Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

33 results about "Fault tolerant architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

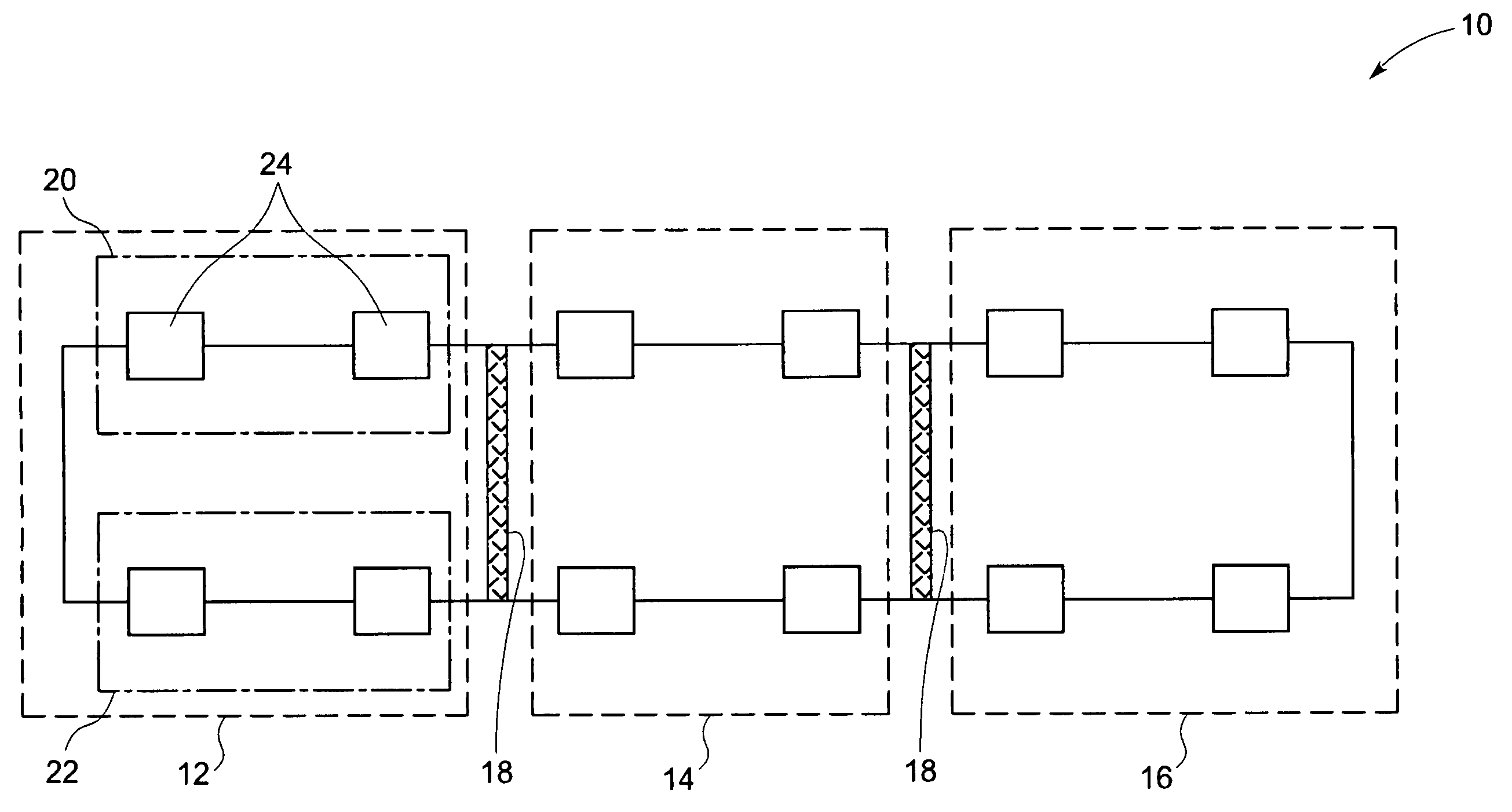

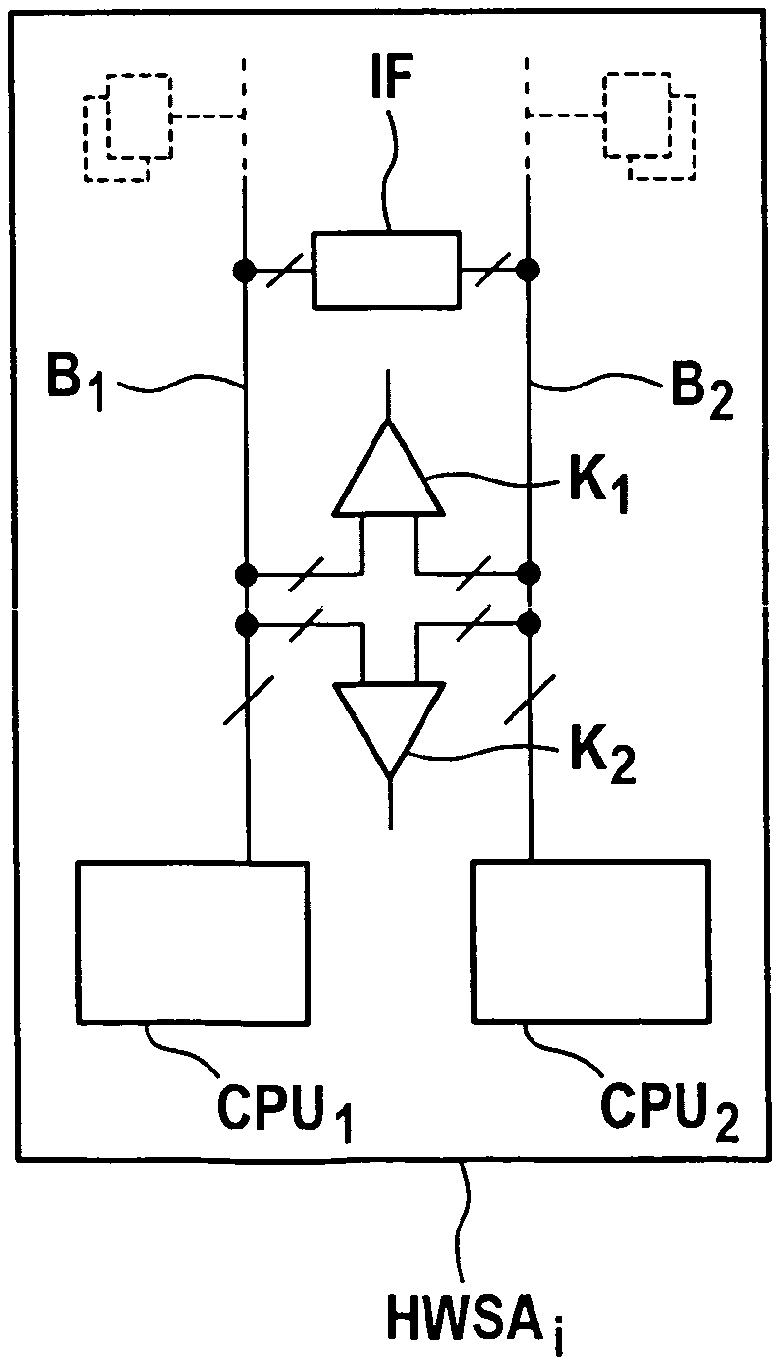

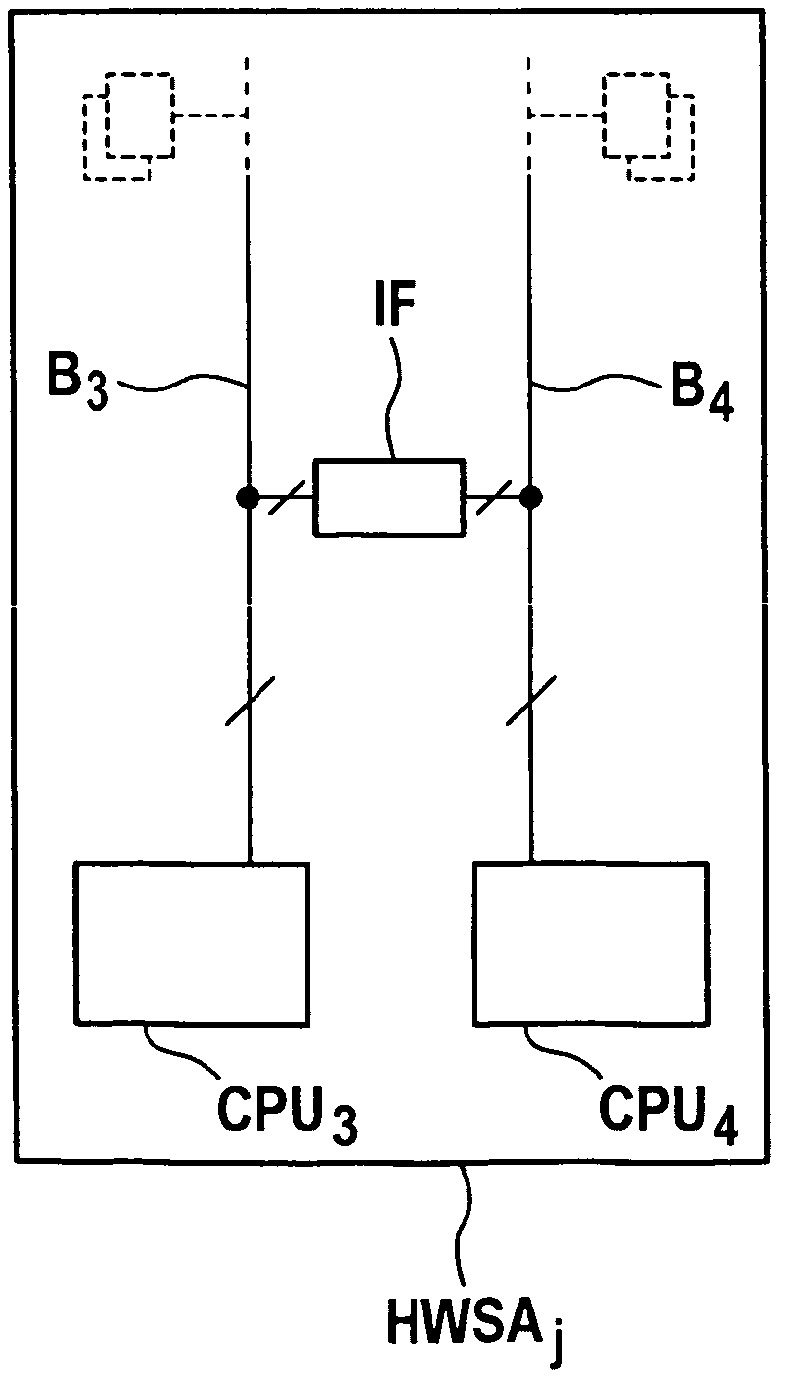

Microprocessor System Having Fault-Tolerant Architecture

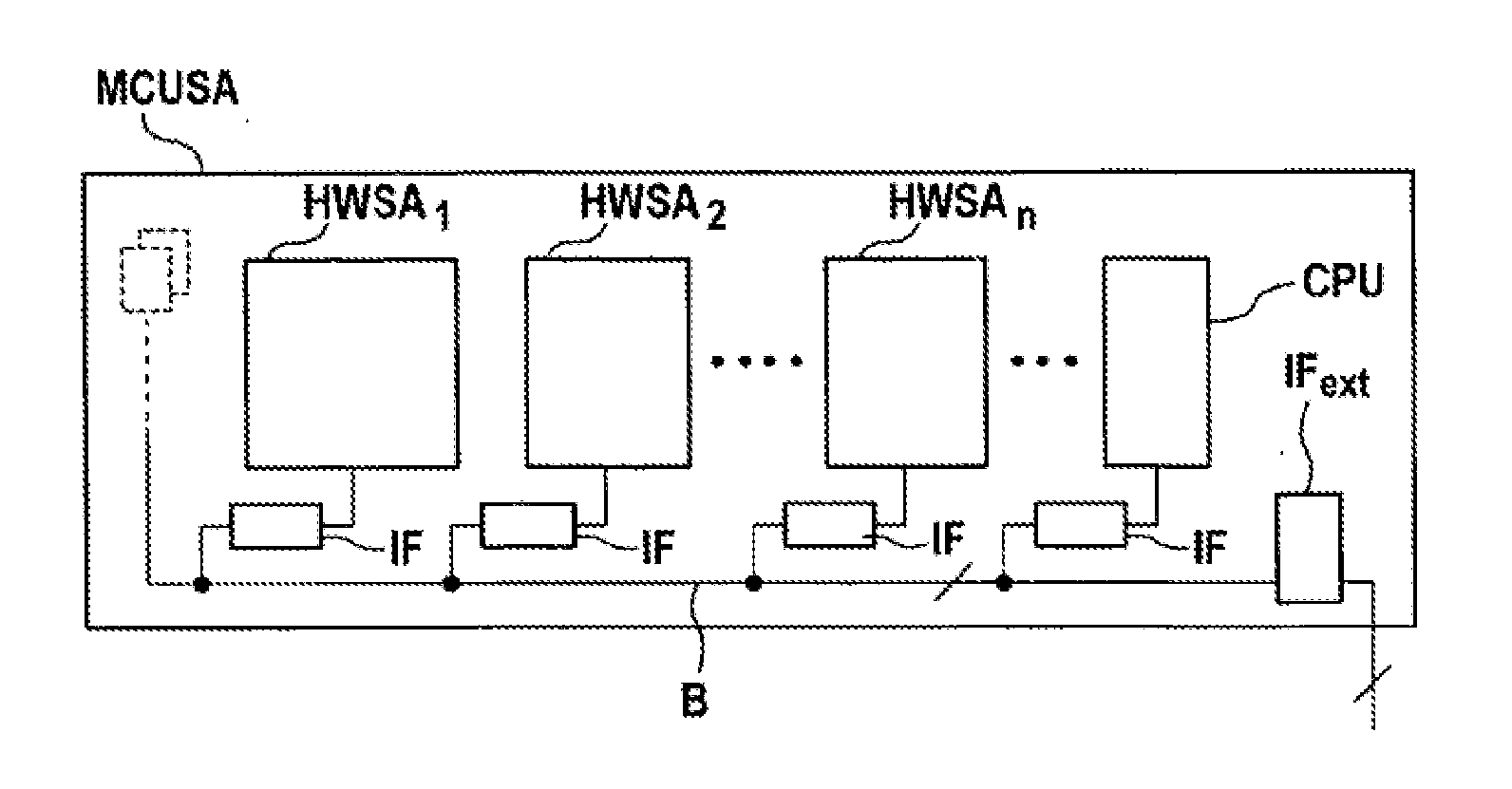

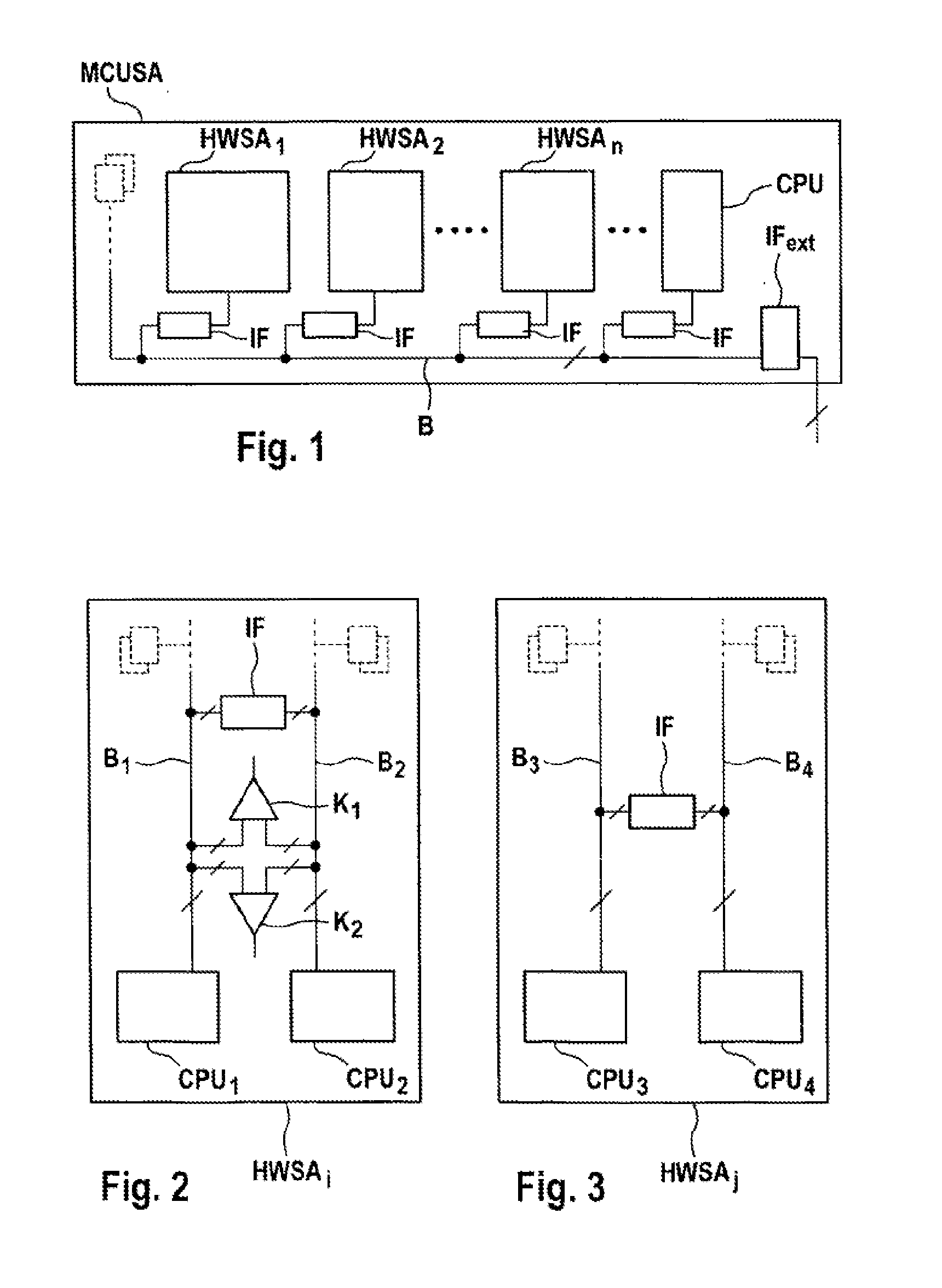

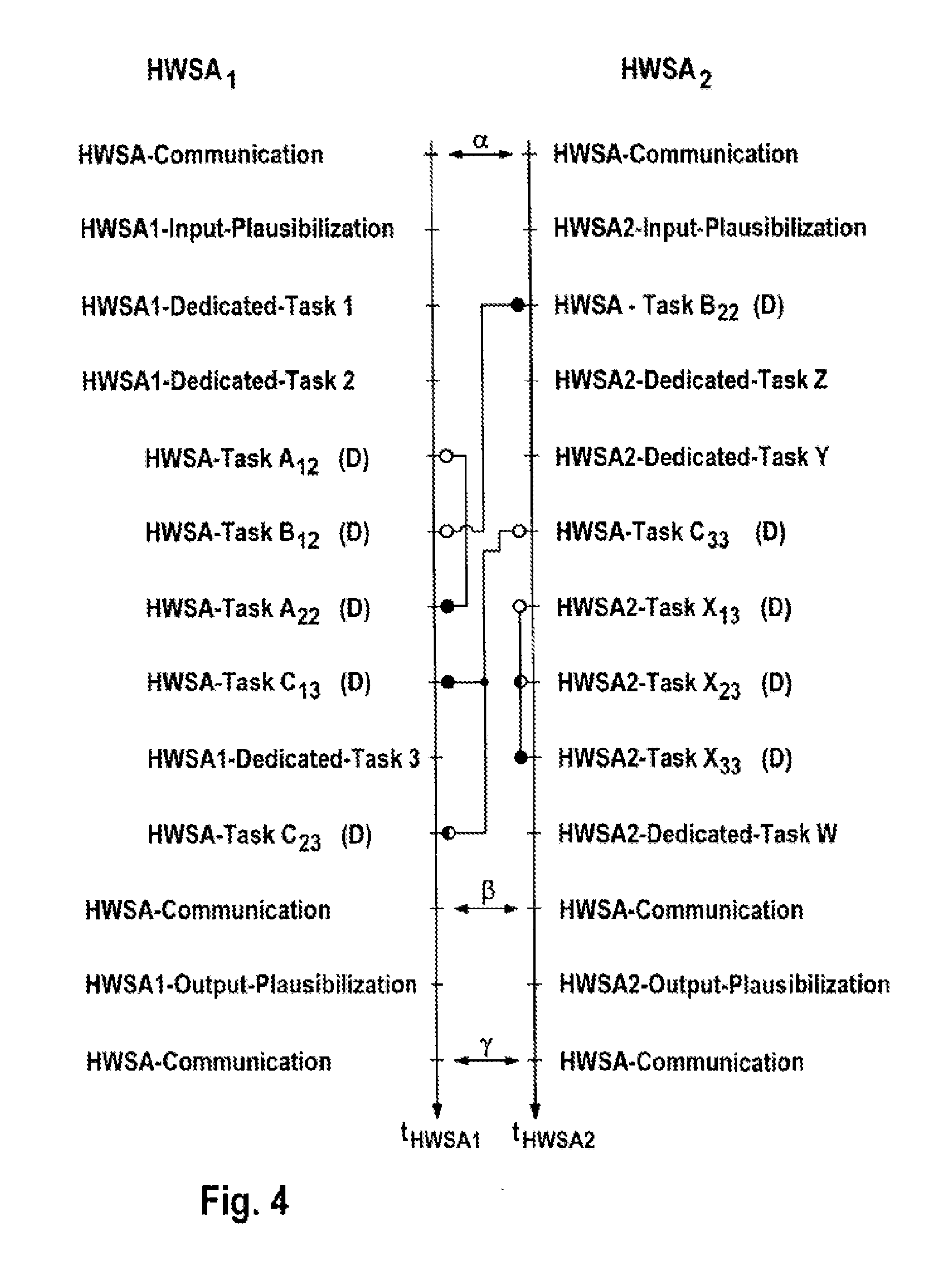

InactiveUS20130268798A1Improve robustnessFurther-increased robustnessSafety arrangmentsError avoidanceFault tolerant architectureIntrinsic safety

The invention relates to a microprocessor system for executing software modules, at least some of which are security critical, within the scope of controlling functions or tasks assigned to the software modules, comprising an intrinsically safe microprocessor module having at least two microprocessor cores. At least one further intrinsically safe microprocessor module having at least two microprocessor cores is provided. At least two microprocessor modules are connected via a bus system, at least two software modules are provided which execute functions, at least some of which overlap, the software modules having at least partially overlapping functions are distributed on a microprocessor module or n at least two microprocessor modules, and means for comparing or arbitrating events generated with the software modules for the identical functions are provided in order to detect software or hardware faults.

Owner:CONTINENTAL TEVES AG & CO OHG

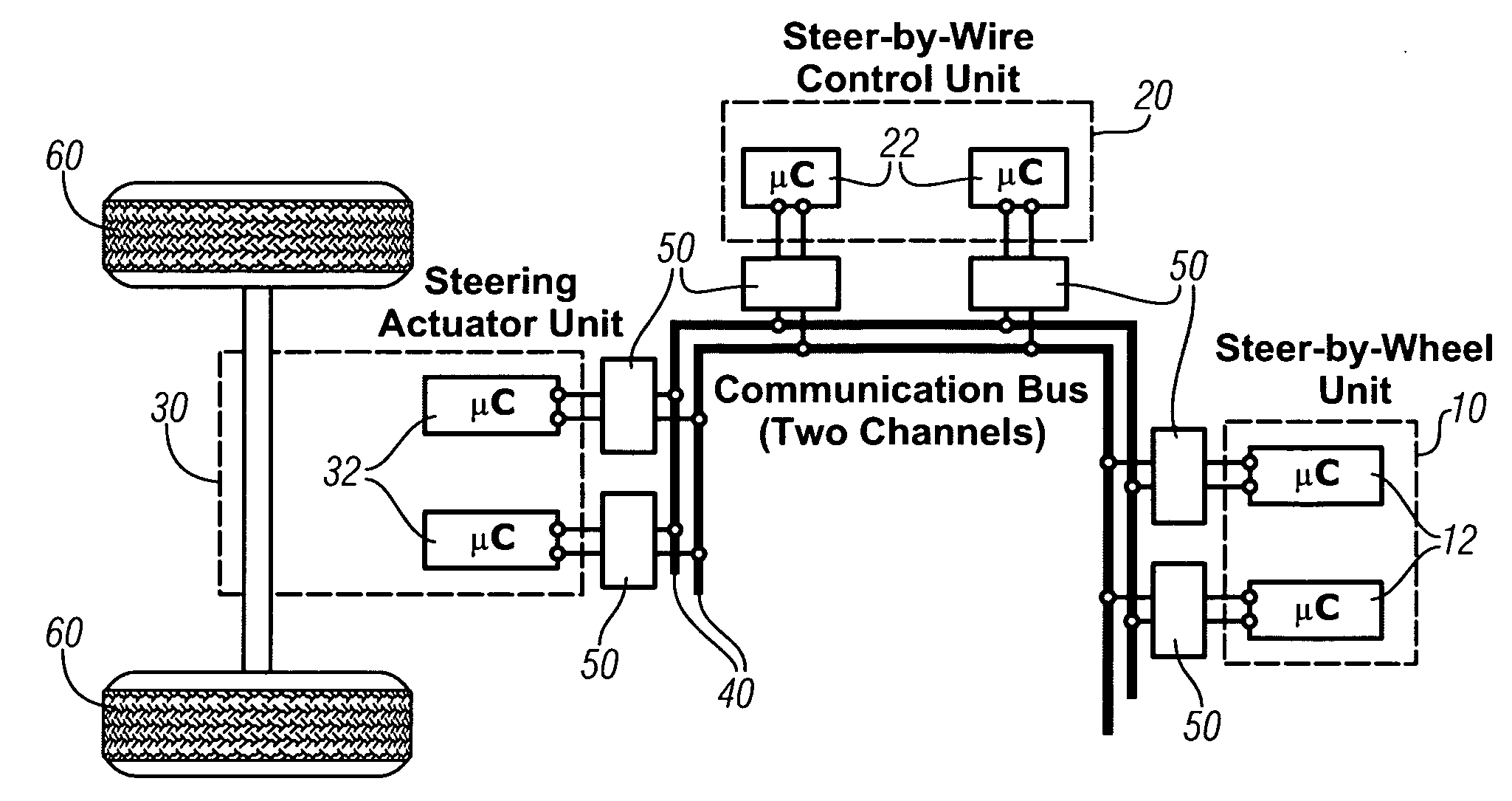

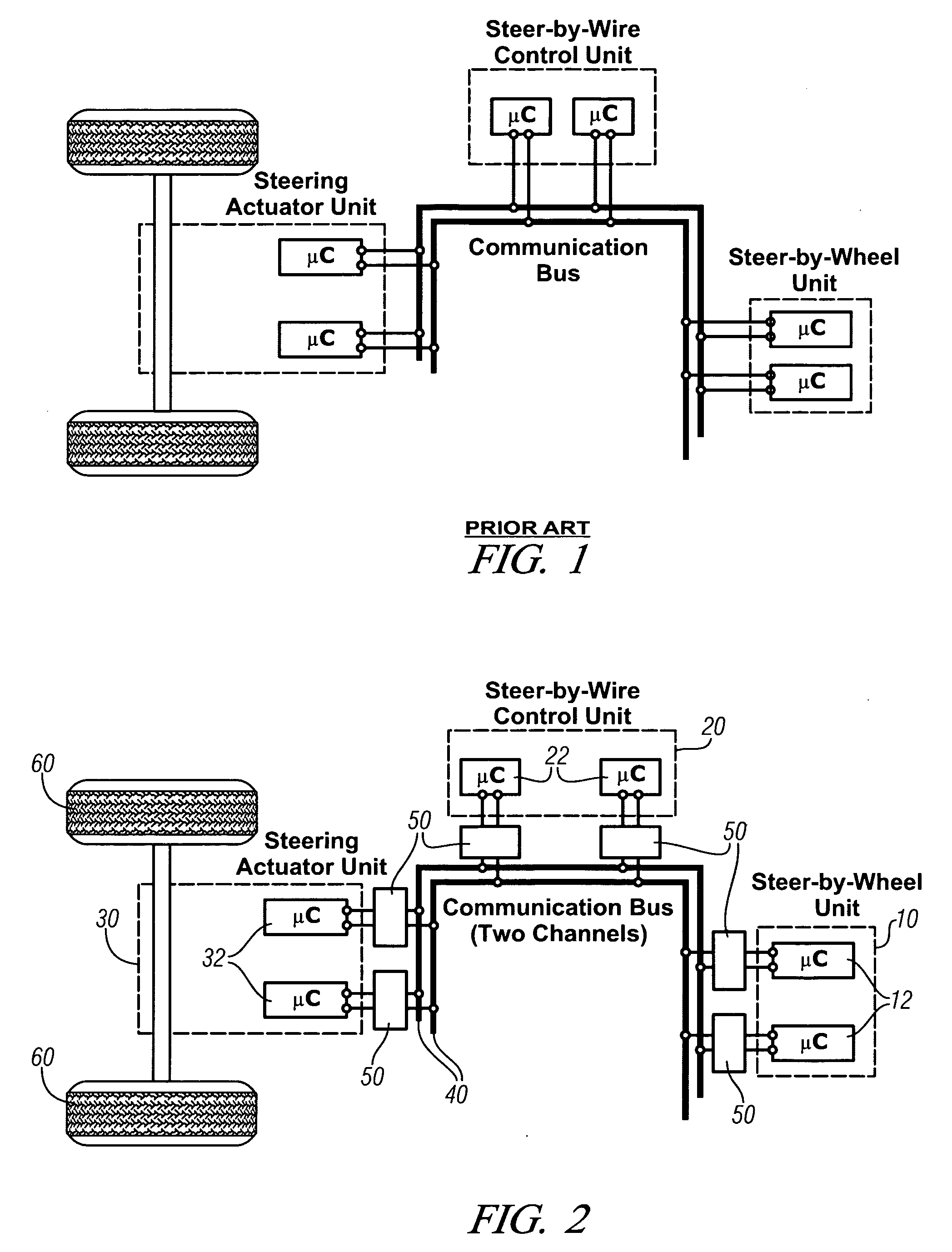

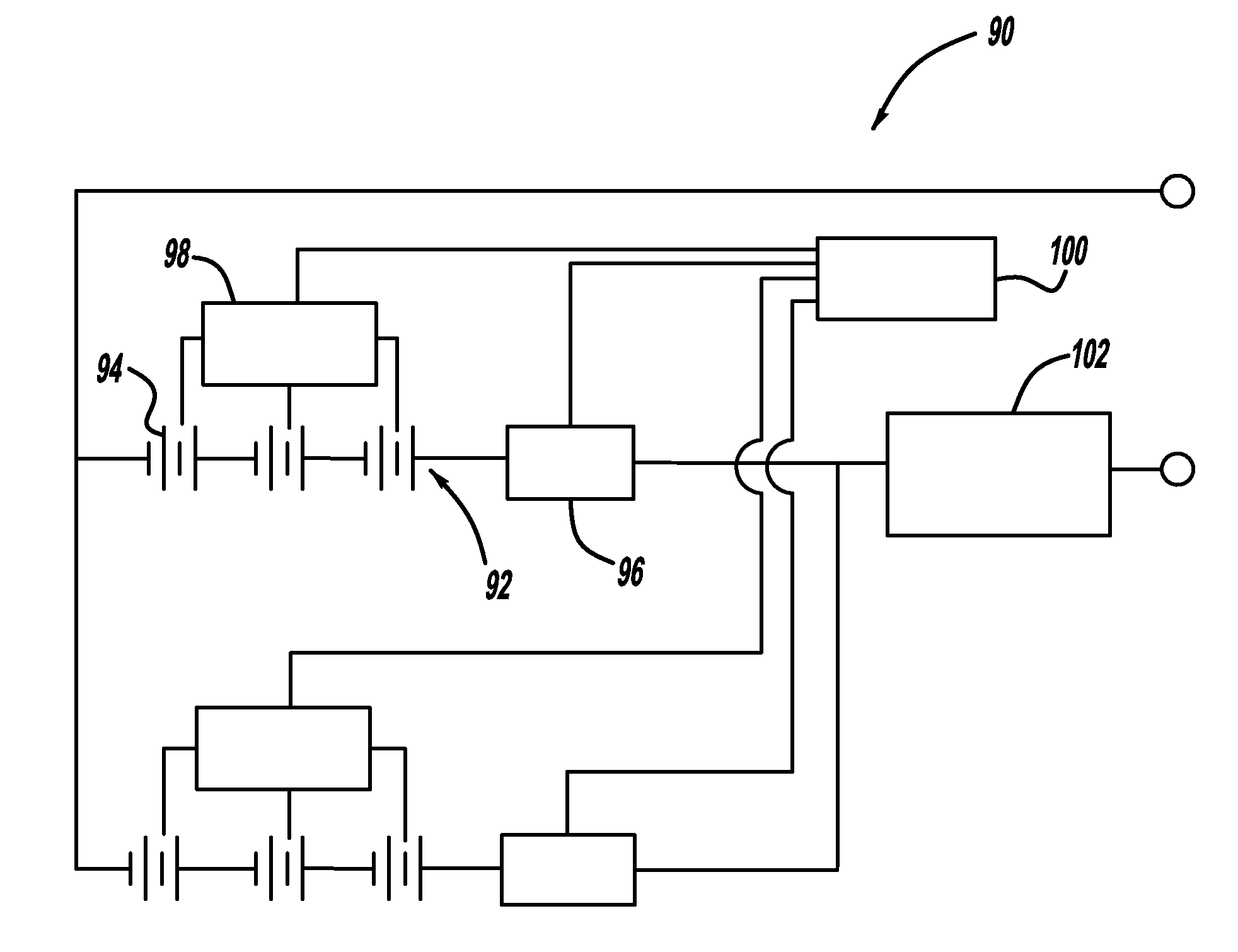

Fault-tolerant architecture for a distributed control system

InactiveUS20060253726A1Improve reliabilityImprove the level ofError detection/correctionBrake control systemsFault tolerant architectureLine sensor

A fault-tolerant architecture, comprising fault tolerant units, a wire-based communication bus, and respective radio transceivers is offered. The fault-tolerant units communicate using the radio transceivers when communication via the wire-based communication bus is compromised by a fault. The intent is to enhance reliability and fault-tolerance of a distributed system architecture, such as a steer-by-wire system for a vehicle. The novel drive-by-wire / wireless architecture uses multiple wireless sensors and short-range low power radio transceivers associated with various micro-controllers. These sensors and radio transceivers allow the micro-controllers to communicate critical control signals and drive commands in the event of a communications fault, e.g. in a vehicle drive-by-wire system.

Owner:GM GLOBAL TECH OPERATIONS LLC

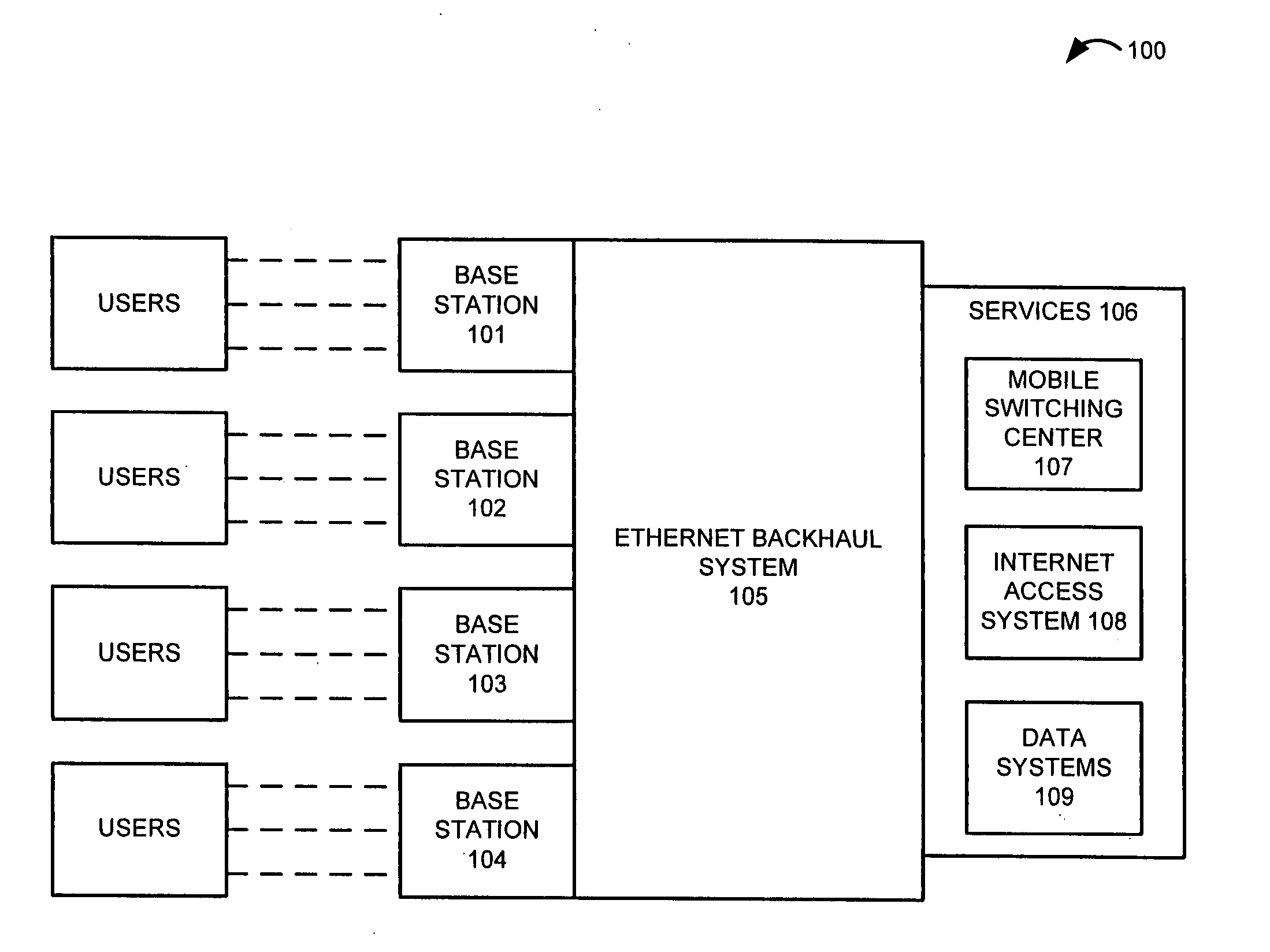

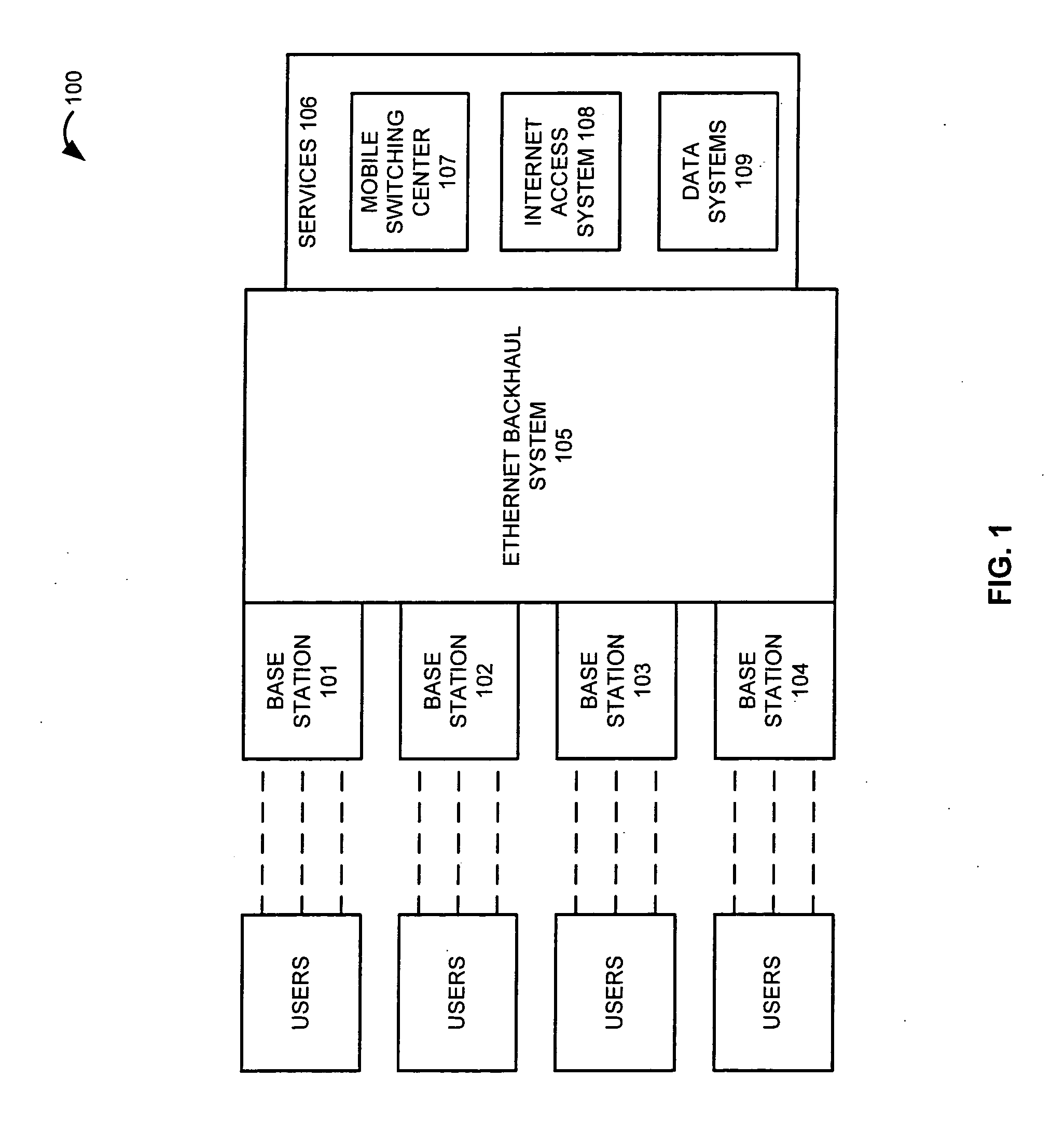

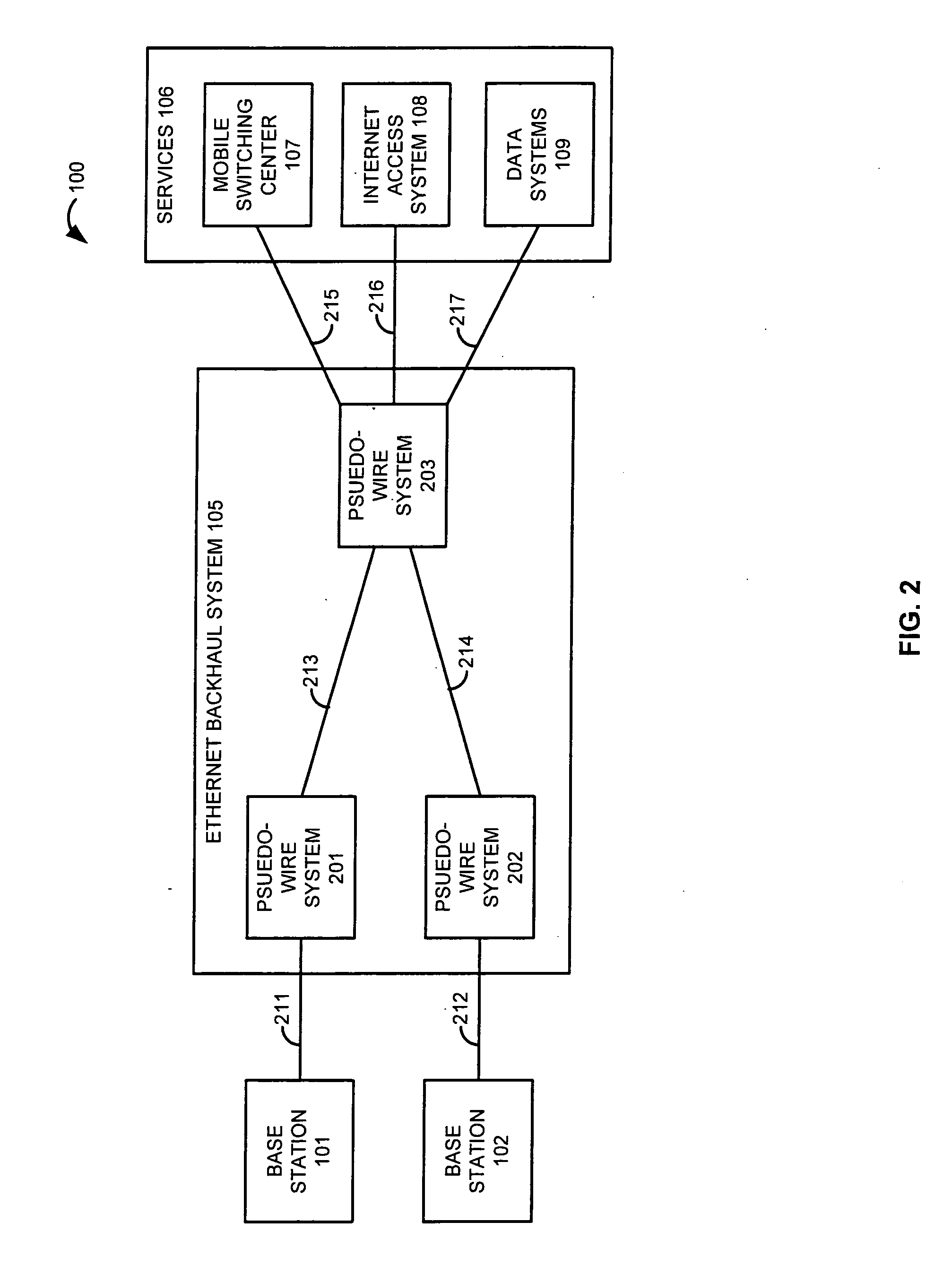

Fault tolerant architecture for wireless base stations using ethernet backhaul

InactiveUS20060227767A1Information formatConnection managementFault tolerant architectureMobile Telephone Service

Base stations exchange information with users over first wireless communication links. A mobile switching center provides mobile telephone service. An Internet access system provides Internet access service. A data system provides a data service. An Ethernet backhaul system uses an Ethernet format to exchange the information between the base stations and the mobile switching center, the Internet access system, and the data system. Wireless interfaces are coupled to the base stations and are configured to exchange the information over second wireless links. Individual base stations detect a fault in the Ethernet backhaul system, and in response, to route the information away from the Ethernet backhaul system and to the wireless interfaces to provide service restoration.

Owner:SPRINT CORPORATION

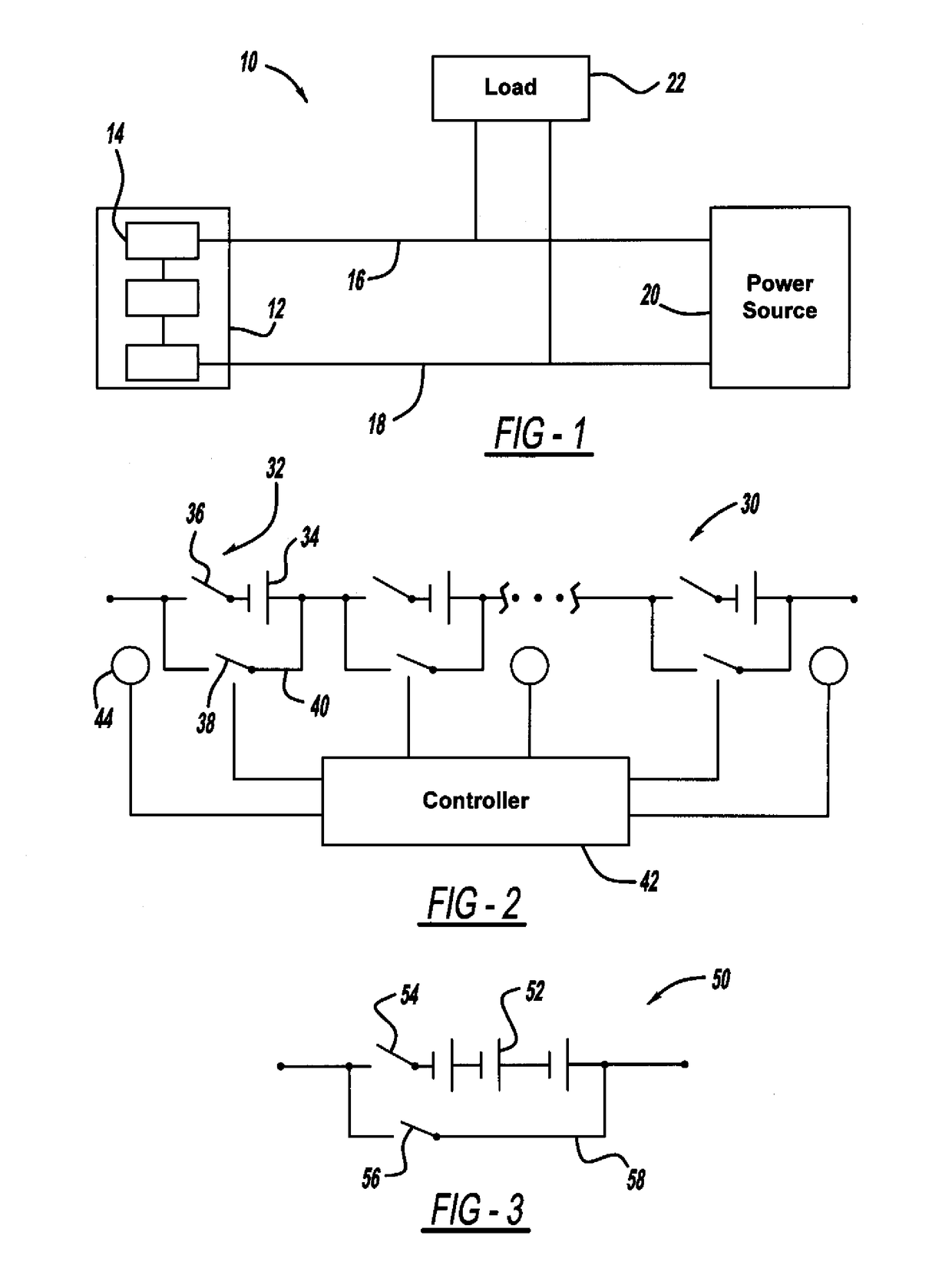

Battery fault tolerant architecture for cell failure modes parallel bypass circuit

ActiveUS20120091963A1LimitedLow failure rateHybrid vehiclesParallel/serial switchingFault tolerant architectureComputer module

A by-pass circuit for a battery system that disconnects parallel connected cells or modules from a battery circuit or controls the current through the parallel connected cells or modules. If a cell has failed or is potentially failing in the system, then the by-pass circuit can disconnect the cell or module from other cells or modules electrically coupled in parallel. If a cell or module has a lower capability than another cell or module, then the by-pass circuit can control the current to the cell or module to maximize the performance of the system and prevent the system from creating a walk-home condition.

Owner:GM GLOBAL TECH OPERATIONS LLC

Battery fault tolerant architecture for cell failure modes series bypass circuit

InactiveUS9024586B2Charge equalisation circuitSafety/protection battery circuitsFault tolerant architectureElectricity

A battery cell by-pass circuit that has particular application for by-passing cells in a high voltage battery for a vehicle. The battery includes a plurality of battery cells electrically coupled in series. The by-pass circuit includes a first switch electrically coupled in series with one or more of the battery cells, a by-pass line electrically coupled around the one or more battery cells and a second switch electrically coupled in the by-pass line and in parallel with the one or more battery cells. During normal cell operation, the first switch is closed and the second switch is open so that current flows through the one or more battery cells. If the one or more battery cells fail or are failing, the first switch is opened and the second switch is closed so that current by-passes the one or more cells and they are removed from the battery circuit.

Owner:GM GLOBAL TECH OPERATIONS LLC

Performance maps for actuator intelligence

InactiveUS20080269922A1High fault toleranceHigh maintenanceProgramme controlAdaptive controlThree levelFault tolerant architecture

A four level fault tolerant architecture for the intelligent machine system is based on the basic component of a self contained actuator module with standardized interfaces. This system architecture organizes all of the operational software to make it universal, high performing, fault tolerant, and use condition-based maintenance. The independent structural layers are structured and prioritized by the advanced electronic controllers. The sensor module creates an accurate parametric representation of the electro-mechanical actuator, and manages all resources in the electro-mechanical actuator. The system will also comprise of operational criteria, maximum performance envelopes, condition-based maintenance, fault tolerance, layered control, and force / motion control. The system allows independent development of different components of the framework, categorized into three levels: the management level, the servo control level, and the senor and communication level. The present disclosure establishes a fully responsive actuator whose intelligence manages a sufficiently broad set of choices.

Owner:TESAR DELBERT

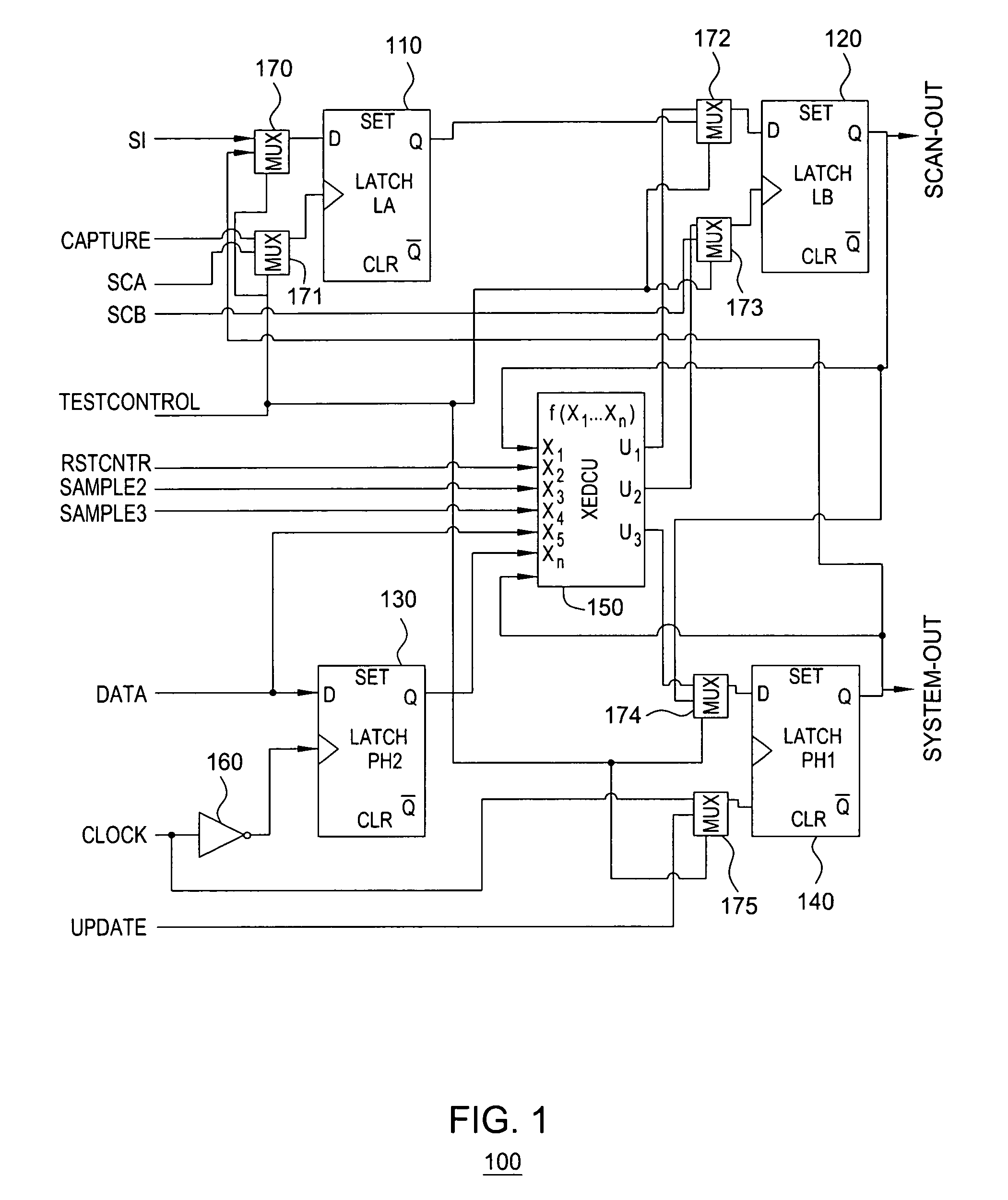

Fault-tolerant architecture of flip-flops for transient pulses and signal delays

ActiveUS7594150B2Reliability increasing modificationsError preventionFault tolerant architectureImage resolution

A method and apparatus for a structure of a flip-flop that is tolerant to the noise pulses occurring due to the presence of crosstalk faults by sampling the input data multiple times before and after the active clock edge. The final stored value at the flip-flop is determined by the resolution of a counter circuit residing in the flip-flop, which is activated at the change of the sampled input data. This counter based resolution mechanism allows for the detection and filtering of the noise pulse induced at the input of the flip-flop due to a crosstalk fault.

Owner:RUTGERS THE STATE UNIV +1

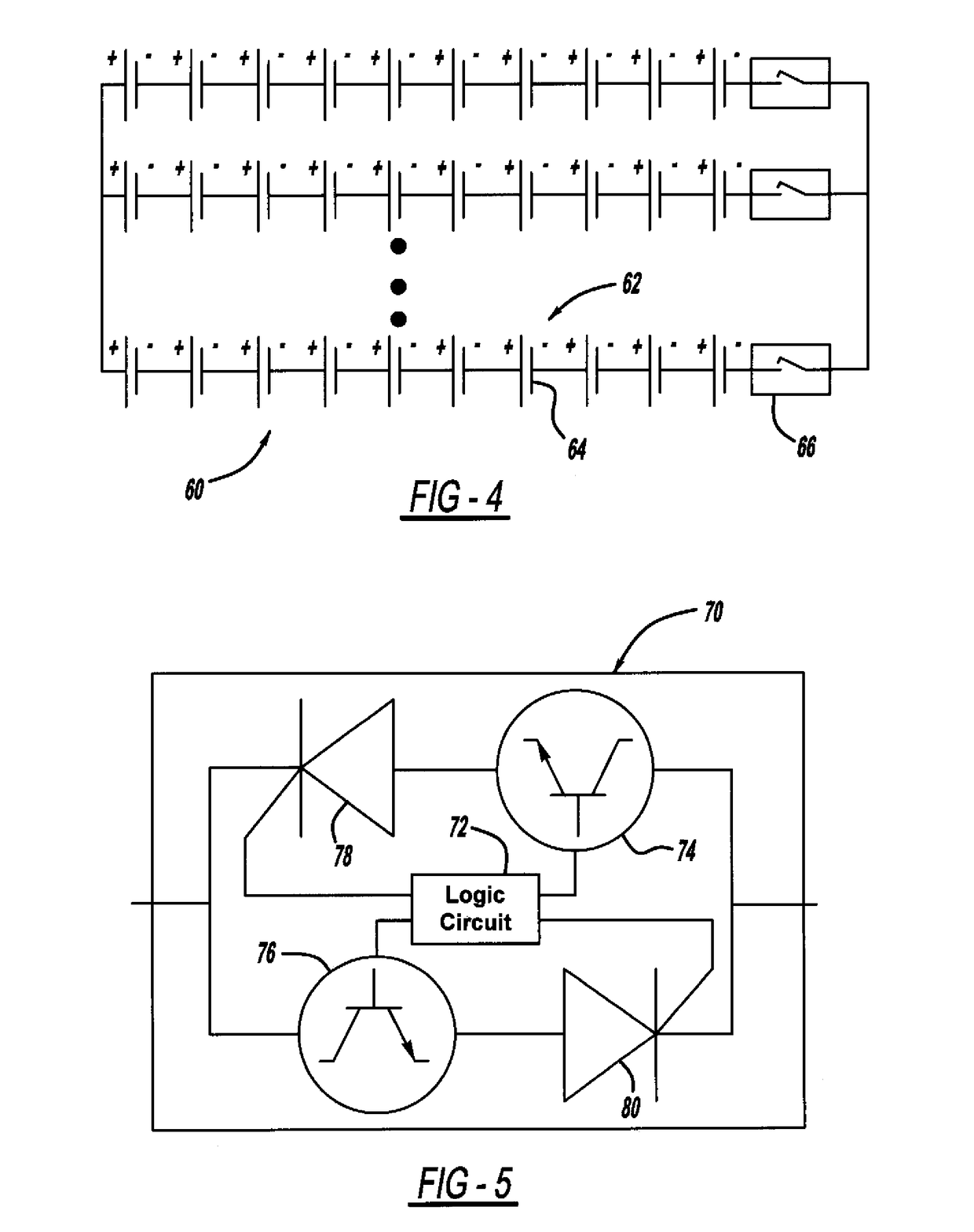

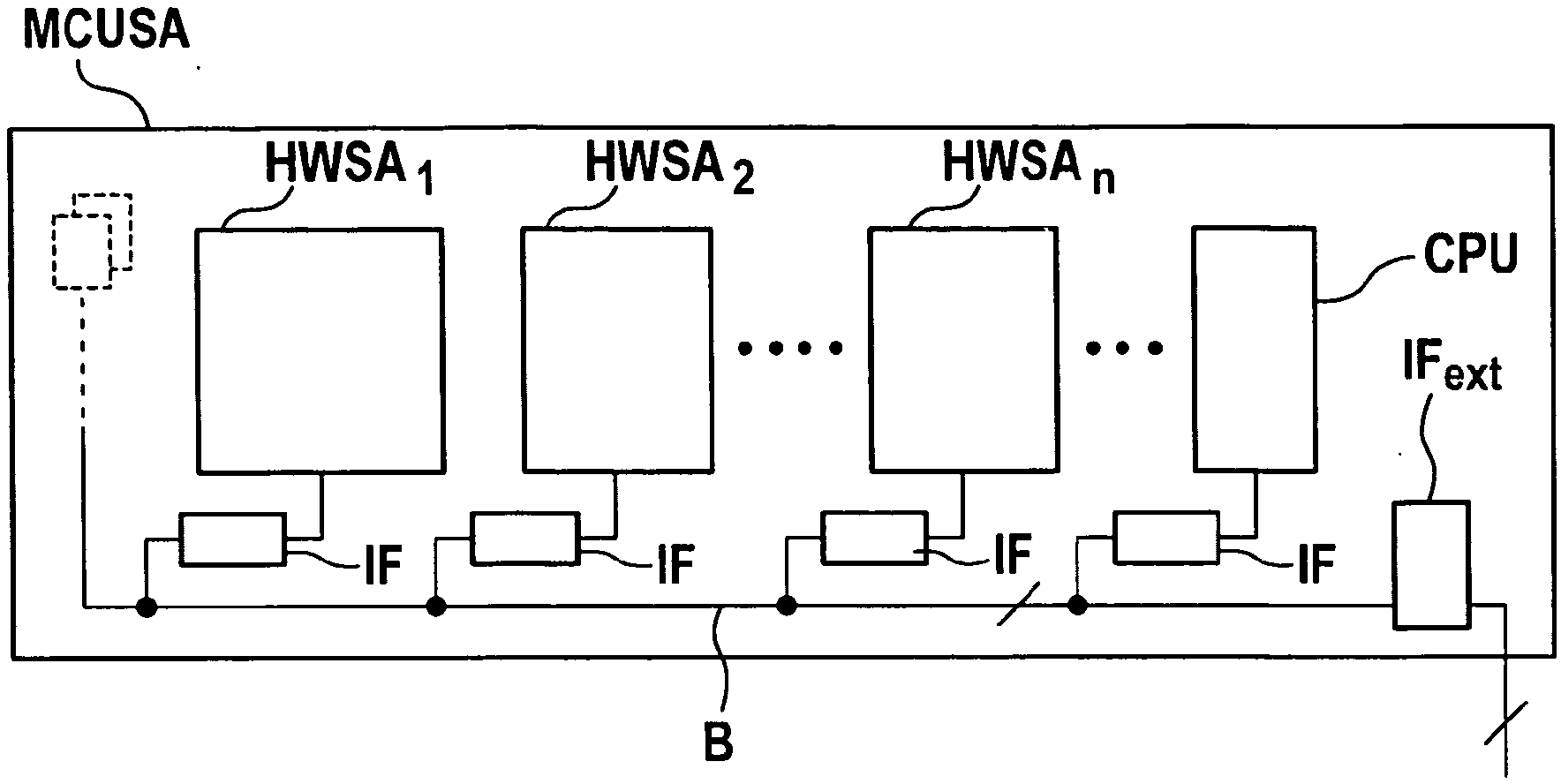

Full fault tolerant architecture for organic electronic devices

InactiveUS7518148B2Static indicating devicesElectroluminescent light sourcesFault tolerant architectureElectricity

An organic device package that provides full fault tolerance against both electrical shorts and electrical opens is presented. An organic device package comprising a plurality of groups of organic electronic elements electrically coupled in series, where at least one of the plurality of groups of organic electronic elements comprises a plurality of sub-groups of organic electronic elements electrically coupled in parallel, and where at least one of the plurality of sub-groups of organic electronic elements comprises a plurality of organic electronic elements electrically coupled in series. Further, various embodiments are contemplated where a plurality of series blocks and parallel blocks may be nested to provide a grid network having increased flexibility and fault tolerance.

Owner:GENERAL ELECTRIC CO

Battery fault tolerant architecture for cell failure modes parallel bypass circuit

ActiveUS8471529B2LimitedLow failure rateParallel/serial switchingMaterial analysis by electric/magnetic meansFault tolerant architectureElectrical battery

Owner:GM GLOBAL TECH OPERATIONS LLC

Full fault tolerant architecture for organic electronic devices

InactiveUS20060226522A1Static indicating devicesSemiconductor/solid-state device detailsFault tolerant architectureGrid network

An organic device package that provides full fault tolerance against both electrical shorts and electrical opens is presented. An organic device package comprising a plurality of groups of organic electronic elements electrically coupled in series, where at least one of the plurality of groups of organic electronic elements comprises a plurality of sub-groups of organic electronic elements electrically coupled in parallel, and where at least one of the plurality of sub-groups of organic electronic elements comprises a plurality of organic electronic elements electrically coupled in series. Further, various embodiments are contemplated where a plurality of series blocks and parallel blocks may be nested to provide a grid network having increased flexibility and fault tolerance.

Owner:GENERAL ELECTRIC CO

Microprocessor system having fault-tolerant architecture

ActiveCN103262045AShort delay timeBest data transfer speedSafety arrangmentsError avoidanceFault tolerant architectureSoftware modules

The invention relates to a microprocessor system (MCUSA) for executing software modules, at least some of which are security-critical, within the scope of controlling functions or tasks assigned to the software modules, comprising an intrinsically safe microprocessor module (HWSAi) having at least two microprocessor cores (CPUi). According to the invention, at least one further intrinsically safe microprocessor module (HWSAi i=1,... n) having at least two microprocessor cores (CPU1, CPU2; CPU3, CPU4) is provided, wherein the at least two microprocessor modules (HWSA1, HWSA2) are connected via a bus system (B), at least two software modules are provided which execute functions, at least some of which overlap, said software modules having at least partially overlapping functions are distributed on a microprocessor module (HWSA1, HWSA2) or on at least two microprocessor modules (HWSA1, HWSA2), and means for comparing and / or arbitrating events generated with the software modules for the identical functions are provided in order to detect software and / or hardware faults.

Owner:CONTINENTAL AUTOMOTIVE TECH GMBH

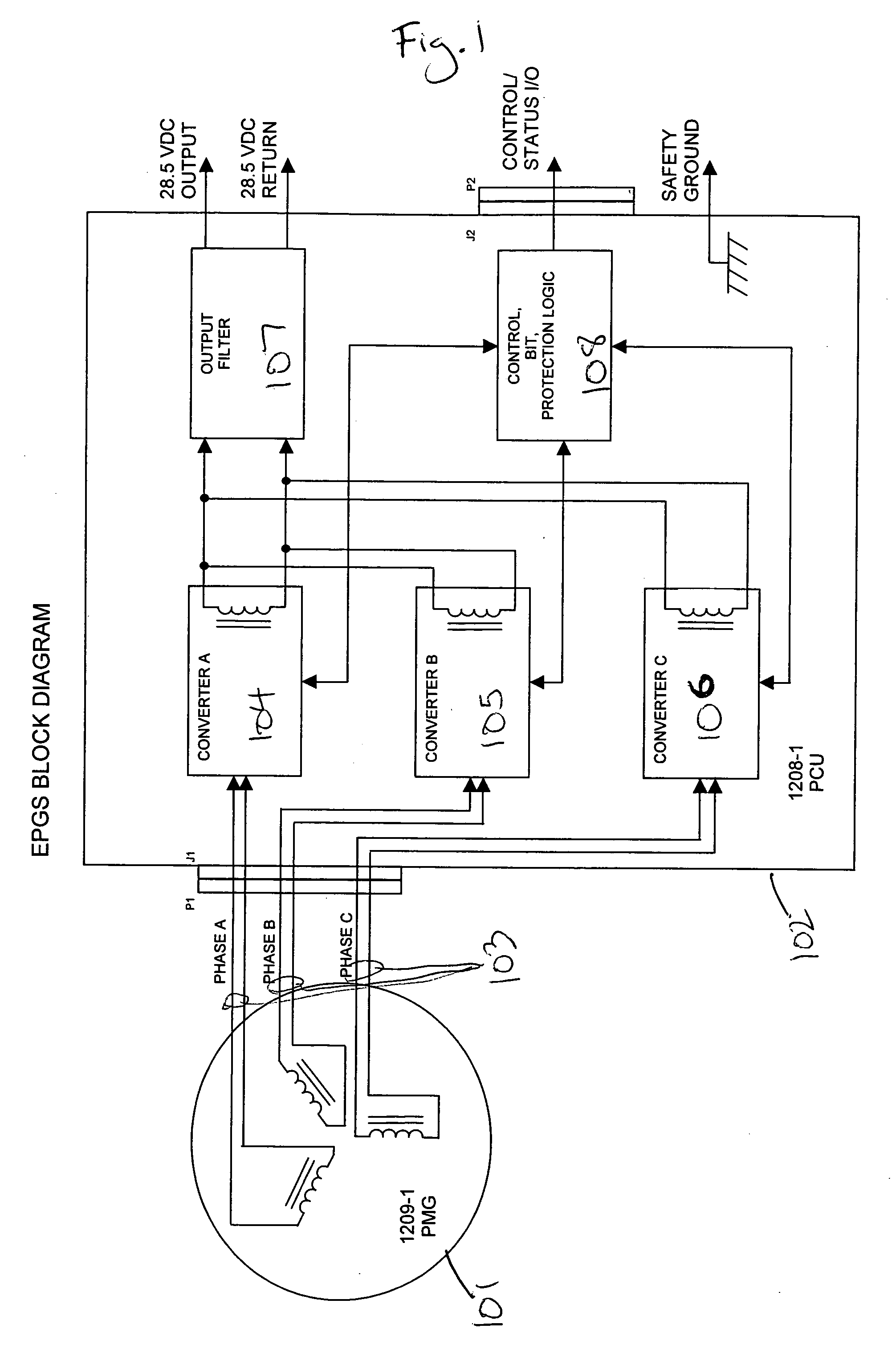

Fault tolerant architecture for permanent magnet starter generator subsystem

ActiveUS20050237034A1Highly reliable and fault tolerant systemOperational securityWindingsMagnetic circuitFault tolerant architectureStarter generator

A permanent magnet starter / generator subsystem configured in a fault tolerant architecture is described herein for small engine applications. The system allows for lighter system weight, improved system reliability, higher performance capability and reduced maintenance.

Owner:ASTRONICS ADVANCED ELECTRONICS SYST

Battery fault tolerant architecture for cell failure modes parallel bypass circuit

ActiveCN102457084AParallel/serial switchingSafety/protection battery circuitsFault tolerant architectureComputer module

A by-pass circuit for a battery system that disconnects parallel connected cells or modules from a battery circuit or controls the current through the parallel connected cells or modules. If a cell has failed or is potentially failing in the system, then the by-pass circuit can disconnect the cell or module from other cells or modules electrically coupled in parallel. If a cell or module has a lower capability than another cell or module, then the by-pass circuit can control the current to the cell or module to maximize the performance of the system and prevent the system from creating a walk-home condition.

Owner:GM GLOBAL TECH OPERATIONS LLC

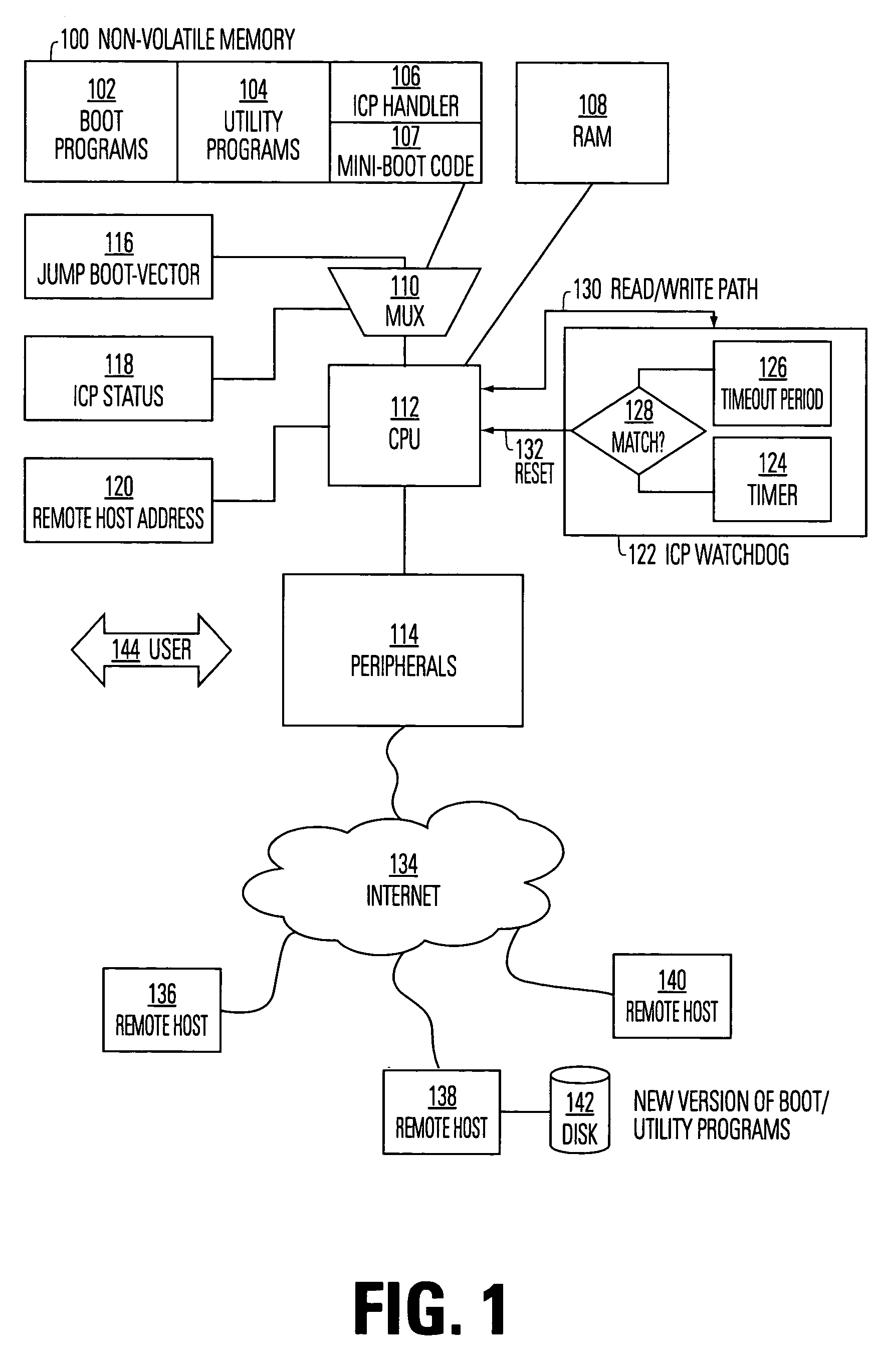

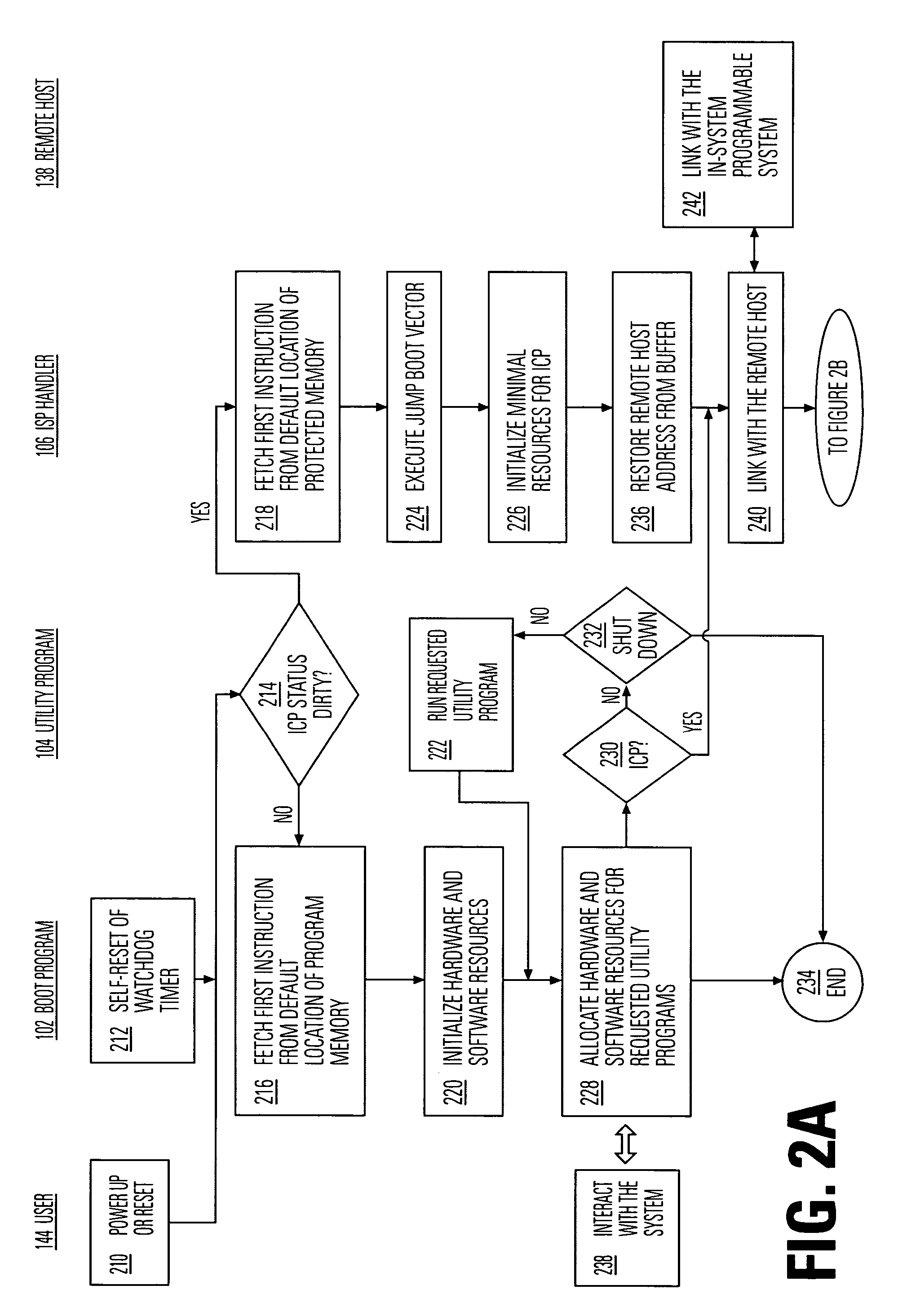

Fault-tolerant architecture for in-circuit programming

InactiveUS7237145B2Communication protocol is improvedIncrease speedEmergency protective arrangements for automatic disconnectionRedundant operation error correctionFault tolerant architectureMultiplexer

The present invention provides a method and apparatus for providing fault-tolerance for in-circuit programming systems. The invention operates by storing a minimal set of code to initialize the in-circuit programming process in a protected memory so that if the in-circuit programming process fails, the in-circuit programming process can be restarted from the protected memory. This type of fault-tolerance is especially important in systems which allow the code which accomplishes the in-circuit programming to be modified by the in-circuit programming process. One embodiment of the present invention provides a multiplexer to selectively switch between a normal boot code sequence and a protected boot code sequence, as well as a watchdog timer to monitor the in-circuit programming process to determine whether the in-circuit programming process is not progressing properly.

Owner:MACRONIX INT CO LTD

Fault-tolerant architecture of flip-flops for transient pulses and signal delays

ActiveUS20070266282A1Reliability increasing modificationsError preventionFault tolerant architectureImage resolution

A method and apparatus for a structure of a flip-flop that is tolerant to the noise pulses occurring due to the presence of crosstalk faults by sampling the input data multiple times before and after the active clock edge. The final stored value at the flip-flop is determined by the resolution of a counter circuit residing in the flip-flop, which is activated at the change of the sampled input data. This counter based resolution mechanism allows for the detection and filtering of the noise pulse induced at the input of the flip-flop due to a crosstalk fault.

Owner:RUTGERS THE STATE UNIV +1

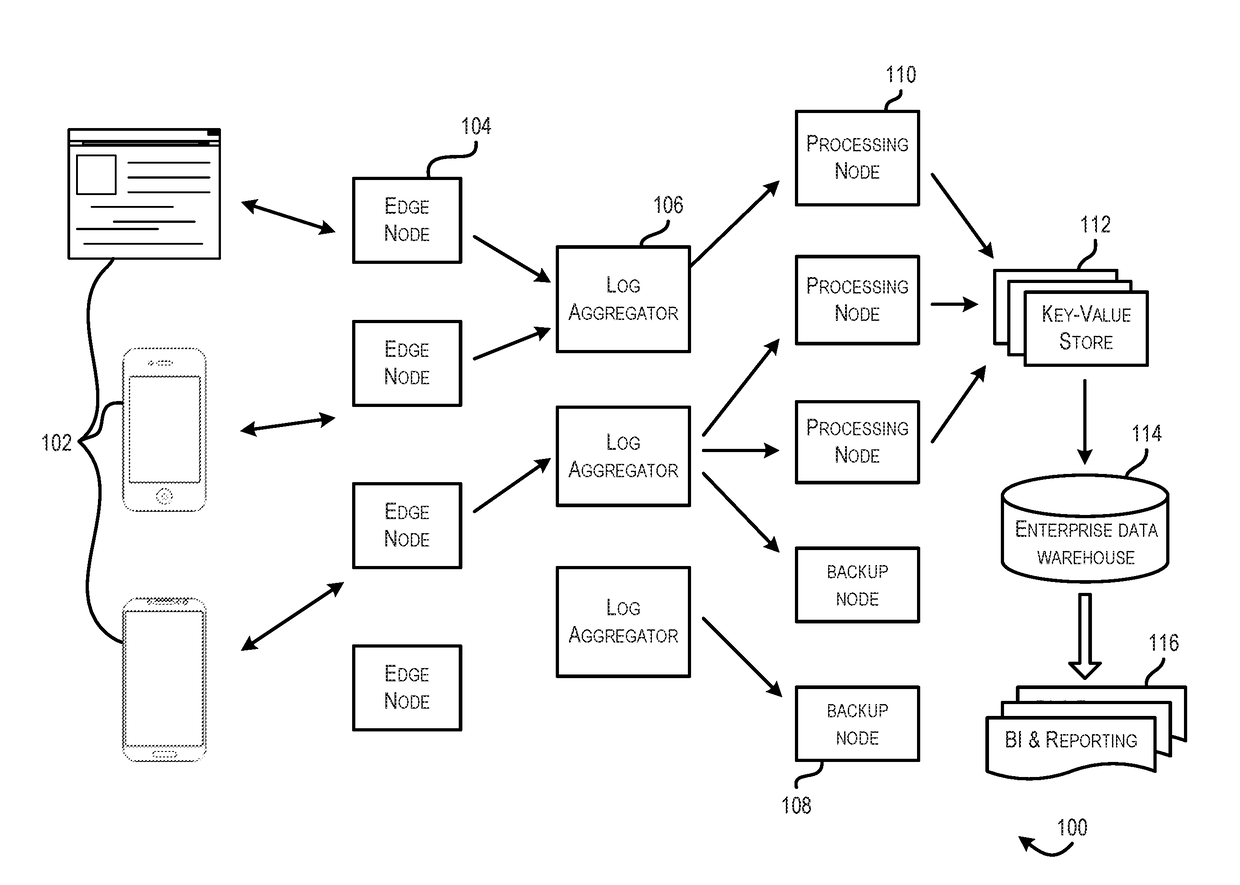

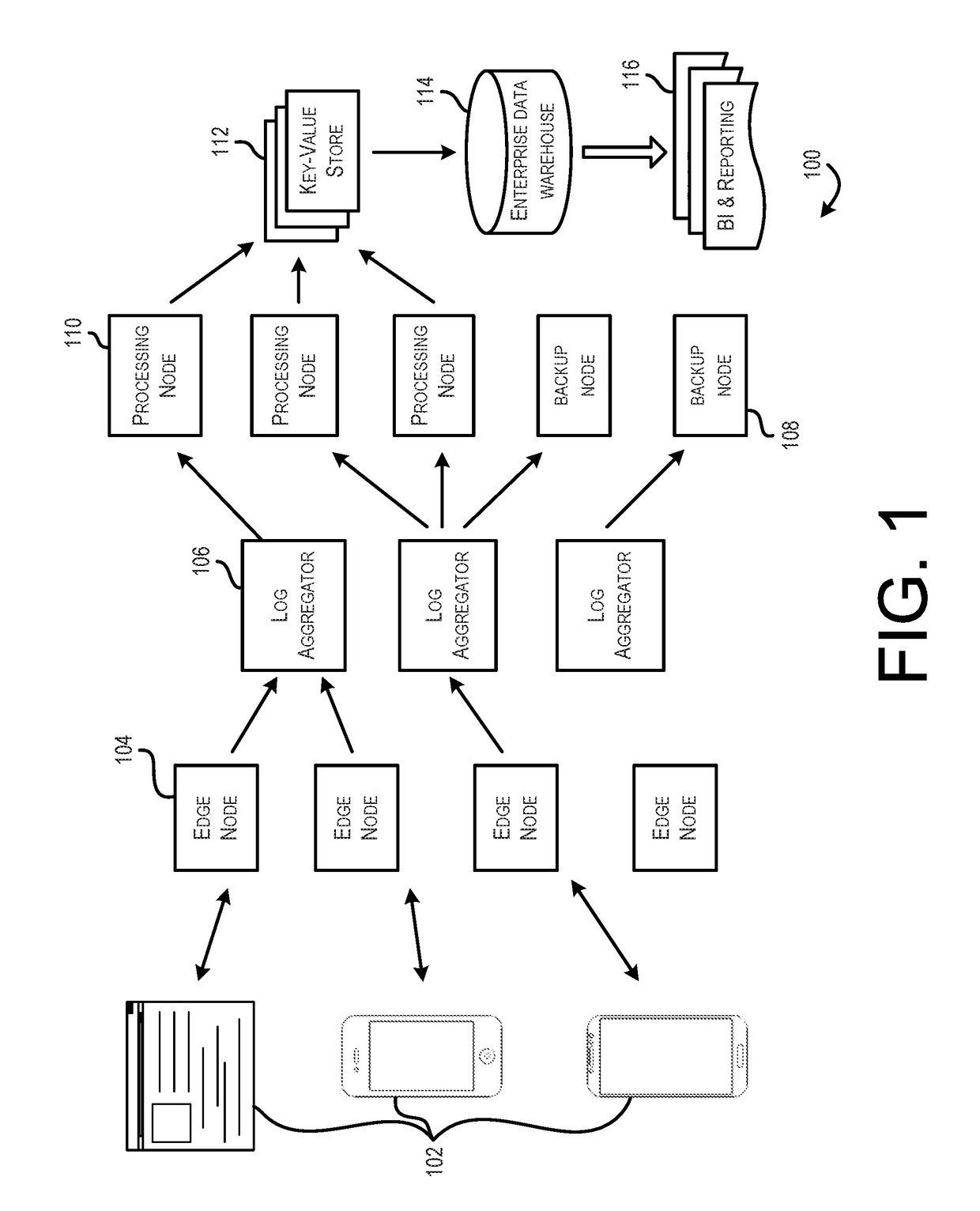

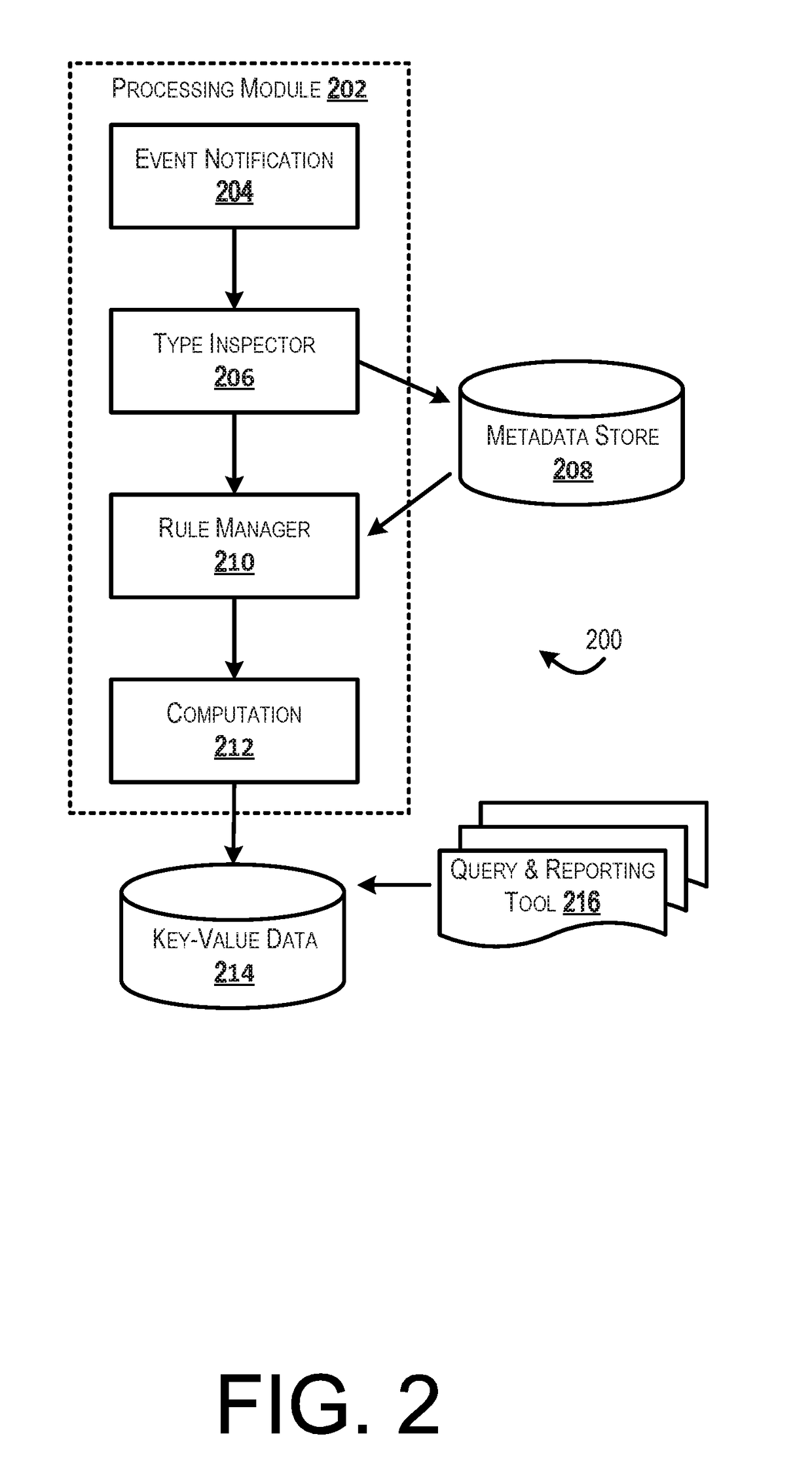

Real-time fault-tolerant architecture for large-scale event processing

ActiveUS20170177442A1Simple queryHardware monitoringData acquisition and loggingFault tolerant architectureComplex event processing

Techniques described herein include an event notification processing platform configured to process large-scale event notifications in relative real time. The platform may receive event notifications from multiple sources and publish them to an event stream, or log. The platform may subsequently process each notification at a processing module according to one or more sets of rules and the processed information may be made available via a data store. Rule sets may be selected based on the type of event received by the platform. A backup data store may record event notifications as they are received or at periodic intervals. Event notification data may also be stored at multiple levels of the platform, so that in the case of a failure of one or more components of the platform, data may continue to be processed.

Owner:BEIJING CHUANGXIN JOURNEY NETWORK TECH CO LTD

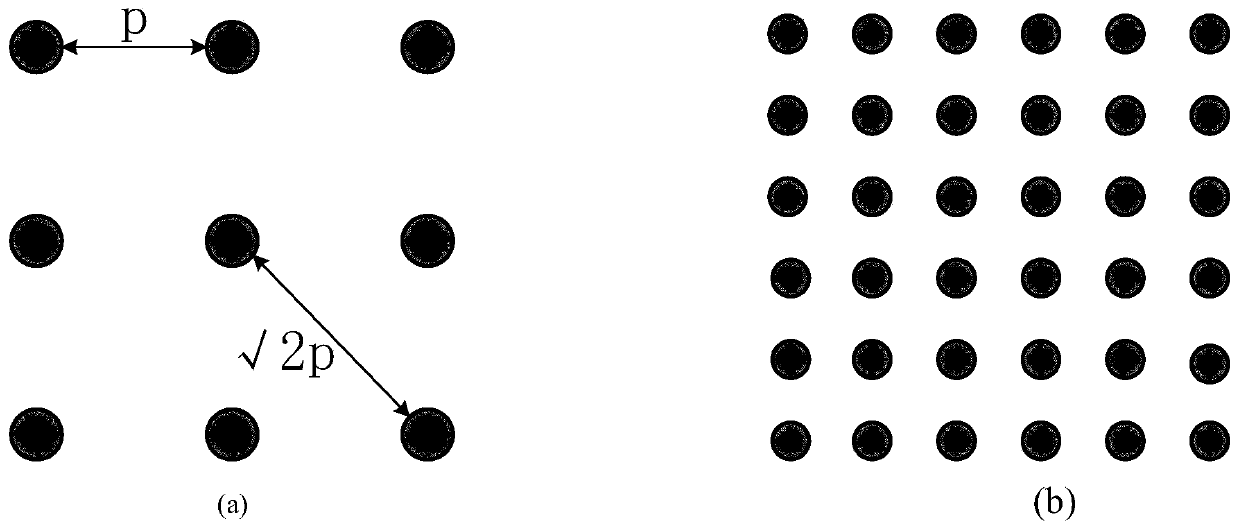

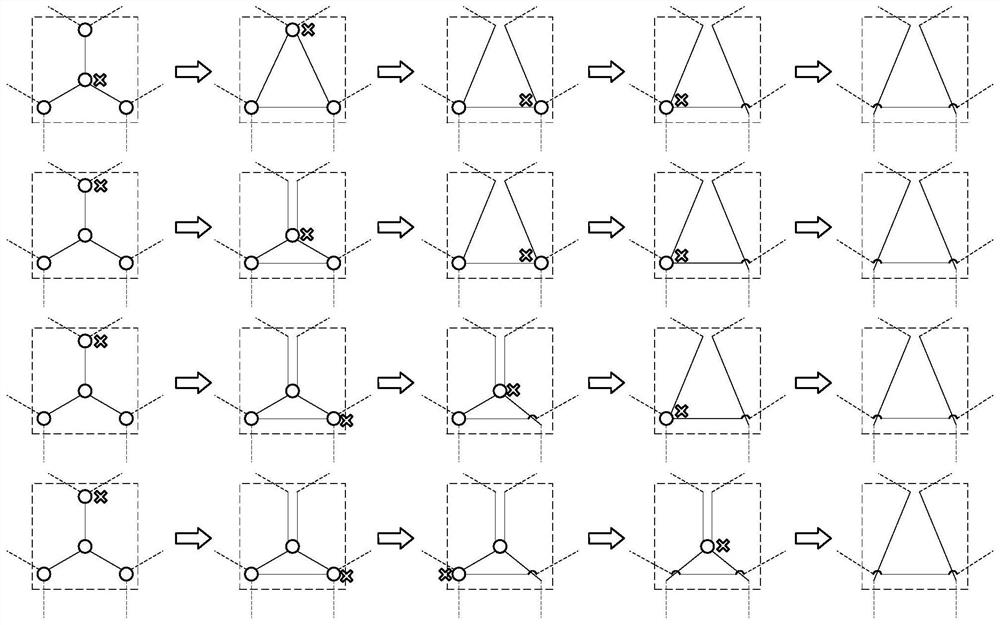

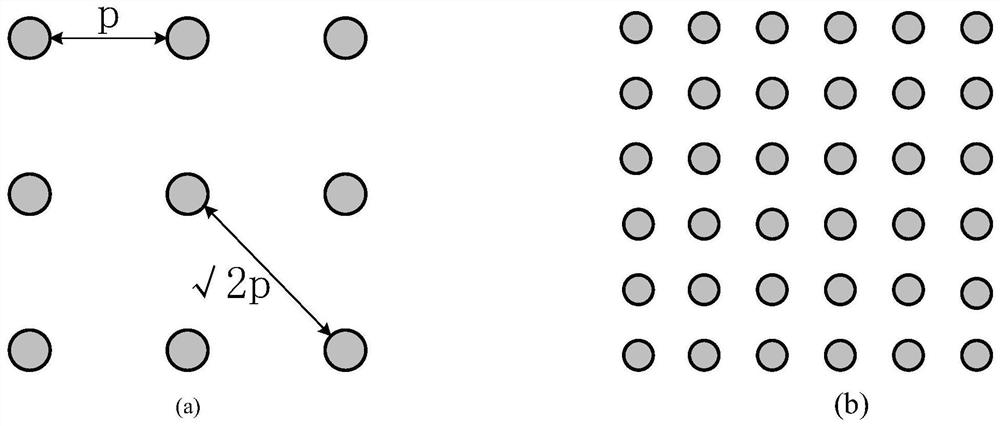

Fault tolerant architecture of TSV oriented to three-dimensional integrated circuit

ActiveCN110323218AImprove repair rateIncrease redundancySemiconductor/solid-state device detailsSolid-state devicesFault tolerant architecturePath length

The invention is suitable for the technical field of the semiconductor, and provides fault tolerant architecture of TSV oriented to three-dimensional integrated circuit. The redundant structure is composed of N layers of annular structures, and N layers of annular structures are equally divided into six regions through six rays; three RTSVs are arranged on each layer of the annular structure, three RTSVs are uniformly distributed on six rays, the RTSVs at the adjacent layers are dislocated and distributed, the RTSV is arranged at the center of the innermost layer of hexagon; the TSVs are arranged by utilizing the specific symmetry and flexibility of the hexagon, and the location for placing the RTSV can be reasonably selected; the redundant structure is divided into multiple uniform regions, and the redundancy rate of each region is improved, thereby guaranteeing the high repair rate of the whole structure; the RTSVs are uniformly distributed in the TSV array, the symmetry of the routing direction is combined, the condition that the repair path length of the fault TSV is large in difference or the time sequence overhead can be avoided, and the overhead is reduced.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY AND SCIENCE

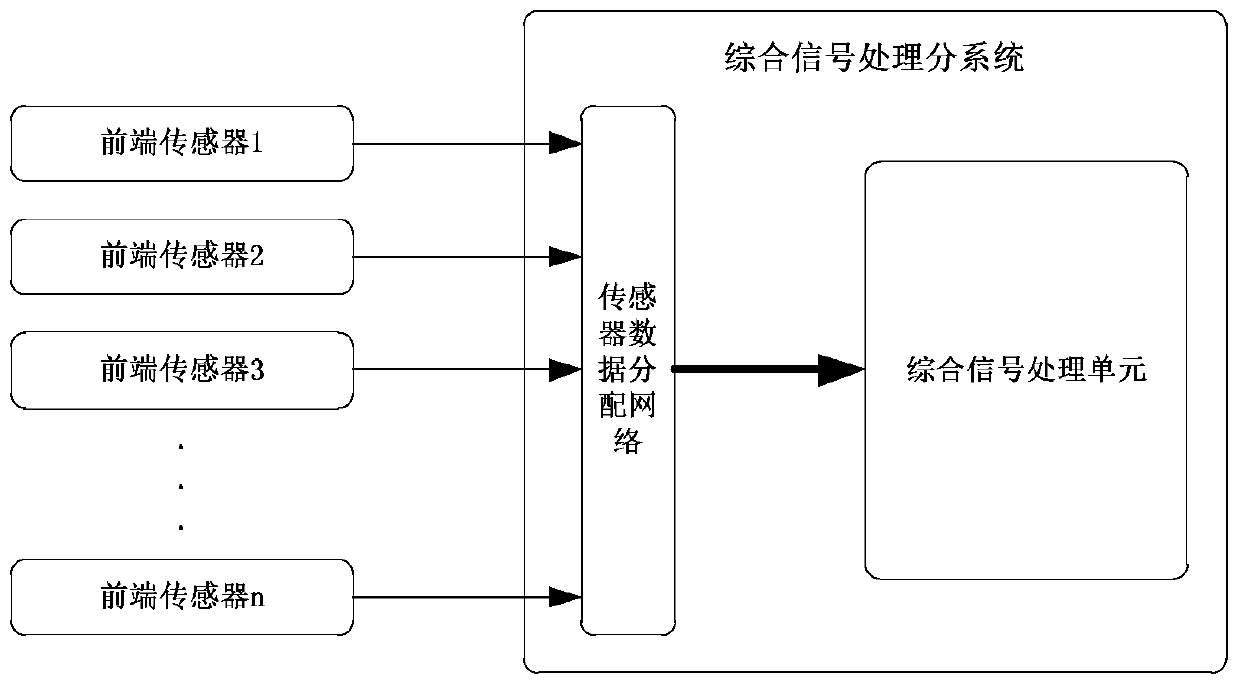

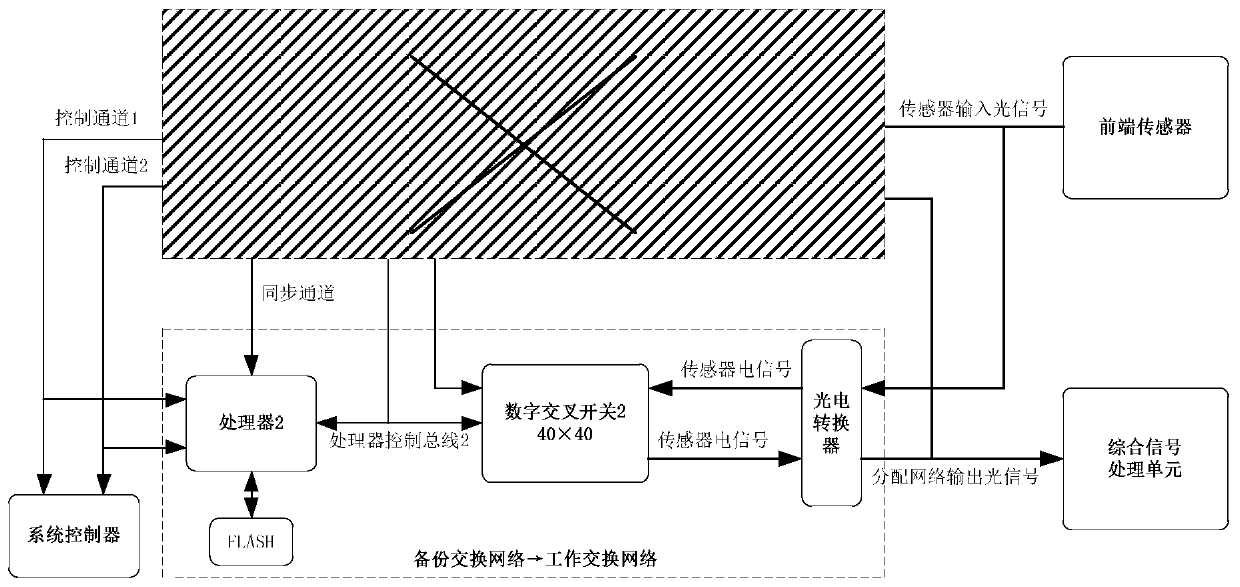

Sensor data distribution network fault tolerance architecture and method

PendingCN111045863AFast exchangeEasy to implementRedundant operation error correctionFault tolerant architectureHeartbeat

The invention provides a sensor data distribution network fault tolerance architecture and method, aiming at the requirement of an integrated avionics system on the reliability of an integrated signalprocessing subsystem. A sensor data distribution network adopts a dual-redundancy design, redundancy adopts a hot backup working mode, fault detection is performed through a heartbeat mechanism, anda system controller manages the sensor data distribution network through a dual-redundancy control channel. According to the fault tolerance method of the sensor data distribution network, the reliability of the comprehensive signal processing subsystem can be effectively improved.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

Fault tolerant architecture for permanent magnet starter generator subsystem

ActiveUS20060033478A1Highly reliable and fault tolerant systemOperational securityMotor/generator/converter stoppersElectric motor controlFault tolerant architectureStarter generator

A permanent magnet starter / generator subsystem configured in a fault tolerant architecture is described herein for small engine applications. The system allows for lighter system weight, improved system reliability, higher performance capability and reduced maintenance.

Owner:ASTRONICS ADVANCED ELECTRONICS SYST

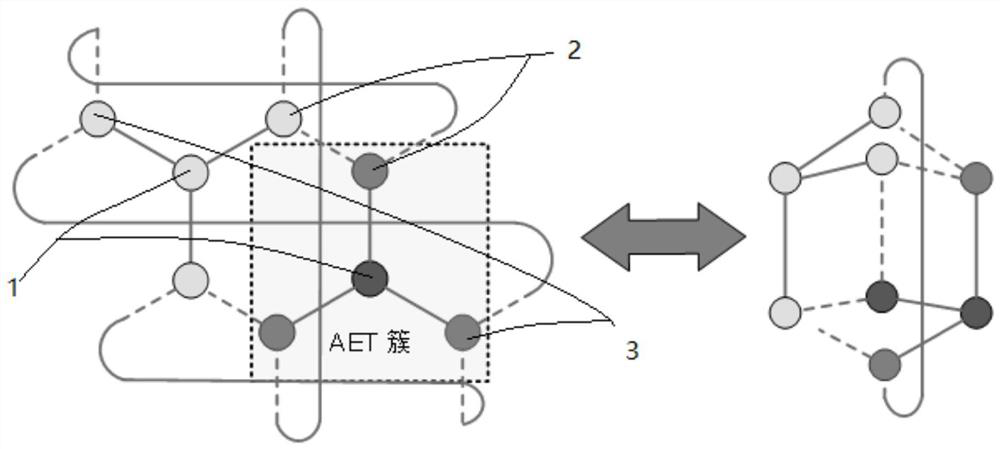

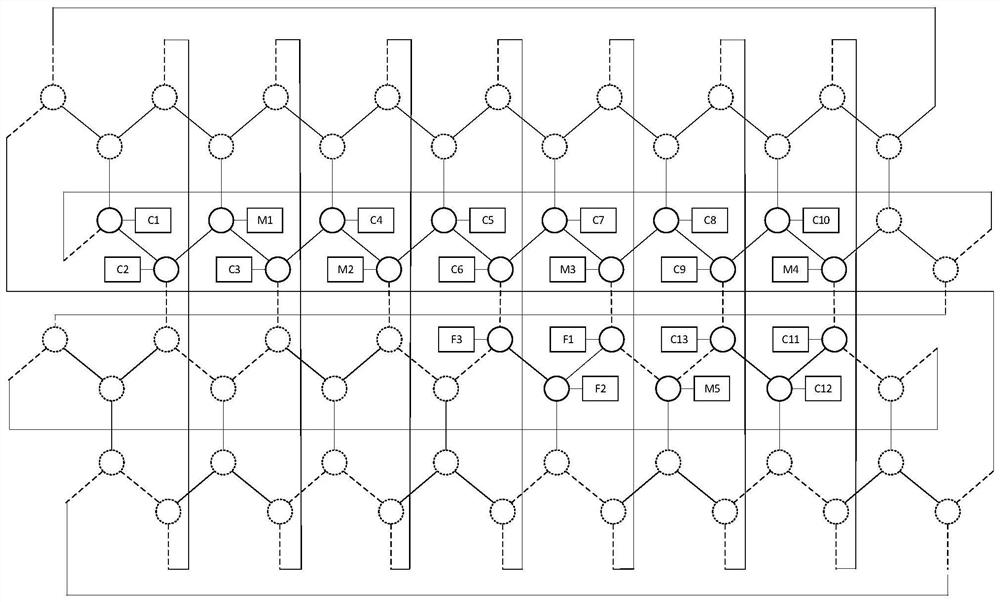

Fault-tolerant architecture system and fault-tolerant architecture control method

InactiveCN112702285ASmooth connectionFully enclosedData switching networksFault tolerant architectureComputer architecture

The invention discloses a fault-tolerant architecture system and a fault-tolerant architecture control method. The fault-tolerant architecture system comprises a processing core unit and a peripheral unit; the processing core unit is used for carrying out local computing, the peripheral unit is used for carrying out global communication and system control, the processing core unit comprises at least two AET cell clusters, each AET cell cluster comprises a central AET unit and three peripheral AET units, the network structures of the central AET unit and the peripheral AET units are the same, and the central AET unit of the AET cell cluster is connected with the three peripheral AET units at an included angle of 120 degrees; each AET unit of at least two AET cell clusters comprises three communication links, the processing core unit is configured with a connection strategy, and the connection strategy comprises that peripheral AET units in different AET cell clusters are connected with each other. The invention provides a fault-tolerant architecture system and a fault-tolerant architecture control method. A fault-tolerant architecture has a telescopic, highly reliable and flexible network structure.

Owner:FUDAN UNIV

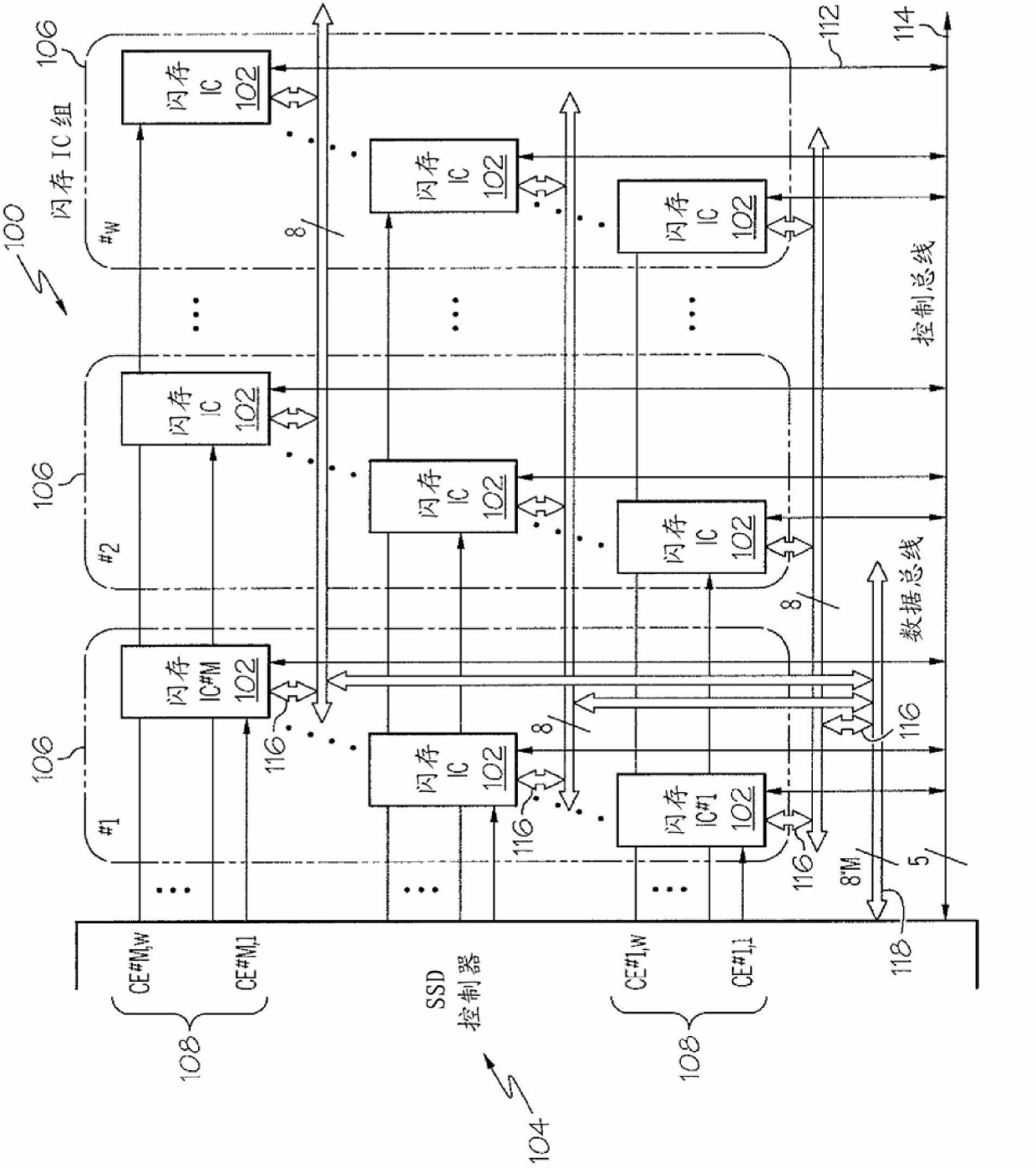

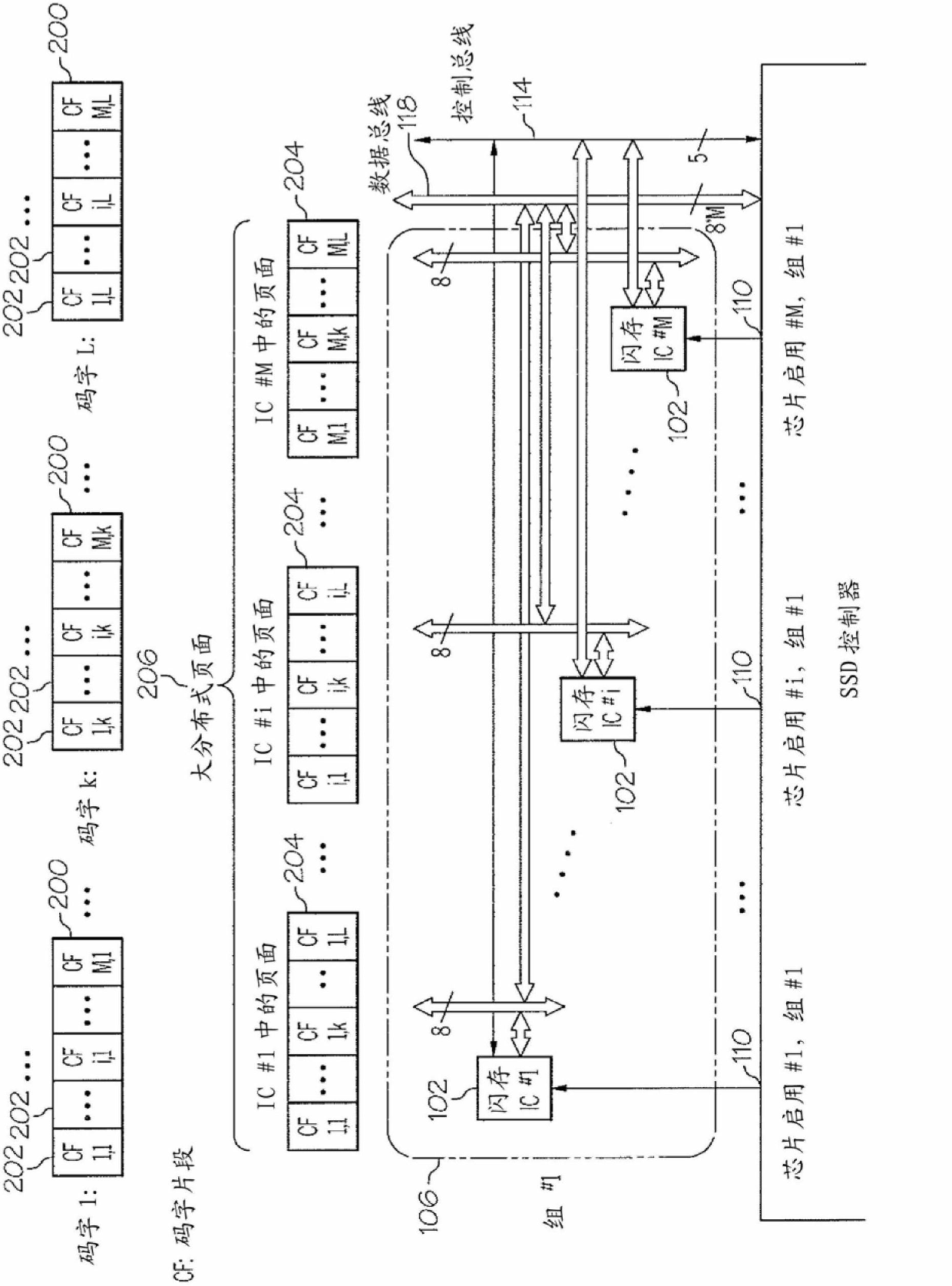

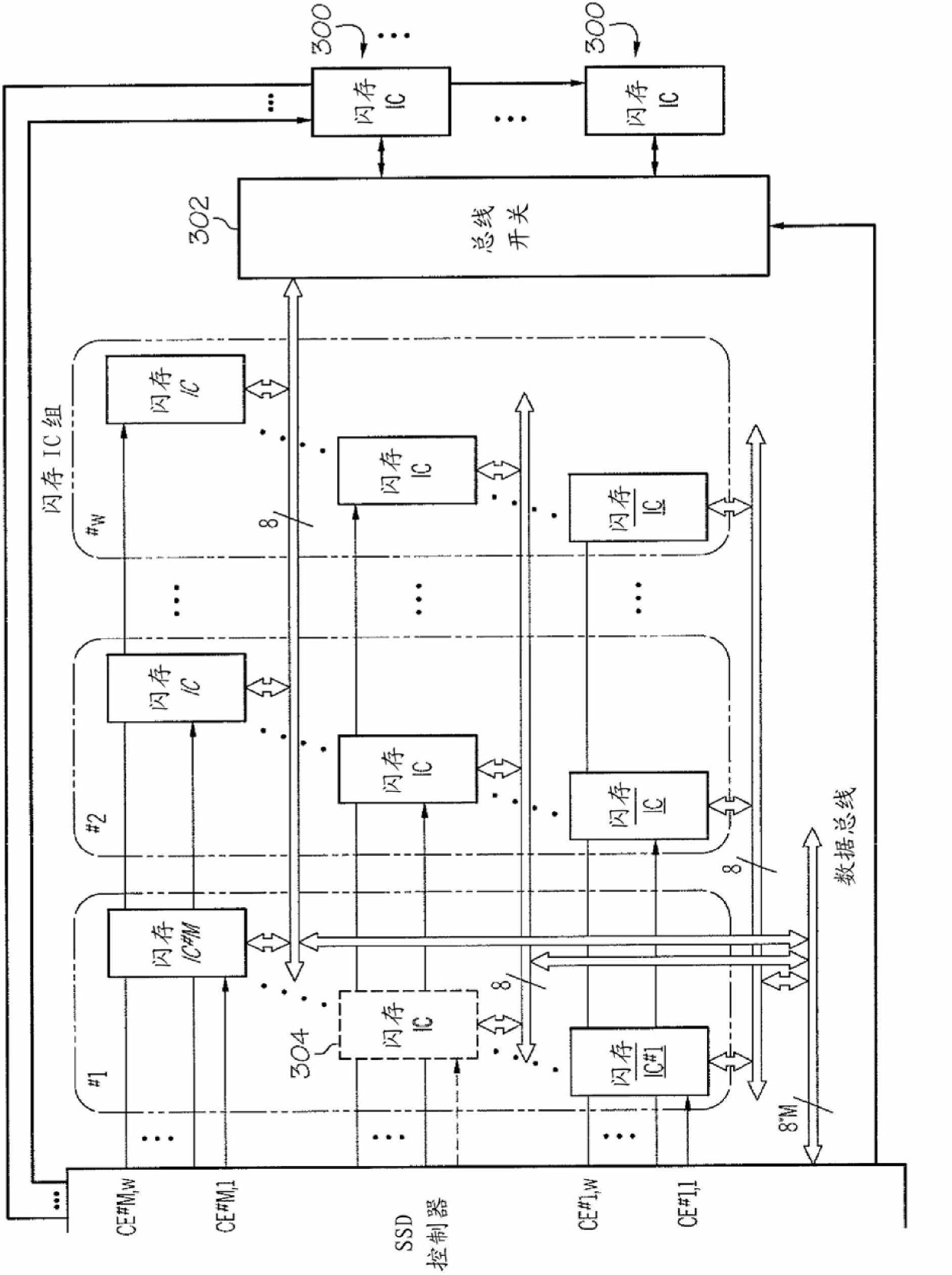

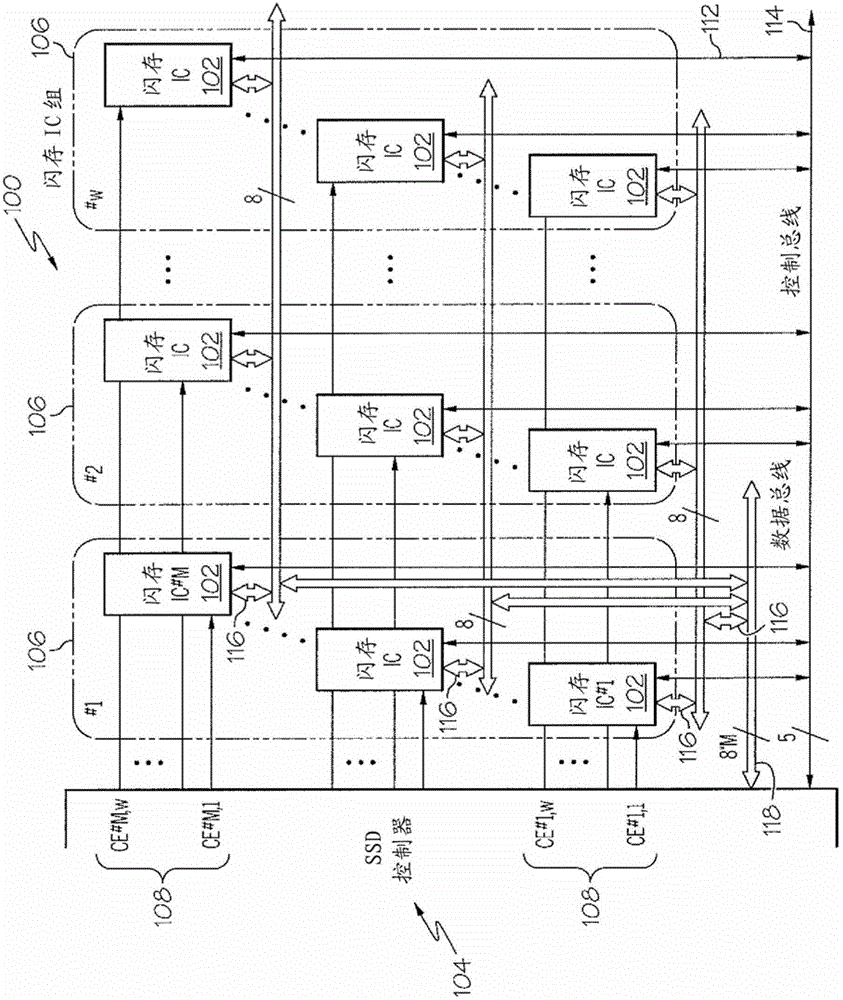

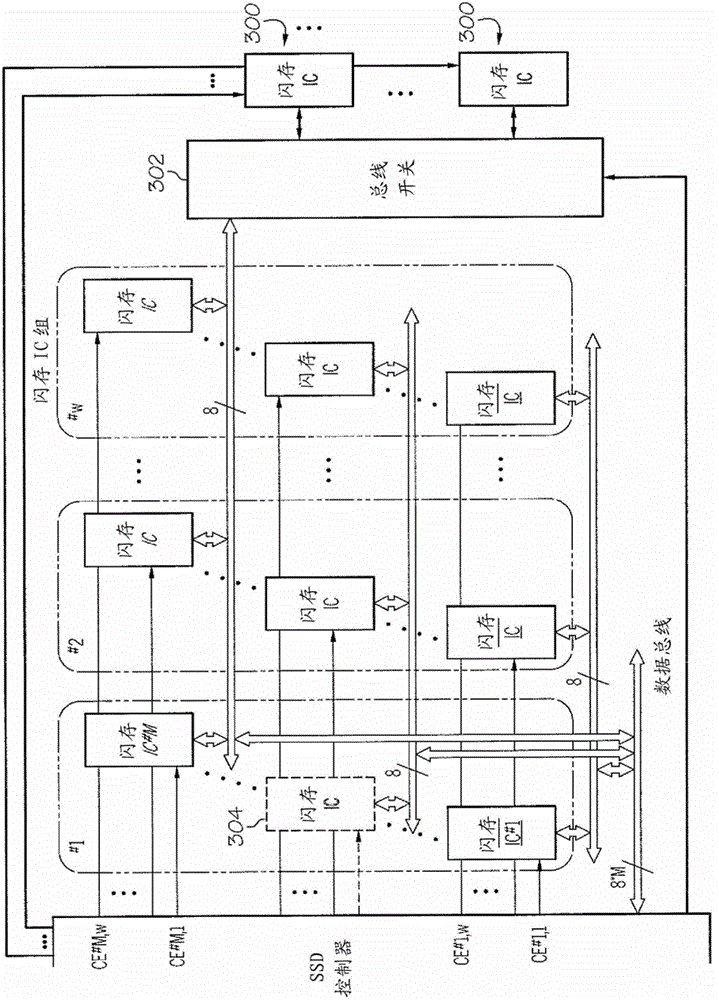

Solid-state storage system with parallel access of multiple flash/PCM devices

ActiveCN102630318AStatic storageRedundant data error correctionFault tolerant architectureSolid-state storage

Systems and methods are provided that confront the problem of failed storage integrated circuits (ICs) in a solid state drive (SSD) by using a fault-tolerant architecture along with one error correction code (ECC) mechanism for random / burst error corrections and an L-fold interleaving mechanism. The systems and methods described herein keep the SSD operational when one or more integrated circuits fail and allow the recovery of previously stored data from failed integrated circuits and allow random / burst errors to be corrected in other operational integrated circuits. These systems and methods replace the failed integrated circuits with fully functional / operational integrated circuits treated herein as spare integrated circuits. Furthermore, these systems and methods improve I / O performance in terms of maximum achievable read / write data rate.

Owner:IBM CORP

Fault-tolerant architecture and method for complex convolutional neural network

PendingCN112862068ATiming stabilityAvoid delayNeural architecturesRedundant hardware error correctionFault tolerant architectureNetwork data

The invention relates to the technical field of network data communication fault tolerance, and discloses a complex convolutional neural network-oriented fault tolerance architecture and method.The complex convolutional neural network-oriented fault tolerance architecture comprises an AET brain-like fault tolerance architecture and a convolutional neural network, the AET brain-like fault tolerance architecture comprises an AET cluster, the AET cluster comprises a plurality of nodes which are connected together, and the convolutional neural network is connected with the AET cluster. A volume base layer, a pooling layer and a full connection layer of the convolutional neural network are mapped to different nodes in a chain structure to form chain mapping nodes, nodes without a mapping relation are used as idle nodes, and when the nodes with the mapping relation have errors, the idle nodes close to the nodes with the mapping relation take over the errors to perform operation and communication tasks; according to the architecture, when an error node occurs, a nearby idle node substitutes for the error node, so that data delay caused by excessive data transmission when the idle node is searched for is avoided, substitution from the idle node to the mapping node can be quickly completed, a new connection architecture is formed, time sequence stability of a network is ensured, and data communication is completed more efficiently.

Owner:FUDAN UNIV

Real-time fault-tolerant architecture for large-scale event processing

ActiveUS10169166B2Data acquisition and loggingRedundant operation error correctionFault tolerant architectureComplex event processing

Techniques described herein include an event notification processing platform configured to process large-scale event notifications in relative real time. The platform may receive event notifications from multiple sources and publish them to an event stream, or log. The platform may subsequently process each notification at a processing module according to one or more sets of rules and the processed information may be made available via a data store. Rule sets may be selected based on the type of event received by the platform. A backup data store may record event notifications as they are received or at periodic intervals. Event notification data may also be stored at multiple levels of the platform, so that in the case of a failure of one or more components of the platform, data may continue to be processed.

Owner:BEIJING CHUANGXIN JOURNEY NETWORK TECH CO LTD

A fault-tolerant architecture for tsv in 3D integrated circuits

ActiveCN110323218BImprove repair rateIncrease redundancySemiconductor/solid-state device detailsSolid-state devicesFault tolerant architectureParallel computing

The present invention is applicable to the field of semiconductor technology, and provides a fault-tolerant architecture for TSVs in three-dimensional integrated circuits. The redundant structure is composed of an N-layer ring structure, and the N-layer ring structure is divided into six regions by six rays, and each ring layer There are three RTSVs in the structure, and the three RTSVs are evenly distributed on the six rays. The RTSVs between adjacent layers are misplaced. The center of the innermost hexagon is equipped with an RTSV, which utilizes the unique symmetry and flexibility of the hexagon. Arrange TSVs in a consistent manner, and select and place RTSVs reasonably, divide the redundant structure into several uniform areas, improve the redundancy rate of each area, and ensure a high repair rate of the entire structure; the uniform distribution of RTSVs in the TSV array, combined with The symmetry of the routing direction can avoid the situation that the repair path length of the faulty TSV is too different or the timing overhead is large, and the overhead can be reduced.

Owner:ANHUI POLYTECHNIC UNIV

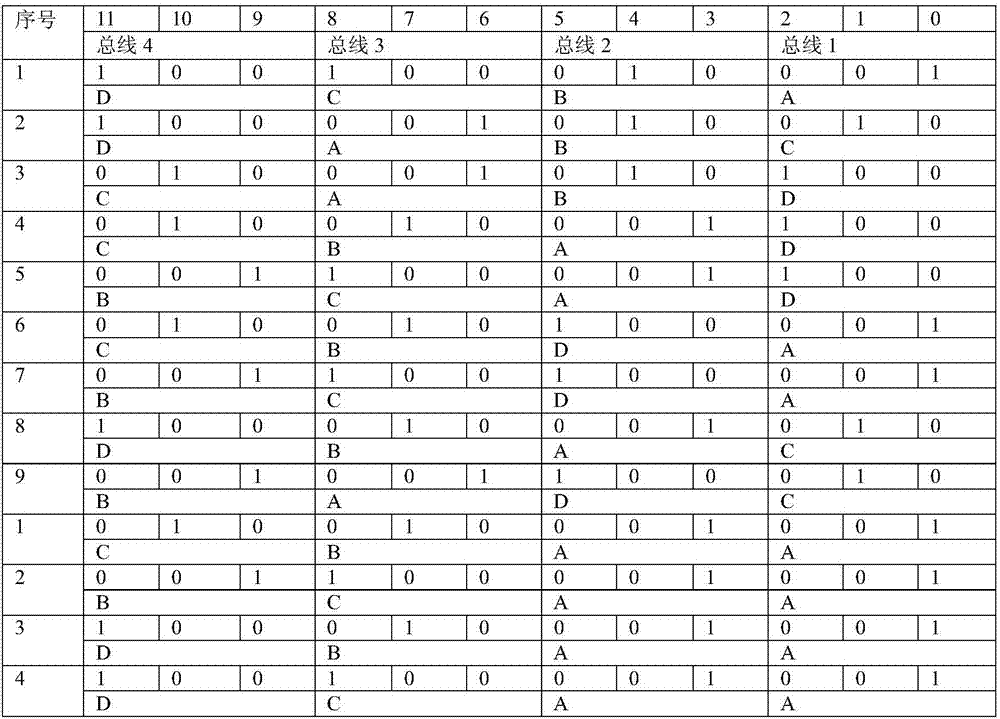

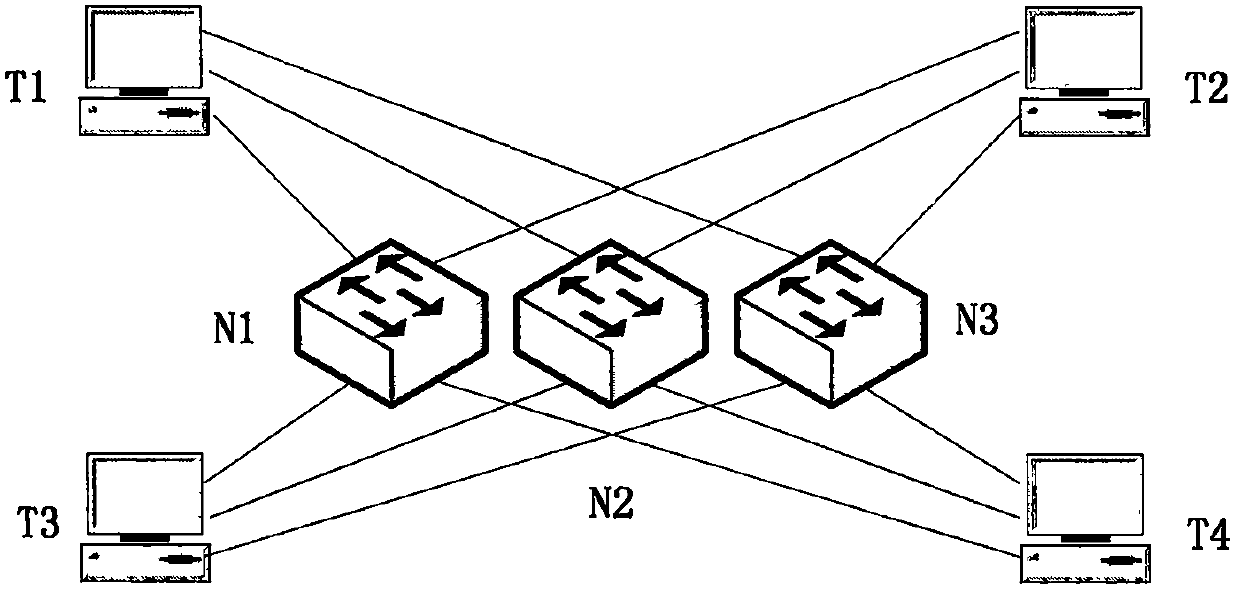

Multimode redundant bus fault-tolerant architecture in hot backup computer and control method thereof

ActiveCN107977289AImprove access efficiencyShorten access timeRedundant hardware error correctionFault tolerant architectureMachine control

The invention relates to a multimode redundant bus fault-tolerant architecture in a hot backup computer and a control method thereof, and belongs to the technical field of communication. According tospaceport guidance navigation control subsystem characteristics, the multimode redundant bus fault-tolerant architecture comprising M buses in the hot backup computer is designed. According to a taskdemand, a plurality of sensors and execution mechanisms are reasonably distributed on the M buses. Each single machine of a spaceport guidance navigation control computer is designed with N bus control circuits which are respectively connected with N buses in the M buses. Under normal condition, each single machine controls one bus, namely, one bus controller of each single machine works in a maincontrol mode, and other N-1 bus controllers serve as redundant backups to work in a monitor / sleep mode. By adoption of the multimode redundant bus fault-tolerant architecture in the hot backup computer and the control method thereof, the performance requirements, for long-term high reliability and high data throughout bandwidth of buses, of complex long-life guidance navigation control subsystemsare satisfied.

Owner:BEIJING INST OF CONTROL ENG

Data consistency method based on unreliable network

InactiveCN107592210AImprove fault toleranceImprove reliabilityError preventionData switching networksFault tolerant architectureInformation processing

The invention provides a data consistency method based on an unreliable network, which is used for achieving data consistency through a fault-tolerant mechanism in a condition of unreliable network transmission. The method comprises the following steps: 1, a redundant fault-tolerant architecture is defined; 2, in the condition of unreliable network transmission, a hypothetical condition for data consistency is defined; and 3, a data interaction process and a redundant information processing method are defined. Thus, the method of the invention can be used in important fields such as space andmilitary, thereby enhancing the fault-tolerant ability of the system and the reliability of the key equipment; and the method is applicable to a distributed architecture and can be promoted for faulttolerance for remote network data communication.

Owner:BEIJING SPACE TECH RES & TEST CENT

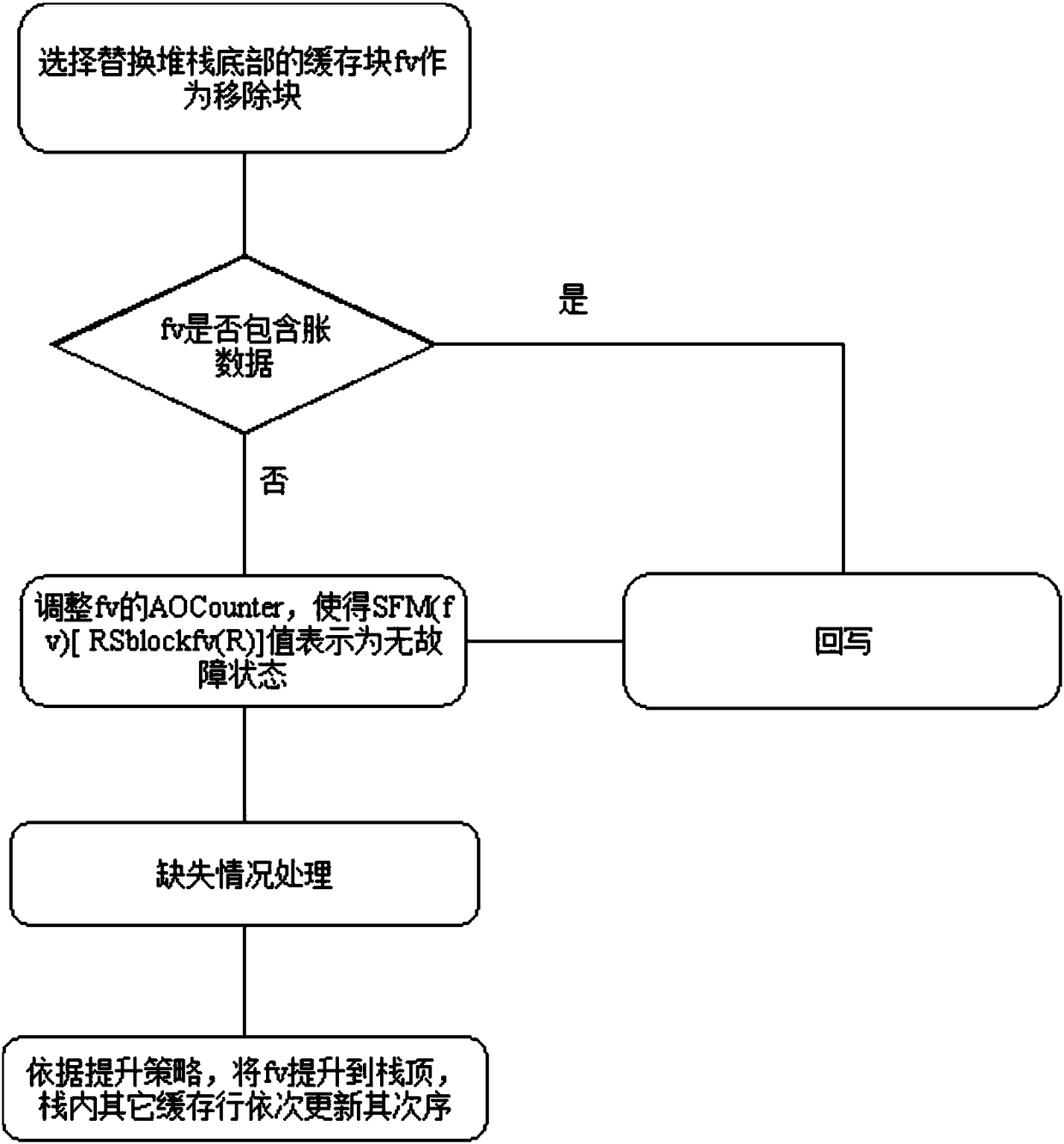

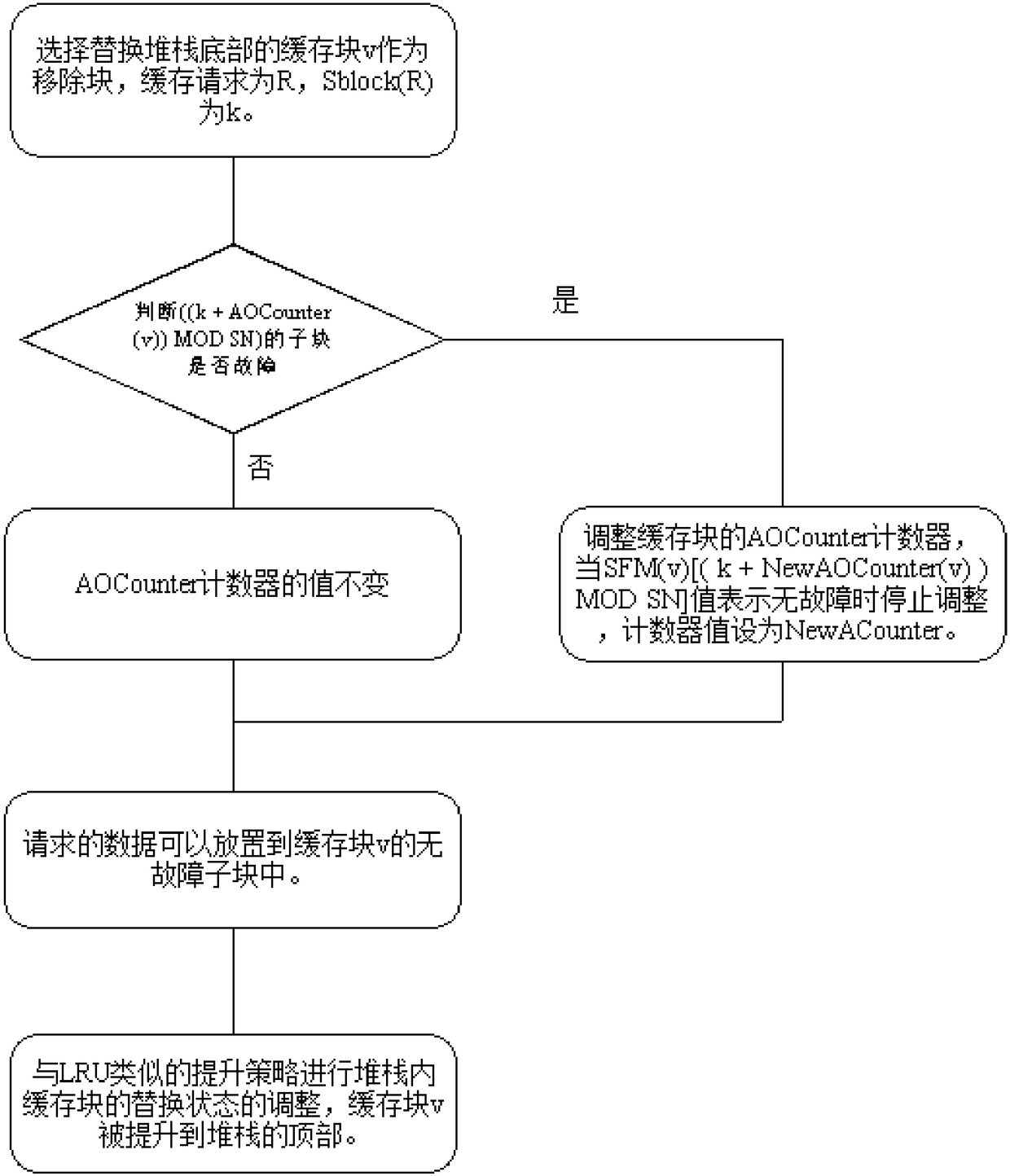

Dynamically patched high-performance on-chip cache fault-tolerant architecture

ActiveCN107122256BGuaranteed to workEfficient repairNon-redundant fault processingFault tolerant architectureParallel computing

The invention puts forward a dynamic repairing high-performance on-chip cache fault-tolerant framework, and can timely and efficiently process intermittent bit failure and permanent faults by low expenditure. Through a fault-sensitive replacement mechanism, new faults can be tolerated at any time, the cache is guaranteed to normally work, then, on the basis of a situation that a cache block is used and accessed, and a fault subblock is dynamically repaired to lighten an influence on the performance of the cache by faults.

Owner:BEIJING UNIV OF POSTS & TELECOMM

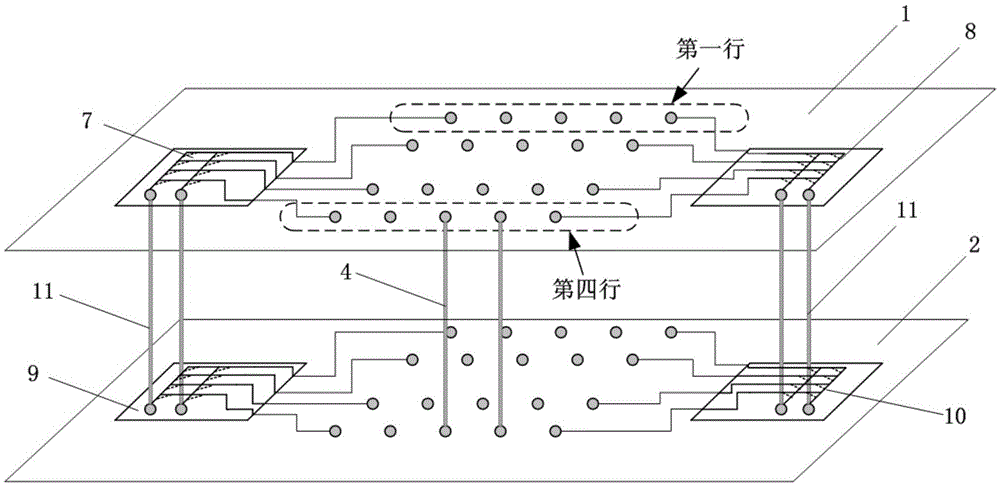

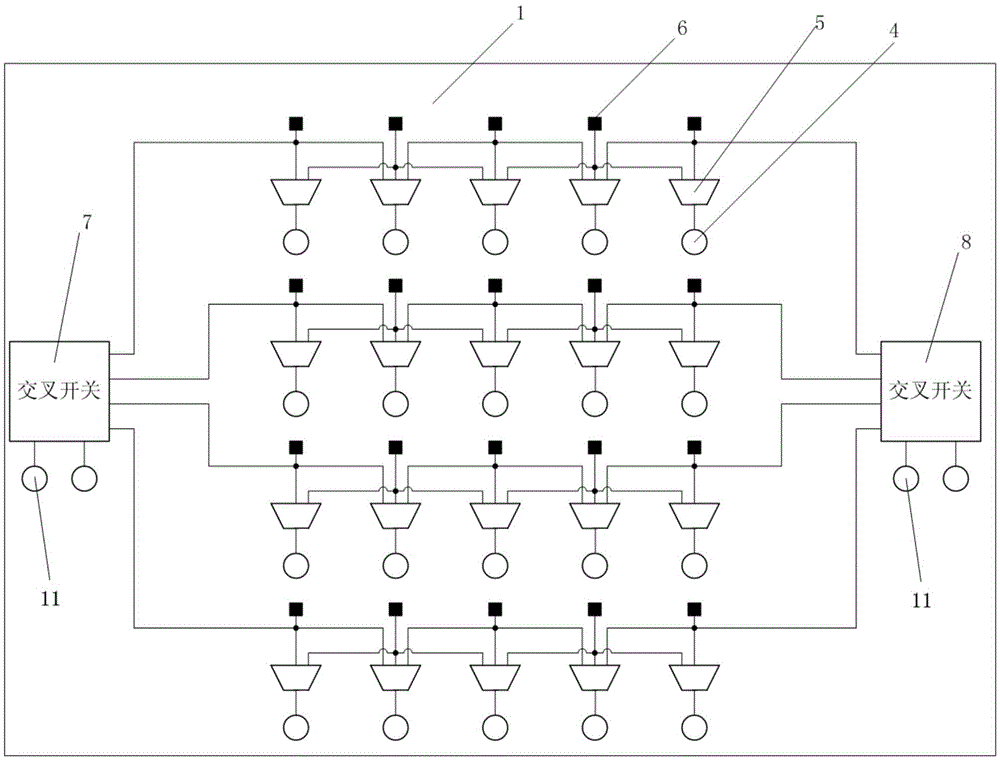

A 3D chip redundant TSV fault-tolerant structure with the function of transferring signals

InactiveCN103780243BImprove yieldLow costReliability increasing modificationsSemiconductor/solid-state device detailsFault tolerant architectureCrossbar switch

The invention discloses a three-dimensional chip redundant TSV fault-tolerant structure with the function of transferring a signal. A three-dimensional chip comprises an upper-layer wafer and a lower-layer wafer. The upper-layer wafer and the lower-layer wafer are respectively provided with circular holes which are vertically and horizontally arrayed to form multiple rows and columns. Each circular hole in the upper-layer wafer and the corresponding circular hole in the lower-layer wafer are connected through a TSV. On the upper-layer wafer and the lower-layer wafer, the ends of all the TSVs are respectively connected with a signal transmission terminal through a multi-way selector. The upper-layer wafer and the lower-layer wafer are respectively provided with two crossbar switches, and all the crossbar switches are connected with the multi-way selectors. The crossbar switches of the upper-layer wafer are correspondingly connected with the crossbar switches of the lower-layer wafer through two redundant TSVs. The three-dimensional chip redundant TSV fault-tolerant structure has the advantages that the problem that a signal cannot be transmitted normally due to a TSV failure can be solved, the yield of the chip is effectively improved, hardware cost is low, the structure is simple, and the fault-tolerant capacity is high.

Owner:HEFEI UNIV OF TECH

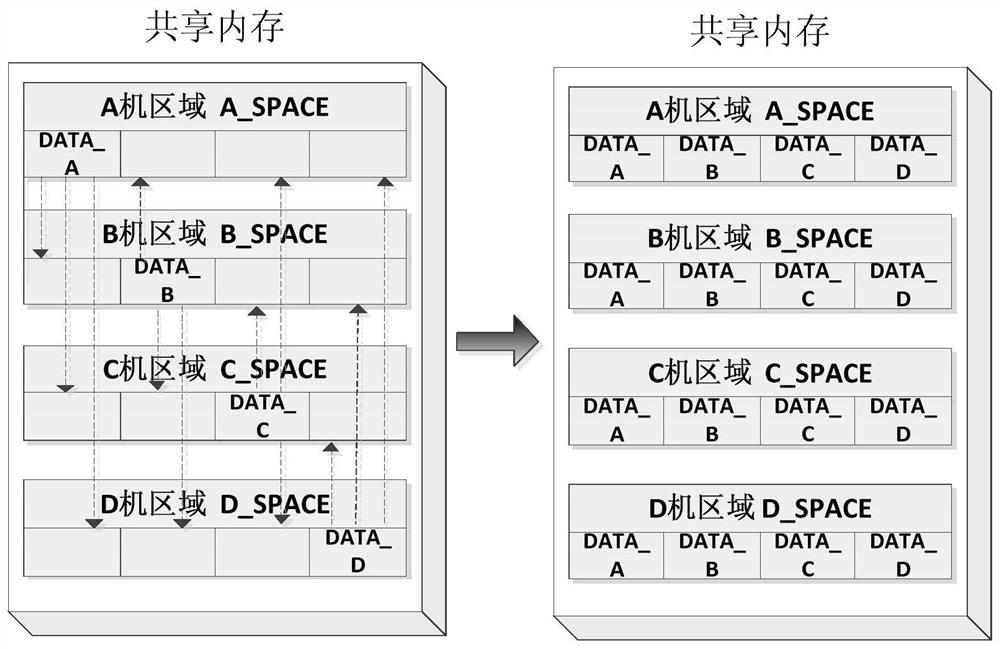

Multi-machine time scale simulation method suitable for multi-machine fault-tolerant architecture of attitude and orbit control system

ActiveCN113438008ASimplify communication implementationAvoid Data ConflictsInterprogram communicationTime-division multiplexFault tolerant architectureSynchronous control

According to the multi-machine time scale simulation method suitable for the multi-machine fault-tolerant architecture of the attitude and orbit control system, independent and mutually exclusive data spaces are designed in a shared memory of multiple machines, a data basis is provided for unified management of time scales, a mode of multiple times of time scale synchronization is adopted, the data exchange and transmission process in the shared memory of the multiple machines is subjected to stage division, multiple machines are in a synchronous state in different data processing stages, non-synchronous data are prevented from being introduced into calculation, task-level multi-machine time scale unification is achieved, then a synchronous controller is designed, the synchronous controller is used for communicating with all the machines, synchronization is carried out with simulation time as a control reference, high-priority synchronous parameters are designed, the single-machine debugging process and the multi-machine time mark unification are no longer contradictory, and the system-level multi-machine time mark unification is realized. Finally, the problem of multi-machine time scale unification under a fault-tolerant architecture is solved, the simulation method not only realizes task-level time scale unification, but also realizes system-level time scale unification, and is successfully applied in a space station simulation environment at present.

Owner:BEIJING INST OF CONTROL ENG

Solid-state storage system with parallel access of multiple flash/PCM devices

ActiveCN102630318BStatic storageRedundant data error correctionFault tolerant architectureSolid-state storage

Systems and methods are provided that confront the problem of failed storage integrated circuits (ICs) in a solid state drive (SSD) by using a fault-tolerant architecture along with one error correction code (ECC) mechanism for random / burst error corrections and an L-fold interleaving mechanism. The systems and methods described herein keep the SSD operational when one or more integrated circuits fail and allow the recovery of previously stored data from failed integrated circuits and allow random / burst errors to be corrected in other operational integrated circuits. These systems and methods replace the failed integrated circuits with fully functional / operational integrated circuits treated herein as spare integrated circuits. Furthermore, these systems and methods improve I / O performance in terms of maximum achievable read / write data rate.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com