Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

102 results about "Design margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Design margin is the measure of the distance from the set point or the mean response to the nearest edge of failure where acceptance criteria will fail and OOS conditions occur. The greater the design margin, the less likely OOS and lot acceptance failures may occur.

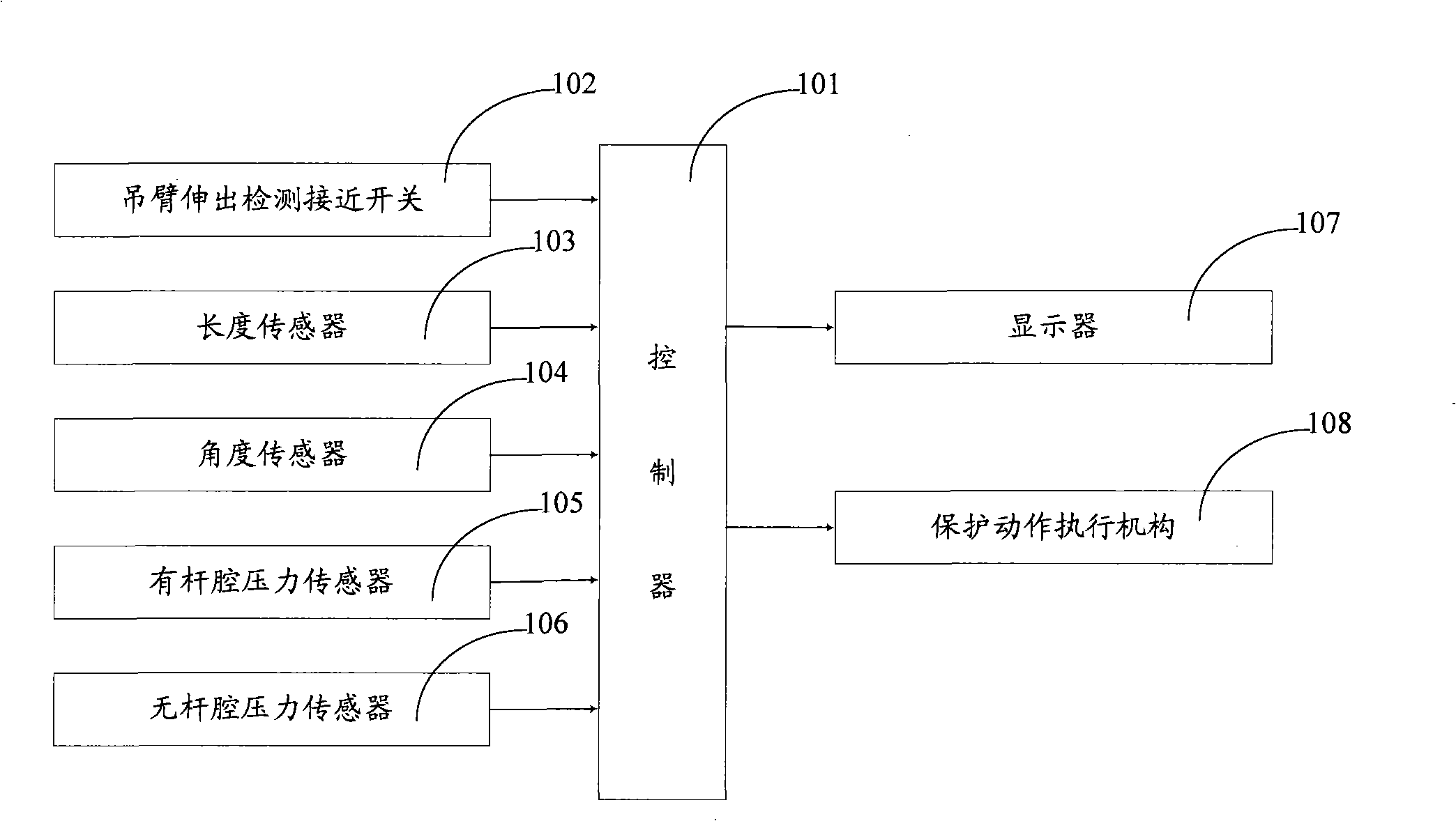

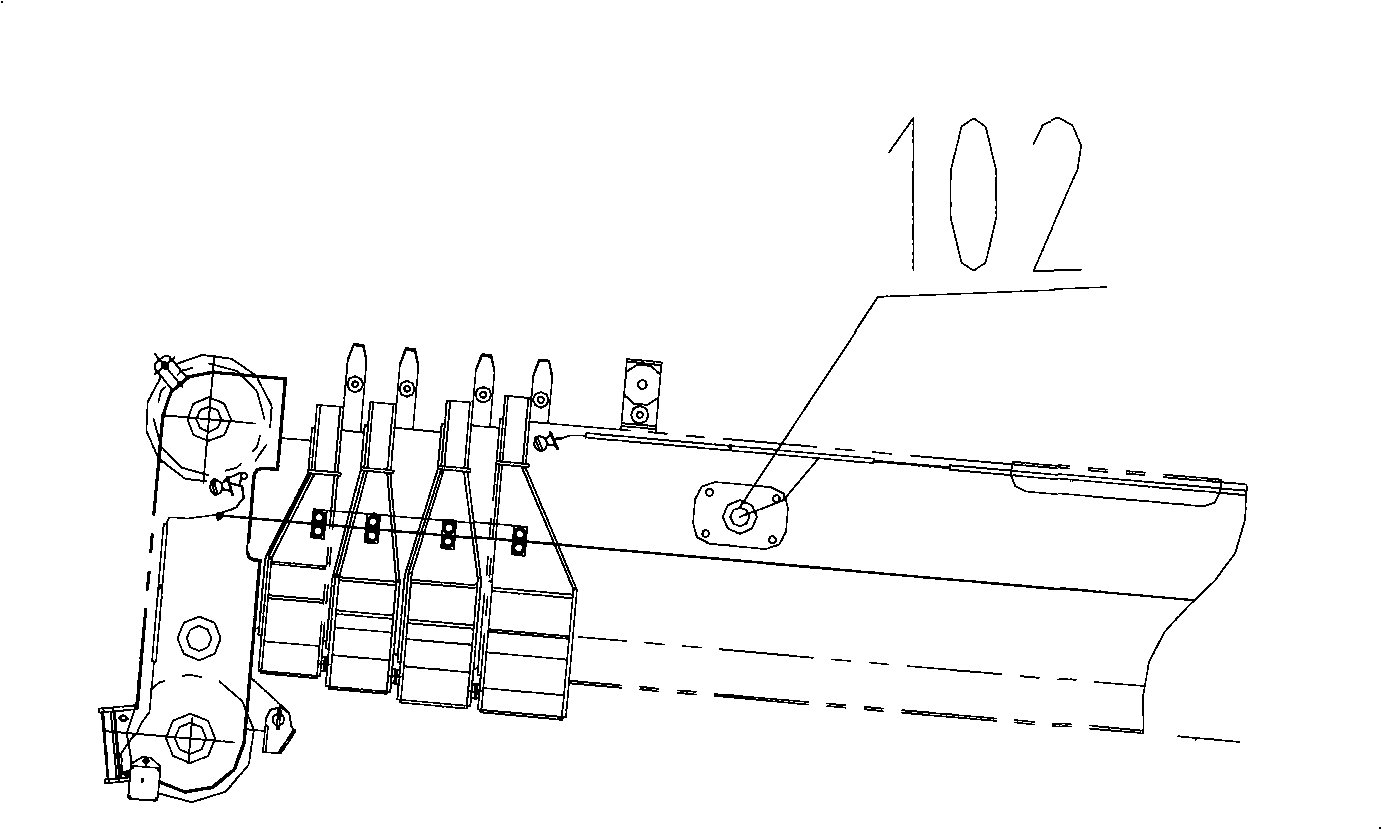

Crane security protection system and crane thereof

InactiveCN101348216AAvoid step changesAccurate estimateLoad-engaging elementsCranesControl signalProtection system

The invention discloses a safety protection system for a crane, comprising a plurality of sensors, a controller and a protection action actuating mechanism. The sensors detect and transmit the working state of the crane to the controller in real time; according to the detection data of the sensors, the controller calculates maximum allowable load determined by the characteristics of the crane under the current working state; the determined maximum allowable load is compared with the maximum allowable load related to the characteristics of the crane, then a minimum value therein is taken, and after predetermined design margin is taken, a rated working load G is obtained; according to the data of the sensors, current actual lifting weight is obtained through calculation; the actual lifting weight is compared with the rated working load, and if the actual lifting weight exceeds a preset safe range, the controller sends out a safety protection control signal limiting the crane to move toward the dangerous direction; and the protection action actuating mechanism limits the crane to move toward the dangerous direction according to the safety protection control signal. The invention provides a crane using simultaneously the safety protection system.

Owner:SANY AUTOMOBILE HOISTING MACHINERY

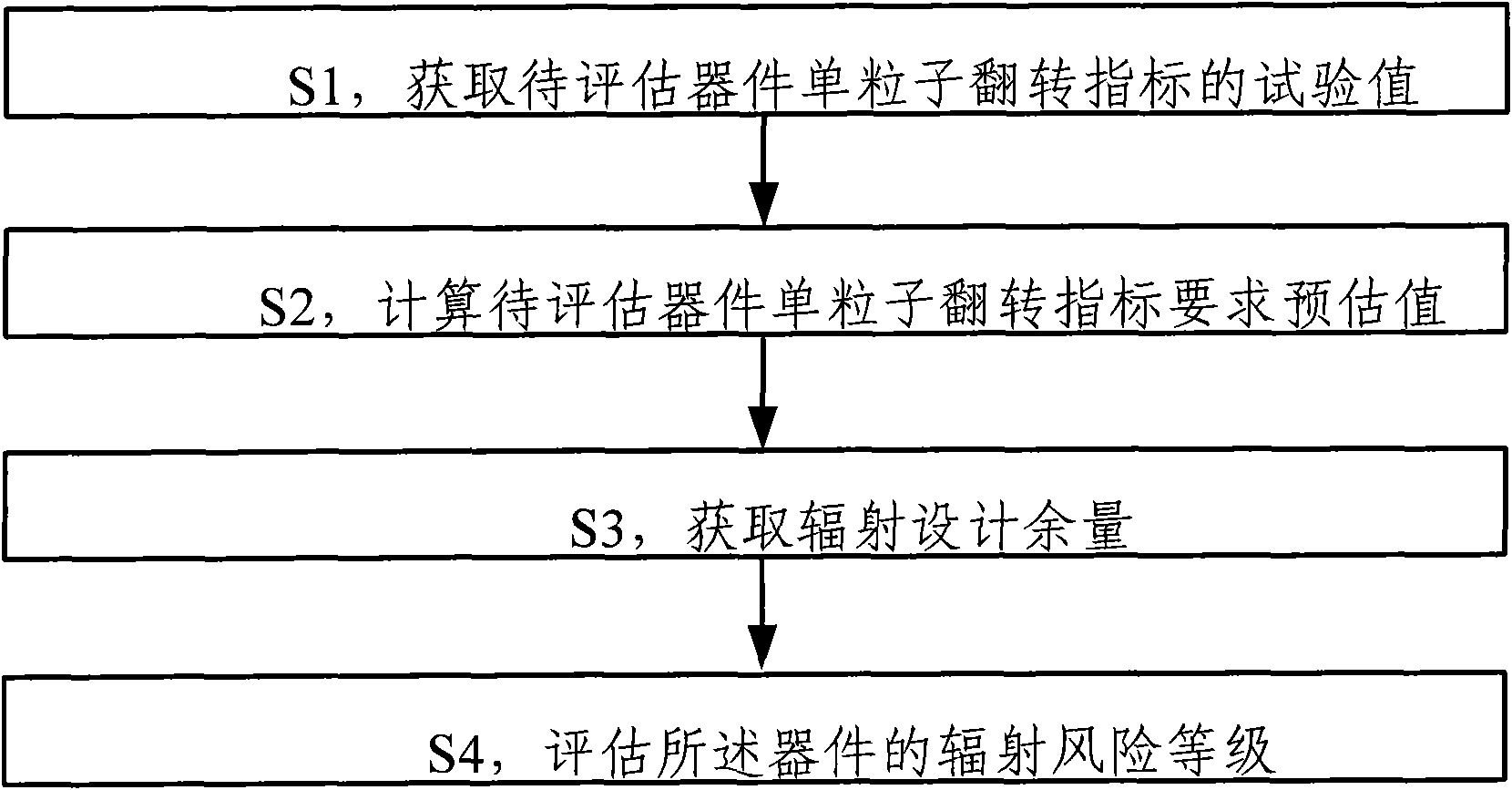

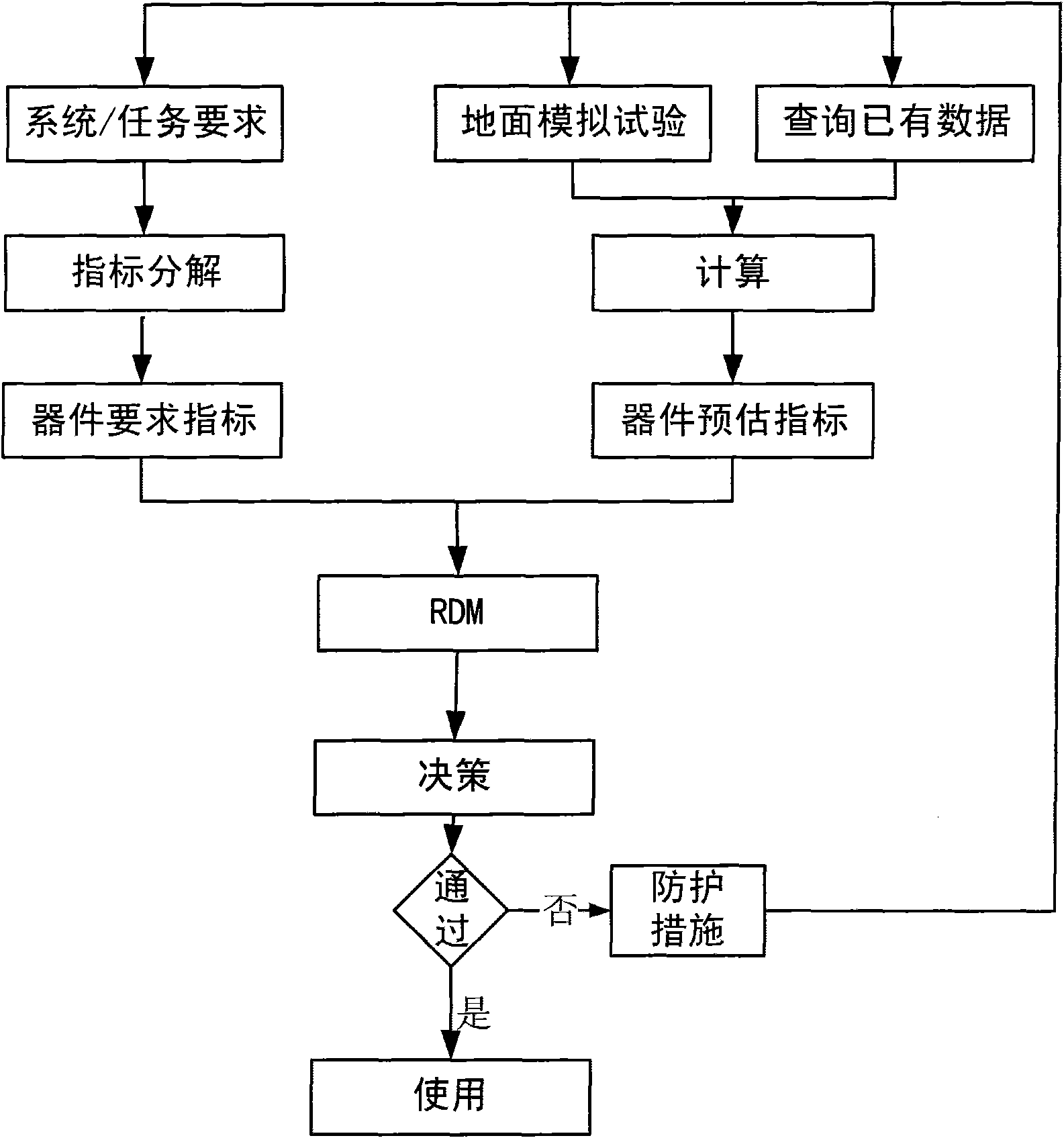

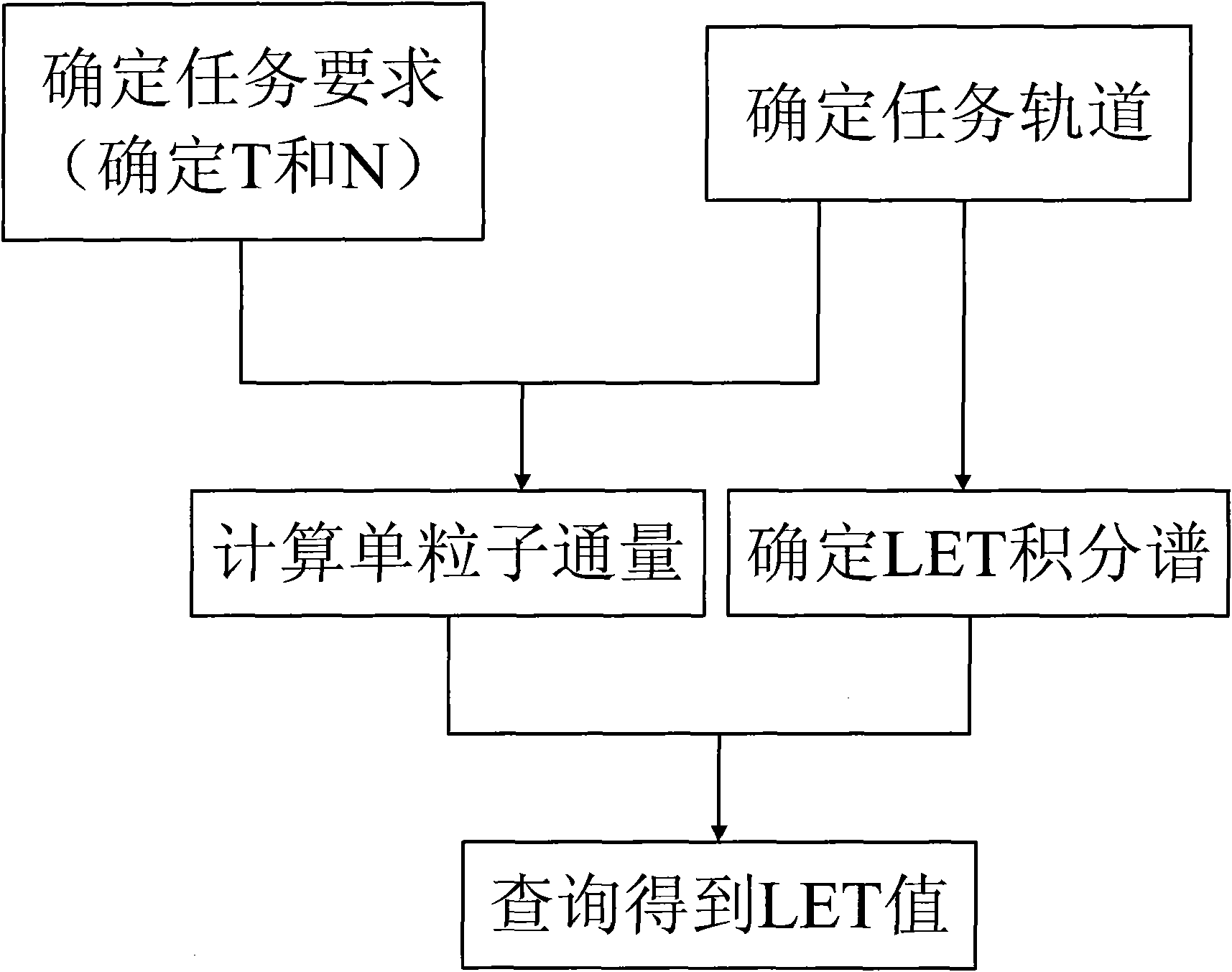

Method and system for evaluating single-particle effect index of satellite device

The invention discloses a method for evaluating a single-particle effect index of a satellite device. The evaluating method comprises the following steps of: acquiring a single-particle turnover test value of a to-be-evaluated device by testing or simulating; calculating a single-particle turnover index required prediction value, required by a task, of the to-be-evaluated device; acquiring a radiation design margin according to a test expected value of the single-particle turnover index of the device and the single-particle turnover index required prediction value; and evaluating the radiation risk level of the device according to the radiation design margin. According to the technical scheme, the method for evaluating the single-particle effect index of the satellite device can effectively direct the model selection of the satellite device by calculating the single-particle turnover rate index of the device, and provide quality assurance for the satellite to victoriously finish the task.

Owner:BEIJING SHENGTAOPING TEST ENG TECH RES INST

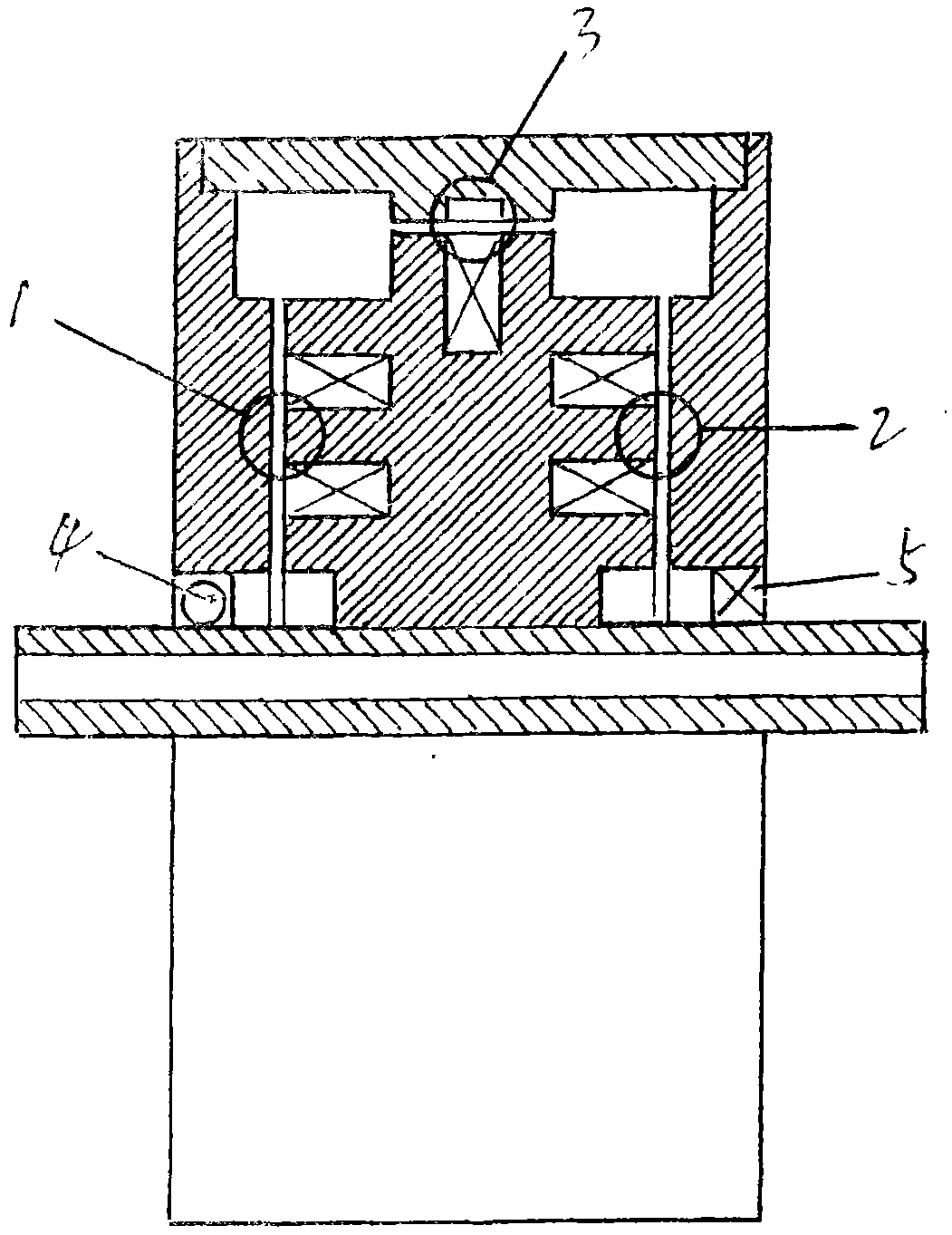

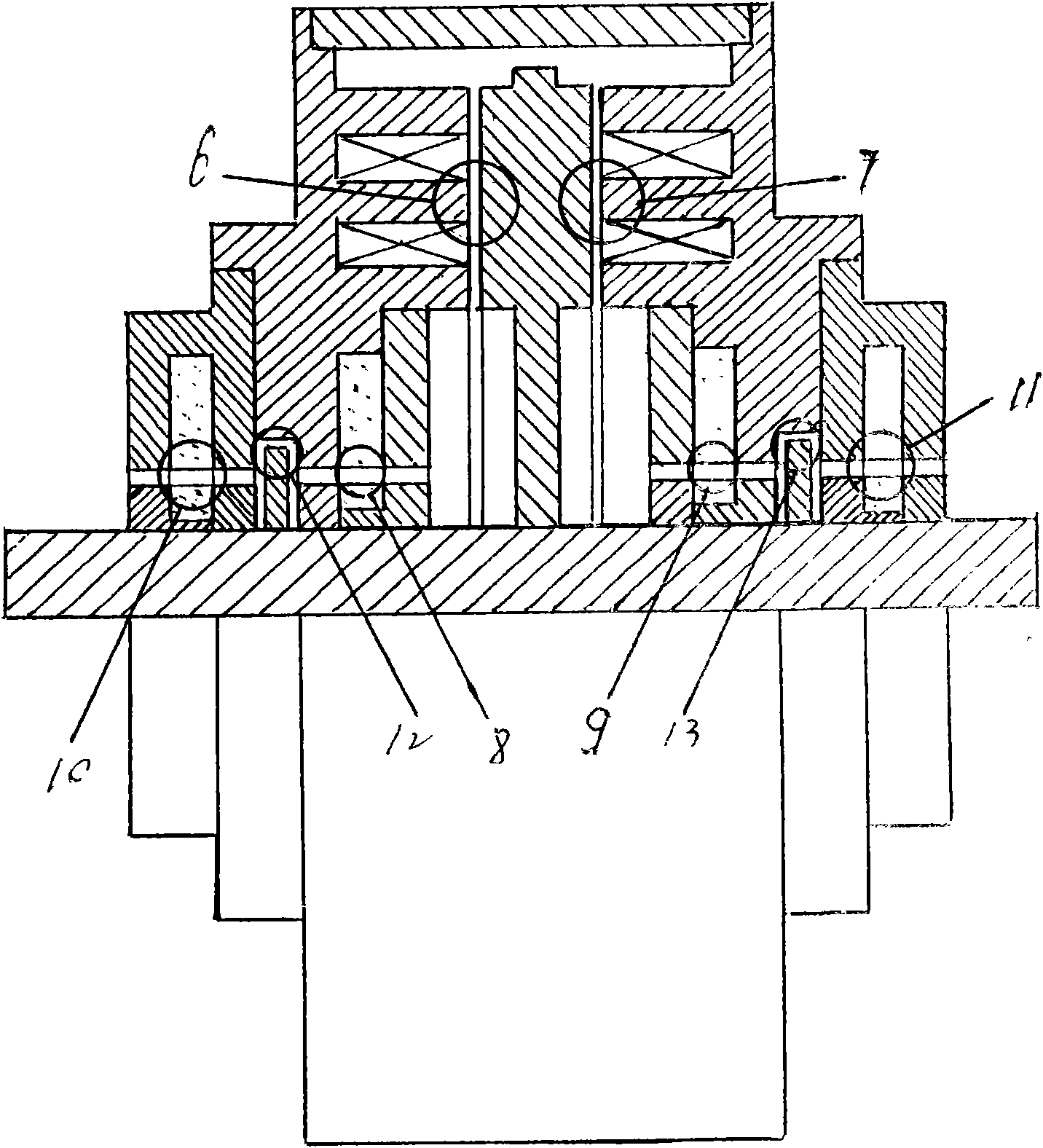

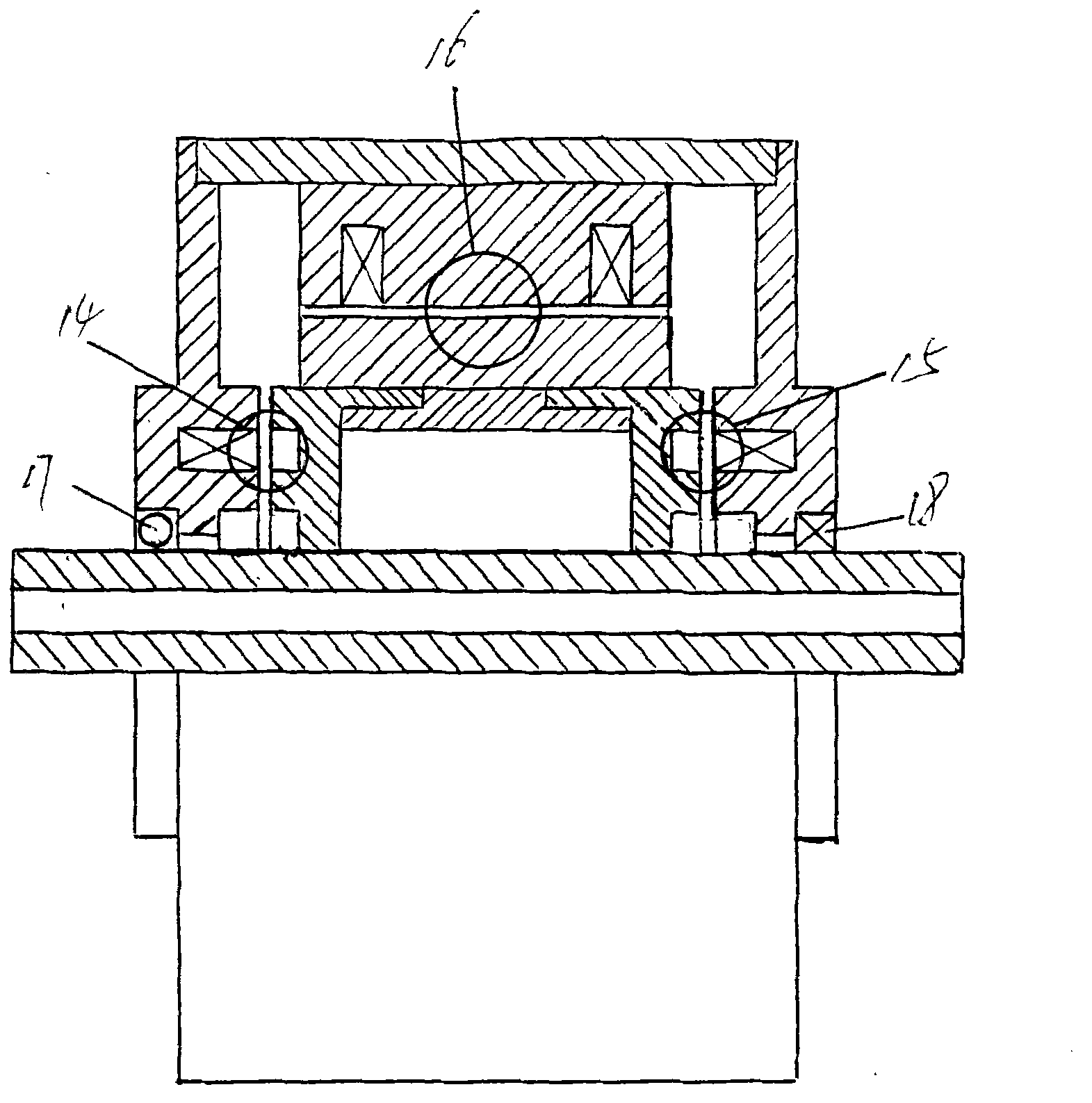

Magnetic levitation rotor support system, magnetic levitation bearing and magnetic biasing weight reducing device

InactiveCN101771308AEliminate and avoid unstable factorsAvoid lostMechanical energy handlingBearingsSupporting systemActive cell

The invention discloses a single freedom degree magnetic levitation rotor support system, a magnetic levitation bearing and a magnetic biasing weight reducing device. The single freedom degree magnetic levitation rotor support system is composed of an attraction type axial magnetic levitation bearing (24), attraction type radial magnetic levitation bearings (25,26), magnetic biasing weight reducing devices (27,28) and air gap limit protective devices (29,30) of the axial and radial magnetic levitation bearings which are all arranged in the same movement mechanism. Active cell parts and stator parts of the axial and radial bearings are composed of a permanent magnetic field or a controllable magnetic device not generating non-work air gap magnetic leakage loss. So long as designing margin of the magnetic field is enough, the system of the invention can operate stably without adopting any form of sensor feedback control technology.

Owner:张玉宝

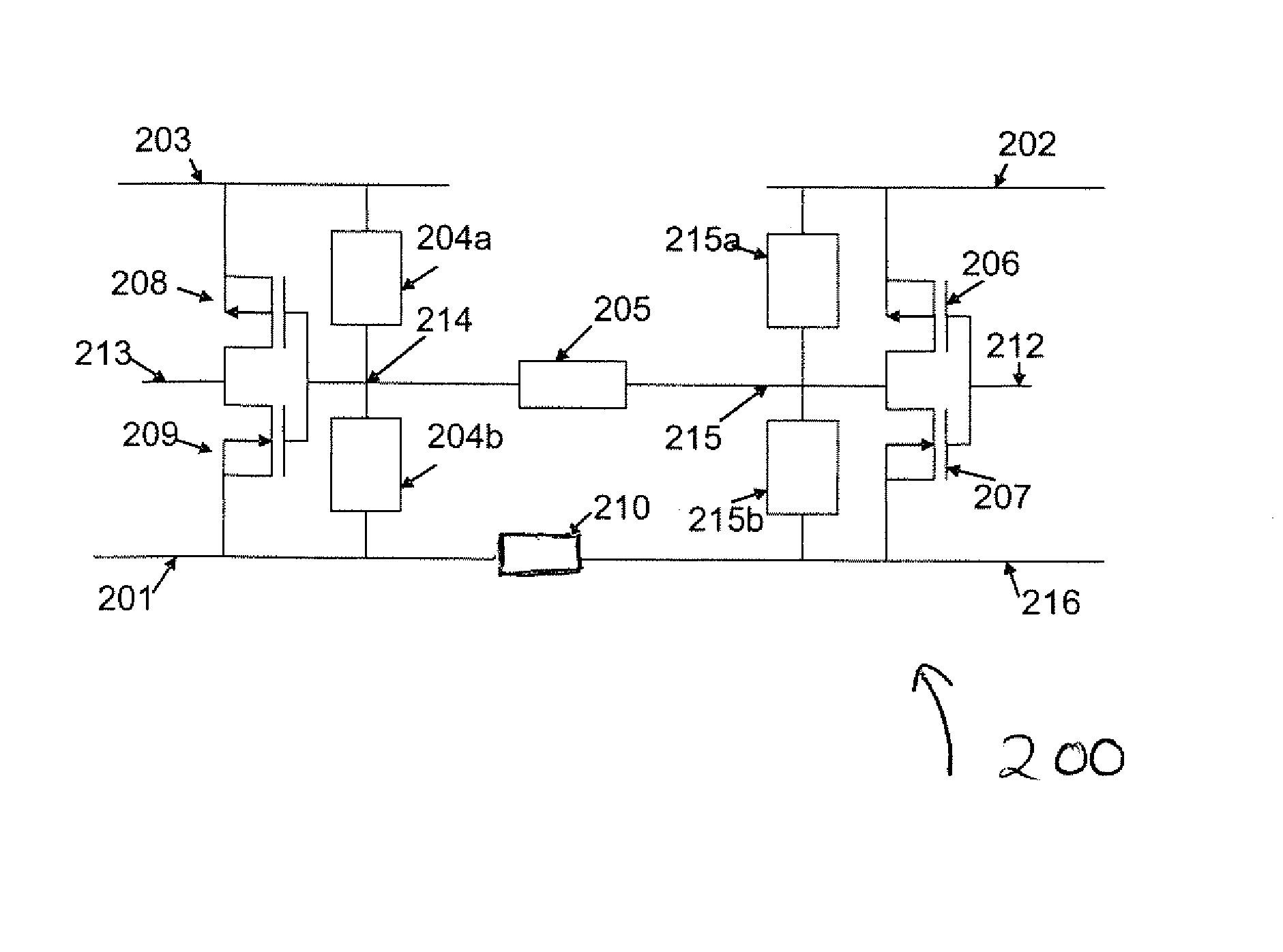

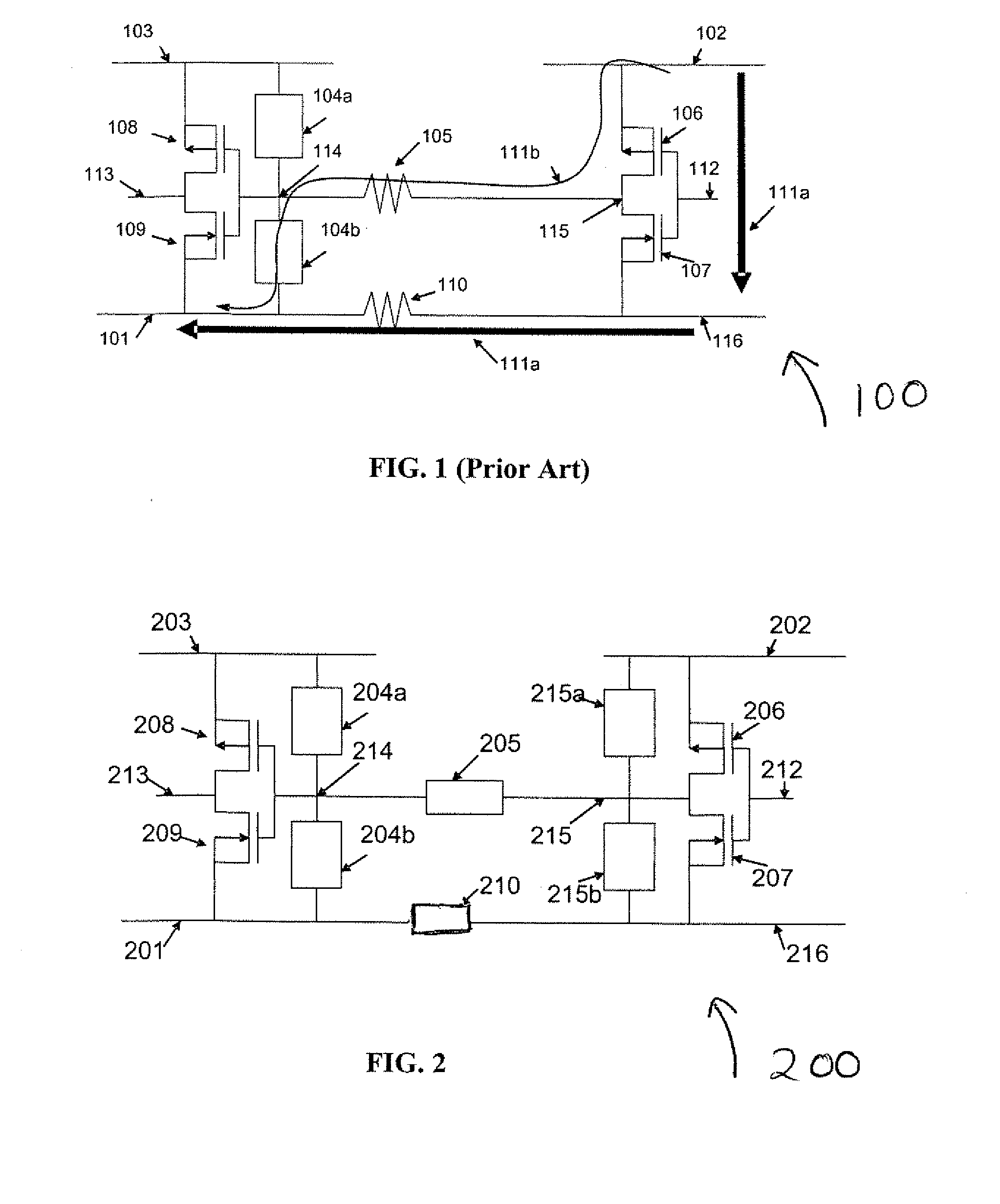

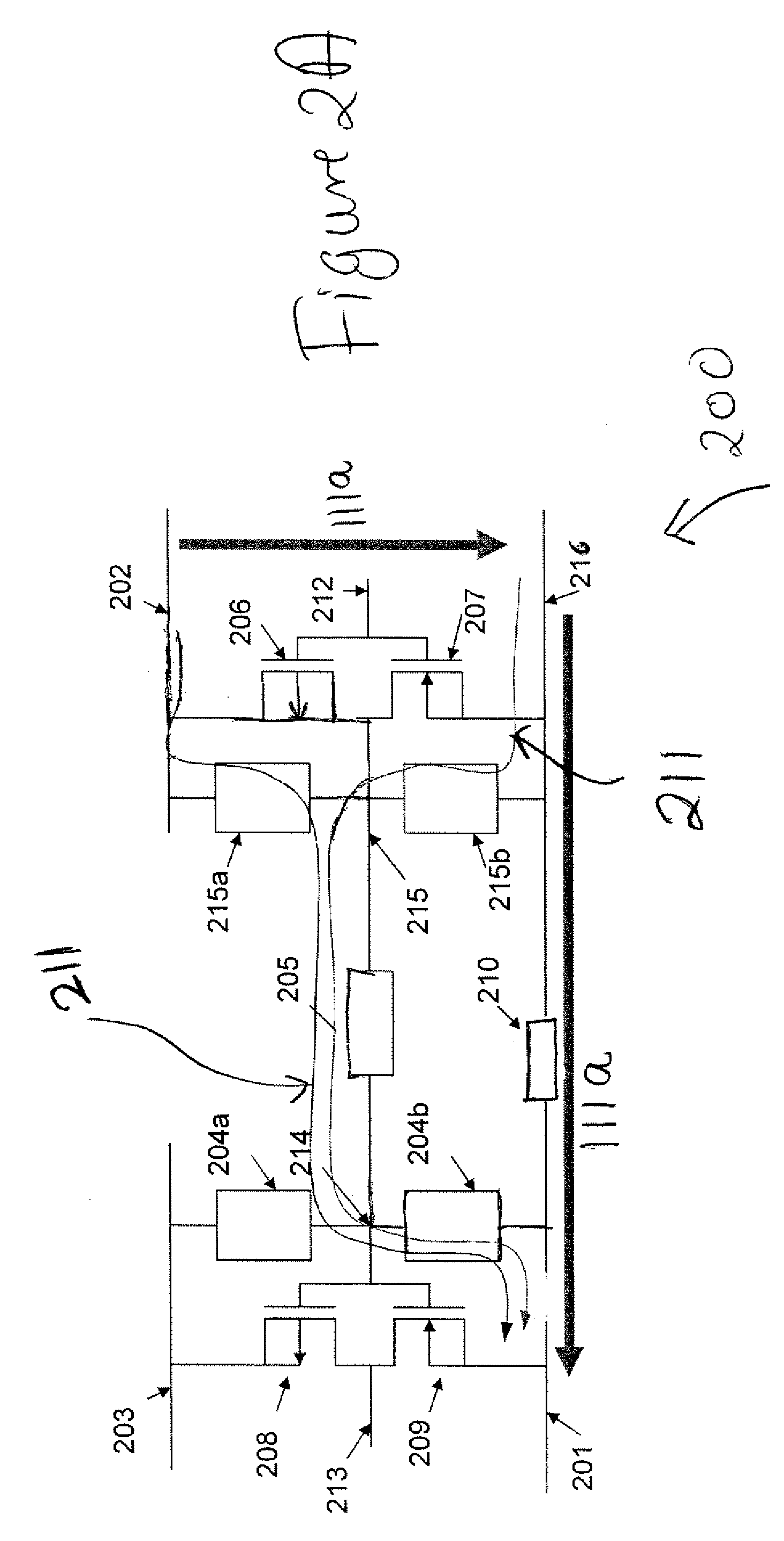

Method and aparatus for improved electrostatic discharge protection

InactiveUS20080218920A1Solid-state devicesEmergency protective arrangements for limiting excess voltage/currentEngineeringPower domains

An apparatus having an inter-domain electrostatic discharge (ESD) protection circuit for protection of an integrated circuit (IC) with multiple power domains. The protection circuit in response to an ESD event provides an ESD protection between different power domains. Specifically, the protection circuit comprises at least one clamp coupled to one power domain, which conducts current during an ESD event to provide extra current in the interface line between the two different power domains. This extra current also in turn increases the voltage over the impedance element on the interface line, thus improving the design margins for the ESD protection and providing a better ESD protection capability for IC products.

Owner:SOFICS BVBA

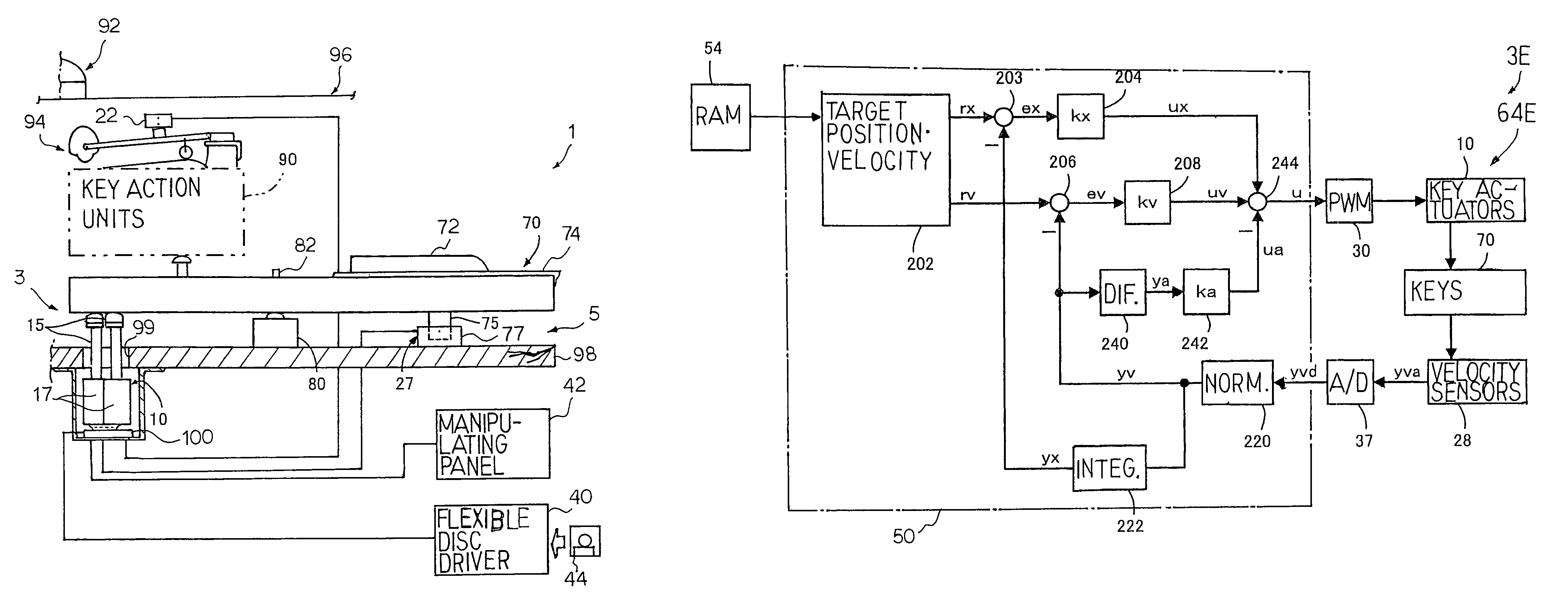

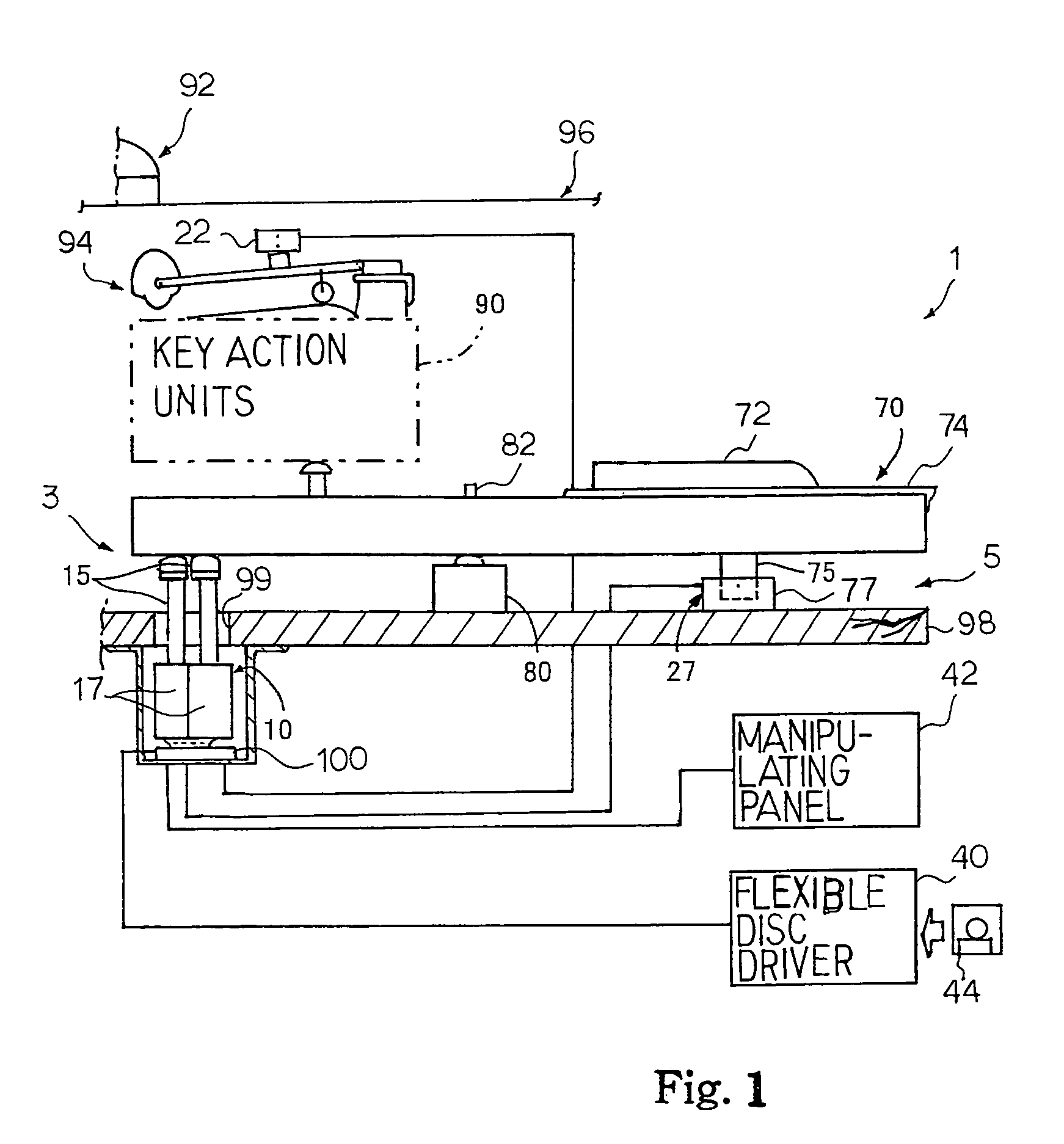

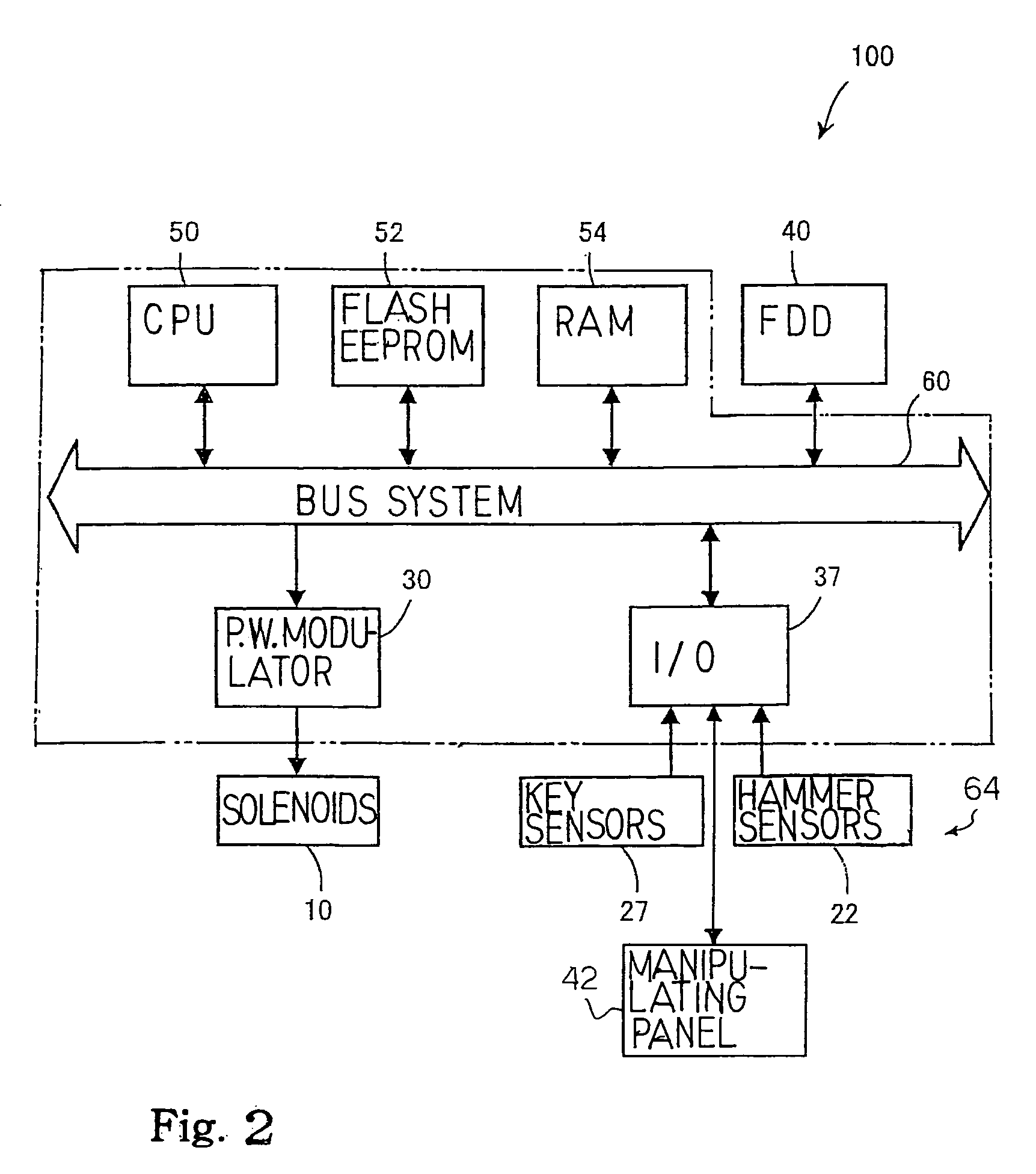

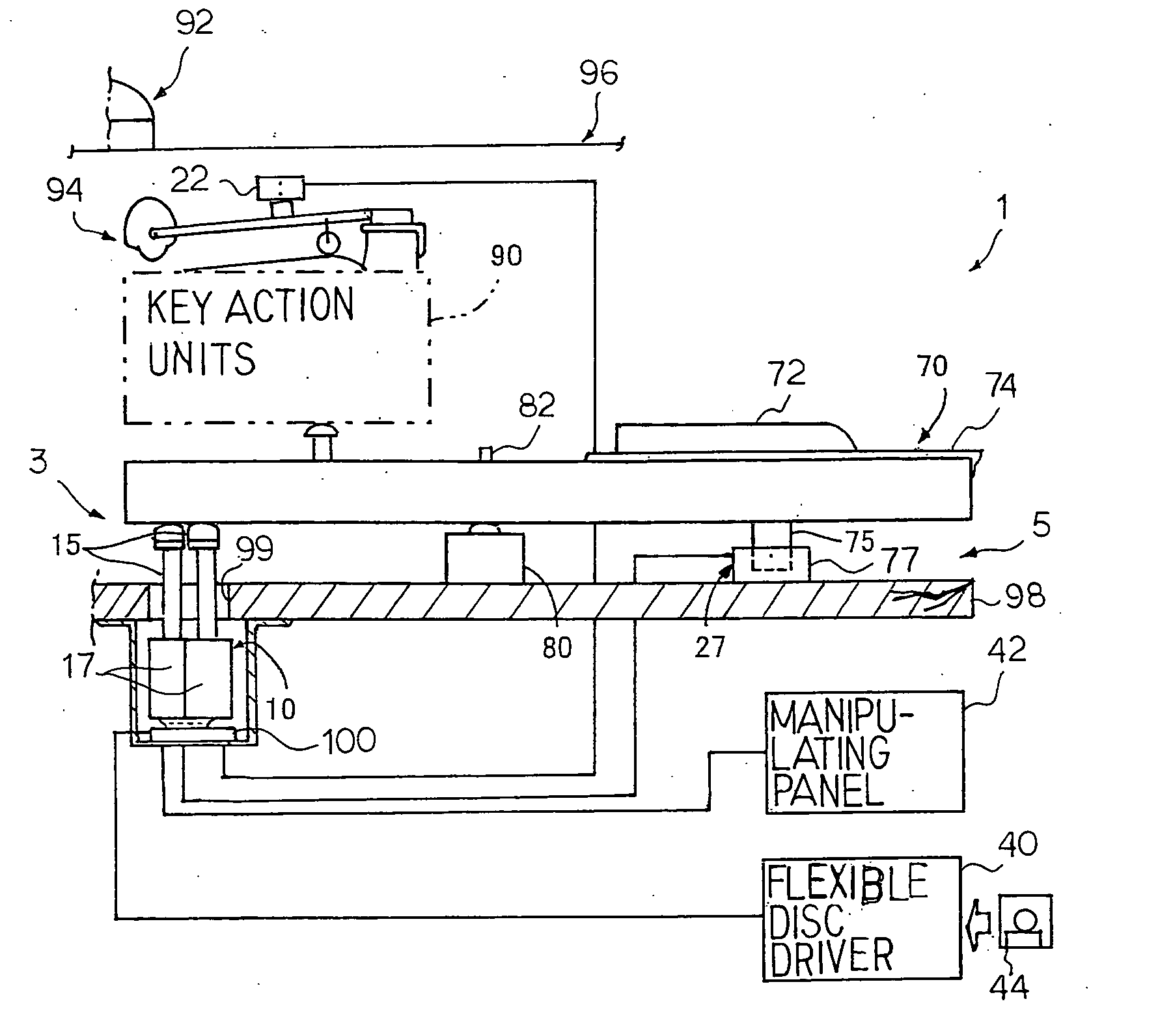

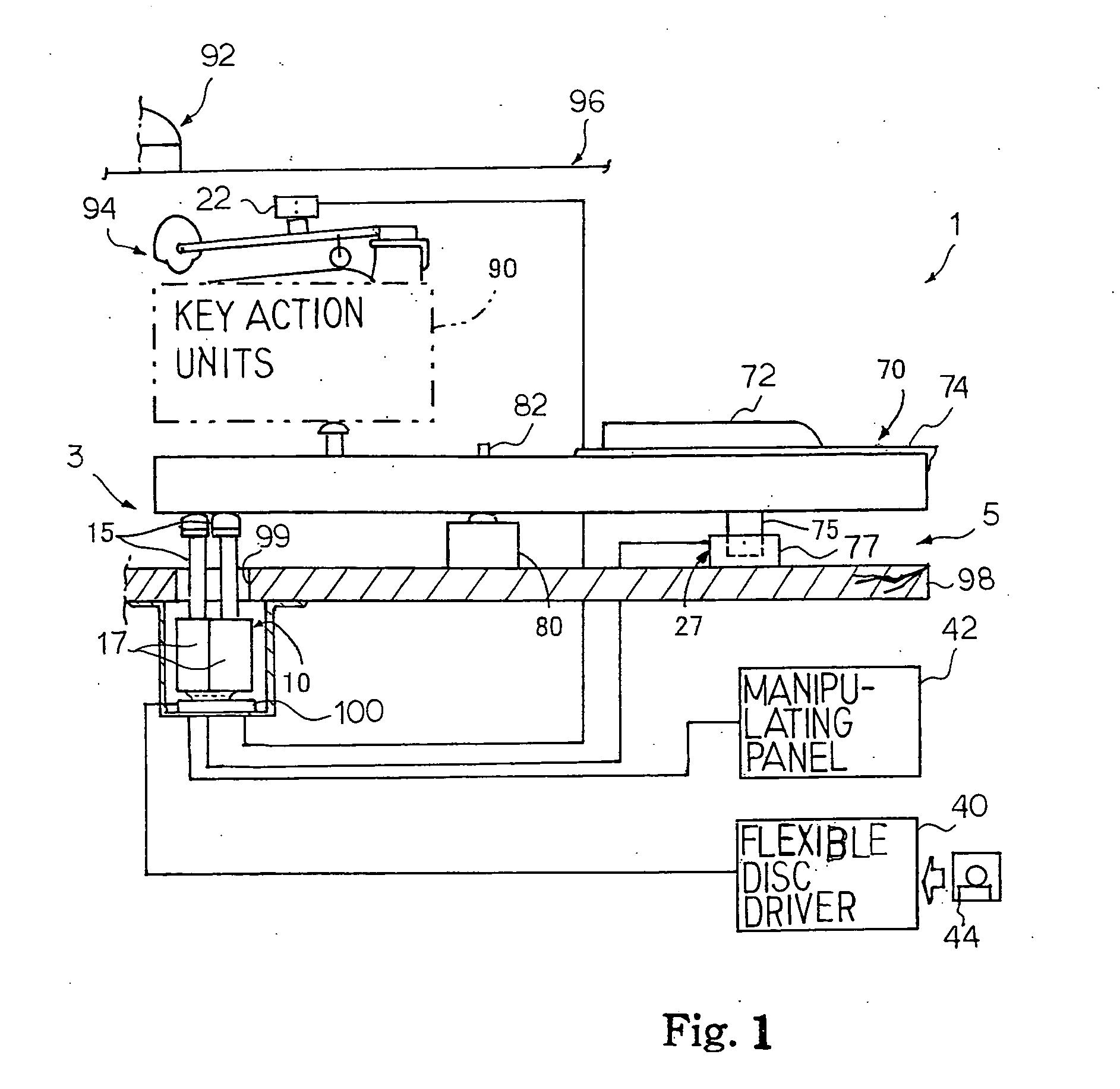

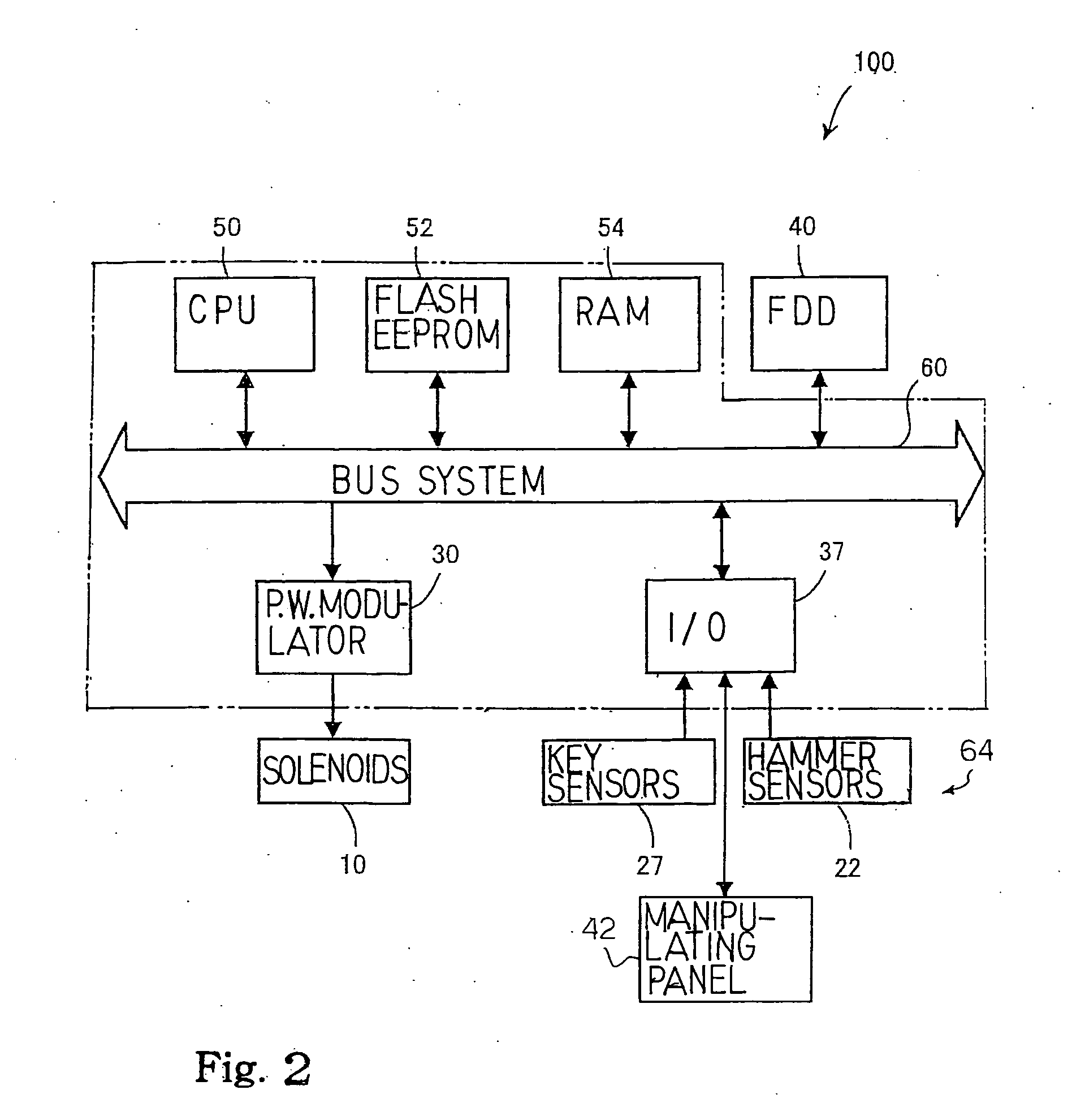

Automatic player keyboard musical instrument equipped with key sensors shared between automatic playing system and recording system

ActiveUS6969791B2Economical without sacrifice of the fidelity in playbackReduce the number of partsElectrophonic musical instrumentsAutomatic musical instrumentsPianoEngineering

An automatic player piano has various sorts of individuality due to differences in size, design margins applied to the component parts and a difference in electric characteristics of system component parts so that key position signals contain error components due to those sorts of individuality; plural feedback control loops are created between the key sensors and key actuators, and the error components are eliminated from the current key positions through the normalization; even if an original performance is reenacted through the automatic player piano different from that used in the recording, the feedback control loops cause the key actuators to force the keys to move along reference trajectories determined on the basis of the music data codes, whereby the manufacturer makes the key sensors shared between the recording system and the automatic playing system.

Owner:YAMAHA CORP

Automatic player keyboard musical instrument equipped with key sensors shared between automatic playing system and recording system

ActiveUS20050211048A1Economical without sacrifice of the fidelity in playbackReduce the number of partsElectrophonic musical instrumentsAutomatic musical instrumentsPianoEngineering

An automatic player piano has various sorts of individuality due to differences in size, design margins applied to the component parts and a difference in electric characteristics of system component parts so that key position signals contain error components due to those sorts of individuality; plural feedback control loops are created between the key sensors and key actuators, and the error components are eliminated from the current key positions through the normalization; even if an original performance is reenacted through the automatic player piano different from that used in the recording, the feedback control loops cause the key actuators to force the keys to move along reference trajectories determined on the basis of the music data codes, whereby the manufacturer makes the key sensors shared between the recording system and the automatic playing system.

Owner:YAMAHA CORP

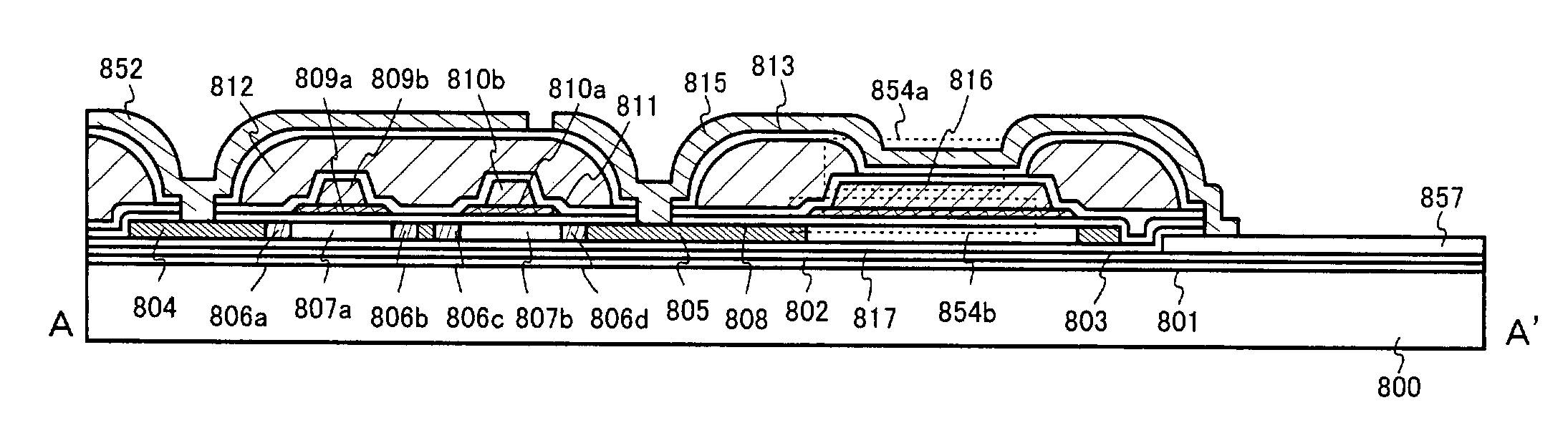

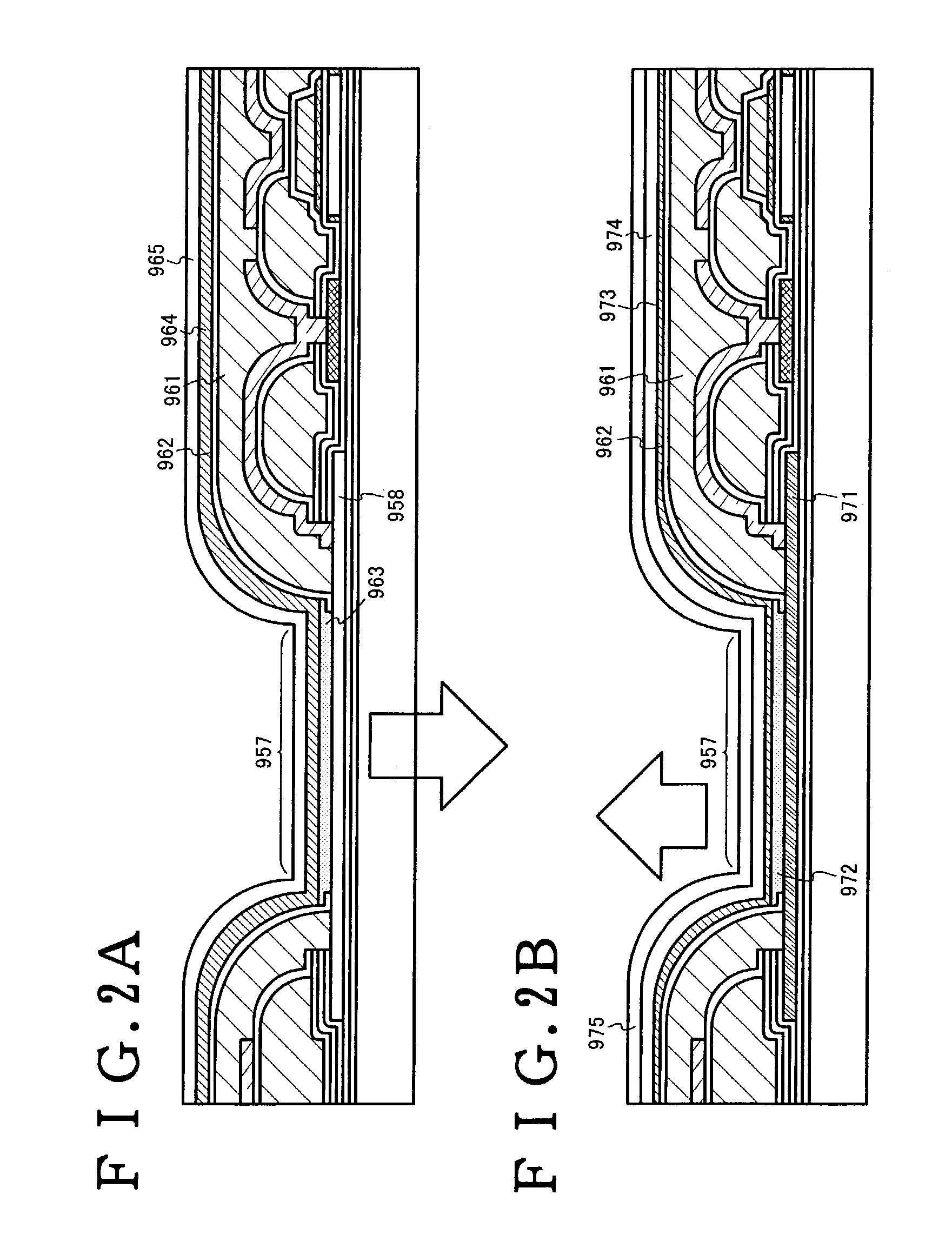

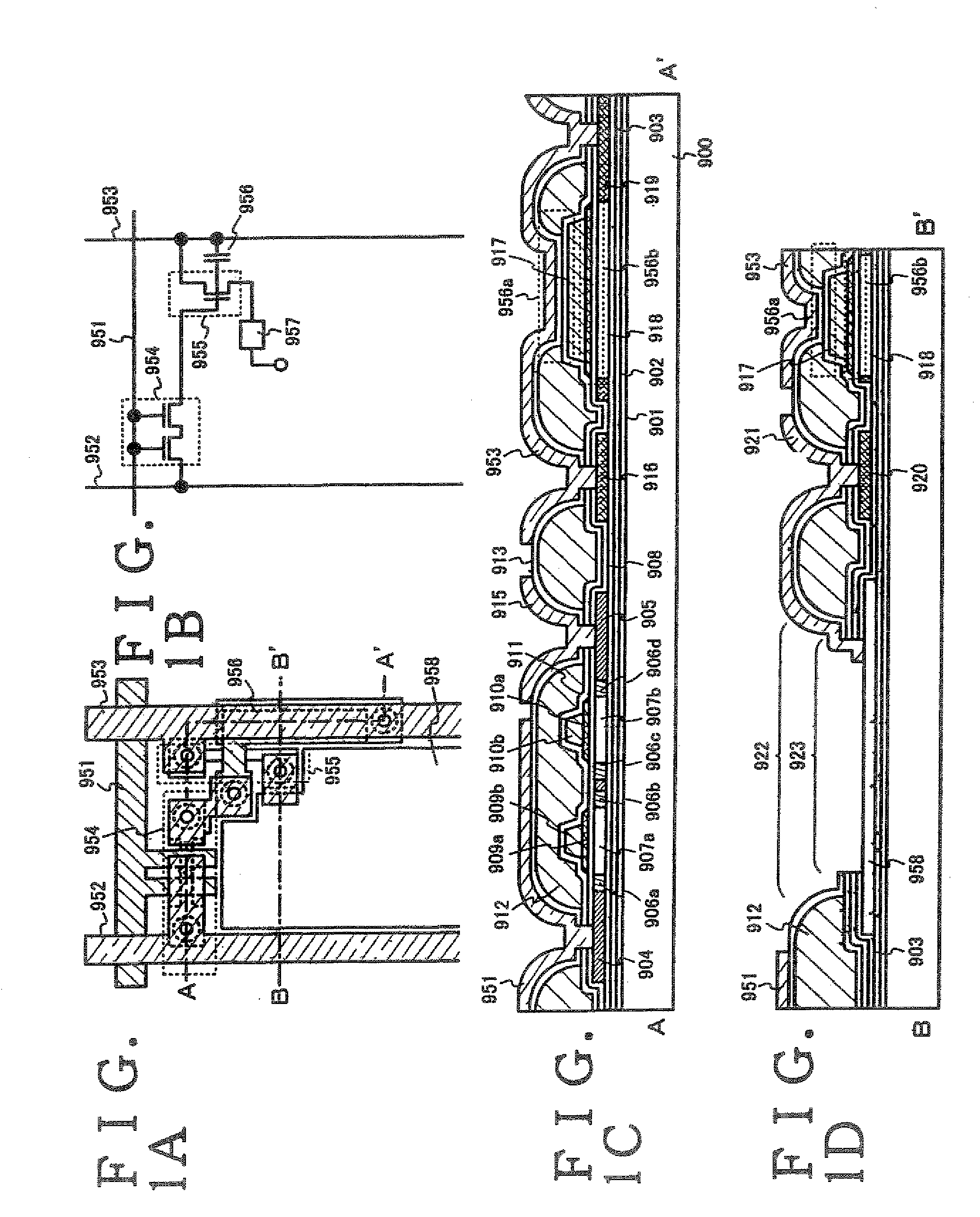

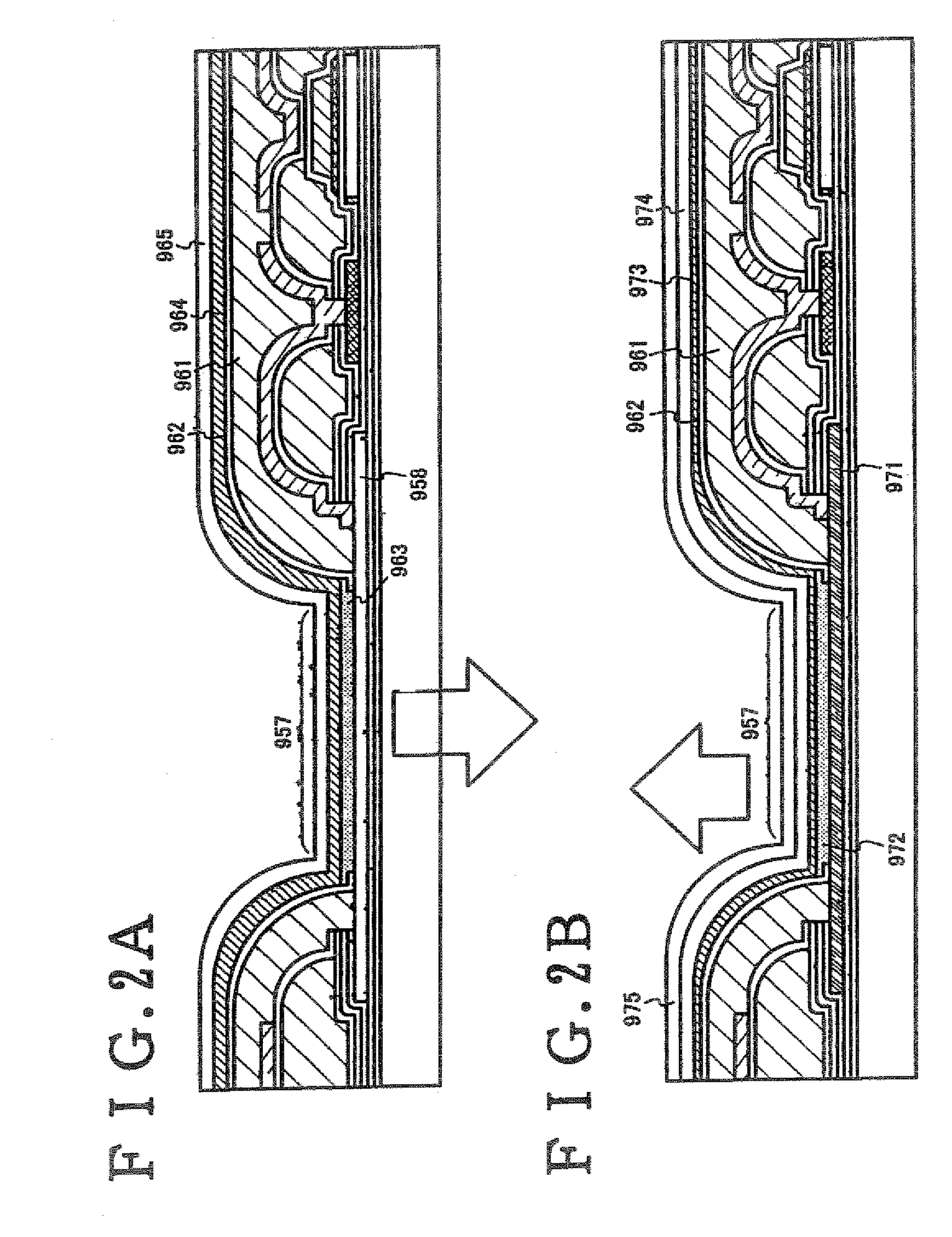

Display device and method of fabricating the same

InactiveUS7411215B2Fabrication process can be shortenedReduce manufacturing costTransistorElectroluminescent light sourcesDisplay deviceEngineering

To achieve promotion of stability of operational function of display device and enlargement of design margin in circuit design, in a display device including a pixel portion having a semiconductor element and a plurality of pixels provided with pixel electrodes connected to the semiconductor element on a substrate, the semiconductor element includes a photosensitive organic resin film as an interlayer insulating film, an inner wall face of a first opening portion provided at the photosensitive organic resin film is covered by a second insulating nitride film, a second opening portion provided at an inorganic insulating film is provided on an inner side of the first opening portion, the semiconductor and a wiring are connected through the first opening portion and the second opening portion and the pixel electrode is provided at a layer on a lower side of an activation layer.

Owner:SEMICON ENERGY LAB CO LTD

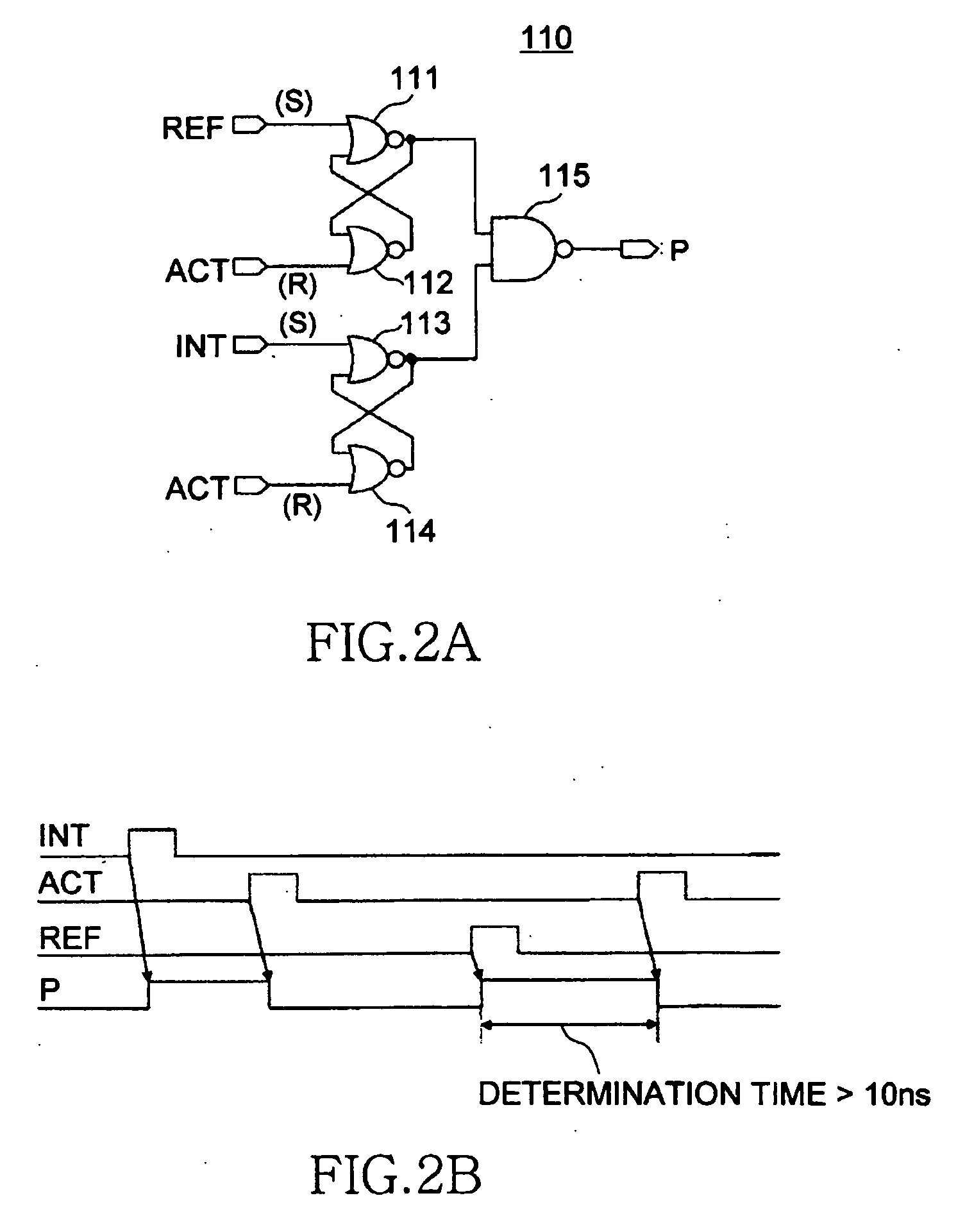

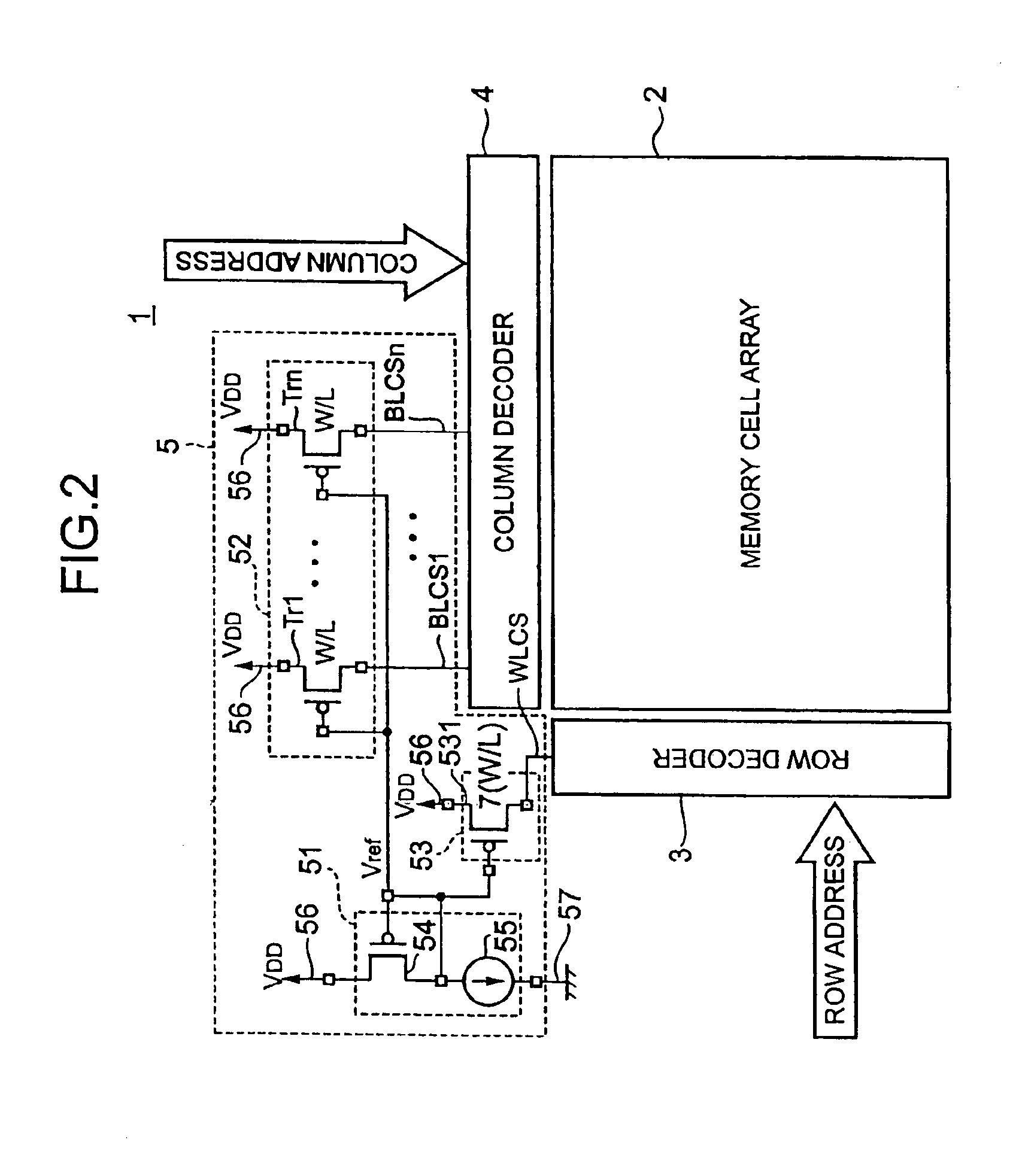

Semiconductor device having delay control circuit

InactiveUS20100085824A1Performance degradation can be preventedIncrease in circuit sizeMultiple input and output pulse circuitsPulse automatic controlEngineeringControl circuit

A first delay circuit and a second delay circuit having different operation conditions from each other, a detection circuit that detects a difference in propagation speed of a pulse signal, which is simultaneously input to the first and second delay circuits, and a setting circuit that generates a selection signal based on a detection result from the detection circuit are provided. The selection signal is supplied to a delay control circuit that generates an operation timing signal by delaying a reference signal, of which a delay amount is controlled by the selection signal. With this arrangement, a necessity to set the delay amount of the delay control circuit with a large design margin can be eliminated considering PVT variation, and as a result, performance degradation can be prevented.

Owner:LONGITUDE LICENSING LTD

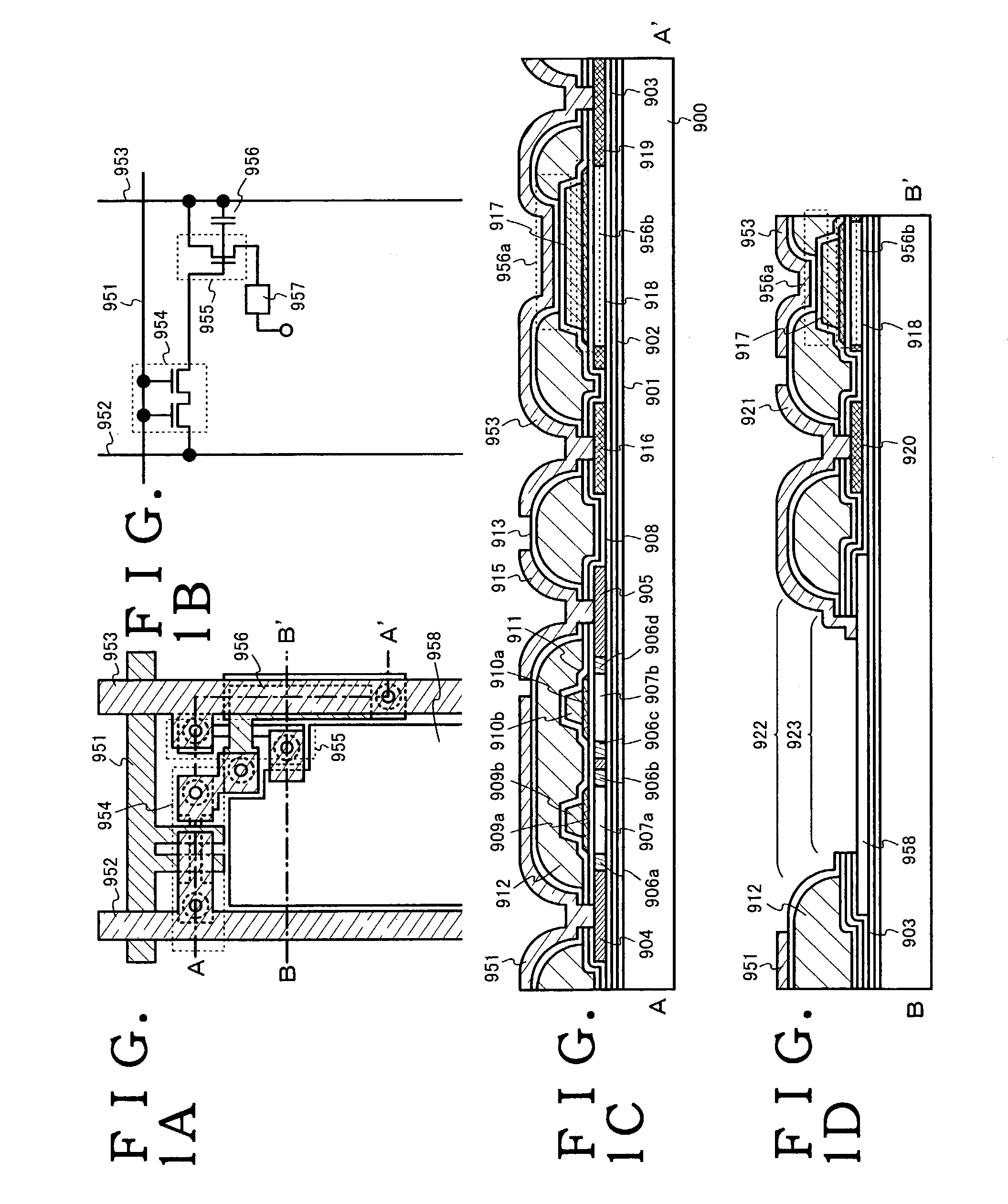

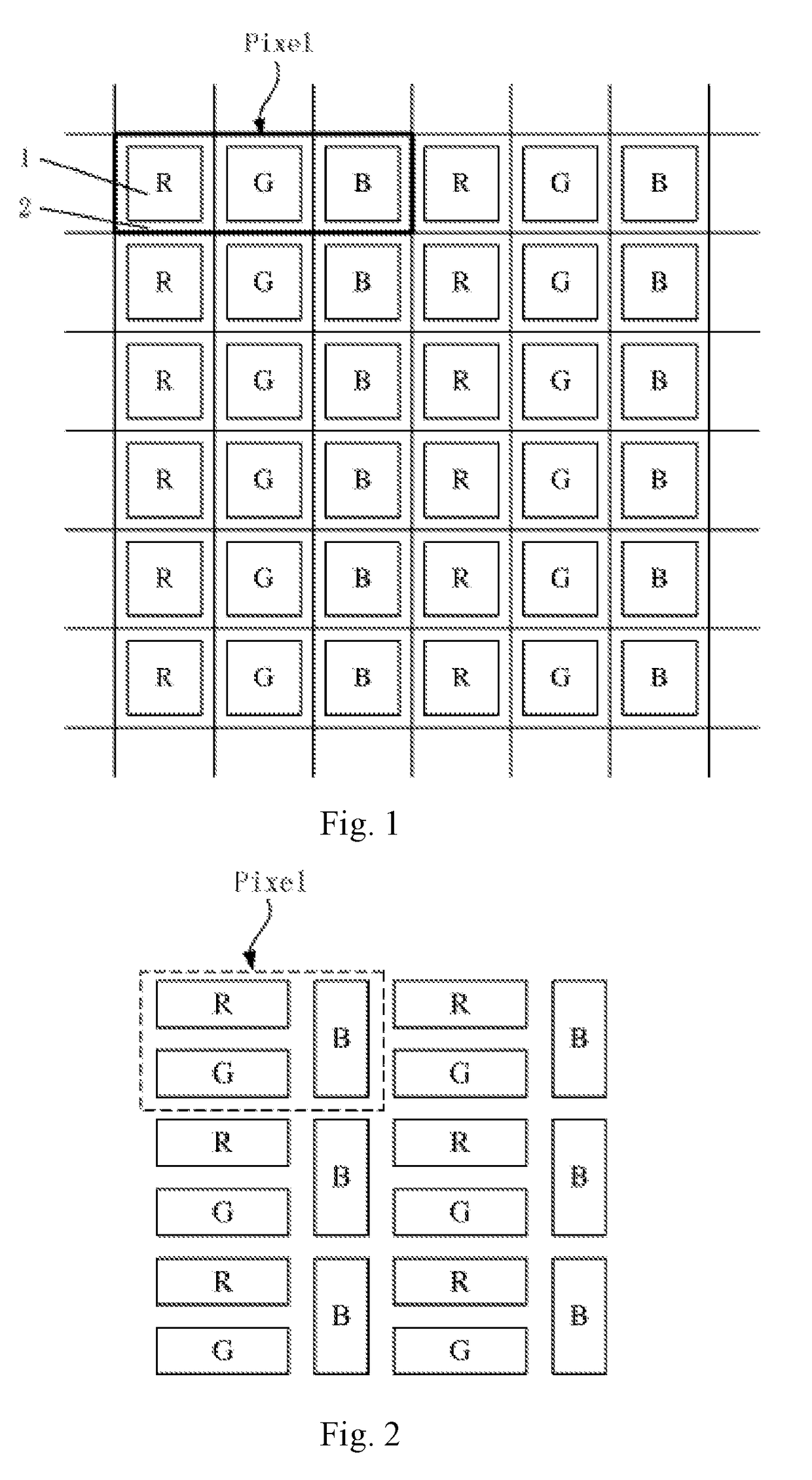

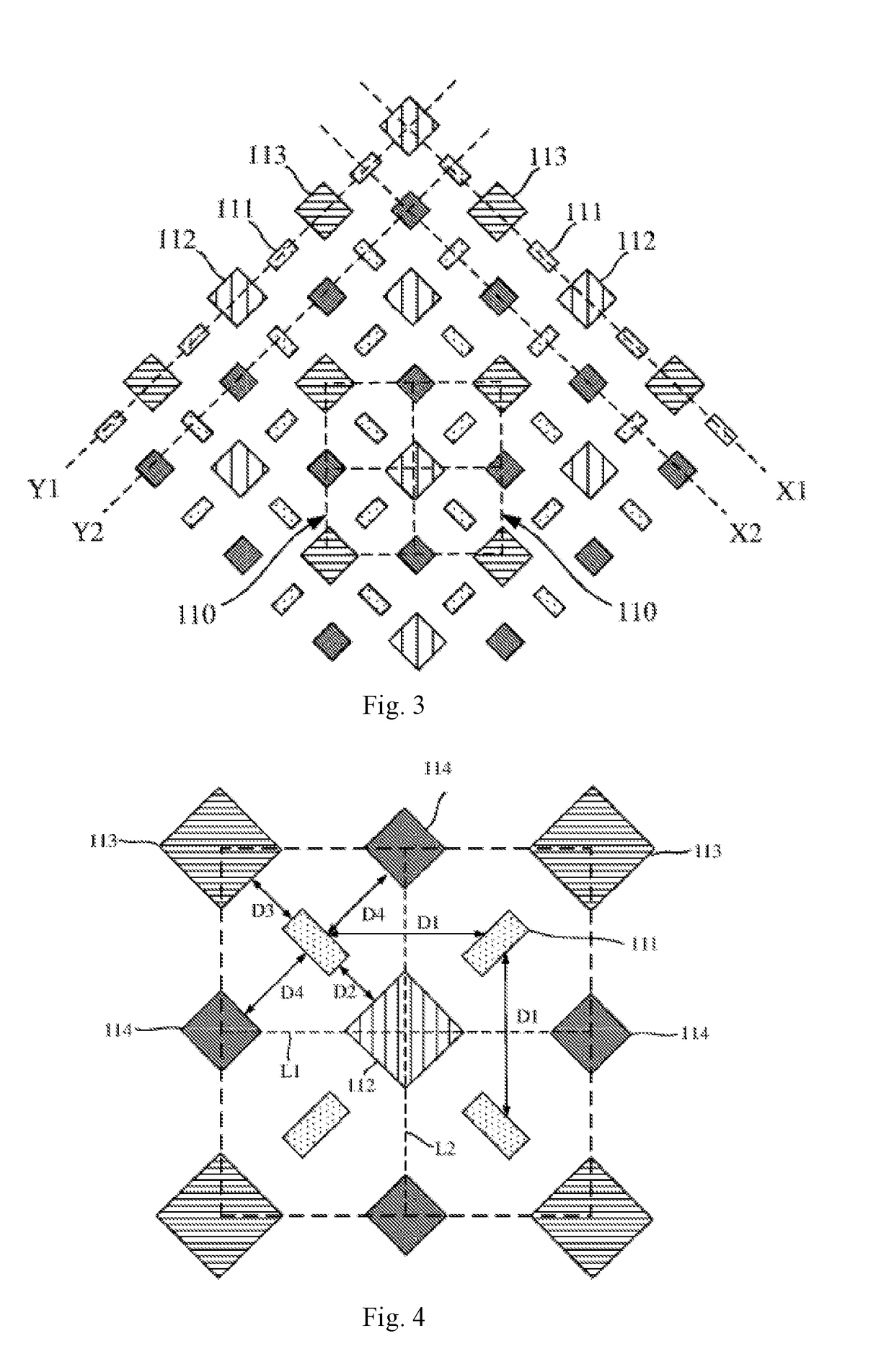

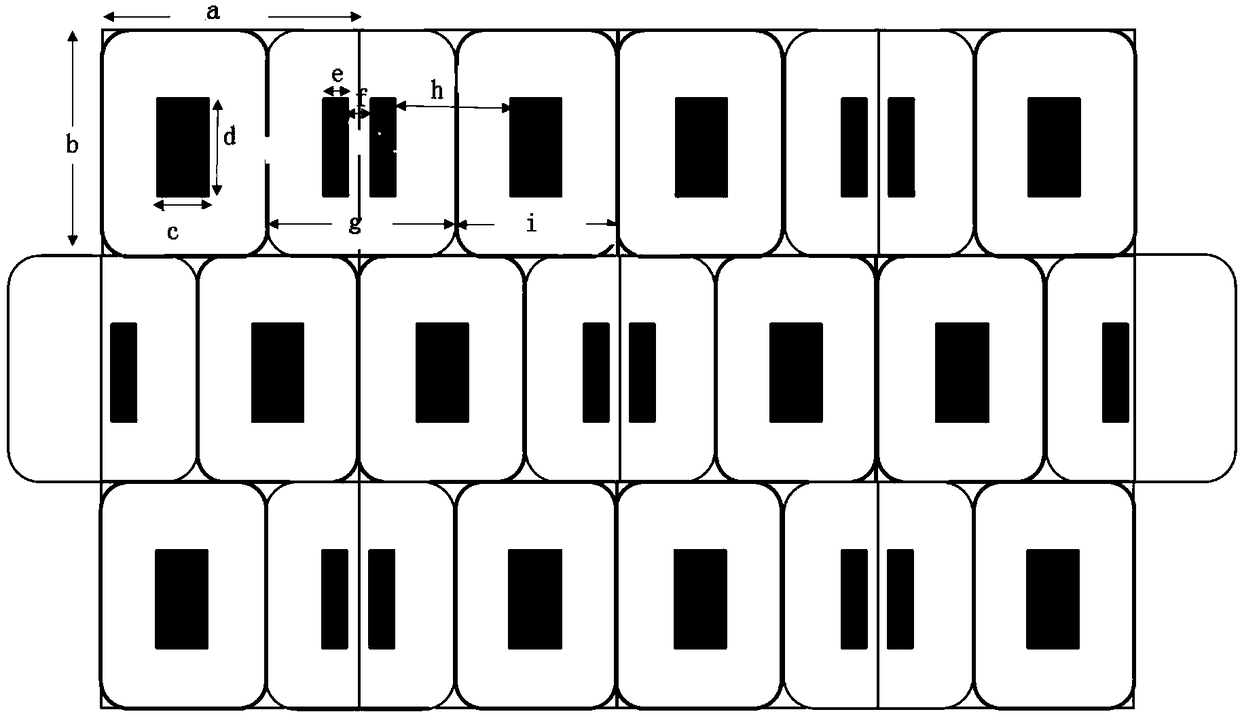

Pixel structure and OLED display panel

ActiveUS20190035861A1Increase opening ratioIncrease design marginStatic indicating devicesSolid-state devicesLight-emitting diodeComputer science

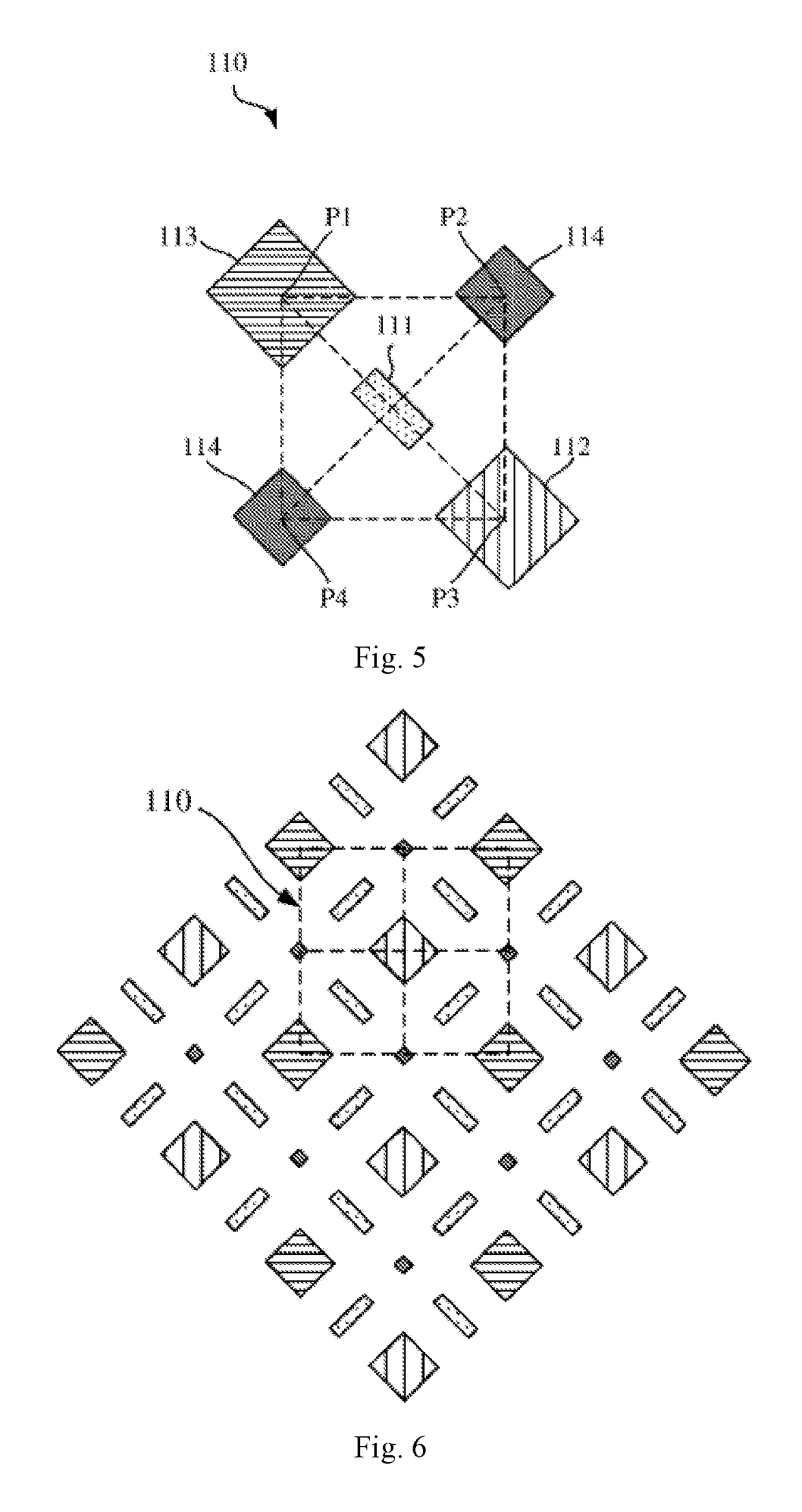

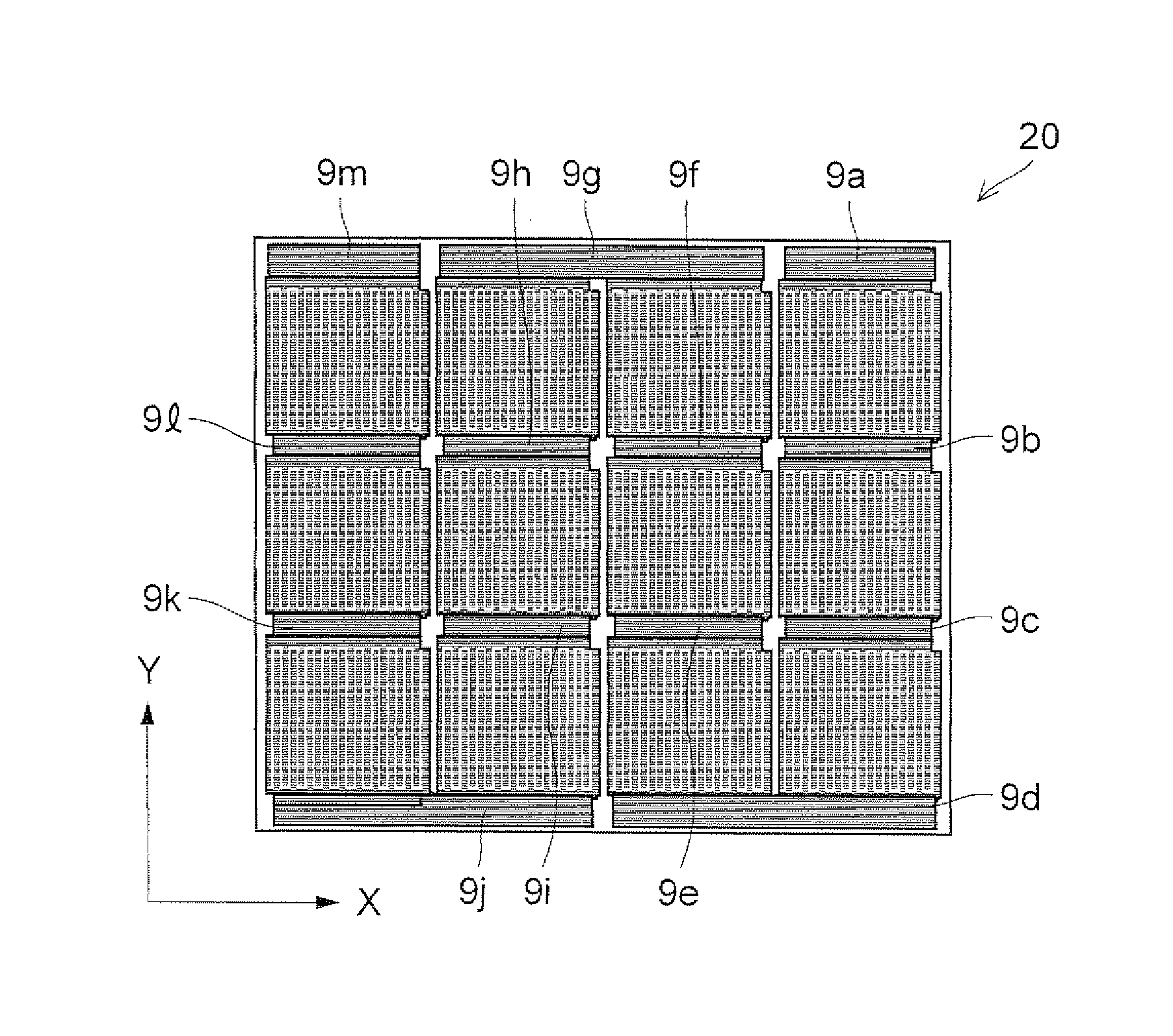

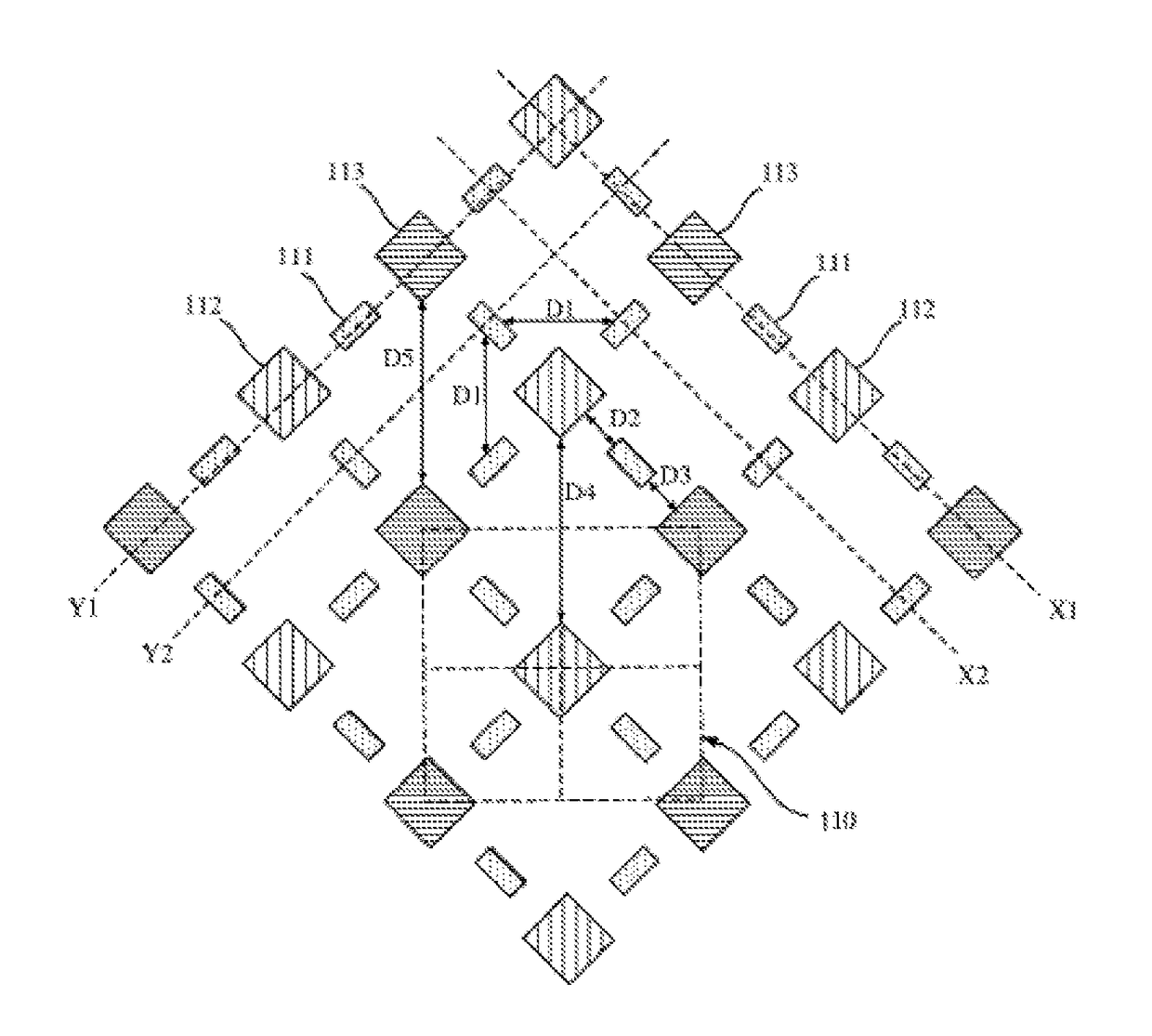

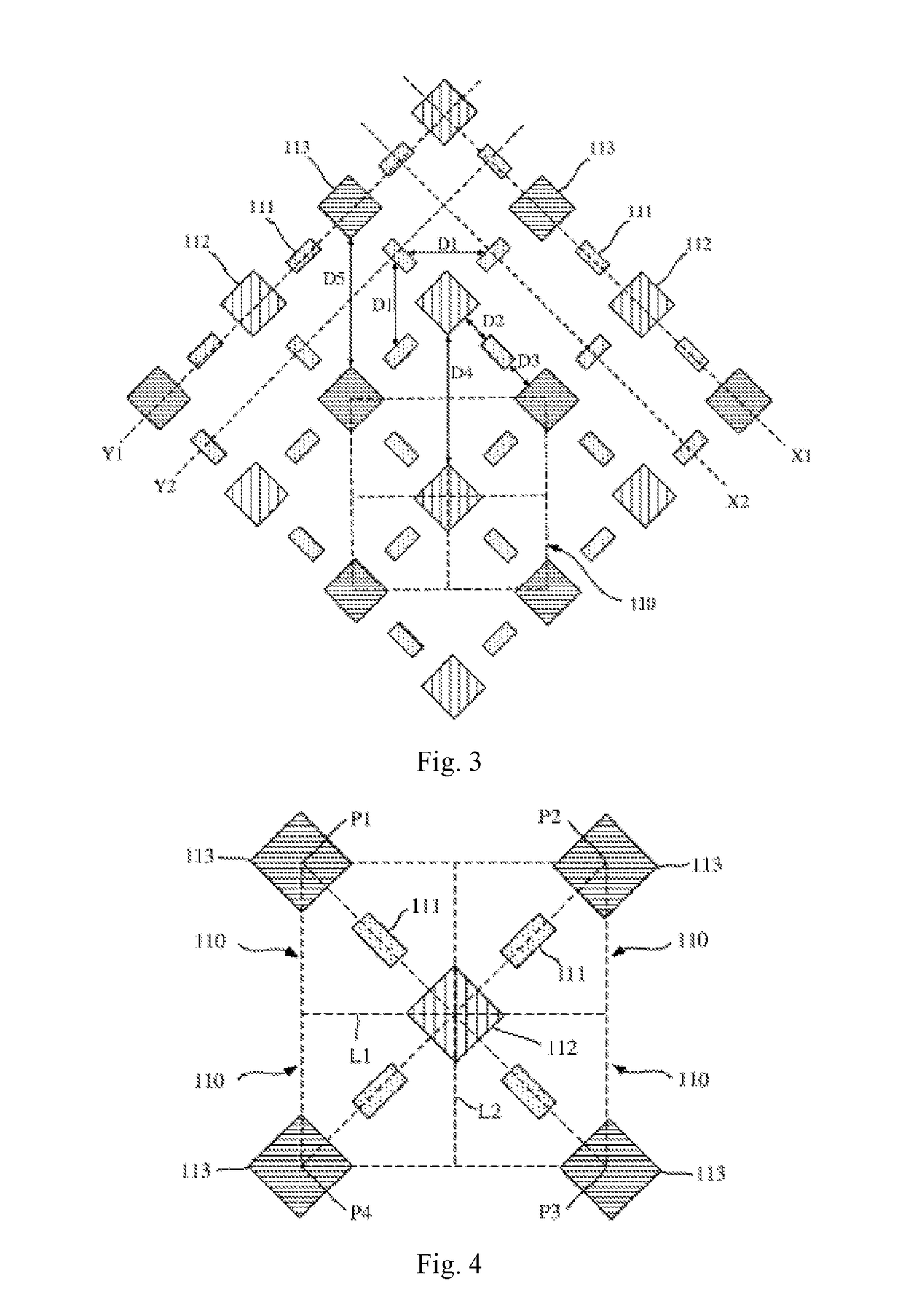

A pixel structure and an organic light-emitting diode (OLED) display panel incorporating the pixel structure are disclosed. Each pixel unit (110) in the pixel structure includes a first sub-pixel (111), a second sub-pixel (112), a third sub-pixel (113) and two fourth sub-pixels (114). The second sub-pixel (112), the third sub-pixel (113) and the fourth sub-pixels (114) are arranged to define a quadrilateral encompassing the first sub-pixel (111) and be common to four adjacent pixel units (110). The first sub-pixel (111) serves as a primary display element, while each of the second sub-pixel (112), the third sub-pixel (113) and the fourth sub-pixels (114) acts as a secondary display element. As a result, a higher aperture ratio of the primary display element can be obtained at the same PPI and design margin, or an increased design margin and reduced process difficulty can be obtained at the same PPI and aperture ratio.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

Solar battery module and method for manufacturing the same

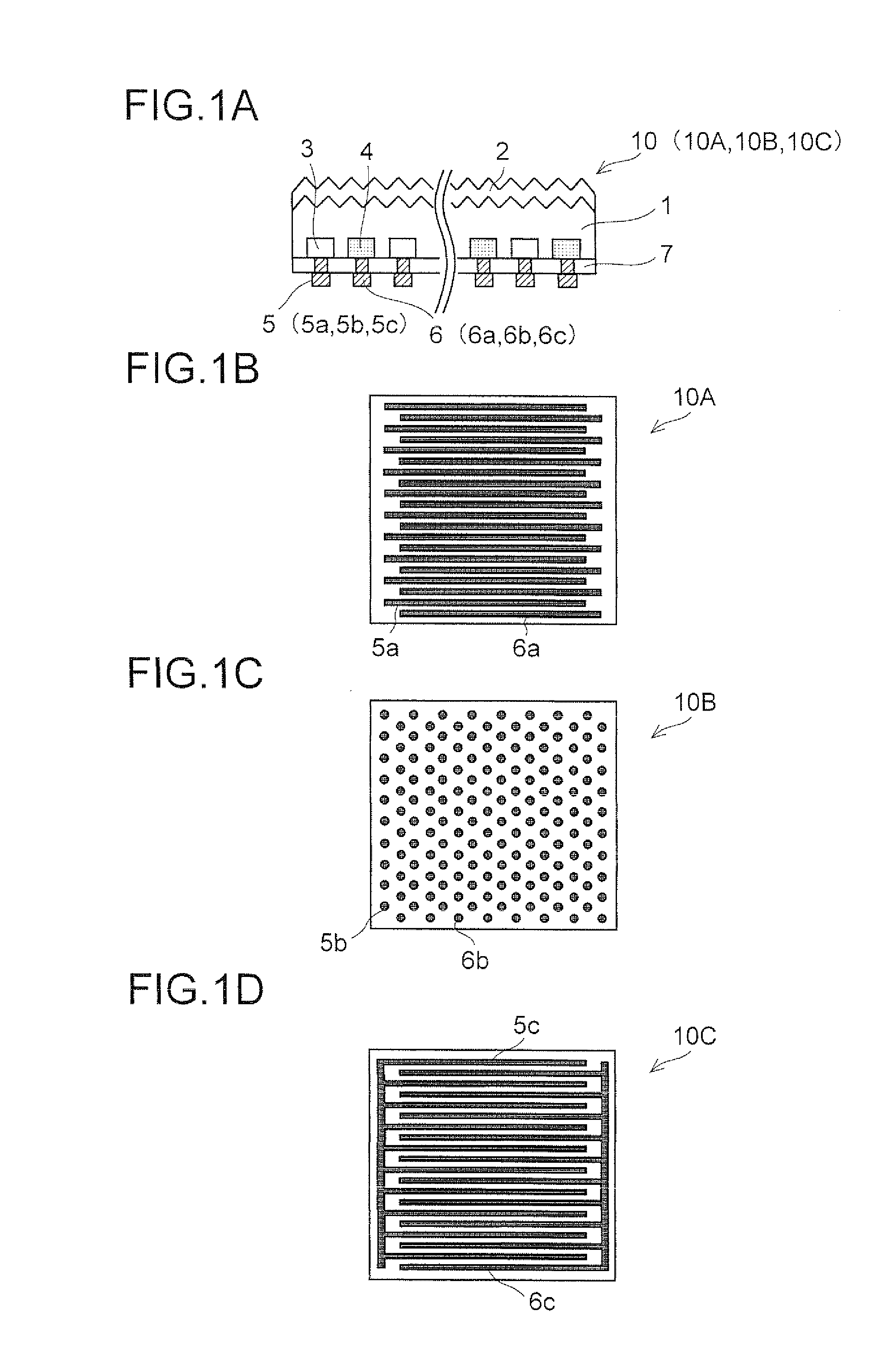

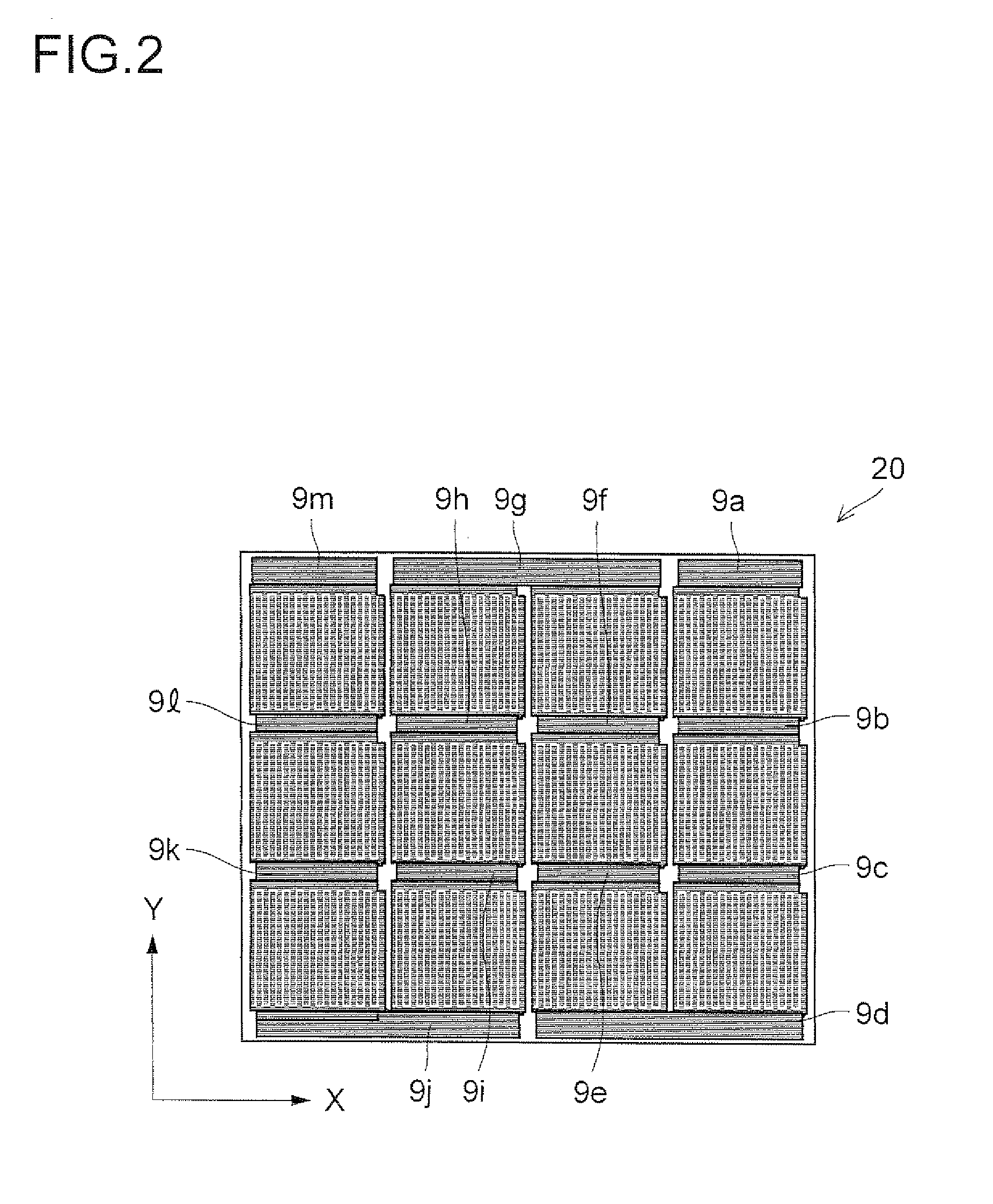

ActiveUS20110094562A1Avoid positioningPV power plantsPrinted circuit aspectsElectricityElectrical battery

Provided is a solar battery module wherein solar battery cells are electrically connected to each other by using a wiring board having a predetermined wiring pattern formed on a resin base material. A method for manufacturing such solar battery module is also provided. In the wiring board of the solar battery module, a direction wherein a design margin is small is permitted to be a direction wherein the thermal contraction ratio of the resin base material is small, by the shape of an electrode pattern on the solar battery cell and that of the wiring pattern on the wiring board. At the time of manufacturing such solar battery module, temperature in a heat treatment step is set at 100° C. or higher but not higher than 180° C. Electrode designing at a fine pitch is made possible and the solar battery module exhibits high solar battery characteristics, even when the solar battery cells are connected by using wiring boards composed of various types of resin materials having thermal compression ratio not sufficiently low.

Owner:SHARP KK

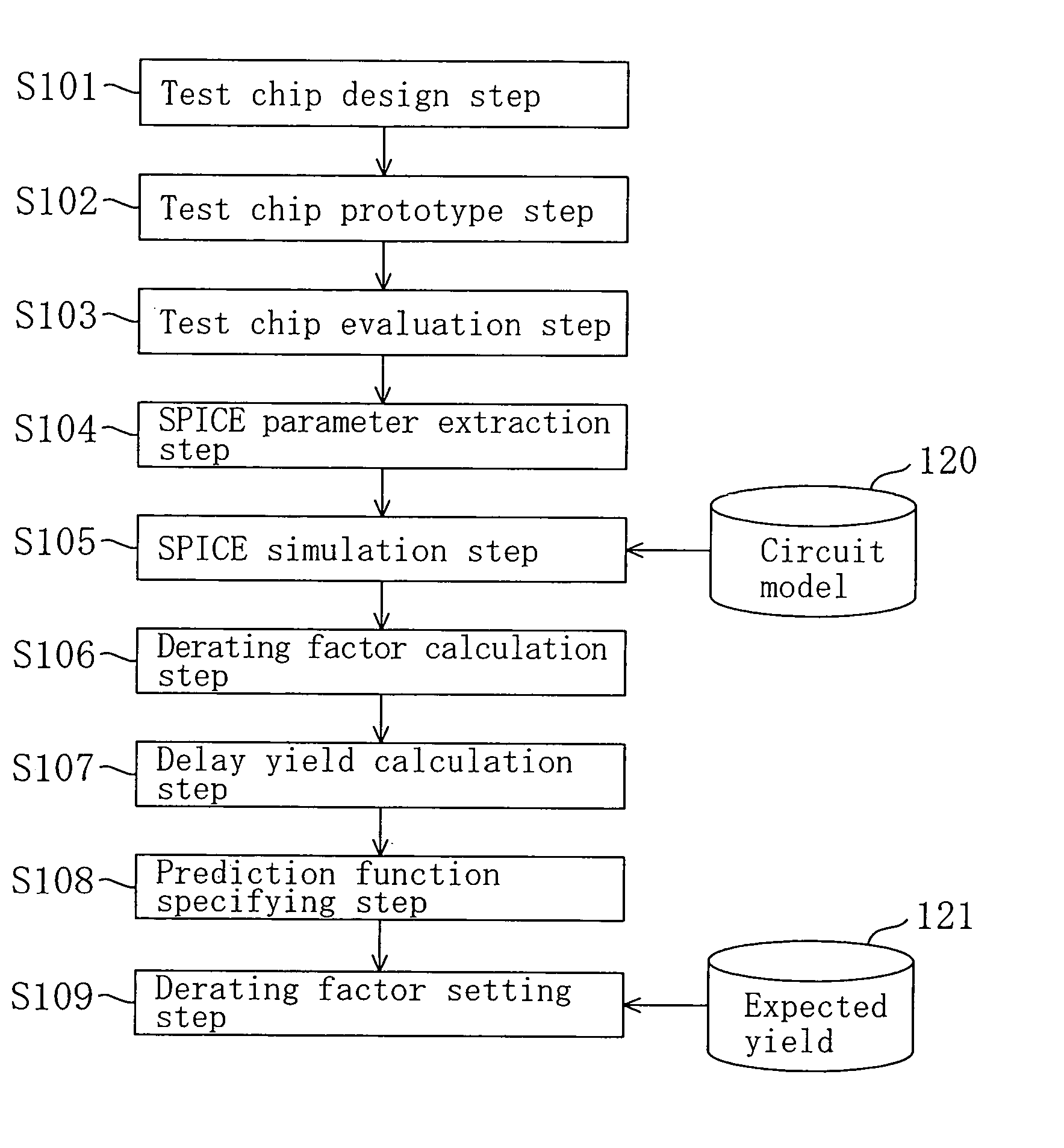

Method for setting design margin for LSI

ActiveUS7197728B2More accurateMore realisticSemiconductor/solid-state device manufacturingComputer aided designEngineeringSignal propagation delay

After predicting a relationship between a design margin set against a fabrication variation in design of an LSI and a yield, a specific design margin for attaining a given yield is calculated based on the predicated relationship. The yield is a delay yield obtained by cumulating a signal propagation delay time thereby achieving a probability that a signal propagated through a logic circuit of the LSI is delayed by a given amount of time, and the design margin is a derating factor indicating a ratio between the signal propagation delay time and a standard value of the signal propagation delay time.

Owner:PANNOVA SEMIC

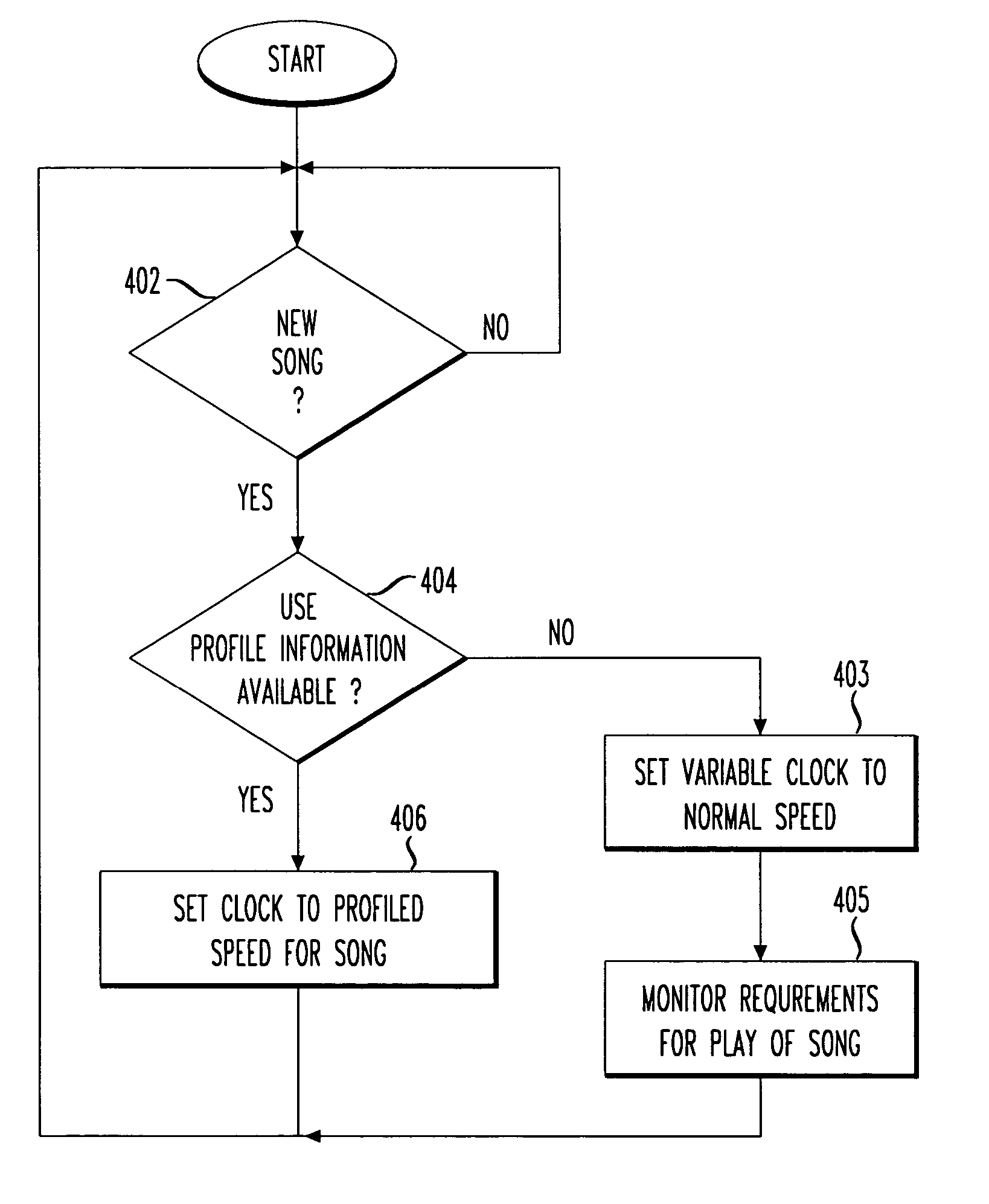

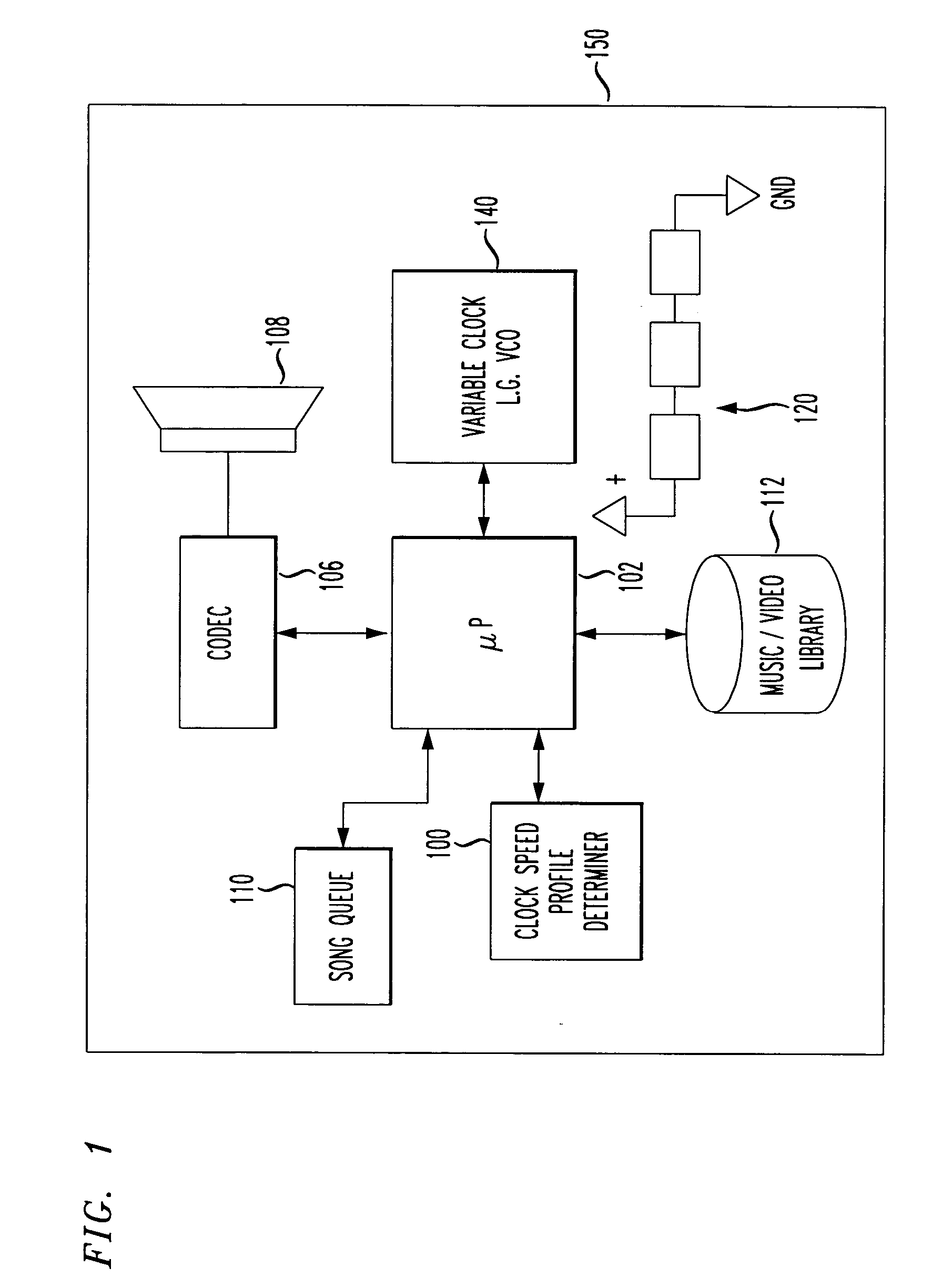

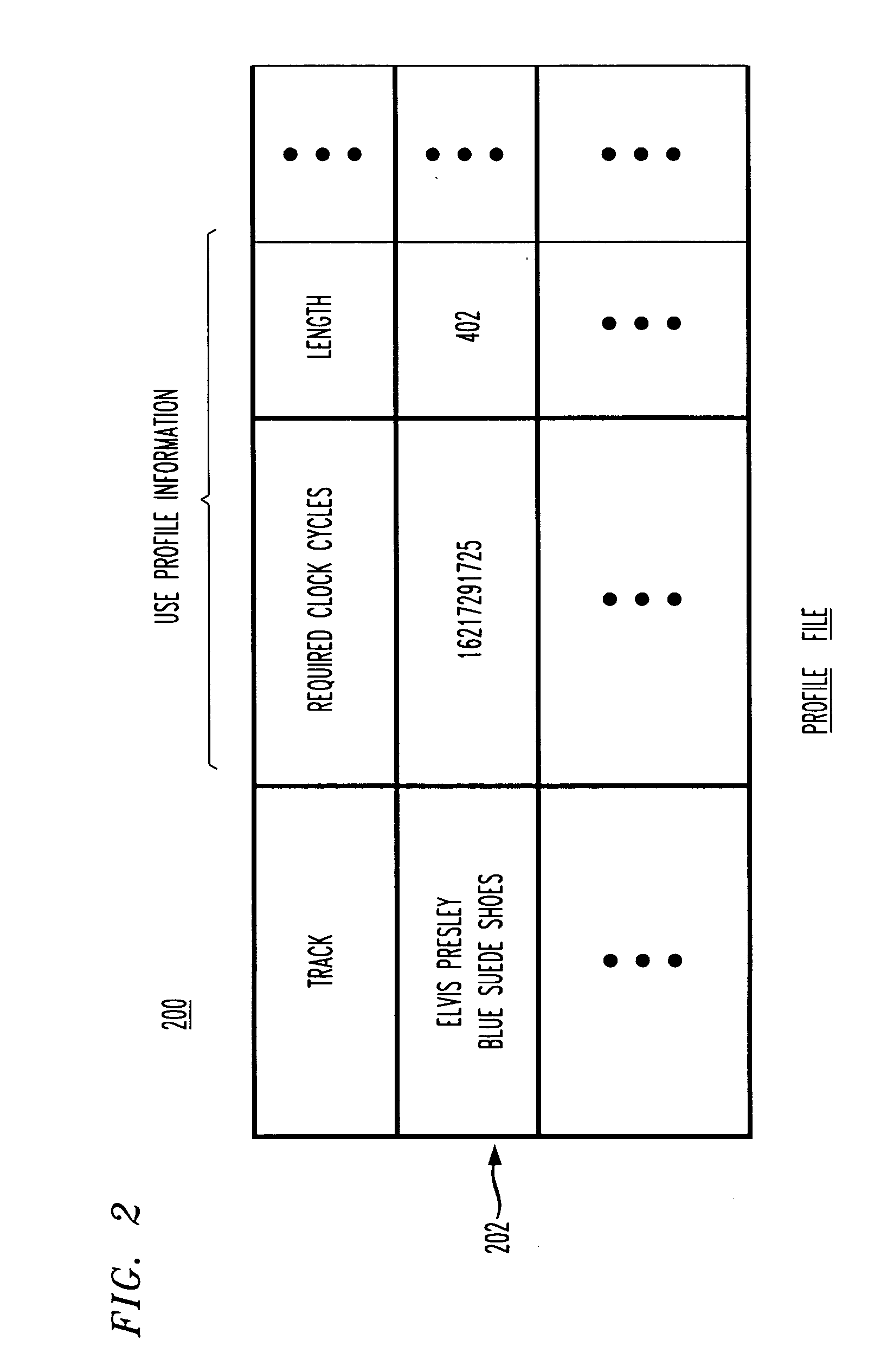

Adaptive power management in portable entertainment device

Battery life in portable entertainment devices that play fixed-length music or video files (e.g., MP3 music files) is extended by adaptively adjusting the speed of a processor in the device such that only a minimum number of MIPS are performed to playback the music or video files. Slowing the processor clock provides significant savings in power usage. A use profile containing required MIPS for each song may be stored on the device, or use profile information may be inserted into the data stream or embedded within the data file. Power savings occurs on every subsequent replay of the same entertainment data file or data stream by adaptively adjusting the processor clock to the desired speed as determined by the use profile information (plus design margin based on the particular playback device).

Owner:AVAGO TECH INT SALES PTE LTD

Pixel structure and OLED display panel

ActiveUS20180247984A1Increase opening ratioIncrease design marginStatic indicating devicesSolid-state devicesLight-emitting diodeComputer science

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

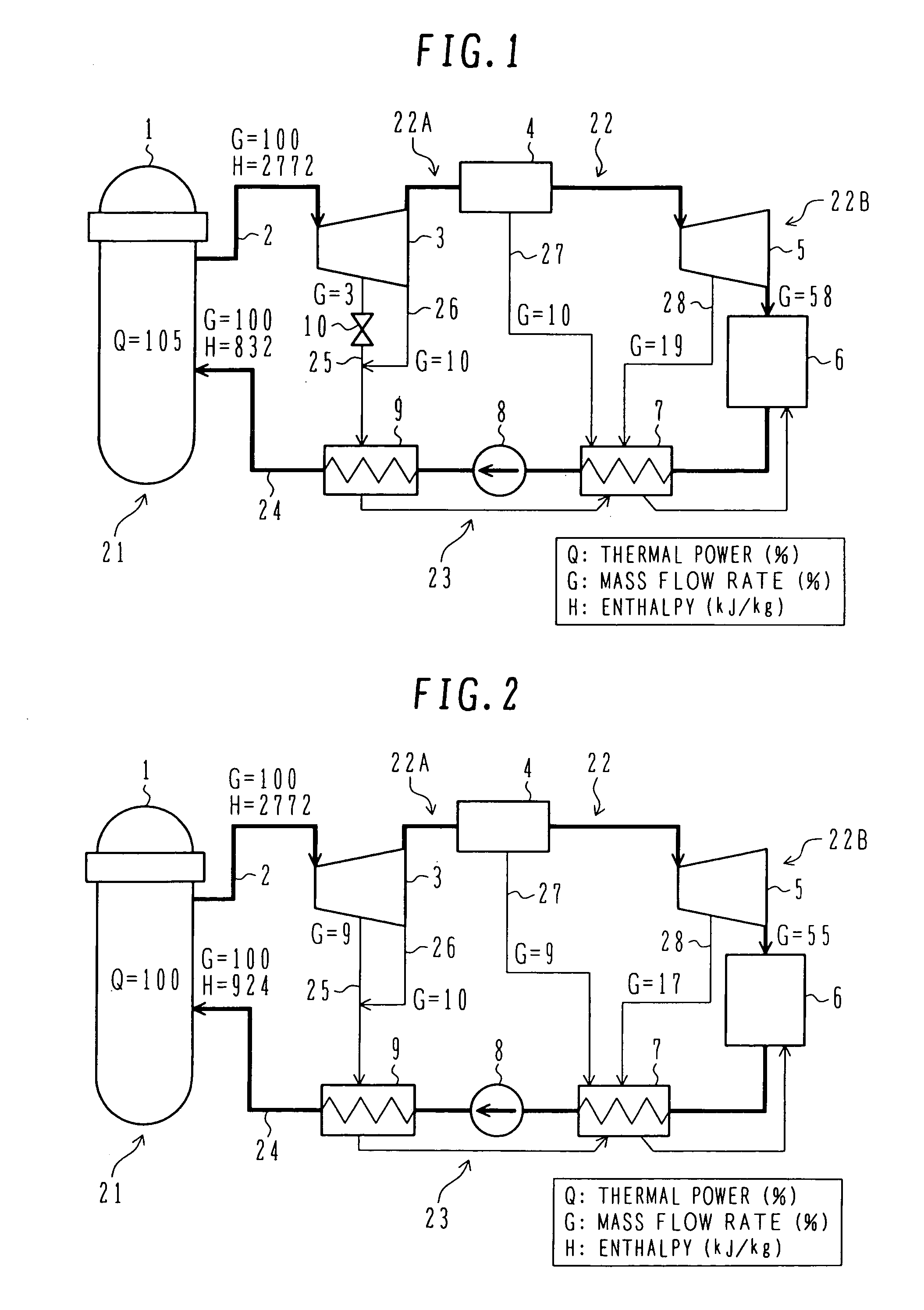

Operation method of nuclear power plant

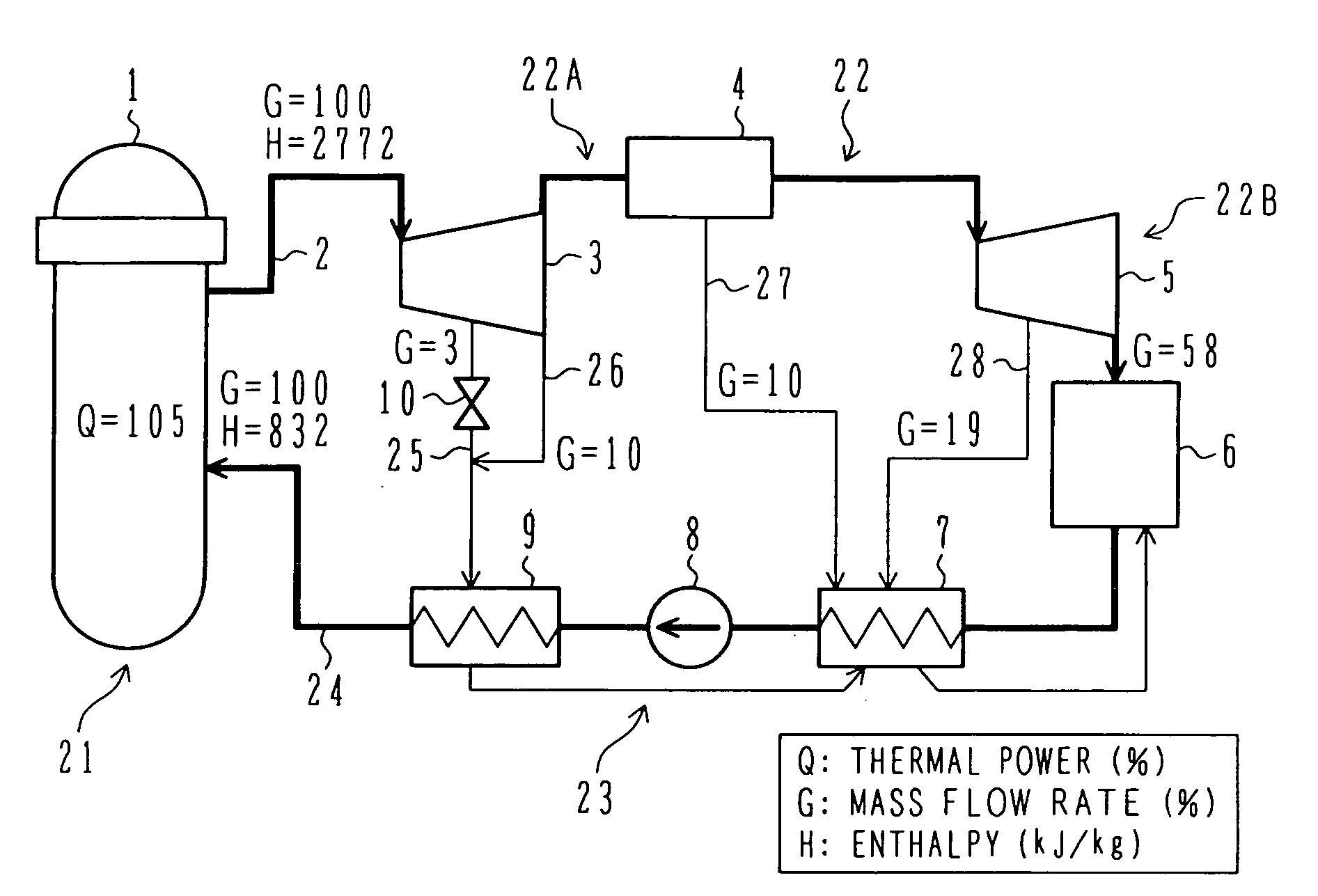

ActiveUS20070000250A1Increase thermal powerIncrease flow rateNuclear energy generationNuclear power plant controlNuclear powerHigh pressure

A nuclear power plant and an operation method of the nuclear power plant, which can uprate plant power without greatly modifying the construction of plant equipment, while keeping a core's pressure loss characteristic, a safety margin, and a design margin in the transient state substantially the same as those before the power uprate. Thermal power in a second operation cycle of a nuclear reactor is uprated from thermal power in a first operation cycle preceding the second operation cycle at least one operation cycle. A proportion of steam extracted from a steam system and introduced to a feedwater heater, which is in particular extracted from an intermediate point and an outlet of a high pressure turbine, with respect to a flow rate of main steam is reduced in the second operation cycle from that in the first operation cycle such that temperature of feedwater discharged from the feedwater heater lowers in the range of 1° C. to 40° C. in the second operation cycle.

Owner:HITACHI-GE NUCLEAR ENERGY LTD

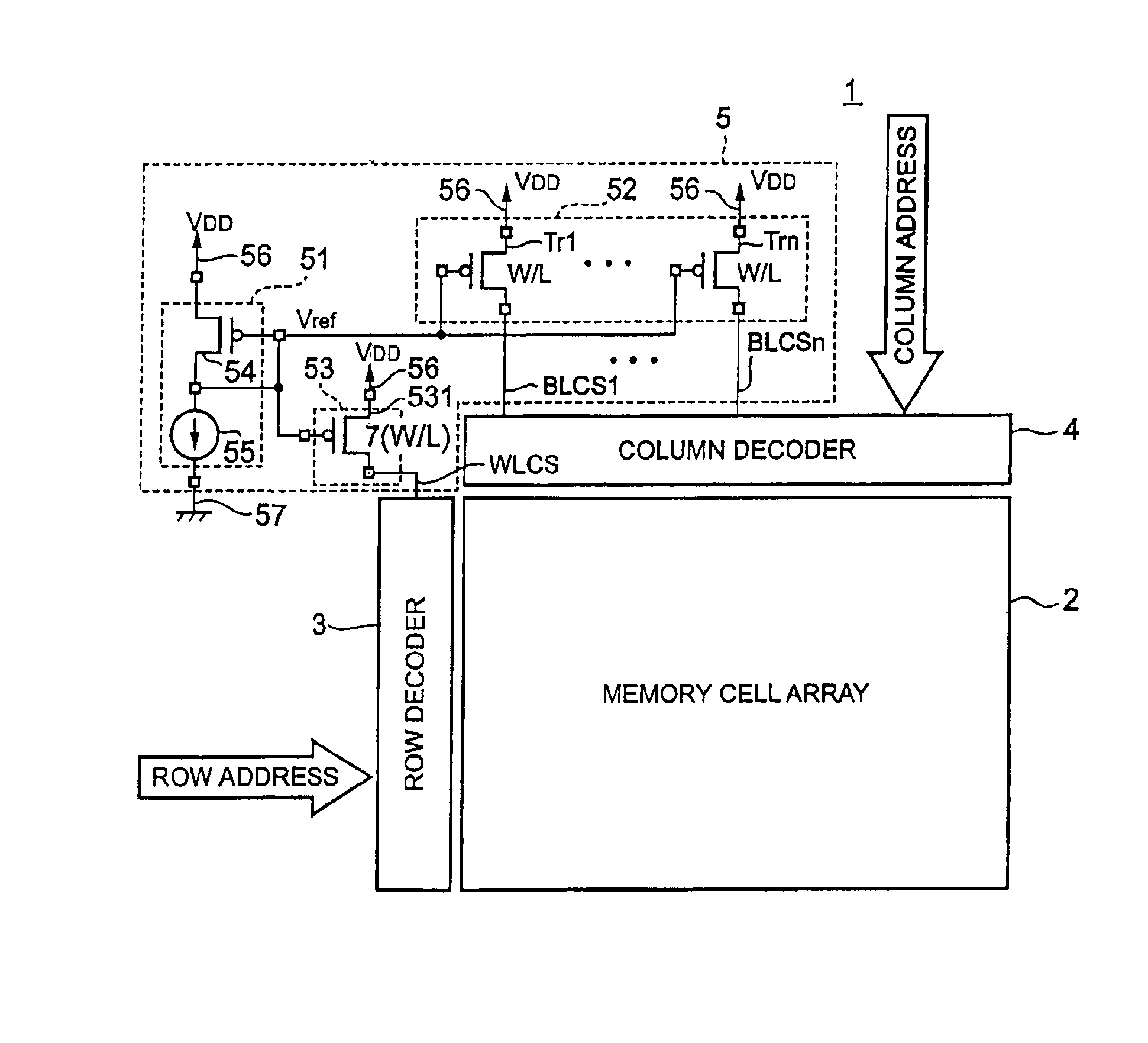

Magnetic memory and method for optimizing write current in a magnetic memory

ActiveUS6992924B2Minimise currentMinimize powerMagnetic-field-controlled resistorsSolid-state devicesWrite bitMagnetic memory

The invention provides methods and apparatus for for determining and providing optimum write bit line current and write word line current in an MRAM. A single reference potential is used to determine the values of the write line current and the bit line current. In determining the optimal values, asteroid curves representing bit line magnetic fields Hx generated by write bit line current IB and word line magnetic fields Hy generated by write word line current Iw for magnetization are considered, and an asteroid curve ACout is defined outside the asteroid curves of all memory cells taking manufacture variations and design margins into account. A write bit line current and a write word line current are selected such that the write current obtained by adding the write bit line current or currents and the write word line current, or the write power consumed by the bit line or lines and the write word line is minimized. Furthermore, in order to prevent multi-selection, the write bit line current and the write word line current are selected so that they generate a synthetic magnetic field on the curve between calculated points of the asteroid curve ACout.

Owner:WESTERN DIGITAL TECH INC

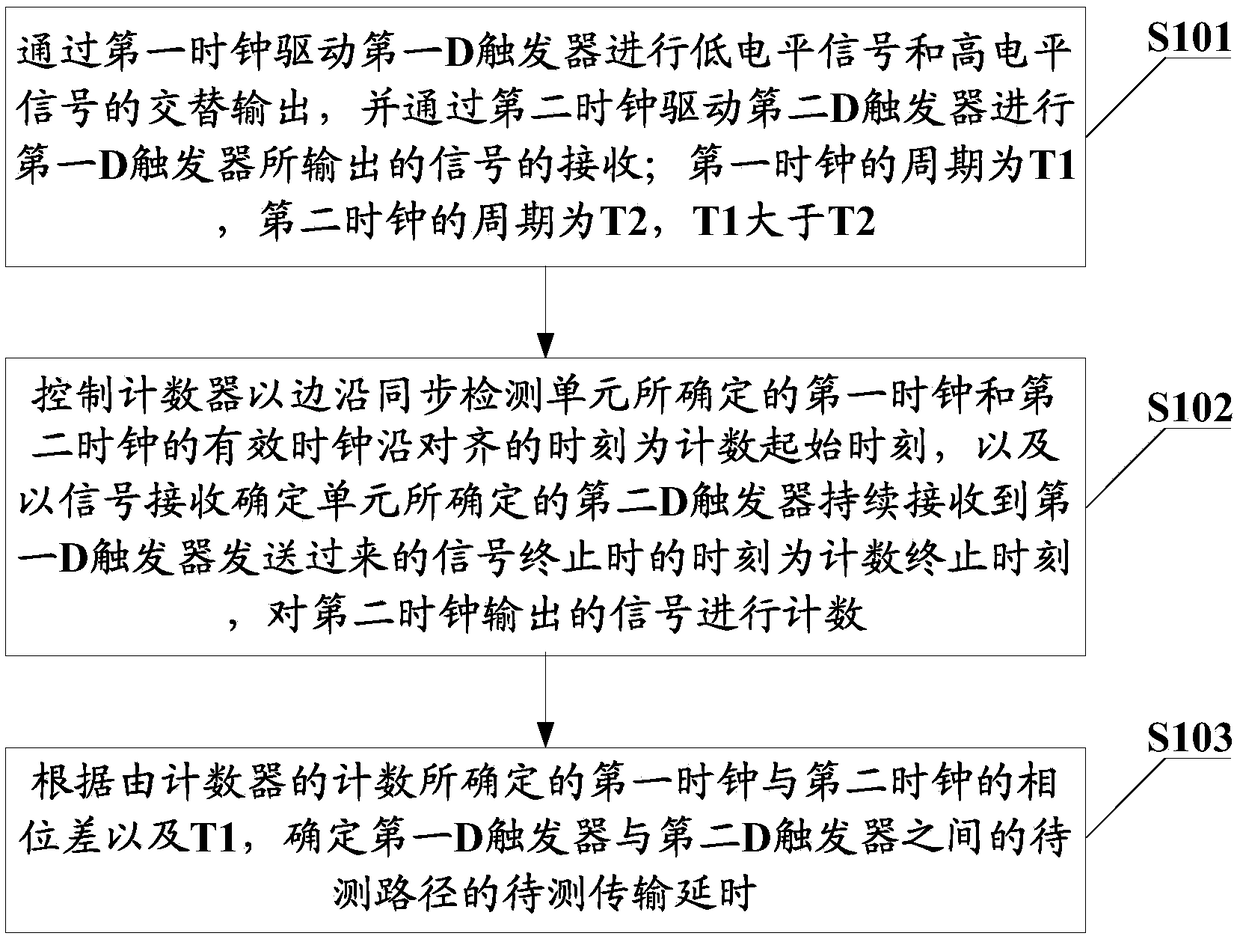

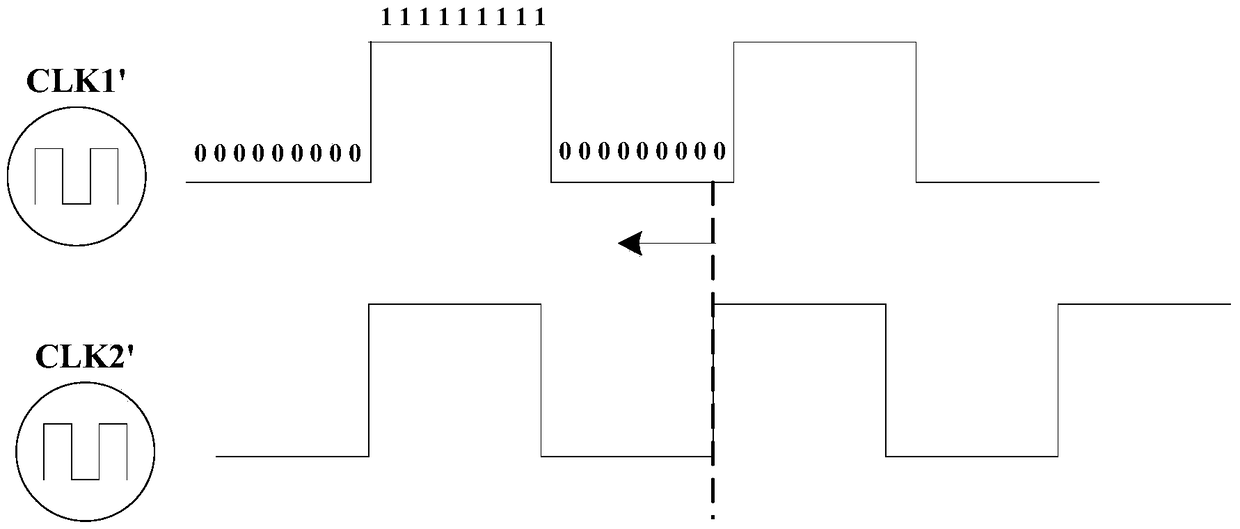

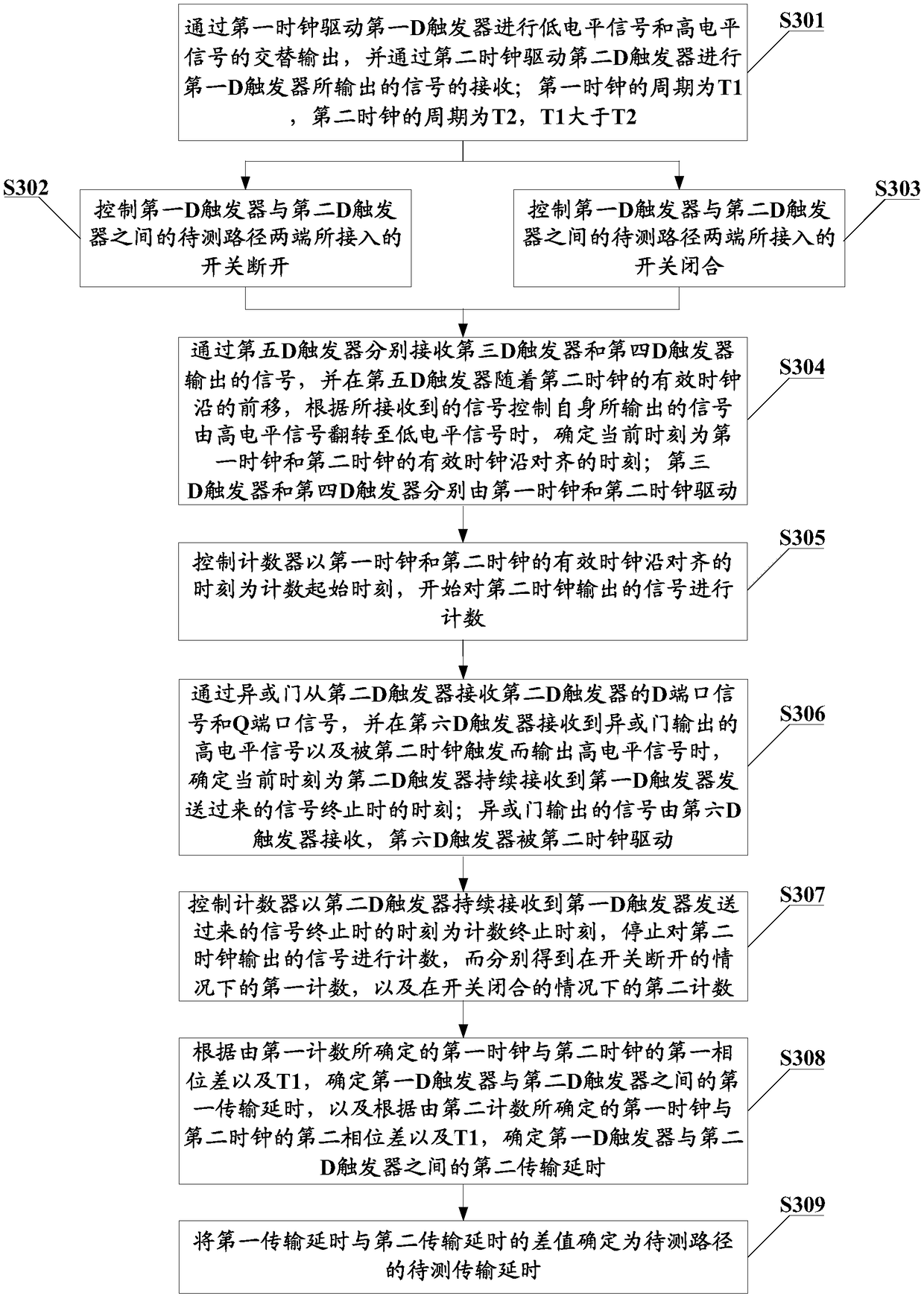

Transmission delay test method and device based on FPGA

ActiveCN109217951AHigh precisionGive full play to the performanceTime-division multiplexTransmission monitoringPhase differenceSynchronous detection

The invention provides a transmission delay test method and a transmission delay test device based on FPGA. Two clock phases that are constantly tightening are simulated by two different cycles of clocks. and an edge synchronization detection unit determines the time at which the effective clock edges of the two clocks are aligned, and the signal reception determination unit determines the time when the fast clock cannot acquire the slow clock signal, A phase difference between the two clocks is then calculated based on the number counted by the counter in the time interval between the alignment of the two clock valid clock edges to the acquisition of the slow clock signal by the fast clock, Then the transmission delay of the circuit to be tested is determined by the phase difference and the period of the slow clock, which effectively improves the accuracy of the transmission delay test, so that the user can reasonably reduce the design margin in the FPGA application, and can give fullplay to the performance of the FPGA chip.

Owner:SHENZHEN PANGO MICROSYST CO LTD

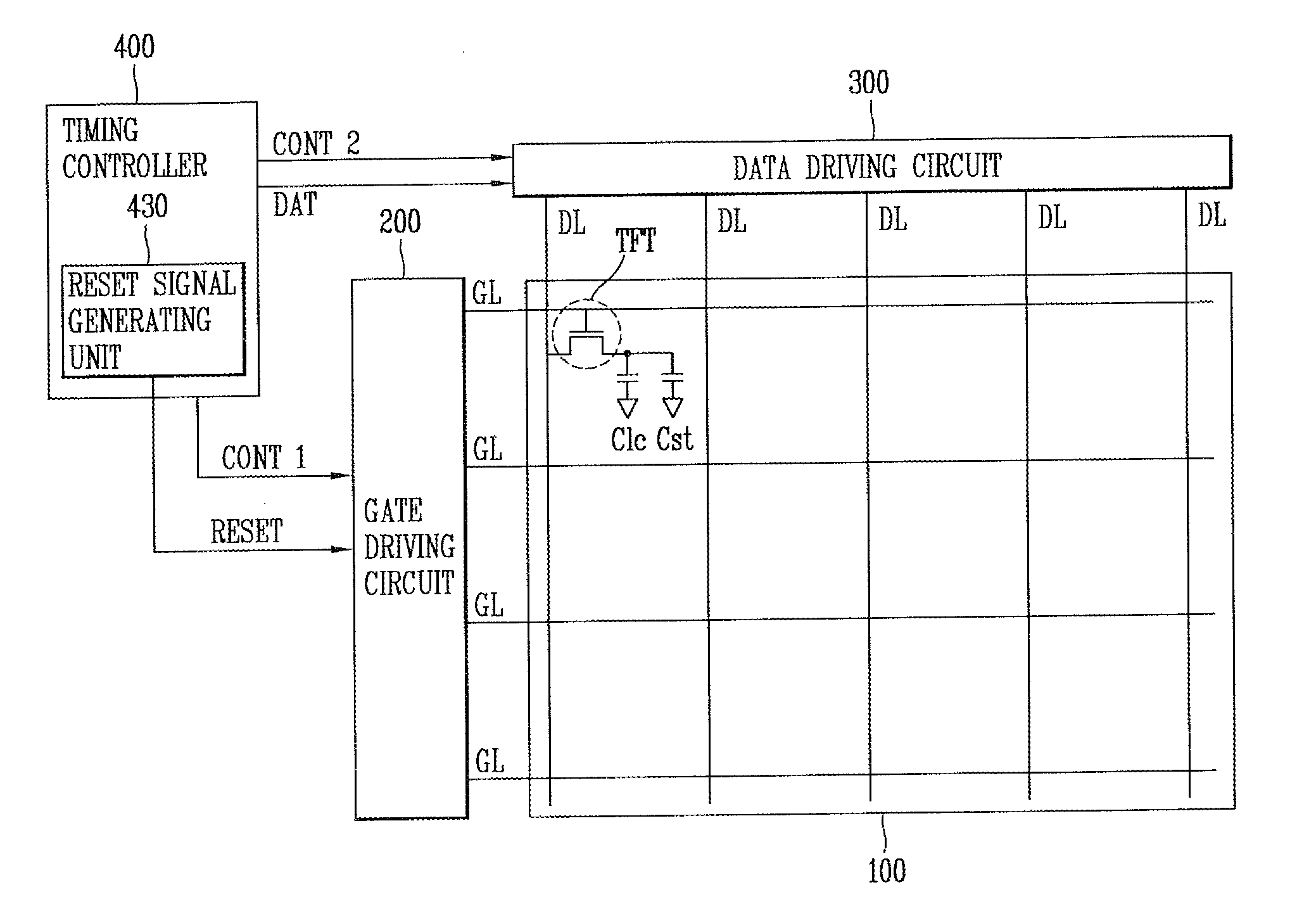

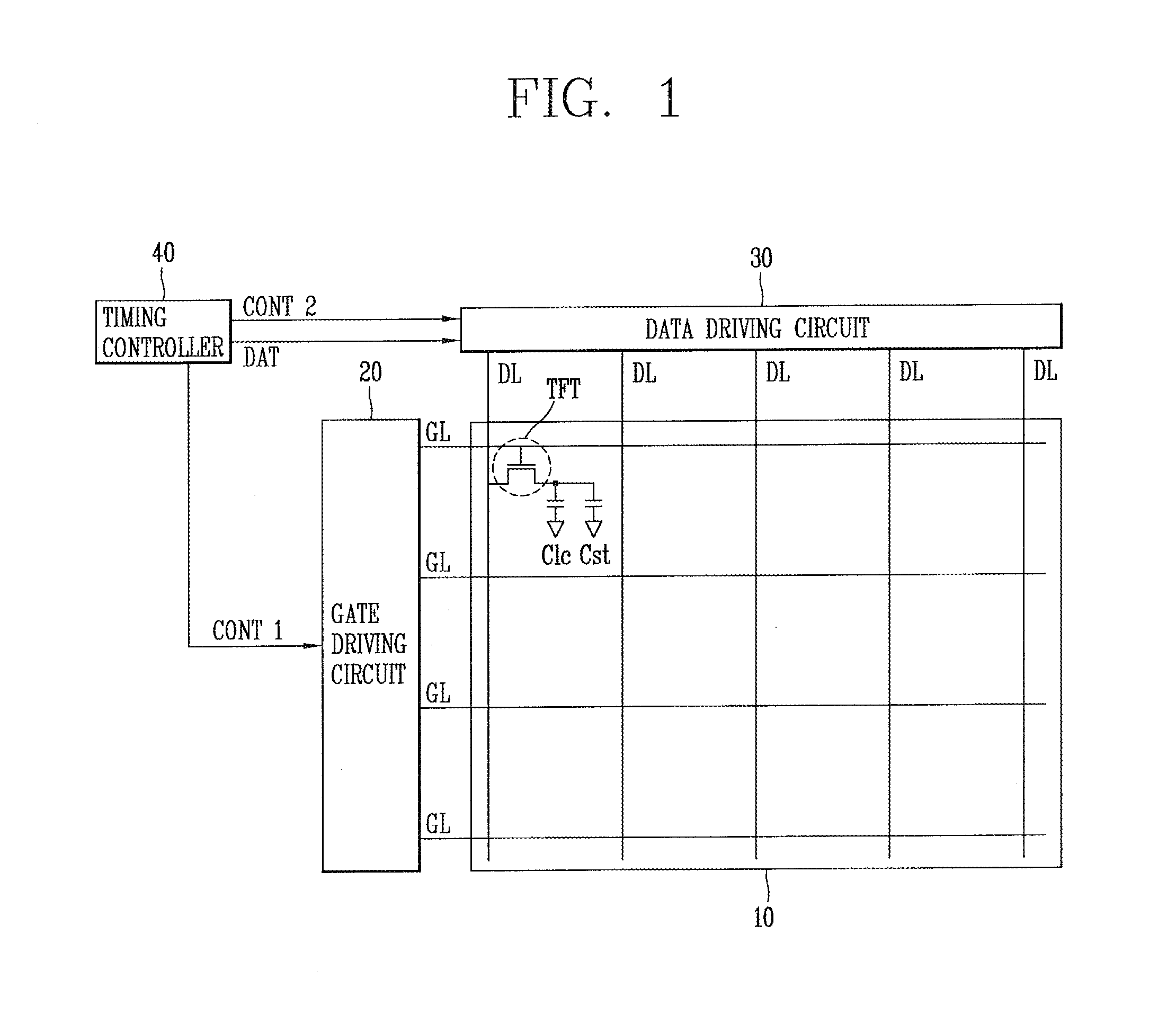

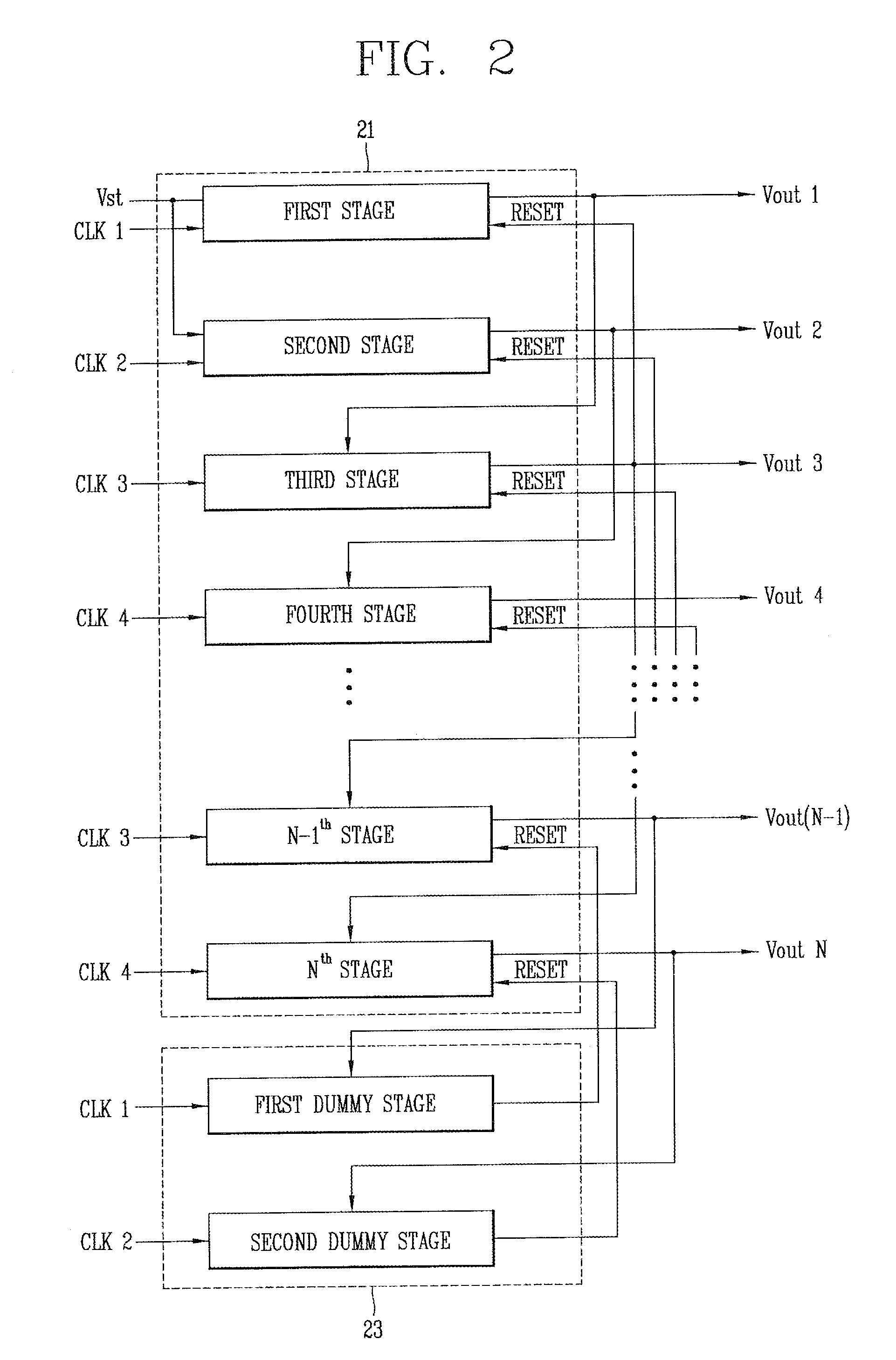

Gate driving circuit and liquid crystal display device having the same

ActiveUS20120001894A1Increase productionReduce manufacturing costCathode-ray tube indicatorsDigital storageManufacturing cost reductionLiquid-crystal display

A gate driving circuit is capable of improving yield by virtue of acquisition of a design margin and reduction of a fabricating cost. The gate driving circuit includes a shift resistor having N stages driven by a start signal and first to fourth clock signals output from the exterior, and an externally input reset signal is applied to reset terminals of the N−1th stage and the Nth stage of the shift resistor, respectively.

Owner:LG DISPLAY CO LTD

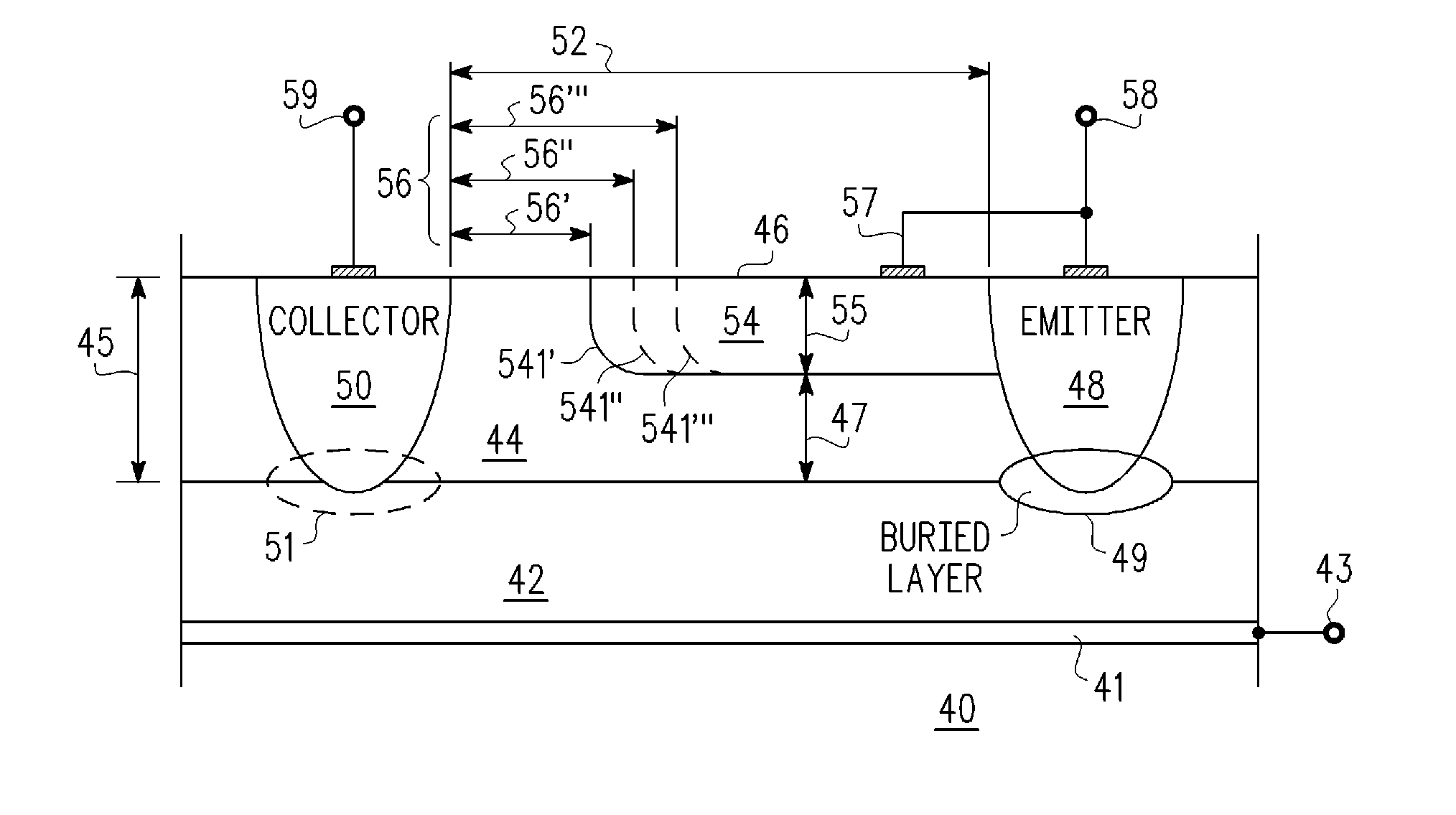

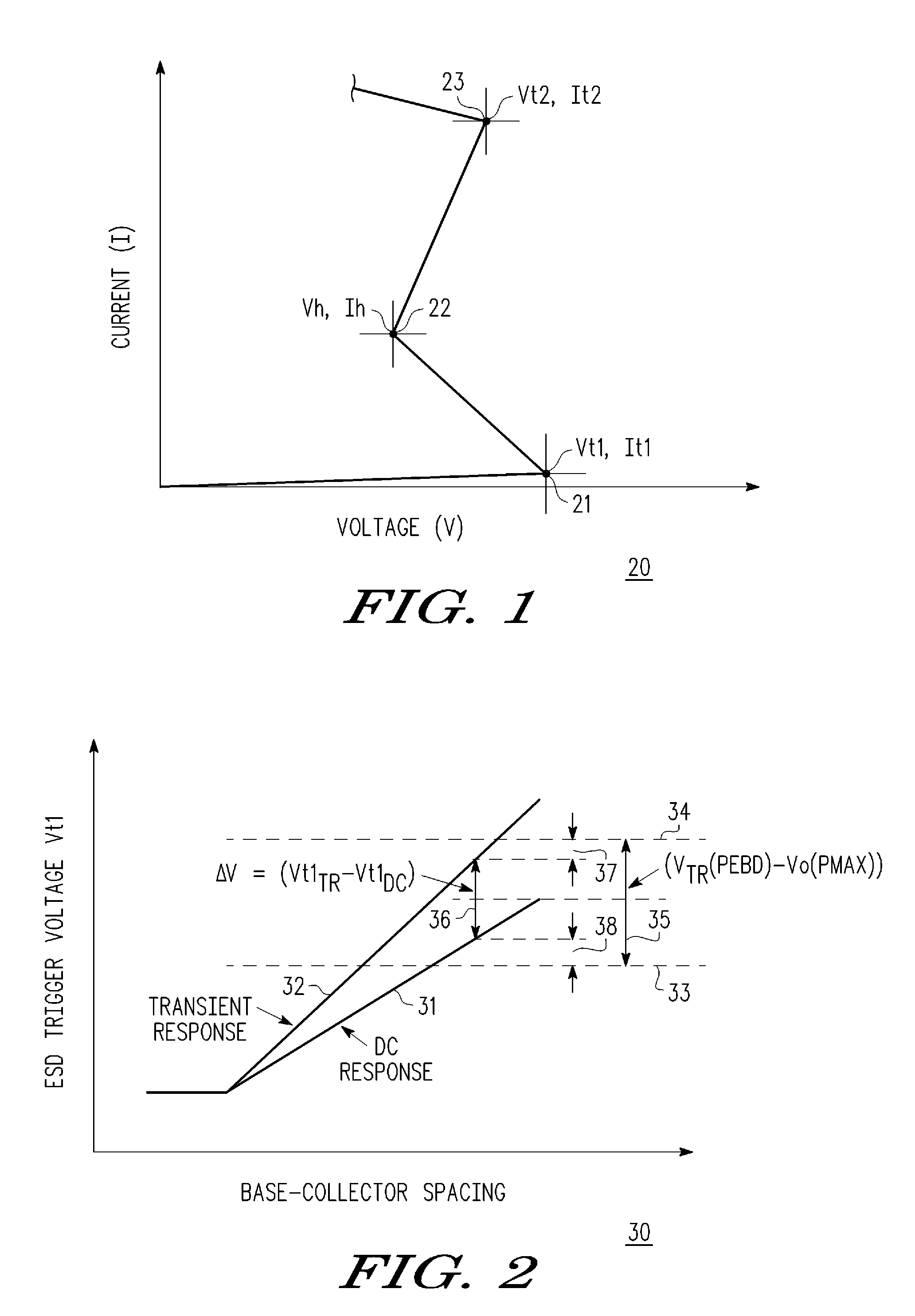

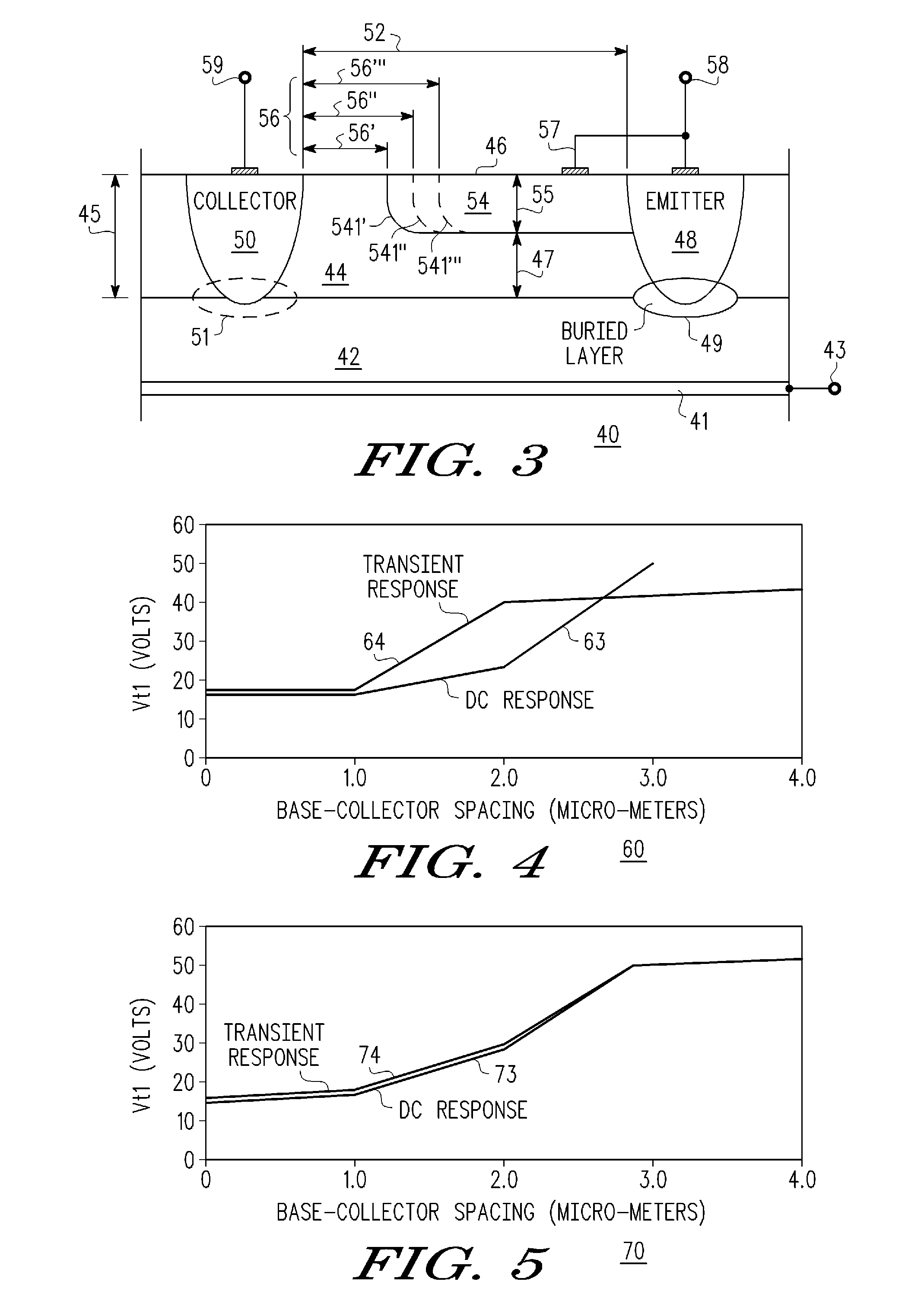

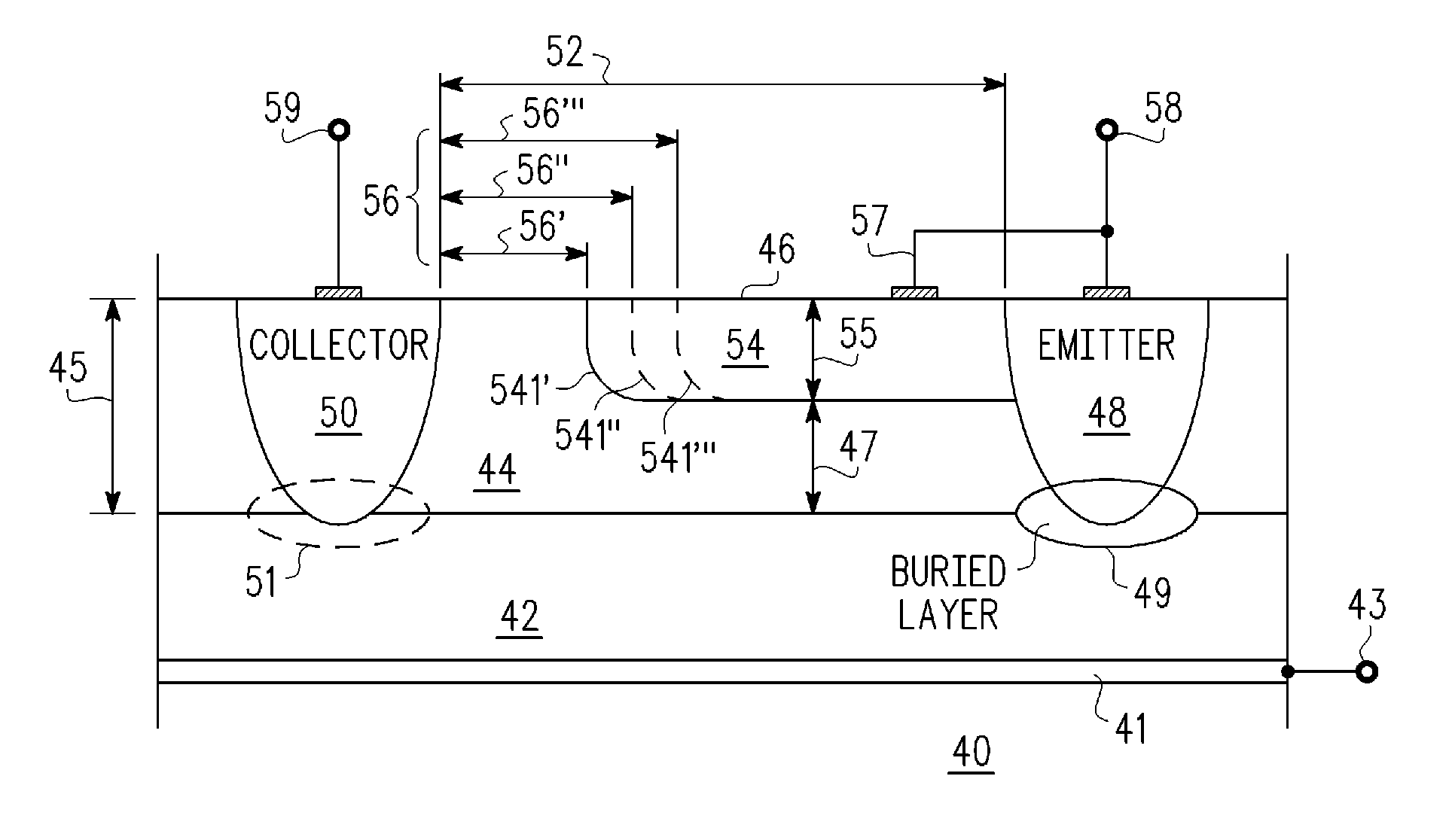

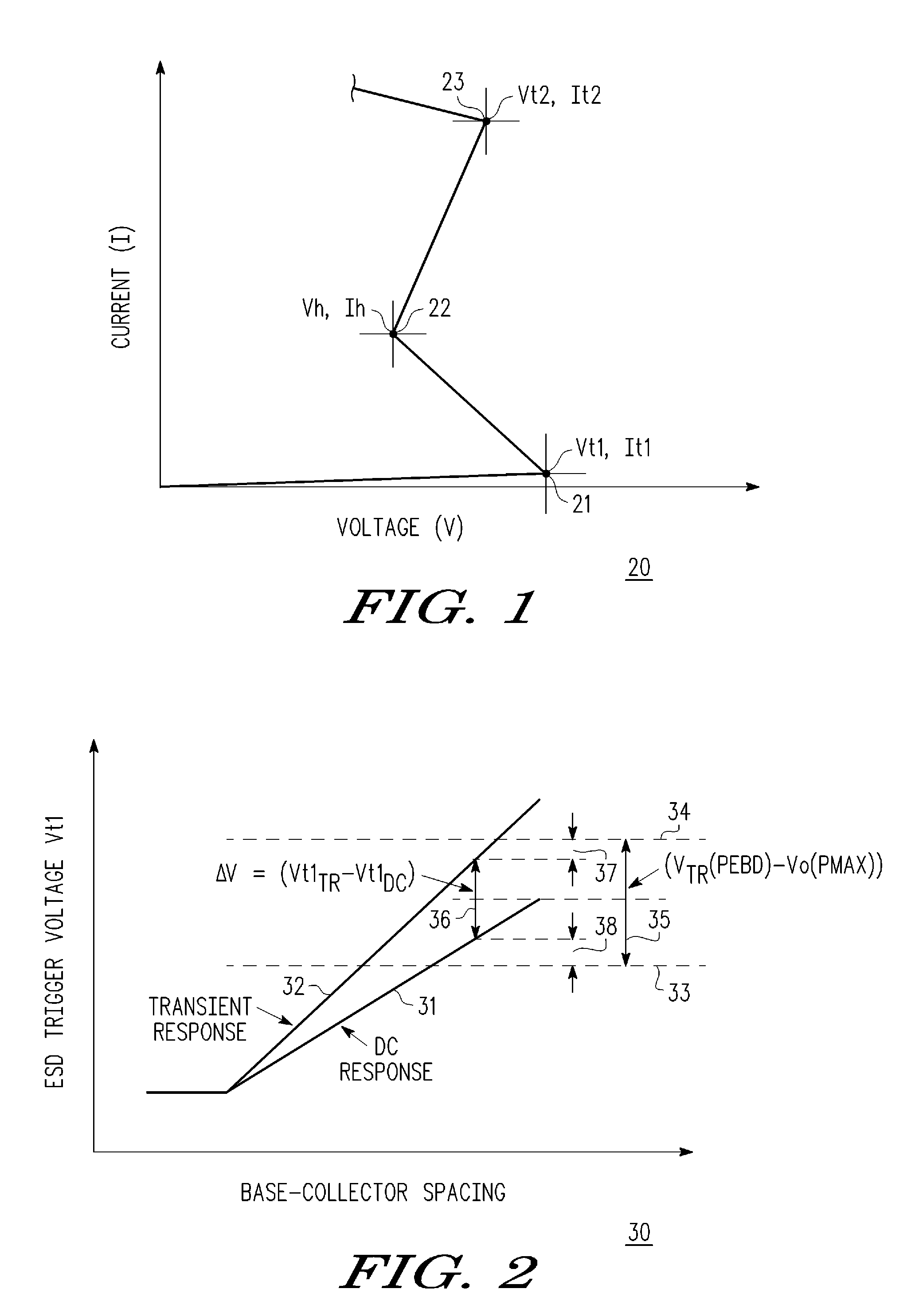

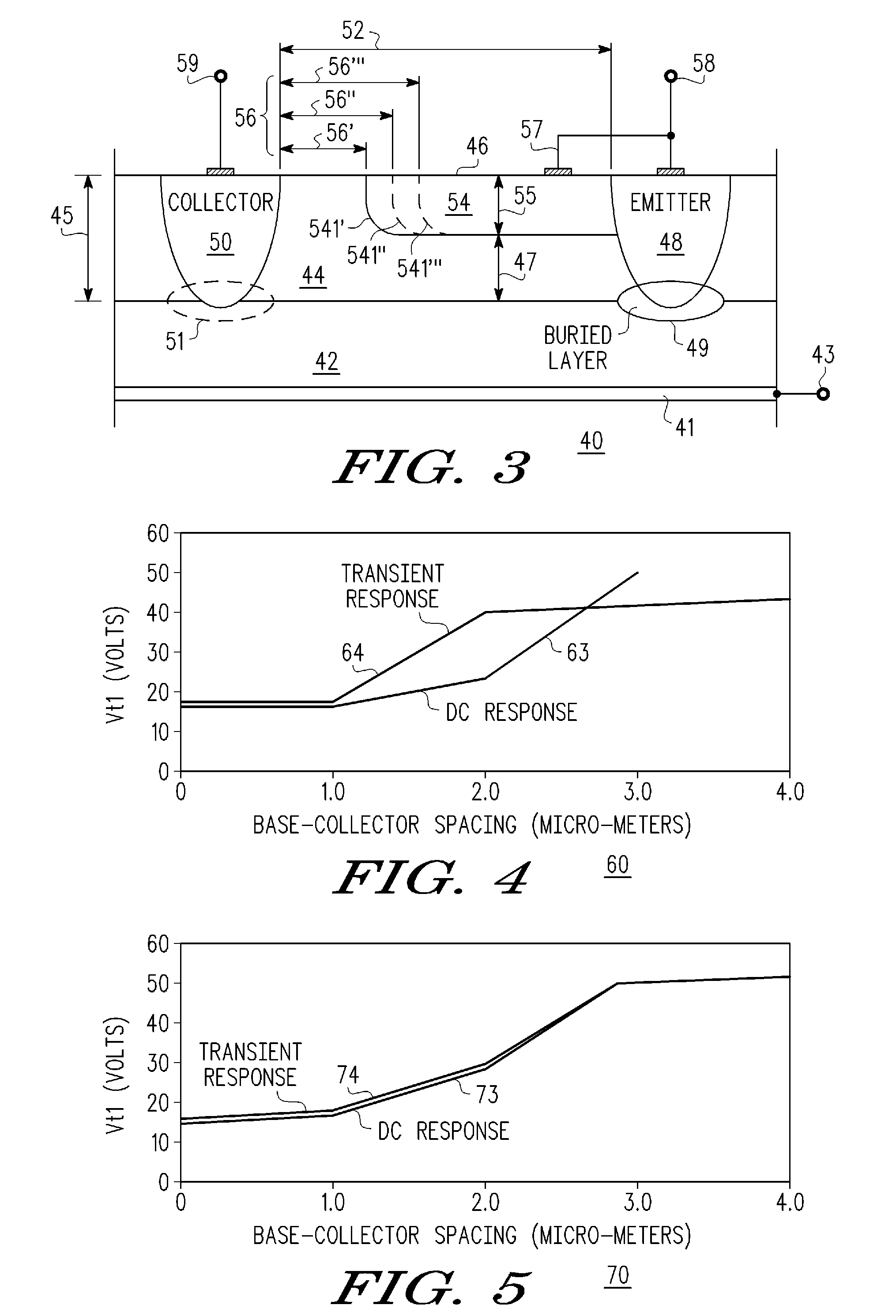

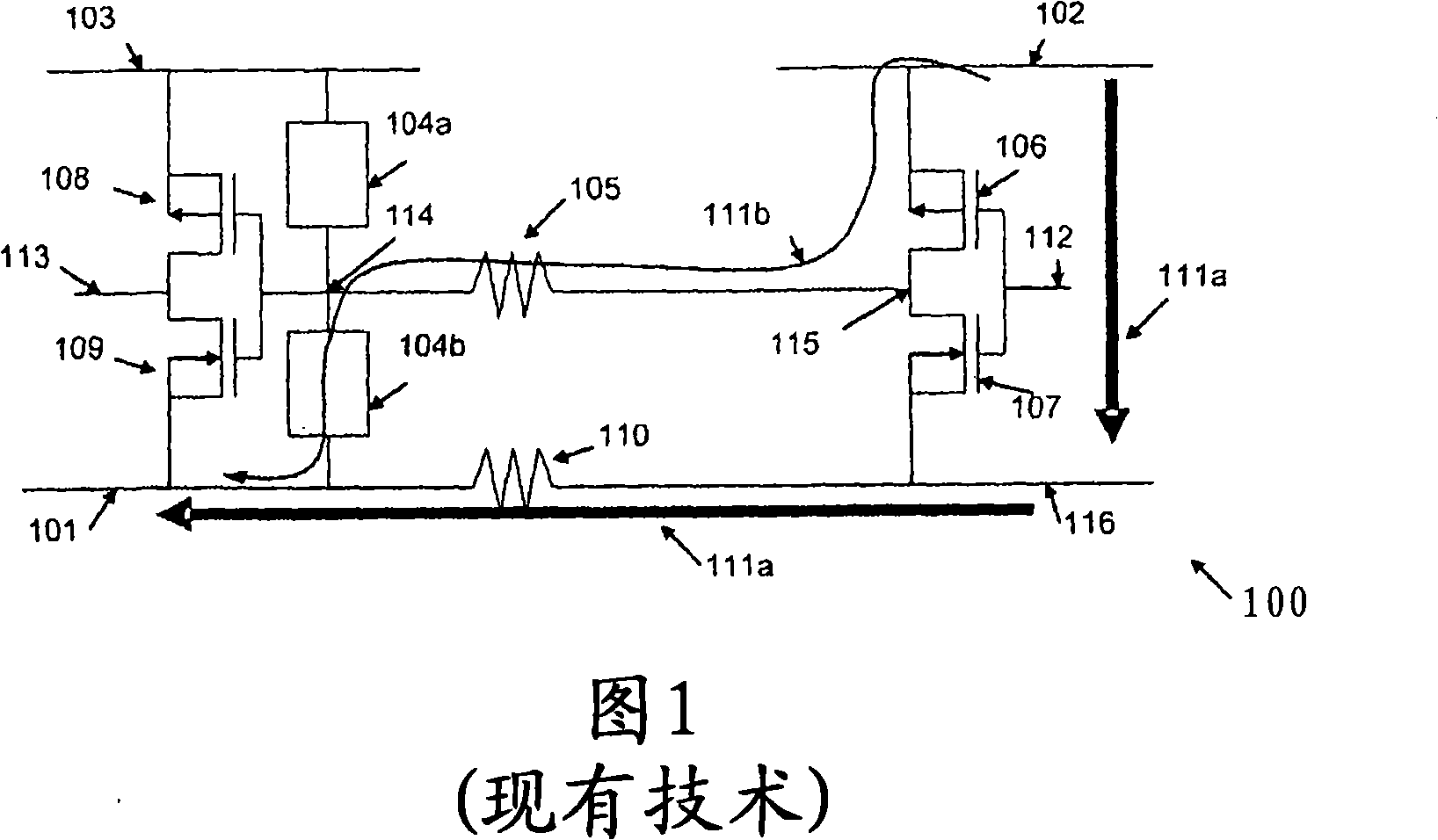

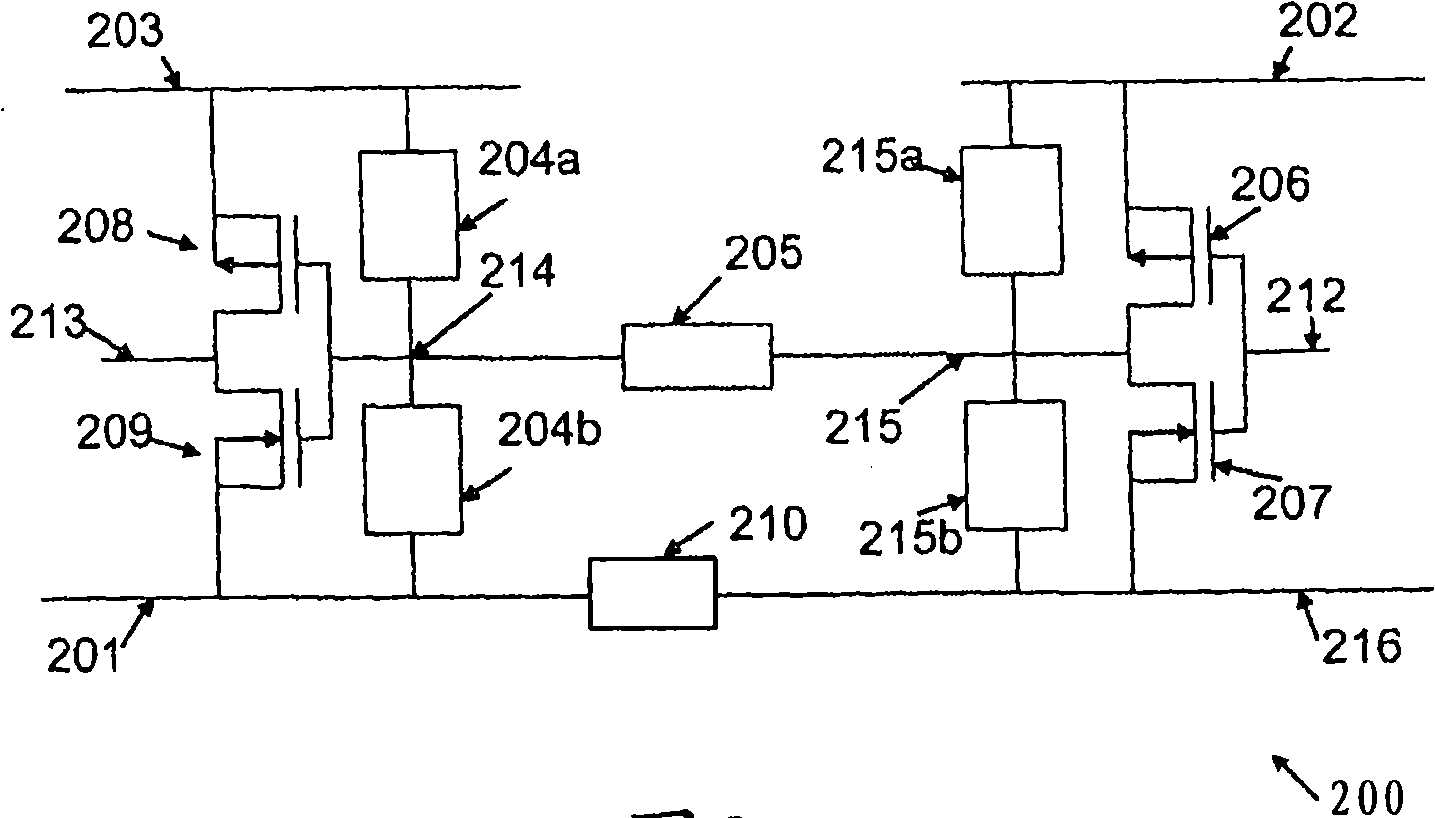

Buried asymmetric junction ESD protection device

An improved lateral bipolar electrostatic discharge (ESD) protection device (40) comprises a semiconductor (SC) substrate (42), an overlying epitaxial SC layer (44), emitter-collector regions (48, 50) laterally spaced apart by a first distance (52) in the SC layer, a base region (54) adjacent the emitter region (48) extending laterally toward and separated from the collector region (50) by a base-collector spacing (56) that is selected to set the desired trigger voltage Vt1. By providing a buried layer region (49) under the emitter region (48) Ohmically coupled thereto, but not providing a comparable buried layer region (51) under the collector region (50), an asymmetrical structure is obtained in which the DC trigger voltage (Vt1DC) and transient trigger voltage (Vt1TR) are closely matched so that ∥Vt1TR−Vt1DC∥˜0. This close matching increases the design margin and provides a higher performance ESD device (40) that is less sensitive to process variations, thereby improving manufacturing yield and reducing cost.

Owner:NXP USA INC

Buried asymmetric junction ESD protection device

An improved lateral bipolar electrostatic discharge (ESD) protection device (40) comprises a semiconductor (SC) substrate (42), an overlying epitaxial SC layer (44), emitter-collector regions (48, 50) laterally spaced apart by a first distance (52) in the SC layer, a base region (54) adjacent the emitter region (48) extending laterally toward and separated from the collector region (50) by a base-collector spacing (56) that is selected to set the desired trigger voltage Vt1. By providing a buried layer region (49) under the emitter region (48) Ohmically coupled thereto, but not providing a comparable buried layer region (51) under the collector region (50), an asymmetrical structure is obtained in which the DC trigger voltage (Vt1DC) and transient trigger voltage (Vt1TR) are closely matched so that |Vt1TR−Vt1DC|˜0. This close matching increases the design margin and provides a higher performance ESD device (40) that is less sensitive to process variations, thereby improving manufacturing yield and reducing cost.

Owner:NXP USA INC

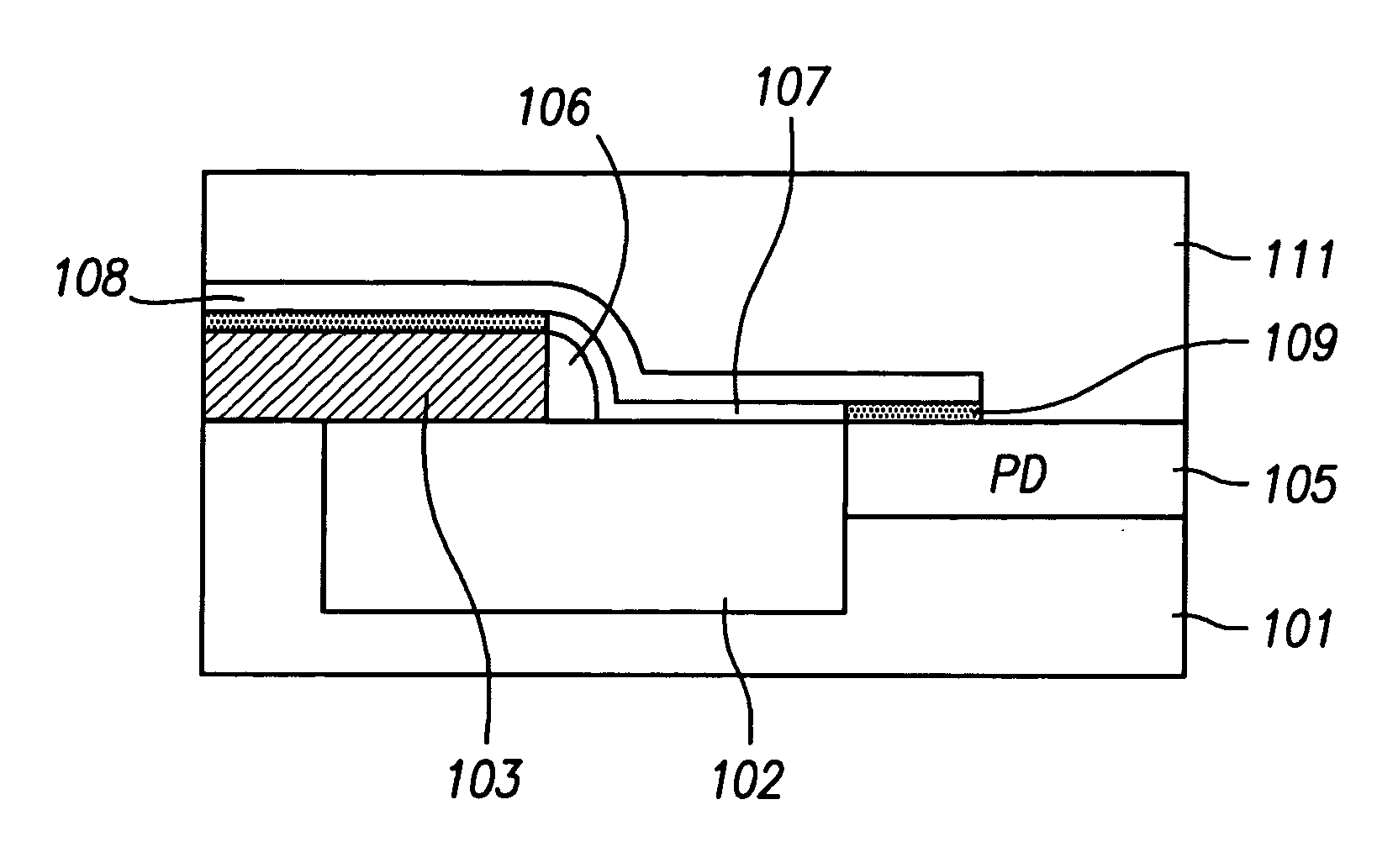

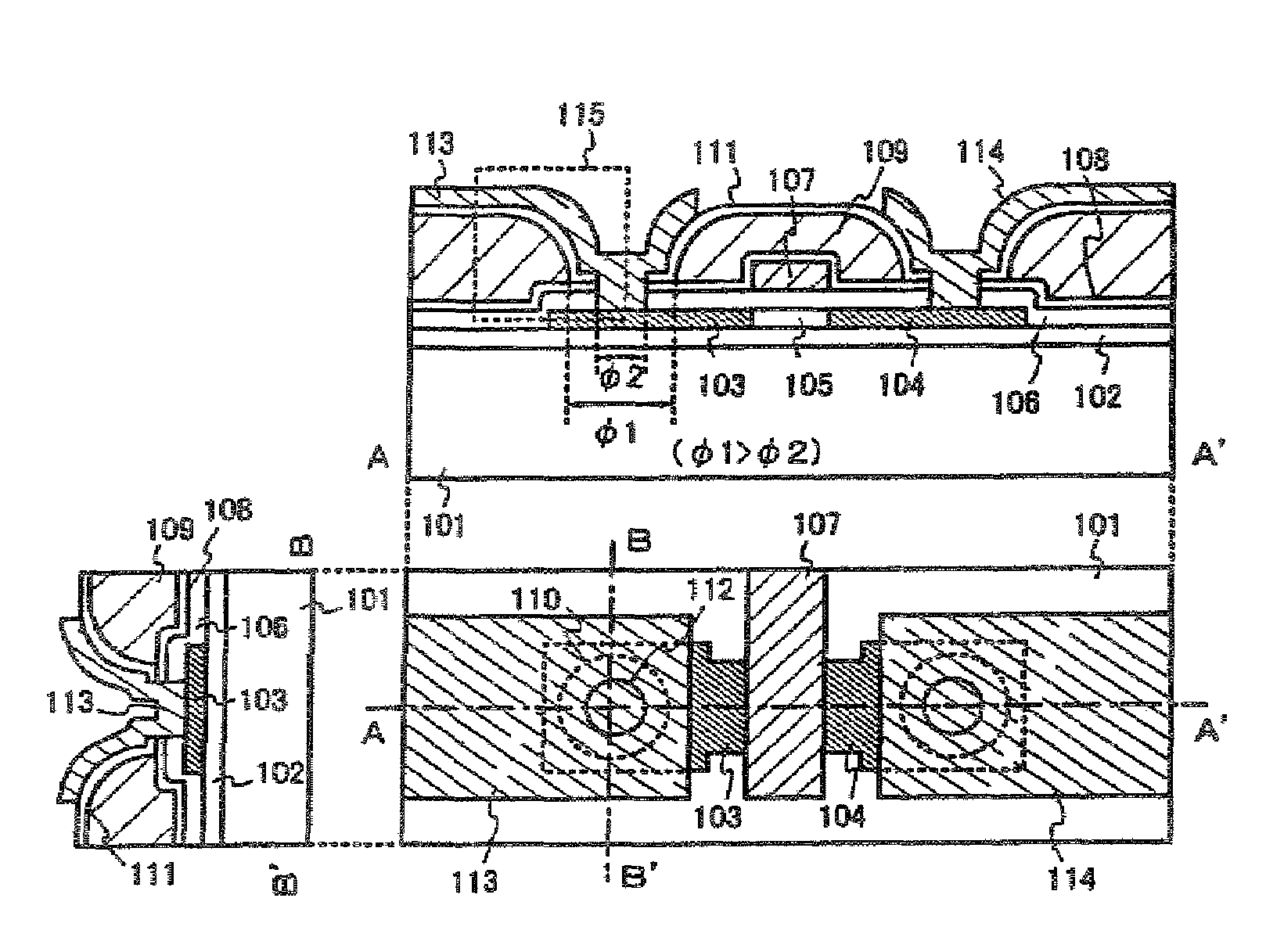

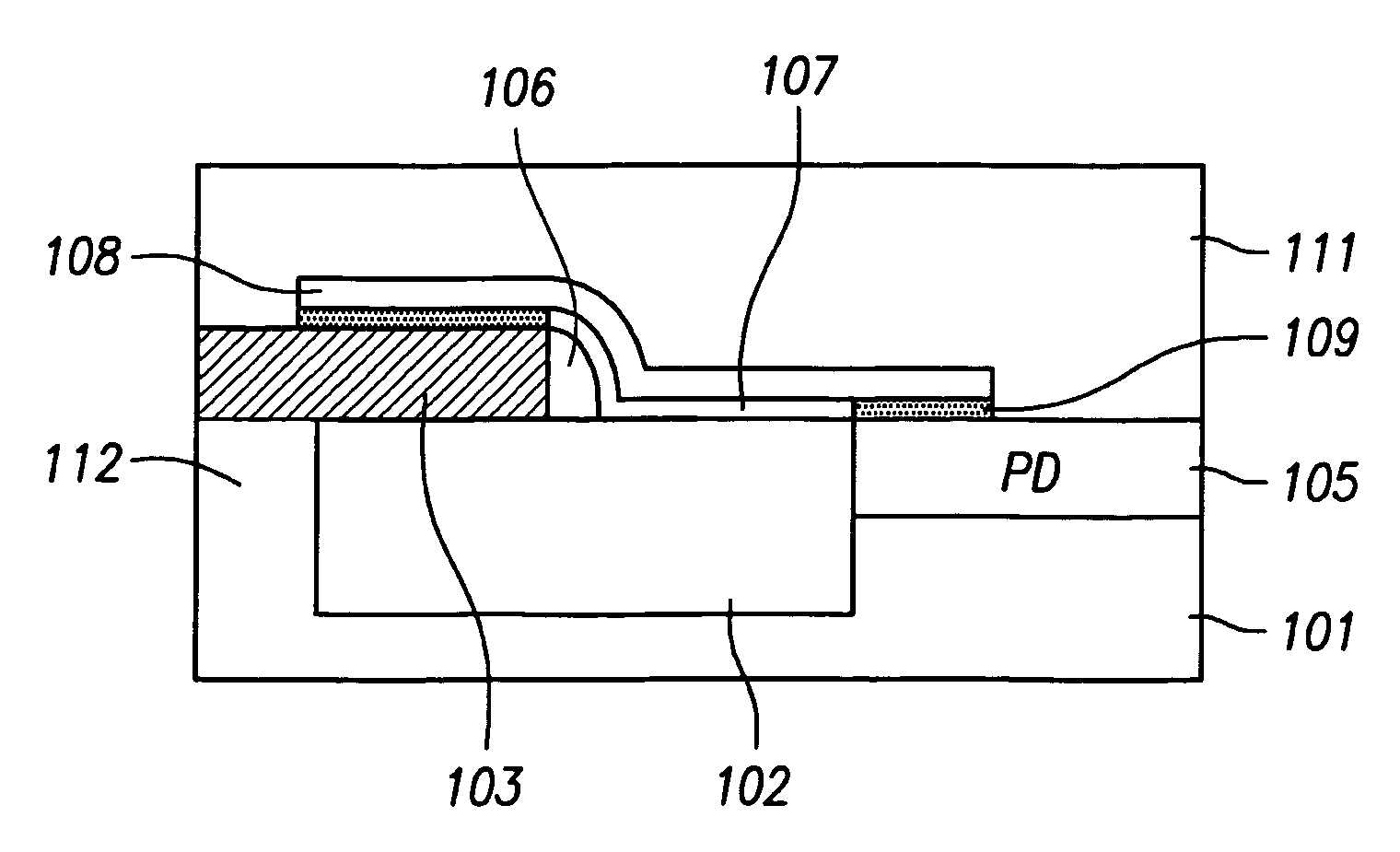

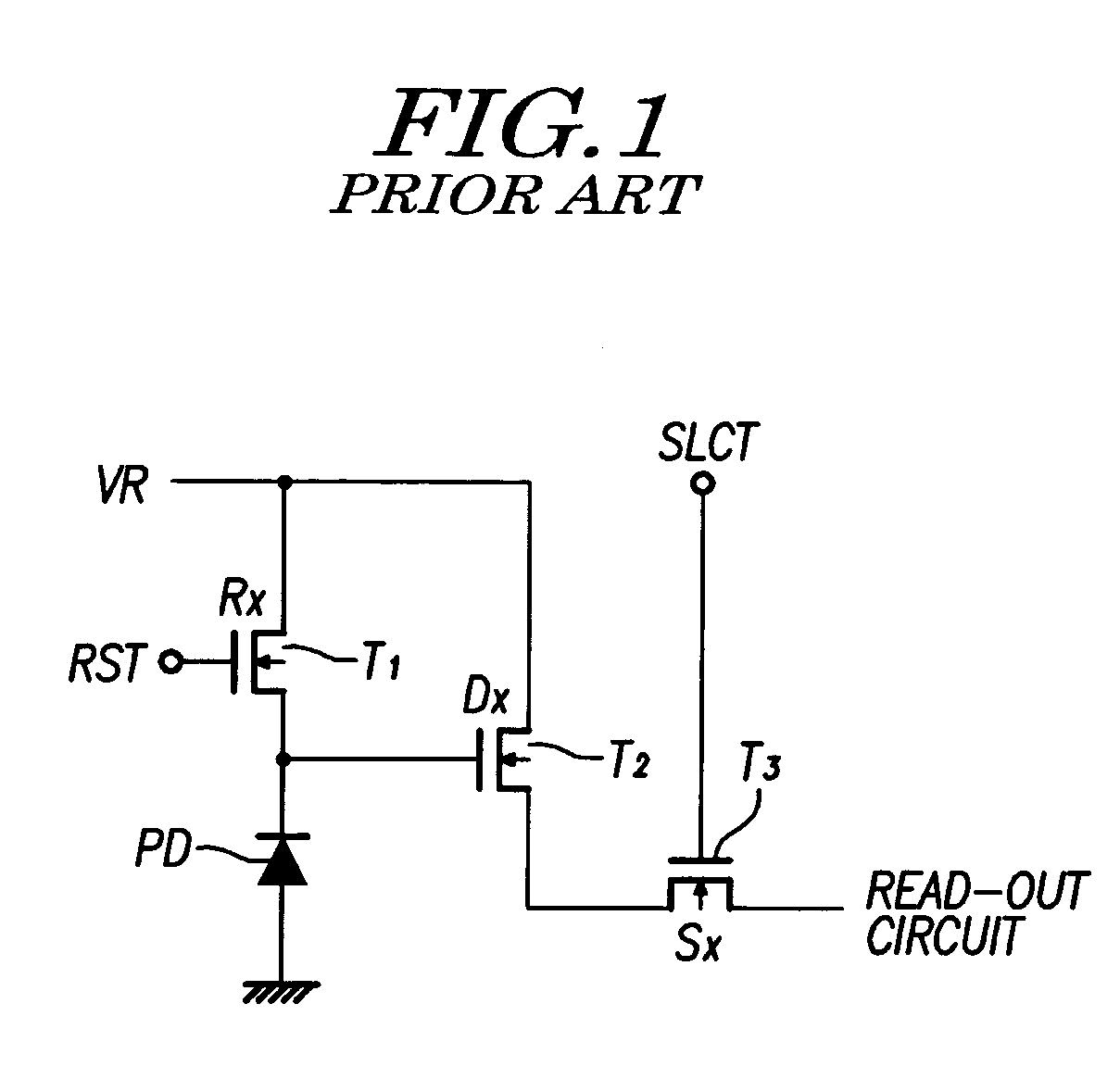

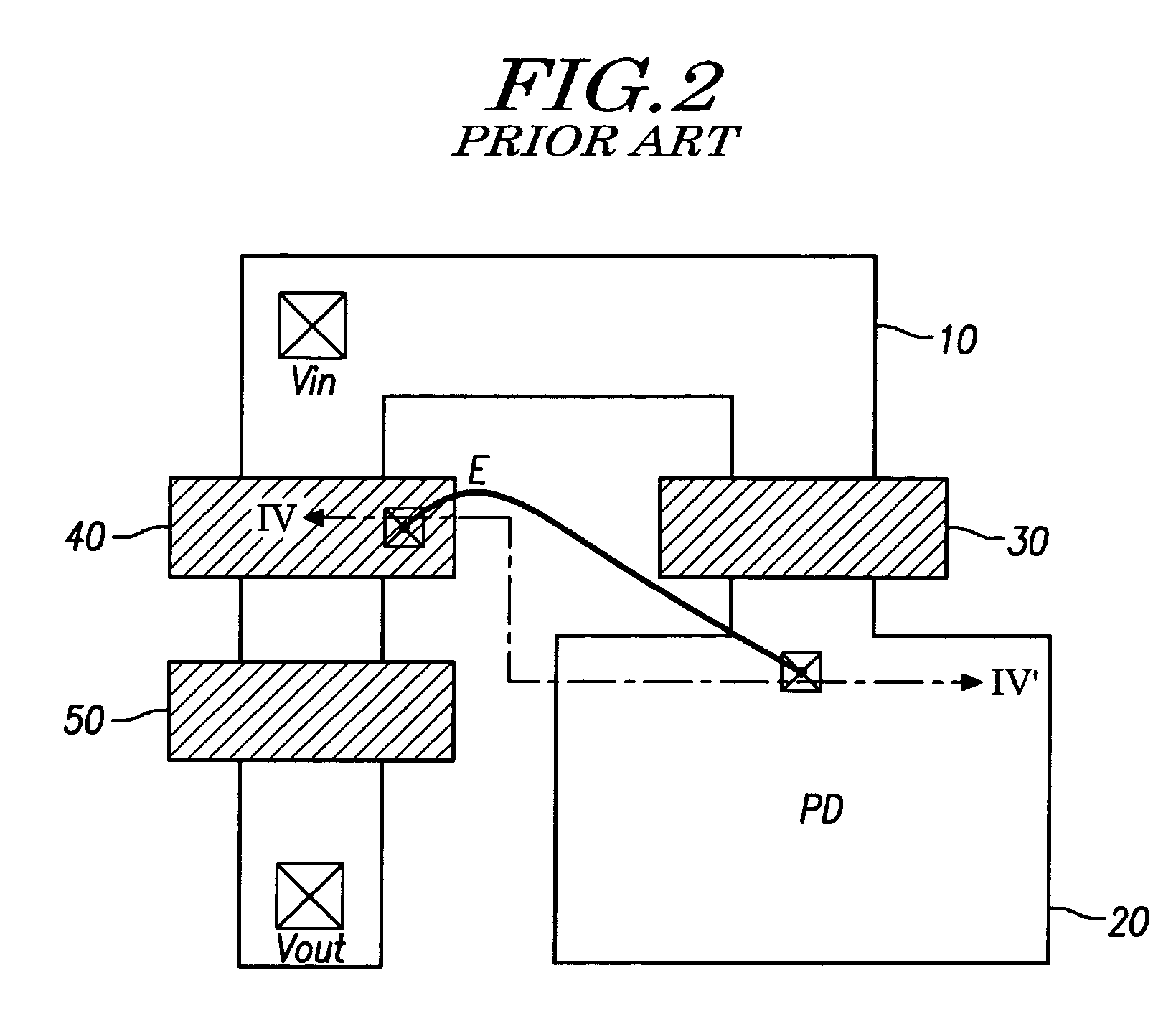

CMOS image sensor and method for manufacturing the same

InactiveUS20070085119A1Reducing and preventing damageIncrease design marginTelevision system detailsSolid-state devicesCMOSMetal silicide

Disclosed are a CMOS image sensor and a method for manufacturing the same, for reducing or preventing damage to a photodiode and improving a pixel design margin to achieve scale down of a pixel. The CMOS image sensor includes an isolation layer in a semiconductor substrate, a gate electrode crossing a part of the isolation layer and the active area, a photodiode area in the active area, an insulating sidewall spacer on sides of the gate electrode, a metal silicide layer on the gate electrode and at least part of a surface of the photodiode area adjacent to the gate electrode, a metal layer electrically connecting the gate electrode to the photodiode area, and a dielectric layer on the entire surface of semiconductor substrate.

Owner:DONGBU ELECTRONICS CO LTD

Display device and method of fabricating the same

InactiveUS8368072B2Promote stability of operational functionIncrease design marginTransistorElectroluminescent light sourcesDisplay deviceEngineering

To achieve promotion of stability of operational function of display device and enlargement of design margin in circuit design, in a display device including a pixel portion having a semiconductor element and a plurality of pixels provided with pixel electrodes connected to the semiconductor element on a substrate, the semiconductor element includes a photosensitive organic resin film as an interlayer insulating film, an inner wall face of a first opening portion provided at the photosensitive organic resin film is covered by a second insulating nitride film, a second opening portion provided at an inorganic insulating film is provided on an inner side of the first opening portion, the semiconductor and a wiring are connected through the first opening portion and the second opening portion and the pixel electrode is provided at a layer on a lower side of an activation layer.

Owner:SEMICON ENERGY LAB CO LTD

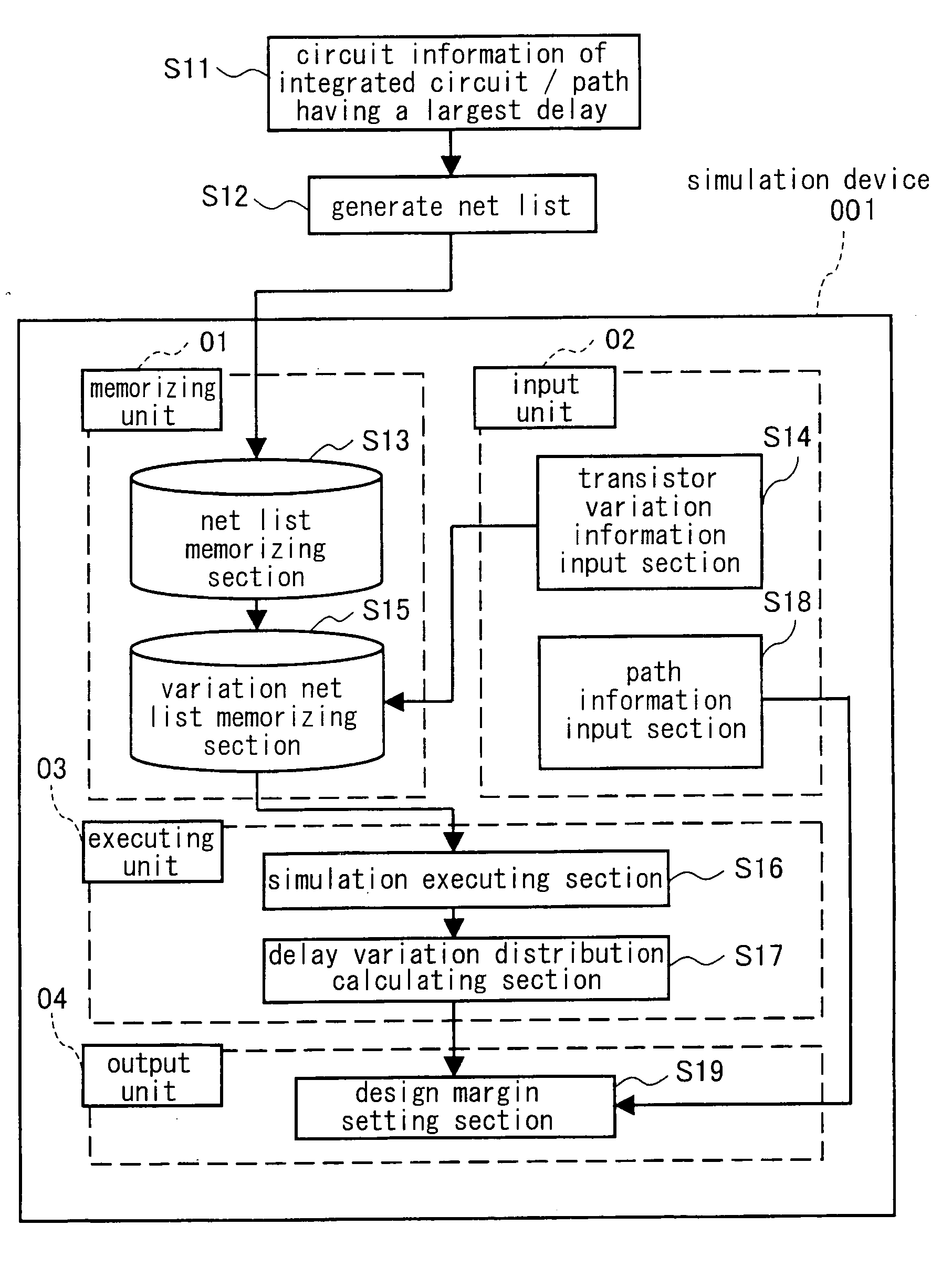

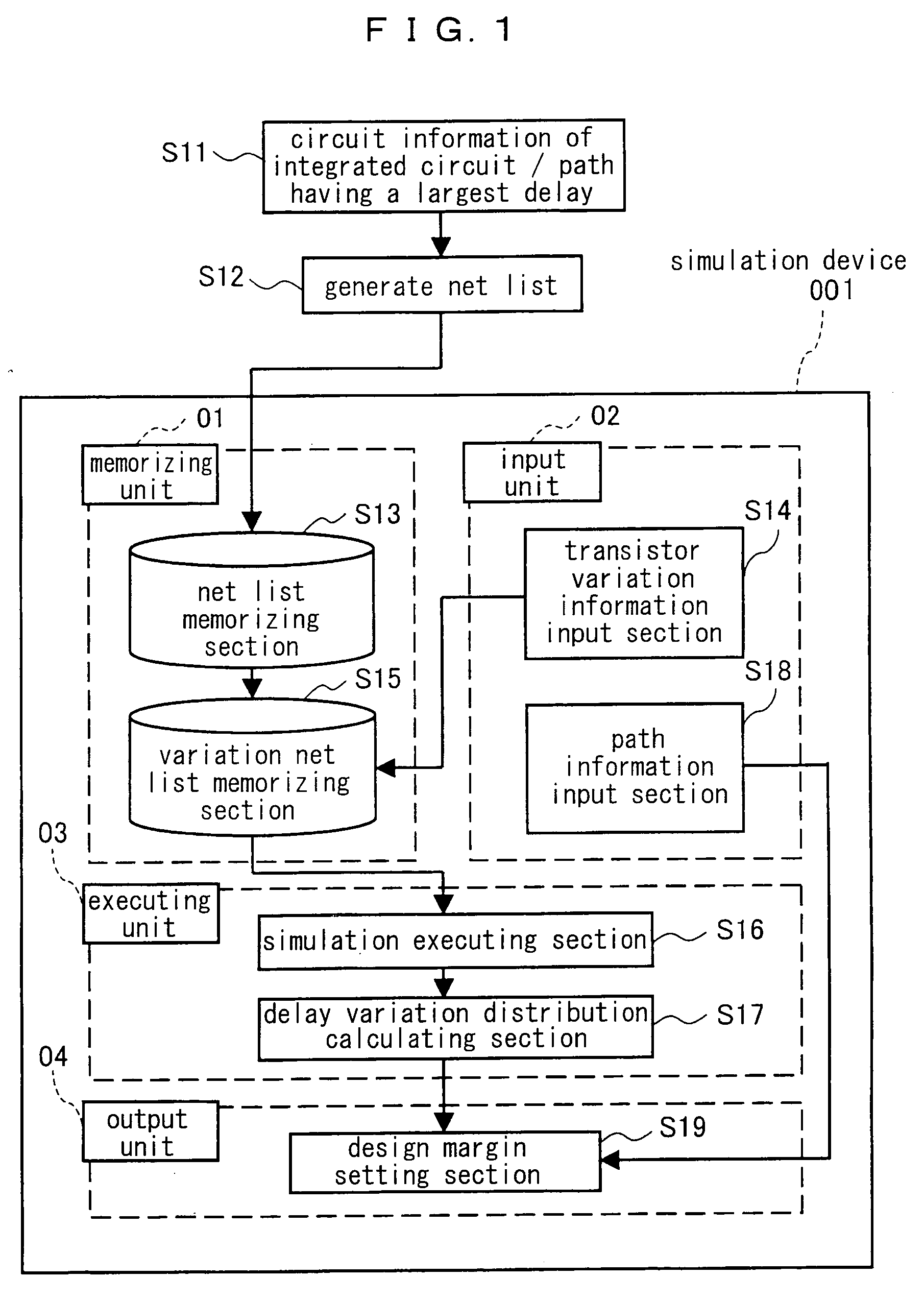

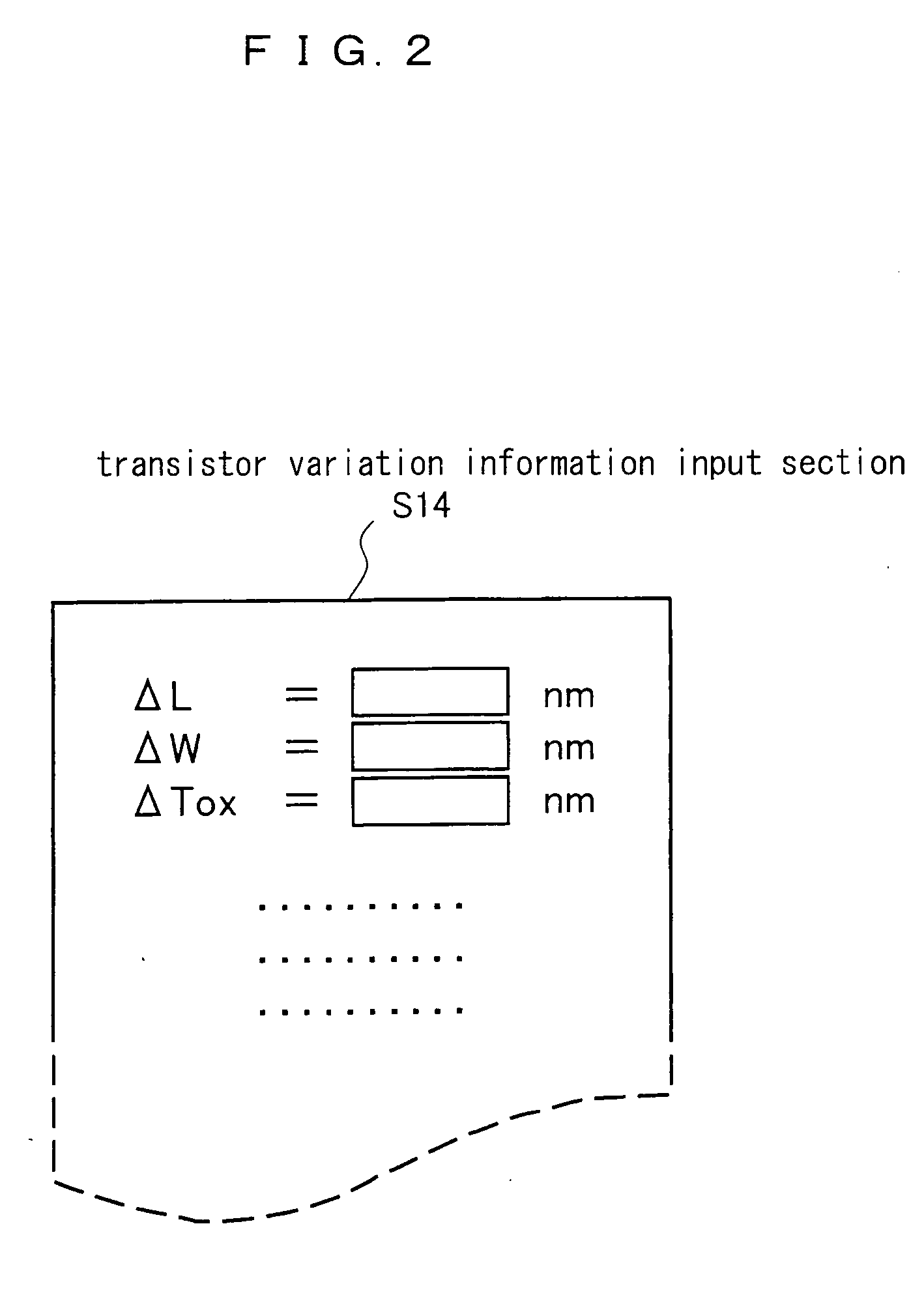

Simulation device for integrated circuit

InactiveUS20060173667A1Improve efficiency levelsPrecise designCAD circuit designSpecial data processing applicationsParallel computingExecution unit

A simulation device for an integrated circuit according to the present invention comprises a first memory unit, a first input unit, a second memory unit, an execute unit, a second input unit and an output unit. A net list of a particular path in inter-cell paths in the integrated circuit comprising a plurality of synchronizing circuit cells is stored in the first memory unit. The first input unit appends a variation information relating to gate lengths, gate widths and the like of transistors to the net list stored in the first memory unit. The variation net list to which the variation information is appended by the first input unit is stored in the second memory unit. The execute unit executes a simulation using the variation net list stored in the second memory unit to thereby calculate a delay variation distribution. The second input unit appends a circuit information to the path. The output unit sets and outputs a design margin of the circuit based on the delay variation distribution calculated by the execute unit and the circuit information appended by the second input unit.

Owner:PANASONIC CORP

Method and aparatus for improved electrostatic discharge protection

InactiveCN101359825ASolid-state devicesEmergency protective arrangements for limiting excess voltage/currentPower domainsInter-domain

Owner:SARNOFF CORP +1

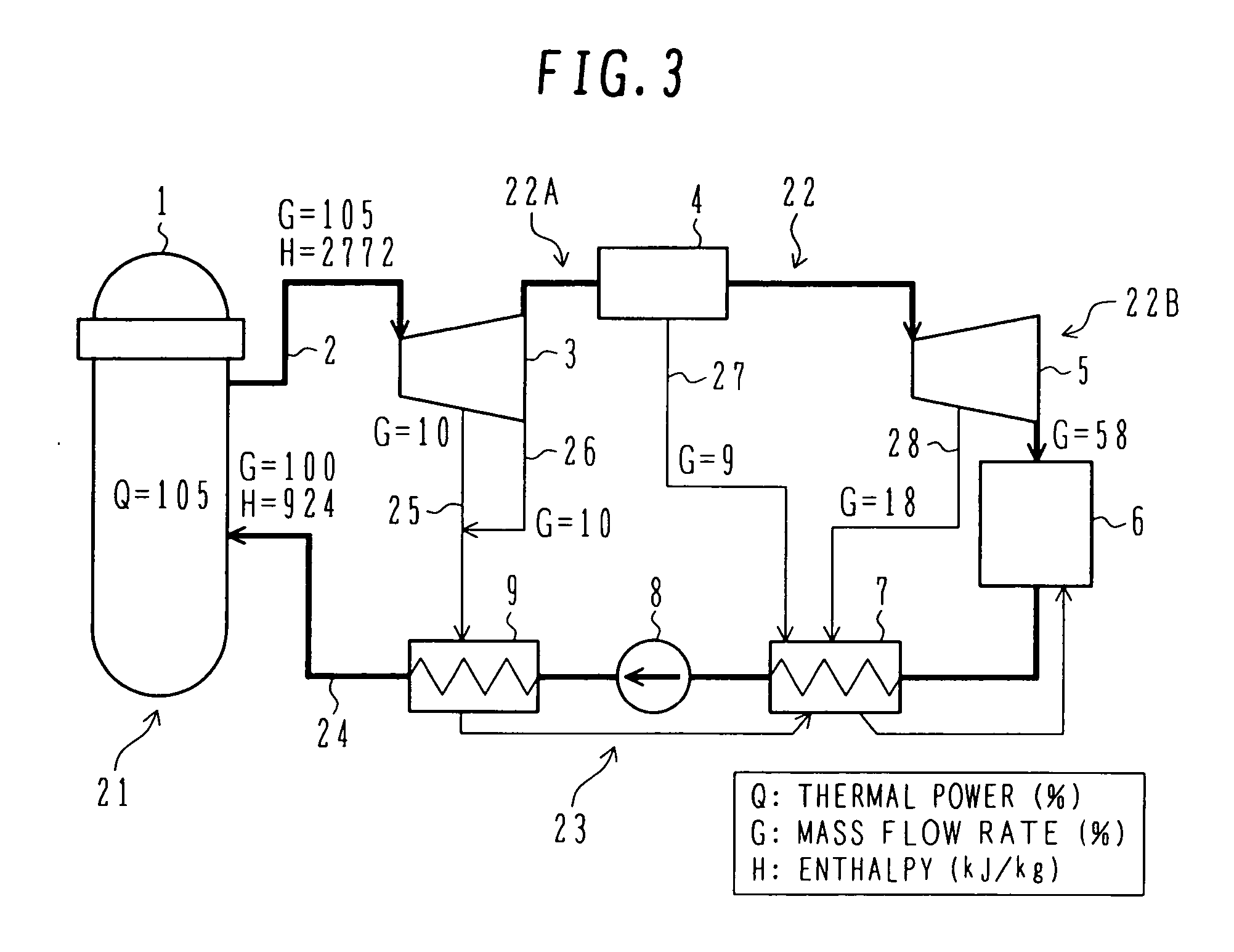

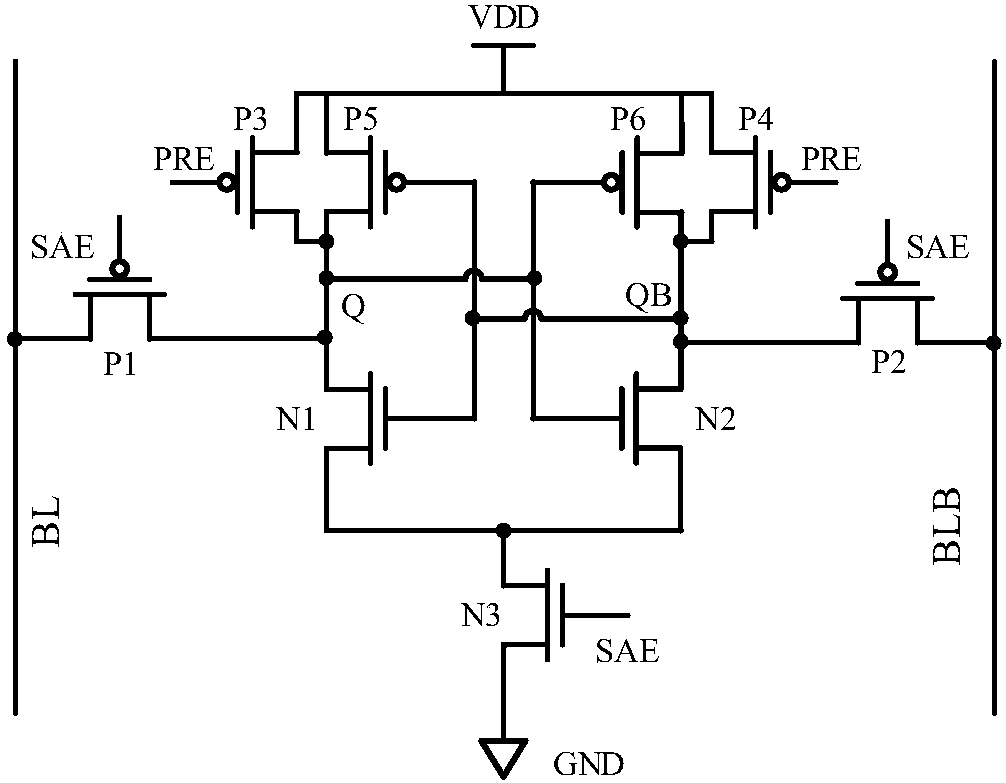

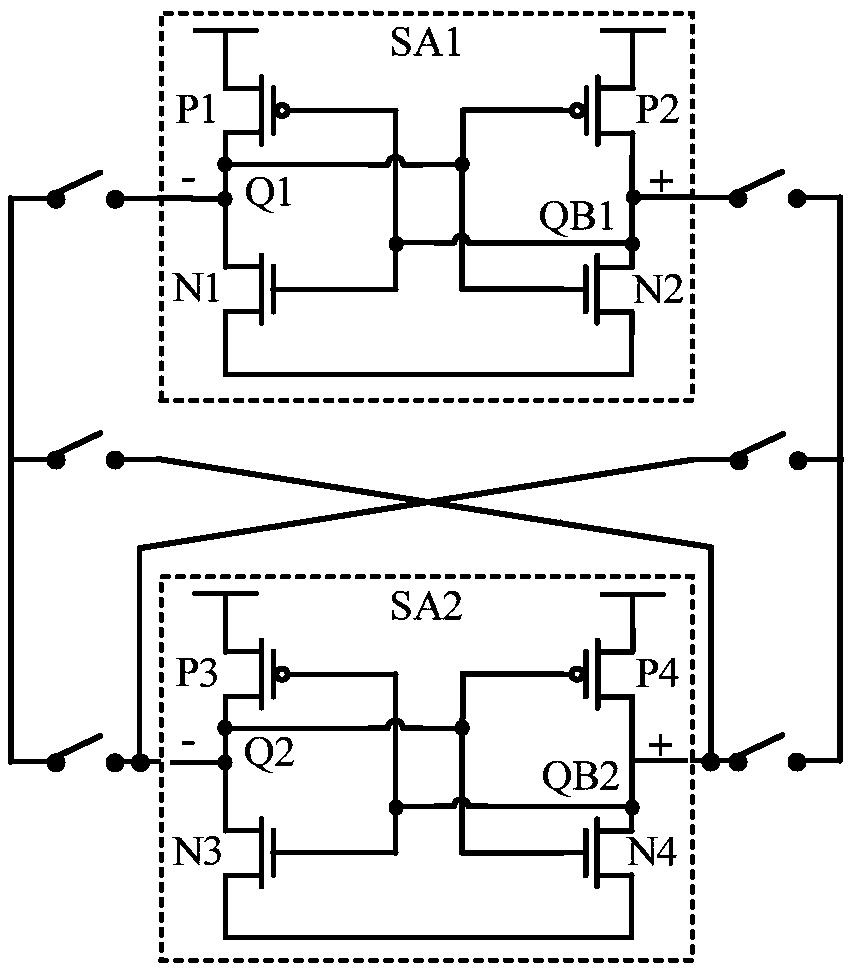

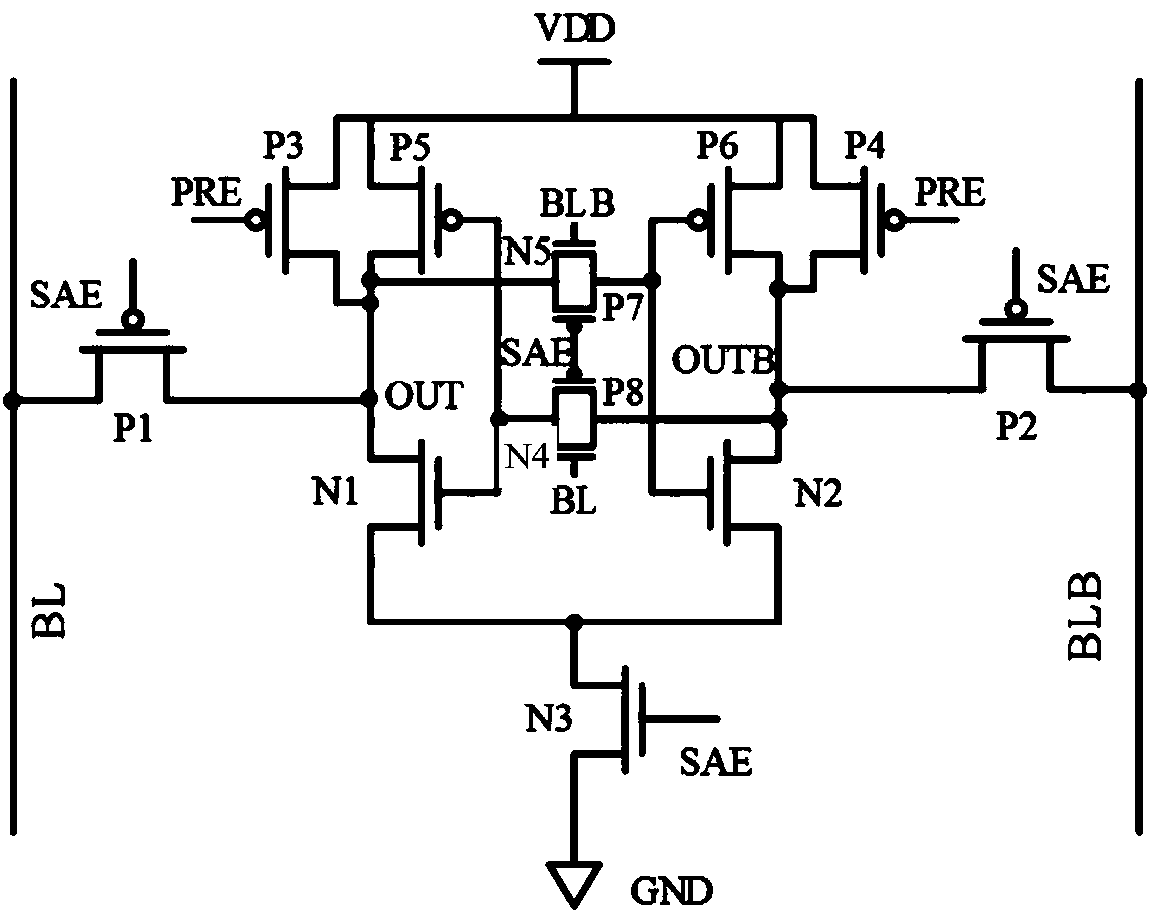

Offset voltage self-adaptive digital calibration type sense amplifier

PendingCN108231100ALower Offset VoltageHigh speedDigital storageStatic random-access memoryAudio power amplifier

The invention discloses an offset voltage self-adaptive digital calibration type sense amplifier, which is a sense amplifier circuit structure capable of effectively lowering offset voltage. The structure utilizes a simple peripheral circuit to realize the calibration compensation of the offset voltage of the sense amplifier and a compensation state latching operation, and a purpose of lowering the offset voltage to a large extent is achieved. Meanwhile, since the offset voltage is lowered, the design margin of a static random access memory reading circuit is effectively improved so as to lower power consumption generated when a unit is read, and the data reading speed of the static random access memory is improved.

Owner:ANHUI UNIVERSITY

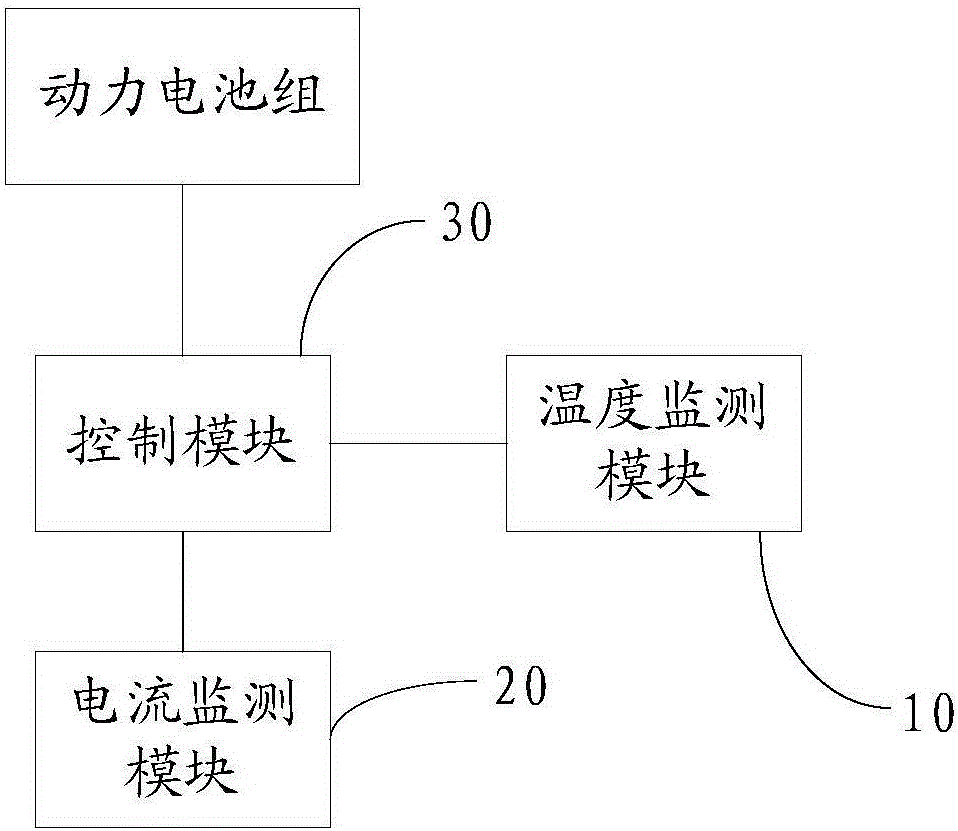

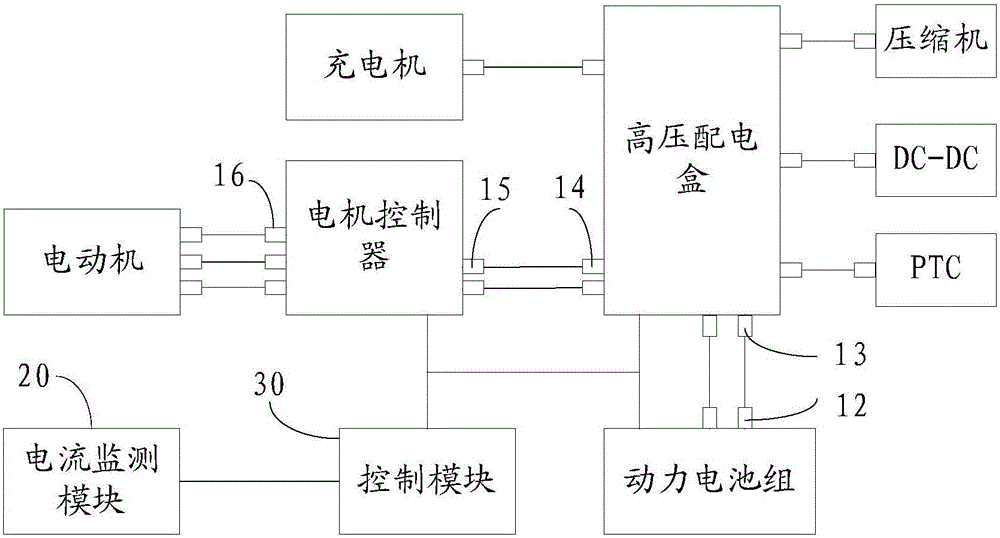

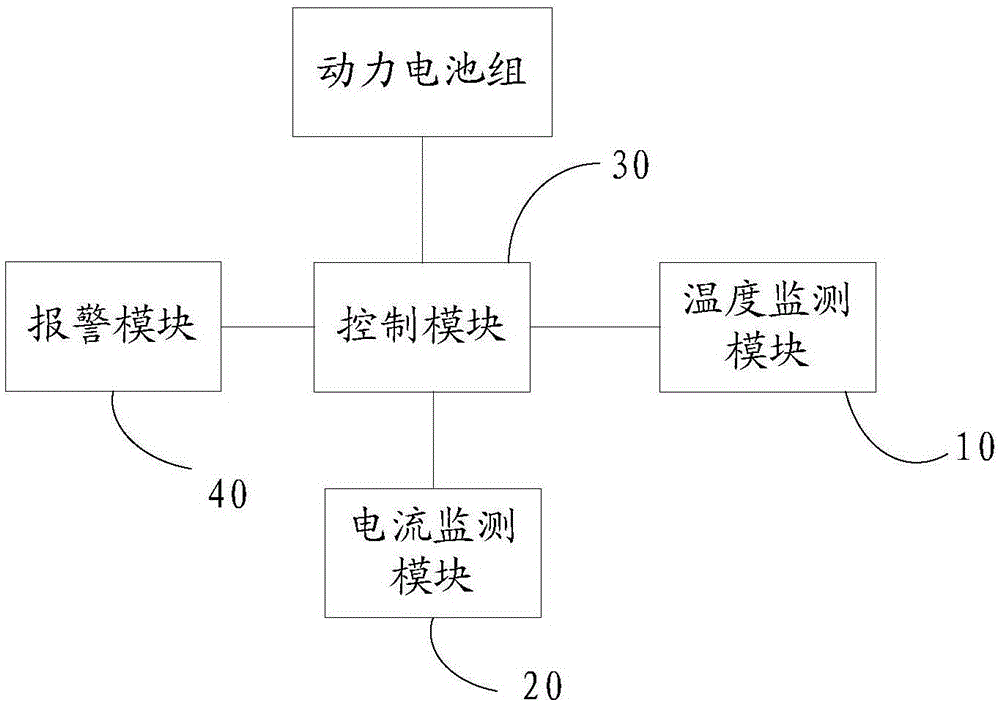

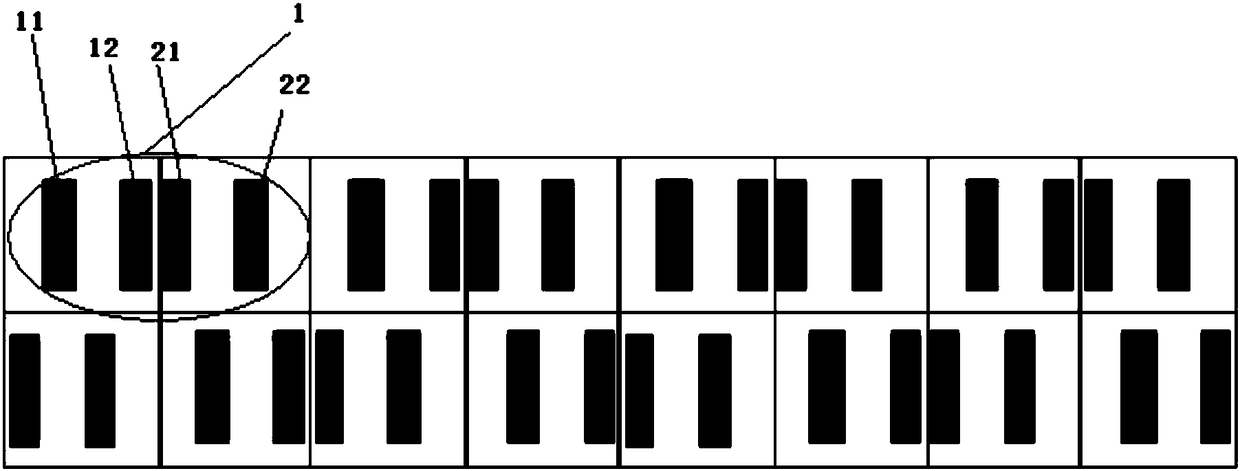

High-voltage loop control device and method for electric automobile

ActiveCN106427621AAvoid burnsReduce output powerVehicular energy storageBattery/fuel cell control arrangementPower batteryLoop control

Owner:CHERY AUTOMOBILE CO LTD

Pixel distribution structure

ActiveCN108510891AHigh-resolutionReduce intervalStatic indicating devicesSolid-state devicesImage resolutionComputer science

The invention provides a pixel distribution structure. The pixel distribution structure comprises a plurality of pixel units which are in repeated distribution, wherein each pixel unit comprises a first pixel, two second pixels which are close to each other, and a third pixel which are arranged in sequence, the distance between the two second pixels is smaller than the distance between the secondpixels and the other pixels, and the first pixel, the second pixels and the third pixel are different pixels. In the technical scheme, the two second pixels can be closer to each other, the demands ofproduction and processing can be satisfied, compared with the conventional manner, the technical scheme provided by the invention has the advantages that the numbers of sub-pixels and pixel circuit units are reduced by 1 / 3, the pixel resolution can be improved, meanwhile, the design margin of an OLED is guaranteed, the aperture ratio of R / G / B sub-pixels is increased, the problem that in the priorart, the pixel aperture ratio can not be guaranteed while the resolution ratio is improved is solved, and the display effect is improved.

Owner:KUNSHAN GO VISIONOX OPTO ELECTRONICS CO LTD

CMOS image sensor and method for manufacturing the same

InactiveUS7651903B2Reducing and preventing damageEnable scale downTelevision system detailsSolid-state devicesCMOSIsolation layer

Disclosed are a CMOS image sensor and a method for manufacturing the same, for reducing or preventing damage to a photodiode and improving a pixel design margin to achieve scale down of a pixel. The CMOS image sensor includes an isolation layer in a semiconductor substrate, a gate electrode crossing a part of the isolation layer and the active area, a photodiode area in the active area, an insulating sidewall spacer on sides of the gate electrode, a metal silicide layer on the gate electrode and at least part of a surface of the photodiode area adjacent to the gate electrode, a metal layer electrically connecting the gate electrode to the photodiode area, and a dielectric layer on the entire surface of semiconductor substrate.

Owner:DONGBU ELECTRONICS CO LTD

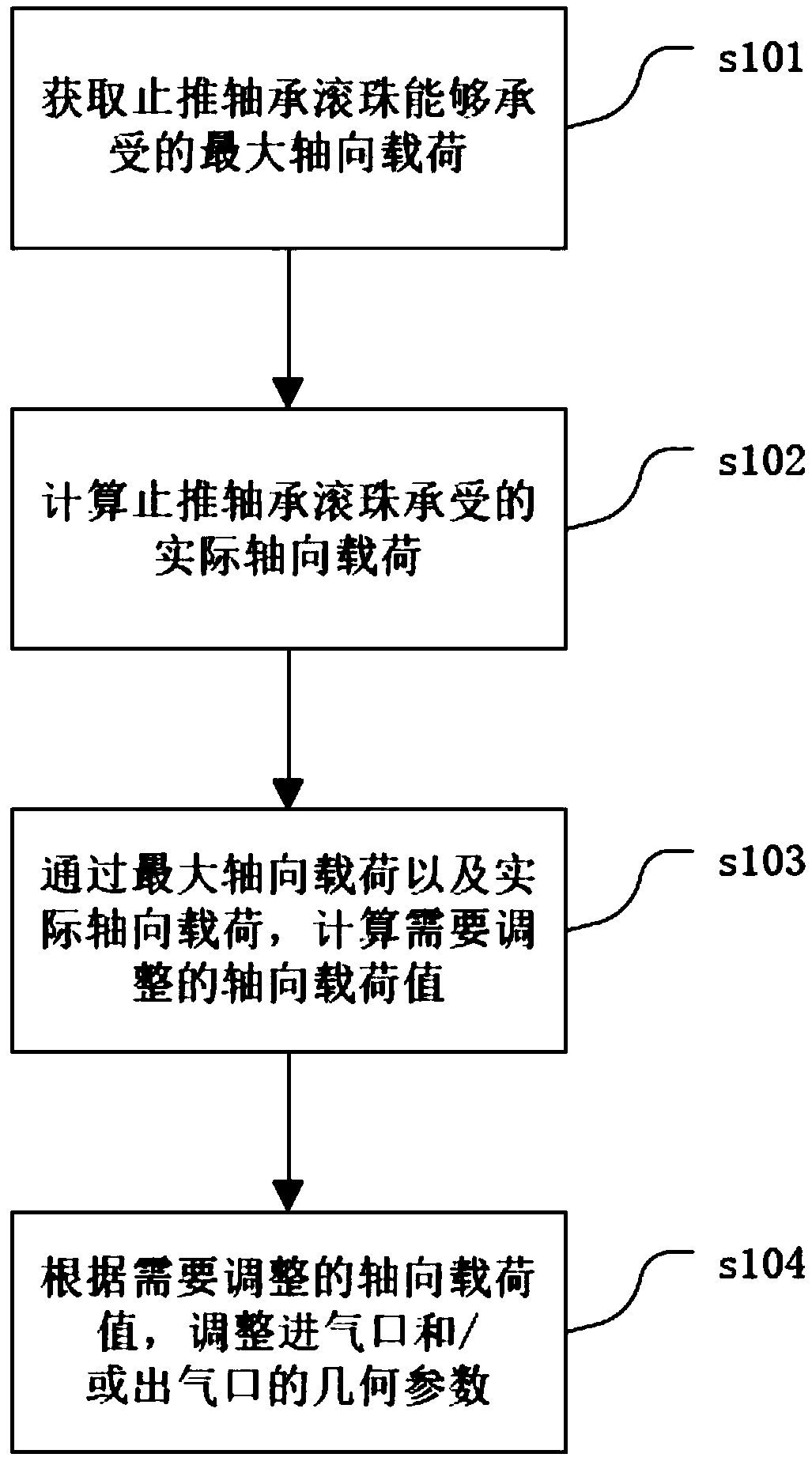

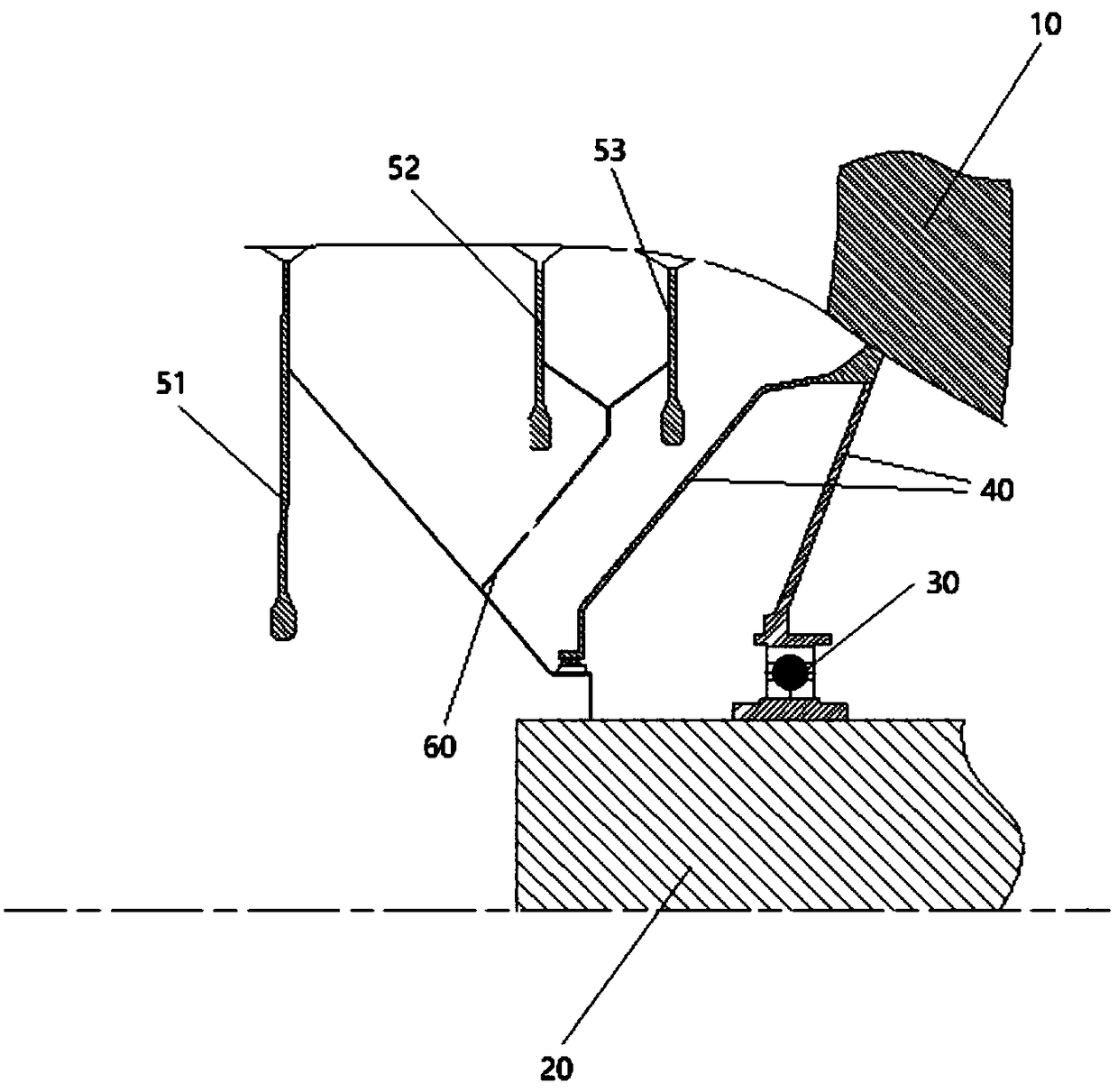

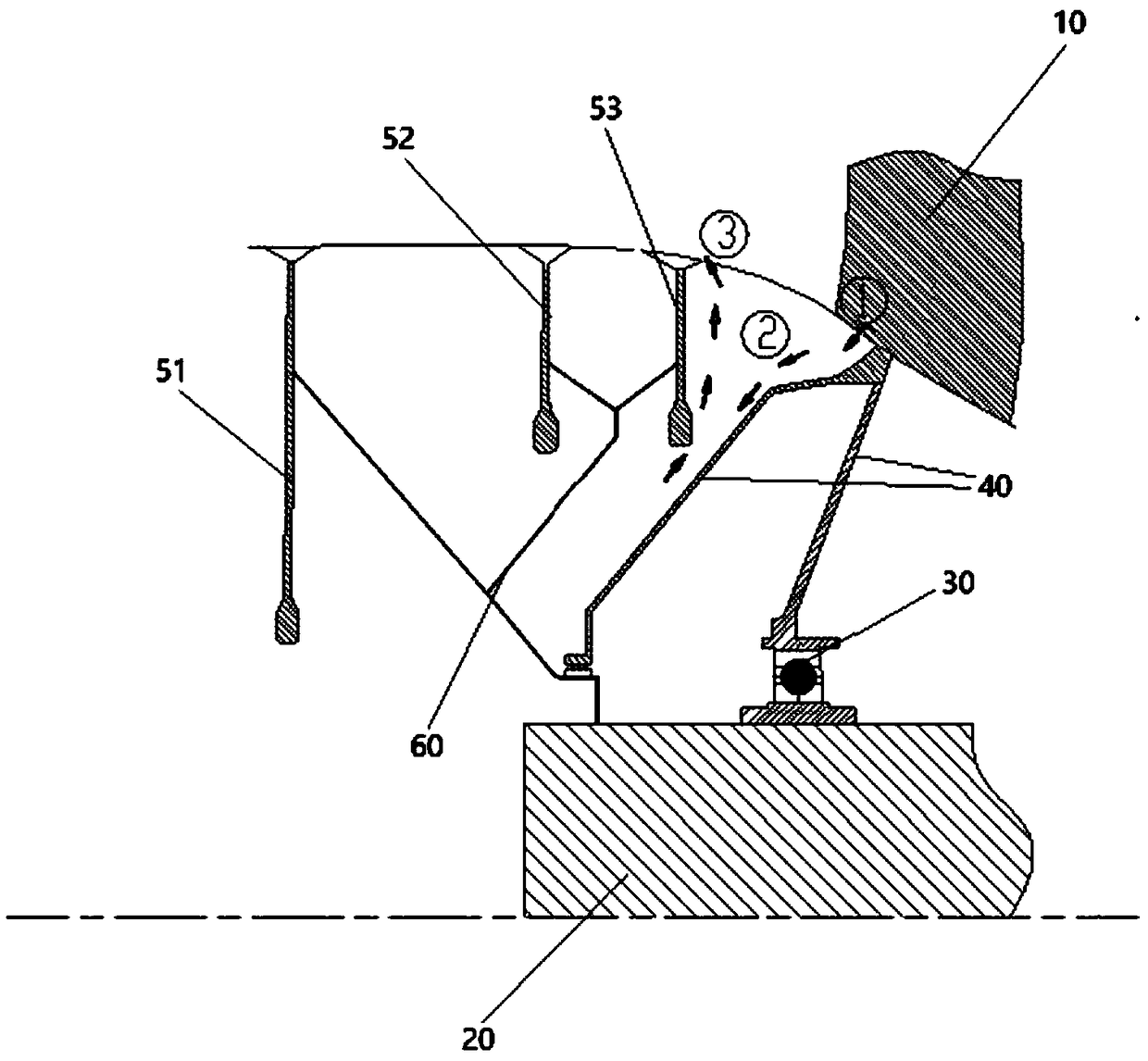

Design method of aero-engine booster chamber

ActiveCN109117509AAchieve Axial Force BalanceIncrease marginGeometric CADSpecial data processing applicationsAviationThrust bearing

The invention discloses a design method of an aero-engine booster chamber. The design method comprises the following steps: obtaining the maximum axial load that a thrust bearing ball can bear; calculating the actual axial load on thrust bearing balls; through the maximum axial load and the actual axial load, the axial load which needs to be adjusted being calculated; adjusting the geometry of theinlet and / or outlet according to the value of the axial load that needs to be adjusted. By controlling the gas pressure in the booster chamber, the invention can realize the axial force balance welland improve the design margin; moreover, the design of the booster chamber is relatively independent, and regulating the pressure in the chamber has no influence on the realization of other system functions.

Owner:AECC SHENYANG ENGINE RES INST

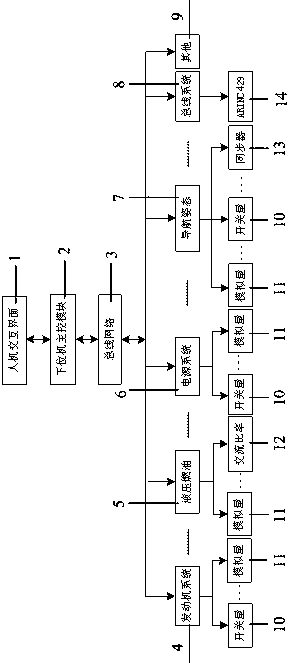

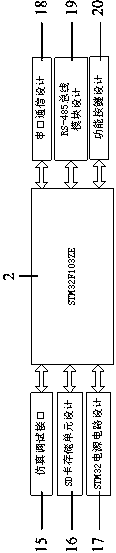

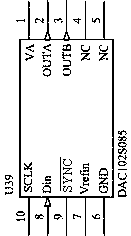

Flight parameter signal generating system

InactiveCN107664967ARun fastReduce power consumptionProgramme controlComputer controlMicrocontrollerData set

The invention discloses a flight parameter signal generating system. The system includes an upper computer man-machine interaction interface and a lower computer signal generating system, wherein thelower computer signal generating system includes an engine system module, a hydraulic pressure fuel oil system module, a power system module, a navigation attitude system module, a bus system module and the like. LabVIEW is adopted for designing the upper computer man-machine interaction interface, an Access database is selected for storing parameter data set by an upper computer and a lower computer communication network is constructed by taking an STM32 as a main control module in combination with RS485 technology. Switching quantity signals are achieved by adopting a single-chip microprocessor in combination with a photovoltaic coupler. Analog quantity signals are generated through controlling a DAC chip by the single-chip microprocessor. AC rate signals are generated through an AC ratetable. Generation of synchronizer signals is realized through a chip AD9959. Generation of ARINC429 is realized through controlling HS-3182 and HS-3282 by the single-chip microprocessor. Generation of AC power signals is realized through a voltage transformer. A DC power supply power source is achieved through a voltage stabilizing chip. Flight parameters are allocated to different signal generation modules. On one hand, management is facilitated. On the other hand, design margin is realized and addition and reduction of signal generation modules are facilitated.

Owner:HENAN POLYTECHNIC UNIV

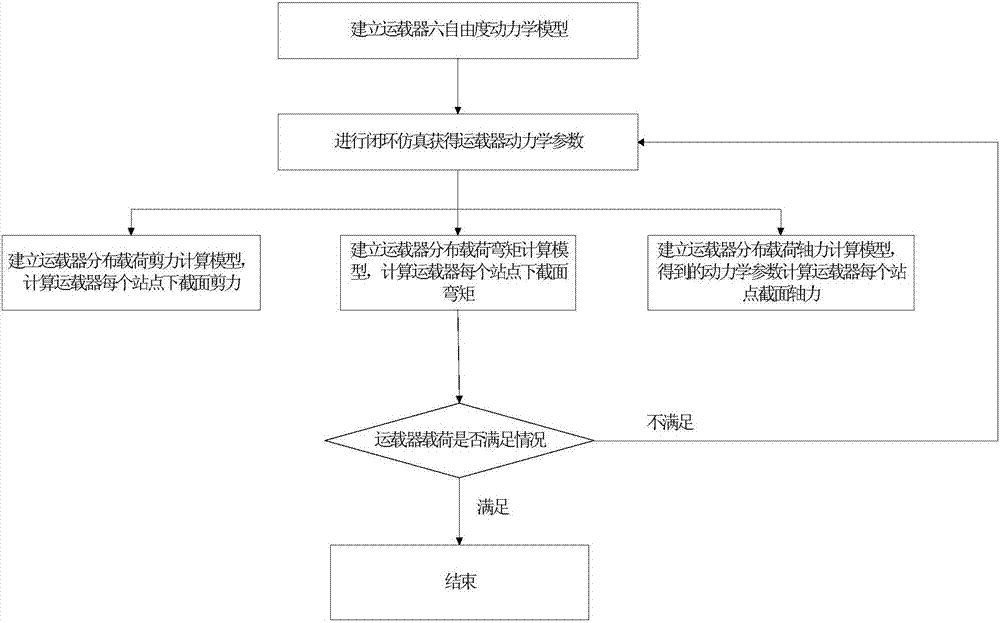

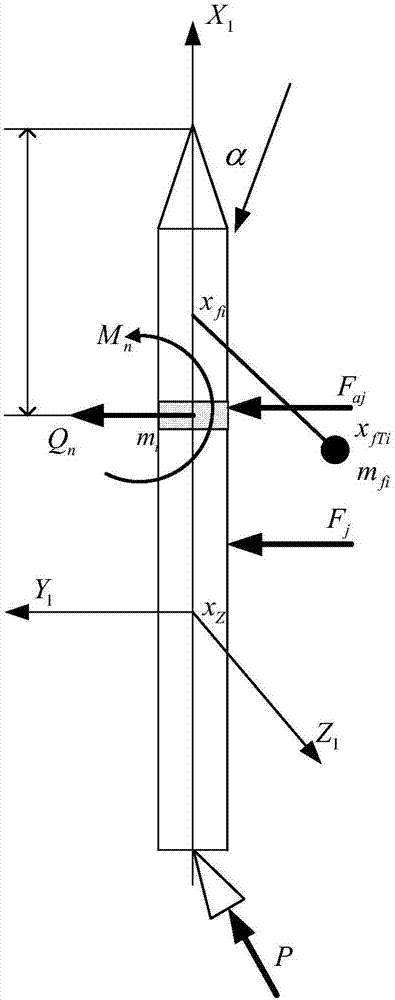

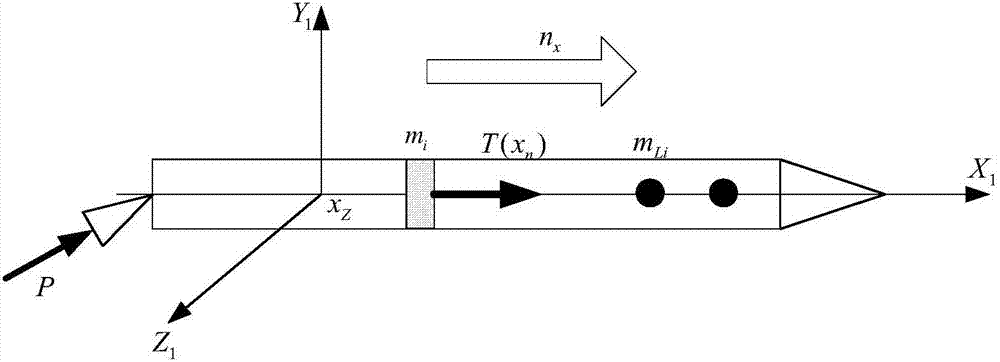

Close-loop simulation-based distributed load optimization design method for carrier

The invention discloses a close-loop simulation-based distributed load optimization design method for a carrier. The method comprises the steps of firstly building a six-degree-of-freedom dynamics model for the carrier, then performing close-loop simulation to obtain dynamics parameters, building a distributed load shear force calculation model, a bending moment calculation model and an axial force calculation model of the carrier, and calculating lower section shear force, lower section bending moment and section axial force of each site of the carrier; and secondly, rechecking the situation on whether loads of the carrier meet the requirements or not, if the loads of the carrier meet the requirements, ending the design, if the loads of the carrier do not meet the requirements, optimizing a close-loop simulation input, re-obtaining the dynamics parameters, and calculating the lower section shear force, the lower section bending moment and the section axial force of each site, until the loads of the carrier meet the requirements. According to the method, the loads on all the sections of the carrier of a rocket in a flight process can be really reflected; and therefore, the method is of great significance for rechecking the completeness and design margin of load design.

Owner:BEIJING INST OF ASTRONAUTICAL SYST ENG +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com