Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53 results about "Delay equalization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

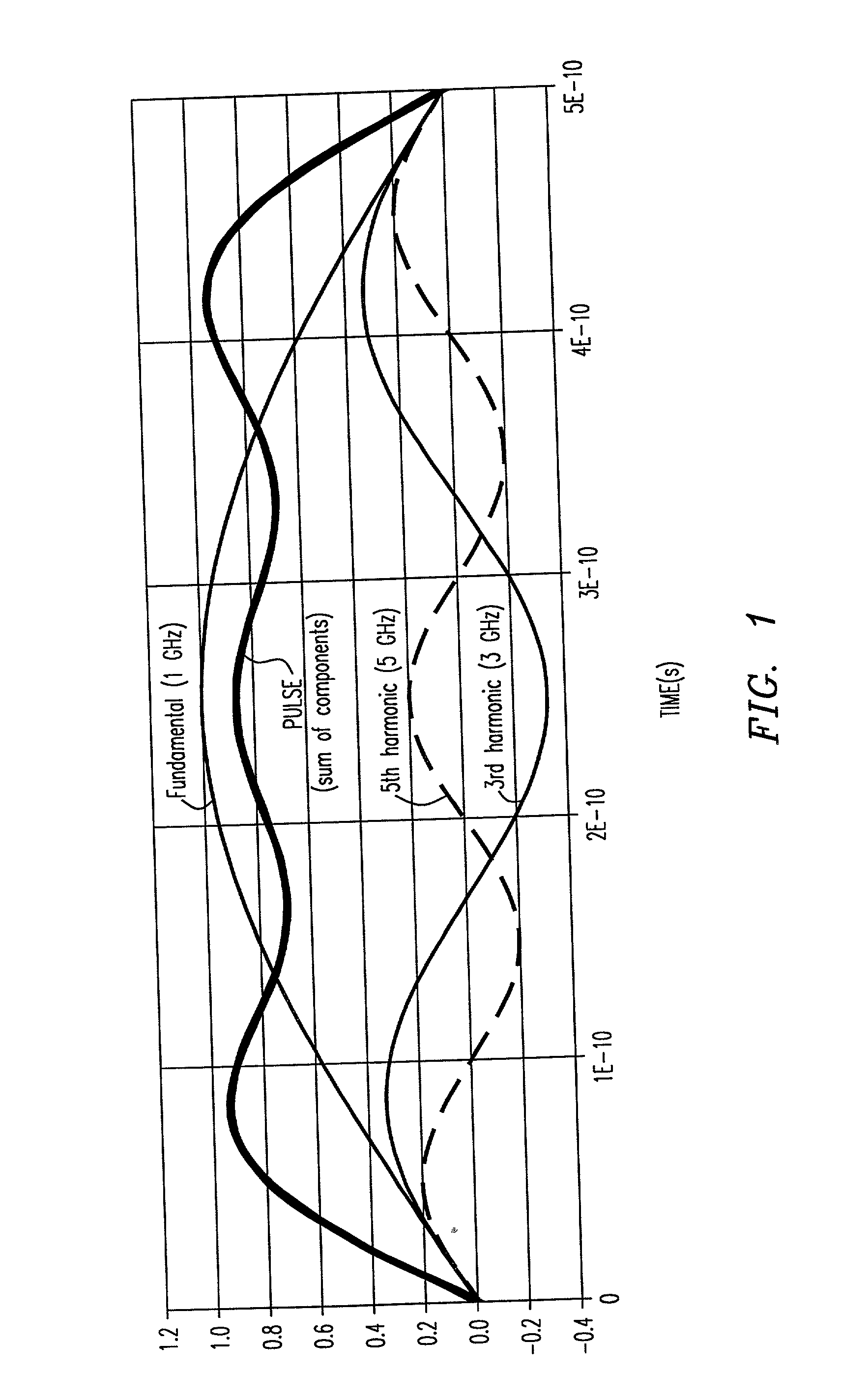

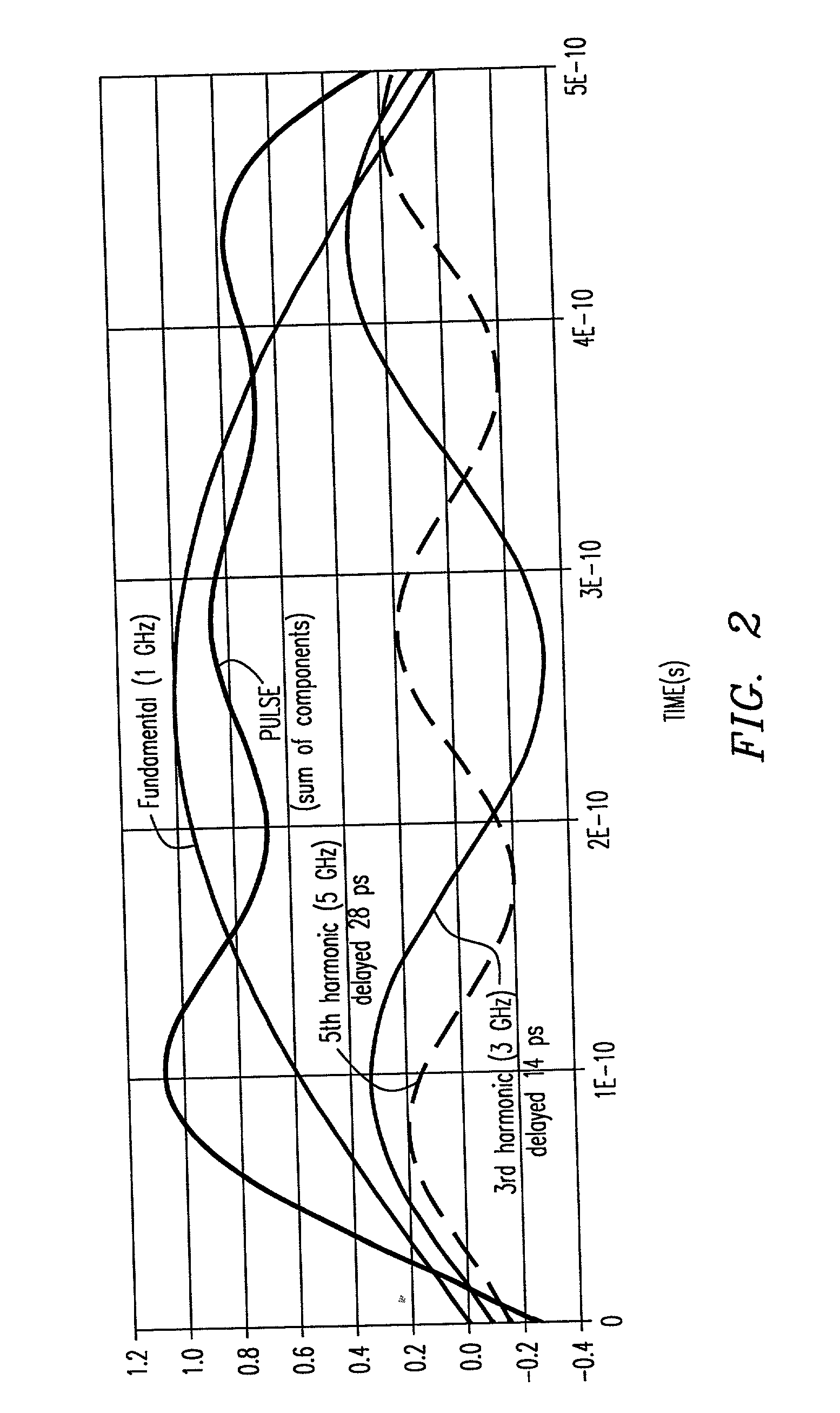

In signal processing, delay equalization corresponds to adjusting the relative phases of different frequencies to achieve a constant group delay, using by adding an all-pass filter in series with an uncompensated filter. Clever machine-learning techniques are now being applied to the design of such filters.

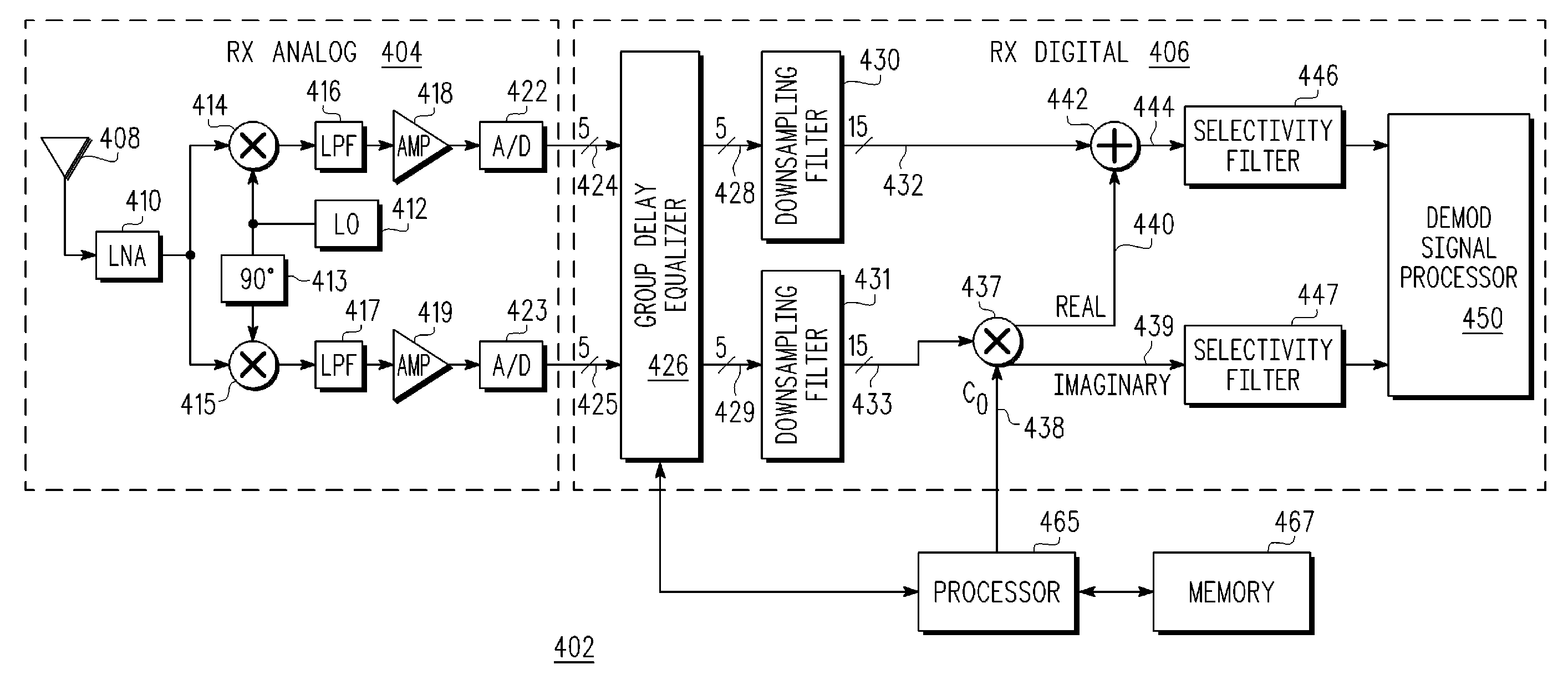

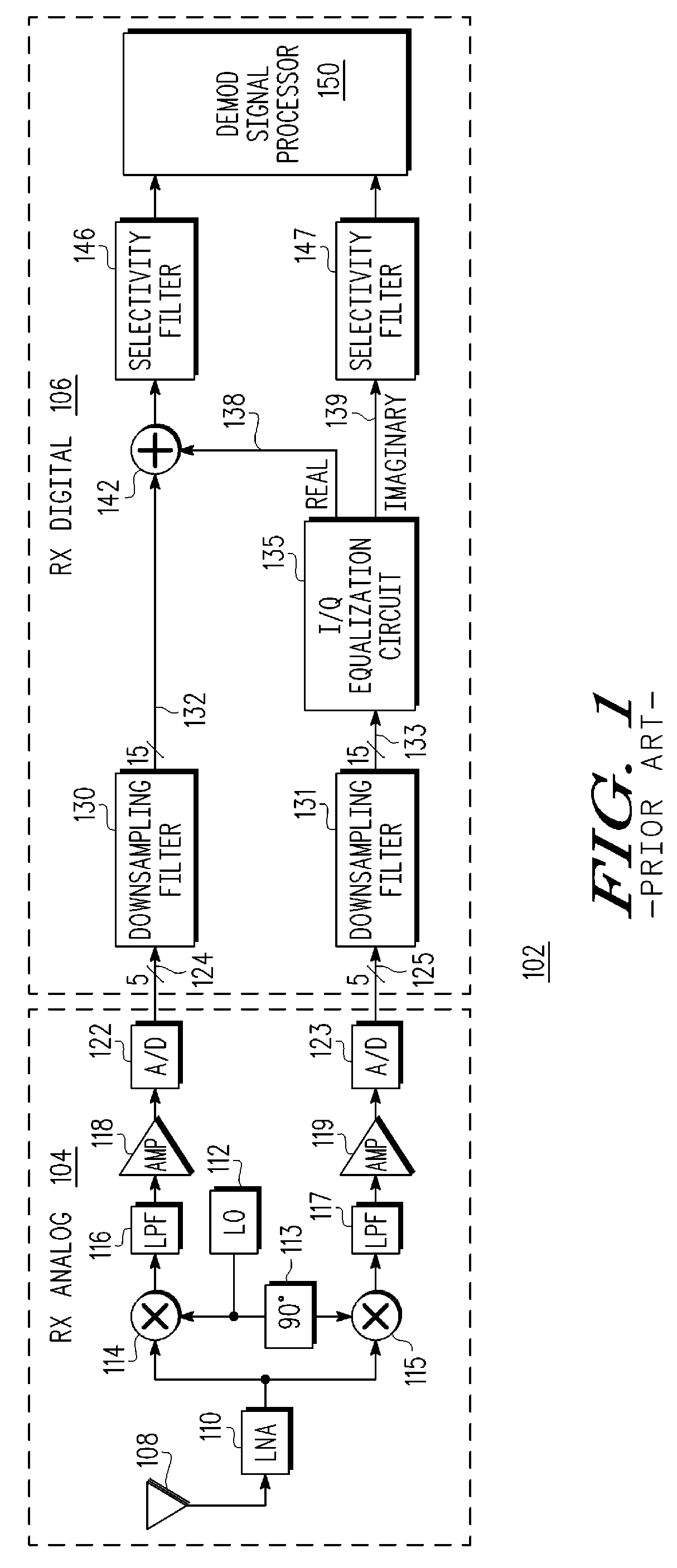

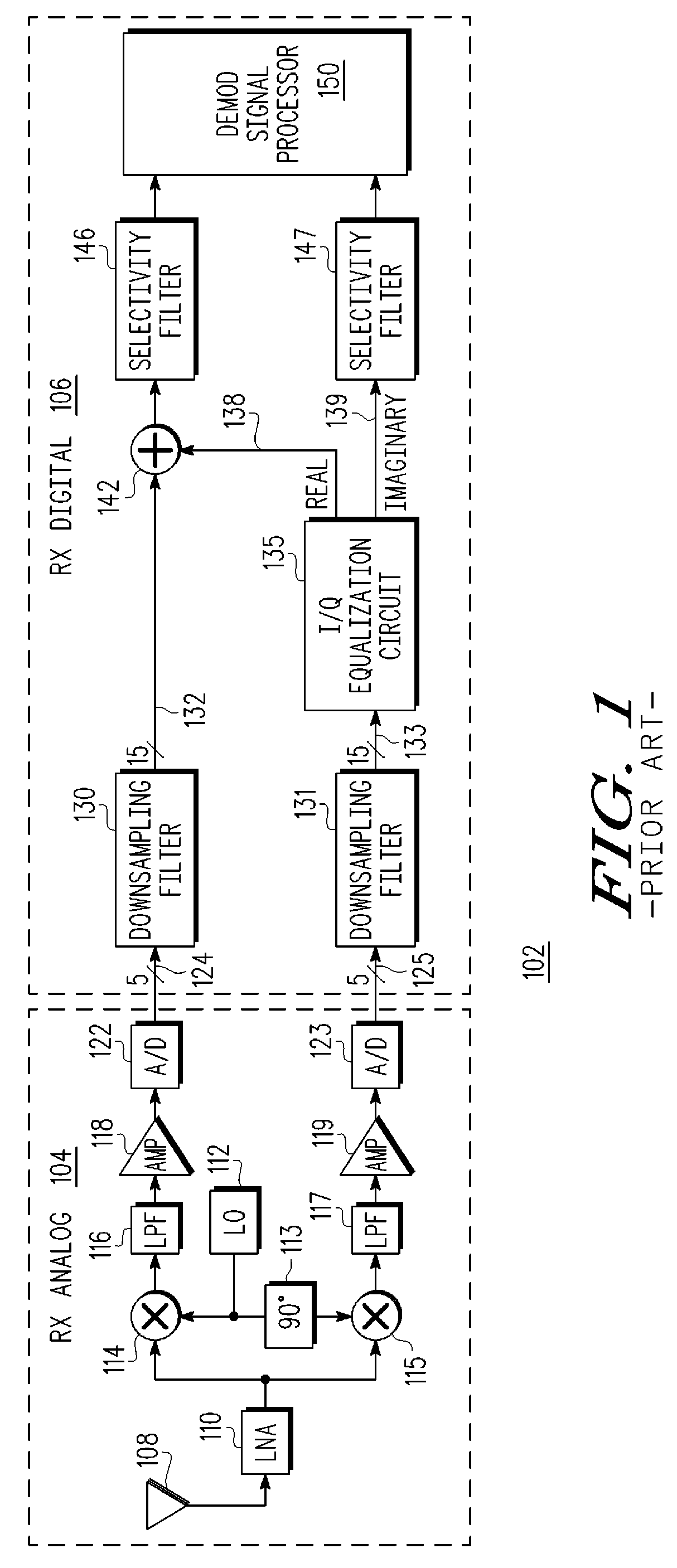

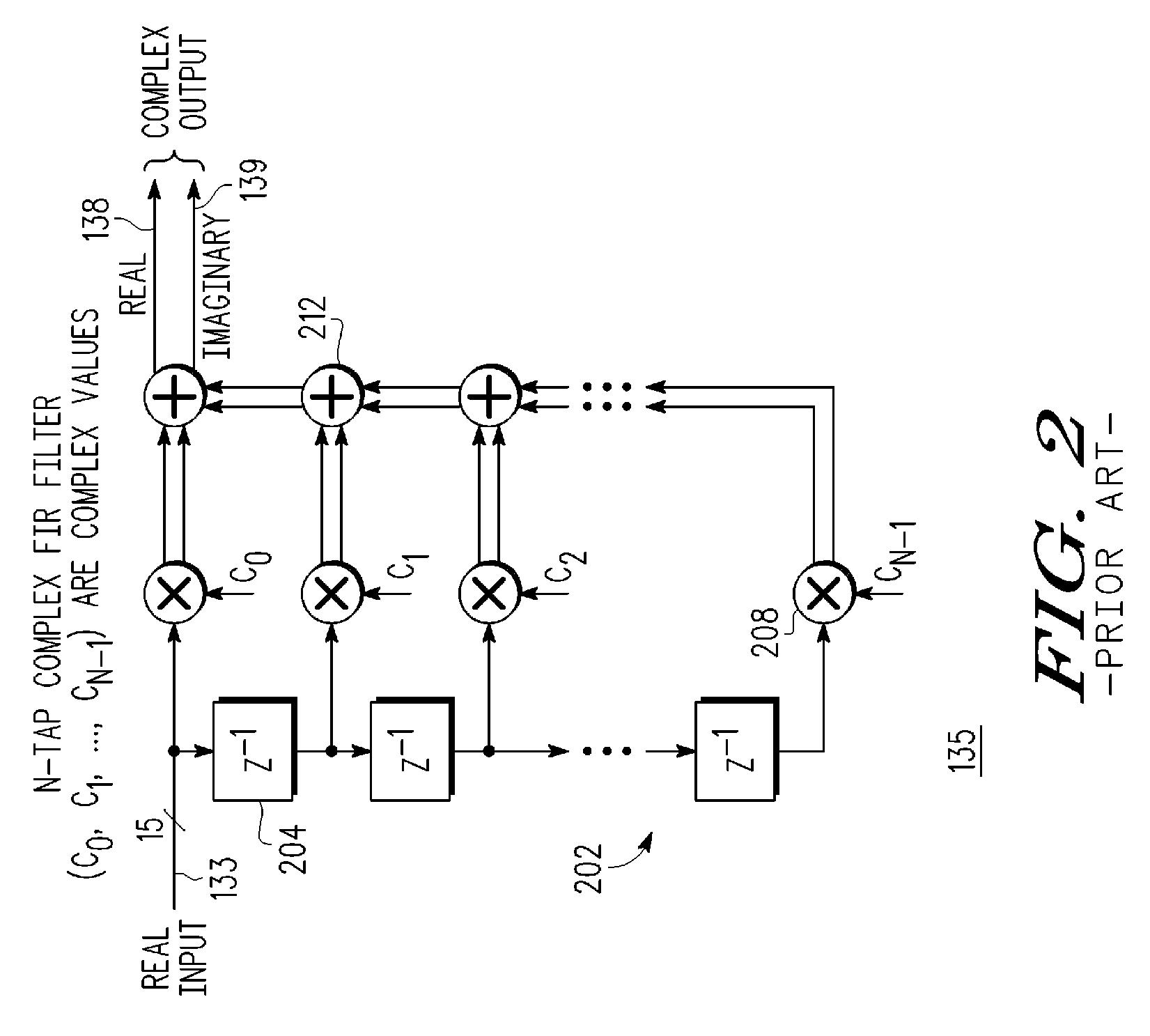

Receiver i/q group delay mismatch correction

A device for minimizing group delay mismatch in a quadrature receiver (402) having an in-phase channel and a quadrature-phase channel. The device includes a microprocessor (465) for determining an I / Q phase imbalance between digital signals on an in-phase channel and digital signals on a quadrature-phase channel, and for calculating a group delay mismatch between the in-phase channel and the quadrature-phase channel, and a group delay equalizer (426). The group delay equalizer includes a delay line (505 and 605) for delaying one of the in-phase channel and the quadrature-phase channel by one of a plurality of delays, based on an amount of group delay mismatch.

Owner:NORTH STAR INNOVATIONS

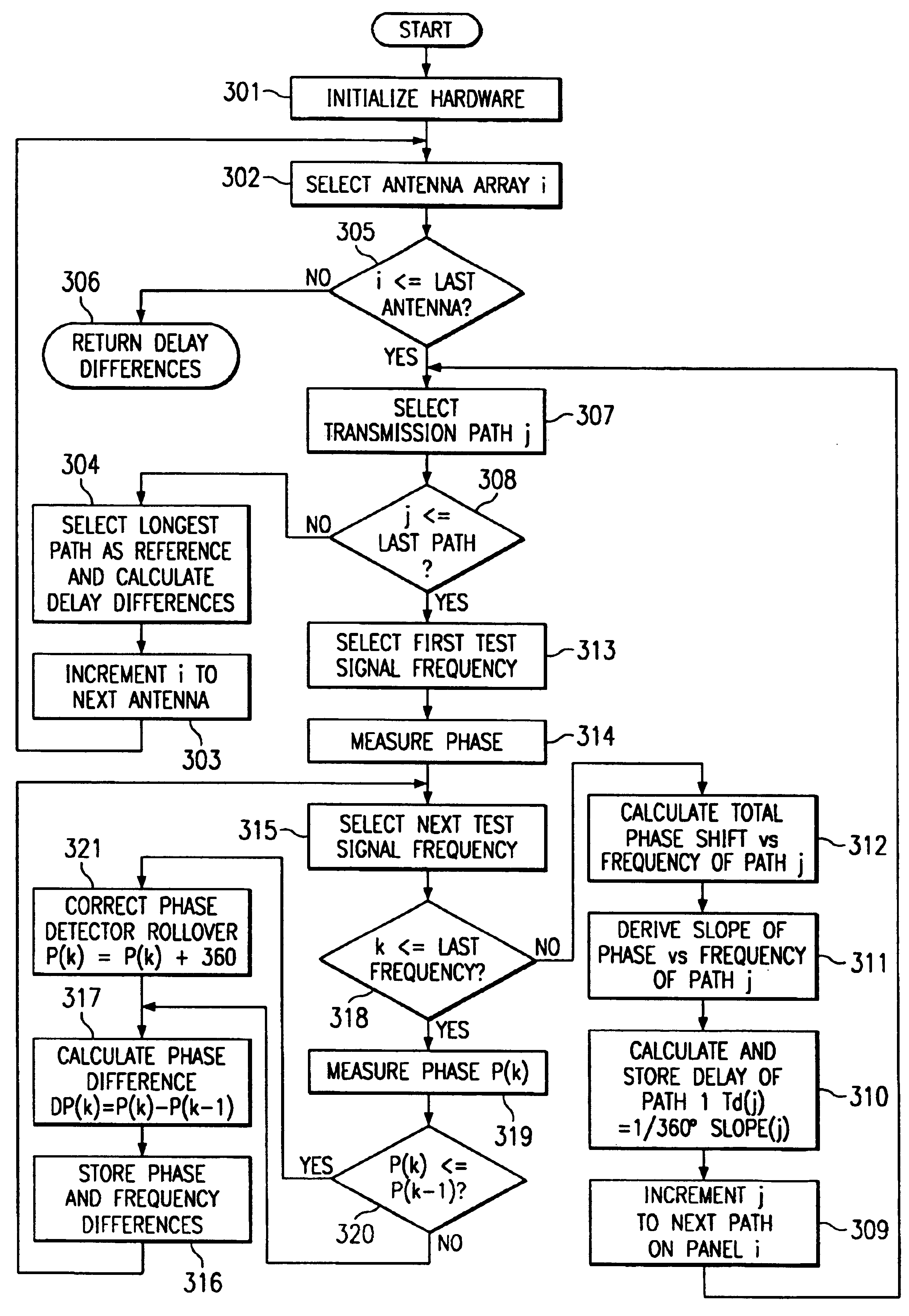

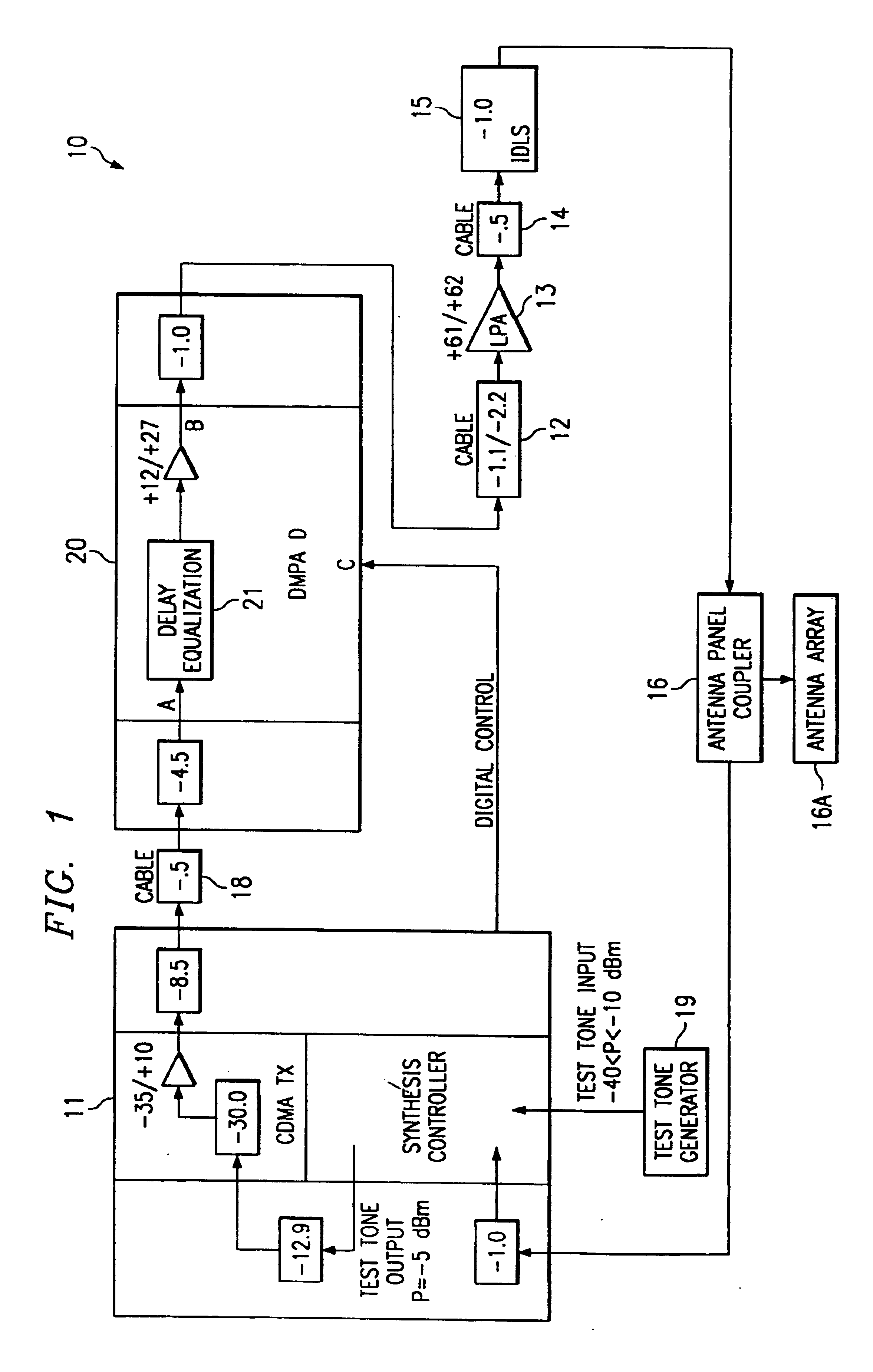

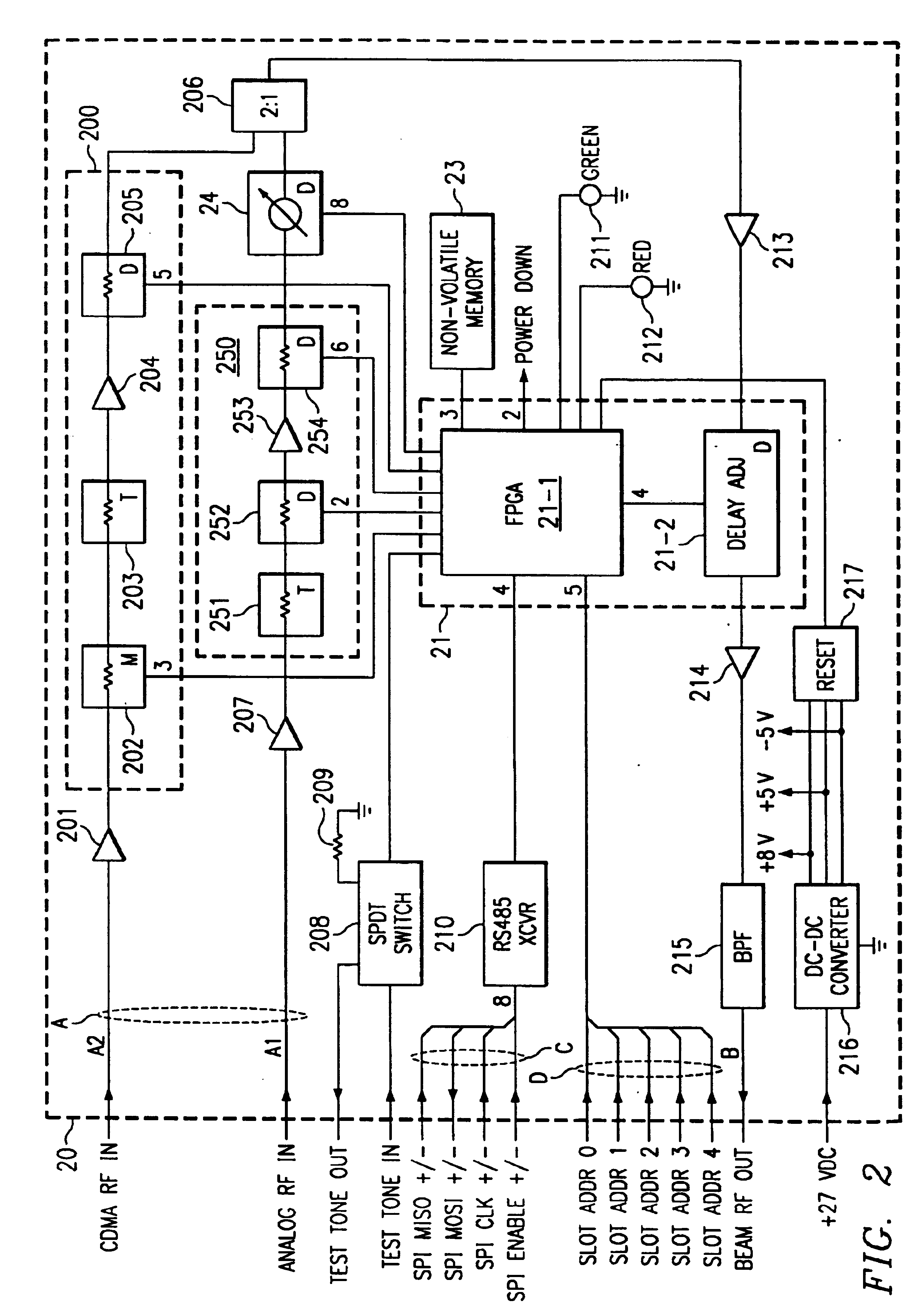

System and method for delay equalization of multiple transmission paths

InactiveUS6895230B1Minimize impactSimplifies accumulationResonant long antennasSpatial transmit diversityElectricityCommunications system

The present invention provides systems and methods for addressing the effects of non-linear phase response, such as by equalizing electrical delays among transmission paths. A preferred embodiment provides phase detection circuitry and phase adjustment circuitry in the signal paths of a multiple beam or phased array antenna to provide delay equalization of the signal paths. Communication systems implementing the systems and methods of the present invention are provided broadband phase calibration and, therefore, are enabled to provide controlled and predictable beam forming over a broad range of frequencies.

Owner:F POSZAT HU

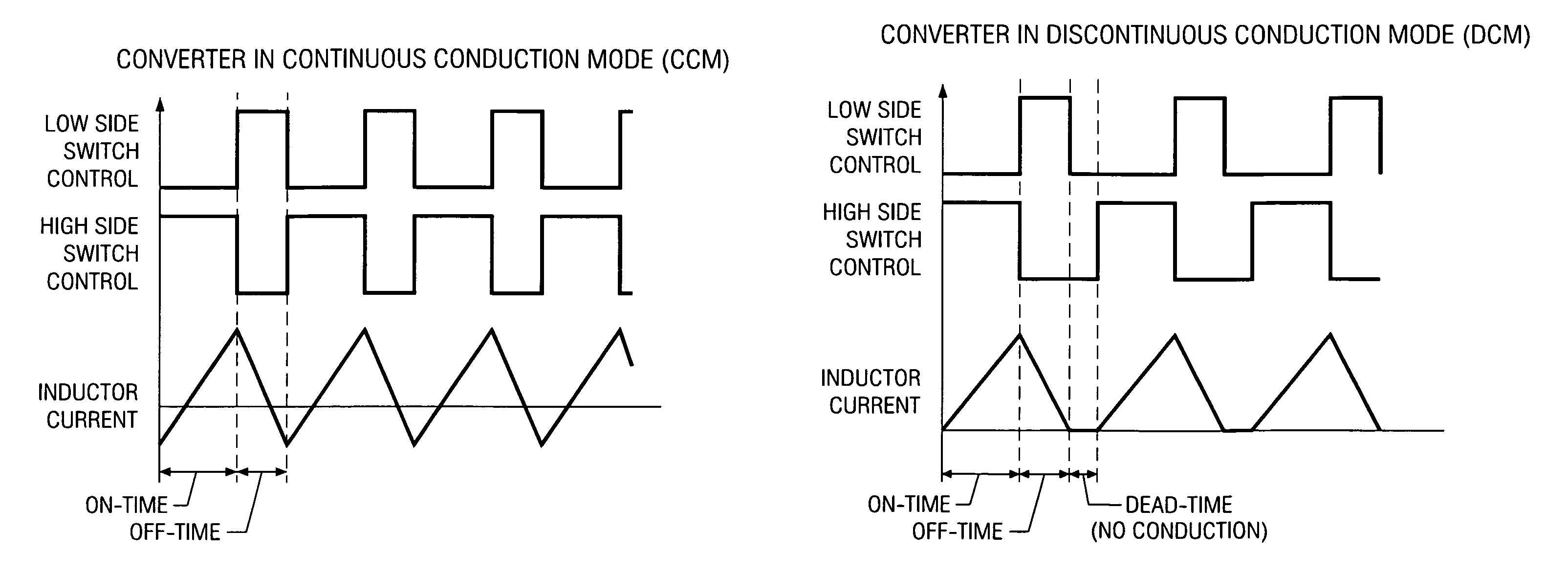

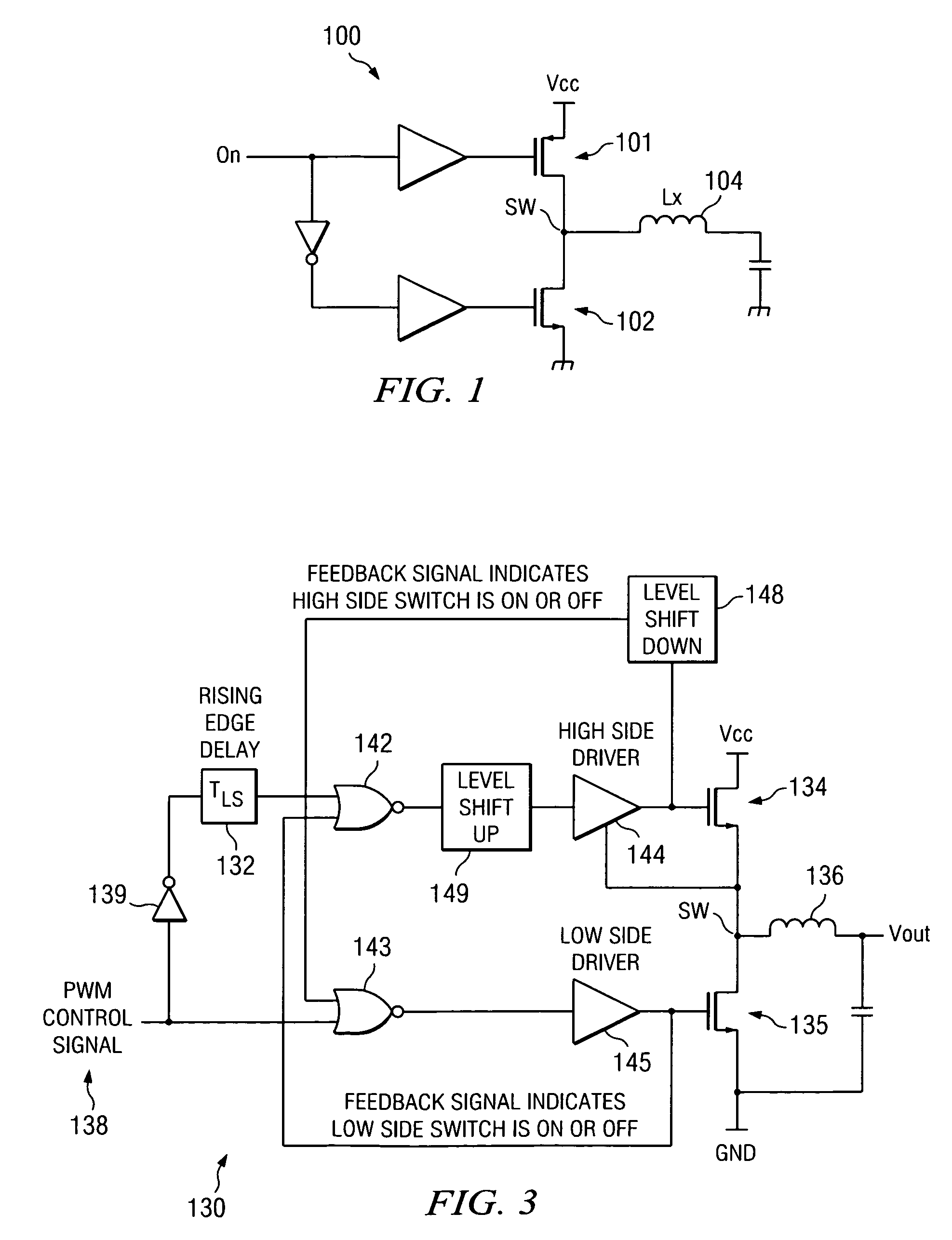

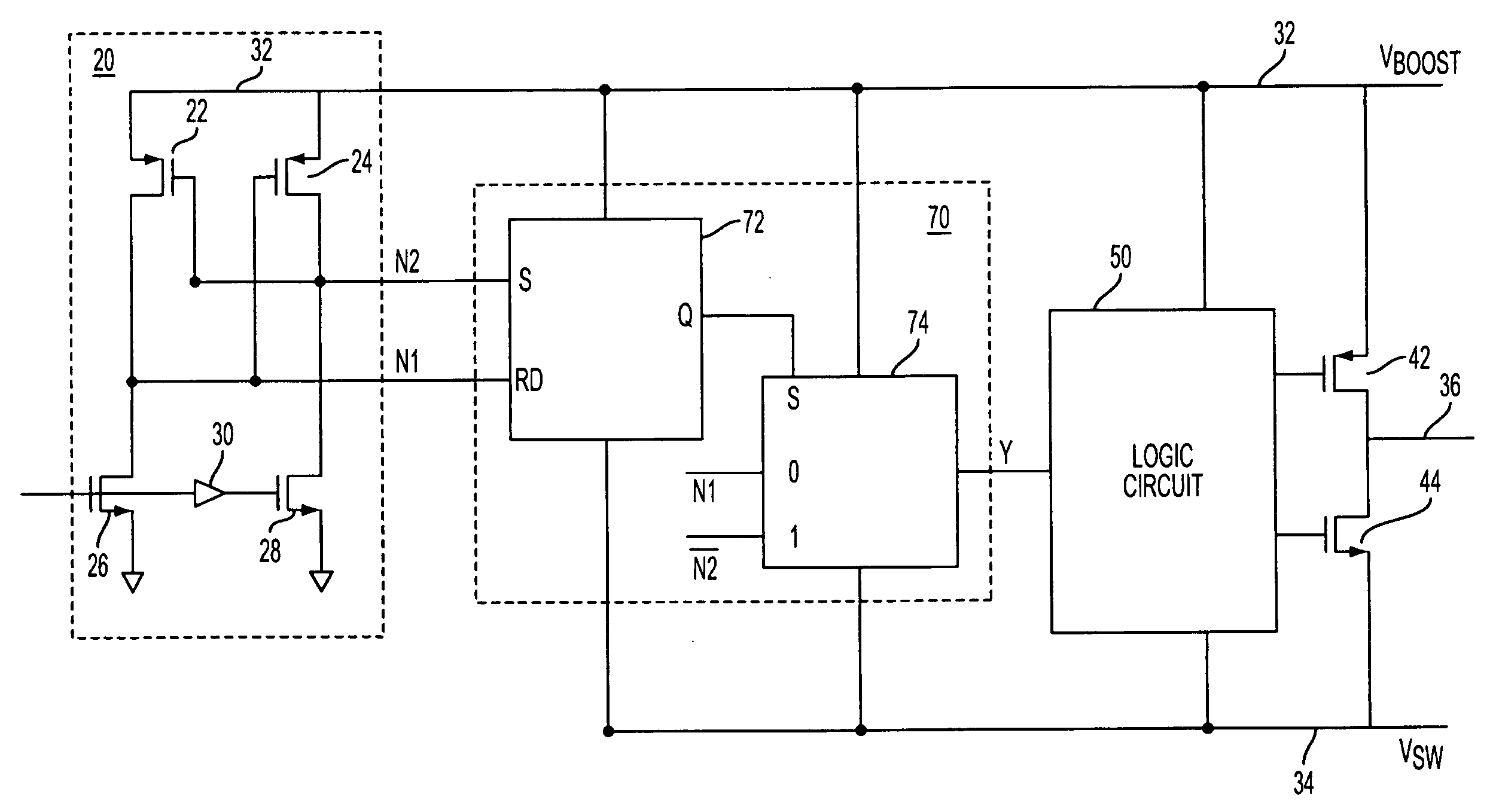

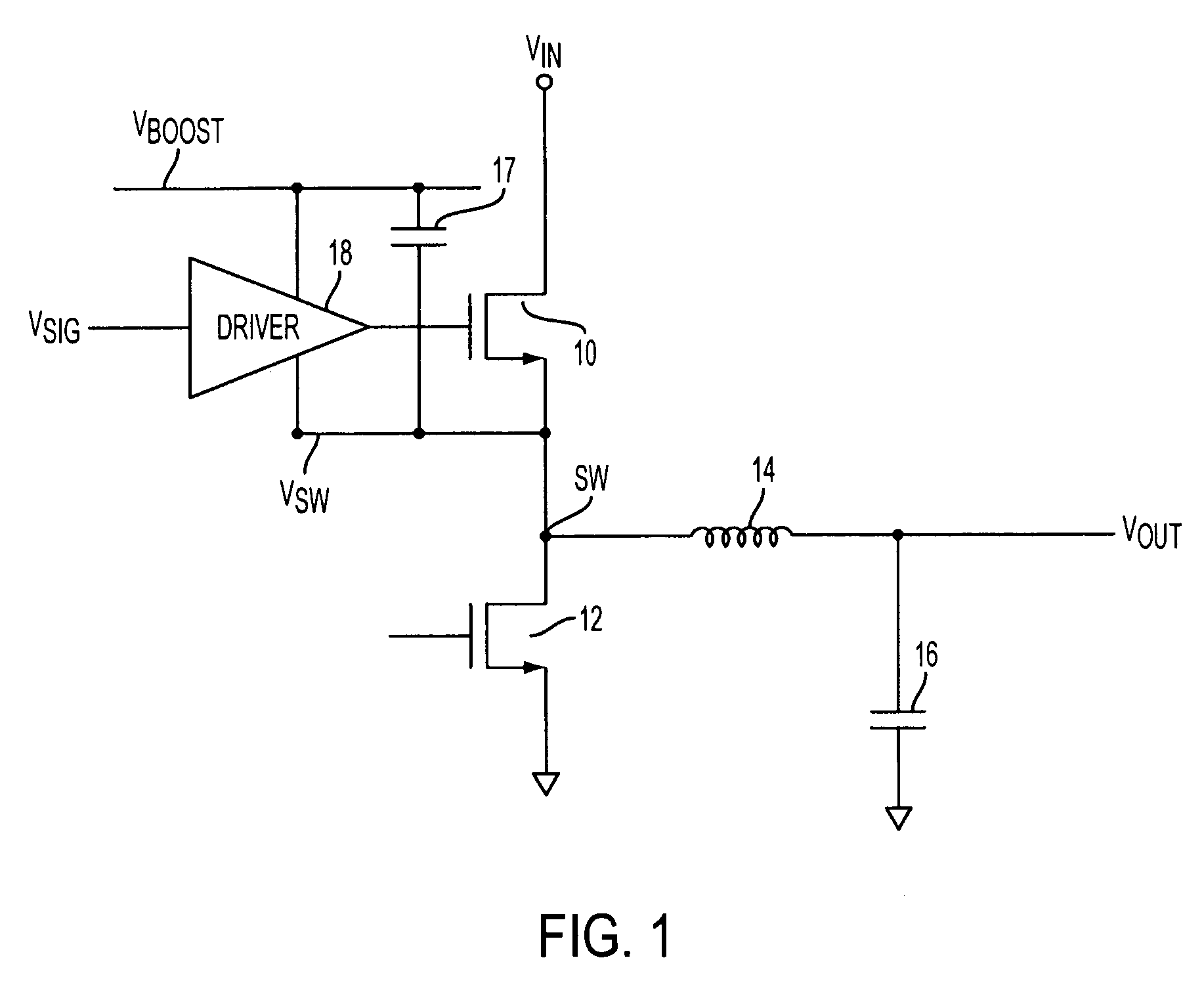

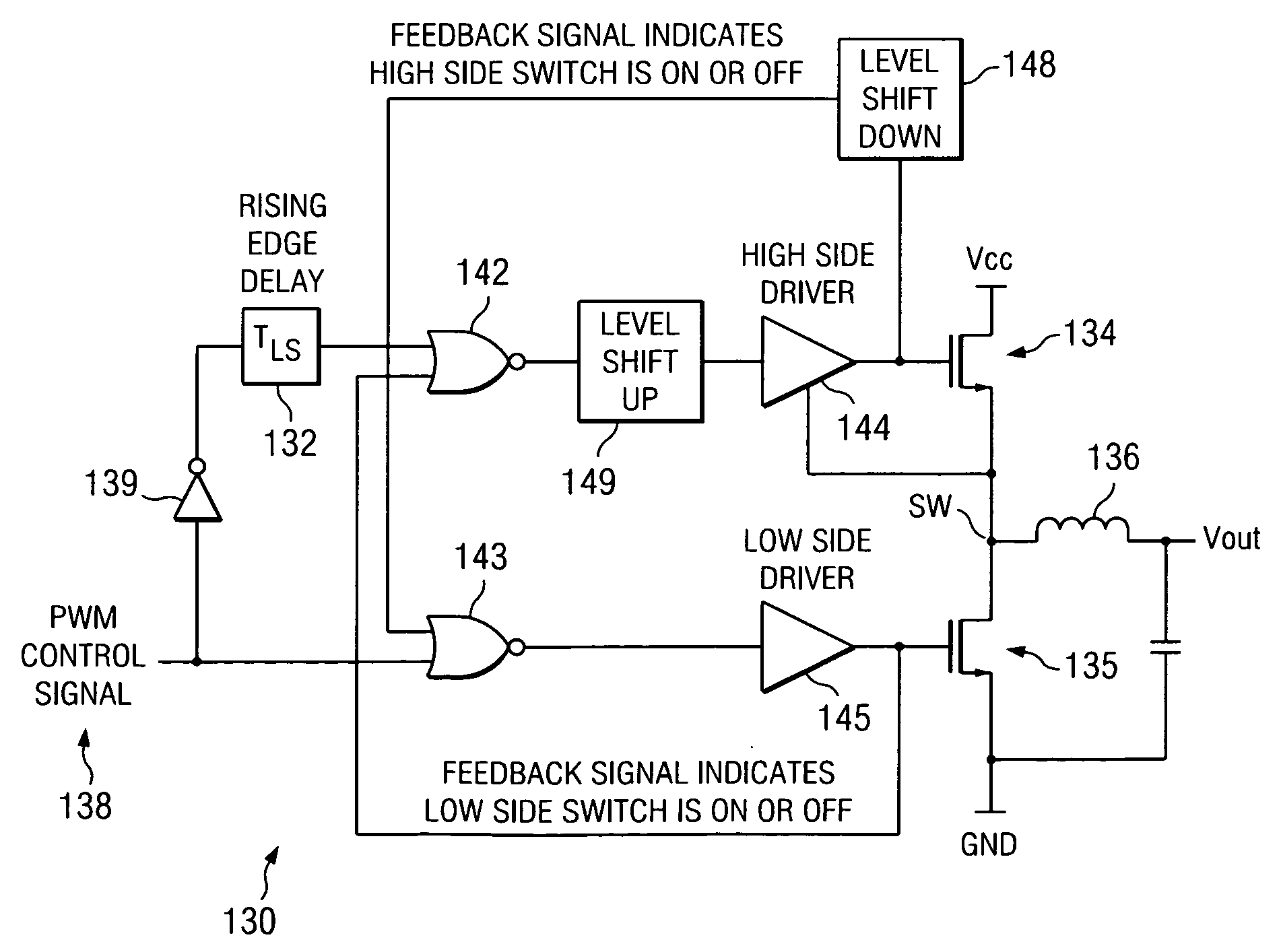

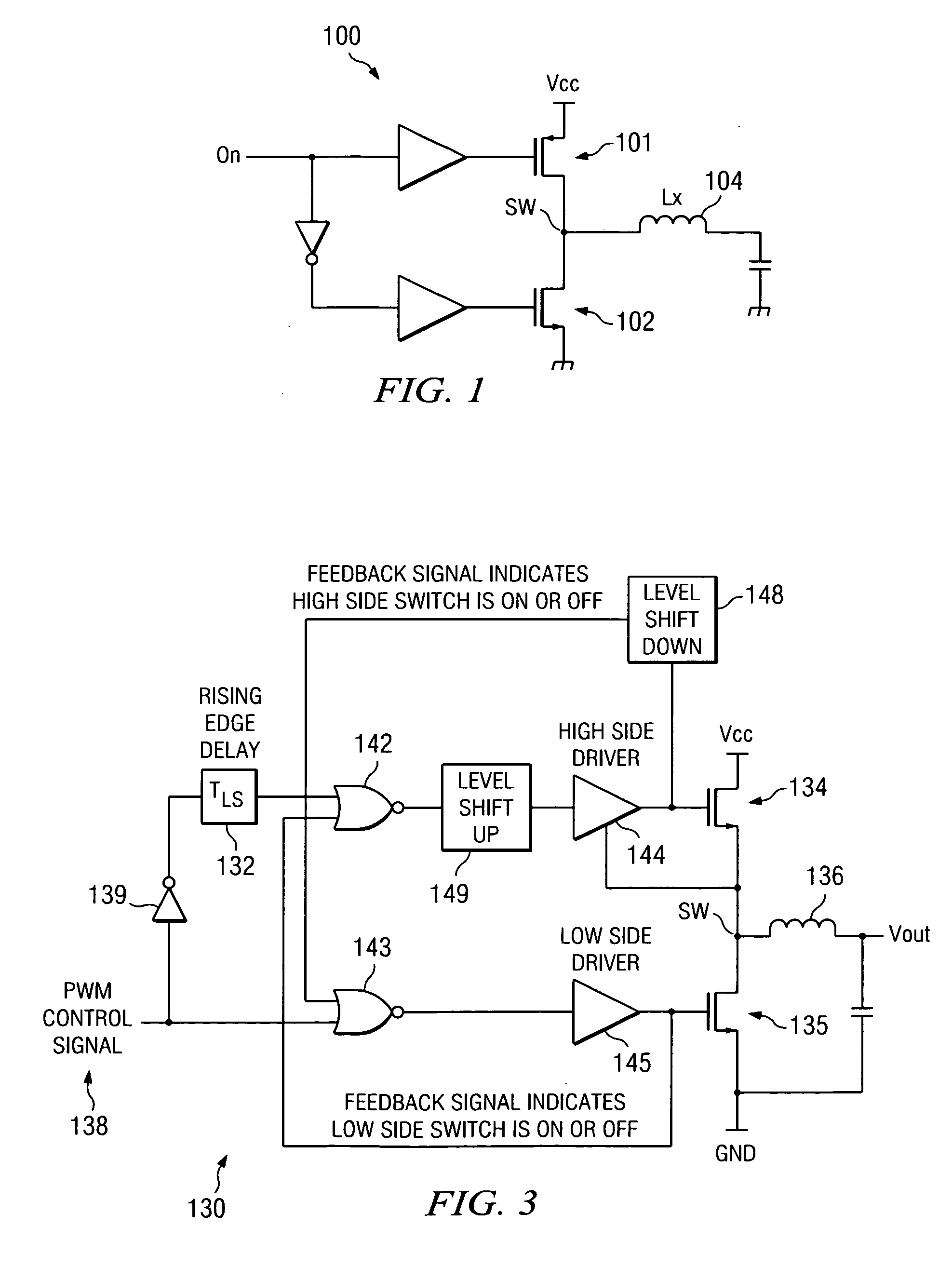

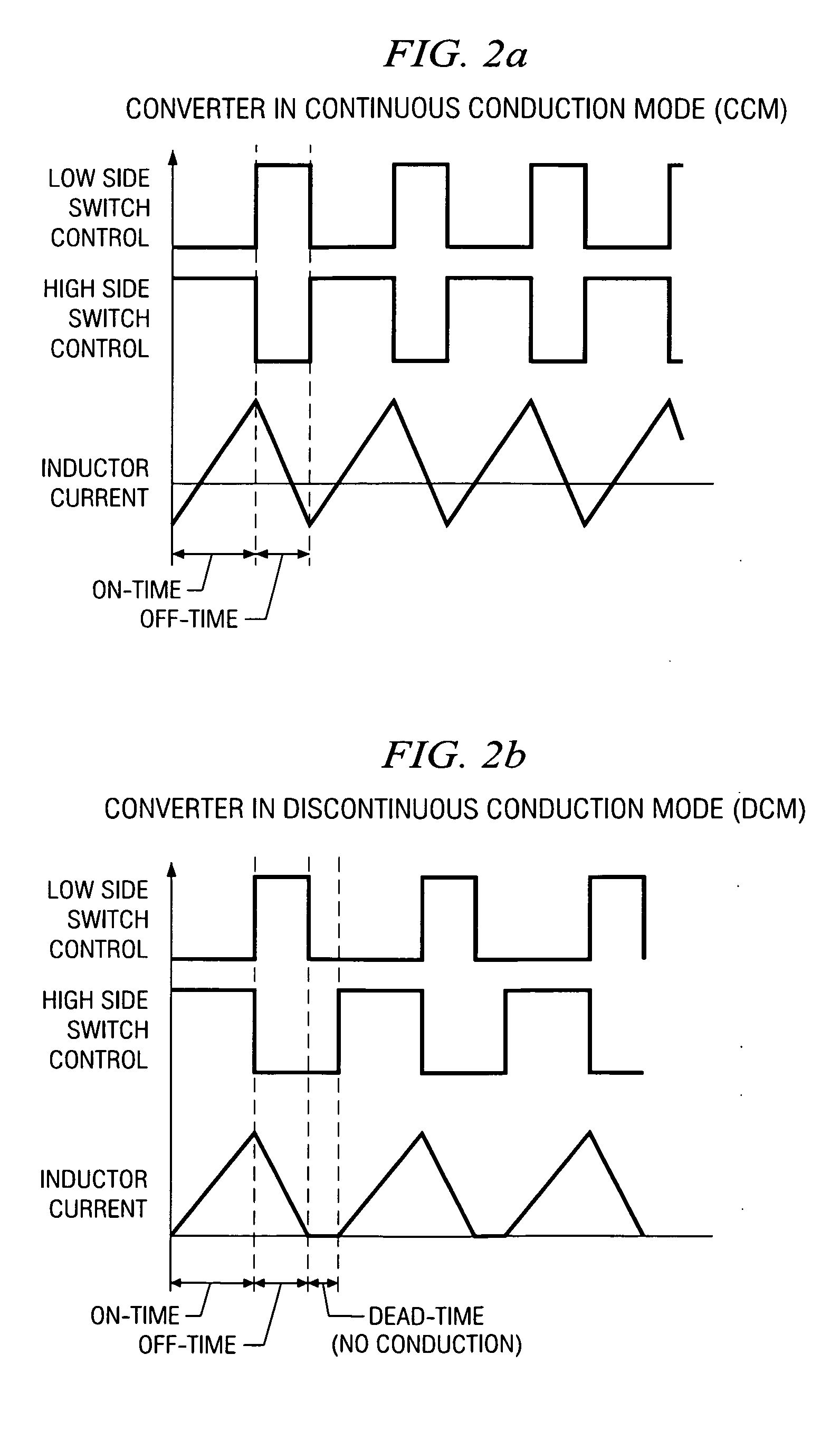

System and method for switch mode power supply delay compensation

ActiveUS7932703B2Avoid oscillationDc-dc conversionElectric variable regulationPropagation delayEngineering

A delay applied to a turn-on time for a high side switch in a switch mode power converter prevents oscillation between continuous and discontinuous conduction modes under light load conditions. The delay equalizes turn-on time for a high side switch with respect to continuous and discontinuous modes, so that turn-on time is not treated differently between the different modes. The delay value can be set for be equivalent to a propagation delay through a driver for a low side switch, in addition to a turn-off time for the low side switch. The addition of the delay element tends to maintain the switch mode power converter in a discontinuous mode under light load conditions and avoids oscillation between discontinuous and continuous conduction modes.

Owner:TEXAS INSTR INC

Receiver I/Q group delay mismatch correction

A device for minimizing group delay mismatch in a quadrature receiver (402) having an in-phase channel and a quadrature-phase channel. The device includes a microprocessor (465) for determining an I / Q phase imbalance between digital signals on an in-phase channel and digital signals on a quadrature-phase channel, and for calculating a group delay mismatch between the in-phase channel and the quadrature-phase channel, and a group delay equalizer (426). The group delay equalizer includes a delay line (505 and 605) for delaying one of the in-phase channel and the quadrature-phase channel by one of a plurality of delays, based on an amount of group delay mismatch.

Owner:NORTH STAR INNOVATIONS

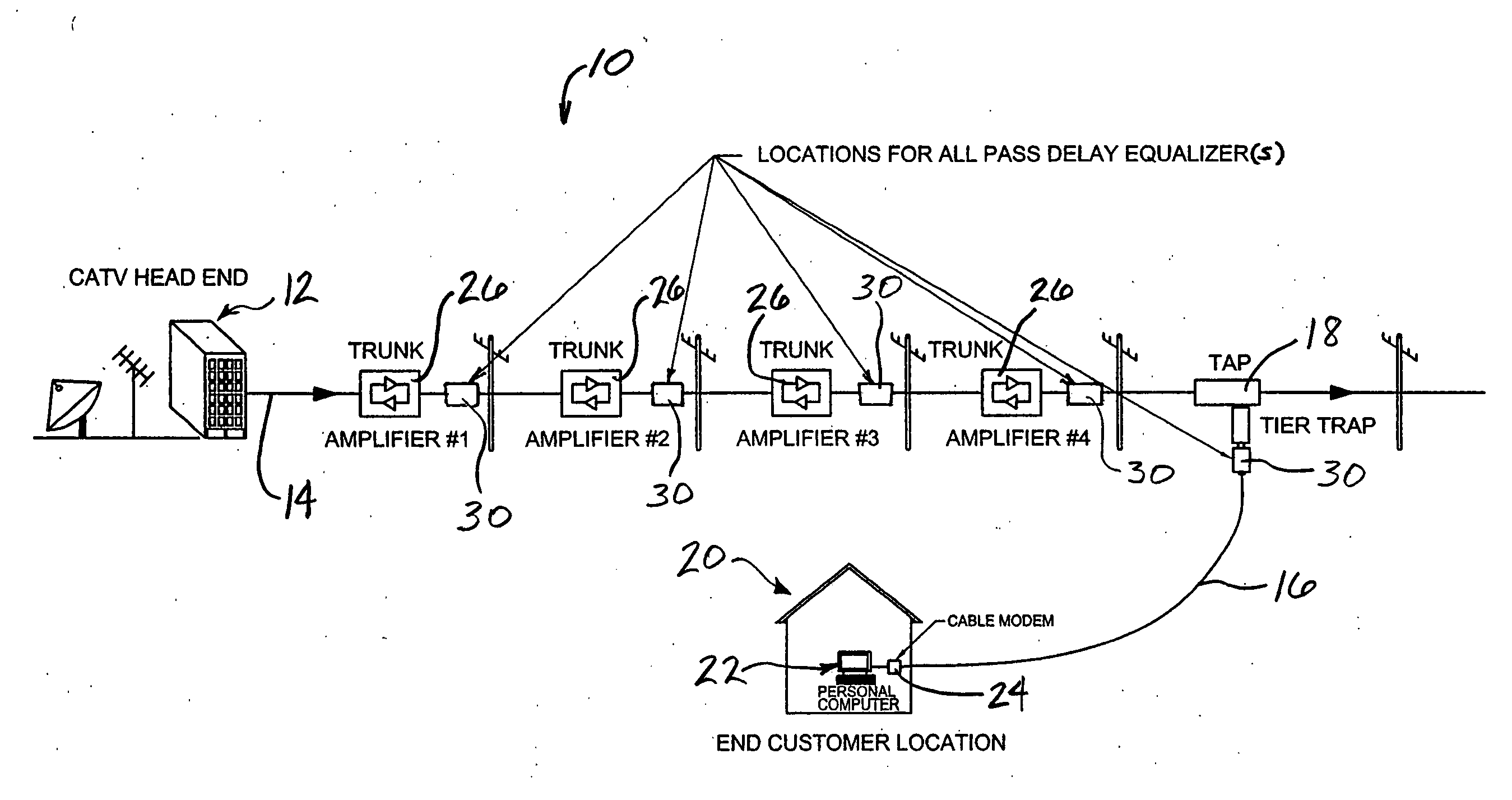

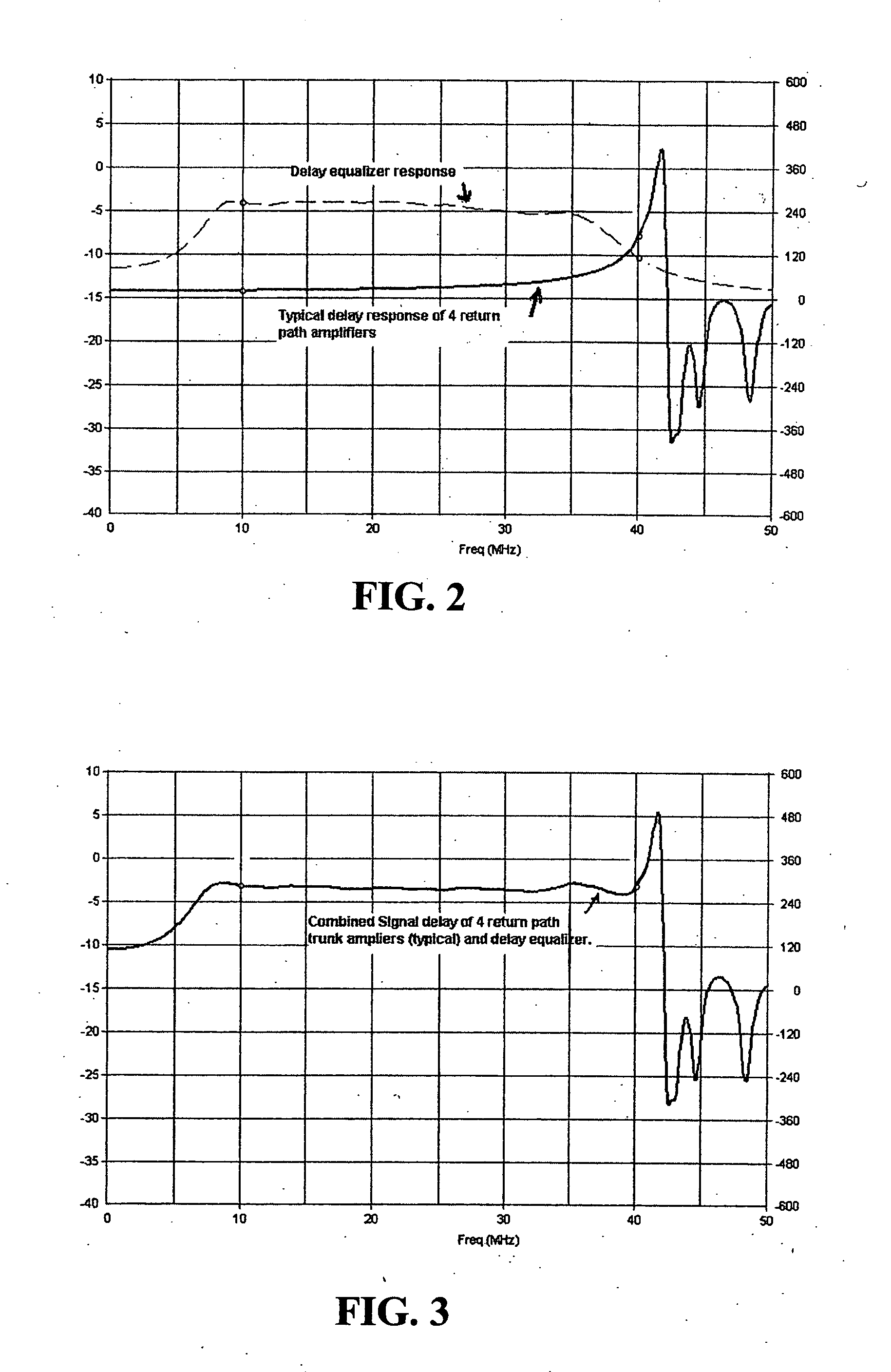

All-pass network for data transmission over a CATV system

InactiveUS20060031911A1Analogue secracy/subscription systemsTwo-way working systemsAudio power amplifierFrequency characteristic

A cable system, and a method for configuring a path of a cable system, wherein the group delay caused by one or more amplifiers having diplex filter networks is substantially equalized over all frequencies within a predetermined band by the use of one or more all-pass delay equalizers. A method of configuring a path includes steps of determining a delay versus frequency characteristic of the path within the predetermined frequency band, and providing from one to a plurality of all-pass delay equalizers in the path, wherein a collective delay versus frequency characteristic of the all-pass delay equalizer(s) within a predetermined frequency band is a mirror image of that caused by the amplifier(s), such that all frequencies within the predetermined frequency band are delayed by substantially the same amount and hence all frequency components of a signal arrive at a receiver at substantially the same time.

Owner:PPC BROADBAND INC

Time delay equalizer for high-temperature superconduction microwave filtering group

InactiveCN1671068AGroup Delay EqualizationLow insertion lossTransmission control/equalisingWaveguide type devicesRF front endTime delays

This invention refers to analog signal process and communication technology, especially refers to the group delay equalization of high temperature superconductive filter used in high temperature superconductive film technology field, which contains high temperature superconductive microstrip filter, 3db mixing coupler and two single end reflection filter, is a plane microstrip structure and adapts for making phase equalization and reducing phase distortion to the high temperature superconductive filter of RF front end in satellite receiving system and receiving front end in base station of mobile communication system. Said invention is integrated in one medium substrate and has more stable performance.

Owner:NANKAI UNIV

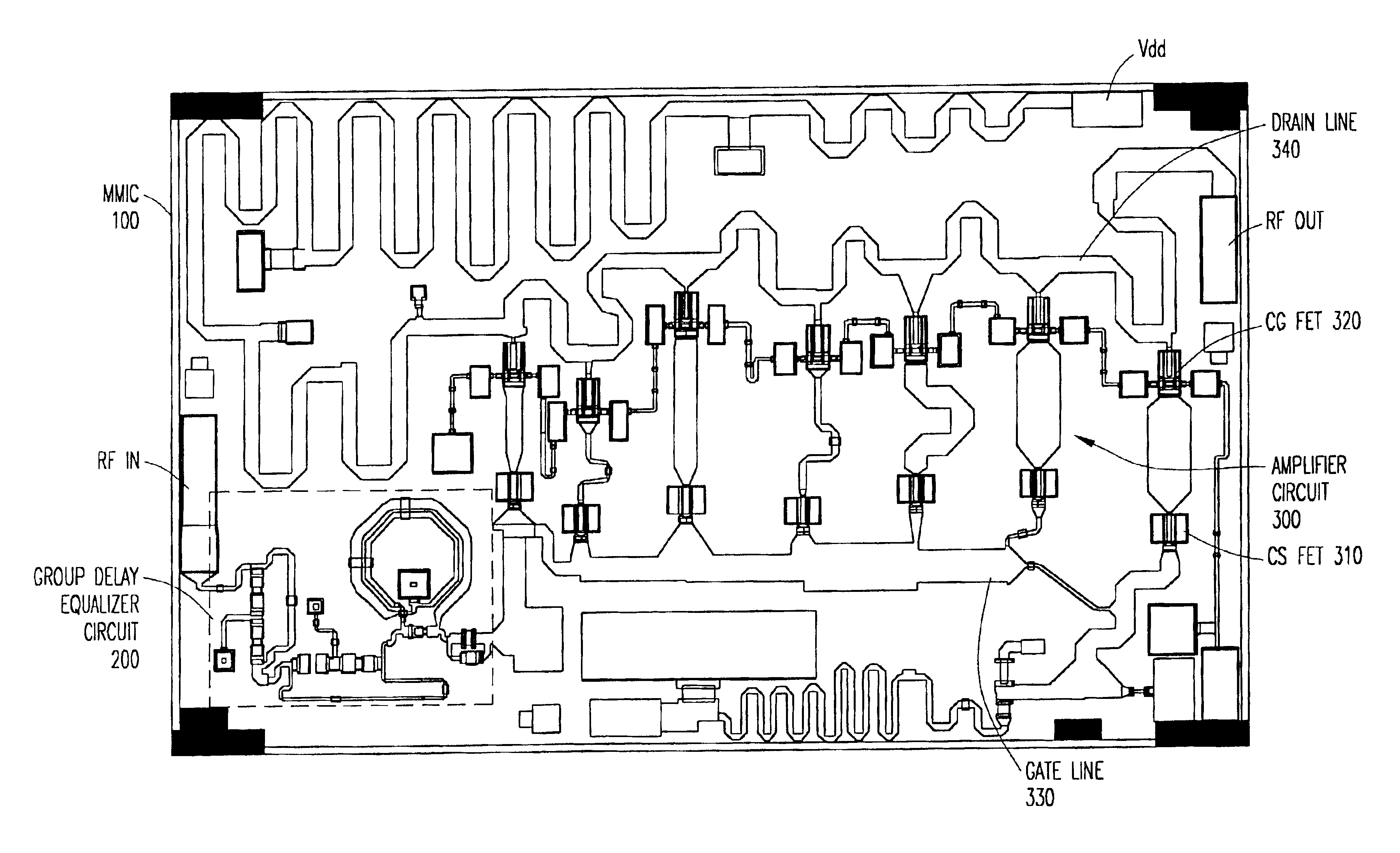

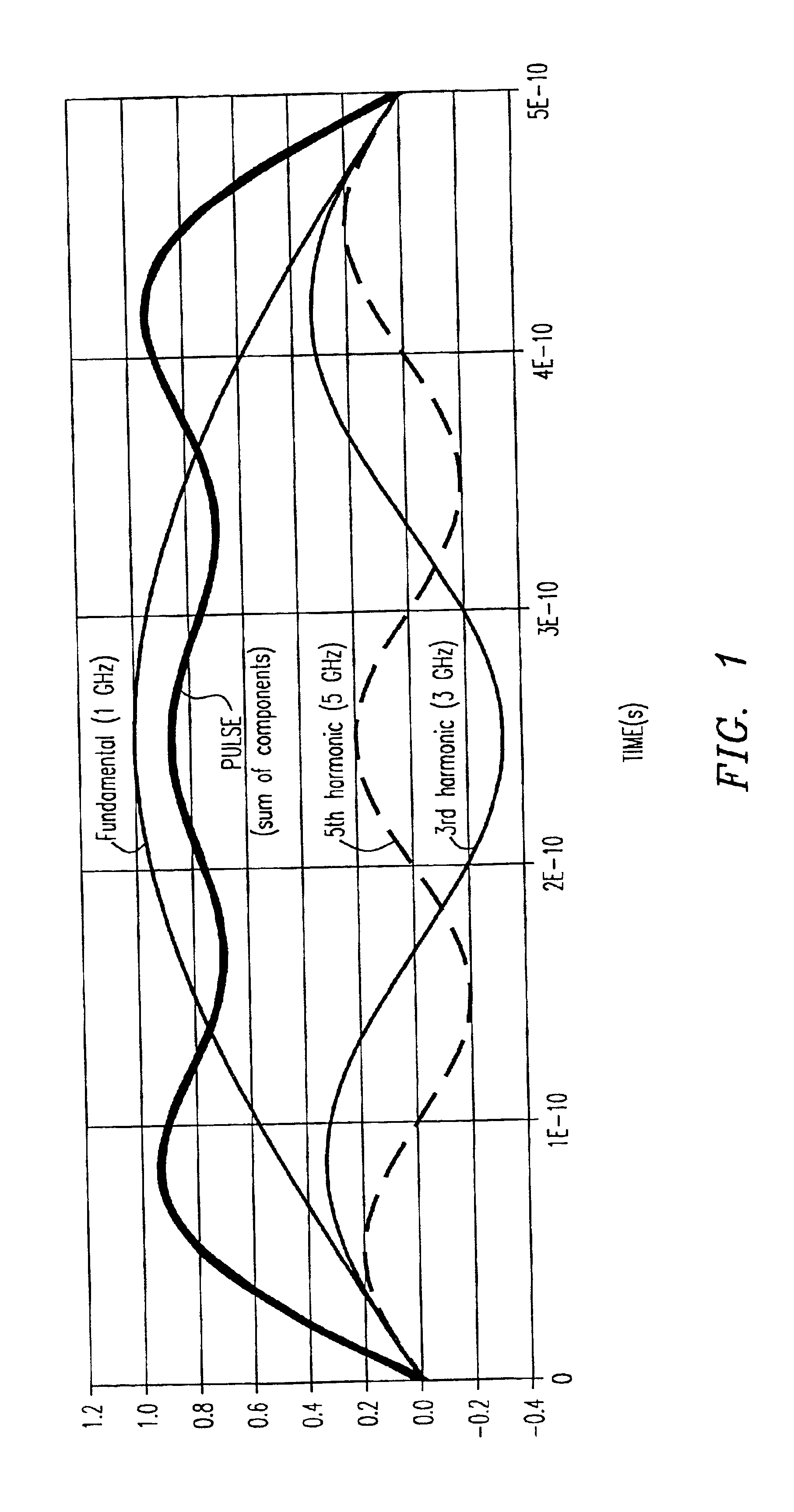

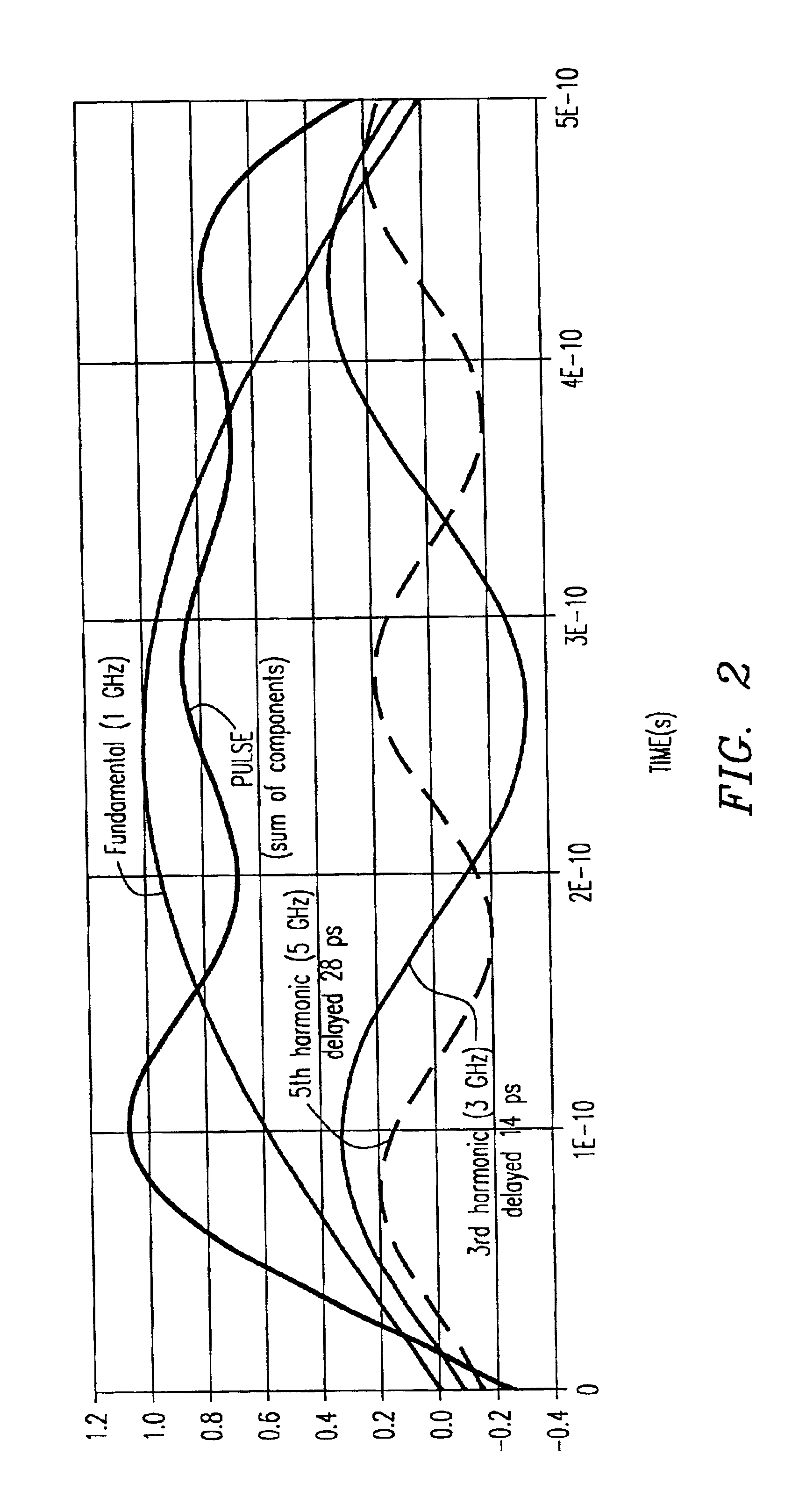

Group delay equalizer integrated with a wideband distributed amplifier monolithic microwave integrated circuit

InactiveUS20030141941A1Transmission control/equlisationAmplifiers wit coupling networksDistributed amplifierAudio power amplifier

A wideband distributed or feedback amplifier monolithic microwave integrated circuit (MMIC) is disclosed that contains an integrated group delay equalizer circuit to compensate for the group delay variation of the amplifier circuitry. The MMIC amplifier is capable of achieving a predicted constant group delay with little variation over a wide frequency range. In addition, the group delay equalizer circuit enables the amplifier to achieve flat (constant) gain over a wide bandwidth, while maintaining constant group delay. Furthermore, the group delay equalizer circuitry requires only a small portion of the total MMIC area.

Owner:REMEC DEFENSE & SPACE INC +1

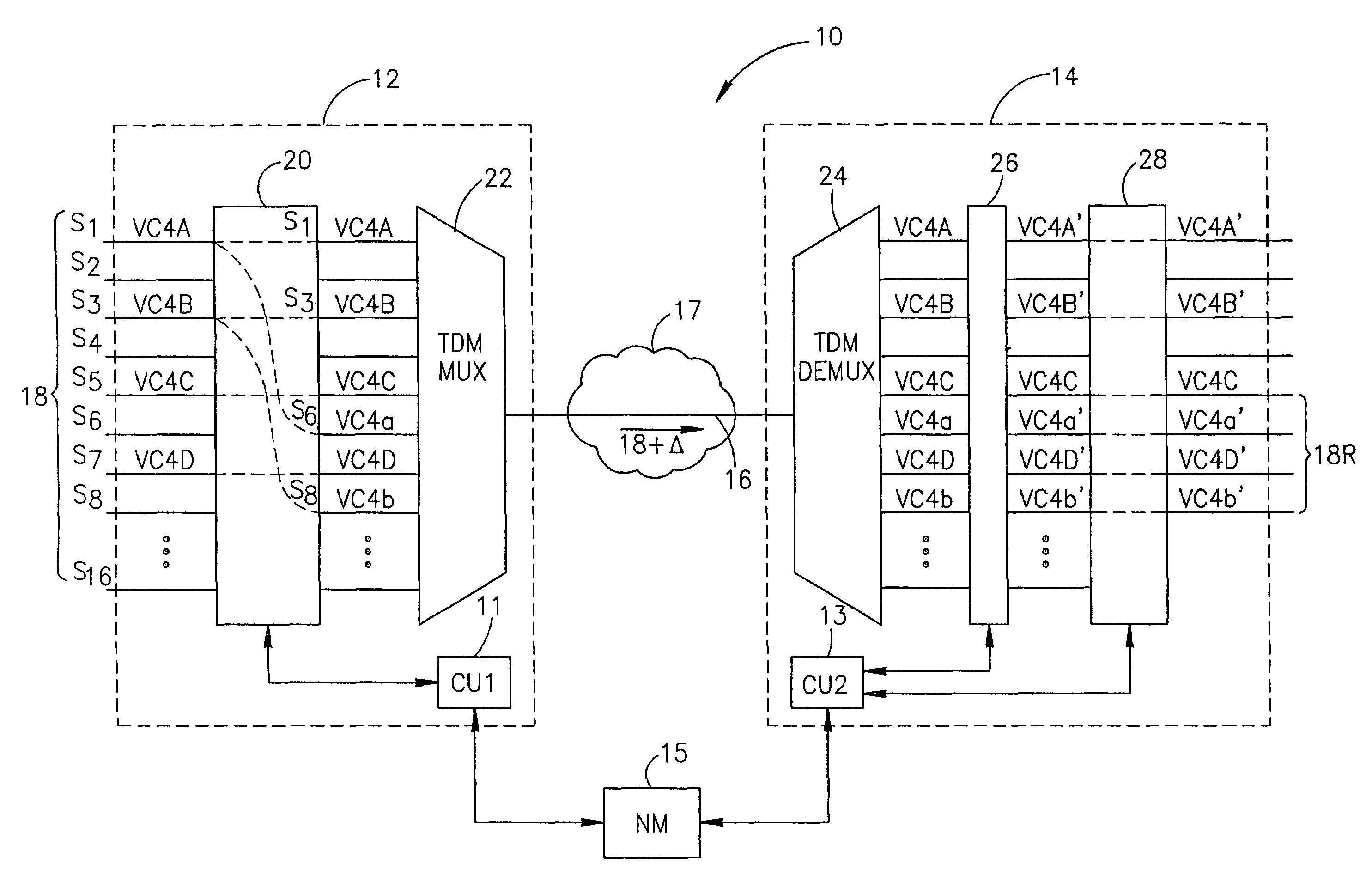

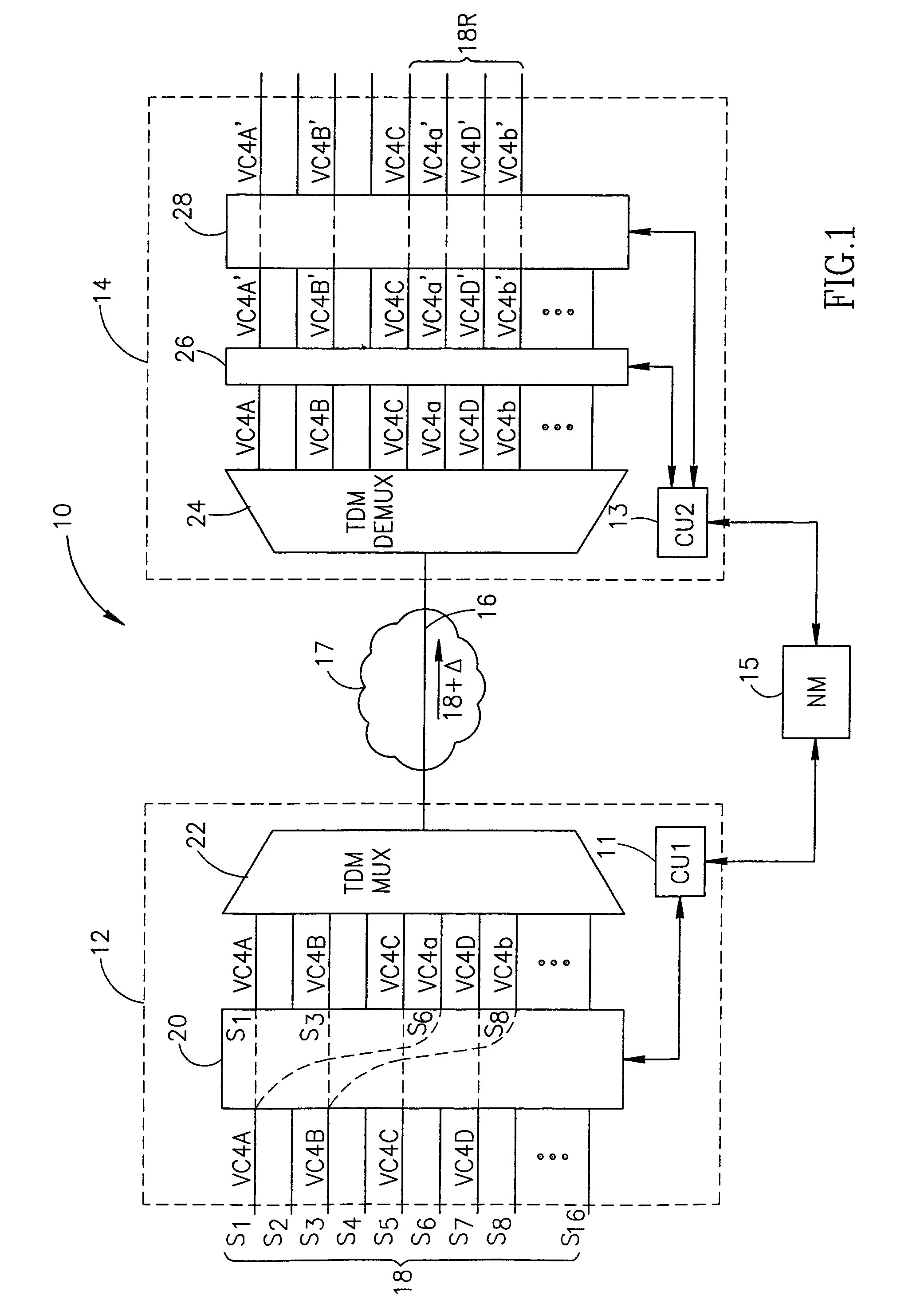

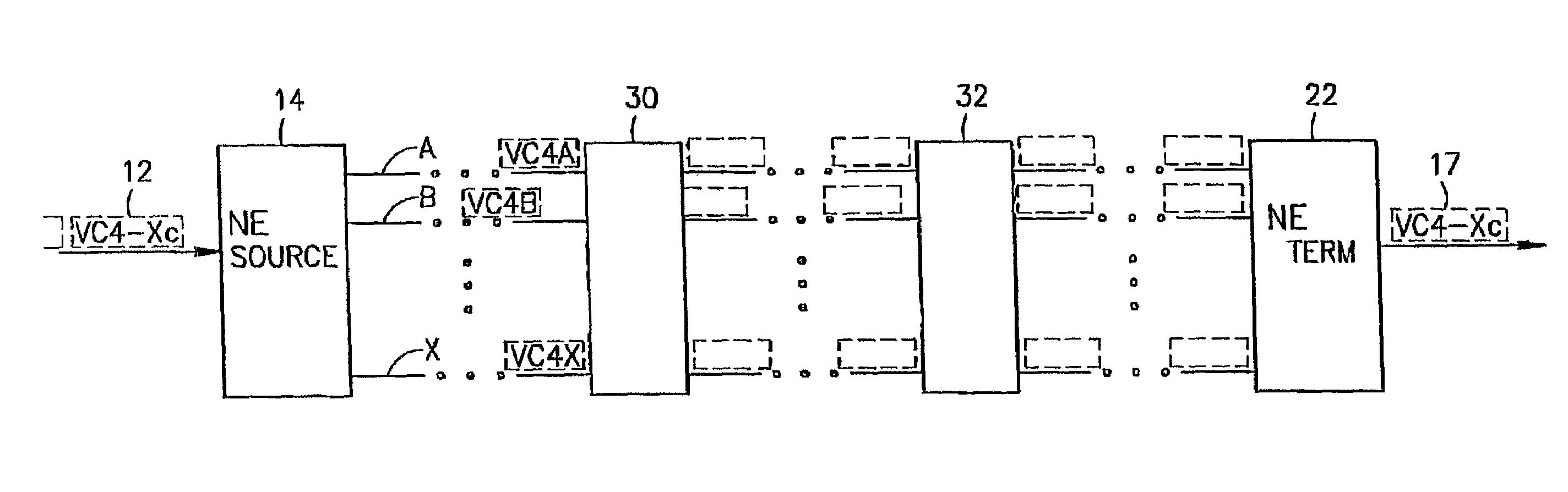

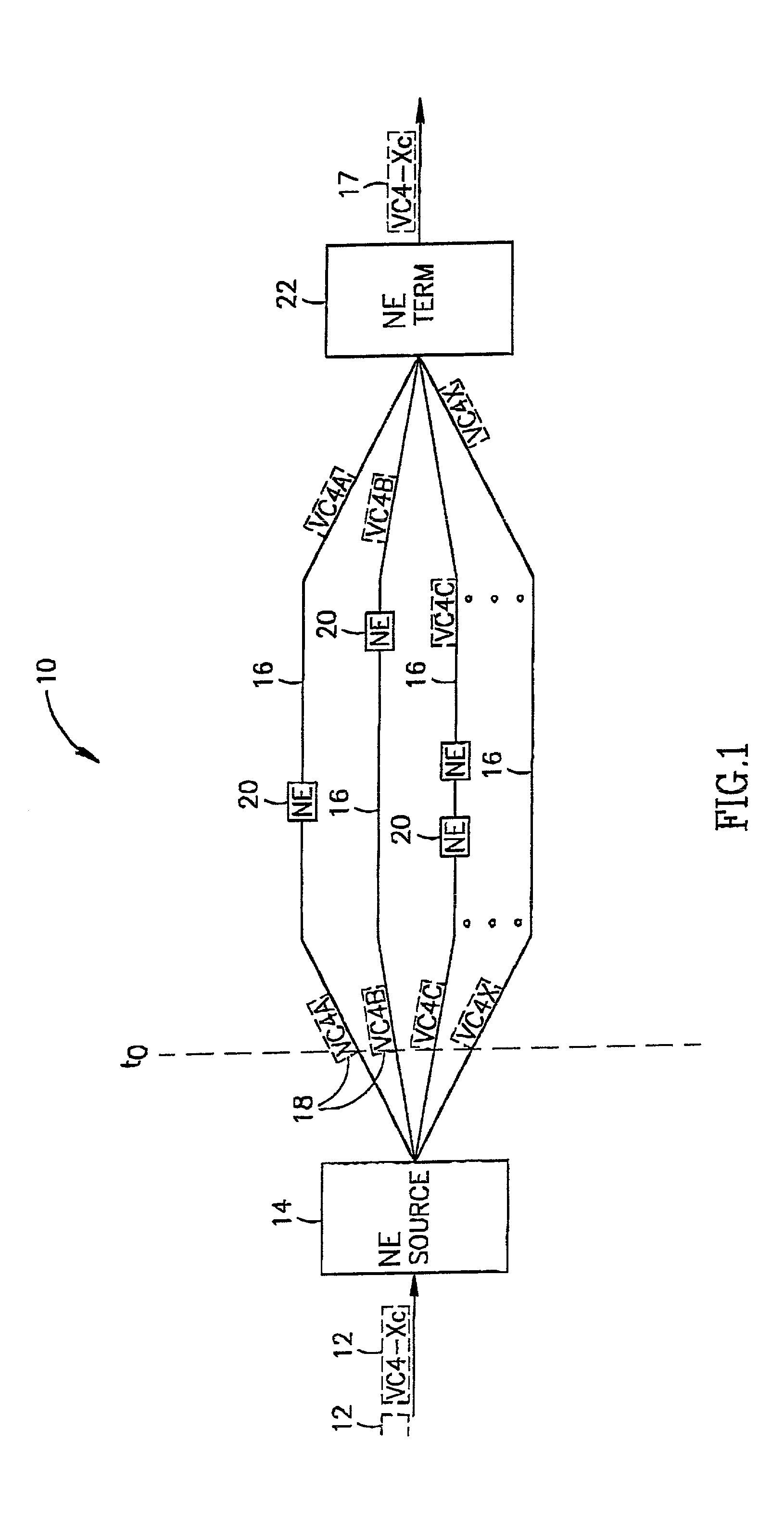

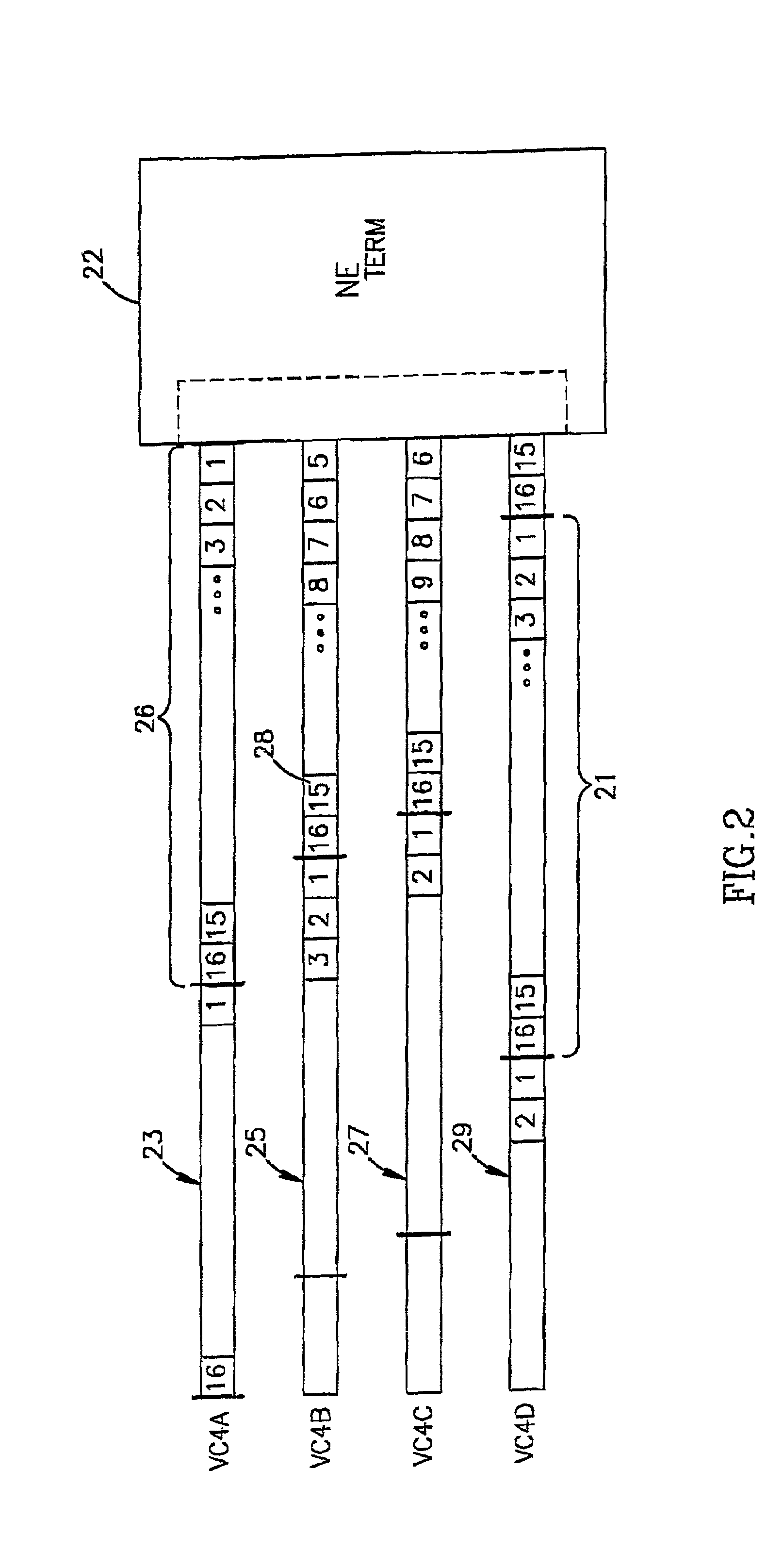

Rearrangement of data streams

InactiveUS7023848B2Time-division multiplexData switching by path configurationTelecommunications networkData stream

A method and a system for errorless switching, in a telecommunication network, from a basic data stream to a copy of the basic data stream obtained by bridging of the basic data stream at a first network node, being characterized in that the switching is performed at a second network node receiving both the basic data stream and the copy data stream, upon performing an operation of delay equalization between the basic data stream and the copy data stream.

Owner:ECE TELECOM LTD

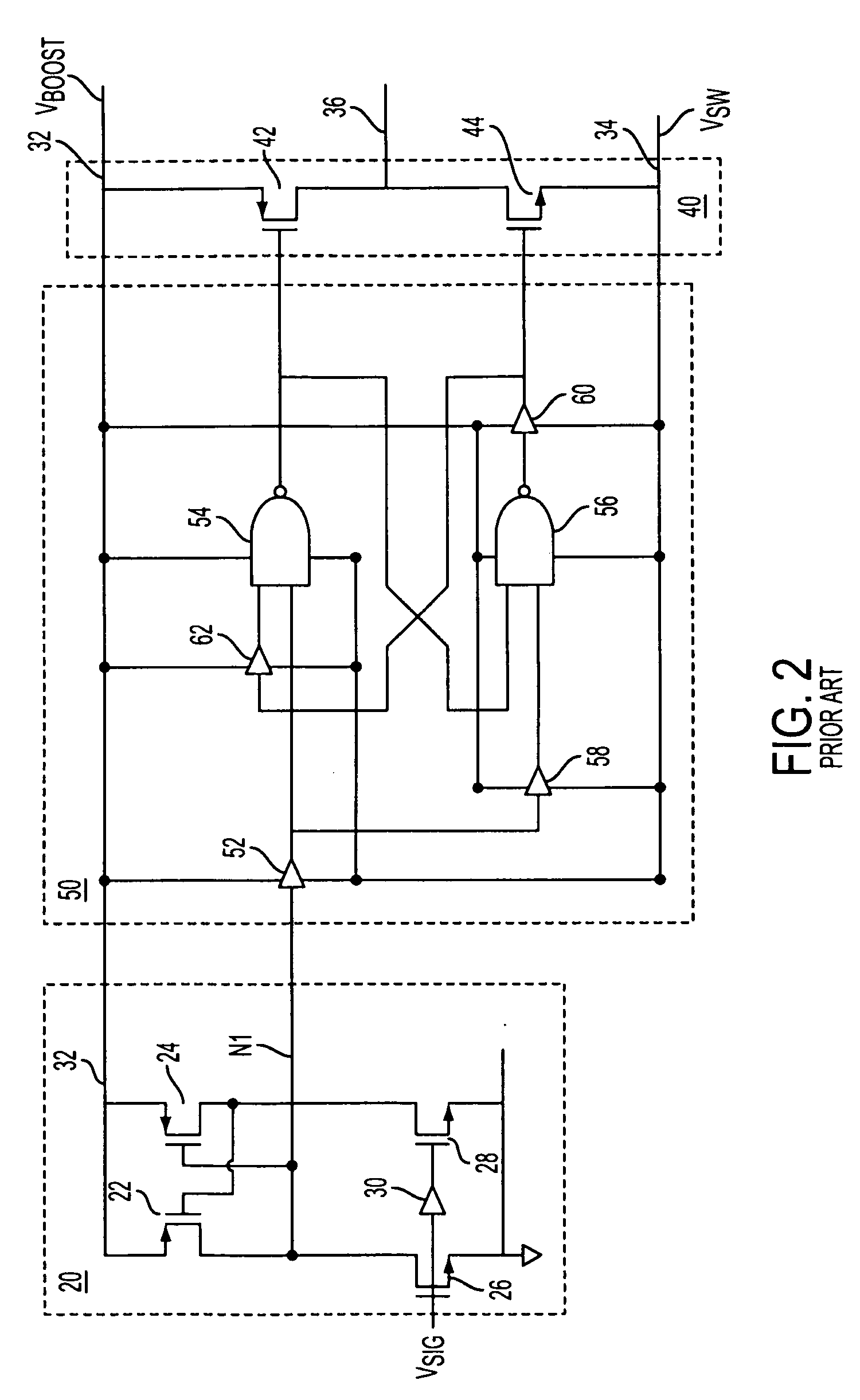

Level shift delay equalization circuit and methodology

ActiveUS20070146007A1Power reduction in field effect transistorsPulse automatic controlState dependentSignal transition

Transition delays in a level shift circuit are equalized by generating a first signal related to the state of the input signal, a second signal inversely related to the state of the input signal, and a third signal that is reciprocal to the second signal. Upon transition of the input signal from a high state to a low state, the third signal is selected for controlling the output until the first signal attains a high state. The first signal is selected for controlling the output when it has reached a high state after the input signal transition. The first signal remains selected upon transition of the input signal from a high state to a low state. Thus, output delays are equalized and reduced to the shortest delay.

Owner:ANALOG DEVICES INT UNLTD

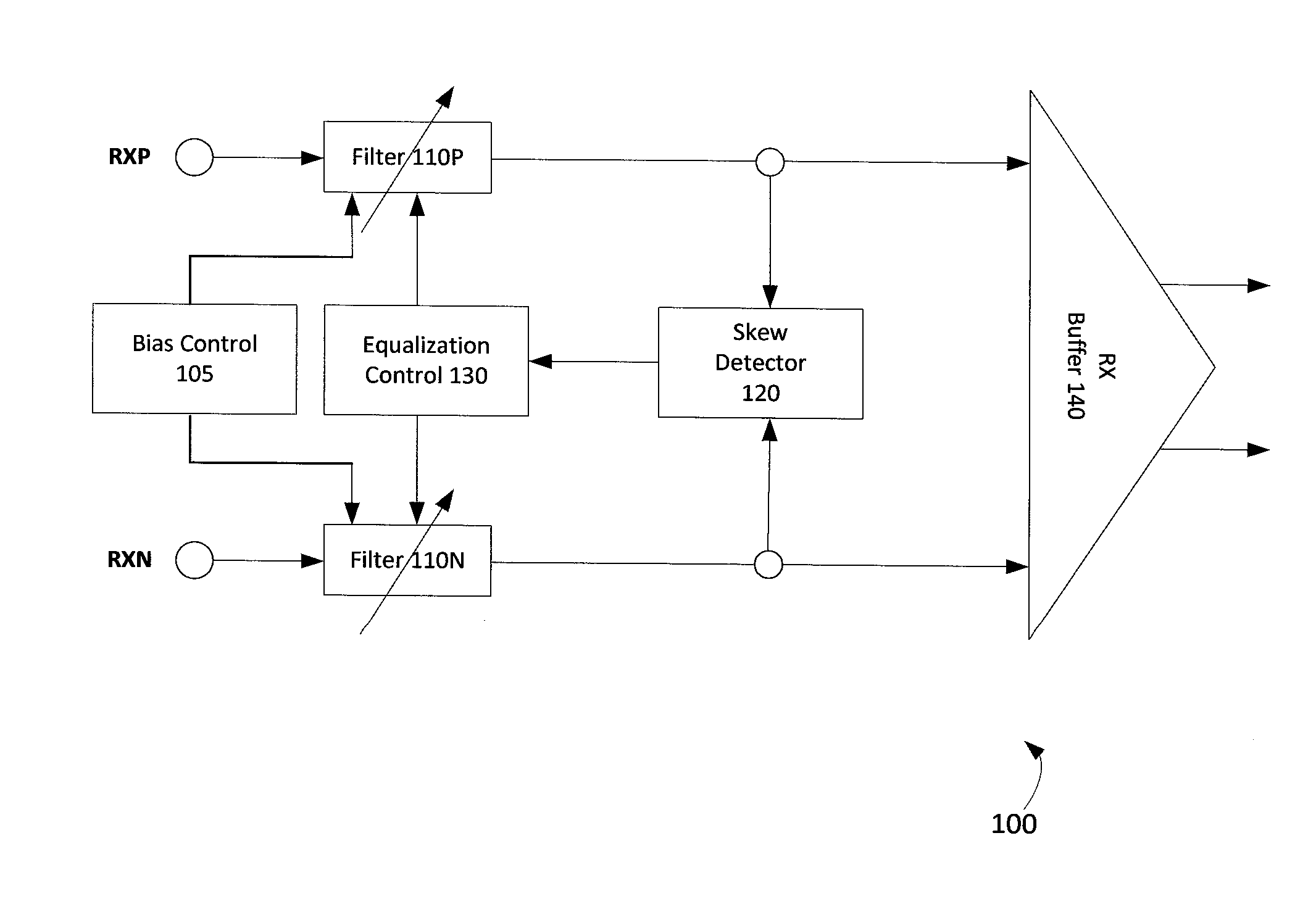

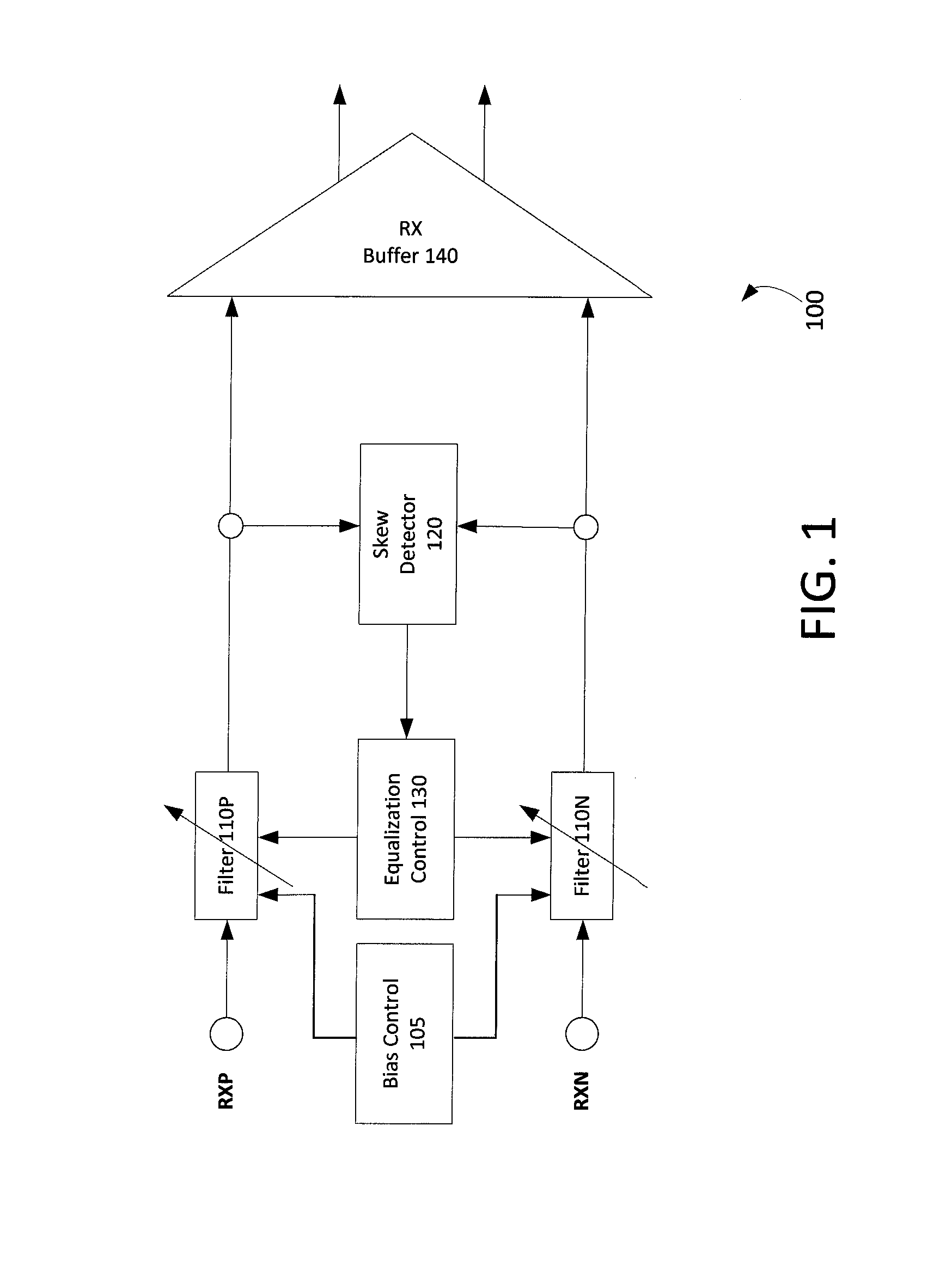

Apparatus and methods for adaptive receiver delay equalization

Disclosed are apparatus and methods for adaptive receiver delay equalization. One embodiment relates to a method for adaptive receiver delay equalization. Filtered positive and negative polarity signals are generated by a first variable-delay filter and a second variable-delay filter, respectively. A delay difference is determined between the filtered positive and negative polarity signals, and a skew-indication signal is generated based on the delay difference. A delay control signal is generated based on the skew-indication signal, and the delay control signal is sent to at least one of the first and second variable-delay filters. Other embodiments and features are also disclosed.

Owner:ALTERA CORP

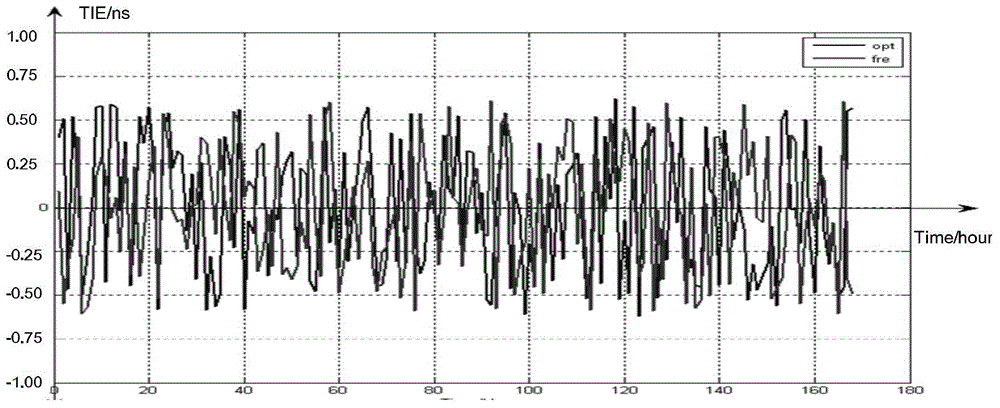

Automatic optical fiber transmission delay locking and equalization method

ActiveCN104426600AEffectively filter out jitter noiseReal-time measurementTime-division multiplexTransmission monitoring/testing/fault-measurement systemsUltrasound attenuationNarrow range

Owner:四川泰富地面北斗科技股份有限公司

Method, device and system for delay equalizing in high rate data streams

InactiveUS7058056B2Minimize and equalize delay differenceError preventionTransmission systemsHigh rateData stream

A method, a device and a system for delay equalizing of fragment data streams transmitted via N individual paths and forming a virtual data stream, wherein the virtual data stream and each of said fragment data streams consisting of data frames; the method including gradual minimization of differential delay of the fragment data streams at one or more intermediate points between a source point and a destination point of the virtual data stream. The gradual minimization of the differential delay can be provided by devices (30, 32) respectively fitted at the intermediate points; each of the devices comprises a control unit (36) and N memory buffer blocks (34), each associated with a respective individual path.

Owner:ECE TELECOM LTD

System and method for switch mode power supply delay compensation

ActiveUS20100002472A1Avoid oscillationContinuous operationDc-dc conversionElectric variable regulationPropagation delayTurn on time

A delay applied to a turn-on time for a high side switch in a switch mode power converter prevents oscillation between continuous and discontinuous conduction modes under light load conditions. The delay equalizes turn-on time for a high side switch with respect to continuous and discontinuous modes, so that turn-on time is not treated differently between the different modes. The delay value can be set for be equivalent to a propagation delay through a driver for a low side switch, in addition to a turn-off time for the low side switch. The addition of the delay element tends to maintain the switch mode power converter in a discontinuous mode under light load conditions and avoids oscillation between discontinuous and continuous conduction modes.

Owner:TEXAS INSTR INC

Group delay equalizer integrated with a wideband distributed amplifier monolithic microwave integrated circuit

InactiveUS6801098B2Transmission control/equlisationOne-port networksDistributed amplifierAudio power amplifier

A wideband distributed or feedback amplifier monolithic microwave integrated circuit (MMIC) is disclosed that contains an integrated group delay equalizer circuit to compensate for the group delay variation of the amplifier circuitry. The MMIC amplifier is capable of achieving a predicted constant group delay with little variation over a wide frequency range. In addition, the group delay equalizer circuit enables the amplifier to achieve flat (constant) gain over a wide bandwidth, while maintaining constant group delay. Furthermore, the group delay equalizer circuitry requires only a small portion of the total MMIC area.

Owner:REMEC DEFENSE & SPACE INC +1

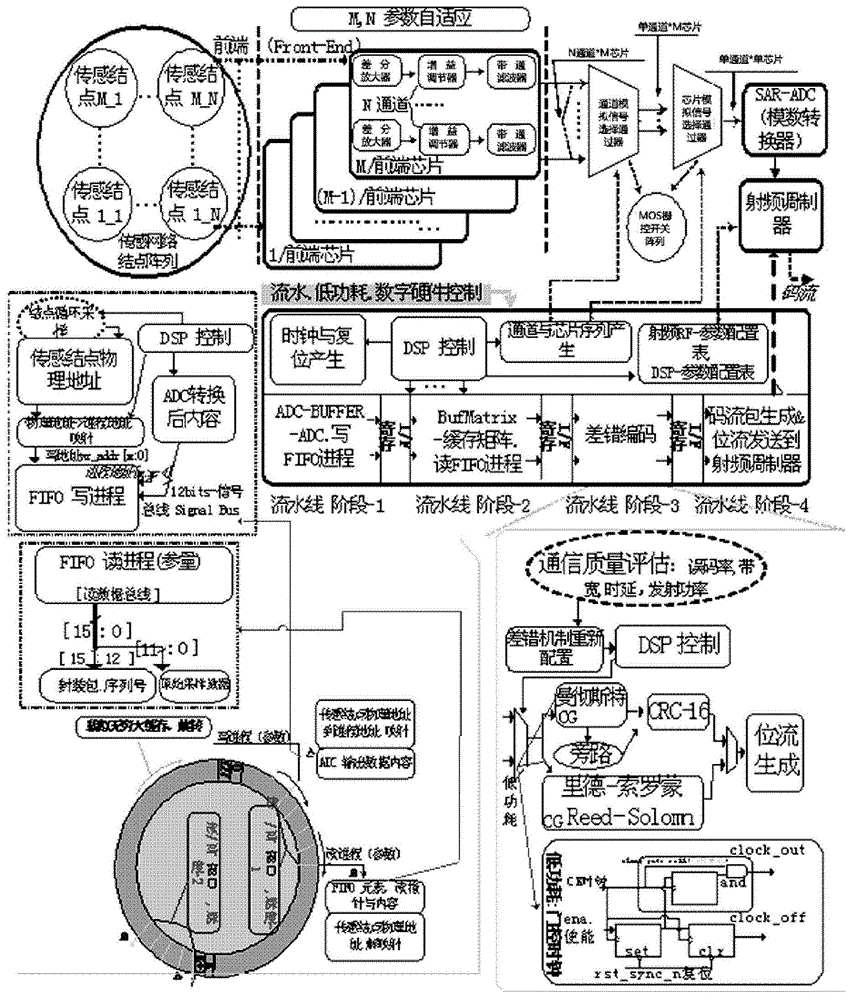

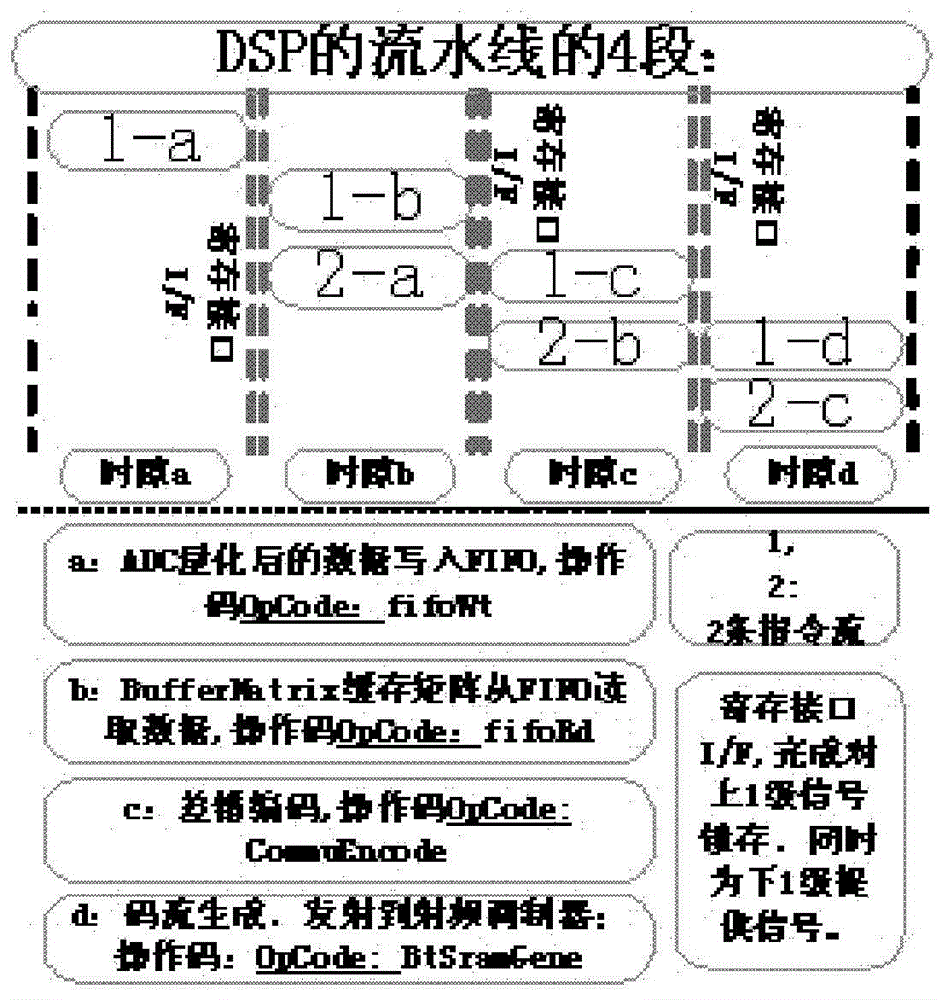

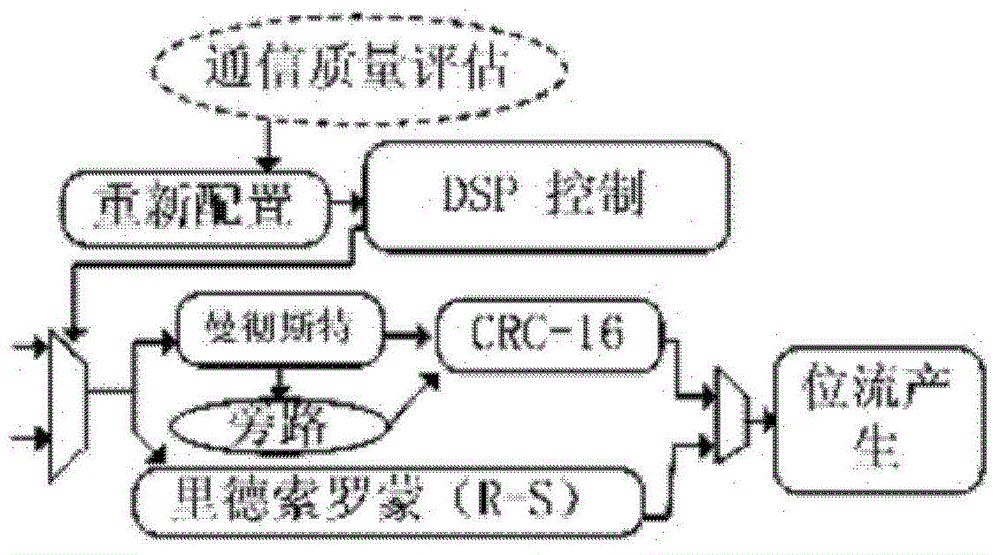

Four stage flow line digital signal processor and wireless on-chip system chip with same

ActiveCN104545902ALower latencyNo riskDiagnostic signal processingSensorsVIT signalsDelay equalization

The invention discloses a four stage flow line digital signal processor (DSP) and a wireless on-chip system chip with the same. The DSP adopts a four stage low power consumption flow line structure allowing delay equalization. The structure includes (1) an ADC quantization data write FIFO buffer process; (2) a ping-pong switch matrix read FIFO process; (3) wireless channel differential coding; (4) bit stream generation and transmission. The SOC can be configured into a transmitting or receiving mode through the DSP, and analog signals of front end OPA and BPF are selected by a multiplexer to transmit to an ADC for analog to digital conversion. The DSP and SOC chip flow mechanism is free of delayed bubbles and hazards and is convenient to expand; the flow line structure is low in power consumption, chip power consumption is reduced by the clock gating technique, and the subjective real-time evaluation is not affected by the multi-stage flow line.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

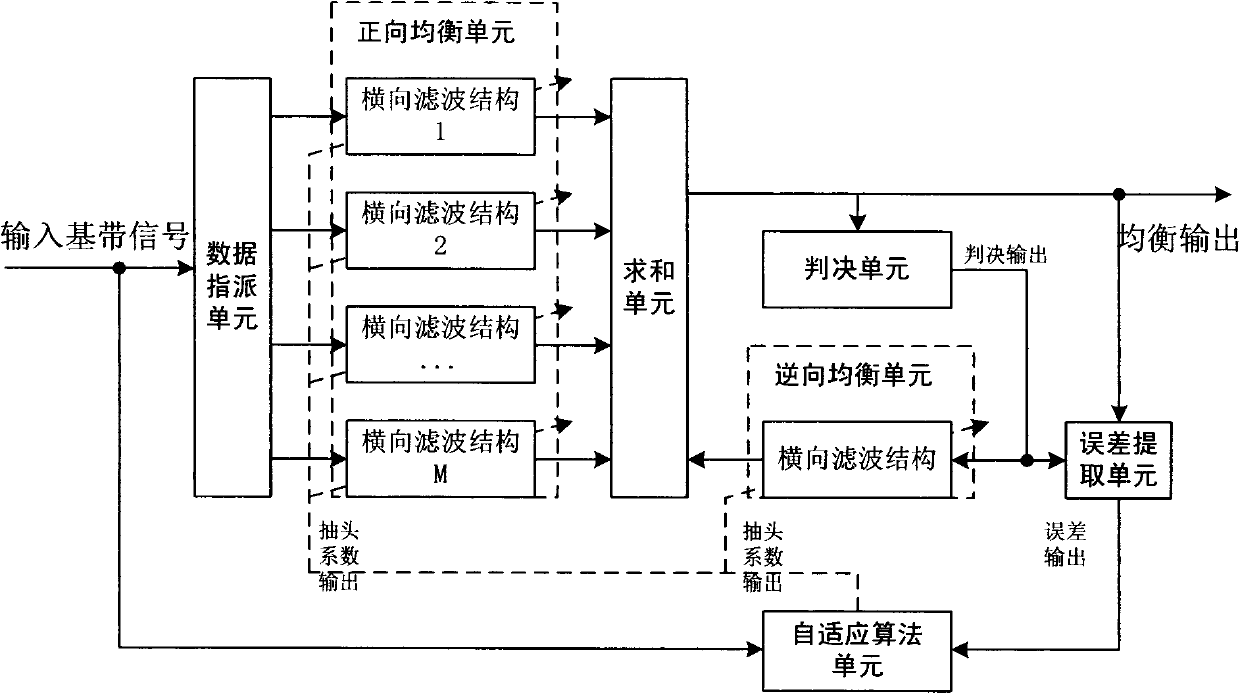

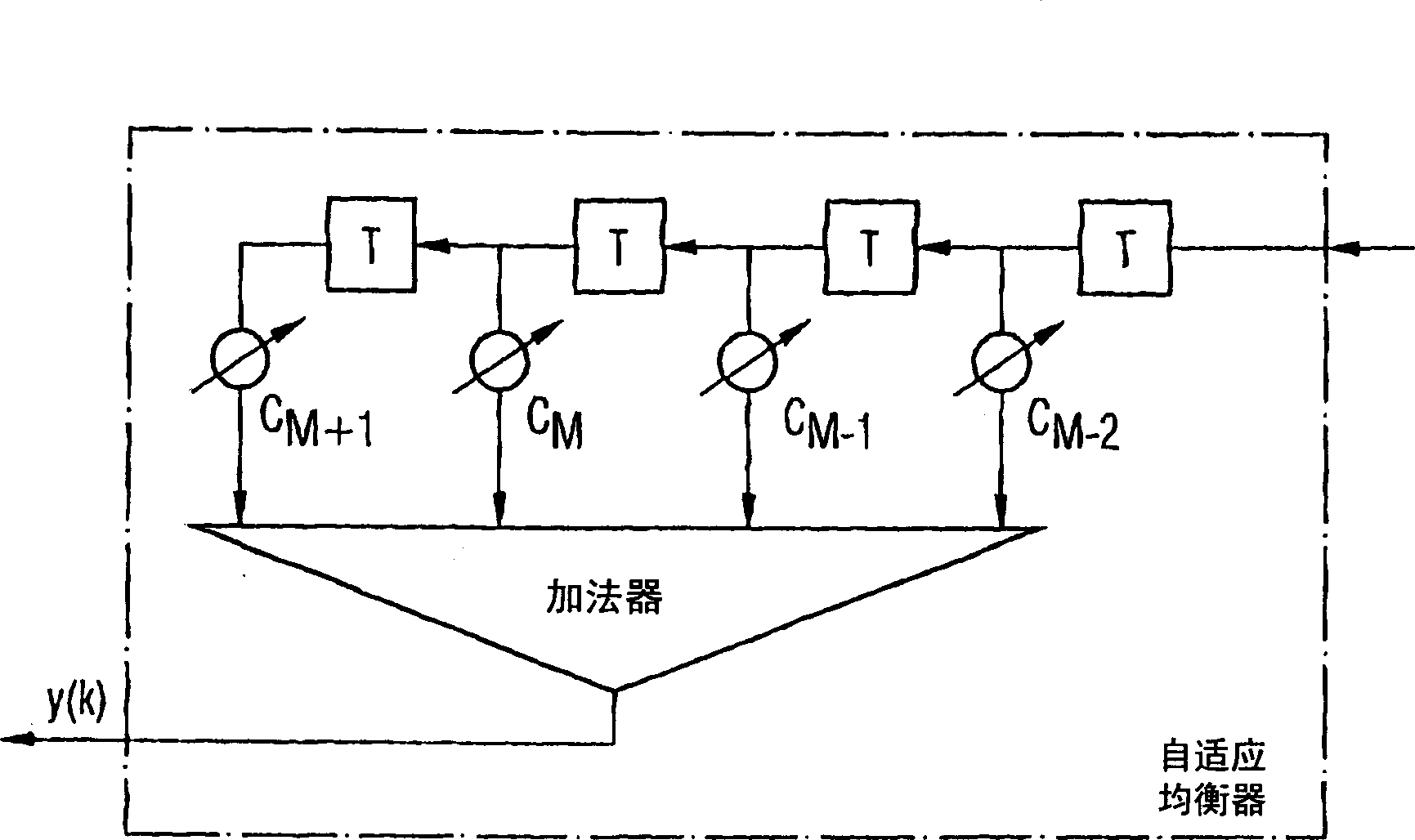

Method for carrying out equalization on 100M magnitude broadband reception signal

InactiveCN102594374AImprove adaptabilityHigh speedEnergy efficient ICTTransmitter/receiver shaping networksBlind equalizationTime domain equalization

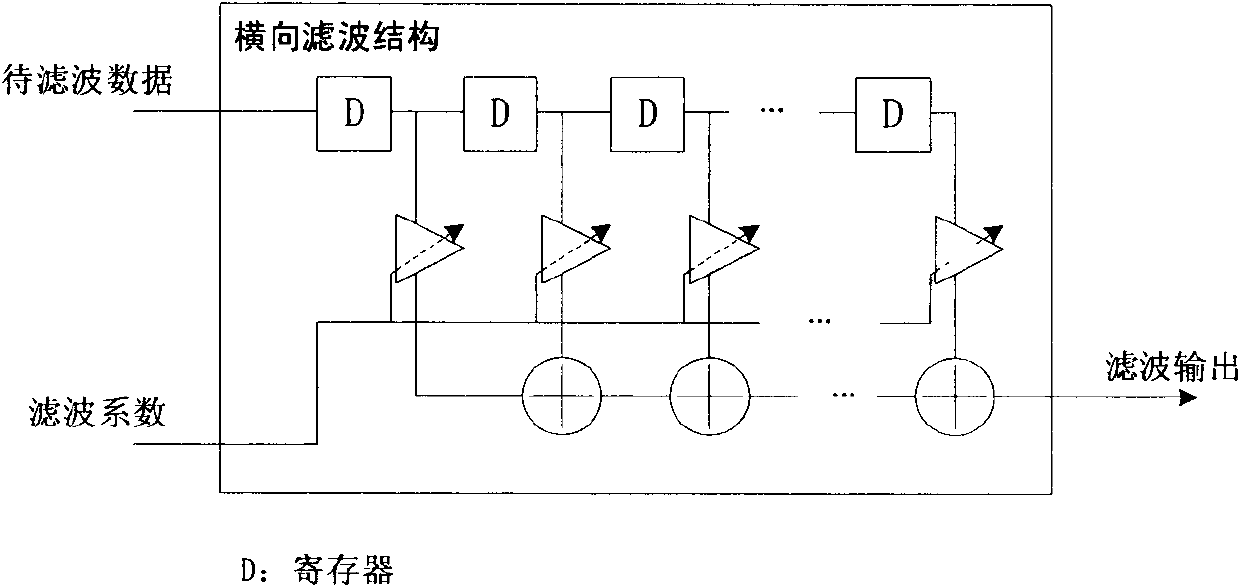

The invention provides a method for carrying out equalization on a 100M magnitude broadband reception signal, and is aimed at providing a method for using a simple time domain parallel structure to carry out time domain equalization on the broadband signal with small resource consumption, a fast operation speed, and no need of changing a transmission system. The method is realized through the following technical scheme: (1) employing a fraction interval adaptive blind equalization digital logic circuit with decision feedback, and receiving over-sampling baseband signal to be equalized in parallel; (2) carrying out addition of output of all transverse filtering structures as equalization output, and sending the baseband signal to be equalized into the transverse filtering structures in a forward direction equalization unit according to a corresponding phase relationship; (3) judging an equalization output result with a decision unit, and solving an error signal e(n) of the output result and a decision result; after e(n) is adjusted through an error convergence factor, carrying out gradient estimation and equalization coefficient updating, and sending an updated equalization coefficient to each transverse filtering structure to carry out an equalization operation. According to the method, contradiction between generating the equalization results and carrying out the equalization coefficient updating simultaneously in a code element is solved.

Owner:10TH RES INST OF CETC

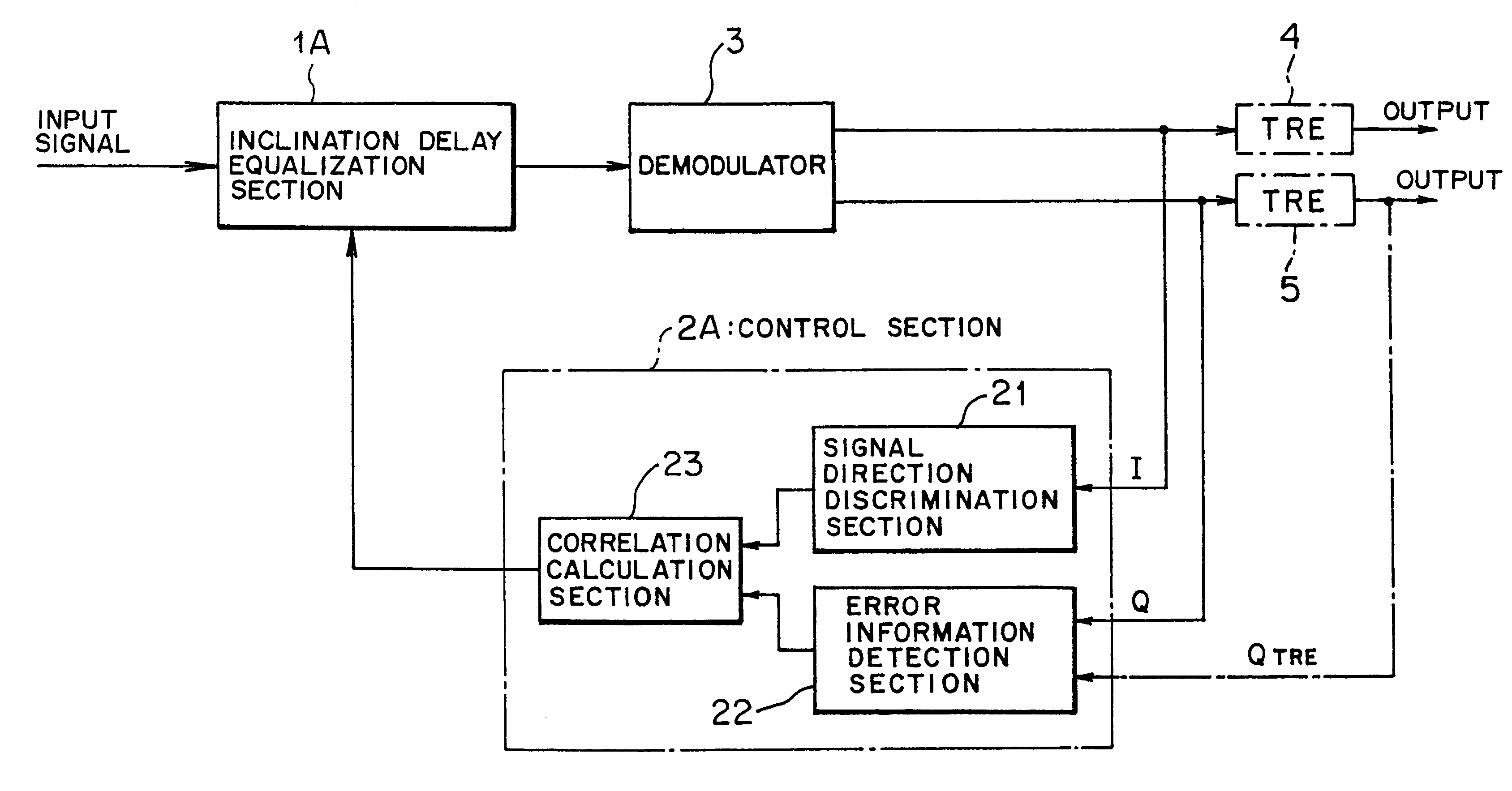

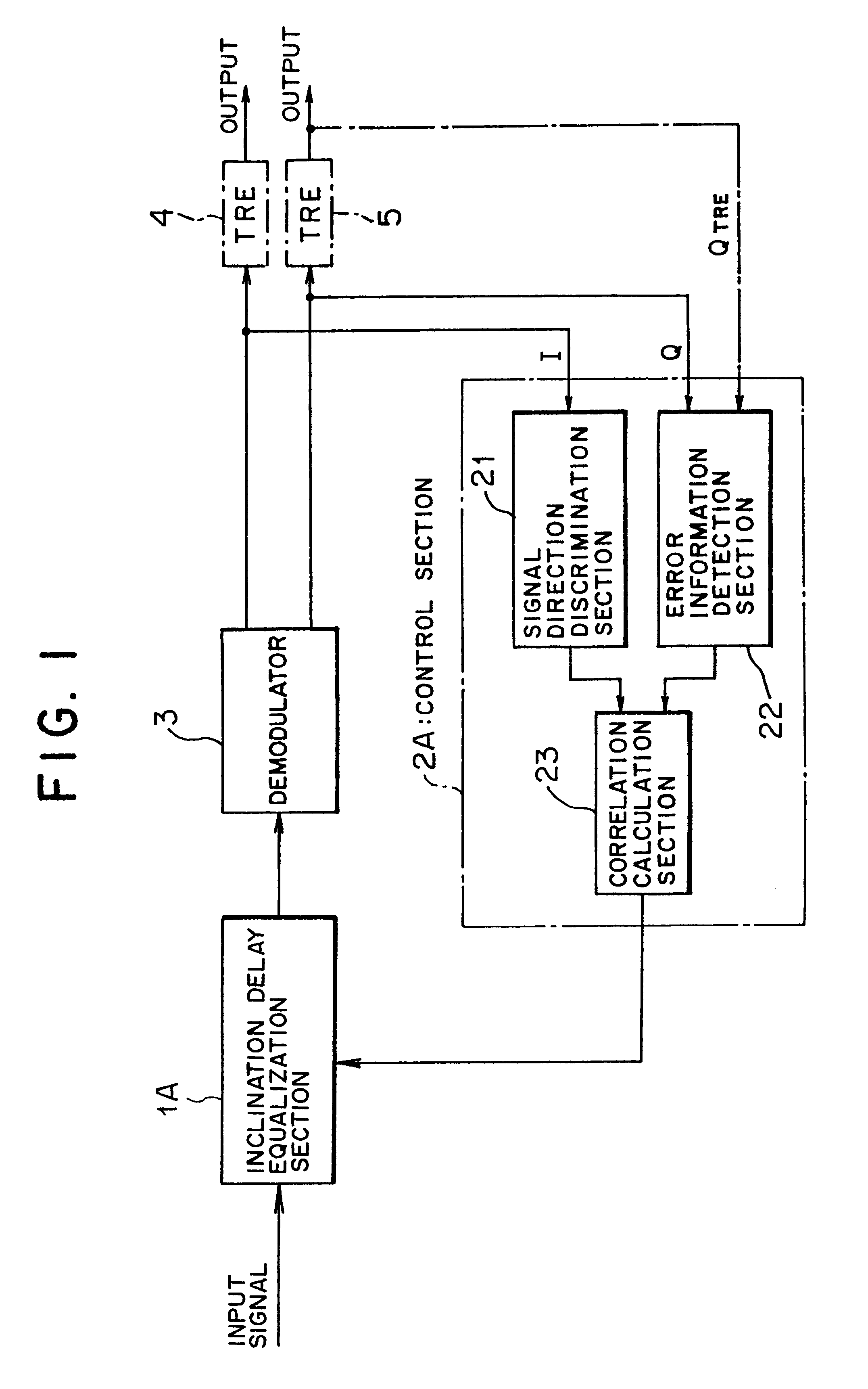

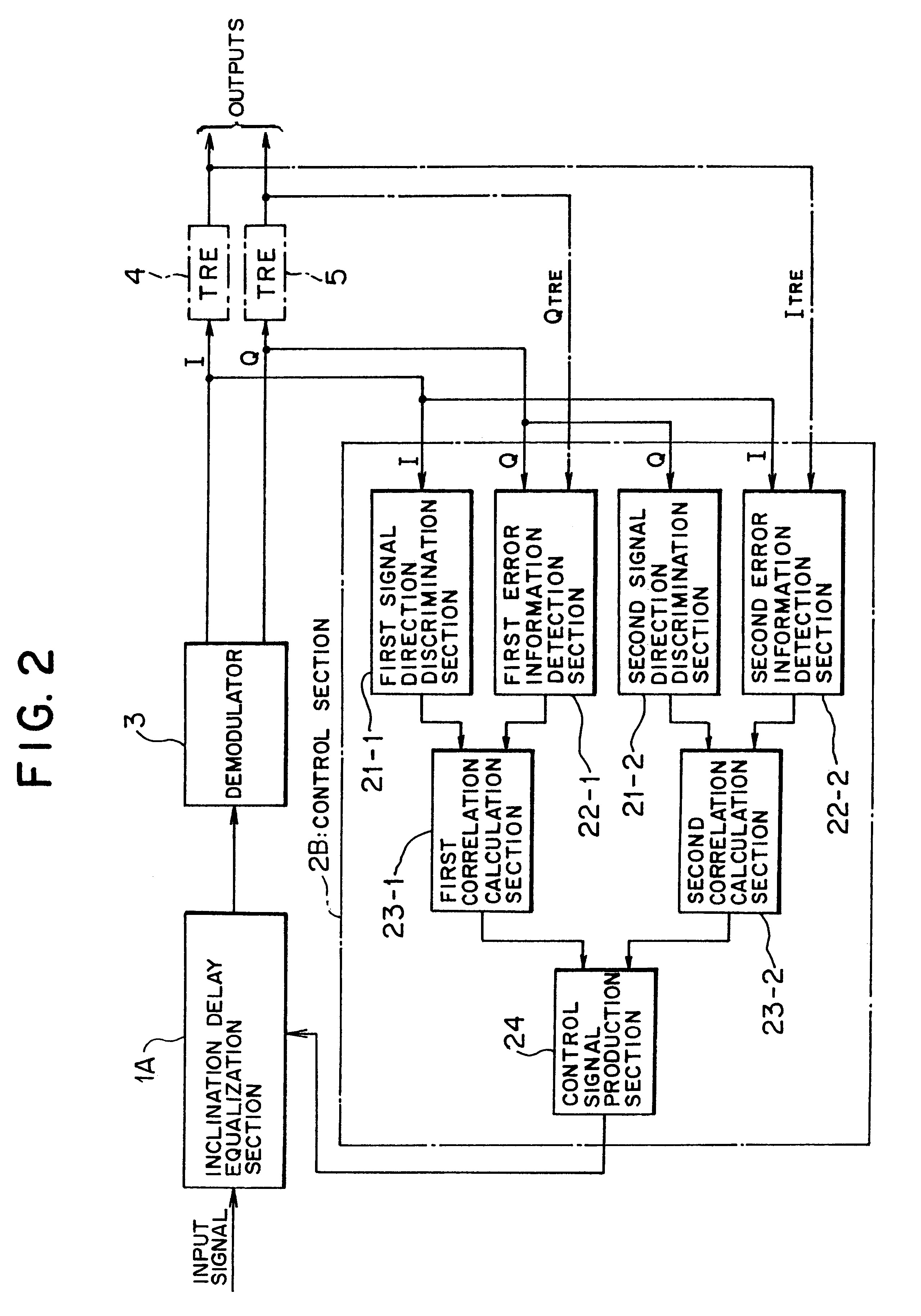

Automatic delay equalizer and automatic delay equalization method as well as automatic delay and amplitude equalizer and automatic delay and amplitude equalization method

InactiveUS6516028B1Delay characteristicSmall sizeMultiple-port networksTransmission control/equlisationControl signalEqualization

The invention provides an automatic delay equalizer and an automatic delay equalization method which can detect a delay characteristic (delay distortion) of an input signal and automatically compensate for the delay characteristic. The equalizer includes an inclination delay equalization section for compensating for the delay characteristic of the input signal in accordance with an inclination delay characteristic, and a control section for discriminating a direction of variation of a value of a first one of a pair of digital demodulated signals of the input signal, detecting error information from a second one of the digital demodulated signals which is orthogonal to the first signal and outputting a control signal for the inclination delay equalization section based on a correlation between the error information and the direction of variation of the value of the first signal.

Owner:FUJITSU LTD

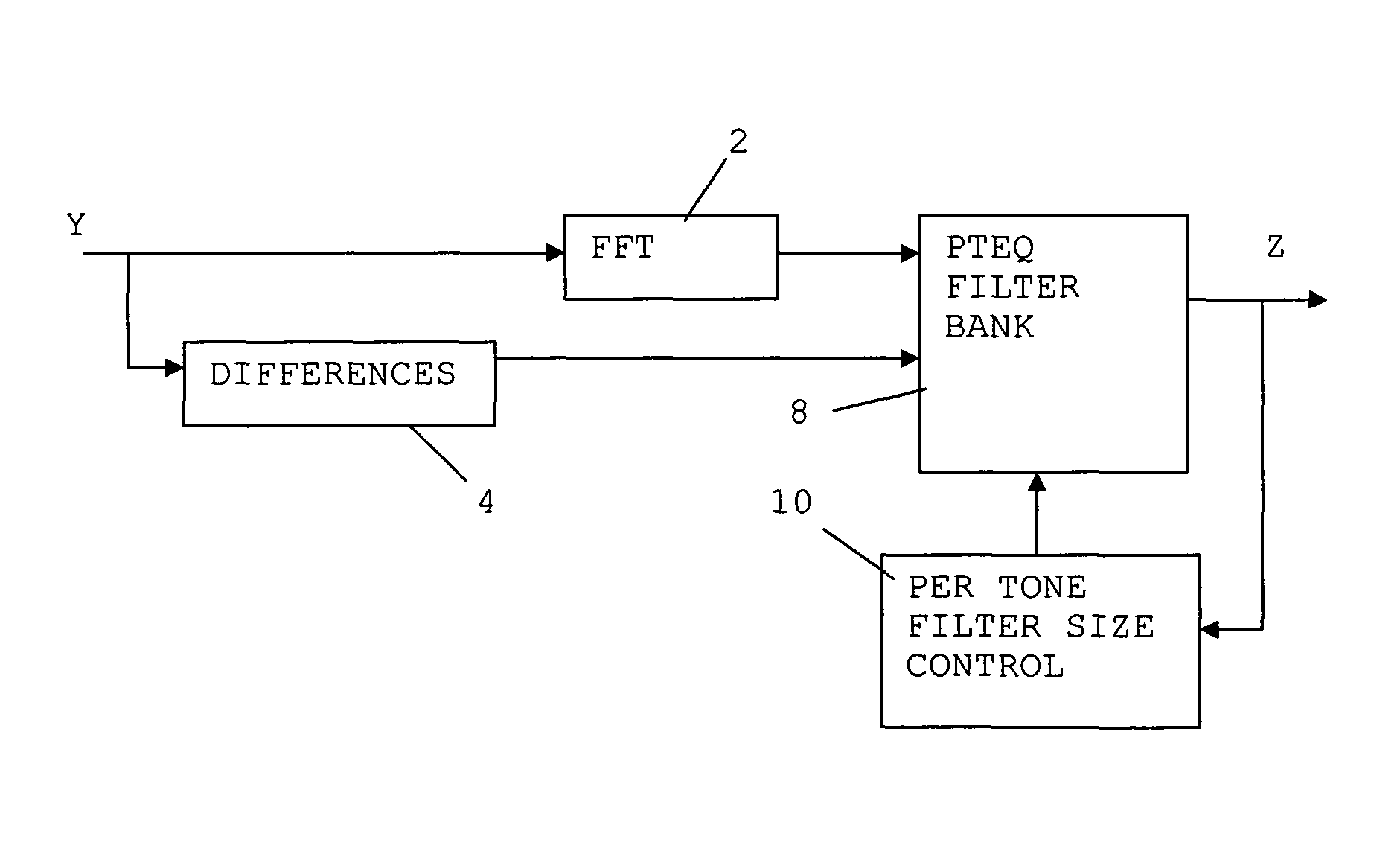

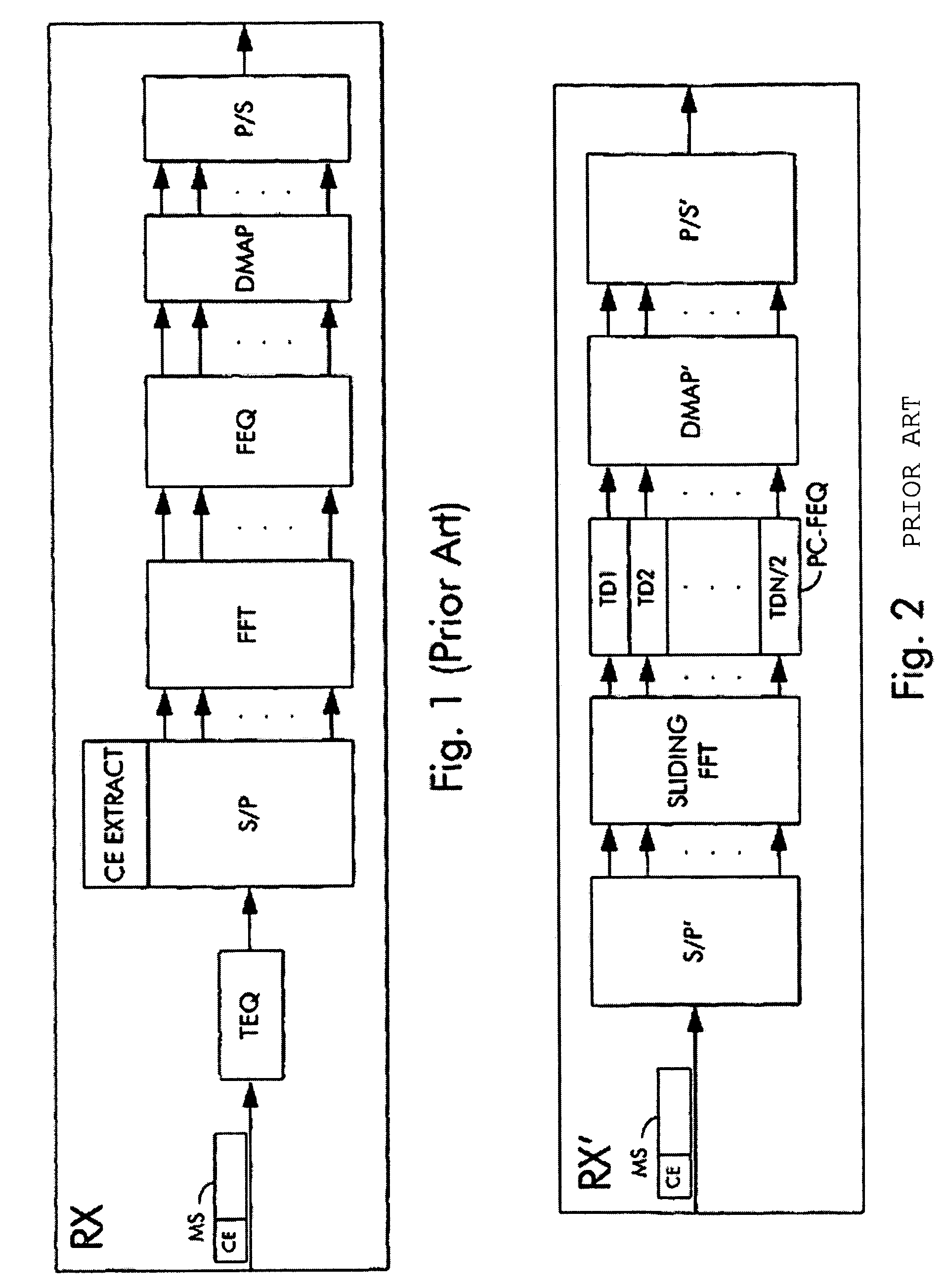

Arrangements and methods for per tone equalization with reduced complexity

ActiveUS8102924B2Improve performanceReduce complexityMultiple-port networksDelay line applicationsAdaptive filterCarrier signal

An equalizer for a multi carrier signal for carrying out equalization adapted to each carrier or group of carriers, Fourier transforms the multi carrier signal, and obtains difference terms of the multi carrier signal. Both are input to an adaptive filter, to output equalized signals, wherein decimation is applied to at least some of the difference terms input to the filter. This enables the complexity to be reduced for a given performance level. In particular since only non-zero filter taps need to be stored and updated, coefficient memory and coefficient calculation capacity can be reduced. Another way to reduce complexity involves measuring noise for at least some of the carriers, and dynamically adapting the size of the filter on a per carrier basis according to global optimizion heuristic algorithms which adapt this filter size based on the comparison between this noise and an optimal performance figure achieved in a previous ISI-ICI free measurement phase.

Owner:STMICROELECTRONICS BELGIUM +1

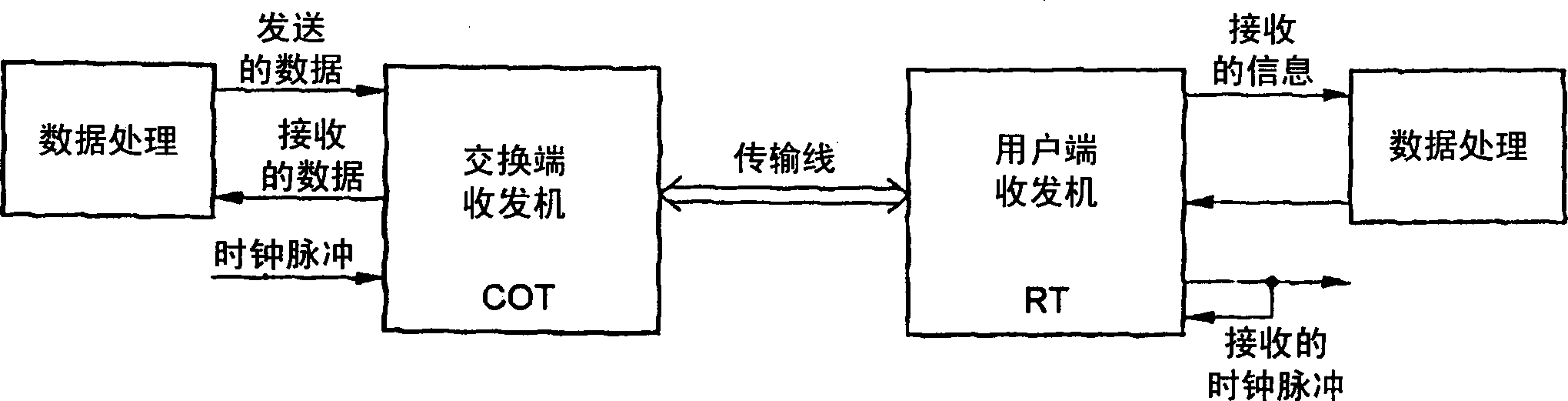

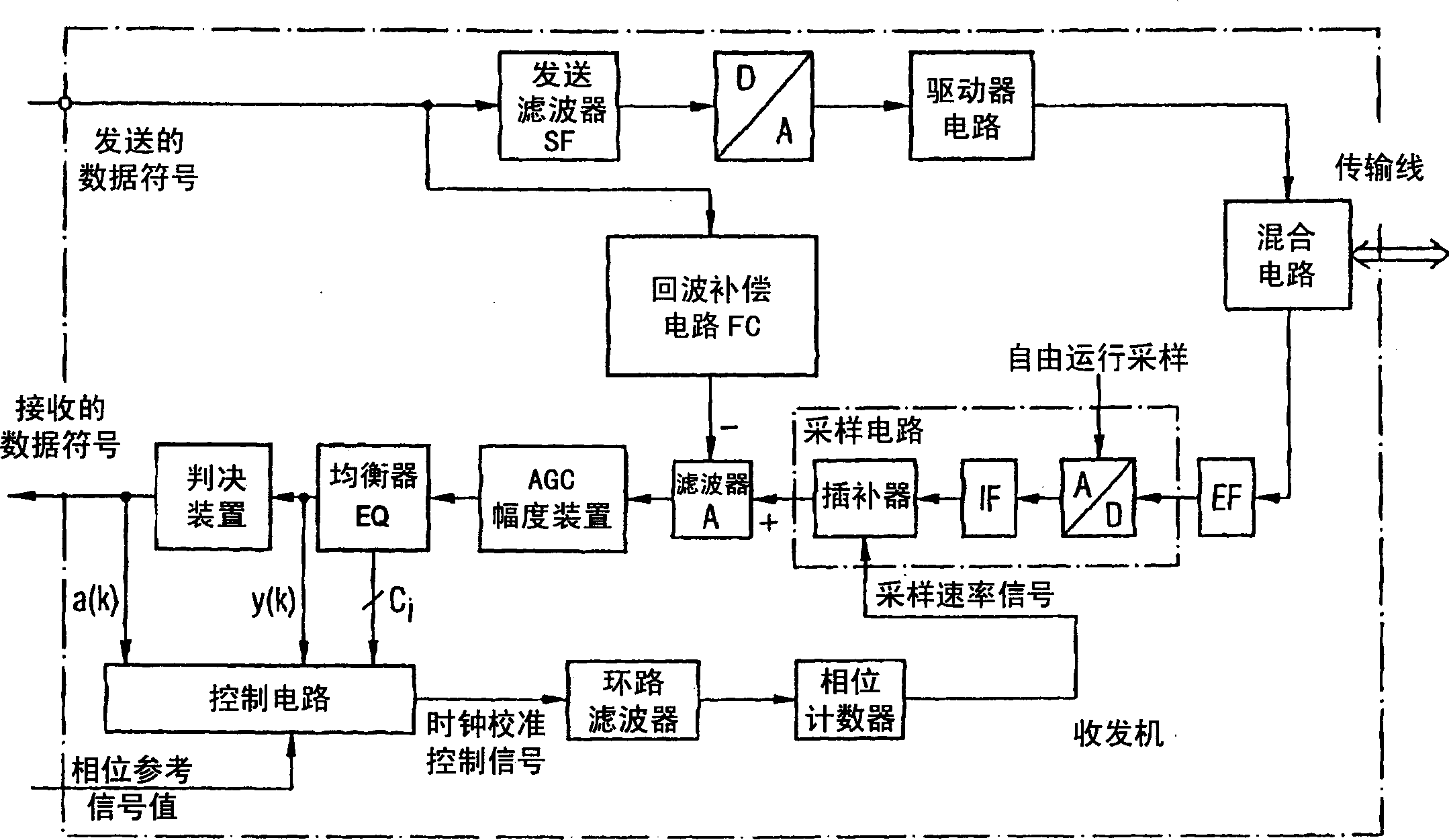

Calculating circuit for calculating sampling phase error

InactiveCN1447556AStability Control ResponseTransmission control/equlisationEqualisersBinary multiplierControl engineering

Owner:INTEL CORP

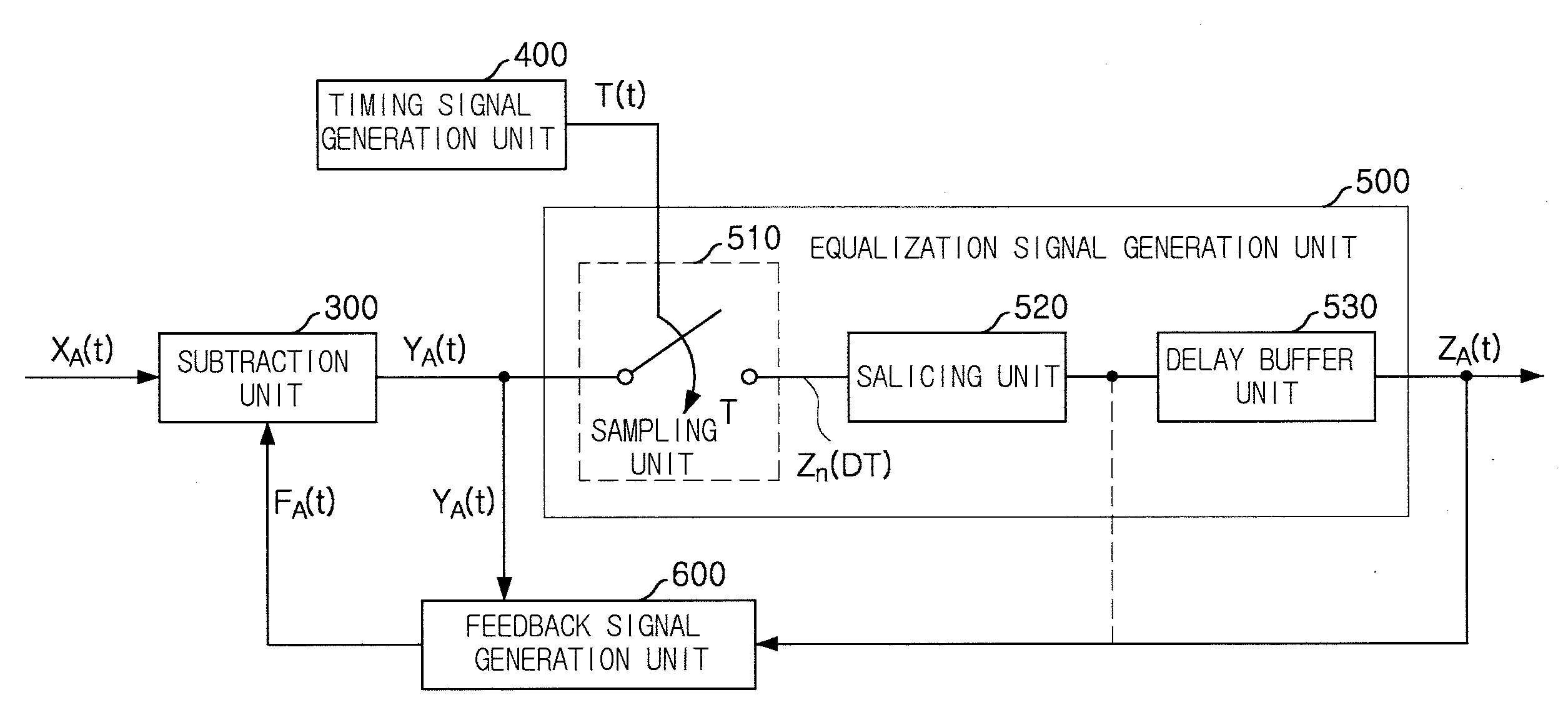

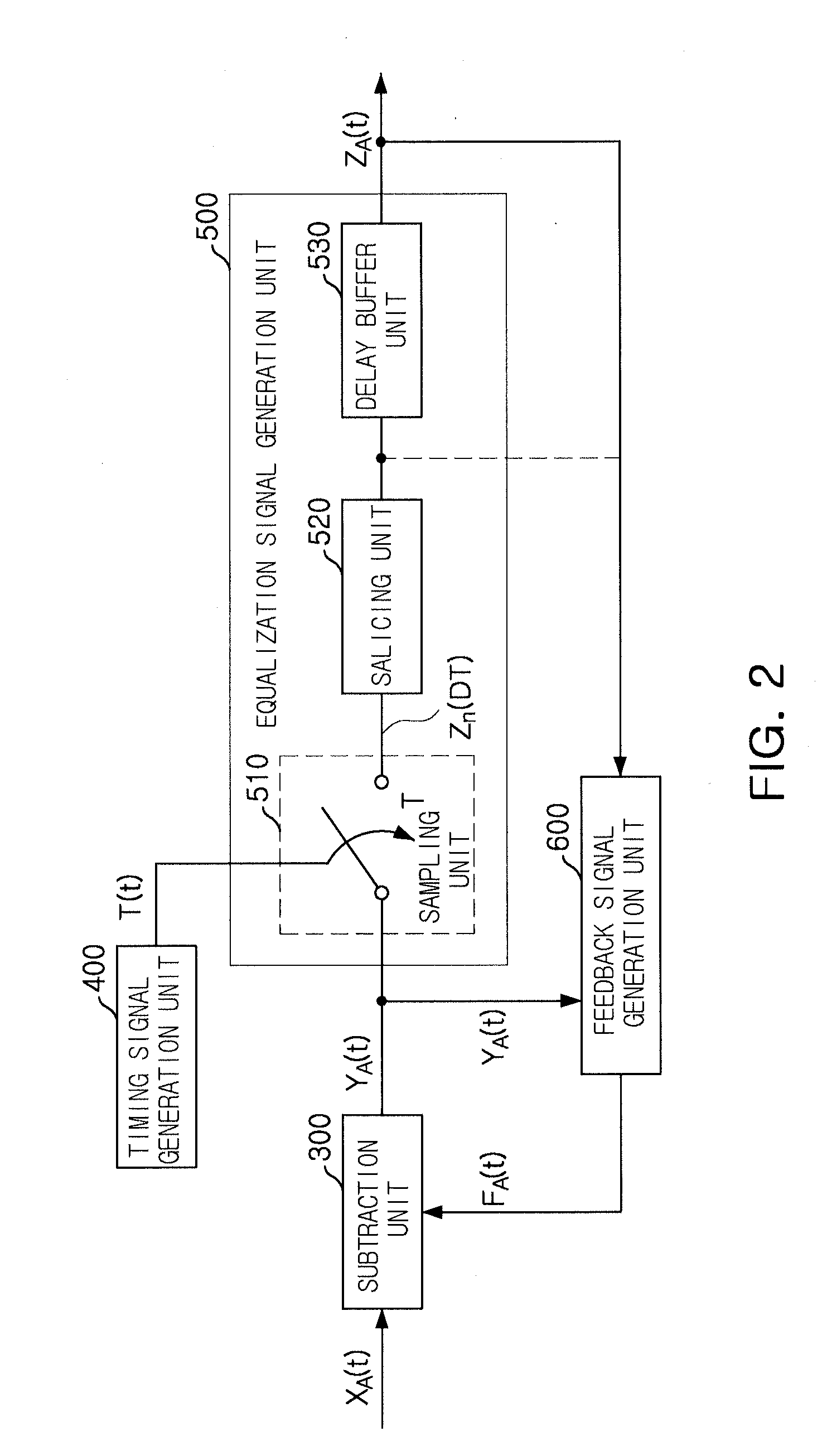

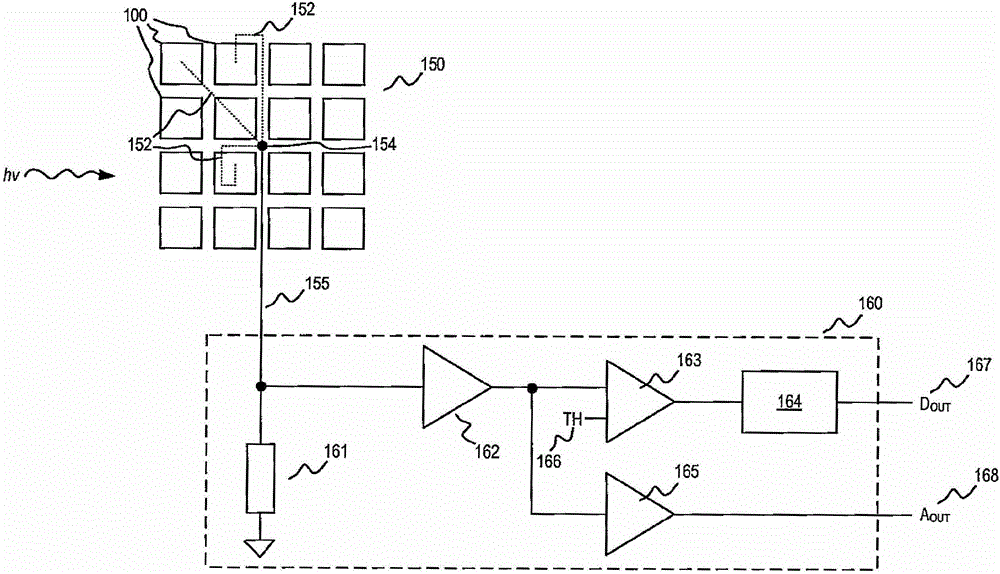

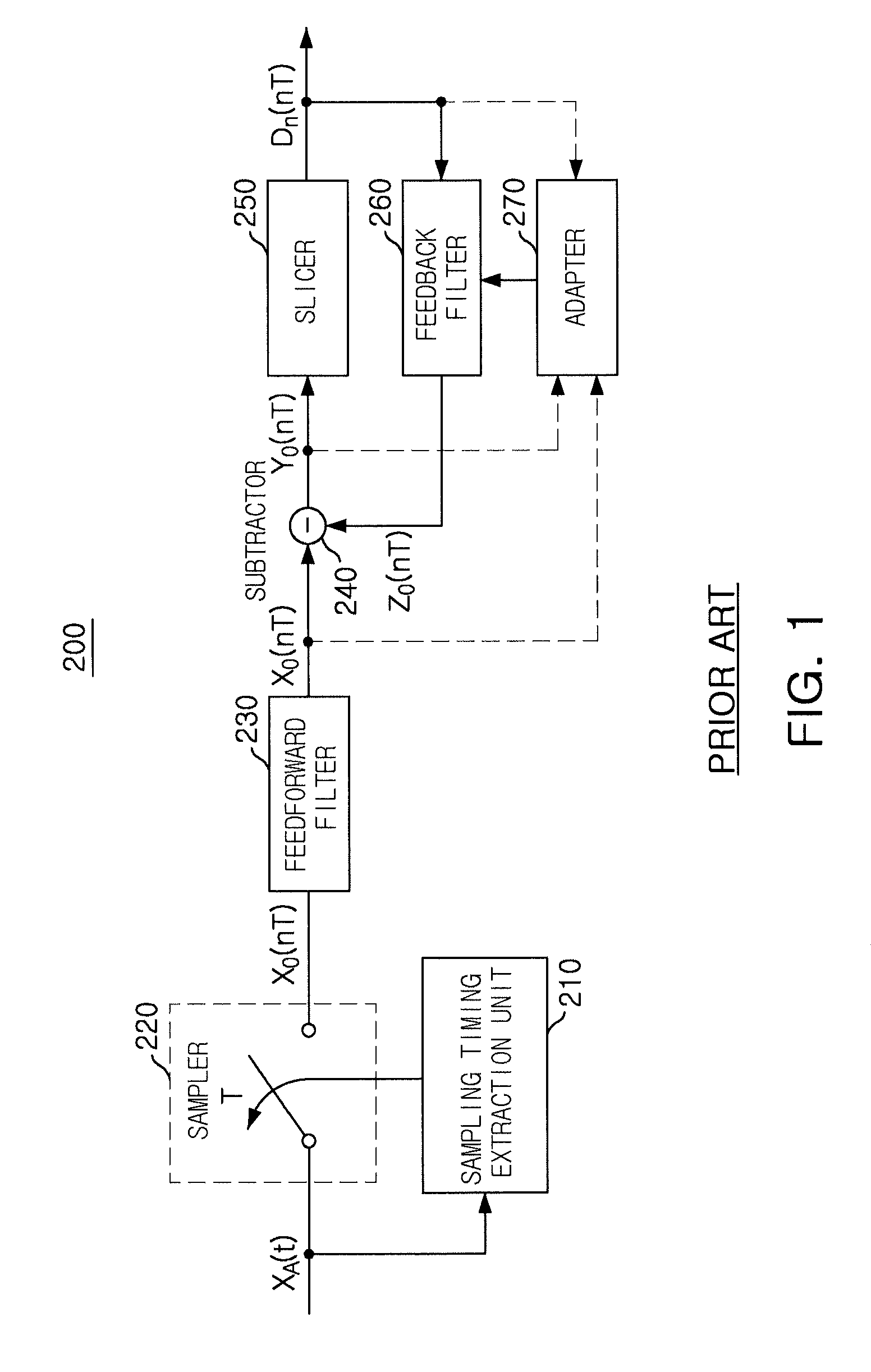

Equalizer employing adaptive algorithm for high speed data transmissions and equalization method thereof

InactiveUS20110317754A1Reduce the impact of interferenceIncrease speedMultiple-port networksDelay line applicationsEqualizationData transmission

Disclosed are an equalizer and an equalization method employing an adaptive algorithm for high speed data transmissions. The equalizer includes: a subtraction unit subtracting a feedback signal from an input signal to generate a subtraction signal; a timing signal generation unit generating a sampling timing signal; an equalization signal generation unit equalizing the subtraction signal according to the sampling timing signal to generate an equalization signal; and a feedback signal generation unit calculating a filter coefficient value by using the subtraction signal and the equalization signal, delaying the equalization signal, and weighting the delayed equalization signal according to the filter coefficient value to generate a feedback signal.

Owner:ELECTRONICS & TELECOMM RES INST

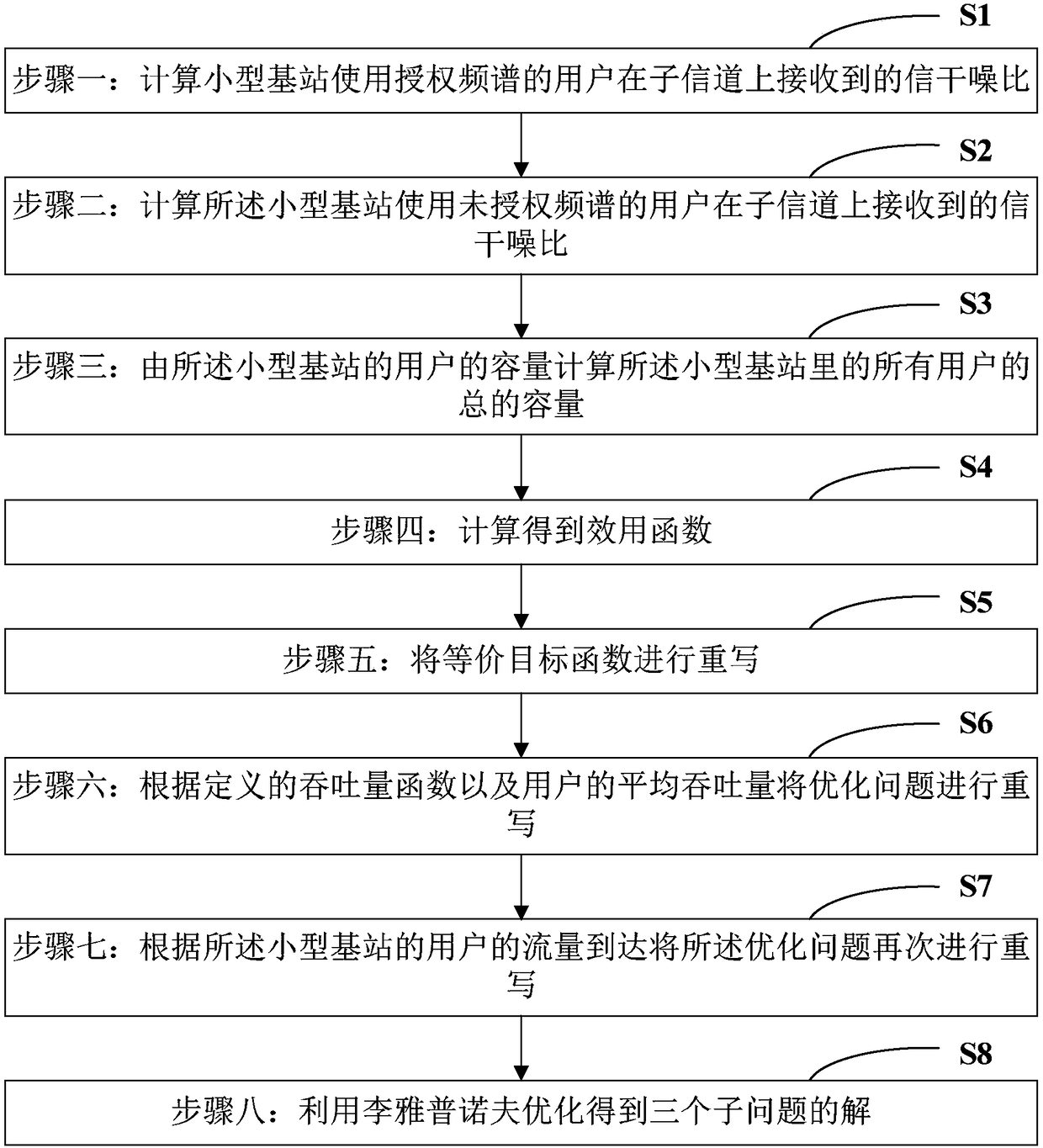

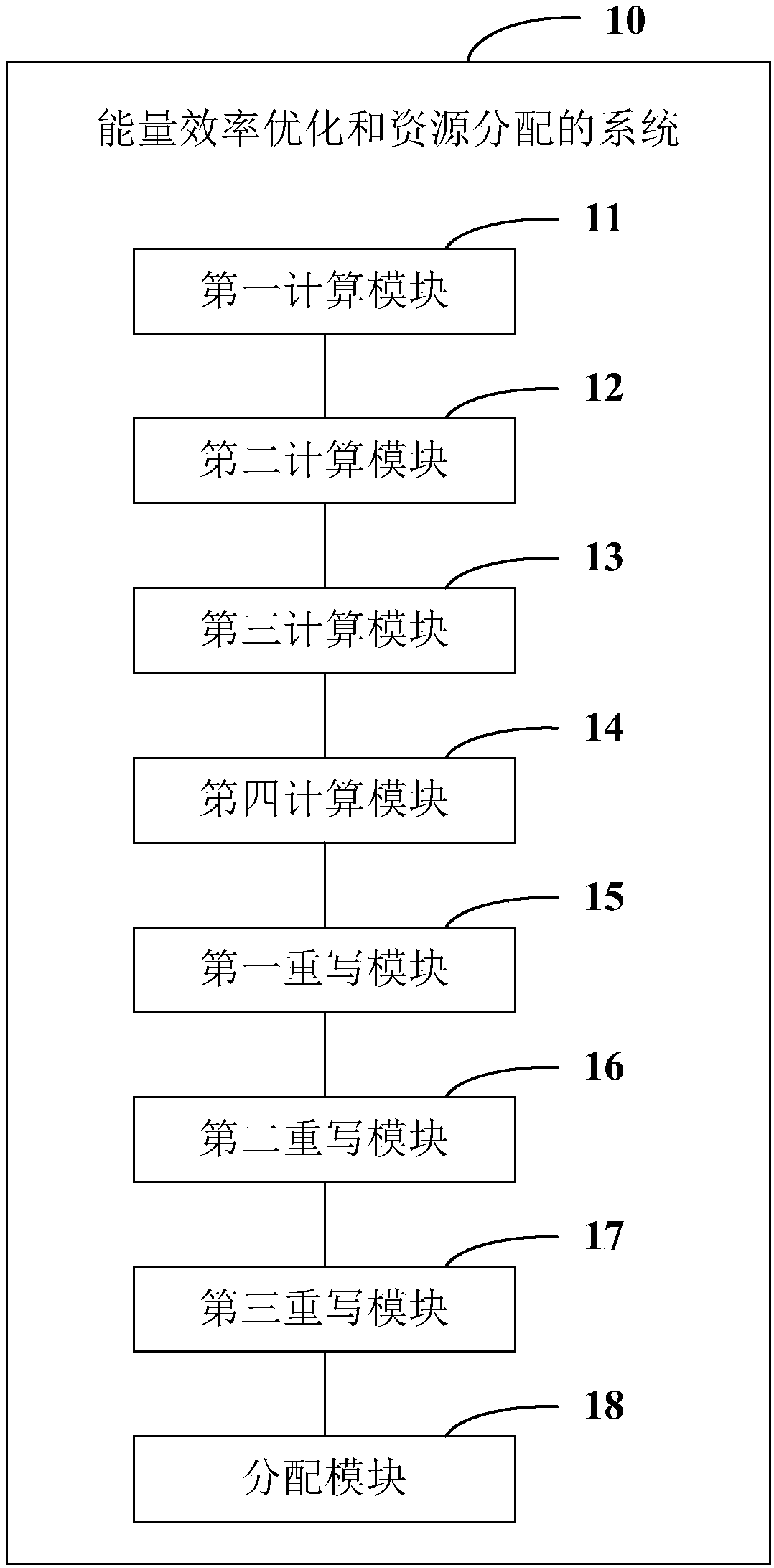

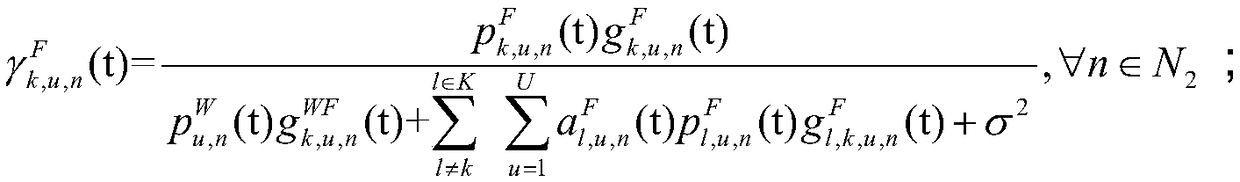

Energy efficiency optimization and resource allocation method and system

The invention provides an energy efficiency optimization and resource allocation method. The method comprises the following steps: calculating a signal-to-interference-noise ratio received by users ofan authorized spectrum in a small base station on a subchannel; calculating a signal-to-interference-noise ratio received by users of an unauthorized spectrum in the small base station on the subchannel; calculating the total capacity of all users in the small base station according to the capacities of the users of the small base station; calculating a utility function; rewriting an equivalent objective function; rewriting an optimization problem according to a defined throughput function and the average throughput of the users; rewriting the optimization problem again according to the arrival of traffic of the users in the small base station; and getting a solution of three sub-problems by means of Lyapunov optimization. The invention also provides an energy efficiency optimization andresource allocation system. Through the technical scheme provided by the invention, the enhancement of utility performance and the balance of energy efficiency delay can be realized under various constraints.

Owner:UNIV OF SCI & TECH BEIJING

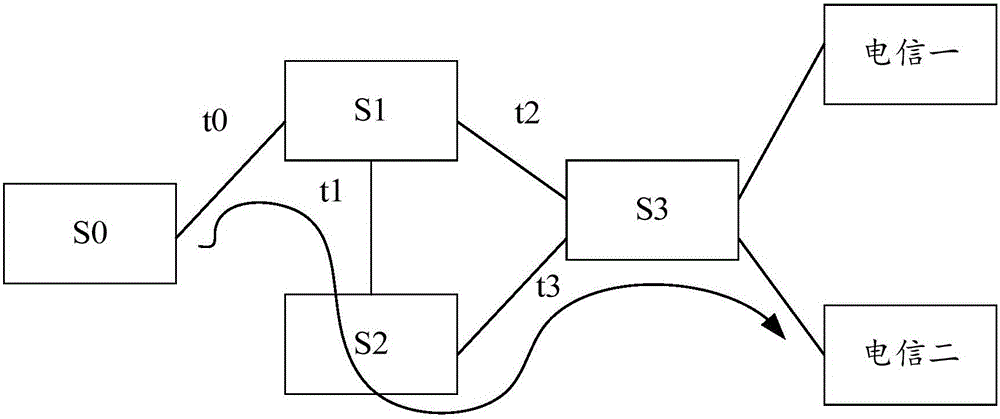

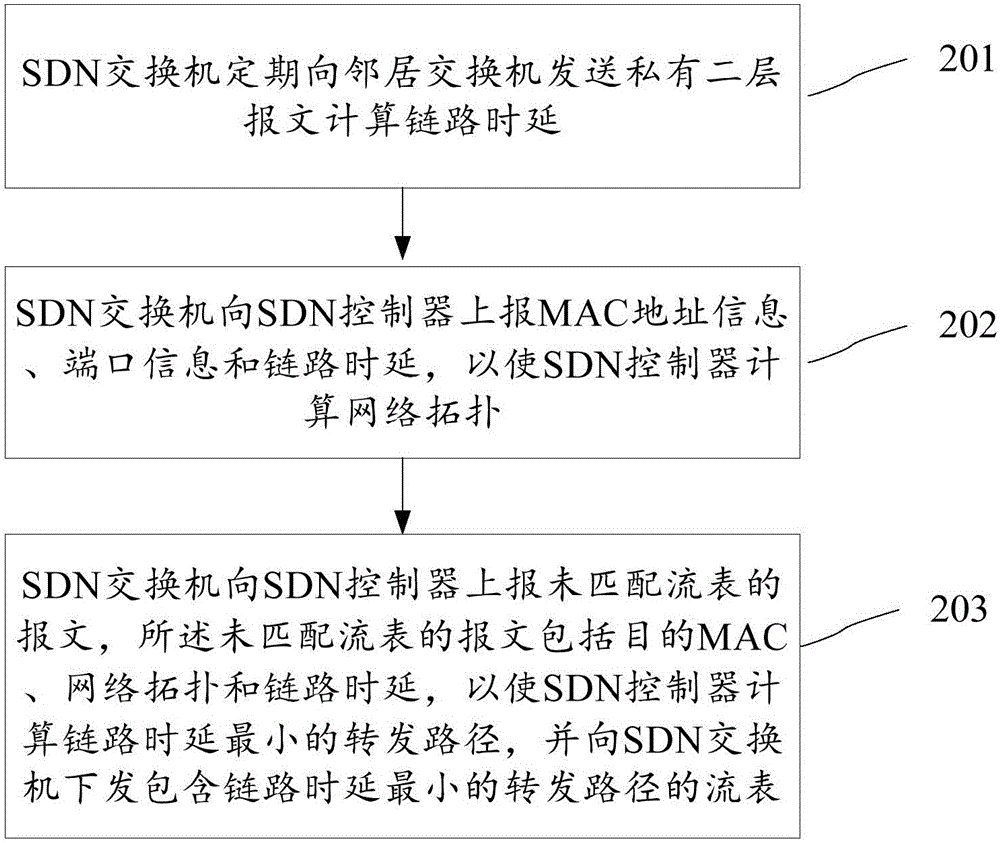

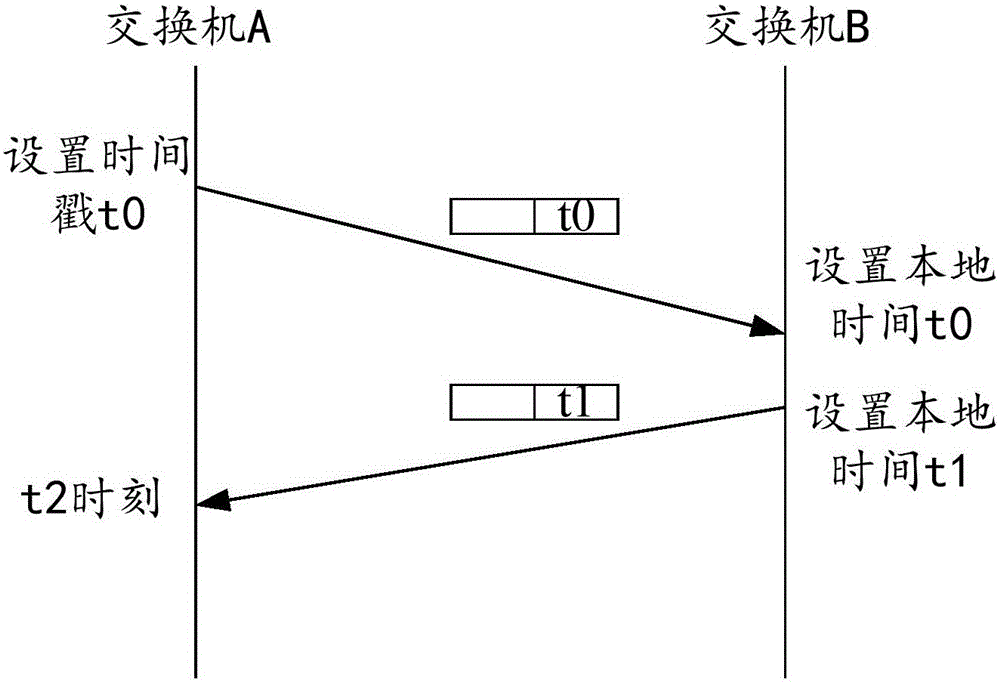

SDN (Software Defined Network)-based multi-link delay equalization method and system

ActiveCN105791113AAvoid the disadvantage of not being able to choose the forwarding path with the least delayData switching networksCentralized computingMulti link

The embodiment of the invention provides an SDN-based multi-link delay equalization method and system. The method comprises the following steps that: an SDN switch transmits private two-layer message calculation link delay to a neighbor switch; the SDN switch reports MAC (Media Access Control) address information, port information and the link delay to an SDN controller in order that the SDN controller calculates network topology; and the SDN switch reports a message of an unmatched flow table to the SDN controller, wherein the message of the unmatched flow table includes destination MAC, the network topology and the link delay in order that the SDN controller calculates a forwarding path with smallest link delay and issues a flow table of the forwarding path with the smallest link delay to the SDN switch. Through adoption of the SDN-based multi-link delay equalization method and system, the forwarding path with the smallest delay can be selected accurately through centralized computing of the controller.

Owner:杭州吉吉知识产权运营有限公司

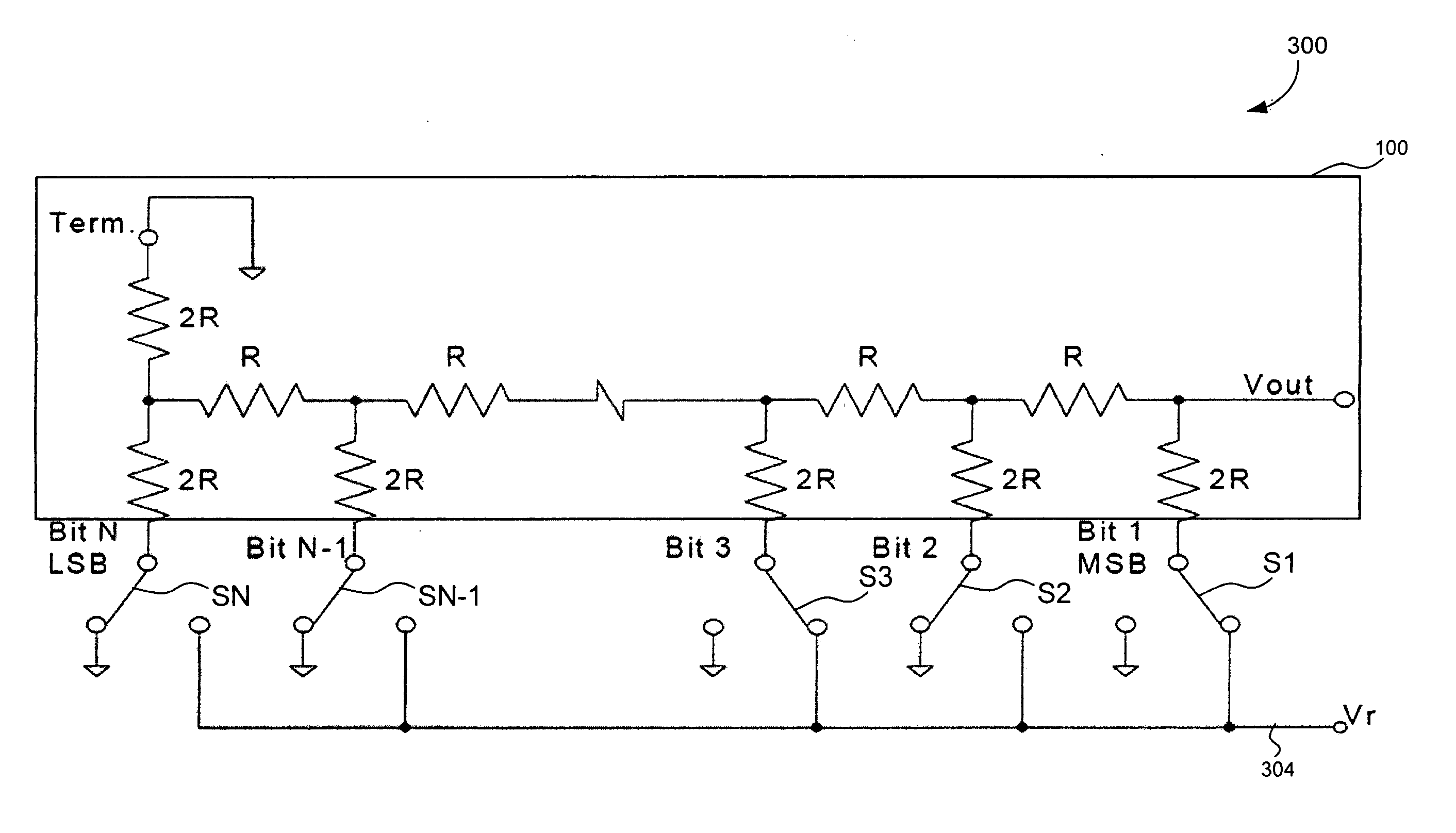

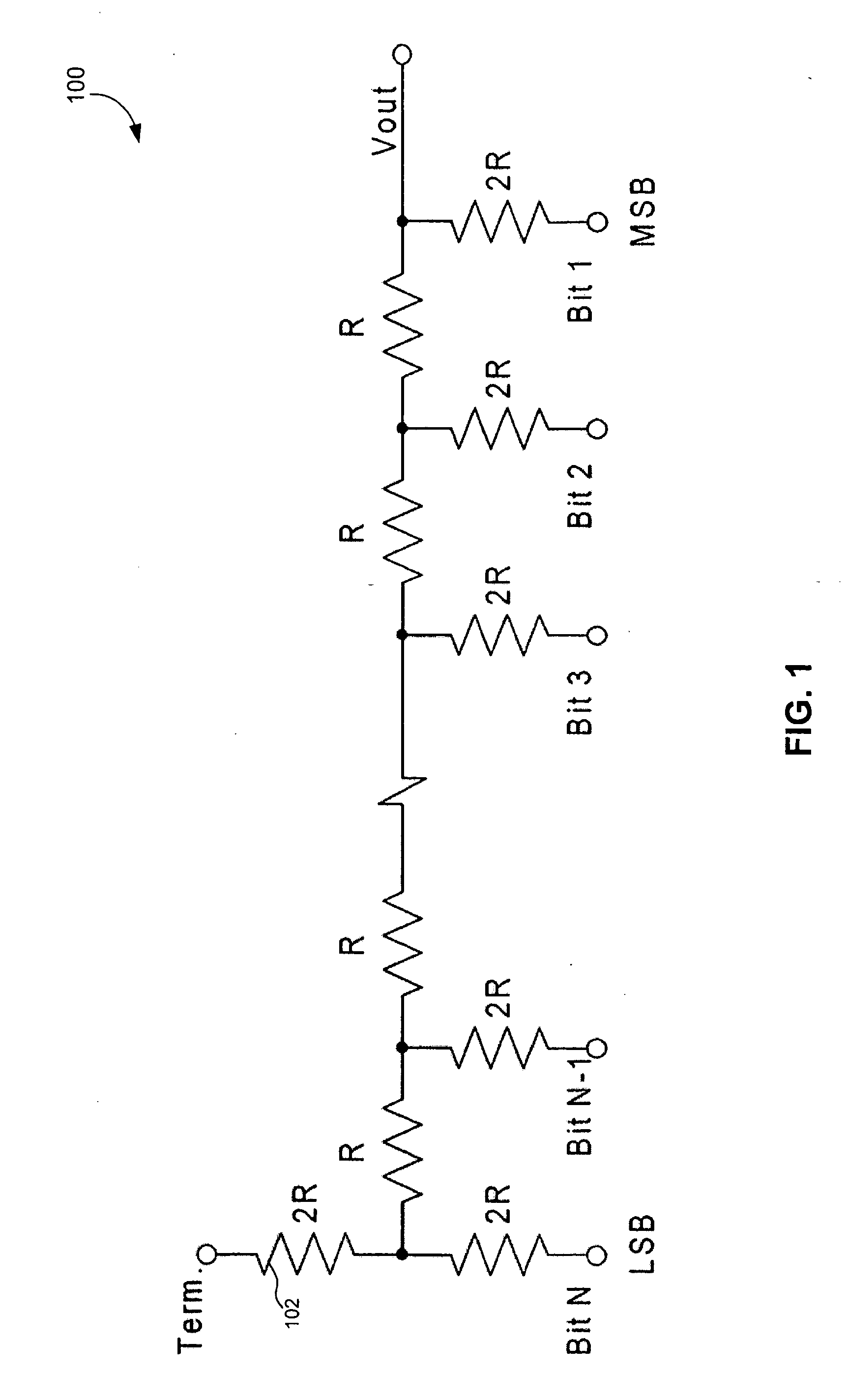

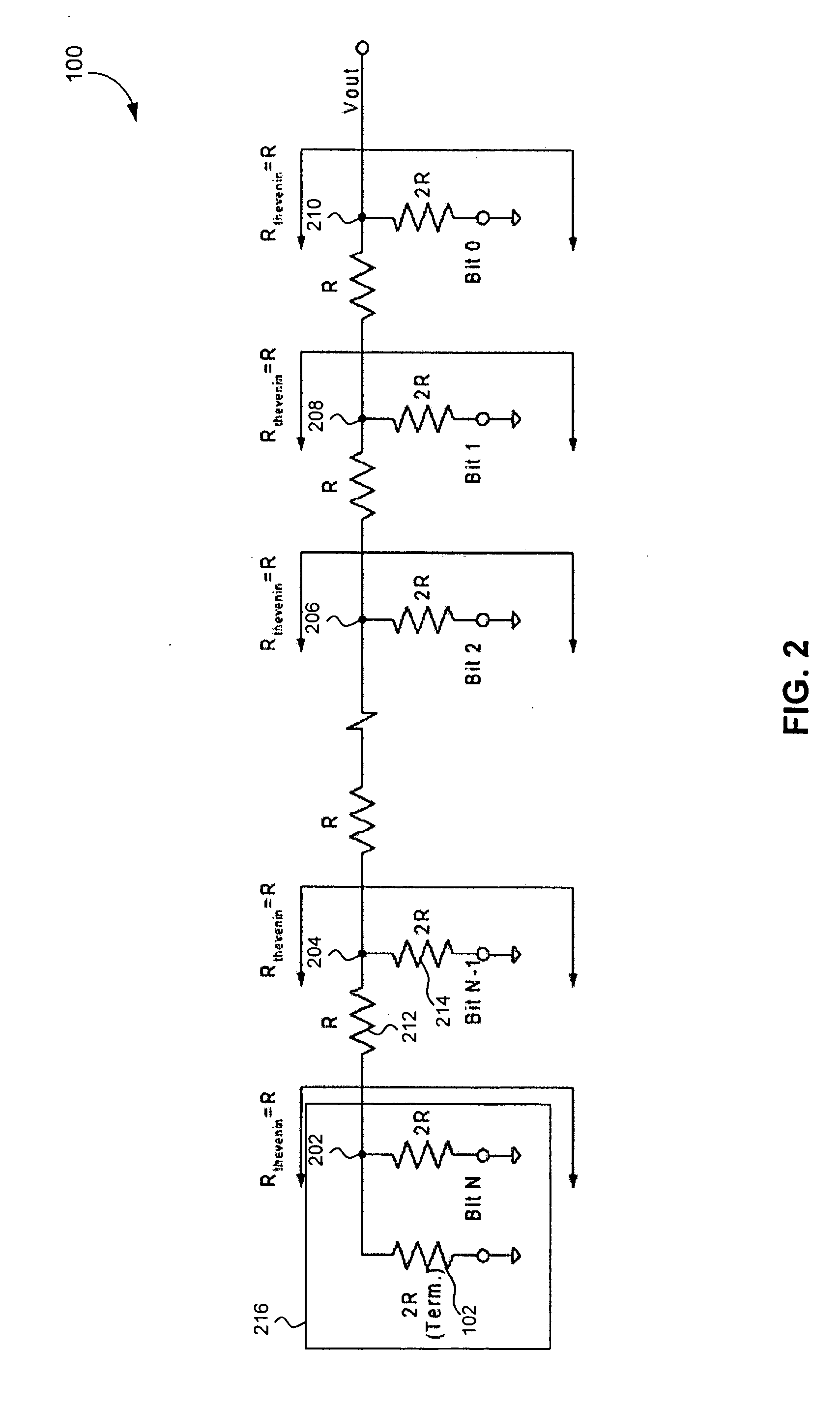

Delay equalized Z/2Z ladder for digital to analog conversion

InactiveUS20060092066A1High resolution DACsIncrease data rateAnalogue/digital conversionElectric signal transmission systemsImage resolutionEngineering

A Z / 2Z ladder network includes an R / 2R ladder network having capacitors coupled across series resistors within the R / 2R ladder network, wherein the capacitors are sized to substantially match delays from nodes within the ladder network to an output node. The Z / 2Z ladder network can be implemented within a digital to analog controller (“DAC”), including higher resolution DACs, and high data rate DACs. In higher resolution DACs, and high data rate DACs, the Z / 2Z ladder network is coupled through switches to corresponding current sources. The Z / 2Z ladder is optionally implemented differentially. The invention can be implemented as a Z / kZ ladder network, where k is a real number.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

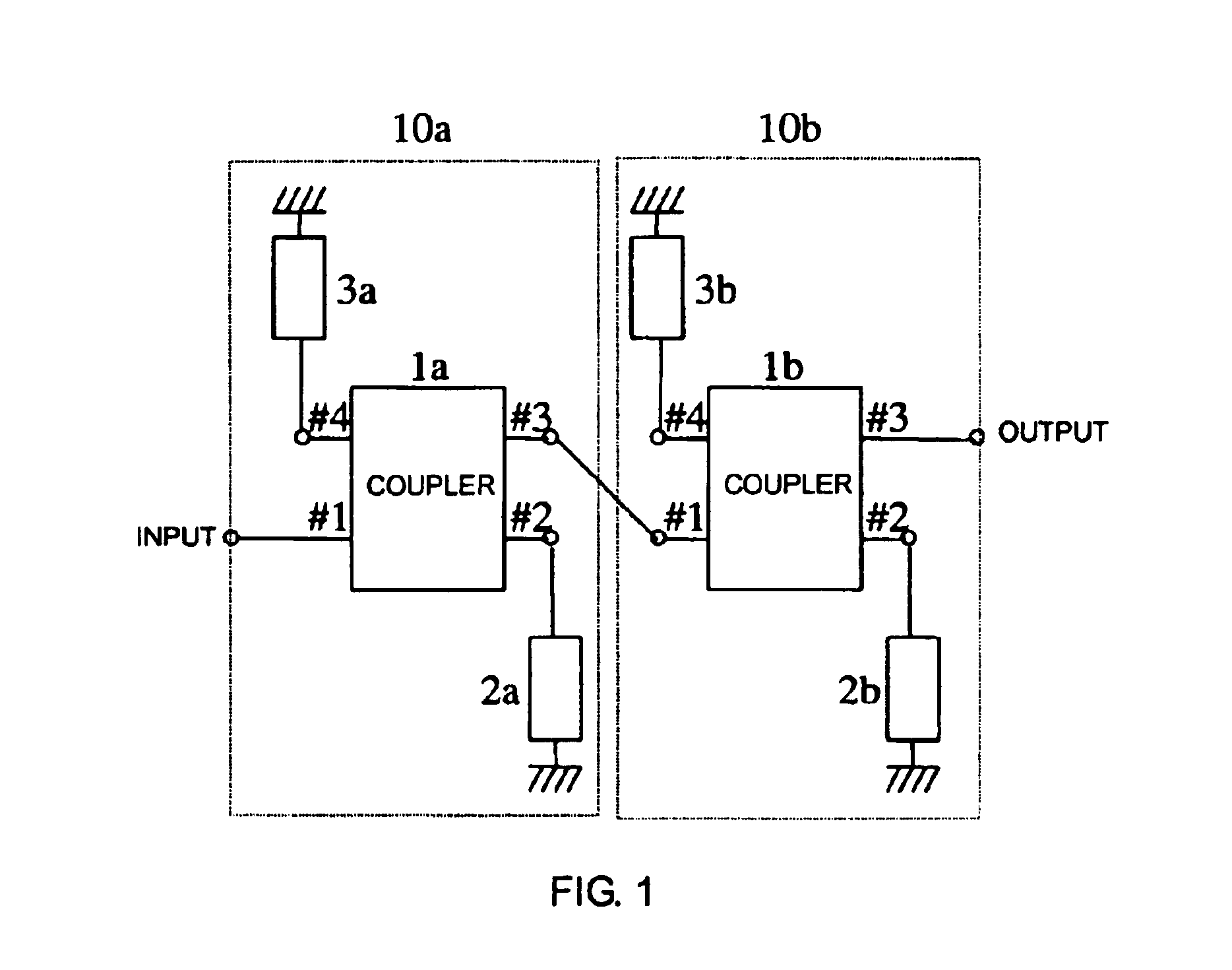

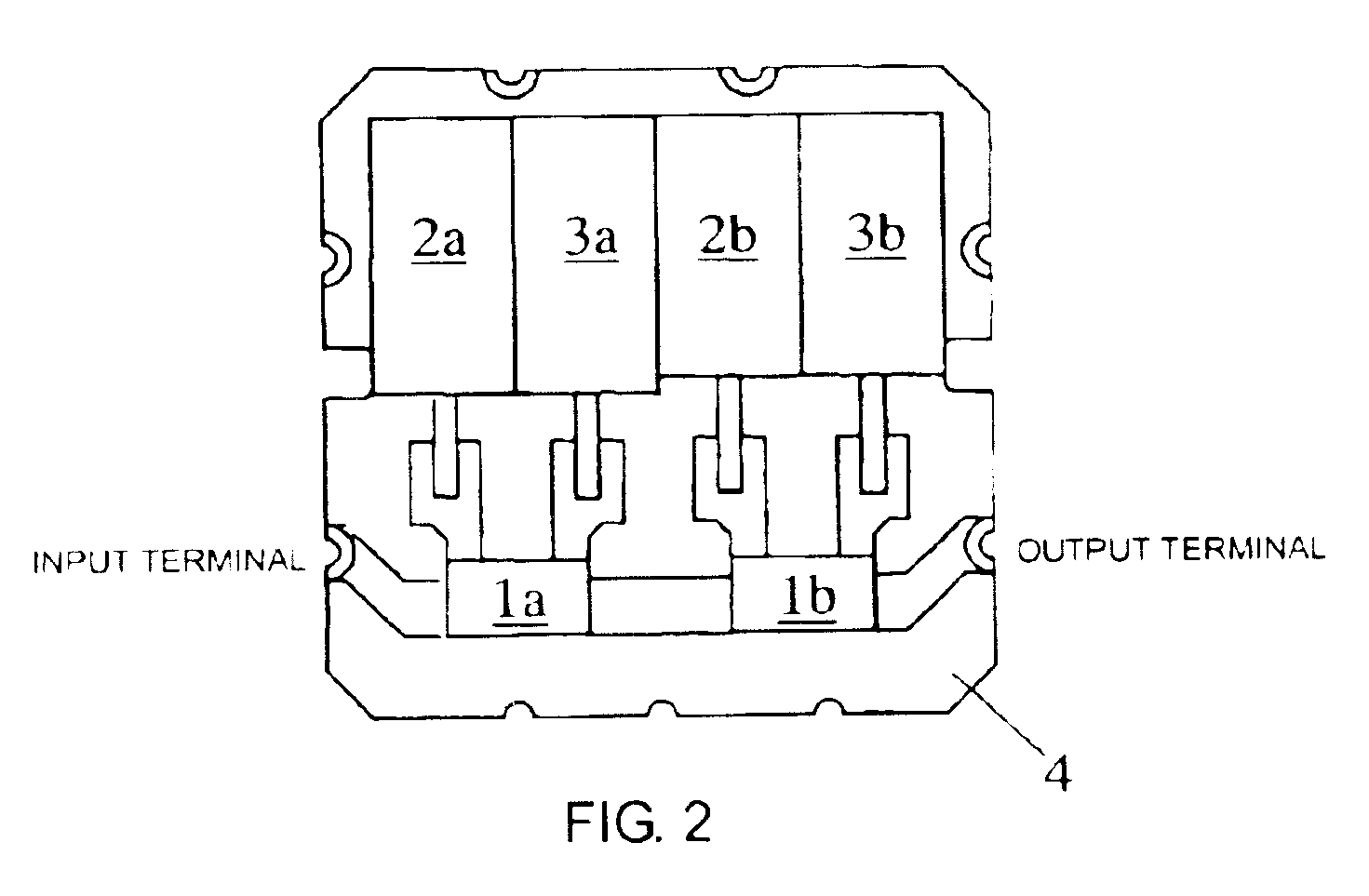

In-band group delay equalizer and distortion compensation amplifier

InactiveUS6958663B2Suppressing to low levelReduce distortion problemsAmplifier modifications to reduce non-linear distortionTransmission control/equlisationLow distortionHybrid coupler

An in-band group delay equalizer is formed in a simple circuit configuration so as to have a flat group delay characteristic over a wide frequency band without having a peak of group delay near each passband edge. The in-band group delay equalizer includes a plurality of convex group delay circuits. Each convex group delay circuit is formed of one hybrid coupler and two resonators connected to respective divided output ports of the hybrid coupler. The center frequencies of the respective convex group delay circuits are set to be different from each other so that the overall group delay characteristic of the in-band group delay equalizer becomes flat. The bandwidth and the group delay can be easily adjusted. A distortion compensation amplifier with very low distortion can be realized using such an in-band group delay equalizer.

Owner:MURATA MFG CO LTD

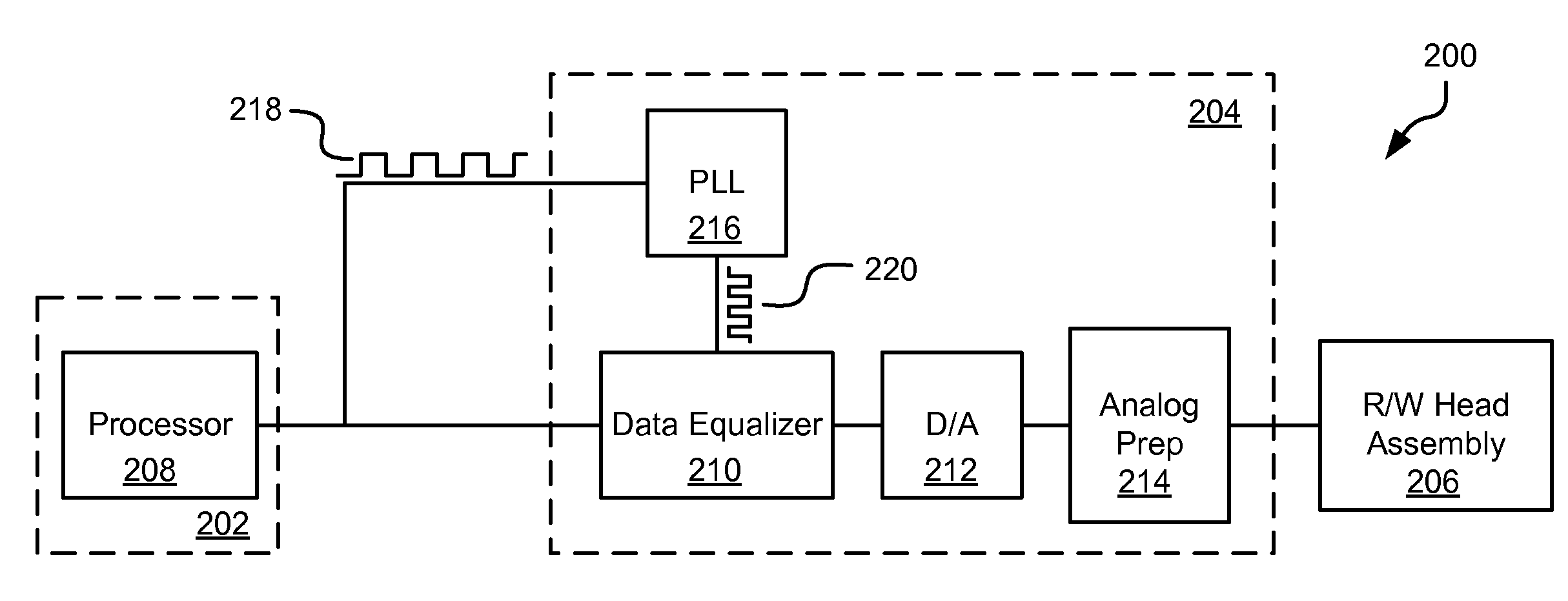

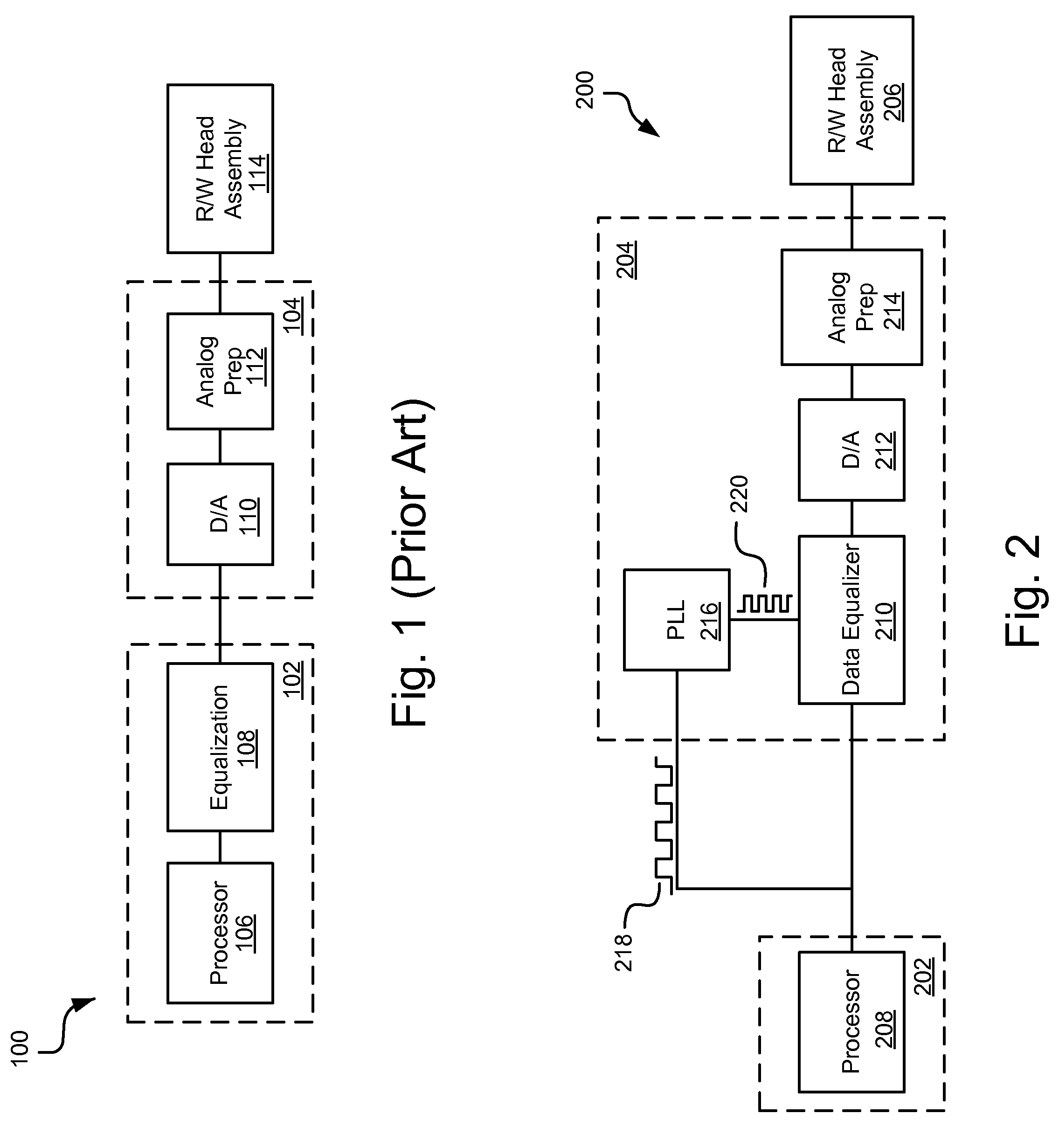

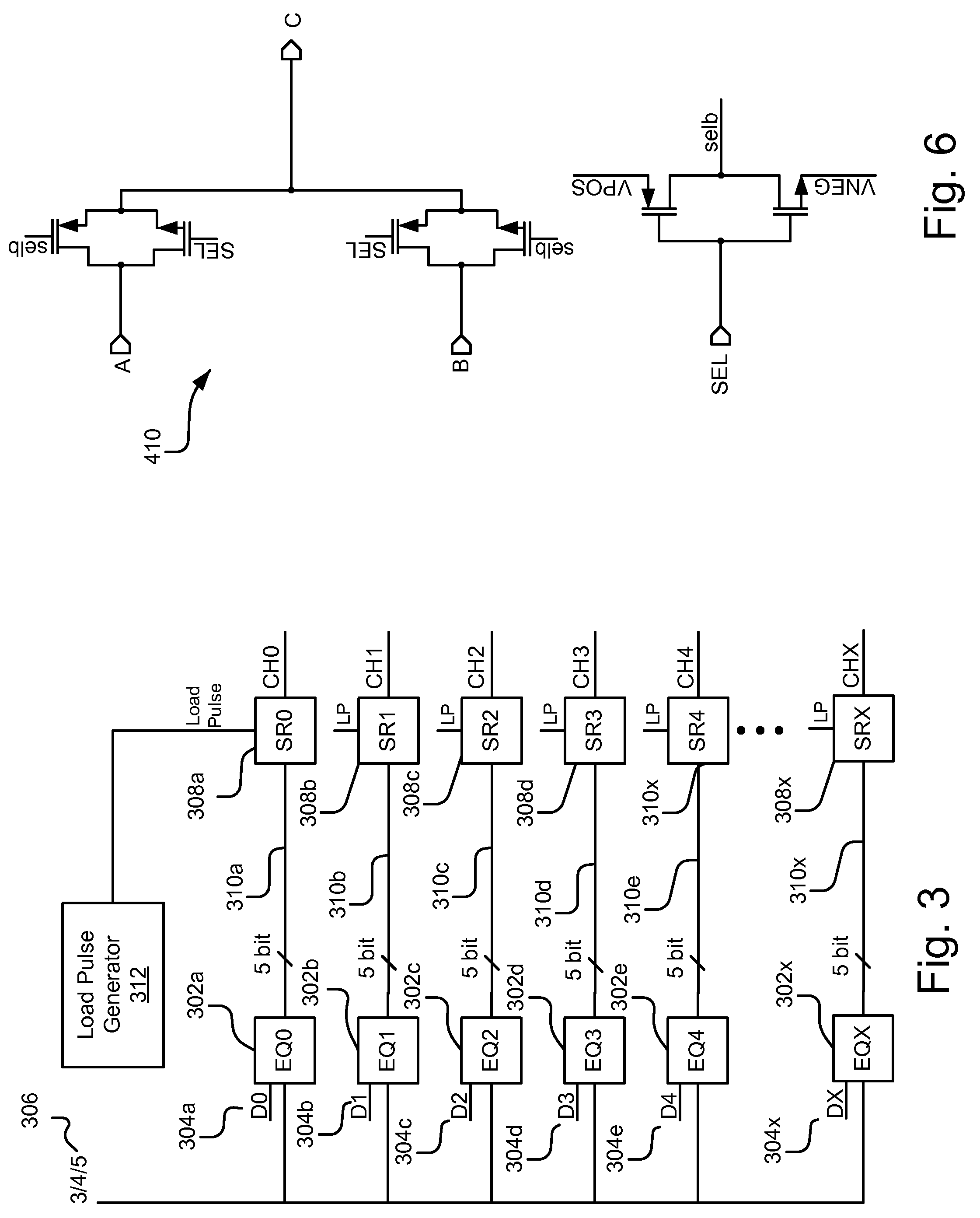

Systems and methods for controlling data equalization

Various embodiments of the present invention provide systems and methods for performing data equalization. For example, various embodiments of the present invention provide data equalization circuits that include an equalization circuit and a transition adjustment circuit. The equalization circuit receives a series of at least two original data bits and replaces at least one of the two original data bits with an equalization pattern including two or more equalization bits. The original data bits correspond to an original data clock, and the two or more equalization bits correspond to an equalization data clock. The transition adjustment circuit is operable to modify an occurrence of a transition from one logic state to another logic state within the equalization pattern on a sub-equalization data clock basis.

Owner:AVAGO TECH INT SALES PTE LTD

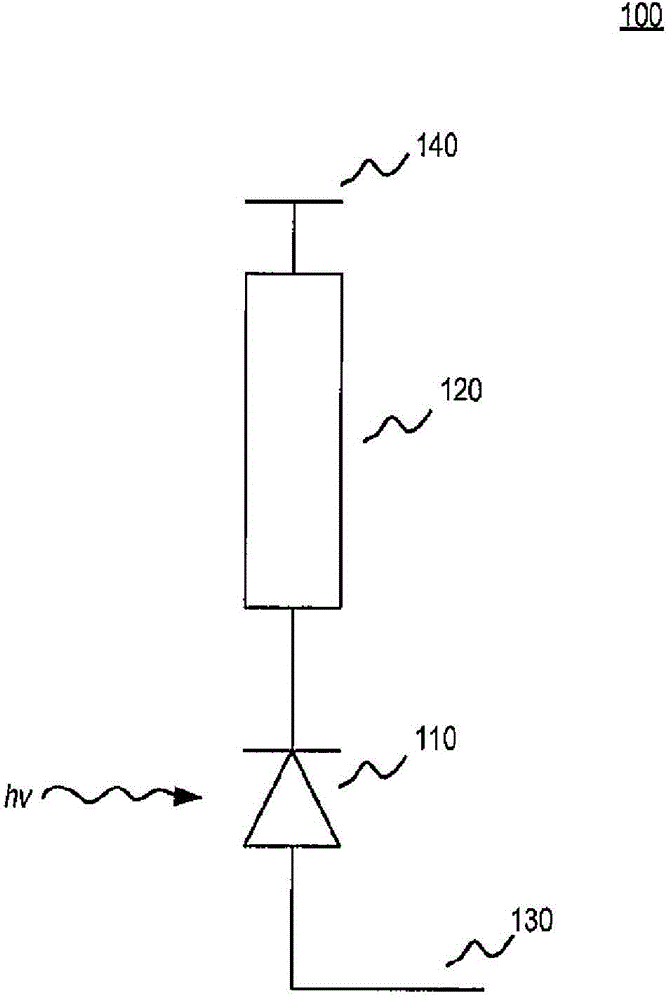

Partitioned silicon photomultiplier with delay equalization

ActiveCN104377250ASolid-state devicesRadiation controlled devicesElectrical conductorSilicon photomultiplier

A photon detection device includes a first wafer having an array of photon detection cells partitioned into a plurality of photon detection blocks arranged in the first wafer. A second wafer having a plurality of block readout circuits arranged thereon is also included. An interconnect wafer is disposed between the first wafer and the second wafer. The interconnect wafer includes a plurality of conductors having substantially equal lengths. Each one of the plurality of conductors is coupled between a corresponding one of the plurality of photon detection blocks in the first wafer and a corresponding one of the plurality of block readout circuits such that signal propagation delays between each one of the plurality of photon detection blocks and each one of the plurality of block readout circuits are substantially equal.

Owner:OMNIVISION TECH INC

Equalizer employing adaptive algorithm for high speed data transmissions and equalization method thereof

InactiveUS8446941B2Reduce the impact of interferenceIncrease speedMultiple-port networksDelay line applicationsEqualizationData transmission

Disclosed are an equalizer and an equalization method employing an adaptive algorithm for high speed data transmissions. The equalizer includes: a subtraction unit subtracting a feedback signal from an input signal to generate a subtraction signal; a timing signal generation unit generating a sampling timing signal; an equalization signal generation unit equalizing the subtraction signal according to the sampling timing signal to generate an equalization signal; and a feedback signal generation unit calculating a filter coefficient value by using the subtraction signal and the equalization signal, delaying the equalization signal, and weighting the delayed equalization signal according to the filter coefficient value to generate a feedback signal.

Owner:ELECTRONICS & TELECOMM RES INST

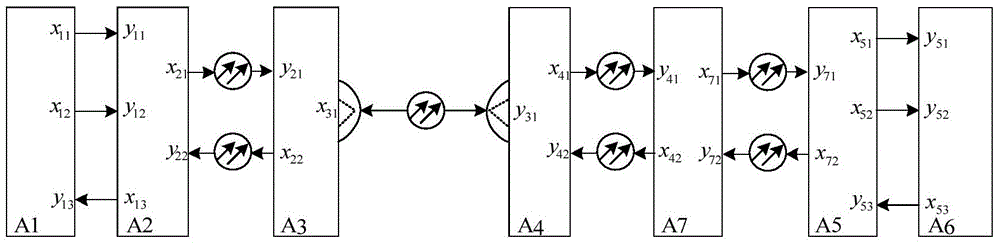

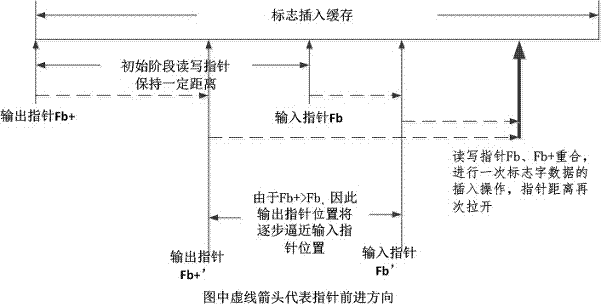

Delay equalization method for realization of service code stream irrelevance by automatic mark insertion

ActiveCN102833060AImprove reliabilityImprove stabilityChannel dividing arrangementsTransmitter/receiver shaping networksChannel dataParallel computing

The invention relates to a delay equalization method for realization of service code stream irrelevance by automatic mark insertion. According to the scheme, a whole set of channel equalization device which includes a sending part and a receiving part, is adapted to a multi-channel and multi-route network environment, and overcomes channel time varying influence is constructed by technical development such as code stream synchronization, cache adjustment, code stream aligning and the like, the device comprises functions of code stream adaption, mark insertion, code stream sending, code stream receiving, synchronous adjustment, cache aligning processing, uniform clock output and the like, the reliability and the stability of channel data transfer can be improved, and accurate and inerrant data transmission performance and stable and constant signal transfer time delay can be provided on the condition of multi-channel switching.

Owner:STATE GRID ELECTRIC POWER RES INST +2

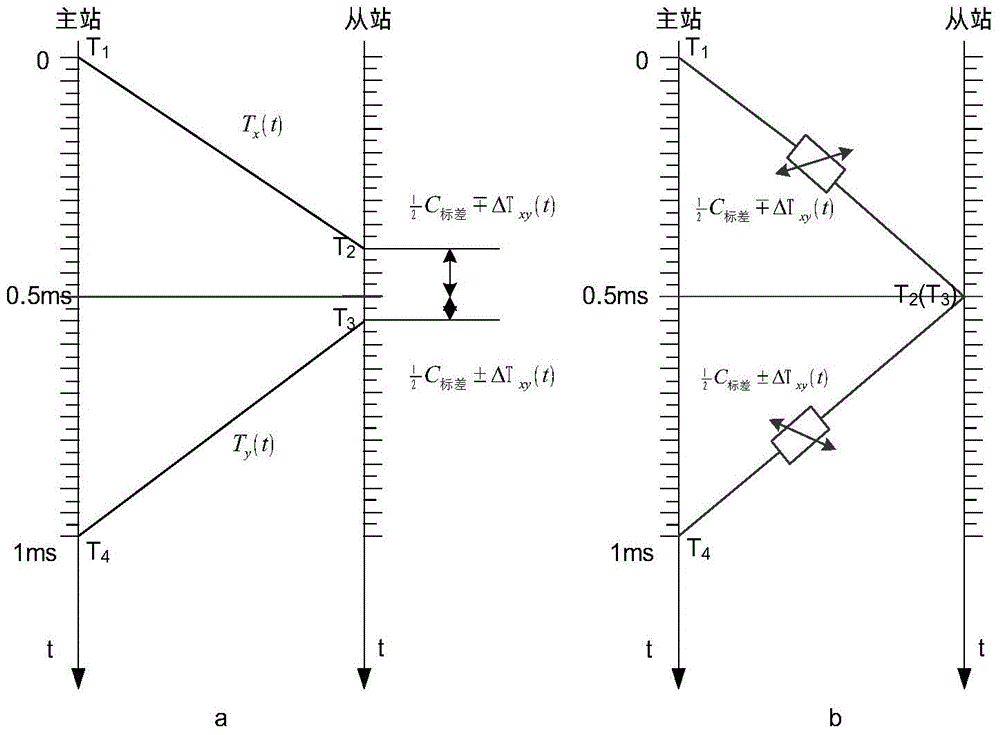

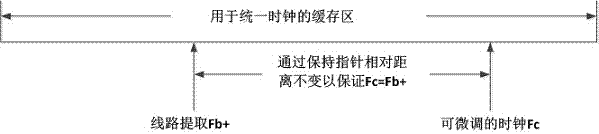

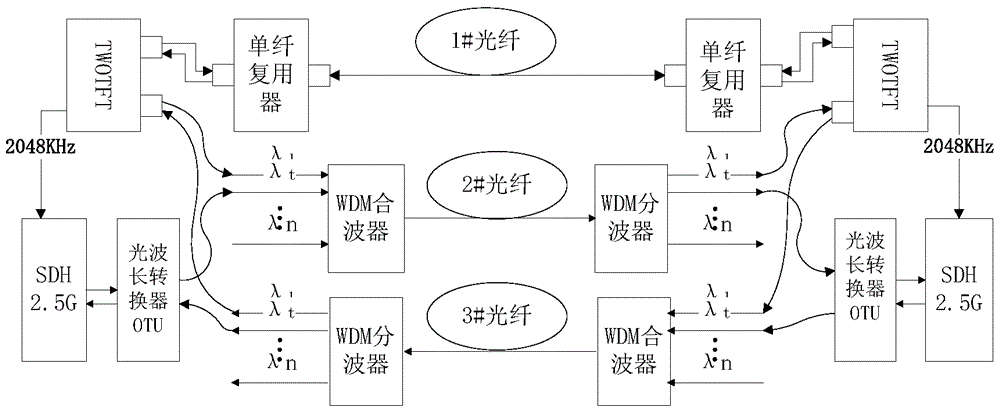

Ultra-precise time-frequency transfer method for dwdm optical transmission system

ActiveCN104038302BSolve the problem that the synchronization accuracy is difficult to improveAccurate automatic compensationWavelength-division multiplex systemsTime-division multiplexFiberMathematical model

Owner:四川泰富地面北斗科技股份有限公司

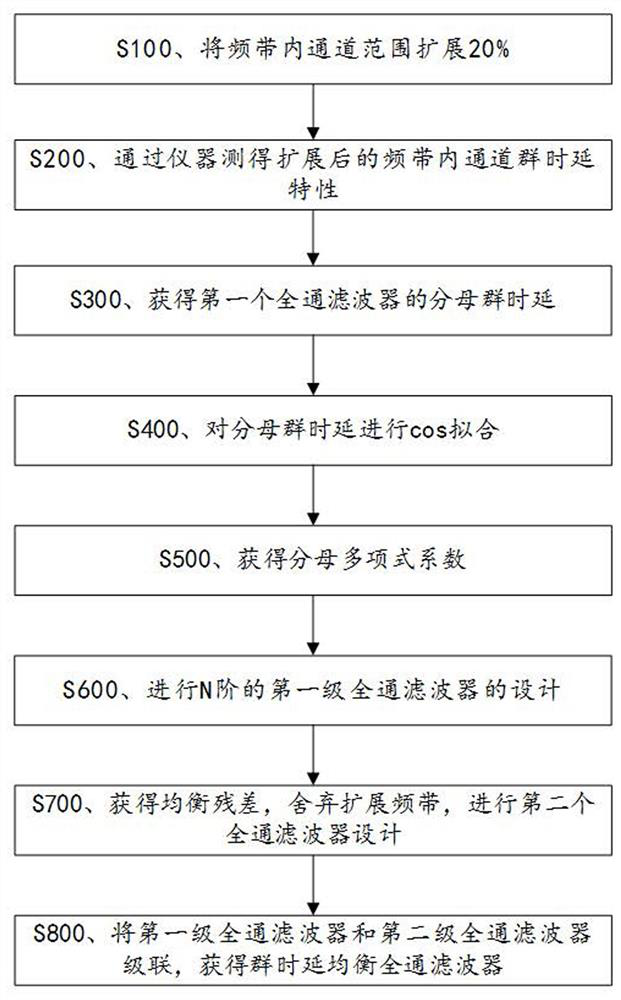

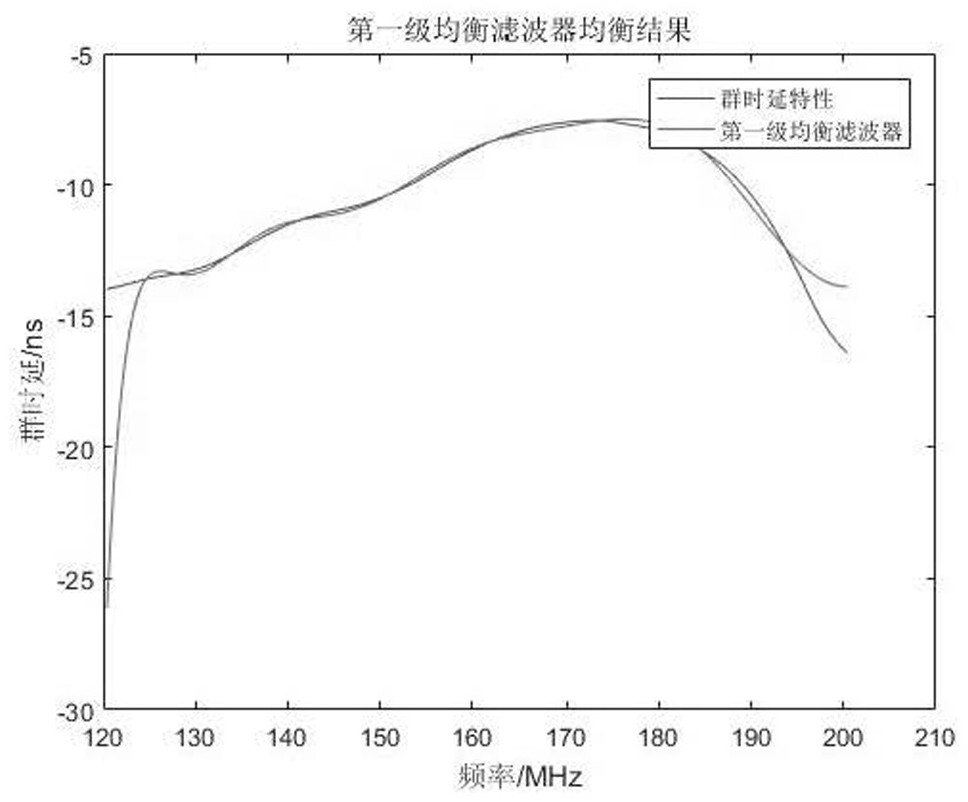

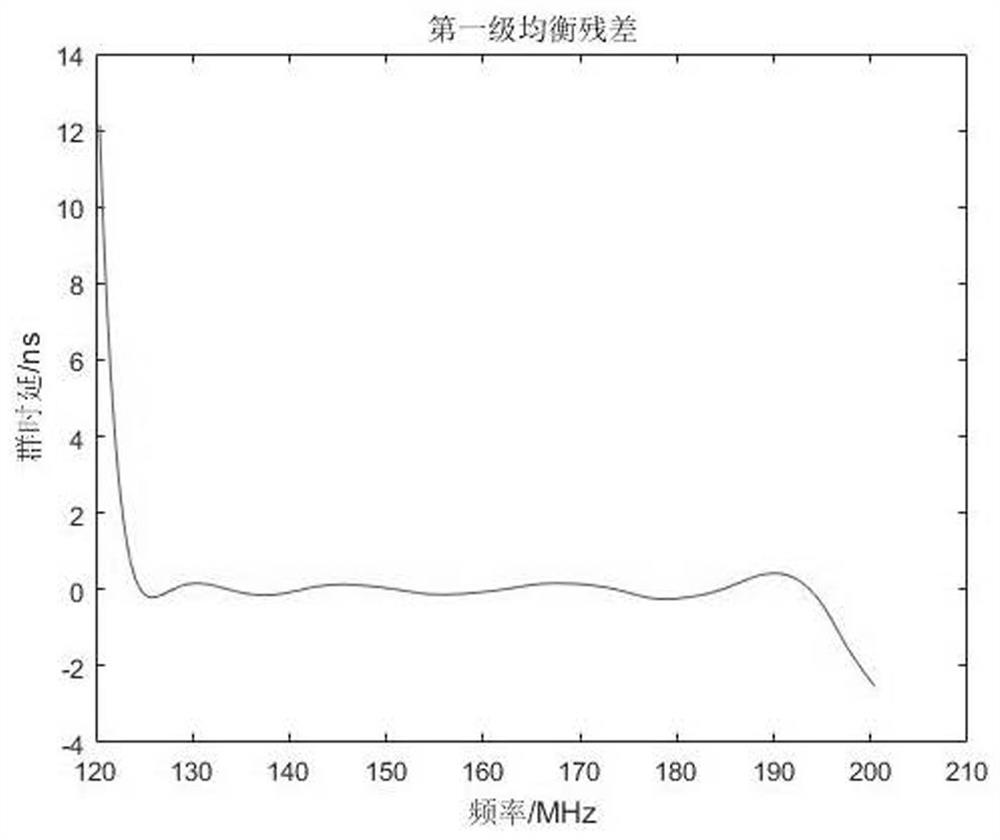

Navigation receiver radio frequency front end group delay characteristic equalization design method and device

ActiveCN113176592AGroup Delay EqualizationHigh frequency of fluctuationsSatellite radio beaconingTransmitter/receiver shaping networksEqualizationControl theory

The invention discloses a navigation receiver radio frequency front end group delay equalization design method and device. The method comprises the following steps: expanding a channel range in a frequency band by M%; measuring the time delay characteristic of the channel group in the expanded frequency band; obtaining denominator group delay of an all-pass filter; carrying out cos fitting on the denominator group time delay, and acquiring a denominator coefficient of the all-pass filter; obtaining a denominator polynomial coefficient; designing a first-stage all-pass filter; acquiring a balanced residual error, abandoning the extended frequency band, and designing a second-stage all-pass filter; and cascading the first-stage all-pass filter and the second-stage all-pass filter to obtain the group delay equalization all-pass filter. According to the invention, the all-pass filter of any group delay is designed by using a complex cepstrum theory, secondary equalization is performed according to the equalization residual error, and finally the group delay can be equalized by using the finite filter order in the specified passband so that the problem of a positioning error caused by related peak distortion brought by the group delay is solved.

Owner:NAT UNIV OF DEFENSE TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com