Four stage flow line digital signal processor and wireless on-chip system chip with same

A digital signal and system chip technology, applied in the direction of diagnostic signal processing, applications, sensors, etc., can solve the problems of non-adjustable anti-interference, no processor analog-to-digital converter integration, high power consumption, etc., to improve continuous working time , reducing the area of the circuit board, the effect of overall delay satisfaction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

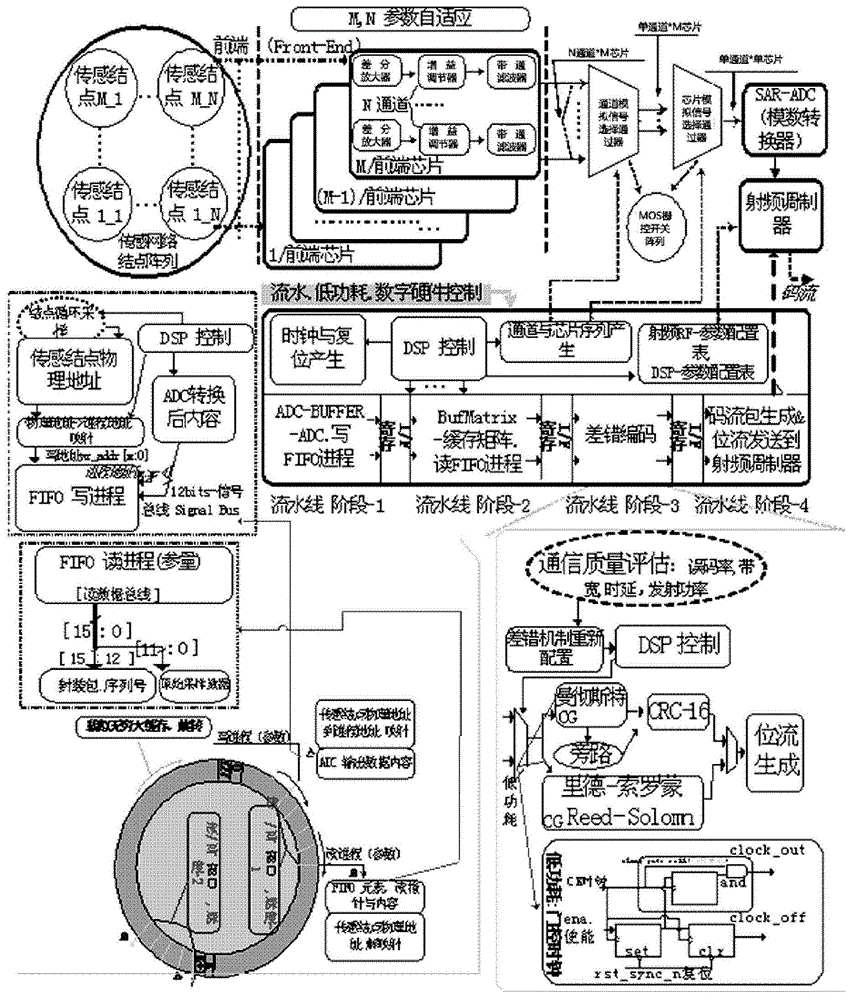

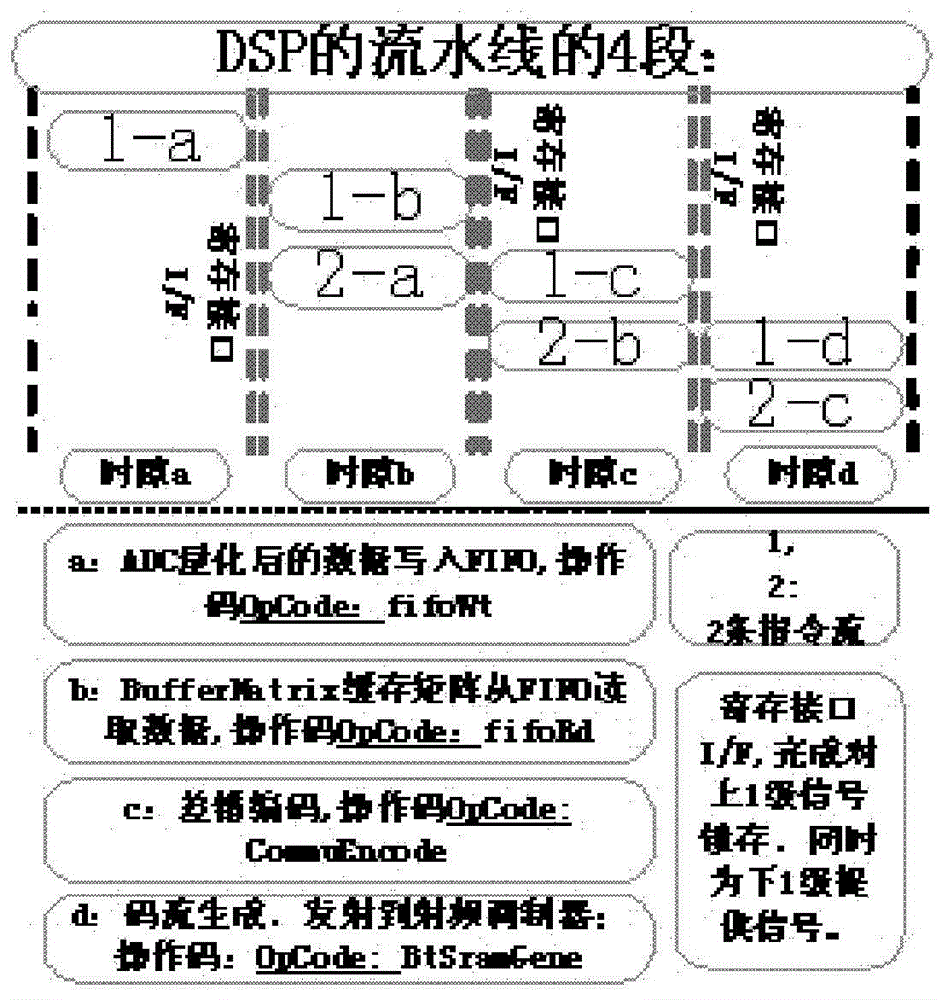

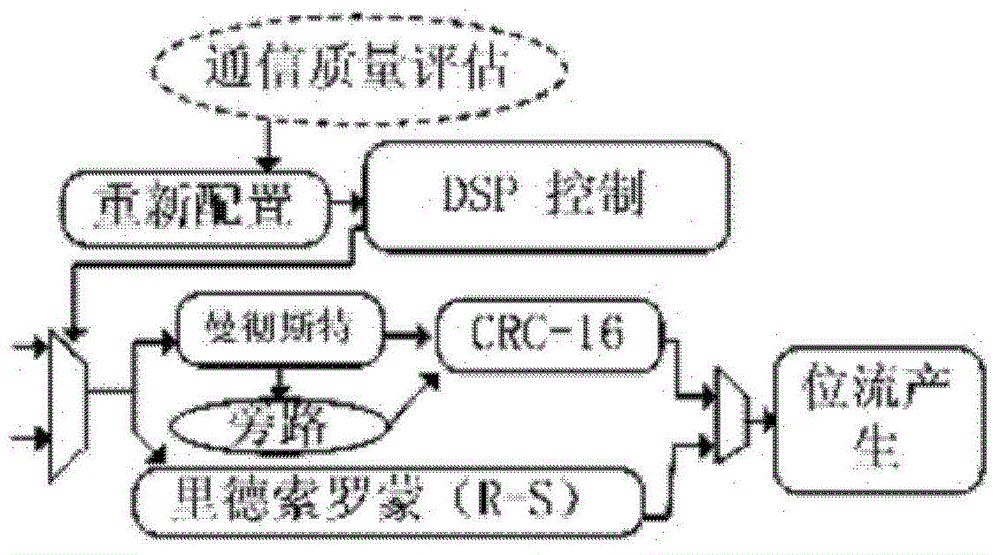

[0048] The invention belongs to the field of integrated circuit SOC chips, and relates to the collection and processing of weak and low-frequency EEG neural network signals. The wireless SOC chip of the invention integrates analog, radio frequency, and digital circuits, and is a portable and wearable design scheme. The power consumption of the SOC system is less than 70mW, can be used continuously for more than 24 hours.

[0049] The entire SOC chip receives and processes the weak low-frequency small signals sent by the network composed of MEMS brain patch sensor nodes. The front-end (Front-End) low-noise differential voltage amplifier (OPA) performs an undistorted closed-loop high-gain amplification of the EEG signal fed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com