Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

179 results about "Cell space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

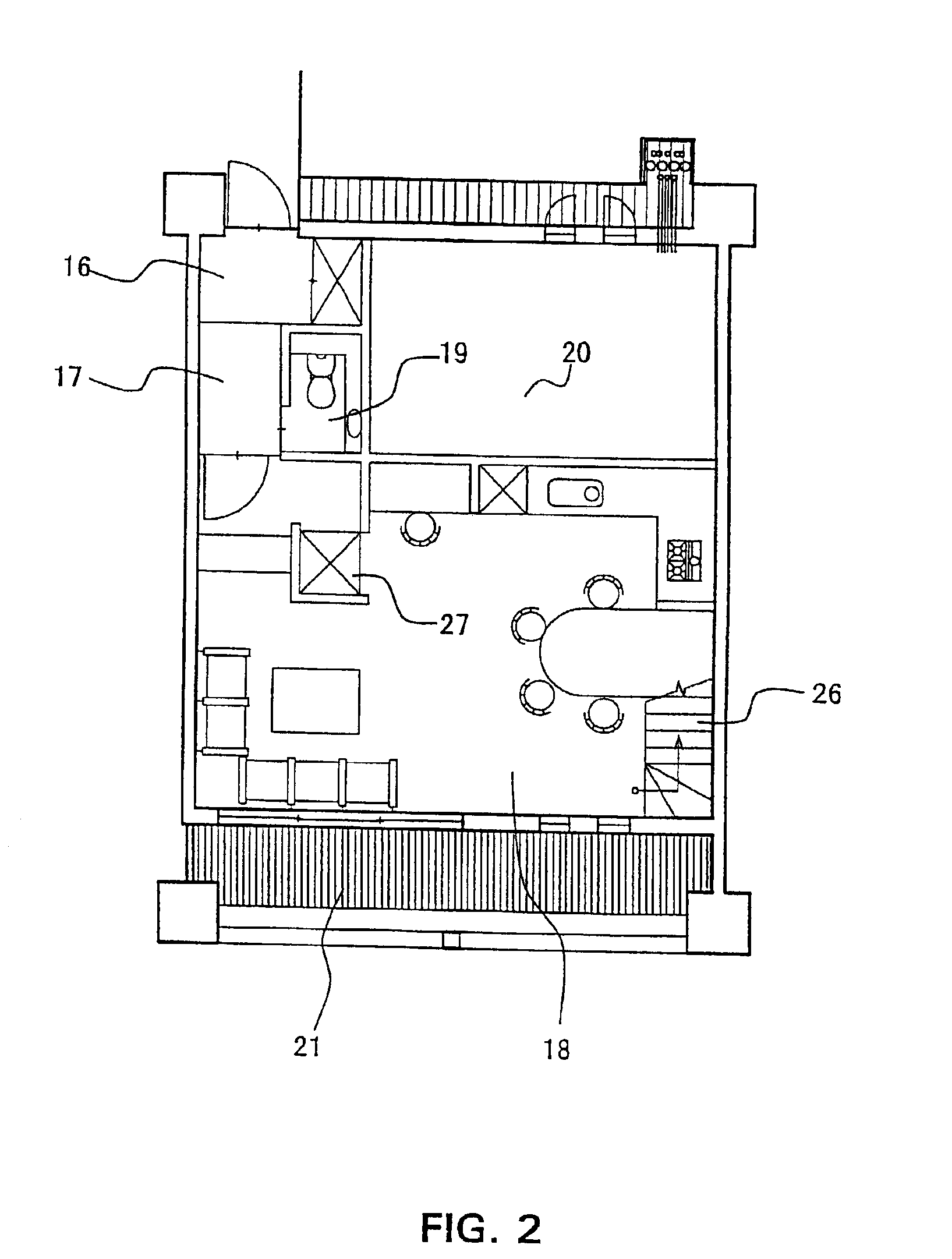

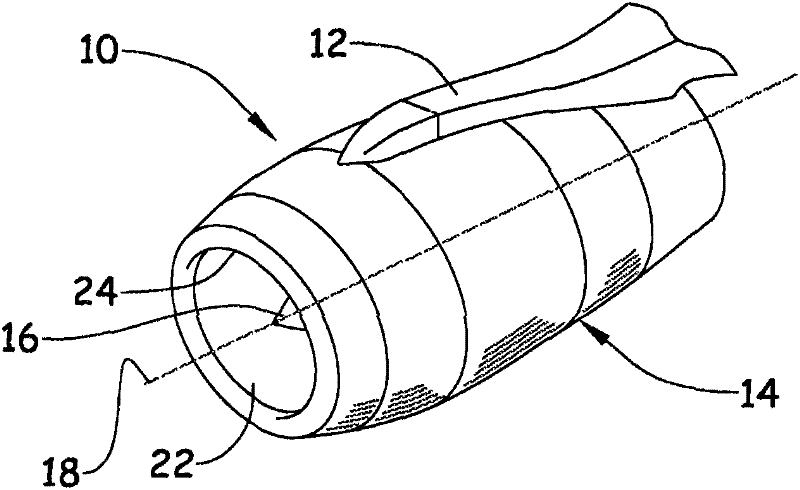

Axially compressible flared stents and apparatus and methods for delivering them

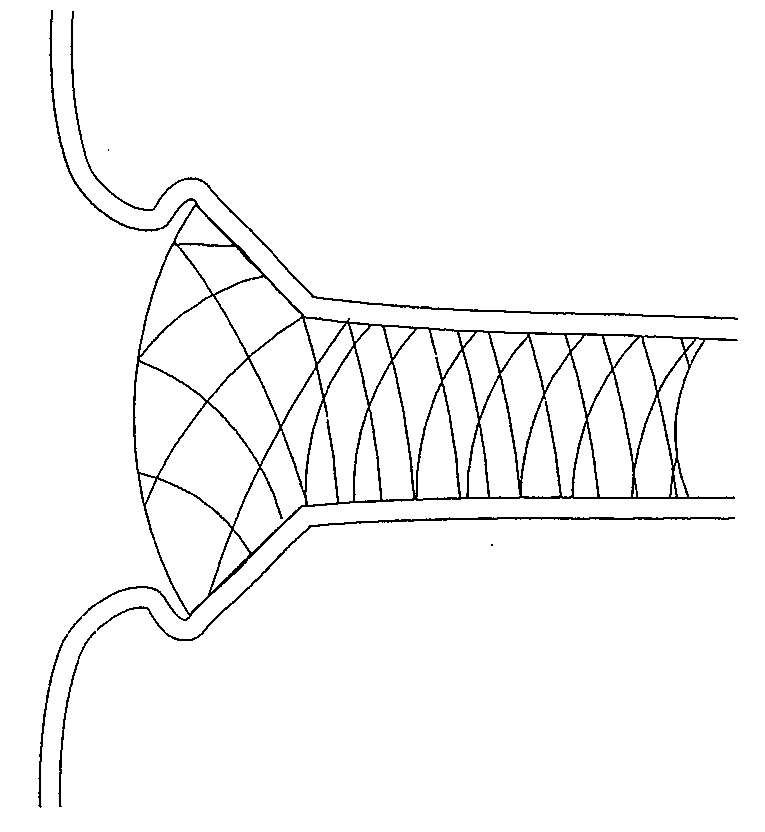

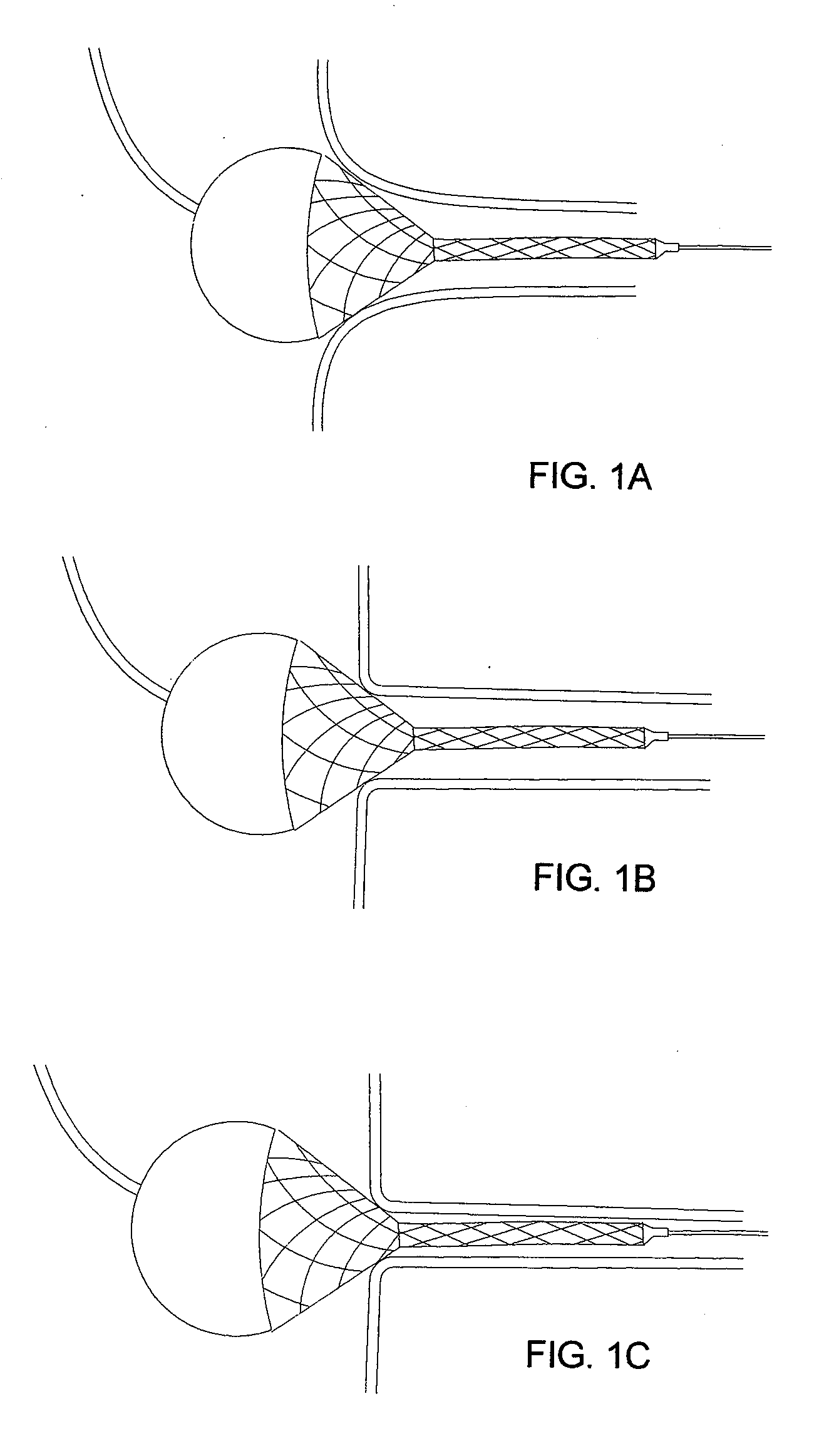

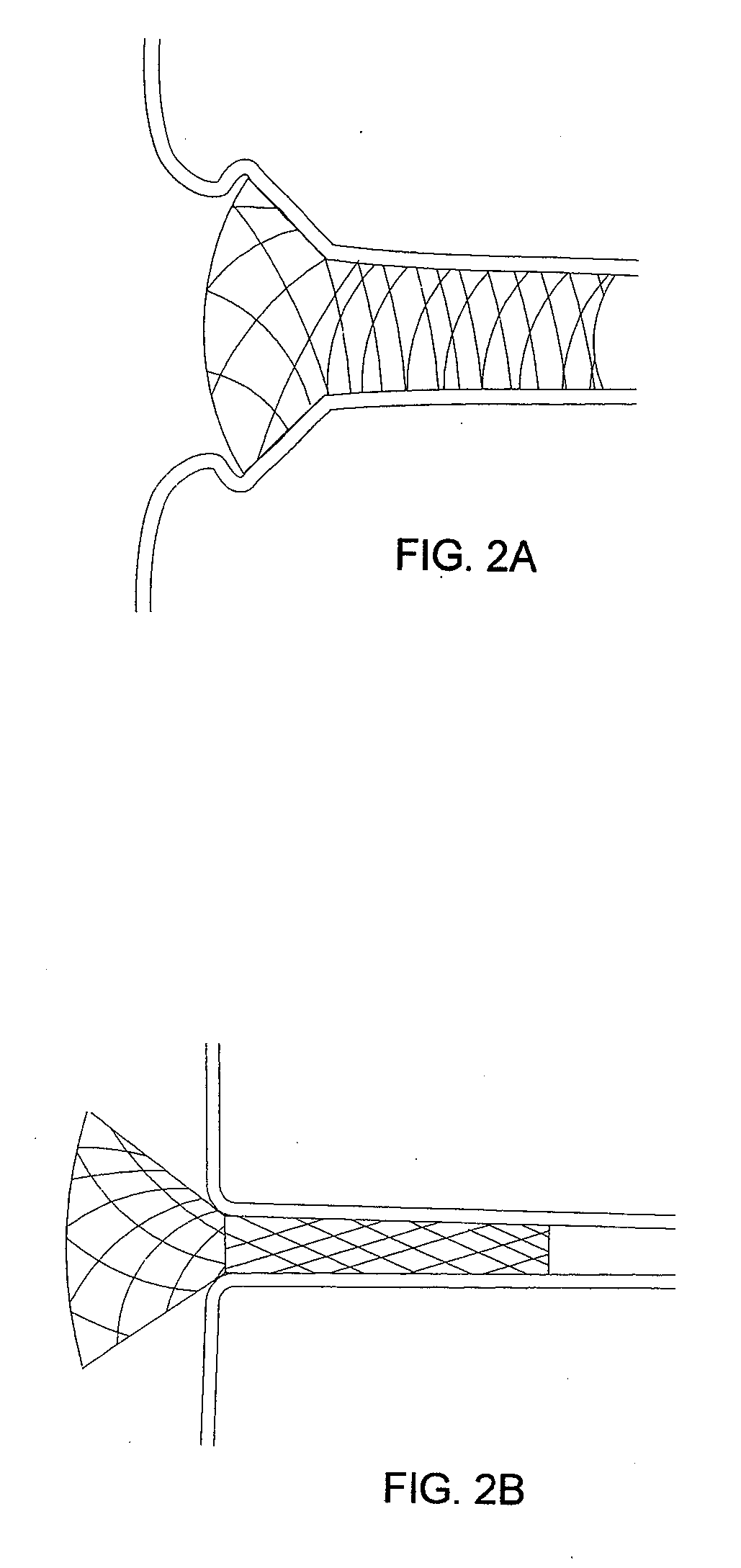

A stent includes a flaring portion and a main portion connected to the flaring portion. The main portion includes a plurality of bands of cells spaced apart axially from one another, adjacent bands of cells being intermittently connected to one another. During use, the stent is introduced into a main vessel in a contracted condition and positioned with the flaring portion adjacent an ostium. The flaring portion is flared, and the stent is advanced at least partially into the ostium. The stent is expanded further such that the main portion expands within the branch body lumen and / or the flaring portion expands adjacent the ostium. The main portion compresses axially during at least one of the steps when the stent is expanded, which may enhance conformance of the stent relative to the ostium and / or enhance reinforcement of the ostium.

Owner:INCEPT LLC

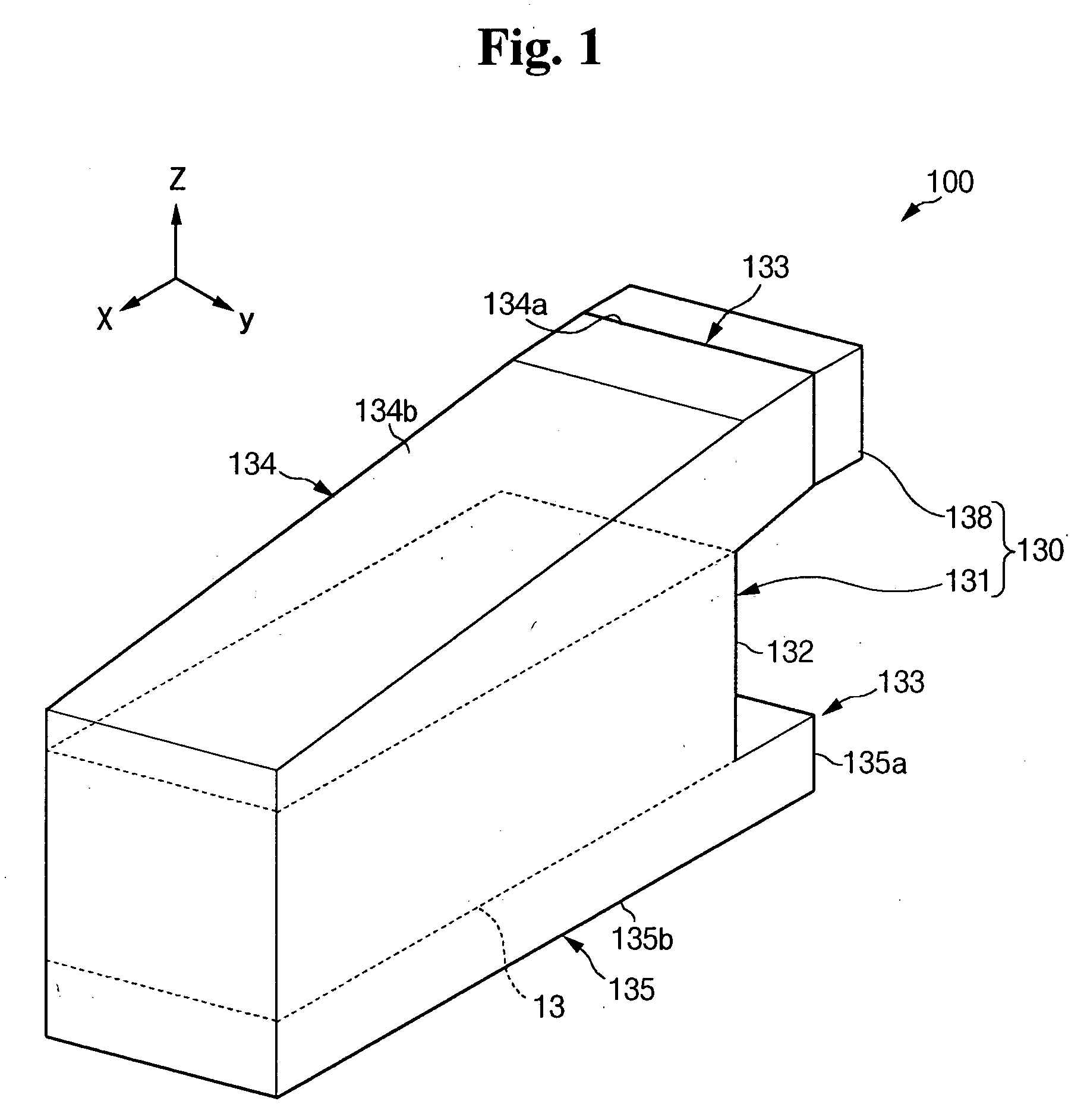

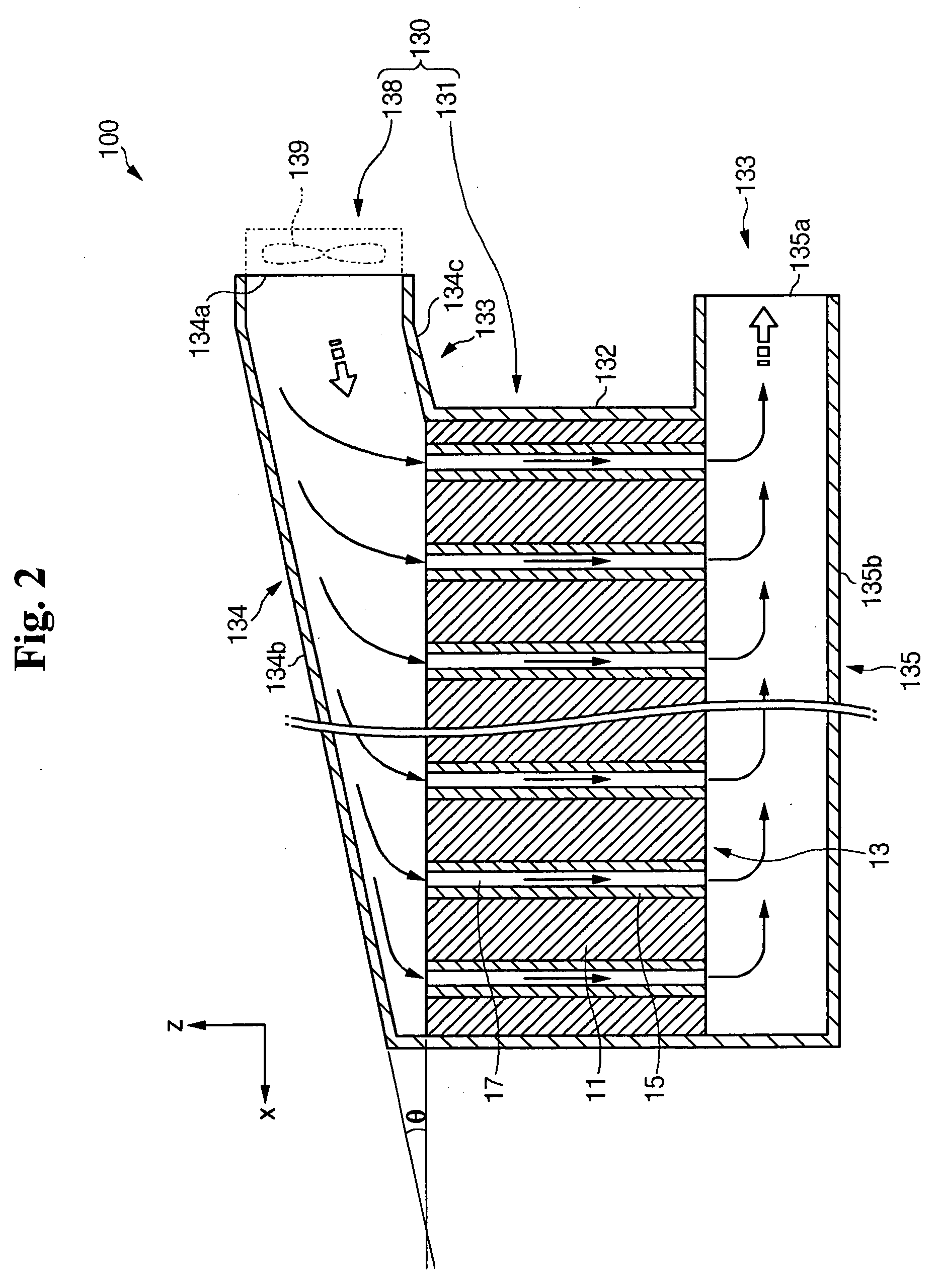

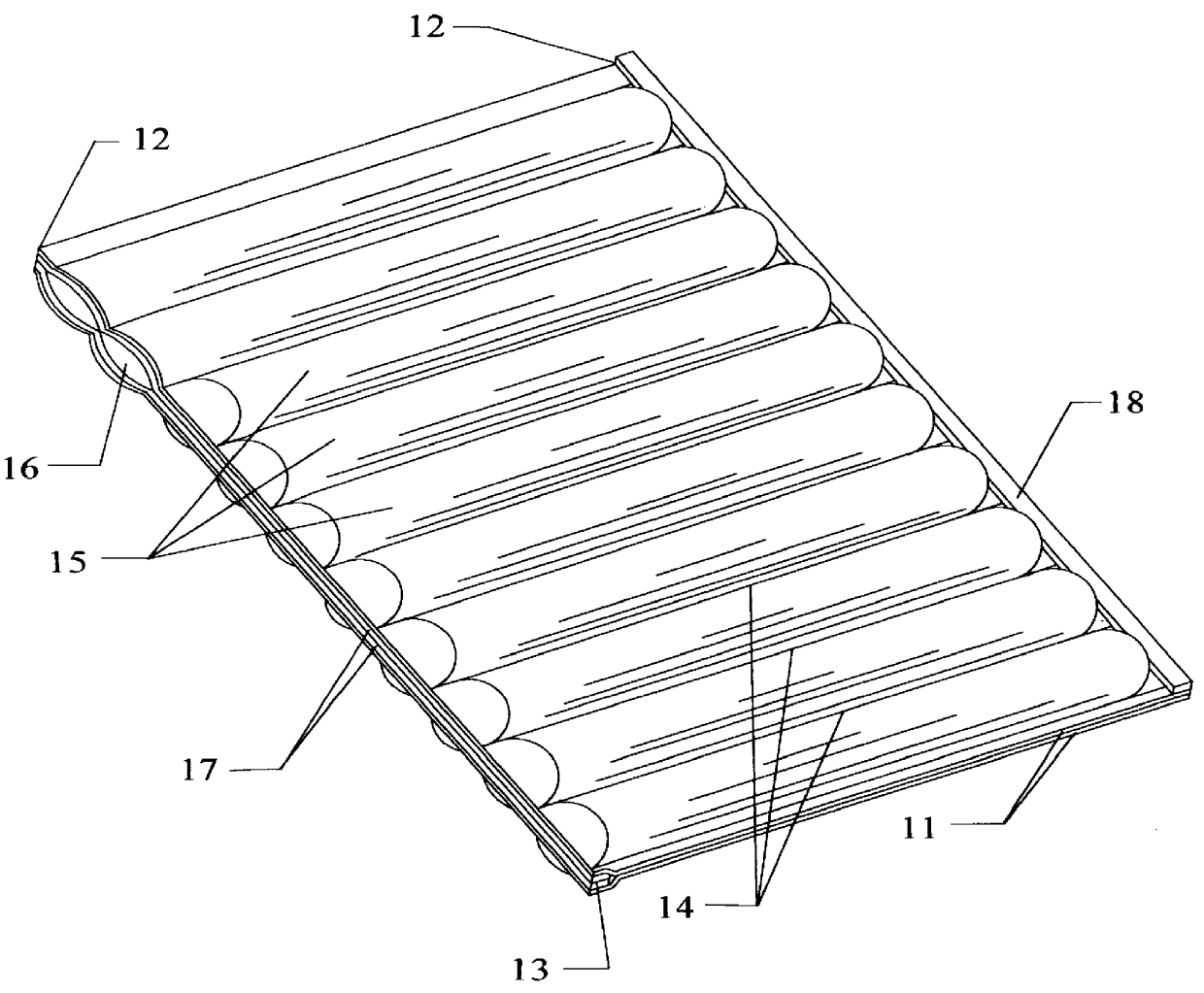

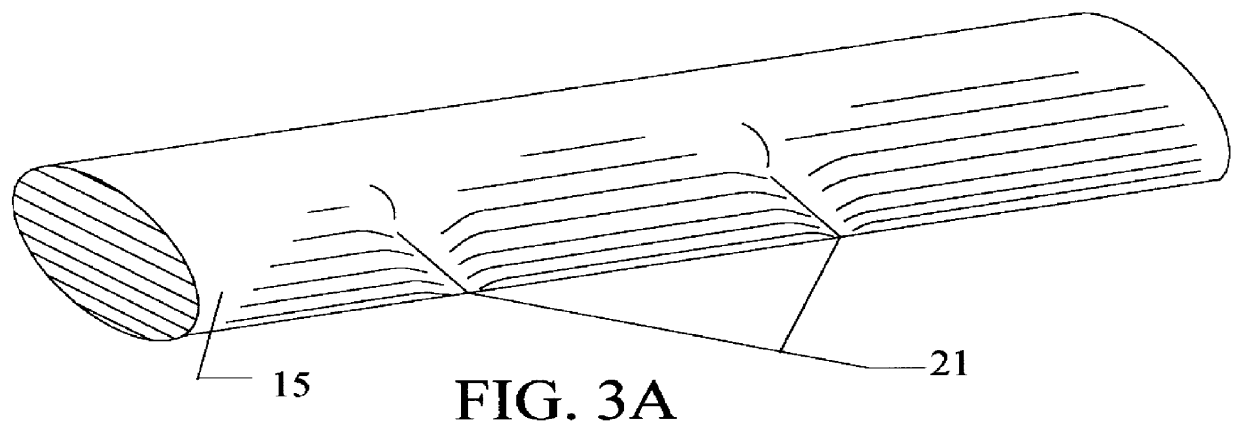

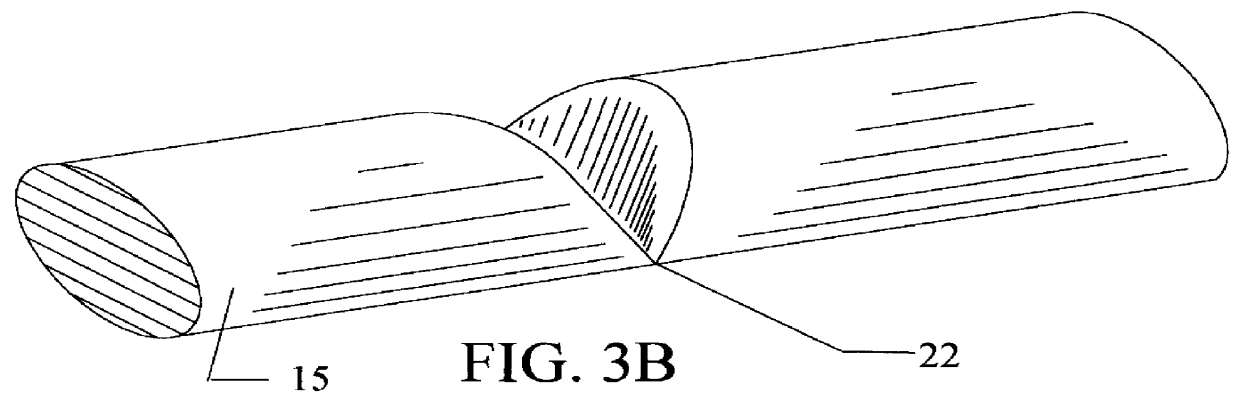

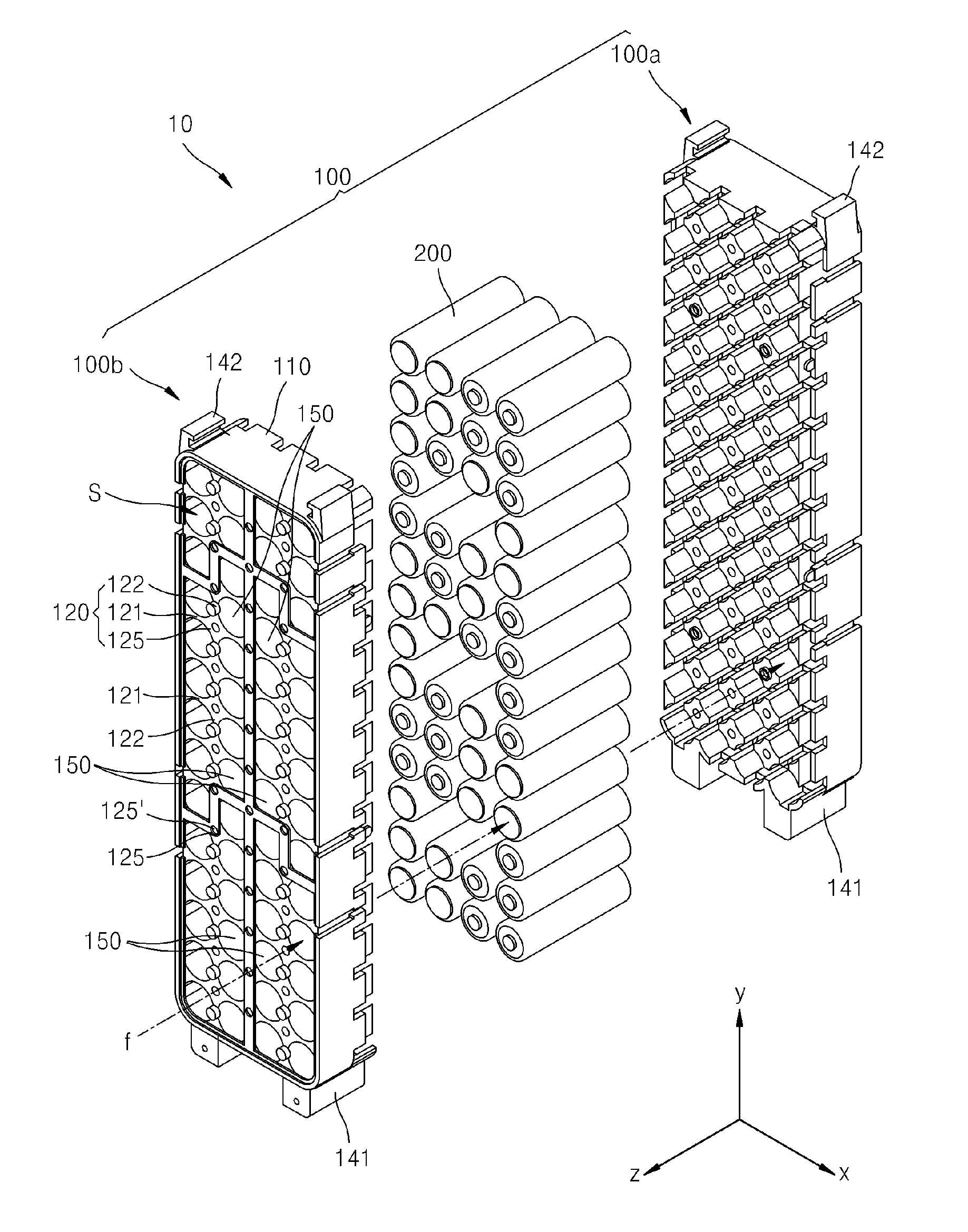

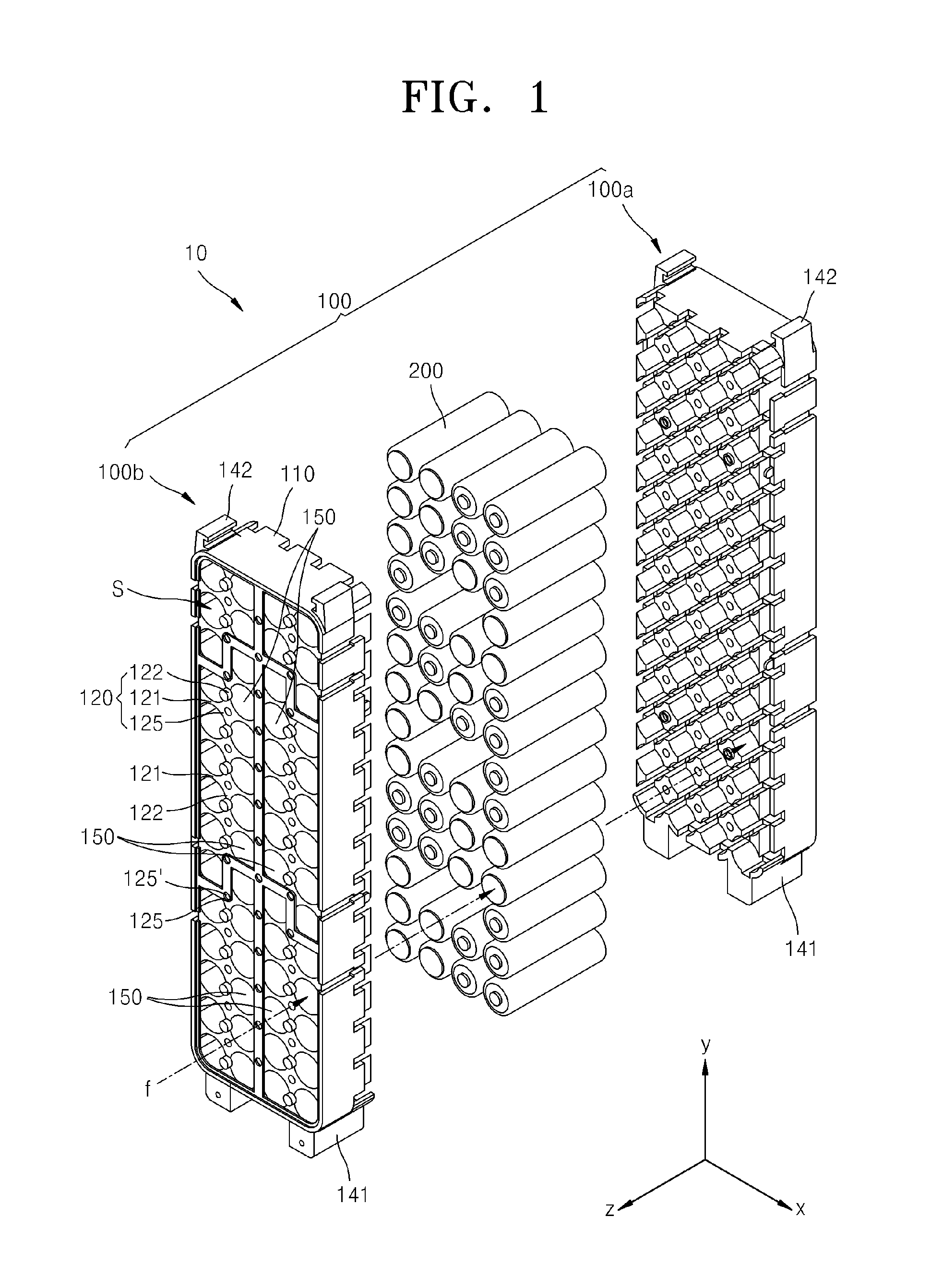

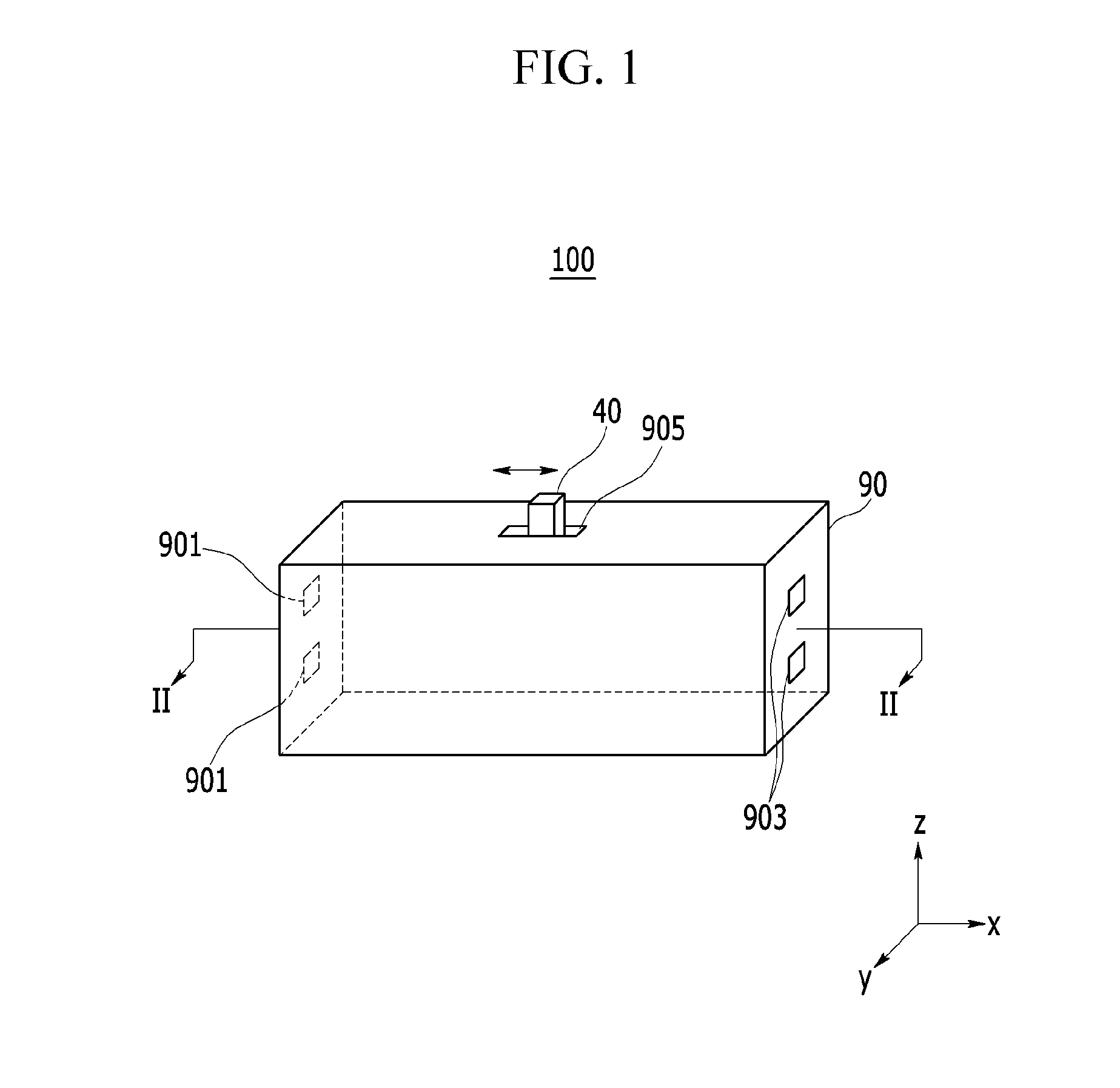

Secondary battery module and cooling apparatus for secondary battery module

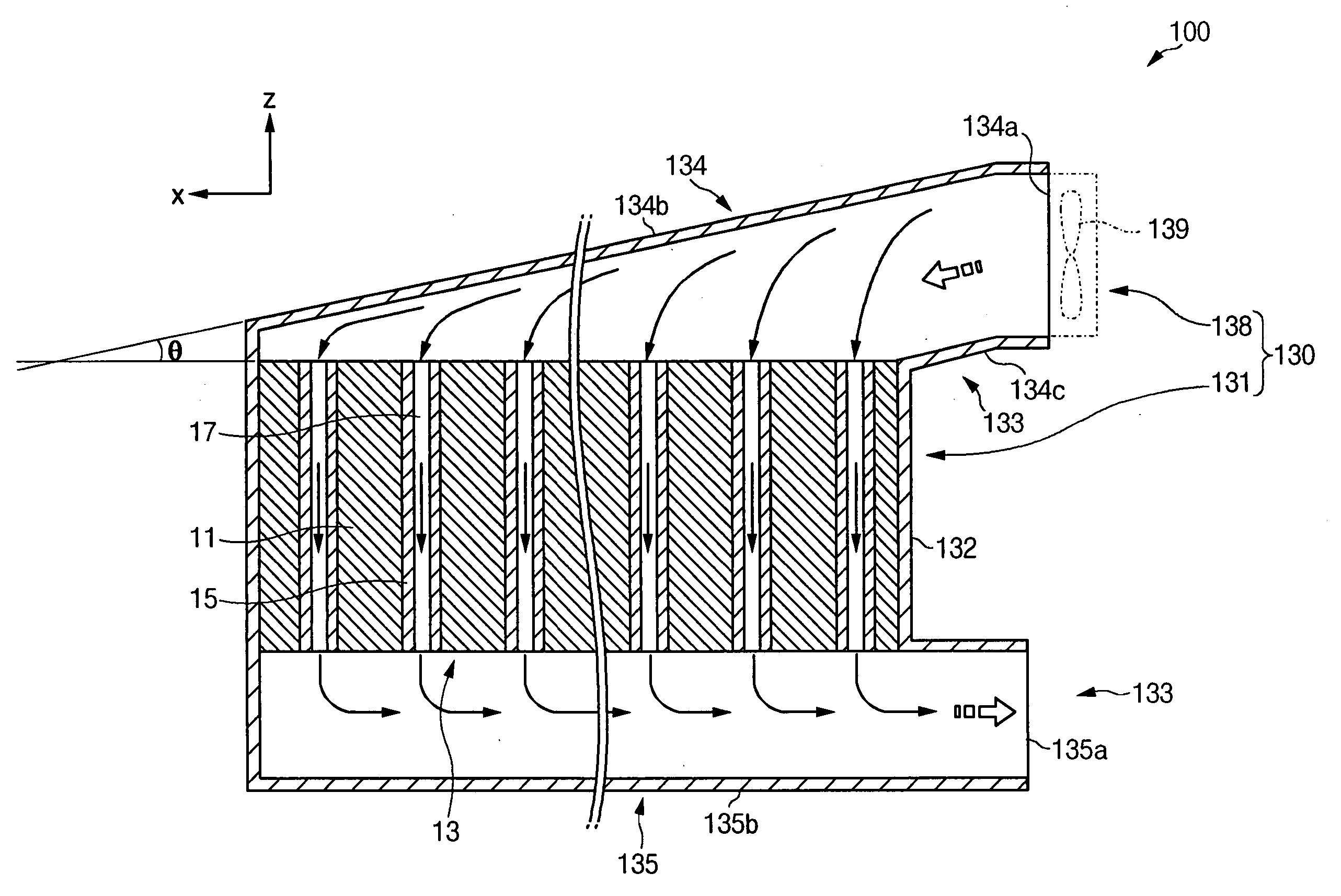

A battery module with a cooling system capable of ventilating a uniform amount of air through the respective unit cells. The battery module includes a plurality of unit cells spaced from each other and a housing for accommodating the unit cells therein. The housing has an inflow guide side inclined with respect to the direction perpendicular to the interfacial surfaces of the plurality of unit cells, an air inlet for introducing a temperature controlling air, and an air outlet for discharging the air ventilated through the unit cells.

Owner:SAMSUNG SDI CO LTD

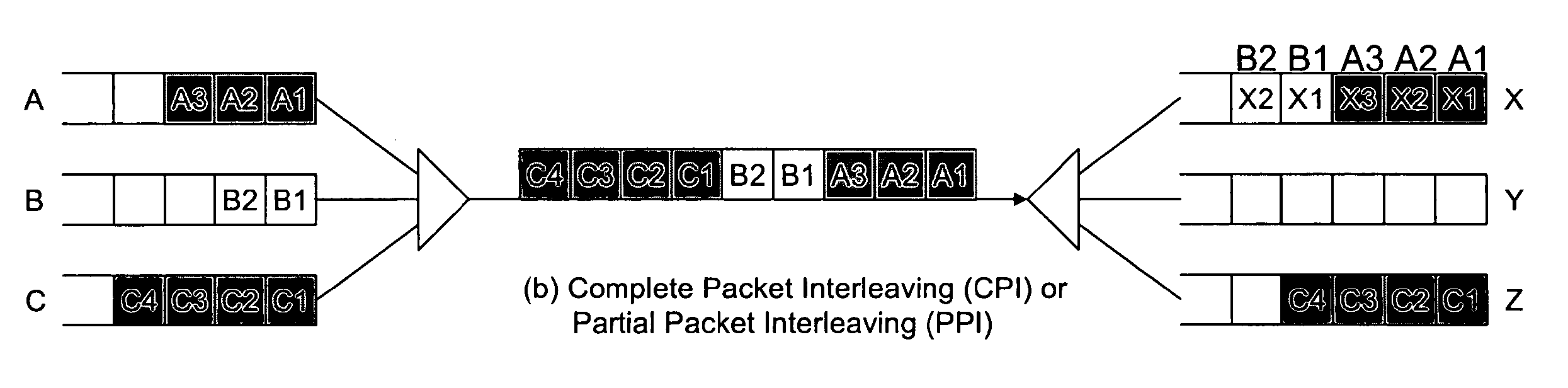

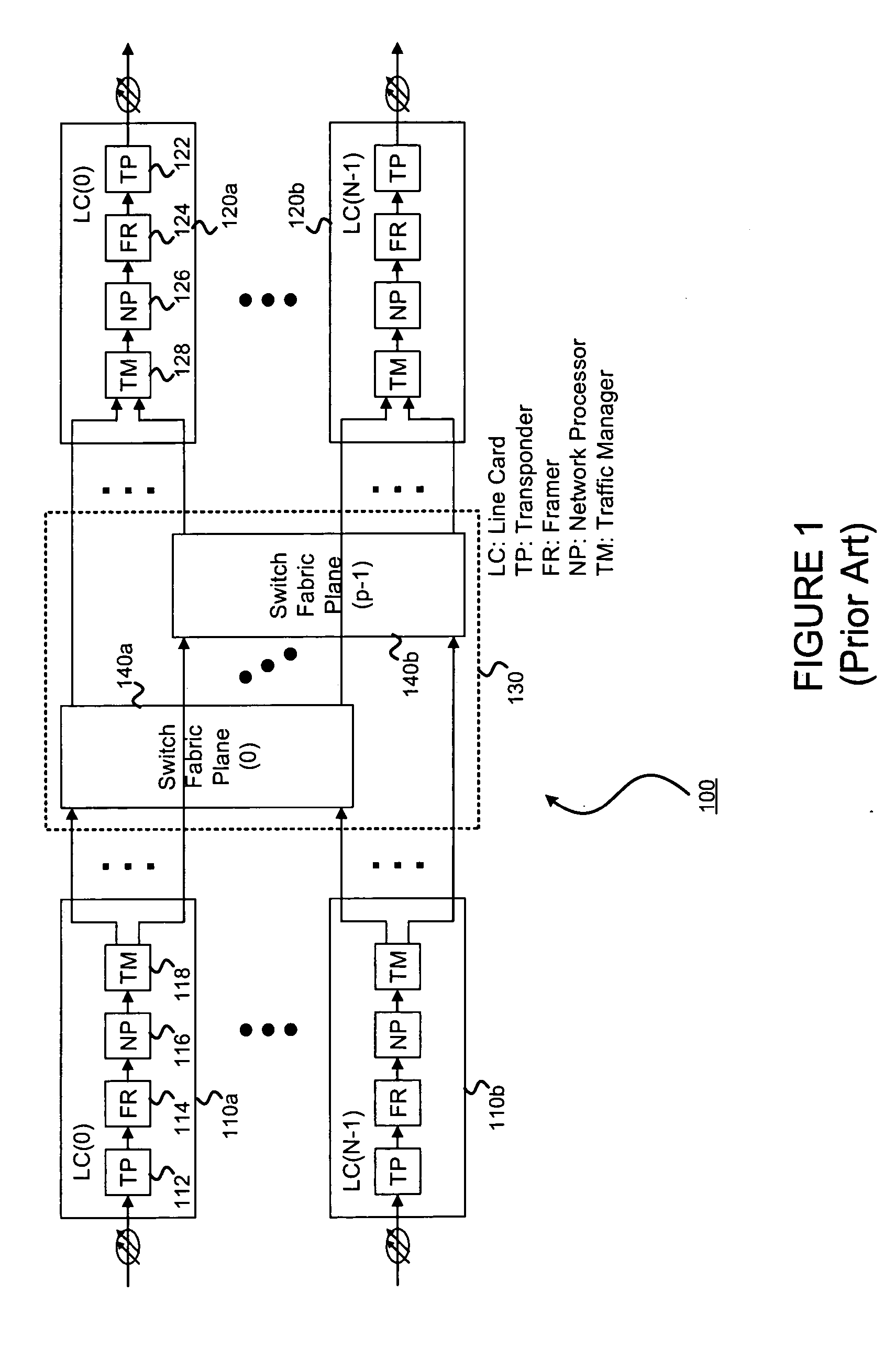

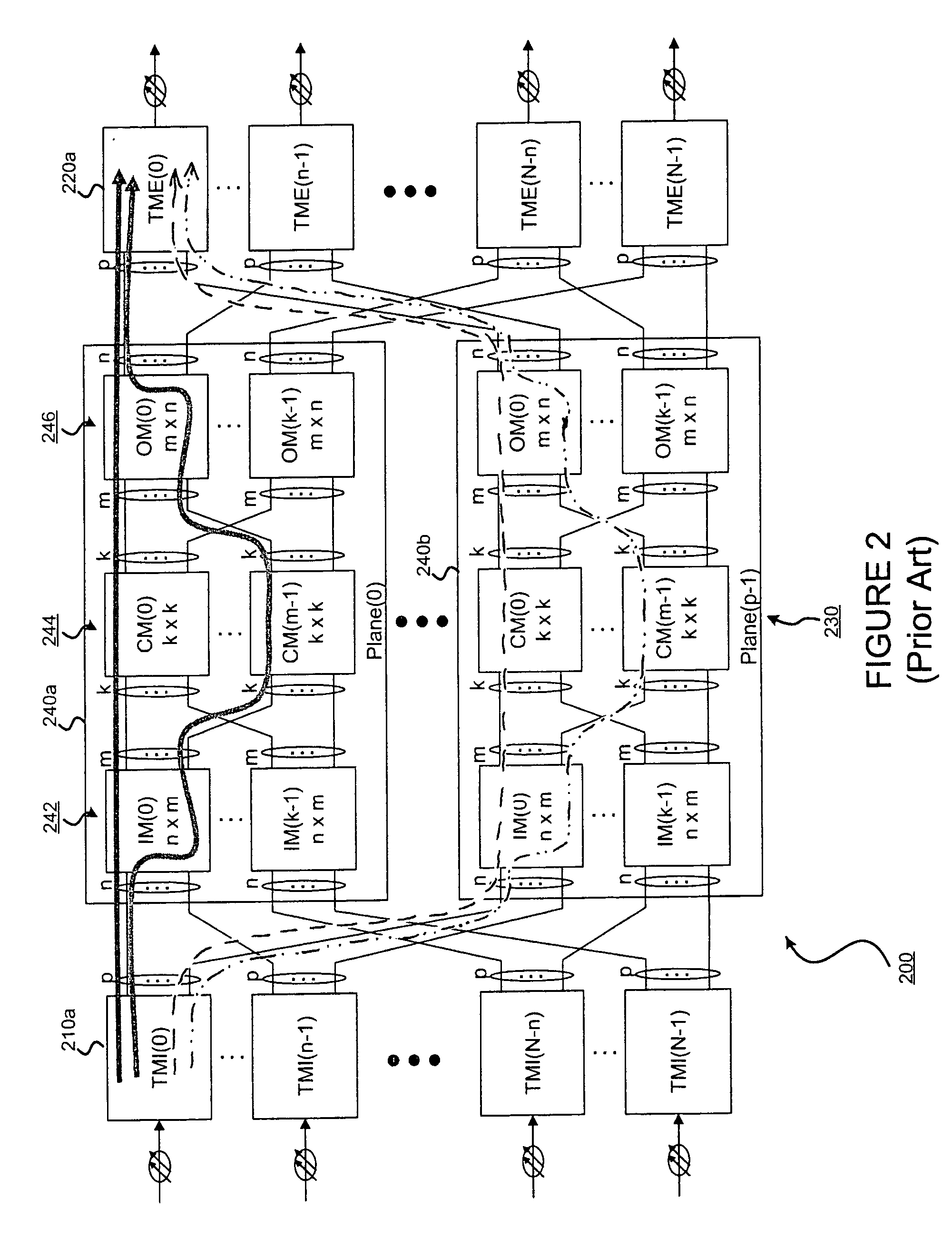

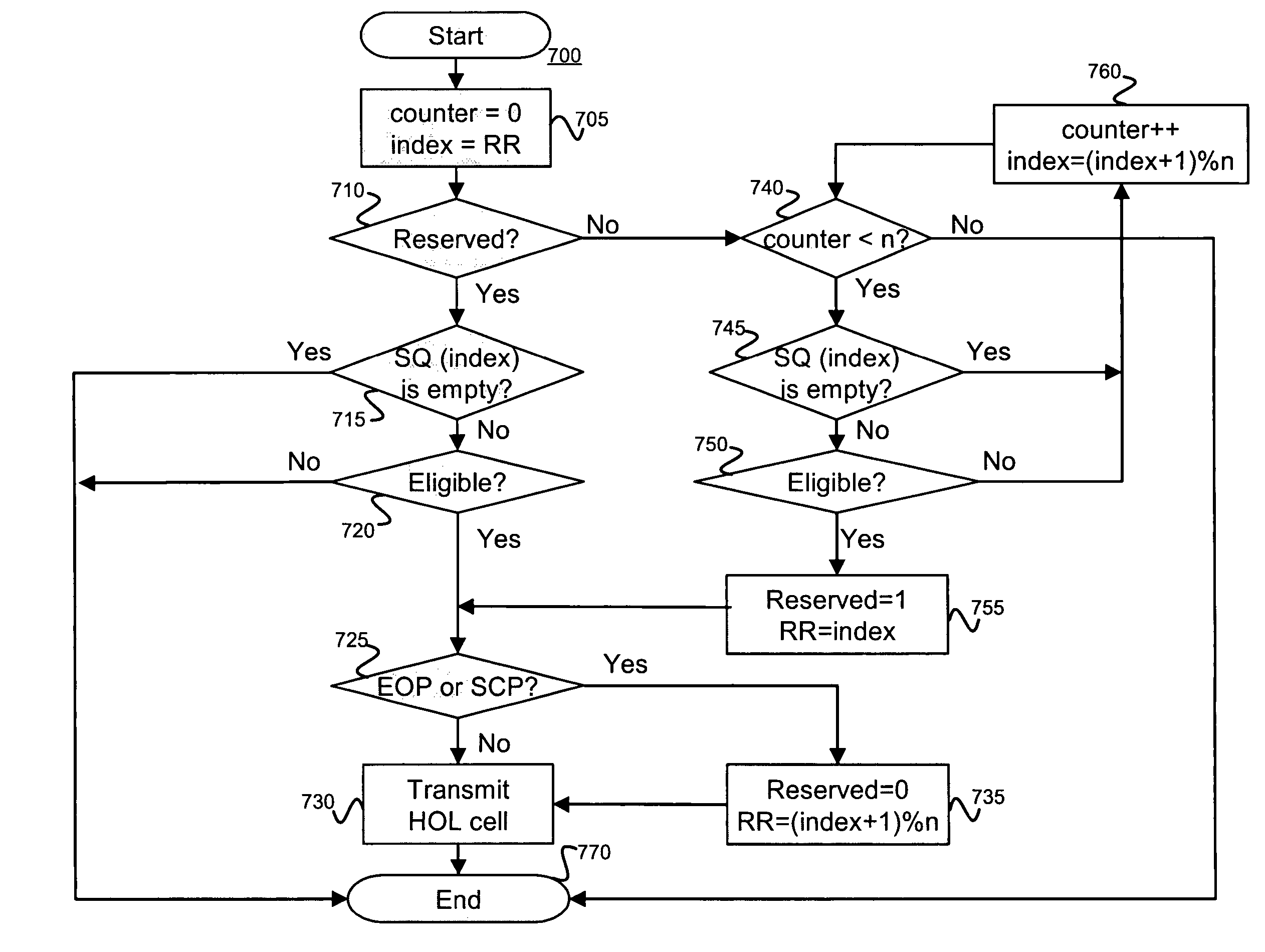

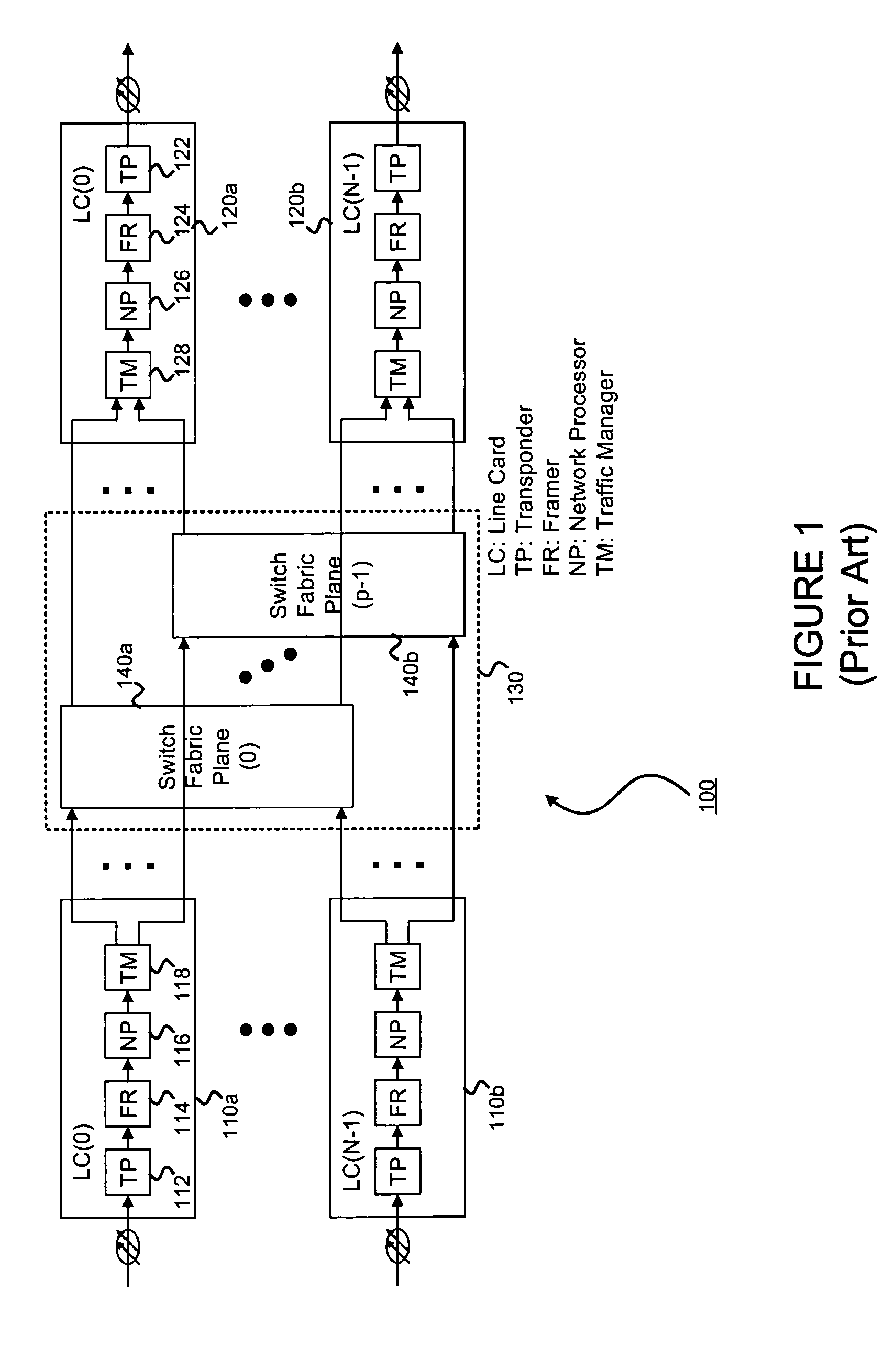

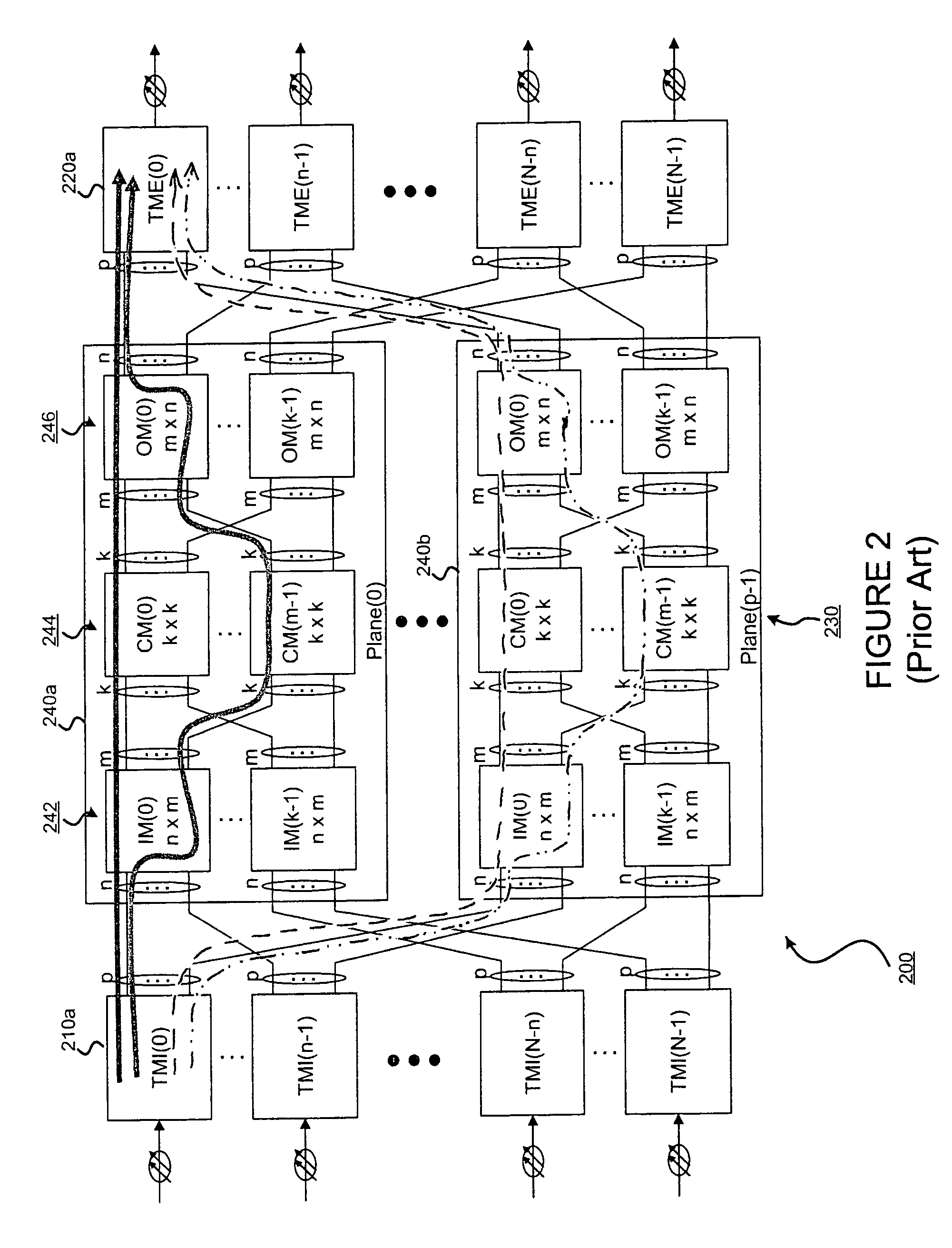

Packet reassembly and deadlock avoidance for use in a packet switch

InactiveUS20050025141A1Multiplex system selection arrangementsData switching by path configurationCell spaceDeadlock

Practical packet reassembly in large, multi-plane, multi-stage switches is possible by using a scheduling technique called dynamic packet interleaving. With dynamic packet interleaving scheduling, if more than one packet is contending for the same output link in a switch module, an arbiter in the switch module gives priority to a partial packet (i.e., to a packet that has had at least one cell sent to the queue). The number of reassembly queues required to ensure reassembly is dramatically reduced (e.g., to the number of paths multiplied by the number of scheduling priorities). Deadlock may be avoided by guaranteeing (e.g., reserving) at least one cell space for all partial packets.

Owner:POLYTECHNIC INST OF NEW YORK

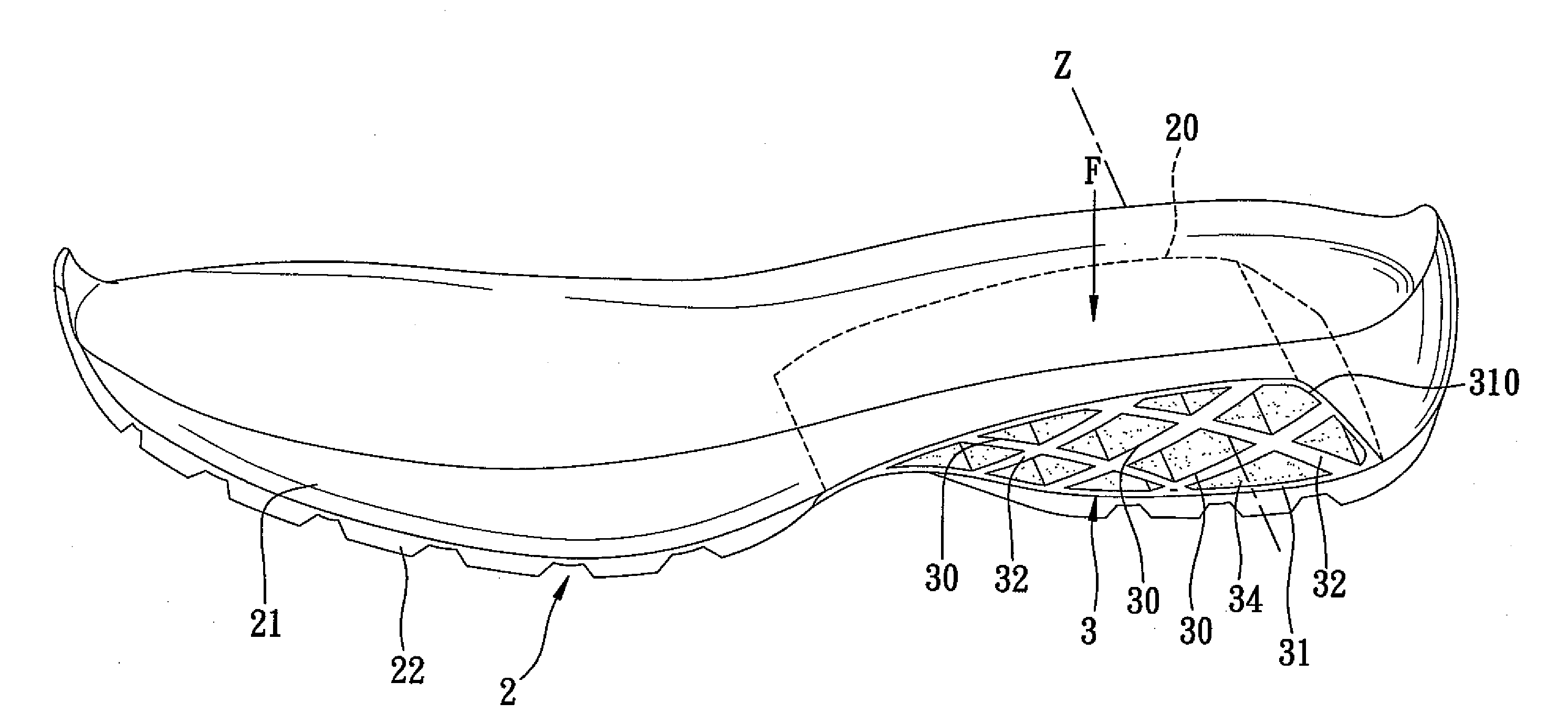

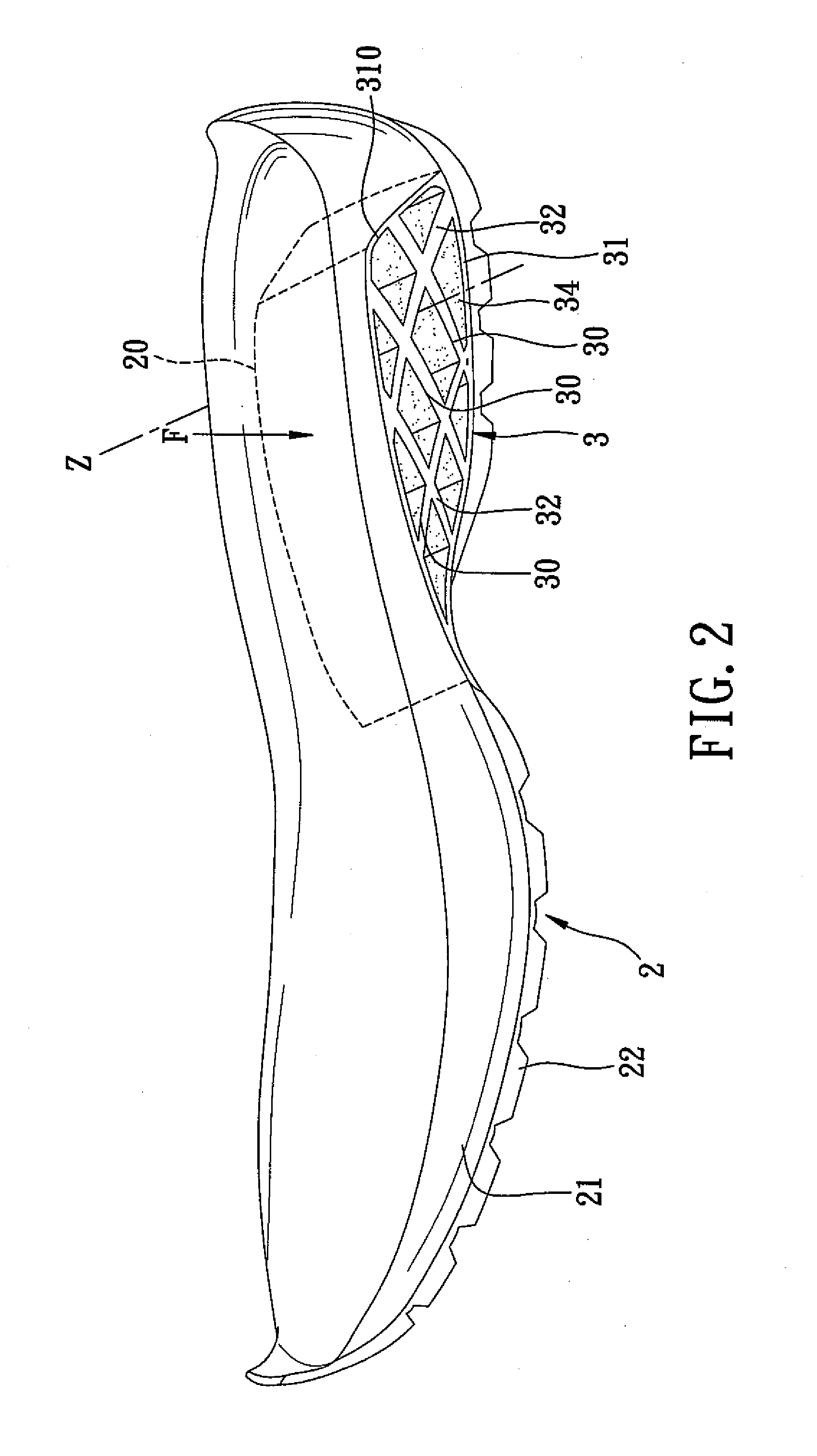

Shoe Sole with Shock Absorbing Capability

A shoe sole includes: a sole unit defining at least one recess; at least one elastic body received in the recess and having a cellular structure that defines at least two levels of cells, the two levels of the cells being disposed one above the other, each of the cells defining a cell space therein; and a filler material that fills the cell space of each of the cells.

Owner:SHYANG SHIN BAO IND

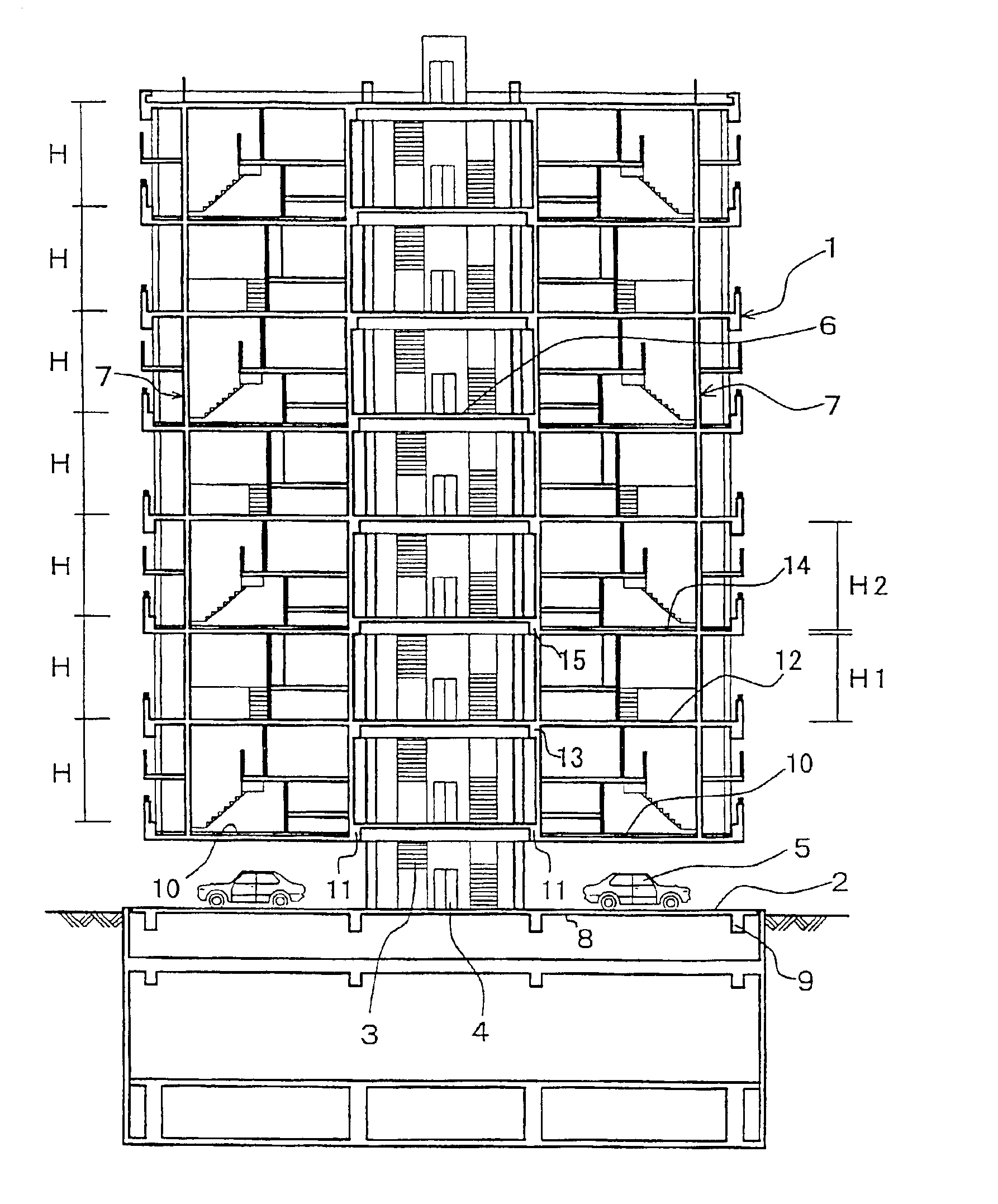

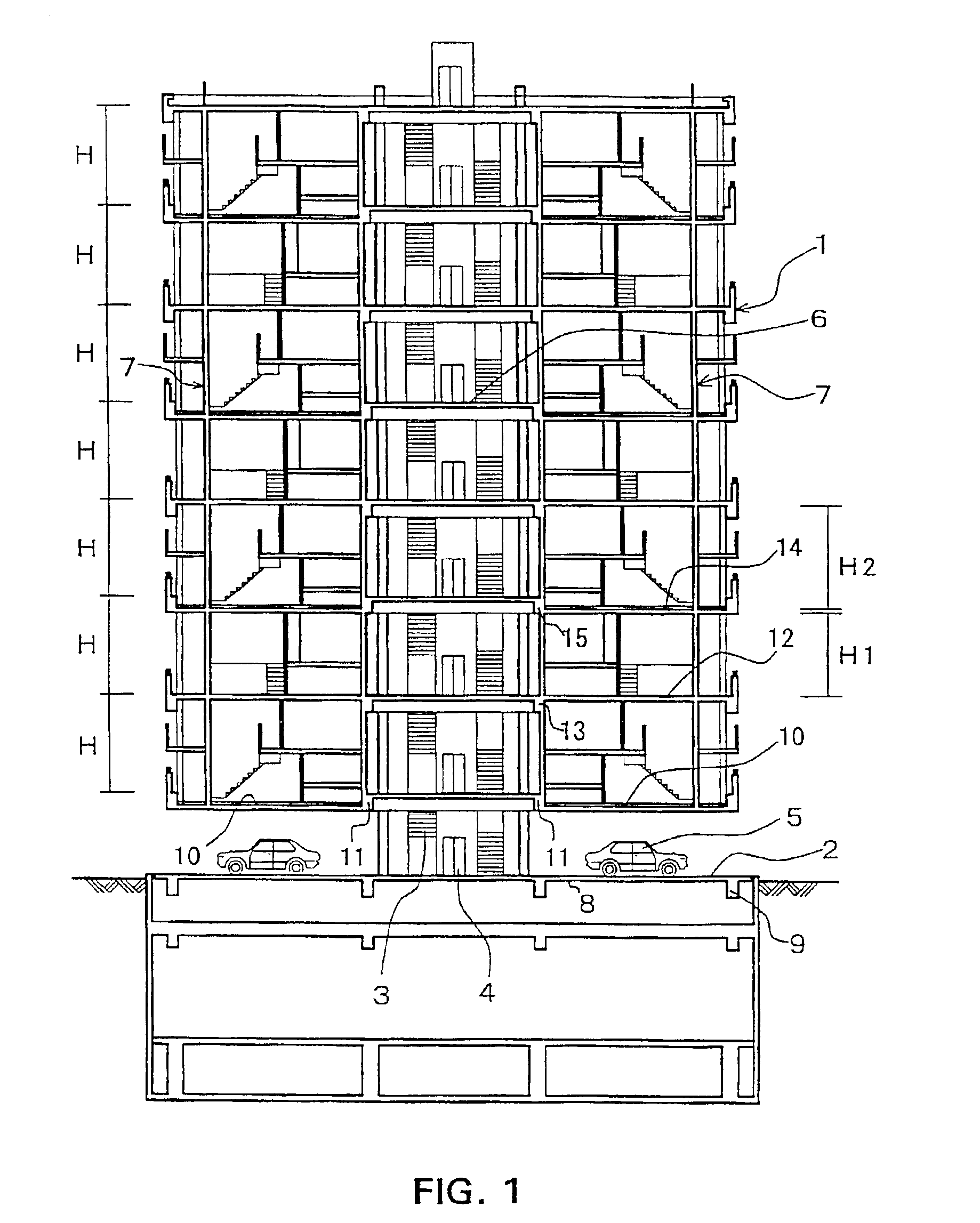

Multiple dwelling house

InactiveUS6922960B2Wide spaceEffective height dimensionPublic buildingsSpecial buildingCell spaceUpper floor

The invention provides a multiple dwelling house in which although its standard floors are constructed to have the same structural floor height, the ceiling heights of individual dwelling units positioned above and below each flat slab can be set to differ from each other so that the multiple dwelling house has ceiling heights capable of meeting a variety of needs of users. The multiple dwelling house includes standard floors constructed to have the same structural floor height dimension, intermediate slabs each of which is made of a flat slab and is disposed between each of adjacent upper and lower floors, and slabs each of which is made of a beam slab and forms a ceiling face of the upper floor and a floor face of the lower floor. One unit made of the adjacent upper and lower floors is constructed in a sequentially repeated manner to make dwelling-unit spaces different in ceiling height between the adjacent upper and lower floors.

Owner:INST OF INT ENVIRONMENT +1

Test device and method for colored particle immunoassay

InactiveUS20060040405A1Minimize false positiveEasy to useEnzymologyLaboratory glasswaresEpitope specificityCell space

Disclosed is a test cell and a method for detection of a preselected ligand in a liquid sample such as a body fluid. The test cell includes an elongate outer casing which houses an interior permeable material capable of transporting an aqueous solution and defining a sample inlet, a test volume, and a reservoir volume. The reservoir volume is disposed in a section of the test cell spaced apart from the inlet and is filled with sorbent material. The reservoir acts to receive liquid transported along a flow path defined by the permeable material and extending from the inlet and through the test volume. In the test volume is a test site which includes a first protein having a binding site specific to a first epitope of the ligand immobilized in fluid communication with the flow path. The test site can be observed through a window of the casing.

Owner:CHARLTON DAVID E +1

Continuous cell mattress overlay with flowable filler material of buckwheat hulls

A mattress overlay consisting of two pieces of fabric joined along the longitudinal, or head to foot, edges and then joined transversely, from side to side, at predetermined distances along the longitudinal axis forming lateral, closed interior cell spaces. In the preferred embodiment, the joining method along at least one of the longitudinal edges uses openable and recloseable cooperating hook and loop pressure strips to allow access to the individual cells after manufacture. To provide even support throughout the resting area, the interior cell spaces are partially filled with a flowable filler material of Buckwheat hulls or a mixture of Buckwheat hulls and any other compatible material. The preferred embodiment allows resting comfort to be customized by adding or removing flowable filler from individual cell spaces as needed. The preferred embodiment has half of an openable and recloseable fastening device joined along longitudinal edge to allow attachment of two or more mattress overlays. The mattress overlay, when Buckwheat hulls are used as a filler material, resists the slippage of the human resting form when a bed is canted for medical purposes.

Owner:HENRY LLOYD W

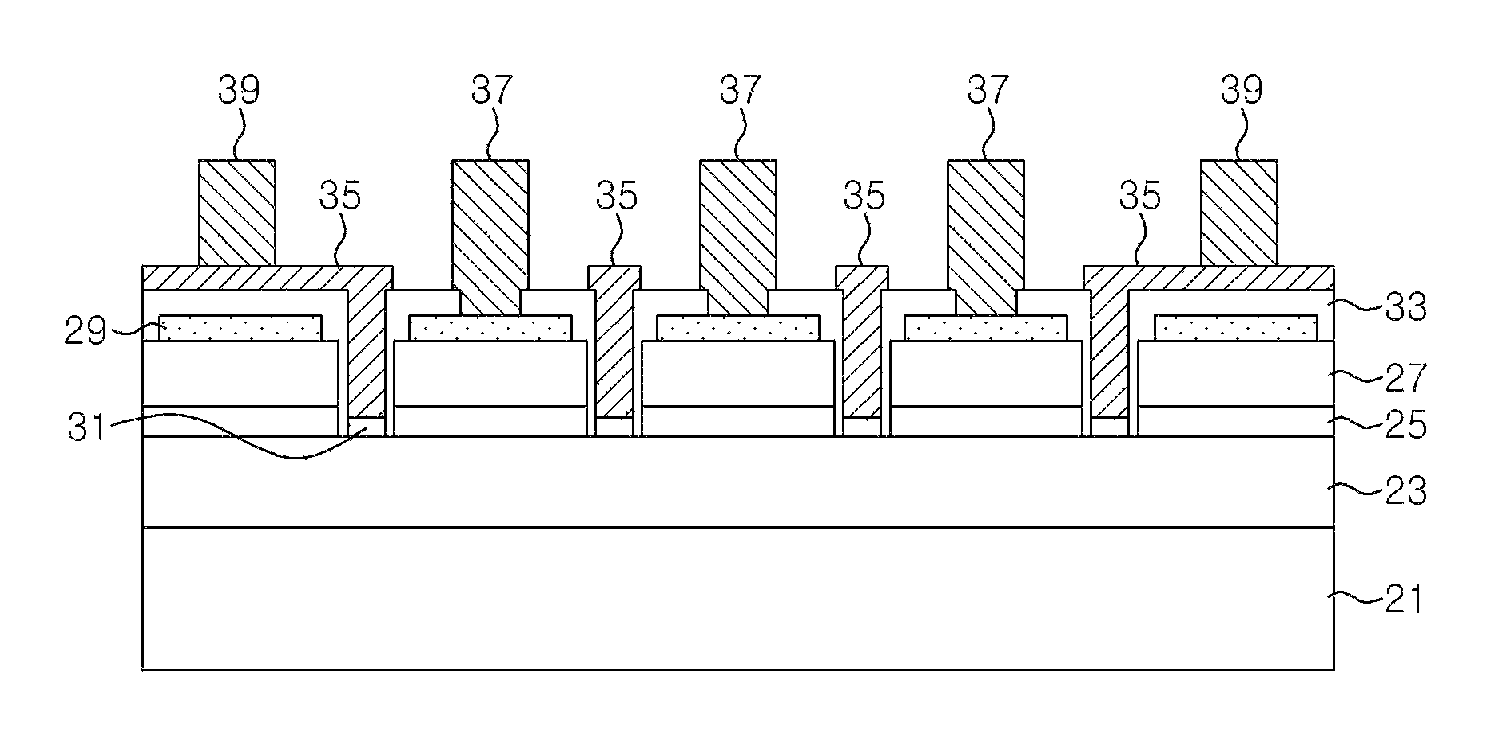

Light emitting diode with improved current spreading performance

ActiveUS7880181B2Evenly distributedImprove luminous efficiencySemiconductor devicesCell spaceEngineering

Owner:SEOUL VIOSYS CO LTD

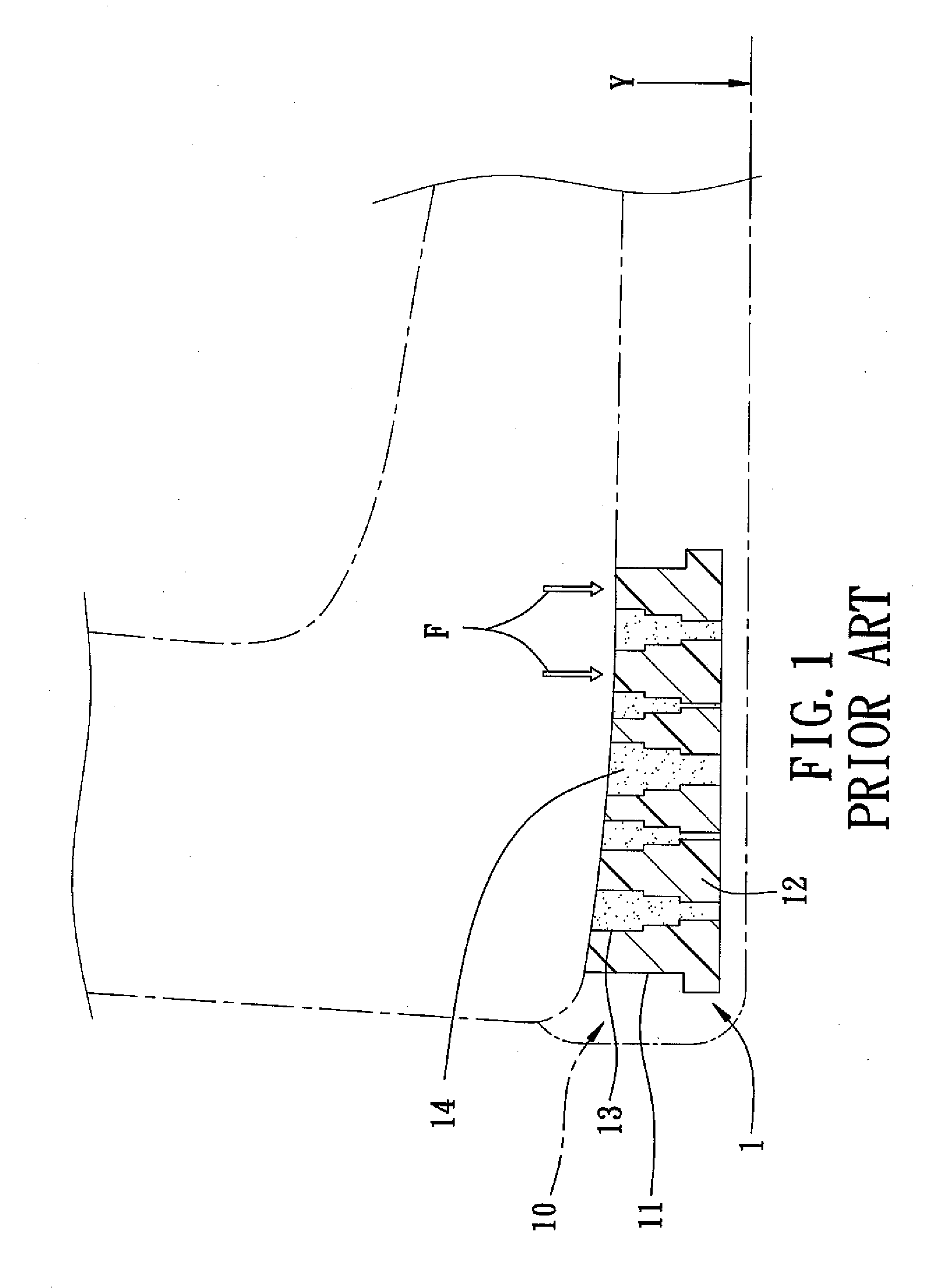

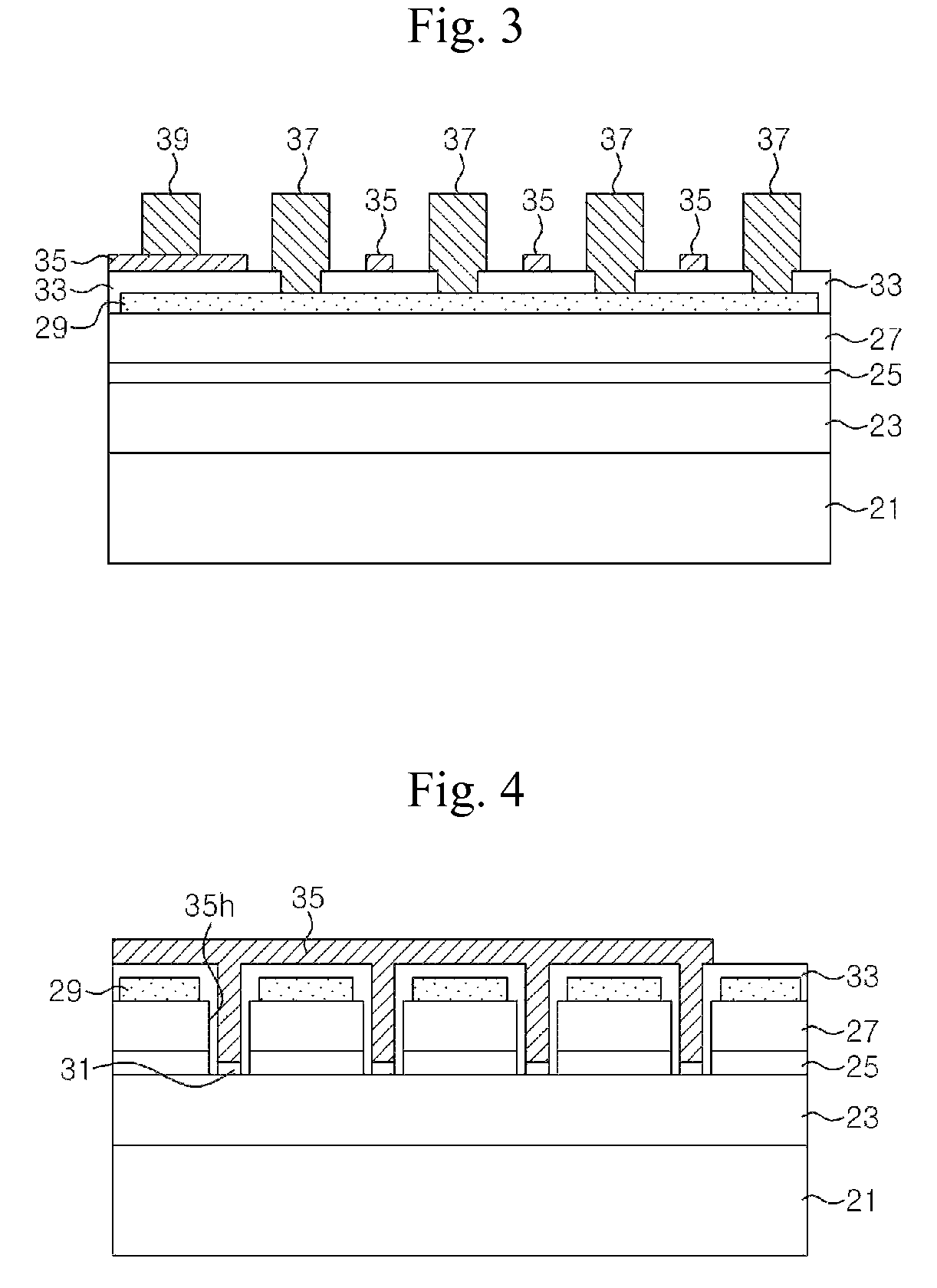

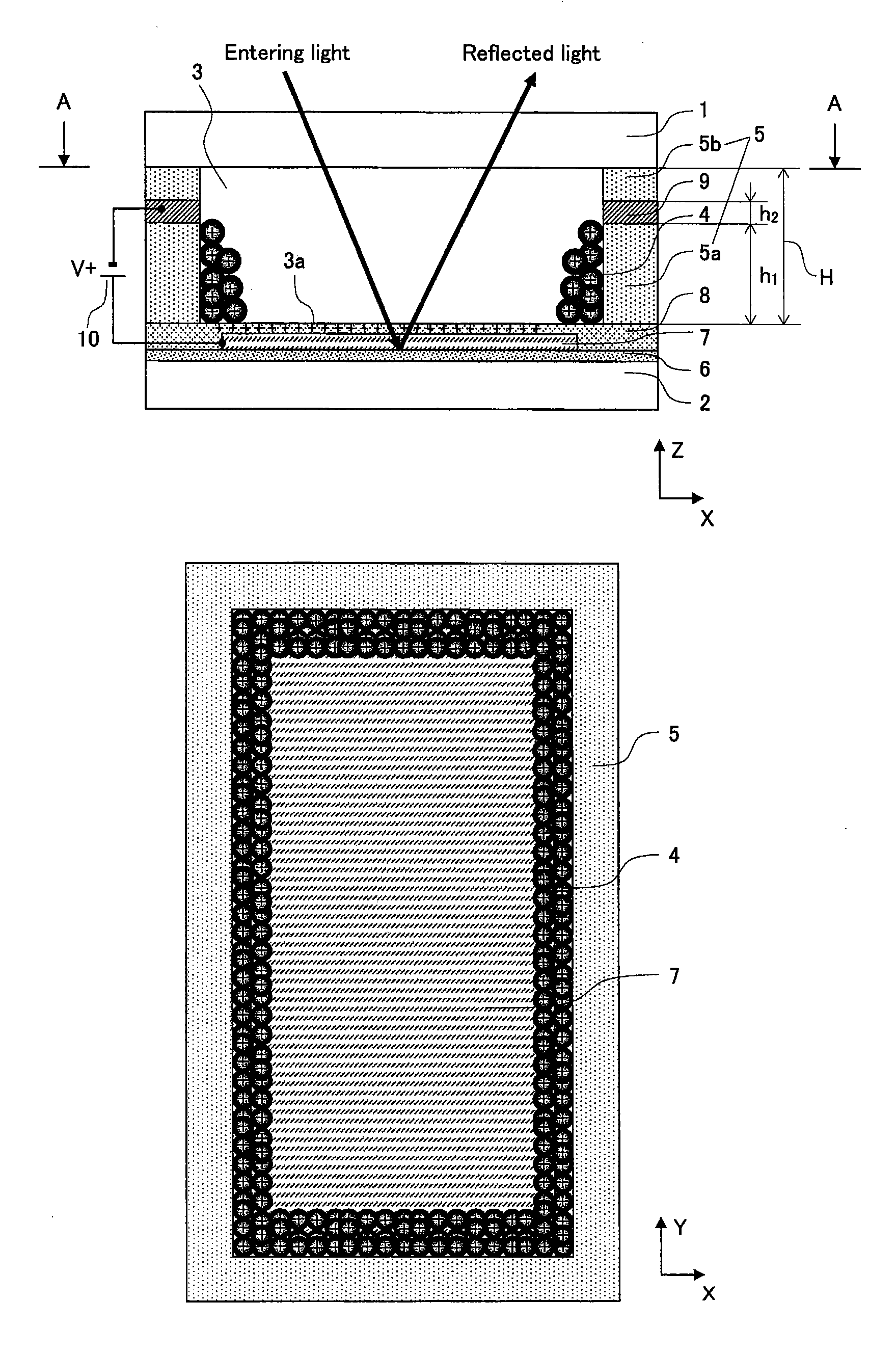

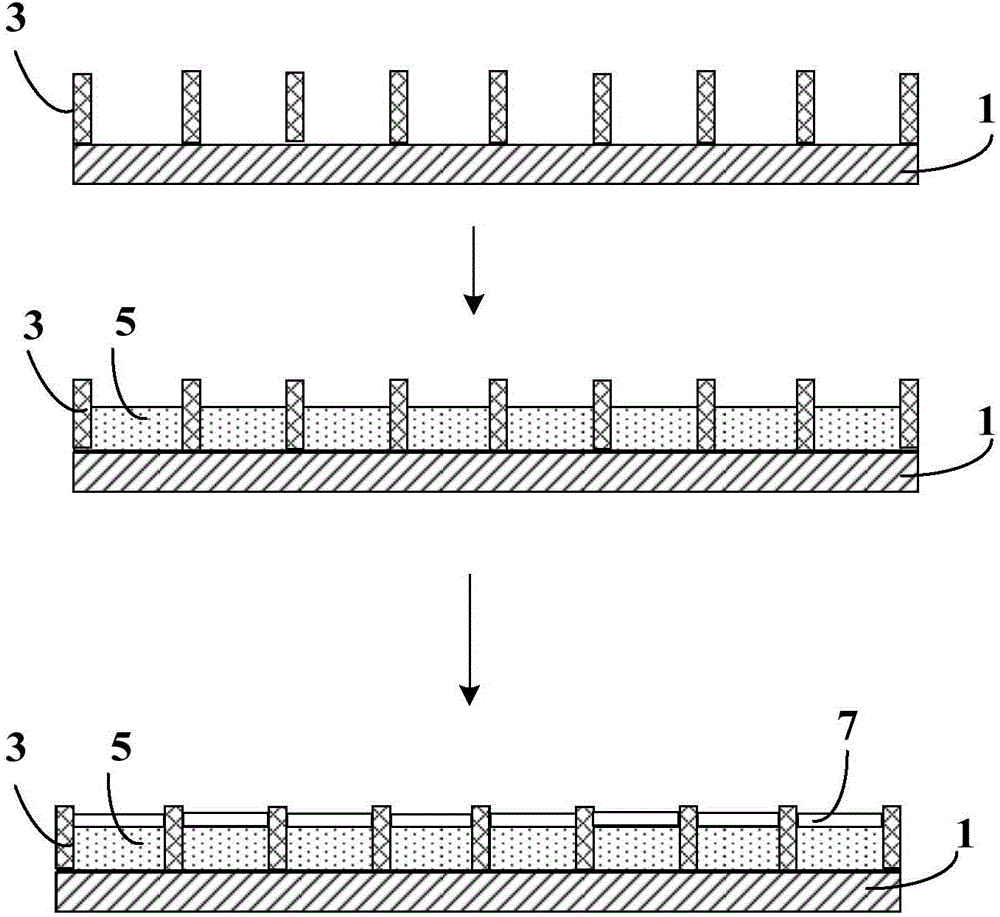

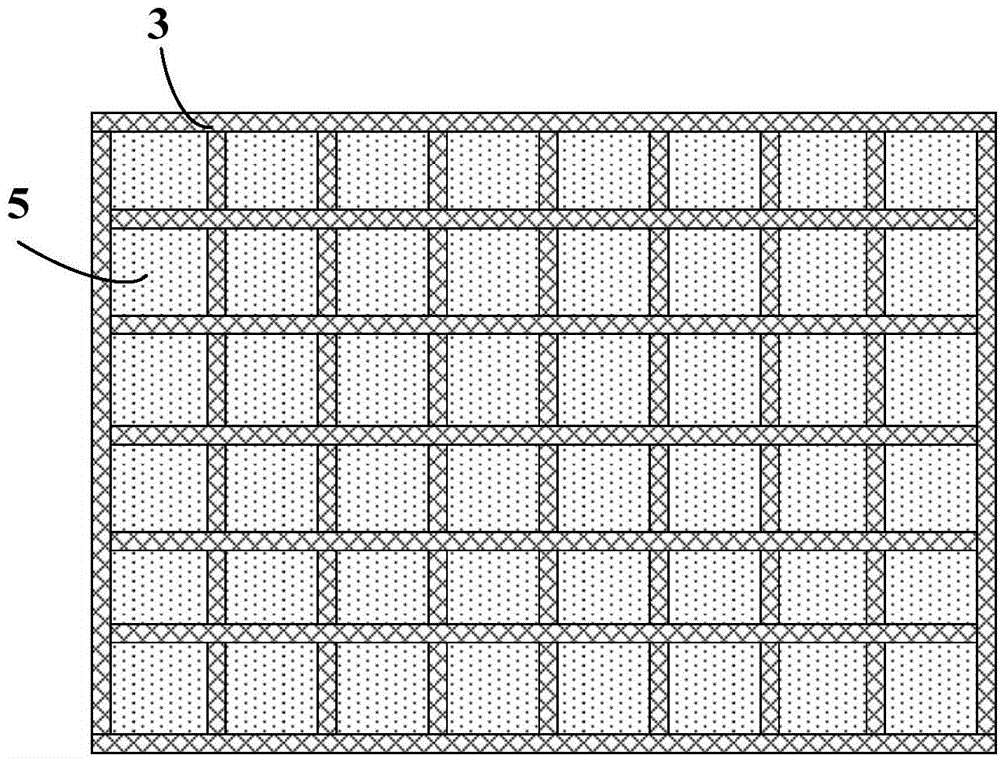

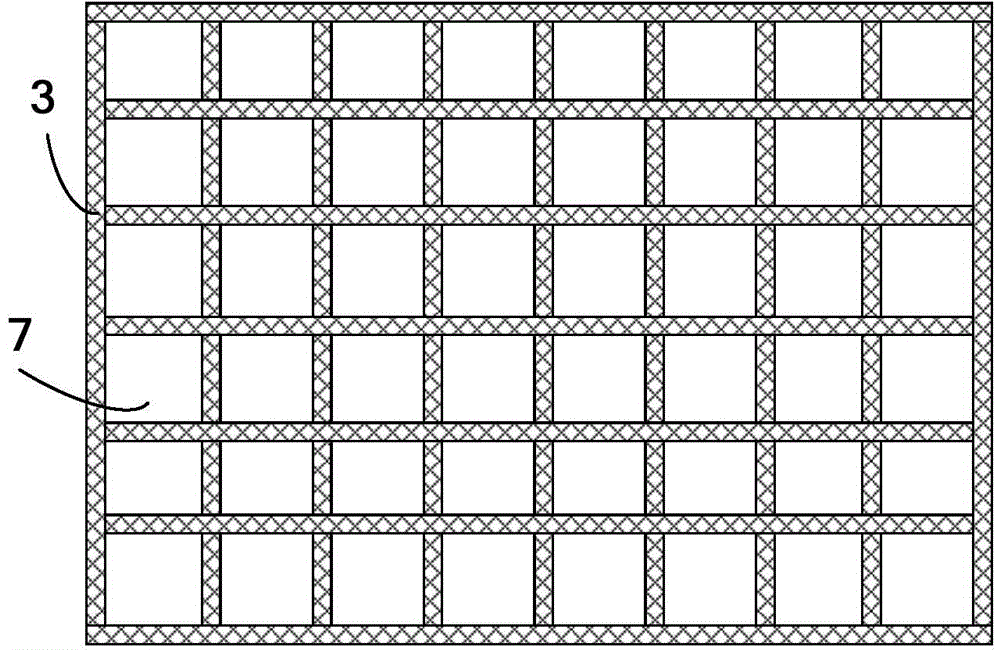

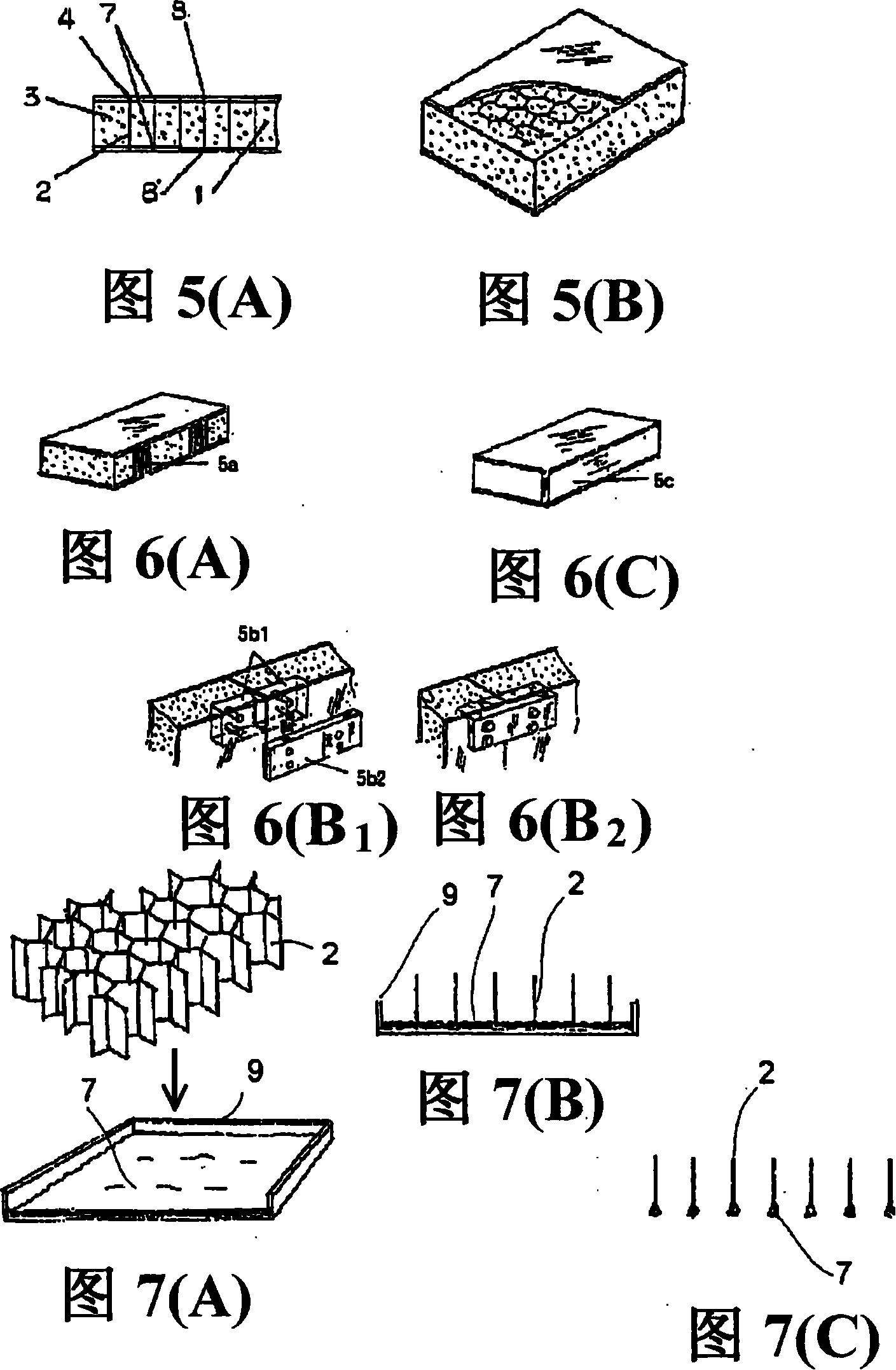

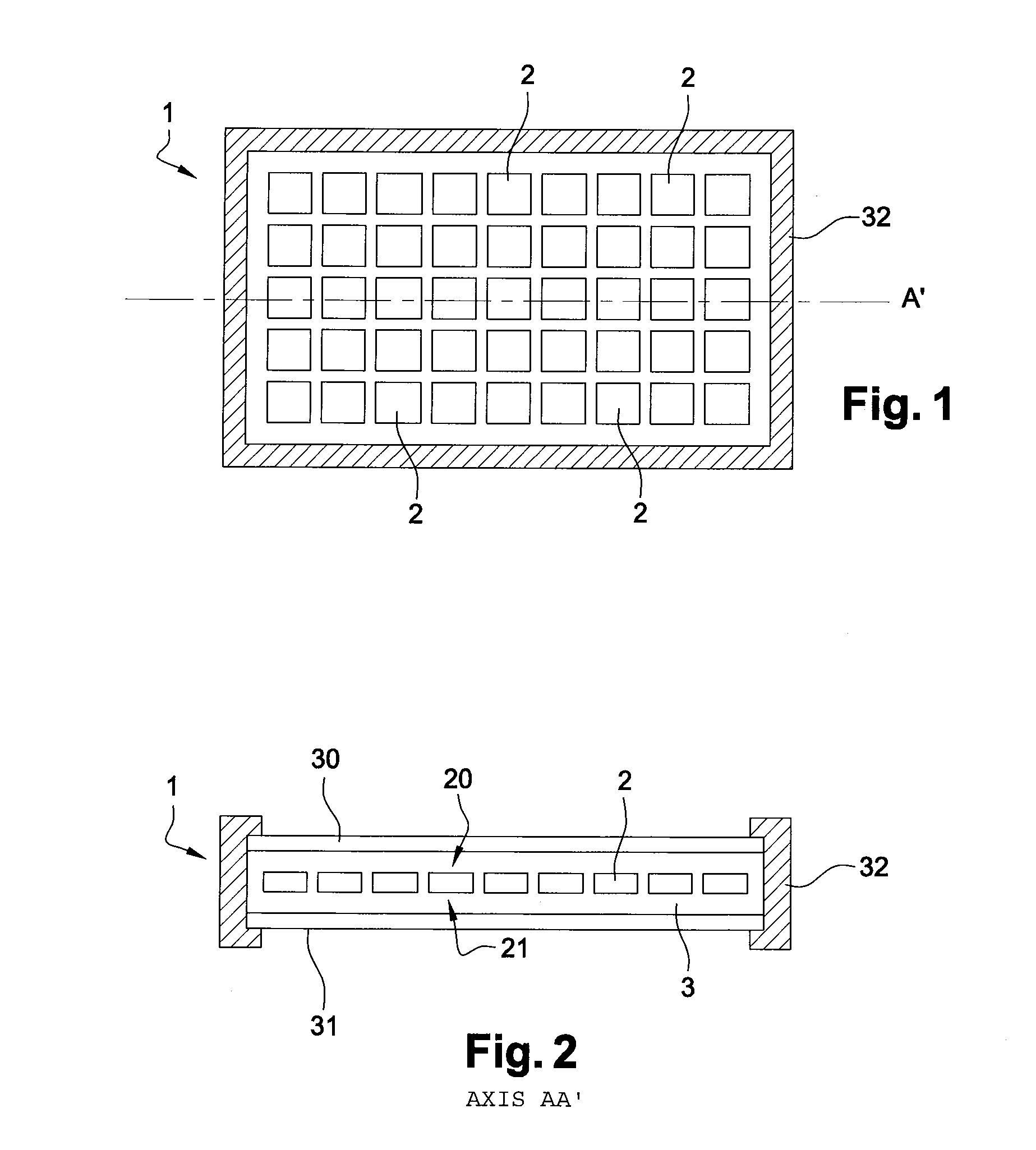

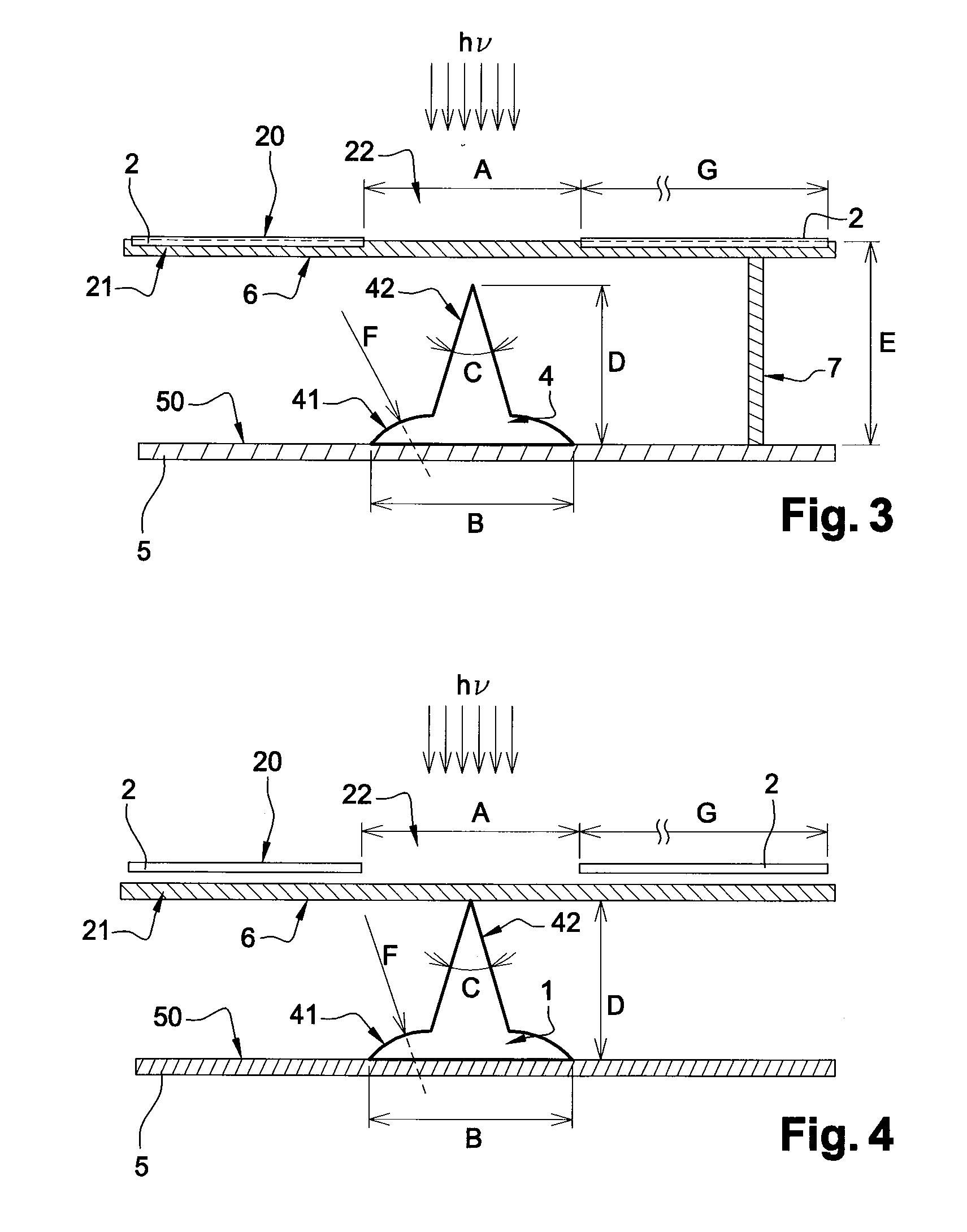

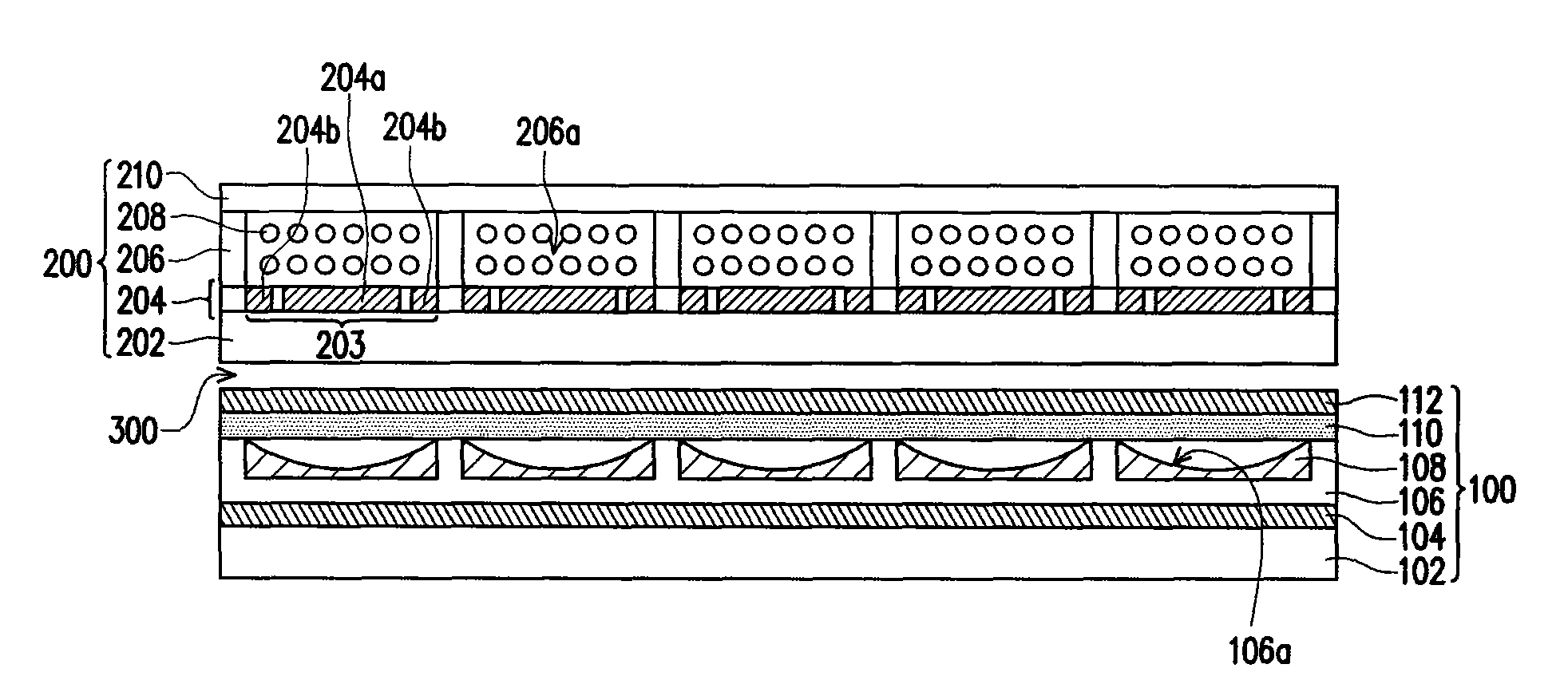

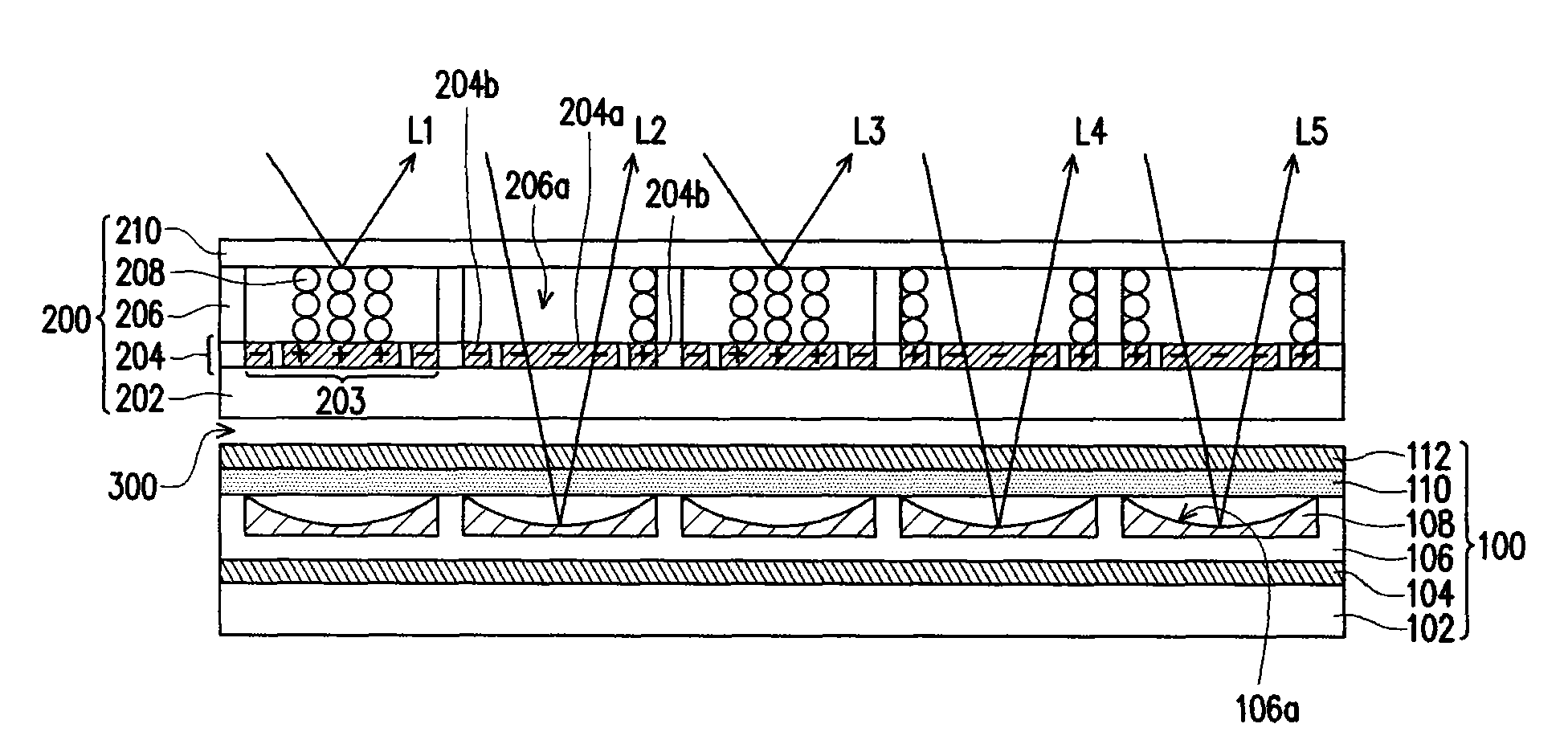

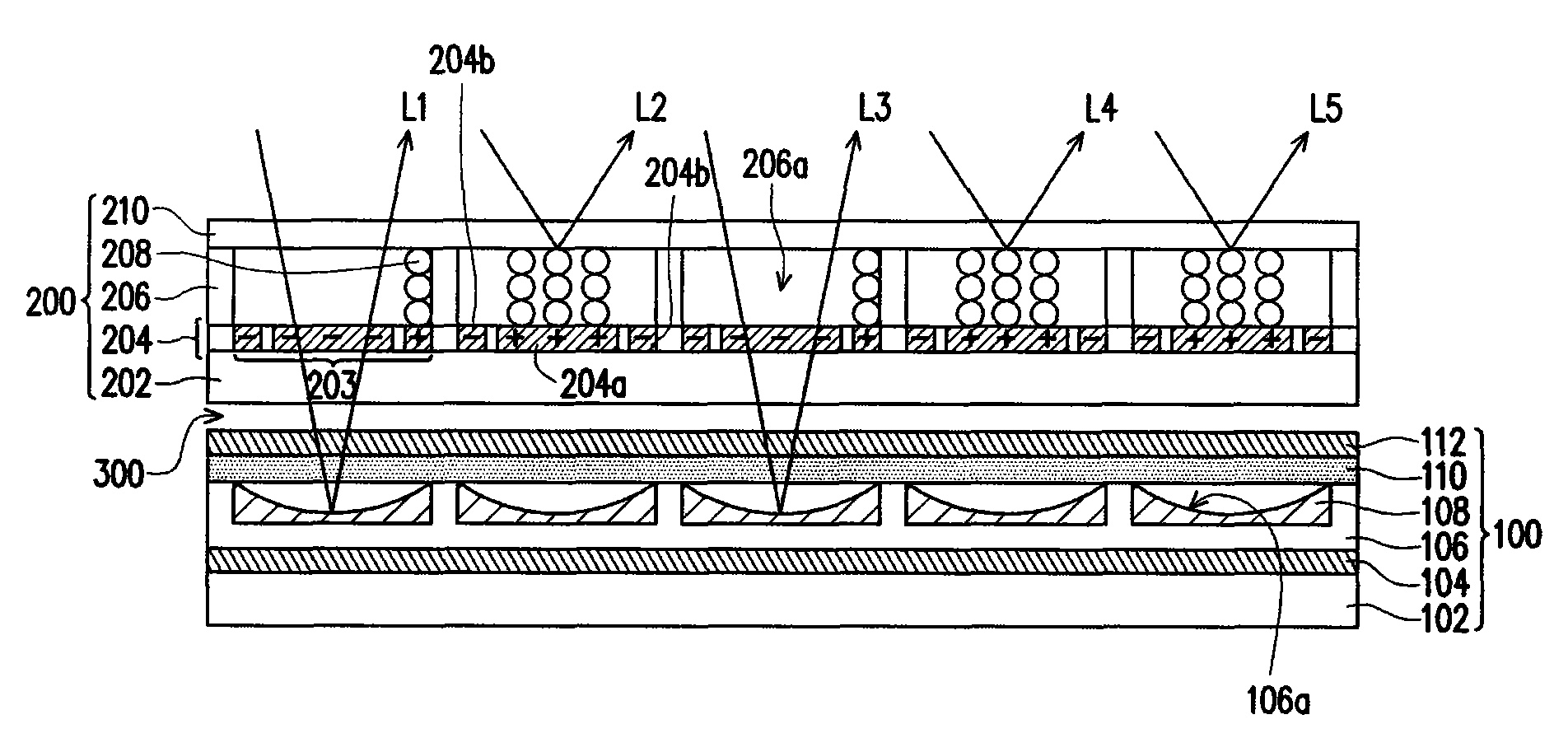

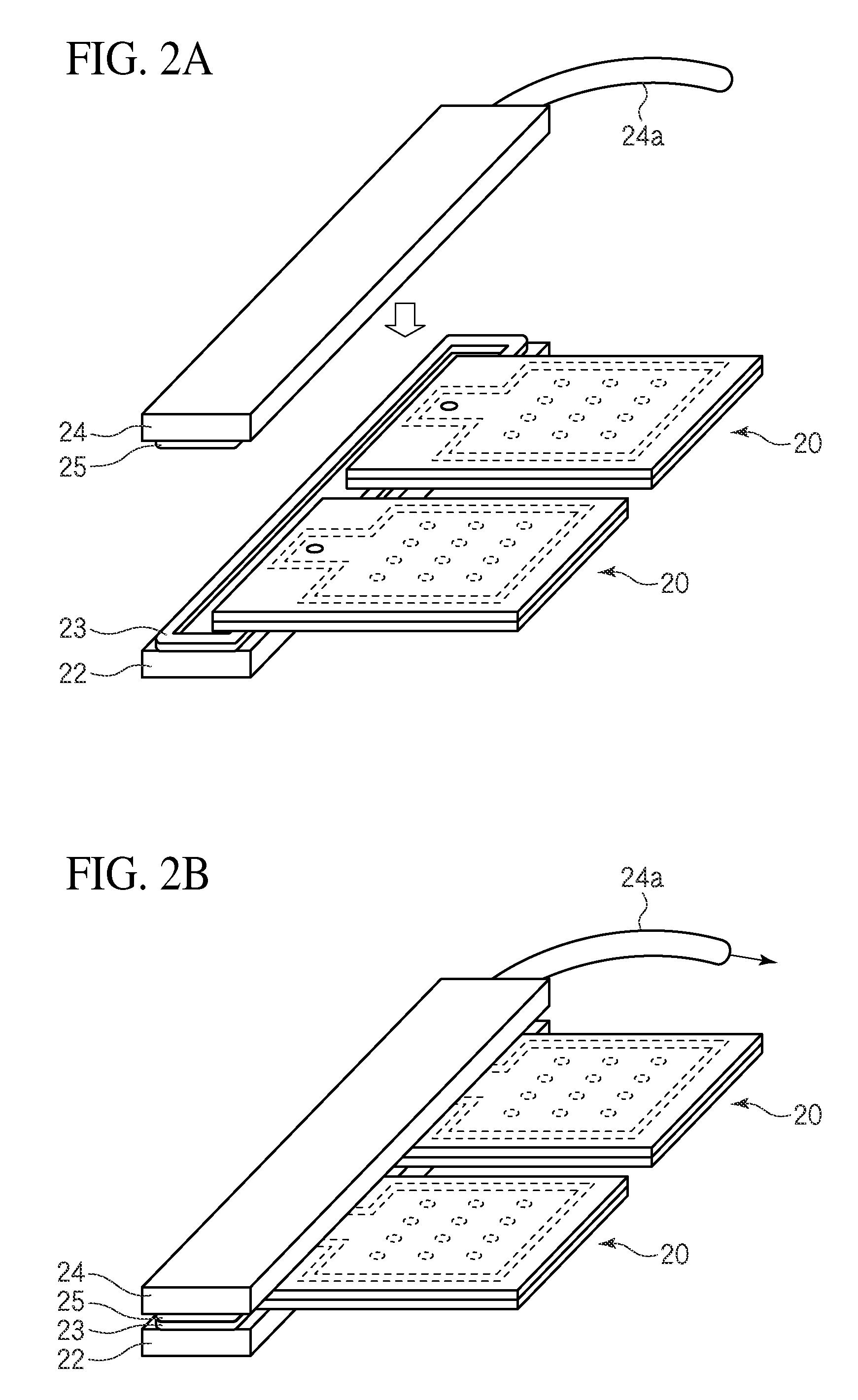

Display device and method of manufacture thereof

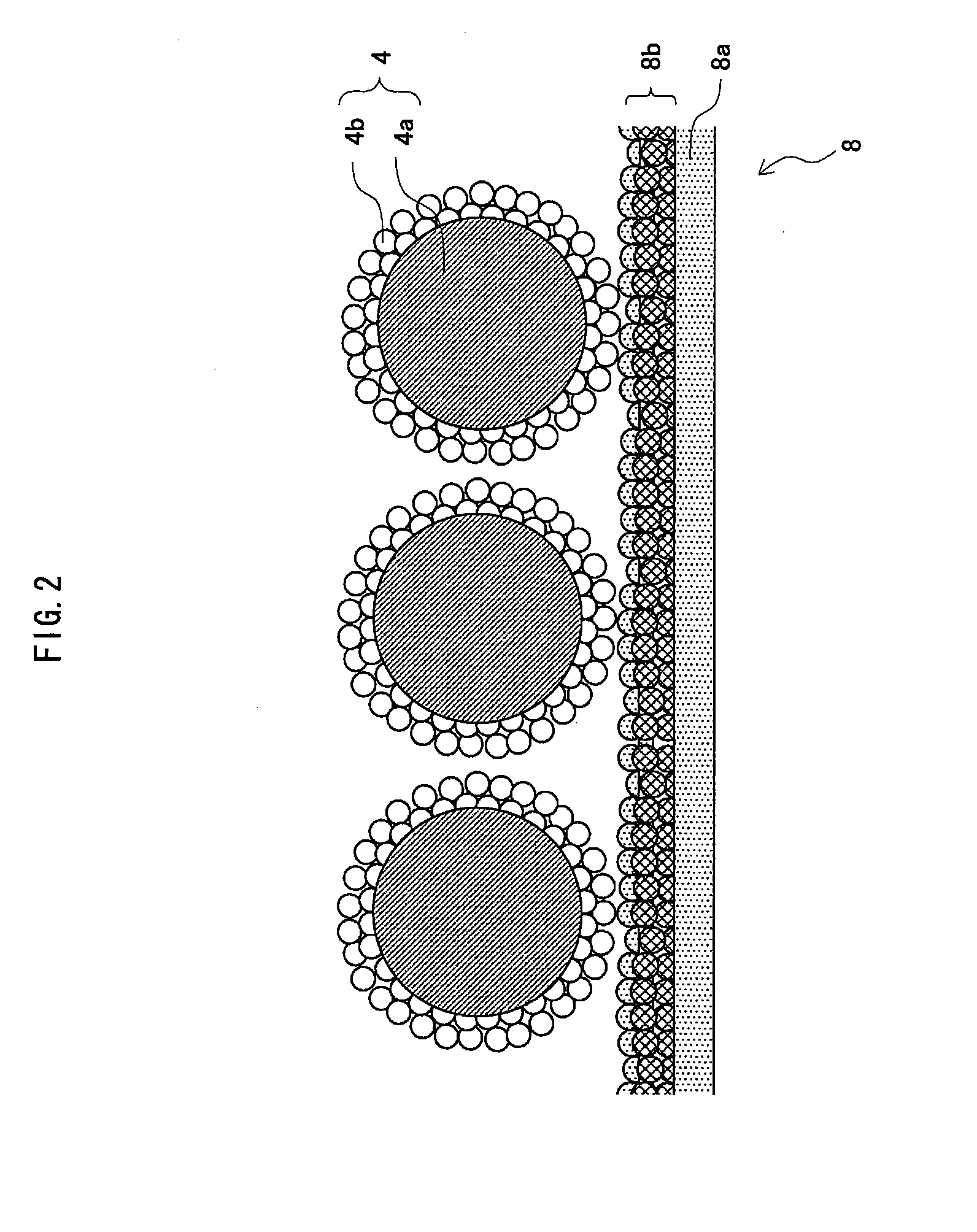

InactiveUS20120069064A1Sufficient distanceIncrease reflectionSolid-state devicesVessels or leading-in conductors manufactureImaging qualityDisplay device

Disclosed is a paper-like display device which has improved contrast and image quality and is capable of high-speed operation. A front substrate 1 and a back substrate 2 are disposed to face each other with a space therebetween, and the space is partitioned by partition walls 5 in the vertical (Y) direction and the horizontal (X) direction in a crisscrossed fashion into cell spaces 3. A predetermined quantity of black-colored particles 4 is enclosed within each cell space 3. A white reflective layer 6, first electrodes 7, and an insulating layer 8 are formed on the inner surface of the back substrate 2. Each first electrode 7 is separately formed for a different pixel and extends along the bottom surface of the cell space 3. Each partition wall 5 includes an upper partition wall 5b, facing the front substrate 1, and a lower partition wall 5a, facing the back substrate 2. A second electrode 9 serving as a common electrode is formed between the upper partition wall 5b and the lower partition wall 5a.

Owner:PANASONIC CORP

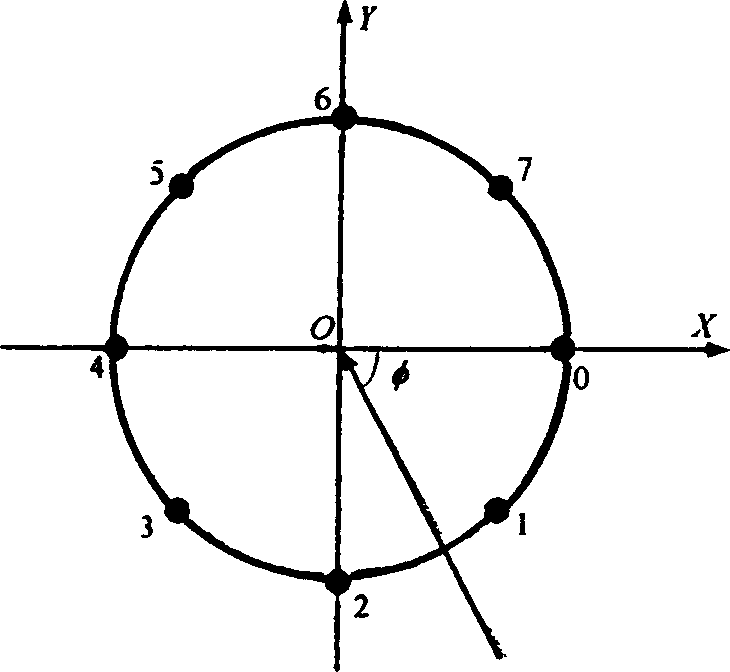

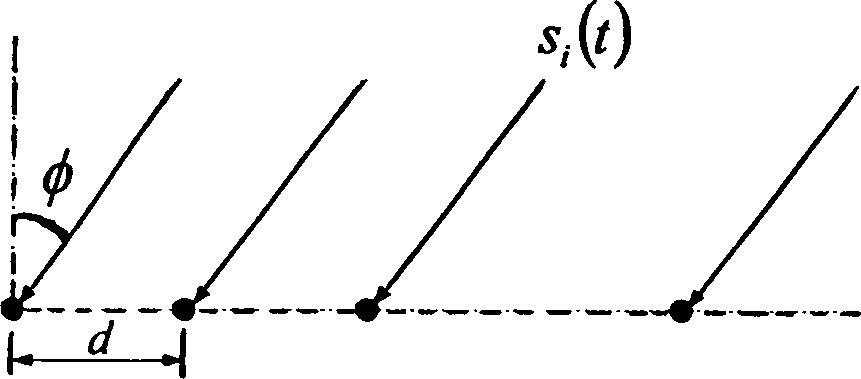

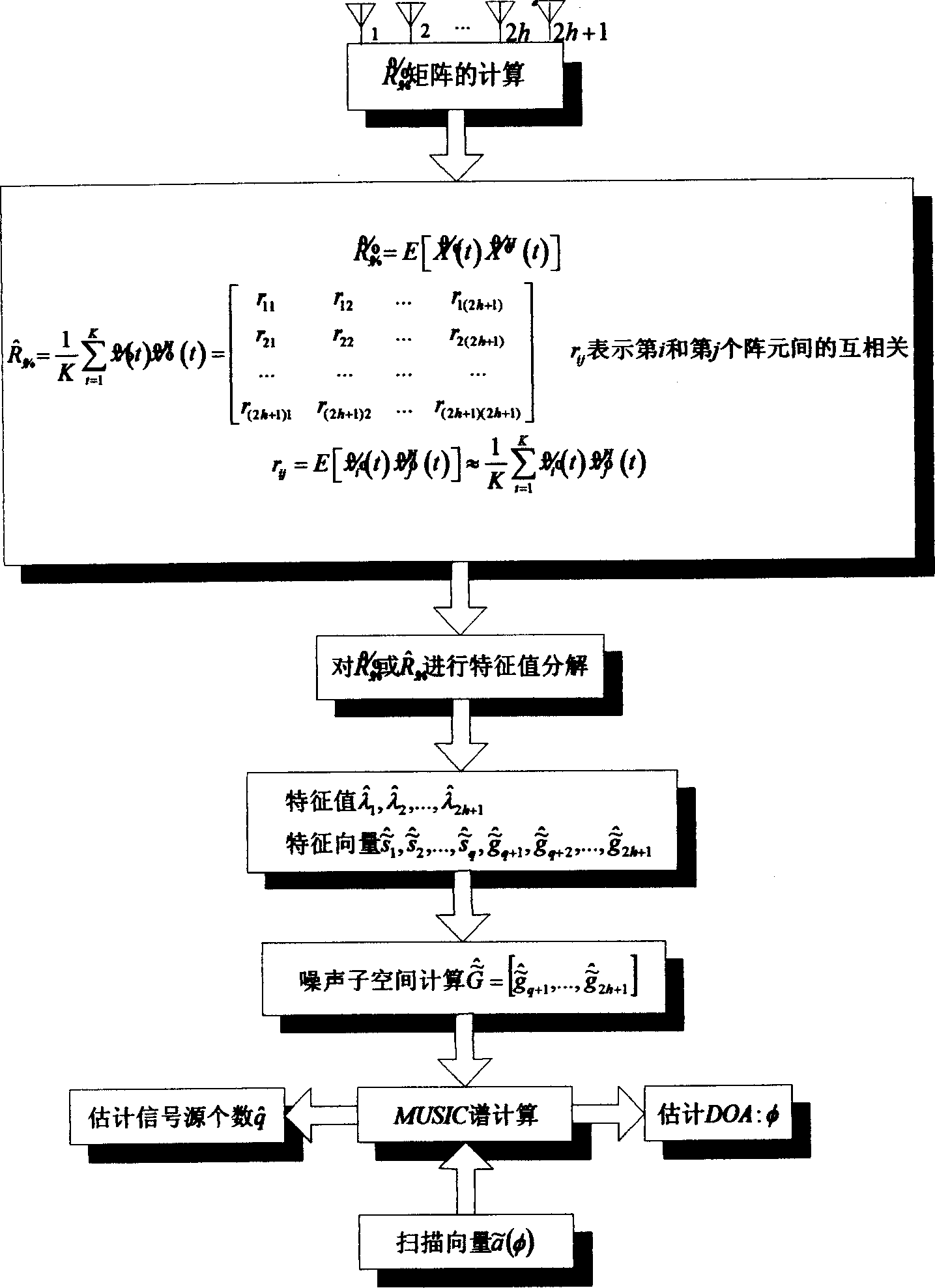

Estimation method for radio orientation incoming wave direction based on TD-SCMA

InactiveCN1523372APosition fixationRadio/inductive link selection arrangementsEstimation methodsSignal classification

The invention is a DOA estimating method to realize circle-angle positioning based on TD-SCMDA standard, firstly adopting multiple signal classifying and correcting algorithms to realize the DOA estimation of intelligent antenna circle-angle positioning; aiming at TD-SCMDA antenna being uniform circle array, converting the array cell-space uniform circle array into mode-space virtual uniform line array; according to eigenvalue and eigenvector characteristic of the data covariance matrix of the virtual line array, advancing a MUSIC algorithm based on mode-space virtual uniform line array and deriving the MUSIC algorithm power chart for the virtual line array and the general implementation algorithm for the mode-space MUSIC algorithm; according to the character of MUSIC algorithm inapplicable to the DOA estimation of relative signal source, advancing the correcting MUSIC algorithm based on the mode-space virtual uniform line array; finally aiming at the problem that the array aperture is small and that the resistance to array cell error disturbance is bad, caused by MUSIC algorithm, advancing four-order cumulant MUSIC algorithm and four-order cumulant correcting MUSIC algorithm based on the mode-space virtual uniform line array.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

Battery pack

ActiveUS20110135993A1Extend lifetime of battery packSecondary cellsCell component detailsCell spaceEngineering

A battery pack including a plurality of battery cells and having improved battery lifetime. The battery pack includes a holder case defining a plurality of cell spaces; and a plurality of battery cells are accommodated in a pattern in a portion of the plurality of cell spaces, wherein some of the plurality of cell spaces are empty.

Owner:SAMSUNG SDI CO LTD

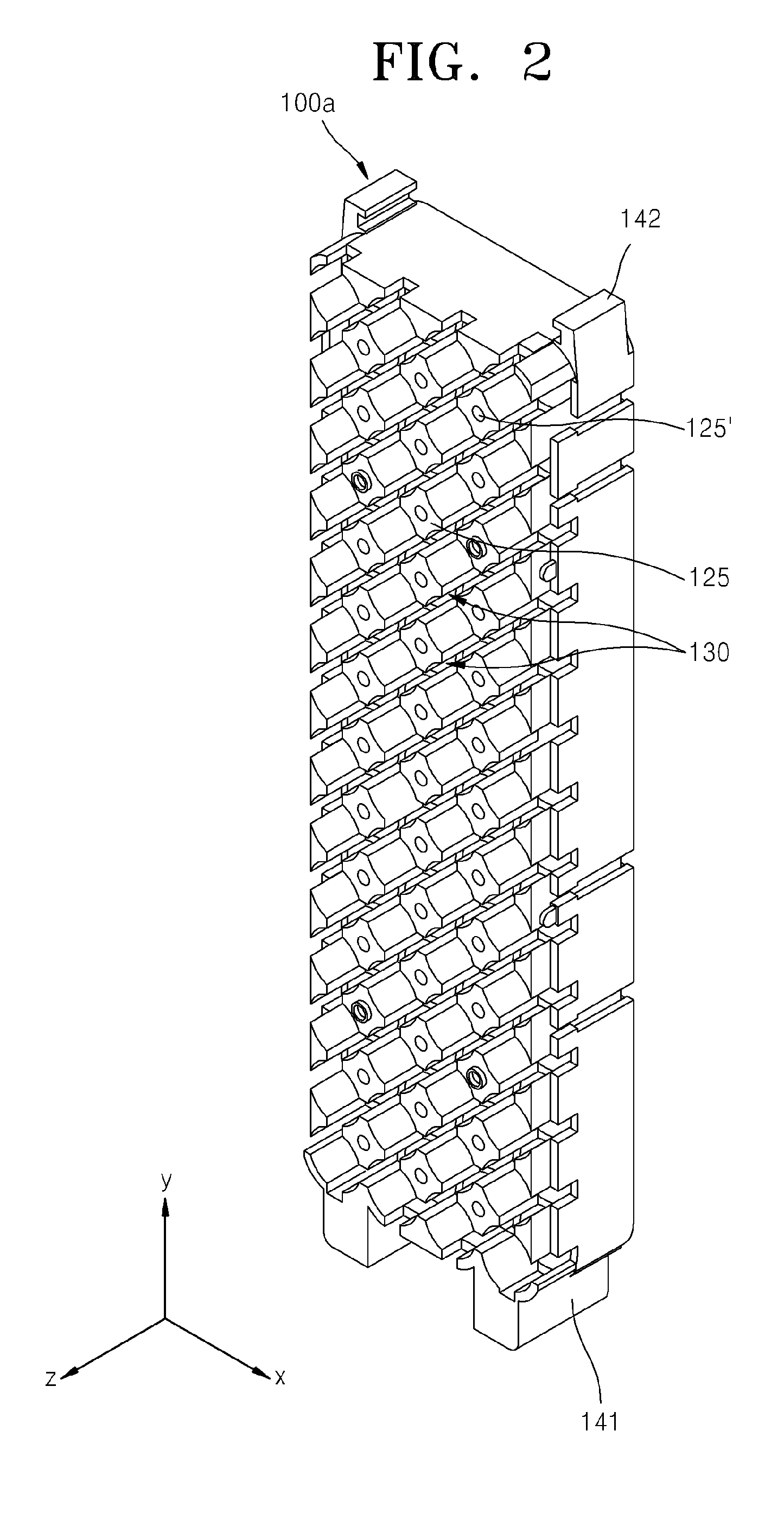

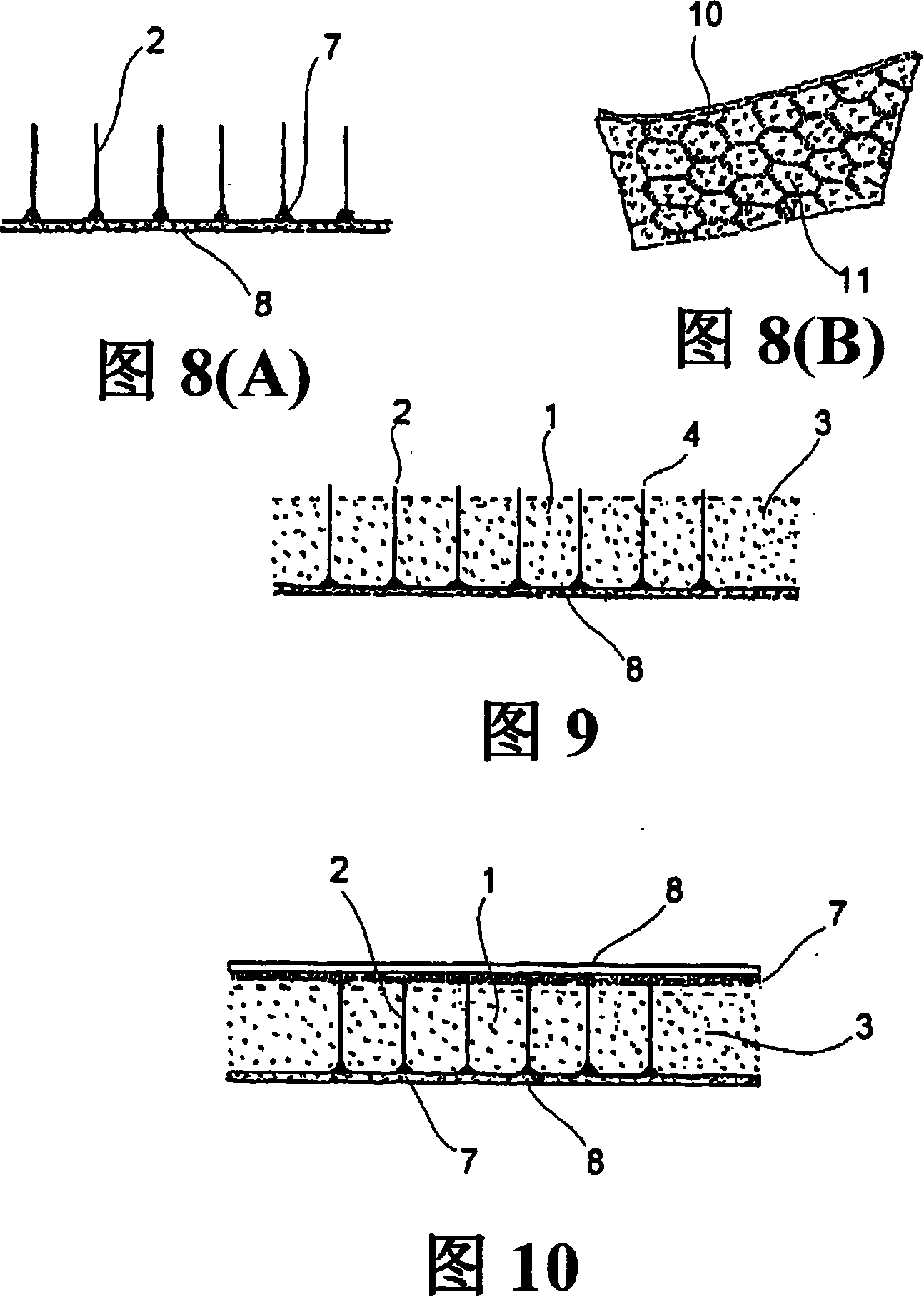

Pole piece, energy storage device and preparation method of pole piece

InactiveCN104600243AGuarantee structureIncreased ion migration rateHybrid capacitor electrodesFinal product manufactureMiniaturizationCell space

The invention discloses a pole piece, an energy storage device, and a preparation method of the pole piece. The method comprises the following steps: (1) preparing a plurality of current collectors and hdrophobic resin adhesive, and forming hydrophobic resin adhesive grids on the current collectors; (2) respectively preparing positive and negative active substance materials, respectively filling cell spaces of the resin grids of the current collectors with the positive and negative active substance materials, and respectively preparing a positive pole piece and a negative pole piece; (3) preparing colloid electrolyte, and respectively covering the active substance materials of the positive pole piece and the negative pole piece with the colloid electrolyte; and (4) carrying out opposite hot-pressing on the positive pole piece and the negative pole piece obtained in the step (3), or carrying out opposite hot-pressing on the positive pole piece or the negative pole piece and another current collector coated with the active substance on the surface to prepare the energy storage device. The energy storage device disclose by the invention has tailorability, can meet the application requirements of miniaturization and individuation, and has high reliability and rapid charge and discharge characteristics.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

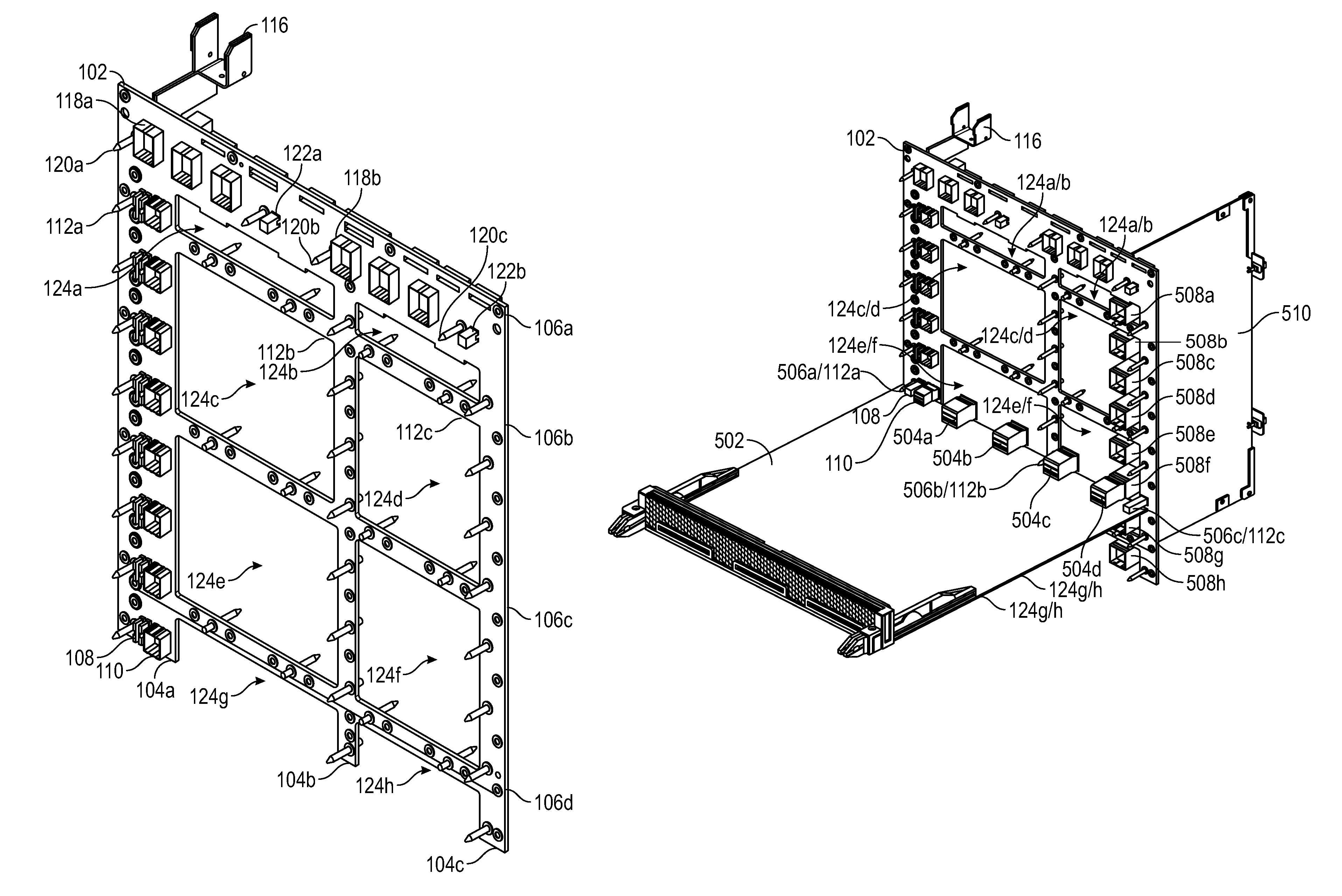

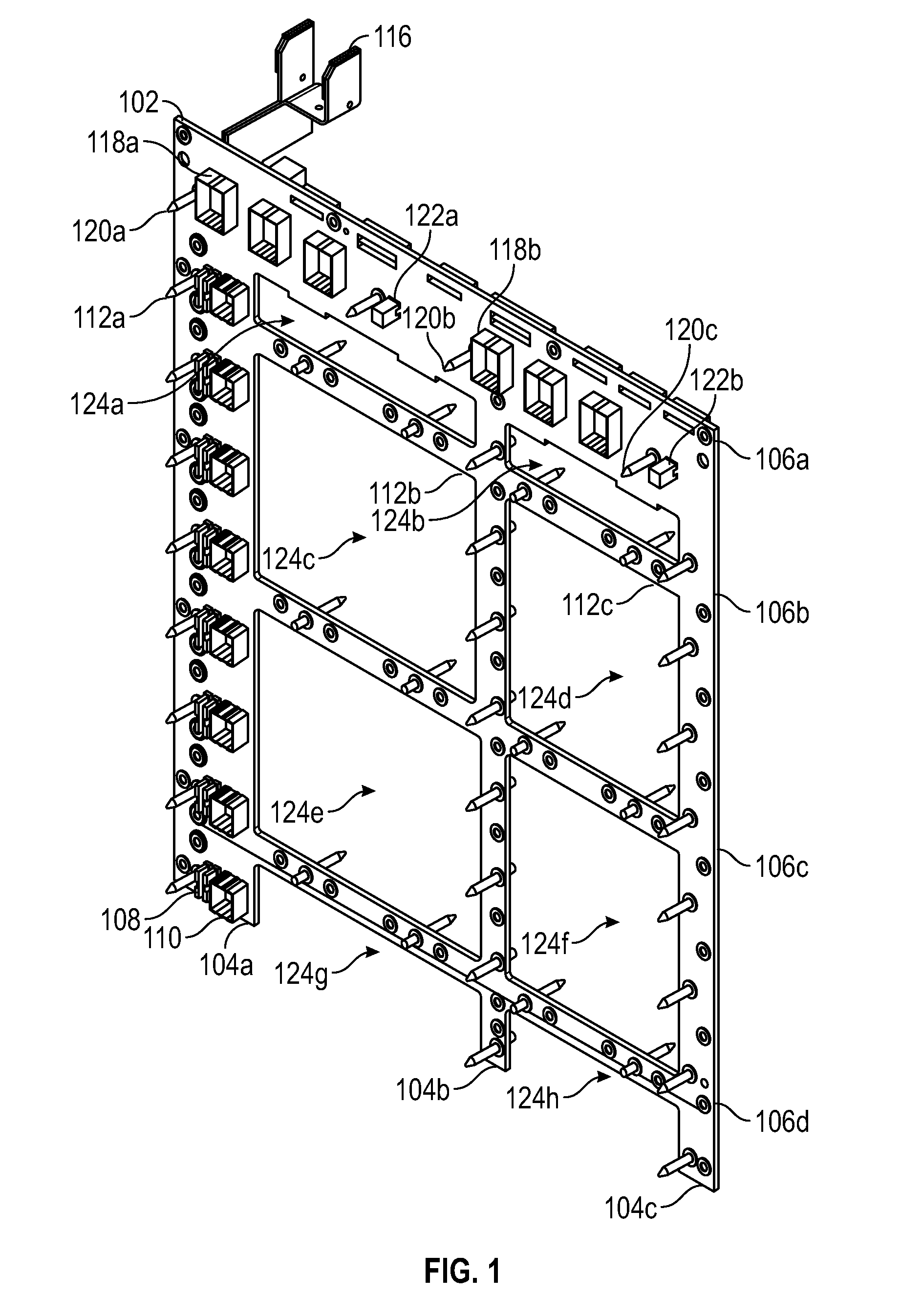

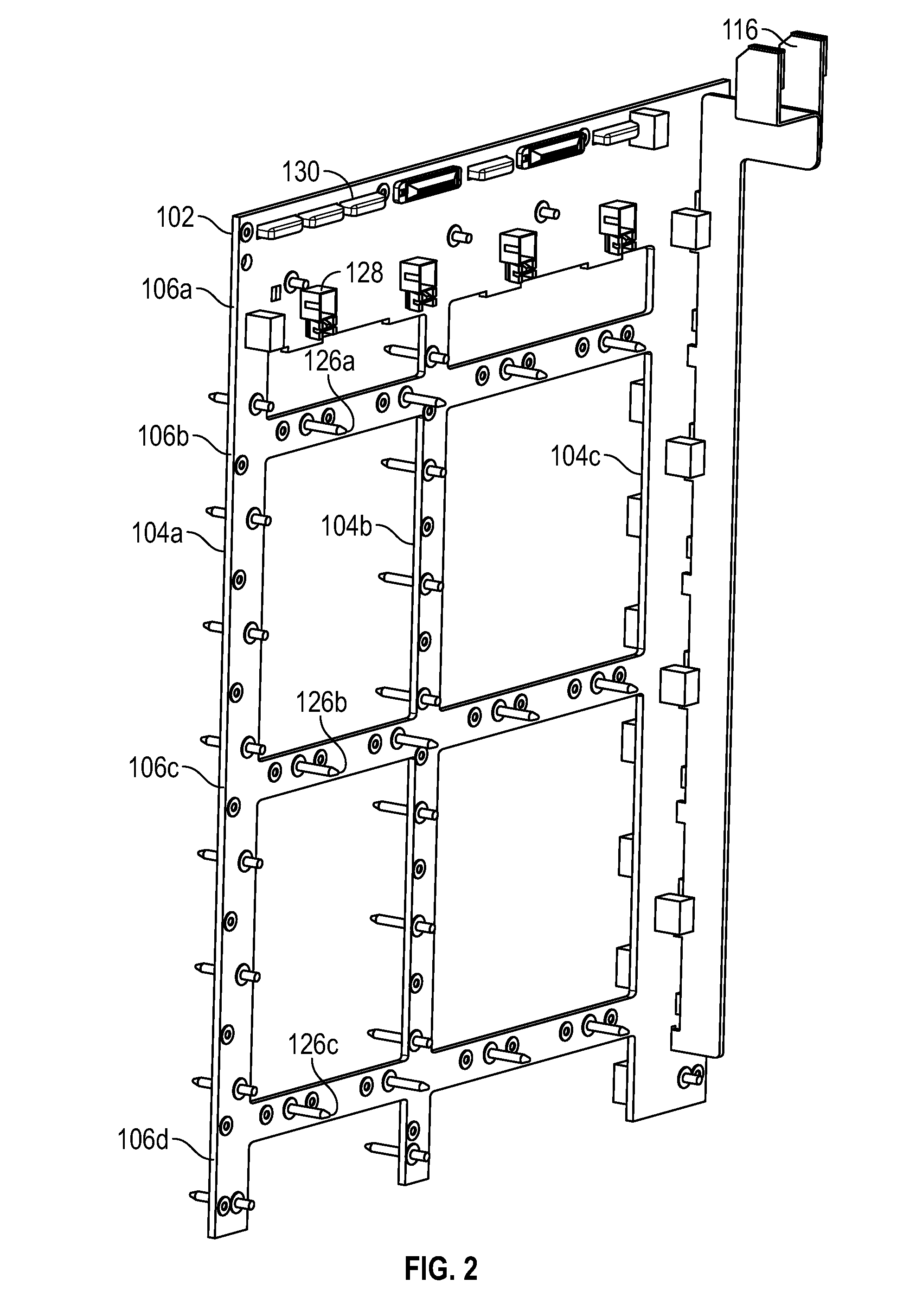

Midplane for orthogonal direct connection

ActiveUS9116660B1Facilitates mechanical registrationEasy alignmentDigital data processing detailsElectrical connection printed elementsRack unitCell space

A novel midplane is shaped with voids through which a dataplane connection is made between components on one side of the midplane and components on the opposite side of the midplane. The voids in the novel midplane offer numerous advantages in the design of network devices, including improved cooling performance, minimizing rack unit space and maximizing interface density, improved signal integrity allowing greater bandwidth through elimination of midplane signaling connections, improved upgradability of orthogonal direct connectors with little or no impact on the midplane or chassis, and proper alignment between the components of the dataplane.

Owner:EXTREME NETWORKS INC

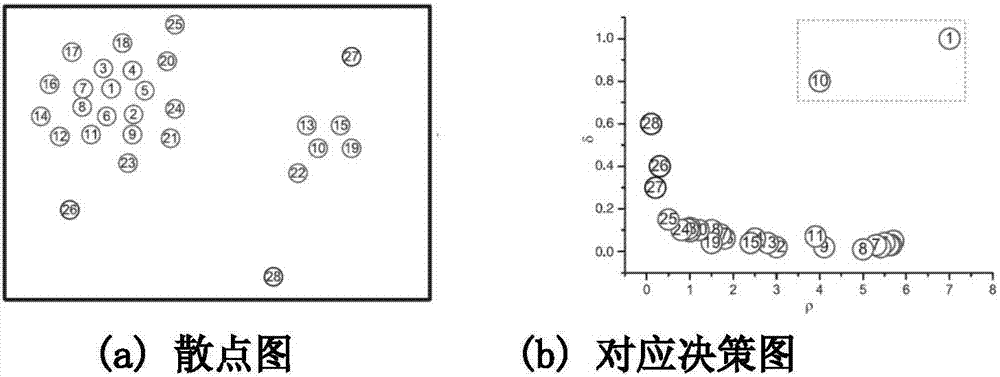

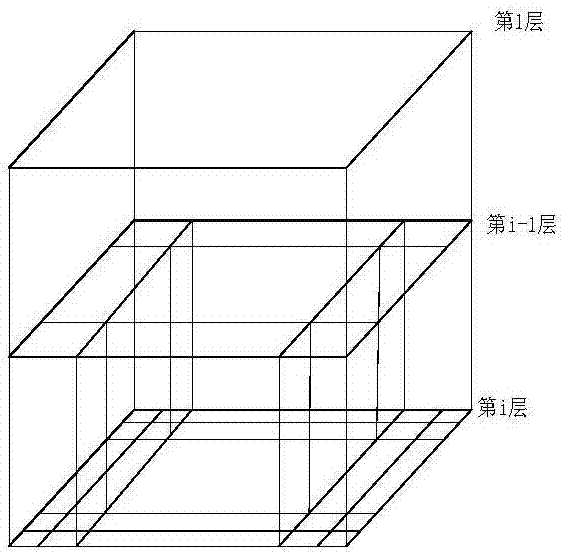

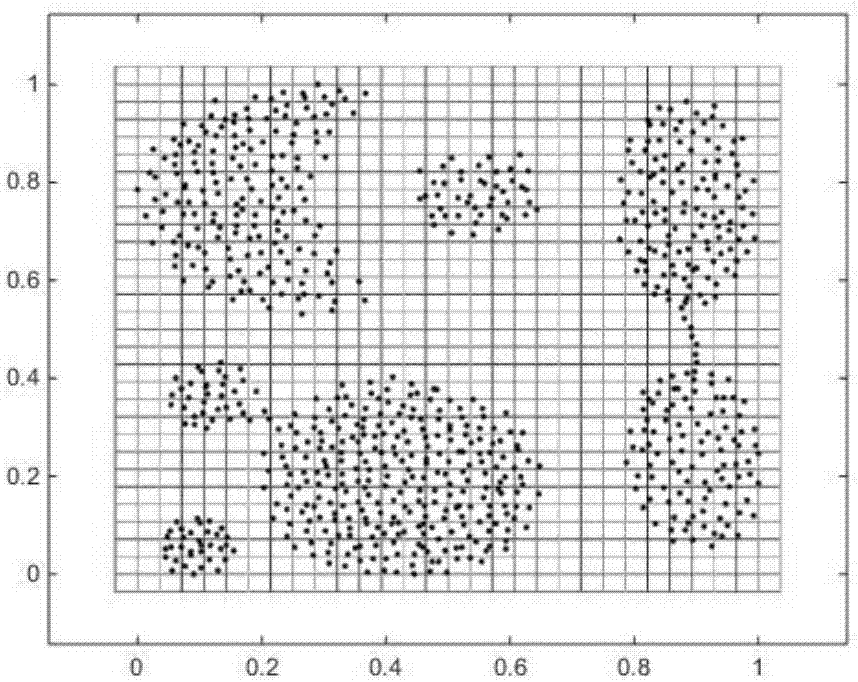

Grid clustering algorithm based on density peak value

InactiveCN107491779AAvoid failureSuitable for handlingCharacter and pattern recognitionCluster algorithmData set

The invention requests to protect a grid clustering algorithm based on a density peak value, and can efficiently processing large-scale data. The algorithm comprises the following steps that: firstly, pelletizing an N-dimensional space into nonintersecting rectangular grid unit, and then, carrying out statistics on the information of unit space; utilizing a thought that a density peak value clustering is used for searching a center point to determine a center unit, i.e., surrounding the center grid unit by certain data units with low local density, and forming a large distance with the grid unit with high self local density; and finally, combining the grid units near the center grid unit so as to obtain a clustering result. A situation experiment result on an UCI (University of CaliforniaIrvine) artificial data set indicates that the algorithm can quickly obtain a clustering center, the clustering problem of large-scale data can be effectively processed, and the algorithm is high in efficiency. Compared with an original density peak value clustering algorithm, the algorithm is characterized in that time loss on different datasets is lowered by 10-100 times and accuracy loss is maintained at 5-8%.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

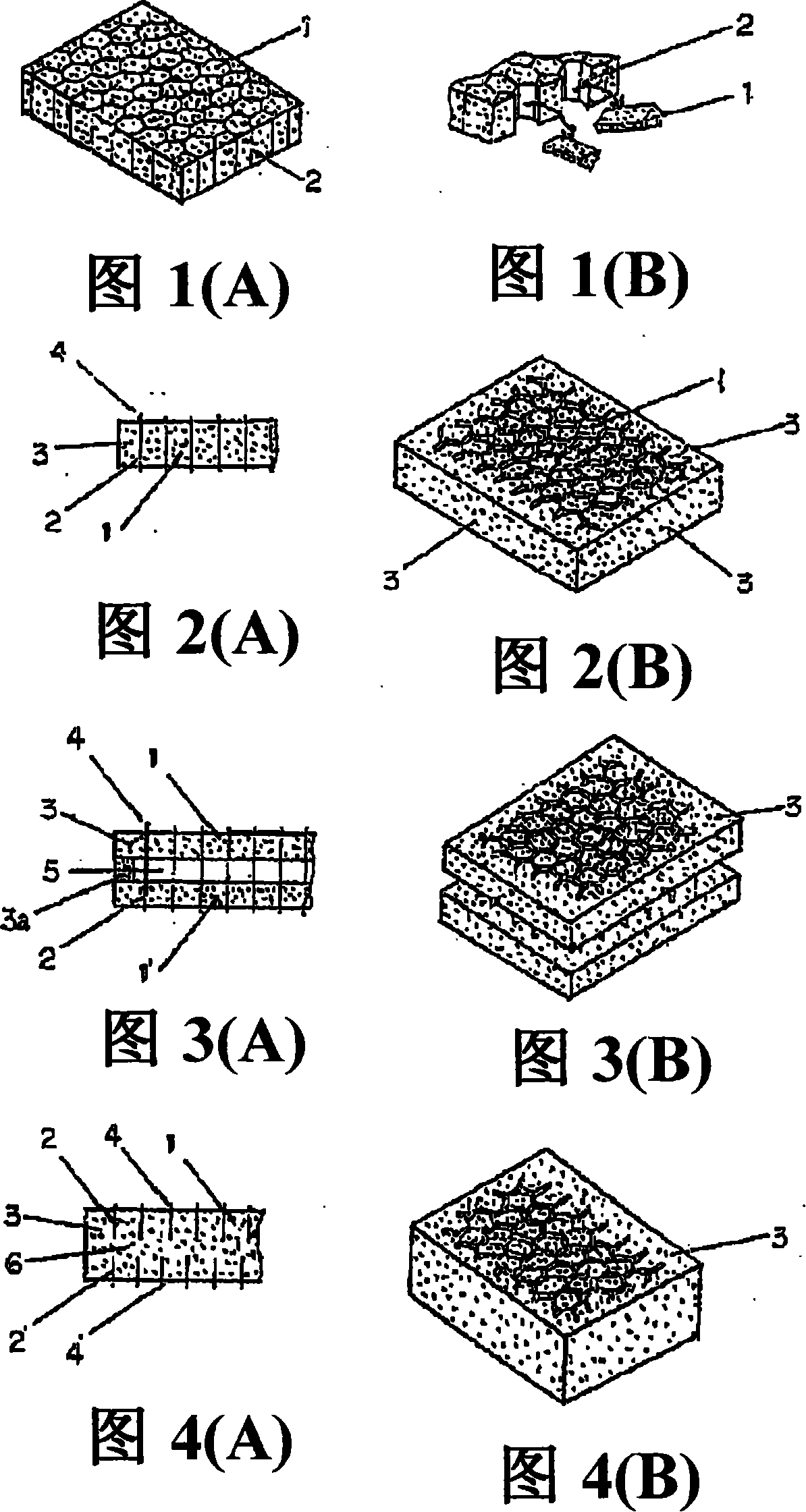

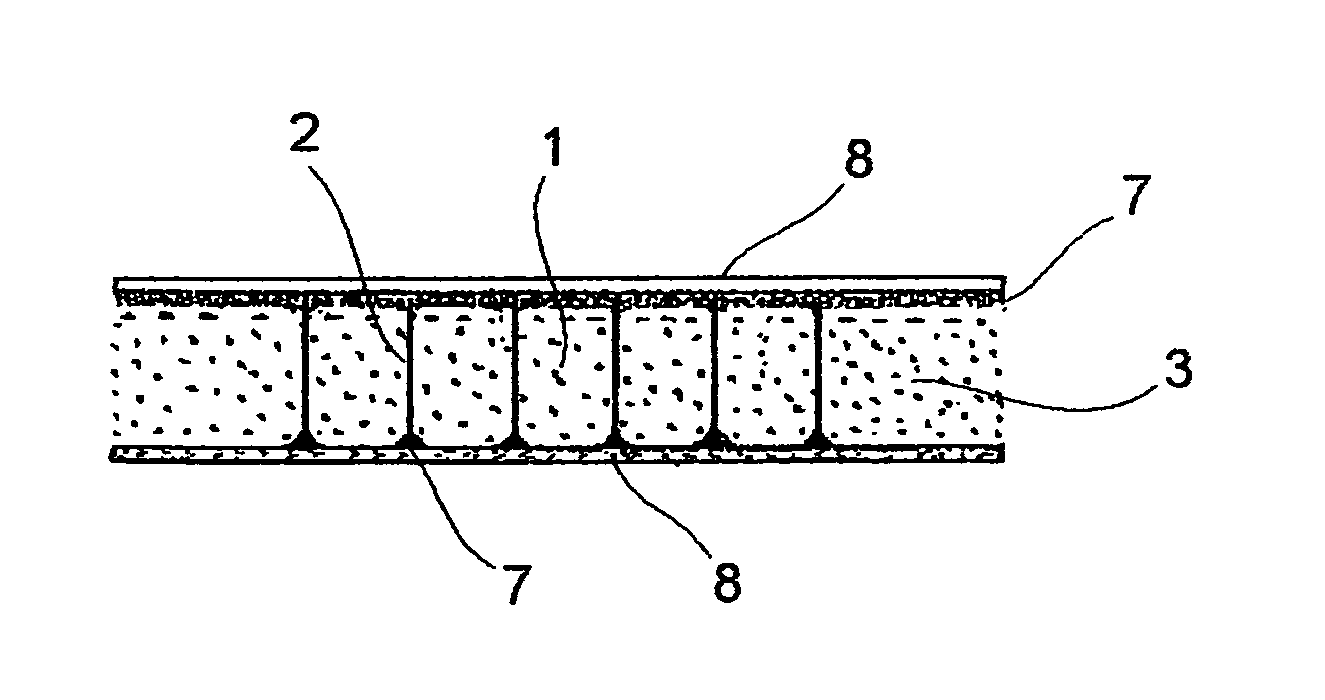

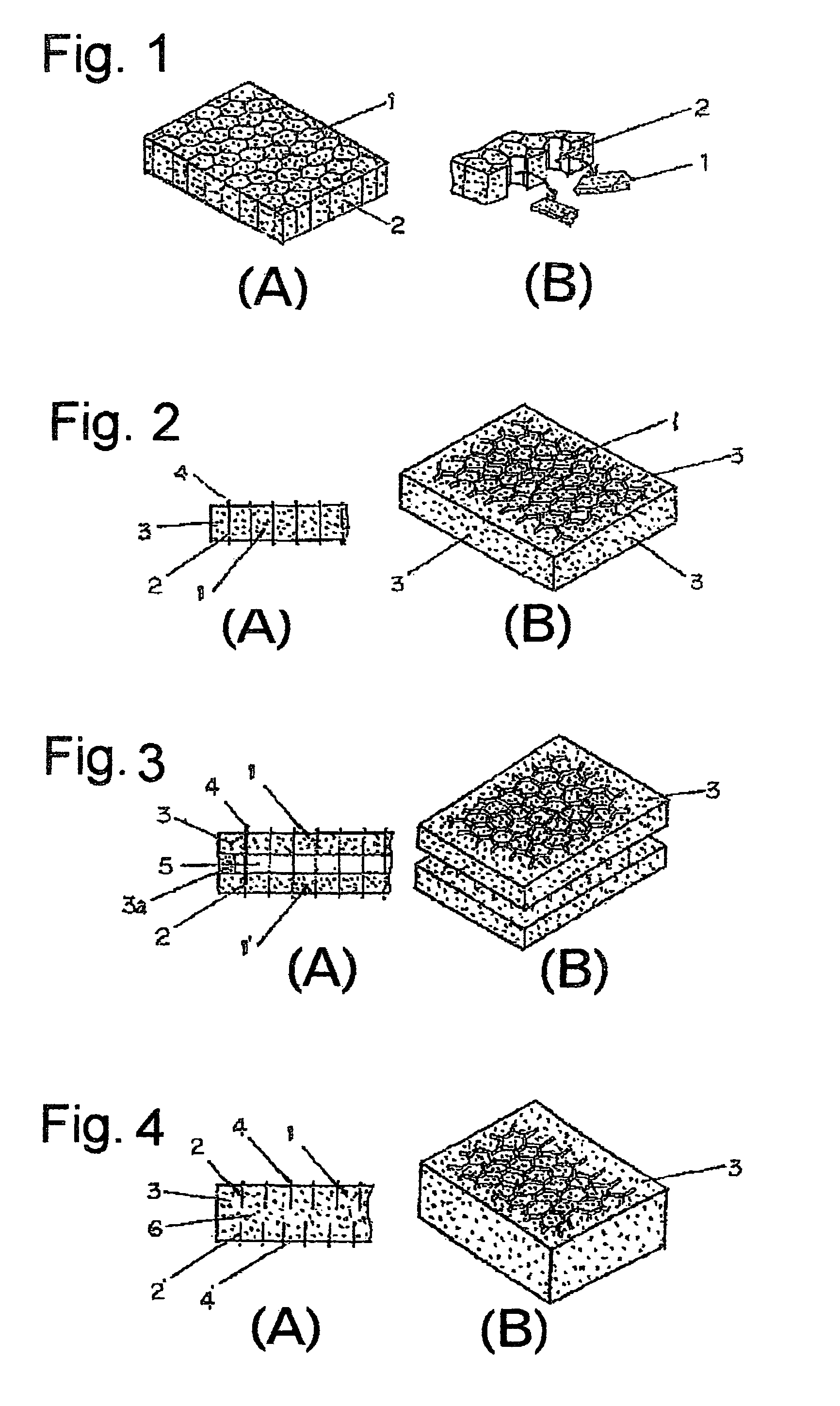

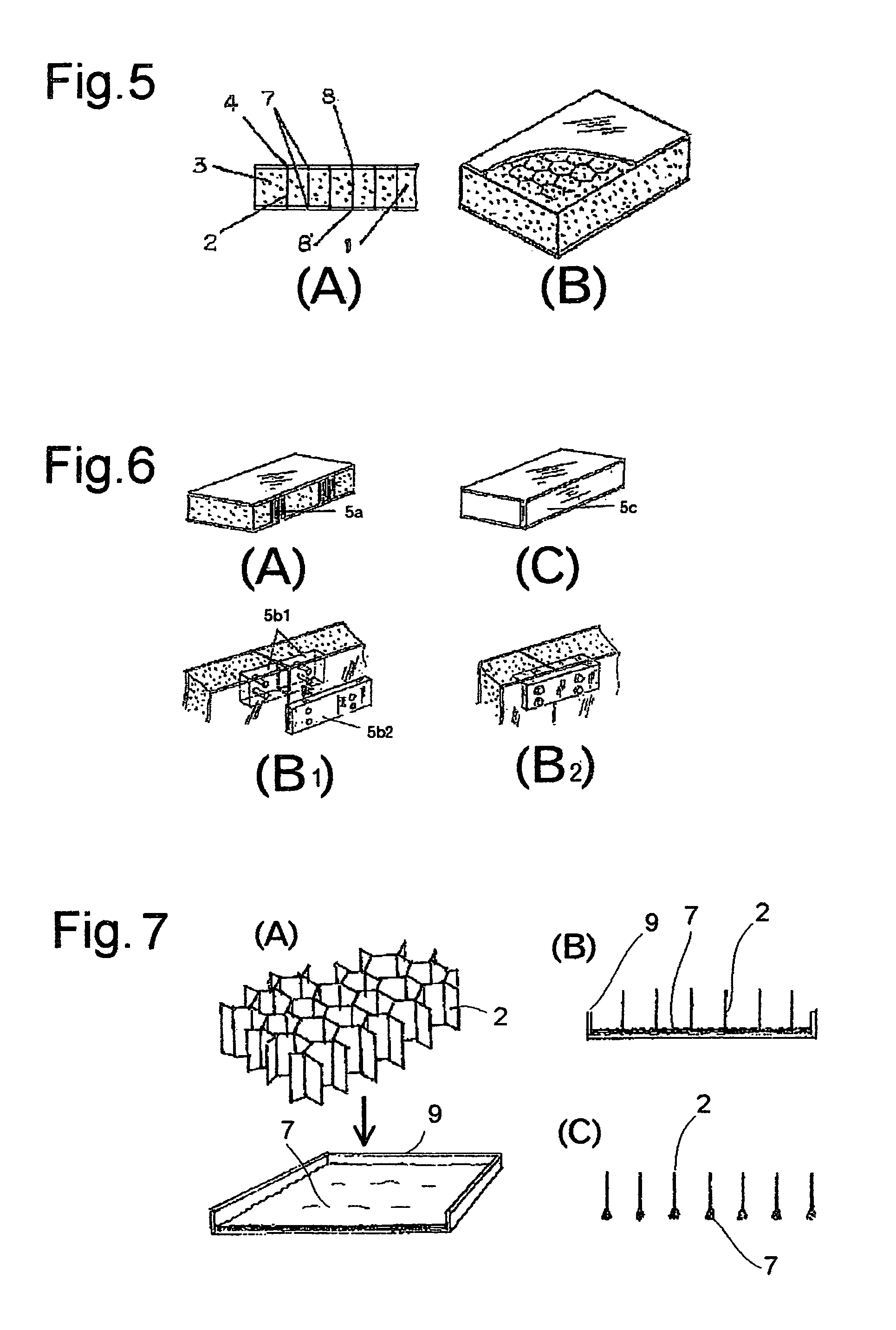

Sandwich panel including honeycomb structure body and method of producing the sandwich panel

ActiveCN101142078AWon't fall offGuaranteed integrityBuilding componentsAdhesivesFilling materialsCell space

The height and width of a sheet-like filler material before it is placed in a cell of a honeycomb material is set greater than those of the honeycomb material, and after the placement, peripheral edges of the honeycomb material are fringed with filler materials to prevent a filler material from falling out of an end section cell. A liquid adhesive agent is applied to the top of cell walls facing one surface of the honeycomb material, and a surface material is pressed to that surface of the honeycomb material to which the adhesive agent is applied. Then, before the adhesive agent hardens, water-absorbing foam materials are placed in cell spaces by pressing them into the cell spaces rom the other surface of the honeycomb material until they are in contact with the adhesive agent. The foam material is quickly adhered to the honeycomb material.

Owner:SHIZUKA

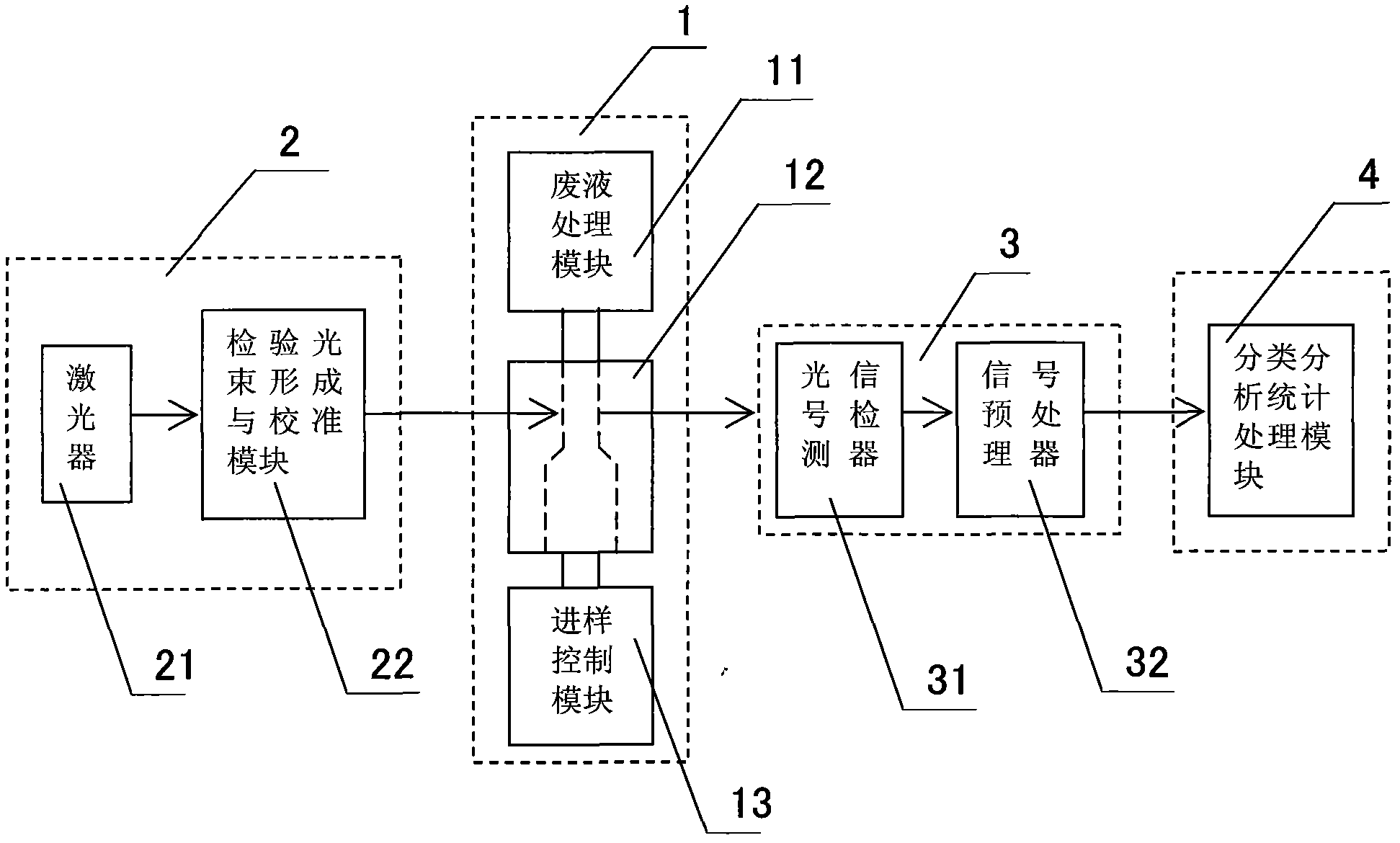

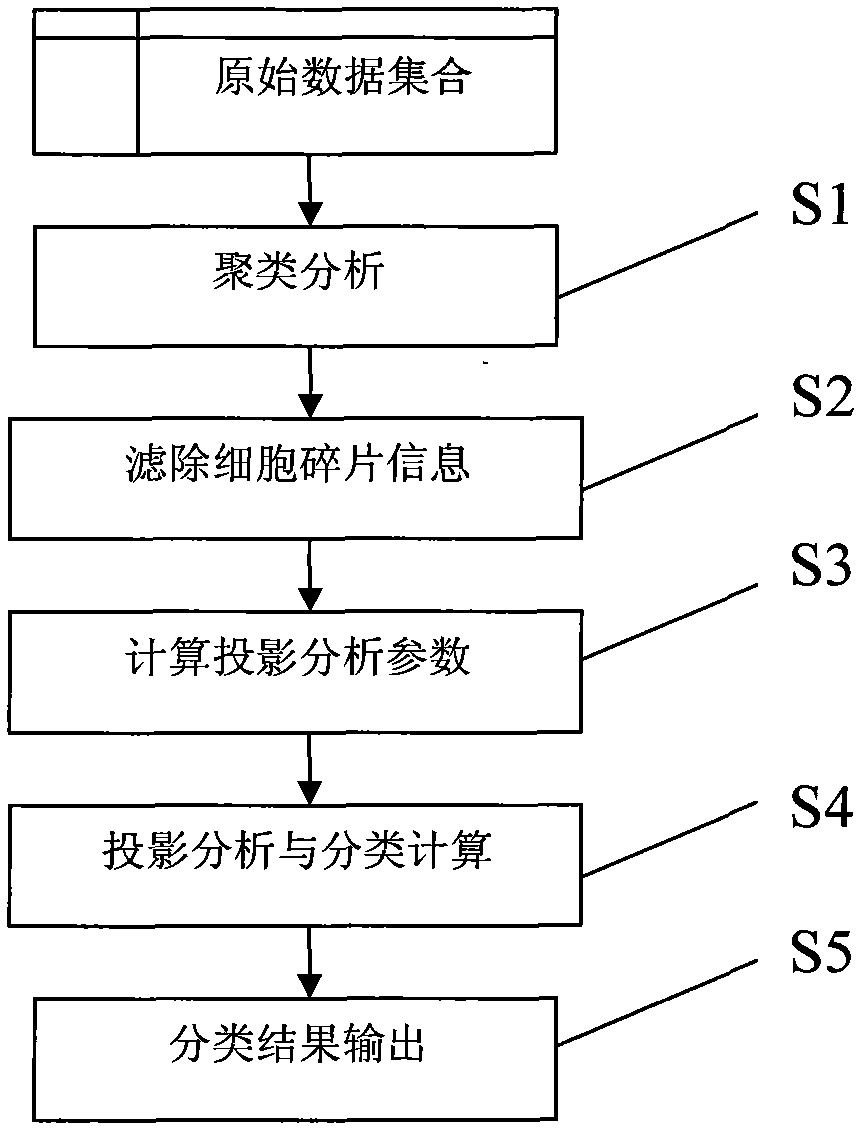

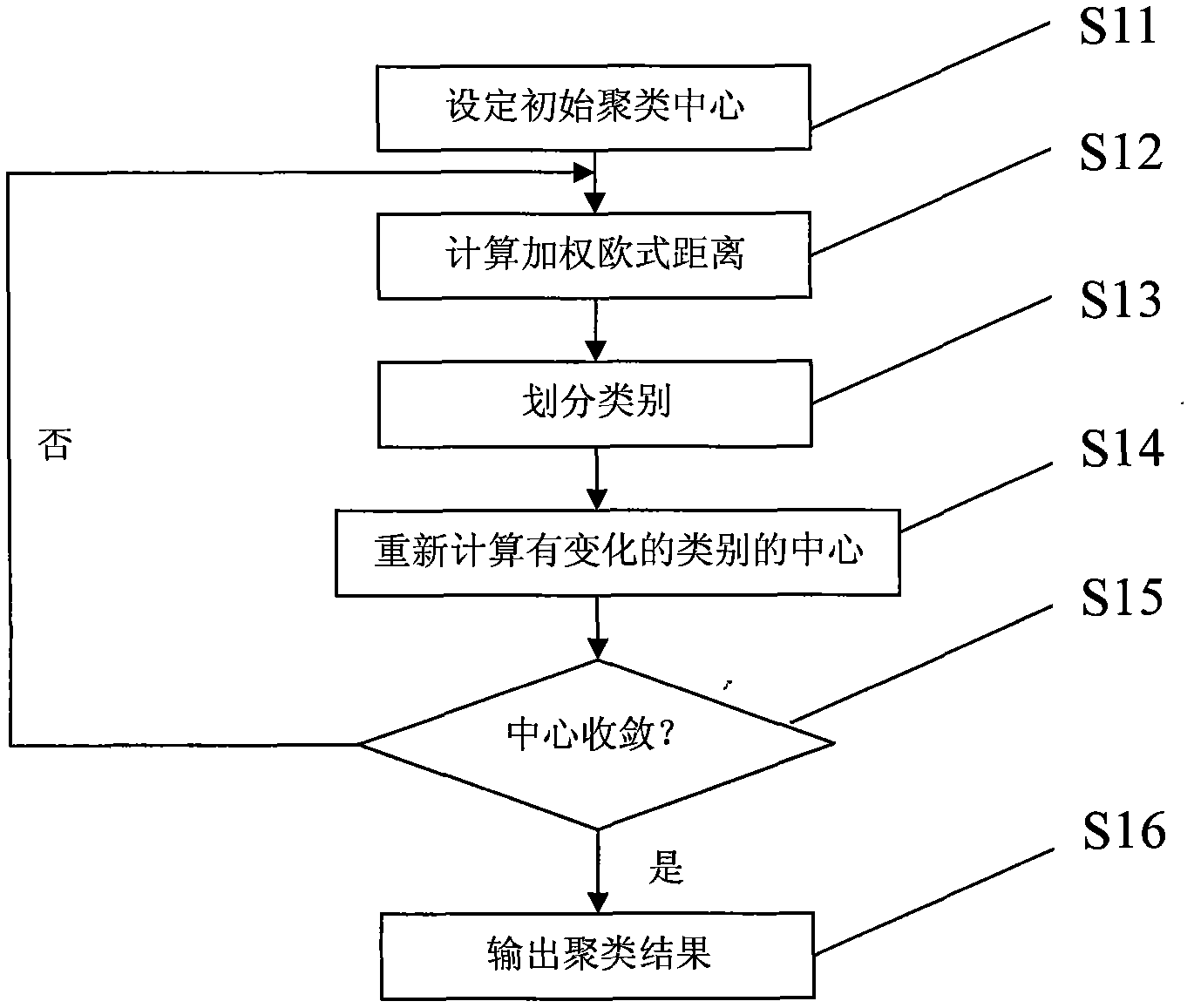

Five classification method of blood cells based on laser sheath flow technology

InactiveCN102279146AImprove accuracyGuaranteed accuracyCharacter and pattern recognitionIndividual particle analysisRed blood cellClassification methods

The invention discloses a five-way classification method of blood cells based on laser sheath flow technology, which includes the following steps: A. Collect at least 4 optical signals of each cell or particle, and characterize them into each optical signal of each cell or particle. Strength-related four-dimensional initial vector; B. Use the K-means clustering method of weighted Euclidean distance to perform the initial clustering of four types of cell collections; C. Sort each cluster and obtain four clusters W1, W2, W3 and W4. Delete the W1 cluster; D. Transform the centroids of the W2 and W4 clusters through spatial coordinates to obtain the rotation matrix and rotation vector used to generate the feature vectors used in classification calculations; E. Use the rotation vector or rotation matrix to transform the The initial vector is converted into a feature vector, the statistical characteristics of the cell feature vector in the corresponding spatial coordinates are calculated and extracted, and the cells are classified into five categories through a decision tree. This method does not require the use of special reagents, has high calculation efficiency and more accurate classification results.

Owner:URIT MEDICAL ELECTRONICS CO LTD

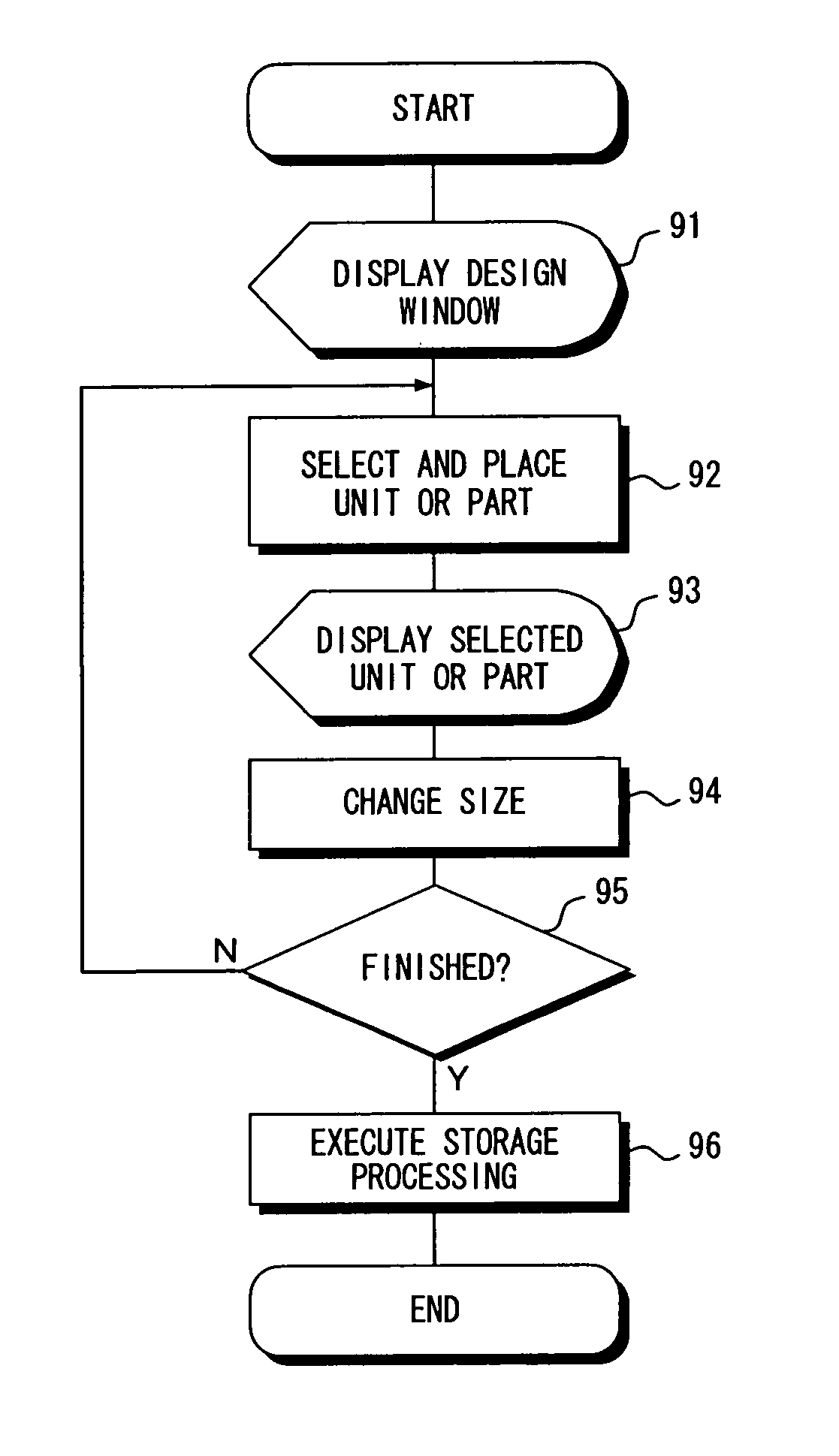

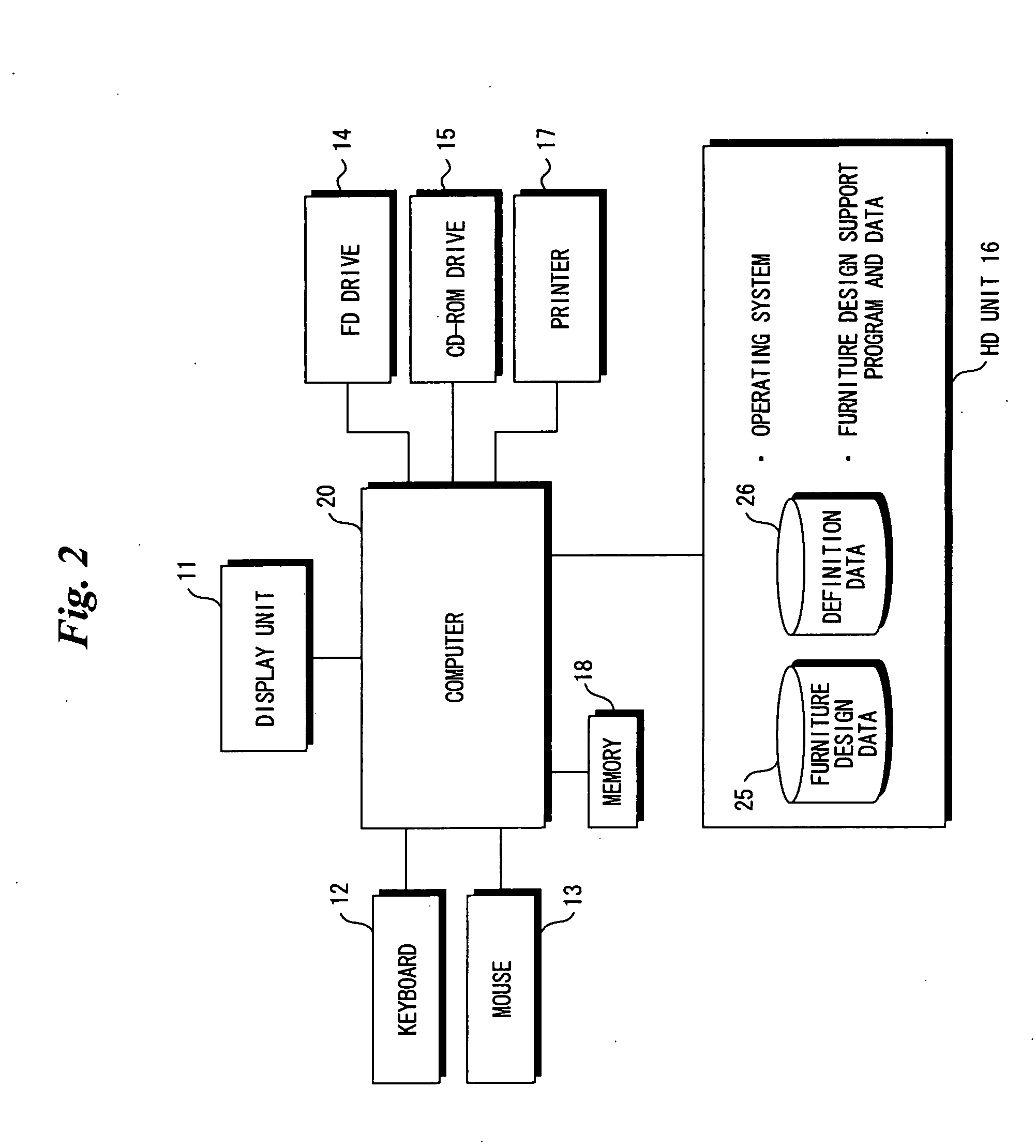

Article Design Support System and Method of Controlling Same

ActiveUS20070262982A1Increase freedomEasy to changeGeometric CADCharacter and pattern recognitionDesign support systemCell space

Provided is an article design support system featuring enhanced degree of freedom in terms of designing articles (for example, an article of furniture). A part space P surrounding a part incorporated in a cell space S is correlated with the cell space S, which is formed by a frame constituting a unit. The position (dimensions) of the part space P in the cell space S is defined by part space data specifying a relative position and relative dimensions using the cell space S as a reference. The position (dimensions) of a part in the part space P is defined by part (element) data specifying a relative position and relative dimensions using the part space P as a reference.

Owner:NINOMIYA KENICHI

Sandwich panel including honeycomb structure body and method of producing the sandwich panel

ActiveUS8367183B2Hardening of the adhesive agent is time consumingHardening is acceleratedDispersed particle filtrationConstructions elementsFilling materialsCell space

Owner:SHIZUKA

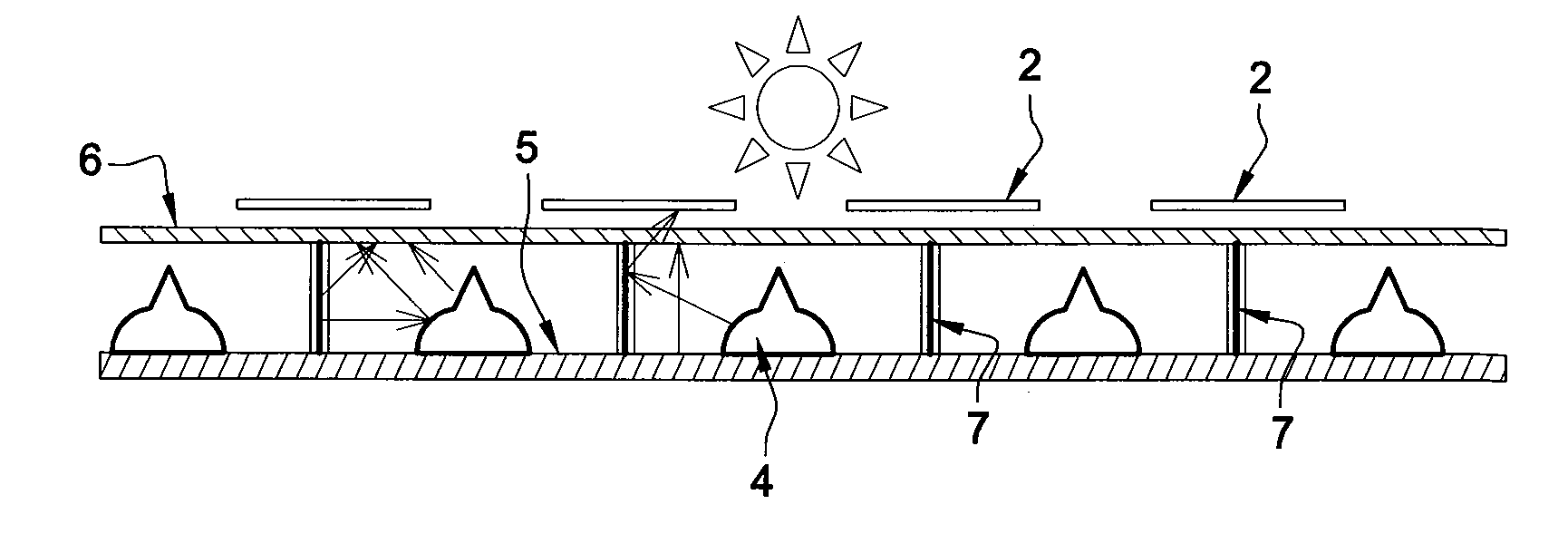

Reflective device for a photovoltaic module with bifacial cells

InactiveUS20120247533A1Easy to captureEfficiently correspondMirrorsPV power plantsCell spaceEngineering

The invention relates to a reflective device for a photovoltaic module formed by a plurality of bifacial photovoltaic cells or rows of said cells spaced apart from one another, each cell having an active front face and an active rear face that can capture photons from incident light rays falling on the front and rear faces. The device comprises at least one reflective module to be placed under the cells substantially in line with the gap(s) separating two adjacent cells or two rows of adjacent cells. The reflective module comprises: a first portion, of which the surfaces that are oriented towards the gap have a first curvature such as to send all or part of the incident photons towards the rear face of the cells; and a second portion mounted on the first portion, of which the surfaces oriented towards the gap have a second curvature such as to send all or part of the incident photons towards the rear face of the cells, the second curvature being different from the first curvature.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

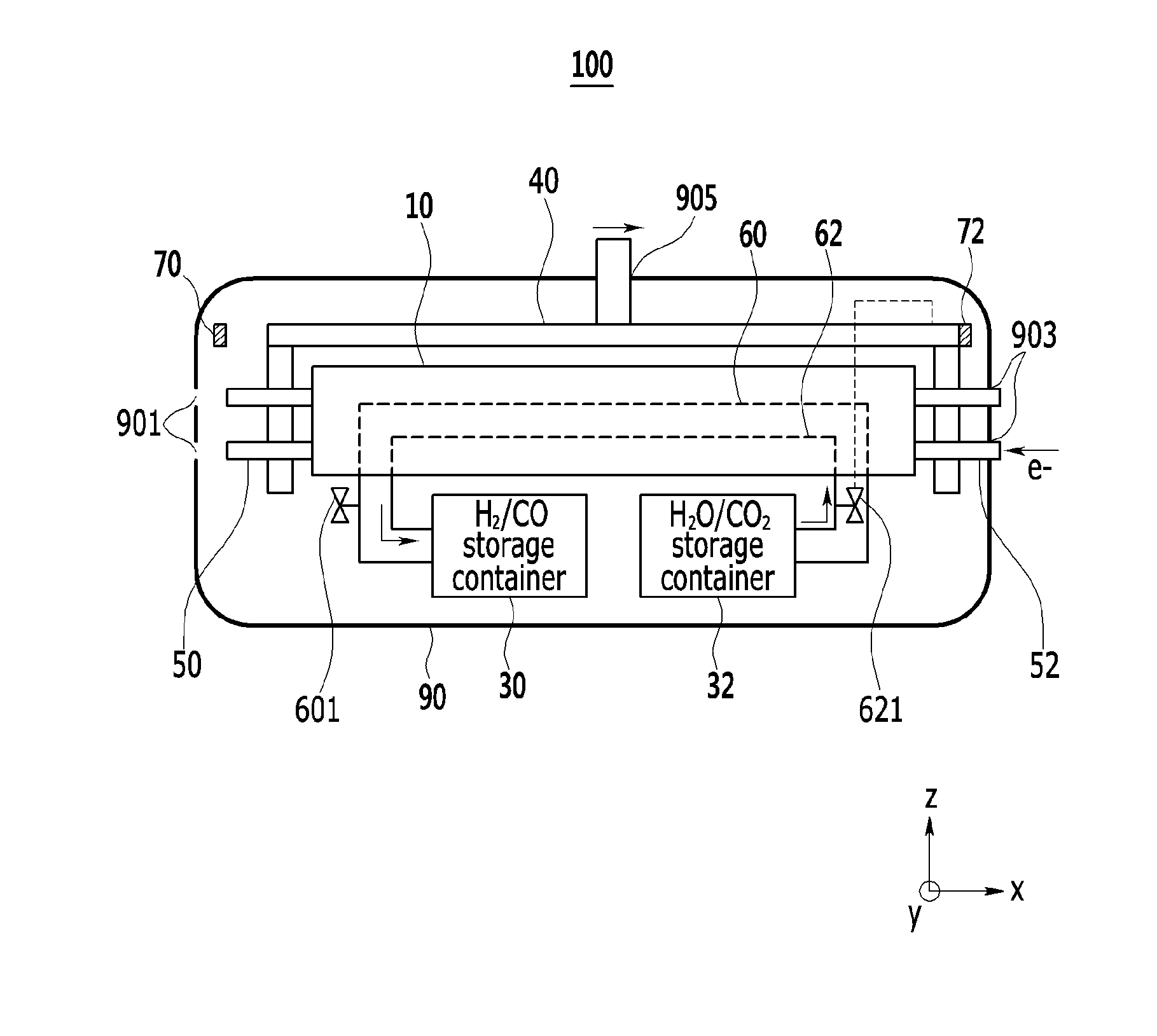

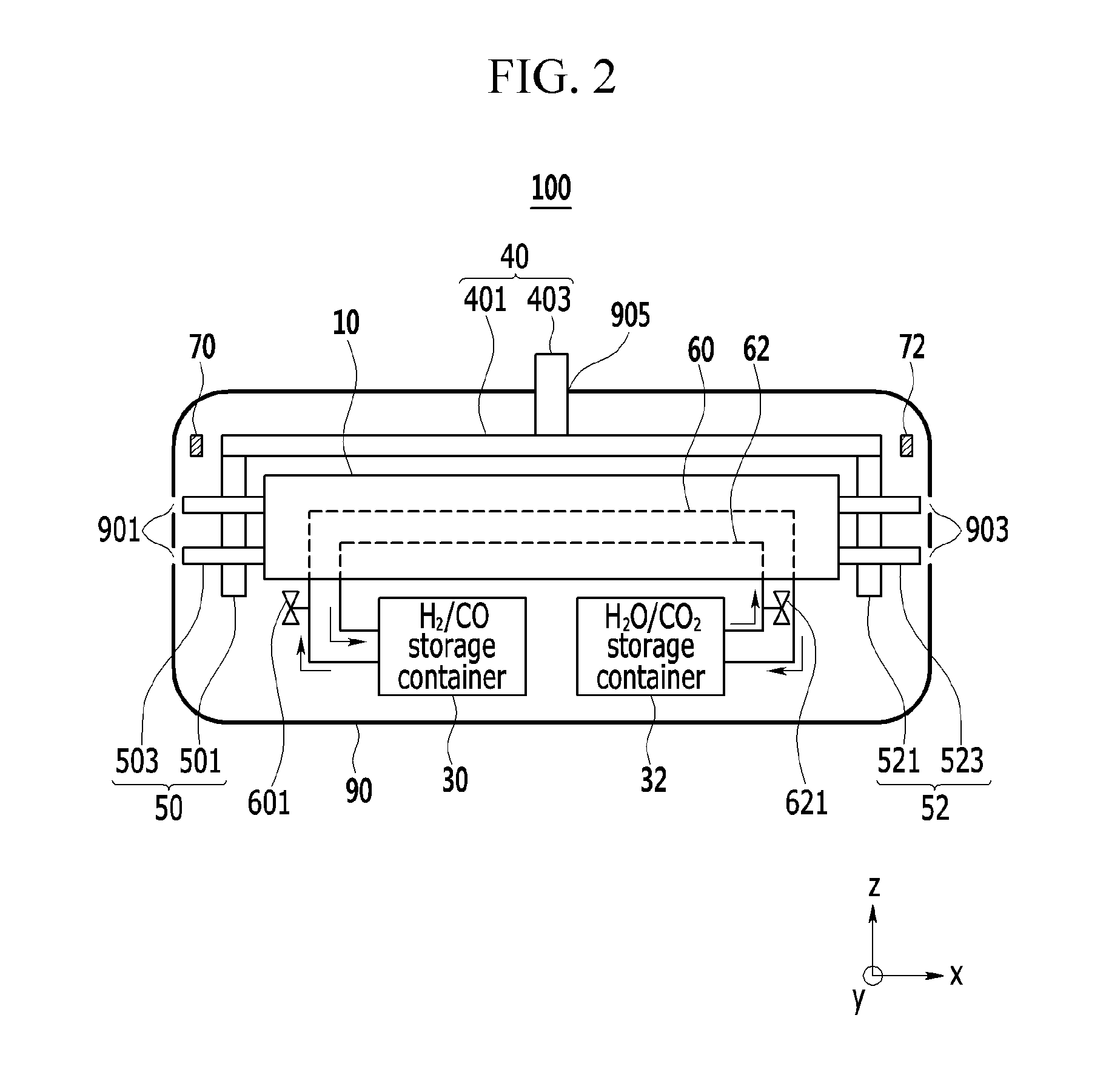

Hybrid electrochemical cell

InactiveUS20160130709A1Improve efficiencyHigh densityCellsFuel and secondary cellsHydrogenCell space

A hybrid electrochemical cell using reversible operation of a solid oxide cell includes: i) solid oxide cell generating power; ii) first storage container storing hydrogen and carbon monoxide discharged from the solid oxide cell supplying the hydrogen and carbon monoxide to the solid oxide cell; iii) second storage container storing steam and carbon dioxide discharged from the solid oxide cell supplying the steam and carbon dioxide to the solid oxide cell; iv) first connection pipe connecting the first storage container, the second storage container, and the solid oxide cell; v) second connection pipe connecting the first storage container, the second storage container, and the solid oxide cell; vi) discharging terminal connected to the solid oxide cell; vii) charging terminal connected to the solid oxide cell spaced apart from the discharging terminal, having the solid oxide cell disposed in between; and viii) mode converter connected to the solid oxide cell.

Owner:KOREA INST OF SCI & TECH

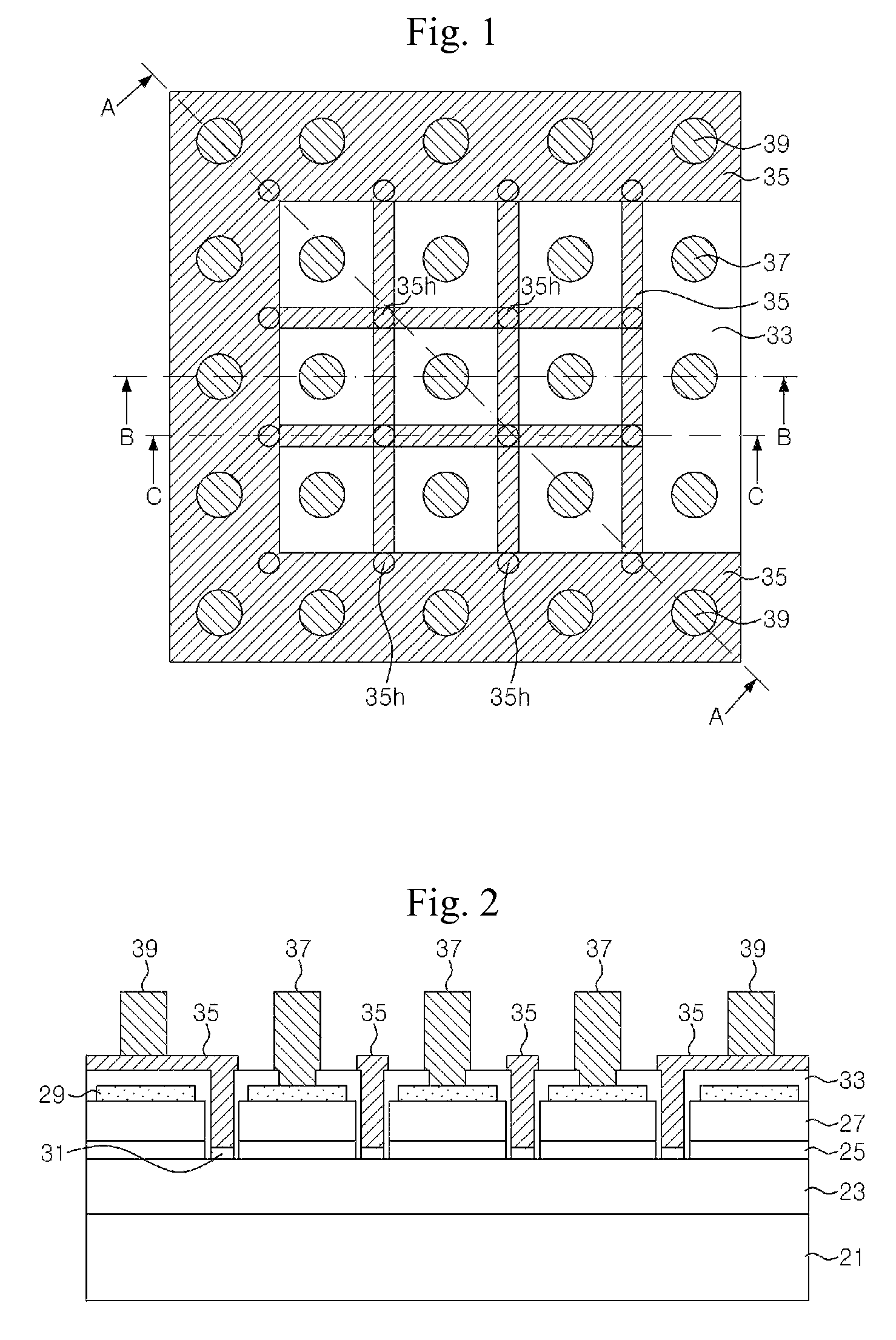

Self generating display and manufacturing method thereof

InactiveCN101614927ACapable of full-color animation displayLight-sensitive devicesFinal product manufactureSolid state electrolyteElectrophoresis

The invention discloses a self generating display and a manufacturing method thereof. The self generating display comprises a dye sensitized solar cell and an electrophoretic display, wherein the dye sensitized solar cell comprises a lower electrode arranged on a first substrate, a partition structure arranged on the lower electrode and provided with a plurality of unit openings, a dye material positioned in the unit openings, solid electrolyte covering on the partition structure, and an upper electrode covering the solid electrolyte; the electrophoretic display is electrically connected with the dye sensitized solar cell, and comprises pixel units arranged on a second substrate, a separation structure arranged above the pixel units, an electrophoretic medium and a protective layer covering on the separation structure, wherein each pixel unit is arranged corresponding to each unit opening, and comprises at least one switch element, a pixel electrode and a plurality of side electrodes; the separation structure has a plurality of unit spaces, and each unit space is arranged corresponding to each pixel unit; and the electrophoretic medium is filled in the unit spaces of the separation structure.

Owner:AU OPTRONICS CORP

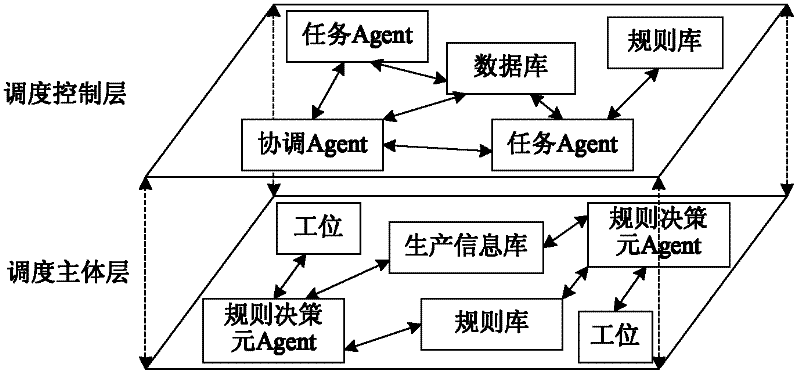

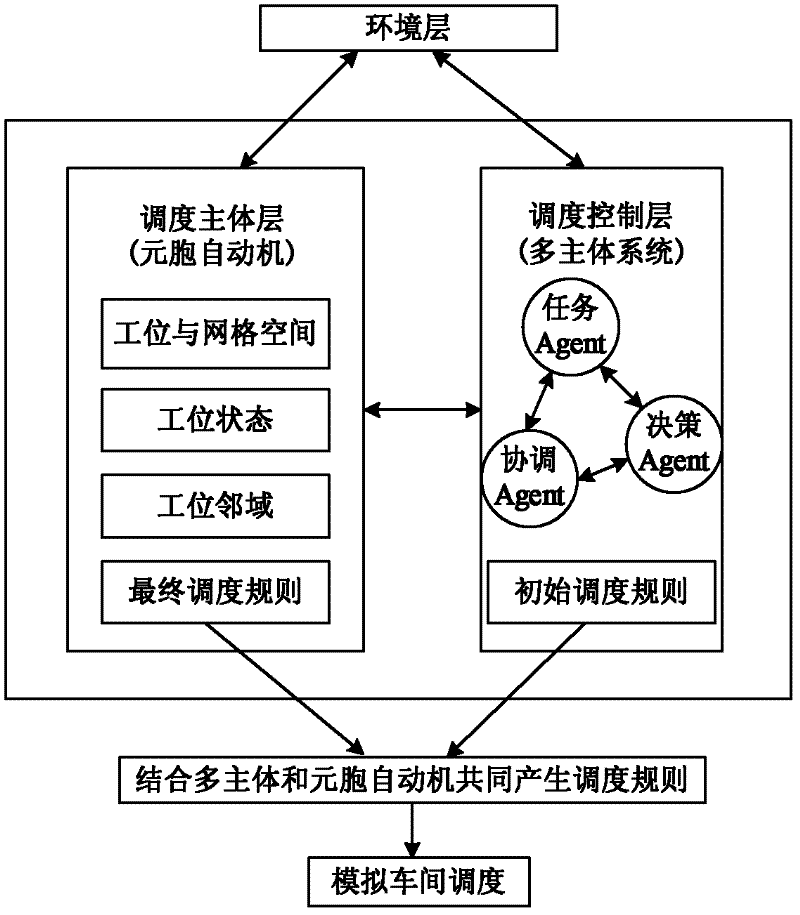

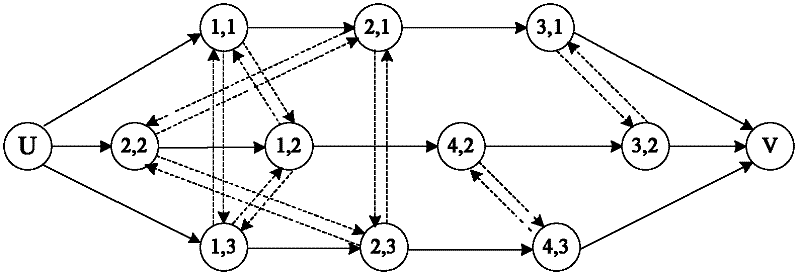

Method for carrying out dispatching control on multi-variety multi-process manufacturing enterprise workshop on basis of ACA (Automatic Circuit Analyzer) model

The invention relates to a method for carrying out dispatching control on a multi-variety multi-process manufacturing enterprise workshop on the basis of an AC (Automatic Circuit Analyzer) model, which comprises the following steps of: 1, setting a target function of the multi-variety multi-process manufacturing enterprise workshop, and when task information of a task Agent is sent to a decision Agent by a coordination Agent, representing the task information with a directed graph G by the decision Agent and using a dispatching rule which is obtained by the decision Agent through a random algorithm as an initial solution of a tabu search algorithm; 2, by a rule decision element Agent, firstly, calculating a target value F, then searching other dispatching methods from the dispatching field by the tabu search algorithm, and using a solution with the minimum target value as the adopted rule; and 3, carrying out state changing on each cell (i.e. a station) in a cell space according to the dispatching rule awarded by the rule decision element. According to the invention, a complex dispatching system can be described, the practical production is well reflected, the computational efficiency of a model is also considered, and the problem of dispatching the dynamic and complex multi-variety multi-process manufacturing enterprise workshop is rapidly and accurately solved.

Owner:ZHEJIANG UNIV OF TECH

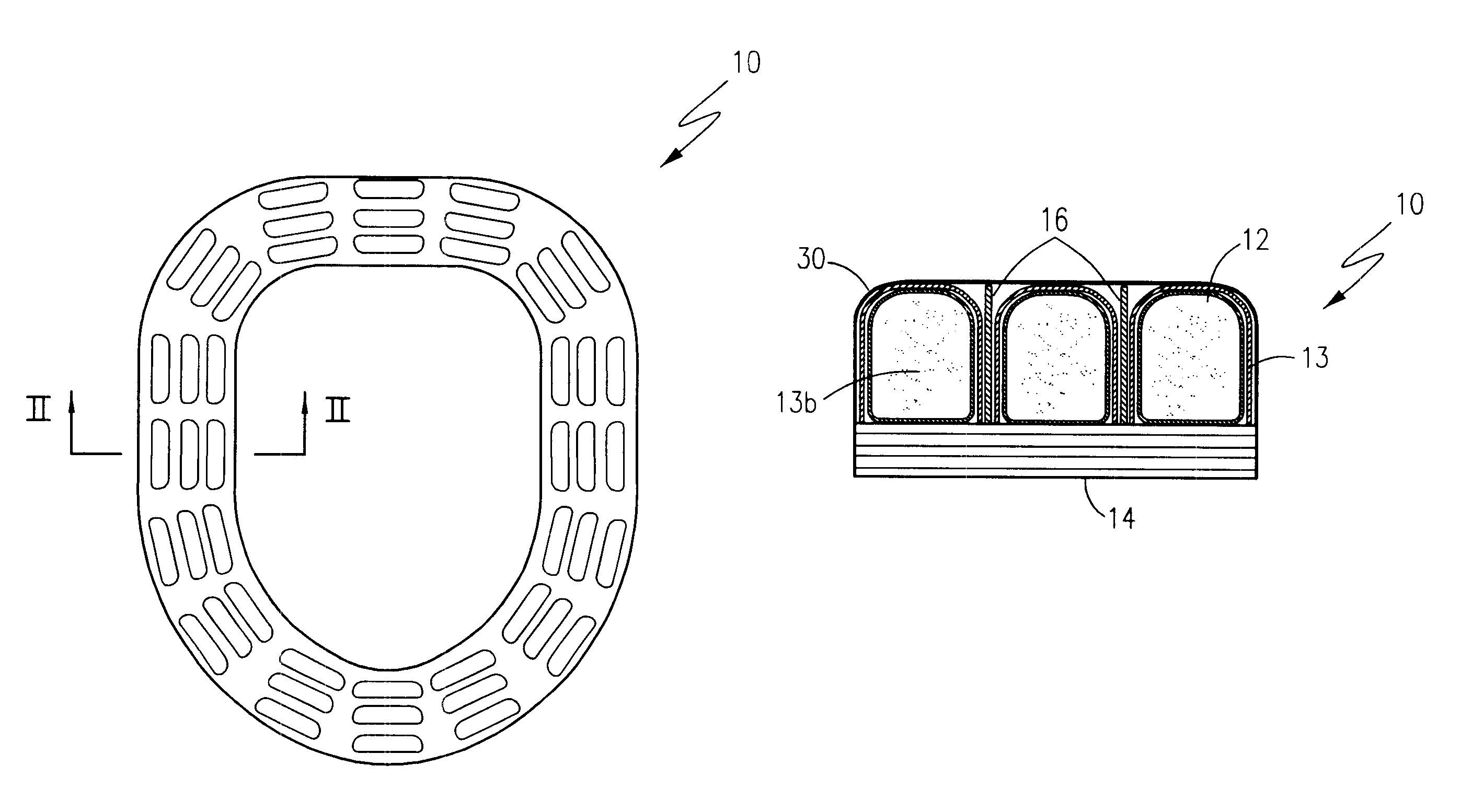

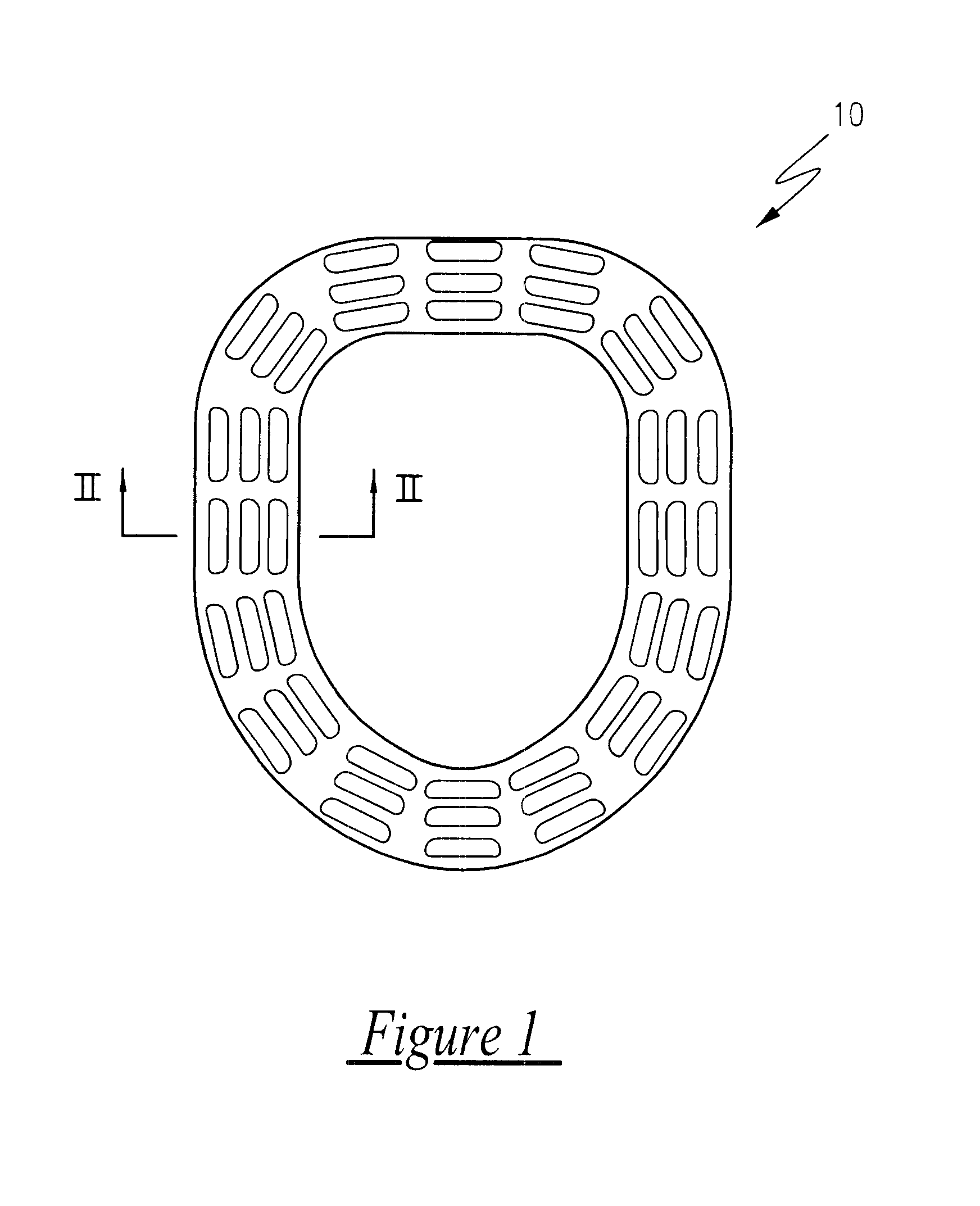

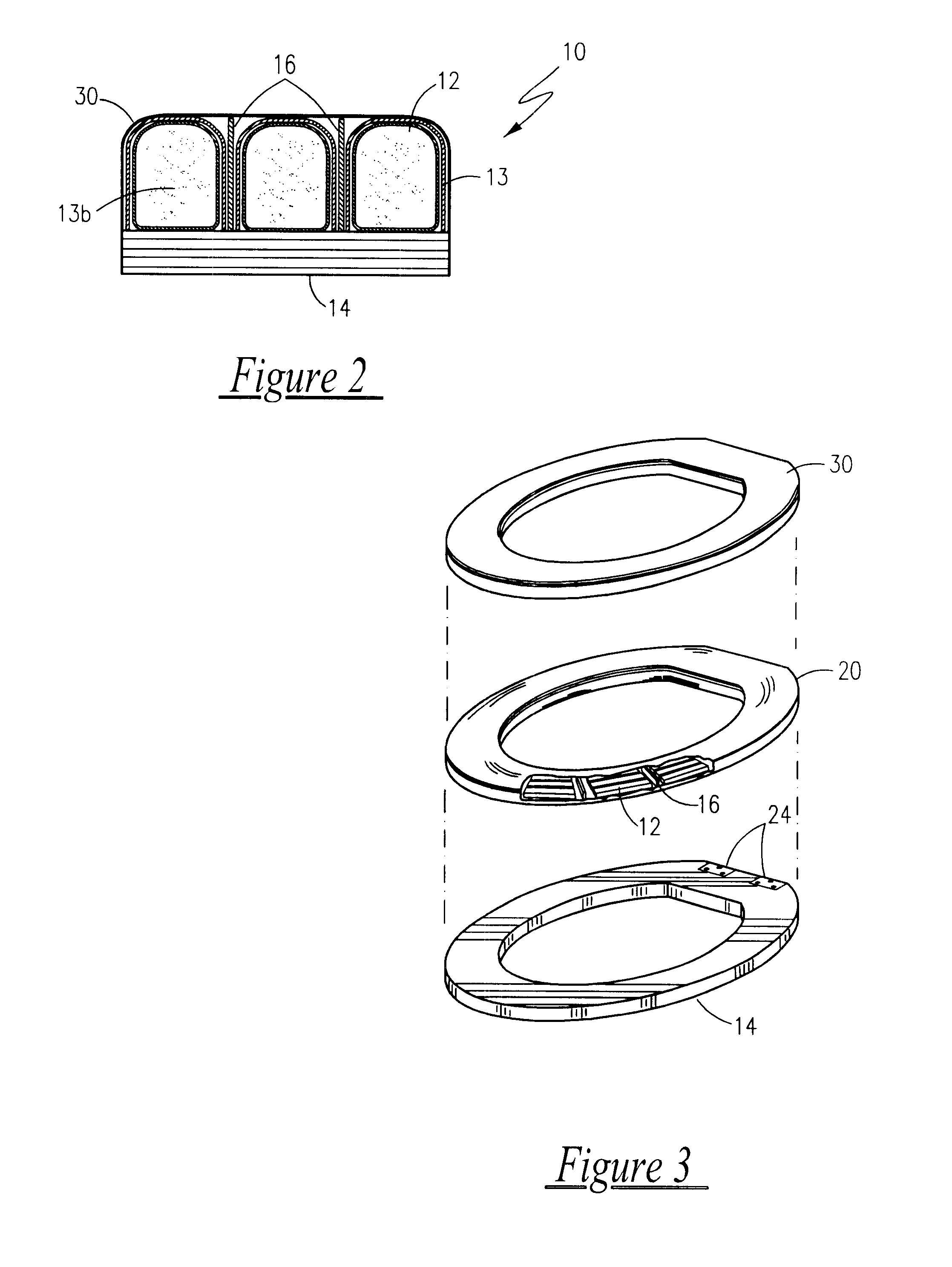

Fluid-cell toilet seat

A toilet seat is formed of three layers: a base; an insert disposed on the top surface of the base; and, an outer cover layer affixed to the base. The insert forms a plurality of radially disposed water or gel filled cells, each water or gel cell spaced from an adjacent cell by a separator. A fluid cell cover overlays the fluid cells, and is formed of a soft, deformable material. Each cell is filled with and contains a fluid, thereby allowing said toilet seat to provide a contouring support when pressed upon.

Owner:WHITE JR CHARLES L

Packet reassembly and deadlock avoidance for use in a packet switch

InactiveUS7852829B2Multiplex system selection arrangementsData switching by path configurationCell spaceDeadlock

Practical packet reassembly in large, multi-plane, multi-stage switches is possible by using a scheduling technique called dynamic packet interleaving. With dynamic packet interleaving scheduling, if more than one packet is contending for the same output link in a switch module, an arbiter in the switch module gives priority to a partial packet (i.e., to a packet that has had at least one cell sent to the queue). The number of reassembly queues required to ensure reassembly is dramatically reduced (e.g., to the number of paths multiplied by the number of scheduling priorities). Deadlock may be avoided by guaranteeing (e.g., reserving) at least one cell space for all partial packets.

Owner:POLYTECHNIC INST OF NEW YORK

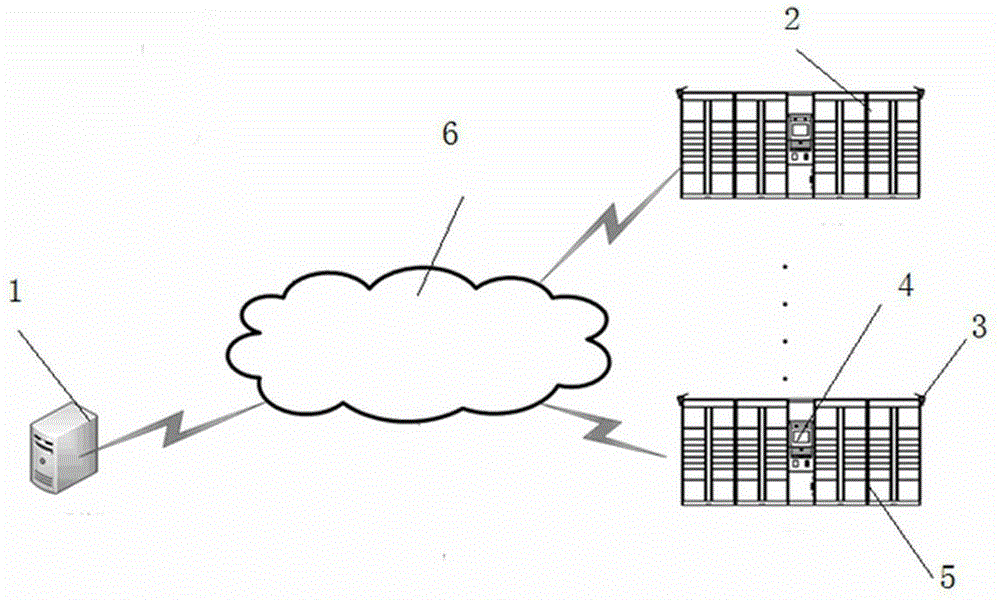

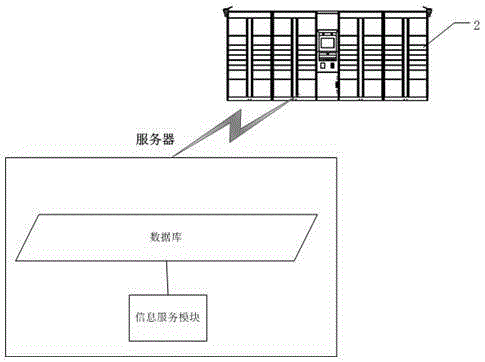

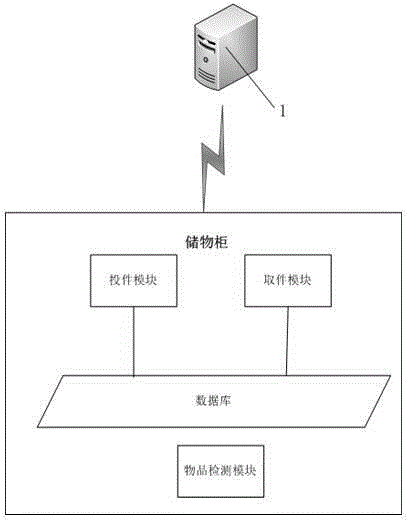

System and method for achieving delivery of multiple express items through one cell of storage cabinet

The invention discloses a system for achieving delivery of multiple express items through one cell of a storage cabinet. The system comprises the storage cabinet and a server, wherein the storage cabinet is in communication with the server through a network, the server comprises a server database and an information service module, the storage cabinet comprises a human-computer interface, cells and a control unit, and the control unit comprises a storage cabinet database, an item delivering module and an item receiving module. In addition, the invention further discloses a method for achieving delivery of multiple express items through one cell of the storage cabinet. The method comprises the steps of item delivery and item receiving. By means of the system and the method, multiple express items of the same recipient can be put in one cell, the cell space is reasonably utilized, the using number of the cells is decreased, the cell utilization rate is improved, each express item can be further traced and managed, and the phenomenon of express item loss is avoided.

Owner:CHENGDU WOLAILA GRID INFORMATION TECH

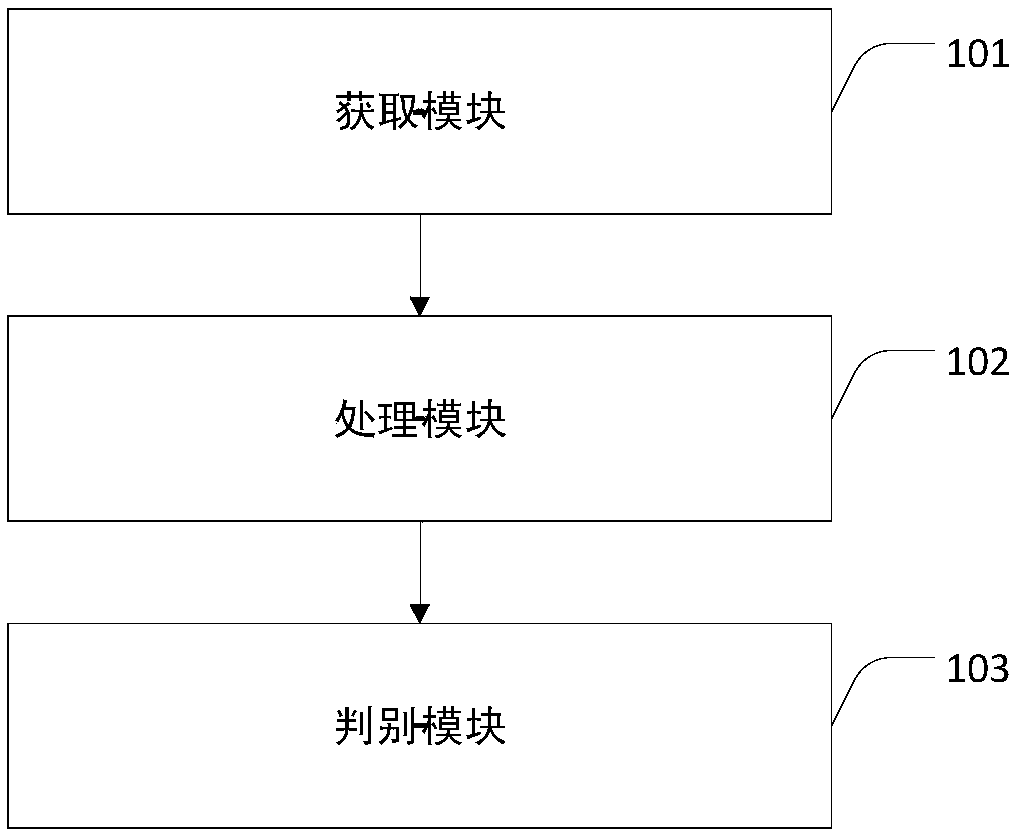

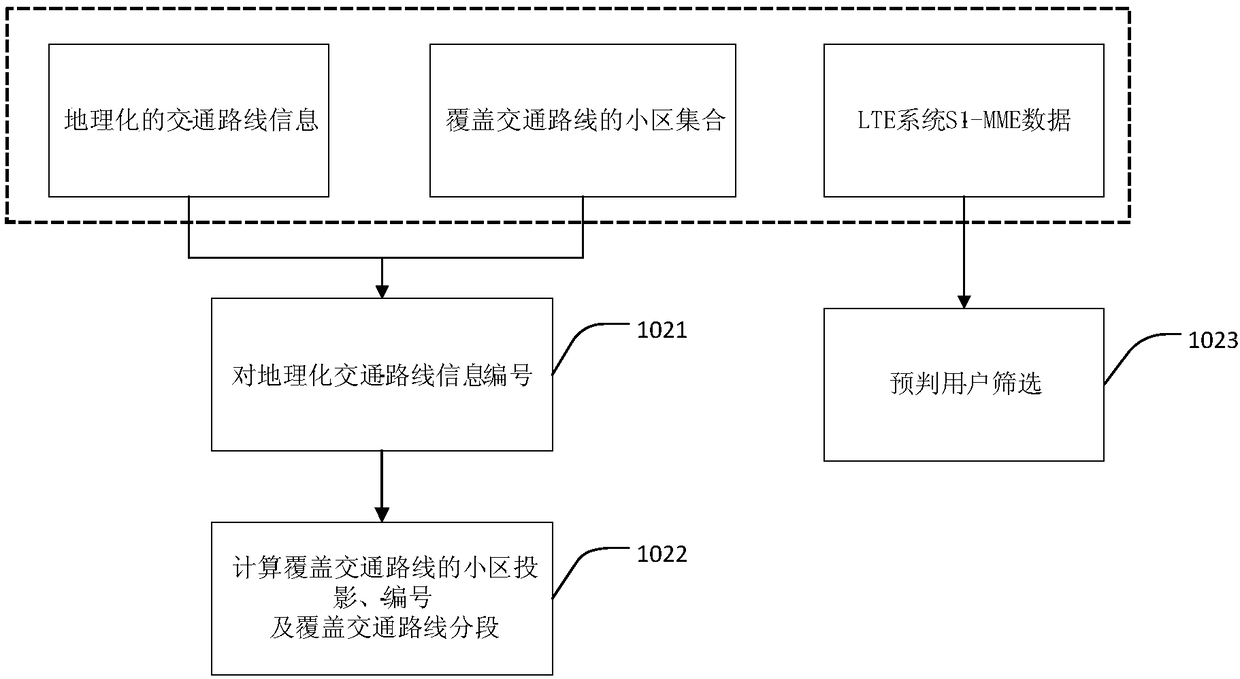

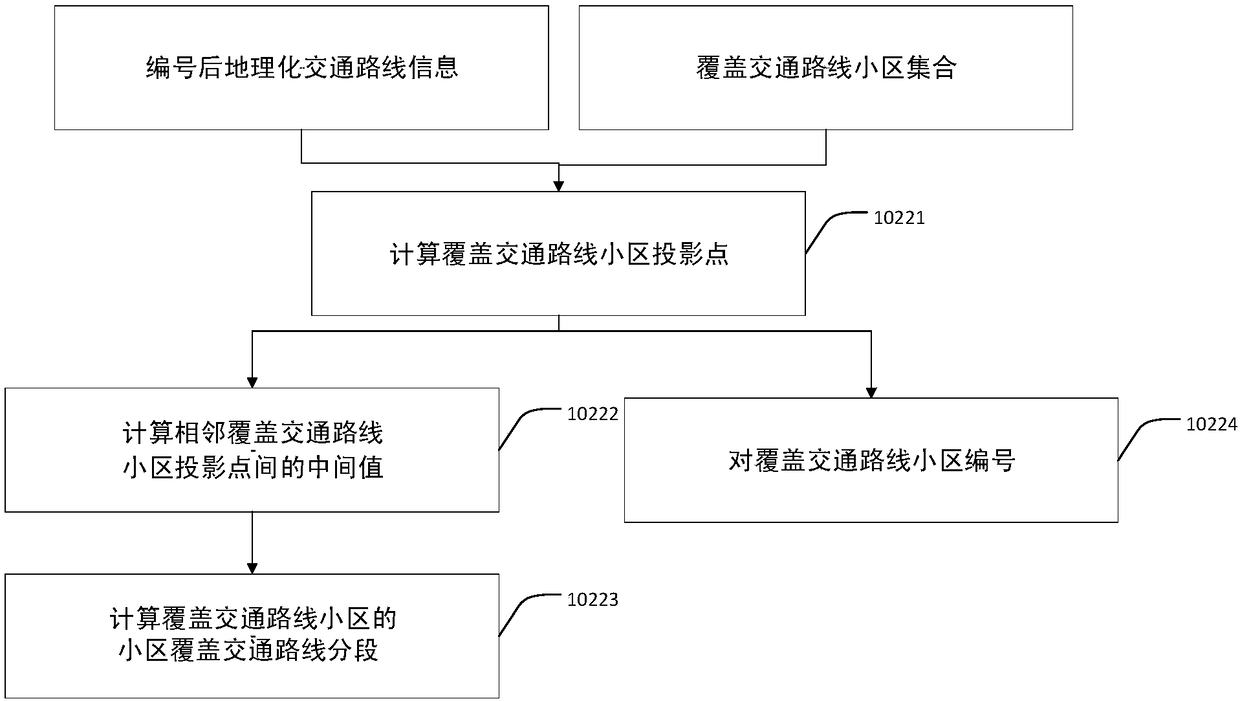

S1-MME data-based method of determining mobile user rapidly and accurately

ActiveCN108307316AHigh discrimination accuracyImprove discrimination accuracyParticular environment based servicesLocation information based serviceProjection algorithmsSlide window

The invention discloses an S1-MME data-based method of determining mobile user rapidly and accurately, belonging to the technical field of data analysis. According to the method, a pre-determined useris screened out by collecting S1-MME interface data in an LTE mobile communication network, and a practical traffic route and a travel distance of the user are simulated and calculated by combining an algorithm calculating a projection of a base station cell set covering the traffic route on a geographic traffic route and a cell coverage track segmentation algorithm. The method replaces a mannerof calculating a user movement speed by using cell space in the prior art, so that the movement distance and speed are determined more accurately; and the user is determined by using both a maximum span determining method and a reverse slide window determining method, so that the determining accuracy is improved, manual intervention factors are reduced, and false negative and false positive problems resulting from the fact that fewer cells cover the traffic route or traffic routes of different mobile attributes are adjacent are solved.

Owner:CHINA TELECOM CORP LTD

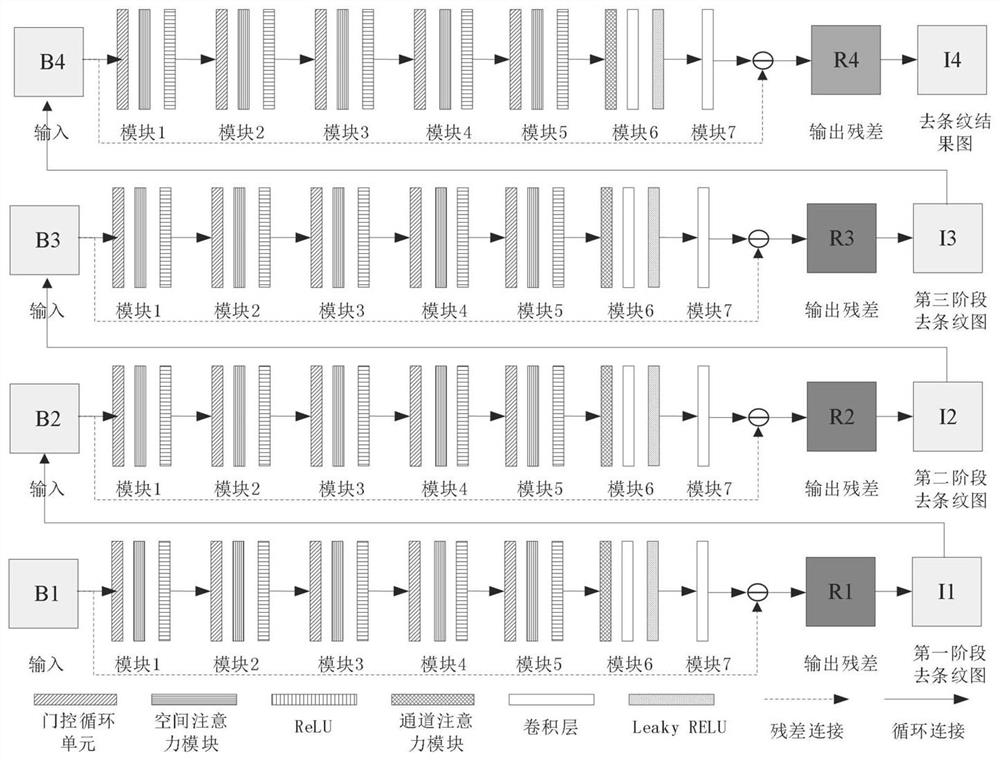

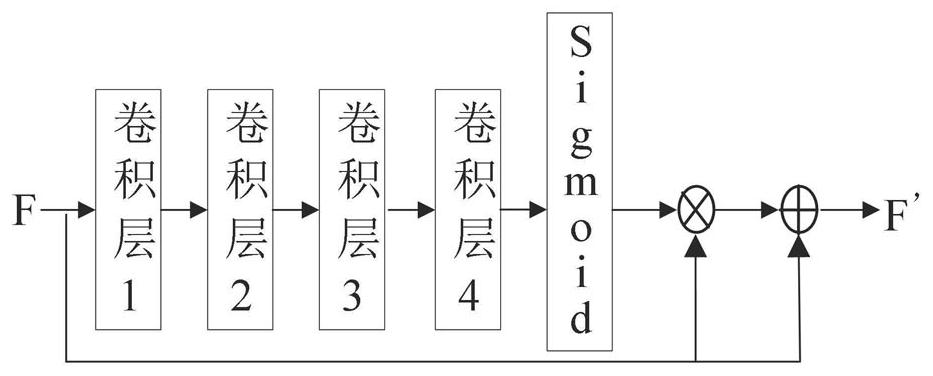

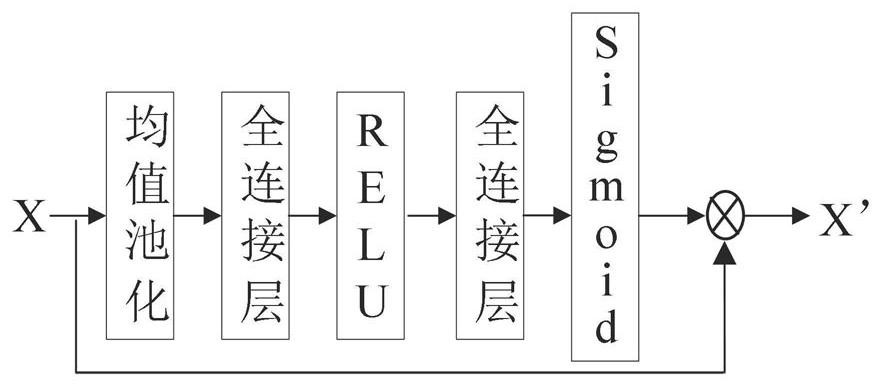

Image rain removing method based on attention mechanism and gating circulation unit

PendingCN111861925AQuality improvementRemarkable effect of removing rainImage enhancementImage analysisActivation functionComputer graphics (images)

The invention provides an image rain removal method based on an attention mechanism and a gating circulation unit, and the method comprises the steps: firstly constructing an image rain removal network architecture based on the attention mechanism and the gating circulation unit, wherein the image rain removal network architecture includes 6 modules, each of the first five modules comprises a gating circulation unit, a spatial attention module and an activation function; wherein the module 1 is used as an encoder, expansion convolution with expansion factors of 1, 2, 4 and 8 is respectively used in the module 2 to the module 5, and the sizes of corresponding receiving domains are respectively 5 * 5, 9 * 9, 17 * 17 and 33 * 33; the module 6 comprises a convolution layer, a channel attentionmodule and an activation function, and a 1 * 1 convolution layer is connected behind the module 6 and serves as a decoder to generate residual error mapping; then, selecting the MSE and the SSIM as loss functions; and finally, training the constructed network architecture. According to the method, the problems of rain stripe residues and detail blurring occurring in processing of the image containing the dense rain stripes are solved, the rain lines in the image are removed, meanwhile, the detail parts of the image are reserved, and the image definition is greatly improved.

Owner:南京信息工程大学滨江学院

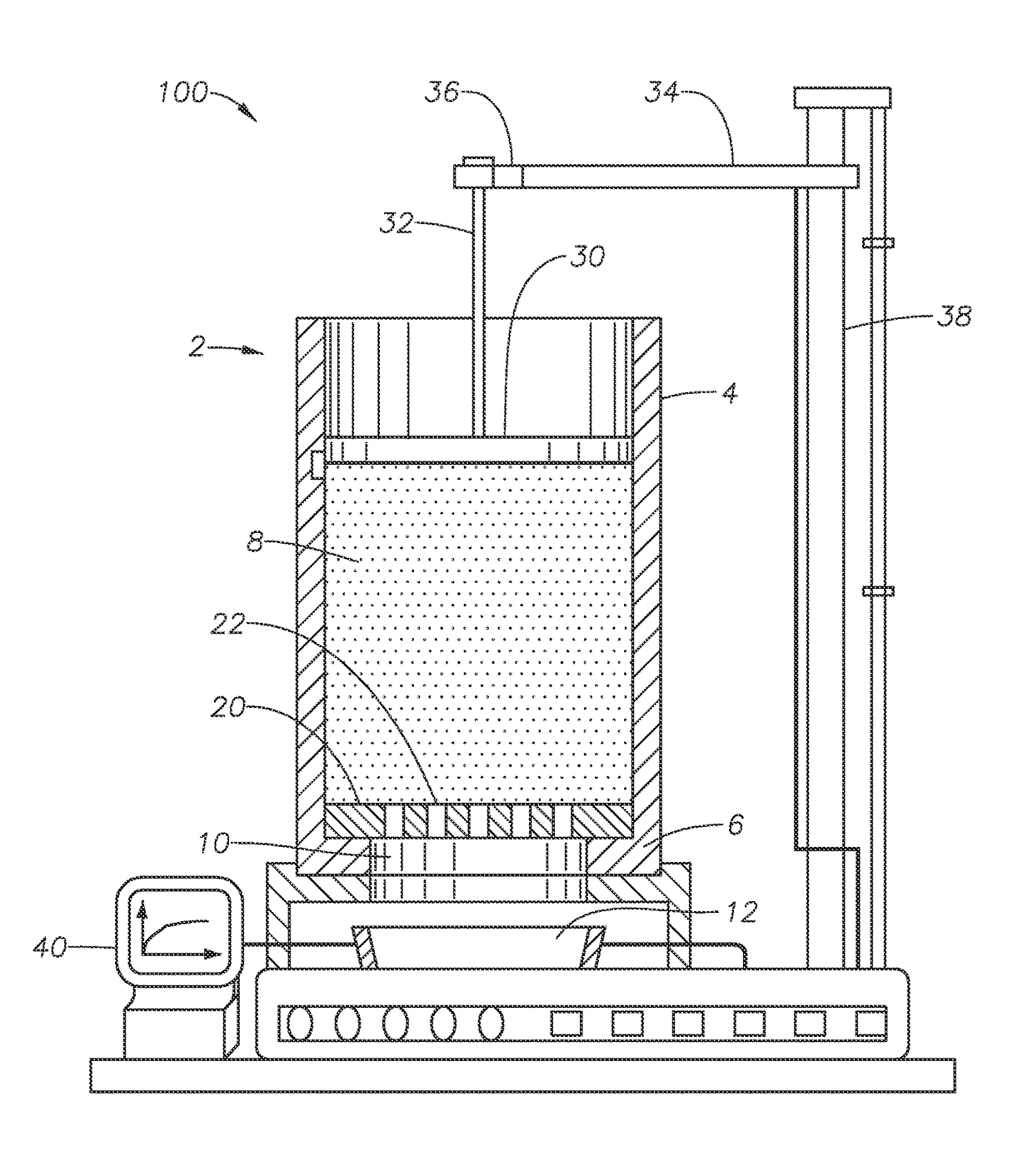

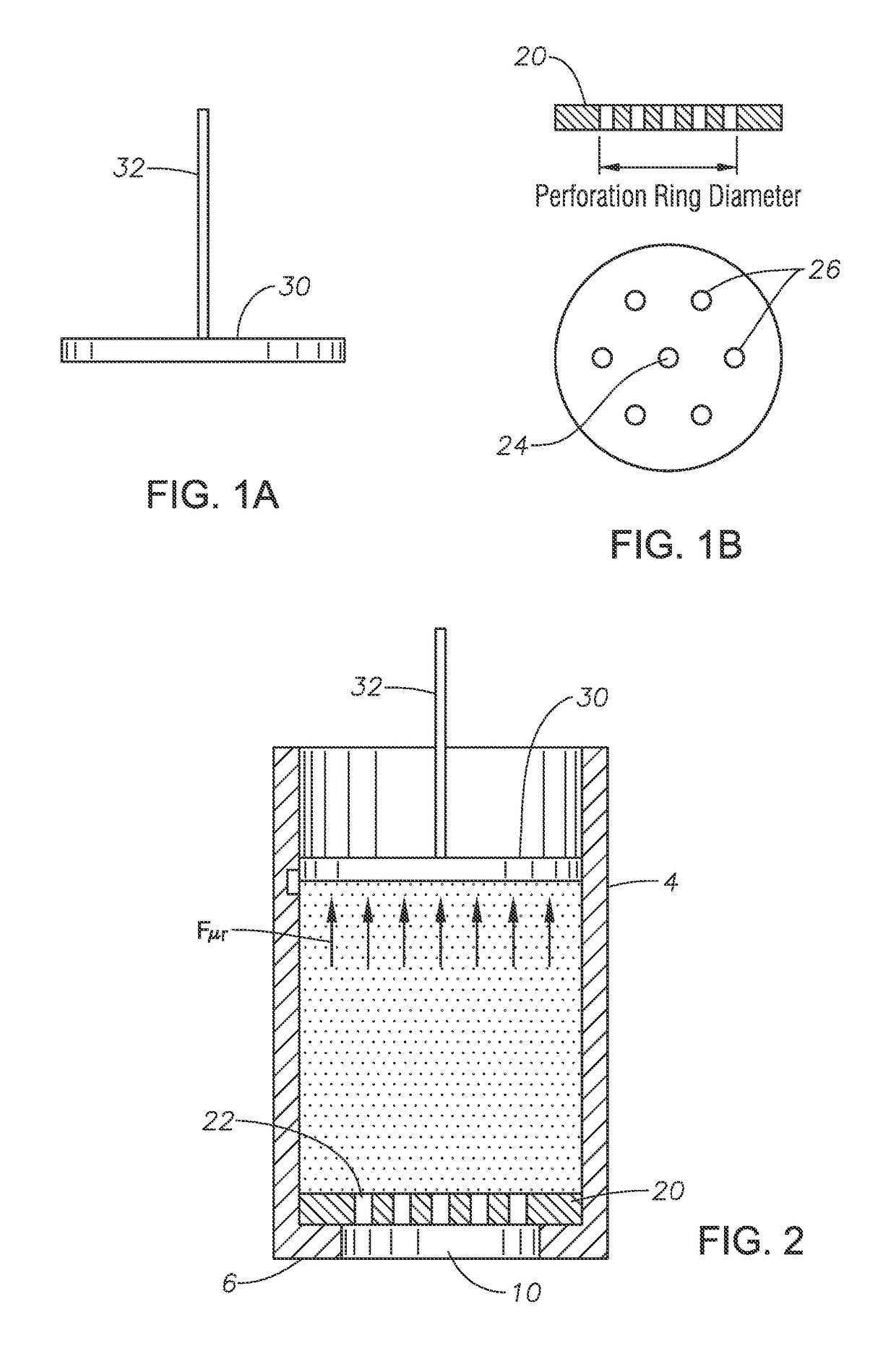

Method and apparatus for testing gel-based lost circulation materials

ActiveUS9739694B2Material strength using tensile/compressive forcesElectrical/magnetic solid deformation measurementCircular discGel based

Owner:SAUDI ARABIAN OIL CO

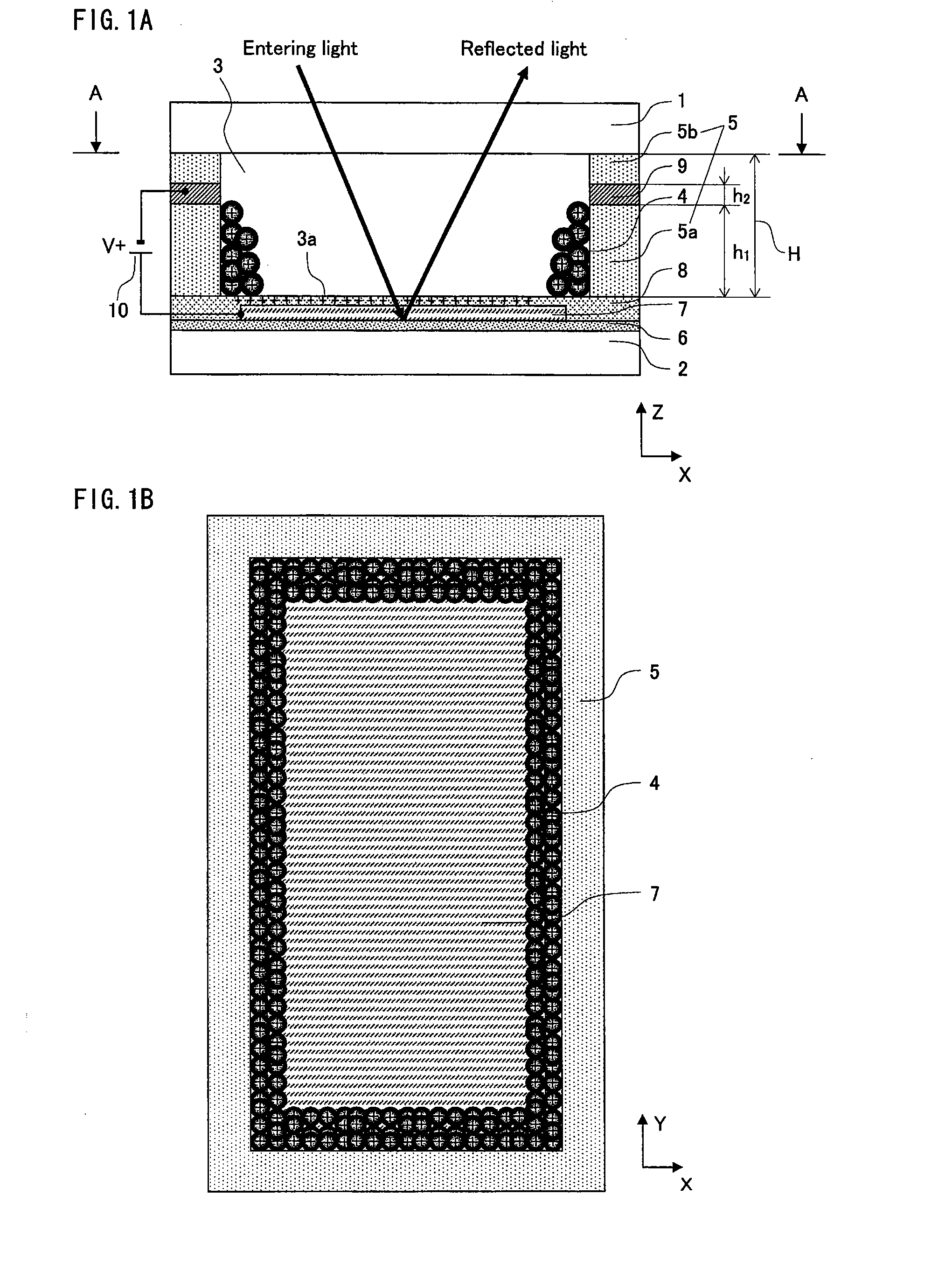

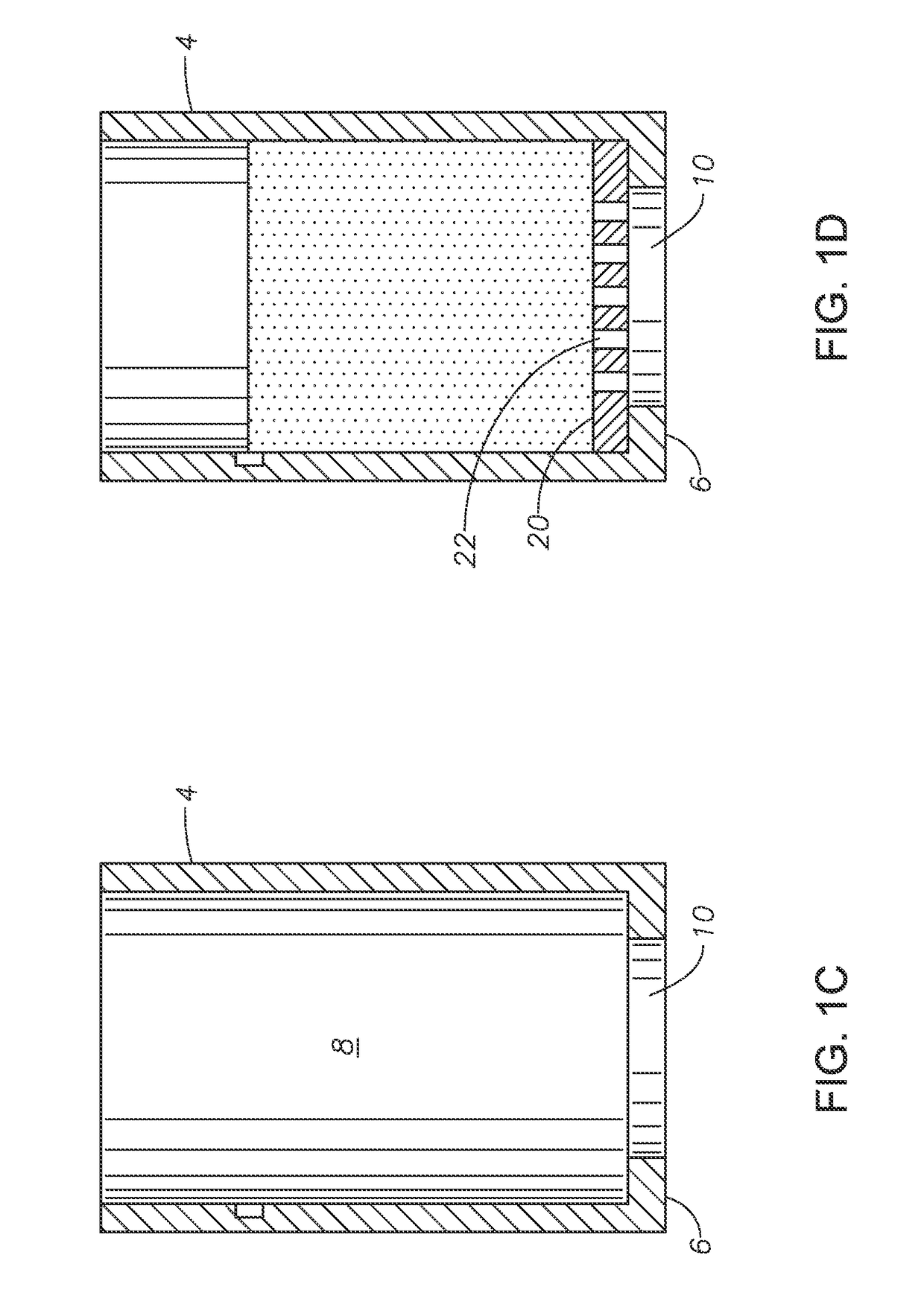

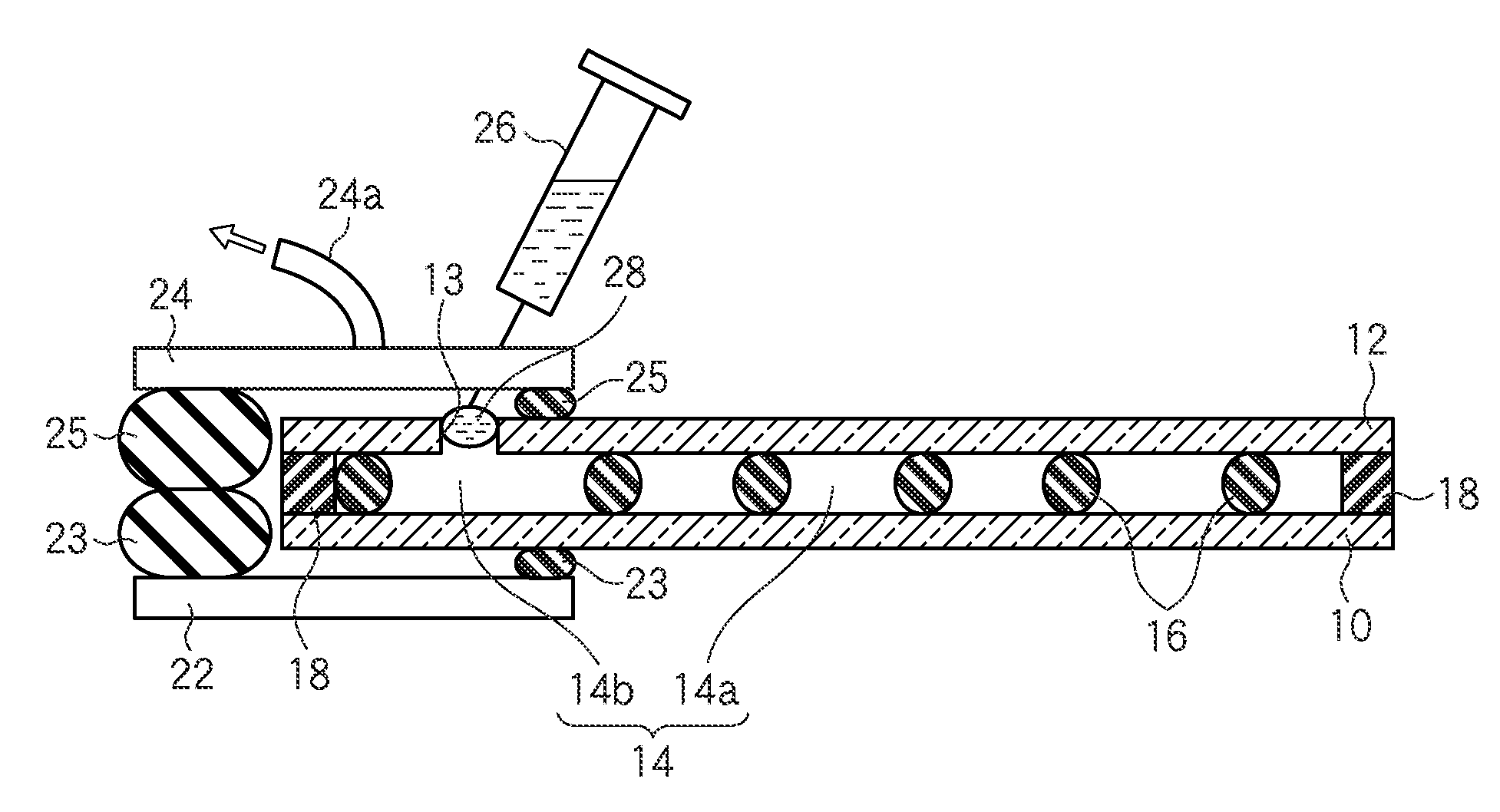

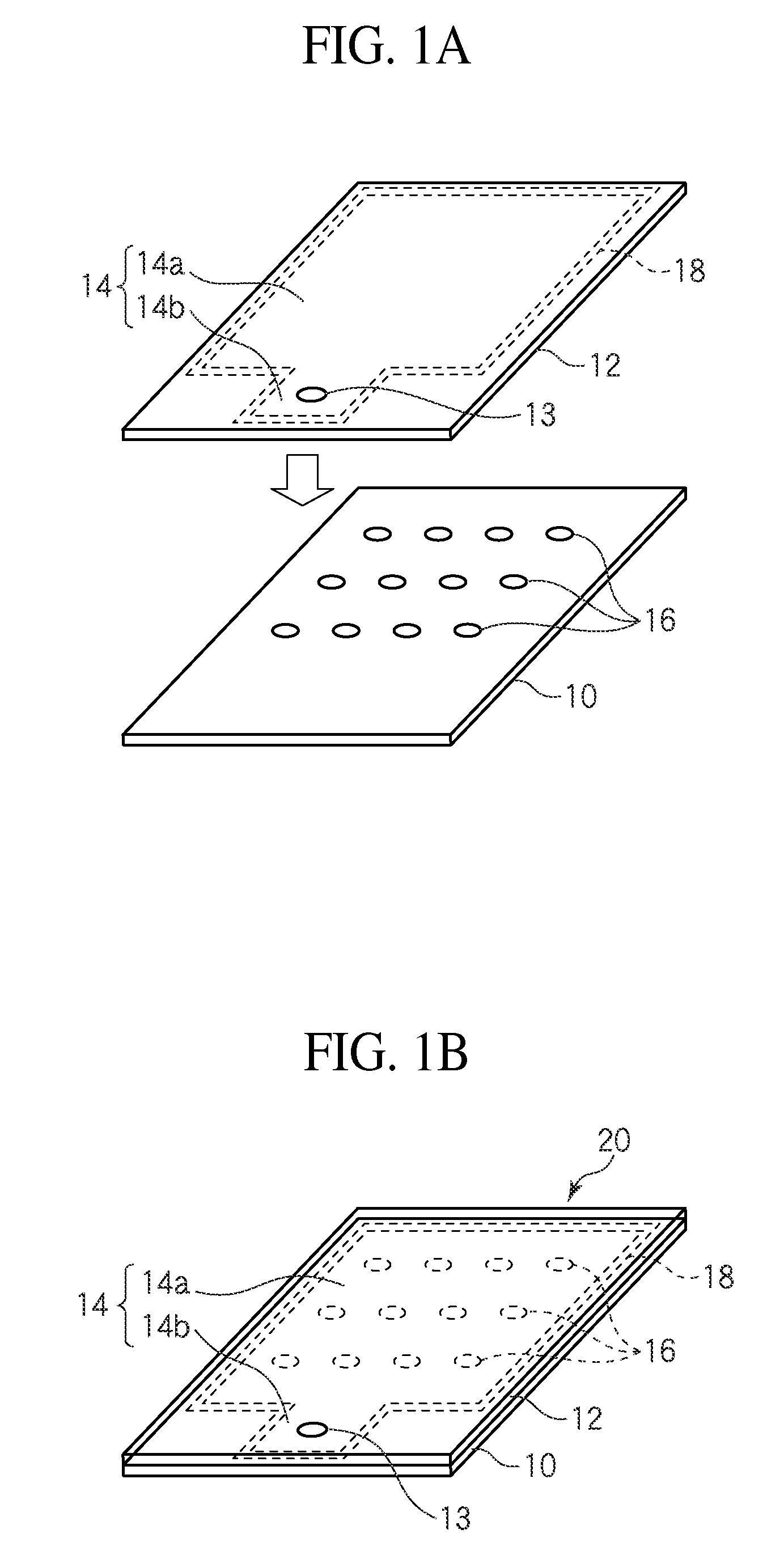

Liquid crystal display panel manufacturing method and device

InactiveUS20090009707A1Semiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayCell region

A liquid crystal display panel 20 is manufactured by applying a seal agent 19 to at least of a pair of substrates 10, 12, enclosing the cell region 14; opposing the pair of substrates 10, 12 at a prescribed gap to define a cell space 14; depressurizing the interior of the cell space 14 through an opening 13 formed in at least one of the pair of substrates 10, 12 to thereby securely bond the pair of substrate 10, 12 to each other; and injecting a liquid crystal into the cell space 14. The atmospheric pressure is applied to the pair of substrates 10, 12, whereby a uniform external pressure is applied, and the glass substrates can be securely bonded to each other in good condition.

Owner:FUJITSU LTD

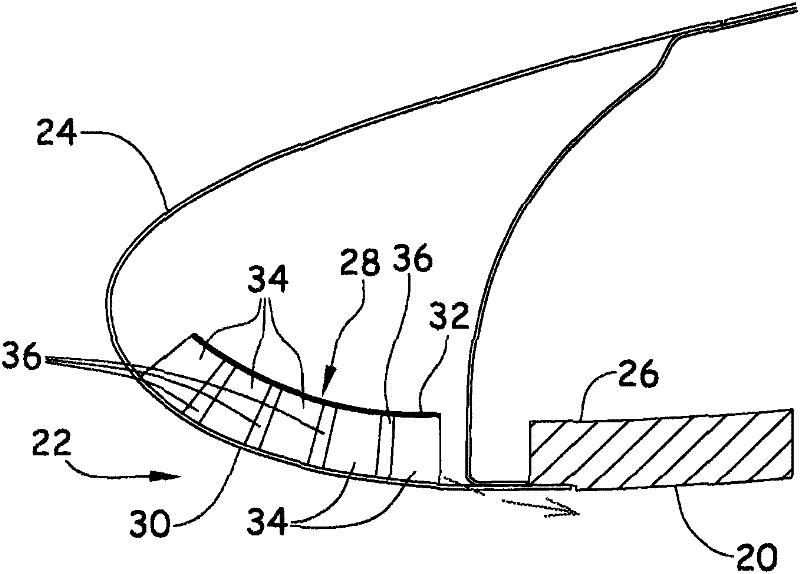

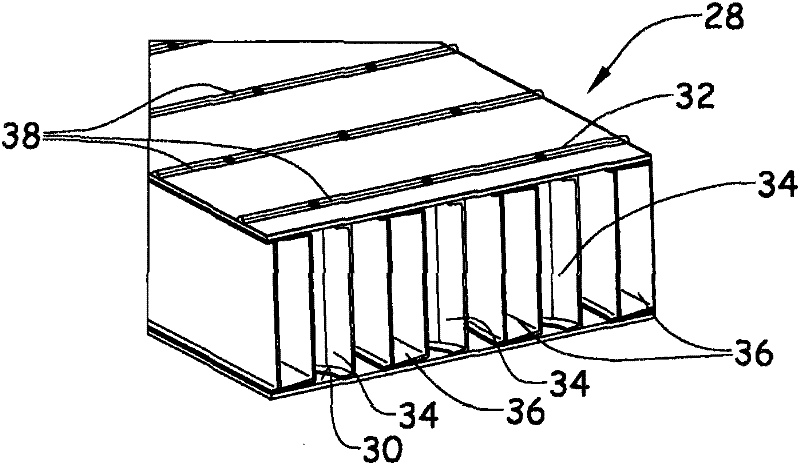

Acoustic processing panel, more particularly adapted for an air intake in an aircraft nacelle

ActiveCN102307783AImprove processing efficiencyImprove drainage efficiencyDe-icing equipmentsGas turbine plantsNacelleCell space

The invention relates to an acoustic processing panel mounted at the air intake of an aircraft nacelle, said panel including at least one acoustically resistive structure (30) and a reflective layer (32), between which are provided, in a direction substantially perpendicular to the longitudinal direction of the nacelle, strips (34) of honeycomb cells spaced apart so as to enable the hot air flow for treating icing, characterised in that it comprises ducts (36) for the hot air, each defined by at least one wall extending from the acoustically resistive layer (30) to the reflective layer (32) so as to insulate said cell strips (34) in the longitudinal direction.

Owner:AIRBUS OPERATIONS (SAS)

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com