Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

39 results about "'Backward reading'" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Monitoring and correcting device for single event upset fault of satellite borne spread spectrum responder

InactiveCN104021051AAvoid Performance Metrics DegradationAvoid functioFault responseComputer moduleSingle event upset

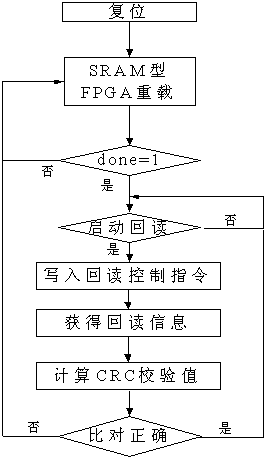

The invention discloses a monitoring and correcting device for a single event upset fault of a satellite borne spread spectrum responder. The monitoring and correcting device is used for monitoring and correcting a communication processing module of the satellite borne spread spectrum responder. The monitoring and correcting device is characterized by comprising an anti-fuse FPGA circuit, a watchdog circuit and an AND gate logic circuit, the anti-fuse FPGA circuit is used for conducting backward reading, backward reading information comparing and heavy load judging on the configuration information of the communication processing module and used for sending first heavy load signals to the AND gate logic circuit, the watchdog circuit is used for sending second heavy load signals to the AND gate logic circuit according to feed dog signals sent by the communication processing module, and the AND gate logic circuit is used for conducting AND logic operation on the received first heavy load signals and the received second heavy load signals and sending heavy load enabling signals to the communication processing module according to AND results.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

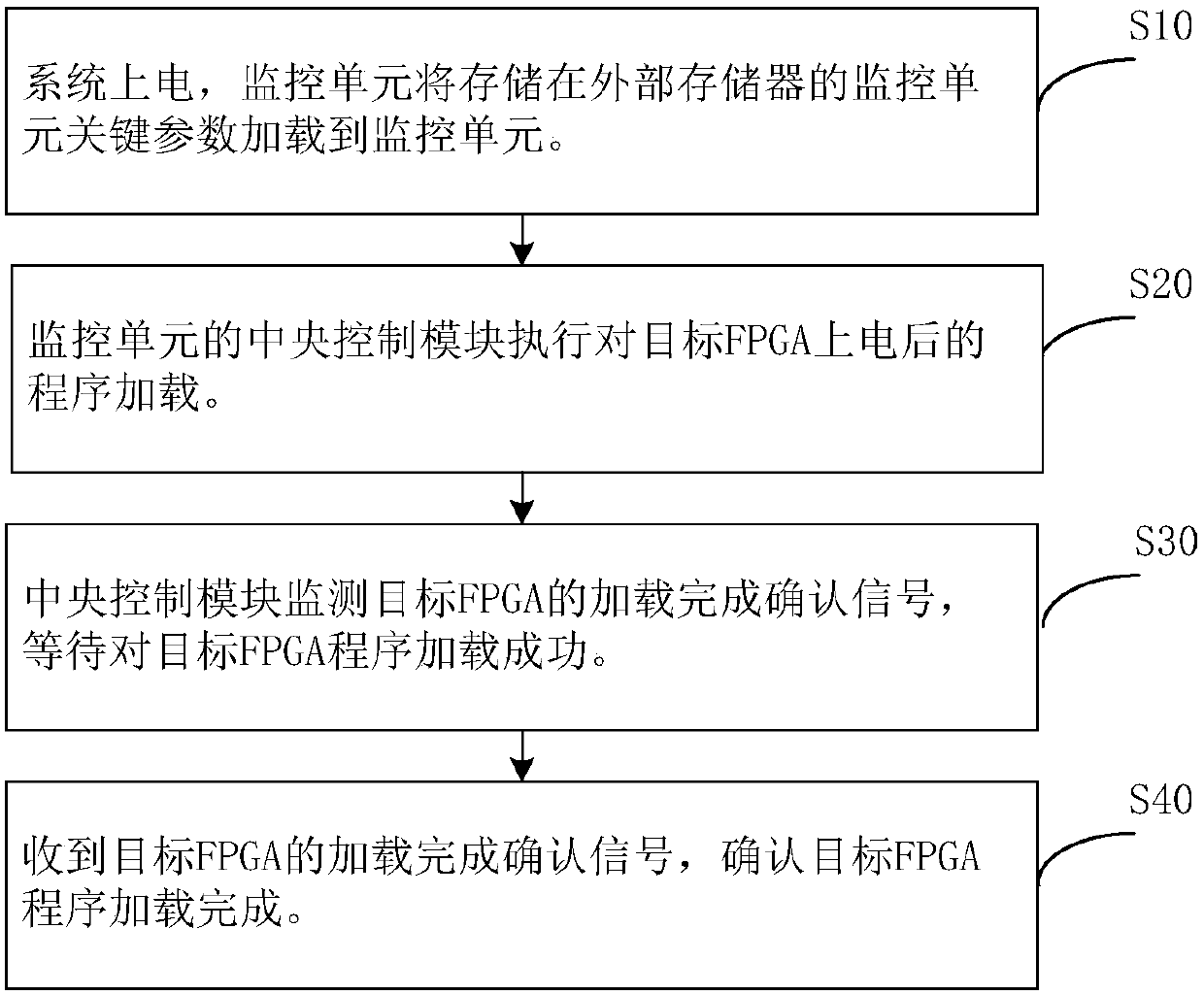

Multifunctional configurable single particle radiation resistance system and method

ActiveCN107678913AAchieve multi-functionImprove the ability to resist single event radiationFault responseHardware monitoringUnit loadElectricity

The invention discloses a multifunctional configurable single particle radiation resistance system and method. A key parameter loading module of a monitoring unit loads a monitoring configuration parameter stored in an external memory to the monitoring unit; the monitoring configuration parameter is put in a storage file generated in a set format; a central control module of the monitoring unit executes program loading after a target FPGA is powered on; the central control module monitors a loading completion confirmation signal of the target FPGA and waits for program loading success of the target FPGA; and when the loading completion confirmation signal of the target FPGA is received, the program loading completion of the target FPGA is confirmed. Different working interfaces can be selected for performing radiation-resistant reinforcement design on any quantity of FPGAs with backward reading functions only by modifying the monitoring configuration parameter in the external memory, so that multifunctional configurable reinforcement design of multiple SRAM type FPGAs can be realized.

Owner:湖南斯北图科技有限公司

Methods, systems, and apparatus for reducing the effects of tape dimensional stability

ActiveUS7738212B2The effect is accurateImprove accuracyDriving/moving recording headsAlignment for track following on tapesComputer graphics (images)'Backward reading'

Owner:QUANTUM CORP

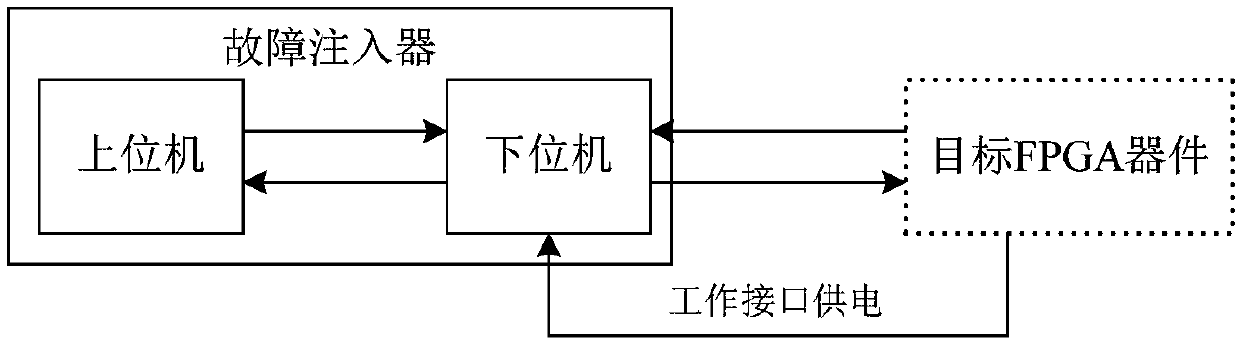

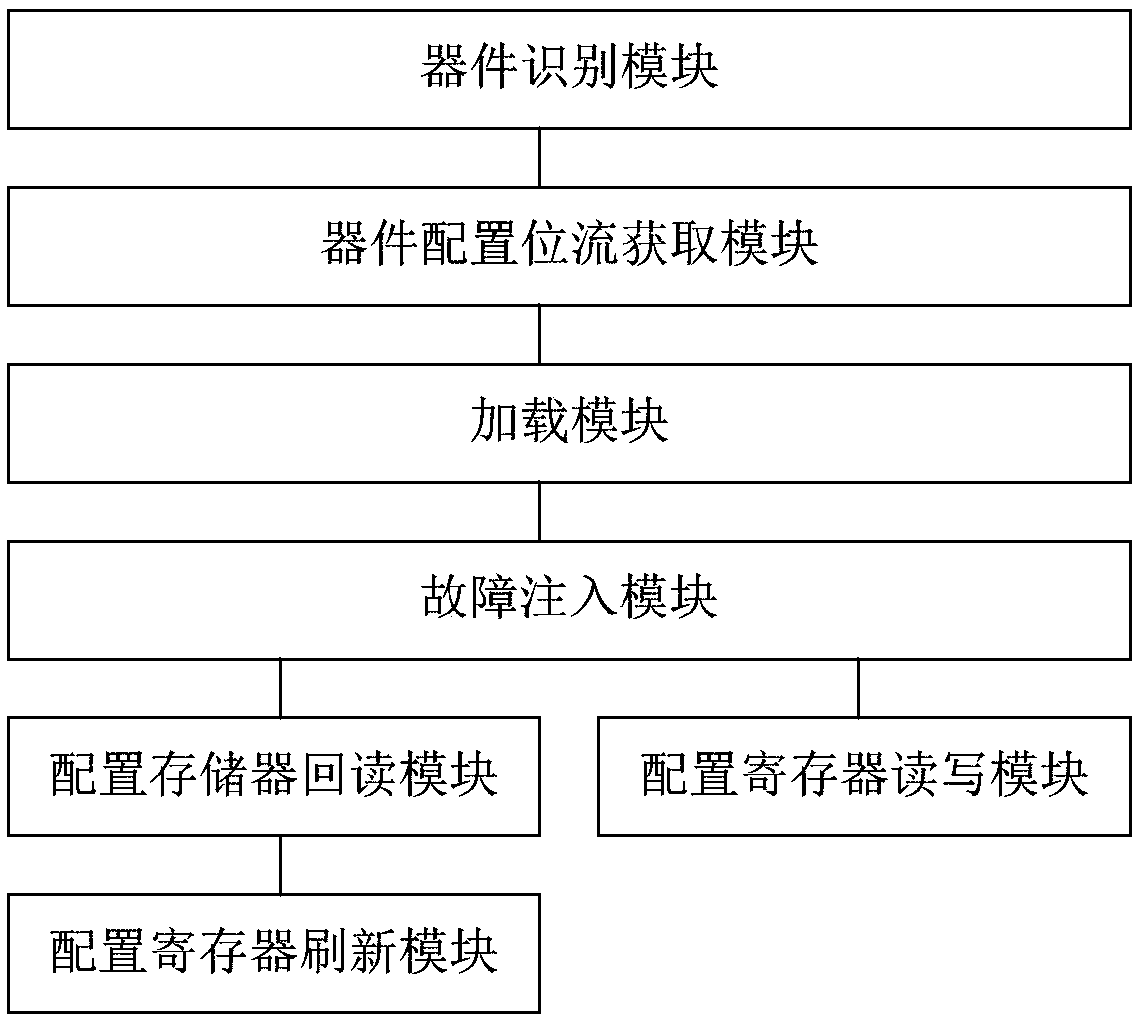

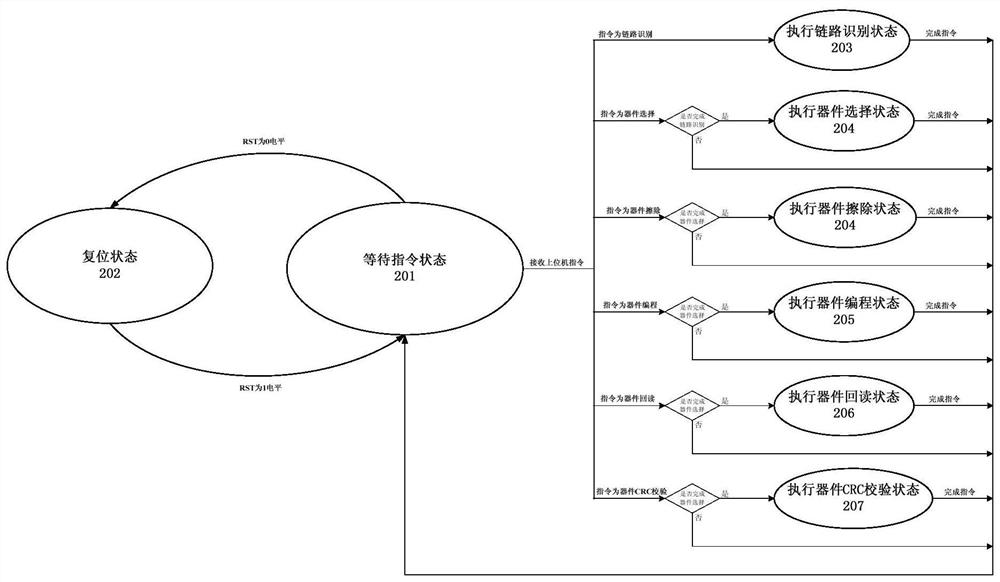

SRAM type FPGA turnover fault injection device and fault injection method

ActiveCN107678896AFault injection implementationFault injection satisfiesReliability/availability analysisFaulty hardware testing methodsDevice typeSoftware fault

The invention provides an SRAM type FPGA turnover fault injection device and fault injection method. An upper computer indicates a lower computer to perform chain device identification, thereby obtaining a device type corresponding to an ID of a target FPGA device; the upper computer selects a working interface and indicates the lower computer to perform configuration bit stream backward reading through the working interface; an original configuration bit stream file of the target FPGA device is obtained; the upper computer indicates the lower computer to finish power-on program loading of thetarget FPGA device by utilizing the original configuration bit stream file of the target FPGA device; the upper computer generates a turnover fault injection bit stream file according to a fault injection type; and the lower computer is indicated to finish fault injection for the target FPGA device through the selected working interface by utilizing the fault injection bit stream file. The shortcomings that an existing hardware fault injection device is complex and high in cost, a test result after injection is low in credibility because an existing fault model for software fault injection isinsufficiently real, and the like can be overcome.

Owner:湖南斯北图科技有限公司

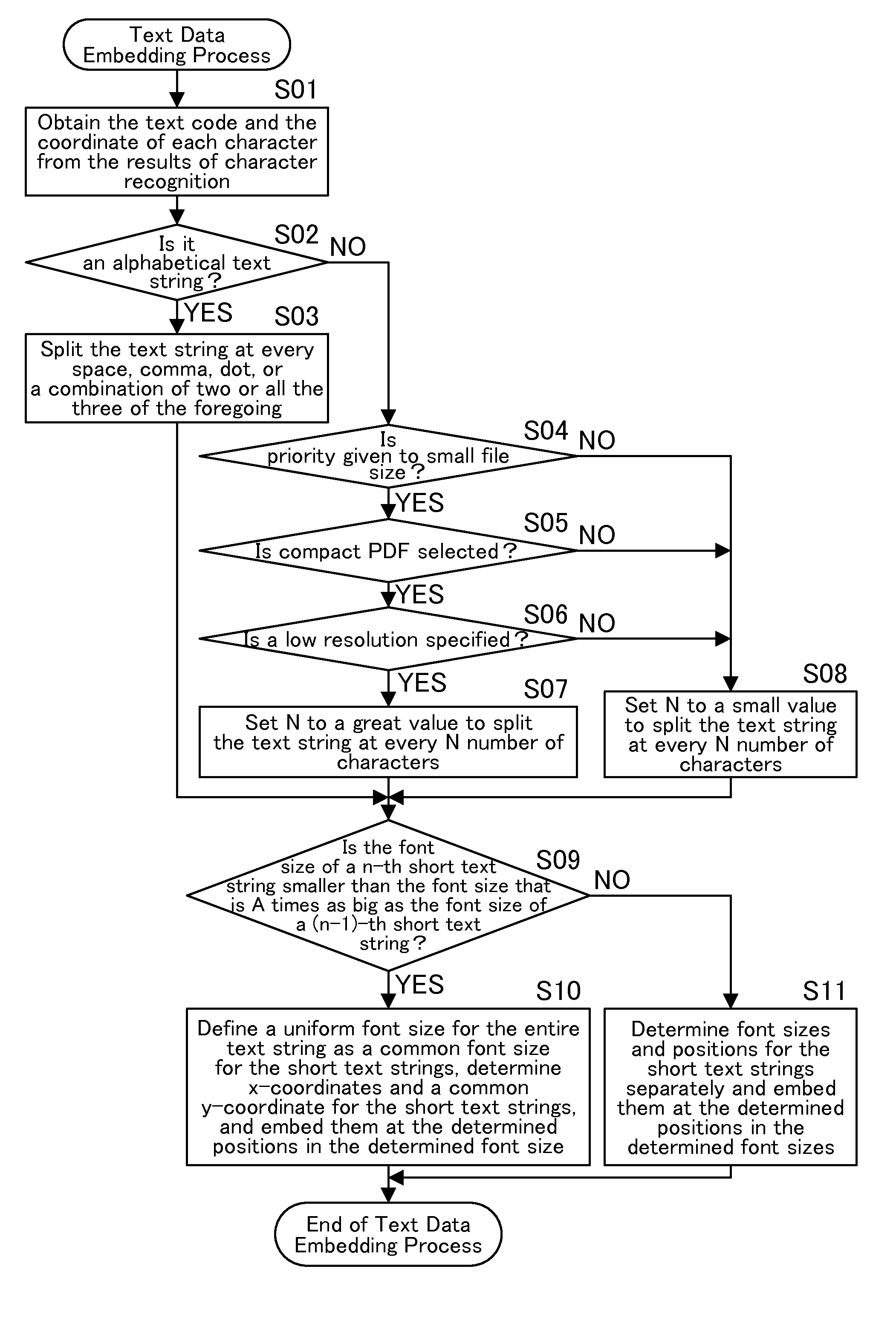

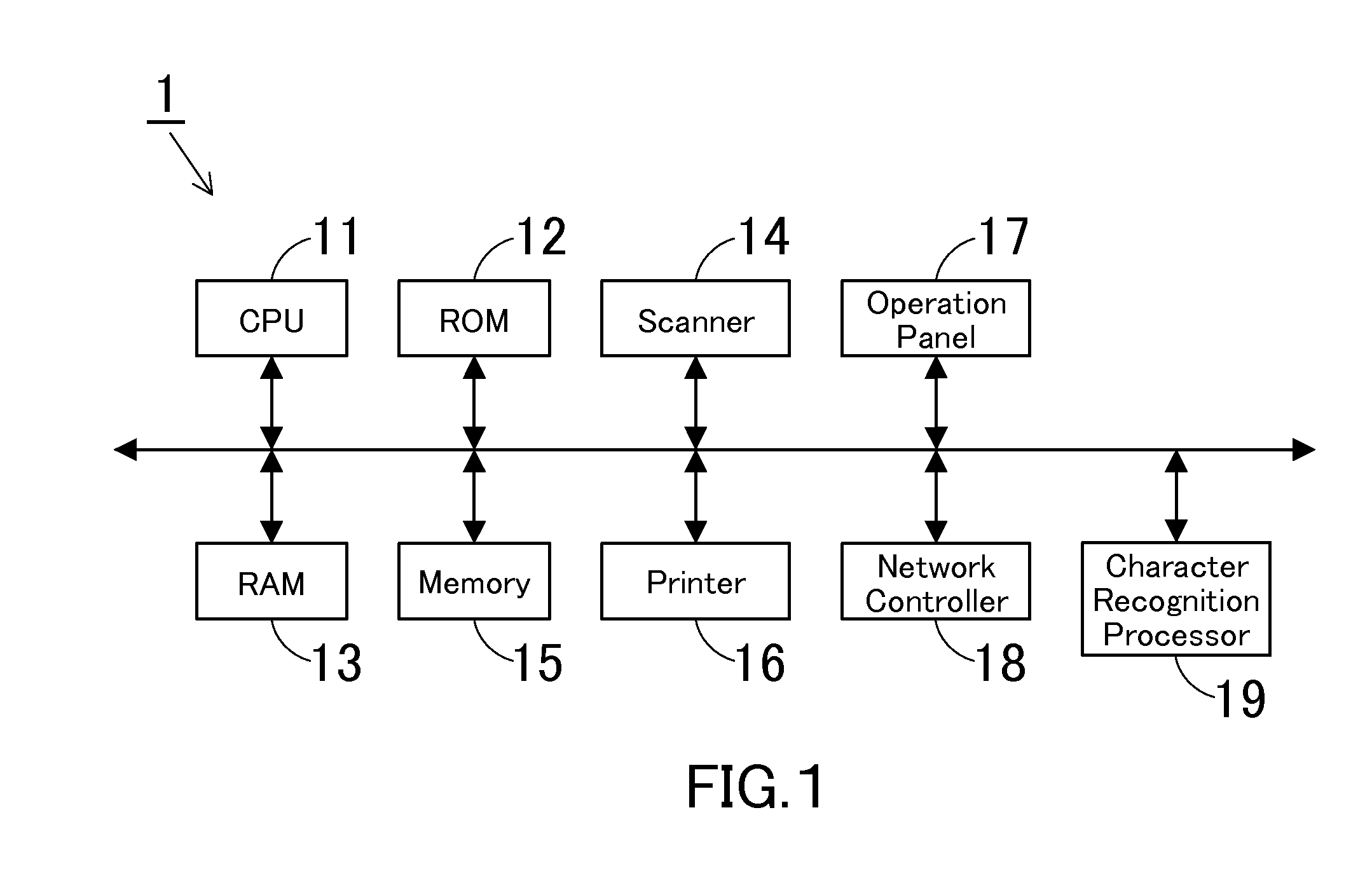

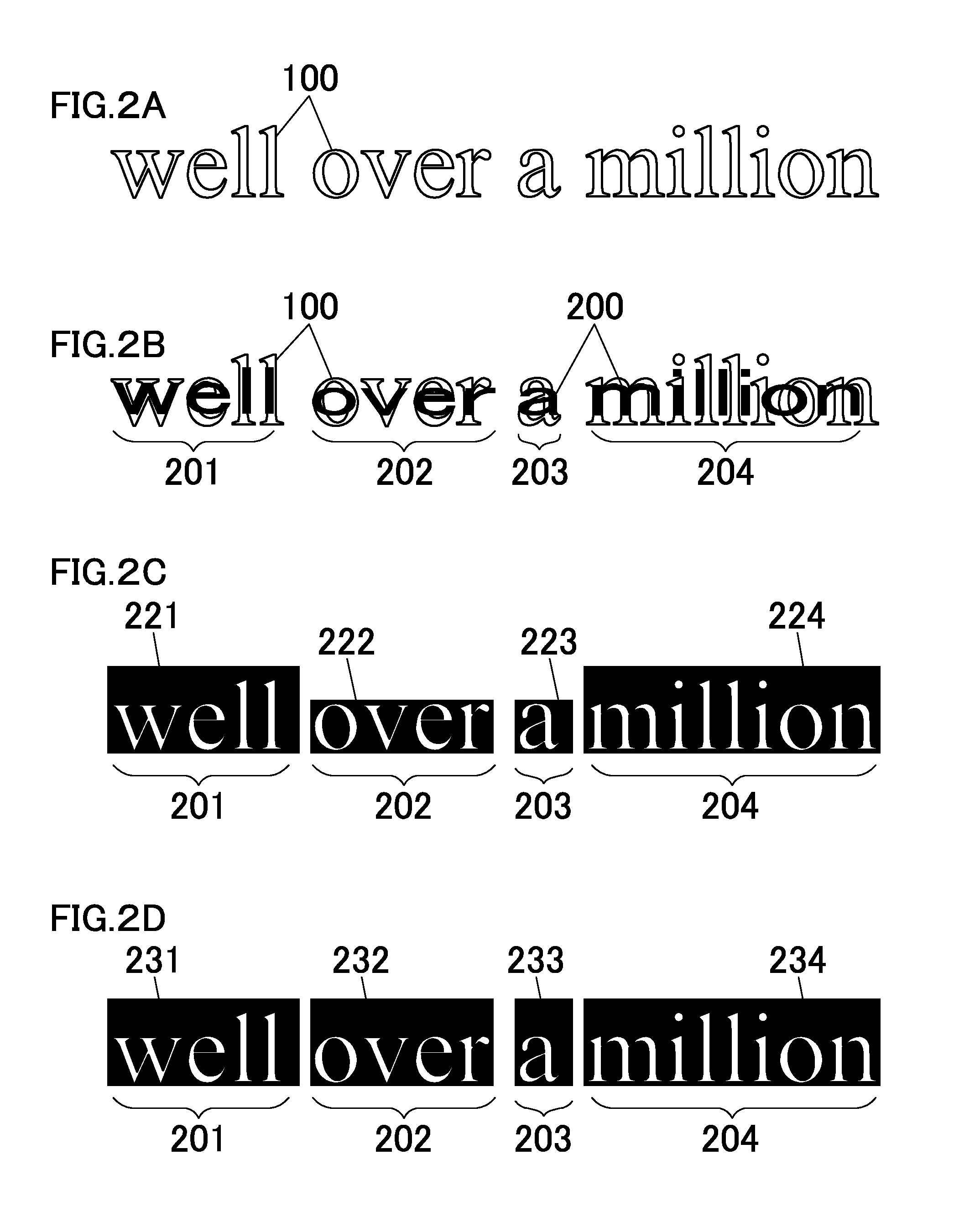

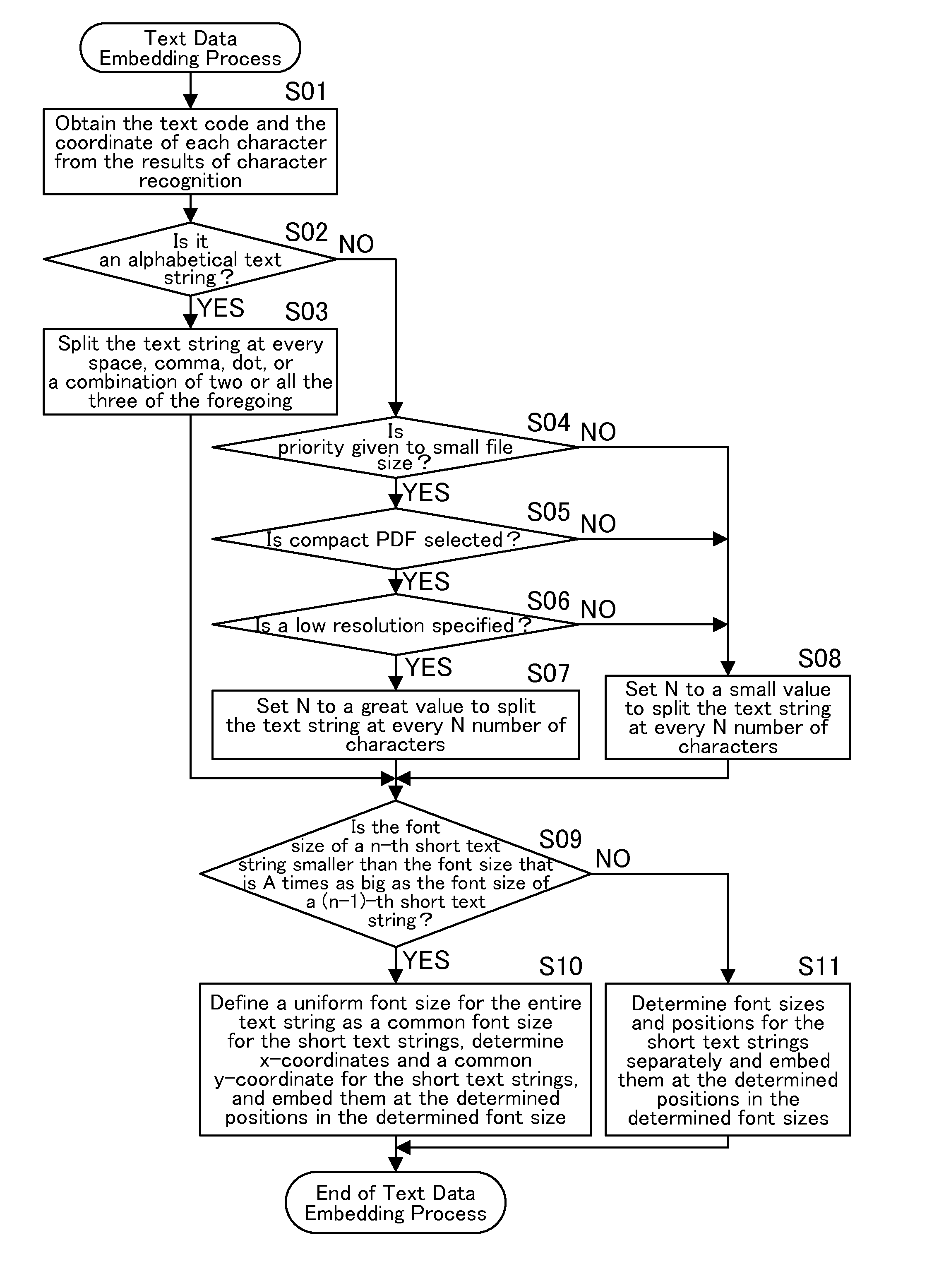

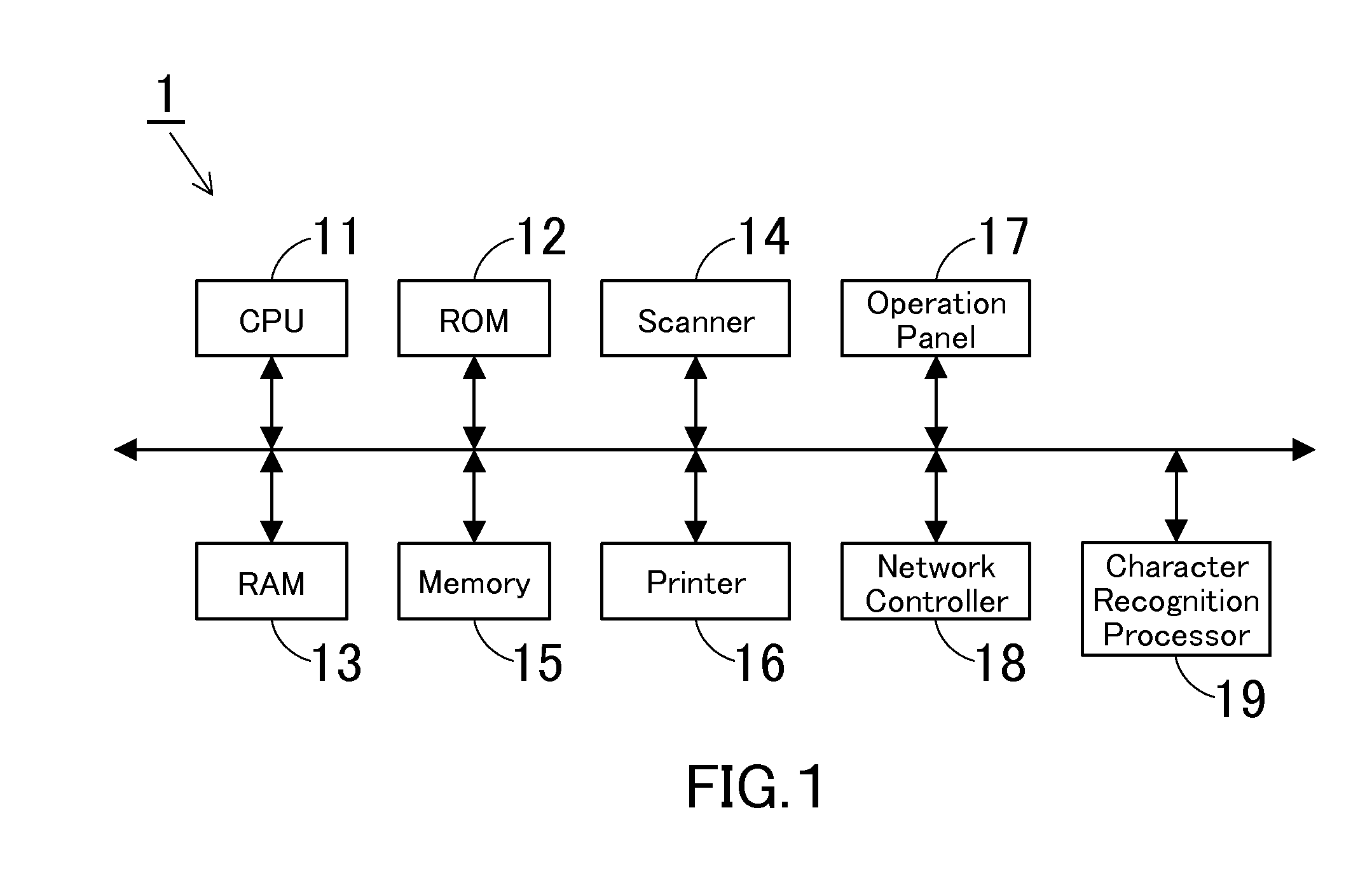

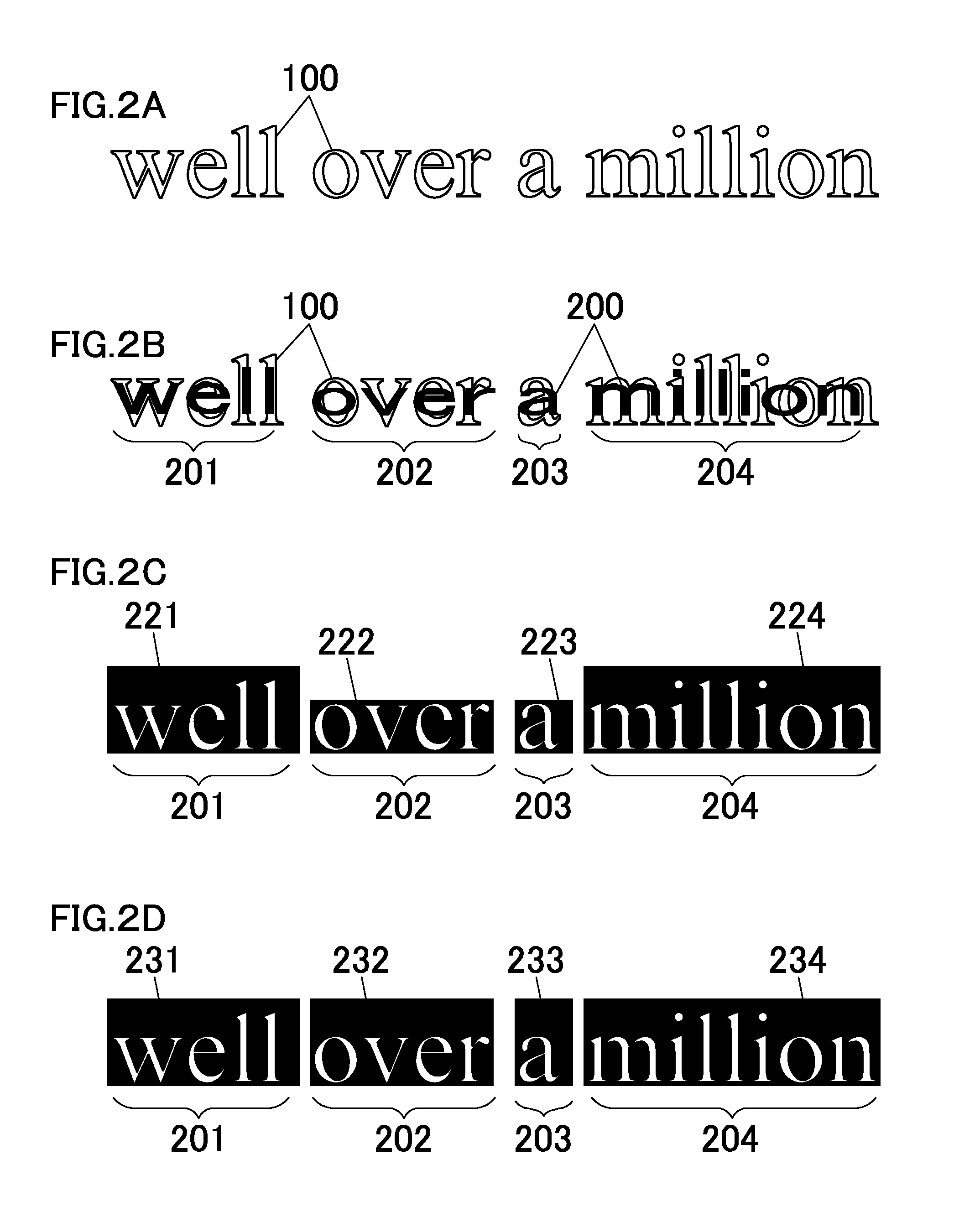

Image forming apparatus, text data embedding method, and recording medium

ActiveUS20150146220A1Digitally marking record carriersDigital computer detailsComputer graphics (images)Image formation

An image forming apparatus includes: a scanner that obtains an image file by document scanning; a character recognition processor that obtains a text string from each line of text by performing character recognition; a text string splitter that splits each the text string into a plurality of short text strings in accordance with a predetermined rule; a font size determining portion that determines a uniform font size for each the text string; a position determining portion that determines x-axis positions for the short text strings on the basis of the x-coordinates of the characters at the forefront in the respective short text strings, the short text strings each having its x-axis in the forward and backward reading directions; and an embedding portion that embeds text data of the short text strings in the image file at the respective x-axis positions in the uniform font size for the entire text string.

Owner:KONICA MINOLTA INC

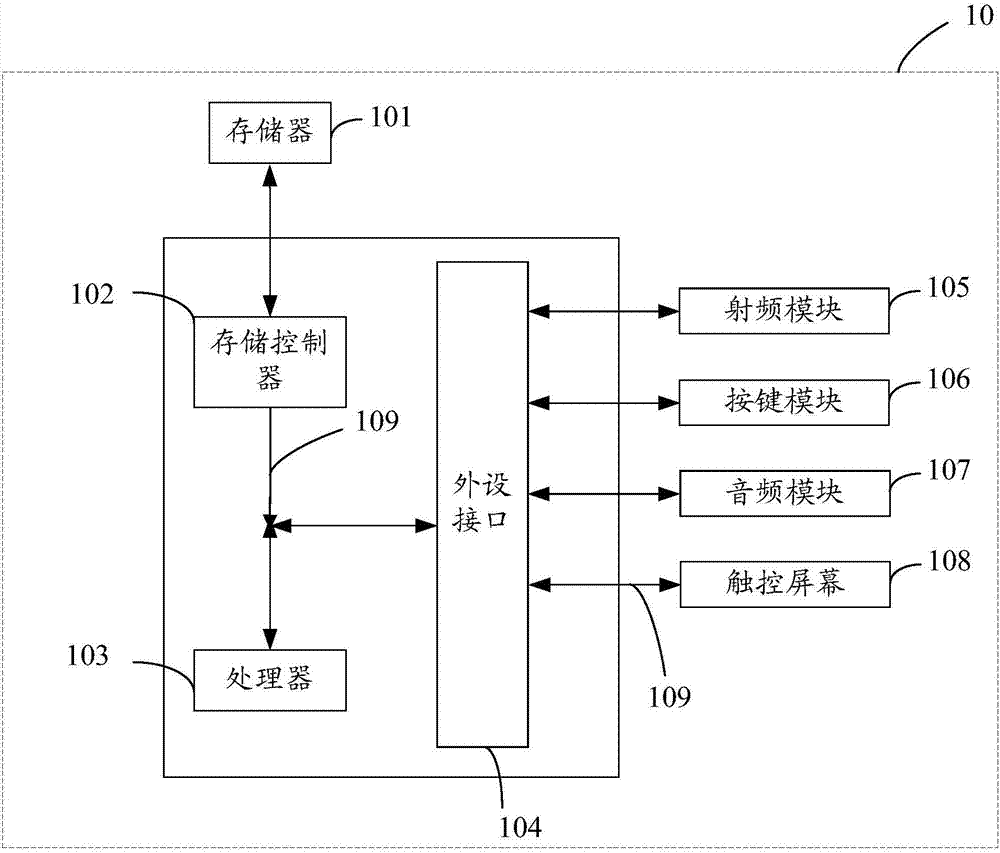

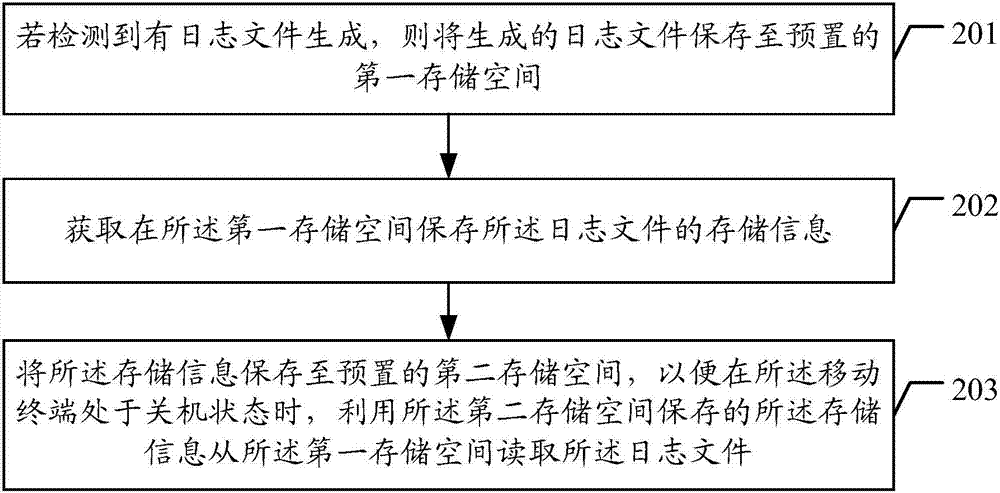

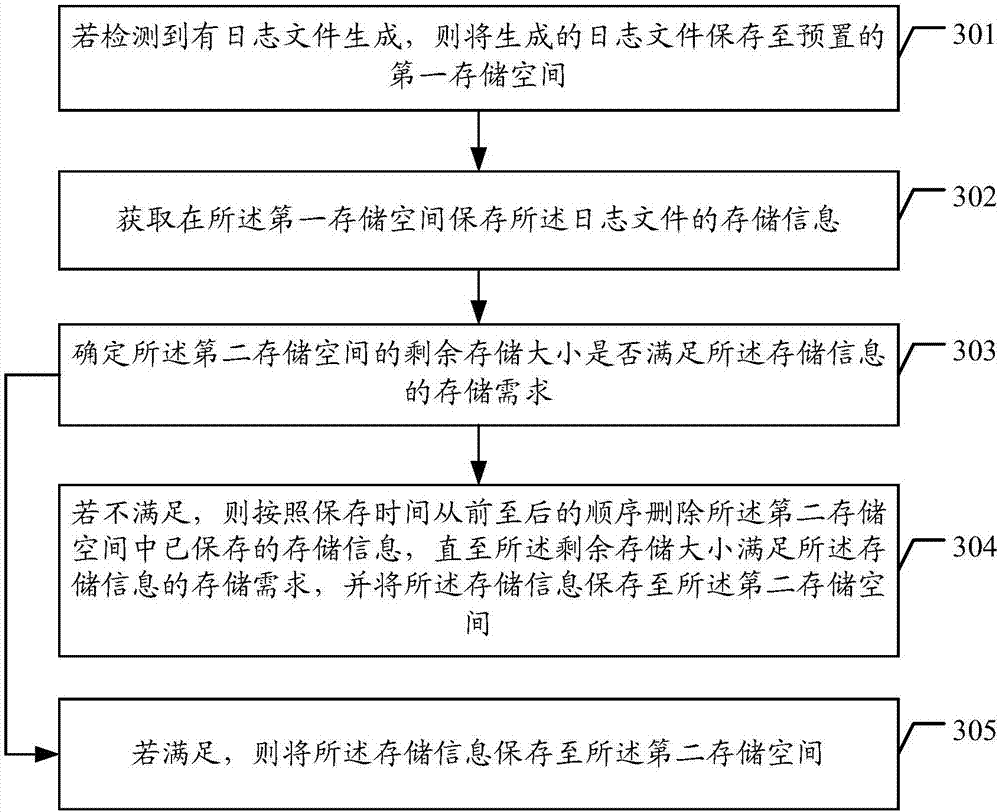

Log file reading method, apparatus and system, and log file writing method, apparatus and system

ActiveCN106951521AShorten the timeImprove reading efficiencySpecial data processing applications'Backward reading'File storage

The invention discloses a log file reading method, apparatus and system, and a log file writing method, apparatus and system. The writing method comprises the steps of storing a generated log file in a preset first storage space if it is detected that the log file is generated; and obtaining storage information of storing the log file in the first storage space, wherein the storage information is stored in a preset second storage space. The reading method comprises the steps of obtaining the storage information when the log file is stored in the first storage space from the preset second storage space after a connection with a mobile terminal in a power-off state is performed; and reading the log file by utilizing the storage information. By setting the second storage space used for storing the storage information during storage of the log file in the mobile terminal, when the mobile terminal is in the power-off state, the log file can be read by utilizing the storage information stored in the second storage space without backward reading of a whole User Data partition, so that the log file reading time is effectively shortened and the reading efficiency is improved.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

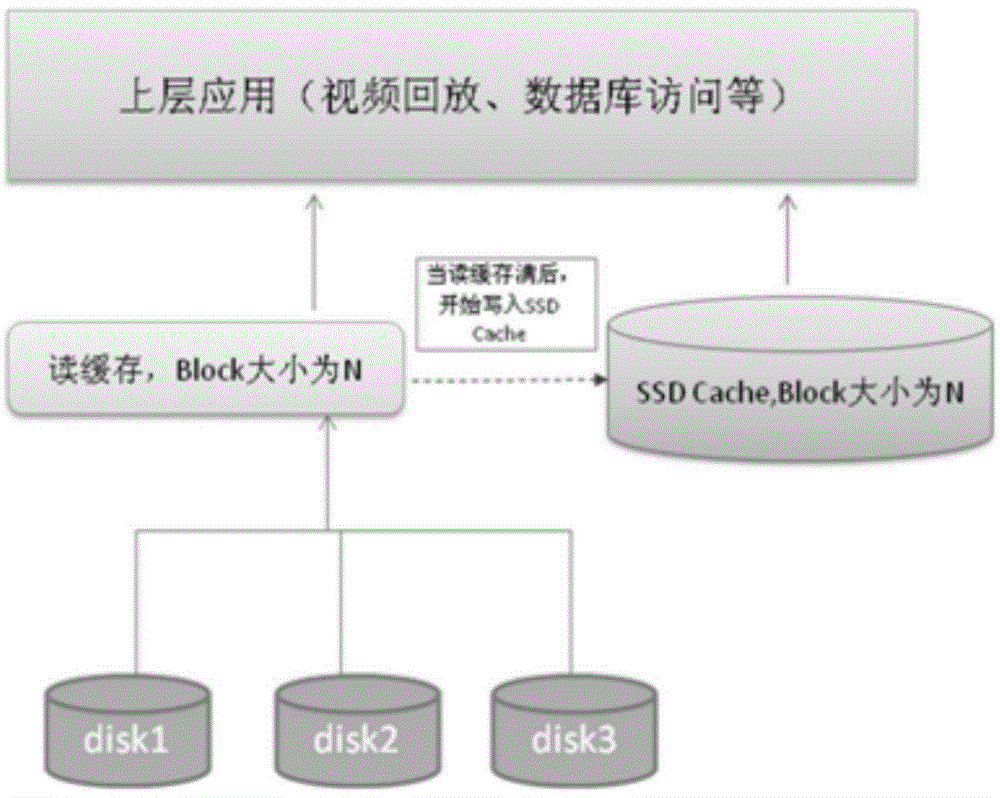

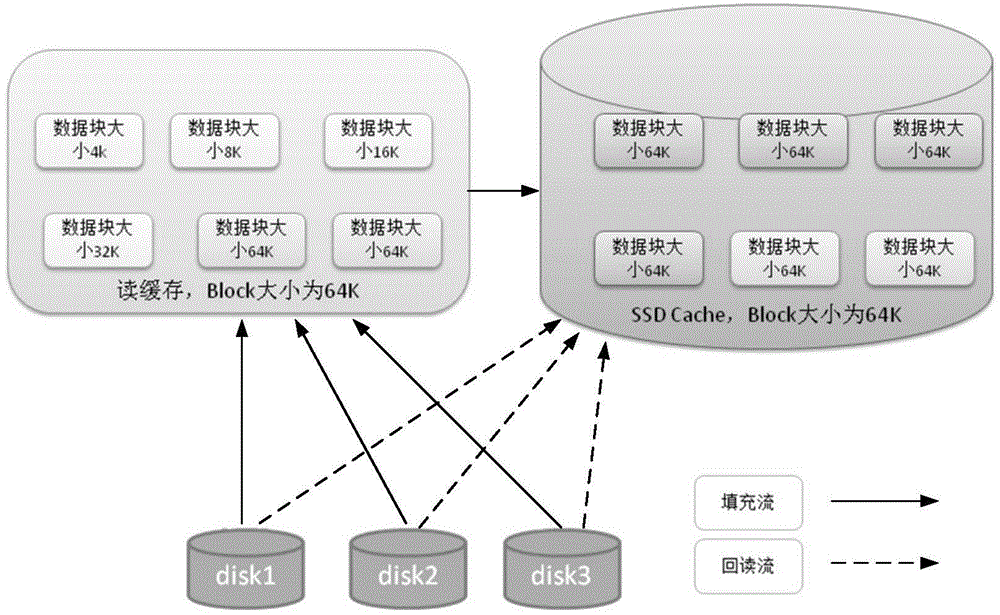

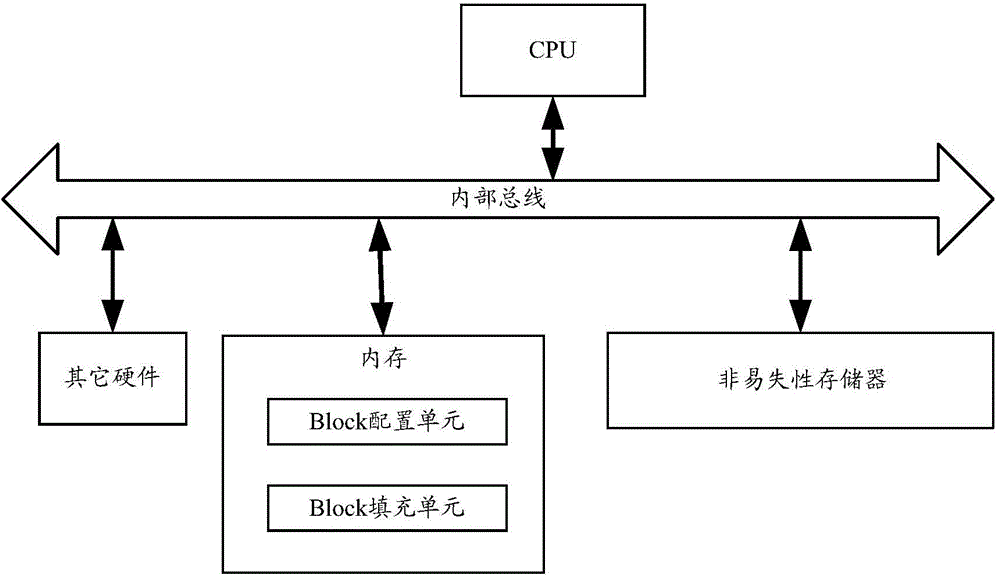

SSD Cache filling method and device

ActiveCN104133642AReduce the number of readbacksReduce random command requestsInput/output to record carriersMemory adressing/allocation/relocationParallel computing'Backward reading'

The invention provides an SSD Cache filling method and device which can be applied to storage equipment. The method comprises the steps of dividing an SSD Cache into a plurality of Blocks with different sizes; according to the size of a data block to be filled, selecting the Block with the most similar size as the data block to be filled for filling the data block to be filled, wherein the size of the data block to be filled is smaller than or equal to the size of the selected Block. According to the SSD Cache filling method and device, the size of the Block needed for filling is selected according to the magnitude of a service command, the backward reading frequency of a magnetic disk is reduced to the greatest extent, and the SSD Cache filling speed is improved.

Owner:ZHEJIANG UNIVIEW TECH CO LTD

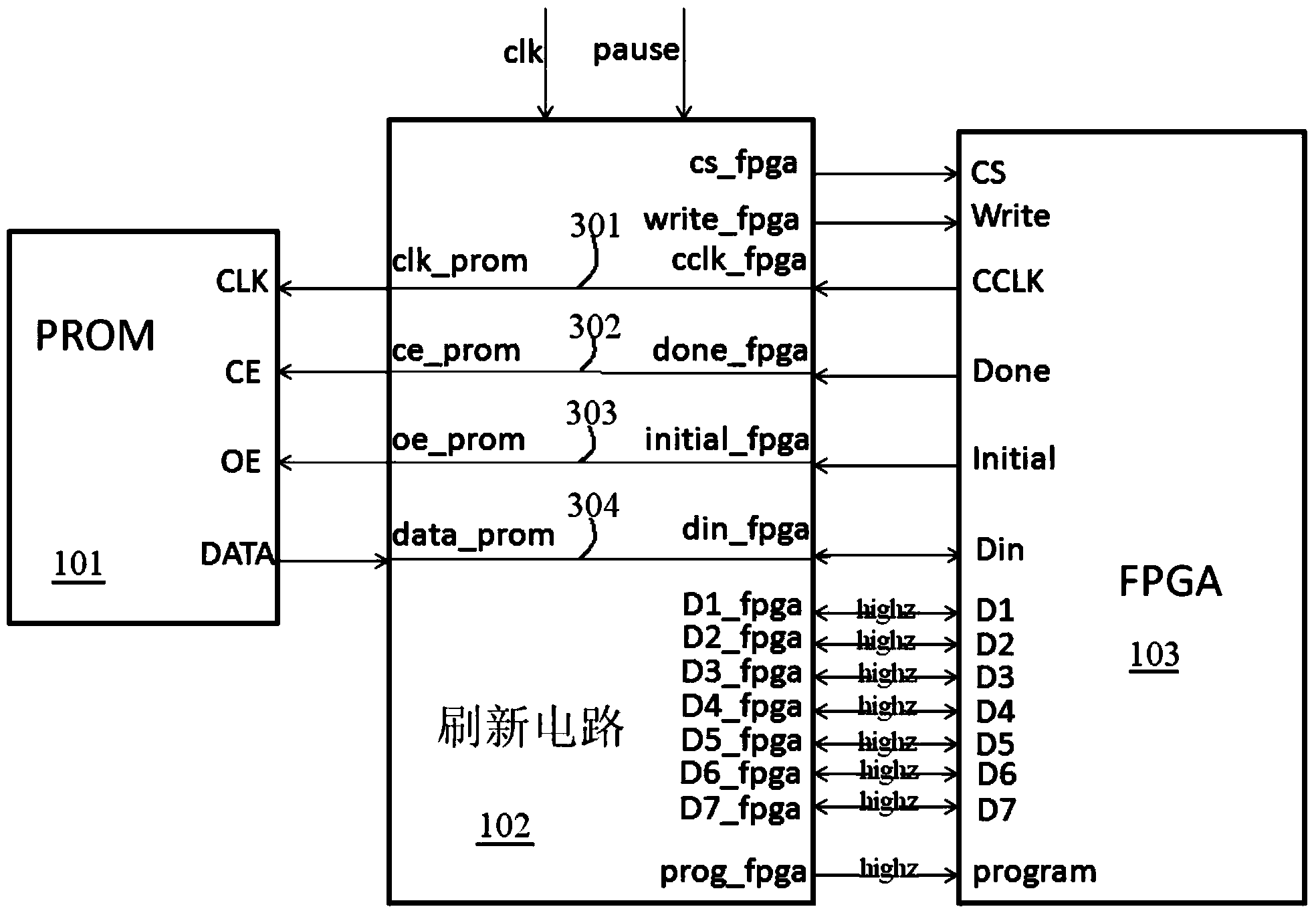

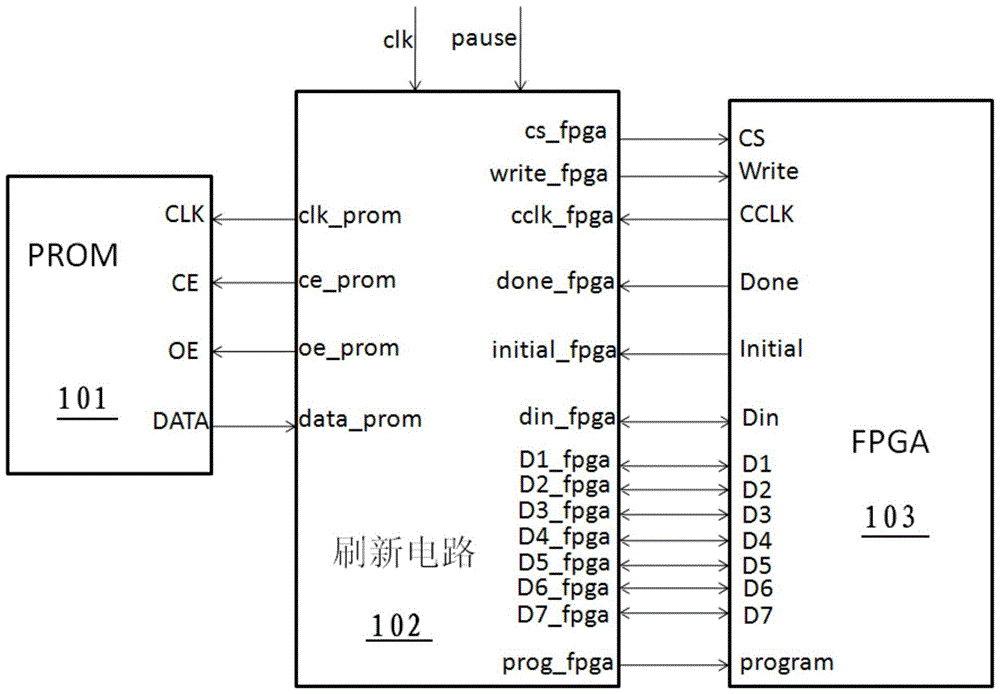

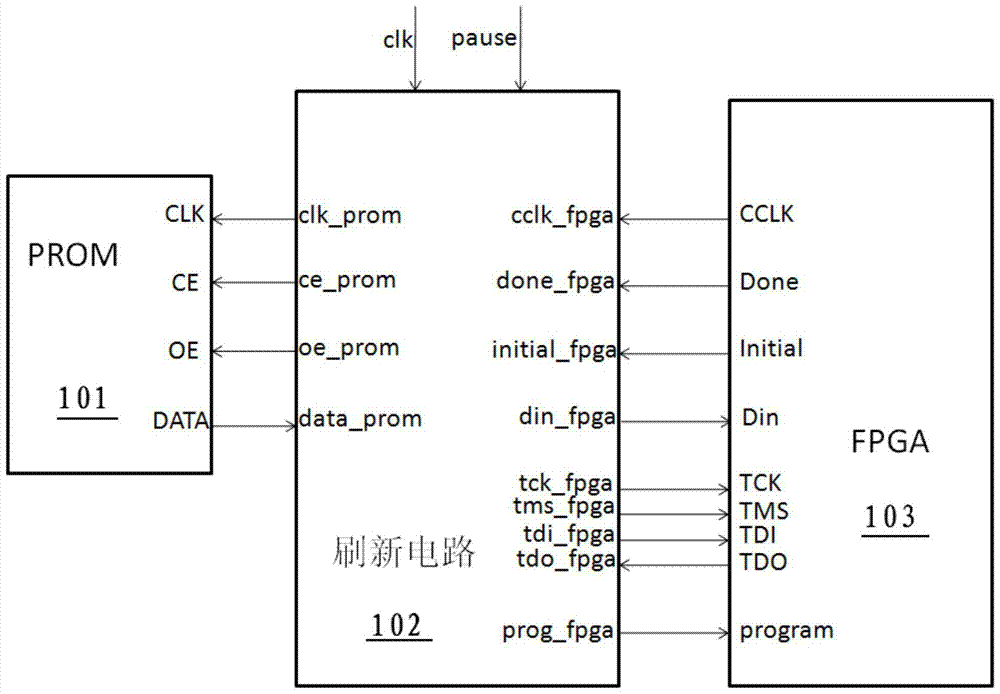

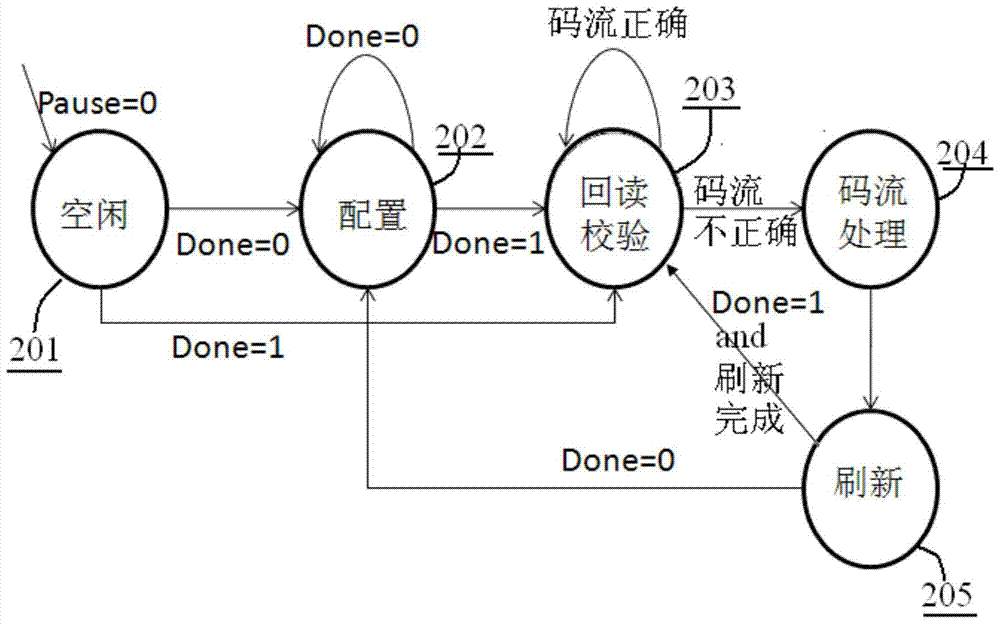

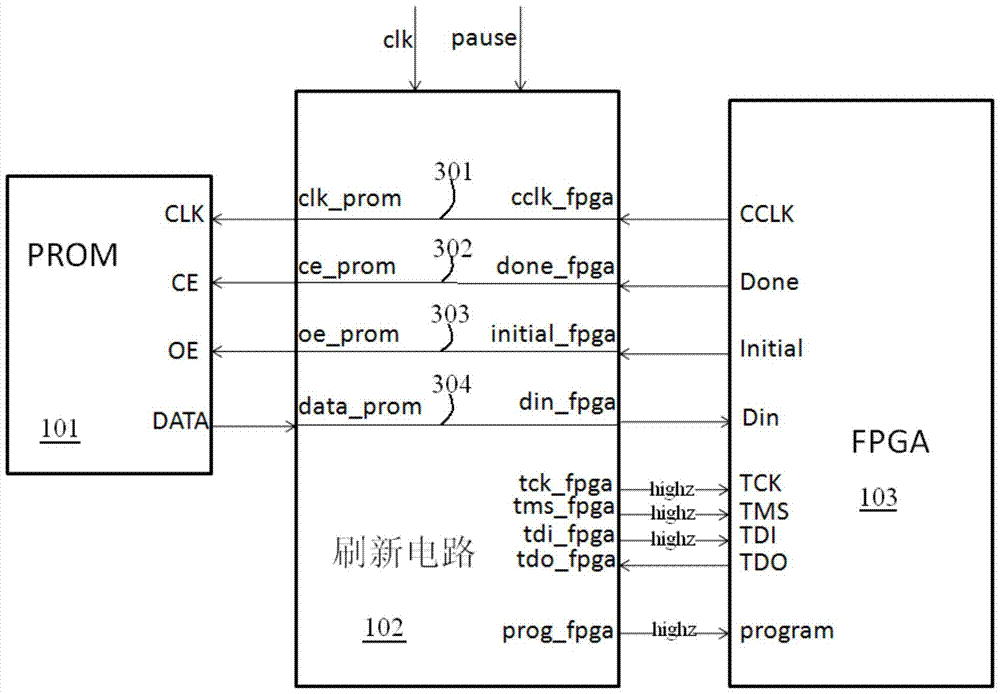

Astronavigation FPGA universal refresh circuit based on JTAG interface and achieving method thereof

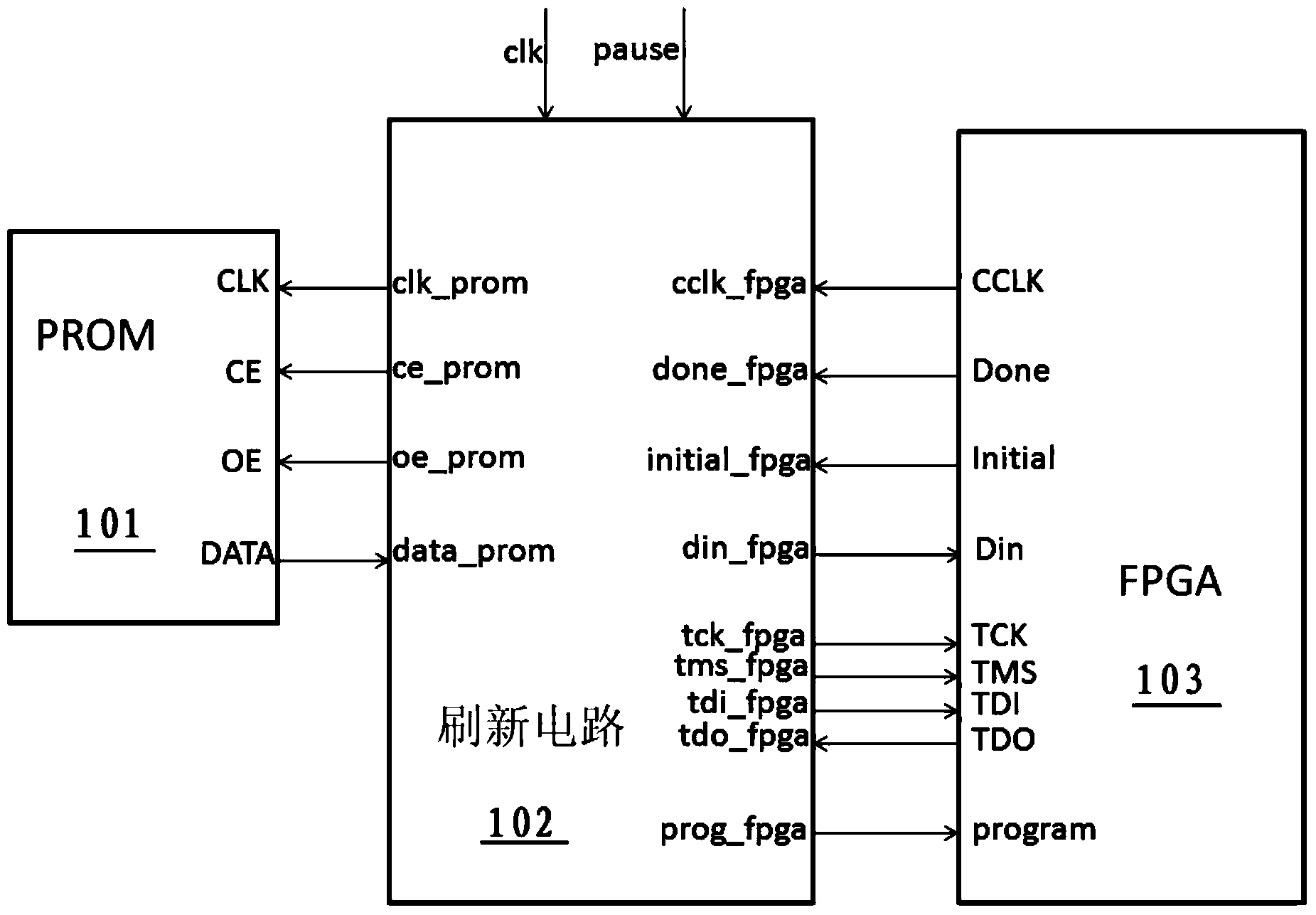

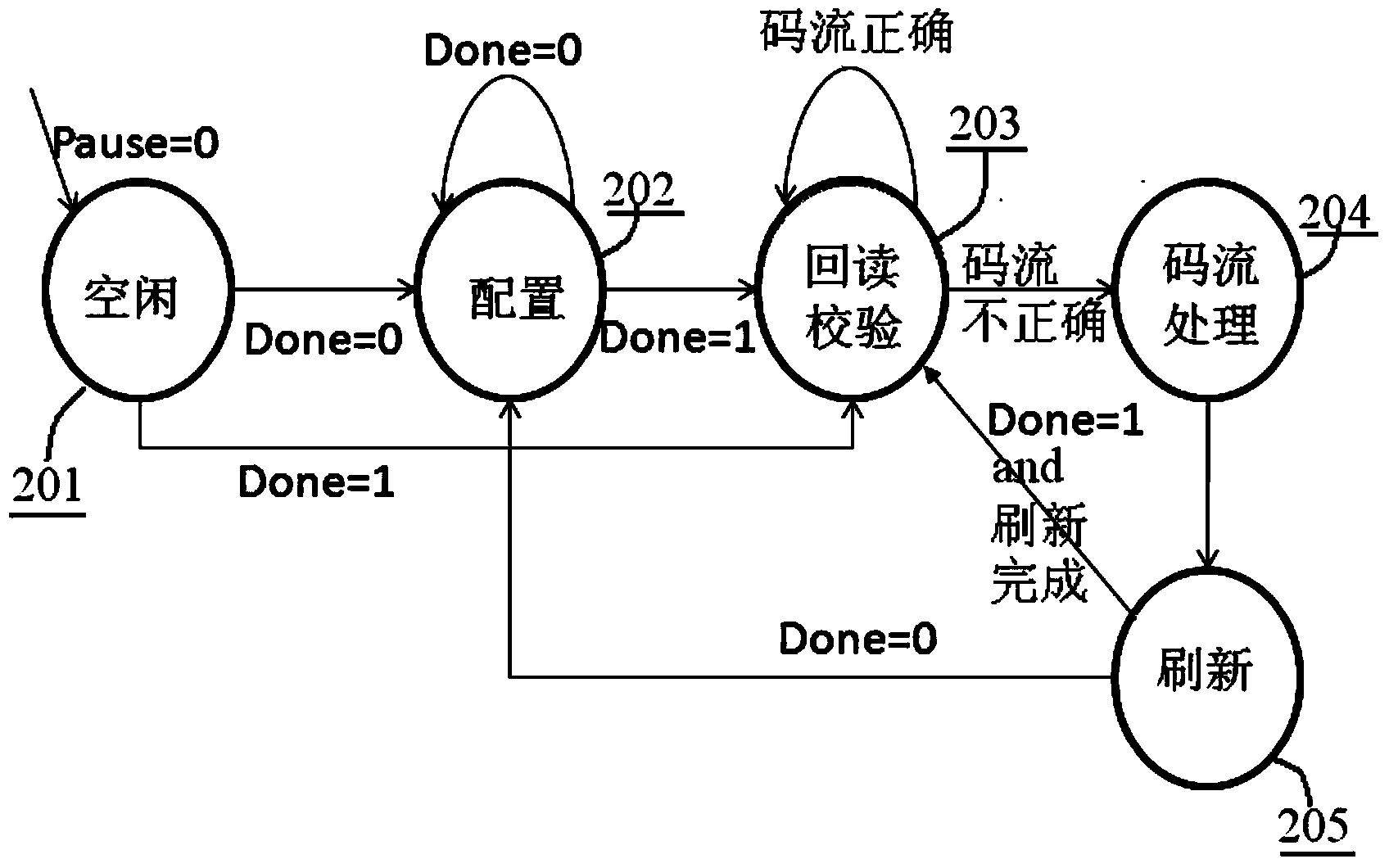

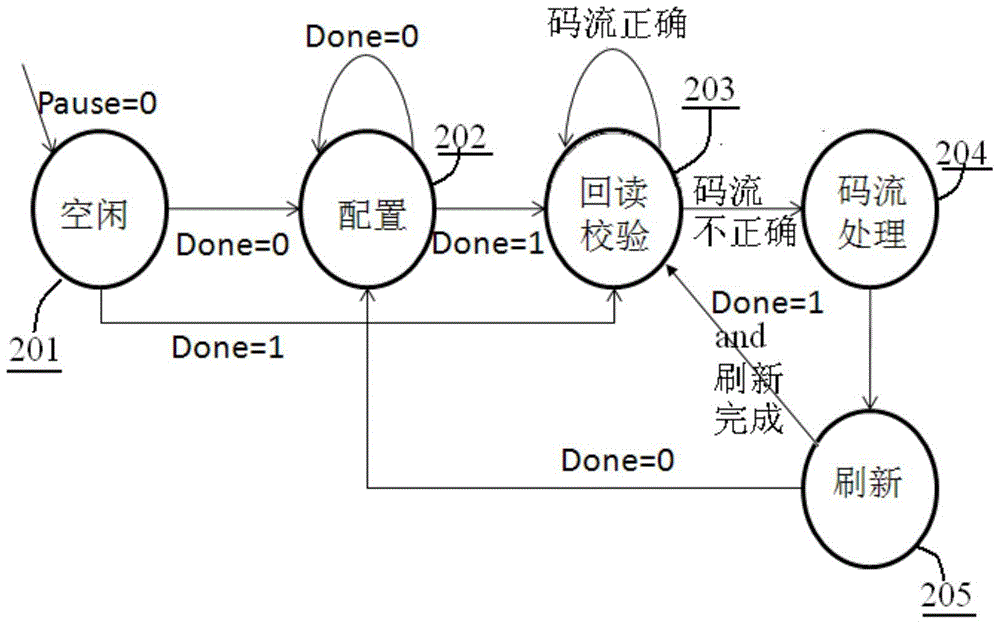

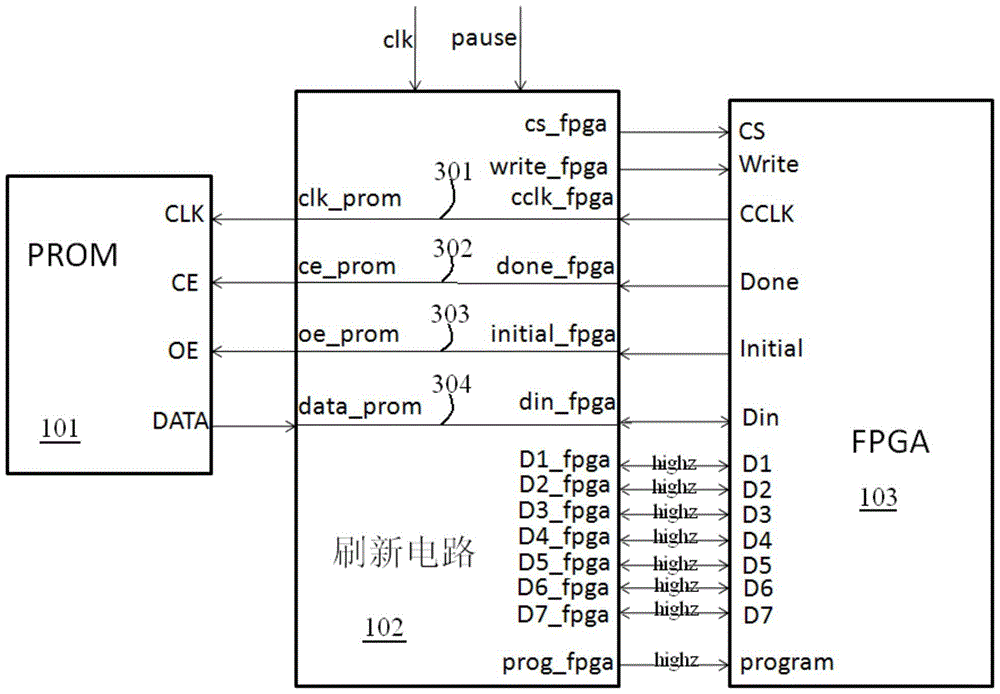

ActiveCN103840823AImprove the reliability of space applicationsReduce adverse effectsLogic circuits using elementary logic circuit componentsData sourceJoint Test Action Group

The invention relates to an astronavigation FPGA universal refresh circuit based on a JTAG interface. The refresh circuit is provided with seven input pins and eight output pins, and the input pins and the output pins are connected with pins of a PROM and pins of an FPGA. The SRAM-type FPGA is subjected to backward reading operation through the JTAG interface, the type of the FPGA is determined, and backward read data are checked; if errors happen, a code stream is read from a correct data source, effective parts are intercepted from the code stream, the effective code stream is written into an inner configuration bit of the FPGA again through the JTAG interface, and accordingly refreshing of a configuration memory is completed. Through the refresh circuit, single event upset of the astronavigation FPGA can be timely detected and corrected, functional faults caused by single event upset of the astronavigation FPGA are eliminated, and astronavigation FPGA space application reliability is improved.

Owner:BEIJING MXTRONICS CORP +1

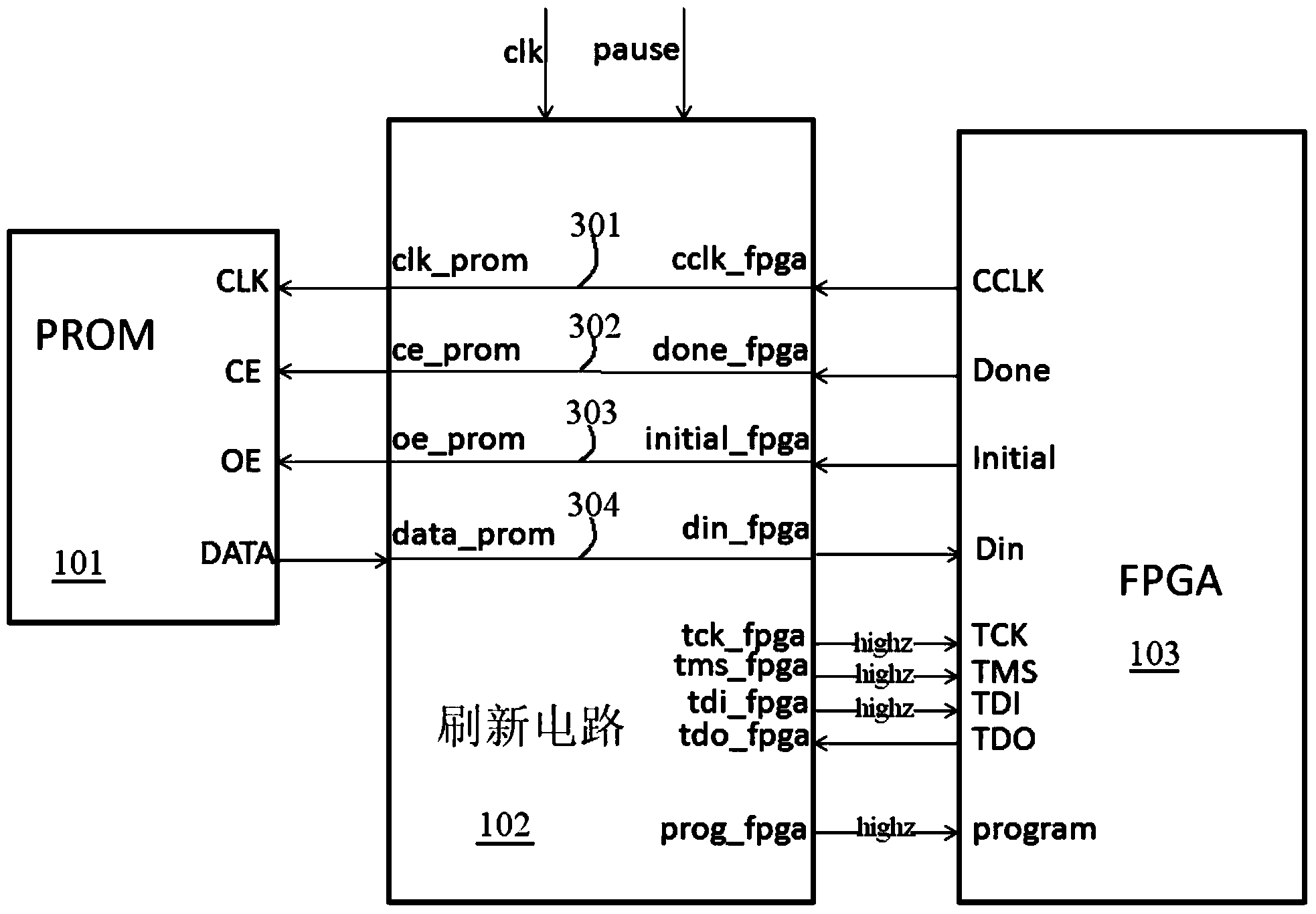

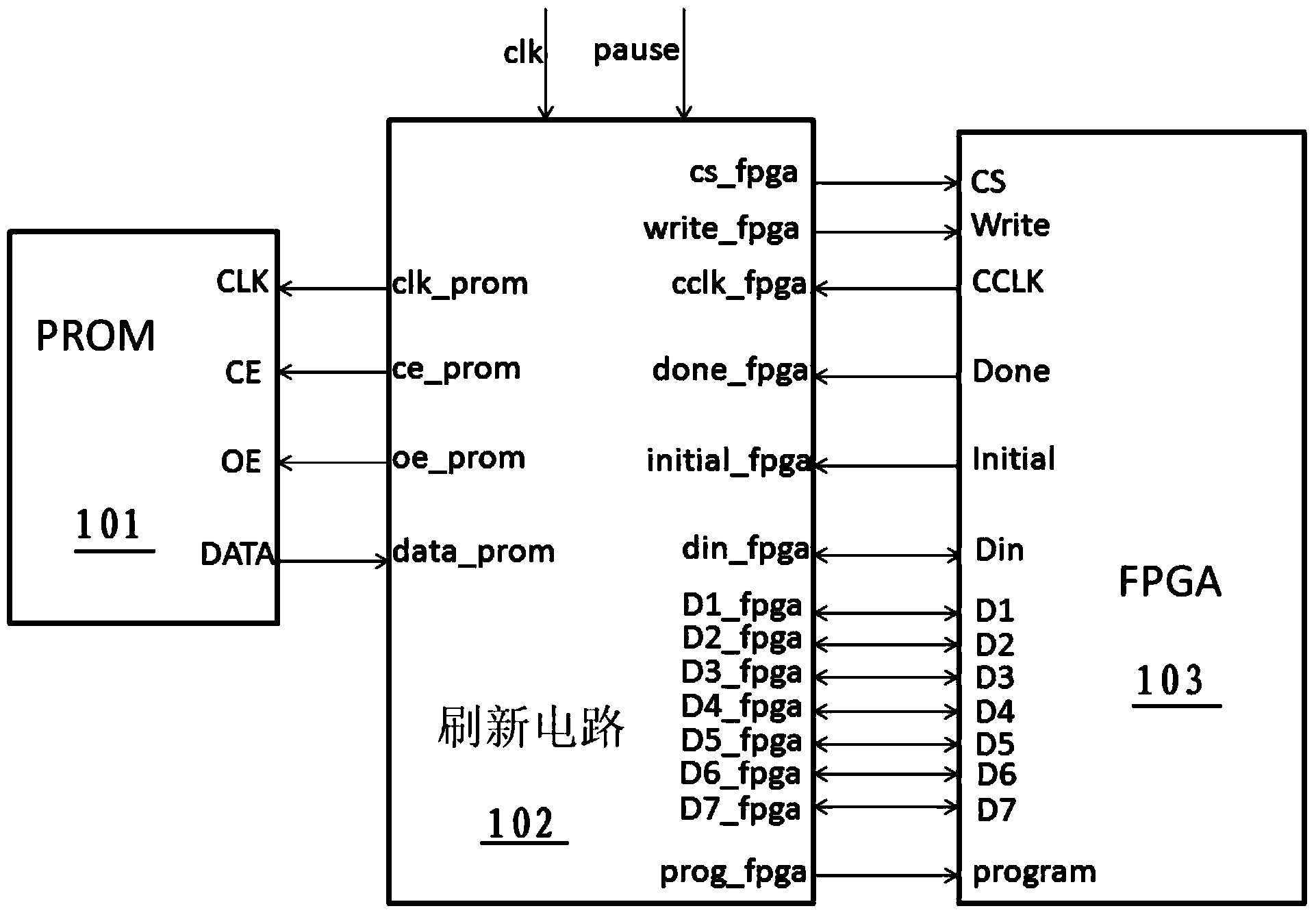

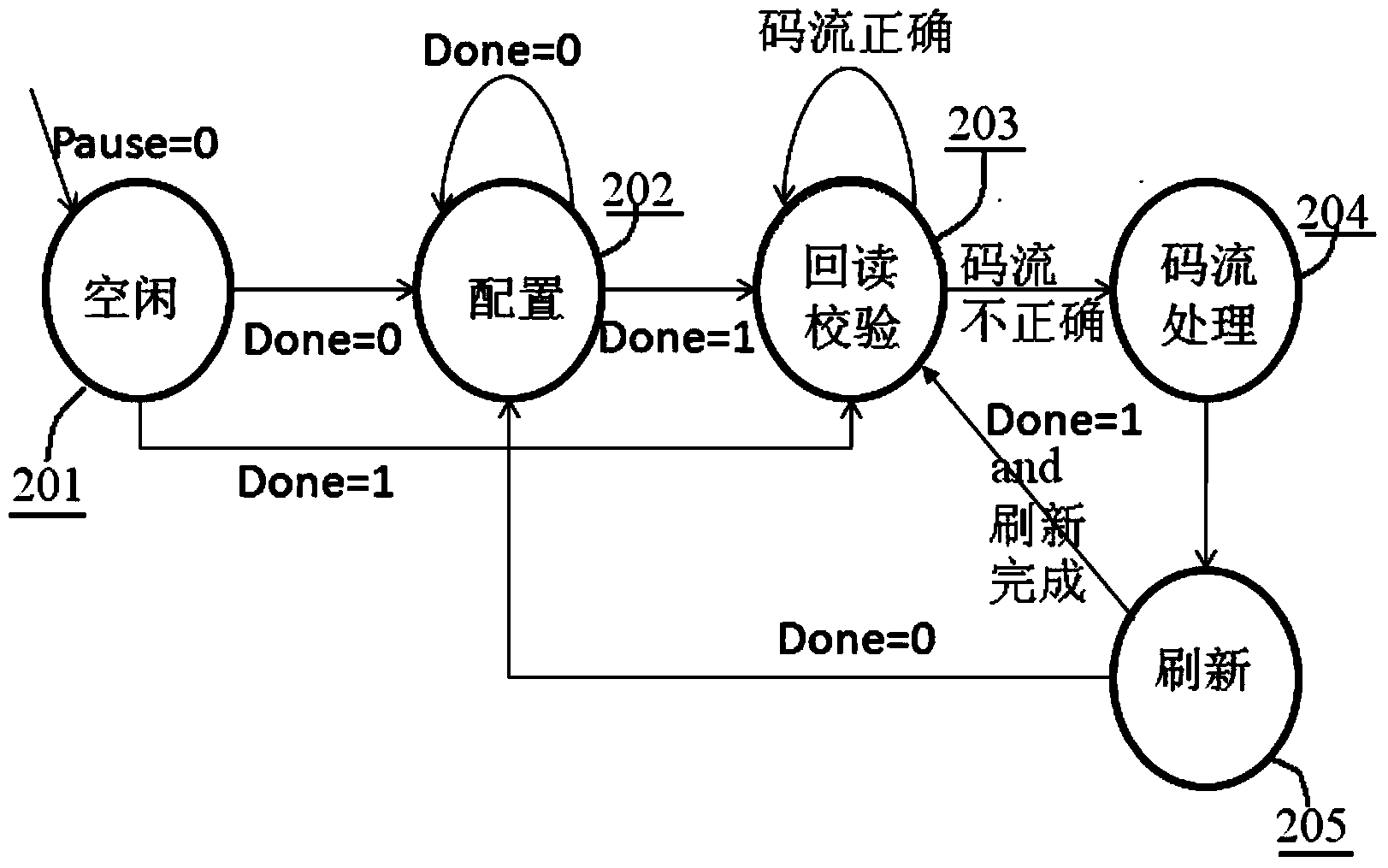

Astronavigation FPGA universal refresh circuit based on SELECTMAP and achieving method thereof

ActiveCN103840822AImprove the reliability of space applicationsReduce adverse effectsLogic circuits using elementary logic circuit componentsCircuit design'Backward reading'

The invention relates to an astronavigation FPGA universal refresh circuit based on SELECTMAP. The refresh circuit is provided with six input pins, six output pins and eight double-direction pins, and the input pins, the output pins and the double-direction pins are connected with pins of a PROM and pins of an FPGA. The SRAM-type FPGA is subjected to backward reading operation through SELECTMAP, the type of the FPGA is determined, and backward read data are checked; if errors happen, a code stream is read from a correct data source, effective parts are intercepted from the code stream, the effective code stream is written into an inner configuration bit of the FPGA again through SELECTMAP, and accordingly refreshing of a configuration memory is completed. Through the refresh circuit, single event upset of the astronavigation FPGA can be timely detected and corrected, functional faults caused by single event upset of the astronavigation FPGA are eliminated, and astronavigation FPGA space application reliability is improved.

Owner:BEIJING MXTRONICS CORP +1

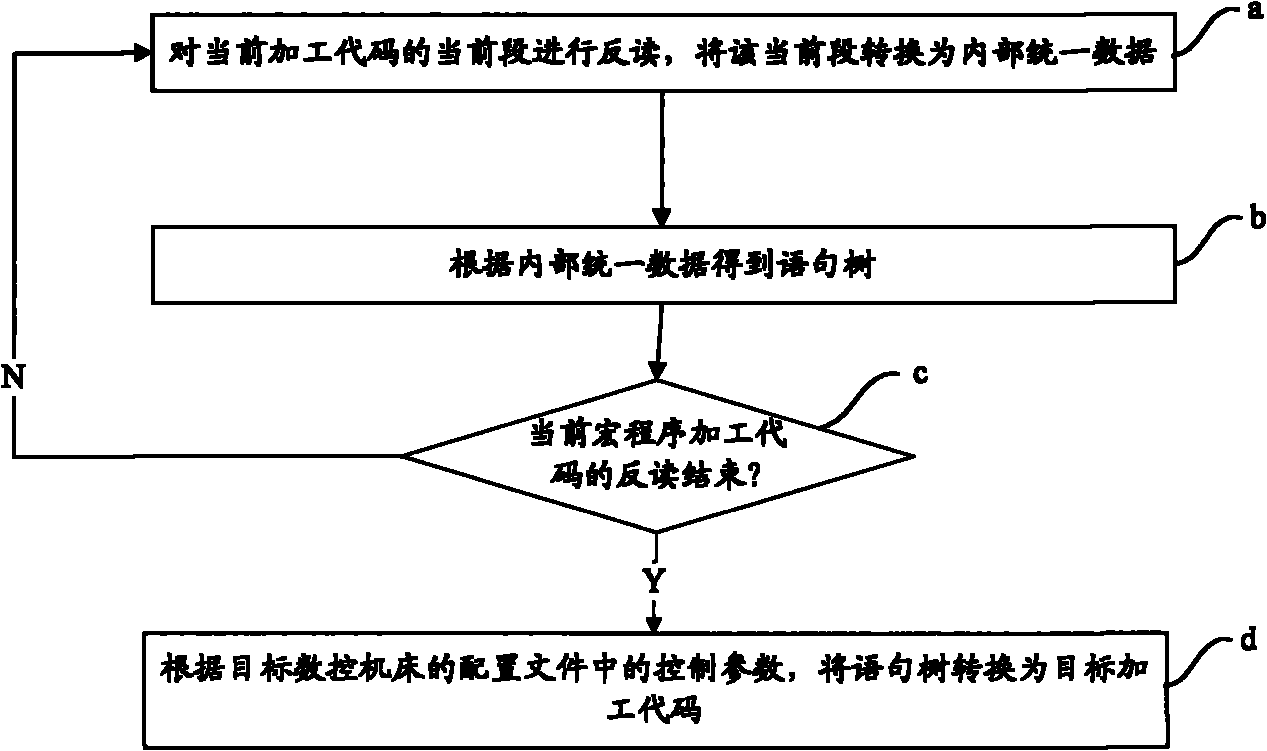

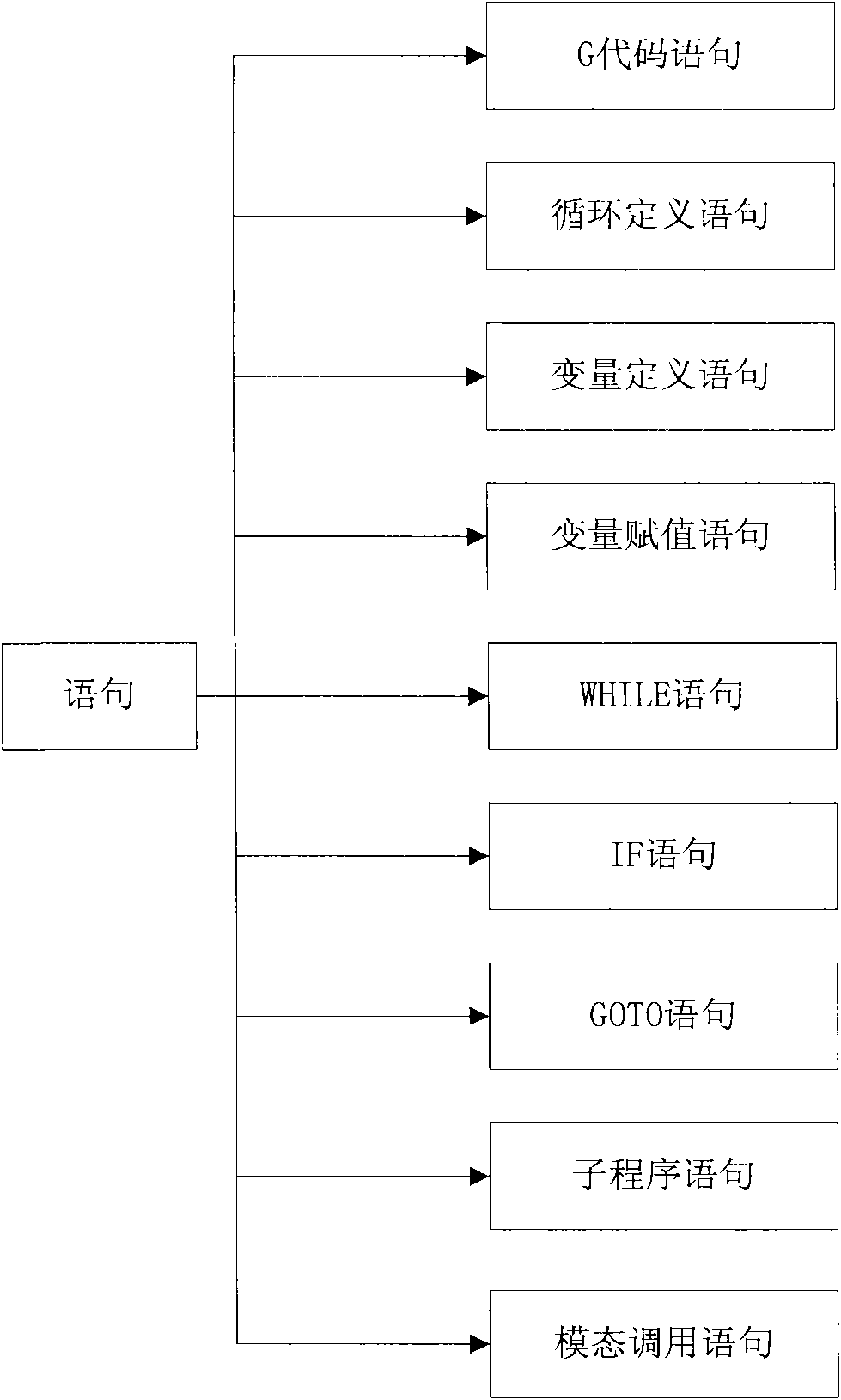

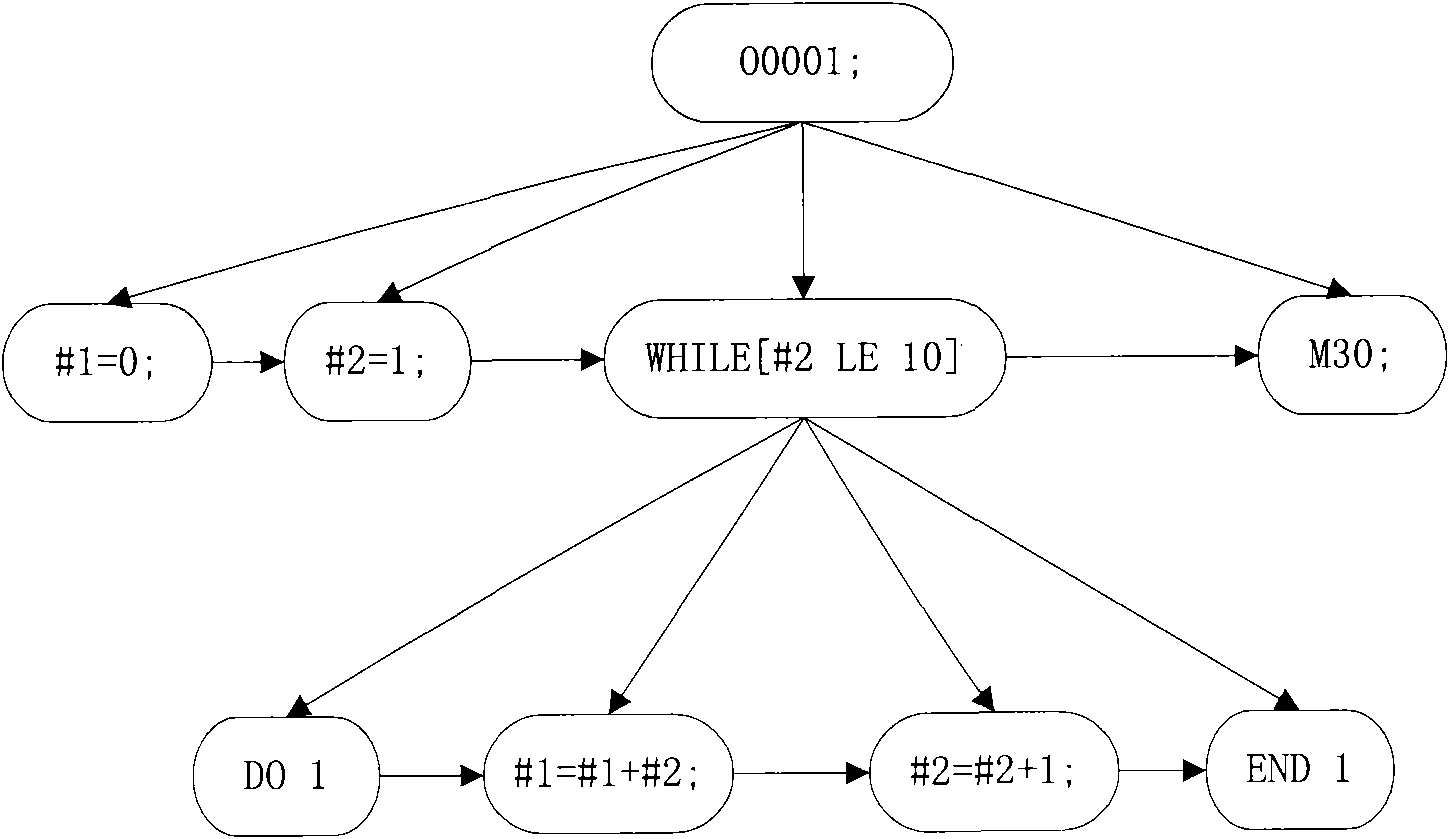

Method and device for converting universal code based on macroprogram

InactiveCN102081378AAvoid mistakesShorten the timeProgramme controlComputer controlNumerical controlComputer architecture

The invention discloses a method and a device for converting a universal code based on a macroprogram. The method comprises the following steps of: a, reading the current section of the current machining code backward, and converting the current section into internal unified data; b, acquiring a statement tree according to the internal unified data; c, judging whether the backward reading of the current macroprogram machining code is finished or not, if so, executing the step d, otherwise, executing the step a; and d, converting the statement tree into a target machining code according to a control parameter in a configuration file of a target numerical control machine. By the method and the device, code conversion time is saved, efficiency is improved, errors which easily occur in manual code conversion are avoided, and the qualification rate of a product is improved.

Owner:CAXA TECH

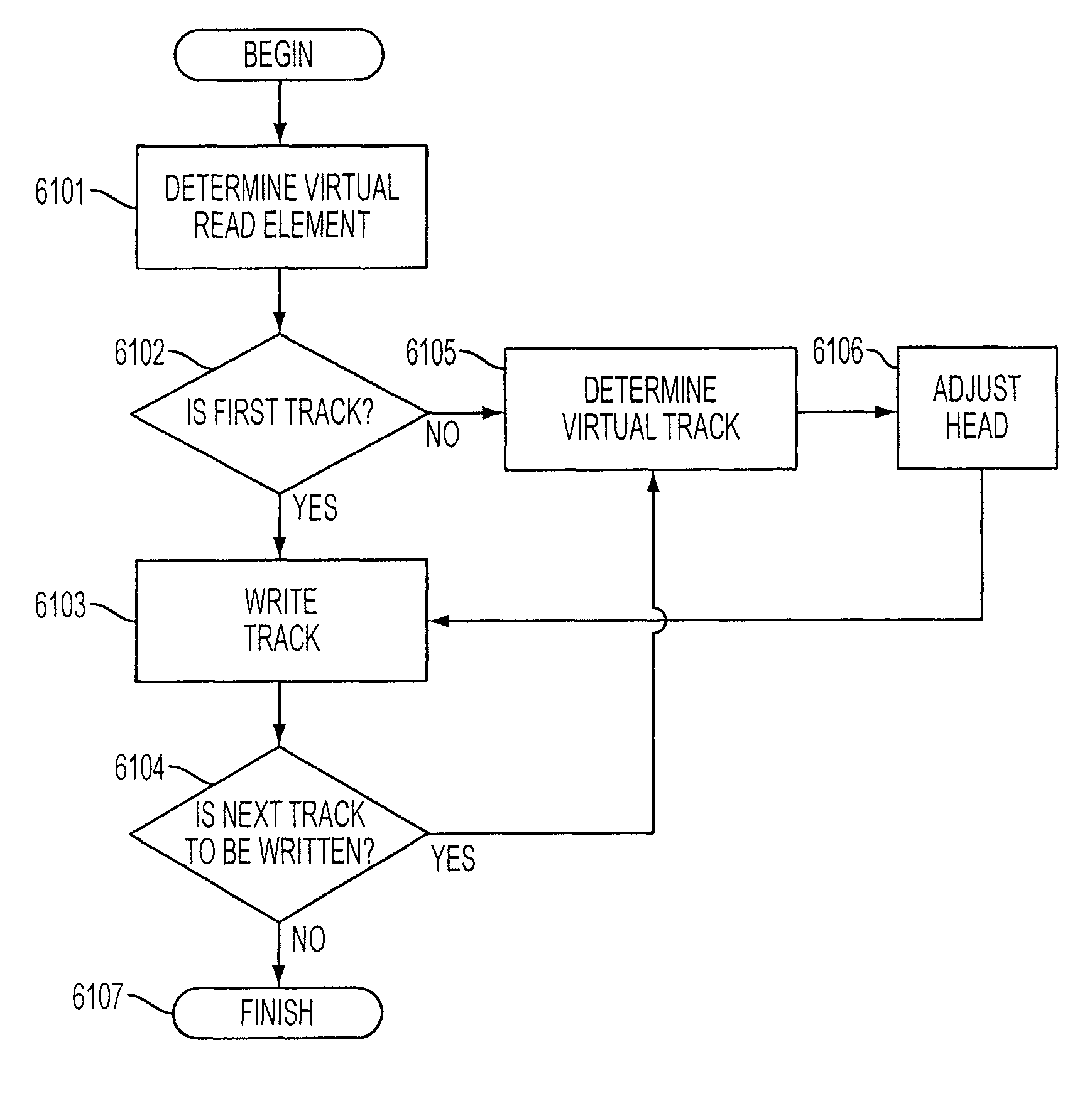

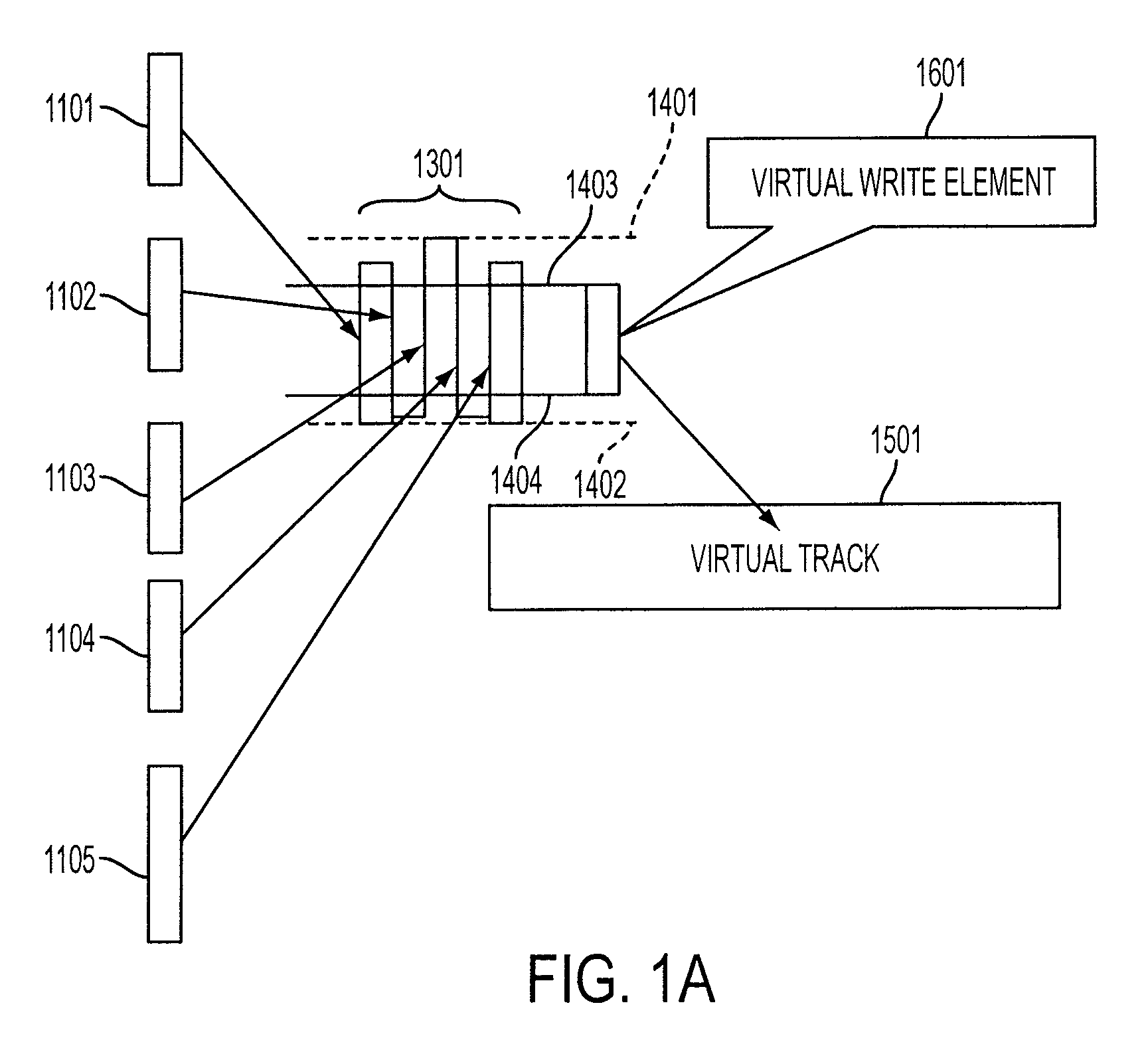

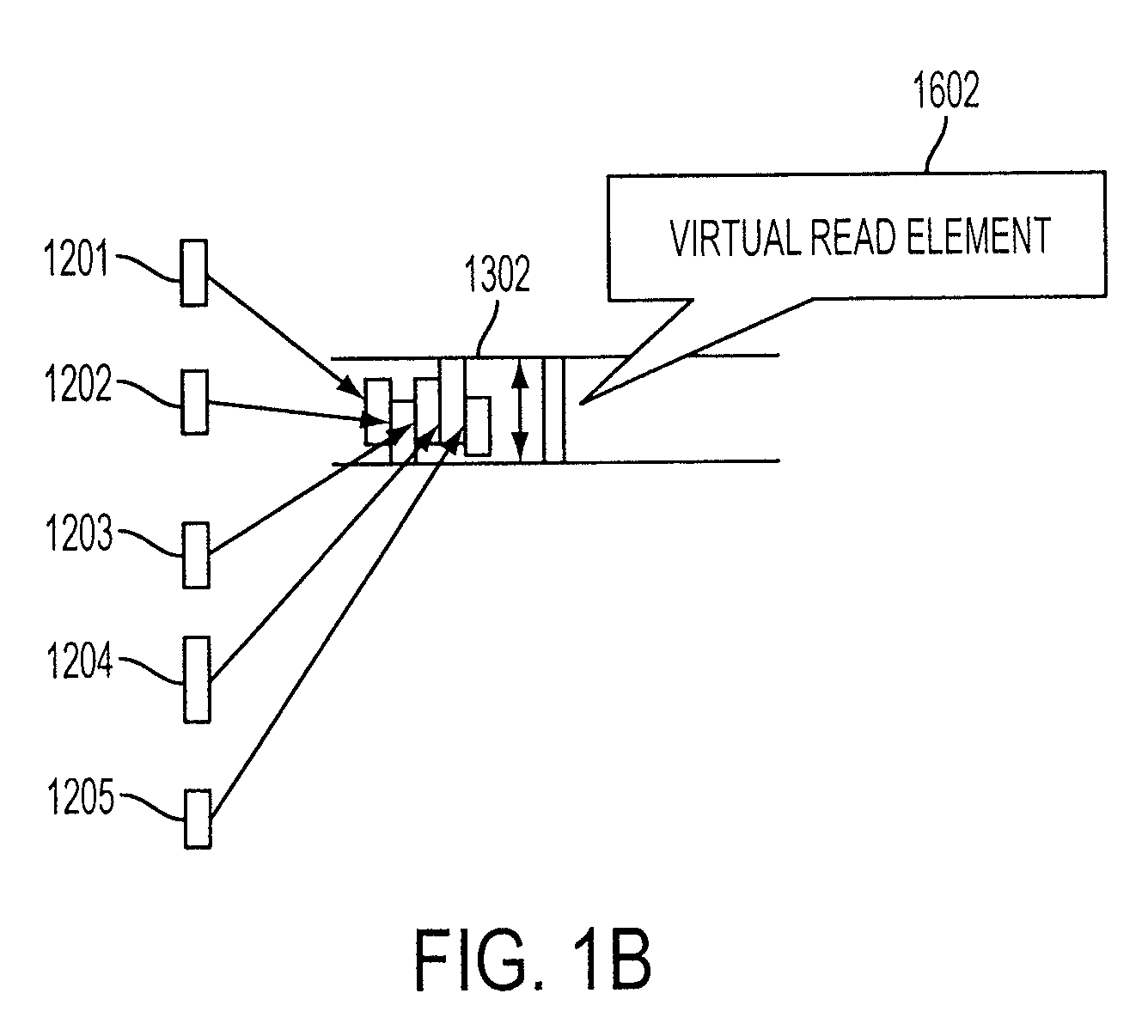

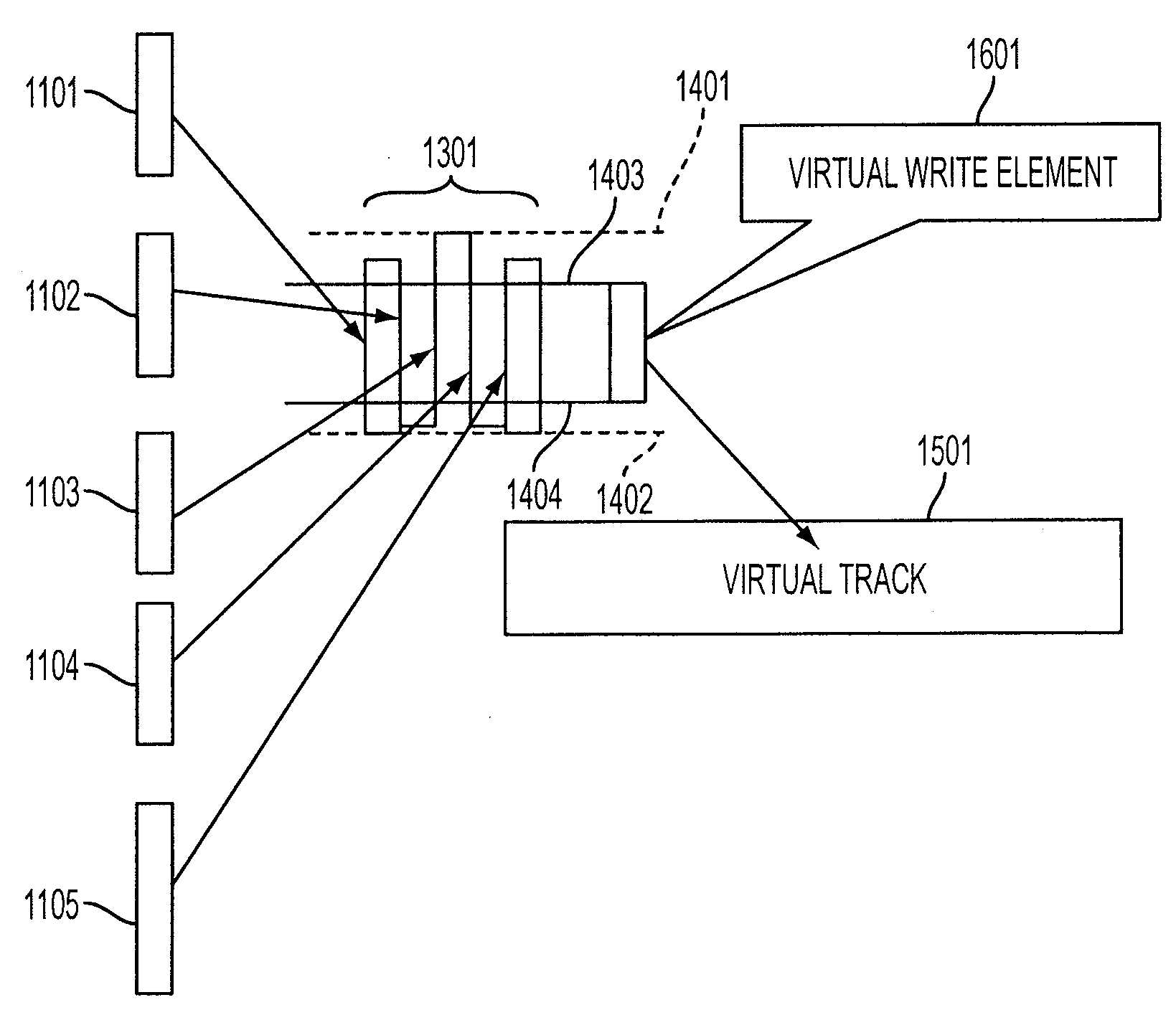

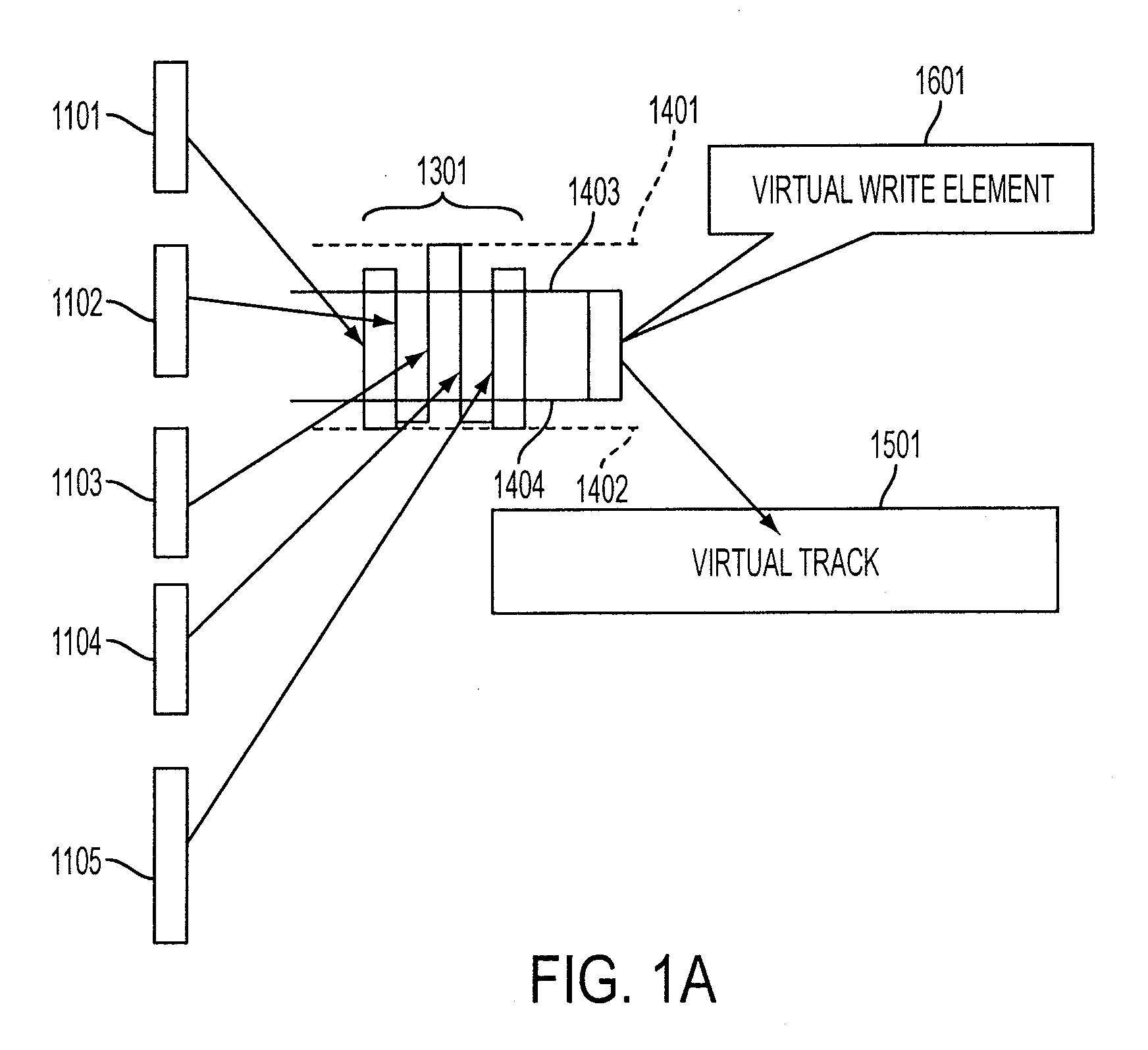

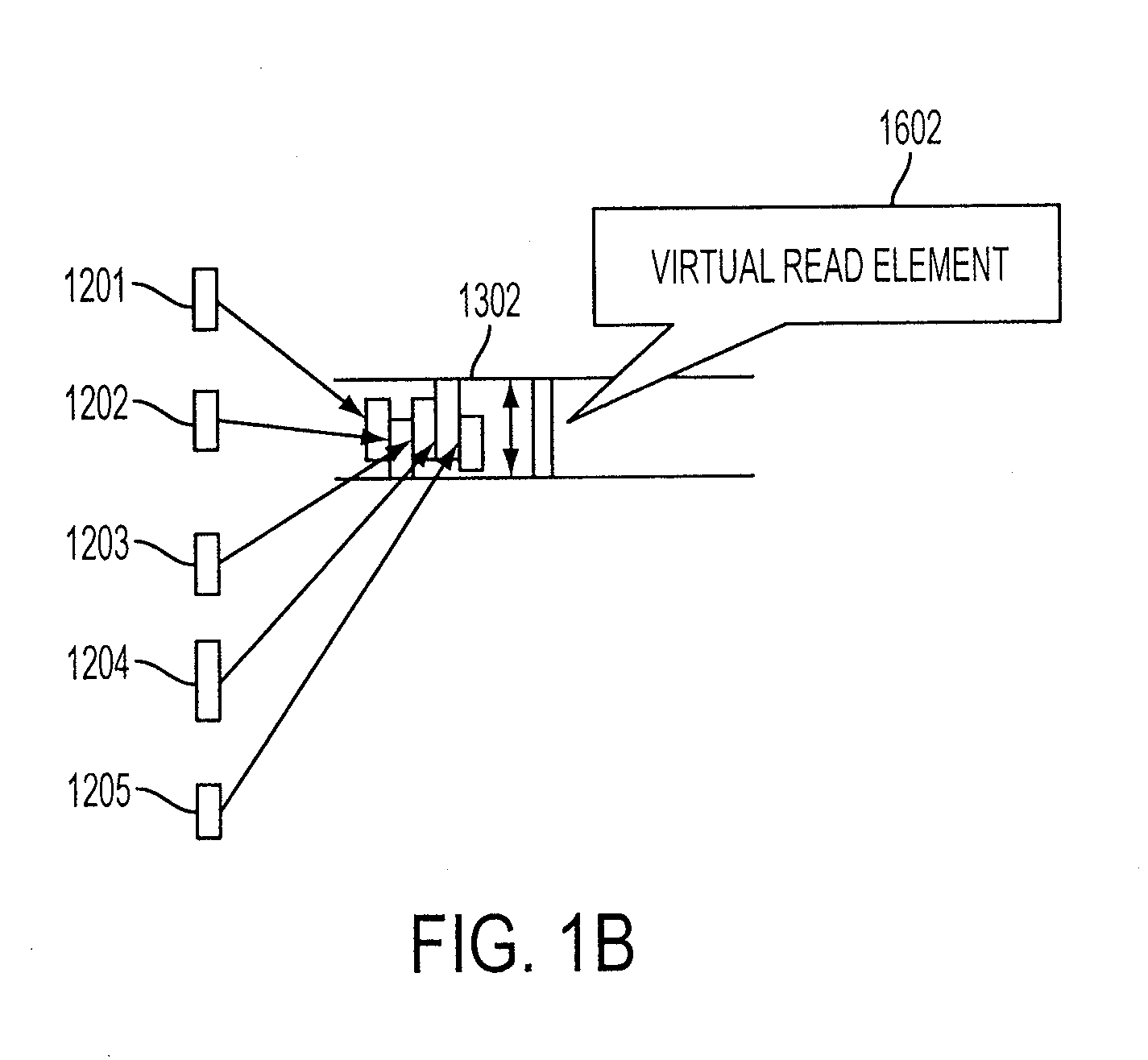

Methods, systems and apparatus for reducing the effects of tape dimensional stability

ActiveUS20090213488A1Accurate measurementAccurate correctionDriving/moving recording headsAlignment for track following on tapesComputer graphics (images)'Backward reading'

A method, system, apparatus, and computer readable medium storing instructions for recording data tracks and a method and system for reading data tracks. For recording data tracks, virtual boundary of a first data track recorded on the storage medium is determined. The recording element is positioned based on the determined virtual boundary of the first track and a second data track is recorded by the positioned recording element. For reading data tracks, a first virtual boundary of a first data track and a second virtual boundary of the first data track are determined and a reading element is positioned at a center of the first data track based on the determined virtual boundaries. In the system of reading recorded data tracks, a number of forward reading elements and backward reading elements are provided. The forward reading elements have different pitches.

Owner:QUANTUM CORP

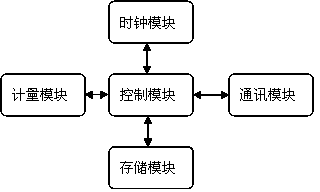

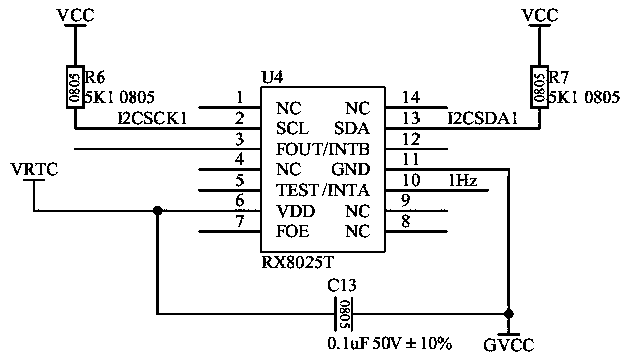

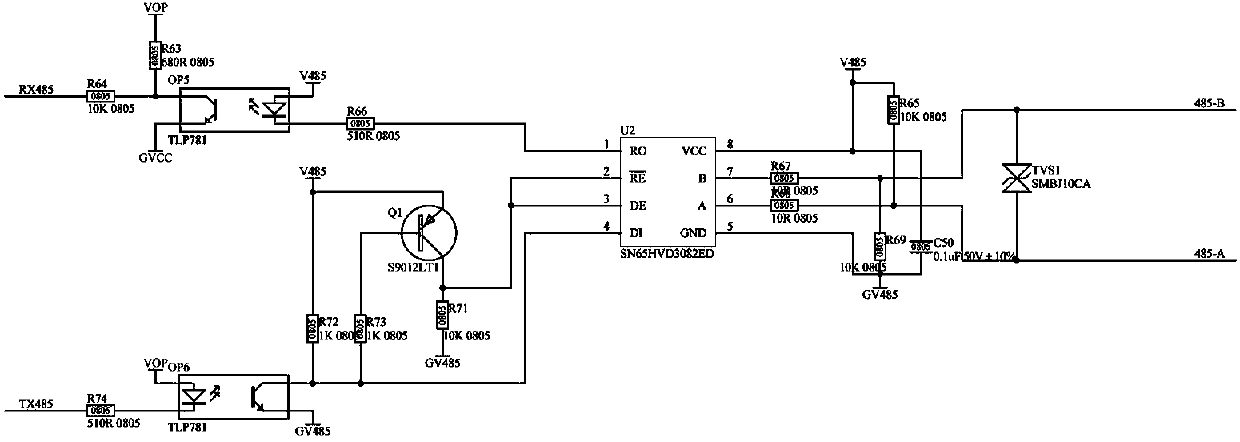

Data backward-reading and storing device and system thereof

InactiveCN103439554AAvoid frequent operationsGuaranteed continuityMulti-tester circuitsComputer module'Backward reading'

The invention provides a data backward-reading and storing device and system thereof. The data backward-reading and storing device comprises: a metering module which is used for acquiring data of at least more than one of power, electric quantity, current and voltage in real time; a control module which is connected with the metering module; a communication module which is connected with the control model; a clock module which is connected with the control module and calibrates current time via the control module and the communication module; and a storage module which is connected with the control module. Timing data freezing is performed by the control module according to current time and presupposed time intervals, and the frozen data and time of data freezing are stored from the metering module and the clock module to the storage module. Data are measuring and acquired in real time by the device. Besides, the data is frozen according to the presupposed time intervals so as to ensure continuity, security and integrity of the data. Furthermore, previous data can be backward read rapidly so that system overhead is reduced.

Owner:ESD ENERGY

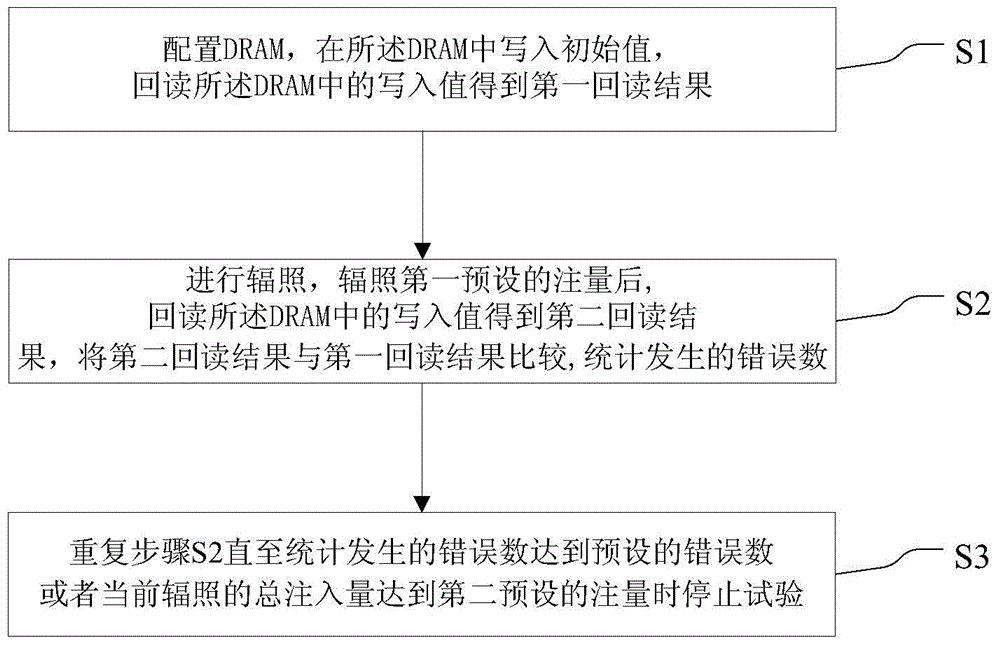

DRAM (dynamic random access memory) neutron single event effect test method

InactiveCN105590651AThe test is validImprove accuracyStatic storageStatic random-access memoryRandom access memory

The invention provides a DRAM (dynamic random access memory) neutron single event effect test method. The DRAM neutron single event effect test method comprises the steps of S1, configuring the DRAM, writing an initial value in the DRAM, and performing backward reading on the writing value in the DRAM to obtain a first backward reading result; S2, performing irradiation, after first preset fluence is irradiated, performing backward reading on the writing value in the DRAM to obtain a second backward reading result; and comparing the second backward reading result with the first backward reading result to make statistics on the number of occurred errors; and S3, repeatedly performing the step S2, and stopping the test until the statistical number of the occurred errors achieves a preset number of errors or the total fluence of the current irradiation achieves a second preset fluence. The DRAM neutron single event effect test method can perform test on the DRAM neutron single event effect, and the accuracy of the test result can be improved.

Owner:BEIJING SHENGTAOPING TEST ENG TECH RES INST

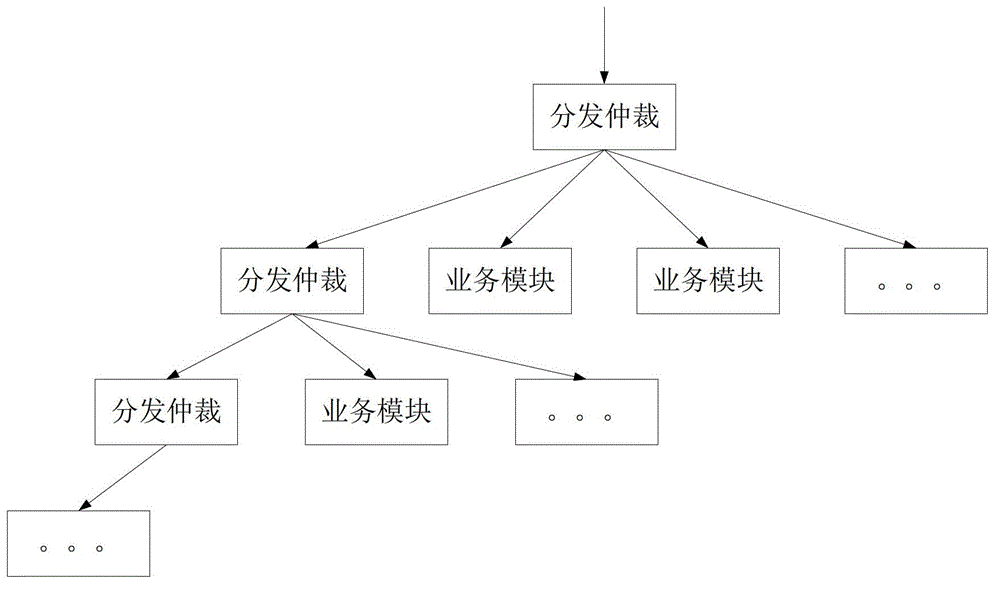

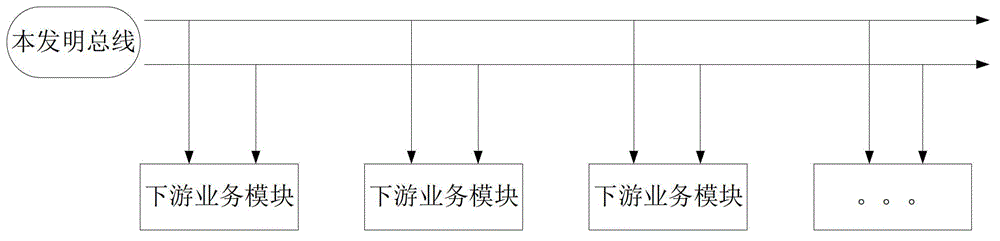

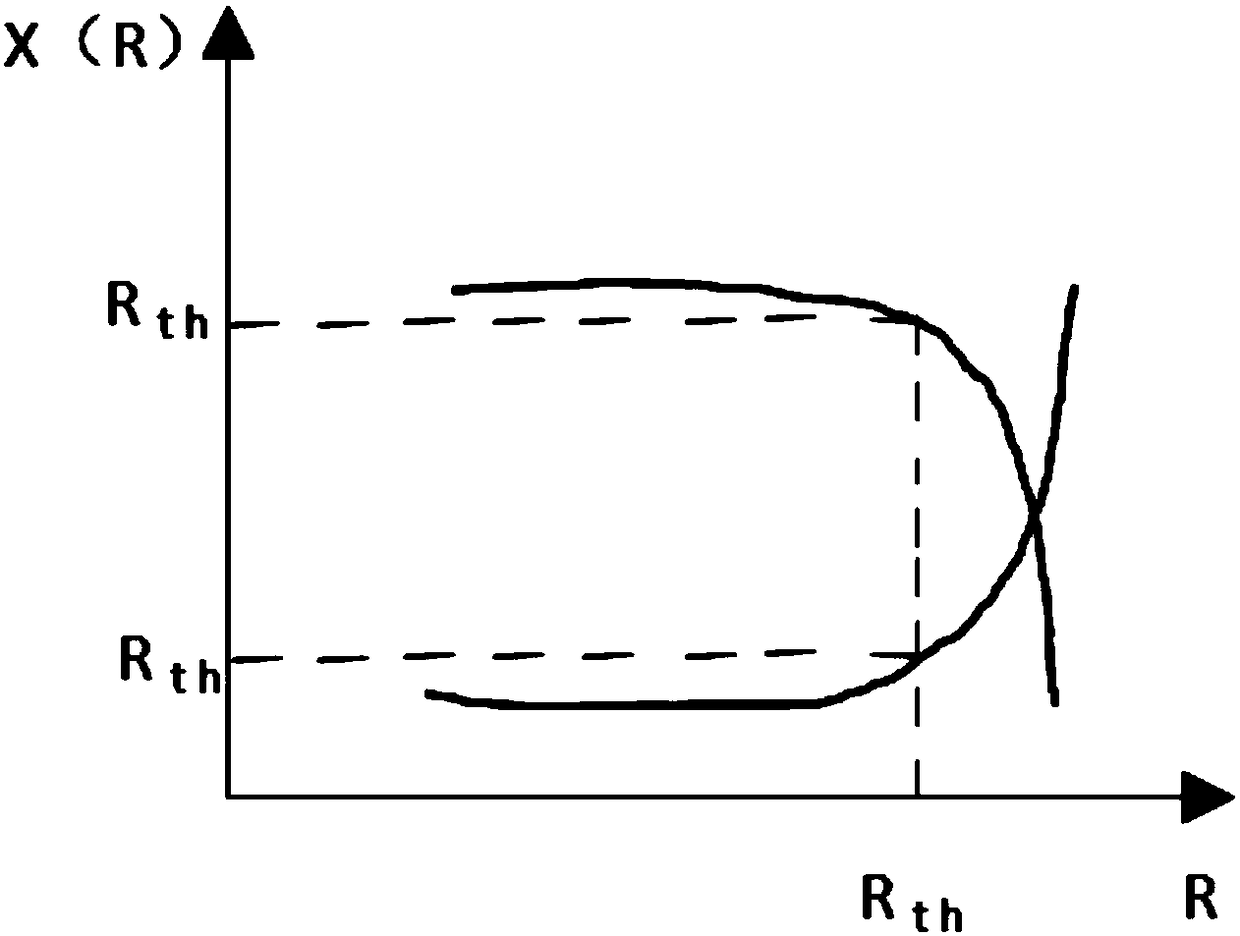

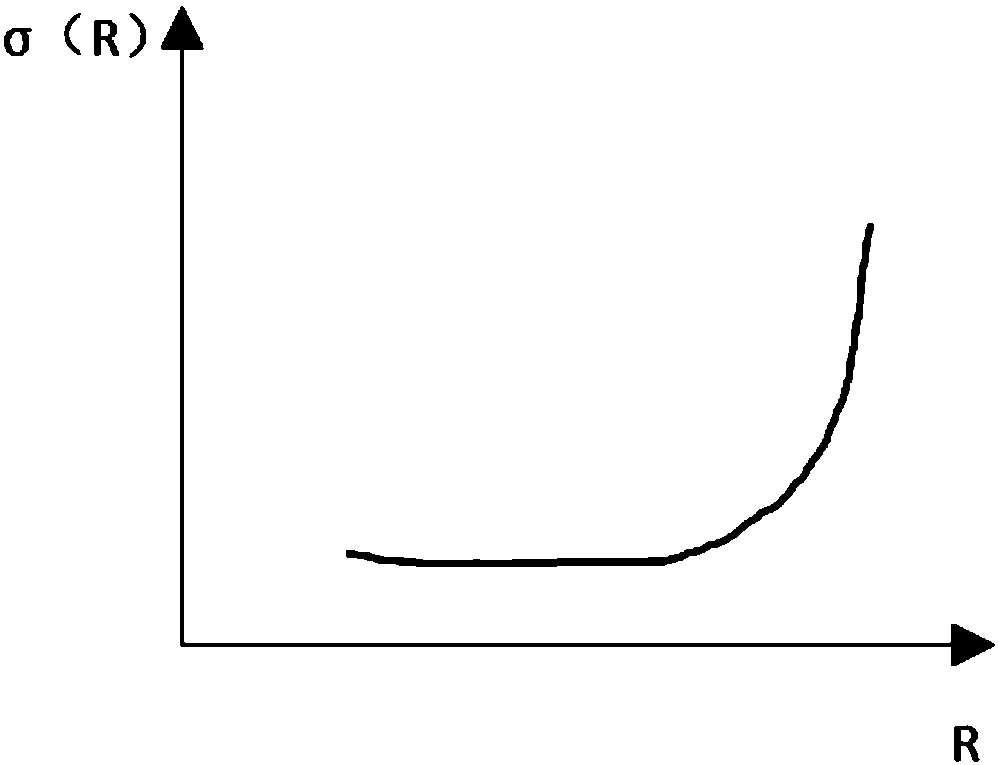

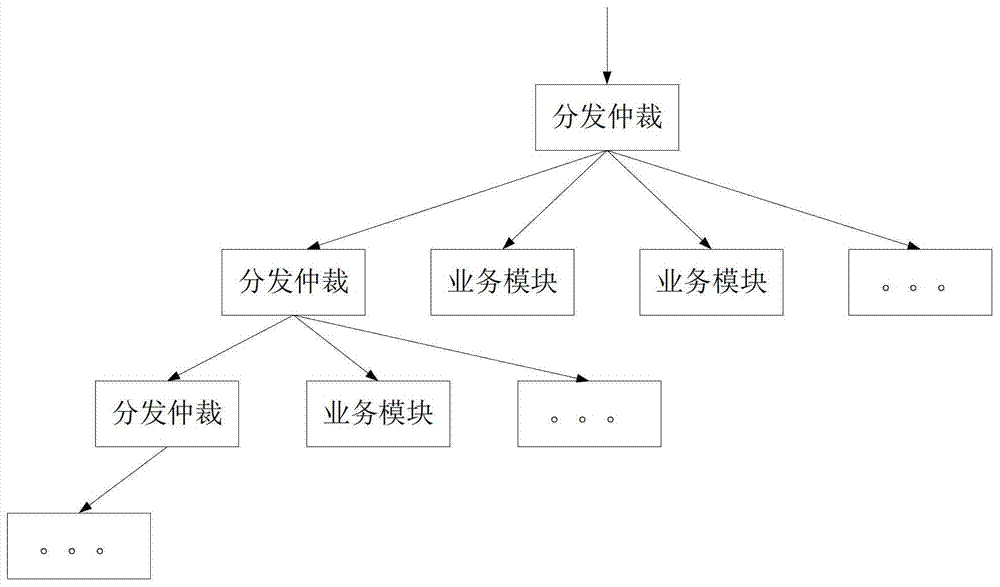

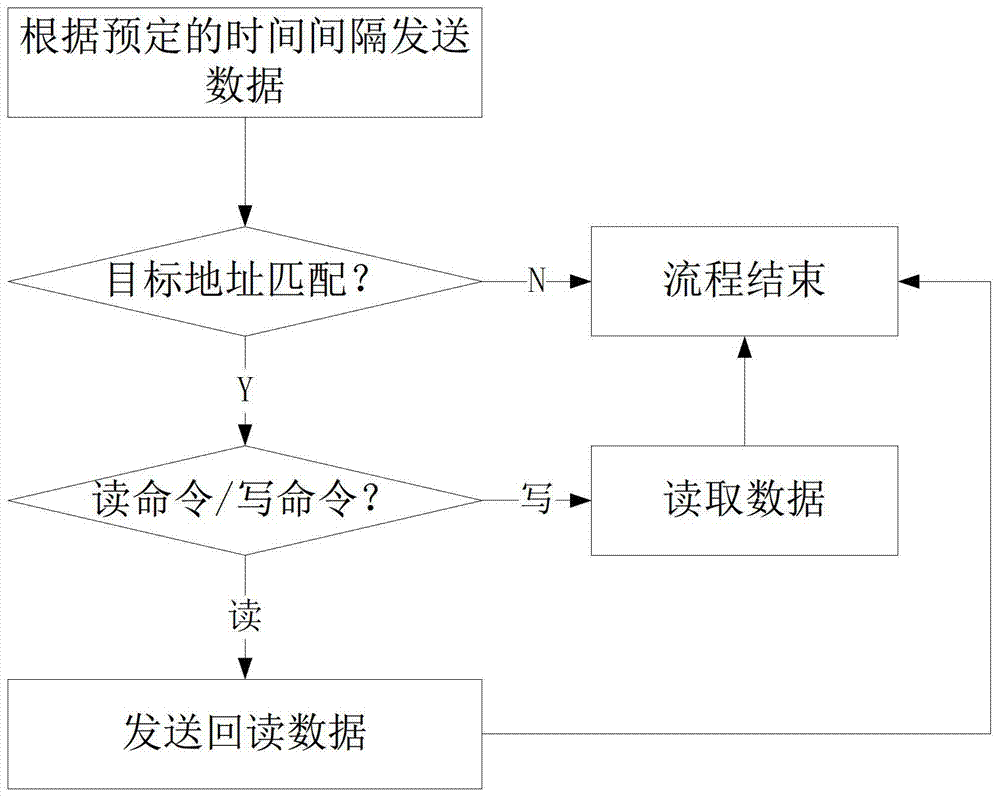

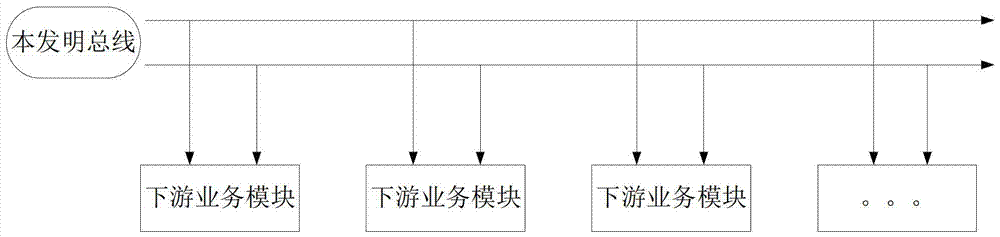

Business processing device

ActiveCN104102604ATroubleshoot layout issuesSave resourcesElectric digital data processingComputer moduleFpga chip

The invention provides a business processing device which is applied to a FPGA (field programmable gate array) chip. The business processing device comprises an upstream business module, a downstream business module and a backward reading main module, wherein all modules are connected together through a bus, the downstream business module receives the data transmitted by the upstream business module, and the data is transmitted by the upstream business module according to a preset time interval; the downstream business module is acquires address information transmitted by the upstream business module through a bus address wire, the address information includes target address information, the downstream business module judges whether the target address information is matched with respective address or not and processing the data if the target address information is matched with the address of the downstream business module, and otherwise, the data is neglected; the backward reading main module is used for caching the data transmitted by the downstream business module to the upstream business module and transmitting the data to the upstream business module. Through the technical scheme, the problems that the expandability of the code is poor and the subsequent function development is not favored when the quantity of the business modules in the FPGA chip is sharply increased can be solved.

Owner:HANGZHOU DPTECH TECH

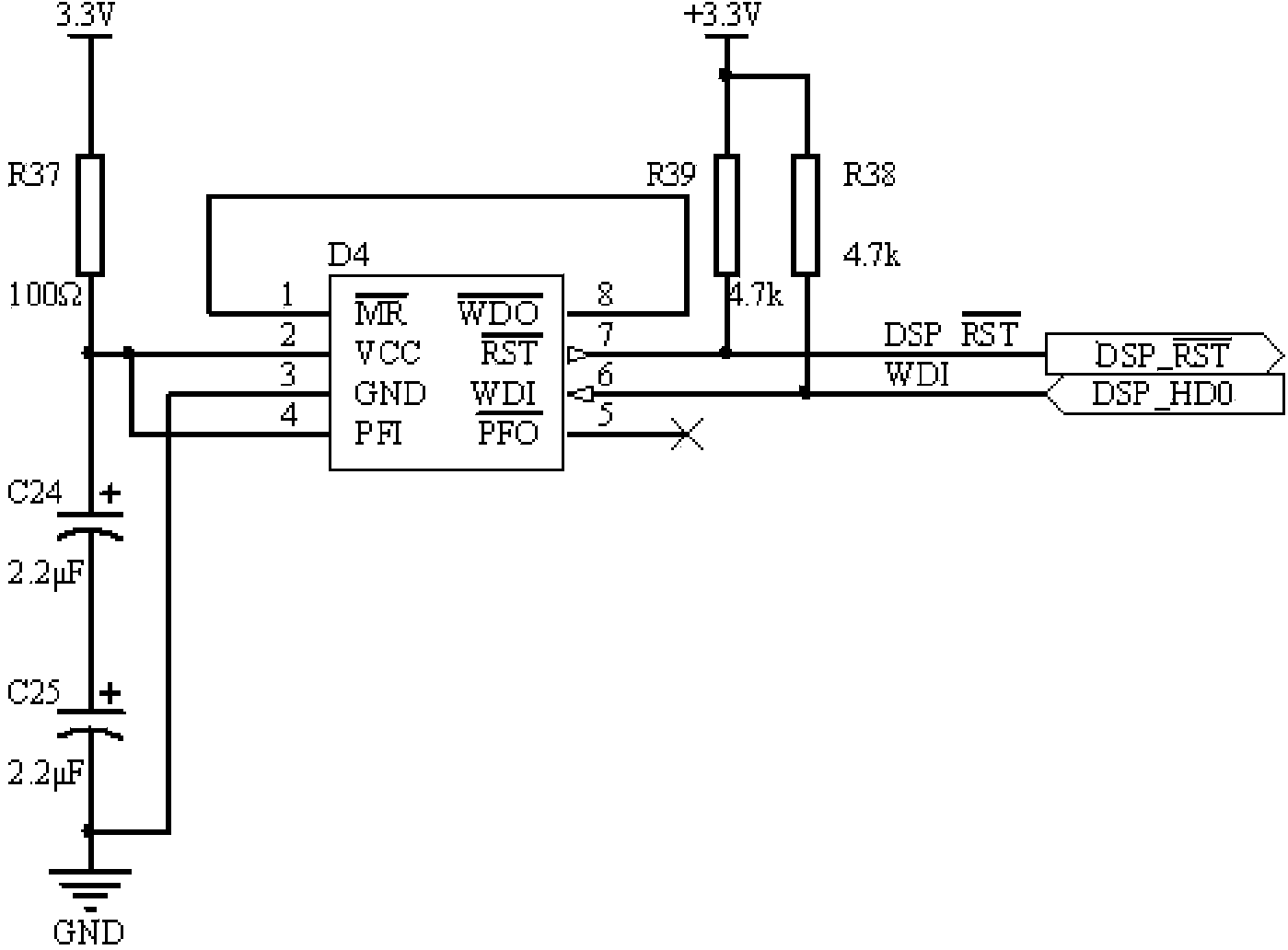

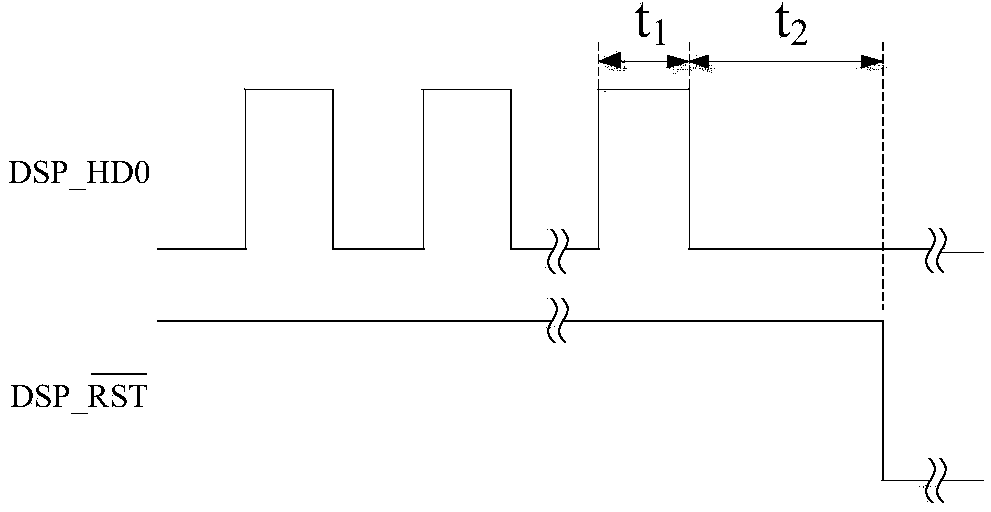

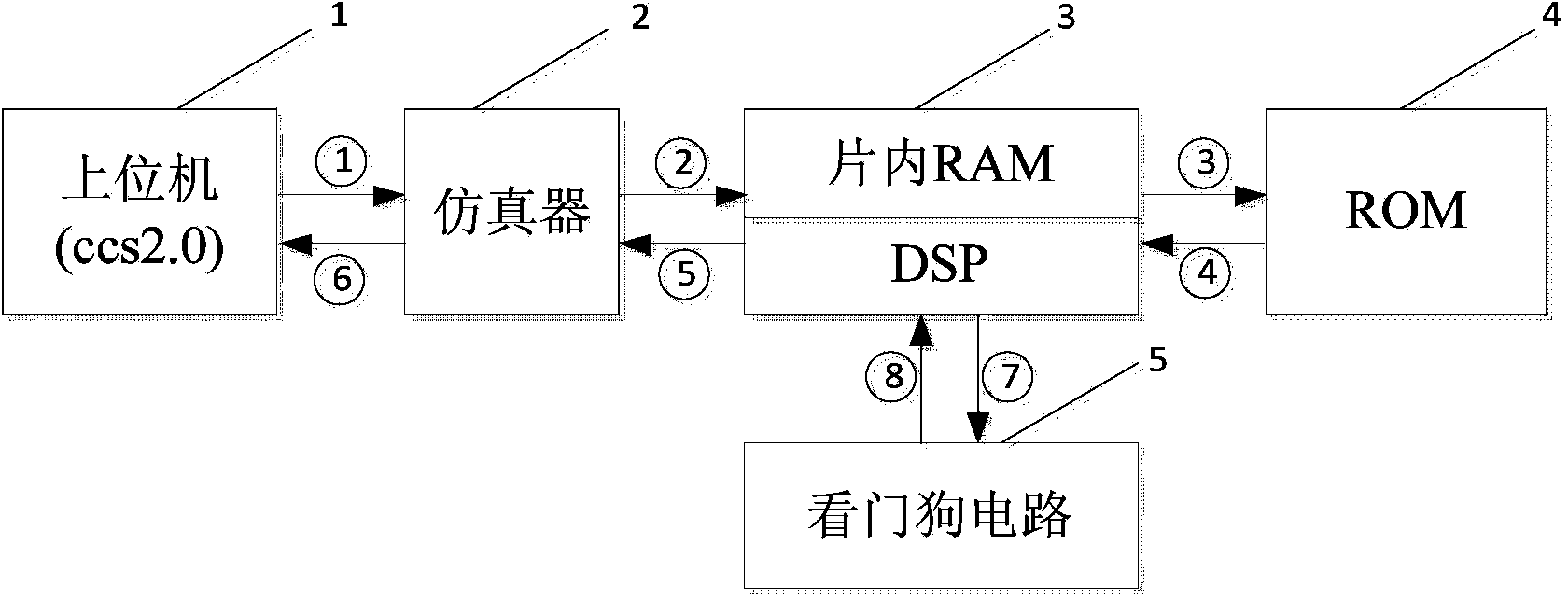

Program burning and backward-reading method with watchdog circuit and based on DSP chip

ActiveCN104063252AReduce complexityReduce difficultyProgram loading/initiatingCanis lupus familiaris'Backward reading'

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

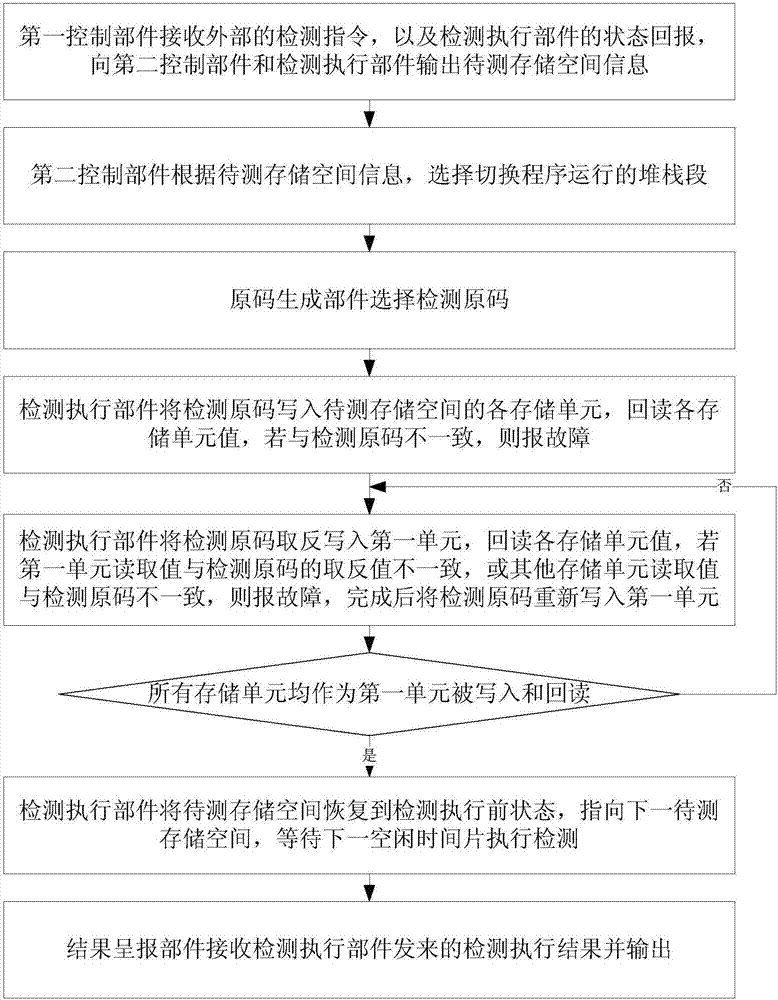

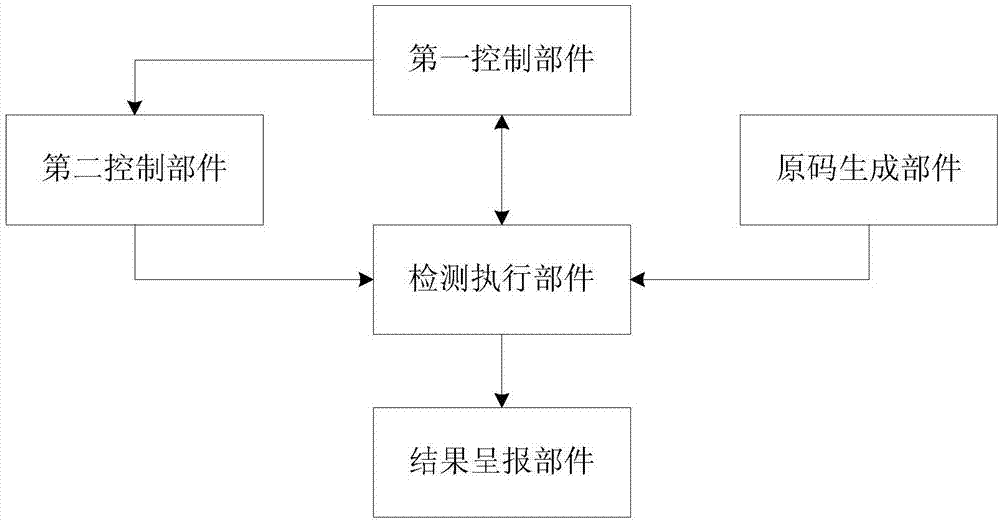

Random access memory (RAM) online detection apparatus and method

ActiveCN107516546AFull Coverage GuaranteedReduce missed detection rateStatic storageStatic random-access memoryNegation

The invention relates to a RAM online detection apparatus, which comprises a first control part, a true form generating part, a second control part, a detection executing part, and a result reporting part. The invention further relates to a RAM online detection method. The method comprises the following steps: receiving a detection command; selecting a stack segment for switching program run; selecting a detection true form; writing the detection true form into each memory unit of a memory space to be detected, backward reading each memory unit value; writing detection true form negation into a first unit, backward reading for judgment; repeating the steps until all memory unit of the memory space are written and backward read; recovering the memory space to a state before the detection, waiting for next detection; and reporting and outputting the results. The provided method and apparatus can detect all areas of a RAM on-line in real time without affecting the normal operation of equipment.

Owner:XIAN FLIGHT SELF CONTROL INST OF AVIC

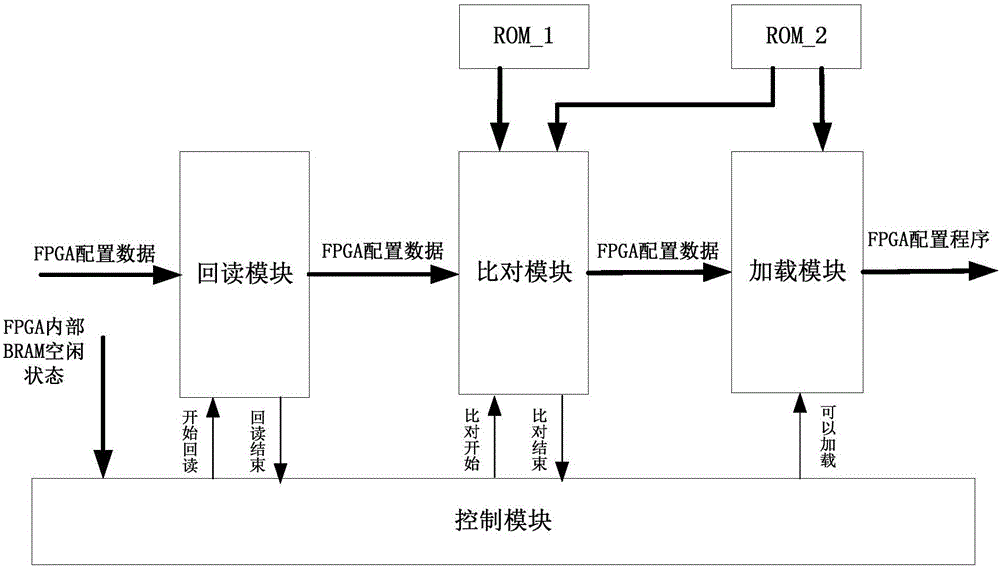

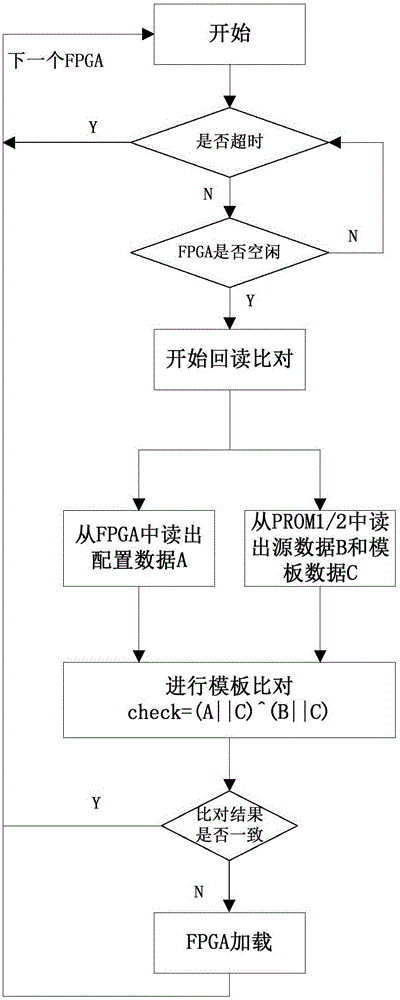

Efficient FPGA configuration backward-reading device and method

InactiveCN105760248AWork reliablyReduce risks from normal workFault responseComplete dataControl signal

The invention provides an efficient FPGA configuration backward-reading device and method.The device and method mainly solve the problem of FPGA function abnormality caused by overturning of an FPGA configuration area in a complex environment of a space.The device comprises a loading module, a backward-reading module, a comparison module and a polling module, wherein the loading module completes data comparison of the FPGA configuration area and re-loading after a mistake is found; the backward-reading module reads FPGA configuration data in the idle state; the comparison module completes comparison between the configuration data read by the backward-reading module and original data and template data; the polling module completes polling of the FPGA state and transmits control signals to all the modules.According to the efficient FPGA configuration backward-reading device and method, the idle detection and overtime exit method is adopted, and high efficiency of the configuration backward-reading device is achieved.

Owner:SHANGHAI SATELLITE ENG INST

Image forming apparatus, text data embedding method, and recording medium

ActiveUS9442899B2Visual presentation using printersCharacter and pattern recognitionComputer graphics (images)Image formation

An image forming apparatus includes: a scanner that obtains an image file by document scanning; a character recognition processor that obtains a text string from each line of text by performing character recognition; a text string splitter that splits each the text string into a plurality of short text strings in accordance with a predetermined rule; a font size determining portion that determines a uniform font size for each the text string; a position determining portion that determines x-axis positions for the short text strings on the basis of the x-coordinates of the characters at the forefront in the respective short text strings, the short text strings each having its x-axis in the forward and backward reading directions; and an embedding portion that embeds text data of the short text strings in the image file at the respective x-axis positions in the uniform font size for the entire text string.

Owner:KONICA MINOLTA INC

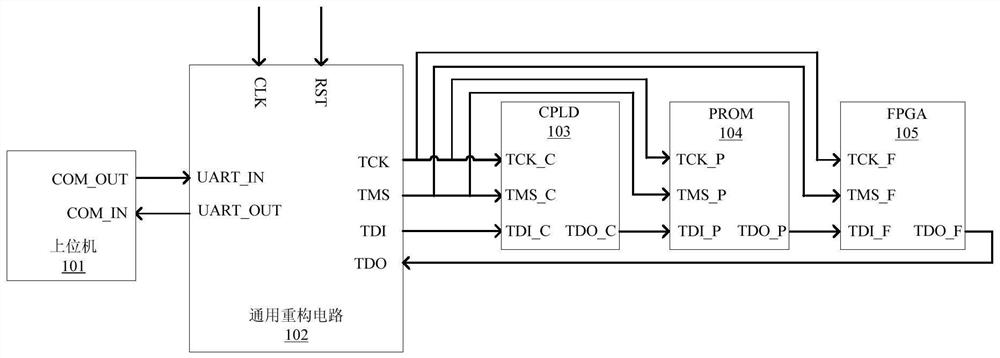

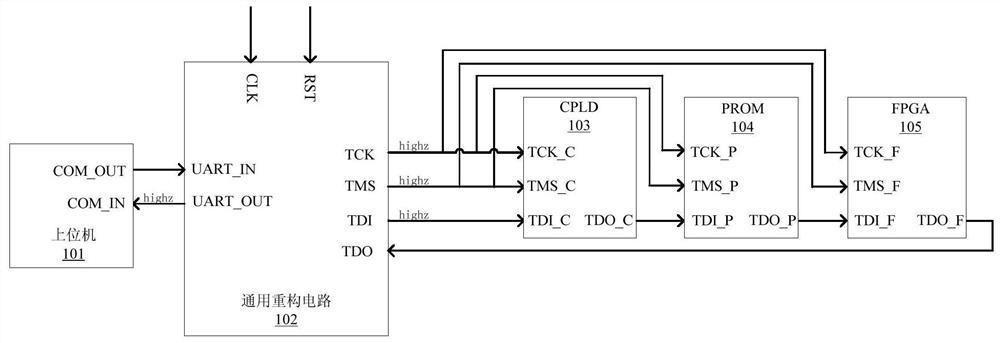

Military FPGA universal reconstruction circuit based on JTAG interface

PendingCN112596743AExtend the field debugging distanceReduce in quantitySoftware deploymentDebugWIRE'Backward reading'

The invention relates to a military FPGA universal reconstruction circuit based on a JTAG interface, and the reconstruction circuit is provided with four input pins and four output pins, can be connected with pins of an FPGA, a CPLD and a PROM, receives an instruction of an upper computer, carries out the backward reading IDCODE operation of the FPGA, the CPLD and the PROM in a link through the JTAG interface, determines the model of a device, and according to an instruction of the upper computer, capable of erasing, programming, reading back and checking the selected device through the JTAG interface; by means of the reconstruction circuit, the purpose of designing FPGA and CPLD design programs in an on-site change system after product installation is achieved, external interfaces of products are effectively reduced, the distance of debugging cables is prolonged, and the on-site debugging efficiency of installed products is improved.

Owner:BEIJING MXTRONICS CORP +1

The realization method of aerospace fpga general refresh circuit based on selectmap

ActiveCN103840822BImprove the reliability of space applicationsReduce adverse effectsLogic circuits using elementary logic circuit componentsData sourceModel Number

The invention relates to an astronavigation FPGA universal refresh circuit based on SELECTMAP. The refresh circuit is provided with six input pins, six output pins and eight double-direction pins, and the input pins, the output pins and the double-direction pins are connected with pins of a PROM and pins of an FPGA. The SRAM-type FPGA is subjected to backward reading operation through SELECTMAP, the type of the FPGA is determined, and backward read data are checked; if errors happen, a code stream is read from a correct data source, effective parts are intercepted from the code stream, the effective code stream is written into an inner configuration bit of the FPGA again through SELECTMAP, and accordingly refreshing of a configuration memory is completed. Through the refresh circuit, single event upset of the astronavigation FPGA can be timely detected and corrected, functional faults caused by single event upset of the astronavigation FPGA are eliminated, and astronavigation FPGA space application reliability is improved.

Owner:BEIJING MXTRONICS CORP +1

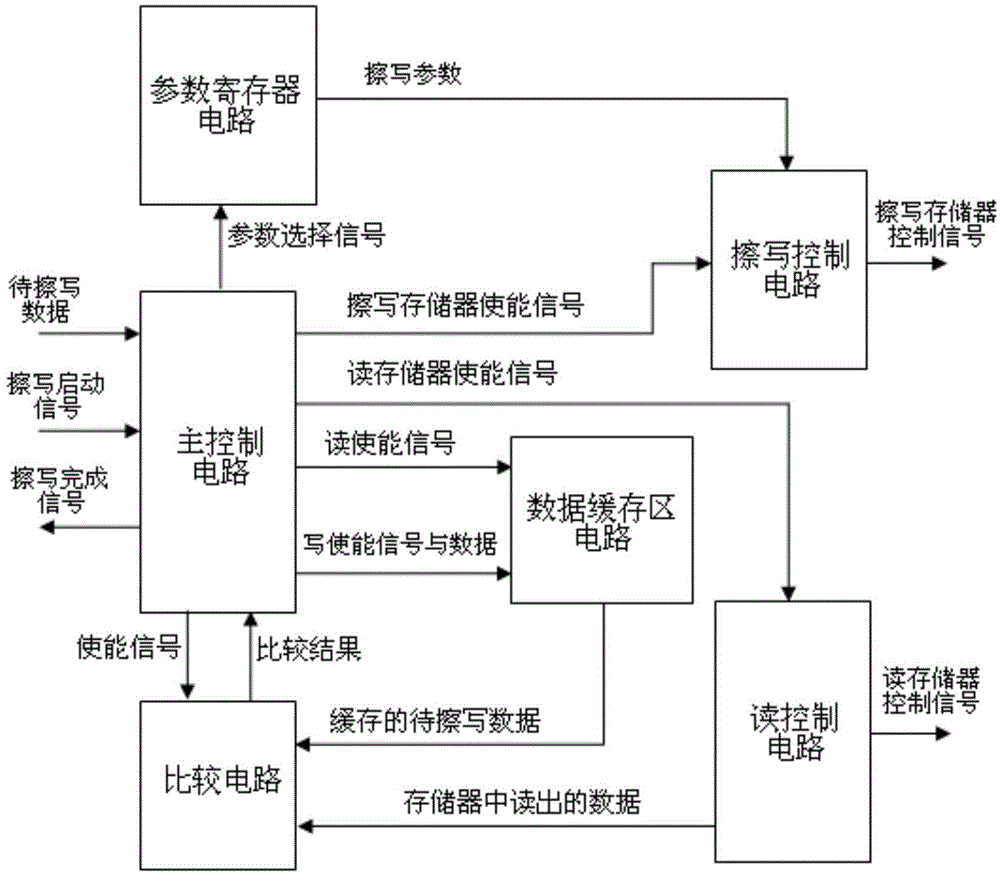

Erasing/writing control circuit and method of nonvolatile memory

InactiveCN106328201AOptimizing Erase and Write Power ConsumptionConvenient timeRead-only memoriesControl circuitData storing

The invention discloses an erasing / writing control circuit of a nonvolatile memory. The erasing / writing control circuit comprises a main control circuit, a parameter register circuit, a comparison circuit, a data cache region circuit, the erasing / writing control circuit and a reading control circuit. The invention furthermore discloses an erasing / writing control method of the nonvolatile memory. In a process of erasing / writing the nonvolatile memory each time, firstly erasing / writing attempts to be performed by using a configuration parameter corresponding to low power consumption and short erasing / writing time. After the current operation of attempting to perform the easing / writing is finished, backward reading is performed and comparison with data stored in an internal cache region of the circuit is carried out. If the data is inconsistent, the erasing / writing attempts to be performed again by using a configuration parameter corresponding to higher power consumption and longer erasing / writing time, and the process is repeated until a comparison result displays that the data is consistent after the backward reading, so that the current erasing / writing work of the nonvolatile memory is finished. According to the control circuit, the erasing / writing time of the nonvolatile memory can be optimized, the power consumption of the erasing / writing period can be reduced, and the erasing / writing performance can be improved.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

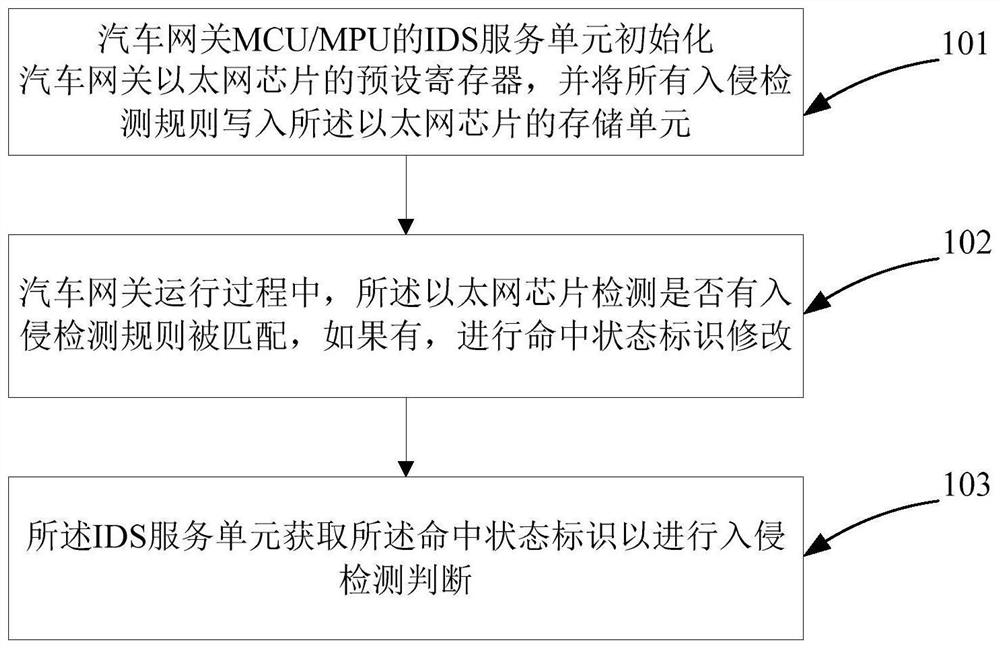

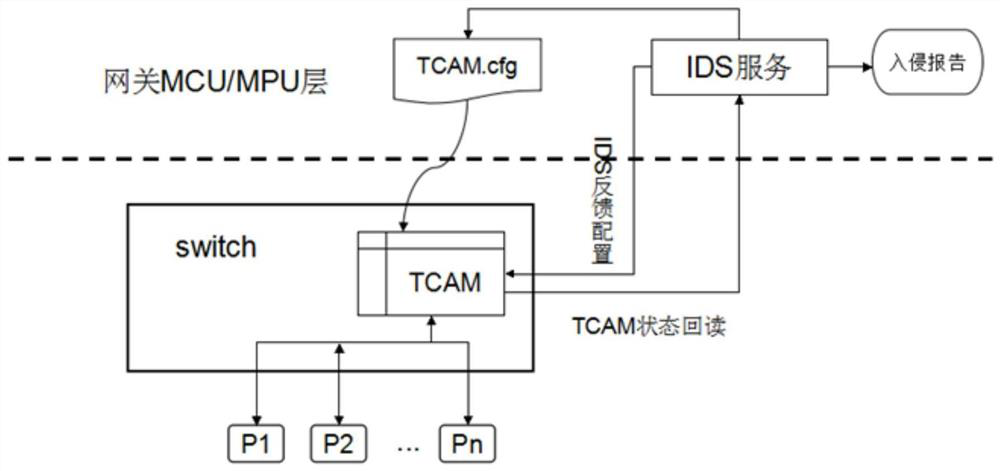

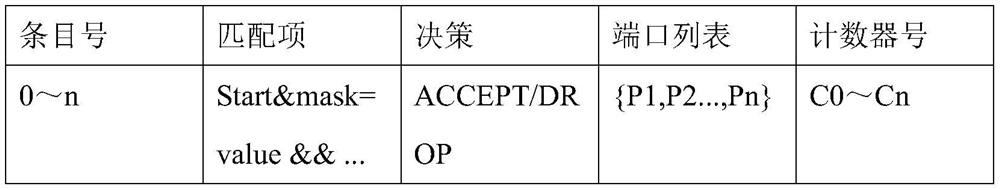

Method and system for realizing network intrusion detection on automobile gateway

The invention discloses a method and system for realizing network intrusion detection on an automobile gateway, and the method comprises the steps: an IDS service unit of an MCU / MPU of the automobile gateway initializes a preset register of an Ethernet chip of the automobile gateway, and writes all intrusion detection rules into a storage unit of the Ethernet chip; in the running process of the automobile gateway, the Ethernet chip detects whether an intrusion detection rule is matched or not, and if yes, the hit state identification modification is carried out; and the IDS service unit obtains the hit state identifier to perform intrusion detection judgment. According to the invention, the Ethernet chip is used for intrusion detection, rapid matching is carried out based on intrusion detection rules, and the IDS service unit on the MCU / MPU only needs to carry out state backward reading and feedback configuration, so that intrusion detection can be realized, large consumption on the performance of the MCU / MPU is not caused, and the processing of the existing service of the MCU / MPU is not influenced.

Owner:XIAMEN YAXON NETWORKS CO LTD

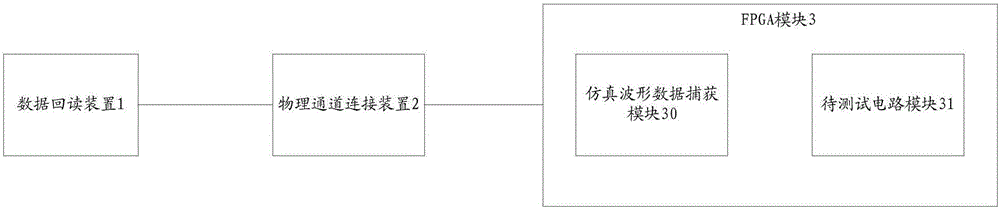

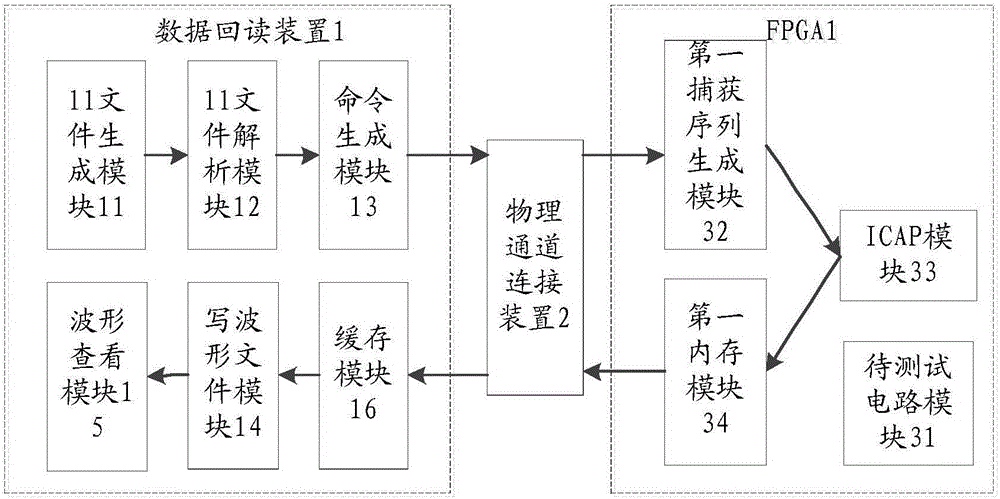

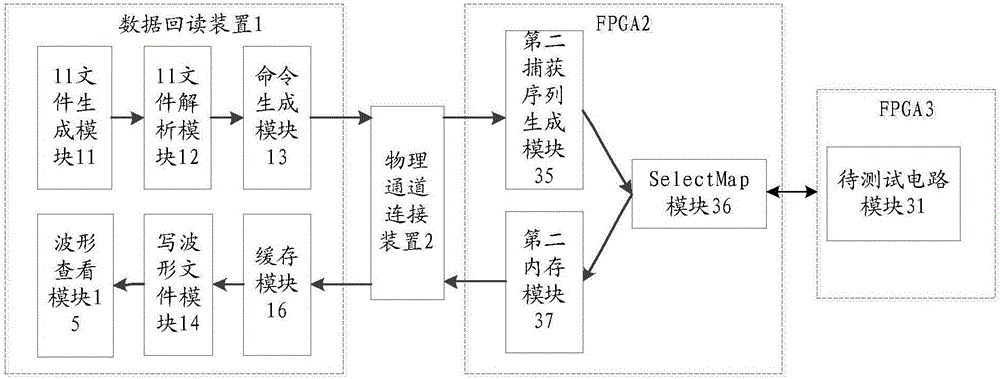

Data backward-reading system

PendingCN106168996AIncrease occupancySimple designSpecial data processing applicationsStatic timing analysis'Backward reading'

The embodiment of the invention provides a data backward-reading system. The data backward-reading system comprises a data backward-reading device, a physical channel connecting device and an FPGA module, wherein the data backward-reading device generates a waveform backward-reading command, sends the waveform backward-reading command to the physical channel connecting device, obtains simulation waveform data from the physical channel connecting device and displays simulation waveforms corresponding to the simulation waveform data; the physical channel connecting device transmits the waveform backward-reading command and the simulation waveform data; the FPGA module comprises a to-be-test circuit module and a simulation-waveform-data capturing module, and is used for obtaining the waveform backward-reading command, capturing simulation waveform data generated by the to-be-test circuit module through the simulation waveform data capturing module according to the waveform backward-reading command and sending the simulation waveform data to the physical channel connecting device. The embodiment of the data backward-reading system is small in occupied logical resource, the occupied logical resource can not be enlarged along with enlargement of the IC design scale, backward reading of the simulation waveform data is quite convenient, and static timing analysis is easy.

Owner:HEFEI HAIBENLAN TECH

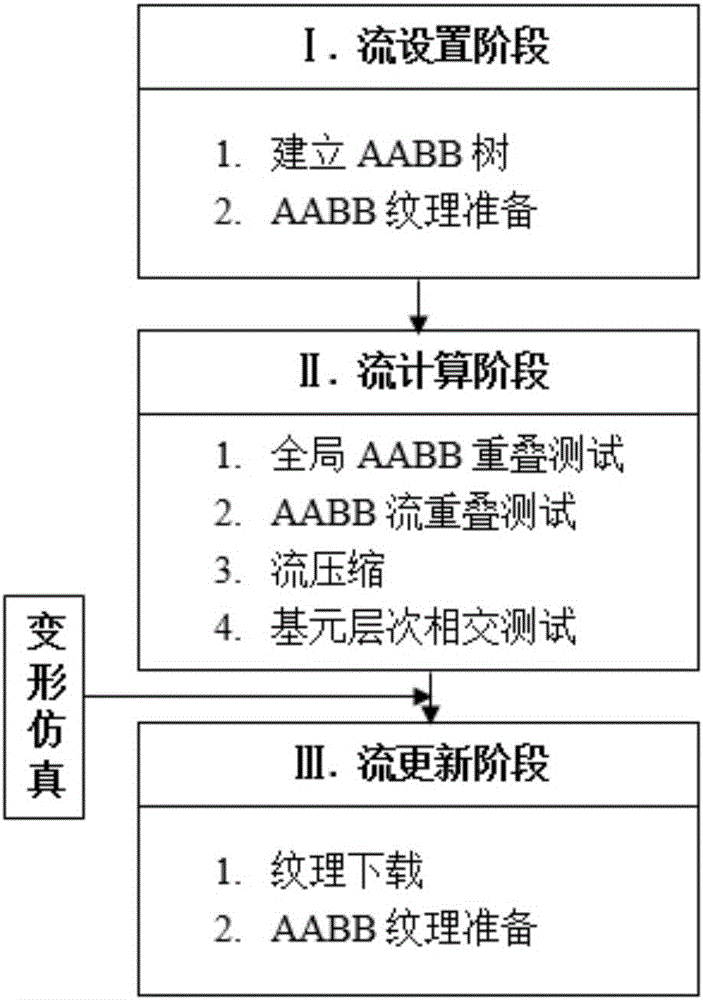

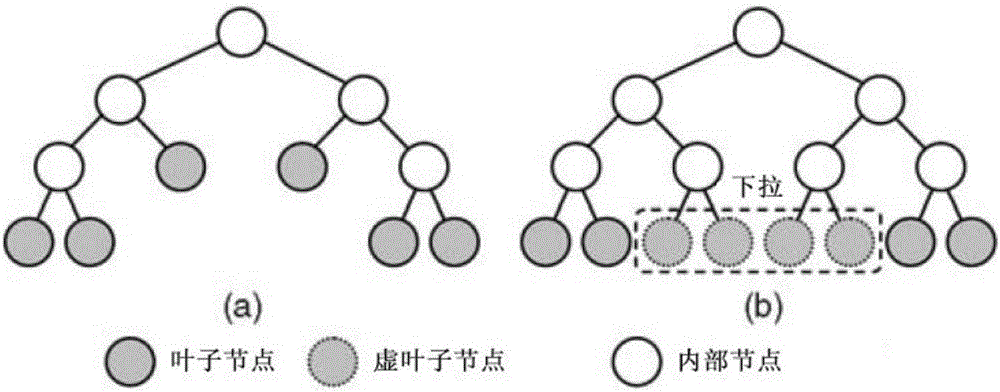

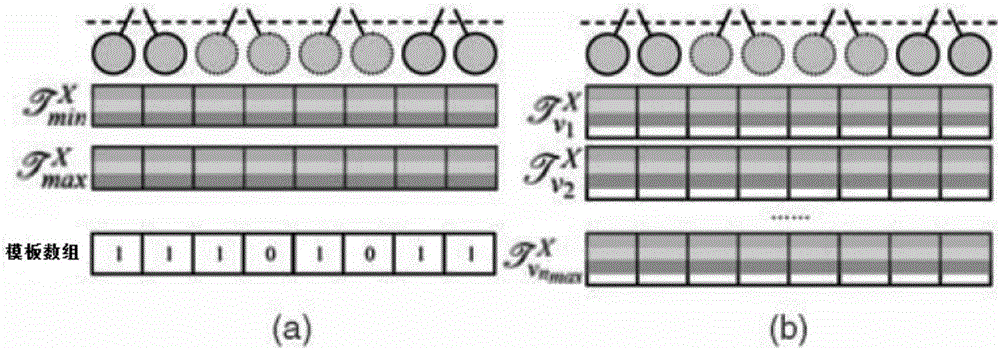

Method for deformable body collision detection based on AABB flow computation

InactiveCN106055740AImprove performanceImprove acceleration performanceSpecial data processing applicationsThree stageCollision detection

The invention provides a method for deformable body collision detection based on AABB flow computation. The method comprises three stages including flow setting, flow computation and flow updating. At the flow setting stage, an AABB tree structure is established, and AABB texture preparation is carried out; at the flow computation stage, a large-scale concurrent AABB flow overlap test is carried out; and at the flow update stage, an AABB flow is updated according to deformation of a model. The collision detection method provided by the invention has the advantages that the complex deformable body collision detection is effectively implemented through implementation of a large-scale concurrent flow computation mode under a GPU; the AABB flow overlap test is optimally applied, the flow updating is conducted in a single-instruction multi-dataflow manner, data backward-reading efficiency is increased by a flow compression technology, the large mode is processed by horizontal texture paving, and so forth; and on the premise that a high interaction rate is ensured, intersections among all the triangular primitives of two seriously deformed models can be detected.

Owner:EAST CHINA NORMAL UNIV

Realization method of aerospace fpga general refresh circuit based on jtag interface

ActiveCN103840823BImprove the reliability of space applicationsReduce adverse effectsLogic circuits using elementary logic circuit componentsData sourceJoint Test Action Group

The invention relates to an astronavigation FPGA universal refresh circuit based on a JTAG interface. The refresh circuit is provided with seven input pins and eight output pins, and the input pins and the output pins are connected with pins of a PROM and pins of an FPGA. The SRAM-type FPGA is subjected to backward reading operation through the JTAG interface, the type of the FPGA is determined, and backward read data are checked; if errors happen, a code stream is read from a correct data source, effective parts are intercepted from the code stream, the effective code stream is written into an inner configuration bit of the FPGA again through the JTAG interface, and accordingly refreshing of a configuration memory is completed. Through the refresh circuit, single event upset of the astronavigation FPGA can be timely detected and corrected, functional faults caused by single event upset of the astronavigation FPGA are eliminated, and astronavigation FPGA space application reliability is improved.

Owner:BEIJING MXTRONICS CORP +1

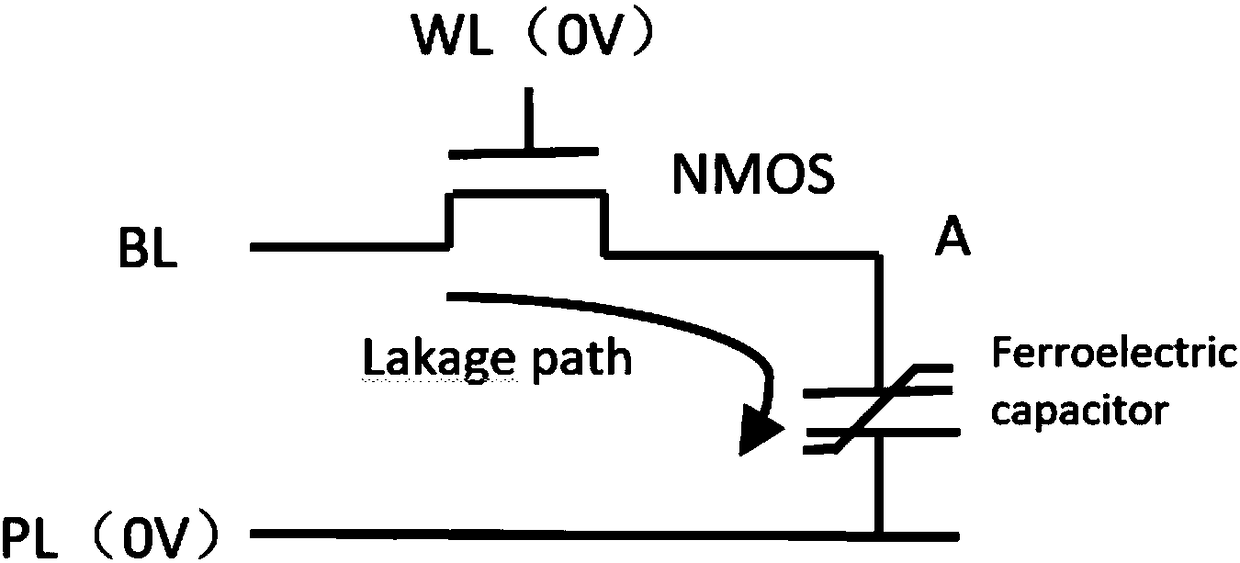

Method for determining sensitive parameters of FeRAM (Ferroelectric Random Access Memory)

The invention discloses a method for determining sensitive parameters of a FeRAM (Ferroelectric Random Access Memory) and belongs to the fields of space radiation damage effects and radiation hardening. The method comprises the following steps: backward reading first data from a FeRAM completing radiation, matching the backward read data and a second data written into the FeRAM before radiation, and determining the FeRAM matched to be qualified as a first FeRAM; acquiring a parameter DC and a parameter AC of the first FeRAM by virtue of a testing instrument when each set radiation dose point is reached, respectively analyzing the parameter DC and the parameter AC by virtue of a QMU formula, and determining that one parameter included in the parameter DC and the parameter AC fails when a confidence ratio determined by the QMU formula is less than 1.

Owner:XIANGTAN UNIV

A business processing device

ActiveCN104102604BTroubleshoot layout issuesSave resourcesElectric digital data processingExtensibilityFpga chip

The invention provides a business processing device which is applied to a FPGA (field programmable gate array) chip. The business processing device comprises an upstream business module, a downstream business module and a backward reading main module, wherein all modules are connected together through a bus, the downstream business module receives the data transmitted by the upstream business module, and the data is transmitted by the upstream business module according to a preset time interval; the downstream business module is acquires address information transmitted by the upstream business module through a bus address wire, the address information includes target address information, the downstream business module judges whether the target address information is matched with respective address or not and processing the data if the target address information is matched with the address of the downstream business module, and otherwise, the data is neglected; the backward reading main module is used for caching the data transmitted by the downstream business module to the upstream business module and transmitting the data to the upstream business module. Through the technical scheme, the problems that the expandability of the code is poor and the subsequent function development is not favored when the quantity of the business modules in the FPGA chip is sharply increased can be solved.

Owner:HANGZHOU DPTECH TECH

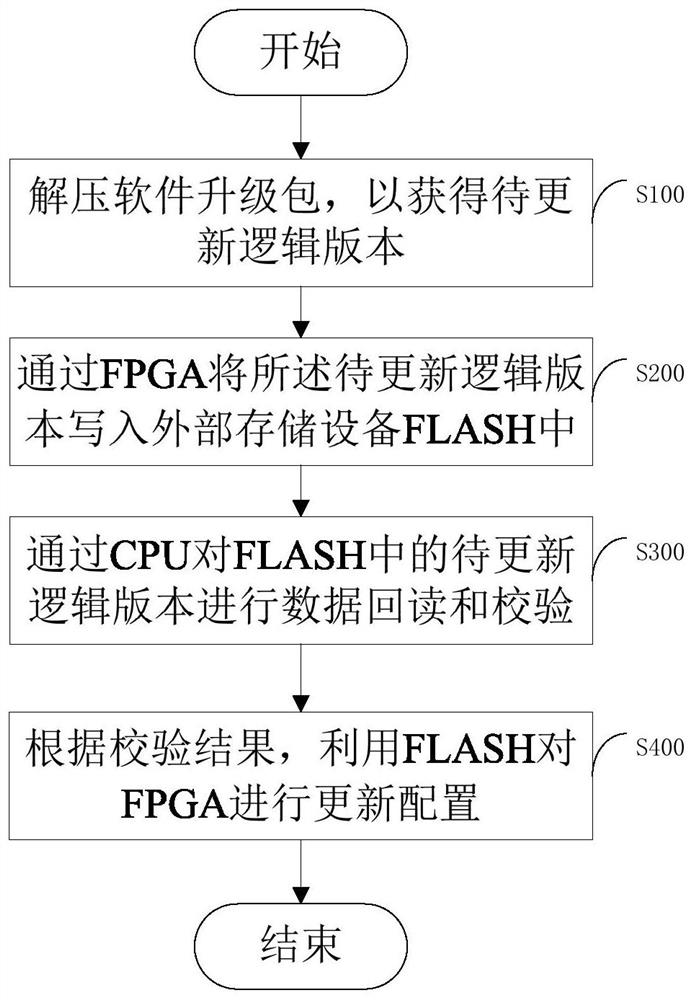

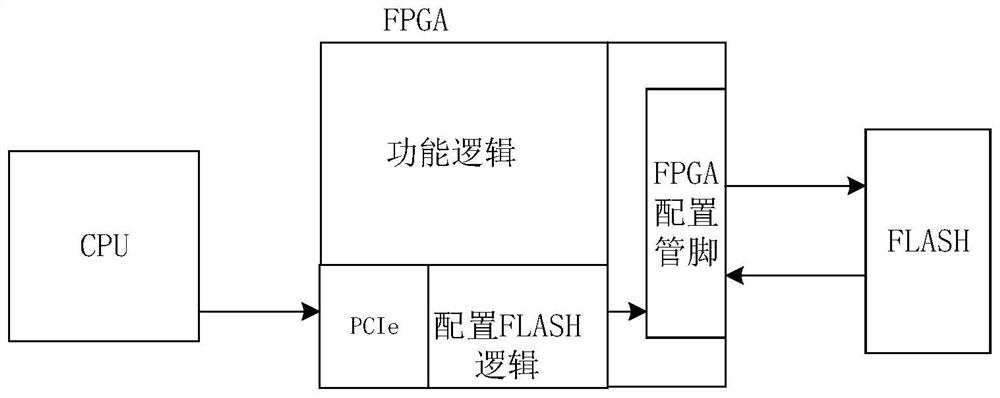

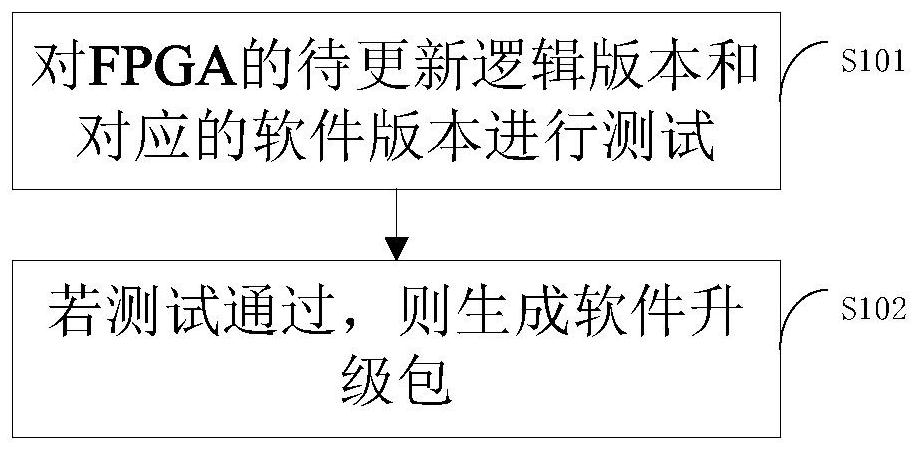

FPGA remote updating method and system, electronic equipment and storage medium

PendingCN114201204ADoes not affect normal system businessIncrease flexibilityVersion controlSoftware deploymentDigital signal processingComputer architecture

The embodiment of the invention provides an FPGA remote updating method and system, electronic equipment and a storage medium, and relates to the technical field of digital signal processing. The method comprises the following steps: decompressing a software upgrade package to obtain a to-be-updated logic version; writing the logic version to be updated into an external storage device FLASH through an FPGA (Field Programmable Gate Array); performing data backward reading and verification on the logic version to be updated in the FLASH through a CPU (Central Processing Unit); according to the verification result, the FLASH is used for updating configuration of the FPGA, the method can remotely update the FPGA without affecting normal system services, and the problems that an existing method cannot remotely update and cannot normally operate during updating are solved.

Owner:BEIJING TOPSEC NETWORK SECURITY TECH +2

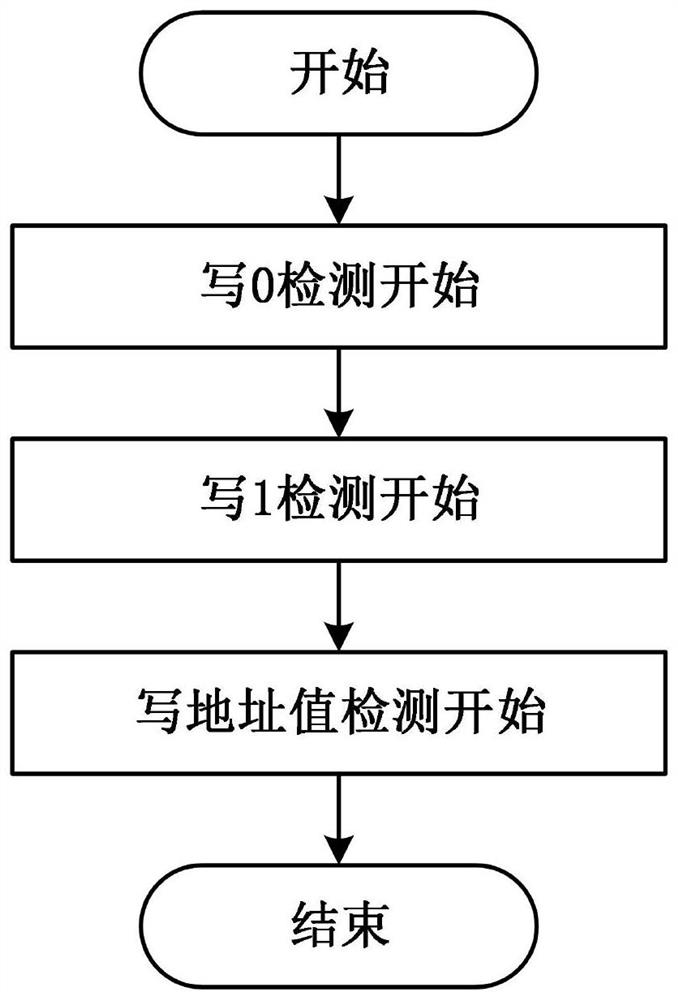

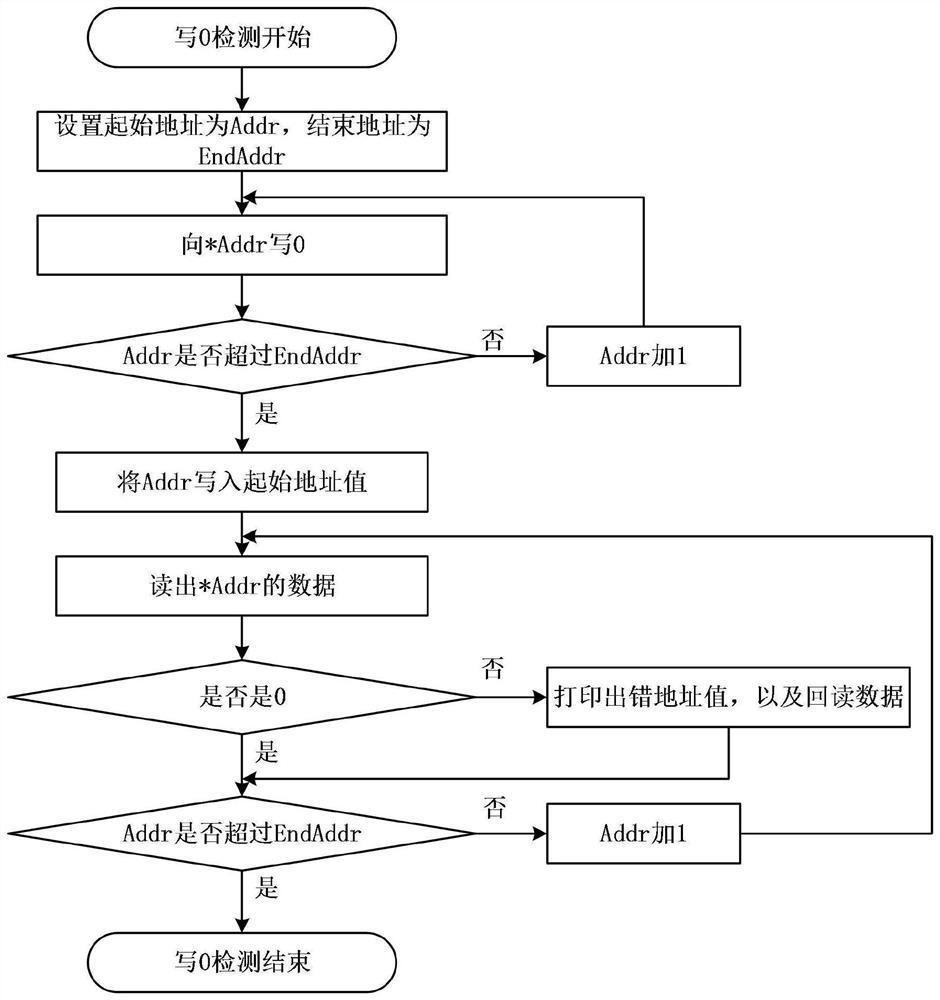

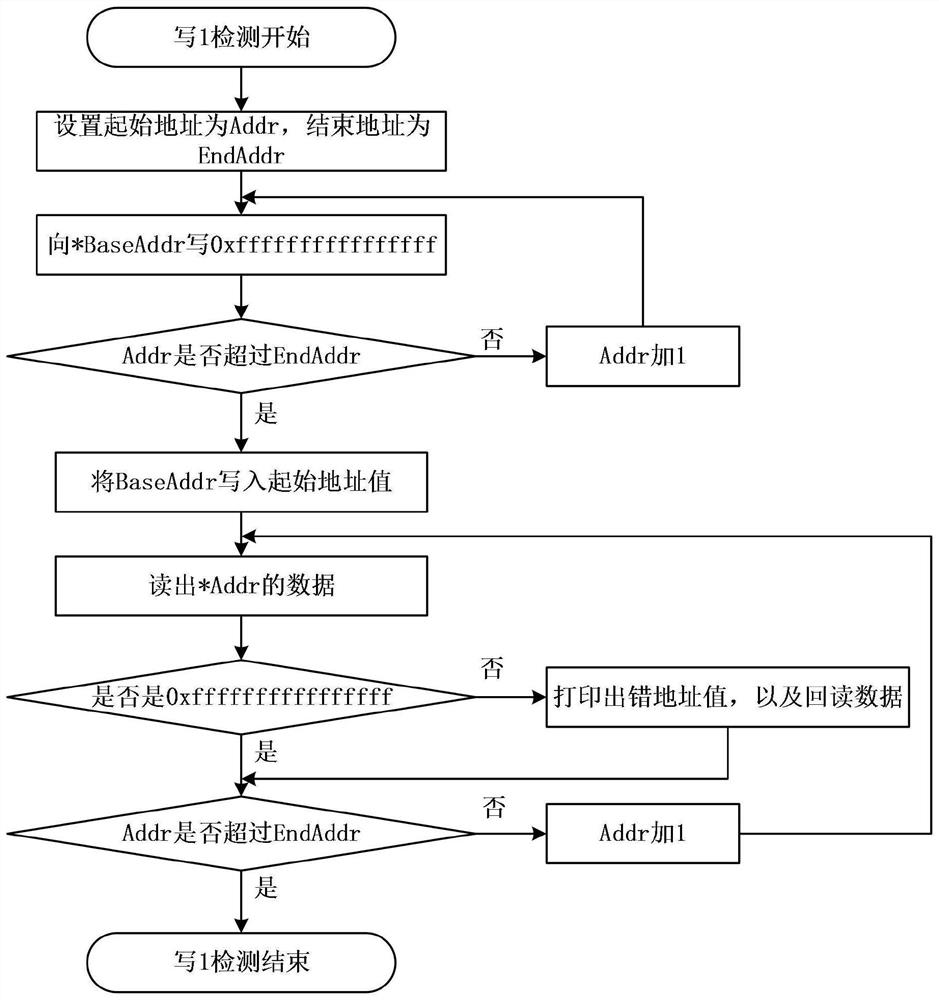

Computer system memory detection method and system independent of operating system

PendingCN113407372ADetect connection problemsDetection constant 0Faulty hardware testing methodsNon-redundant fault processingOperational systemTerm memory

According to the computer system memory detection method and system independent of the operating system, a memory detection program is written into a computer system memory through JTAG equipment, so that the computer system memory can run in the initial starting stage of the computer system, namely, the execution of a solidified code segment of the computer system is finished after basic hardware is initialized and before a bootloader runs; and the memory is circularly detected for multiple times in three modes of writing 0 and 1 into the memory and writing the processed address value and performing backward reading. The memory detection method provided by the invention can be applied to a scene that a computer operating system cannot work or does not have an operating system, can quickly and accurately detect whether the problem of connection of the address line and the data line exists in the memory equipment or not, and can detect the problems of constant 0, constant 1 and short circuit of the address line and the data line of the memory equipment.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

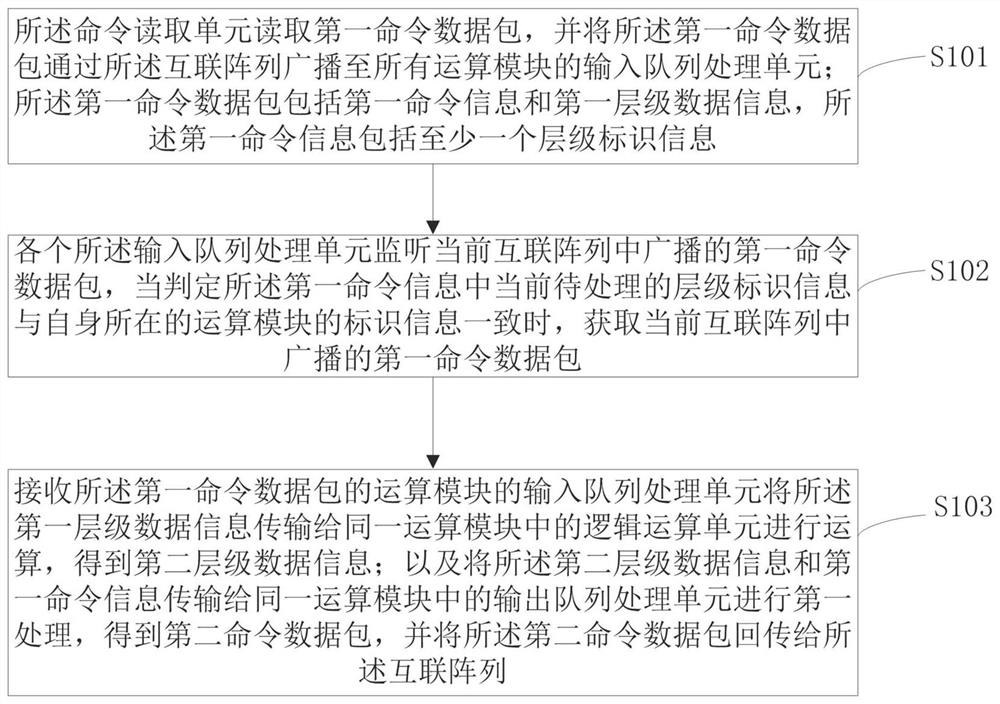

Operation acceleration method and circuit for SSD (Solid State Disk) main control chip with high flexibility and low bandwidth

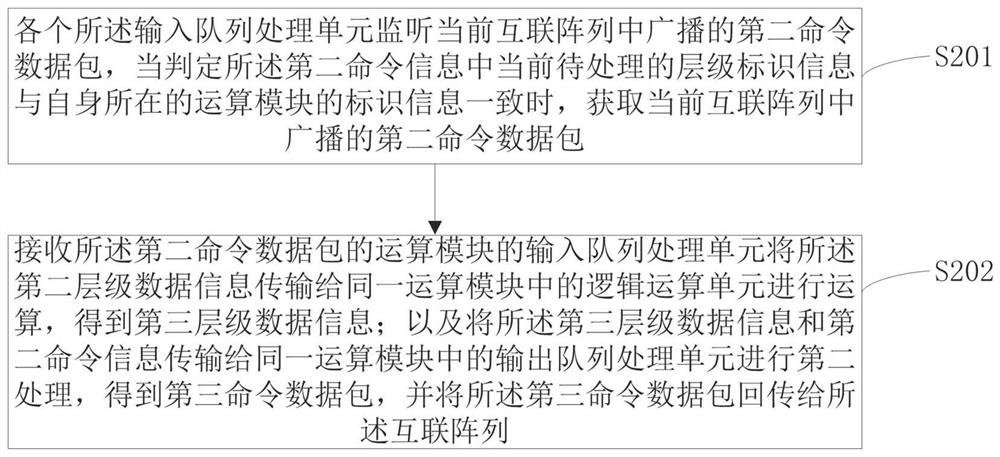

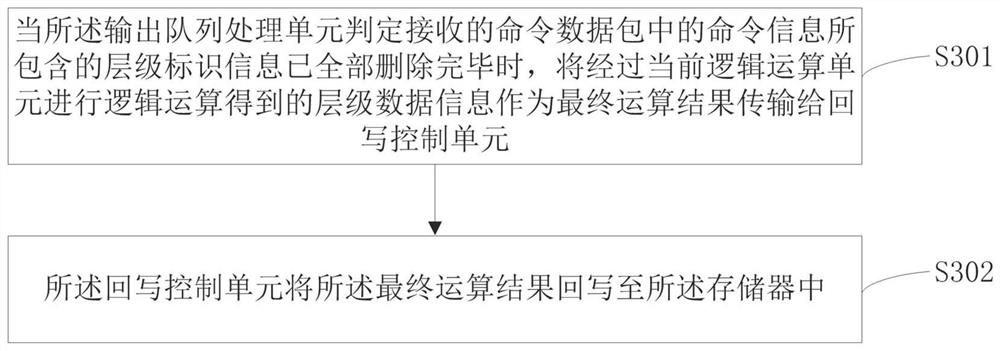

PendingCN112835553AImprove efficiencyIncrease flexibilityDigital data processing detailsArchitecture with single central processing unitData packLogical operations

The invention discloses an operation acceleration method and circuit for SSD main control chip with high flexibility and low bandwidth. The circuit comprises an interconnection array, an operation array and a memory, the operation array comprises a command reading unit, a write-back control unit and a plurality of operation modules; each operation module comprises an input queue processing unit, a logic operation unit and an output queue processing unit; according to the scheme, all the logic operation units are connected through the interconnection array, each operation module automatically sends the operation result to the next operation module through the interconnection array after completing the corresponding logic operation of the operation module, and the final operation result is stored in the memory through the writing control unit after all the operations are completed; and backward reading is carried out through the command reading unit. When different logical operations need to be carried out, only the command data packets of the corresponding levels need to be edited and input into the acceleration circuit, so that the efficiency and the flexibility of the logical operations are greatly improved.

Owner:深圳安捷力特新技术有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com