SRAM type FPGA turnover fault injection device and fault injection method

A fault injection and device technology, applied in fault hardware testing methods, detecting faulty computer hardware, instruments, etc., can solve the problems of low reliability of test results, unreal fault models, and complex equipment, and achieve test results. Real and reliable, low cost, flexible configuration effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

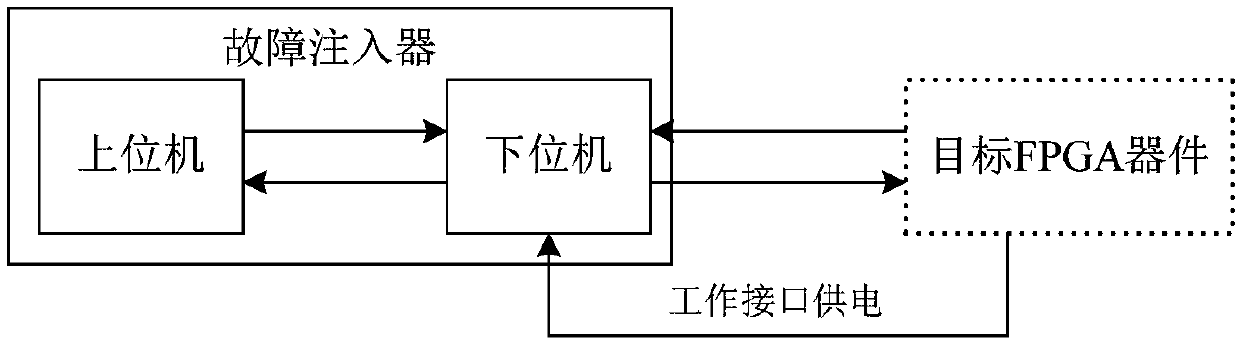

[0045] This embodiment provides a kind of SRAM type FPGA flipping fault injector, its structure is as follows figure 1 As shown, the fault injector includes:

[0046] Upper computer, lower computer. The lower computer is provided with a working interface, and the working interface communicates with the fault injection interface of the target FPGA device. The upper computer and the lower computer communicate through the Ethernet protocol, such as UDP protocol, TCP protocol and other communications.

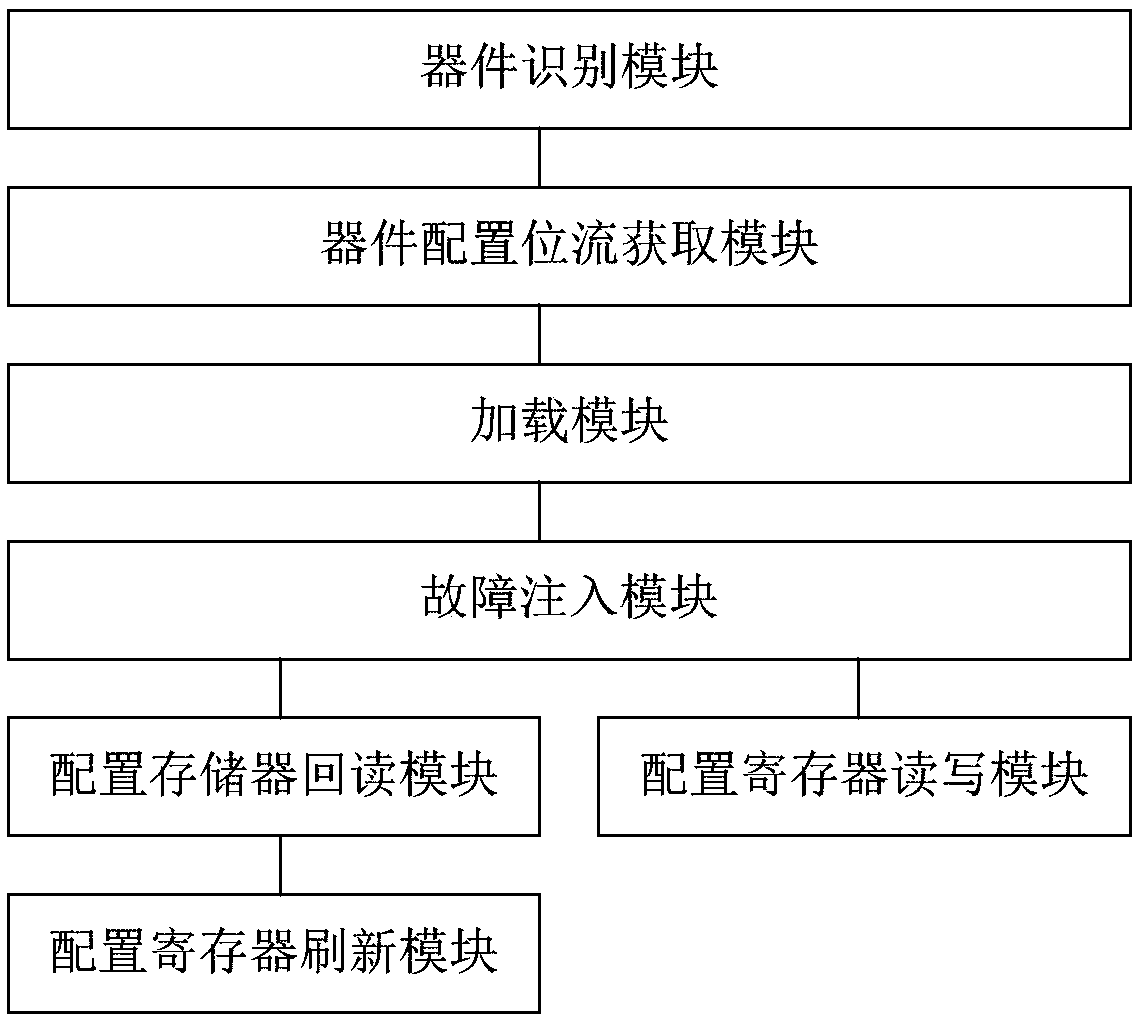

[0047] The upper computer is used for parameter setting, configuration bit stream generation, and instruction sending; the lower computer is responsible for performing related operations. The upper computer sends a device identification request command, and determines the corresponding device model according to the target FPGA device ID fed back by the lower computer; and instructs the lower computer to implement fault injection on the target FPGA device through the fault injection...

Embodiment 2

[0142] Embodiment 2 of the present invention also provides a SRAM type FPGA flipping fault injection method, the specific implementation process of which is the same as that of the fault injector in Embodiment 1, and will not be described in detail here.

[0143] In the second embodiment above, step S60-step S70 may not be included. In this case, the fault injection method lacks the function of reading back and refreshing the configuration memory of the target FPGA device.

[0144] Step S80 may also not be included in the second embodiment above. In this case, the fault injection method lacks the function of reading and writing configuration registers of the target FPGA device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com