The realization method of aerospace fpga general refresh circuit based on selectmap

An implementation method and circuit technology, applied in the direction of logic circuits using basic logic circuit components, logic circuits using specific components, etc., can solve problems such as internal function disorder, connection short circuit, function failure, etc., to achieve a complete state and improve the circuit Reliable, practical results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

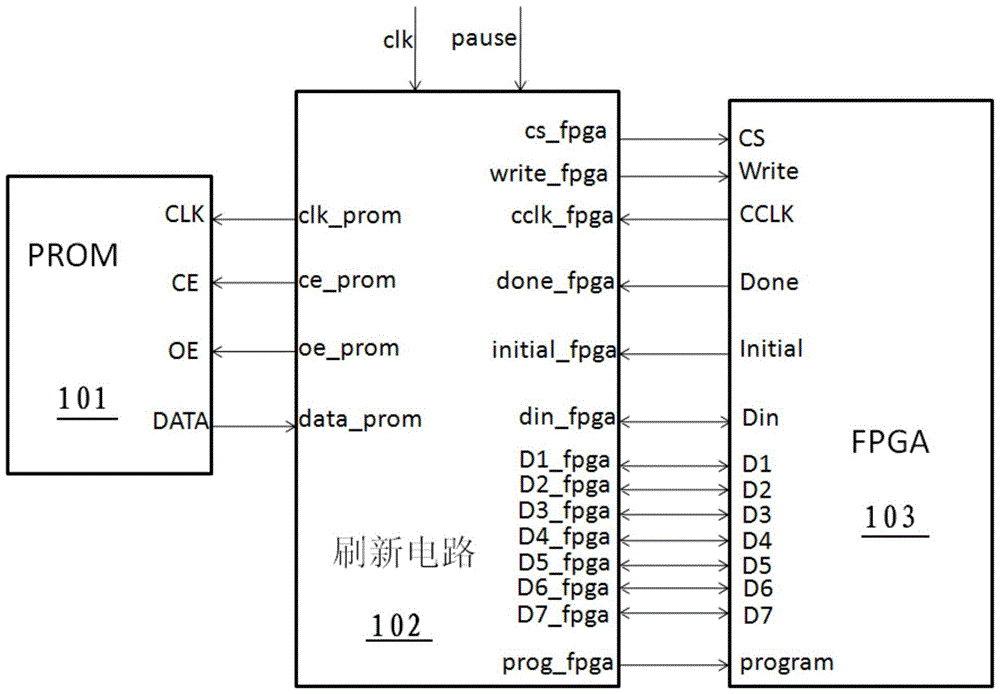

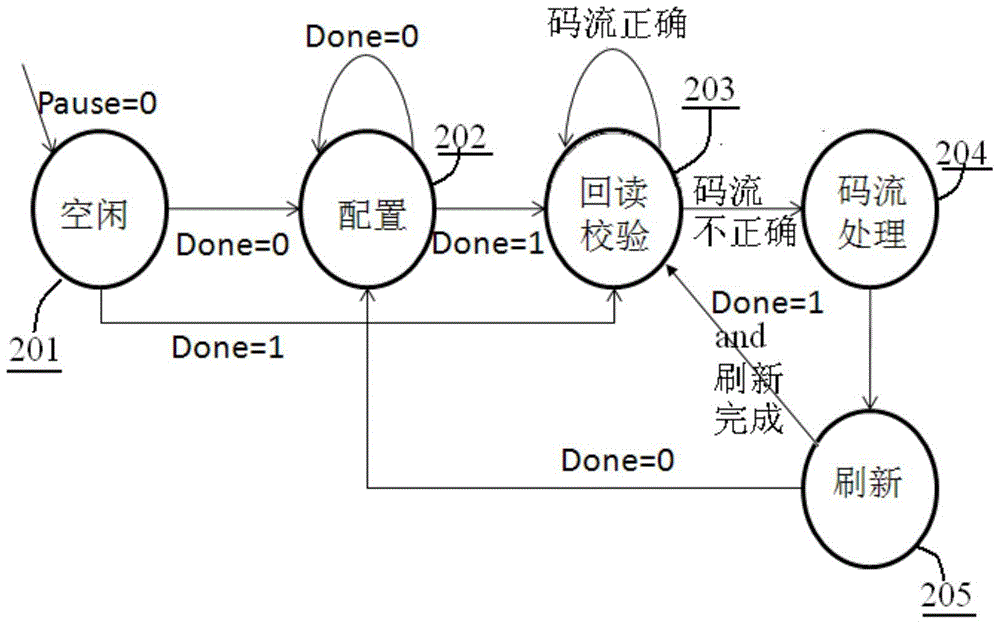

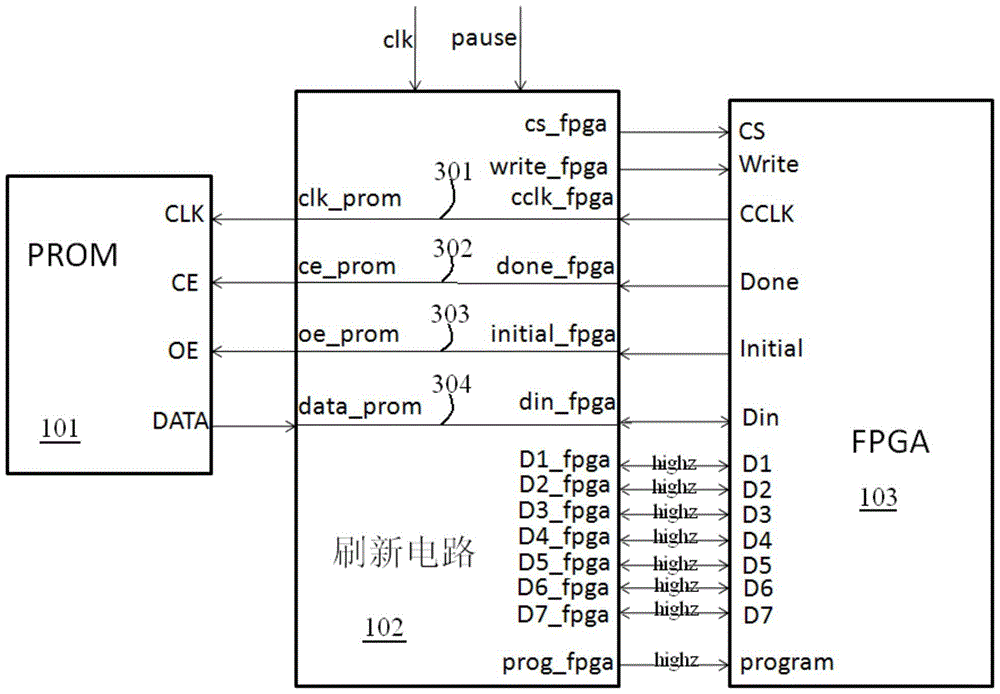

[0071] After power-on, connect the pause pin of the refresh circuit 102 to the "0" level, then the refresh circuit 102 suspends work, enters and remains in the idle state 201; in the idle state, the refresh circuit, such as image 3 Shown is a schematic diagram of the internal wiring and pin level of the refresh circuit of the present invention in the idle state, connecting the internal wiring 301, 302, 303, 304, and connecting the corresponding pins of PROM101 and FPGA103 together, that is, the CLK tube of PROM101 The pin is connected to the CCLK pin of FPGA103, the CE pin of PROM101 is connected to the Done pin of FPGA103, the OE pin of PROM101 is connected to the Initial pin of FPGA103, and the DATA pin of PROM101 is connected to the Din pin of FPGA103; at the same time, the refresh circuit 102 D1_fpga pins, D2_fpga pins, D3_fpga pins, D4_fpga pins, D5_fpga pins, D6_fpga pins, D7_fpga pins, cs_fpga pins, write_fpga pins, and prog_fpga output are in a high impedance state. At ...

Embodiment 2

[0073] After power-on, the pause pin of the refresh circuit 102 is connected to the "1" level, the clk pin is connected to a fixed-frequency clock signal, and the input signal of the done_fpga pin is detected. If the refresh circuit 102 detects that the done_fpga level is "0", the refresh circuit 102 will enter the configuration state 202, otherwise it will directly jump to the readback verification state 203. In the configuration state 202, such as image 3 , The refresh circuit 102 connects the internal wires 301, 302, 303, 304, and connects the corresponding pins of PROM101 and FPGA103, that is, the CLK pin of PROM101 is connected to the CCLK pin of FPGA103, and the CE pin of PROM101 is connected to Done of FPGA103. The OE pin of PROM101 is connected to the Initial pin of FPGA103, and the DATA pin of PROM101 is connected to the Din pin of FPGA103; in the FPGA configuration process, the Done pin of FPGA103 that has not been configured is output as "0" level. The CCLK pin will...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com