Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90results about How to "Smooth waveform" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Heart-sound detecting apparatus and pulse-wave-propagation-velocity-relating-information obtaining system using the heart-sound detecting apparatus

InactiveUS6845263B2Accurately determineAccurately determinedElectrocardiographyStethoscopeBiological bodyHeart sounds

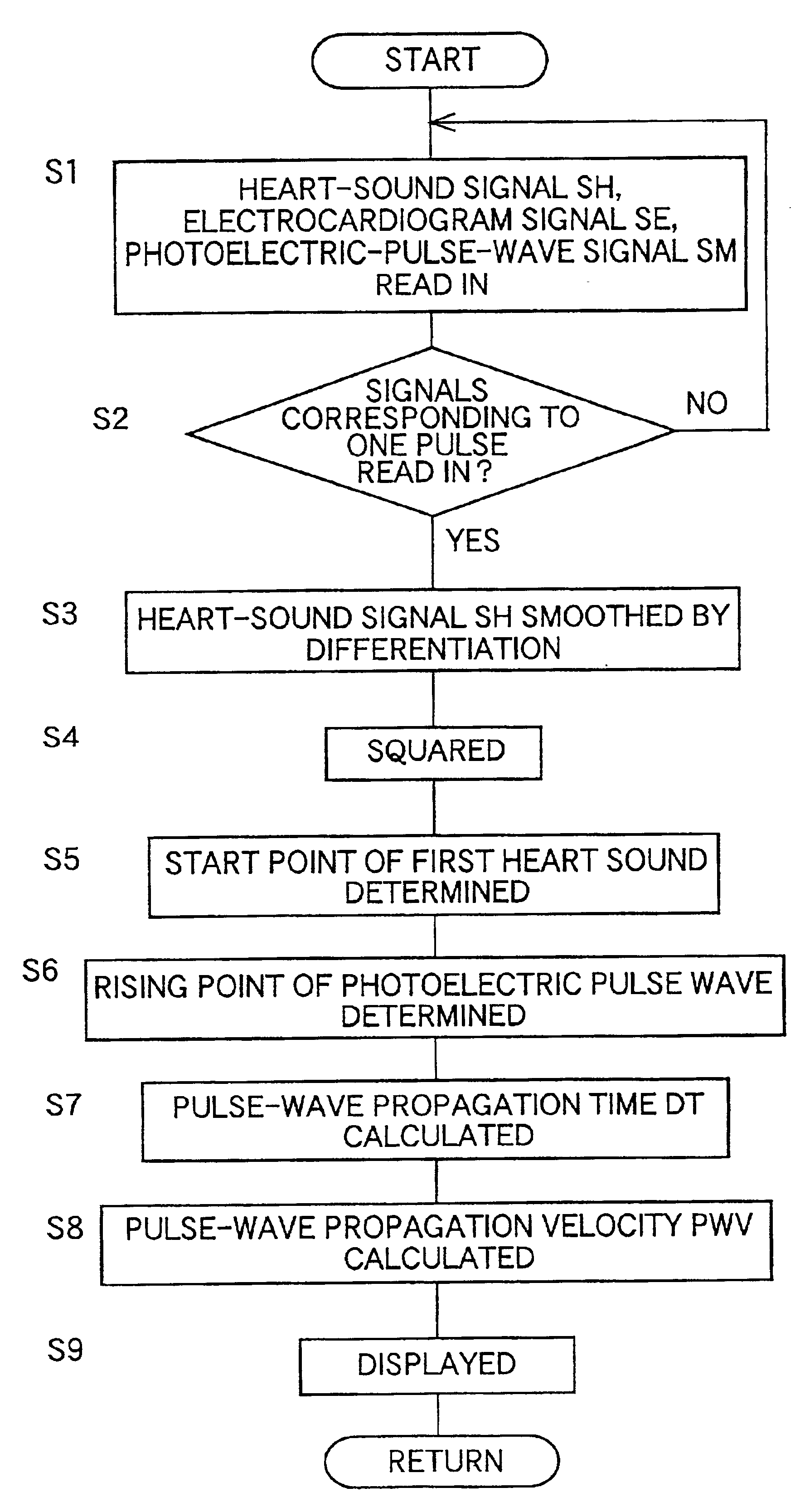

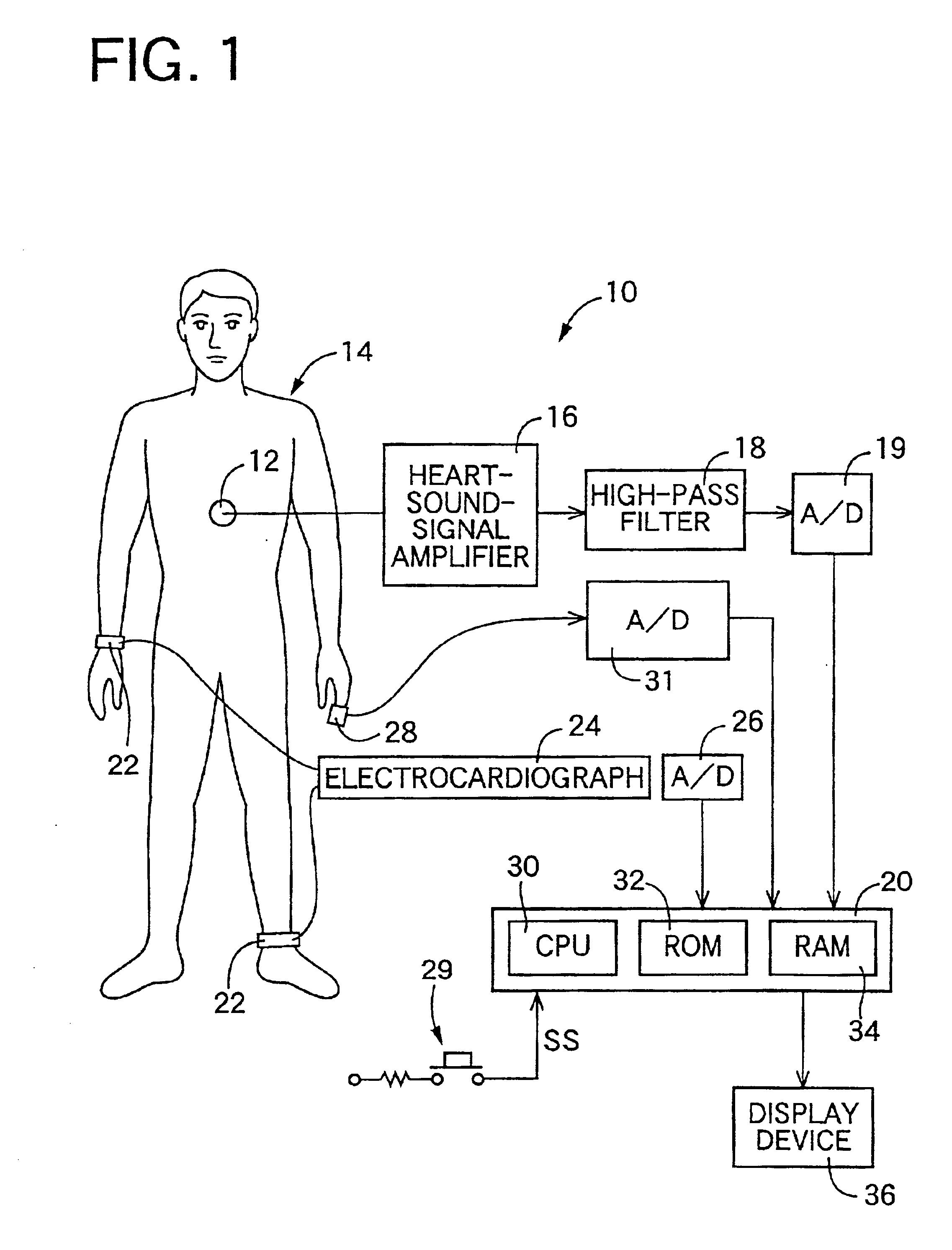

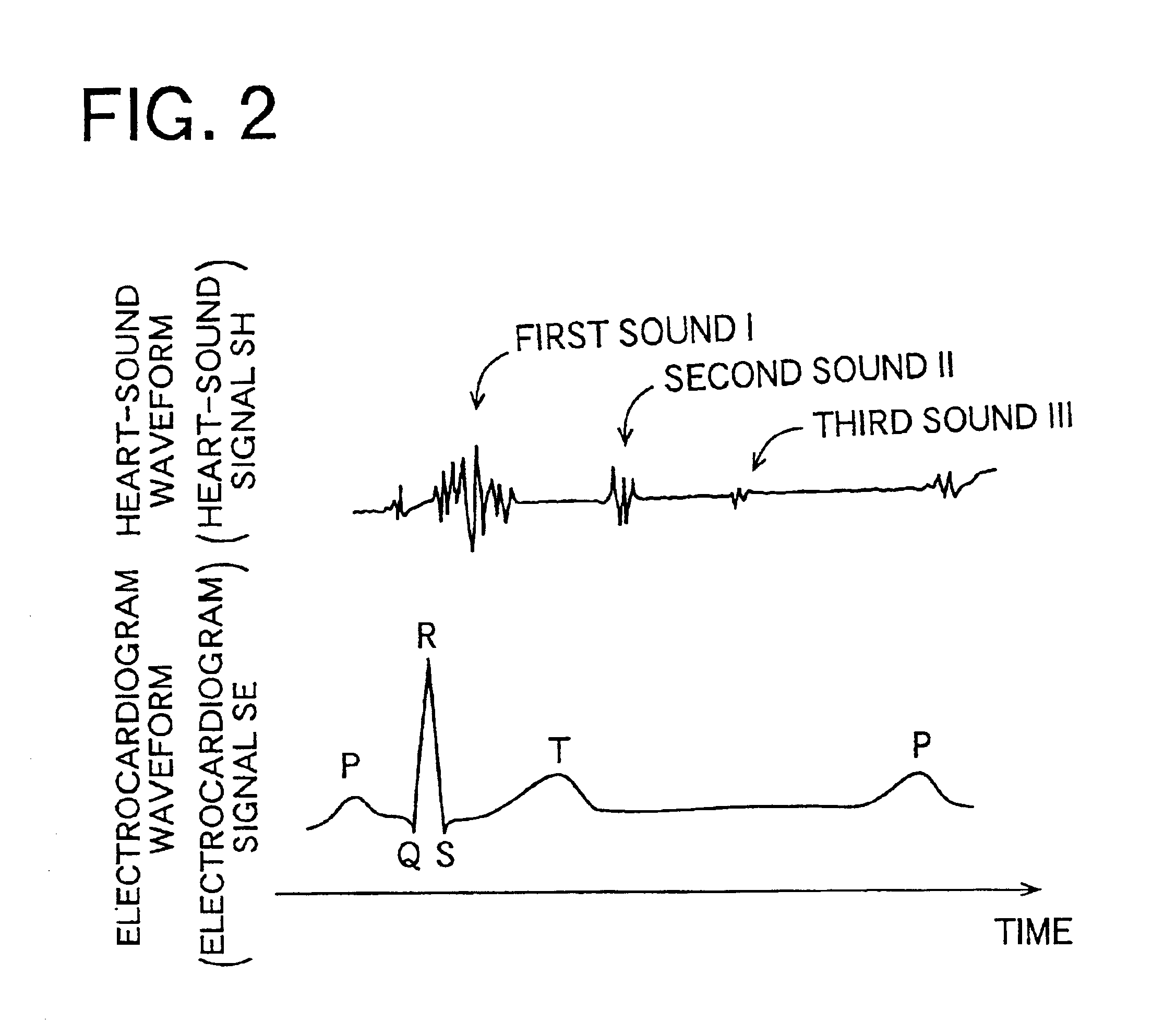

A heart-sound detecting apparatus, including: a heart-sound microphone which detects a plurality of heart sounds produced by a heart of a living subject and outputs a heart-sound signal representative of the detected heart sounds; a smoothing device for smoothing, by differentiation, a waveform of the heart-sound signal output from the heart-sound microphone; a squaring device for squaring an amplitude of the smoothed waveform with respect to a base line of the heart-sound signal; and a start-point determining device for determining a start point of a first heart sound I as one of the detected heart sounds, based on that the squared amplitude is greater than a prescribed threshold value.

Owner:OMRON HEALTHCARE CO LTD

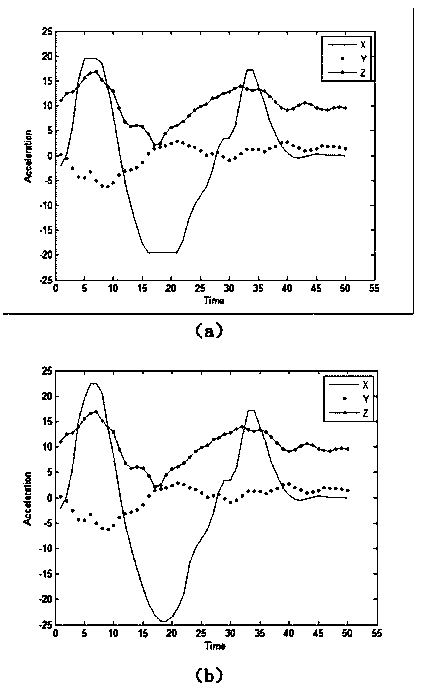

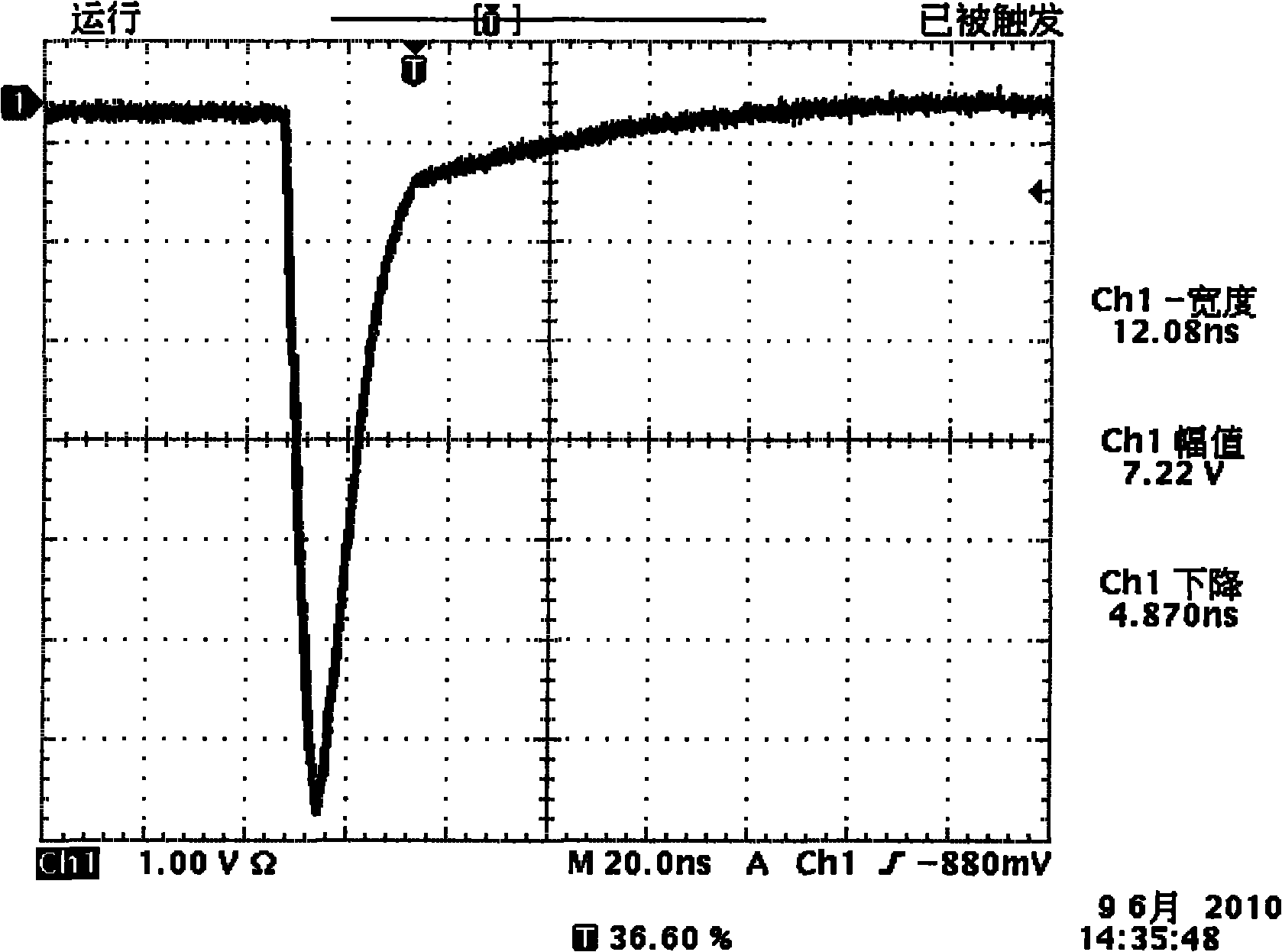

Gesture recognition method based on acceleration sensor

InactiveCN103984416ASmooth waveformWaveform Regularization and UnificationInput/output for user-computer interactionCharacter and pattern recognitionAdaptive matchingCompressed sensing

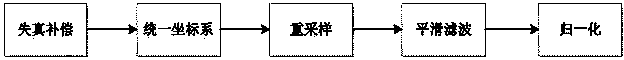

The invention discloses a gesture recognition method based on an acceleration sensor. The gesture recognition method based on an acceleration sensor comprises the following steps: automatically collecting gesture acceleration data, preprocessing, calculating the similarity of all gesture sample data so as to obtain a similarity matrix, extracting a gesture template, constructing a gesture dictionary by utilizing the gesture template, and carrying out sparse reconstruction and gesture classification on the gesture sample data to be recognized by adopting an MSAMP (modified sparsity algorithm adaptive matching pursuit) algorithm. According to the invention, the compressed sensing technique and a traditional DTW (dynamic time warping) algorithm are combined, and the adaptability of the gesture recognition to different gesture habits is improved, and by adopting multiple preprocessing methods, the practicability of the gesture recognition method is improved. Additionally, the invention also discloses an automatic collecting algorithm of the gesture acceleration data; the additional operation of traditional gesture collection is eliminated; the user experience is improved; according to the invention, a special sensor is not required, the gesture recognition method based on the acceleration sensor can be used for terminals carried with the acceleration sensor; the hardware adaptability is favorable, and the practicability of the recognition method is enhanced. The coordinate system is uniform, and can be adaptive to different multiple gesture habits.

Owner:BEIJING UNIV OF POSTS & TELECOMM

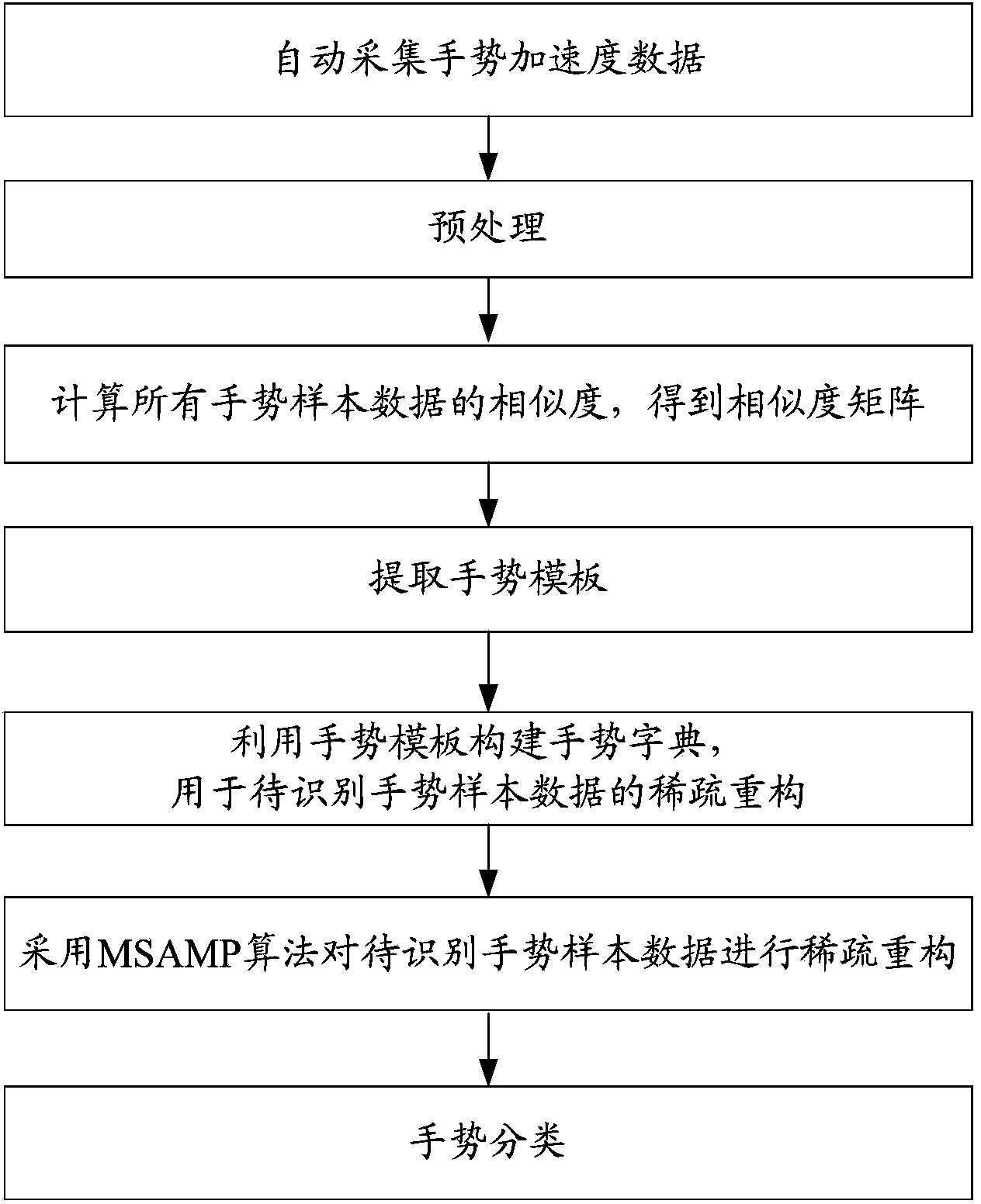

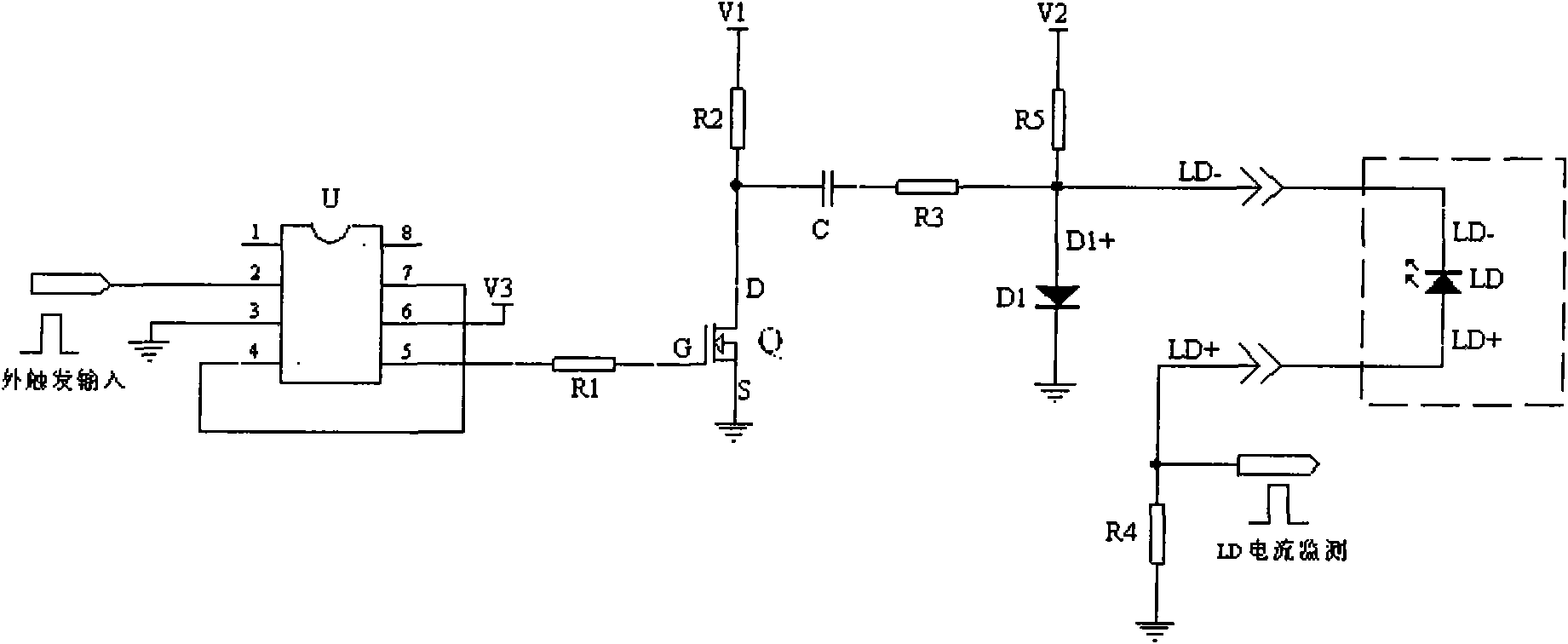

High-speed narrow pulse modulation driving power supply for semiconductor laser

ActiveCN101895058AHigh frequencyCutting edge fastLaser detailsLaser output parameters controlCapacitanceMOSFET

The invention discloses a high-speed narrow pulse modulation driving power supply for a semiconductor laser. The high-speed narrow pulse modulation driving power supply comprises a semiconductor laser driving circuit and a high-precision temperature control circuit, wherein the semiconductor laser driving circuit adopts a high-speed MOSFET as a switch. The driven semiconductor laser can output the required laser pulse with high frequency, quick advancing front, narrow pulse width, controllable pulse peak and smooth waveform according to the parameters of the semiconductor laser by changing the power supply voltage, resistance and capacitance in the driving power supply circuit.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

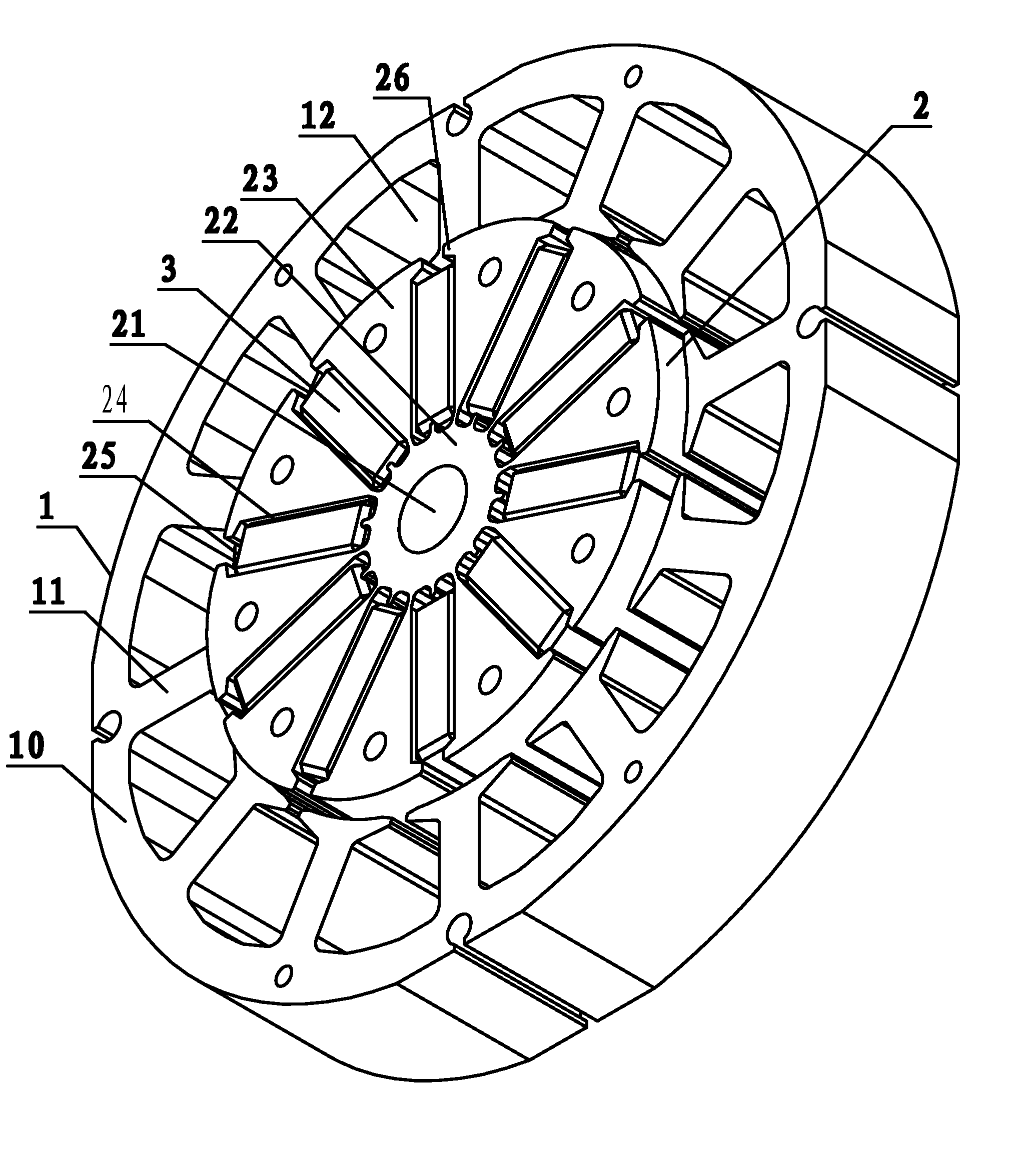

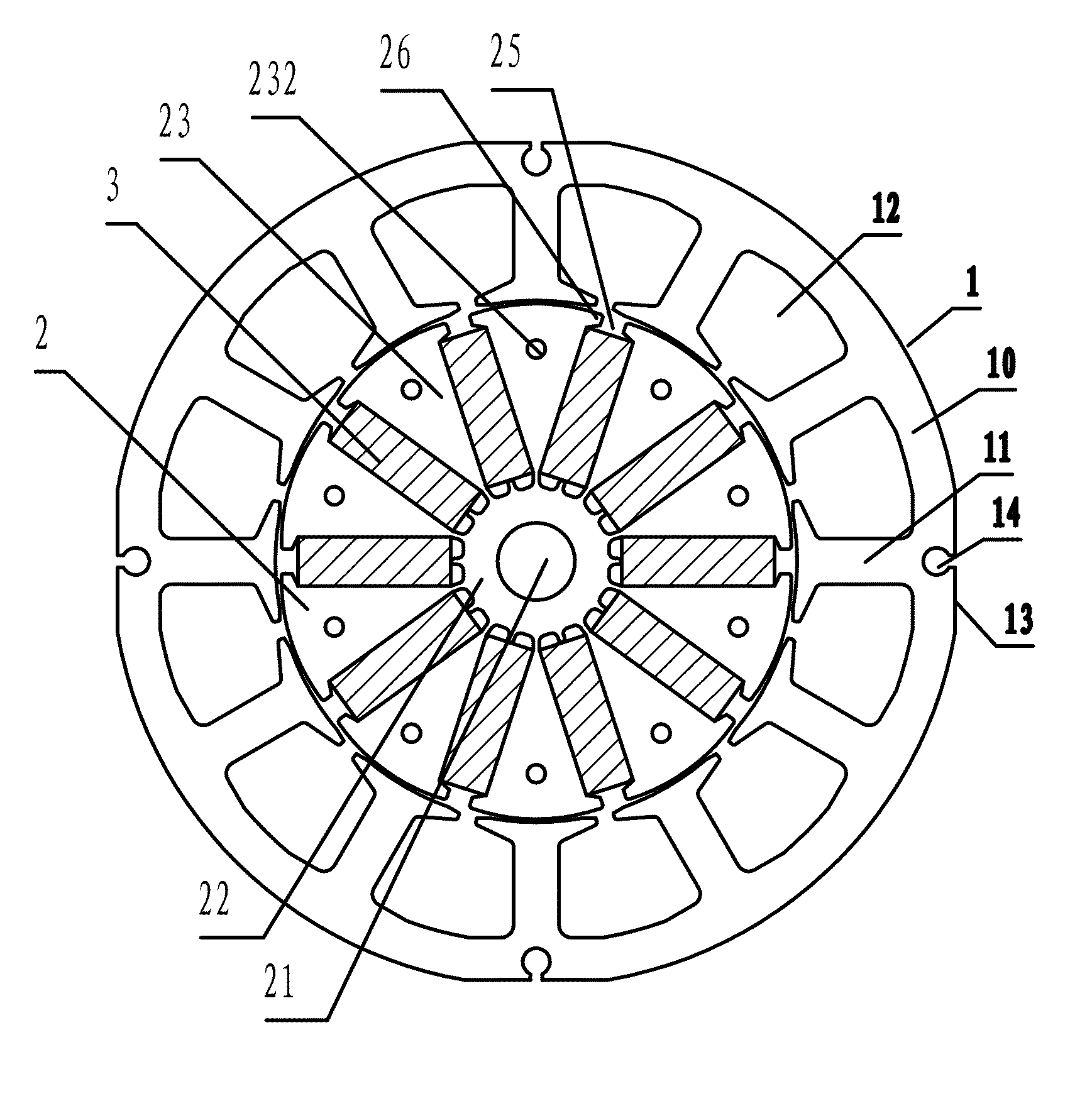

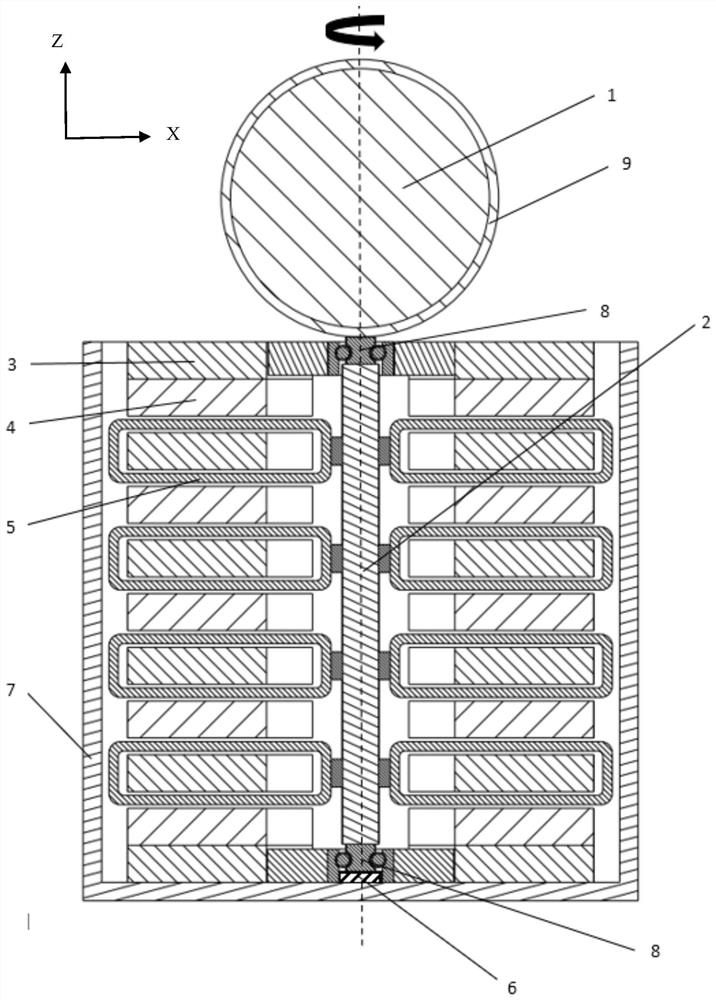

Motor

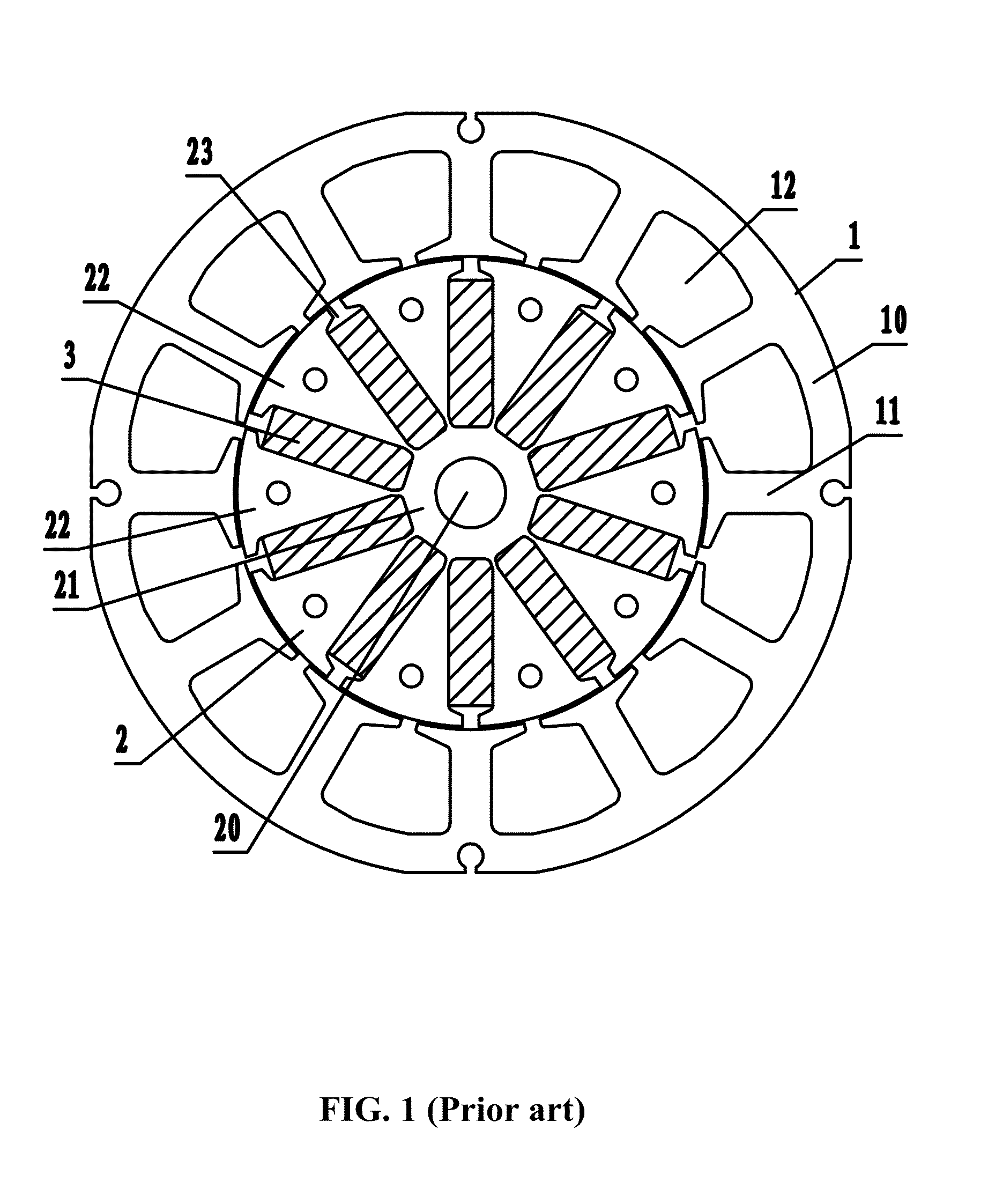

InactiveUS20130038162A1Simple structureSmall sizeMagnetic circuit rotating partsSynchronous machines with stationary armatures and rotating magnetsEngineeringConductor Coil

A motor including a stator assembly and a rotor assembly. The stator assembly includes a stator core and a winding; the stator core includes a yoke and a plurality of teeth protruding inwards from the yoke; between two adjacent teeth formed is a winding slot; the winding is arranged in the winding slot, and winded on the teeth. The rotor assembly includes a rotor core and a permanent magnet. The rotor core includes an annular ring having a central axial bore and a plurality of magnetic induction blocks protruding outwards from an outer side of the annular ring. Between two adjacent magnetic induction blocks formed is a radial recess for mounting the permanent magnet. The magnetic induction blocks at both sides of an opening of the radial recess protrude with a hook block. The thickness of the rotor core is larger than that of the stator core.

Owner:ZHONGSHAN BROAD OCEAN MOTOR MFG

Non-contact method for detecting physiological signal and motion in real time

ActiveUS20170007185A1Reduce in quantityImprove accuracyOptical sensorsMeasuring/recording heart/pulse rateSkin complexionSkin color

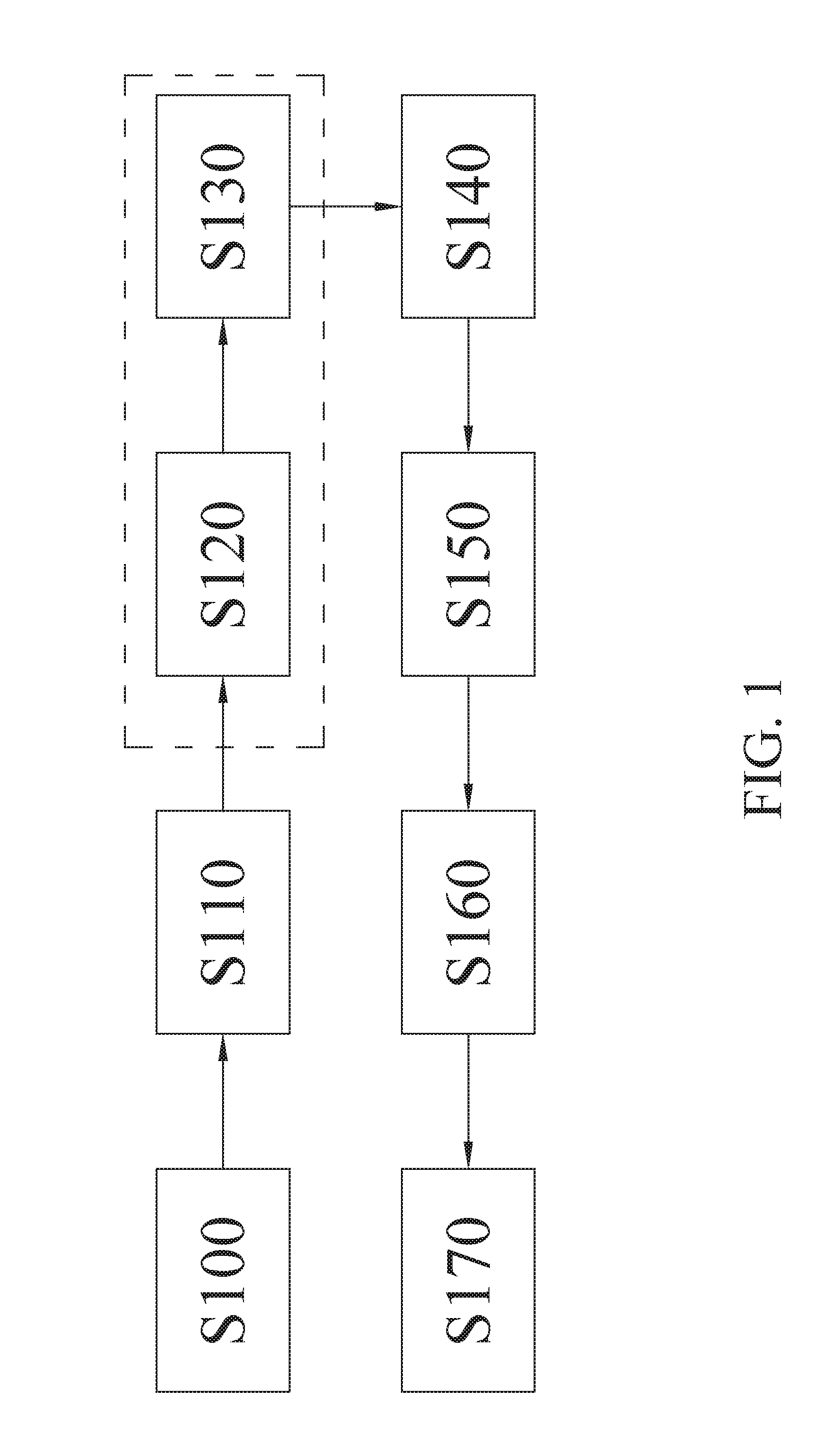

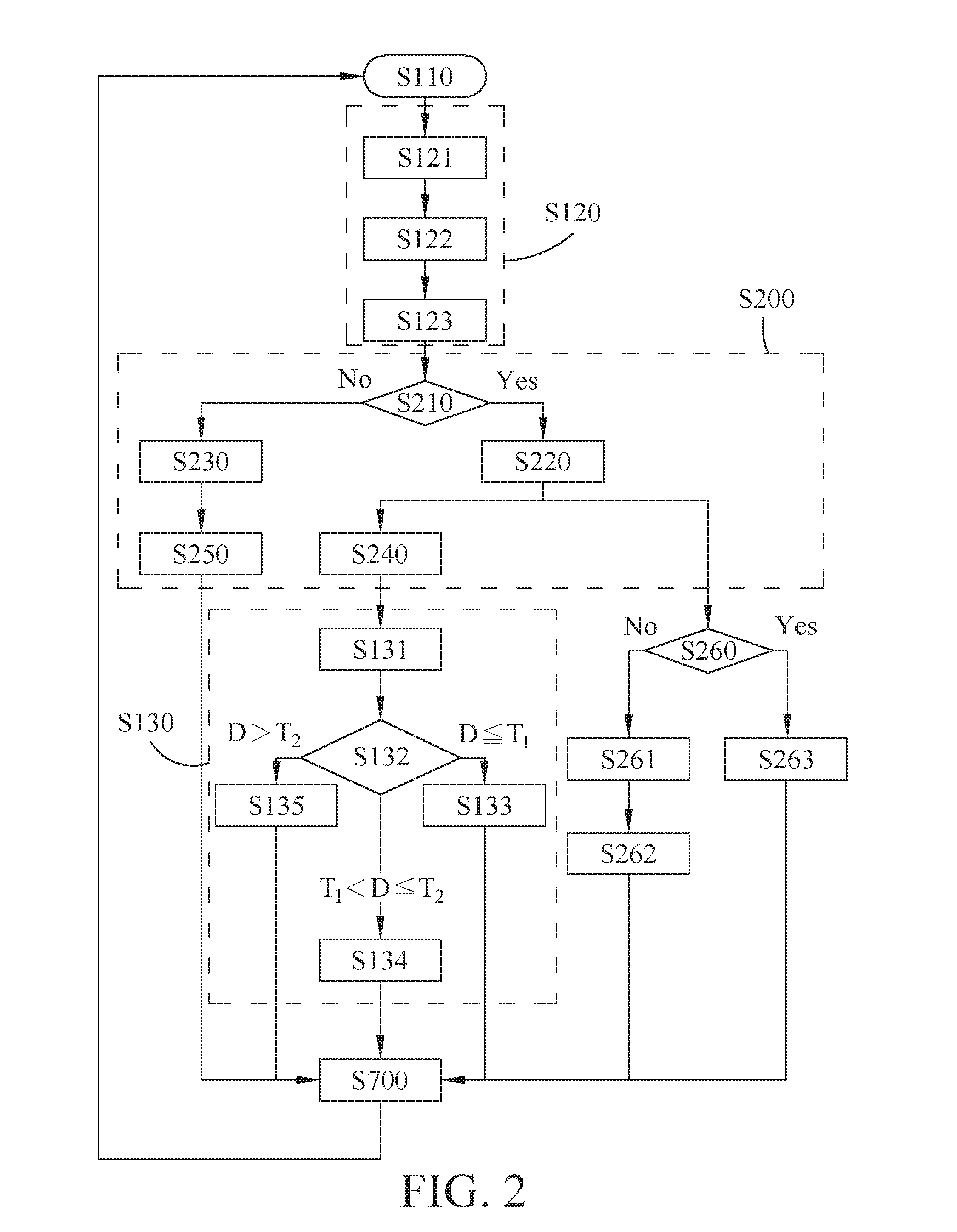

A non-contact method for detecting physiological signals and motion in real time comprises: sensing a portion of a human body to generate a series of image frames by an optical sensing element; determining a complexion region from each of the image frames; then calculating a central coordinate of the complexion region; determining a sample block by expanding a surrounding range from the central coordinate, for getting a complexion fluctuation waveform; comparing said central coordinate with a central coordinate of a later image frame, to calculate a displacement in a unit time for determining whether the portion of the human body is in a static state. In the static state, an operating unit performs noise filter and peak detecting for complexion fluctuation waveform, and calculates a physiological signal. Said method can reduce the amount of data required to be processed in physiological signal detection, and improve the accuracy of the detection.

Owner:NAT TAIWAN UNIV OF SCI & TECH

Dual-frequency receiving antenna and dual-frequency rectifying antenna

InactiveCN103474778AImprove matchHigh gainSimultaneous aerial operationsAntenna earthingsDual frequencyCircuit reliability

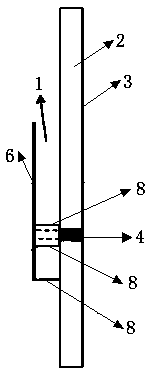

The invention discloses a dual-frequency receiving antenna and a dual-frequency rectifying antenna. The dual-frequency receiving antenna and the dual-frequency rectifying antenna are used for solving the problems that an existing dual-frequency receiving antenna is large in size and small in gain, an existing dual-frequency rectifying antenna is large in size, can not receive weak energy and is not suitable for remote transmission, and a rectifying circuit is poor in reliability. The dual-frequency receiving antenna comprises a rectangular radiating patch. A Z-type groove used for achieving dual-frequency characteristics is formed in the radiation patch. The lower end of the radiation patch is sequentially connected with a dielectric substrate layer and a metal earth plate through a coaxial line. The coaxial line is in circuit connection with the rear end of the radiation patch. An air dielectric layer is formed between the radiation patch and the dielectric substrate layer. The portions, arranged between the radiation patch and the dielectric substrate layer, outside the coaxial line are provided with metal sheets in a bilaterally-symmetric mode. The upper ends of the metal sheets are connected with the radiation patch. The lower ends of the metal sheets are connected with the dielectric substrate layer. One end face of the radiation patch is further connected with the metal sheets connected with the dielectric substrate layer. The dual-frequency receiving antenna and the dual-frequency rectifying antenna can be widely applied in the fields of communication, medical treatment, industry and the like, for microwave power transmission.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

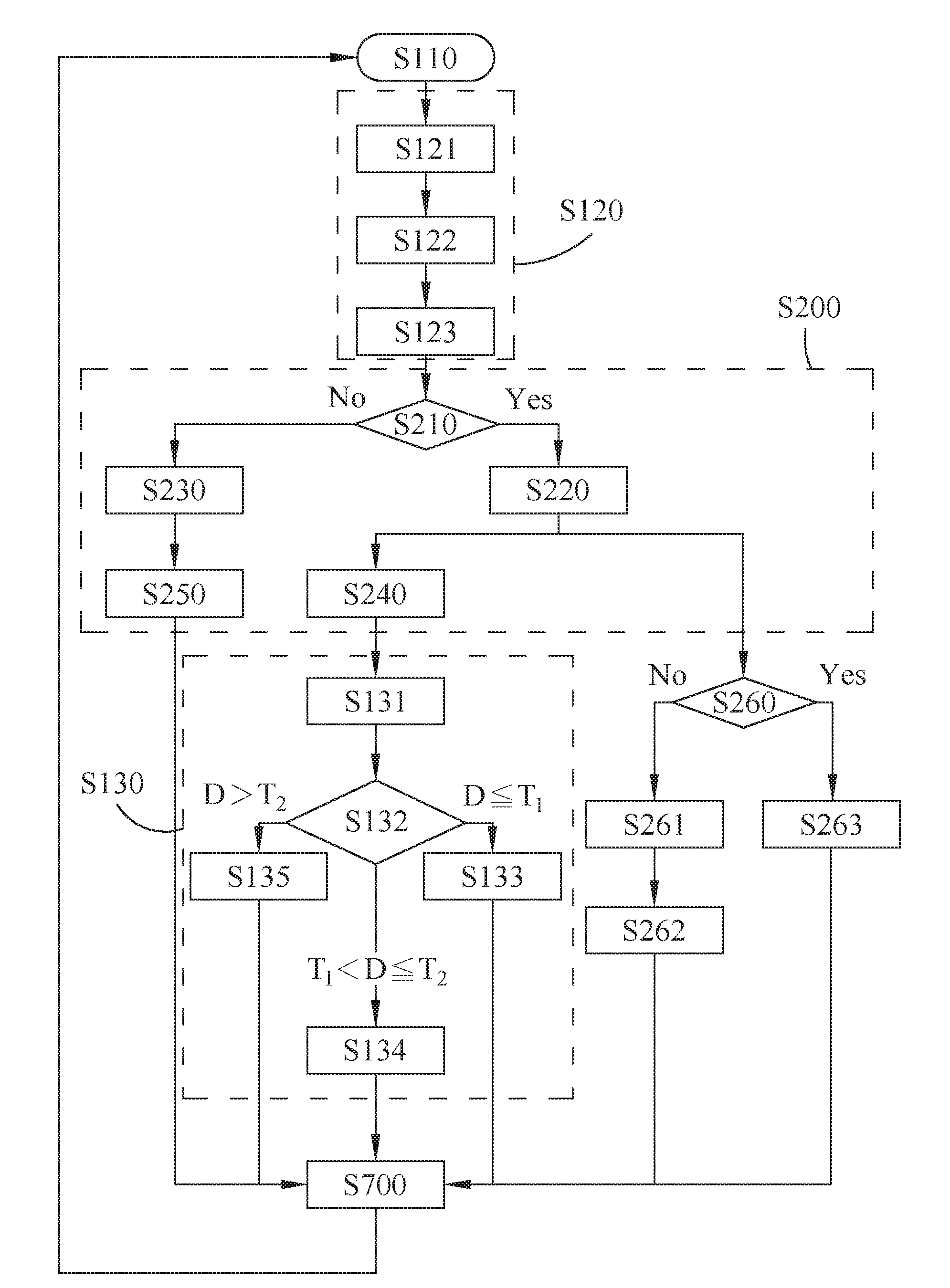

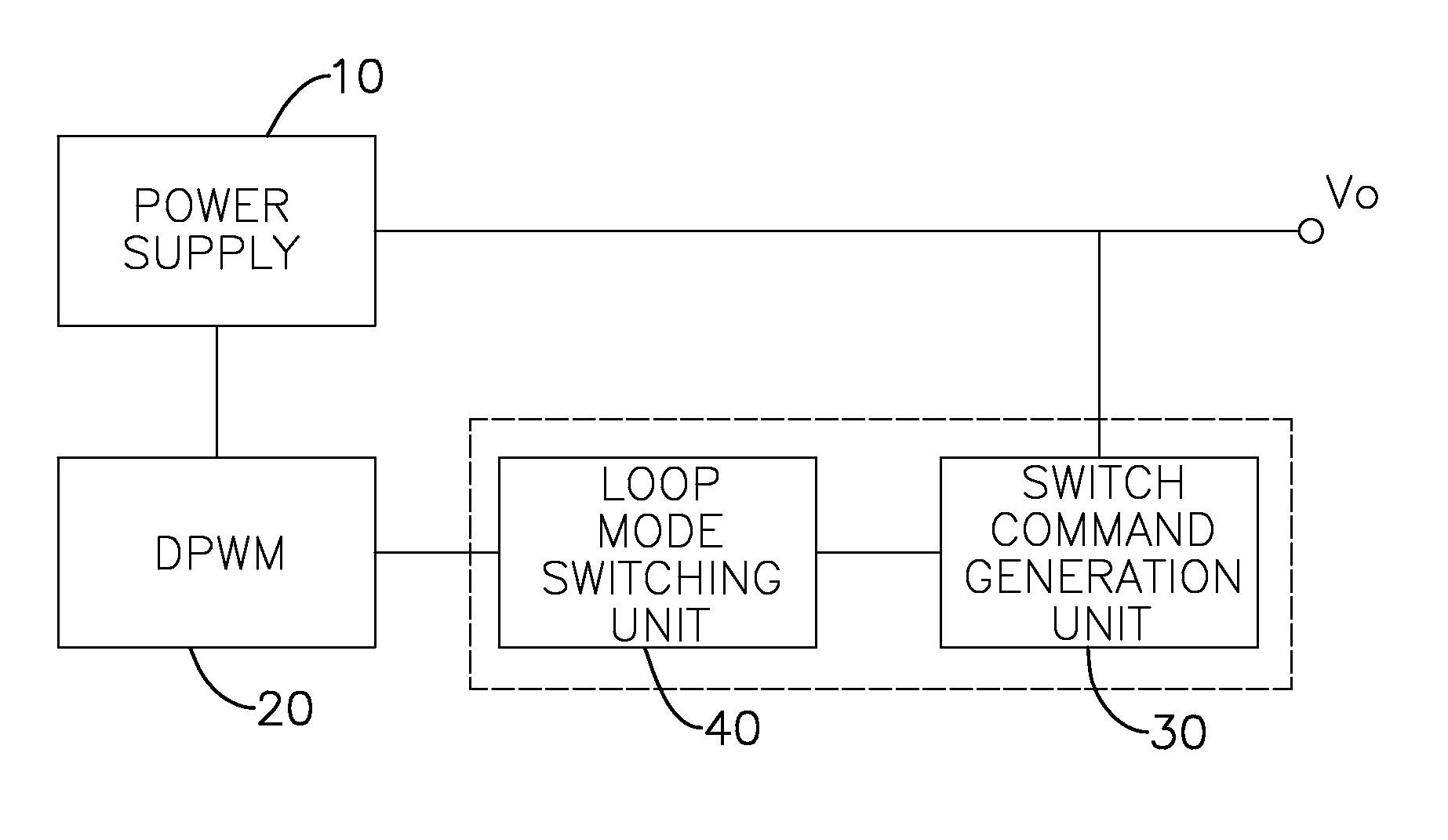

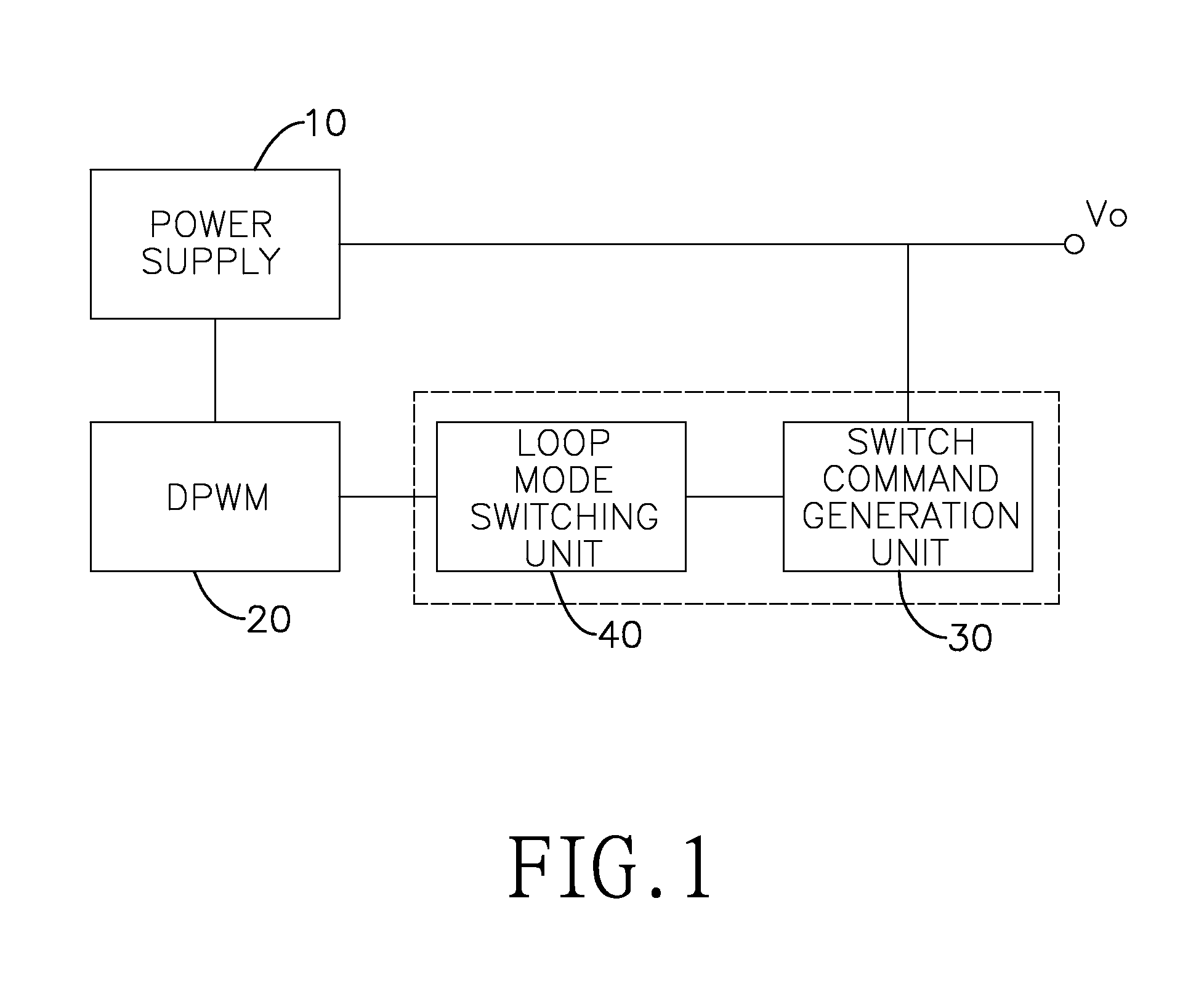

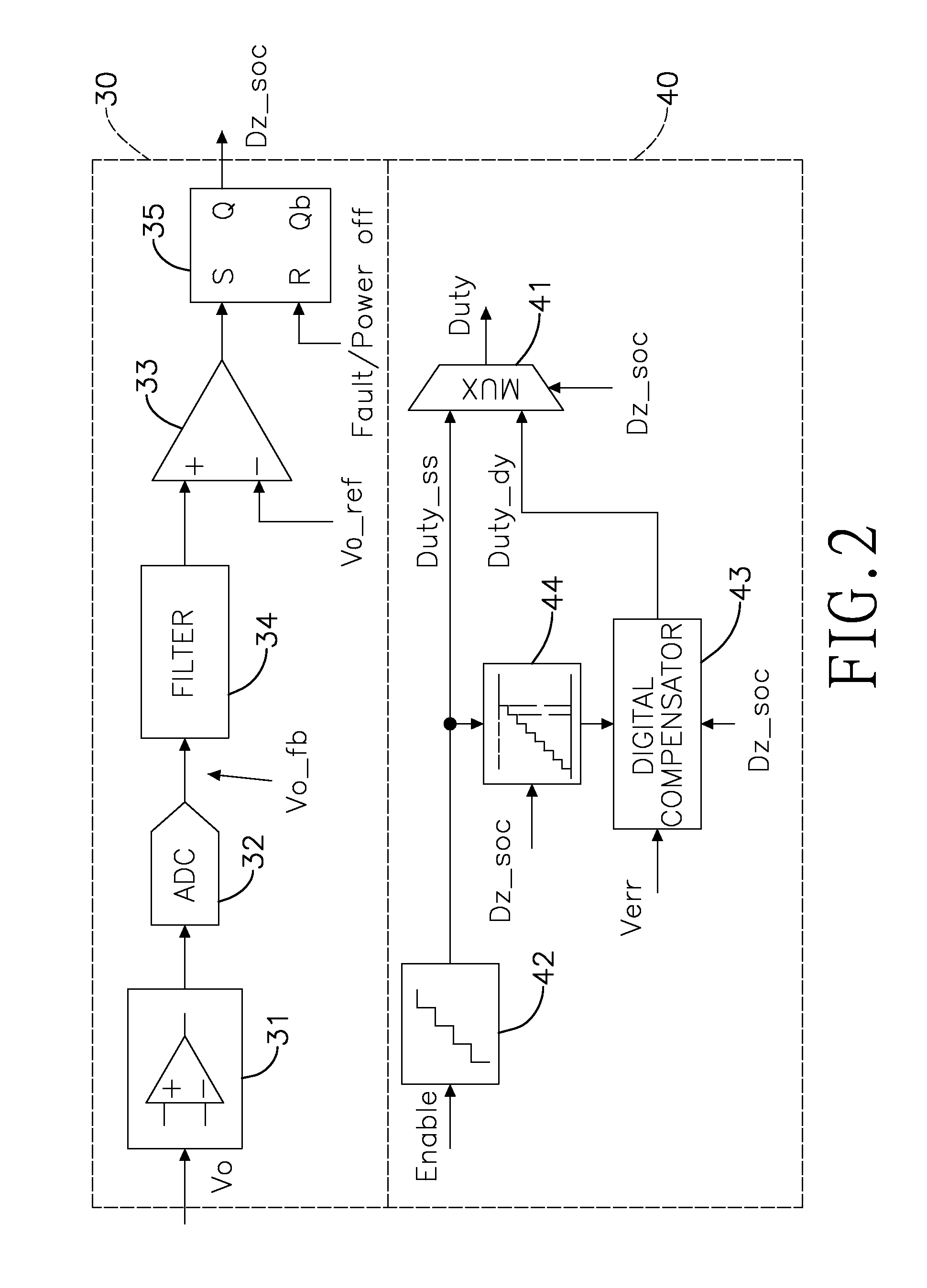

Method and device for controlling soft start of a power supply

InactiveUS20130106370A1Efficient integrationImproving bit length utilization rateDc-dc conversionAc network voltage adjustmentDigital dataLoop control

A method for controlling soft start of a power supply performs soft start under an open loop control mode after the power supply is started, enters a switching control mode when output voltage of the power supply reaches a reference value, starts to convert the output voltage of the power supply into digital data using an analog-to-digital converter for determining if the power supply is switched to a closed loop control mode and the output voltage is adjusted under the switching control mode. Using the foregoing technique can enhance the bit length utilization rate of the analog-to-digital converter, ensure a smooth waveform of the output voltage and suppress maximum excess or minimum deficiency or a transient response at the switching control mode.

Owner:ACBEL POLYTECH INC

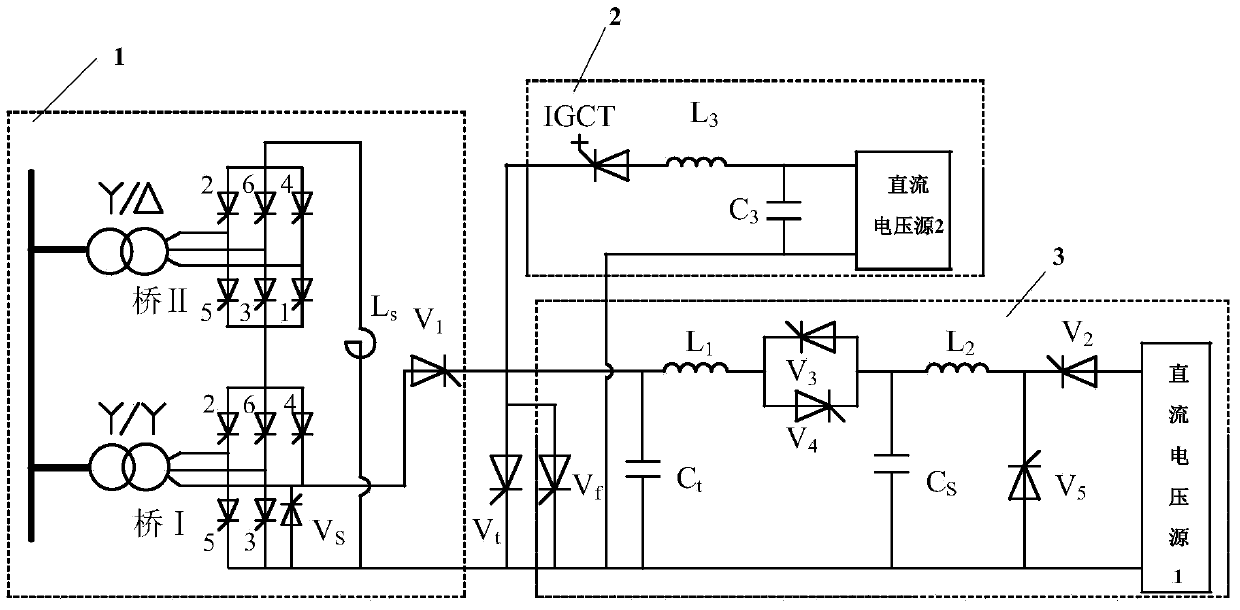

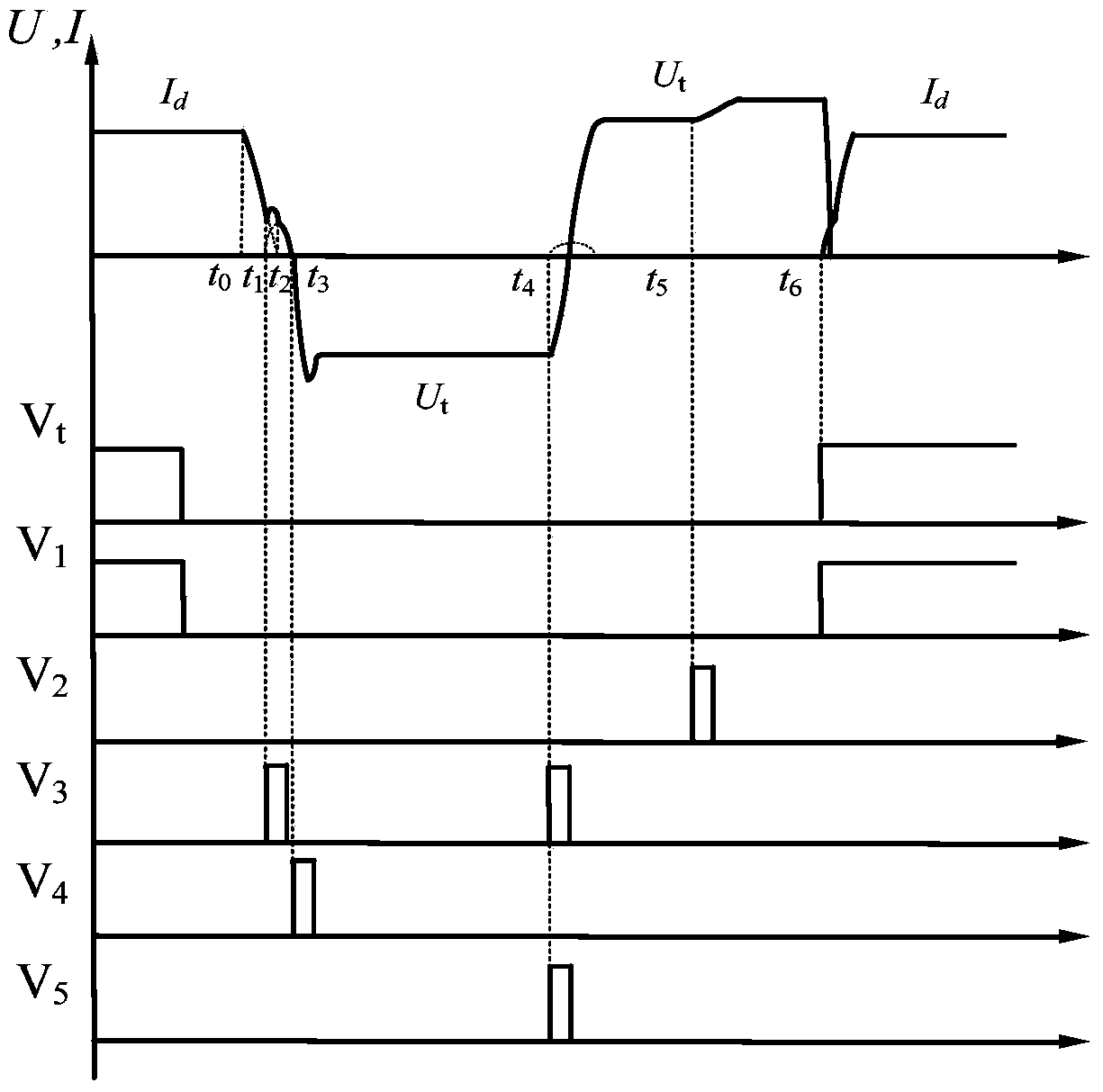

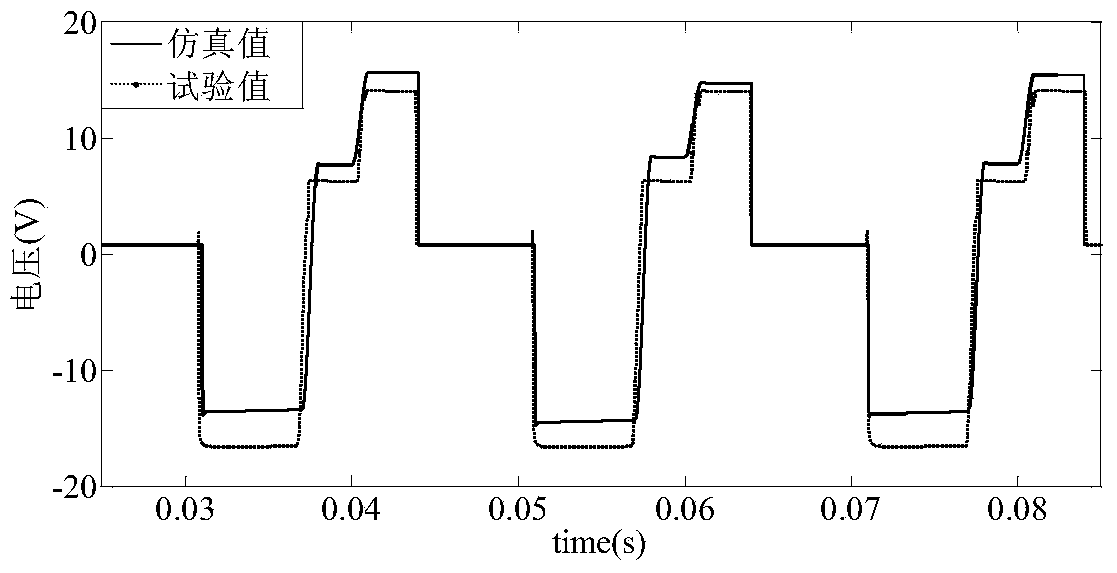

Operation synthesis tester for ultrahigh voltage direct current converter valve

InactiveCN103744017AEasy to adjustTo achieve the purpose of voltage reversalCircuit interrupters testingHigh voltage igbtVoltage loop

The invention relates to an operation synthesis tester for an ultrahigh voltage direct current converter valve, which comprises a 12-pulse wave converter loop, a high voltage loop and a large current loop which are connected two by two, wherein the ultrahigh voltage loop provides a reverse restore voltage and a positive voltage for a valve to be tested; the large current loop provides a large current for flowing the valve to be tested; the 12-pulse wave converter loop provides high voltage, fault overcurrent and direct current intermittent current needed by the valve to be tested. Compared with the prior art, the operation synthesis tester for the ultrahigh voltage direct current converter valve has the advantages of good equivalence, wide applicable range, good economy, high test precision and the like.

Owner:SHANGHAI JIAO TONG UNIV

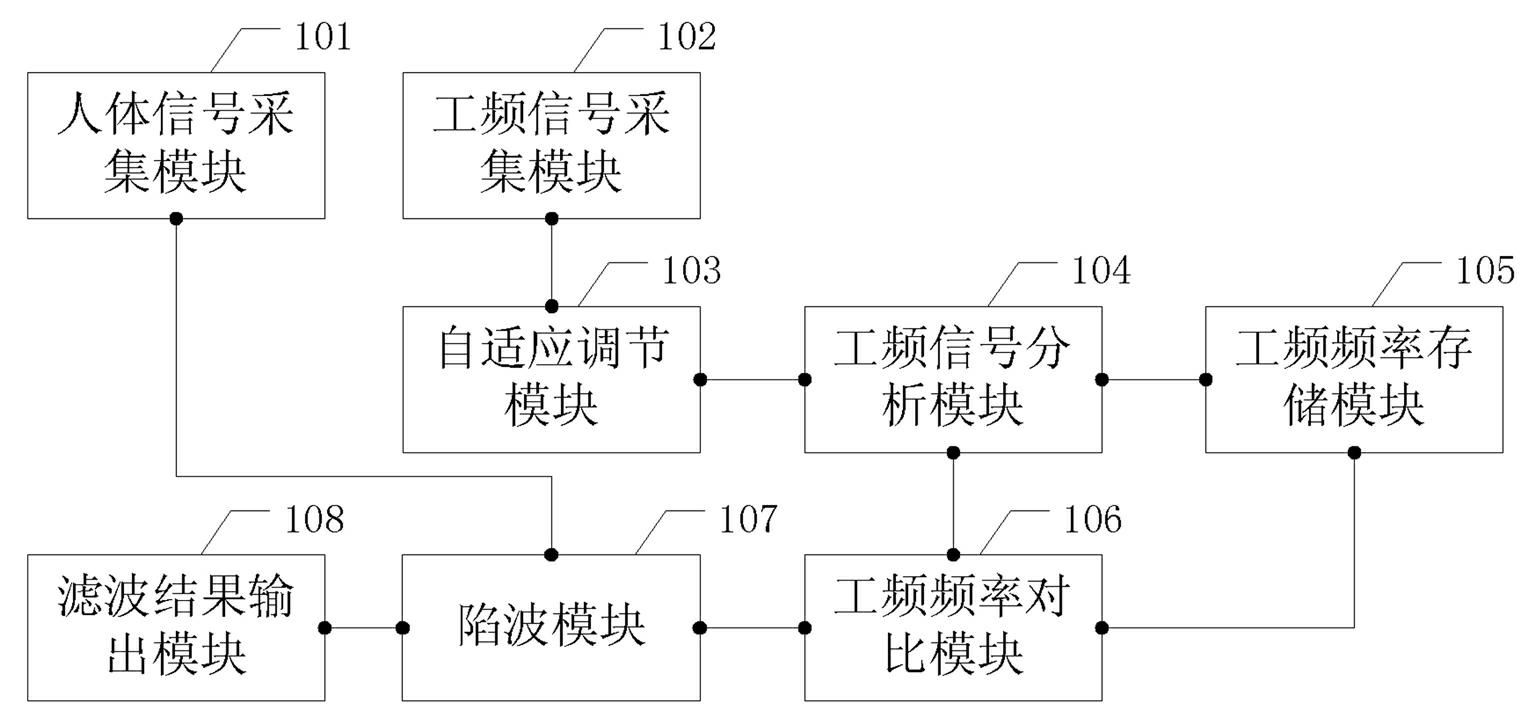

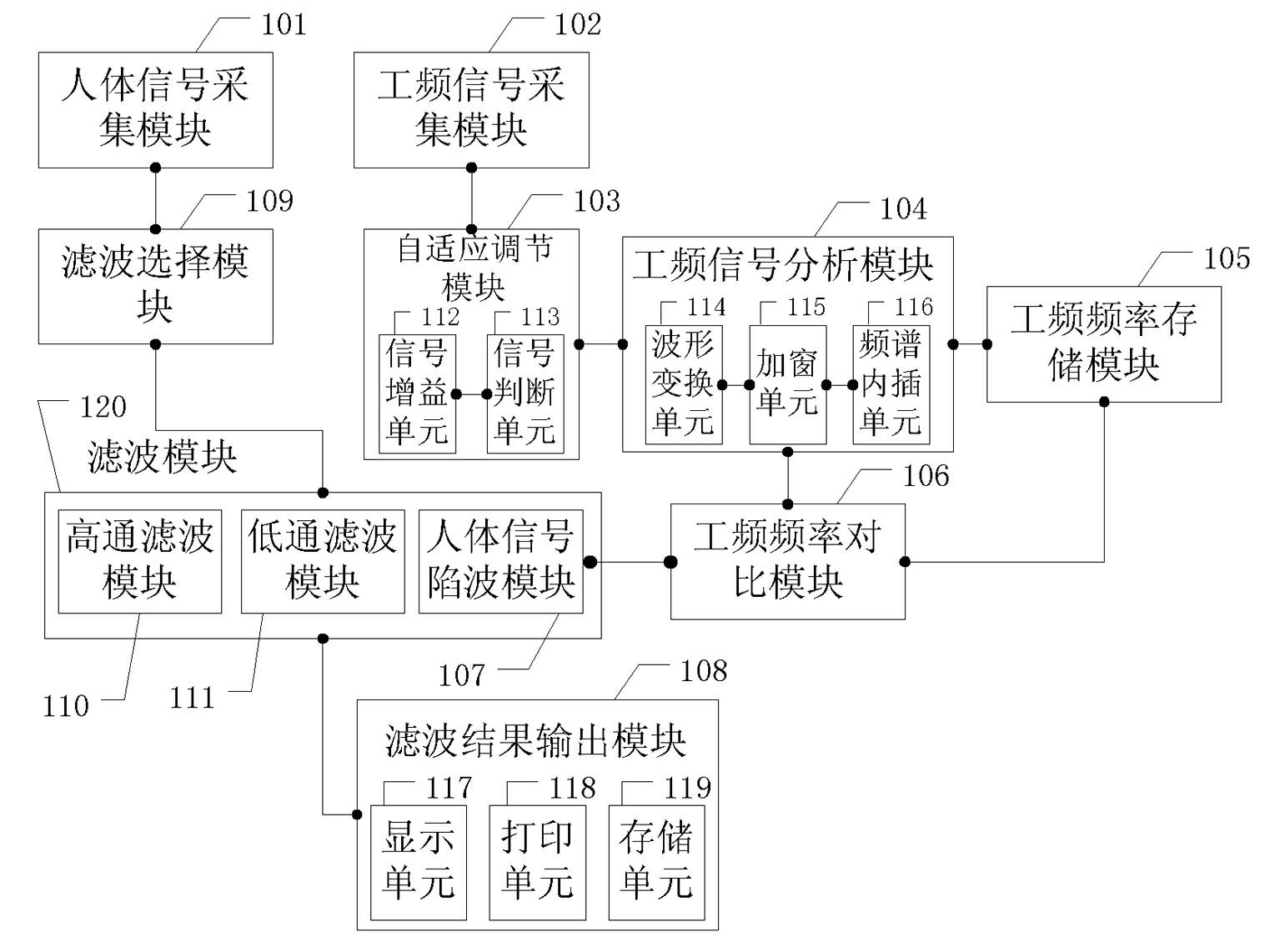

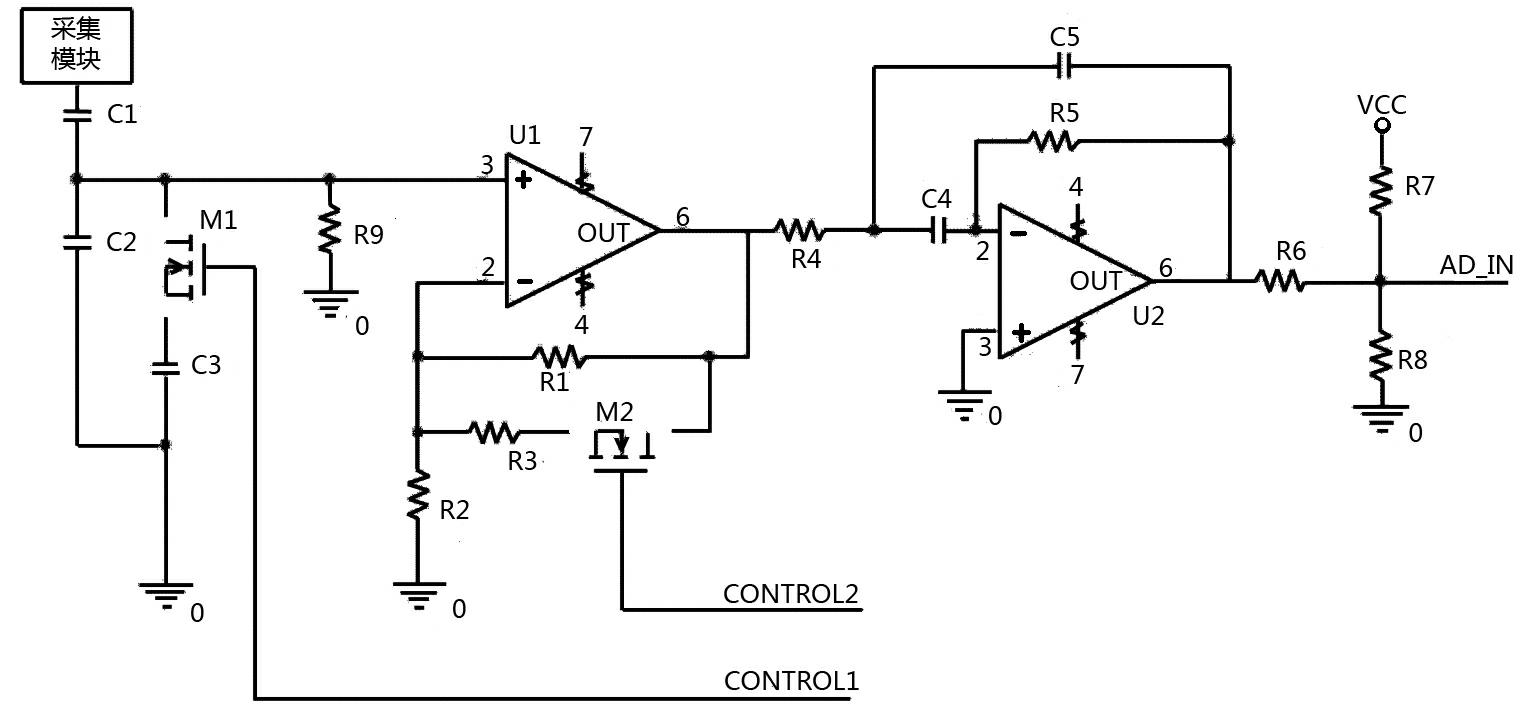

Power frequency digital notch device and method based on frequency track

ActiveCN102176667AAccurate collectionReduce distractionsDigital technique networkUltrasound attenuationSignal on

The invention relates to the technical field of digital notch, in particular relates to a power frequency digital notch device and method based on frequency track. The power frequency digital notch method based on the frequency track comprises the following steps: singly collecting power frequency signals and adaptively regulating, analyzing and comparing; and if a comparison result exceeds a set threshold, regulating the coefficient of a power frequency notch filter, and notching a human signal so as to obtain a filtering result, and outputting the filtering result. According to the method, the space power frequency signal can be correctly acquired in real time, the notch is timely traced, the interference of the power frequency signal on a useful signal is effectively attenuated, and the problems that digital notch attenuation amplitude is in lack because of frequency fluctuation of power frequency and the like are solved. In a clinic application, through the device and the method, a wave form is smooth, which is beneficial to correct diagnosis, thereby avoiding misdiagnosis.

Owner:EDAN INSTR

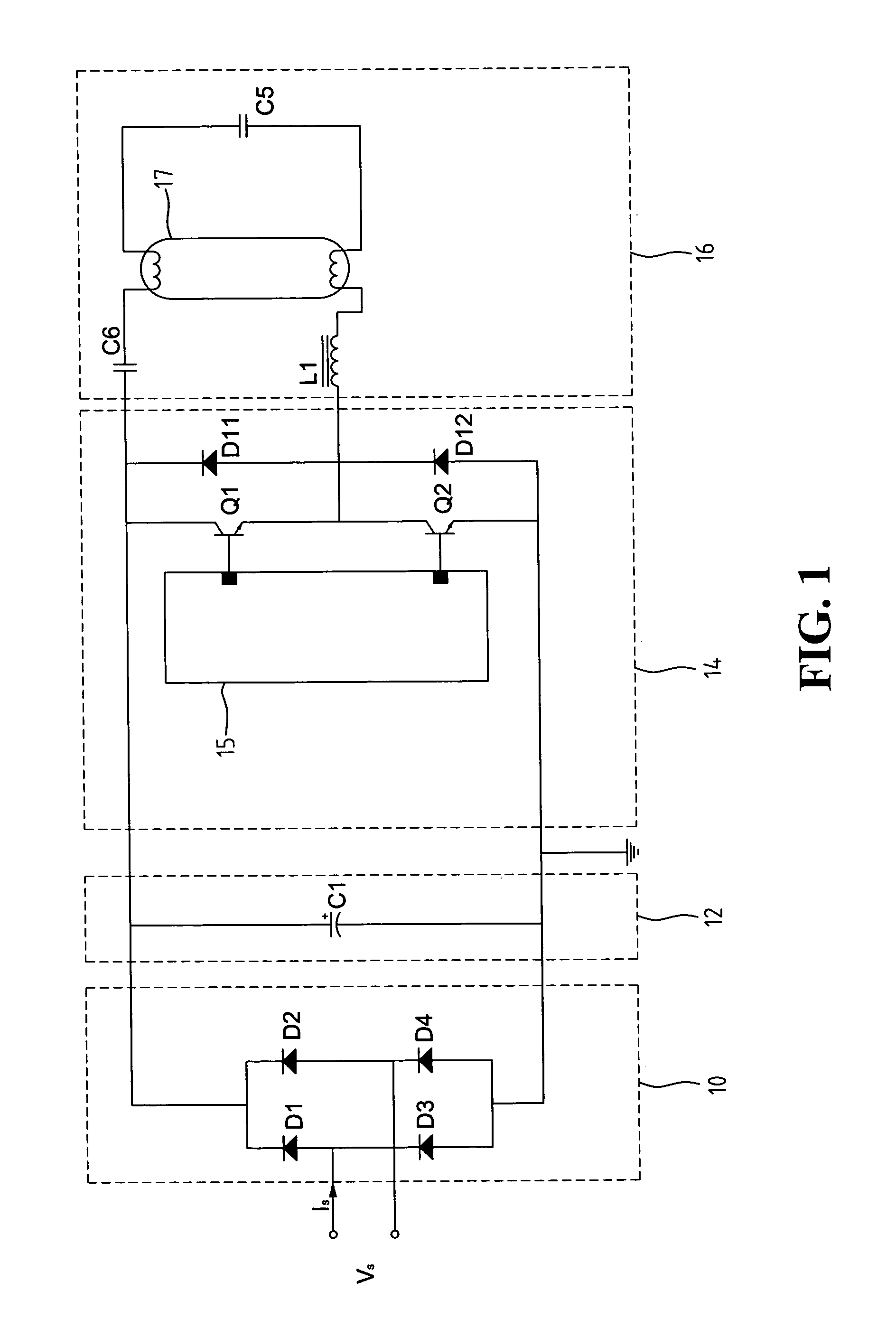

Power factor correction circuit for electronic ballast

InactiveUS6998795B2Smooth waveformLess amountElectric light circuit arrangementElectric discharge lampsTotal harmonic distortionLamp current

A power factor correction circuit for the electronic ballast of a fluorescent lamp is provided. The power factor correction circuit is located between a bridge rectifier circuit and A high frequency oscillation circuit of the electronic ballast, and includes a filtering capacitor charge / discharge circuit and a feedback circuit taking input from a filament of the fluorescent lamp. The electronic ballast equipped with the power factor correction circuit achieves a power factor >0.95, a lamp current crest factor <1.7, and a total harmonic distortion <10%.

Owner:CHIOU YIH FANG

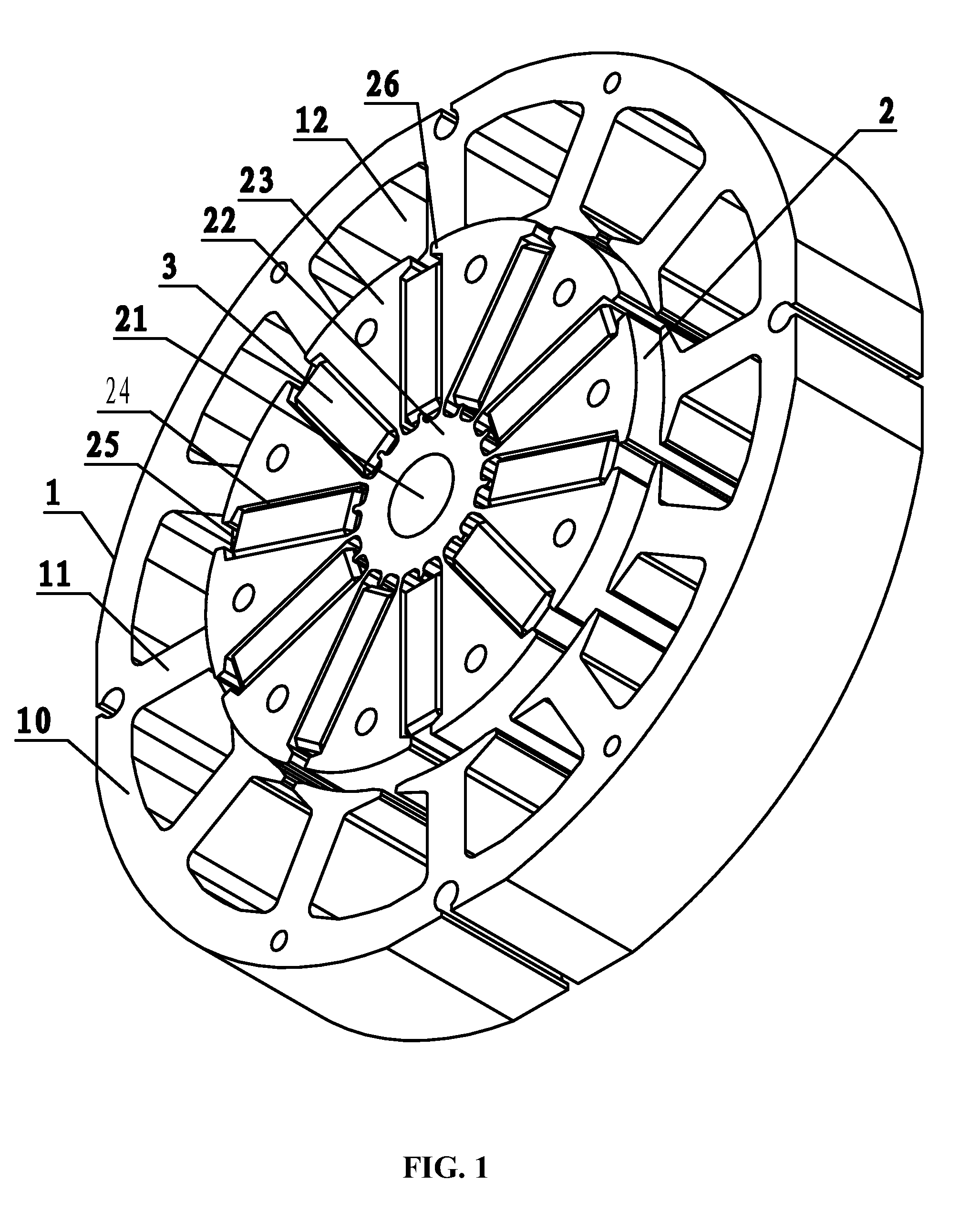

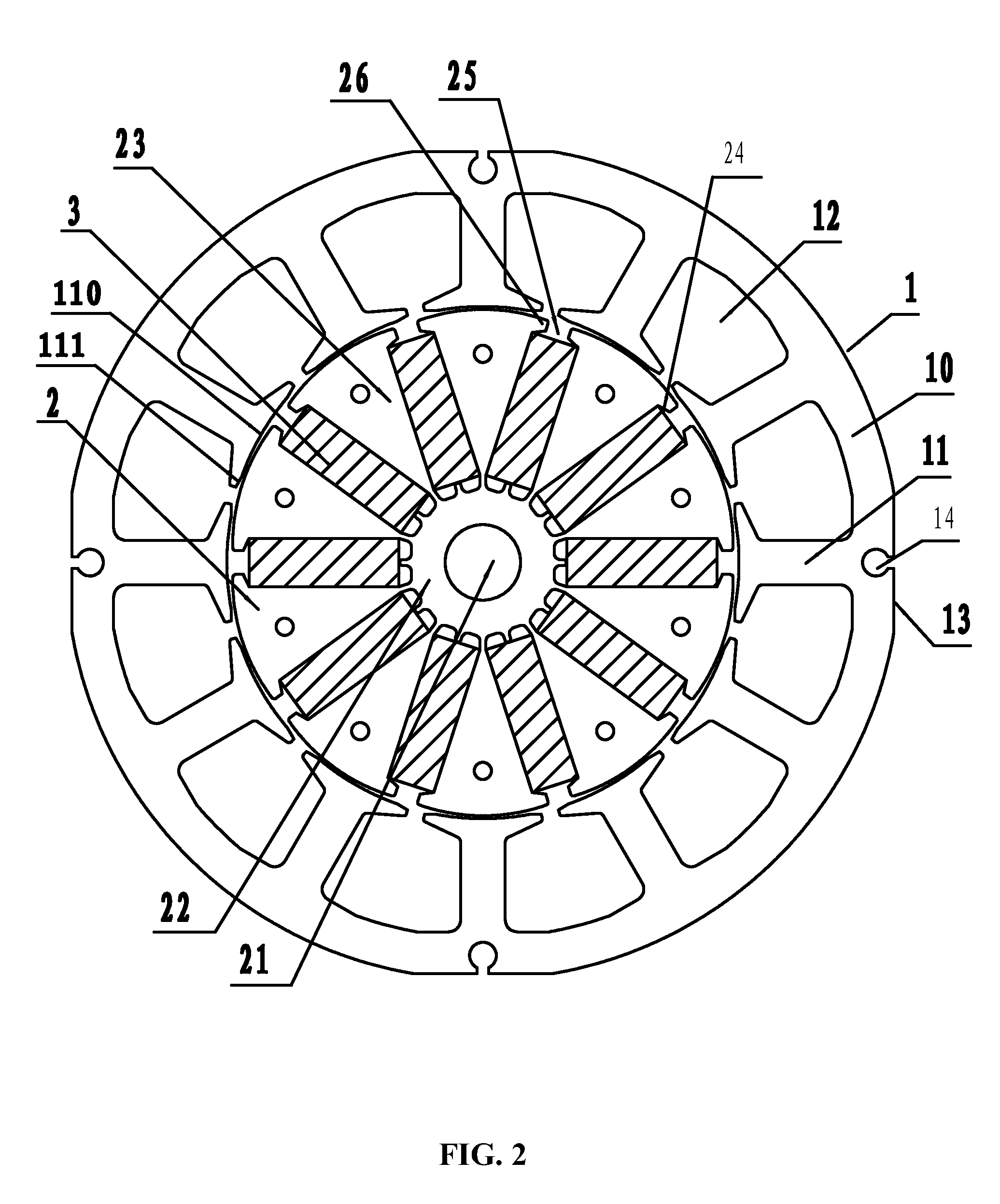

Motor structure

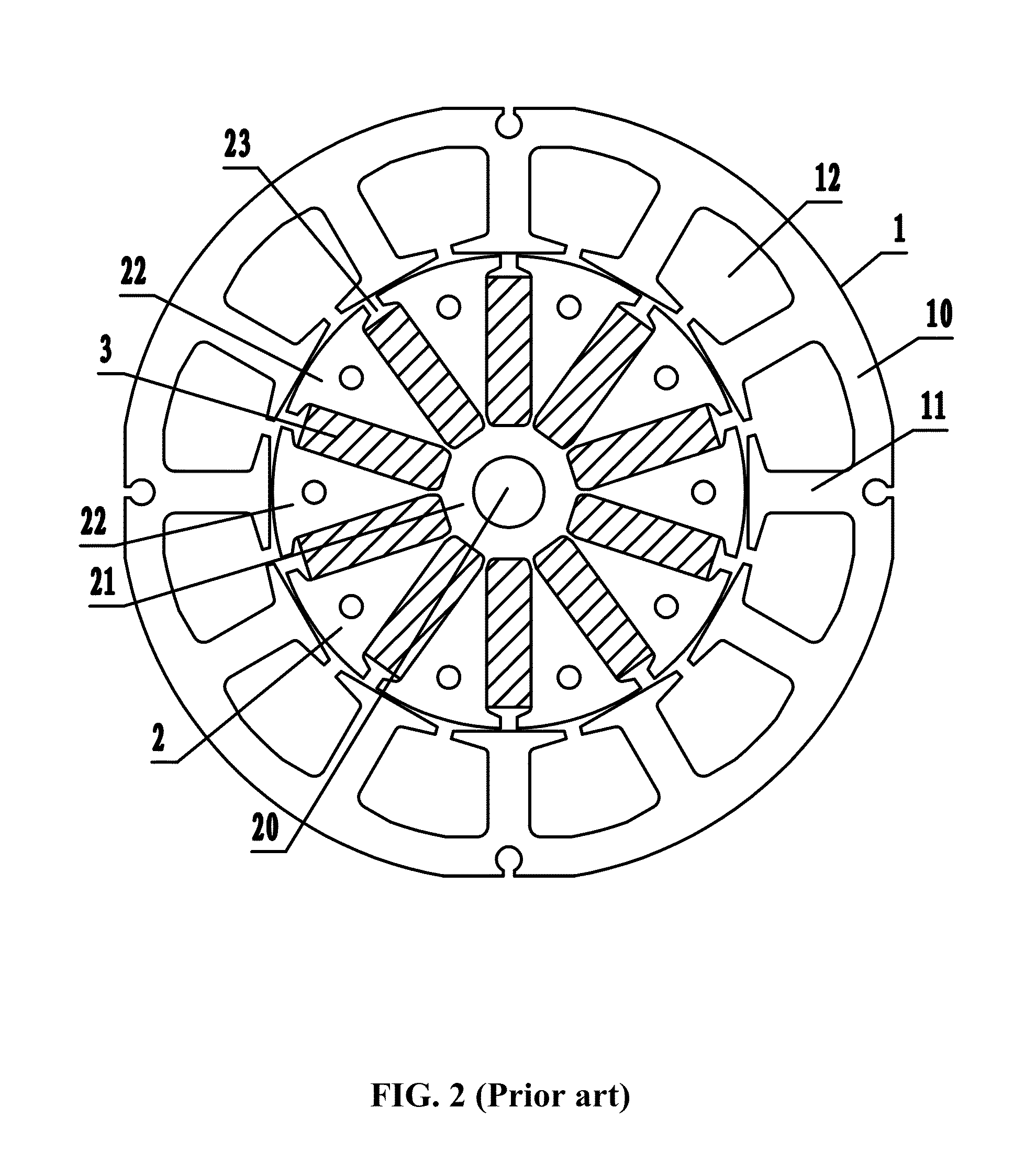

ActiveUS8564166B2Simple structureReduce Flux LeakageMagnetic circuit shape/form/constructionSynchronous machines with stationary armatures and rotating magnetsEngineeringConductor Coil

A motor structure including a stator assembly having a stator core and a winding and a rotor assembly embedded therein having a rotor core and a permanent magnet. The stator core includes a yoke and a plurality of teeth protruding inwards from the yoke. Two adjacent teeth form a wire embedding slot and the winding is placed inside the wire embedding slot and winds around the teeth. The rotor core includes an annular ring having a central axial pore and a plurality of magnetic induction blocks protruding outwards from an outer side of the annular ring. Two adjacent magnetic induction blocks form a radial recess for mounting the permanent magnet. The section of an outer side surface of the magnetic induction blocks is a circular-arc line. The outer side surface employs a point with a distance deviating from the center of the central axial pore as a center of circle.

Owner:ZHONGSHAN BROAD OCEAN MOTOR MFG

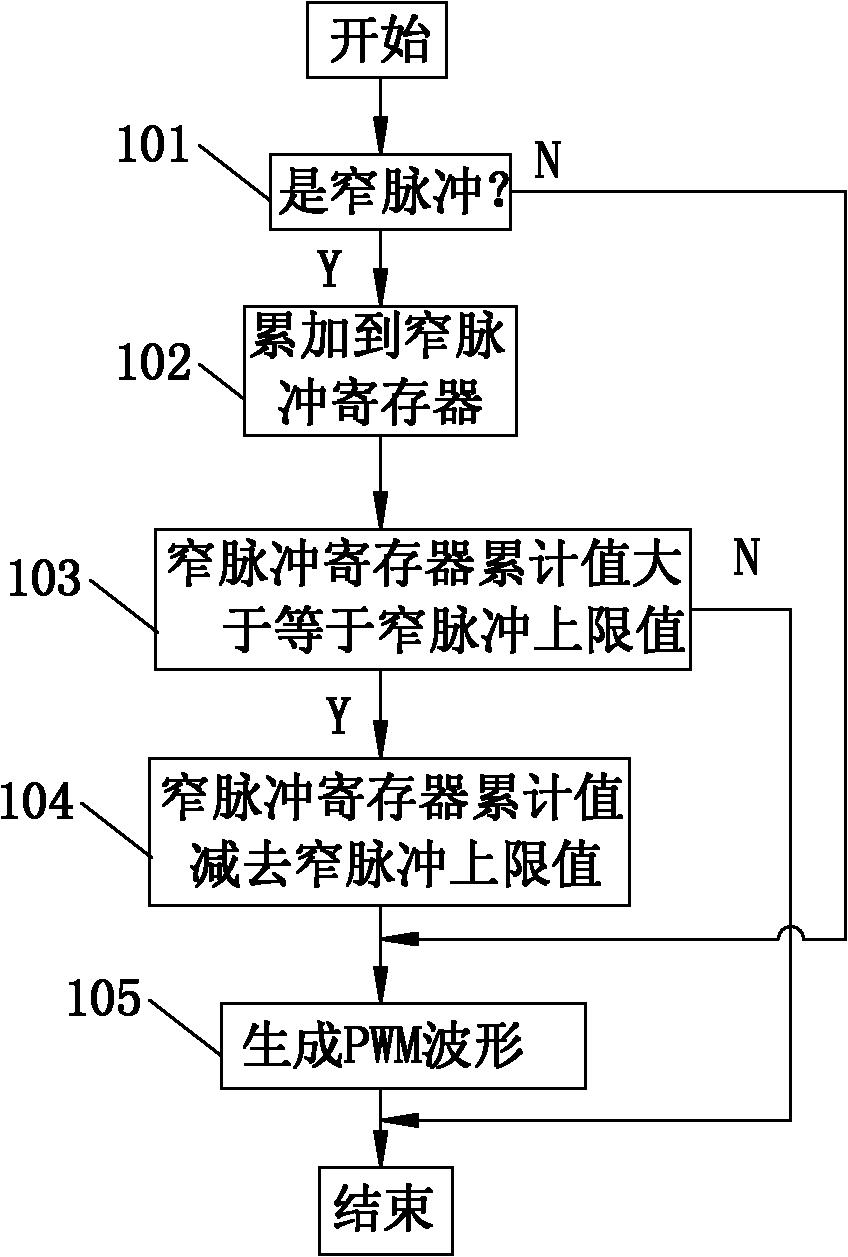

Smooth narrow pulse compensating method of FPGA in frequency converter

InactiveCN102118103ASmooth waveformReduce the number of conductionsAC motor controlEnergy industryTransverterHarmonic

The invention discloses a smooth narrow pulse compensating method of an FPGA (field programmable gate array) in a frequency converter, which comprises the steps as follows: judging whether an input modulating wave is a narrow pulse, if not, outputting the waveform, and if the value is stored in a narrow pulse register, not generating a waveform currently; inputting the modulating wave again, and judging whether the value is a narrow pulse, if not, outputting the waveform, if yes, accumulating the value; judging whether the sum of accumulated values is larger than or equal to the narrow pulse upper limit, if yes, outputting the waveform; and if the modulating wave is a narrow pulse, and the sum of accumulated values of the narrow pulse register is smaller than the narrow pulse upper limit, accumulating the current value in the narrow pulse register, and not outputting the wave. By taking the measure, an additional hardware circuit is not needed, thus being capable of guaranteeing smooth waveforms to be output at a position of a sinusoidal wave at which a narrow pulse is generated, effectively reducing the switching frequency of a power device, the heat generated by the device and harmonic content of the system, increasing the effective output level of the device, and improving the efficiency of the whole system.

Owner:CHINESE ELECTRICAL EQUIP GRP CO LTD

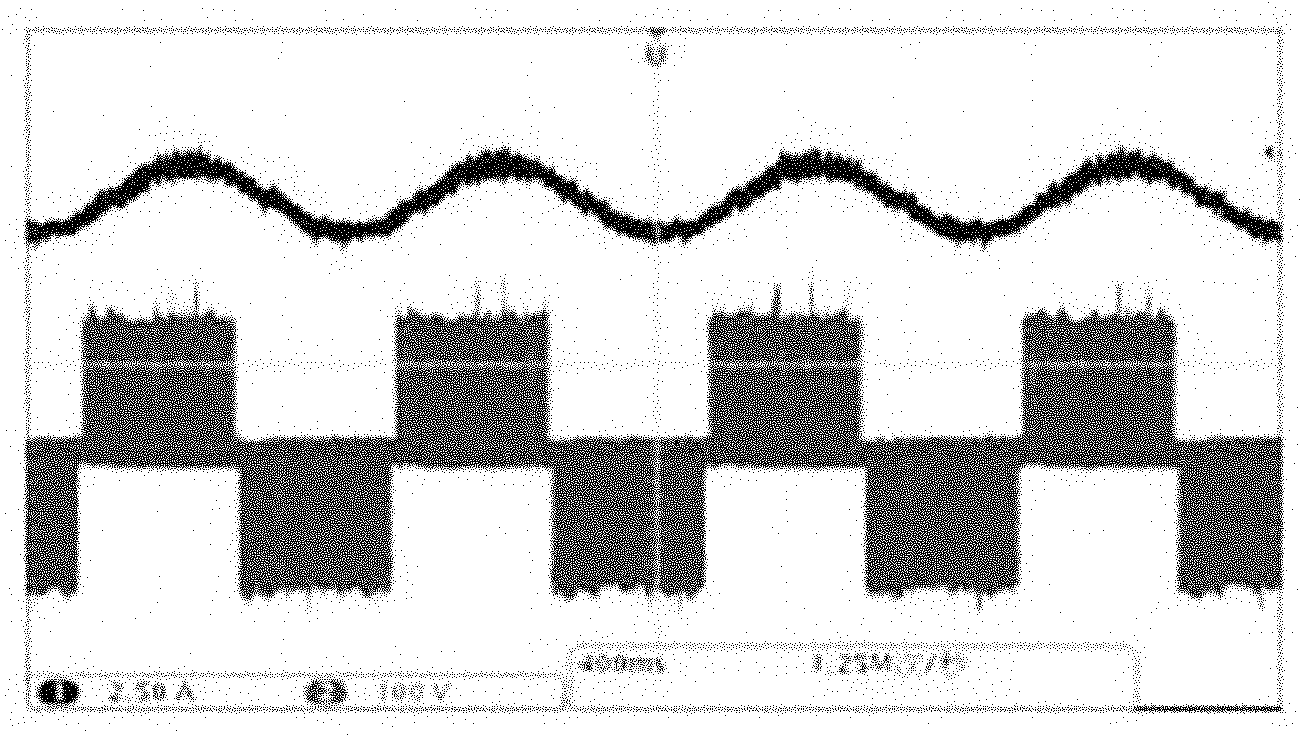

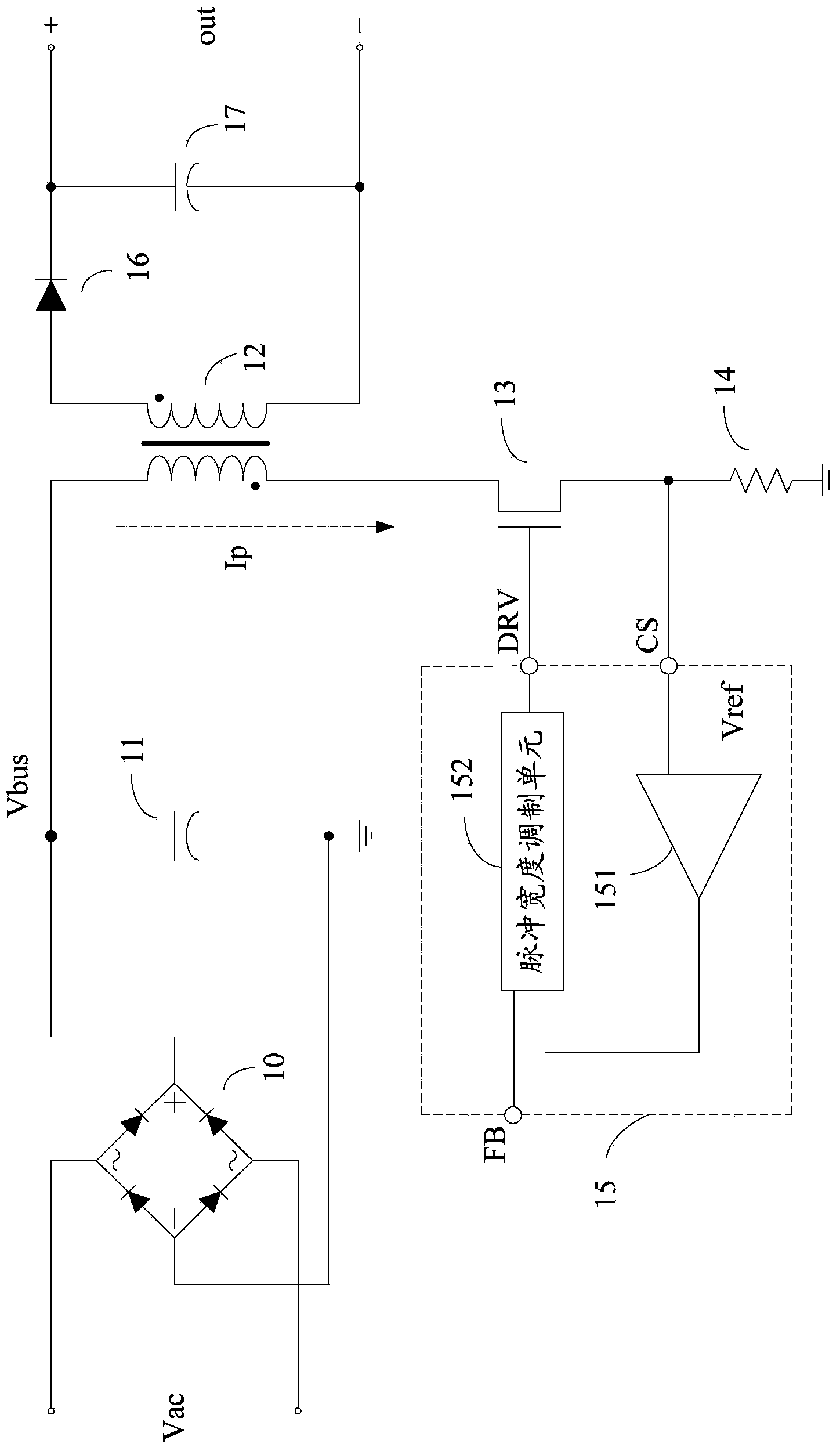

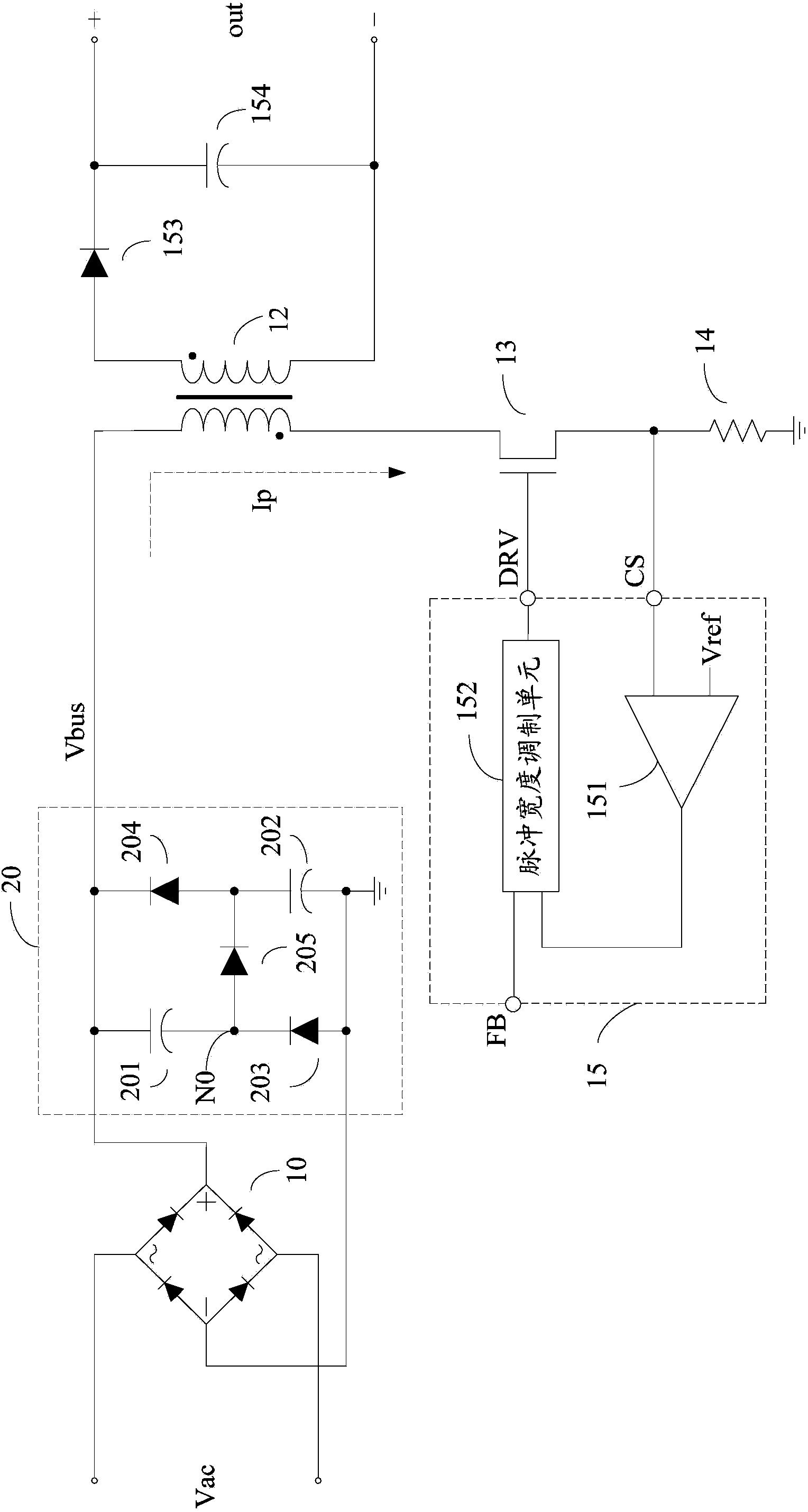

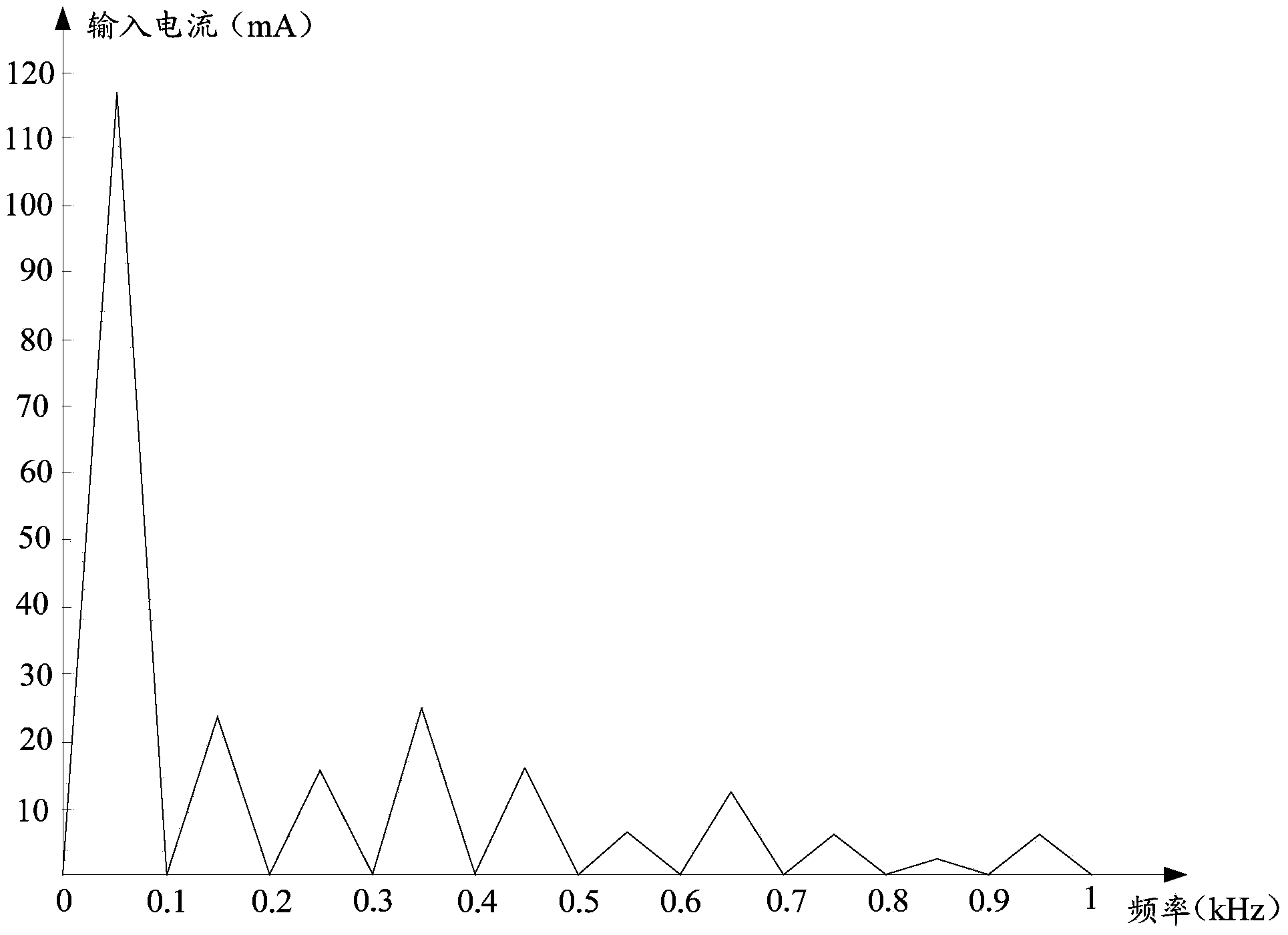

Switching power supply and control circuit thereof

ActiveCN103916020AReduce Harmonic DistortionSimple structureEfficient power electronics conversionDc-dc conversionPower flowTotal harmonic distortion

The invention discloses a switching power supply and a control circuit of the switching power supply. The control circuit of the switching power supply comprises a peak current detection end, a feedback end, a driving end, a first voltage comparator and a pulse width modulation unit. The control circuit of the switching power supply further comprises a control end and a reference voltage adjusting unit, wherein the control end is suitable for receiving control voltage, the reference voltage adjusting unit is suitable for generating a peak value comparison reference voltage according to control voltage, and when the value of the control voltage is equal to zero V, or the value is larger than a first voltage value, the value of the peak value comparison reference voltage is a second voltage value. When the value of the control voltage is larger than zero V and smaller than or equal to the first voltage value, the value of the peak value comparison reference voltage is equal to the sum of a third voltage value and the value of the control voltagea, and the sum of the third voltage value and the first voltage value is equal to the second voltage value. According to the switching power supply and the control circuit of the switching power supply, the total harmonic distortion of the switching power supply is reduced.

Owner:SHANGHAI LUMIXESS TECH

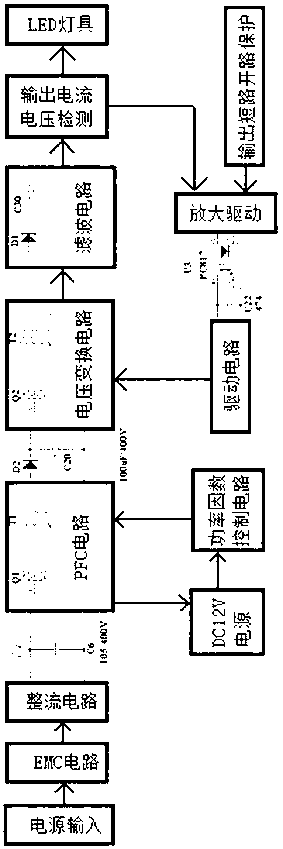

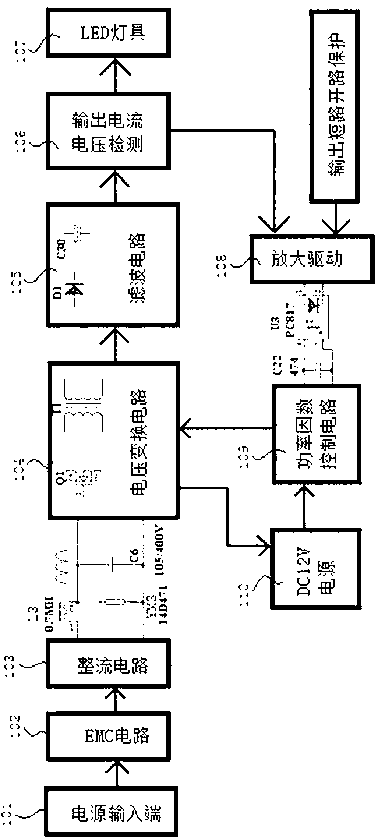

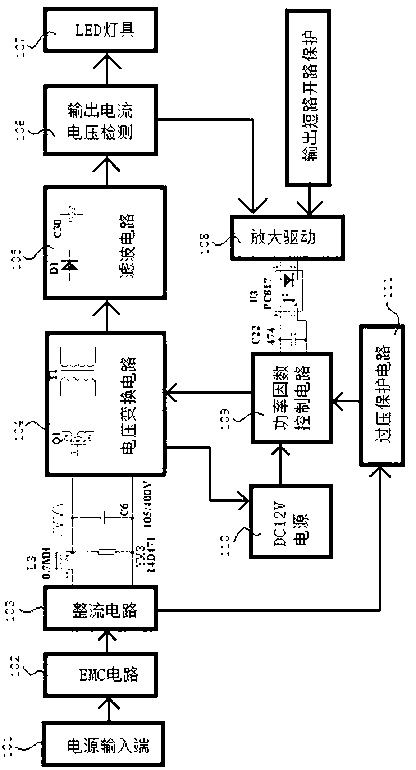

Light-emitting diode (LED) driving power supply

InactiveCN103068129AIncrease in sizeLarge capacityElectric light circuit arrangementPower gridCurrent voltage

The invention relates to the light-emitting diode (LED) manufacturing field and provides a LED driving power supply. The LED driving power supply comprises a power input end, an electro magnetic compatibility (EMC) circuit, a rectifying circuit, a voltage conditioning circuit, a filtering circuit, an output current voltage detecting circuit and an LED lamp at the output end of the output current voltage detecting circuit, and further comprises a constant current and constant voltage controlling circuit, wherein the power input end, the EMC circuit, the rectifying circuit, the voltage conditioning circuit, the filtering circuit, the output current voltage detecting circuit and the LED lamp are connected in sequence, the constant current and constant voltage controlling circuit is connected with an output end of the output current voltage detecting circuit and an input end of the voltage conditioning circuit, an inductance and a piezoresistor are arranged between the rectifying circuit and the voltage conditioning circuit, the inductance is connected with the rectifying circuit and the voltage conditioning circuit in series, the piezoresistor is connected with the rectifying circuit and the voltage conditioning circuit in parallel, and the input end of the piezoresistor is connected with the output end of the inductance. The LED driving power supply has the advantages that elements with big sizes, high failure rates and high prices are greatly reduced, the structure is simple and reasonable, the cost is lowered and application is stable and reliable. The inductance is added between the rectifying circuit and the voltage conditioning circuit, so that undesirable effects due to the fact that different-mode signals transit to a power grid are restrained, meanwhile the piezoresistor is added, and thereby the ability of the power supply to reject outside surge is improved.

Owner:ZHONGSHAN YALESI ELECTRIC CO LTD

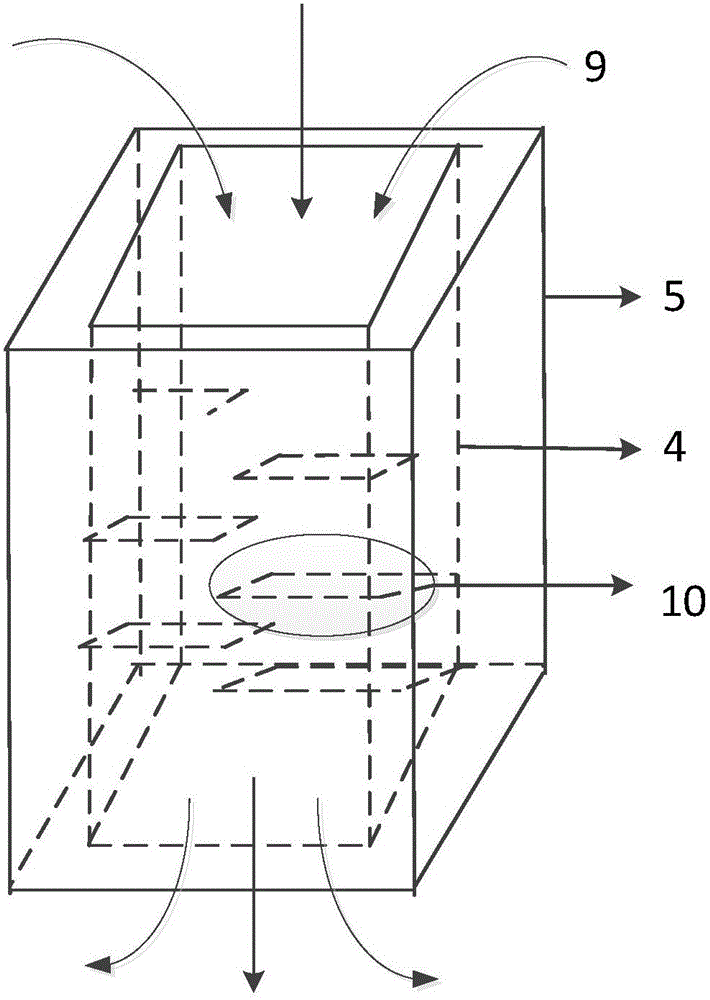

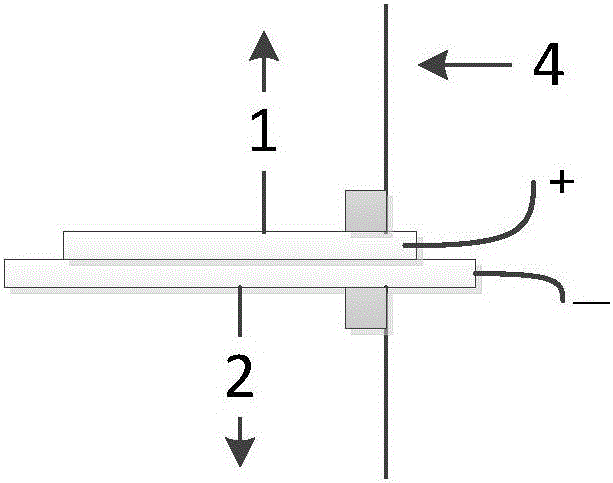

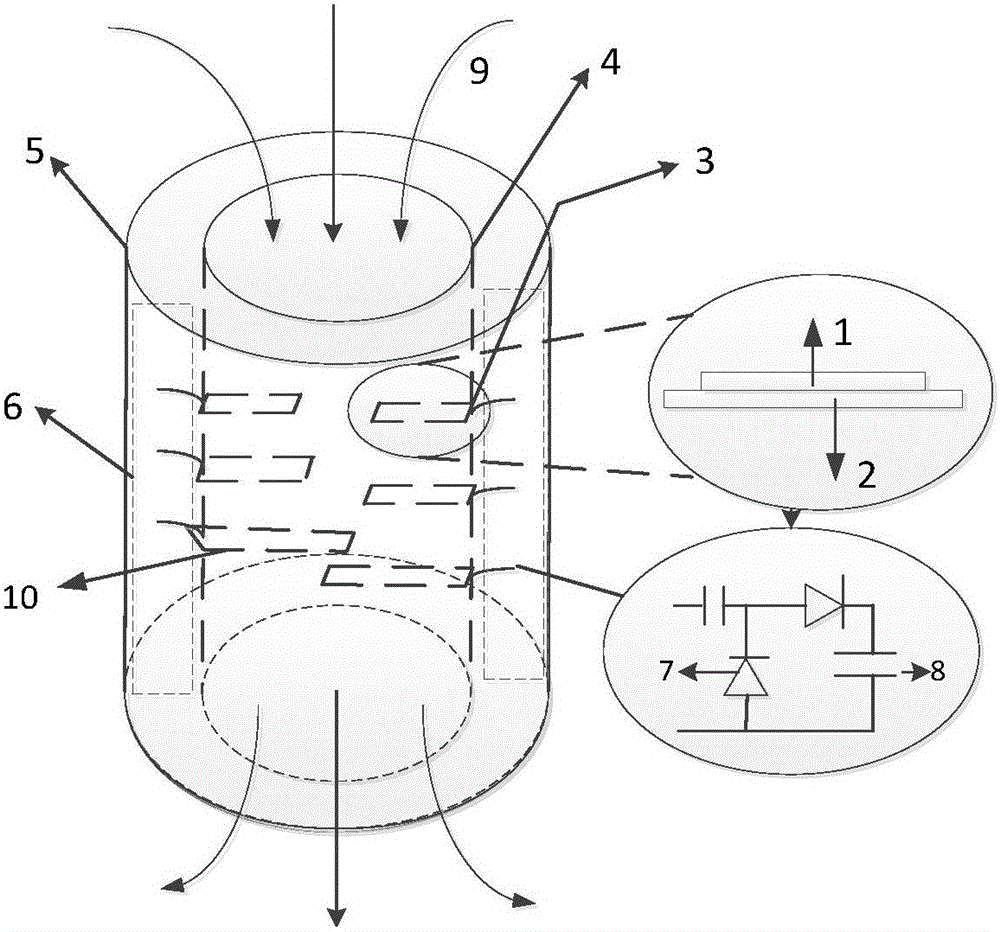

Piezoelectric material based fluid vibration energy collection apparatus

InactiveCN105811803AAchieve the effect of recyclingSave resourcesPiezoelectric/electrostriction/magnetostriction machinesElectricityBroadband

The invention discloses a piezoelectric material based fluid vibration energy collection apparatus. The fluid vibration energy collection apparatus comprises a first container and a second container, wherein the first container and the second container are cuboids or cylinders; the second container is sleeved by the first container; multiple transduction circuits arranged on a PCB are arranged between the first container and the second container; the upper and lower end planes between the first container and a second container are sealed; multiple sockets are formed in the inner side of the second container; one ends of piezoelectric transduction sheets are fixed in the sockets while the other ends of the piezoelectric transduction sheets extend to the center of the second container; the piezoelectric transduction sheets comprise piezoelectric ceramics and substrates; the piezoelectric ceramics are connected with the positive ends of the corresponding transduction circuits through wire-outlet circuits; the substrates are connected with the negative ends of the corresponding transduction circuits through the wire-outlet circuits; the number of the transduction circuits is equal to that of the piezoelectric transduction sheets, and the transduction circuits are in one-to-one correspondence connection with the piezoelectric transduction sheets. According to the apparatus, the broadband is realized and the energy collection effect is improved due to different lengths, shape structures and position relations of the piezoelectric transduction sheets.

Owner:JIANGSU UNIV

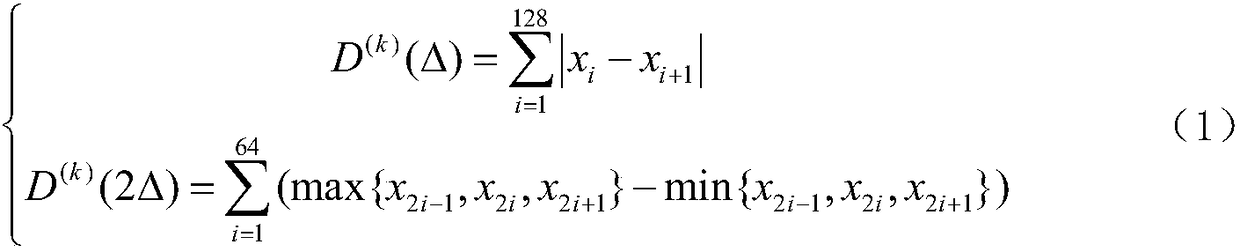

Improved harmonic detection method for double-feed wind power generation system

InactiveCN108061821ASmall attenuationImprove denoising effectFrequency analysisElectricityWavelet denoising

The invention discloses an improved harmonic detection method for a double-feed wind power generation system, and the method comprises the steps: sampling current signals, comprising harmonic waves, in the double-feed wind power system at different wind speeds and under wind conditions; 2), continuously adjusting the threshold parameters of wavelet denoising according to the fractal dimensions ofa harmonic wave signal, and removing noise in a segmented manner through wavelet transformation; 3), enabling the denoised signal to pass through a high-pass digital filter based on a Chebyshev type I, carrying out the EMD decomposition of the harmonic through an improved EMD method, carrying out the Hilbert transformation of each IMF component, and detecting the harmonic component at each order in a harmonic signal of a wind power plant. The method provided by the invention is used for the harmonic analysis of the double-feed wind power generation system, can achieve the accurate detection ofthe harmonic component at each order in the harmonic signal of the wind power plant, also can achieve the reflection of a moment of the abrupt change of the harmonic signal, and enables the decomposition result of the harmonic signal to be more accurate.

Owner:NANJING UNIV OF SCI & TECH

Data/commands through audio channel

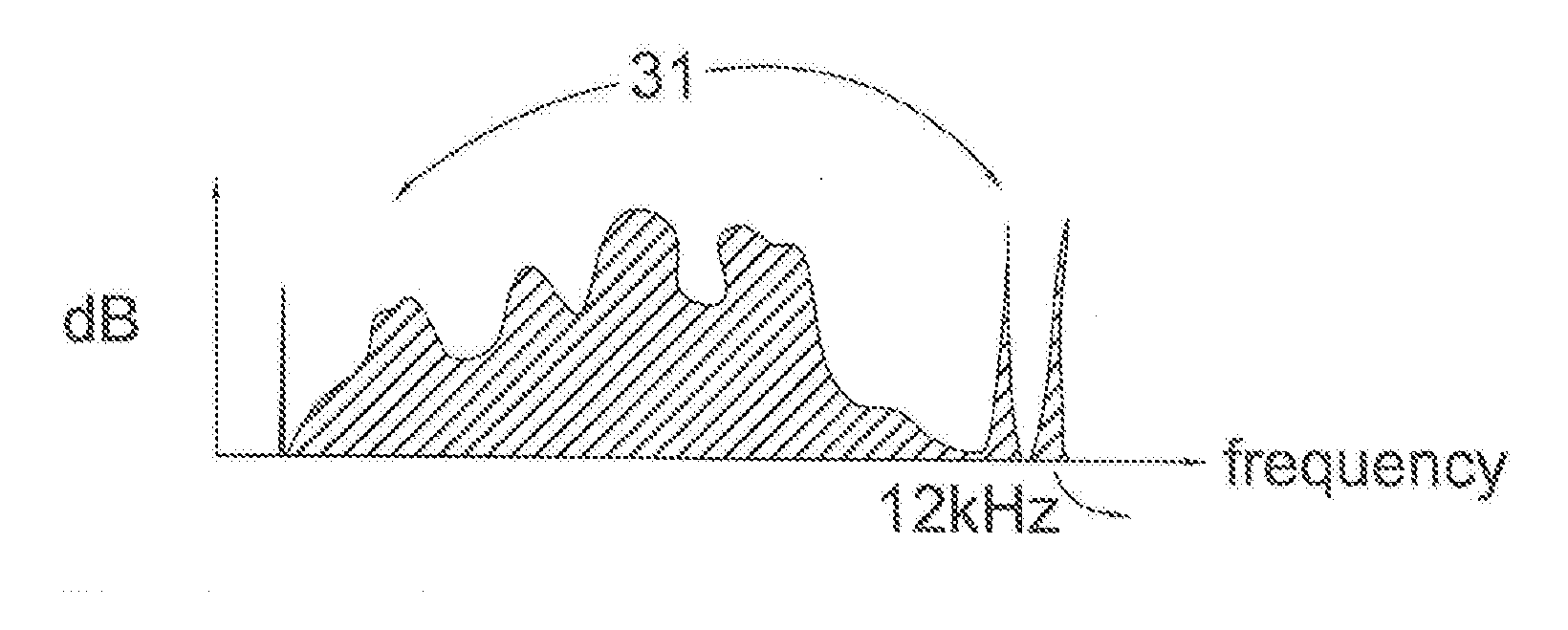

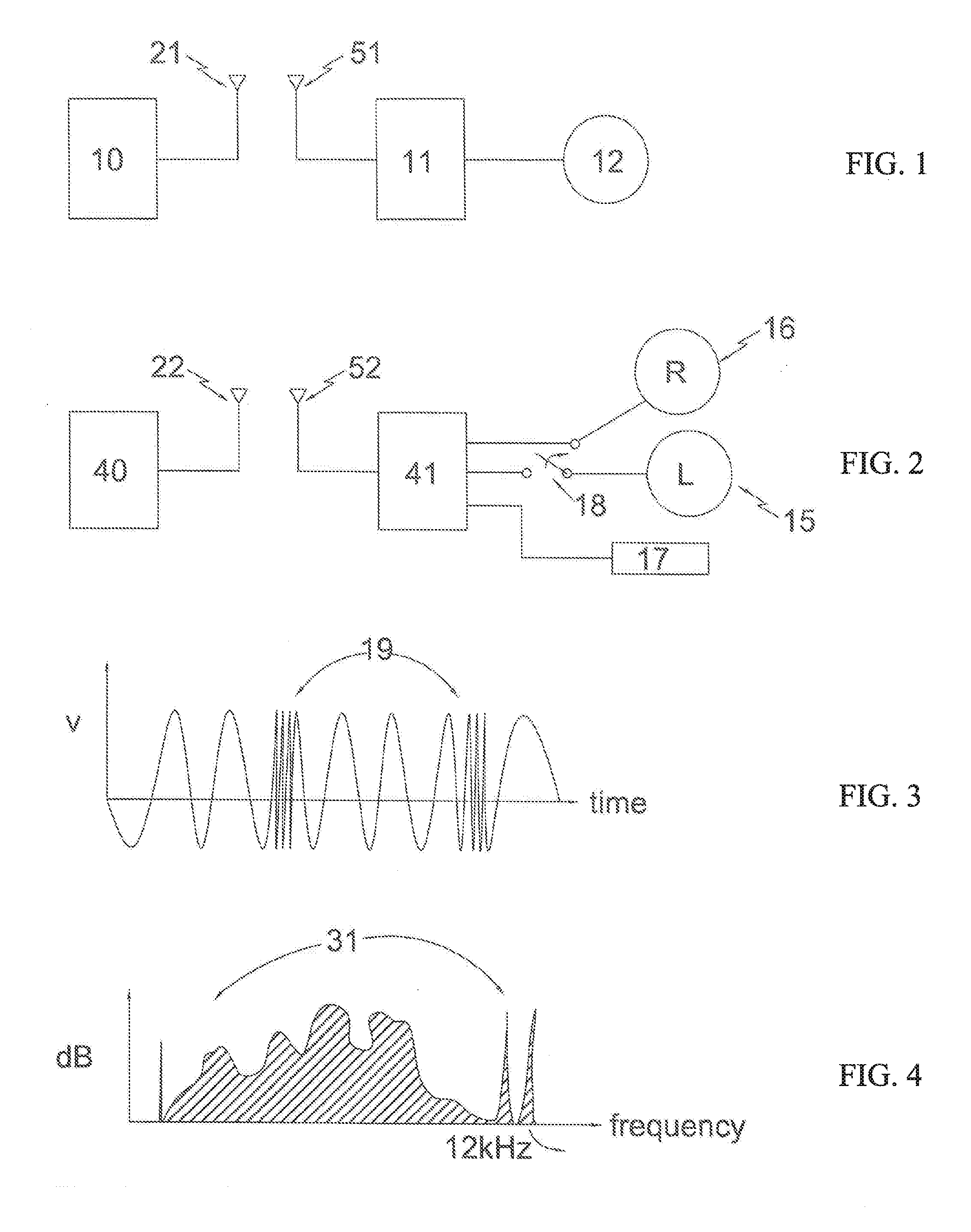

InactiveUS20160140839A1Less and even no interruptionSmoothing tone(s)Non-electrical signal transmission systemsSpeech analysisLoudspeakerComputer science

A method to send data or commands through streaming audio signal by using special tone(s) or waveform at a short period of time or using inaudible tone(s) or waveform, filterable tone(s) or waveform mixed into music or audio signal to send for data / commands. In audio stereo channels, by using one of stereo channels or adaptively arranged by time to use one of channels for sending special tone(s) or waveform for data or command purpose as well switching the speaker of sending command channel to other streaming music or audio channel without creating further noise or interruption.

Owner:HSIEH MINGCHIH

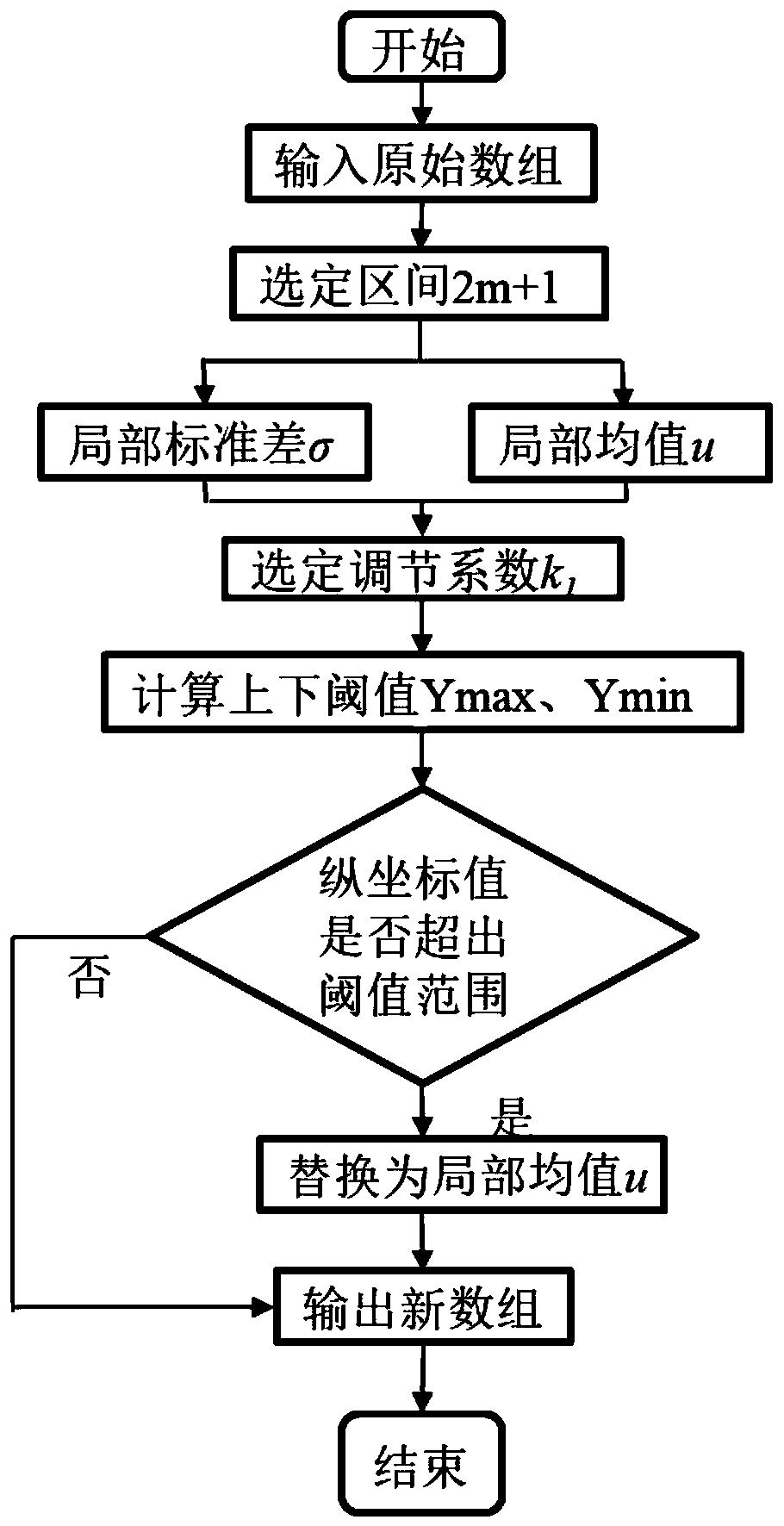

Contour data processing method based on sliding window mean filtering

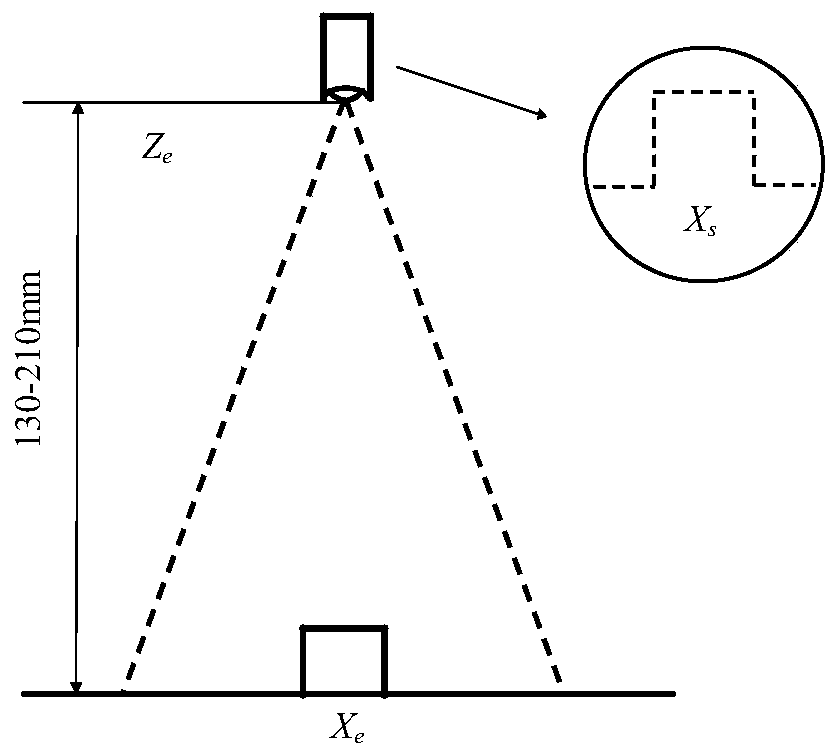

InactiveCN111156921AEasy to measureAccurate removalImage enhancementImage analysisLight sensingThree dimensional measurement

The invention discloses a contour data processing method based on sliding window mean filtering, and relates to the field of material processing engineering. The invention aims to solve the problems of random noise, image distortion and detail loss in a large complex profile contour extraction process. The contour data processing method based on sliding window mean filtering comprises the steps that a laser vision sensor projects linear stripe light to a target profile, and according to light stripe information received by a light sensing module, space coordinates of a target object are obtained through calibration information of the sensor and laser stripe contour information. The laser vision sensor projects one linear scanning light to the surface of the target object each time to obtain the profile of one section, and the measurement mode is simple and efficient. The method is applied to the field of three-dimensional measurement.

Owner:HARBIN INST OF TECH

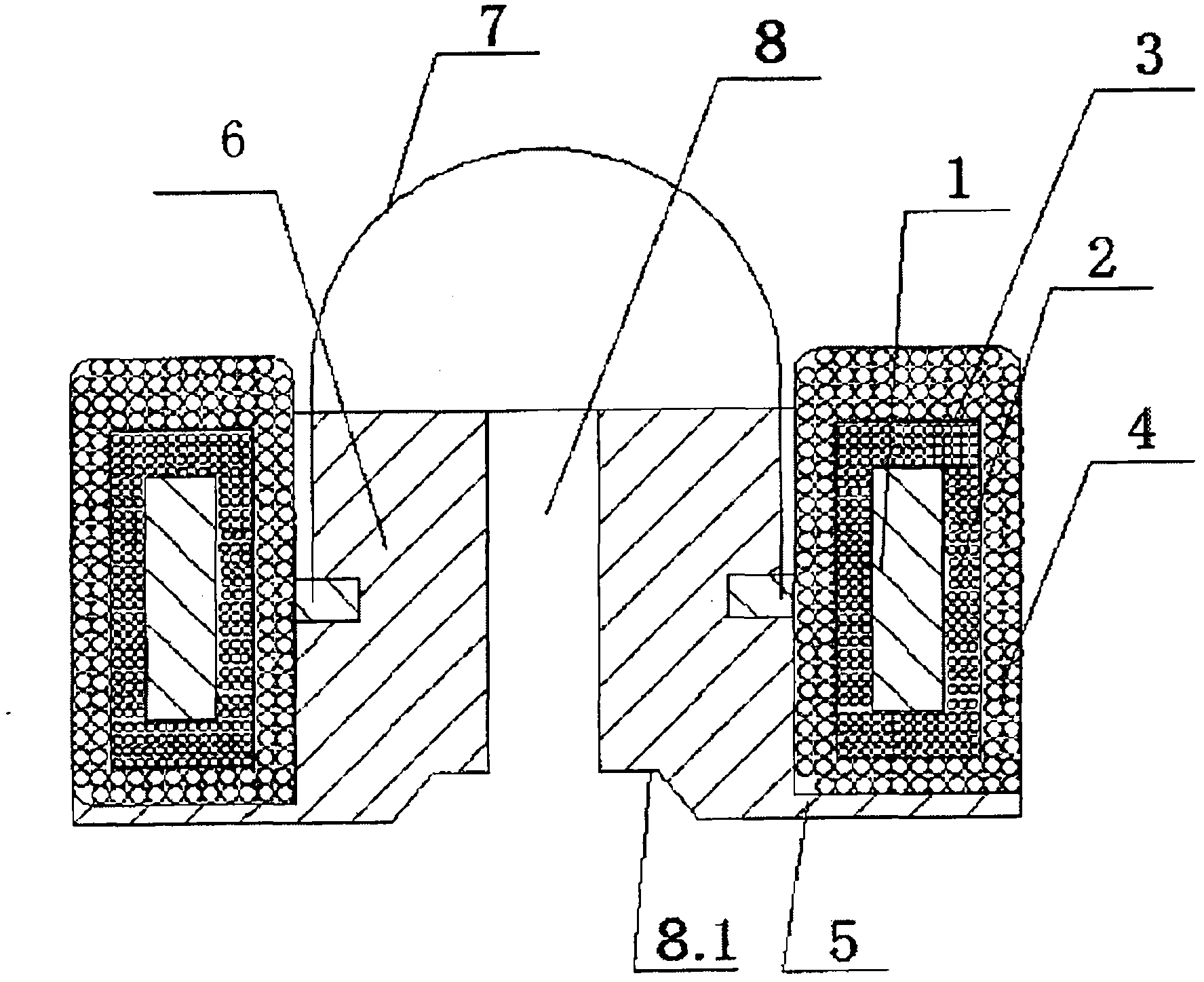

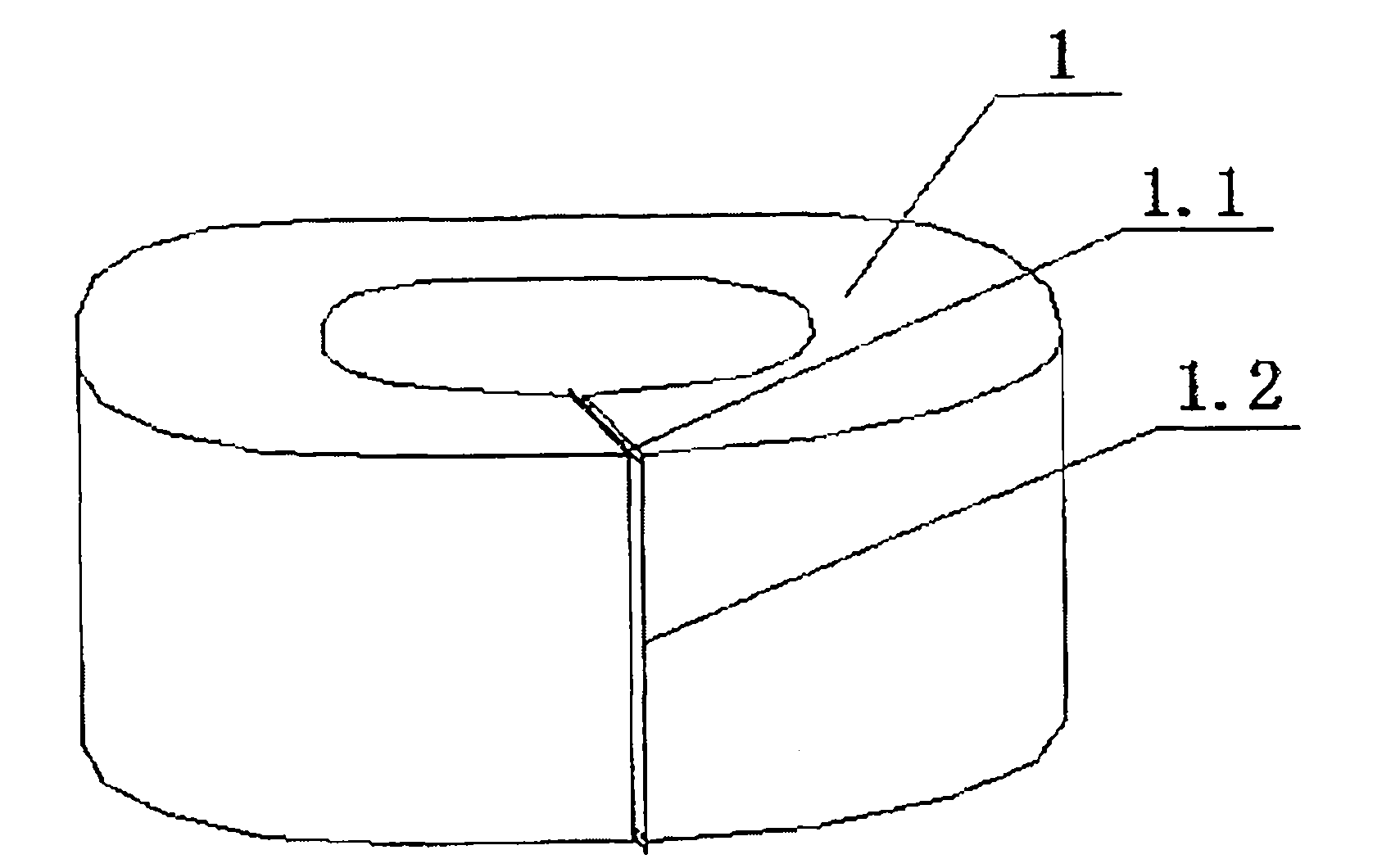

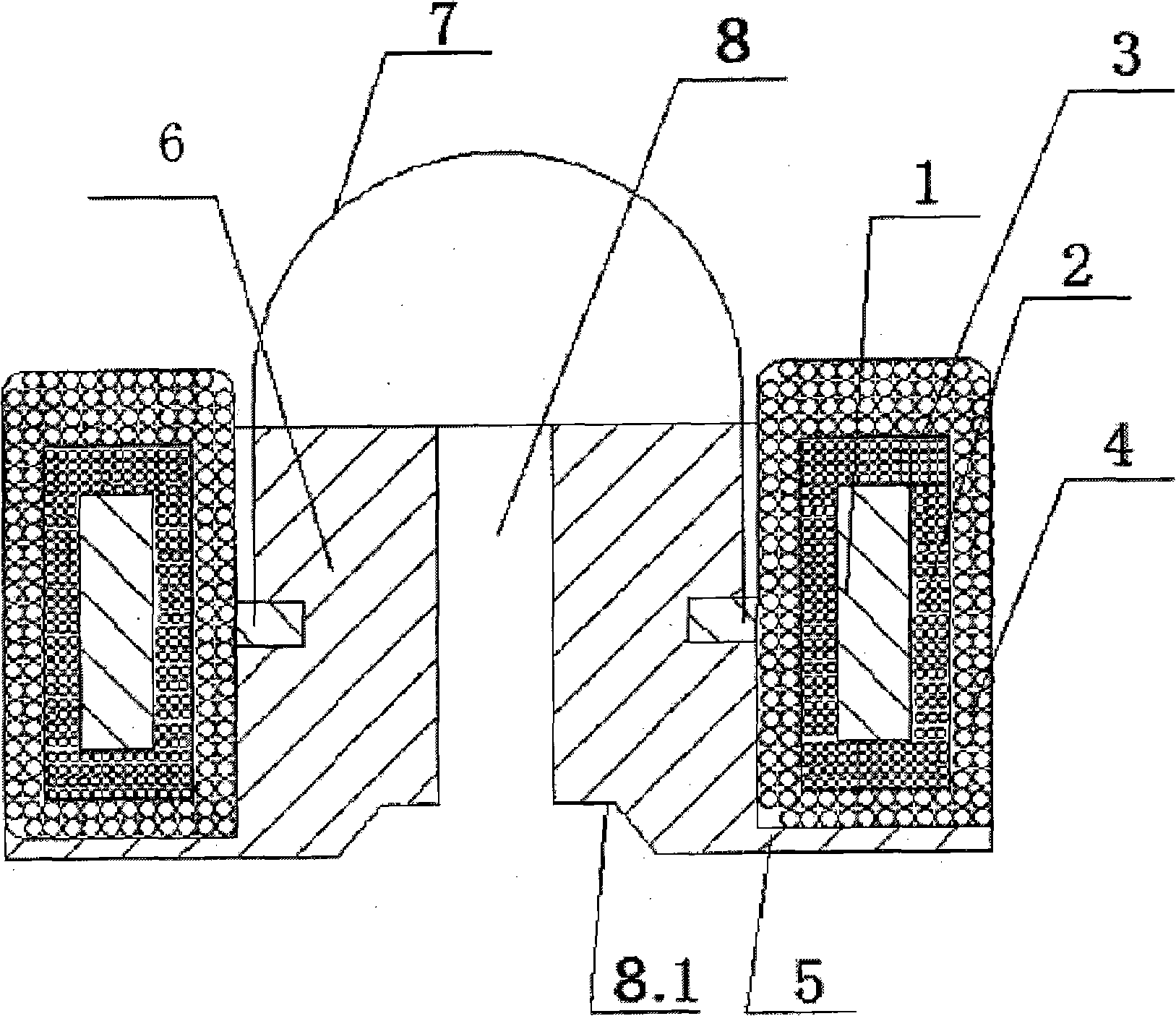

Magnetic leakage-preventing annular transformer

ActiveCN102360861AImprove efficiencyReduce temperature riseUnwanted magnetic/electric effect reduction/preventionFixed transformersTransformerEngineering

The invention relates to a magnetic leakage-preventing annular transformer, which comprises an annular iron core, a primary coil and a secondary coil both of which are sequentially wound on the annular iron core. The annular iron core is a non-closed annular iron core provided with a gap; an insulated film is lined at the gap; an epoxy core is arranged at an inner circle of the annular transformer; an epoxy layer is arranged on the bottom surface of the annular transformer; the bottom surface of the epoxy layer is a flat surface; the epoxy core and the epoxy layer are integrated as a whole; the opposite surface of the gap is a flat surface; the gap is 0.02-0.12 mm in width; shielding layers are arranged between the primary coil and the secondary coil; the materials of the shielding layersare covered on the entire surface of the primary coil of the transformer; the shielding layers are uniform in width; and the shielding layers are overlapped and covered at 1 / 4 of the width of each shielding layer on the surface of the primary coil.

Owner:NINGBO ZHONGCE E T ELECTRONICS

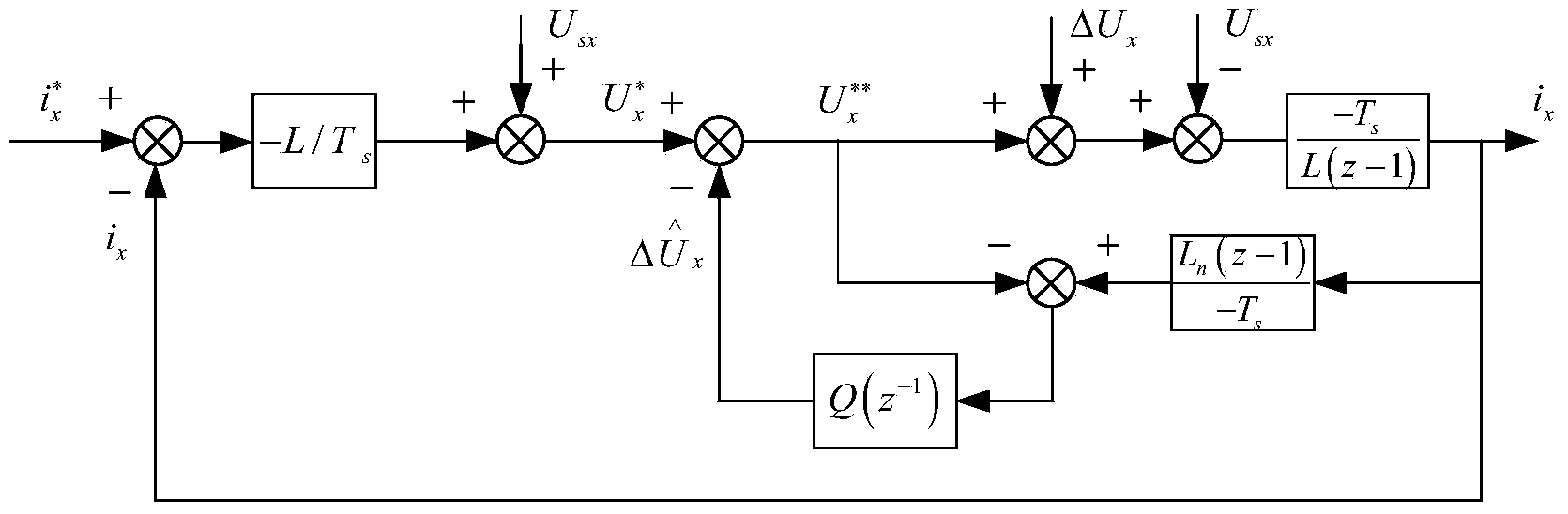

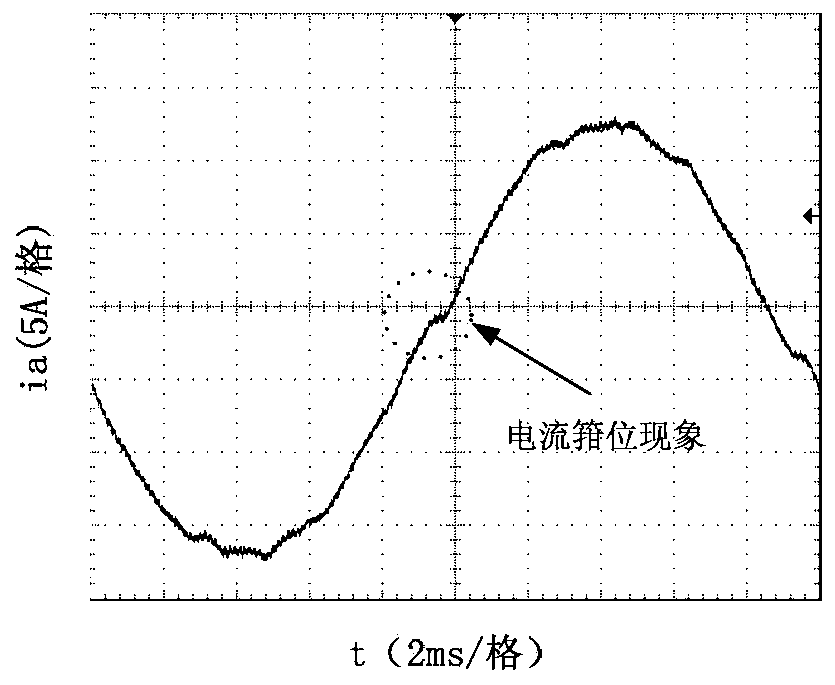

Self-adaptation dead-time compensation method for H-bridge cascade STATCOM (static synchronous compensator)

InactiveCN104037768AHarmonic reductionSmooth waveformFlexible AC transmissionHarmonic reduction arrangementControl systemDead time compensation

The invention discloses a self-adaptation dead-time compensation method for H-bridge cascade STATCOM (static synchronous compensator) and aims to solve the problem of lack of dead-time compensation directly targeting the H-bridge cascade STATCOM. According to a circuit topological structure of the H-bridge cascade STATCOM, the method includes steps of acquiring a discrete mathematic model of the H-bridge cascade STATCOM in a three-phase coordinate system; converting the discrete mathematic model into a transfer function mode in the discrete state; online monitoring difference between STATCOM output voltage and reference voltage caused by the dead-time effect by a discrete disturbance monitor in real time, utilizing the monitored difference as compensation capacity to introduce into a H-bridge cascade STATCOM control system, and self-adaptation dead-time compensation is realized.

Owner:哈尔滨同为电气股份有限公司

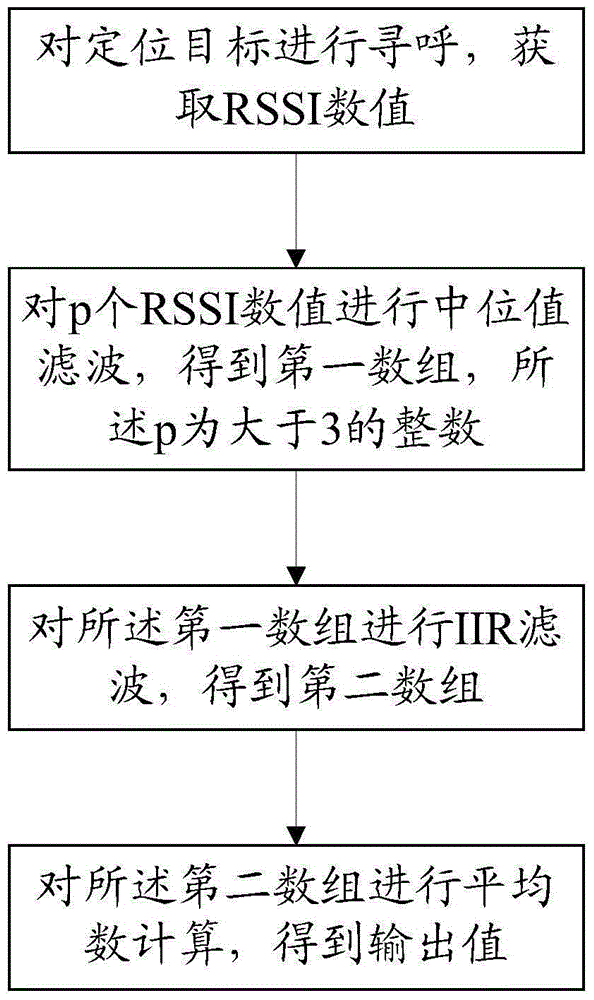

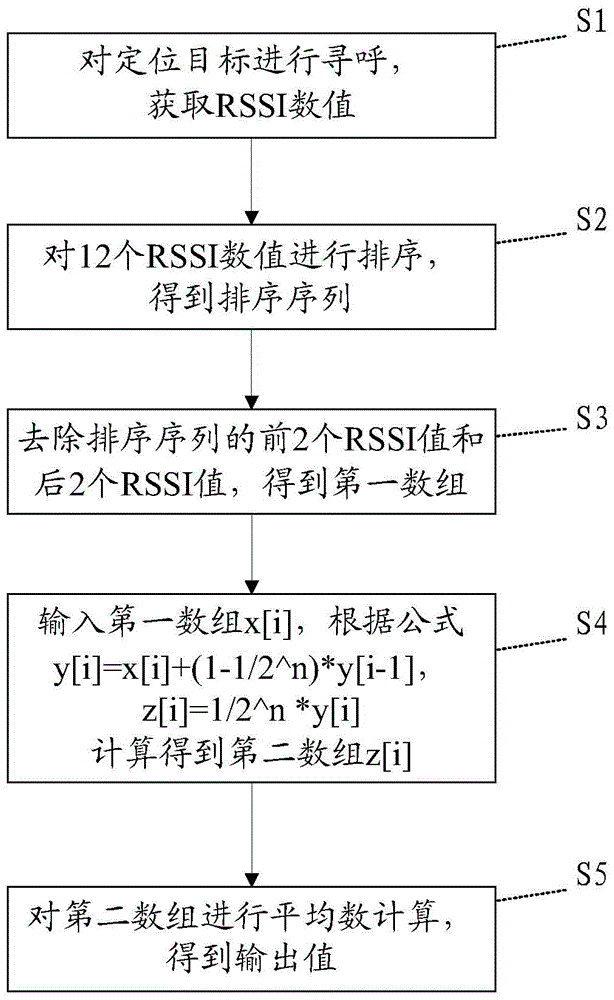

RSSI (Received Signal Strength Indication)-based filtering method and system

ActiveCN105720943AOvercome the shortcomings of instability and large fluctuationsReduce the impact of pulse interferenceDigital technique networkPosition fixationIir filteringArray data structure

The invention discloses an RSSI (Received Signal Strength Indication)-based filtering method and system. The method comprises the following steps: paging a positioning target to obtain RSSI numerical values; performing median value filtering on p RSSI numerical values to obtain a first array, wherein p is an integer being greater than 3; performing IIR (Infinite Impulse Response) filtering on the first array to obtain a second array; and calculating a mean value of the second array to obtain an output value. The median value filtering is performed on the RSSI numerical values, so that the influence on pulse interference is lowered, and the defects of unstable input RSSI values and great fluctuation can be overcome. Through the IIR filtering, the contradiction of excessive output fluctuation due to an overlarge input proportion is overcome. The IIR filtering is performed on the RSSI numerical values being subjected to the median value filtering, so that an output waveform is smoothened effectively, and becomes more stable.

Owner:XIAMEN MEIYA PICO INFORMATION

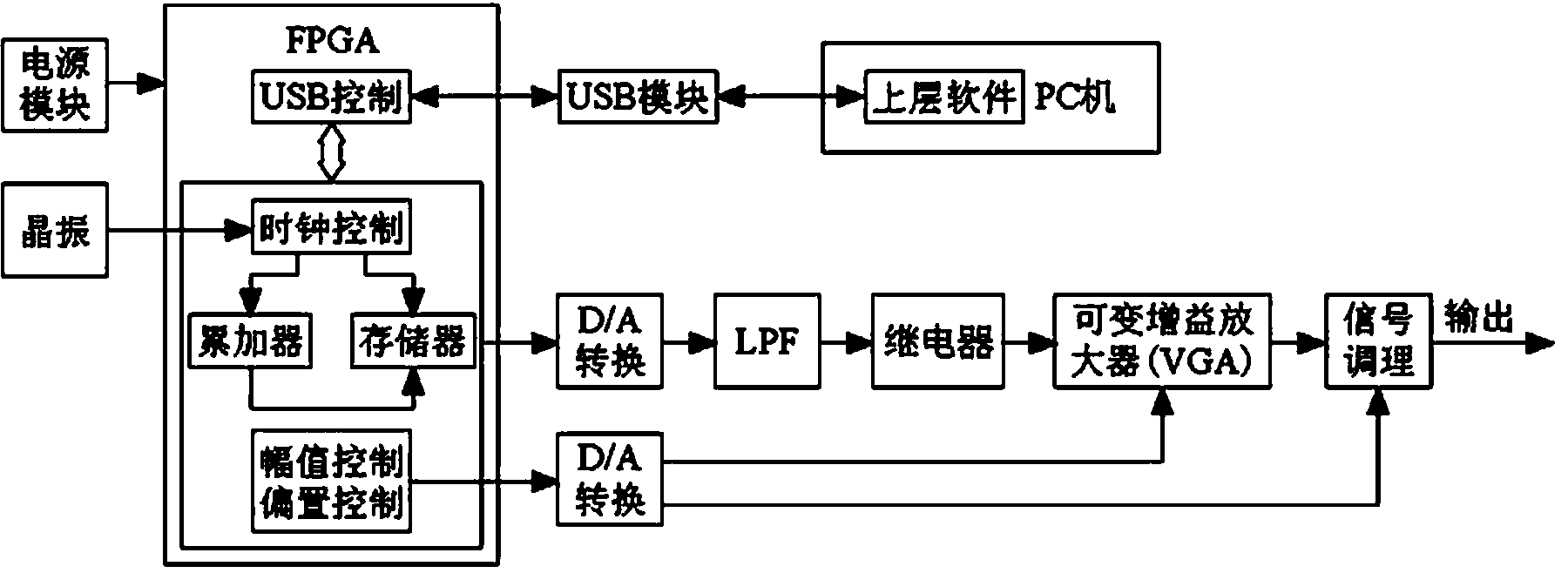

Arbitrary waveform generator

InactiveCN103812473AFast conversionRealize generationElectric pulse generator circuitsDigital function generatorsSignal conditioning circuitsVariable-gain amplifier

The invention belongs to the technical field of generators and particularly relates to an arbitrary waveform generator. The arbitrary waveform generator, simple in structure and low in cost, comprises an FPGA (Field Programmable Gate Array), a power module, a crystal oscillator, a communication module, a first D / A conversion module, a second D / A conversion module, a low pass filter, a variable gain amplifier and a signal conditioning circuit. The structural key points of the arbitrary waveform generator are that ports of the FPGA are respectively connected with ports of the power module, the crystal oscillator, the communication module, the first D / A conversion module and the second D / A conversion module; the port of the communication module is connected with the port of a PC machine; the first D / A conversion module, the low pass filter, the relay, the variable gain amplifier and the signal conditioning circuit are connected in sequence; and the ports of the second D / A conversion module are respectively connected with the port of the variable gain amplifier and the port of the signal conditioning circuit.

Owner:孙仁

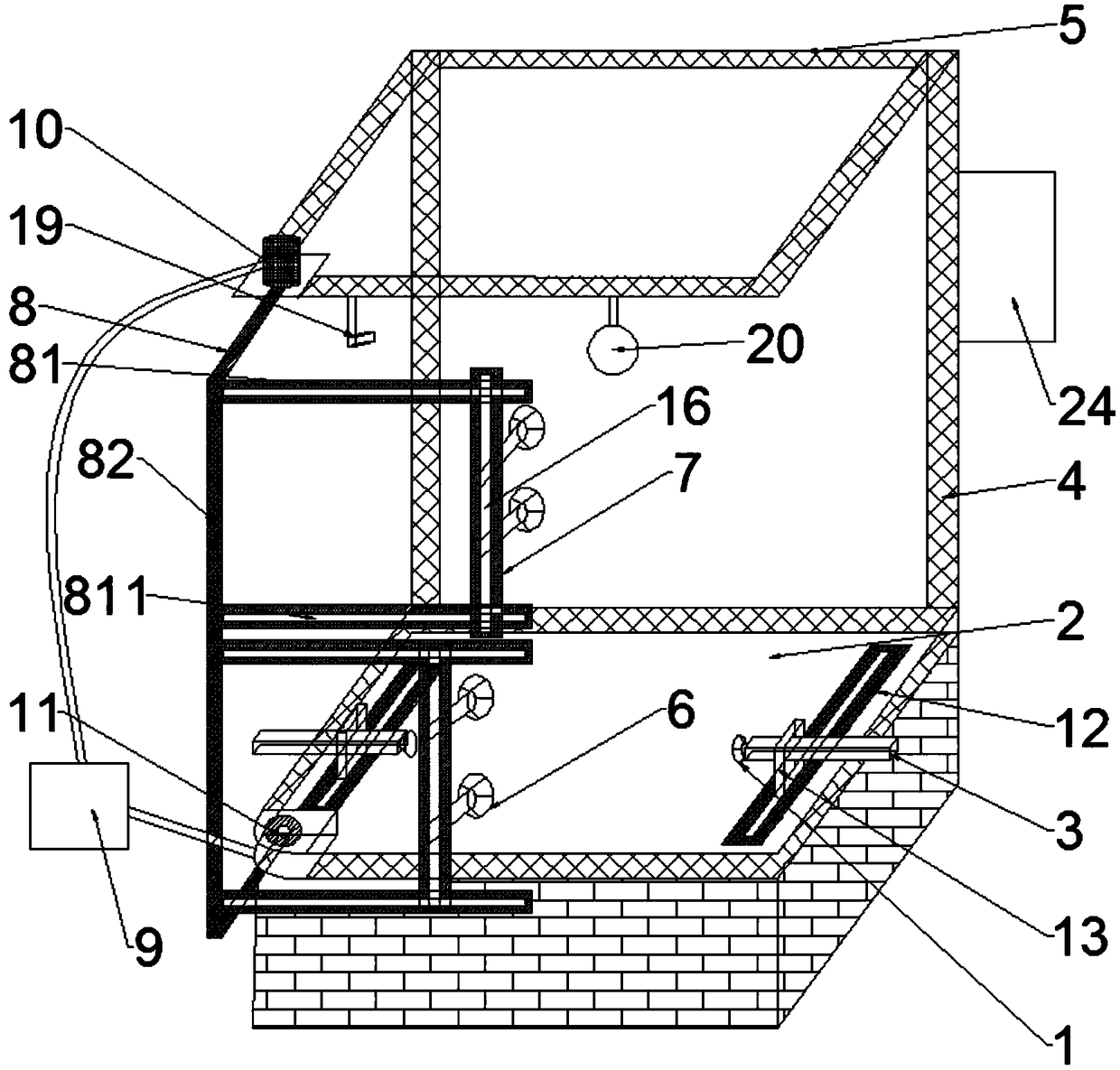

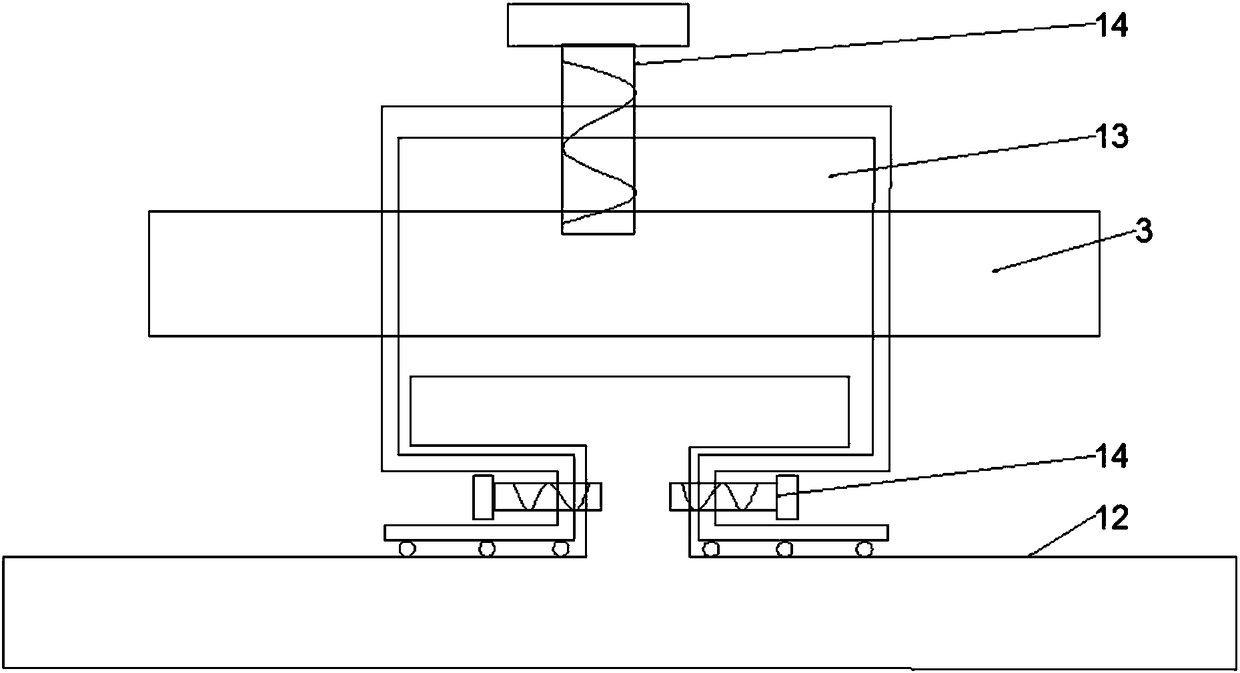

Uninterruptible power supply door operator for refrigerator door test

ActiveCN108562428AExtended service lifeReduced output voltage ripple factorMachine part testingFailure rateRefrigerator car

The invention relates to the technical field of test equipment and discloses an uninterruptible power supply door operator for refrigerator door test. The uninterruptible power supply door operator comprises a fixation connection device for fixing a test refrigerator, a door opening connection device for connecting a refrigerator door, a power device fixedly arranged on the fixation connection device and used for driving the door opening connection device, and an uninterruptible power supply module for providing power supply to the power device. The uninterruptible power supply door operator can prevent the case of power supply abnormity, provides steady and uninterrupted power supply, realizes fast matching of various types of refrigerators and well solves the problem of refrigerator dooropening and closing track matching, is convenient and fast to install, can realize automatic repeated opening and closing of upper and lower doors of the refrigerator, and is high in safety stabilitycoefficient, low in failure rate, not easy to damage the refrigerator, high in automation degree, simple in structure and low in cost.

Owner:合肥羿振电力设备有限公司

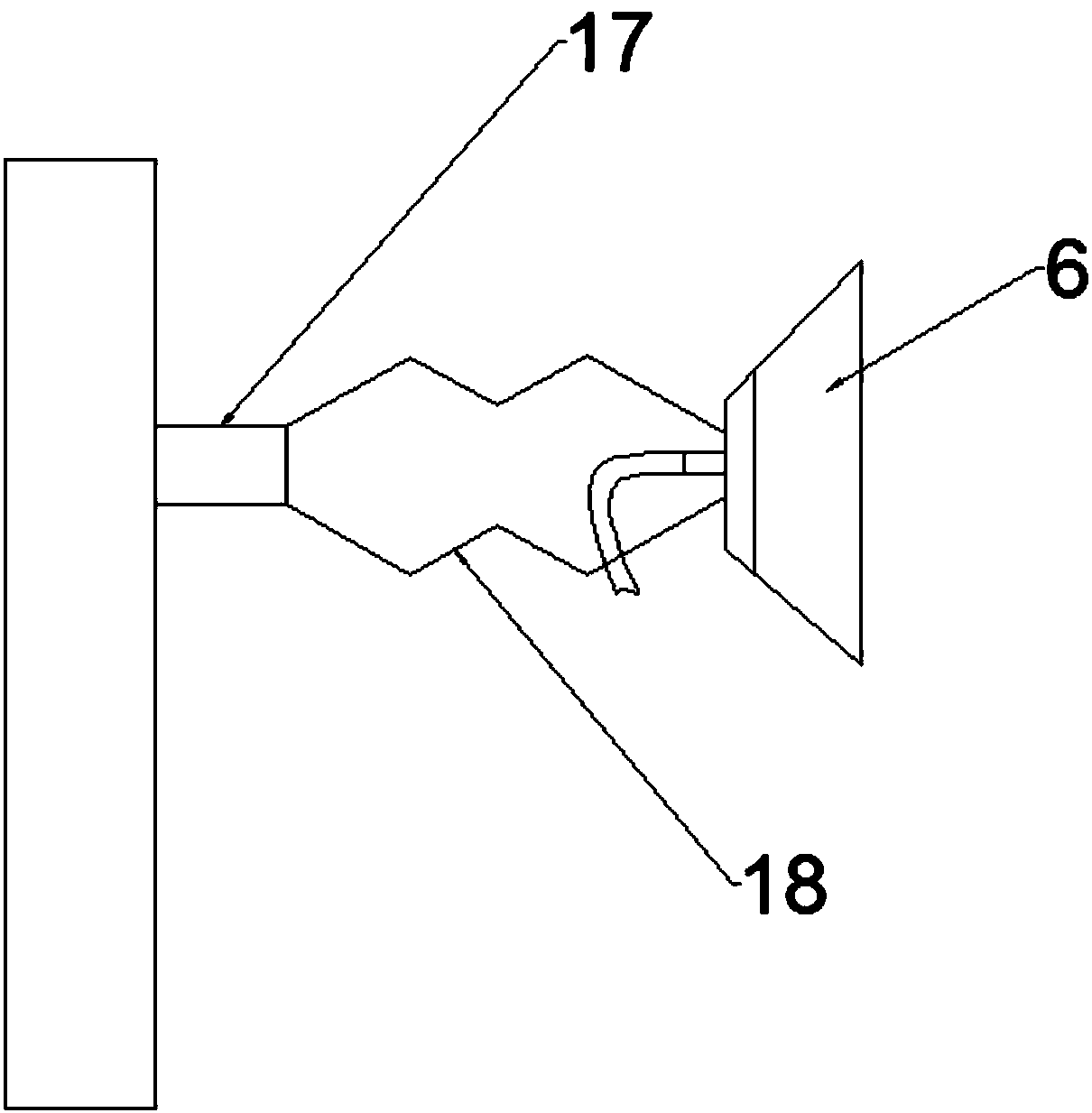

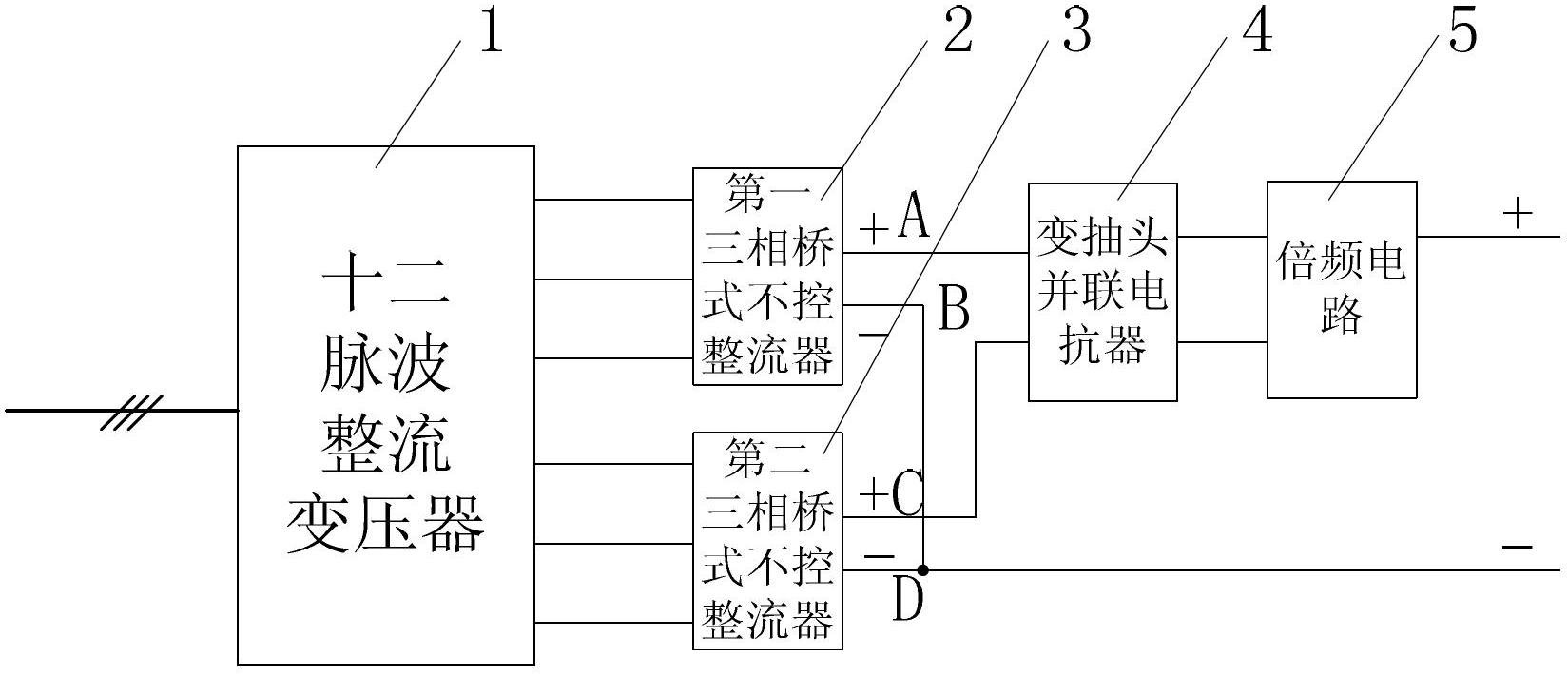

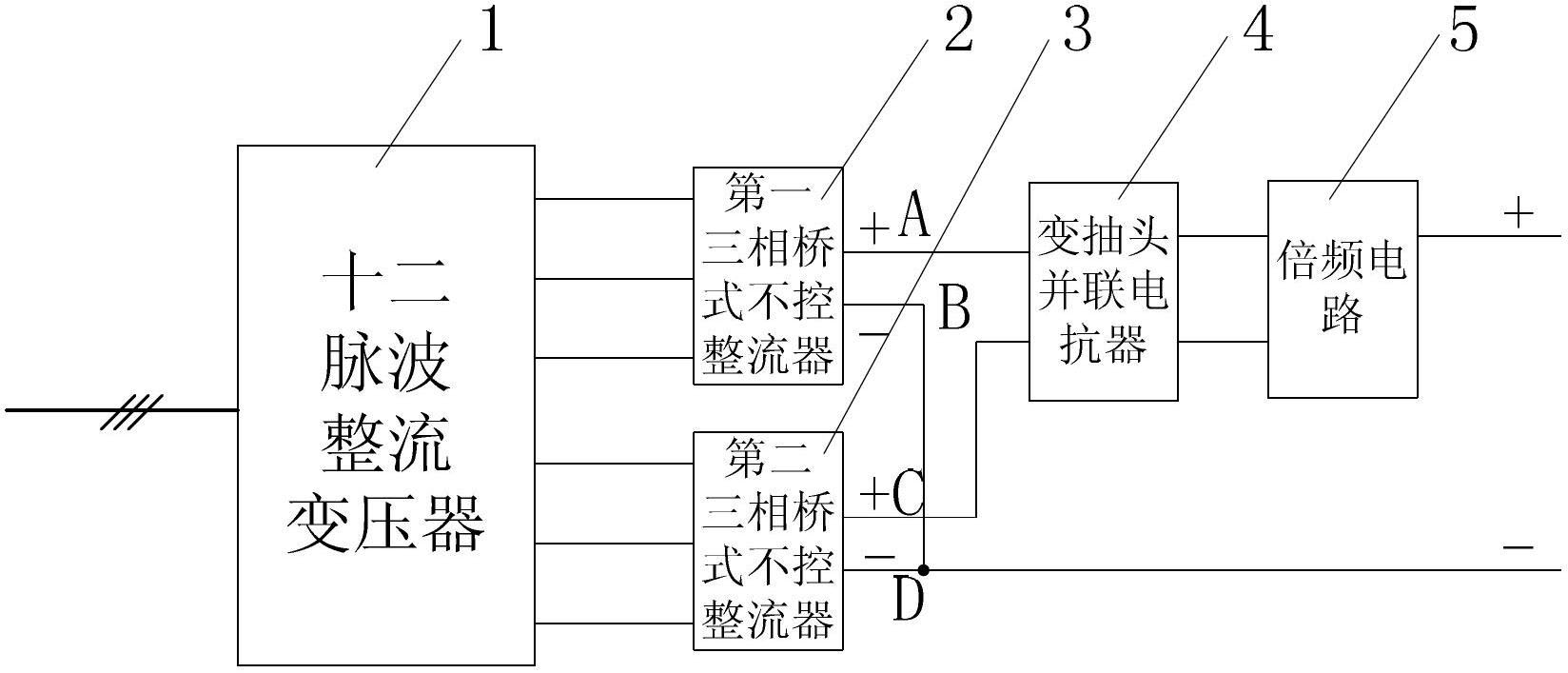

Equivalent 24 pulse wave non-control rectification DC thawing apparatus

ActiveCN102664379ASimple structureLess investmentOverhead installationAc-dc conversion without reversalWave shapeShunt reactor

The invention discloses an equivalent 24 pulse wave non-control rectification DC thawing apparatus which is composed of a 12 pulse wave rectifier transformer (1), a first three-phase bridge non-control rectifier (2), a second three-phase bridge non-control rectifier (3), a variable-tap parallel reactor (4) and a frequency multiplier circuit (5) which are connected in series, wherein the 12 pulse wave rectifier transformer (1) is provided with a three-phase output end connected with the input end of the first three-phase bridge non-control rectifier (2), and the three-phase output end is connected with the input end of the second three-phase bridge non-control rectifier (3). Two output ends of the variable-tap parallel reactor (4) are correspondingly connected with two input ends of the frequency multiplier circuit (5). The apparatus has the advantages of simple structure, wide thawing applicability, low investment, small occupation area, high cost performance, low pollution on the power grid, and smooth waveform, and is easy to operate and simple to maintain, thereby saving both human resources and material resources.

Owner:STATE GRID HUNAN ELECTRIC POWER +3

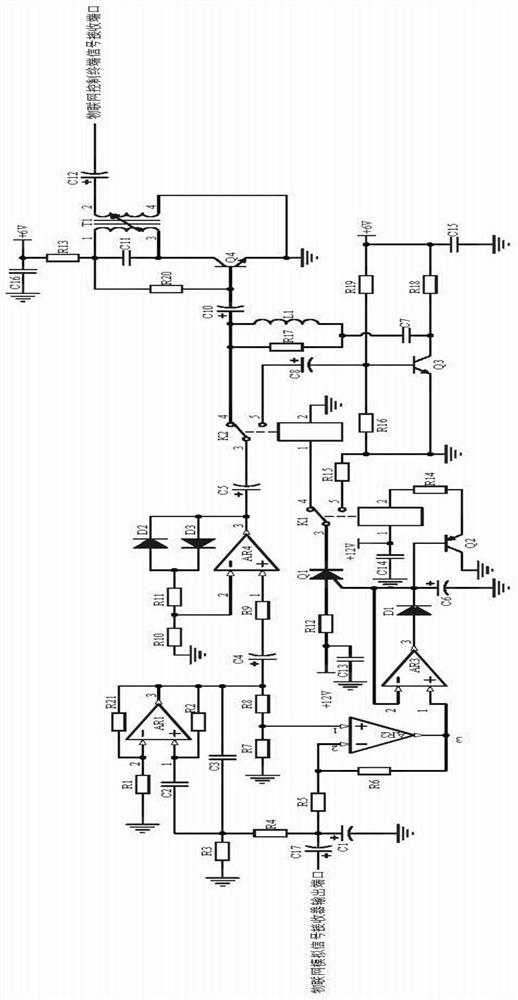

Internet-of-Things signal transmission noise reduction system

InactiveCN112003579AImprove vibrationAccurate resonant frequencyMultiple-port networksElectronic switchingBandpass filteringSilicon-controlled rectifier

The invention discloses an Internet-of-Things signal transmission noise reduction system. The circuit comprises a band-pass filter circuit, a phase detection compensation circuit, an amplitude stabilization circuit and a frequency selection output circuit. Band-pass filtering is carried out on the received analog signal; the amplitude stabilization circuit utilizes the characteristic that the sumof parallel dynamic resistances of a diode D2 and a diode D3 changes along with the current of a feedback loop to adjust the amplification factor of the amplitude stabilization circuit, signal amplitudes are stabilized, the phase detection compensation circuit adopts operational amplifiers AR2 and AR3 to detect signal phase differences before and after band-pass filtering and takes amplitudes of the signal phase differences; the conduction states of the silicon controlled rectifier Q1 and the triode Q2 are controlled; the frequency selection output circuit utilizes parallel resonance of the adjustable transformer T1 and the capacitor C11 to achieve signal frequency selection, noise reduction processing is carried out on analog signals of the Internet of Things, and meanwhile the problem ofsignal distortion caused by nonlinear phase shift of an analog filter is solved.

Owner:ELECTRIC POWER RES INST OF GUANGXI POWER GRID CO LTD +1

Disk drive

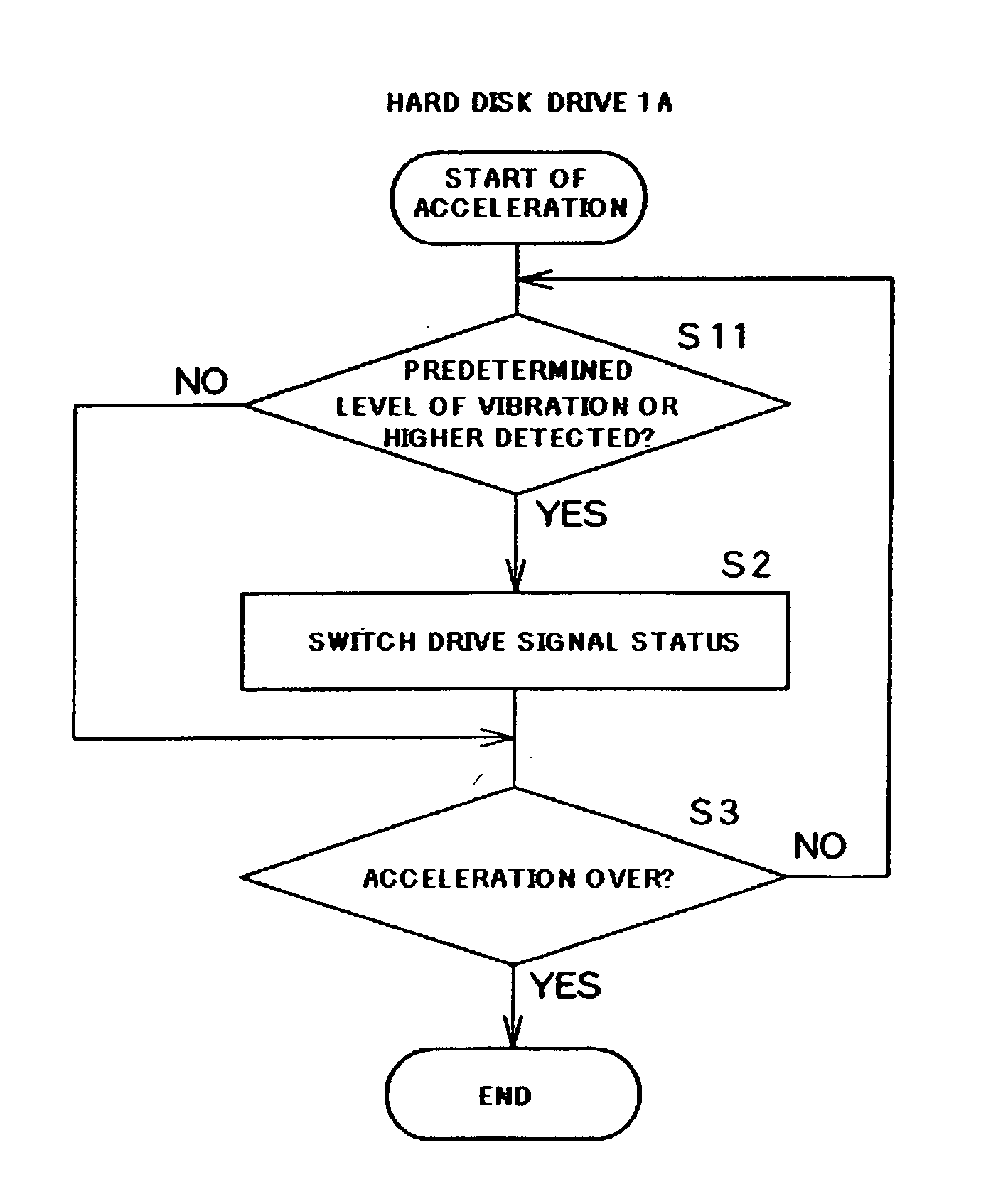

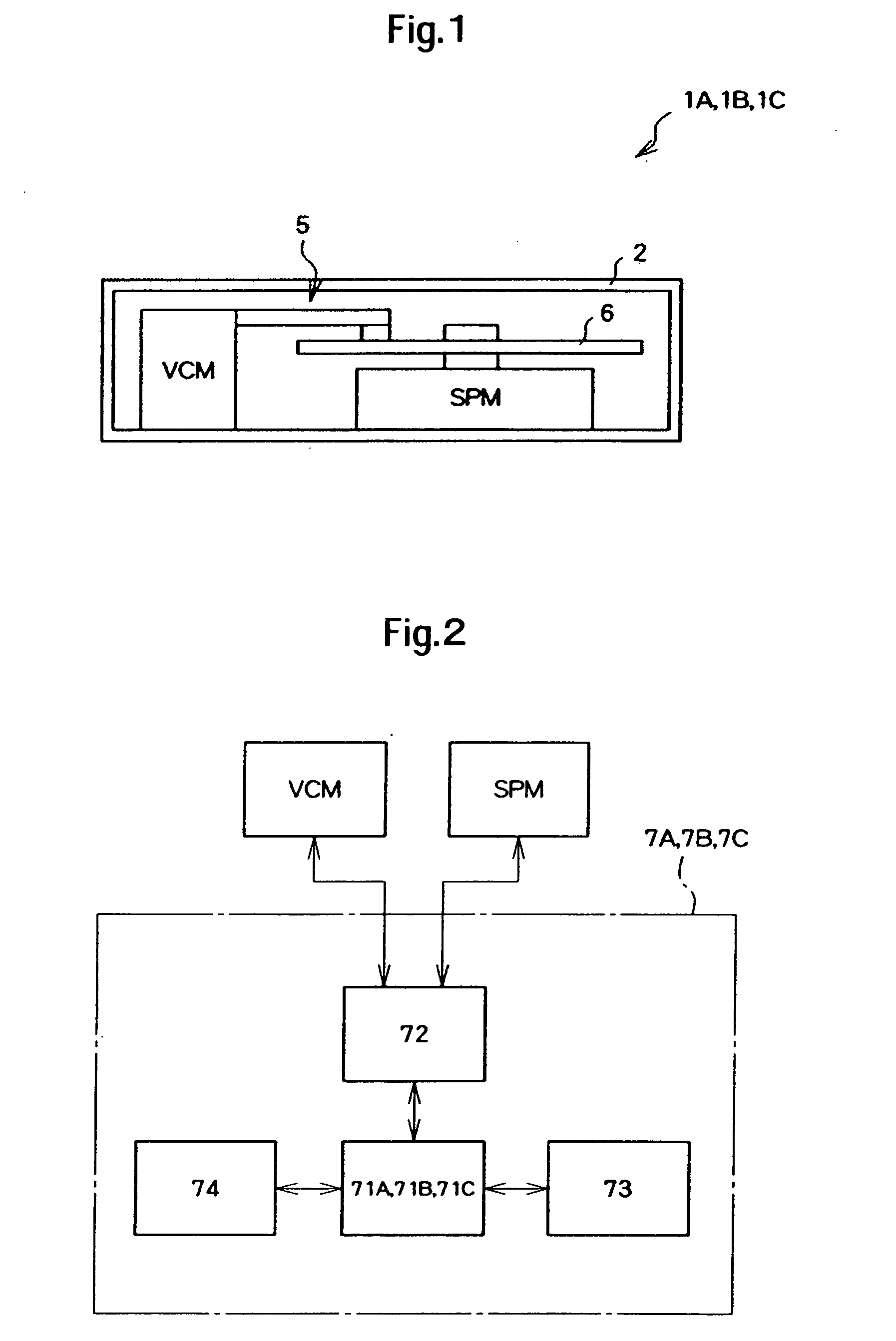

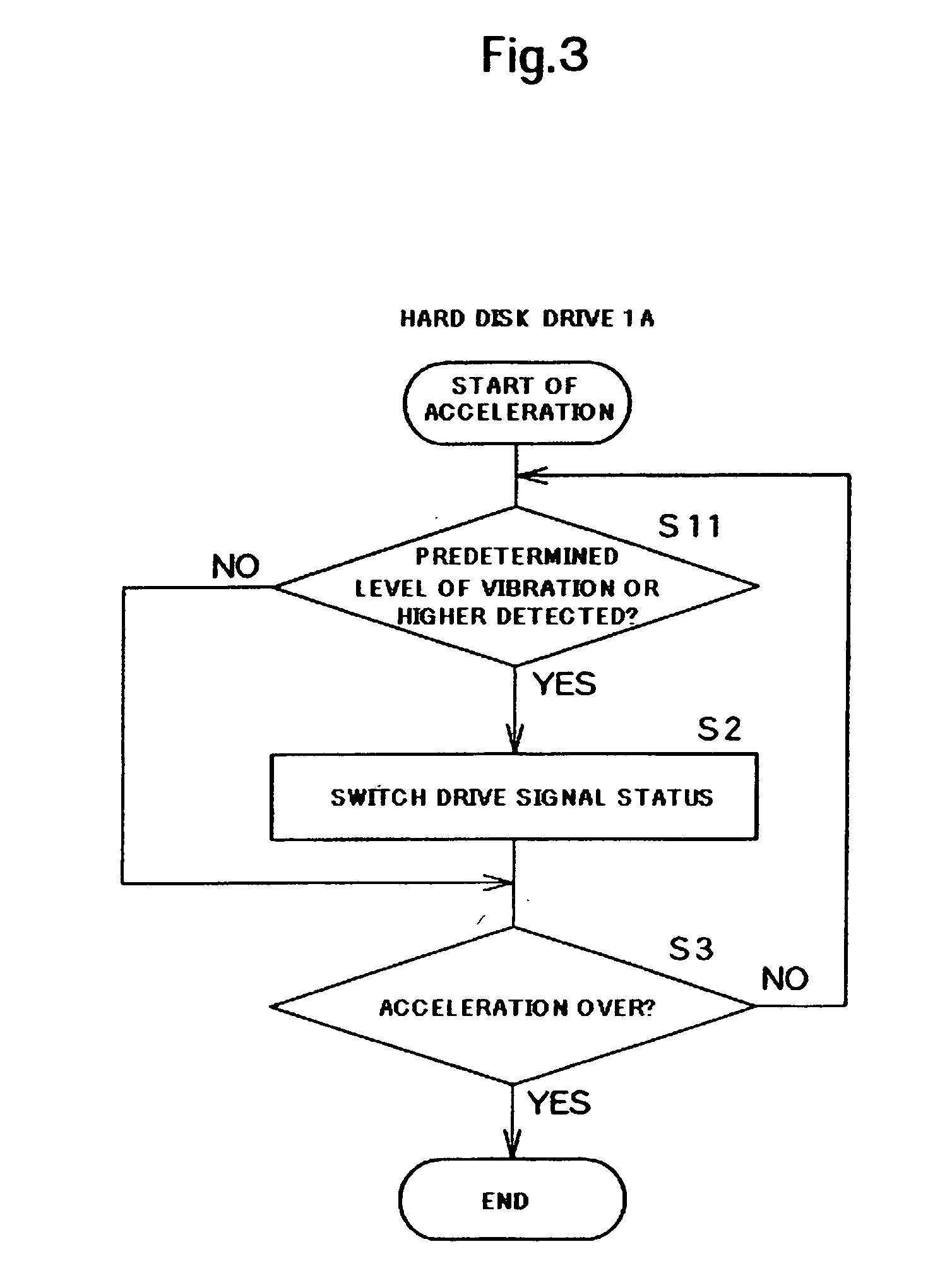

InactiveUS20070253089A1Reduce current levelSmooth waveformCombination recordingRecord information storageHard disc driveVoltage

Embodiments in accordance with the present invention provide a disk drive that ensures quieter rotational acceleration of a recording disk. Certain embodiments relate to a hard disk drive that detects the vibration of an enclosure by monitoring, via a driver, a counter electromotive voltage generated in a voice coil motor. If the hard disk drive detects a predetermined level of vibration or higher in the enclosure, it switches the status of a drive signal applied to a spindle motor so as to reduce the current level or smooth the waveform. This ensures reduced vibration of the enclosure.

Owner:WESTERN DIGITAL TECH INC

Method for speeding up rotation of liquid crystal molecule and liquid crystal panel drive circuit used in the method

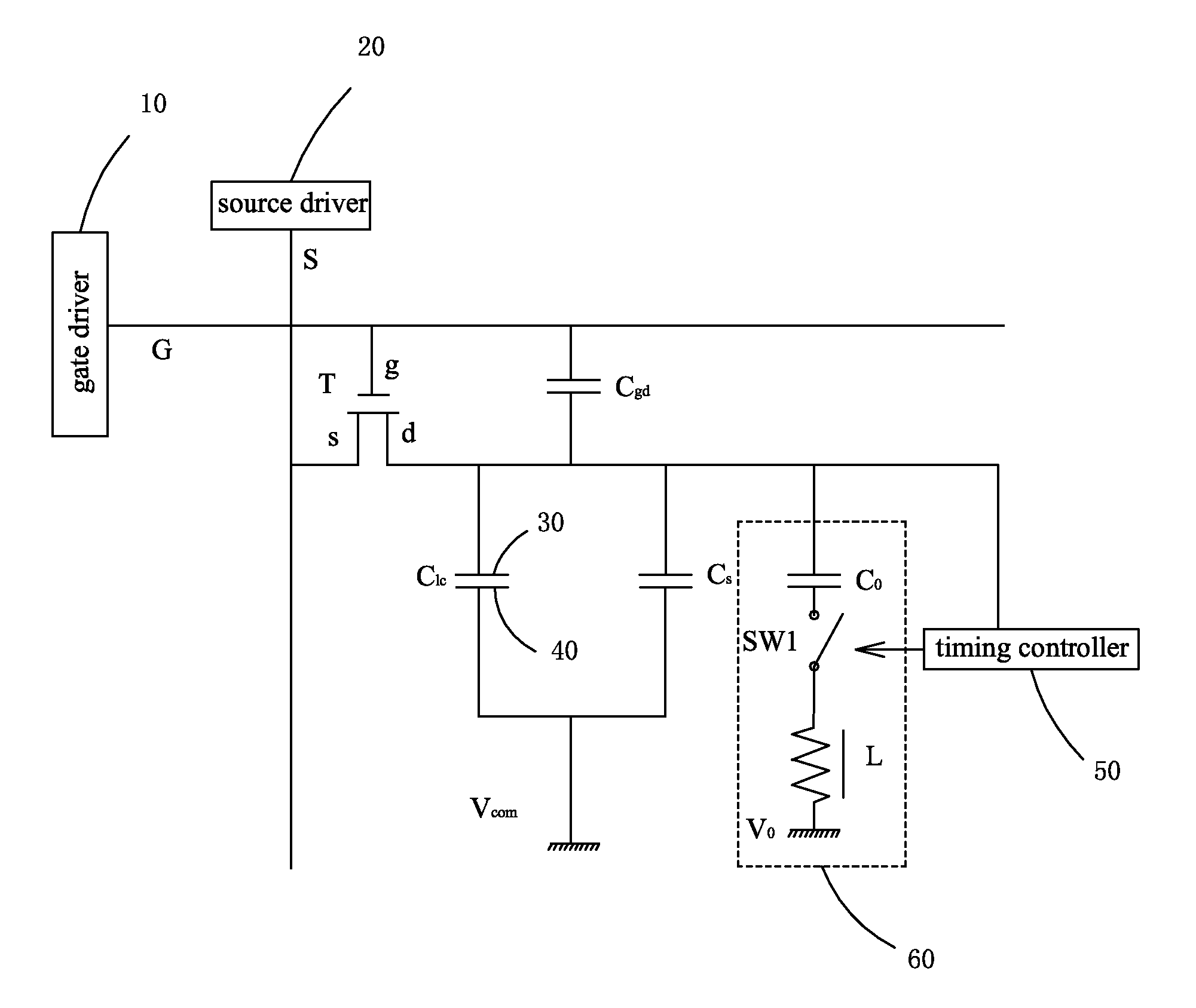

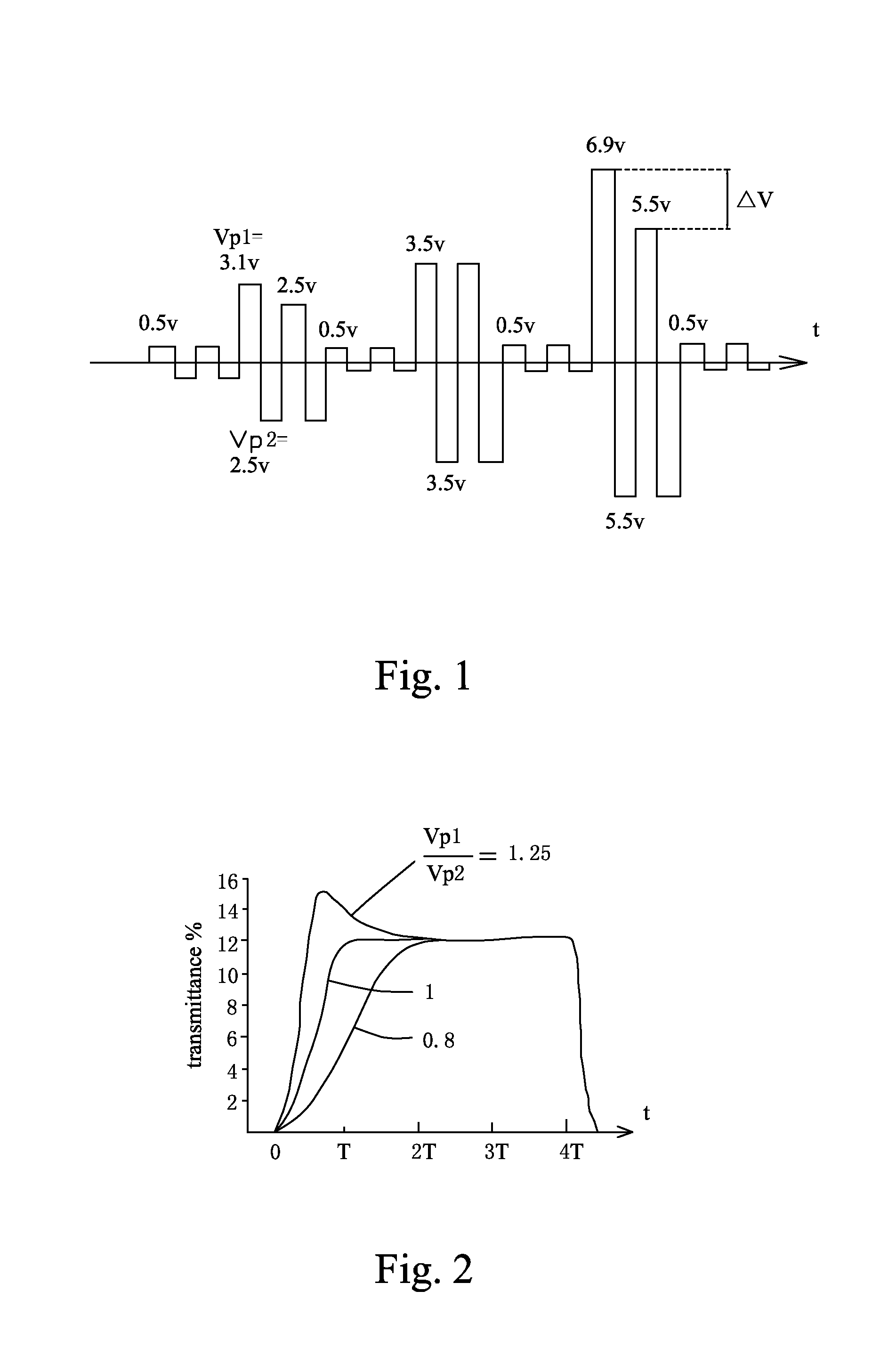

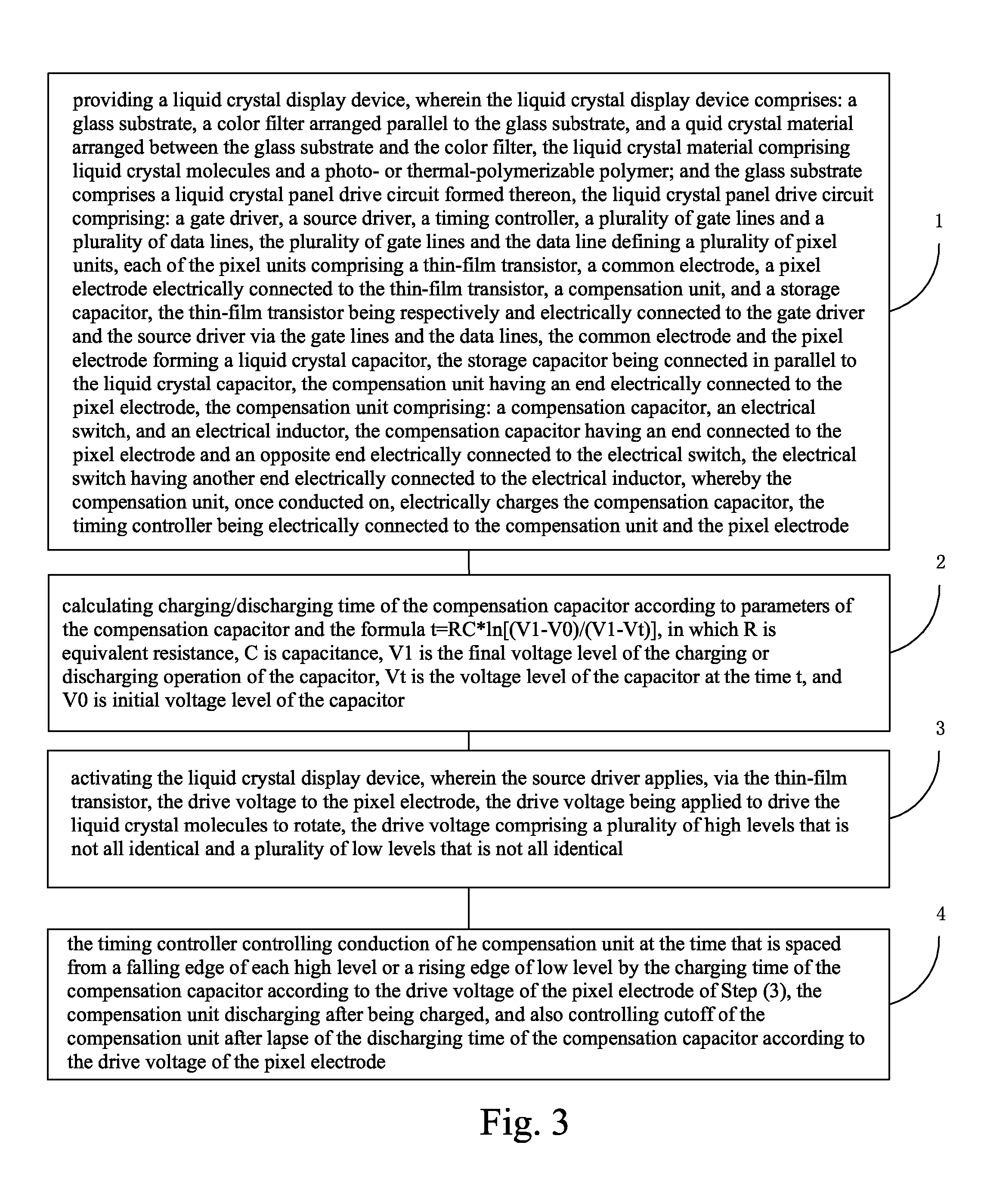

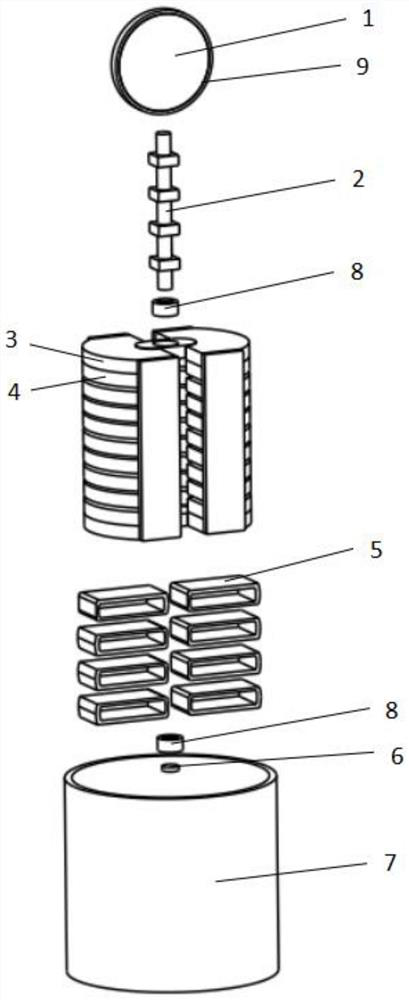

ActiveUS20140111722A1Smooth rotationShort response timeStatic indicating devicesNon-linear opticsCapacitanceElectricity

The present invention provides a method for speeding up rotation of liquid crystal molecule and a liquid crystal panel drive circuit used in the method. The method includes providing a liquid crystal display device, which includes a glass substrate having a liquid crystal panel drive circuit formed thereon and including a timing controller and pixel units each including a thin-film transistor, a common electrode, a pixel electrode electrically connected to the thin-film transistor, a compensation unit, and a storage capacitor, the compensation unit including a compensation capacitor, the timing controller being electrically connected to the compensation unit and the pixel electrode; calculating discharging / charging time of the compensation capacitor; activating the liquid crystal display device, where the source driver applies a drive voltage via the thin-film transistor to the pixel electrode; and the timing controller controlling the compensation unit to conduct on or cut off according to the drive voltage.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

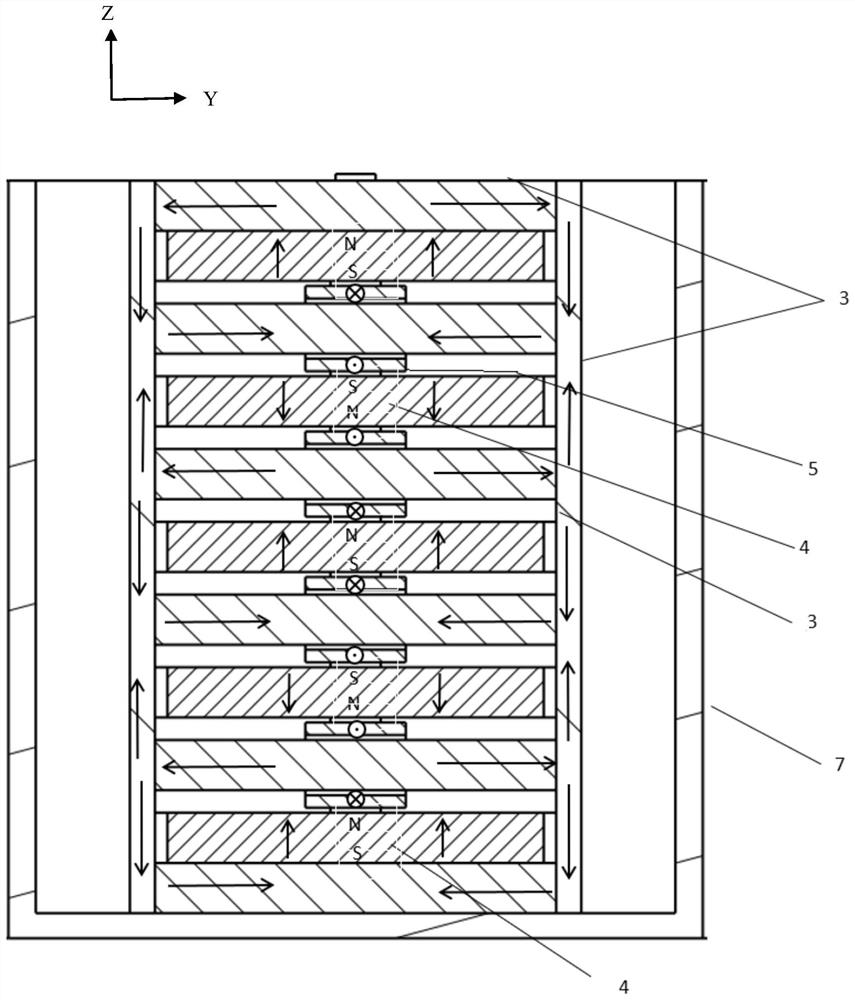

One-dimensional high-speed heavy-load limited rotation actuator

The invention discloses a one-dimensional high-speed heavy-load limited rotation actuator which comprises a rotating shaft, two groups of coils, two groups of magnet assemblies and a shell, wherein the two groups of coils are symmetrically fixed to two sides of the rotating shaft, and each group of coils comprises n coils which are axially distributed along the rotating shaft; each group of magnet assemblies comprises n+2 layers of magnetizers and n+1 layers of permanent magnets which are longitudinally arranged in a staggered manner; each group of coils corresponds to one group of magnet assemblies, and the n coils are respectively and correspondingly sleeved on the magnetizers from the second layer to the (n+1) th layer, so that the upper part and the lower part of each coil are respectively provided with a layer of permanent magnet; when current flows through the two groups of coils, the magnet assembly generates a bias magnetic field to drive the two groups of coil assemblies to drive the rotating shaft to rotate around the axis of the rotating shaft. By adopting a multi-layer structure, the magnet is effectively utilized, the size and the weight are small, the torque is large, and the requirement for bearing large loads is met.

Owner:北京瑞控信科技股份有限公司

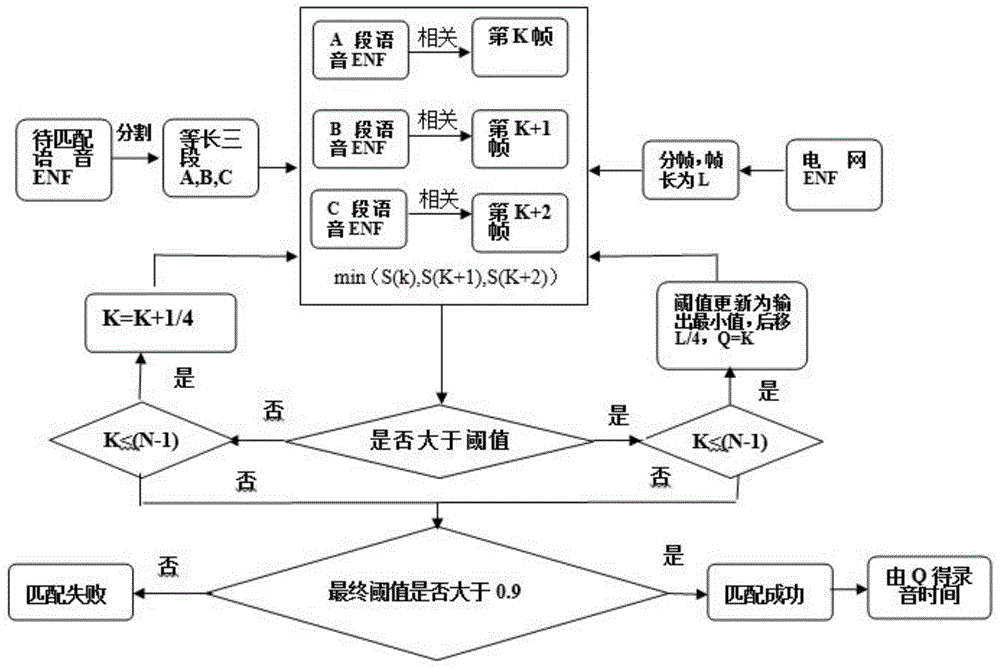

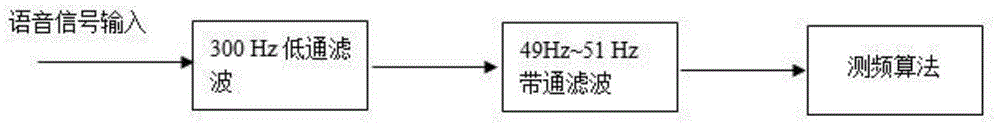

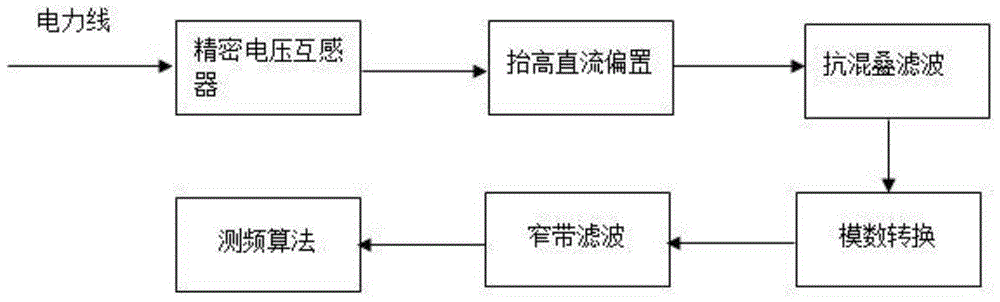

Recording time identification method

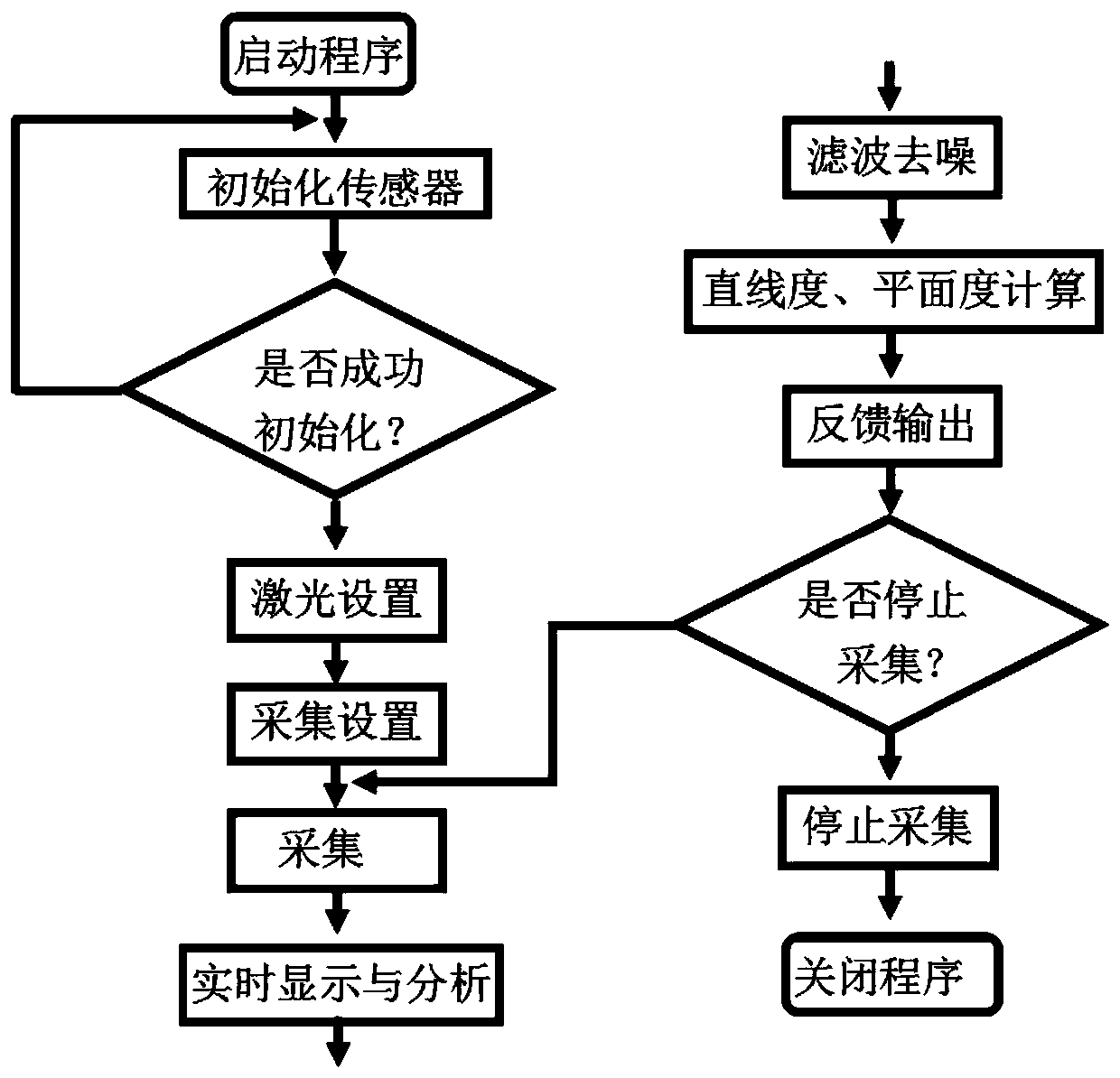

ActiveCN104156578AImprove matching efficiencyImprove matching accuracySpecial data processing applicationsSpeech soundComputer science

The invention provides a recording time identification method. The recording time identification method includes voice signal preprocessing, power-grid frequency extraction, normalization, design of a correlator and parallel matching algorithm, matching-signal median filtering and output of matching results. The recording time identification method includes firstly extracting power-grid frequency signals in audio frequency to be matched, dividing the power-grid frequency signals into three channels to be matched with frames in power-grid frequency in power lines in parallel so as to obtain correlation degree of the power-grid frequency signals and the power-grid frequency, comparing the correlation degree with the threshold value, judging the frames with the maximum correlation degree, and finally acquiring recording time of audio frequency signals. The recording time identification method adopts a parallel mechanism, matching efficiency is improved. Meanwhile, the recording time identification method is more accurate in recording time identification and is of great significance in audio frequency forensics.

Owner:NANJING INST OF TECH

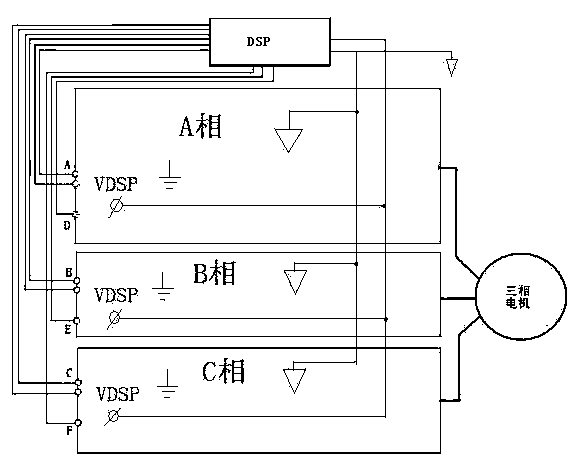

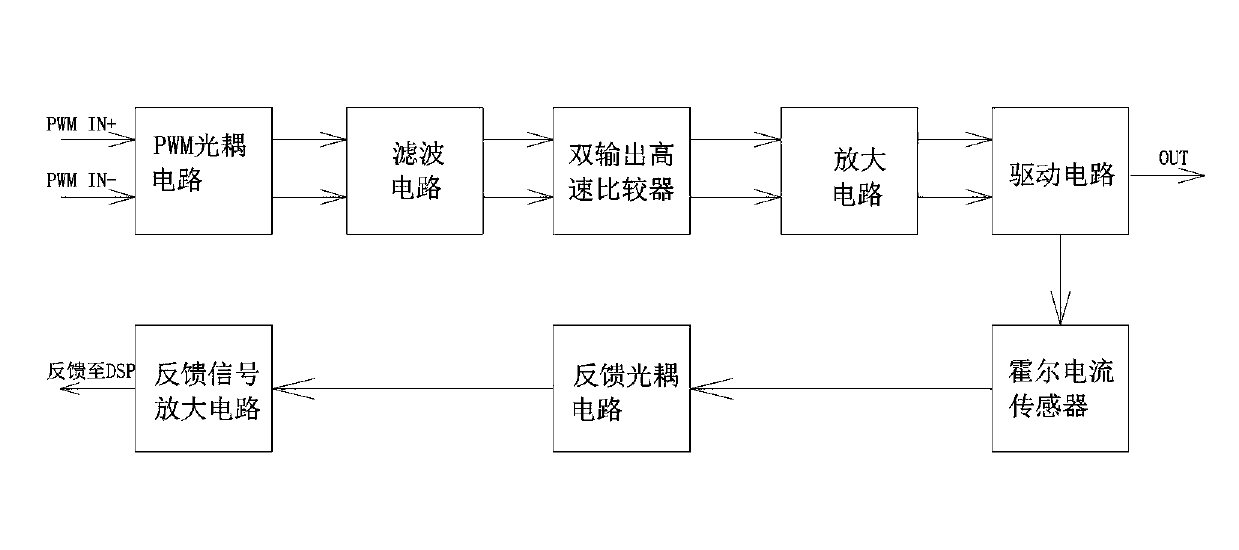

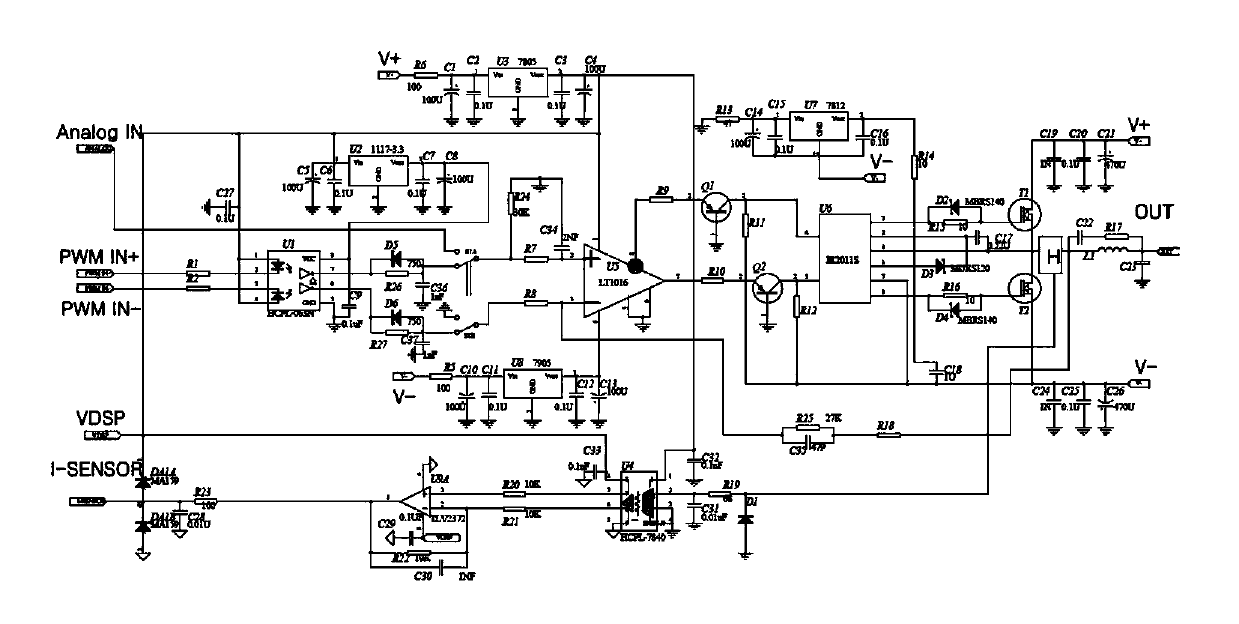

Three-phase motor variable frequency speed control system capable of outputting sine waves with frequency as high as 20000Hz

InactiveCN103475308ASmooth waveformReduce running noiseAC motor controlDynamo-electric converter controlHemt circuitsControl theory

A three-phase motor variable frequency speed control system capable of outputting sine waves with the frequency as high as 20000Hz comprises a DSP processor, three groups of three-phase drive PWM signals used for outputting phases with the difference of 120 degrees and three-phase amplifying channels, wherein the structures of the three-phase amplifying channels are identical, and the three-phase amplifying channels are distributed in parallel, receive the corresponding three-phase drive PWM signals sent by the DSP processor respectively, improve the frequency of the three-phase drive PWM signals to be larger than or equal to 20000Hz and are used for controlling a drive circuit to drive a motor. The three-phase motor variable frequency speed control system has the advantages of being smooth in output wave shape, low in motor operation noise, smooth, high in signal-noise ratio, little in signal distortion, wide in dynamic range, good in circuit stability, strong in anti-interference performance, capable of allowing digital or analog signals to be input, and flexible to use.

Owner:四川峰谷源新能源有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com