Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60results about How to "Save pin resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

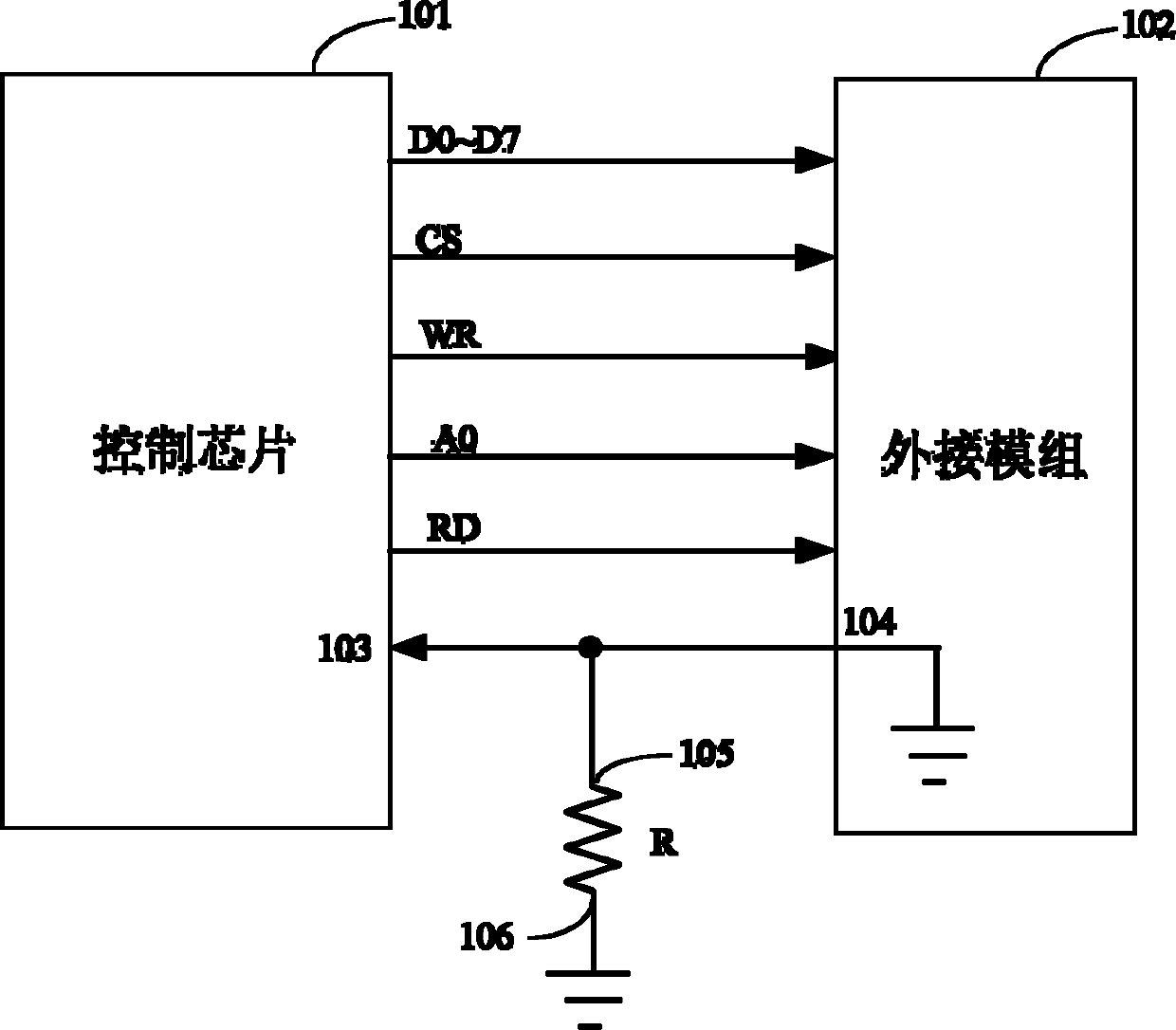

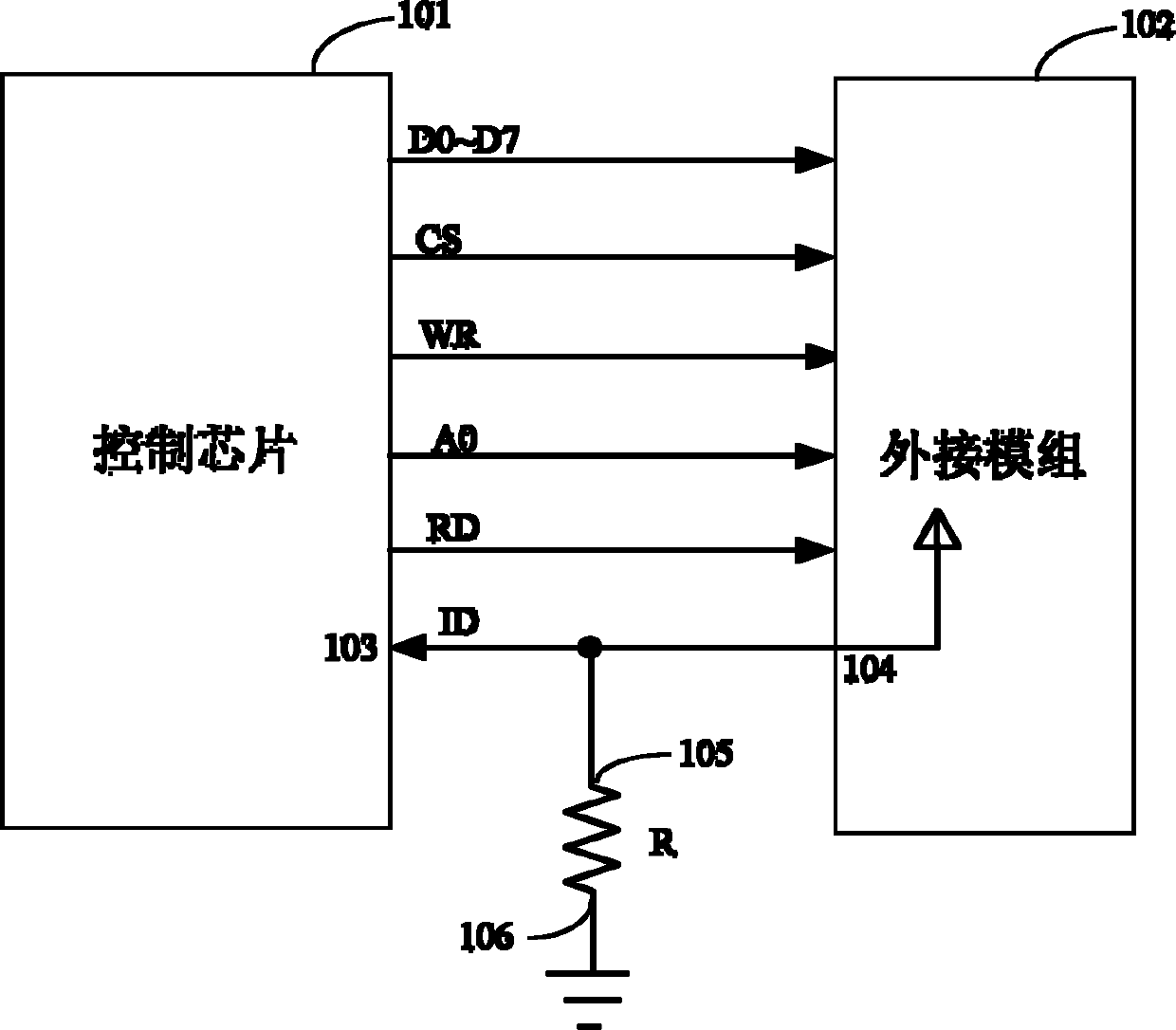

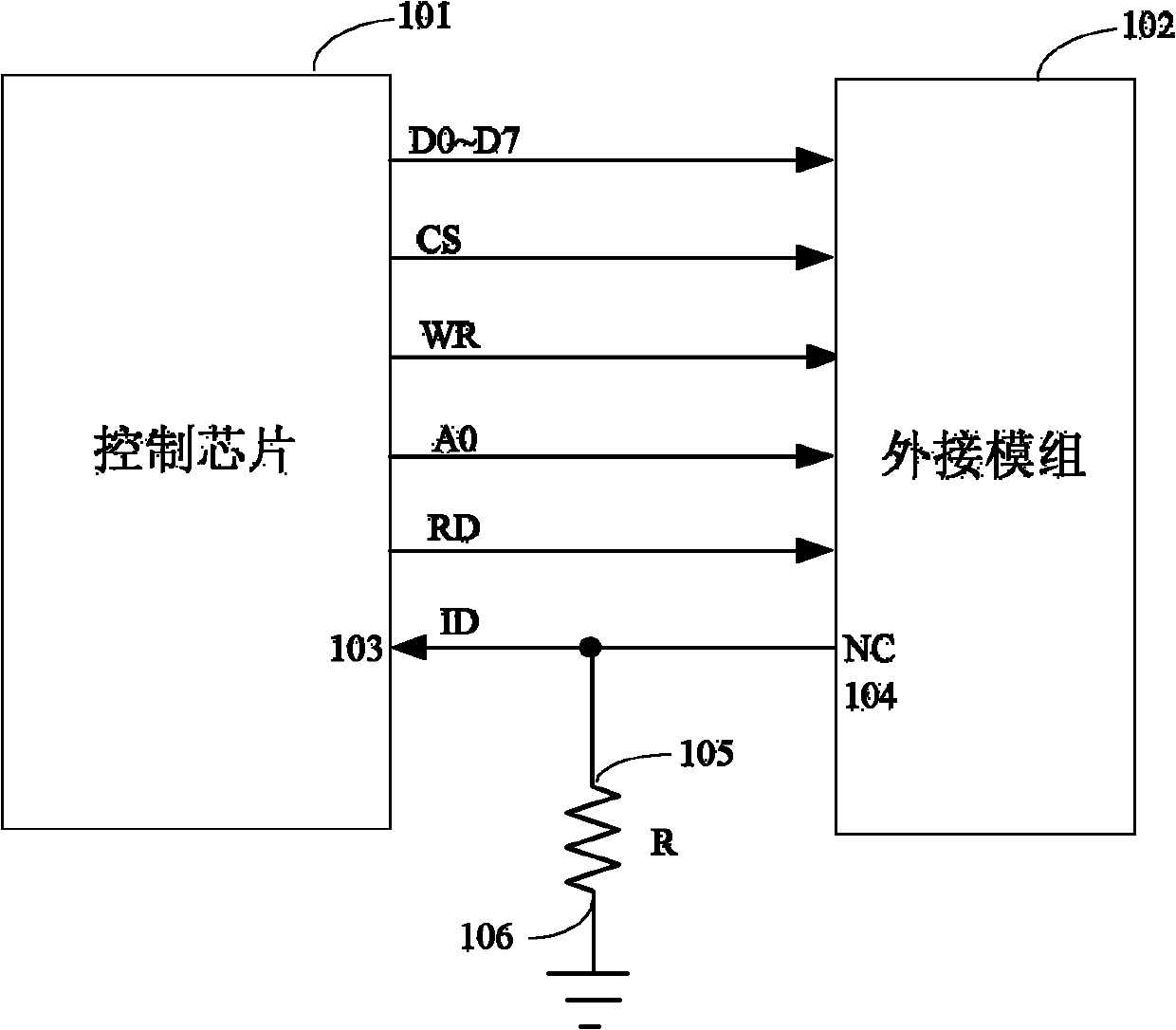

Identification method for external module and electronic equipment using same

ActiveCN102169468ALow costSave pin resourcesElectric digital data processingElectrical resistance and conductanceEngineering

The invention discloses an identification method for an external module. The method comprises the following steps of: connecting a first port of a control chip with a second port of the external module; connecting one end of a resistor between the first port and the second port; grounding the other end of the resistor; setting the first port as an output mode and an input mode; outputting a high level in the output mode; further reading pins levels of the first port in the output mode and the input mode; and judging the connection mode of the second port according to the pin levels to judge the type of the external module. The invention also discloses electronic equipment. In the mode, the technical scheme provided by the invention can save cost and pin resources, and has the advantages of simplicity and practicability.

Owner:HUIZHOU TCL MOBILE COMM CO LTD

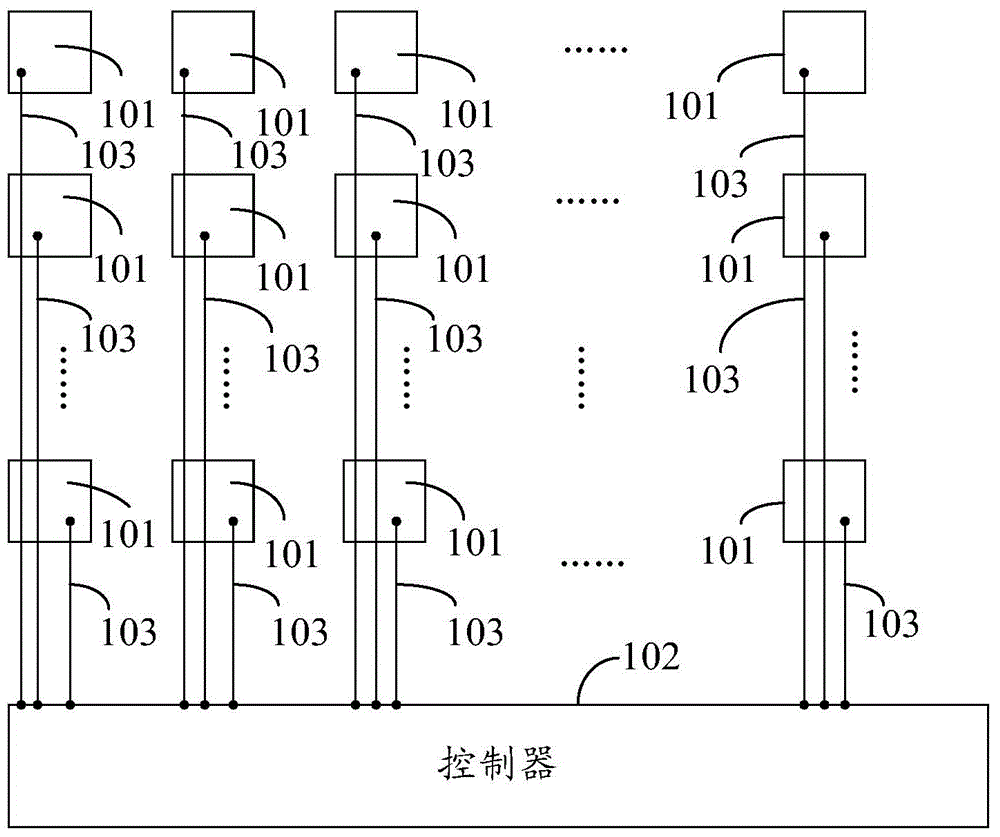

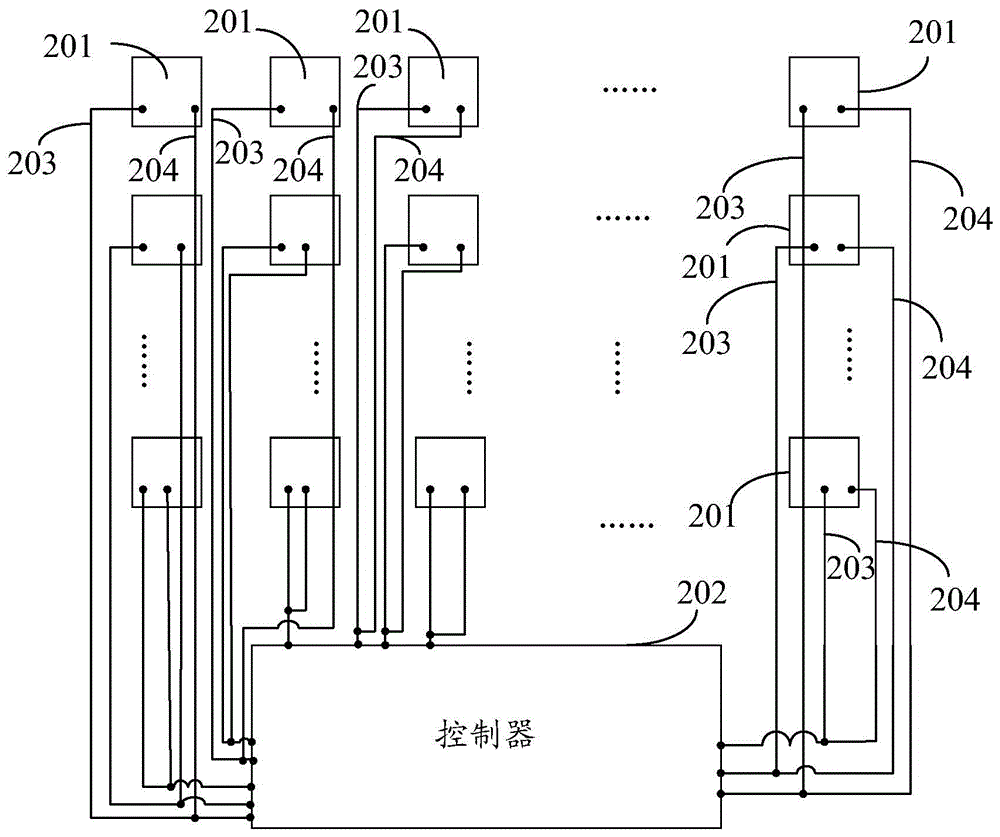

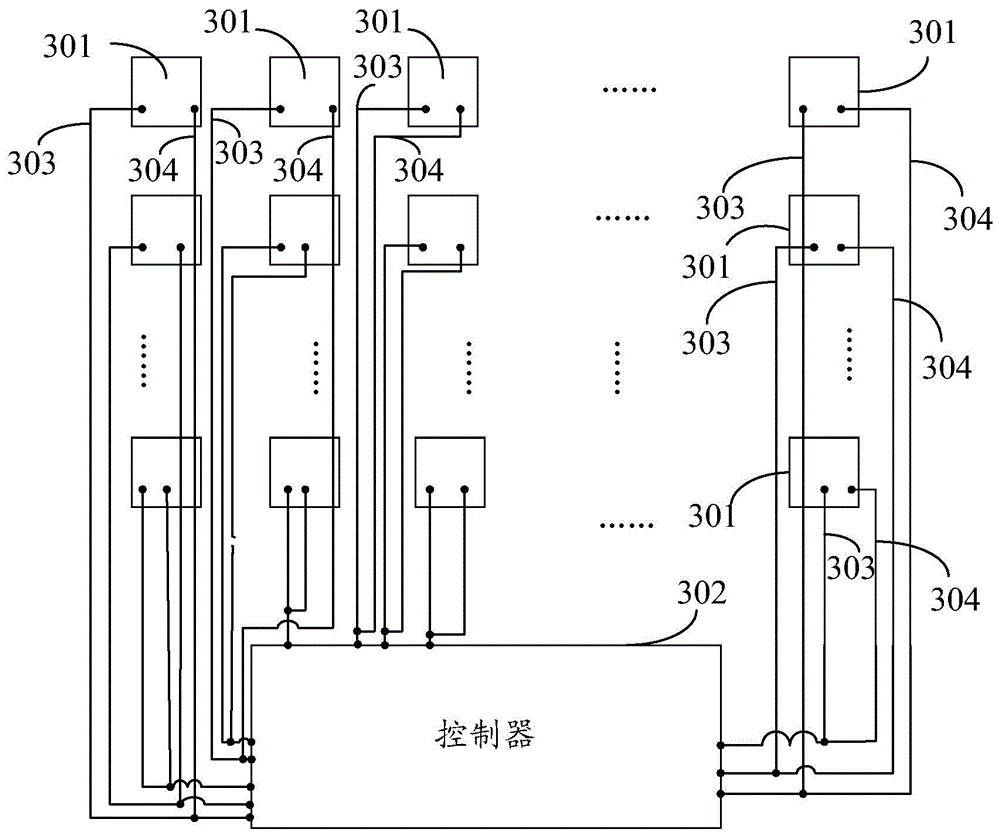

Touch panel and touch type display device

InactiveCN104391601AReduce disconnectionSave pin resourcesNon-linear opticsInput/output processes for data processingDisplay deviceHuman–computer interaction

The invention discloses a touch panel and a touch type display device. The touch panel comprises a controller and a plurality of arrayed touch electrodes, and each touch electrode is electrically connected with the same pin of the controller through at least two leads. By the mode, the problem of disconnection of the leads among the touch electrodes and the controller can be effectively improved, defective rate is decreased, and the service life of the touch panel is prolonged.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

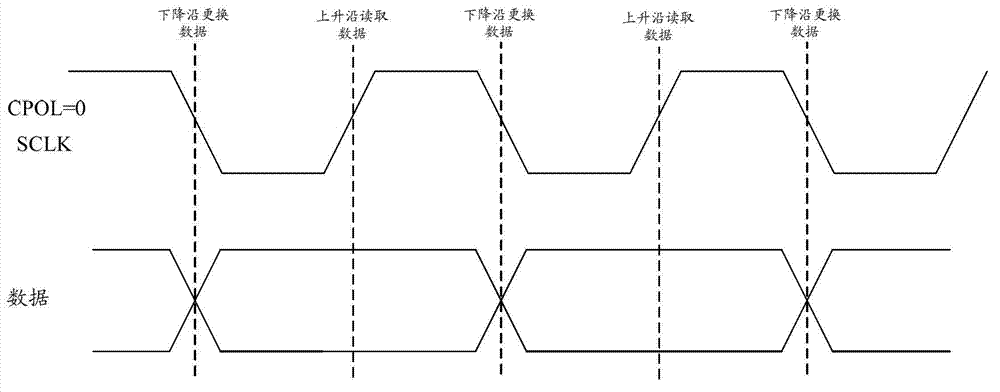

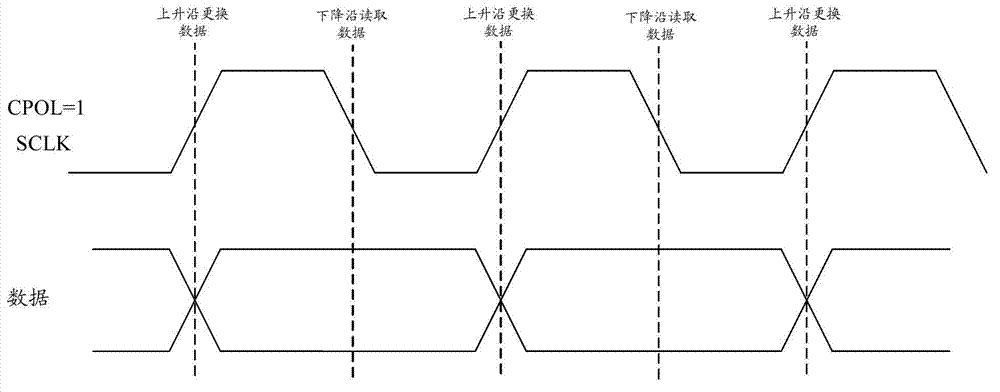

Data transmission method and data transmission system based on serial peripheral interface (SPI) data transmission timing sequences

InactiveCN103092806AFast transmissionImprove transmission efficiencyElectric digital data processingByteSerial Peripheral Interface Bus

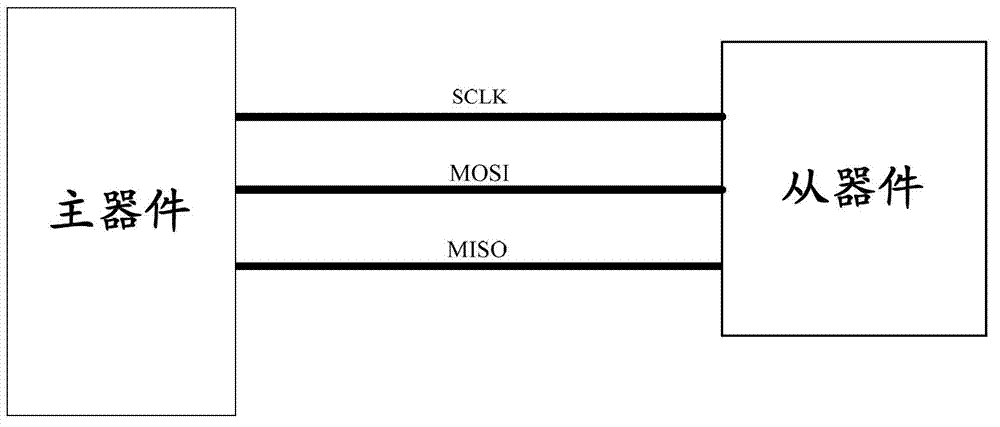

The invention discloses a data transmission method and a data transmission system based on serial peripheral interface (SPI) data transmission timing sequences. The data transmission method based on the SPI data transmission timing sequences comprises the following steps: outputting SPI clock in effective status by a main device and sending a read\write mark of 1 byte, a start address (SA) of 2 byte and read\write data length (Len) of the 2 byte, receiving the read\write mark, SA and Len by a secondary device according to the SPI clock output by the main device and the SPI data transmission timing sequences, and sending data with SA and Len byte as a first address to the main device according to the SPI data transmission timing sequences and the read\write mark or storing the data of the Len byte received by the main device to local storage space with SA as the first address. Due to the fact that the Len byte is sent continuously in one frame data, and the data of the Len byte do not need to be sent by being placed on Len frame data like the prior art, transmission effects are improved largely.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

Data transmission method, device and system of data storage system

InactiveCN104239252ASave pin resourcesIncrease profitElectric digital data processingData transmissionData store

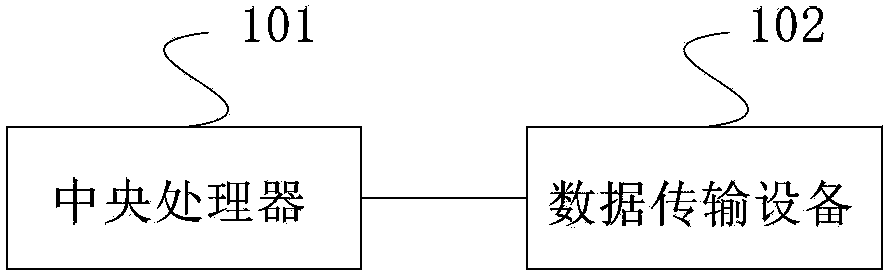

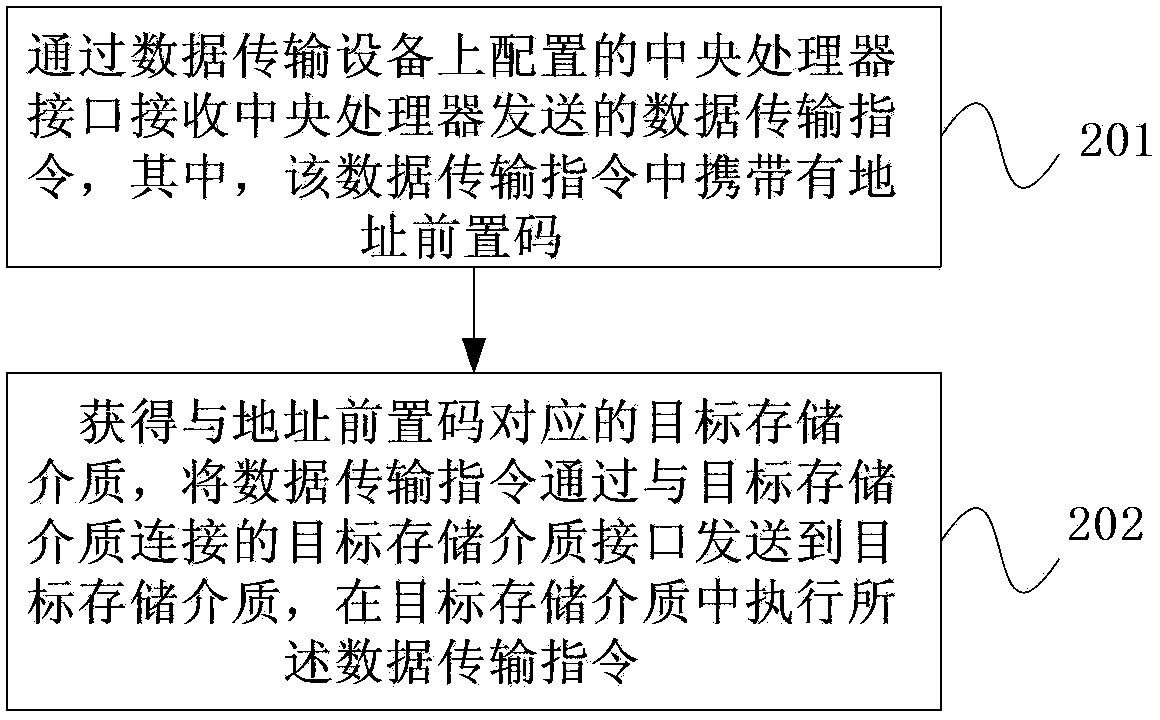

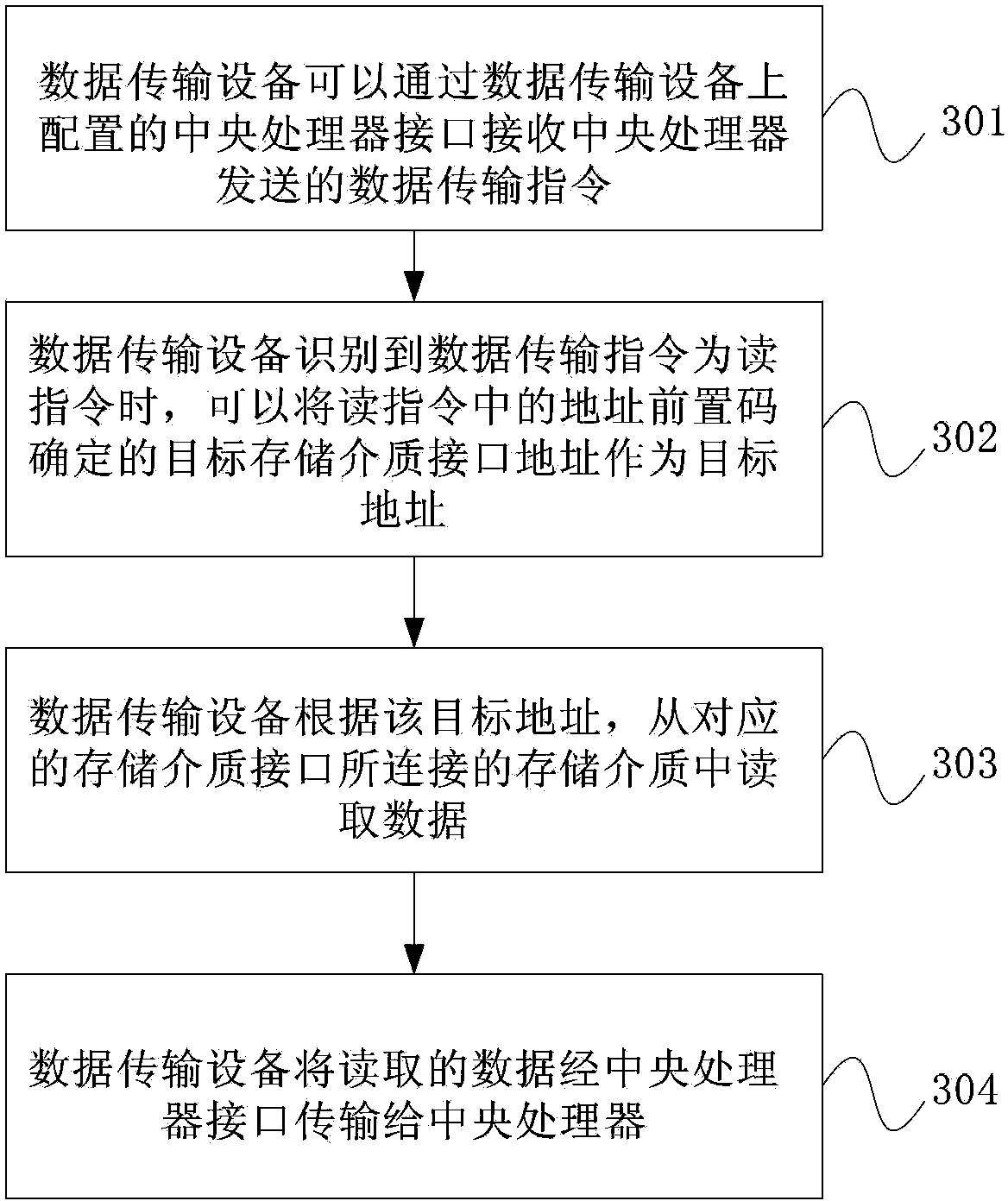

An embodiment of the invention provides a data transmission method, device and system of a data storage system. The data transmission method includes: a central processing unit interface configured on data transmission equipment receives a data transmission instruction transmitted by a central processing unit so as to obtain target storage media corresponding to address precedence codes, the data transmission instruction is transmitted to the target storage media through target storage medium interfaces connected with the target storage media, and the data transmission instruction is executed in the target storage media, wherein each address precedence code corresponds to one of at least two storage media of different types. The method has the advantages that the central processing unit can be connected with different storage media by being connected with one central processing unit interface disposed on the data transmission equipment, the pin resources of the central processing unit are saved, and the utilization rate of the pin resources of the central processing unit is increased.

Owner:HUAWEI TECH CO LTD +1

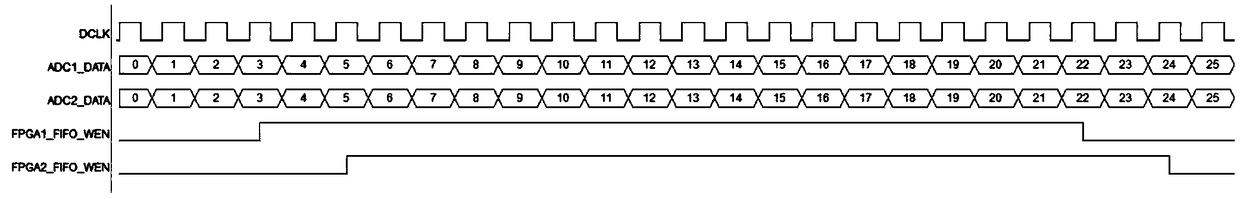

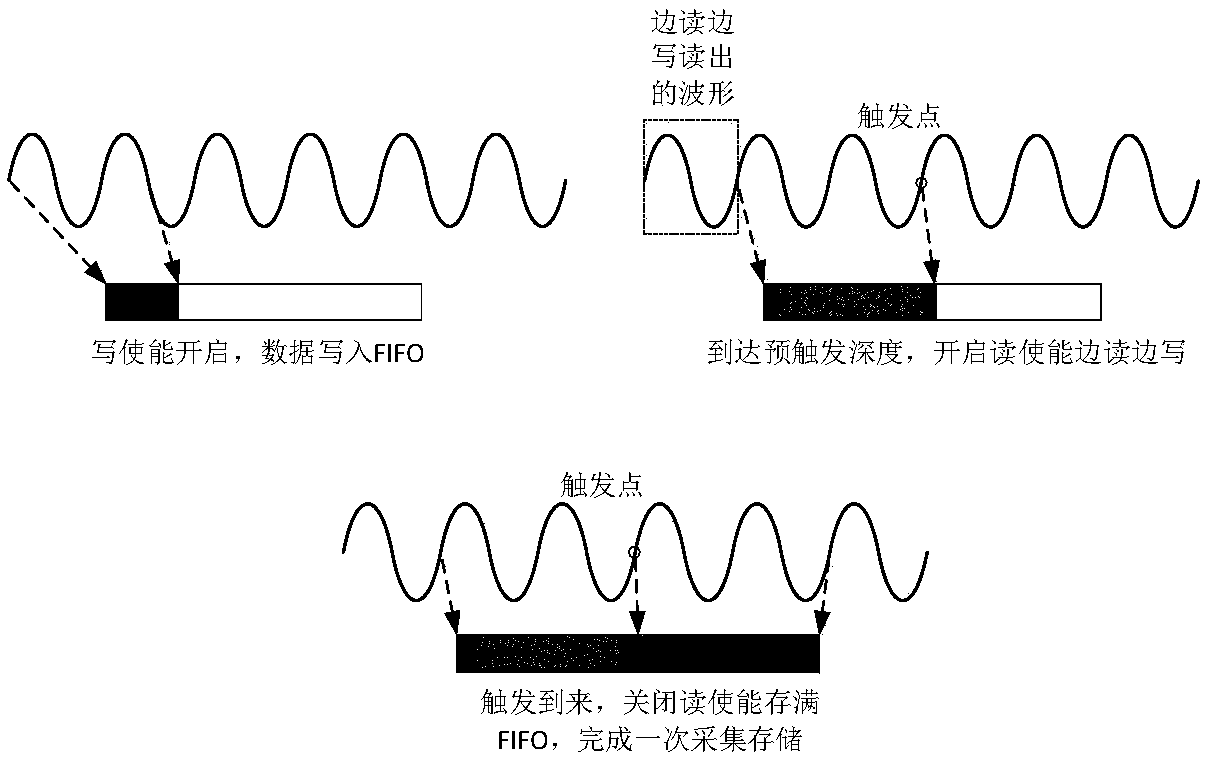

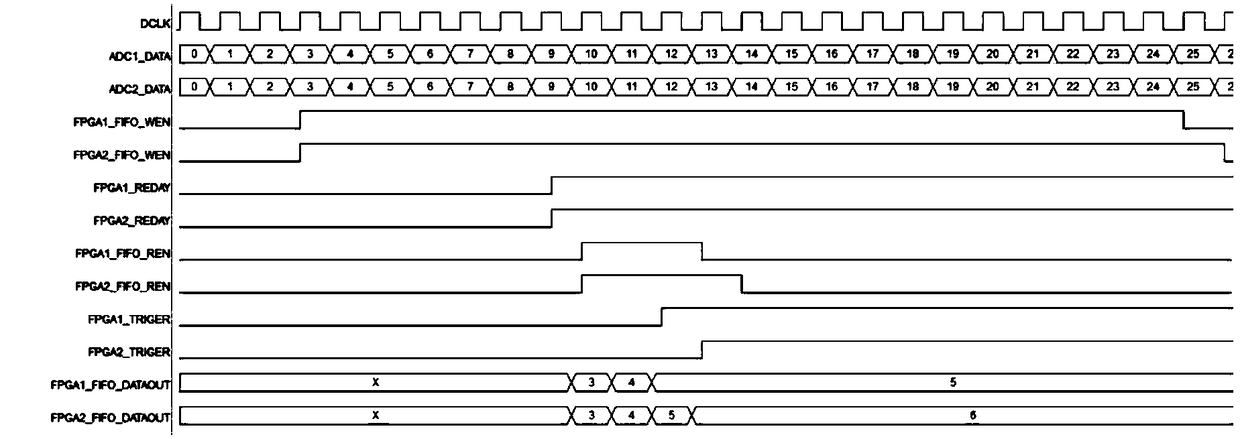

A storage synchronization method of multi-channel acquisition system based on multi-FPGA

ActiveCN109284247ASave pin resourcesStable display of trigger waveformProgramme controlComputer controlInterconnectionComputer engineering

The invention discloses a storage synchronization method of a multi-channel acquisition system with multi-FPGA, the interconnection relationship between FPGAs is established by using the interconnection lines between FPGAs. According to the trigger source, the master-slave trigger property is selected, and the master FPGA synchronously collects the write enable of the slave FPGA, the digital trigger precise positioning, and the digital trigger positioning value synchronously realizes the storage, read and write synchronization of the multi-FPGA multi-channel acquisition system.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

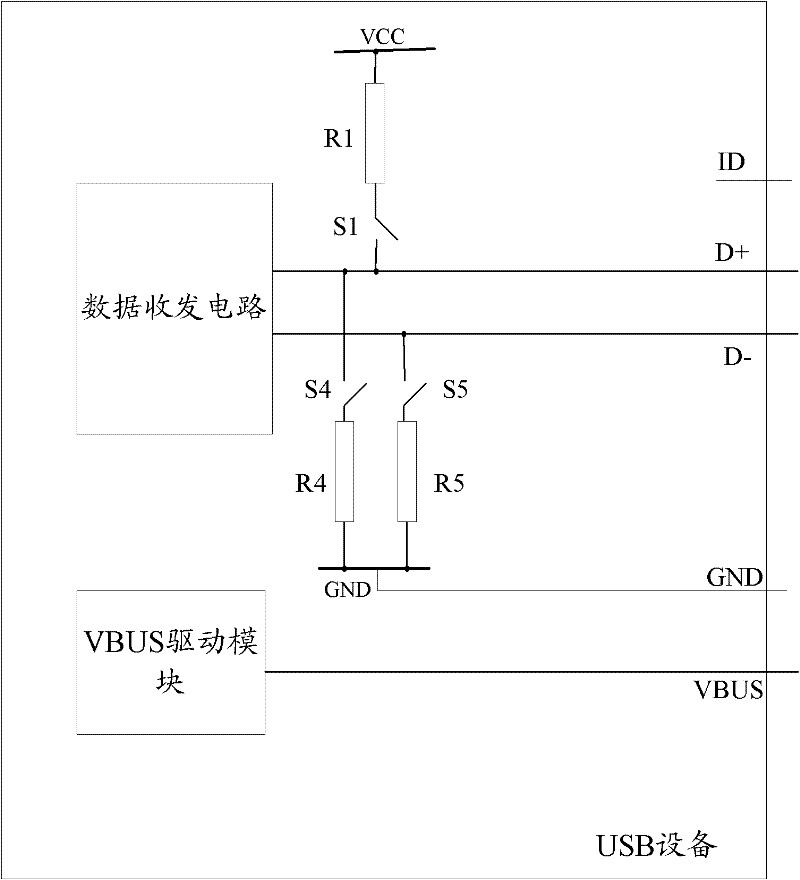

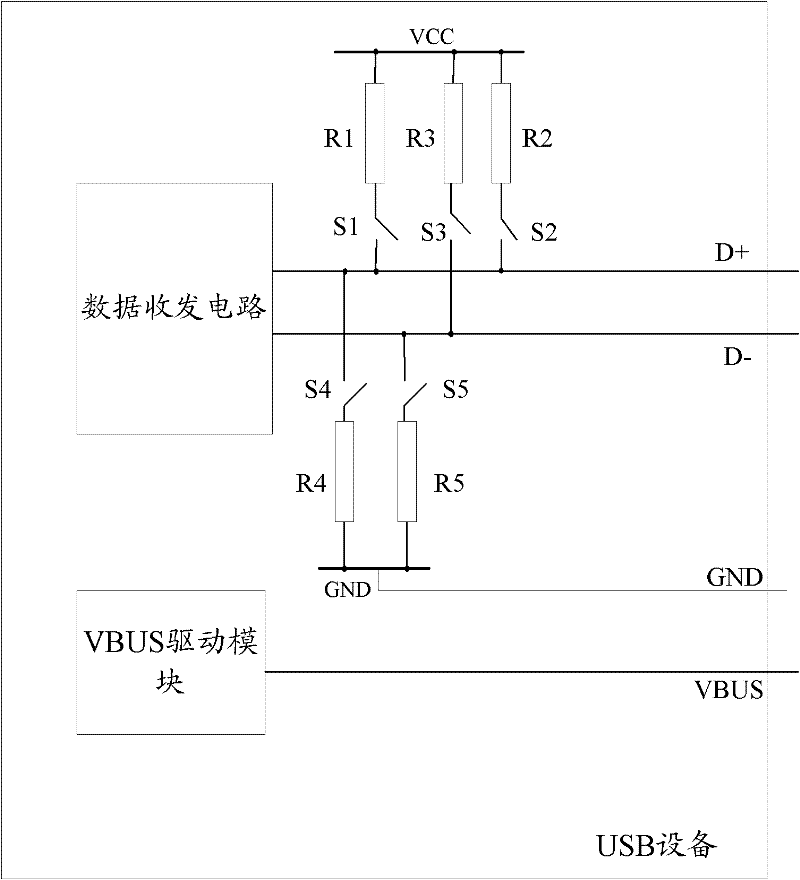

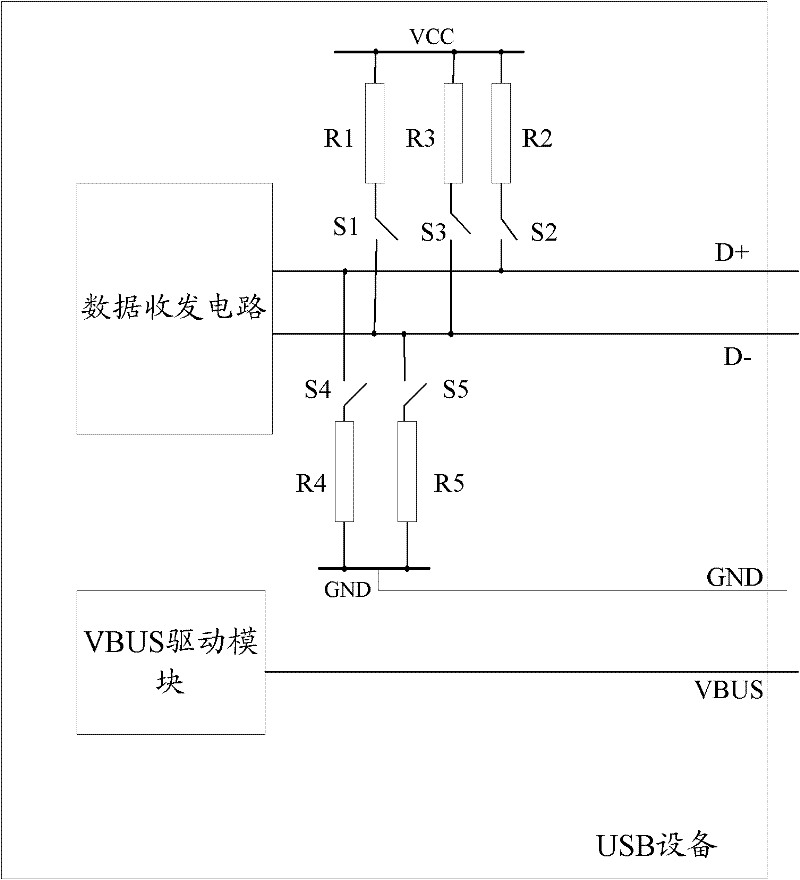

USB (Universal Serial Bus) equipment and detection method thereof

ActiveCN102479133ASave pin resourcesError detection/correctionElectrical resistance and conductancePull-up resistor

The invention relates to the field of communication equipment and discloses USB (Universal Serial Bus) equipment and a detection method thereof. The USB equipment can be detected to be host equipment or slave equipment without an ID (Identification) base pin, and thus, the base pin resources of the USB equipment are saved. The USB equipment disclosed by the invention comprises a series branch (1) consisting of a first pull-up resistor and a first switch, a series branch (2) consisting of a second pull-up resistor and a second switch, a series branch (3) consisting of a third pull-up resistor and a third switch, a series branch (4) consisting of a fourth pull-down resistor and a fourth switch, a series branch (5) consisting of a fifth pull-down resistor and a fifth switch, wherein one end of the series branch (1) is connected with a VCC (Virtual Channel Connection), the other end of the series branch (1) is connected with a D+ data line or a D- data line, one end of the series branch (2) is connected with the VCC, the other end of the series branch (2) is connected with the D+ data line, one end of the series branch (3) is connected with the VCC, the other end of the series branch (3) is connected with the D- data line, one end of the series branch (4) is grounded, the other end of the series branch (4) is connected with the D+ data line, one end of the series branch (5) is grounded, the other end of the series branch (5) is connected with the D- data line.

Owner:ACTIONS ZHUHAI TECH CO

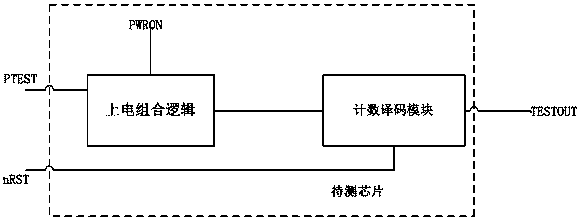

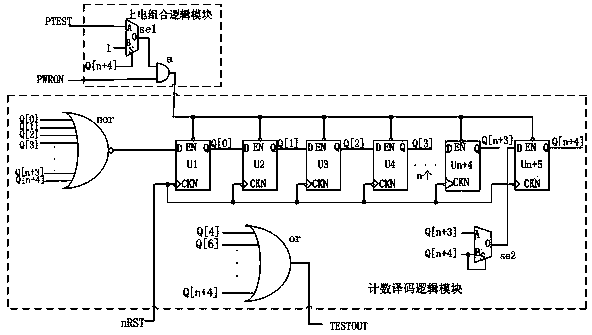

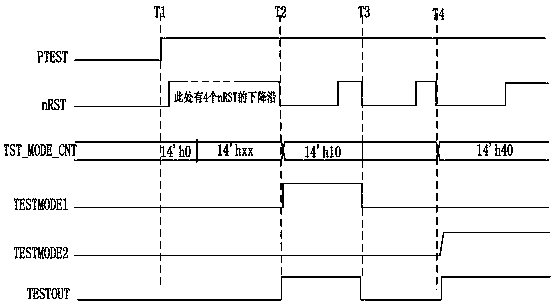

Circuit for accessing chip test mode and control method of circuit

PendingCN108414924ASave pin resourcesSimple circuitDigital circuit testingEnergy efficient computingElectricityPower-on reset

The invention relates to a circuit for accessing a chip test mode and a control method of the circuit. The circuit comprises a power-on reset logic module and a counting decoding logic module, an existing chip pin is reused, the counting decoding logic module based on one-hot encoding counting is designed to access and switch various test modes, pin sources of a chip are saved, test efficiency ofthe chip is improved, chip test is in a scan chain test mode when clock jump is driven, and the test coverage rate of a scan chain can be increased.

Owner:AMICRO SEMICON CORP

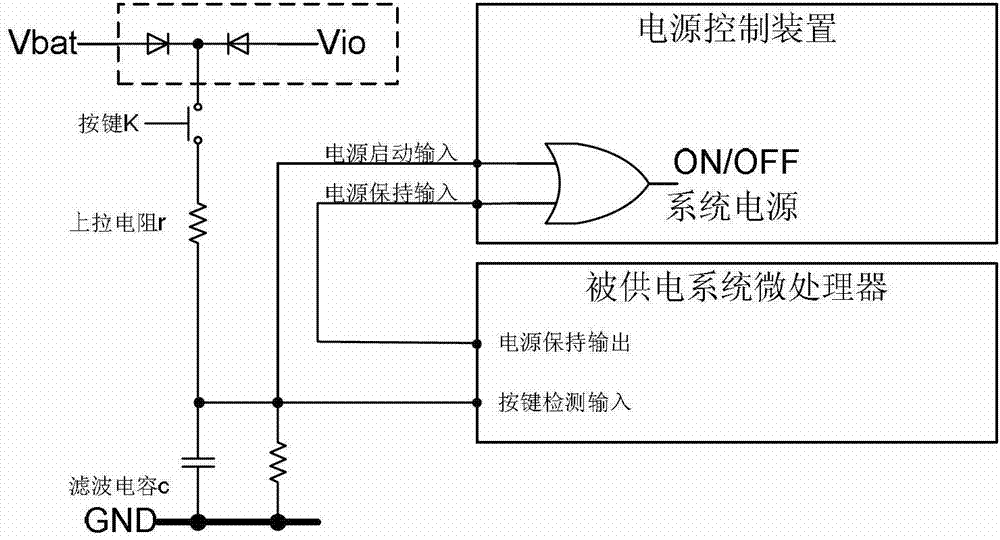

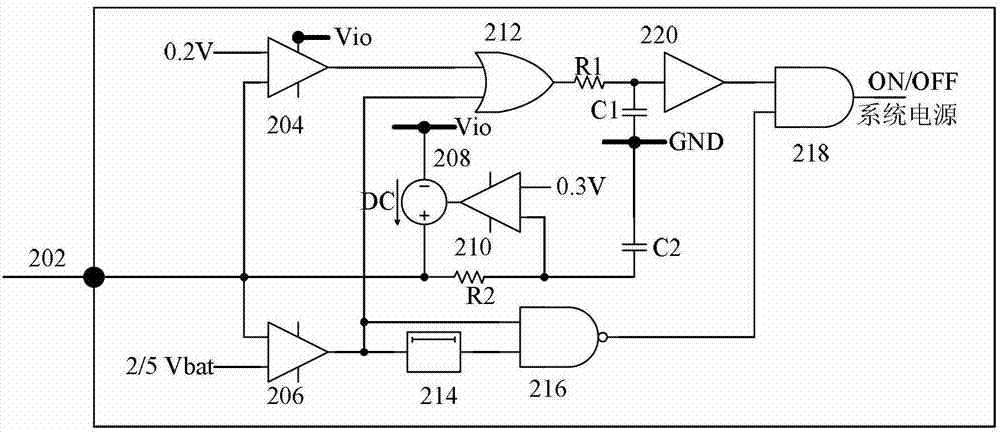

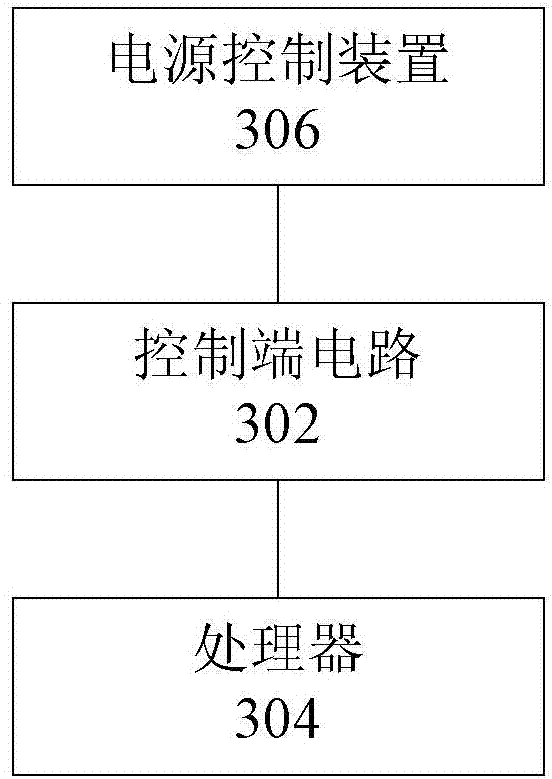

Power supply control device and power supply control system

ActiveCN102780246ASave pin resourcesReduce system costBatteries circuit arrangementsElectric powerEmbedded systemControlled source

The invention provides a power supply control device and a power supply control system. The device comprises a first input node, a first comparator, a second comparator, a controlled source, an amplifier, an or logic gate circuit, a delay circuit, a first NAND logic gate circuit and a second NAND logic gate circuit. By the power supply control device and the power supply control system, the problem that a power supply system in the related technology occupies much pin resources is solved; the pin resources and the system cost are saved; and the utilization rate of pins is improved.

Owner:SG MICRO

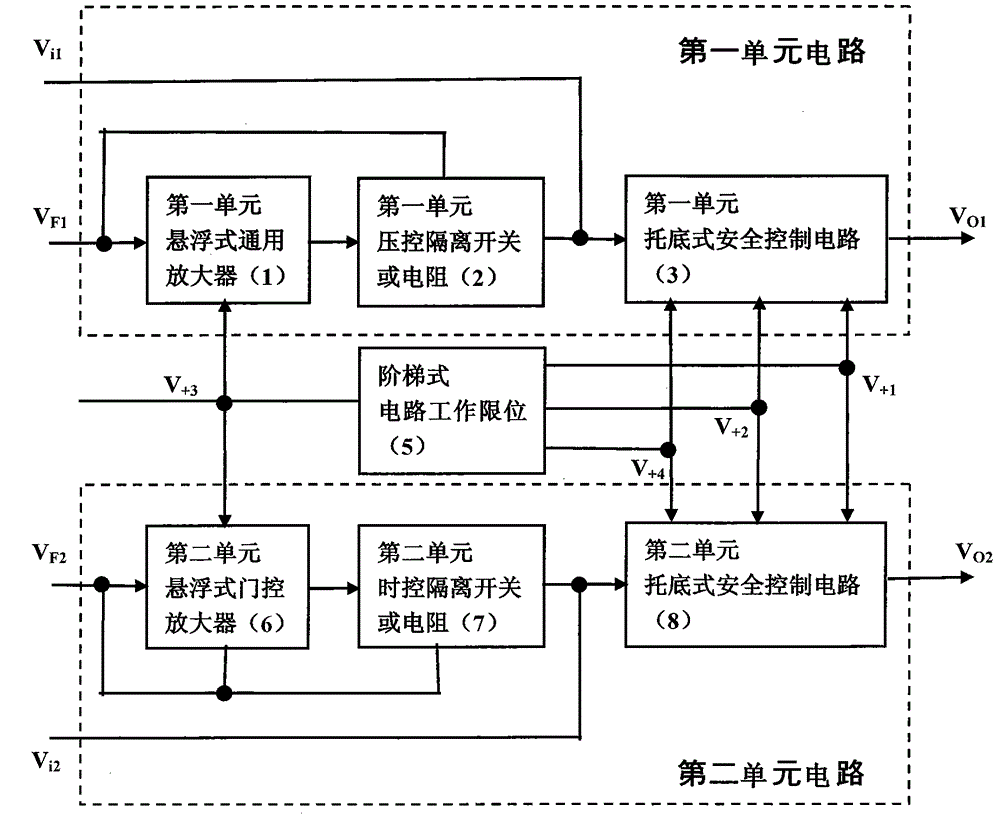

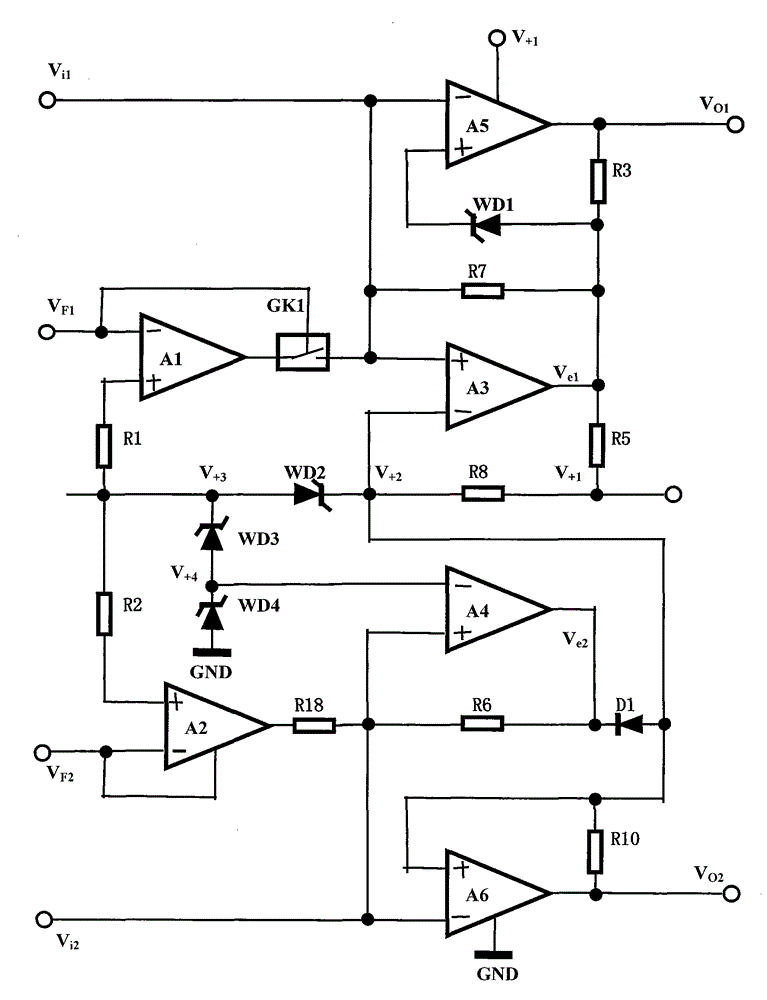

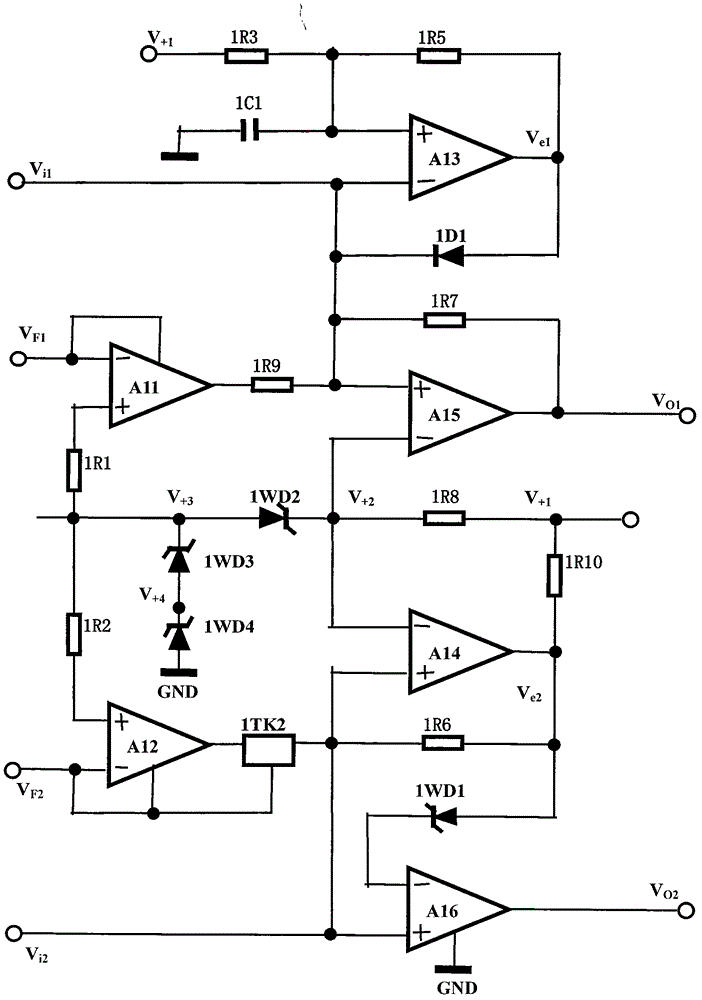

Current and effect stabilizing control circuit chip and safe control electric appliance thereof

PendingCN104950779AImprove securityEnsure control securityProgramme controlComputer controlAudio power amplifierSafety control

The invention relates to a current and effect stabilizing control circuit chip and a safe control electric appliance of the control circuit chip. The current and effect stabilizing control circuit chip and the safe control electric appliance adopt the technical scheme that two parallel and complementary unit circuits are adopted for forming the current and effect stabilizing control circuit chip, wherein the input end of an isolation switch arranged in each unit circuit is connected with an amplifier; the output end of the isolation switch arranged in each unit circuit is connected with a bottom supporting type safe control circuit; weak sensing signals are amplified and are then transmitted to the bottom supporting type safe control circuit to be processed by the isolation switch; the strong sensing signals can be directly sent to the bottom supporting type safe control circuit to be processed directly from the level input end; each bottom supporting type safe control circuit has the bottom supporting protection and limit exceeding safety control function; in addition, the two bottom supporting type safe control circuits are mutually locked; if the inputs of the two unit circuits are used for parallelly detecting the sensing signals and the outputs of the two unit circuits are used for serially connecting a peripheral driving executing circuit, and the capability of comprehensively preventing the fault control loss is realized, so that when the current and effect stabilizing control circuit chip is applied to safety protection and test control circuits for the temperature, the pressure, the water level, the timing and the like, the safety performance can be improved, the control loss accident can be avoided, and the purposes are wide.

Owner:刘圣平

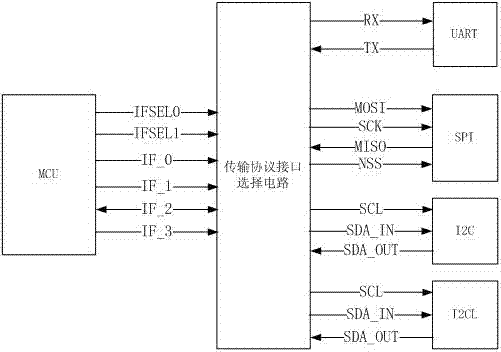

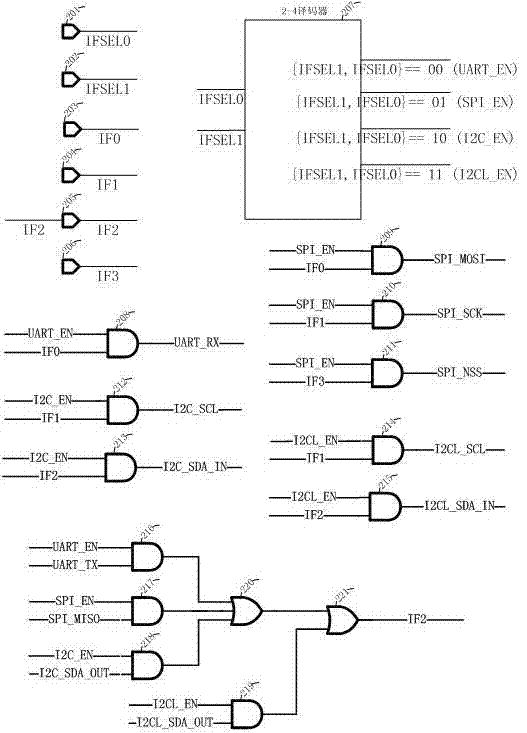

Port multiplexing circuit capable of supporting SPI, I2C, I2CL and UART protocols

InactiveCN105446929ALow costSave pin resourcesElectric digital data processingTransmission protocolData control

The present invention discloses a port multiplexing circuit capable of supporting SPI, I2C, I2CL and UART protocols. Multiple transmission protocol ports are integrated to four ports to perform selective multiplexing. The overall structure comprises an MCU processor, a transmission protocol port selection circuit, transmission protocol data control circuits, and the like. The transmission protocol port selection circuit is connected with the MCU processor, and a selected and used transmission protocol is determined through values of MCU inputs IFSEL0 and IFSEL1. Meanwhile, states of four private ports are also determined, and then data circulation transmission of a specific transmission protocol can be achieved. According to the port multiplexing circuit disclosed by the present invention, the problem in port private integrated multiplexing is solved, and the integrated and easily controlled use is realized.

Owner:WUHAN XINCHANG TECH CO LTD

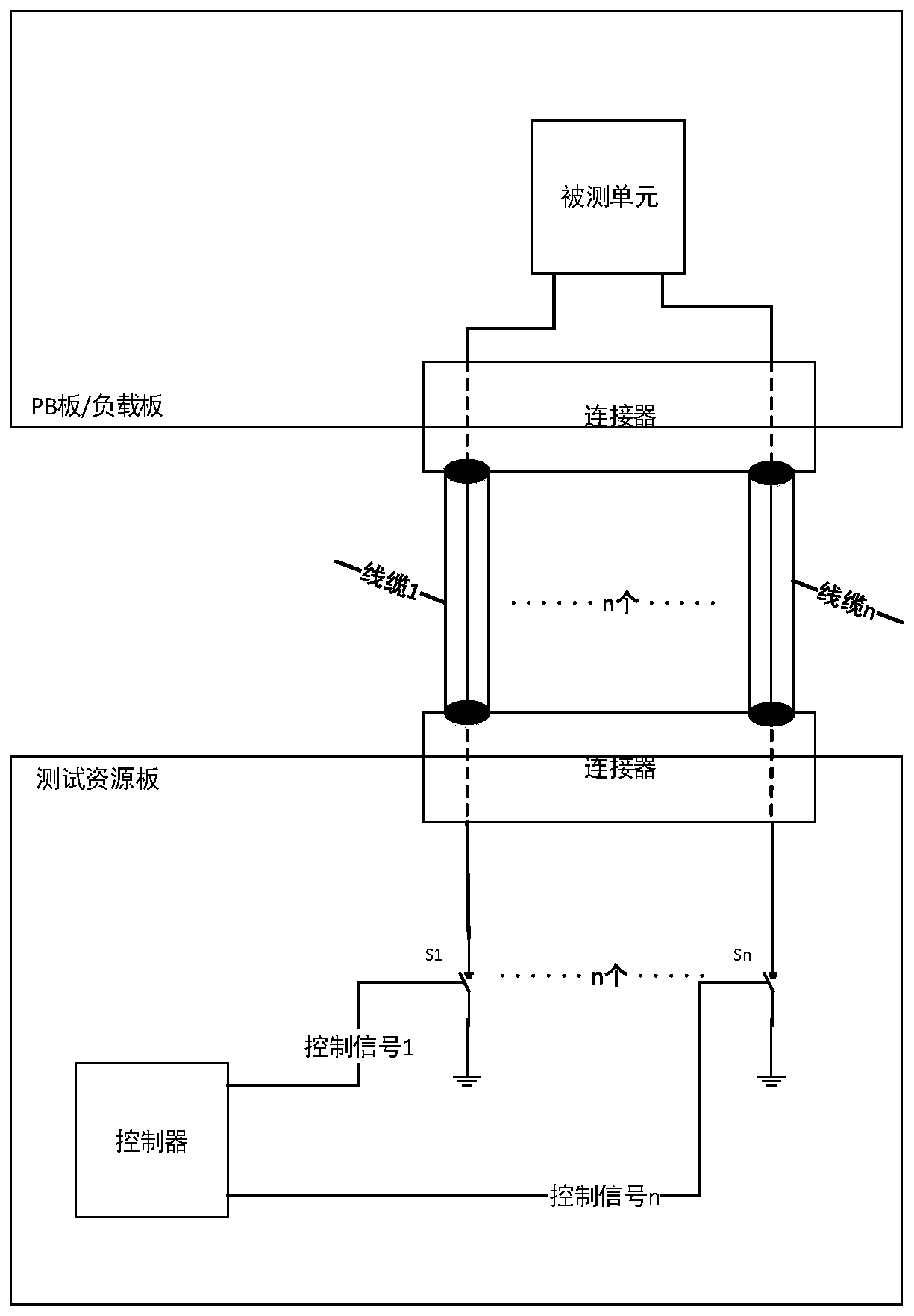

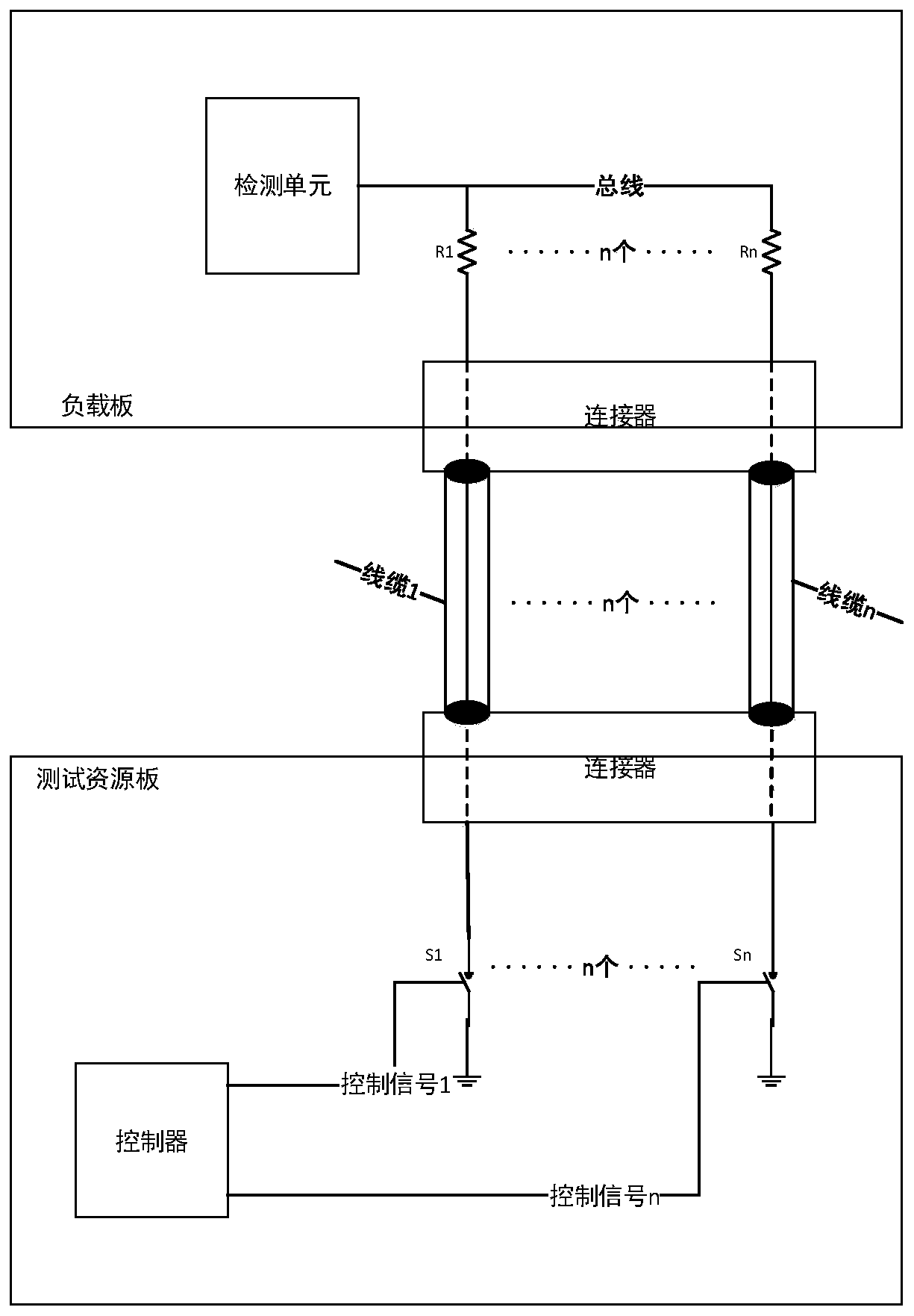

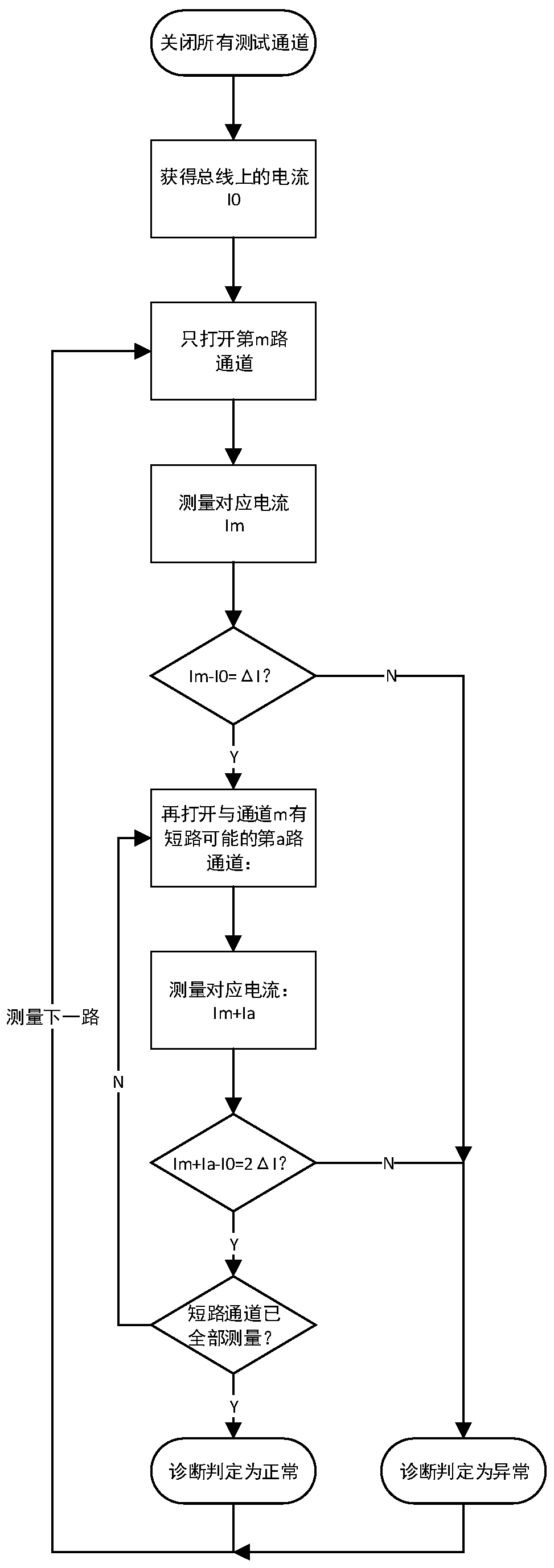

Detection structure and method of ATE system

InactiveCN110687373ALow costEasy to manageShort-circuit testingContinuity testingElectrical resistance and conductanceBus

The invention discloses a detection structure of an ATE system. The structure comprises a test resource board and a load board. The test resource board comprises a controller and n test channels connected with the controller. The load board comprises a detection unit, a bus and n resistors with a same resistance value R. The n test channels are connected with one ends of the n resistors, and the other ends of the n resistors are connected to the detection unit through the bus. A voltage Vbus is applied to the detection unit, a first test channel to the Nth test channel are sequentially opened,a current Im on the bus is measured, and whether a mth test channel is normal is judged according to the Im. By using the detection structure and method of the ATE system, a position of the test channel with a fault can be accurately positioned, and a reason why the test channel has the fault can be quickly judged.

Owner:SHANGHAI NCATEST TECH CO LTD

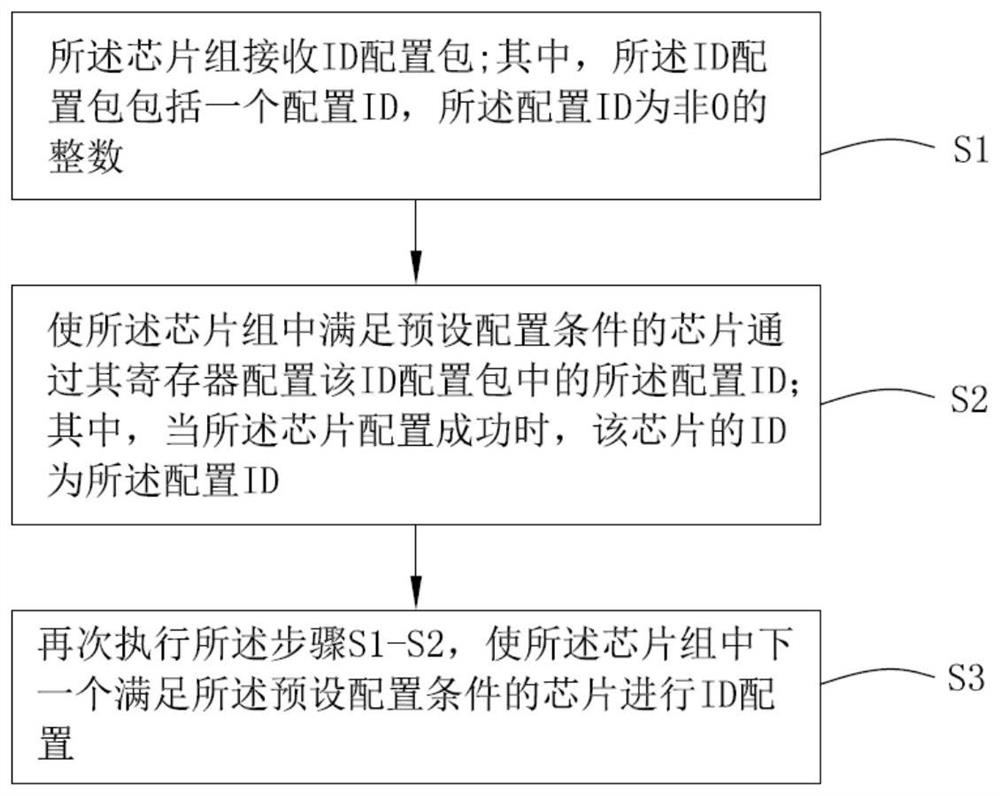

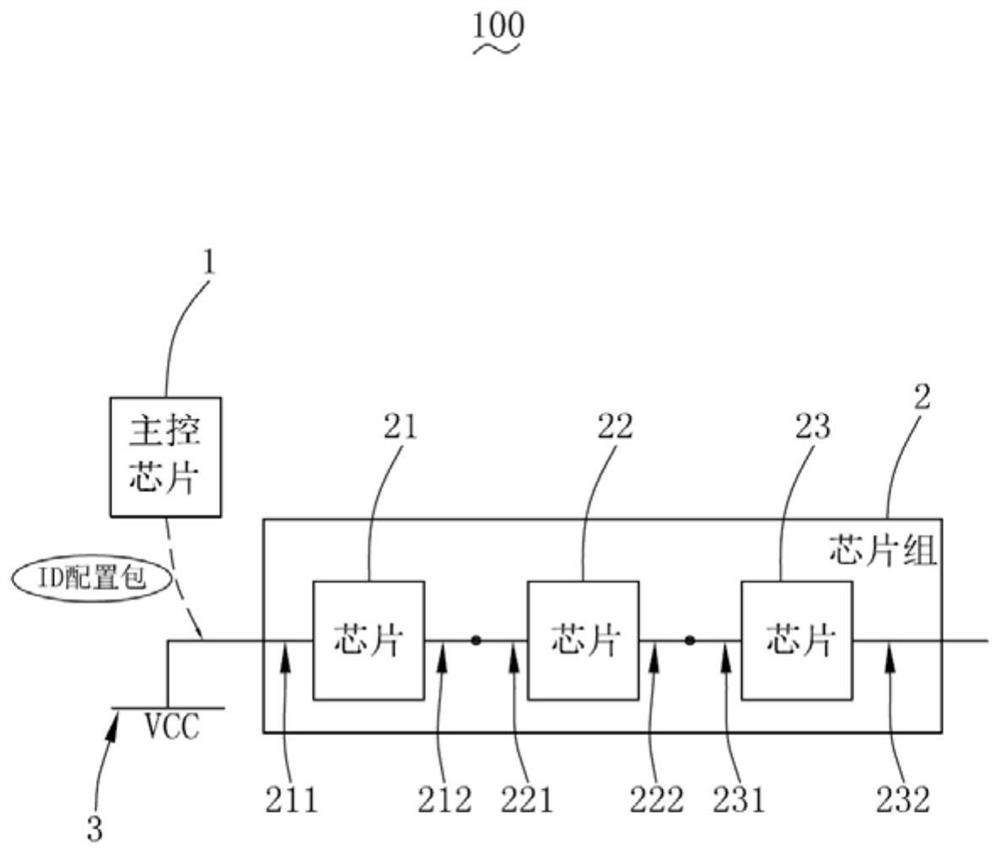

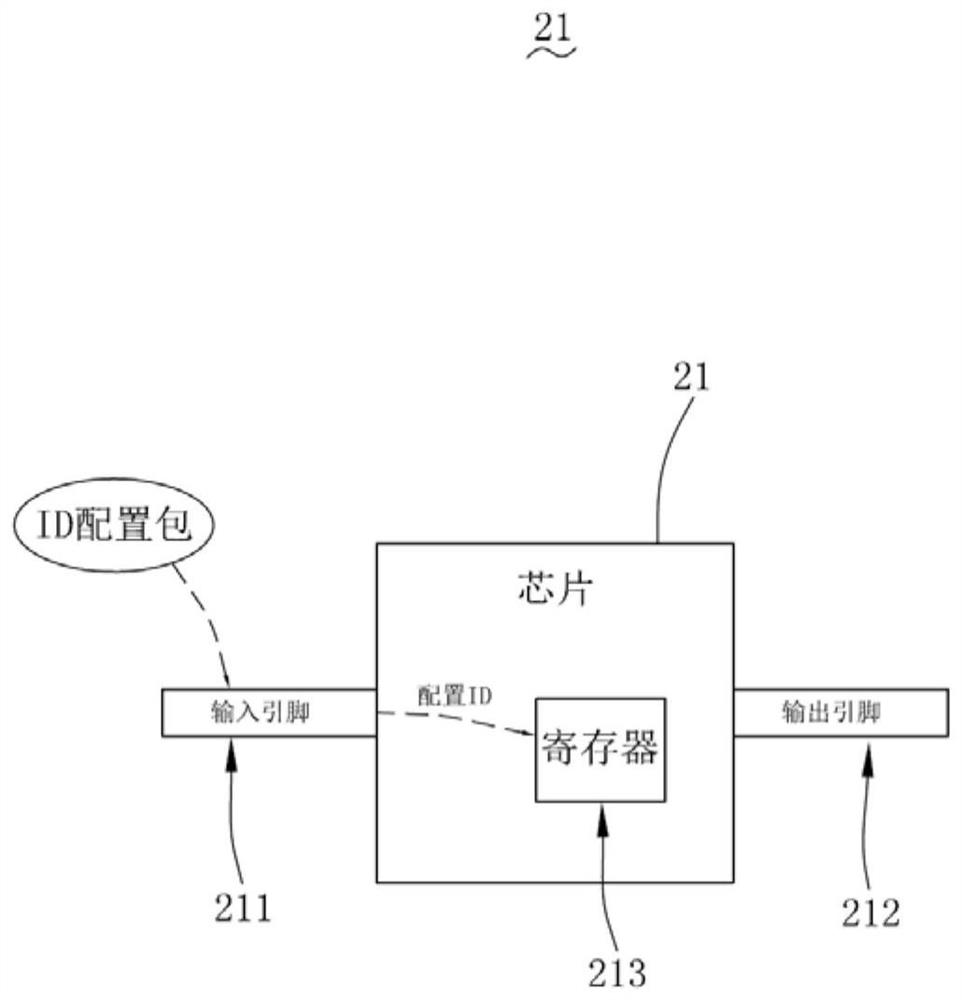

ID configuration method of series circuit, series circuit and related equipment

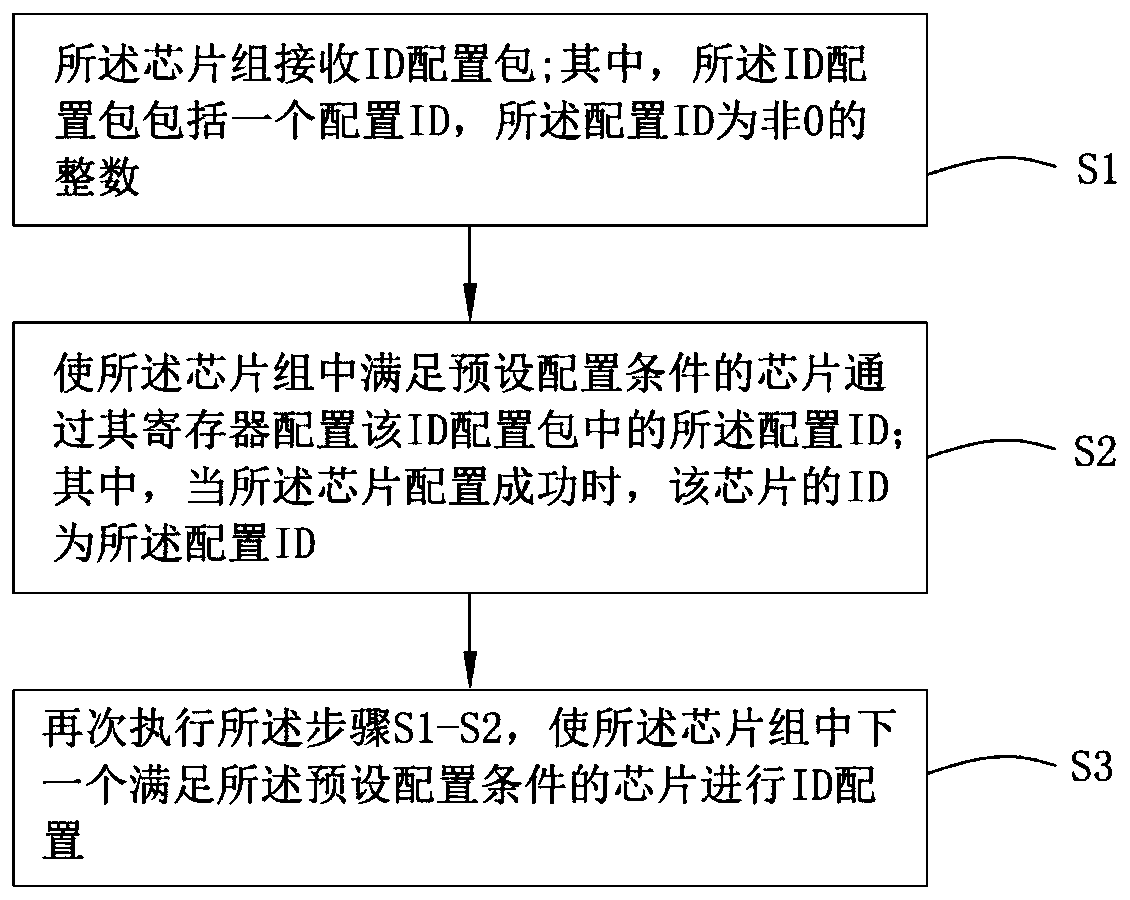

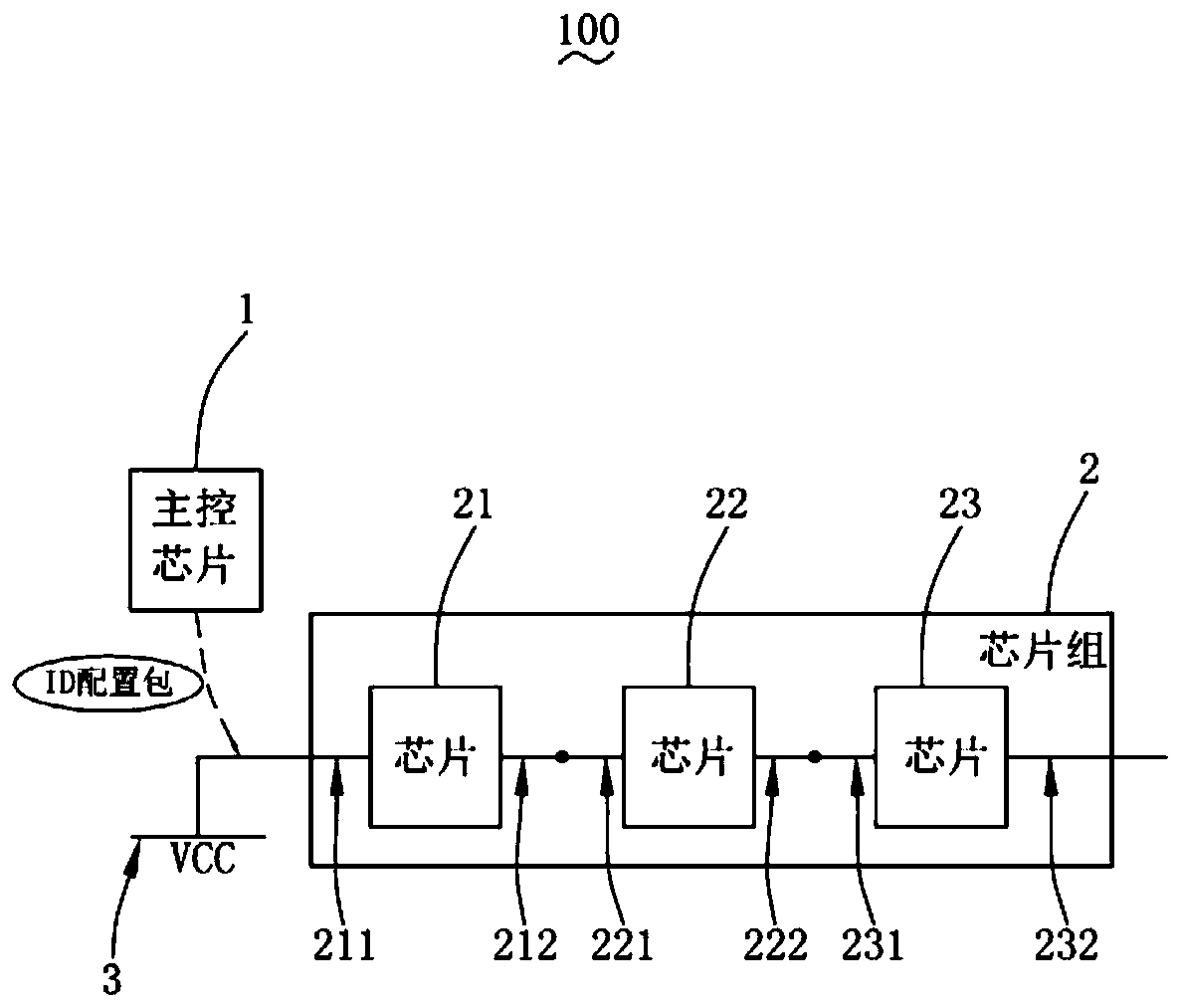

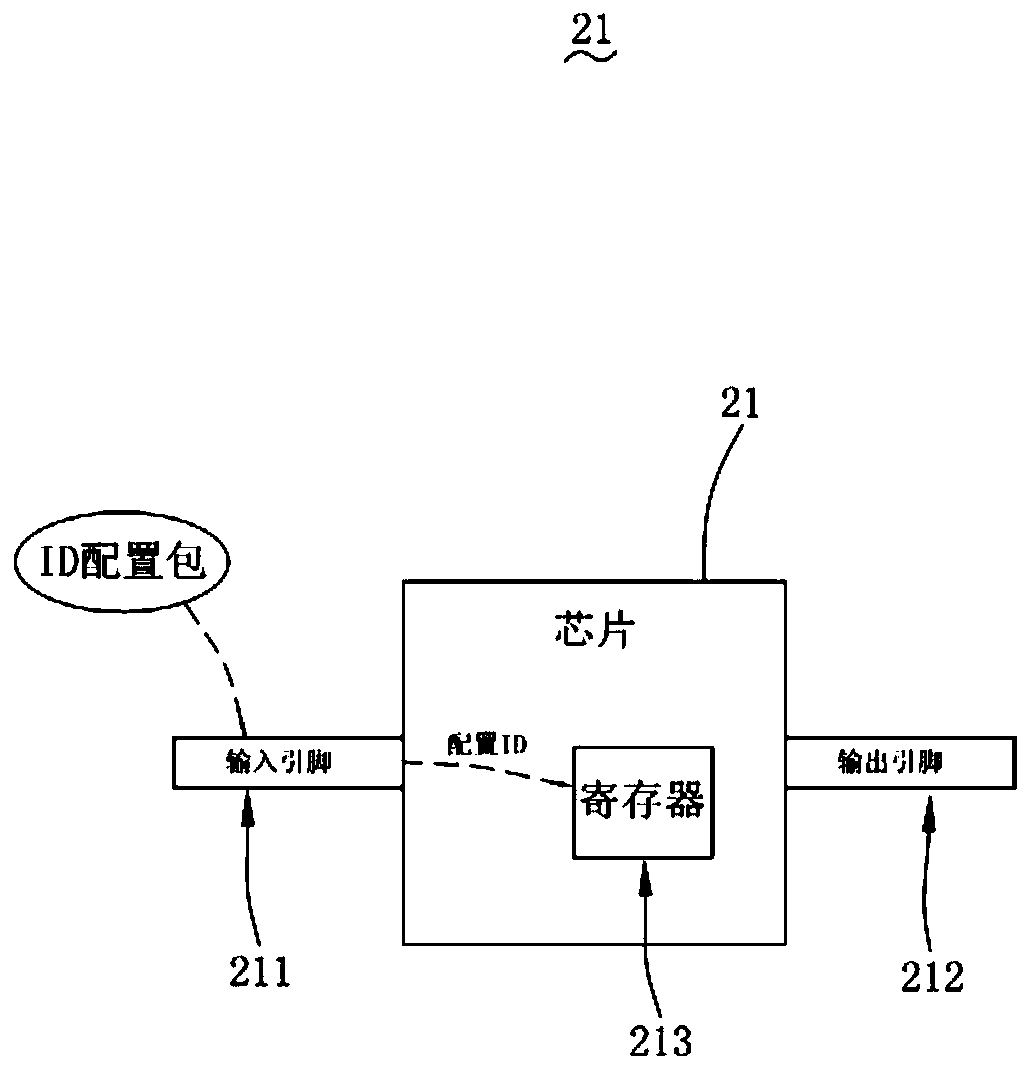

ActiveCN110162340ARich varietyIncrease flexibilityBootstrappingRegister allocationProcessor register

The invention provides an ID configuration method of a series circuit, the series circuit comprises a chipset, and the chipset comprises a plurality of chips which are sequentially connected in series, wherein the chip located at the head end of the chipset is connected to a power supply end through an input pin of the chip, an input pin of the ith chip in the chipset is connected to an output pinof the (i-1) th chip, and i is an integer greater than 1; the method comprises the steps that S1, the chipset receives an ID configuration package; s2, configuring a configuration ID in the ID configuration packet by a chip meeting a preset configuration condition in the chipset through a register of the chip; and S3, executing the steps S1 to S2 again, so that the next chip meeting the preset configuration condition in the chipset is subjected to ID configuration. The invention further provides a control terminal. The invention further provides a control terminal applying the method and a computer readable storage medium. Compared with the prior art, pin resources of the chip are saved, the ID configuration range is expanded, and the types of the configured IDs are rich.

Owner:莫冰 +2

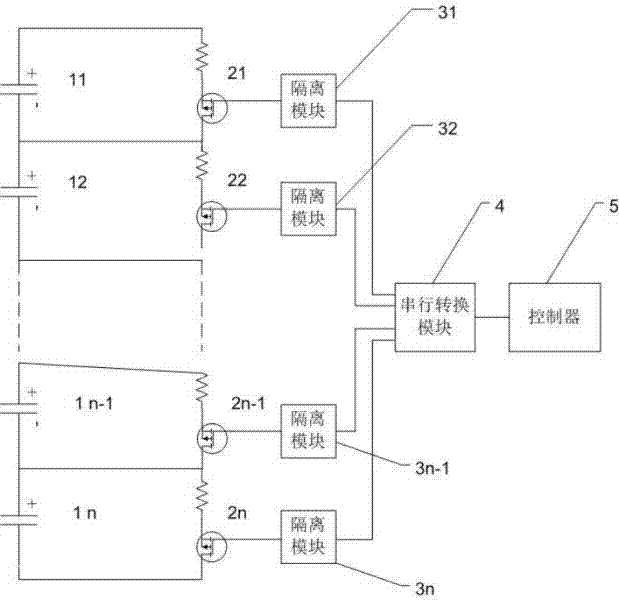

Multi-parallel-and-serial super capacitor system balancing method

ActiveCN102856984AImprove efficiencyImprove performanceElectrical storage systemCapacitanceInterference resistance

The invention relates to the relevant technical field of capacitor balancing, and in particular relates to a multi-parallel-and-serial super capacitor system balancing method. A super capacitor is formed by the combination of a plurality of monomer capacitors in a serial and / or parallel mode. The system comprises the super capacitor and a controller; a discharge resistor is connected in parallel to two ends of each monomer; each discharge resistor is connected with a switch module in series; and each switch module is connected with the controller, and is conducted or stopped by the control of the controller, thus the connection and disconnection of a discharge loop are controlled. According to the invention, by designing a passive balancing circuit, an appropriate balanced strategy is matched, the integral performance of a capacitor group is improved, the capacitor using rate is improved, and the service life of the capacitor group is prolonged. The balancing scheme provided by the invention is simple and reliable, and is high in interference prevention capability; and by means of a serial communication module, pin resources of the controller are saved greatly.

Owner:HUIZHOU EPOWER ELECTRONICS

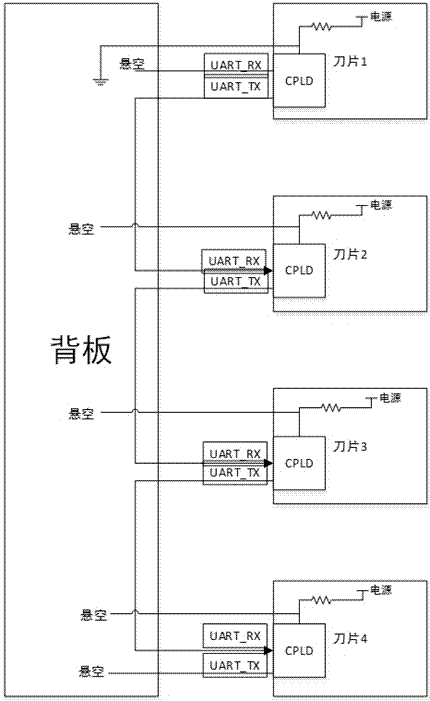

Automatic allocation method for blade server management internal network IPs

ActiveCN106993068ASave pin resourcesSuitable for promotion and applicationTransmissionBlade serverIp address

The invention particularly relates to an automatic allocation method for blade server management internal network IPs. According to the automatic allocation method for the blade server management internal network IPs, each calculation blade in a blade server is configured with a CPLD (Complex Programmable Logic Device) chip; UART (Universal Asynchronous Receiver / Transmitter ) interfaces of the CPLD chips are connected with a backboard; a UART RX end of a first calculation blade is hung; a UART TX end of the first calculation blade is connected with the RART RX end of a second calculation blade, the rest can be done in the same manner, and the UART TX end of an nth calculation blade is connected with the UART RX end of an n+1th calculation blade, until the final calculation blade is finished; and the UART TX end of the final calculation blade is hung. According to the automatic distribution method for the blade server management internal network IPs, only three pins are connected with the backboard and a demand of allocating different IP addresses to dozens of blades can be realized; the method is stable and reliable; BMC IO resources and backboard connector pin resources can be saved; and the method is superior to the prior art and is applicable to popularization and application.

Owner:GUANGDONG INSPUR BIG DATA RES CO LTD

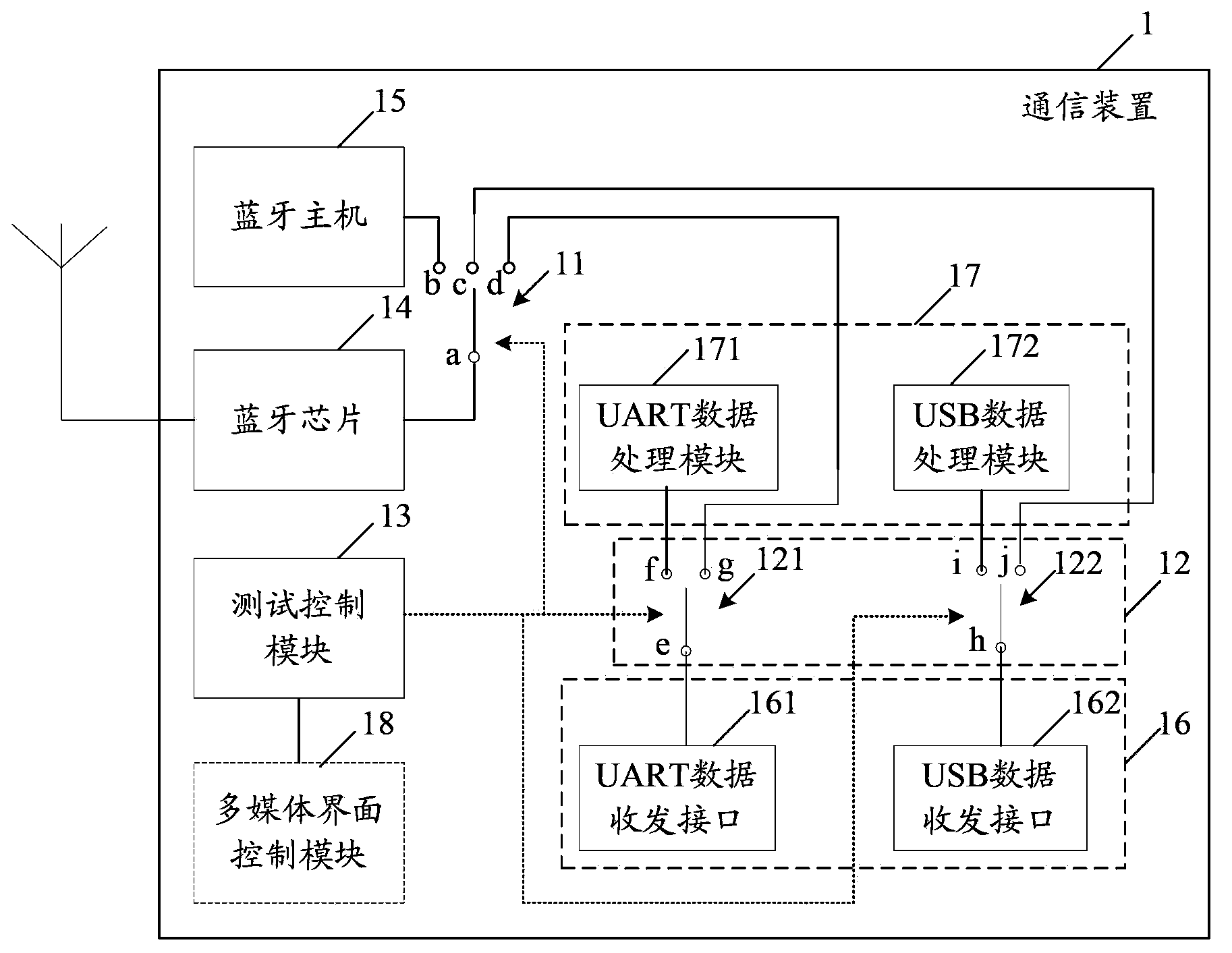

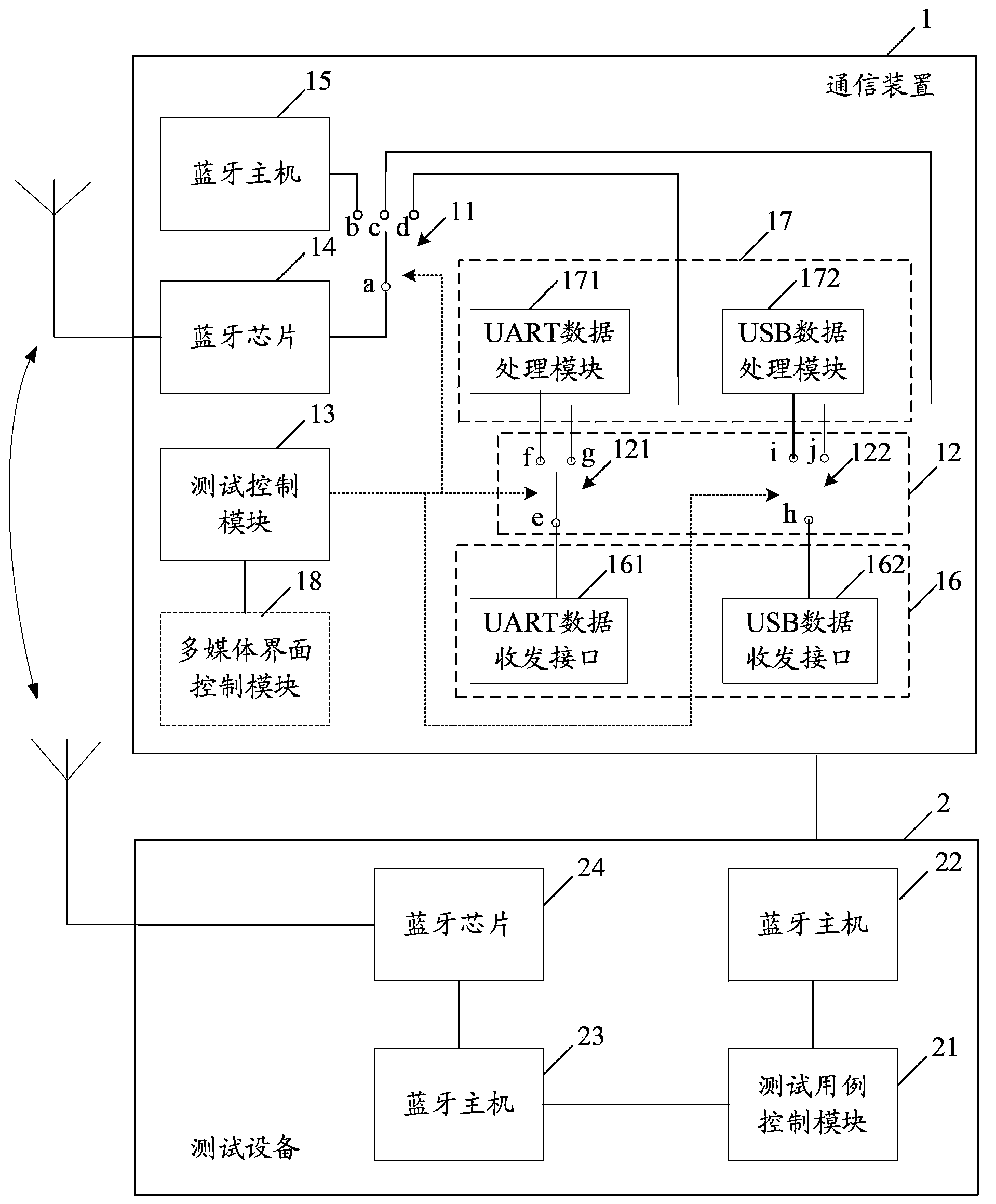

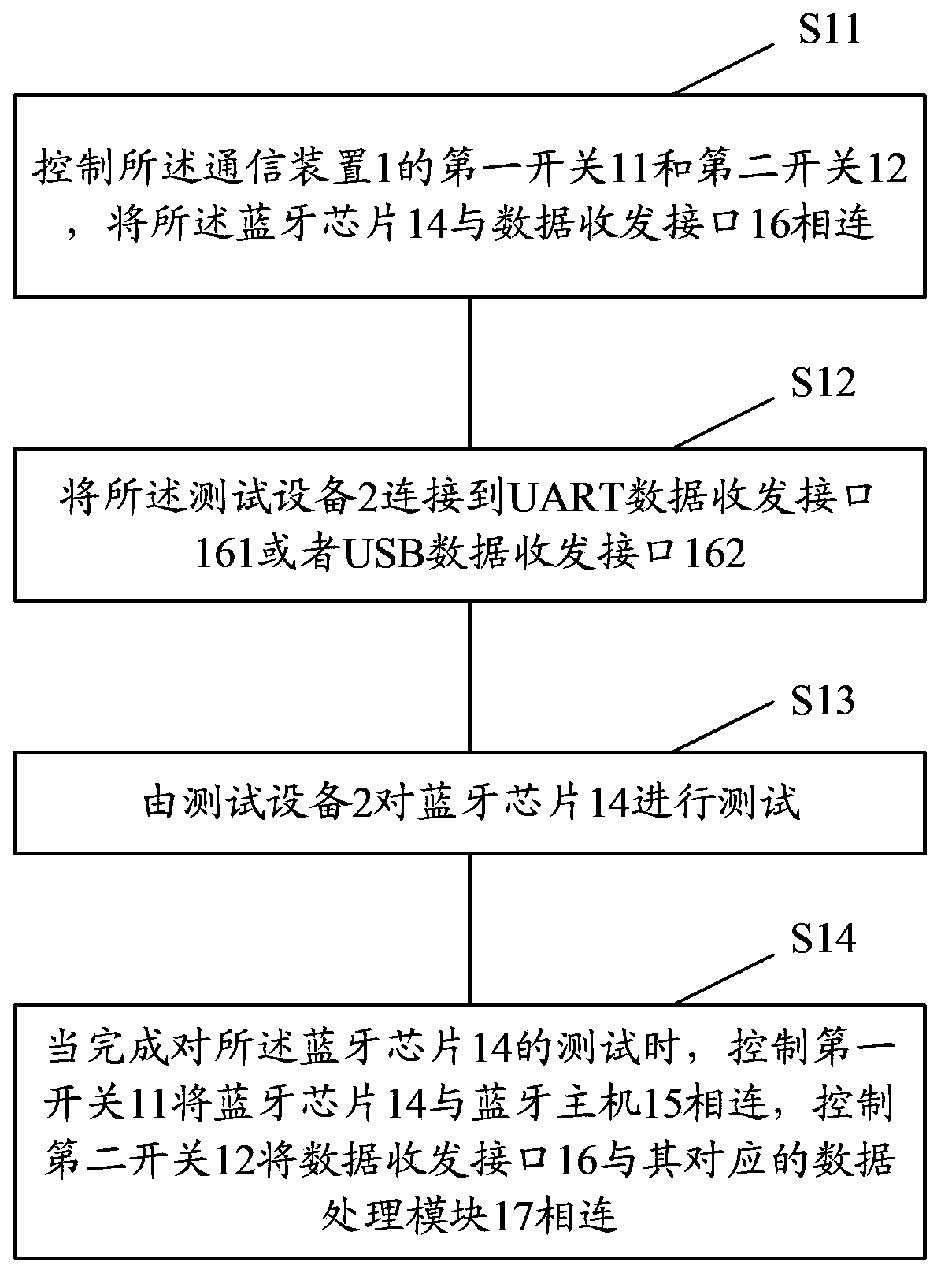

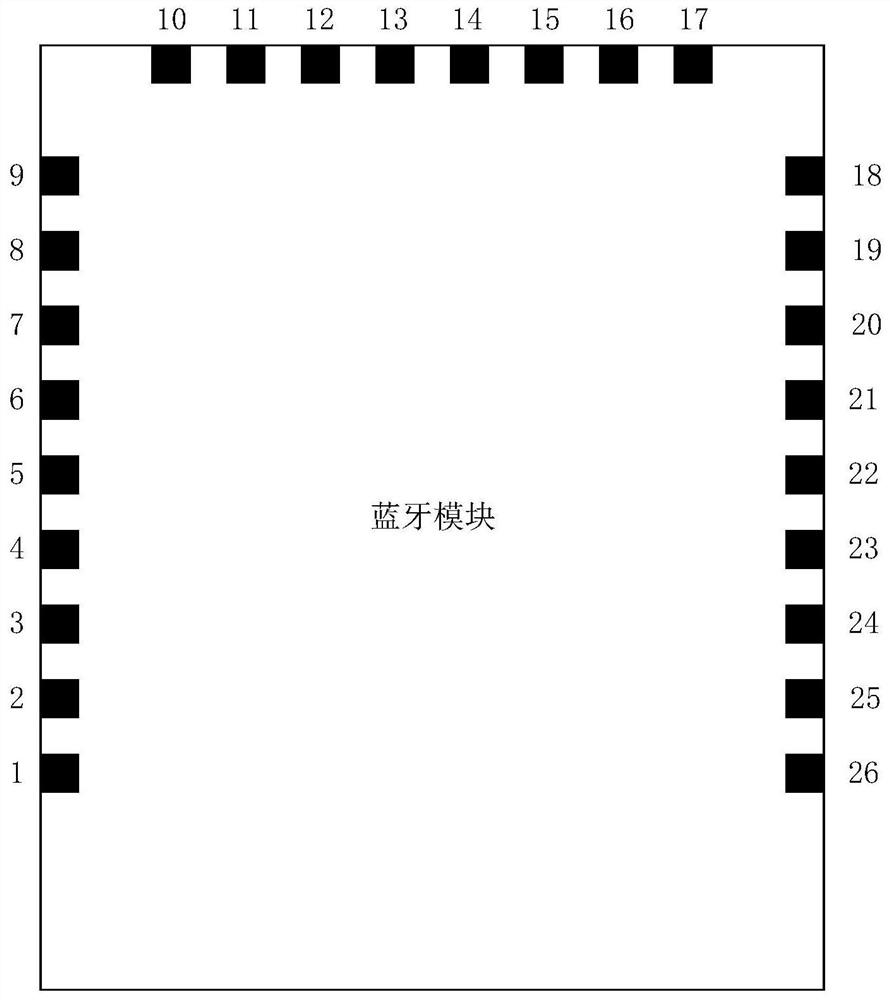

Communication device, test system and test method thereof

ActiveCN104219003AImplement testImprove system performanceElectrical testingDevices with bluetooth interfacesComputer moduleEngineering

The present invention provides communication device, test system and test method thereof, the communication device comprising: a baseband chip, and a target test chip, an upper processing module on the target test chip, at least one data receiving and transmitting interface and a data processing module thereof, a first switch, a second switch and a test control module integrated in the baseband chip, wherein the first switch is used for achieving connection between the target test chip and the data receiving and transmitting interface or the upper processing module; the second switch is used for achieving connection between the data receiving and transmitting interface and the data processing module or the target test chip; the test control module is used for controlling the first and second switches to connect the data receiving and transmitting interface with the target test chip, so that the communication device is suitable for testing the target test chip. The technical solution of the present invention does not need additional test pins while testing the target chip, saves resources for the communication device and reduces cost.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

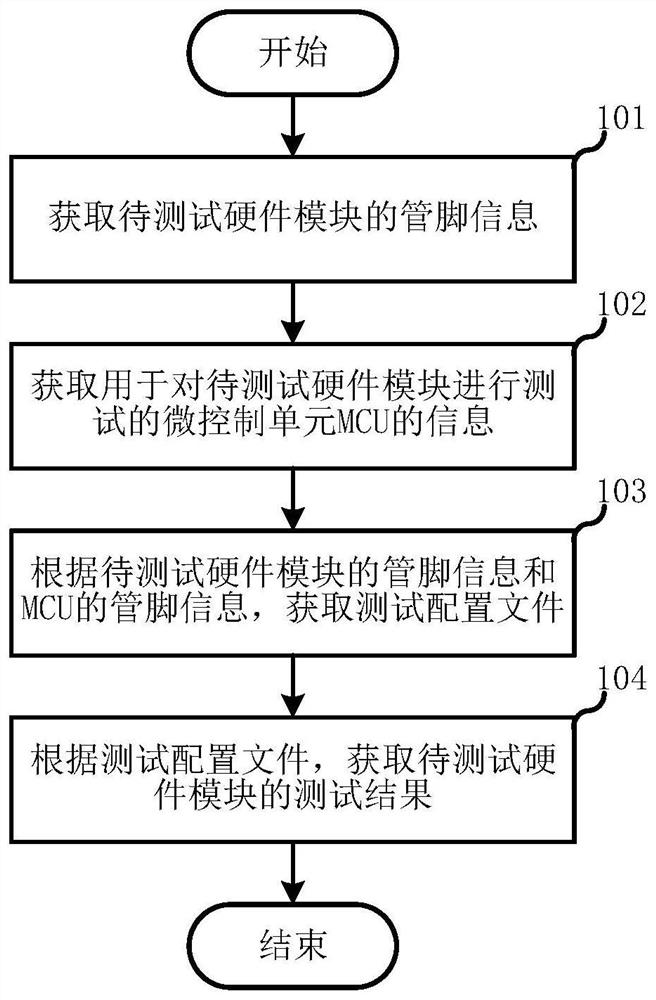

Hardware module testing method and system, electronic equipment and storage medium

PendingCN112463498ALong test timeLow efficiencyDetecting faulty hardware by configuration testFunctional testingComputer hardwareControl cell

The embodiment of the invention relates to the technical field of communication, and discloses a hardware module testing method and system, electronic equipment and a storage medium. The hardware module test method comprises the steps of obtaining pin information of a to-be-tested hardware module; acquiring information of a micro control unit (MCU) for testing the hardware module to be tested, wherein the information of the MCU at least comprises pin information of the MCU; obtaining a test configuration file according to the pin information of the hardware module to be tested and the pin information of the MCU; and obtaining a test result of the to-be-tested hardware module according to the test configuration file. According to the hardware module test method provided by the embodiment ofthe invention, complex instruments and meters are not needed, the test cost can be reduced, the test process of the hardware module is flexibly configured, and the operability and expandability of the test process are greatly improved.

Owner:QUECTEL WIRELESS SOLUTIONS

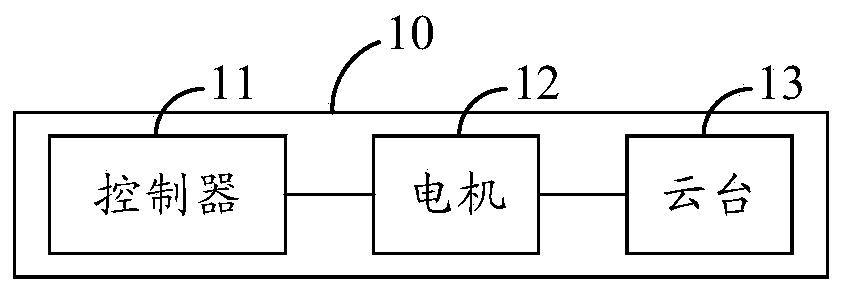

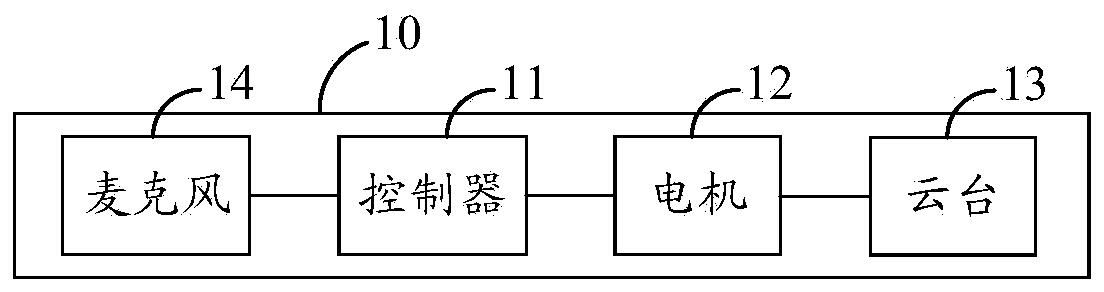

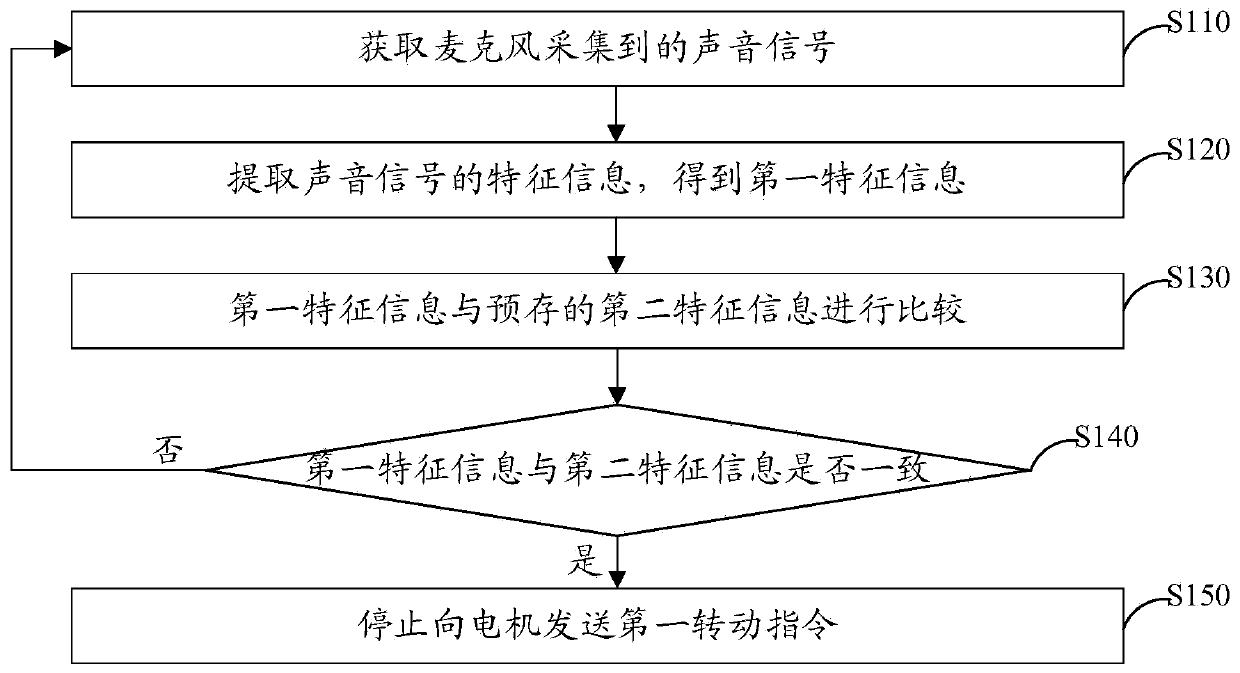

Pan-tilt motor limiting method and device, pan-tilt camera and storage medium

InactiveCN111447362ASave pin resourcesReduce impact noiseTelevision system detailsColor television detailsElectric machineNoise

The invention discloses a pan-tilt motor limiting method and device, a pan-tilt camera and a storage medium. The method comprises the following steps: acquiring a sound signal acquired by a microphone; extracting feature information of the sound signal to obtain first feature information; comparing the first feature information with pre-stored second feature information, wherein the second featureinformation is feature information of impact sound generated when the motor and / or the holder impacts the limiting structural member; and if the first feature information is consistent with the second feature information, stopping sending a first rotation instruction to the motor, the first rotation instruction being used for controlling the motor to rotate. In this way, impact noise can be reduced.

Owner:ZHEJIANG DAHUA TECH CO LTD

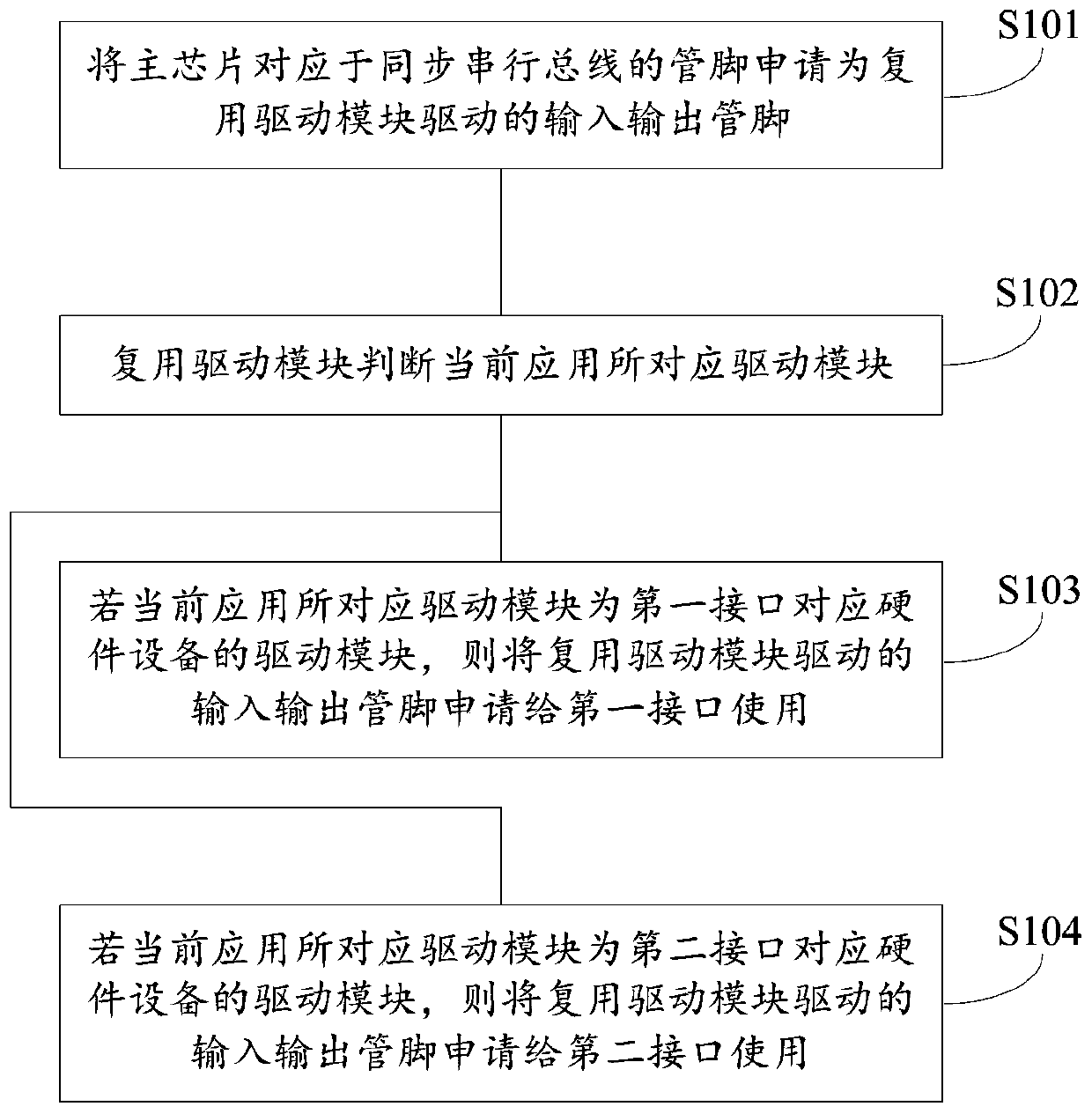

Synchronous serial bus multiplexing method and device, terminal, and non-temporary computer readable storage medium

ActiveCN110990319ADoes not affect data transferSave pin resourcesElectric digital data processingComputer hardwareMultiplexing

The invention relates to the field of embedded chips, and provides a synchronous serial bus multiplexing method and device, a terminal and a non-temporary computer readable storage medium. The invention aims to reduce the number of consumed pins when a main chip is connected with VGA and IC interfaces. The method comprises the following steps that an input / output pin driven by a multiplex drivingmodule is applied for as a pin, corresponding to a synchronous serial bus, of a main chip; the multiplexing driving module judges a driving module corresponding to a current application; if the driving module corresponding to the current application is a driving module of hardware equipment corresponding to a first interface, the input / output pin driven by the multiplexing driving module is applied to the first interface; and if the driving module corresponding to the current application is a driving module of hardware equipment corresponding to a second interface, the input / output pin drivenby the multiplexing driving module is applied to the second interface. According to the invention, pin resources of the main chip are saved, convenience is provided for adding other more functions tothe main chip, and multiplexing of the synchronous serial bus is realized on a software level.

Owner:BEIJING THUNDERSTONE TECH CO LTD

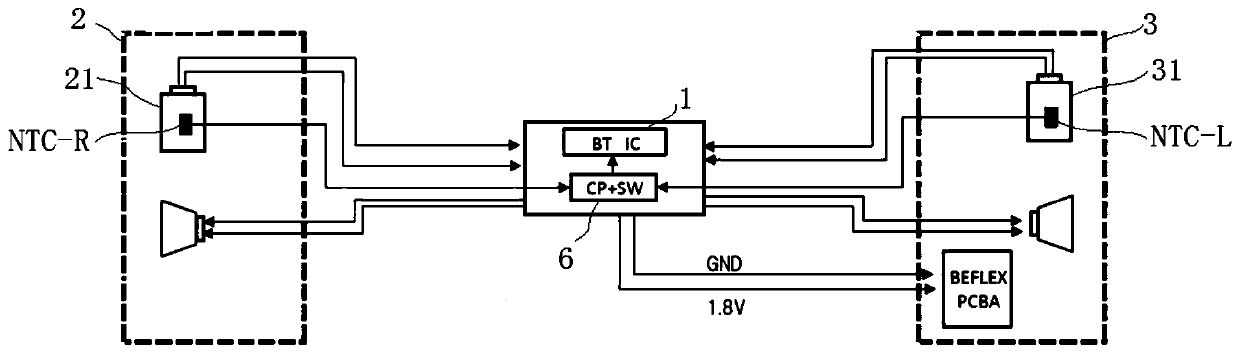

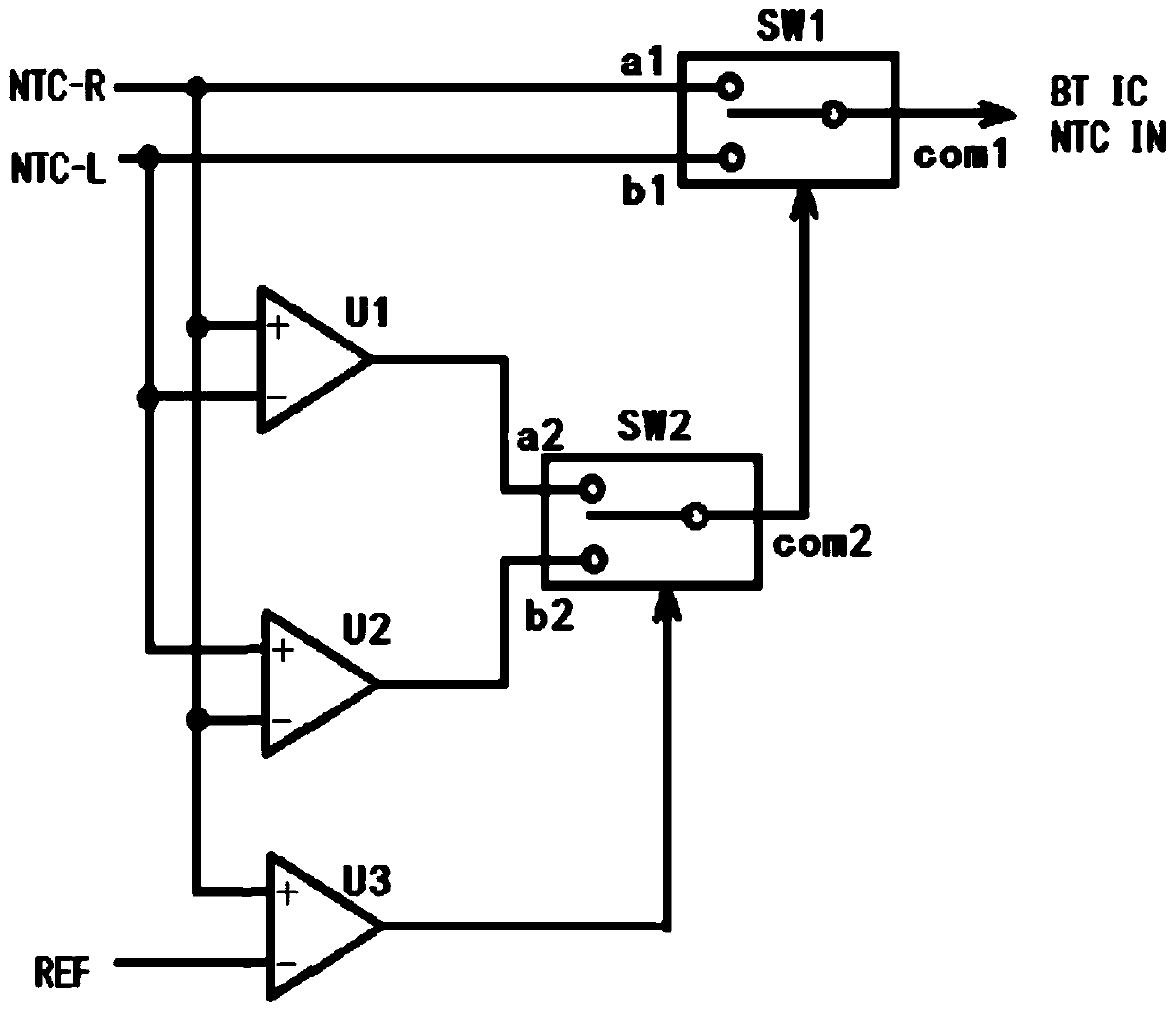

Bluetooth headset and temperature screening circuit therein

The invention relates to a temperature screening circuit. The temperature control circuit comprises comparators U1, U2 and U3, multistage electric control switches SW1 and SW2 and two temperature acquisition points used for acquiring output voltage of a temperature sensing device, wherein one temperature acquisition point is respectively connected with the non-inverting input end of the comparatorU1 and the inverting input end of the comparator U2, and the other temperature acquisition point is respectively connected with the inverting input end of the comparator U1 and the non-inverting input end of the comparator U2; the output end of the comparator U3 is connected with the controlled end of the multi-stage electric control switch SW2; the output ends of the comparator U1 and the comparator U2 are respectively connected with two wiring ends of a multi-stage electric control switch SW2, and the output end of the multi-stage electric control switch SW2 is connected with the controlledend of a multi-stage electric control switch SW1, and two temperature acquisition points are respectively connected with two wiring ends of the multi-stage electric control switch SW1; and if the voltage output by the temperature sensing device is negatively correlated with the temperature, the reverse input end of the comparator U3 is used for receiving the reference voltage, and the same-direction input end of the comparator U3 is connected with the temperature acquisition point, and otherwise, the connection method of the input end of the comparator U3 is opposite.

Owner:广东思派康电子科技有限公司

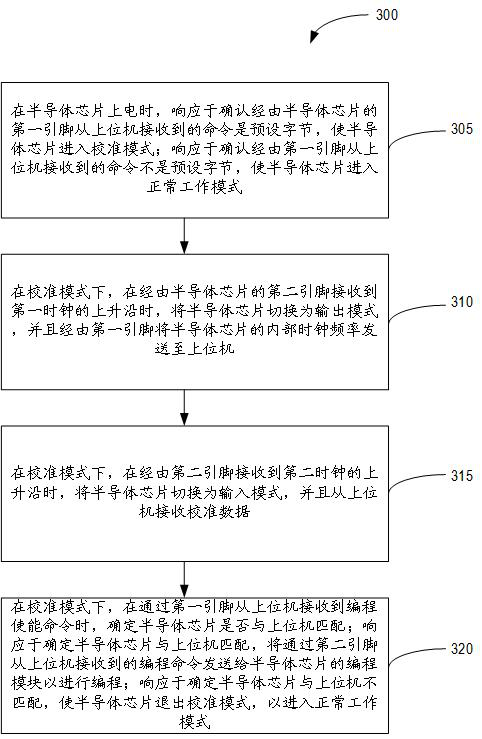

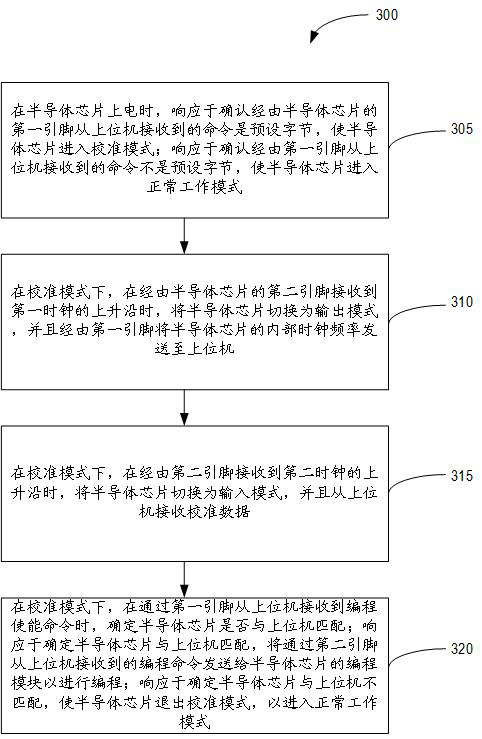

Semiconductor chip and control method thereof

ActiveCN112148064ASave pin resourcesReduce power-on stabilization wait timeFaulty hardware testing methodsGenerating/distributing signalsEngineeringVolatile memory

Owner:HANGZHOU SDIC MICROELECTRONICS

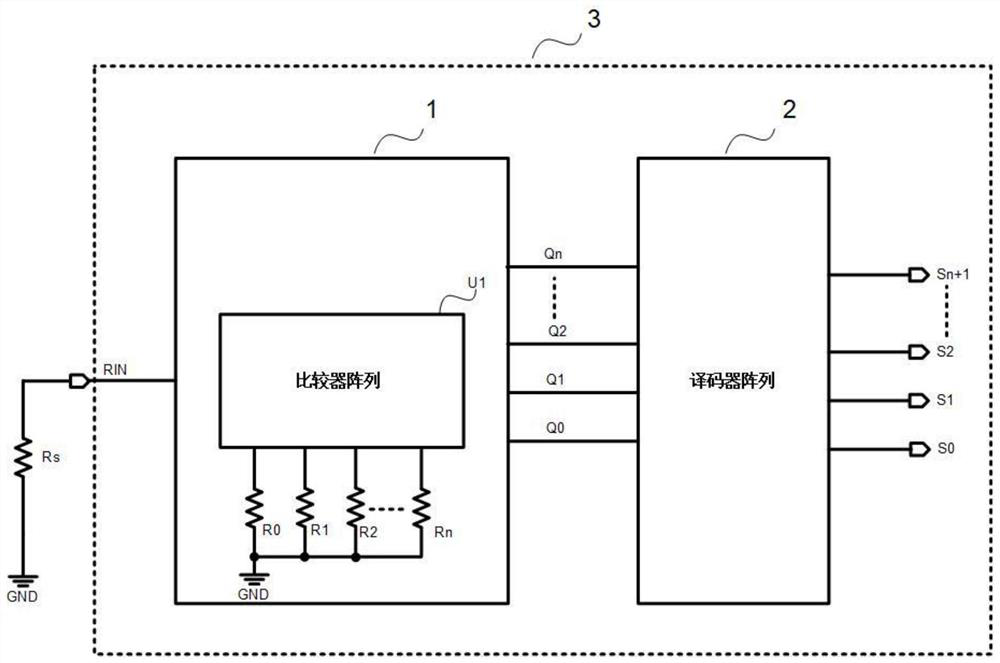

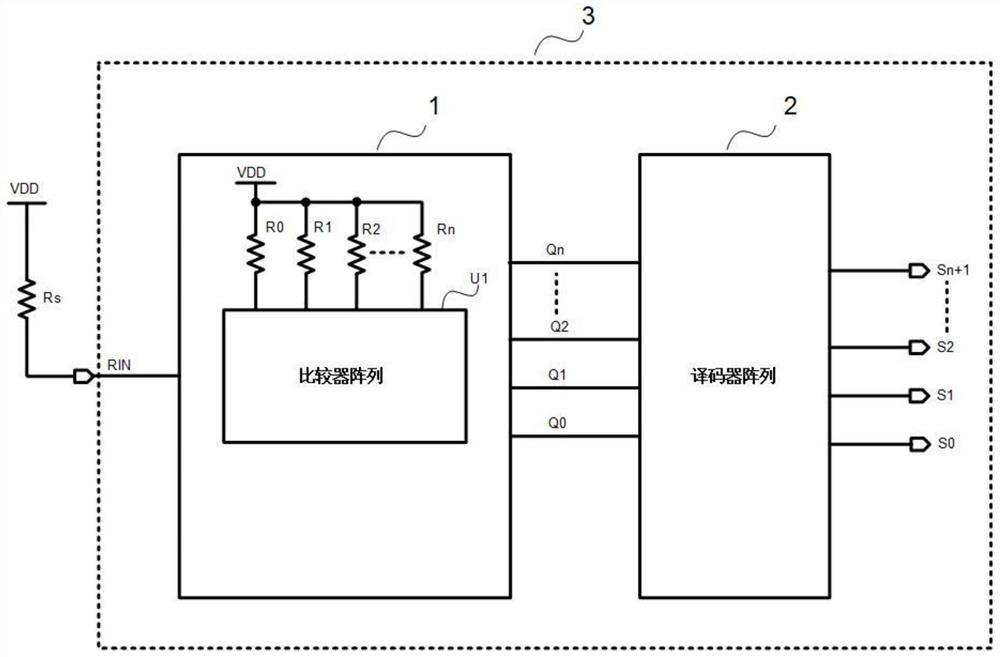

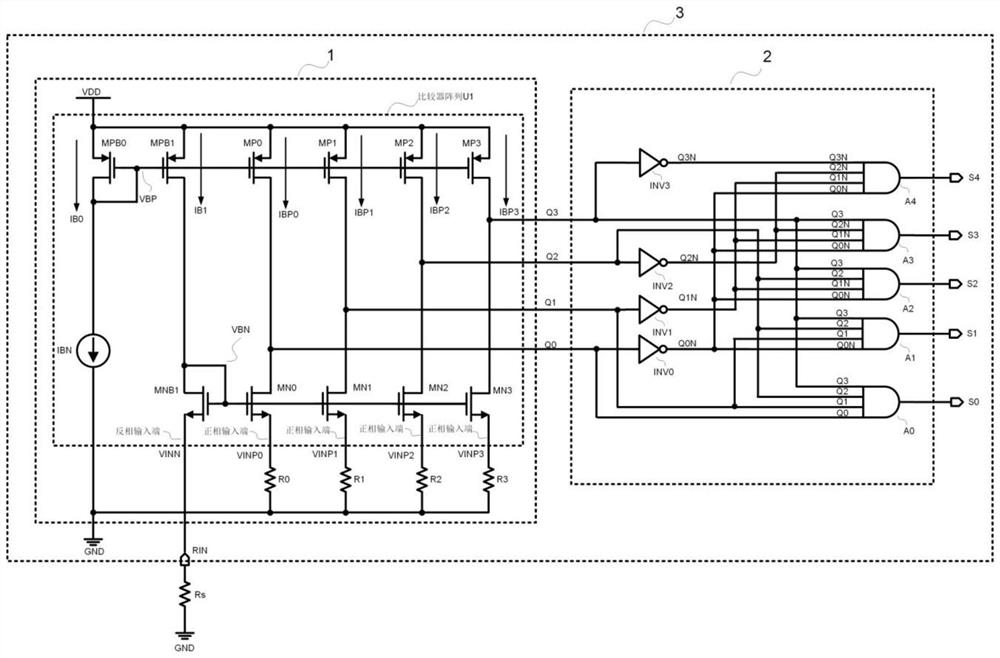

Integrated circuit option setting circuit

PendingCN114124081ASave pin resourcesReduce manufacturing costLogic circuitsHemt circuitsEmbedded system

An integrated circuit option setting circuit comprises an integrated circuit and a peripheral resistor Rs, and a comparator module and a decoder module are arranged in the integrated circuit. The comparator module comprises a comparator array U1 and resistor arrays R0-Rn; one ends of the resistor arrays R0-Rn are connected with the comparator array U1, and the other ends of the resistor arrays R0-Rn are connected with the ground GND or a power supply VDD; a pin RIN of the integrated circuit is an input end of the comparator module, and Q0-Qn are output ends of the comparator module; the decoder module comprises a decoder array, the input end of the decoder array is connected to Q0-Qn, and the port S0-Sn + 1 is the output end of the decoder module; one end of the external resistor Rs is connected with the input end RIN of the comparator module, and the other end of the external resistor Rs is connected with the ground GND or a power supply VDD; and corresponding circuit options are set by selecting different resistance values of the external resistor Rs. Compared with the prior art, the method has the beneficial effects that more than two options can be set through one pin of the integrated circuit, so that the pin resources of the integrated circuit are greatly saved, and the manufacturing cost is reduced.

Owner:岱昆半导体(上海)有限公司

Data transmission method and device

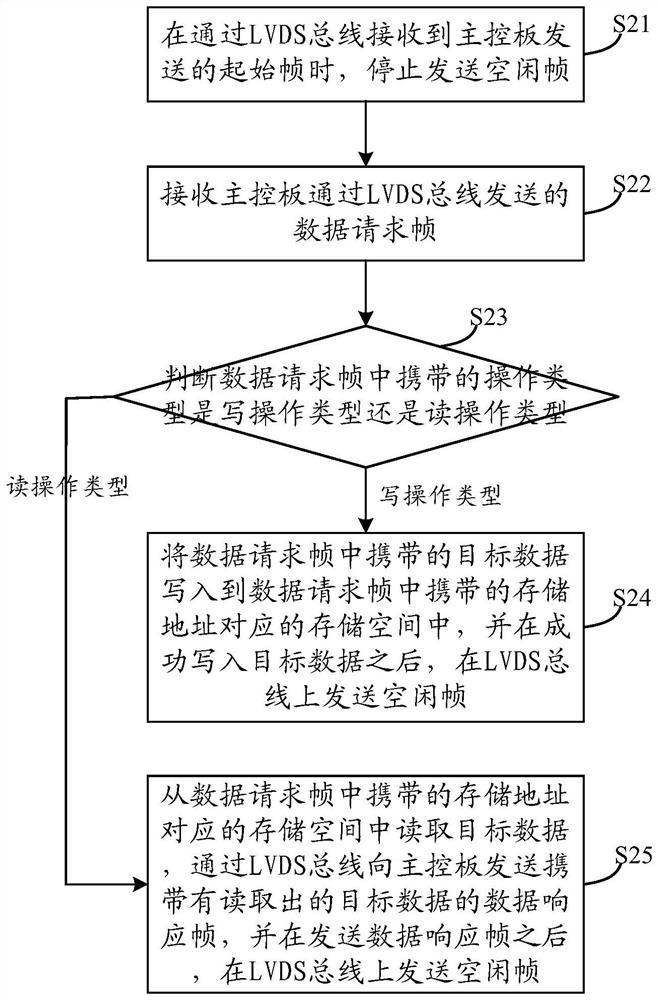

The invention provides a data transmission method and device, the method is applied to a main control board in routing equipment, an LVDS bus is arranged between the main control board and any one line card board in the routing equipment, and the method comprises the following steps: when it is detected that the LVDS bus has an idle frame and target data needs to be read / written on any one line card board, sending the idle frame to the LVDS bus; sending the start frame to the line card board through the LVDS bus, so that the line card board stops sending the idle frame when receiving the start frame; and after the start frame is sent, a data request frame is sent to the line card board through the LVDS bus, so that the line card board executes related read / write operation on the basis of receiving the data request frame. According to the routing equipment, data transmission between the main control board and the line card board in the routing equipment is realized through the LVDS bus, less pin resources can be occupied, and thus the space of a PCB (Printed Circuit Board) is saved.

Owner:NEW H3C TECH CO LTD

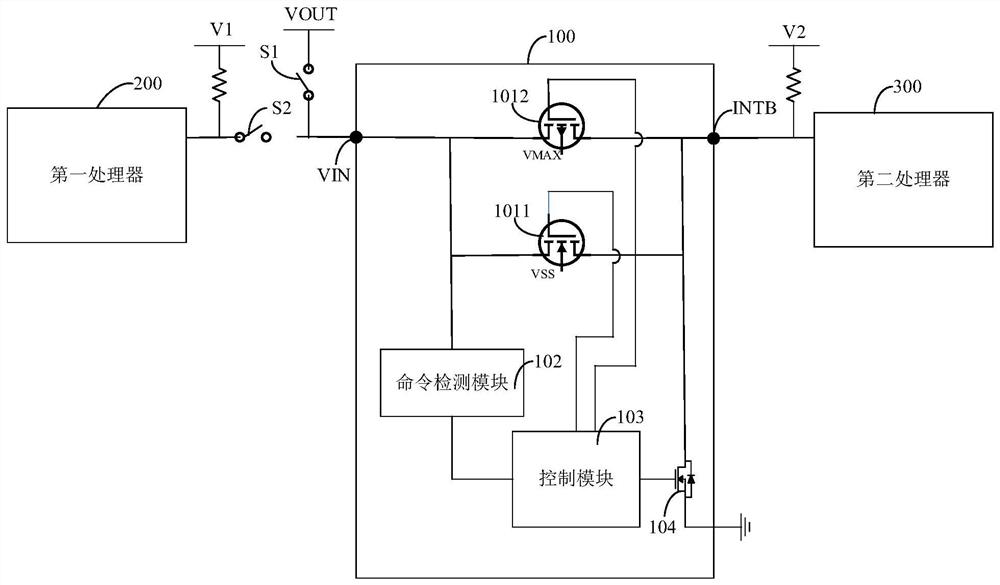

Communication circuit and electronic equipment

ActiveCN112260680AIncrease profitReduce in quantityLogic circuit coupling/interface arrangementsControl communicationsMiniaturization

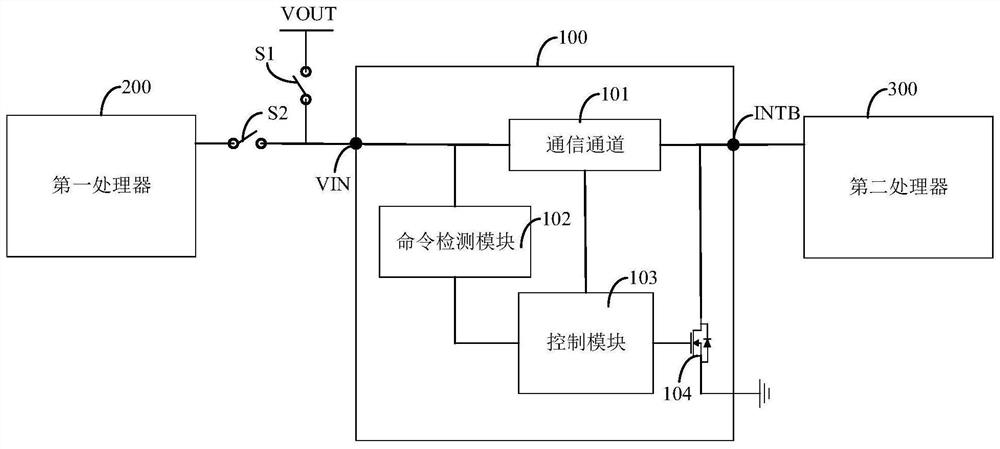

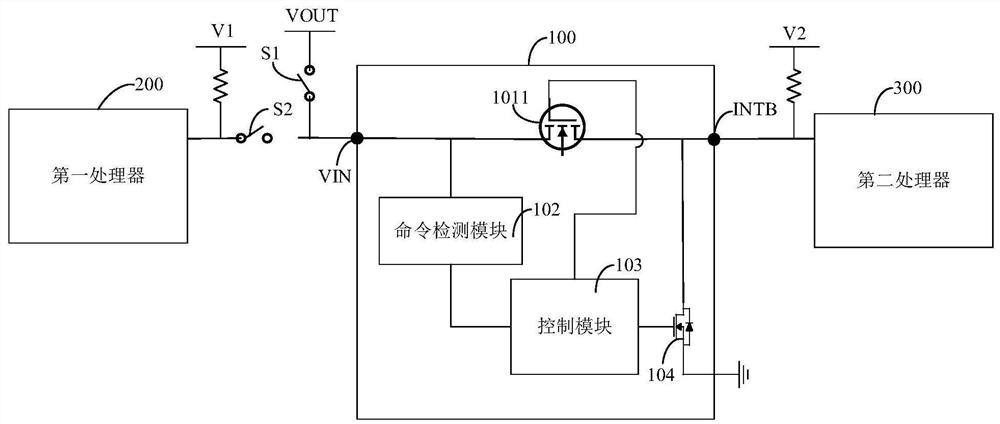

According to the communication circuit and the electronic equipment provided by the invention, the circuit function is newly added by multiplexing the power supply input pin and the interrupt pin, sothat the size miniaturization is facilitated. The communication circuit is provided with a power input pin and an interrupt pin; the power input pin is connected with a first IO port of the first processor through a first switch; the interrupt pin is connected with a second IO port of the second processor; the communication circuit comprises a communication channel, a command detection module anda control module. The communication channel is connected between the power supply input pin and the interrupt pin; the command detection module is used for outputting a first notification signal to the control module when detecting that the power input pin receives a logic control command output from the first IO port; and the output end of the control module is connected with the switching circuit, and the control module is used for controlling the communication channel to be communicable in response to the first notification signal so as to realize communication between the first IO port andthe second IO port through the power input pin, the communication channel and the interrupt pin.

Owner:SHANGHAI YAOHUO MICROELECTRONICS CO LTD

ID configuration method of series circuit, series circuit and related equipment

The invention provides an ID configuration method for a series circuit, the series circuit includes a chipset, and the chipset includes a plurality of chips connected in series in sequence; the chip at the head end of the chipset is connected to the power supply end through the input pin of the chip, The input pin of the i-th chip in the group is connected to the output pin of the i-1-th chip, and i is an integer greater than 1; the method includes: step S1, the chipset receives an ID configuration packet; step S2, makes the chip The chips in the group that meet the preset configuration conditions configure the configuration ID in the ID configuration package through their registers; step S3, and execute steps S1-S2 again, so that the next chip in the chipset that meets the preset configuration conditions performs ID configuration. The invention also provides a control terminal. The invention also provides a control terminal applying the method and a computer-readable storage medium. Compared with related technologies, the present invention saves pin resources of the chip, expands the range of ID configuration, and enriches the types of configured IDs.

Owner:莫冰 +2

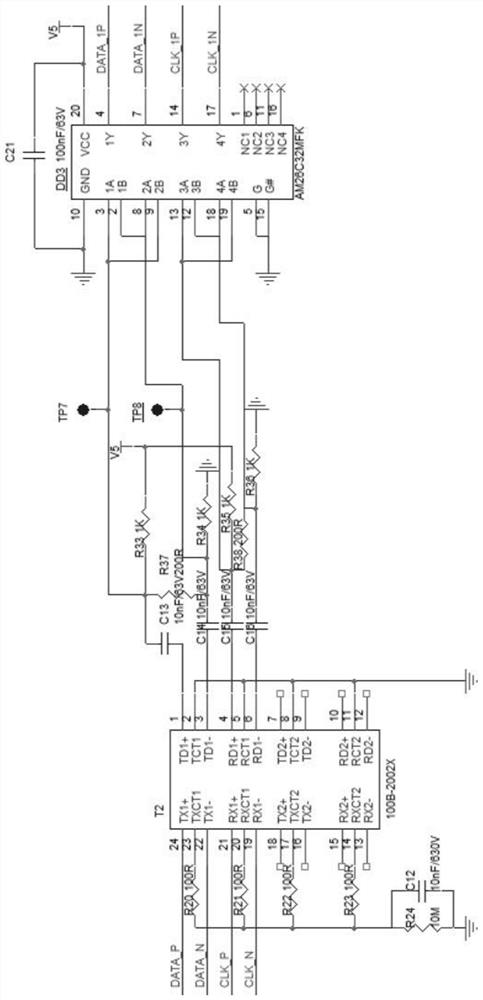

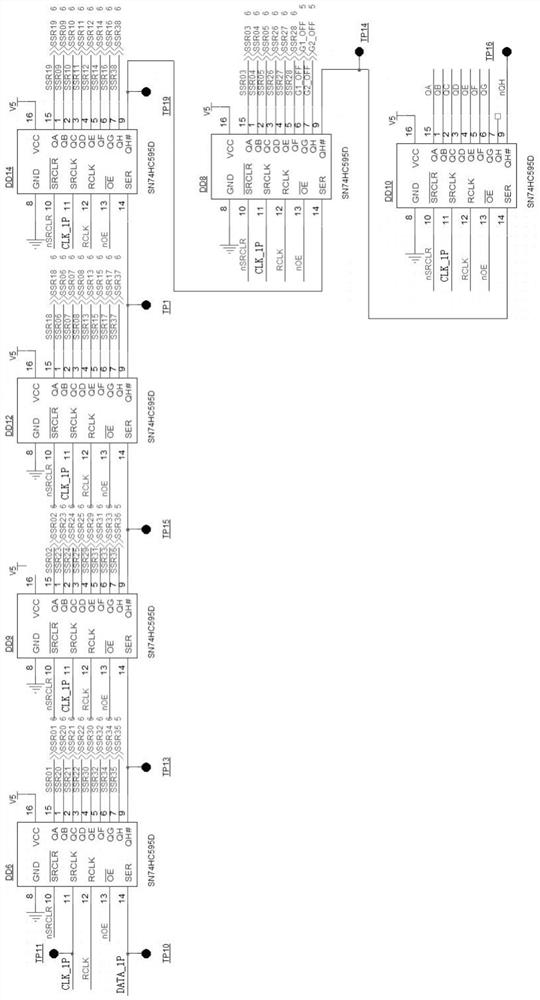

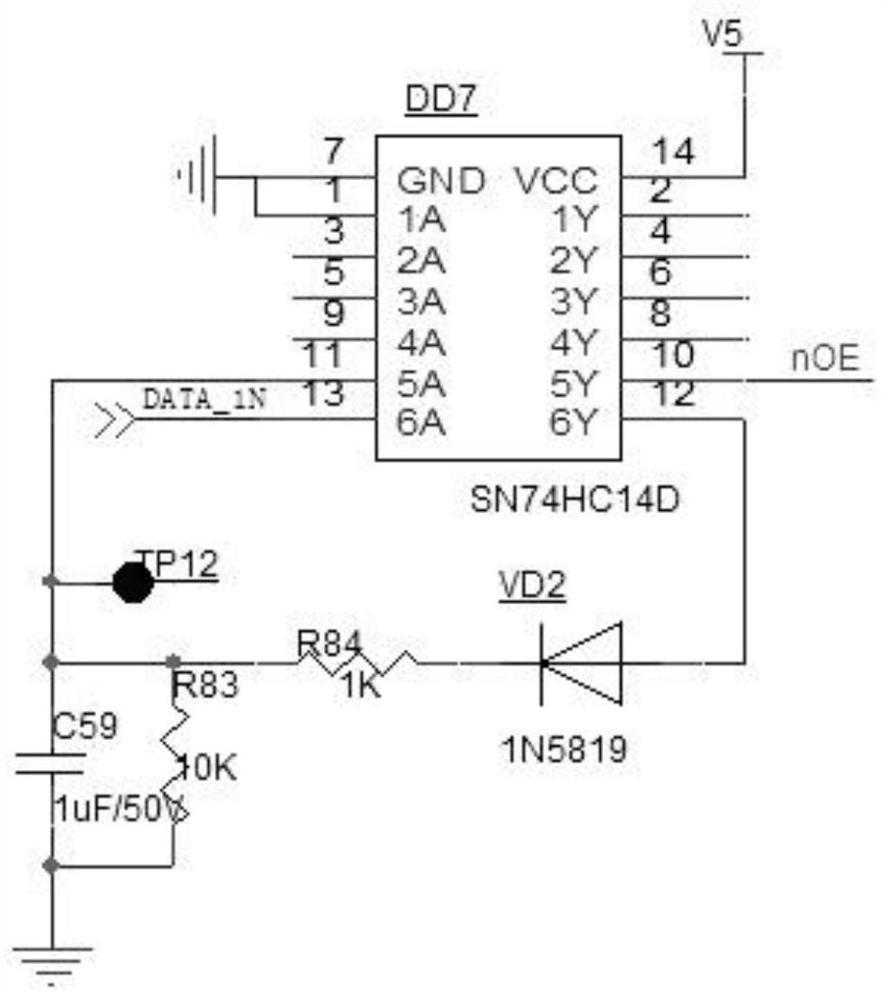

Serial multi-channel power distribution switch control circuit

ActiveCN111123800BSave pin resourcesStable stateProgramme controlComputer controlShift registerFlip-flop

The invention discloses a serial multi-channel power distribution switch control circuit, including FPGA, a shift register group, the serial data input end of the first shift register in the shift register group and the data signal output end of the control module DATA_P connection, the serial data input terminal of other shift registers in the shift register group is connected to the serial data output terminal of the previous shift register adjacent to it, the signal clock input terminal of the shift register is connected to the clock signal of the control module The output terminal CLK_P is connected, the latch clock input terminal of the shift register is connected to the first output terminal of the D flip-flop, the clear signal input terminal of the shift register is connected to the second output terminal of the D flip-flop, and the output of the shift register The enable signal input terminal is connected to the output terminal of the inverter, the input terminal of the inverter is connected to the data signal output terminal DATA_N of the control module, and multiple parallel data output terminals of the shift register are respectively connected to multiple power distribution switches. It saves time and effort, and saves FPGA pin resources.

Owner:武汉卓目科技有限公司

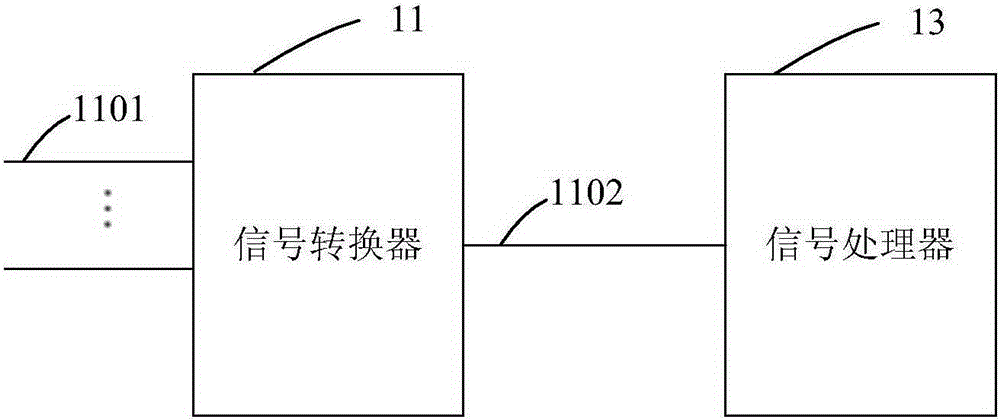

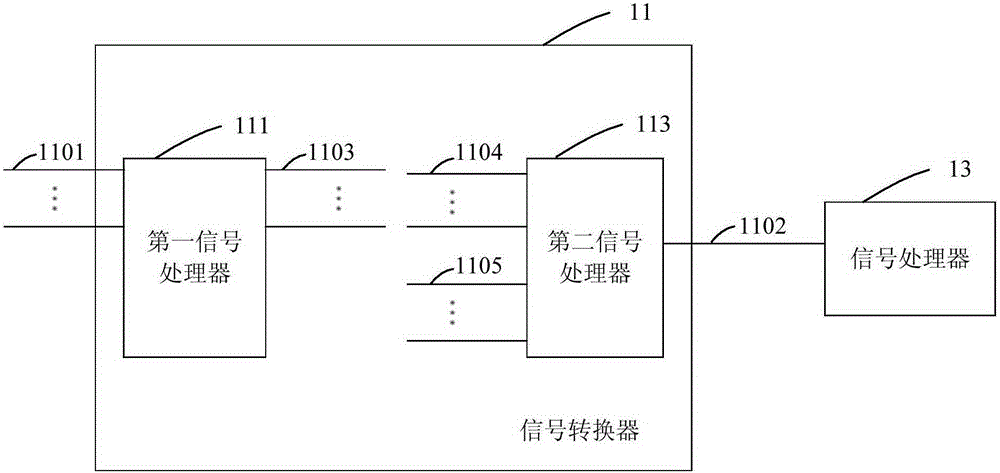

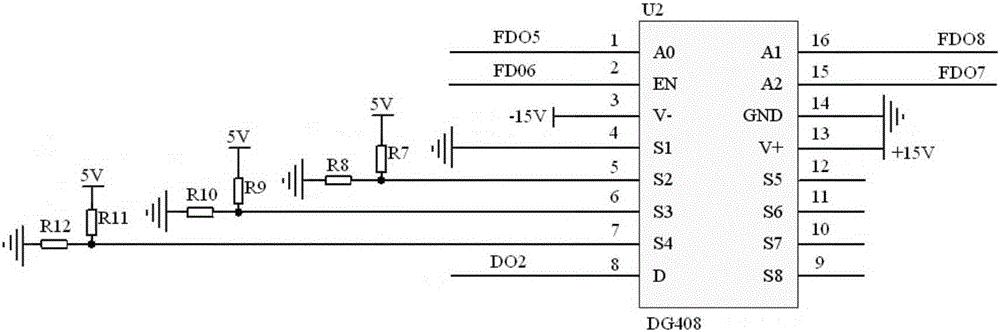

Electric locomotive traction controller state feedback device and system

ActiveCN106681197ASave pin resourcesImprove resource utilizationProgramme controlComputer controlResource utilizationControl theory

The invention provides an electric locomotive traction controller state feedback device and a system. the electric locomotive traction controller state feedback device comprises a signal converter and a signal processor, wherein the signal converter comprises at least two ways of signal input ends and one way of signal output end; the at least two ways of signal input ends is connected with a traction converter cabinet feedback device of the electric locomotive; the one way of signal output end is connected with the signal processor; the signal converter is used for converting digital state feedback signals inputted by the at least two ways of signal input ends respectively to a way of analog output signals, and the way of analog output signals is outputted to the signal processor; and the signal processor is used for carrying out signal analysis on the way of analog output signals to obtain digital state feedback signals. According to the electric locomotive traction controller state feedback device provided by the invention, the resource utilization rate of a core control chip can be enhanced.

Owner:CRRC DALIAN R & D CO LTD

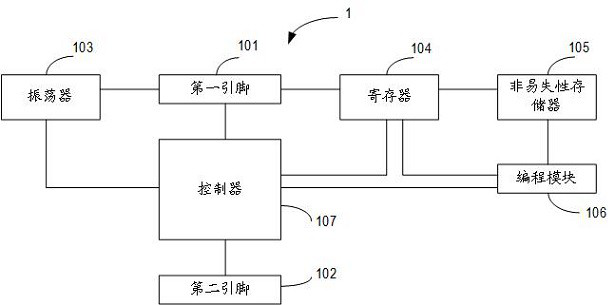

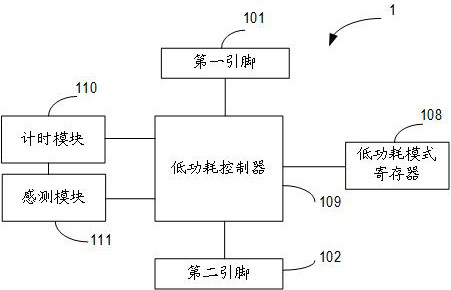

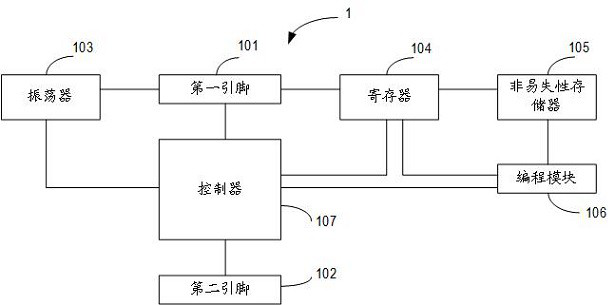

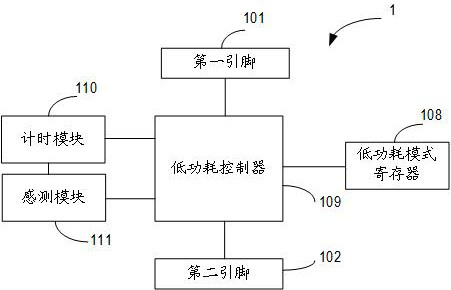

Semiconductor chip and control method thereof

ActiveCN112148064BSave pin resourcesReduce power-on stabilization wait timeFaulty hardware testing methodsGenerating/distributing signalsComputer architectureClock rate

Embodiments of the present disclosure provide a semiconductor chip and a control method thereof. The semiconductor chip includes: a first pin; a second pin; a non-volatile memory; a programming module configured to program calibration data into the non-volatile memory when a programming command is received; and a controller coupled to The first pin, the second pin and the programming module are configured to: when the semiconductor chip is powered on, if the command received from the host computer via the first pin is a preset byte, the semiconductor chip enters the calibration mode, if it is not a preset byte, the semiconductor chip enters the normal working mode; in the calibration mode, the internal clock frequency is output through the first pin; the calibration data is received through the first pin; the programming is received through the first pin enable command; and cause the programming module to program using the calibration data based on the program enable command. The semiconductor chip described here can utilize two pins to realize various functions.

Owner:HANGZHOU SDIC MICROELECTRONICS

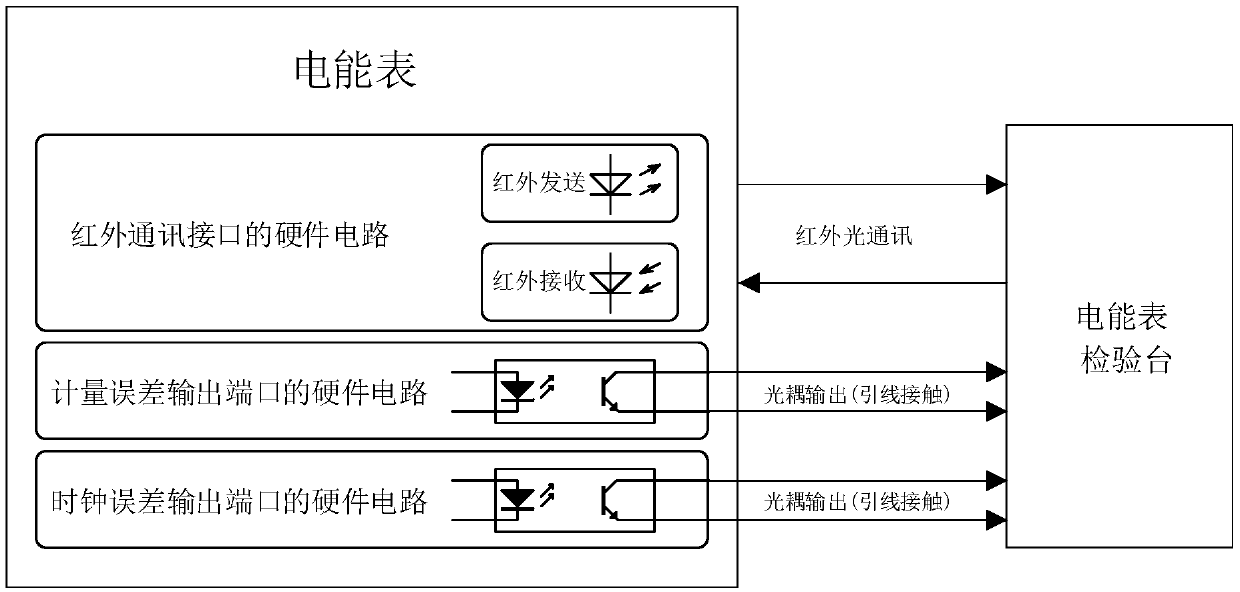

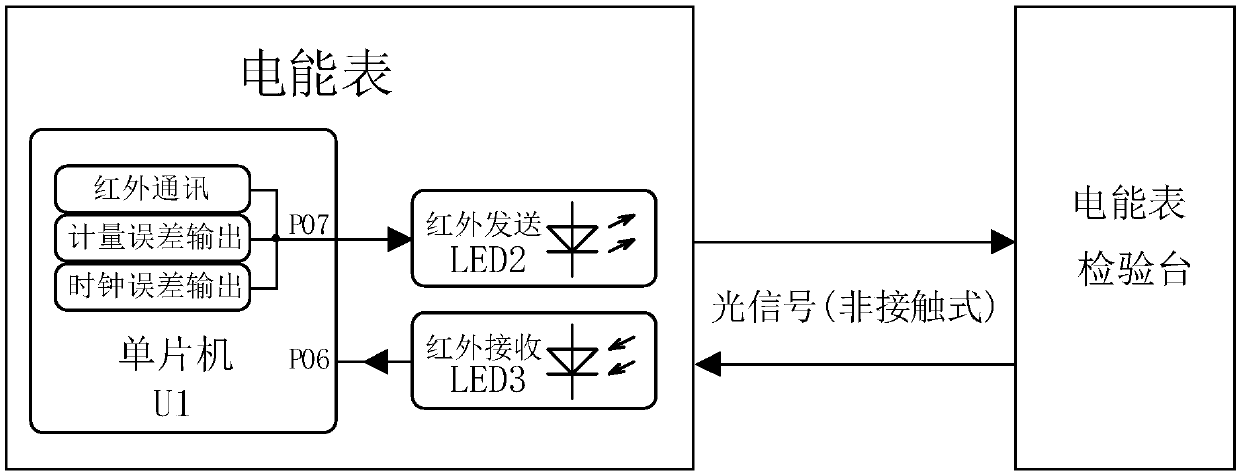

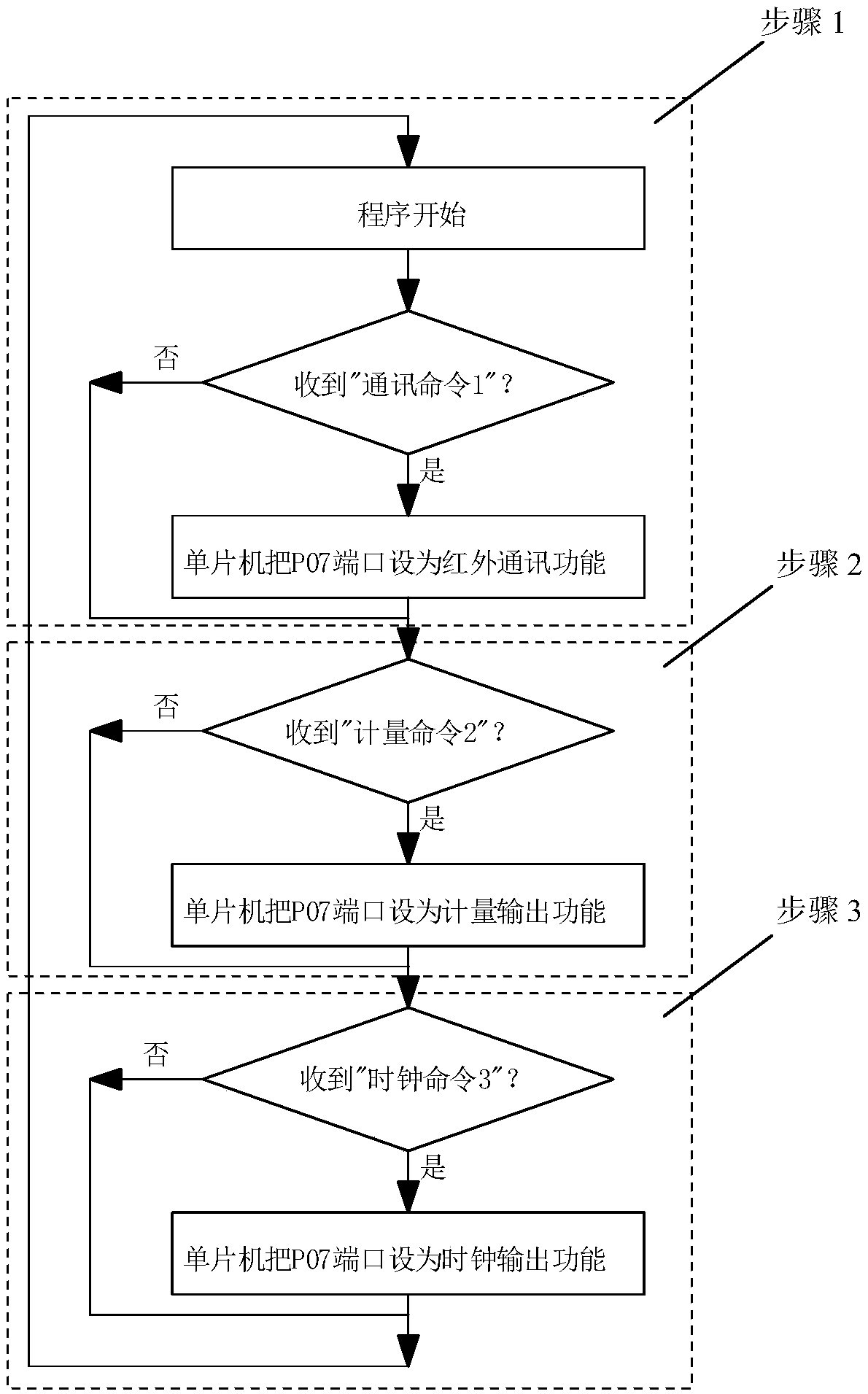

Multifunctional infrared electric energy meter and detection method thereof

PendingCN109557499AImprove antistatic levelIncrease the level of automationTime integral measurementMicrocomputerMicrocontroller

The invention discloses a multifunctional infrared electric energy meter. The multifunctional infrared electric energy meter comprises a single chip microcomputer and an infrared transmitting tube andan infrared receiving tube connected to the single chip microcomputer. The single chip microcomputer receives a detection instruction of an external electric energy meter detecting device through theinfrared receiving tube. The detection instruction comprises a communication command, a measurement command, and a clock command. The single chip microcomputer controls the infrared transmitting tubeto output a signal to be detected according to the detecting instruction. The electric energy meter detecting device detects the electric energy meter according to the signal to be detected outputtedby the infrared transmitting tube. The signal to be detected comprises an infrared communication signal, a measurement error signal, and a clock error signal. The multifunctional infrared electric energy meter has advantages that the IP54 waterproof rating of the electric energy meter is realized at a low cost, the antistatic level of the electric energy meter is improved, and the overall productquality is improved; and the production efficiency is improved, the production cost is reduced by a non-contact detection method, the automation level of the electric energy meter production is improved, and the quality of electric energy meter products is improved.

Owner:ZHANGZHOU CANNET ELECTRICAL APPLIANCE

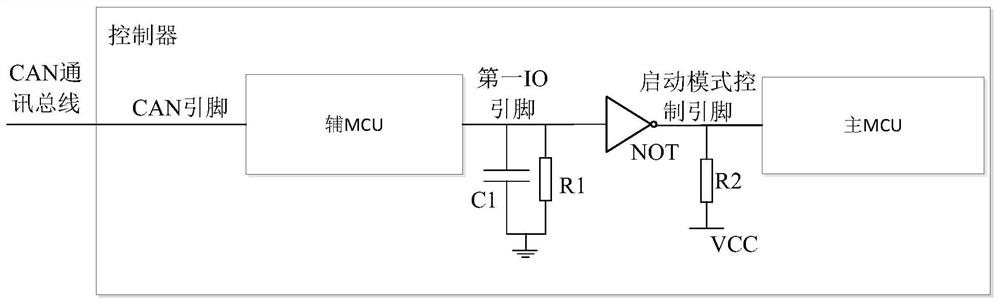

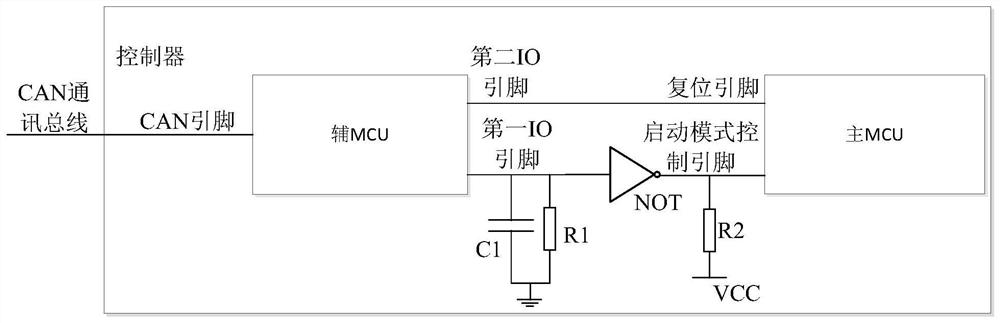

A startup control system and startup method

ActiveCN110488726BSave pin resourcesProgramme controlComputer controlComputer hardwareControl signal

Owner:WEICHAI POWER CO LTD

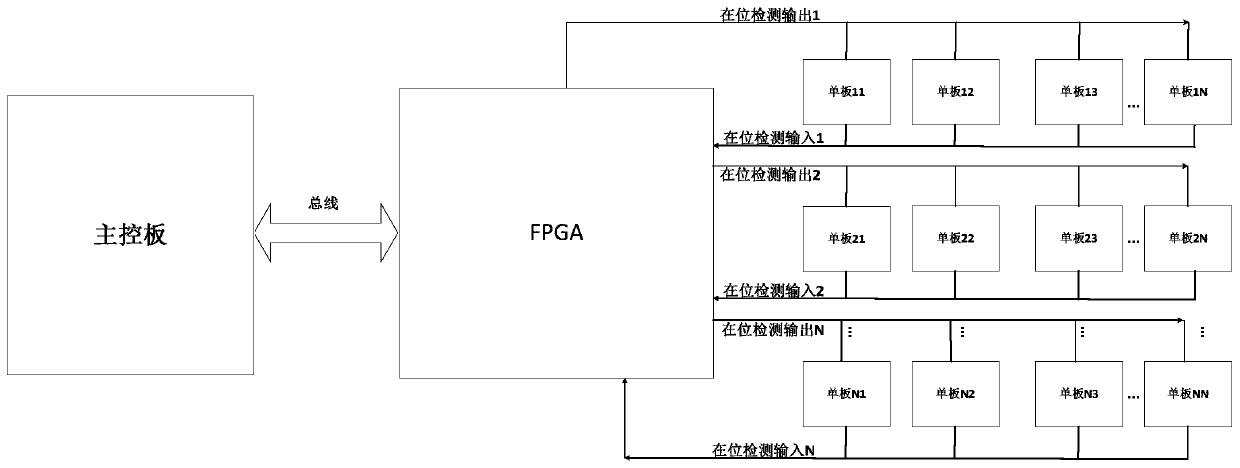

In-position real-time monitoring device for single boards in train signal system

InactiveCN109814528ASave pin resourcesFast FPGA presence detectionElectric testing/monitoringTime-sharingVIT signals

The invention discloses an in-position real-time monitoring device for single boards in a train signal system. The device is used for performing in-position real-time monitoring on a plurality of single boards under the control of a main control board, and comprises an FPGA connected with the main control board, wherein the FPGA is provided with an in-position monitoring output module, an in-position monitoring input module and an in-position real-time monitoring module, the in-position monitoring output module outputs in-position detection output signals to the single boards, the in-positiondetection output signals are high levels or low levels which are output in sequence position by position, the in-position monitoring input module receives in-position input signals from the single boards, the in-position real-time monitoring module detects the in-position input signals to judge whether or not the single boards are in position, the FPGA saves detected data into a register, and themain control board inquires the in-position states of the single boards through a bus in real time. The in-position real-time monitoring device for the single boards in the train signal system has theadvantages that the in-position states of the single boards can be detected in real time; the time-sharing reuse of pins can be achieved, it is achieved that the in-position detection of the multipleboards is achieved by using a small number of pins, and the pin resources are saved.

Owner:浙江众合科技股份有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com