Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "Reduce recovery loss" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

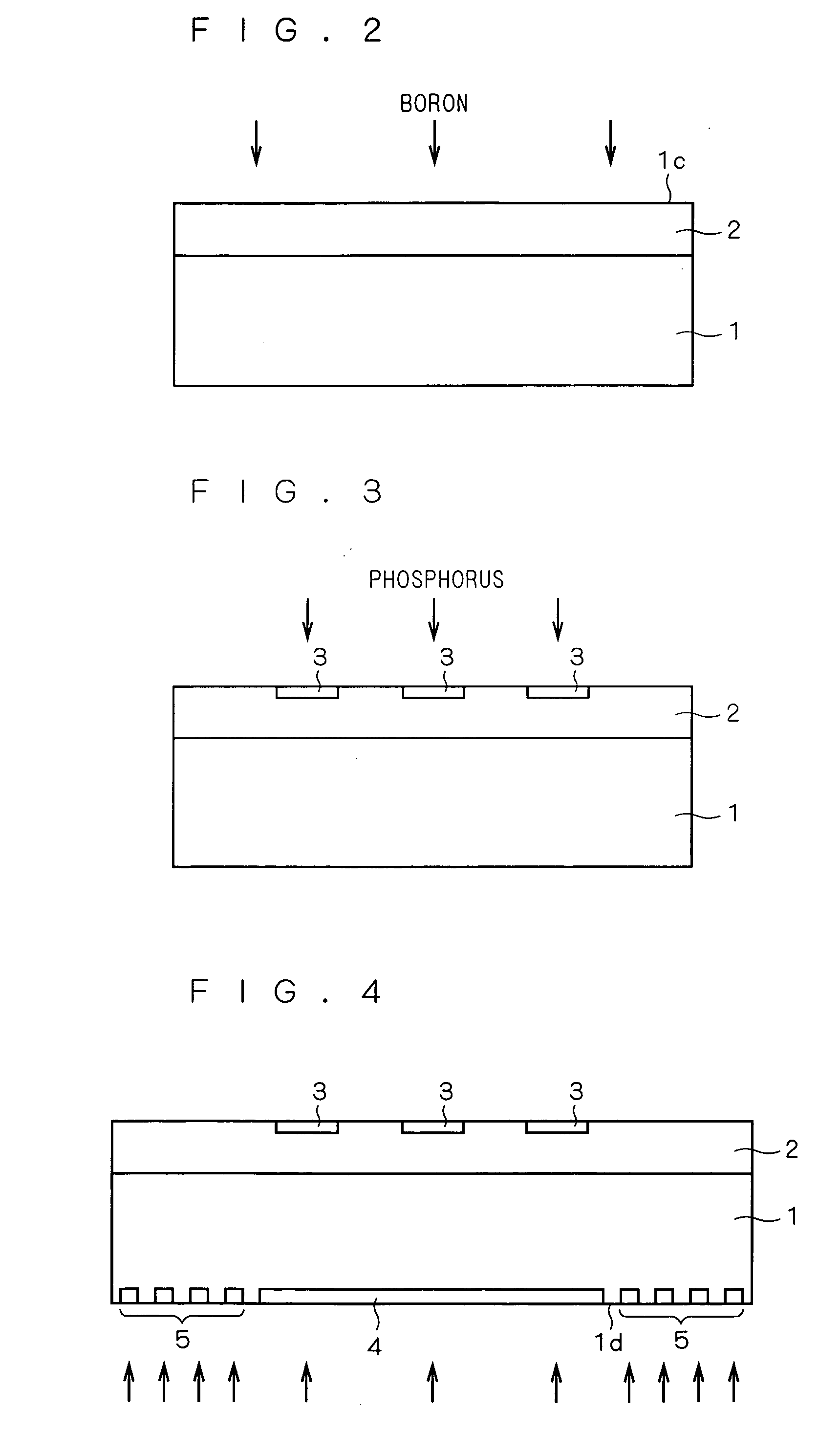

Semiconductor device

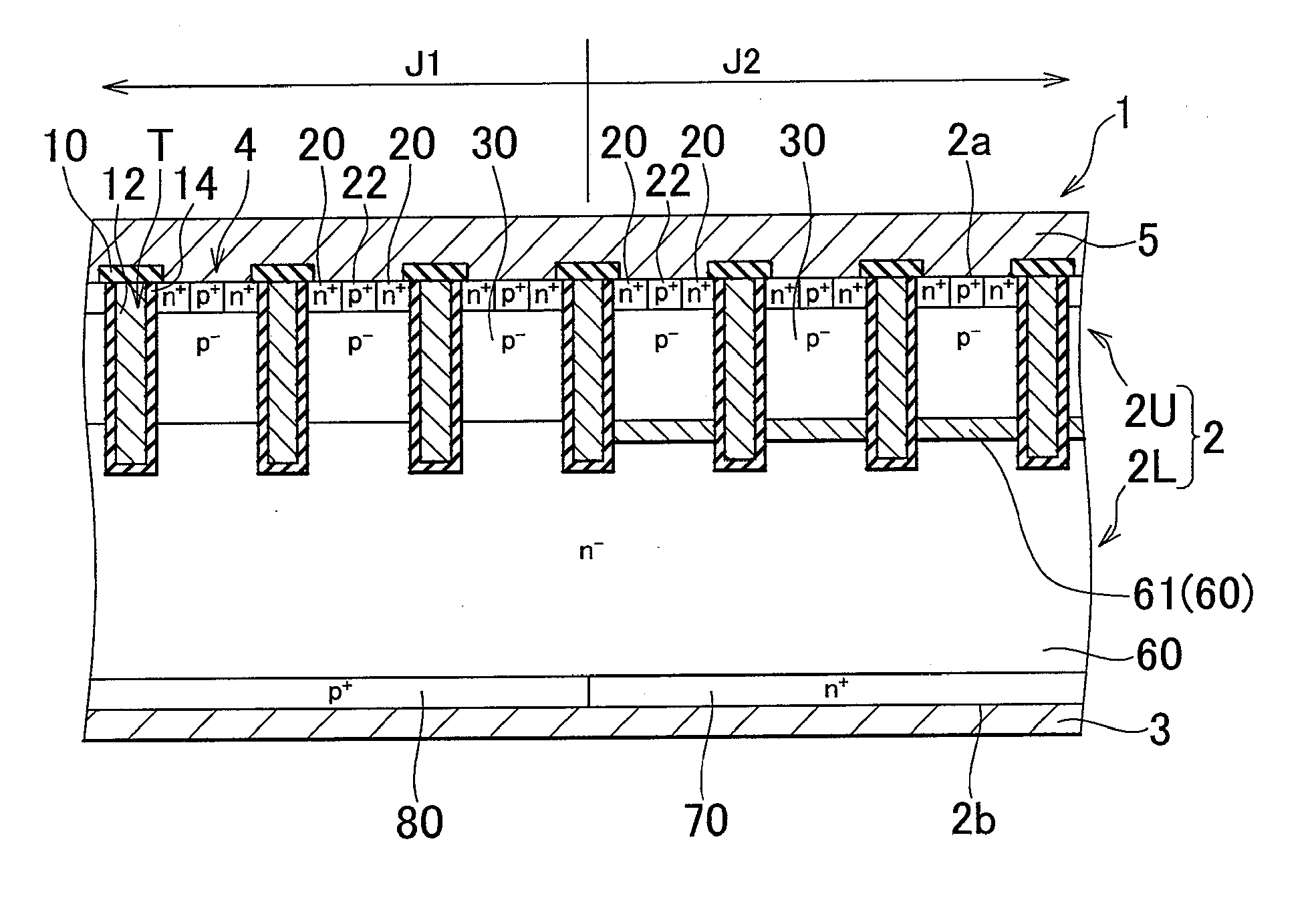

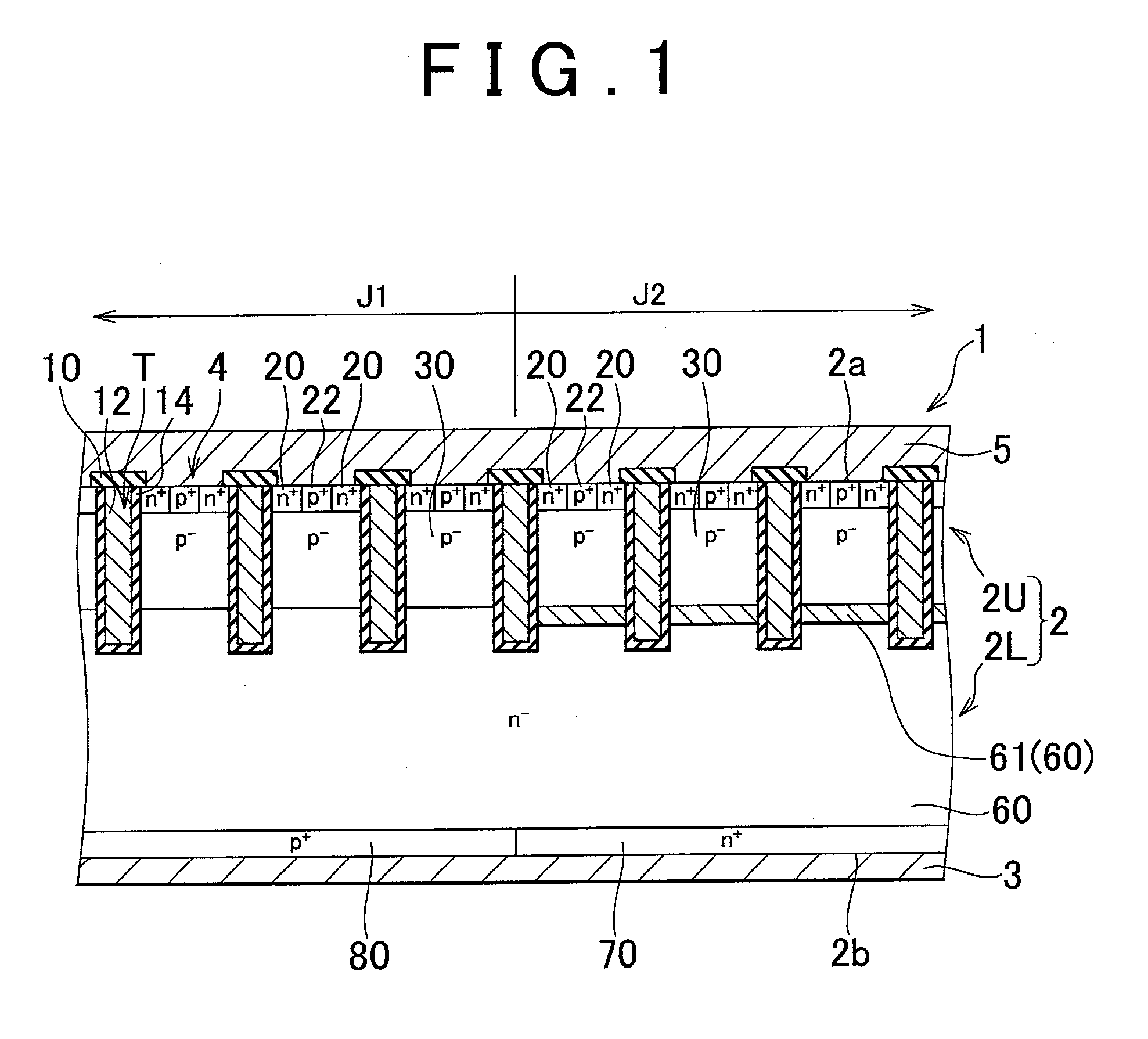

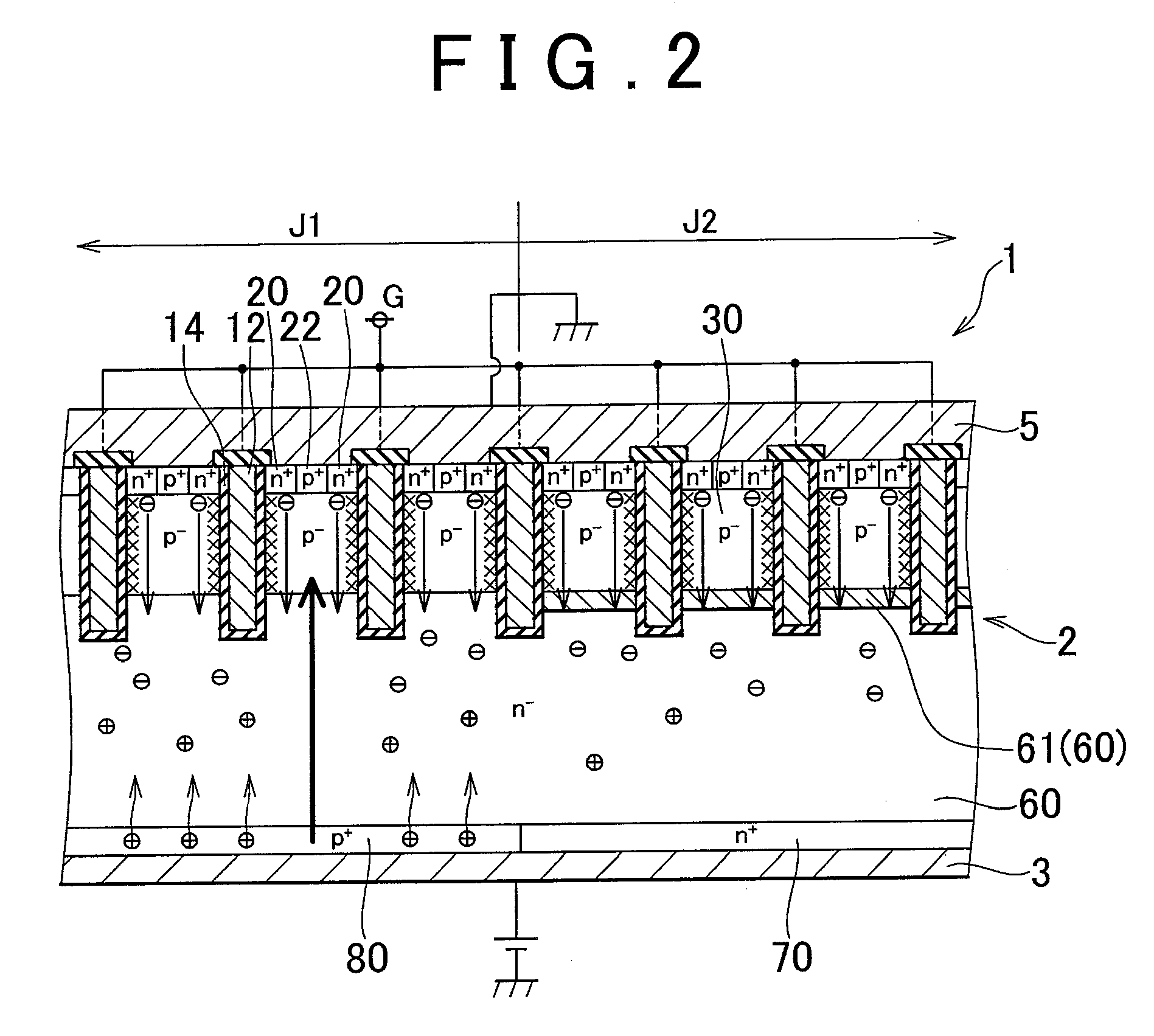

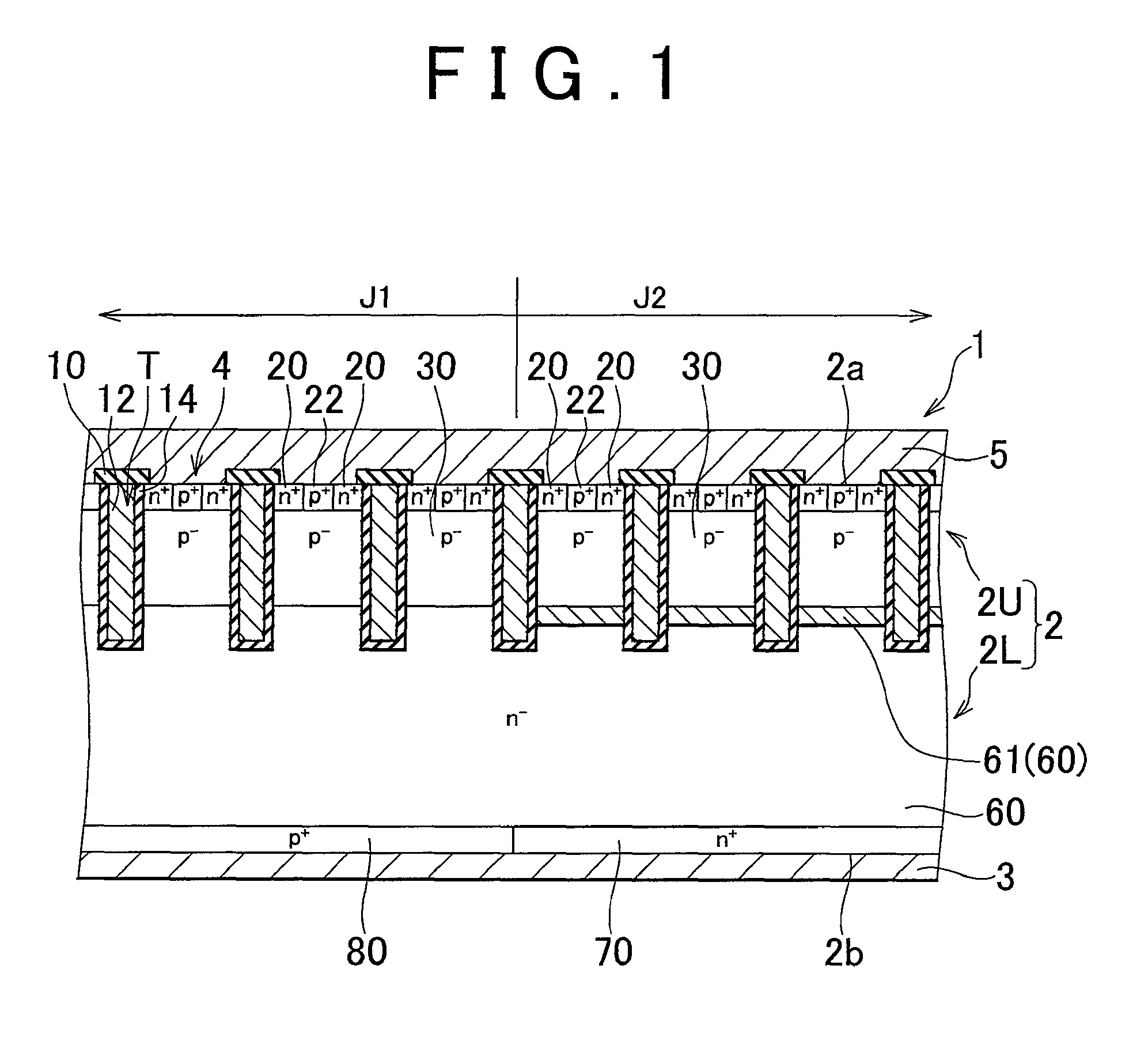

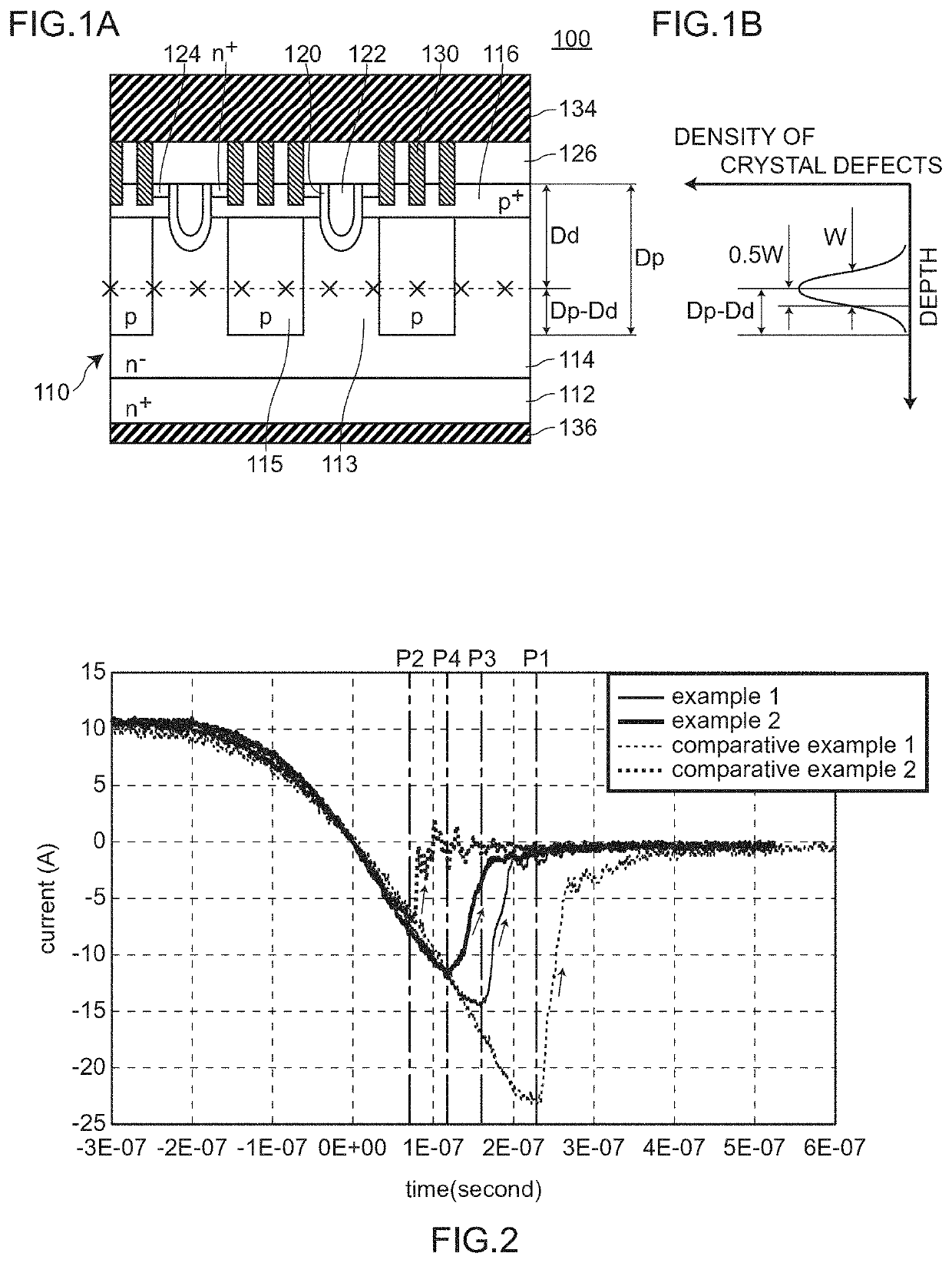

InactiveUS20090278166A1Reduce recovery lossReduced life-timeTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

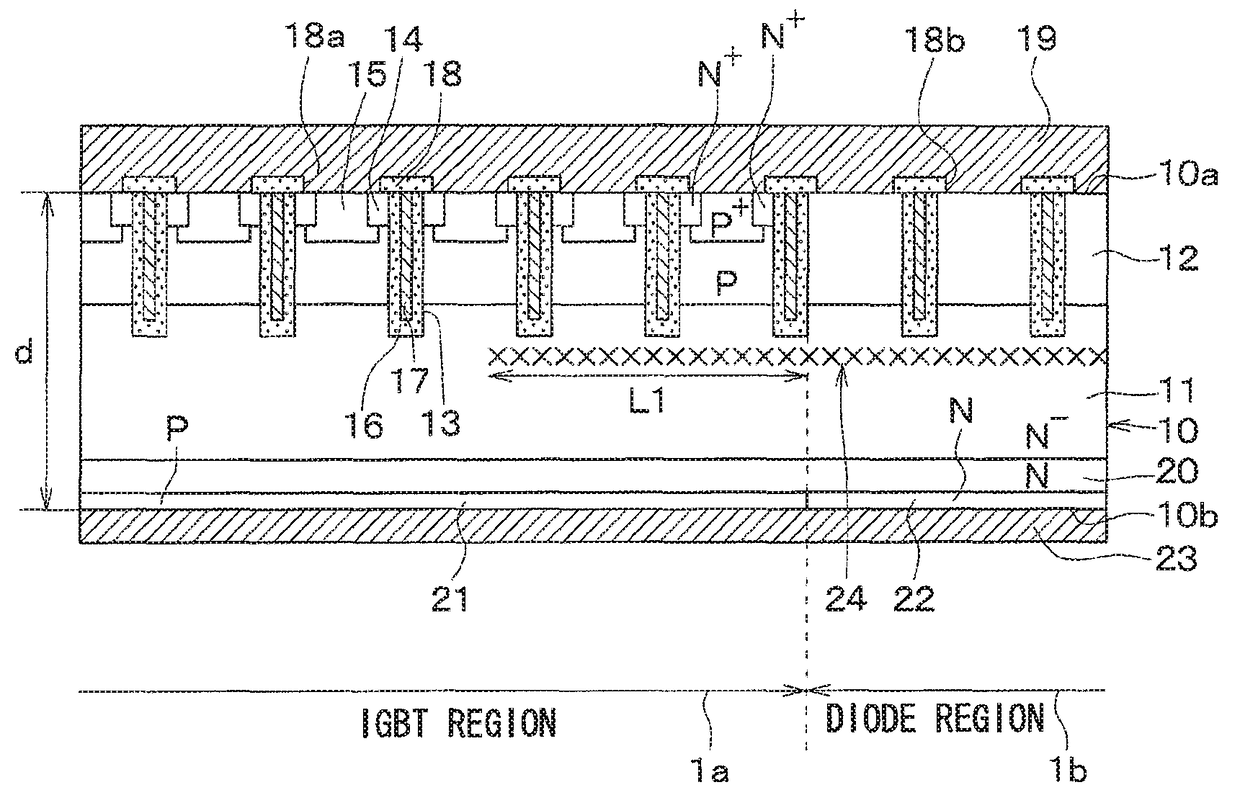

A semiconductor device in which both an IGBT element region and a diode element region exist in the same semiconductor substrate includes a low lifetime region, which is formed in at least a part of a drift layer within the diode element region and shortens the lifetime of holes. A mean value of the lifetime of holes in the drift layer that includes the low lifetime region is shorter within the IGBT element region than within the diode element region.

Owner:TOYOTA JIDOSHA KK

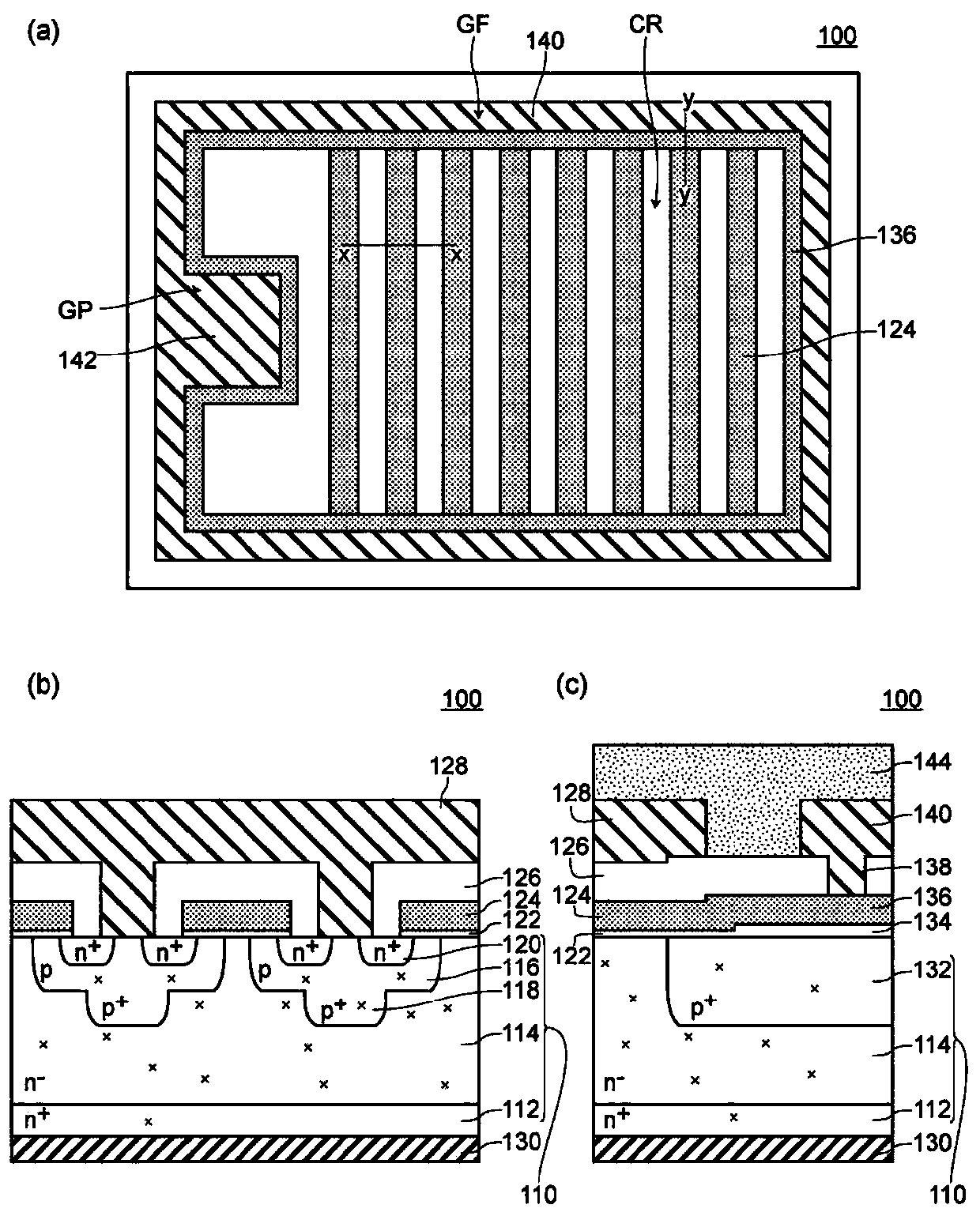

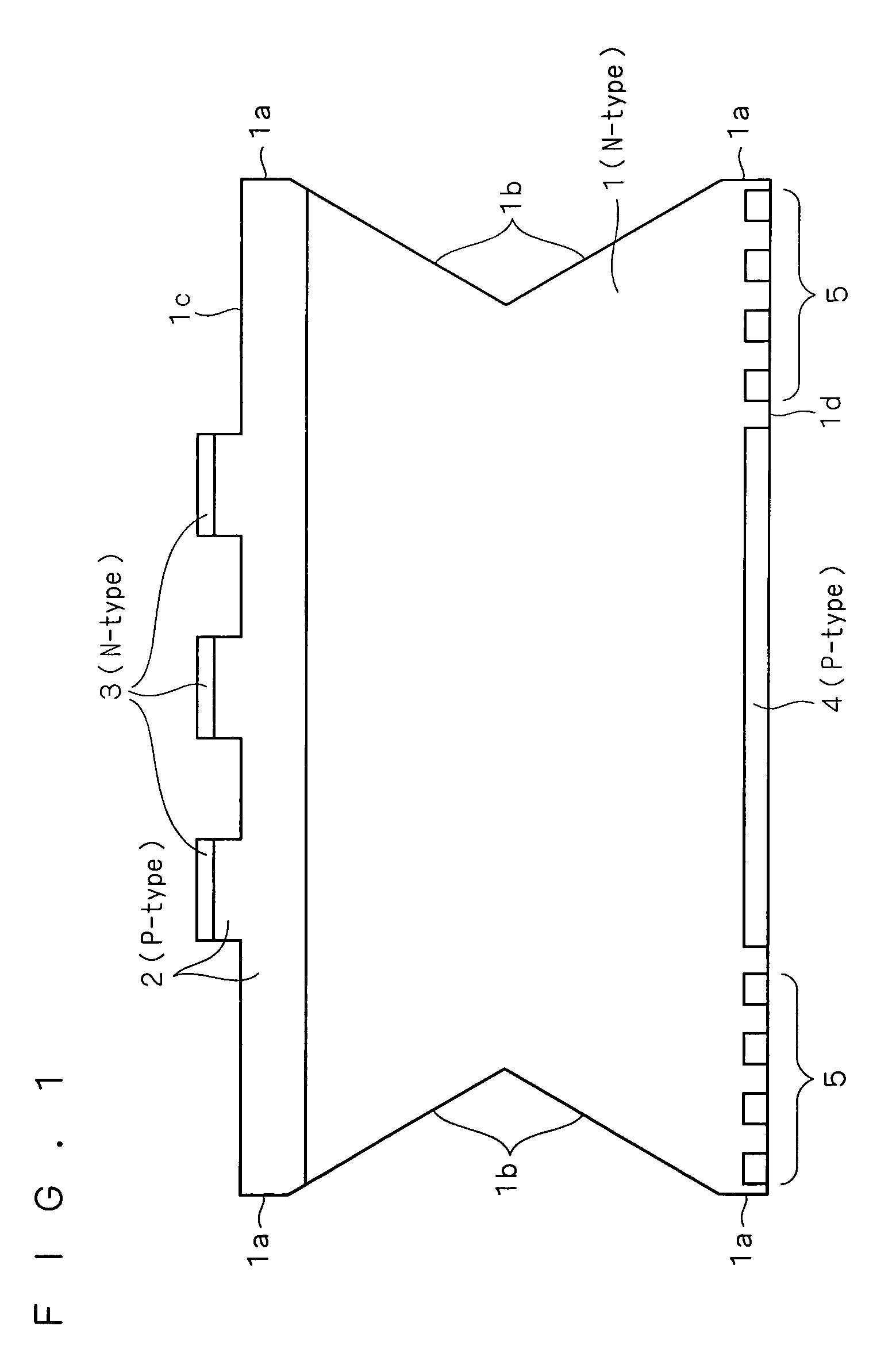

Semiconductor device having IGBT and diode

ActiveUS20070170549A1Sufficient performanceSufficient surge withstand voltageTransistorDiodeSemiconductorSemiconductor device

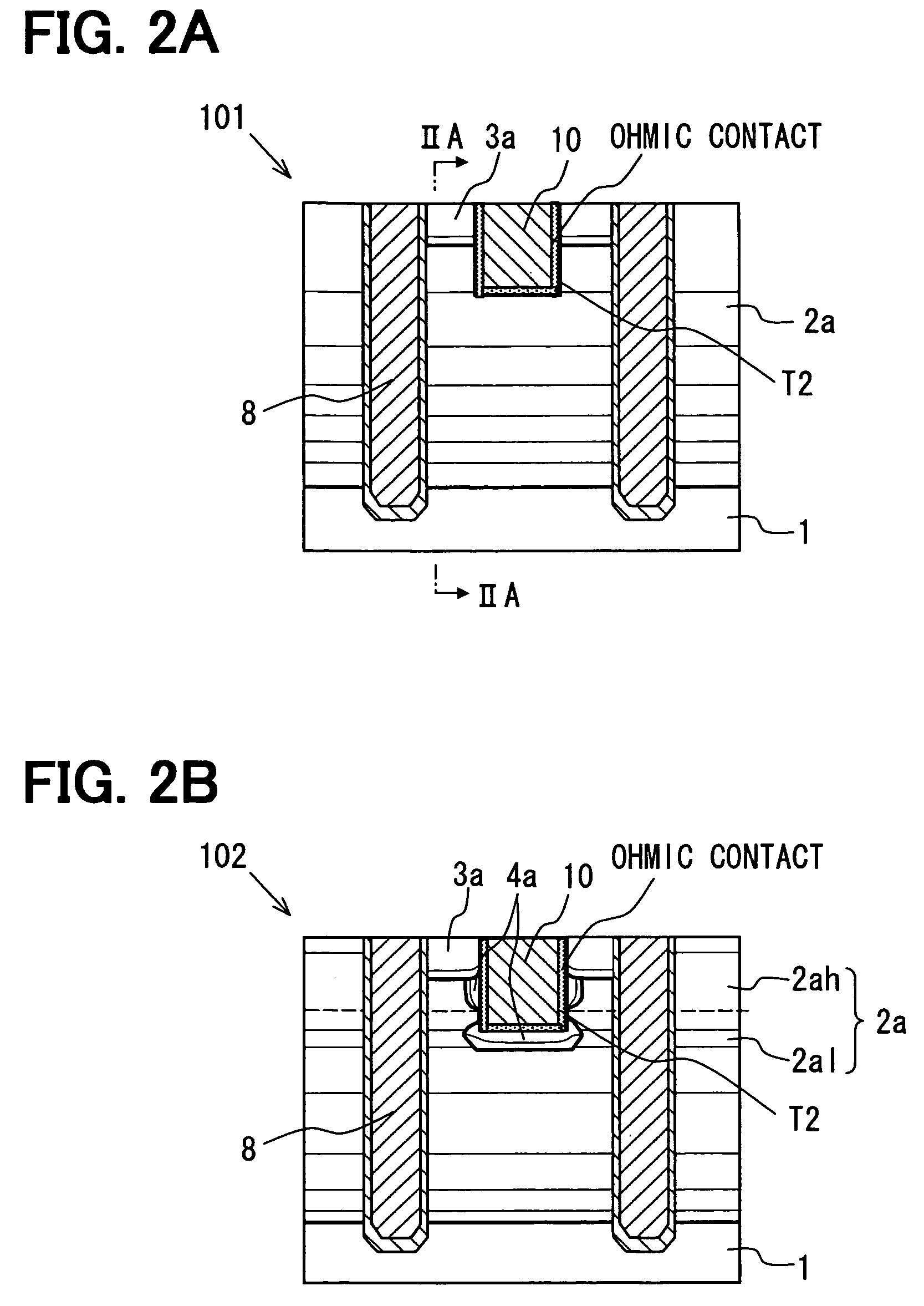

A semiconductor device includes: a substrate having a first side and a second side; an IGBT; and a diode. The substrate includes a first layer, a second layer on the first layer, a first side N region on the second layer, second side N and P regions on the second side of the first layer, a first electrode in a first trench for a gate electrode, a second electrode on the first side N region and in a second trench for an emitter electrode and an anode electrode, and a third electrode on the second side N and P regions for a collector electrode and a cathode. The first trench penetrates the first side N region and the second layer, and reaches the first layer. The second trench penetrates the first side N region, and reaches the second layer.

Owner:DENSO CORP

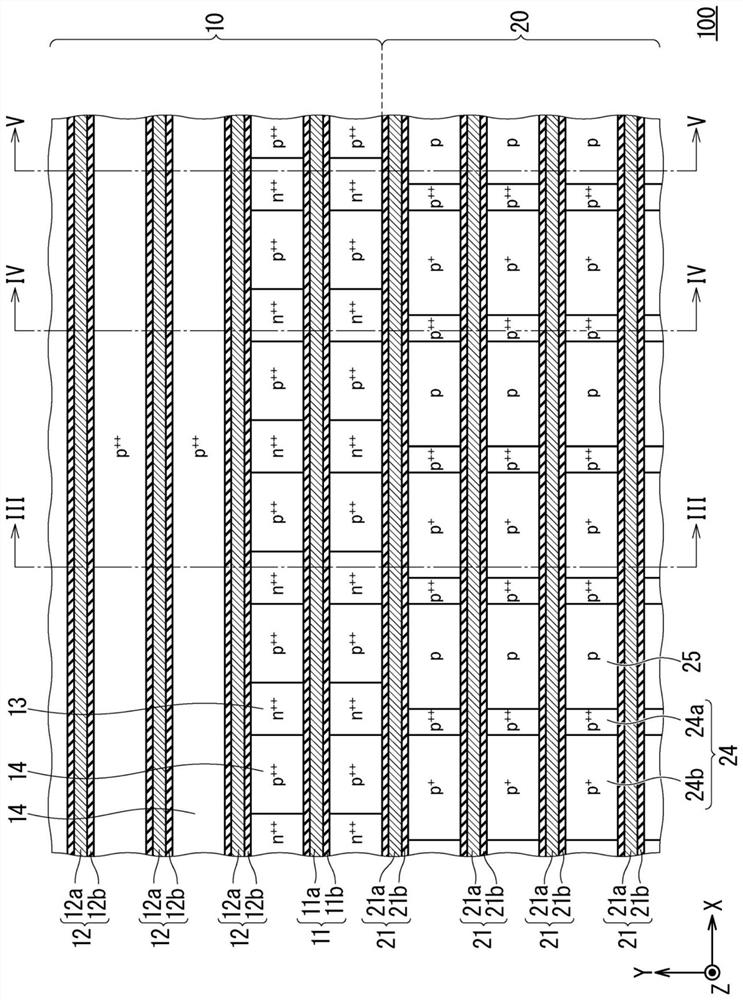

Semiconductor device

ActiveUS20170077216A1Improve featuresImproved recovery propertiesTransistorConversion constructional detailsSemiconductorSemiconductor device

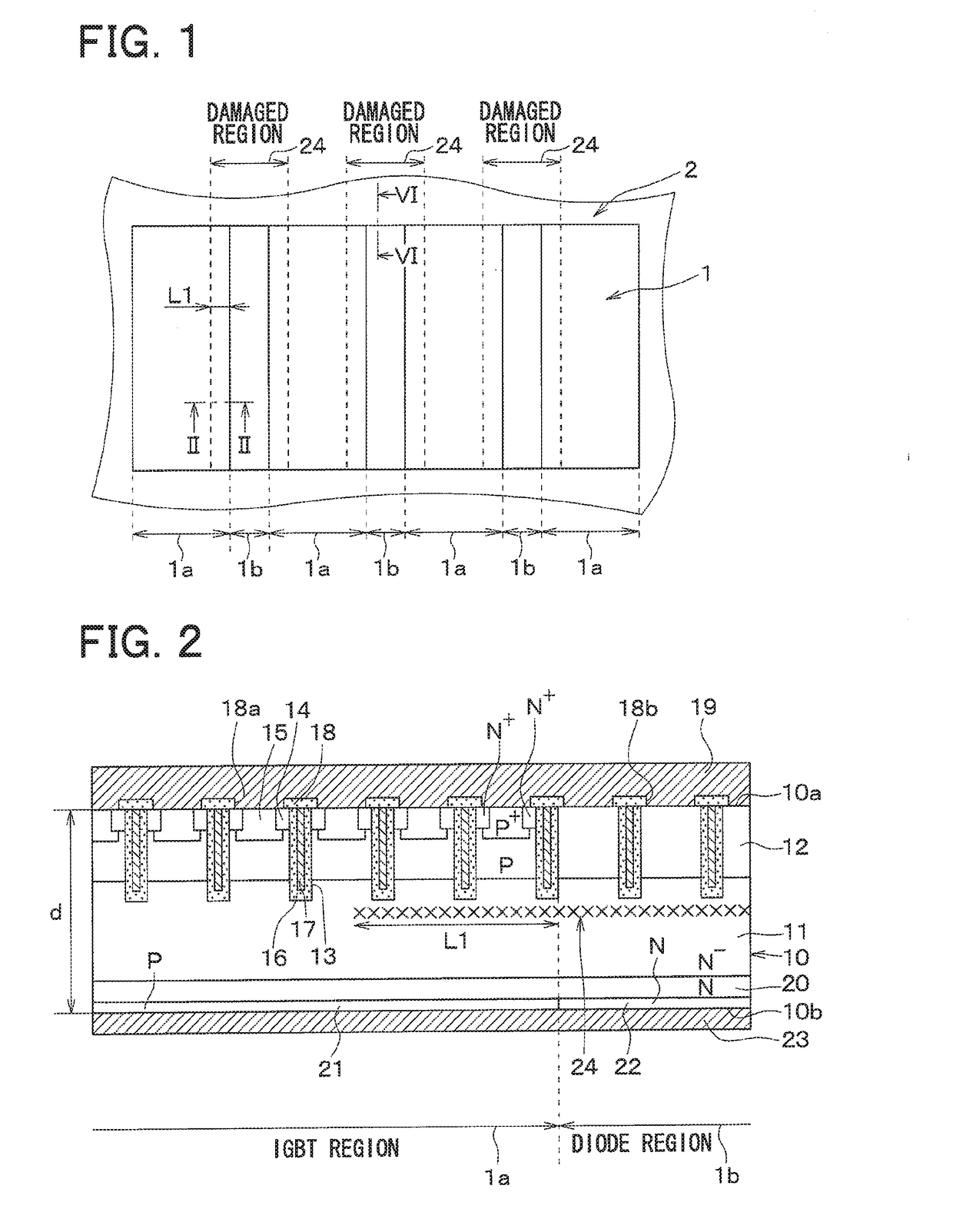

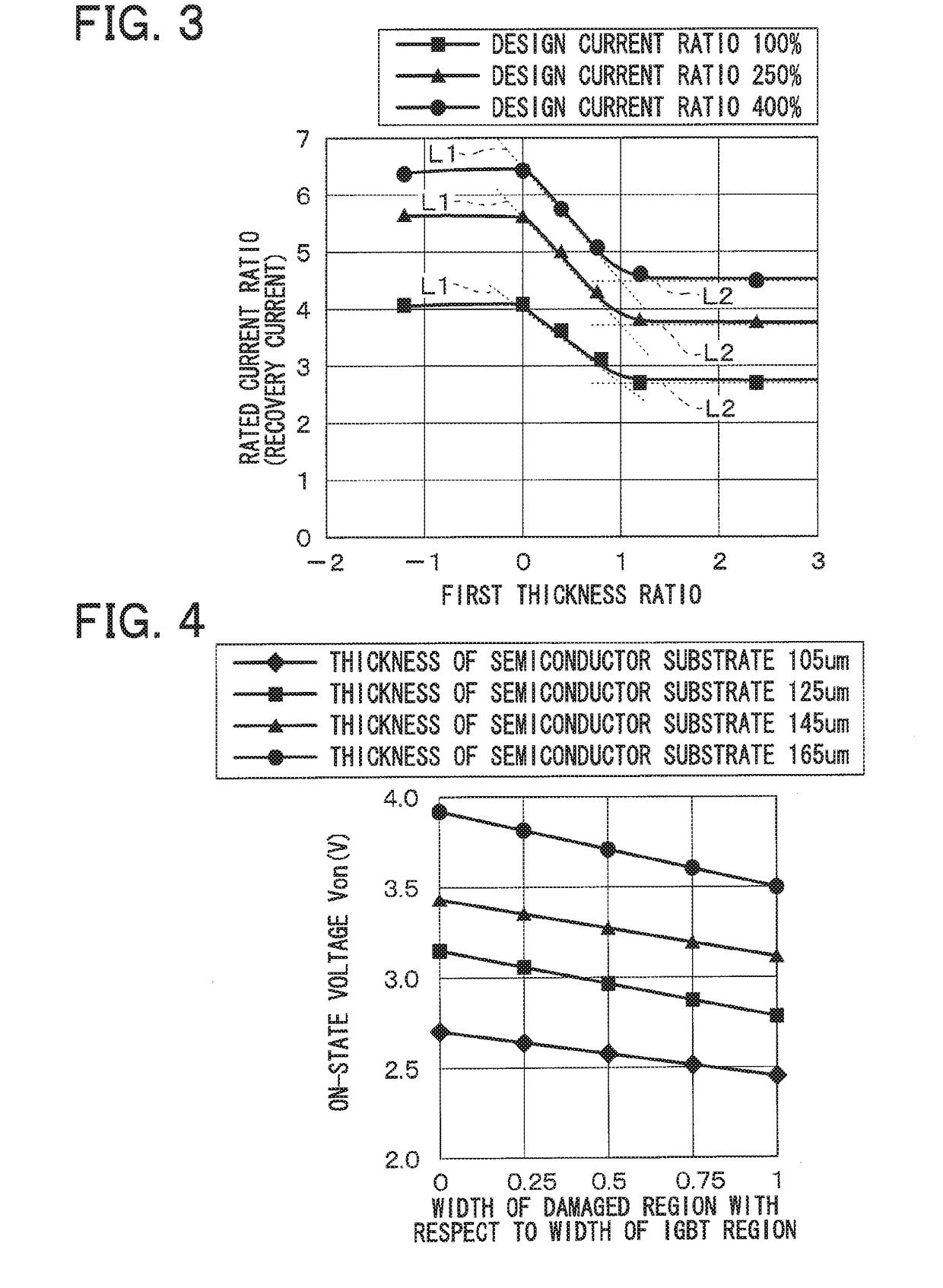

A semiconductor device includes a semiconductor substrate with: a drift layer; a base layer; and a collector layer and a cathode layer. In the semiconductor substrate, when a region operating as an IGBT device is an IGBT region and a region operating as a diode device is a diode region, the IGBT and diode regions are arranged alternately in a repetitive manner; a damaged region is arranged on a surface portion of the diode region in the semiconductor substrate. The IGBT and diode regions are demarcated by a boundary between the collector and cathode layers; and a surface portion of the IGBT region includes: a portion having the damaged region at a boundary side with the diode region; and another portion without the damaged region arranged closer to an inner periphery side relative to the boundary side.

Owner:DENSO CORP

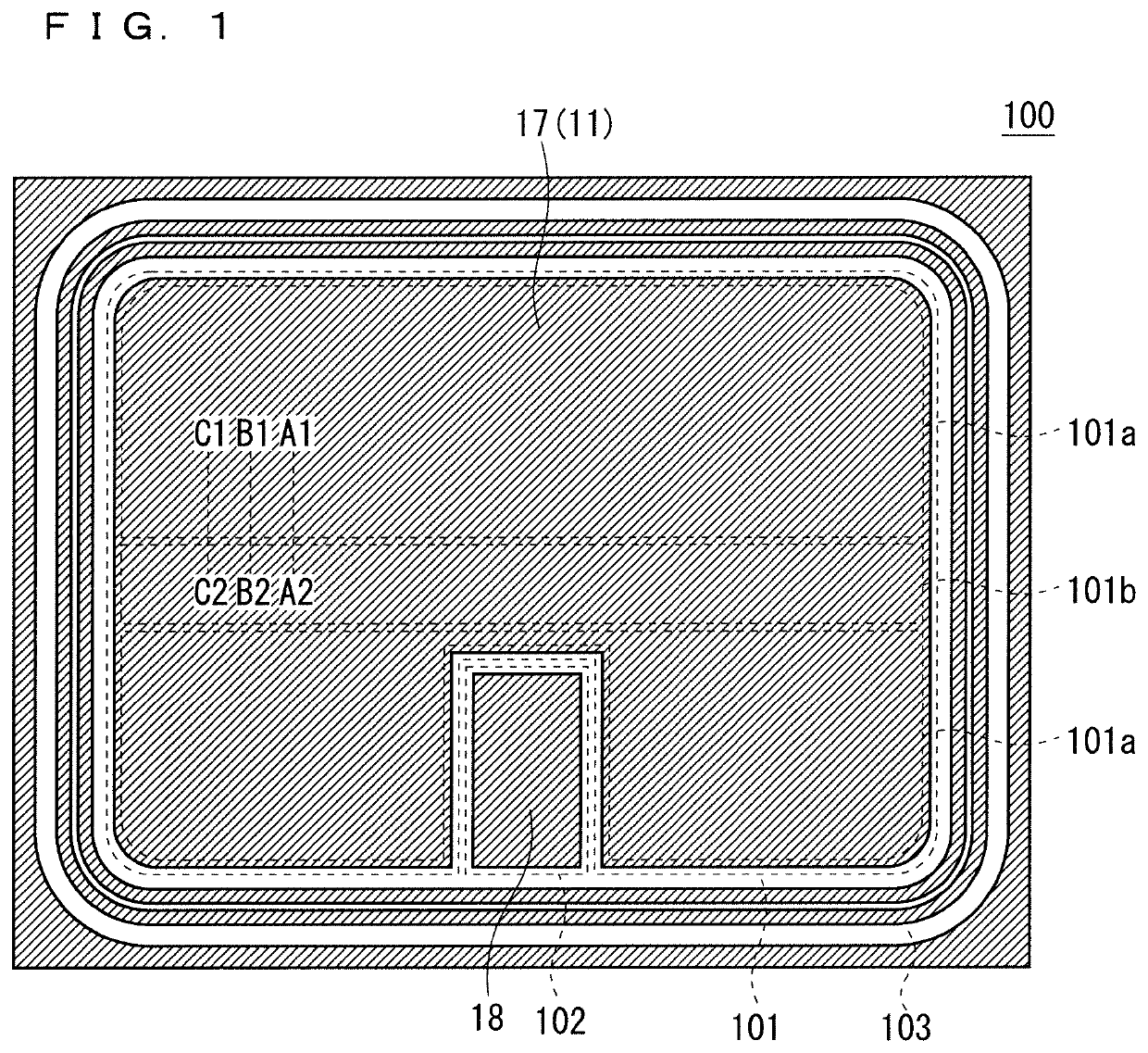

Semiconductor device

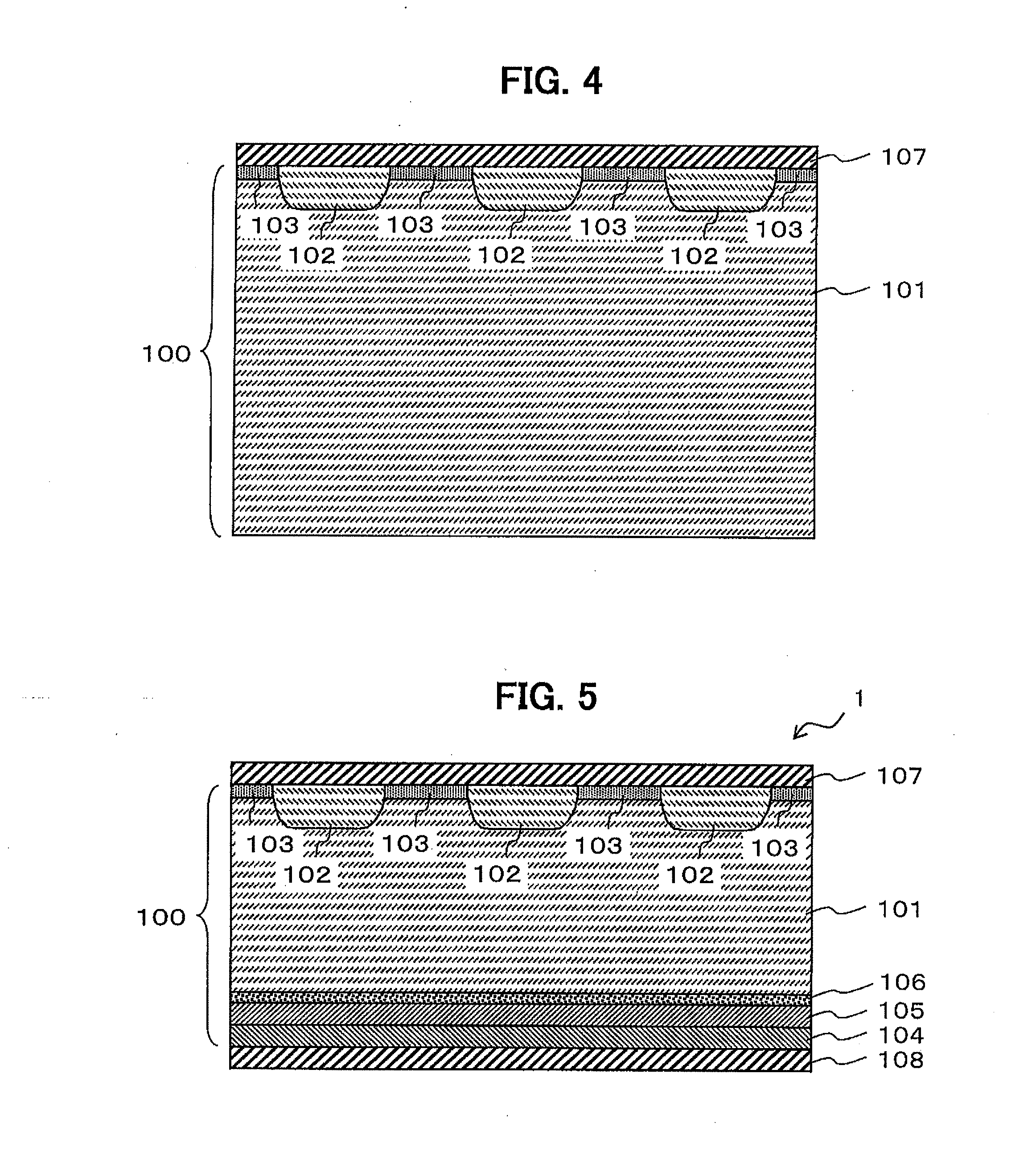

ActiveCN102479788AReduce recovery lossReduce recoverySolid-state devicesSemiconductor devicesPower semiconductor deviceSemiconductor device

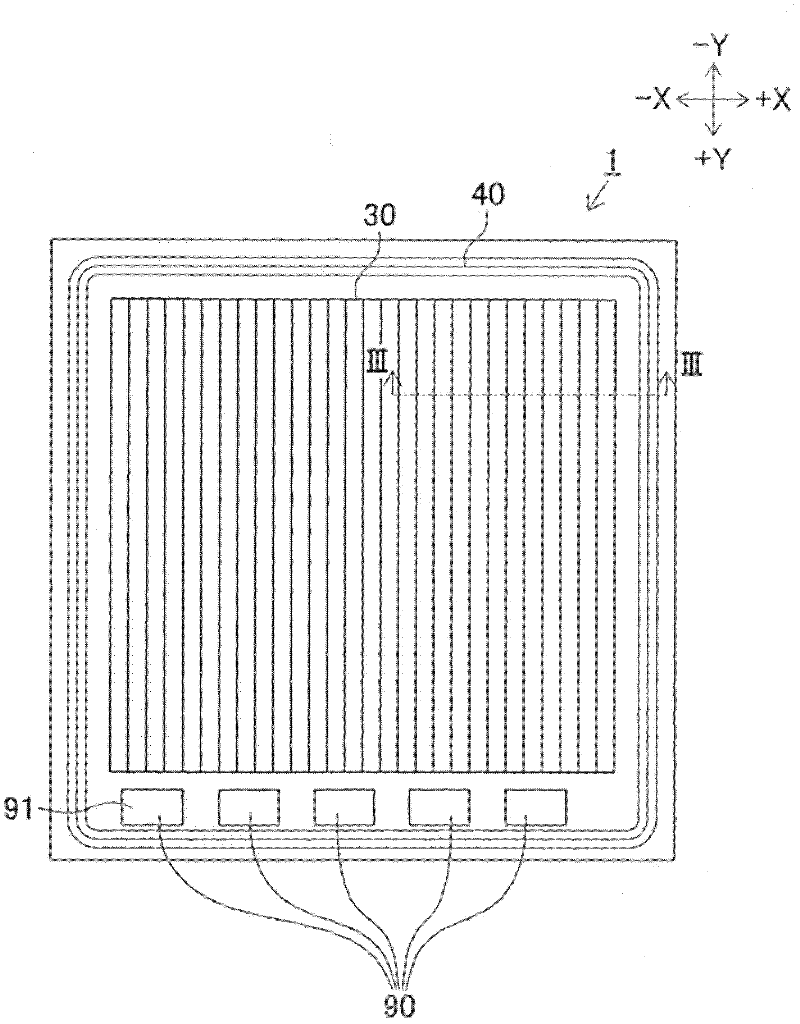

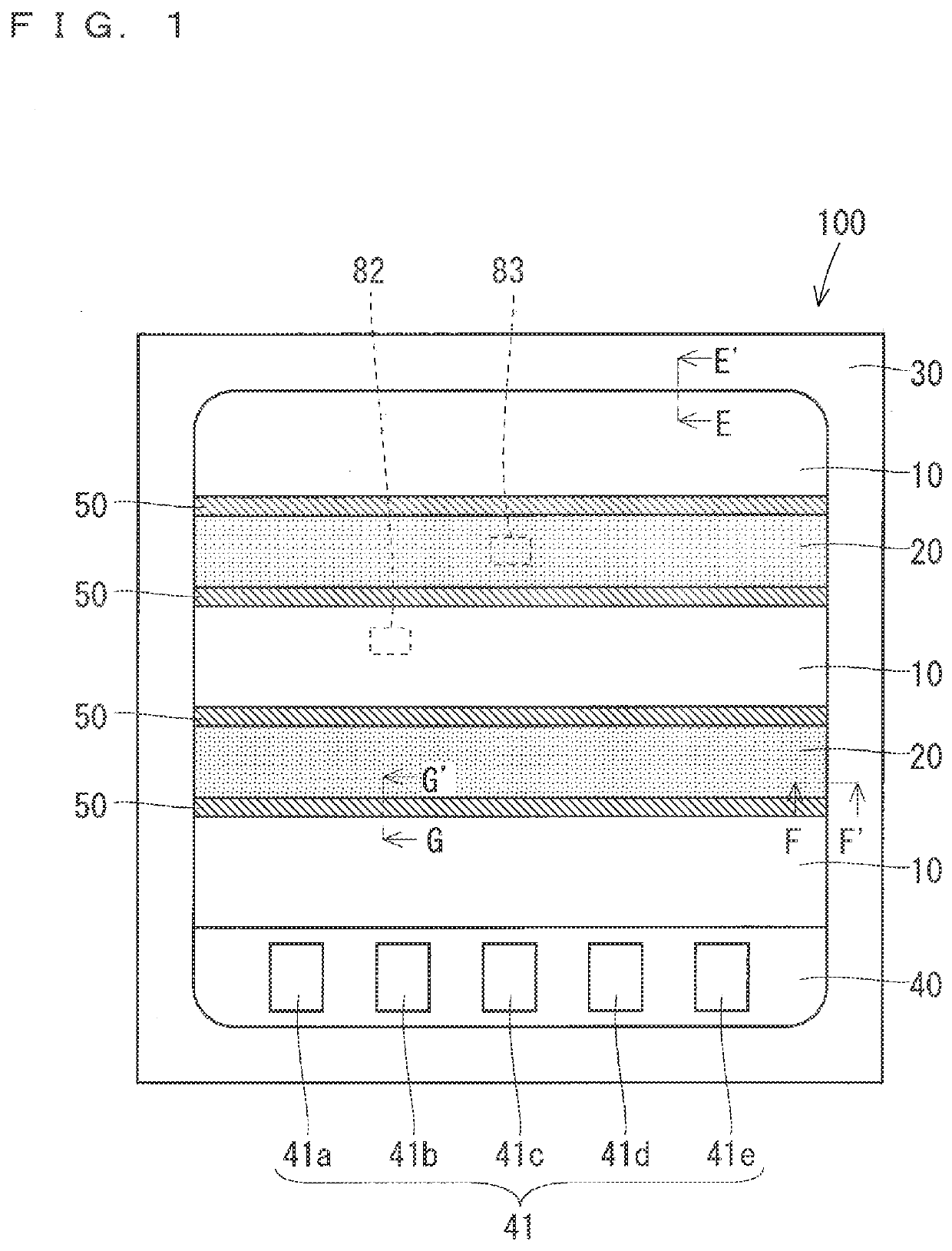

Provided is a semiconductor device, comprising semiconductor substrates (101, 210, 301, 401) and having a first surface and a second surface. The semiconductor substrate has element zones (30, 330, 430) composed of an IGBT zone (Xi) and a diode zone (Xf) arranged adjacent to the IGBT zone. An IGBT element (100) is formed in the IGBT zone. A diode element (20) is formed in the diode zone. The heavily doped zones (40, 208, 340, 440) of the first conduction type are located upon the first surface side around the element zone. The absorption zones (22, 222, 322, 422, 522) of the first conduction type are located upon the second surface side around the element zone. The third conductor zone (523) of the second conduction type are located upon the second surface side around the element zone.

Owner:DENSO CORP

Semiconductor device having IGBT and diode

ActiveUS7498634B2Sufficient performanceSufficient surge withstand voltageTransistorDiodeSemiconductorSemiconductor device

Owner:DENSO CORP

Semiconductor device having IGBT and diode

ActiveCN101000911ASufficient IGBT performanceSufficient surge withstand voltageSolid-state devicesSemiconductor devicesSemiconductorCathode

A semiconductor device includes: a substrate having a first side and a second side; an IGBT; and a diode. The substrate includes a first layer, a second layer on the first layer, a first side N region on the second layer, second side N and P regions on the second side of the first layer, a first electrode in a first trench for a gate electrode, a second electrode on the first side N region and in a second trench for an emitter electrode and an anode electrode, and a third electrode on the second side N and P regions for a collector electrode and a cathode. The first trench penetrates the first side N region and the second layer, and reaches the first layer. The second trench penetrates the first side N region, and reaches the second layer.

Owner:DENSO CORP

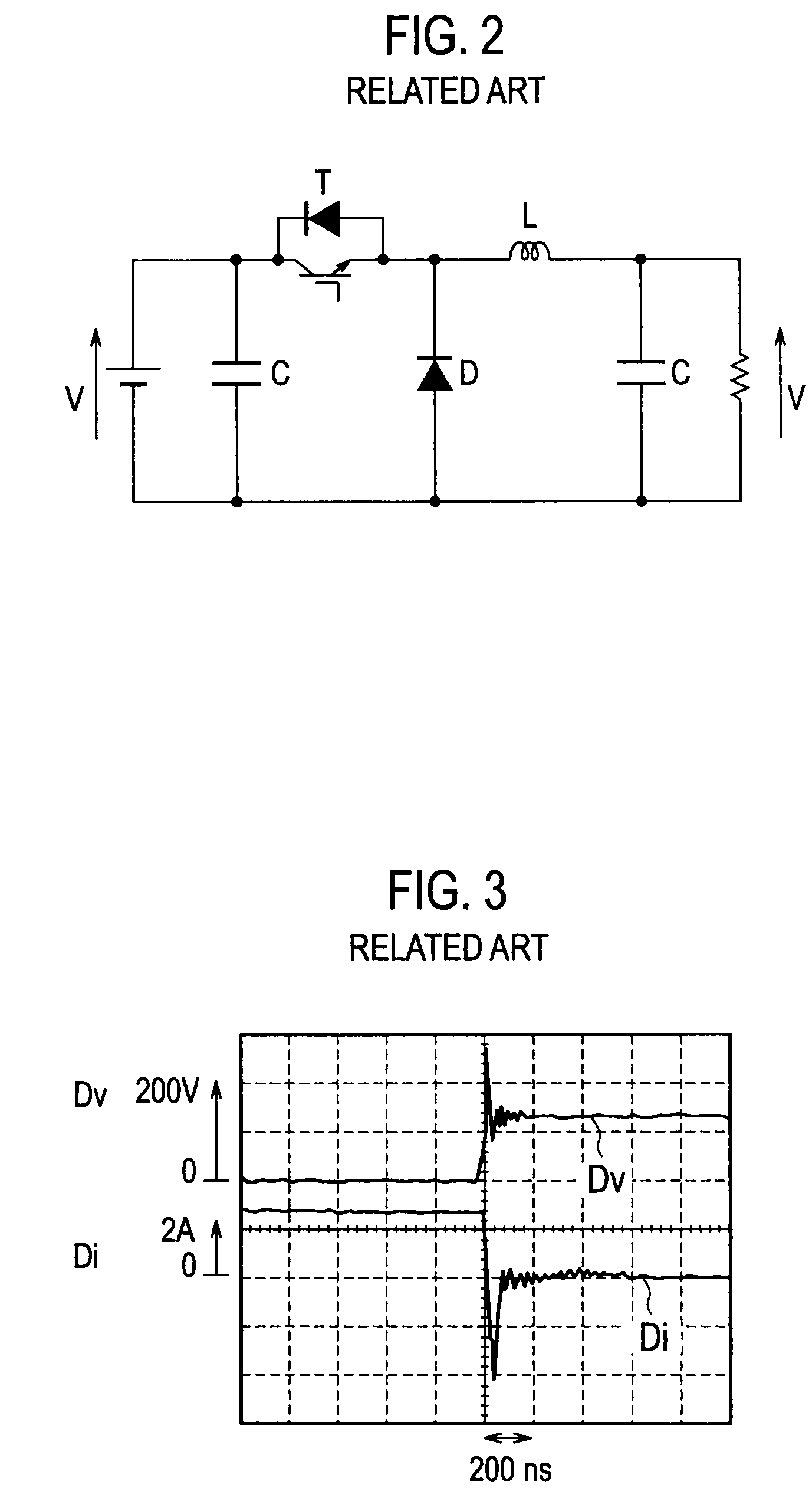

Diode and Power Conversion System

InactiveUS20140070379A1Improve breakdown voltageLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesDopantHigh concentration

A diode includes: a first semiconductor layer of a first conductive type; a second semiconductor layer of a second conductive type arranged adjoining to the first semiconductor layer; a third semiconductor layer of the first conductive type arranged on a side, opposite to the second semiconductor layer, of the first semiconductor layer, and contains a dopant of the first conductive type at a higher concentration than the first semiconductor layer; a first electrode ohmically connected to the second semiconductor layer; a second electrode ohmically connected to the third semiconductor layer; and a fourth semiconductor layer arranged at a position adjoining to the third semiconductor layer between the first and third semiconductor layers, contains a dopant of a type being the same as a type of the dopant of the first conductive type contained in the third semiconductor layer, and has a carrier lifetime shorter than the third semiconductor layer.

Owner:HITACHI POWER SEMICON DEVICE

Semiconductor device

ActiveUS10056450B2Improved recovery propertiesReduce conduction voltage dropTransistorConversion constructional detailsSemiconductorSemiconductor device

A semiconductor device includes a semiconductor substrate with: a drift layer; a base layer; and a collector layer and a cathode layer. In the semiconductor substrate, when a region operating as an IGBT device is an IGBT region and a region operating as a diode device is a diode region, the IGBT and diode regions are arranged alternately in a repetitive manner; a damaged region is arranged on a surface portion of the diode region in the semiconductor substrate. The IGBT and diode regions are demarcated by a boundary between the collector and cathode layers; and a surface portion of the IGBT region includes: a portion having the damaged region at a boundary side with the diode region; and another portion without the damaged region arranged closer to an inner periphery side relative to the boundary side.

Owner:DENSO CORP

Semiconductor device and power converter using it

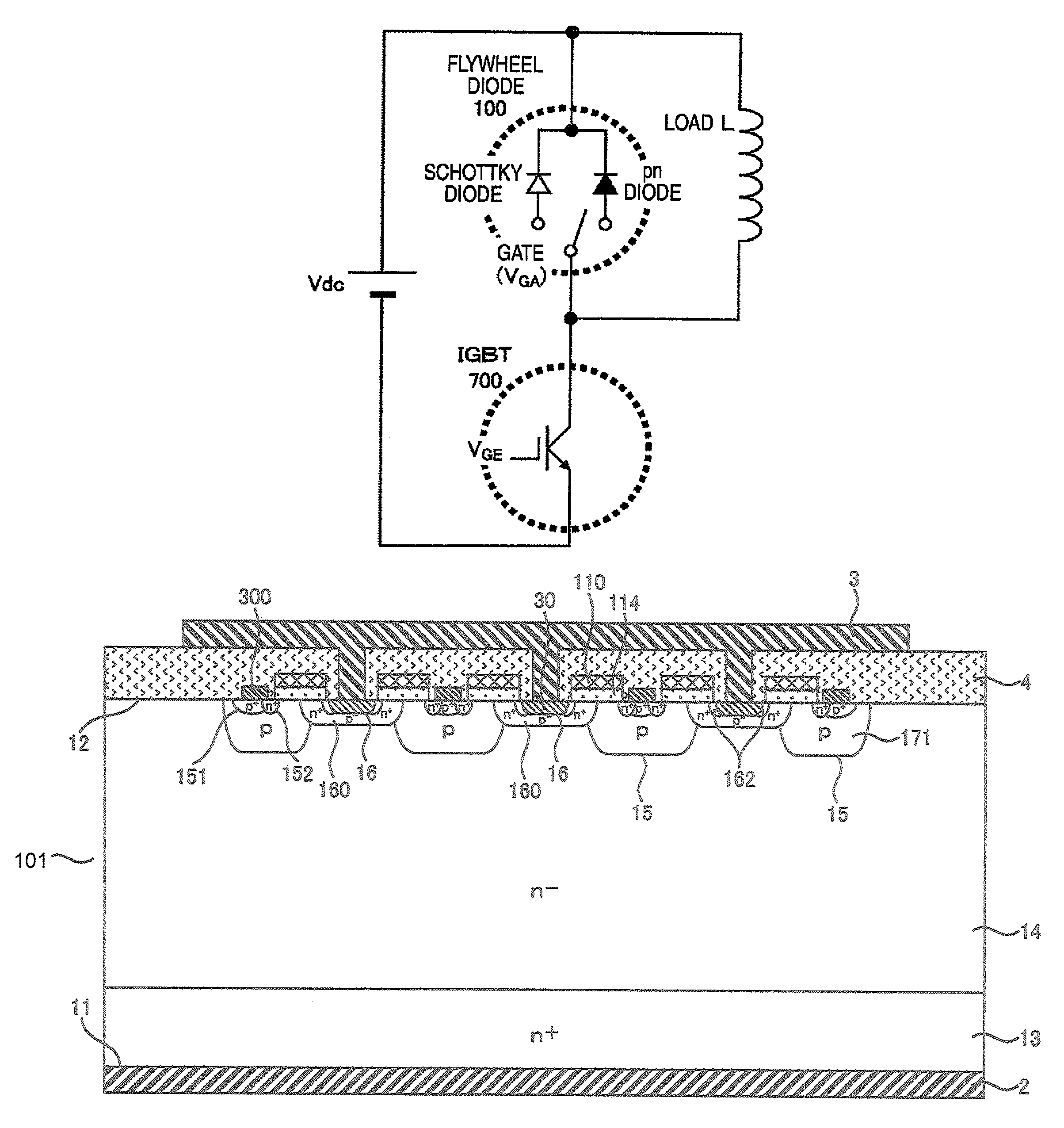

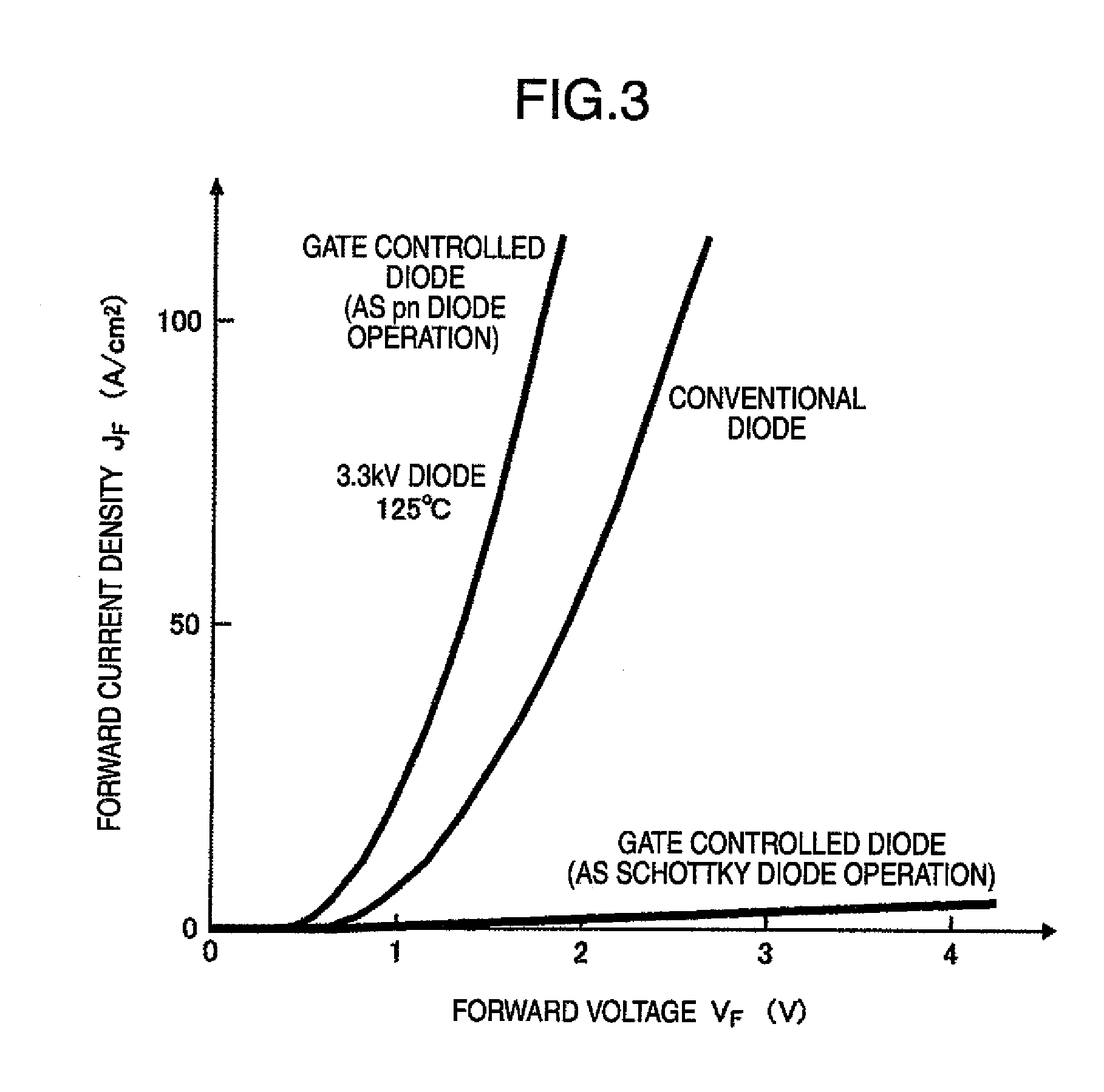

ActiveUS20110073905A1Lower forward voltage dropTotal current dropTransistorSolid-state devicesFlyback diodeSchottky diode

A semiconductor device and a power converter using it wherein a switching power device and a flywheel diode are connected in series, the flywheel diode includes a region having a Schottky junction to operate as a Schottky diode and a region having a pn junction to operate as a pn diode and control operation is performed such that when current flows forwardly through the flywheel diode, the pn diode operates and when the flywheel diode recovers backwardly, the Schottky diode operates mainly.

Owner:HITACHI LTD

Semiconductor device having IGBT and diode

InactiveUS7952143B2Reduce recovery lossIncrease the turn-on voltageTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSemiconductor

Owner:TOYOTA JIDOSHA KK

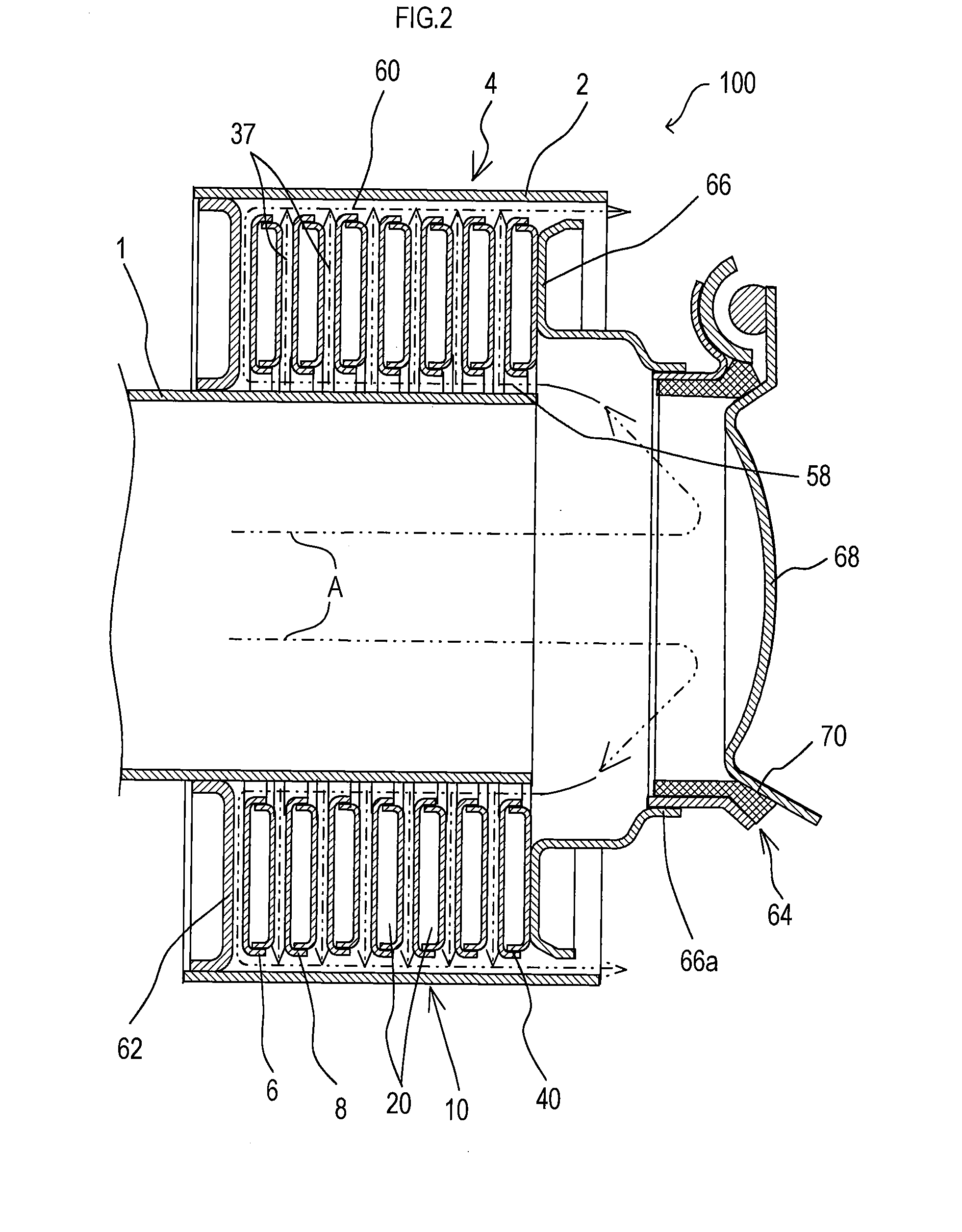

Exhaust gas heat recovery device

ActiveUS20140352286A1Improve efficiencyShort timeInternal combustion piston enginesRecuperative heat exchangersExhaust fumesProcess engineering

An exhaust gas heat recovery device of the present invention recovers heat of an exhaust gas from an internal combustion engine. The exhaust gas heat recovery device includes an exhaust pipe that leads the exhaust gas from an upstream side to a downstream side, a cylindrical shell that covers an outside of the exhaust pipe, and an exhaust gas heat recovery section that is interposed between the exhaust pipe and the cylindrical shell and that performs heat exchange between the exhaust gas and a heat exchange medium. The exhaust gas heat recovery section includes a stacked body that is composed by stacking a plurality of jacket each having a heat exchange medium conduit provided thereinside. In the stacked body, the respective heat exchange medium conduits in the plurality of jacket parts are serially connected to each other.

Owner:FUTABA IND CO LTD

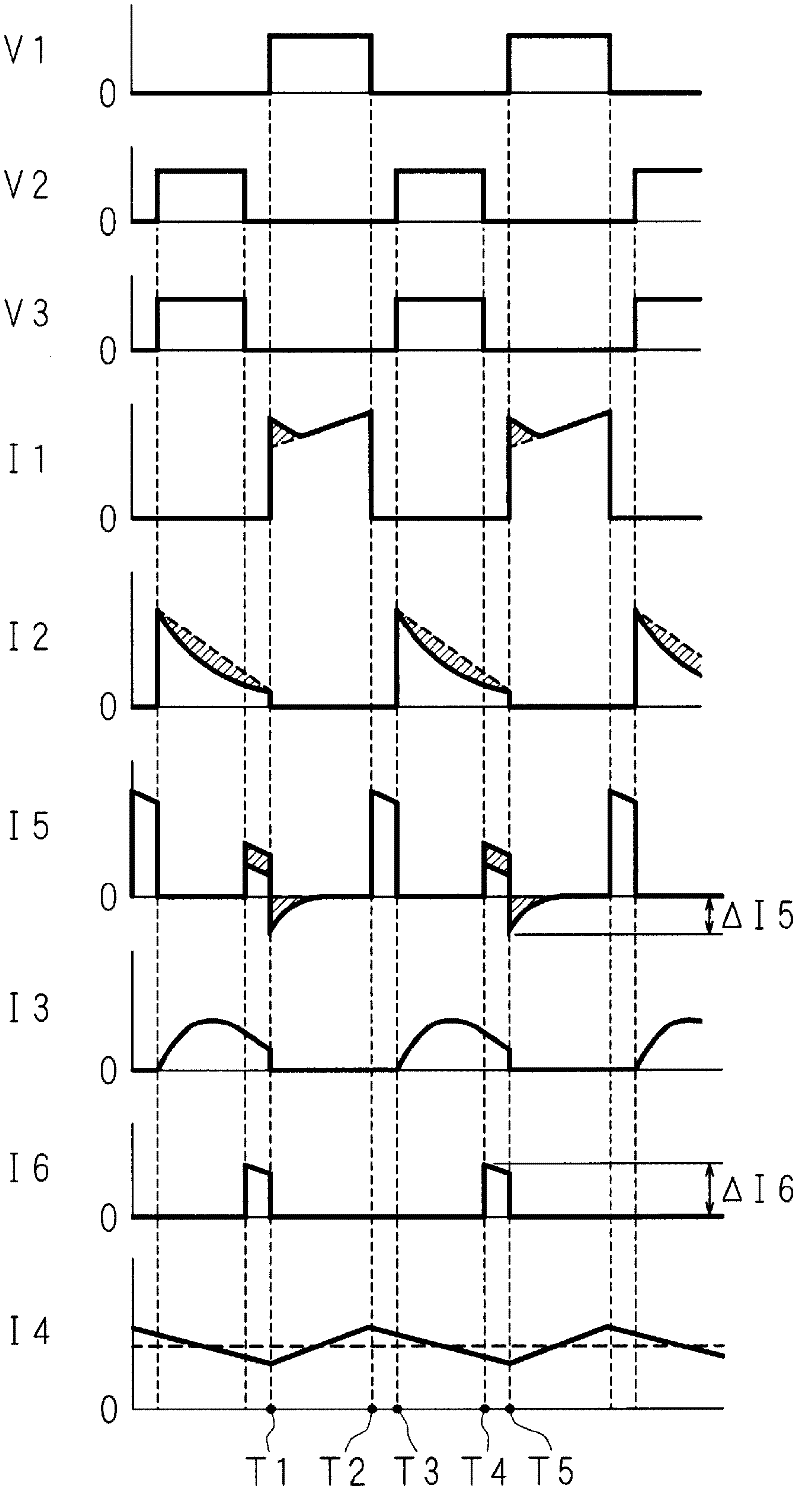

Bi-directional DC-DC converter

ActiveUS7638900B2Reduce recovery lossReduce lossesDc network circuit arrangementsDc-dc conversionDc dc converterEngineering

A bi-directional DC-DC converter includes a first series circuit connected to ends of a first DC power source and including a first winding of a first reactor and a first switch; a second series circuit connected to ends of the first switch and including a second winding of the first reactor, a second reactor, a second switch, a third switch, and a second DC power source; a third series circuit connected to the ends of the first switch and including a fourth switch and the second DC power source; and a control circuit configured to turn on / off the switches and thereby carry out step-up and step-down operations between the first and second DC power sources.

Owner:NAGOYA UNIVERSITY +1

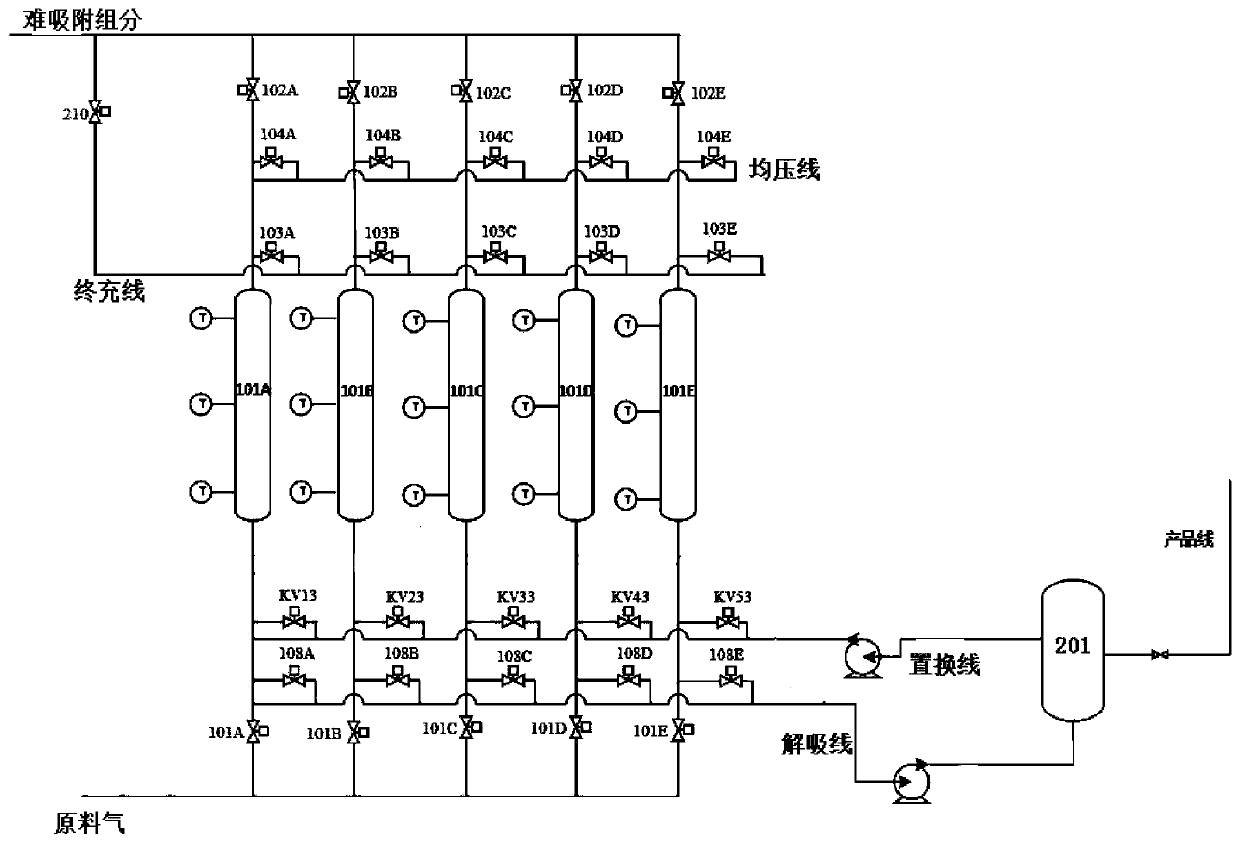

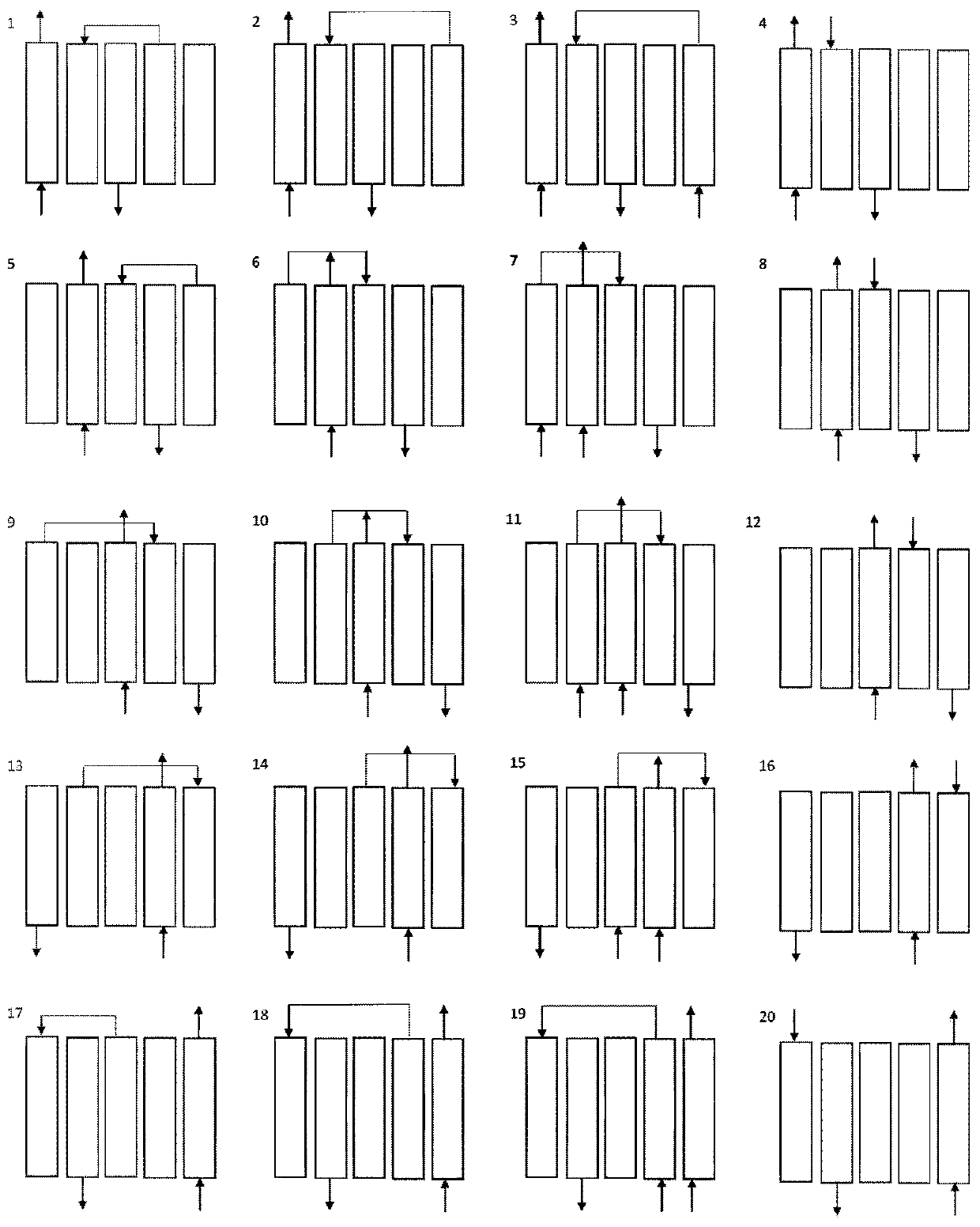

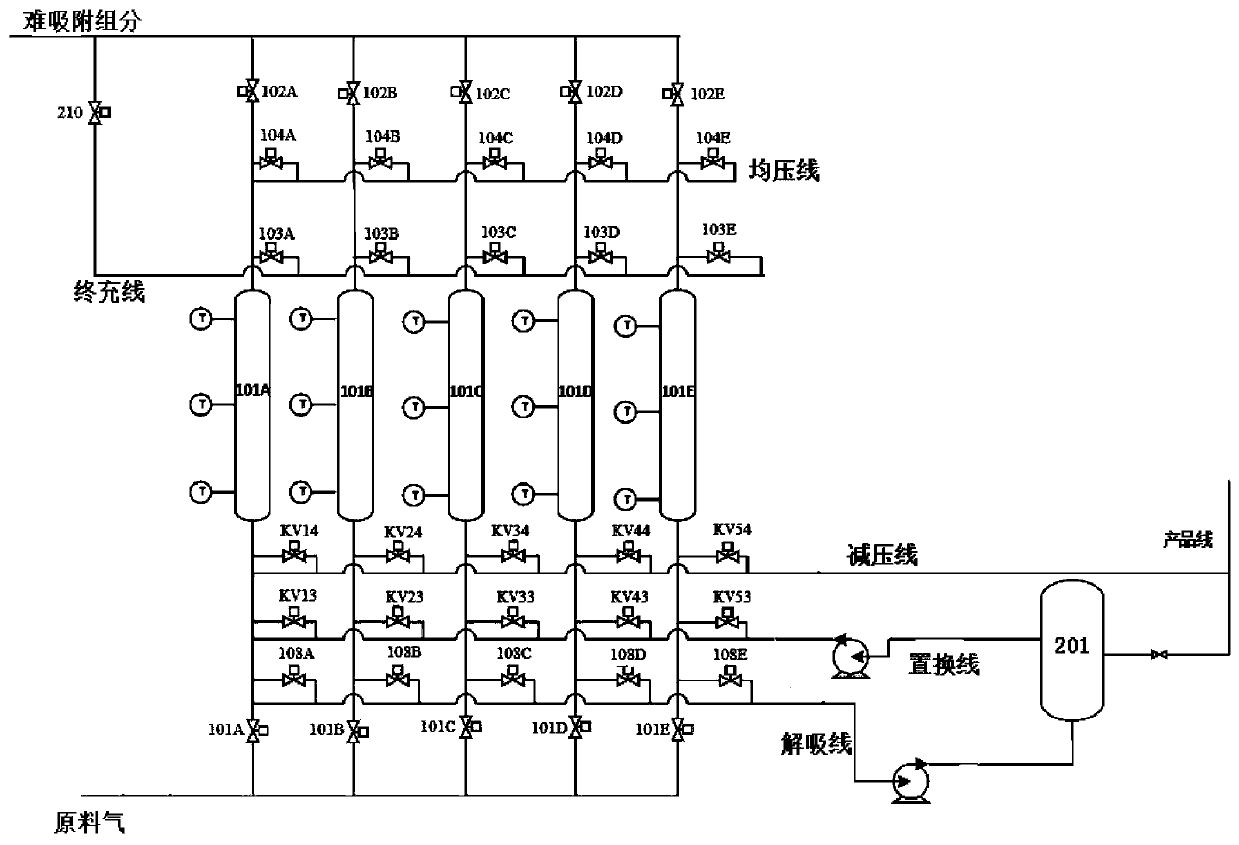

Method for increasing concentration of gas easy to adsorb by using pressure swing adsorption method

ActiveCN110354637ATo achieve mutual cooperationIncrease processing rateDispersed particle separationSorbentDesorption

The invention provides a method for increasing the concentration of a gas easy to adsorb by using a pressure swing adsorption method. The method comprises the following steps: (1) feeding a raw material gas into a first adsorption tower, and performing adsorption operation till an adsorbent is saturated; (2) performing pressure equalizing operation on a first adsorption tower after adsorption; (3)introducing a product gas into an unadsorbed gas for exchange, and blowing an exchanged gas into other adsorption towers; (4) performing pressure equalizing operation on the first adsorption tower after exchange for a second time; (5) performing vacuum desorption on the first adsorption tower so as to obtain a product gas; (6) pressurizing the first adsorption tower after desorption. Through theprocedures, multiple adsorption towers cooperate to achieve concentration increase of the gas easy to adsorb, particularly the product gas is adopted as an exchange gas, the exchanged gas is fed intoother adsorption towers, and pressure equalizing operation is implemented after exchange, so that not only is the exchange effect improved, but also the concentration and the recycling rate of a component easy to adsorb can be increased.

Owner:盖氏科技 +1

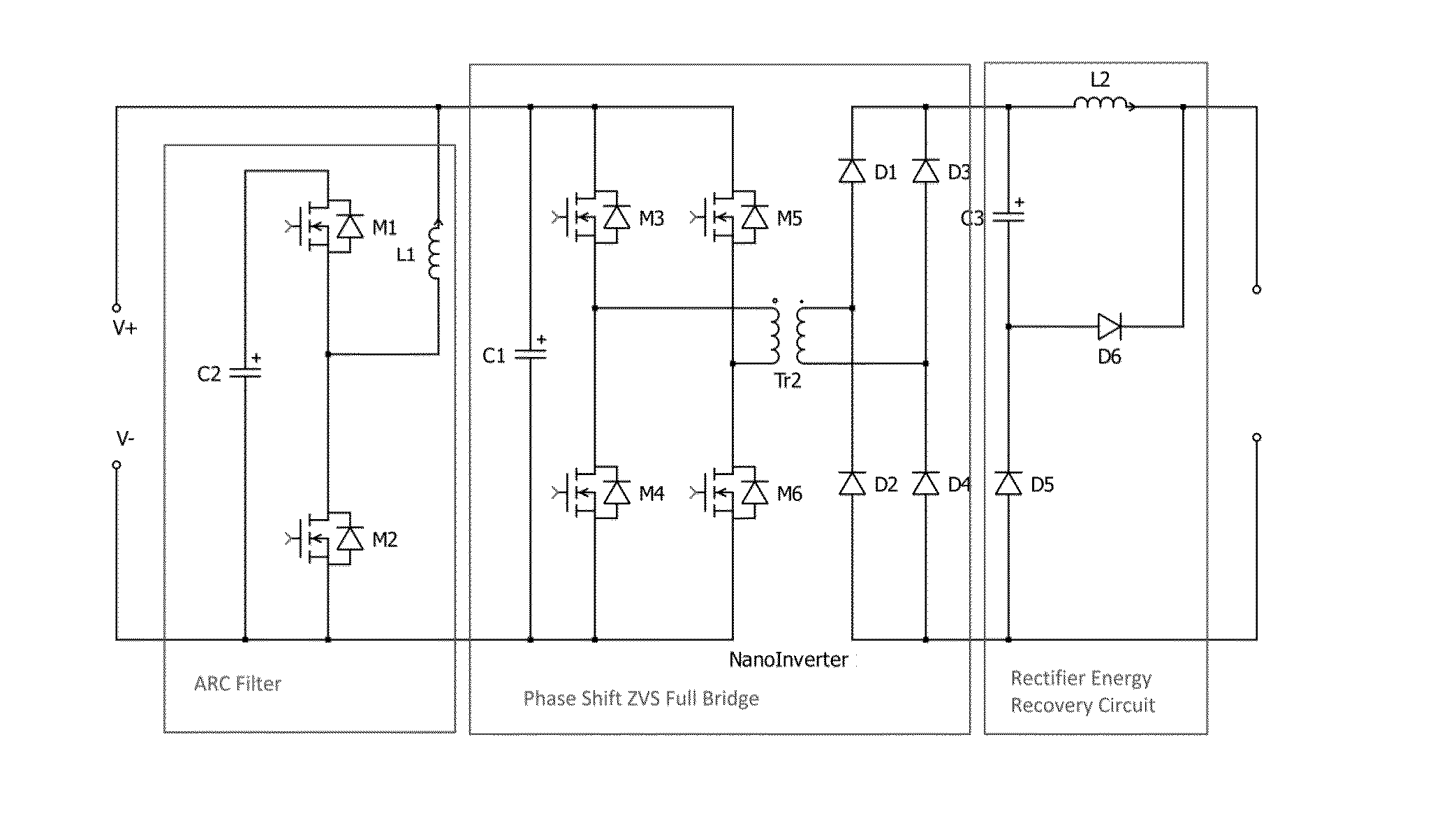

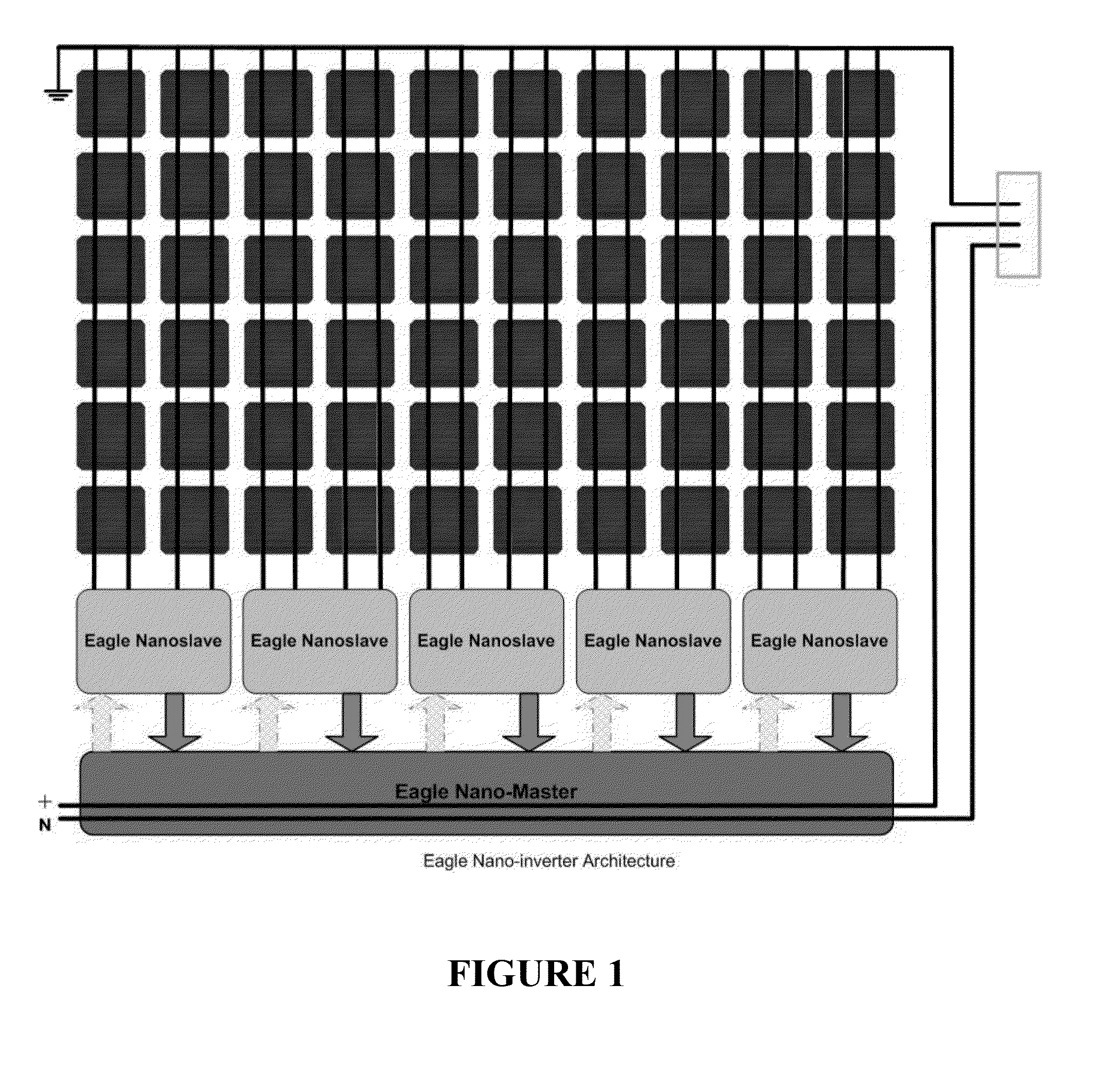

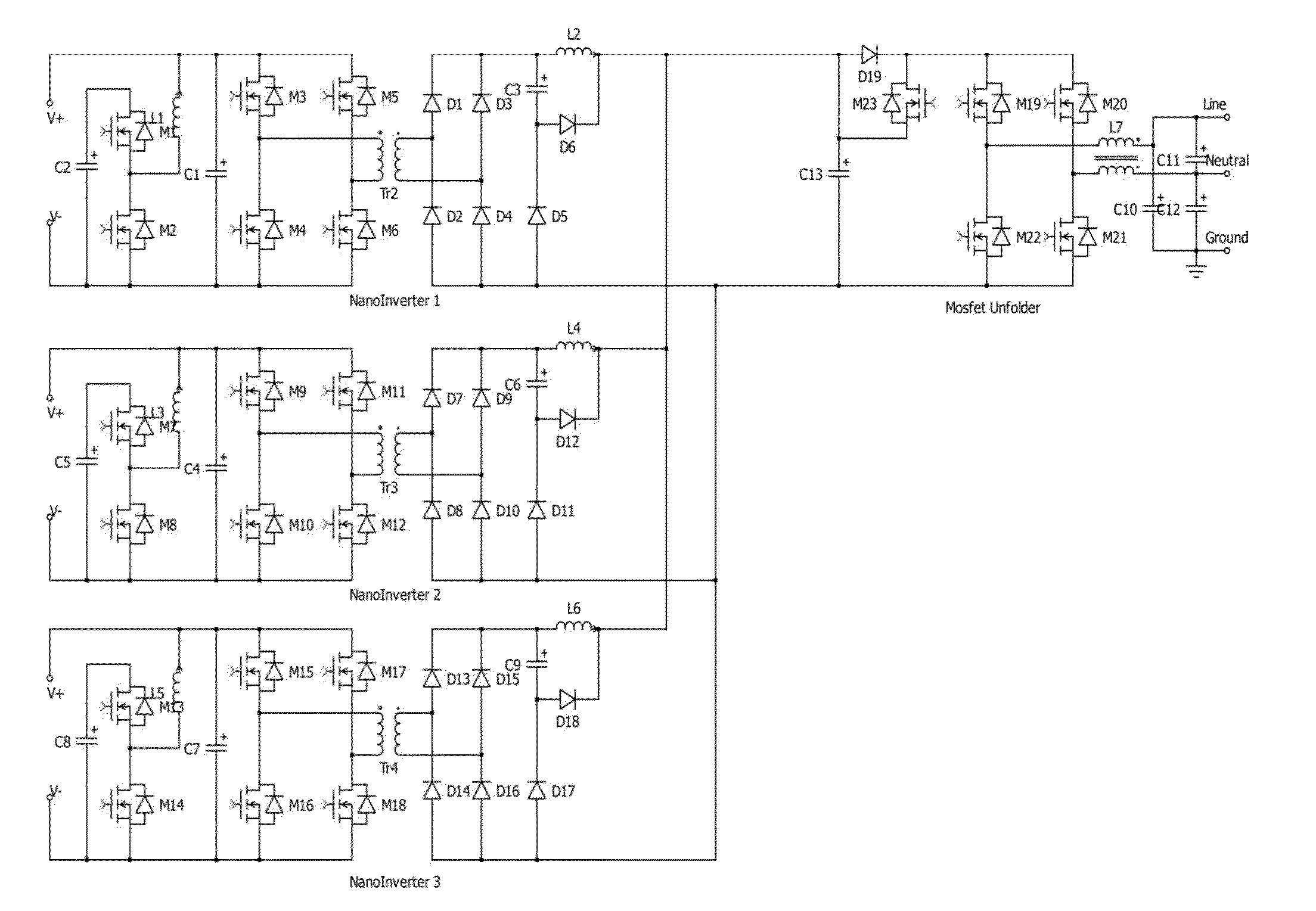

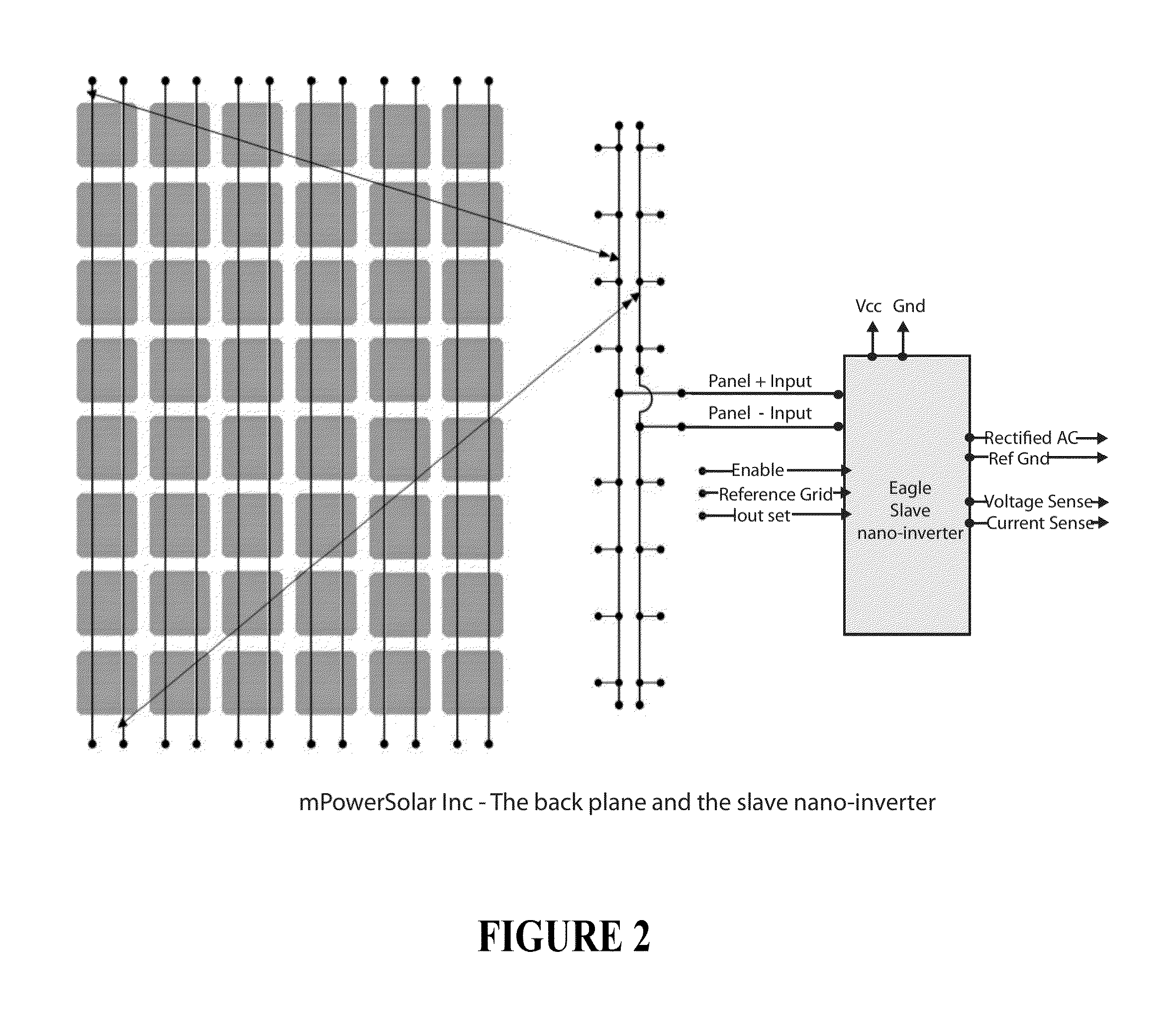

Slave circuit for distributed power converters in a solar module

ActiveUS20140119085A1Achieve benefitsReduce recovery lossEfficient power electronics conversionAc-dc conversionReverse recoveryEnergy recovery

An inverter device for a solar module. The inverter device comprises a slave circuit device that includes an input comprising a DC input from a solar cell group and a preliminary boost circuit. A DC boost circuit is coupled to the preliminary boost circuit and configured to boost the intermediary voltage to an AC RMS peak voltage. A rectifier circuit is coupled to the DC boost circuit. An energy recovery circuit comprises a storage device coupled to the rectifier output. The energy recovery circuit is configured to temporarily store a reverse recovery charge and transfers the reverse recovery charge to an output of a DC bus structure to reduce a diode recovery loss in the rectifier circuit.

Owner:SUNEDISON MICROINVERTER PROD

Diode and power conversion system

Owner:HITACHI POWER SEMICON DEVICE

Dc-dc converter, module, power supply device and electronic apparatus

InactiveCN102460924AReduce recovery lossEfficient power electronics conversionSolid-state devicesMicrochiropteraPower flow

A controller CT1 switches on a first switch SW1, and the direct-current voltage given from a power source BAT flowing through a first inductor L1 is smoothed by a capacitor C1 and is output from an output terminal OUT1. After a specified period of time has elapsed since the first switch SW1 was turned off by the controller CT1, the second switch SW2 and the third switch SW3 are turned on approximately at the same time. The electric current which was flowing through the first inductor L1 is branched into the second switch SW2 and the third switch SW3, and the electric current flowing through the parasitic diode Dp1 of the second switch SW2 is reduced. As a result, when the second switch SW2 is turned off, the recovery current flowing through the parasitic diode Dp1 is reduced.

Owner:FUJITSU LTD

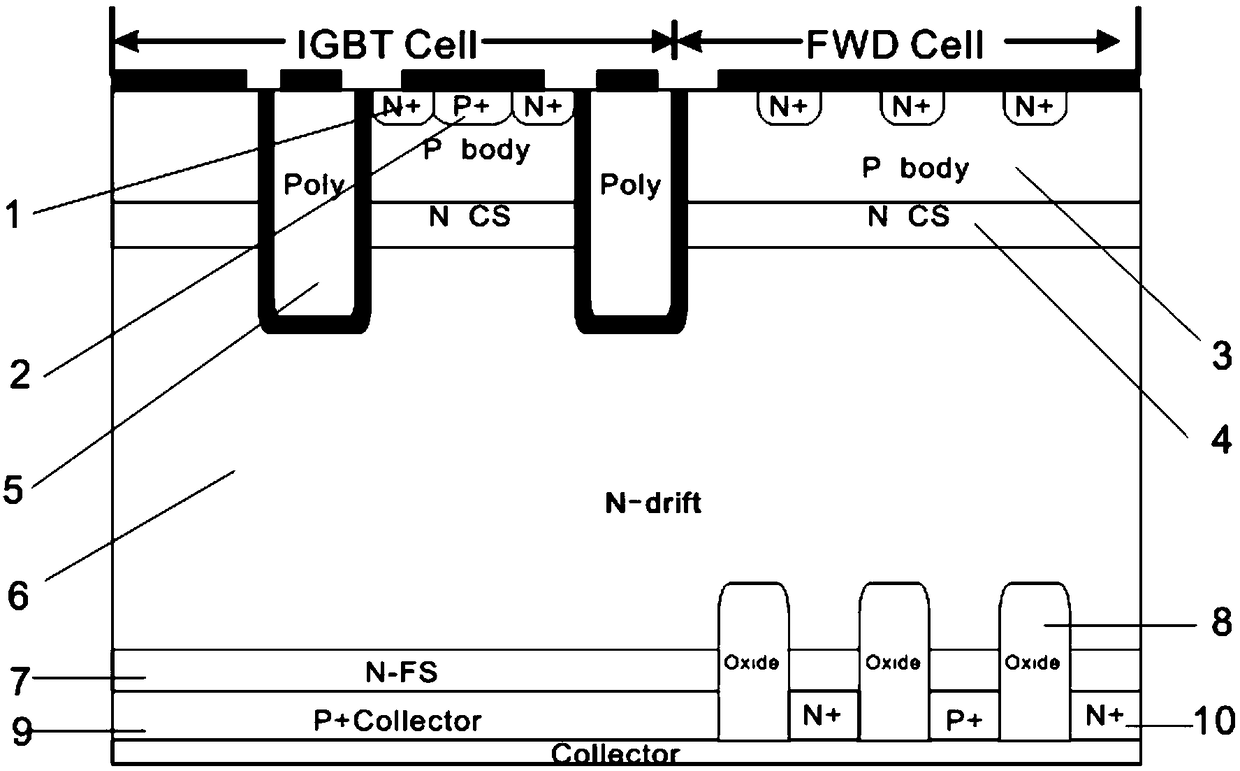

Oxide tank alternating isolation type insulated gate bipolar transistor and a preparation method thereof

ActiveCN109256423AEliminate the Snapback problemIncrease potential differenceTransistorSolid-state devicesEngineeringBody region

The invention discloses an oxide tank alternating isolation type insulated gate bipolar transistor, comprising N + emitter regions sequentially arranged from top to bottom, and P1 emitter areas sequentially arranged from top to bottom, P2 emitter regions sequentially arranged from top to bottom. Body, a N- CS Carrier Storage Area, an N-aDrift drift area , an N-FS field cut-off area and a P +collector area ; The N + emitter region located in the middle of the transistor is provided with a gate area and the P + emitter area located in the middle of the transistor is provided with a gate area.The upper surface of the body region has a P + emitter area spaced apart from the N + emitter area, and the NThe lower surface of the FS field cutoff area is also provided with an N + collector area,The N + collector areais spaced apart from the P + collector area located at the edge of the transistor, and an oxidation groove is formed between the P + collector area near the edge of the transistor and the N + collector area. The transistor of the invention can reduce the recovery loss while eliminating the Snapback phenomenon by optimizing the design of a plurality of places.

Owner:XIAN UNIV OF TECH

Semiconductor device manufacturing method

ActiveCN109997215AReduce lossReduce recovery lossTransistorSemiconductor/solid-state device manufacturingMOSFETLattice defects

A semiconductor device manufacturing method of the present invention is characterized by comprising, in this order: a MOS structure forming step of forming a gate electrode on a first major surface side of a semiconductor substrate with a gate insulating film interposed therebetween, and then forming an interlayer insulating film so as to cover the gate electrode; a metal layer forming step of forming, over the interlayer insulating film, a metal layer in a state of being connected to the gate electrode; an electron beam irradiating step of irradiating the semiconductor substrate with an electron beam in a state in which the metal layer is at ground potential, to thereby generate a lattice defect in the semiconductor substrate; a metal layer dividing step of dividing the metal layer into aplurality of electrodes; and an anneal processing step of heating the semiconductor substrate to repair the lattice defect in the semiconductor substrate. In a MOSFET according to the present invention, a parasitic internal diode recovery loss can be reduced compared with when the electron beam irradiating step is not implemented, and the semiconductor device manufacturing method provided makes it possible to manufacture a semiconductor device having a VTH characteristic comparable to that when the electron beam irradiating step is not implemented.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

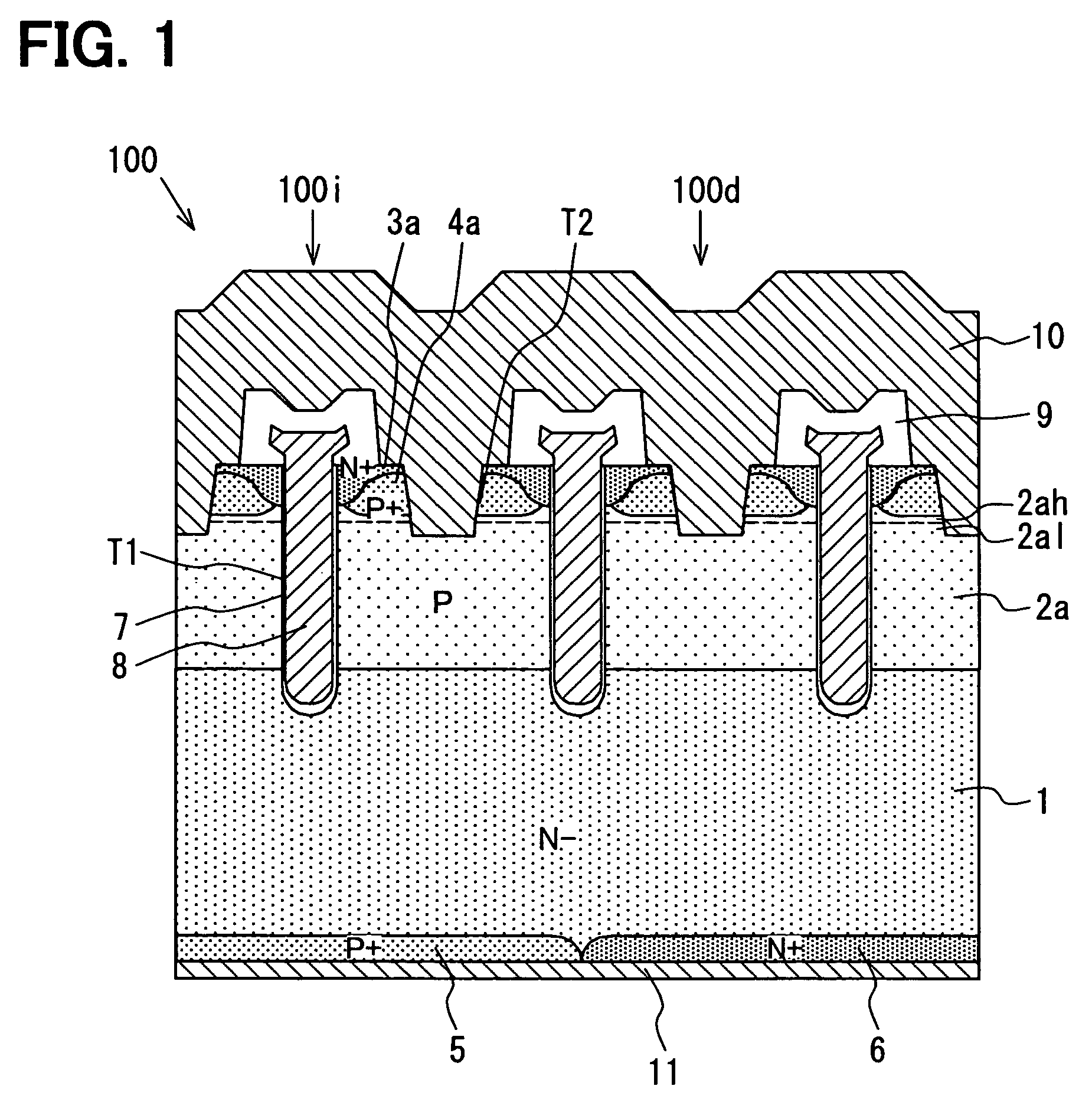

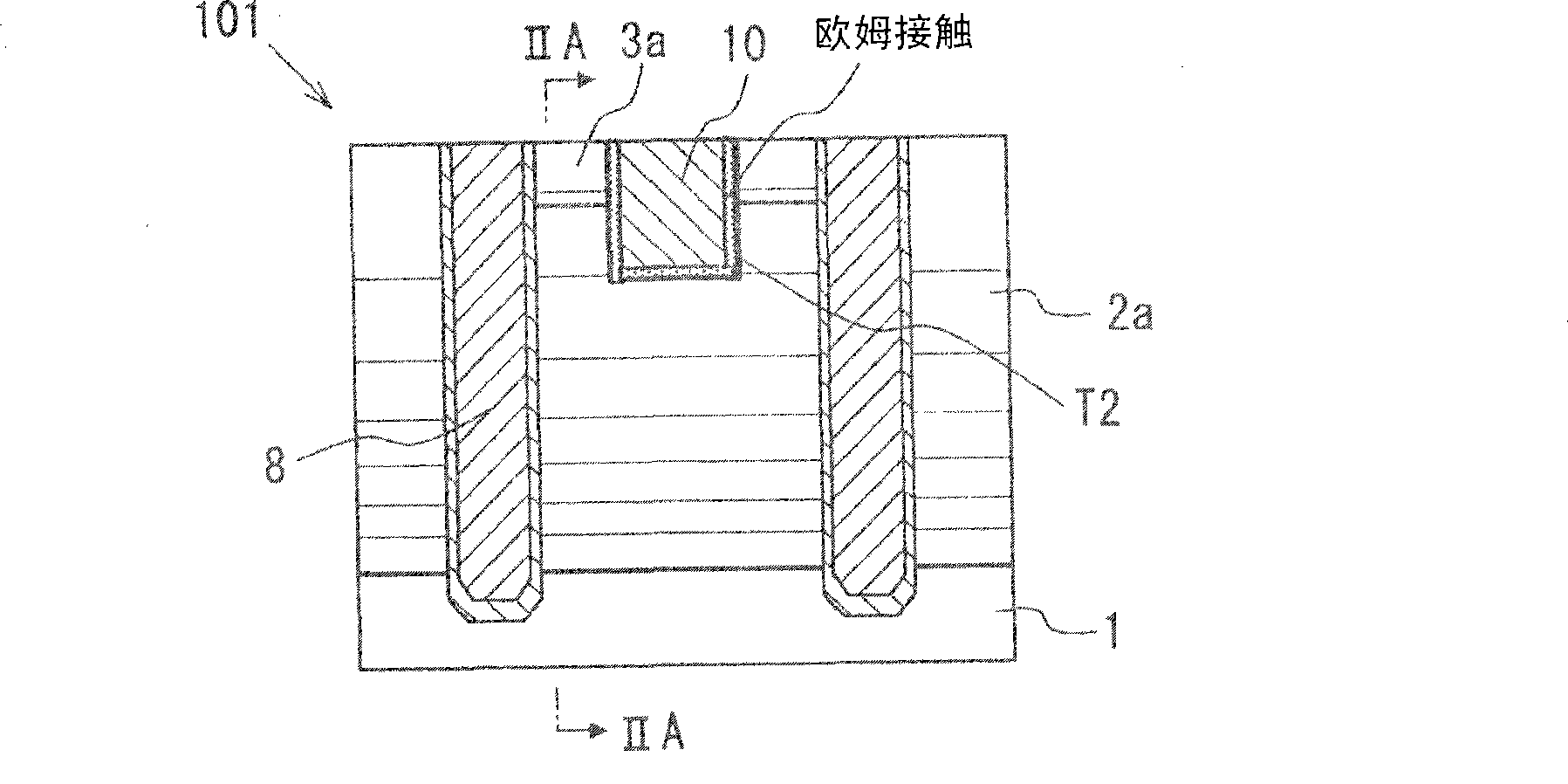

Semiconductor device having IGBT and diode

ActiveCN100521207CSufficient IGBT performanceSufficient surge withstand voltageSolid-state devicesSemiconductor devicesSemiconductorSemiconductor device

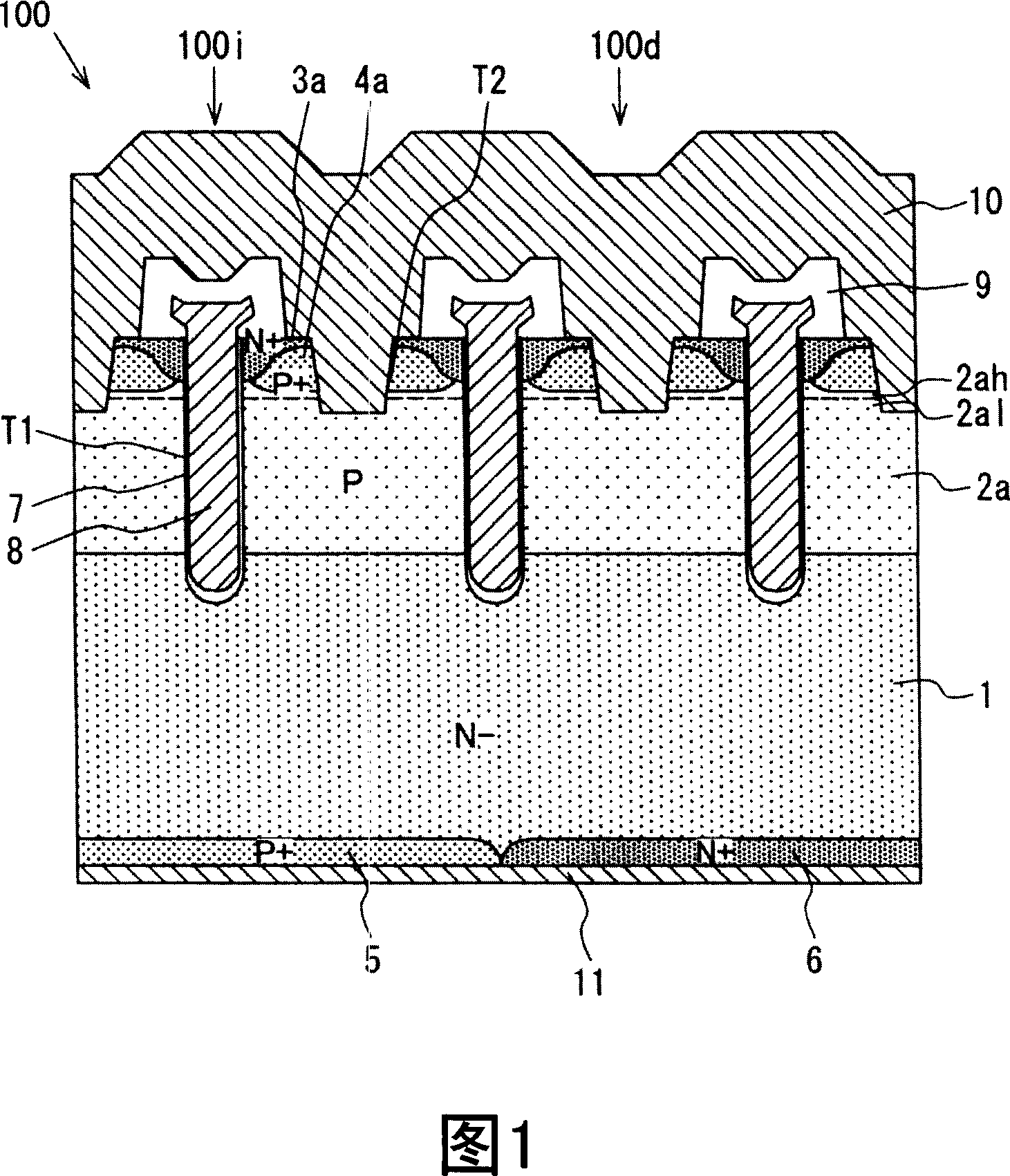

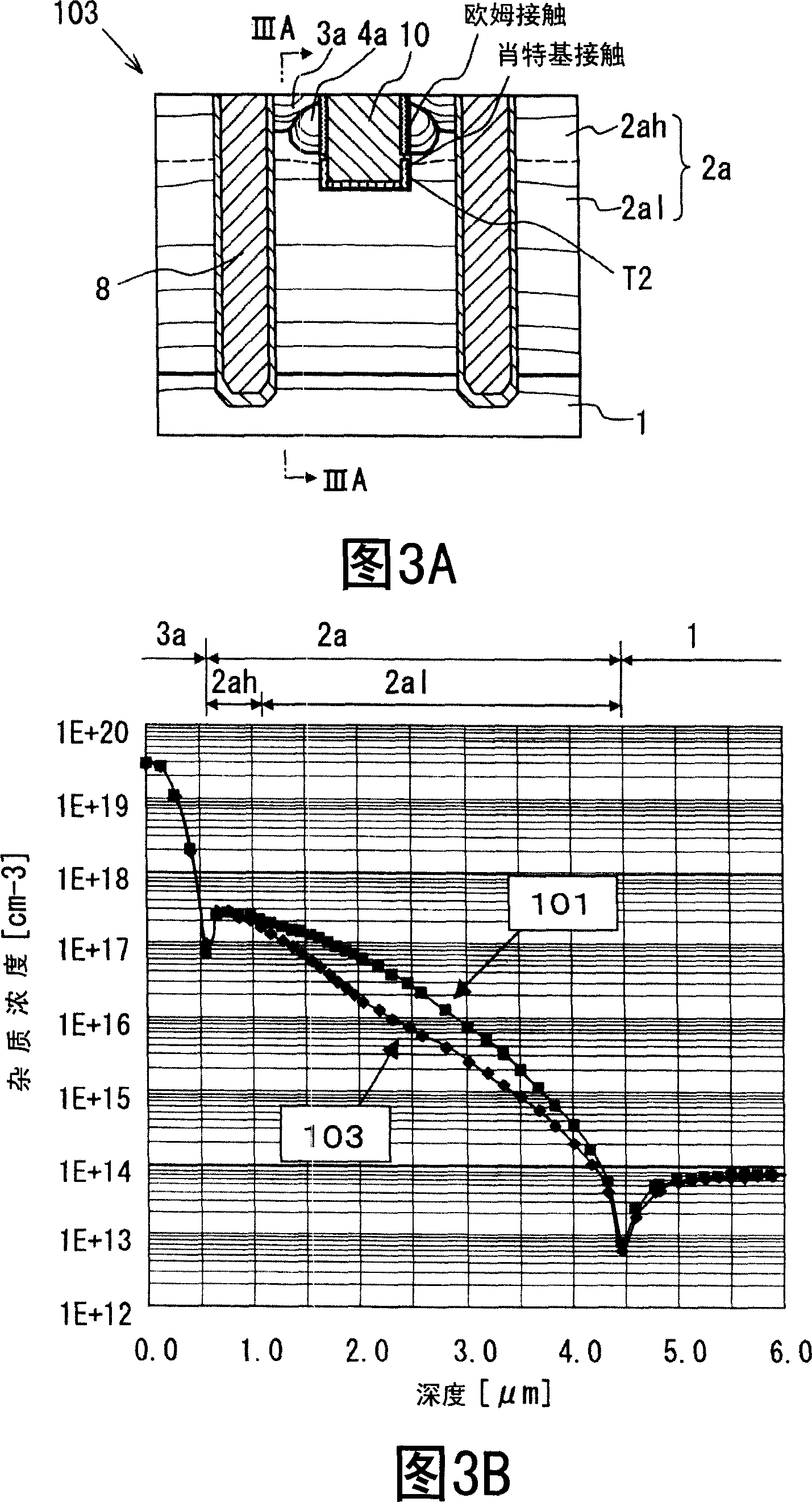

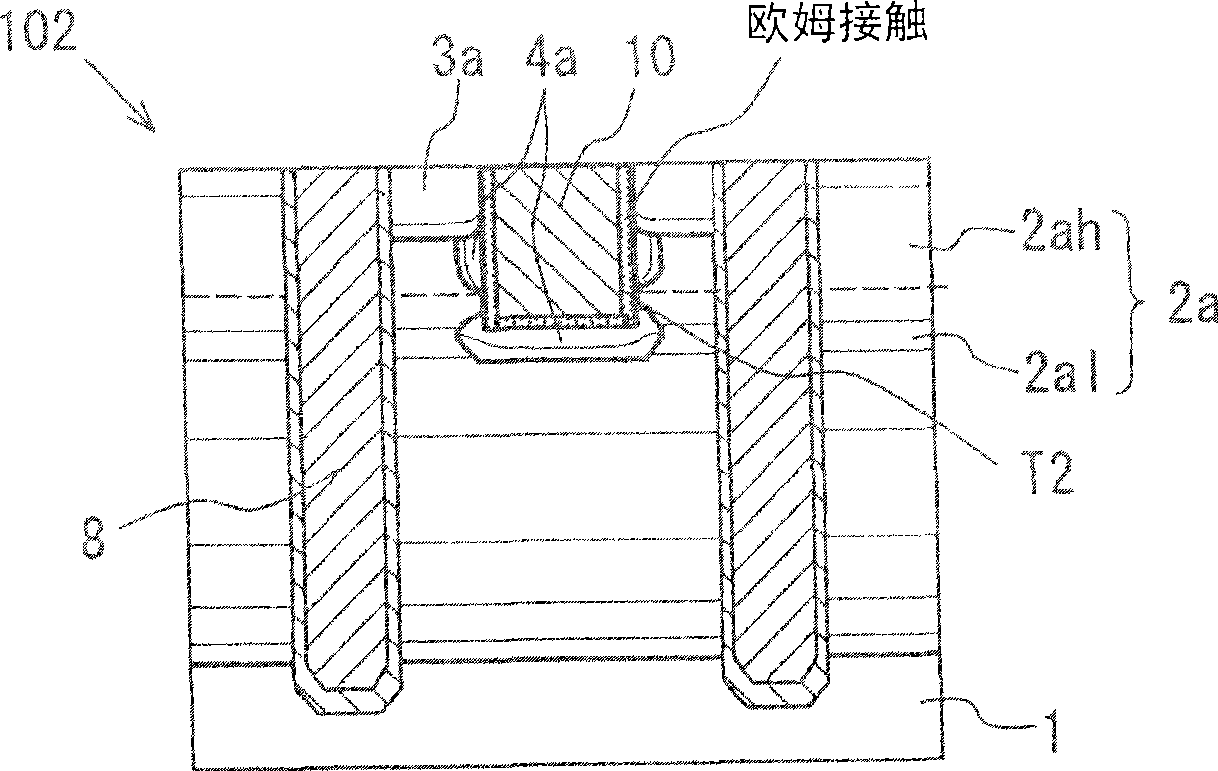

A semiconductor device comprising: a substrate (1, 1a, 2a, 2b, 3a, 4a, 5, 6, 8, 10, 11, T1, T2) having a first side and a second side; an IGBT (100i, 104i , 105i); and diodes (100d, 104d, 105d). The substrate (1, 1a, 2a, 2b, 3a, 4a, 5, 6, 8, 10, 11, T1, T2) comprises: a first layer (1); a second layer ( 2a); the N region (3a) on the first side on the second layer (2a); the N region and the P region (5, 6) on the second side, located on the second side of the first layer (1); the first The first electrode (8) in the trench (T1) serves as a gate; the second electrode (10) is located on the N region (3a) on the first side and in the second trench (T2) and serves as an emitter and an anode; and a third electrode (11), located on the N and P regions (5, 6) on the second side, serving as a collector and a cathode. The first trench (T1) passes through the N region (3a) on the first side and the second layer (2a), and reaches the first layer (1). The second trench (T2) passes through the N region (3a) on the first side and reaches the second layer (2a).

Owner:DENSO CORP

Semiconductor device

In plan view of an RC-IGBT, a boundary region has an occupancy rate of an n+-type source layer per unit area, the occupancy rate being smaller than an occupancy rate of the n+-type source layer per unit area in an IGBT region, and the boundary region has an occupancy rate of a p+-type contact layer per unit area, the occupancy rate being smaller than an occupancy rate of the p+-type contact layer per unit area in an IGBT region.

Owner:MITSUBISHI ELECTRIC CORP

Method for treating lithium ion battery waste

PendingUS20200263276A1Excessive wasteReduce recovery lossWaste processingTransportation and packagingSmelting processPhysical chemistry

A method for treating a lithium ion battery waste according to the present invention is a method for treating a lithium ion battery waste using a converter furnace in a copper smelting process, wherein, prior to a treatment for charging a copper mat produced in a flash smelter in a copper smelting process into a converter furnace and blowing oxygen into the converter furnace to produce crude copper, the lithium ion battery waste is introduced into the converter furnace or a ladle that is used for the charging of the copper mat into the converter furnace and then the lithium ion battery waste is burned with residual heat in the converter furnace or the ladle.

Owner:SUMITOMO METAL MINING CO LTD

Semiconductor device

InactiveCN107112324AReduce recovery lossDoes not make loss worseTransistorSolid-state devicesPower semiconductor deviceImpurity

An IGBT 1 has: an n type drift layer 5; a p type base layer 6 and an n type emitter layer 7, which are formed on the front surface of the n type drift layer 5; and a p type collector layer 8 formed on the rear surface of the n type drift layer 5. An FWD 2 has: the n type drift layer 5; a p type anode layer 10 formed on the front surface of the n type drift layer 5; and an n type cathode layer 11 formed on the rear surface of the n- type drift layer 5. In a wiring region 3 and a terminal region 4, a p type well 12 is formed in the front surface of the n- type drift layer 5. In the wiring region 3, wiring 13 is formed on the p type well 12. The p type well 12 has a higher impurity concentration and more depth compared with the p type anode layer 10. The p type well 12 is not formed directly above the n type cathode layer 11, and is separated from a region directly above the n type cathode layer 11.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device and power converter using it

ActiveUS8853736B2Lower forward voltage dropTotal current dropTransistorSolid-state devicesFlyback diodeSchottky diode

A semiconductor device and a power converter using it wherein a switching power device and a flywheel diode are connected in series, the flywheel diode includes a region having a Schottky junction to operate as a Schottky diode and a region having a pn junction to operate as a pn diode and control operation is performed such that when current flows forwardly through the flywheel diode, the pn diode operates and when the flywheel diode recovers backwardly, the Schottky diode operates mainly.

Owner:HITACHI LTD

Semiconductor device having crystal defects and method of manufacturing the semiconductor device having crystal defects

ActiveUS10818496B2Reduce the amount requiredFast switching speedSemiconductor/solid-state device manufacturingDiodeMOSFETDevice material

A MOSFET includes: a semiconductor base substrate having n-type column regions and p-type column regions, the n-type column regions and the p-type column regions forming a super junction structure; and a gate electrode which is formed on a first main surface side of the semiconductor base substrate by way of a gate insulation film, wherein crystal defects whose density is increased locally as viewed along a depth direction are formed in the n-type column regions and the p-type column regions, using the first main surface as a reference and assuming a depth to a deepest portion of the super junction structure as Dp, a depth at which density of the crystal defects exhibits a maximum value as Dd, and a half value width of density distribution of the crystal defects as W, a relationship of 0.25Dp≤Dd<0.95Dp and a relationship of 0.05Dp<W<0.5Dp are satisfied.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

Power semiconductor device

ActiveUS7244969B2Reduce recovery lossDegree of reductionThyristorDiodePower semiconductor deviceImpurity diffusion

A power semiconductor device comprises a semiconductor substrate, a gate electrode region (control electrode region), a cathode electrode region (first main electrode region), an anode electrode region (second main electrode region) and a guard ring. The semiconductor substrate has a side surface portion having a vertical portion formed substantially vertical to a main surface and a mesa portion connected to the vertical portion in a cross section. The gate electrode region is formed in a first main surface of the semiconductor substrate. The cathode electrode region is formed in part of a surface of the gate electrode region. The anode electrode region is formed in a second main surface of the semiconductor substrate. The guard ring is formed in the second main surface of the semiconductor substrate and annularly surrounds the anode electrode region. With this constitution provided is a power semiconductor device which makes the impurity diffusion length of the anode electrode region shallower in order to ensure reduction in recovery loss.

Owner:MITSUBISHI ELECTRIC CORP

Reverse conduction semiconductor device and method for manufacturing reverse conduction semiconductor device

PendingCN114388610AReduce manufacturing costHigh latch-up toleranceSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialContact layer

The invention relates to a reverse conducting semiconductor device and a manufacturing method of the reverse conducting semiconductor device. Provided is a reverse-conducting semiconductor device having high latch-up tolerance and low recovery loss while avoiding a significant increase in manufacturing cost. The semiconductor substrate (50) has a first main surface (F1) and a second main surface (F2). The base contact layer (14) is disposed between the base layer (15) and the first main surface (F1) and constitutes a part of the first main surface (F1). The anode contact region (24) is disposed between the anode layer (25) and the first main surface (F1), constitutes a part of the first main surface (F1), and has a second conductivity-type impurity concentration peak higher than that of the anode layer (25). The anode contact region (24) includes a first anode contact layer (24b) having a lower net concentration than the base contact layer (14) and a higher first conductivity type impurity concentration than the base contact layer (14).

Owner:MITSUBISHI ELECTRIC CORP

Power semiconductor device

ActiveUS20060151805A1Reduce recovery lossDegree of reductionThyristorDiodePower semiconductor deviceImpurity diffusion

A power semiconductor device comprises a semiconductor substrate, a gate electrode region (control electrode region), a cathode electrode region (first main electrode region), an anode electrode region (second main electrode region) and a guard ring. The semiconductor substrate has a side surface portion having a vertical portion formed substantially vertical to a main surface and a mesa portion connected to the vertical portion in a cross section. The gate electrode region is formed in a first main surface of the semiconductor substrate. The cathode electrode region is formed in part of a surface of the gate electrode region. The anode electrode region is formed in a second main surface of the semiconductor substrate. The guard ring is formed in the second main surface of the semiconductor substrate and annularly surrounds the anode electrode region. With this constitution provided is a power semiconductor device which makes the impurity diffusion length of the anode electrode region shallower in order to ensure reduction in recovery loss.

Owner:MITSUBISHI ELECTRIC CORP

Slave circuit for distributed power converters in a solar module

ActiveUS9356537B2Reduce recovery lossLess costlyEfficient power electronics conversionAc-dc conversionReverse recoveryComputer module

An inverter device for a solar module. The inverter device comprises a slave circuit device that includes an input comprising a DC input from a solar cell group and a preliminary boost circuit. A DC boost circuit is coupled to the preliminary boost circuit and configured to boost the intermediary voltage to an AC RMS peak voltage. A rectifier circuit is coupled to the DC boost circuit. An energy recovery circuit comprises a storage device coupled to the rectifier output. The energy recovery circuit is configured to temporarily store a reverse recovery charge and transfers the reverse recovery charge to an output of a DC bus structure to reduce a diode recovery loss in the rectifier circuit.

Owner:SUNEDISON MICROINVERTER PROD

Converter and power conversion device using same

ActiveUS10630195B2Reducing size and costReduce recovery lossAc-dc conversion without reversalEfficient power electronics conversionConvertersWide-bandgap semiconductor

A converter includes a first diode having an anode and a cathode connected respectively to an input terminal and a first output terminal, a second diode having an anode and a cathode connected respectively to a second output terminal and the input terminal, a first transistor connected between the first output terminal and the input terminal, a second transistor connected between the input terminal and the second output terminal, and a bidirectional switch connected between the input terminal and a third output terminal and including third to sixth diodes and a third transistor. Each of the first diode, the second diode, and the third transistor is made of a wide bandgap semiconductor. Each of the first and second transistors and the third to sixth diodes is made of a semiconductor other than the wide bandgap semiconductor.

Owner:TOSHIBA MITSUBISHI-ELECTRIC IND SYST CORP

Semiconductor device

ActiveUS20200135717A1Reduce recovery lossReduced Tolerance RequirementsTransistorSolid-state devicesDevice materialEngineering

A semiconductor device includes an IGBT as a switching element, and a diode. The IGBT includes: a p type channel doped layer formed in a surface layer part on a front side of a semiconductor substrate; a p+ type diffusion layer and an n+ type source layer individually selectively formed in a surface layer part of the p type channel doped layer; and an emitter electrode connected to the n+ type source layer and the p+ type diffusion layer. A part of the p type channel doped layer reaches a front-side surface of the semiconductor substrate and is connected to the emitter electrode. On the front-side surface of the semiconductor substrate, the p+ type diffusion layer is interposed between the p type channel doped layer and an n+ type source layer, and the p type channel doped layer and the n+ type source layer are not adjacent to each other.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com