Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

59results about How to "Improve ESD performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

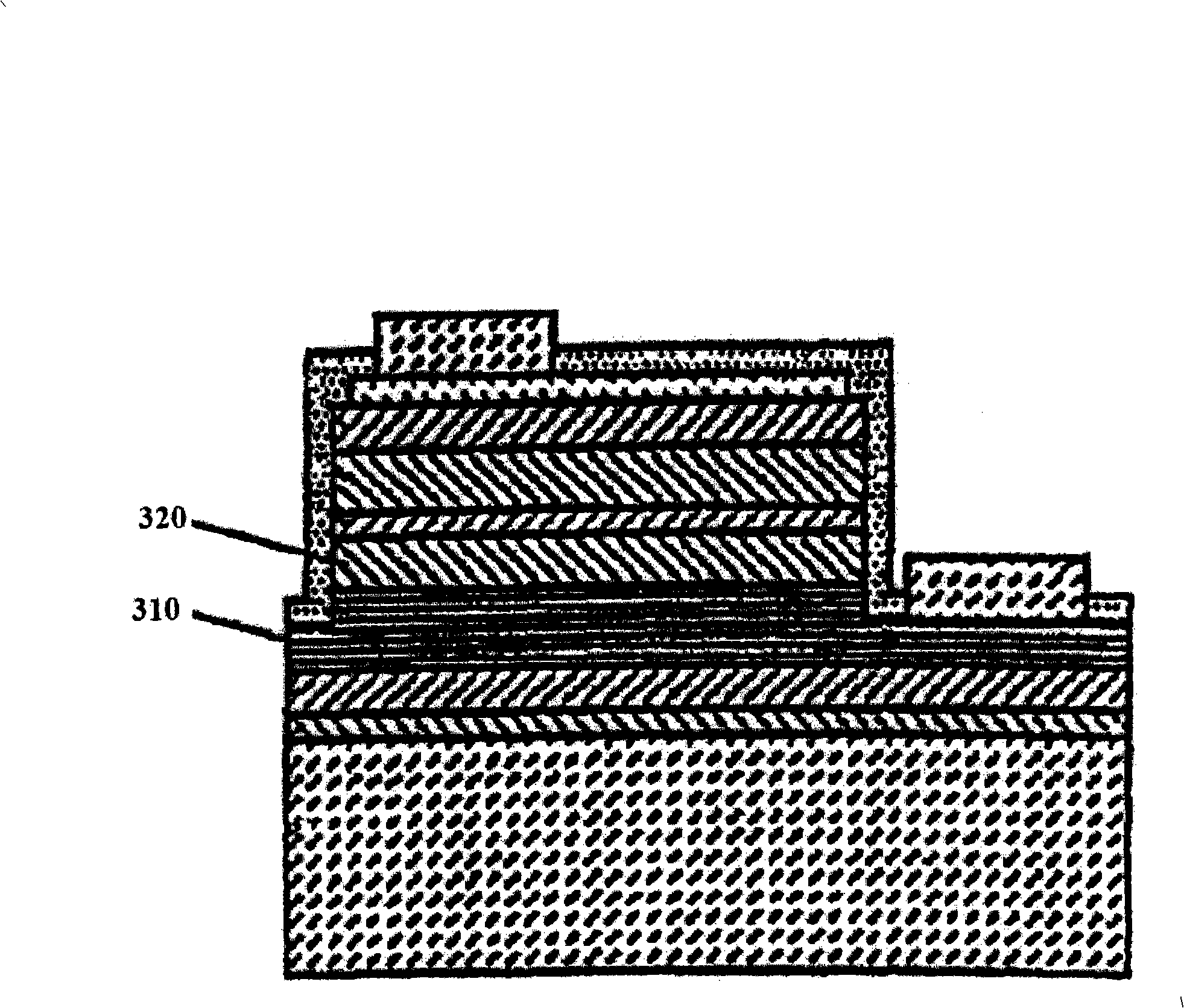

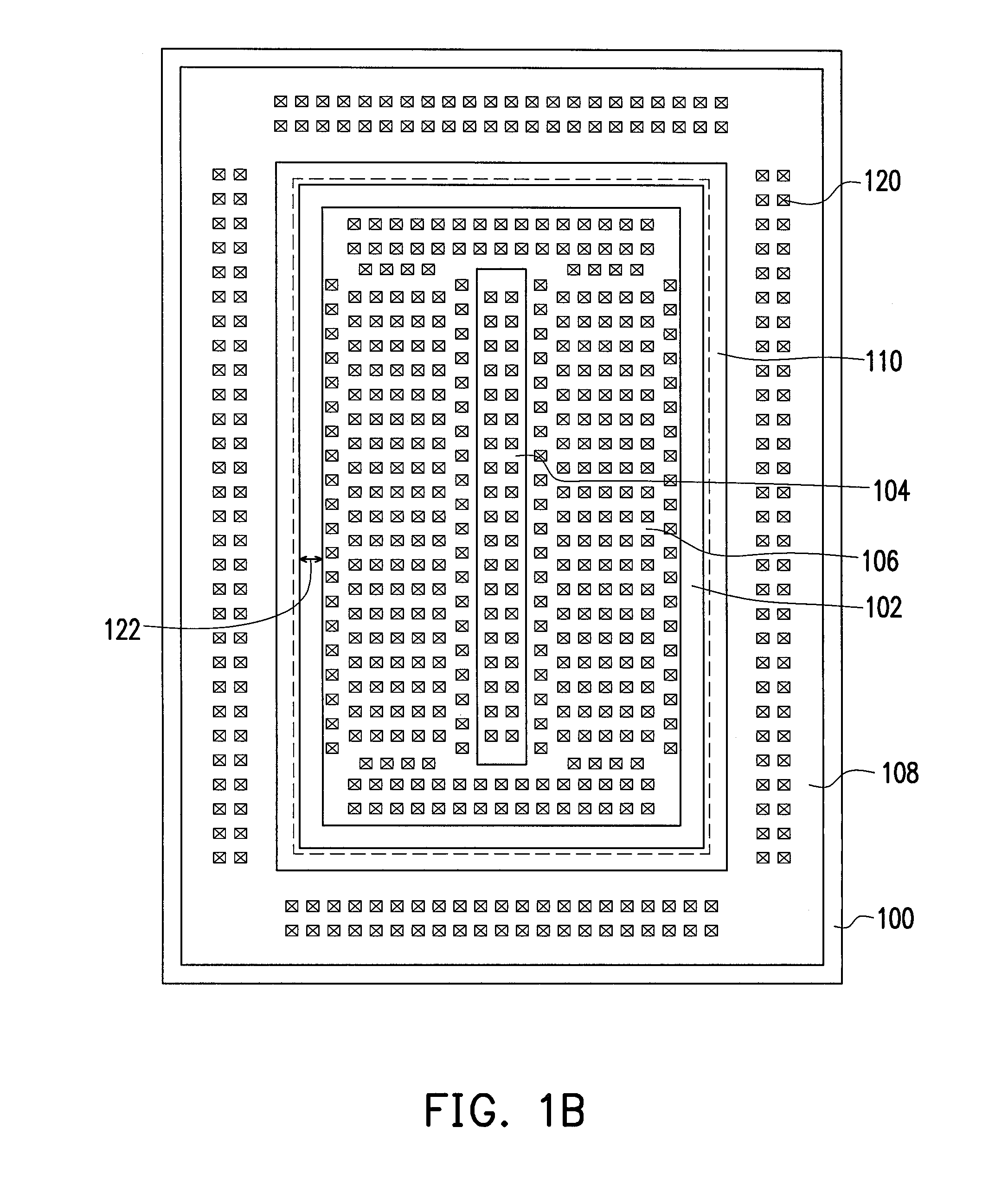

Semiconductor device and method for fabricating the same

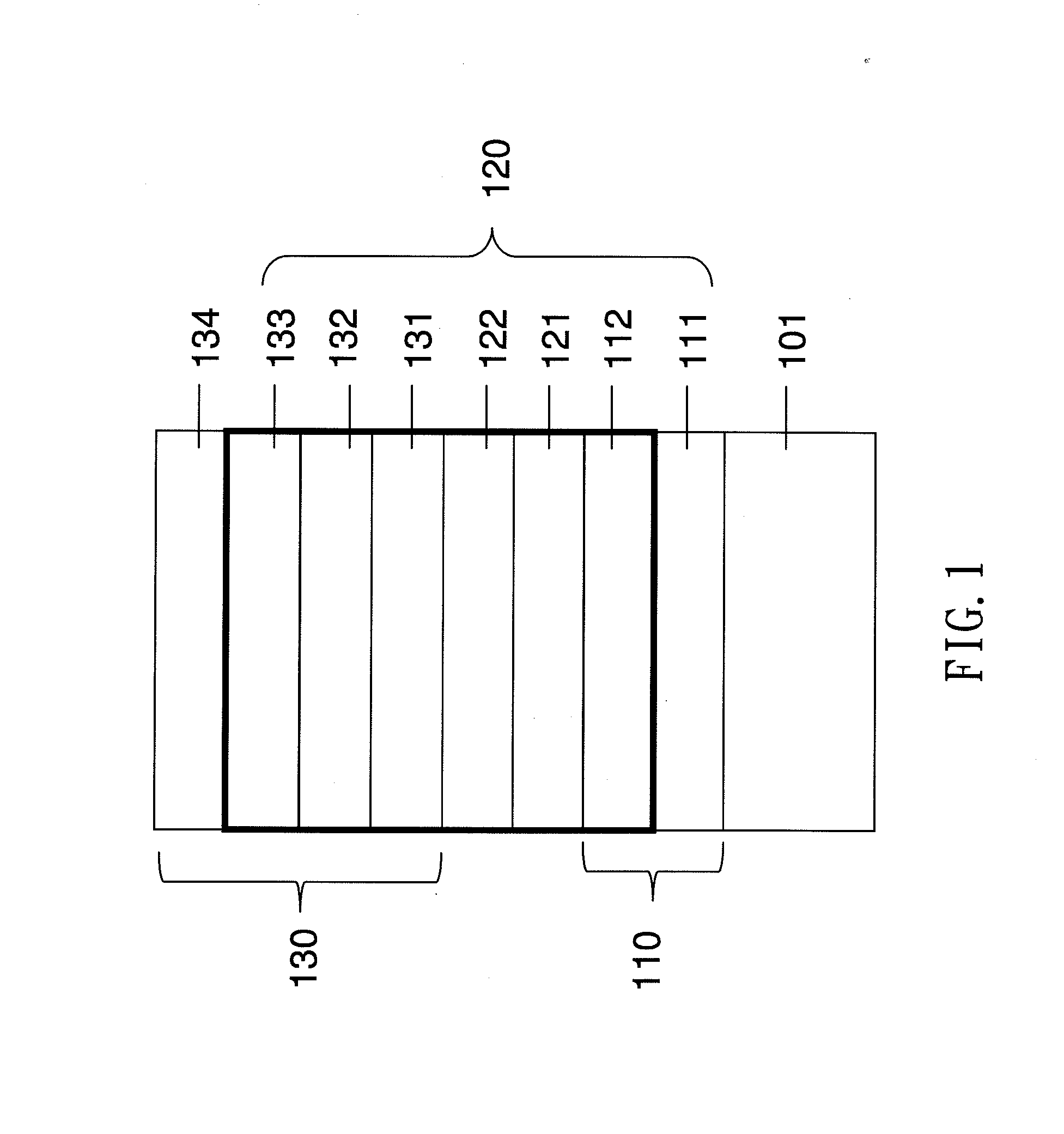

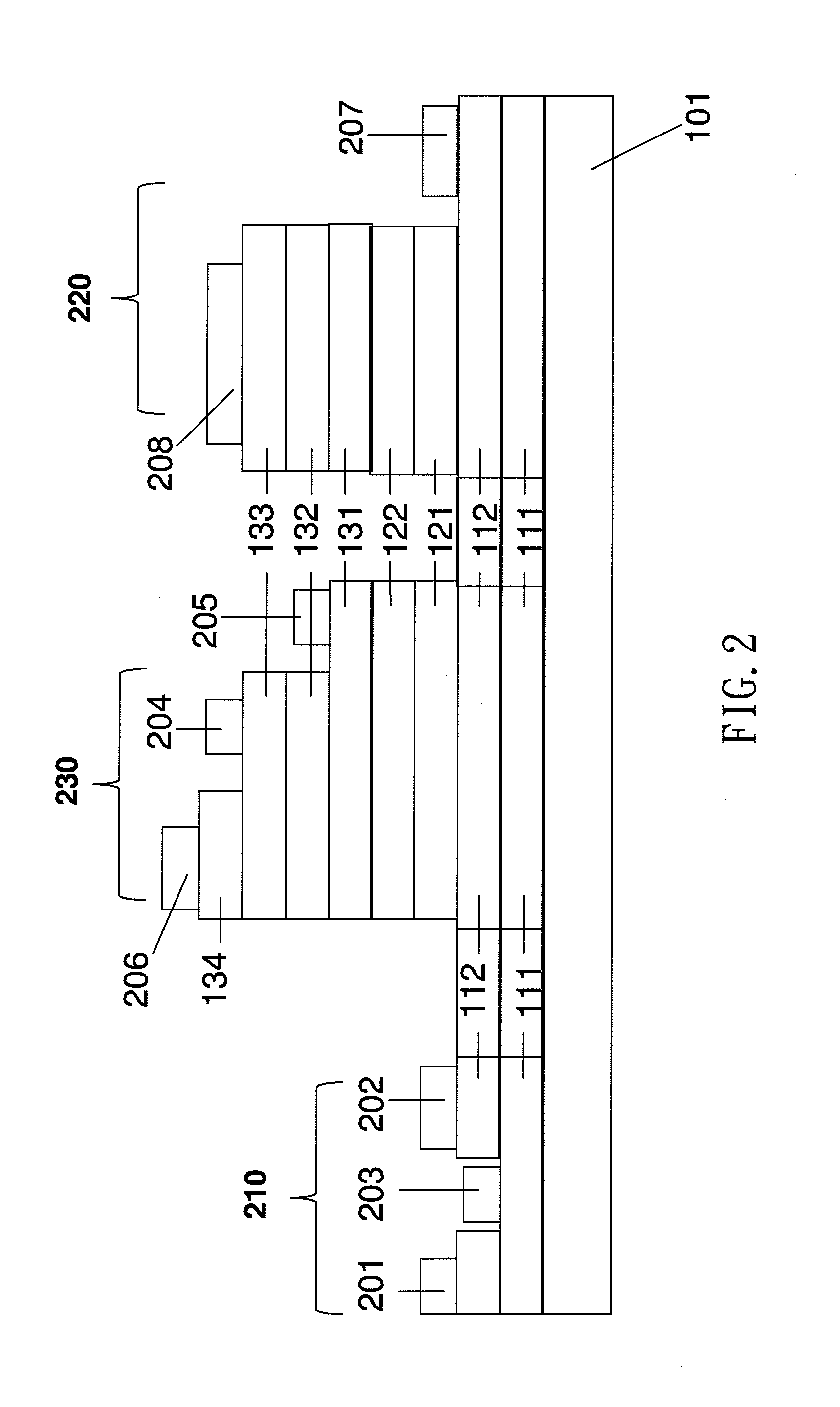

ActiveUS20130126972A1Easy to manufactureImprove ESD performanceSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceEngineering

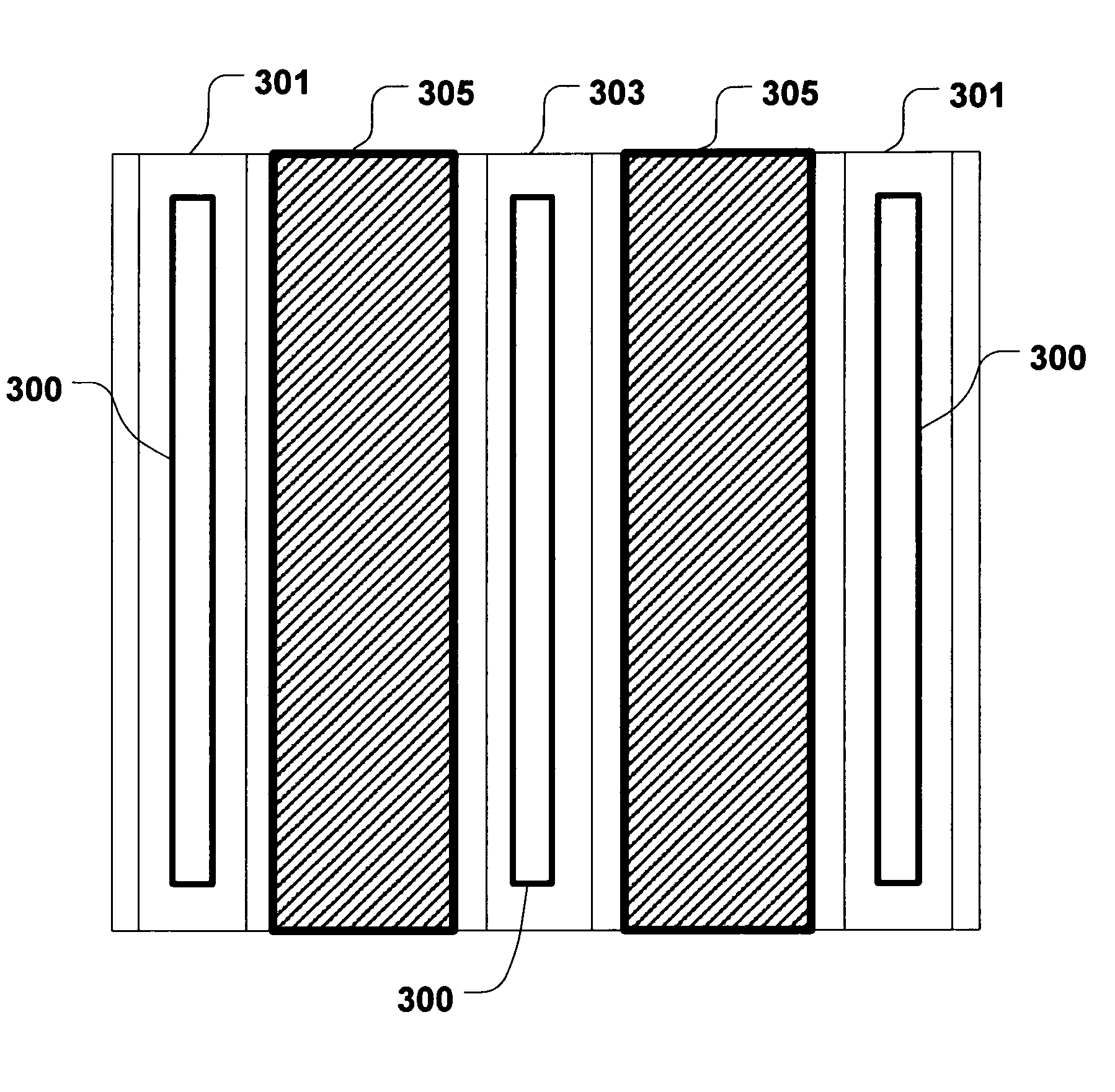

A semiconductor device and a fabricating method thereof are provided. The semiconductor device includes a substrate of a first conductivity type, a fin, a gate, source and drain regions of a second conductivity type, and a first doped region of the second conductivity type. A plurality of isolation structures is formed on the substrate. The fin is disposed on the substrate between two adjacent isolation structures. The gate is disposed on the isolation structures and covers a portion of the fin, wherein the portion of the fin covered by the gate is of the first conductivity type. The source and drain regions is configured in the fin at respective sides of the gate. The first doped region is configured in the fin underlying the source and drain regions and adjoining the substrate. The first doped region has an impurity concentration lower than that of the source and drain regions.

Owner:MARLIN SEMICON LTD

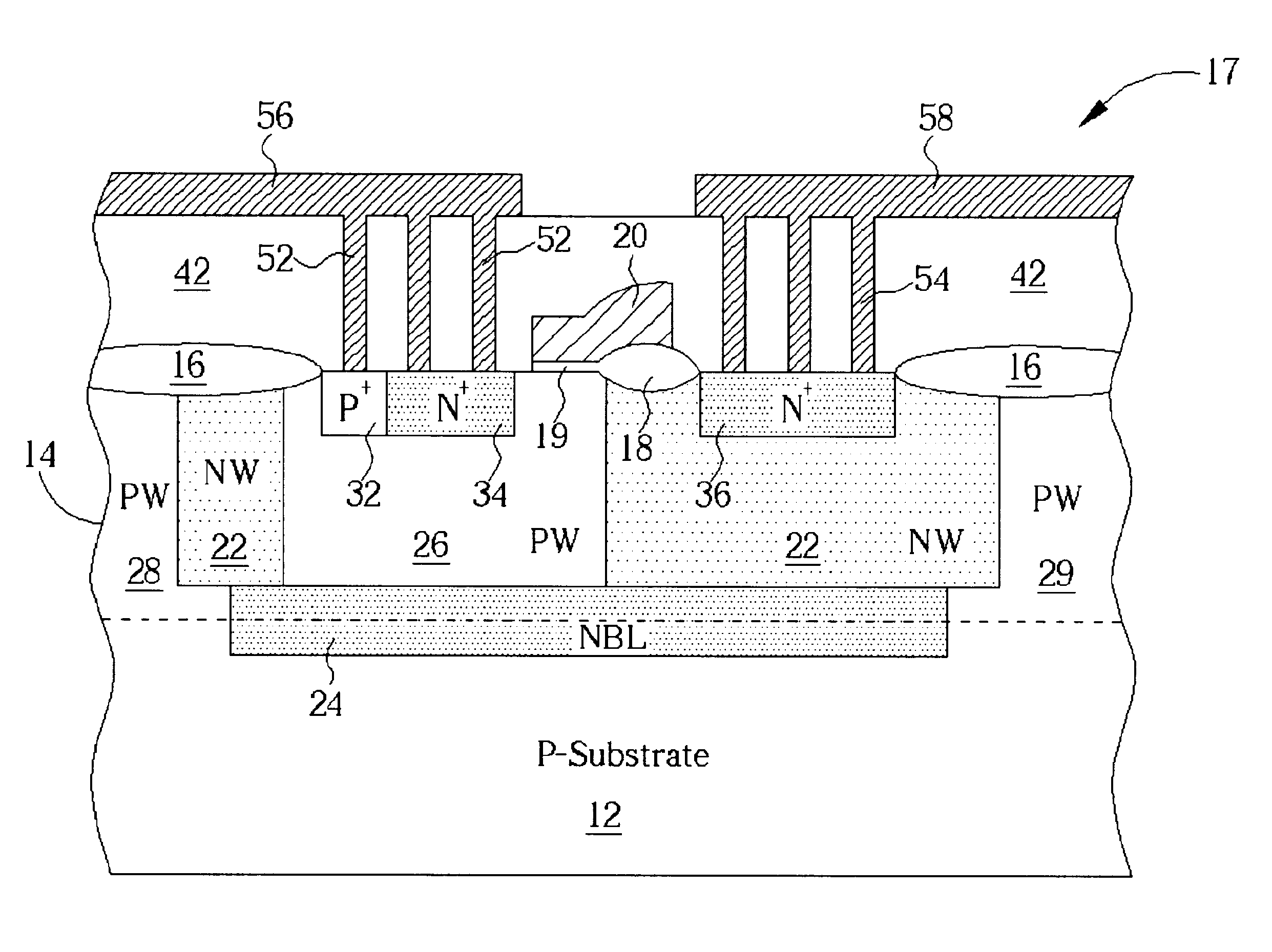

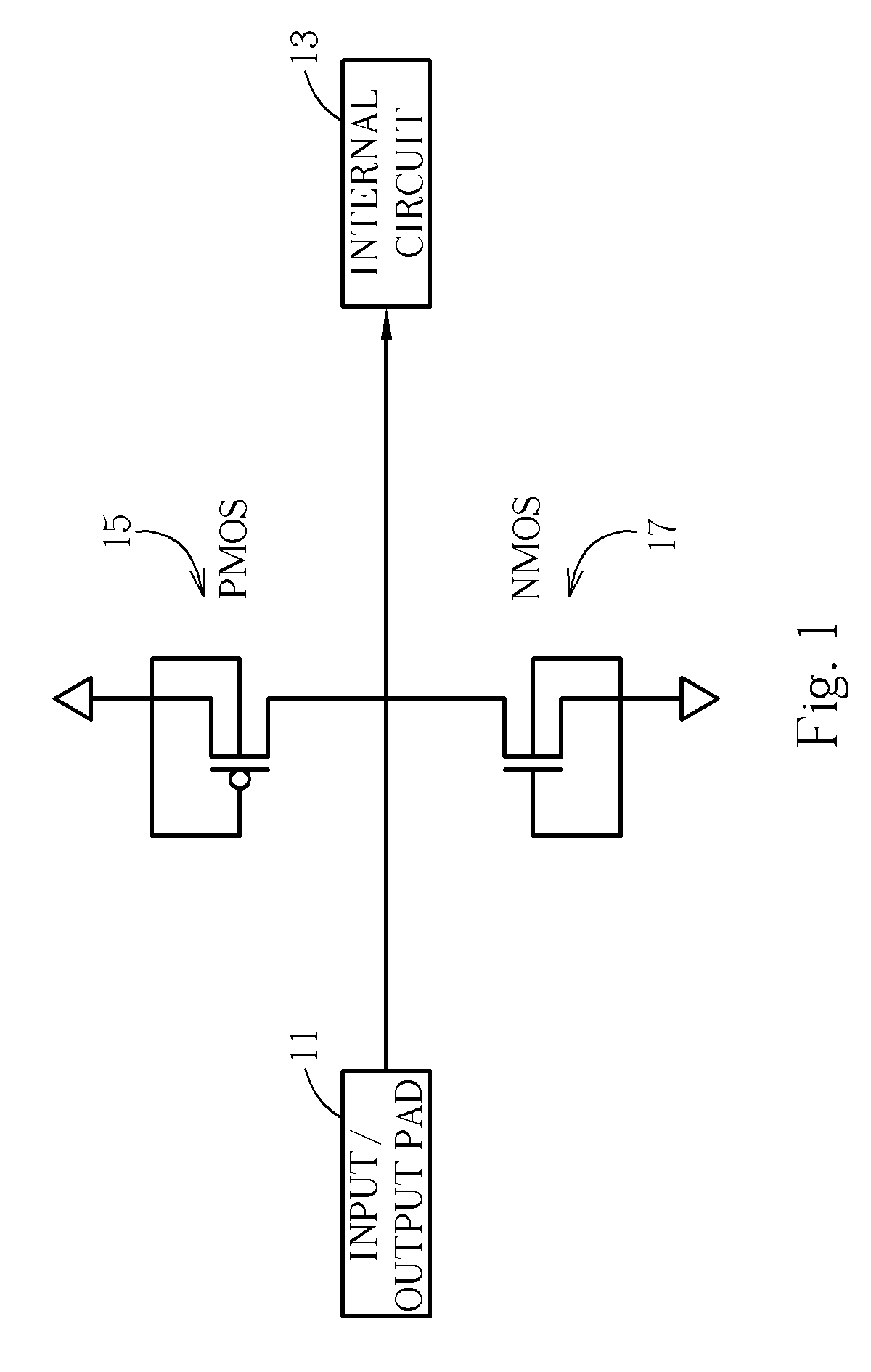

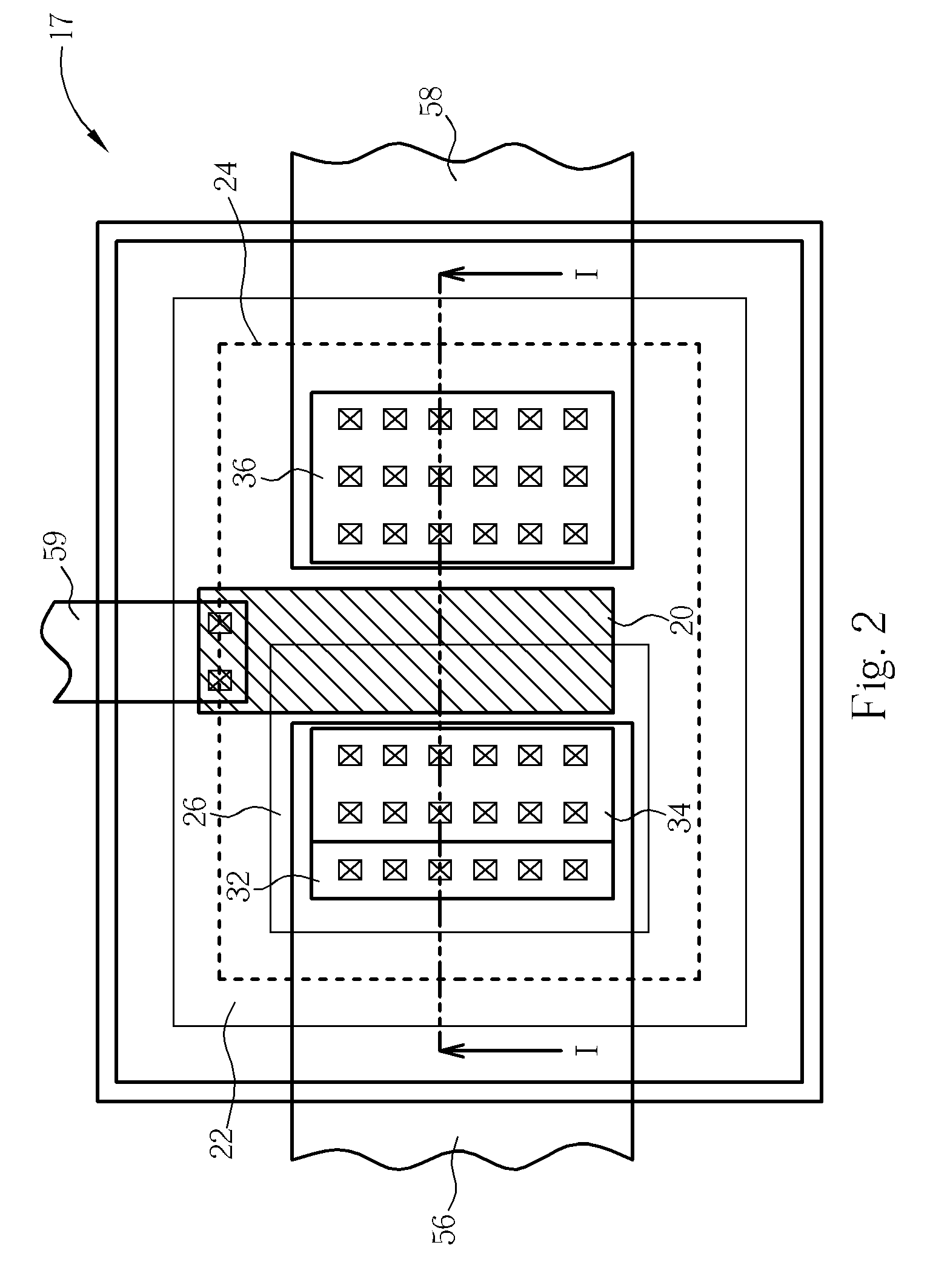

Electrostatic discharge (ESD) protection MOS device and ESD circuitry thereof

ActiveUS6879003B1Improved ESD performance and robustnessImprove ESD performanceTransistorSemiconductor/solid-state device detailsEngineeringElectrostatic discharge protection

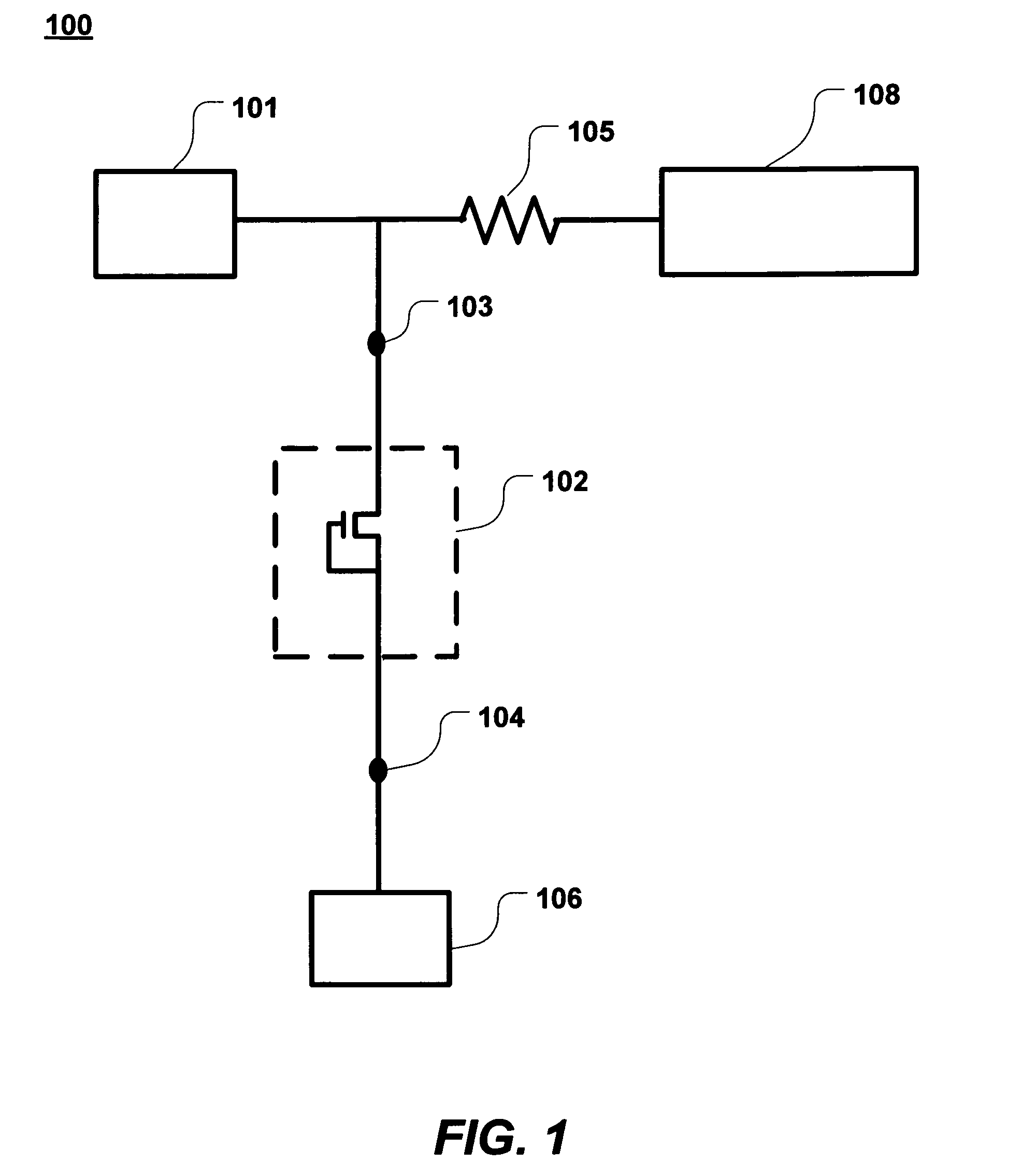

An NMOS device having protection against electrostatic discharge. The NMOS device includes a P-substrate, a P-epitaxial layer overlying the P-substrate, a P-well in the P-epitaxial layer, an N-well in the P-epitaxial layer and encompassing the P-well, an N-Buried Layer (NBL) underneath the P-well and bordering the N-well. The P-well is fully isolated by the N-well and the NBL. The NMOS device further includes a first isolation structure consisting of a gate-insulating layer connected with a field oxide layer, which is formed on the P-epitaxial layer. A gate overlies the first isolation structure. A second isolation structure laterally spaced apart from the first isolation structure is approximately situated on the N-well. An N+ source doping region, which functions as a source of the NMOS device, is disposed in the P-well. An N+ drain doping region, which functions as a drain of the NMOS device, is disposed in the N-well.

Owner:UNITED MICROELECTRONICS CORP

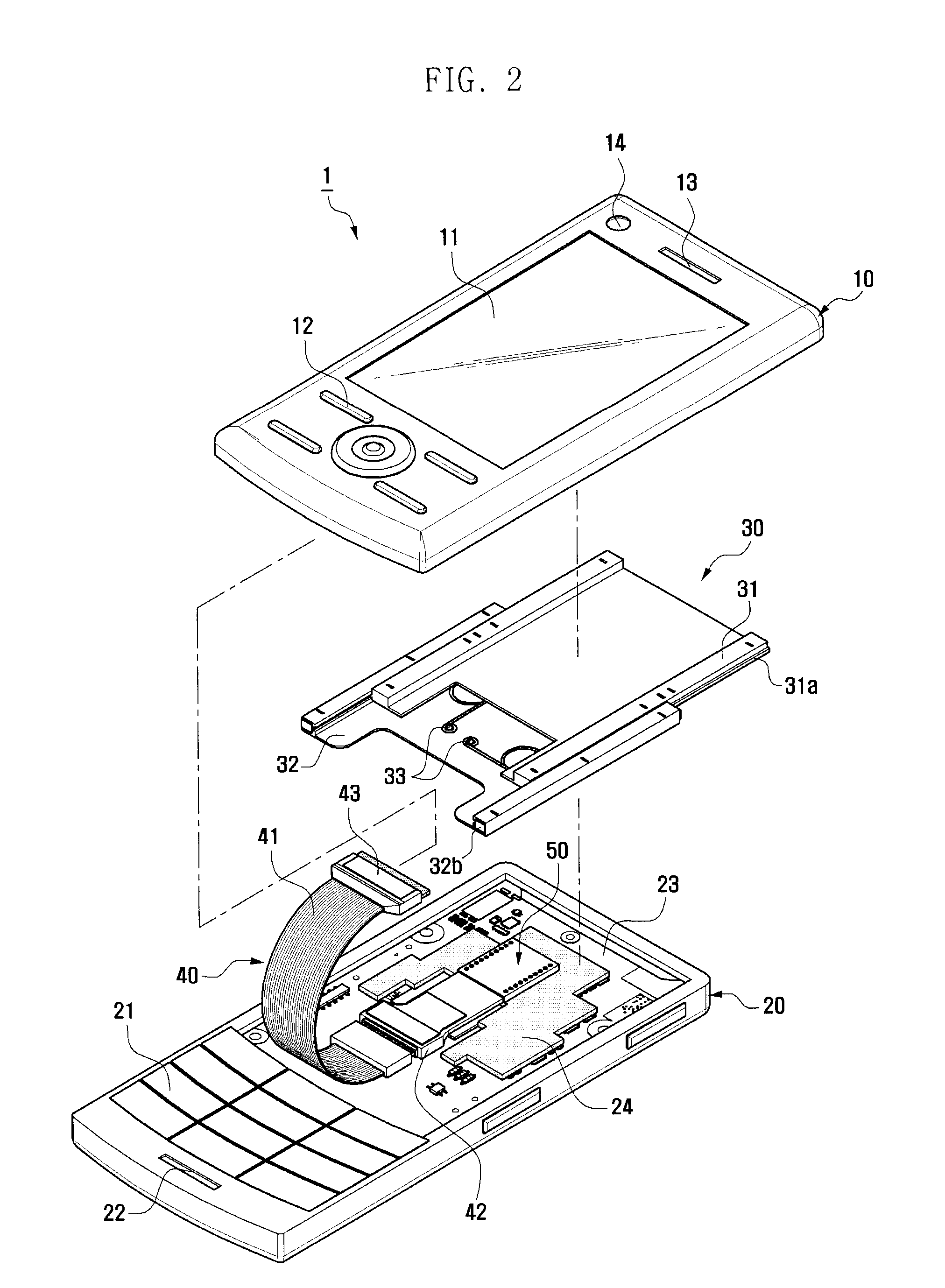

Mobile terminal having flexible printed circuit board

ActiveUS20100273539A1Improve Radiation PerformanceImprove ESD performancePrinted circuit detailsSubstation equipmentElectricityEngineering

A mobile terminal having a flexible printed circuit board (FPCB) is includes: a first main body having a first electronic circuit board therein; a second main body slidably connected to the first main body and having a second electronic circuit board therein; a FPCB for transferring an electronic signal by electrically connecting the first electronic circuit board and the second electronic circuit board; and a ground extension portion connected to one end of the FPCB connected to the first electronic circuit board, having a ground layer connected to a ground line of the FPCB therein, and connected to a noise shielding portion for shielding noise generated from one or more electronic components mounted on the first electronic circuit board. By extending the ground, the influences of noise and static electricity is minimized on an electronic circuit board mounted on the electronic components.

Owner:SAMSUNG ELECTRONICS CO LTD

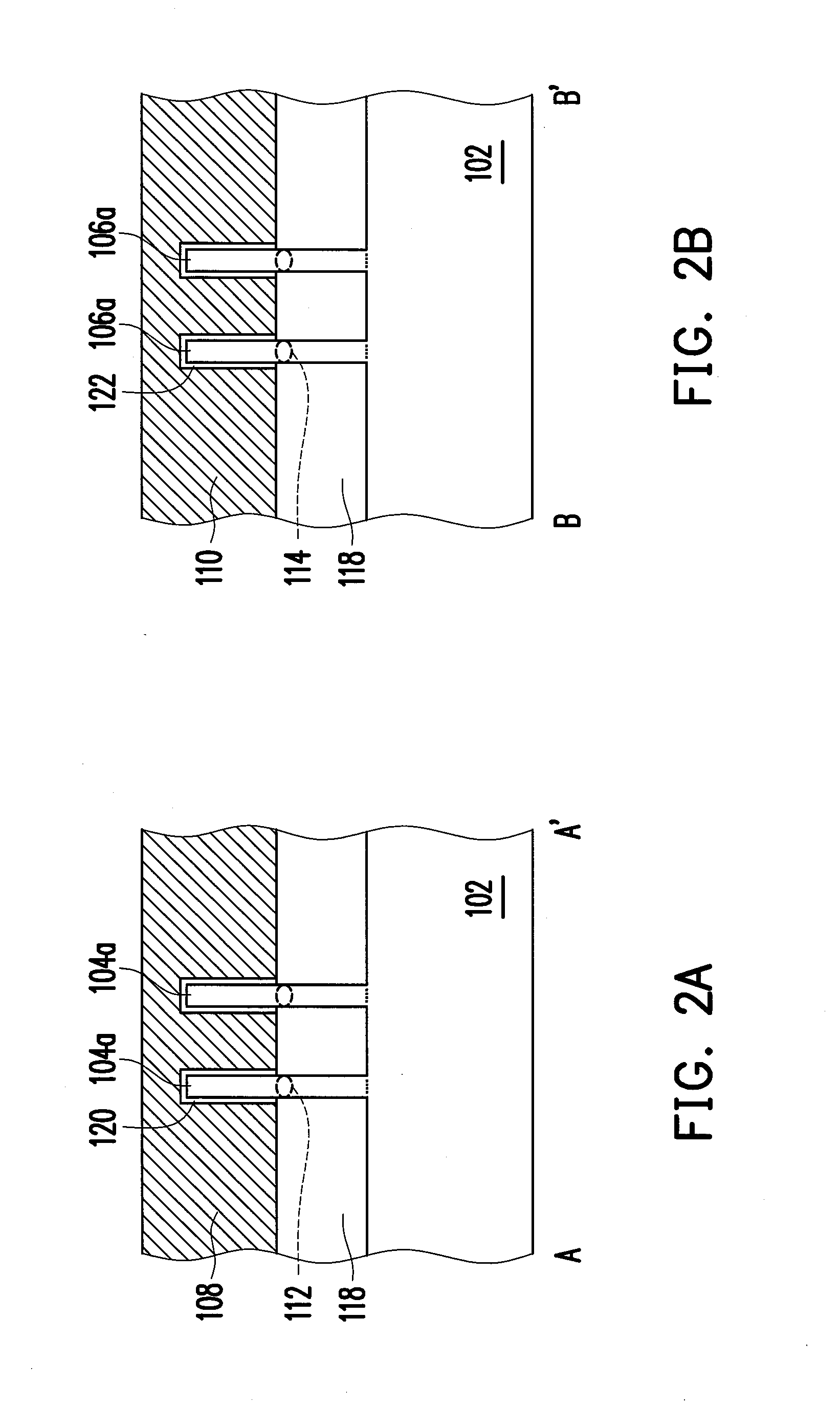

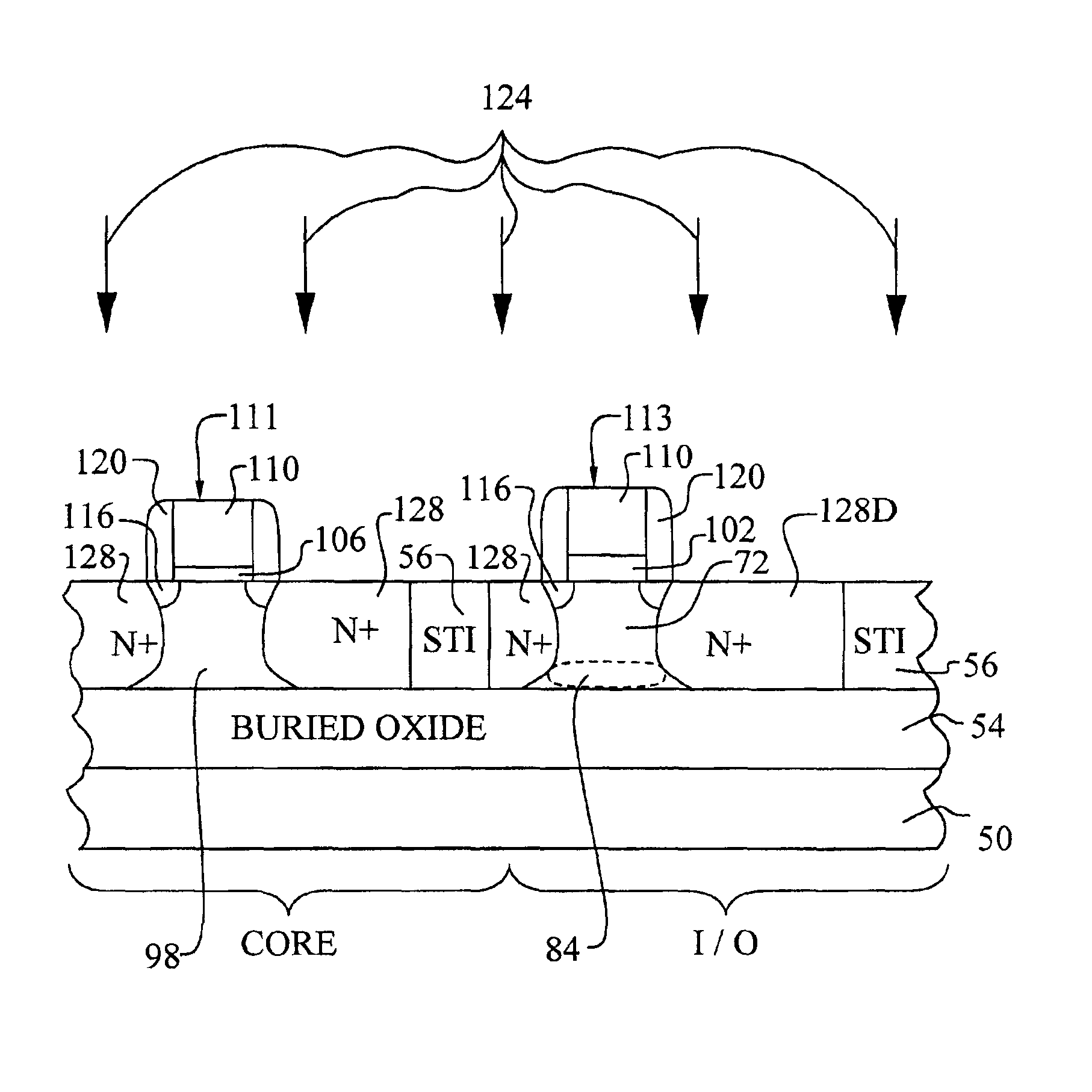

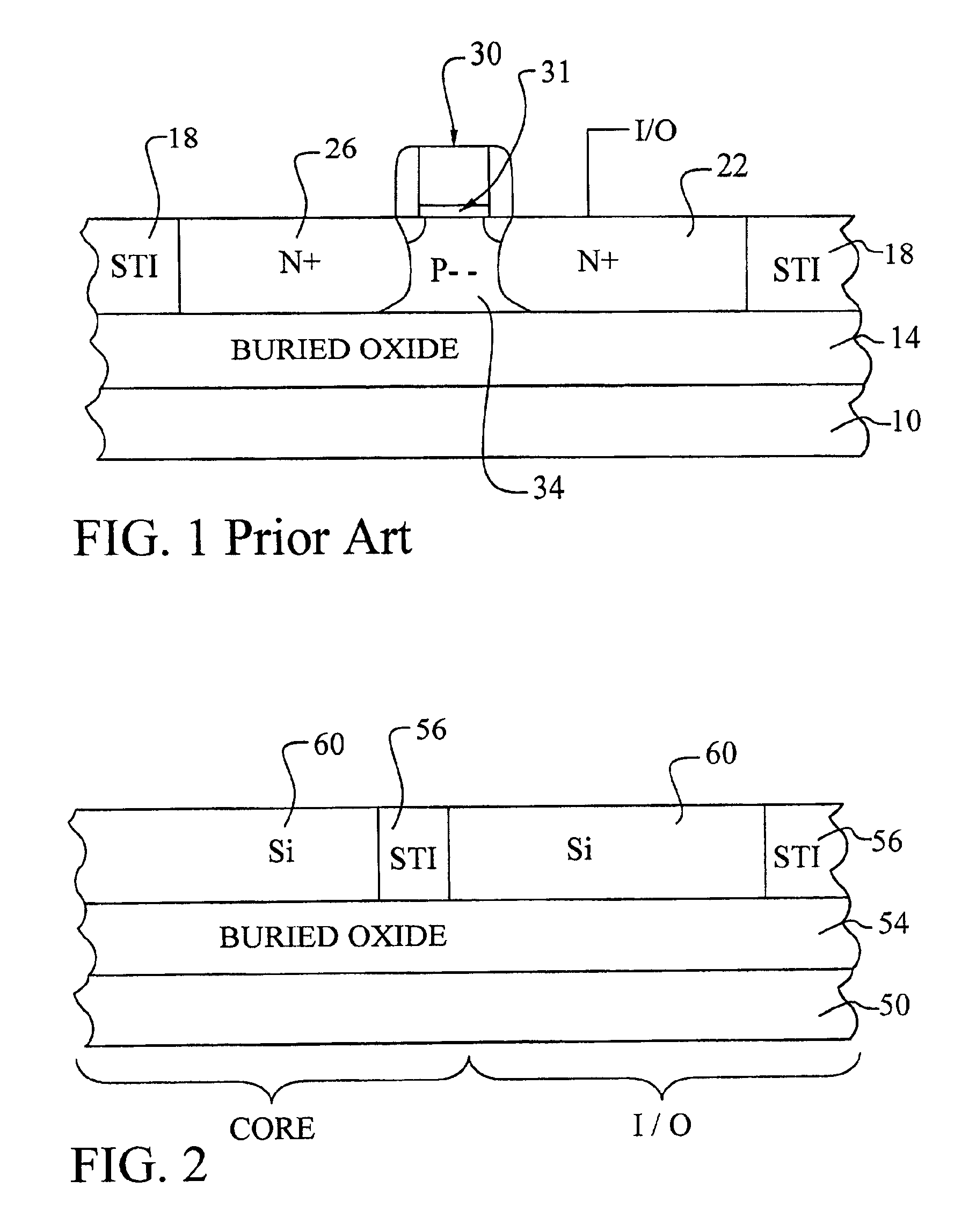

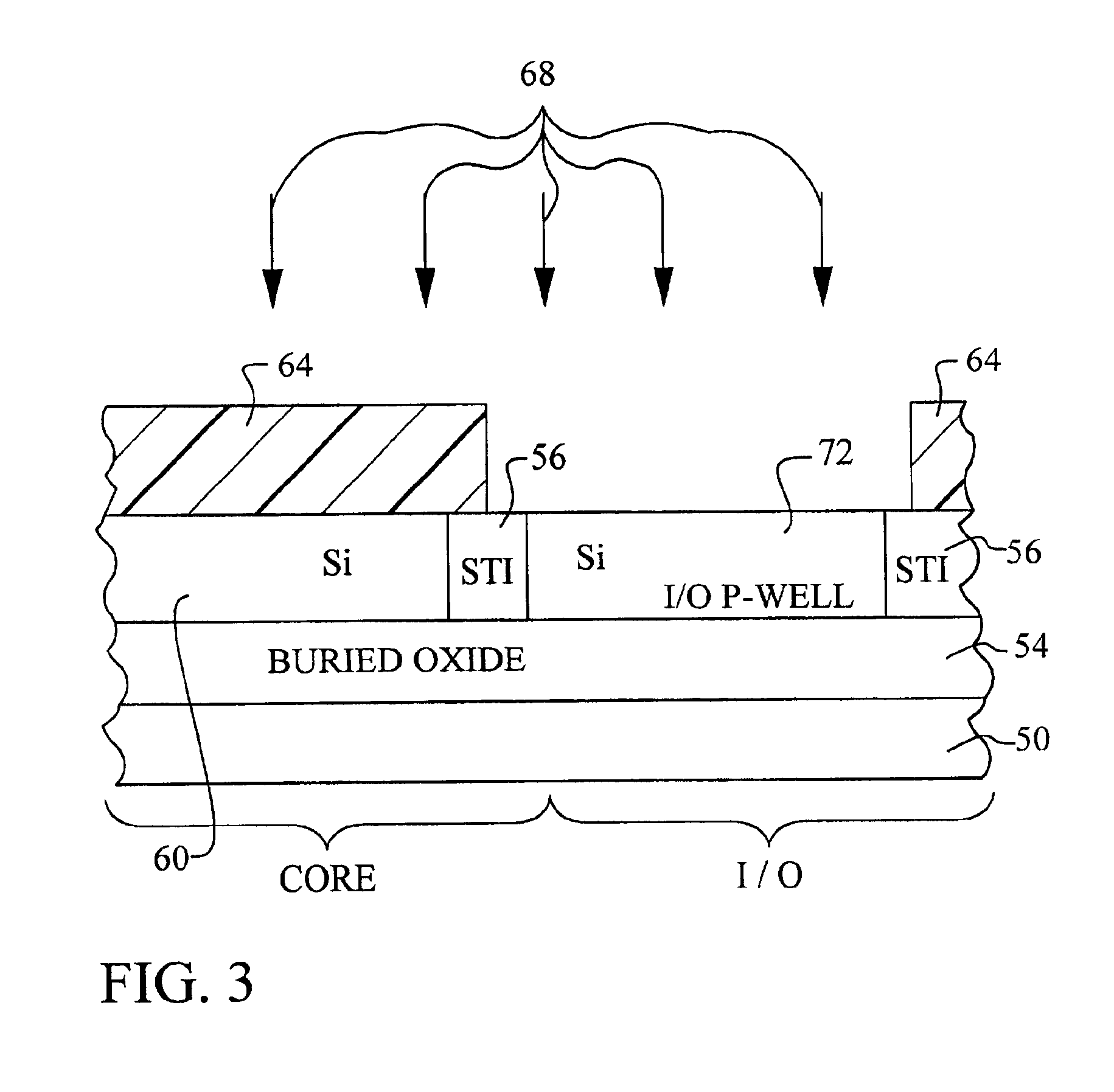

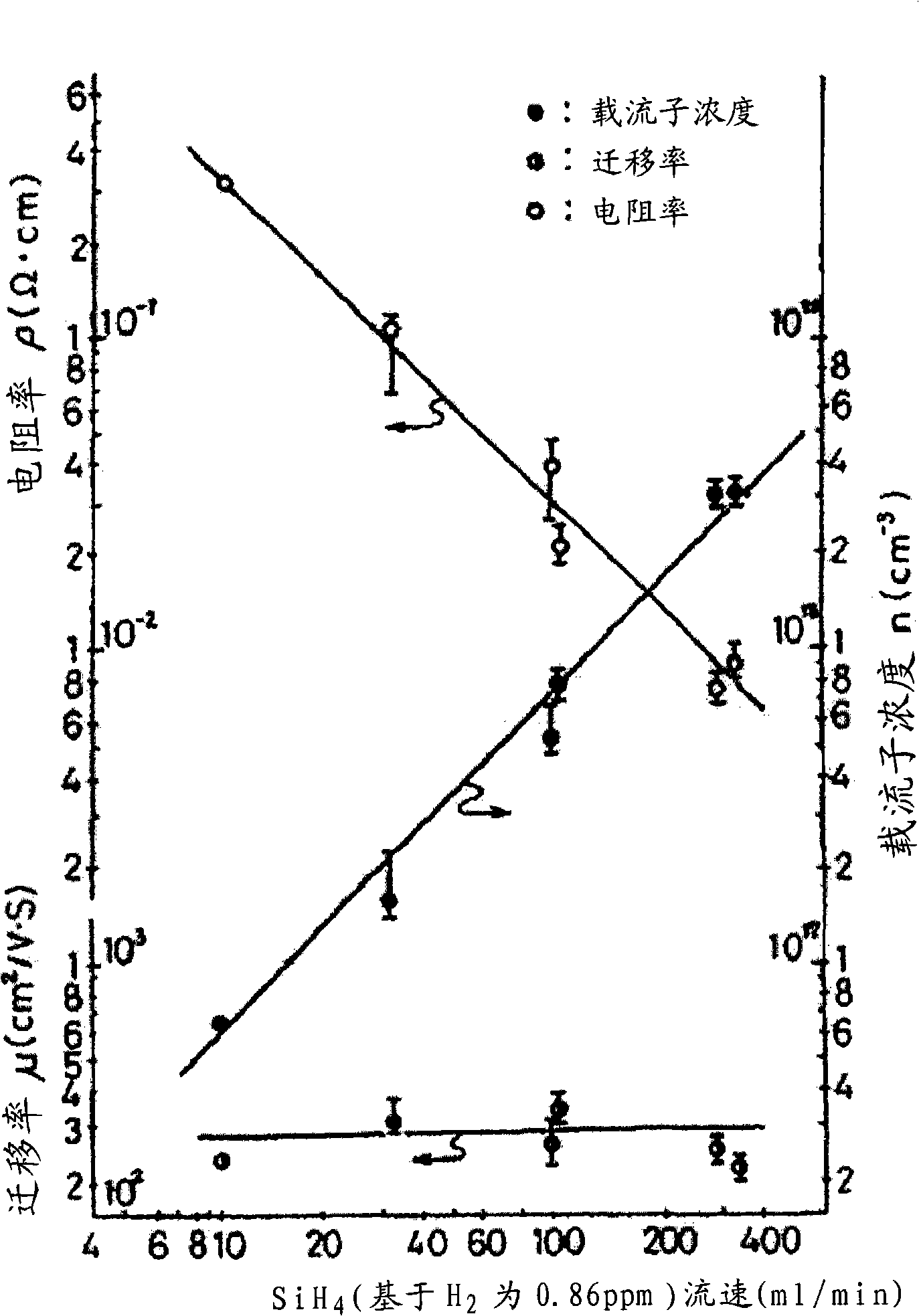

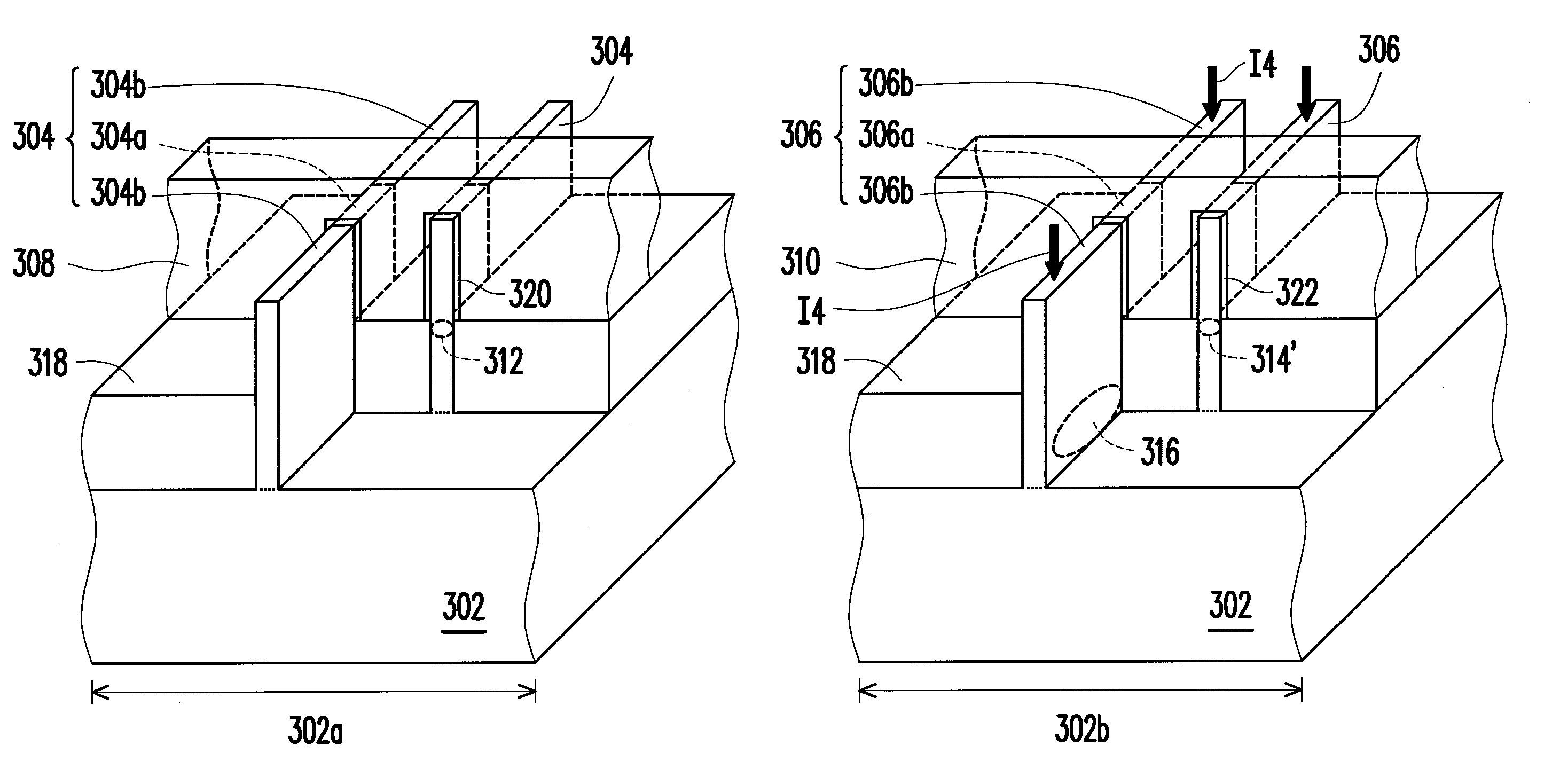

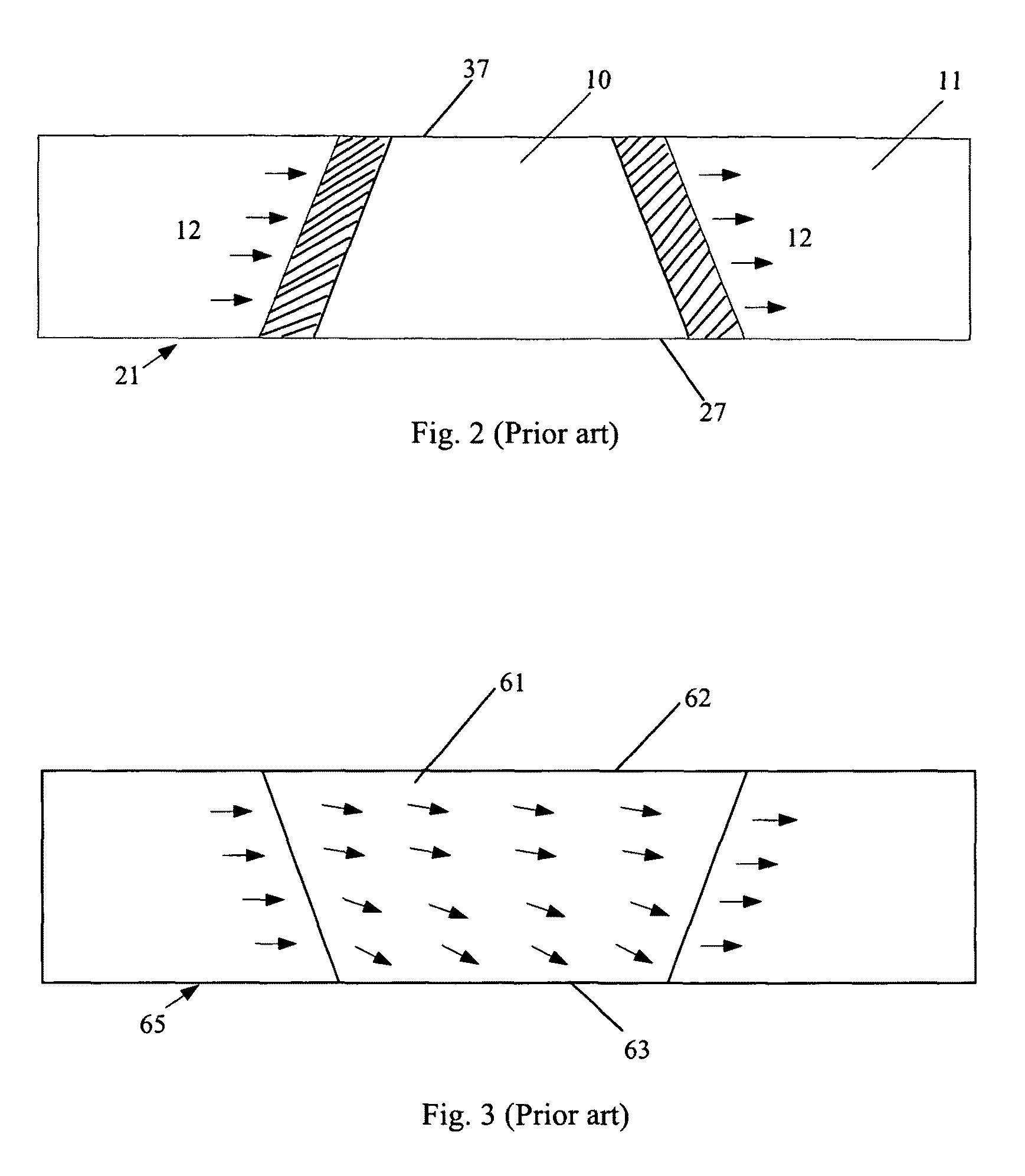

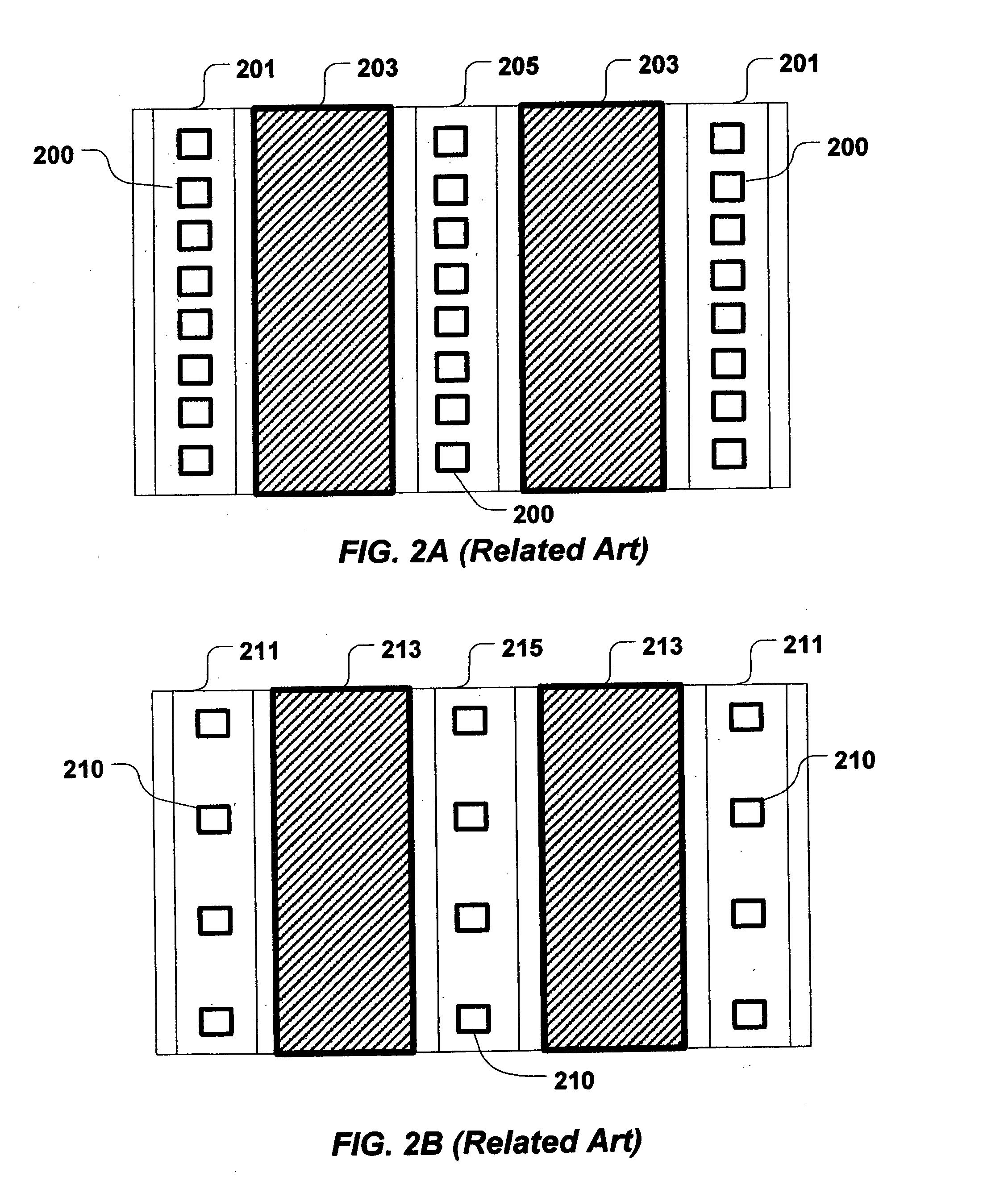

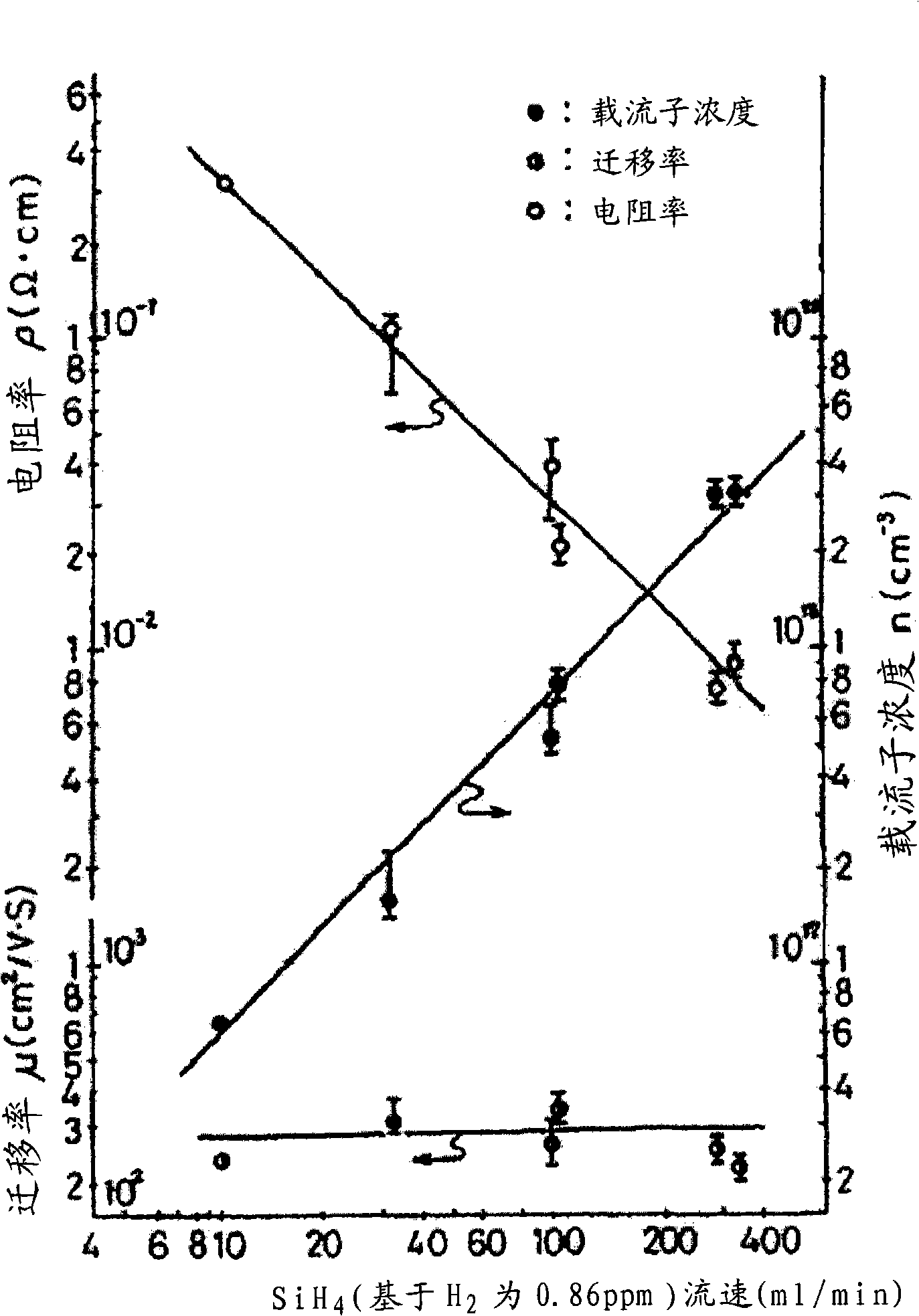

Method of fabricating an ESD device on SOI

InactiveUS6867103B1Improve ESD performanceLower breakdown voltageTransistorSolid-state devicesHigh concentrationSoi substrate

A method to form transistors having improved ESD performance in the manufacture of an integrated circuit device is achieved. The method includes providing a SOI substrate with a doped silicon layer and a buried oxide layer. The doped silicon layer has a first conductivity type and overlies the buried oxide layer. Ions are implanted into the SOI substrate to form higher concentration regions in the doped silicon layer. The higher concentration regions have the first conductivity type and are formed substantially below the top surface of the doped silicon layer. MOS gates are formed. These MOS gates include an electrode layer overlying the doped silicon layer with a gate oxide layer therebetween. Source and drain regions are formed in the doped silicon layer to complete the transistors in the manufacture of the integrated circuit device. The source and drain regions contact the higher concentration regions and have a second conductivity type.

Owner:TAIWAN SEMICON MFG CO LTD

Electrostatic discharge (ESD) protection mos device and ESD circuitry thereof

ActiveUS20050280092A1Improved ESD performance and robustnessImprove ESD performanceTransistorSemiconductor/solid-state device detailsEngineeringElectrostatic discharge protection

An NMOS device having protection against electrostatic discharge. The NMOS device includes a P-substrate, a P-epitaxial layer overlying the P-substrate, a P-well in the P-epitaxial layer, an N-well in the P-epitaxial layer and encompassing the P-well, an N-Buried Layer (NBL) underneath the P-well and bordering the N-well. The P-well is fully isolated by the N-well and the NBL. The NMOS device further includes a first isolation structure consisting of a gate-insulating layer connected with a field oxide layer, which is formed on the P-epitaxial layer. A gate overlies the first isolation structure. A second isolation structure laterally spaced apart from the first isolation structure is approximately situated on the N-well. An N+ source doping region, which functions as a source of the NMOS device, is disposed in the P-well. An N+ drain doping region, which functions as a drain of the NMOS device, is disposed in the N-well.

Owner:UNITED MICROELECTRONICS CORP

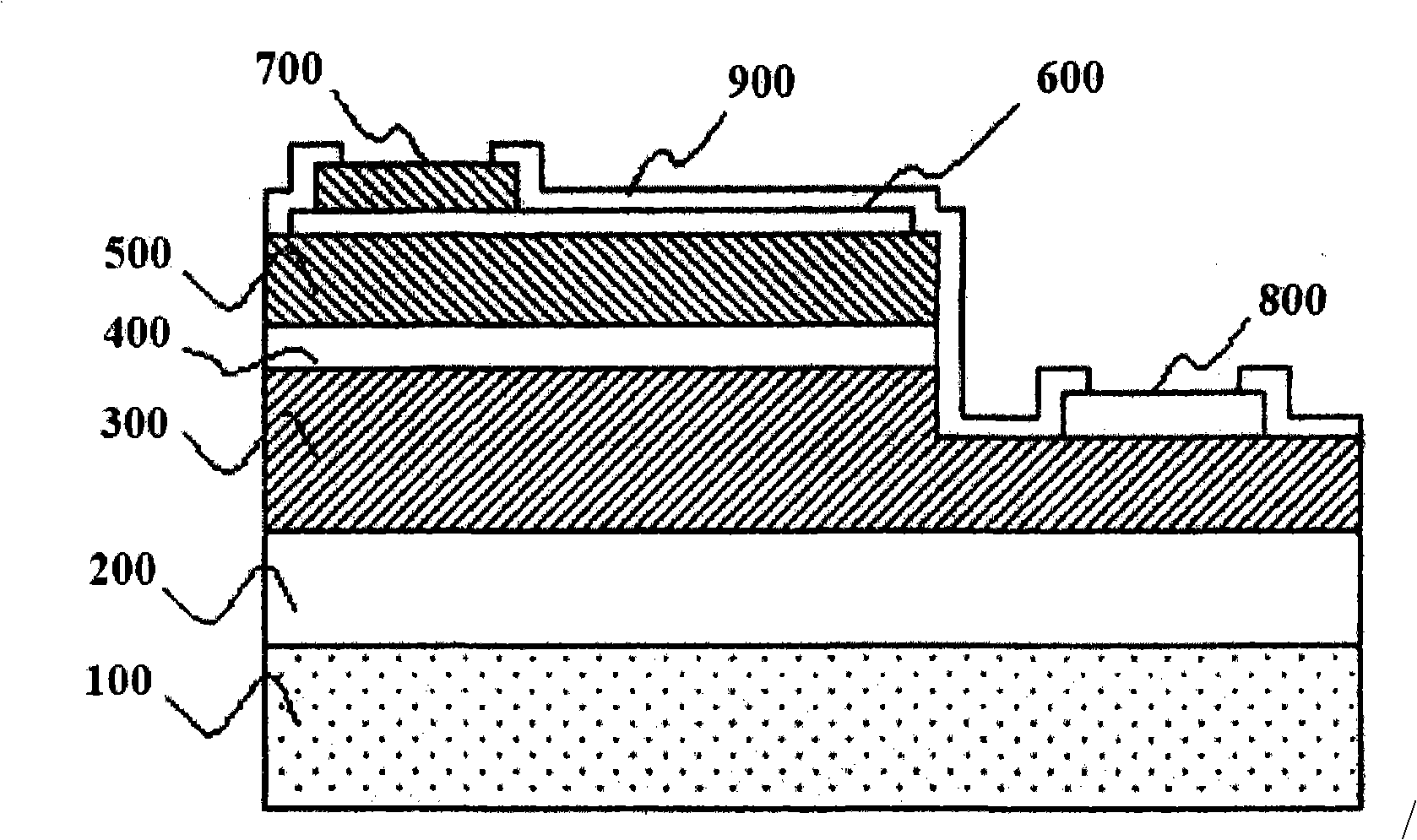

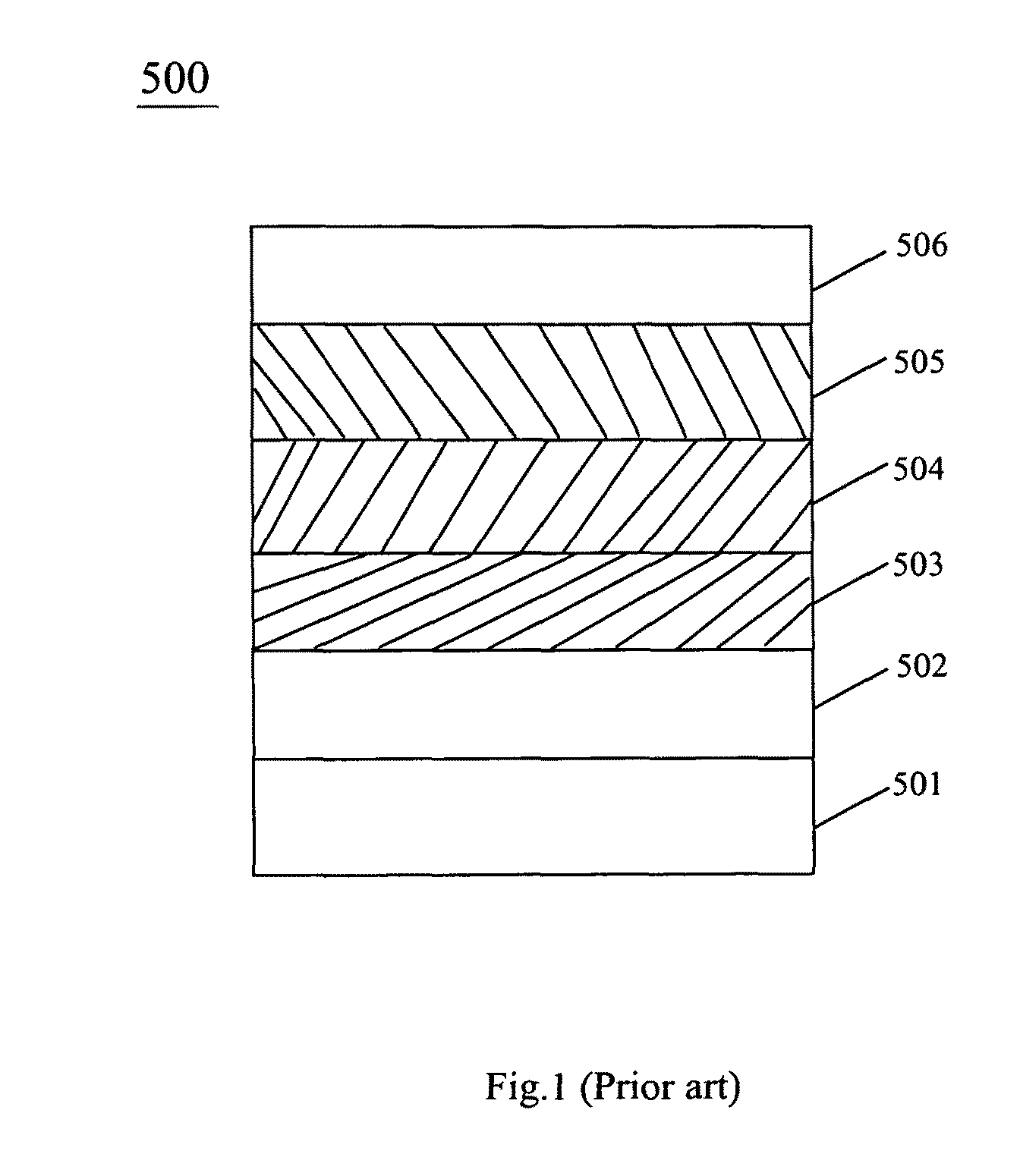

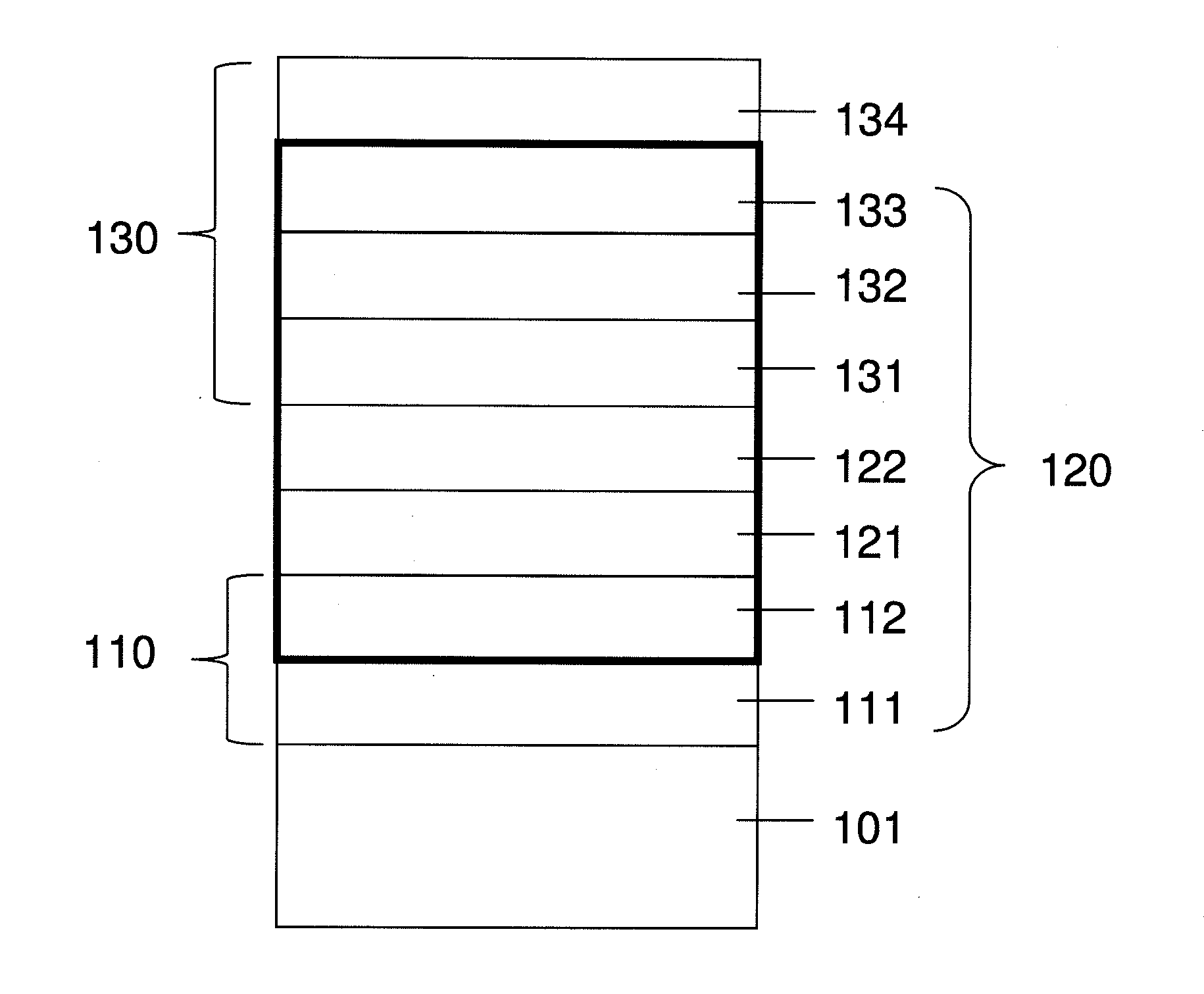

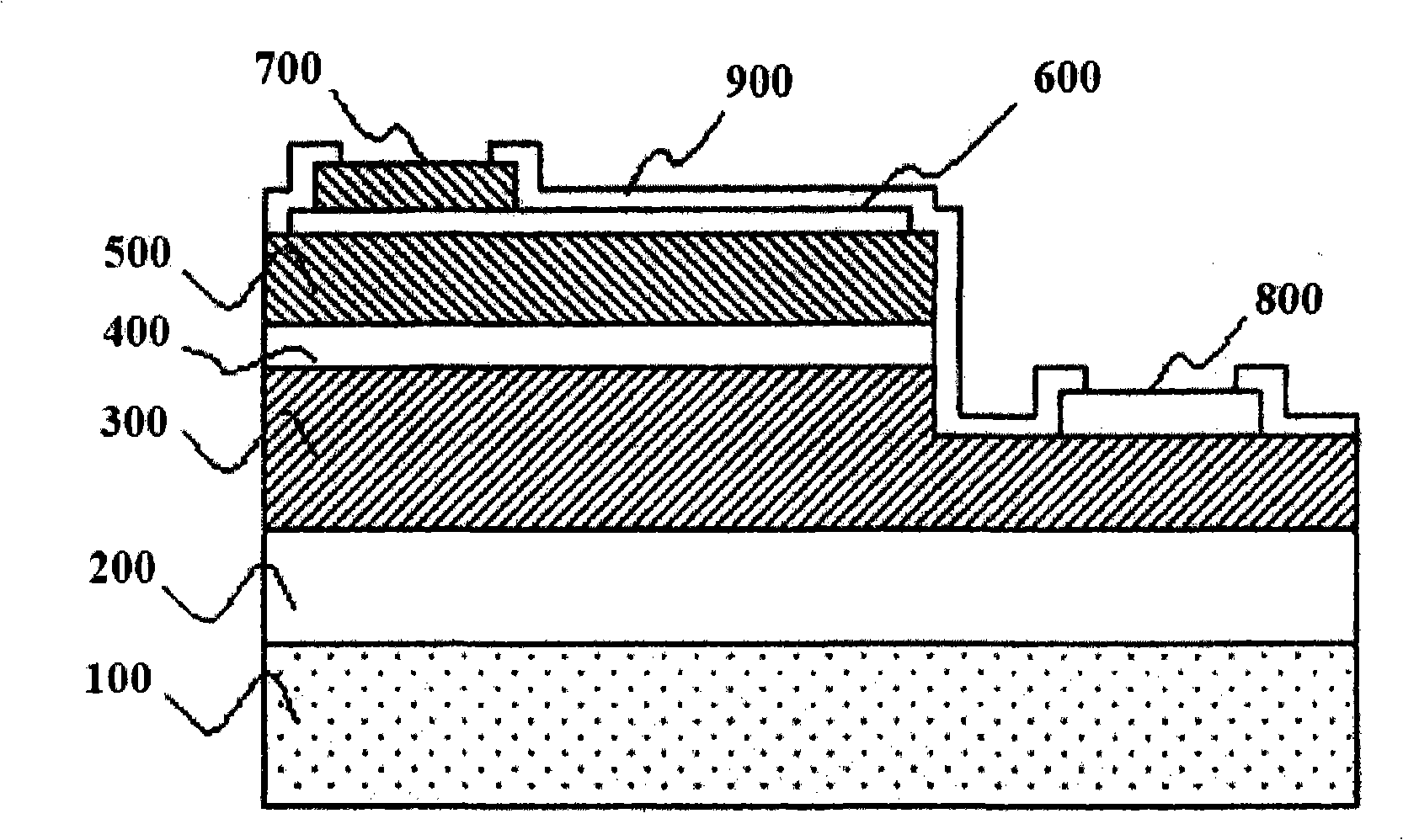

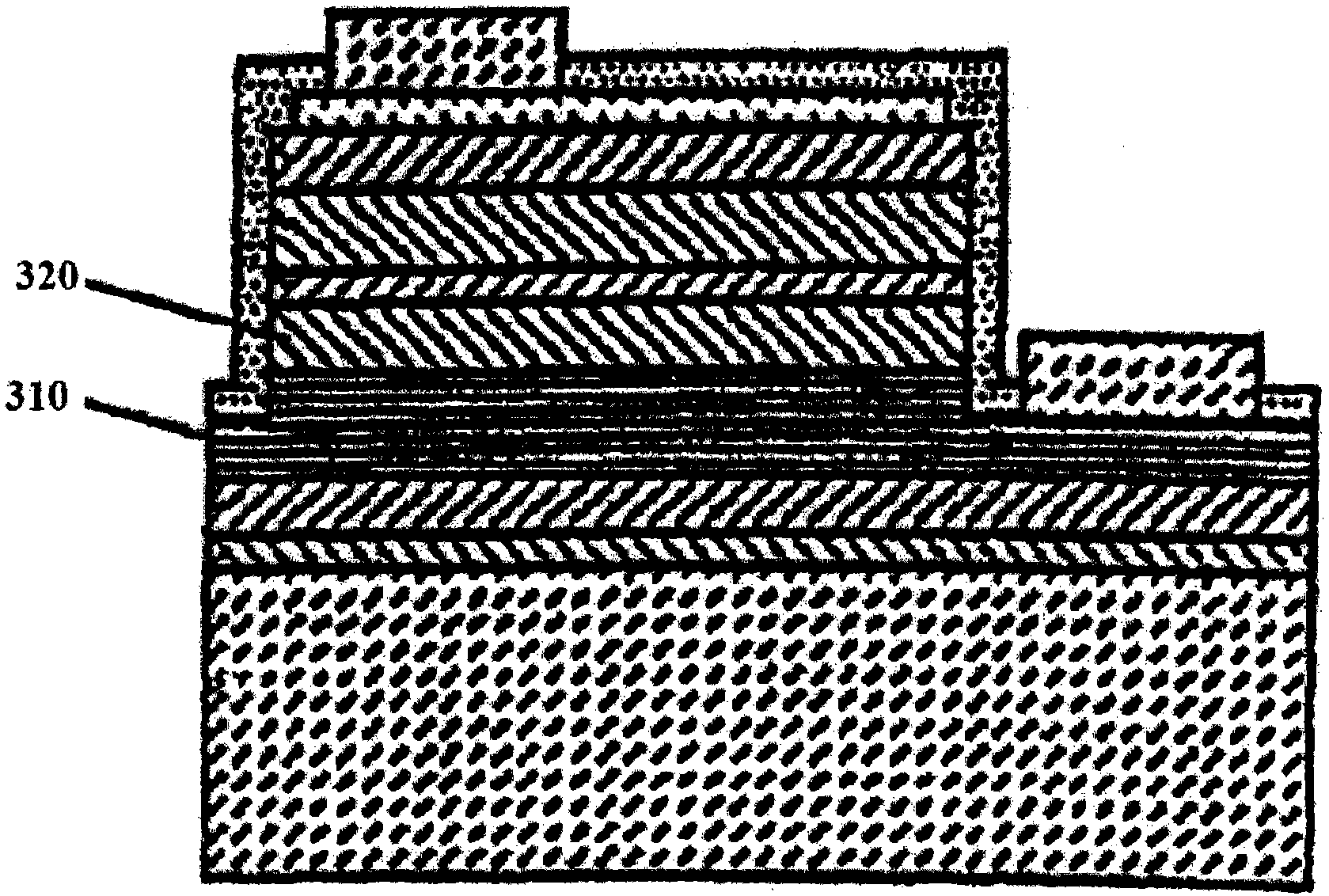

III-nitride semiconductor light emitting device

InactiveCN101404315ACurrent extension can promoteImproved ESD performanceSemiconductor devicesContact layerLight emitting device

The present invention relates to a III-nitride semiconductor light emitting device, and more particularly, to a III-nitride semiconductor light emitting device which can facilitate current spreading and improve electrostatic discharge characteristic by providing an undoped GaN layer with a thickness over 100 A in an n-side contact layer.

Owner:EPIVALLEY

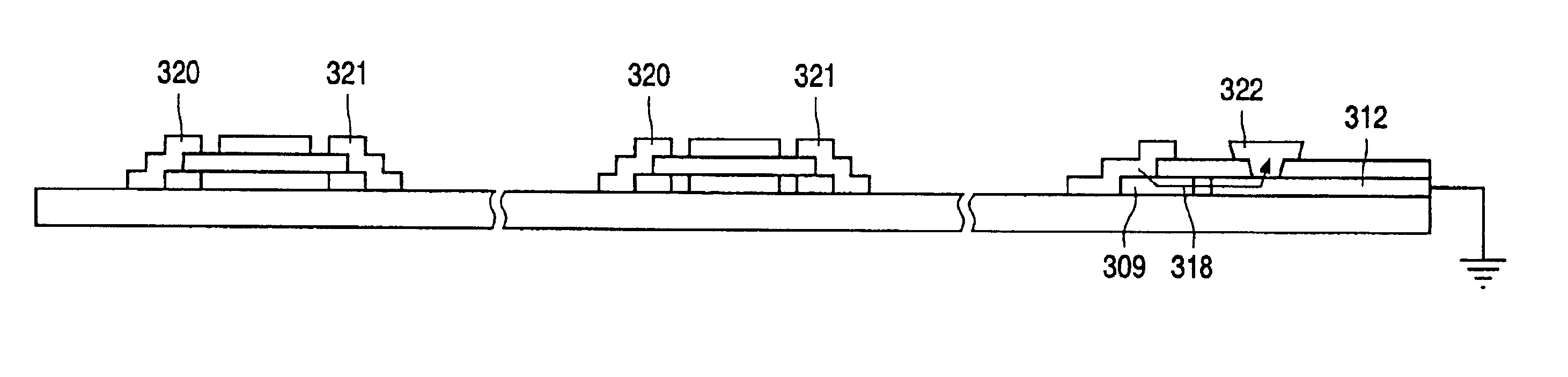

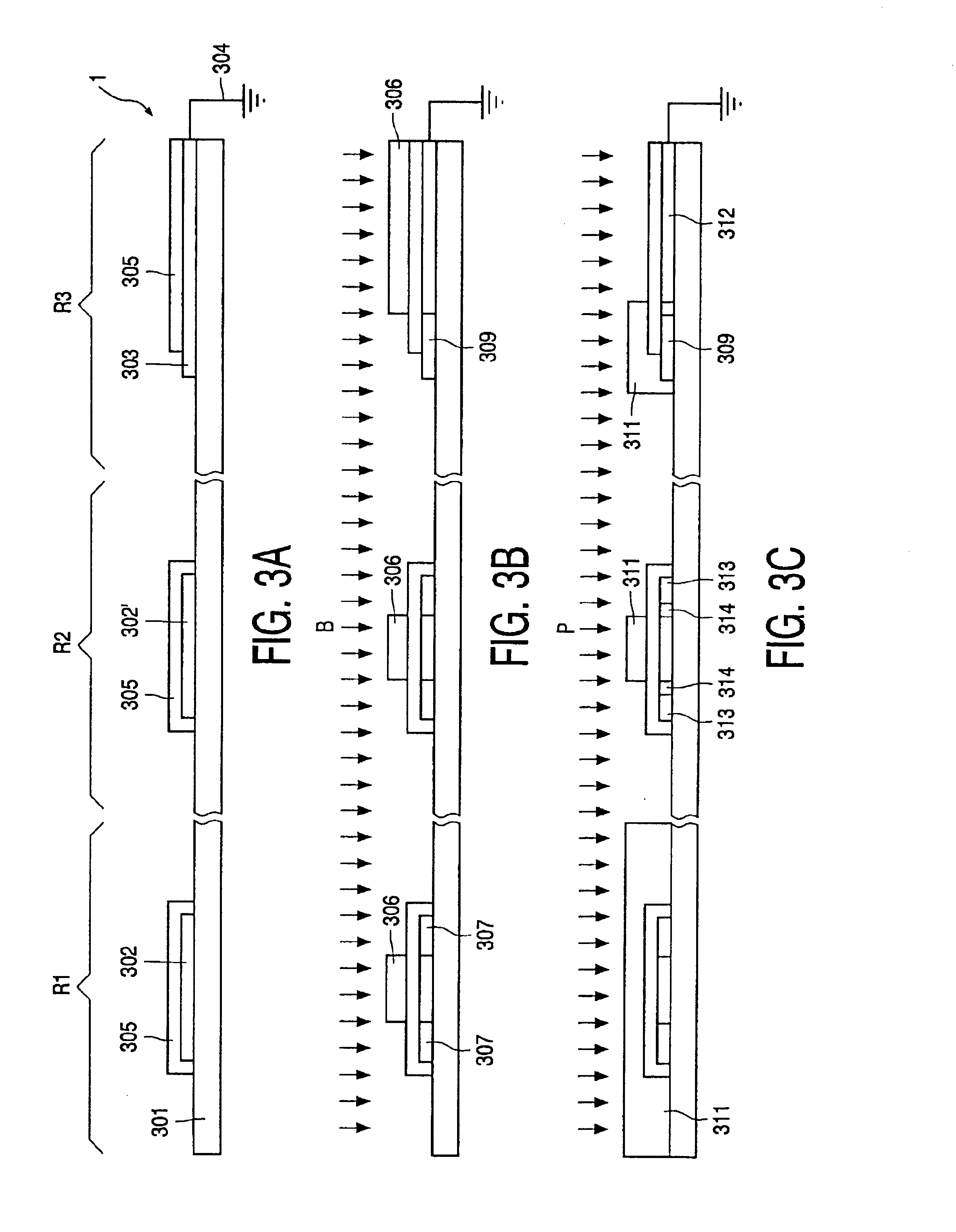

Semiconductor device having ESD device

ActiveUS8604548B2Induce punch-through currents more easilyEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Owner:MARLIN SEMICON LTD

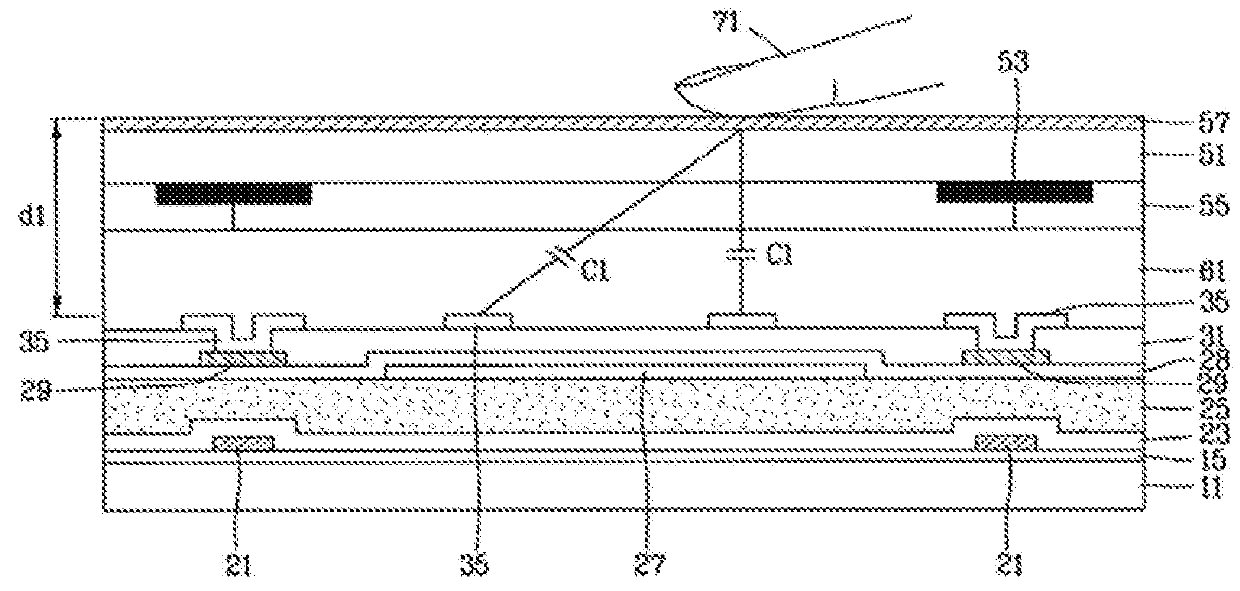

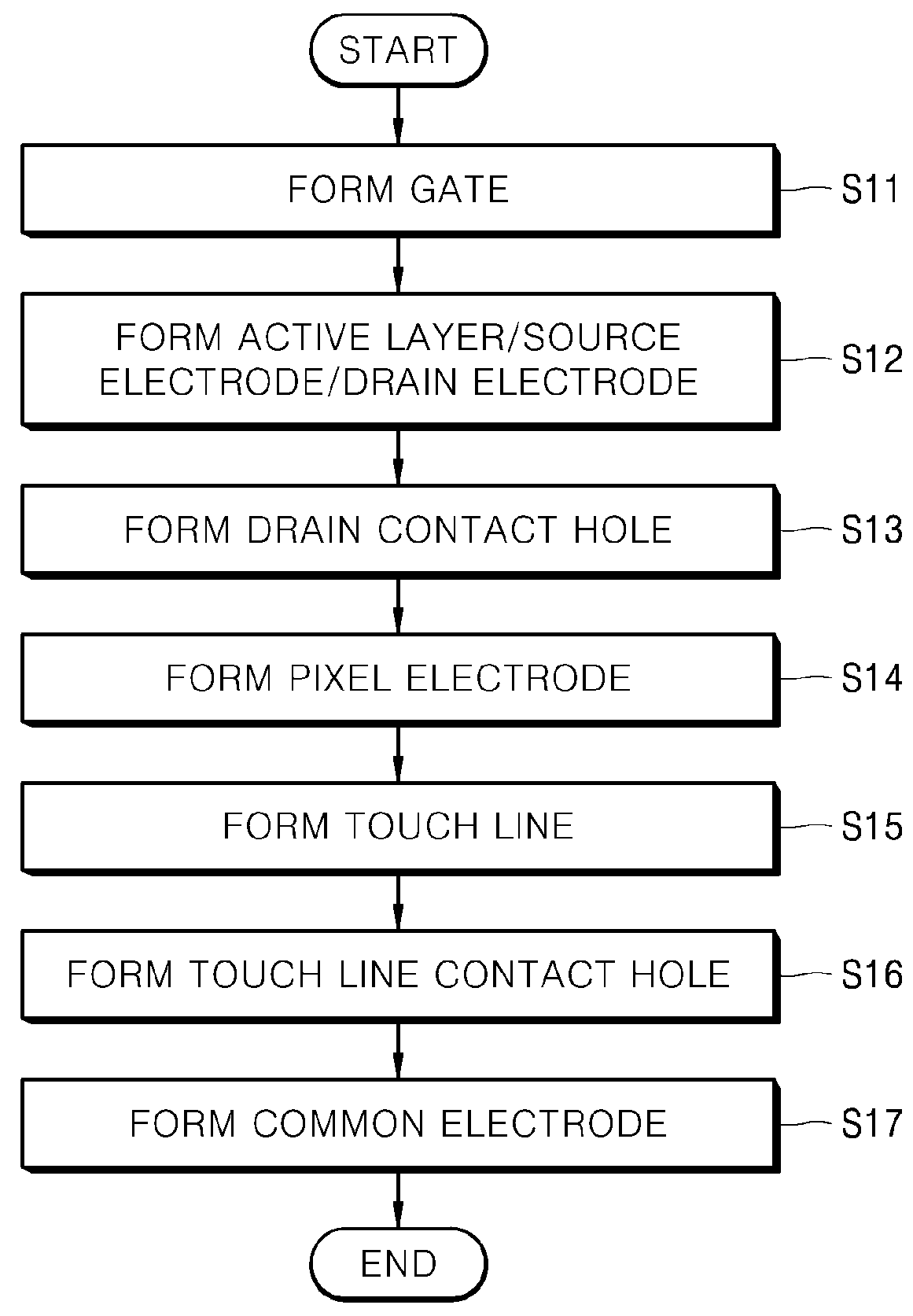

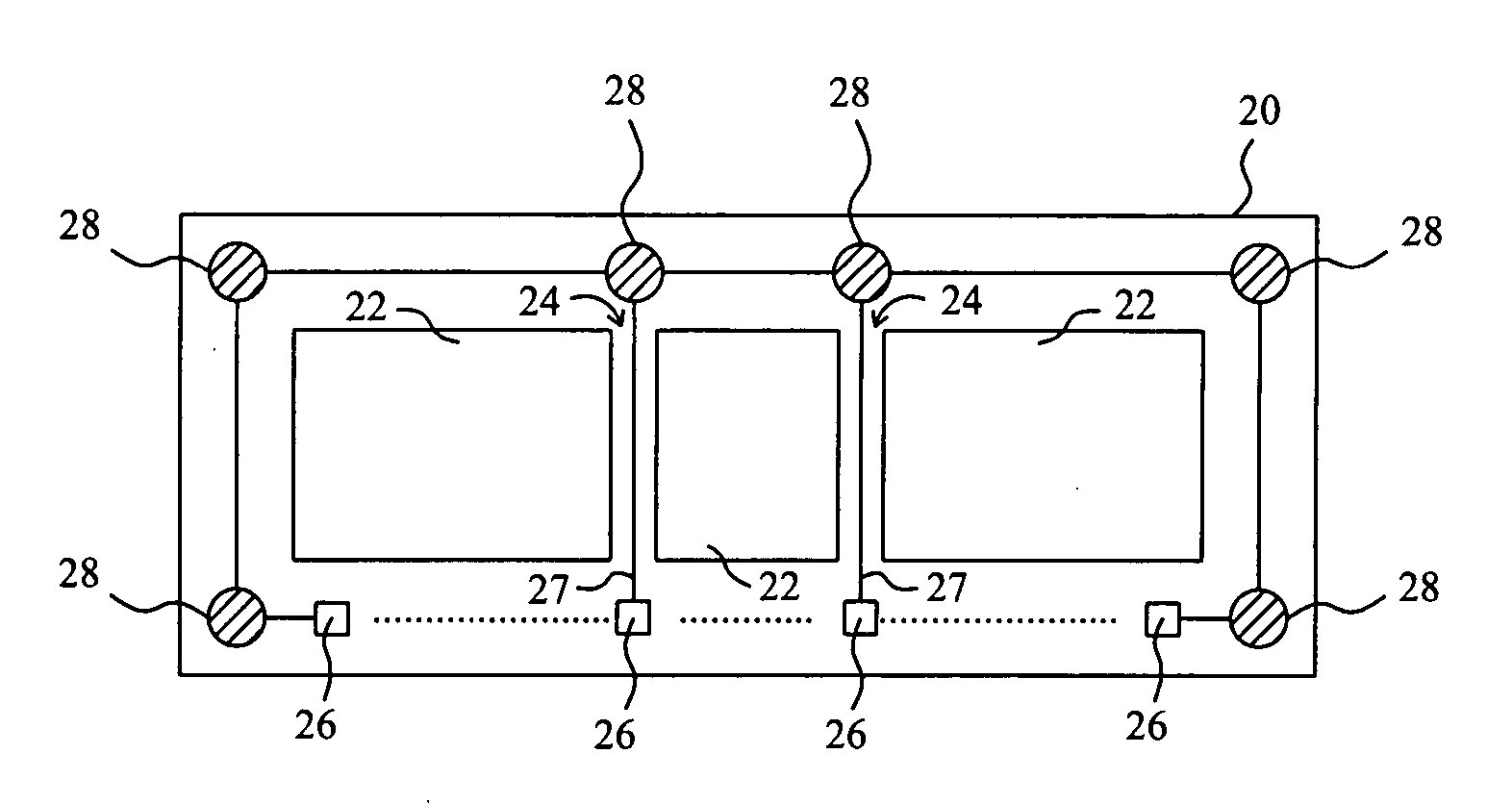

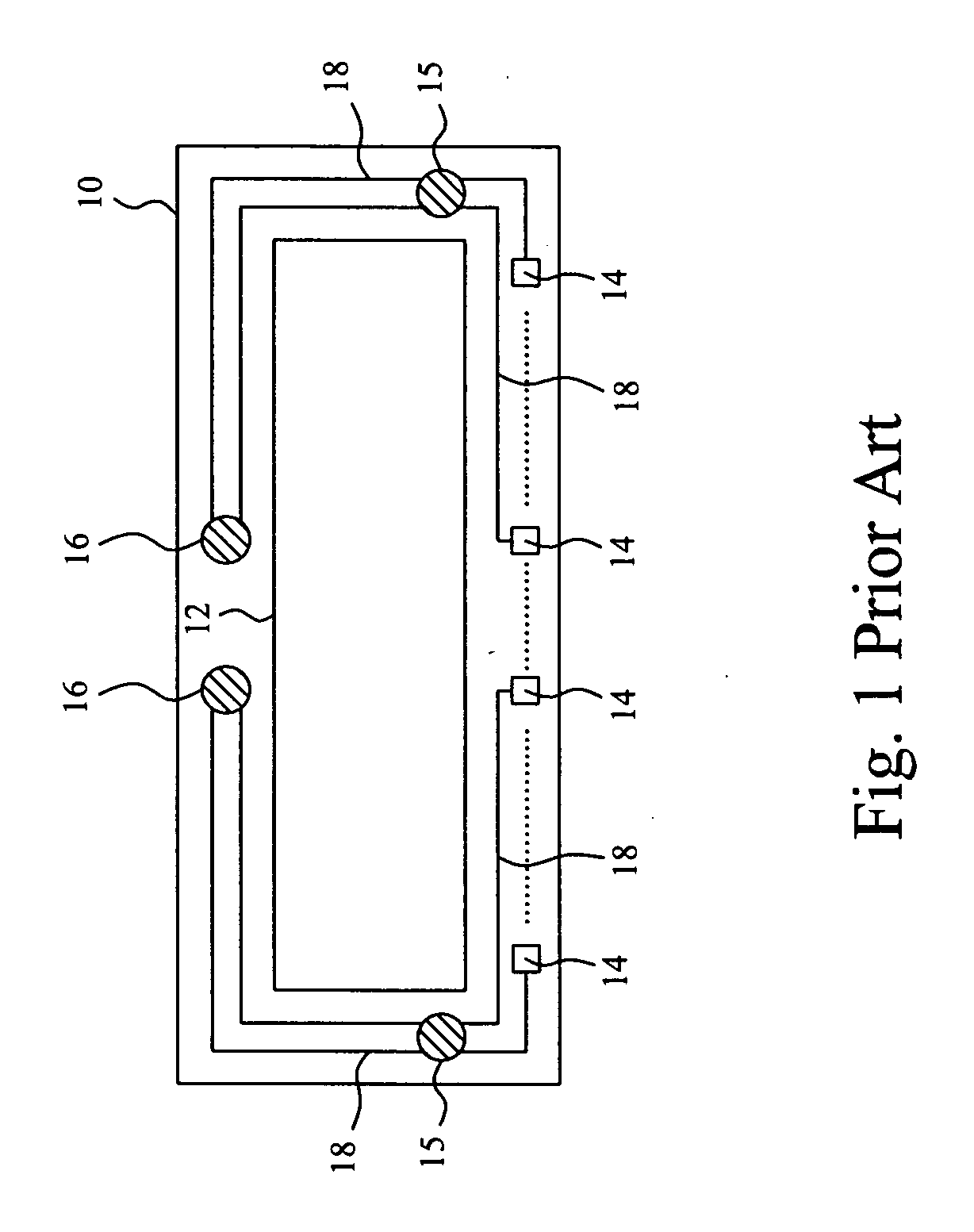

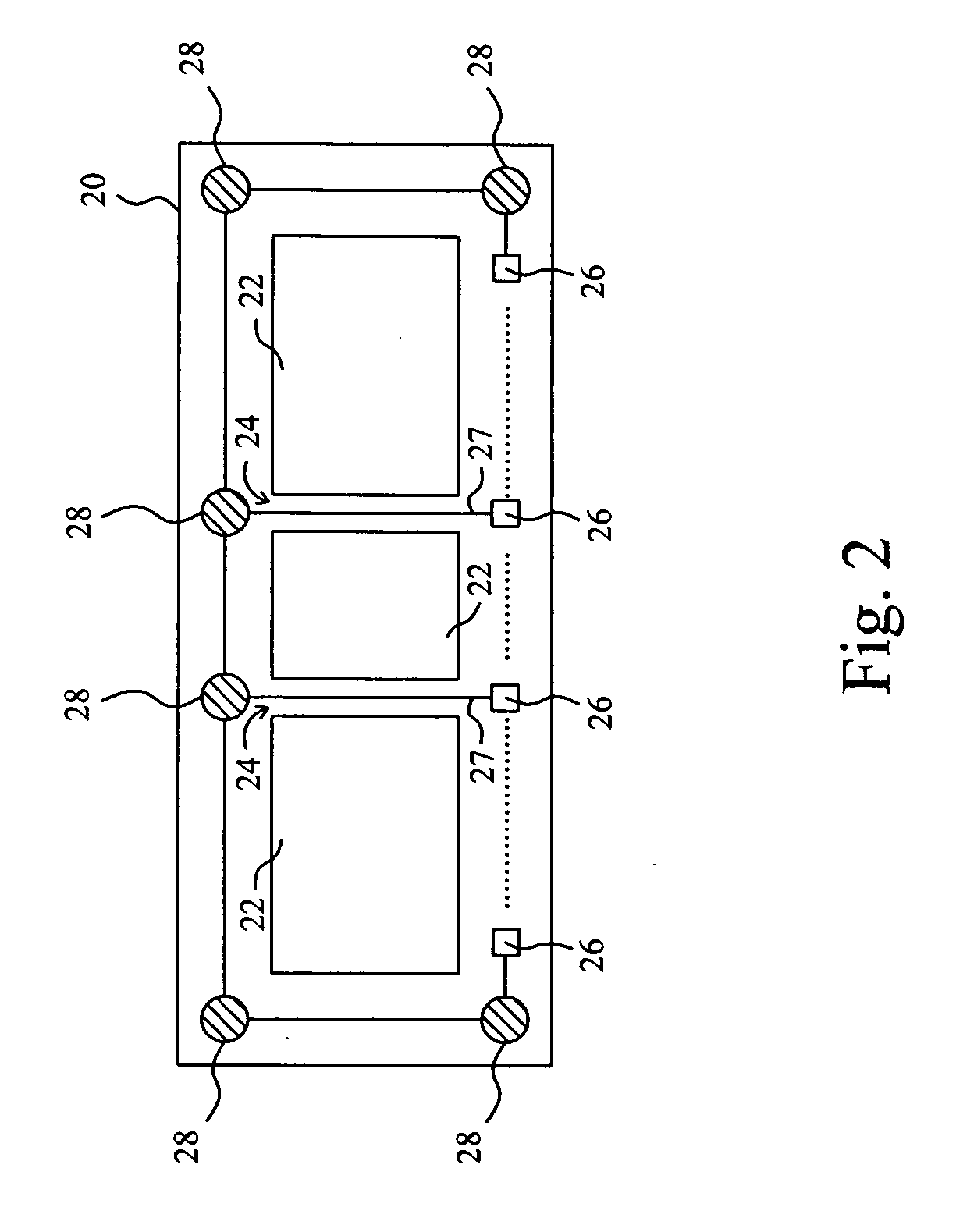

In-cell touch liquid crystal display device and method of manufacturing the same

ActiveUS20180095318A1Improve touch performanceImprove ESD performanceDigital data processing detailsSolid-state devicesManufacturing cost reductionLiquid-crystal display

An in-cell touch LCD device and a method of manufacturing the same are discussed. The in-cell touch LCD device may implement a screen display and a screen touch through a thin-film transistor substrate, which has an area larger than that of a color filter substrate, thus improving touch performance and ESD performance and simplifying a manufacturing process and reducing manufacturing costs.

Owner:LG DISPLAY CO LTD

LCD source driver for improving electrostatic discharge

InactiveUS20070057327A1Improve ESD performanceIncrease chip areaSemiconductor/solid-state device detailsSolid-state devicesElectrostatic dischargePower cord

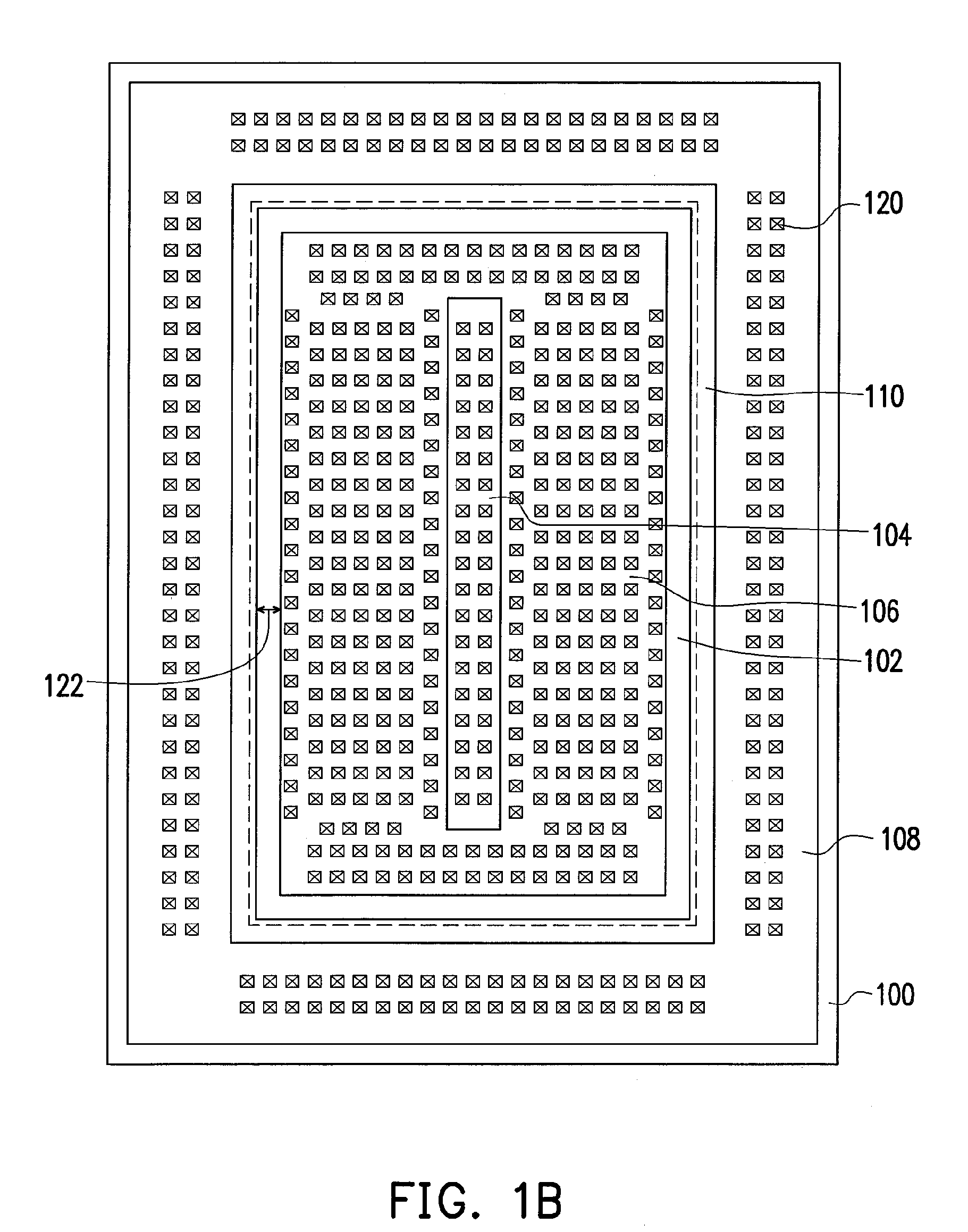

In an LCD source driver, to enhance the ESD performance thereof, there is provided a path in a device area penetrating thereacross such that an internal power wire or an internal ground wire to connect between an output pad and a power-rail ESD clamp circuit on two margins, respectively, of the LCD source driver could pass through the path to shorten the internal power wire or the internal ground wire and thereby to avoid chip area increase for the ESD mechanism.

Owner:ELAN MICROELECTRONICS CORPORATION

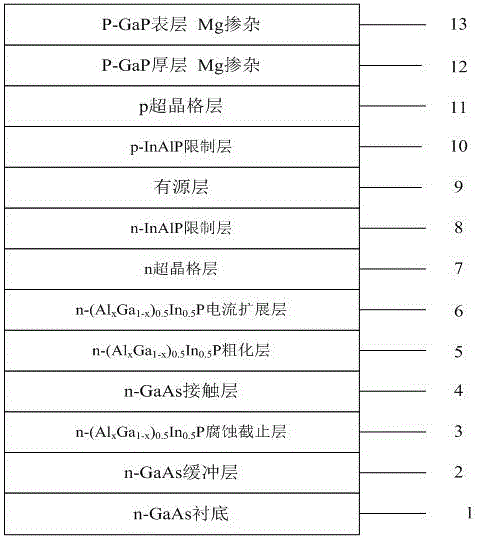

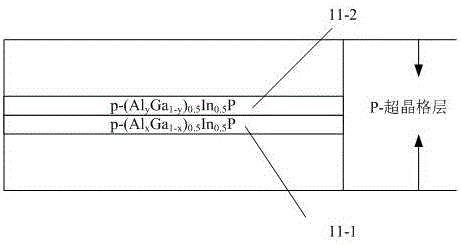

Epitaxial wafer for inverted LED chip and fabrication method of epitaxial wafer

InactiveCN106129196AImprove current spreading effectImprove luminous efficiencySemiconductor devicesPotential wellLight-emitting diode

The invention relates to an epitaxial wafer for an inverted LED chip and a fabrication method of the epitaxial wafer, belongs to the technical field of epitaxy of a light emitting diode. An n-(Al<x>Ga<1-x>)<0.5>In<0.5>P potential well layer and an n-(Al<y>Ga<1-y>)<0.5>In<0.5>P barrier layer are periodically, alternatively and epitaxially grown during growth of an n-type superlattice, and a p-(Al<x>Ga<1-x>)<0.5>In<0.5>P potential well layer and a p-(Al<y>Ga<1-y>)<0.5>In<0.5>P barrier layer are periodically, alternatively and epitaxially grown during growth of a p-type superlattice. The fabrication process is simple and reasonable, the transverse motion of an electron in an n-(Al<x>Ga<1-x>)<0.5>In<0.5>P current extension layer can be effectively improved by the n-type superlattice, and the luminous efficiency of an AlGaInP epitaxial structure is further improved. With the product fabricated by the method, the luminous efficiency, the photoelectric property and the yield of an AlGaInP-based inverted LED epitaxial wafer can be effective enhanced.

Owner:YANGZHOU CHANGELIGHT

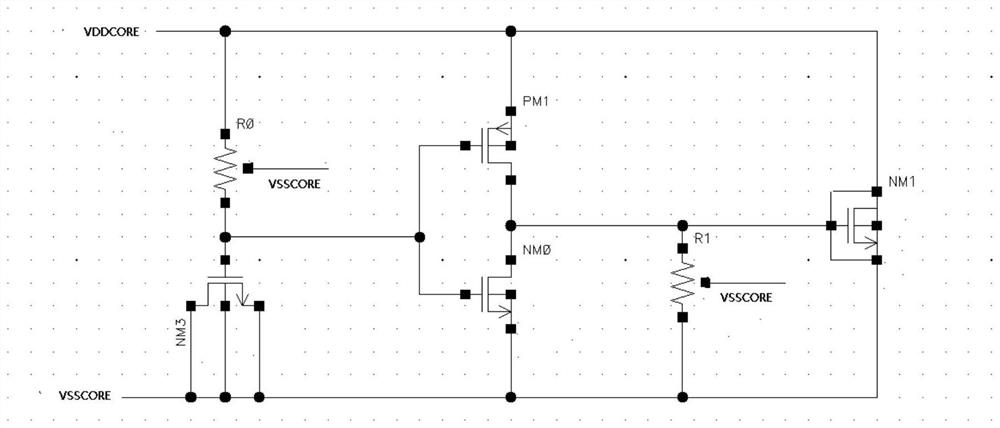

Static discharging circuit

InactiveCN102611093AExcellent ESD performanceIncreased maximum withstand voltageEmergency protective arrangements for limiting excess voltage/currentEngineeringHigh pressure

The invention relates to a static discharging circuit, which comprises a voltage division circuit, a first N-channel metal oxide semiconductor (NMOS) tube and a second NMOS tube, wherein a positive electrode input end of the voltage division circuit is connected with a high-voltage input end, a negative electrode input end of the voltage division circuit is coupled with the ground, and an output end is connected with a grid electrode of the first NMOS tube and is used for outputting bias voltage conducting the first NMOS tube; a drain electrode of the first NMOS tube is connected with the high-voltage input end, and a source electrode is connected with a drain electrode of the second NMOS tube; and a source electrode of the second NMOS tube is grounded, and a grid electrode of the second NMOS tube is coupled with the ground. The static discharging circuit has the advantages that the circuit voltage resistant value is improved, and meanwhile, the static discharging performance of the static discharging circuit is also improved.

Owner:SHANGHAI AWINIC TECH CO LTD

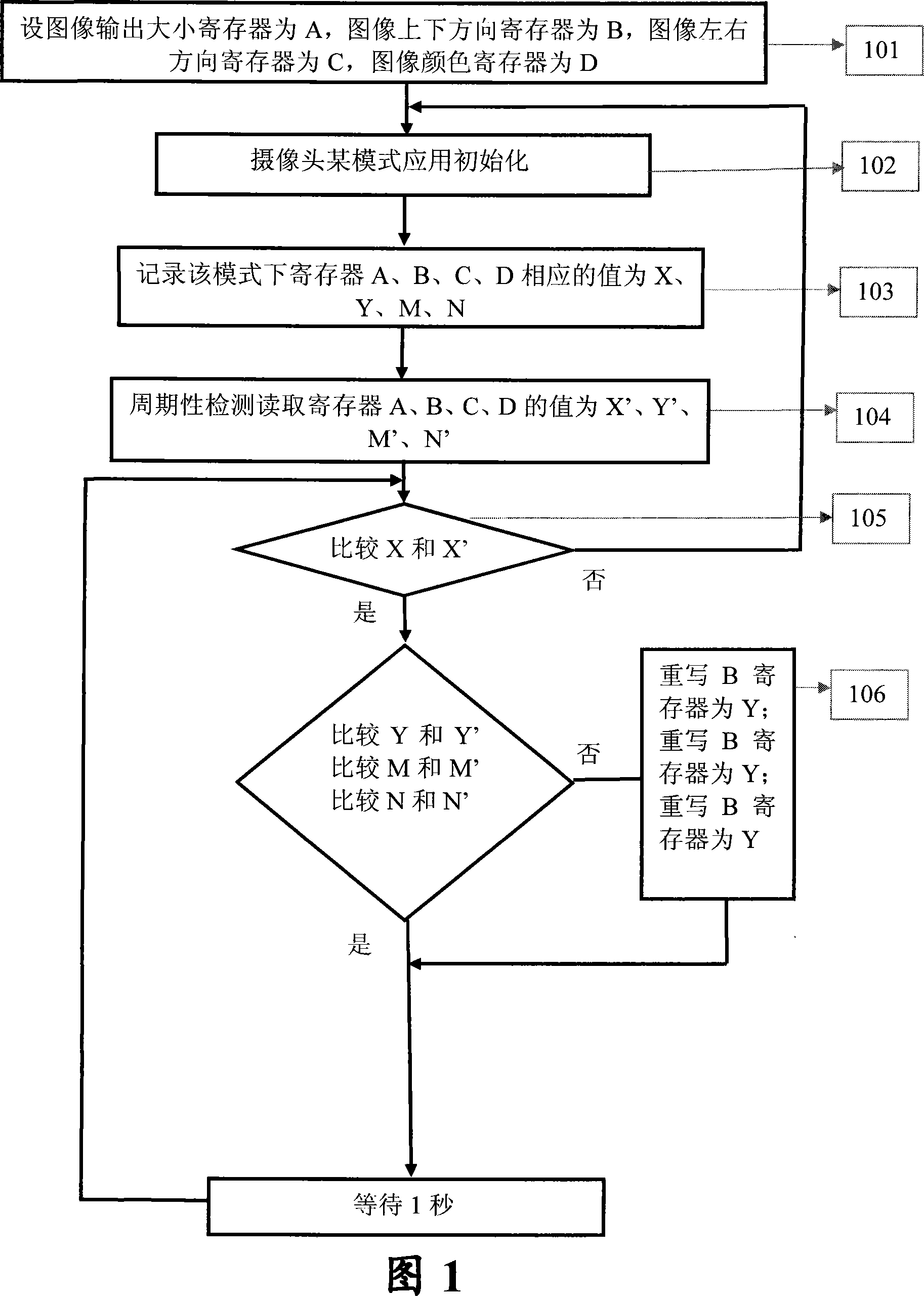

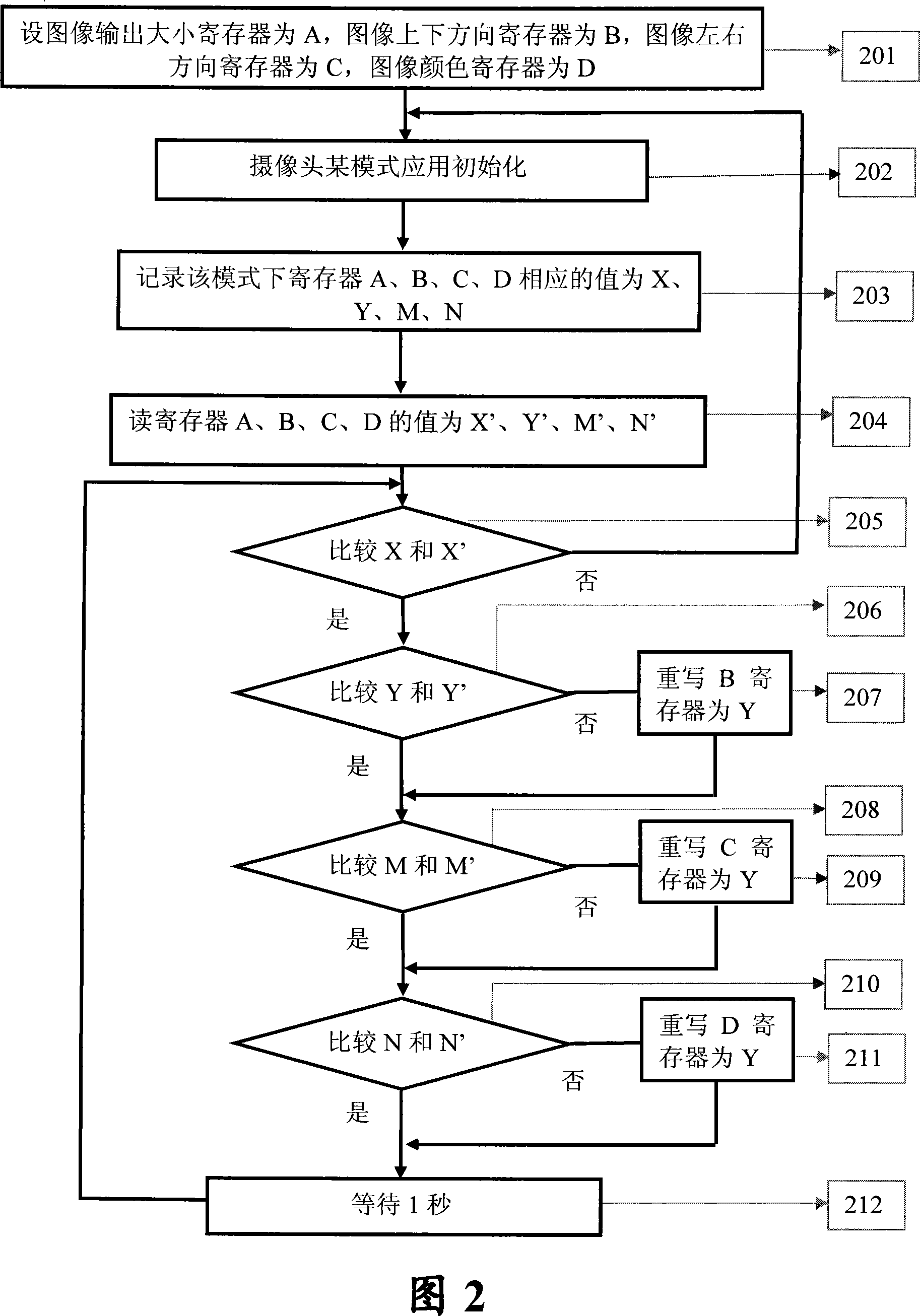

Method for improving issue for releasing static charge for pick-up head of handset

InactiveCN101094325AImproved ESD performanceGuaranteed validityTelevision system detailsColor television detailsComputer hardwareProcessor register

The method comprises: 1) setting up several image feature registers into the solid image sensor in the pick-up head of mobile phone; 2) when initializing the different mode of the mobile phone pick-up head, the initial image feature value is saved in the image feature register; 3) in application of each mode of the mobile phone pick-up head, periodically detecting the current different image feature value in said image feature registers, and comparing those initial image feature value saved in said image features registers; if a certain image feature value is different with the initial value, then re-writing the image feature register value as the initial image feature value; if they are the same, after a waiting time, re-executing the step 3.

Owner:ZTE CORP

ESD protection device

ActiveUS20100295157A1Improve ESD performanceTransistorSemiconductor/solid-state device detailsP type dopingPhysics

Owner:UNITED MICROELECTRONICS CORP

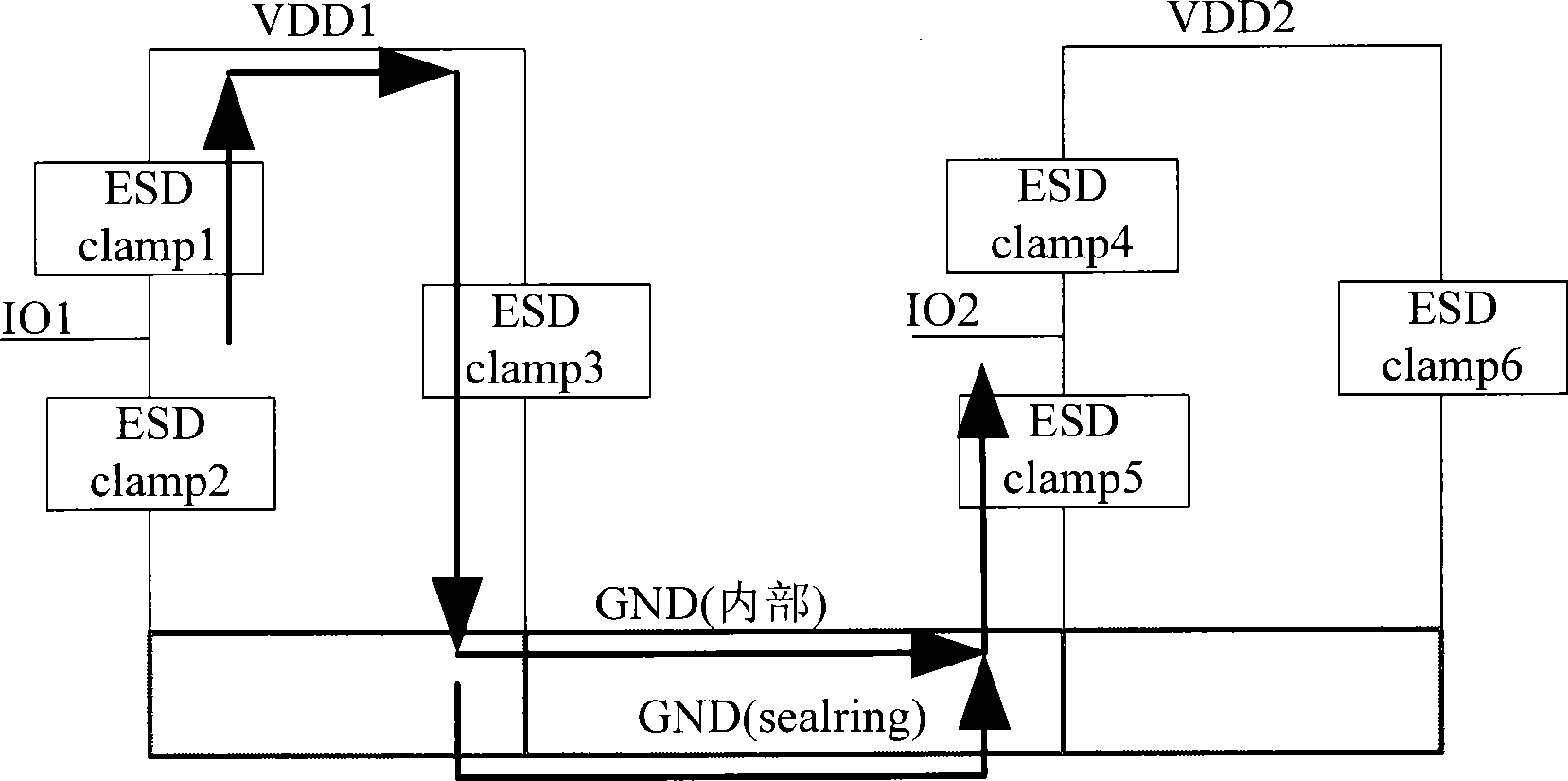

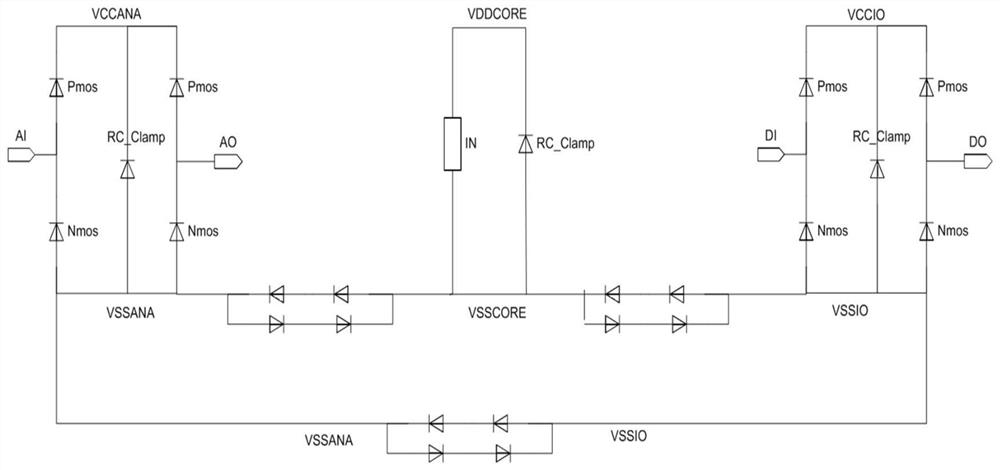

Electrostatic discharge protection method of chip with multiple power systems and multiple package types

InactiveCN104347621AReduce areaImprove ESD performanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceElectrostatic discharge protection

The invention discloses an electrostatic discharge protection method of a chip with multiple power systems and multiple package types. According to the method, in addition to using a common ground wire path in the chip, a ground potential in a seal ring is utilized, and a ground wire of each power system is connected, so that the electrostatic discharge current is released through two parallel paths, and thus the condition of damage caused by excessive potential of a circuit in the chip due to overlarge parasitic resistance on a discharge path is avoided. According to the method, the ESD (Electronic Static Discharge) performance of the chip is enhanced without increasing the area of the chip.

Owner:BEIJING CEC HUADA ELECTRONIC DESIGN CO LTD

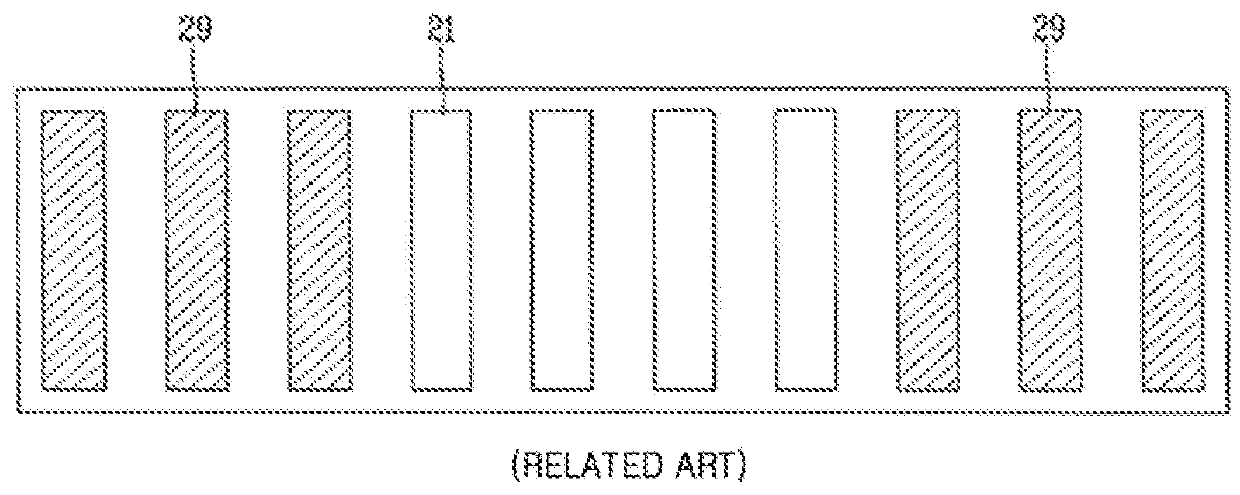

Active matrix substrate

InactiveUS6838700B2Prevent current flowDissipating negative charge build-upTransistorDischarge tube luminescnet screensElectrical conductorActive matrix

An active matrix substrate includes a row and column array of active elements. Each element is associated with a TFT having a gate electrode connected to a corresponding row conductor and source and drain (electrodes connected to corresponding column conductors. Circuitry for protecting against electrostatic discharge (ESD) is connected to at least one of the row conductors for protecting the TFTs against ESD.

Owner:TPO HONG KONG HLDG

Monolithic compound semiconductor structure

ActiveUS9087923B2Small surface areaImprove ESD performanceTransistorSolid-state devicesCompound semiconductorThyristor

Owner:WIN SEMICON

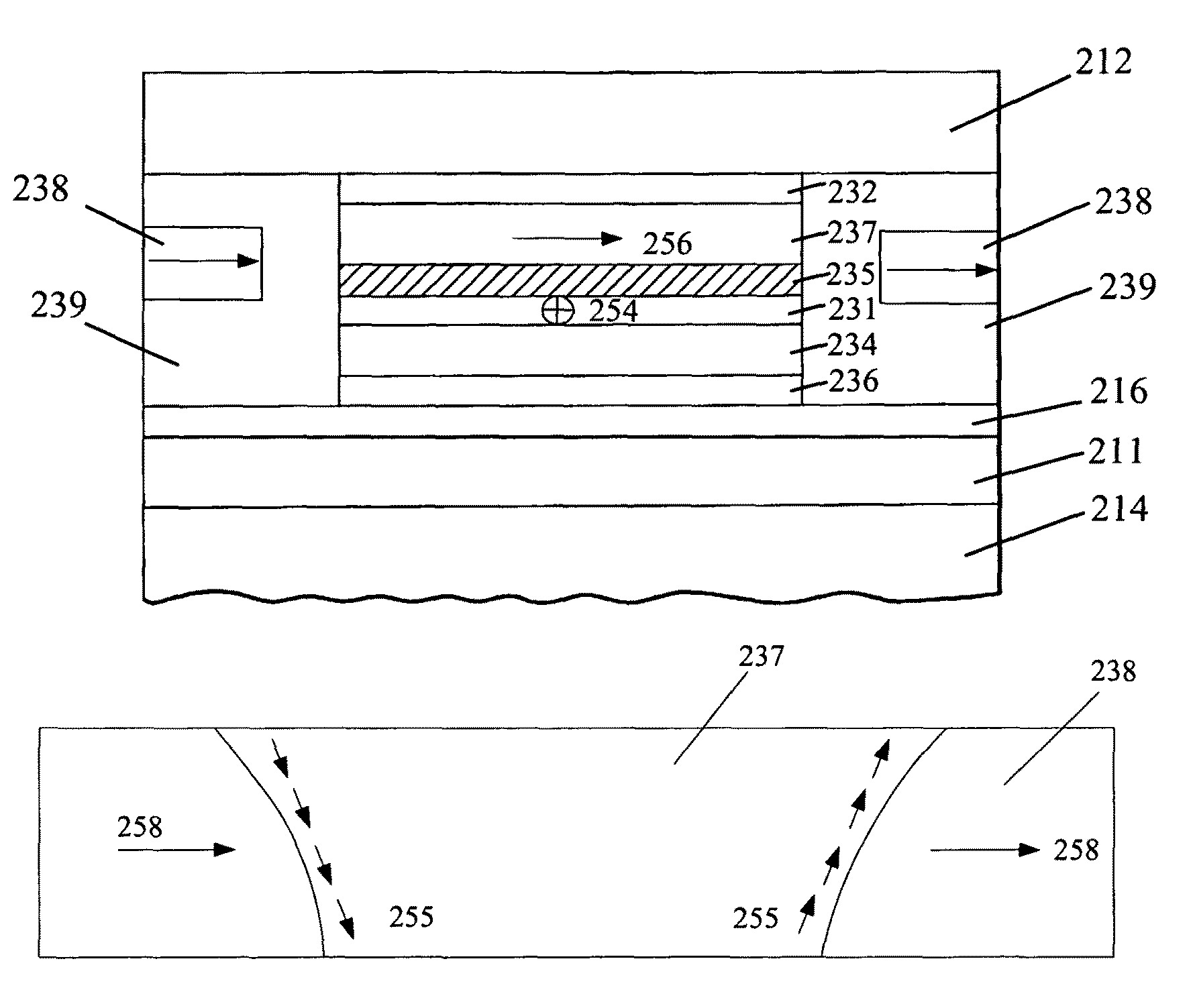

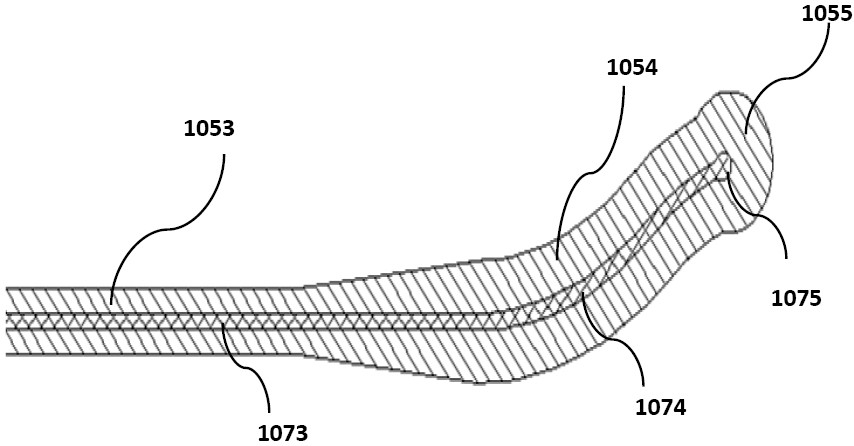

Magnetoresistive sensor with funnel-shaped free layer, magnetic head, head gimbal assembly, and disk drive unit with the same

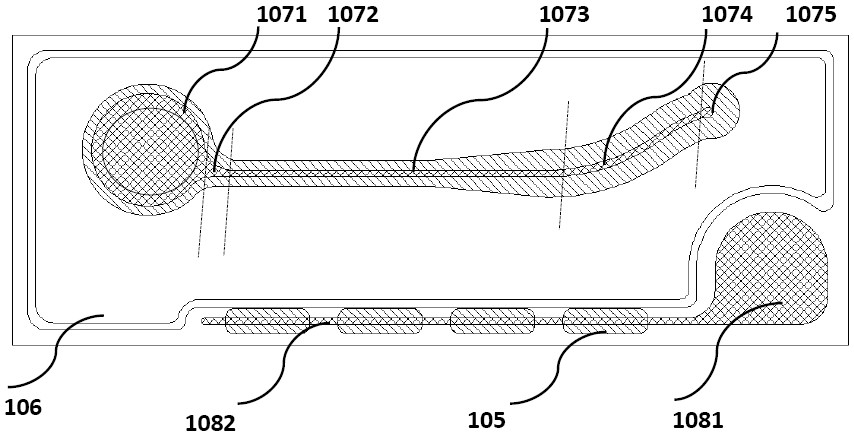

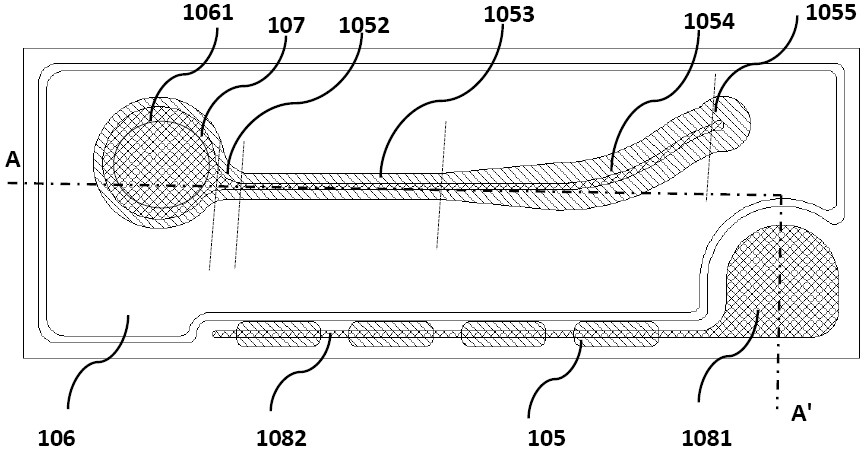

InactiveUS8767356B2Improve controlImprove ESD performanceNanomagnetismDisposition/mounting of recording headsEngineeringAir bearing surface

An MR sensor includes a first shielding layer, a second shielding layer, an MR element formed therebetween, and a pair of hard magnet layers respectively placed on two sides of the MR element. The MR element includes an AFM layer formed on the first shielding layer, a pinned layer formed on the AFM layer and a free layer formed between the pinned layer and the second shielding layer. The free layer is funnel-shaped, which has a first edge facing an air bearing surface and a second edge opposite the first edge, and the first edge has a narrower width than that of the second edge. The MR sensor can improve MR height control performance, and improve the ESD performance and decrease the PCN and RTN and, in turn, get a more stable performance. The present invention also discloses a magnetic head, an HGA and a disk drive unit.

Owner:SAE MAGNETICS (HK) LTD +1

ESD protection device

Owner:UNITED MICROELECTRONICS CORP

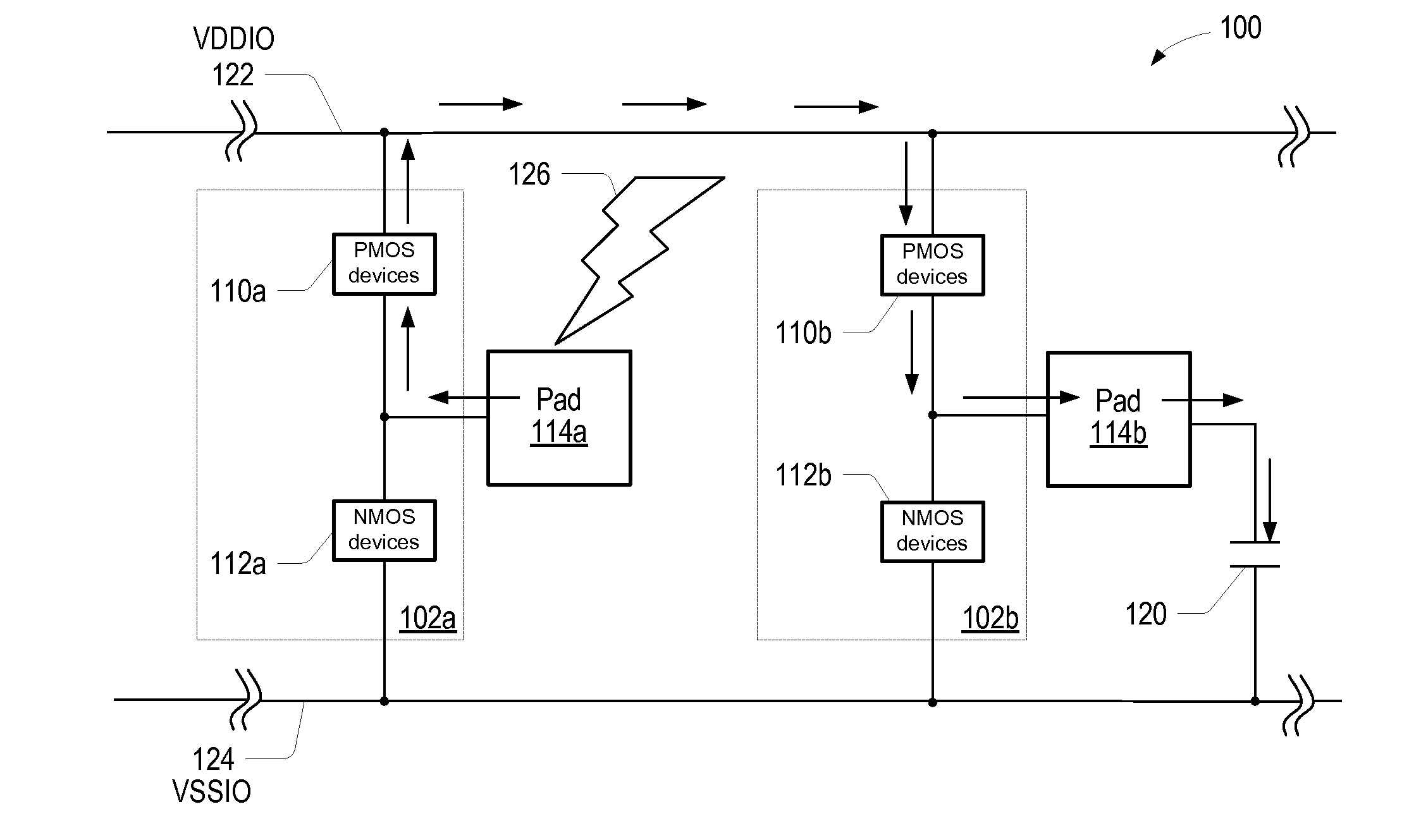

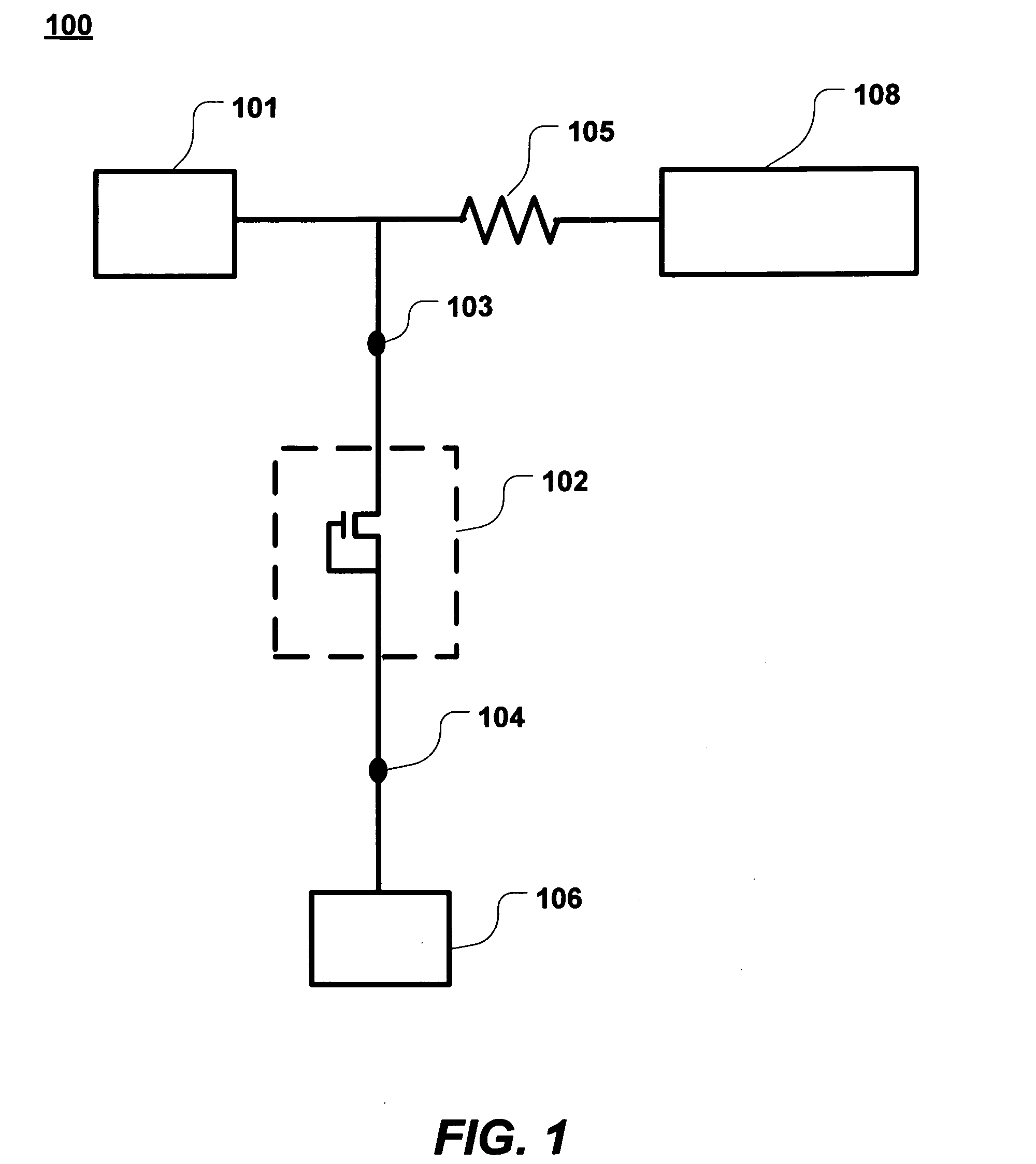

Pad ESD Spreading Technique

ActiveUS20080165459A1Reduce peak voltageImprove performanceEmergency protective arrangements for limiting excess voltage/currentCapacitanceΠ pad

A system, e.g. an integrated circuit or part, may include a plurality of pads, e.g. digital I / O pads, each comprising a physical pad and associated pad circuit. In case of an ESD event affecting one or more of the digital I / O pads, PMOS devices configured in an output buffer section between an I / O pad supply rail and the physical output pad—within their respective pad circuits in the affected digital I / O pads—may all be turned on in response to the ESD event. This may allow the capacitance of each pad, in some cases approximately 3 pF capacitance per pad, to charge up, absorbing the energy of the ESD event and reducing the peak voltage the integrated circuit or part experiences as a result of the ESD event. The reduced peak voltage may be directly correlated with improved ESD performance of the product.

Owner:MICROCHIP TECH INC

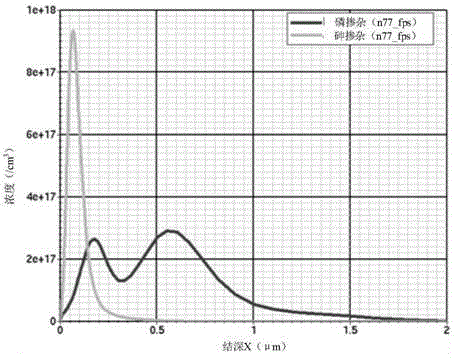

Semiconductor device and manufacturing method thereof, and electronic device

ActiveCN106298966AImprove ESD performanceImprove current withstand capabilitySemiconductor/solid-state device detailsSolid-state devicesSemiconductorIon implantation

The invention provides a manufacturing method of a semiconductor device. The manufacturing method comprises the steps of: providing a semiconductor substrate; performing first ion implantation by using a first photomask, so as to form a first well region of a first conductivity type in the semiconductor substrate; performing second ion implantation by using a second photomask, so as to form a second well region of the first conductivity type in the semiconductor substrate; forming a first diffusion region of a second conductive type in the first well region; and forming a second diffusion region of the first conductivity type in the second well region, wherein the second well region positions on the outer side of the first well region, and a concentration of ions of the first conductivity type in the first well region is lower than that that of ions of the first conductivity type in the second well region. The invention further provides a semiconductor device manufactured by adopting the semiconductor device, and an electronic device. Compared with the prior art, the semiconductor diode device manufactured by adopting the manufacturing method and the electronic device comprising the same can improve the ESD voltage tolerance and current tolerance, and effectively reduce electric leakage and improve the ESD performance of the devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP

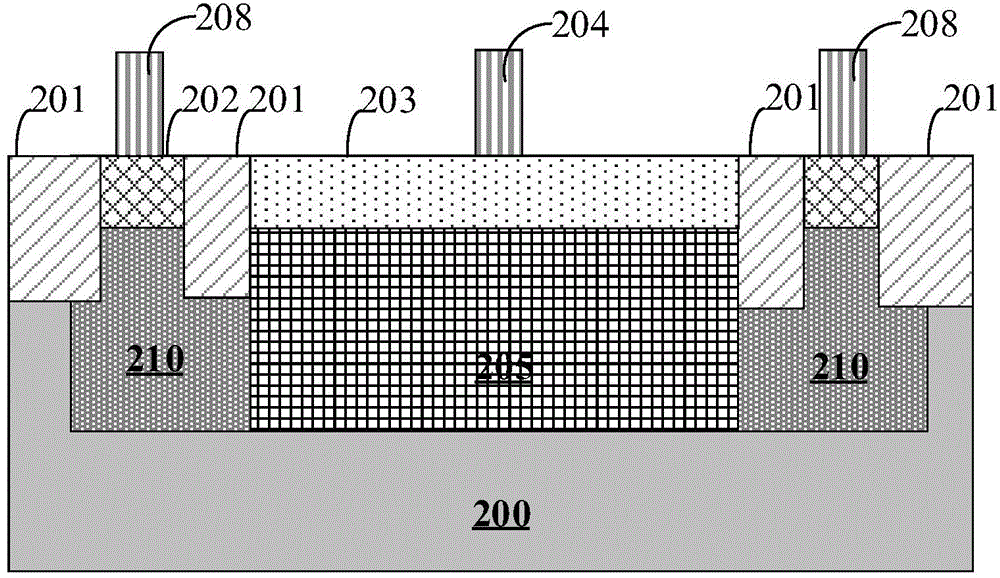

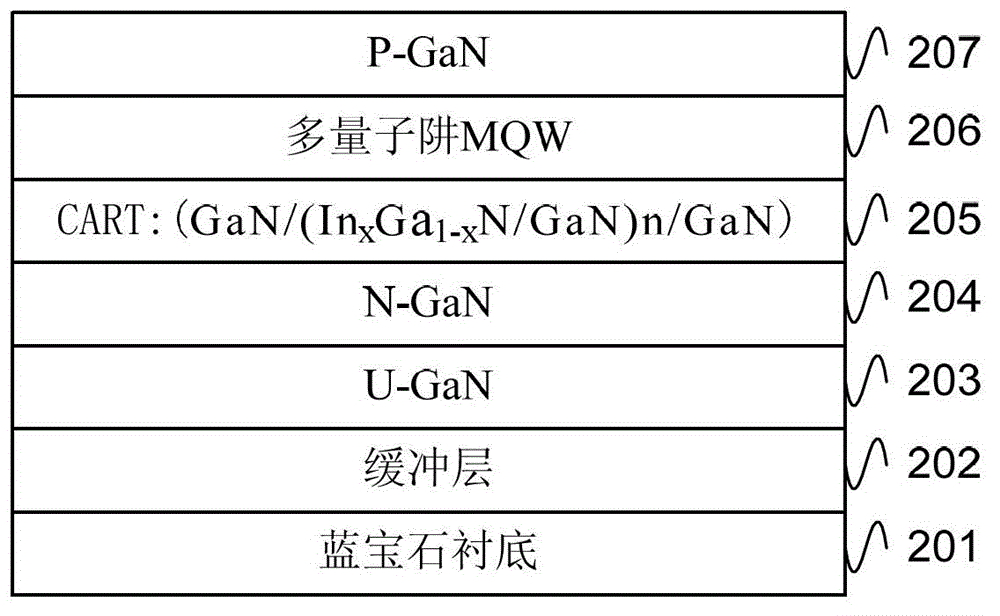

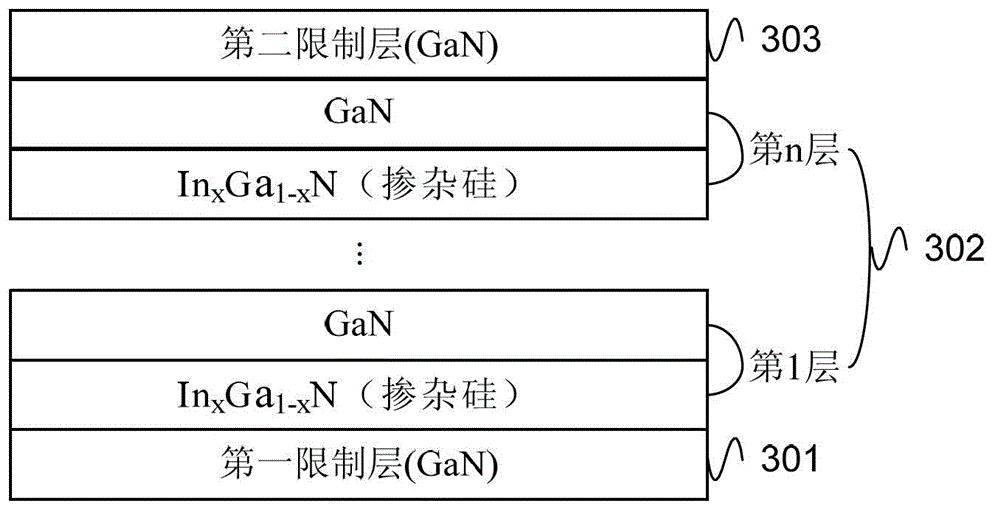

LED epitaxy structure

ActiveCN103560185AImproved ESD performanceImprove the ability to resist ESDSemiconductor devicesOptoelectronicsElectrostatic discharge

The invention provides an LED epitaxy structure. The LED epitaxy structure comprises a substrate. A buffer layer is arranged on the substrate. The surface of the buffer layer is provided with an undoped GaN layer. The surface of the undoped GaN layer is provided with an N-type doped GaN layer. The surface of the N-type doped GaN layer is provided with an asymmetric resonant tunnel CART structure layer. The surface of the CART structure layer is provided with a multiple quantum well MQW layer. A P-type doped GaN layer is arranged on the MQW layer. According to the embodiments of the invention, the LED electrostatic discharge (Electro-Static Discharge, ESD) resistance capability can be effectively improved.

Owner:EPITOP PHOTOELECTRIC TECH

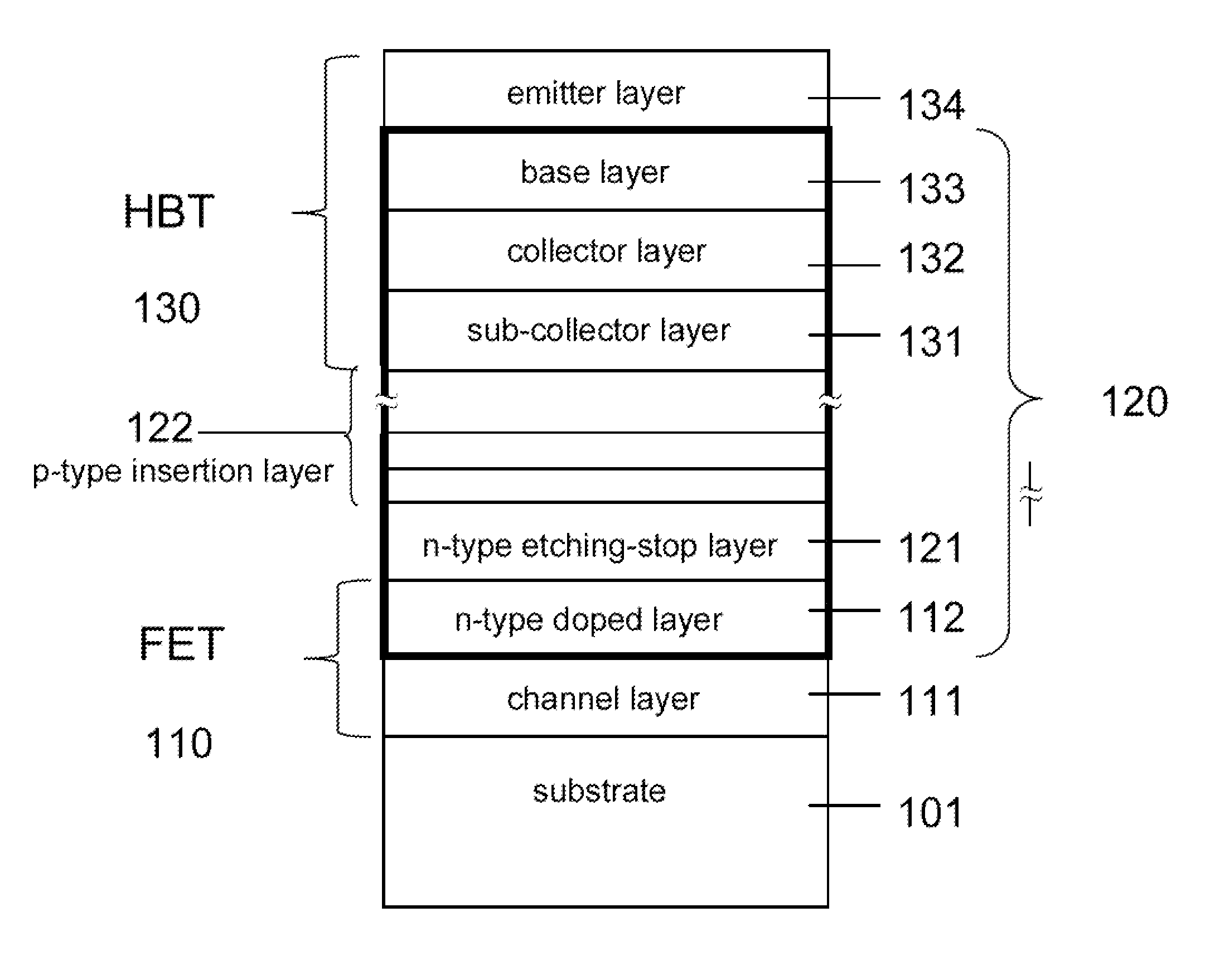

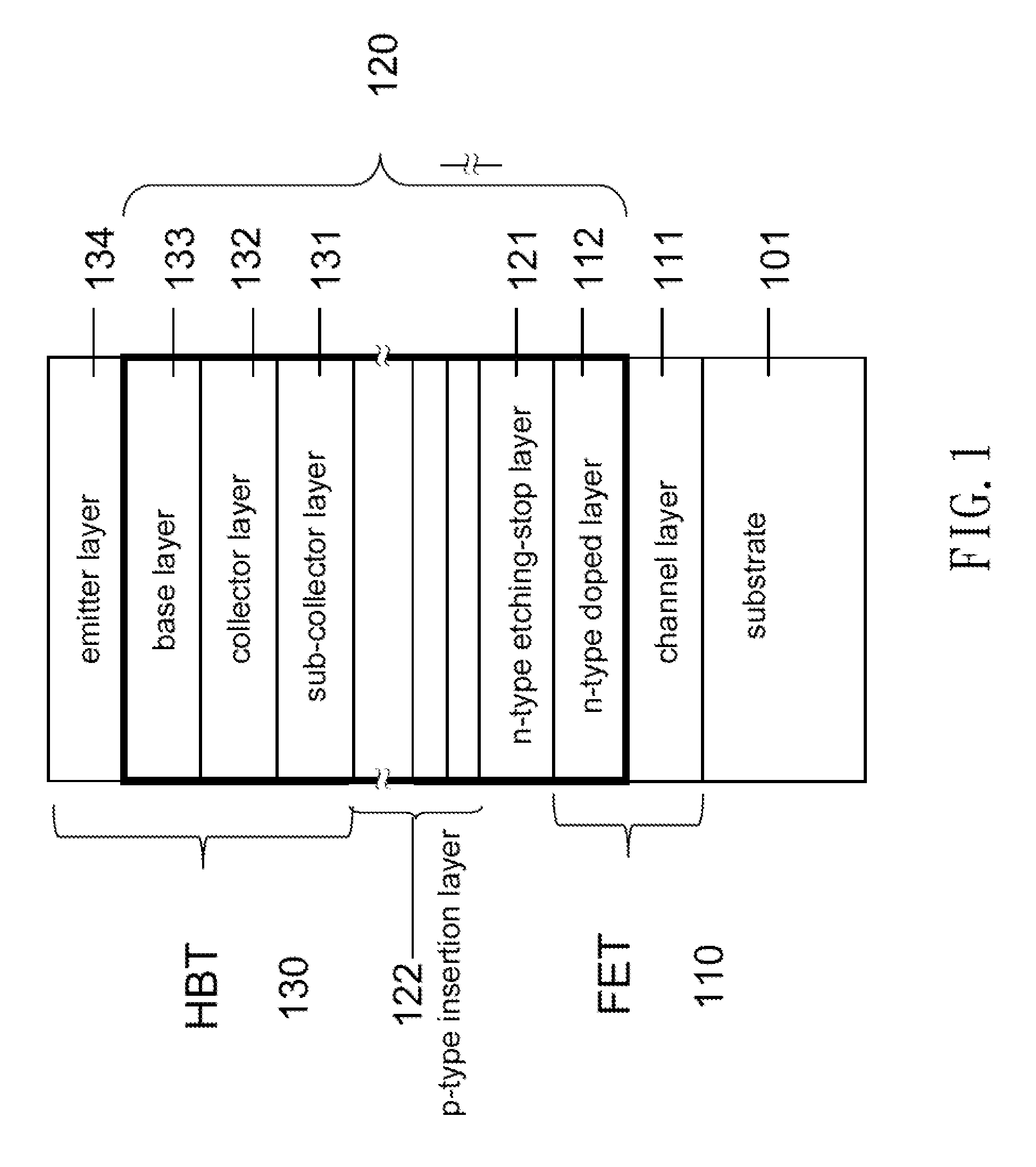

Monolithic compound semiconductor structure

ActiveUS20130334564A1Small surface areaImprove ESD performanceTransistorThyristorCompound semiconductorPhysics

A monolithic compound semiconductor structure is disclosed. The monolithic compound semiconductor structure comprises a substrate, an n-type FET epitaxial structure, an n-type etching-stop layer, a p-type insertion layer, and an npn HBT epitaxial structure, and it can be used to form an FET, an HBT, or a thyristor.

Owner:WIN SEMICON

Semiconductor light emitting element and light emitting device

PendingCN112086544AImprove distribution too concentrated phenomenonImprove reliabilitySemiconductor devicesMetal electrodesActive layer

A semiconductor light emitting element includes: a first conductivity type semiconductor layer, a second conductivity type semiconductor layer, and an active layer therebetween; a current blocking layer, comprising a strip-shaped part arranged on a local surface of the first conductive type semiconductor layer; a first metal electrode, comprising a first metal electrode pad and a first metal electrode extension strip extending out of the first metal electrode pad, and the first metal electrode extension strip being located on the strip-shaped part of the current blocking layer; the first metalelectrode extension strip comprises an extension section and an end part; and the strip-shaped part of the current blocking layer, which is positioned below part of the extension section, is providedwith a widening part which is gradually widened along the extension direction which is gradually far away from the first metal electrode pad.

Owner:XIAMEN SANAN OPTOELECTRONICS CO LTD

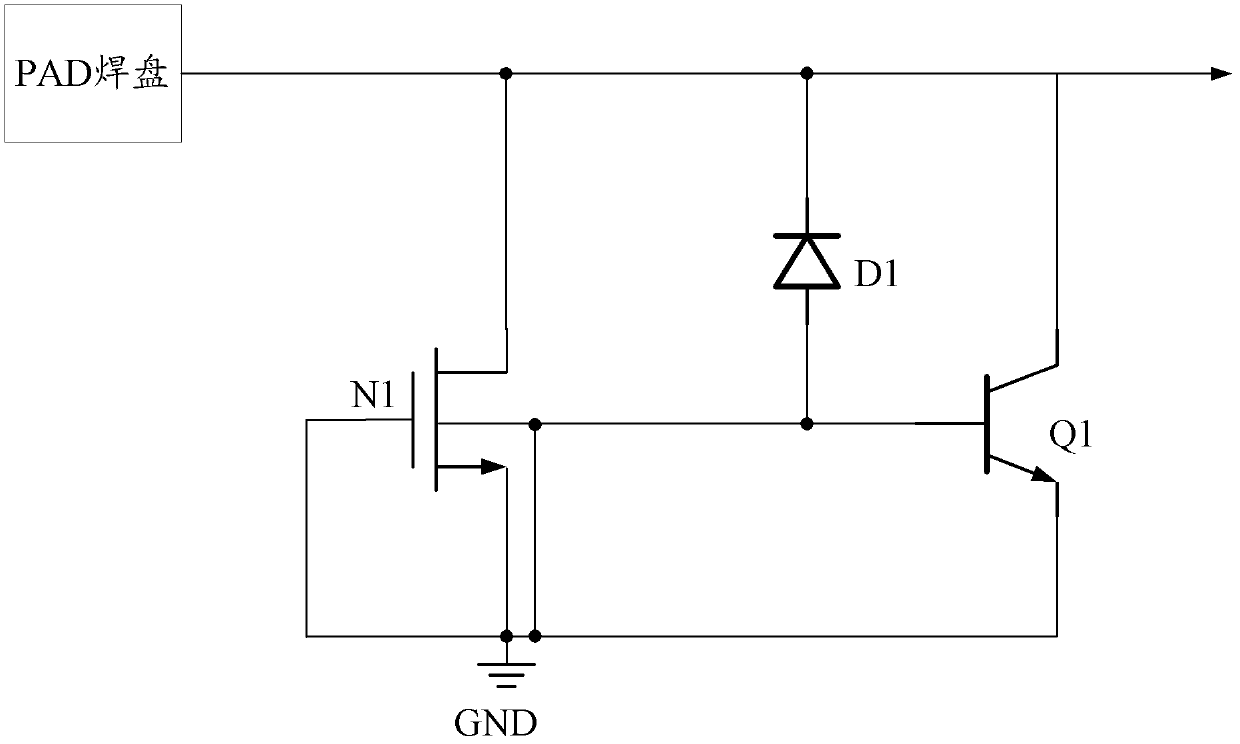

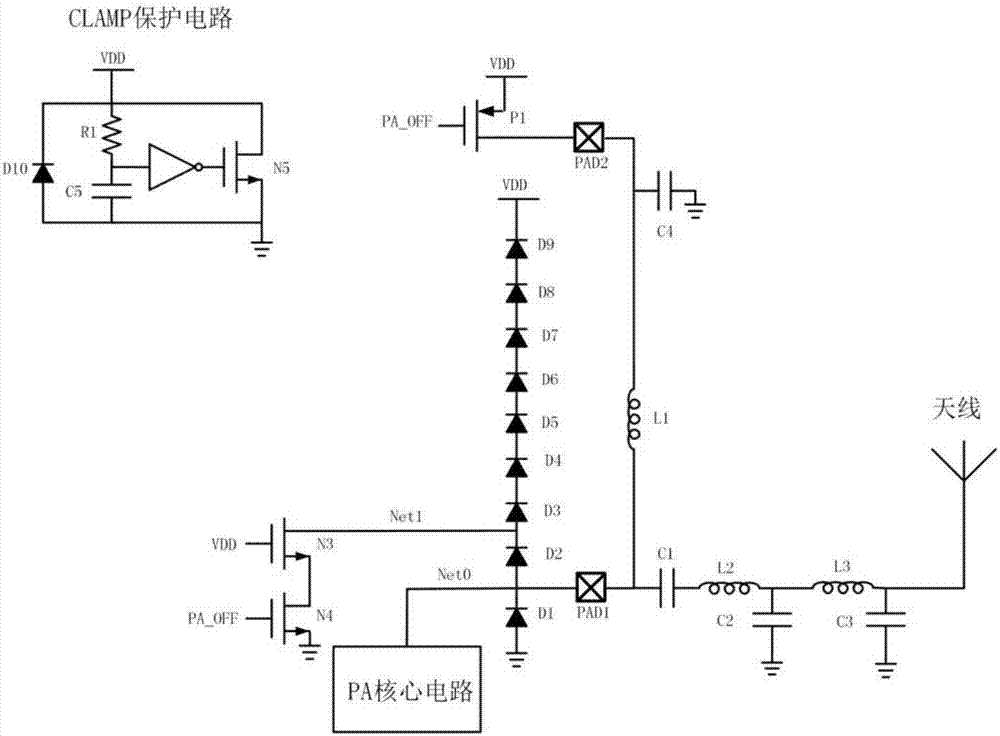

Antistatic protection circuit of radio frequency chip high-power amplifier

ActiveCN107493084AHighlight substantive featuresSignificant progressHigh frequency amplifiersPower amplifiersAudio power amplifierPower switching

The invention provides an antistatic protection circuit of a radio frequency chip high-power amplifier. The antistatic protection circuit comprises a PA core circuit, a PA output matching circuit, an ESD protection circuit and a power switch circuit; the power switch circuit is connected with the PA output matching circuit; the ESD protection circuit comprises a diode D1, a diode D2, a MOS tube N3 and a MOS tube N4; the anode of the diode D1 is grounded, and the cathode of the diode D1 is connected with the drain of the MOS tube N3 through the diode D2; the source of the MOS tube N3 is connected with the drain of the MOS tube N4, the source of the MOS tube N4 is grounded; the grid of the MOS tube N3 is connected with a power supply VDD, the cathode of the diode D2 is connected with the power supply VDD by orderly passing through the diodes D3 to D9 in a forward direction; the grid of the MOS tube N4 is connected with the power switch circuit; the cathode of the diode D1 is connected with the PA core circuit, and the cathode of the diode D1 is connected with the PA output matching circuit through the PAD1. The antistatic protection circuit of the radio frequency chip high-power amplifier provided by the invention has the advantages of being scientific in design, strong in practicability, simple in structure, high in EDS performance and low in cost.

Owner:WUXI ZETAI MICROELECTRONICS

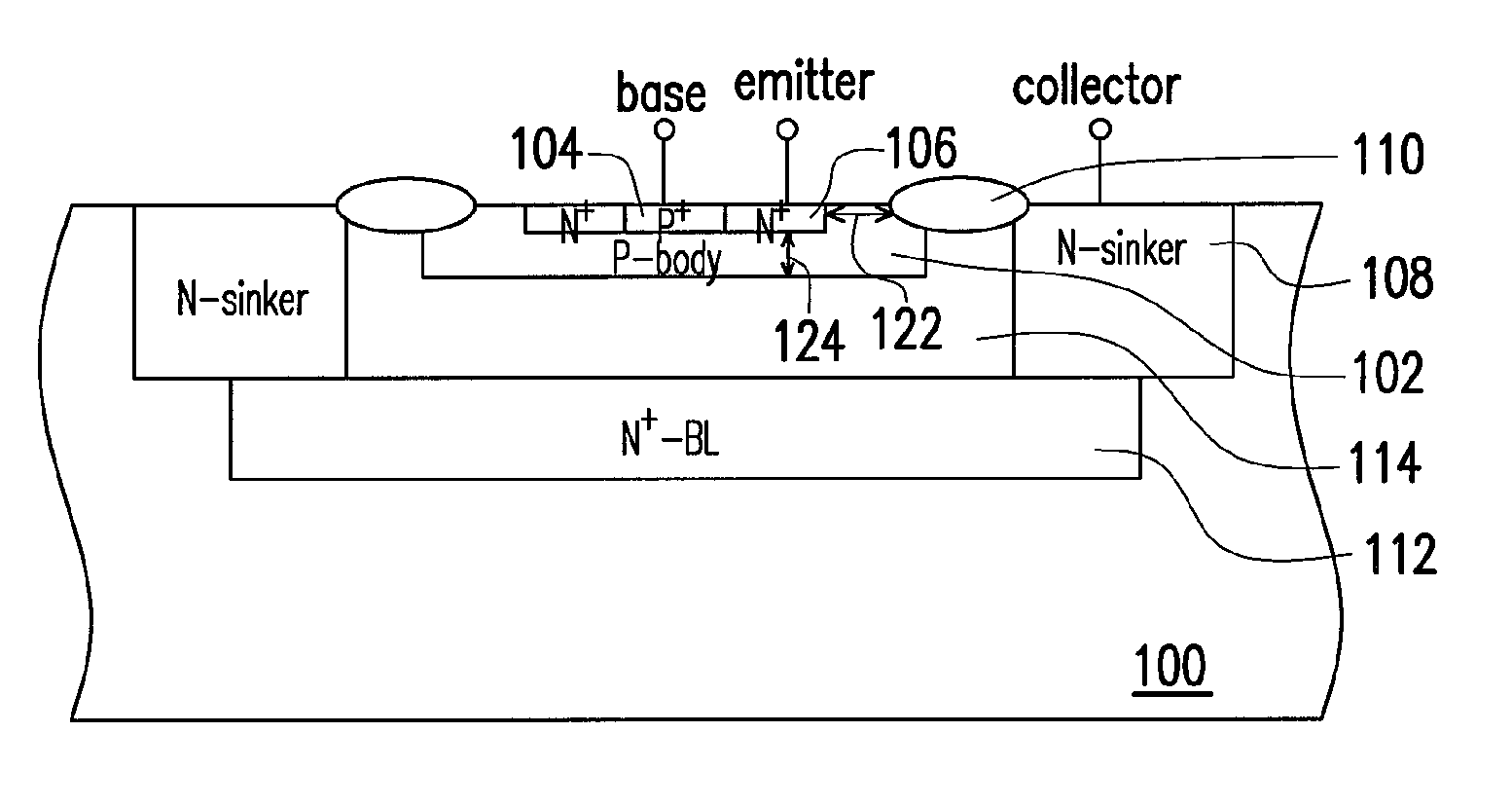

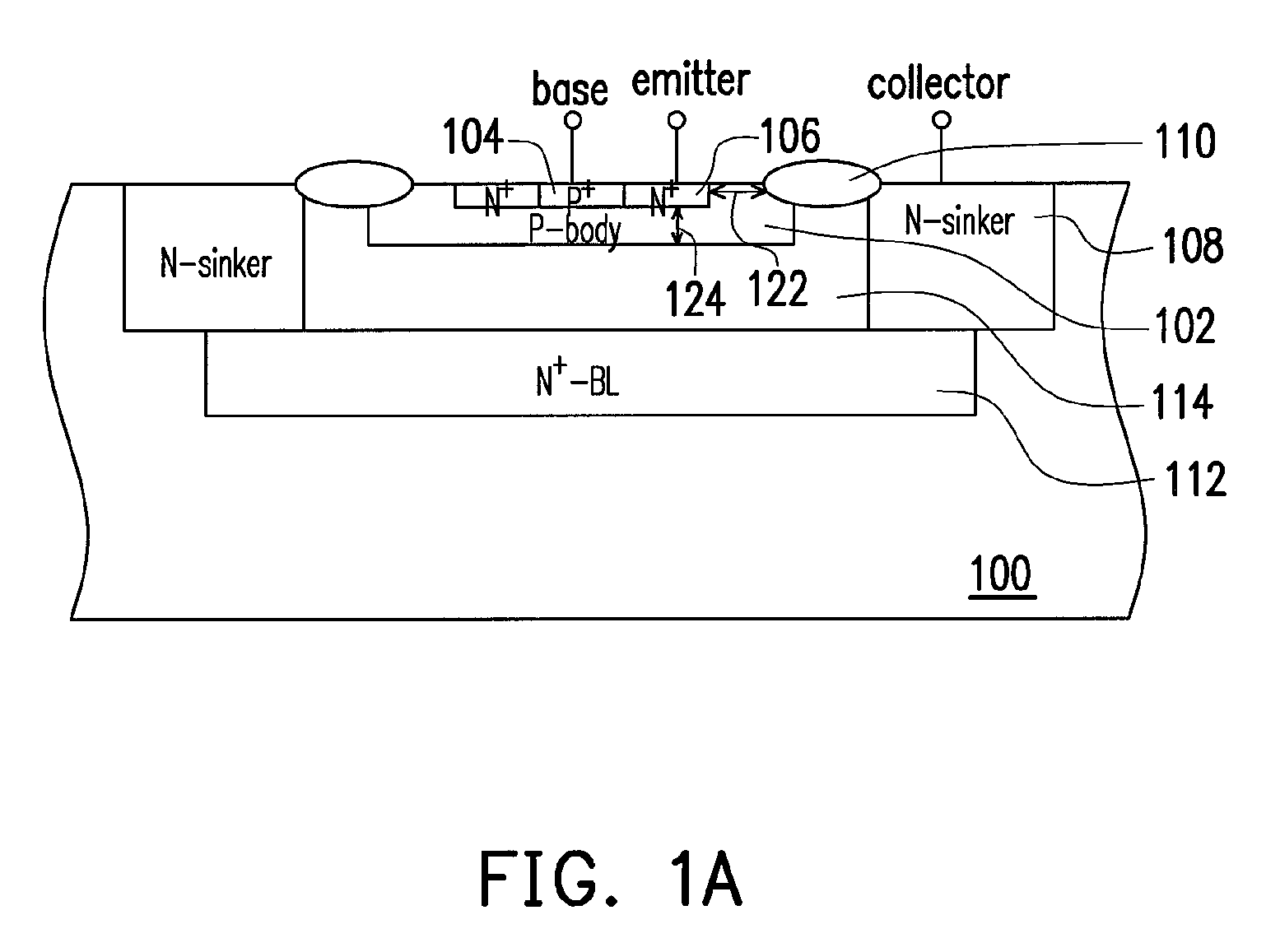

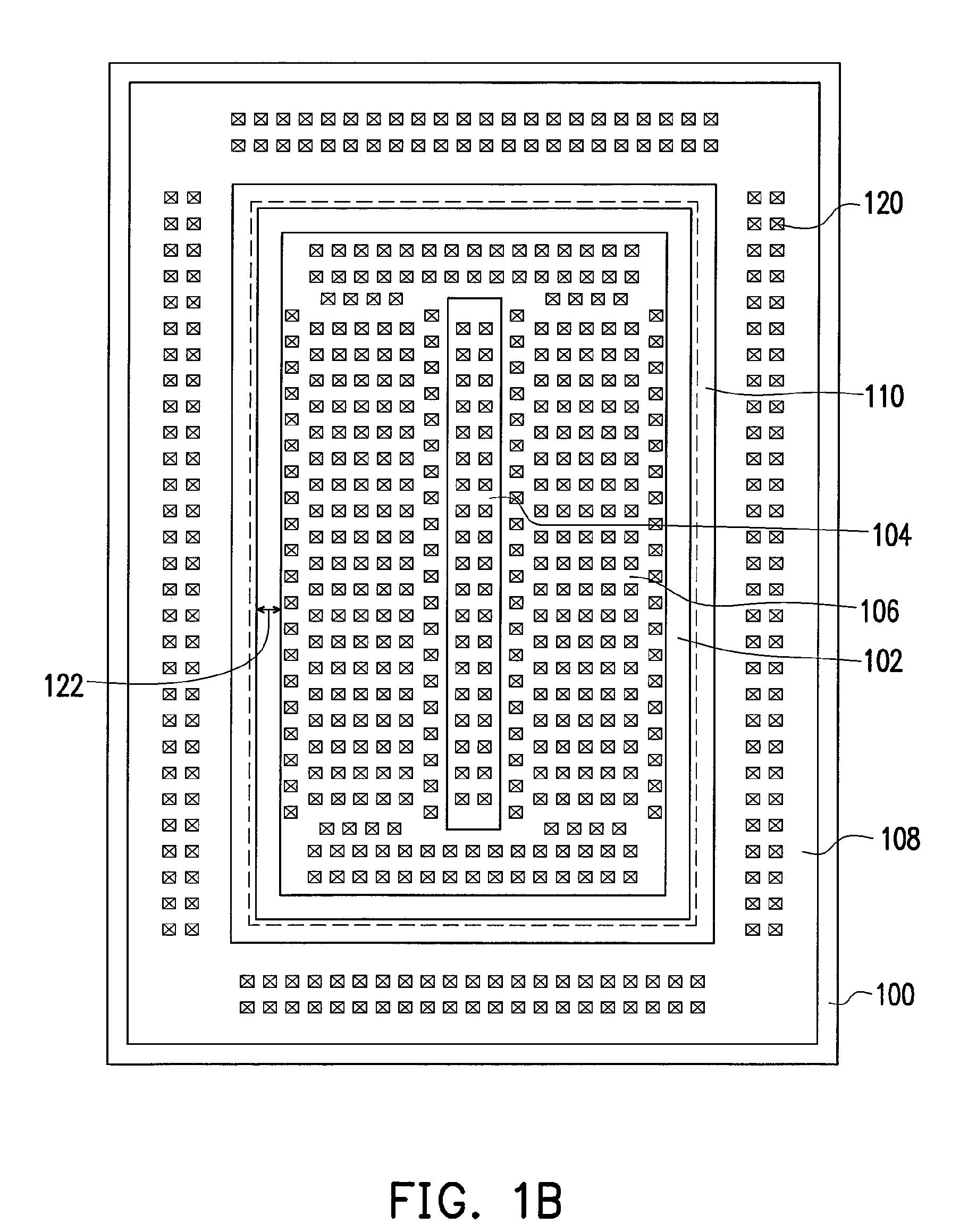

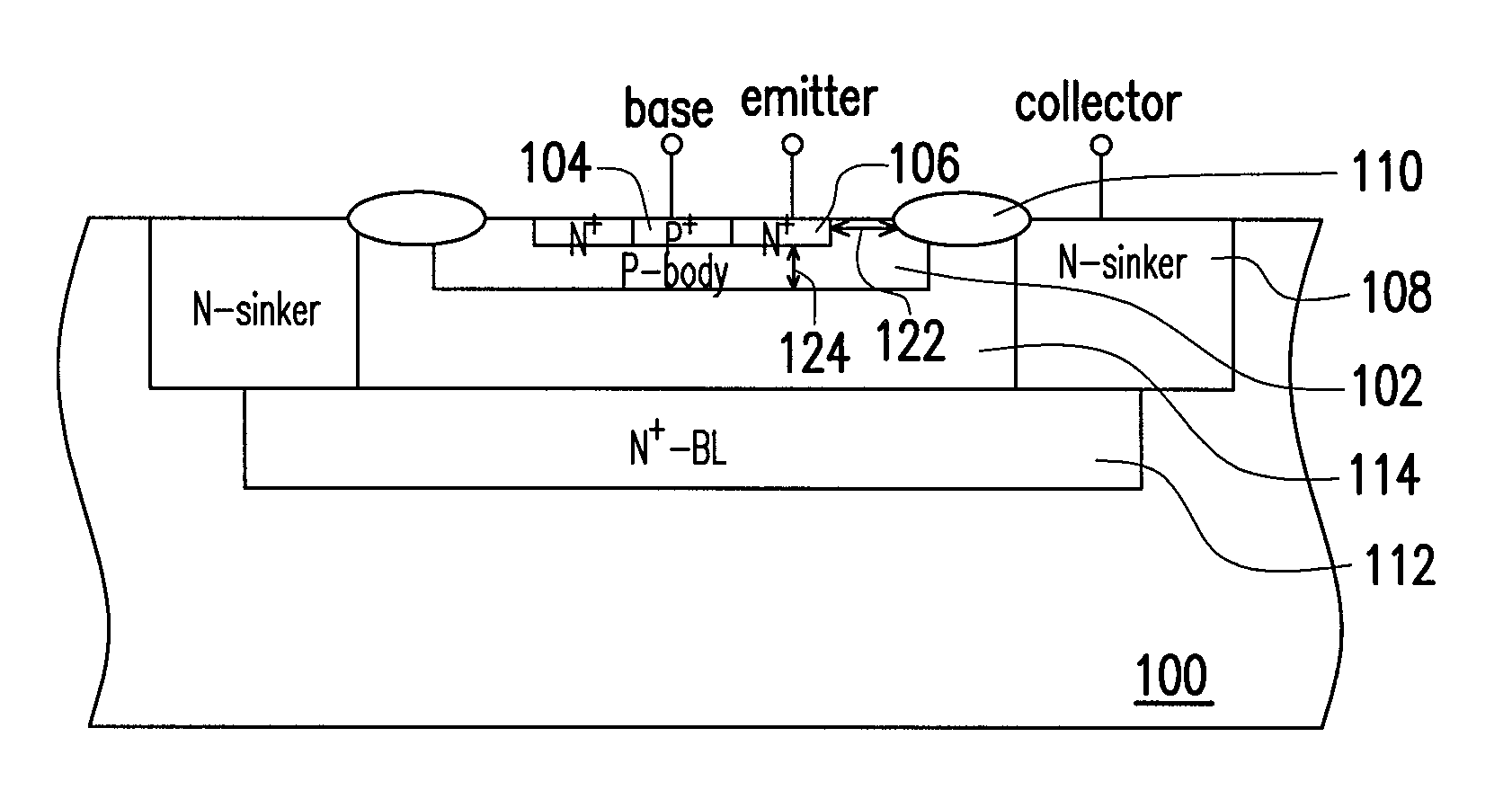

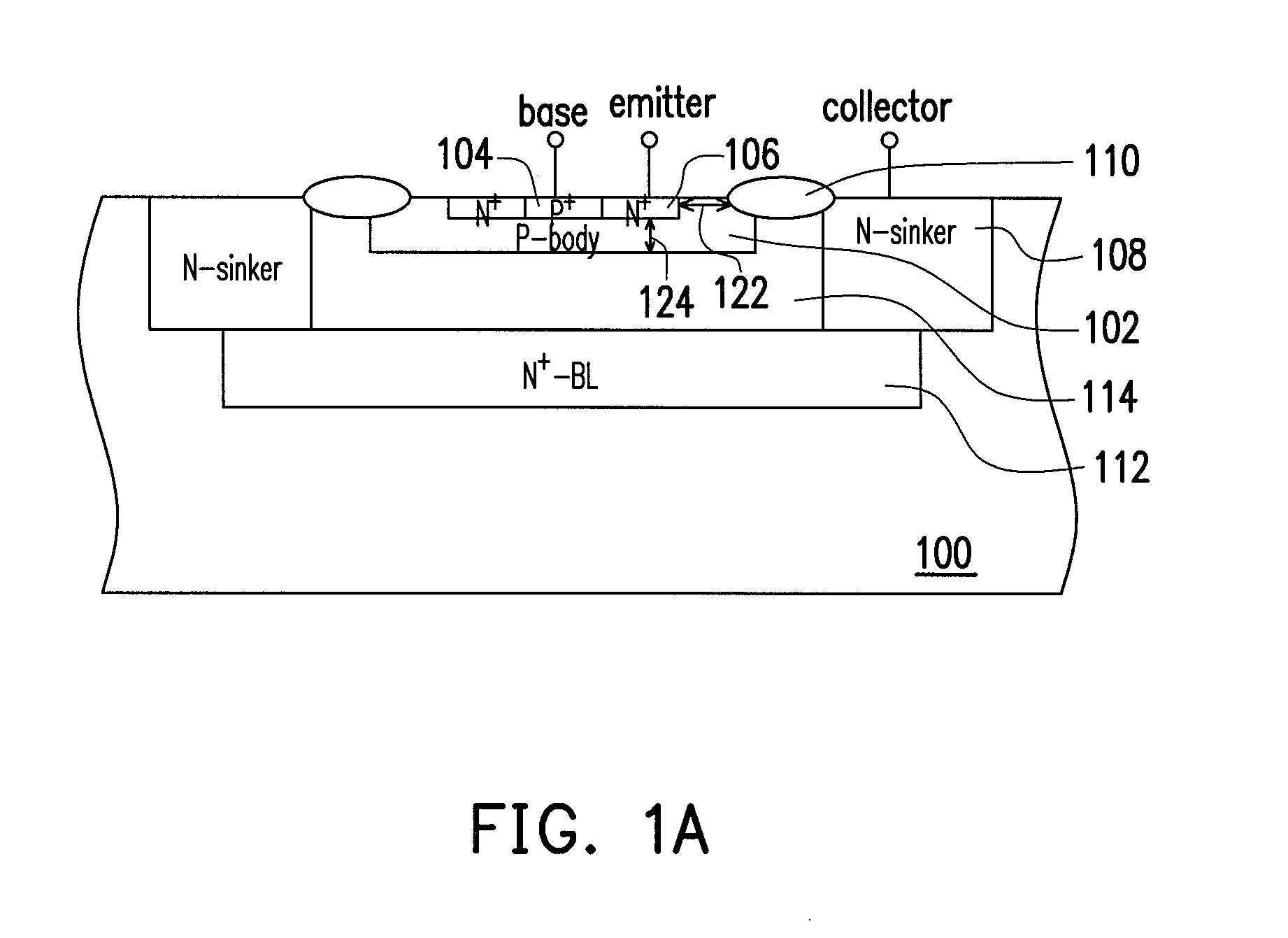

ESD protection device

An ESD protection device is described, which includes a P-body region, a P-type doped region, an N-type doped region and an N-sinker region. The P-body region is configured in a substrate. The P-type doped region is configured in the middle of the P-body region. The N-type doped region is configured in the P-body region and surrounds the P-type doped region. The N-sinker region is configured in the substrate and surrounds the P-body region.

Owner:UNITED MICROELECTRONICS CORP

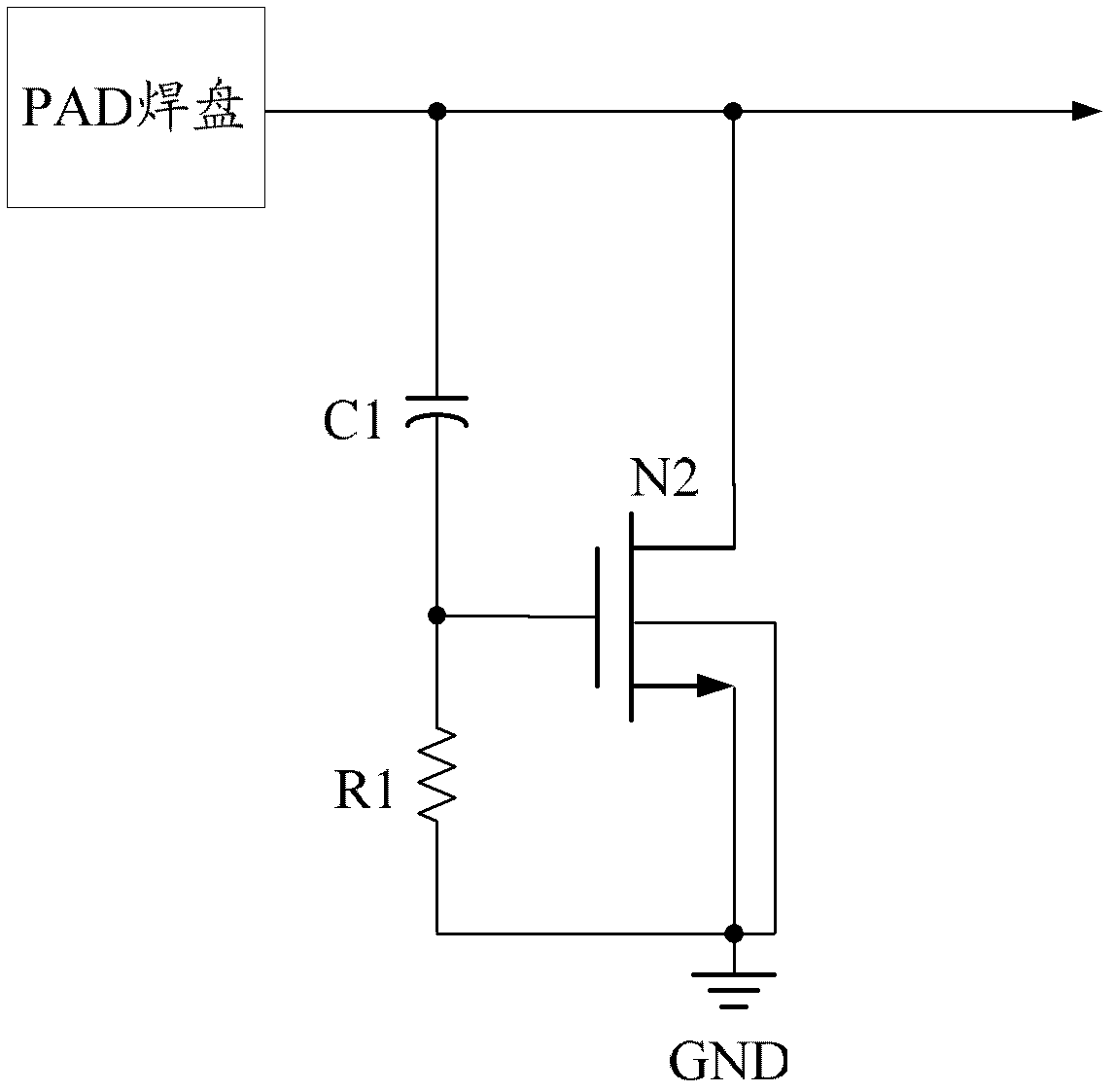

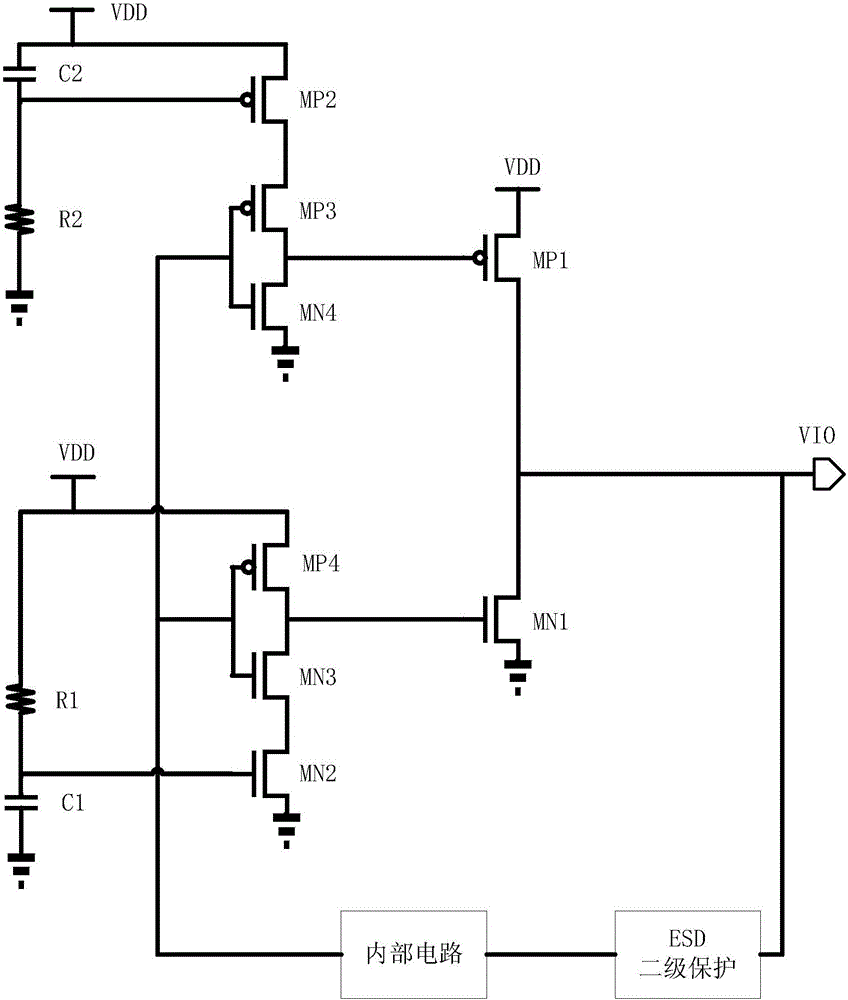

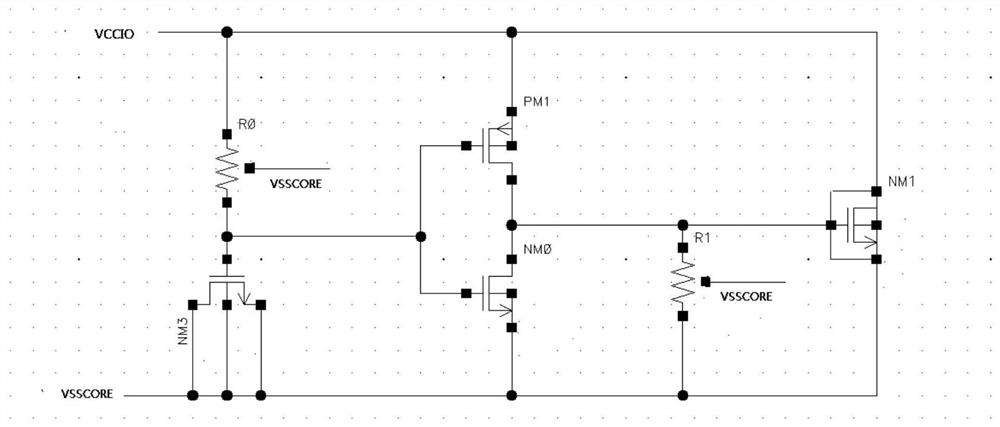

IO circuit used for enhancing ESD performance

ActiveCN105049027AImprove ESD performanceImprove the level ofLogic circuits coupling/interface using field-effect transistorsSolid-state devicesCapacitanceControl switch

The invention discloses an IO circuit used for enhancing ESD performance. The IO circuit comprises a detection circuit, a preceding-stage driving circuit, an ESD protection tube and an IO driving tube. The detection circuit is formed through connecting a resistor and a capacitor in series. The preceding-stage driving circuit is formed by a MOS with a moderate size. The ESD protection tube and the IO driving tube are reused and are formed by a large-size NMOS and a large-size PMOS. The resistor R and the capacitor C form the detection circuit. The detection circuit can detect an ESD event and is served as input of preceding stage driving. The preceding-stage driving circuit controls switches of the large-size NMOS and the large-size PMOS. The large-size NMOS and the large-size PMOS timely and effectively release static electricity in the ESD event and are taken as driving tubes of the IO circuit during normal working. Compared to a conventional method, by using the IO circuit of the invention, in order to reach a same ESD level, needed NMOS and PMOS areas are greatly reduced and a circuit area is effectively decreased through reusing of an ESD protection device and the driving tube.

Owner:CHIPSEA TECH SHENZHEN CO LTD

Electrostatic discharge protection circuit

PendingCN114123141AIncrease the areaIncrease costEmergency protective arrangements for limiting excess voltage/currentHemt circuitsControl theory

The embodiment of the invention provides an electrostatic discharge protection circuit. The electrostatic discharge protection circuit comprises a first power supply, a second power supply, a first electrostatic discharge protection device, a second electrostatic discharge protection device, a first ground electrically connected with the first power supply, and a second ground electrically connected with the second power supply, the first power supply and the second power supply are mutually independent, the first ground and the second ground are electrically connected through the first electrostatic discharge protection device, and the first ground and the second power supply are electrically connected through the second electrostatic discharge protection device. Therefore, the first electrostatic discharge protection device and the second electrostatic discharge protection device are added to first improve the ESD performance, the electrostatic discharge protection devices are manufactured according to the existing process, the size is not adjusted, only the device is increased, the area of an integrated circuit is increased, the cost increase can be ignored, and the cost of the integrated circuit is effectively saved.

Owner:GREE ELECTRIC APPLIANCES INC

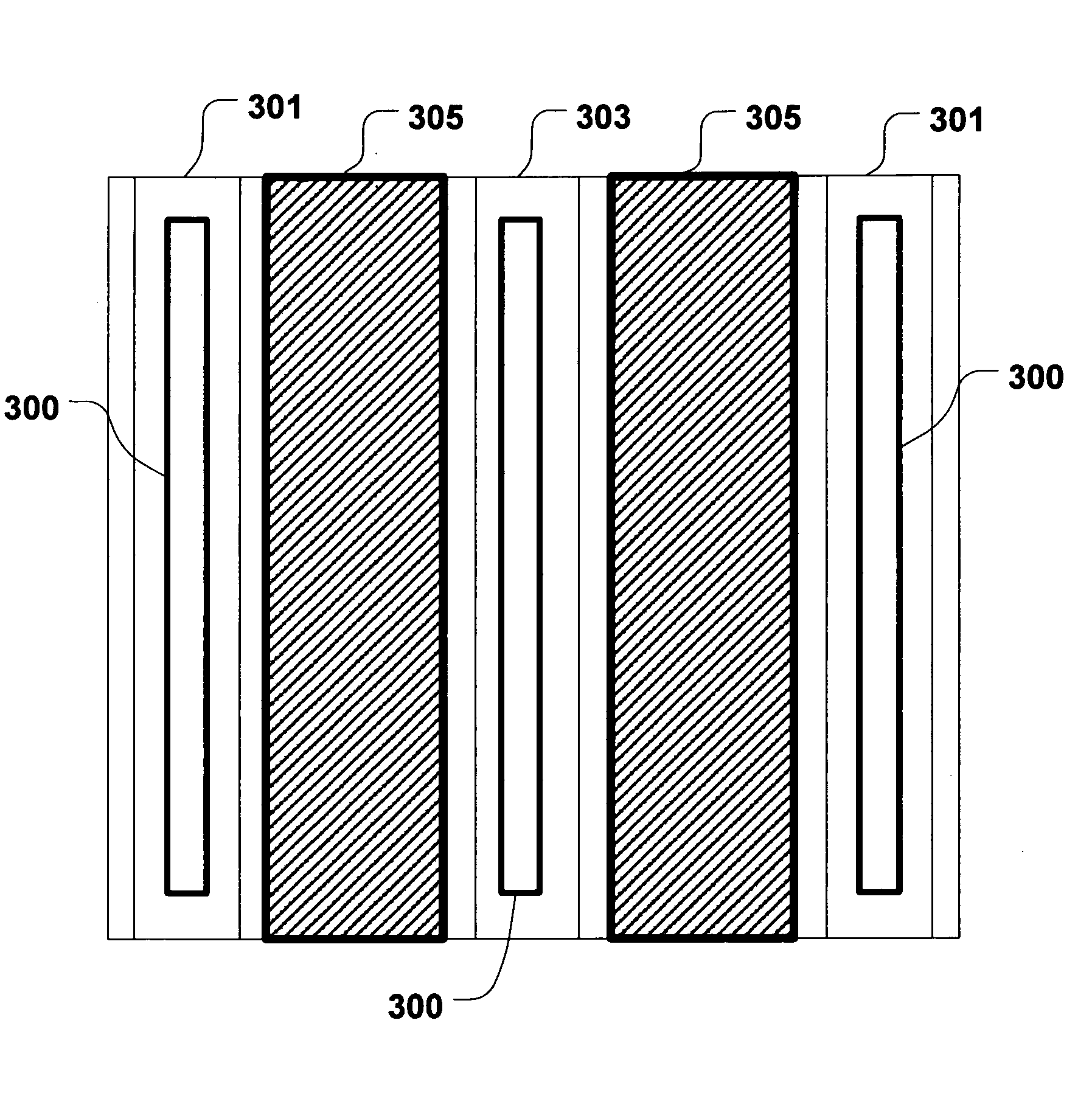

String contact structure for high voltage ESD

ActiveUS20080093672A1Broad range of applicationImprove ESD performanceSemiconductor/solid-state device detailsSolid-state devicesElectrostatic dischargeEngineering

The present invention relates to an electrostatic discharge (ESD) protection scheme and particularly to a string contact structure for an improved ESD performance. In an embodiment, the invention provides a method for forming an ESD protection circuit for protecting an internal circuit from damage due to an ESD voltage appearing on a pad coupled to a clamp device including a first terminal and a second terminal. The method includes forming a string contact along the first terminal and the second terminal of the clamp device. The method further includes forming one or more conductive layers on the string contact to couple the first terminal and the second terminal of the clamp device to the pad and a ground pad.

Owner:TAIWAN SEMICON MFG CO LTD

String contact structure for high voltage ESD

ActiveUS7826193B2Improve ESD performanceHigh currentSemiconductor/solid-state device detailsSolid-state devicesEngineeringHigh voltage

The present invention relates to an electrostatic discharge (ESD) protection scheme and particularly to a string contact structure for an improved ESD performance. In an embodiment, the invention provides a method for forming an ESD protection circuit for protecting an internal circuit from damage due to an ESD voltage appearing on a pad coupled to a clamp device including a first terminal and a second terminal. The method includes forming a string contact along the first terminal and the second terminal of the clamp device. The method further includes forming one or more conductive layers on the string contact to couple the first terminal and the second terminal of the clamp device to the pad and a ground pad.

Owner:TAIWAN SEMICON MFG CO LTD

III-nitride semiconductor light emitting device

InactiveCN101404315BCurrent extension can promoteImprove ESD performanceSemiconductor devicesContact layerLight emitting device

The present invention relates to a III-nitride semiconductor light emitting device, and more particularly, to a III-nitride semiconductor light emitting device which can facilitate current spreading and improve electrostatic discharge characteristic by providing an undoped GaN layer with a thickness over 100 A in an n-side contact layer.

Owner:EPIVALLEY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com