Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

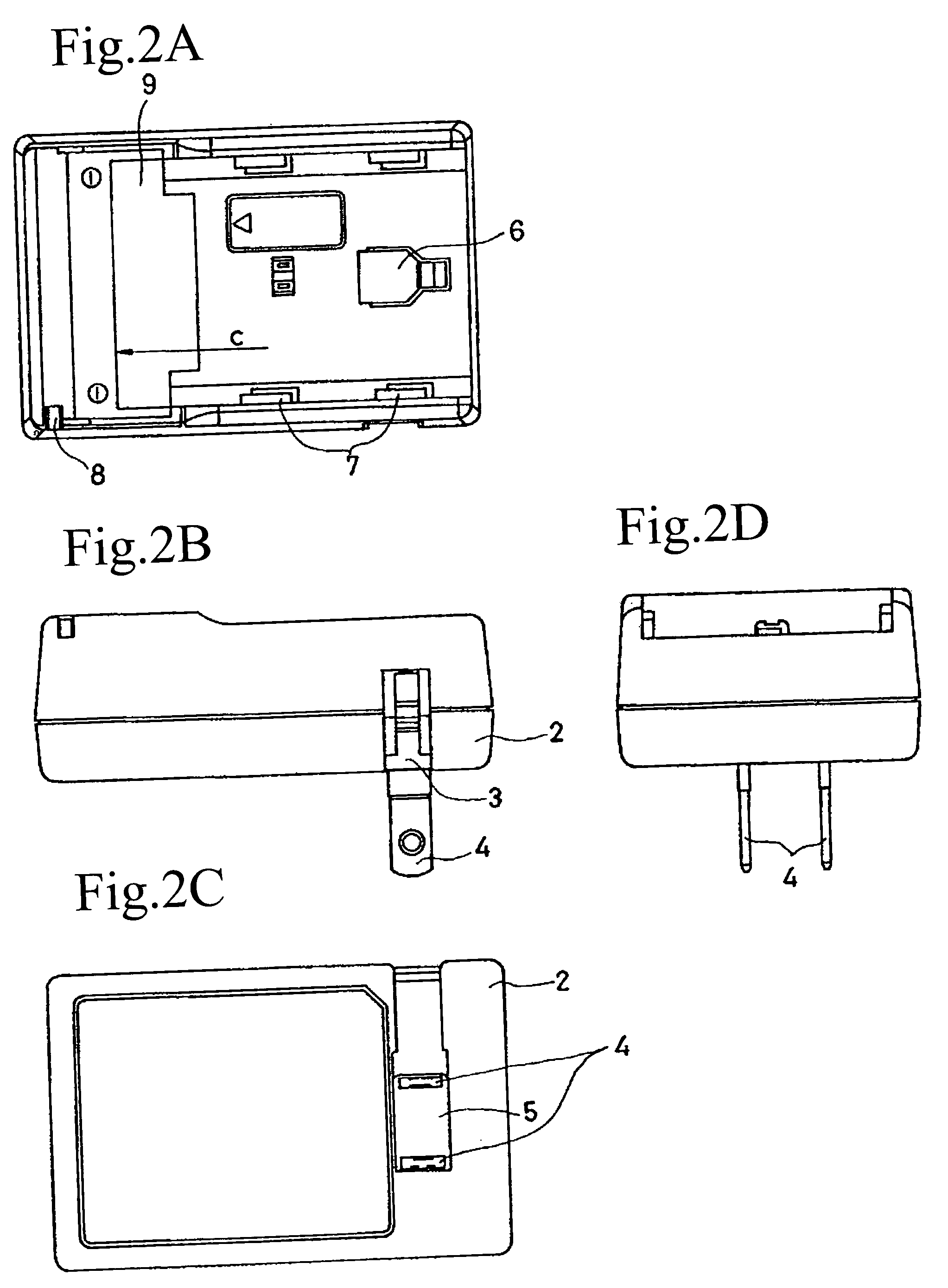

42results about How to "Hinders miniaturization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

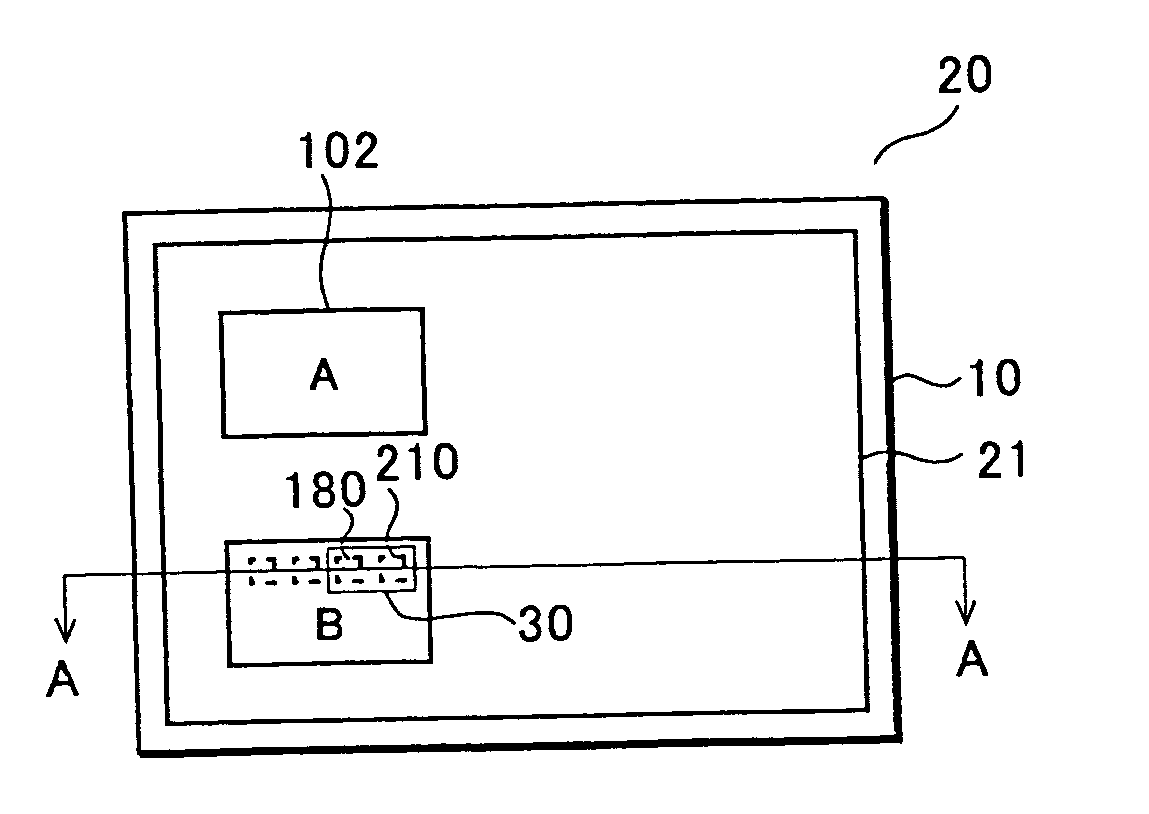

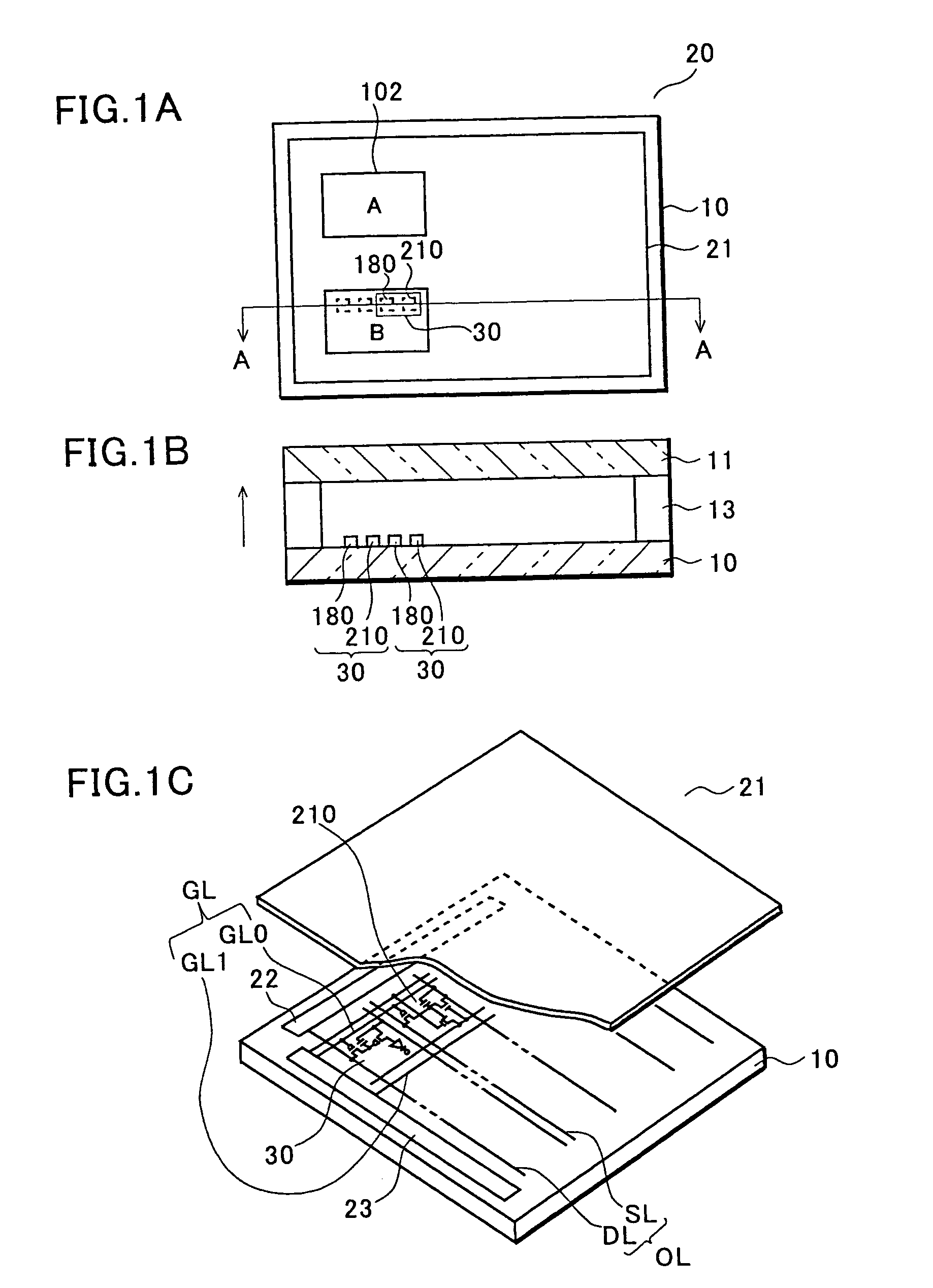

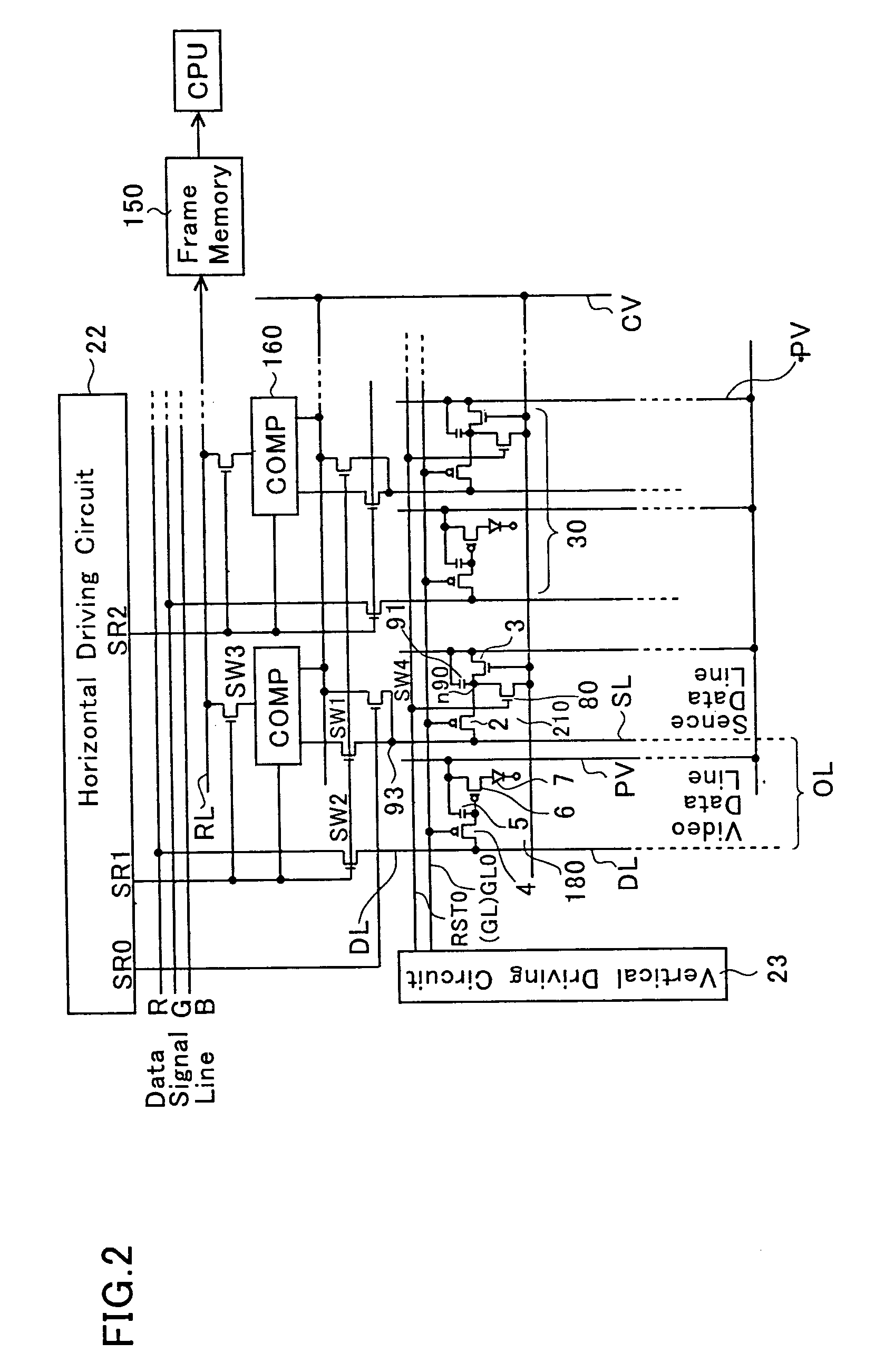

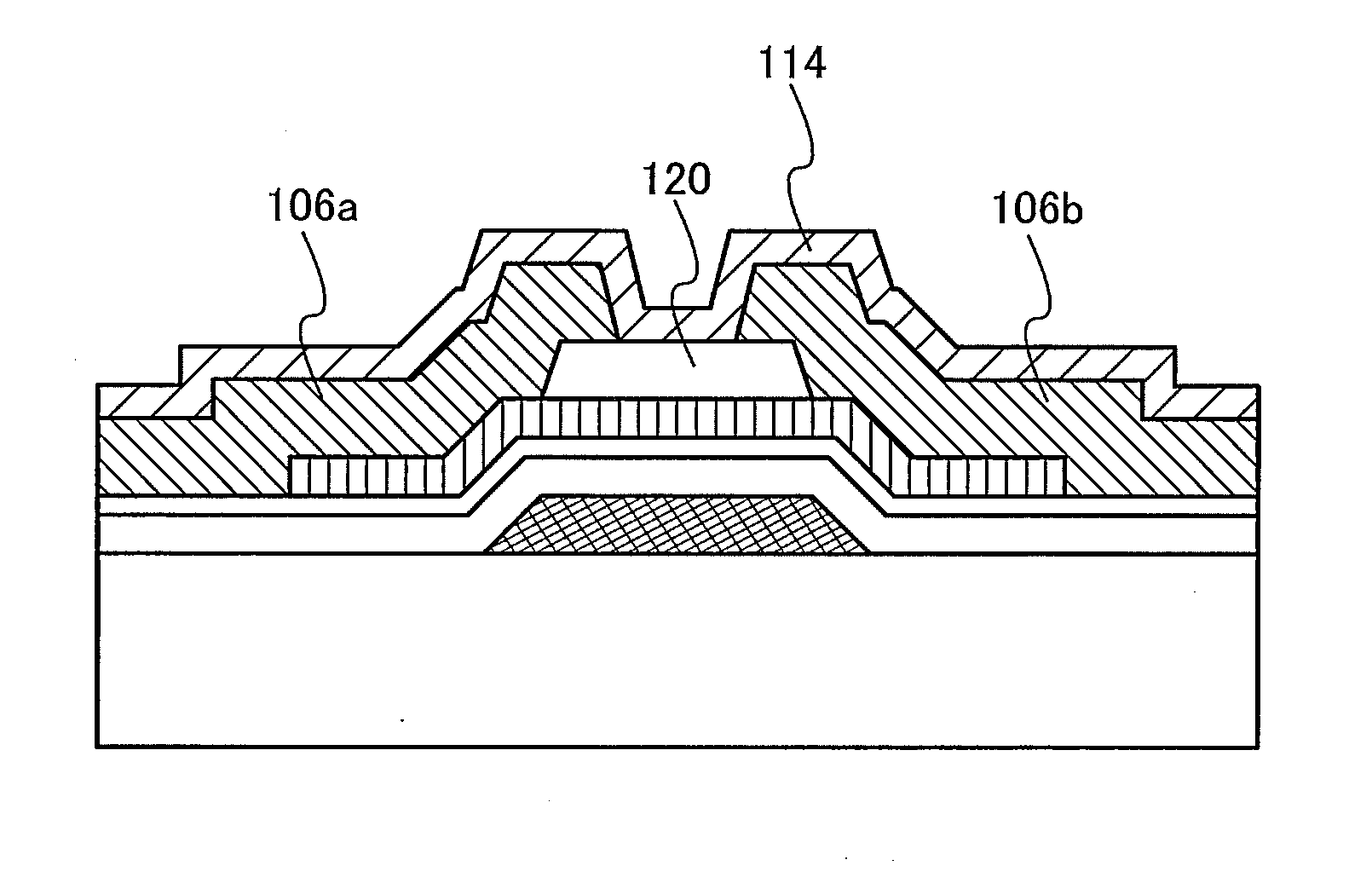

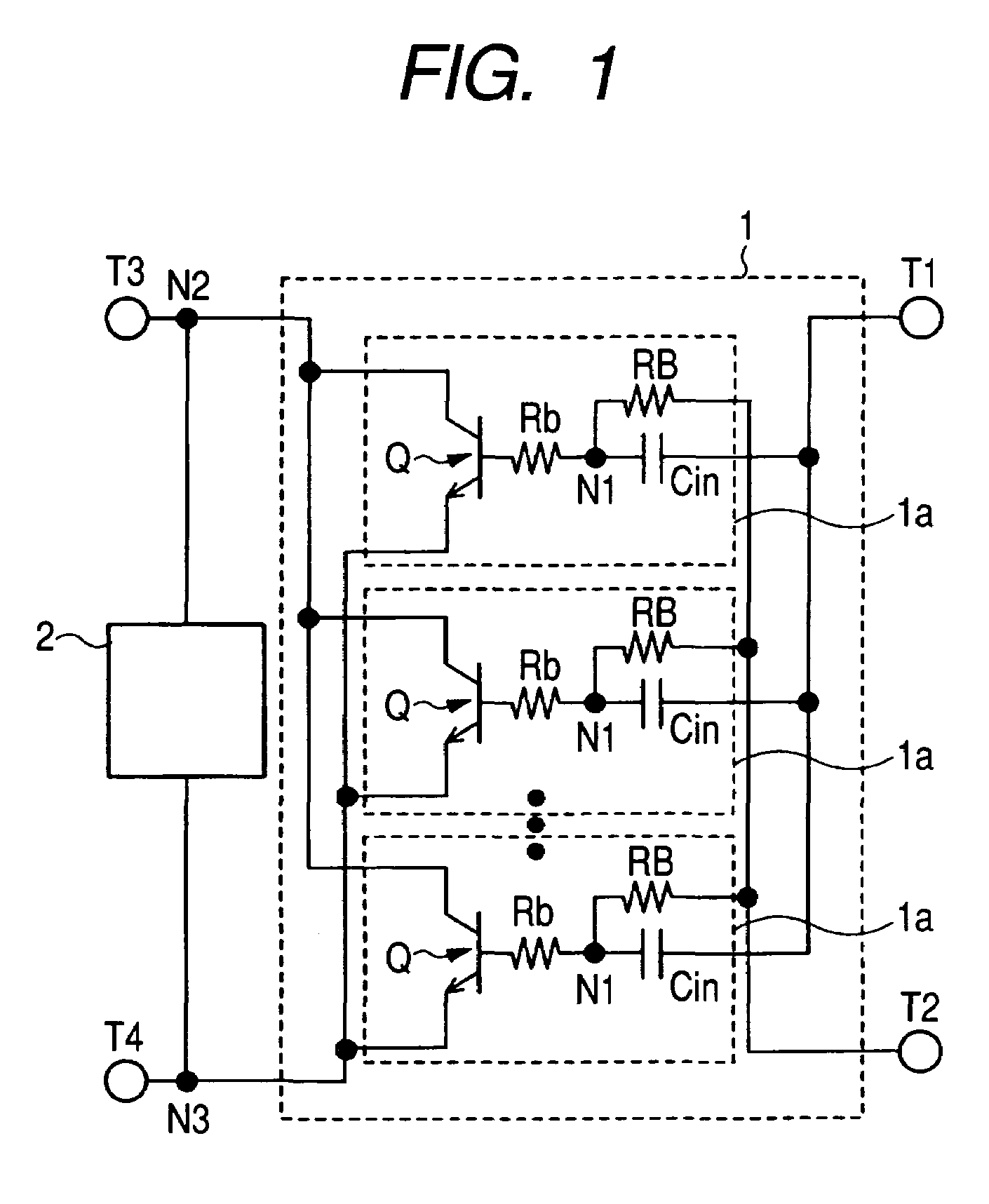

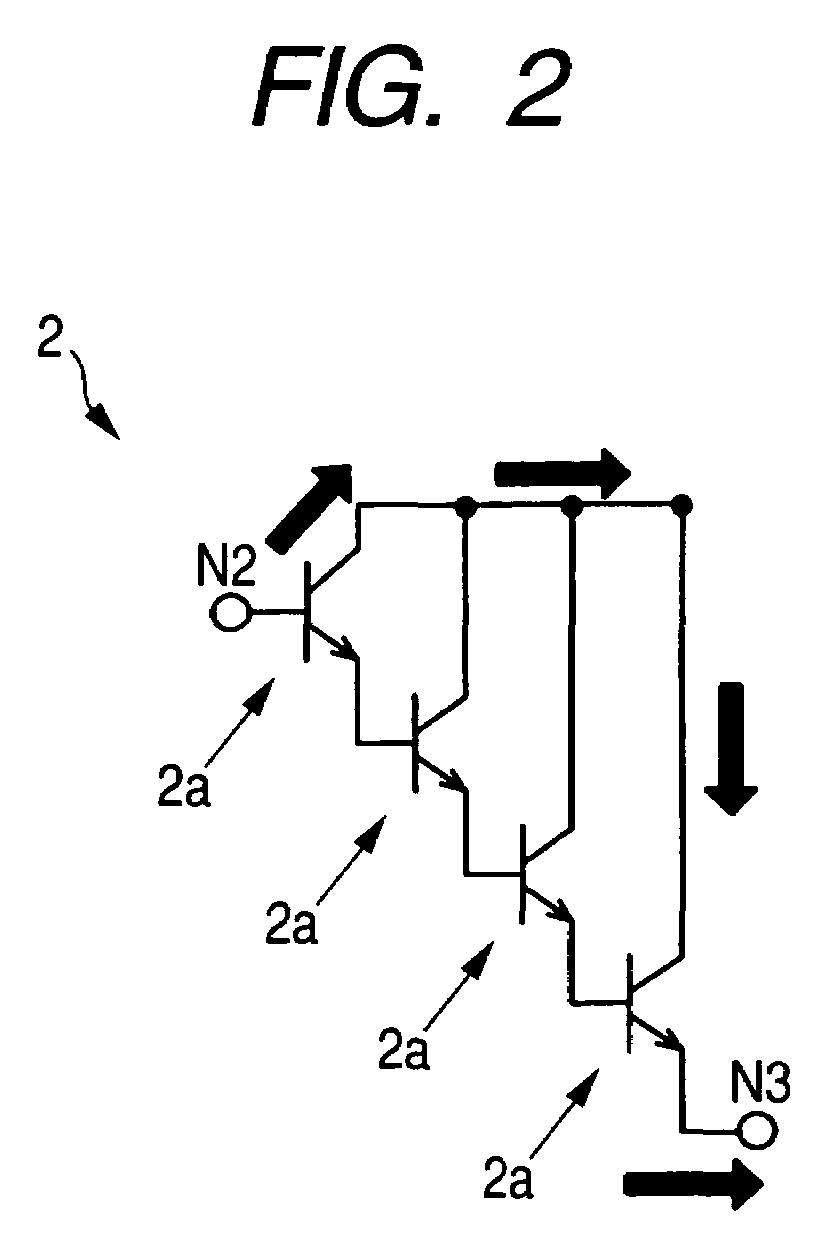

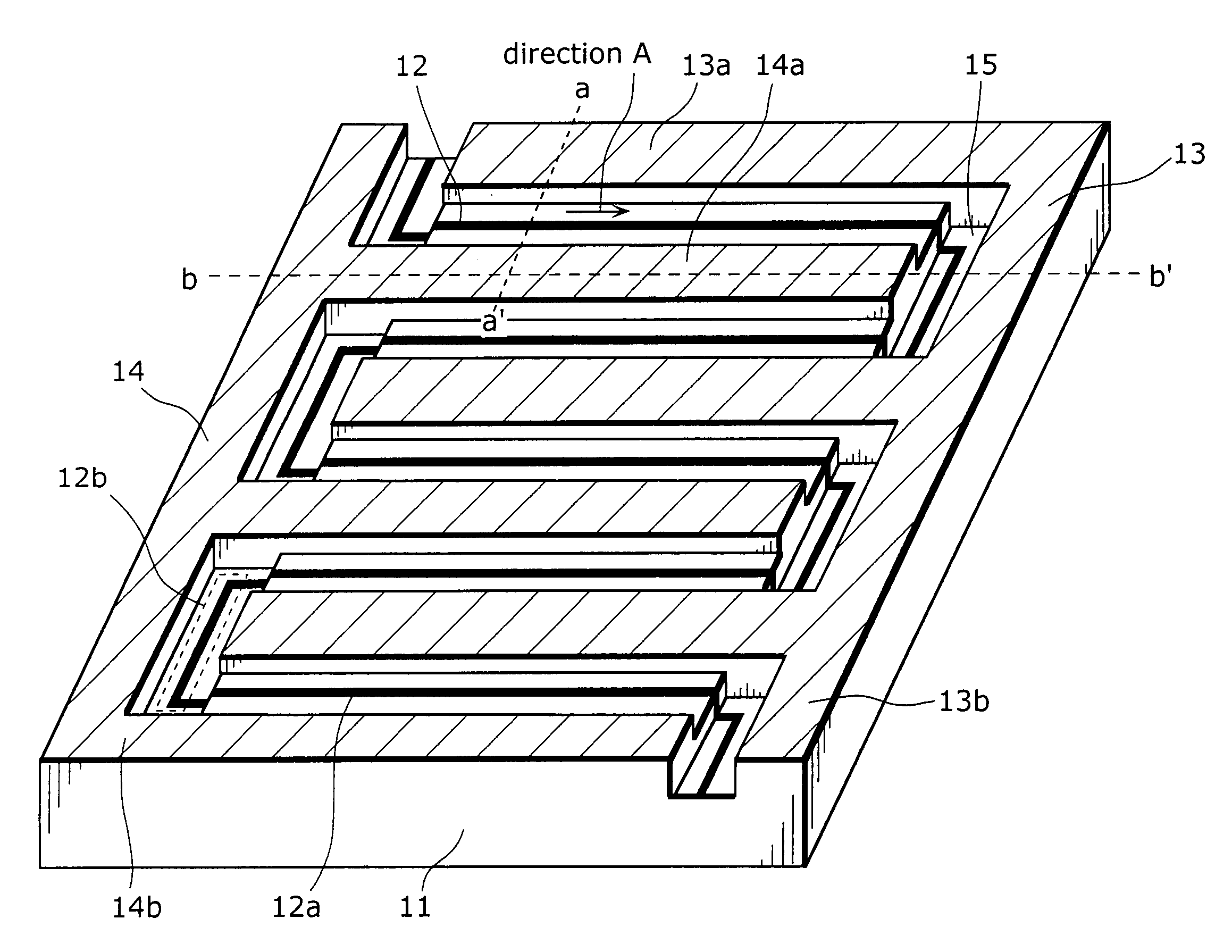

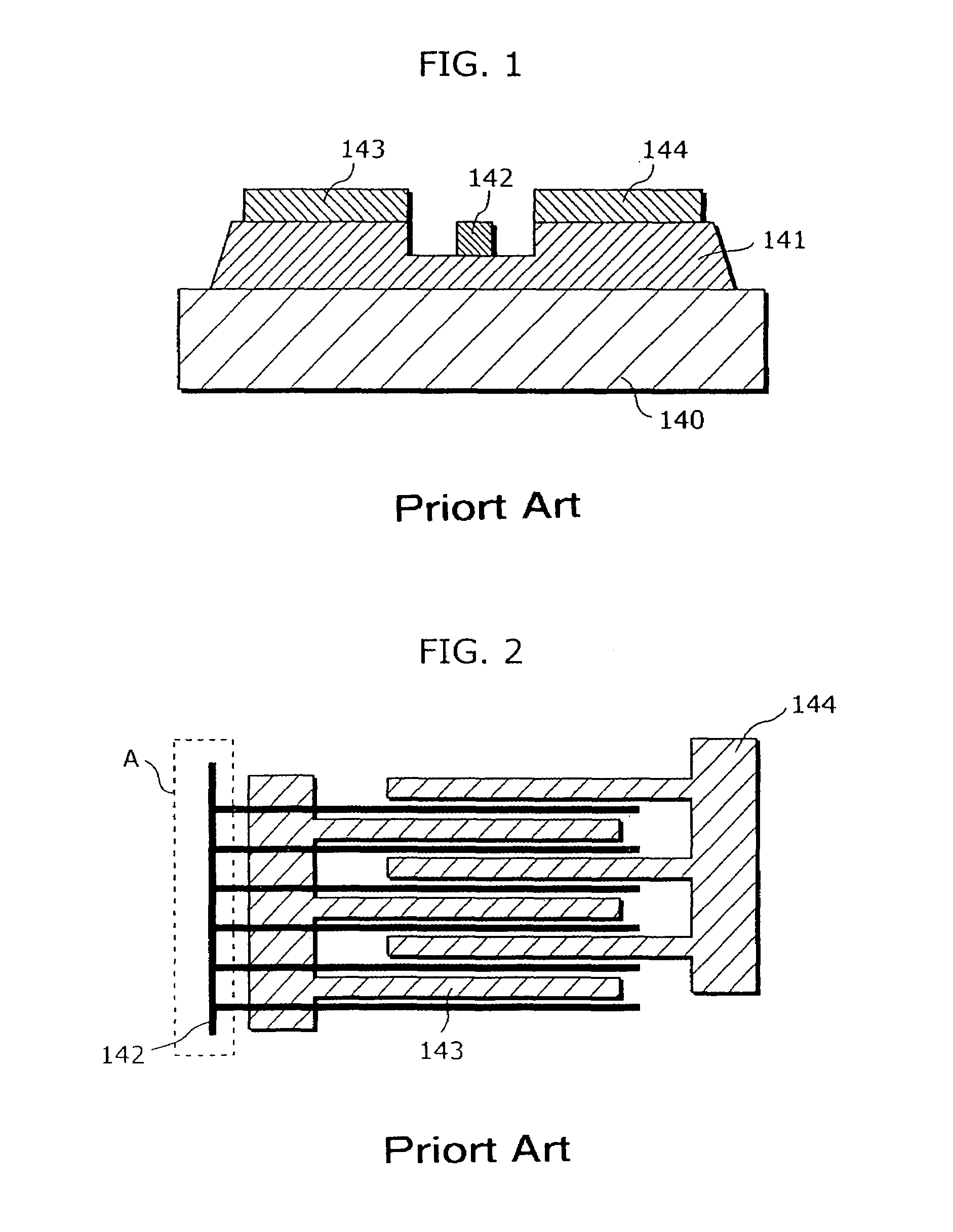

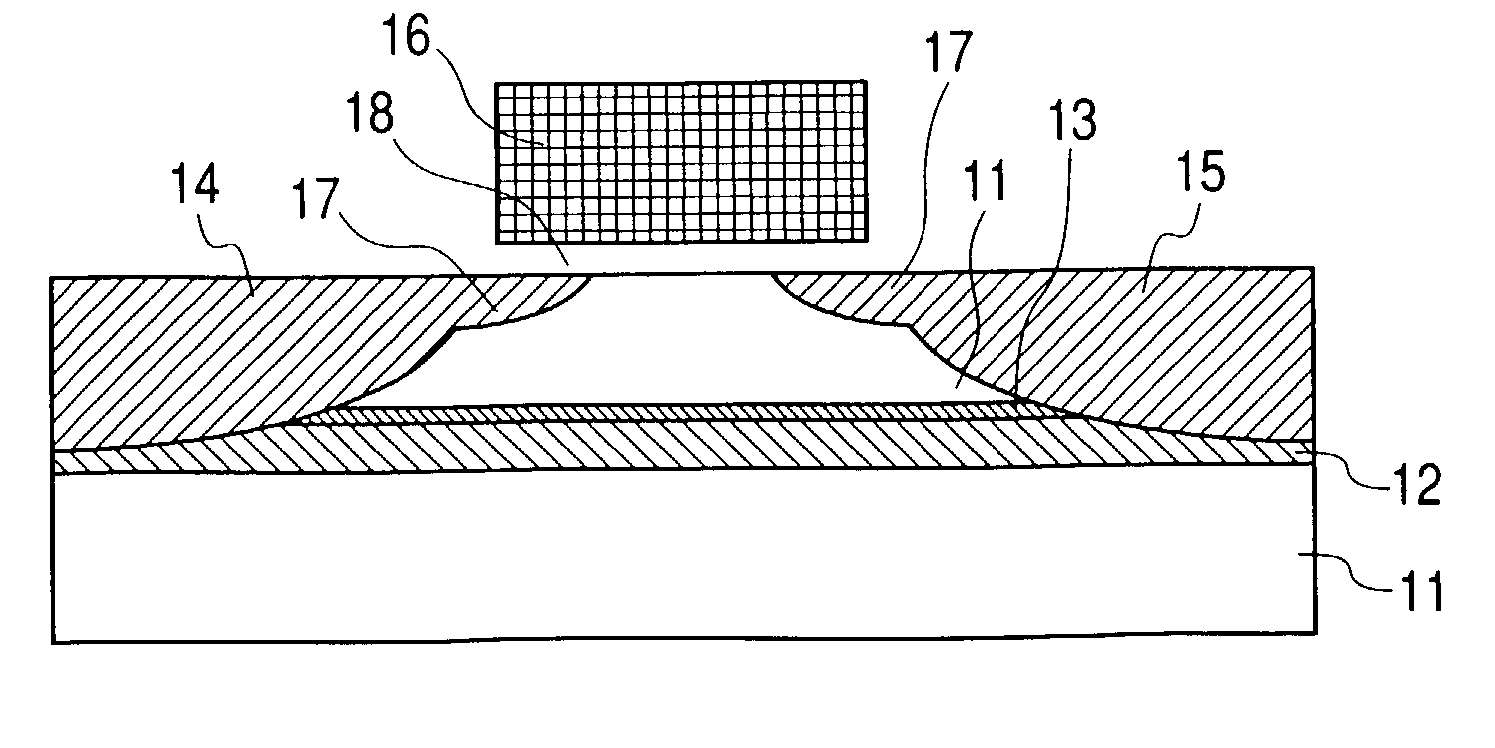

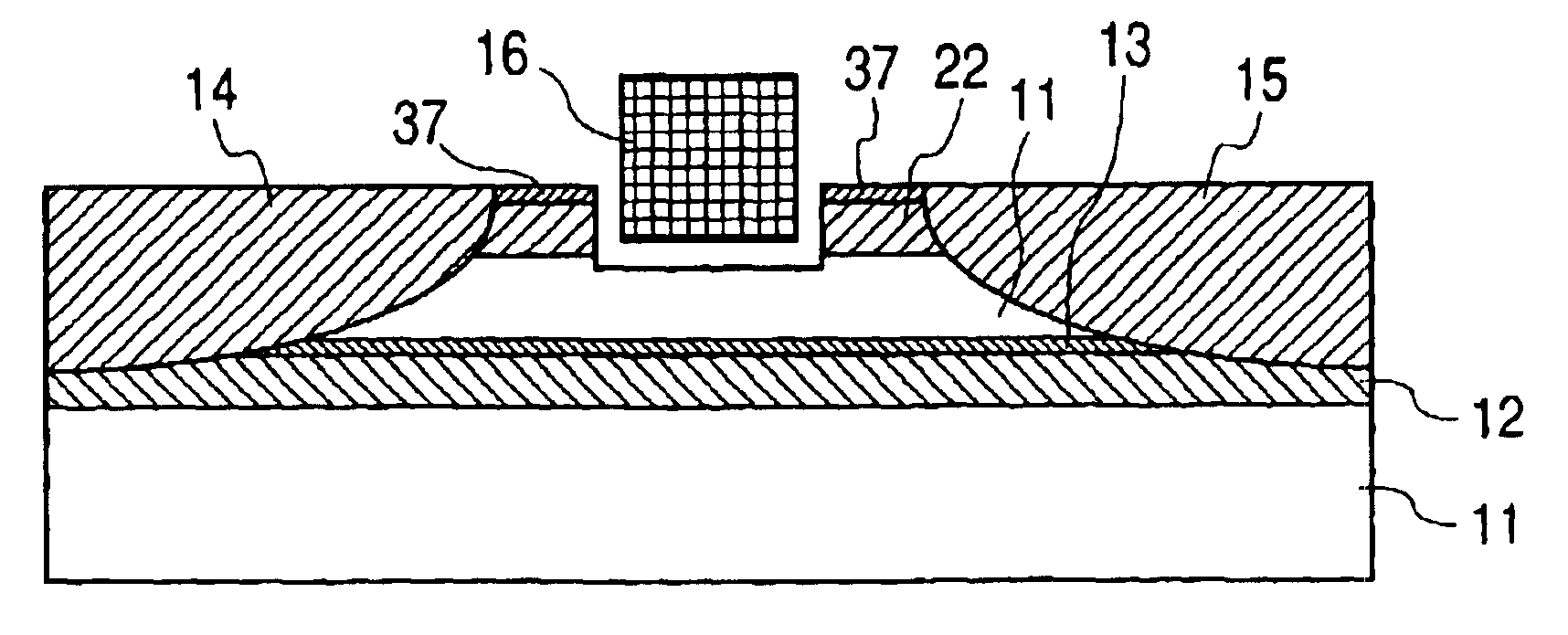

Touch panel

InactiveUS20060033016A1Precise positioningHinders miniaturizationMaterial analysis by optical meansCounting objects on conveyorsTouch panelEngineering

A photosensor and a display unit are fabricated on the same substrate. Input coordinates are identified by comparing the light quantities at positions (pixels) which is and is not touched by a finger or the like by use of a comparison circuit. Thus, TFTs to form the photosensor can be fabricated on the same substrate in the same process, and also reductions in manufacturing cost and the number of parts can be realized. A region required for disposing a sensor in the circumference becomes unnecessary, thus realizing the miniaturization of the device. Moreover, since a region to be a blind spot is eliminated in the display unit, it is possible to utilize the display unit effectively. It is possible to improve the precision of an input recognition and to uniformly perform detection all over the display unit. Furthermore, since the photosensor is constituted of a photoreceptor circuit which is capable of adjusting the sensitivity of receiving light, it is possible to make the sensitivity of receiving light (detection) uniform in the display unit.

Owner:SANYO ELECTRIC CO LTD

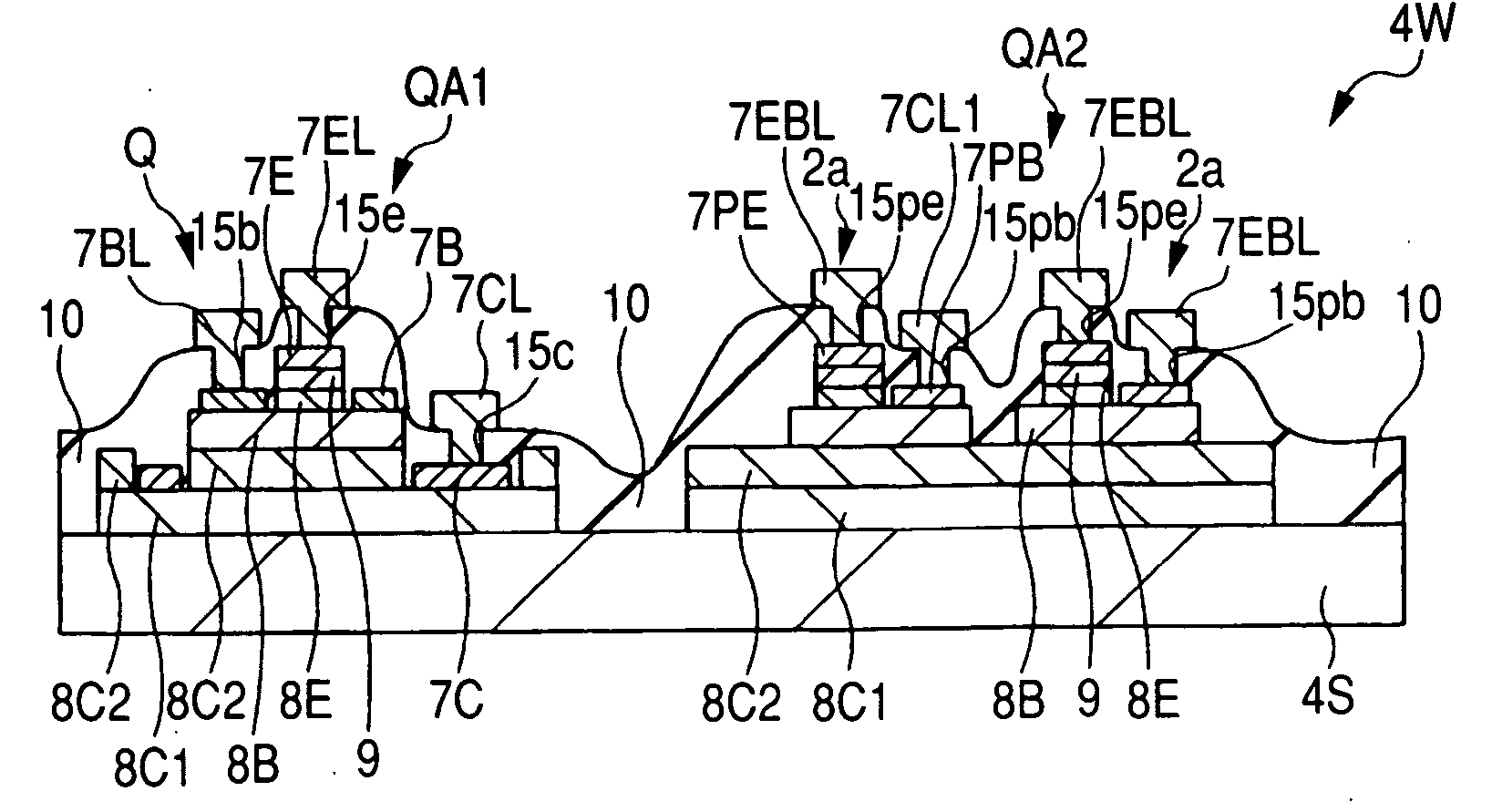

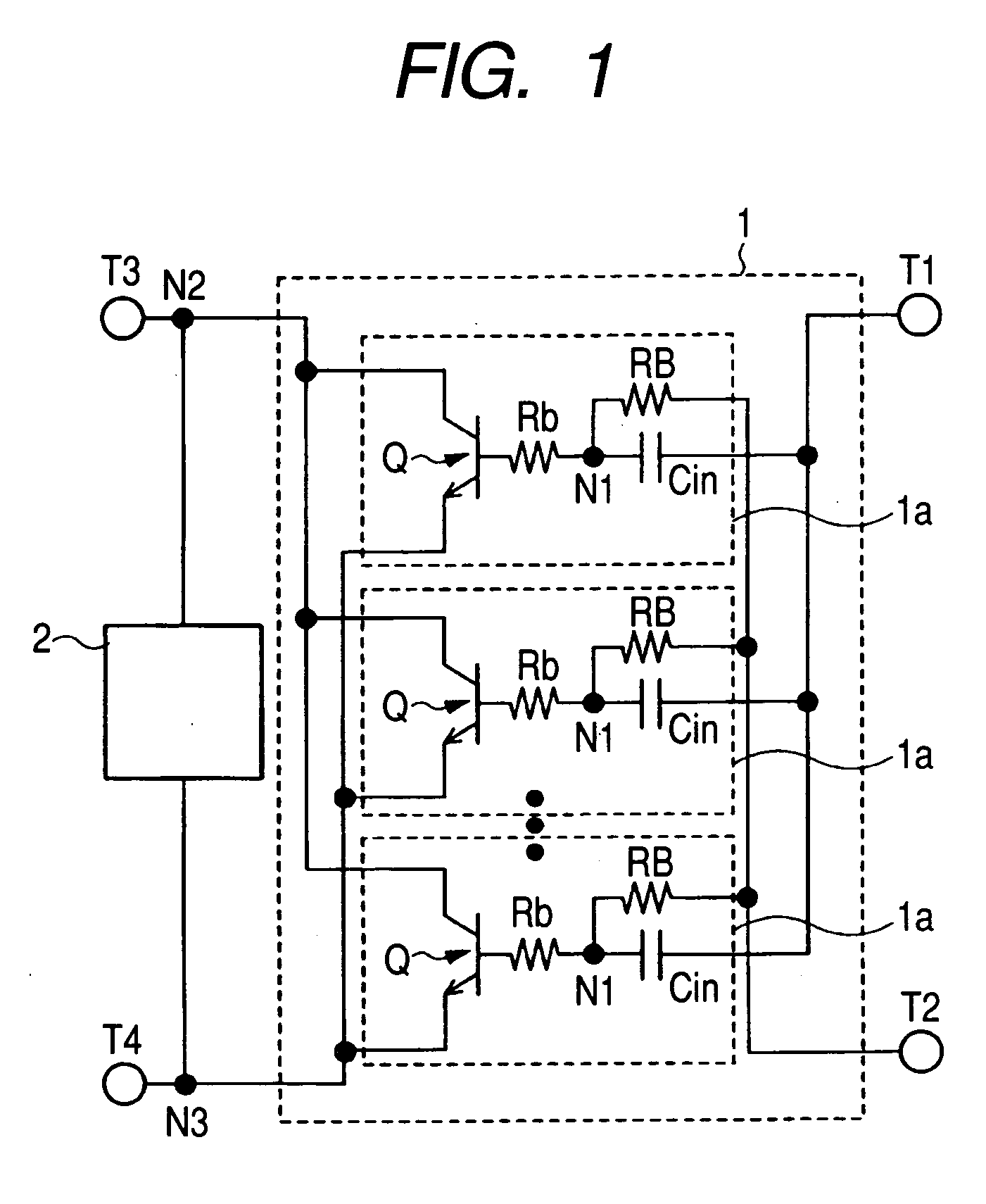

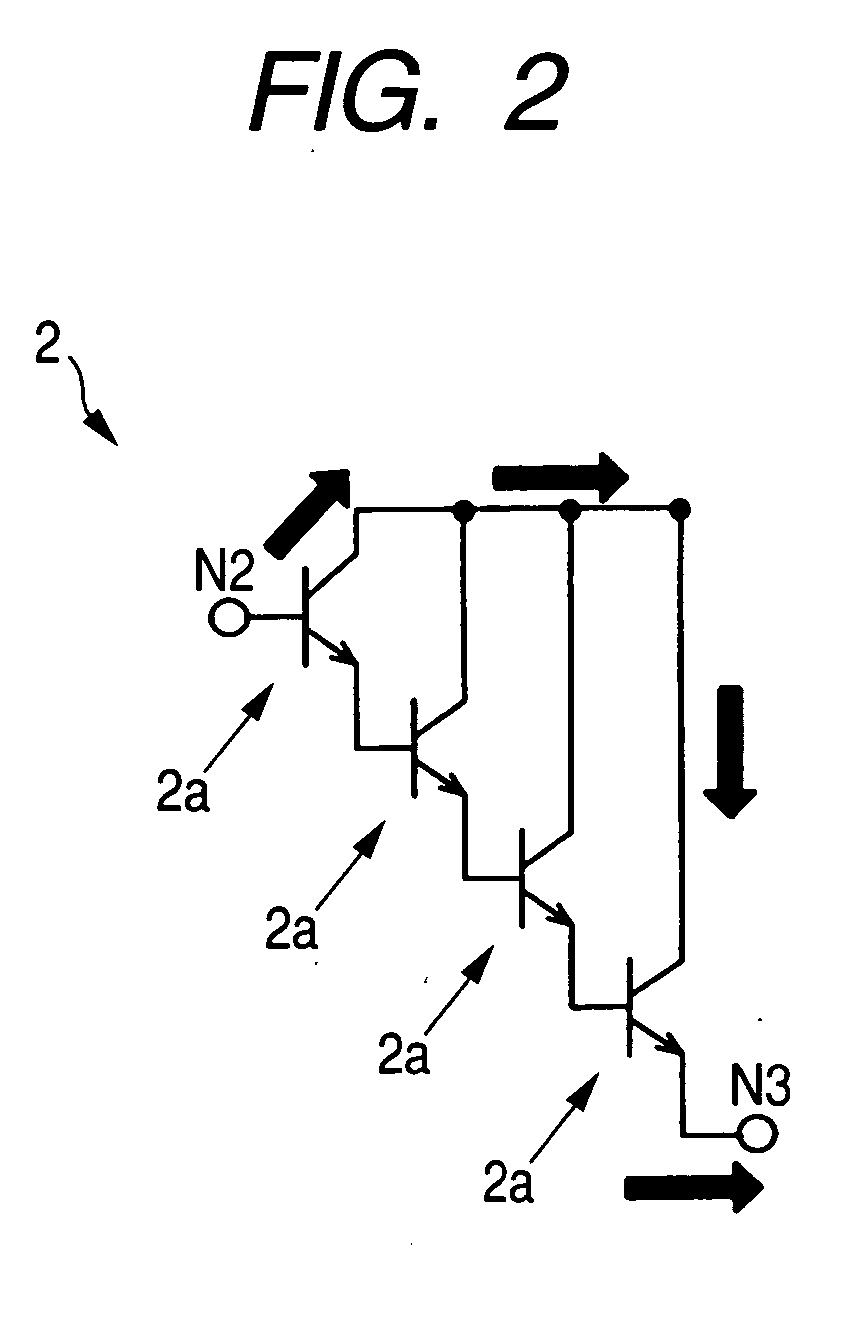

Semiconductor device and radio communication device

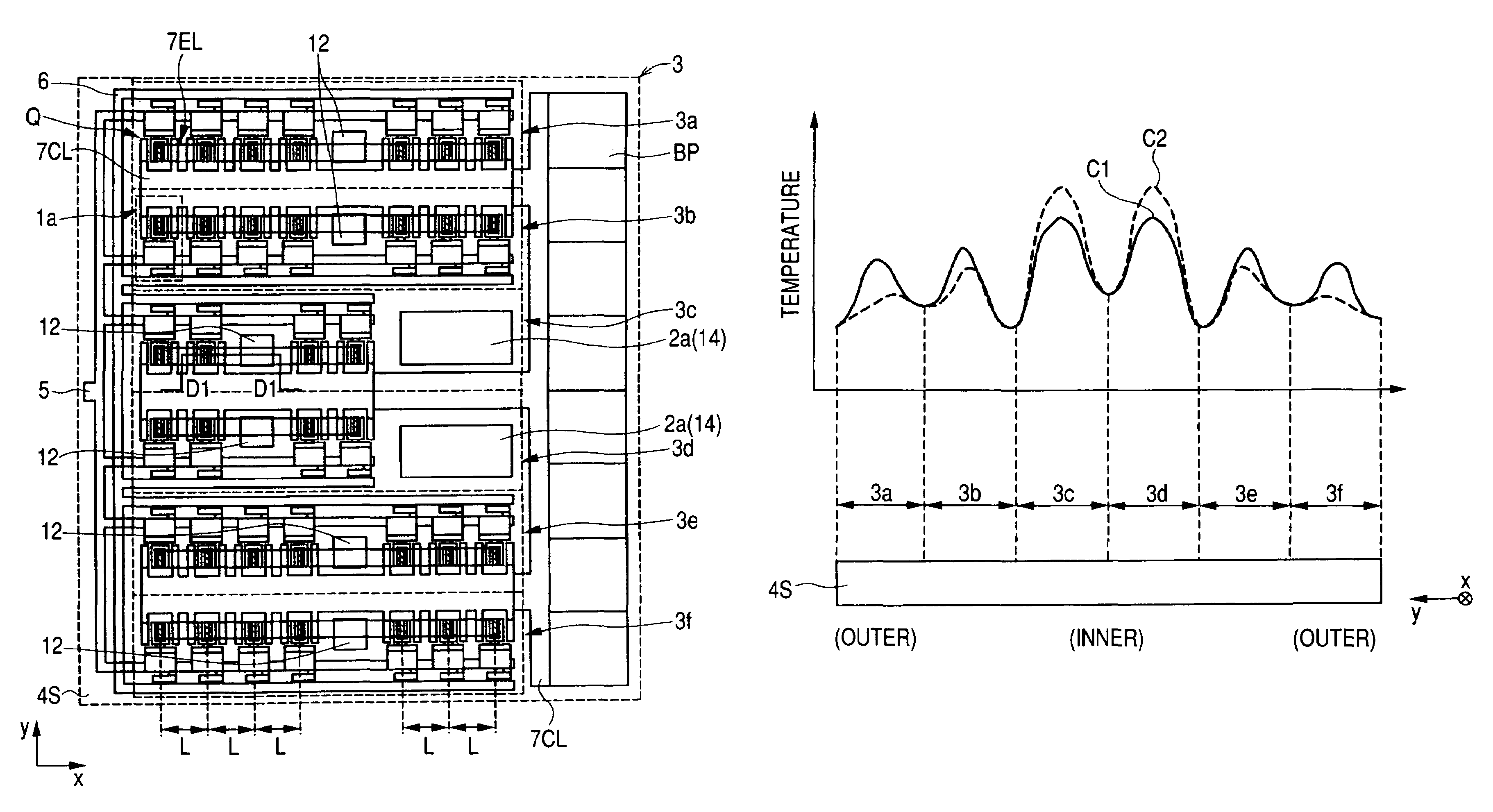

ActiveUS20060138460A1Lower temperature riseEnlarge regionTransistorSemiconductor/solid-state device detailsDevice materialMiniaturization

A technology which allows a reduction in the thermal resistance of a semiconductor device and the miniaturization thereof is provided. The semiconductor device has a plurality of unit transistors Q, transistor formation regions 3a, 3b, and 3e each having a first number (seven) of the unit transistors Q, and transistor formation regions 3c and 3d each having a second number (four) of the unit transistors Q. The transistor formation regions 3c and 3d are located between the transistor formation regions 3a, 3b, 3e, and 3f and the first number is larger than the second number.

Owner:MURATA MFG CO LTD

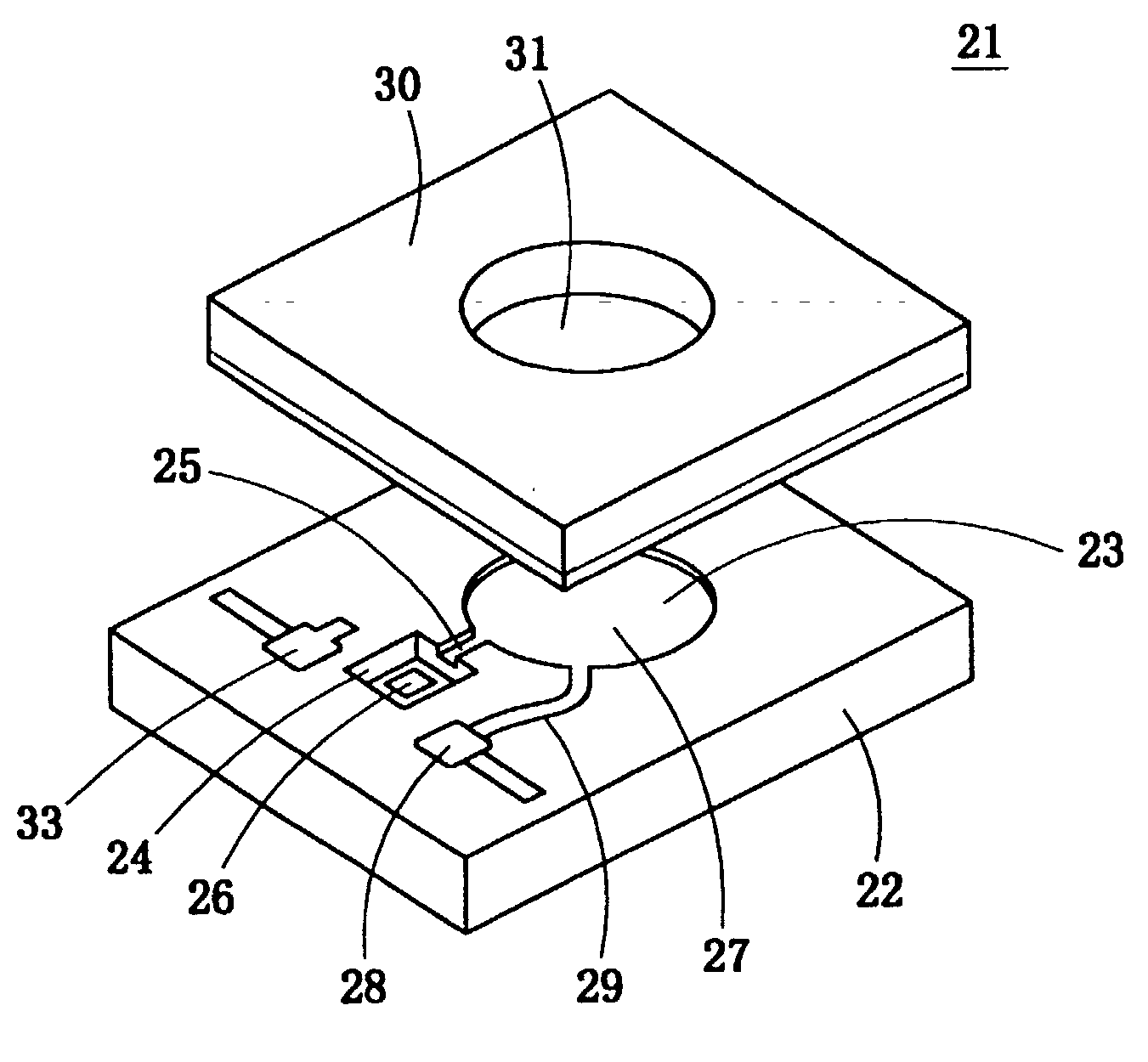

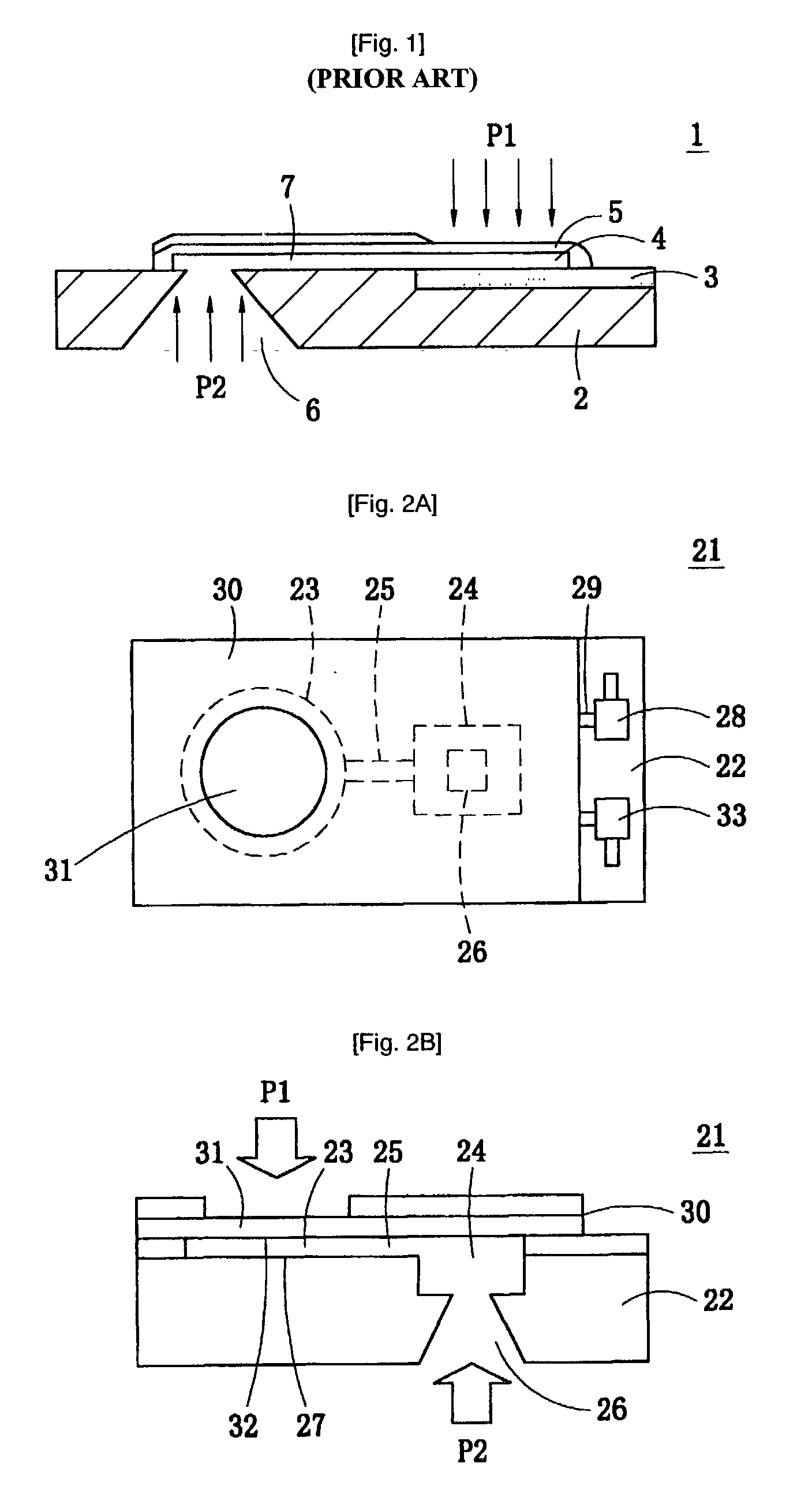

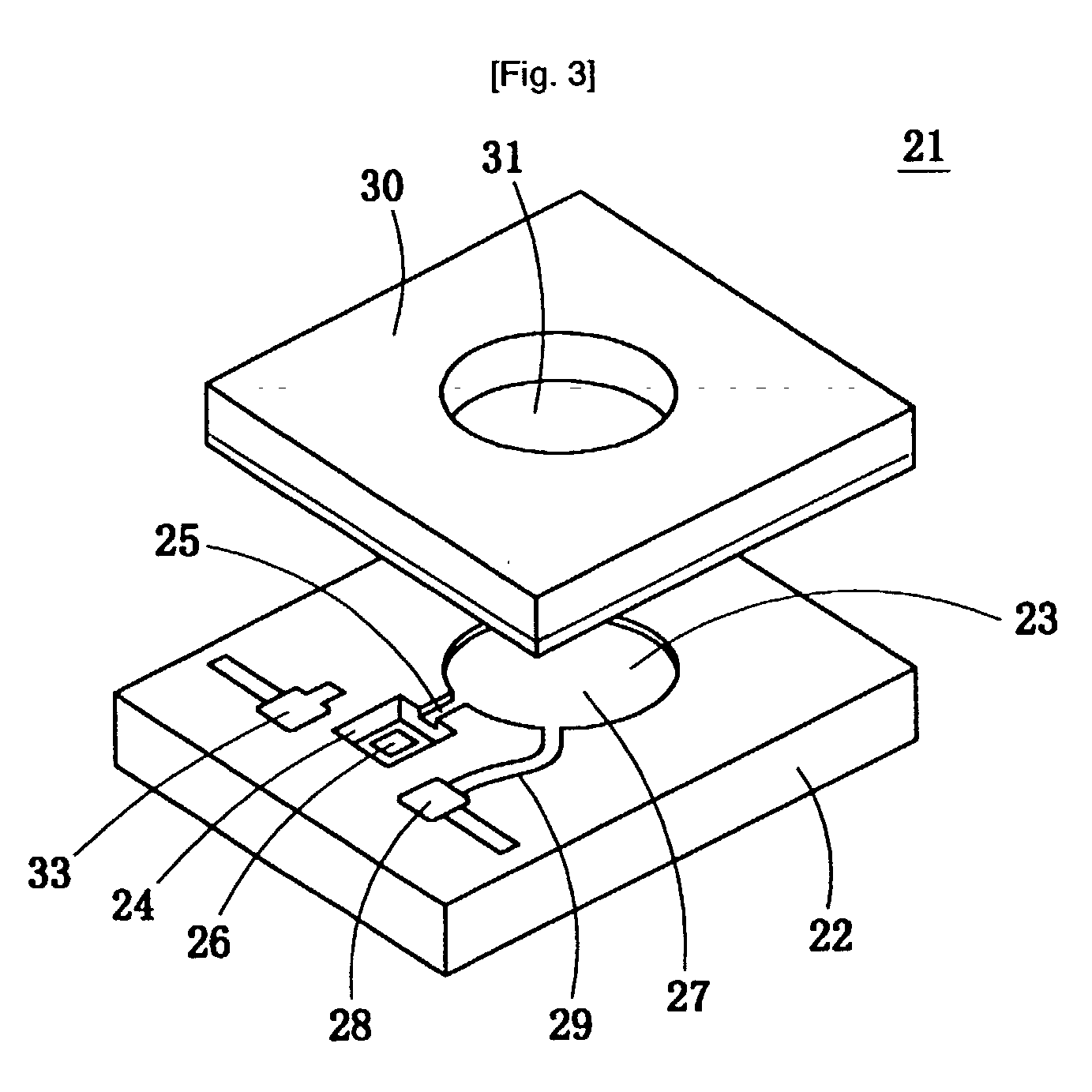

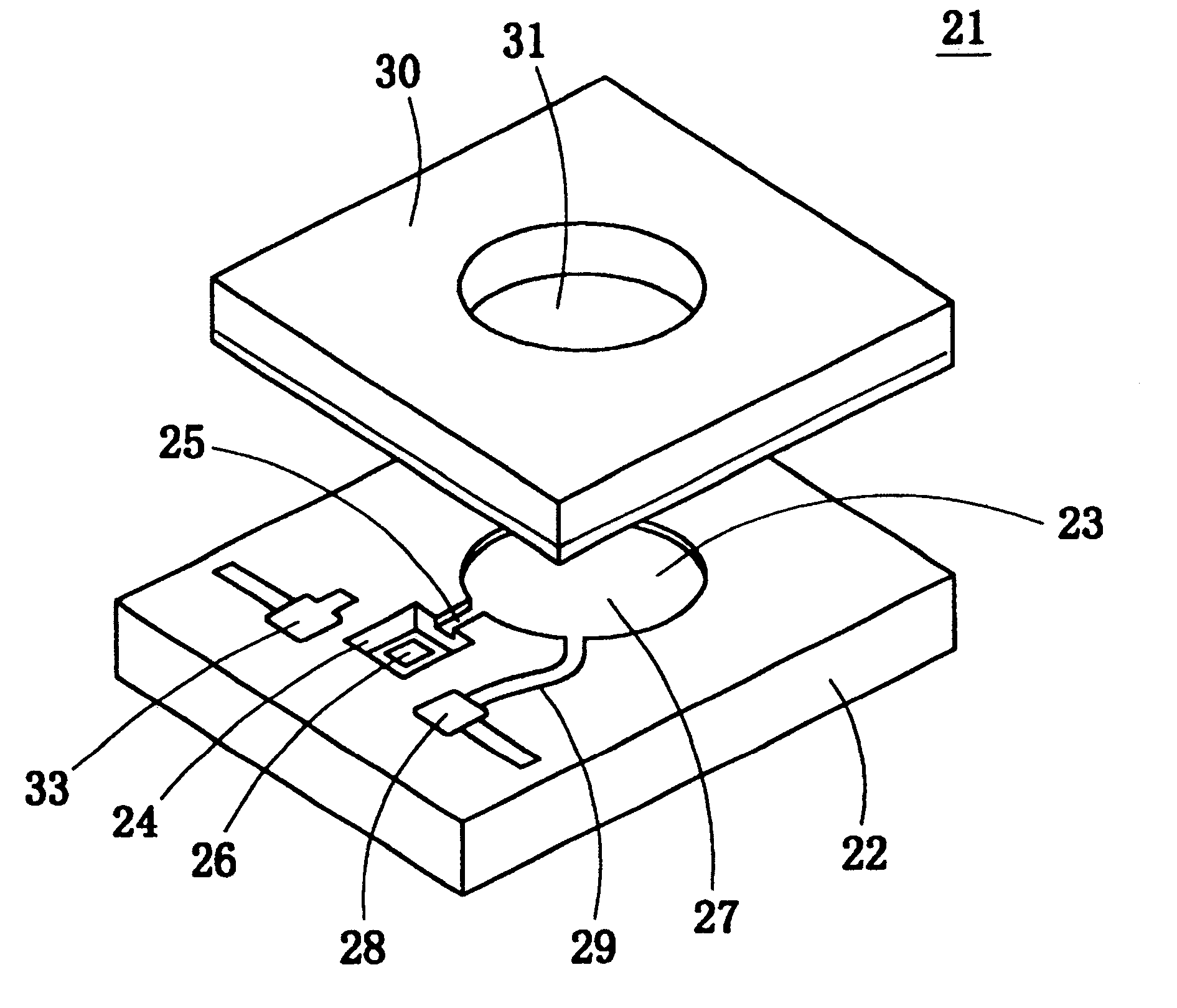

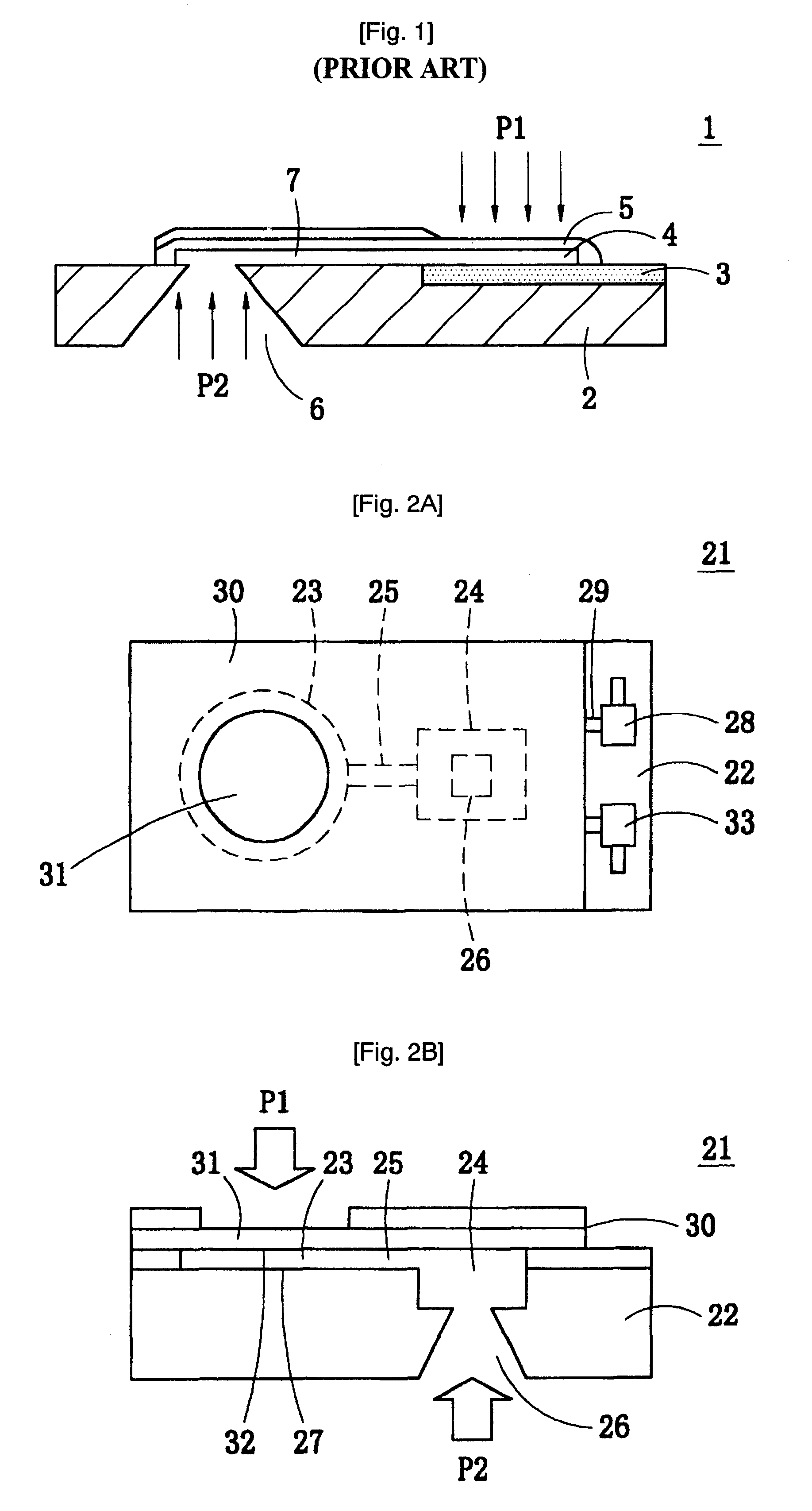

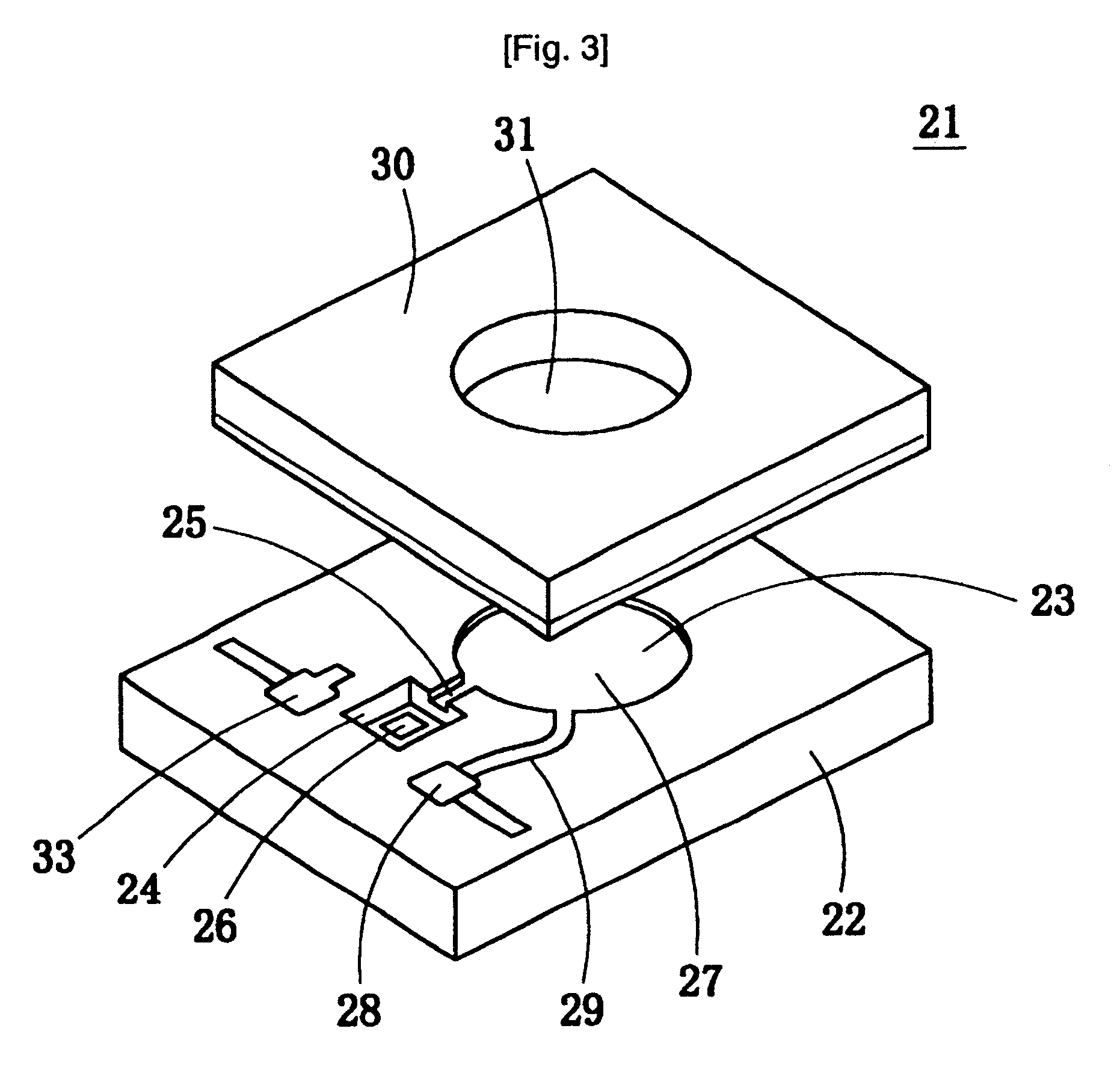

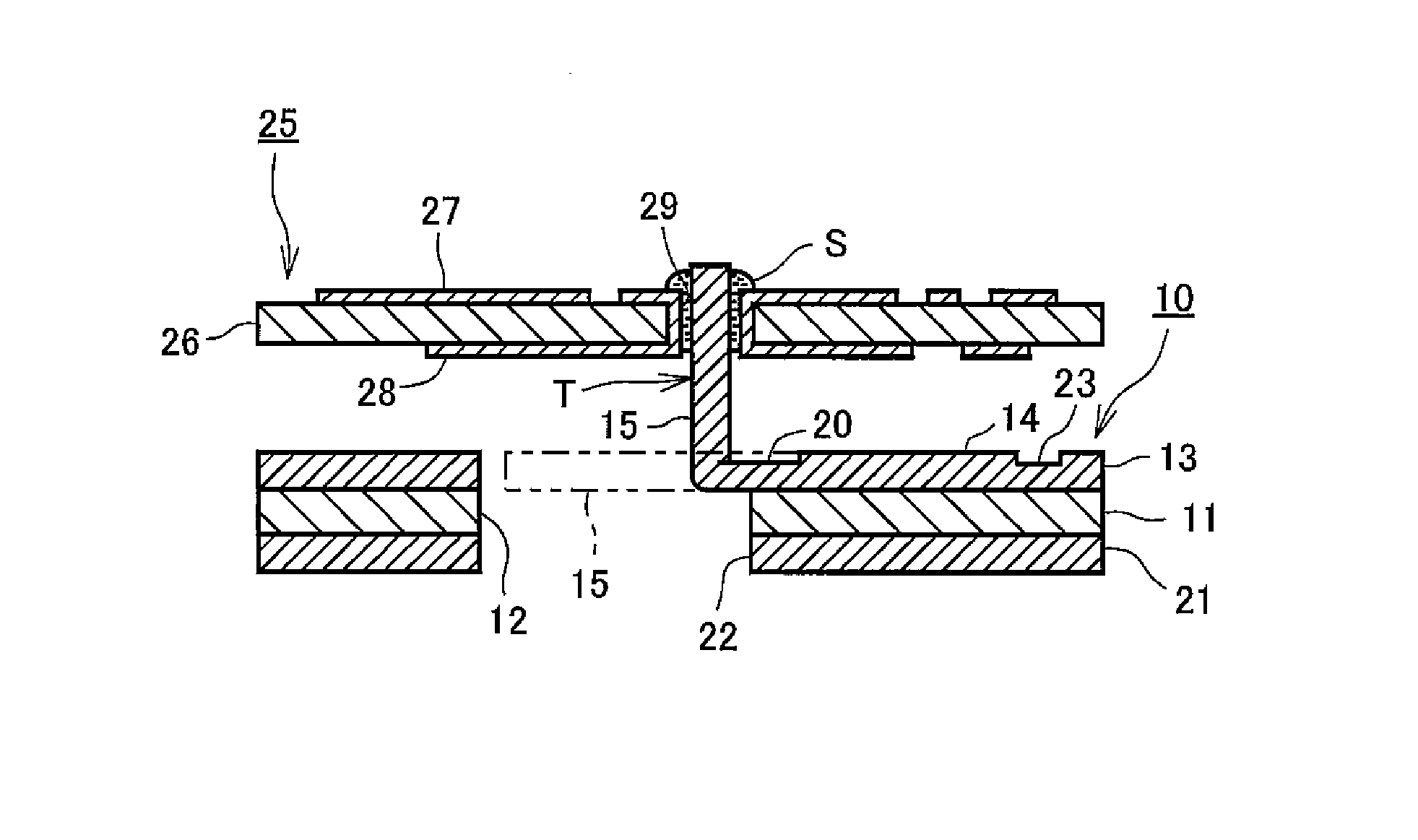

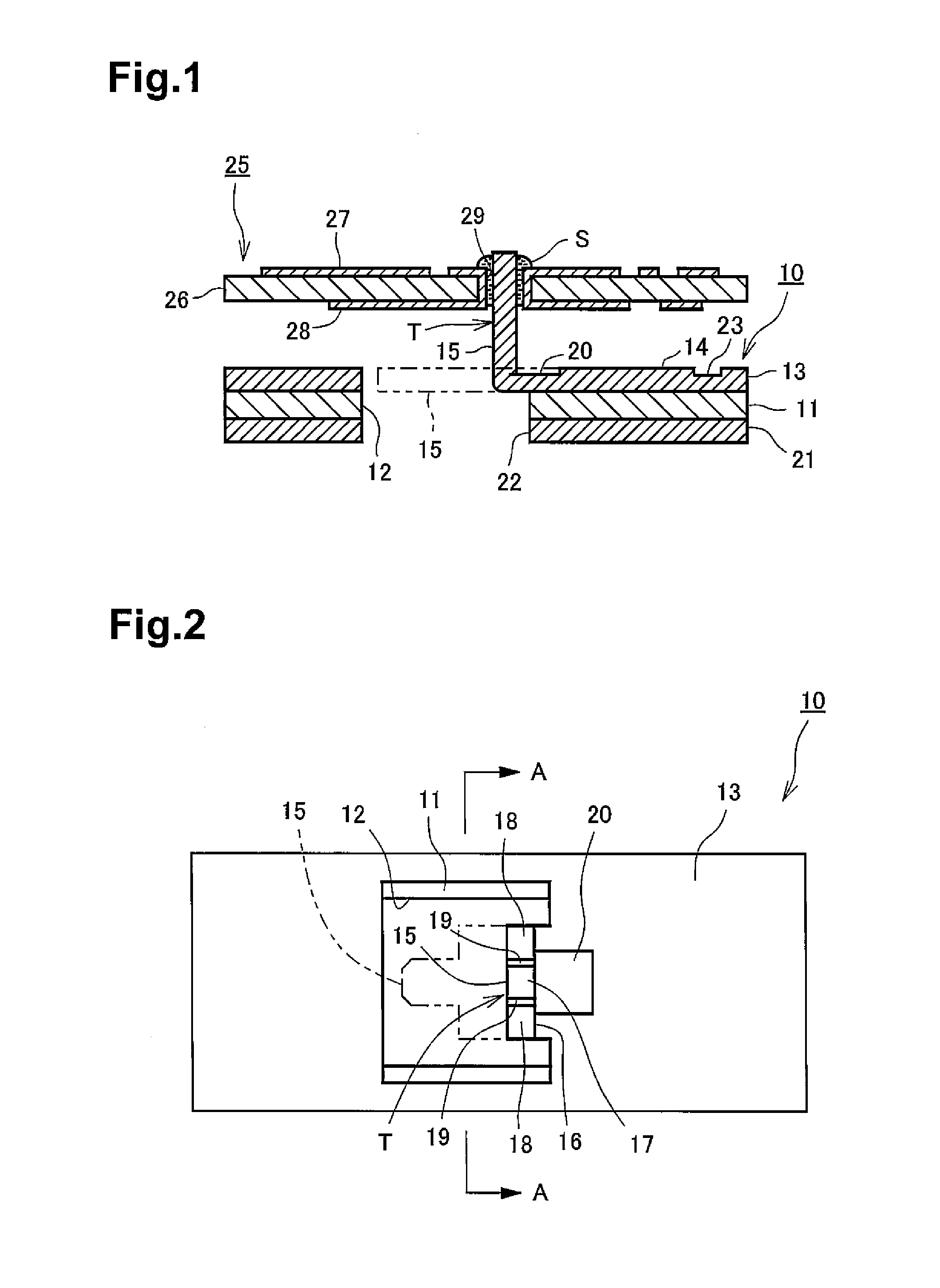

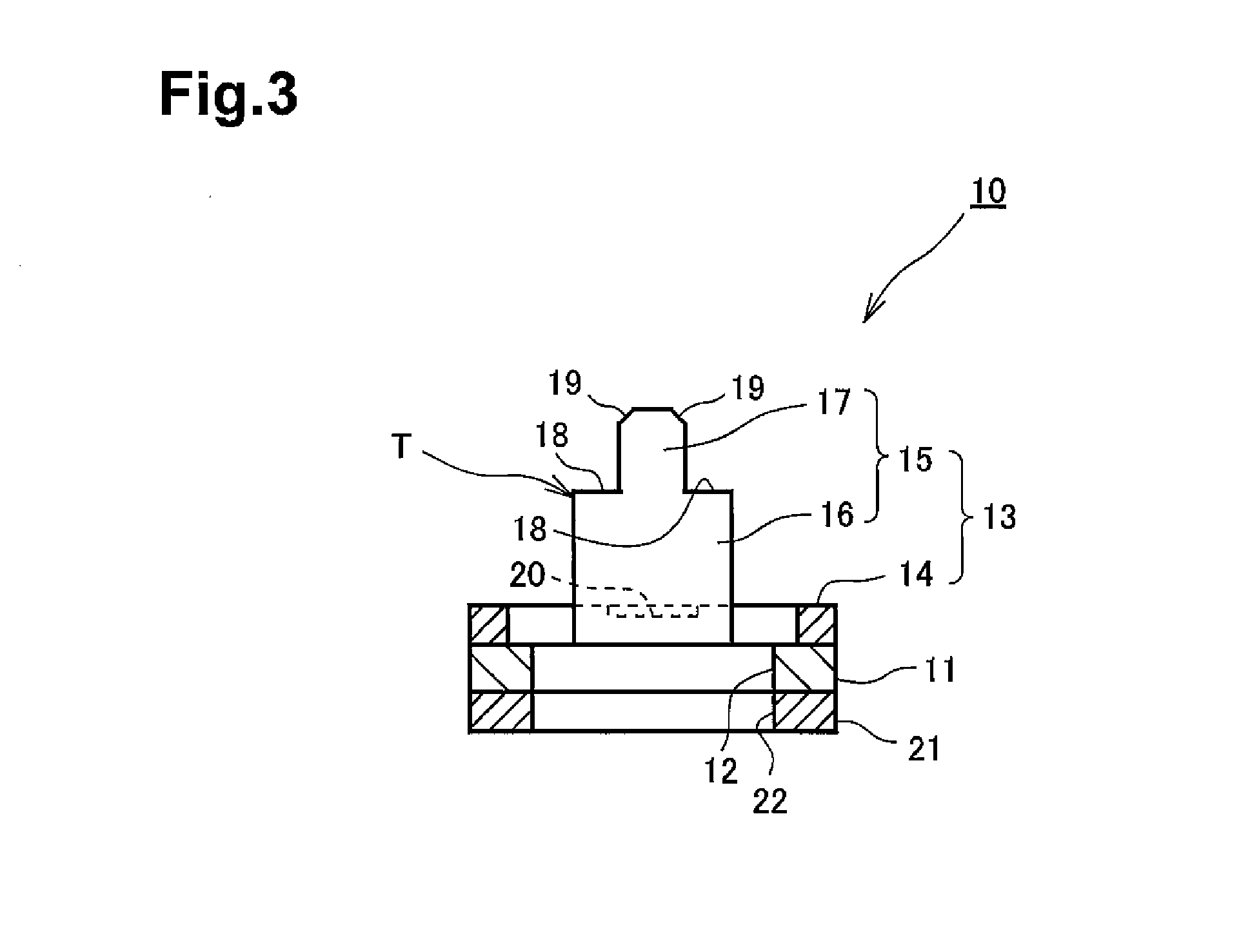

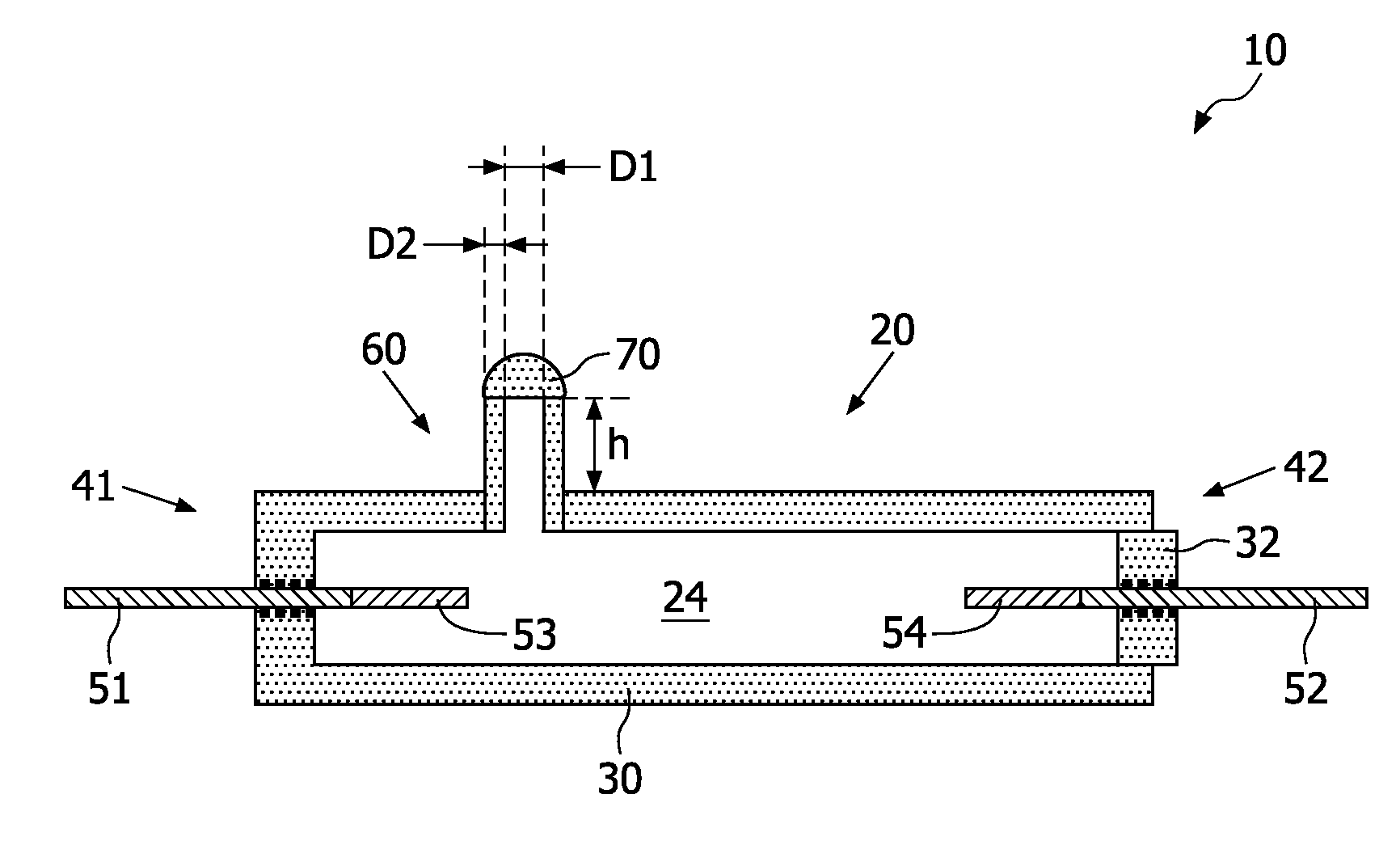

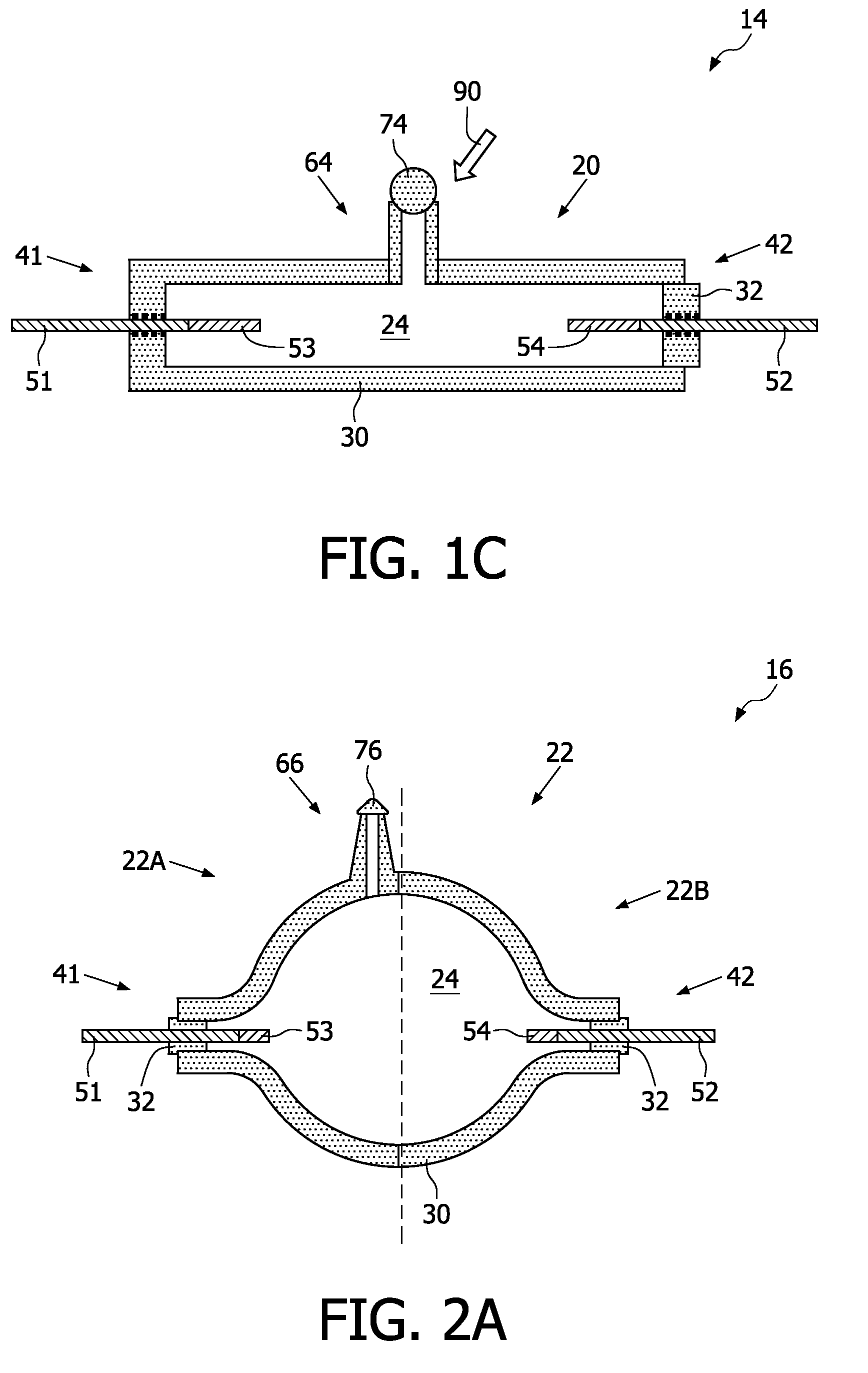

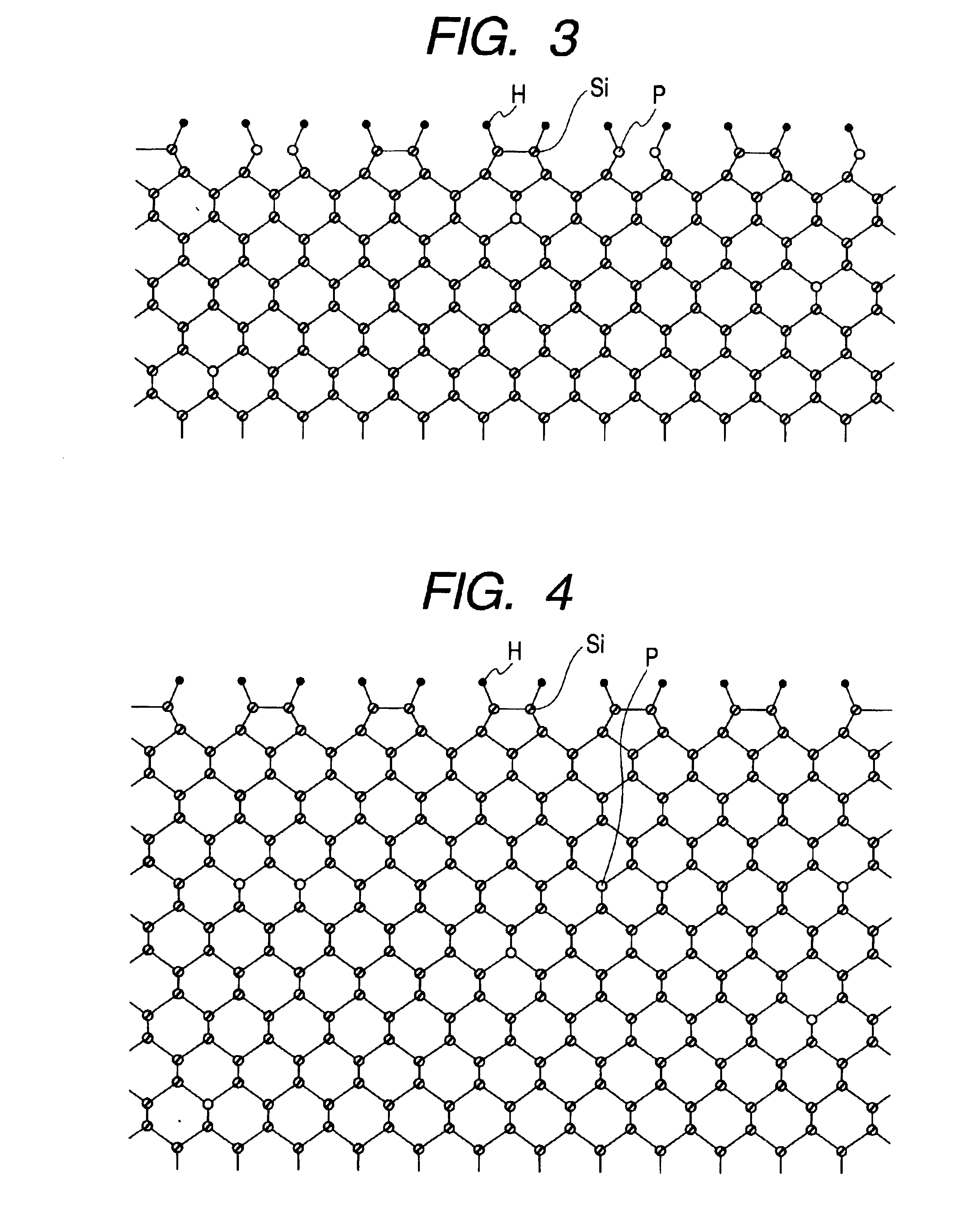

Pressure sensor and pressure-measuring apparatus

InactiveUS20030056598A1Hinders miniaturizationFluid pressure measurement using ohmic-resistance variationEvaluation of blood vesselsMiniaturizationDirect path

A pressure-detecting chamber 23, a pressure-directing path 25 and a buffer space 24 are formed on the upper face of a main-body-side substrate 22 as recessed portions, and the upper face of the pressure-detecting chamber 23 is covered with a thin-type diaphragm 31, and upper faces of the pressure-directing path 25 and the buffer space 24 are covered with a cover substrate 30. A pressure-introducing unit 26 formed on the lower face of the main-body-side substrate 22 is connected to the lower face of the buffer space 24. The cross-section of the buffer space 24 is greater than the cross-section of the pressure-introducing unit 26, and the capacity of the buffer space 24 is greater than the capacity of the pressure-directing path 25. With this arrangement, it is possible to provide a pressure sensor which can control the response characteristic of the pressure sensor to a pressure change with high precision without causing serious adverse effects on the other characteristics of the pressure sensor, without preventing the miniaturization of the sensor.

Owner:ORMON CORP

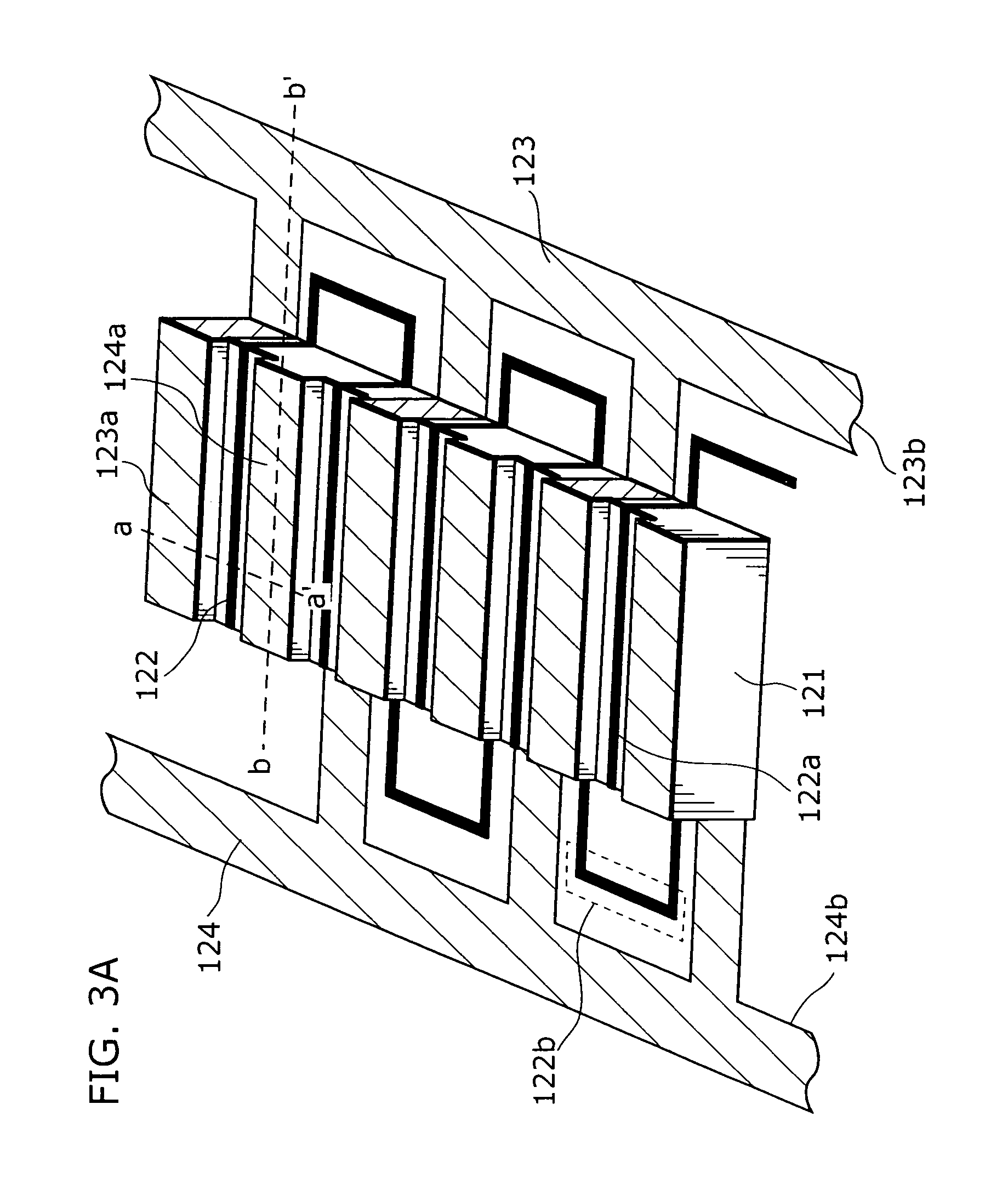

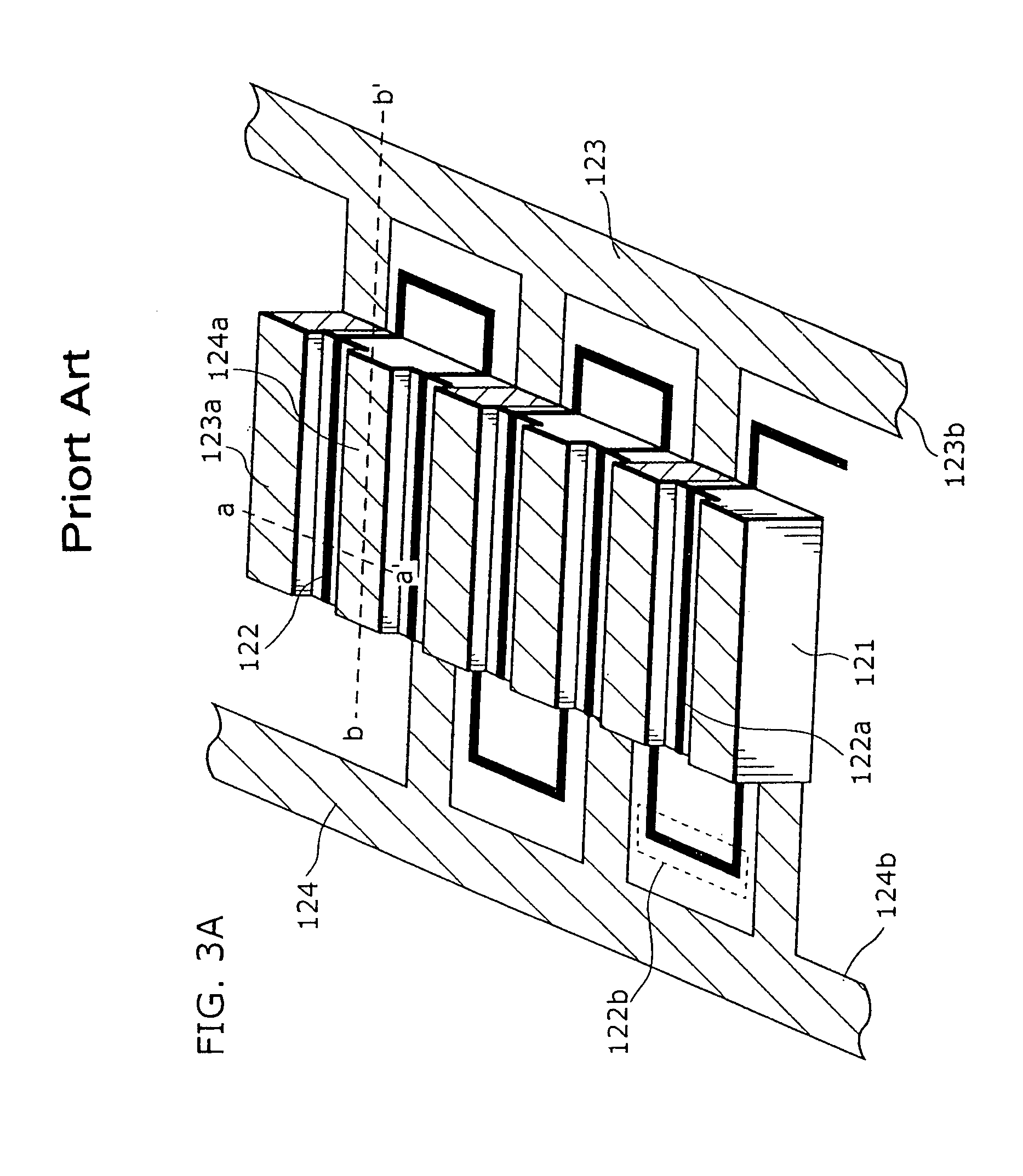

Field-effect transistor

InactiveUS20060022218A1Reduced characteristicsReduce impactSemiconductor devicesMiniaturizationEngineering

The present invention, which aims to provide a gallium arsenide field-effect transistor that can reduce degradation of field-effect transistor characteristics, and to realize miniaturization of the transistor, includes: a substrate; a mesa which includes a channel layer and is formed on the substrate; a source electrode formed on the mesa; a drain electrode; and a gate electrode, wherein, on the mesa, a top pattern is formed in which finger portions of the source electrode and the drain electrode which are formed in comb-shape are located so as to interdigitate, and a gate electrode is formed between the source electrode and the drain electrode, while common portions, which are base parts of the finger portions of the source and drain electrodes, are formed on the surface of the mesa, and the part located below the straight portion which is parallel to the finger portions of the gate electrode is electrically separated from the part located below a corner portion that connects neighboring straight portions of the gate electrode.

Owner:COLLABO INNOVATIONS INC

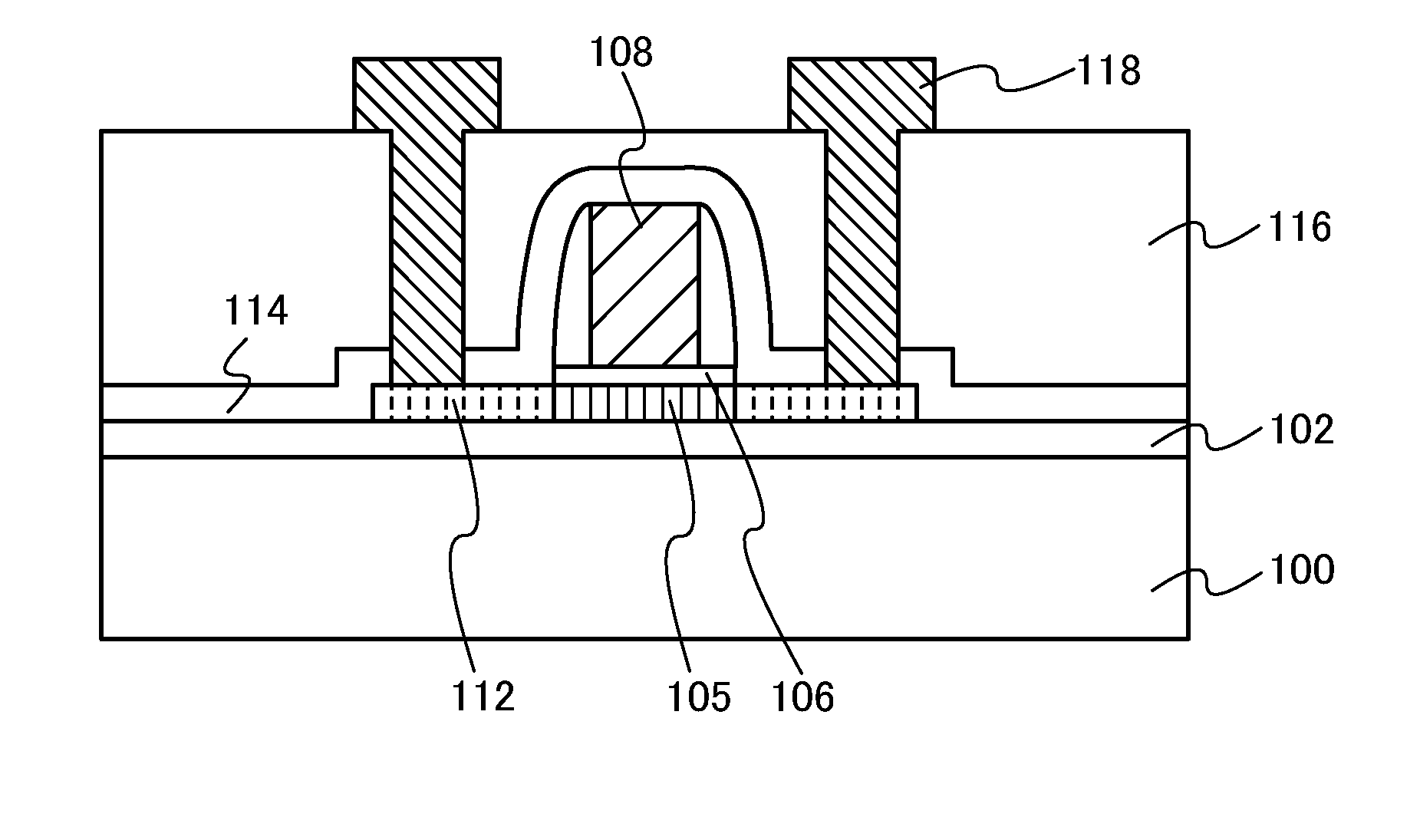

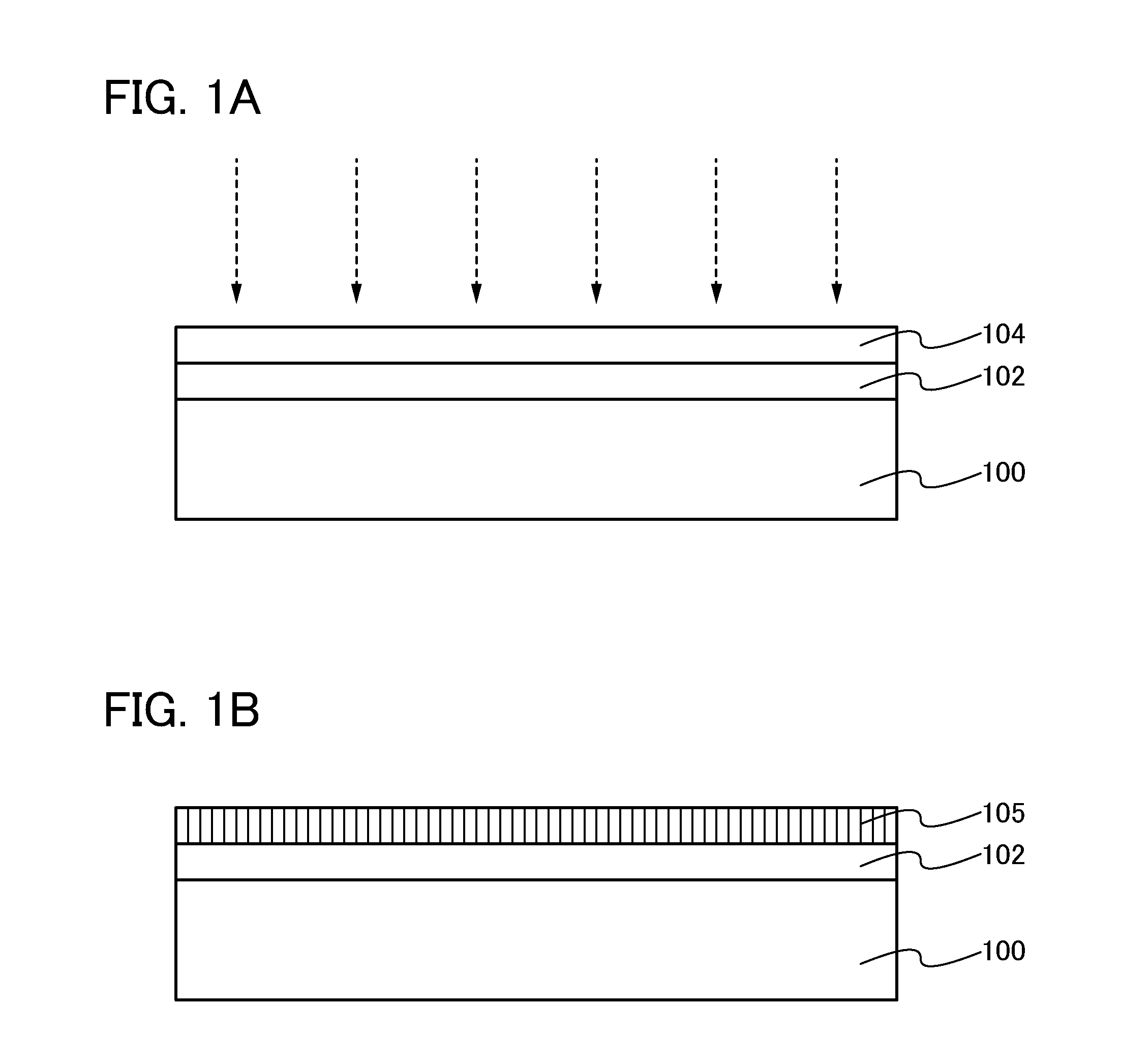

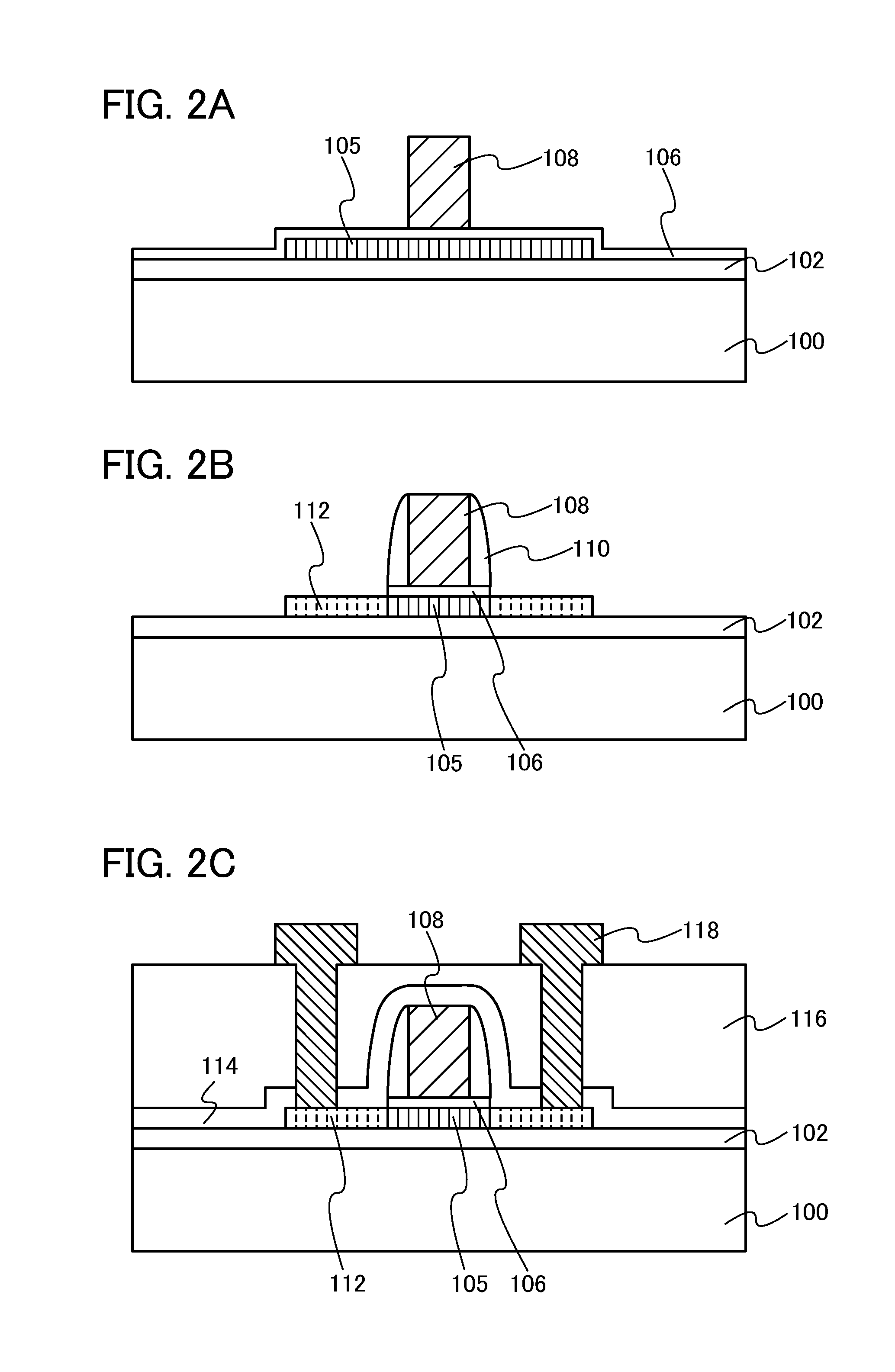

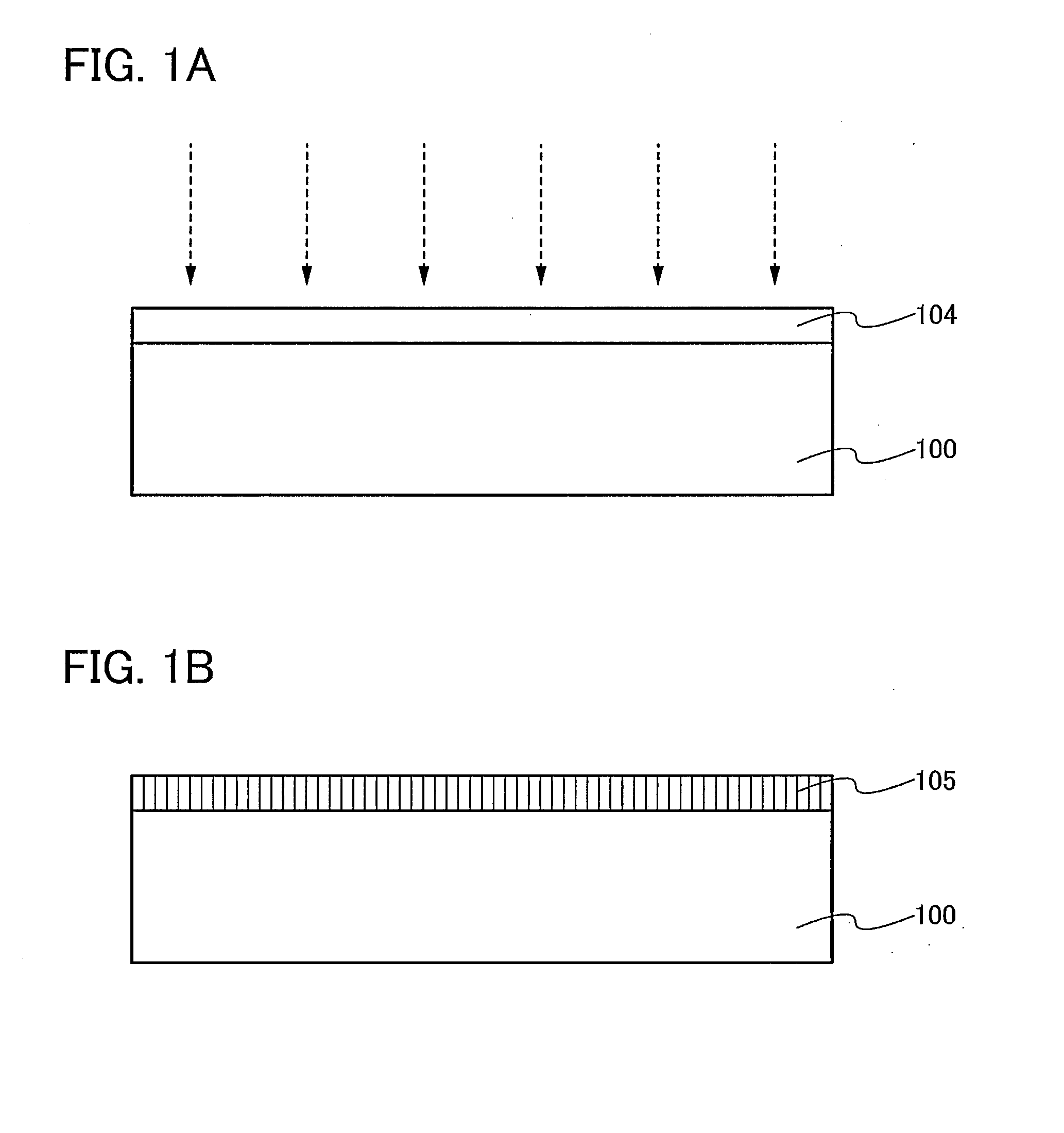

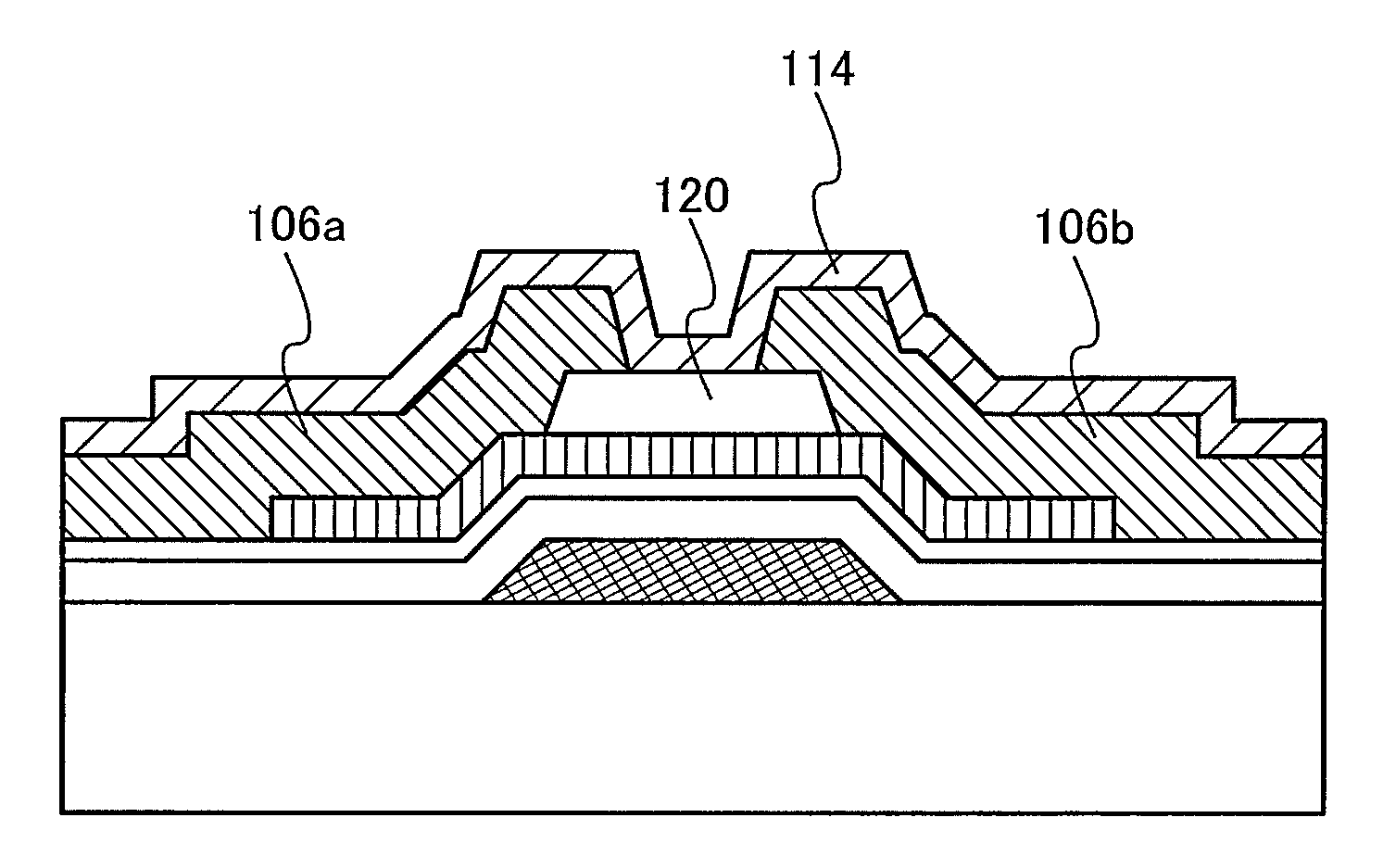

Method for manufacturing oxide semiconductor film, method for manufacturing semiconductor device, and semiconductor device

ActiveUS20130009147A1Improvement in reliability of elementImprove propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceSemiconductor

In an oxide semiconductor film formed over an insulating surface, an amorphous region remains in the vicinity of the interface with the base, which is thought to cause a variation in the characteristics of a transistor and the like. A base surface or film touching the oxide semiconductor film is formed of a material having a melting point higher than that of a material used for the oxide semiconductor film. Accordingly, a crystalline region is allowed to exist in the vicinity of the interface with the base surface or film touching the oxide semiconductor film. An insulating metal oxide is used for the base surface or film touching the oxide semiconductor film. The metal oxide used here is an aluminum oxide, gallium oxide, or the like that is a material belonging to the same group as the material of the oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

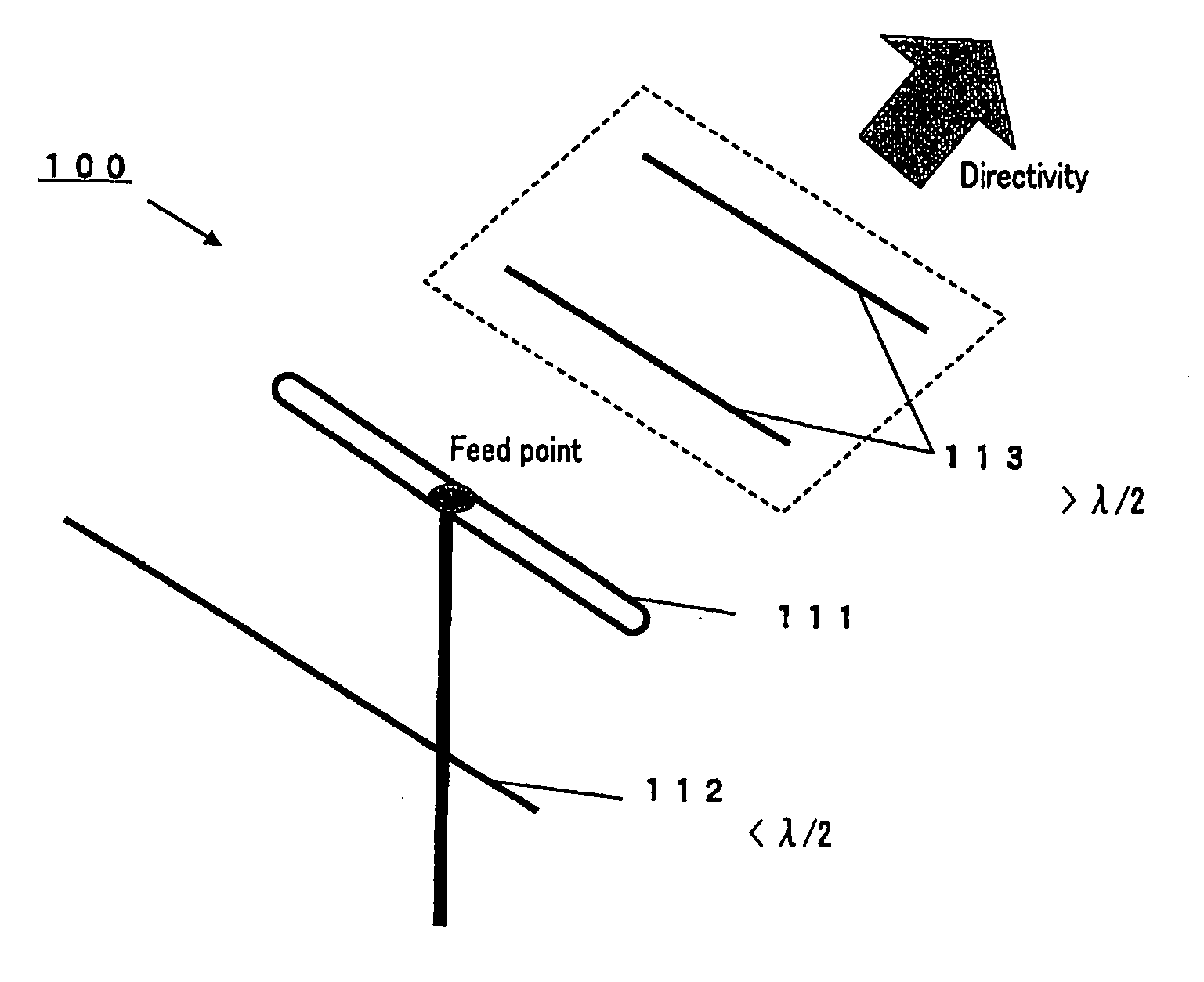

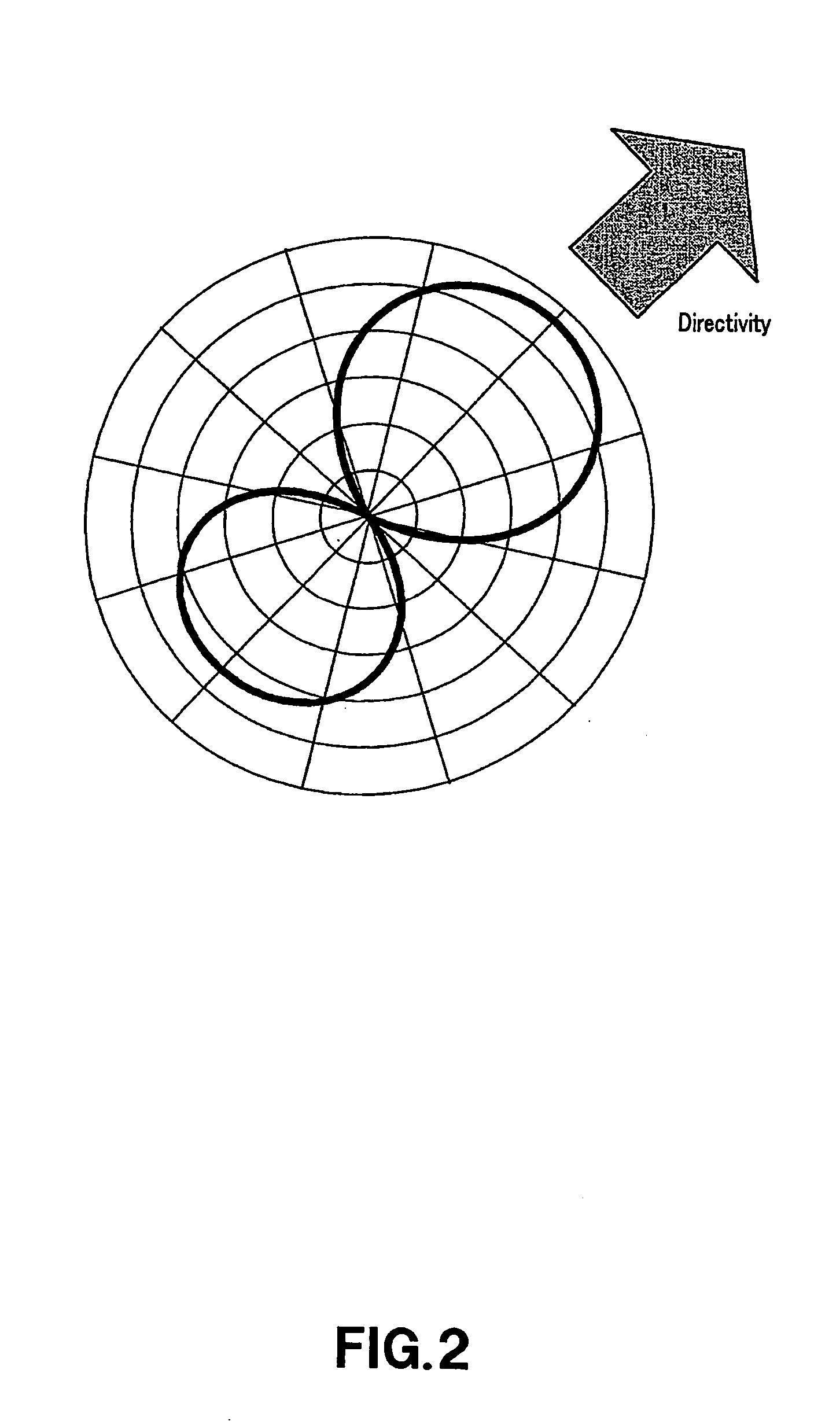

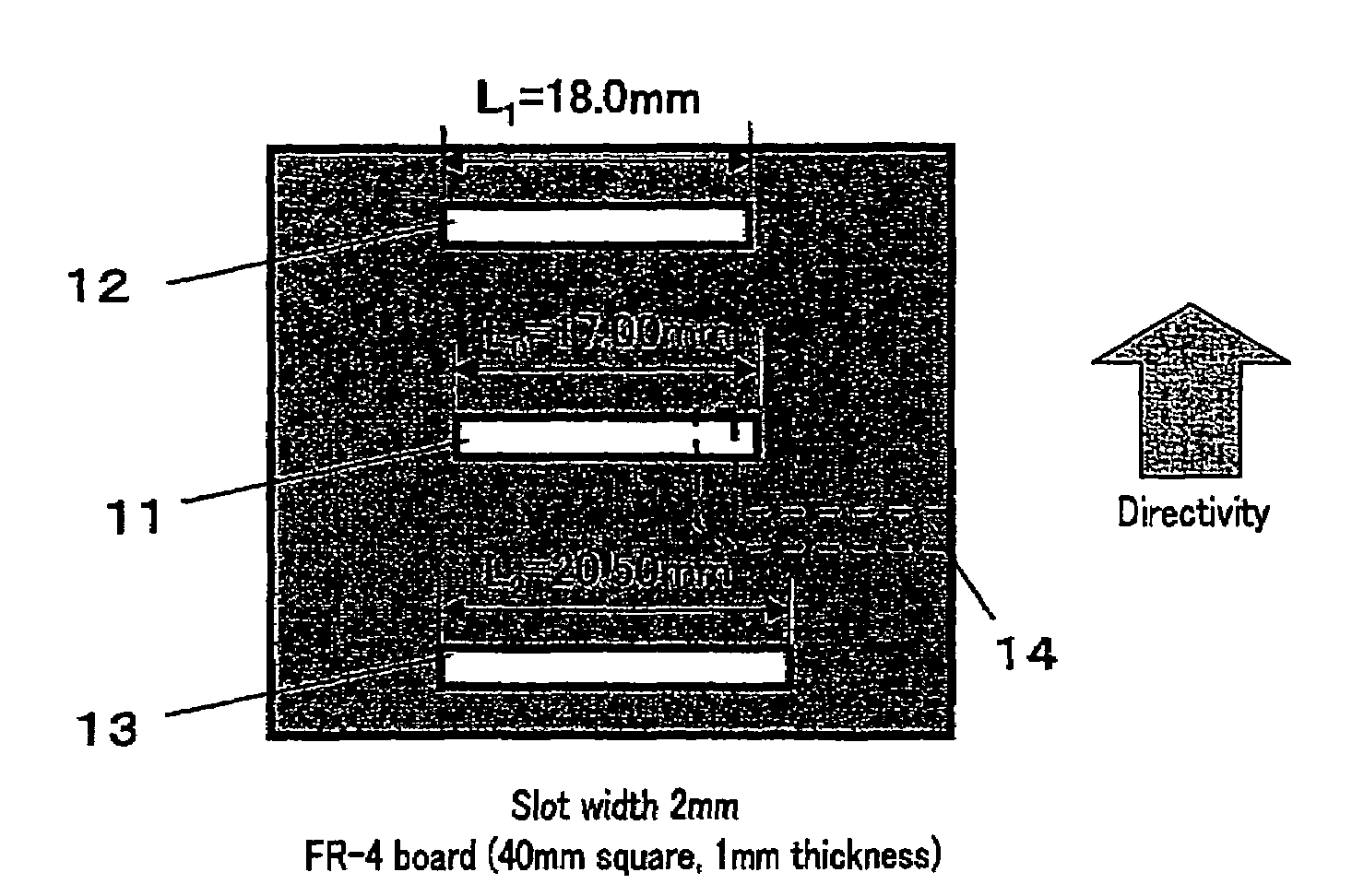

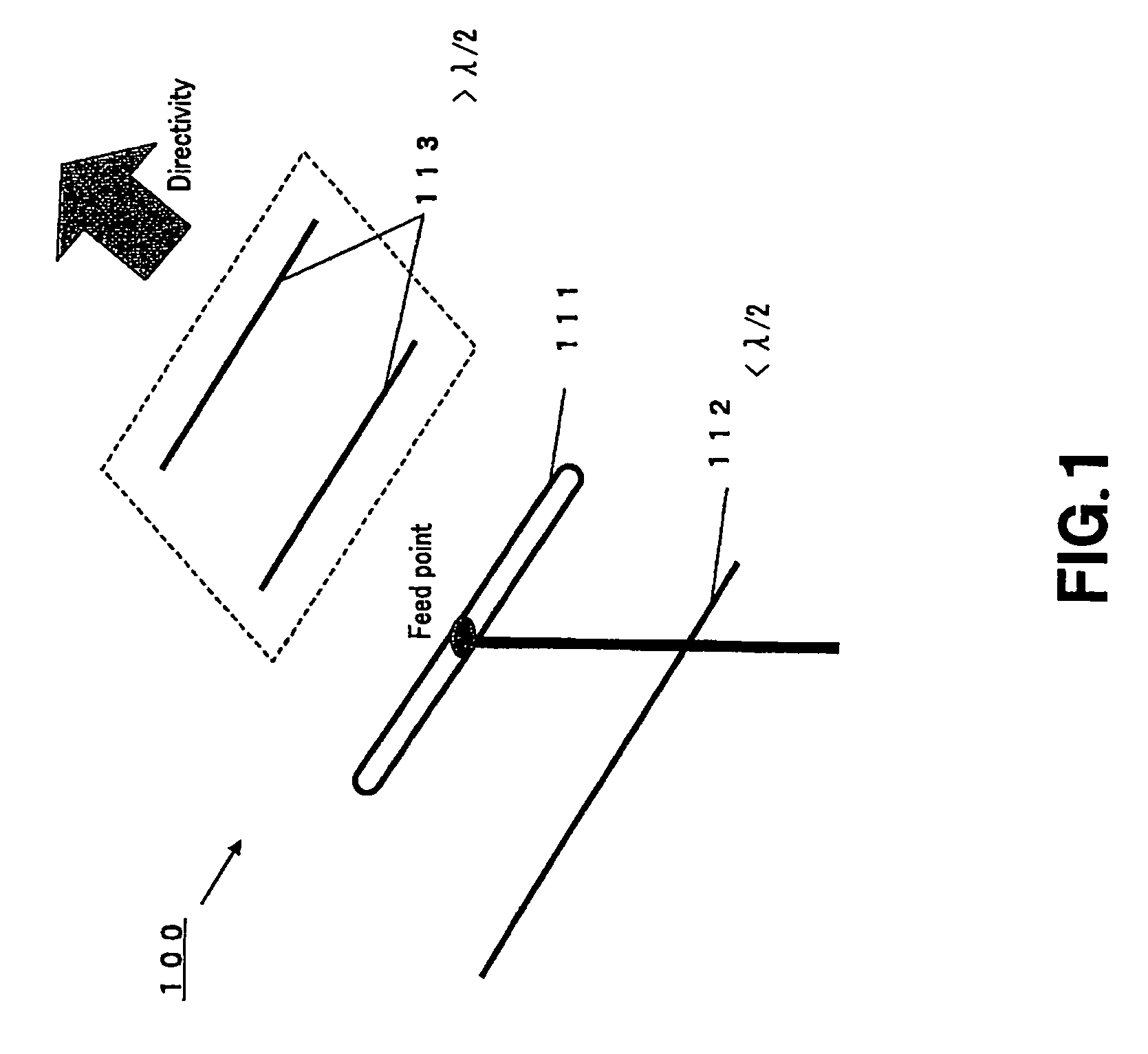

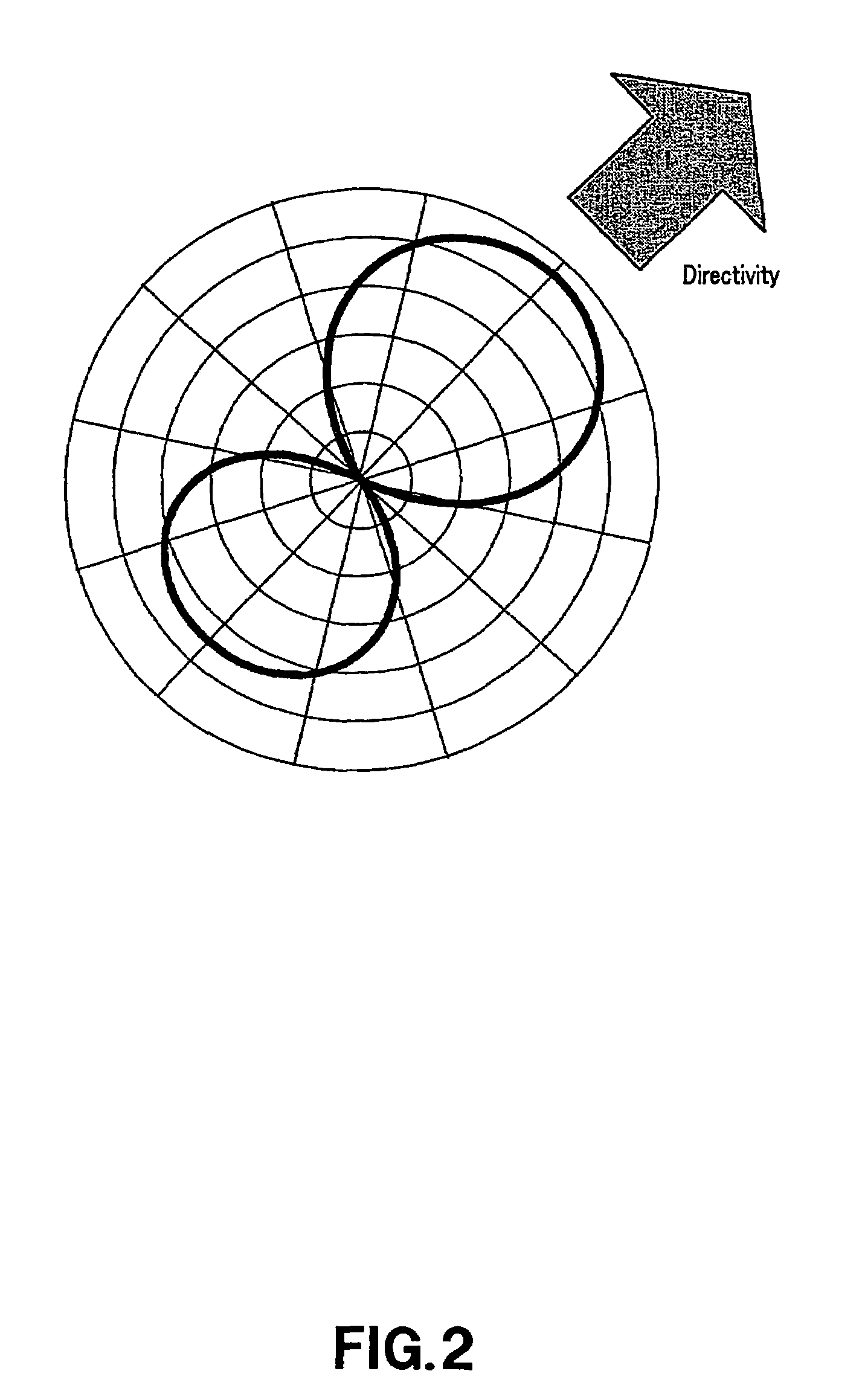

Multibeam antenna

InactiveUS20060044200A1Small sizeReduce in quantityIndividually energised antenna arraysSlot antennasElectricityAntenna element

The present invention has been made to reduce the size and thickness of a multibeam antenna capable of switching the directivity in multi directions. The present invention provides a multibeam antenna including an antenna element array including one or more feed element and N (N: natural number) parasitic elements, wherein the electrical length of one or more parasitic elements are made variable.

Owner:SONY CORP

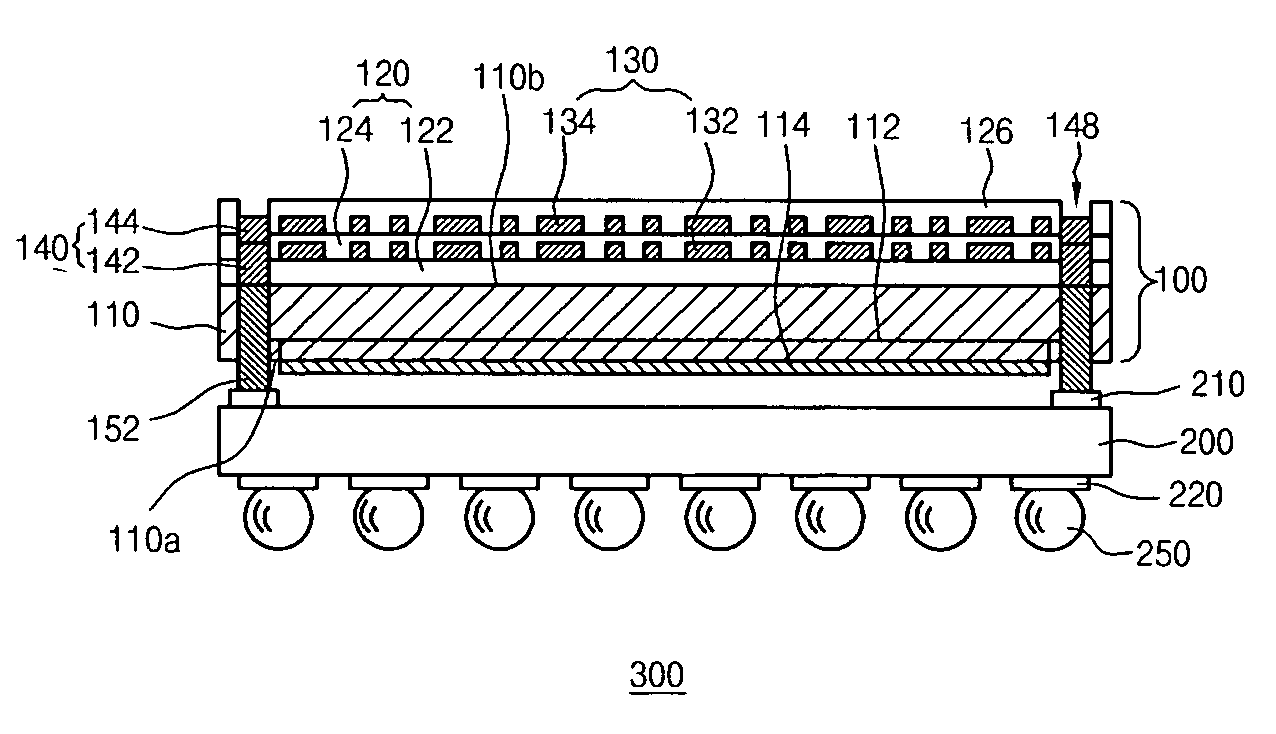

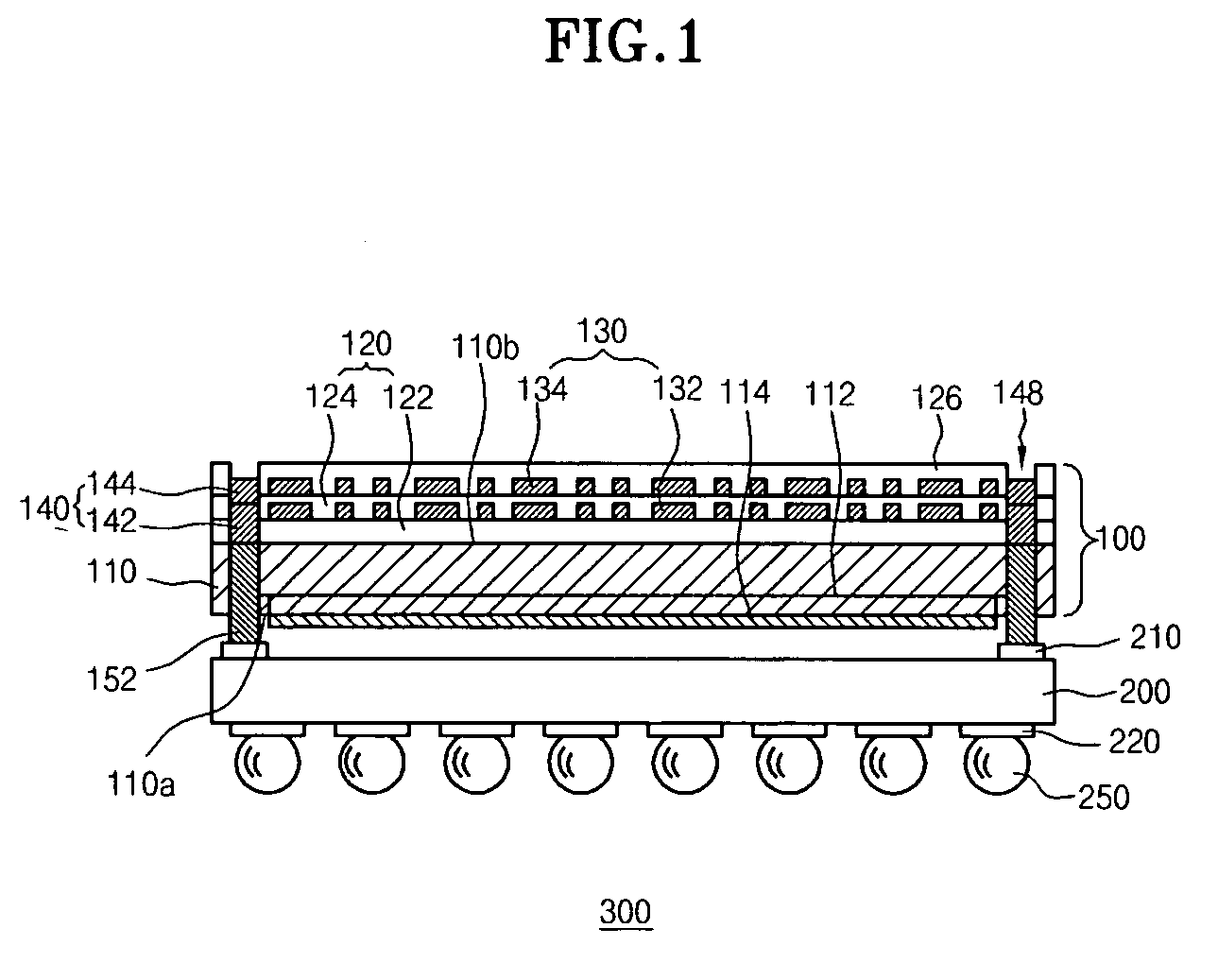

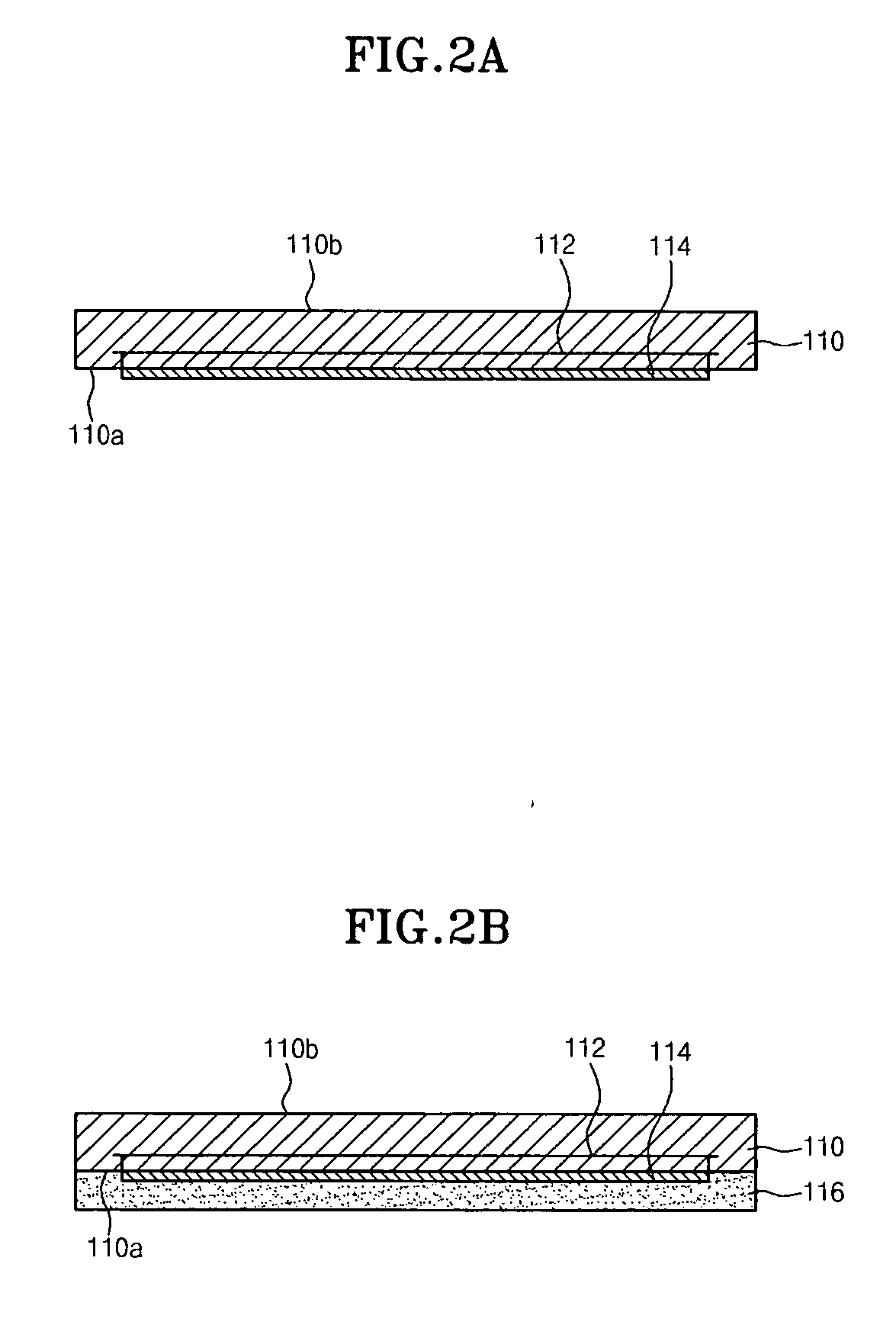

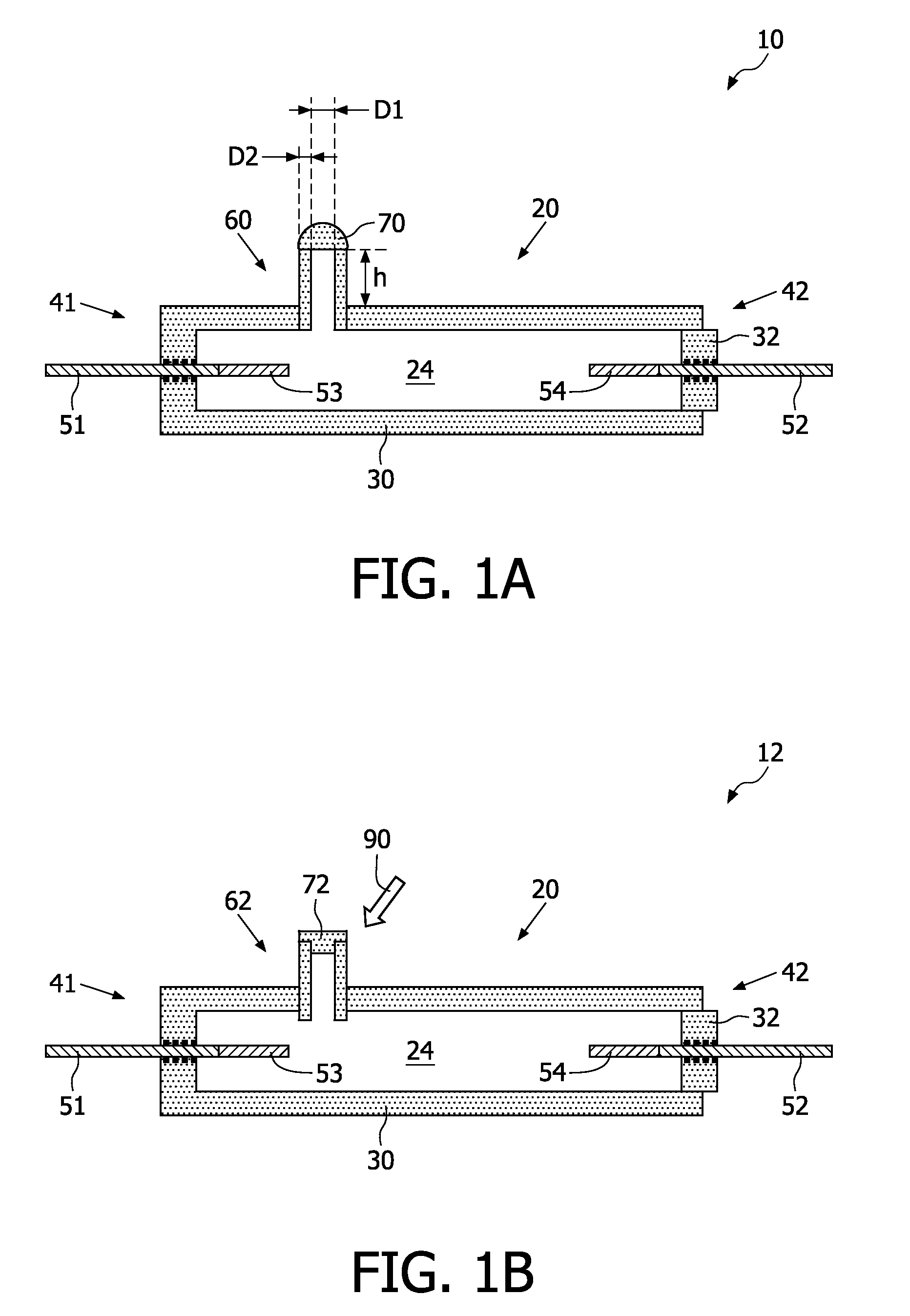

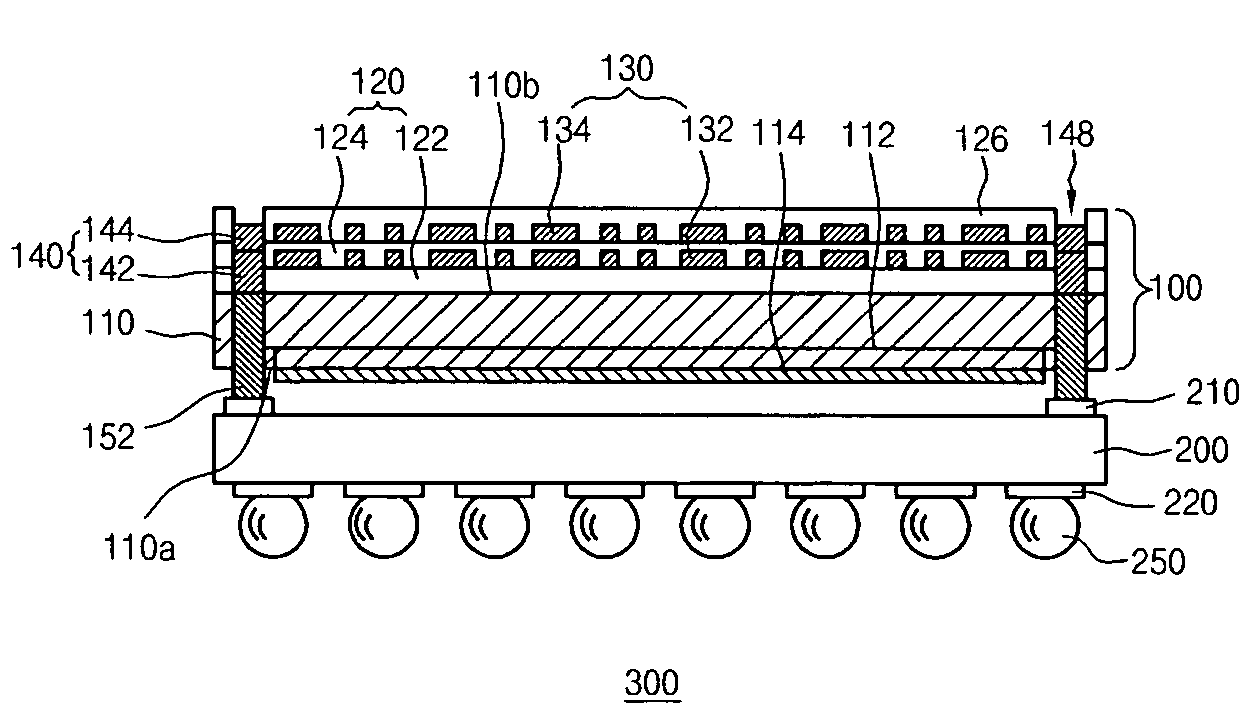

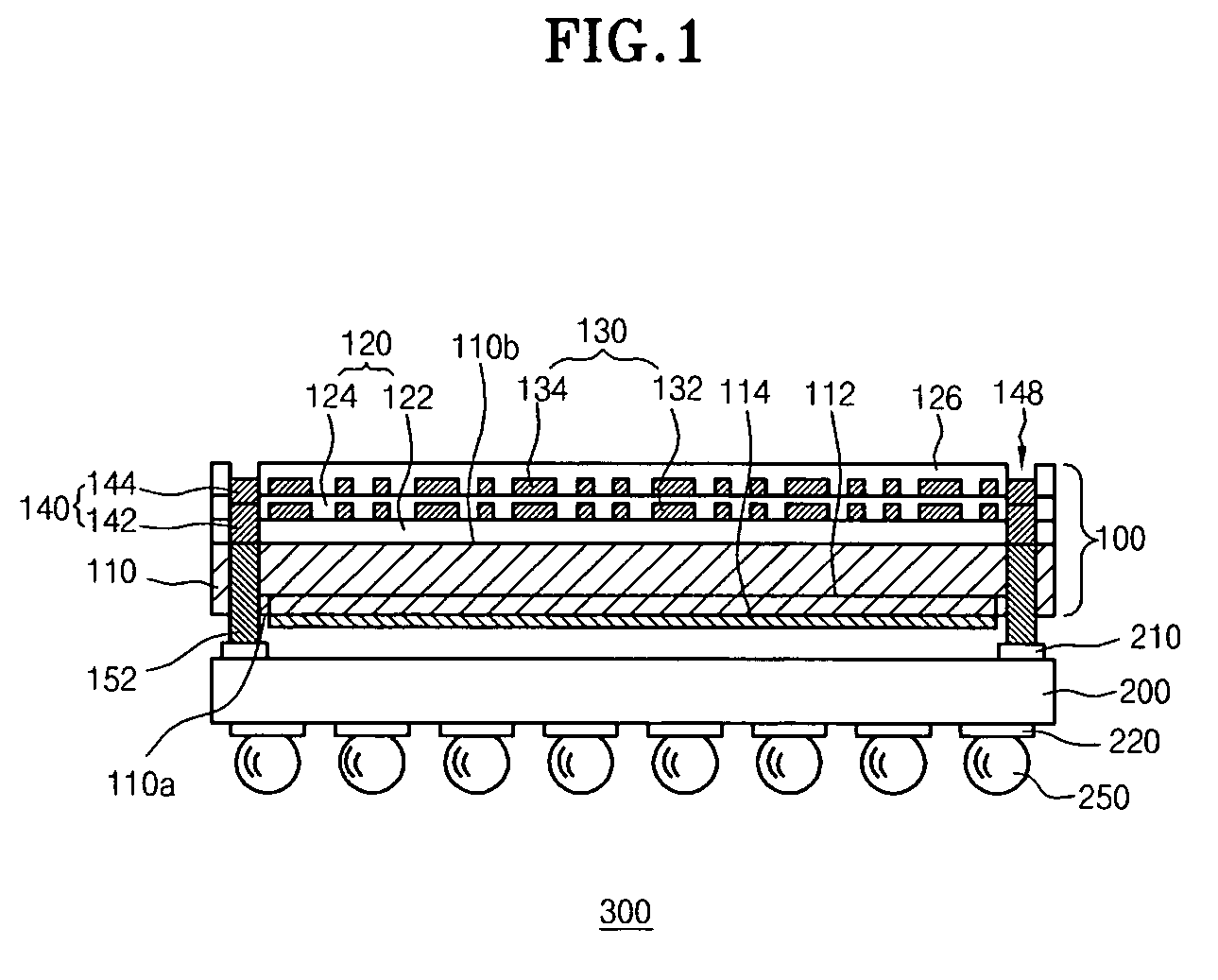

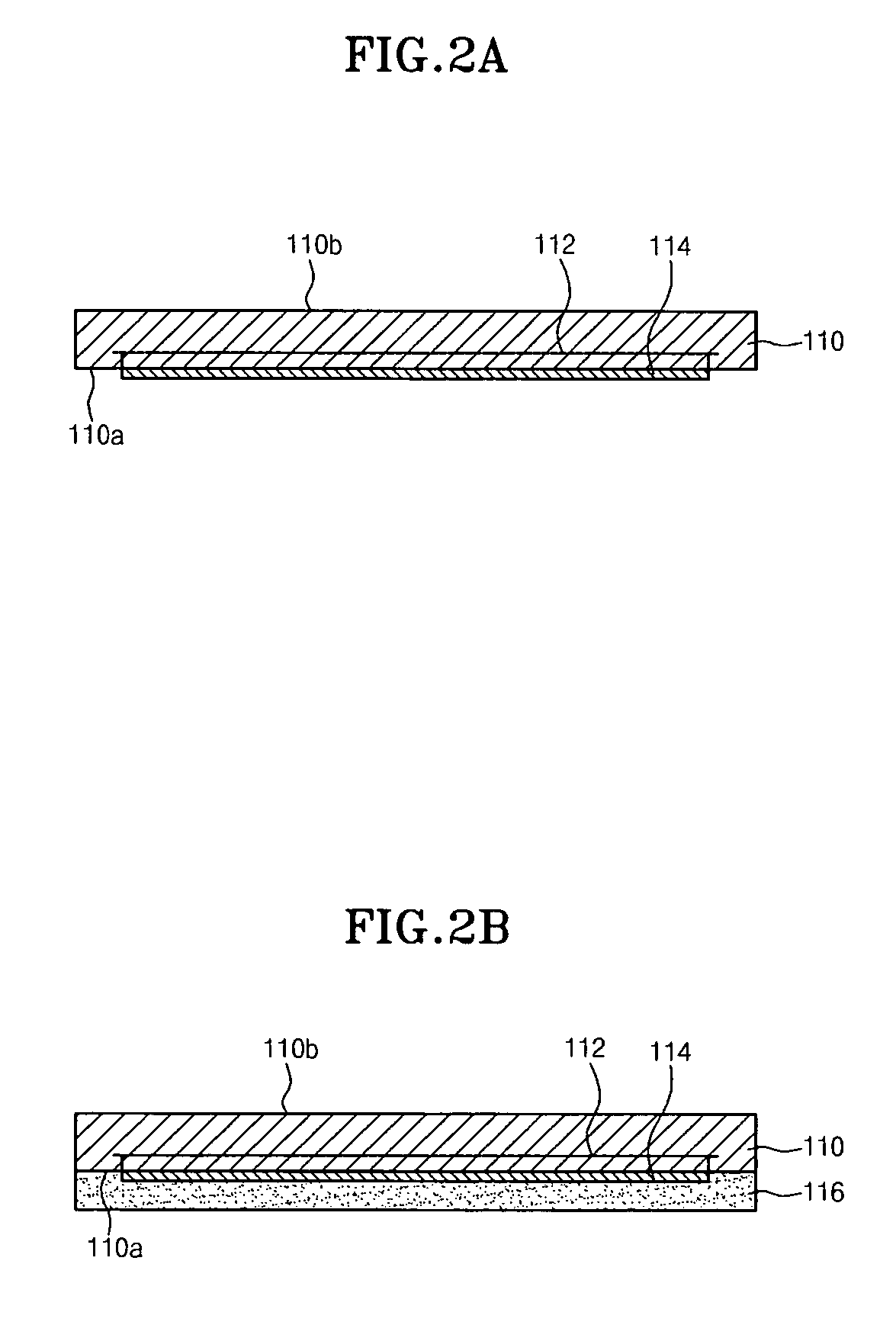

Semiconductor package having embedded passive elements and method for manufacturing the same

ActiveUS20080001285A1Hinders miniaturizationMinimizes electrical connection lengthSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

A semiconductor package includes a base substrate on which a semiconductor chip is placed so that a first surface thereof faces the base substrate. A circuit section is formed adjacent to the first surface. An insulation layer is formed on a second surface of the semiconductor chip which faces away from the first surface. Passive elements are formed on the insulation layer. Via patterns are formed to pass through the insulation layer and are connected to the passive elements. Via wirings are formed to pass through the semiconductor chip and connected to the circuit section, the via patterns and the base substrate. Outside connection terminals are attached to a first surface of the base substrate, which face away from a second surface of the base substrate on which the semiconductor chip is placed.

Owner:SK HYNIX INC

Pressure sensor and pressure-measuring apparatus using pressure buffering

InactiveUS6584854B2Hinders miniaturizationEasy to useFluid pressure measurement using ohmic-resistance variationEvaluation of blood vesselsMiniaturizationEngineering

A pressure-detecting chamber 23, a pressure-directing path 25 and a buffer space 24 are formed on the upper face of a main-body-side substrate 22 as recessed portions, and the upper face of the pressure-detecting chamber 23 is covered with a thin-type diaphragm 31, and upper faces of the pressure-directing path 25 and the buffer space 24 are covered with a cover substrate 30. A pressure-introducing unit 26 formed on the lower face of the main-body-side substrate 22 is connected to the lower face of the buffer space 24. The cross-section of the buffer space 24 is greater than the cross-section of the pressure-introducing unit 26, and the capacity of the buffer space 24 is greater than the capacity of the pressure-directing path 25. With this arrangement, it is possible to provide a pressure sensor which can control the response characteristic of the pressure sensor to a pressure change with high precision without causing serious adverse effects on the other characteristics of the pressure sensor, without preventing the miniaturization of the sensor.

Owner:ORMON CORP

Multibeam antenna

InactiveUS7388552B2Hinders miniaturizationReduce thicknessIndividually energised antenna arraysSlot antennasElectricityAntenna element

Owner:SONY CORP

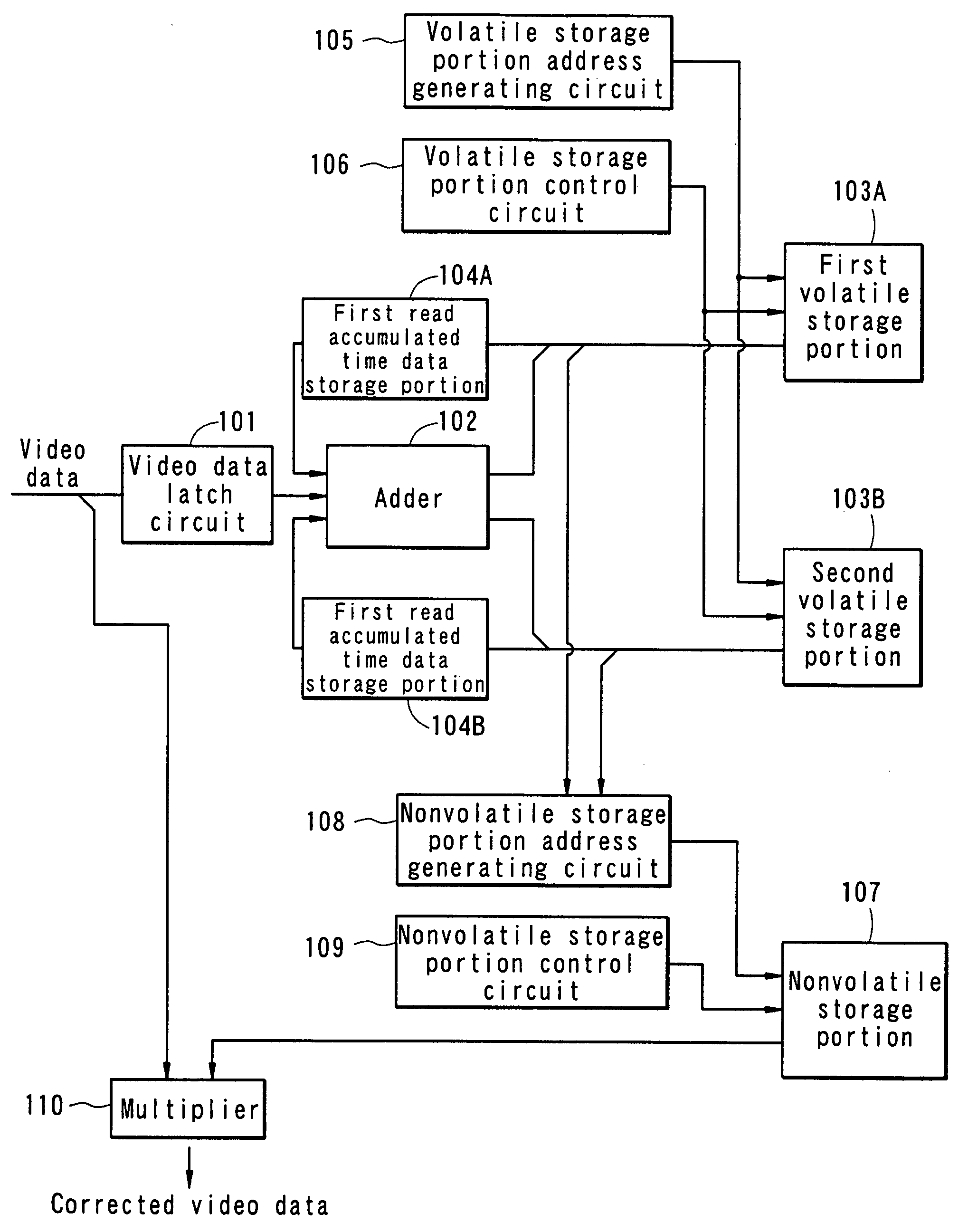

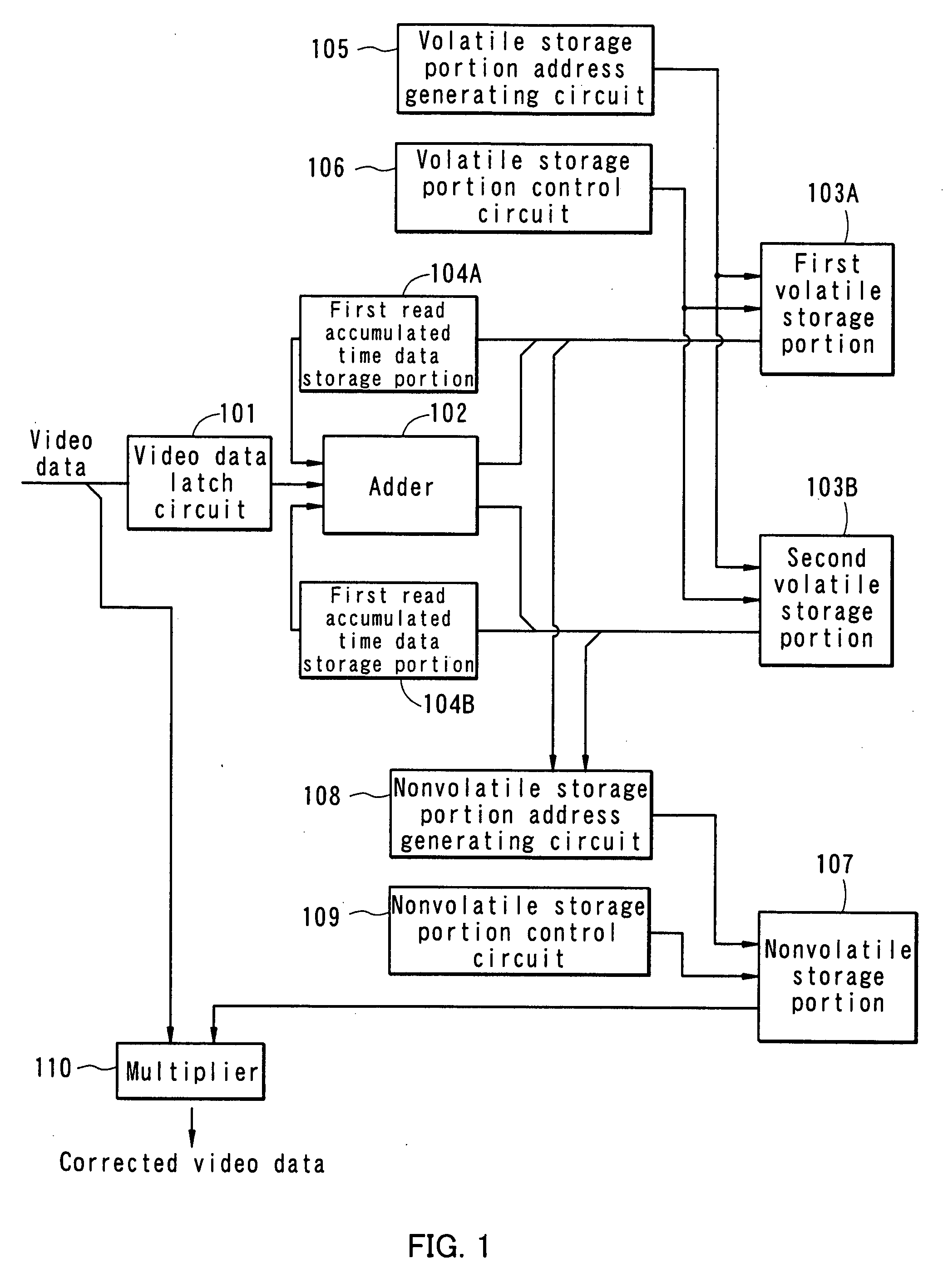

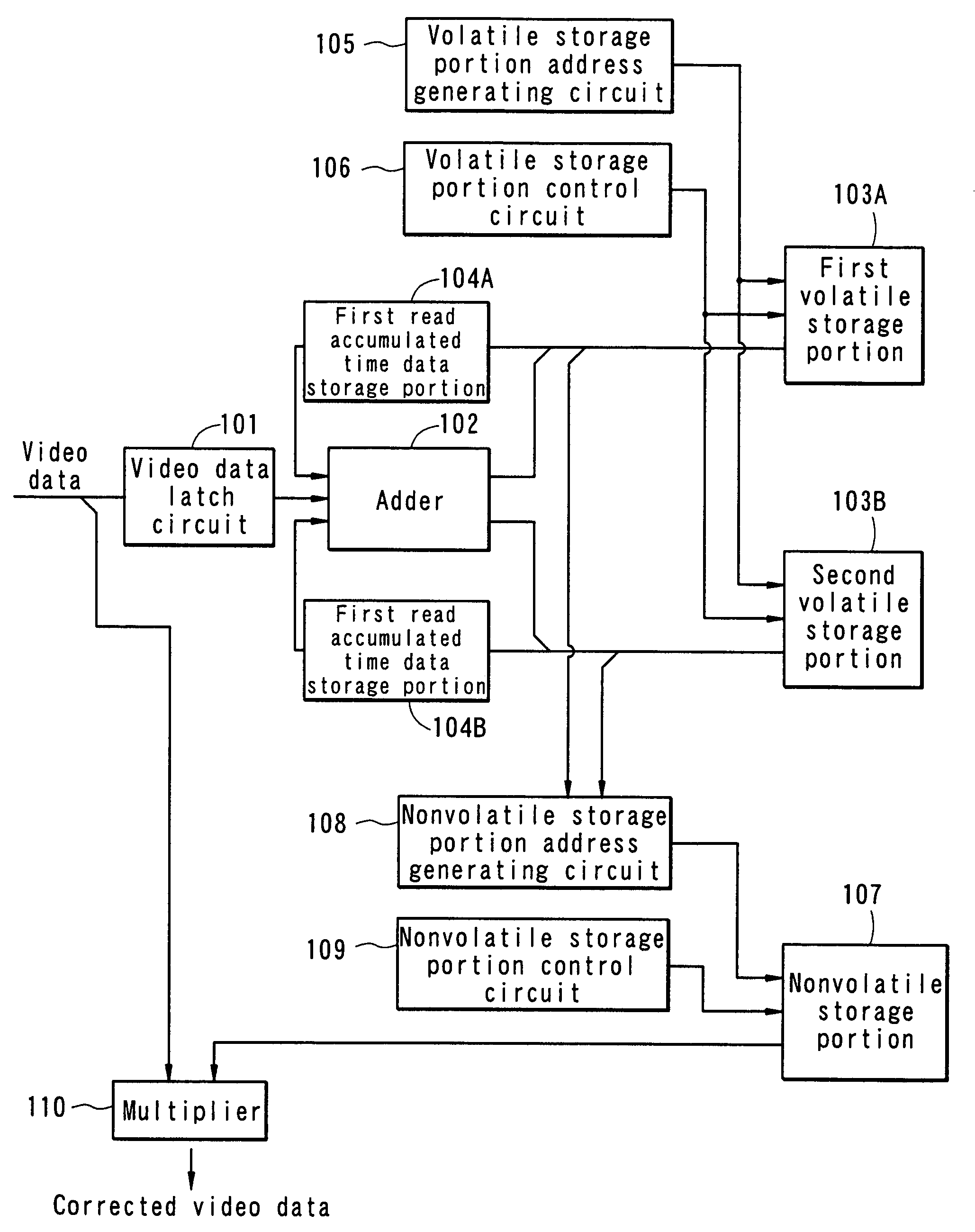

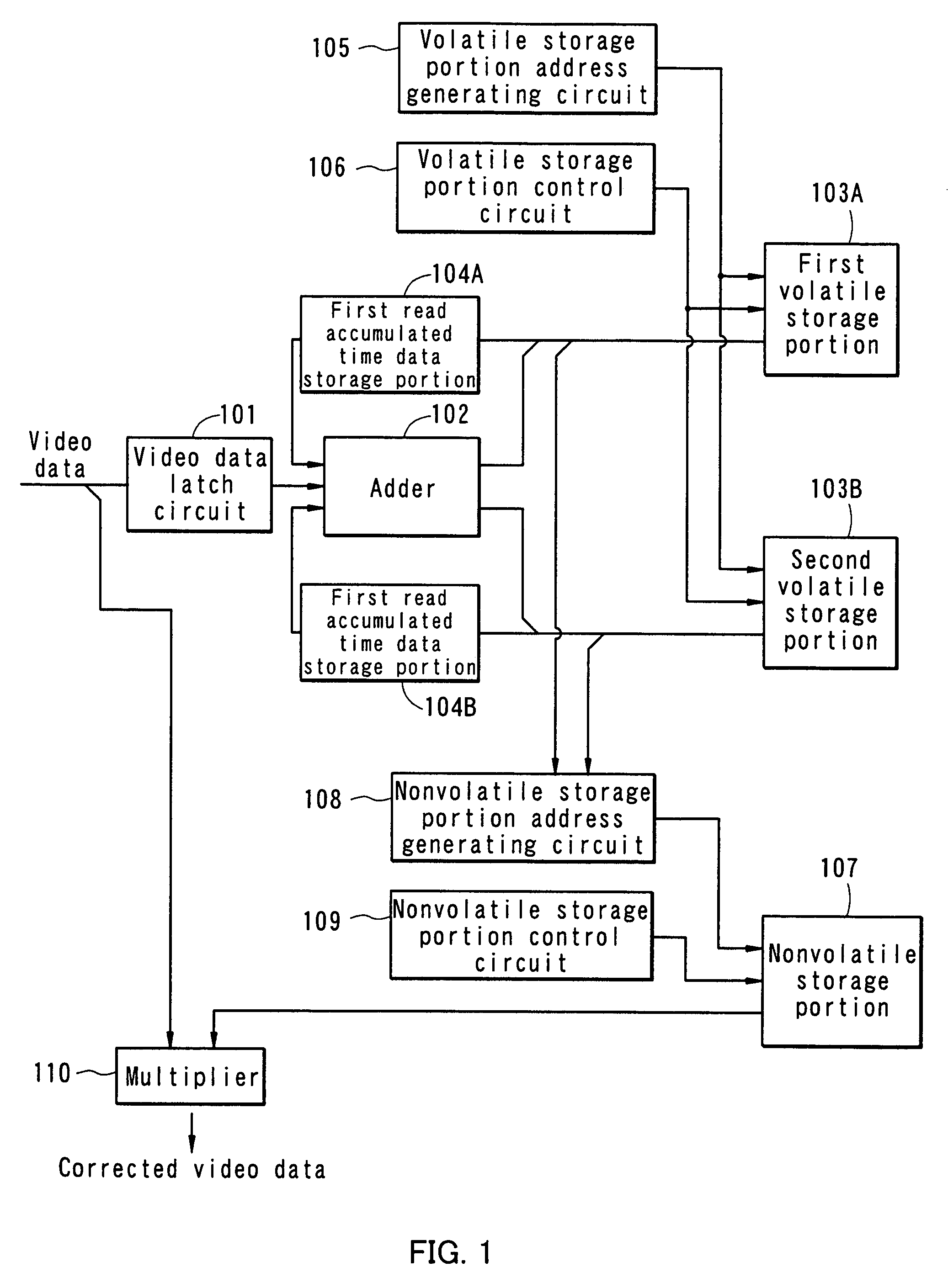

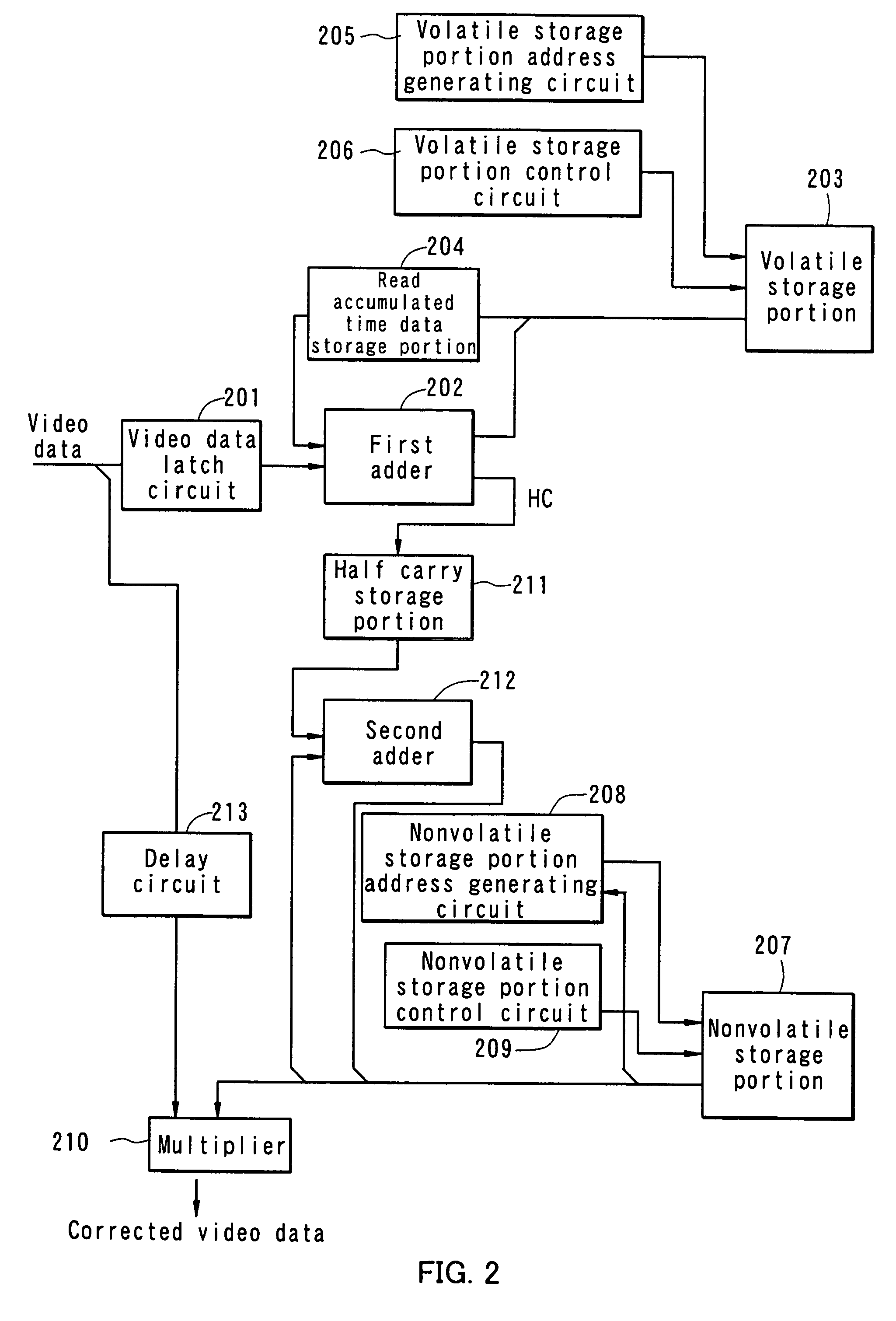

Video data correction circuit, control circuit of display device, and display device and electronic apparatus incorporating the same

InactiveUS20060011846A1Low production costReduce in quantityElectrical apparatusStatic indicating devicesComputer hardwareDisplay device

Accumulated usage data of each pixel of the correction circuit is divided into a plurality of data portions, each of which is stored in a different storing means. For example, the accumulated usage data is divided into the upper bit and the lower bit to be stored separately, and the upper bit of the accumulated usage data is obtained by adding the upper bit to a half carry generated by the calculation of the lower bit of the accumulated usage data. A degradation coefficient selected based on the thus obtained accumulated usage data is multiplied by video data to obtain corrected video data. The invention also provides a control circuit of a display device integrated with such a correction circuit.

Owner:SEMICON ENERGY LAB CO LTD

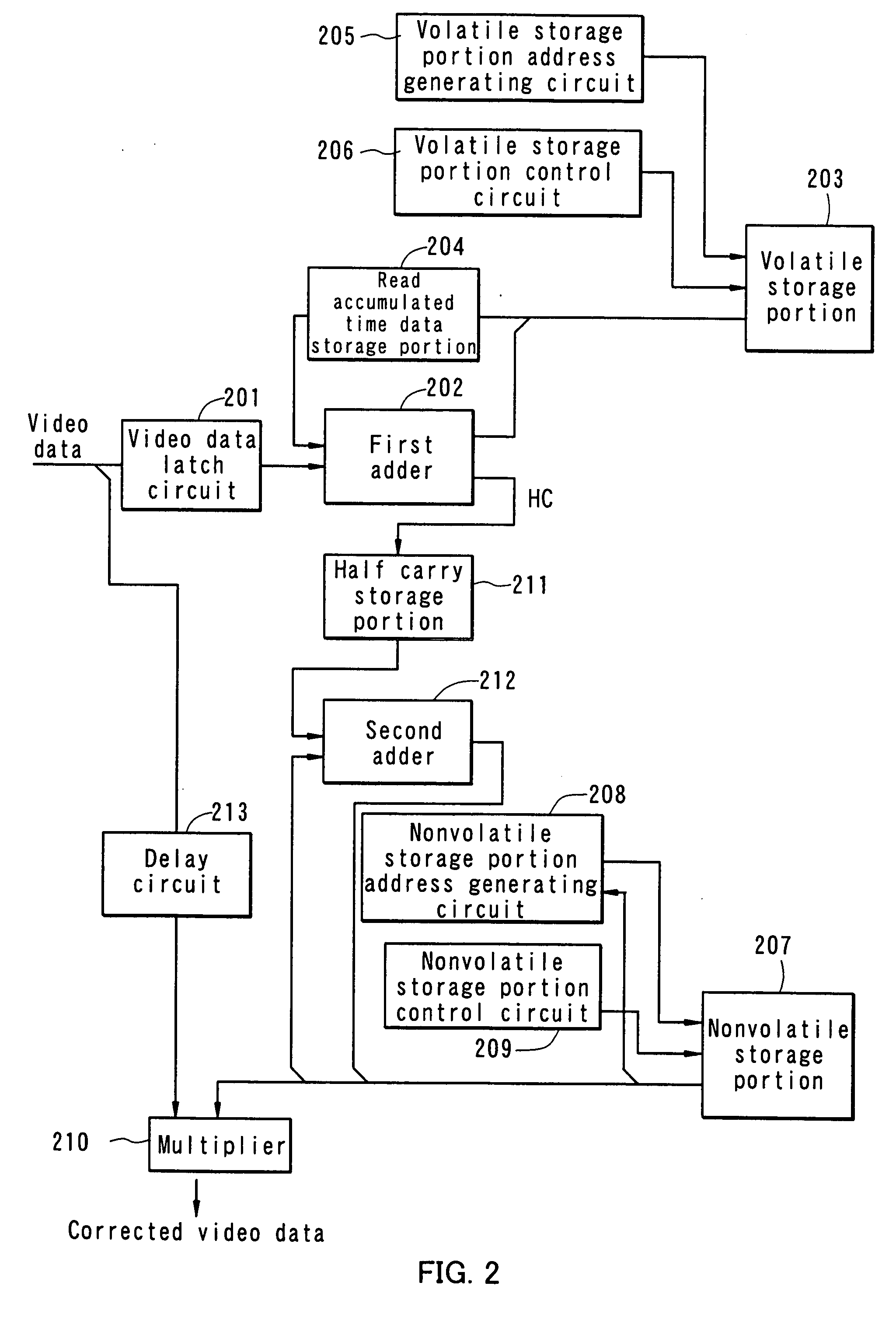

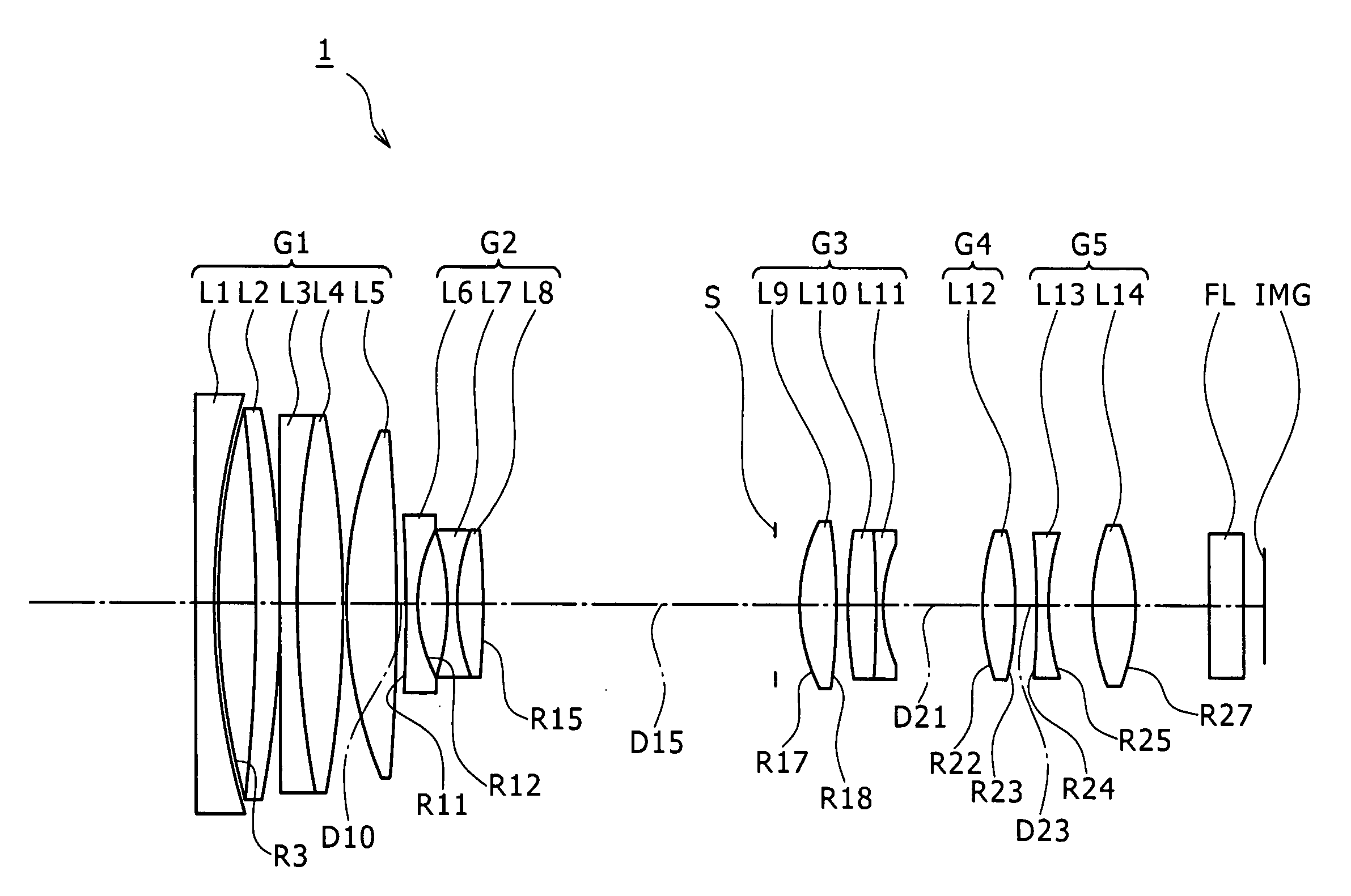

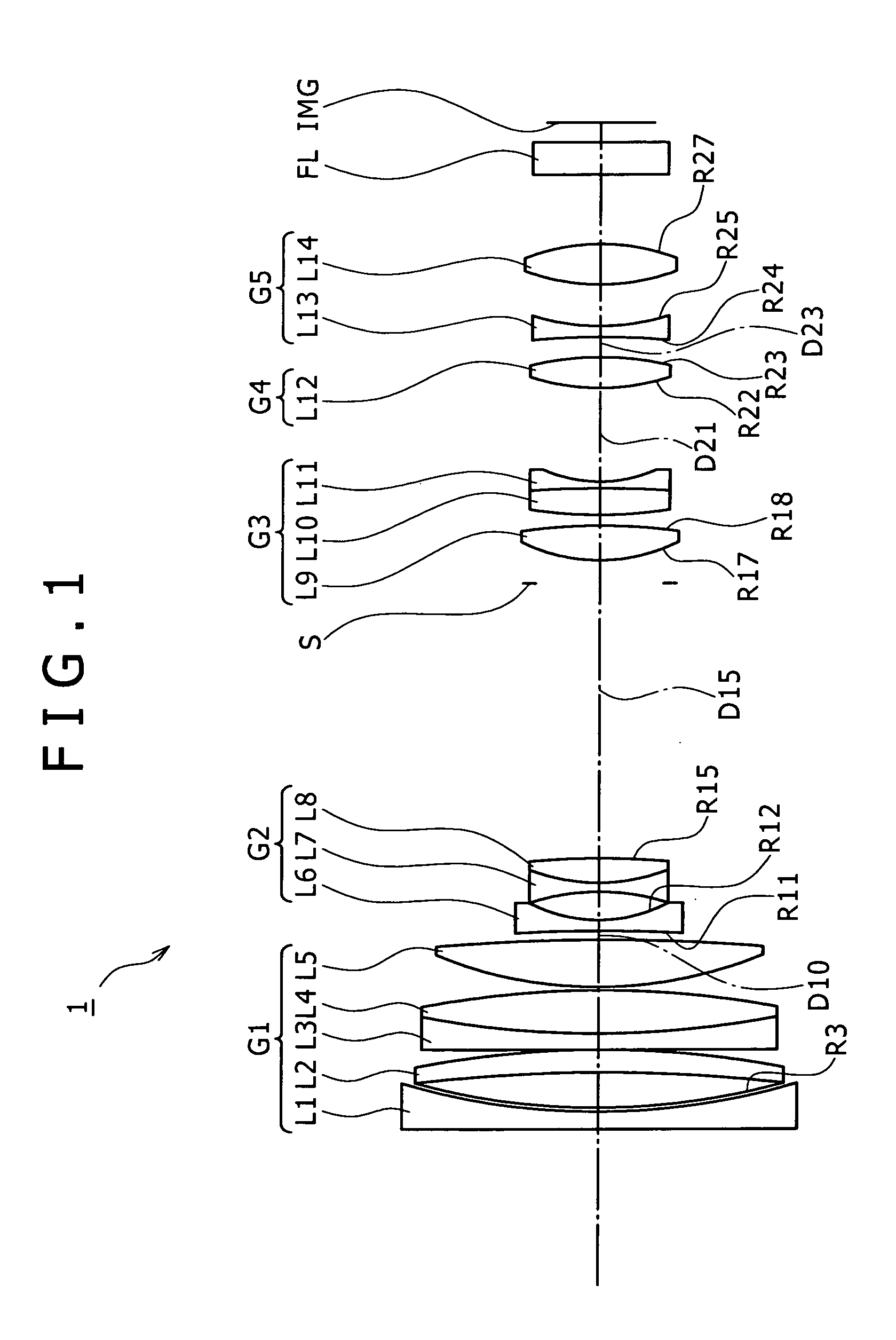

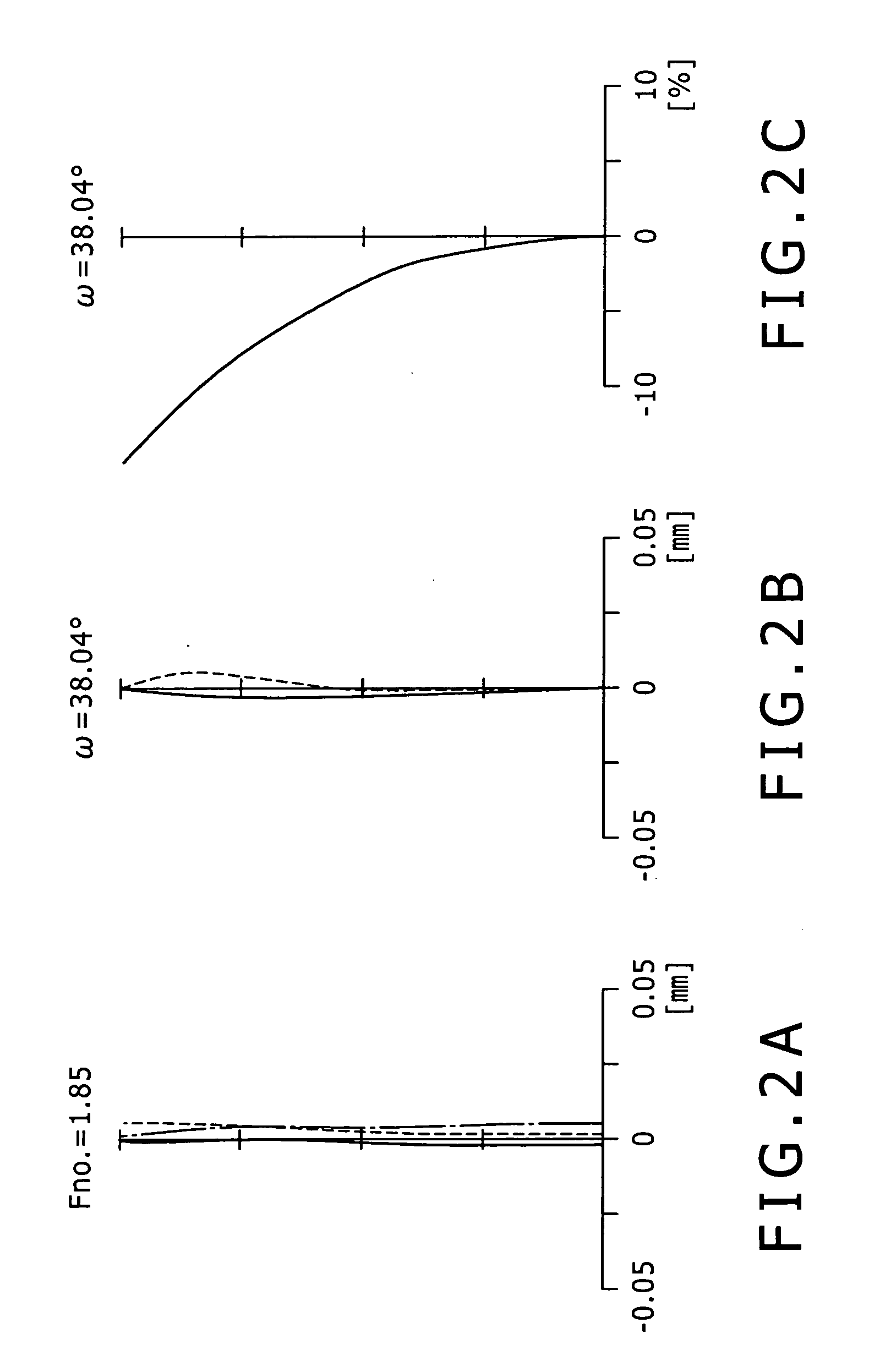

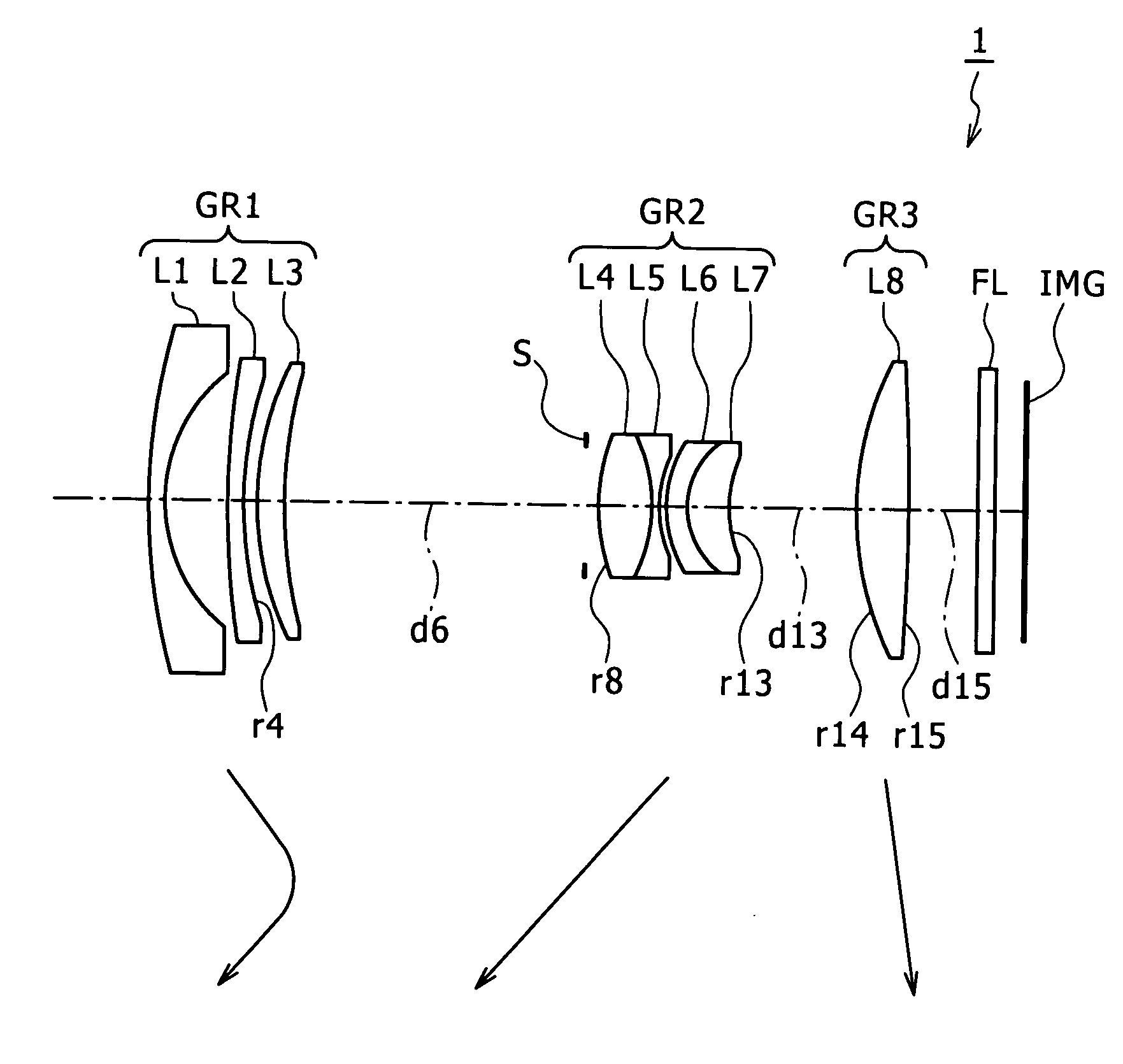

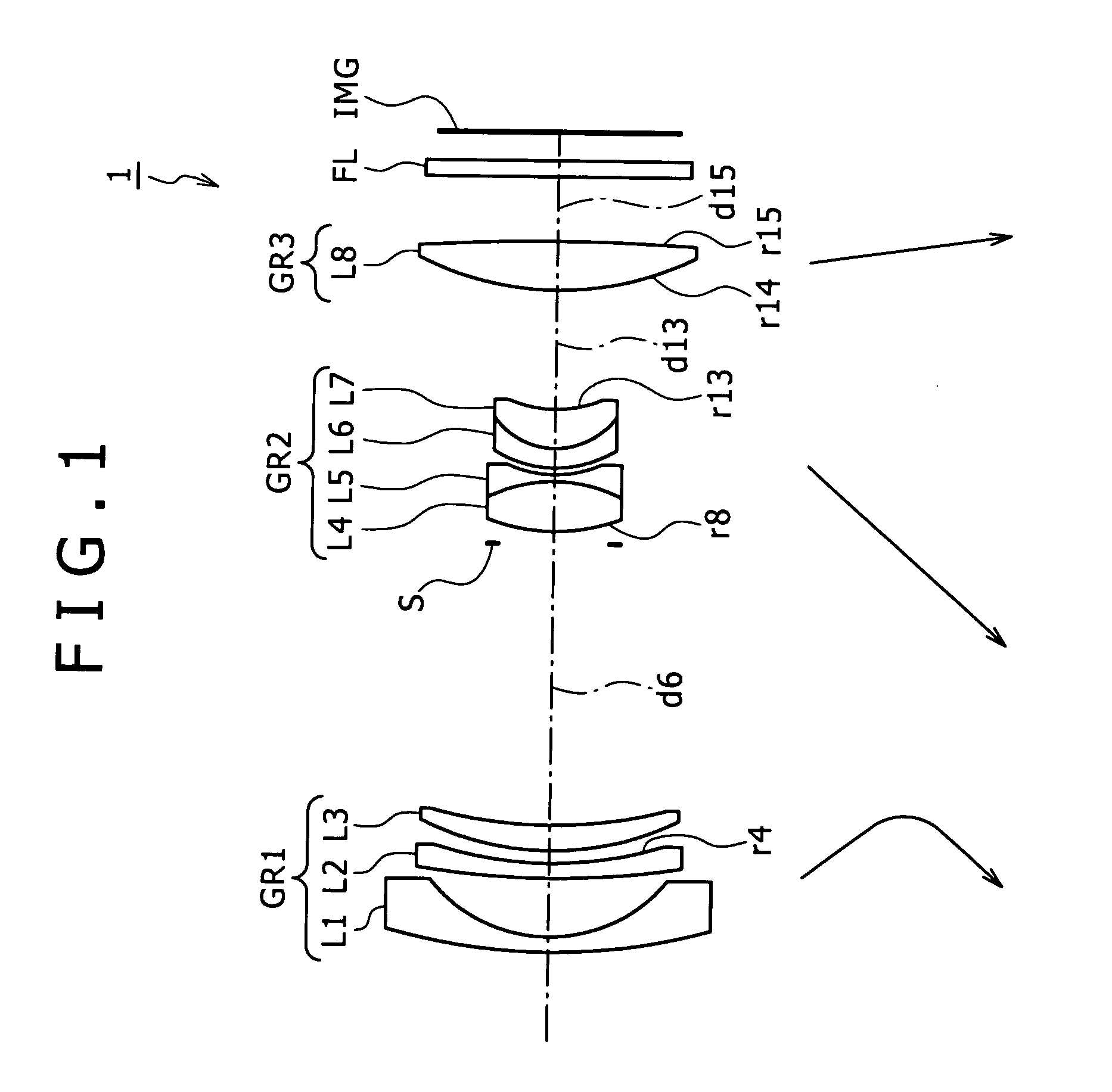

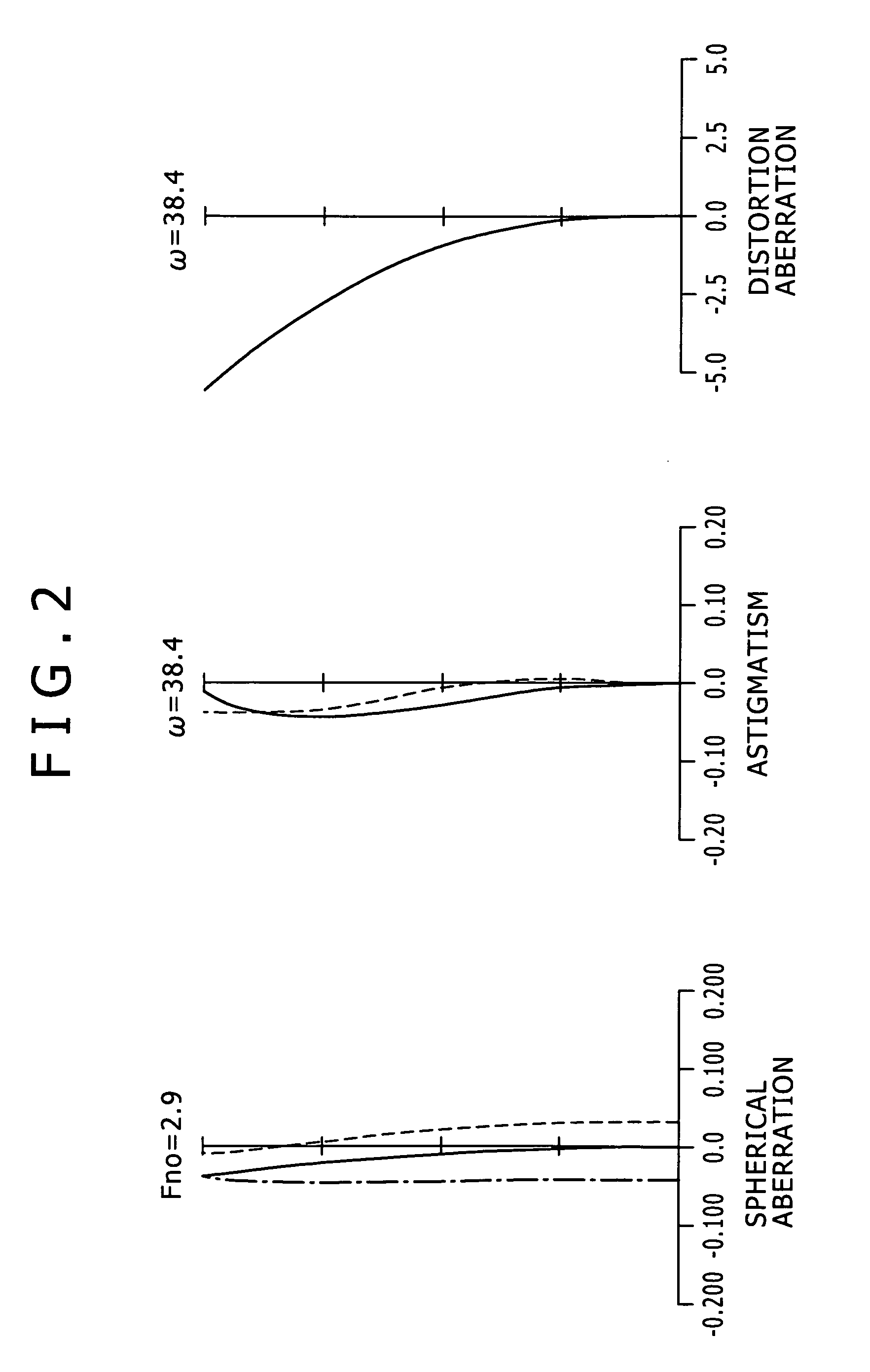

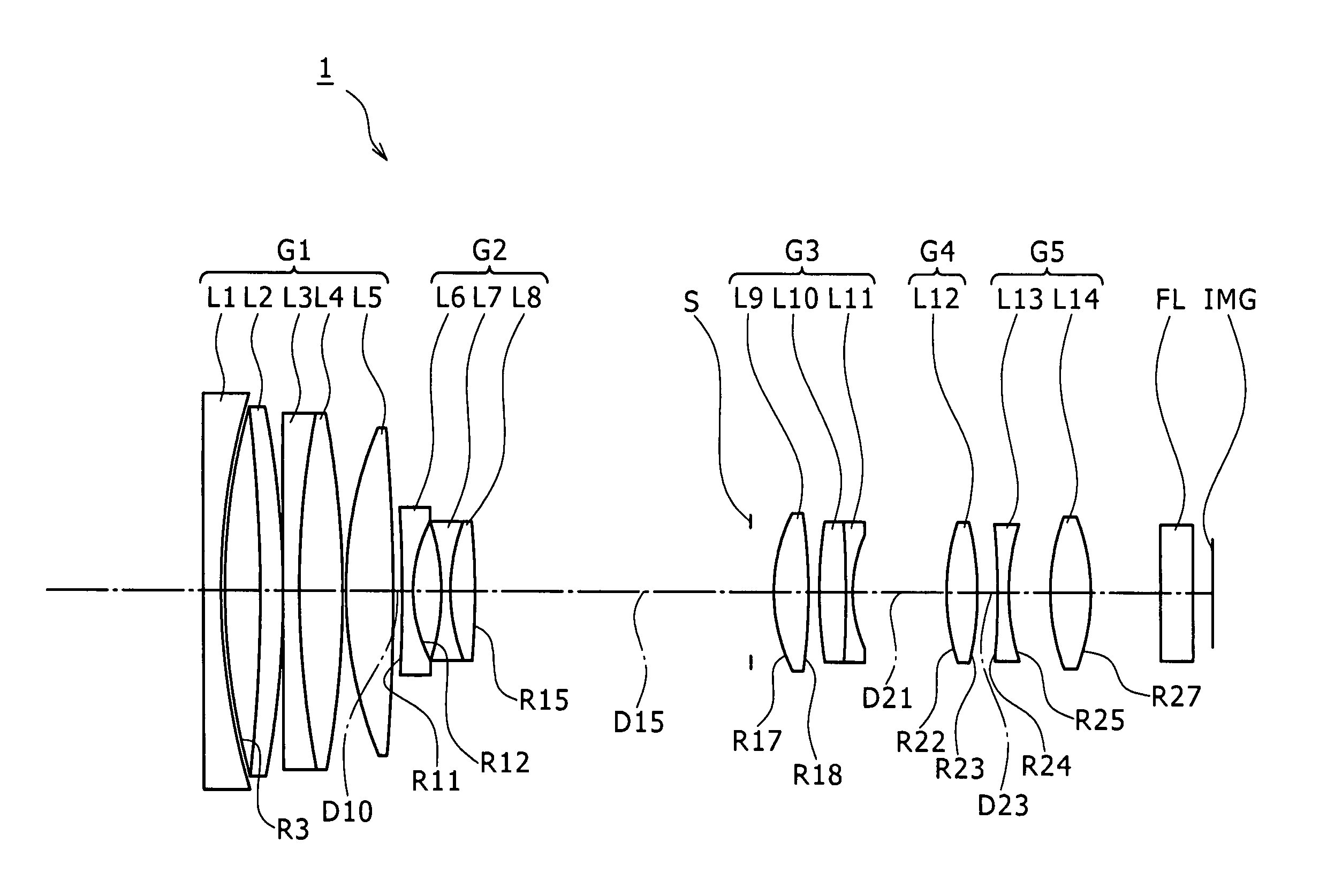

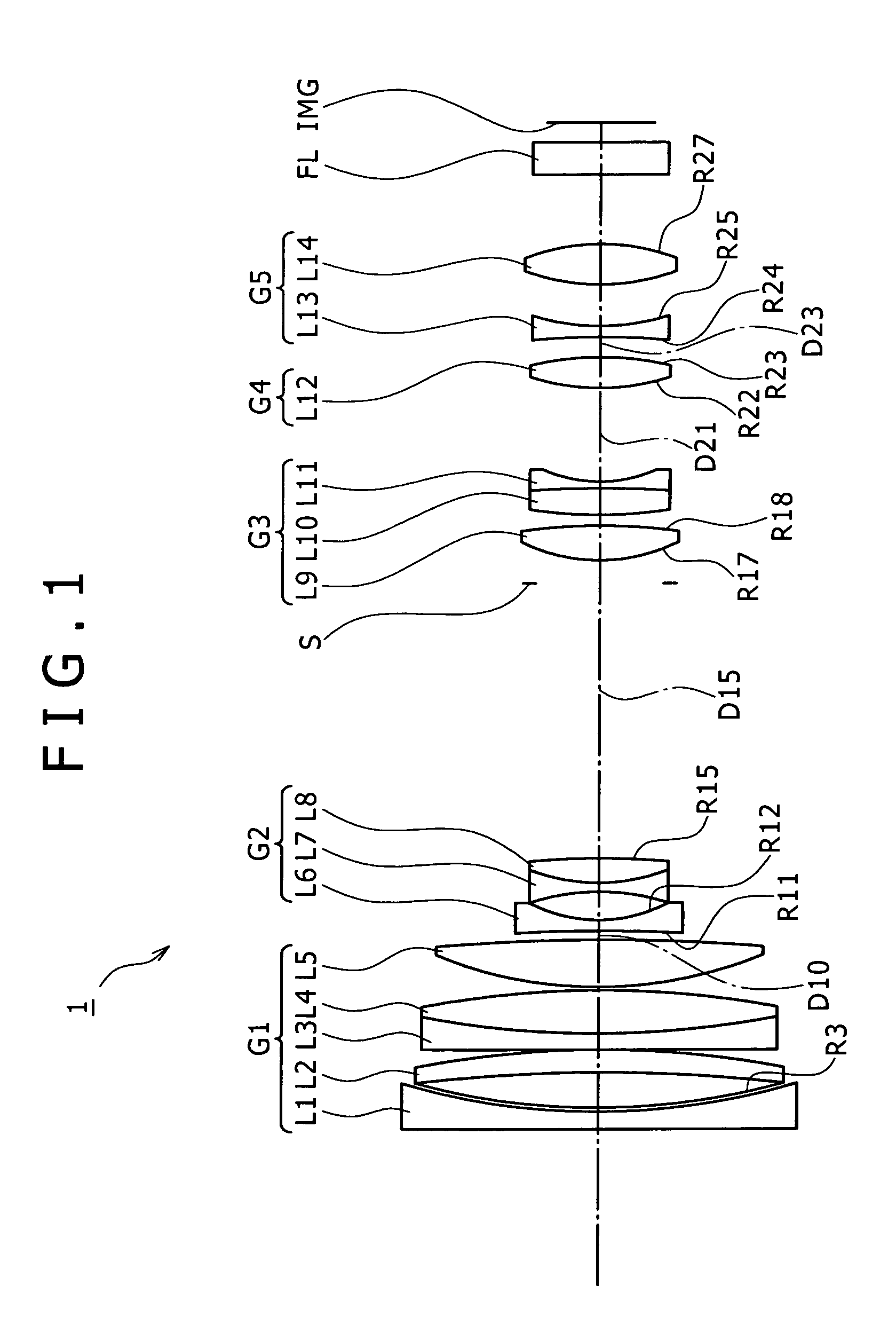

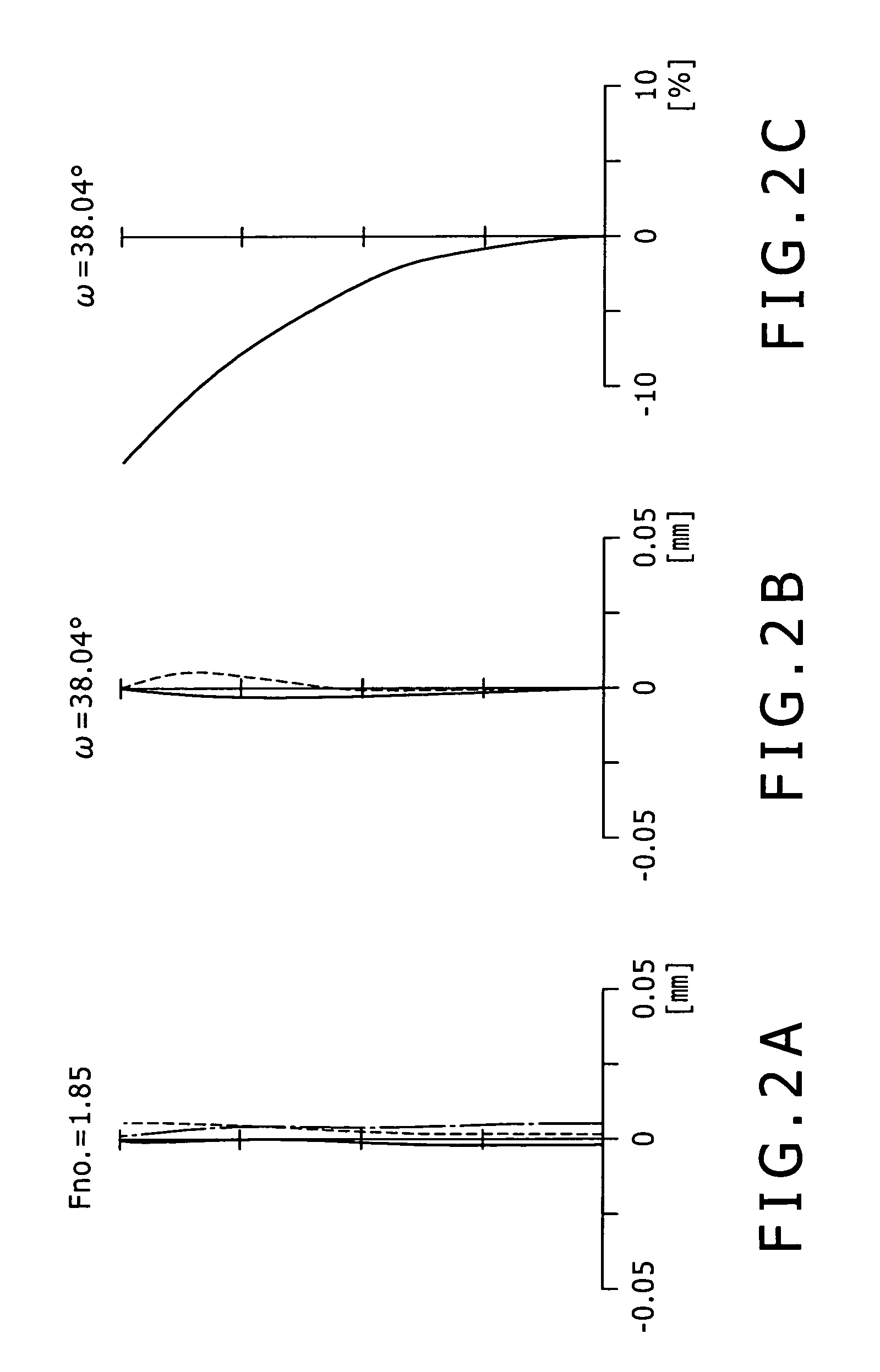

Zoom lens and image pickup device

ActiveUS20110157429A1Wide viewing angleSmall sizeTelevision system detailsColor television detailsOphthalmologyConditional expression

Disclosed herein is a zoom lens including a first lens group, a second lens group, a third lens group, a fourth lens group, and a fifth lens group. The zoom lens satisfies following conditional expressions (1) and (2),0.03<H1′ / f1<0.3 (1)0.3<|f2| / √(fw·ft)<0.65 (2)where H1′ is an interval from a vertex of a surface nearest to the image side in the first lens group to a principal point on the image side of the first lens group (− denotes the object side, and + denotes the image side), f1 is focal length of the first lens group, f2 is focal length of the second lens group, fw is focal length of an entire lens system at a wide-angle end, and ft is the focal length of the entire lens system at a telephoto end.

Owner:SONY CORP

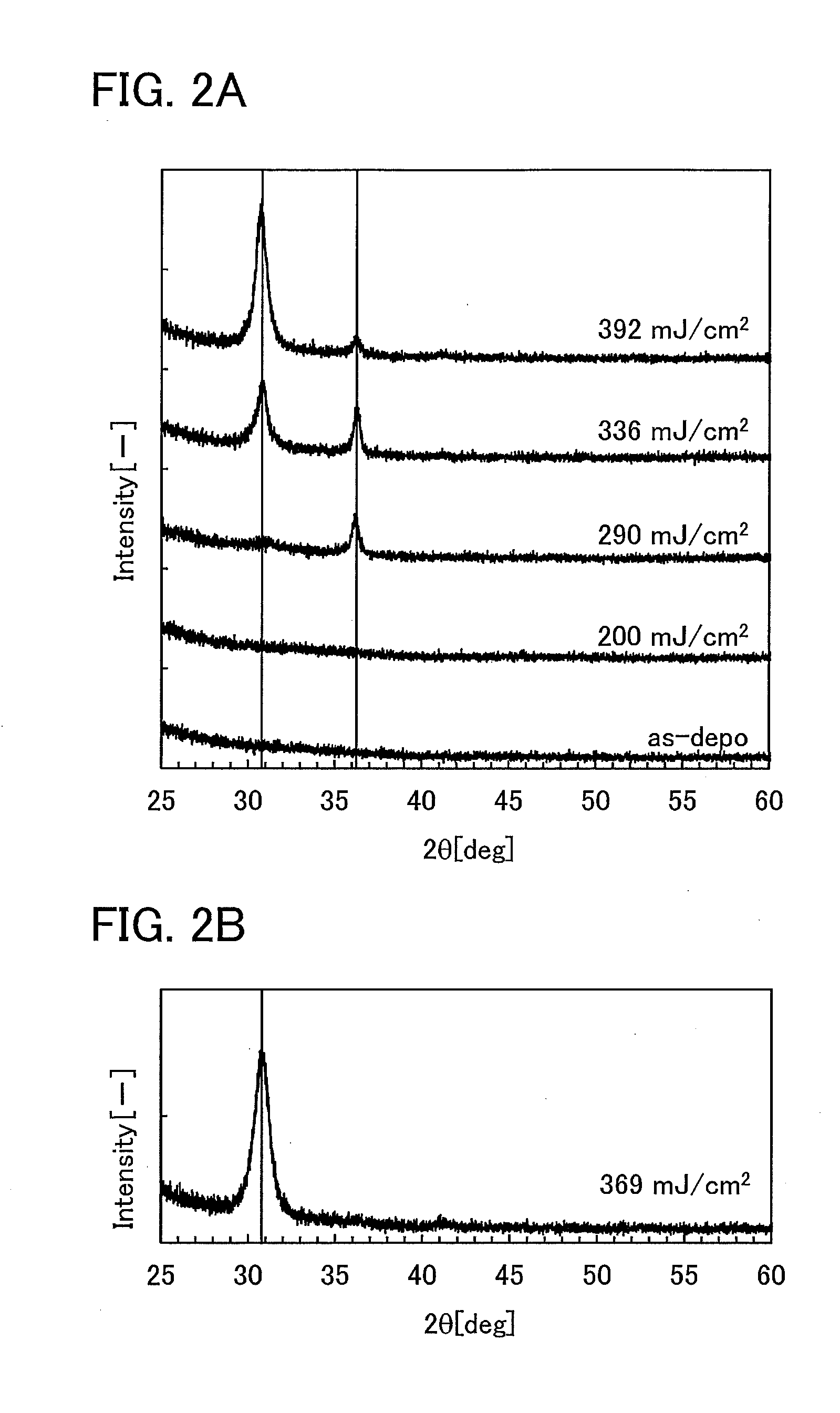

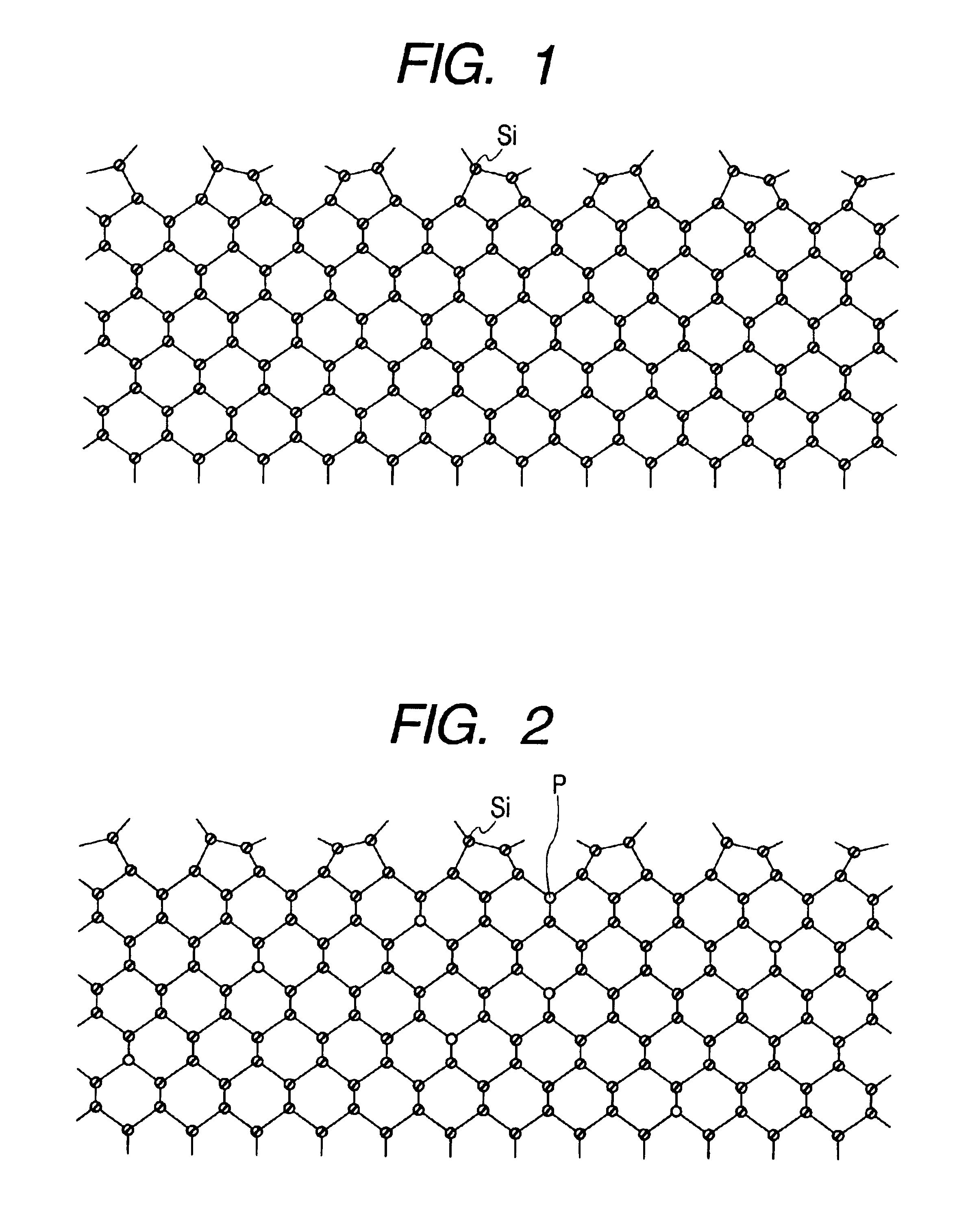

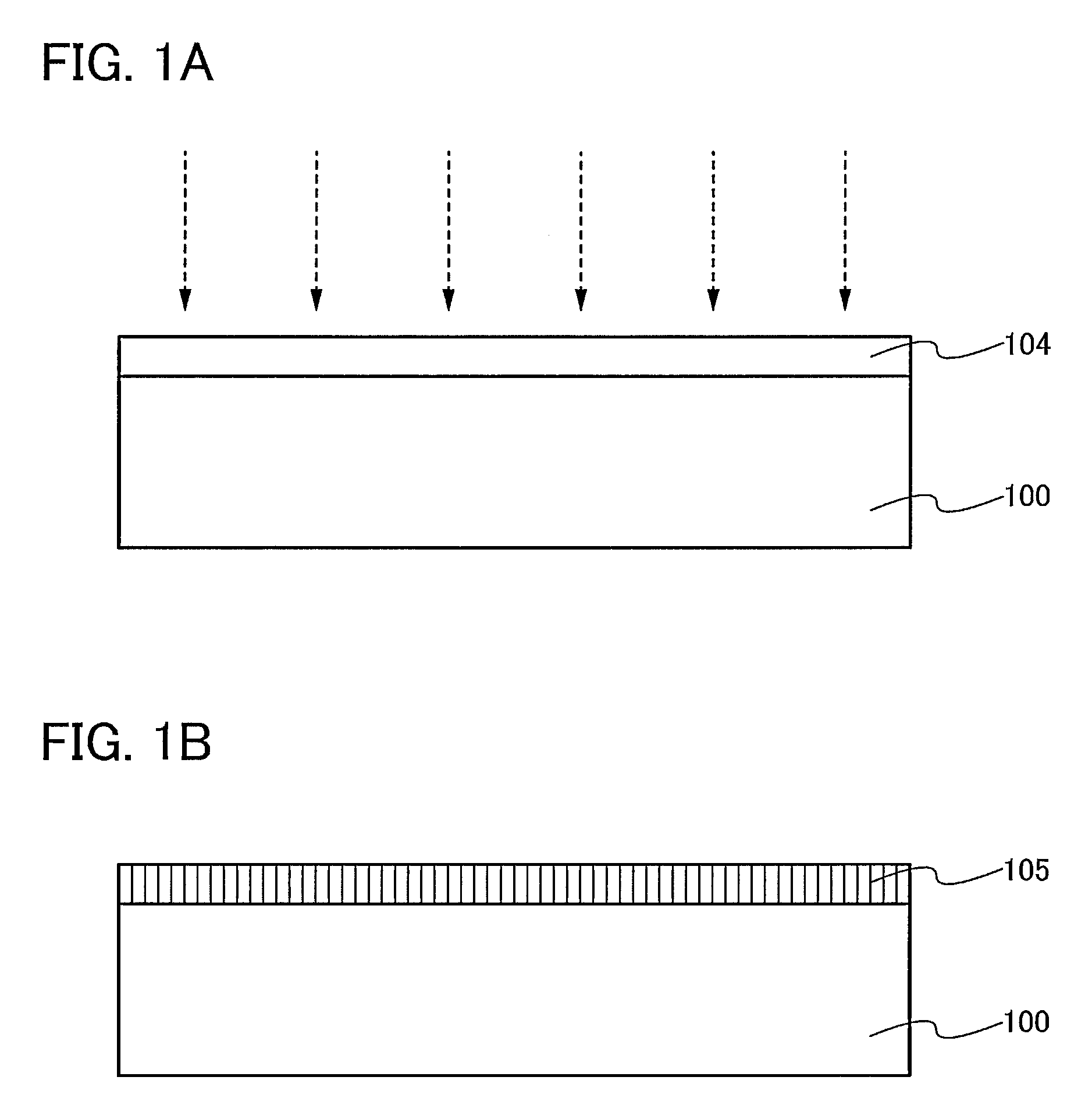

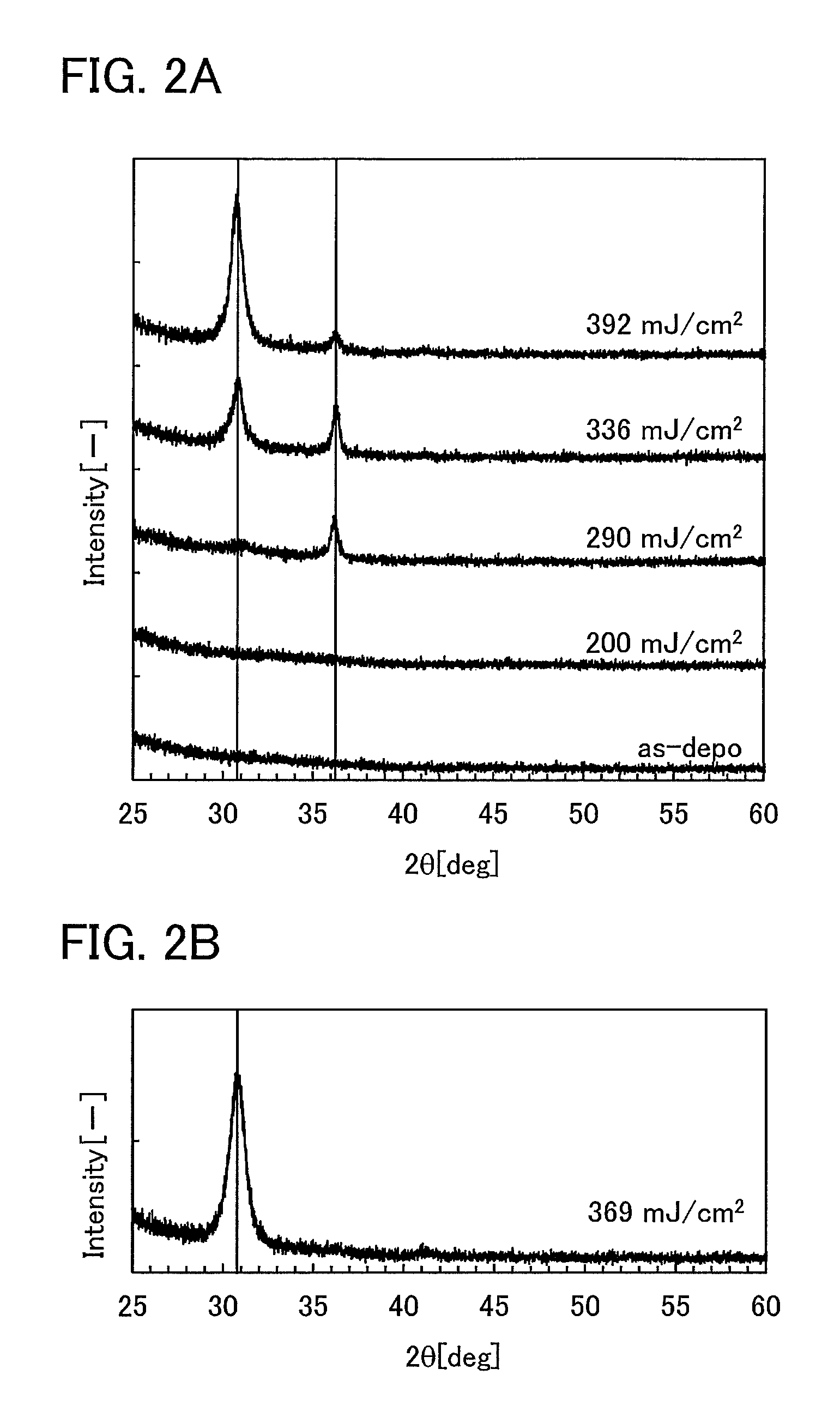

Oxide semiconductor film and method for forming oxide semiconductor film

ActiveUS20140284597A1High crystallinityReduce power consumptionTransistorSemiconductor/solid-state device manufacturingCrystalline oxideIndium

To improve crystallinity of an oxide semiconductor. To provide a crystalline oxide semiconductor film in which a crystallized region extends to the interface with a base or the vicinity of the interface, and to provide a method for forming the oxide semiconductor film. An oxide semiconductor film containing indium, gallium, and zinc is formed, and the oxide semiconductor film is irradiated with an energy beam, thereby being heated. Note that the oxide semiconductor film includes a c-axis aligned crystal region or microcrystal.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and radio communication device

ActiveUS7622756B2Lower temperature riseEnlarge regionTransistorSemiconductor/solid-state device detailsMiniaturizationEngineering

Owner:MURATA MFG CO LTD

Zoom lens and image pickup device

InactiveUS20100123958A1Improve performanceEase of mass productionTelevision system detailsColor television detailsOphthalmologyZoom lens

Disclosed herein is a zoom lens formed by arranging a first lens group having a negative refractive power, a second lens group having a positive refractive power, and a third lens group having a positive refractive power in order from an object side to an image side, wherein at a time of varying power from a wide-angle end to a telephoto end, the first lens group is moved, the second lens group is moved to the object side, and the third lens group is moved to the image side such that an air interval between the first lens group and the second lens group is decreased and such that an air interval between the second lens group and the third lens group is increased.

Owner:SONY CORP

Field-effect transistor

InactiveUS7250642B2Reduced characteristicsReduce impactSemiconductor devicesMiniaturizationEngineering

The present invention, which aims to provide a gallium arsenide field-effect transistor that can reduce degradation of field-effect transistor characteristics, and to realize miniaturization of the transistor, includes: a substrate; a mesa which includes a channel layer and is formed on the substrate; a source electrode formed on the mesa; a drain electrode; and a gate electrode, wherein, on the mesa, a top pattern is formed in which finger portions of the source electrode and the drain electrode which are formed in comb-shape are located so as to interdigitate, and a gate electrode is formed between the source electrode and the drain electrode, while common portions, which are base parts of the finger portions of the source and drain electrodes, are formed on the surface of the mesa, and the part located below the straight portion which is parallel to the finger portions of the gate electrode is electrically separated from the part located below a corner portion that connects neighboring straight portions of the gate electrode.

Owner:COLLABO INNOVATIONS INC

Zoom lens and image pickup device

ActiveUS8040614B2Decrease the inclinationHinders miniaturizationLensOphthalmologyConditional expression

Disclosed herein is a zoom lens including a first lens group, a second lens group, a third lens group, a fourth lens group, and a fifth lens group. The zoom lens satisfies following conditional expressions (1) and (2), 0.03<H1′ / f1<0.3 (1) 0.3<|f2| / √(fw·ft)<0.65 (2) where H1′ is an interval from a vertex of a surface nearest to the image side in the first lens group to a principal point on the image side of the first lens group (− denotes the object side, and + denotes the image side), f1 is focal length of the first lens group, f2 is focal length of the second lens group, fw is focal length of an entire lens system at a wide-angle end, and ft is the focal length of the entire lens system at a telephoto end.

Owner:SONY CORP

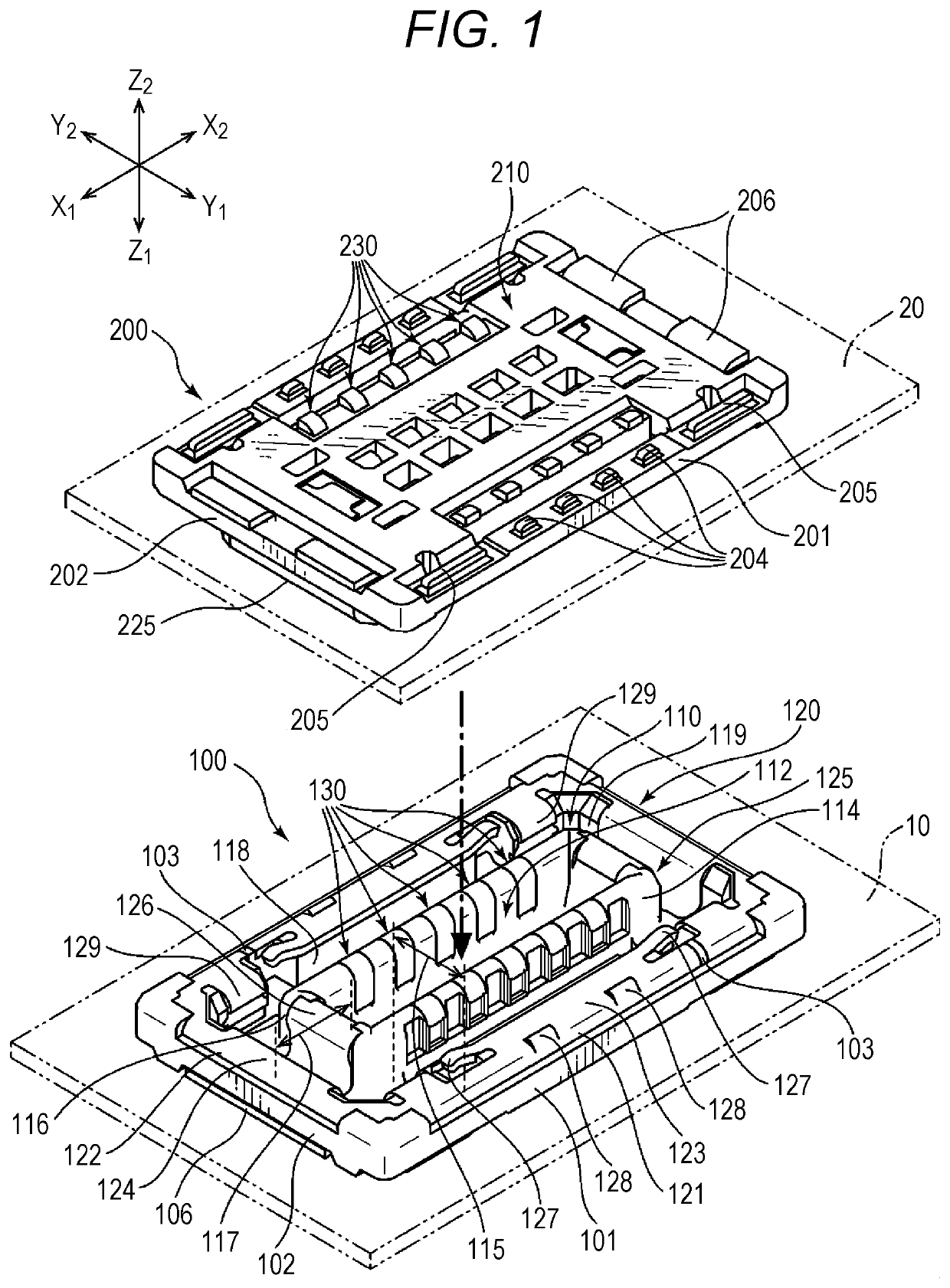

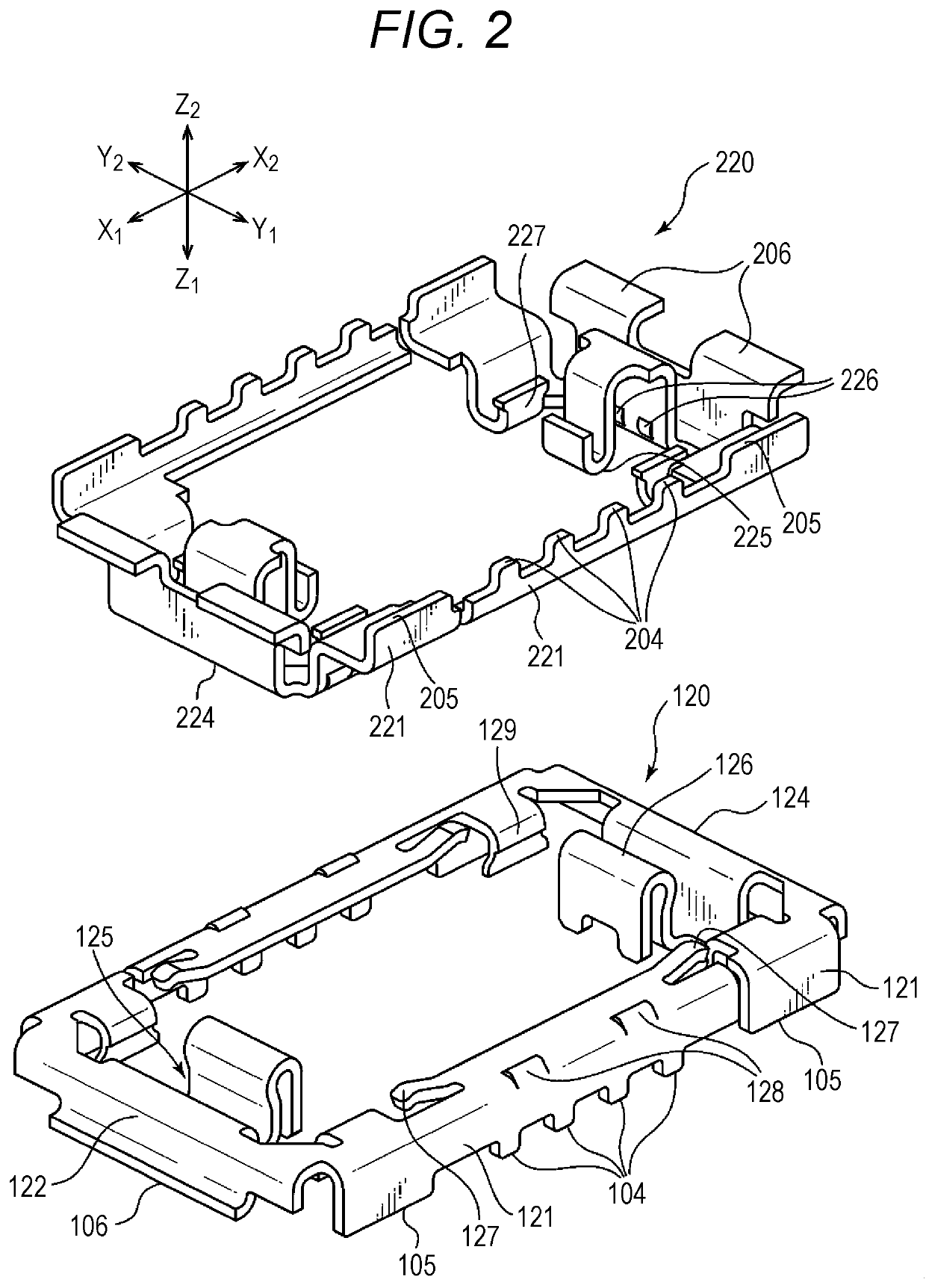

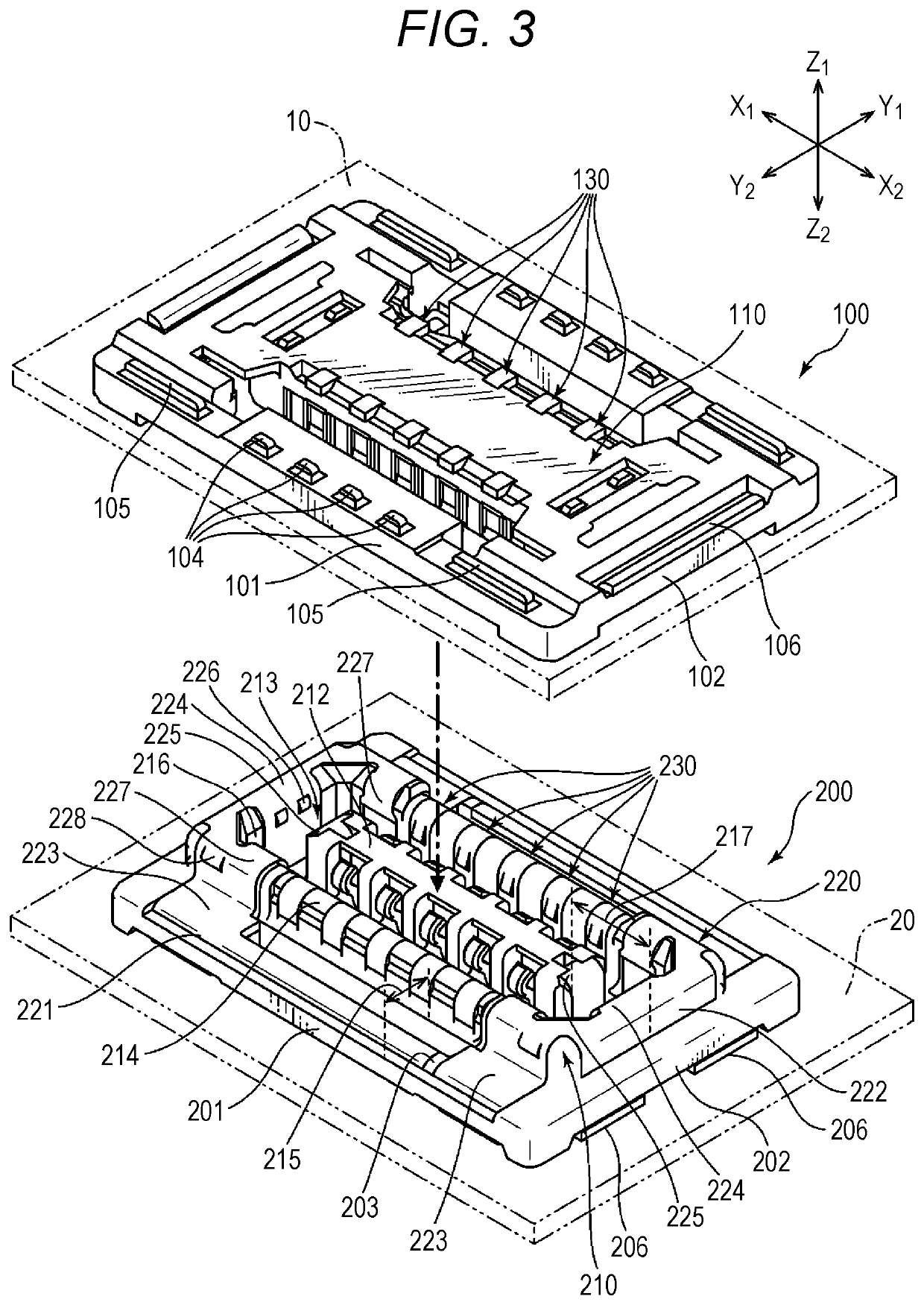

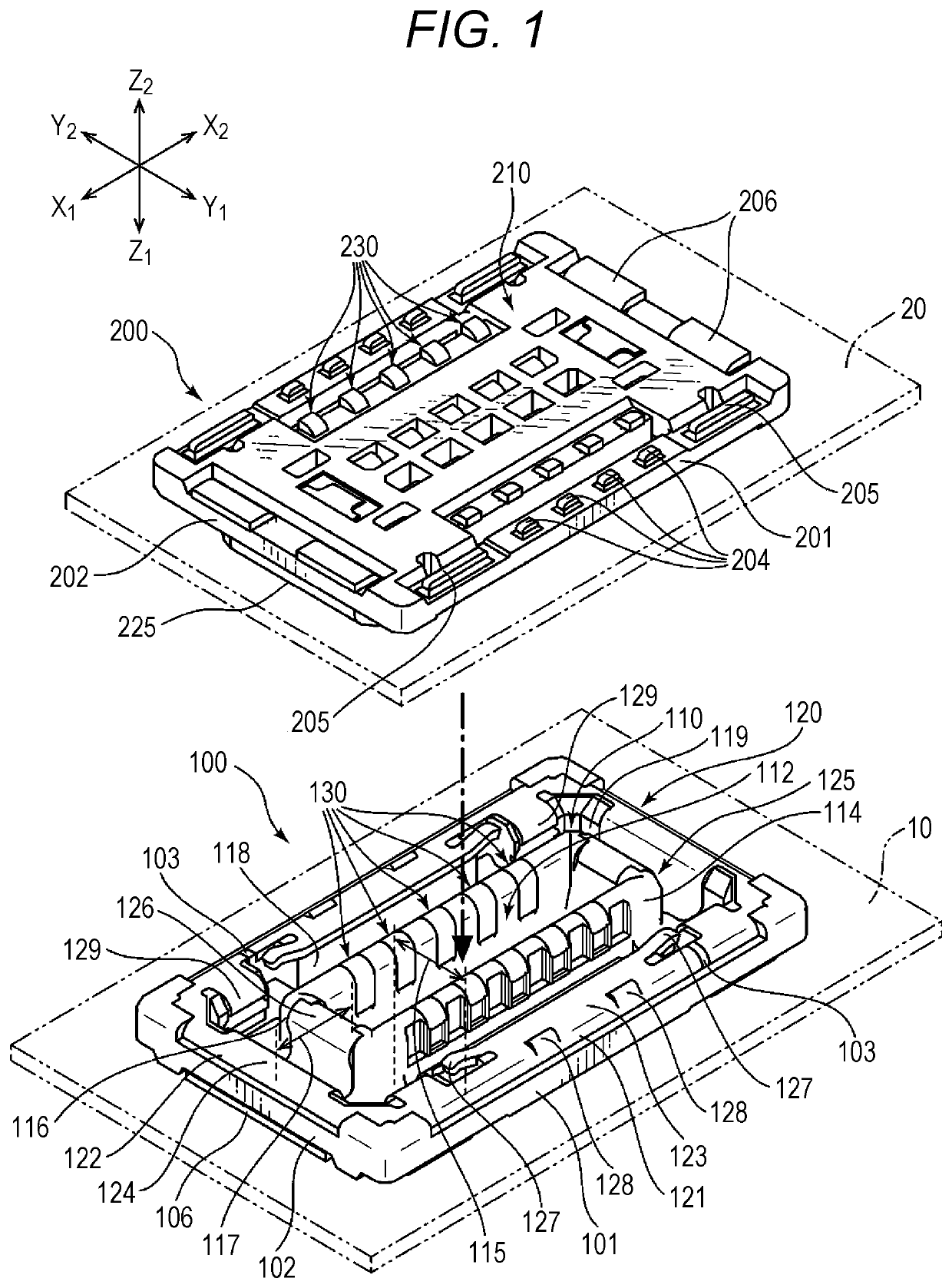

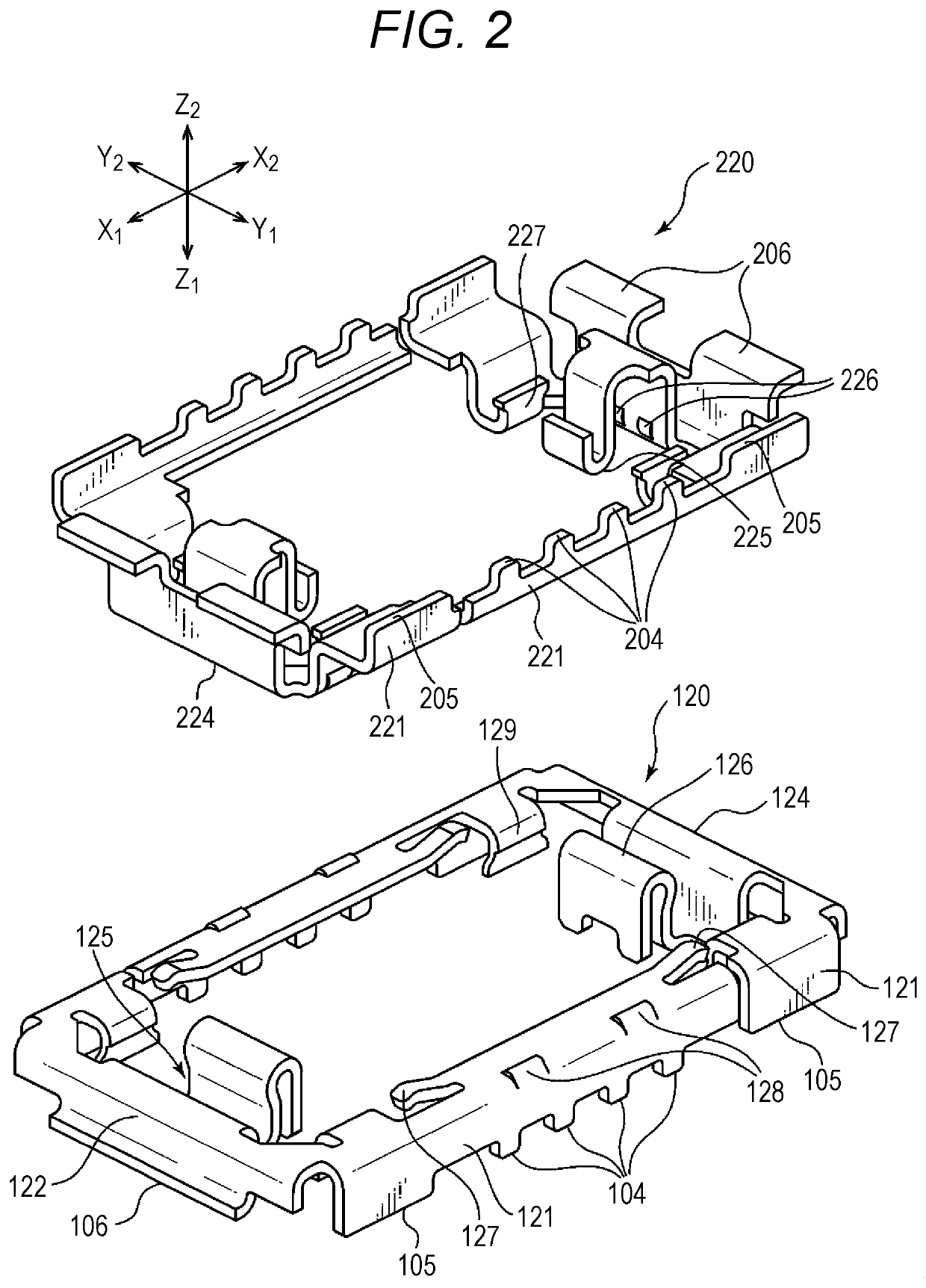

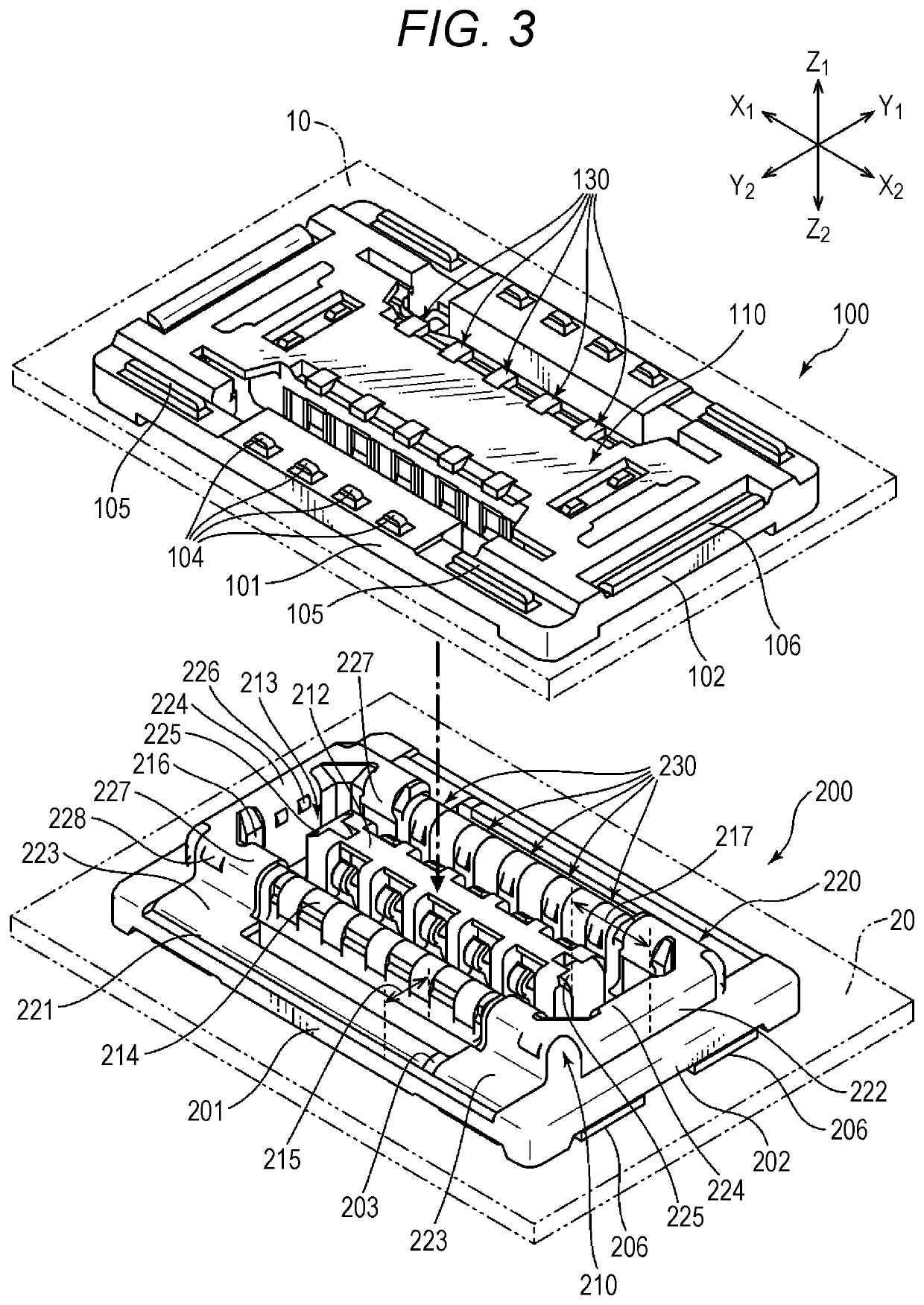

Connector and connector device

ActiveUS20210119386A1Sufficient electromagnetic shielding effectHinders miniaturizationCoupling contact membersTwo-part coupling devicesElectrical connectionEngineering

Owner:HIROSE ELECTRIC GROUP

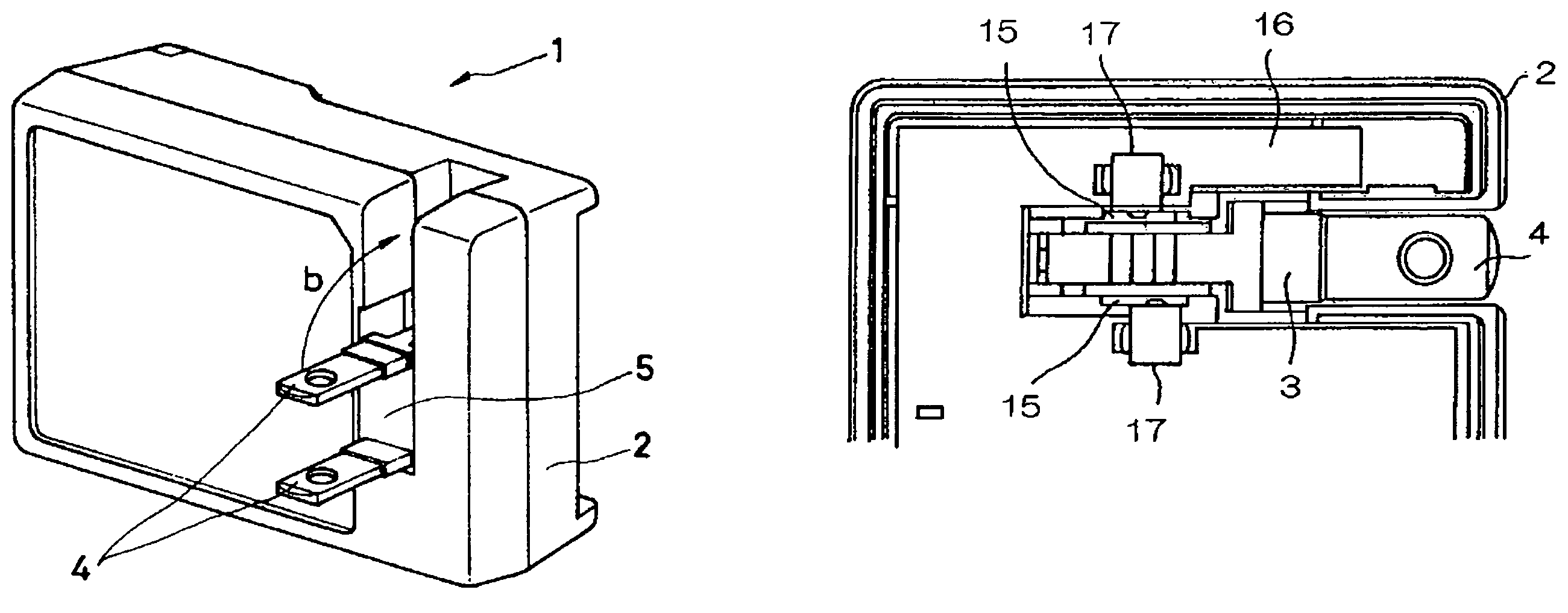

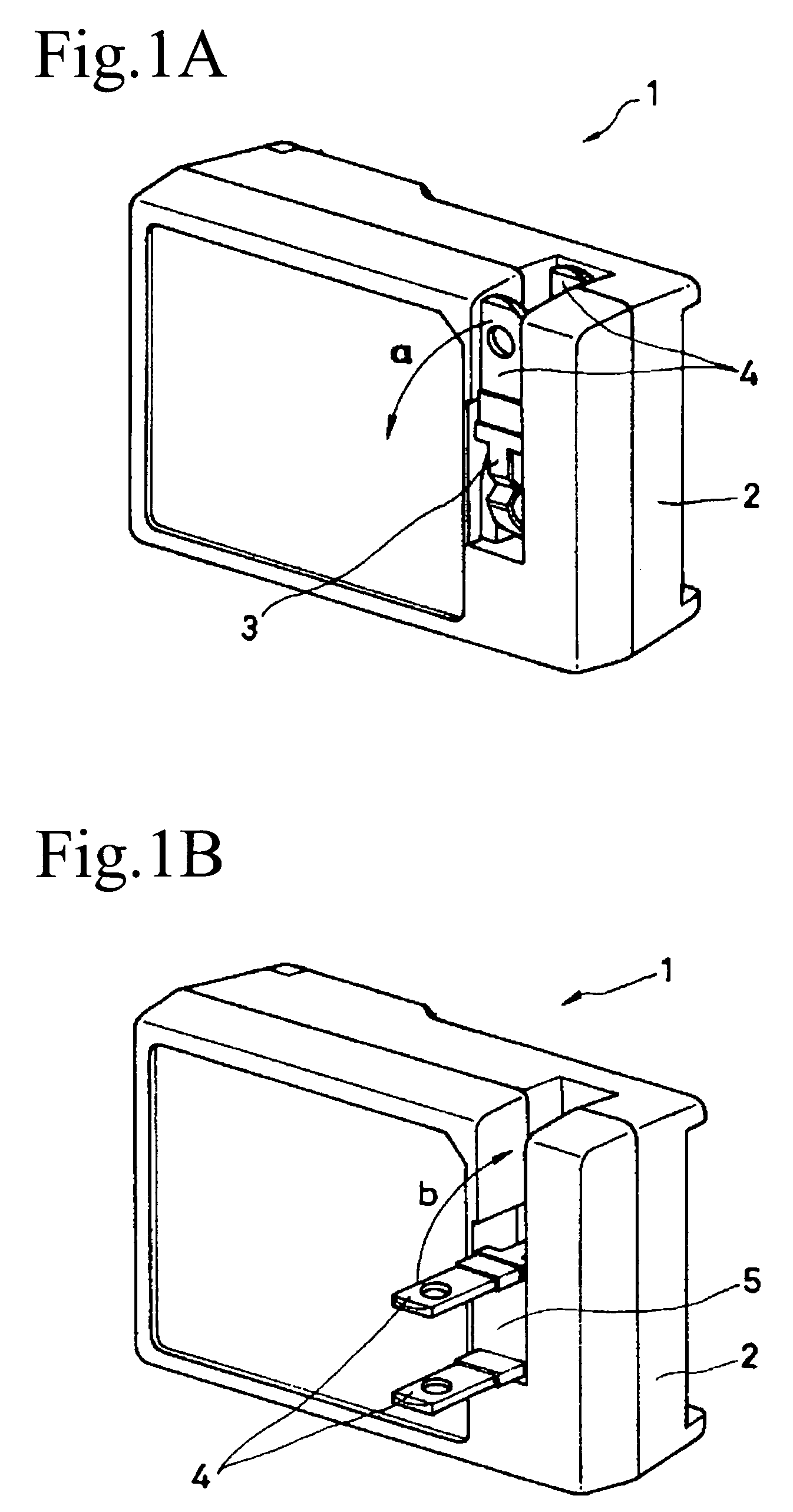

Battery charger

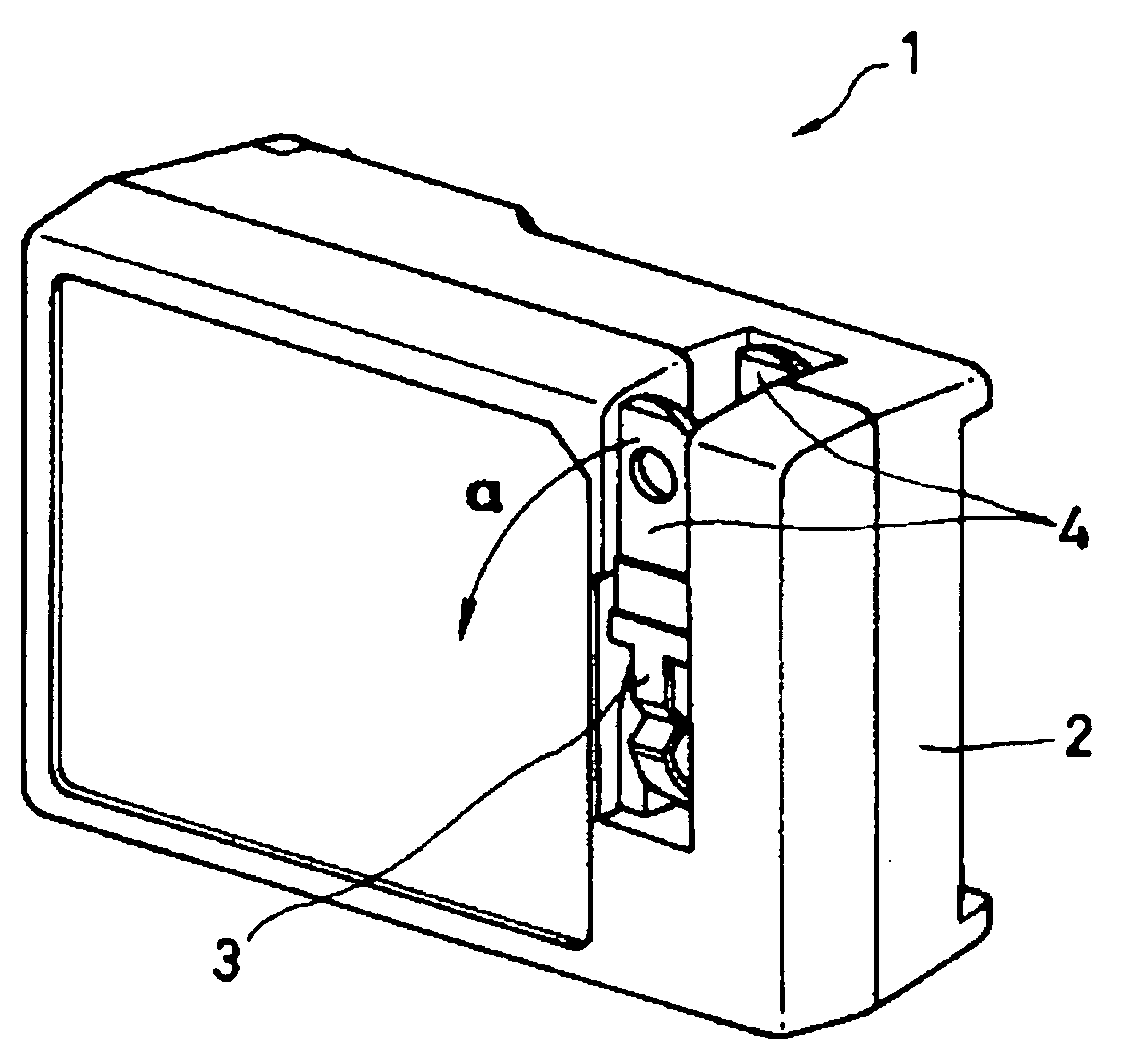

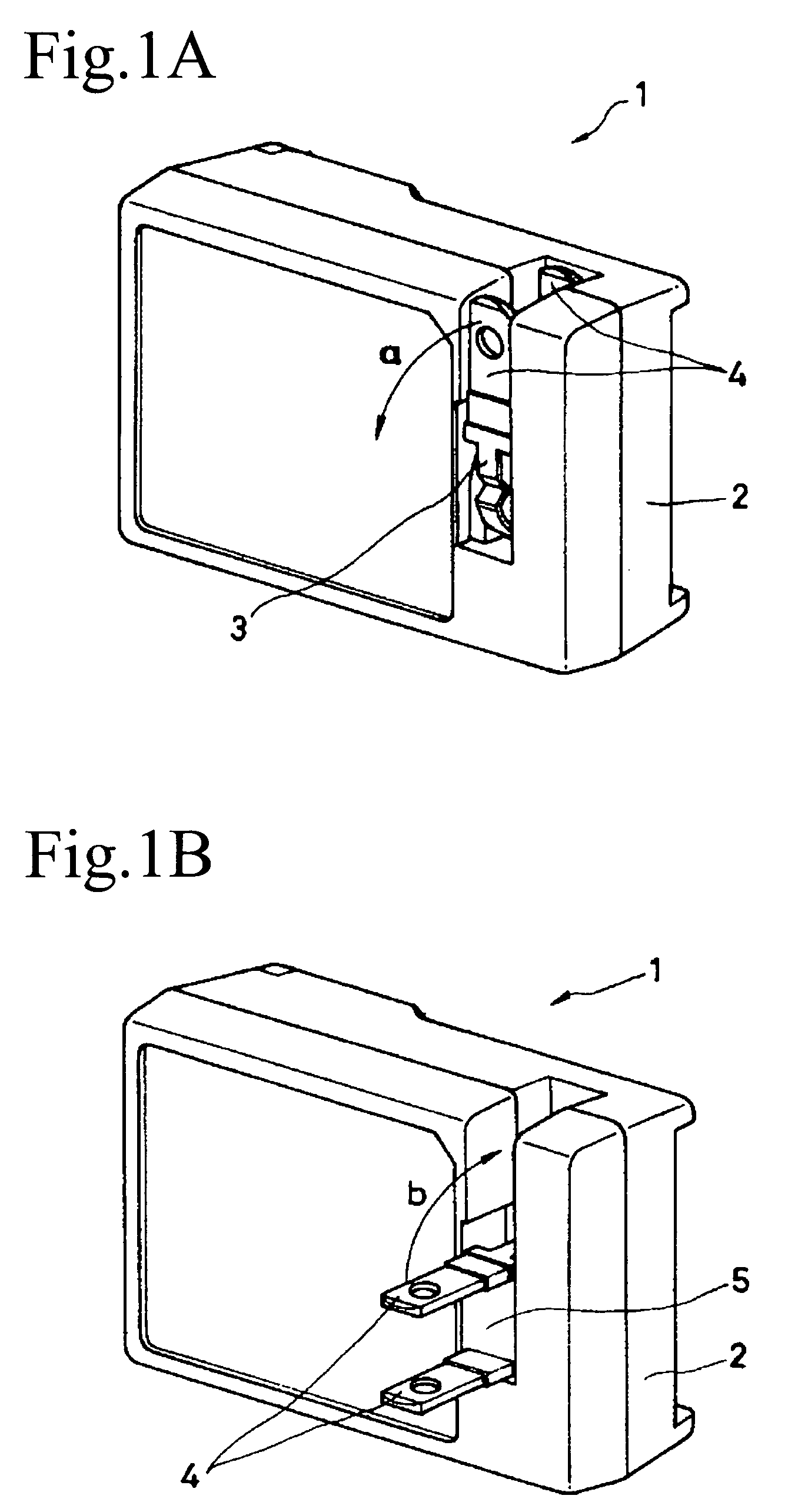

InactiveUS20050106908A1Increase in sizeHinders miniaturizationBatteries circuit arrangementsElectric discharge tubesEngineeringMechanical engineering

Owner:SONY CORP

Wiring substrate

InactiveUS20140027170A1Long time for assemblingMiniaturization is preventedPrinted circuit detailsFinal product manufactureEngineeringElectrical and Electronics engineering

Owner:TOYOTA IND CORP

Ceramic burner for ceramic metal halide lamp

InactiveUS8575838B2Reduce generationSmall sizeTube/lamp vessel fillingSolid cathode detailsElectrical conductorCombustor

A ceramic burner, a ceramic metal halide lamp, and a method of sealing the ceramic burner is provided. The ceramic burner comprises a discharge vessel enclosing a discharge space that is provided with an ionizable filling comprising one or more halides. The discharge vessel comprises a ceramic wall arranged between a first and a second end portion. The first and the second end portion are arranged such that current supply conductors are passed through the end portions to respective electrodes arranged in the discharge space for maintaining a discharge. The ceramic wall of the discharge vessel comprises a tube for introducing the ionizable filling into the discharge vessel during manufacture of the ceramic burner. The tube projects from the ceramic wall and is provided with a gastight seal. The effect of using the tube is that it enables the gastight seal to be arranged away from the ceramic wall of the discharge vessel at a projecting end of the tube.

Owner:KONINK PHILIPS ELECTRONICS NV +1

Video data correction circuit, control circuit of display device, and display device and electronic apparatus incorporating the same

InactiveUS7663576B2Large capacitanceIncrease the number ofElectrical apparatusStatic indicating devicesComputer hardwareData selection

Owner:SEMICON ENERGY LAB CO LTD

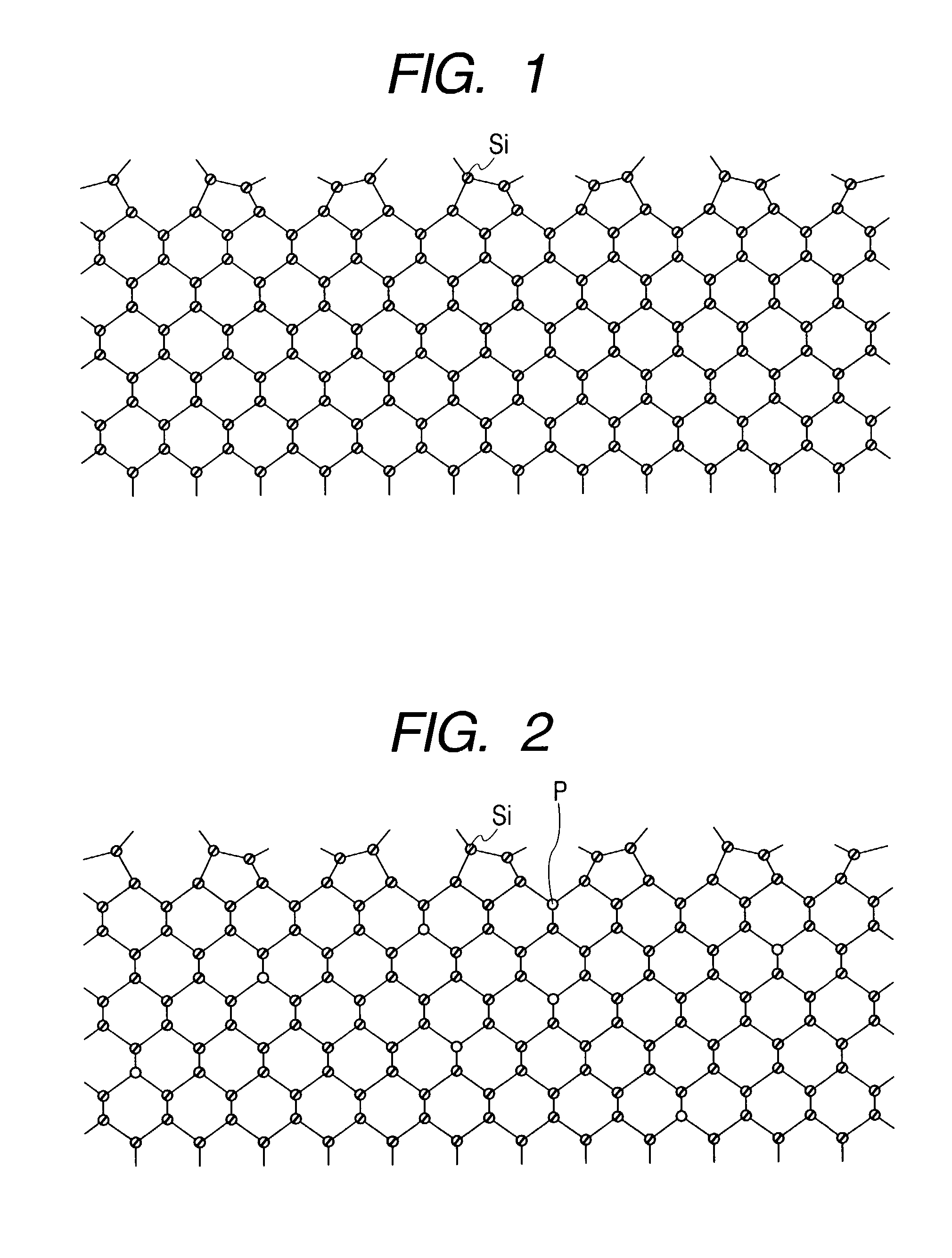

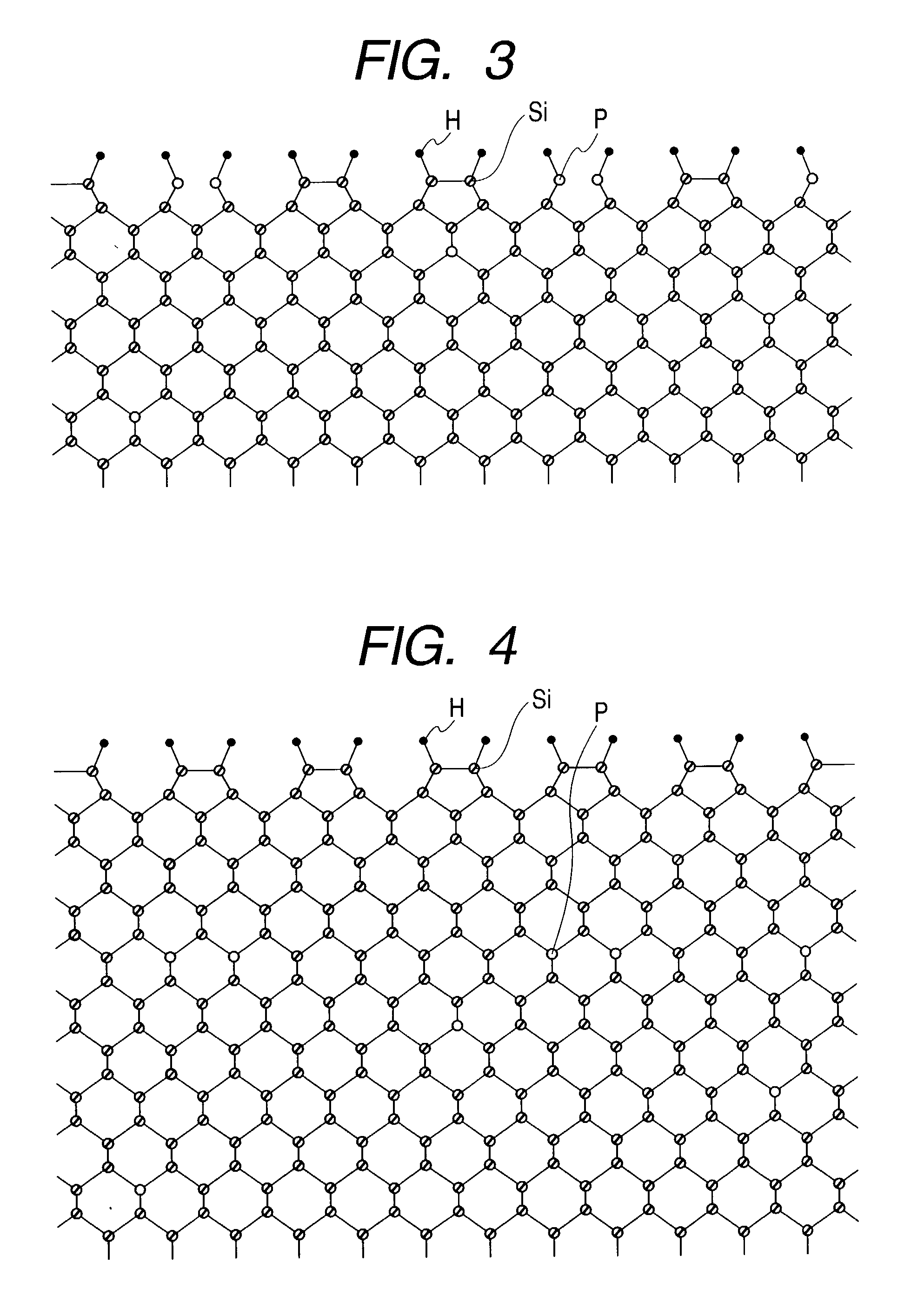

Semiconductor device and its production method

InactiveUS20030119247A1Accurate and stable and inexpensive mannerHinders miniaturizationTransistorSemiconductor/solid-state device manufacturingPhysicsMOSFET

A method for producing a semiconductor device which comprises causing a dopant present in a semiconductor substrate to segregate in the surface of said semiconductor substrate, thereby forming a thin layer which has a higher dopant concentration than said substrate. The thin layer formed by segregation prevents punch-through which occurs as the result of miniaturization of MOSFET. This method permits economical delta doping without sacrificing the device characteristics.

Owner:HITACHI LTD

Semiconductor package having embedded passive elements and method for manufacturing the same

ActiveUS7652347B2Hinders miniaturizationMinimizes electrical connection lengthSemiconductor/solid-state device detailsSolid-state devicesInsulation layerSemiconductor chip

A semiconductor package includes a base substrate on which a semiconductor chip is placed so that a first surface thereof faces the base substrate. A circuit section is formed adjacent to the first surface. An insulation layer is formed on a second surface of the semiconductor chip which faces away from the first surface. Passive elements are formed on the insulation layer. Via patterns are formed to pass through the insulation layer and are connected to the passive elements. Via wirings are formed to pass through the semiconductor chip and connected to the circuit section, the via patterns and the base substrate. Outside connection terminals are attached to a first surface of the base substrate, which face away from a second surface of the base substrate on which the semiconductor chip is placed.

Owner:SK HYNIX INC

Connector and connector device

ActiveUS11239612B2Sufficient electromagnetic shielding effectHinders miniaturizationCoupling contact membersTwo-part coupling devicesElectrical connection

Owner:HIROSE ELECTRIC GROUP

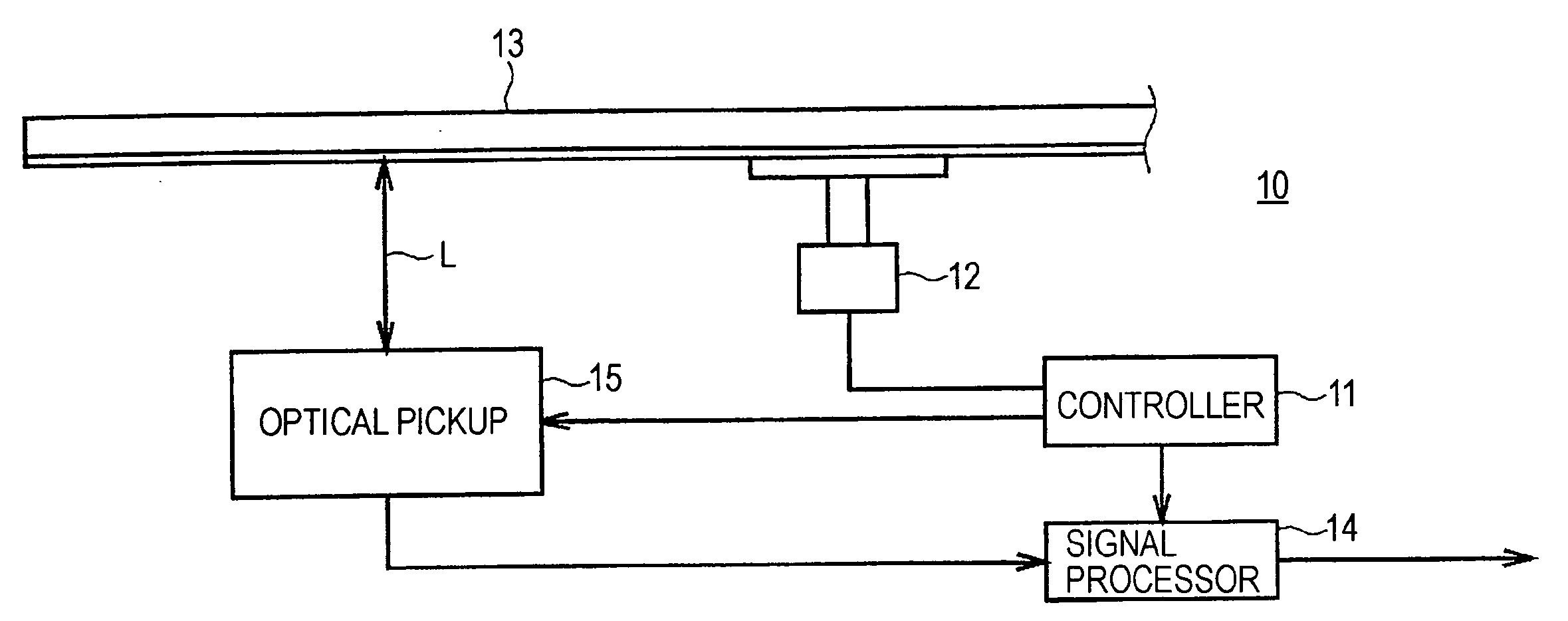

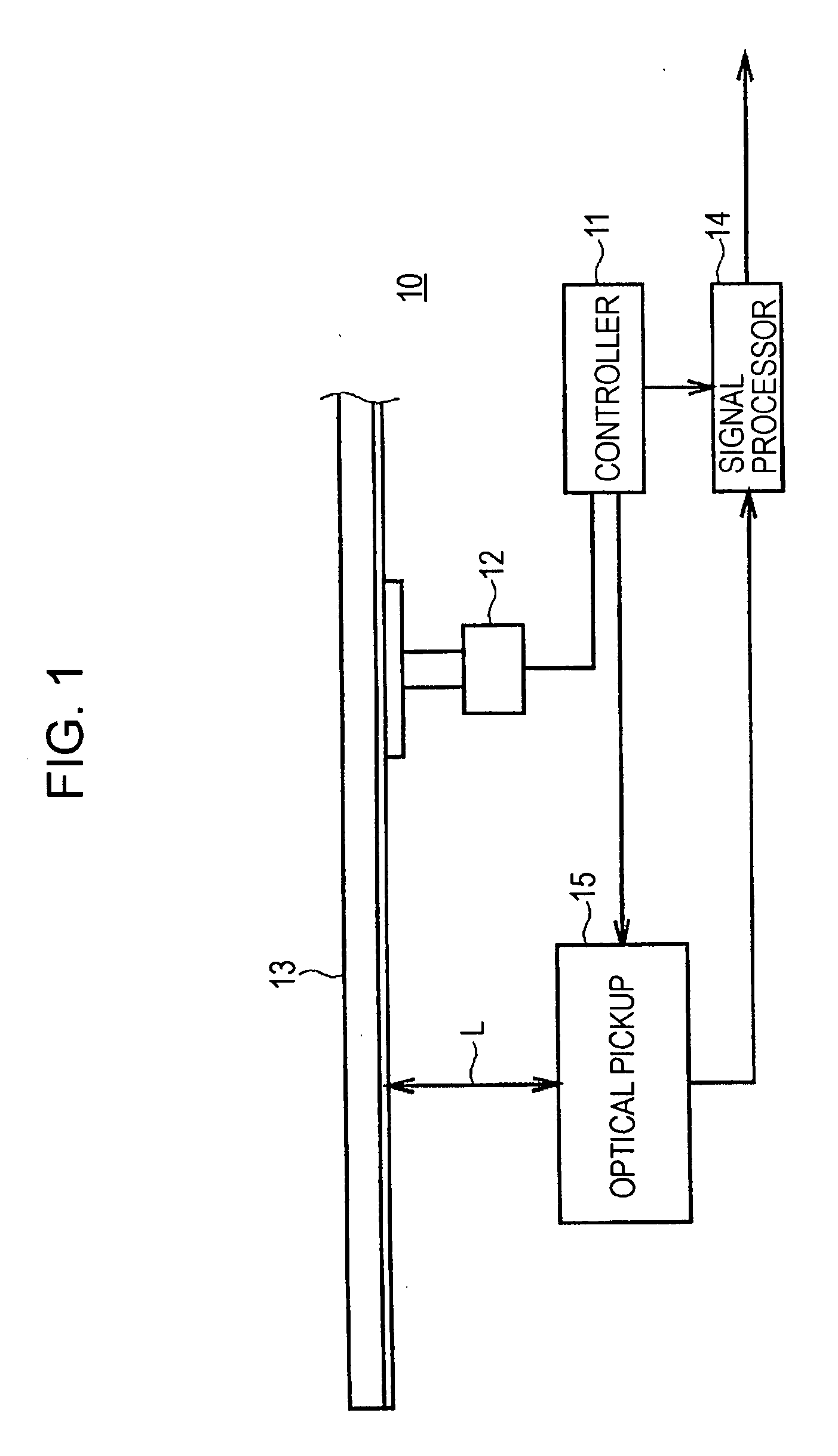

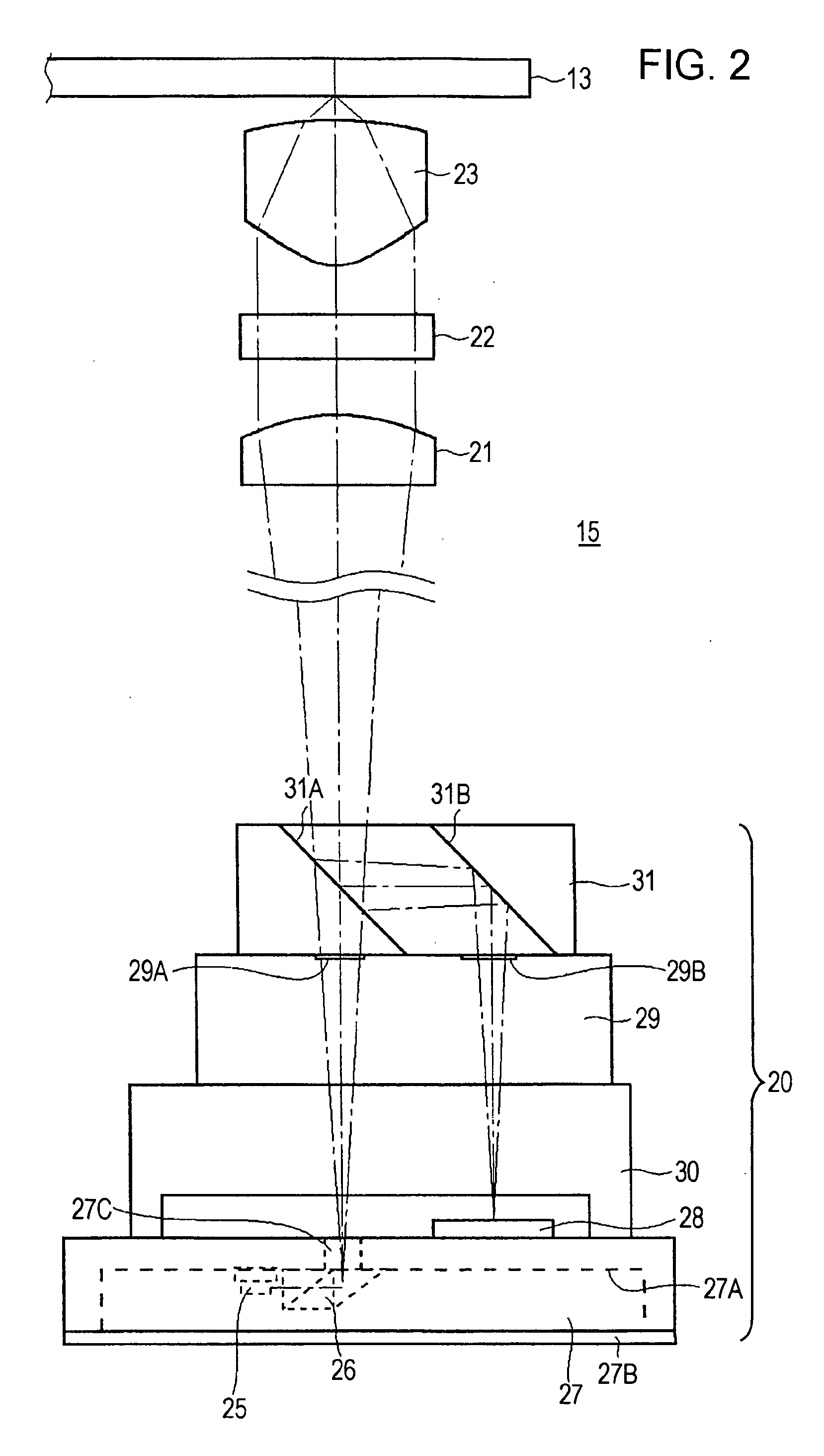

Optical pickup and optical disk apparatus

InactiveUS20080130471A1Minimize widthHinders miniaturizationPrismsOptical beam sourcesPrismOptical pickup

An optical pickup includes a light emitting device, a prism, and an objective lens. The light emitting device emits a laser beam. The prism has an entrance face and an exit face. In the prism, the laser beam emitted from the light emitting device is perpendicularly incident on the entrance face, is parallel-shifted, is perpendicularly reflected, and is emerged from the exit face. The objective lens focuses the laser beam emerged from the prism on a recording surface of an optical disk.

Owner:SONY CORP

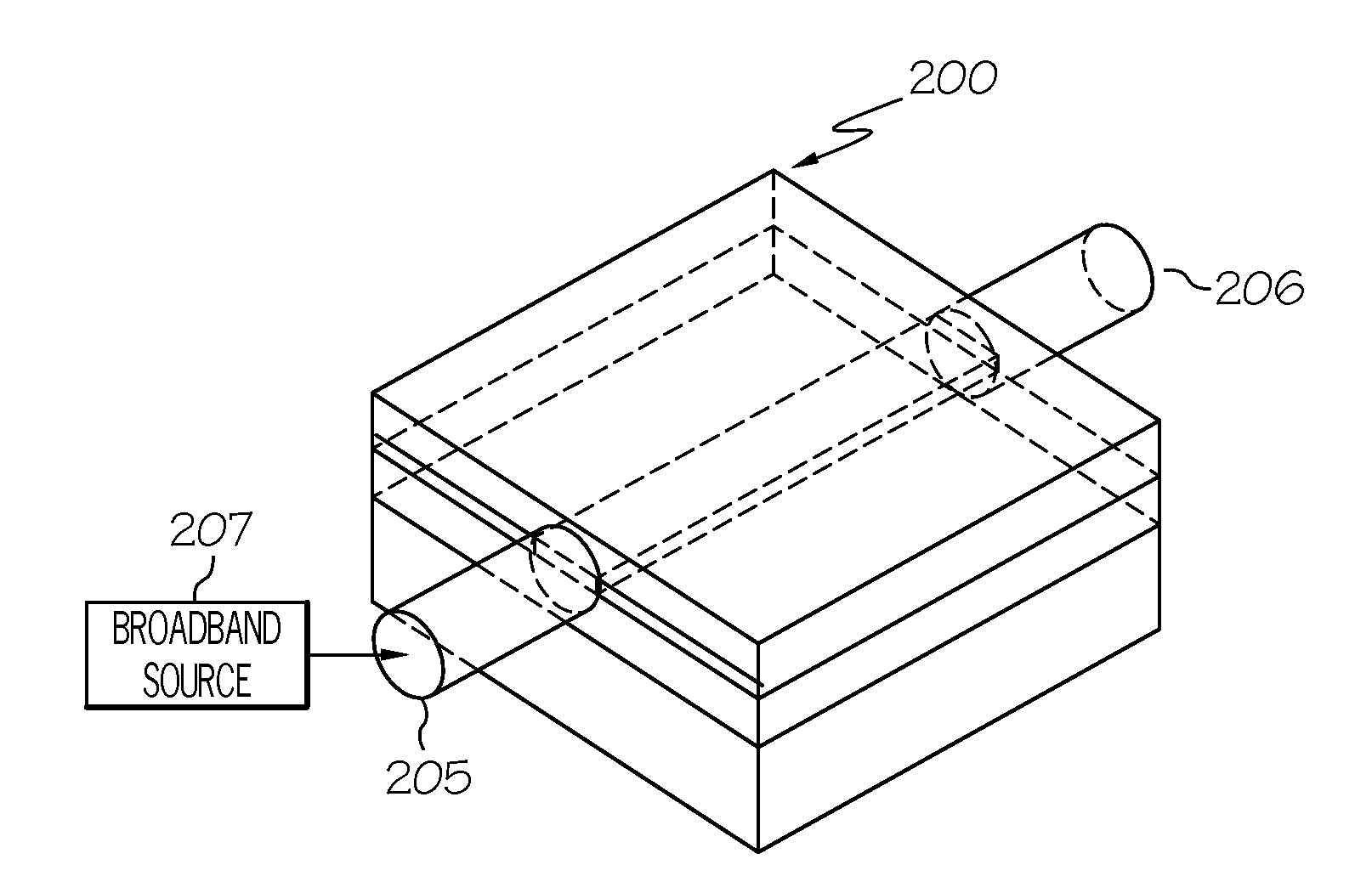

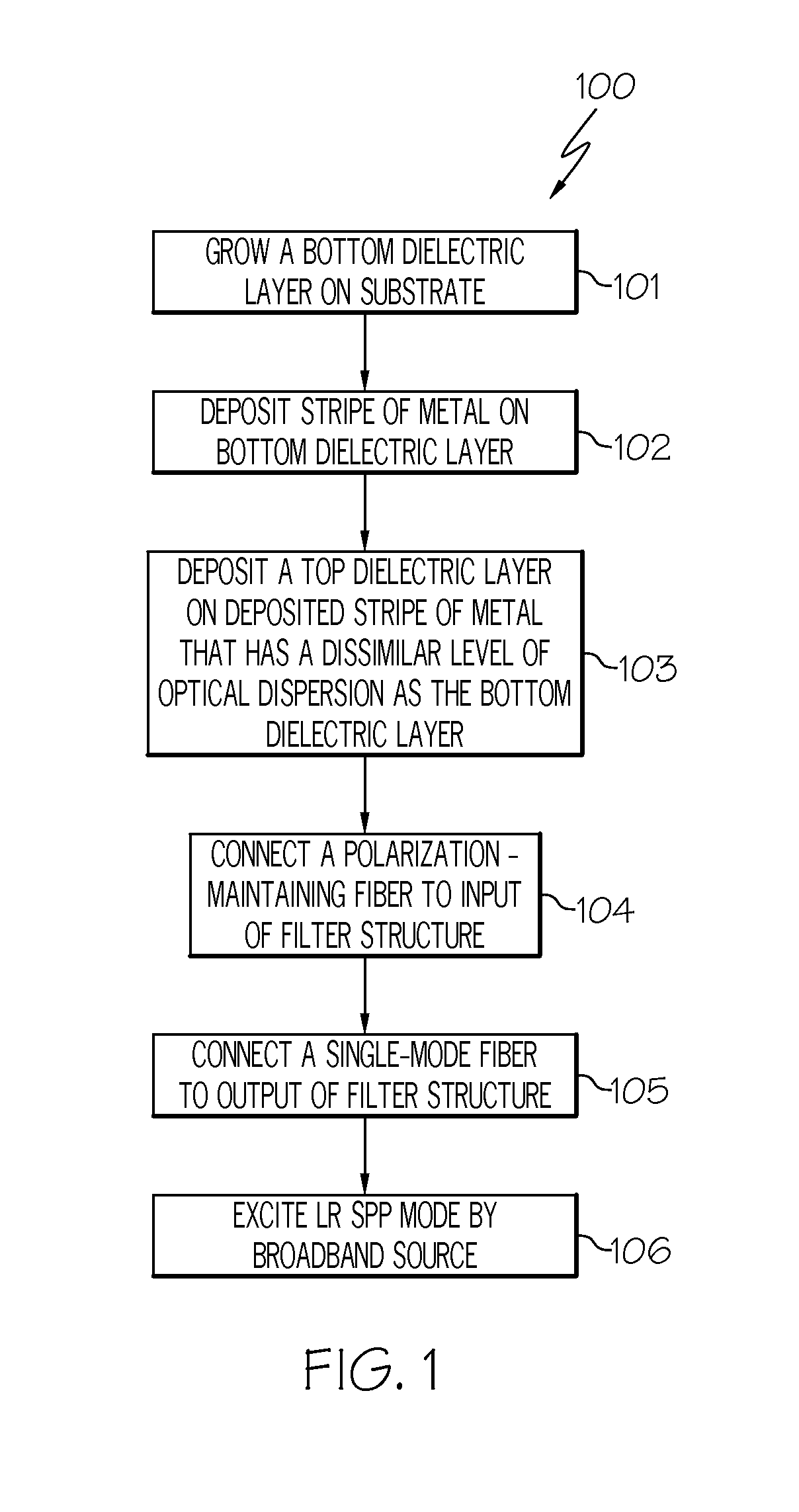

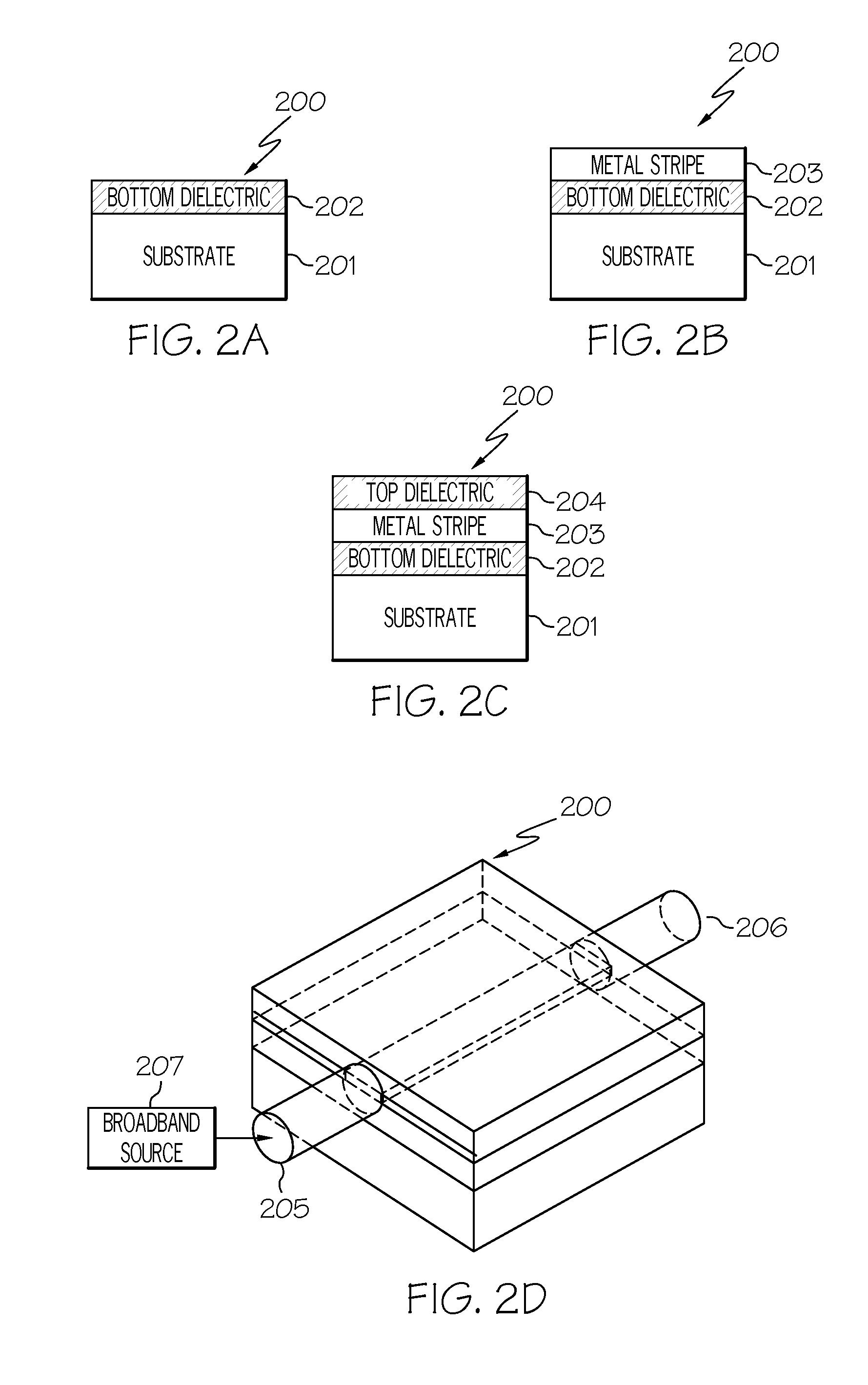

Tunable optical filter utilizing a long-range surface plasmon polariton waveguide to achieve a wide tuning range

InactiveUS20120243821A1Hinders miniaturizationLimited tuning rangeNanoopticsOptical light guidesSurface plasmon polaritonRefractive index matching

An optical filter and a method for fabricating an optical filter with a wide tuning range and a structure subject to miniaturization. The optical filter includes a bottom and a top dielectric layer with a stripe or film of metal between the dielectric layers which have dissimilar refractive index dispersion. The stripe of metal functions as a waveguide supporting a long-range surface plasmon polariton mode which will be achieved at wavelengths for which the refractive indices of the dielectric layers are the same thereby providing a bandpass filter. Furthermore, one of the dielectric layers is made of a material that allows its refractive index to be tuned, such as by changing its applied voltage or temperature. By tuning the refractive index of the dielectric layer, the wavelength at which the refractive indices of the dielectric layers match changes thereby effectively tuning the optical filter.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

Semiconductor device and its production method

InactiveUS6780698B2Accurate and stable and inexpensive mannerHinders miniaturizationTransistorSemiconductor/solid-state device manufacturingDopantMOSFET

A method for producing a semiconductor device which comprises causing a dopant present in a semiconductor substrate to segregate in the surface of said semiconductor substrate, thereby forming a thin layer which has a higher dopant concentration than said substrate. The thin layer formed by segregation prevents punch-through which occurs as the result of miniaturization of MOSFET. This method permits economical delta doping without sacrificing the device characteristics.

Owner:HITACHI LTD

Battery charger

InactiveUS6969269B2Increase in sizeHinders miniaturizationBatteries circuit arrangementsElectric discharge tubesEngineeringMechanical engineering

Owner:SONY CORP

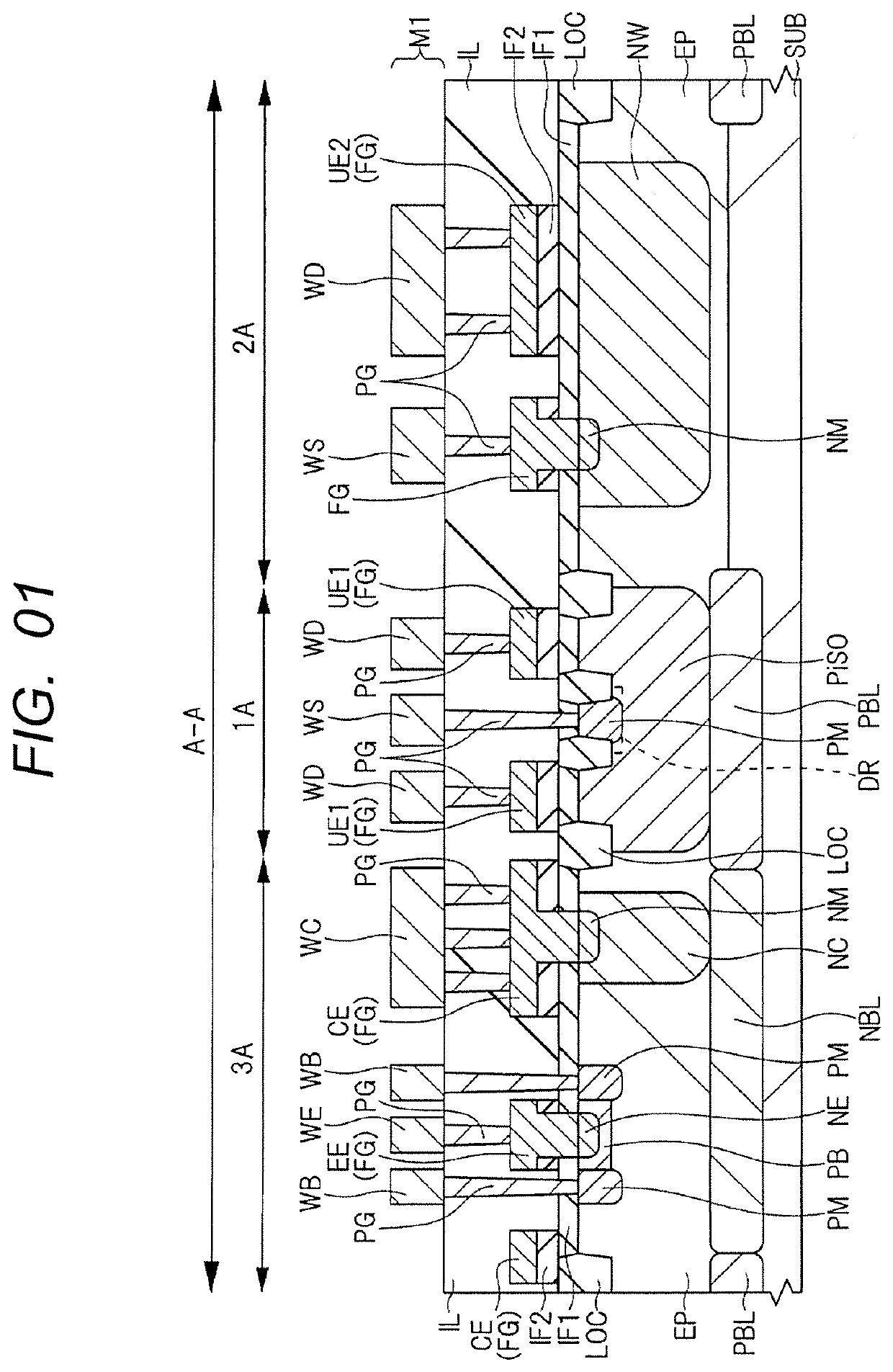

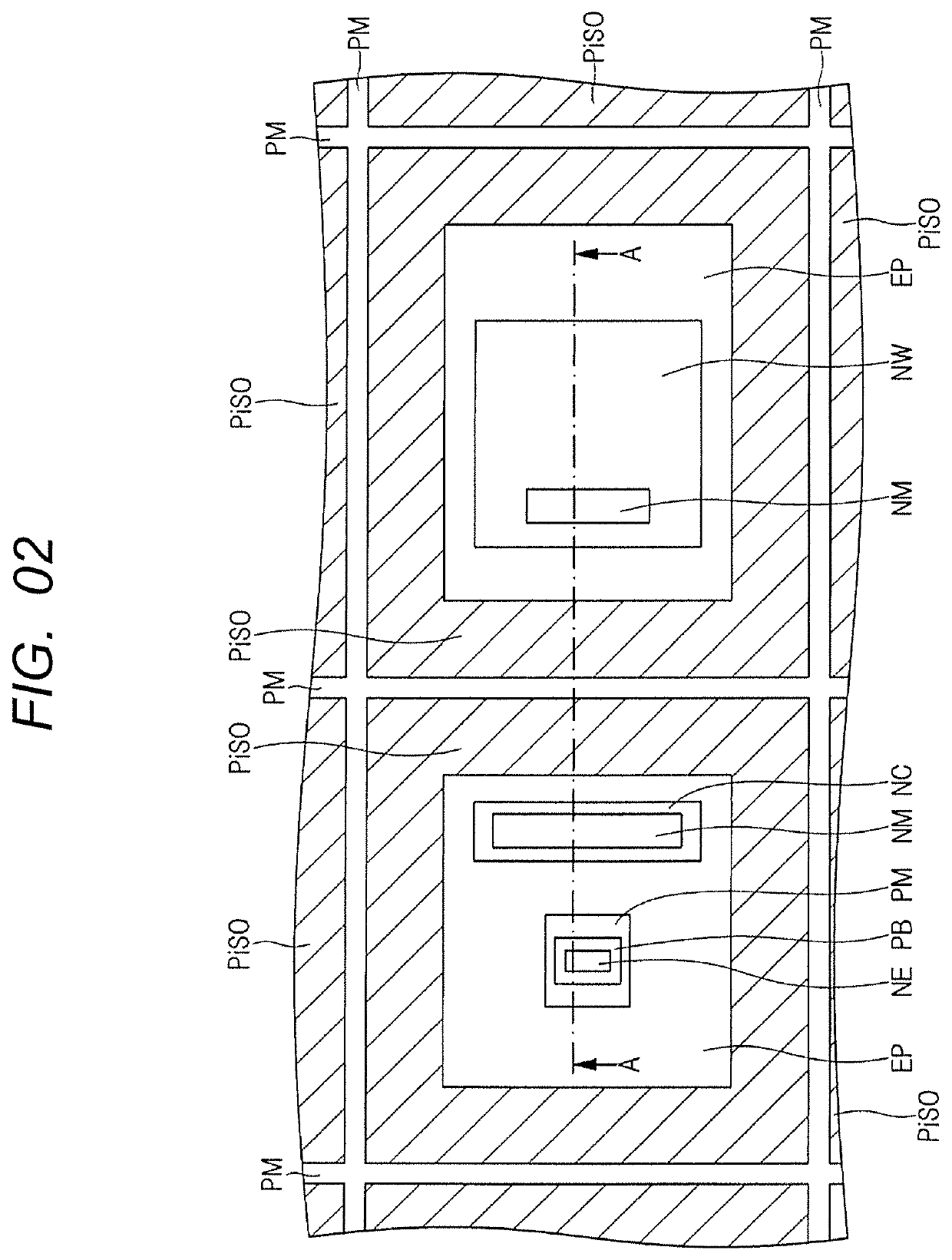

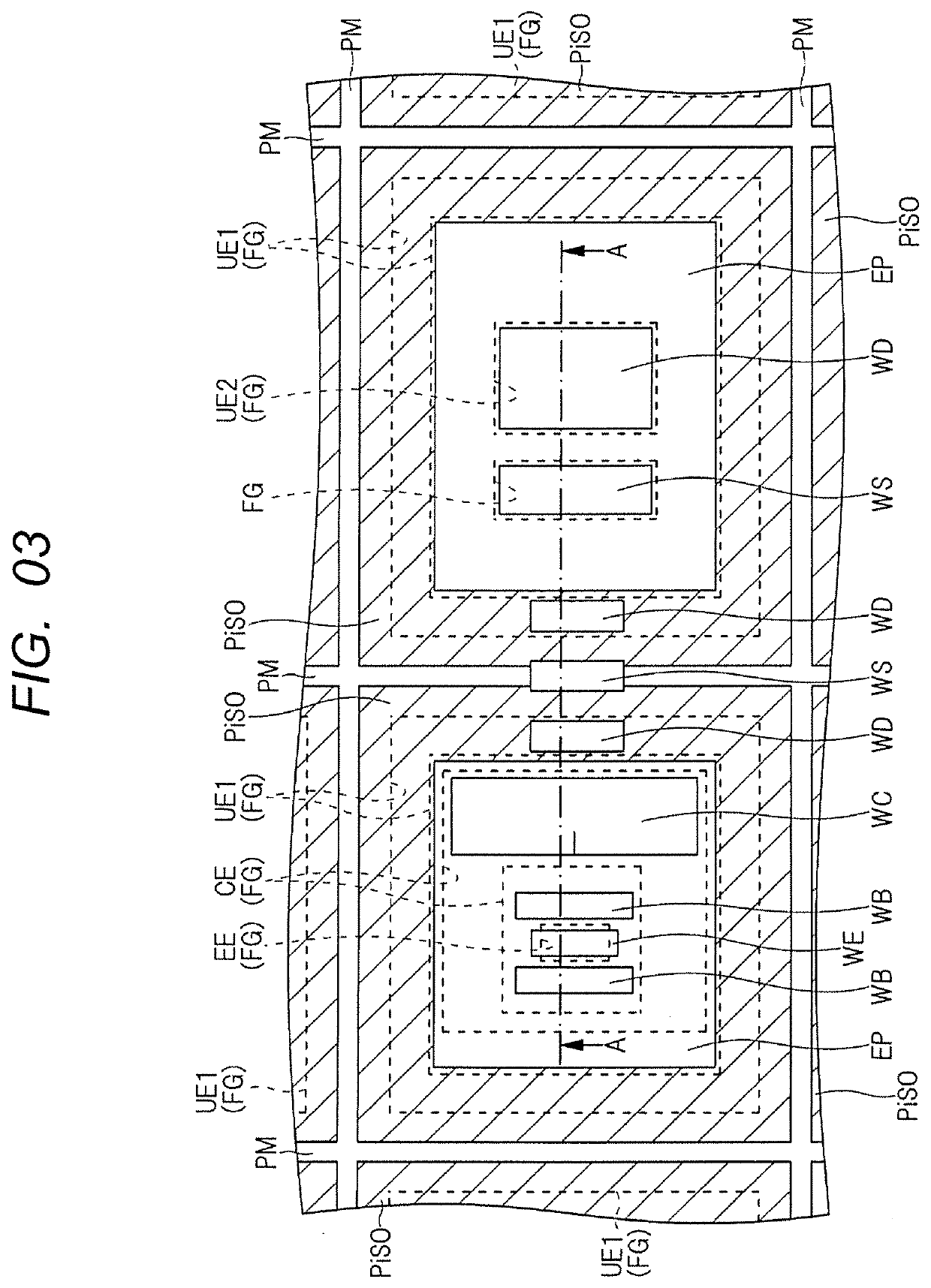

Semiconductor device and method of manufacturing the same

ActiveUS20200294985A1Improve semiconductor device performanceImprove performanceTransistorSolid-state devicesCapacitanceDevice material

A semiconductor device includes a semiconductor substrate SUB, a semiconductor layer EP formed on the semiconductor substrate SUB, a buried layer PBL formed between the semiconductor layer EP and the semiconductor substrate SUB, an isolation layer PiSO formed in the semiconductor layer EP so as to be in contact with the buried layer PBL, and a conductive film FG formed over the isolation layer PiSO via an insulating film IF, whereby a first capacitive element including the conductive film FG as an upper electrode, the insulating film IF as a capacitive insulating film, and the isolation layer PiSO as a lower electrode, is formed over the semiconductor substrate SUB.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com