Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83results about How to "Guaranteed operation speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

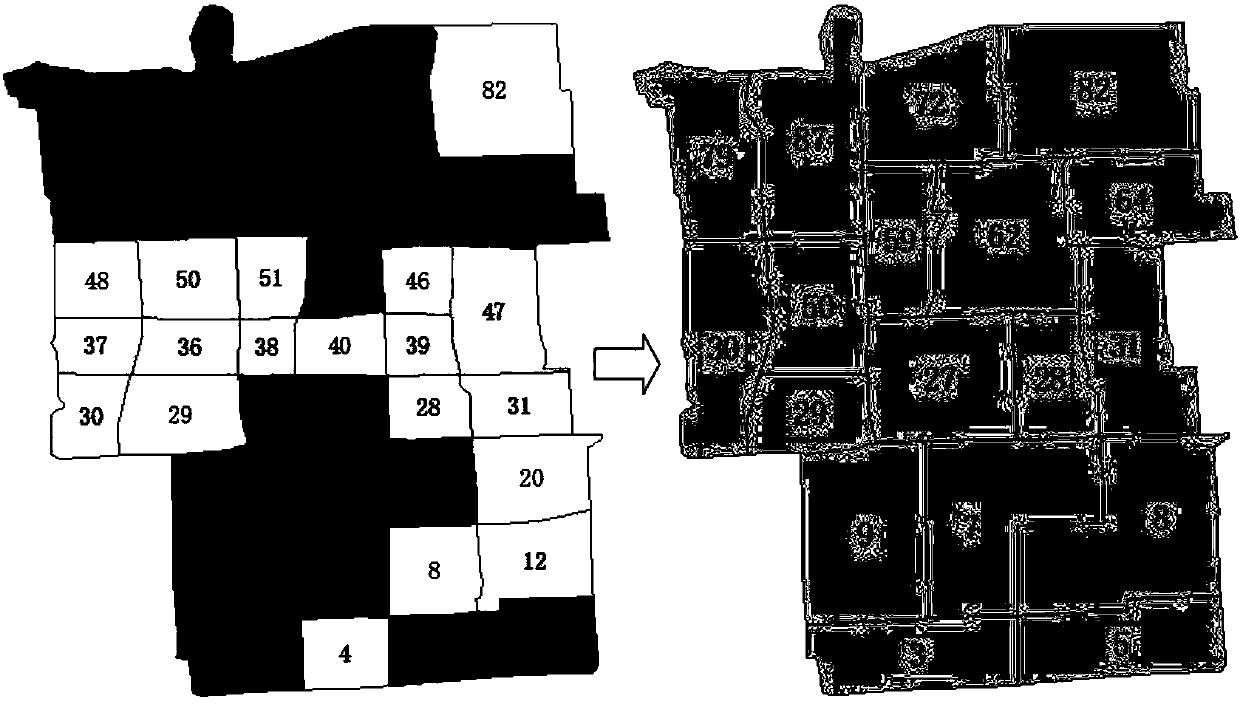

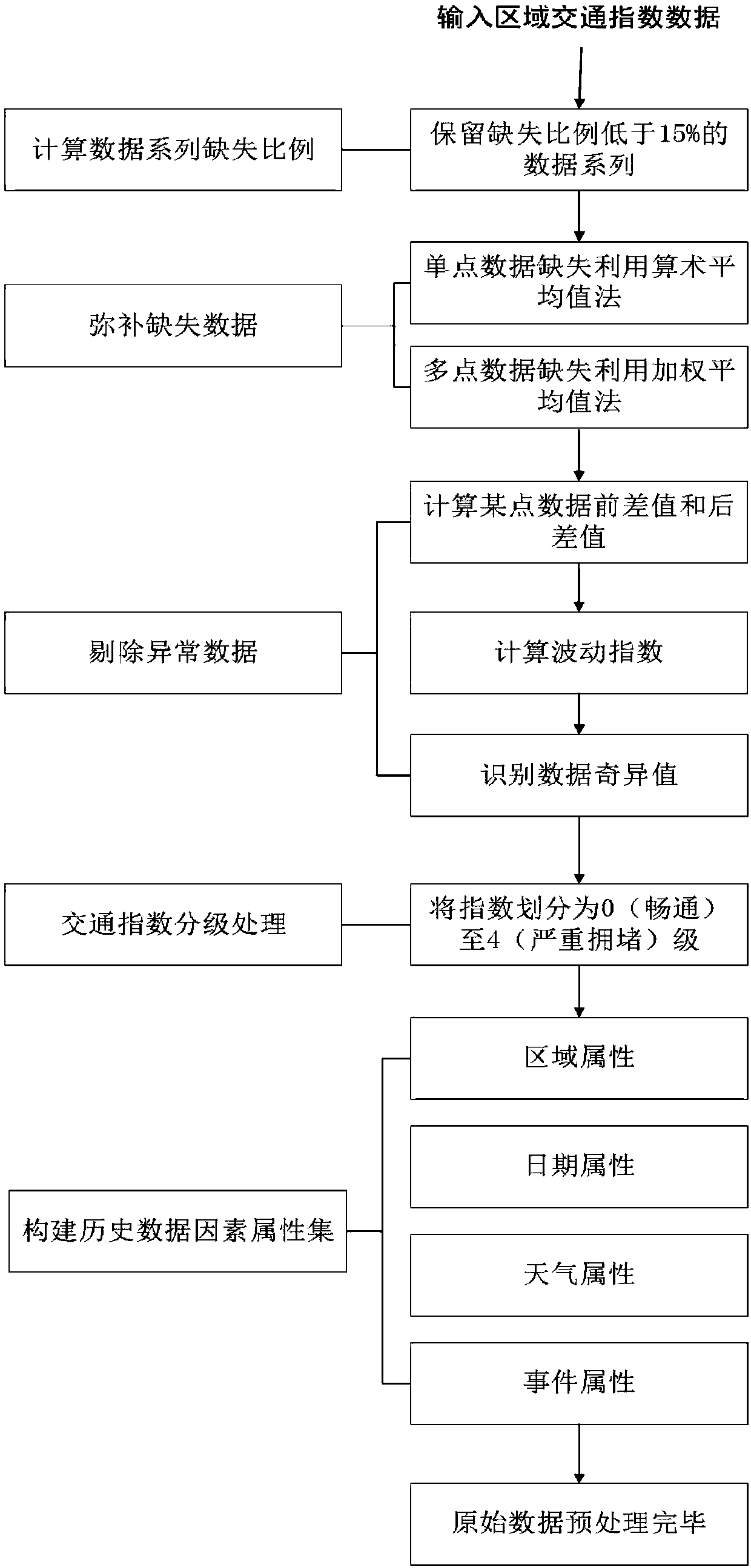

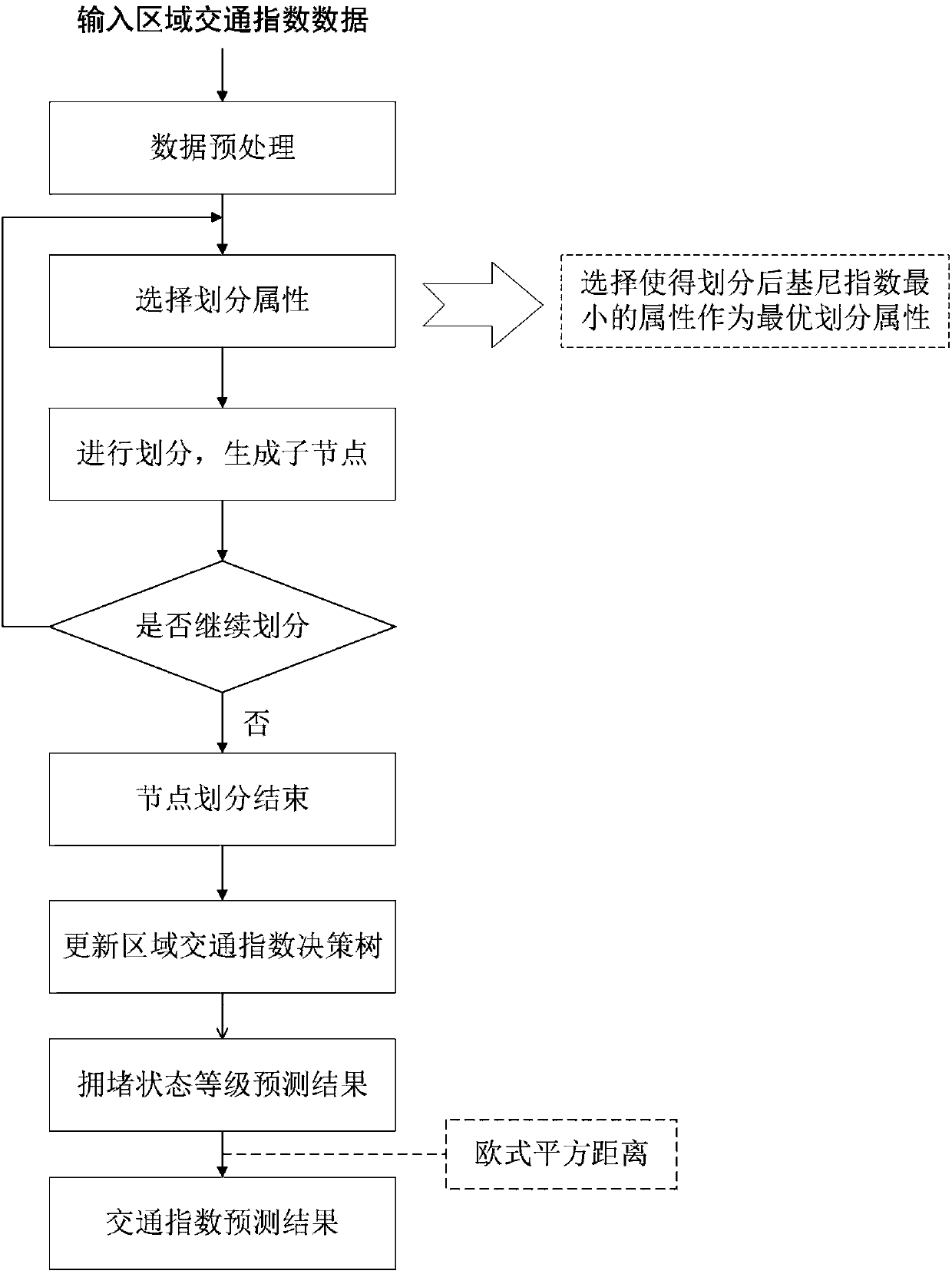

Day-dimension regional traffic index prediction method considering influences of multiple factors

ActiveCN107610469AAccurate portrayalEasy to operateDetection of traffic movementForecastingState predictionOriginal data

The invention discloses a day-dimension regional traffic index prediction method considering influences of multiple factors. The method comprises the steps that regions are divided and aggregated; regional traffic index original data preprocessing is carried out; the influences of multiple factors are considered, and regional traffic index prediction under the day dimension is carried out. According to the specific technical scheme of the method, on the basis of traffic cell division, traffic cells with the same aggregation property are aggregated, and regional traffic indexes are calculated;on the basis of road network operation early warning requirements, a prediction time period and a prediction cycle are determined; regional traffic data is extracted, made up for and removed, and preprocessing such as comprehensive building of a historical data factor attribute set from different angles is conducted on the data; on the basis of a decision tree theory, regional road network operation congestion state prediction is carried out; a final prediction result of the regional traffic indexes is determined by means of the square euclidean distance. By means of the method, on the one hand, monitoring and application of the urban road network operation state is deepened, and on the other hand, technical support is provided for early warning and forecasting work of the road network operation state.

Owner:BEIJING UNIV OF TECH

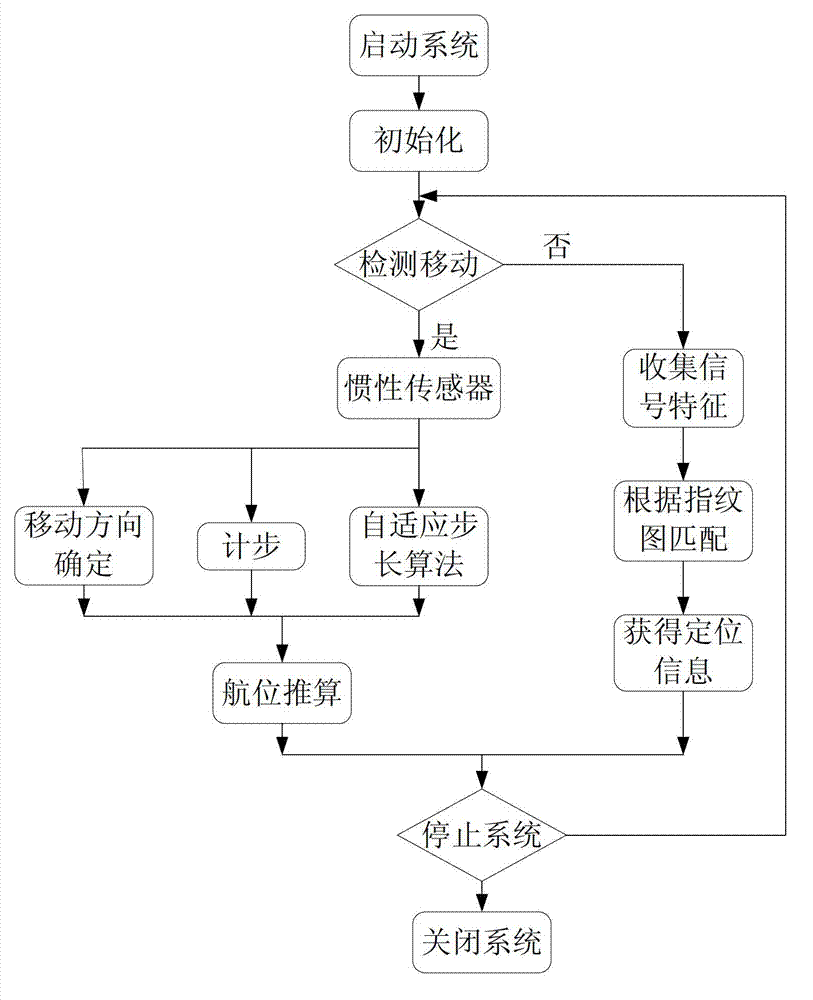

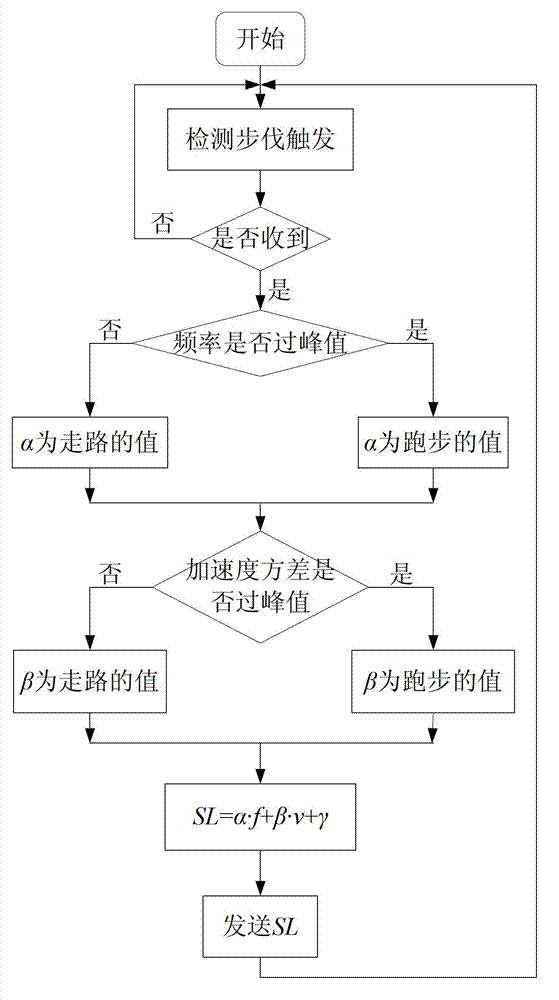

Method and system for indoor positioning based on inertial sensor and wireless signal characteristics

ActiveCN102932742AHigh precisionCorrect cumulative errorWireless commuication servicesHand held devicesBackground process

The invention relates to a method and a system for indoor positioning based on an inertial sensor and wireless signal characteristics. The method comprises the following steps of: initializing the position of a positioning target in the space by a wireless signal characteristics method; detecting the motion state of the positioning target, if the positioning target is in an idle state, positioning the positioning target by the wireless signal characteristics method; if the positioning target is in a moving state, taking the last positioning point in idle state as the starting point to generate the movement locus of the positioning target by the inertial sensor, displaying the position and movement locus of the positioning target on a handheld device in real time, and simultaneously uploading the real-time position information to a background processing device via a wireless network. The system provided by the invention comprises the handheld device with the inertial sensor, wireless receiving nodes arranged in the indoor space, and the background processing device connected with the inertial sensor. Compared with the prior art, the method and the system have the advantages of high positioning precision, association of activity and inertia, and the like.

Owner:SHANGHAI JIAO TONG UNIV

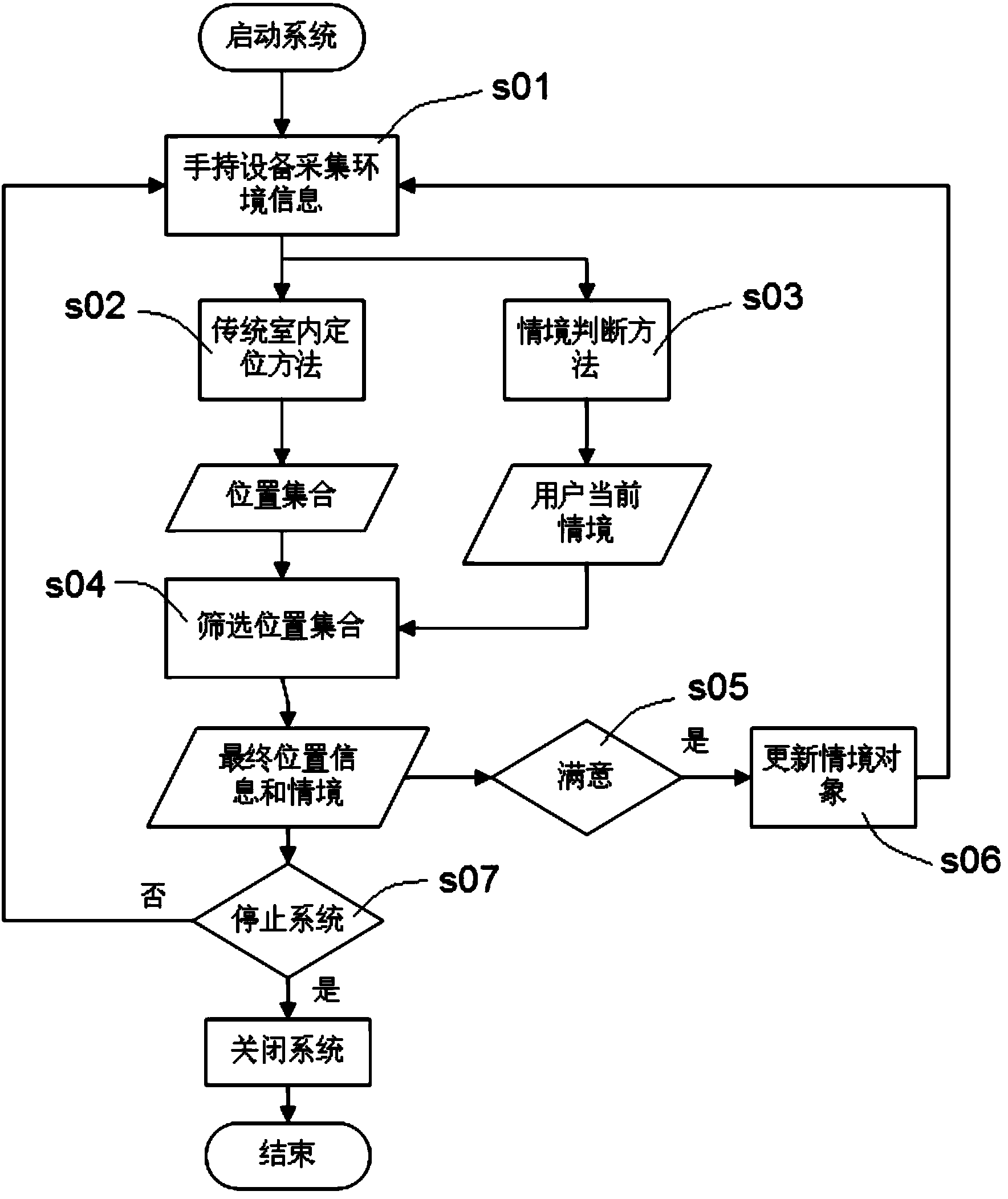

Situation-related indoor positioning method and system

ActiveCN103644905AOvercome experience shortcomingsCorrection errorNavigation instrumentsEngineeringComputer vision

The invention relates to a situation-related indoor positioning method and system. The method comprises the following steps of (1) acquiring environment information through intelligent handheld equipment in real time; (2) obtaining position sets of a target by a conventional indoor positioning method according to the environment information; (3) obtaining the current situation in which the target is positioned by a situation judgment method according to the environment information; (4) screening the position sets according to a situation result obtained in the step (3) to obtain a final positioning result, and displaying the final positioning result; and (5) judging whether a target satisfaction instruction is received, if so, uploading the real-time position information and situation object information to a background processing device through a wireless network, and updating the situation object information. The system comprises the intelligent handheld equipment, the background processing device and a plurality of wireless receiving nodes. Compared with the prior art, the method and the system which are disclosed by the invention have the advantages of high positioning precision, low arrangement cost, excellent user experience and the like.

Owner:SHANGHAI JIAO TONG UNIV

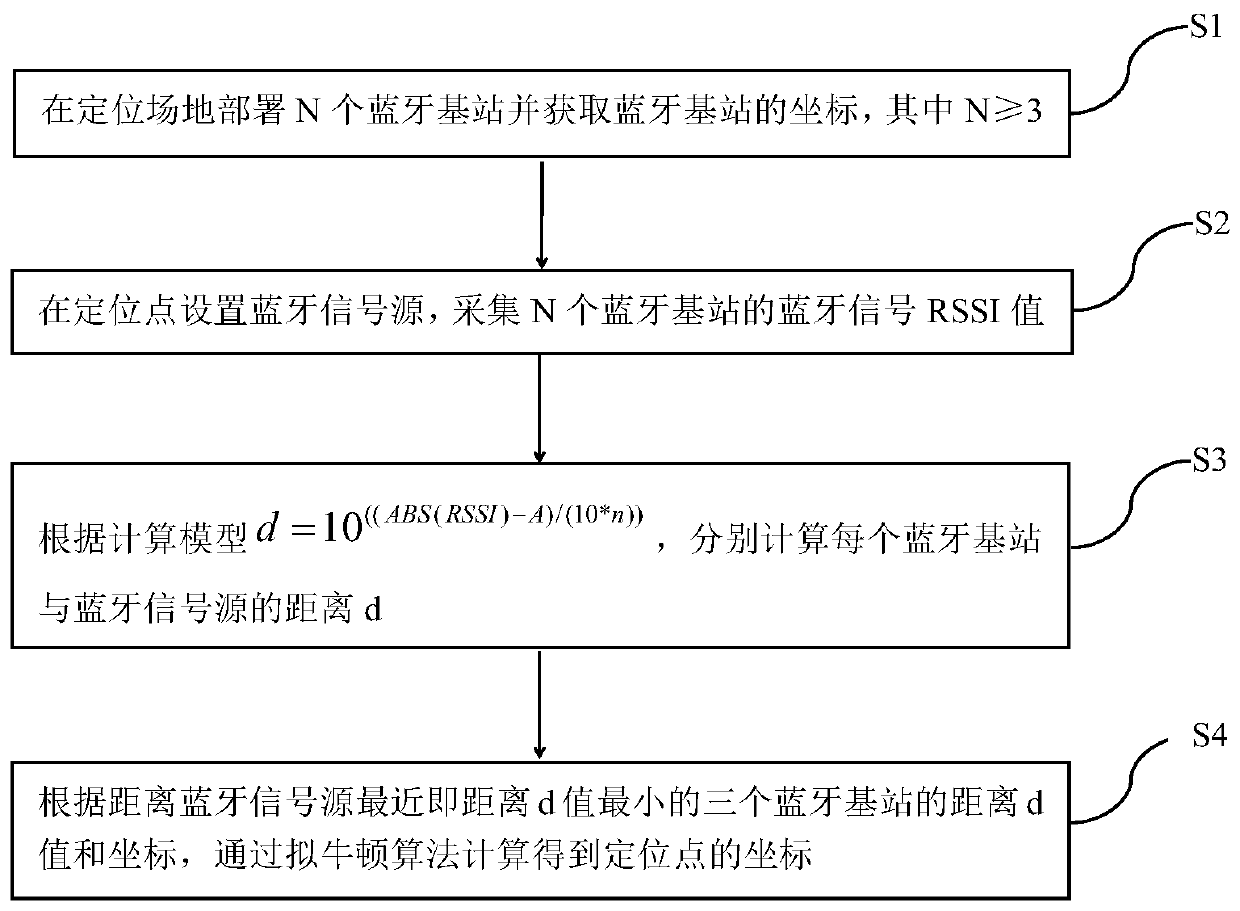

Indoor positioning method based on Bluetooth signal RSSI

InactiveCN109782227AGuaranteed accuracyGuaranteed operation speedPosition fixationTransmission monitoringSignal strengthBase station

An embodiment of the invention discloses an indoor positioning method based on a Bluetooth signal RSSI. The method comprises the following steps of disposing N Bluetooth base stations at a positioningposition and acquiring the coordinate of a Bluetooth base station; setting a Bluetooth signal source at a positioning point, and acquiring Bluetooth signal RSSI values of N Bluetooth base stations; respectively calculating the distance d between each Bluetooth base station and the Bluetooth signal source according to a calculating model d=10((ABS(RSSI)-A) / (10*n)), wherein A is the measured Bluetooth signal strength of the bluetooth base station at a position which is separated from the Bluetooth signal source by 1m, n is an environment attenuating factor; and according to the distances d andcoordinates of three Bluetooth base stations with lowest distances d to the Bluetooth signal source, and obtaining the coordinate of the positioning point through calculation of a quasi-Newton method.The new method prevents a condition of solving an ill-conditioned equation set, and ensures high accuracy of the positioned coordinate. Furthermore compared with a traditional Newton algorithm, the method according to the invention has advantages of simplifying a calculation process and improving operation speed.

Owner:核芯互联科技(青岛)有限公司

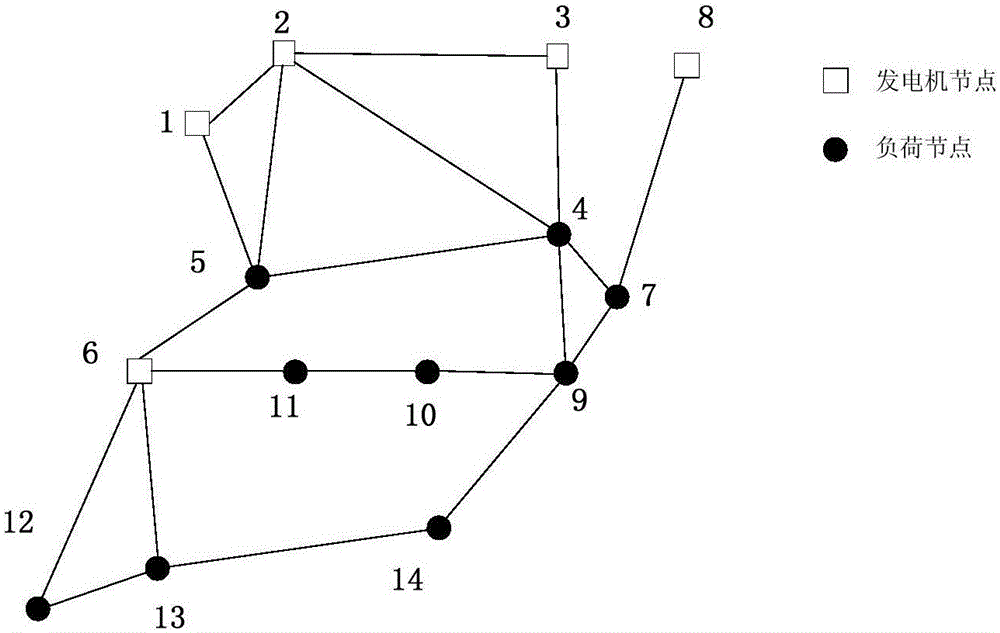

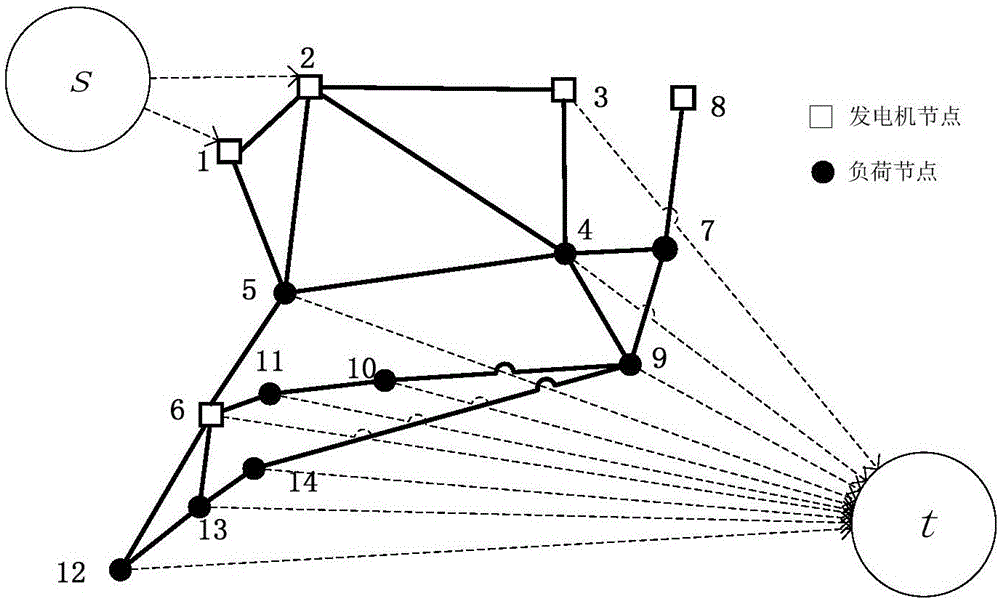

Security analysis method for power system suffering from terror attack

InactiveCN105095998AAvoid solving nestedSatisfy the convergence conditionForecastingResourcesBilevel optimizationAlgorithm

The invention relates to a security analysis method for a power system suffering from a terror attack. The method comprises the following steps: 1) establishing a double-layer mixed integer nonlinear optimization model regarding the terror attack; 2) replacing an inner layer optimization model in the double-layer mixed integer nonlinear optimization model by adopting a KKT (Karush-Kuhn-Tucker) condition to transform the double-layer optimization model into a single-layer optimization model; 3) performing active and reactive power decoupling on the single-layer optimization model to decompose the single-layer optimization model into an active power optimization sub-model and a reactive power adjusting sub-model; 4) simplifying the active power optimization model into a combined model according to a Lagrangian multiplier of the KKT condition, and performing approximate solving by using a max-flow min-cut model; and 5) alternatively solving the active power optimization sub-model and the reactive power adjusting sub-model till the voltage difference of two times of iteration satisfies a corresponding convergence condition, and finally obtaining an optimal solution. Compared with the prior art, the method has the advantages that solution nesting is avoided, the model is comprehensive, the result is accurate and the like.

Owner:TONGJI UNIV

Heating furnace temperature control method based on simulation model

ActiveCN106636606AEasy to controlReduce oxidation burnFurnace typesHeat treatment process controlTemperature controlFurnace temperature

The invention relates to the technical field of control over metallurgical heating furnaces and discloses a heating furnace temperature control method based on a simulation model. The heating furnace temperature control method based on the simulation model comprises the following steps that (1) mechanism modeling is carried out according to the principle of heat convection inside a heating furnace, and a steel billet temperature change model is created; (2) the final discharging billet temperature of each single steel billet is worked out based on the steel billet temperature change model of the step (1), and compared with the set discharging billet temperature, and the adjustment quantities of each single steel billet for the furnace temperature set values of different heating sections are finally determined according to the self-optimization function of a steel billet temperature compensation module; (3) through combination of the quantity and types of the steel billets in each heating section and the feeding billet temperature of each steel billet with the weight coefficients of the different types of steel billets, a steel billet gathering module works out the final adjustment quantity of the furnace temperature set point of each heating section, and outputs the final adjustment quantity to an actuating mechanism; and (4) related parameters in the simulation model are adjusted according to the deviation between the actual discharging billet temperature and the set value, and accordingly the whole simulation model achieves the real-time online function.

Owner:北京和隆优化科技股份有限公司

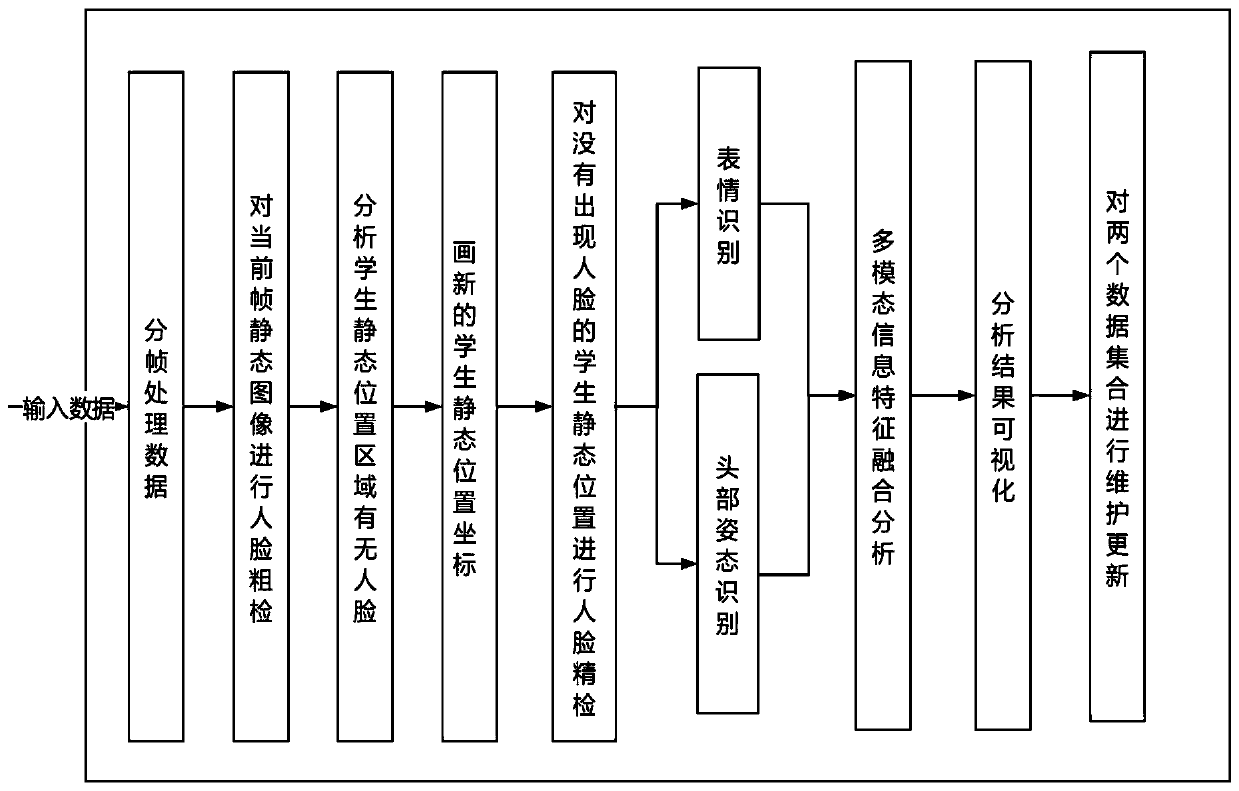

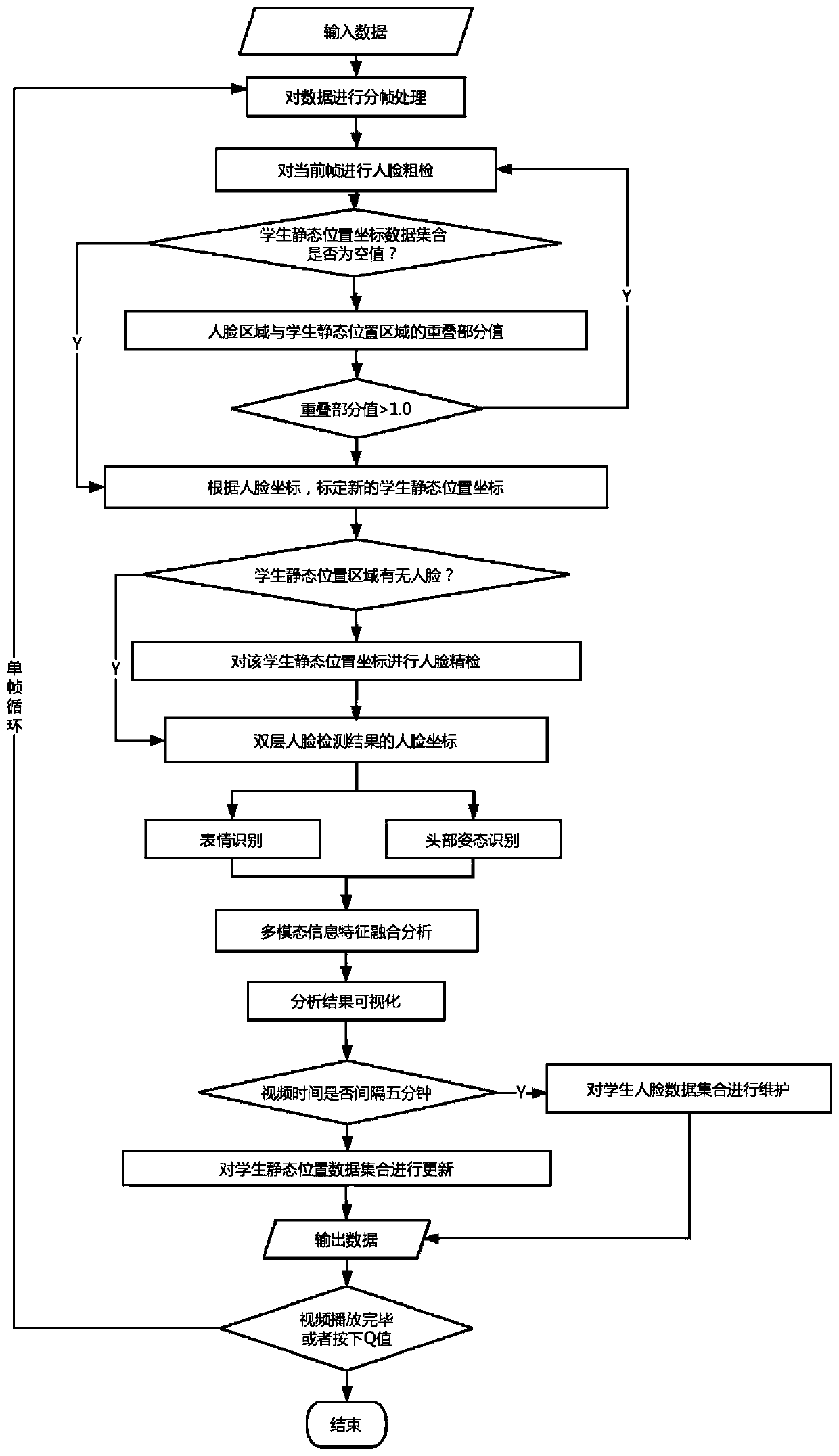

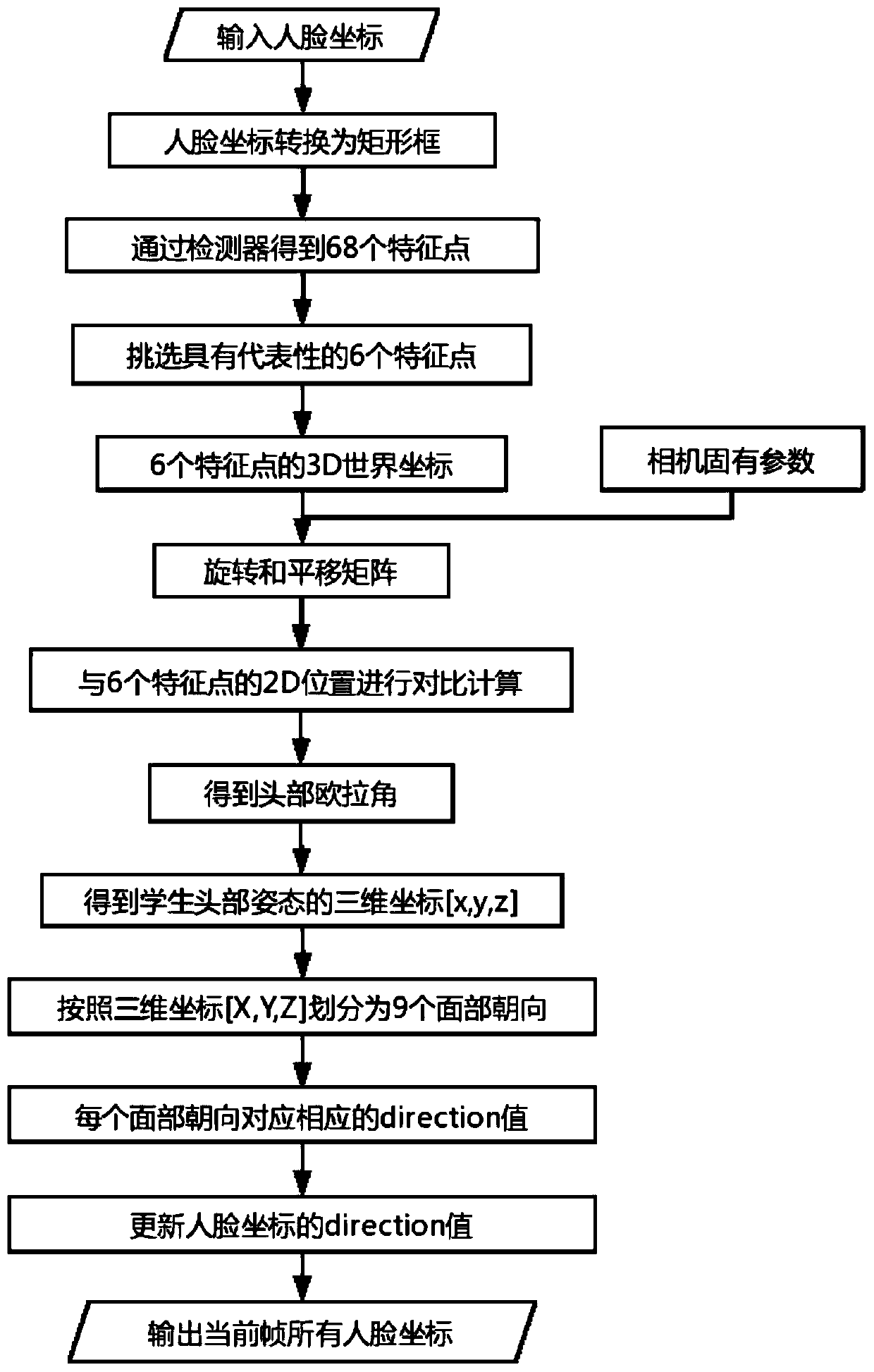

Learning state hybrid analysis method for static multi-person scene

ActiveCN110287790AFocusImprove reliabilityData processing applicationsNeural architecturesFace detectionAlgorithm

The invention provides a learning state hybrid analysis method for a static multi-person scene. At the beginning of a class, the concentration degrees of the students are highly concentrated, according to the invention, the face is detected by using an algorithm with high front face detection speed and high precision, and the static position areas of the students are estimated; then, the life values and the hit values of the static positions of the students are judged, an algorithm with high side face detection precision is called, so that through the double-layer face detection, the accuracy of face detection in the static multi-person scene, such as a classroom, etc., is greatly improved, and the operation speed is ensured. For the recognized and obtained head postures and facial expressions of the students, the concentration degrees of the students are obtained by comparing and calculating the head postures of the students with the head postures of the surrounding students, the expressions of the students are classified in a plurality of ways, and the diversity of the expression classification and the calculation of the concentration degree of the students can improve the reliability of the analysis result of a multi-modal feature analysis module.

Owner:HUAZHONG NORMAL UNIV

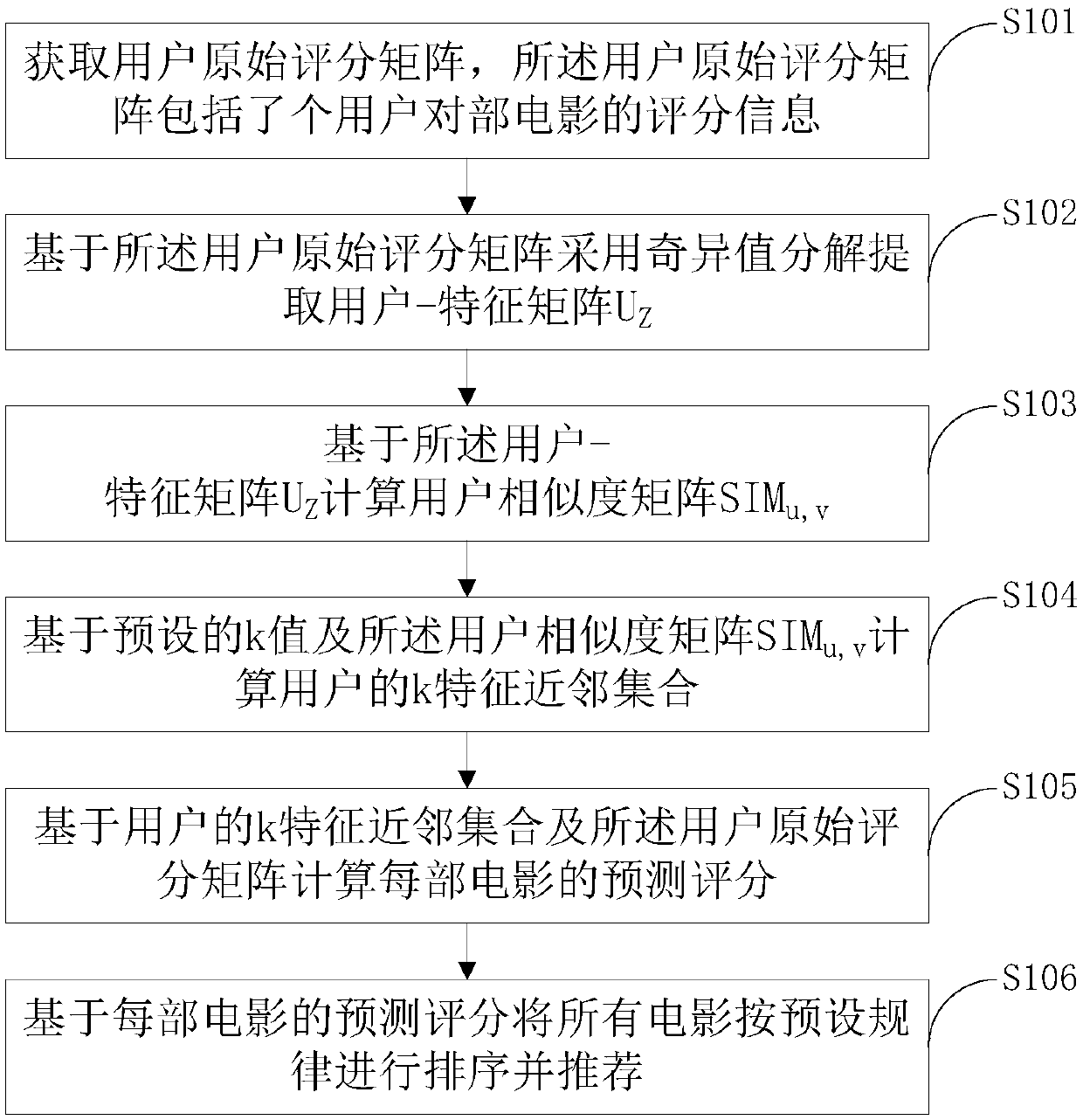

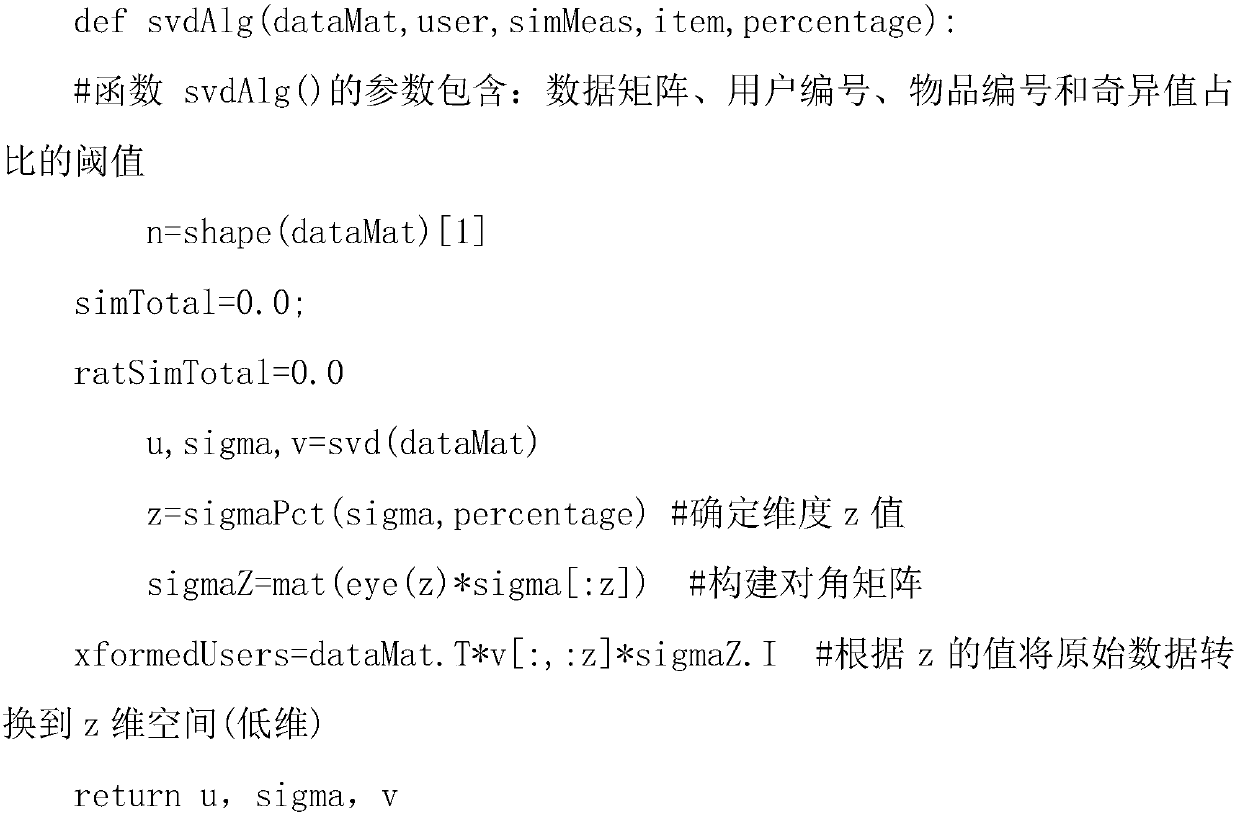

Matrix decomposition and collaborative filter algorithm combined movie recommendation method

ActiveCN108804683AGuaranteed operation speedImprove recommendation accuracySpecial data processing applicationsSingular value decompositionPersonalization

The invention discloses a matrix decomposition and collaborative filter algorithm combined movie recommendation method. The method comprises the following steps of: obtaining a user original scoring matrix, wherein the user original scoring matrix comprises scoring information, for M movies, of N users; extracting a user-feature matrix UZ on the basis of the user original scoring matrix by adoption of singular value decomposition; calculating a user similarity matrix SIMu, v on the basis of the user-feature matrix UZ; calculating k nearest neighbor feature set of the users on the basis of a preset k value and the user similarity matrix SIMu, v; calculating a predicted score of each movie on the basis of the k nearest neighbor set of the users and the user original scoring matrix; and sorting and recommending all the movies according to a preset law on the basis of the predicted score of each movie. According to the method, the recommendation correctness of a slope one algorithm in movie recommendation systems can be enhanced, the personalization degree can be improved while the operation speed of the algorithm is ensured, and influences caused to the slope one algorithm by matrix sparseness can be decreased.

Owner:CHONGQING UNIV OF TECH

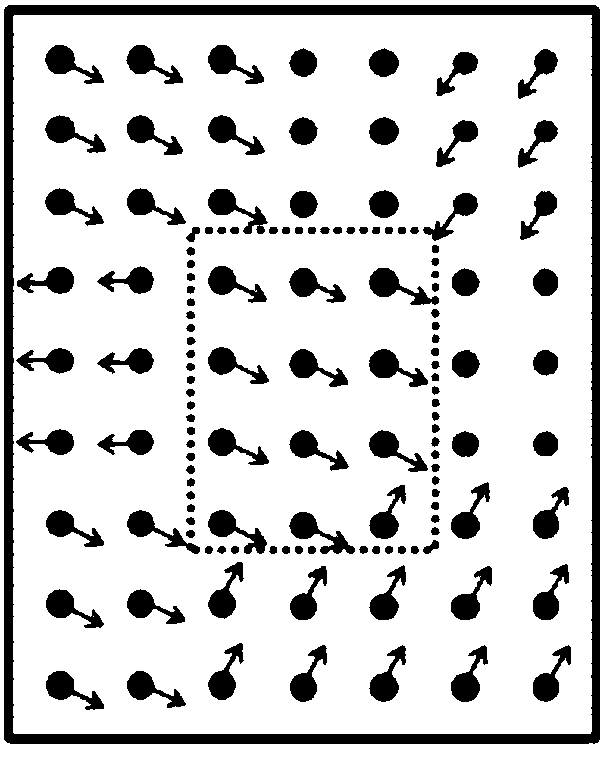

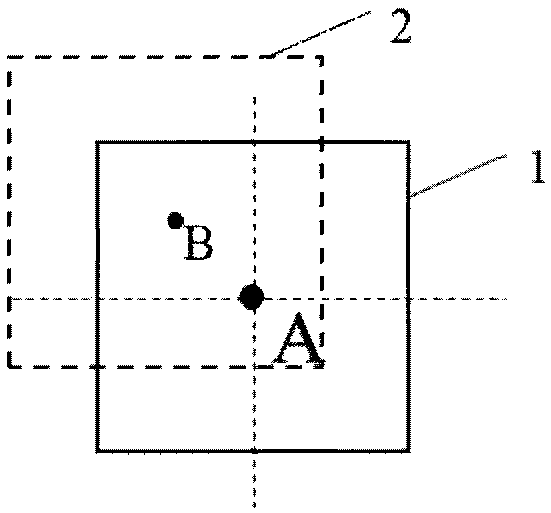

Reinspection method used during tracking failure of monocular long-time visual tracking method

InactiveCN107492114AImprove boundary effectImprove tracking performanceImage enhancementImage analysisCorrelation filterBoundary effects

The invention discloses a reinspection method used during the tracking failure of a monocular long-time visual tracking method. A weighting matrix is used for updating an STC (Spatio-Temporal Context) model, and the characteristics of the STC model for saptio-temporal context modeling are taken as reinspection equipment. When a kernel-related filter response can not meet inspection requirements, the STC model is used for carrying out reinspection to finish position inspection under a covering situation. A method that an HSV (Hue, Saturation and Value) space assists in determining a position is used for improving a boundary effect brought to a WSTC (Weighted Spatio-Temporal Context) algorithm by a Hamming window under a situation that operation speed is guaranteed, and the tracking ability of the WSTC algorithm for a quick movement object is improved.

Owner:HANGZHOU DIANZI UNIV

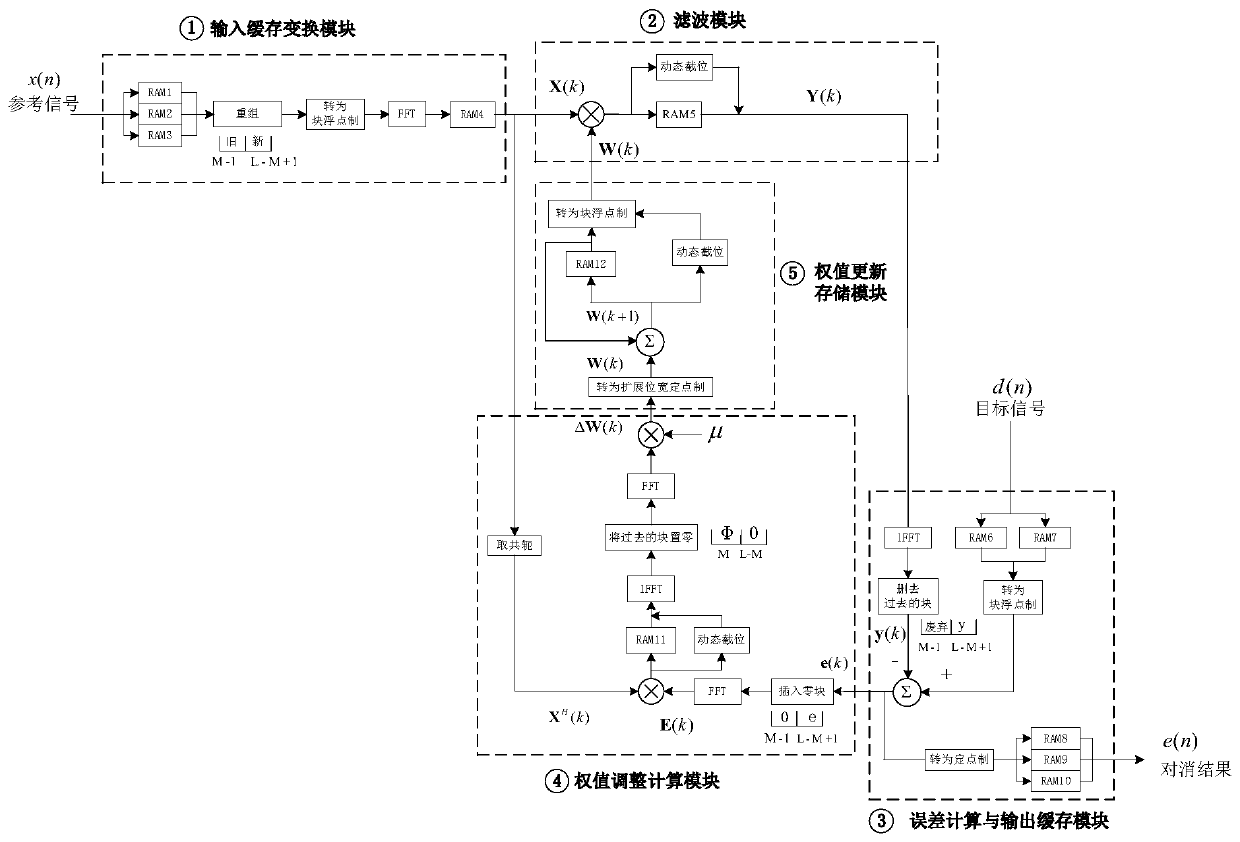

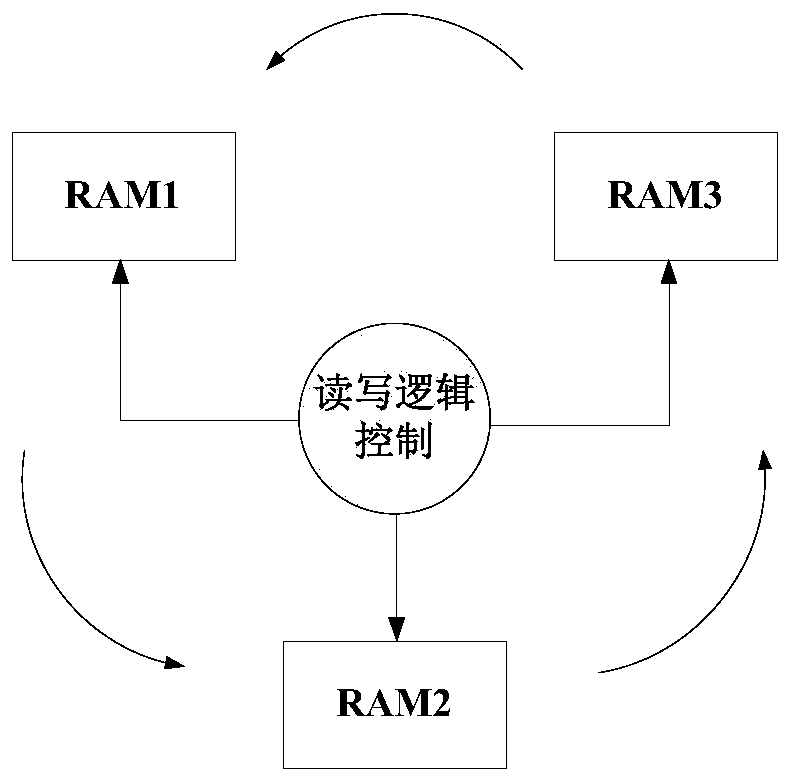

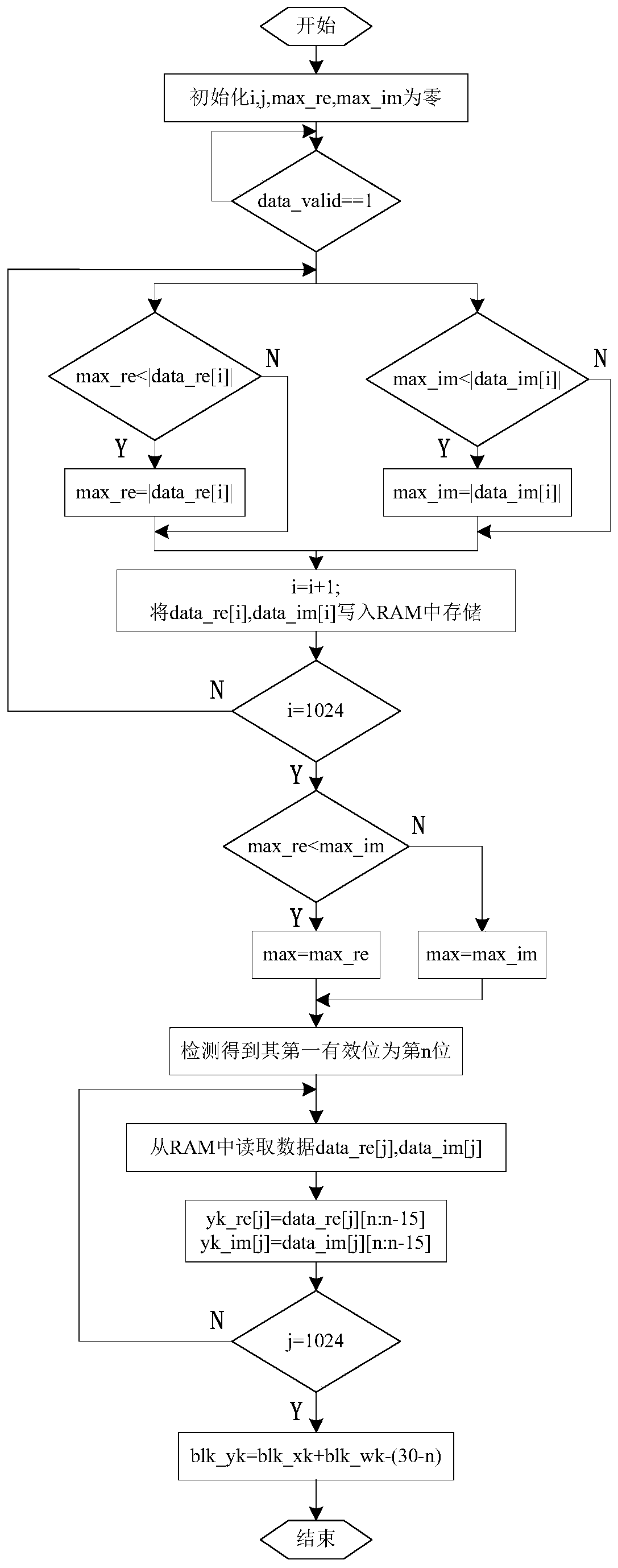

FPGA implementation device and method based on FBLMS algorithm of block floating points

ActiveCN111506294AGuaranteed accuracyHigh precisionDigital data processing detailsCAD circuit designModularityBlock floating-point

The invention belongs to the technical field of real-time adaptive signal processing, particularly relates to an FPGA implementation device and method of an FBLMS algorithm based on a block floating point, and aims to solve the problem that conflicts exist among performance, speed and resources when an existing FPGA device implements the FBLMS algorithm. The method comprises the following steps that an input cache transformation module performs block cache recombination on a reference signal, converts the reference signal into block floating points and then performs FFT transformation; a filtering module carries out filtering in a frequency domain and carries out dynamic bit cutting; an error calculation and output caching module performs block caching on the target signal, subtracts the filtered output after the target signal is converted into a block floating point, and converts the result into a fixed-point system to obtain a final cancellation result; and a weight adjustment calculation module and a weight update storage module obtain the adjustment amount of the weight and update the weight block by block. Aiming at a recursive structure of the FBLMS algorithm, a block floating point data format and a dynamic bit cutting method are adopted, so the data is ensured to have a large dynamic range and high precision, conflicts among performance, speed and resources are solved,and the reusability and expansibility are also improved through modular design.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI +1

Visual odometer implementation method based on ORB feature points and GMS matched filter

ActiveCN111882602AAchieve rotation invarianceImprove match qualityImage enhancementImage analysisPattern recognitionSingular value decomposition method

The invention discloses a visual odometer implementation method based on ORB feature points and a GMS matched filter. The visual odometer implementation method comprises the steps: employing an RGBD camera or a binocular camera for collecting video streams; for each frame of image, based on the current pose of the camera, obtaining feature points (including two-dimensional pixel coordinates, three-dimensional world coordinates and a brief descriptor of angular points corresponding to the feature points) in the image; matching the feature points between the current frame and the previous framein combination with a GMS matching filter; solving a PnP problem according to the matched feature points of the previous frame to obtain a camera pose of the current frame; simultaneously optimizing the camera pose and the three-dimensional world coordinates of the feature points of a plurality of nearest continuous frames by using a Bundle AdJustment; calculating a bag-of-word vector of the current frame by using a bag-of-word model, and judging whether the current frame needs to be stored as a key frame or whether loopback occurs or not; if loopback occurs, optimizing the related key framesby using fast loopback optimization. According to the method, under the condition of ensuring that the re-projection error of the camera is small enough, compared with a traditional singular value decomposition method, operation is simpler and more convenient, and real-time performance is ensured.

Owner:NANJING UNIV OF SCI & TECH +1

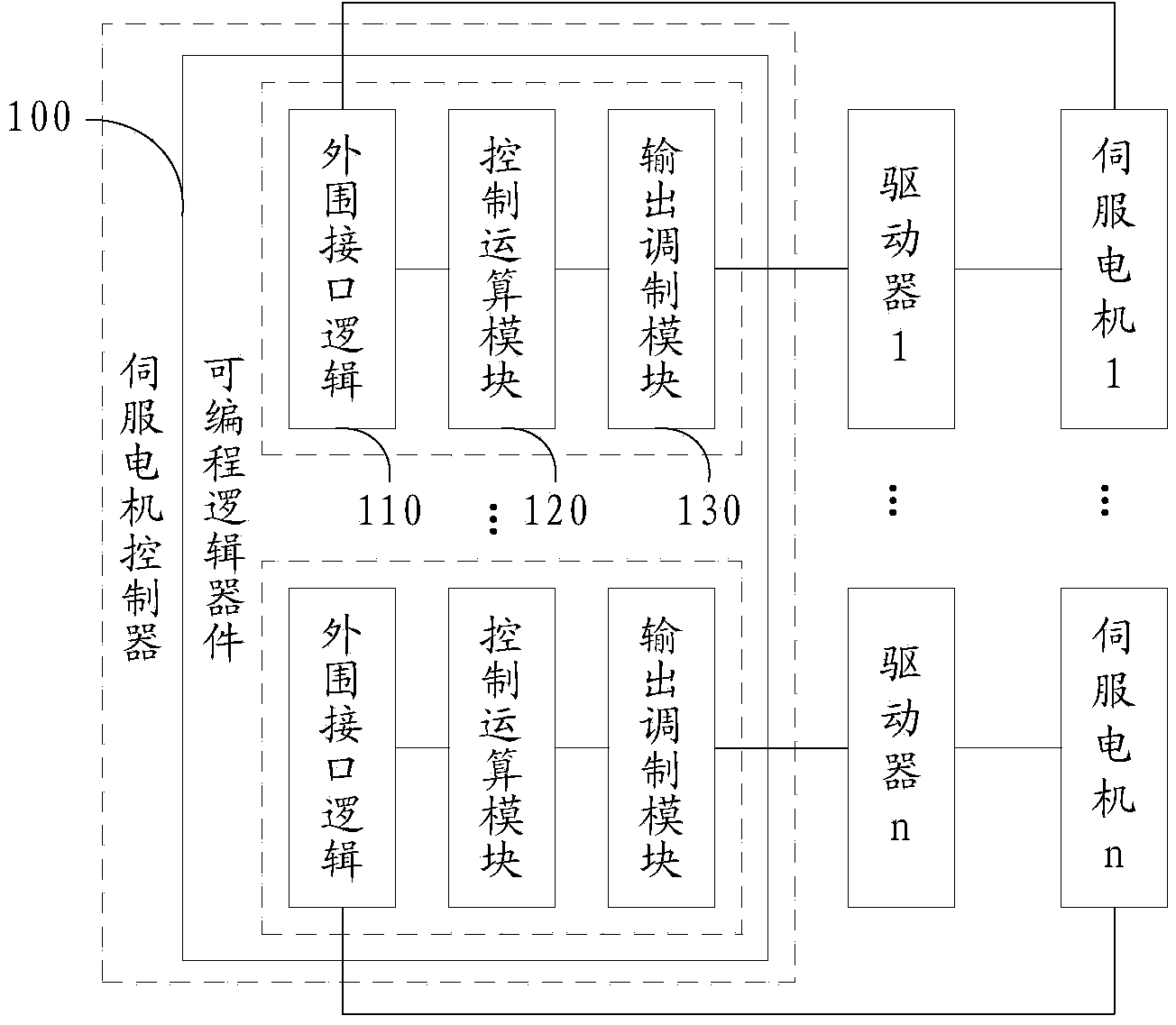

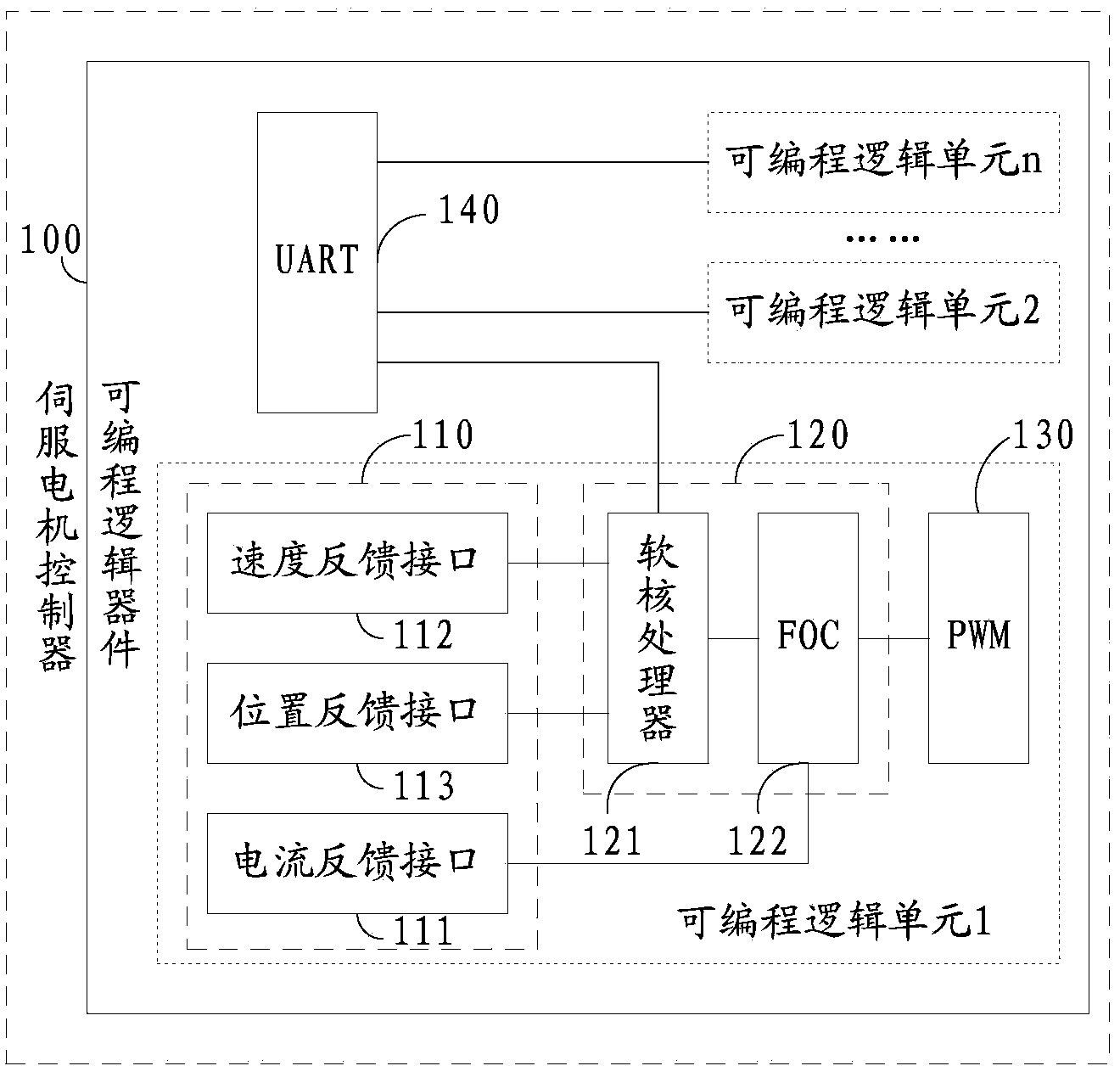

Controller and control method for servo motors

ActiveCN103441727AReduce the numberReduce weightElectronic commutation motor controlVector control systemsCoprocessorProgrammable logic device

The invention discloses a controller for servo motors, which is applied to a servo control system. The controller is characterized by comprising a programmable logic device, wherein the programmable logic device comprises peripheral interface-logic devices, output modulation modules and controlling operation modules, wherein the controlling operation modules are obtained through online programming. According to the controller, the control algorithm of servo motors is implemented by only using the programmable logic device without multiple hardware processors, so that the number of chips is reduced, the weight of a circuit board is reduced, the difficulty of circuit wiring is lowered, and the interface complexity between a main processor and a coprocessor is lowered, so that the cost of the controller is significantly reduced; meanwhile, controlled parameters of each servo motor are subjected to corresponding controlling operation through multiple controlling operation modules in the programmable logic device, so that the operation speed is ensured, and the response speed of a servo system is improved. Therefore, the controller and the control method disclosed by the invention solve the problems in the prior art.

Owner:BEIJING RUNKE GENERAL TECH

Echeloned torsion transmission and shock absorbing combined coupling

InactiveCN105041893AImprove extrusion strengthAvoid destructionSlip couplingFrequency changerGas compressor

The invention provides an echeloned torsion transmission and shock absorbing combined coupling which comprises an input end half-coupling, a sheath, an elastic sleeve group, a middle joint, a variable-rigidity membrane group and an output end half-coupling. A flange of the input end half-coupling is connected with the sheath through the elastic sleeve group to form an elastic torsion transmission and impact absorbing loop. Outer teeth of the tail end of the input end half-coupling are matched with inner teeth of the sheath to form a torsion transmission strengthening loop. The front end of the middle joint is connected with the sheath, and the rear end of the middle joint is connected with the output end half-coupling through the variable-rigidity membrane group. By means of the echeloned torsion transmission and shock absorbing combined coupling, high-frequency torsion vibration of a diesel engine set, a reciprocating compressor unit and a frequency changer set can be effectively eliminated, and the problem that because the torsion is enlarged, connection and transmission of units become difficult in work of a chemical raw material gas compressor unit, an ethylene granulating machine group and the like is solved; and an optimal scheme is provided for long-distance transmission of a frequency-conversion renovation unit.

Owner:沈阳申克动力机械有限公司

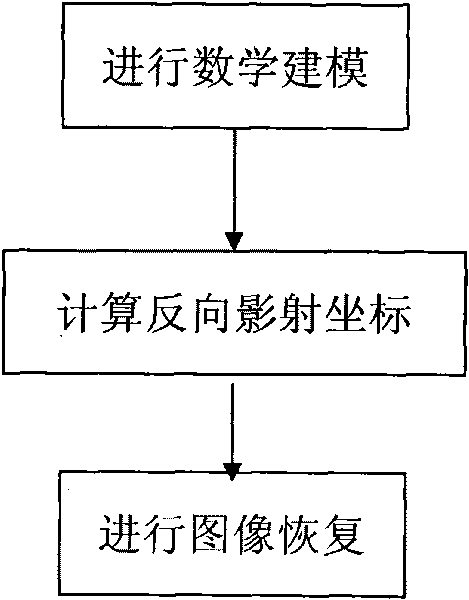

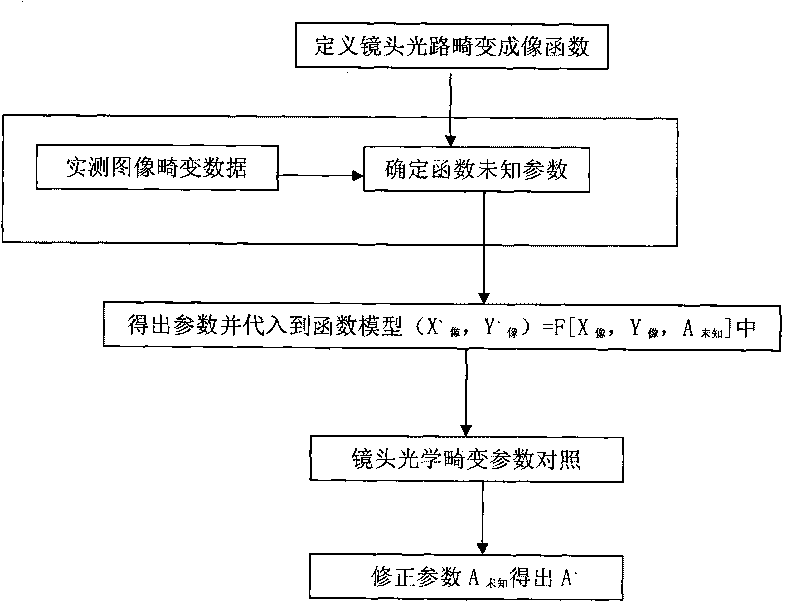

Method for rectifying deviation of image

InactiveCN101729739AImprove the correction speed and output effectOmit stepsImage enhancementPictoral communicationOptical pathDistortion

Owner:潘林岭 +2

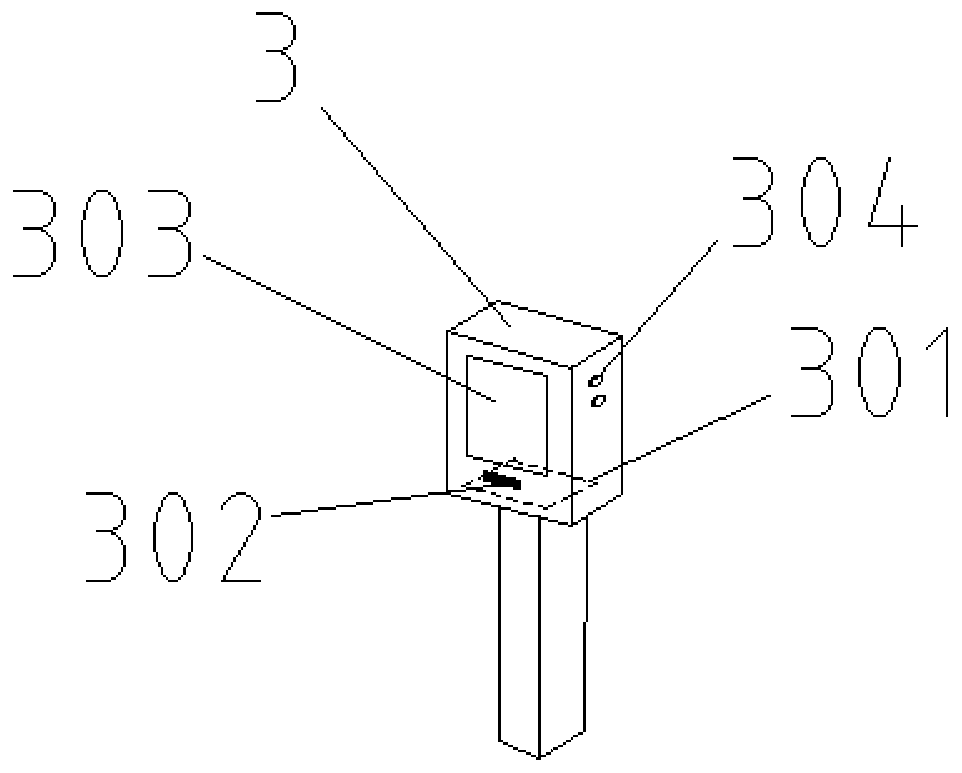

Barrier gate system of intelligent parking garage and barrier gate control method

PendingCN110685480AAvoid the hassle of reversingMeet strict screening requirementsUsing optical meansElectromagnetic wave reradiationAutomatic controlEmbedded system

The invention provides a barrier gate system of an intelligent parking garage and a barrier gate control method, and belongs to the technical field of measuring equipment. The system comprises a control case, a barrier gate case, a barrier gate railing and a car size measuring device. A driving device is arranged in the barrier gate case, and one end of the barrier gate railing is connected with the driving device. A control host is arranged in the control case, and a parking information display panel is arranged on the outer surface of the control case. The control method comprises the stepsthat whether a vehicle enters an area to be measured or not is judged; the size of the vehicle is measured and calculated according to left laser radar, right laser radar, rear laser radar and an automatic control element; and the measured vehicle size value and a parked vehicle size requirement of the intelligent parking garage are compared to determine whether the vehicle is permitted through ornot. The barrier gate system is combined with the measuring technology of the laser radar, the vehicle size testing result is more accurate through calculation correction, and the strict screening requirement of the intelligent parking garbage for the size of the vehicle is met.

Owner:广西云高智能停车设备有限公司

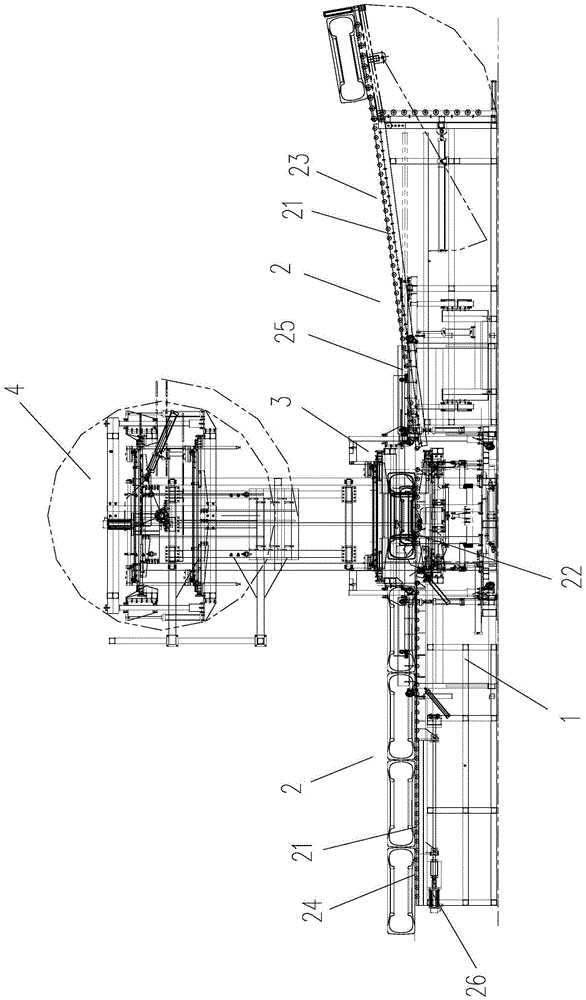

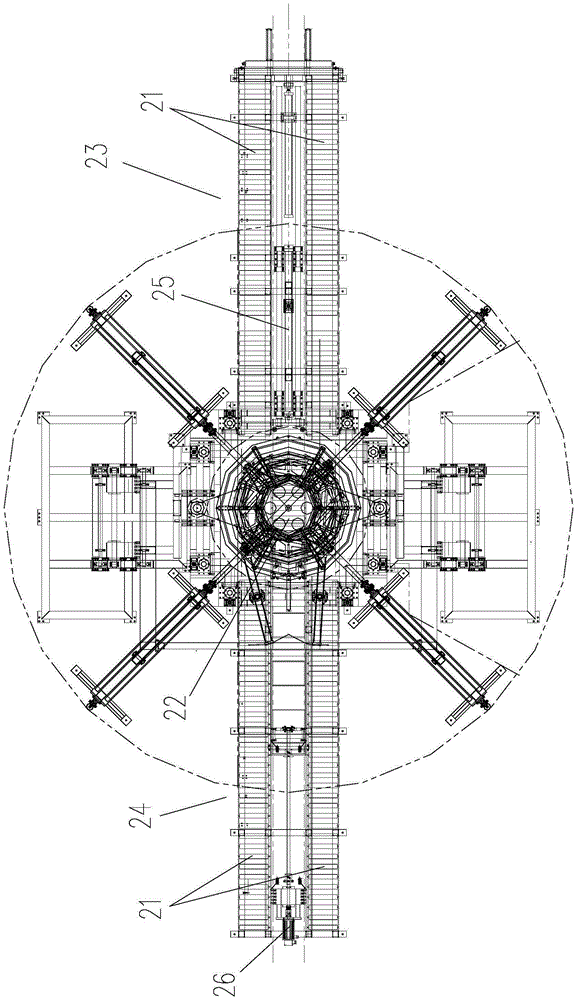

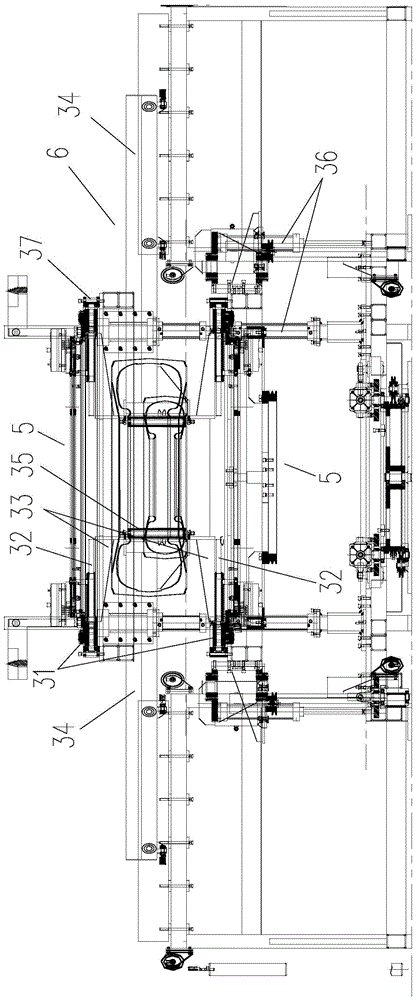

Tyre's inner tire mat belt installing machine

ActiveCN105196807ASimple structureReduce the probability of misfitsTyre repairingEngineeringFill device

A tyre's inner tire mat belt installing machine comprises a frame, on which a tyre conveying device, a tyre flaring device and tyre filling device. The tyre flaring device is positioned at the middle part of the tyre conveying device. The tyre filling device is positioned above the tyre flaring device. The tyre's inner tire mat belt installing machine has a relatively simple structure. Tyre flaring and filling of inner tire mat belts can be simultaneously carried out at only a station. Probability of matching errors between working procedures during the working process is reduced, occupation space of equipment is also saved. Accuracy requirement is low, and long-term stable and efficient operation can be realized.

Owner:青岛胜迈自动化科技有限公司

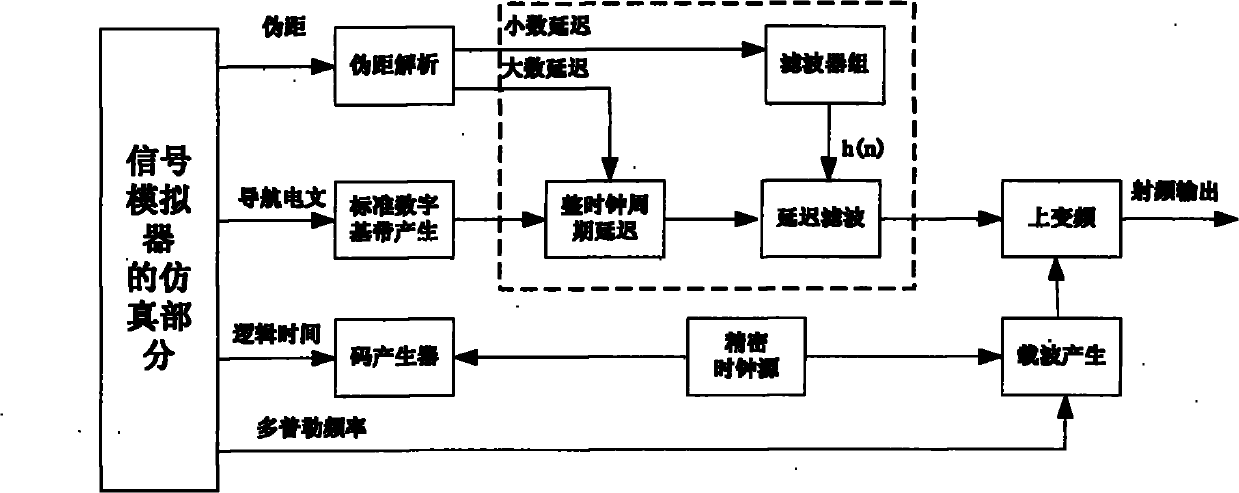

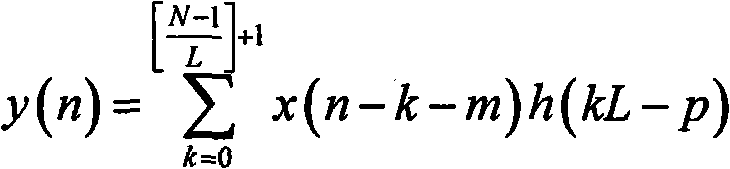

Precise delay implementation method for satellite navigation digital baseband signal

ActiveCN101907715AAvoid complex calculationsGuaranteed variation range of pseudorangeSatellite radio beaconingDigital signal processingAnti-aliasing

The invention relates to a precise delay implementation method for a satellite navigation digital baseband signal. In the method, a pseudo range is decomposed into great number delay and small number delay, wherein the great number delay is realized by the delay of a plurality of entire clock periods; and the small number delay is realized by digital delay processing. The digital delay processing comprises the processes of data interpolation, digital delay filtering and selection. A small number delay signal is subjected to reverse mirror image filtering after the data interpolation and is subjected to anti-aliasing filtering before the selection. Not only the variation range of the pseudo range but also the control accuracy can be ensured by using a great number implementation method and a small number implementation method respectively.

Owner:NAT UNIV OF DEFENSE TECH

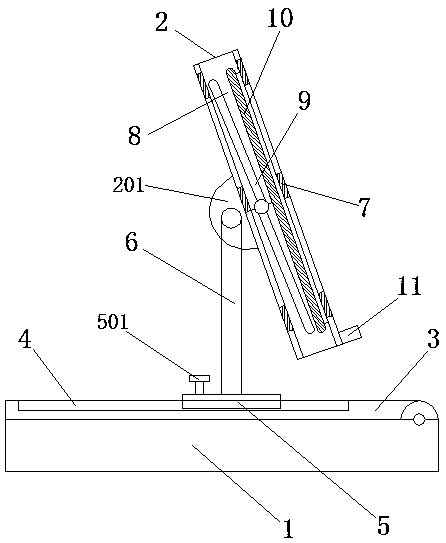

Adjustable mobile phone cooling holder

InactiveCN108200254AEffective regulationAdjustable mobile phone cooling is effectiveStands/trestlesModifications by conduction heat transferEngineeringMechanical engineering

The invention discloses an adjustable mobile phone cooling holder, comprising a base and a support plate set on the base. Two sides of the support plate comprise a support surface and a fixing surface. An adjustment plate is hinged with one end of the top of the base. A slide slot is set on the top of the adjustment plate along a length direction. A slide base is set in the slide slot in a slide mode. The top of the slide base is movably connected with the fixing surface of the support plate through a fixedly set support rod. A plurality of heat dissipation holes are uniformly set on the support surface and fixing surface of the support plate. A cooling cavity is set in the support plate. A cooling fan is set in the cooling cavity. According to the holder, multi-angle and multi-direction adjustment can be carried out for operation demands of a mobile phone, a high speed operation mobile phone can be cooled, and the service life of a mobile phone battery is prolonged.

Owner:郑州浩蓝智能科技有限公司

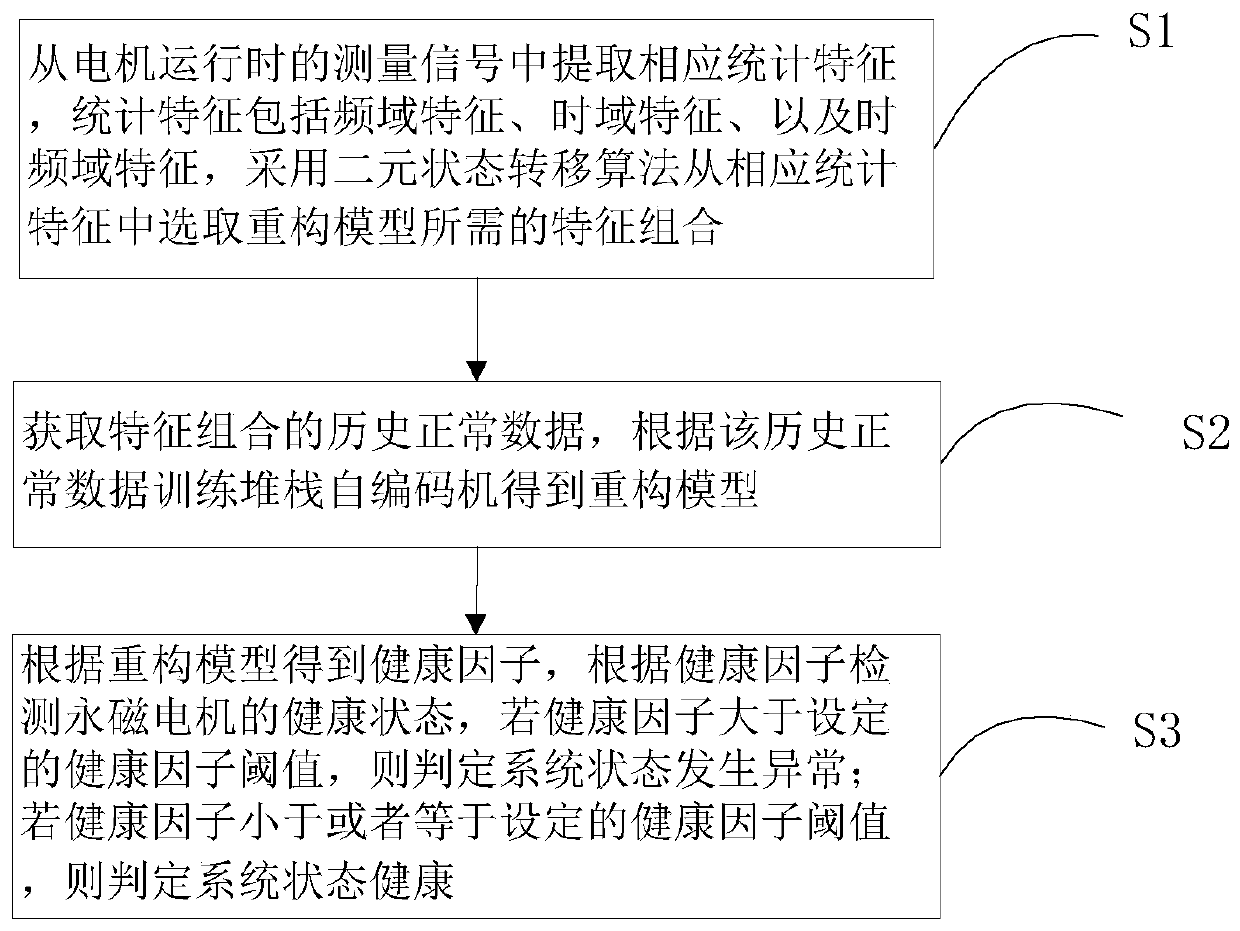

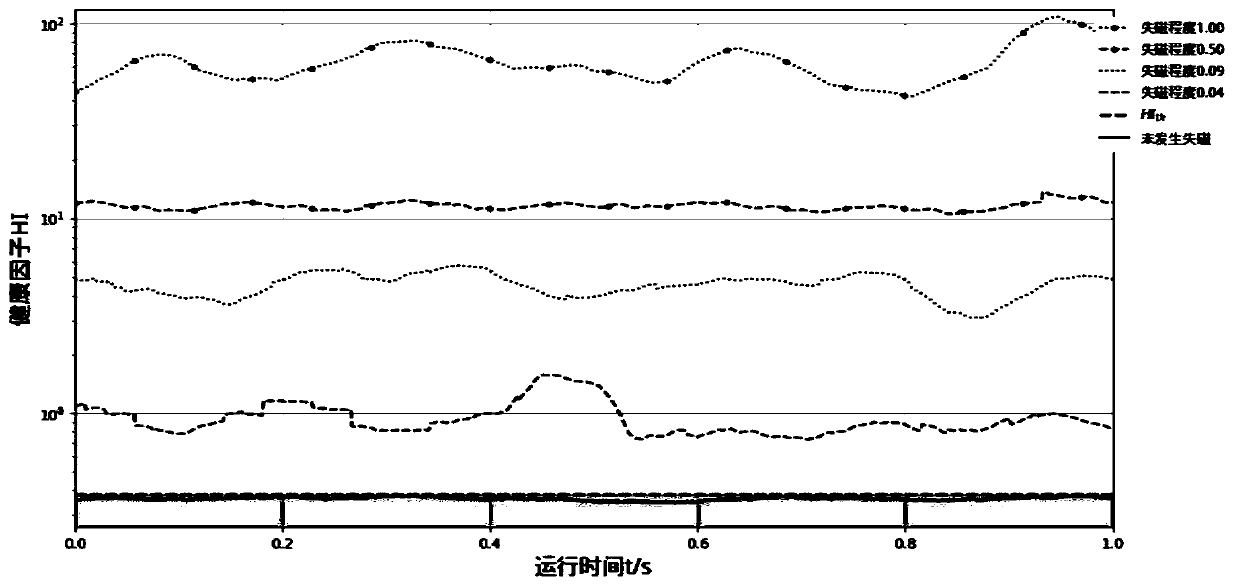

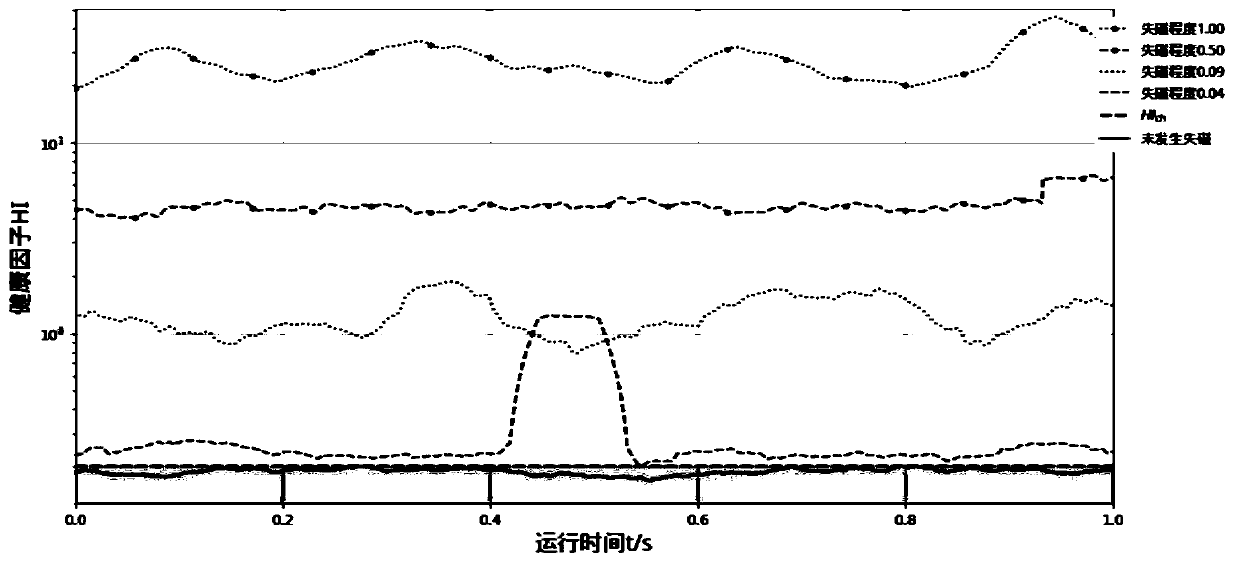

Method and system for detecting health state of permanent magnet motor

ActiveCN110187275AHigh precisionAccurate reconstructionDynamo-electric machine testingTime frequency domainPermanent magnet motor

The invention relates to the field of permanent magnet motor health monitoring, and discloses a method and a system for detecting a health state of a permanent magnet motor, so as to realize accuratedetection of a permanent magnet motor health state. The method disclosed by the invention comprises the steps of: extracting corresponding statistical features from a measurement signal during the operation of the motor, wherein the statistical features comprise a frequency domain feature, a time domain feature and a time-frequency domain feature, and selecting a feature combination necessary fora reconstruction model from the corresponding statistical features by using a binary state transition algorithm; and obtaining historical normal data of the feature combination, training a stacking self-encoding machine according to the historical normal data to obtain the reconstruction model, obtaining a health factor according to the reconstruction model, and detecting the health state of the permanent magnet motor by using the health factor.

Owner:CSR ZHUZHOU ELECTRIC LOCOMOTIVE RES INST

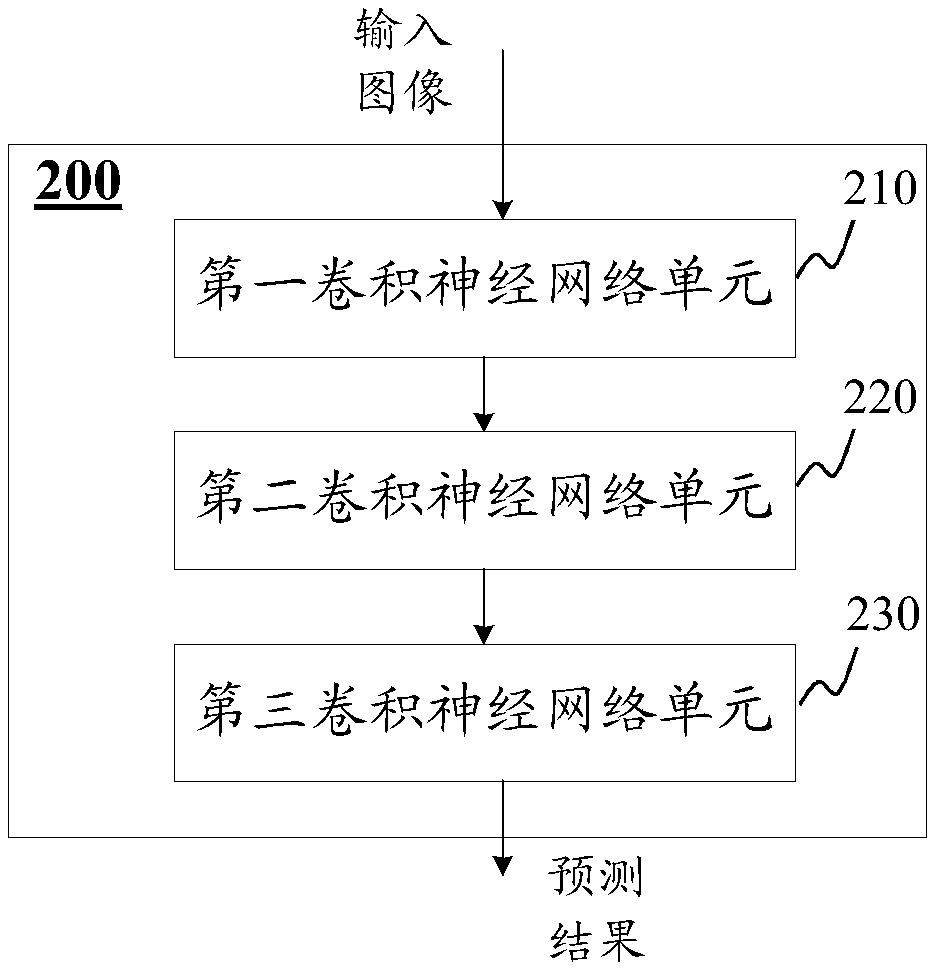

Target detection method and device, equipment and computer readable medium

PendingCN110163057AFast operationGuaranteed operation speedCharacter and pattern recognitionNeural architecturesConvolutionConvolutional neural network

The invention discloses a target detection method and device and equipment and a computer readable medium. The method comprises the following steps: extracting an input feature image from an input image by utilizing a first convolutional neural network, wherein the size of the input feature image is smaller than that of the input image; performing convolution processing on the input feature imageby using a second convolutional neural network; and utilizing a third convolutional neural network to predict the convolutional input feature image output by the second convolutional neural network, and determining the position of the region where the target is located according to the prediction result output by the third convolutional neural network.

Owner:TENCENT TECH (SHENZHEN) CO LTD

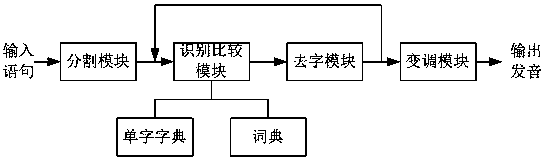

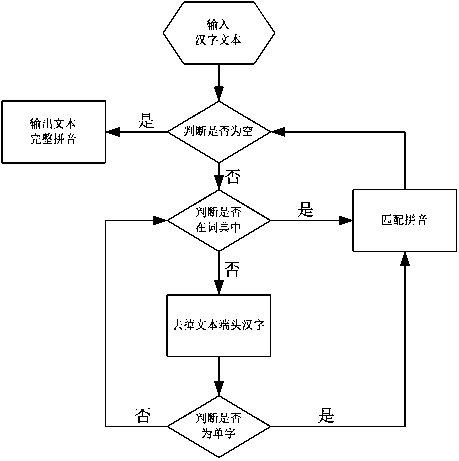

Chinese character pinyin conversion method and conversion system

PendingCN110083711AGuaranteed operation speedSolve the pronunciation problem of tone transpositionNatural language data processingSpecial data processing applicationsHabitConversion method

A Chinese character pinyin conversion system comprises a segmentation module, a recognition comparison module, a character removal module and a tone modification module which are sequentially connected. The recognition comparison module is connected with a single character dictionary and a dictionary database, the single character dictionary comprises each single character, and a unique corresponding pinyin default pronunciation is set for each single character. The words of the dictionary comprise more than two Chinese characters, and at least one of the Chinese characters is a word of a polyphone. The invention further discloses a Chinese character pinyin conversion method. By the adoption of the Chinese character pinyin conversion method and system, the single-character dictionary and the dictionary are designed respectively, word segmentation and pronunciation matching algorithms are combined, and under the condition that the operation speed is guaranteed. The problem of tone-changing pronunciation in most polyphone characters and pronunciation habits can be effectively solved. After tone modification calibration is adopted, the pronunciation is closer to the real pronunciationhabit.

Owner:成都启英泰伦科技有限公司

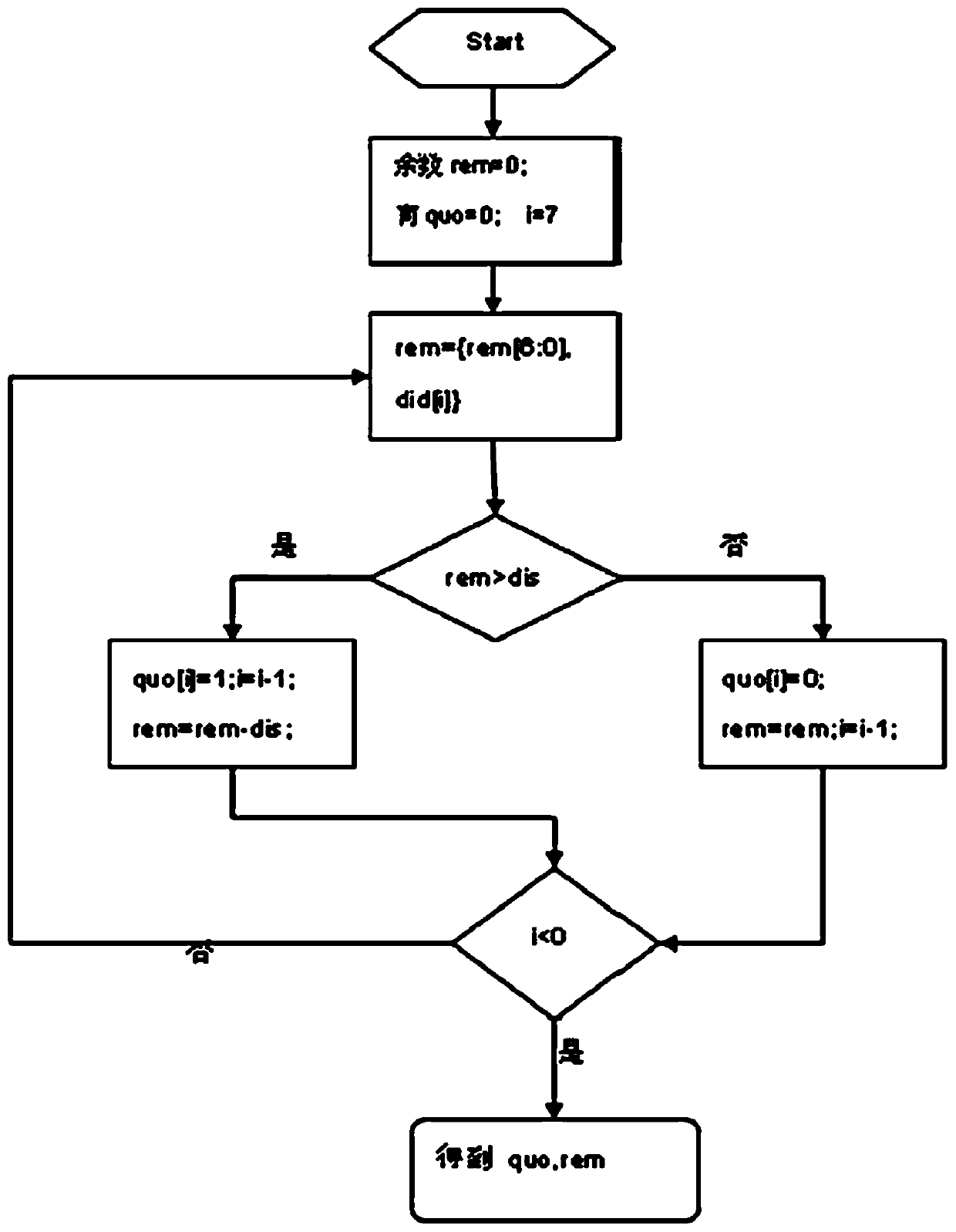

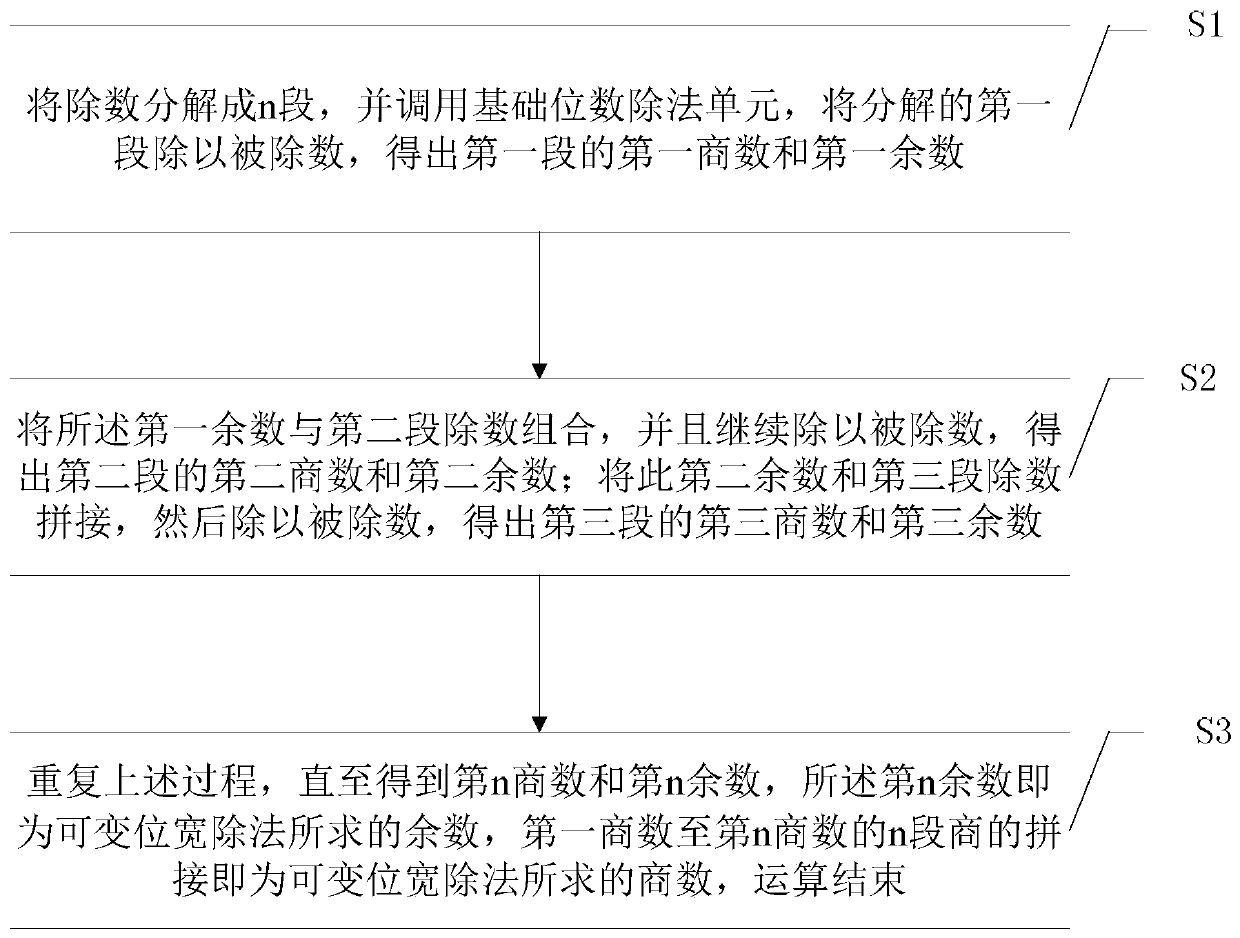

Method and device for achieving variable bit width division method through FPGA

InactiveCN109783053AHigh speedMake up for limitationsDigital data processing detailsFpga implementationsComputer science

Owner:EHIWAY MICROELECTRONIC SCI & TECH SUZHOU CO LTD

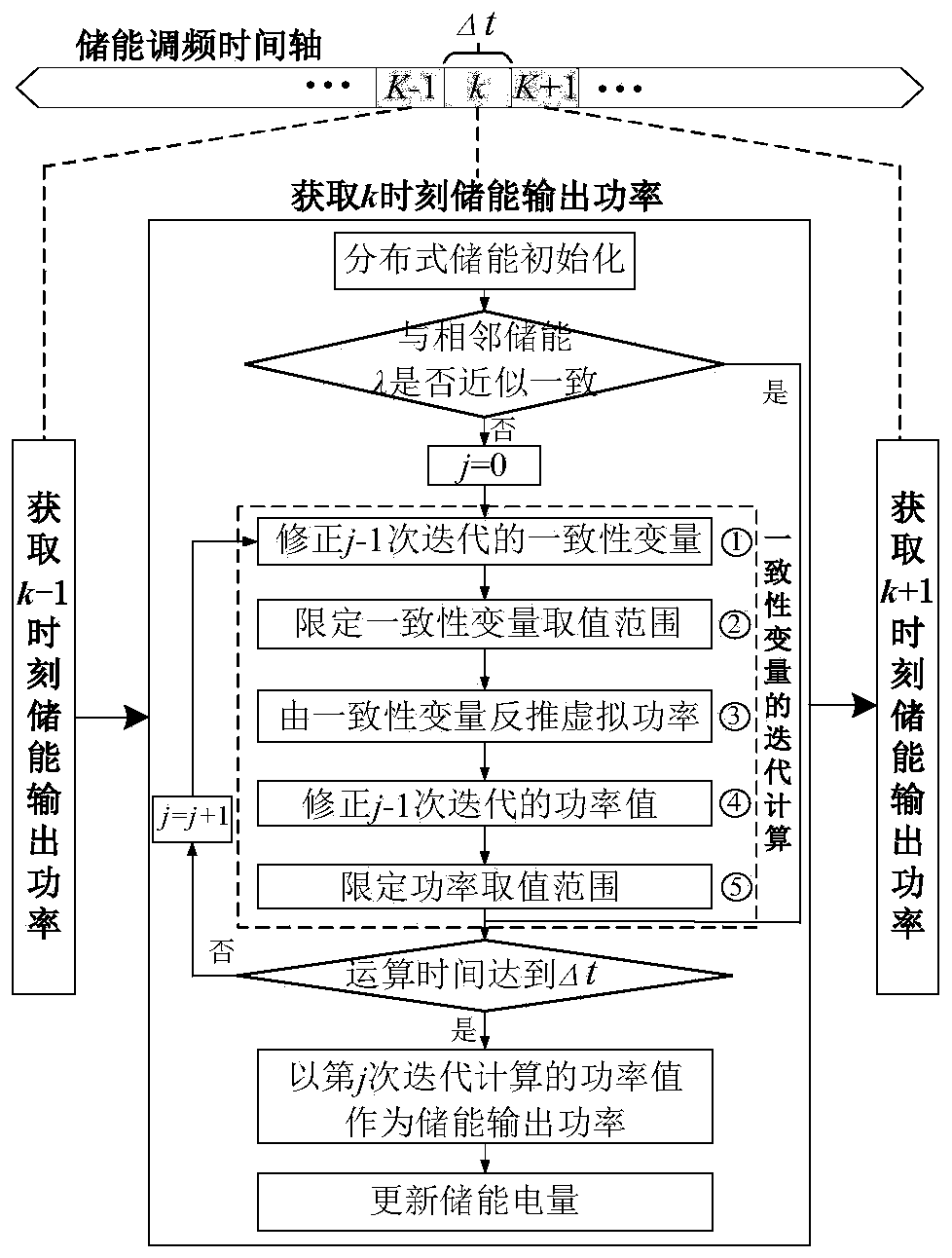

Distributed energy storage aggregator AGC method based on consistency algorithm

ActiveCN110137981AExtended service lifeLow costAc network load balancingPower oscillations reduction/preventionElectricityPower grid

The invention discloses a distributed energy storage aggregator AGC method based on a consistency algorithm and belongs to the technical field of power generation in which energy storage participatesin power grid frequency modulation. The method comprises a step of initially allocating an AGC signal through a filtering link, a step of allowing an aggregator to integrates distributed energy storage into a whole to participate in AGC, externally tracks a frequency modulation signal, and internally controlling the frequency modulation output of different technical features of the energy storage,a step of taking energy storage frequency modulation cost functions established according to energy storage technology characteristic parameters and real-time electricity as key indicators for distributing the output of each energy storage frequency, and a step of using a multi-agent consistency algorithm inside an aggregator and locally calculating the distributed energy storage by exchanging aconsistency variable with adjacent energy storage to obtain an optimized energy storage output plan. The method performs integrated control of small-scale and modular distributed energy storage of different types, so that distributed energy storage meets the minimum admission capacity requirement of an AGC market, the frequency modulation capability of a power grid is effectively improved, the rapid response advantage of the energy storage is exerted, and the service life of the energy storage is extended at the same time.

Owner:SOUTHEAST UNIV

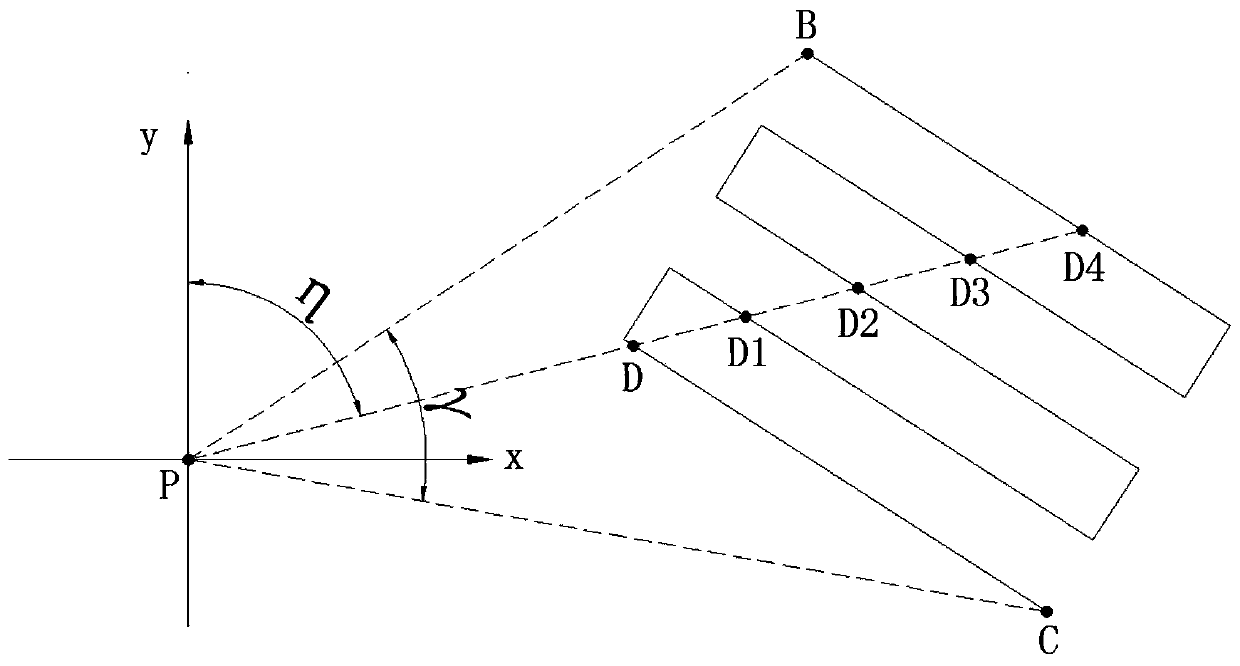

Safe return route planning method for unmanned aerial vehicle

PendingCN110864682AAvoiding the risk of a crashSolve the problem of crashingNavigation instrumentsInternal combustion piston enginesAutomotive engineeringRoute planning

The invention discloses a safe return route planning method for an unmanned aerial vehicle. The method comprises the following steps of establishing a rectangular coordinate system, determining a course azimuth angle, searching an elevation digital map in an azimuth angle range, storing marks and corresponding angle values by the unmanned aerial vehicle, and automatically planning a safety path bya lost unmanned aerial vehicle. The invention discloses a safe return route planning method for the unmanned aerial vehicle. Before the unmanned aerial vehicle takes off, an elevation lookup table ismade through a ground PC end according to corresponding parameters and transmitted to the unmanned aerial vehicle to be stored, a safe path can be selected as a return route through calculation afterthe unmanned aerial vehicle is out of contact, and the problem that the unmanned aerial vehicle crashes due to the fact that the ground elevation cannot be determined by the unmanned aerial vehicle is solved; meanwhile, the problem that the unmanned aerial vehicle cannot store a large-area elevation digital map is also solved.

Owner:CHENGDU JOUAV AUTOMATION TECH

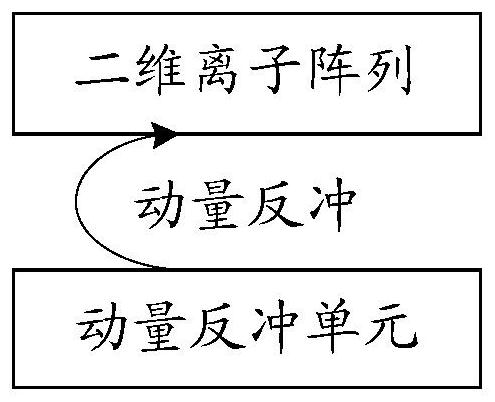

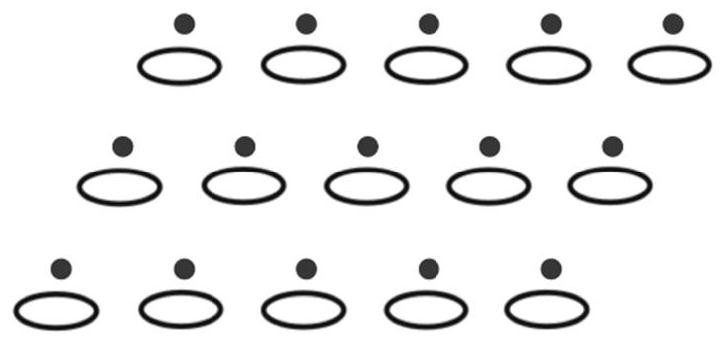

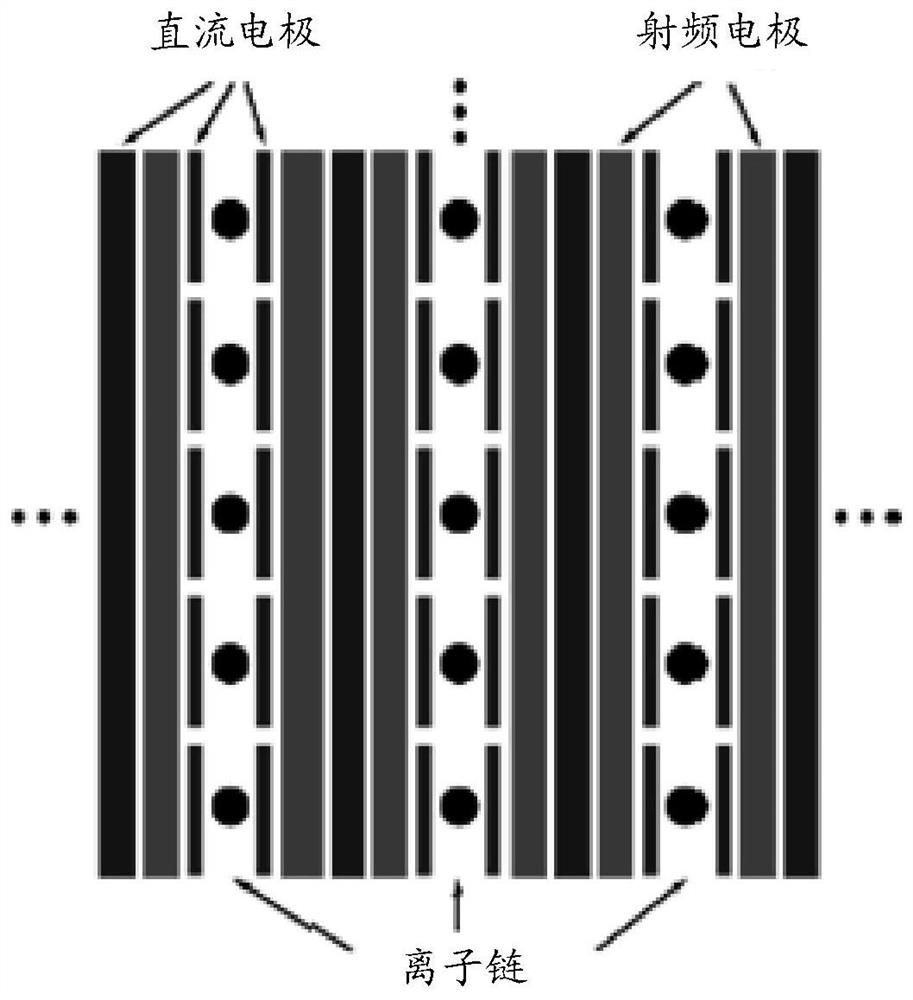

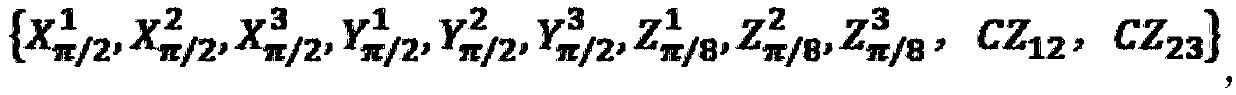

Quantum bit logic gate

The embodiment of the invention discloses a quantum bit logic gate, which is based on a two-dimensional ion array in which each ion is constrained by a preset simple harmonic potential in a selected direction, and realizes a double-quantum bit logic gate by enabling momentum recoil to act on any two adjacent ions in the two-dimensional ion array. The quantum bit logic gate realized based on the two-dimensional ion array is not limited in ion number; and the operation speed of the double-quantum bit logic gate is ensured through momentum recoil.

Owner:TSINGHUA UNIV

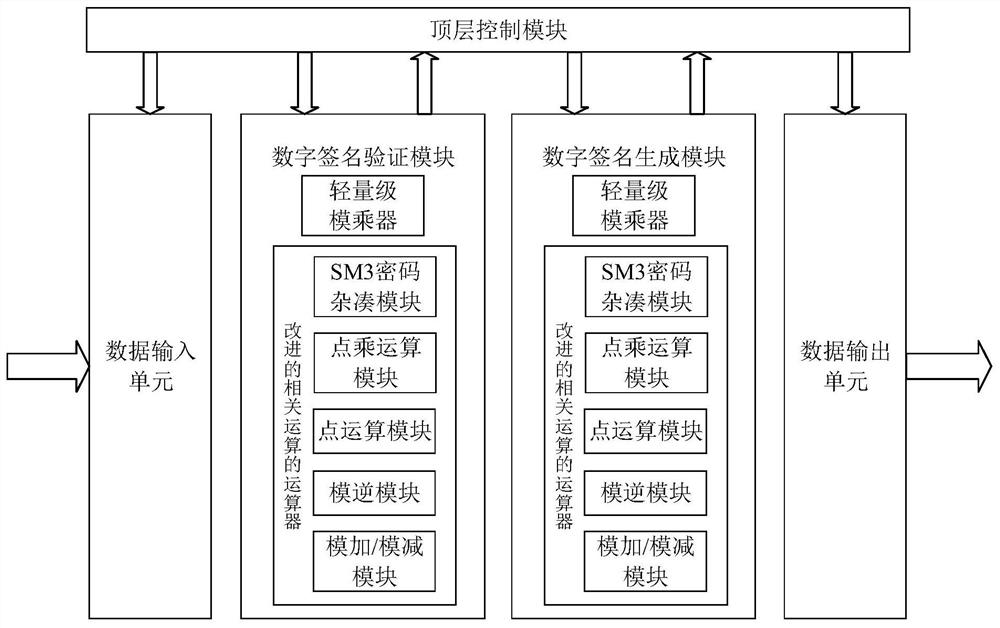

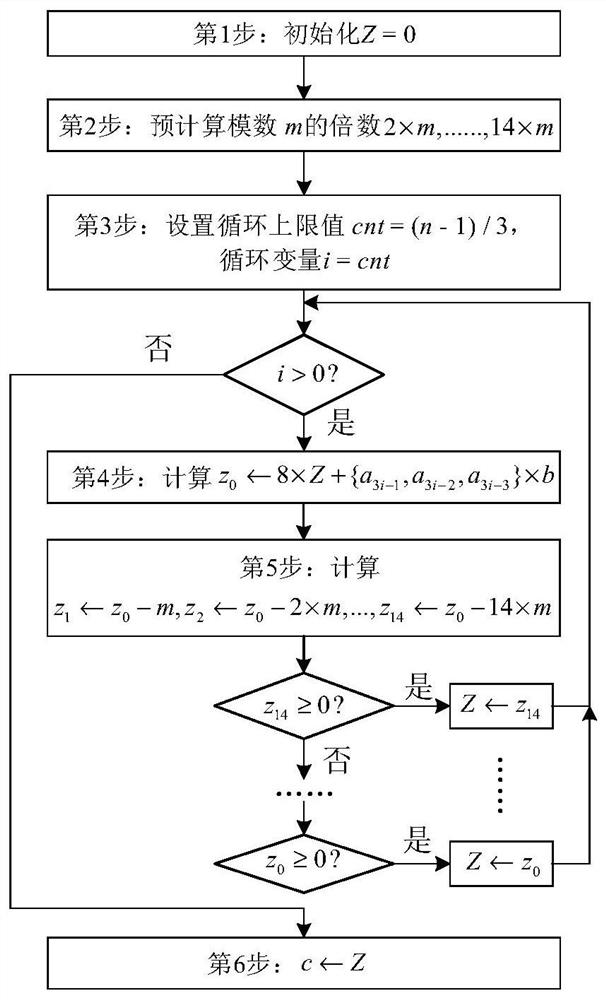

SM2 digital signature generation and verification device based on lightweight modular multiplication

ActiveCN113193962AReduce space complexityReduce resource areaUser identity/authority verificationHigh level techniquesParallel computingDigital Signature Algorithm

The invention provides an SM2 digital signature generation and verification device based on lightweight modular multiplication. The device at least comprises a top layer control module, a data input unit, a data output unit, a lightweight modular multiplier, an SM2 digital signature generation module, an SM2 digital signature verification module and a set of improved arithmetic units for correlation operation. According to the method, a complex modular multiplication algorithm is simplified into common addition, subtraction and shifting operations by utilizing the idea of simultaneous multiplication and modular multiplication of the staggered modular multiplication algorithm, so that the resource area is consumed as little as possible while the modular multiplication speed is increased, and the efficiency of an upper-layer algorithm is further influenced; and a quicker way is provided for the finally constructed SM2 digital signature algorithm of the application layer.

Owner:ANHUI NORMAL UNIV

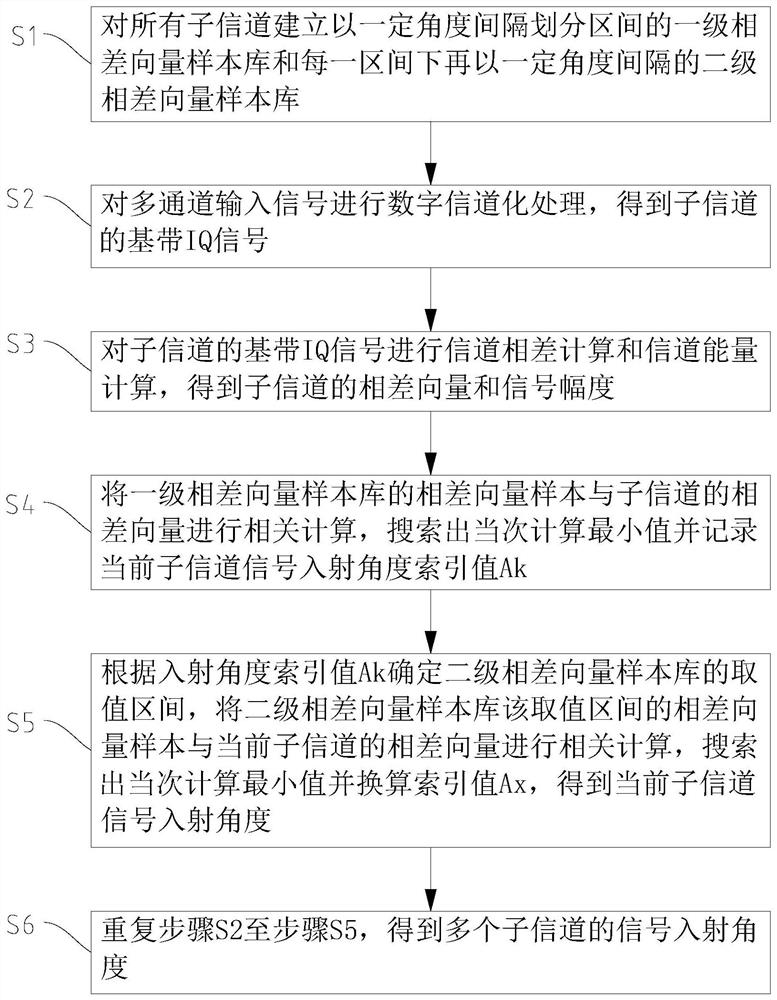

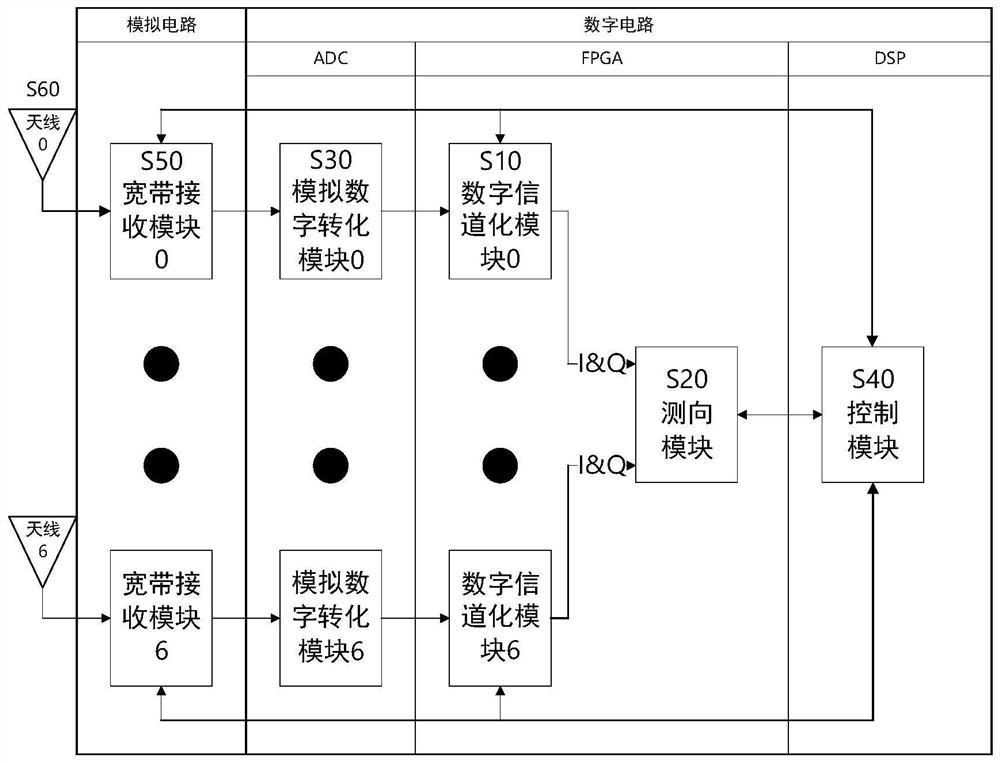

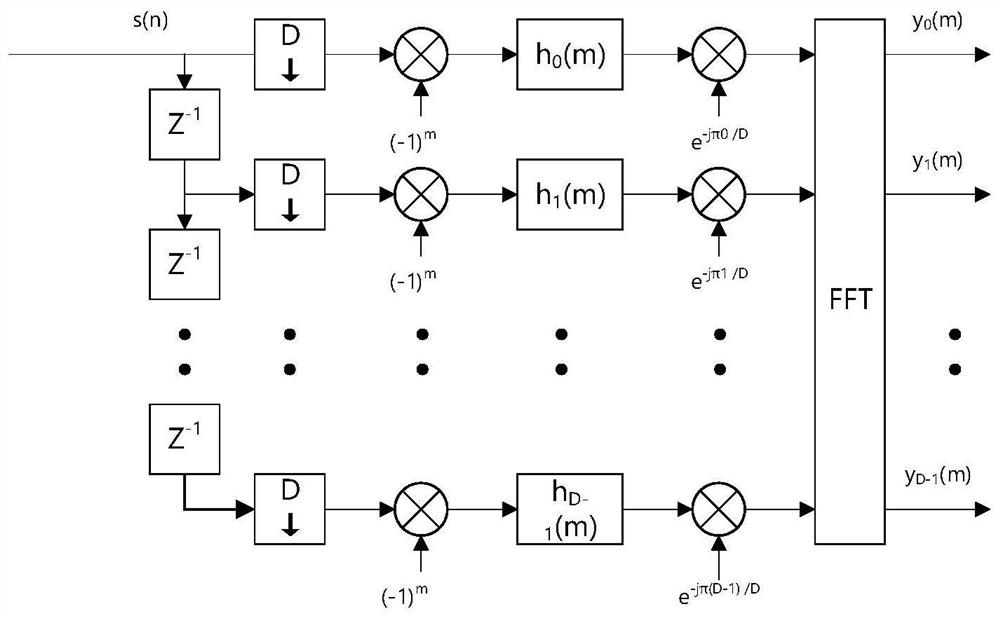

Correlation interferometer real-time direction finding method based on channelization processing

PendingCN113376570ASave resourcesSmall amount of calculationRadio wave direction/deviation determination systemsChannelizedBroadbanding

The invention provides a correlation interferometer real-time direction finding method based on channelization processing. The correlation interferometer real-time direction finding method comprises the following steps: establishing a first-level phase difference vector sample library with intervals divided at certain angle intervals and a second-level phase difference vector sample library with certain angle intervals in each interval for all sub-channels; performing digital channelization processing on the multi-channel input signal; performing channel phase difference calculation and channel energy calculation; carrying out correlation calculation, searching a minimum value calculated at the time, and recording an incident angle index value of a current sub-channel signal; and determining a value interval of the secondary phase difference vector sample library, performing correlation calculation on a phase difference vector sample in the value interval of the secondary phase difference vector sample library and a phase difference vector of the current sub-channel, searching a minimum value calculated at the time, and converting the minimum value into an index value to obtain a signal incident angle. According to the invention, the two-stage operation strategy is adopted to carry out correlation calculation and the large-scale parallel pipeline is adopted to accelerate the operation speed, so that the real-time direction finding of short-time burst signals in a broadband frequency band is realized.

Owner:嘉兴军创电子科技有限公司

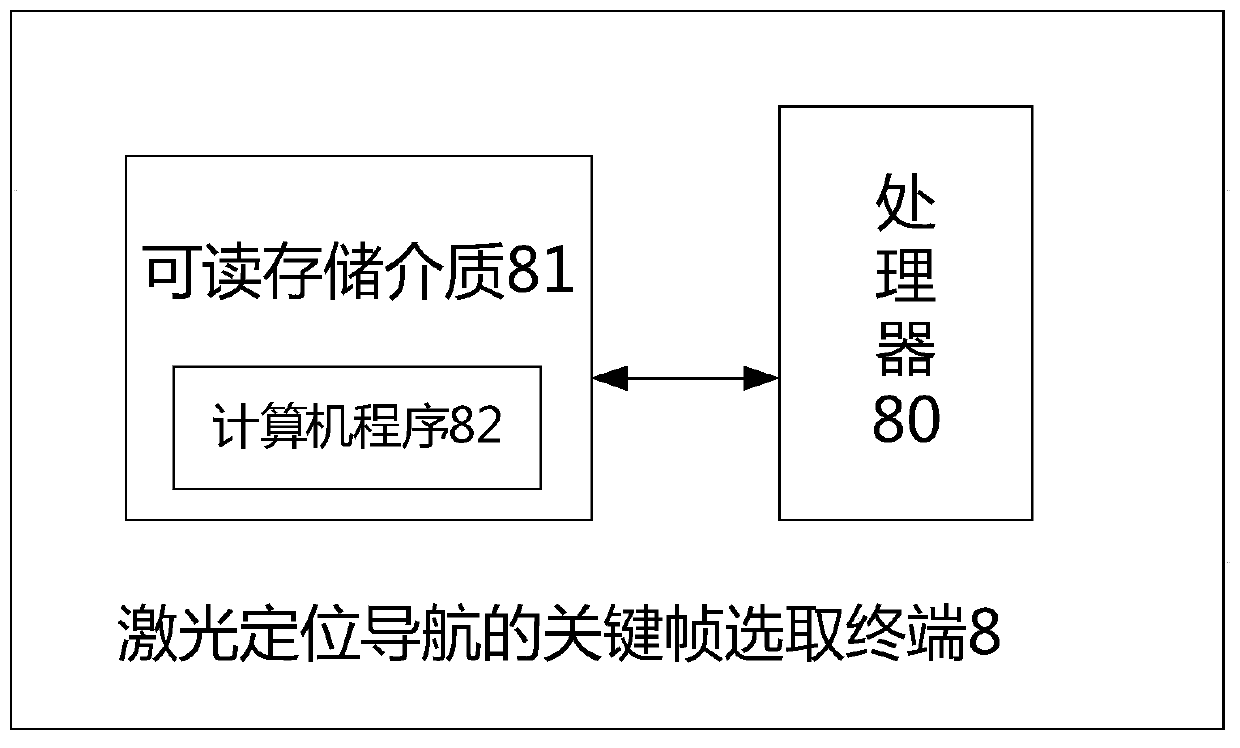

Laser positioning navigation key frame selection method, medium, terminal and device

ActiveCN110887490AImprove efficiencyImprove effectivenessNavigational calculation instrumentsHigh level techniquesEngineeringComputer vision

The invention discloses a laser positioning navigation key frame selection method, a medium, a terminal and a device. The accurate position of the robot is estimated in the mapping process; rasterizing laser, calculating the sum of front and back variations of all cell entropies accessed by the laser beams and the map entropy change caused by the current laser rasterization is obtained; and whether the current laser is the key frame or not is determined according to the variation of the map entropy so that the effectiveness of key frame laser selection is improved under the condition of ensuring the operation speed, the redundancy of map feature information is not liable to generate, the efficiency of laser SLAM is improved and the method has important significance in practical application.

Owner:SHANGHAI YOGO ROBOTICS CO LTD

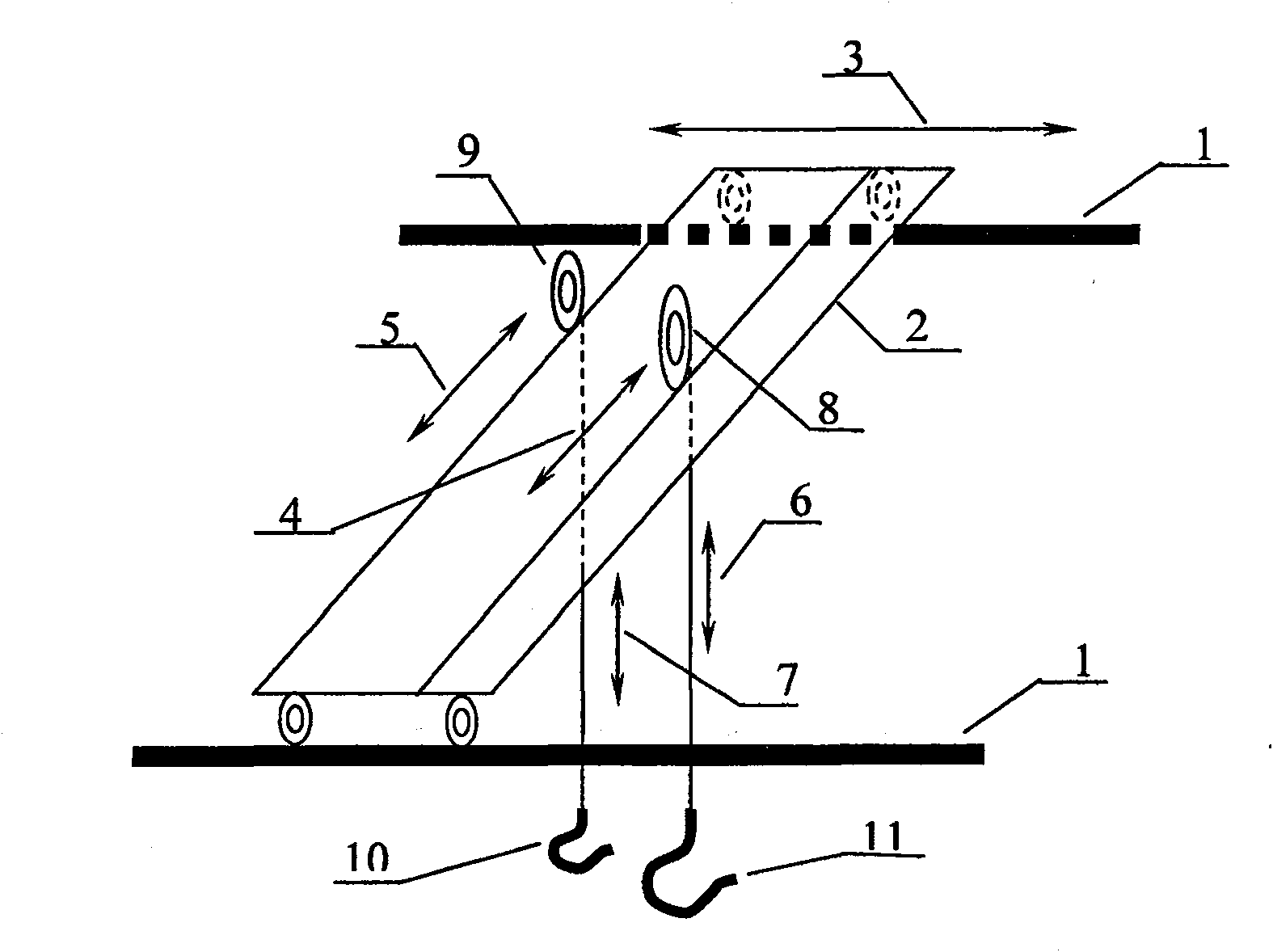

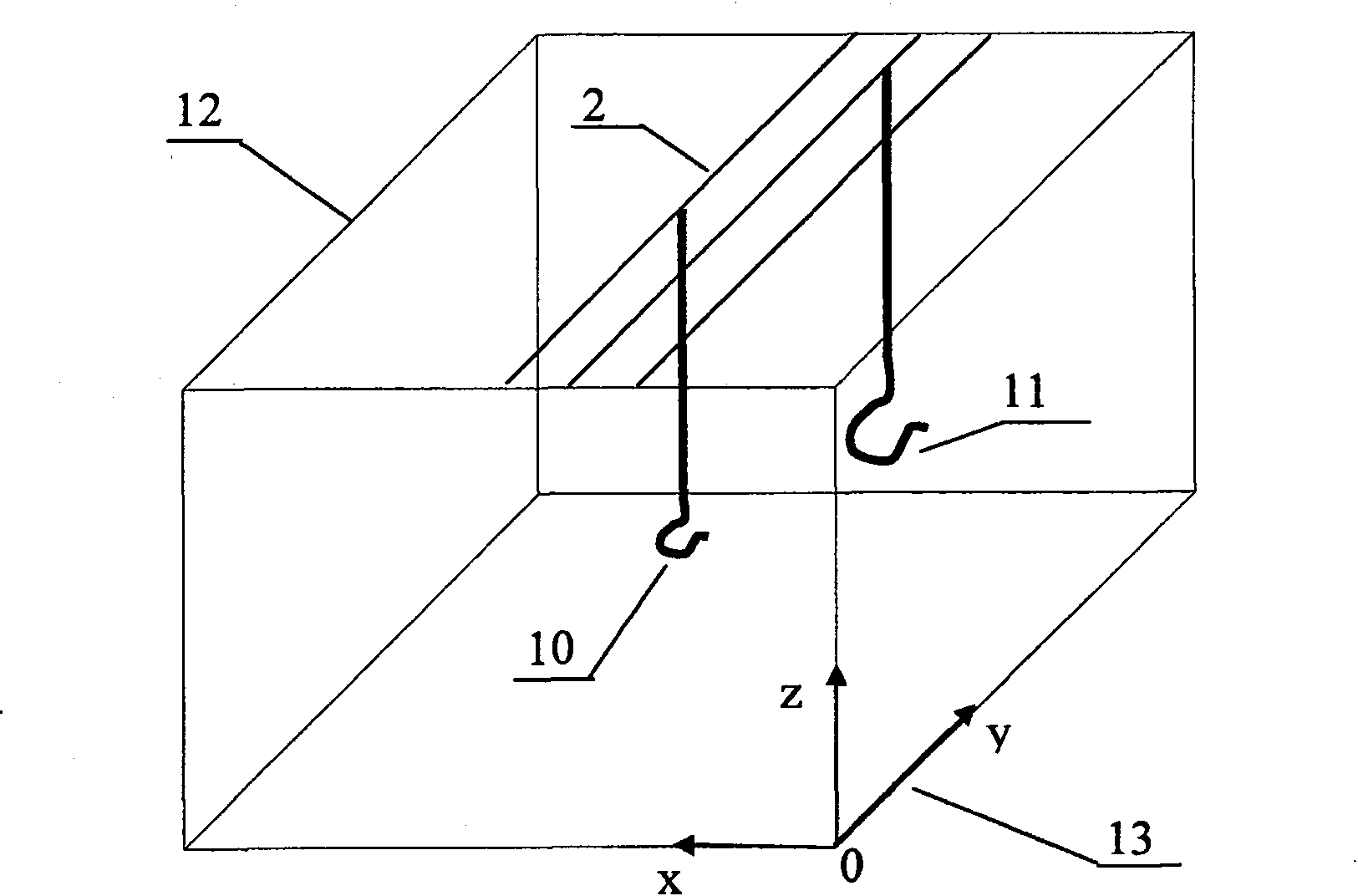

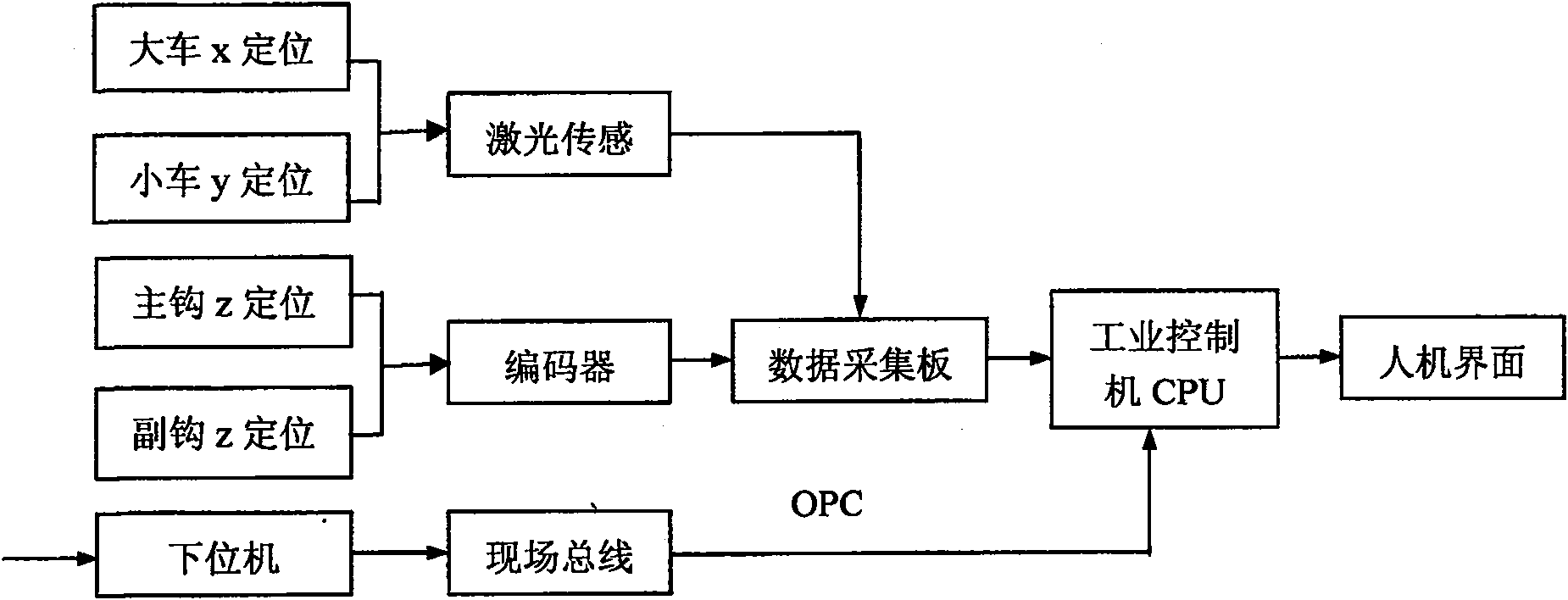

Traveling crane positioning system and positioning method

InactiveCN100567130CAccurately run reference dataIntuitive surface informationLoad-engaging elementsVisual BasicData acquisition

A crane positioning system and positioning method. The invention adopts the industrial control computer as the core, organically integrates the industrial control computer, the data acquisition card, the lower computer PLC and the sensor, and fully exerts their respective advantages. On the basis of not affecting the design and control scheme of the original crane, the system uses high-precision laser sensors and encoders to measure the distances of the crane in the three directions of x, y, and z, and sends them to the industrial control through different types of data acquisition cards. In the computer CPU, at the same time, OPC technology is used to read the running status of the crane from the lower computer PLC to the upper computer-industrial control computer in real time through the field bus, and then use Visual Basic and other advanced languages to write data processing and interface in the industrial control computer. The display program achieves the purpose of displaying the running position and status of the crane in real time, thereby providing the crane operator with accurate data on the operation of the crane, and at the same time providing a solid research foundation for the realization of high-precision unmanned driving of the crane.

Owner:TIANJIN UNIVERSITY OF TECHNOLOGY

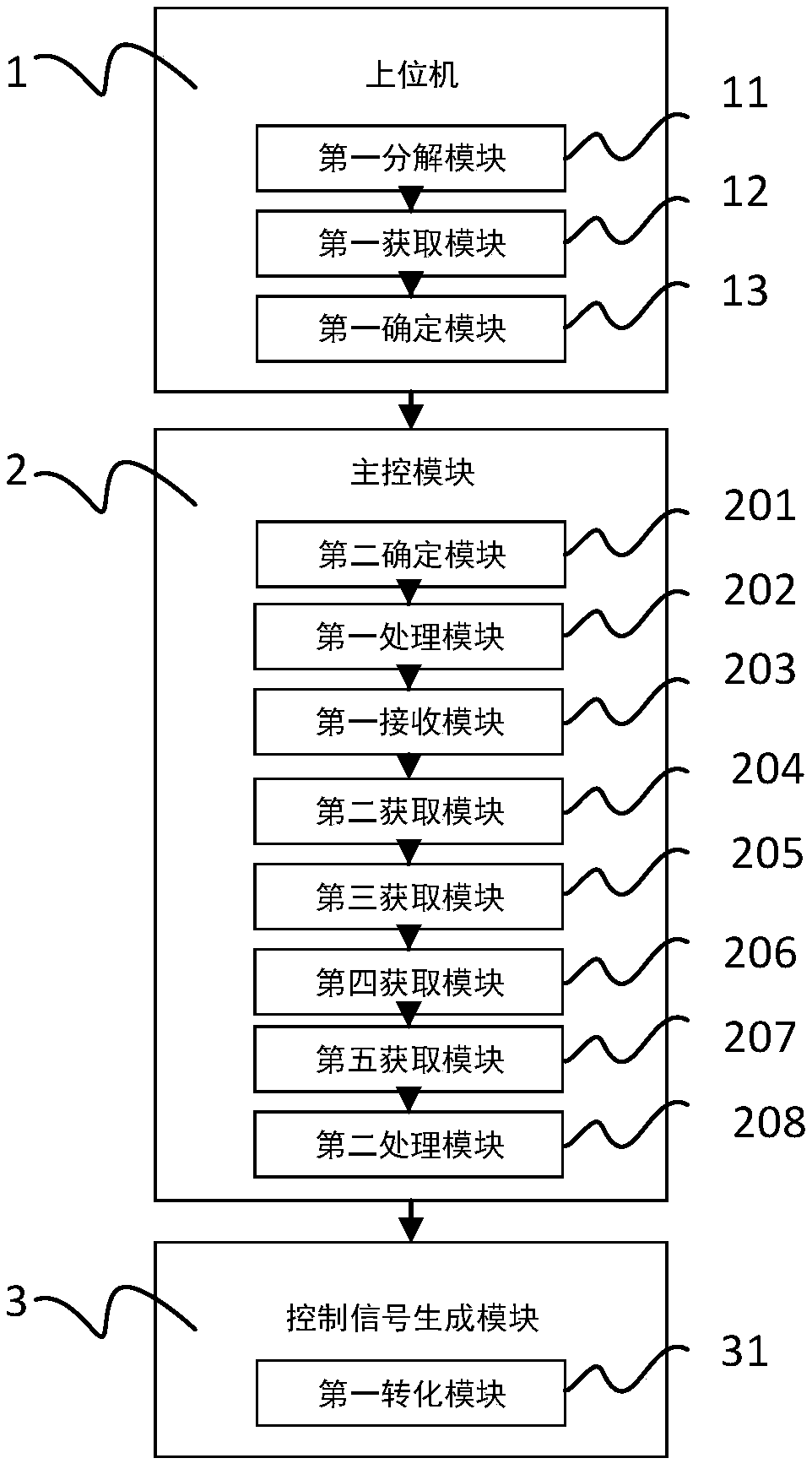

Quantum bit control signal generation system

ActiveCN109615079AQuick responseReduce capacity storage requirementsQuantum computersControl signalComputer engineering

The invention relates to the technical field of signal generation, and particularly discloses a quantum bit control signal generation system. A target label code and a target time code are issued through an upper computer through a main control module; the control signal generation module is controlled to generate a quantum bit control signal; the control signal corresponding to the quantum logicgate is pre-stored in the main control module in the form of the first standard signal; a to-be-processed signal is generated by adopting a target tag code and a form of storing a first address code corresponding to the first standard signal in the main control module; the capacity storage requirement on the main control module is greatly reduced from the source; according to the quantum bit control method and the quantum bit control device, the quantum bit control signal can be rapidly provided, the response speed of the control signal generation module is greatly improved, and the speed of post-stage quantum operation is ensured.

Owner:ORIGIN QUANTUM COMPUTING TECH (HEFEI) CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com