Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

201results about "Phase shifter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

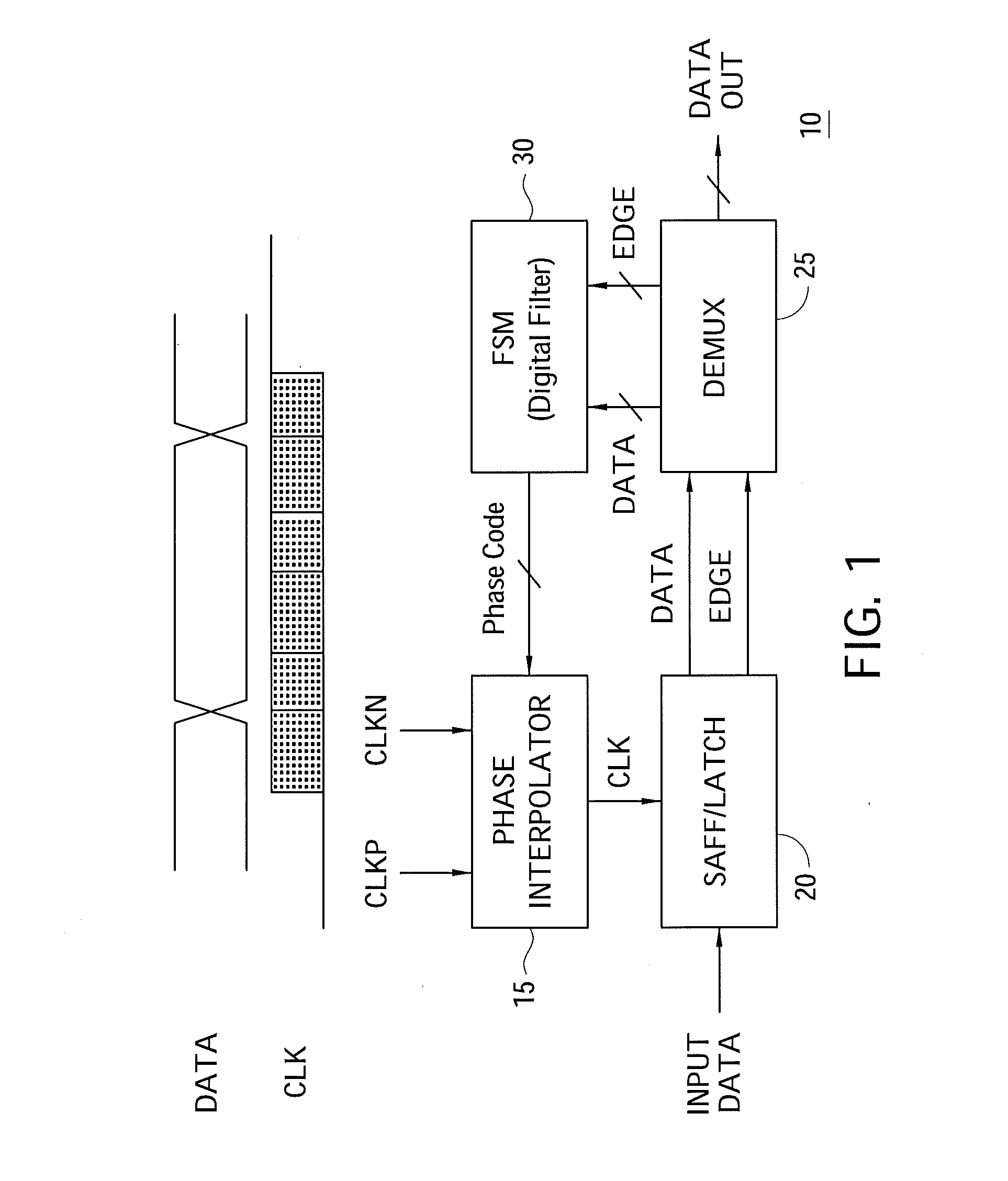

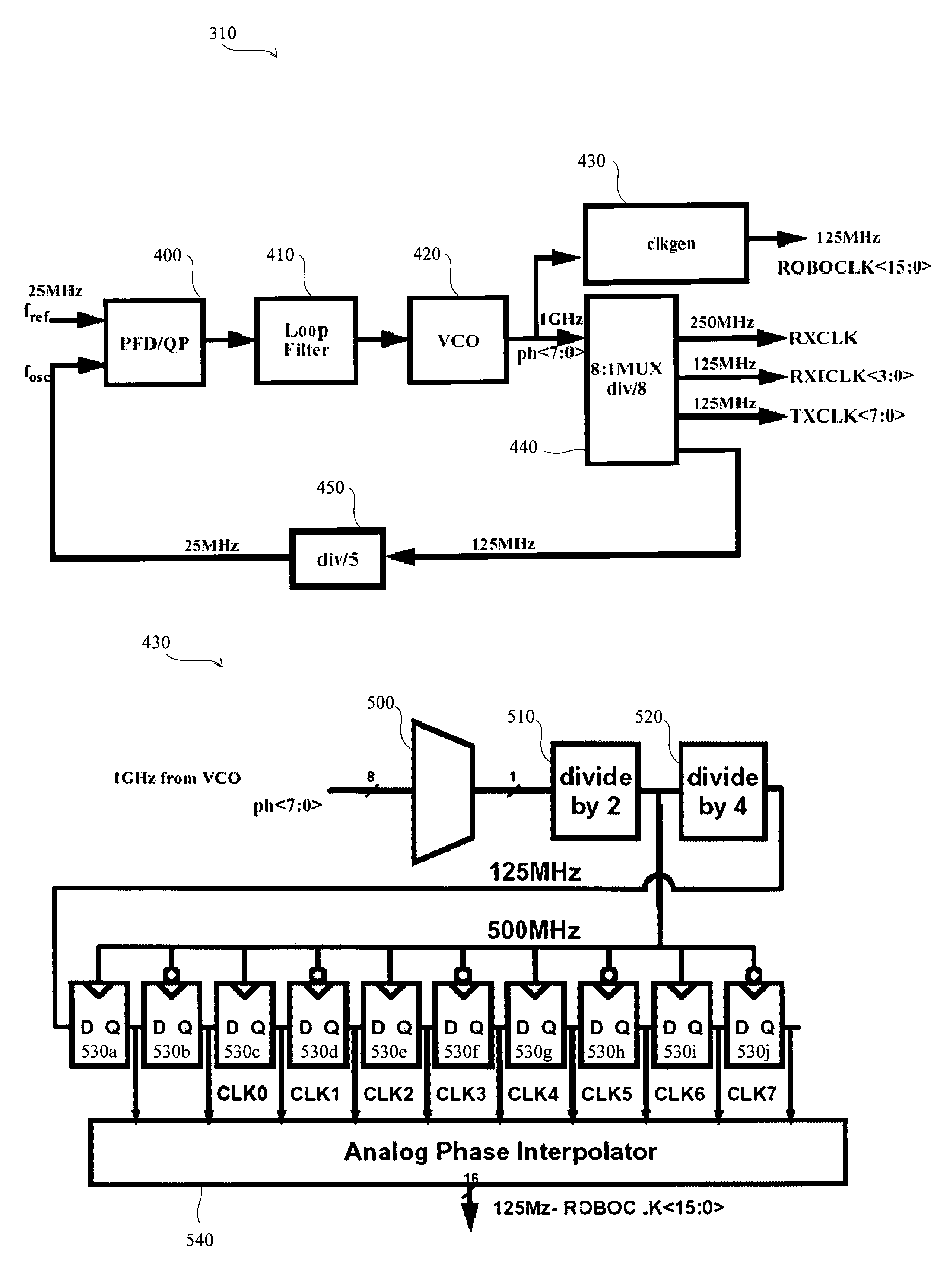

Phase interpolator to interpolate between a plurality of clock phases

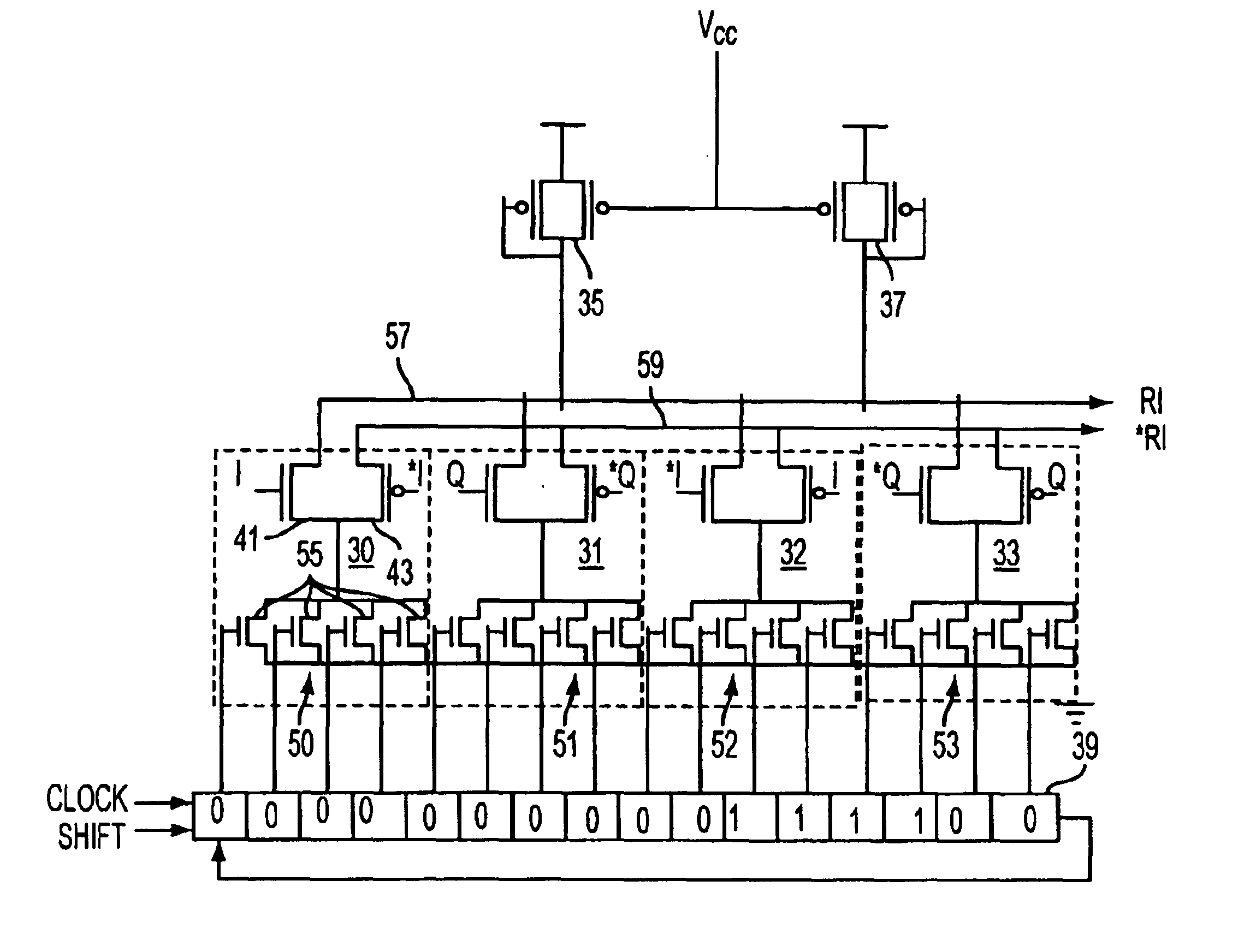

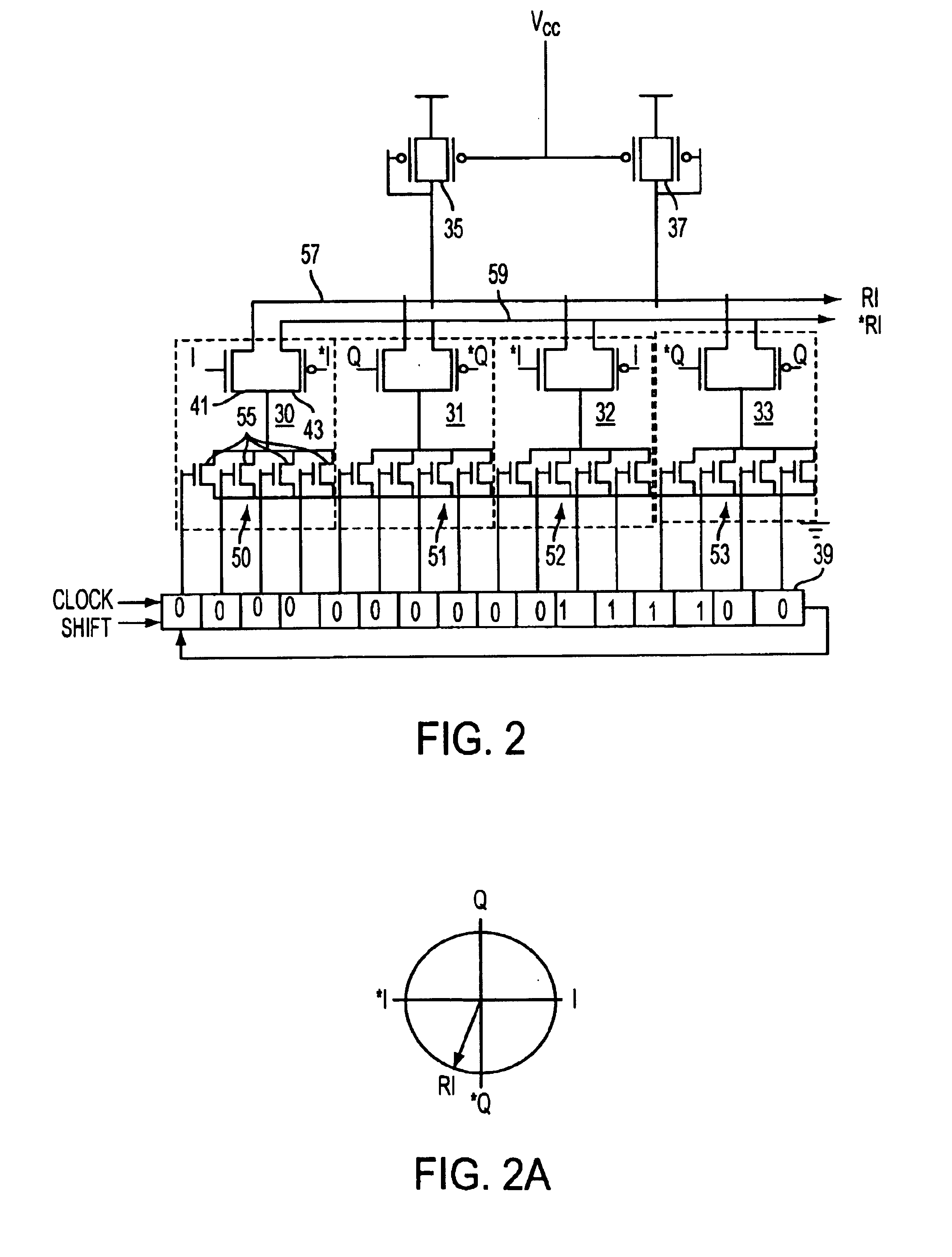

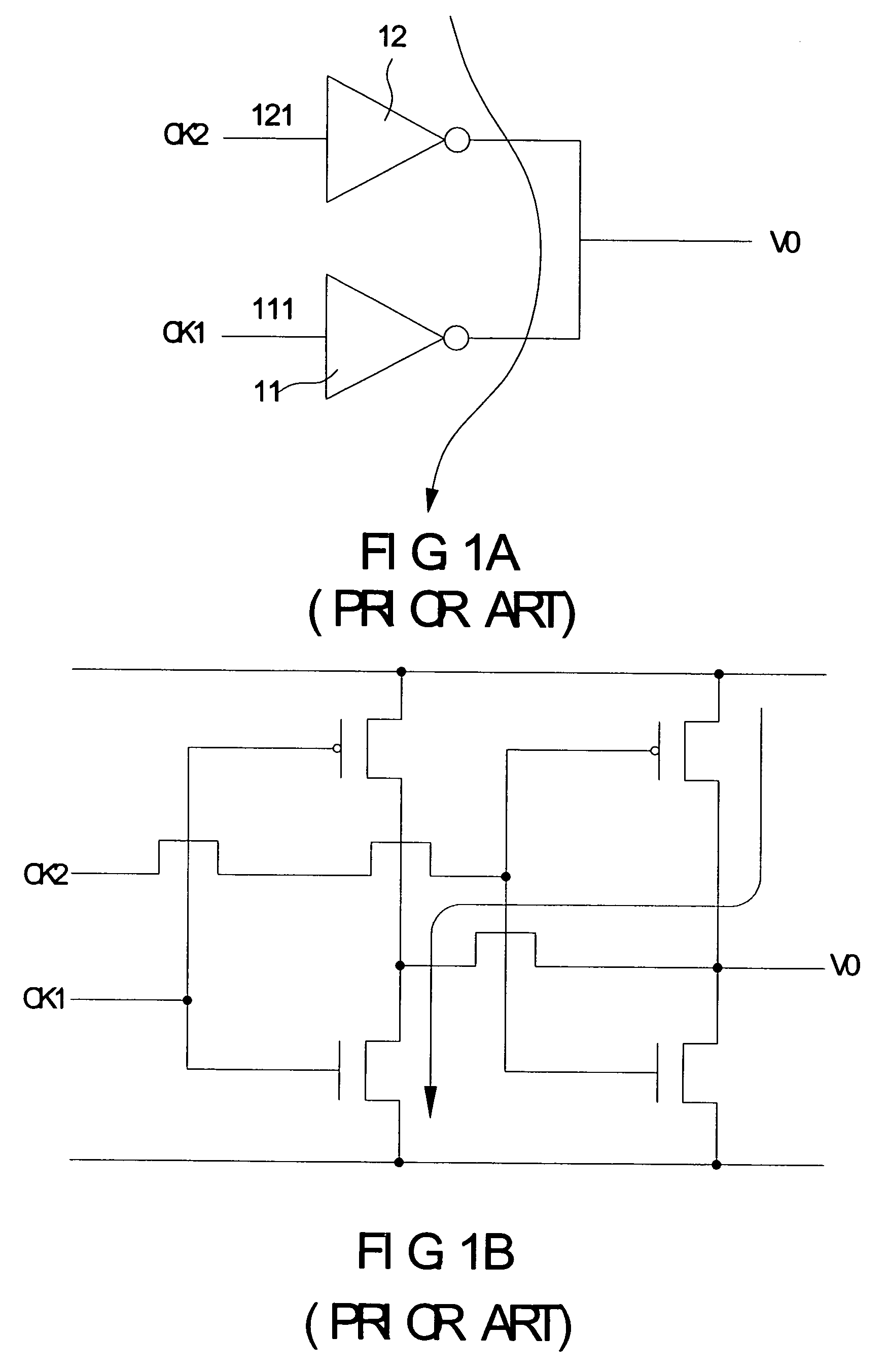

A phase interpolator interpolates between a plurality of clock phases using a plurality of switching legs coupled to a common output. Each switching leg includes a pair of differential switching transistors each having a gate and two additional terminals, one of which is coupled to said common output. The gates are coupled to respective ones of the plurality of clock phases and their complements. Tails couple the other terminals of said switching transistors to ground. Each tail made up of a plurality of transistors. A load coupling the common output to a voltage.

Owner:INTEL CORP

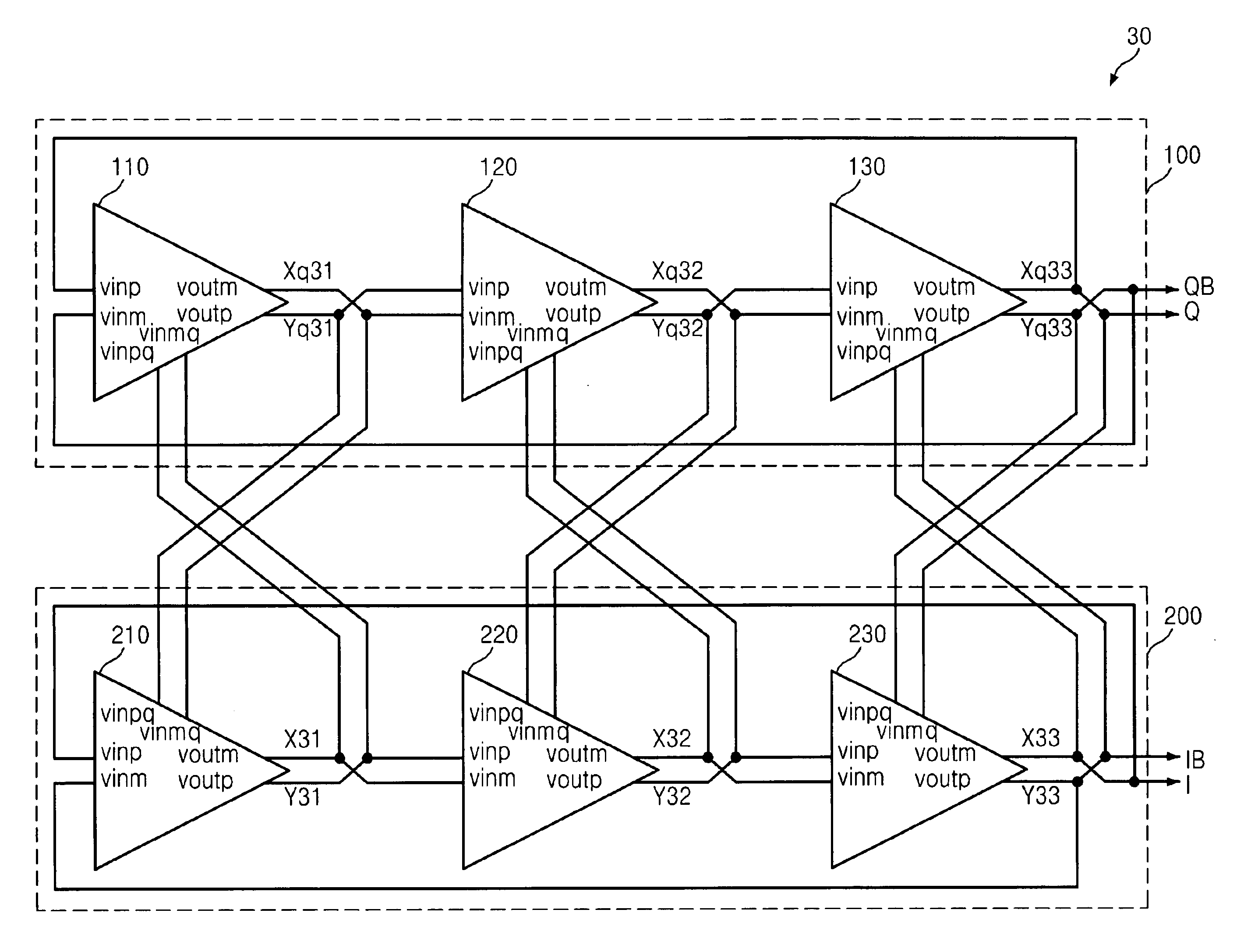

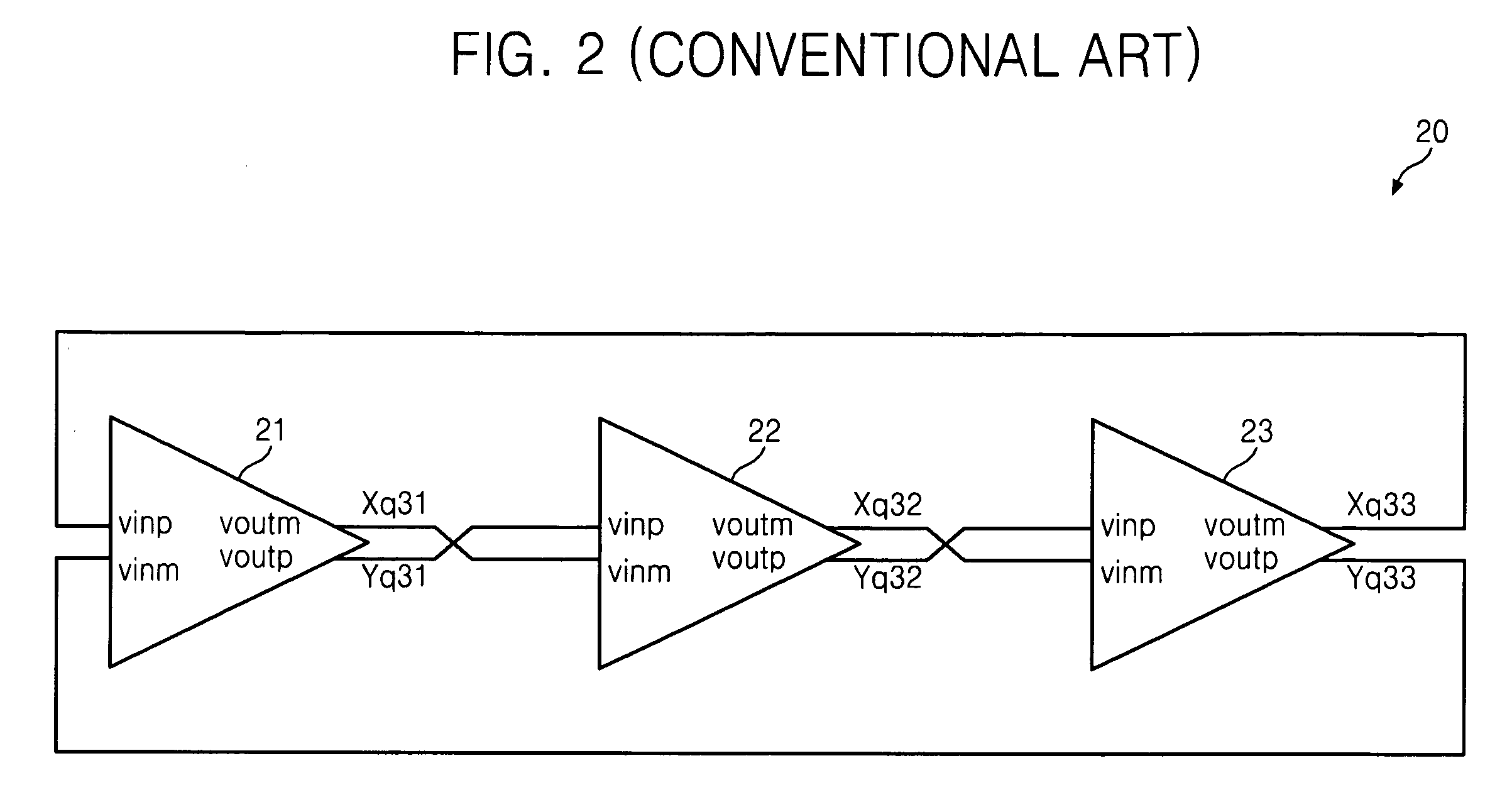

Phase interpolation circuit

InactiveUS7466179B2Inhibit currentSingle output arrangementsElectric pulse generatorEngineeringMulti phase

Owner:REALTEK SEMICON CORP

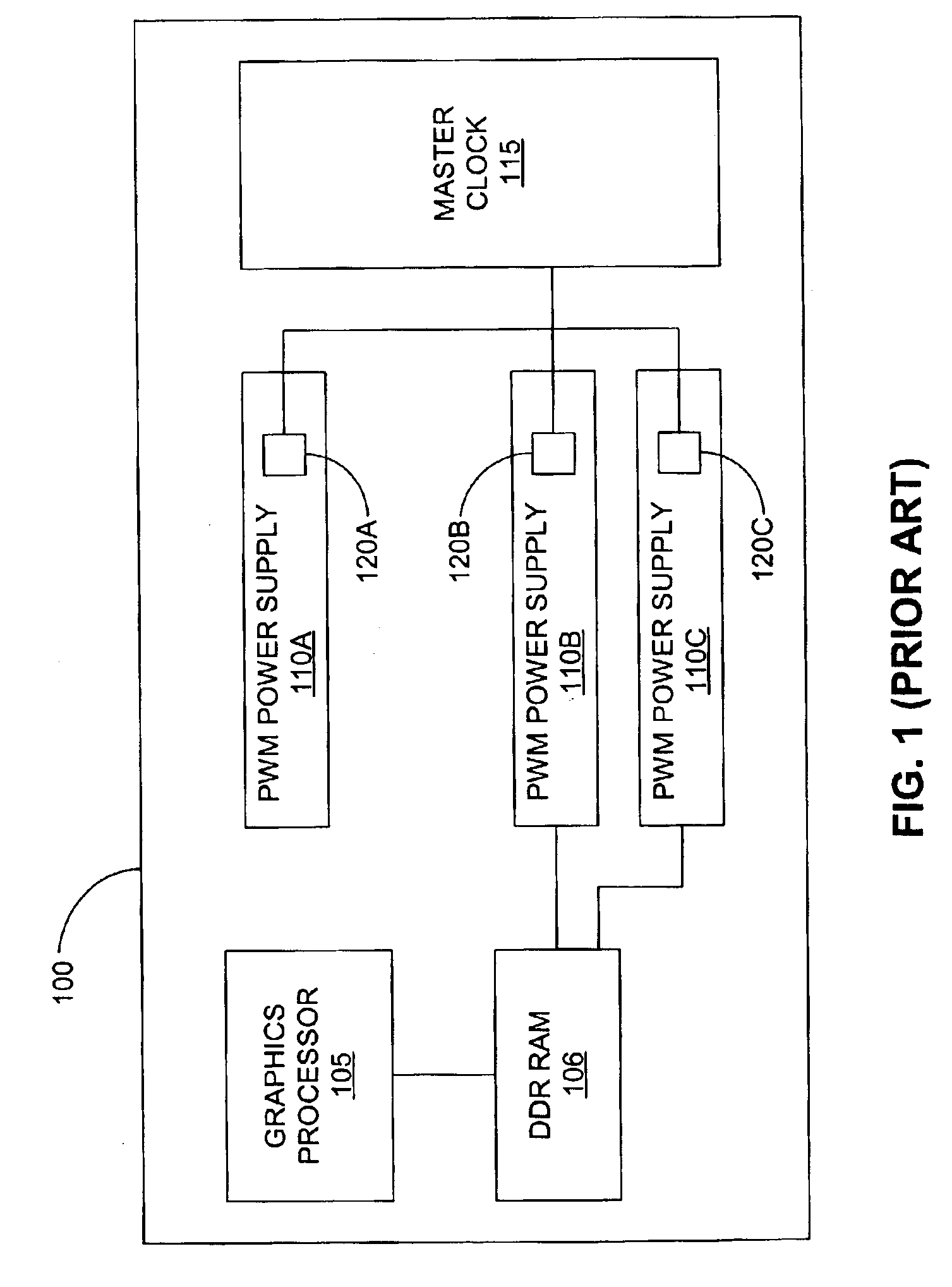

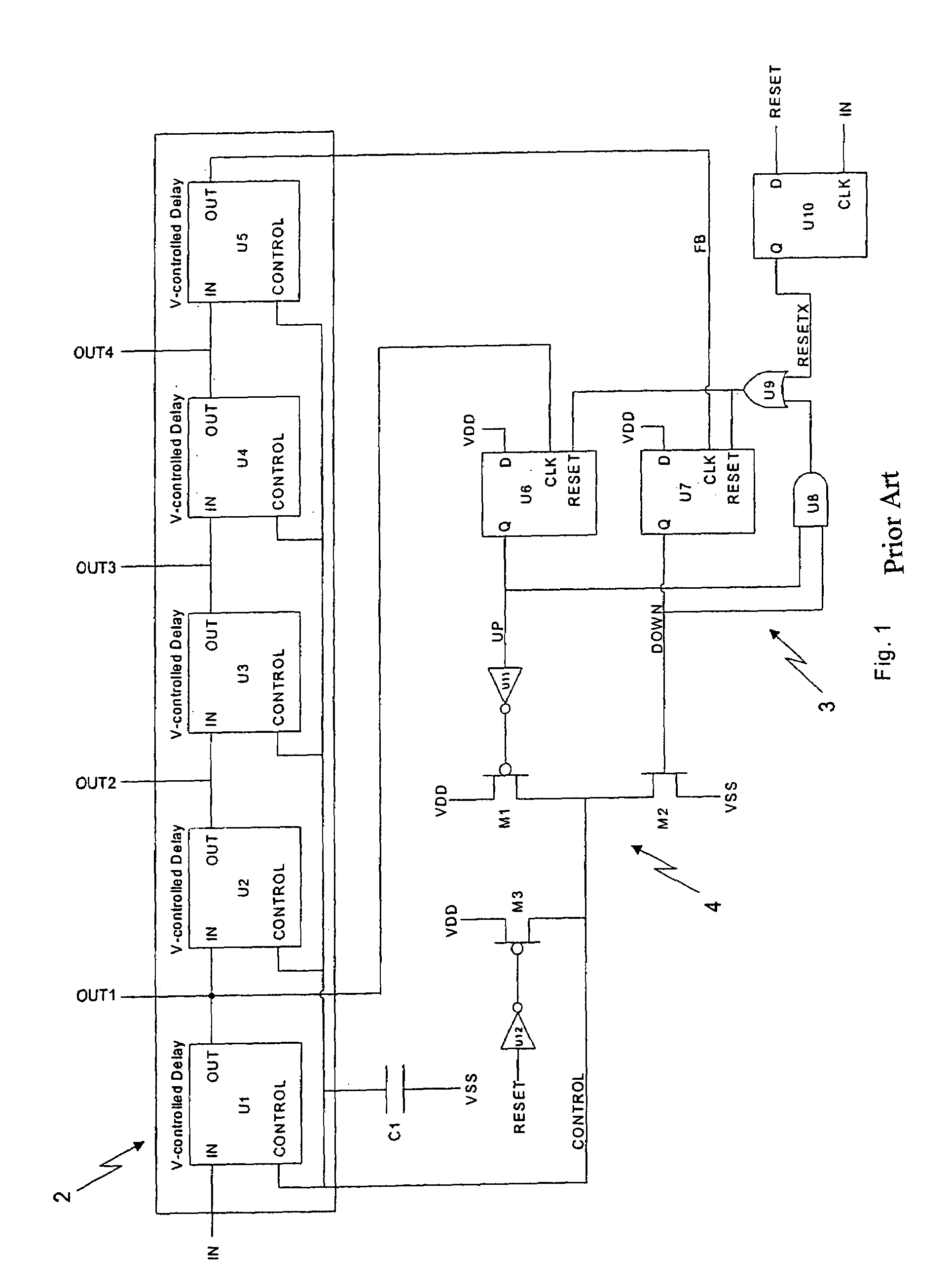

Multiphase clock generator

InactiveUS7545188B1Consumes less power and areaConsumes less power and chip areaModulation transferencePulse automatic controlPhase shiftedControl signal

A clock generator generates multiple clock signals based on an input signal and adjusts the phases of the clock signals relative to a phase of the input signal, based on a control signal. The clock generator includes a phase locked loop that includes a phase shift unit. The phase shift unit selects some of the clock signals based on the control signal and generates a feedback signal based on the selected clock signals. The feedback signal has a phase based on the phases of the selected clock signals. The phase locked loop aligns the phase of the feedback signal with the phase of the input signal. In this process, the phase locked loop shifts the phase of each of the clock signals relative to the phase of the input signal.

Owner:INTEGRATED DEVICE TECH INC

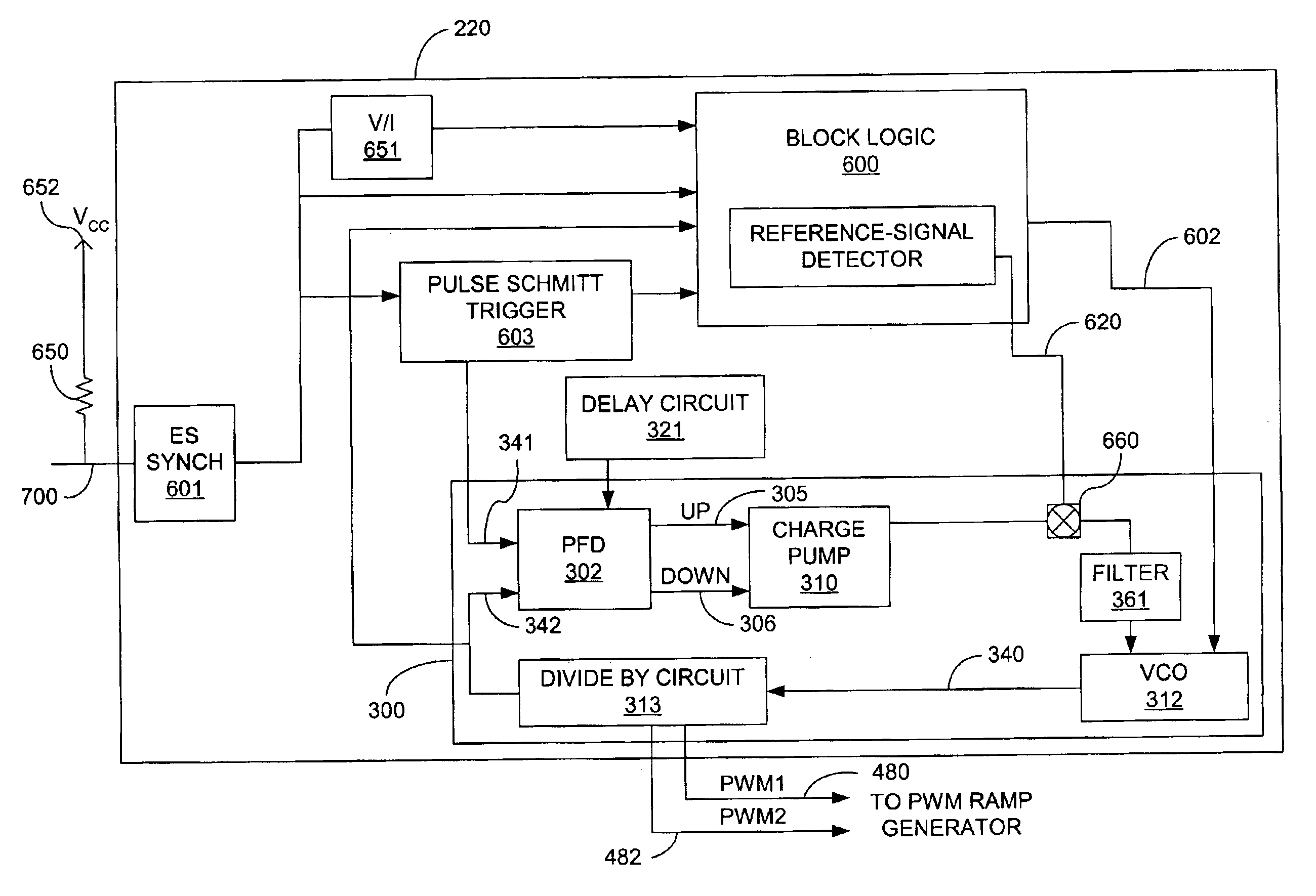

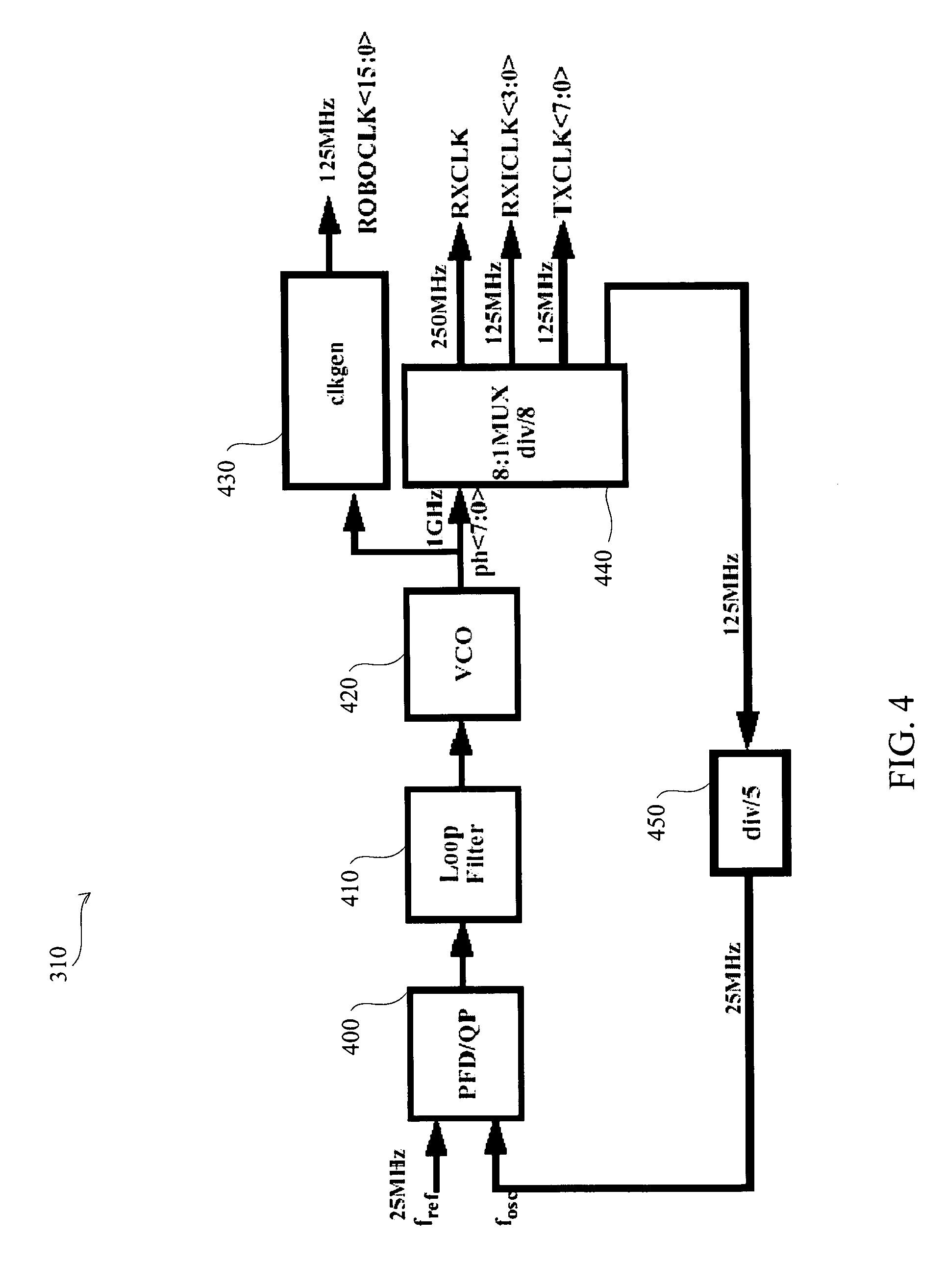

Phase-lock loop having programmable bandwidth

InactiveUS6853252B2Reducing PFD gainReducing PLL bandwidthPulse automatic controlCounting chain pulse countersPhase differencePhase frequency detector

A phase-locked loop having a programmable loop bandwidth is provided. A PLL comprises an oscillator operable to receive an error-correction signal and to generate an oscillator signal having a frequency that is related to the error-correction signal. The PLL further comprises a phase-frequency detector (PFD) coupled to the oscillator and operable to receive a reference signal and to generate the error-correction signal based upon a phase difference between the reference signal and a feedback signal derived from the oscillator signal. The PLL further comprises an error-correction signal suppression circuit coupled to the PFD and operable to control the loop bandwidth of the PLL by periodically enabling the PFD.

Owner:INTERSIL INC

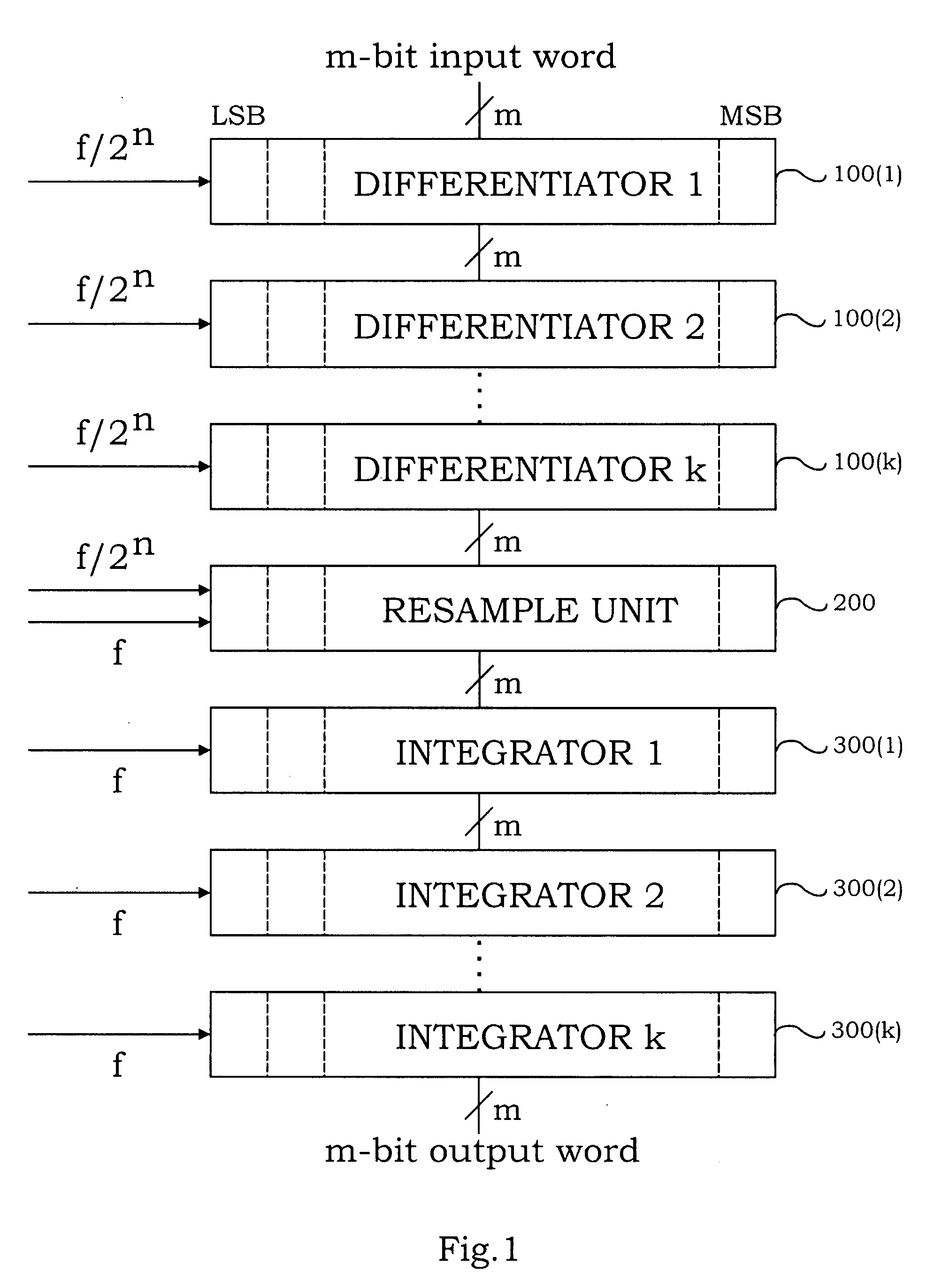

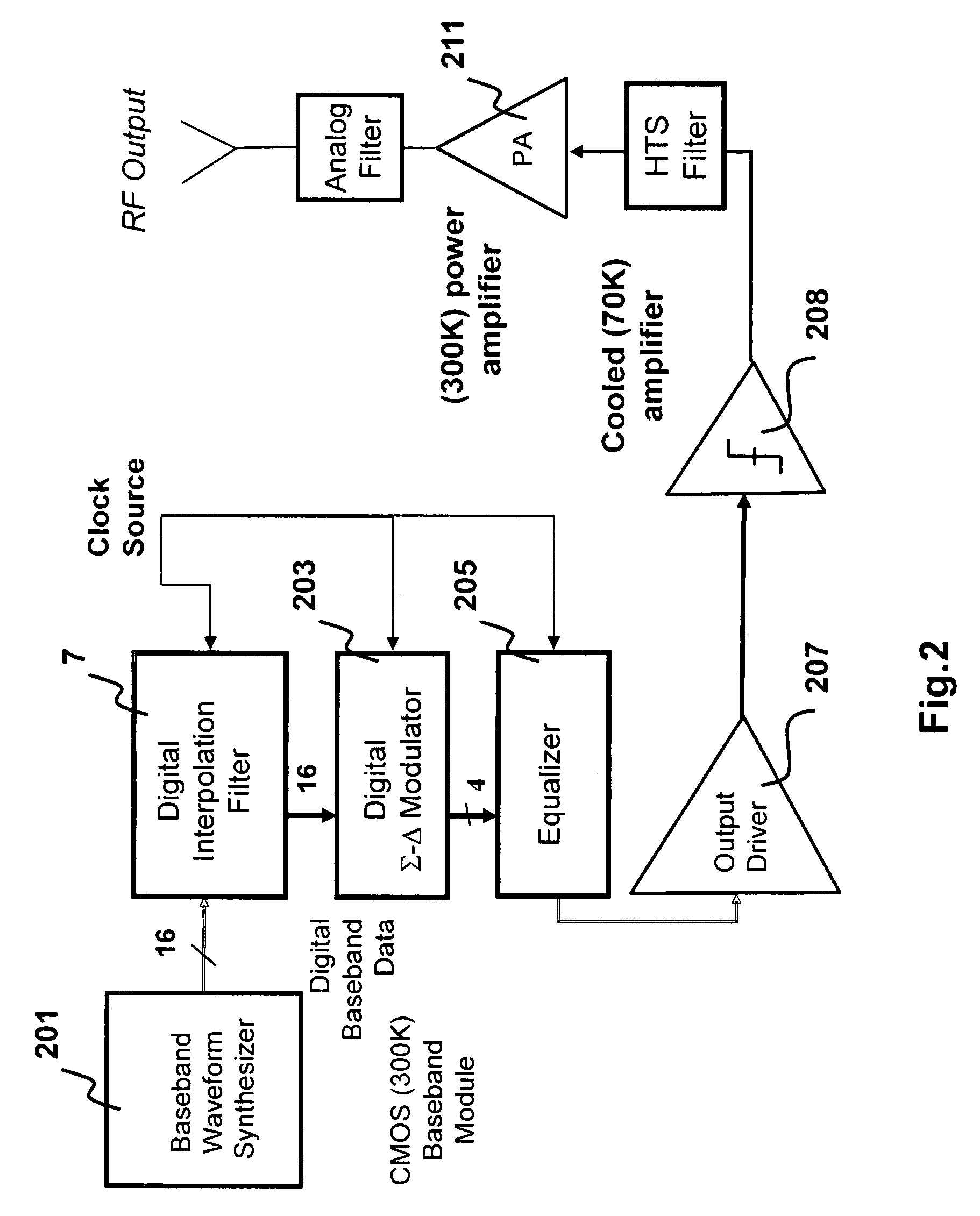

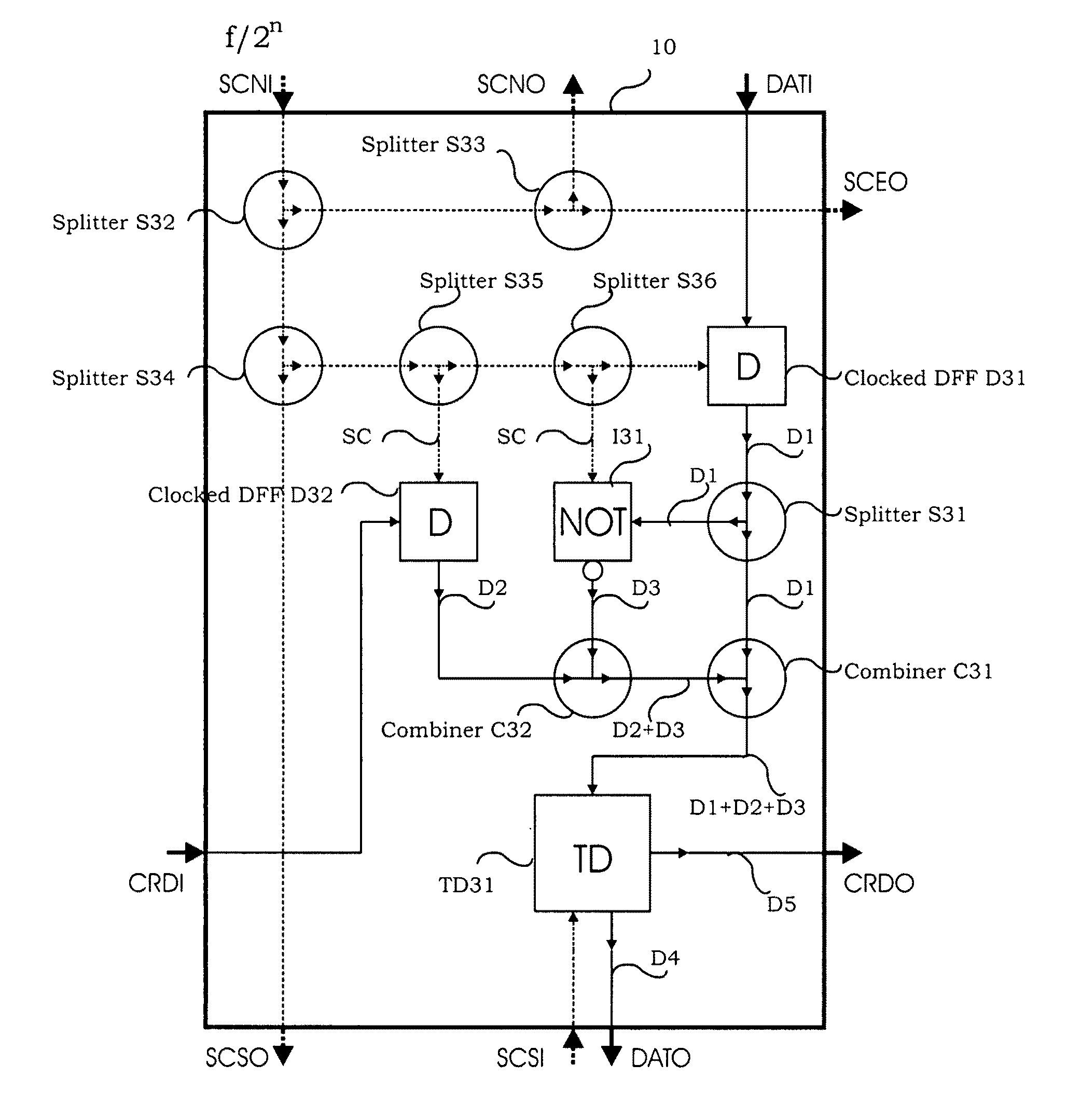

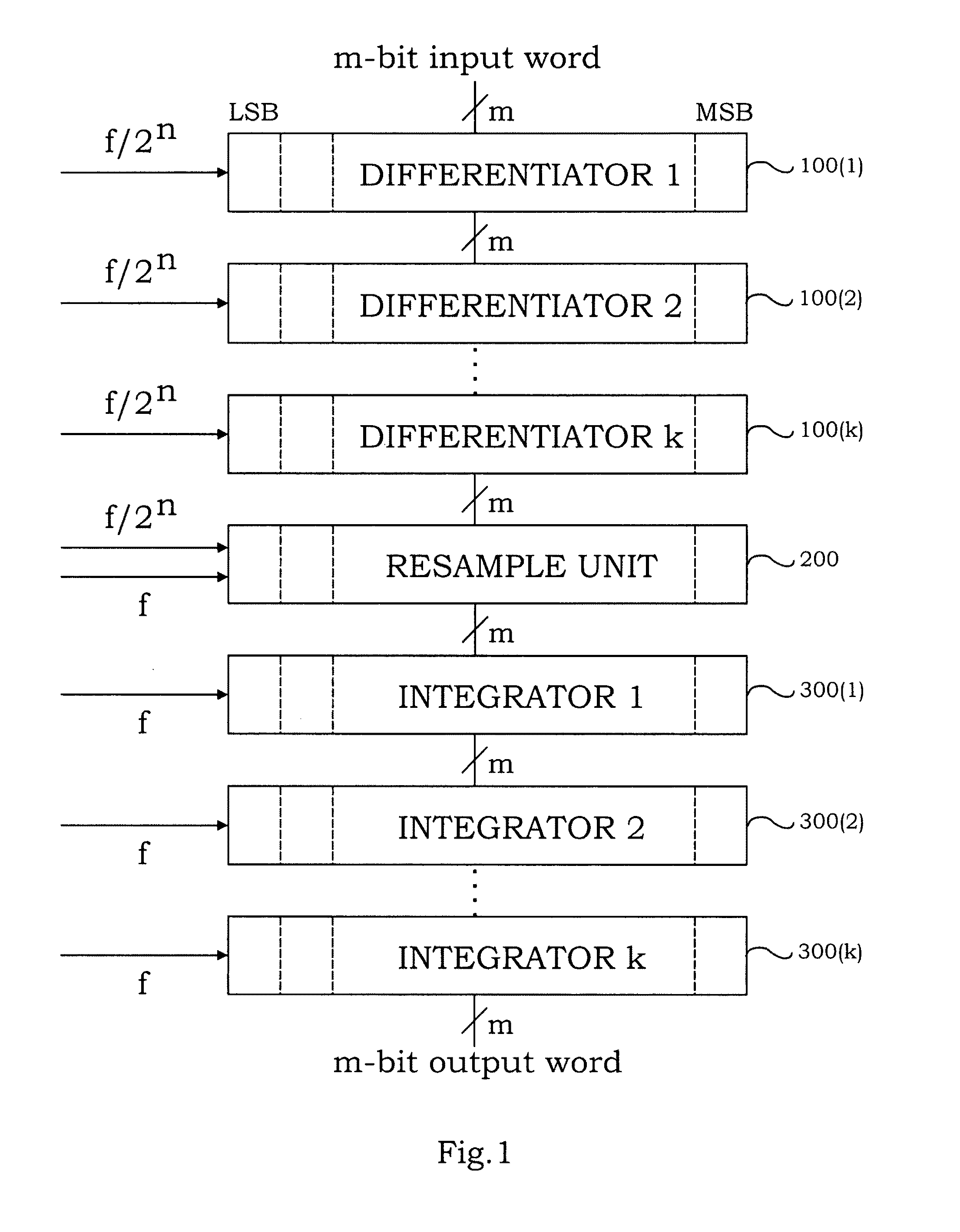

Ultra fast circuitry for digital filtering

ActiveUS20080231353A1Accurate timingEasy to operateComputation using non-contact making devicesSolid-state devicesUltra high speedNon destructive

The invention includes a novel differentiator cell, a novel resample unit cell, and precision synchronization circuitry to ensure proper timing of the circuits and systems at the anticipated ultra-high speed of operation. The novel differentiator cell includes circuitry for combining a carry input signal, a data bit signal and the output signal of a NOT cell and applying the signals as distinct and separate pulses to the input of a toggle flip-flop (TFF) for producing an asynchronous carry output and a clocked data output. The novel differentiator cells can be interconnected to form a multi-bit differentiator circuit using appropriate delay and synchronization circuitry to compensate for delays in producing the carry output of each cell which is applied to a succeeding cell. The novel resample cell includes a non-destructive reset-set flip-flop (RSN) designed to receive a data bit, at its set input, at a slow clock rate, which data is repeatedly read out of the RSN at a fast clock rate, until the RSN is reset. The novel differentiator and resampler cells can be interconnected, for example, to form the differentiator and up-sampling sections of a digital interpolation filter (DIF). Also, the relative clocking of bit slices (columns) in such a DIF may be achieved by using the fast clock signal to synchronize the slow clock which controls data entry. The circuits of the invention can be advantageously implemented with Josephson Junctions in rapid-single-flux-quantum (RSFQ) logic.

Owner:SEEQC INC

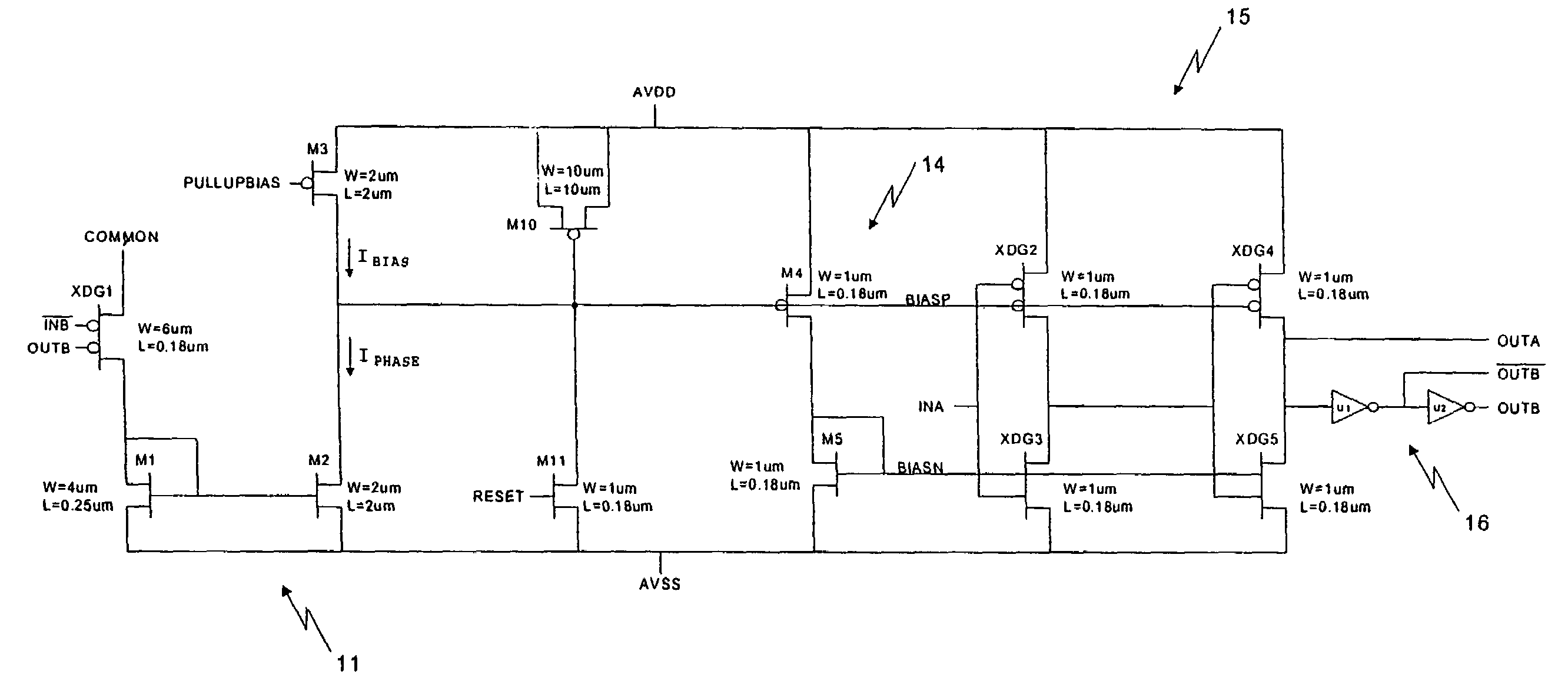

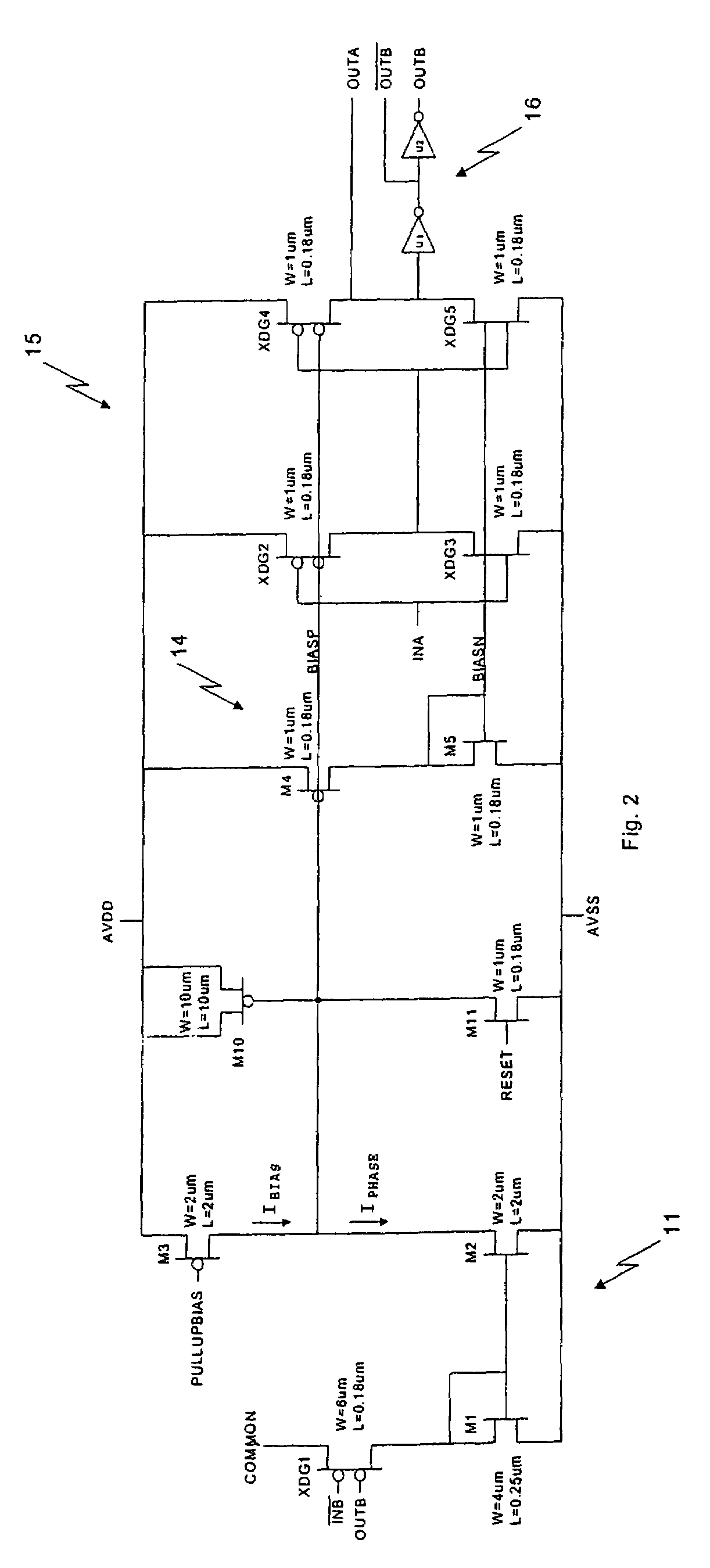

Low power small area static phase interpolator with good linearity

InactiveUS20110241746A1Reduce areaReduce power consumptionPhase shifterTime-delay networksPhase controlEngineering

A static phase interpolator includes first and second plurality of inverters coupled in parallel between an output node and first and second input nodes for receiving first and second clock signals, and first and second plurality of switch elements coupled to the first and second plurality of inverters for selectively turning on individual ones of the inverters in response to a phase control signal. An inverter is coupled the output node. The interpolator may include a slew rate controller coupled to the first and second input nodes. Also, each inverter of the interpolator may include a PMOS transistor in series with an NMOS transistor and have a respective one of the switch elements disposed between the PMOS and NMOS transistors.

Owner:TAIWAN SEMICON MFG CO LTD

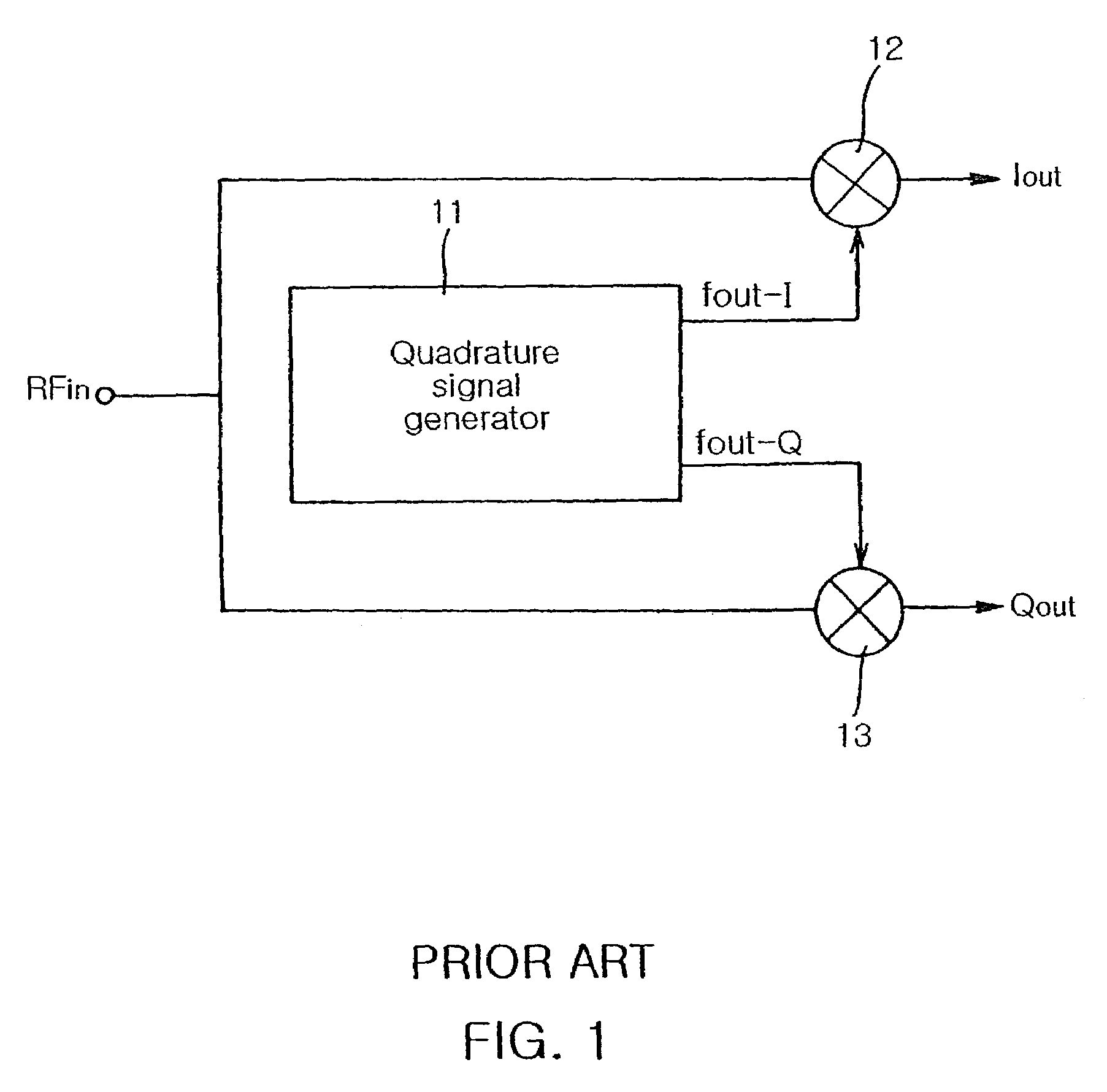

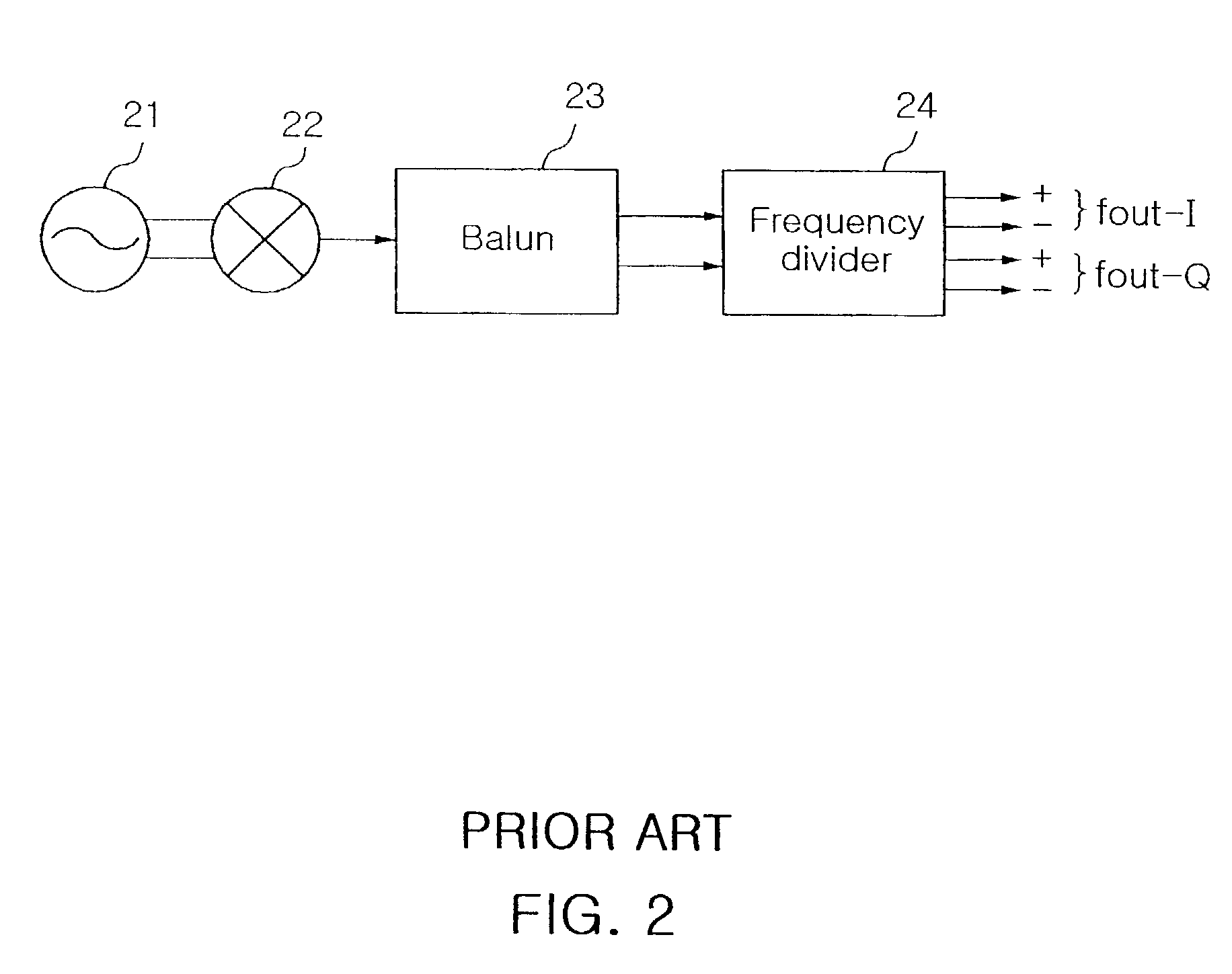

Quadrature signal generator with feedback type frequency doubler

InactiveUS7010287B2Reliable characteristicVessel manufacturingPulse automatic controlType frequencyControl system

Disclosed is a quadrature signal generator for generating an in-phase signal and a quadrature-phase signal, which is capable of generating a quadrature signal having the same frequency as a differential oscillating frequency, using a feedback control system. The quadrature signal generator includes an oscillator for generating a differential oscillation frequency signal having predetermined differential oscillation frequencies; a feedback type frequency doubler for generating a differential frequency signal having differential frequency components corresponding to differential frequency components of a frequency sum signal obtained by summing the differential oscillation frequency signal received from the oscillator and a differential feedback signal received at the differential feedback terminal; and a frequency divider for dividing the differential frequency signal received at the differential input terminal thereof by 2, thereby generating a quadrature signal consisting of two differential output frequency signals to supply at least one differential output frequency signal of the quadrature signal to the feedback type frequency doubler as the differential feedback signal.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

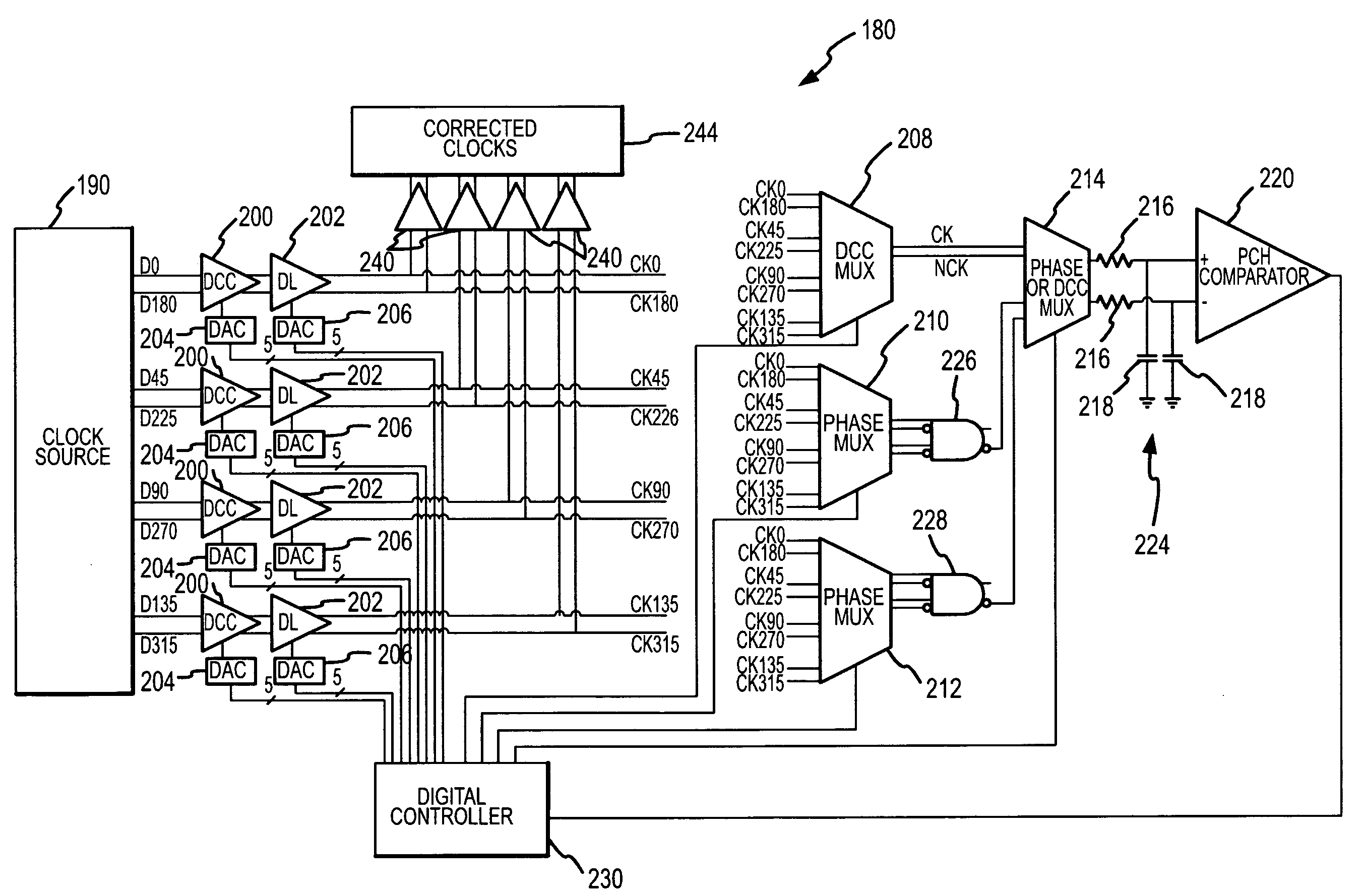

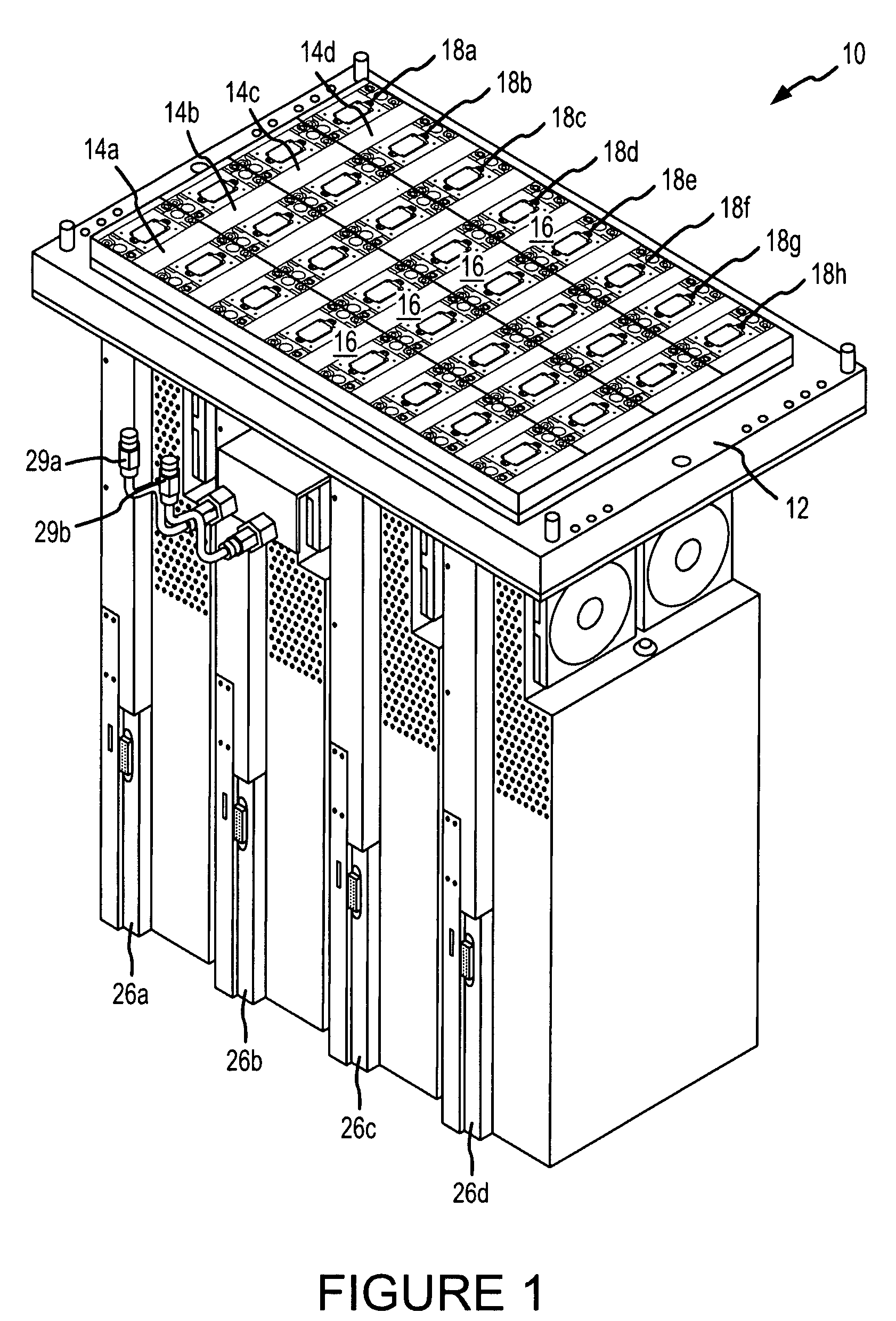

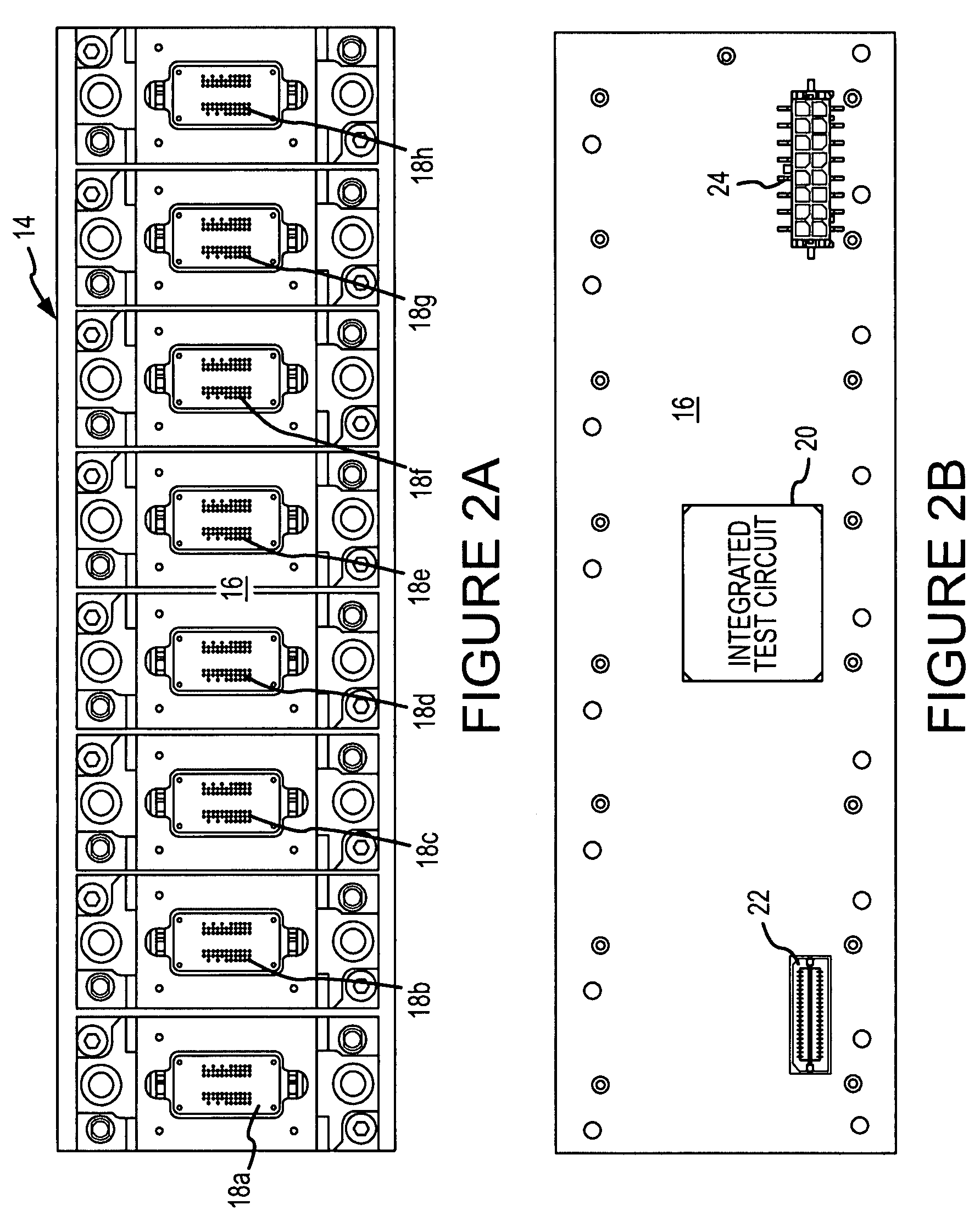

System and method for conditioning differential clock signals and integrated circuit load board using same

Owner:MICRON TECH INC

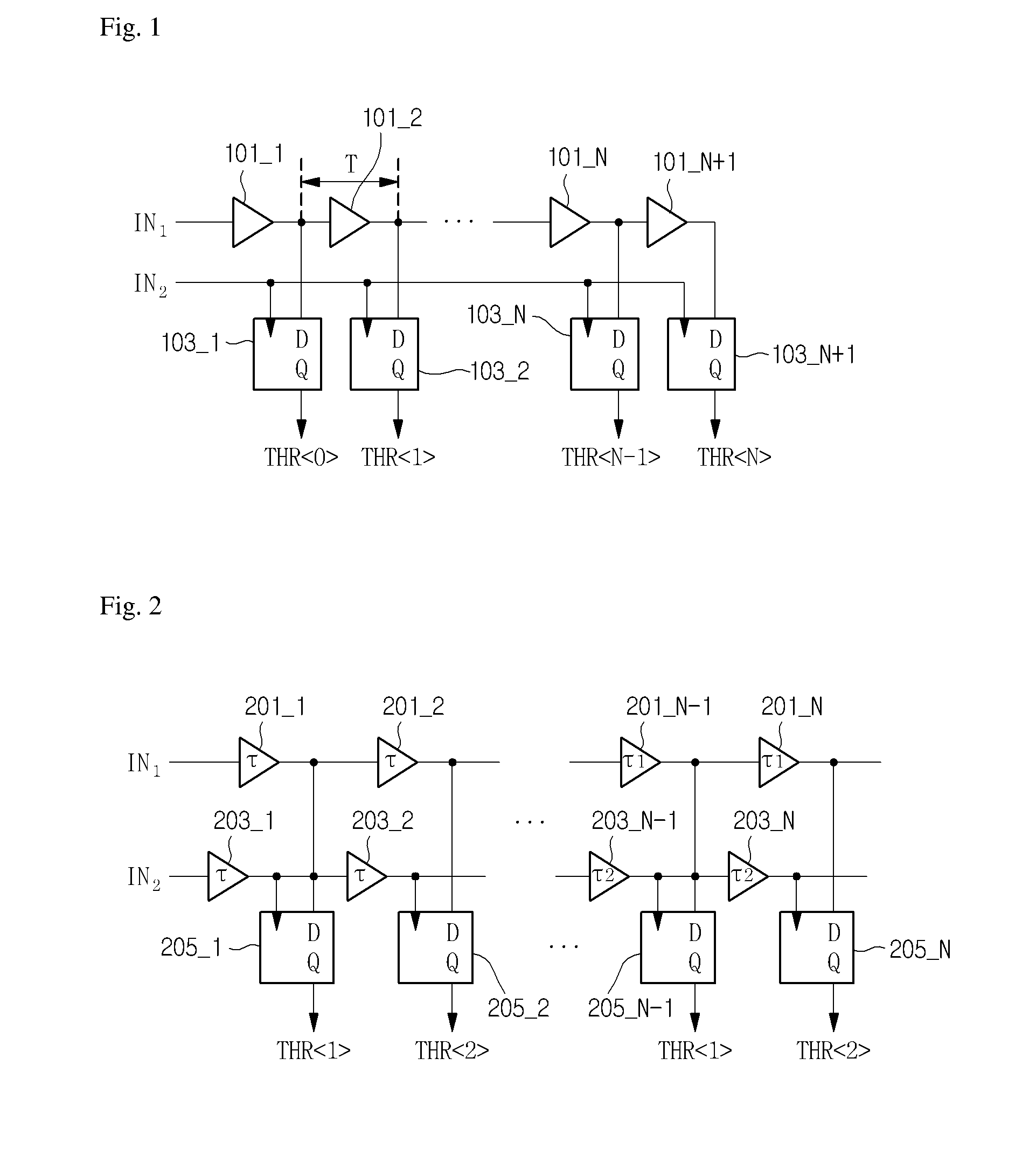

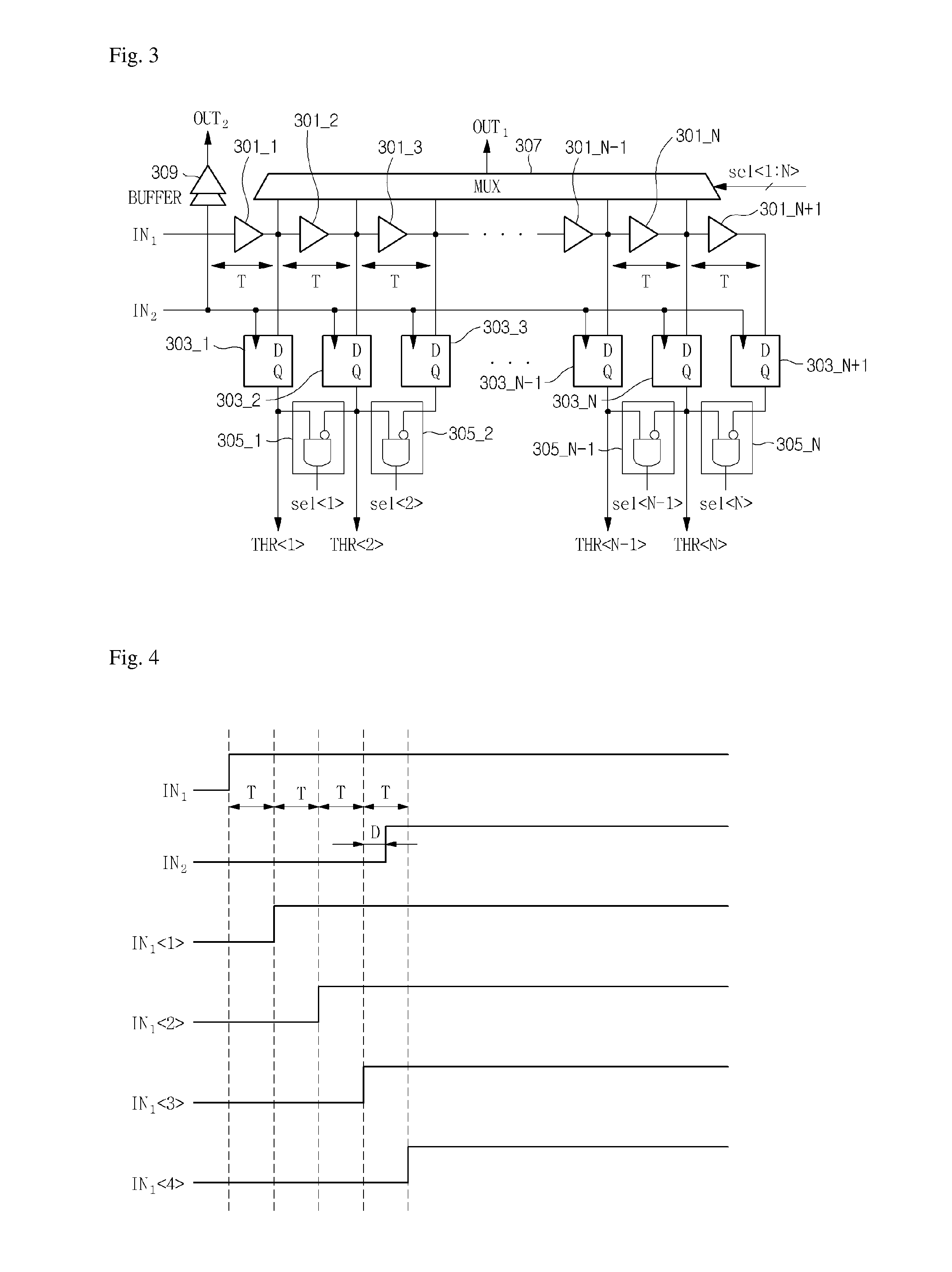

Phase-digital converter having hierarchical structure

InactiveUS20090028274A1Small sizeHigh resolutionAnalogue/digital conversionMultiple-port networksDigital down converterPhase difference

A time to digital converter having a hierarchical structure is provided. The time to digital converter includes: a plurality of delay stages for sequentially delaying a first signal for a specific delay time; a plurality of flip-flops for comparing delay signals of the first signal delayed by the delay stages with a second signal, and generating different outputs before and after a phase difference between the delay signals of the first signal and the second signal becomes smaller than a resolution of the phase detector; a selection signal generator for generating a selection signal for selecting a signal most similar to the second signal among the delay signals of the first signal from the outputs of the flip-flops; and a Multiplexer (MUX) for receiving the delay signals of the first signal and the selection signal, and outputting the signal most similar to the second signal among the delay signals of the first signal.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

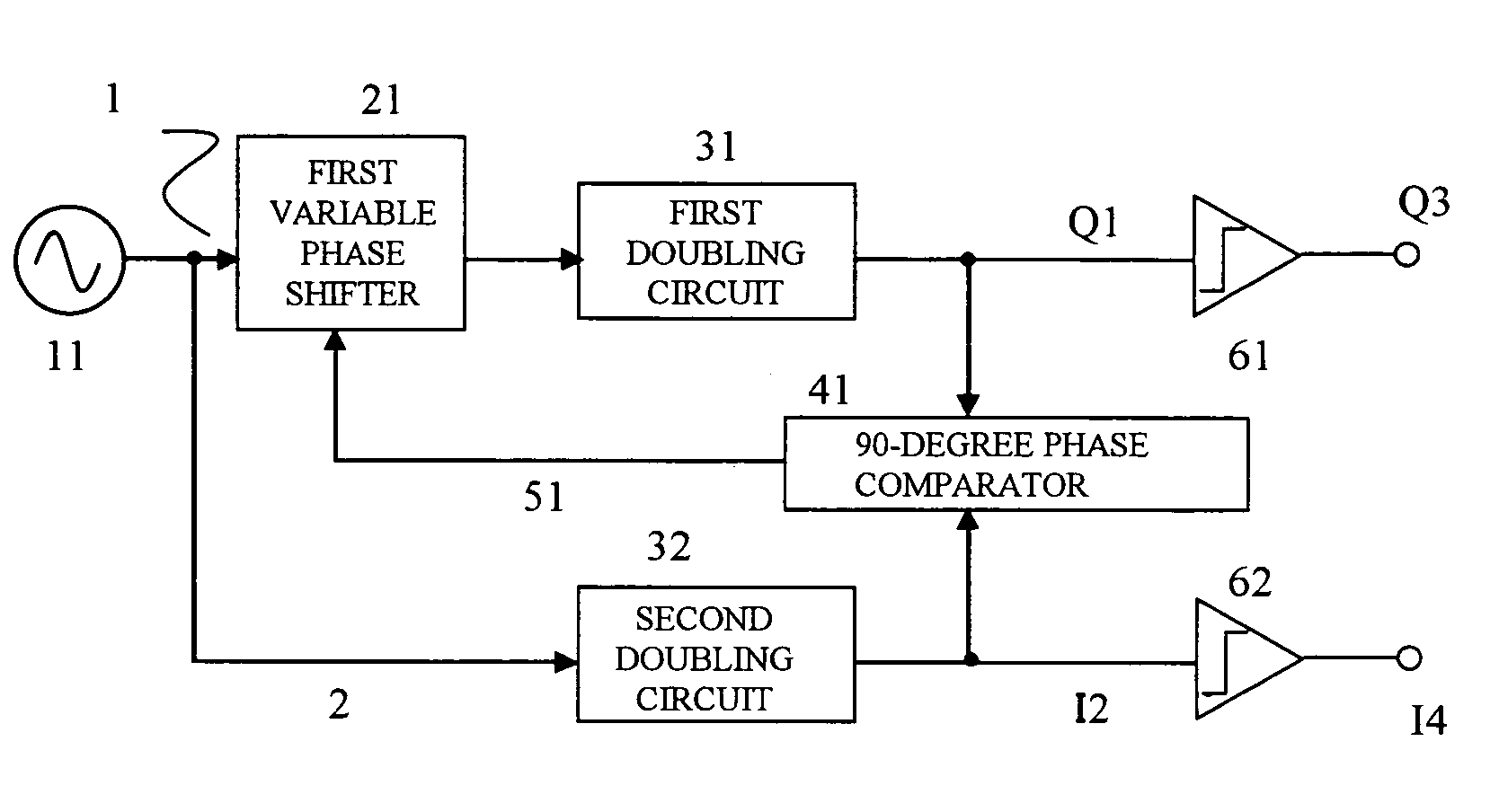

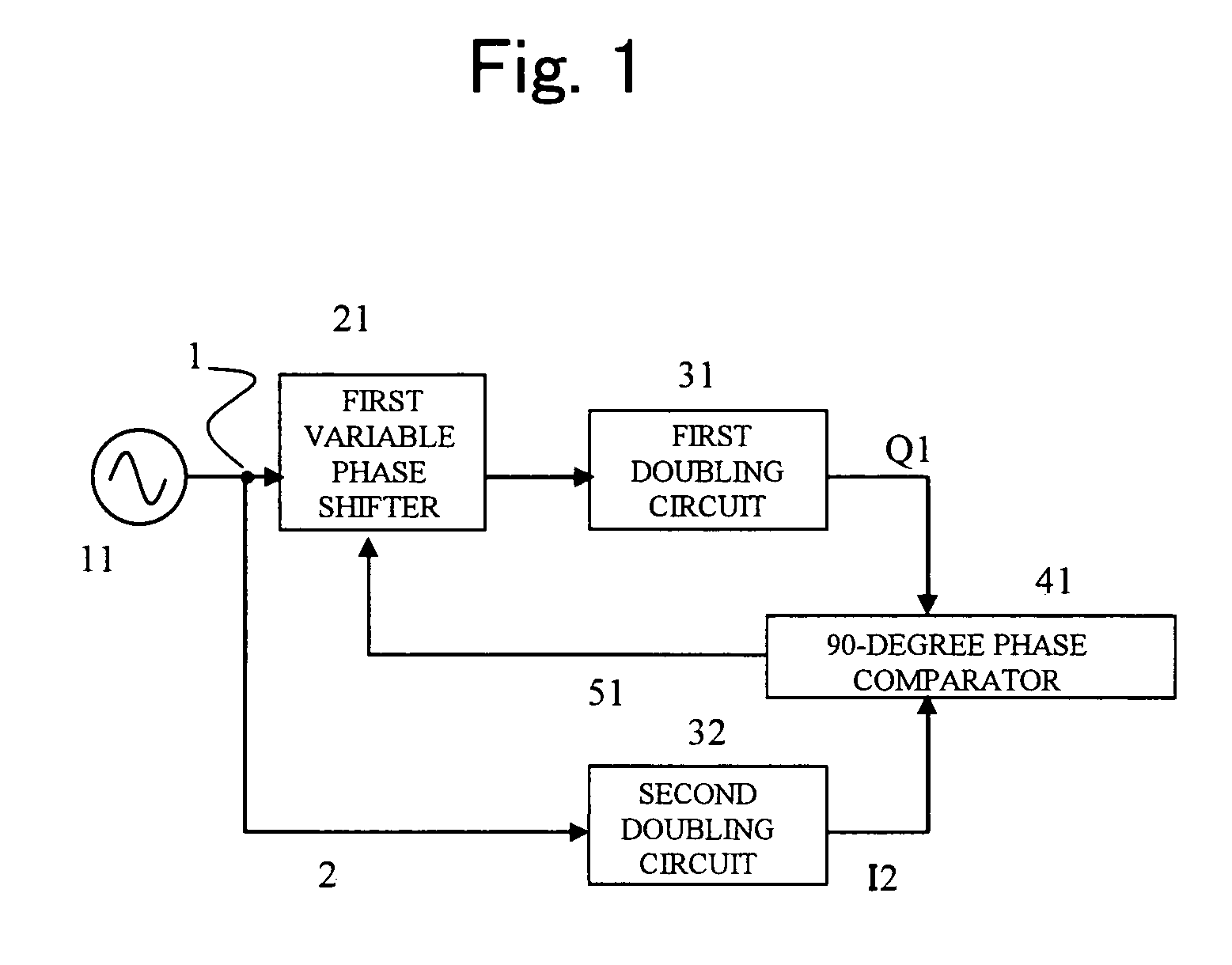

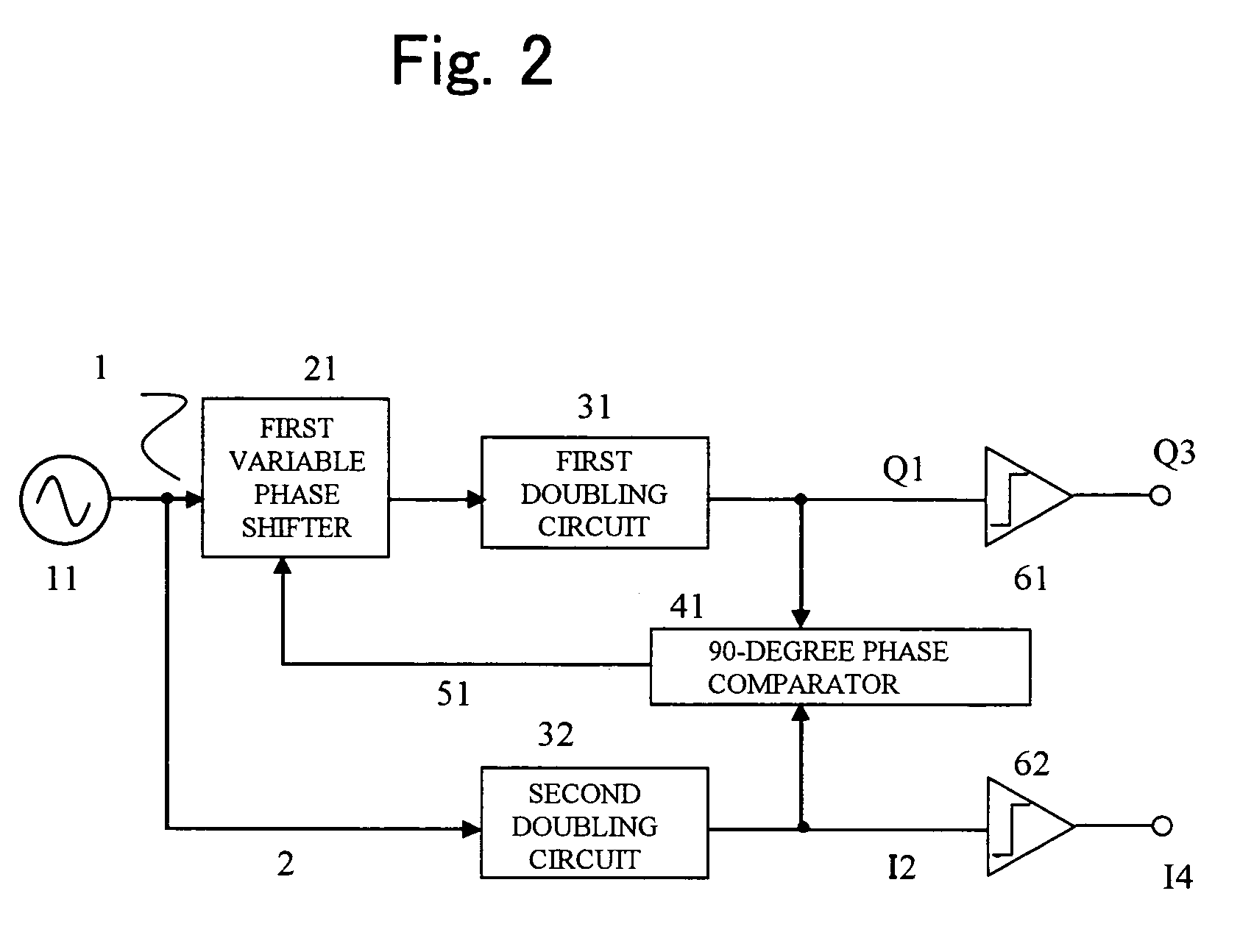

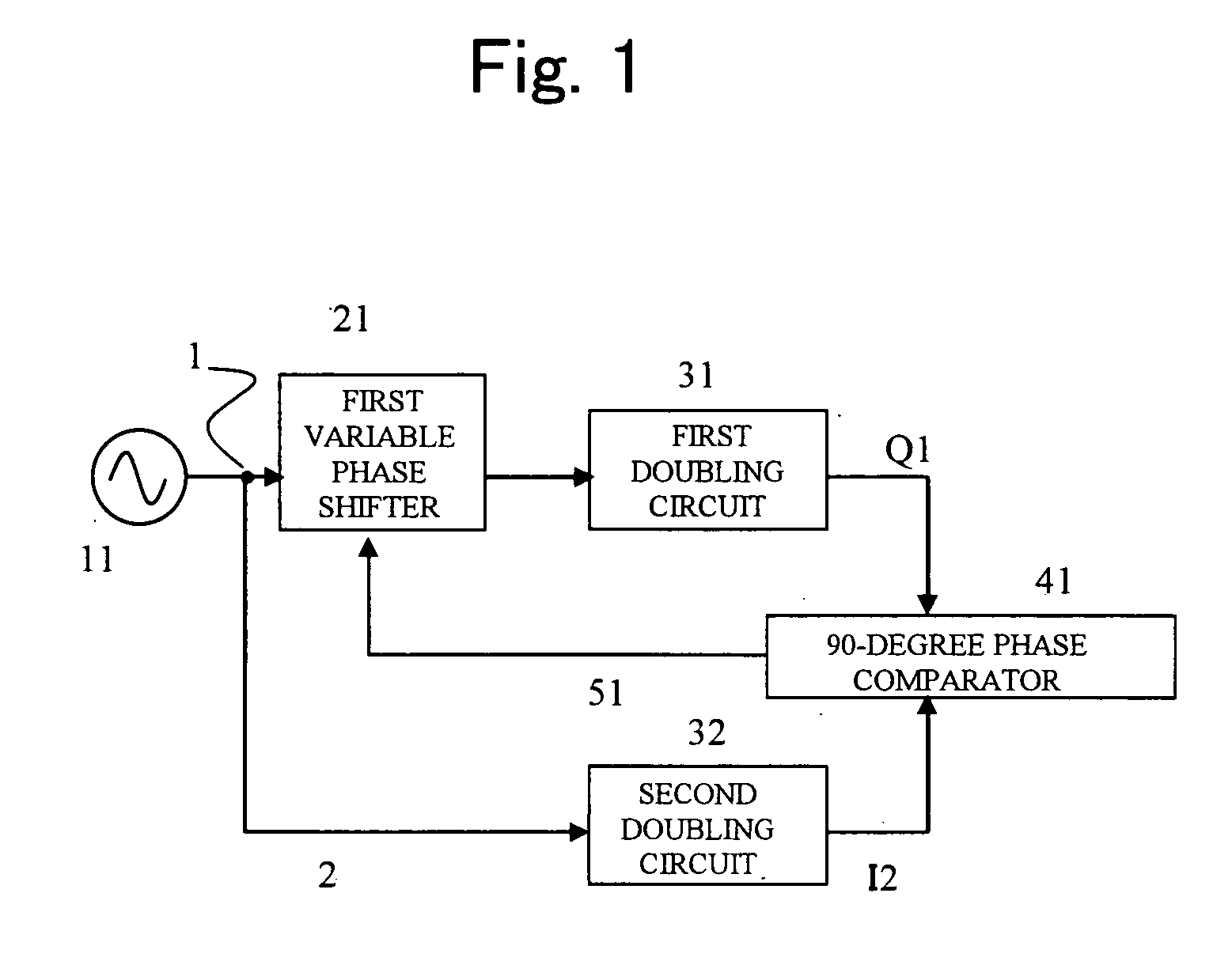

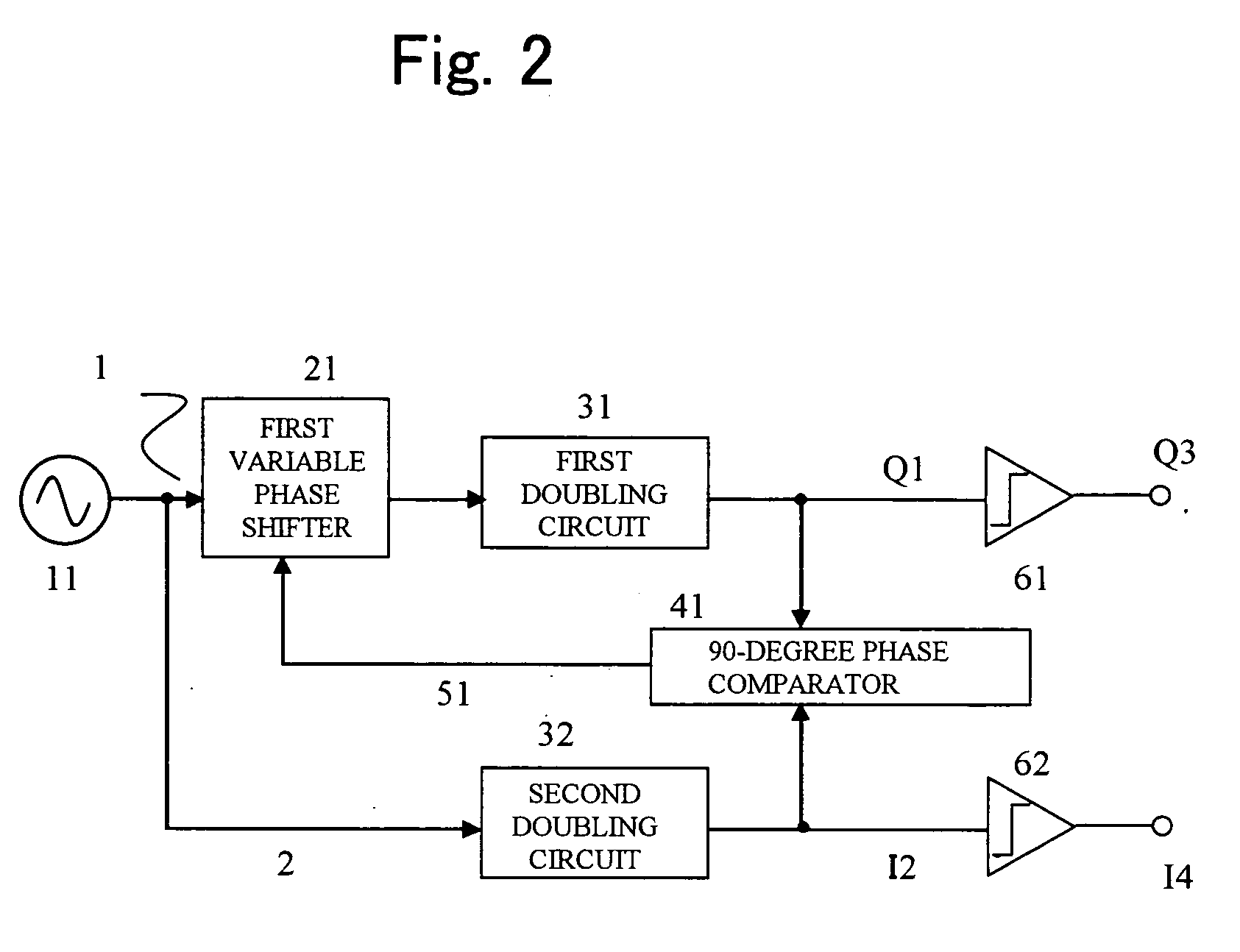

Phase shifting device

InactiveUS7282979B2Highly accurate orthogonal phase modulation/demodulation schemeMultiple-port networksPulse automatic controlPhase shift controlPhase shifted

A phase shifting device includes a signal source; a variable phase shifter; first and second doubling circuits; and a 90-degree phase comparator. An output from the signal source is connected to an input of the variable phase shifter and to an input of the second doubling circuit, an output from the variable phase shifter is connected to an input of the first doubling circuit, an output from the first doubling circuit serves as a first output signal, and an output from the second doubling circuit serves as a second output signal. The first output signal and the second output signal are inputted to the 90-degree phase comparator. The amount of phase shift rotation of the variable phase shifter is changed by a phase shift control signal outputted from the 90-degree phase comparator. By this, an exact 90-degree phase shift is obtained.

Owner:PANASONIC CORP

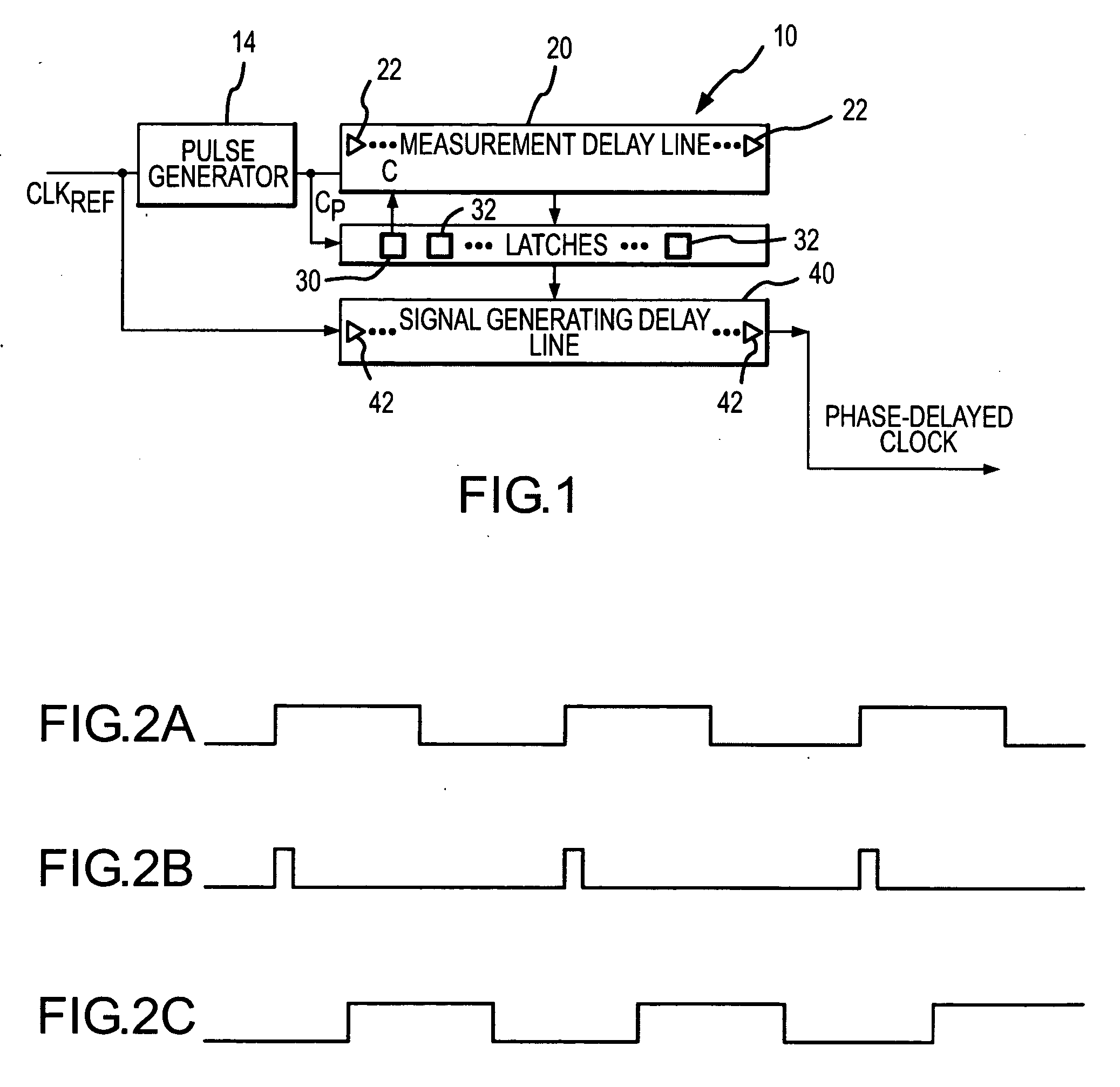

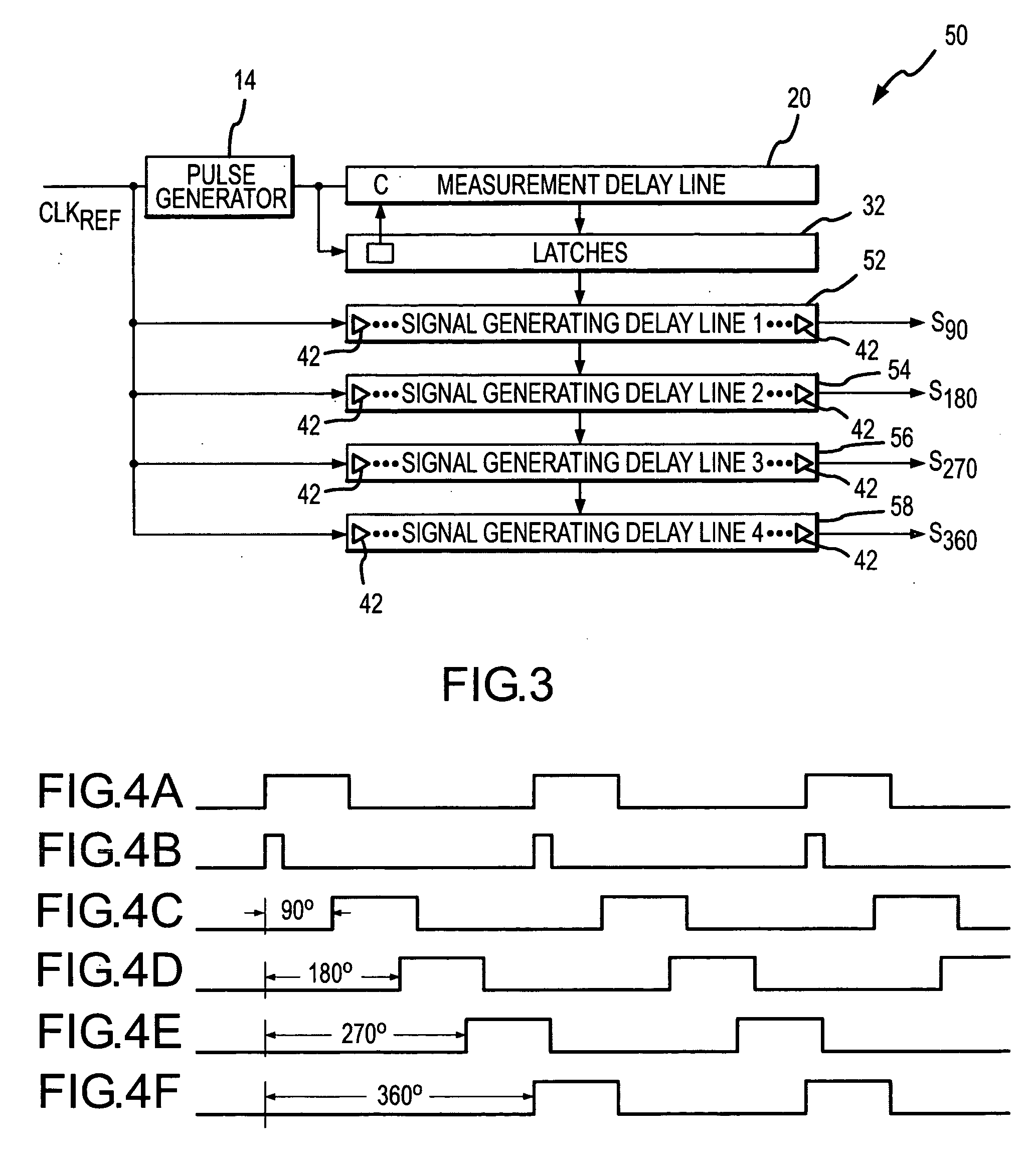

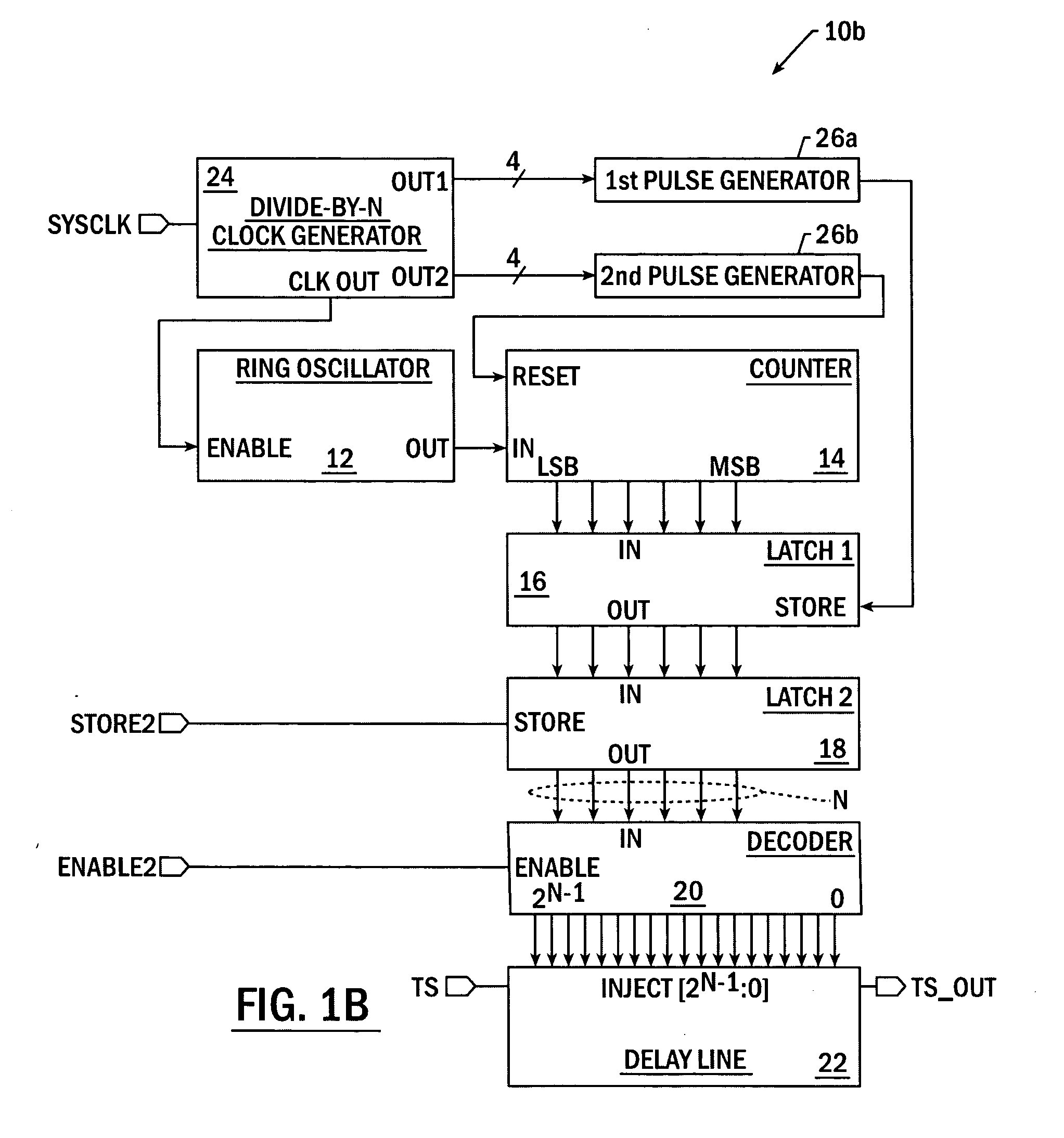

System and method generating a delayed clock output

ActiveUS7012474B2Reduce the possibilityEliminate spacePulse automatic controlError detection/correctionClock signalEngineering

Owner:AVAGO TECH INT SALES PTE LTD

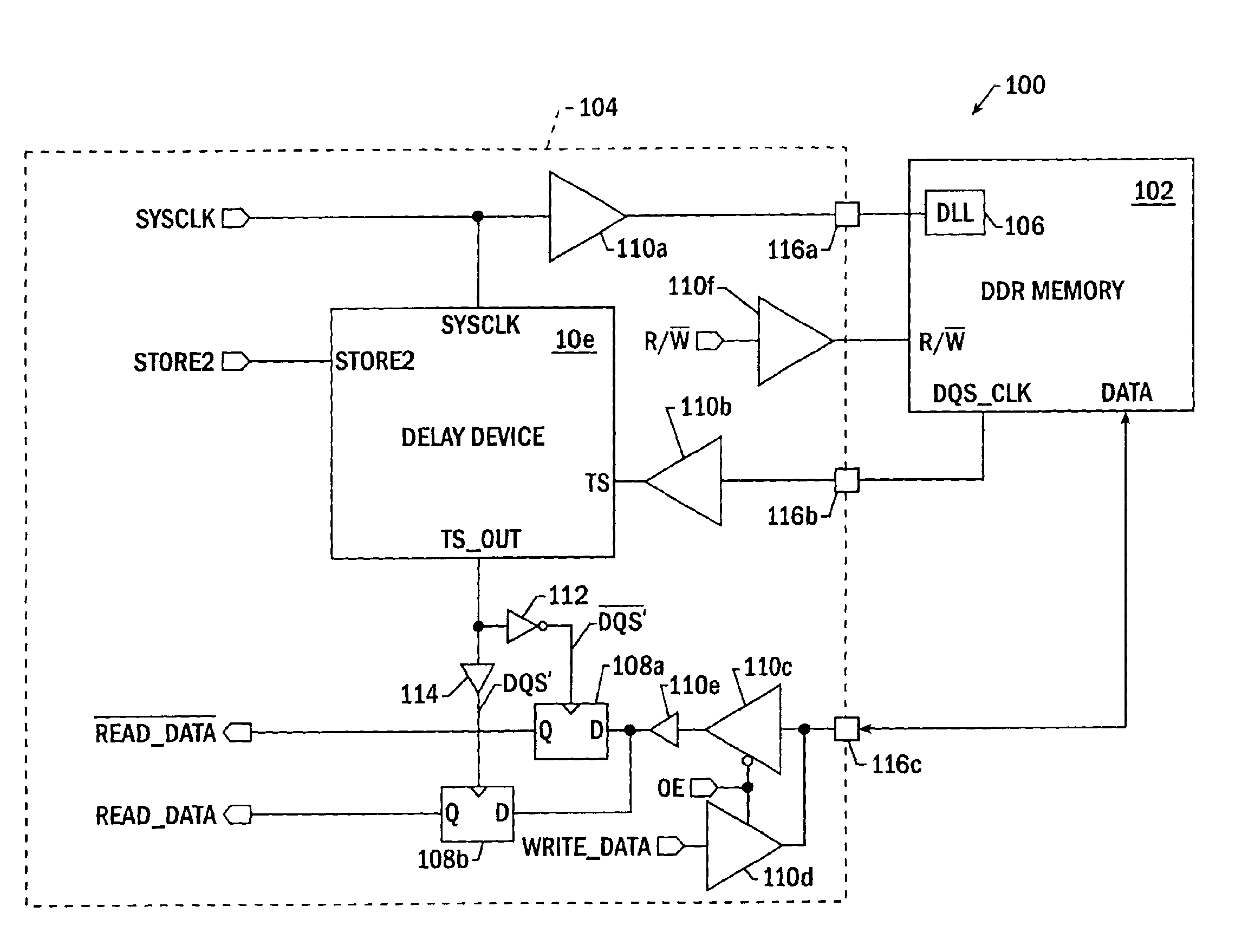

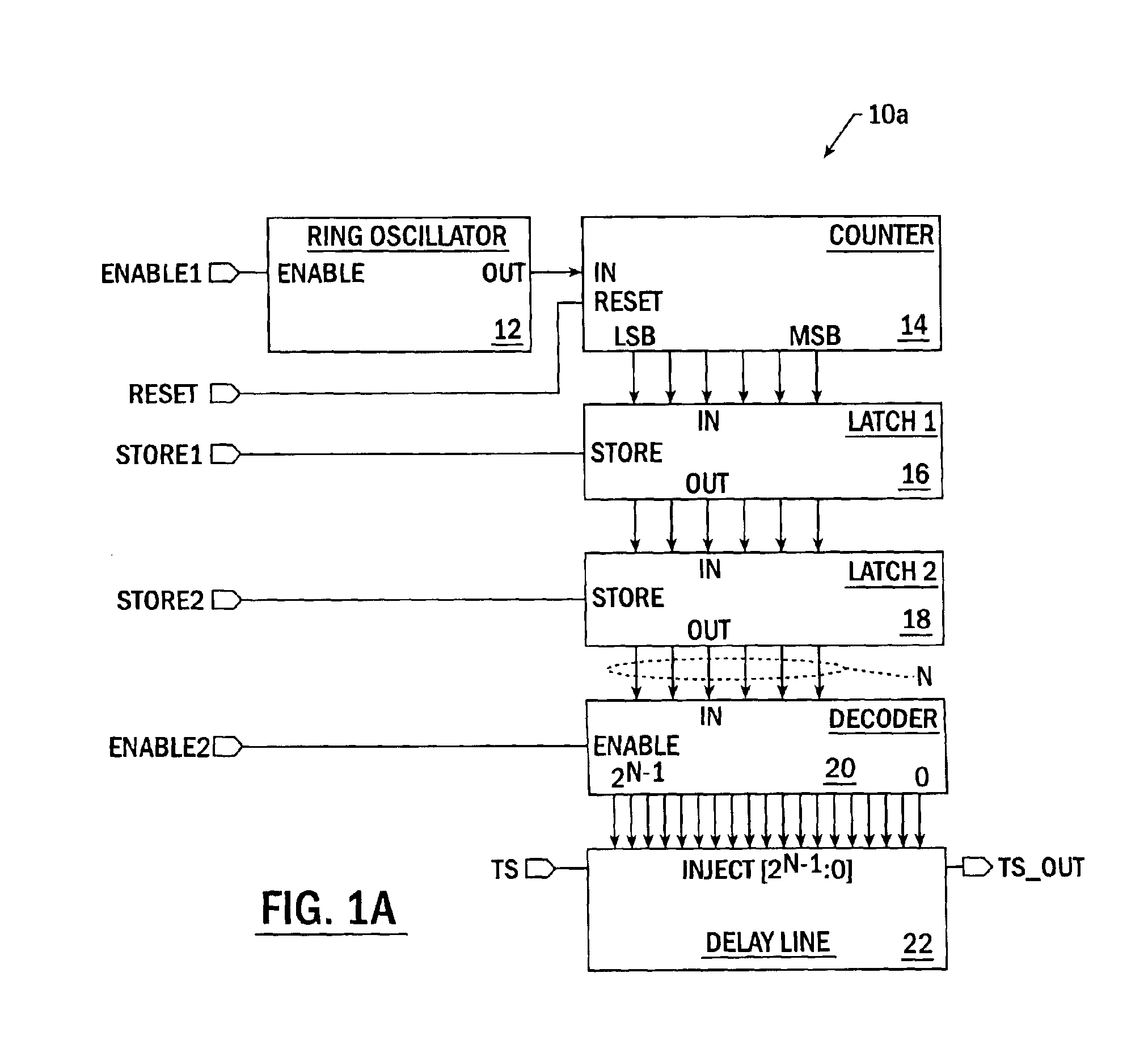

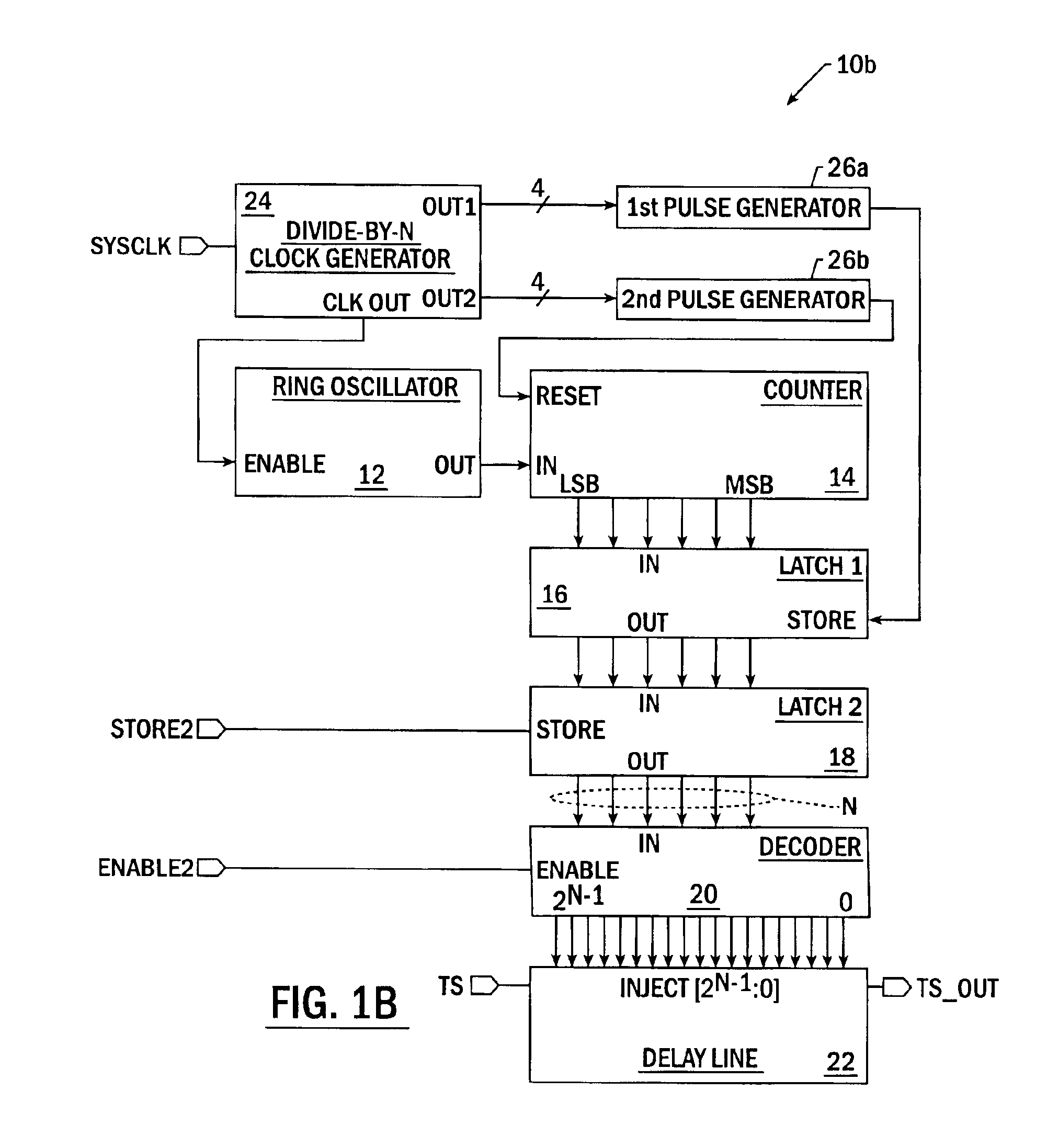

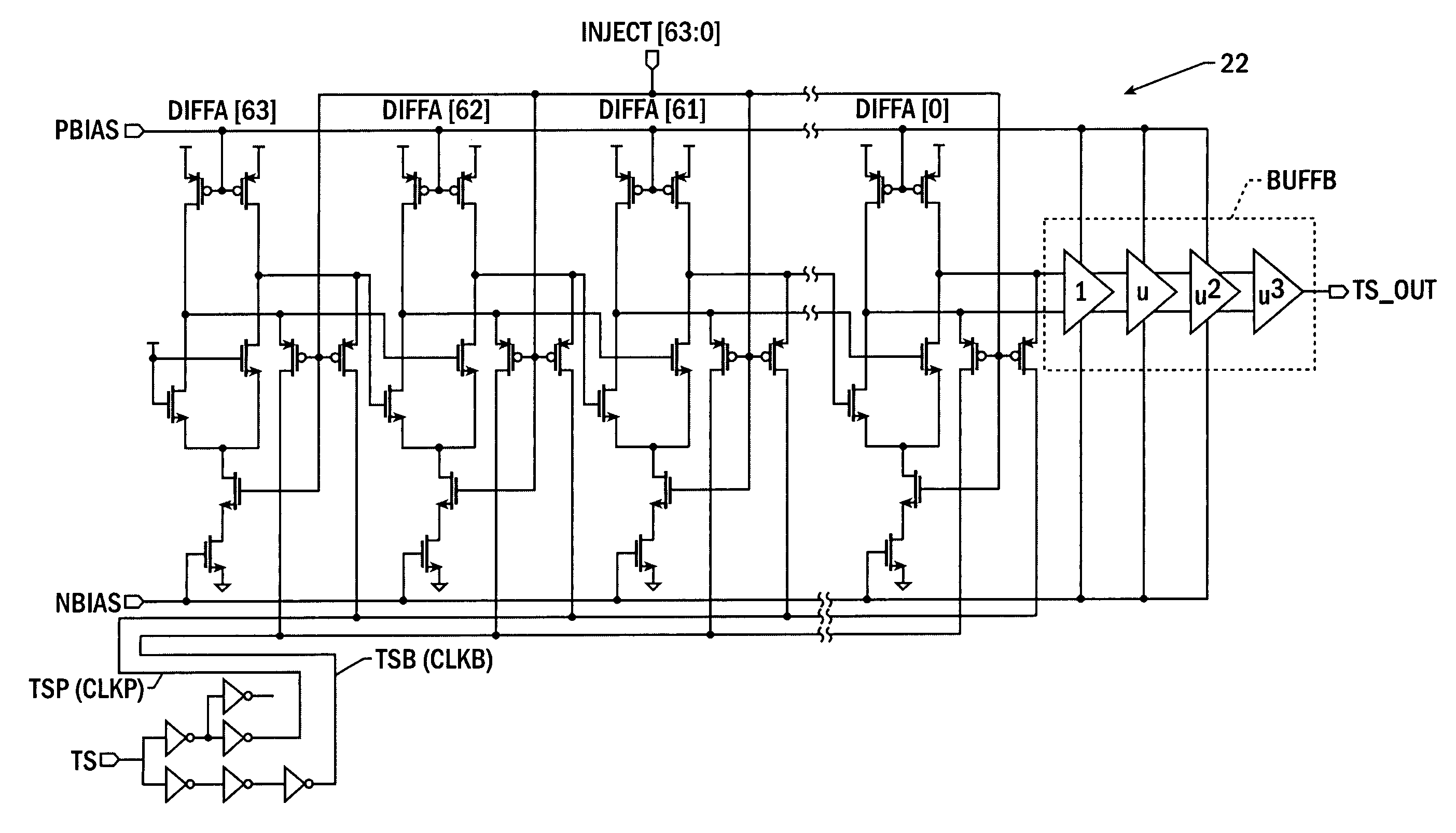

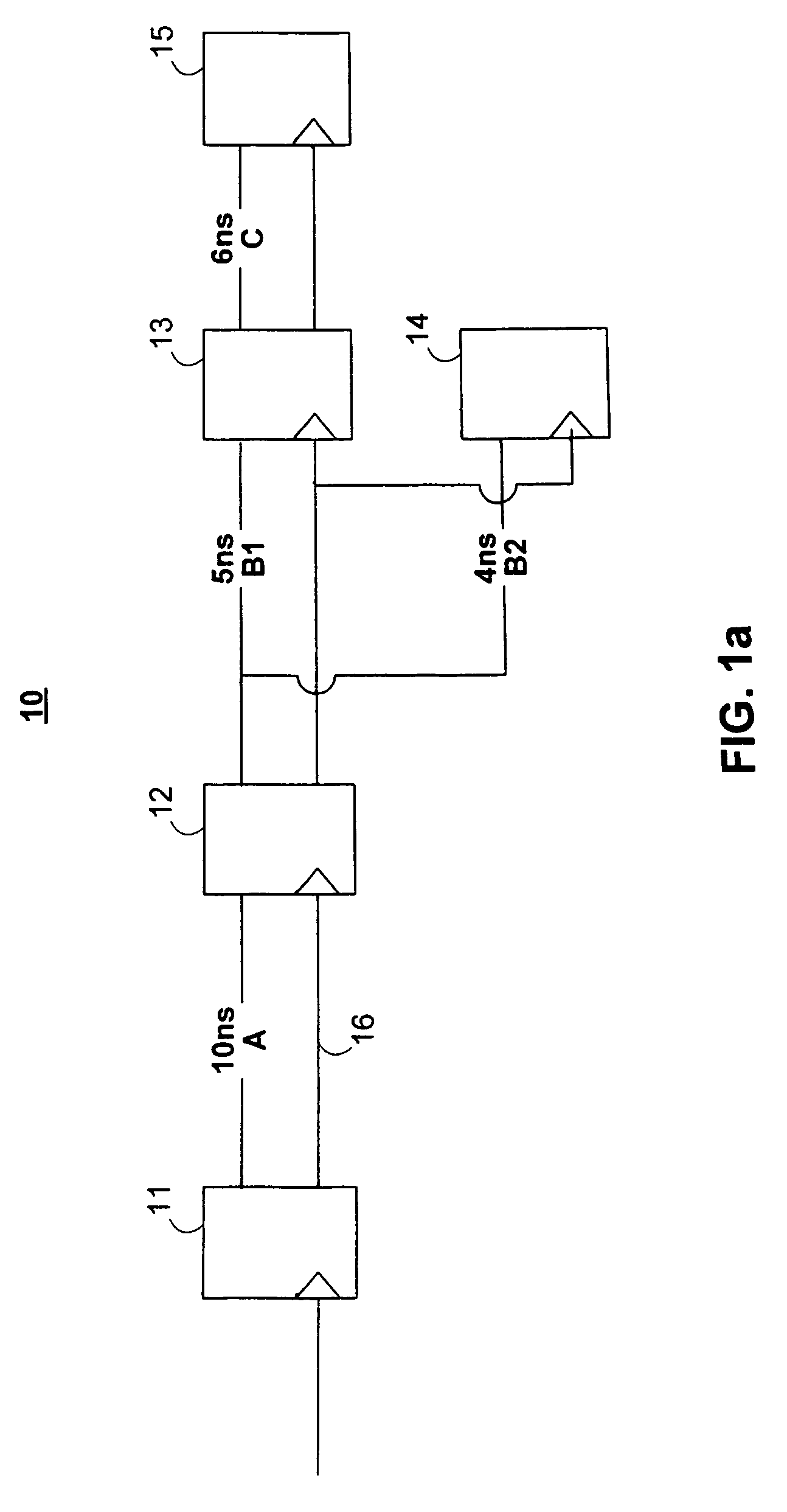

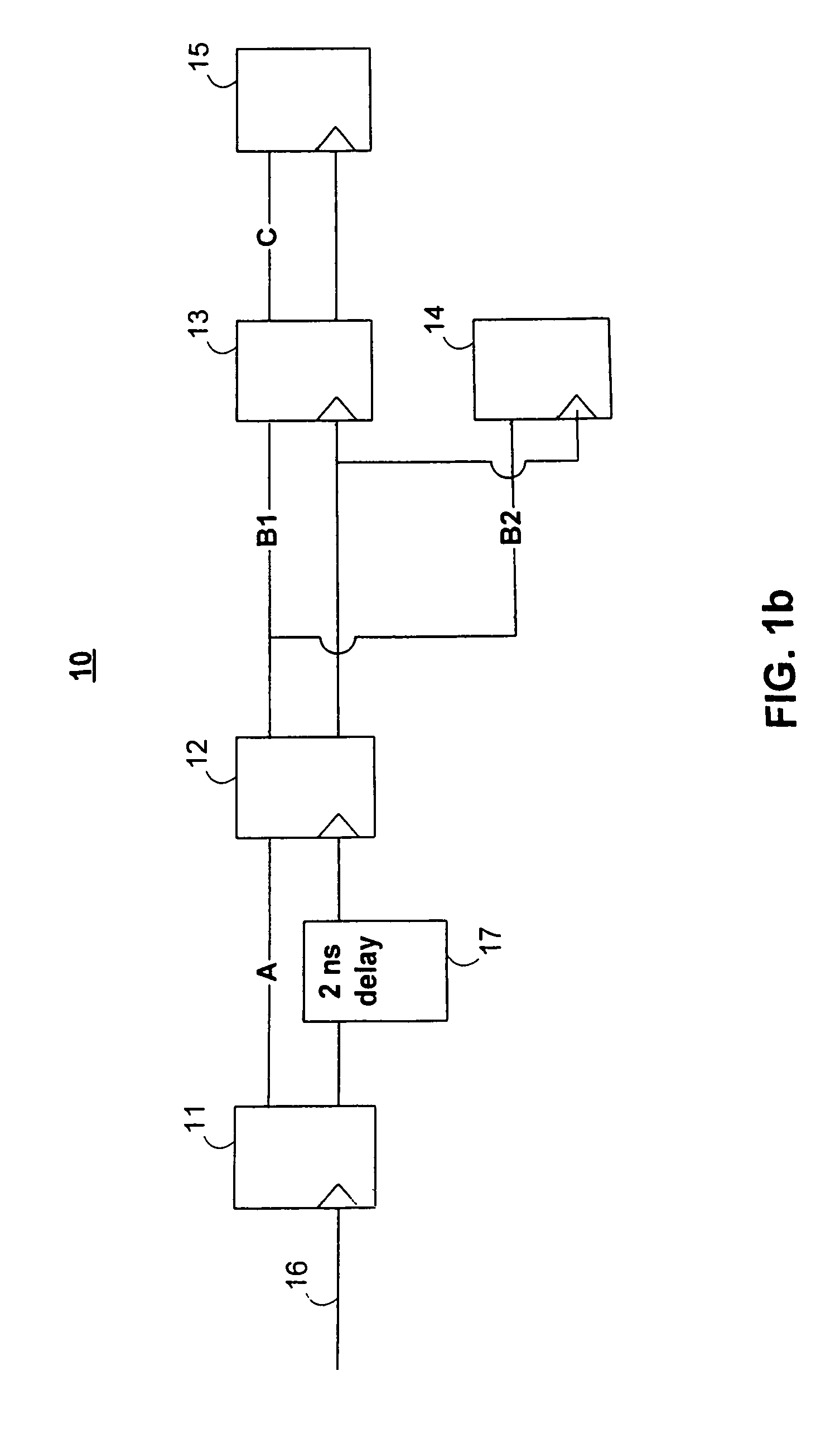

Integrated circuit devices having high precision digital delay lines therein

InactiveUS6856558B1High resolutionConvenient power supplyPulse automatic controlPulse generation by logic circuitsInjection portControl signal

Integrated circuit delay devices include a digital delay line that is configured to provide a percent-of-clock period delay to a timing signal accepted at an enabled one of a plurality of injection ports thereof. The digital delay line may be responsive to an injection control signal having a value that sets a length of the delay by specifying a location of the enabled one of the plurality of injection ports, with the end of the delay line being a fixed output port. A delay line control circuit is also provided that is responsive to a clock signal having a period from which the percent-of-clock period delay is preferably measured. The delay line control circuit is configured to generate the injection control signal by counting multiple cycles of a high frequency ring oscillator signal having a period less than, and typically substantially less than, the clock period, over a time interval having a duration greater than, and typically substantially greater than, the clock period. The ring oscillator signal may be generated by a ring oscillator having a relatively small number of stages and the time interval may be sufficiently long so that a large number of cycles of the ring oscillator signal may be counted over many periods of the clock signal.

Owner:SK HYNIX INC

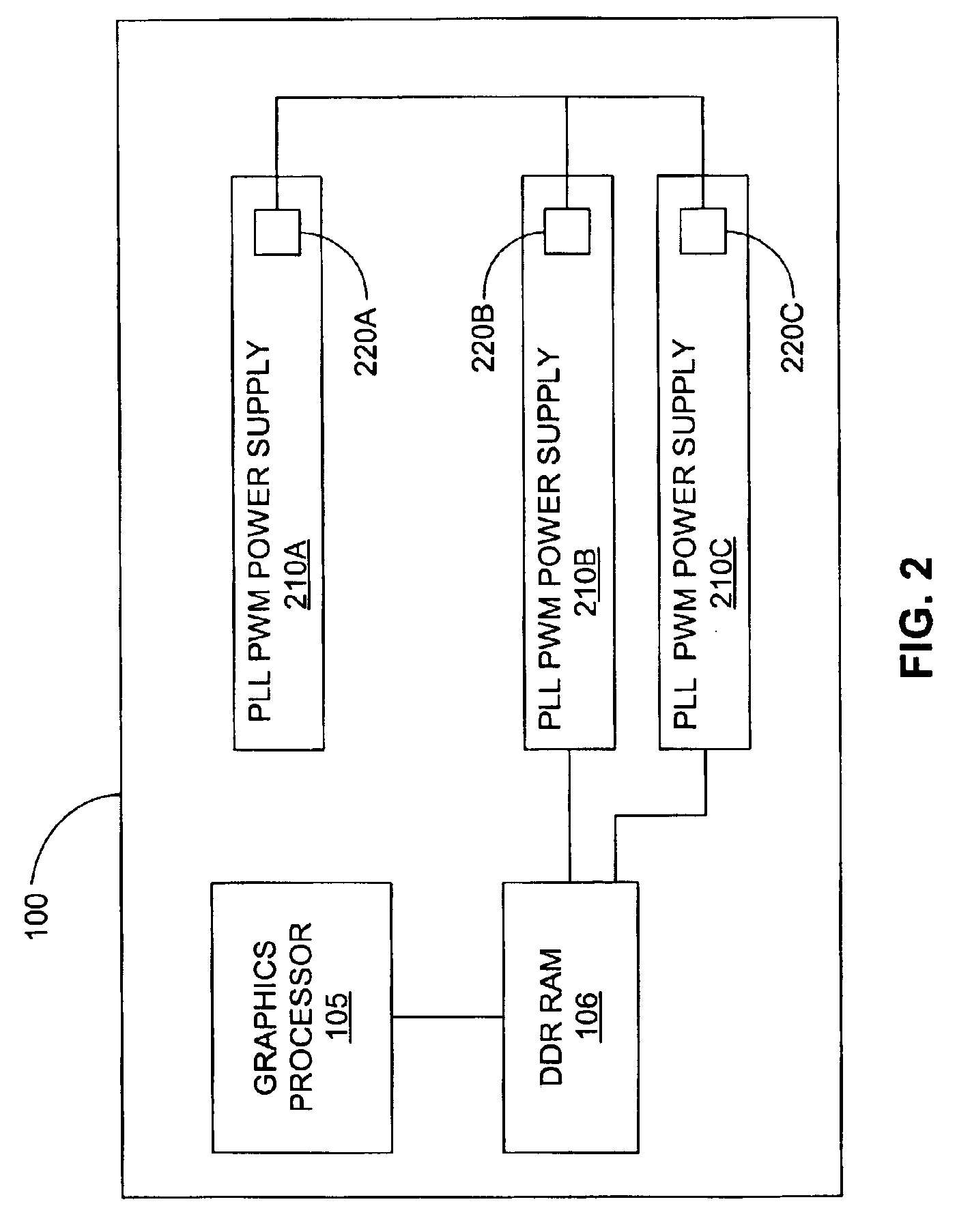

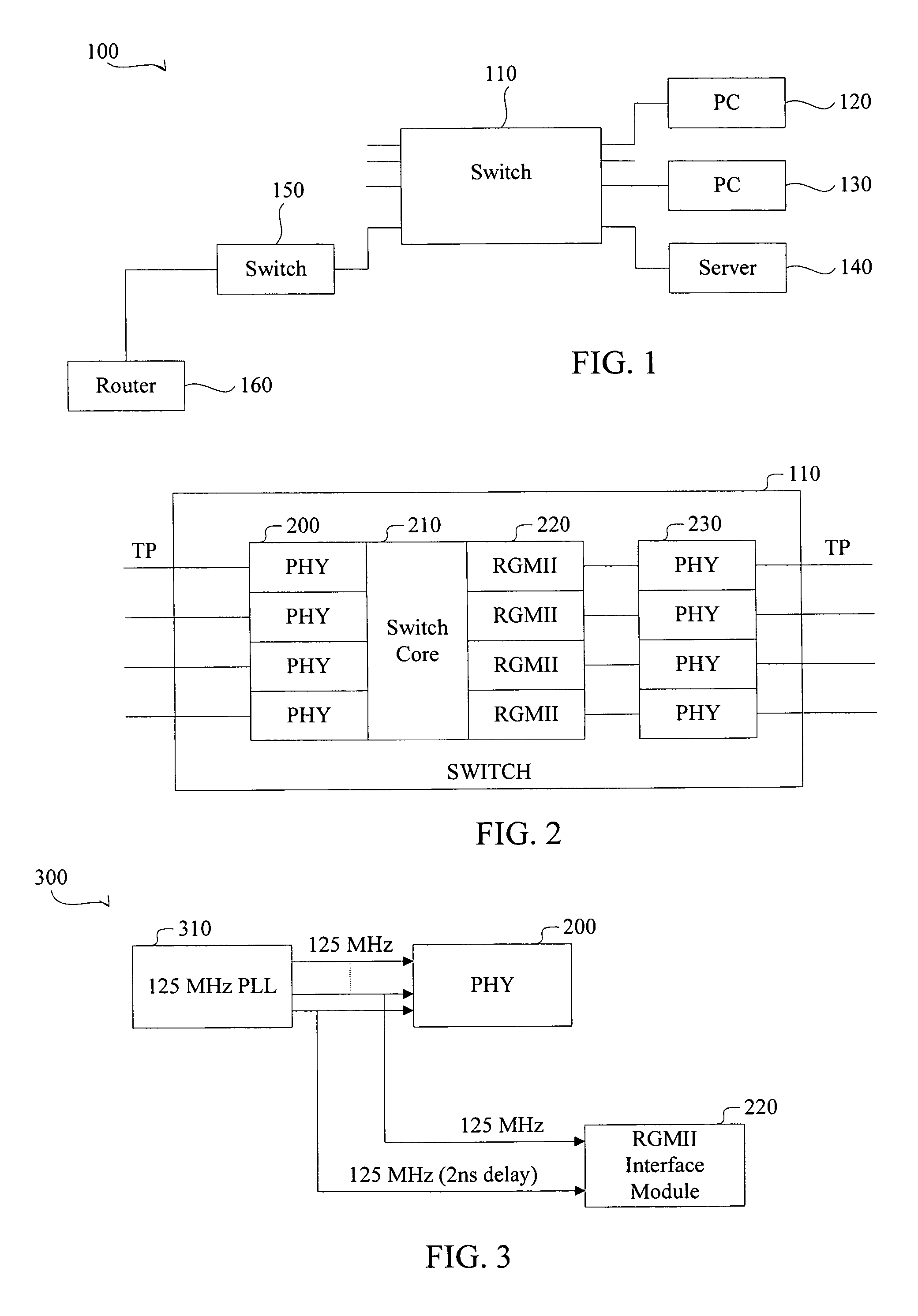

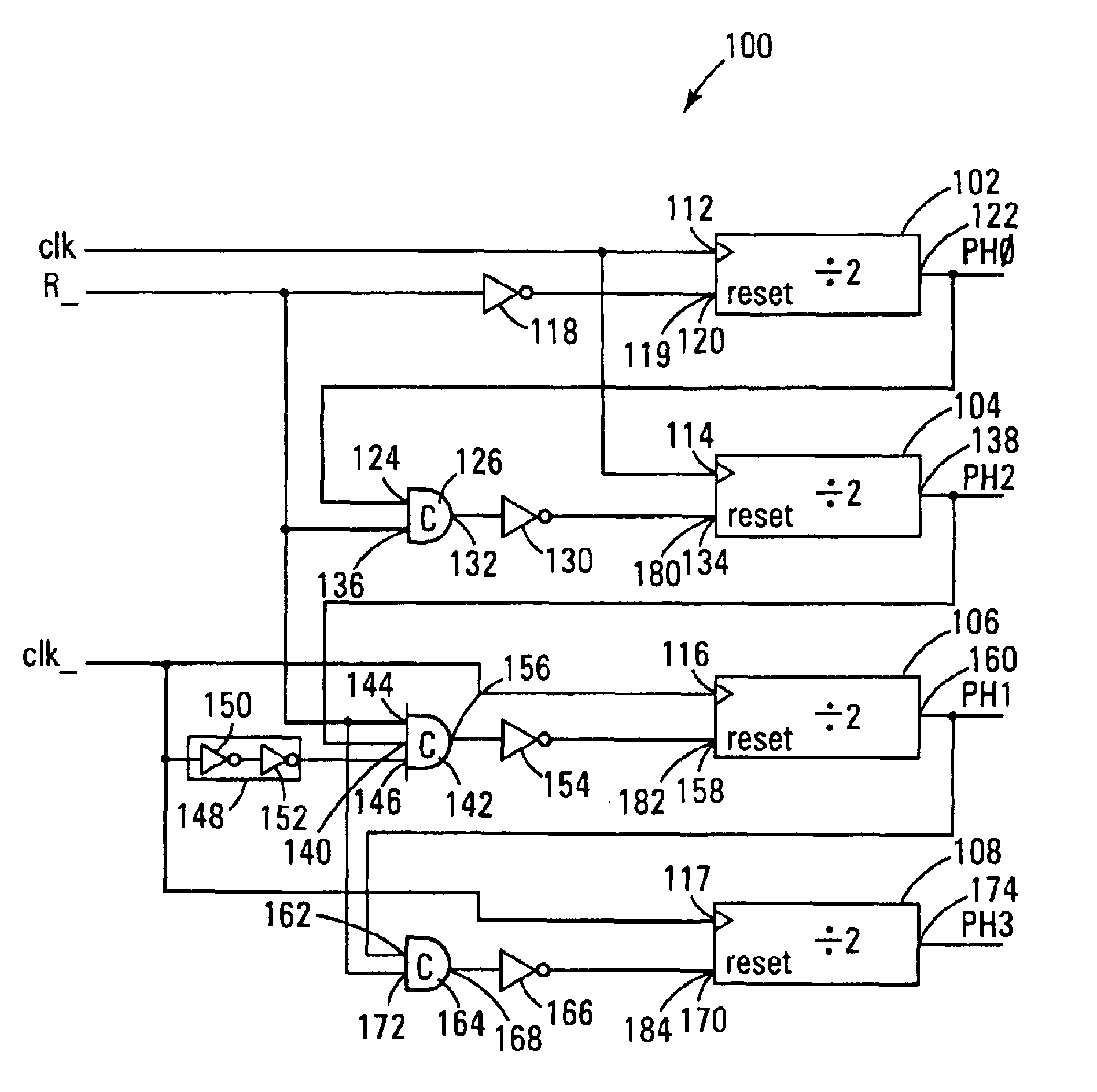

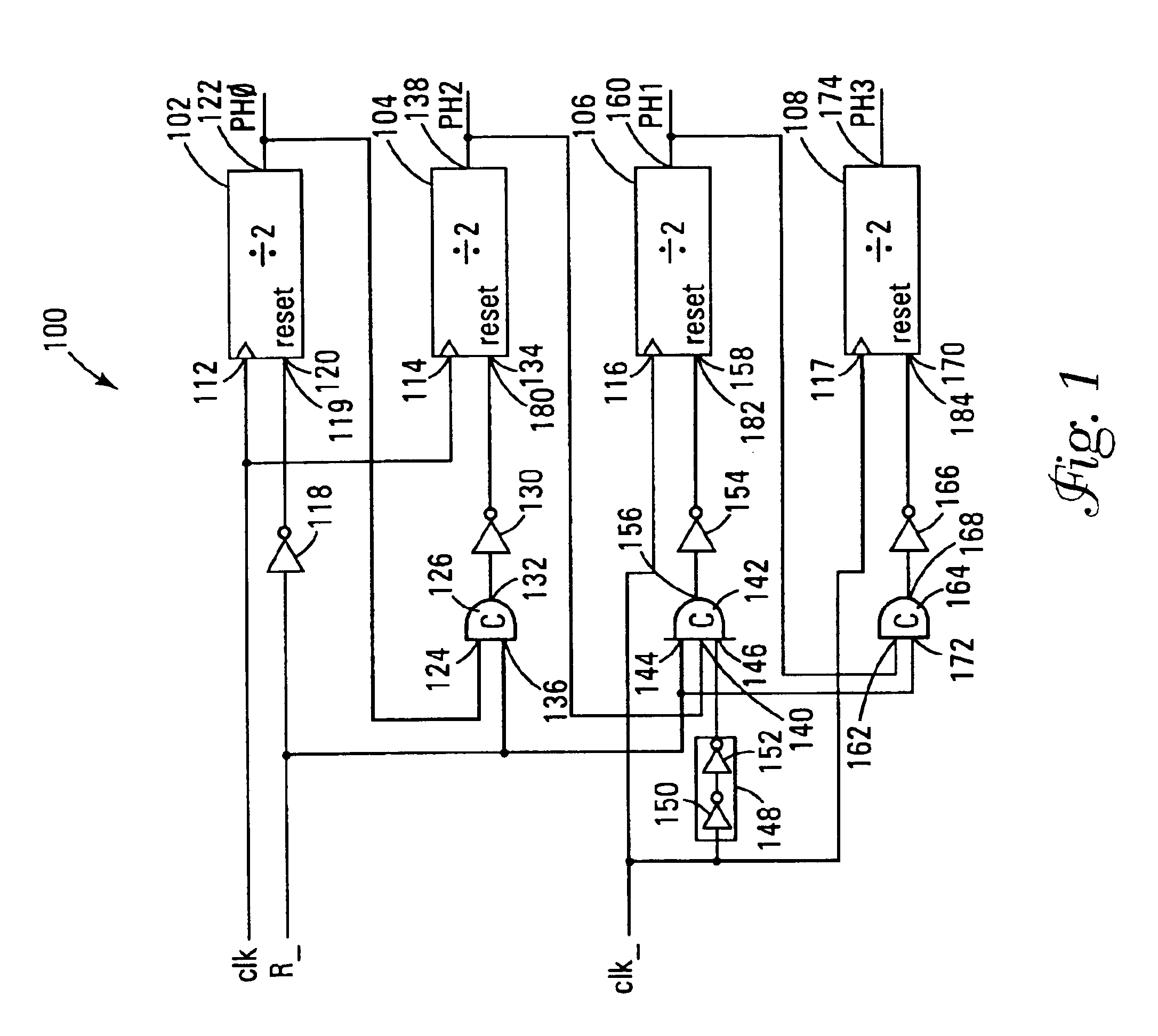

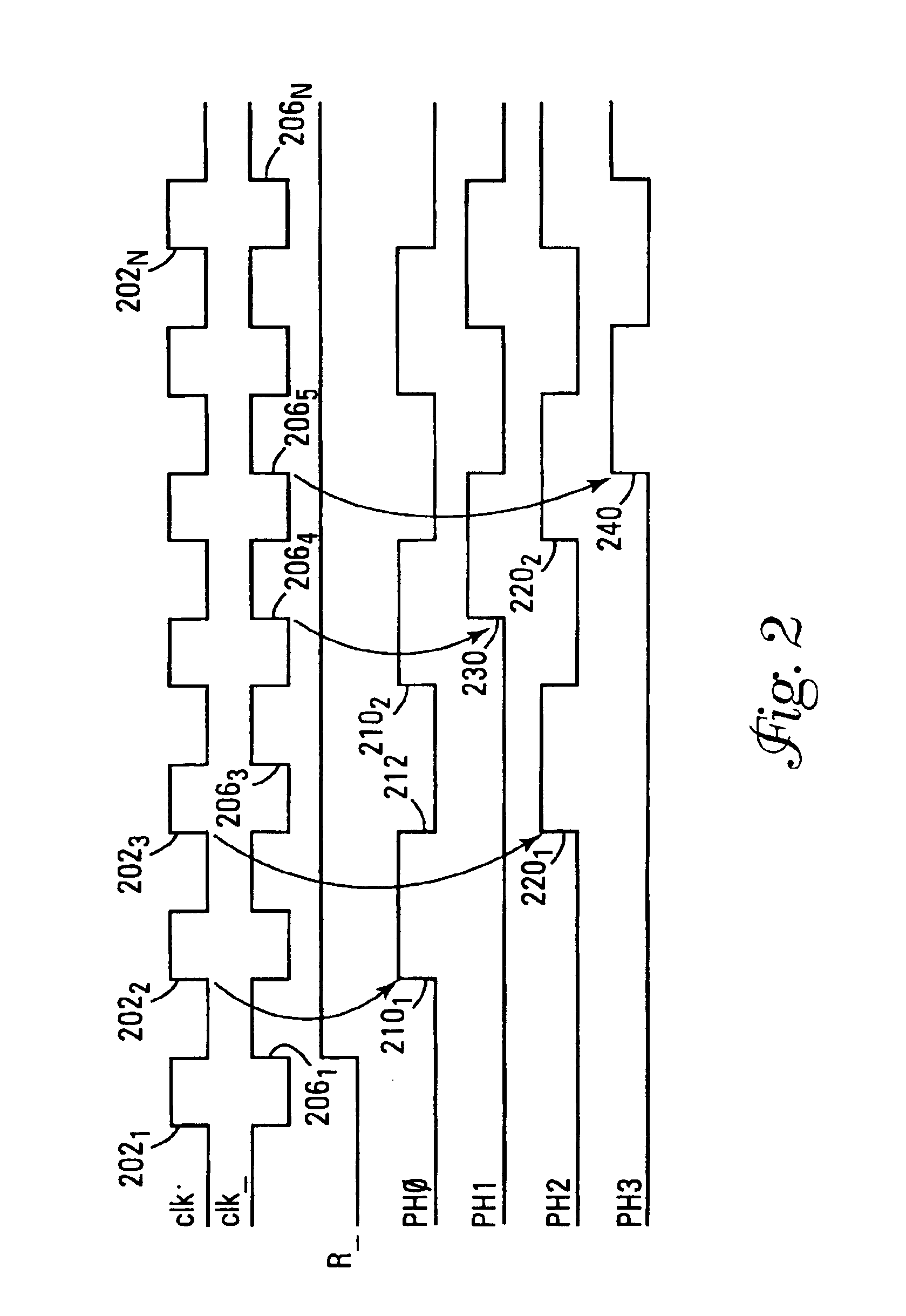

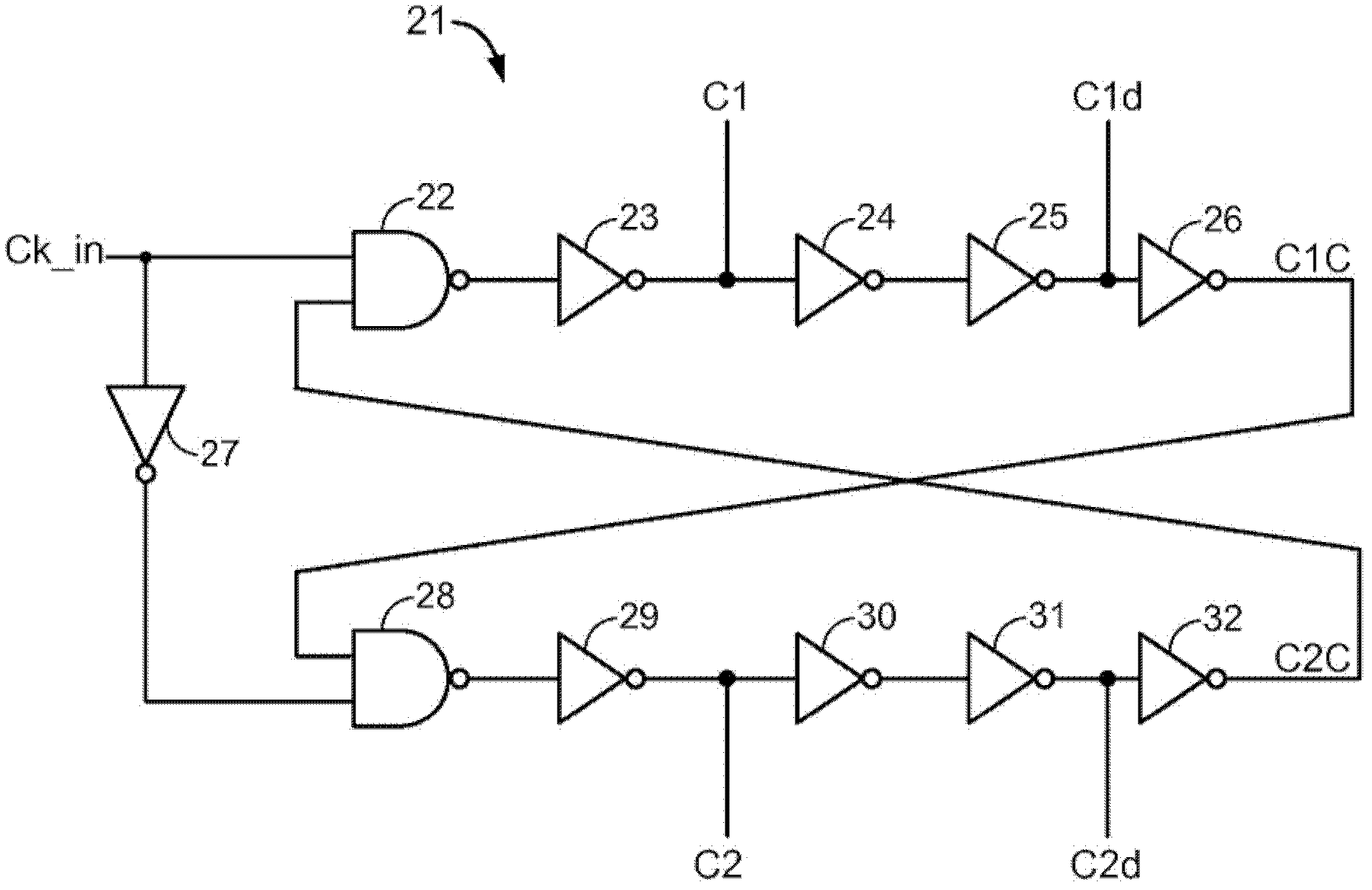

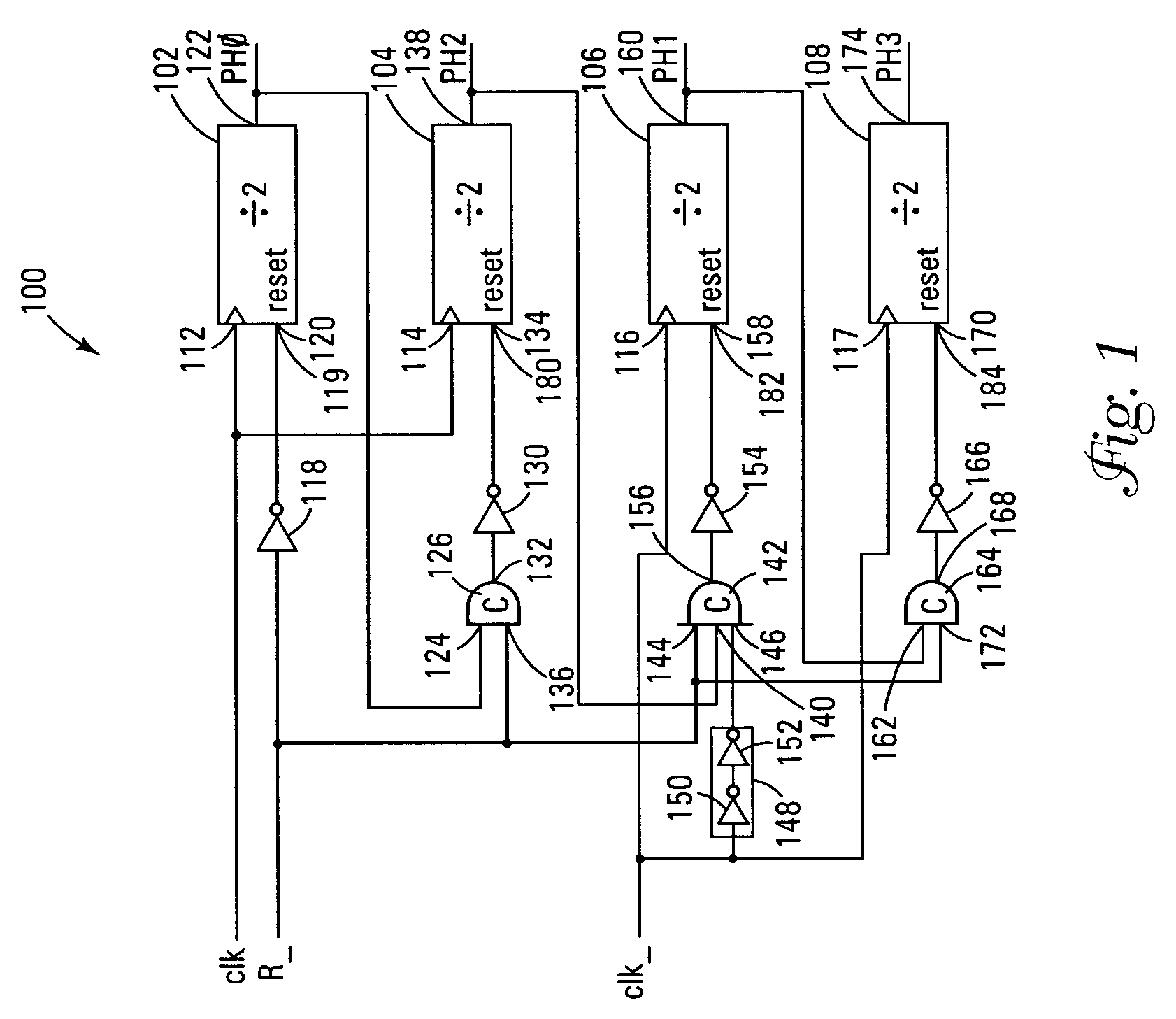

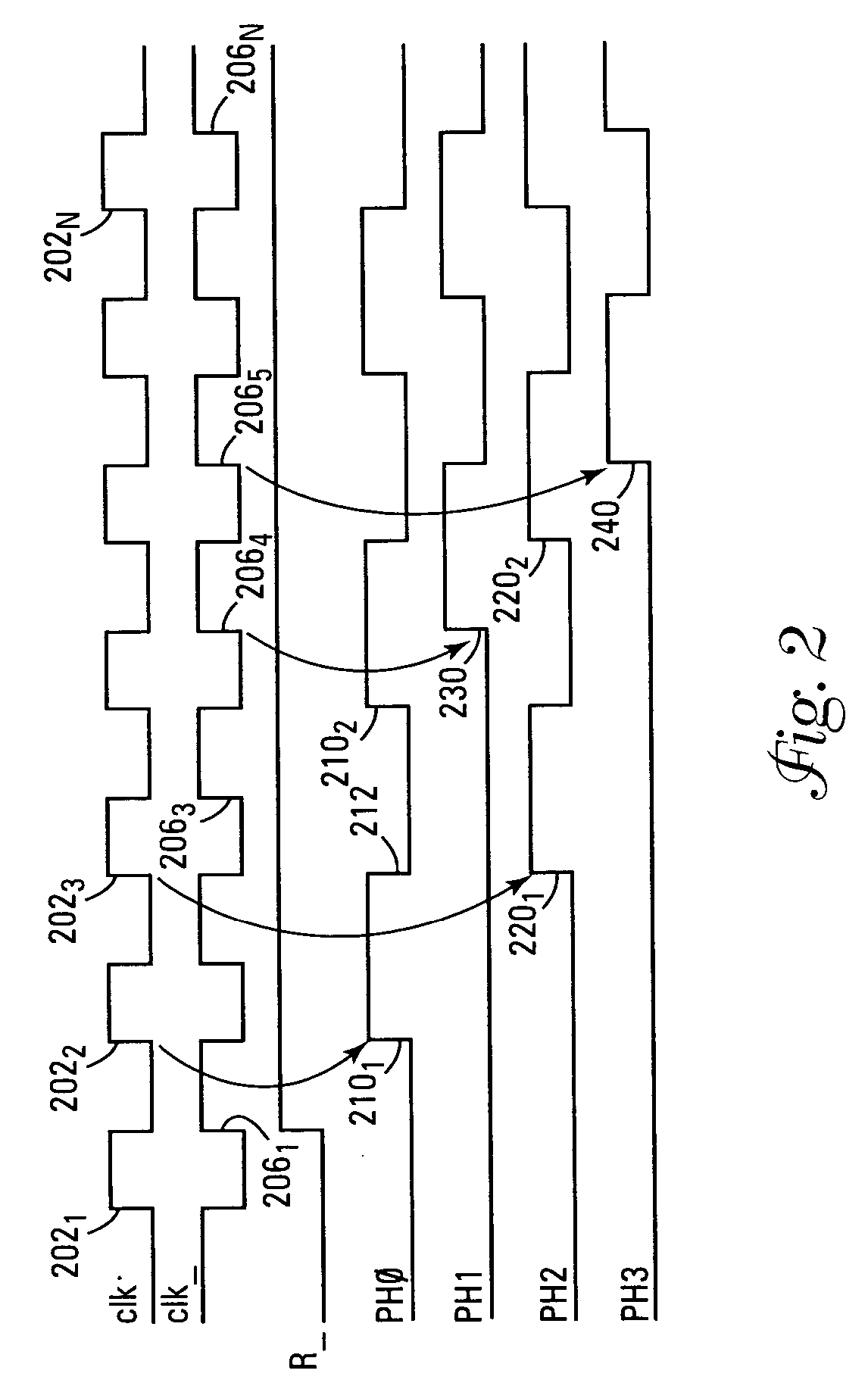

Multiphase clock generators

Multiphase clock generators and methods are provided. A multiphase clock generator has a first clock divider for generating a first-phase clock signal from a first input clock signal. A first logic gate is connected to an output port of the first clock divider. A second clock divider is connected to an output port of the first logic gate. The second clock divider is for generating a second-phase clock signal from the first input clock signal. A second logic gate is connected to an output port of the second clock divider. A third clock divider is connected to an output port of the second logic gate. The third clock divider is for generating a third-phase clock signal from a second input clock signal.

Owner:MICRON TECH INC

Generating multi-phase clock signals using hierarchical delays

Circuits and methods for generating multi-phase clock signals using digitally-controlled hierarchical delay units (HDs) are provided. A plurality of serially-coupled HDs outputs clock signals that are phase-shifted relative to a reference clock signal. Each HD includes either one or two variable delay lines that provide coarse phase adjustment of an associated input signal. Each HD also includes one or more phase mixers that provide fine phase adjustment of the input signal.

Owner:ROUND ROCK RES LLC

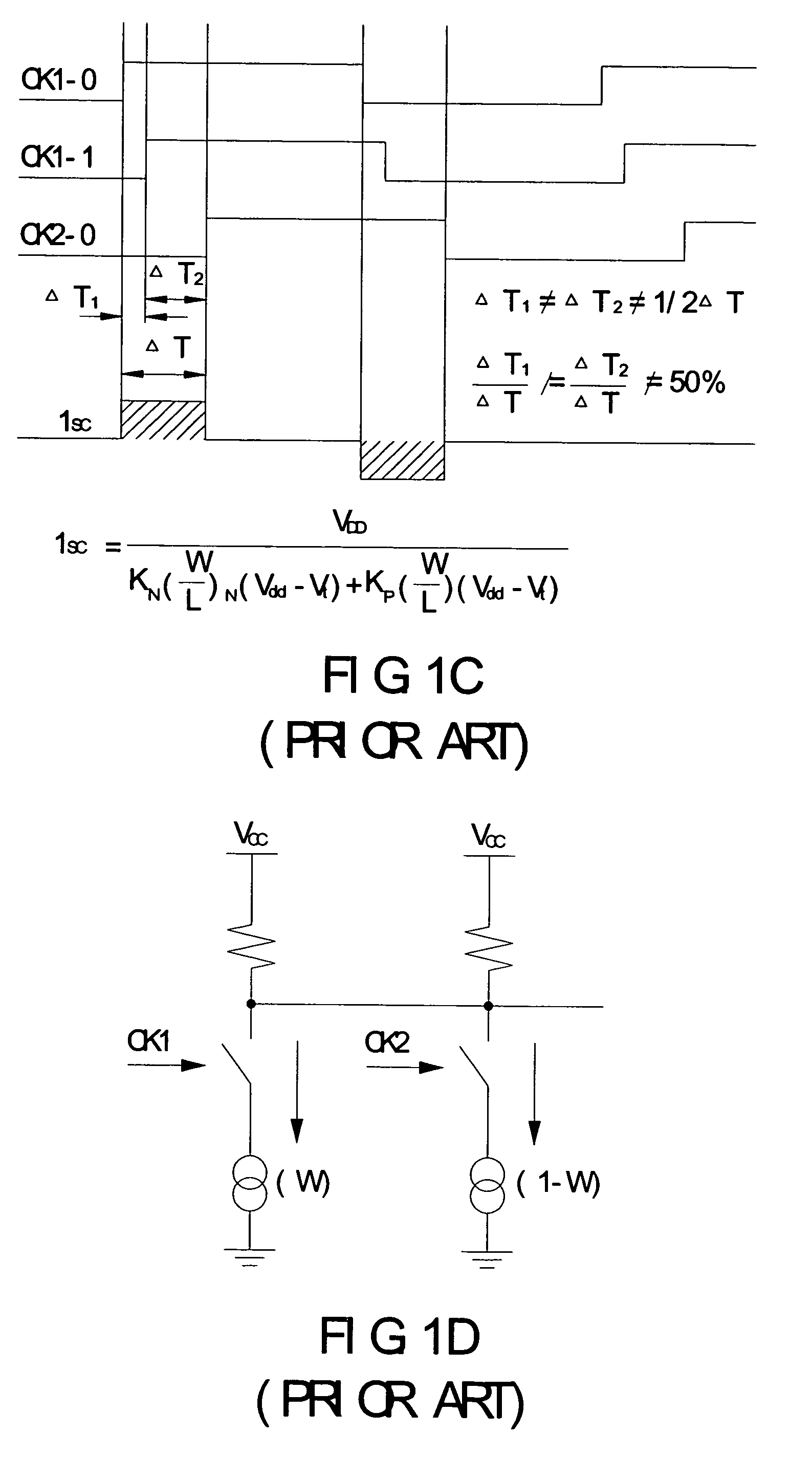

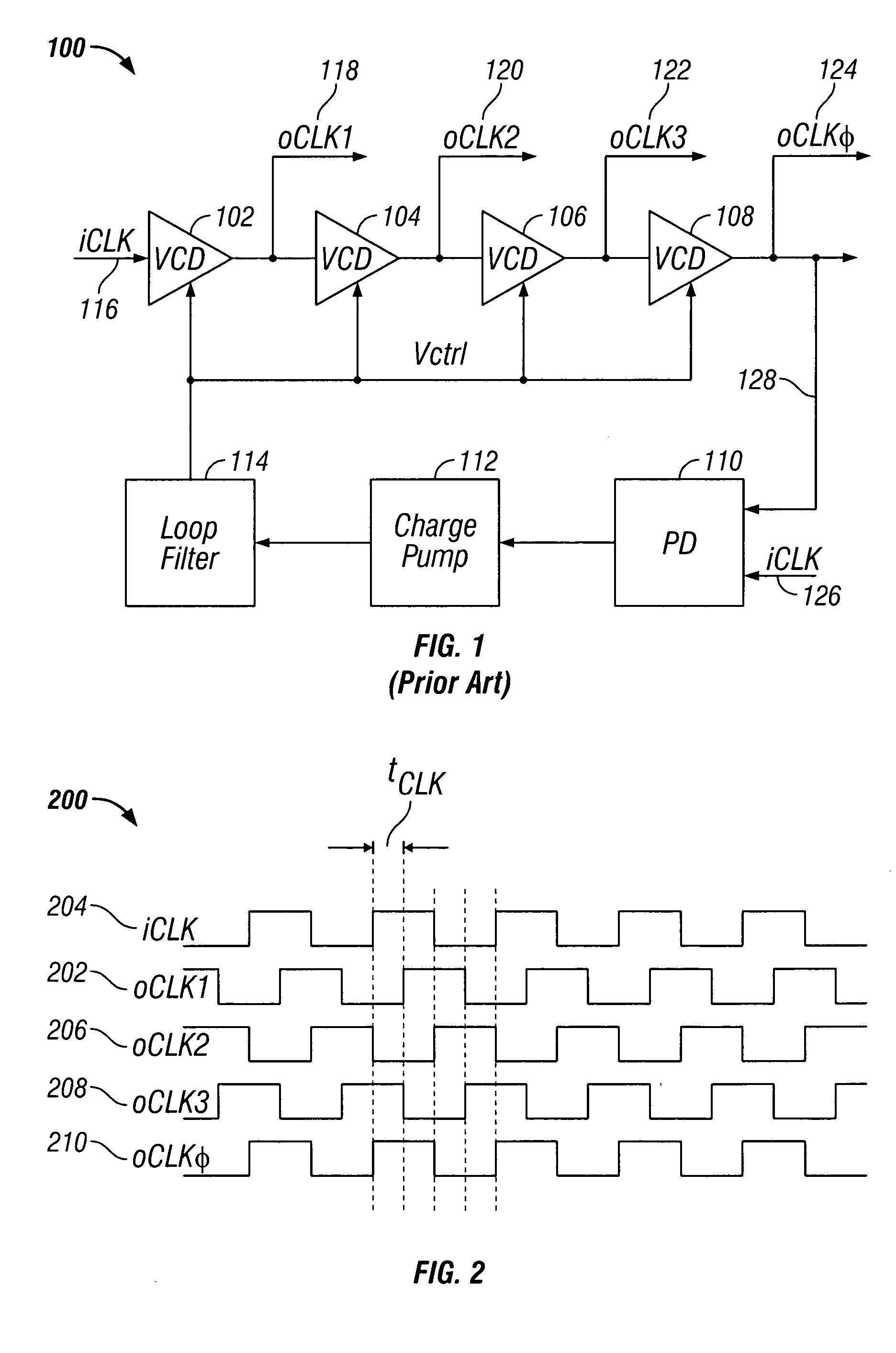

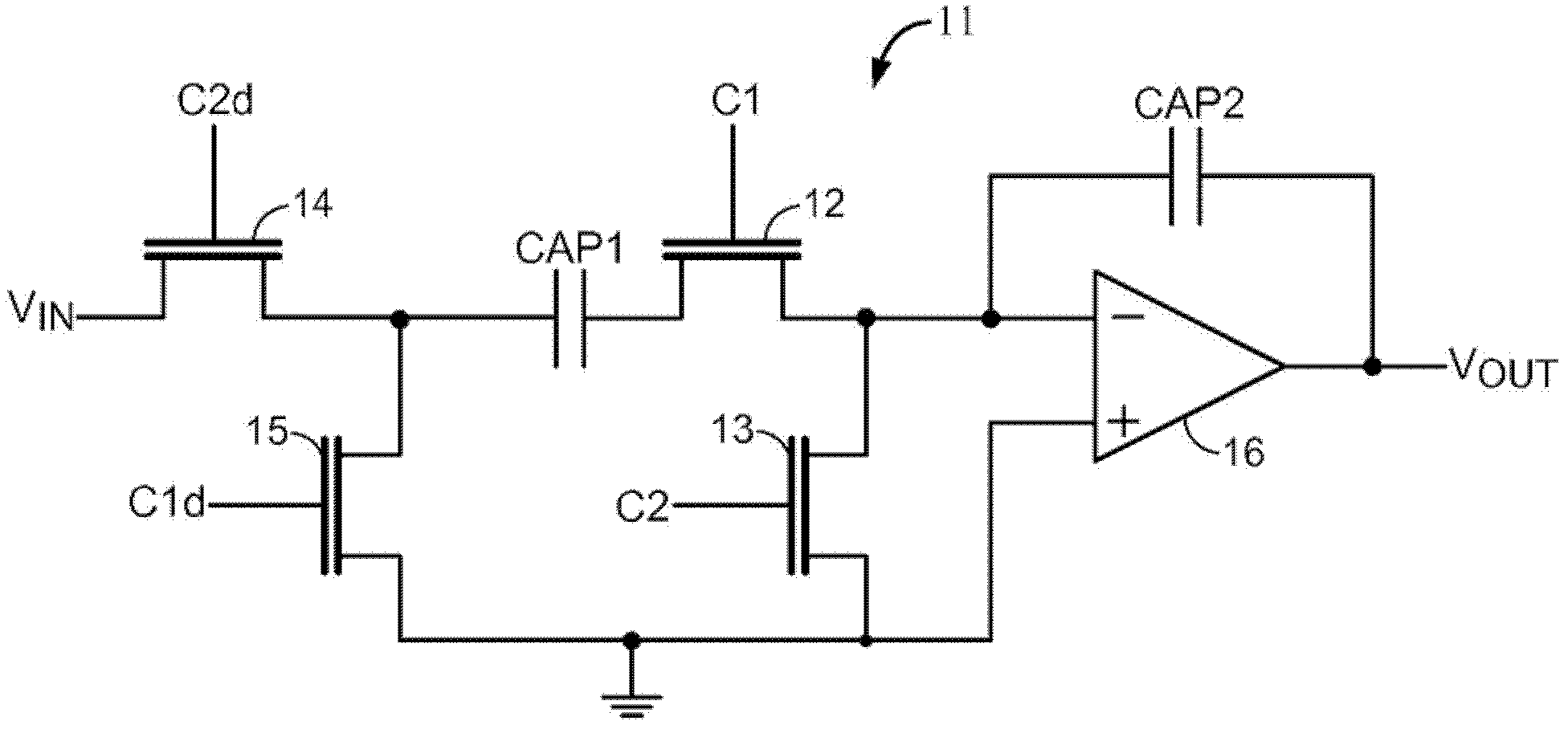

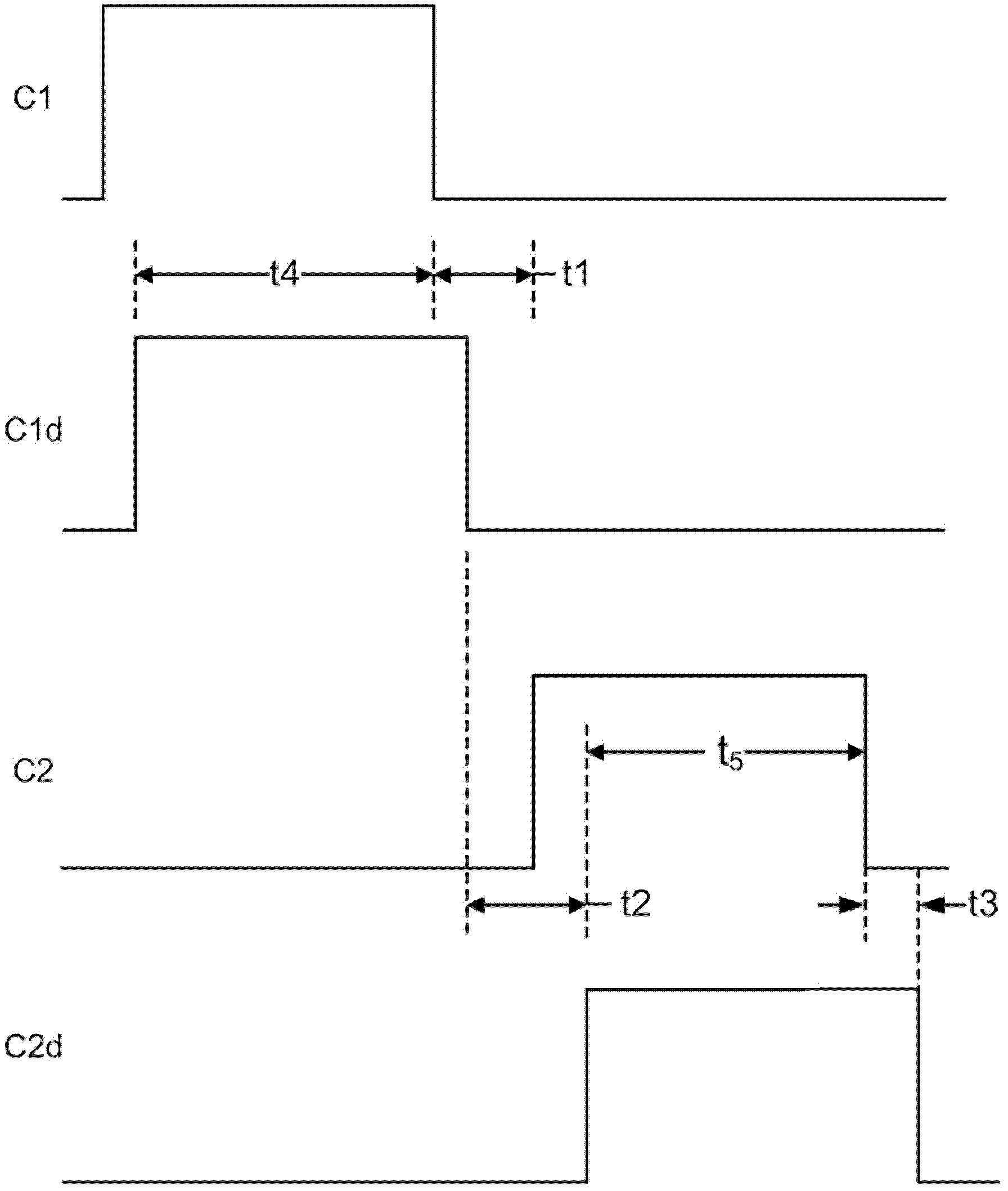

Techniques for non-overlapping clock generation

Techniques for generating precise non-overlap time and clock phase delay time across a desired frequency range are provided. In one configuration, a device includes a non-overlapping clock generation circuit which comprises a delay lock loop (DLL) circuit that in turn generates a control voltage to a clock generator circuit coupled thereto. The control voltage operates to maintain precise timing relationship of non- overlapping delayed clock signals generated by the clock generator circuit. In one aspect, the DLL circuit receives an input clock with a known duty cycle and derives an output control voltage to fix the unit delay to a certain portion of the input clock cycle. In a further aspect, the clock generator circuit includes a plurality of voltage-controlled delay cells coupled to the DLL circuit to generate a first set of clock signals and a second set of clock signals delayed from the first set of clock signals by a non- overlapping time (tnlp) that is independent of manufacturing process variations.

Owner:QUALCOMM INC

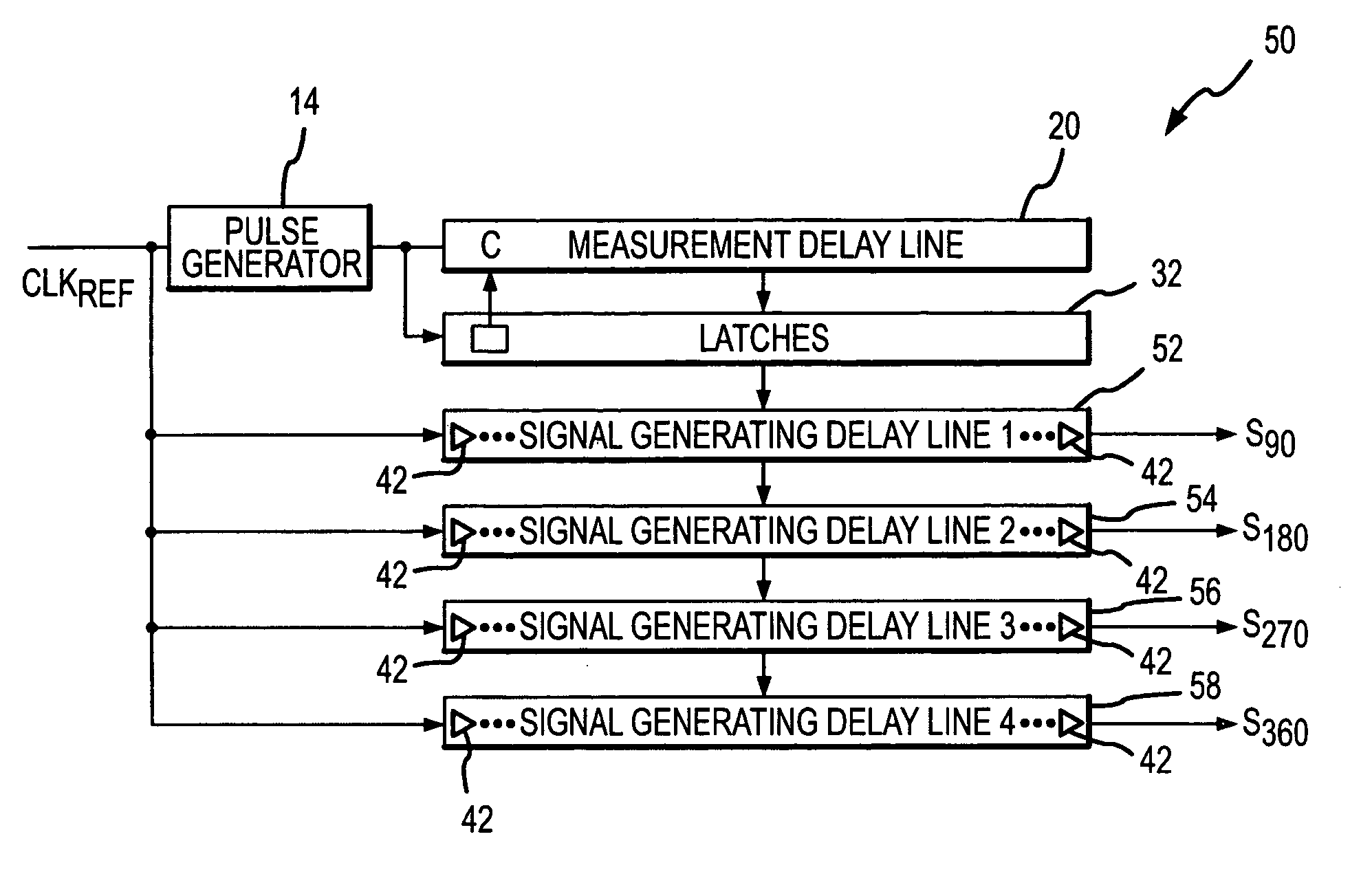

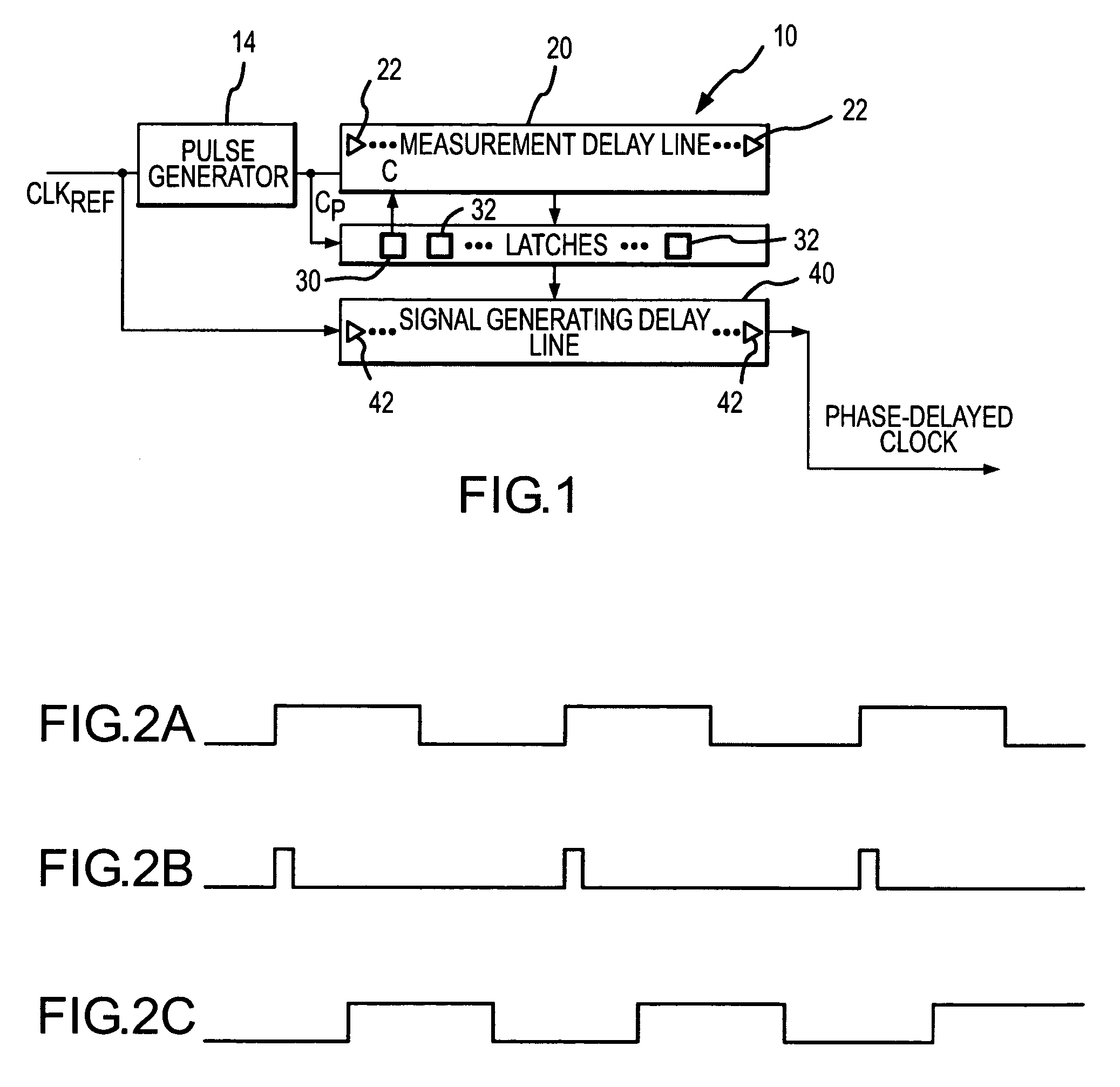

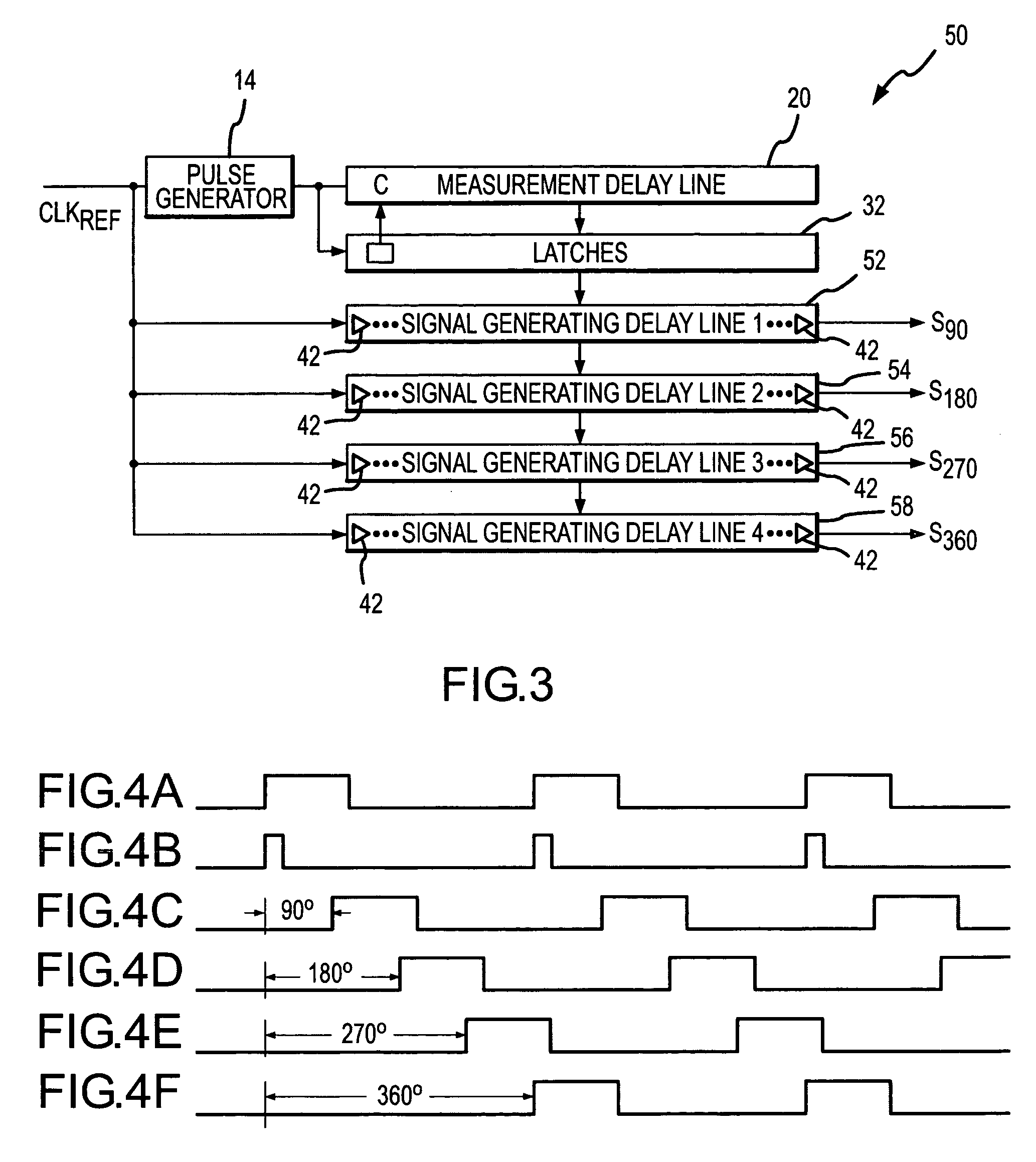

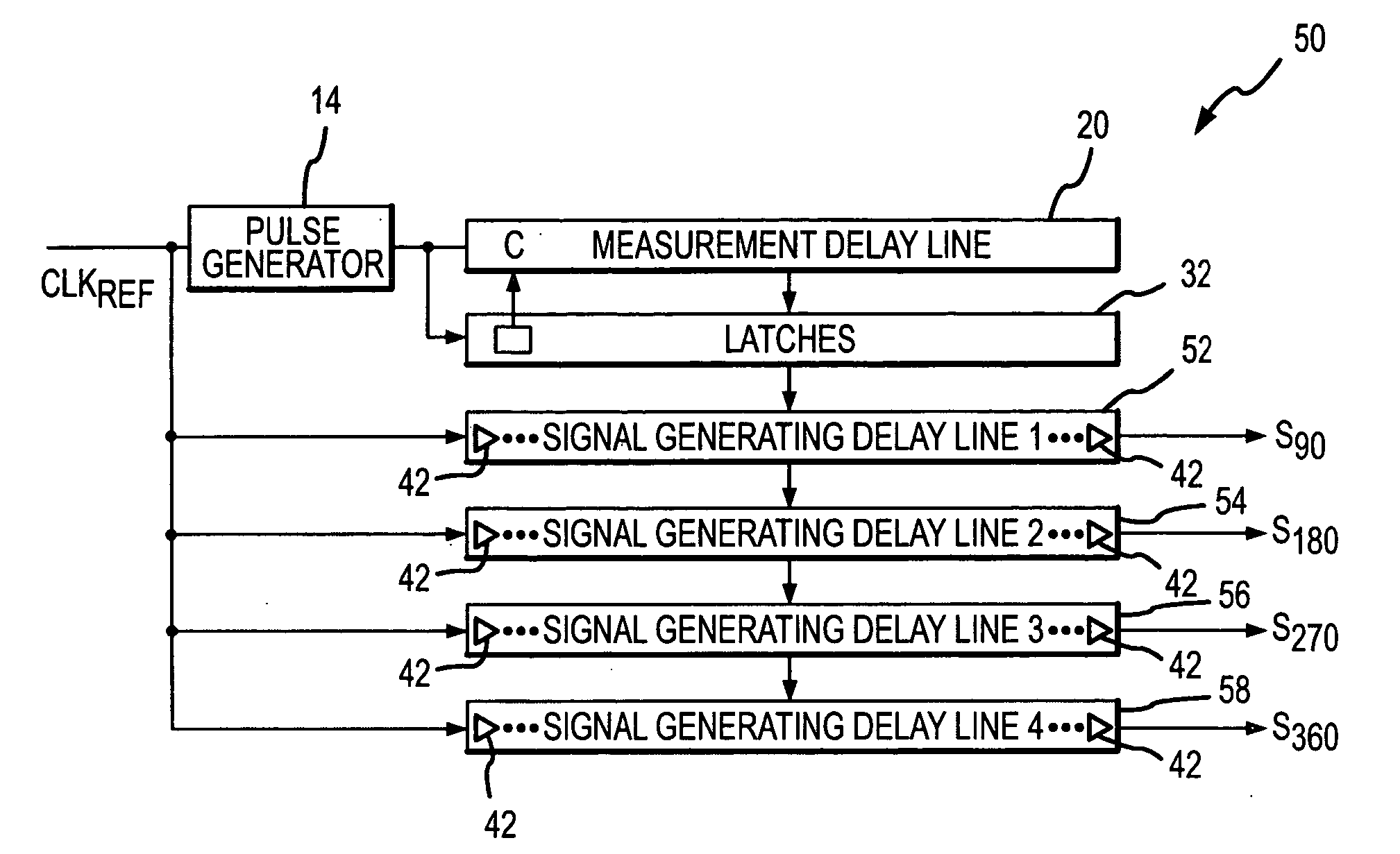

System and method for reduced power open-loop synthesis of output clock signals having a selected phase relative to an input clock signal

InactiveUS7078951B2Reduce degradationReduce power consumptionDigital storagePhase shifterEngineeringMeasurement delay

A signal generating circuit includes a pulse generator generating a pulse responsive to a periodic clock reference signal. The pulse propagates through a plurality of series-connected delay elements in a measurement delay line. The measurement delay line is coupled to a series of latches that correspond to respective groups of delay elements in the measurement delay line. The delay element to which the pulse has propagated when the next pulse is received causes a corresponding latch to be set. The clock reference signal propagates through a signal generating delay line, which contains a sub-multiple of the number of delay elements in the measurement delay line, starting at a location corresponding to the set latch. The latch may remain set for a large number of periods of the clock reference signal so that it is not necessary for the clock reference signal to propagate through the measurement delay line each cycle.

Owner:MICRON TECH INC

System and method for reduced power open-loop synthesis of output clock signals having a selected phase relative to an input clock signal

InactiveUS20060044037A1Reduce delay of delay lineReduce power consumptionDigital storagePhase shifterEngineeringMeasurement delay

A signal generating circuit includes a pulse generator generating a pulse responsive to a periodic clock reference signal. The pulse propagates through a plurality of series-connected delay elements in a measurement delay line. The measurement delay line is coupled to a series of latches that correspond to respective groups of delay elements in the measurement delay line. The delay element to which the pulse has propagated when the next pulse is received causes a corresponding latch to be set. The clock reference signal propagates through a signal generating delay line, which contains a sub-multiple of the number of delay elements in the measurement delay line, starting at a location corresponding to the set latch. The latch may remain set for a large number of periods of the clock reference signal so that it is not necessary for the clock reference signal to propagate through the measurement delay line each cycle.

Owner:MICRON TECH INC

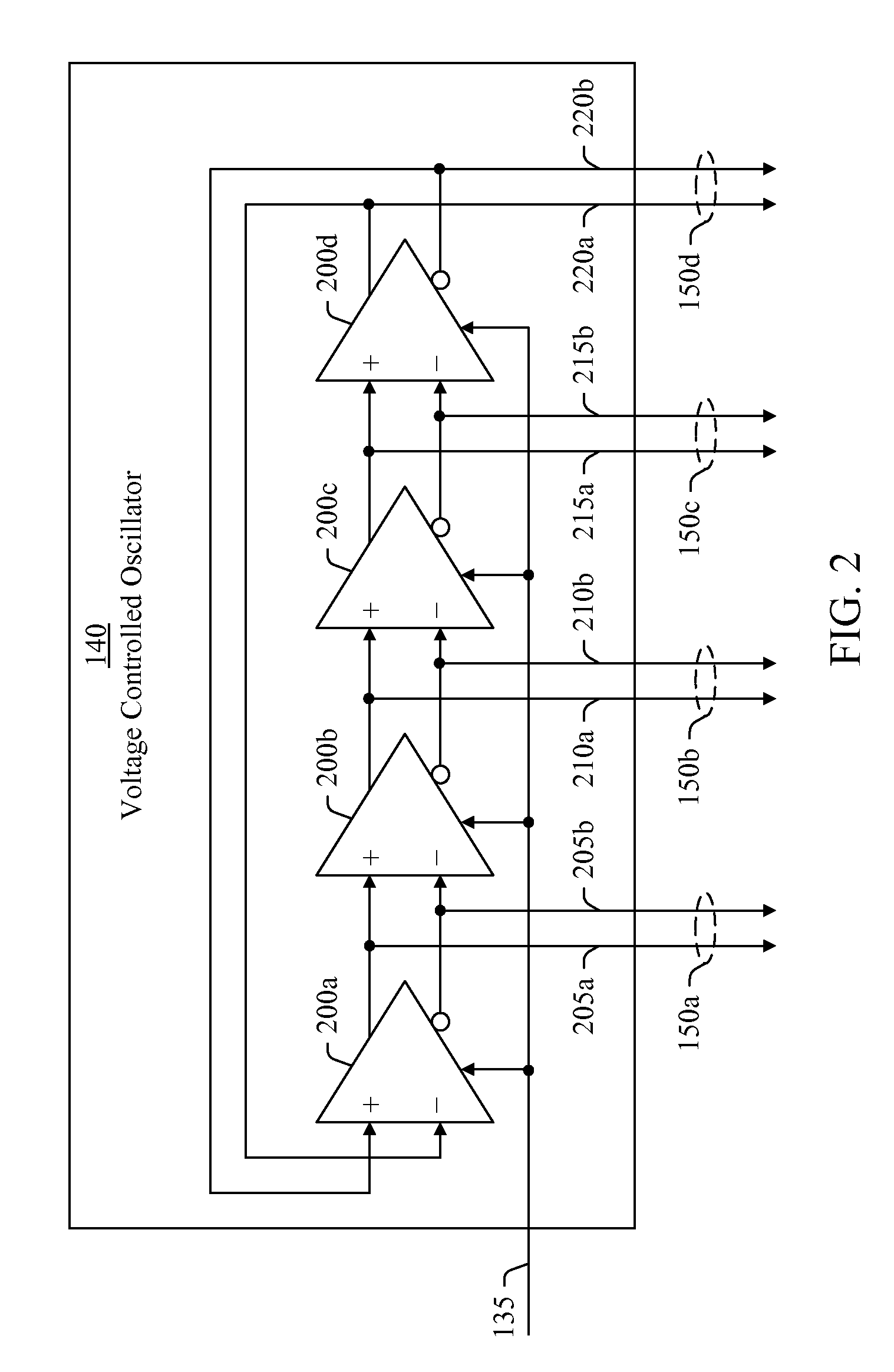

Quadrature-phase voltage controlled oscillator

InactiveUS20080252386A1Reduce power consumptionPulse automatic controlPulse generation by logic circuitsControl signalEngineering

A voltage controlled oscillator (VCO) is provided. The VCO may include a first ring oscillation circuit that may have a plurality of delay cells and may output first differential oscillation signals, and a second ring oscillation circuit that may have a plurality of delay cells and may output second differential oscillation signals. The delay cells of the first ring oscillation circuit may be respectively cross-coupled to the corresponding delay cells of the second ring oscillation circuit. Each of the delay cells may include a differential amplification circuit that may output a first differential signal based on a first control signal, and a negative resistance circuit that may be connected in parallel to a pair of output terminals of the differential amplification circuit, may receive a second differential signal, may adjust the phase of the first differential signal based on a second control signal, and may then output the first differential signal.

Owner:SAMSUNG ELECTRONICS CO LTD

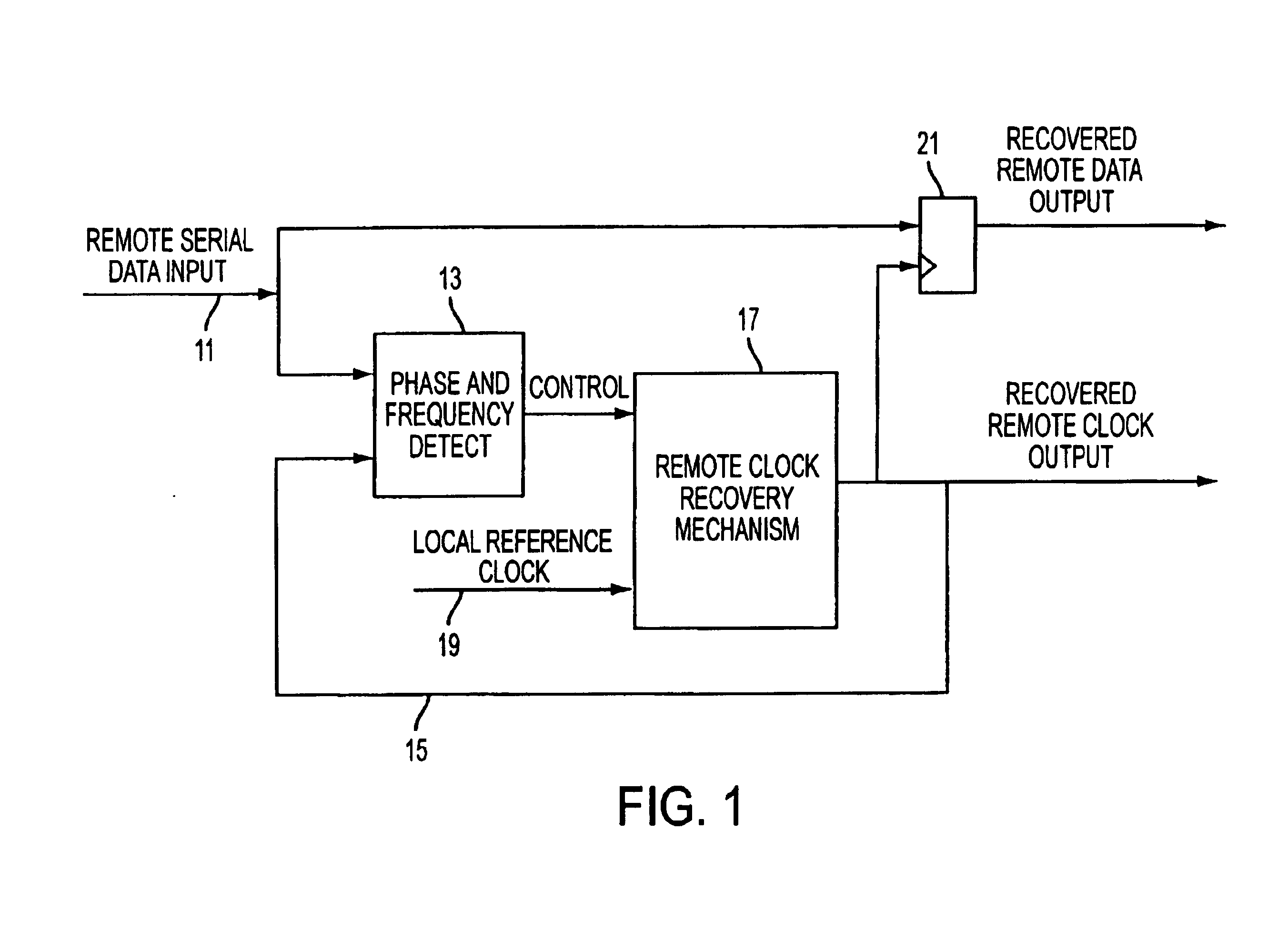

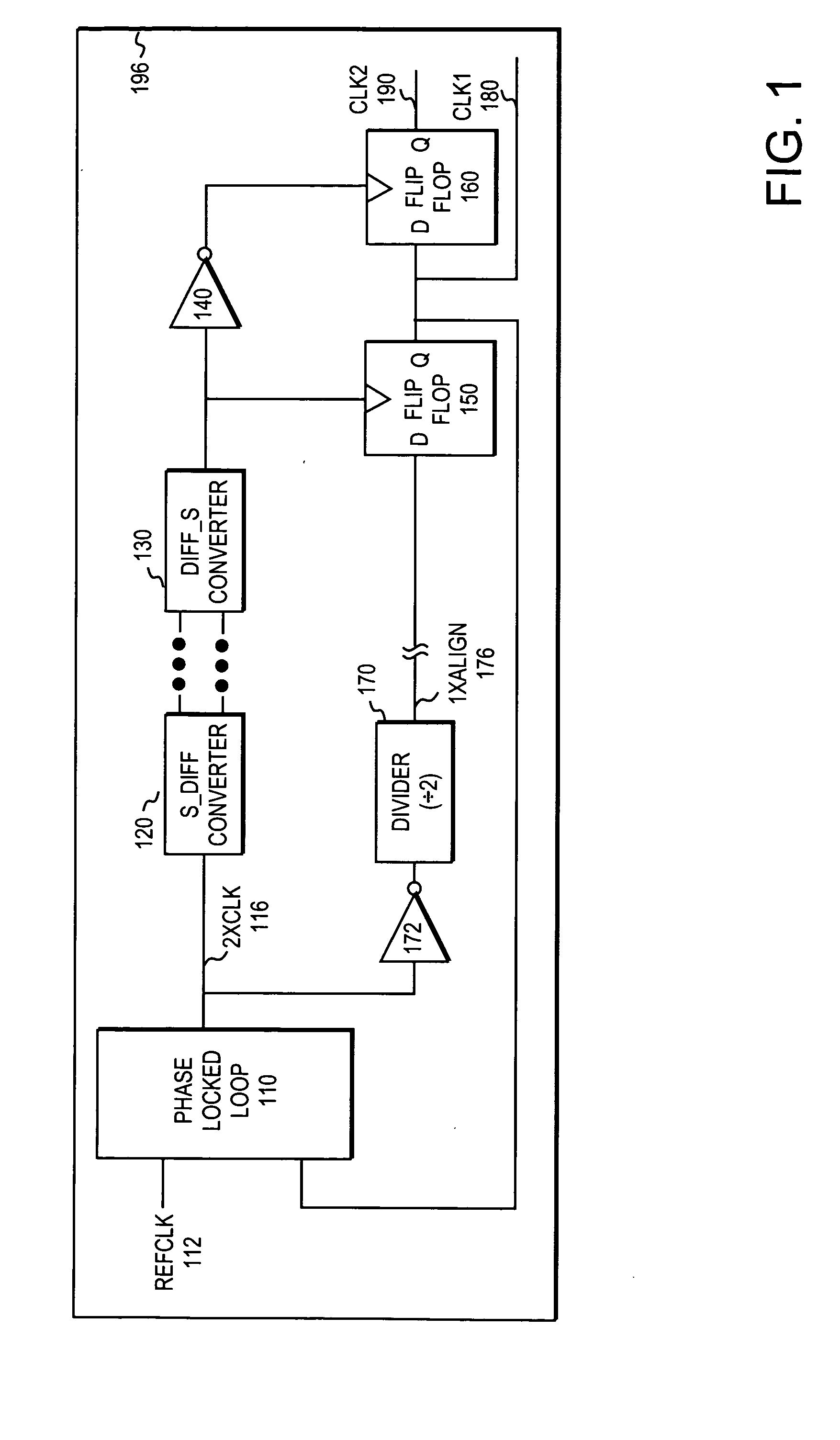

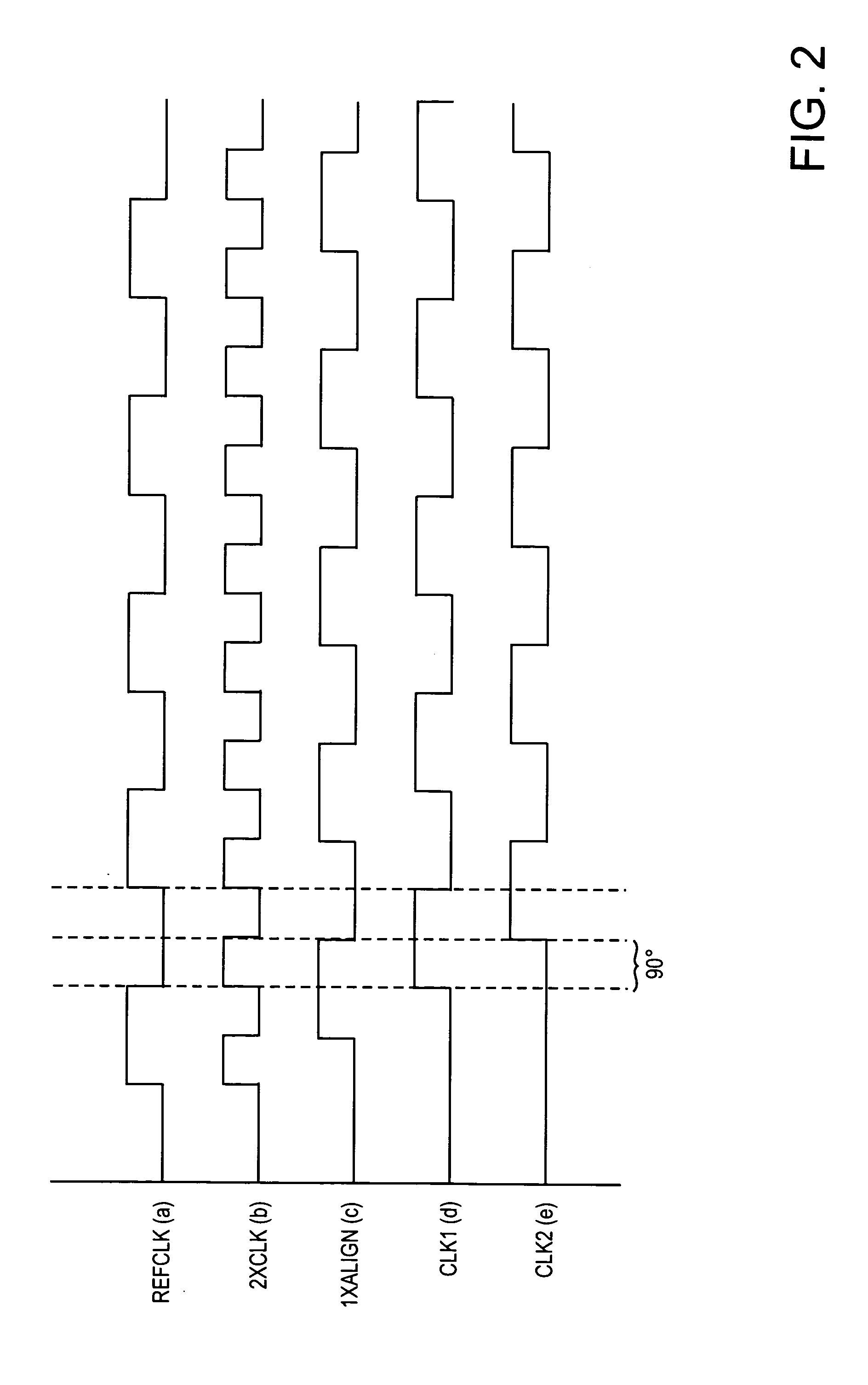

Method and apparatus for generating a quadrature clock

A quadrature clock generating apparatus includes a clock generator providing a double clock having a frequency that is twice that of a received reference clock. Divider circuitry is coupled to provide an alignment signal having half the frequency of the double clock. A recovery circuit recovers a first clock and a second clock from the double clock in accordance with the alignment signal. The first and second clocks have substantially a 90° phase difference.

Owner:HEWLETT PACKARD DEV CO LP

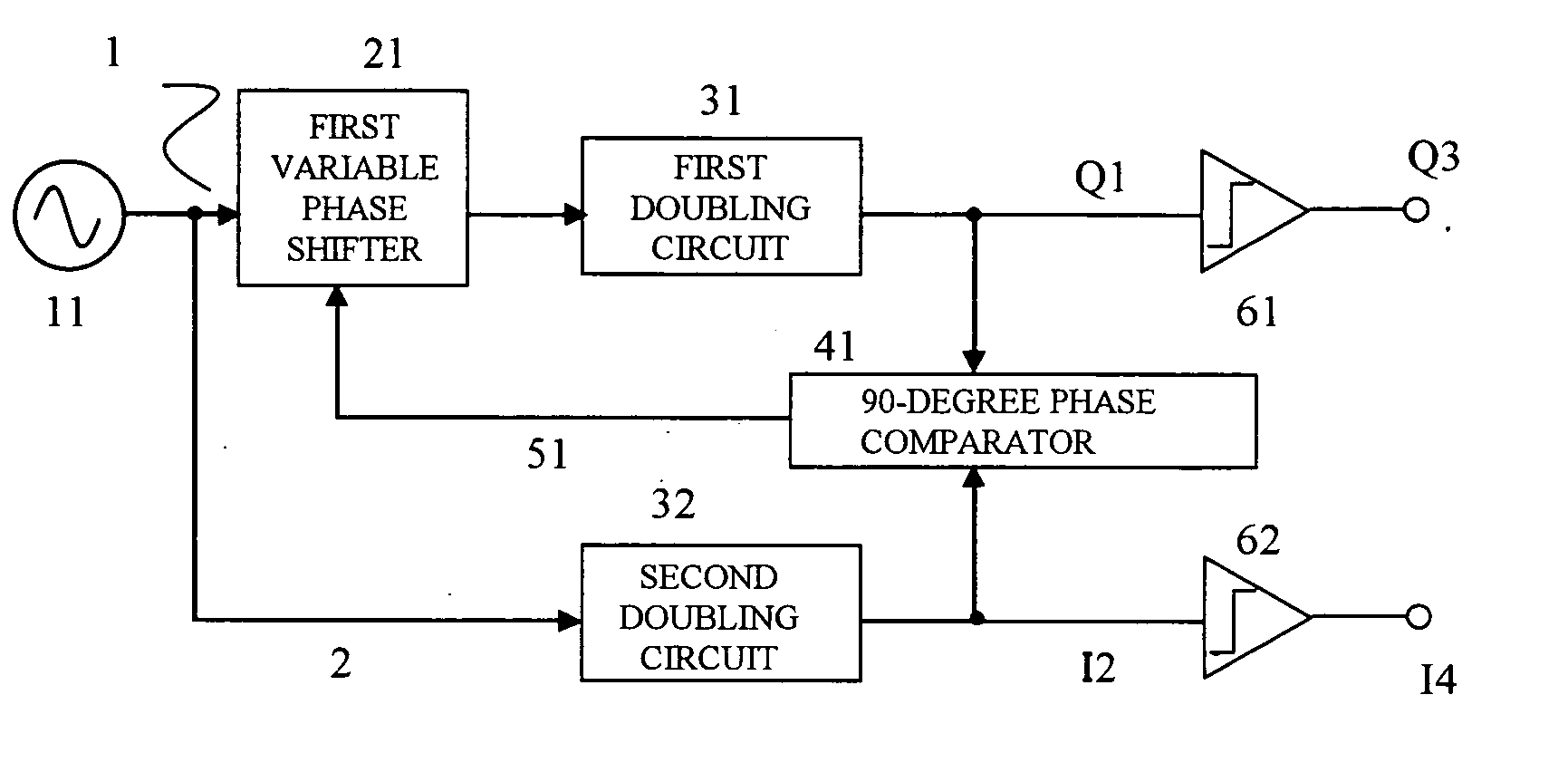

Phase shifting device

InactiveUS20060055442A1Highly accurate orthogonal phase modulation/demodulation schemeMultiple-port networksPulse automatic controlPhase shift controlPhase shifted

A phase shifting device includes a signal source; a variable phase shifter; first and second doubling circuits; and a 90-degree phase comparator. An output from the signal source is connected to an input of the variable phase shifter and to an input of the second doubling circuit, an output from the variable phase shifter is connected to an input of the first doubling circuit, an output from the first doubling circuit serves as a first output signal, and an output from the second doubling circuit serves as a second output signal. The first output signal and the second output signal are inputted to the 90-degree phase comparator. The amount of phase shift rotation of the variable phase shifter is changed by a phase shift control signal outputted from the 90-degree phase comparator. By this, an exact 90-degree phase shift is obtained.

Owner:PANASONIC CORP

Ultra fast circuitry for digital filtering

InactiveUS7991814B2Easy to operateComputation using non-contact making devicesSolid-state devicesUltra high speedNon destructive

Owner:SEEQC INC

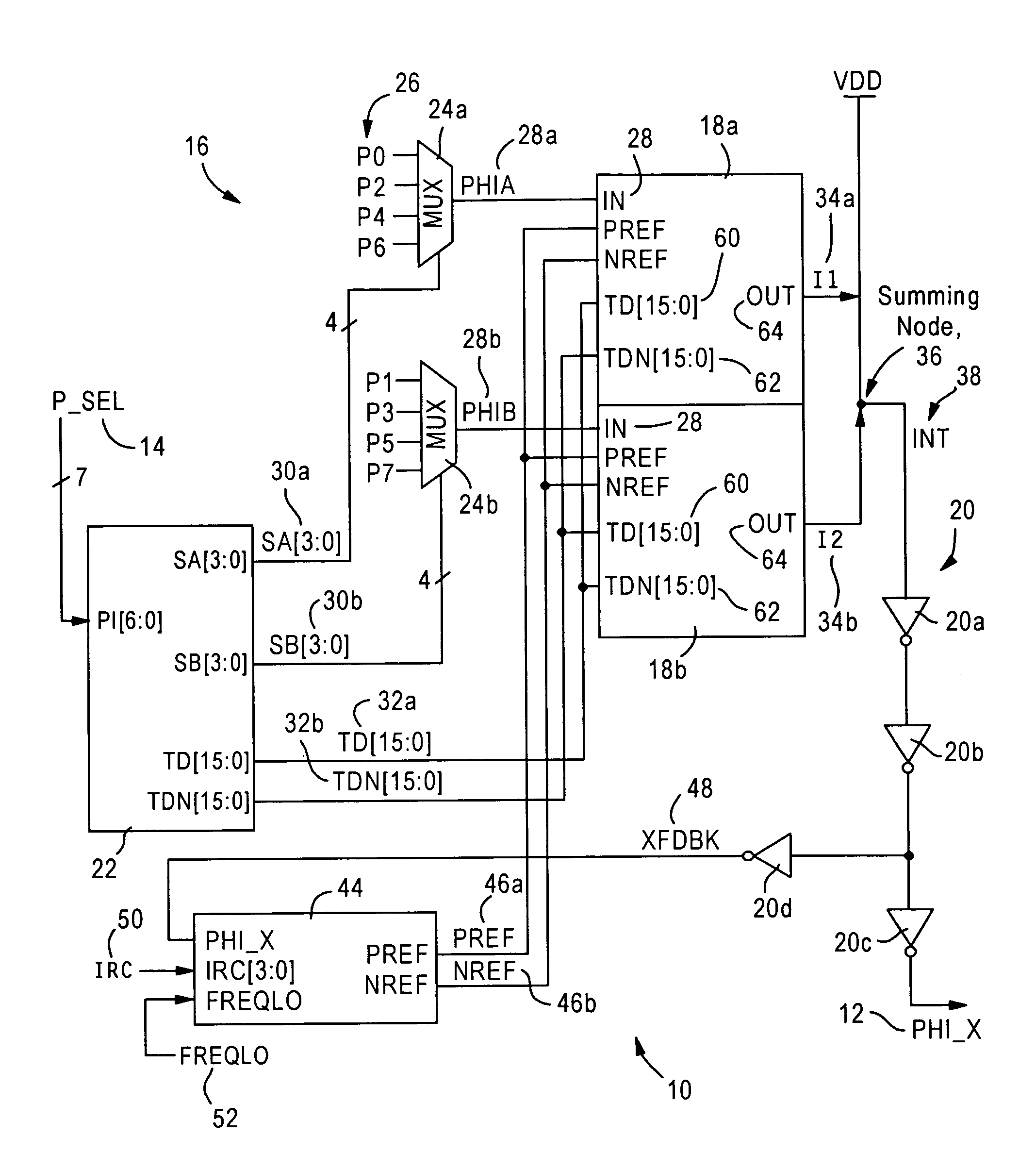

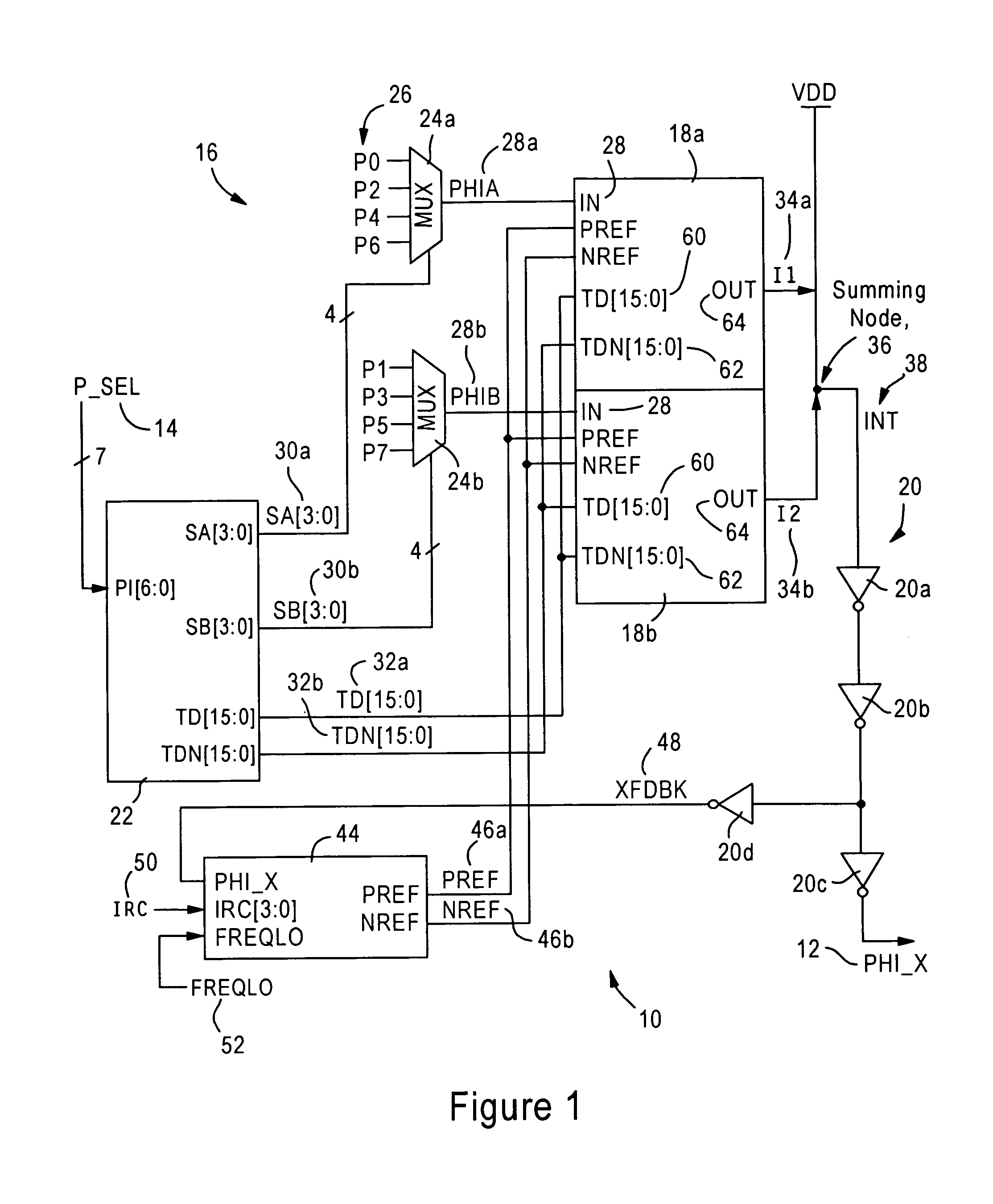

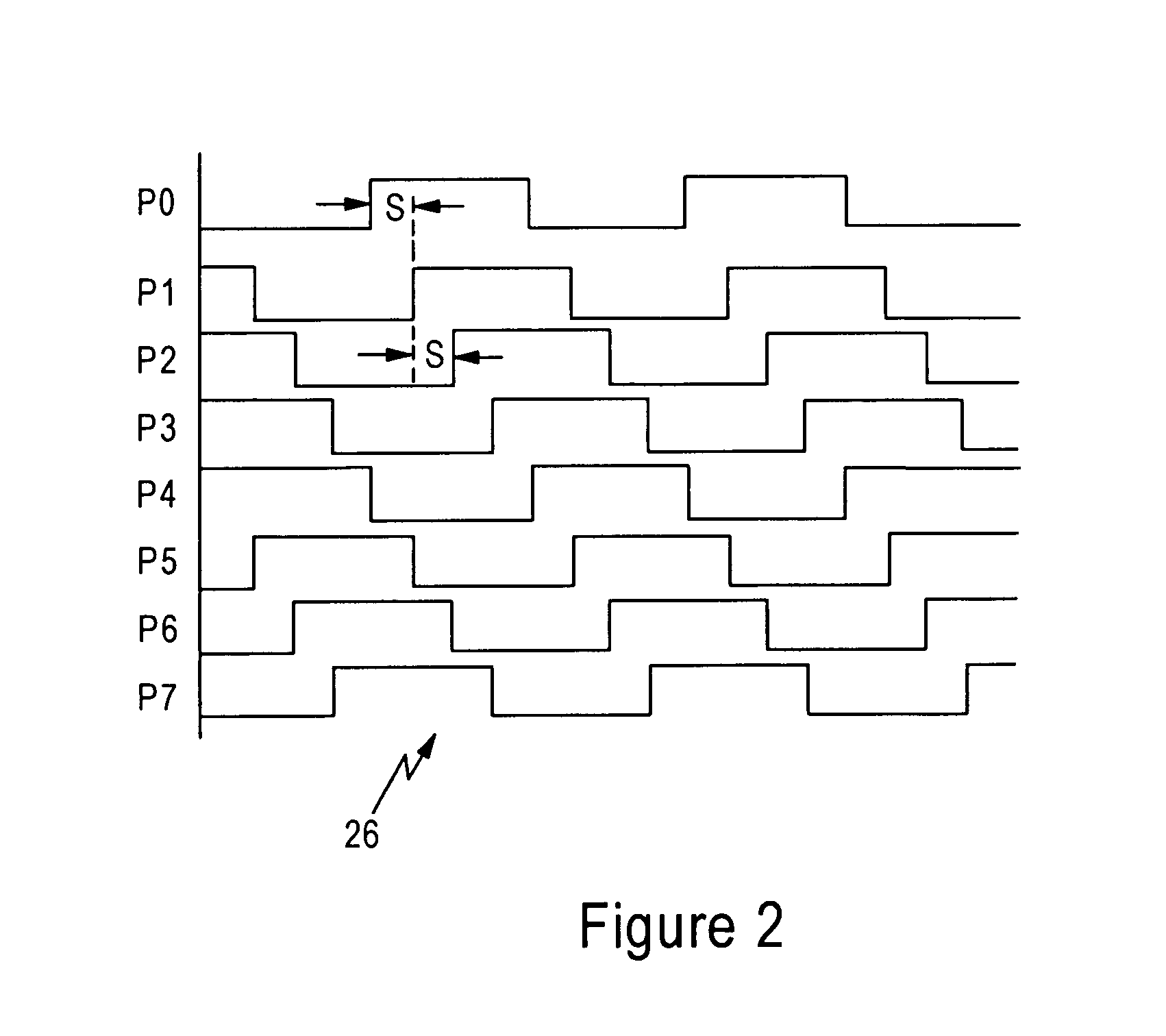

Binary controlled phase selector with output duty cycle correction

ActiveUS7613266B1Pulse automatic controlSynchronisation signal speed/phase controlAudio power amplifierBinary control

A phase selection circuit having a selection circuit, binary weighted current sources, and an amplifier circuit. The phase selection circuit is configured for selecting adjacent phase signals from a number of equally-spaced phases of a clock signal, based on a phase selection value. The selection circuit outputs the adjacent phase signals to respective first and second binary weighted current sources, along with a digital interpolation value. The first current source outputs a contribution current onto a summing node based on the first adjacent phase signal and the digital interpolation control value, and the second current source outputs a second contribution current to the summing node based on the second adjacent phase signal and an inverse of the digital interpolation control value, resulting in an interpolated signal. An amplifier circuit outputs the interpolated signal as a phase-interpolated clock signal according to the phase selection value.

Owner:GLOBALFOUNDRIES US INC

Phase interpolator

ActiveCN103297004ASuppresses the effects of phaseReduce phase errorSingle output arrangementsPhase shifterPower flowVoltage reference

A phase interpolator includes a first to a fourth differential pair. Each of the differential pairs includes a first and a second transistor and a stabilizing capacitor connected between a source coupled node and a reference voltage. The phase interpolator also includes a plurality of current sources and a group of switches to switch connections between the source coupled nodes of the differential pairs and the current sources so that (i) a first operating current is supplied to a first selected one of the first and second differential pairs and (ii) a second operating current is supplied to a second selected one of the third and fourth differential pairs. Drains of the first transistors in the differential pairs are commonly connected and drains of the second transistors in the differential pairs are commonly connected to form a first and a second output node so that a differential output signal is output.

Owner:MEGACHIPS

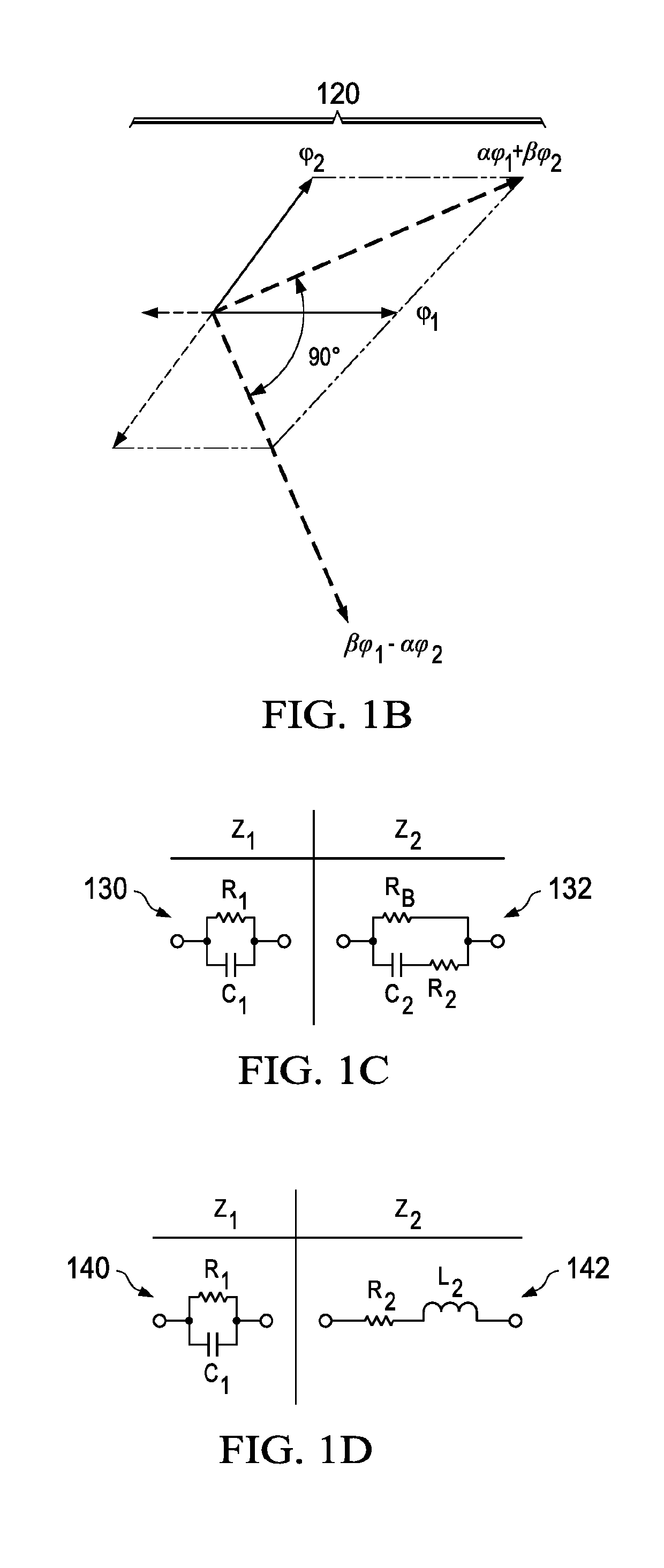

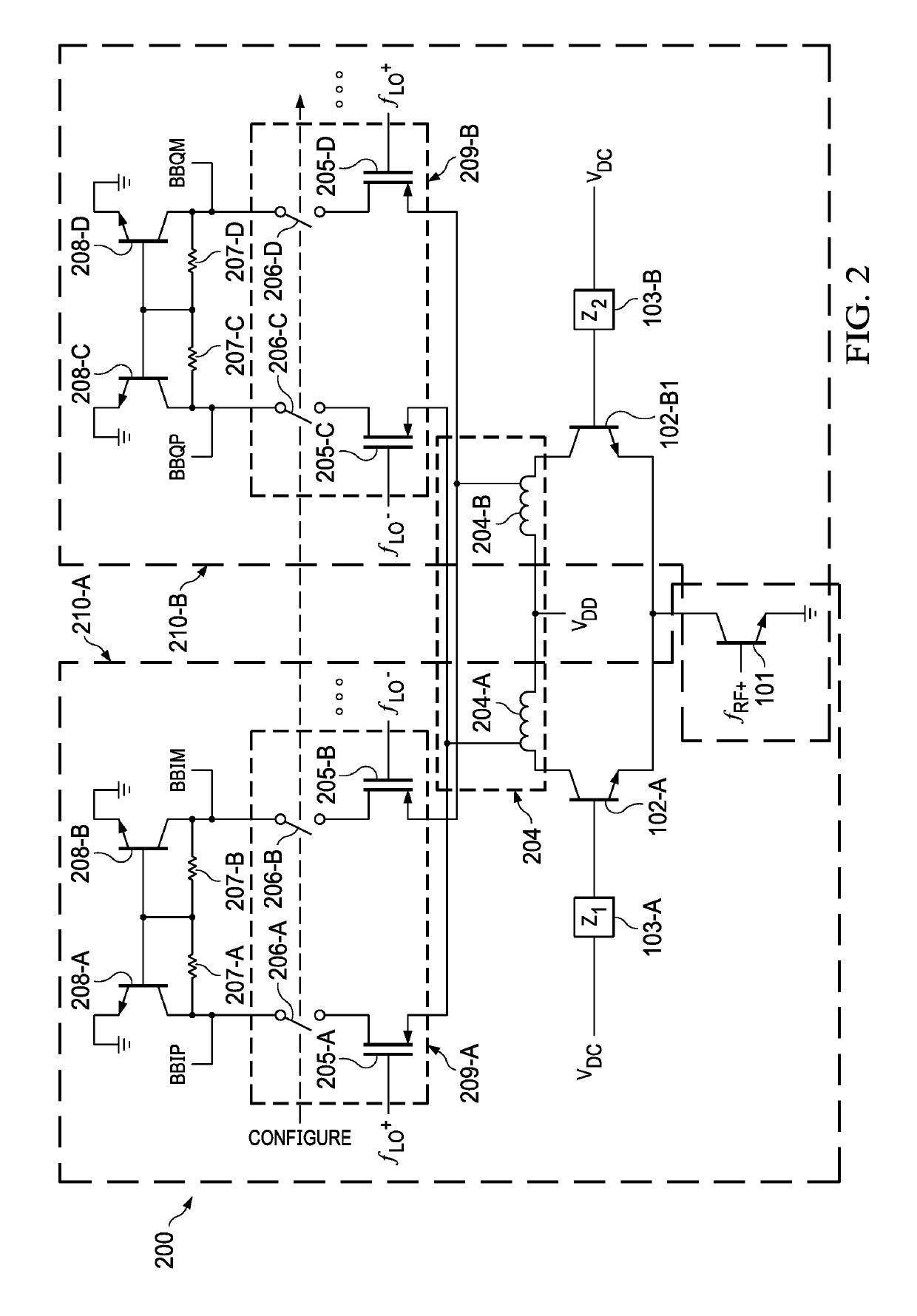

Polyphase phase shifter

ActiveUS20190199334A1Made preciselySpatial transmit diversityFrequency-division multiplex detailsLow noiseCommunications system

In described examples, a quadrature phase shifter includes digitally programmable phase shifter networks for generating leading and lagging output signals in quadrature. The phase shifter networks include passive components for reactively inducing phase shifts, which need not consume active power. Output currents from the transistors coupled to the phase shifter networks are substantially in quadrature and can be made further accurate by adjusted by a weight function implemented using current steering elements. Example low-loss quadrature phase shifters described herein can be functionally integrated to provide low-power, low-noise up / down mixers, vector modulators and transceiver front-ends for millimeter wavelength (mmwave) communication systems.

Owner:TEXAS INSTR INC

Integrated circuit devices having high precision digital delay lines therein

InactiveUS6944070B1High resolutionConvenient power supplyPulse automatic controlPulse generation by logic circuitsInjection portControl signal

Owner:SK HYNIX INC

Multiphase clock generators

Multiphase clock generators and methods are provided. A multiphase clock generator has a first clock divider for generating a first-phase clock signal from a first input clock signal. A first logic gate is connected to an output port of the first clock divider. A second clock divider is connected to an output port of the first logic gate. The second clock divider is for generating a second-phase clock signal from the first input clock signal. A second logic gate is connected to an output port of the second clock divider. A third clock divider is connected to an output port of the second logic gate. The third clock divider is for generating a third-phase clock signal from a second input clock signal.

Owner:MICRON TECH INC

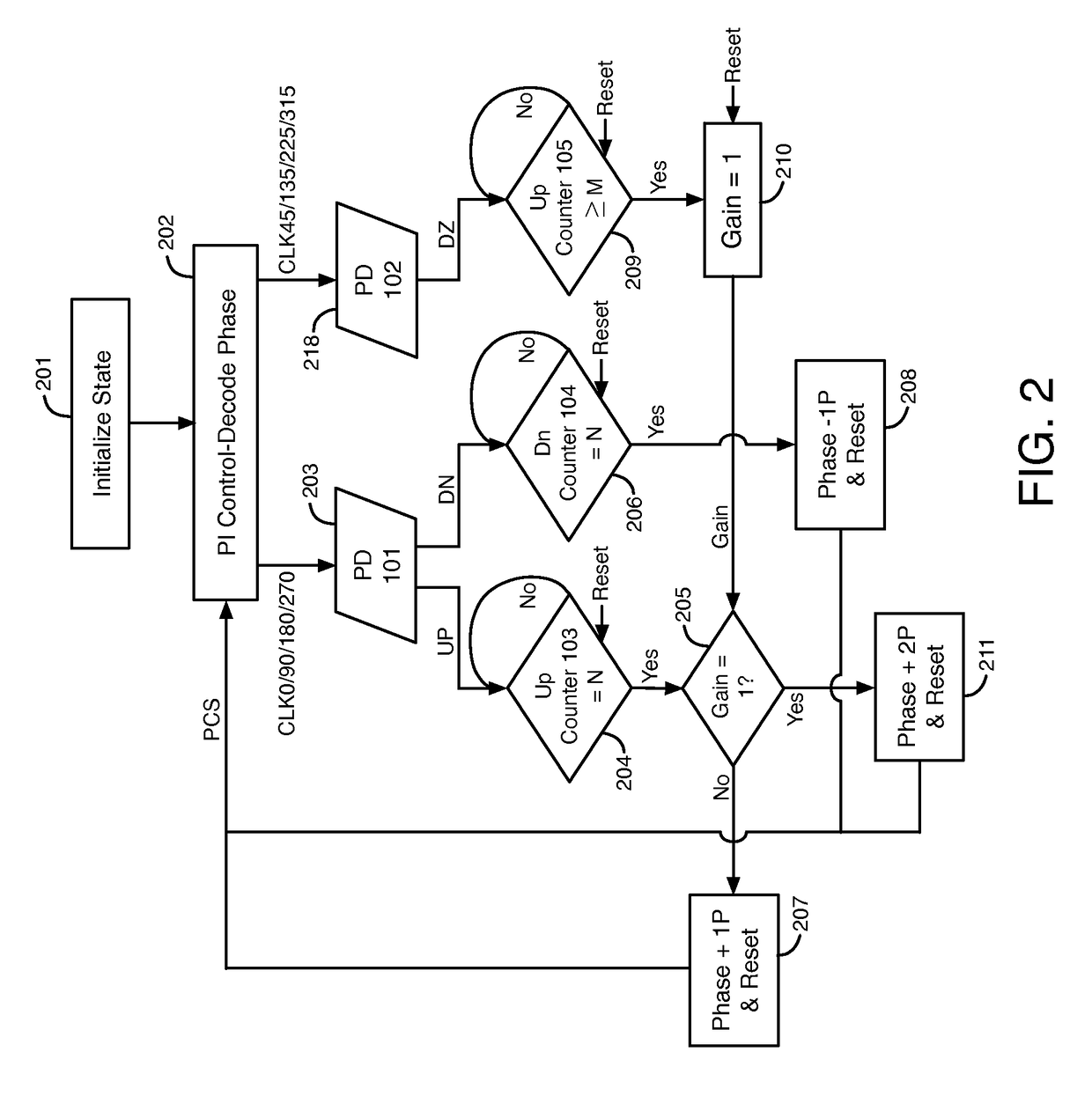

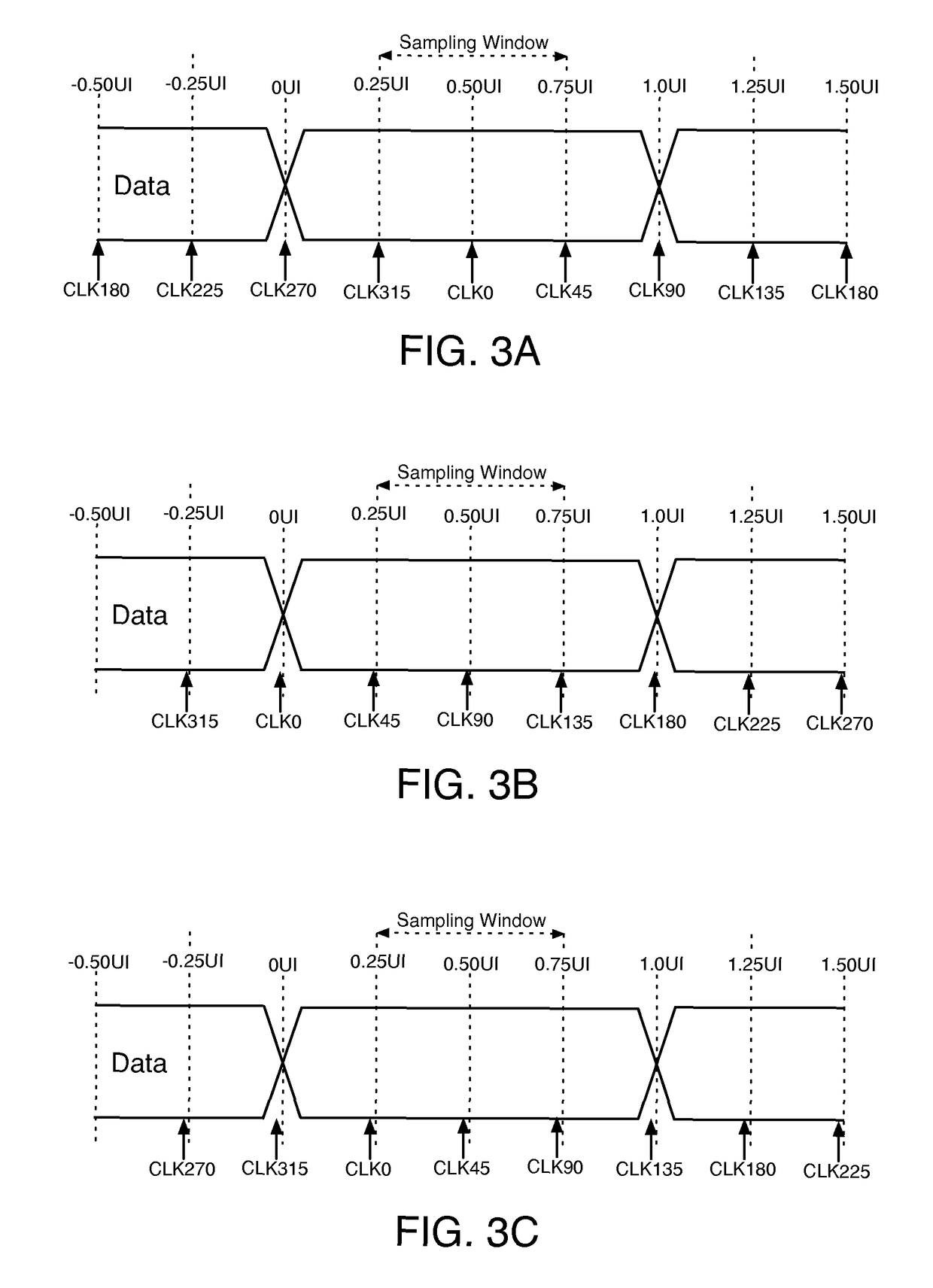

Techniques for varying phase shifts in periodic signals

A circuit includes a phase detection circuit and a phase change circuit. The phase detection circuit compares a phase of a first periodic signal to an input signal to generate a gain signal. The phase change circuit provides phase shifts to the first periodic signal in first and second directions when the gain signal has a first value. The phase change circuit increases phase shifts provided to the first periodic signal in the first direction in response to the gain signal changing from the first value to a second value. The phase change circuit provides phase shifts to the first periodic signal in the second direction when the gain signal has the second value that are smaller than the phase shifts provided to the first periodic signal in the first direction when the gain signal has the second value.

Owner:ALTERA CORP

Programmable logic devices with skewed clocking signals

InactiveUS7464286B1Improve frequency performanceImproves operating frequency characteristicError detection/correctionData resettingComputer Aided DesignPath length

A programmable logic device has programmable phase-shifting circuitry. The phase-shifting circuitry is used to generate a set of skewed clock signals that is used to adjust the relative timing of device elements in a circuit synthesized in the programmable logic device. By suitably adjusting the relative timing of the device elements, the circuit critical path lengths are effectively reduced leading to improved circuit frequency performance. Algorithms are provided for establishing clock skew values that lead to improved circuit performance. The algorithms are incorporated in computer aided design tools to enable automatic optimization of circuit designs.

Owner:ALTERA CORP

Phase multiplier circuit

InactiveUS7009441B2Even and accurate spacingPulse automatic controlElectronic switchingNegative feedbackLoop filter

Owner:FIEDLER ALAN

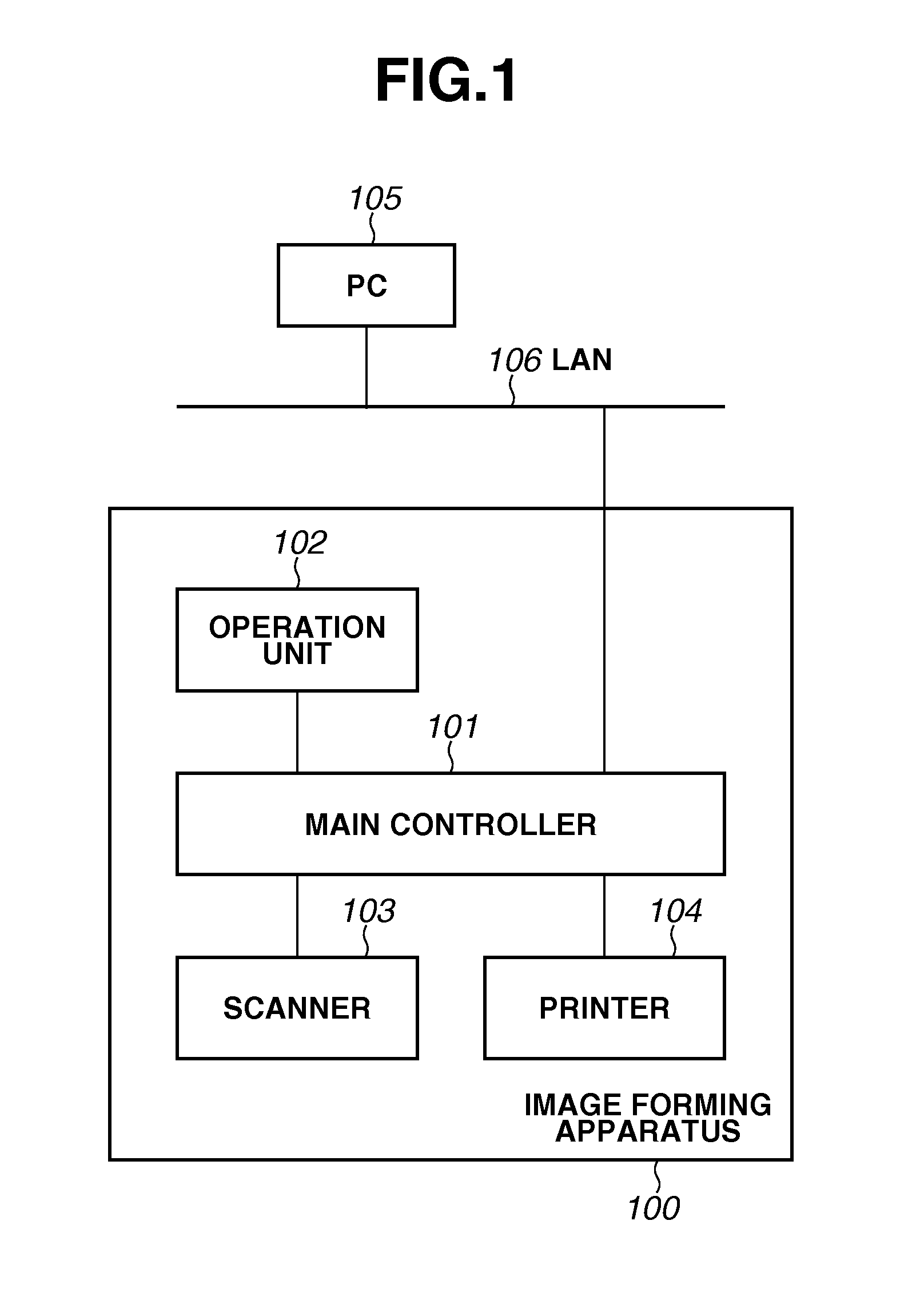

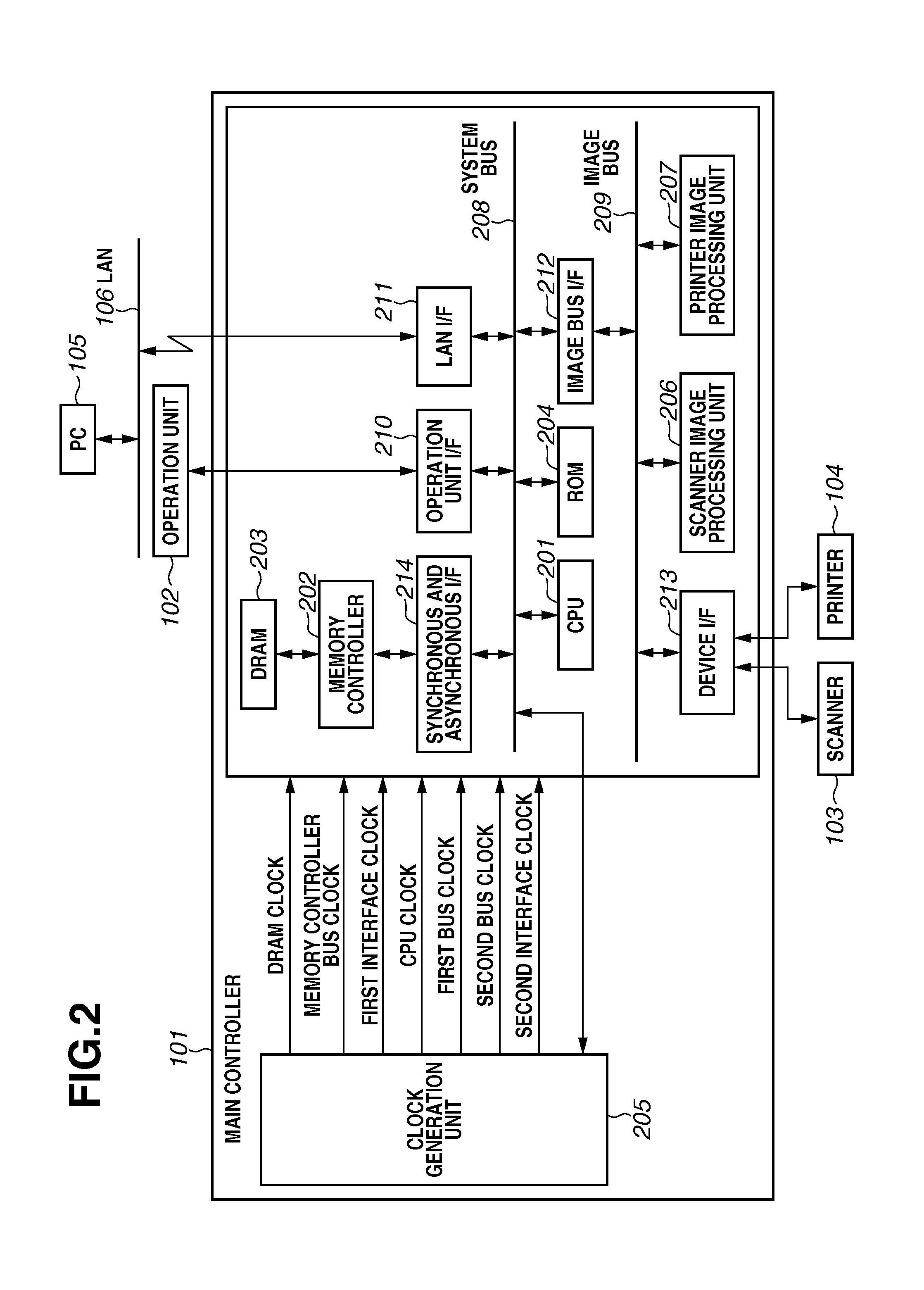

Semiconductor integrated circuit, apparatus with semiconductor integrated circuit, and clock control method in semiconductor integrated circuit

ActiveUS20160087618A1Counting chain pulse countersPulse counters with static storageData translationEngineering

A semiconductor integrated circuit includes, a fixed frequency-division clock generation unit configured to generate a fixed frequency-division clock with a fixed frequency based on an output clock of a clock source, a variable frequency-division clock generation unit configured to generate a variable frequency-division clock with a variable frequency based on the output clock of the clock source, and a data path selection unit configured to select a data path. The data path selection unit selects a data path with or without a synchronization unit for converting the data into clock-synchronous data on a receiving side according to whether the variable frequency-division clock is or is not, respectively, generated by the variable frequency-division clock generation unit.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com