Techniques for non-overlapping clock generation

A clock generation circuit, non-overlapping technology, applied in the direction of pulse technology, pulse generation, generation of electrical pulses, etc., can solve the problems of consuming the effective time of the clock, multi-current, consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021] The word "exemplary" is used herein to mean "serving as an example, illustration, or illustration." Any embodiment or design described herein as "exemplary" is not to be construed as preferred or advantageous over other embodiments or designs.

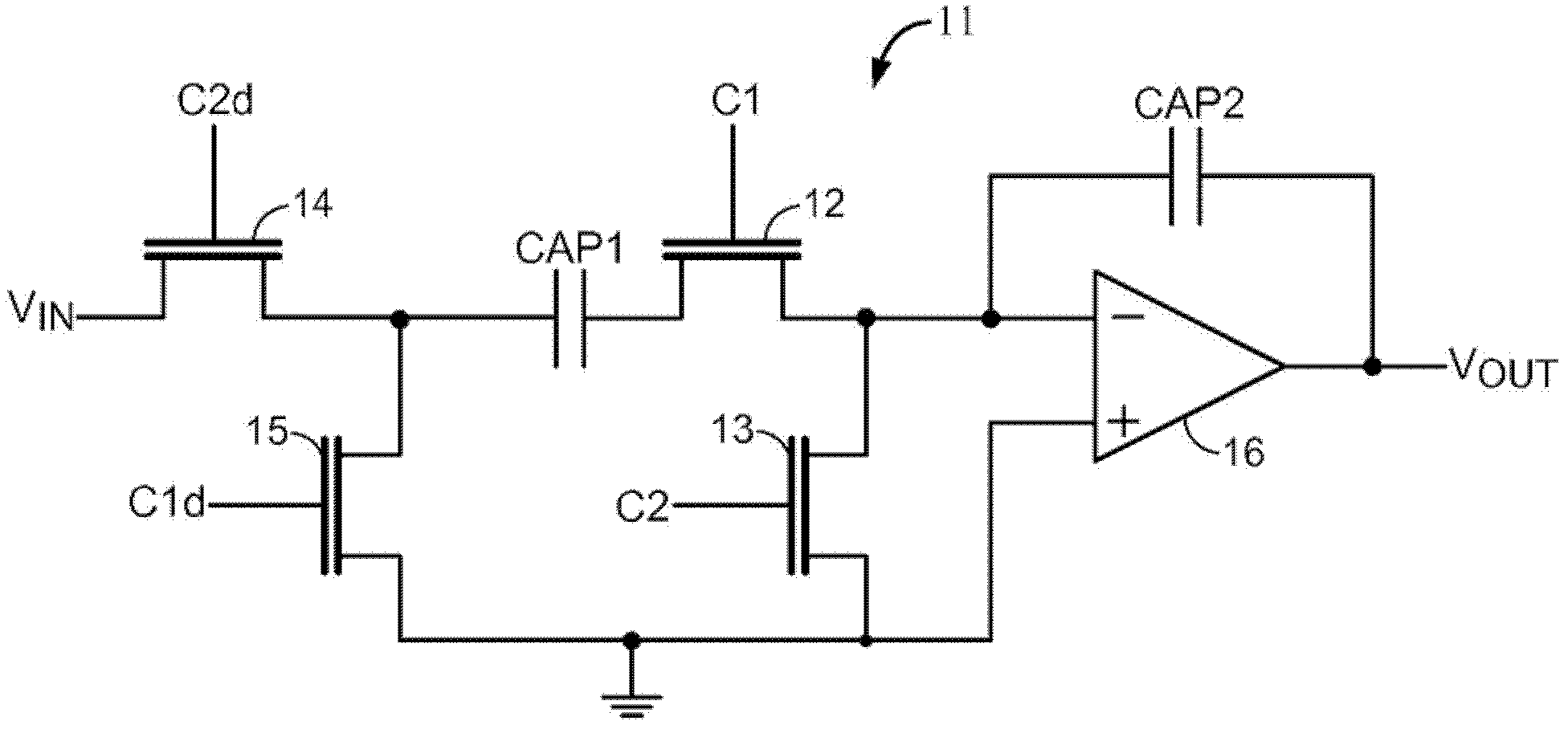

[0022] Typically, non-overlapping clock signals are used in switched capacitor circuits to minimize errors. FIG. 1 is a schematic diagram of a prior art non-inverting switched capacitor integrator circuit 11 known to those skilled in the art. The switched capacitor integrator circuit 11 includes switches 12 , 13 , 14 and 15 , capacitors CAP1 and CAP2 , and an amplifier 16 . Switches 12, 13, 14 and 15 receive non-overlapping clock signals C1, C2, C2d (C2-delay) and C1d (C1-delay), respectively.

[0023] In a first phase of operation, switches 13 and 14 are enabled to charge capacitor CAP1 to a voltage applied to input Vin. A switch 14 connects the input Vin to the first terminal of the capacitor CAP1. Switch 13 connects the s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com