Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

76 results about "Digital delay line" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

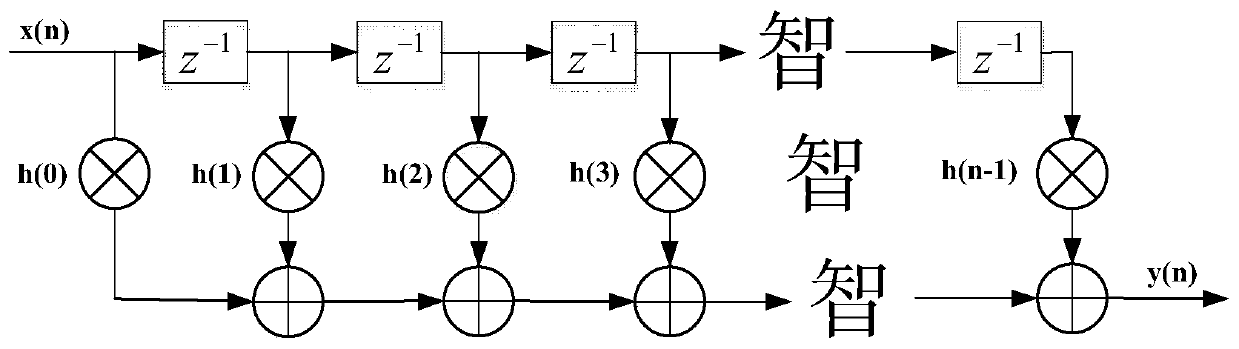

Inventor

A digital delay line is a discrete element in digital filter theory, which allows a signal to be delayed by a number of samples. If the delay is an integer multiple of samples, digital delay lines are often implemented as circular buffers. This means that integer delays can be computed very efficiently. The delay by one sample is notated z⁻¹ and delays of N samples is notated as z⁻ᴺ motivated by the role the z-transform plays in describing digital filter structures.

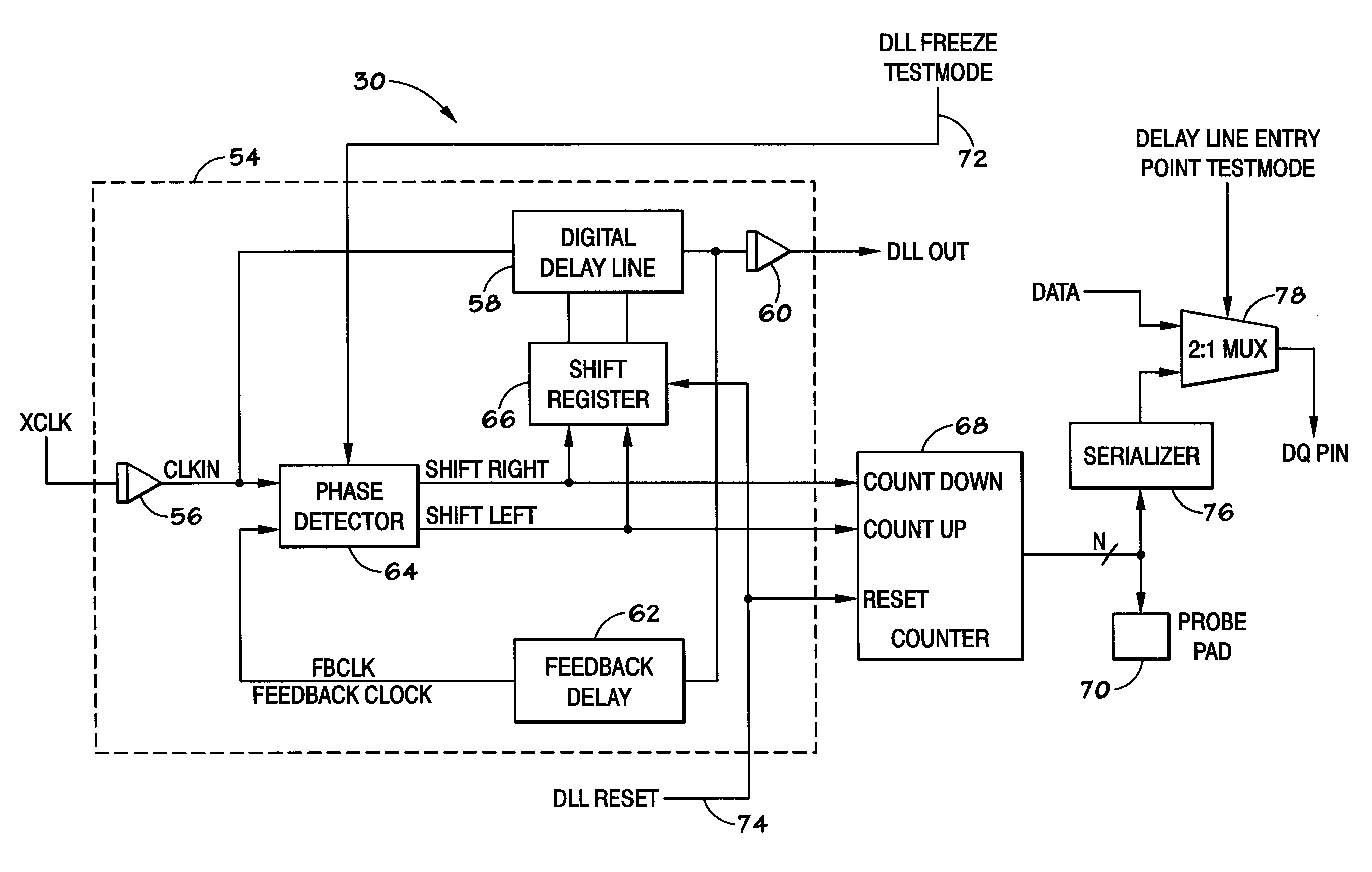

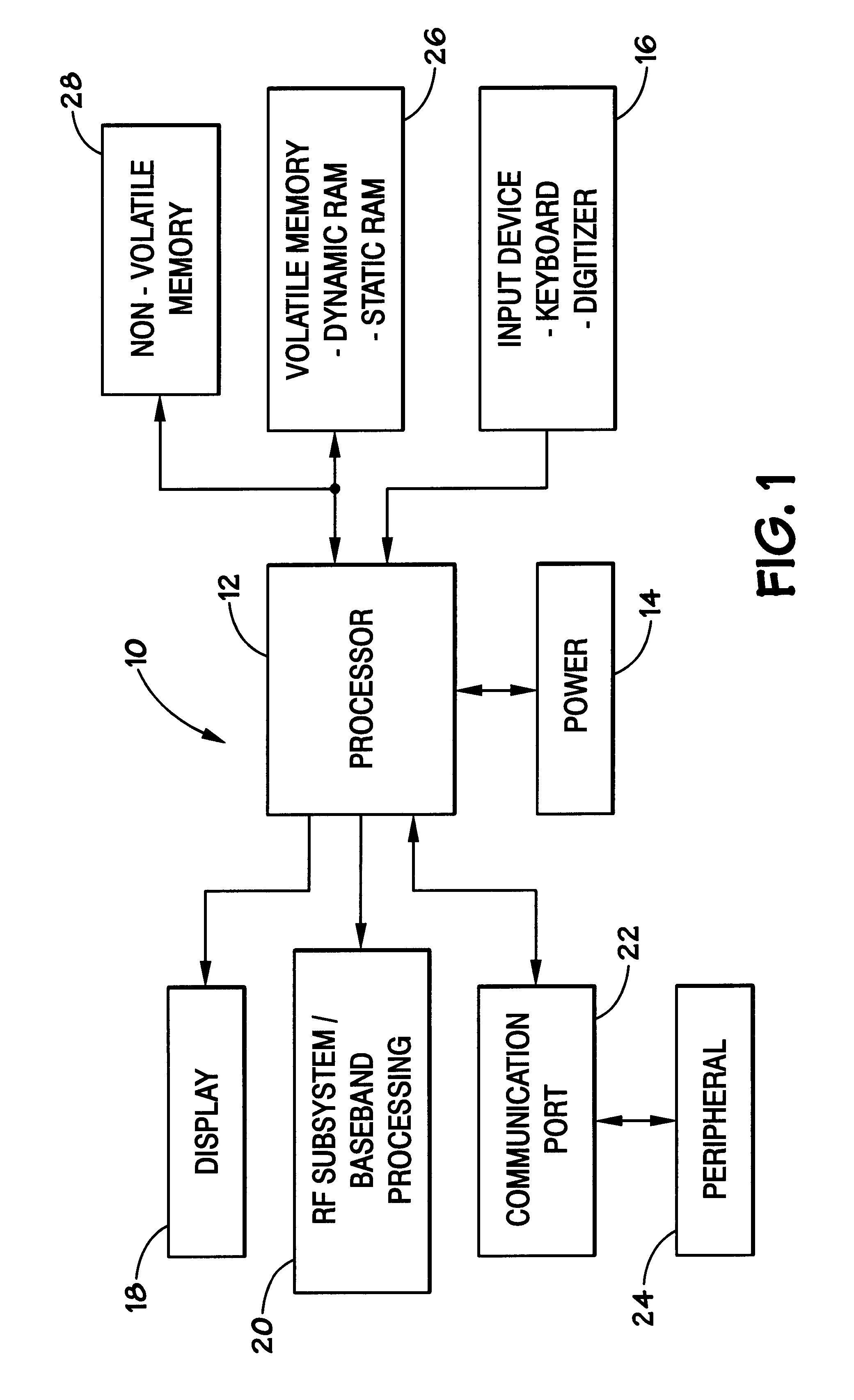

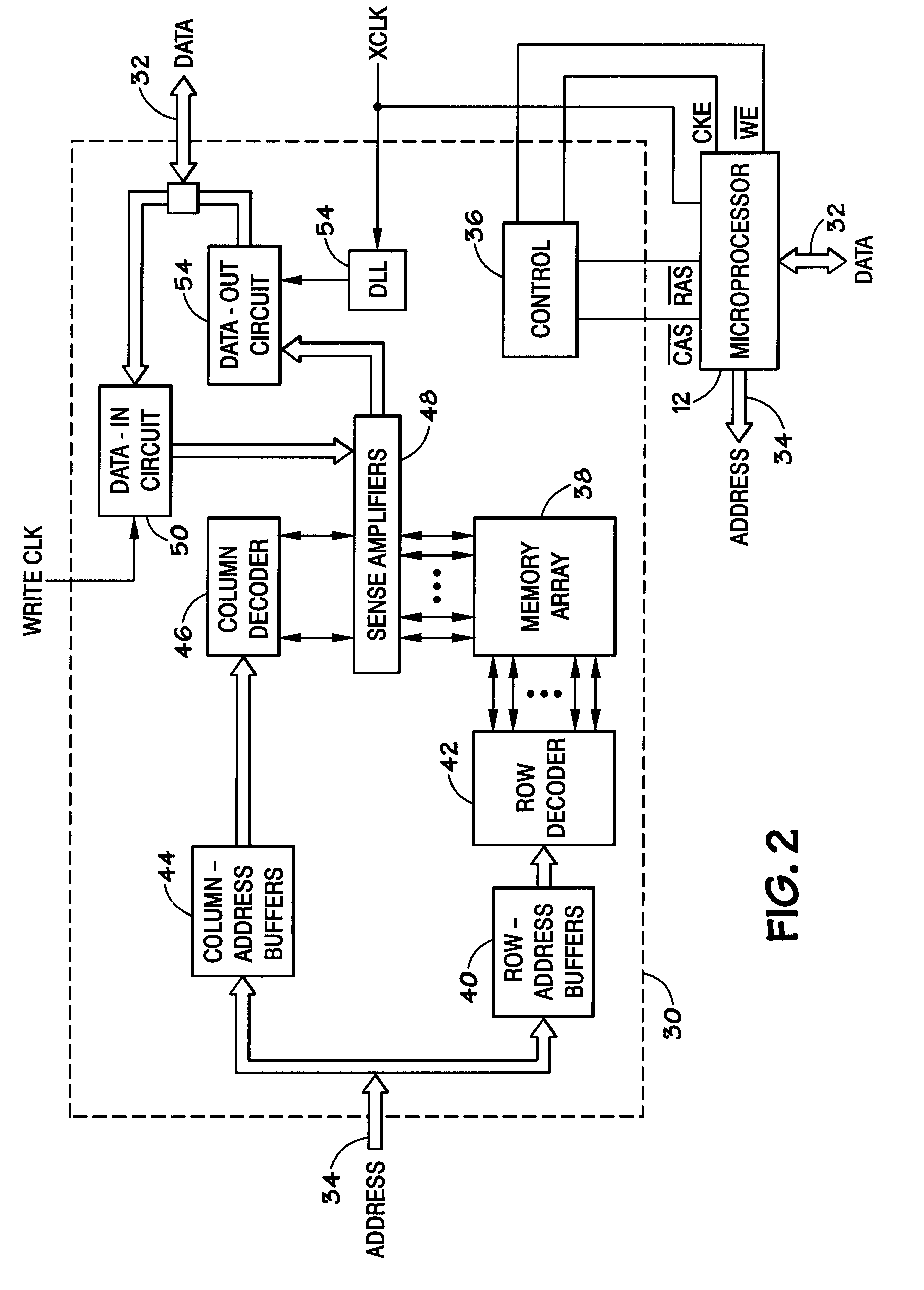

Method and apparatus for determining digital delay line entry point

A method and apparatus to characterize a synchronous device after it is packaged. For synchronous devices, such as SDRAMs implementing a Delay Locked Loop (DLL) to synchronize one signal, such as an external clock signal with a second signal, such as a data signal, a counter is coupled to the phase detector of the DLL to track the entry point of the delay line. The entry point information can be taken over a variety of voltages, temperatures, and frequencies to characterize the DLL. The counter may be located on the synchronous device or external to the device.

Owner:ROUND ROCK RES LLC

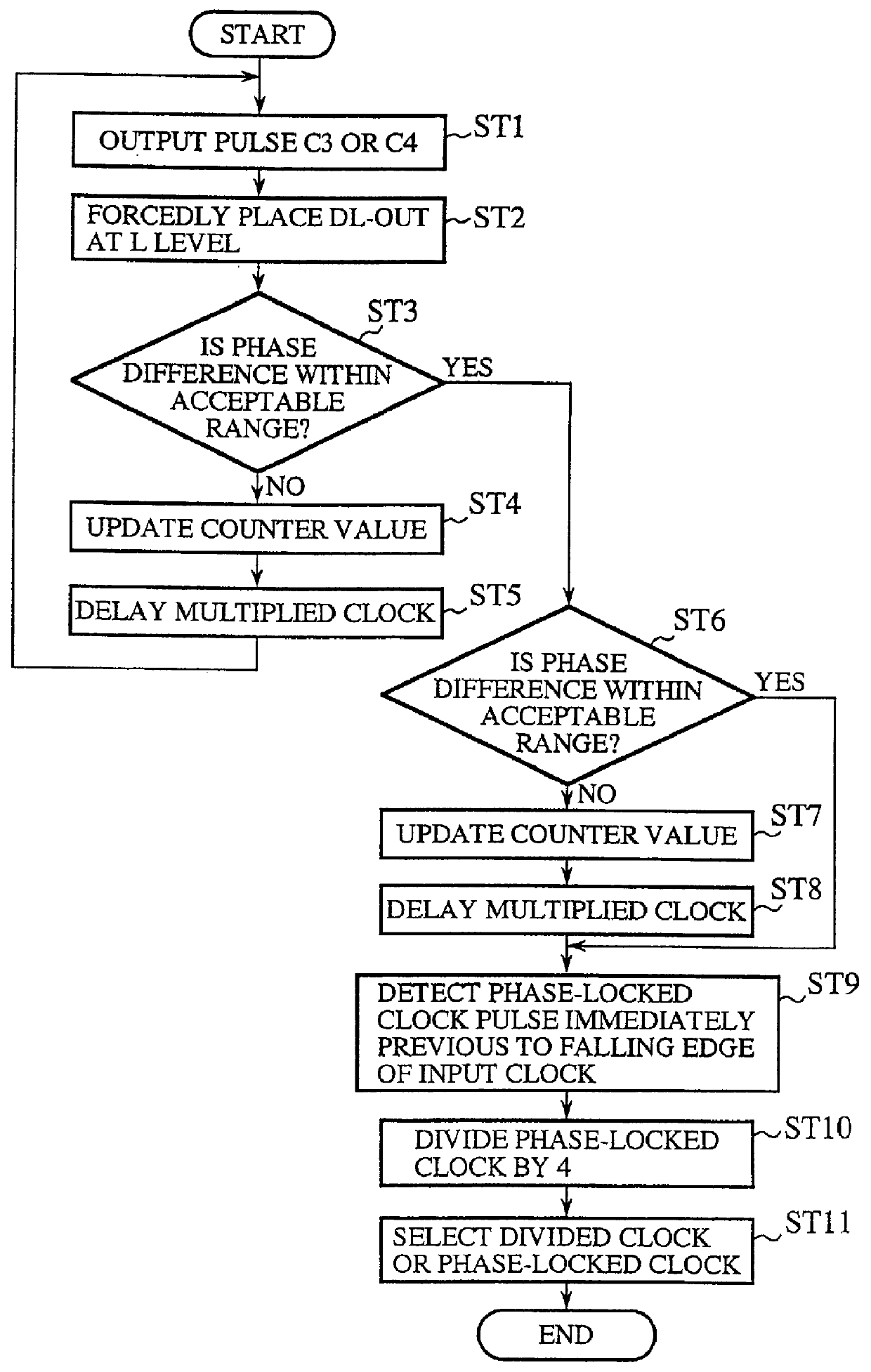

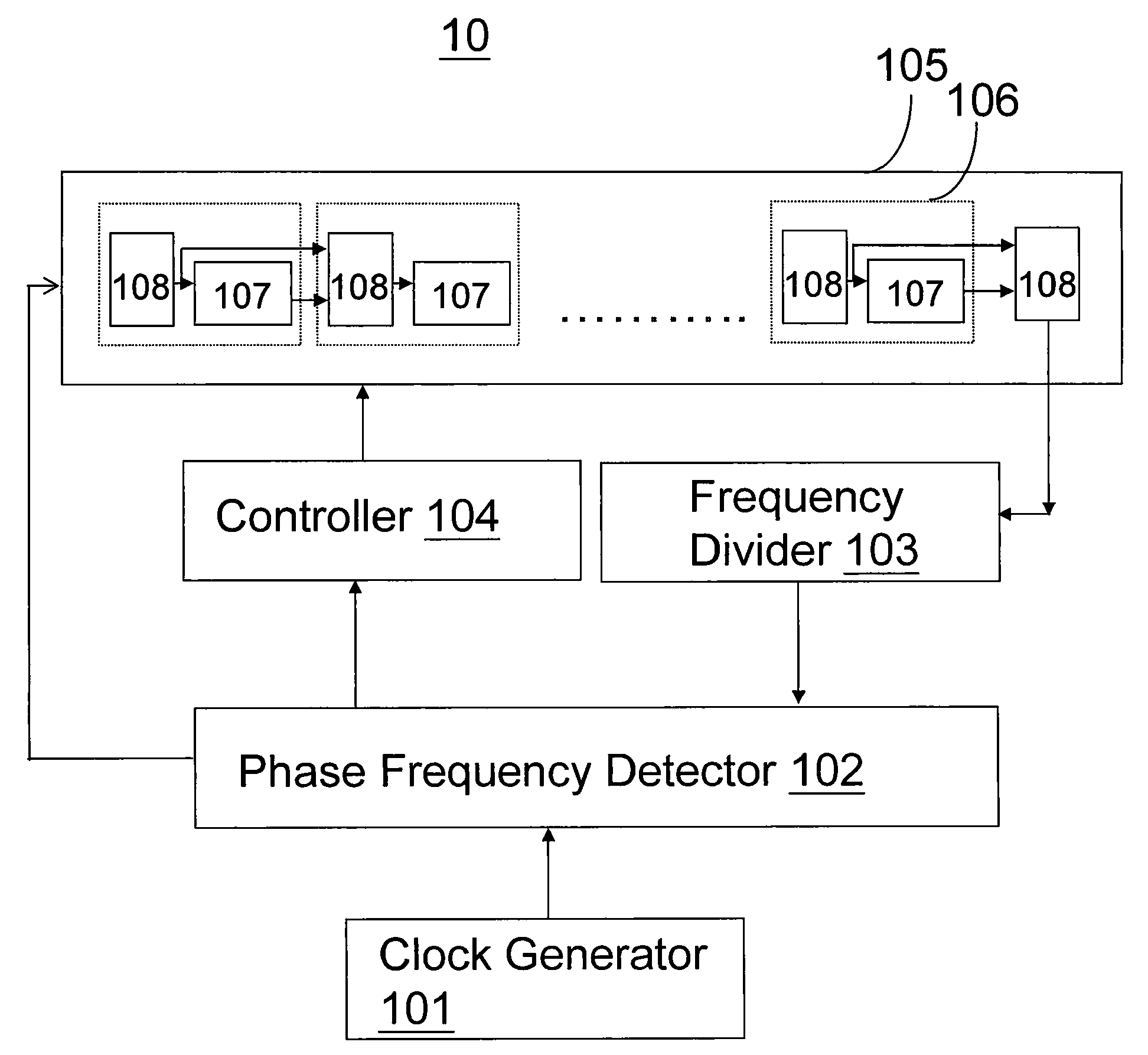

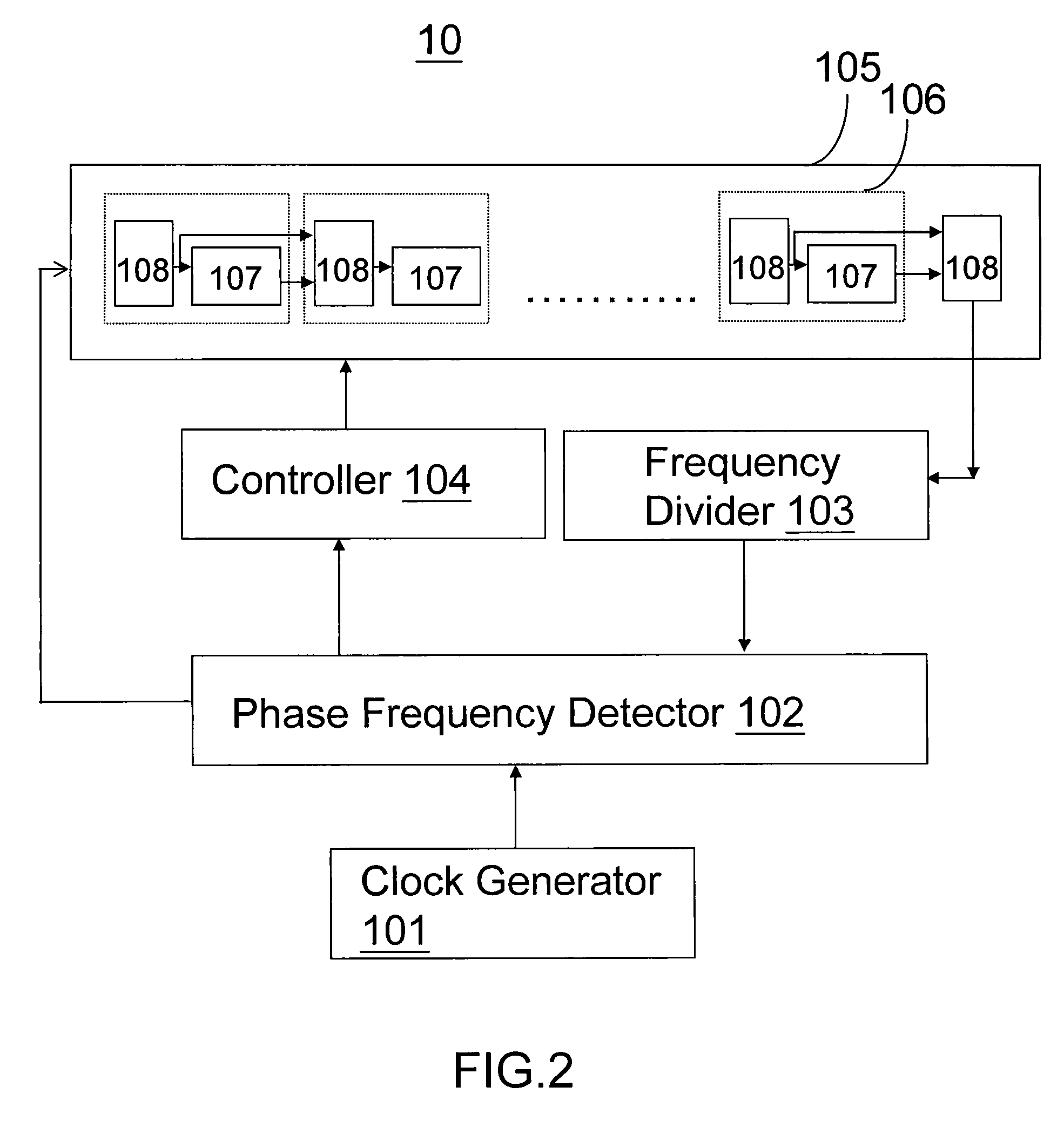

Clock generator and clock generating method capable of varying clock frequency without increasing the number of delay elements

InactiveUS6049238AReduce frequencyDelay lines pulse generationPulse automatic controlPhase differenceDelayed time

A clock generator including a frequency multiplier, a phase lock circuit and a frequency divider. The frequency multiplier generates a frequency multiplied clock by multiplying the frequency of an input clock. The phase lock circuit detects a phase difference between the input clock and a frequency divided clock, and generates, by delaying the frequency multiplied clock by an amount corresponding to the phase difference, a phase-locked clock with its phase locked with the input clock. The frequency divider detects in every fixed cycle a particular pulse of the phase-locked clock, and generates the frequency divided clock by dividing the phase-locked clock with reference to the particular pulse of the phase-locked clock. In particular, the frequency divider detects the particular pulse immediately previous to a falling edge of the input clock. This can reduce the phase difference between the input clock and the phase-locked clock, and hence to solve a problem of a conventional clock generator in that a delay time of a digital delay line in a phase lock circuit must be lengthened with a reduction in the multiplication number of the frequency multiplied clock, which requires a greater number of delay elements because of a large occupying area of the delay elements and a decoder, thereby increasing the circuit scale and cost of a chip to reduce the multiplication number of the frequency multiplied clock.

Owner:RENESAS ELECTRONICS CORP

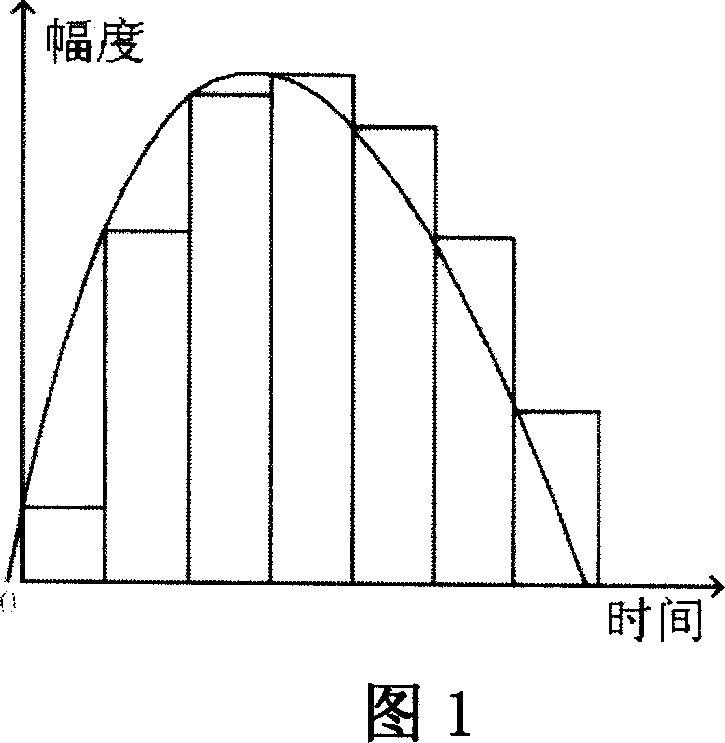

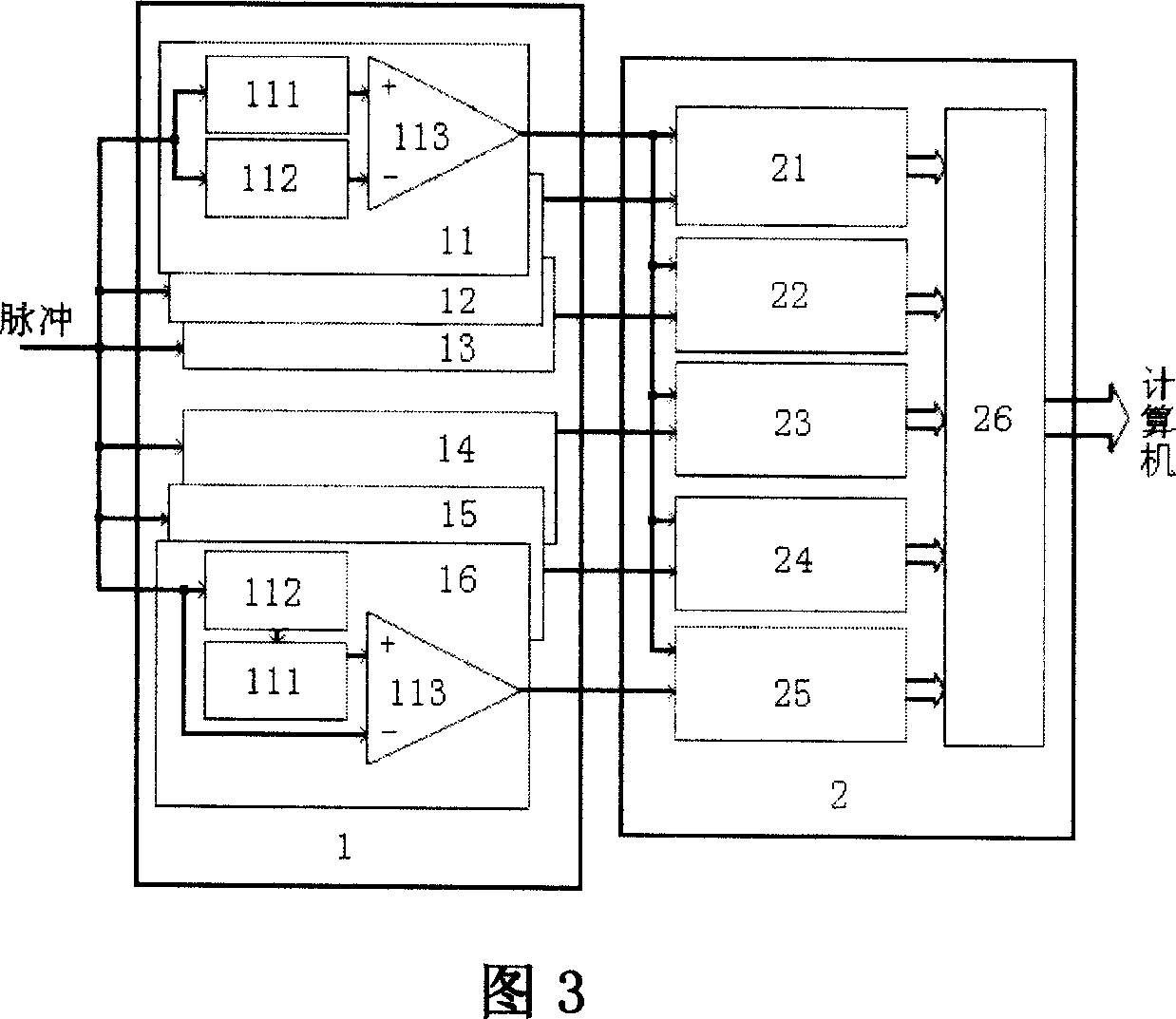

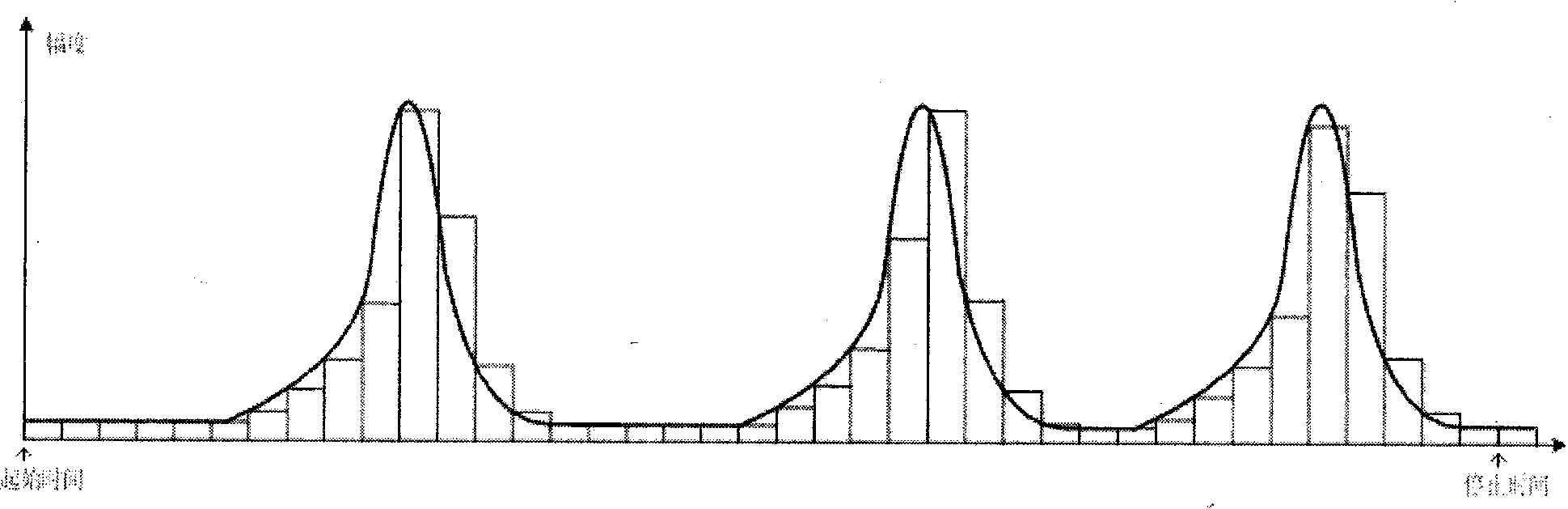

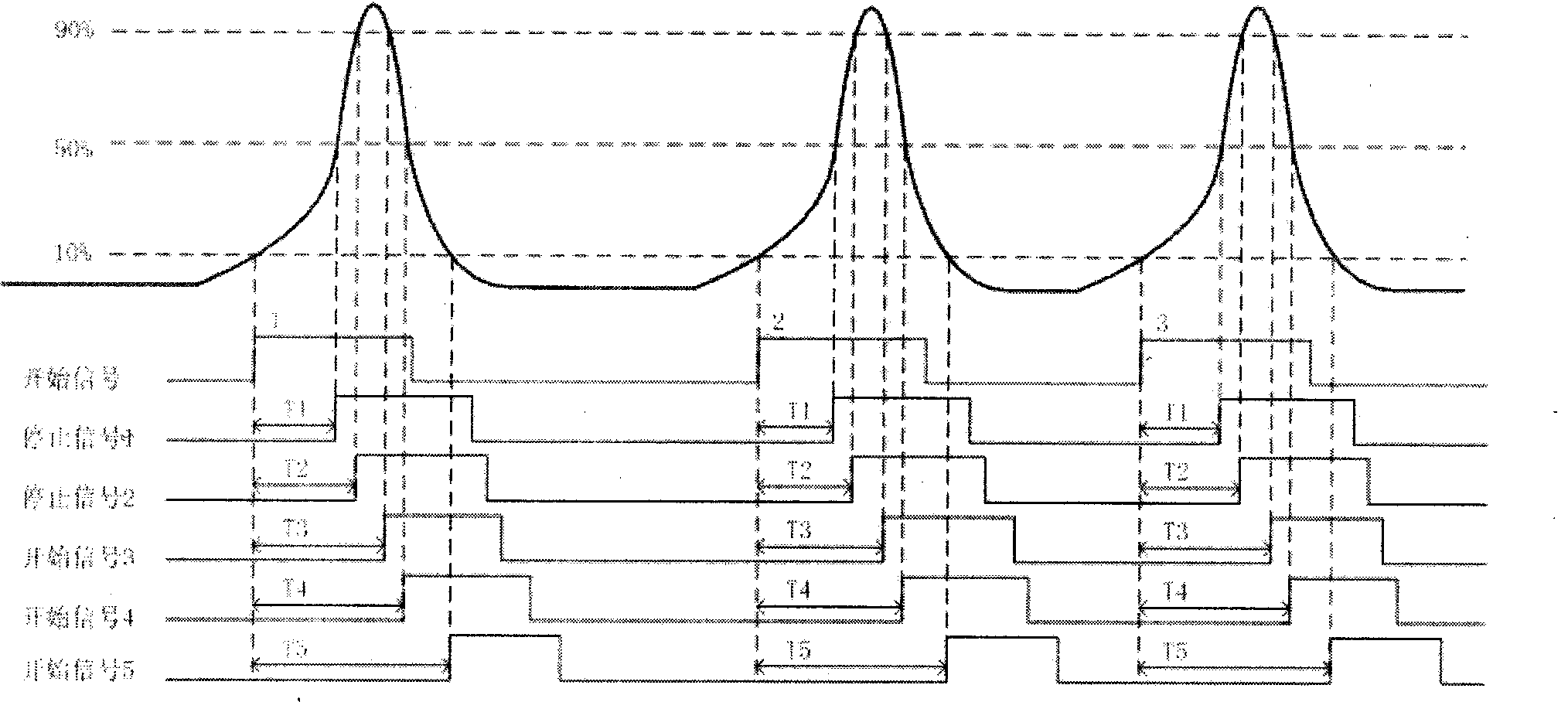

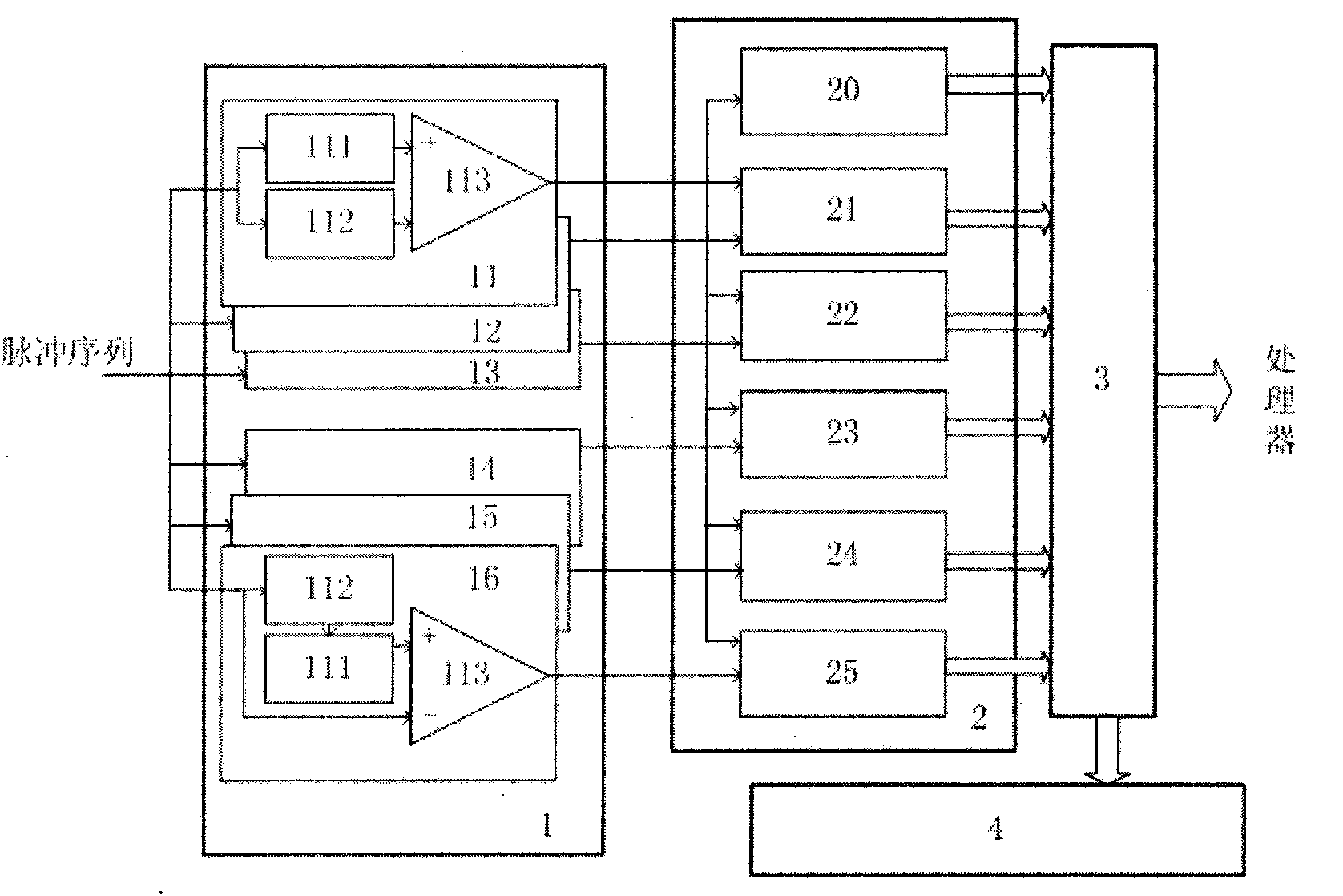

Pulse shape measuring device and measuring method thereof

InactiveCN101034120AHighly integratedGood value for moneyOptical rangefindersPulse characteristics measurementsDiscriminatorMeasurement device

This invention relates to a measuring method and device of impulse form. The invention includes one constant proportion timing discriminate module and one time-to-digital conversion module. Data of time-to-digital conversion modular enter calculator for handling. Constant proportion timing discriminate module has a group of leading edge discriminator and a group of back edge discriminator, which separately discriminate a series of points where the ratio of pulse front edge and back edge voltage and spike voltage are certain worth corresponding time. multipass time-to-digital conversion module convert time interval between first time and subsequently time to digital quantity, adopt digital counting method and combine digital delay line bracketing method, realize at a piece of field programmable logic array FPGA. sending obtained data into computer for calculation to gain time interval, base on voltage peak ratio of every time to indirectly reduce impulse form, and obtain pulsewidth. The invention has low cost, small bulk, and light weight, can apply to laser range finder.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Digital PLL (Phase-Locked Loop) based phase noise measuring device and method

ActiveCN105306053AImprove stabilityAvoid ADC SaturationPulse automatic controlLow noiseDiscriminator

The invention provides a digital PLL (Phase-Locked Loop) based phase noise measuring device. The digital PLL based phase noise measuring device comprises a frequency power measuring unit, a phase discrimination unit, a filtering unit, a DC (Direct Current) bias compensation unit, a low-noise amplification unit, an acquisition, frequency discrimination and phase discrimination unit, a digital loop filtering unit, a phase discrimination constant detection unit, a self-adaptive digital gain control unit, a reference source unit, and a signal processing and displaying unit. According to the digital PLL based phase noise measuring device, a double-balanced mixer is adopted as a phase discriminator, the phase noise of a measured source is extracted through a digital PLL, the specific noise extraction mode is divided into frequency mixer phase discrimination and digital delay line frequency discrimination, and DC caused by a loop circuit is counteracted through a DC bias compensation circuit, so that too big DC after amplification, induced ADC saturation and induced loop lock-losing are prevented. The implementation scheme of the digital PLL based phase noise measuring device is simple, totally excellent phase noise measuring sensitivity can be realized, the realized analysis frequency spectrum range is also very wide, and phase noise testing demands of most signal sources can be satisfied.

Owner:THE 41ST INST OF CHINA ELECTRONICS TECH GRP

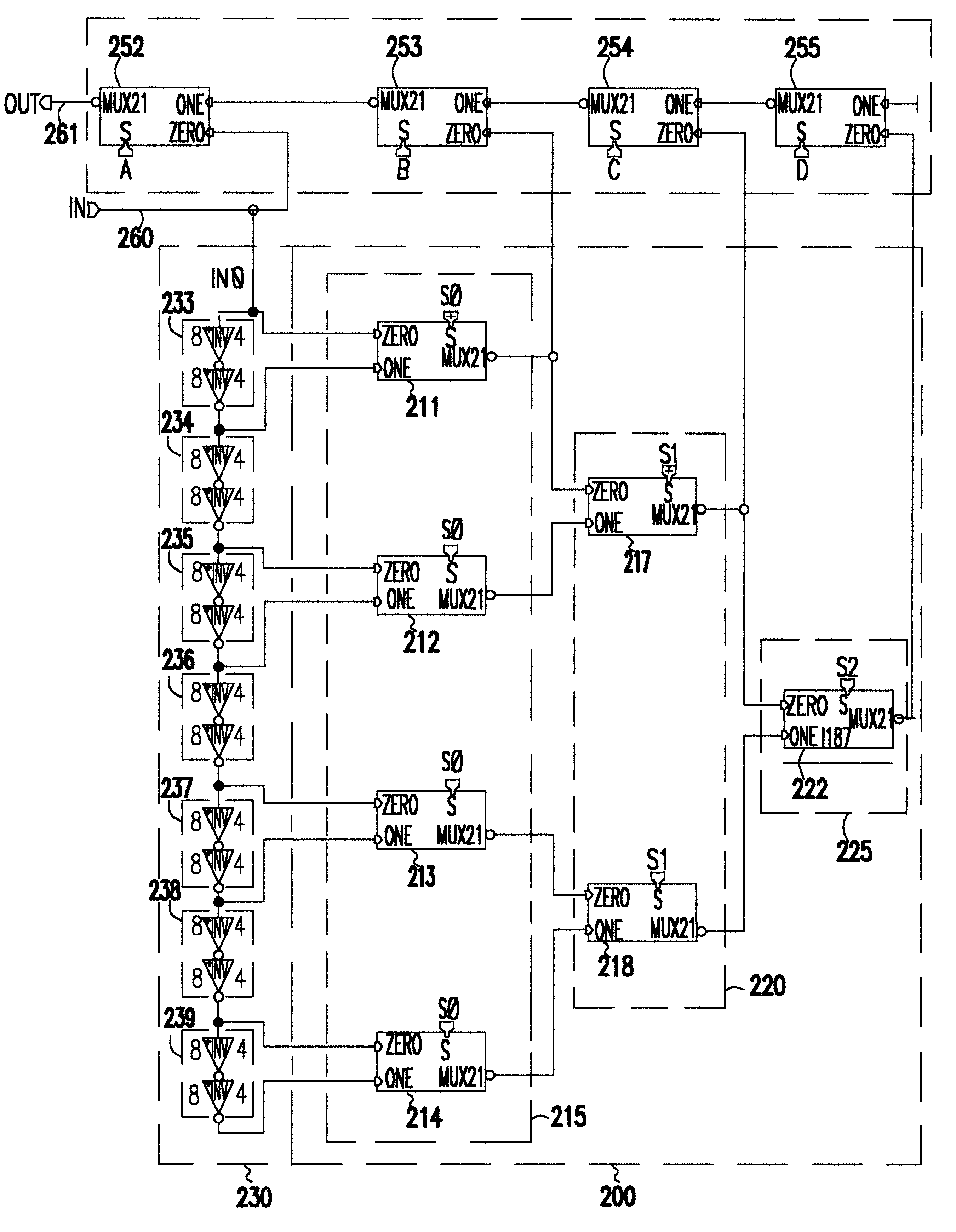

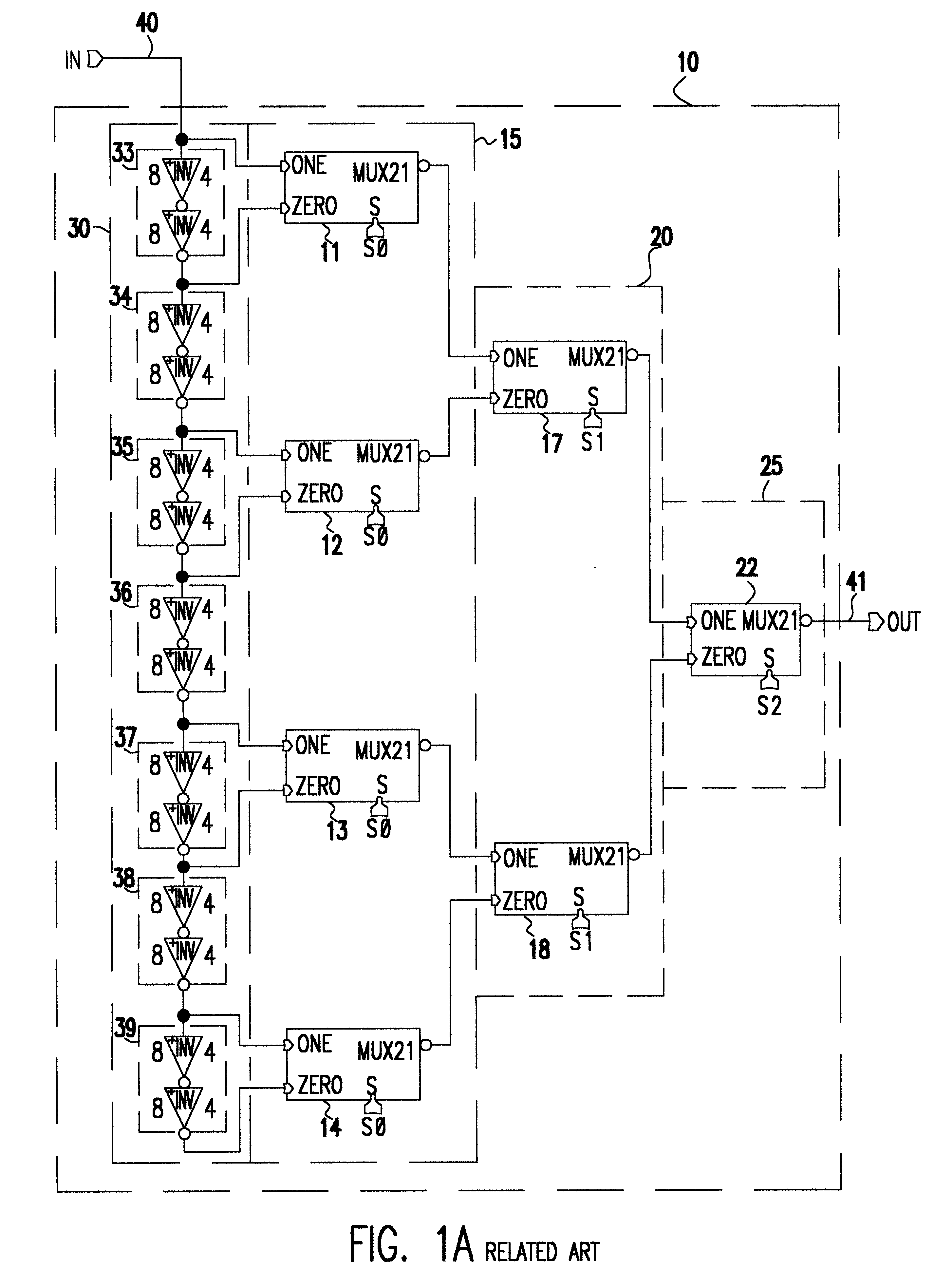

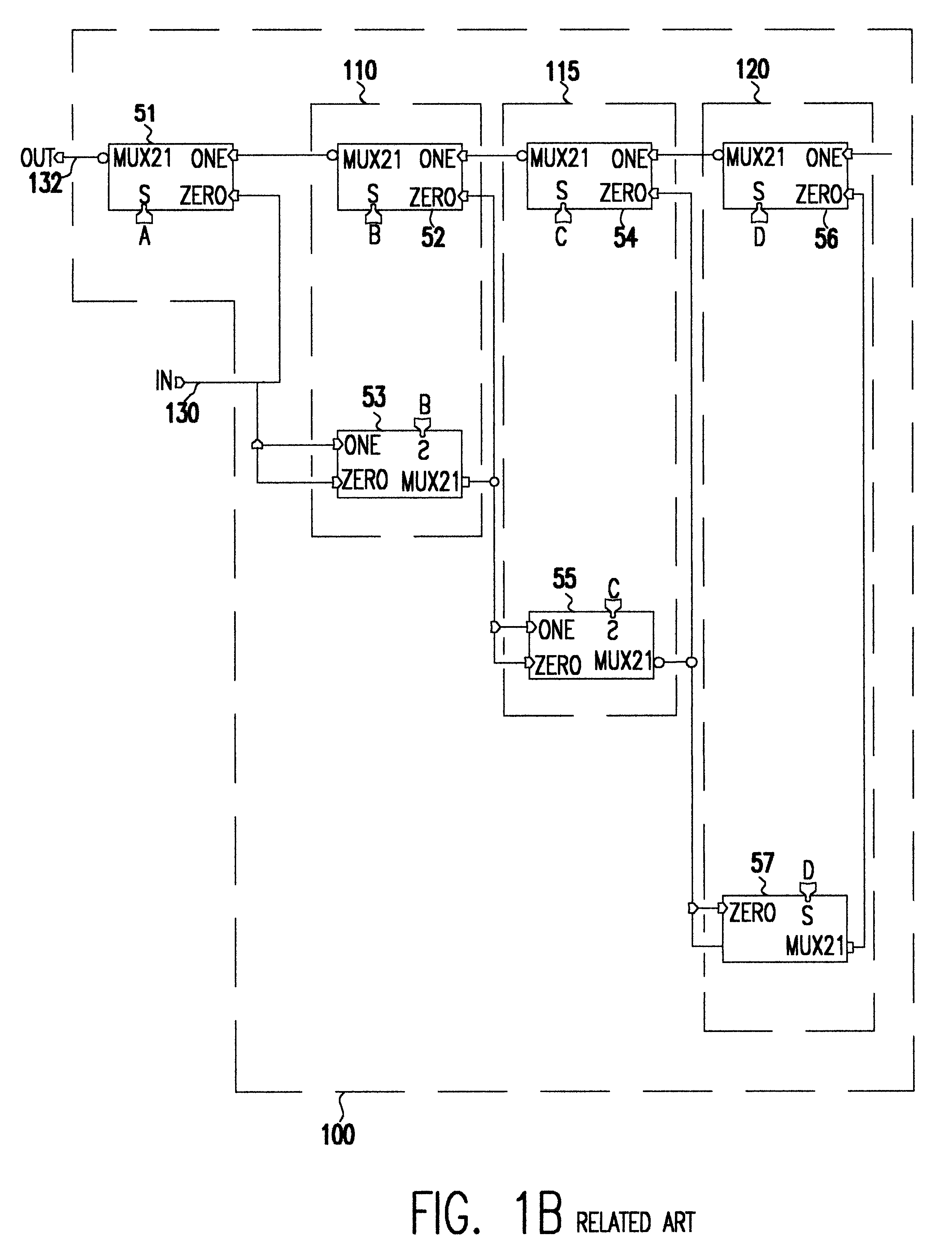

Digital delay line with low insertion delay

InactiveUS6285229B1Increased frequency rangeReduce chip areaSingle output arrangementsTime-delay networksDigital delay lineEngineering

A variable digital delay line with an insertion delay as low as a single delay element yet capable of providing a large programmable delay with a small simple control mechanism. A loop connects an input to an output through selectable first delay elements such as 2:1 muxes and selectable second delay elements such as pairs of inverters by way of a plurality of intermediate nodes having a tap. A plurality of sneak paths are available wherein the loop by passes a remainder of first delay elements and / or second delay elements by way of the taps at the intermediate nodes.

Owner:IBM CORP

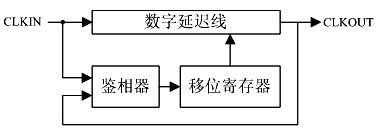

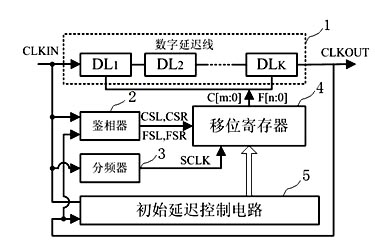

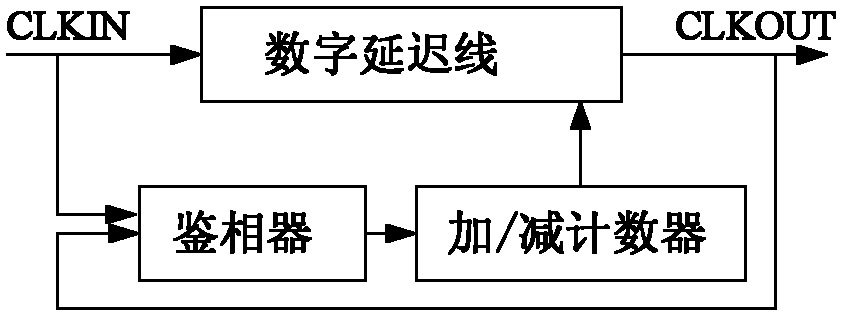

Digital delay phase locked loop circuit

InactiveCN101951260ASolve the speed problemSolve the problem of wrong lockPulse automatic controlShift registerDiscriminator

The invention relates to a digital delay phase locked loop circuit. In the circuit, a clock frequency divider and an initial delay control circuit are added; meanwhile, a shift register is improved; each delay unit of a digital delay line is controlled by an output signal of the improved shift register; a phase discriminator compares the phase of an input clock CLKIN and the phase of a delayed output clock CLKOUT; shift of the improved shift register is controlled according to a phase comparison result; the initial delay control circuit measures delay time from the input clock CLKIN to the output clock CLKOUT when started and then generates a setting signal to set the improved shift register; and the input clock CLKIN is output to serve as the input clock for the improved shift register after the frequency is divided by the clock frequency divider. The circuit solves the problems of slow locking speed and error locking of the conventional DLL structure, has a wider frequency range and is favorable for improving chip yield.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

Programmable delay line compensated for process, voltage, and temperature

A delay line compensated for process, voltage, and temperature variations, includes a delay locked loop (DLL) configured to delay a digital signal by the clock period of the digital signal, the DLL including a DLL delay line arranged as a plurality of cascaded sub-delay lines each sub-delay line providing one of a plurality of delay quanta in response to a digital control signal. A fractionating circuit is configured to generate a digital delay line control signal that is a fraction of the digital control signal. A digital delay line is arranged as a plurality of cascaded sub-delay lines each sub-delay line providing one of a plurality of delay quanta in response to the digital delay line control signal.

Owner:MICROSEMI SOC

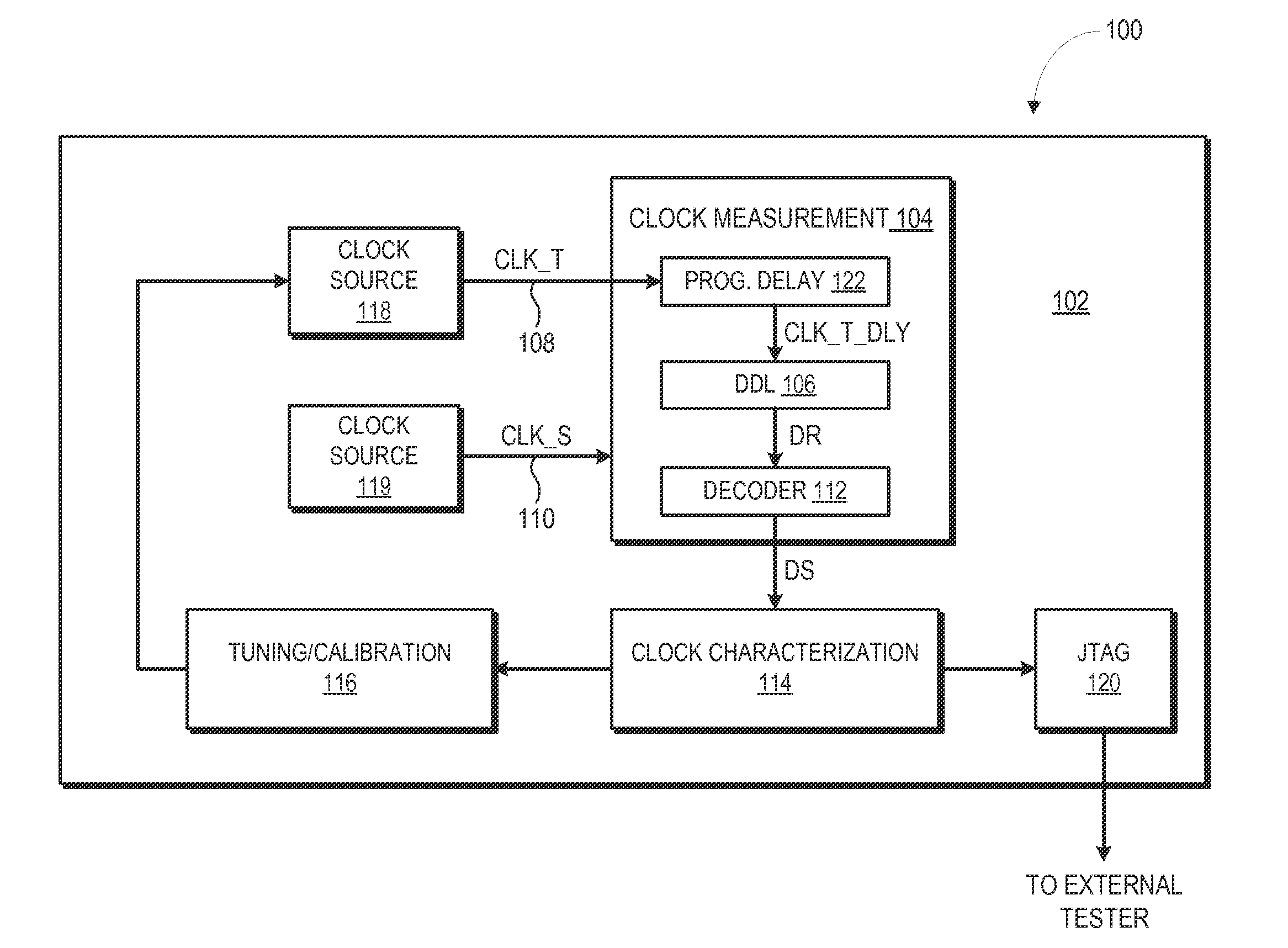

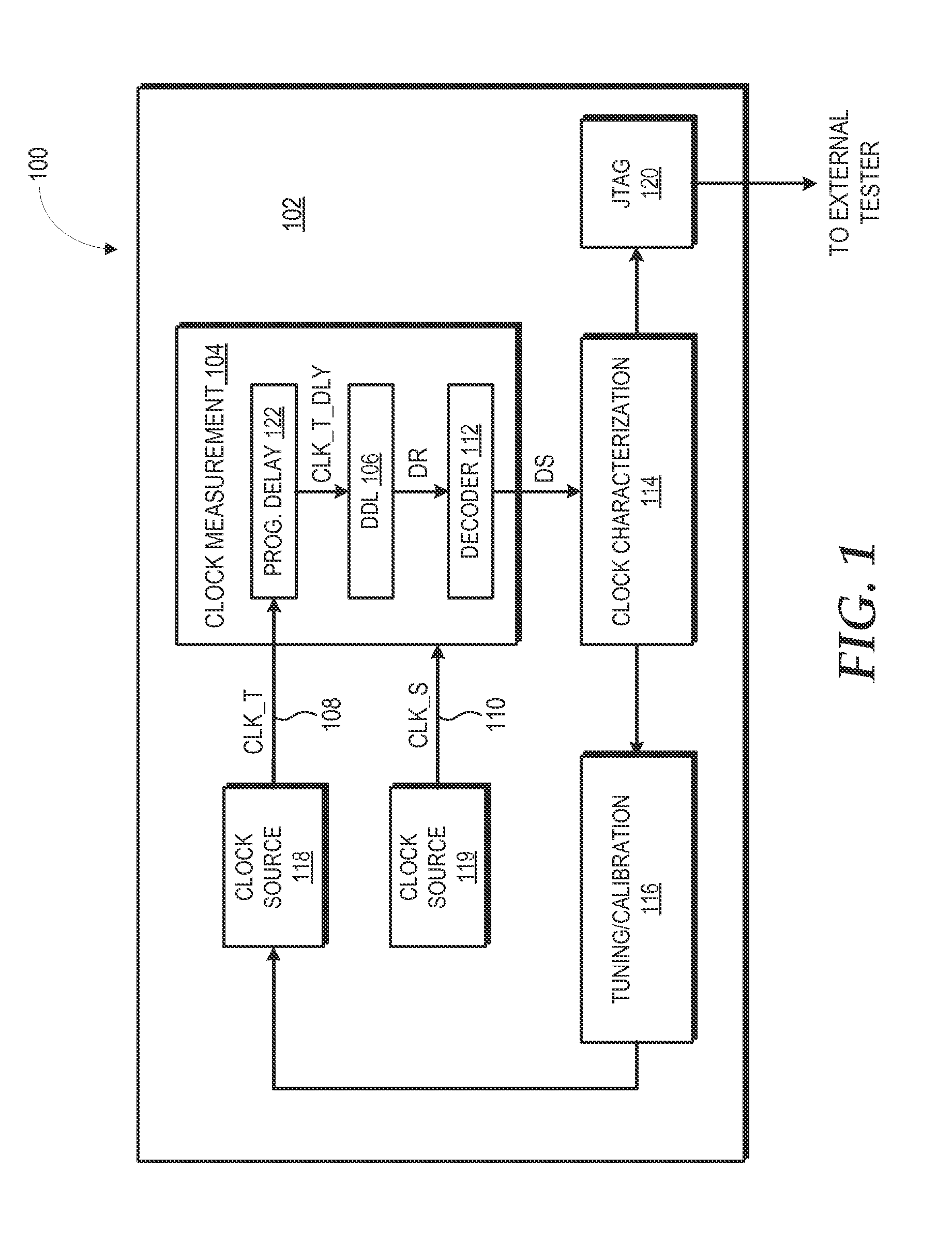

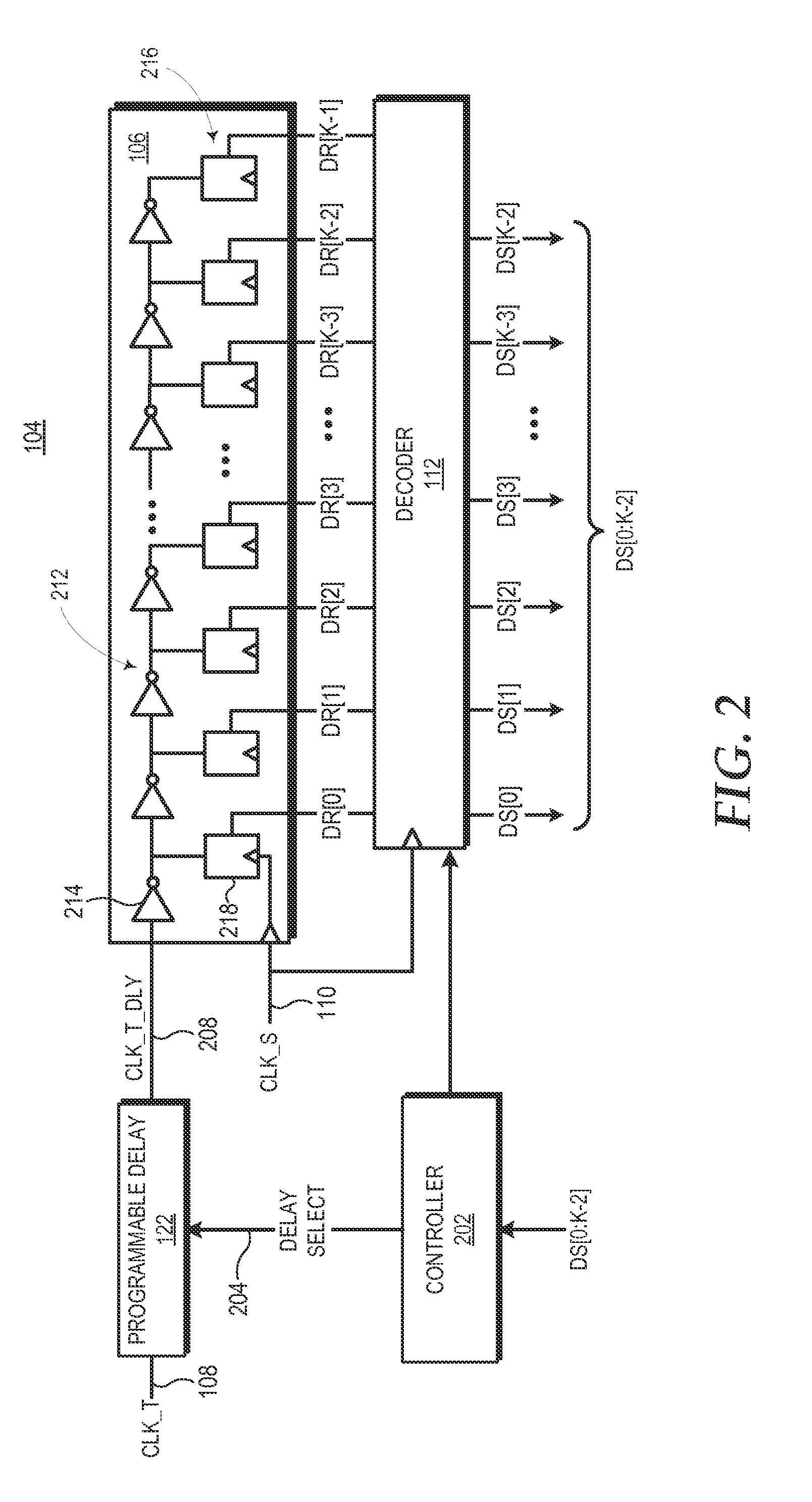

Adaptive digital delay line for characterization of clock uncertainties

An integrated circuit (IC) measures uncertainties in a first signal. The IC comprises a programmable delay circuit to introduce a programmable delay to the first signal to generate a first delayed signal. The IC further comprises a digital delay line (DDL) comprising a first delay chain of delay elements having input to receive the first delayed signal. The DDL further comprises a set of storage elements, each storage element having an input coupled to an output of a corresponding delay element of the first delay chain, and an output to provide a corresponding bit of a digital reading. The DDL additionally comprises a decoder to generate a digital signature from the digital reading and a controller to iteratively adjust the programmed delay of the programmable delay circuit to search for a failure in a resulting digital signature.

Owner:ADVANCED MICRO DEVICES INC

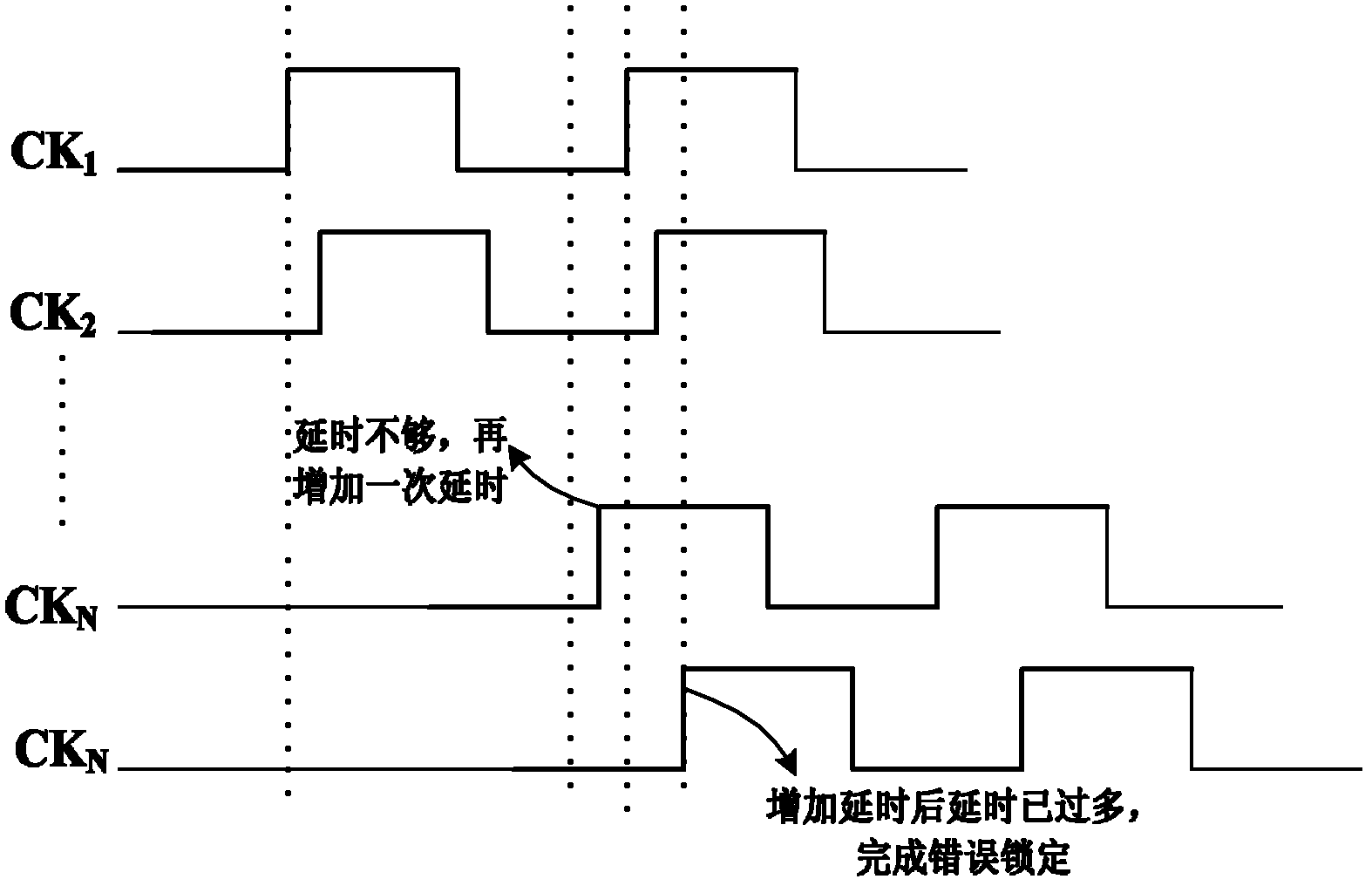

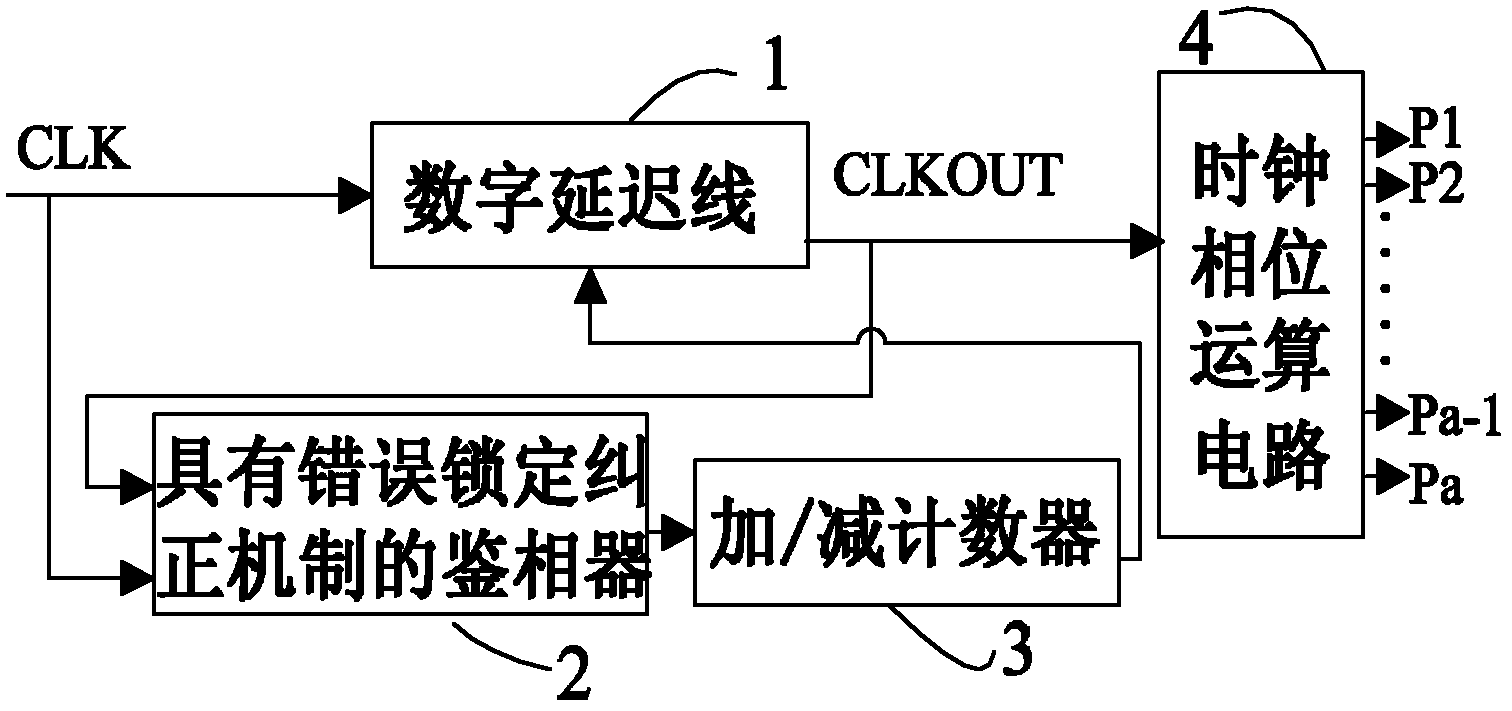

Counter control type delay-locked loop circuit with mistaken locking correction mechanism

ActiveCN102594338ASolve the problem of easy mislockingImprove yieldPulse automatic controlDiscriminatorDelay-locked loop

The invention relates to a counter control type delay-locked loop (DLL) circuit with a mistaken locking correction mechanism. The circuit comprises a digital delay line, a phase discriminator, an addition / subtraction counter and a clock phase arithmetic circuit. An input reference clock signal CLK is connected to the digital delay line and the phase discriminator respectively. The output of the digital delay line is connected to the phase discriminator and the clock phase arithmetic circuit. The output of the phase discriminator is connected to the input of the addition / subtraction counter. The output of the addition / subtraction counter is connected to the digital delay line. Whether the delay of a delayed output clock signal is consistent with a locking condition or not is judged through a locking process detection window, and the delay is timely regulated according to a detection result, so that mistaken locking is avoided, and a delay locking function is accurately realized. The circuit has the advantages that: the problem that the conventional DLL structure is easily mistakenly locked is effectively solved; moreover, the circuit has a wide frequency range and much phase output; and the yield of a chip can be improved.

Owner:58TH RES INST OF CETC

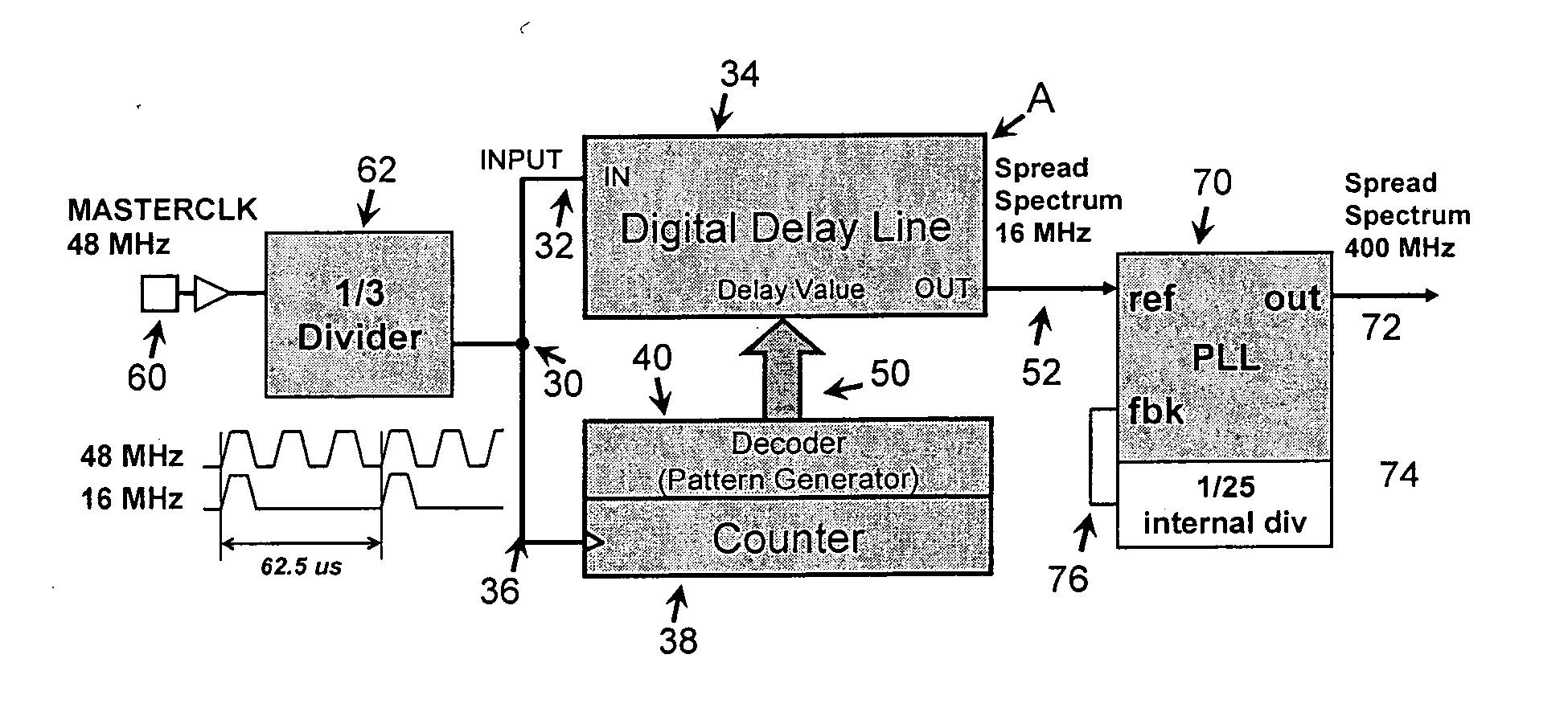

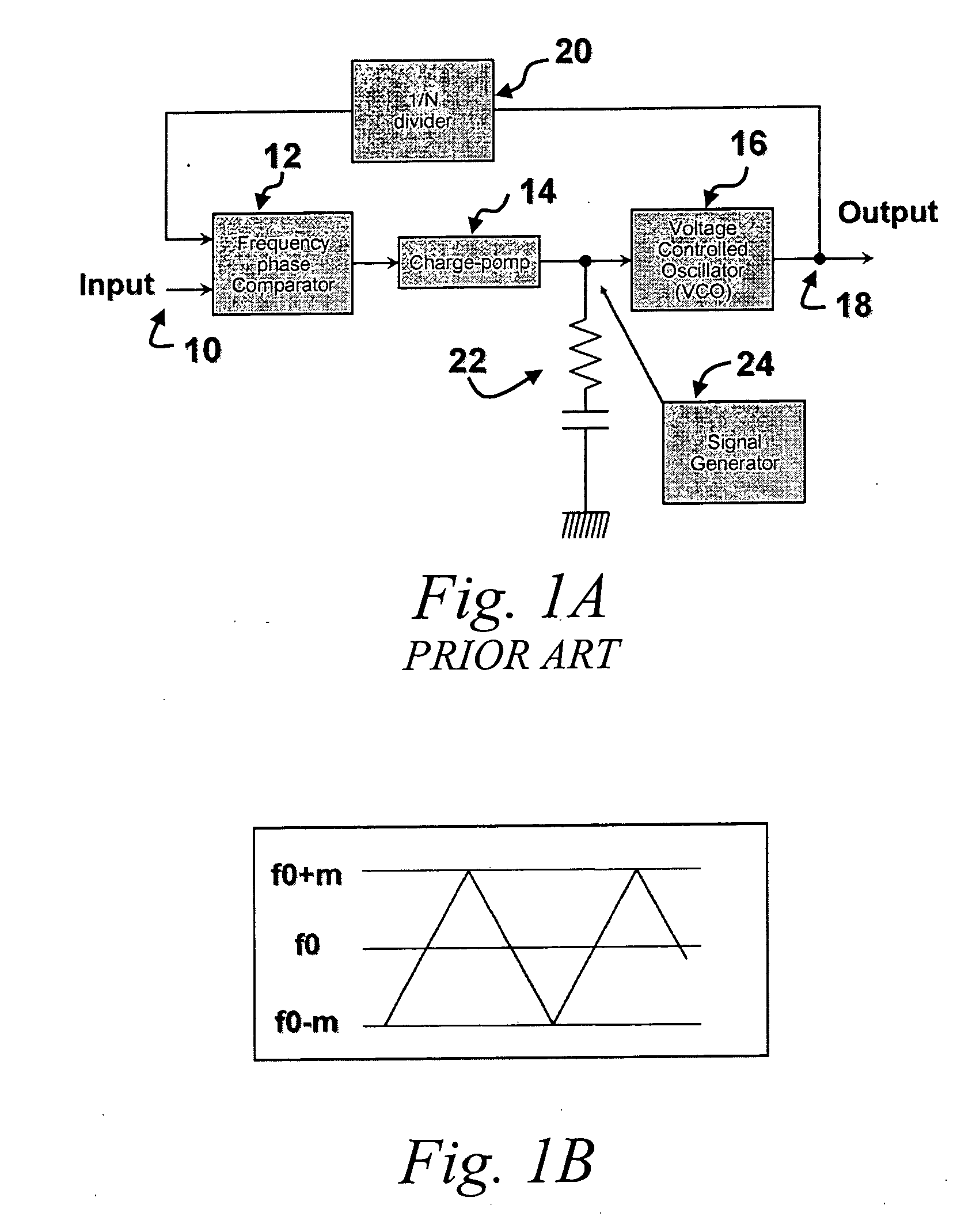

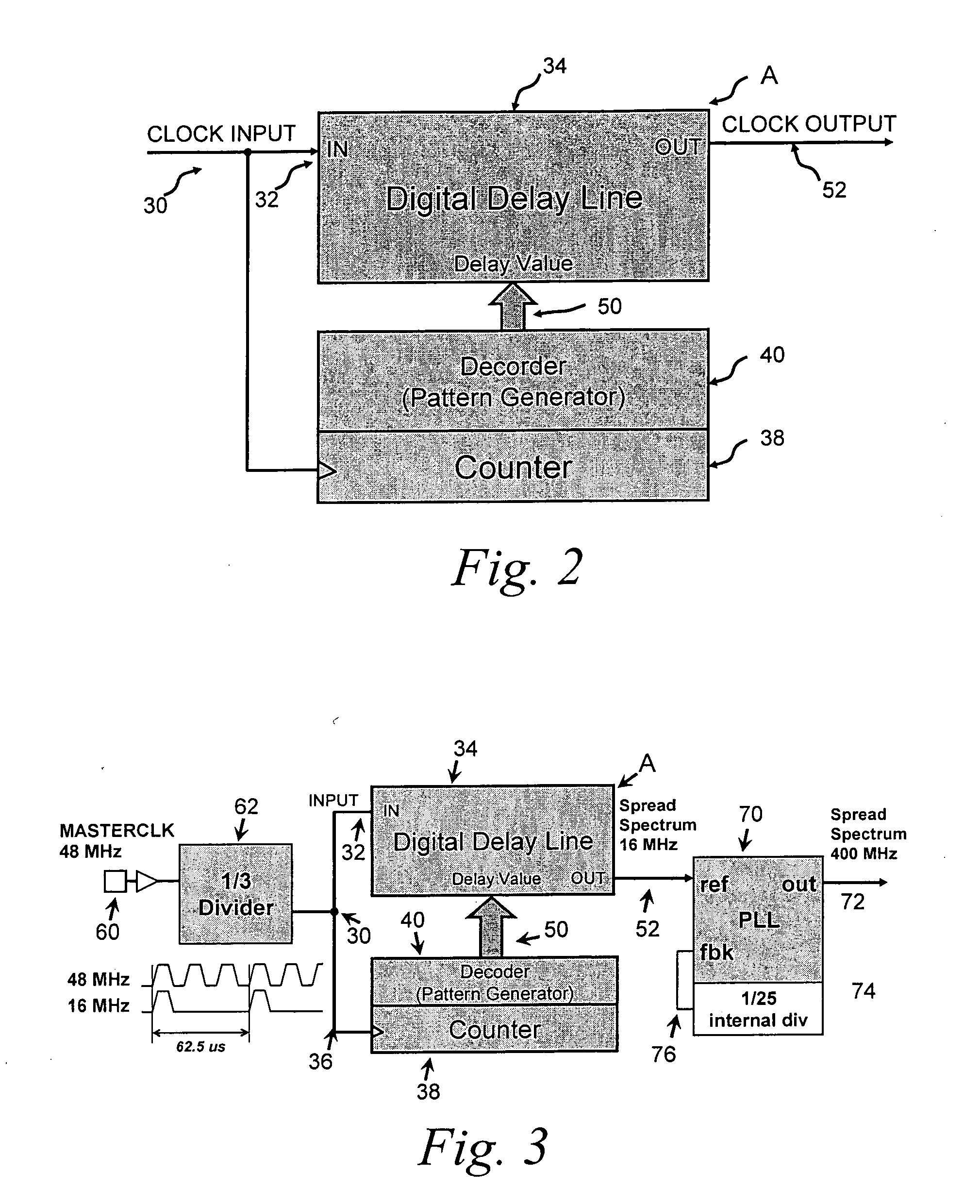

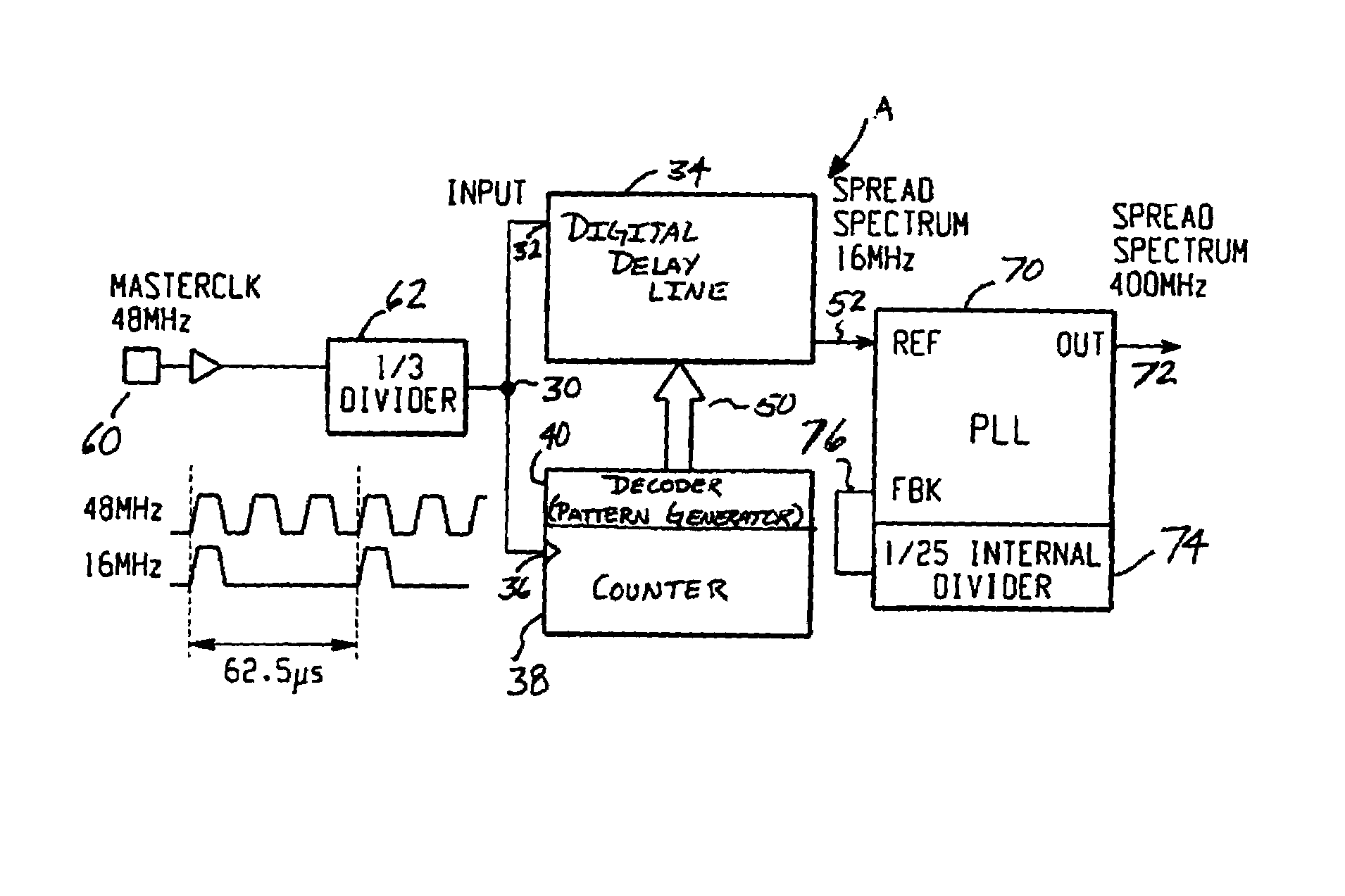

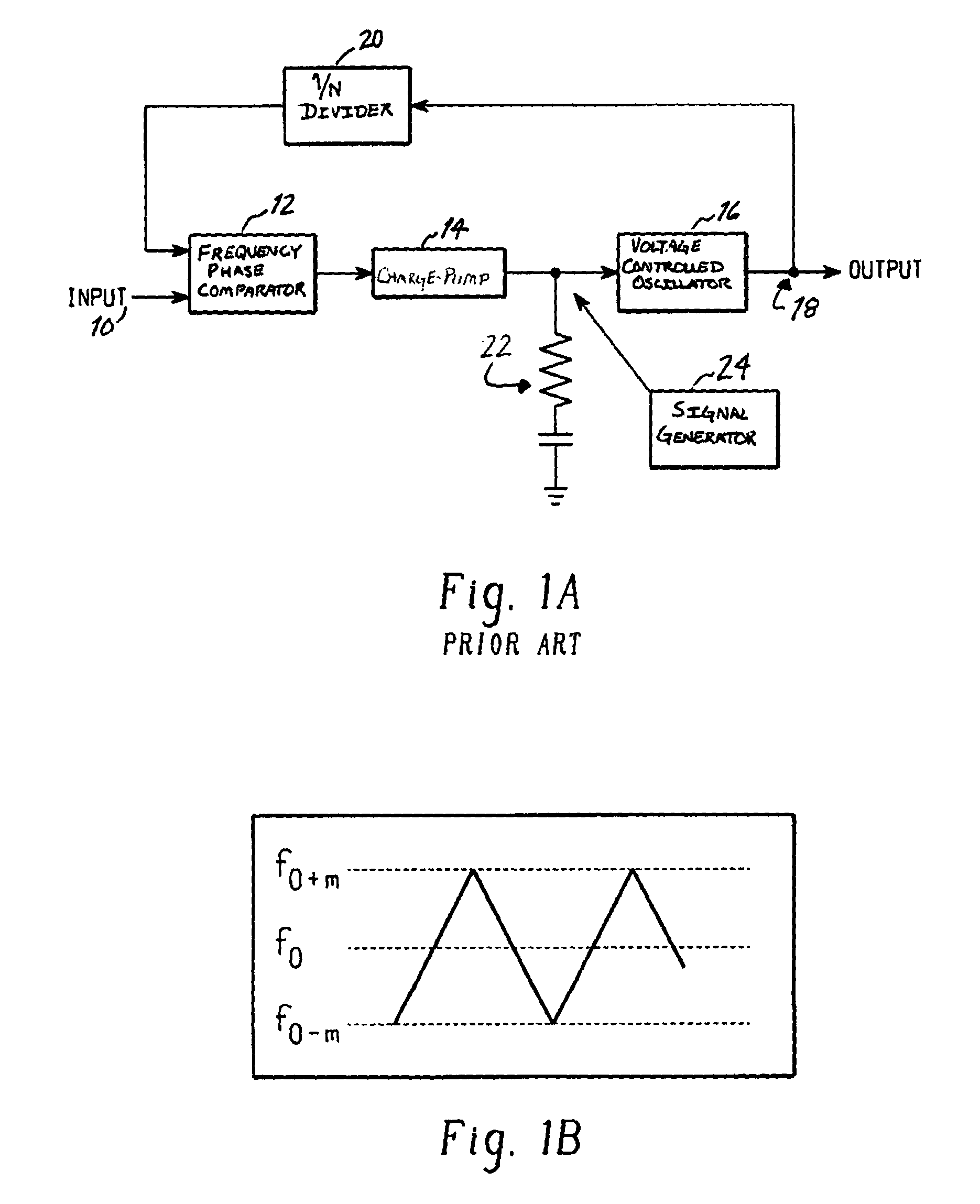

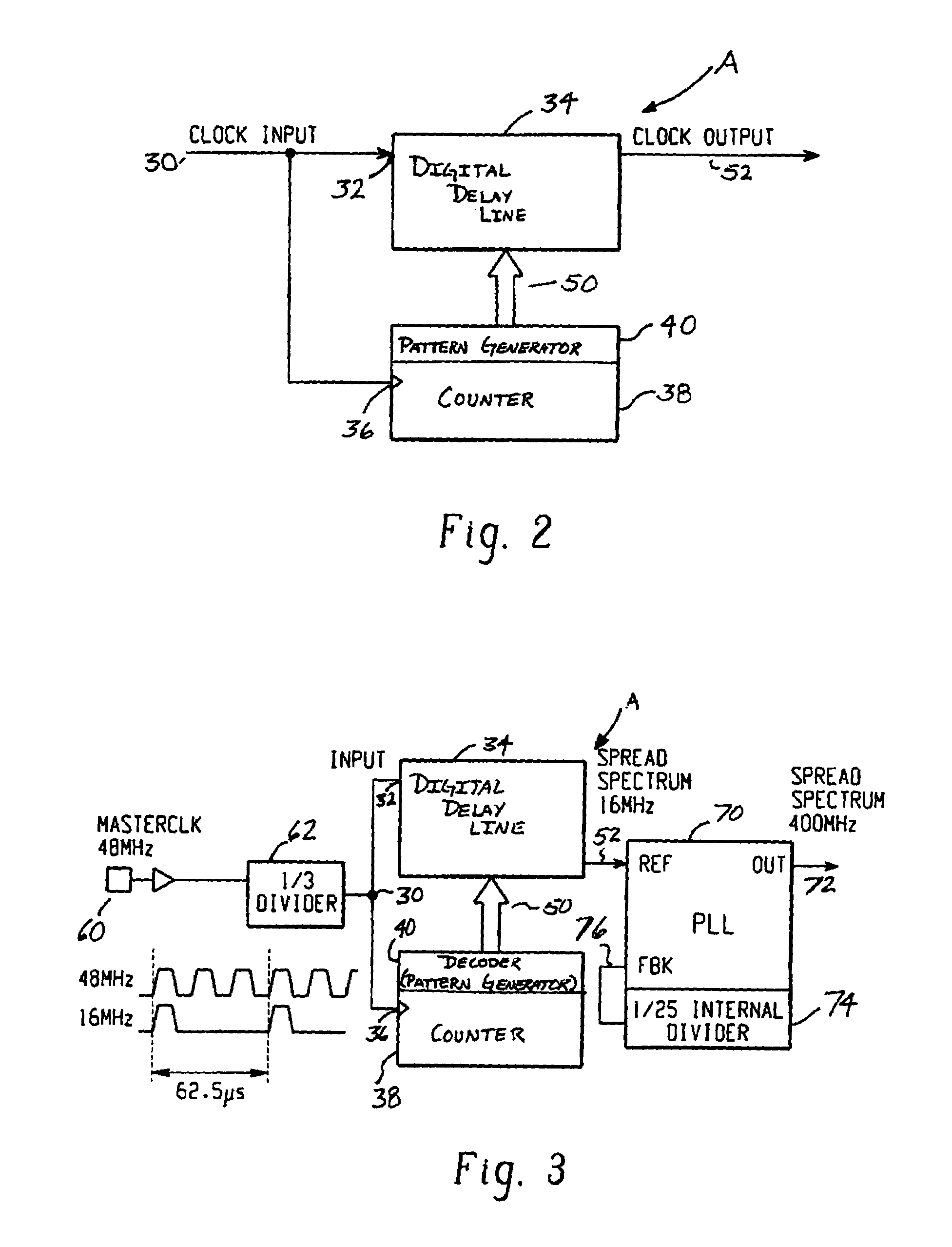

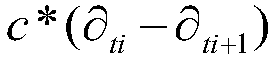

Spread spectrum clock generator

InactiveUS20050069019A1Angle modulation detailsDigital data processing detailsDigital dataDigital clock

A clock signal generator varies a frequency of a digital clock over a selected range of frequencies. The generator employs a divider for lowering a frequency of a clock signal. A counter increments synchronously with the signal, and causes a selected sequence of outputs to be generated by a pattern generator. The pattern generator output forms an input to a digitally controllable delay line which receives the lower frequency clock signal. The pattern generator causes the digital delay line to vary a frequency of the lowered frequency clock signal between selected boundaries. The varying frequency clock signal is then raised up again such that a final clock has a varying frequency, and will exhibit less EMI spiking during switching of an associated, synchronous digital data device. The solid state nature of the generator allows for simple fabrication, inexpensive manufacture and ready integration into digital circuitry, such as multifunction integrated circuits.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

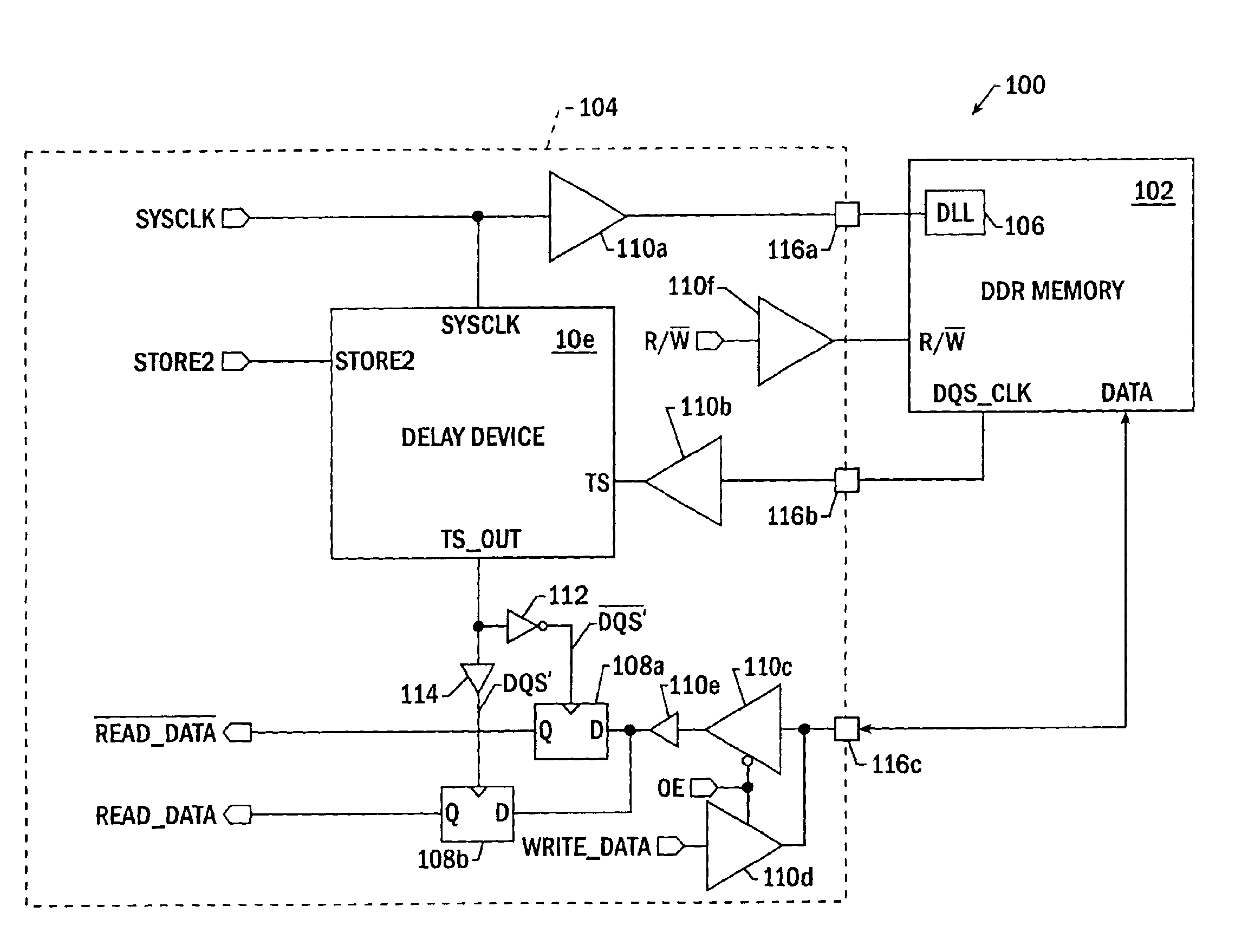

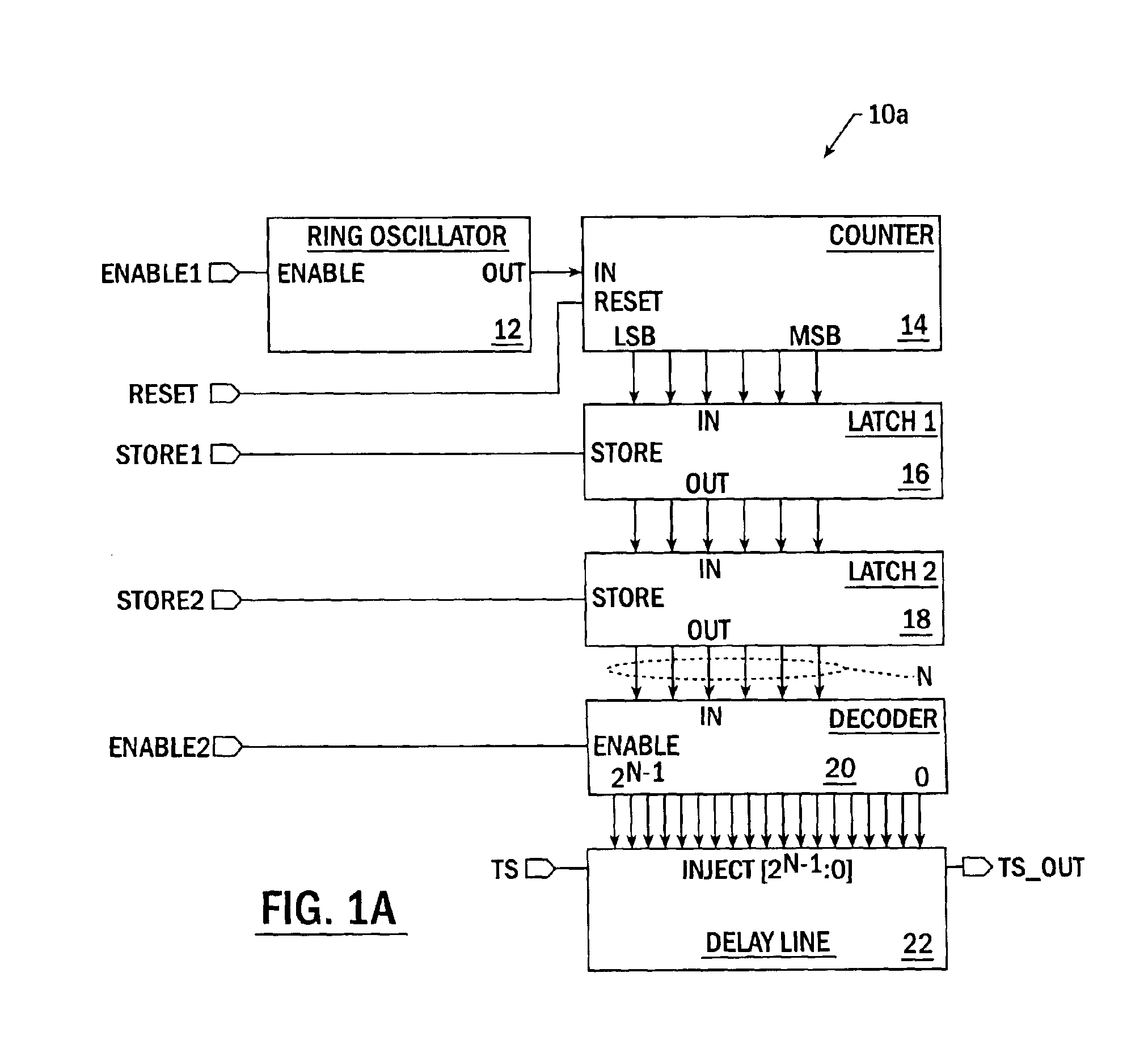

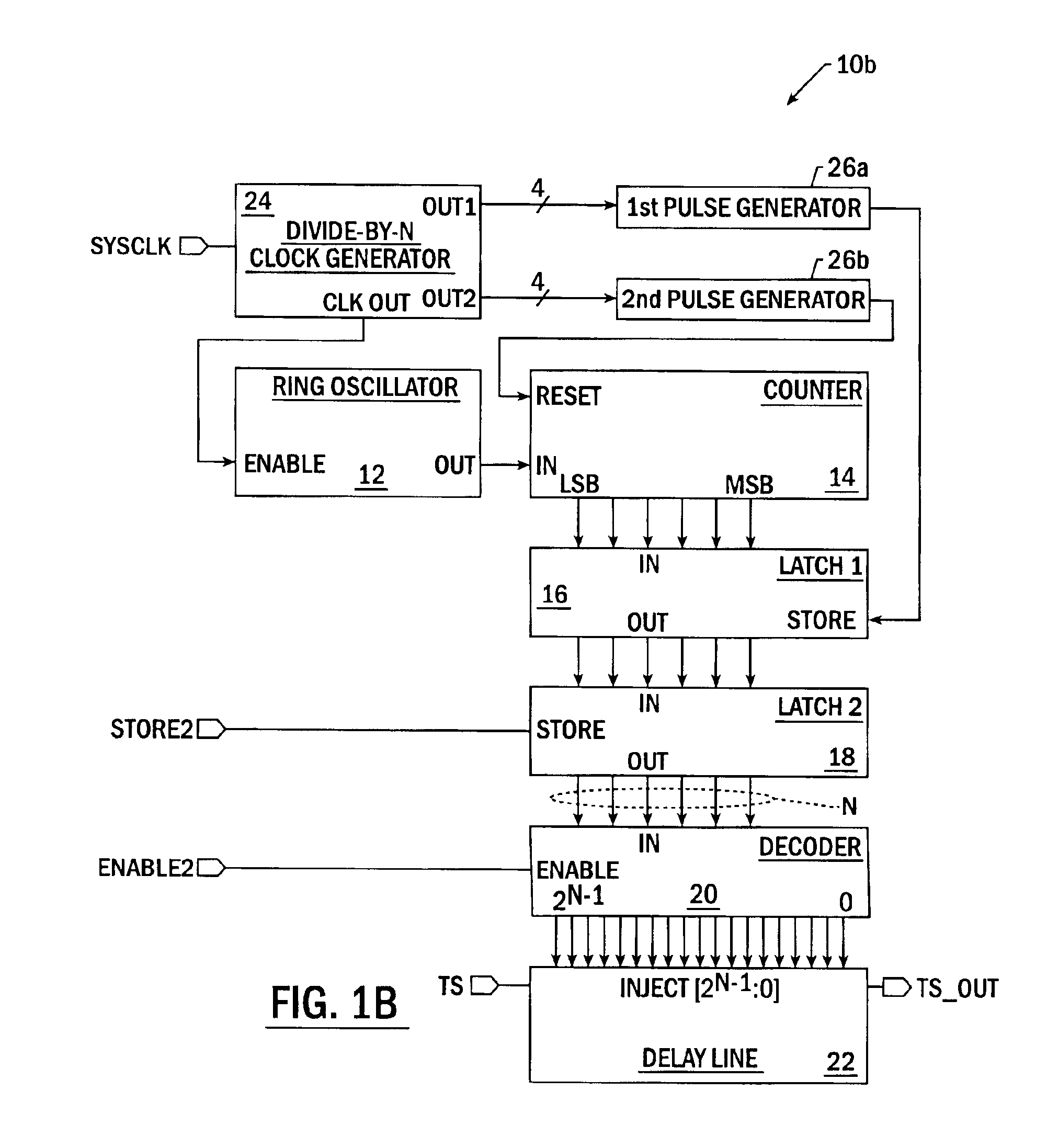

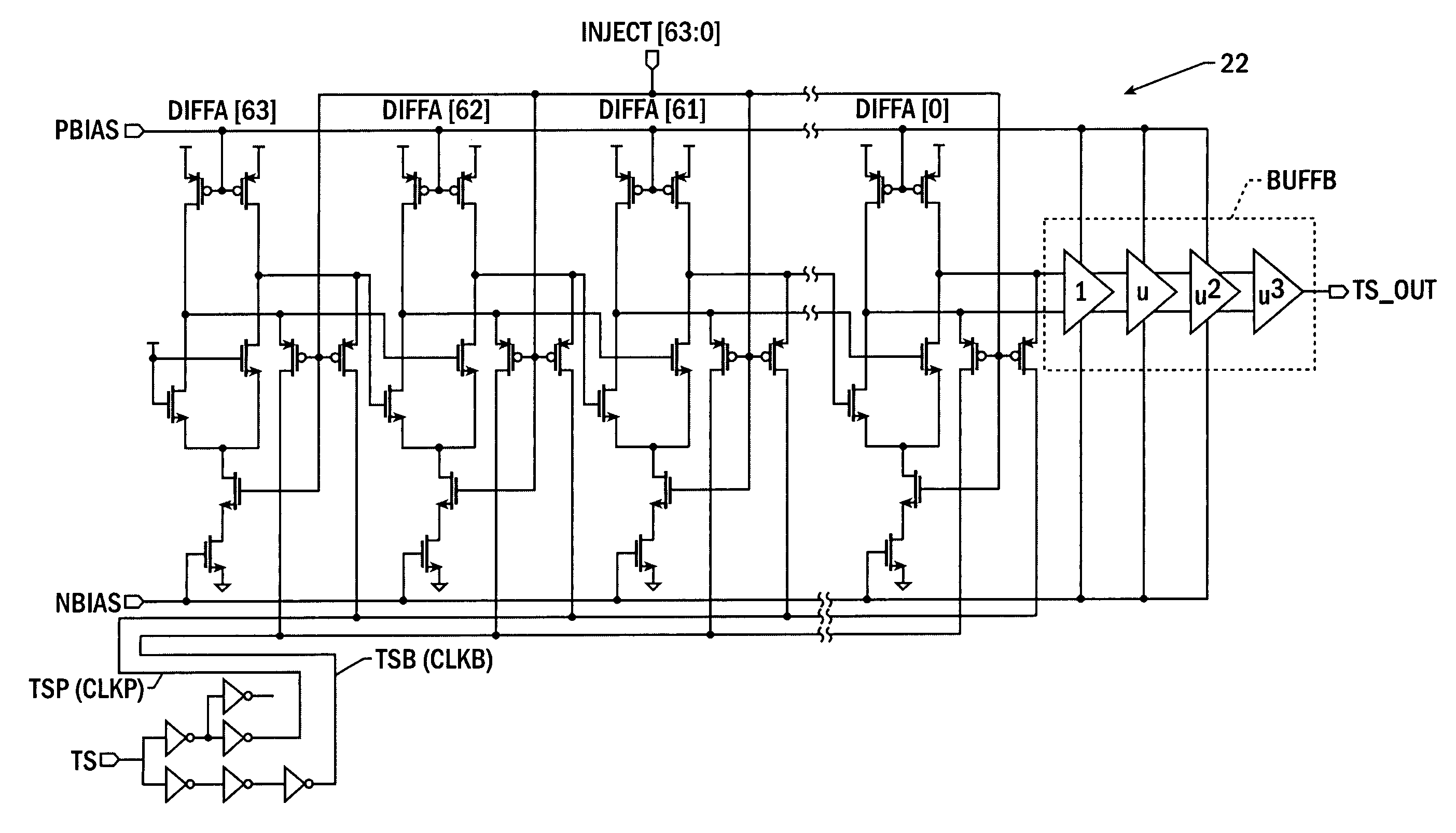

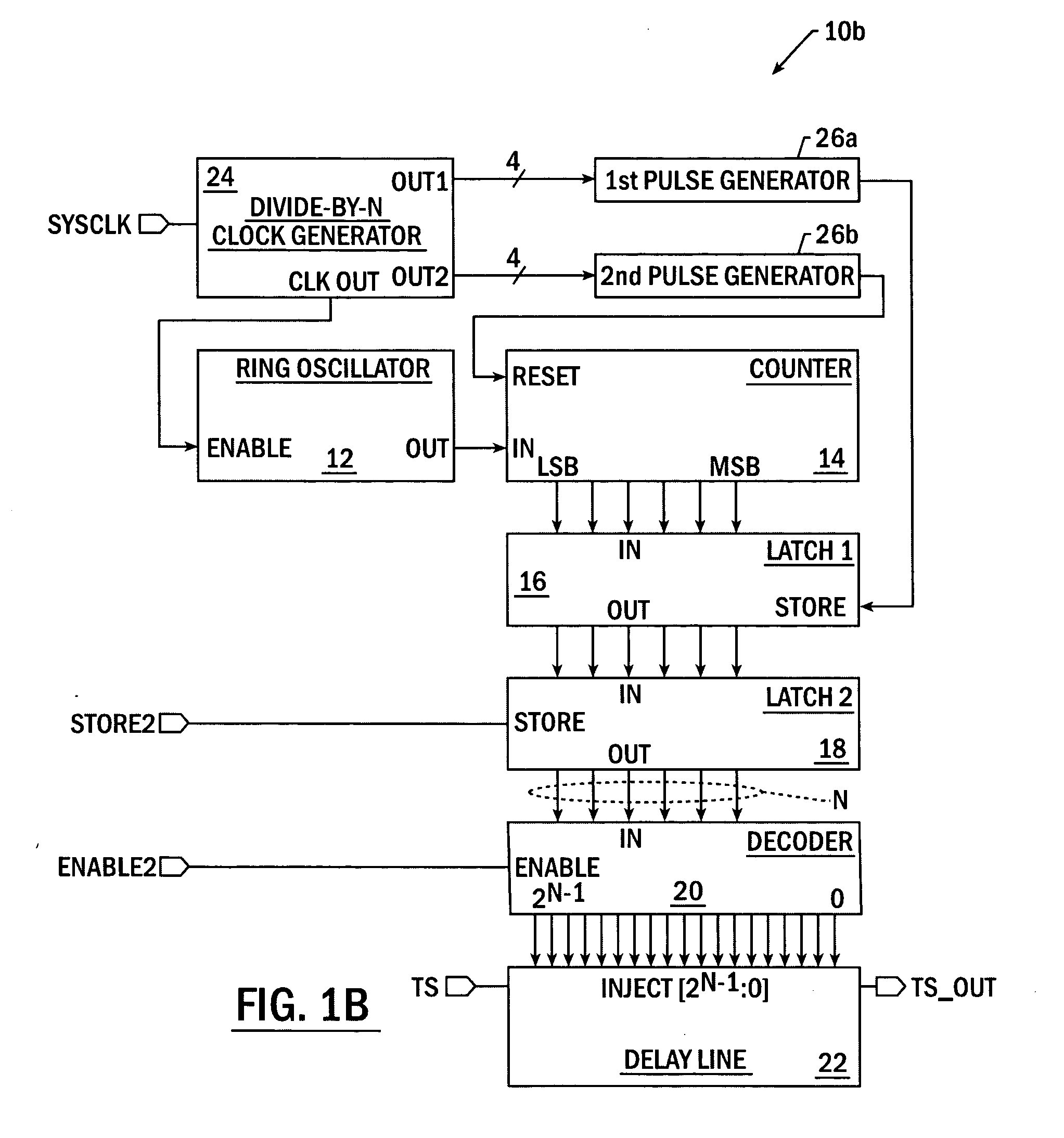

Integrated circuit devices having high precision digital delay lines therein

InactiveUS6856558B1High resolutionConvenient power supplyPulse automatic controlPulse generation by logic circuitsInjection portControl signal

Integrated circuit delay devices include a digital delay line that is configured to provide a percent-of-clock period delay to a timing signal accepted at an enabled one of a plurality of injection ports thereof. The digital delay line may be responsive to an injection control signal having a value that sets a length of the delay by specifying a location of the enabled one of the plurality of injection ports, with the end of the delay line being a fixed output port. A delay line control circuit is also provided that is responsive to a clock signal having a period from which the percent-of-clock period delay is preferably measured. The delay line control circuit is configured to generate the injection control signal by counting multiple cycles of a high frequency ring oscillator signal having a period less than, and typically substantially less than, the clock period, over a time interval having a duration greater than, and typically substantially greater than, the clock period. The ring oscillator signal may be generated by a ring oscillator having a relatively small number of stages and the time interval may be sufficiently long so that a large number of cycles of the ring oscillator signal may be counted over many periods of the clock signal.

Owner:SK HYNIX INC

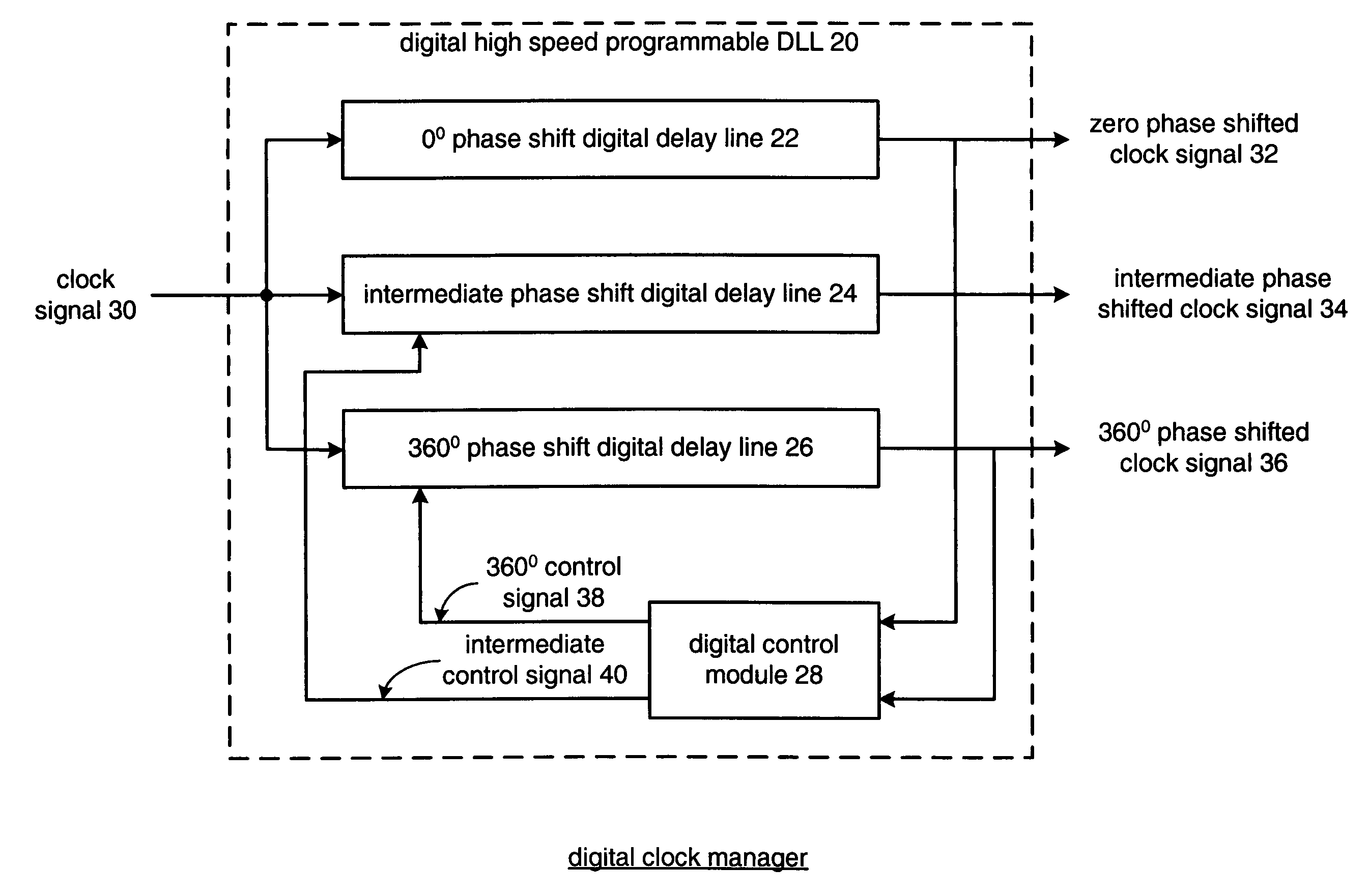

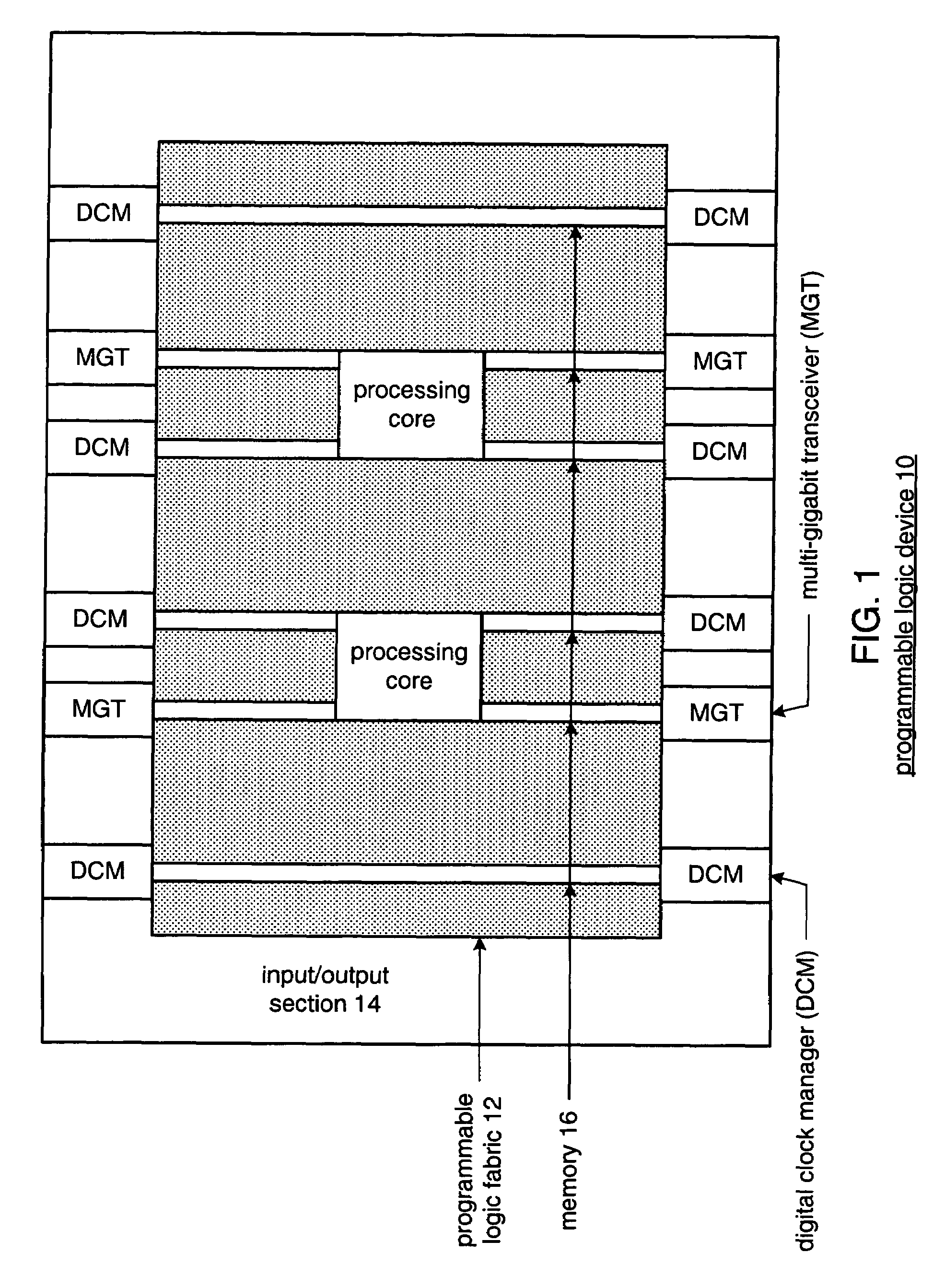

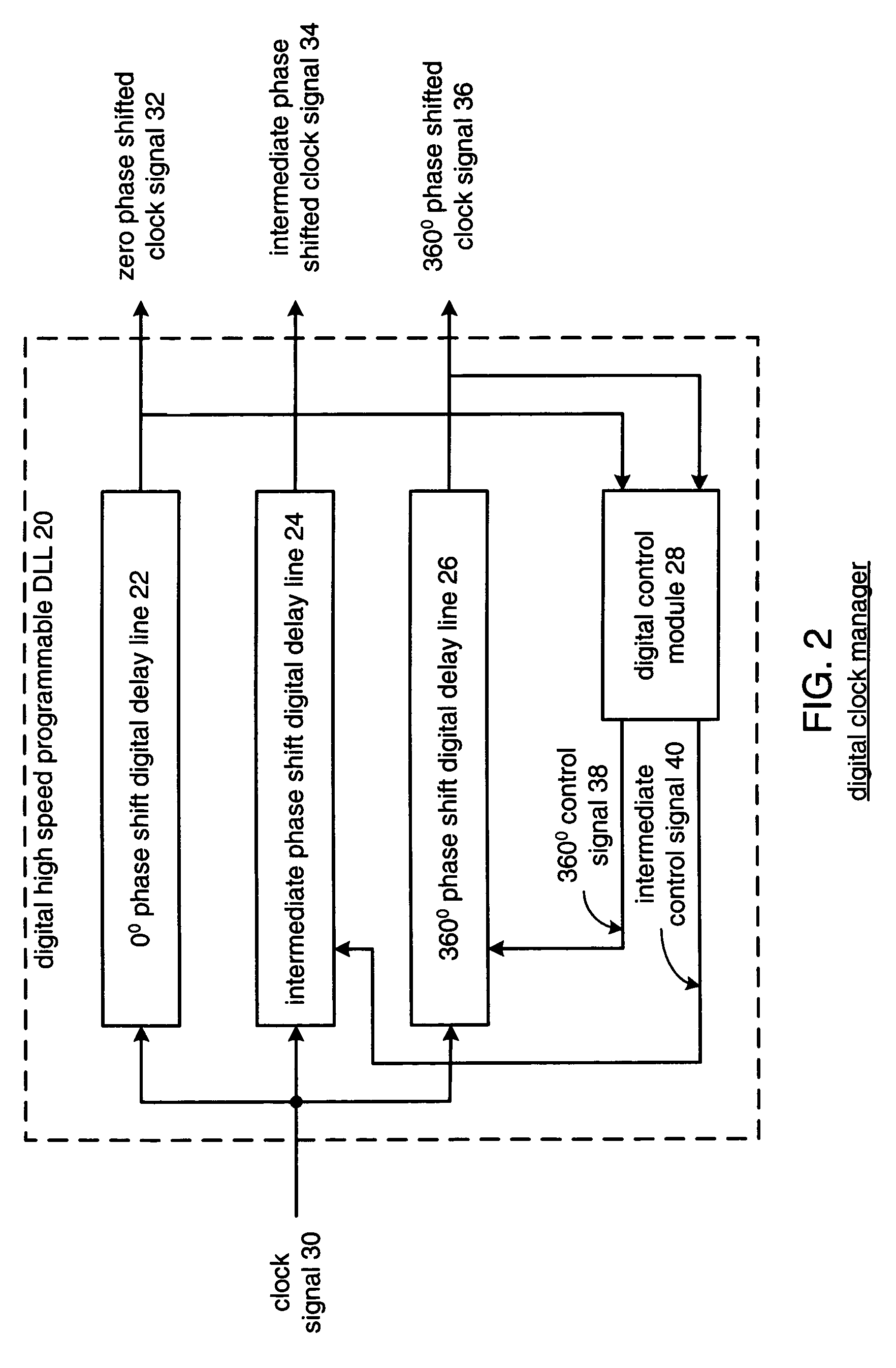

Digital high speed programmable delayed locked loop

A digital high speed programmable delayed locked loop (DLL) includes a zero degree phase shift digital delay line, at least one intermediate phase shift digital delay line, a three hundred and sixty degree phase shift digital delay line, and a digital control module. The zero degree phase shift, intermediate phase shift, and 360 degree phase shift digital delay lines are operably coupled to produce, from a clock signal, zero phase shifted, intermediate phase shifted, and 360 phase shifted representations, respectively, of the clock signal. The digital control module is operably coupled to produce an intermediate control signal for the intermediate phase shift digital delay line and a 360 degree control signal for the 360 degree phase shift digital delay line based on a phase difference between the zero phase shifted representation of the clock signal and the three hundred and sixty degree phase shifted representation of the clock signal.

Owner:XILINX INC

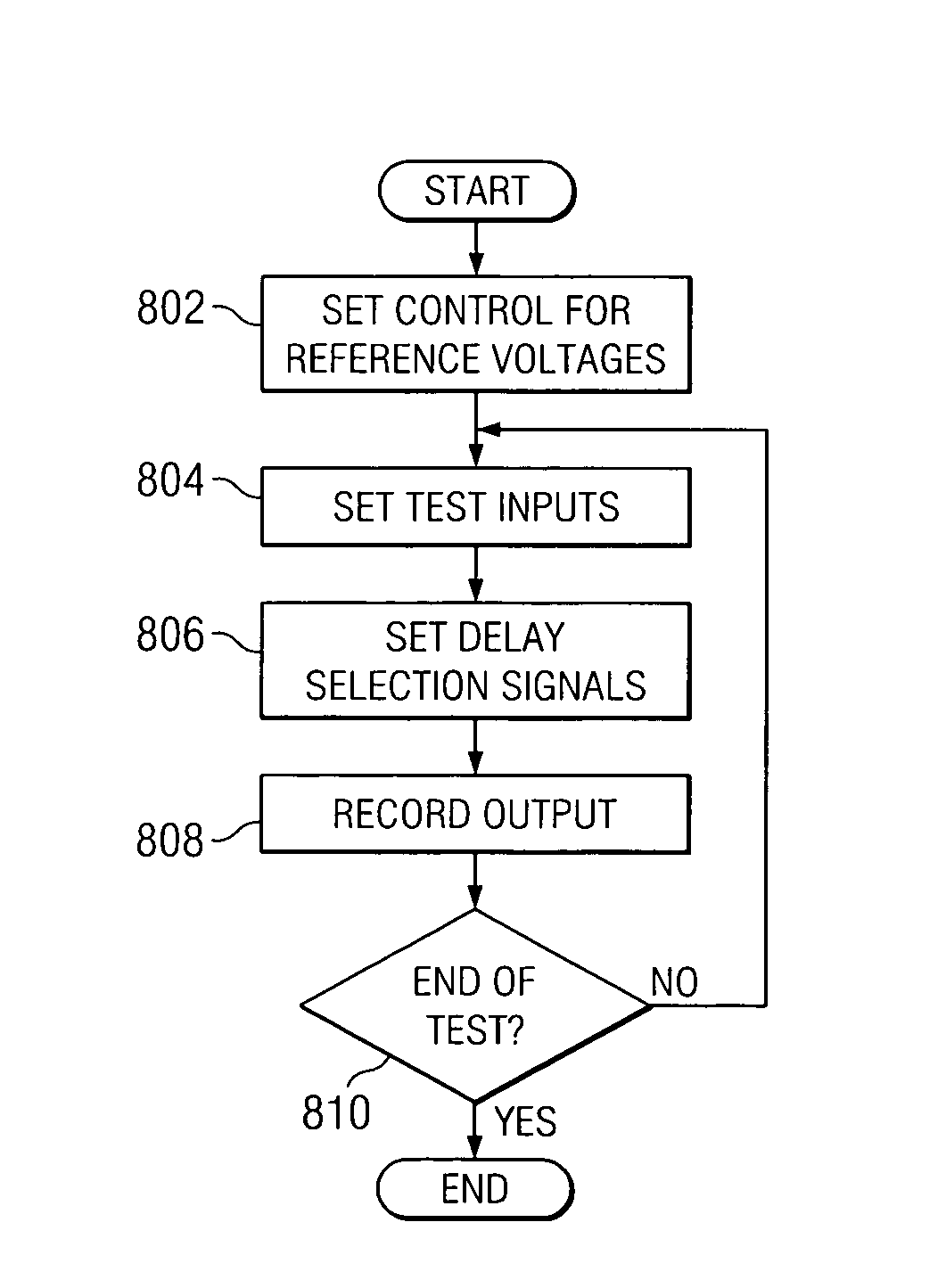

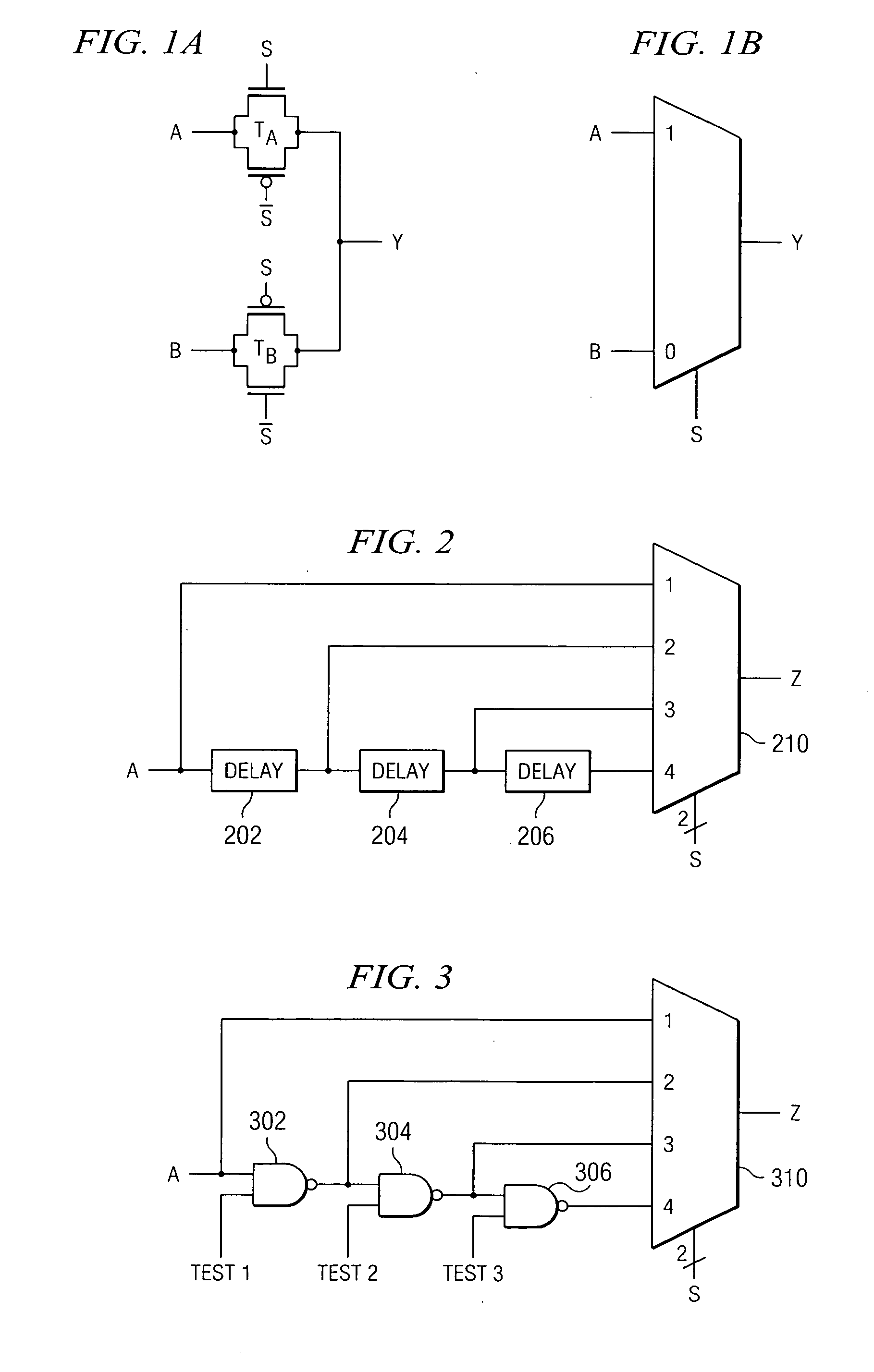

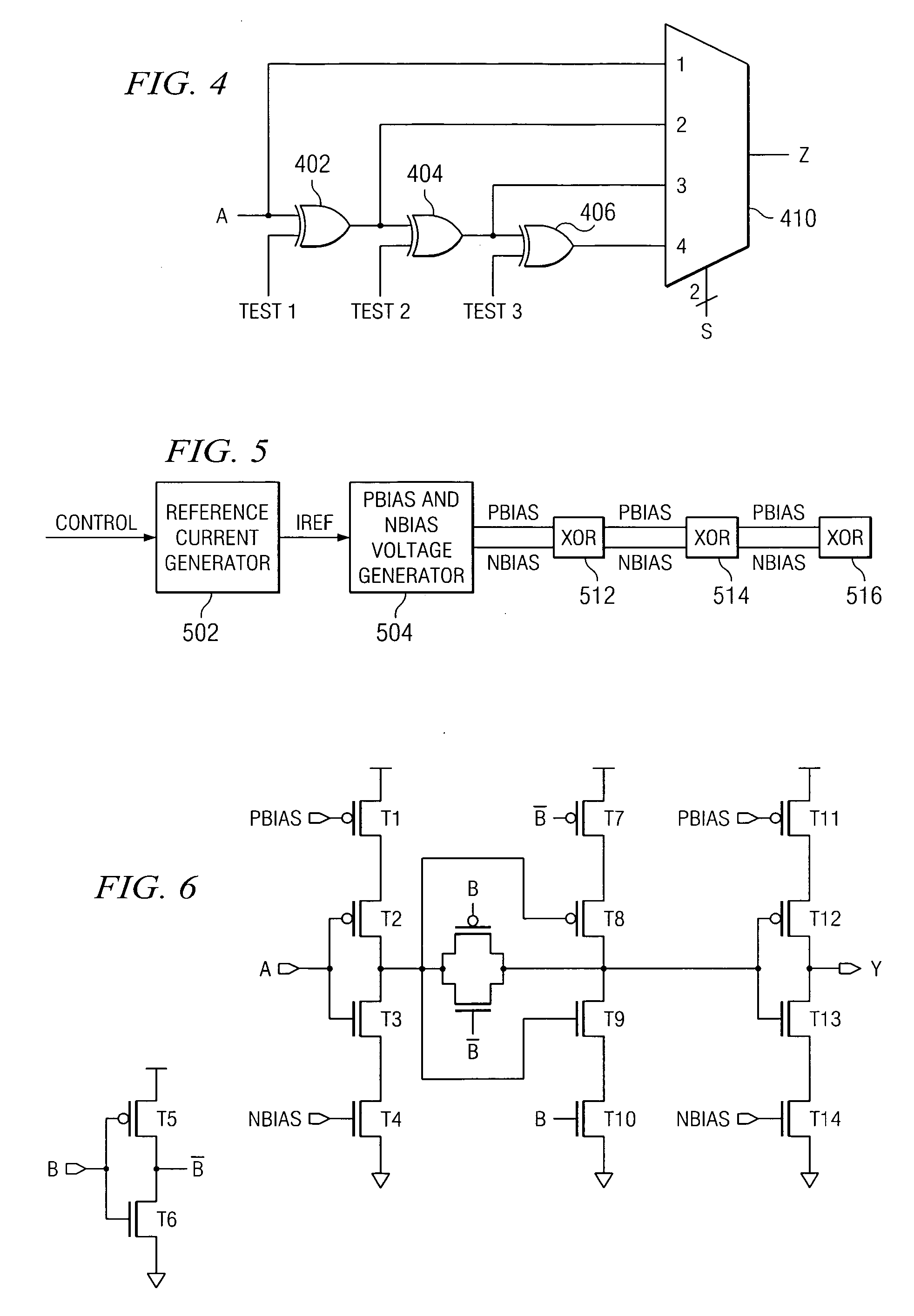

Testable digital delay line

InactiveUS20060247880A1Robust pattern fault coverageTime indicationSynchronous motors for clocksFault coverageVoltage generator

A testable digital delay line that uses XOR gates as delay elements is provided. The use of XOR gates enables independent control of each input to the multiplexer. With test inputs that enable each delay element, the multiplexer inputs can be assigned any value during test, thus giving the delay line very robust pattern fault coverage. The XOR gate may consist of three current limiting inverters. A reference voltage generator generates constant voltages between a source voltage, bias voltages, and ground. These constant voltages decide the amount of current through the current limiting inverters. Selecting a different set of reference voltages programs a different current flowing in the current limiting inverters. This programmable current causes a programmable unit delay to be introduced by each XOR gate delay element.

Owner:IBM CORP

Spread spectrum clock generator

A clock signal generator varies a frequency of a digital clock over a selected range of frequencies. The generator employs a divider for lowering a frequency of a clock signal. A counter increments synchronously with the signal, and causes a selected sequence of outputs to be generated by a pattern generator. The pattern generator output forms an input to a digitally controllable delay line which receives the lower frequency clock signal. The pattern generator causes the digital delay line to vary a frequency of the lowered frequency clock signal between selected boundaries. The varying frequency clock signal is then raised up again such that a final clock has a varying frequency, and will exhibit less EMI spiking during switching of an associated, synchronous digital data device. The solid state nature of the generator allows for simple fabrication, inexpensive manufacture and ready integration into digital circuitry, such as multifunction integrated circuits.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

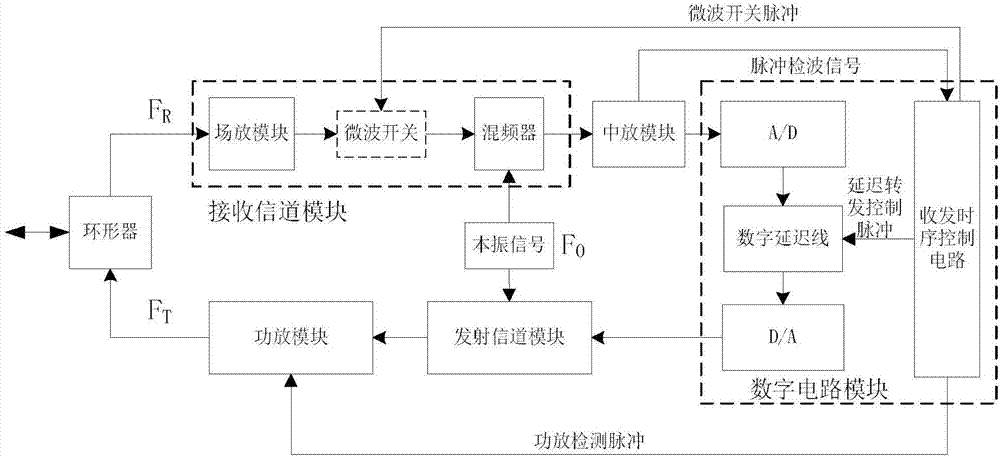

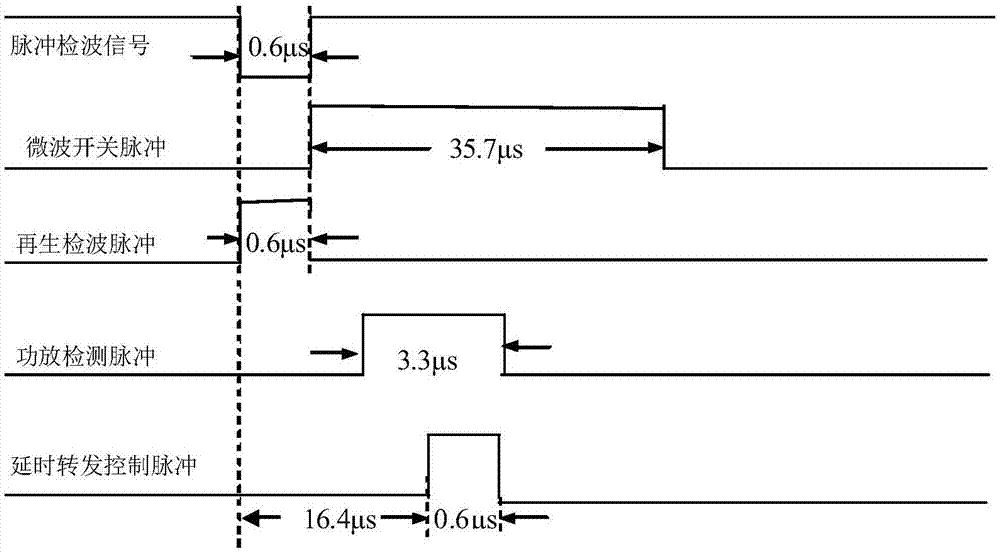

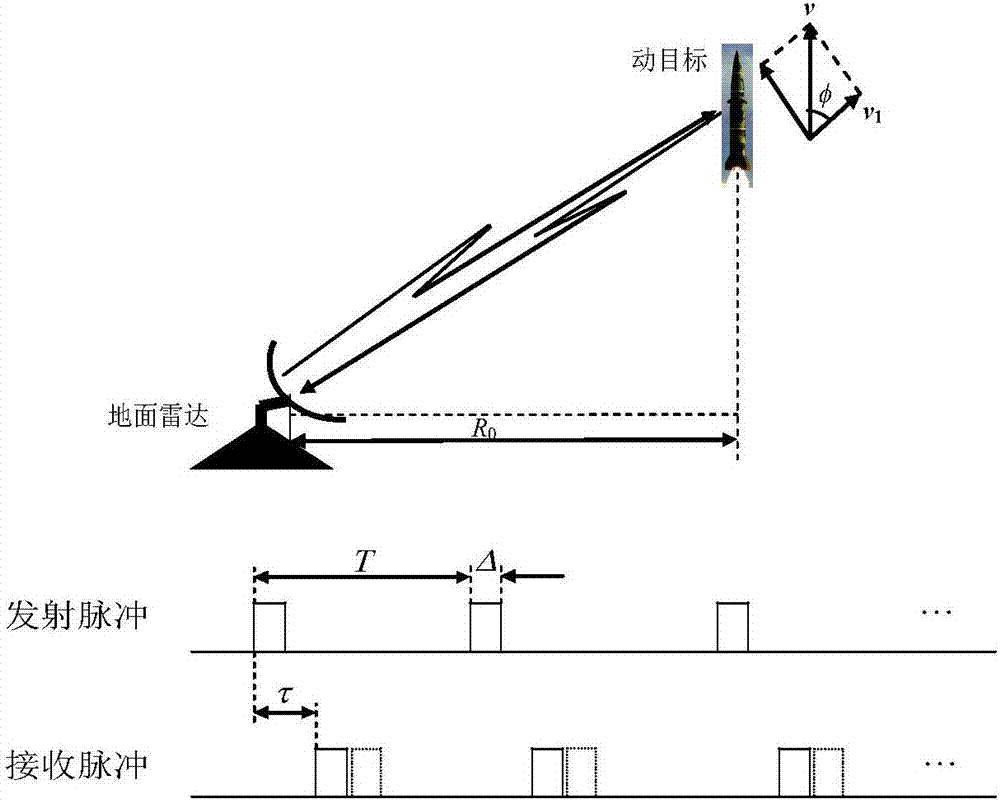

Co-channel interference processing system for pulse coherent answering machine

ActiveCN107271967ASimplify channel designFlexibleWave based measurement systemsIntermediate frequencyCo-channel interference

The invention provides a co-channel interference processing system for a pulse coherent answering machine, which can solve the self-excitation problem of co-channel interference of a pulse coherent answering machine and ensure the working stability of the answering machine. The method is achieved by the following technical scheme that after the pulse answering machine antenna receives a radio frequency signal, the radio frequency signal FR enters a field amplifier module through a circulator, after the signal is filtered and amplified by the field amplifier module and then controlled by a microwave switch, the controlled radio frequency signal is mixed with a local oscillation signal to output an intermediate frequency signal, the intermediate frequency is amplified and detected by a middle amplifier module and then sent to a digital circuit module for A / D acquisition, a collected signal is stored and transmitted through a digital delay line, the timing control of the digital delay line is controlled by a sending and receiving timing control circuit, a forwarding signal is sent to a D / A converter for outputting an intermediate frequency signal which is subjected to up conversion by a transmitting channel module and then amplified by a power amplifier module, and an amplified signal FT is output by the circulator. The system solves the self-excitation problem of pulse transmit-receive same frequency.

Owner:10TH RES INST OF CETC

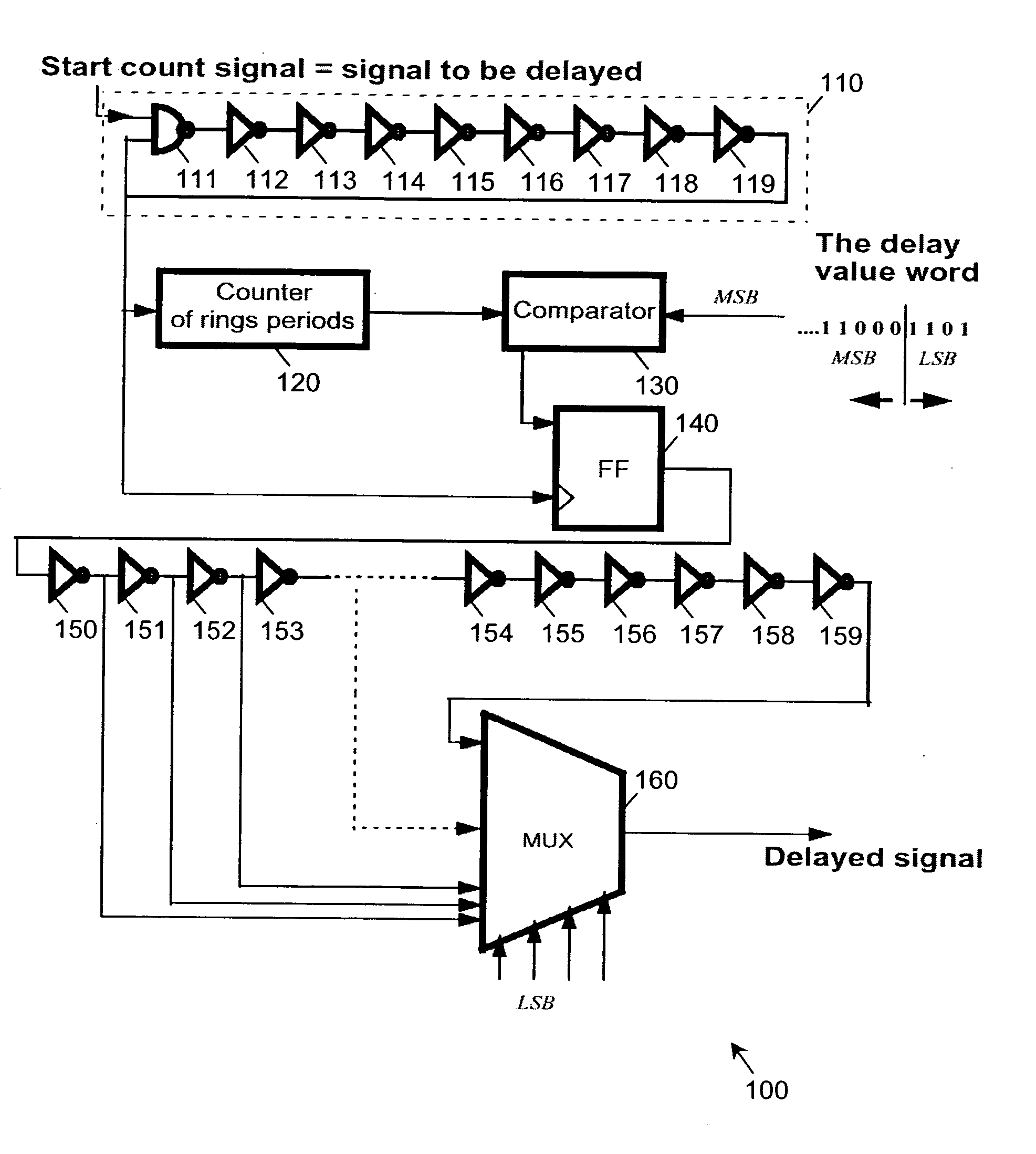

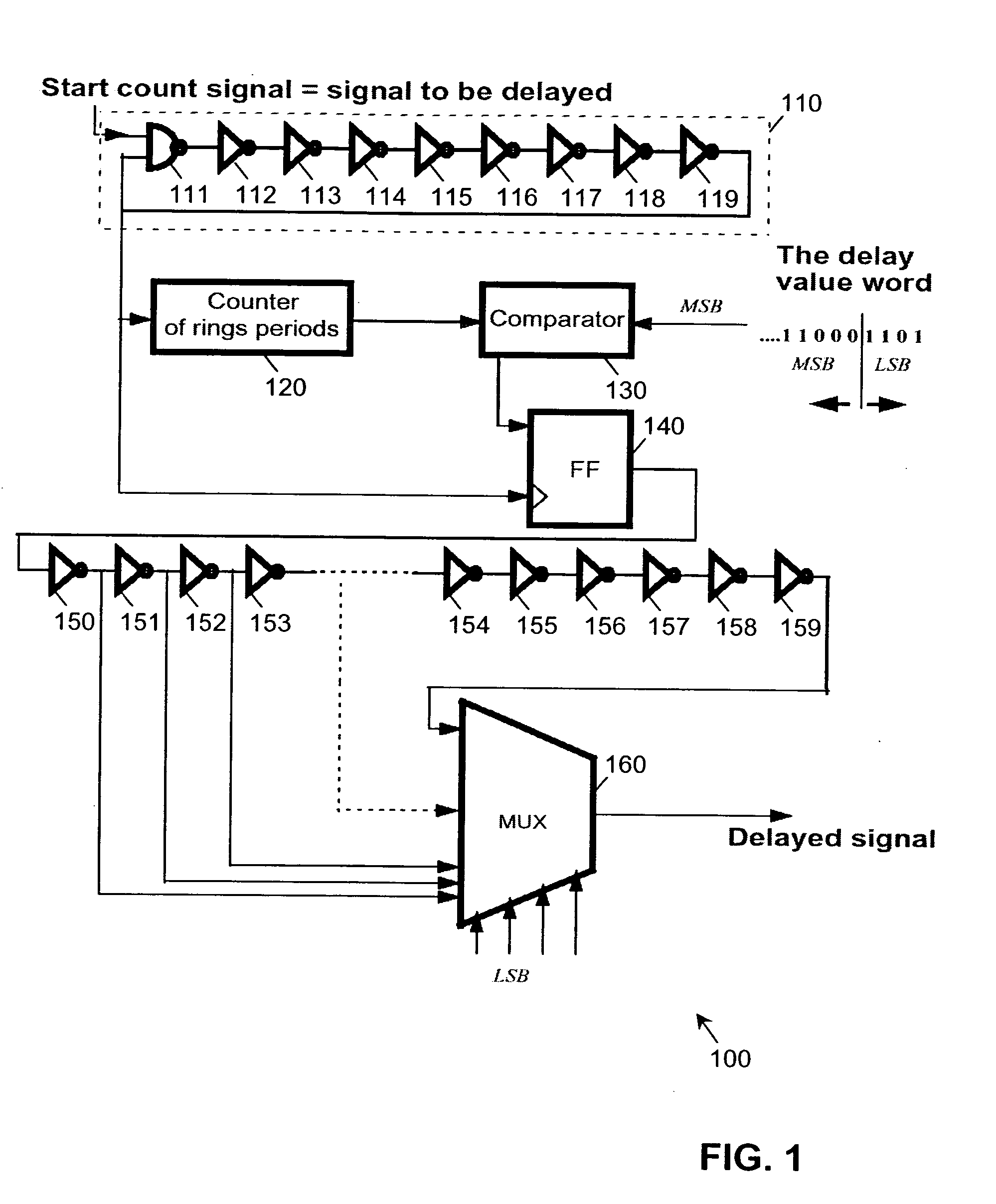

Arrangement and method for digital delay line

ActiveUS20040263266A1Pulse automatic controlPulse generation by logic circuitsLow distortionDigital delay line

An arrangement (100) and method for a high precision and low distortion digital delay line with infinite delay. The digital delay line has an oscillating ring (110) with an odd number of inverting elements that triggers a counter (120). A comparator (130) compares the counter and the MSB of a given delay word. A line of inverters (150-159), double the odd number in the ring oscillator, is connected to a MUX (160) controlled by the LSB of the delay word. This provides the advantages of: high resolution due to use of a small, basic component, self-delay ring oscillator; small silicon area due to use of a special decoding scheme use the rings number to produce large delays; and easy implementation as a digital block in an integrated circuit using a standard cells library to build the ring and the decoder.

Owner:NXP USA INC

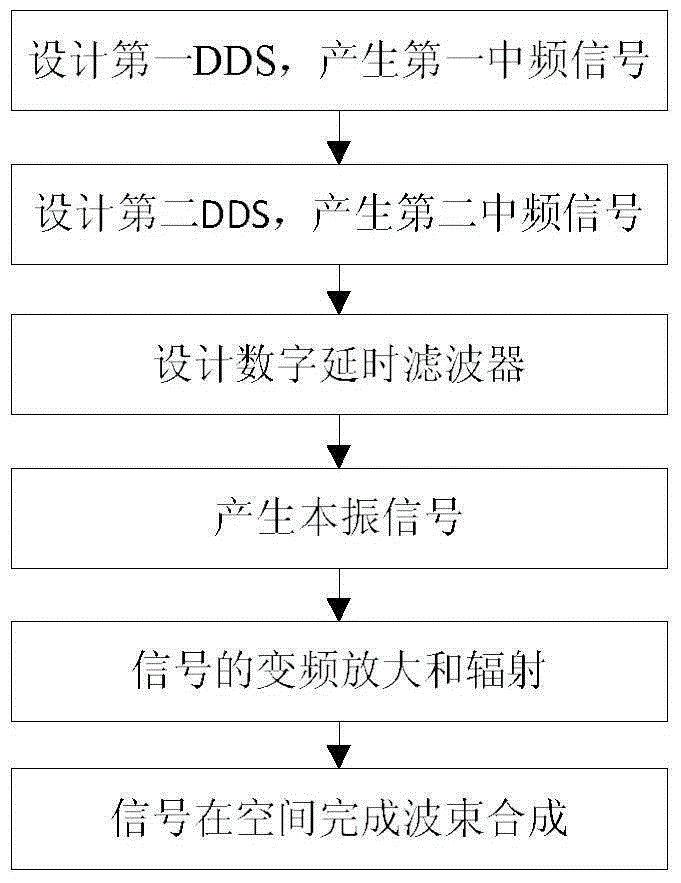

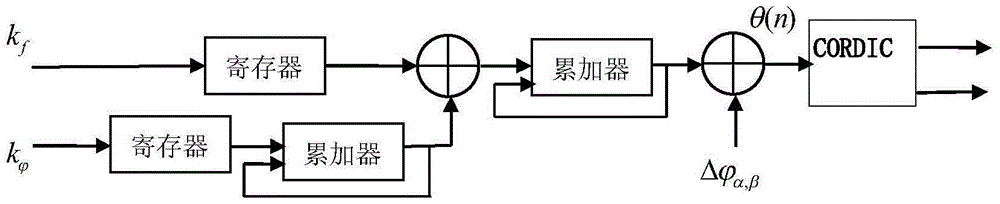

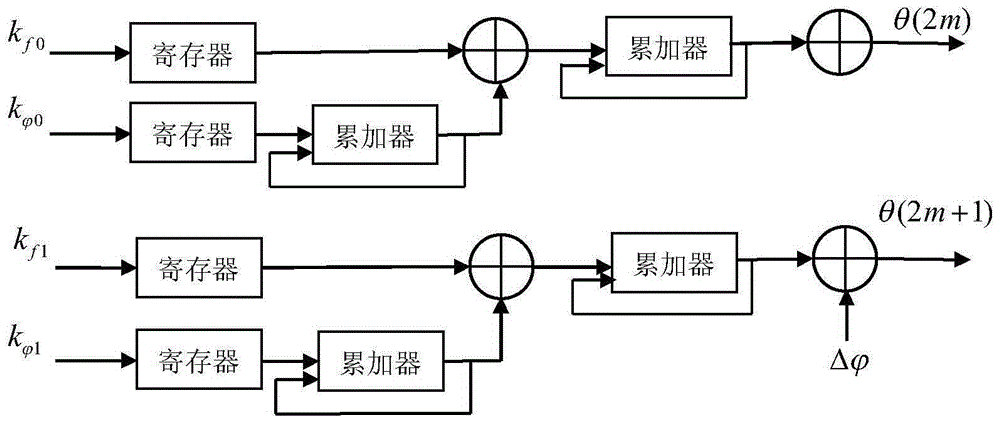

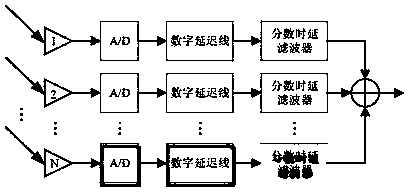

Transmitting digital beam forming method based on digital delay and phase compensation

ActiveCN105204004AEffective generationWave based measurement systemsFiltrationIntermediate frequency

The invention discloses a digital transmitting beam forming method based on digital delay and phase compensation. According to the method, a first DDS is designed by means of two accumulators and the CORDIC algorithm in an FPGA, and a simulative first intermediate-frequency signal is obtained; a second DDS is designed by means of the multiphase processing technique in an FPGA, a digital baseband signal of a second intermediate-frequency signal is obtained by means of two accumulators and the CORDIC algorithm, and a simulative second intermediate-frequency signal is obtained through interpolated filter digital frequency conversion; a frictional delay filter and an integral delay filter are designed, and a digital delay filter is realized in four phases; a first local oscillation signal and a second local oscillation signal are generated by means of output reference clock signals and frequency agility local oscillation signals, and a radio-frequency signal is generated through frequency mixing filtration; the radio-frequency signal is transmitted through an antenna array after being amplified, and beam forming is achieved in the space. According to the method, a narrow-band signal and a broad-band signal are generated by means of multiple DDS combinations, and narrow-band signal and broad-band signal transmitting beam forming is achieved by means of phase control and continuously variable digital delay.

Owner:HOHAI UNIV

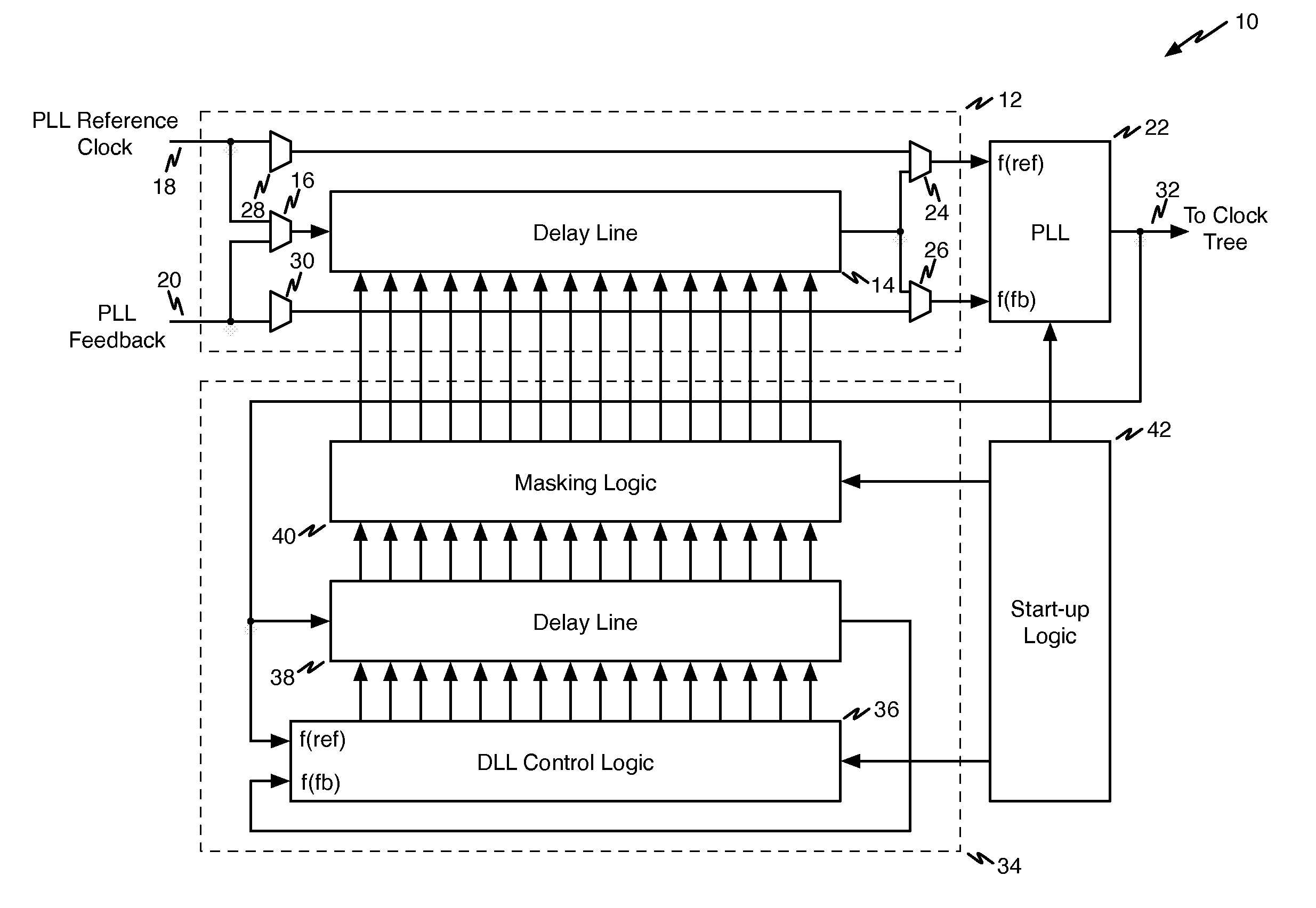

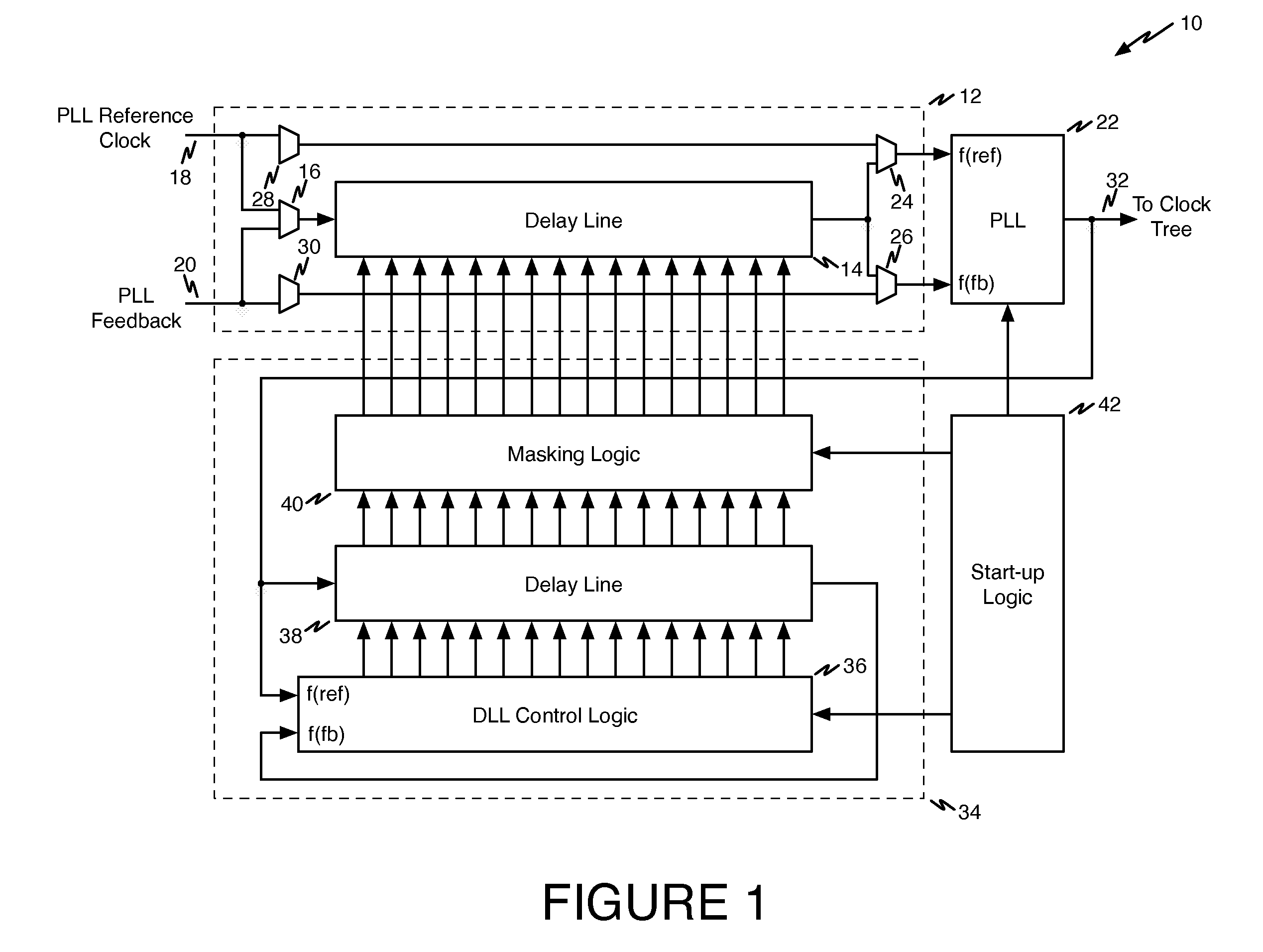

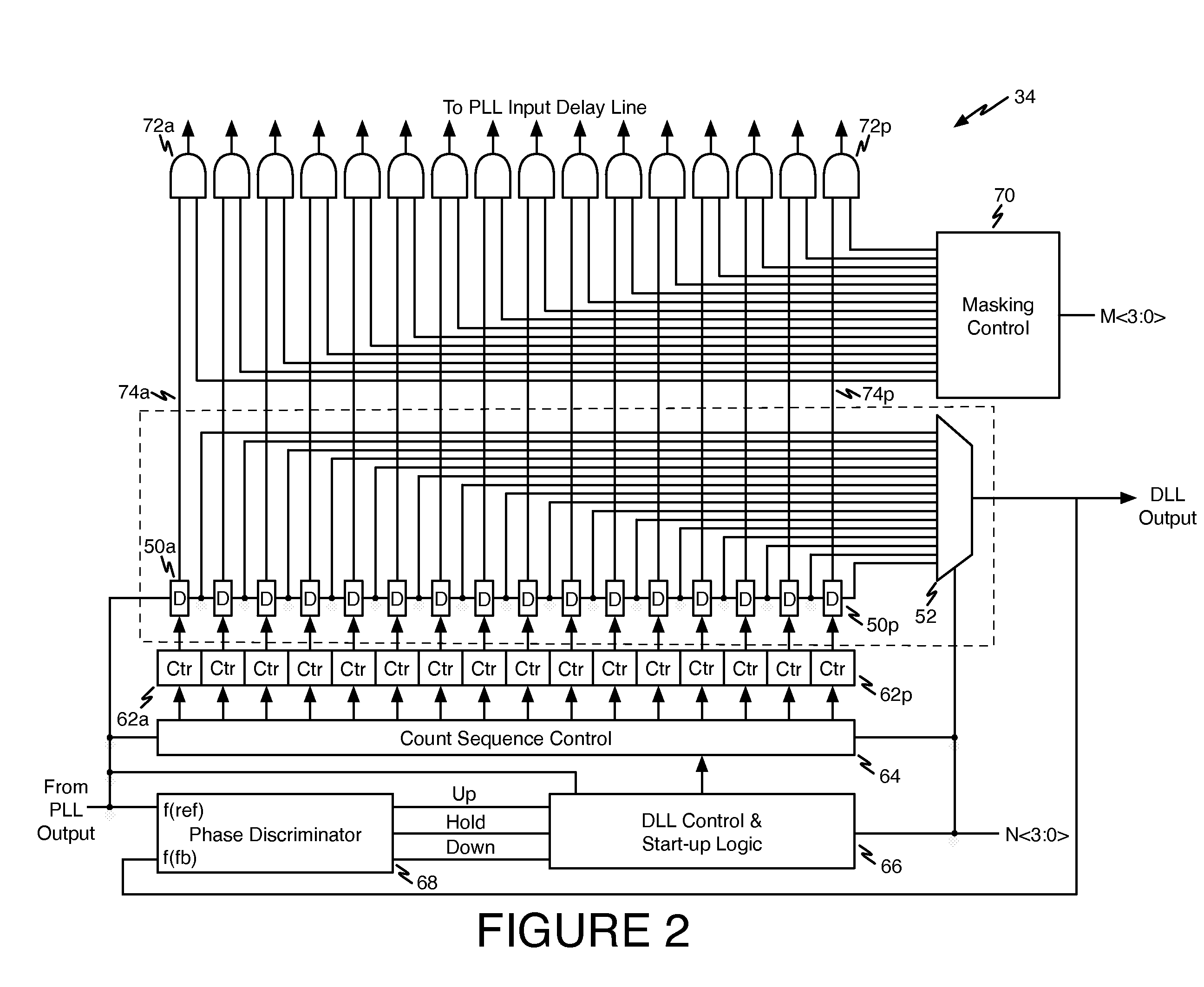

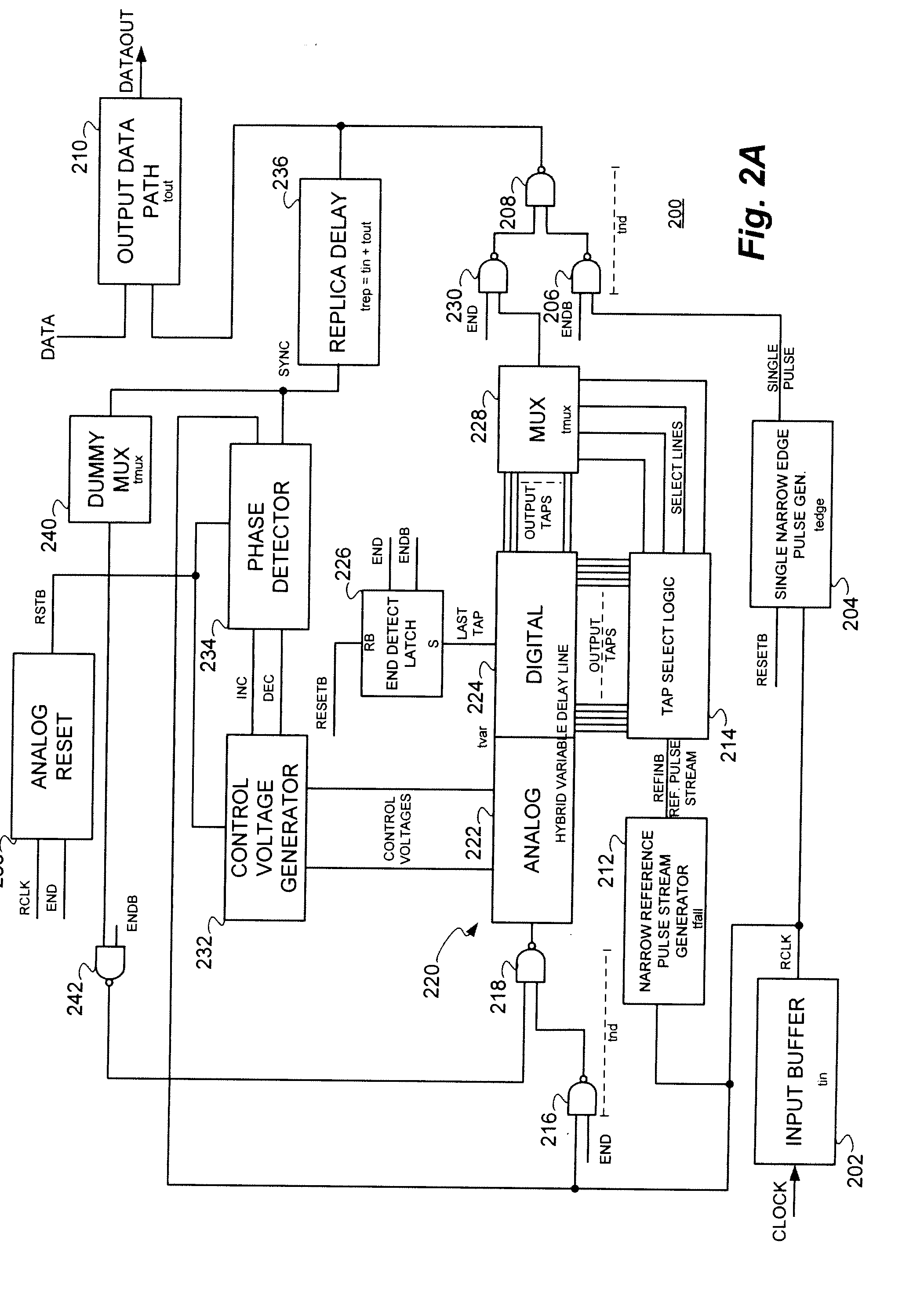

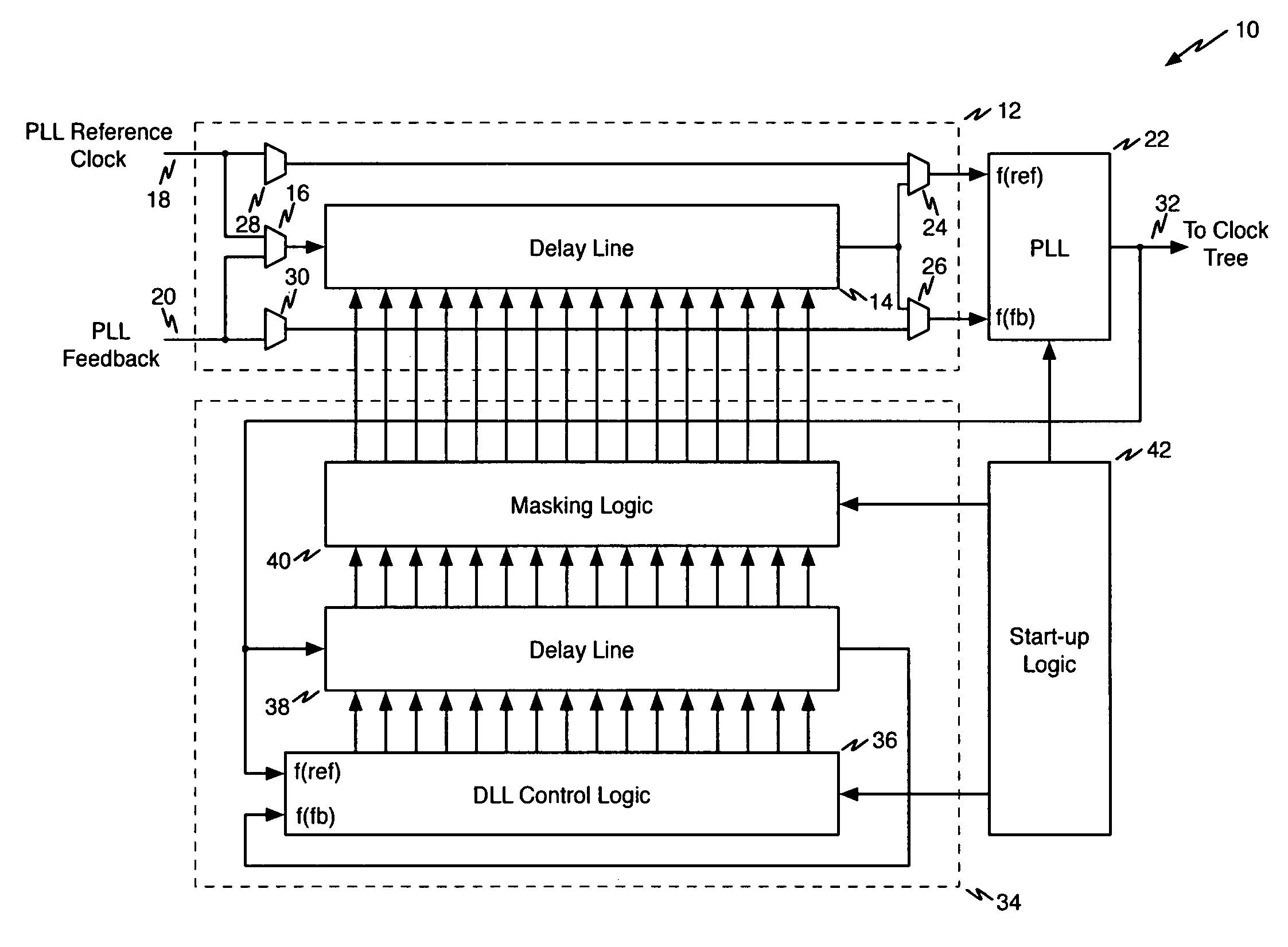

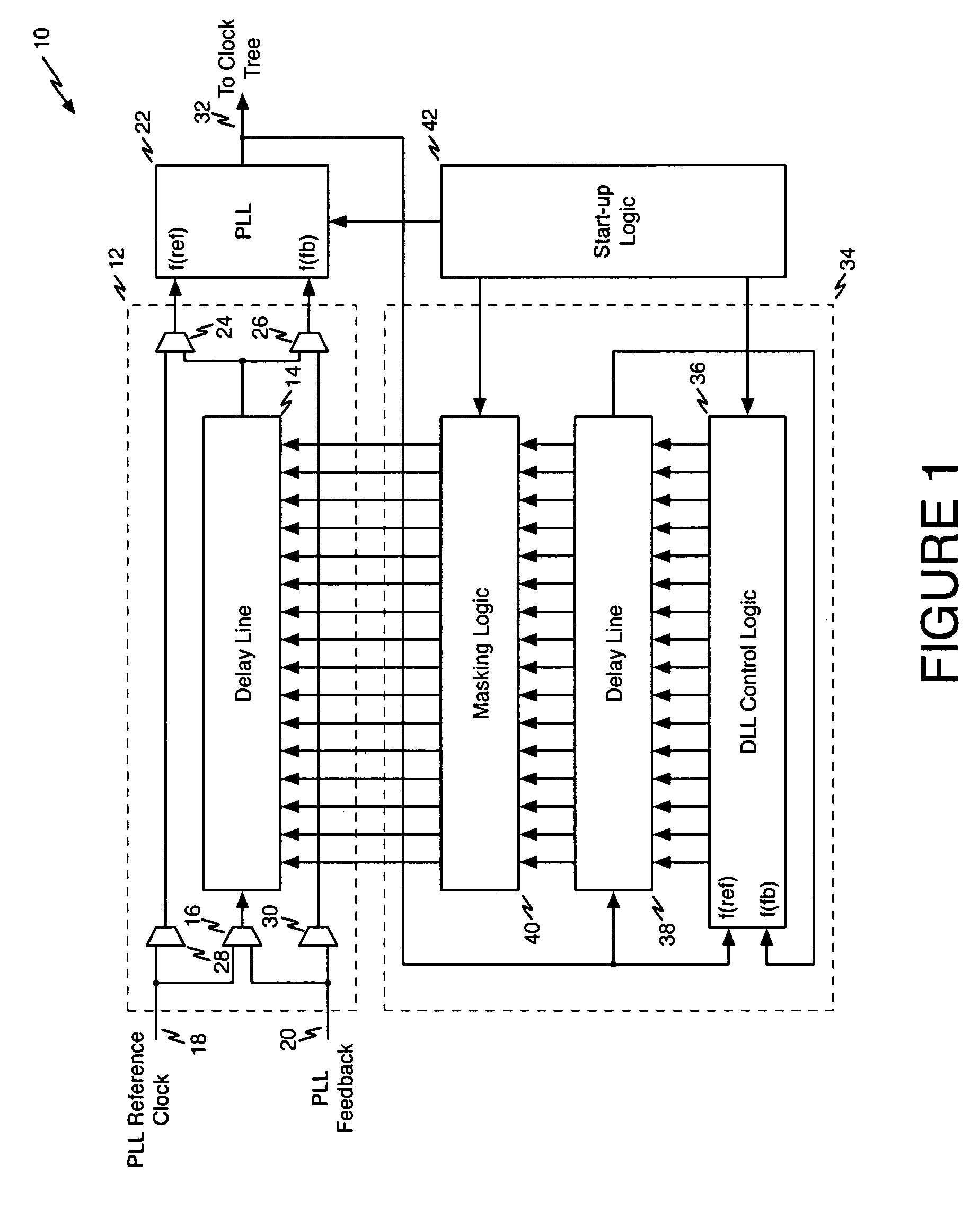

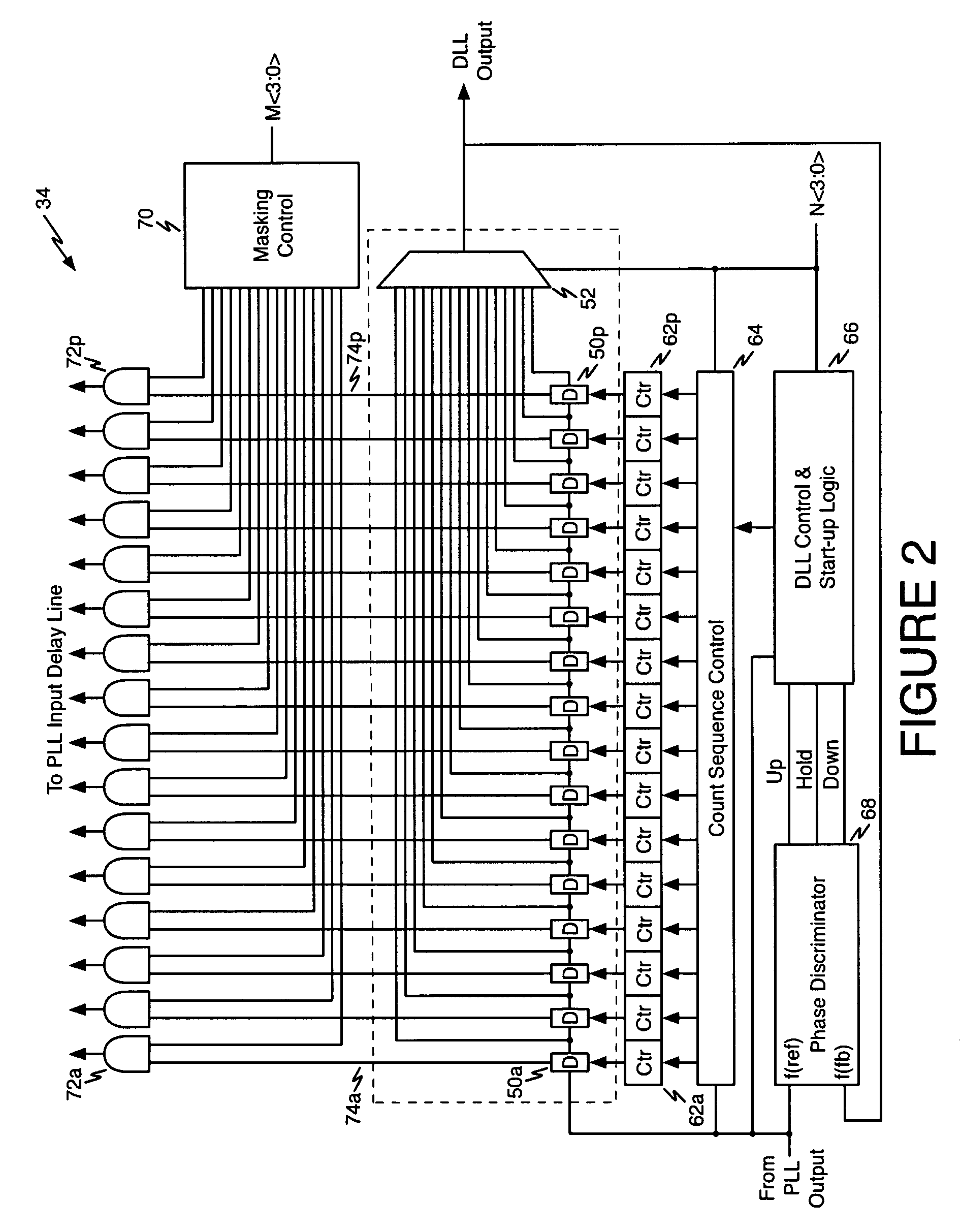

Configurable architecture hybrid analog/digital delay locked loop (DLL) and technique with fast open loop digital locking for integrated circuit devices

A configurable architecture, hybrid analog / digital delay locked loop and technique with fast open loop digital locking for integrated circuit dynamic random access memory (DRAM) devices and devices incorporating embedded DRAM. The DLL design and technique disclosed employs a hybrid analog / digital delay line, but does not use conventional closed loop architecture during the digital phase of the locking process.

Owner:PROMOS TECH INC

Integrated circuit devices having high precision digital delay lines therein

InactiveUS6944070B1High resolutionConvenient power supplyPulse automatic controlPulse generation by logic circuitsInjection portControl signal

Owner:SK HYNIX INC

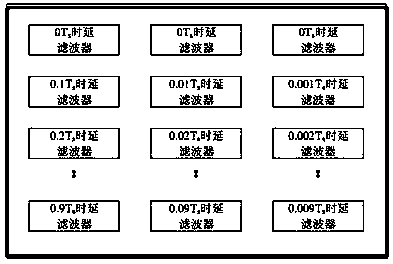

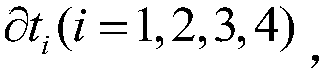

Broadband beam forming method based on multistage filter bank

ActiveCN109889186ARealize delay compensationSave hardware resourcesAdaptive networkDigital technique networkTime delaysDigital delay line

The invention discloses a broadband beam forming method based on a multi-stage filter bank, and provides a multi-stage filter bank method to realize the delay compensation of broadband signals from the perspective of saving hardware resources and practical application according to the design difference of various delay filters. The method aims at fractional time delay filtering compensation, integer time delay can be compensated by adopting a digital delay line method, and accurate time delay compensation can be realized by carrying out hierarchical filtering on each array element receiving signal of an array. Through the structure of the multi-stage filter bank provided by the invention, the delay filtering time is realized. Due to the fact that the filtering coefficients of all sets of delay filters are only related to the sampling period of the signal, only a small number of filtering coefficients need to be stored, the whole filter bank can be designed in advance to be stored, real-time calculation of the coefficients is avoided, and the method has important value in practical application.

Owner:HOHAI UNIV

Spread spectrum clock generator

InactiveUS20060146971A1Angle modulation detailsDigital data processing detailsDigital dataDigital clock

A clock signal generator varies a frequency of a digital clock over a selected range of frequencies. The generator employs a divider for lowering a frequency of a clock signal. A counter increments synchronously with the signal, and causes a selected sequence of outputs to be generated by a pattern generator. The pattern generator output forms an input to a digitally controllable delay line which receives the lower frequency clock signal. The pattern generator causes the digital delay line to vary a frequency of the lowered frequency clock signal between selected boundaries. The varying frequency clock signal is then raised up again such that a final clock has a varying frequency, and will exhibit less EMI spiking during switching of an associated, synchronous digital data device. The solid state nature of the generator allows for simple fabrication, inexpensive manufacture and ready integration into digital circuitry, such as multifunction integrated circuits.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

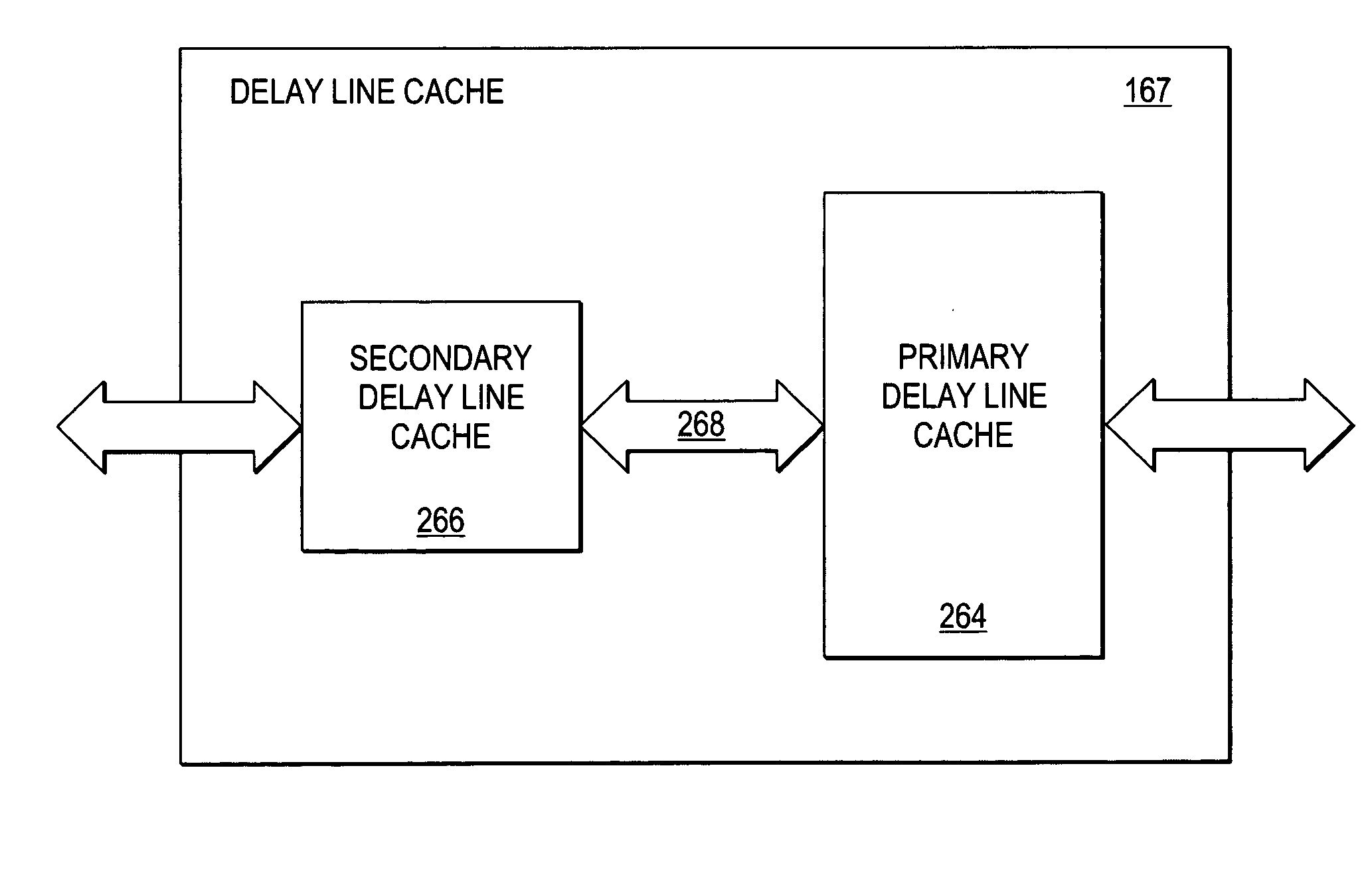

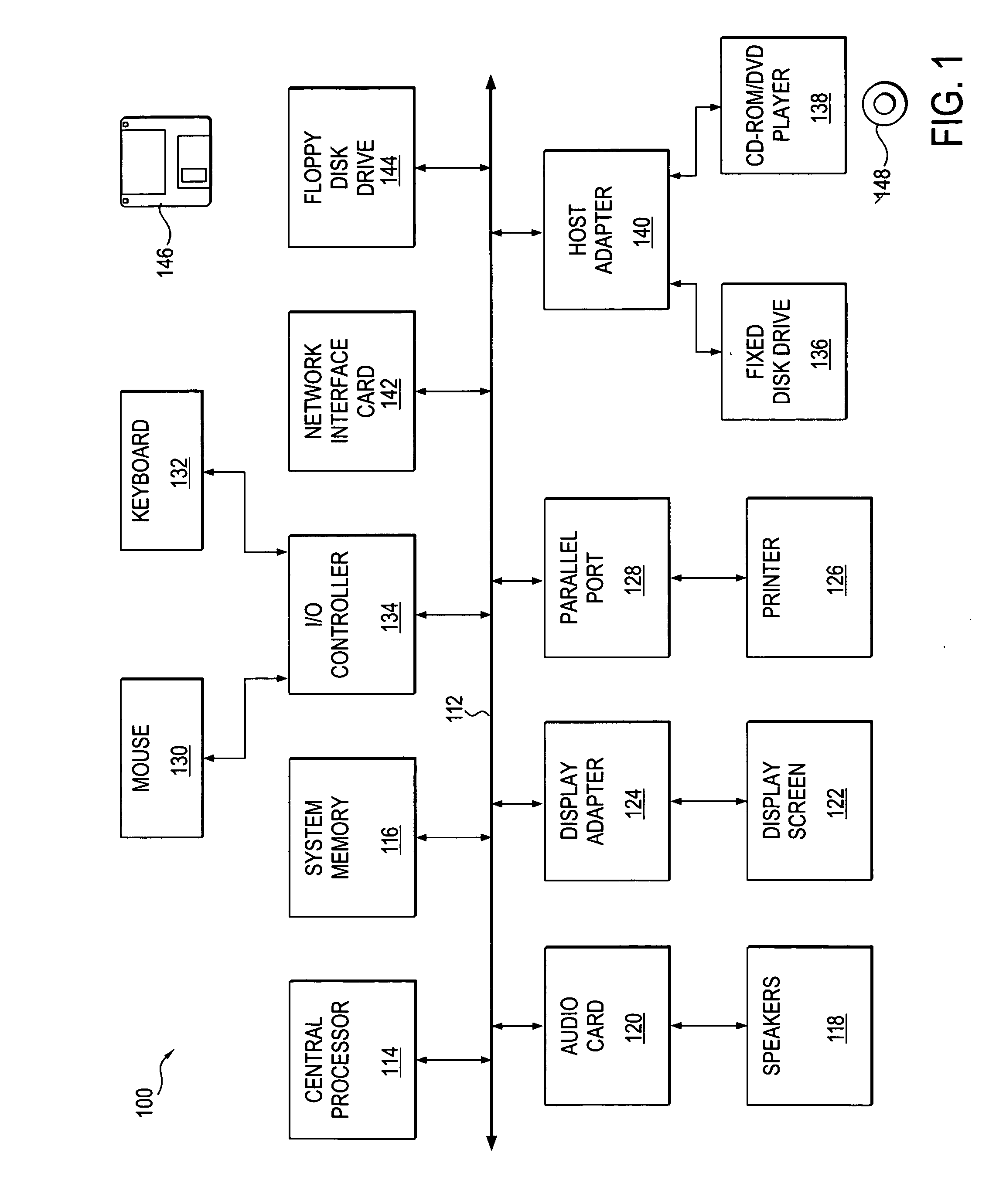

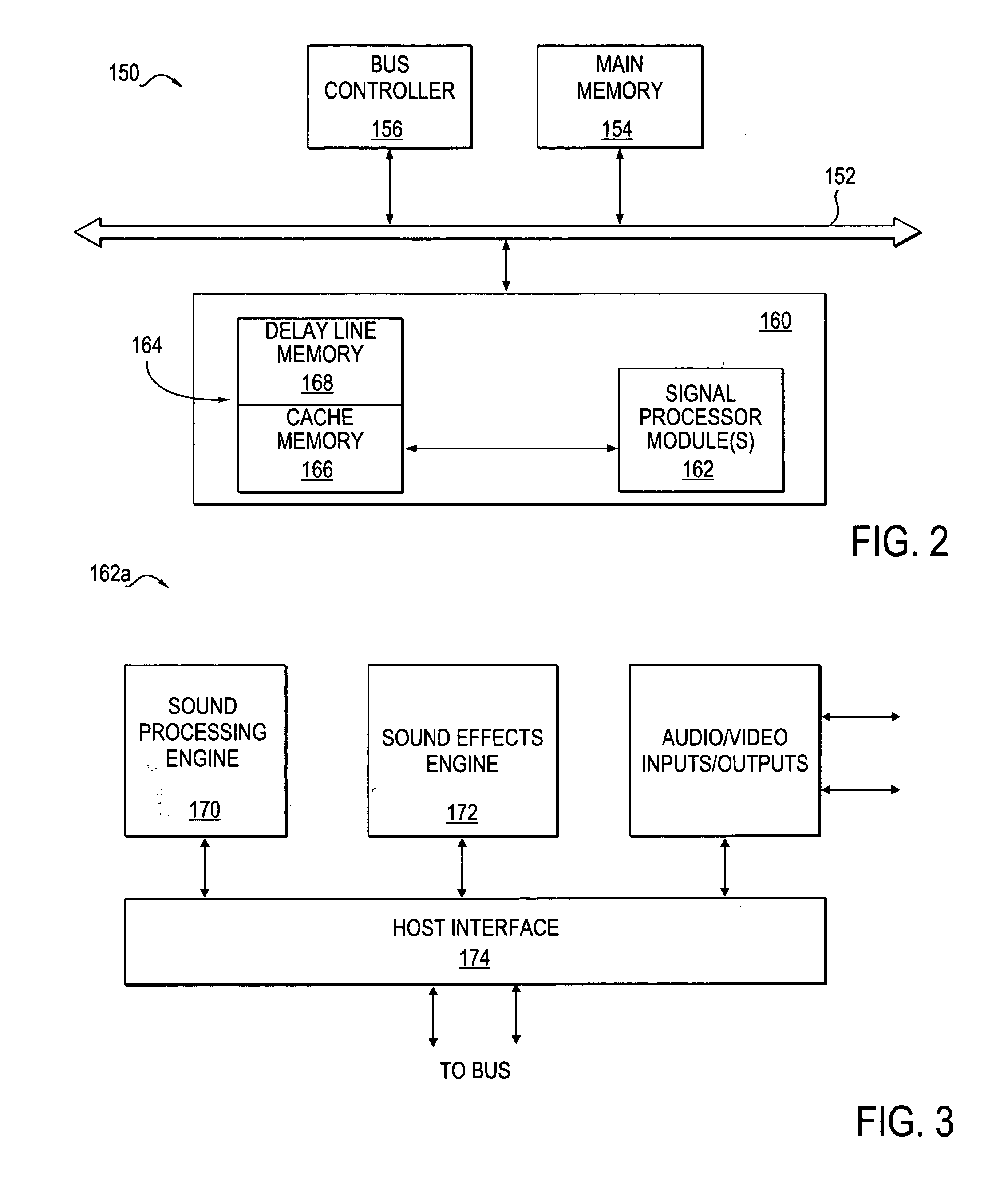

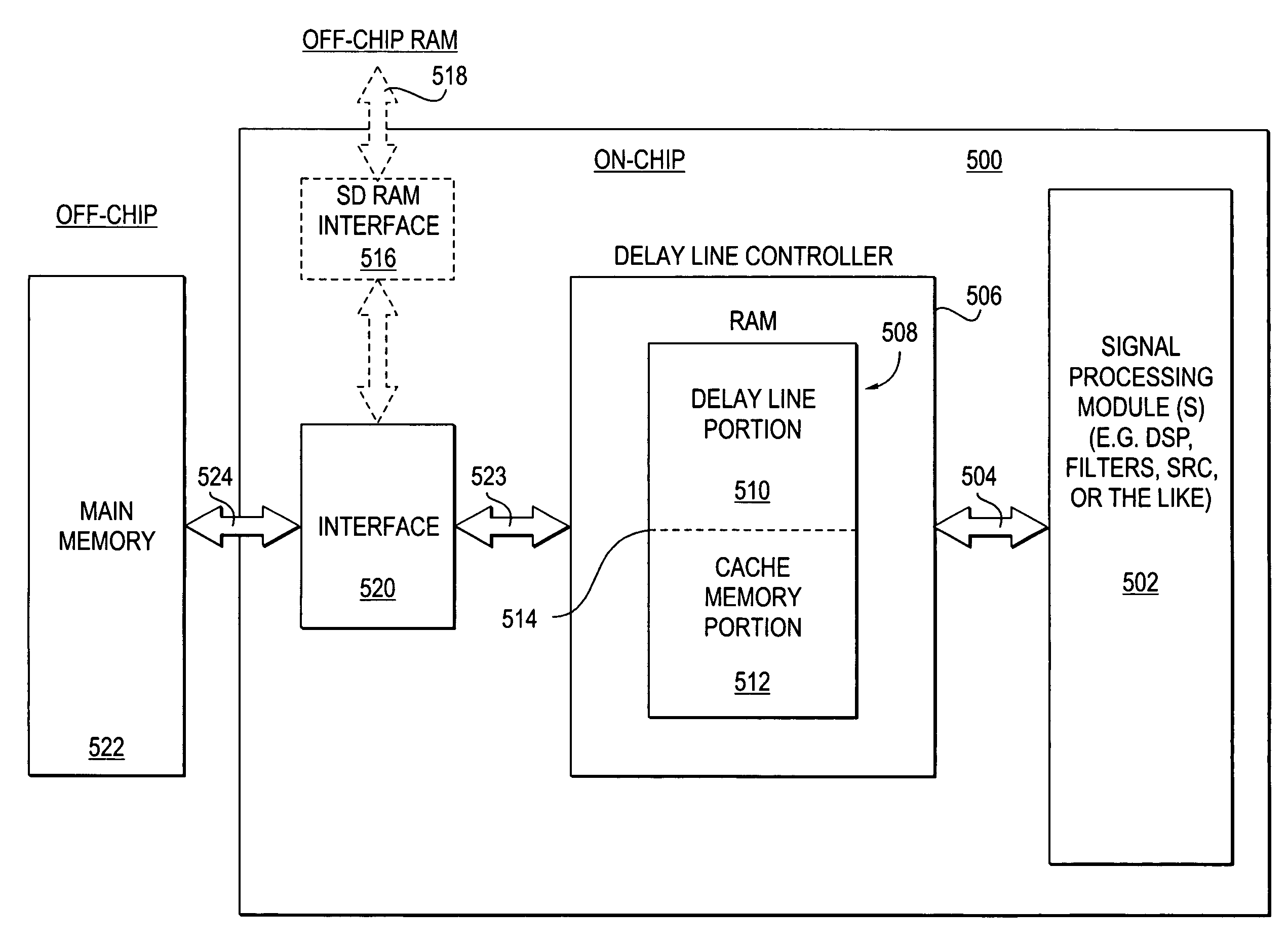

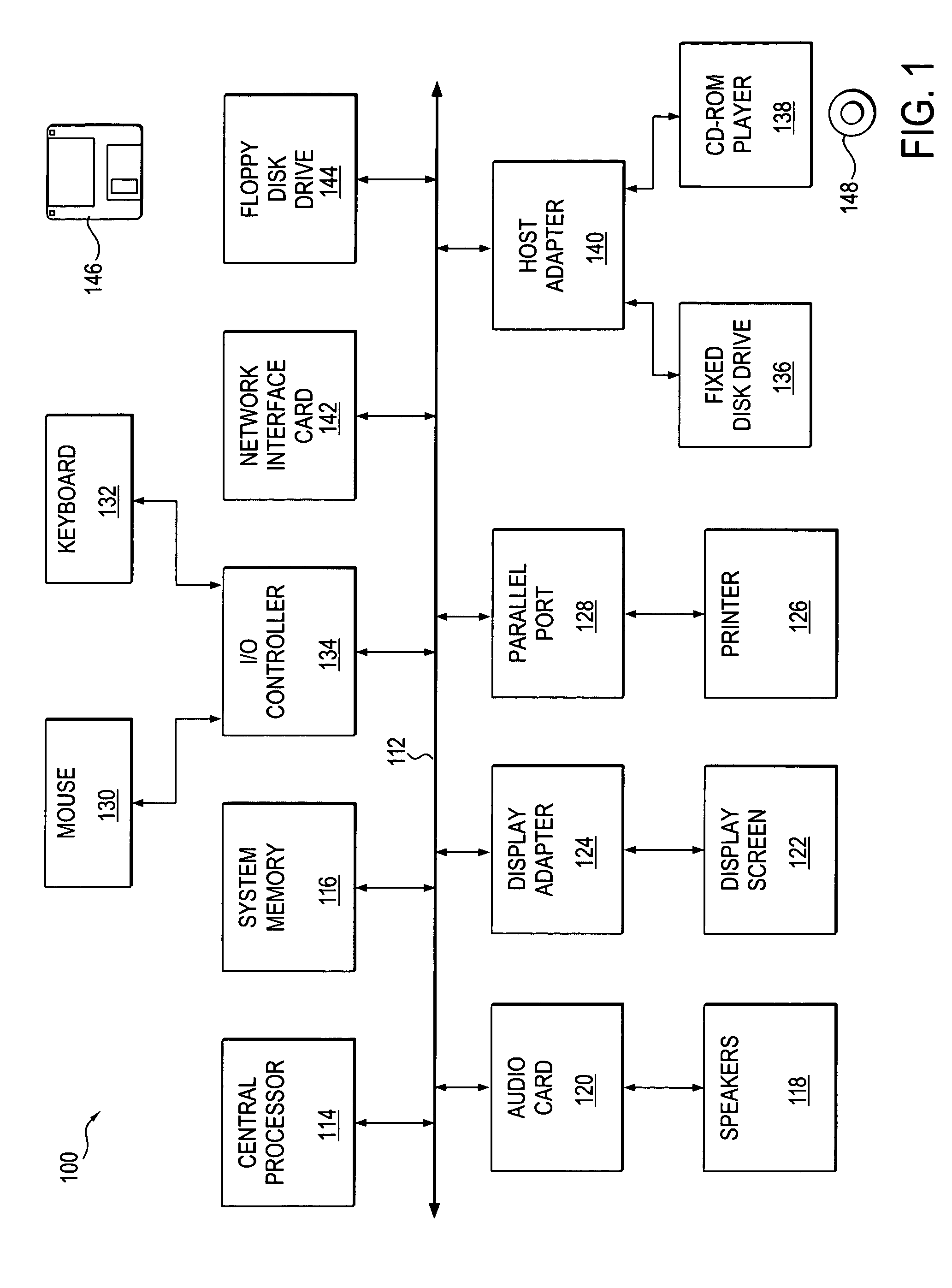

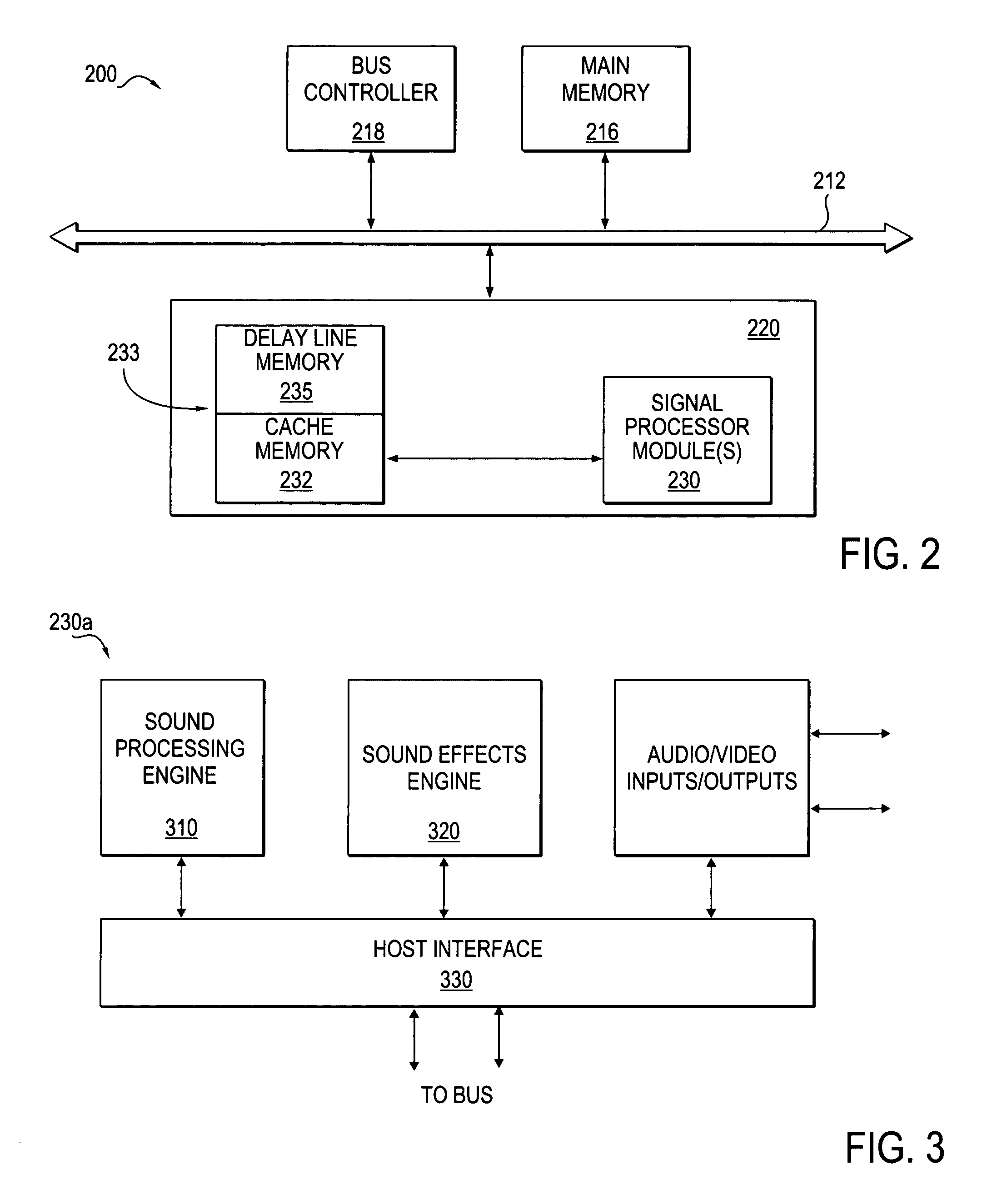

Method and circuit to implement digital delay lines

ActiveUS20050289298A1Electrophonic musical instrumentsMemory adressing/allocation/relocationDigital dataParallel computing

A delay line circuit and method to delay digital data in a main memory is provided. The delay line circuit may comprise primary delay line cache, secondary delay line cache, and a cache controller to control communication of data between the secondary delay cache and the primary delay cache. The primary delay line cache may receive digital data to be delayed from a signal processor module, and secondary delay line cache may be connected to the primary delay line cache and the main memory to send data to and receive delayed data from the main memory. Data in the secondary delay line cache may be updated with data from the main memory or with data from the primary delay line cache. The invention extends to a machine-readable medium comprising a set of instructions for executing any of the methods described herein.

Owner:CREATIVE TECH CORP

Spread spectrum clock generator

A clock signal generator varies a frequency of a digital clock over a selected range of frequencies. The generator employs a divider for lowering a frequency of a clock signal. A counter increments synchronously with the signal, and causes a selected sequence of outputs to be generated by a pattern generator. The pattern generator output forms an input to a digitally controllable delay line which receives the lower frequency clock signal. The pattern generator causes the digital delay line to vary a frequency of the lowered frequency clock signal between selected boundaries. The varying frequency clock signal is then raised up again such that a final clock has a varying frequency, and will exhibit less EMI spiking during switching of an associated, synchronous digital data device. The solid state nature of the generator allows for simple fabrication, inexpensive manufacture and ready integration into digital circuitry, such as multifunction integrated circuits.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

Fixed target protection-based satellite navigation signal repeater deception jamming system and method thereof

InactiveCN105891845ADetect and respond effectivelyIncrease success rateSatellite radio beaconingDigital delay lineMarine navigation

The invention provides a fixed target protection-based satellite navigation signal repeater deception jamming system and a method thereof. The system comprises multiple satellites, multiple repeaters, a real target point and a set false target point, wherein the number of the repeaters is the same as that of the satellites, one repeater receives navigation satellite signals broadcasted by one satellite, the multiple repeaters receive navigation satellite signals broadcasted by multiple satellites respectively and time delay of the multiple repeaters is controlled respectively through a digital delay line technology, the multiple navigation satellite signals after certain time delay are broadcasted via the multiple repeaters respectively, and thus, an enemy weapon guided by using the navigation satellite signals in an effective jamming area is further deceived to deviate from the real target point and advance to the set false target point. The problem that the traditional repeater deception can not handle receiver inertial navigation detection can be solved, and an important role is played in protecting a fixed important target.

Owner:NAT UNIV OF DEFENSE TECH

Method and circuit to combine cache and delay line memory

ActiveUS7107401B1General purpose stored program computerDigital storageDigital delay lineParallel computing

A method and a digital processor circuit to process digital delays are provided. The digital processor circuit may comprise circuit memory and a processor module such as a digital signal processor (DSP), a delay line module, a filter module and a sample rate converter module. The circuit memory may comprise a digital delay line memory portion to provide a plurality of digital delay lines; and a cache memory portion to perform a pre-fetch data transfer operation from the main memory to the cache memory portion. The cache memory portion may comprise a plurality of delay caches that are updated with data samples from corresponding delay lines in the main memory. The sizes (e.g., the relative sizes) of the delay line memory portion and the cache memory portion of the circuit memory may be adjustable. The sizes may be dependent upon algorithms executed by the processor module.

Owner:CREATIVE TECH CORP

Full-waveform digital detection device

InactiveCN104251986ASolve the problem that the signal cannot be restoredHighly integratedWave based measurement systemsDiscriminatorResting time

The invention relates to a full-waveform digital detection device comprising a constant fraction timing module, a time digital conversion module, a data interface module and a data storage module. A leading-edge discriminator set and a lagging-edge discriminator set of the constant fraction timing module discriminates that amplitude ratio of voltage, at pulse leading edge and pulse lagging edge, and peak voltage is a series of point corresponding moments of certain values. By integrating the digital counting method and digital delay line interpolation method, the time digital conversion module converts time intervals between the first time and each of the rest time into digital values so as to acquire data, then the data is sent to the data storage module through the data interface module. Implementation of the time digital conversion module and the data interface module is facilitated on an FPGA (field programmable gate array). The full-waveform digital detection device has the advantages such as high precision, integration and low cost and is applicable to the three-dimensional imaging laser scanner.

Owner:HANGZHOU ZHONGKE TIANWEI TECH

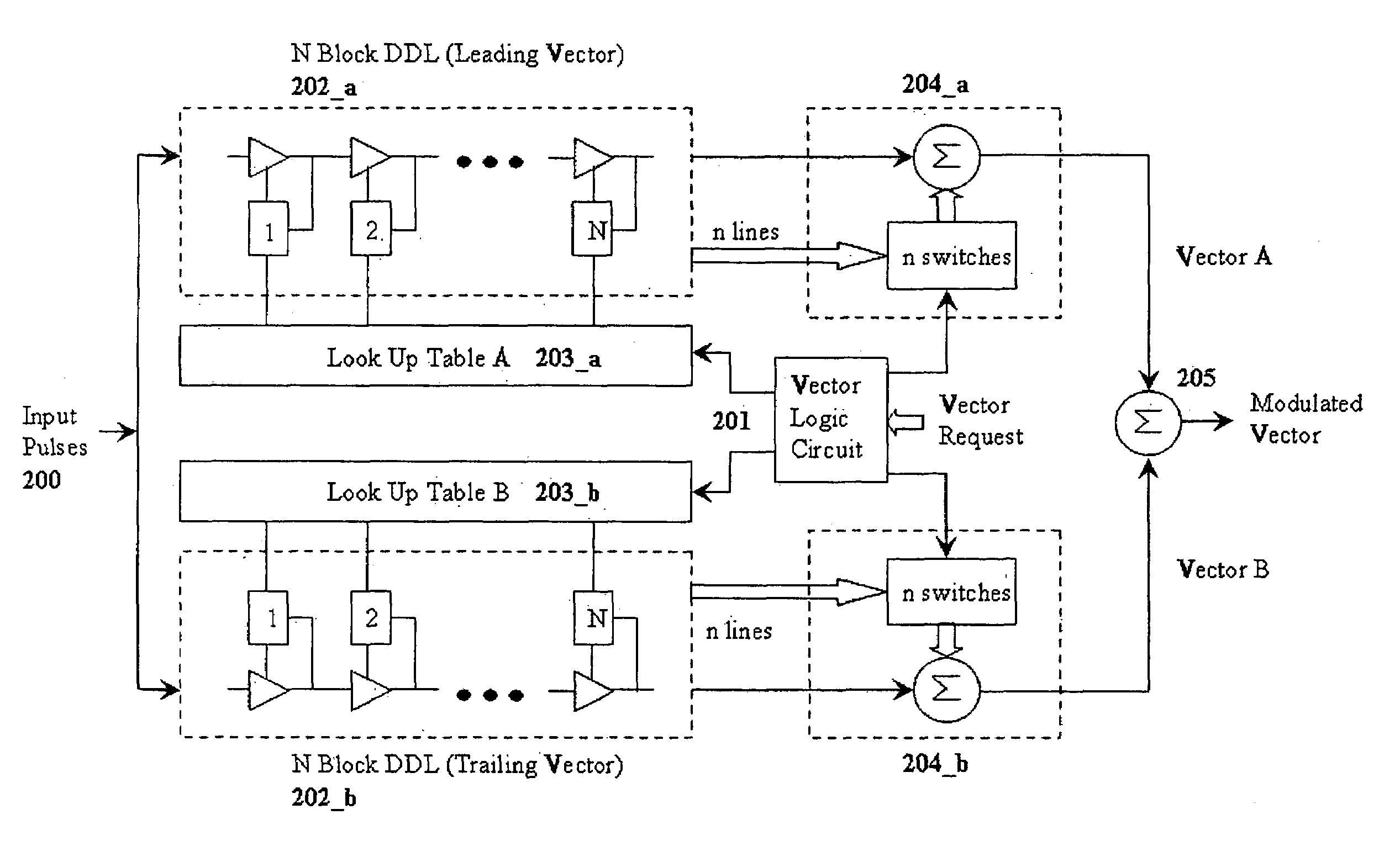

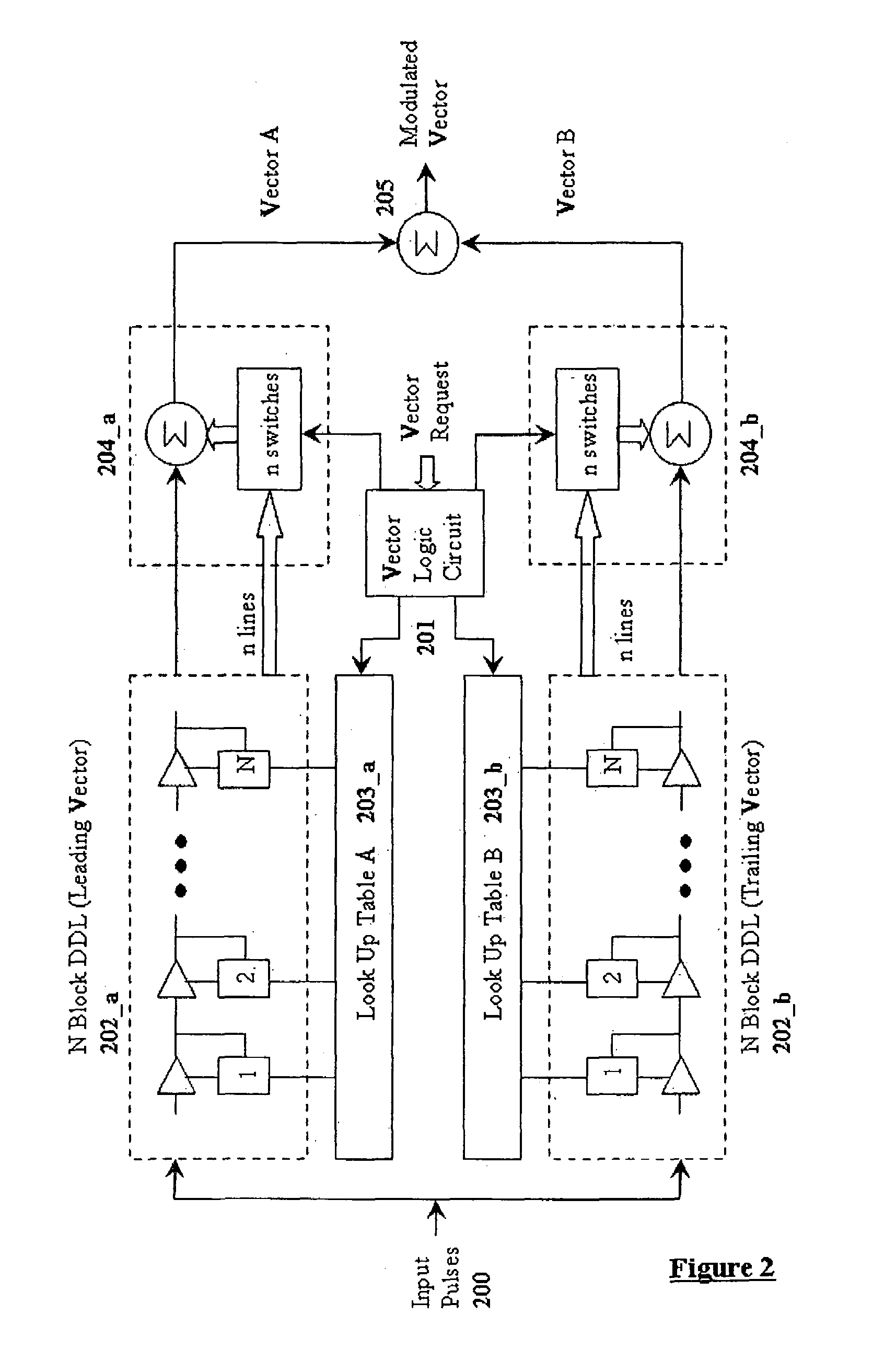

Modulation using discrete amplitude adjustment and dual digital delay lines

The present invention provides a means to implement amplitude and phase modulation digitally and directly at an RF frequency that benefits from high output power without the use of amplifiers. This is accomplished by the combination of two varying amplitude and phase vectors. A reference oscillator produces a carrier signal, which is supplied to two digital delay lines composed of a sequence of delay banks. The delay lines are controlled by lookup tables that are updated by the vector control circuit, used to determine the delay of each digital delay line. The output of each delay line is multiplexed to a switching bank which is also controlled by the vector control circuit. The output of the switching bank, in combination with a summer, is used to produce discrete amplitude adjustment of the vector. The delay of the lines and the summation adjustment are set in such a way as to produce two vectors with the desired phase shift and magnitude the summation of these two vectors produces a resultant vector with the desired phase and amplitude characteristics.

Owner:VECIMA NETWORKS

Digital delay line and application thereof

InactiveUS20100013533A1Reduce areaReduce power consumptionPulse automatic controlElectric pulse generatorHysteresisElectricity

A digital delay line includes a plurality of hysteresis-based delay cells electrically connected in series. These hystersis delay units in the hysteresis-based delay cells may be similar or different. All of the hysteresis delay units respectively have an inverter mode and a hesteresis mode. The delay and resolution of the hysteresis delay unit may be derived from the time difference in the inverter mode and hysteresis mode. Such a digital delay line applied to a digital phase locked loop may reduce consumption of area and power.

Owner:NAT CHIAO TUNG UNIV

Programmable delay line compensated for process, voltage, and temperature

A delay line compensated for process, voltage, and temperature variations, includes a delay locked loop (DLL) configured to delay a digital signal by the clock period of the digital signal, the DLL including a DLL delay line arranged as a plurality of cascaded sub-delay lines each sub-delay line providing one of a plurality of delay quanta in response to a digital control signal. A fractionating circuit is configured to generate a digital delay line control signal that is a fraction of the digital control signal. A digital delay line is arranged as a plurality of cascaded sub-delay lines each sub-delay line providing one of a plurality of delay quanta in response to the digital delay line control signal.

Owner:MICROSEMI SOC

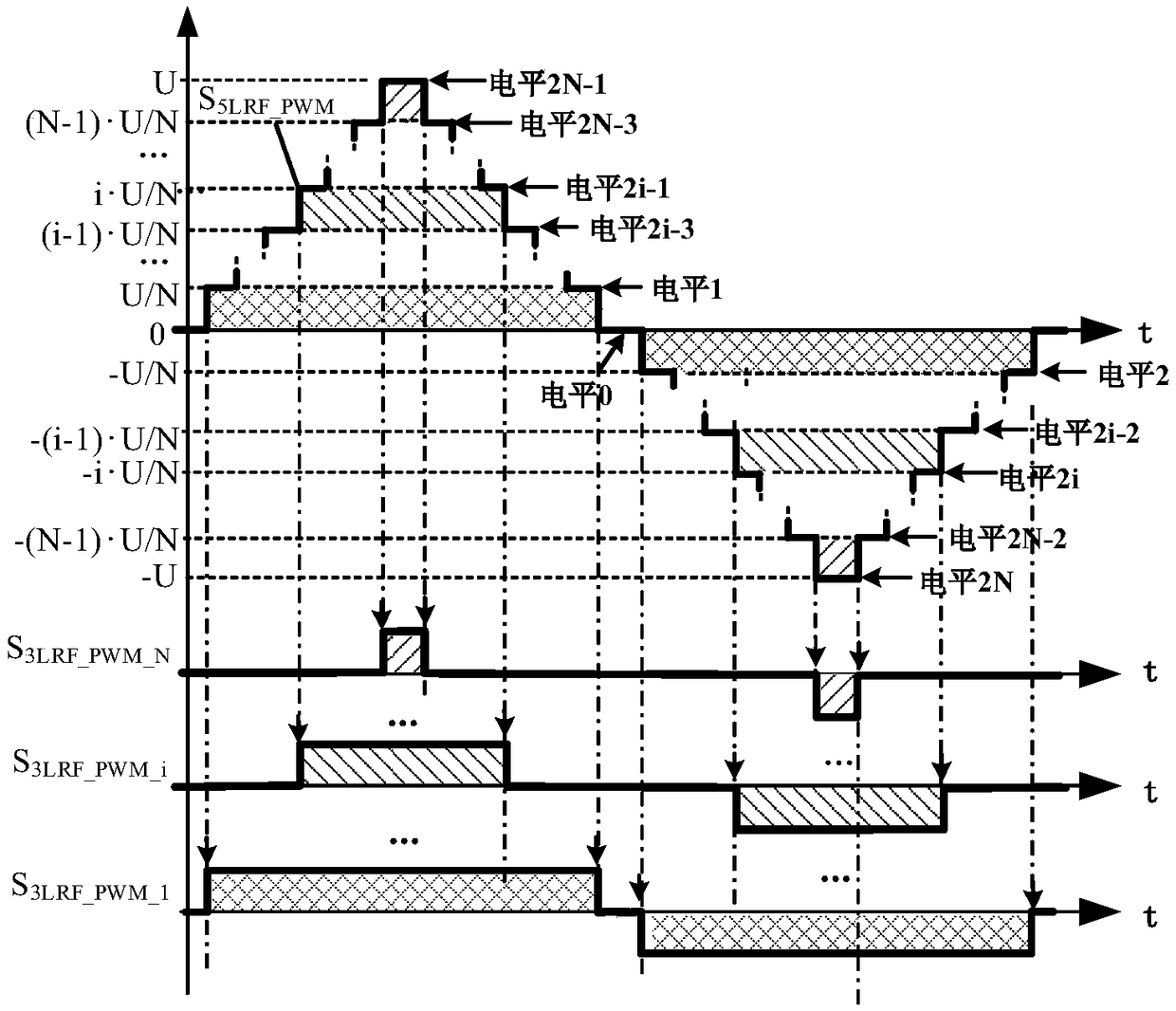

Power equalization method and modulator for modulation of specific harmonic elimination multilevel radio frequency pulse width

ActiveCN109510633AImprove performanceRealize simple structurePulse duration/width modulationTransmissionPhase shift controlHarmonic

The invention discloses a power equalization method and a modulator for modulation of a specific harmonic elimination multilevel radio frequency pulse width. The method comprises the steps of: decomposing a specific harmonic elimination multi-level RF-PWM signal into a plurality of 3-level RF-PWM signals with equal pulse areas by using the area equivalence principle based on a multi-level radio frequency pulse signal output from the specific harmonic elimination multi-level RF-PWM, according to the rise and fall of the pulse outputting the multi-level RF-PWM signal; driving a rear-stage SMPA unit, so that multi-level RF-PWM output pulse sequence specific harmonics are eliminated, while achieving the power equalization between the rear-stage SMPA units and between the power tubes in the unit. The radio frequency pulse width modulator is based on the power equalization method, and generates a phase shift control signal for driving a rear-stage 5-level SMPA unit by using a digital delay line unit, thereby realizing active cancellation of a 3X times specific harmonic. The power equalization method for modulation of a specific harmonic elimination multilevel radio frequency pulse widthdoes not need an additional power equalization control circuit, which simplifies the modulator structure.

Owner:NAT UNIV OF DEFENSE TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com