Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38 results about "Square law detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

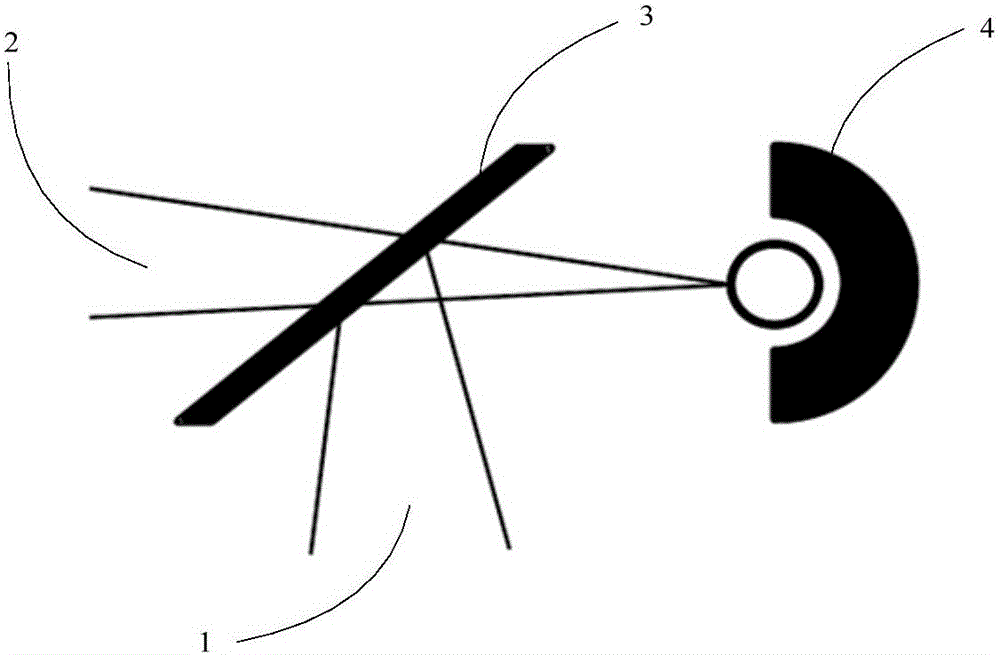

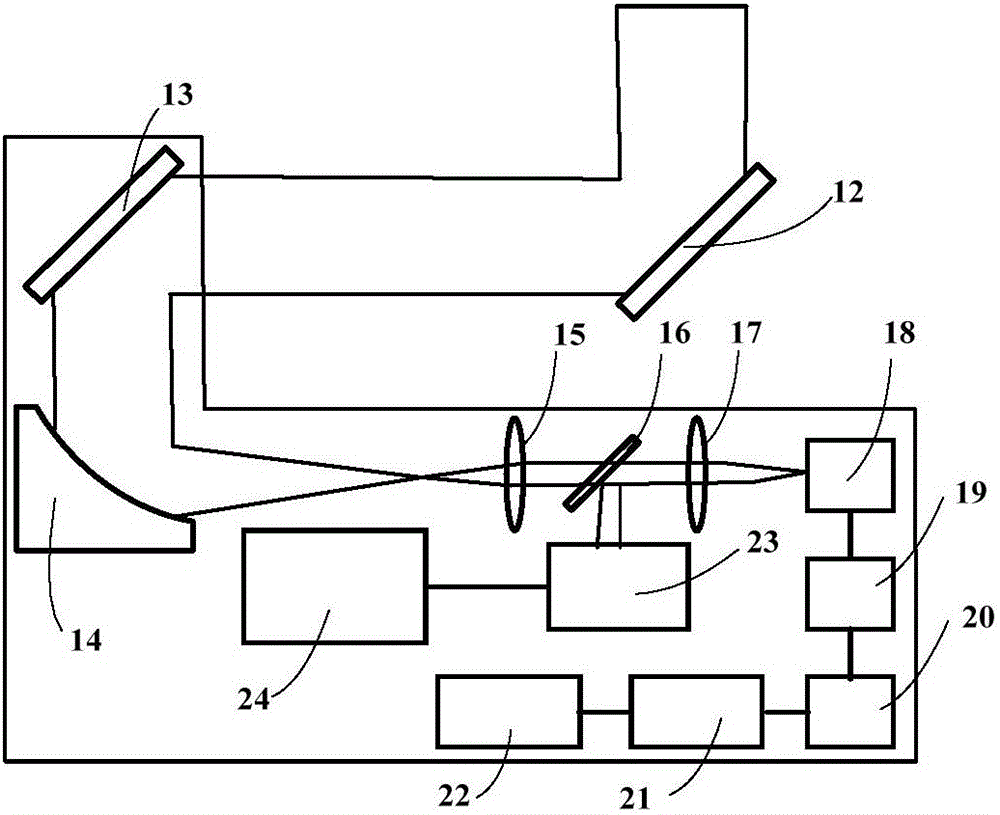

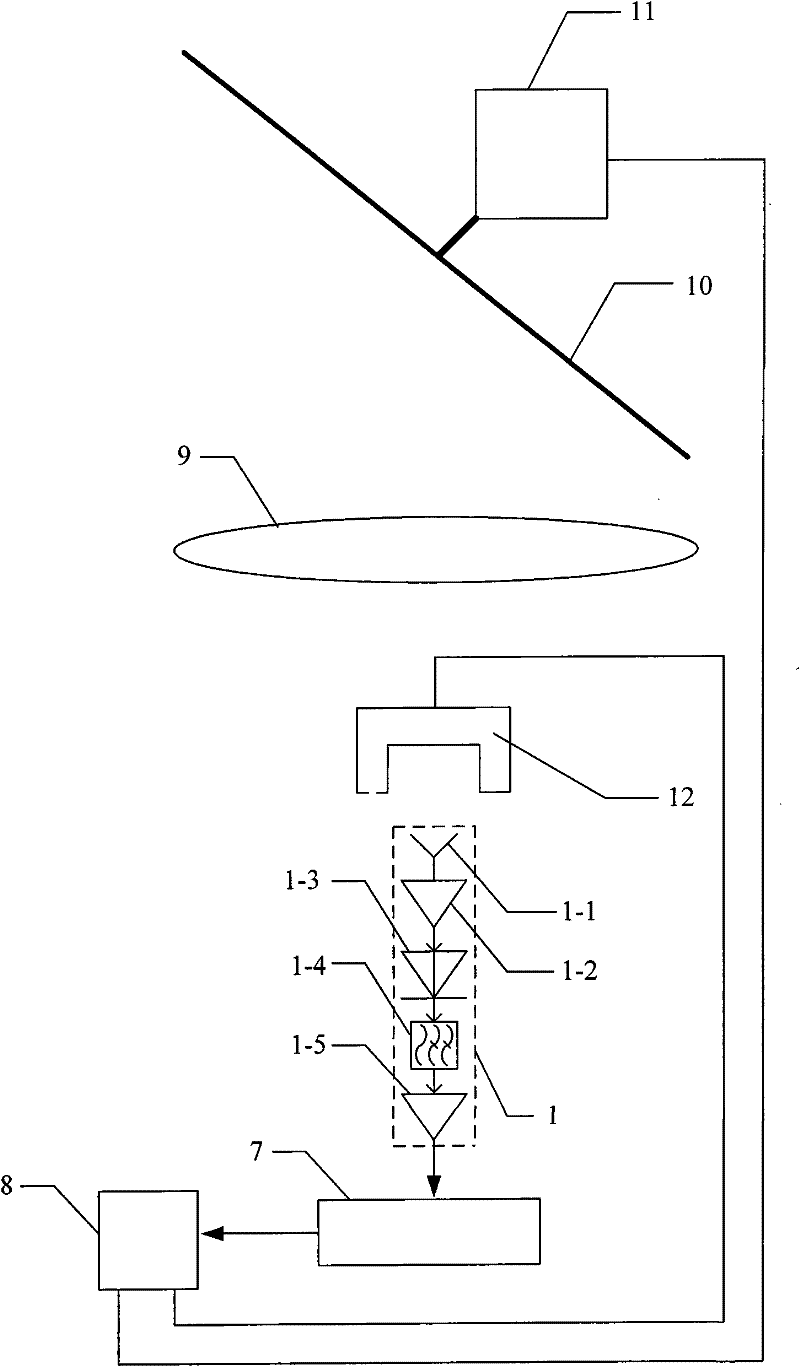

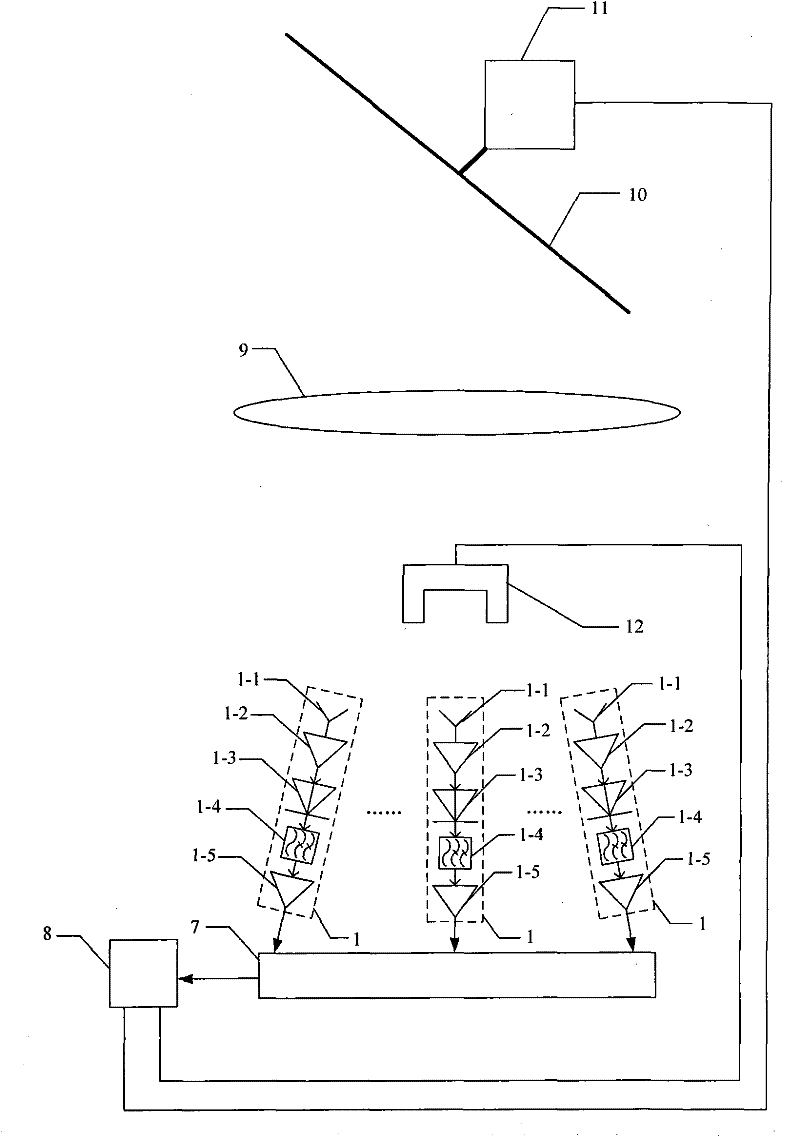

Passive millimeter wave imaging system

ActiveCN101644770AHigh resolutionImaging time is shortRadio wave reradiation/reflectionLow-pass filterMillimeter

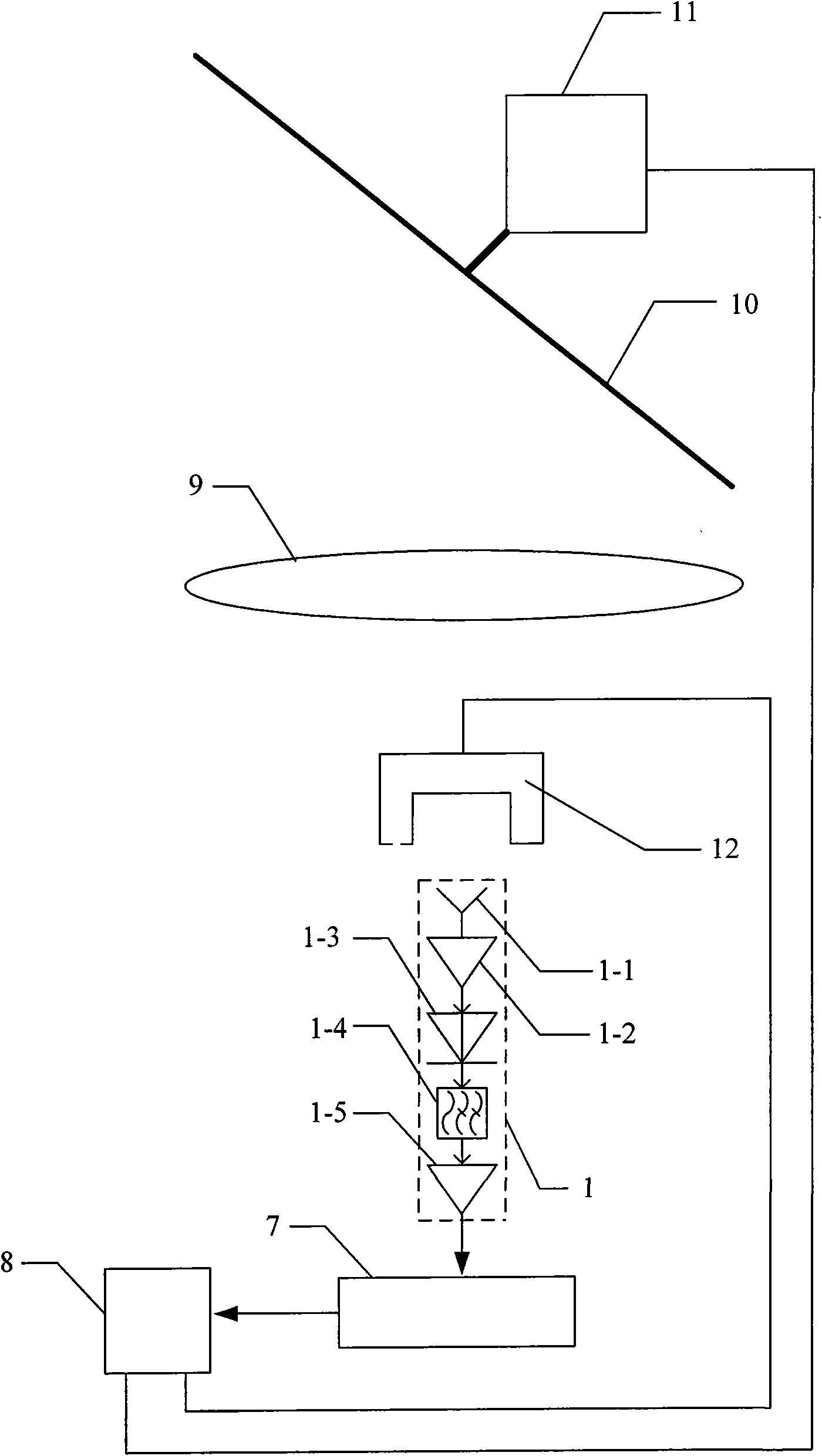

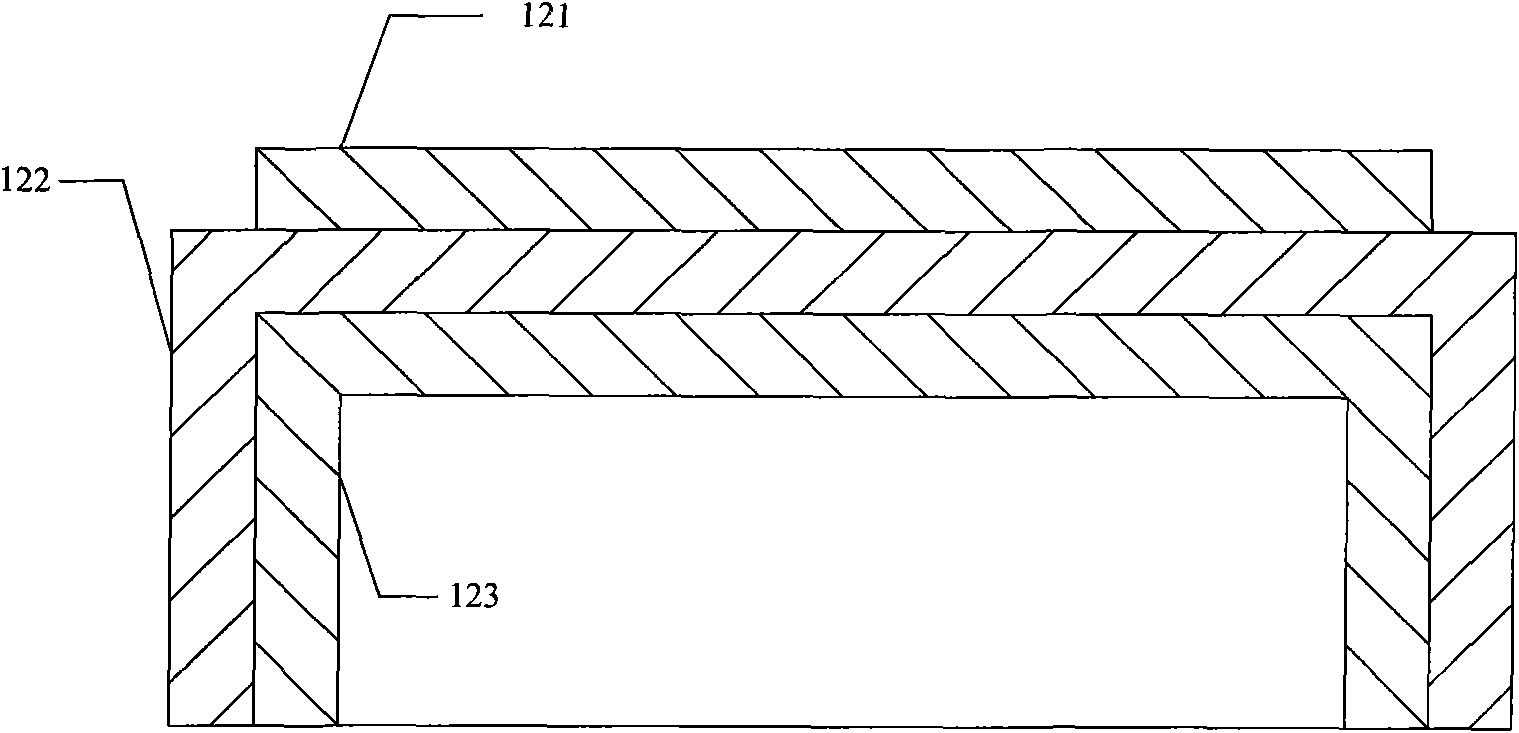

The invention discloses a passive millimeter wave imaging system and relates to a millimeter wave imaging system. The passive millimeter wave imaging system solves the problems of long imaging time ofthe system, poor real-time property and low resolution of an obtained image caused by the way of focal plane array imaging of the existing millimeter wave imaging system. A metal reflection plate ofthe passive millimeter wave imaging system reflects electromagnetic waves radiated by a target to be tested onto a receiving antenna by aggregation via a medium lens, the received signals are processed by a millimeter wave band high-gain low-noise amplifier, a high-sensitivity square law detector, a low-pass filter and a low-frequency amplifier in sequence and then collected by a digital collection circuit, and the collected signals are transmitted into a computer for carrying out imaging processing. The passive millimeter wave imaging system is applicable to the field of security.

Owner:HARBIN INST OF TECH

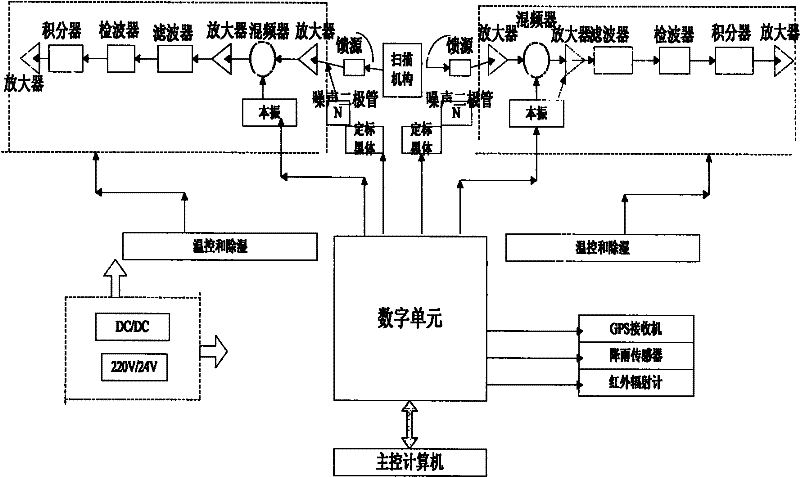

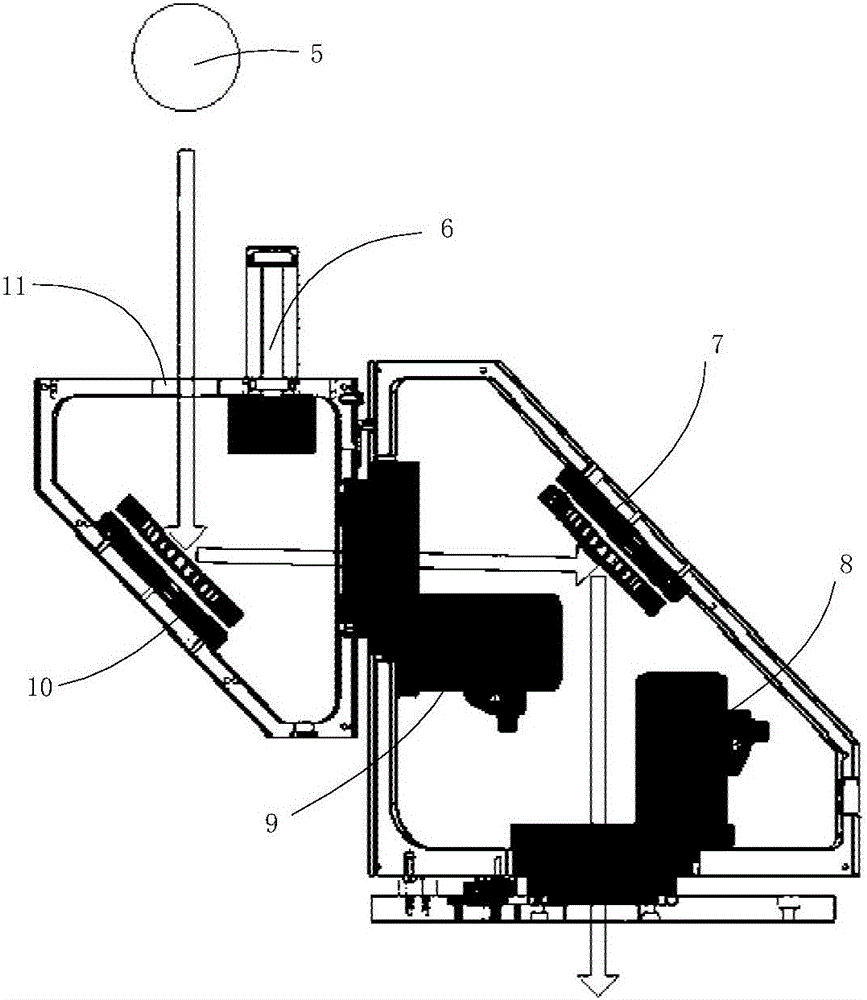

Foundation-based atmosphere profile microwave detector

InactiveCN102243304AReduce axial (transverse) dimensionsIncrease in sizeICT adaptationRadio wave reradiation/reflectionIntegratorIntermediate frequency

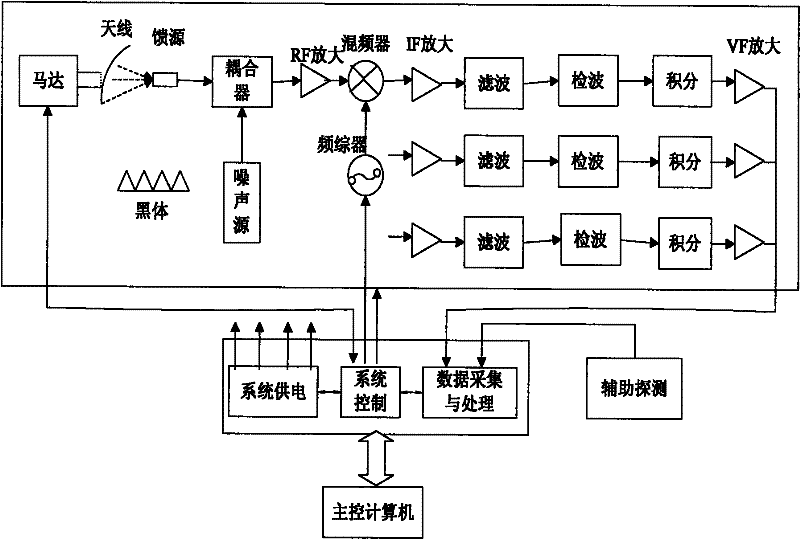

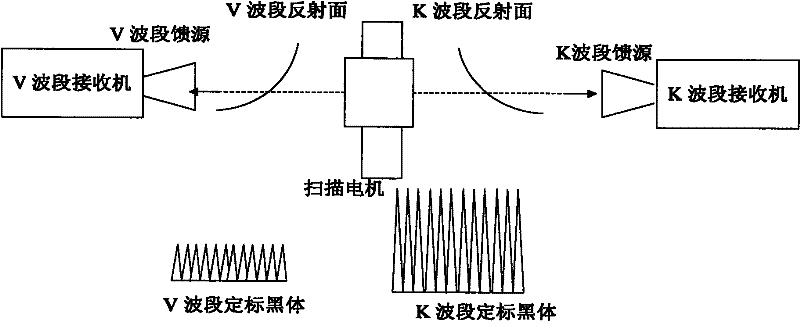

The invention provides a foundation-based atmosphere profile microwave detector. The detector is characterized by comprising an antenna feeder unit, a radiometer receiving unit and a scanning mechanism unit, wherein the antenna feeder unit comprises two independent antenna feeder sub-units for two wavebands and is provided with two-frequency independent reflective surfaces; the two independent antenna reflective surfaces are arranged at two ends of the output shaft of a scanning motor respectively, can realize beam scanning through motor rotation, and are used for receiving microwave radiation of atmosphere and an internal calibration reference source; the radiometer receiving unit comprises a directional coupler, a radio amplifier, a power divider, a band pass filter, a square law detector, an integrator and a video amplifier, and is used for realizing intermediate frequency detection of a received signal; the scanning mechanism unit comprises a scanning shaft, a scanning step motor, two front ends and a sub-miniature type A (SMA) connector; and driven by the scanning motor, the scanning shaft drives the two reflective surfaces to circumferentially scan so as to realize observation on sky in different incident angles and measurement on an internal calibration blackbody and acquire data which is acquired in a measurement and periodic internal calibration unit.

Owner:NAT SPACE SCI CENT CAS

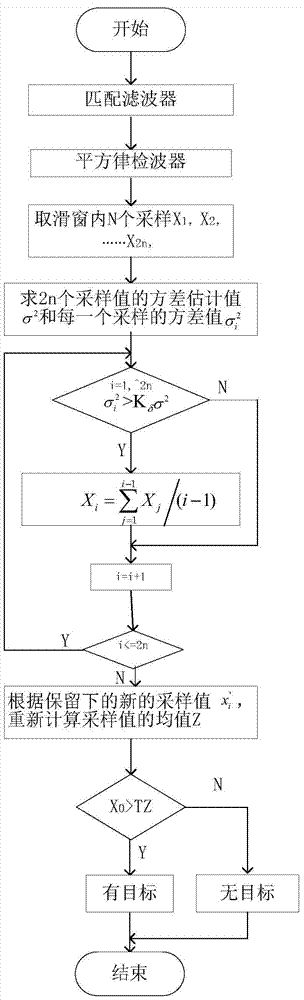

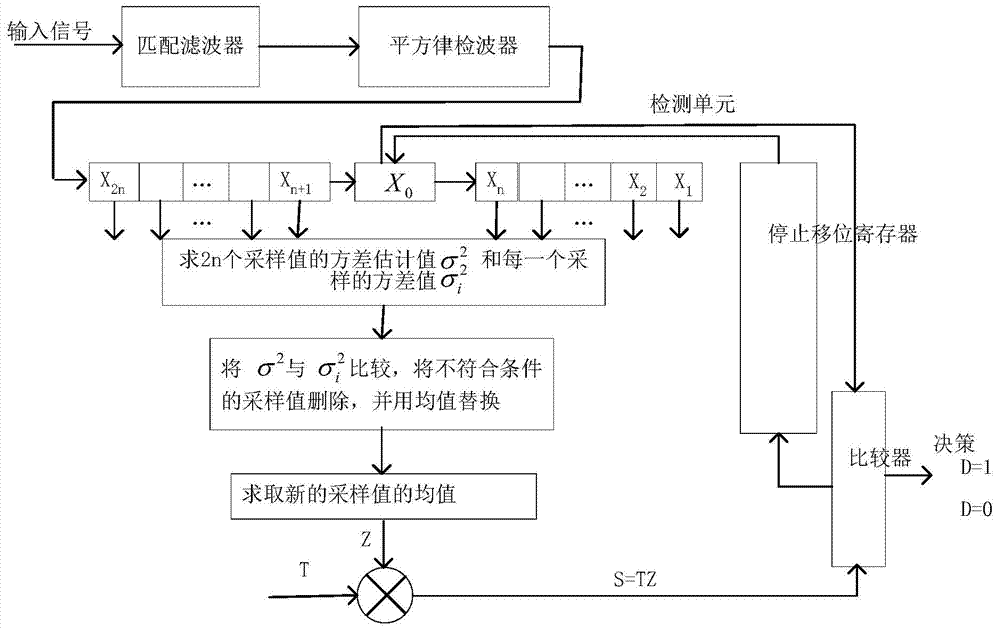

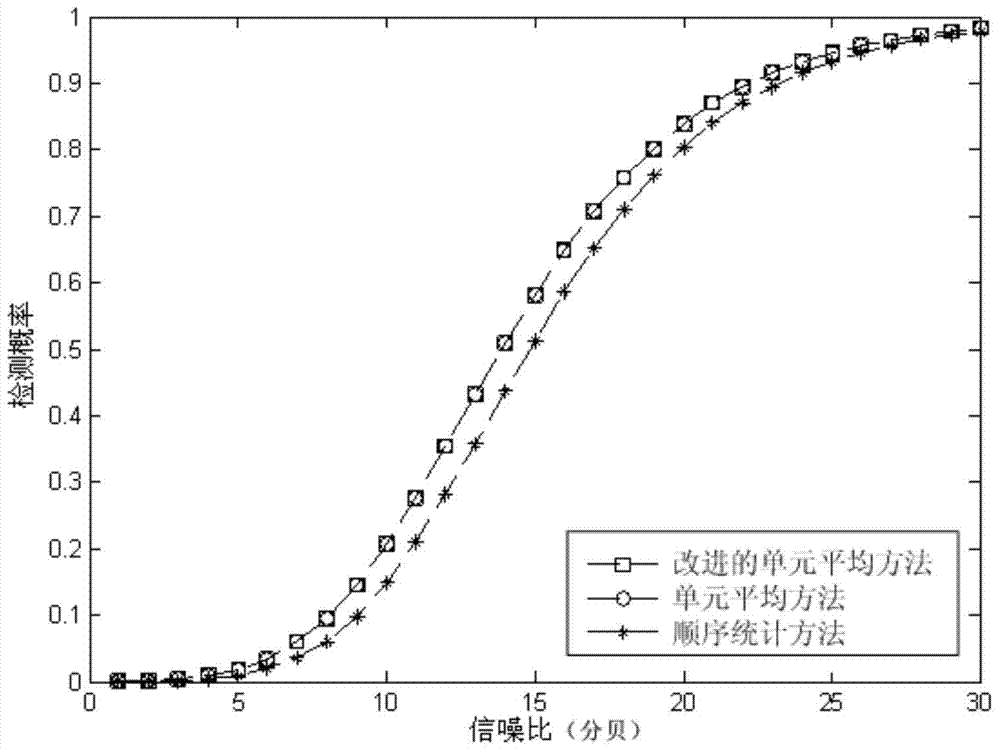

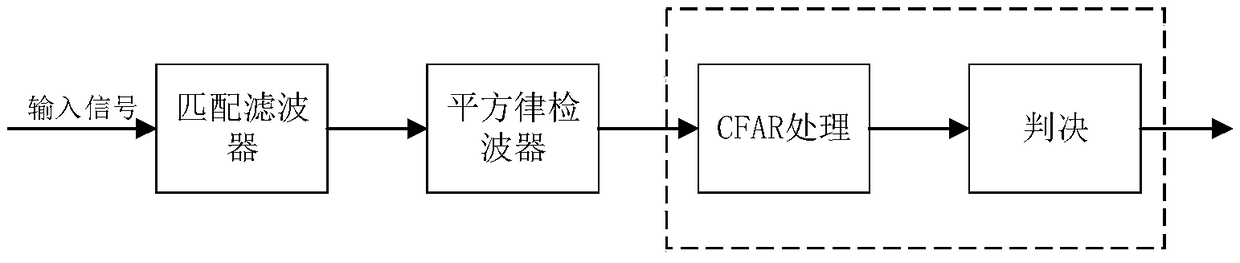

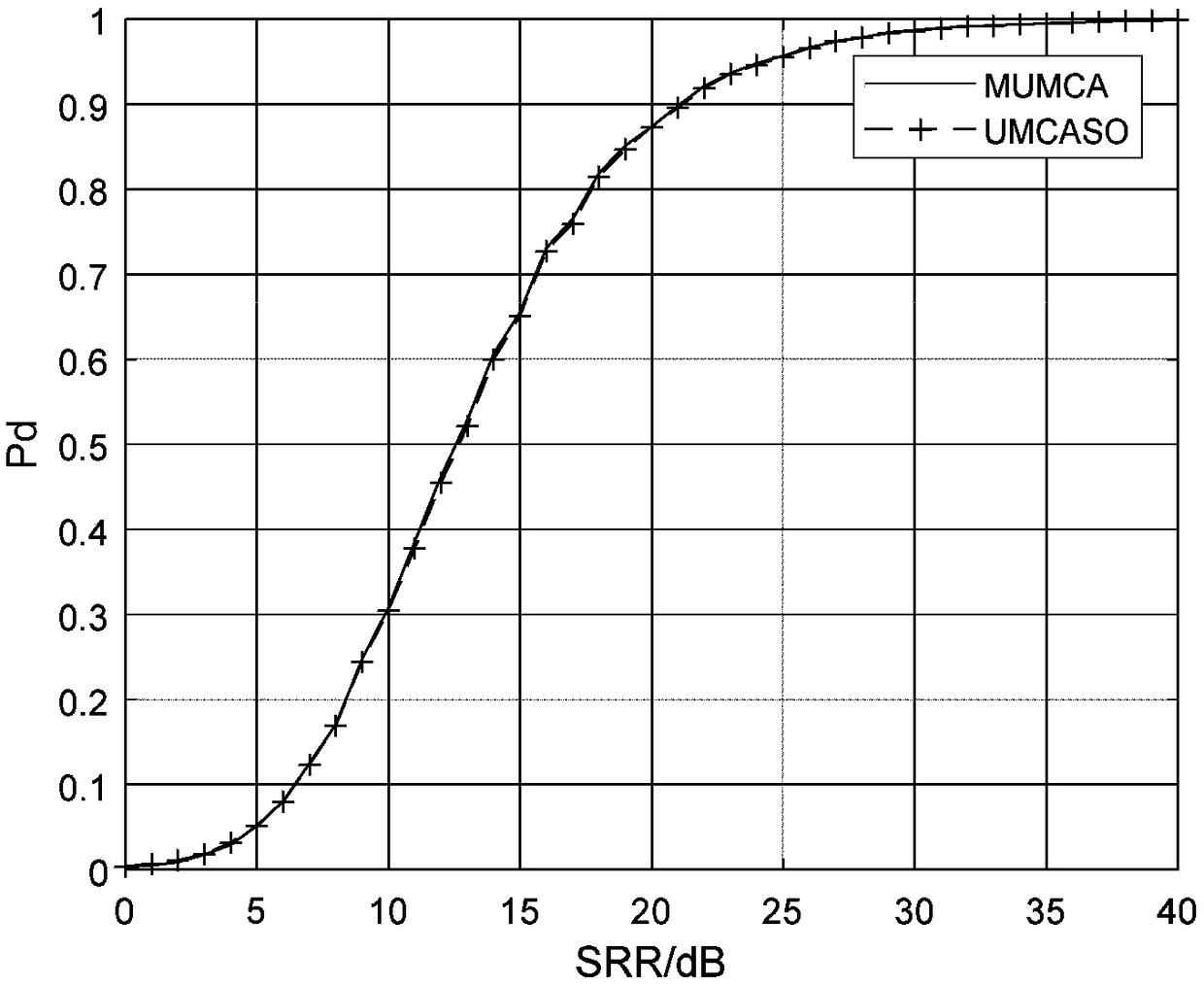

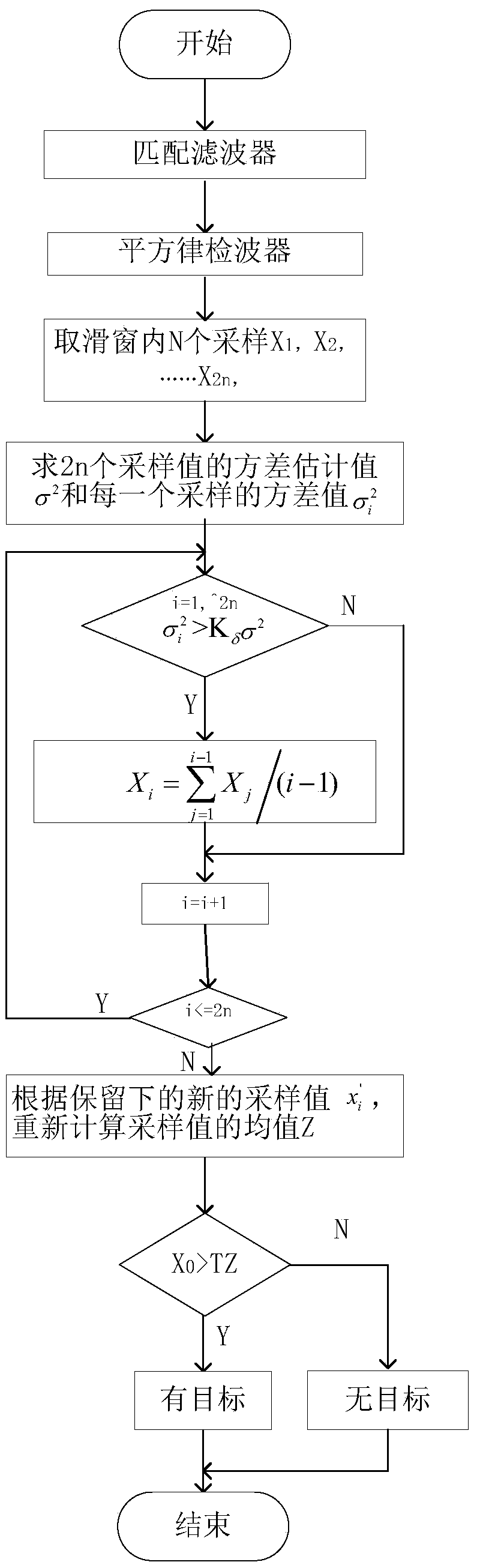

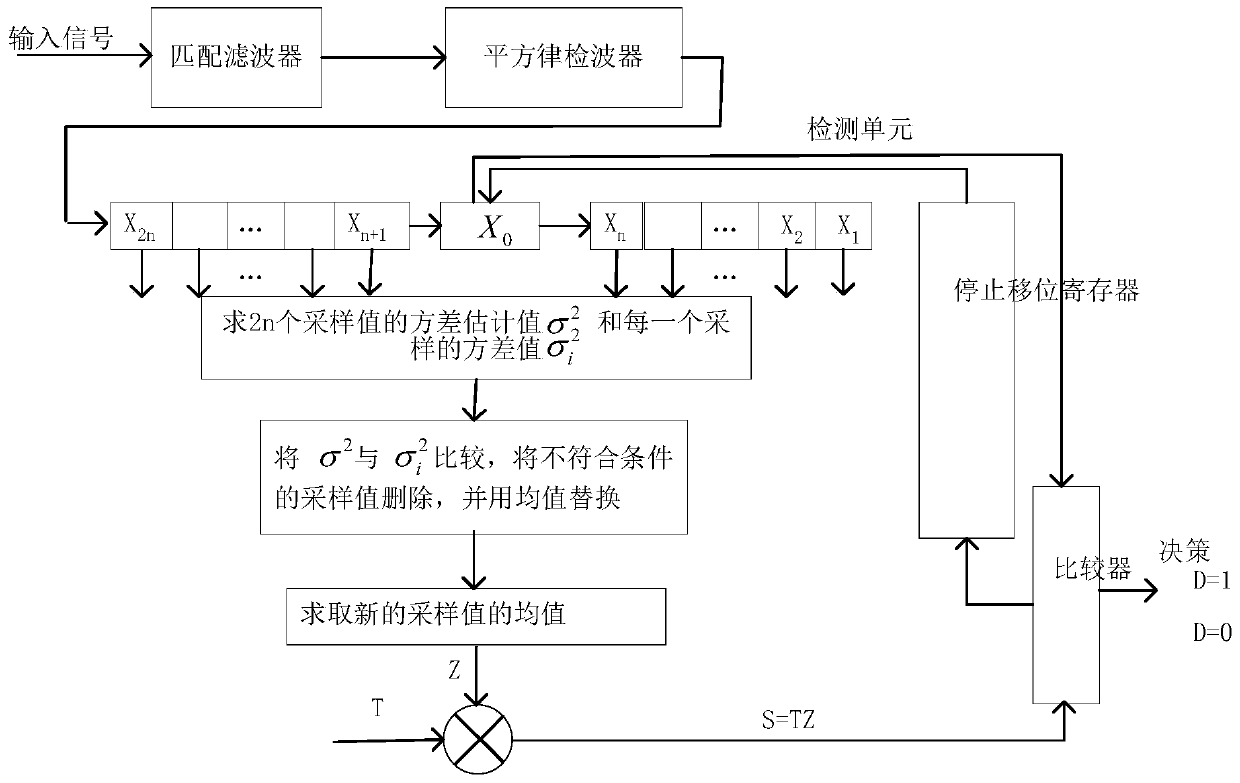

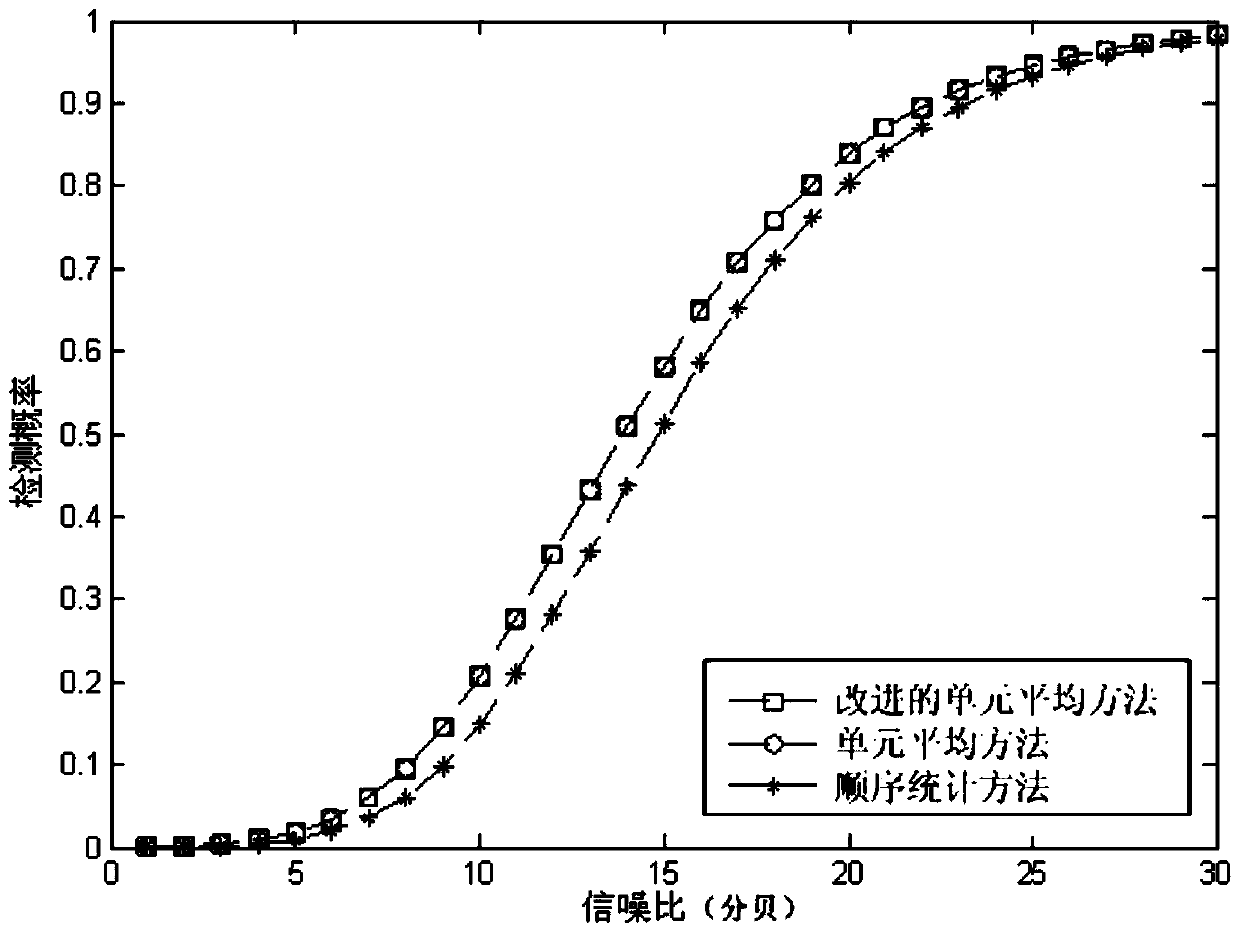

Self-adaptive constant false alarm rate target detection method

InactiveCN104502899AAutomatic adjustment of detection thresholdEfficient removalWave based measurement systemsRadarSlide window

The invention relates to a self-adaptive constant false alarm rate target detection method. The method includes the following steps: 1), transmitting data received by radar into a matching filter; 2), transmitting signals output by the matching filter into a square-law detector for processing; 3), transmitting signals output by the square-law detector into a CFAR (constant false alarm rate) detector for processing, and acquiring an estimation value Z of cluster power level generated by a reference unit according to a corresponding CFAR algorithm through sampling; 4), outputting a final judgment by the CFAR detector according to the estimation value Z acquired in step 3), namely detecting whether a target exists in the unit or not. In the method, according to statistical average value and variance of sampling values in a reference sliding window, the sampling value with the variance larger than a certain numerical value is deleted, an average value of remaining valid sampling values is used to replace the sampling value, and an average value of the sampling values is recalculated.

Owner:CHANGAN UNIV

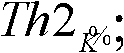

High-resolution radar dual-threshold detector based on energy accumulation

ActiveCN102323577AImprove robustnessWell formedRadio wave reradiation/reflectionEnergy basedHigh resolution radar

The invention discloses a high-resolution radar dual-threshold detector based on energy accumulation, belonging to the field of signal processing. Values of all distance units in a distance window, passing through a square-law detector, are compared with a first threshold, quantity and positions a target scattering center are extracted, then energy of the scattering centers is accumulated and compared with a second threshold to obtain a final detection judgment. Compared with the traditional detection, the detector deduces a calculation formula of the threshold to ensure that actual application is more convenience and flexible, is simple in form, is easy to engineering realization, and has better robustness and detection property under the condition of unknown distribution of the scattering centers.

Owner:北京理工雷科电子信息技术有限公司

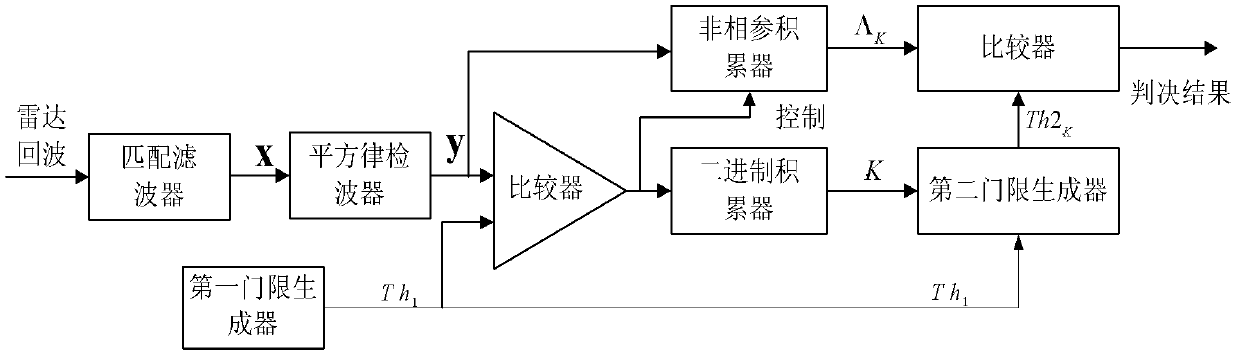

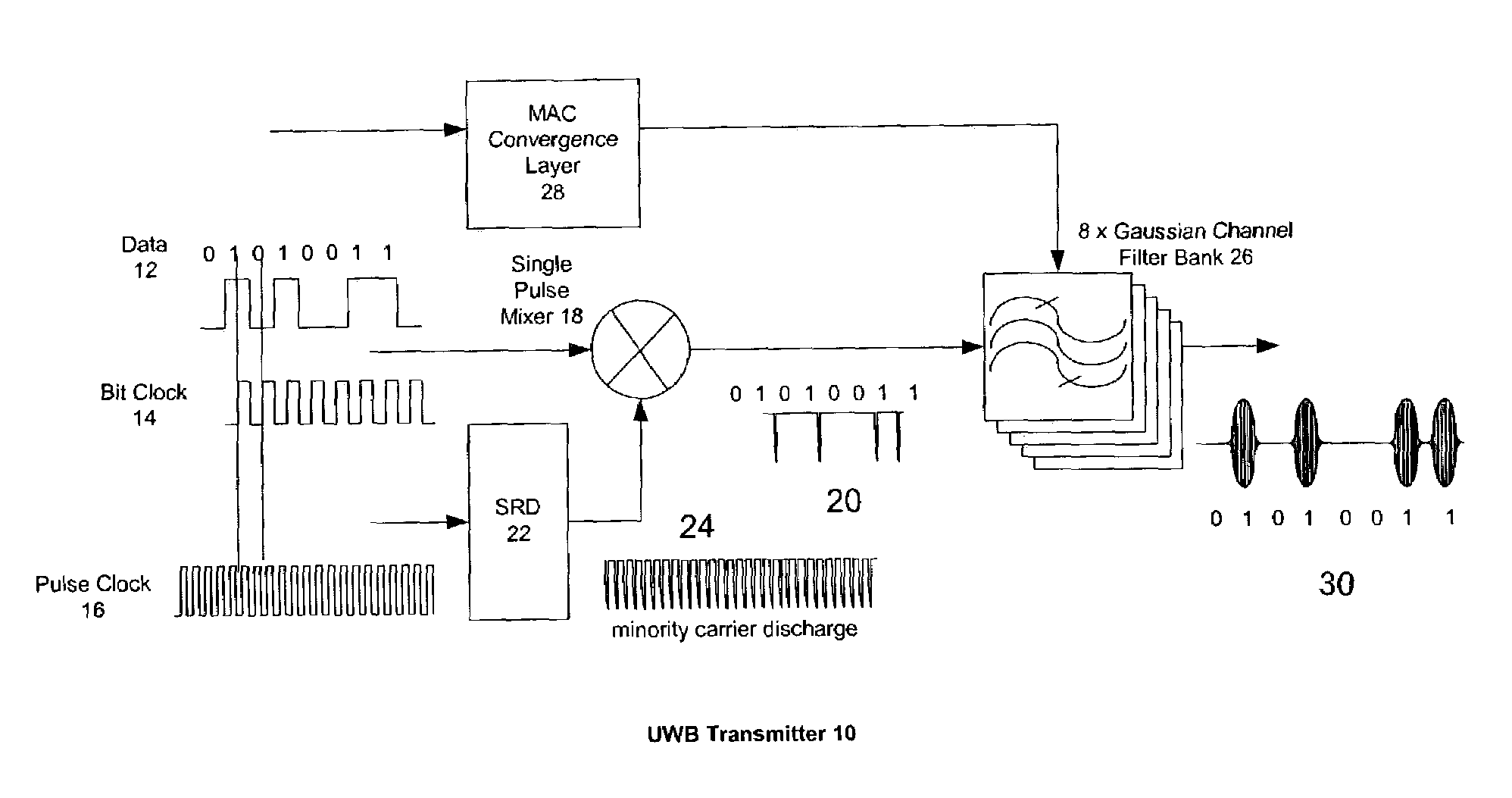

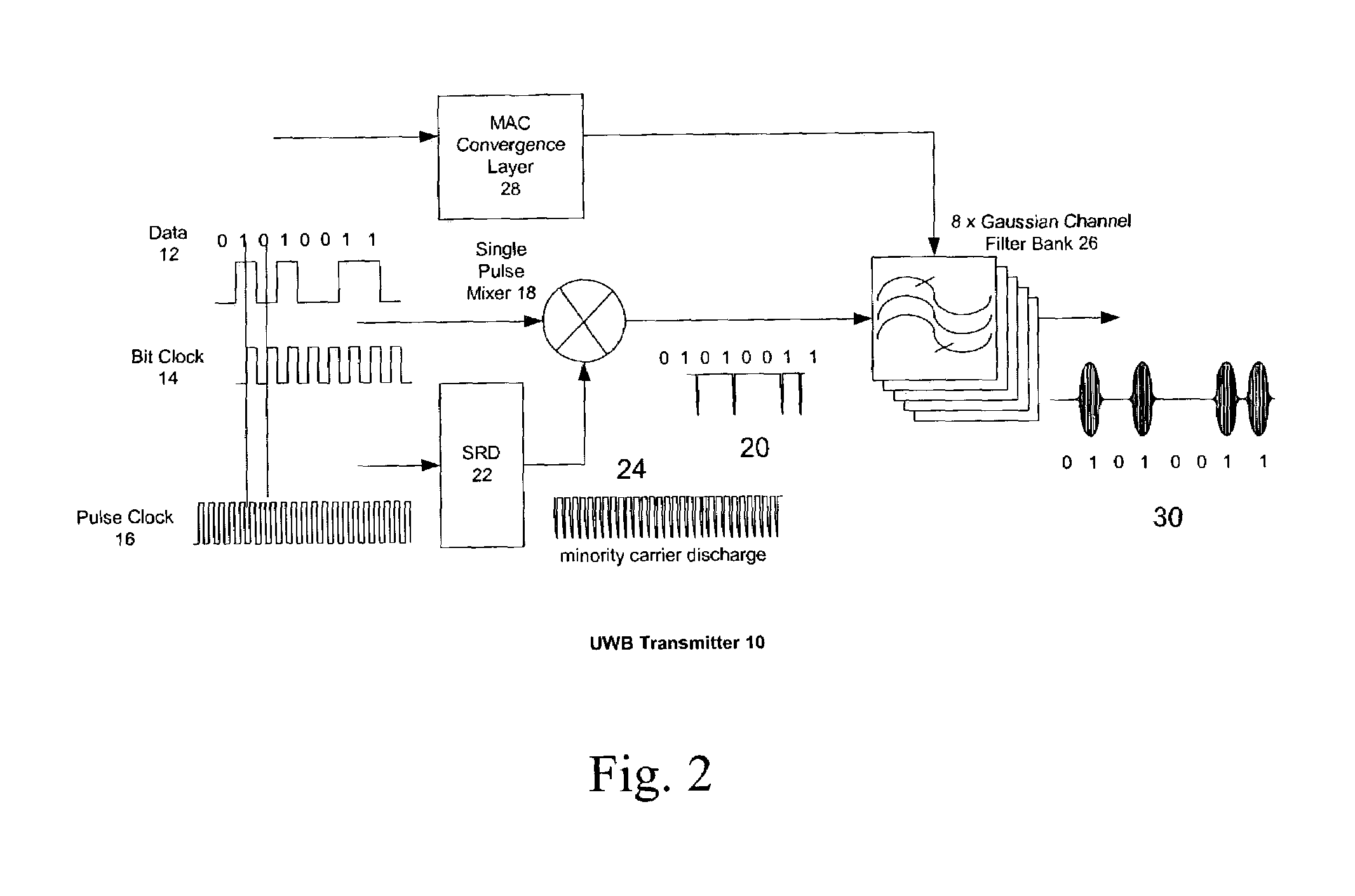

Method and design of data communications transceiver for ultra wide band (UWB) operation in 3.1 GHz to 10.6 GHz frequency band

InactiveUS7286599B1Multiplex communicationDuration/width modulated pulse demodulationTransceiverEngineering

An ultra wide band (UWB) communication system includes a channel filter bank to cover the 3.1 to 10.6 GHz band in channels having approximately equal bandwidth. A transmitter and a receiver may share the filter bank when the communication system is configured as a transceiver. The transmitter produces short duration, wide bandwidth RF pulses by triggering the impulse response of one or more of the filters of the filter bank. The impulse response is triggered by applying a very short duration time domain signal produced using a single pulse mixer and a step recovery diode circuit. The receiver uses a square-law detector to detect RF signals passed by the channel filter bank and the detected signals are further processed to extract a data signal and a confidence level in the data signal.

Owner:FEMTO DEVICES

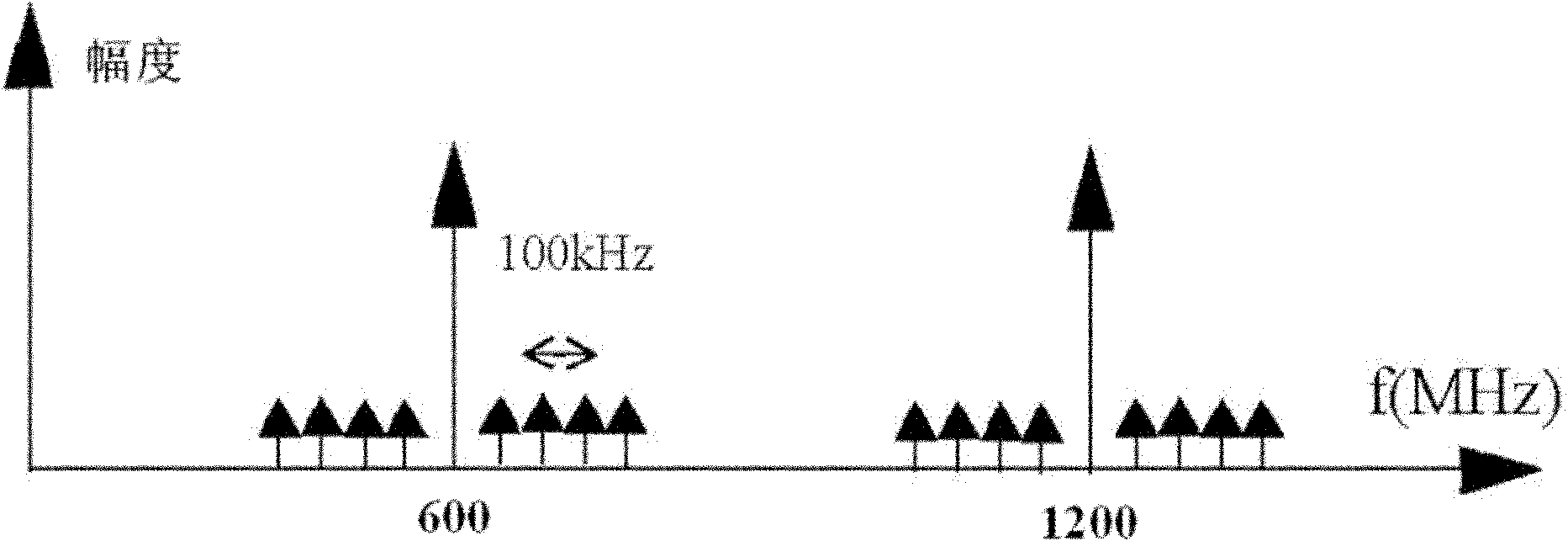

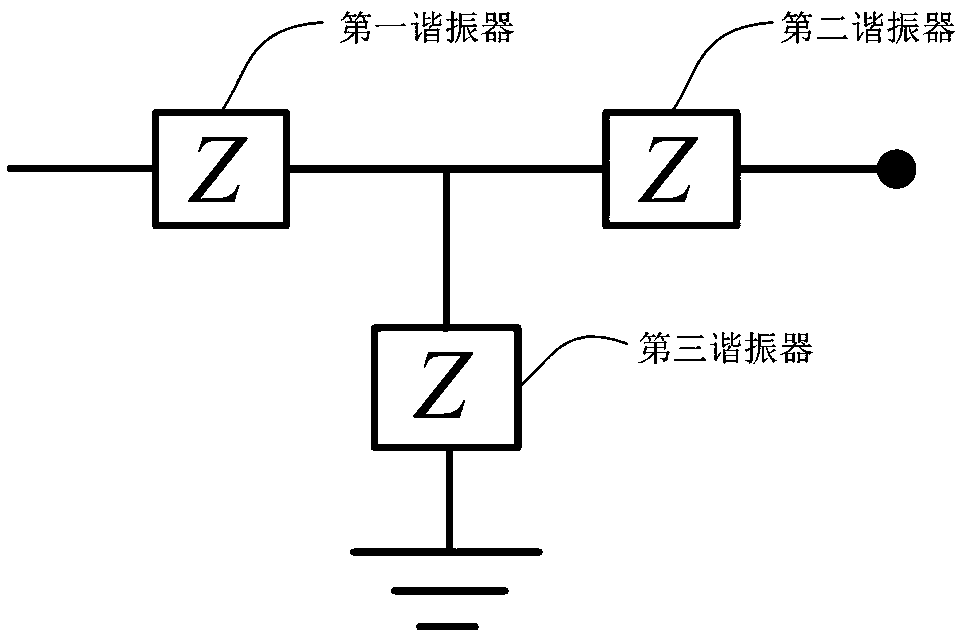

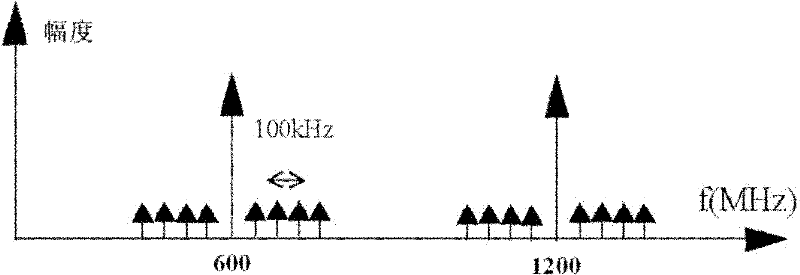

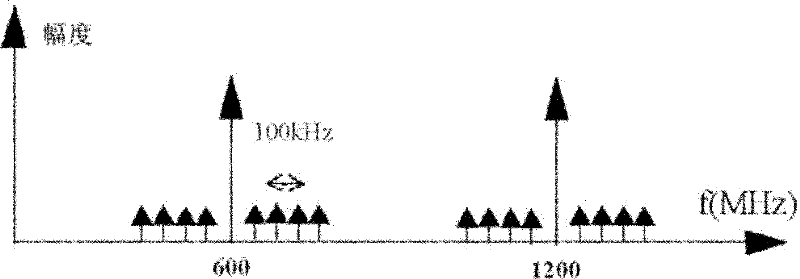

Phase response calibration method of nonlinear vector network analyzer based on fine frequency grid calibration

InactiveCN102087346AAchieving Phase AlignmentPhase calibration with high frequency resolutionResistance/reactance/impedencePhase responseImage resolution

The invention relates to a nonlinear vector network analyzer calibration method, in particular relating to a phase response calibration method of a nonlinear vector network analyzer based on fine frequency grid calibration. The method provided by the invention can be used for the problem that the existing phase response calibration method of a nonlinear network analyzer has low phase calibration frequency resolution. The method comprises: constructing an amplitude modulation signal xAM(t); constructing a fine frequency grid on both sides of a carrier frequency fc; calibrating the phase of a square law detector by use of the fine frequency grid to obtain the phase transmission standard of the fine frequency grid; and carrying out fine frequency phase calibration of the nonlinear vector network analyzer by use of the phase transmission standard of the fine frequency grid. The method is applicable to the phase calibration of the nonlinear vector network analyzer.

Owner:HARBIN INST OF TECH

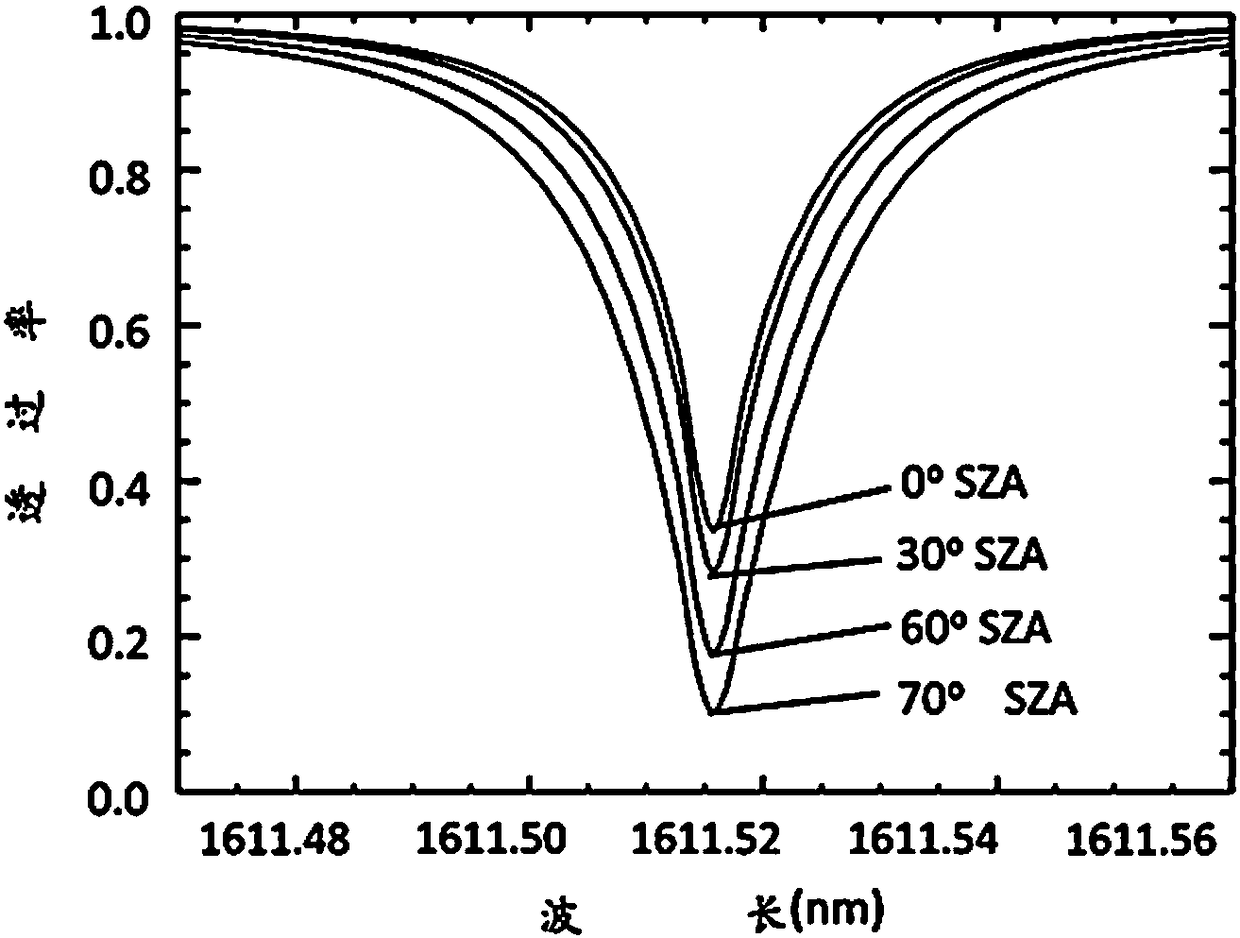

High-spectrum-resolution total atmospheric spectral transmittance measuring method

InactiveCN105928902ANarrow line width and heightHigh resolutionColor/spectral properties measurementsIntermediate frequencyLine width

The invention discloses a high-spectrum-resolution total atmospheric spectral transmittance measuring method. The method includes: using a target tracking device for acquiring sunlight or starlight penetrating the atmosphere as signal light, taking a high-coherence narrow linewidth laser as local oscillation laser, subjecting the signal light penetrating the atmosphere and the local oscillation laser to optical mixing in a heterodyne detector prior to passing through an intermediate-frequency filter and a square-law detector, sending to a band-pass filter to remove noise, enabling a computer to collect for obtaining a heterodyne signal generated by combination of the signal light penetrating the atmosphere and the local oscillation laser, and processing the heterodyne signal to obtain a high-resolution spectrum of weak signal light penetrating the atmosphere. The high-spectrum-resolution total atmospheric spectral transmittance measuring method is used for real-time measurement of total atmospheric spectral transmittance and applicable to fields of atmospheric optics, meteorological research, atmospheric pollution monitoring, detection and the like, and quick response and real-time measurement of high-spectrum-resolution total atmospheric spectral transmittance can be realized according to the method.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

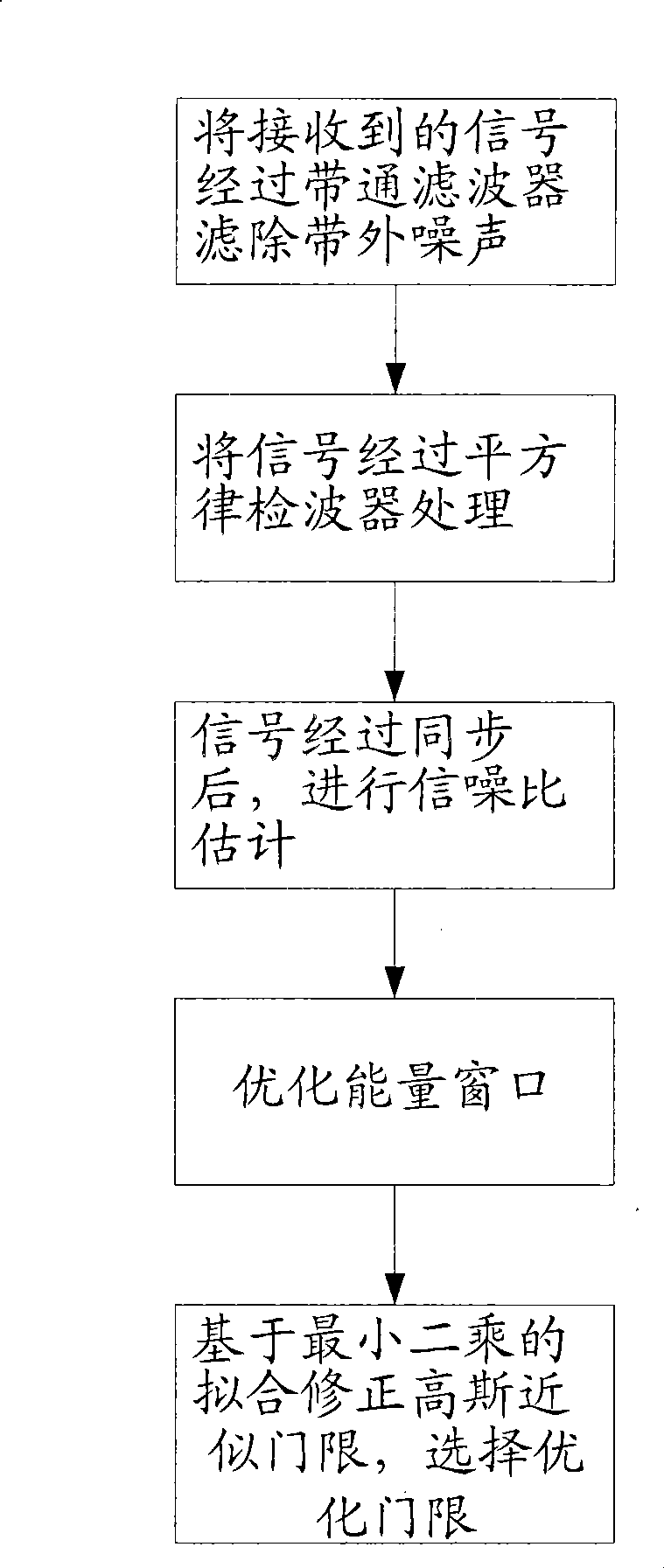

UWB receiver error rate performance optimizing method by noncoherent energy detection

The invention provides an error rate performance optimizing method of a noncoherent energy detecting UWB receiver, comprising the following steps: the outside band noise of a received signal is filtered via a bandpass filter; the signal is processed by a square-law detector, and after the synchronism process, the SNR estimation is carried out; an energy window is optimized; and an optimized threshold is selected based on a least square fitting correction gauss approximate threshold. The error rate performance optimizing method of a noncoherent energy detecting UWB receiver enables the receiver performance to be greatly improved by the combined optimization of the judgment threshold of the receiver and an energy integral window.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

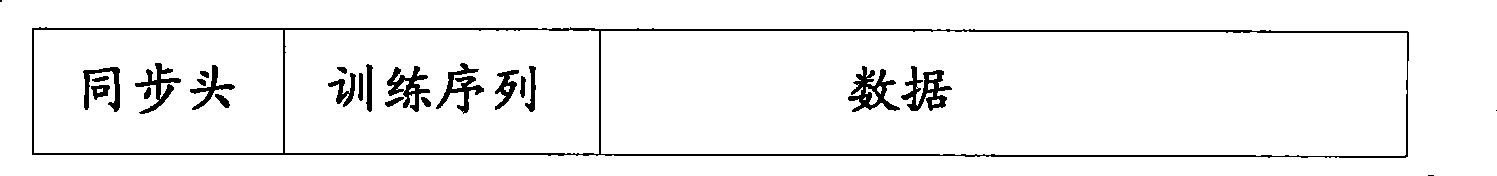

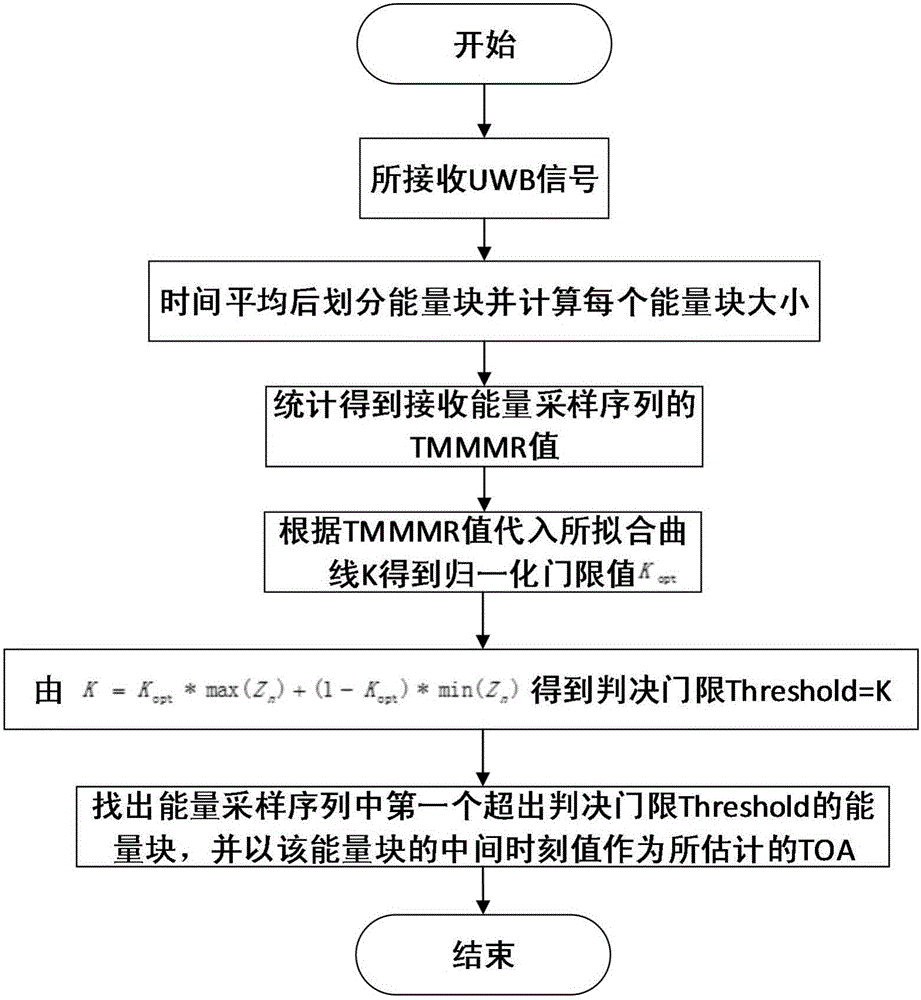

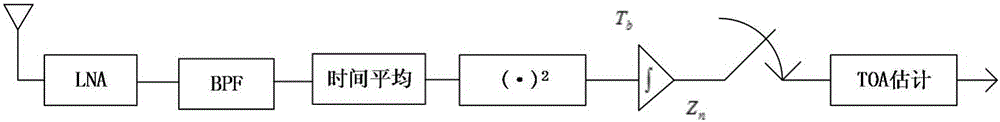

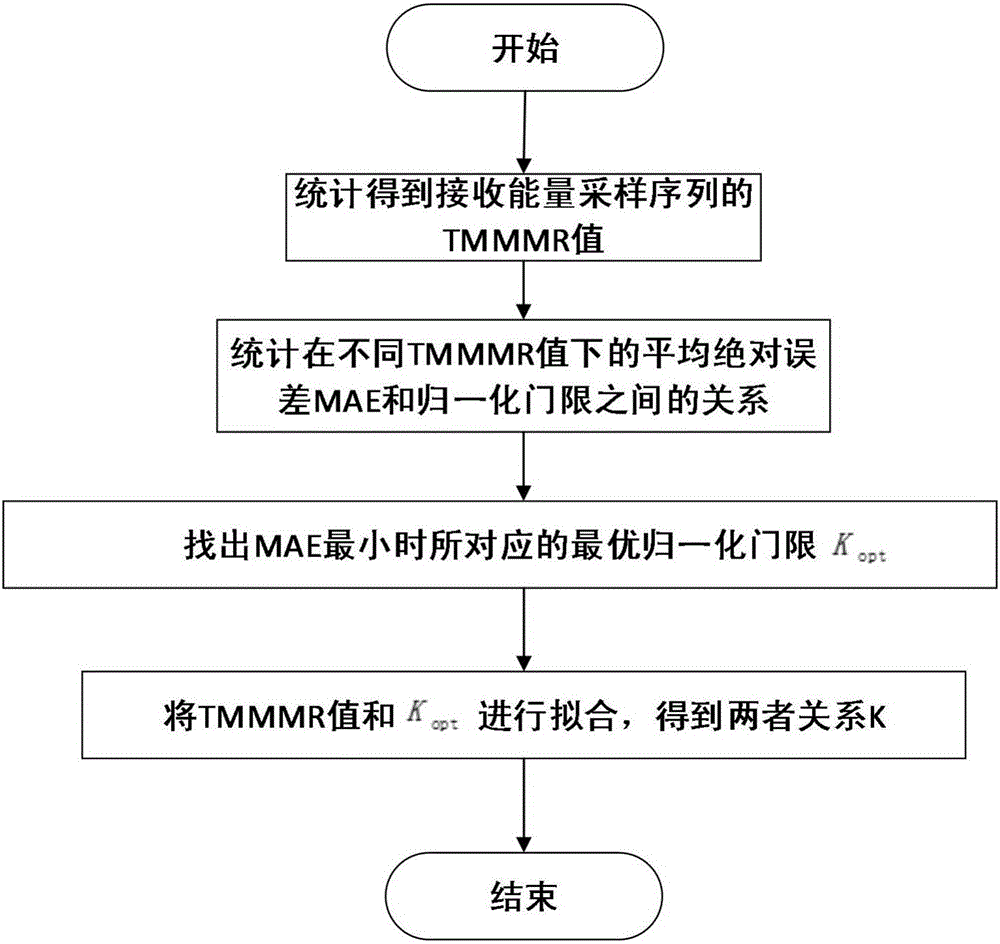

Time of arrival estimation method based on energy mean detection

ActiveCN106131949ALower estimated impactImprove performancePosition fixationWireless communicationSample sequenceEngineering

The invention relates to a time of arrival estimation method based on energy mean detection. The method comprises the steps of carrying out time averaging on multiple pulse receiving signals, thereby obtaining frame synchronous ultra wide band receiving signals; obtaining energy signals through a square-law detector, and sampling the energy signals, thereby obtaining an energy sampling sequence of the receiving signals; obtaining a maximum and minimum to mean energy sample ratio of the receiving signal after time averaging according to the obtained energy sampling sequence, obtaining an optimum normalization threshold through a function relationship between the maximum and minimum to mean energy sample ratio and the optimum normalization threshold, and determining a judgment threshold; and selecting a middle position of an energy block first exceeding the judgment threshold as a time of arrival estimation value. According to the method, the high performance can be realized in a working signal to noise ratio range.

Owner:SHANGHAI INTERNET OF THINGS

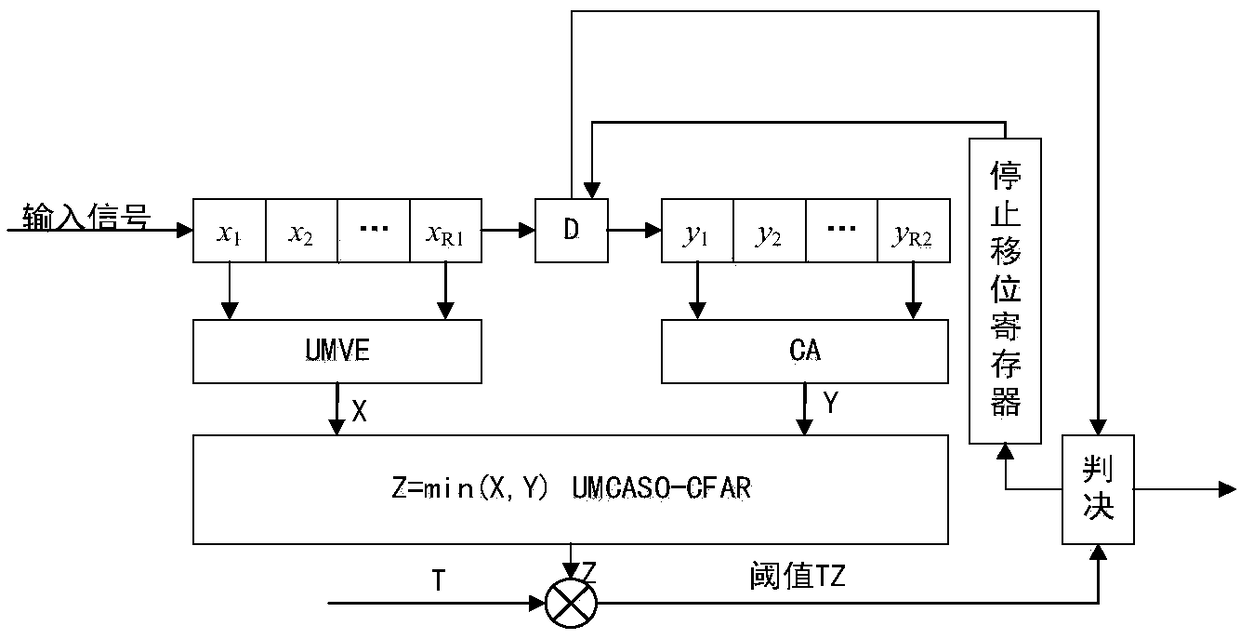

Multi-target interference resistant constant false alarm detection method

ActiveCN109188388AWith anti-interference abilityReduce performanceWave based measurement systemsShift registerSlide window

The invention discloses a multi-target interference resistant constant false alarm detection method. The method includes the following steps: step 1) a sonar performs sampling at intervals at a rightside and a left side of a location D of a detection unit, acquired sampling values sequentially pass through a matched filter and a square-law detector, and are sent to a shift register subsequently,and the shift register stores R1 sampling values (x<1>,x<2>...x<R1>) of the left side of D as a front reference sliding window, and stores R2 sampling values (x<1>,x<2>...x<R2>) of the right side of Das a back reference sliding window; step 2) the front reference sliding window is processed by an unbiased minimum variance estimating method to obtain front local estimation X, and the back reference sliding window is processed by a unit averaging method to obtain back local estimation Y; step 3) the smaller of X and Y is used as a final background noise power estimator Z; and step 4) after being multiplied by a threshold factor T, Z is compared with detection statistical quantity S to perform judgment, and a judgment result of whether the detection unit is a target is obtained.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

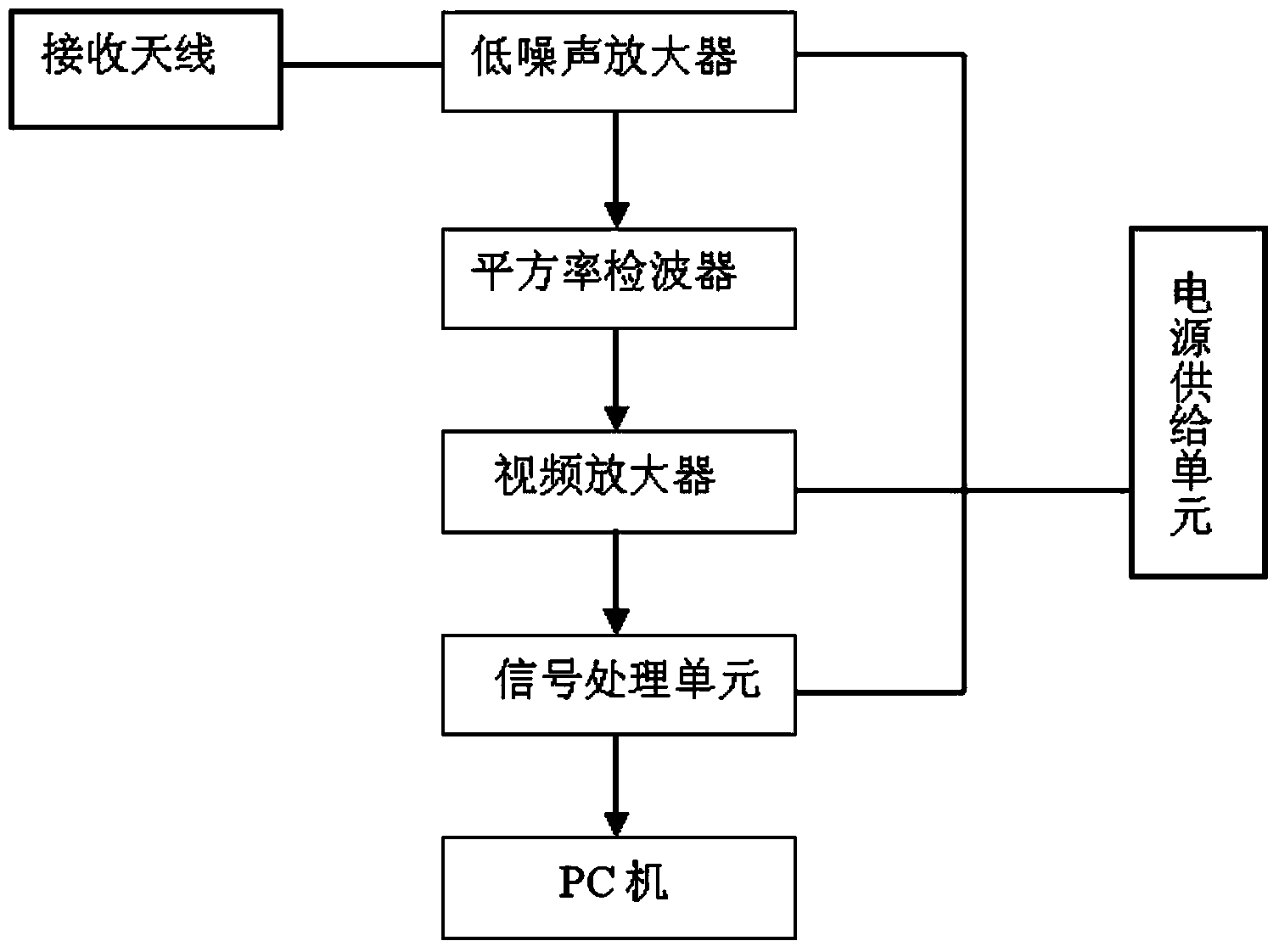

System and method for recognizing motor vehicles in intelligent transportation system

InactiveCN103489315AEasy maintenanceImprove detection accuracyRoad vehicles traffic controlMobile vehicleEngineering

The invention discloses a system for recognizing motor vehicles in an intelligent transportation system. The recognizing system comprises a detector, a receiving antenna and a PC. The detector is a passive millimeter wave detector and is composed of a low noise amplifier, a square-law detector, a video amplifier, a signal processing unit and a power supply unit. The receiving antenna is a millimeter wave antenna. The recognizing method includes the steps that first, the millimeter wave detector works, and a vehicle moves towards a detection area of the detector; second, the millimeter wave detector observes the detection area and outputs signals; third, the PC compares the voltages of output signals of the detector with preset threshold voltages for detecting whether the vehicle can pass or not, and a judgment is made; fourth, under the condition that the judgment that the vehicle can pass is made, the PC compares the voltages of the output signals of the detector with preset threshold voltage ranges of different vehicle models, and according to the fact that the voltages of the output signals of the detector fall into the threshold voltage range of a certain vehicle model, the PC makes a corresponding vehicle type recognizing judgment for allowing the vehicle to pass.

Owner:CHANGZHOU OUJIA COMM EQUIP

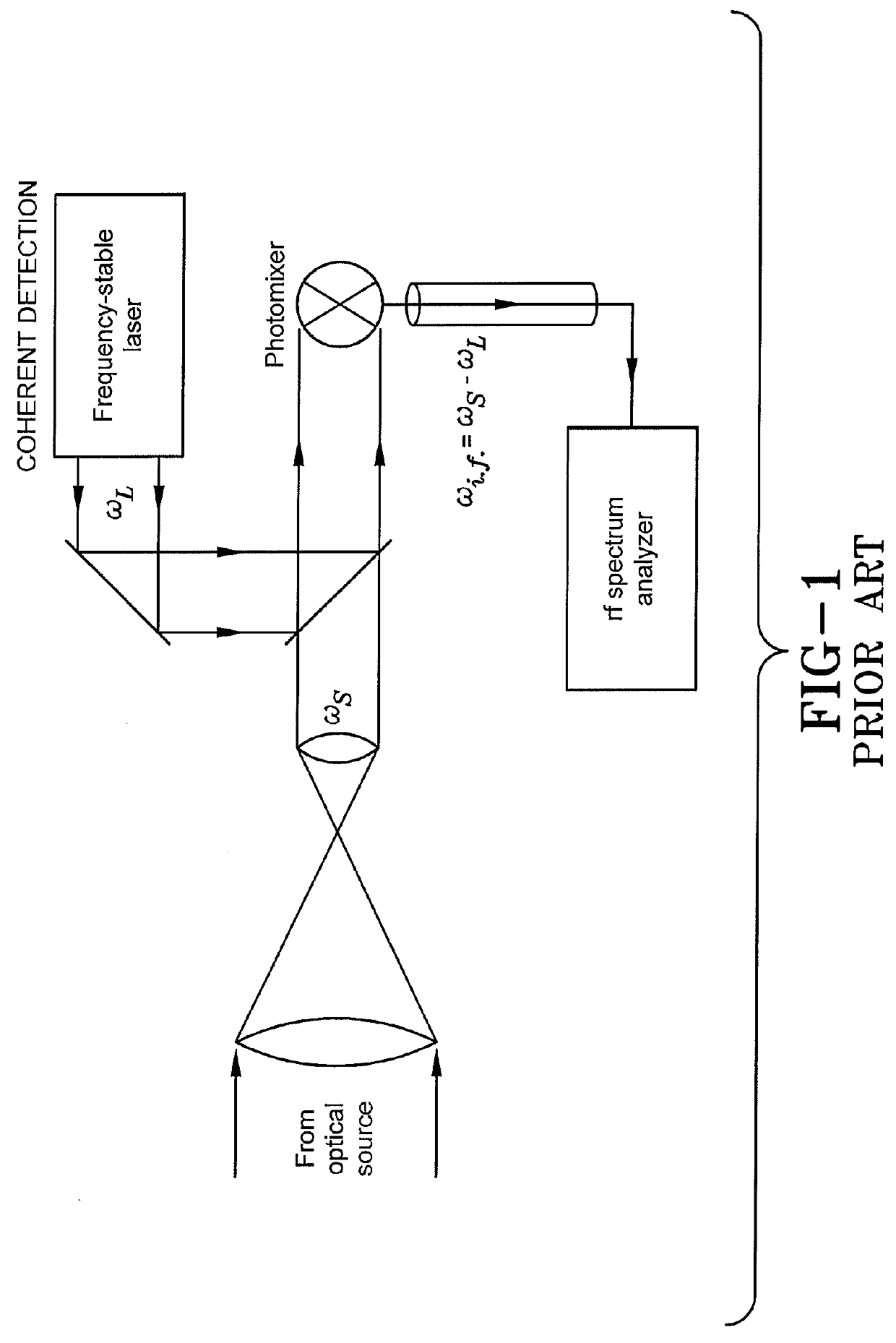

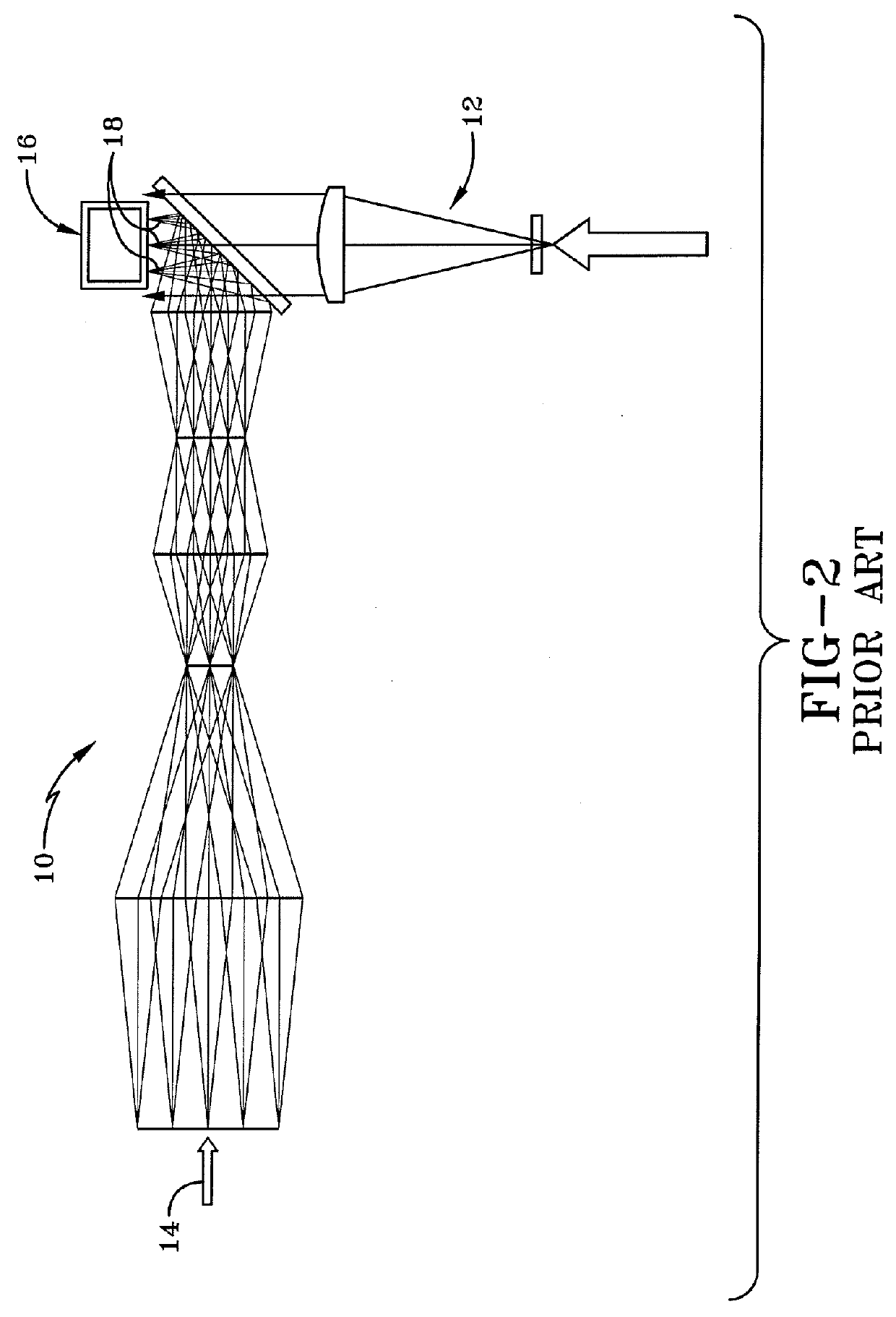

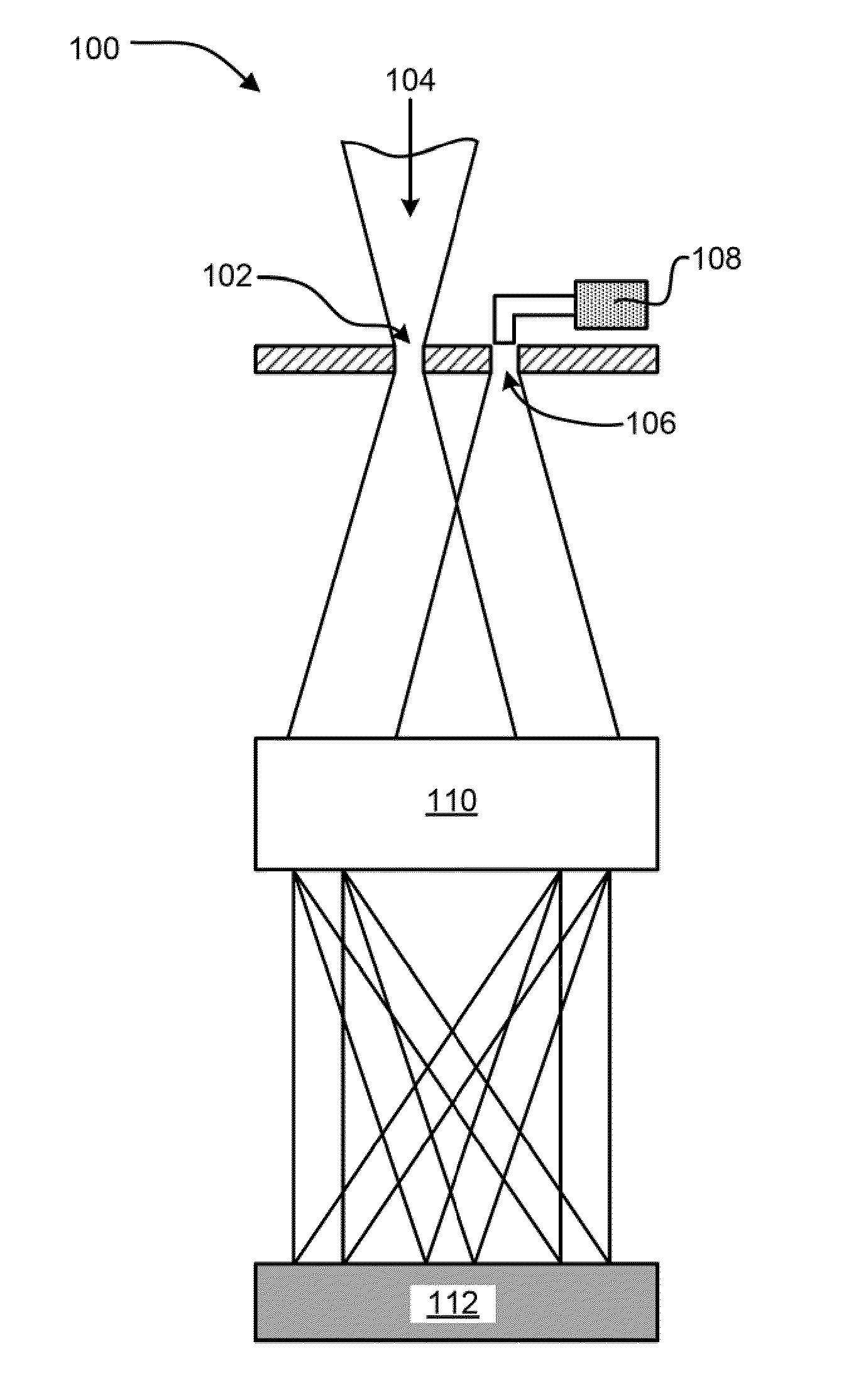

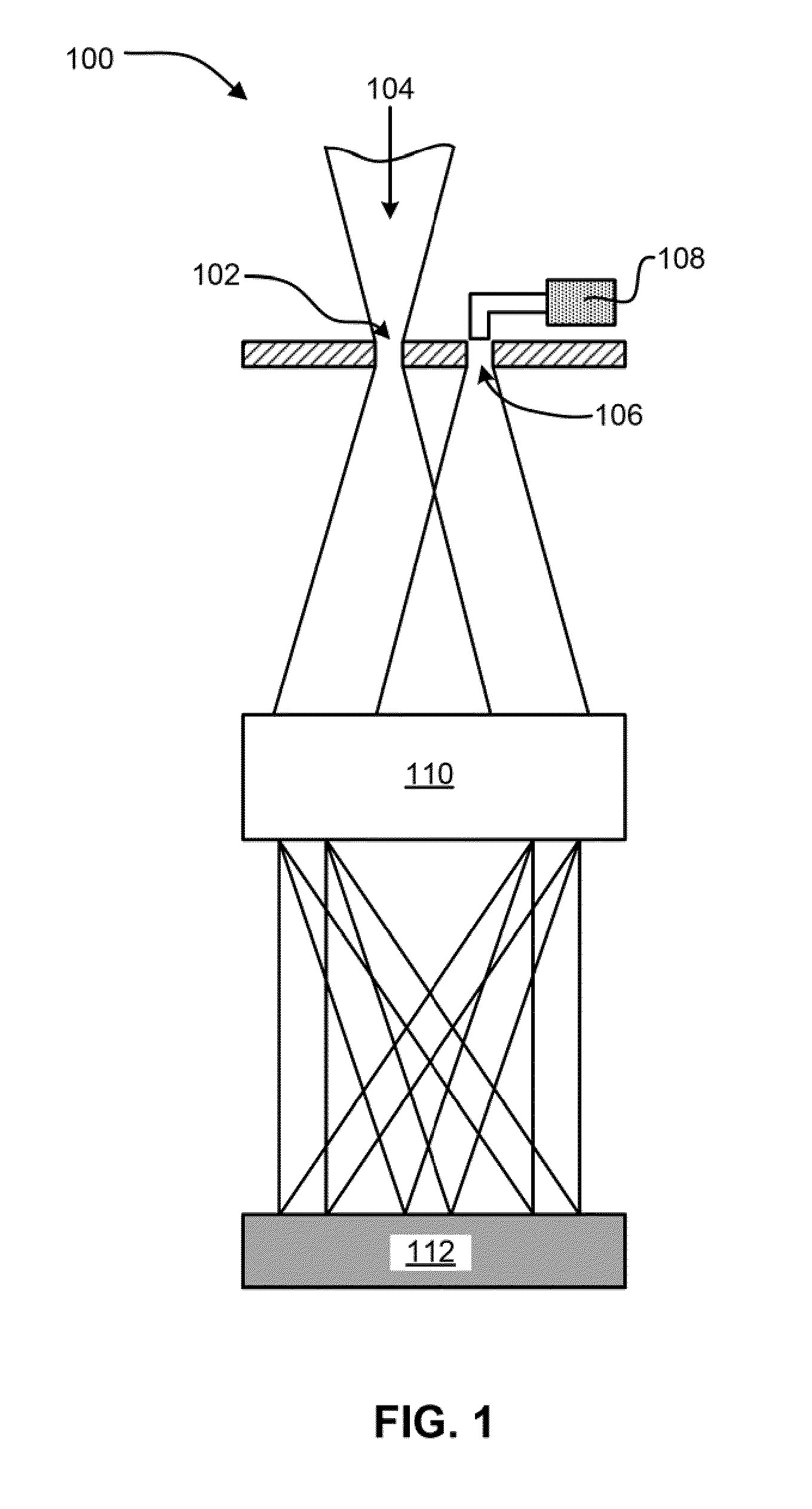

High efficiency coherent imager

ActiveUS20160036535A1Reduced effectivenessDetection is limitedOptical measurementsElectromagnetic receiversBeam splitterParticle physics

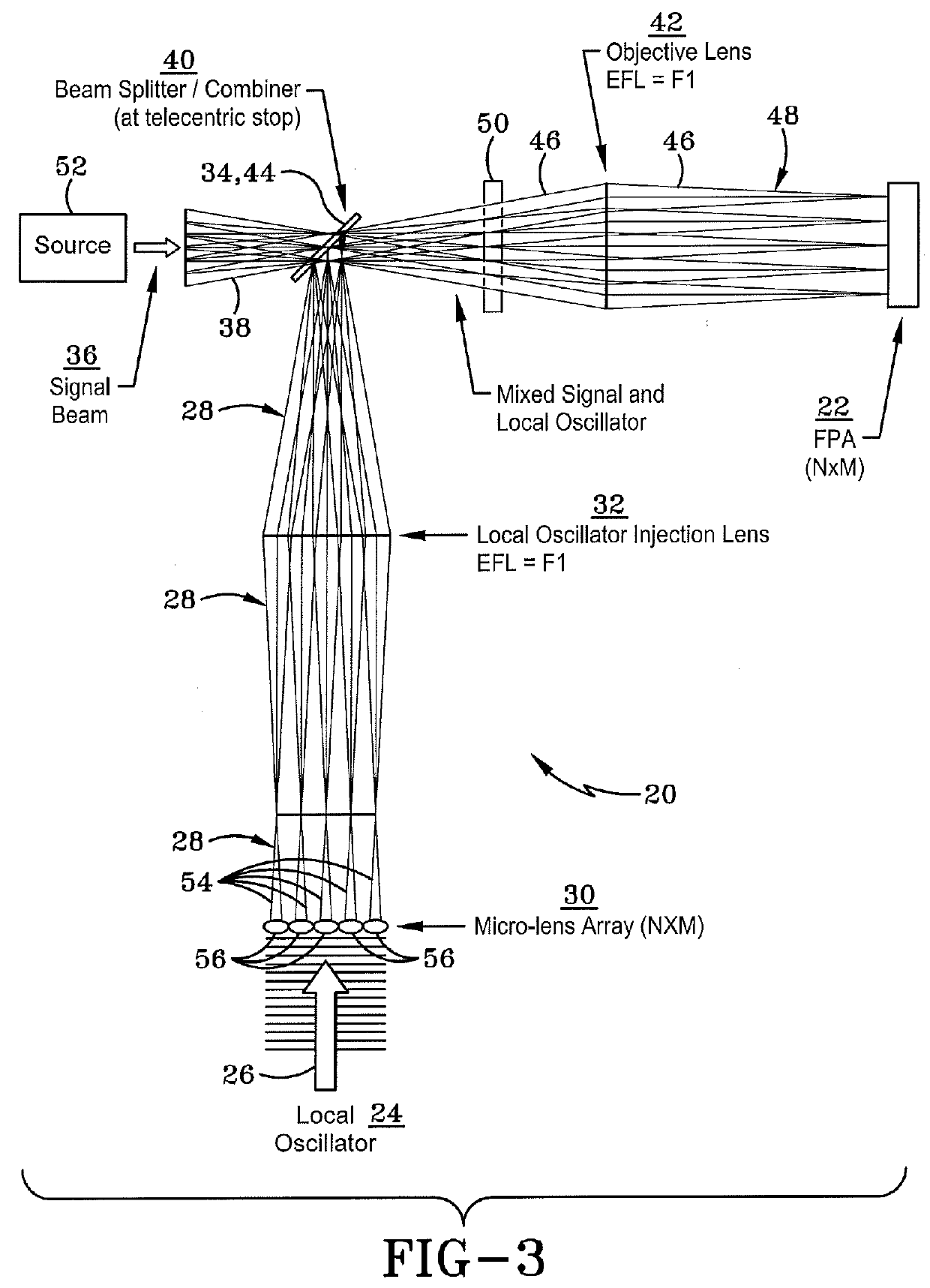

An extended field heterodyne detection apparatus comprises a local signal oscillator, a micro-lens array set in optical relation to the local signal oscillator to multiplex a beam from the local signal oscillator, a local oscillator injection lens in the optical path of the local oscillator and the micro-lens array, a semi-reflective beam splitter at the telecentric stop of the local oscillator injection lens to reflect the beam of the local oscillator in parallel to a signal beam passing through the semi-reflective beam splitter, an objective lens, with a stop, located at the semi-reflective beam splitter, and a focal plane array, situated to receive the source beam. The extended field heterodyne detection apparatus solves the problem of creating a local oscillator beam that is mode-matched for an incoming signal beam, for the eventual process of mixing both the signal beam and the local oscillator using a conventional, square-law detector.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

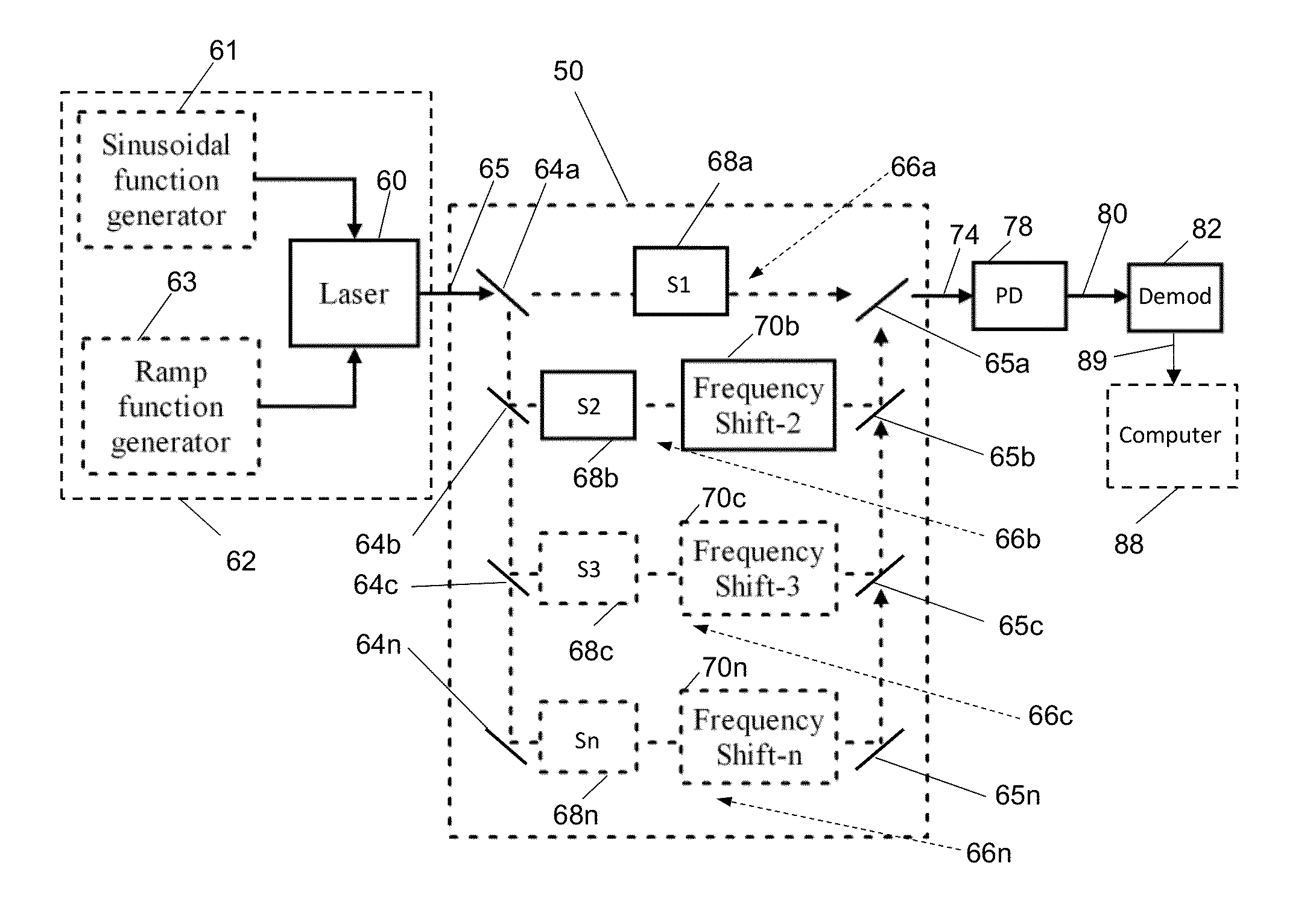

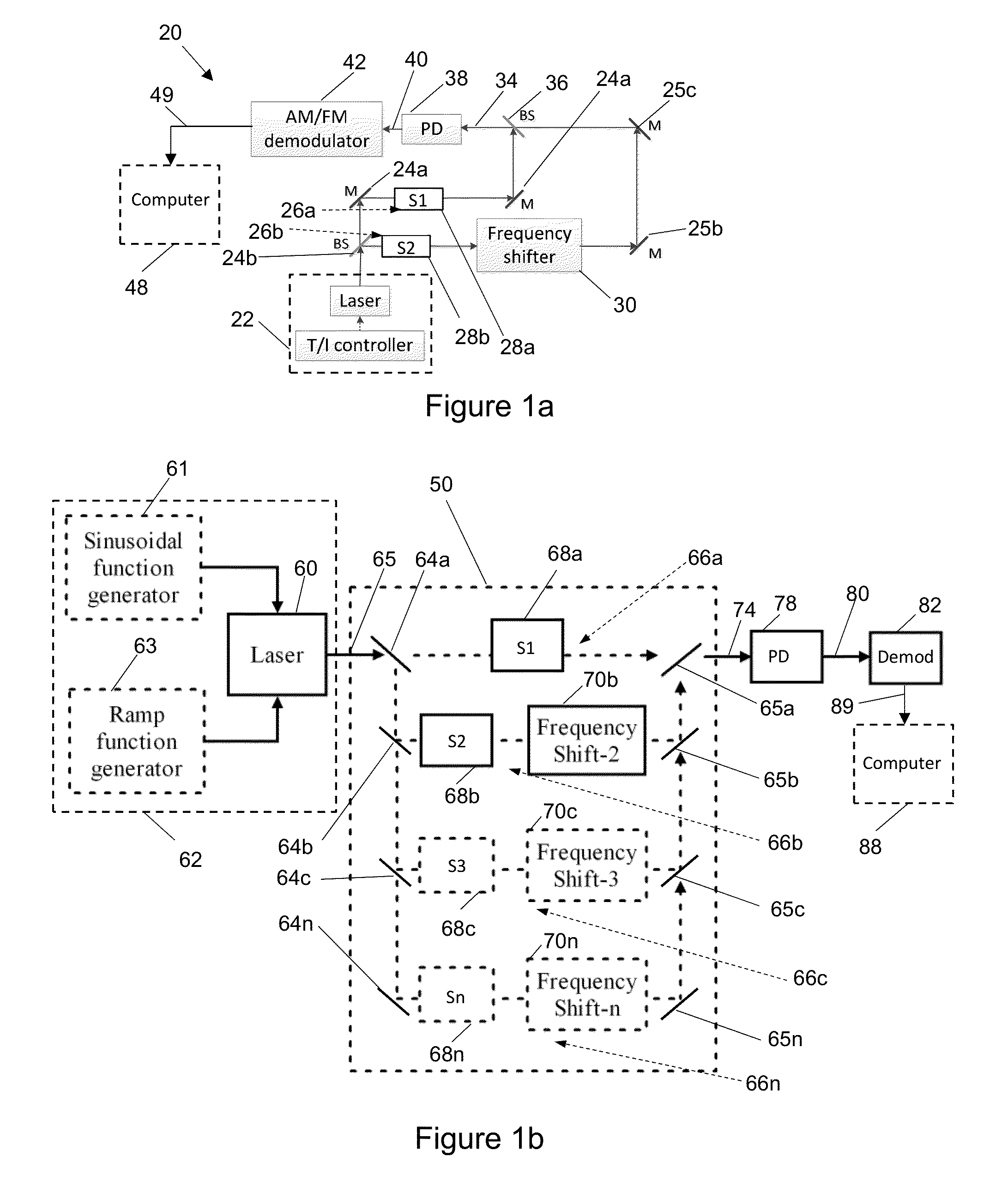

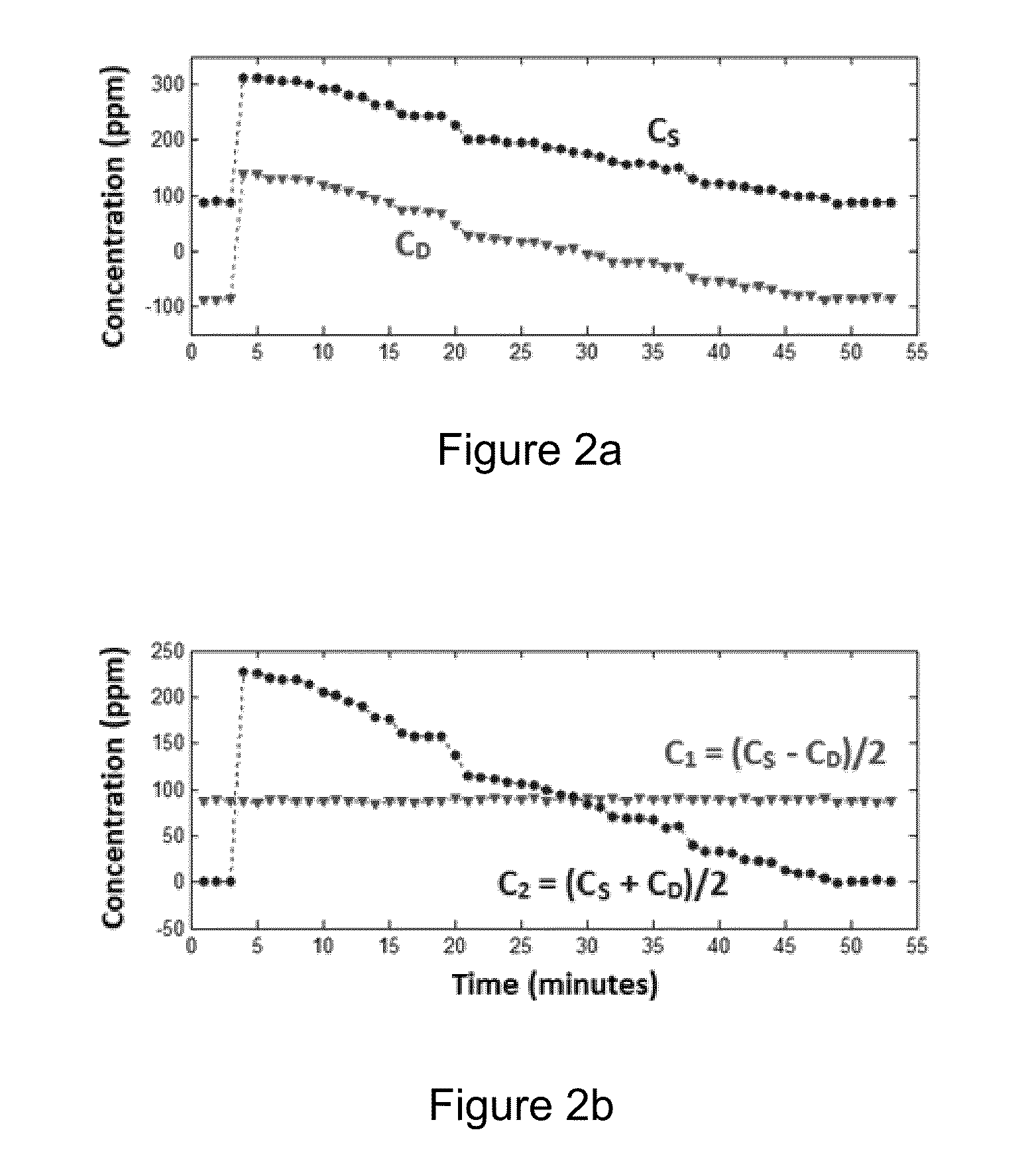

Optical subtraction of molecular dispersion signals enabled by differential optical dispersion spectroscopy

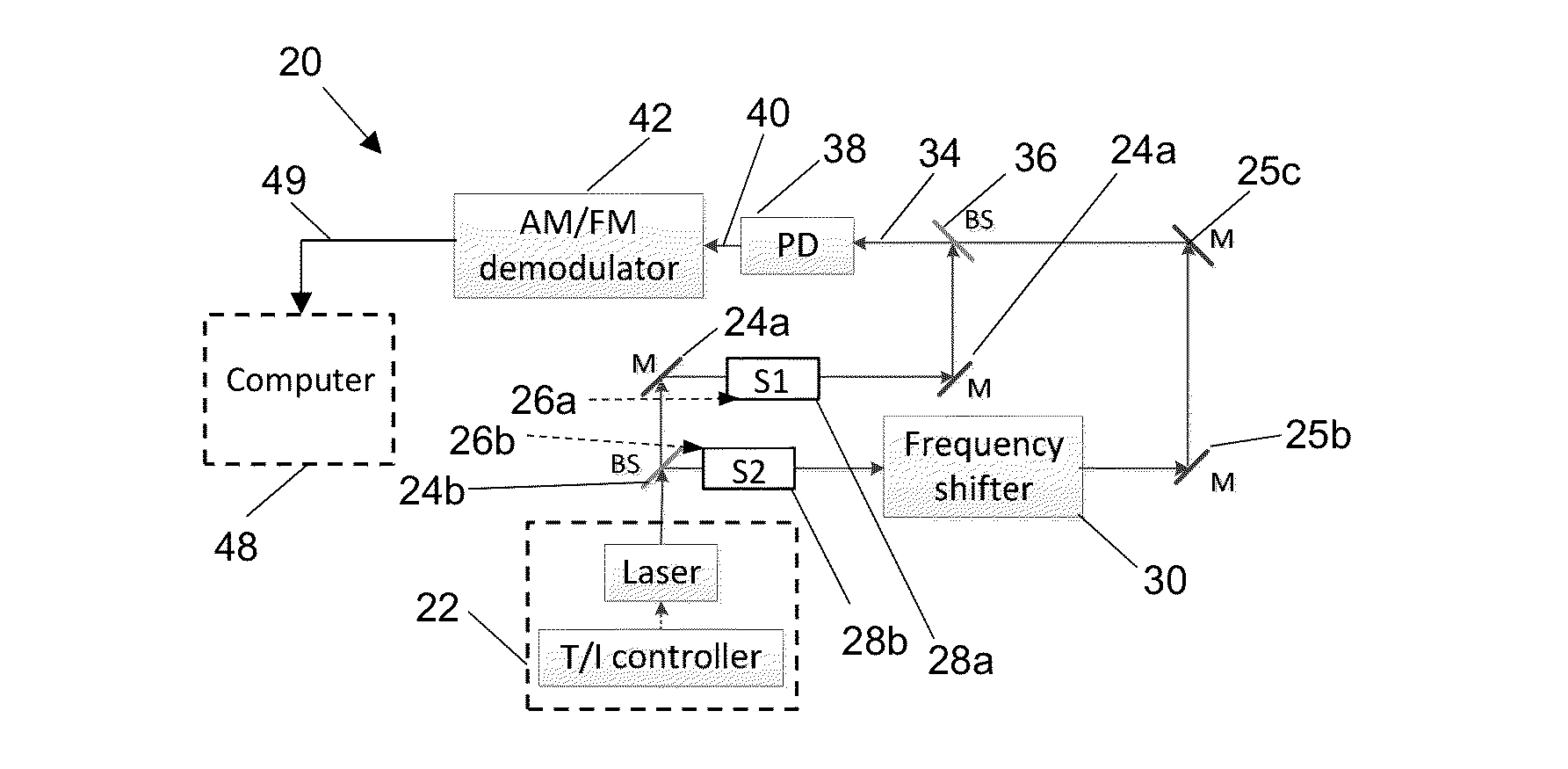

ActiveUS20140111808A1Transmissivity measurementsColor/spectral properties measurementsBeam splitterSpectroscopy

An apparatus and method for differential optical dispersion using a first sample and a second sample are disclosed. The apparatus includes a single frequency chirped laser source configured to generate a single frequency chirped laser beam. A first beam splitter is configured to split the single frequency chirped laser beam into first and second optical branches, the first sample being located in the first optical branch, the second sample being located in the second optical branch. A frequency shifter is located in the second optical branch, downstream of the second sample. A second beam splitter is configured to combine the first and second optical branches and generate a chirp-modulated mixed light beam. A square law detector is configured to detect the chirp-modulated mixed light beam and generate a heterodyne beatnote signal. A demodulator is configured for detection of the heterodyne beatnote signal to generate a transmission / differential optical dispersion spectrum.

Owner:THE TRUSTEES FOR PRINCETON UNIV

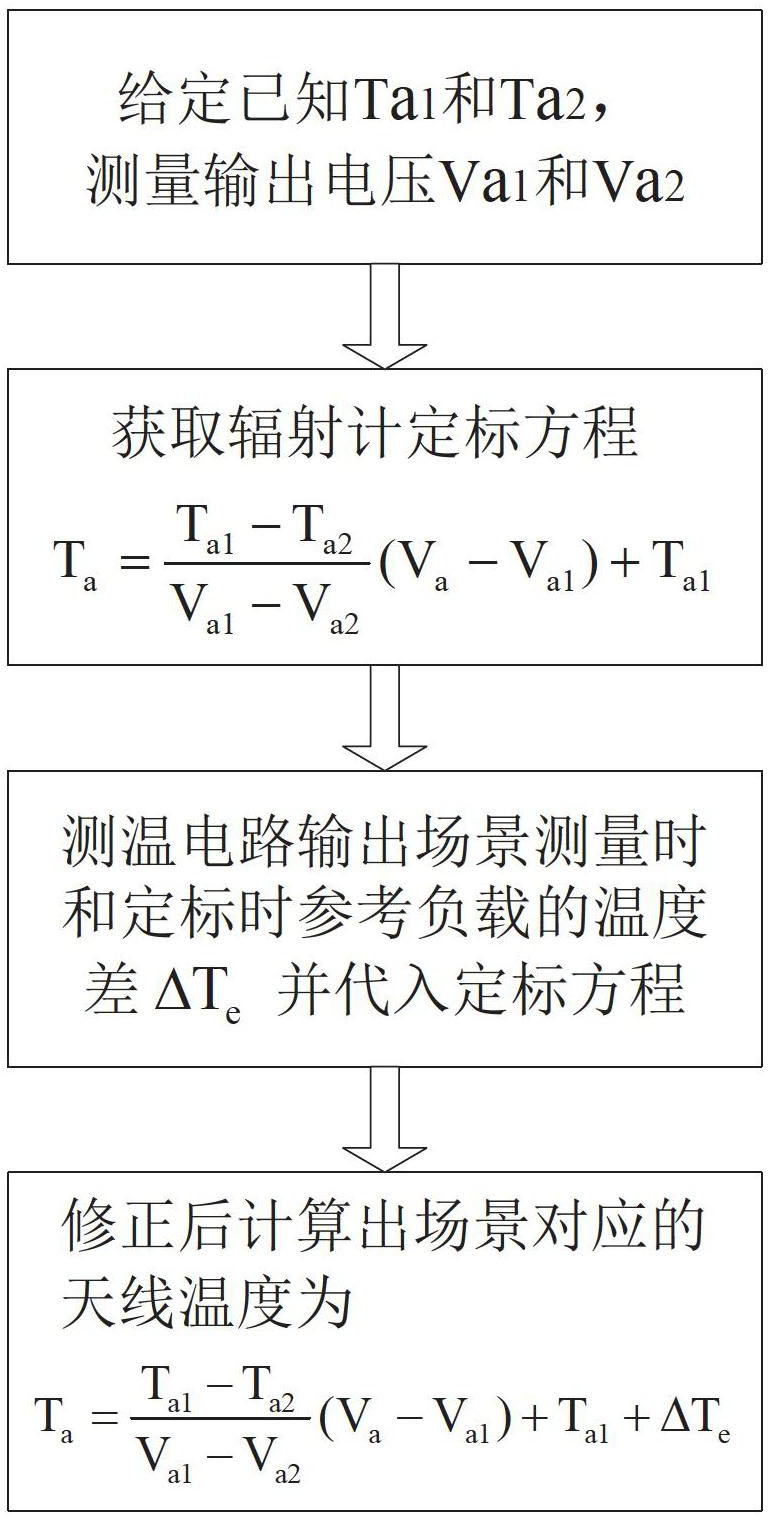

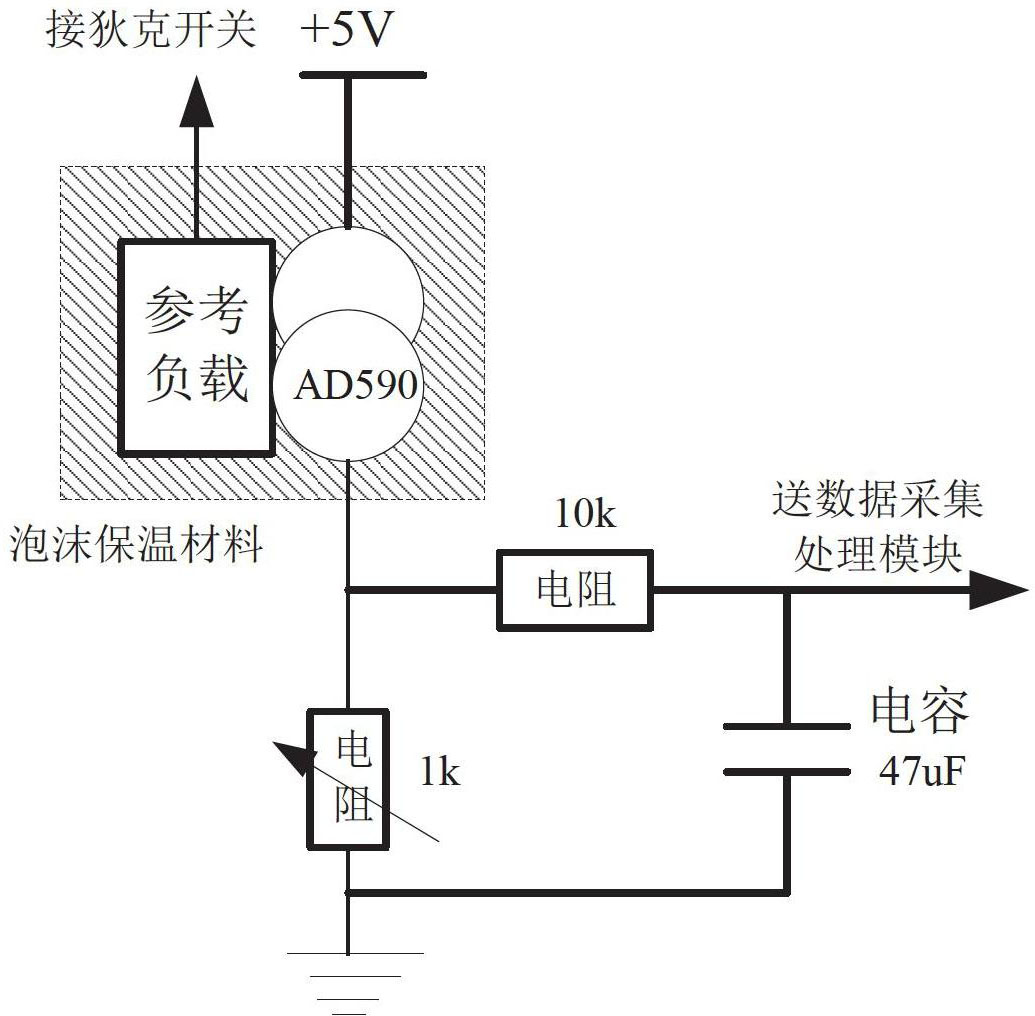

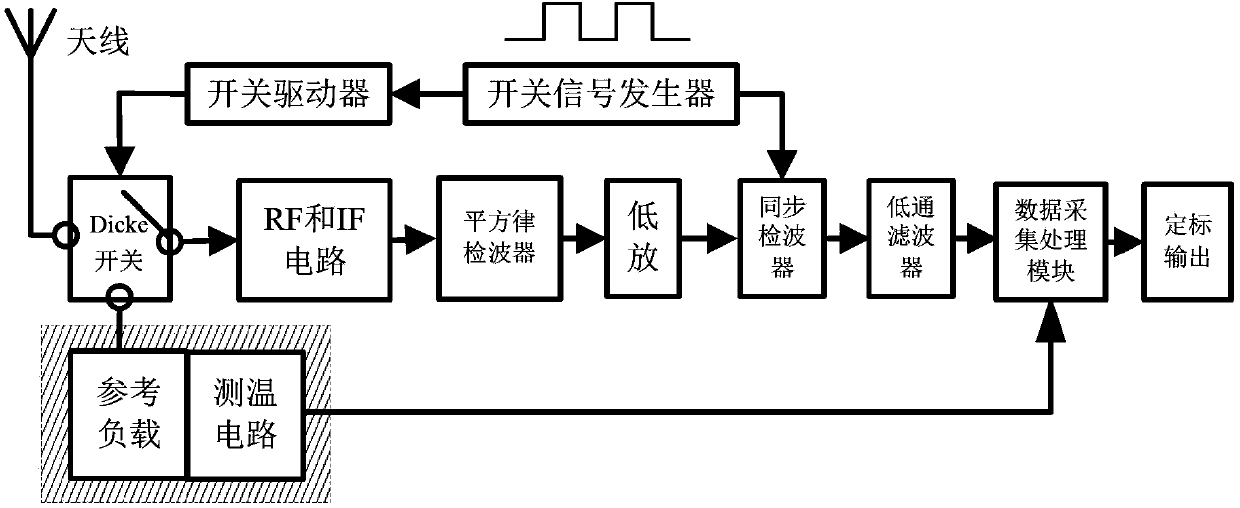

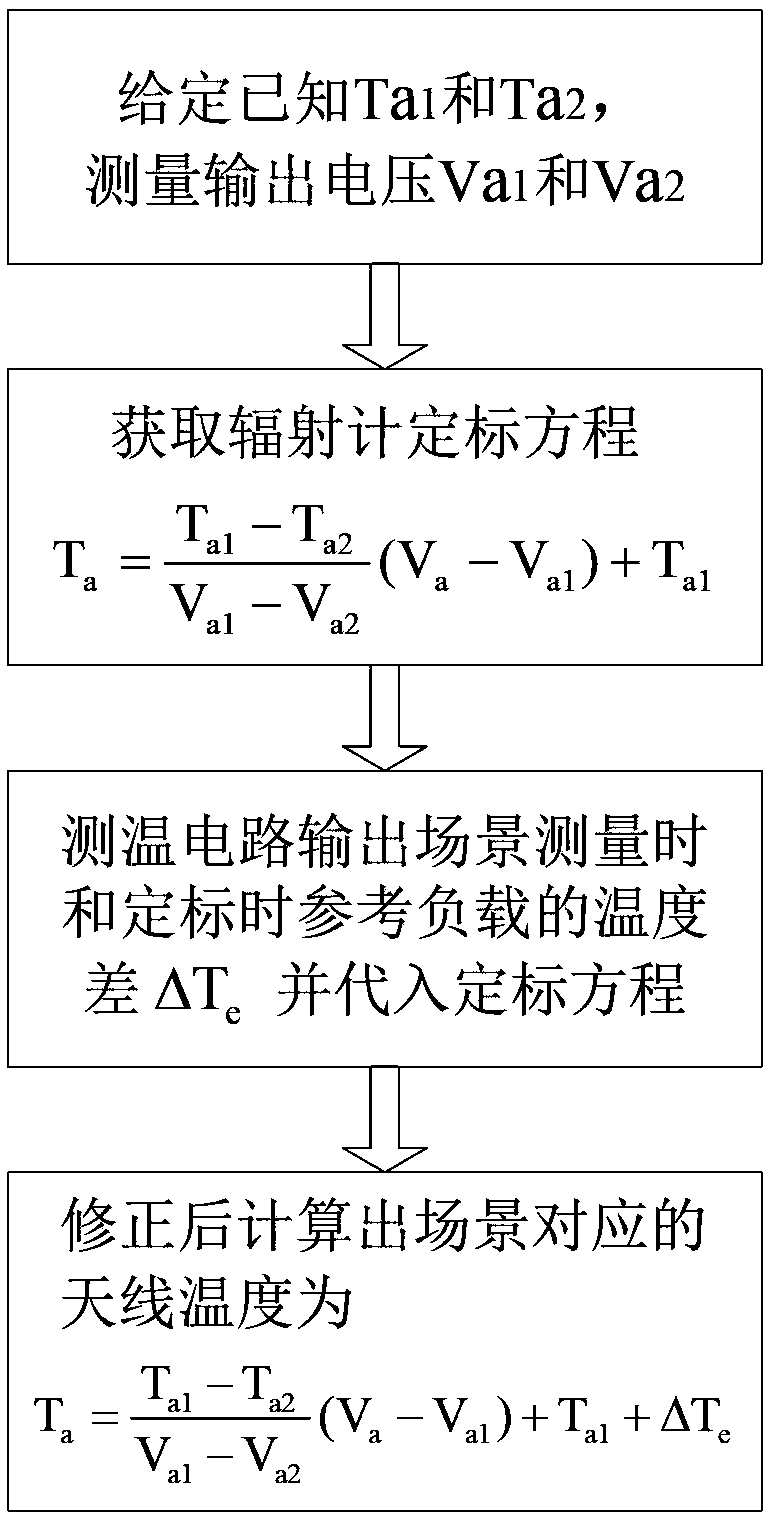

Real-time monitoring microwave dicke radiometer based on reference load temperature

InactiveCN102680803ASimple structureElectromagentic field characteristicsTransmissionLow-pass filterIntermediate frequency

The invention discloses a real-time monitoring microwave dicke radiometer based on a reference load temperature and belongs to the field of microwave passive remote sensing. The radiometer comprises a dicke input switch, wherein a first end of the dicke input switch is sequentially connected with a radio frequency and intermediate frequency amplifying circuit, a square law detector, a low frequency amplifier, a synchronous detector, a low pass filter and a data collecting and processing module, a second end of the dicke input switch is switched between a reference load and an antenna under the driving of a switch signal generator, and a temperature measuring circuit is arranged on the reference load and connected with the data collecting and processing module. The reference load of the microwave dicke radiometer is not required to be kept in a constant temperature state, only the temperature measuring circuit is used for monitoring the temperature changes of the reference load in real time, the monitored variable quantity of the temperature of the reference load is plugged into a radiometer scaling equation for modification, and an antenna temperature of the measured scene is obtained. According to the real-time monitoring microwave dicke radiometer based on the reference load temperature, the measuring accuracy is improved and the structure of the existing microwave dicke radiometers is simplified.

Owner:HUAZHONG UNIV OF SCI & TECH

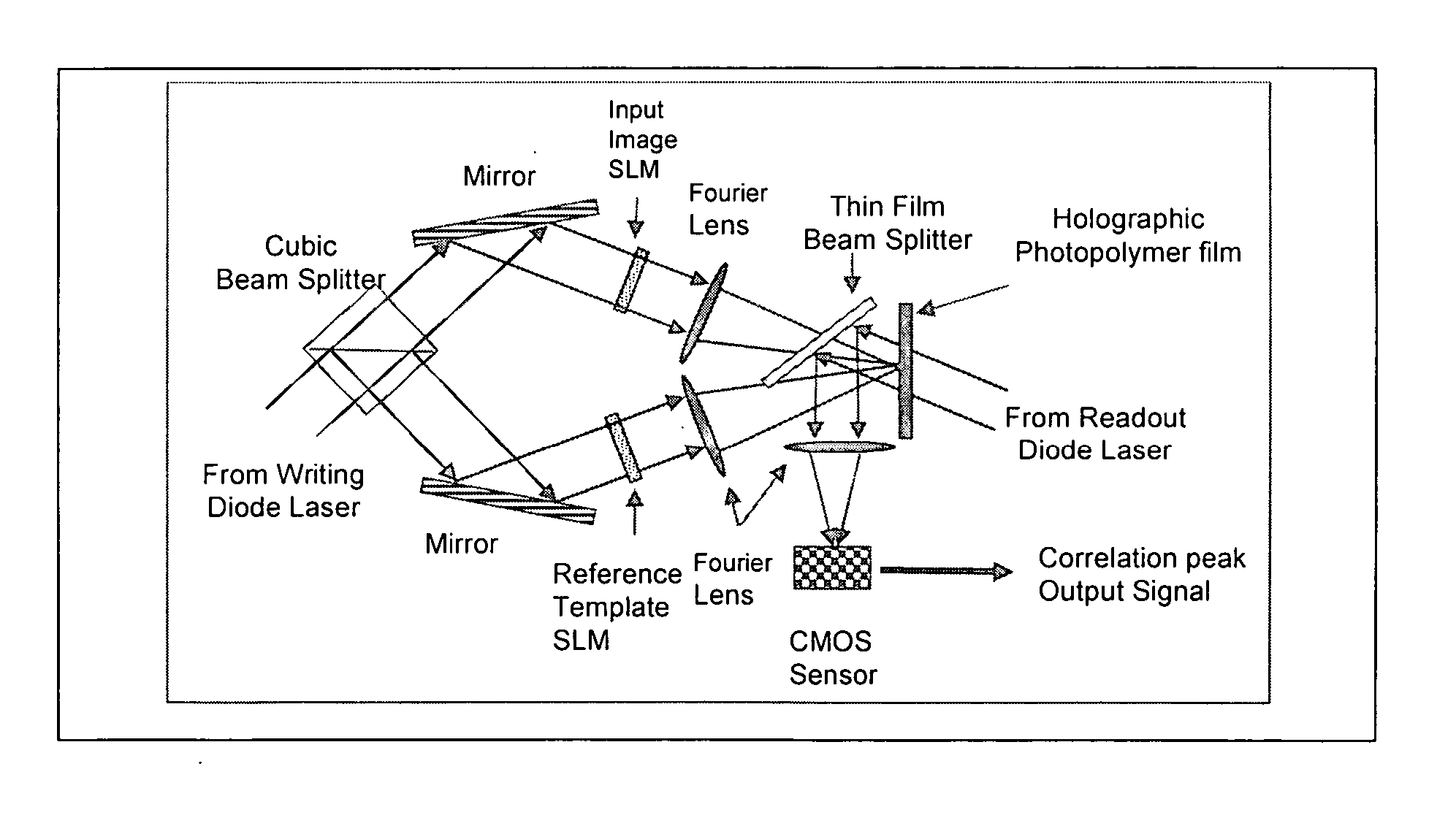

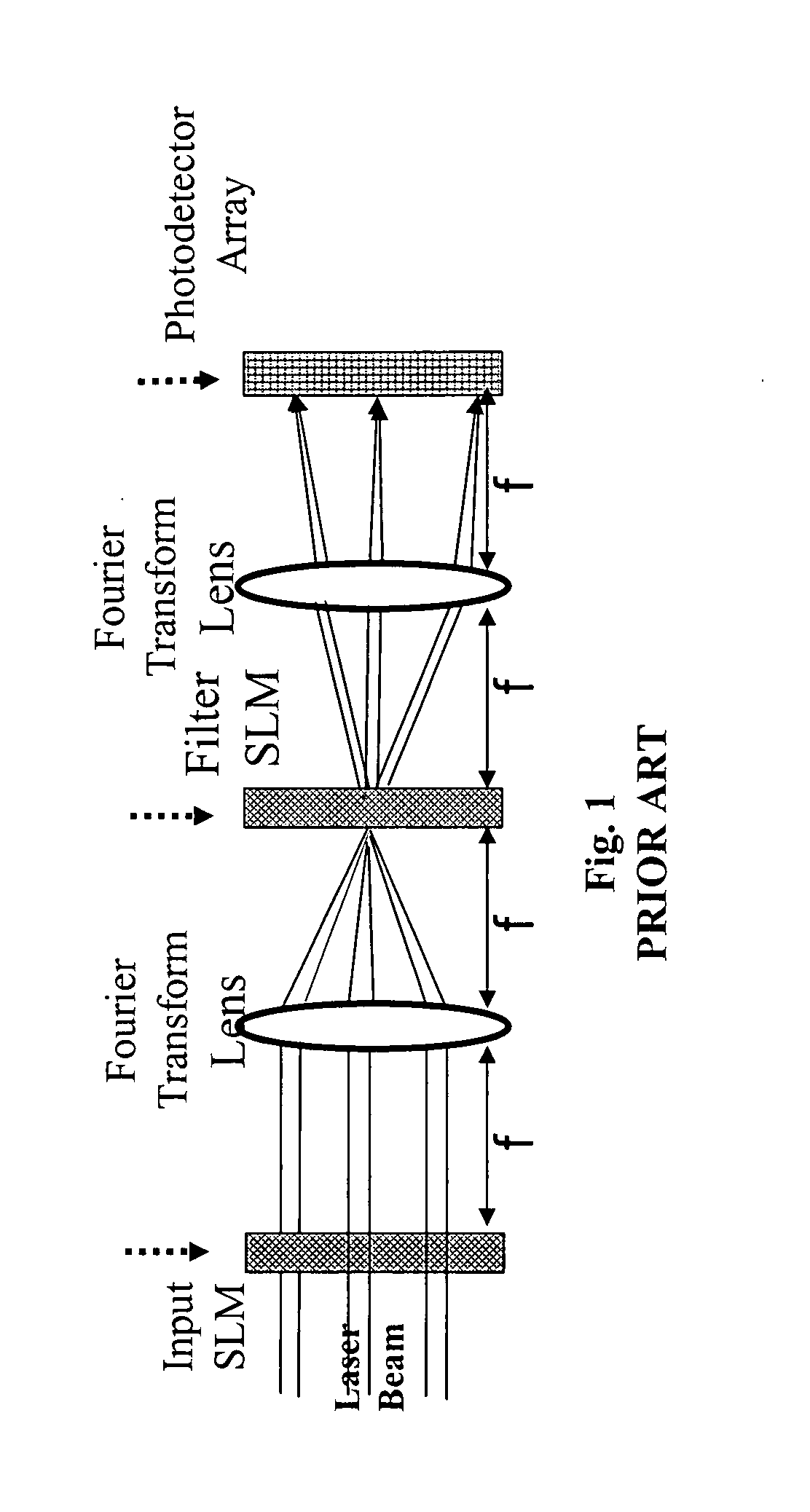

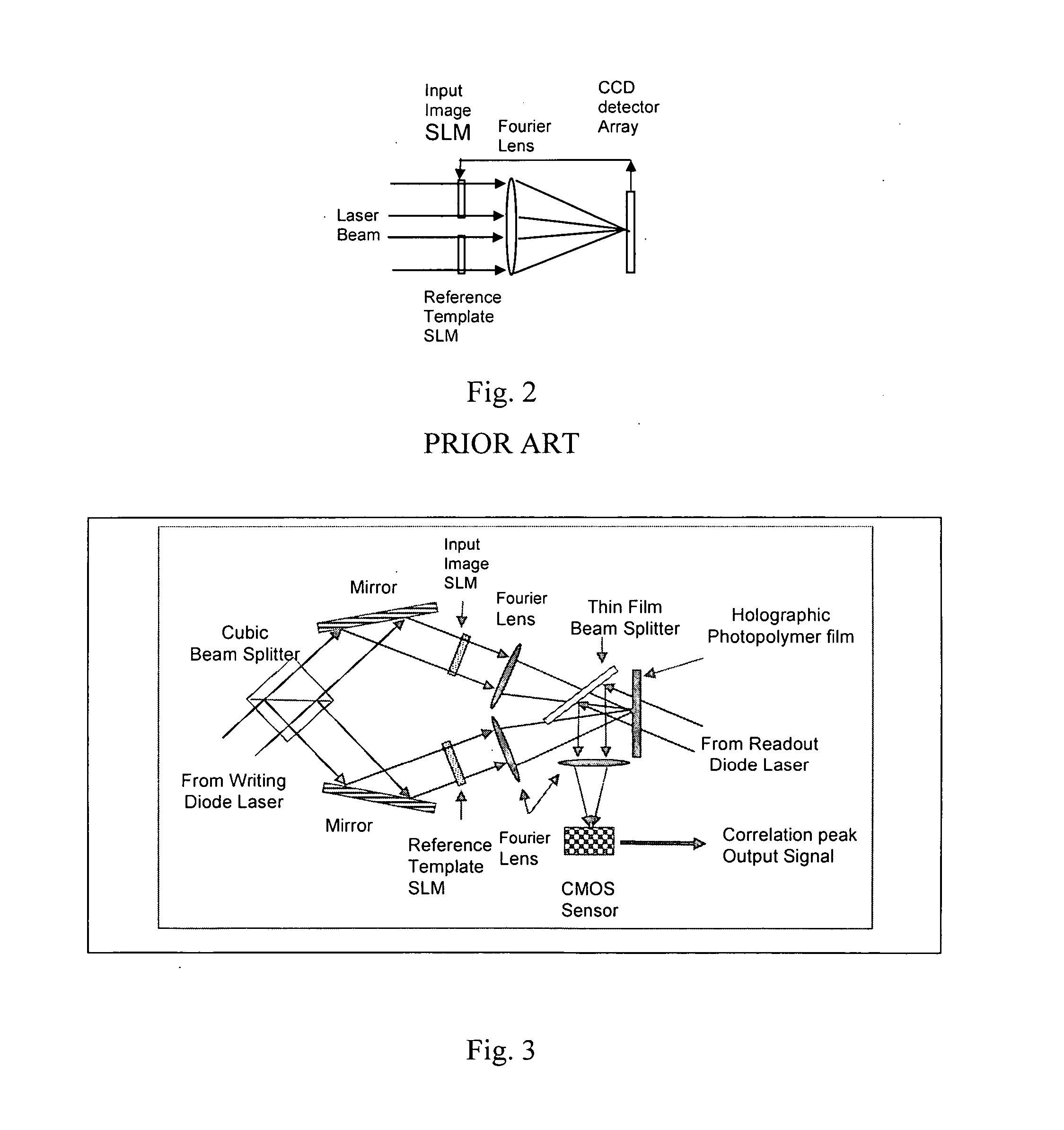

Real-time pattern recognition processor using holographic photopolymer and method of use thereof

InactiveUS20070188838A1Character and pattern recognitionHologram recording materialPattern recognitionPhotopolymer

We have designed, built and operated an innovative JTOC system utilizing a holographic photopolymer as the square law detector to record the holographic data for one-step correlation signal requisition in real time. The resultant high-resolution, high-speed JTOC is useful to perform real-time pattern recognition. An example application that has been demonstrated is fingerprint verification.

Owner:CALIFORNIA INST OF TECH

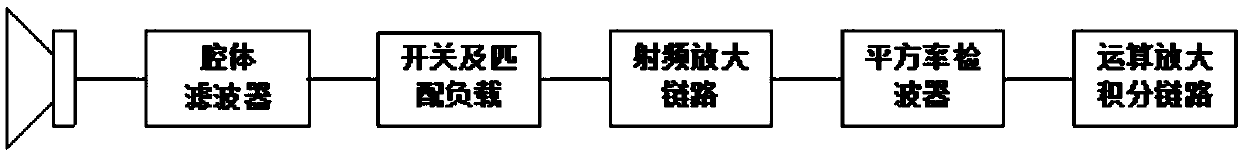

Passive receiving link for active and passive joint detection

ActiveCN109520523AReduce distractionsOut-of-band signal suppressionMeasurement devicesTransmission systemsMicrowaveRadar

The invention discloses a passive receiving link for active and passive joint detection of adjacent frequency bands. The passive receiving link comprises a radiometer feed source, a cavity filter, a single-pole double-throw switch, a load, a radio frequency amplification link, a square-law detector and an integral amplification link, wherein the radiometer feed source is used for receiving a target radiation noise signal; the cavity filter is used for suppressing the radar emission signals of the adjacent frequency bands; the radio frequency amplification link is used for amplifying the noisesignal so as to meet the input requirement of the square-law detector; and the integral amplification link is used for outputting detection and performing amplified integral output. The passive receiving link can be applied to the active and passive integrated microwave detecting instrument system of terrestrial water resource satellites, and can also be widely applied to various adjacent satellite-borne active and passive joint detection systems.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

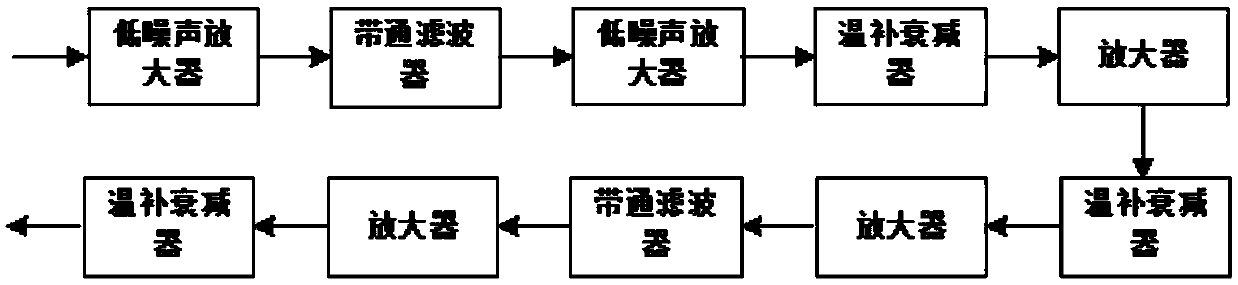

Coherent detector for atmosphere greenhouse gas

PendingCN108593576AHigh spectral resolutionColor/spectral properties measurementsWater vaporRadio frequency

The invention discloses a coherent detector for atmosphere greenhouse gas. The coherent detector comprises a light cylinder, a solar tracking device, a collimation optical telescope, a chopper, a local oscillation laser, an optical fiber combiner, a high-speed photoelectric detector, a square law detector, a radio frequency amplifier, a video frequency amplifier, a locking amplifier and a microprocessor. According to the coherent detector for the atmosphere greenhouse gas, by referring concepts of a wireless heterodyne receiver and coherent detection, only when sunlight radiation components ofwhich wavelength is equal to that of laser output by the local oscillation laser are subjected to coherent detection, signals required by people can be output, and the spectral resolution of a sun photometer is increased. The coherent detector for the atmosphere greenhouse gas has the advantages that the contradiction between the sunlight detectivity and spectral resolution of an original photometer is solved, and the coherent detector is suitable for measurement of column concentration of atmosphere greenhouse gas components such as water vapor, carbon dioxide and methane.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

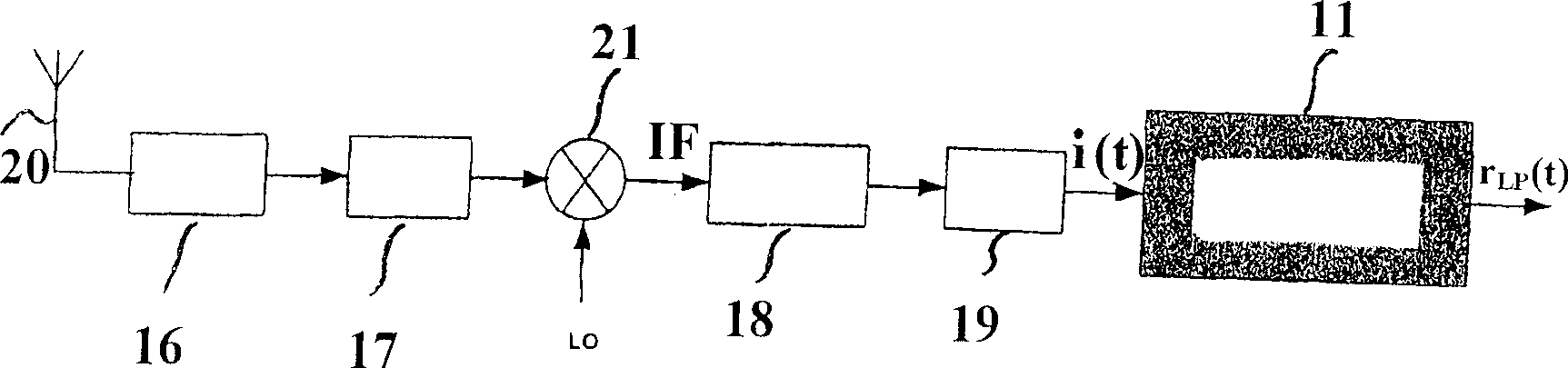

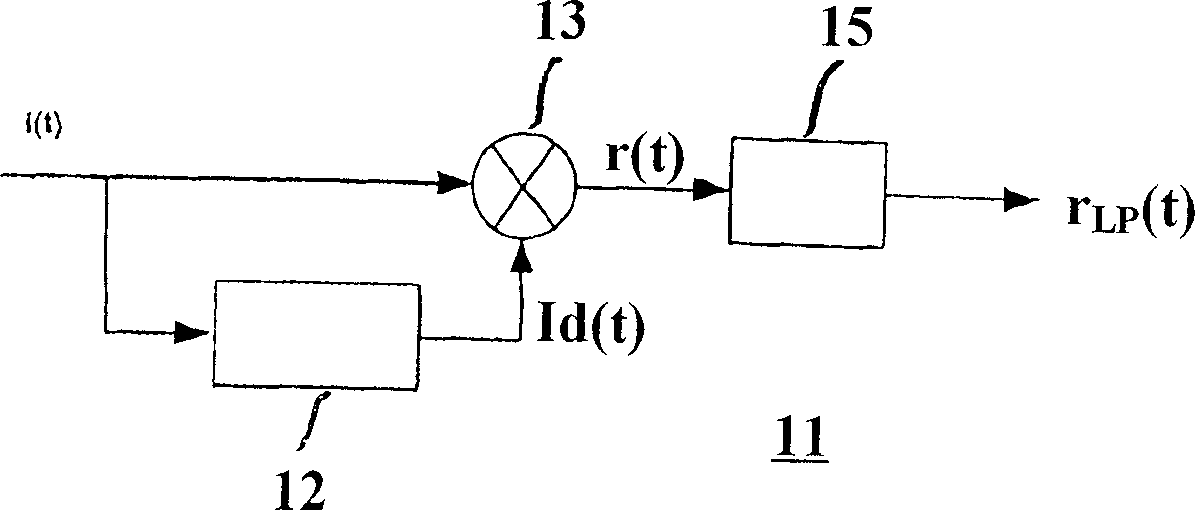

Frequency-shift-keying demodulator and method of frequency-shift-keying

InactiveCN1756245AReduce power consumptionReduce complexityFrequency-modulated carrier systemsLow-pass filterData signal

The present invention relates to a frequency-shift-keying demodulator (1,1') comprising a phase shifter 2 for shifting the phase of an input signal i(t) by a predetermined degree and for outputting a shifted signal Id(t), a combining unit (3, 4; 31, 32, 33, 41, 42) for combining the input signal i(t) and the shifted signal Id(t) output by the phase shifter 2 and for outputting a corresponding signal r(t) and a low-pass filter 5 for filtering the signal r(t) output by the combining unit (3, 4; 31, 32, 33, 41, 42), and for outputting a low-pass filtered signal r LP (t) the bandwidth of said low-pass filter 5 being matched with the bandwidth of a data signal contained in said input signal i(t). According to the present invention said combining unit (3, 4; 31, 32, 33, 41, 42) comprises at least one adder (3; 31, 32) for adding the input signal i(t) and the shifted signal Id(t) output by the phase shifter 2 and for outputting an added signal and at least one square law detector (4; 41, 42) for receiving the added signal output by the adder (3; 31, 32) and for outputting a squared signal r(t) which is the square of the added signal wherein the combining unit (3, 4;31, 32, 33, 41, 42) outputs the squared signal r(t) to the low-pass filter 5. Furthermore, the present invention relates to a method of frequency-shift-keying demodulating an input signal i(t).

Owner:SONY DEUT GMBH

Real-time monitoring microwave dicke radiometer based on reference load temperature

InactiveCN102680803BSimple structureElectromagentic field characteristicsTransmissionIntermediate frequencyLow-pass filter

The invention discloses a real-time monitoring microwave dicke radiometer based on a reference load temperature and belongs to the field of microwave passive remote sensing. The radiometer comprises a dicke input switch, wherein a first end of the dicke input switch is sequentially connected with a radio frequency and intermediate frequency amplifying circuit, a square law detector, a low frequency amplifier, a synchronous detector, a low pass filter and a data collecting and processing module, a second end of the dicke input switch is switched between a reference load and an antenna under the driving of a switch signal generator, and a temperature measuring circuit is arranged on the reference load and connected with the data collecting and processing module. The reference load of the microwave dicke radiometer is not required to be kept in a constant temperature state, only the temperature measuring circuit is used for monitoring the temperature changes of the reference load in real time, the monitored variable quantity of the temperature of the reference load is plugged into a radiometer scaling equation for modification, and an antenna temperature of the measured scene is obtained. According to the real-time monitoring microwave dicke radiometer based on the reference load temperature, the measuring accuracy is improved and the structure of the existing microwave dicke radiometers is simplified.

Owner:HUAZHONG UNIV OF SCI & TECH

Passive millimeter wave imaging system

ActiveCN101644770BHigh resolutionImaging time is shortRadio wave reradiation/reflectionLow-pass filterMillimeter

The invention discloses a passive millimeter wave imaging system and relates to a millimeter wave imaging system. The passive millimeter wave imaging system solves the problems of long imaging time of the system, poor real-time property and low resolution of an obtained image caused by the way of focal plane array imaging of the existing millimeter wave imaging system. A metal reflection plate ofthe passive millimeter wave imaging system reflects electromagnetic waves radiated by a target to be tested onto a receiving antenna by aggregation via a medium lens, the received signals are processed by a millimeter wave band high-gain low-noise amplifier, a high-sensitivity square law detector, a low-pass filter and a low-frequency amplifier in sequence and then collected by a digital collection circuit, and the collected signals are transmitted into a computer for carrying out imaging processing. The passive millimeter wave imaging system is applicable to the field of security.

Owner:HARBIN INST OF TECH

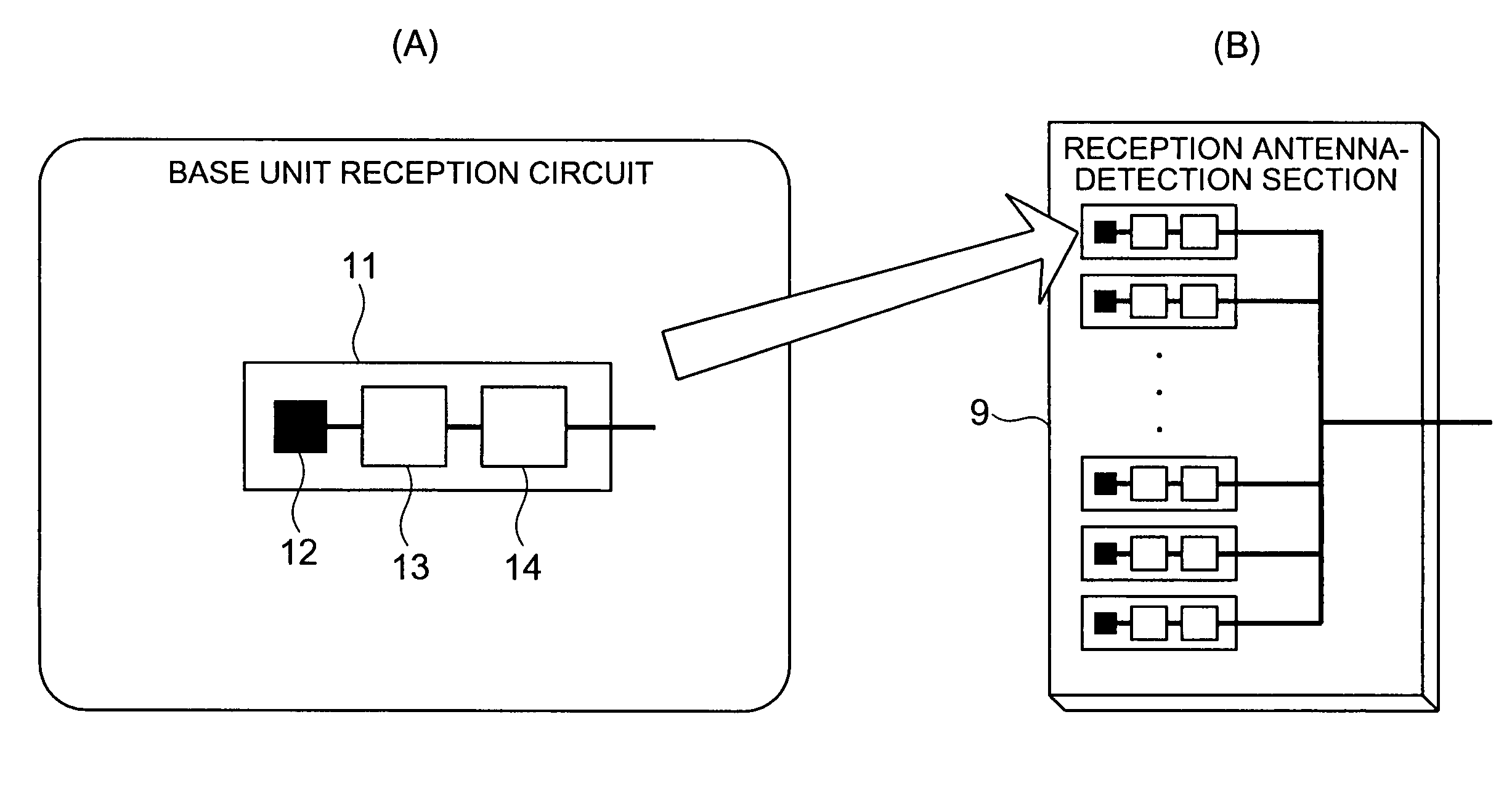

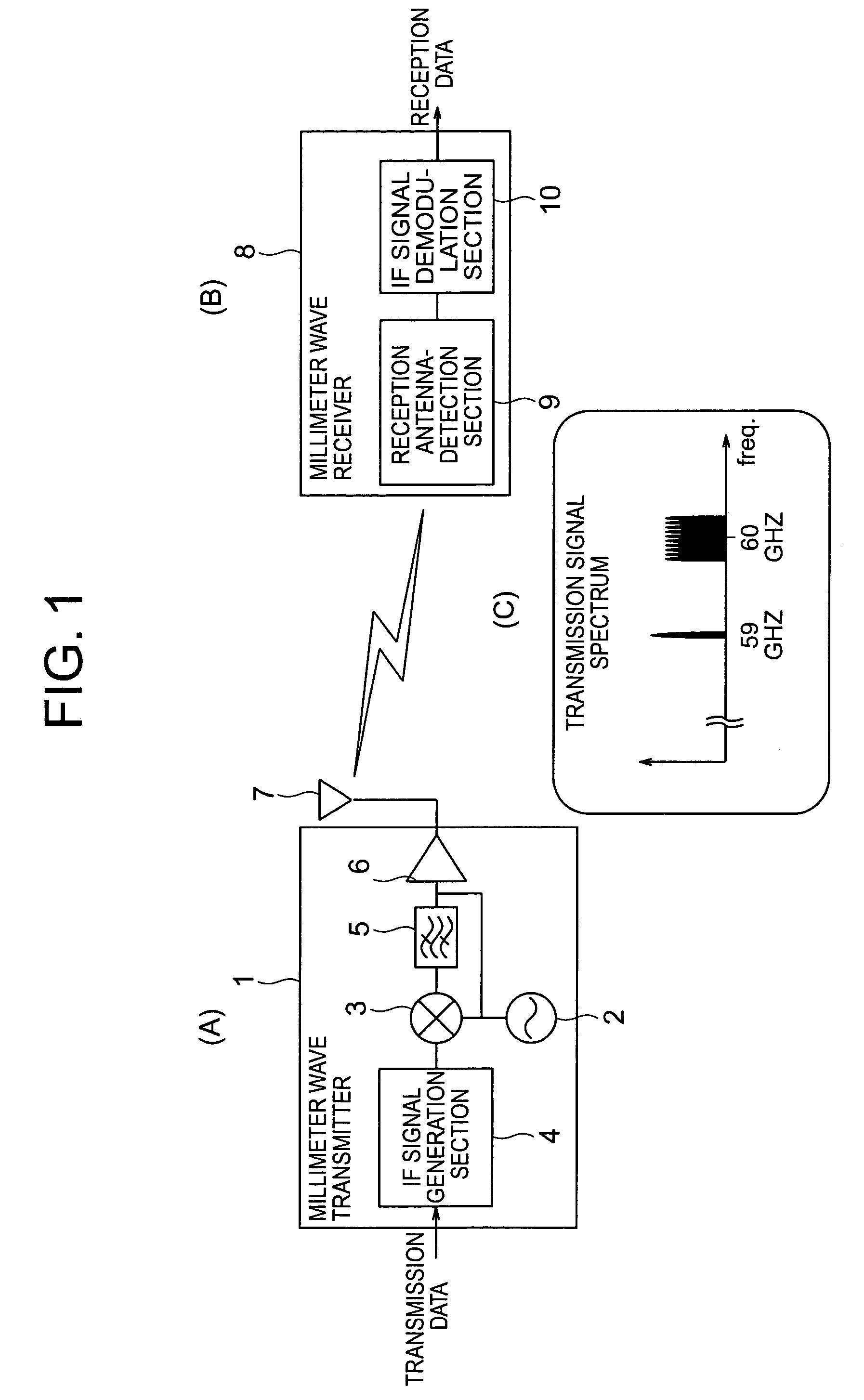

Radio communicate method and system

InactiveUS7292831B2Spatial transmit diversityAntenna supports/mountingsAudio power amplifierWide beam

Owner:NAT INST OF INFORMATION & COMM TECH

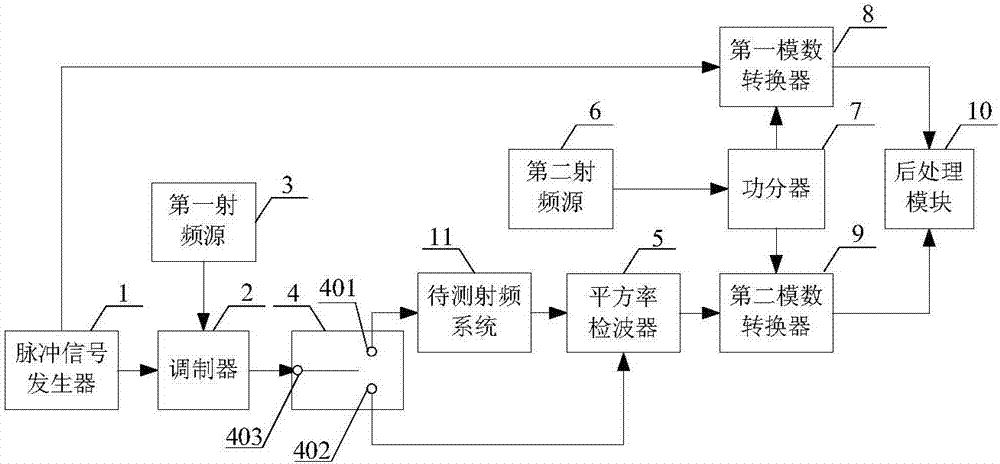

RF system group delay parameter measuring method

InactiveCN103516451ASimple structureAvoid introducing errorsRelay systems monitoringTime delaysCarrier signal

The invention discloses an RF system group delay parameter measuring method which comprises the steps as follows: the moving contact of a single-pole double-throw switch is combined with a first fixed terminal; a first pulse signal is sent to a first analog-digital converter through a pulse signal generator, and a second pulse signal is sent to a modulator through the pulse signal generator; a first carrier signal is sent to the modulator through a first RF source; the second pulse signal is modulated into the first carrier signal through the modulator; a signal with a new time delay is demodulated through a square law detector; a first synchronous sampling clock signal is sent to a power divider through a second RF source, and the first synchronous sampling clock signal from the second RF source is divided into two paths through the power divider. The measuring method utilizes the square law detector to demodulate a modulated signal, so as to avoid the introducing errors and improve the measuring accuracy which is better than 1 ns. The applicable frequency range of the measuring method is 100 MHz-50 GHz.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

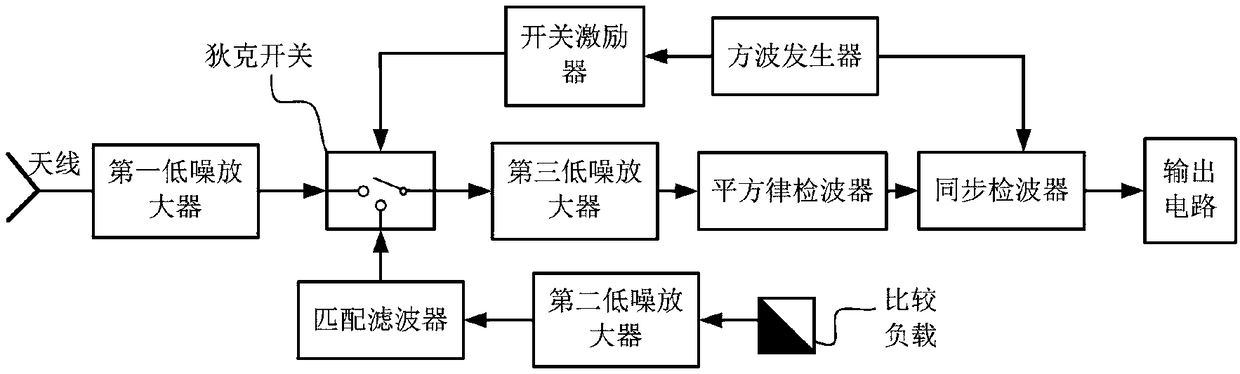

Improved Dick radiometer for detecting stealth plane

InactiveCN108761543AReduce lossHigh sensitivityGeological detection using milimetre wavesOptical detectionAudio power amplifierSquare waveform

The invention discloses an improved Dick radiometer for detecting a stealth plane. The improved Dick radiometer includes an antenna, a first low noise amplifier, a second low noise amplifier, a thirdlow noise amplifier, a comparative load, a matched filter, a Dick switch , a square law detector, a synchronous detector, a square wave generator, a switch actuator and an output circuit. To overcomethe defect that a bandwidth filter in the conventional radiometers loses an antenna signal, the bandwidth filter is removed; and in order to prevent the signal from being overwhelmed by noise due to the interference of the Dick switch, the matched filter is added in a reference channel, the structure of the Dick radiometer is optimized and improved so as to improve the sensitivity.

Owner:NANJING UNIV OF SCI & TECH

Optical subtraction of molecular dispersion signals enabled by differential optical dispersion spectroscopy

Owner:THE TRUSTEES FOR PRINCETON UNIV

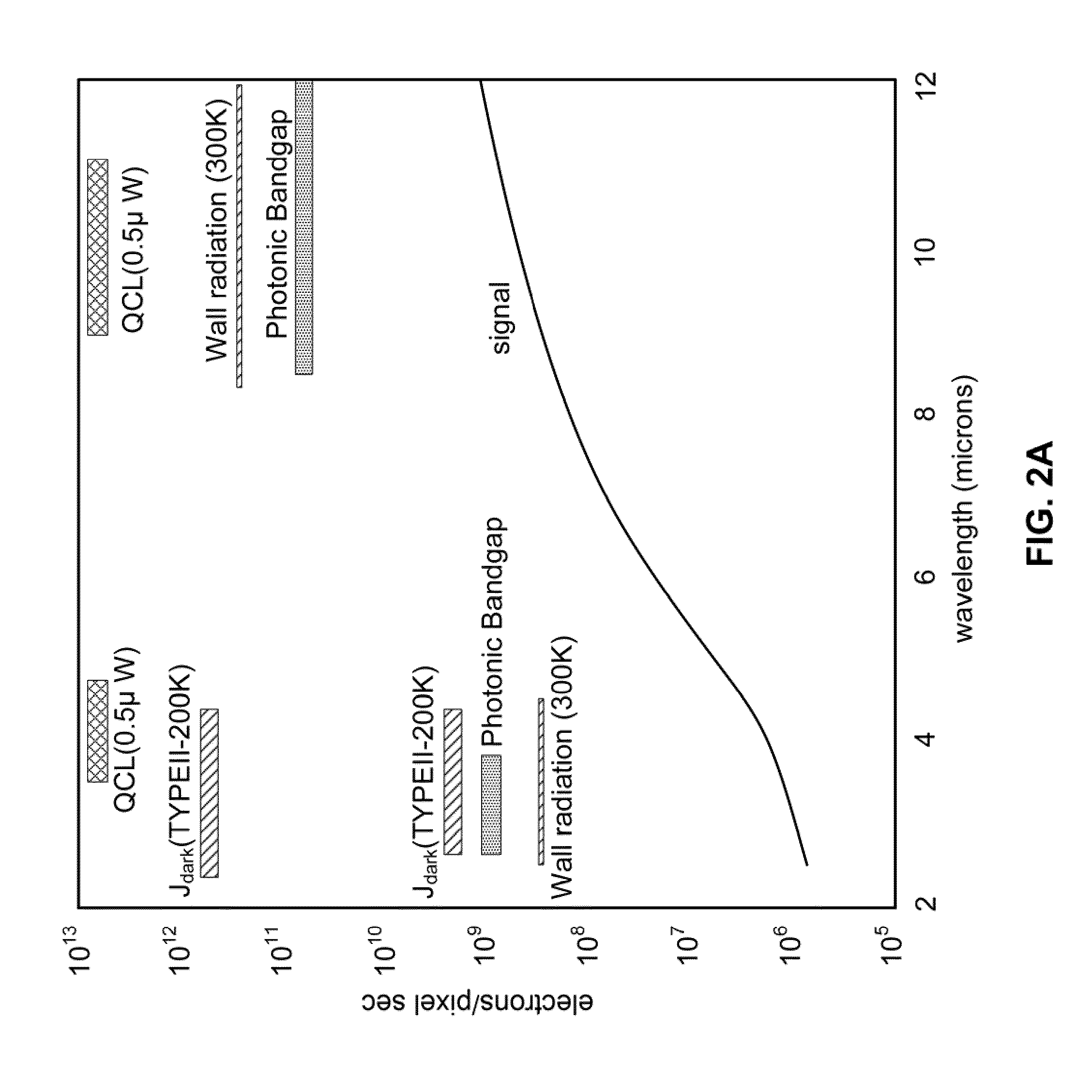

Room-temperature quantum noise limited spectrometry and methods of the same

In one embodiment, a heterodyne detection system for detecting light includes a first input aperture adapted for receiving first light from a scene input, a second input aperture adapted for receiving second light from a local oscillator input, a broadband local oscillator adapted for providing the second light to the second input aperture, a dispersive element adapted for dispersing the first light and the second light, and a final condensing lens coupled to an infrared detector. The final condensing lens is adapted for concentrating incident light from a primary condensing lens onto the infrared detector, and the infrared detector is a square-law detector capable of sensing the frequency difference between the first light and the second light. More systems and methods for detecting light are described according to other embodiments.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

RF system group delay parameter measuring device

InactiveCN103516450ASimple structureHigh measurement accuracyRelay systems monitoringMeasurement deviceComputer module

The invention discloses an RF system group delay parameter measuring device which comprises a pulse signal generator (1), a modulator (2), a first RF source (3), a square law detector (5), a second RF source (6), a power divider (7), a first analog-digital converter (8), a second analog-digital converter (9) and a postprocessing module (10); a single-pole double-throw switch (4) comprises a first fixed terminal (401), a second fixed terminal (402) and a moving contact (403). The measuring device utilizes the square law detector to demodulate a modulated signal, so as to avoid introducing errors, and improve the measurement accuracy which is better than 1 ns. The measuring device utilizes the pulse signal generator to generate a code pattern and code rate controllable pulse signal, so as to enable the apertures and time for measurement of the group delay parameters to be adjustable. The measuring device utilizes the single-pole double-throw switch to realize the switching of a signal channel at the output terminal of the modulator, so that the measuring process is simplified. The applicable frequency range of the measuring device is 100 MHz-50 GHz.

Owner:BEIJING INST OF RADIO METROLOGY & MEASUREMENT

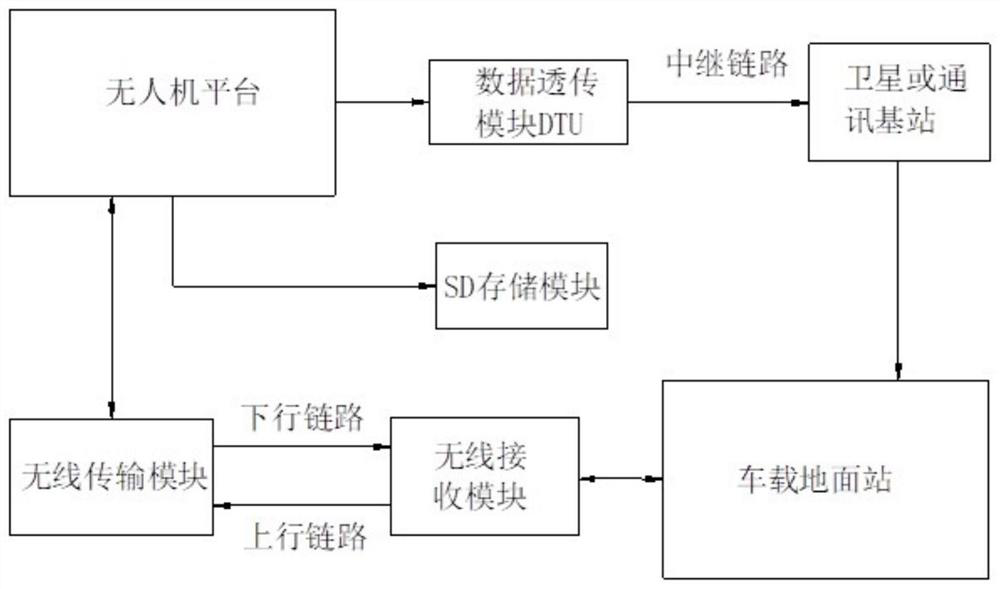

Unmanned aerial vehicle-mounted Ka-band microwave radiometer system

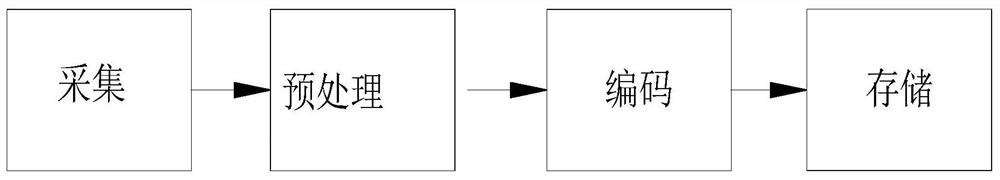

PendingCN112904335AReduce power consumptionReduce volumeRadio wave reradiation/reflectionICT adaptationLow noiseControl cell

The invention discloses an unmanned aerial vehicle-mounted Ka-band microwave radiometer system. The system comprises a Ka wave band antenna, a radio frequency switch, a matching load, a first low noise amplifier, a second low noise amplifier, a band-pass filter, a local oscillator, a frequency mixing circuit, an intermediate frequency amplifier, a variable gain amplifier, a square law detector, a video amplifier, an AD sampling unit, a micro control unit MCU, a temperature measuring unit, an SD storage module, a DA control circuit, a GPS module, a data unvarnished transmission module DTU and a wireless transmission module. Compared with a traditional constant-temperature design, the unmanned aerial vehicle-mounted Ka-band microwave radiometer system adopts a digital gain automatic compensation algorithm and a multi-point temperature correction algorithm, so that a temperature control module and a feedback circuit can be omitted, the power consumption is reduced, and the size and the mass are reduced.

Owner:NORTHEAST INST OF GEOGRAPHY & AGRIECOLOGY C A S

An Adaptive Constant False Alarm Rate Target Detection Method

InactiveCN104502899BAutomatic adjustment of detection thresholdEfficient removalWave based measurement systemsSlide windowRadar

The invention relates to an adaptive constant false alarm rate target detection method, comprising the following steps: 1): inputting data received by a radar into a matched filter; 2): inputting a signal output by a matched filter into a square law processing in the detector; 3): Finally, the signal output from the square law detector is passed to the CFAR detector for processing, and the estimated value Z of the clutter power level generated by the reference unit sampling according to the corresponding CFAR algorithm is obtained; 4): according to 3) Obtained reference unit sampling According to the estimated value Z of the clutter power level generated by the corresponding CFAR algorithm, the CFAR detector outputs the final decision, that is, whether there is a target in the detection unit. According to the statistical mean value x and variance of the sampling values in the reference sliding window, the method deletes the sampling values whose variance is greater than a certain value, replaces the sampling value with the mean value of the remaining effective sampling values, and recalculates the mean value of the sampling values.

Owner:CHANGAN UNIV

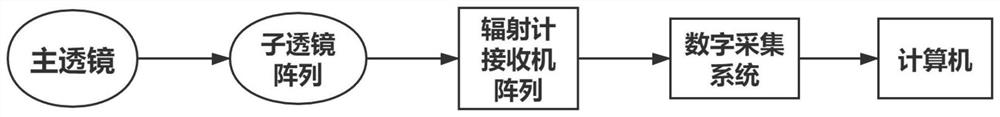

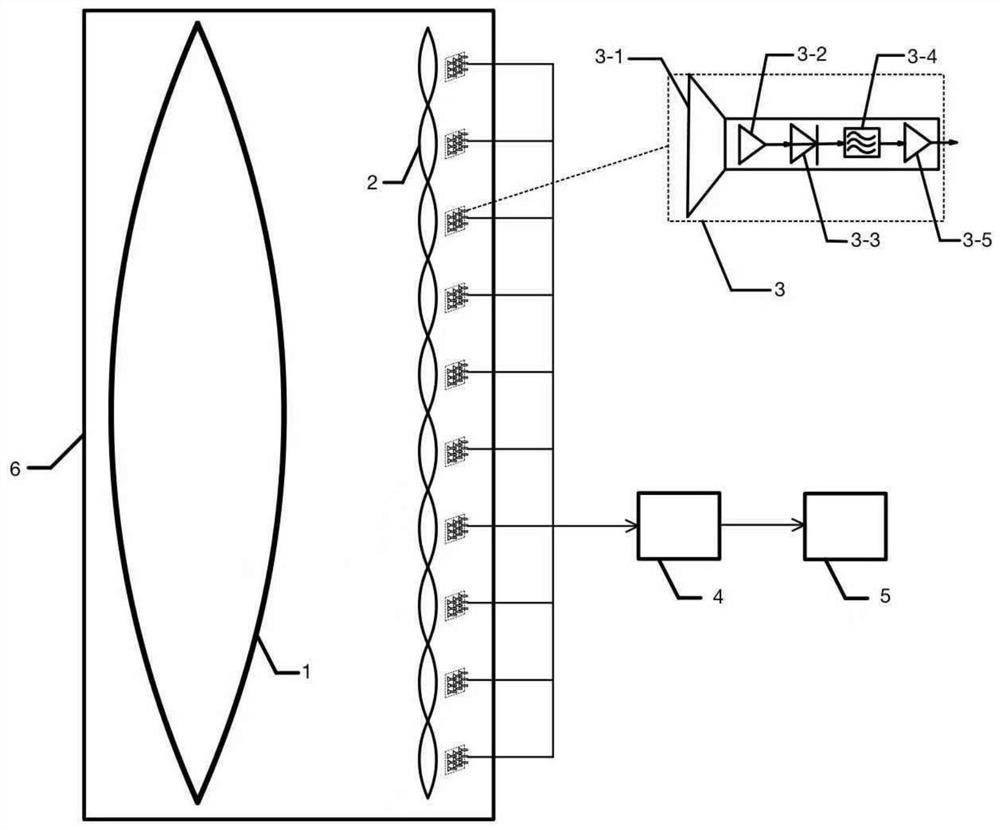

Passive millimeter wave three-dimensional imaging system and imaging method thereof

PendingCN113777605ARealize large depth of field imagingAdapt to the needs of fast and convenient security imagingRadio wave reradiation/reflectionLow-pass filterRadiometer

The invention relates to a passive millimeter wave three-dimensional imaging system and an imaging method thereof. The system comprises a main dielectric lens, a sub dielectric lens array, a radiometer receiver array, a digital acquisition circuit and a computer; electromagnetic waves radiated by an object in a field are converged to a sub-lens array plane through the main dielectric lens and then are focused to a radiometer receiver array plane through different sub-lenses, a receiving antenna on a radiometer receiver array receives the electromagnetic waves, signals are sequentially output to a millimeter wave band low noise amplifier, a high-sensitivity square law detector, a low-pass filter, and alow-frequency amplifier; and the output end of the low-frequency amplifier is connected with the input end of the digital acquisition circuit, and the digital acquisition circuit transmits sampling signals to the computer for data processing.

Owner:HARBIN INST OF TECH

Phase response calibration method of nonlinear vector network analyzer based on fine frequency grid calibration

InactiveCN102087346BAchieving Phase AlignmentPhase calibration with high frequency resolutionResistance/reactance/impedencePhase responseImage resolution

The invention relates to a nonlinear vector network analyzer calibration method, in particular relating to a phase response calibration method of a nonlinear vector network analyzer based on fine frequency grid calibration. The method provided by the invention can be used for the problem that the existing phase response calibration method of a nonlinear network analyzer has low phase calibration frequency resolution. The method comprises: constructing an amplitude modulation signal xAM(t); constructing a fine frequency grid on both sides of a carrier frequency fc; calibrating the phase of a square law detector by use of the fine frequency grid to obtain the phase transmission standard of the fine frequency grid; and carrying out fine frequency phase calibration of the nonlinear vector network analyzer by use of the phase transmission standard of the fine frequency grid. The method is applicable to the phase calibration of the nonlinear vector network analyzer.

Owner:HARBIN INST OF TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com