Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

132 results about "Nanowire transistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

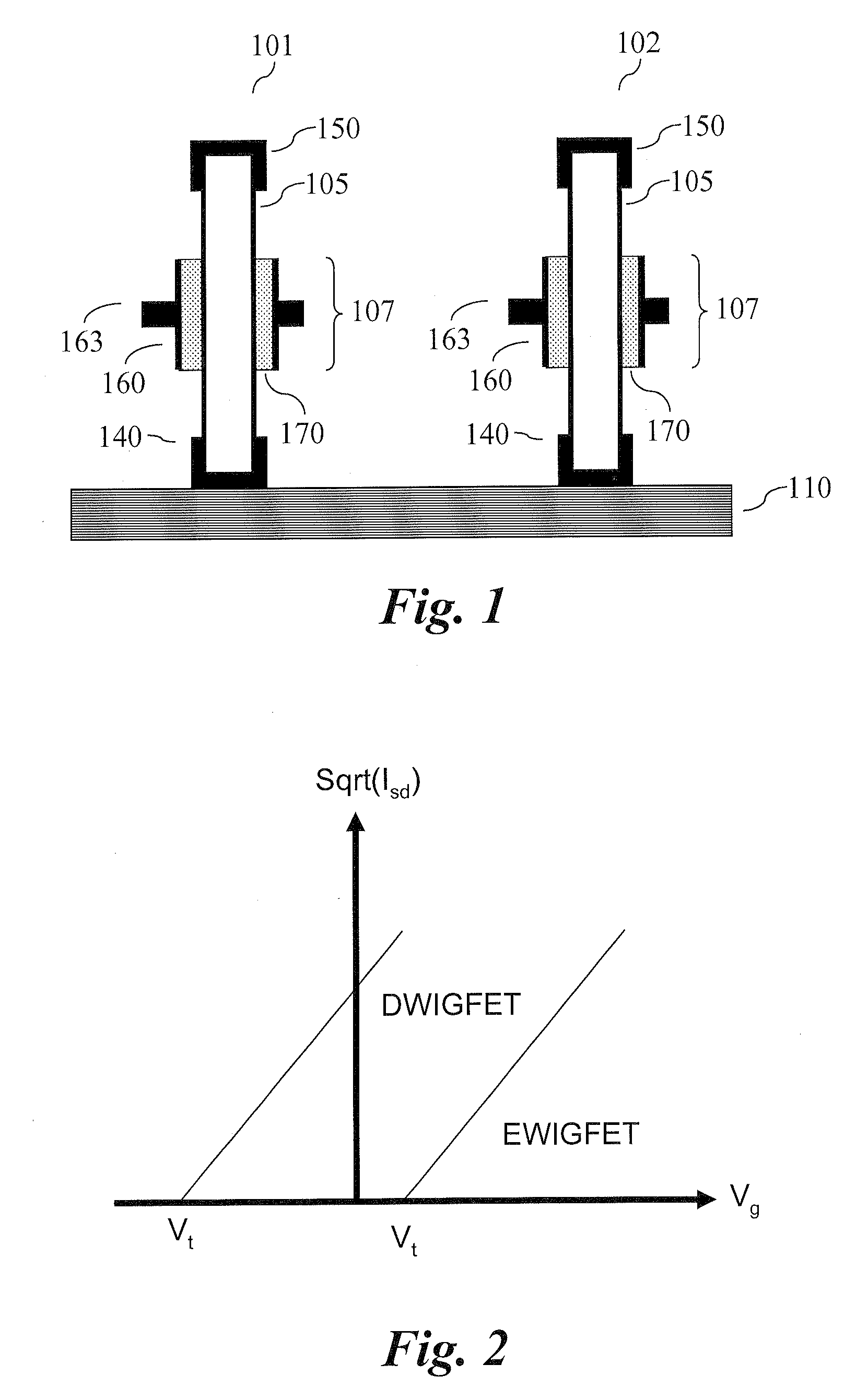

Assembly of nanoscaled field effect transistors

InactiveUS8063450B2Improve critical high-frequency performanceReduce resistanceTransistorNanoinformaticsNanowireWork function

Owner:QUNANO

Assembly of nanoscaled field effect transistors

InactiveUS20100176459A1Improve critical high-frequency performanceReduce resistanceTransistorNanoinformaticsNanowireWork function

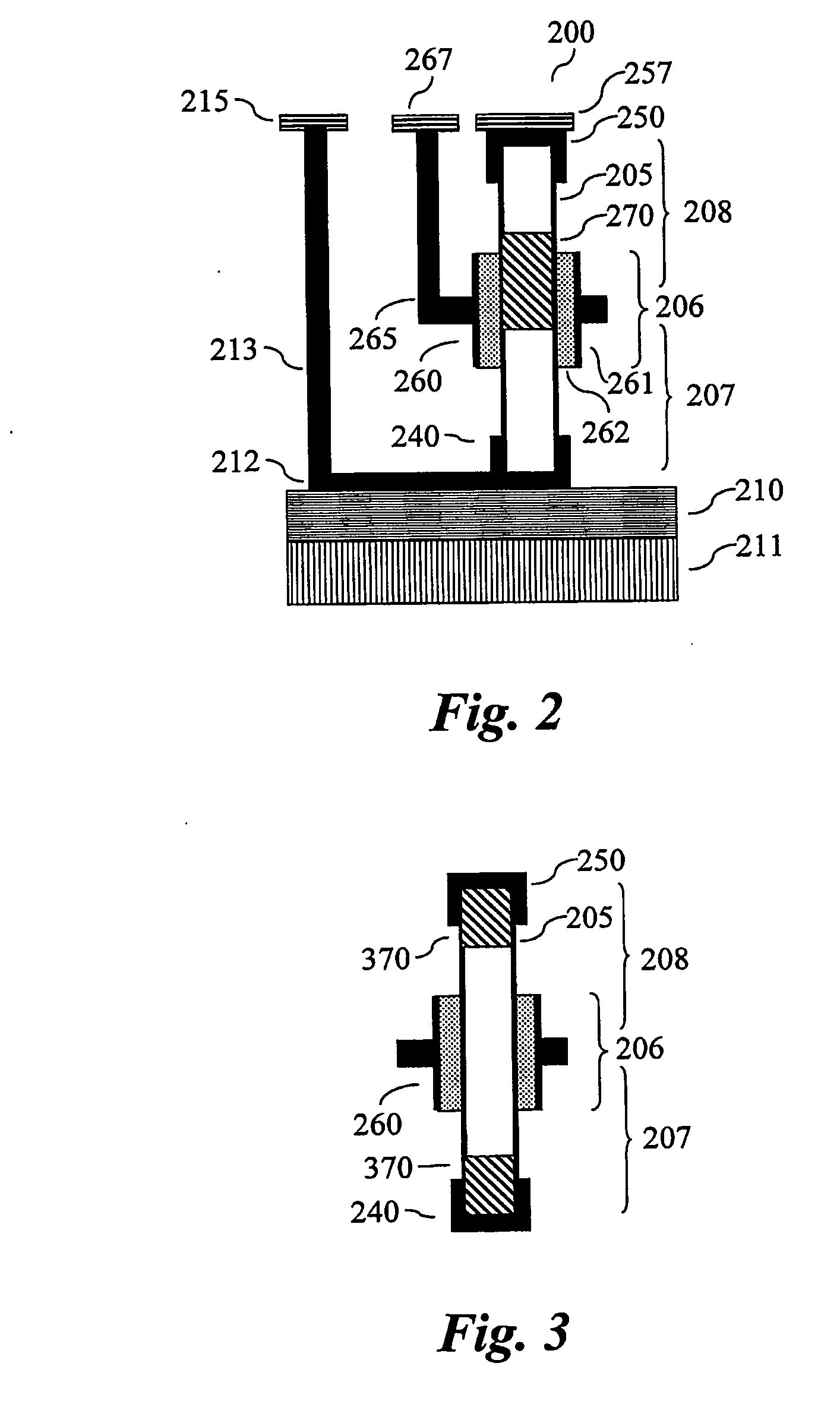

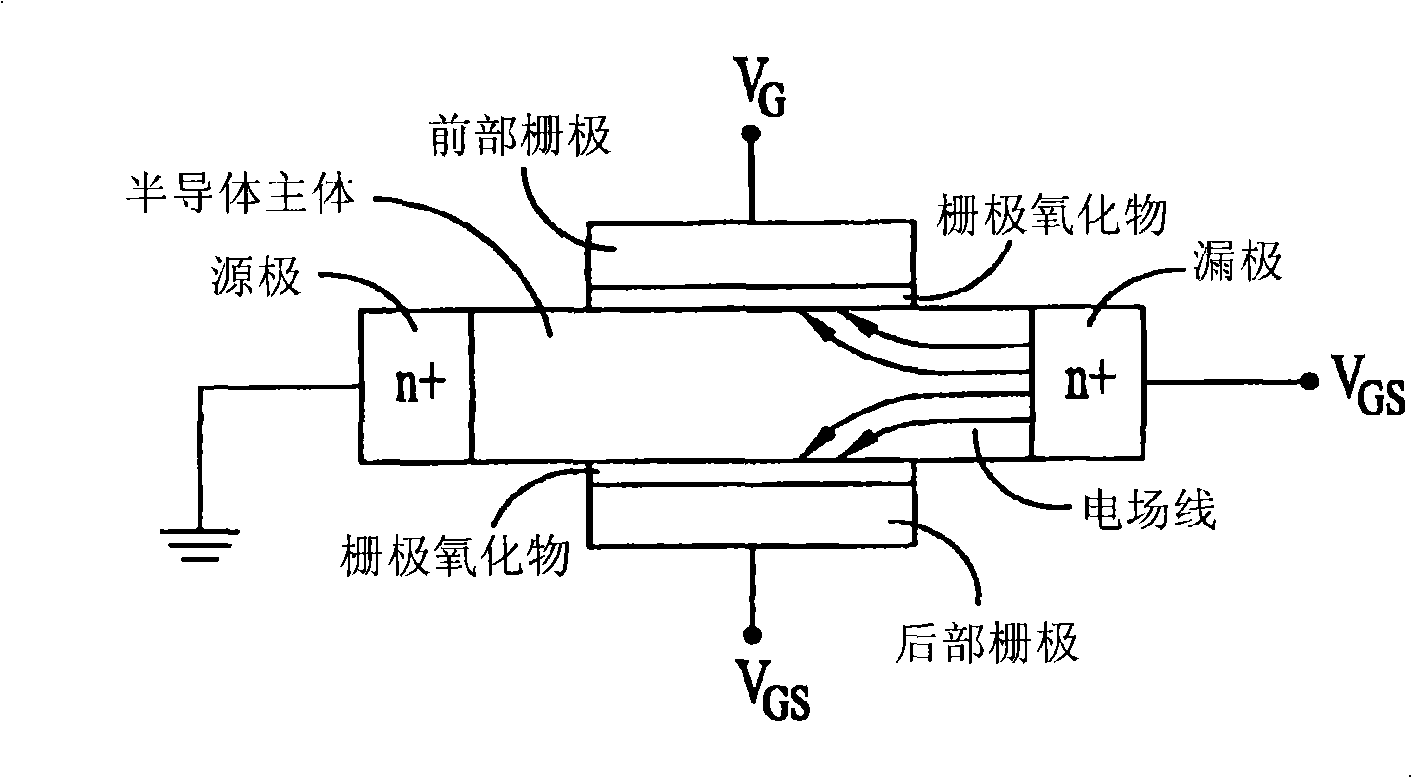

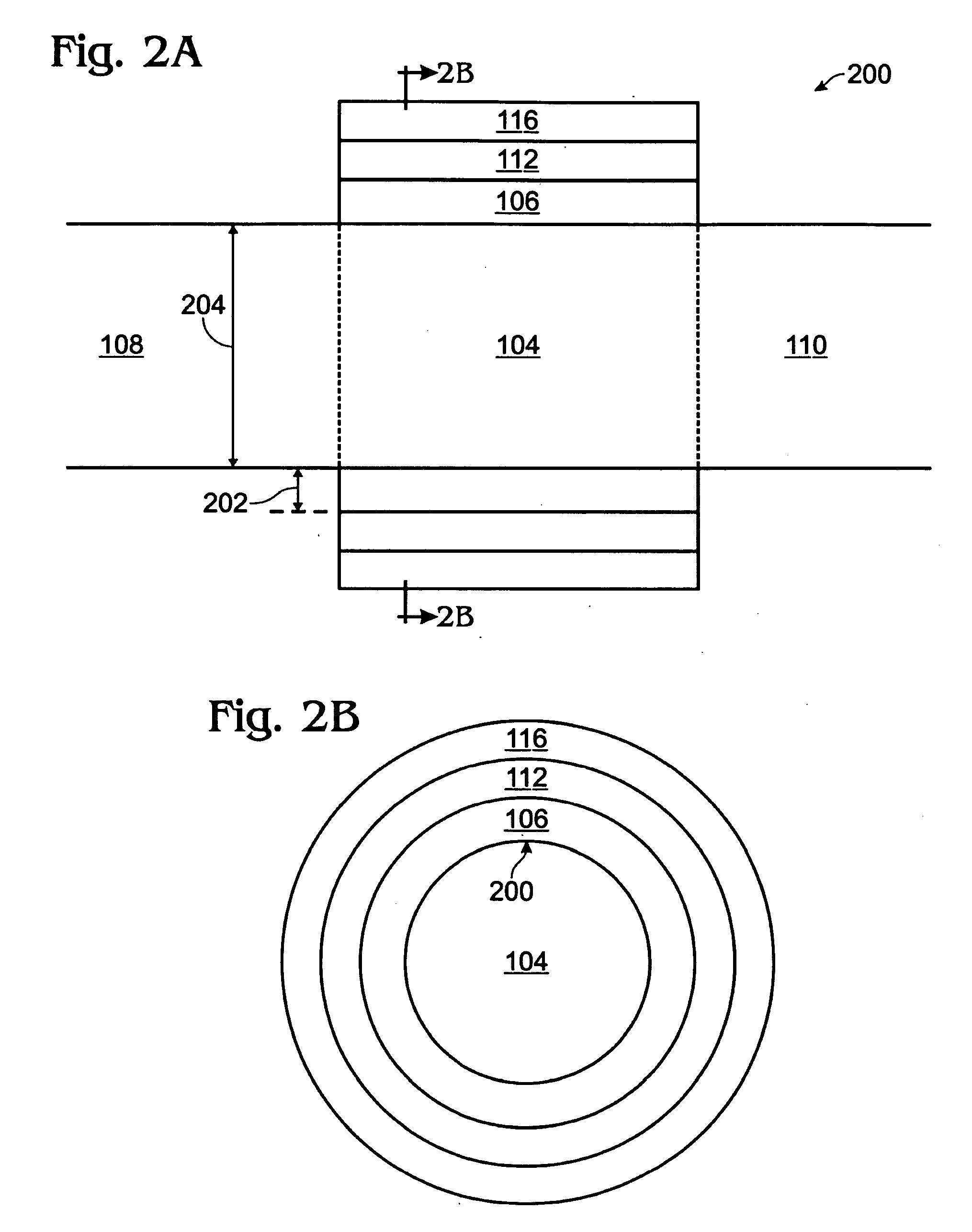

The present invention relates to vertical nanowire transistors with a wrap-gated geometry. The threshold voltage of the vertical nanowire transistors is controlled by the diameter of the nanowire, the doping of the nanowire, the introduction of segments of heterostructures in the nanowire, the doping in shell-structures surrounding the nanowire, tailoring the work function of the gate stack, by strain engineering, by control of the dielectrica or the choice of nanowire material. Transistors with varying threshold voltages are provided on the same substrate, which enables the design of advanced circuits utilizing the shifts in the threshold voltages, similar to the directly coupled field logic.

Owner:QUNANO

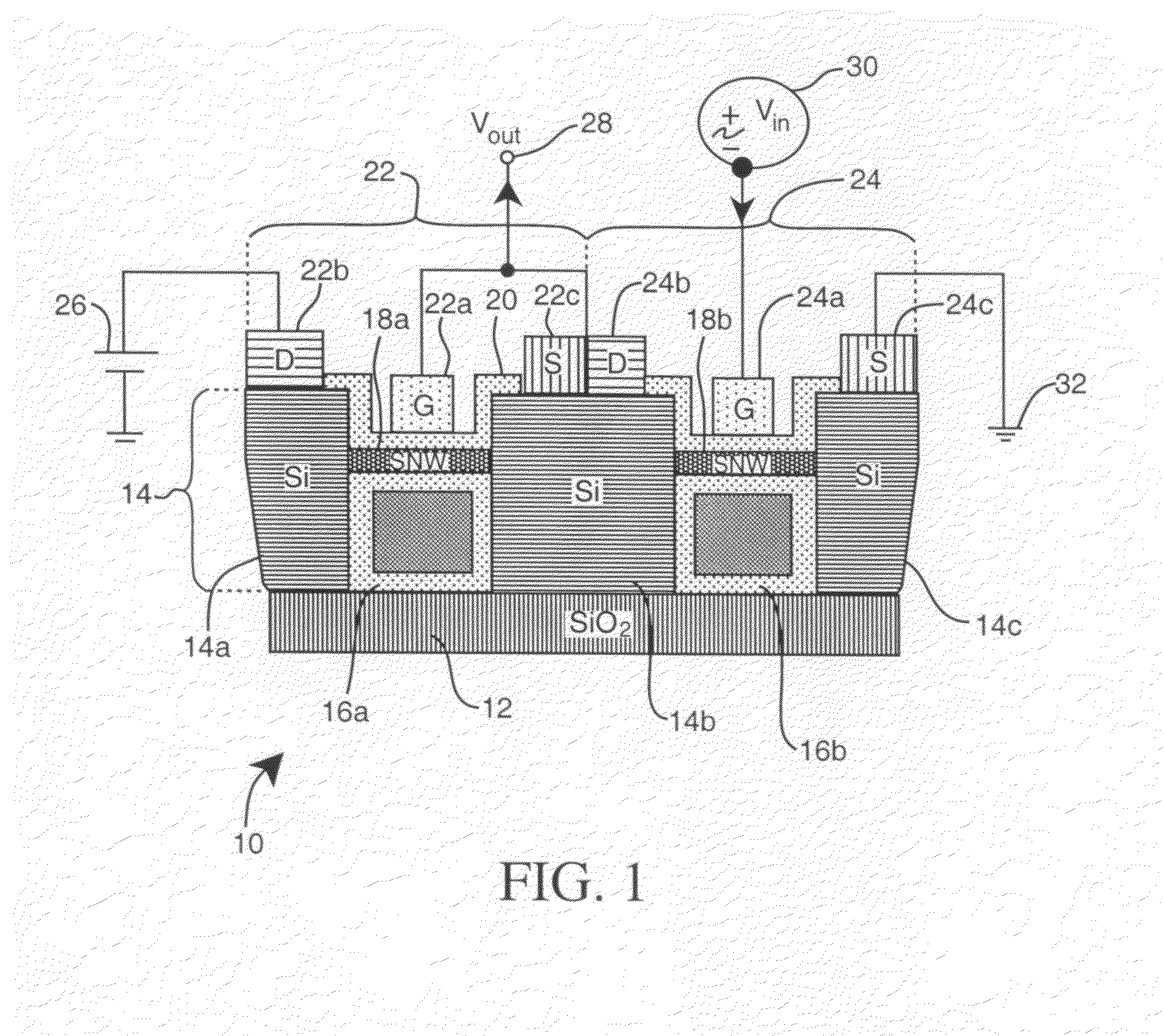

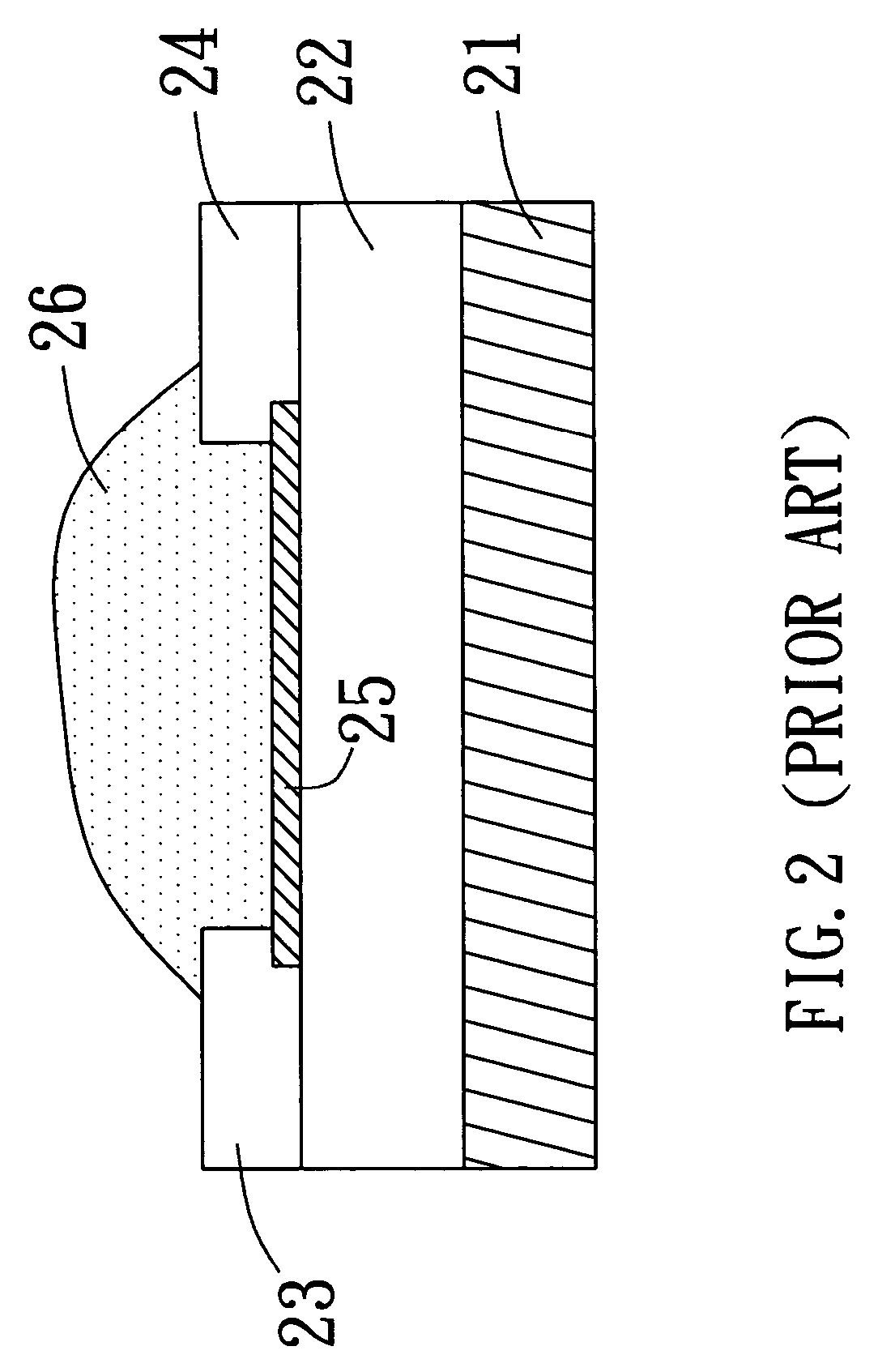

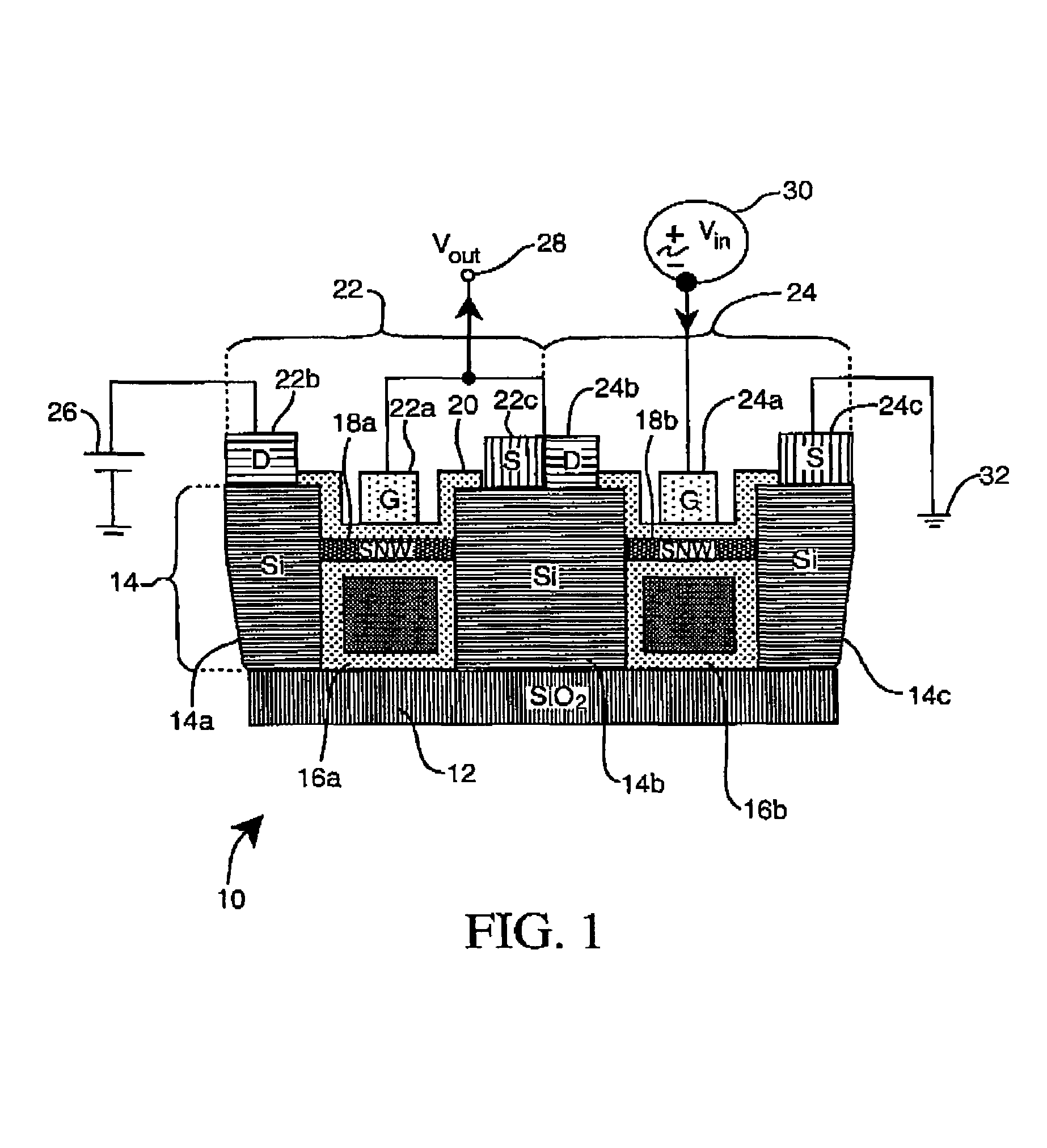

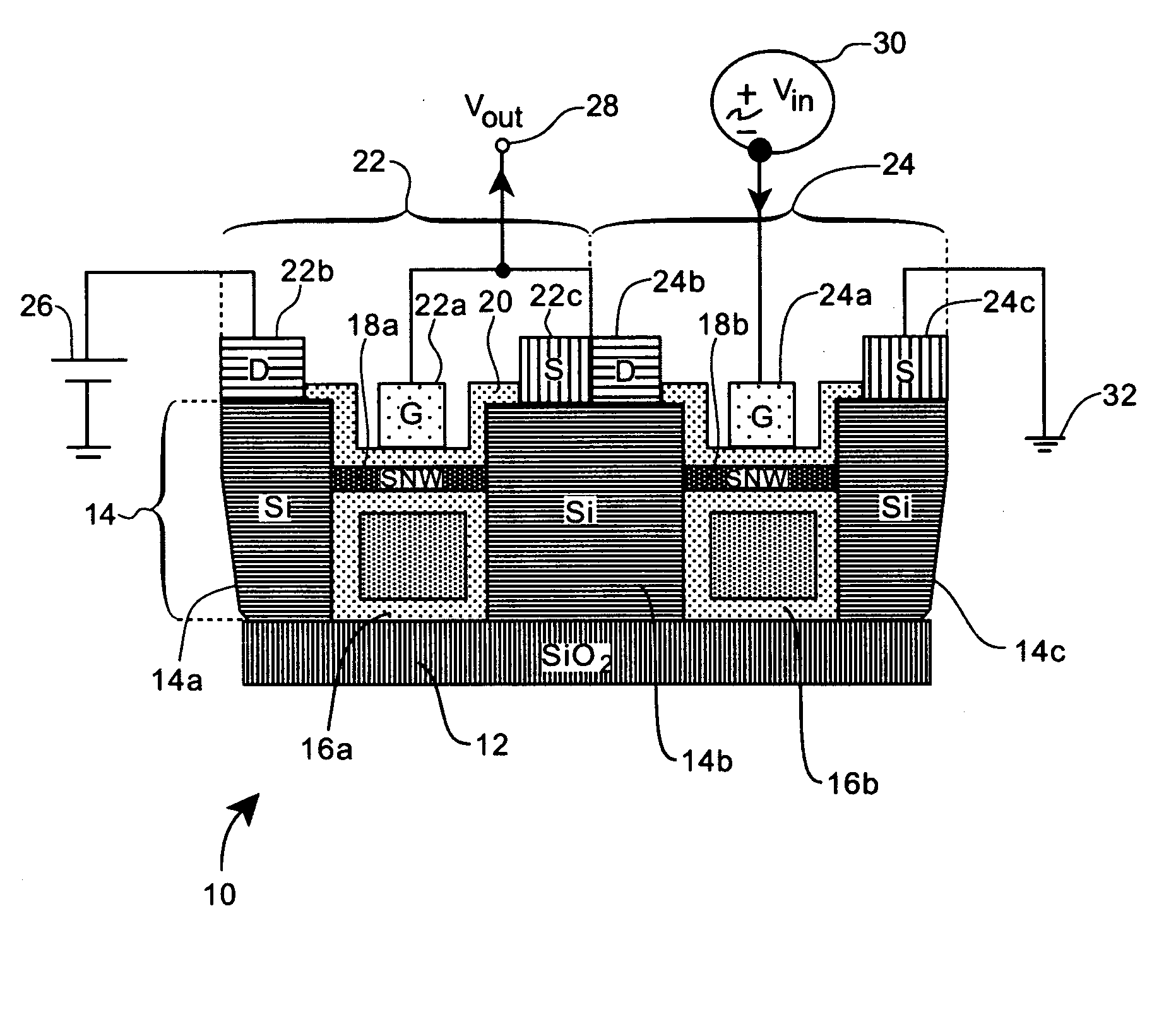

Insulated gate silicon nanowire transistor and method of manufacture

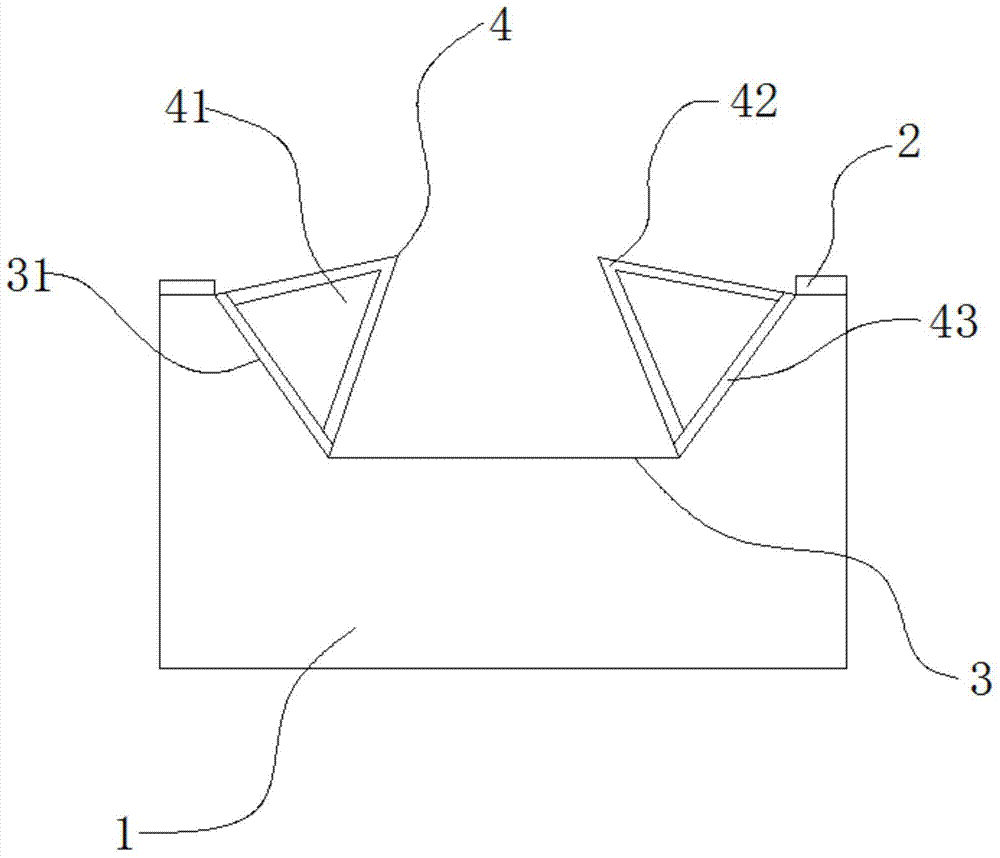

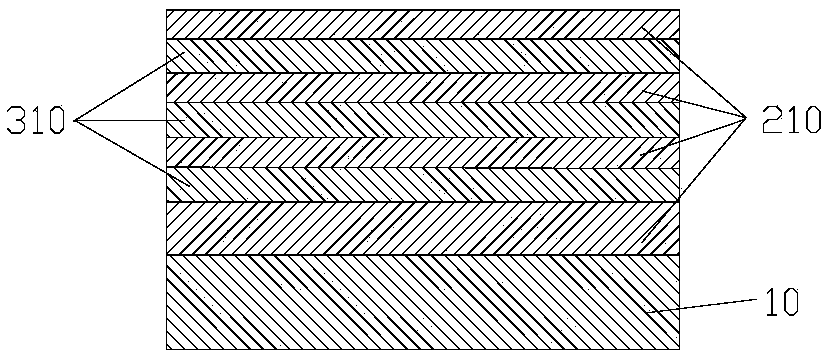

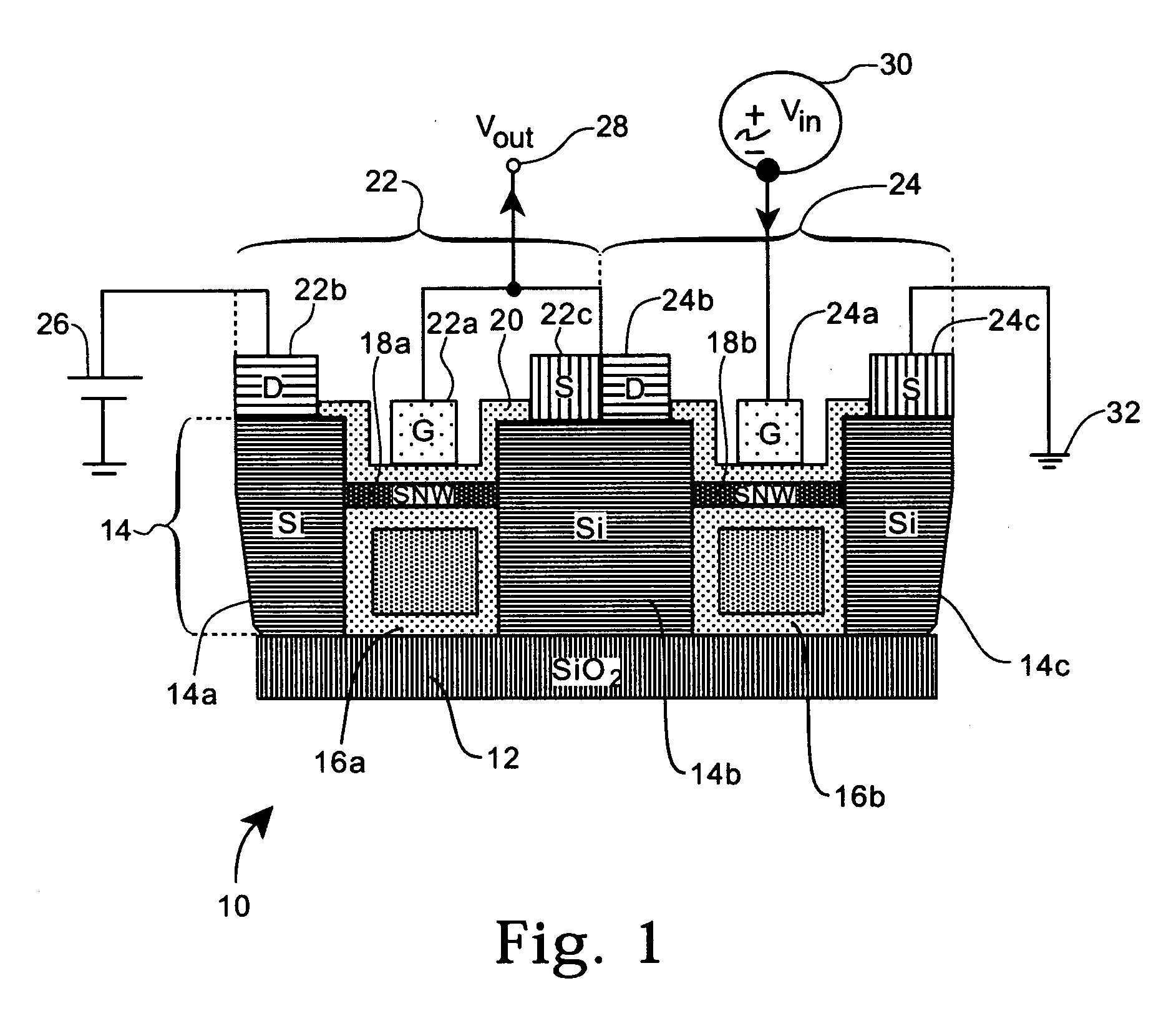

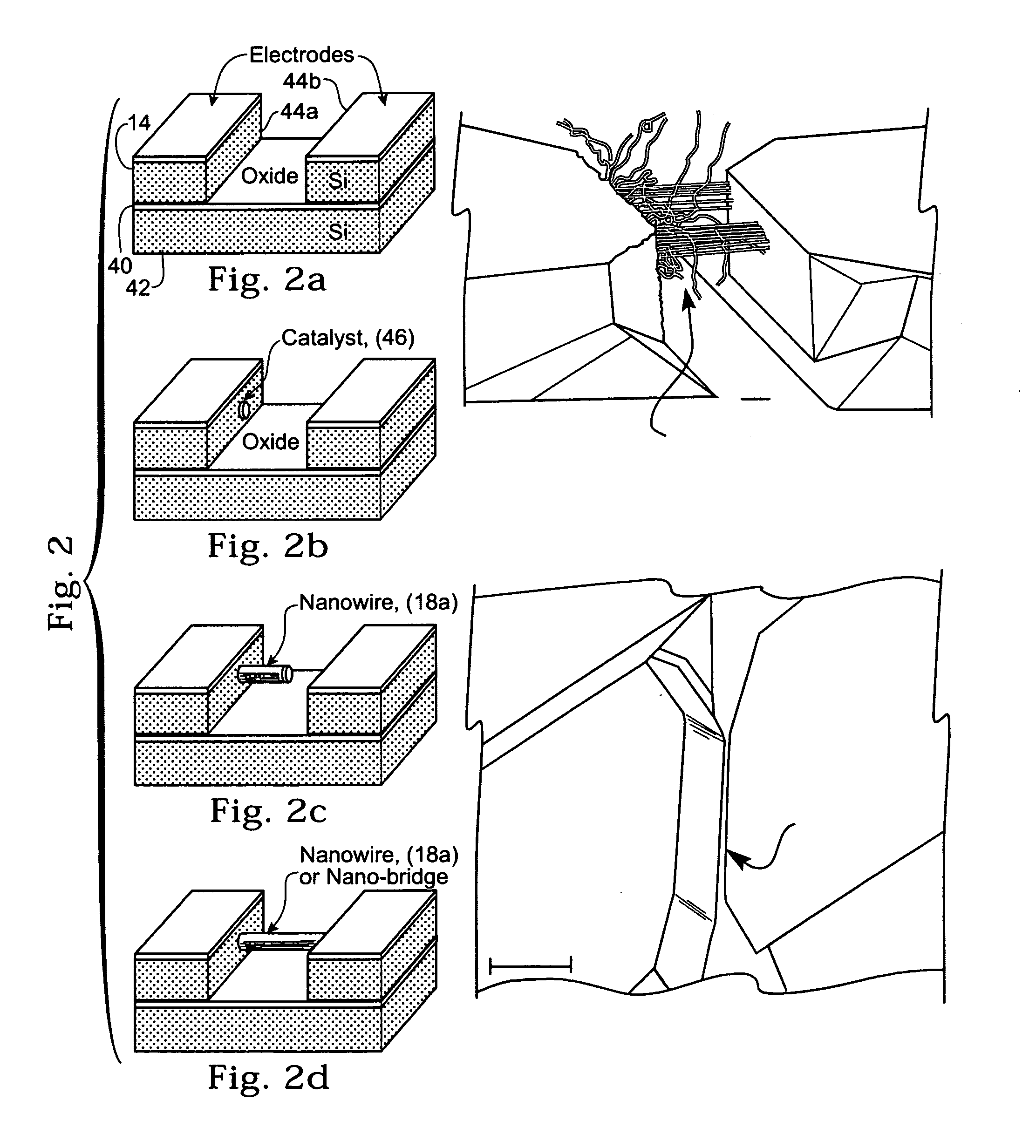

An insulated gate silicon nanowire transistor amplifier structure is provided and includes a substrate formed of dielectric material. A patterned silicon material may be disposed on the substrate and includes at least first, second and third electrodes uniformly spaced on the substrate by first and second trenches. A first nanowire formed in the first trench operates to electrically couple the first and second electrodes. A second nanowire formed in the second trench operates to electrically couple the second and third electrodes. First drain and first source contacts may be respectively disposed on the first and second electrodes and a first gate contact may be disposed to be capacitively coupled to the first nanowire. Similarly, second drain and second source contacts may be respectively disposed on the second and third electrodes and a second gate contact may be disposed to be capacitively coupled to the second nanowire.

Owner:THE UNITED STATES OF AMERICA AS REPRESETNED BY THE SEC OF THE AIR FORCE

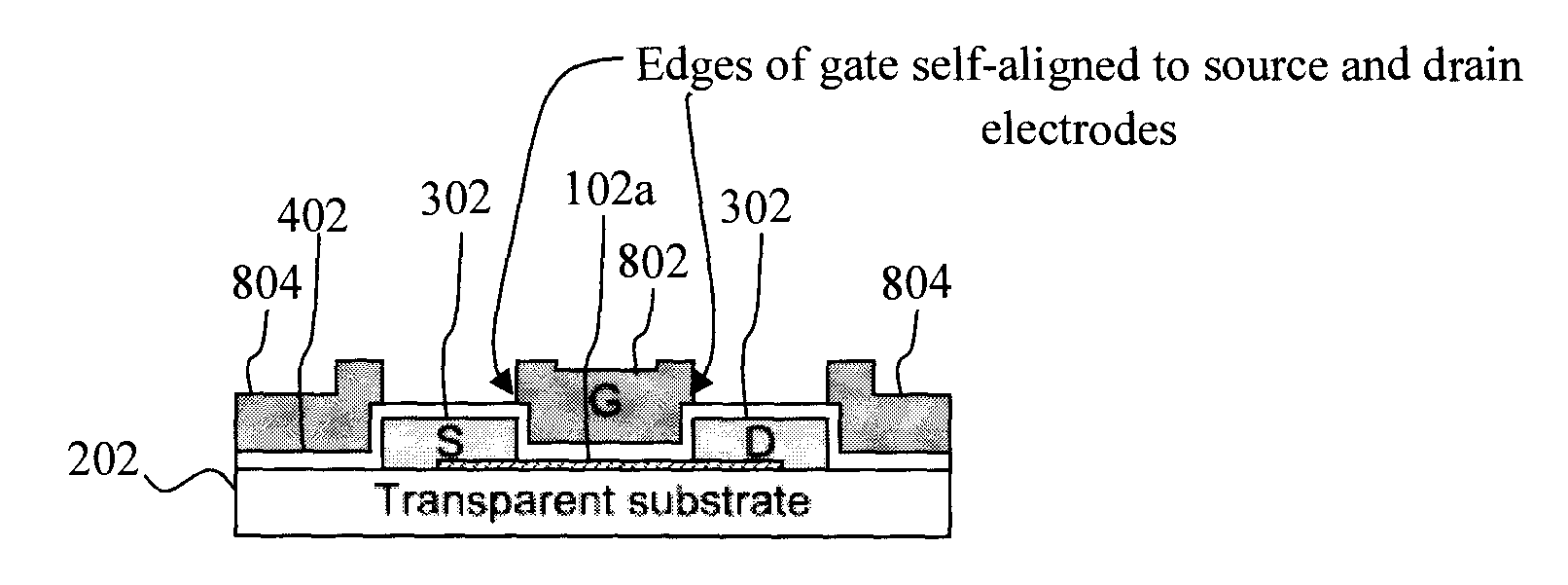

Graphene and Nanotube/Nanowire Transistor with a Self-Aligned Gate Structure on Transparent Substrates and Method of Making Same

Transistor devices having a self-aligned gate structure on transparent substrates and techniques for fabrication thereof are provided. In one aspect, a method of fabricating a transistor device includes the following steps. A channel material is formed on a transparent substrate. Source and drain electrodes are formed in contact with the channel material. A dielectric layer is deposited on the channel material. A photoresist is deposited on the dielectric layer and developed using UV light exposure through the transparent substrate. A gate metal(s) is deposited on the exposed portions of the dielectric layer and the undeveloped portions of the photoresist. The undeveloped portions of the photoresist are removed along with portions of the gate metal over the source and drain regions to form a gate of the device on the dielectric layer over the channel material which is self-aligned to the source and drain electrodes.

Owner:GLOBALFOUNDRIES US INC

Horizontal gate all around nanowire transistor bottom isolation

ActiveUS20170179248A1Avoid etchingNanoinformaticsSemiconductor/solid-state device manufacturingDopantMOSFET

A method of forming a GAA MOSFET includes providing a substrate having source, drain and channel regions, the substrate doped with one of a p-type and an n-type dopant. Disposing an etch stop-electric well (ESEW) layer over the substrate, the ESEW layer doped with the other of the p-type and the n-type dopant. Disposing a sacrificial layer over the ESEW layer, the sacrificial layer doped with the same type dopant as the substrate. Disposing a channel layer over the sacrificial layer. Patterning a fin out of the ESEW layer, sacrificial layer and channel layer in the channel region. Selectively etching away only the sacrificial layer of the fin to form a nanowire from the channel layer of the fin while the ESEW layer of the fin functions as an etch stop barrier to prevent etching of trenches in the substrate.

Owner:GLOBALFOUNDRIES US INC

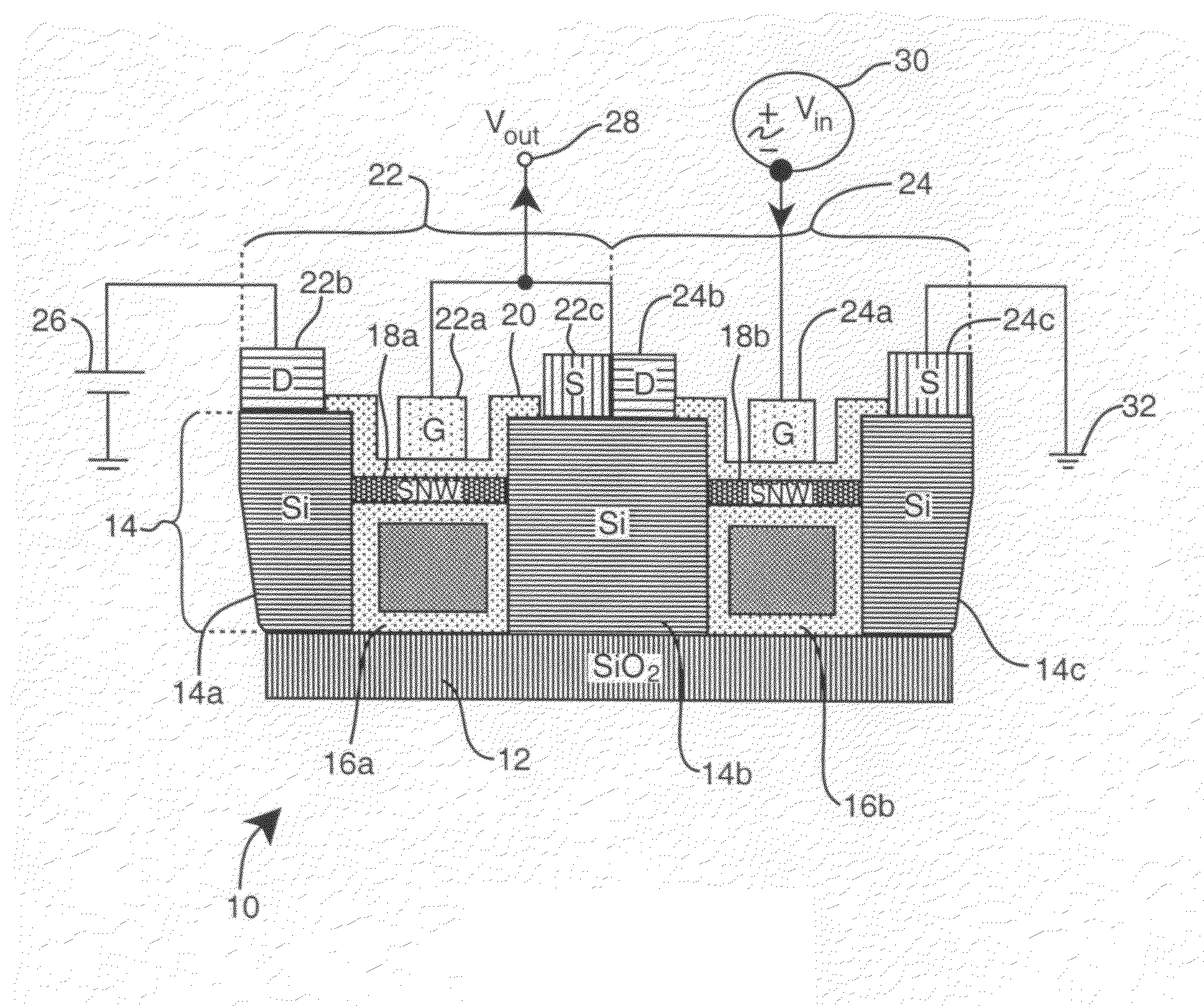

Nanowire circuit architecture

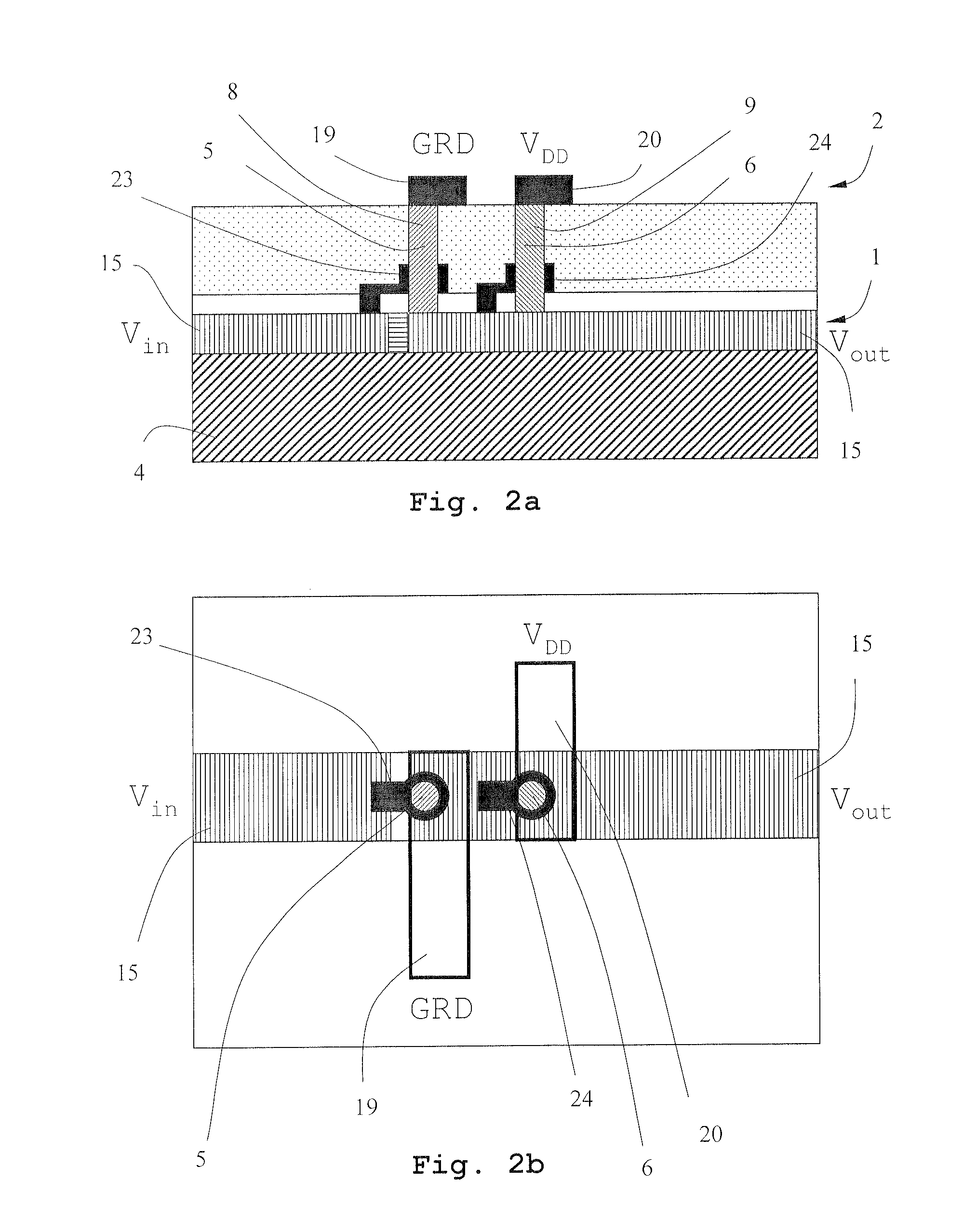

InactiveUS20100155702A1High resolutionIncreased clock-frequency of the oscillatorTransistorAnalogue/digital conversionNanowireEngineering

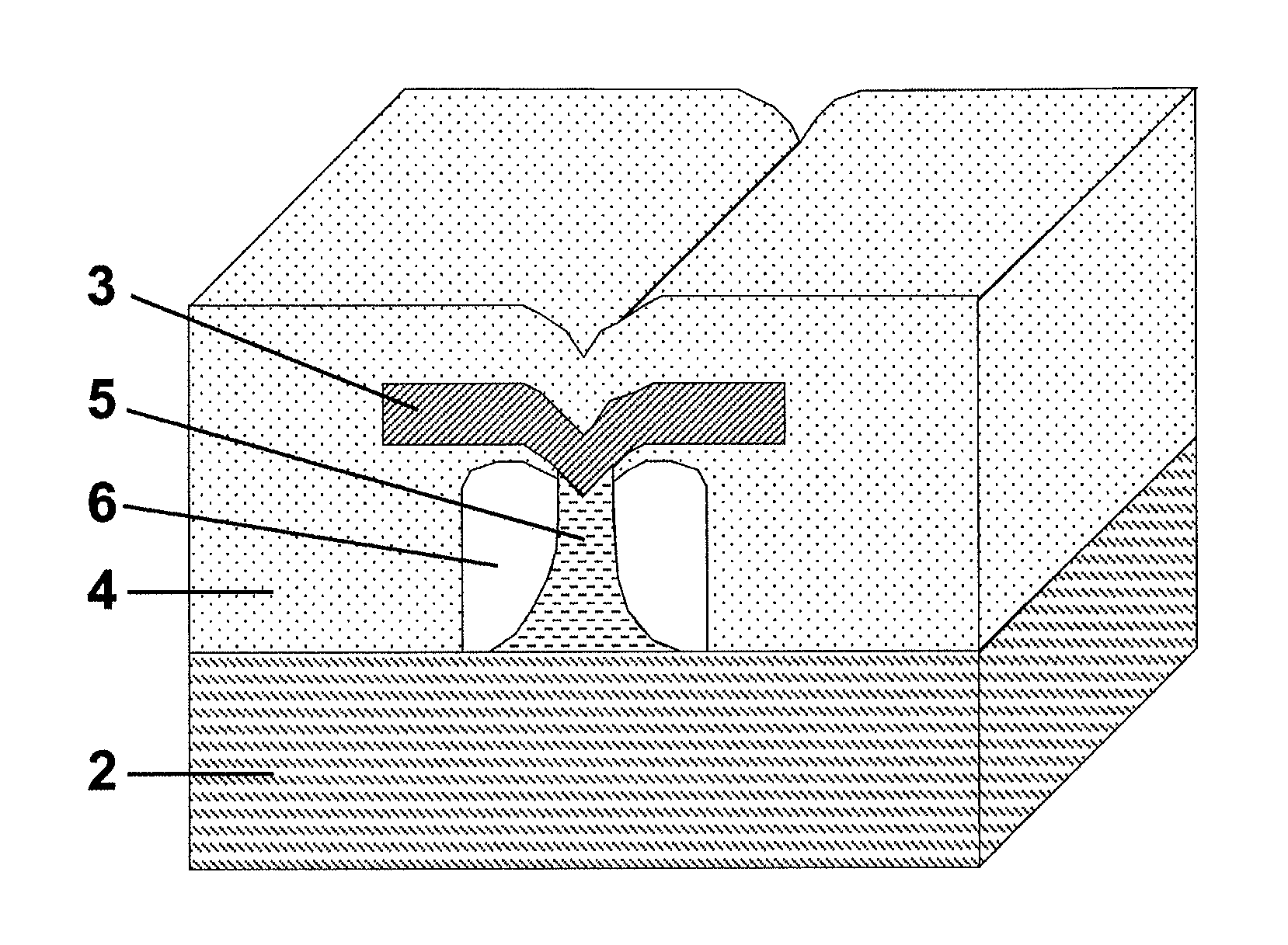

A nanowire circuit architecture is presented. The technology comprises of nanowire transistors (8,9), and optionally nanowire capacitors (12) and nanowire resistors (11), that are integrated using two levels of interconnects only (1,2). Implementations of ring-oscillators, sample- and-hold circuits, and comparators may be realized in this nanowire circuit architecture. Circuit input and circuit output as well as the transistor connections within each circuit are provided in the two levels of interconnects (1,2).

Owner:QUNANO

Structure and manufacturing process of a nano device transistor for a biosensor

ActiveUS7182914B2Bioreactor/fermenter combinationsBiological substance pretreatmentsNano-deviceNanowire

Owner:IND TECH RES INST

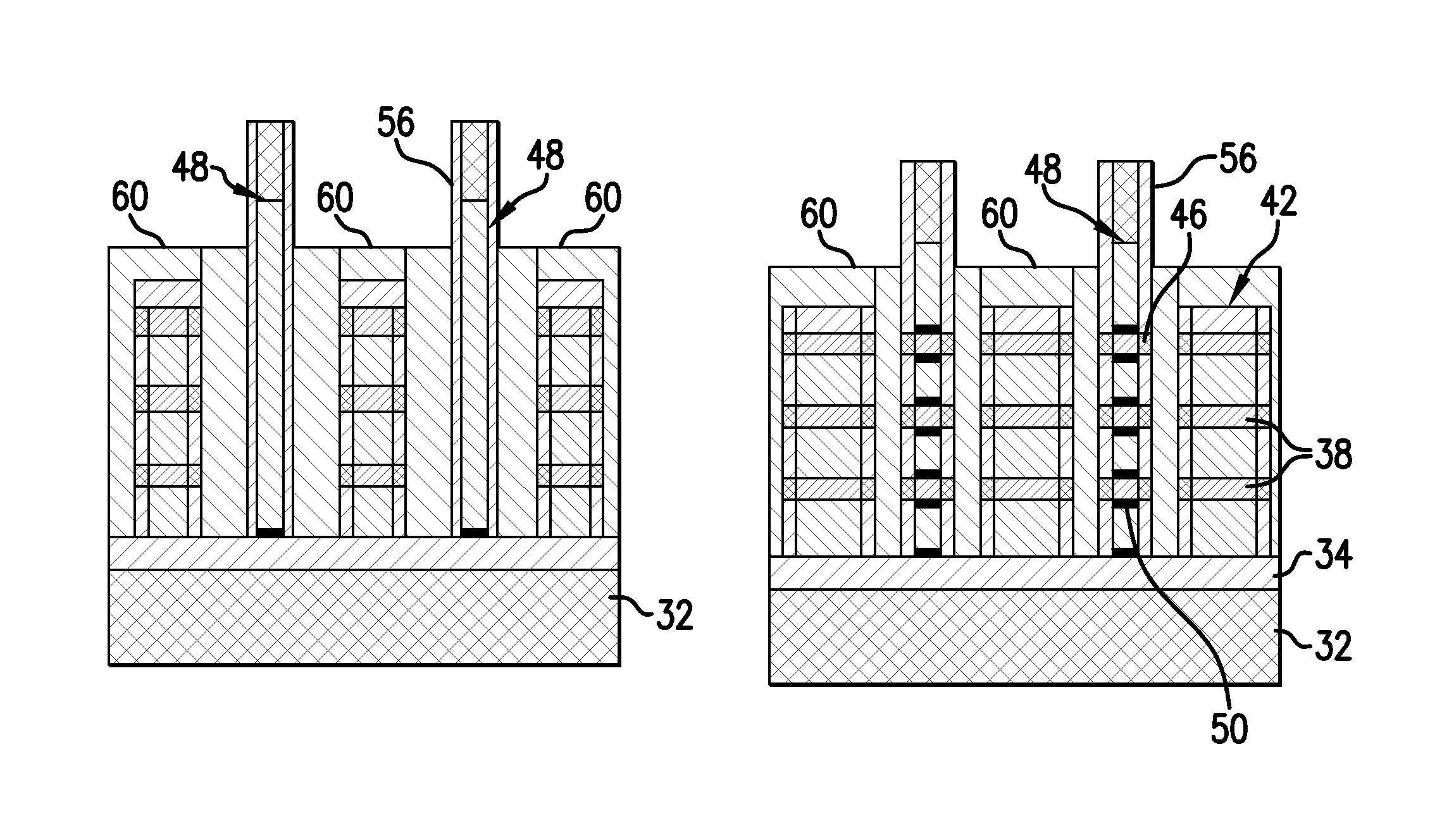

Nanowire transistor structures with merged source/drain regions using auxiliary pillars

A nanowire transistor structure is fabricated by using auxiliary epitaxial nucleation source / drain fin structures. The fin structures include semiconductor layers integral with nanowires that extend between the fin structures. Gate structures are formed between the fin structures such that the nanowires extend through the gate conductors. Following spacer formation and nanowire chop, source / drain regions are grown epitaxially between the gate structures.

Owner:IBM CORP

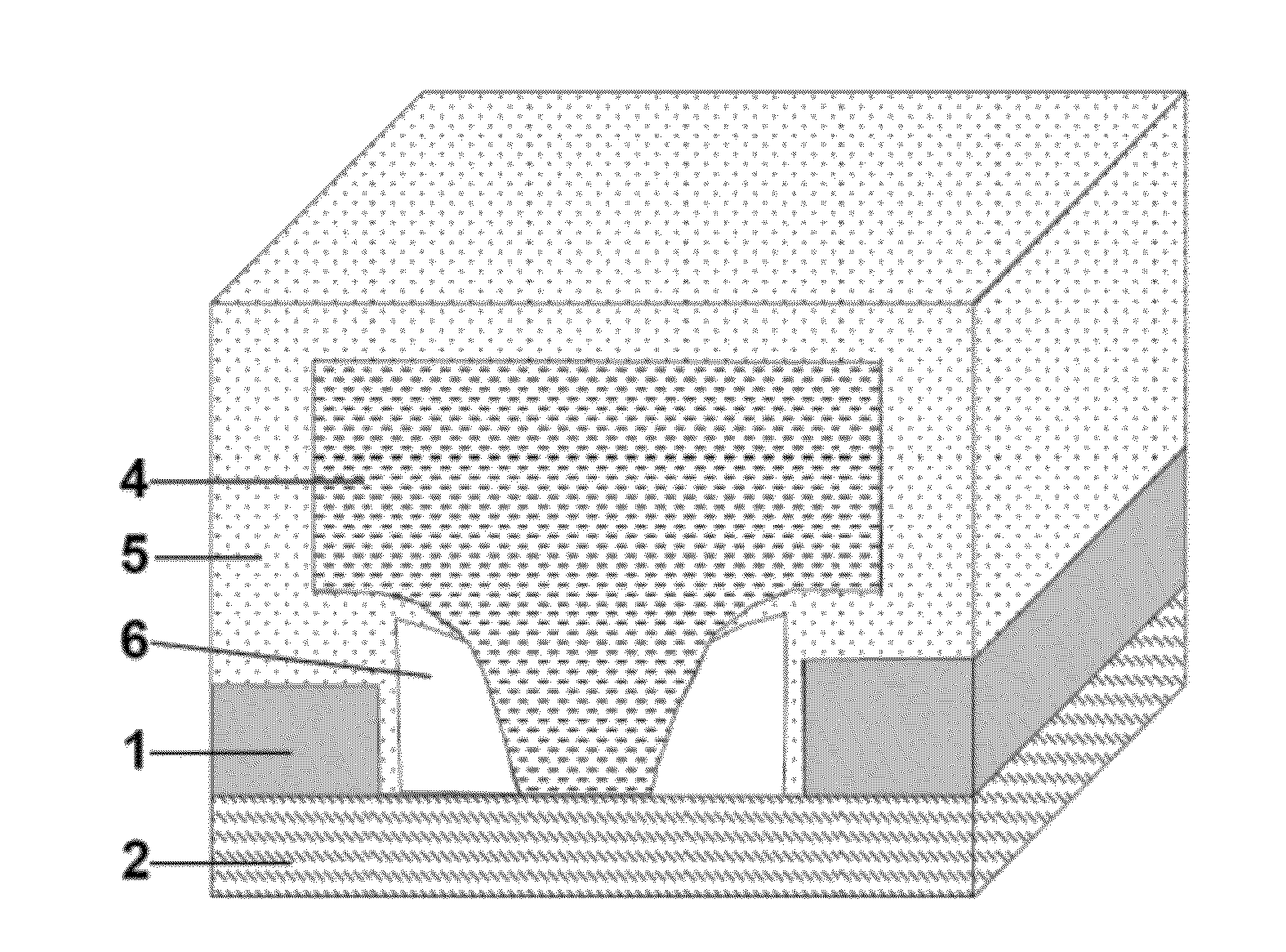

Parasitic capacitance reduction structure for nanowire transistors and method of manufacturing

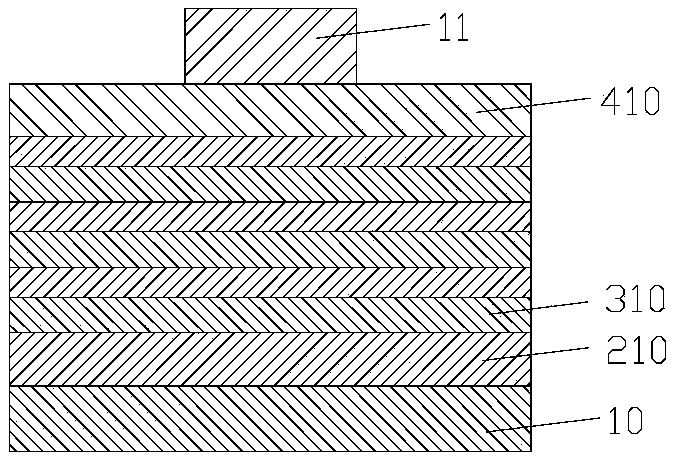

ActiveUS20160315167A1High dielectric constantTransistorSemiconductor/solid-state device manufacturingNanowireParasitic capacitance

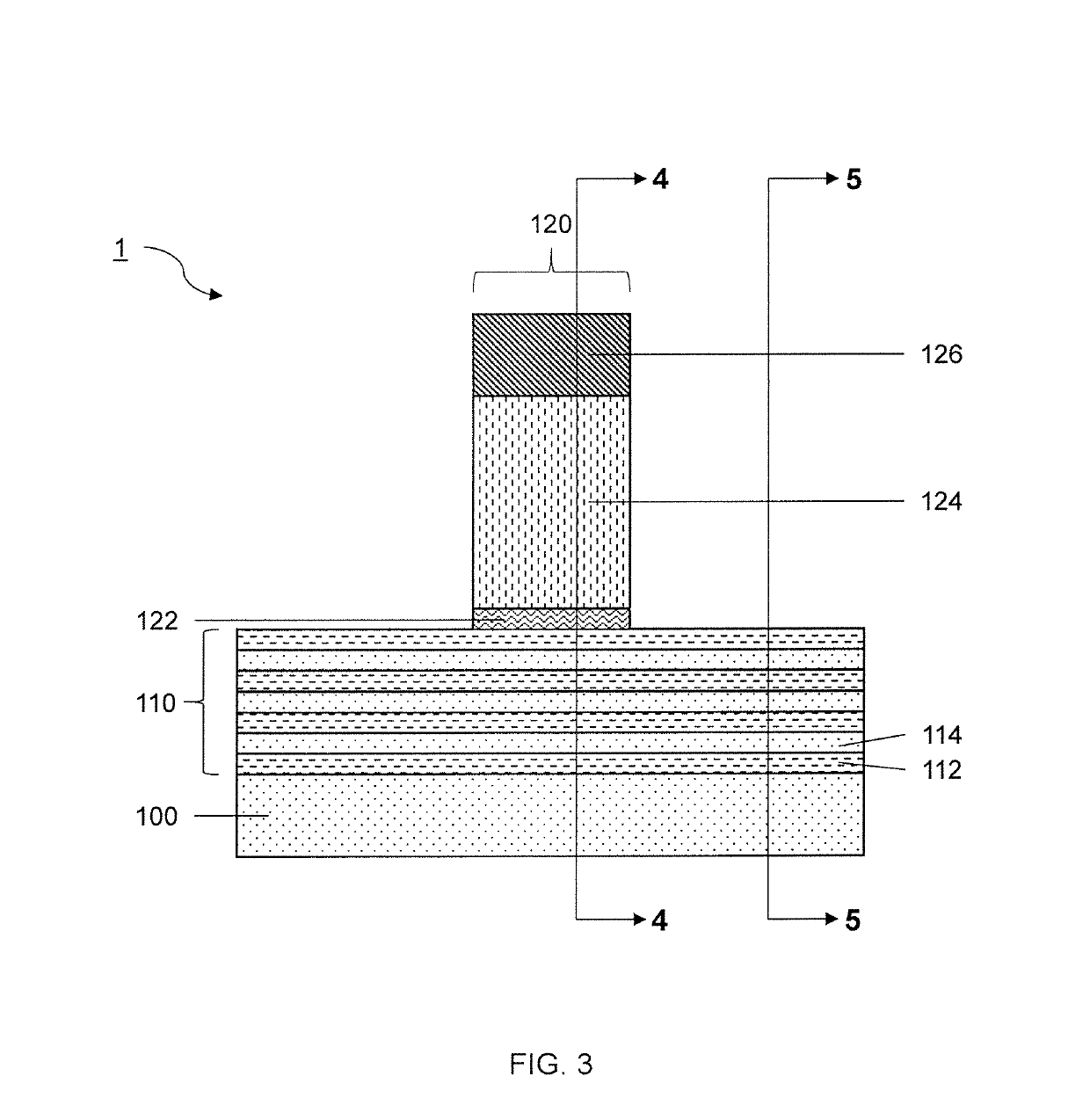

Embodiments of the invention describe parasitic capacitance reduction structure for nanowire transistors and method of manufacturing. According to one embodiment the method includes providing a substrate, forming a first nanowire on the substrate, forming a second nanowire on the first nanowire, forming a first dielectric layer between the substrate and the first nanowire, and forming a second dielectric layer between first dielectric layer and the second nanowire, where the second dielectric layer has a higher dielectric constant than the first dielectric layer. According to one embodiment, a nanowire transistor includes a first nanowire on a substrate, a second nanowire on the second nanowire, a first dielectric layer between the substrate and the first nanowire, and a second dielectric layer between the first dielectric layer and the second nanowire, where the second dielectric layer has a higher dielectric constant than the first dielectric layer.

Owner:TOKYO ELECTRON LTD

Semiconductor device and manufacturing method of same

ActiveCN101546770ATransistorSemiconductor/solid-state device manufacturingGate insulatorPerpendicular direction

A FinFET and nanowire transistor with strain direction optimized in accordance with the sideface orientation and carrier polarity and an SMT-introduced manufacturing method for achieving the same are provided. A semiconductor device includes a pMISFET having a semiconductor substrate; a rectangular solid-shaped semiconductor layer formed at upper part of the substrate to have a top surface parallel to a principal plane of the substrate and a sideface with a (100) plane perpendicular to the substrate's principal plane; a channel region formed in the rectangular semiconductor layer; a gate insulating film formed at least on the sideface of the rectangular layer; a gate electrode on the gate insulator film; and source / drain regions formed in the rectangular semiconductor layer to interpose the channel region therebetween. The channel region is applied a compressive strain in the perpendicular direction to the substrate principal plane. A manufacturing method of the device is also disclosed.

Owner:TOSHIBA MEMORY CORP

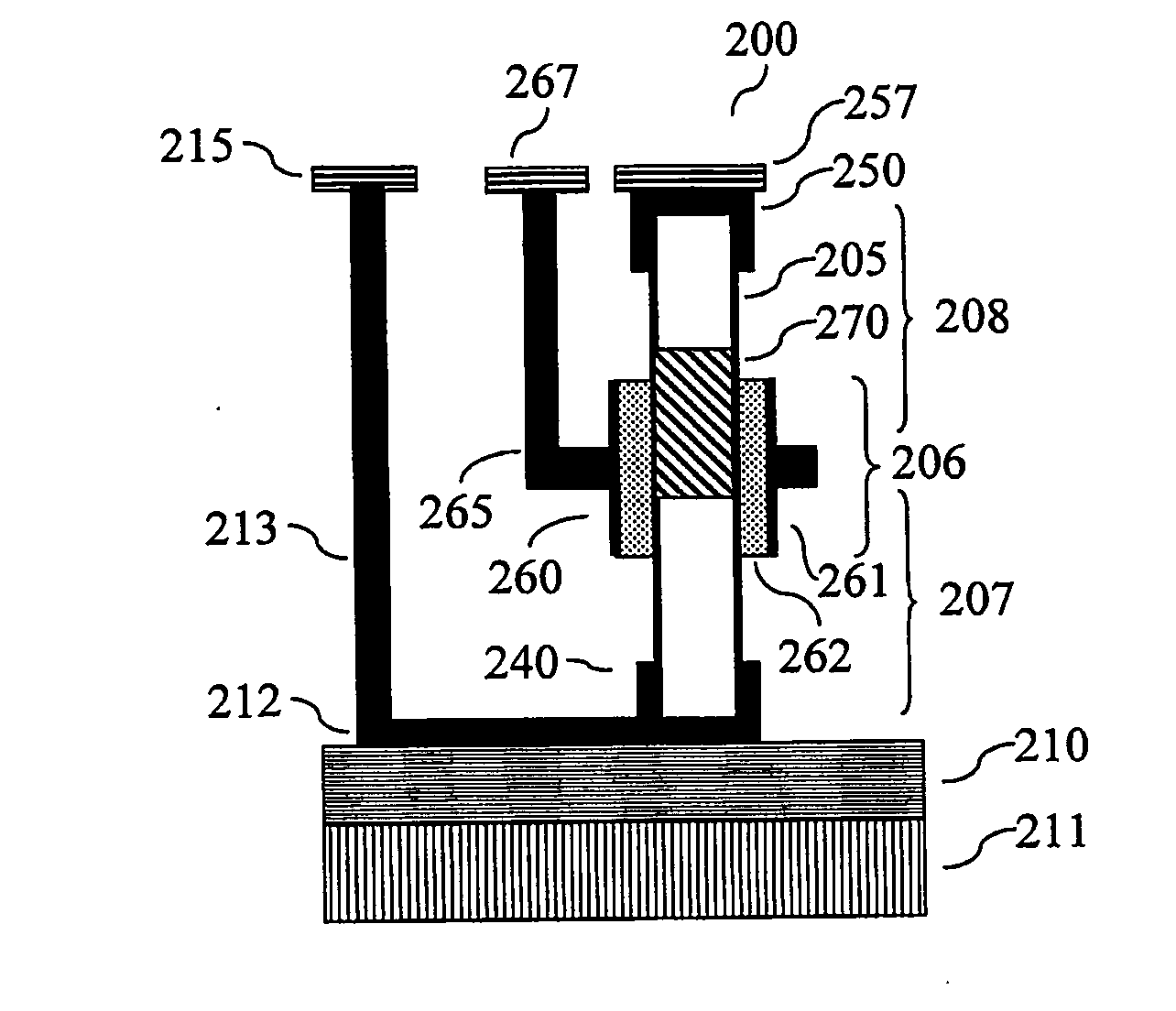

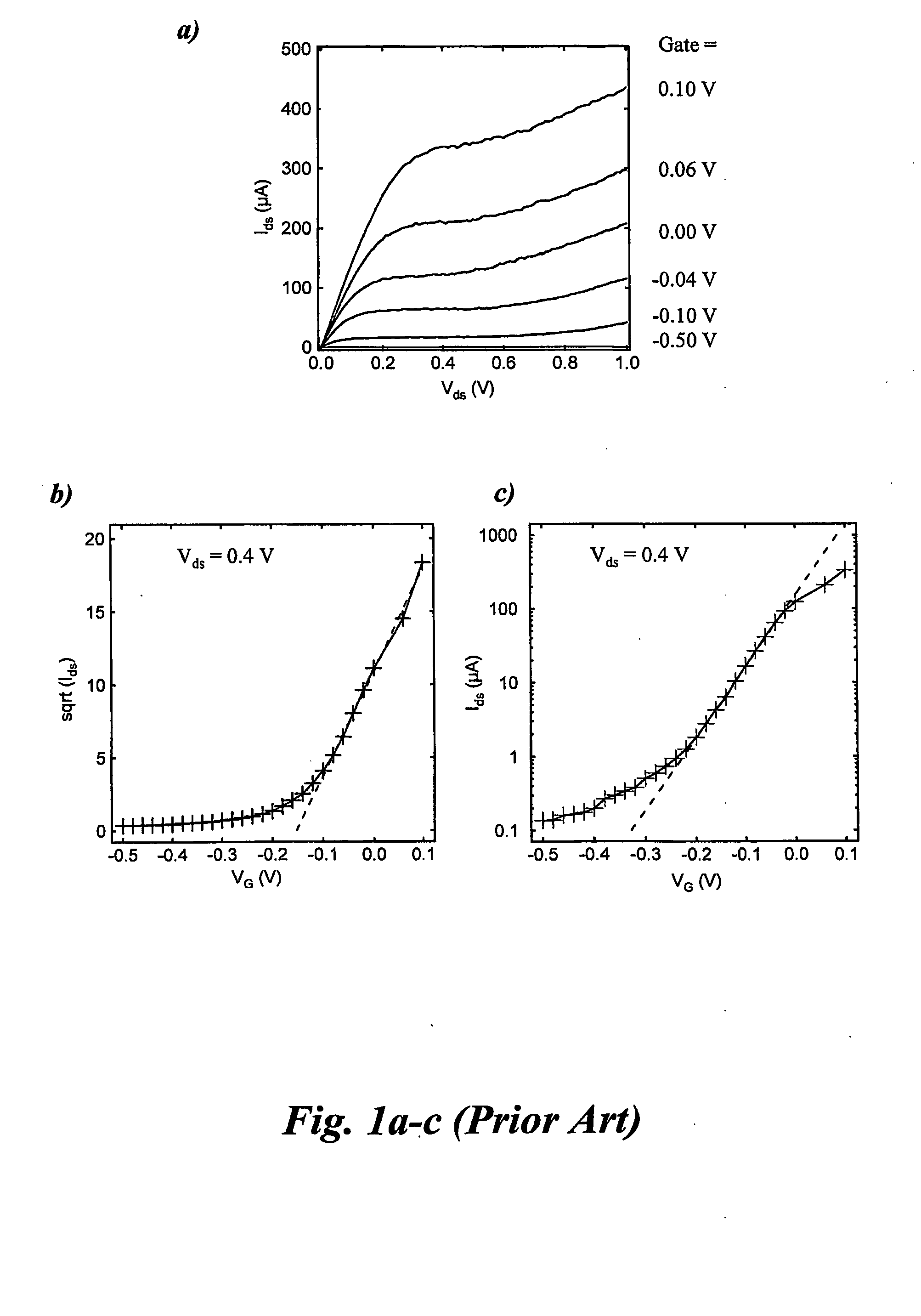

Semiconductor Nanowire Transistor

ActiveUS20090321716A1Improve performanceReduce outputTransistorNanoinformaticsSemiconductor materialsNanowire

A nanowire wrap-gate transistor is realised in a semiconductor material with a band gap narrower than Si. The strain relaxation in the nanowires allows the transistor to be placed on a large variety of substrates and heterostructures to be incorporated in the device. Various types of heterostructures should be introduced in the transistor to reduce the output conductance via reduced impact ionization rate, increase the current on / off ratio, reduction of the sub-threshold slope, reduction of transistor contact resistance and improved thermal stability. The parasitic capacitances should be minimized by the use of semi-insulating substrates and the use of cross-bar geometry between the source and drain access regions. The transistor may find applications in digital high frequency and low power circuits as well as in analogue high frequency circuits.

Owner:QUNANO

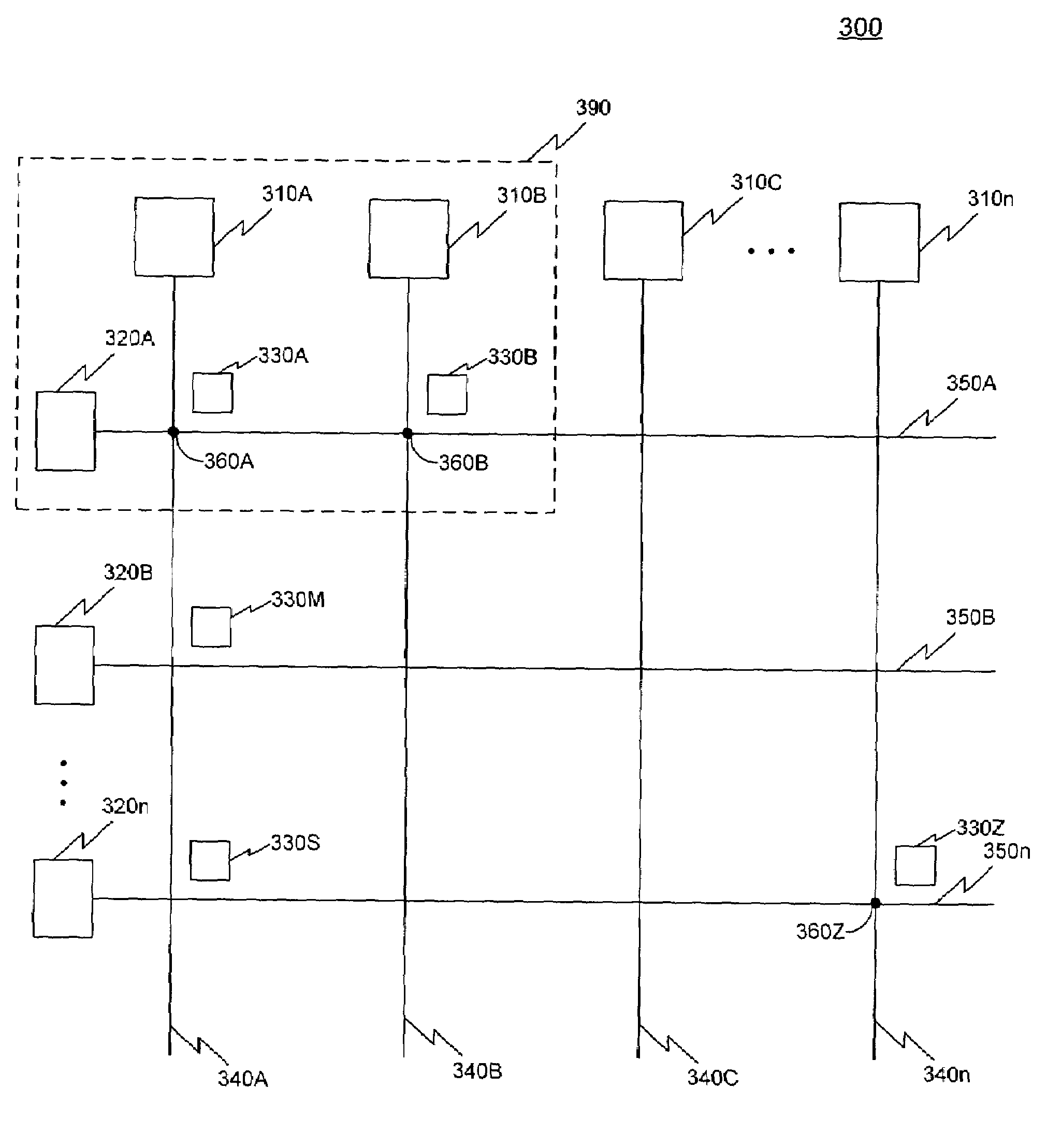

Integrated displays using nanowire transistors

ActiveUS7102605B2Improve performanceIncreased ratio of screen sizeMaterial nanotechnologyNanoinformaticsVoltageNanowire transistors

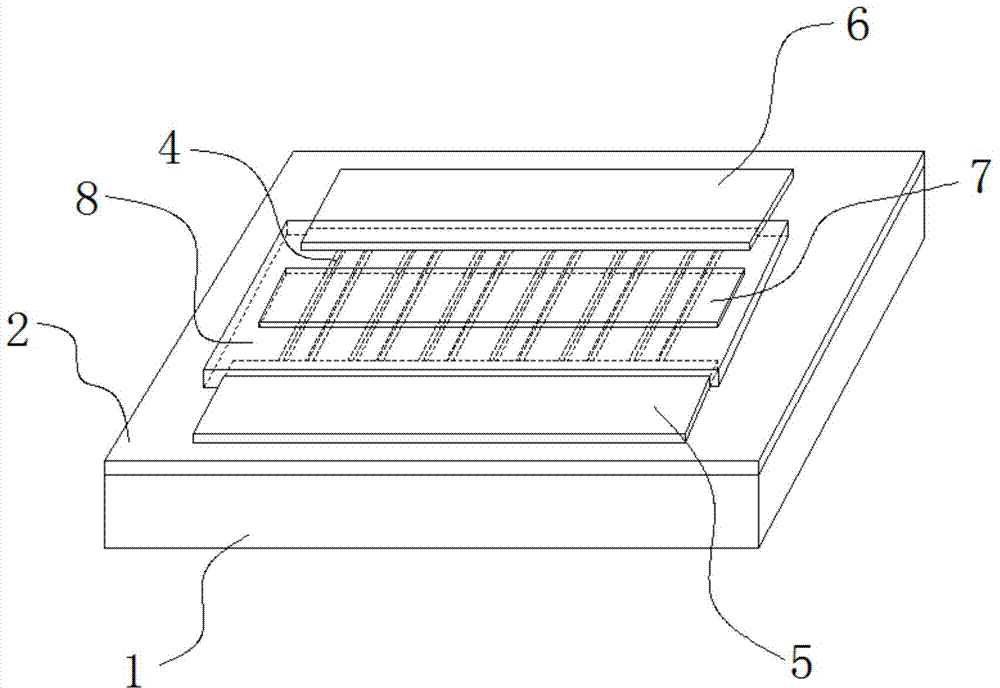

The present invention is directed to a display using nanowire transistors. In particular, a liquid crystal display using nanowire pixel transistors, nanowire row transistors, nanowire column transistors and nanowire edge electronics is described. A nanowire pixel transistor is used to control the voltage applied across a pixel containing liquid crystals. A pair of nanowire row transistors is used to turn nanowire pixel transistors that are located along a row trace connected to the pair of nanowire row transistors on and off. Nanowire column transistors are used to apply a voltage across nanowire pixel transistors that are located along a column trace connected to a nanowire column transistor. Displays including organic light emitting diodes (OLED) displays, nanotube field effect displays, plasma displays, micromirror displays, micoelectromechanical (MEMs) displays, electrochromic displays and electrophoretic displays using nanowire transistors are also provided.

Owner:ONED MATERIAL INC

Junctionless silicon nanowire transistor based on bulk-silicon material and method for manufacturing junctionless silicon nanowire transistor

InactiveCN102916048AReduce manufacturing costImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesIsolation effectSilicon nanowires

The invention discloses a junctionless silicon nanowire transistor based on a bulk-silicon material and a method for manufacturing the junctionless silicon nanowire transistor. The junctionless silicon nanowire transistor comprises a bulk-silicon substrate, a polycrystalline grid, a drain electrode, a source electrode and a grid electrode, a P-type doped layer or an N-type doped layer is manufactured on the bulk-silicon substrate, an N-type doped layer or a P-type doped layer with a doping type opposite to the first P-type doped layer or first the N-type doped layer is manufactured on the first P-type doped layer or the first N-type doped layer, and a PN junction is formed by the different types of doped layers and realizes an electric isolation effect; a source region, a drain region and a silicon nanowire are manufactured on the second N-type doped layer or the second P-type doped layer, and the source region and the drain region are connected with each other by the silicon nanowire to form conducting channels; an insulating dielectric layer is manufactured on the surface of the integral silicon nanowire, the surface of the source region and the surface of the drain region; the polycrystalline grid is manufactured between the source region and the drain region and completely wraps the silicon nanowire; the drain electrode is manufactured on the drain region of silicon; the source electrode is manufactured on the source region of the silicon; and the grid electrode is manufactured on the polycrystalline grid. The junctionless silicon nanowire transistor and the method have the advantage that the junctionless silicon nanowire transistor can be manufactured on the bulk-silicon substrate.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

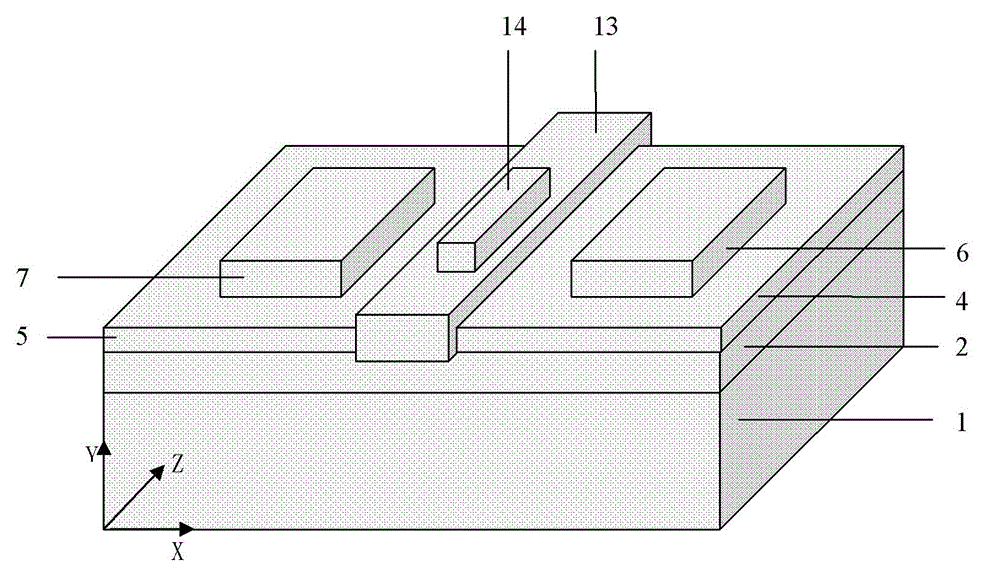

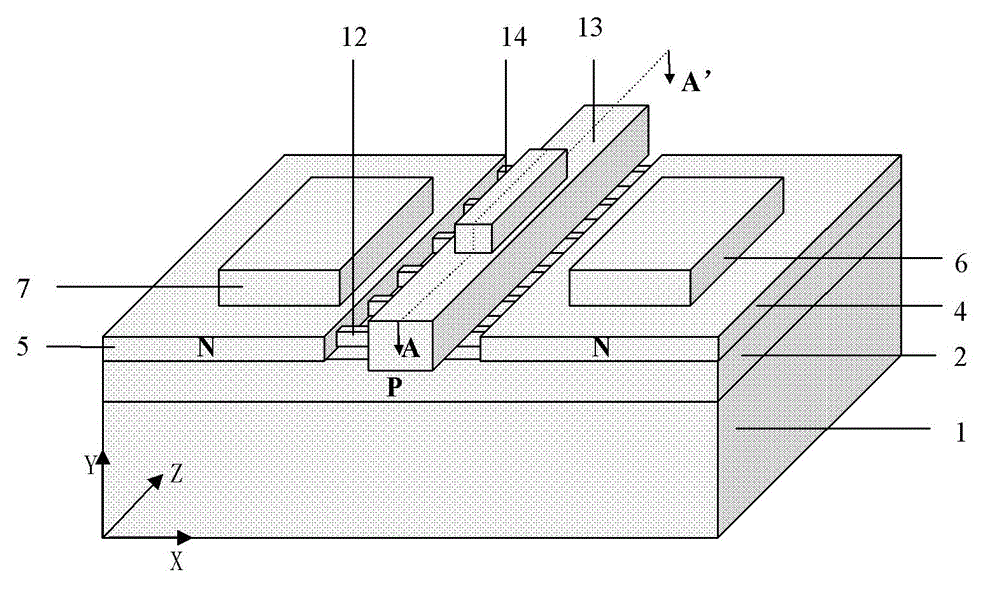

Nanowire transistor and method for fabricating the same

ActiveUS20120156833A1Improve reliabilityImprove propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireSingle crystal

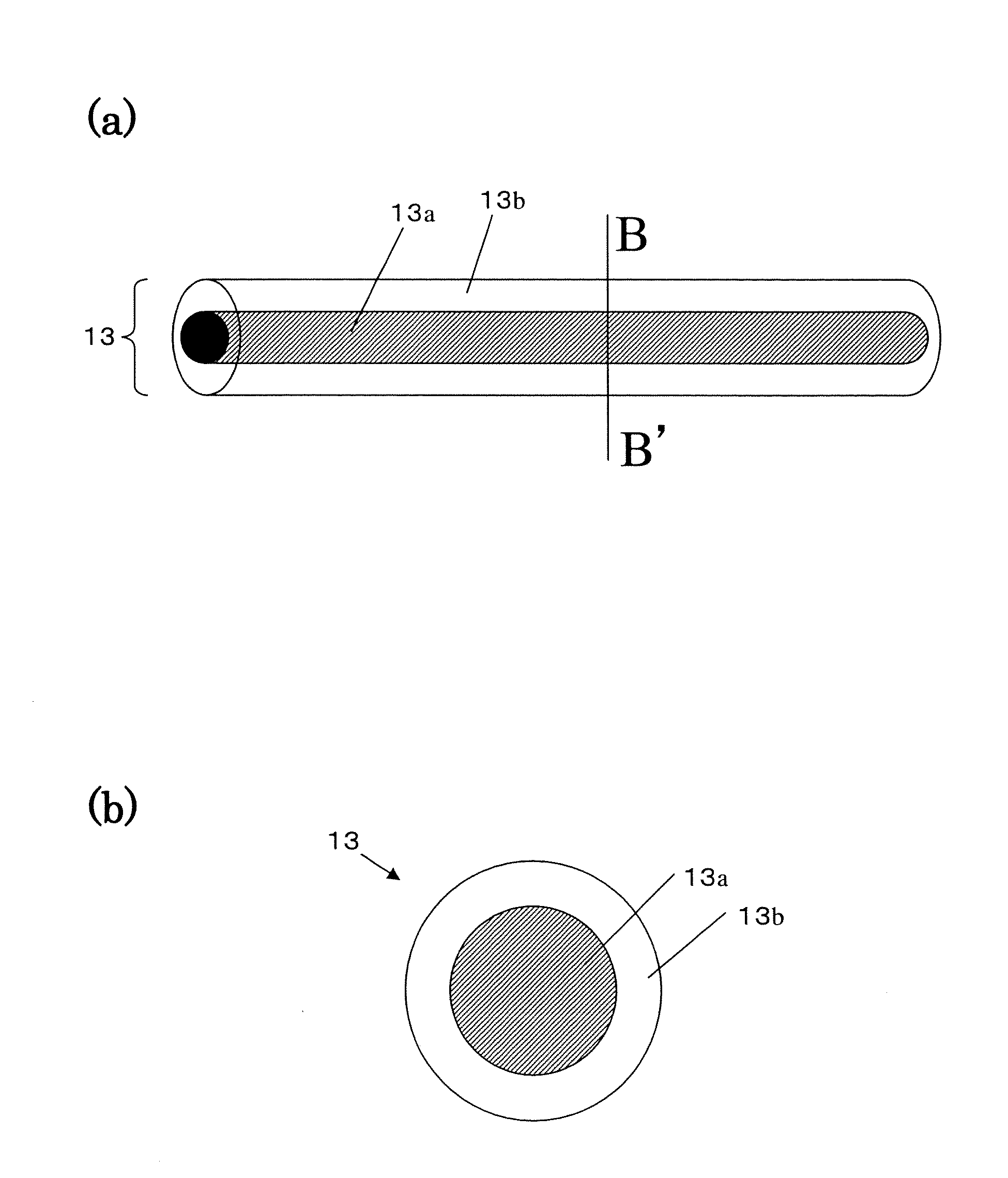

A nanowire transistor according to the present invention includes: at least one nanowire 13 including a core portion 13a that functions as a channel region and an insulating shell portion 13b that covers the surface of the core portion 13a; source and drain electrodes 14 and 15, which are connected to the nanowire 13; and a gate electrode 21 for controlling conductivity in at least a part of the core portion 13a of the nanowire 13. The core portion 13a is made of semiconductor single crystals including Si and has a cross section with a curved profile on a plane that intersects with the longitudinal axis thereof. The insulating shell portion 13b is made of an insulator including Si and functions as at least a portion of a gate insulating film.

Owner:JOLED INC

Nano-wire field effect transistor

ActiveCN101740619AReduce off-state currentReduce static power consumptionSemiconductor devicesGate dielectricNanowire

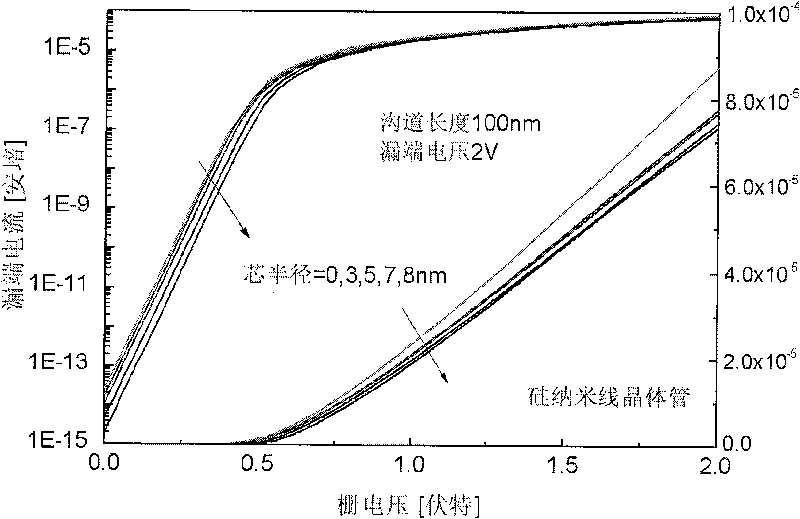

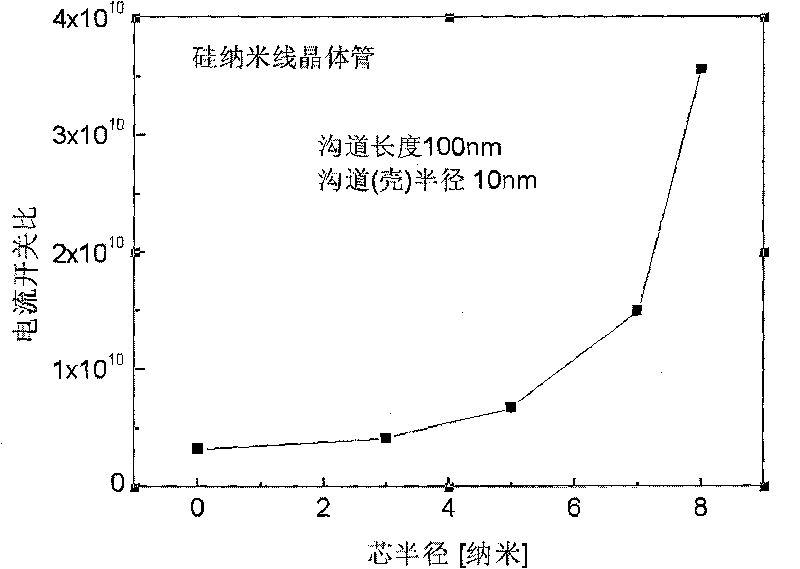

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure and the shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Integrated nonpolar GaN nanowire transistor high in electron mobility and preparation method thereof

ActiveCN104124272AThe process steps are simpleSolve uncontrollabilityNanoinformaticsSemiconductor/solid-state device manufacturingHeterojunctionNanowire

The invention discloses an integrated nonpolar GaN nanowire transistor high in electron mobility and a preparation method thereof. The transistor comprises a substrate and an insulating dielectric layer located on the substrate, a plurality of grooves at intervals are etched in the insulating dielectric layer, heterojunction nanowires are respectively grown in the grooves, a source electrode and a drain electrode are formed on the insulating dielectric layer and are respectively located at two ends of the heterojunction nanowires and respectively connected with each heterojunction nanowire, a gate electrode is formed between the source electrode and the drain electrode, and a gate dielectric layer is arranged between the gate electrode and the heterojunction nanowires. According to the transistor, epitaxial growth and device preparation are united organically, process steps are greatly simplified, and the method is simplified. The transistor solves the problem of uncontrollability and disorder caused by the solution dilution and coating for current nanowire transistors, the nanowire transistor preparation success rate is effectively improved. The nanowire transistor can be widely applied to the field of semiconductors.

Owner:JIANGSU INST OF ADVANCED SEMICON CO LTD

Nanowire transistor with source and drain induced by electrical contacts with negative schottky barrier height

A nanowire transistor includes undoped source and drain regions electrically coupled with a channel region. A source stack that is electrically isolated from a gate conductor includes an interfacial layer and a source conductor, and is coaxially wrapped completely around the source region, extending along at least a portion of the source region. A Schottky barrier between the source conductor and the source region is a negative Schottky barrier and a concentration of free charge carriers is induced in the semiconductor source region.

Owner:ACORN SEMI LLC

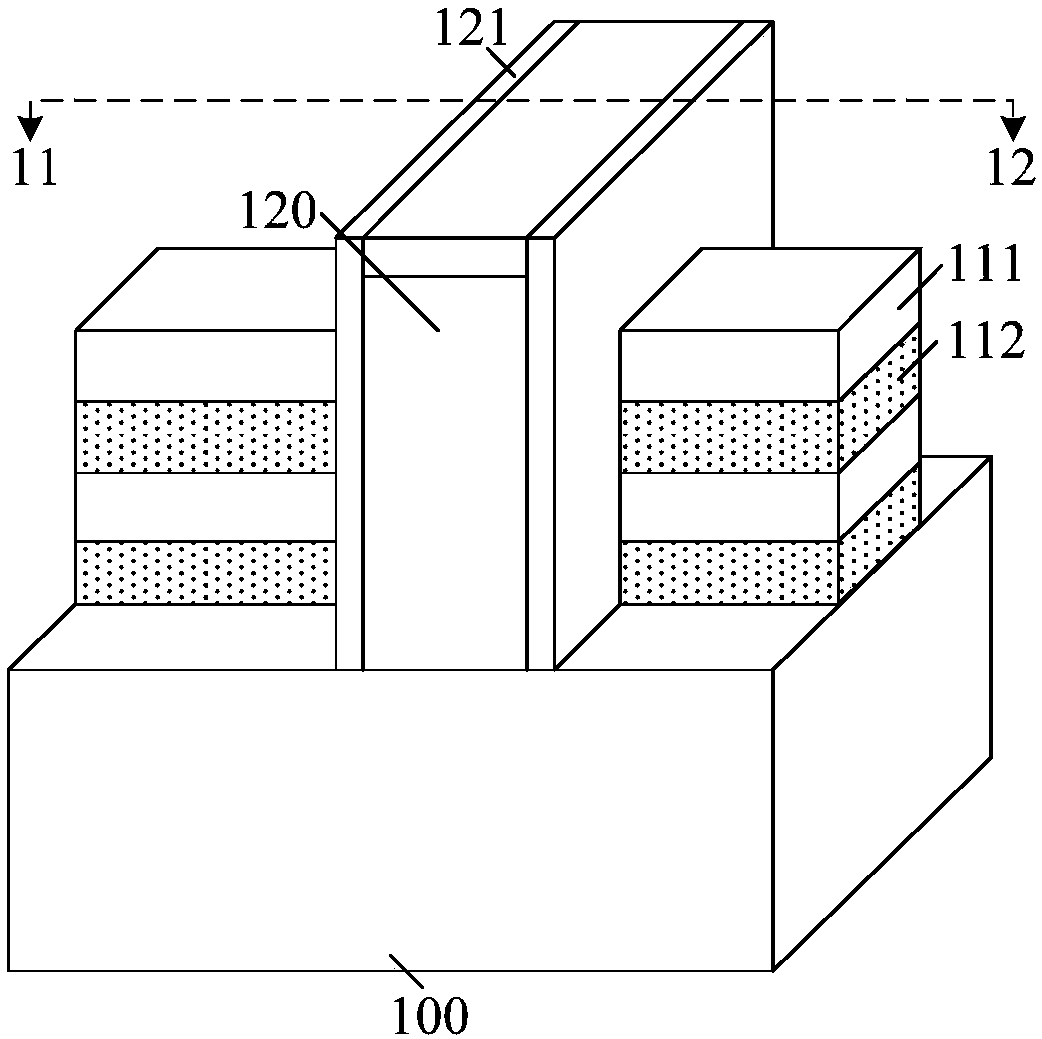

Vertically stacked ring gate nanowire transistor and preparation method thereof

ActiveCN107749421AImprove application competitivenessPerformance parameter impactSemiconductor/solid-state device manufacturingSemiconductor devicesAND gateGate length

The invention provides a vertically stacked ring gate nanowire transistor and a preparation method thereof. First, a substrate with channel layers and sacrificial layers on the surface is provided, the channel layers and the sacrificial layers are alternately stacked along a direction away from the substrate, and a mask layer is formed on the outermost sacrificial layer. Then, etching is carried out inwards by starting from the exposed surface of each sacrificial layer so that the two ends with exposed surfaces of the sacrificial layers are recessed inwards relative to the channel layers to form recesses. The recesses are filled with a dielectric material, and thus, the sacrificial layers have substantially the same length. The sacrificial layers are removed to form second grooves, and gate oxide layers and gates are formed in the second grooves. Thus, the finally formed vertically stacked ring gate nanowire transistor has the same gate length. The influence of gate length difference on the performance parameters of devices is effectively avoided. The application competitiveness of the vertically stacked ring gate nanowire transistor is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Nanowire transistor and forming method thereof

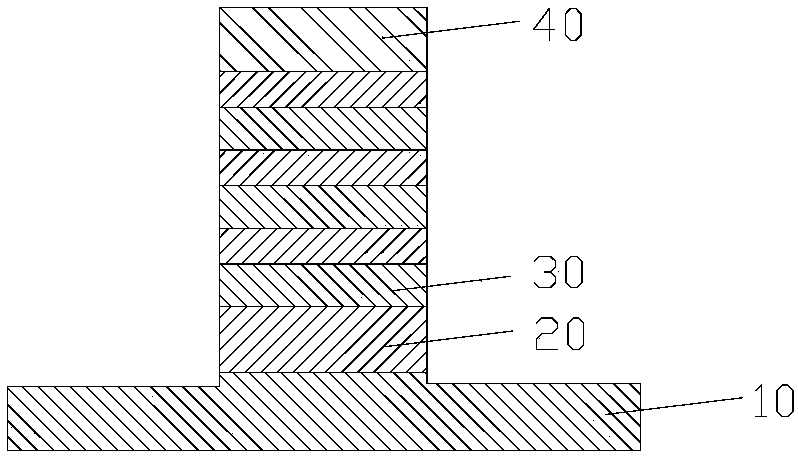

InactiveCN109216454AImprove performanceIncrease spacingNanoinformaticsSemiconductor/solid-state device manufacturingNanowireParasitic capacitance

The invention provides a nanowire transistor and a forming method thereof, wherein the forming method comprises the following steps of: providing a substrate; Forming a composite structure on the substrate, the composite structure comprising one or more laminated composite layers, the composite layers comprising a sacrificial layer on the substrate and a channel layer on the sacrificial layer, thechannel layer and the sacrificial layer being different in material; Etching a sacrificial layer of the side wall of the composite structure to form a depression on the surface of the side wall of the composite structure; Forming an isolation layer on the surface of the sacrificial layer exposed by the recess; Forming a source-drain doping layer on a substrate on both sides of the composite structure after forming the isolation layer, wherein the isolation layer is provided between the source-drain doping layer and the sacrificial layer; Removing the remaining sacrificial layer after the source-drain doping layer is formed; Forming a gate structure surrounding the channel layer. The resulting transistor reduces parasitic capacitance and improves transistor performance.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

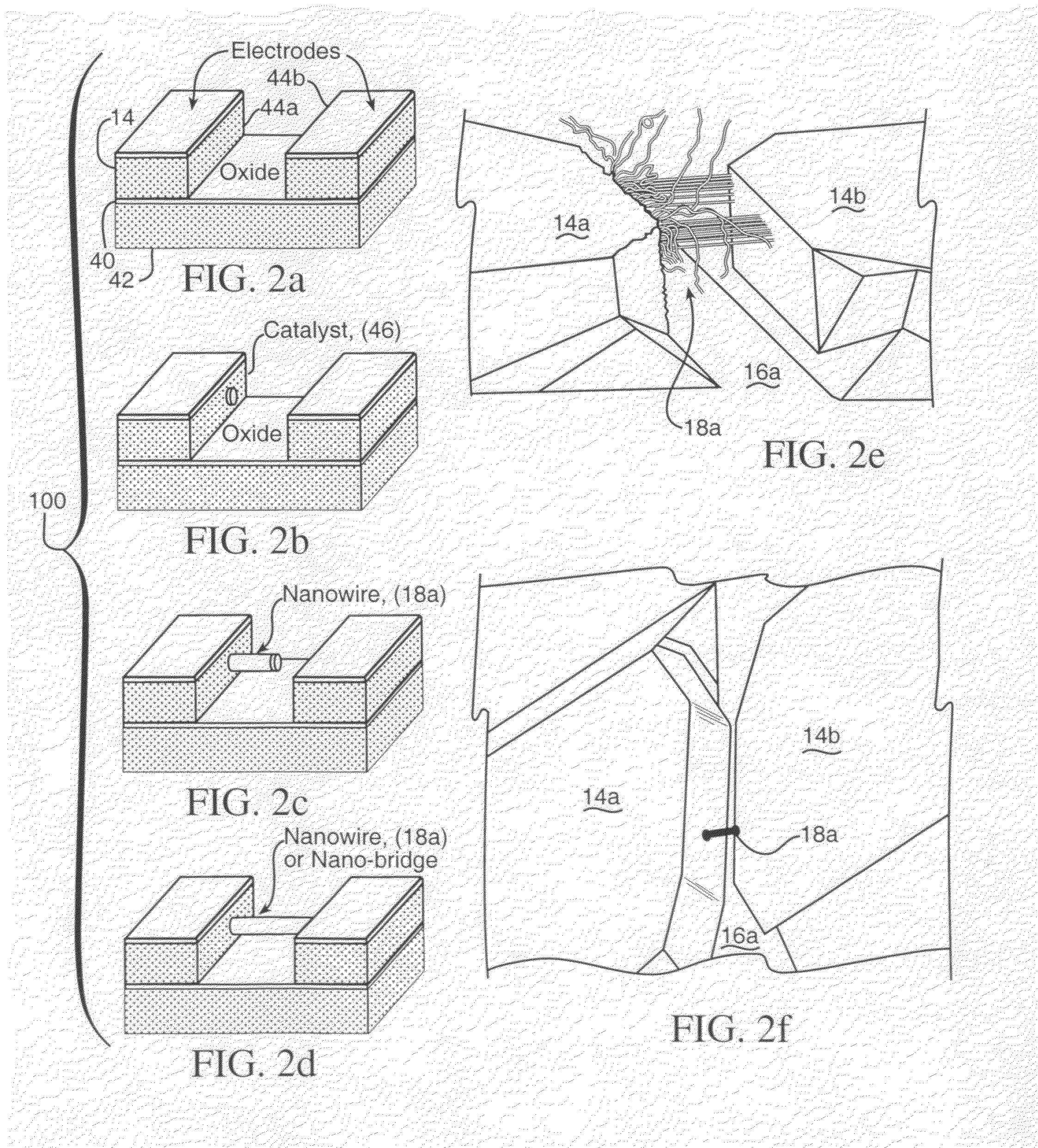

Structure and manufacturing process of a nano device transistor for a biosensor

ActiveUS20050045875A1Bioreactor/fermenter combinationsBiological substance pretreatmentsAntigenNanowire

The present invention relates to a structure and manufacturing process of a nano device transistor for a biosensor. The structure, the manufacturing process and the related circuit for a carbon nano tube or nano wire transistor biosensor device are provided. The refurbished nano device is used for absorbing various anti-bodies so as to detect the specific antigens or absorbing various biotins. Therefore, the object of the present invention to detect the specific species for bio measurement can be achieved.

Owner:IND TECH RES INST

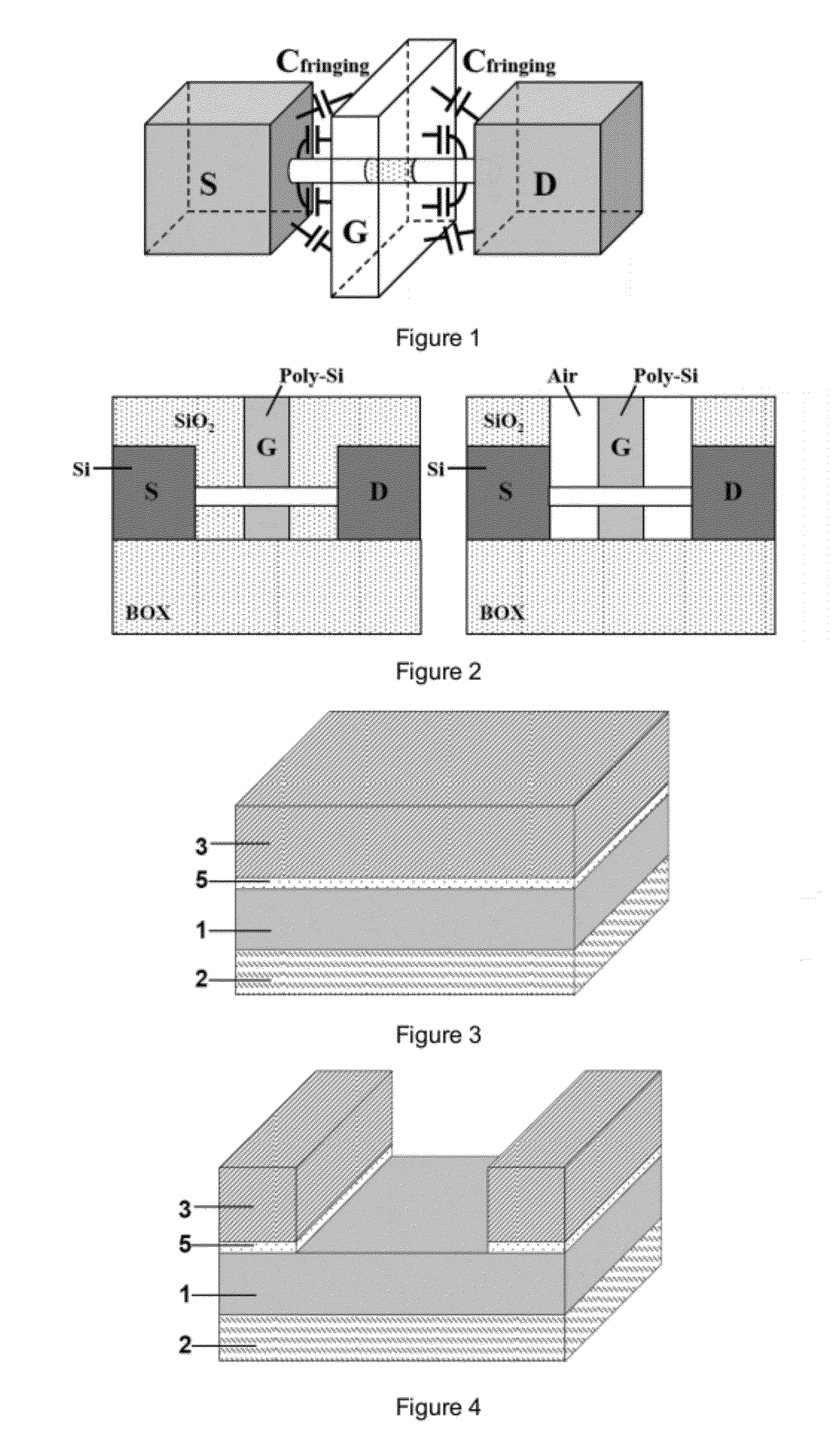

Method for fabricating surrounding-gate silicon nanowire transistor with air sidewalls

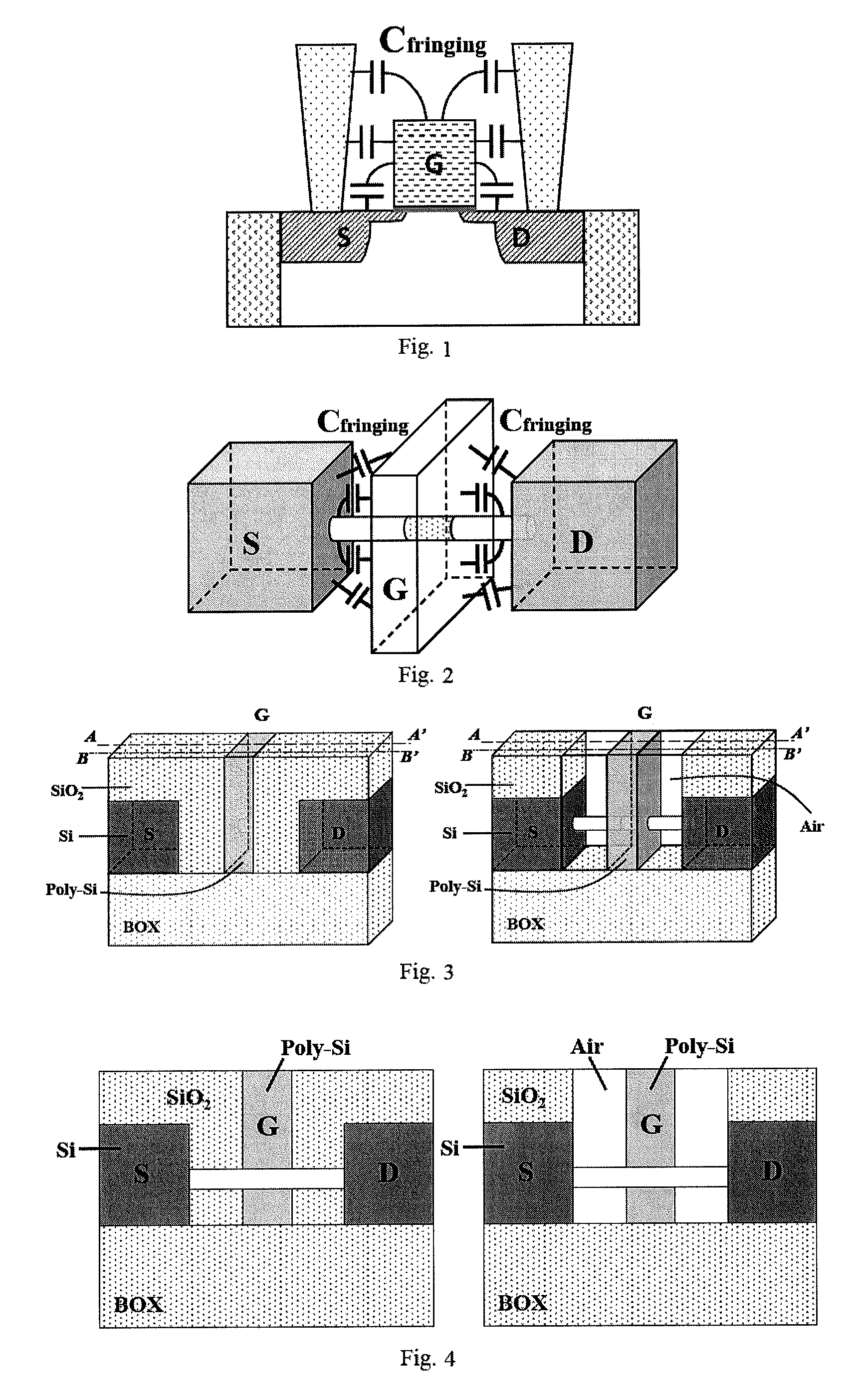

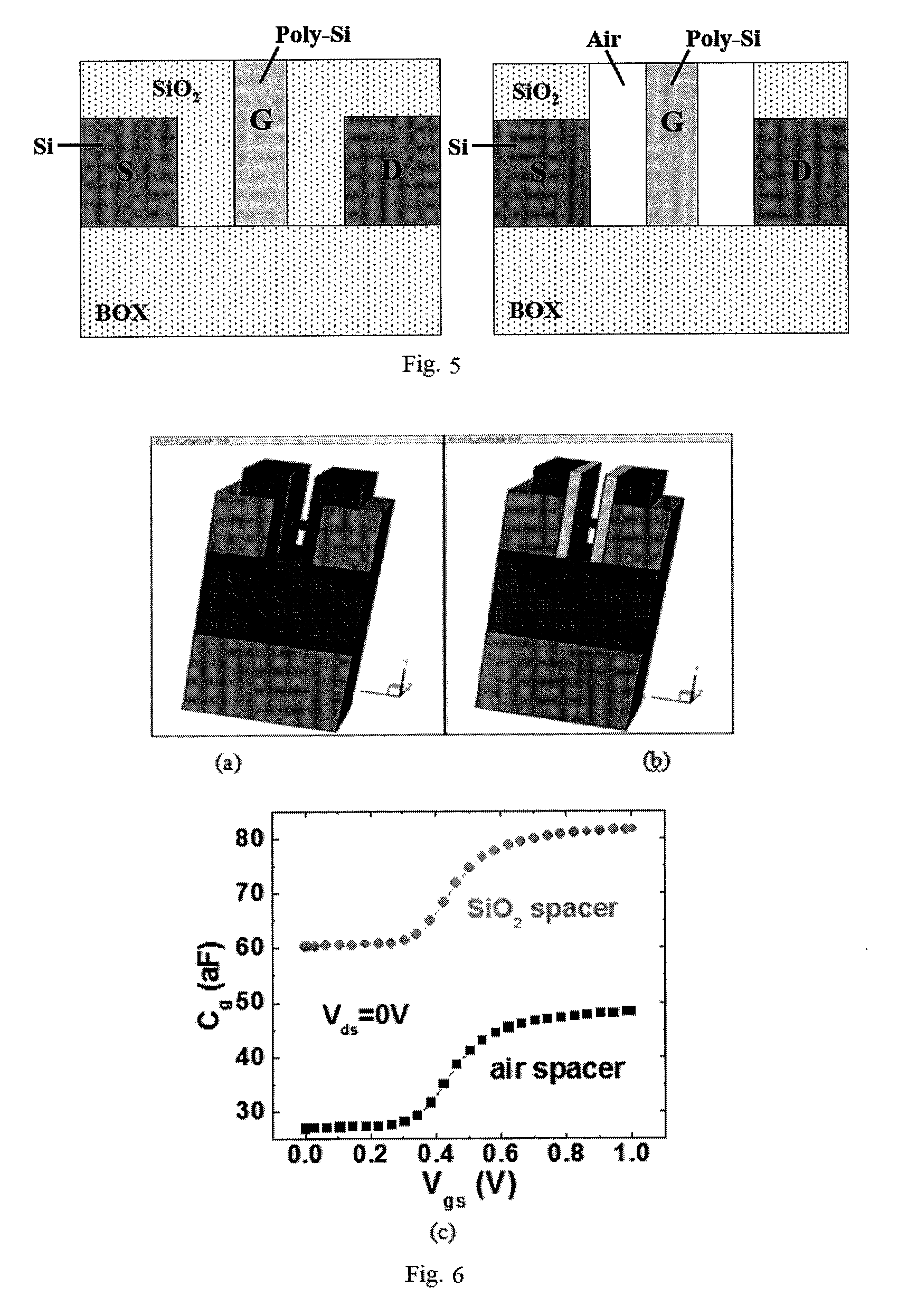

ActiveUS20120302014A1Reduce parasitic capacitanceImprove transient response characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon nanowiresParasitic capacitance

A method for fabricating a surrounding-gate silicon nanowire transistor with air sidewalls is provided. The method is compatible with the CMOS process; the introduced air sidewalls can reduce the parasitic capacitance effectively and increase the transient response characteristic of the device, thus being applicable to a high-performance logic circuit.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Integrated displays using nanowire transistors

ActiveUS20060256059A1Improve performanceIncreased ratio of screen sizeMaterial nanotechnologyStatic indicating devicesNanowireDisplay device

Owner:ONED MATERIAL INC

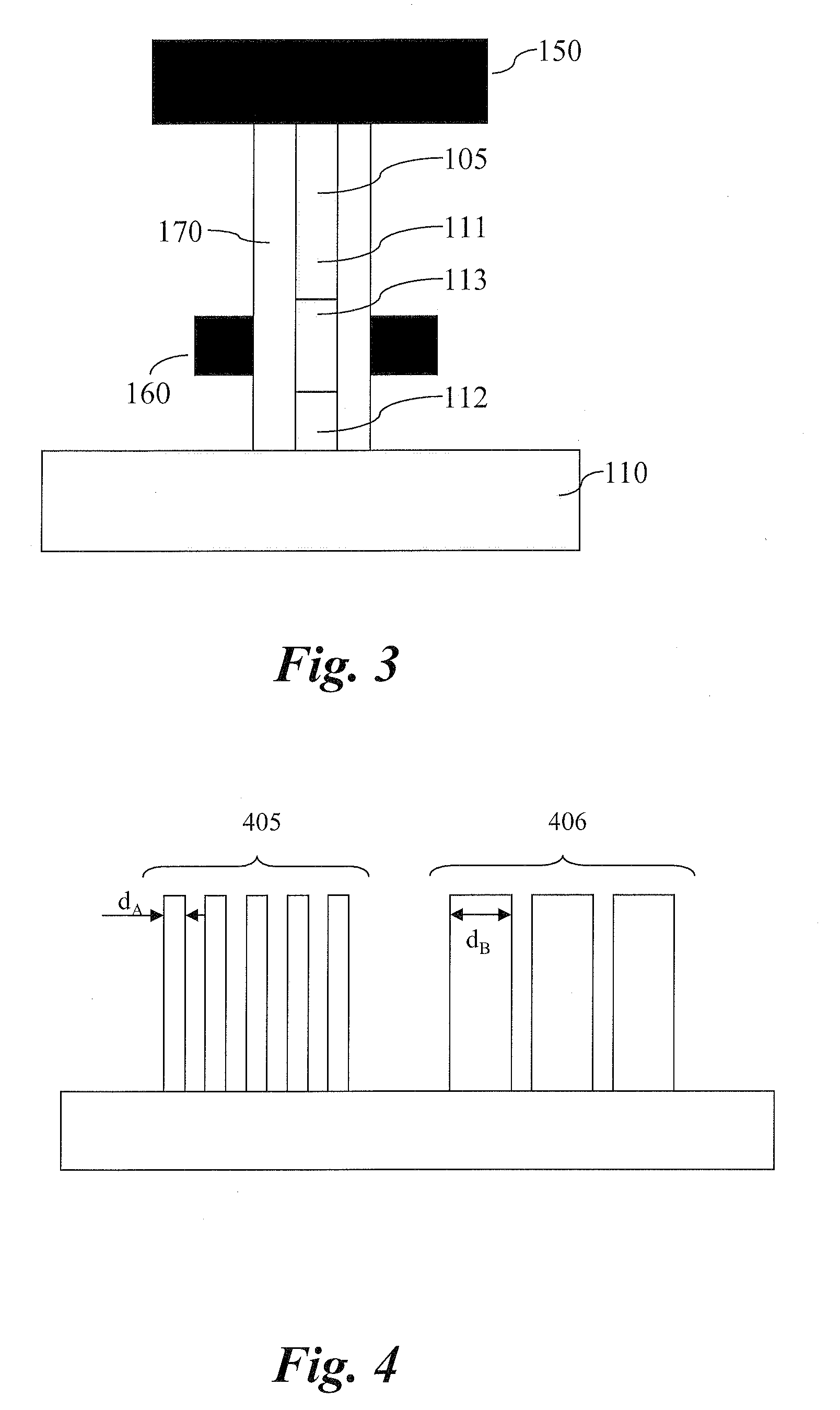

Insulated gate silicon nanowire transistor and method of manufacture

An insulated gate silicon nanowire transistor amplifier structure is provided and includes a substrate formed of dielectric material. A patterned silicon material may be disposed on the substrate and includes at least first, second and third electrodes uniformly spaced on the substrate by first and second trenches. A first nanowire formed in the first trench operates to electrically couple the first and second electrodes. A second nanowire formed in the second trench operates to electrically couple the second and third electrodes. First drain and first source contacts may be respectively disposed on the first and second electrodes and a first gate contact may be disposed to be capacitively coupled to the first nanowire. Similarly, second drain and second source contacts may be respectively disposed on the second and third electrodes and a second gate contact may be disposed to be capacitively coupled to the second nanowire.

Owner:THE GOVERNMENT OF THE US SEC THE AIR FORCE

Insulated gate silicon nanowire transistor and method of manufacture

An insulated gate silicon nanowire transistor amplifier structure is provided and includes a substrate formed of dielectric material. A patterned silicon material may be disposed on the substrate and includes at least first, second and third electrodes uniformly spaced on the substrate by first and second trenches. A first nanowire formed in the first trench operates to electrically couple the first and second electrodes. A second nanowire formed in the second trench operates to electrically couple the second and third electrodes. First drain and first source contacts may be respectively disposed on the first and second electrodes and a first gate contact may be disposed to be capacitively coupled to the first nanowire. Similarly, second drain and second source contacts may be respectively disposed on the second and third electrodes and a second gate contact may be disposed to be capacitively coupled to the second nanowire.

Owner:THE GOVERNMENT OF THE US SEC THE AIR FORCE

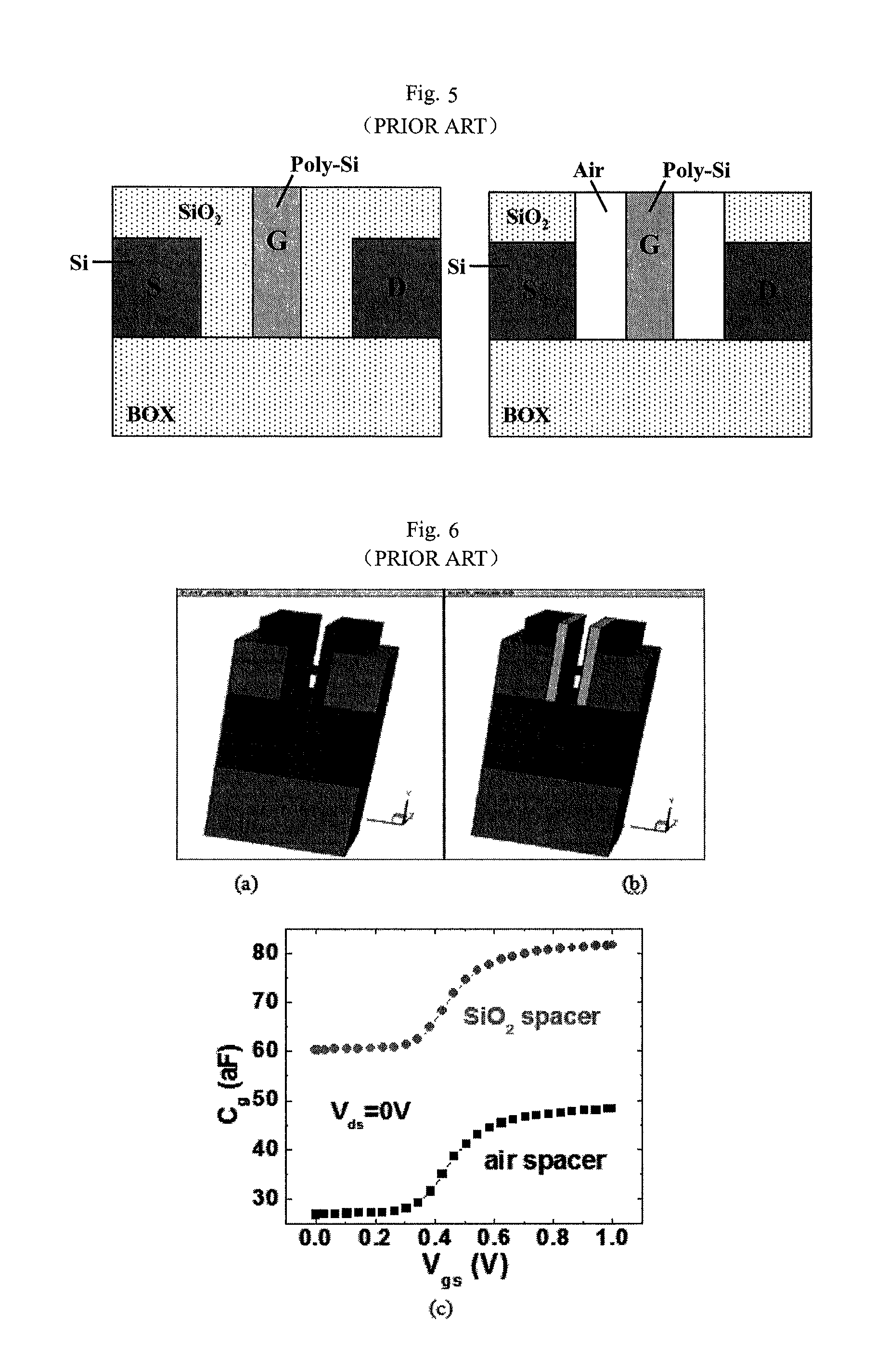

Fabrication method for surrounding gate silicon nanowire transistor with air as spacers

ActiveUS20130017654A1Reduce parasitic capacitanceImprove transient responseNanoinformaticsSemiconductor/solid-state device manufacturingDopantSilicon nanowires

The invention discloses a fabrication method for a surrounding gate silicon nanowire transistor with air as spacers. The method comprises: performing isolation, and depositing a material A which has a higher etch selectivity ratio with respect to Si; performing photolithography to define a Fin hard mask; etching the material A to form the Fin hard mask; performing source and drain implantation; performing photolithography to define a channel region and large source / drain regions; forming the Si Fin and the large source / drains; removing the hard mask of the material A; forming a nanowire; etching the SiO2 to form a floating nanowire; forming a gate oxide layer; depositing a polysilicon; performing polysilicon injection; performing annealing to activate dopants; etching the polysilicon; depositing SiN; performing photolithography to define a gate pattern; etching the SiN and the polysilicon to form the gate pattern; separating the gate and the source / drain with a space in between filled with air; depositing SiO2 to form air sidewalls; performing annealing to densify the SiO2 layer; using subsequent processes to complete the device fabrication. The invention is compatible with the CMOS process flow. The introduction of the air sidewalls can effectively reduce the parasitic capacitance of the device, and improve the transient response of the device, so that the method is applicable for a logic circuit with high performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Nanowire transistor with surrounding gate

Owner:MICRON TECH INC

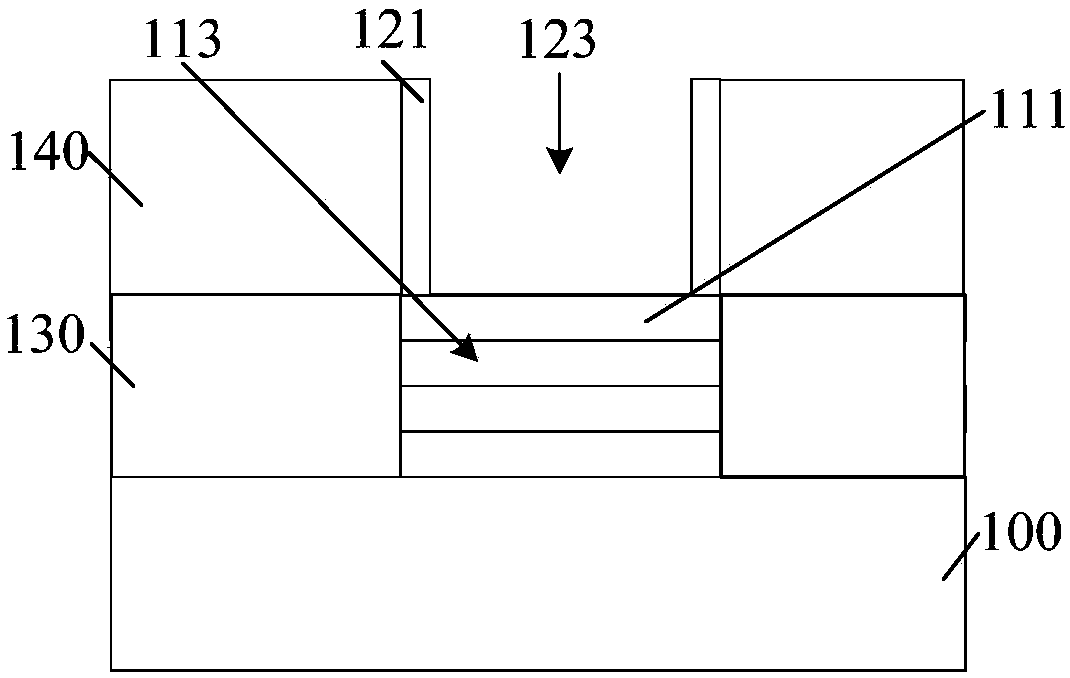

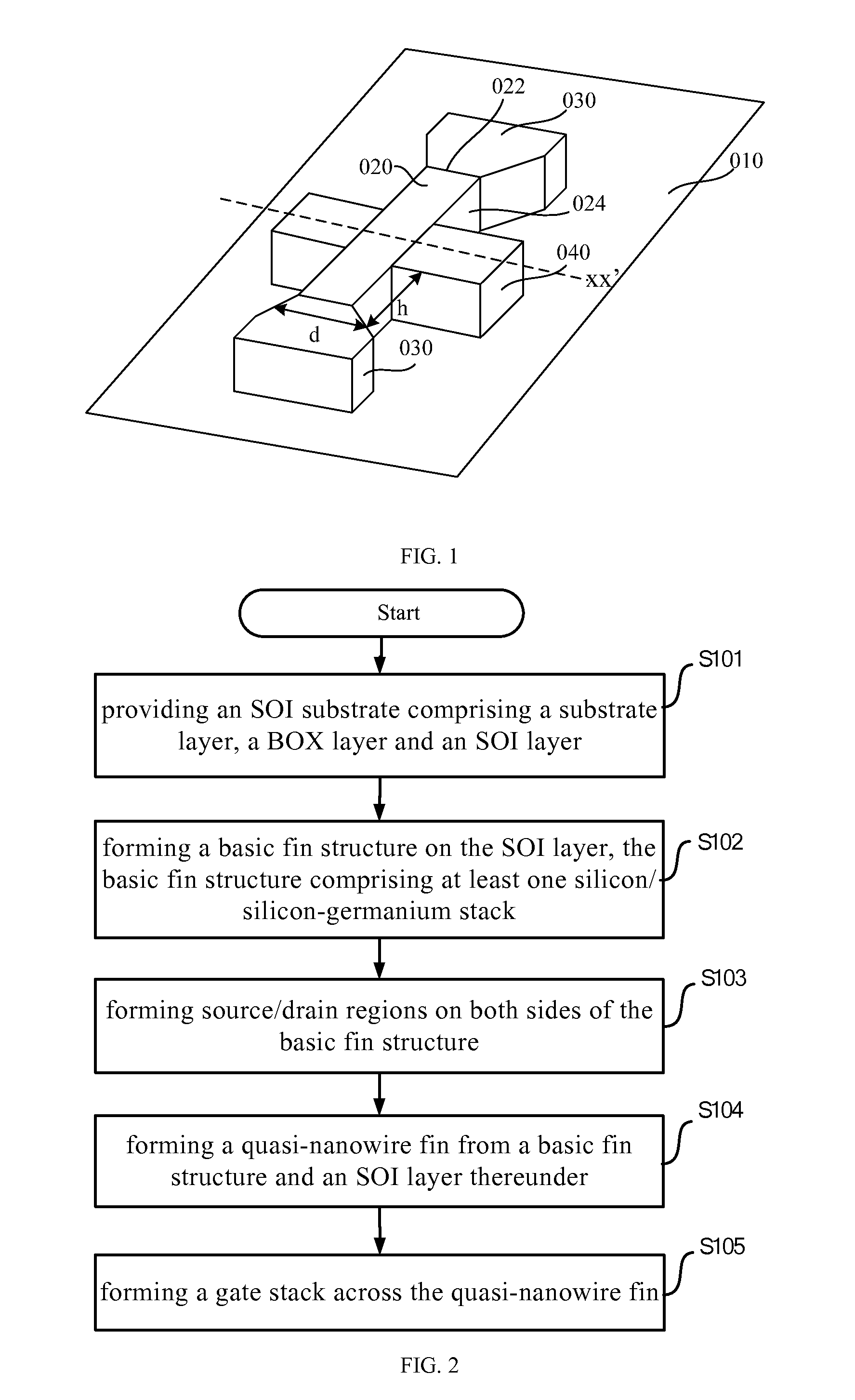

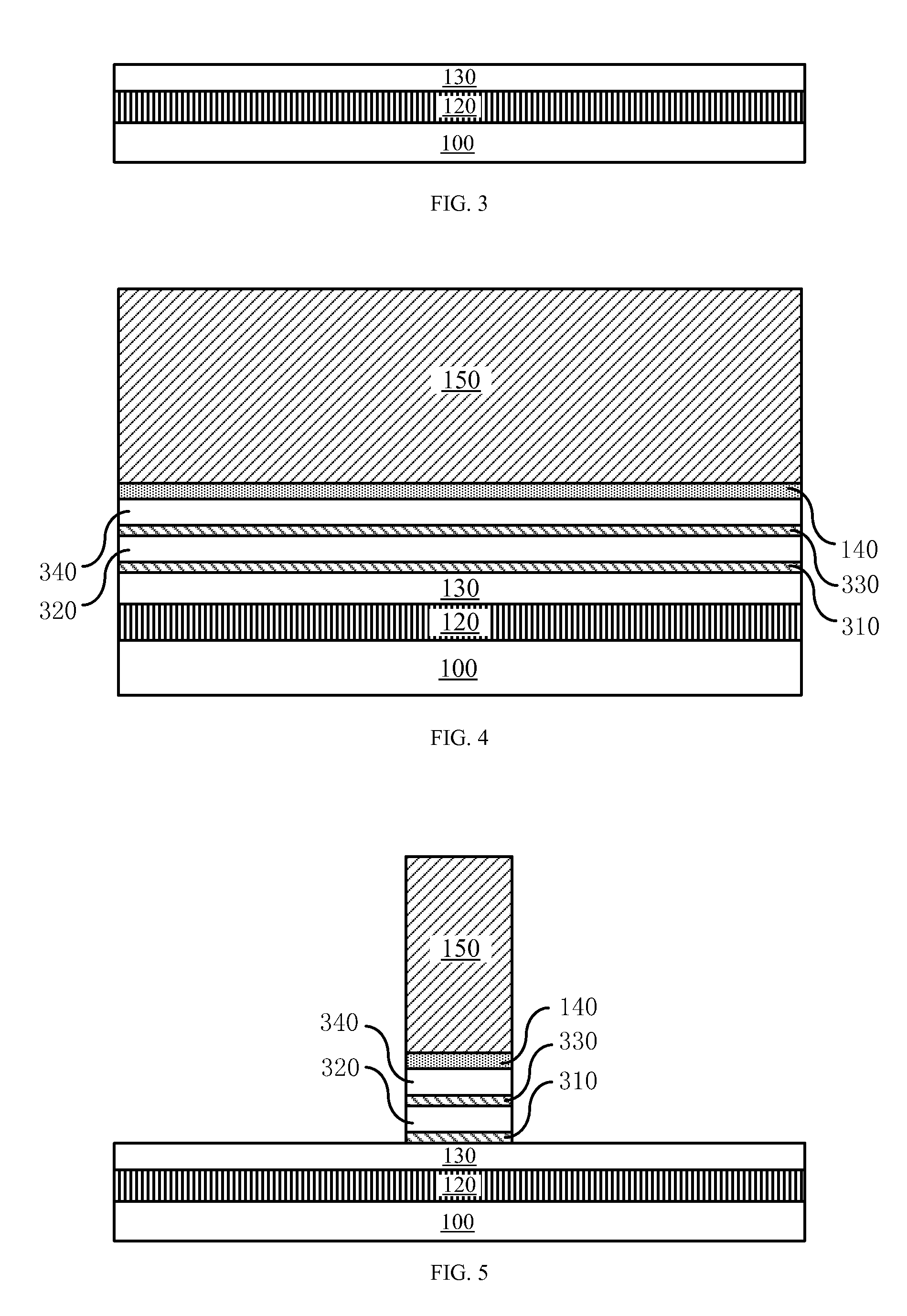

Quasi-nanowire transistor and method of manufacturing the same

InactiveUS20150255594A1Suppression of short channel effectsImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingNanowireSemiconductor structure

A quasi-nanowire transistor and a method of manufacturing the same are provided, the quasi-nanowire transistor comprising: providing an SOI substrate comprising a substrate layer (100), a BOX layer (120) and an SOI layer (130); forming a basic fin structure on the SOI layer, the basic fin structure comprising at least one silicon / silicon-germanium stack; forming source / drain regions (110) on both sides of the basic fin structure; forming a quasi-nanowire fin from a basic fin structure and an SOI layer thereunder; and forming a gate stack across the quasi-nanowire fin. The method can effectively control gate length characteristics. A semiconductor structure formed by the above method is also provided.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

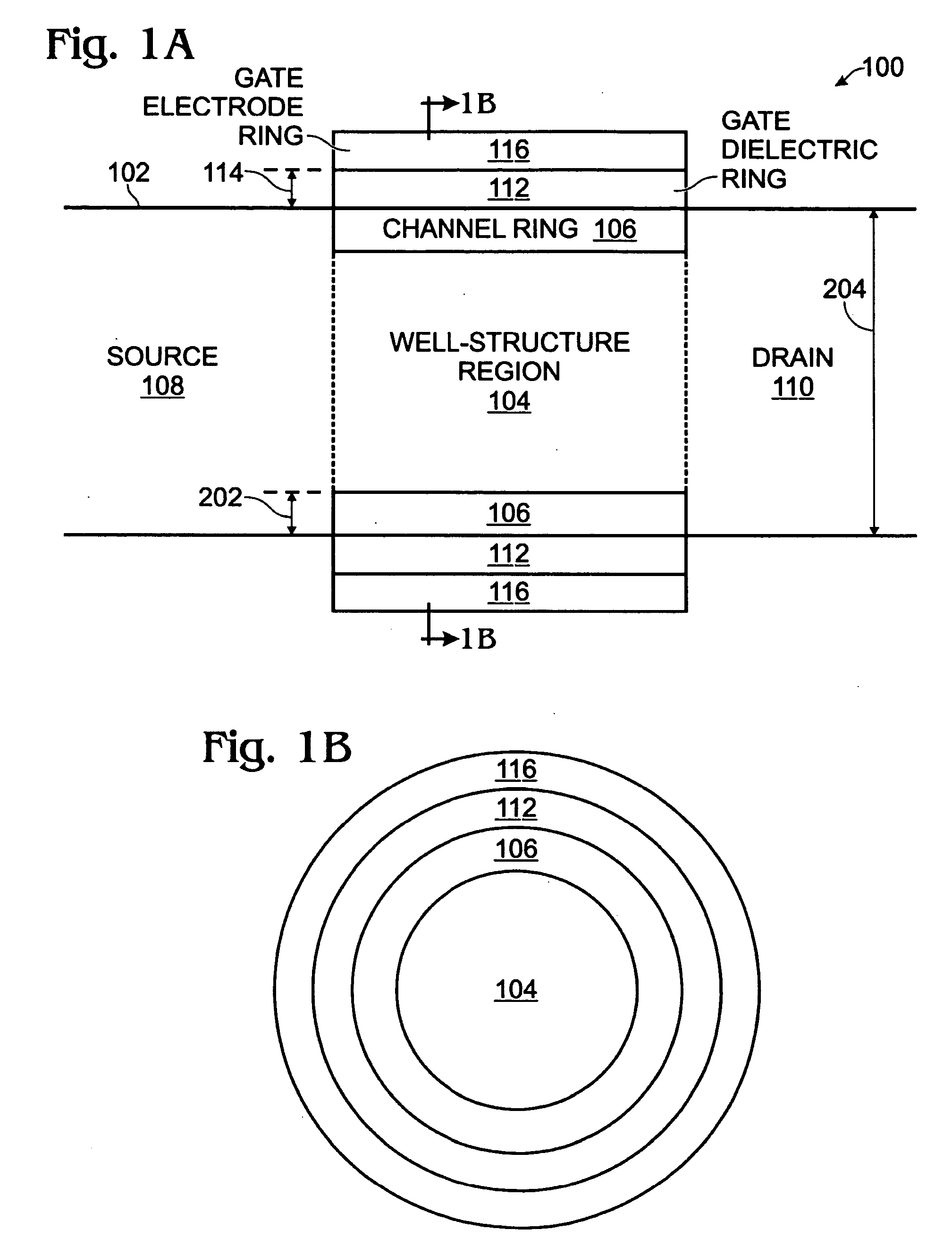

Well-Structure Anti-Punch-through Microwire Device

InactiveUS20100072455A1High yieldImprove uniformityNanoinformaticsSemiconductor/solid-state device manufacturingDopantGate dielectric

A well-structure anti-punch-through microwire device and associated fabrication method are provided. The method initially forms a microwire with alternating highly and lightly doped cylindrical regions. A channel ring is formed external to the microwire outer shell and surrounding a first dopant well-structure region in the microwire, between source and drain (S / D) regions of the microwire. The S / D regions are doped with a second dopant, opposite to the first dopant. A gate dielectric ring is formed surrounding the channel ring, and a gate electrode ring is formed surrounding the gate dielectric ring. The well-structure, in contrast to conventional micro or nanowire transistors, helps prevent the punch-through phenomena.

Owner:SHARP KK

Low contact resistance nanowire fets

ActiveUS20190280088A1Reduce contact resistanceTransistorSemiconductor/solid-state device manufacturingNanowireElectrical conductor

Systems and methods for forming a low contact resistance nanowire transistor are described. The transistor includes a gate formed over a substrate including a gate conductor. Gate spacers are formed on sides of the gate. At least one semiconductor nanowire is formed through the gate such that the at least one semiconductor nanowire extends through the gate conductor and the gate spacers and into source and drain regions grown from surfaces of the at least one semiconductor nanowire adjacent to sides of the gate to increase the surface area of the source drain region contacting the semiconductor nanowire.

Owner:IBM CORP

Fabrication method for surrounding gate silicon nanowire transistor with air as spacers

ActiveUS8513067B2Reduce parasitic capacitanceImprove transient responseNanoinformaticsSemiconductor/solid-state device manufacturingDopantSilicon nanowires

The invention discloses a fabrication method for a surrounding gate silicon nanowire transistor with air as spacers. The method comprises: performing isolation, and depositing a material A which has a higher etch selectivity ratio with respect to Si; performing photolithography to define a Fin hard mask; etching the material A to form the Fin hard mask; performing source and drain implantation; performing photolithography to define a channel region and large source / drain regions; forming the Si Fin and the large source / drains; removing the hard mask of the material A; forming a nanowire; etching the SiO2 to form a floating nanowire; forming a gate oxide layer; depositing a polysilicon; performing polysilicon injection; performing annealing to activate dopants; etching the polysilicon; depositing SiN; performing photolithography to define a gate pattern; etching the SiN and the polysilicon to form the gate pattern; separating the gate and the source / drain with a space in between filled with air; depositing SiO2 to form air sidewalls; performing annealing to densify the SiO2 layer; using subsequent processes to complete the device fabrication. The invention is compatible with the CMOS process flow. The introduction of the air sidewalls can effectively reduce the parasitic capacitance of the device, and improve the transient response of the device, so that the method is applicable for a logic circuit with high performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com