Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

205results about How to "Save packing space" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

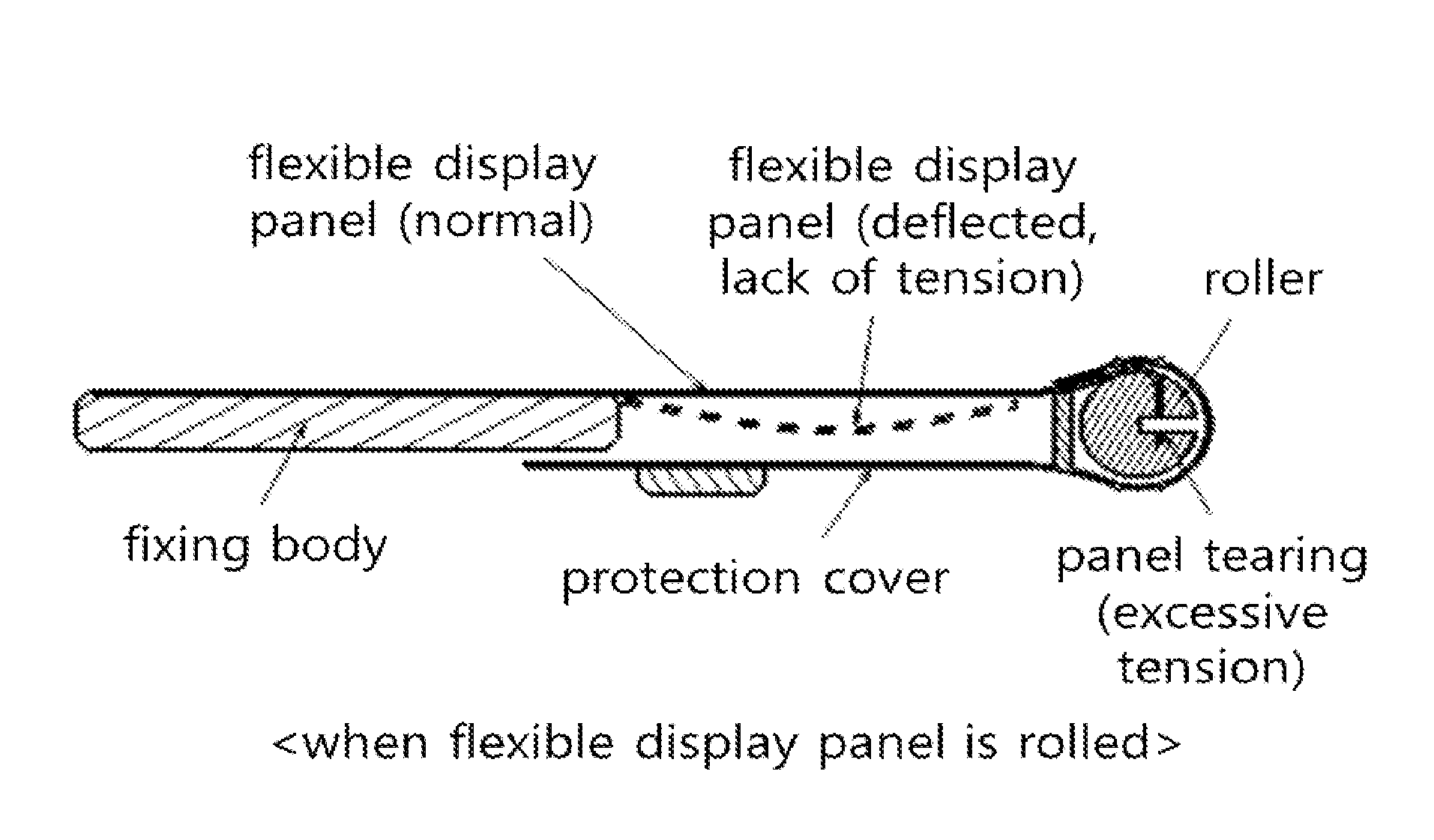

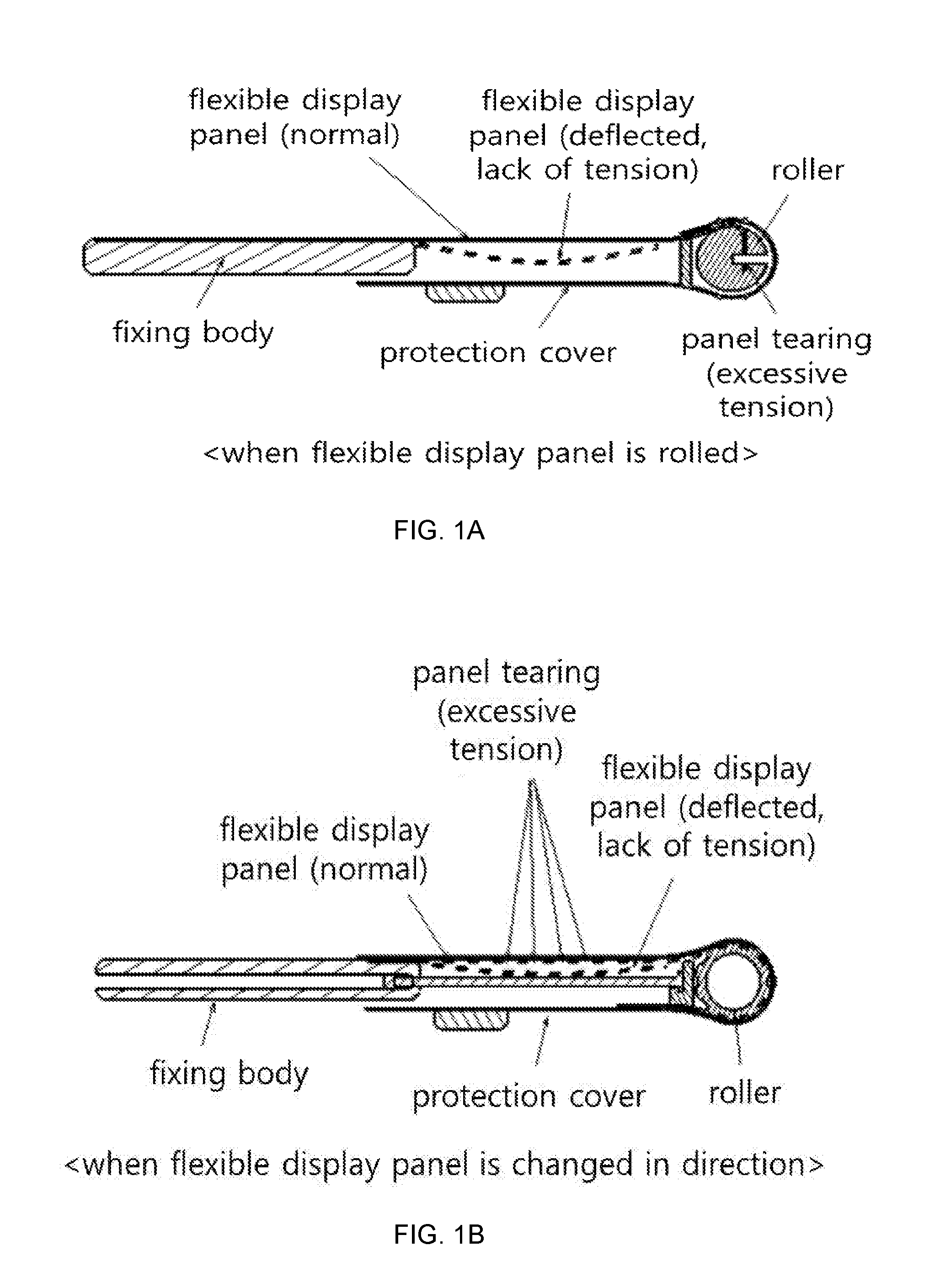

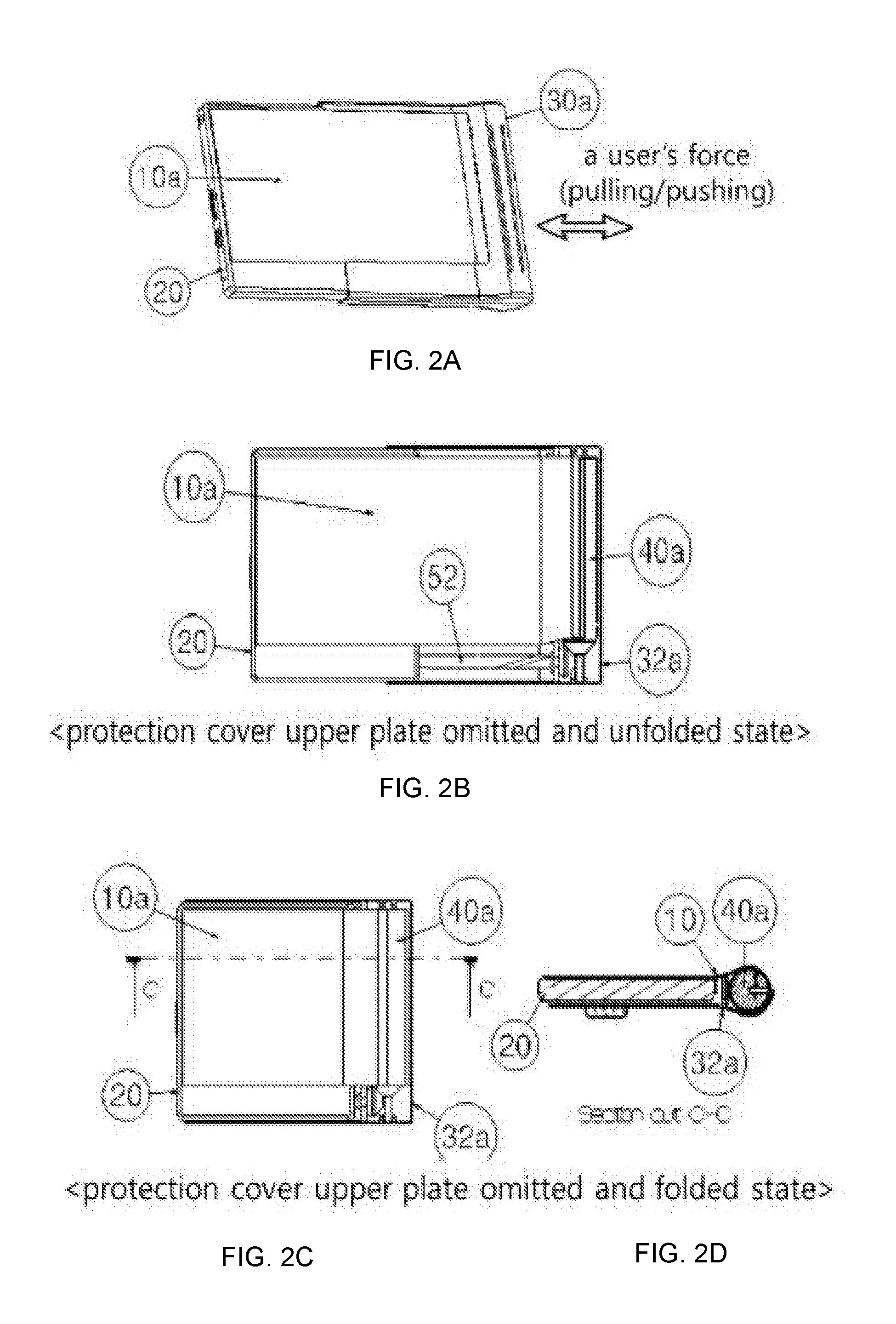

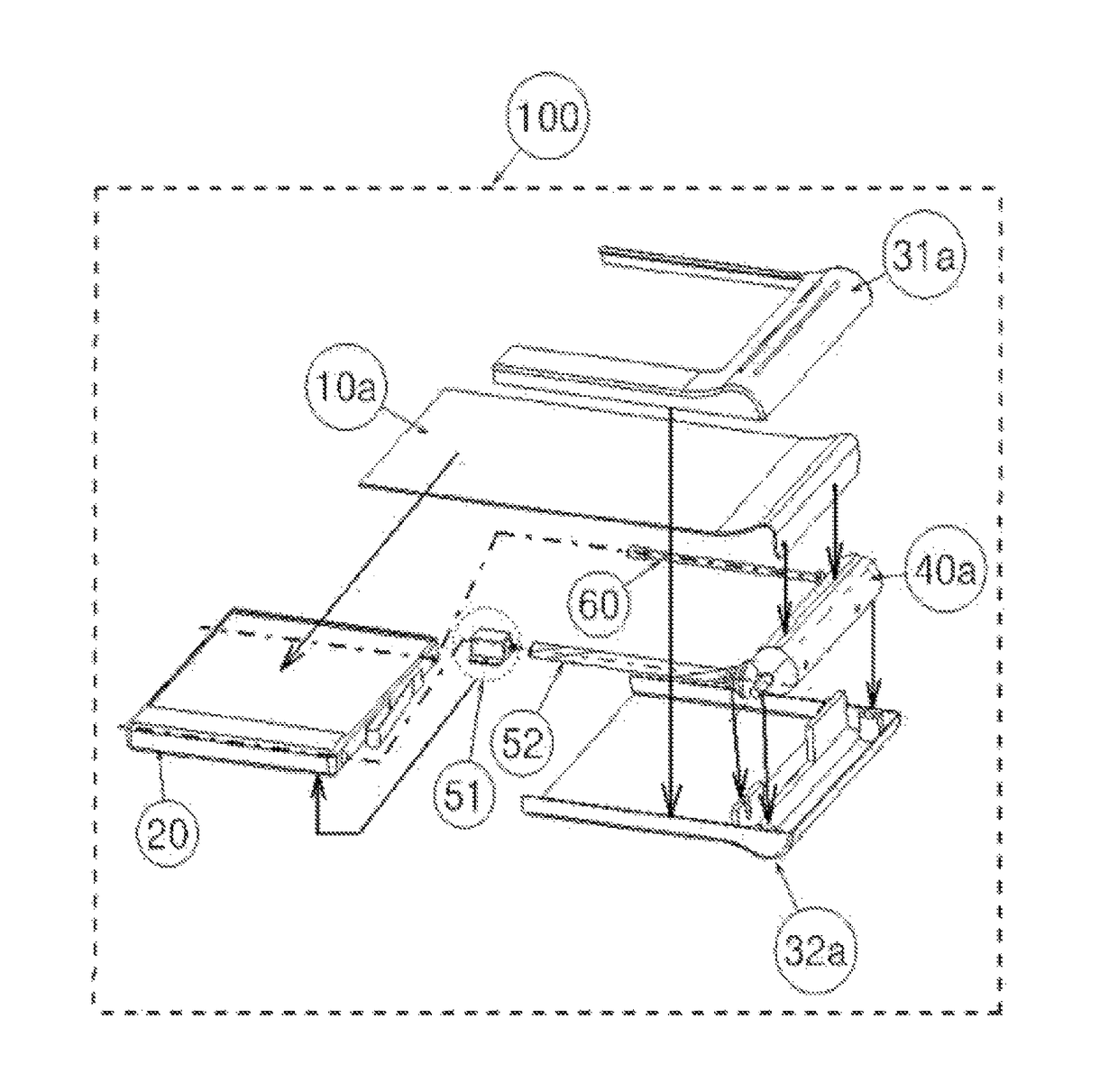

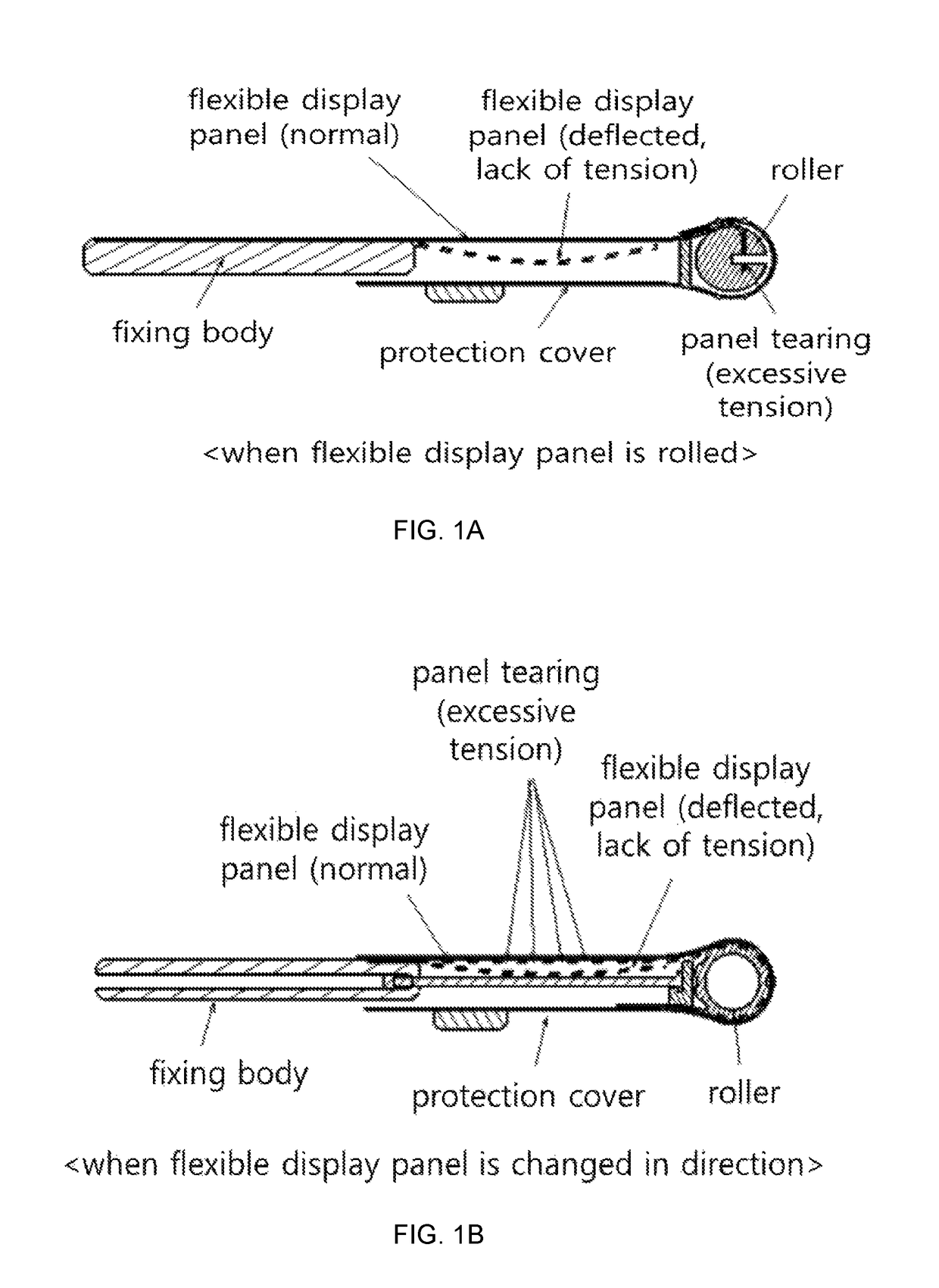

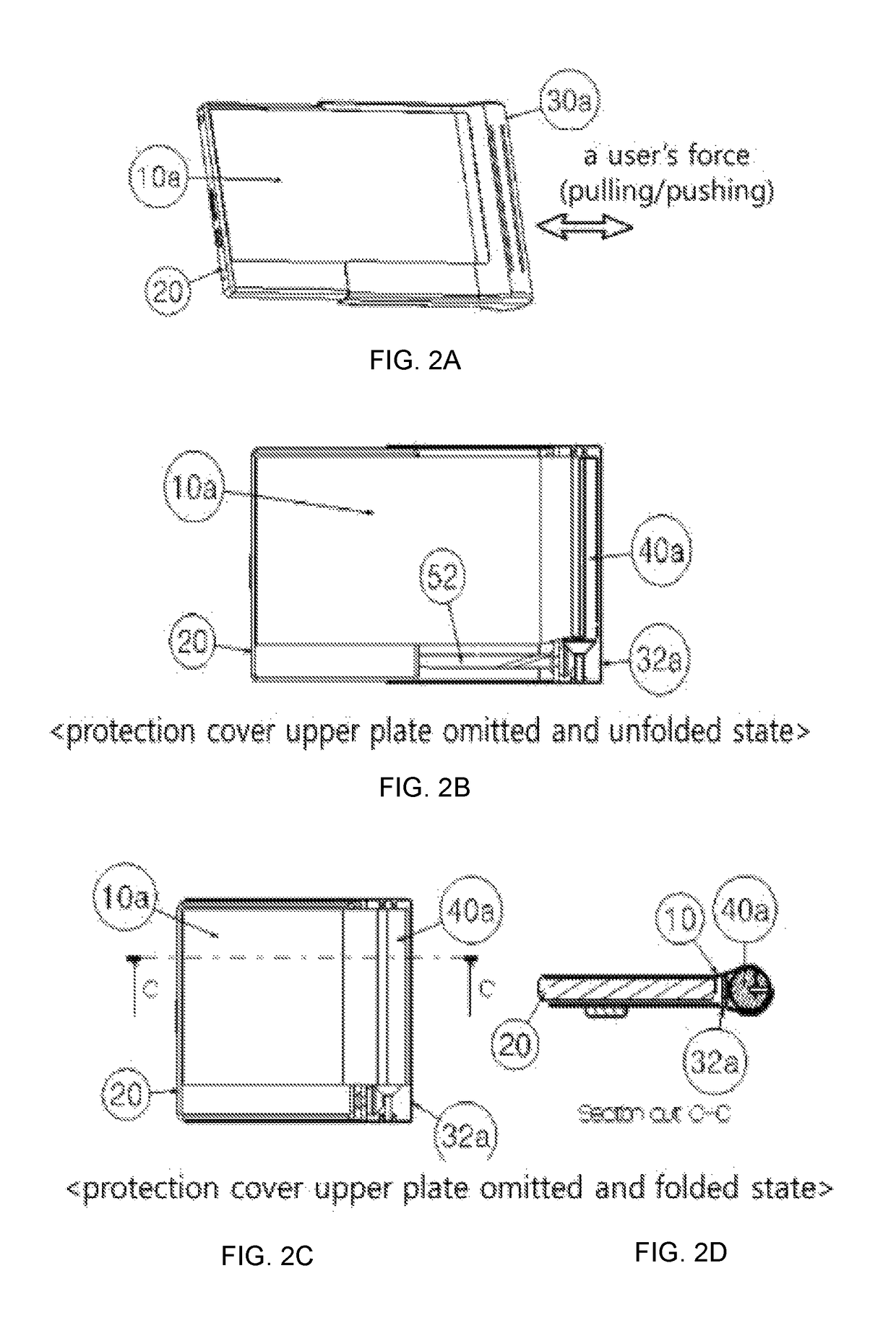

Flexible display apparatus having roller that rotates by unfolding operation-force of user

ActiveUS20170064847A1Save packing spaceLow costDigital data processing detailsCasings with display/control unitsMechanical componentsDisplay device

The present invention relates to a rollable flexible display apparatus to which an operation-force conversion apparatus is applied, wherein the operation-force conversion apparatus converts an unfolding or a folding operation-force linearly applied by a user to a housing of the rollable flexible display apparatus without the application of a motor or a spring into a rotation force with which a roller can rotate using the screw thread principle through an internal mechanical component, and conveys the converted rotational force to the roller.

Owner:LIM YOUSEOB

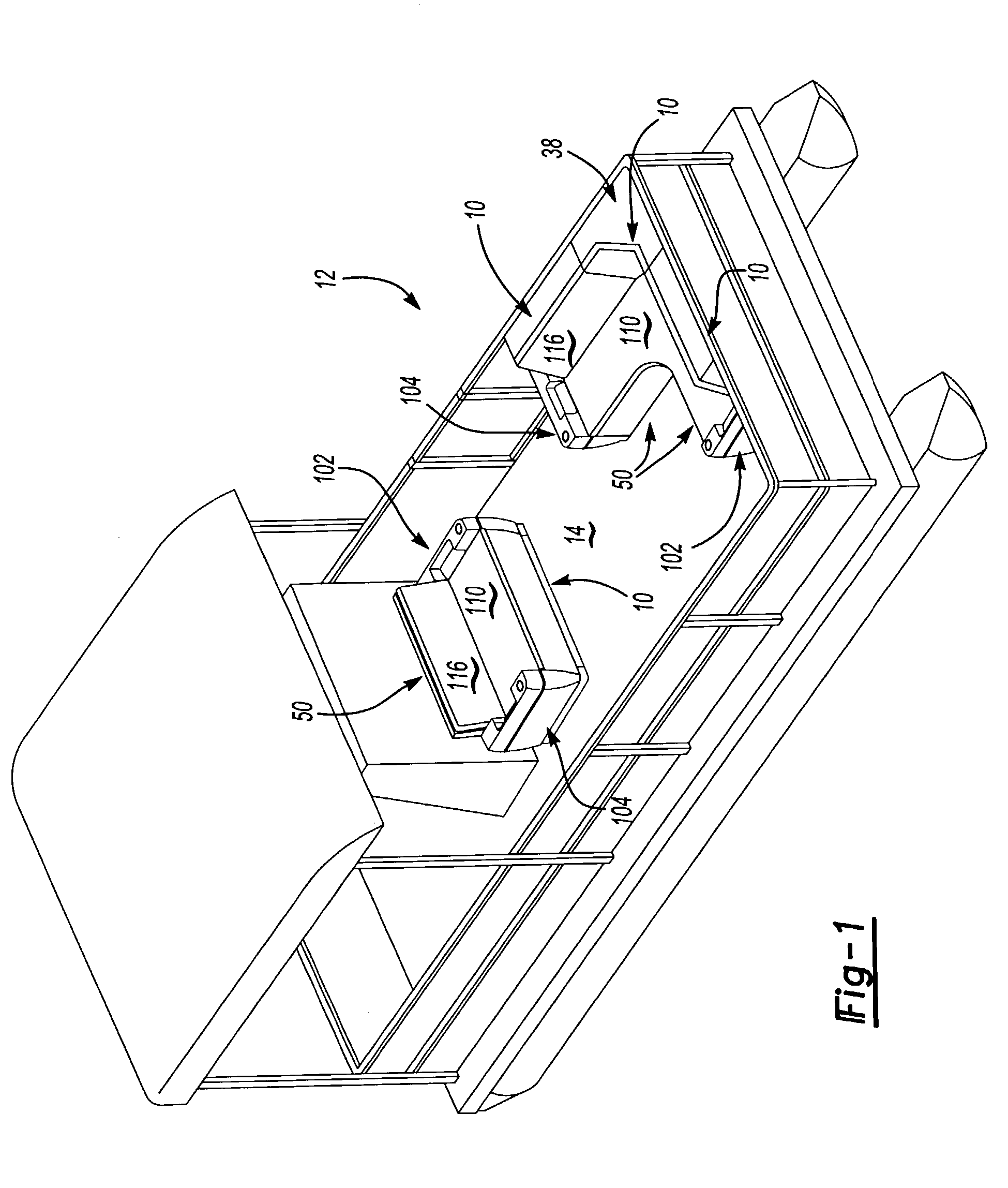

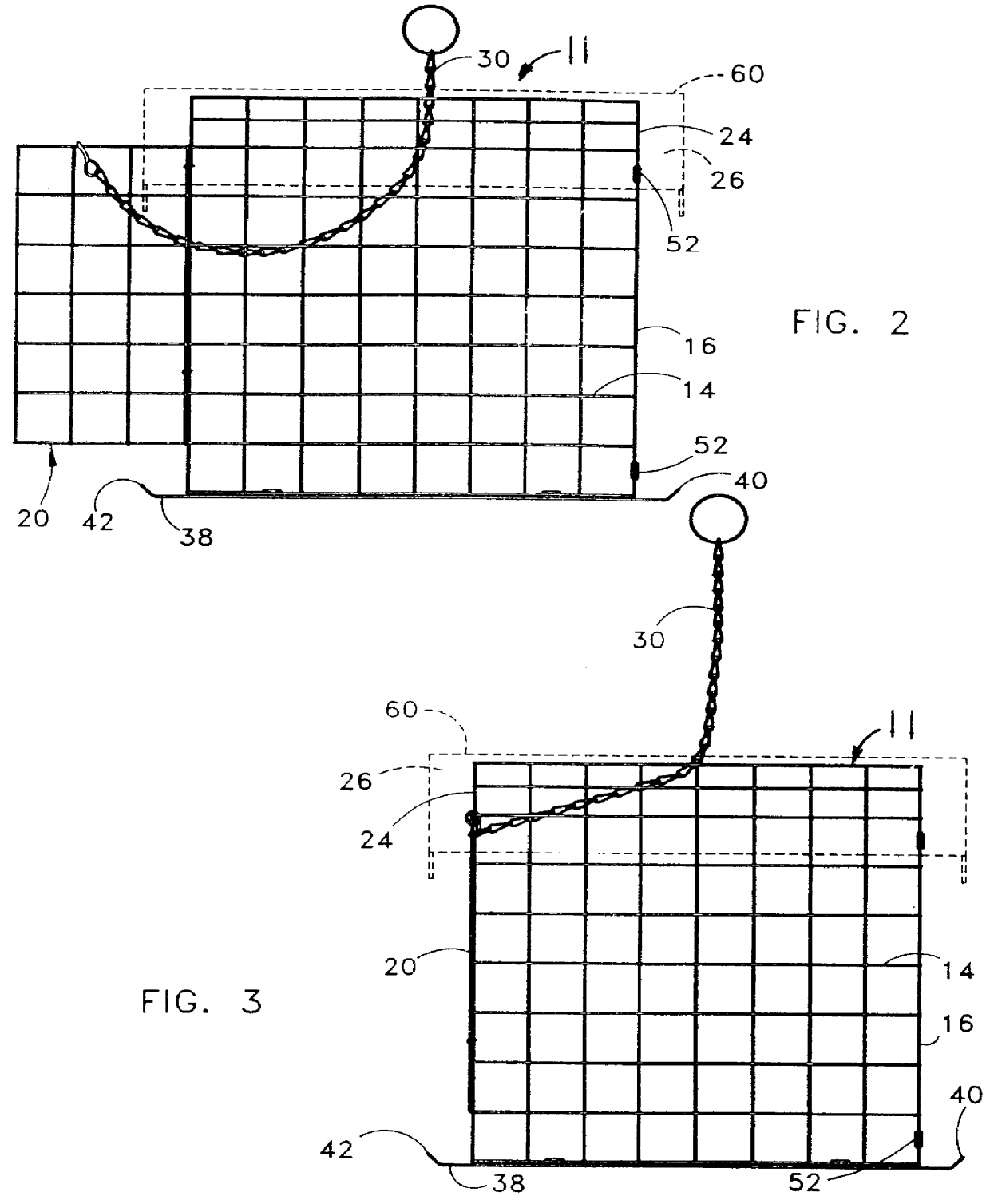

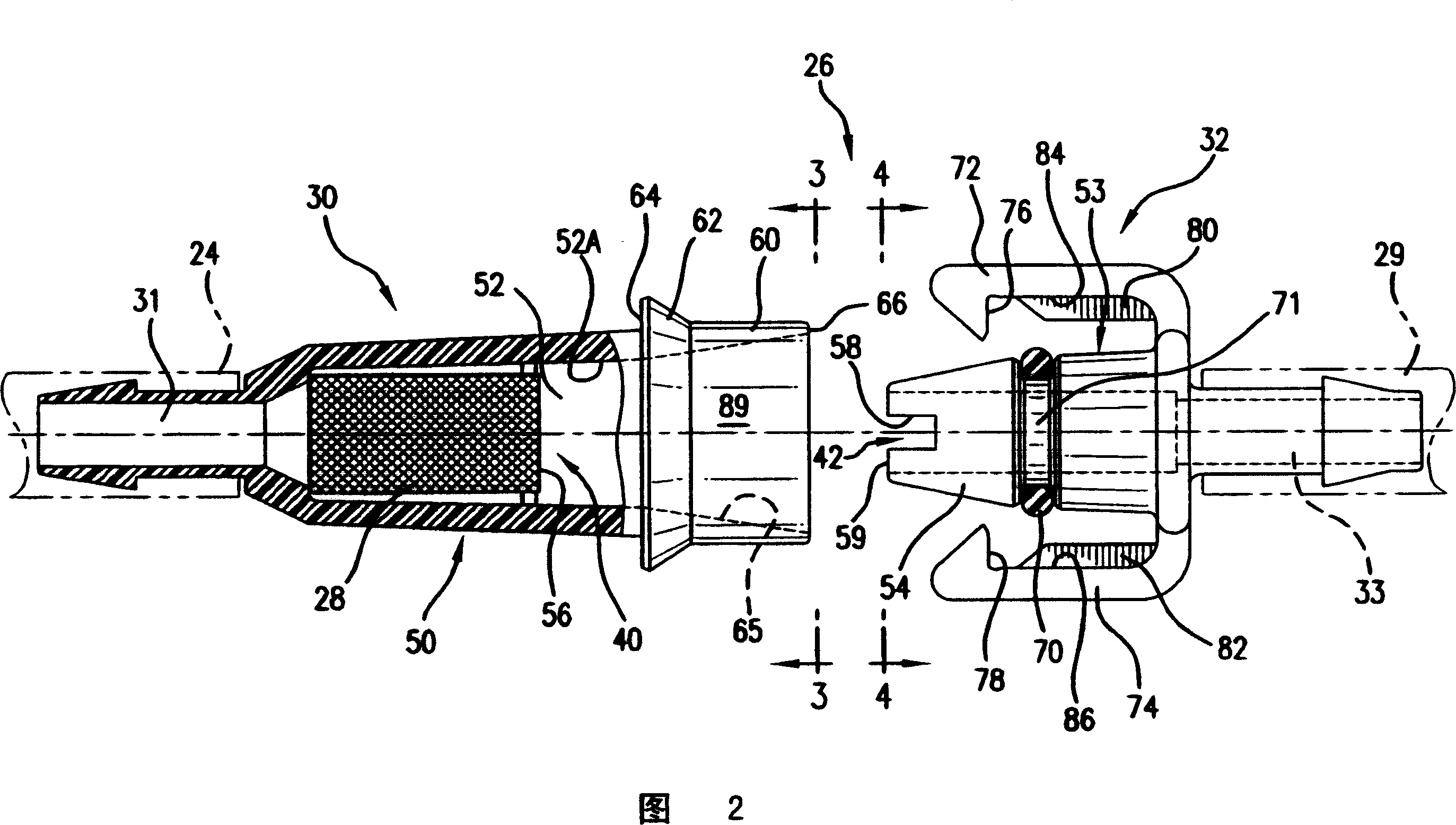

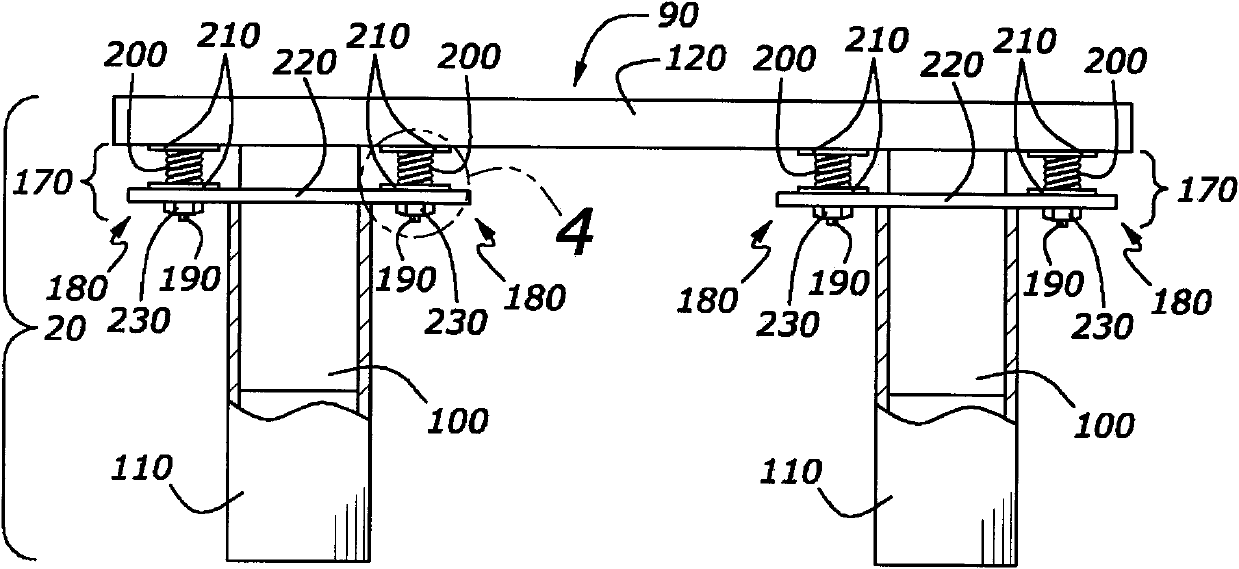

Take-down seating

InactiveUS7066548B2Save packing spaceReduce shipping expenseStands/trestlesRigid containersEngineeringMechanical engineering

A seat assembly (10) for use in a watercraft (12) having a deck (14) is provided. The seat assembly (10) comprises a first portion (16) and a second portion (18) spaced from the first portion (16). First (52) and second (54) connector panels that are separable from and independent of the first (16) and second (18) portions interconnect the first (16) and second (18) portions. A plurality of locking tabs (56) extend from each of the connector panels (52,54) and are inserted into a plurality of slots (58) defined in the portions (16,18) to connect the connector panels (52,54) to the first (16) and second (18) portions. A mounting bracket (84) is attached to a base (82) of each of the connector panels (52,54) and perpendicularly extends from the connector panels (52,54) to mount the connector panels (52,54) to the deck (14) thereby securing the first (16) and second (18) portions to the deck (14).

Owner:MOELLER MARINE PRODS

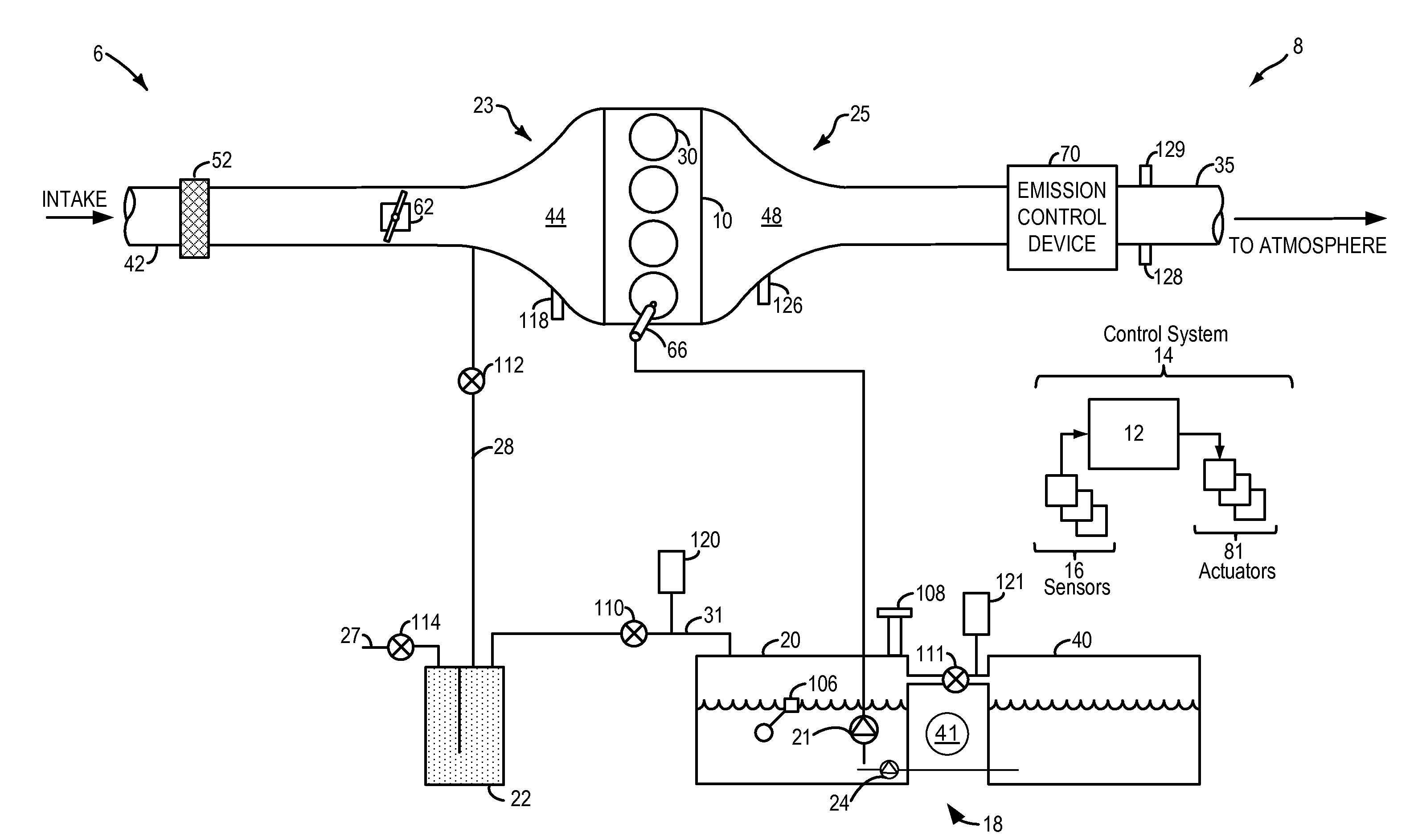

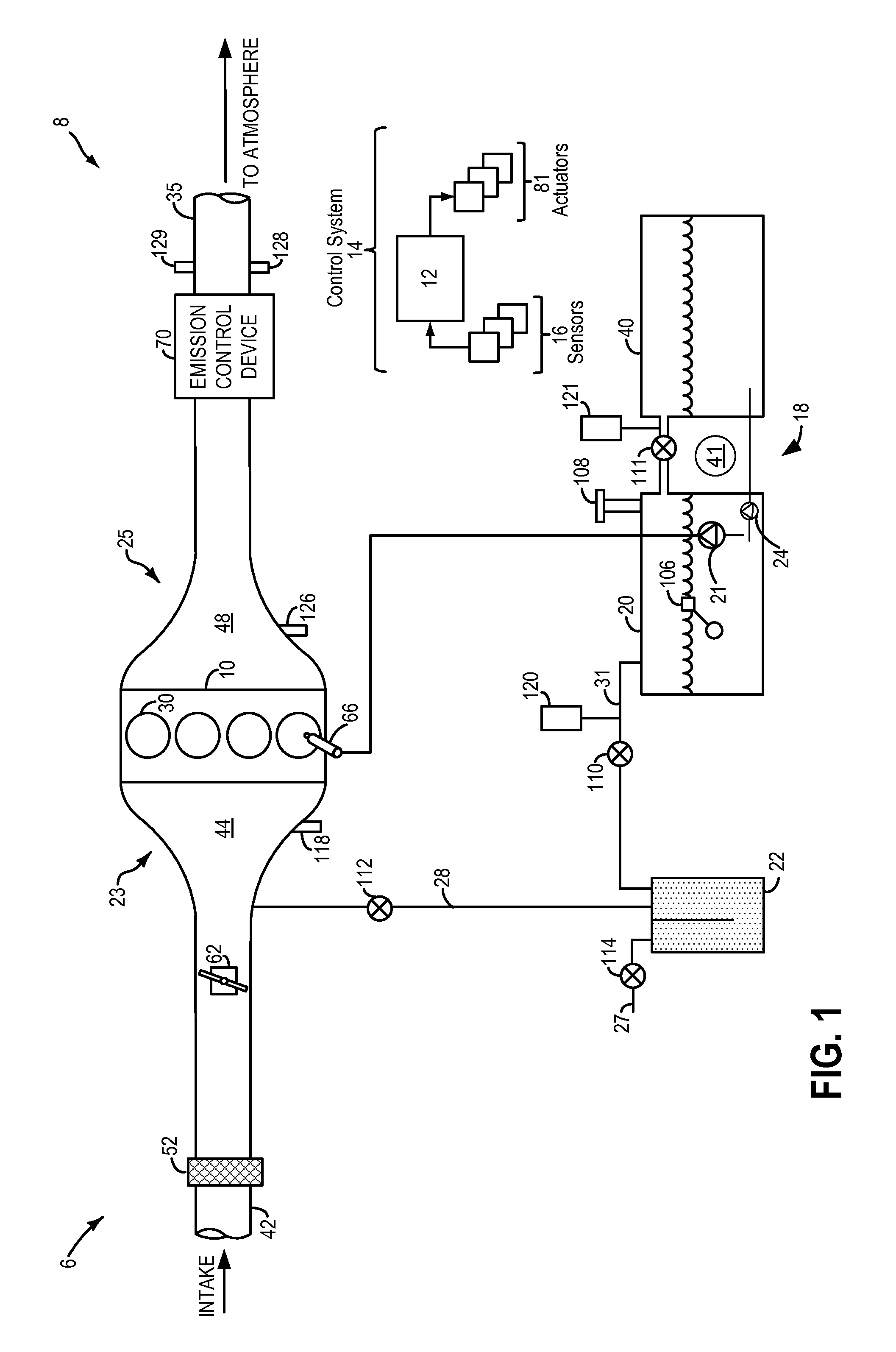

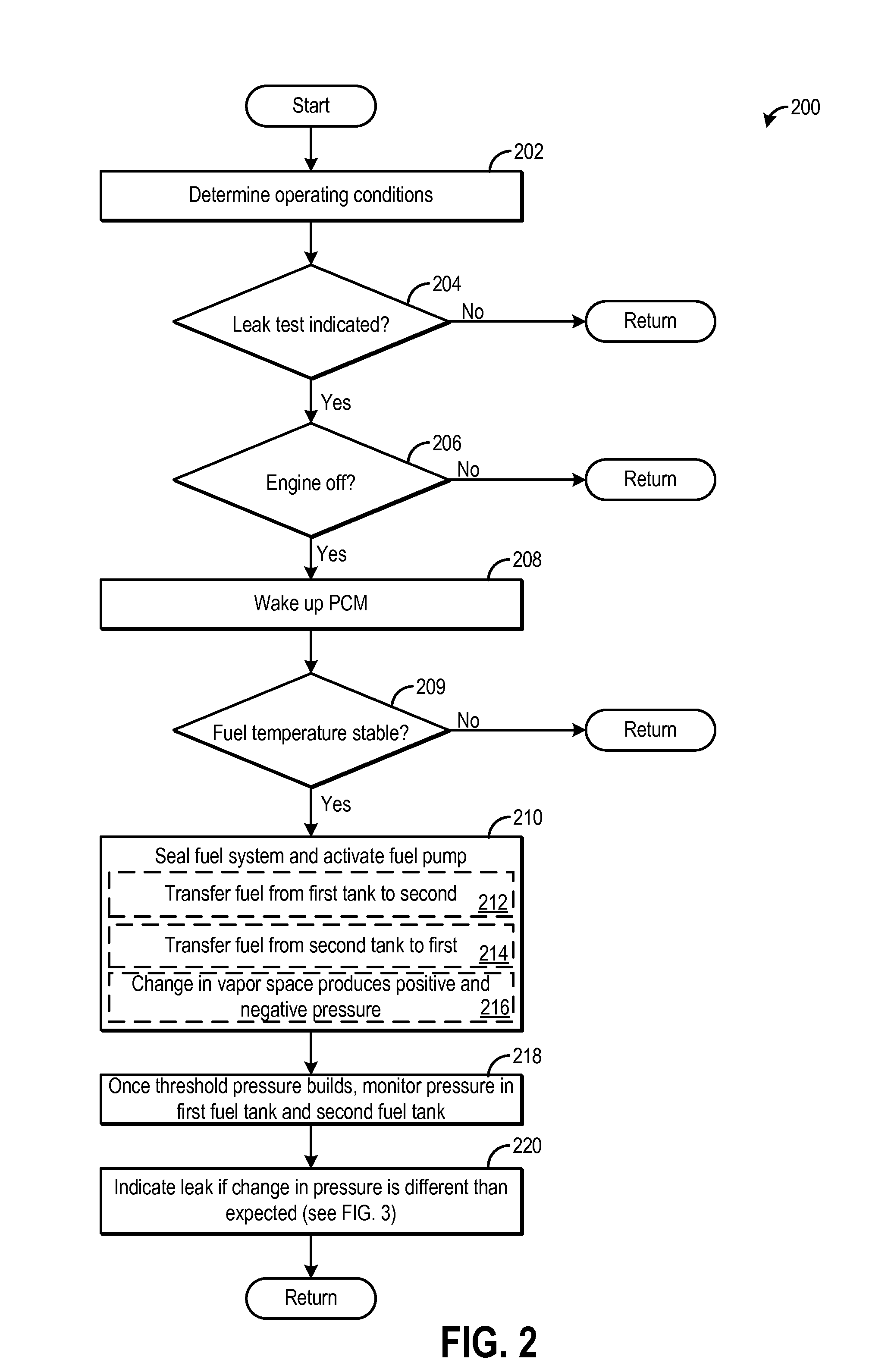

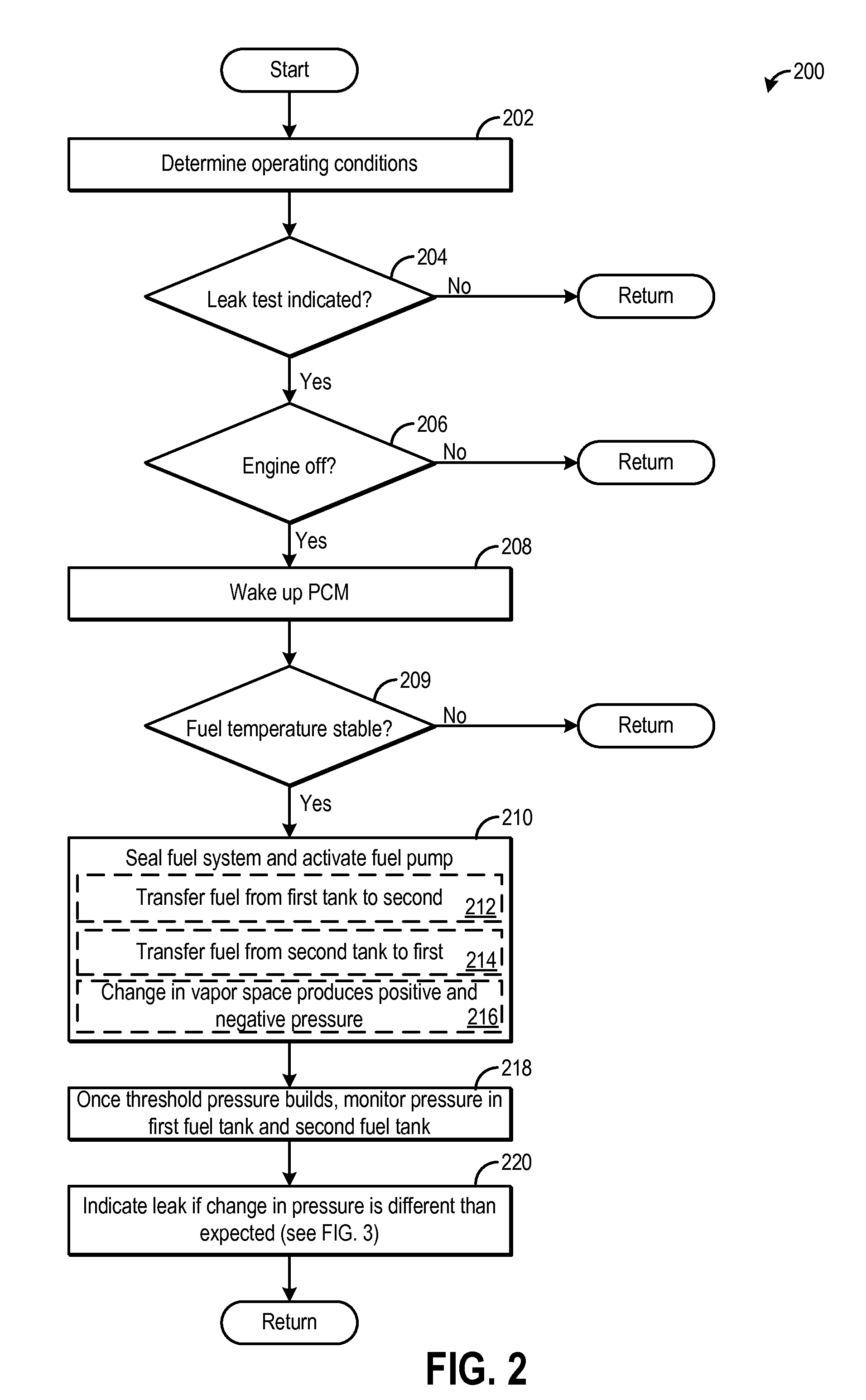

Fuel system degradation test using two fuel tanks

ActiveUS20140107906A1Saving engine packaging spaceImprove engine efficiencyHybrid vehiclesAnalogue computers for vehiclesSystem pressureFuel tank

Embodiments for monitoring fuel system degradation are provided. In one example, a method for a vehicle comprises evacuating fuel from a first fuel tank to a second fuel tank, and indicating fuel system degradation in response to a change in fuel system pressure following the evacuation of fuel. In this way, fuel system degradation may be indicated without use of a separate pressure building device.

Owner:FORD GLOBAL TECH LLC

Integrated two-speed motor

InactiveUS7316627B2Save packing spaceReduce weightElectric devicesElectric propulsion mountingLow speedGear wheel

A vehicle drive assembly includes an integrated two-speed motor that can selectively drive an output at a high operating speed or a low operating speed. The two-speed motor includes a stator mounted to a non-rotating outer housing, and a rotor that is mounted for rotation relative to the stator. The rotor is supported an inner rotor support that defines an inner cavity. A two-speed shifting mechanism is incorporated into the inner cavity and is used to drive an output. The two-speed shifting mechanism includes a gear assembly and first and second clutch assemblies that cooperate with each other to provide low and high speed output capability as needed.

Owner:ARVINMERITOR TECH

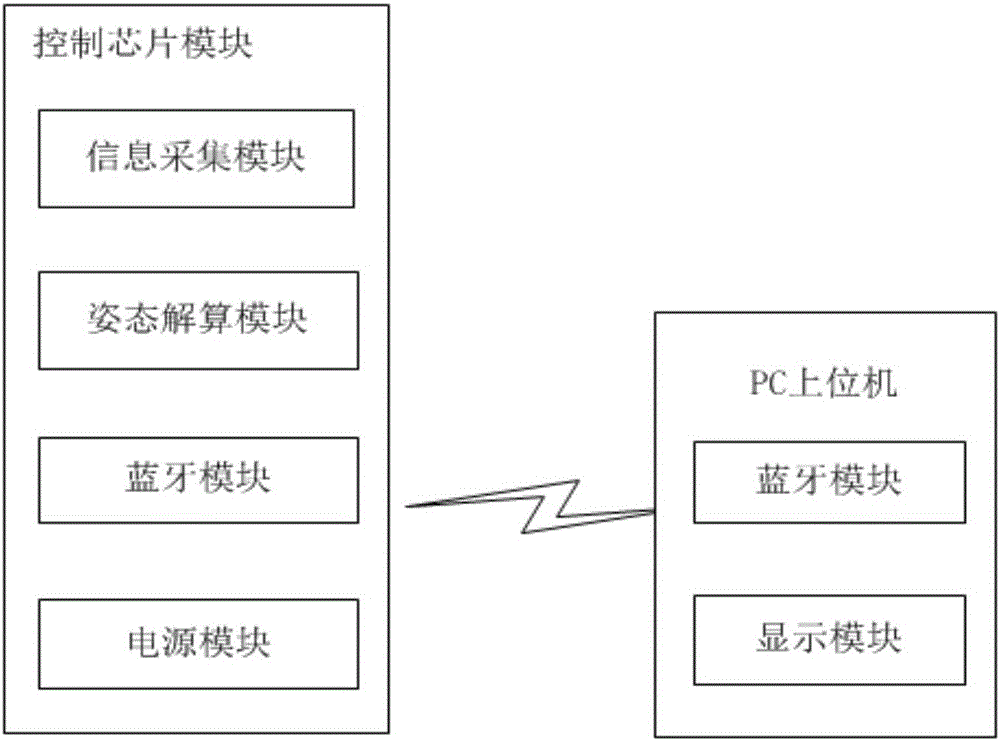

Device and method for monitoring of pig attitudes based on micro-inertial sensor

InactiveCN105850773AReduce volumeRealize complementary advantagesDiagnostic recording/measuringSensorsPhysical medicine and rehabilitationSimulation

A pig posture monitoring device and method based on a micro-inertial sensor, the device includes an information collection module for collecting individual information of pigs; a posture calculation module for fusing and filtering the information collected by the information collection module and outputting the posture angle; and The PC host computer used to recognize the attitude of pigs according to the output results of the attitude calculation module, the invention saves packaging space, and adopts the fourth-order Runge-Kutta optimization algorithm to update the attitude information, through the dynamic Kalman filter model, using the acceleration The gyroscope and magnetometer compensate the drift of the gyroscope, realize the complementary advantages of the gyroscope attitude and the accelerometer and magnetometer attitude, improve the accuracy and reliability of the dynamic measurement of the system, not only significantly reduce the equipment cost, but also have strong applicability. It can meet the requirements of real-time monitoring, and can replace the breeders to observe the posture of the pigs at each moment, so as to detect the suspected pigs early and reduce economic losses.

Owner:NORTHWEST A & F UNIV

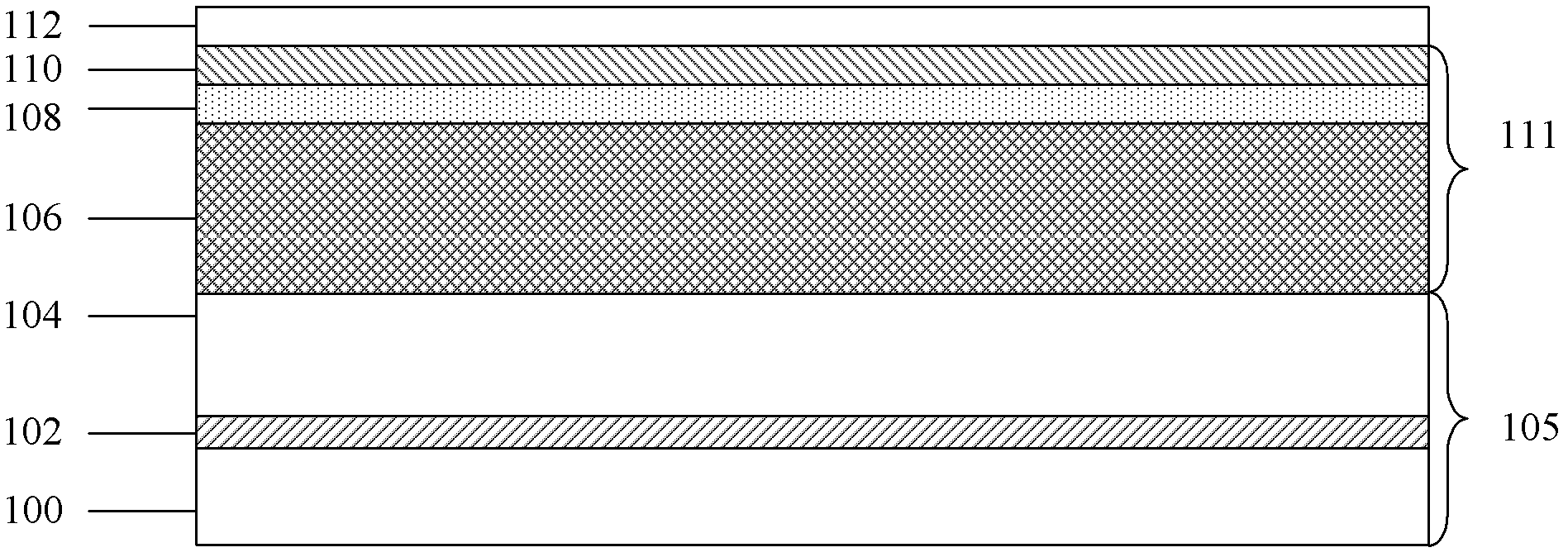

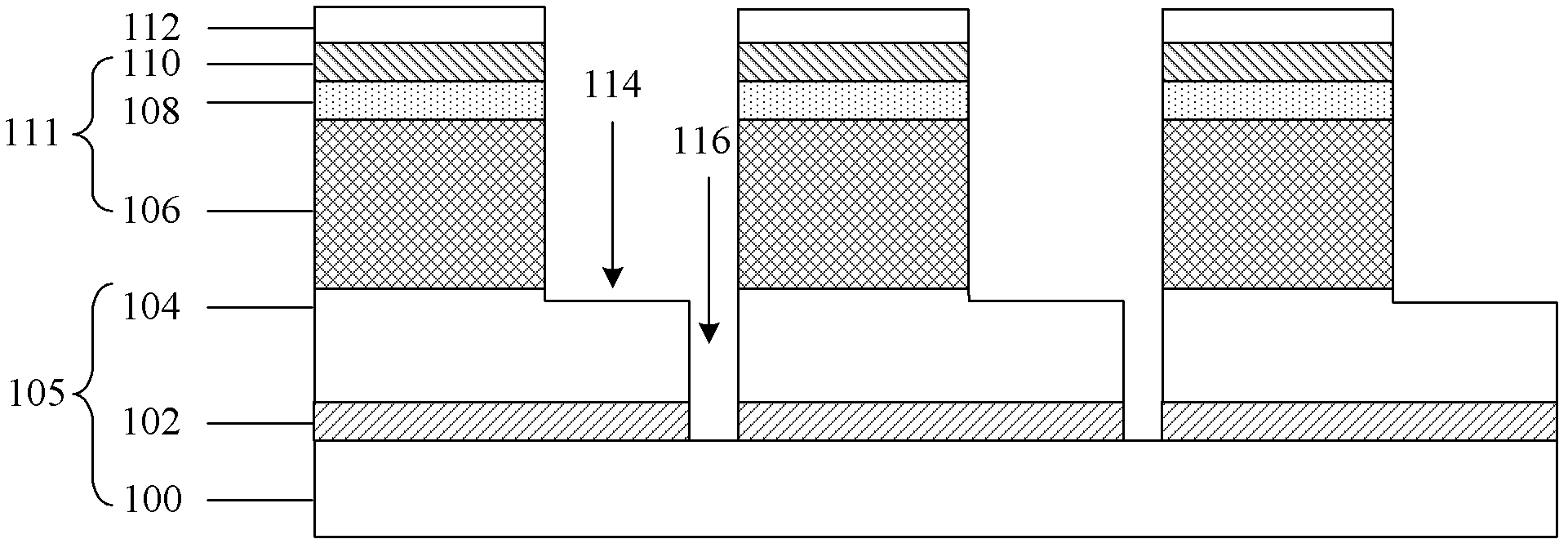

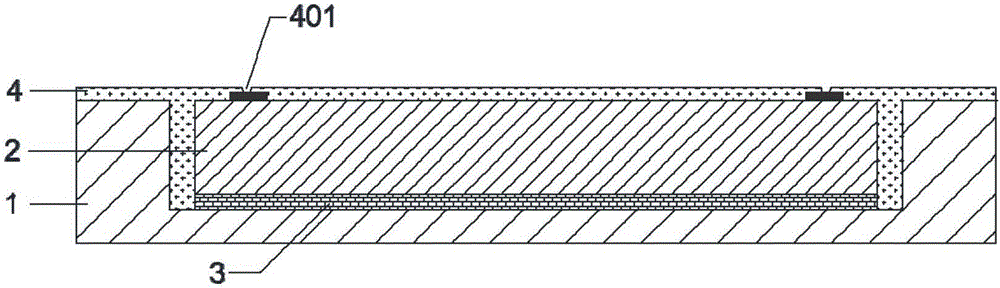

LED (light-emitting diode) packaging structure and manufacturing method thereof

InactiveCN102214649AImprove light extraction efficiencyAchieve integrationSolid-state devicesSemiconductor devicesOn boardEngineering

The invention discloses an LED (light-emitting diode) packaging structure which is characterized in that an LED device module structure is adopted, thus respective scribing is not carried out on each LED chip, thereby saving processes and reducing manufacturing cost; and an inversion structure is adopted to improve overall performances of LEDs. The invention also discloses a manufacturing method of the LED packaging structure. In the manufacturing method, the LED module, an LED drive circuit and an ESD protection circuit are invertedly fixed on the substrate of a COB (chip on board) packagingbonding tray directly by metal bump spot welding balls, so that the overall performances of the LEDs are improved; and because each LED module comprises a plurality of LED chip units which are connected by the same substrate, the respective scribing is not required to carry out on each LED chip, thus saving the processes and reducing the manufacturing cost.

Owner:ENRAYTEK OPTOELECTRONICS

Fastening clip for releasably fastening a dispensing device for dispensing active substances into the flushing liquid on a downward pointing edge element of a toilet bowl, and dispensing device provided with a fastening clip of this type

InactiveUS20070204389A1Save packing spaceEasy to installLavatory sanitoryMechanical engineeringToilet

The invention relates to a fastening clip (3) for releasably fastening a dispensing device (1) for the dispensing one or more active substances into the flushing liquid in a toilet bowl, and to a dispensing device provided with a corresponding fastening clip. The fastening clip (3) comprises and inner clamping limb (4) and an outer clamping limb (5), these clamping limbs (4, 5) being joined to one another at one end either directly or via a joining element (6). The clamping limbs (4, 5) are pretensioned toward one another and, with regard to shape and tensioning force, are designed in such a manner that when the fastening clip is in a fastening position inside a toilet bowl, the clamping limbs (4, 5) seize a downward pointing edge element of the toilet bowl in a clamping manner.

Owner:HENKEL KGAA

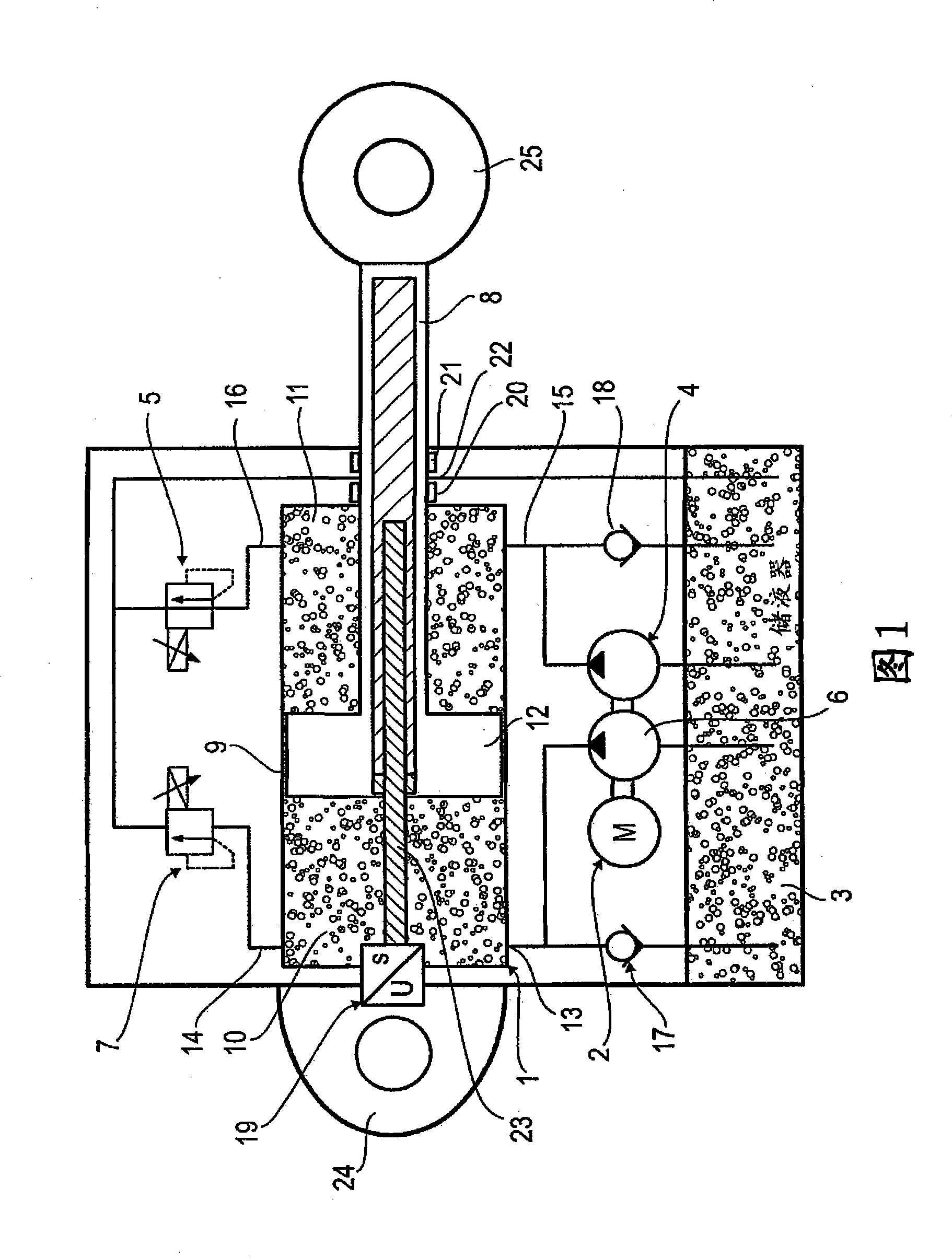

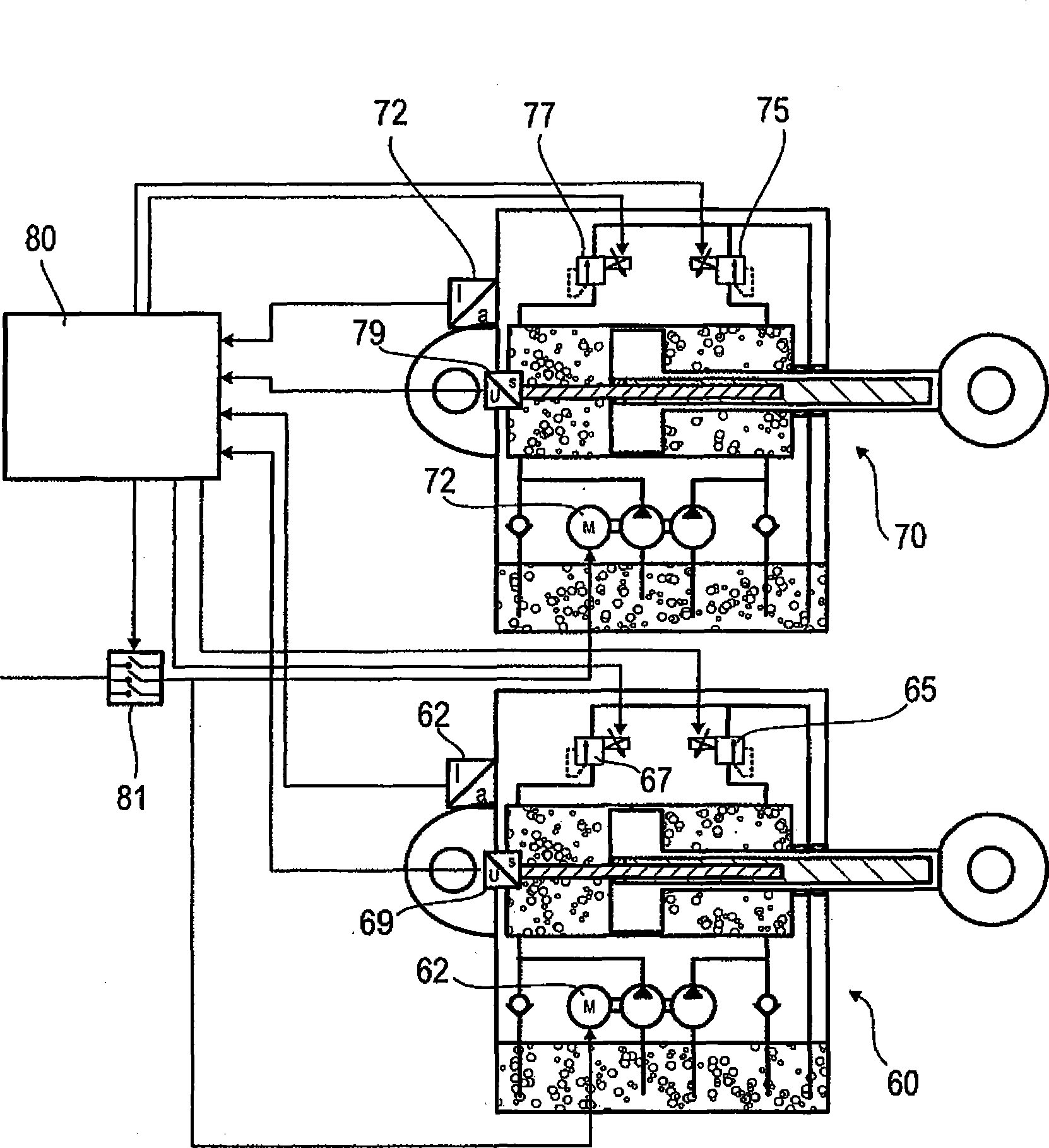

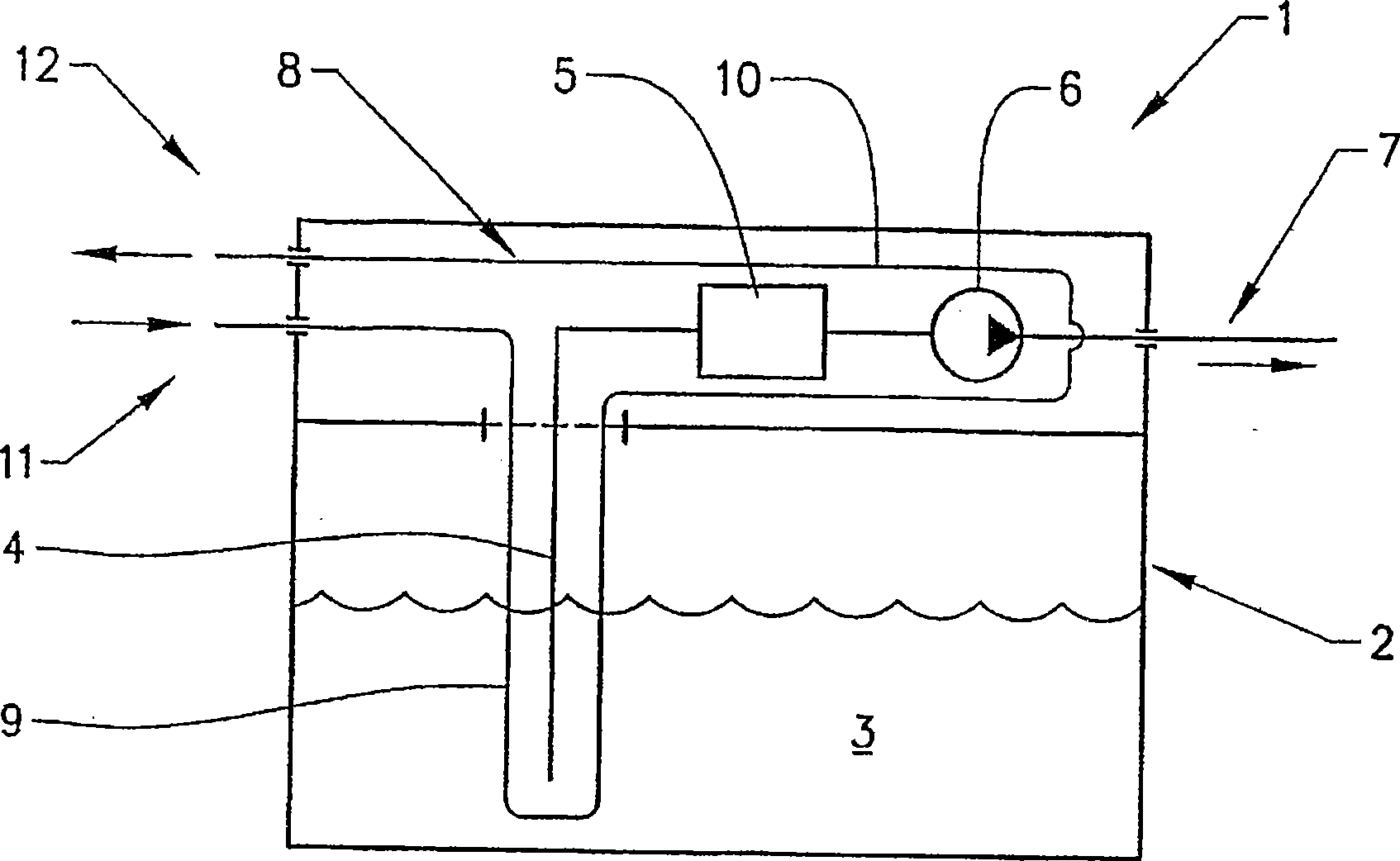

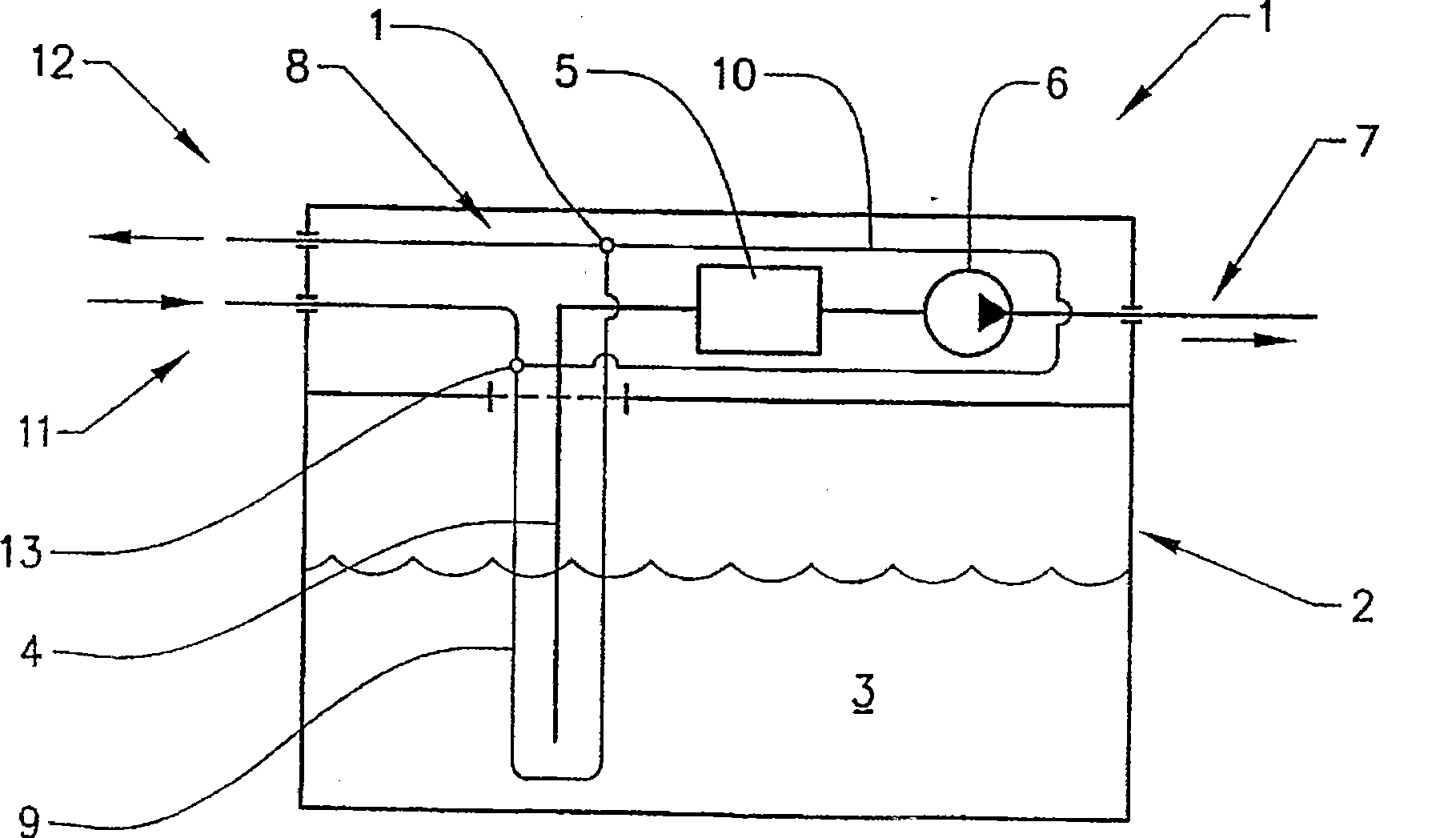

Active hydraulic damper and hydraulic actuator

ActiveCN101392809ASave packing spaceReduce weightSpringsLiquid based dampersHydraulic cylinderActuator

The invention relates to an active hydraulic damper specially for railway vehicles, comprising a hydraulic cylinder, an electric motor, a hydraulic accumulator, at least a pump and at least a control valve. According to the invention, all components of the active hydraulic damper are arranged at the hydraulic cylinder.

Owner:利勃海尔运输系统股份有限公司

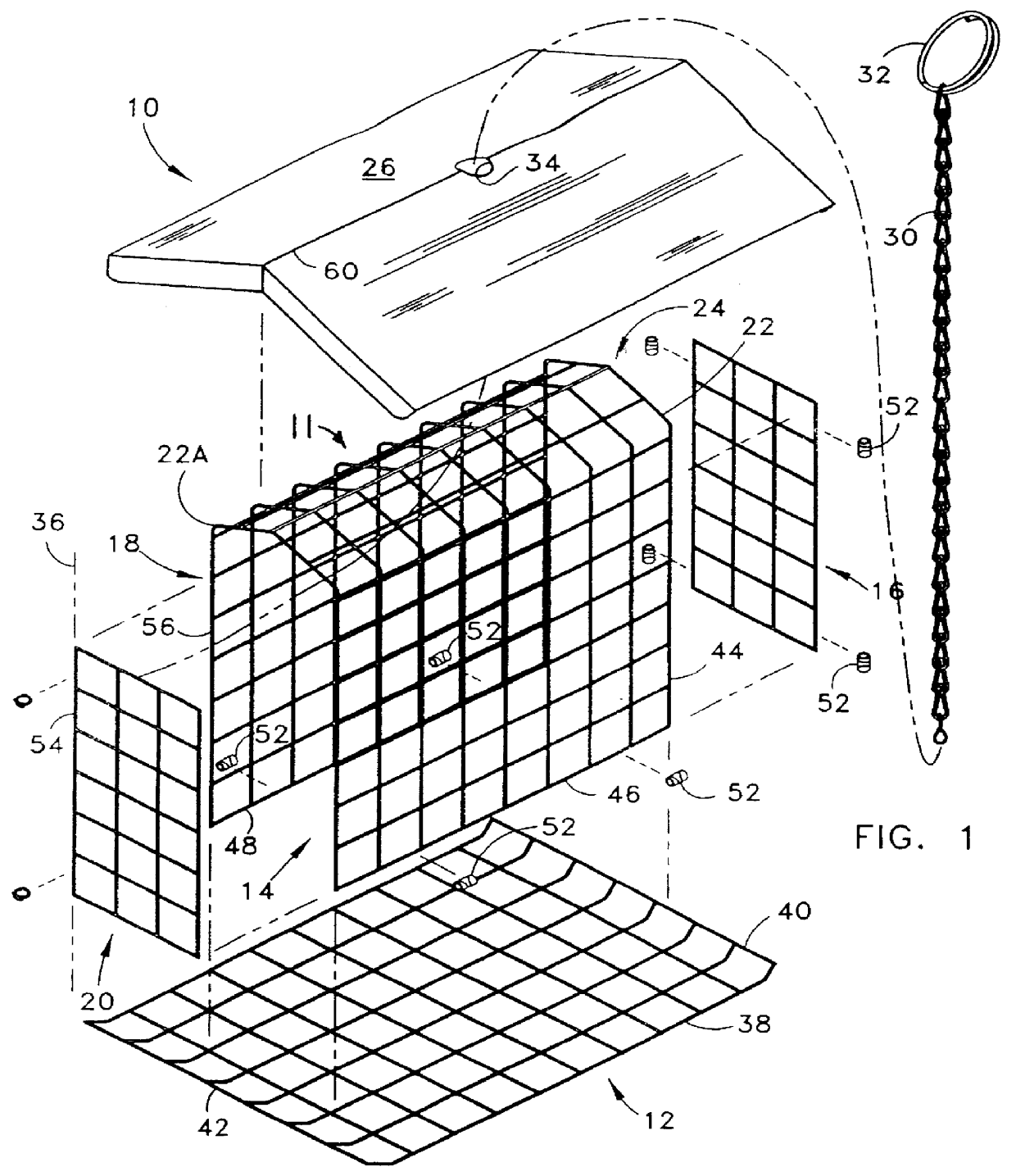

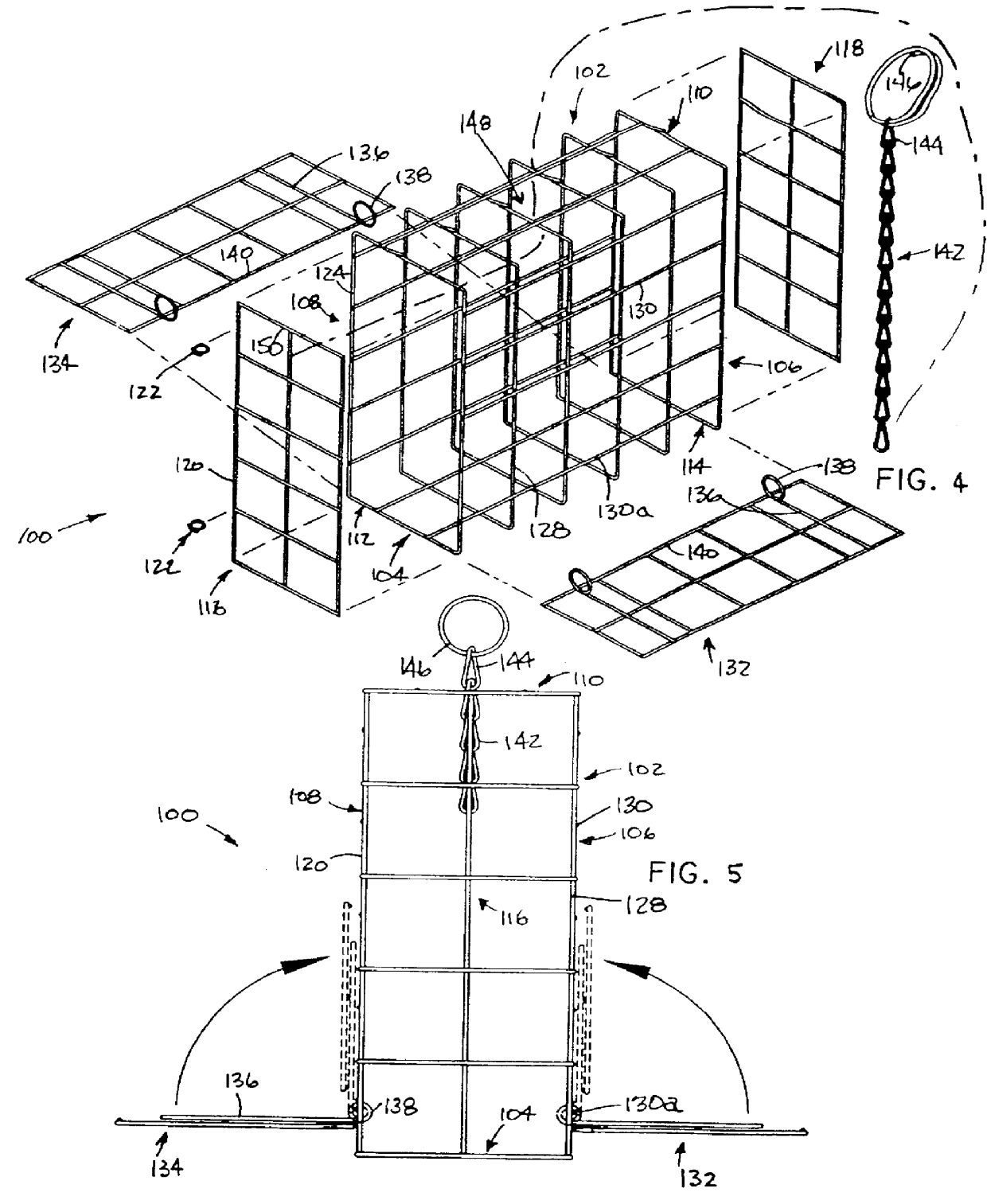

Bird feeder

InactiveUS6024047ASave packing spaceEasy accessAnimal feeding devicesAnimal housingBird feederEngineering

A bird feeder for retaining compressed suet-seed cakes is provided having a construction permitting easier refill of the feeder as well as making it more difficult for squirrels and other animals from raiding the feeder. Two embodiments of the feeder are disclosed including a hinged side door which is kept closed under tension equal to the weight of the suspended feeder and one having foldable perches which conserves packing material and space.

Owner:UNITED PET GRP INC

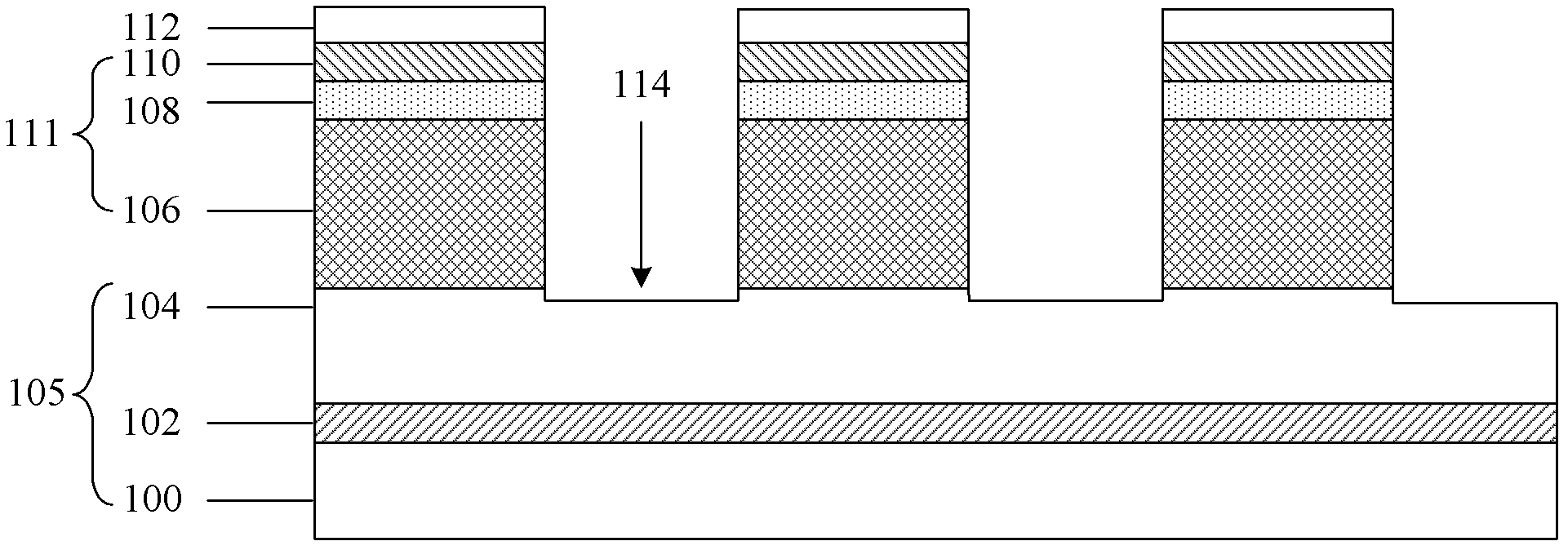

High-voltage nitride-based LED (light emitting diode) device and manufacturing method thereof

InactiveCN102354699AImprove yieldImprove packaging efficiencySolid-state devicesSemiconductor devicesLaser scribingPolymer light emitting diodes

The invention provides a manufacturing method of a high-voltage nitride-based LED (light emitting diode) device, which comprises the following steps of: providing a substrate, and sequentially forming N-type nitride nucleating layers and epitaxial layers on the substrate; etching the epitaxial layers to form N-type contact electrode steps; sequentially etching the N-type nitride nucleating layers to form LED isolation trenches which are exposed out of the surface of the substrate; manufacturing N-type contact electrodes on the N-type contact electrode steps and manufacturing P-type contact electrodes on the epitaxial layers to form a plurality of LED unit chips; and carrying out photoelectric performance test on the LED unit chips, and carrying out laser scribing on the LED unit chips selectively according to a test result so as to cut the LED unit chips in groups to form at least one LED module. The invention also provides the high-voltage nitride-based LED device, so that the cost of the whole LED chip industry is reduced, and the yield is improved.

Owner:ENRAYTEK OPTOELECTRONICS

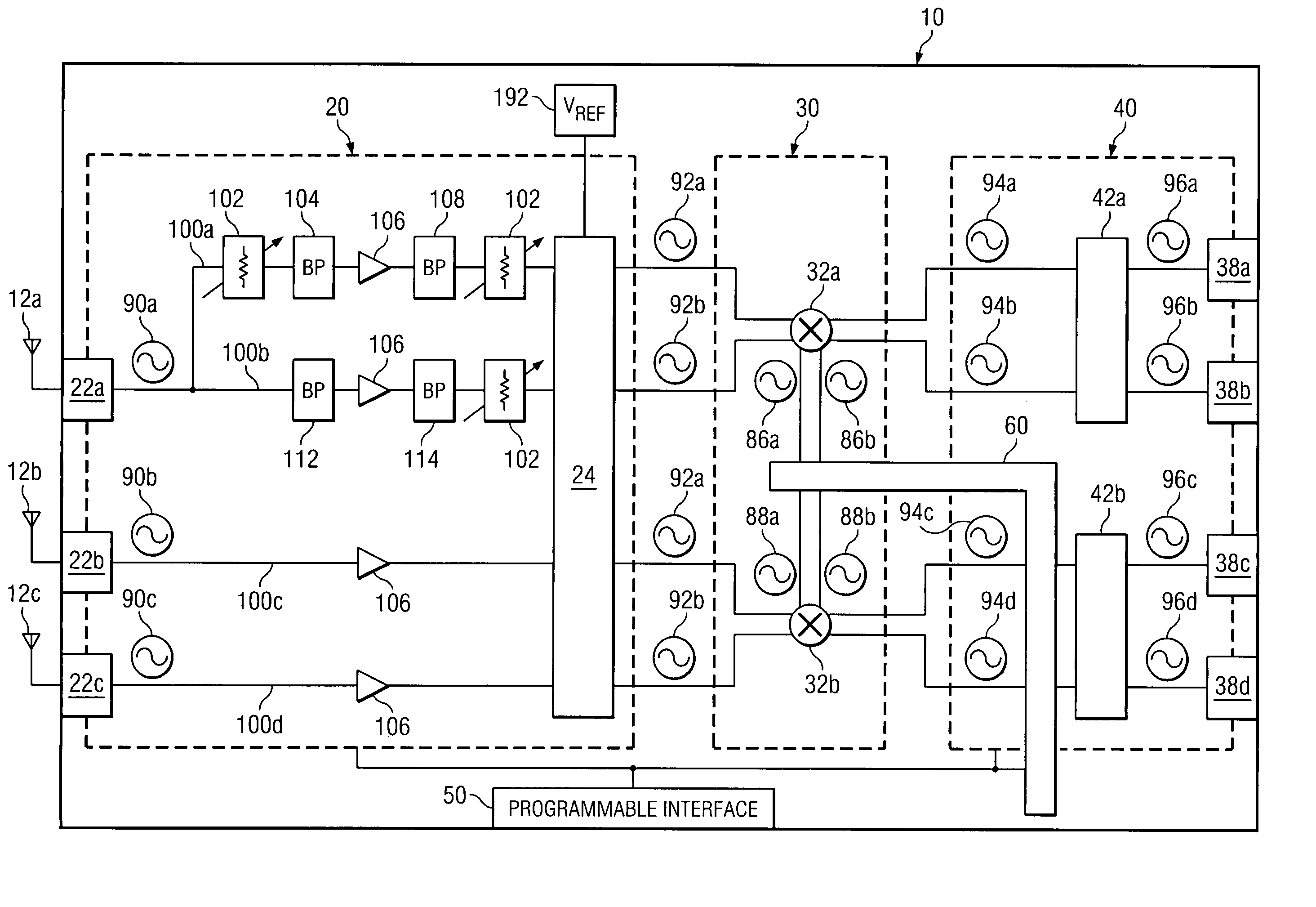

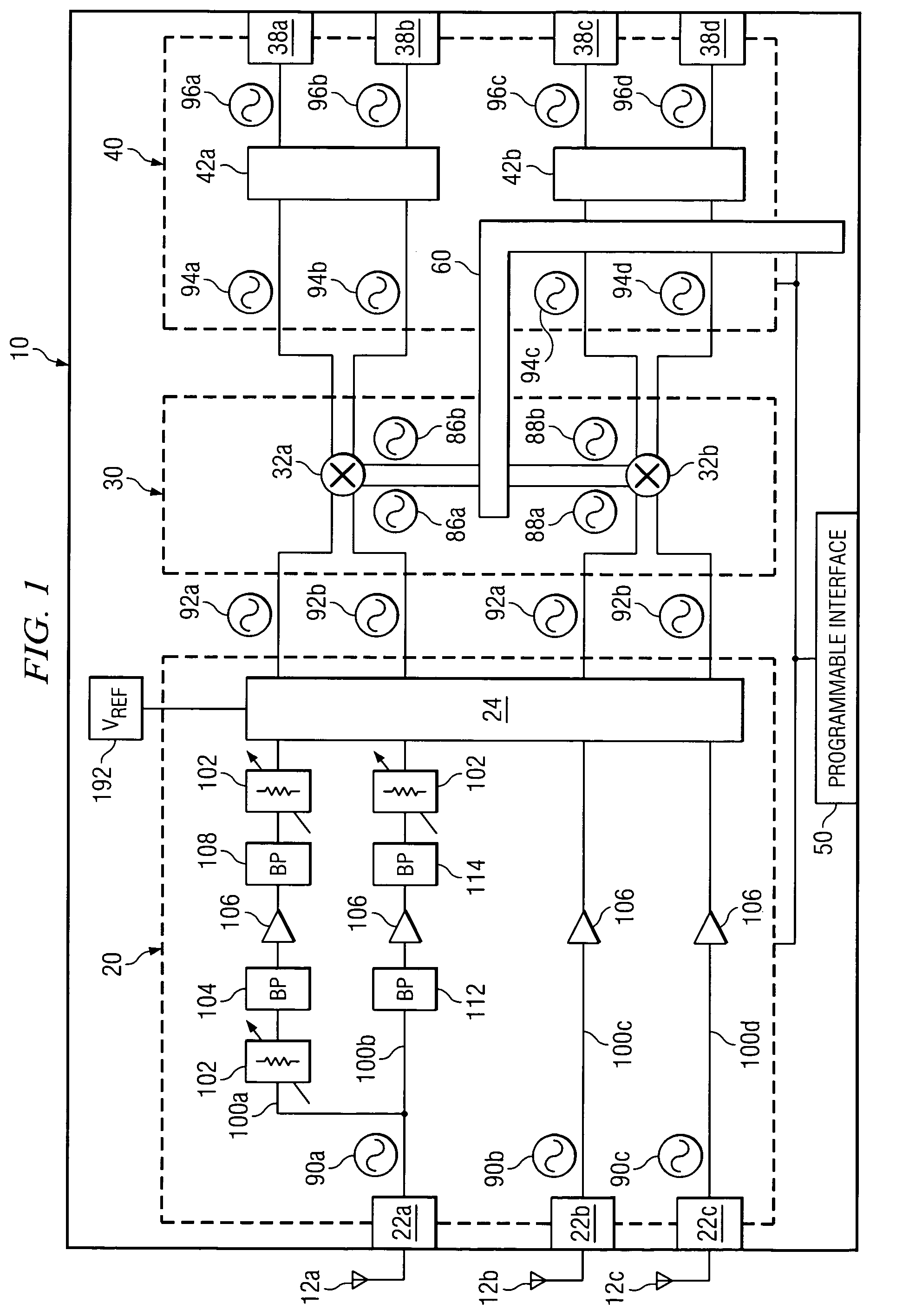

Radio-frequency tuner with differential converter

InactiveUS20070049224A1Improve operational flexibilityReduce headroomPolarisation/directional diversityResonant circuits using central processing unitsFrequency mixerRadio frequency signal

A system for tuning a radio-frequency signal includes a first input path, a second input path, a common reference generator, a selector, a mixer, and a filter. The first input path and the second input path propagate a first single-ended input signal and a second single-ended input signal, respectively, to the selector. The selector converts the first single-ended input signal and the second single-ended input signal into a first differential input signal and a second differential input signal, respectively, using a reference signal generated by the common reference generator. The selector selectively couples one of the first and the second input path to an input of the mixer. The mixer downconverts a selected on of the differential input signals received from the selector. The filter attenuates a portion of the downconverted input signal outside a passband associated with the filter.

Owner:CSR TECH INC

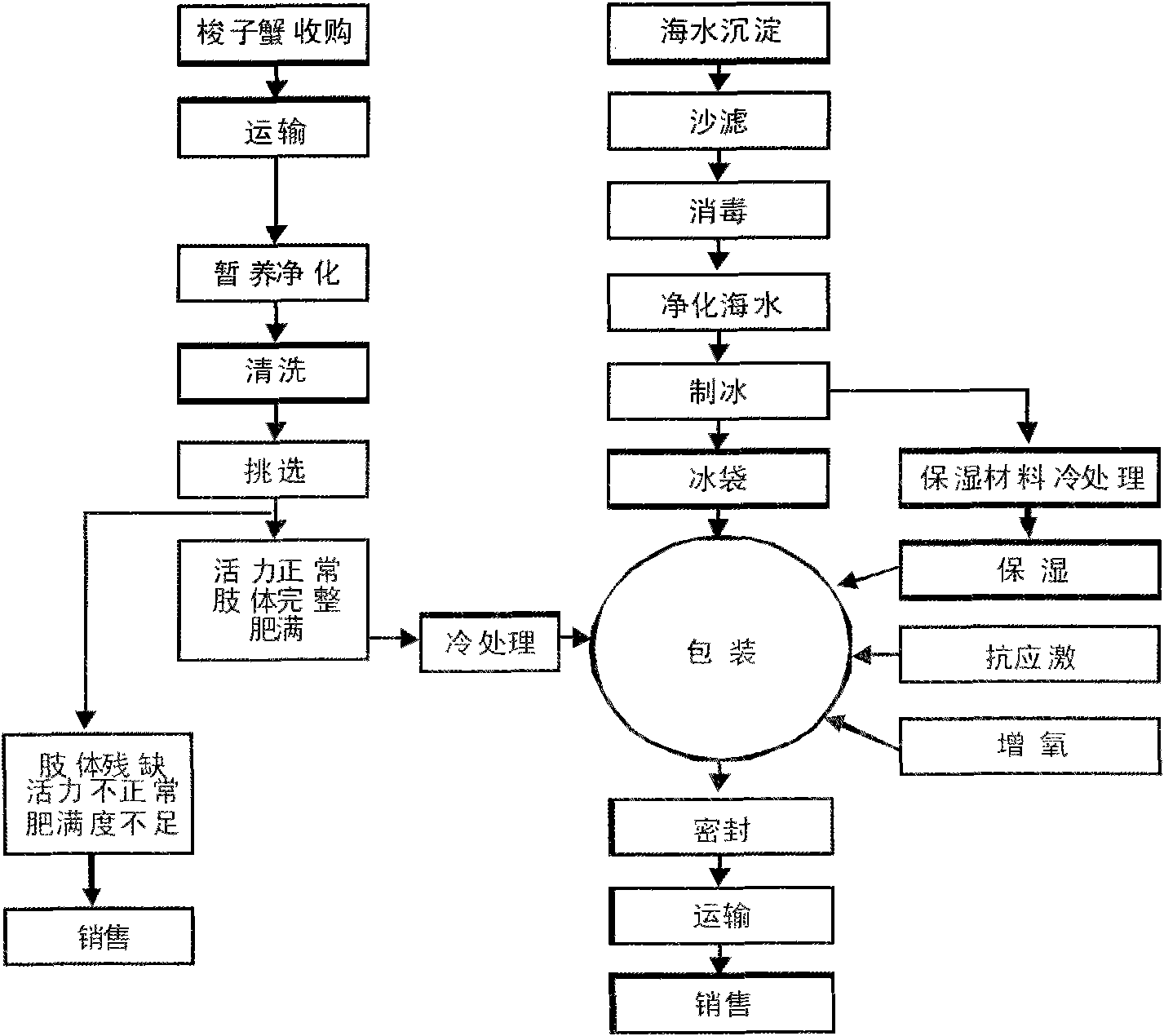

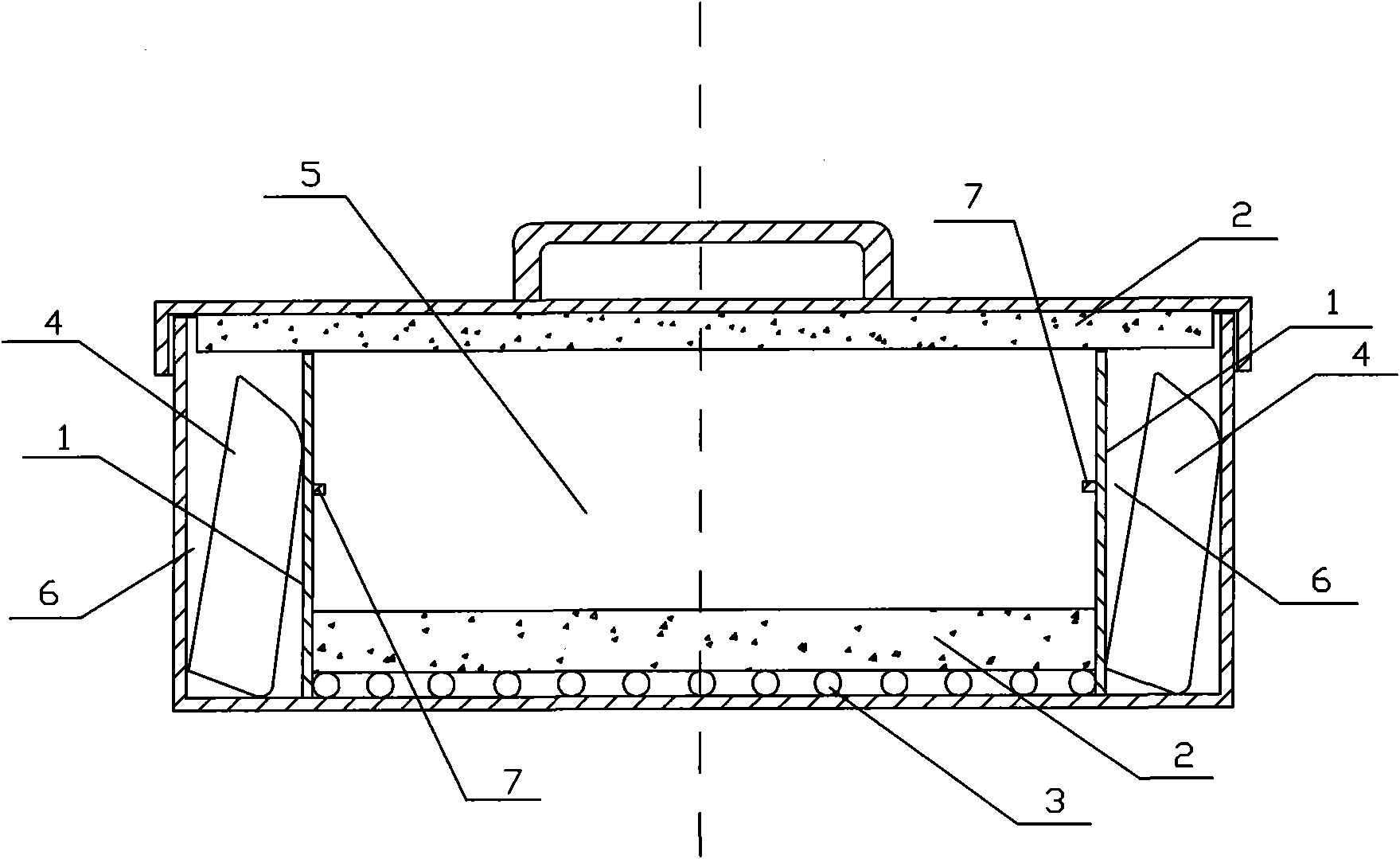

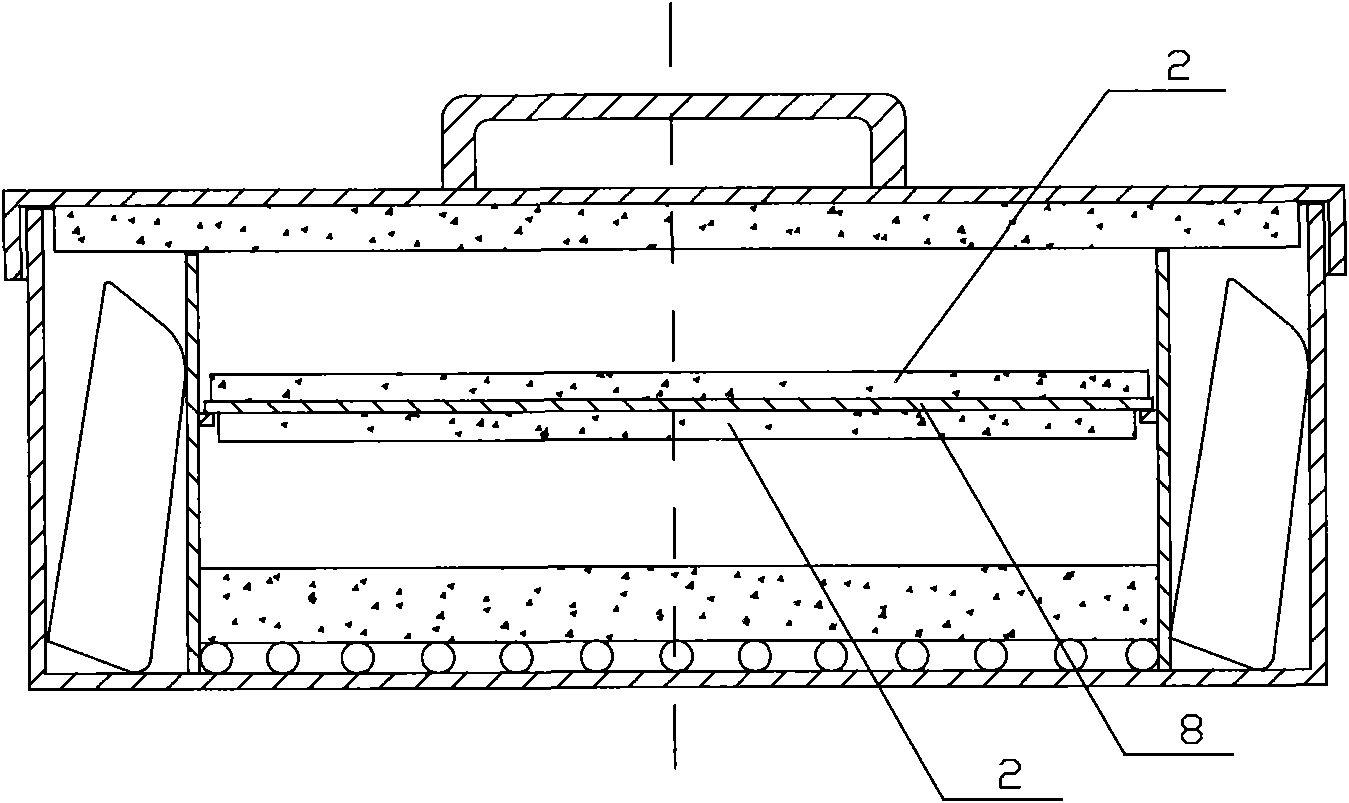

Method for refreshing water-detacted live portunus tritubercularus

InactiveCN102084836AReduce in quantityReaching to clean the surface of PortunusClimate change adaptationPisciculture and aquariaVitamin CSeawater

The invention discloses a method for refreshing water-detacted live portunus tritubercularus, which comprises the steps of: 1, purifying the portunus tritubercularus in seawater, and then putting the portunus tritubercularus in the 2-5 DEG C seawater for soaking for 3-5min to ensure that the portunus tritubercularus is in a narcosis state, wherein the 2-5 DEG C seawater contains 0.1 percent of stable vitamin C; 2, putting a moisturizing material in the 2-5 DEG C seawater containing 0.1 percent of stable vitamin C for soaking until the moisturizing material is saturated; and 3, firstly placingan oxygenating agent in a cavity in the middle of a package box, then laying one layer of moisturizing material above the oxygenating agent, placing the portunus tritubercularus above the moisturizing material, placing one layer of moisturizing material, i.e. a second layer of moisturizing material, above the portunus tritubercularus and covering the packaging box by the cover thereof. The methoddisclosed by the invention has the advantages of long survival time of the portunus tritubercularus, capability of effectively ensuring the edible value and enlarging the marketing range, clean surface of the portunus tritubercularus body, and low cost.

Owner:伊焱垚

Flexible display apparatus having roller that rotates by unfolding operation-force of user

ActiveUS9829925B2Save packing spaceLow costDigital data processing detailsCasings with display/control unitsMechanical componentsDisplay device

The present invention relates to a rollable flexible display apparatus to which an operation-force conversion apparatus is applied, wherein the operation-force conversion apparatus converts an unfolding or a folding operation-force linearly applied by a user to a housing of the rollable flexible display apparatus without the application of a motor or a spring into a rotation force with which a roller can rotate using the screw thread principle through an internal mechanical component, and conveys the converted rotational force to the roller.

Owner:LIM YOUSEOB

Photoelectric chip assembly and packaging method

ActiveCN102569431AAvoid corrosionAvoid heat damageFinal product manufactureSemiconductor devicesEngineeringSealant

The invention provides a photoelectric chip assembly and a packaging method. The photoelectric chip assembly comprises a first photoelectric chip, an optical fiber assembly, a circuit board and a sealing cap. The first photoelectric chip and the optical fiber assembly are fixed on the circuit board. A light receiving surface of the first photoelectric chip is opposite to a light emitting surface of the optical fiber assembly. The first photoelectric chip is connected electrically with the circuit board. The sealing cap is located above the first photoelectric chip and the optical fiber assembly and forms a sealed space with the circuit board. The chip is packaged by a packaging structure in the photoelectric chip assembly so as to avoid corrosion and high temperature damage caused by a sealant to the photoelectric chip, reduce the packaging volume and simplify the flow of packaging operation.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

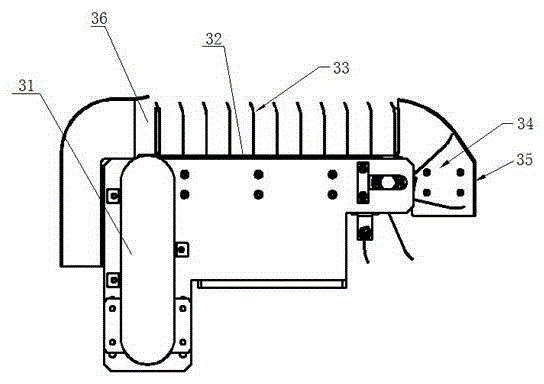

Automotive glass washer arrangement

InactiveCN101032951ASave packing spaceImprove reliabilityMembrane filtersVehicle cleaningFluid couplingEngineering

An automotive glass washer arrangement includes a washer pump having an outlet in fluid connection with at least one automotive glass washer nozzle. The arrangement comprises a fluid coupling having a female element with a chamber therein. A replaceable filter is disposed in the chamber. The fluid coupling further has a male element connected to the female element wherein the female element is in fluid communication with the washer pump and the male element is in fluid communication with the at least one nozzle. In a preferred embodiment, the female element is connected to the washer pump with a first hose and the male element is connected to the washer nozzle with a second hose.

Owner:GM GLOBAL TECH OPERATIONS LLC

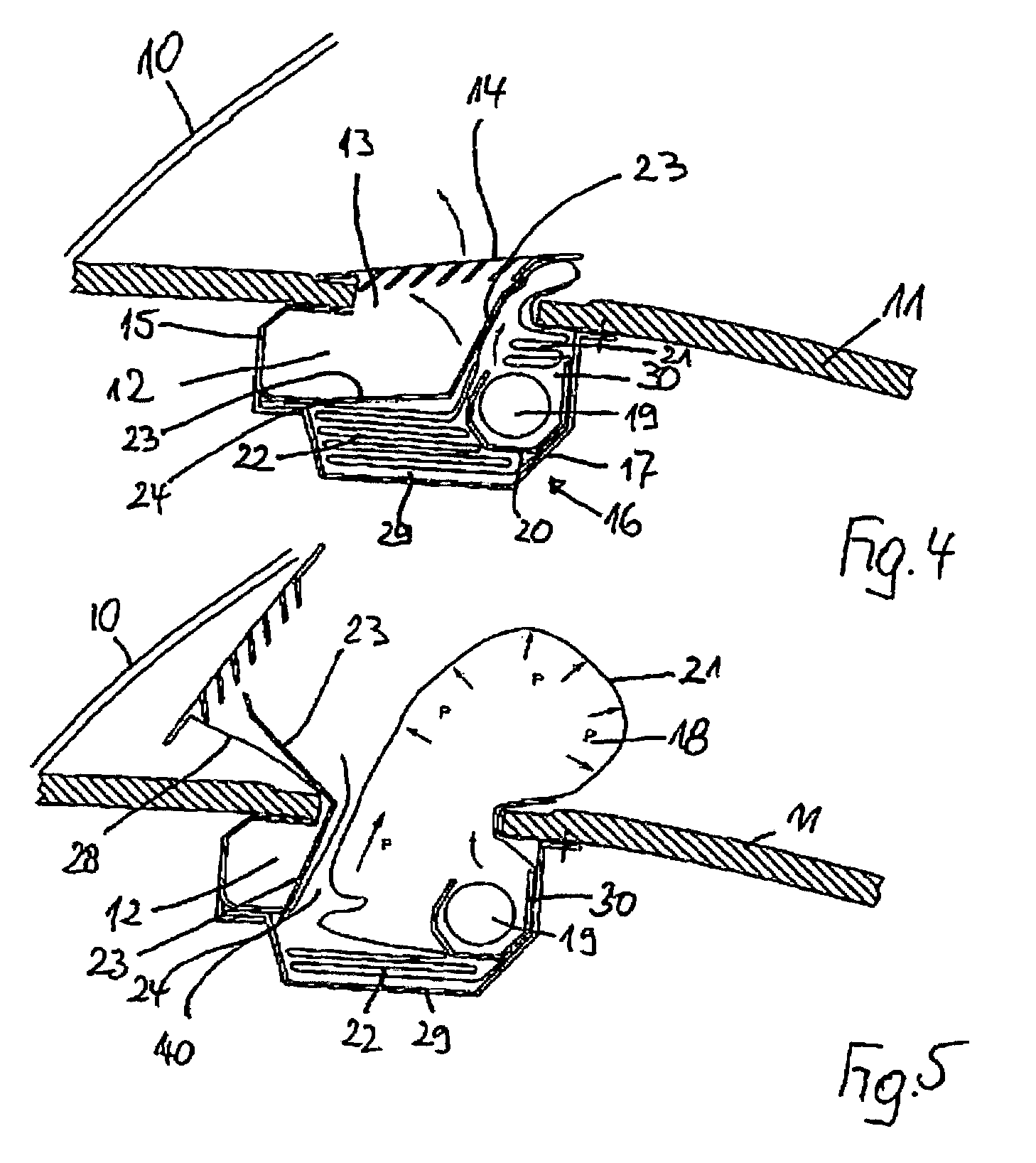

Instrument panel for a motor vehicle having an airbag device integrated in a ventilation arrangement

InactiveUS20070018440A1Reduce depthSave packing spaceAir-treating devicesDashboard fitting arrangementsMobile vehicleEngineering

An airbag module and instrument panel assembly for a motor vehicle having at least one ventilation outlet and a ventilation duct attached thereto and arranged behind an instrument panel. The airbag module is fastened behind the instrument patent and has a gas generator and a folded airbag arranged within its housing wherein a ventilation outlet is closed by a grid that opens when the airbag module is triggered and is provided within the instrument panel for the unfolding airbag. The airbag module is arranged adjacent to the ventilation duct in such a manner that when the airbag module is triggered, the airbag unfolds into the ventilation duct and from there unfolds out of the instrument panel through the ventilation outlet. The pressure of the unfolding airbag moves away from the ventilation outlet which is arranged within the instrument panel.

Owner:AUTOLIV DEV AB

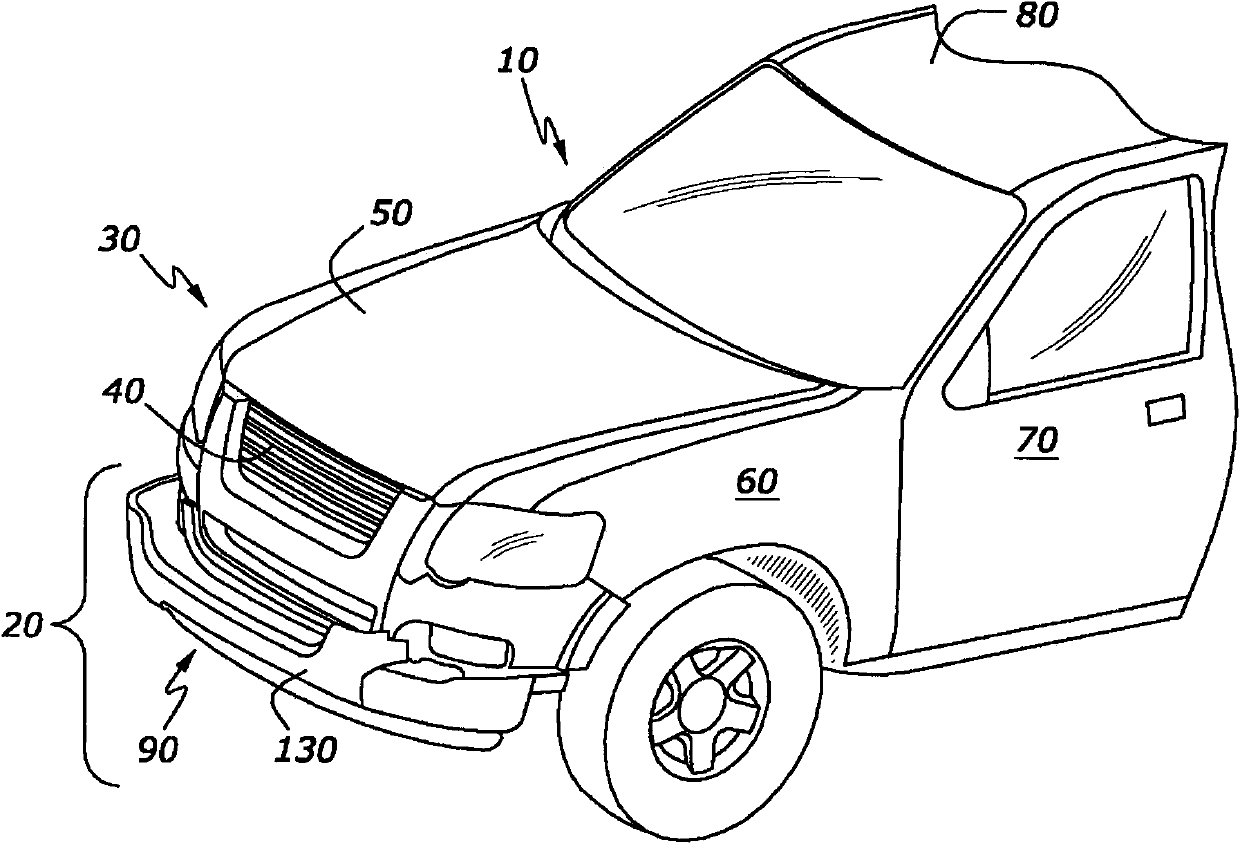

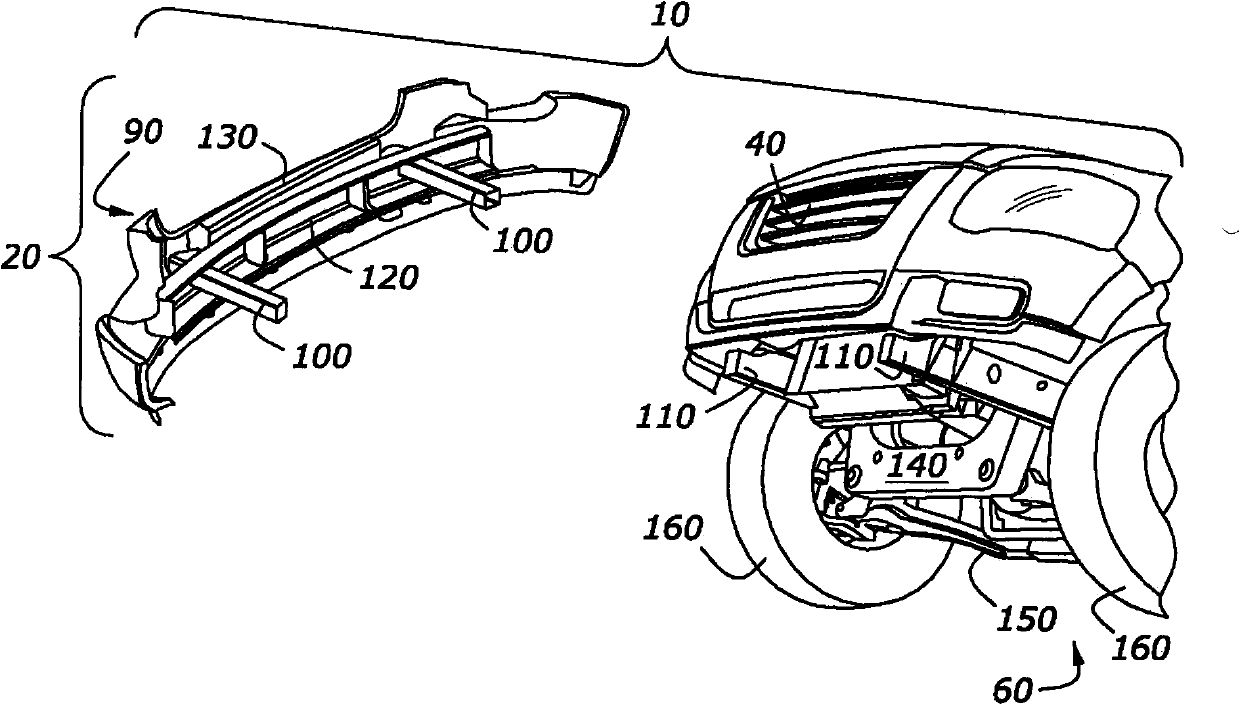

Vehicle impact mitigation system

The present disclosure relates to a vehicle impact mitigation system. The impact mitigation system can be configured to mitigate front impact situations. A main rail and an extendable rail-configured to move with respect to the main rail-are provided. A front module is attached to the extendable rail and attachable to the main rail. A spring is positioned between the front module and main rail, the spring is configured to apply a force to the front module when the front module is detached from the main rail. An actuator is configured to control attachment of the front module to the main rail.

Owner:FORD GLOBAL TECH LLC

Food packaging technology

ActiveCN105235946AEasy to storeEasy to transportWrapper twisting/gatheringMaterial resourcesEngineering

The invention discloses a food packaging technology and relates to the technical field of the food packaging technology. The food packaging technology includes a material conveying step, a material overturning and arranging step, a material sorting step, a bag taking step, a bag opening step and a packaging step. According to the packaging technology, after food is packaged in small bags through an outer packaging machine, the small bagged food is overturned, arranged, sorted and laminated; and finally, the small bagged food is packaged into food packaged in large bags. The whole technologic process is full automatic and mechanical, manual packaging is not needed, and a large amount of manpower and material resources are saved. The packaging technology is high in automatic and mechanical degree, packaging efficiency can be improved easily, and storage and transportation of the food packaged in bags are facilitated.

Owner:FOSHAN SOONTRUE MACHINERY EQUIP

Instrument panel for a motor vehicle having an airbag device integrated in a ventilation arrangement

InactiveUS7325827B2Save packing spaceReduce depthAir-treating devicesDashboard fitting arrangementsMobile vehicleEngineering

An airbag module and instrument panel assembly for a motor vehicle having at least one ventilation outlet and a ventilation duct attached thereto and arranged behind an instrument panel. The airbag module is fastened behind the instrument patent and has a gas generator and a folded airbag arranged within its housing wherein a ventilation outlet is closed by a grid that opens when the airbag module is triggered and is provided within the instrument panel for the unfolding airbag. The airbag module is arranged adjacent to the ventilation duct in such a manner that when the airbag module is triggered, the airbag unfolds into the ventilation duct and from there unfolds out of the instrument panel through the ventilation outlet. The pressure of the unfolding airbag moves away from the ventilation outlet which is arranged within the instrument panel.

Owner:AUTOLIV DEV AB

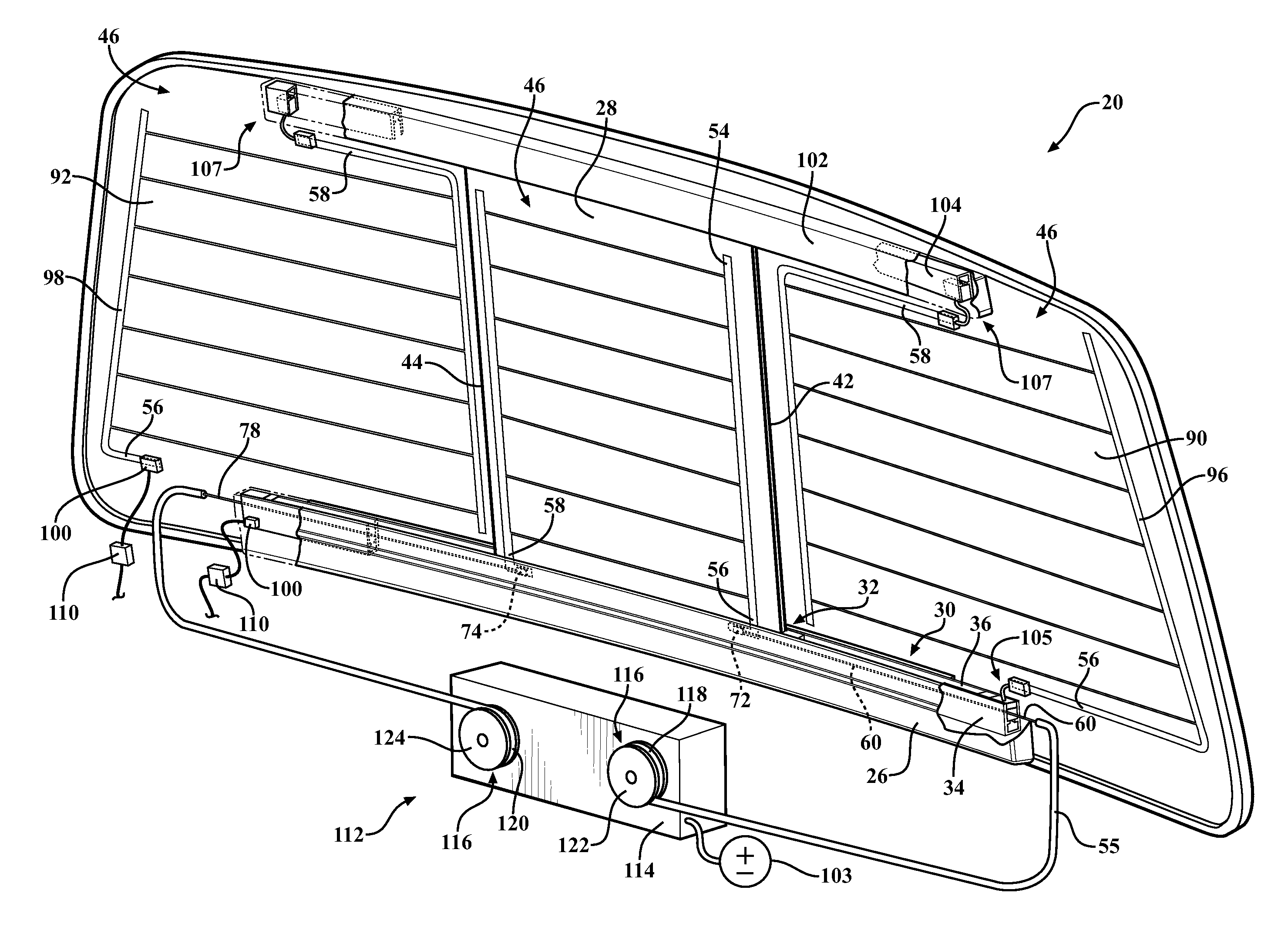

Sliding window assembly

A sliding window assembly for a vehicle, a cable drive system for a vehicle, and methods of operating the same, are disclosed. The sliding window assembly includes a track adapted to be coupled to the vehicle, and a sliding panel movable relative to the track between an open position and a closed position. A heating element is coupled to the sliding panel for heating the sliding panel. The sliding window assembly further includes a conductive cable coupled to the sliding panel and the heating element. The conductive cable is configured to transfer electrical current to energize the heating element and to undergo mechanical force to move the sliding panel relative to the track between the open and closed positions.

Owner:AGC AUTOMOTIVE AMERICAS

Chip packaging structure for slowing down electromagnetic interference and packaging method

ActiveCN106169428AReduce crosstalkImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceInsulation layer

The invention discloses a chip packaging structure for slowing down electromagnetic interference and a packaging method thereof. The packaging method comprises the following steps: producing a sinking groove in a silicon substrate, and embedding a chip whose front surface is upwards arranged and provided with welding pads into the sinking groove to save the packaging space; and forming horizontally-arranged or vertically-arranged inductance distribution wires on the front surface of the chip and a first surface of the silicon substrate, forming horizontally-arranged or vertically-arranged capacitance distribution wires on a first insulation layer, and extending a first metal redistribution wire or a second metal redistribution wire and solder balls to the surface of the silicon substrate to ensure that the welding pads of the chip are electrically fanned out of the surface of the silicon substrate and purposes of improving the packaging reliability and achieving simple process and low cost can be achieved. The horizontally-arranged or vertically-arranged inductance distribution wires form an inductor, and the horizontally-arranged or vertically-arranged capacitance distribution wires and dielectric layers among the capacitance distribution wires form a capacitor; and by adopting the inductor and capacitor with filter characteristics, the signal crosstalk among circuits in the chip can be reduced, unnecessary electric signals can be removed by filtration, the reliability and performance of packaged products can be enhanced, and the cost can also be reduced.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

A liquid receptacle for a vehicle

InactiveCN101432161AReduce the numberEasy to installInternal combustion piston enginesExhaust apparatusEngineeringMechanical engineering

Owner:VOLVO LASTVAGNAR AB

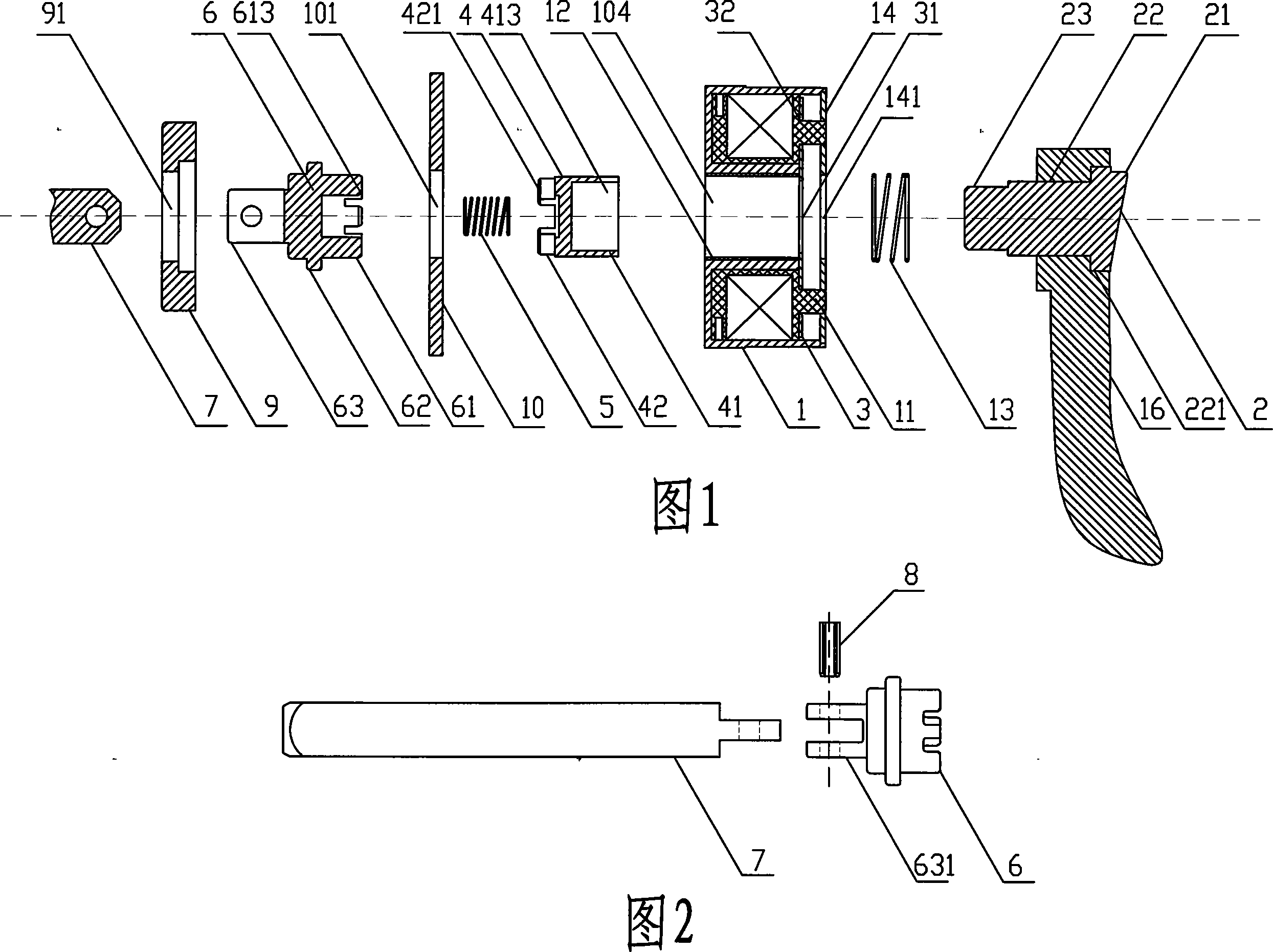

Clutch mechanism of electromagnetic lock

InactiveCN101182741AHave a positive effectHigh concentricityNon-mechanical controlsMagnetically actuated clutchesLocking mechanismElectromagnetic lock

The clutch mechanism of the electromagnetic lock consists of an electromagnet assembly, a push piece connected in sequence, a push piece return spring, a movable piece, a transmission piece, a transmission piece return spring, a square bar linkage block, and a square bar. A sliding shaft and a stopper are arranged on the top end surface of the electromagnet assembly, and the stopper is fixedly connected with the sliding shaft; the movable piece is slidably sleeved on the sliding shaft; the head of the transmission part is provided with a first blind hole cavity; the pushing part The protruding part of the main body passes through the central hole of the movable piece and fits into the first blind hole cavity of the transmission part, and the square rod linkage block is movably connected with the square rod, which facilitates the replacement and folding of the square rod. The clutch mechanism is mainly used in a dual-purpose electromagnetic lock that can be opened and closed mechanically and controlled by an electric circuit.

Owner:GUANGDONG ARCHIE HARDWARE

Damping corrugated board

InactiveCN105035530ANo need to increase the number of layersImprove impact resistanceFlexible coversWrappersPulp and paper industryPaper sheet

The invention discloses a damping corrugated board which comprises outer-layer case board paper and inner-layer case board paper. The damping corrugated board is characterized in that a waterproof glue layer is arranged below the outer-layer case board paper; a first glue layer is arranged below the waterproof glue layer; a corrugated paper core is arranged below the first glue layer; a second glue layer is arranged below the corrugated paper core; the inner-layer case board paper is arranged below the second glue layer; the corrugated paper core is formed by arranging and combining hexagonal paper cores and buffer layers at intervals; and each hexagonal paper core is internally provided with a center circular paper core body and multiple small circular paper core bodies tangent with the outer circumference of the center circular paper core. The damping corrugated board has the beneficial effects that the corrugated paper core is formed by arranging and combining the hexagonal paper cores and the buffer layers at intervals, so that the damping effect of the corrugated board is achieved; the number of layers of corrugated paper does not need to be increased; and the packaging space is better saved.

Owner:东莞华成环保包装科技股份有限公司

Method for refreshing water-detacted live portunus tritubercularus

InactiveCN102084836BReduce in quantityReaching to clean the surface of PortunusClimate change adaptationPisciculture and aquariaVitamin CPortunus trituberculatus

The invention discloses a method for refreshing water-detacted live portunus tritubercularus, which comprises the steps of: 1, purifying the portunus tritubercularus in seawater, and then putting the portunus tritubercularus in the 2-5 DEG C seawater for soaking for 3-5min to ensure that the portunus tritubercularus is in a narcosis state, wherein the 2-5 DEG C seawater contains 0.1 percent of stable vitamin C; 2, putting a moisturizing material in the 2-5 DEG C seawater containing 0.1 percent of stable vitamin C for soaking until the moisturizing material is saturated; and 3, firstly placingan oxygenating agent in a cavity in the middle of a package box, then laying one layer of moisturizing material above the oxygenating agent, placing the portunus tritubercularus above the moisturizing material, placing one layer of moisturizing material, i.e. a second layer of moisturizing material, above the portunus tritubercularus and covering the packaging box by the cover thereof. The methoddisclosed by the invention has the advantages of long survival time of the portunus tritubercularus, capability of effectively ensuring the edible value and enlarging the marketing range, clean surface of the portunus tritubercularus body, and low cost.

Owner:伊焱垚

Sliding window assembly

ActiveUS20170238371A1Heating of heating elementProvide goodWindowsWindscreensSlide windowElectrical current

A sliding window assembly, a cable drive system and methods of operating the same, are disclosed. The sliding window assembly includes a guide track and a sliding window movable relative to the guide track. A heating element is coupled to the sliding window for heating the sliding window. A drum of a drive assembly rotates and includes a conductive terminal connected to a power supply of the vehicle. A cable is coupled between the sliding window and heating element and the drum. The drum rotates to mechanically wind or unwind the cable for moving the sliding window. A conductive element is coupled to at least one of the drum and the cable and is electrically connected to the cable and is movable during movement of the sliding window. The conductive element contacts the conductive terminal to provide electrical current to the cable for energizing the heating element.

Owner:AGC AUTOMOTIVE AMERICAS CO A DIV OF AGC FLAT GLASS NORTH AMERICA INC +2

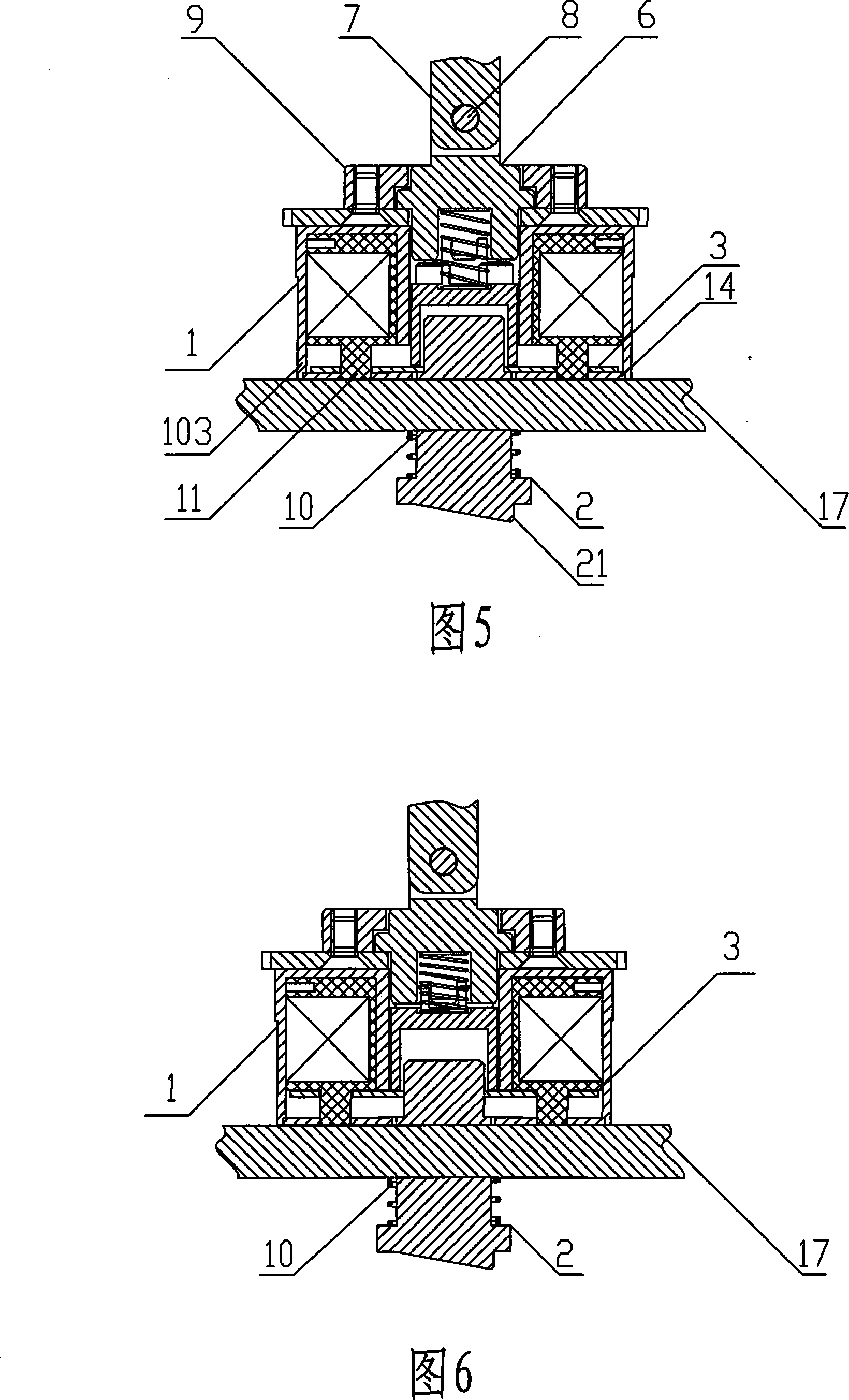

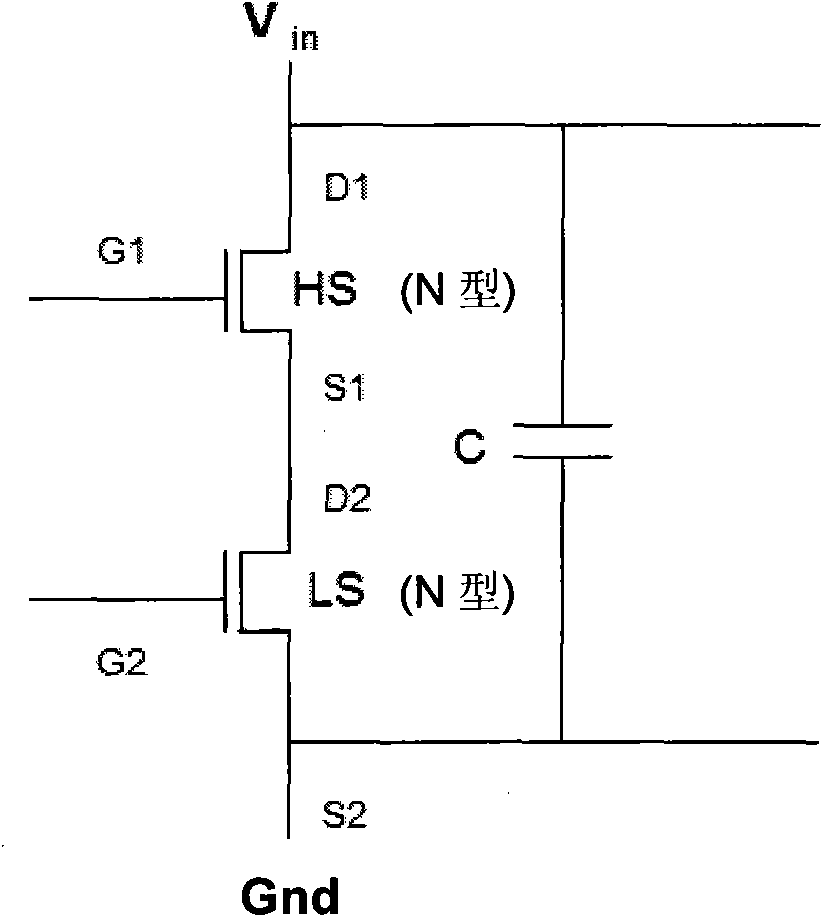

Semiconductor packing structure applied to power switcher circuit

ActiveCN102169873AReduce in quantitySave packing spaceSemiconductor/solid-state device detailsSolid-state devicesCapacitanceMOSFET

The invention discloses a semiconductor packaging structure applied to a power switcher circuit. A power switcher is formed by stacking and connecting two MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor) chips, and a bypass capacitor is packaged in the same package horizontally or vertically; moreover, a PIC (Positive-Impedance Converter) chip is arranged in the same package for forming a DC-DC (Direct Current to Direct Current) switcher. The semiconductor packaging structure provided by the invention ensures that the bypass capacitor is closest to the MOSFET chip, the generated parasitic inductance is the minimum, and thus the size of the semiconductor structure is effectively reduced while the performance of the power switcher or DC-DC switcher is effectively improved.

Owner:ALPHA & OMEGA SEMICON INT LP

Fuel system degradation test using two fuel tanks

InactiveUS9086040B2Save packing spaceImprove engine efficiencyHybrid vehiclesElectrical controlSystem pressureFuel tank

Embodiments for monitoring fuel system degradation are provided. In one example, a method for a vehicle comprises evacuating fuel from a first fuel tank to a second fuel tank, and indicating fuel system degradation in response to a change in fuel system pressure following the evacuation of fuel. In this way, fuel system degradation may be indicated without use of a separate pressure building device.

Owner:FORD GLOBAL TECH LLC

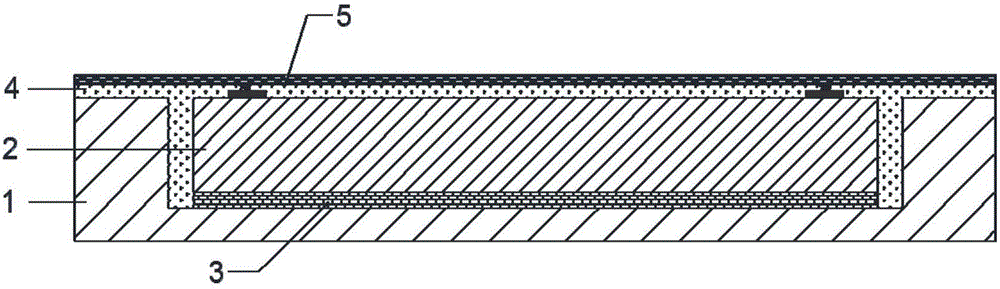

LED (light emitting diode) packaging structure and preparation method thereof

InactiveCN102214652AImprove light extraction efficiencyOmit the step of bondingSolid-state devicesSemiconductor devicesOn boardEngineering

The invention discloses an LED (light emitting diode) packaging structure. An LED device module structure is adopted for the LED packaging structure, so each LED chip unit does not need to be scribed independently, the process can be saved and the manufacturing cost can be reduced; the LED module is of a vertical electrode structure which can be directly packaged, thus the overall performance of the LED can be improved; as the connection between the LED chips of each LED module is in series-parallel connection, so the LED module can be conveniently applied to the high-power illumination field. The invention also discloses a preparation method for an LED packaging structure. By using the method, an LED module, an LED driving circuit and an ESD (Electronic Static Discharge) protection circuit can be directly fixed on a COB (chip on board) bonding plate substrate, thus the overall performance of the LED can be improved; and each LED chip unit does not need to be scribed independently, thus the process can be saved and the manufacturing cost can be reduced; as the connection between the LED chips of each LED module is in series-parallel connection, so the LED module can be conveniently applied to the high-power illumination field.

Owner:ENRAYTEK OPTOELECTRONICS

Electric lifting media wall

ActiveCN110173610AEasy to adjust the lifting heightIncreased load-bearing capacityFurniture partsStands/trestlesDisplay deviceEngineering

The invention discloses an electric lifting media wall which comprises a base, a lifting assembly, a supporting frame and a wall cover body. The lifting assembly comprises at least one group of lifting stand columns and a driving mechanism for driving the lifting stand columns to ascend or descend; the lower ends of the lifting stand columns are connected with the base; the supporting frame is used for being connected with a display mounting frame, is connected onto the lifting stand columns, and ascends or descends synchronously along with the lifting stand columns; the wall cover body coversa table leg component and the outer side of the supporting frame; the wall cover body is connected with the lifting stand columns or the supporting frame, and ascends or descends synchronously alongwith the lifting stand columns; the outer surfaces of two opposite side plates of the wall cover body are of plane structures; and at least one group of connecting holes are formed in at least one outer side surface, and are used for allowing connecting pieces connected with the display mounting frame to penetrate through the wall cover body from outside to inside and be connected with the supporting frame in the wall cover body. The electric lifting media wall has the advantages that the height can be adjusted, the bearing capacity is strong, the function is diversified, the assembly and thedisassembly are convenient, the later maintenance is facilitated, and the packing size is small.

Owner:美国乐歌有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com