Semiconductor packing structure applied to power switcher circuit

A packaging structure, semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device components, circuits, etc., can solve the problem of bypass capacitor CMOSFET, save packaging space, improve the performance of DC-DC converters, and reduce the number of Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

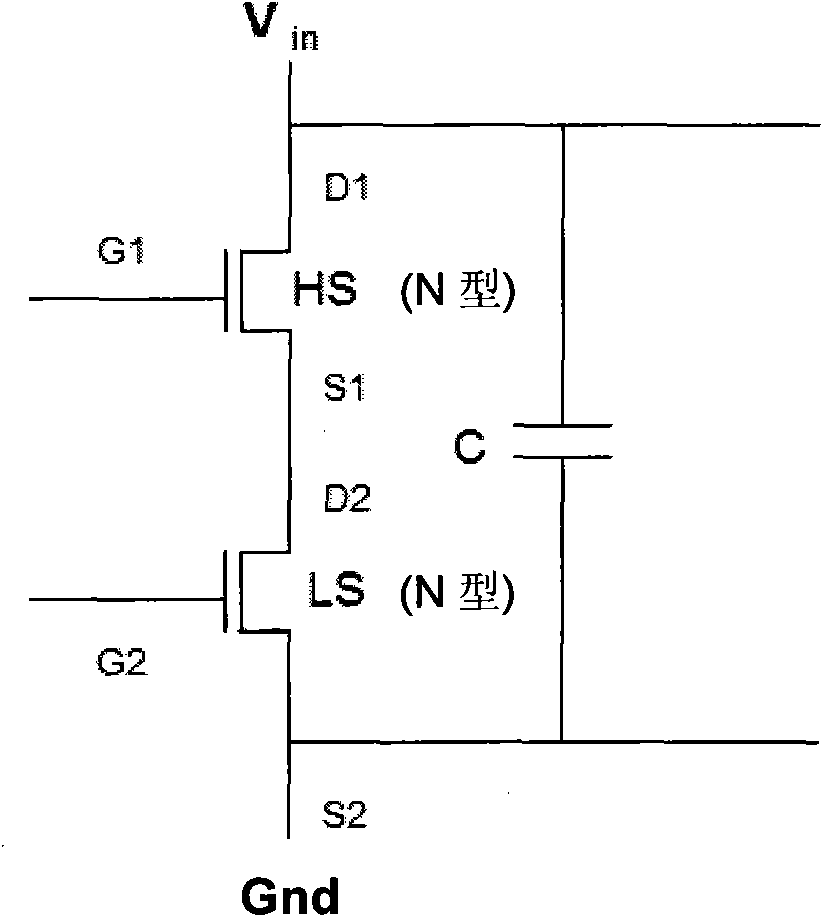

[0049] In this embodiment, the high-end MOSFET chip is stacked on the low-end MOSFET chip, and the bypass capacitor is connected in parallel, and the connecting leads are used to make corresponding electrical connections. Finally, the three circuit elements are mixed and packaged in the same semiconductor package. Realization basis figure 1 The circuit diagram is connected to form the power switch.

[0050] Such as Figure 3A Shown is a top view of Embodiment 1 provided by the present invention; Figure 3B For along Figure 3A A cross-sectional view in the A-A direction. The package includes a lead frame with a carrier 1 and a number of pins. According to figure 1 In the circuit diagram of the power switch shown, the pins include a low-end source pin 21, a low-end gate pin 22, a high-end drain pin 23, and a high-end gate pin 24, where these leads The feet are separated from the slide table 1 and electrically connected. The low-side MOSFET 3 is glued and attached to the stage 1,...

Embodiment 2

[0054] Figure 4A It is a top view of Embodiment 2 provided by the present invention; Figure 4B For along Figure 4A Sectional view in the A-A direction; Figure 4C For along Figure 4A Sectional view in the direction of B-B. This embodiment 2 is basically the same as the package structure described in the above embodiment 1, except that: in this embodiment, a metal connection plate 62' (or a metal connection body such as a metal connection tape) is used instead of implementation. Several connecting leads 62 in Example 1 are used to bond and connect the first metal layer 71 and the low-end source pin 21, and a metal connecting plate 63' is used instead of several connecting leads 63 in Example 1 to bond and connect the second metal layer. For 72 and the high-side drain pin 23, a metal connecting plate 65' is used instead of the several connecting leads 65 in the first embodiment to bond and connect the top source 42 of the high-side MOSFET 4 and the stage 1.

[0055] Similarly, ...

Embodiment 3

[0058] The package structure features provided by the third embodiment are still similar to those of the first embodiment. The core structure is still to stack the high-end MOSFET chip on the low-end MOSFET chip, but in this embodiment, a vertical structure capacitor element is used. The electrodes at both ends of the capacitive element are respectively located on the top surface and the bottom surface.

[0059] Figure 5A It is a top view of Embodiment 3 provided by the present invention; Figure 5B For along Figure 5A A cross-sectional view in the A-A direction. Wherein, the lead frame structure is as shown in embodiment 1, including a stage 1 and a number of pins that are separated from the stage 1 and are not electrically connected; these pins include low-end source pins 21, Low-side gate pin 22, high-side drain pin 23, and high-side gate pin 24. The low-end MOSFET 3 is glued and attached to the stage 1, and its bottom drain (not shown in the figure) is electrically connect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com