Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

38results about How to "Reduce photomask process" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

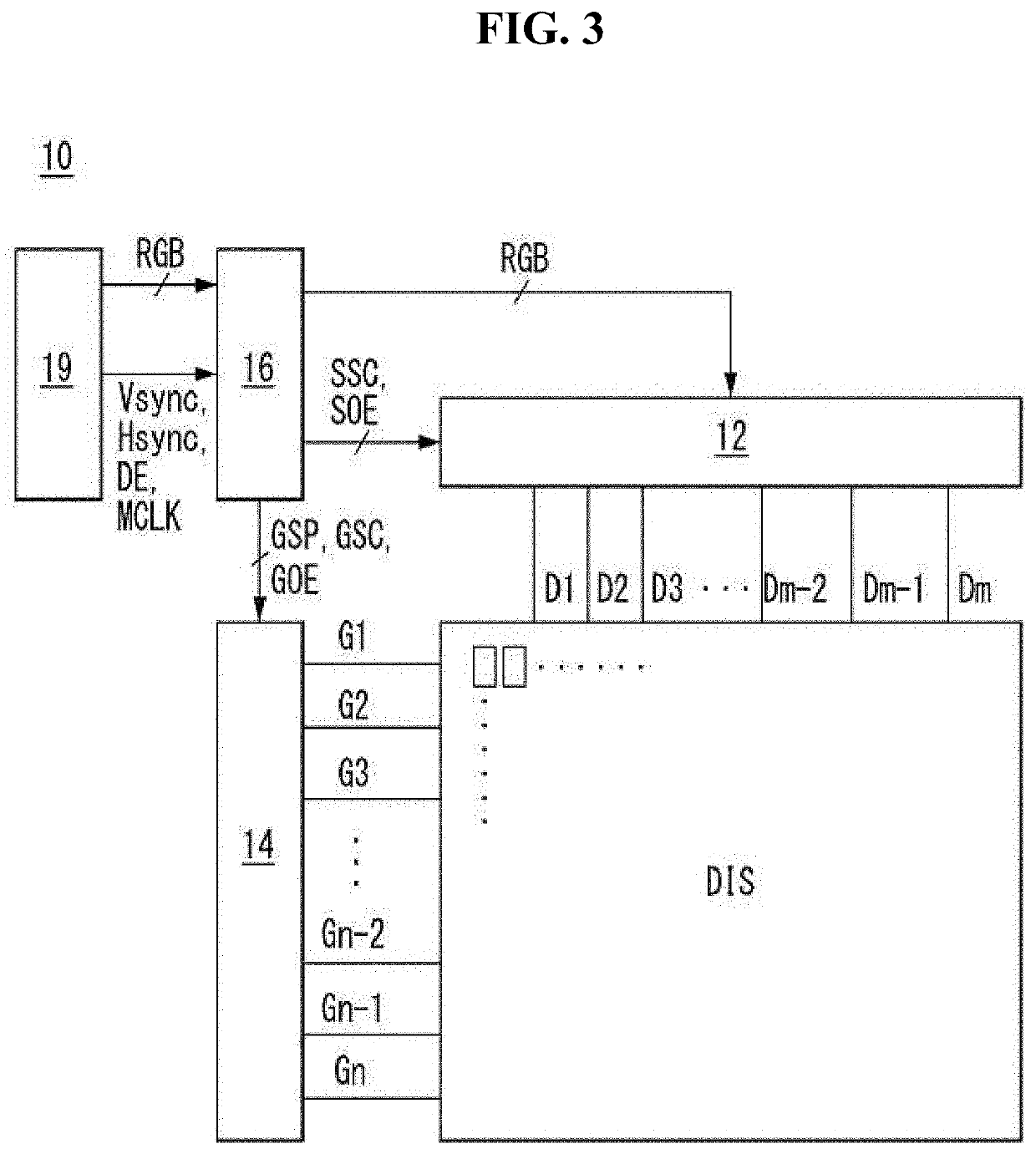

Flexible electroluminescent display device

ActiveUS20180151662A1Reducing stress appliedReduce photomask processStatic indicating devicesSolid-state devicesInsulation layerSignal lines

An electroluminescent display device includes: a substrate including: an active area, and bezel area outside the active area and including a bending area, a first organic insulation layer (OIL) in the active area, covering a first signal line extending from the active area to the bezel area, a second OIL in the bending area, the second OIL being in a same layer as the first organic insulation film, first and second touch electrodes crossing over each other and sealing the active area on an encapsulation layer above the first OIL with a third OIL therebetween, a first signal line link pattern connected to the first signal line, and on the second OIL in the bending area, and second and third signal lines respectively connected to the first and second touch electrodes, and on the second OIL in parallel with the first signal line link pattern.

Owner:LG DISPLAY CO LTD

Flat panel display device and method of manufacturing the same

InactiveUS6958252B2Improve production yieldReduce photomask processElectroluminescent light sourcesSolid-state devicesTransmittanceEngineering

A flat panel display includes a pixel electrode having an opening portion formed on an insulating substrate, a semiconductor layer formed over a surface of the insulating substrate, spaced apart from the pixel electrode, having source and drain regions formed to both end portions thereof, a first insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode, a gate electrode formed on the first insulating layer over the semiconductor layer, and a second insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode. The present invention provides an organic EL display manufactured with reduced mask processes which has excellent electrical characteristics and improved light transmittance.

Owner:SAMSUNG DISPLAY CO LTD

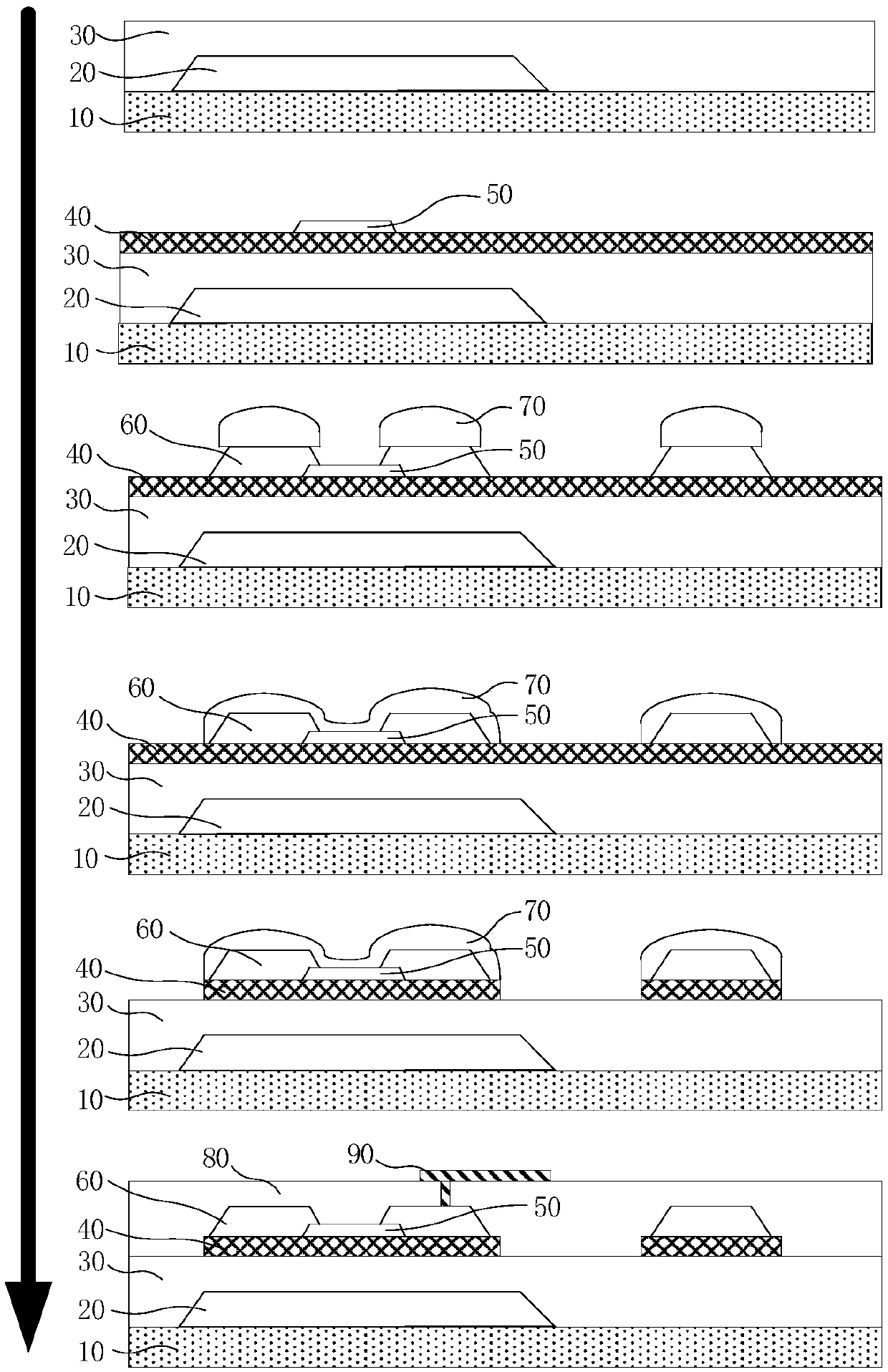

Oxide film transistor and manufacturing method thereof

InactiveCN104617152ASimple manufacturing processImprove featuresTransistorSemiconductor/solid-state device detailsOxide thin-film transistorSemiconductor

The invention discloses an oxide film transistor and a manufacturing method thereof. The manufacturing method comprises sequentially forming a grid electrode, a grid electrode insulating layer and an oxide semiconductor film layer; sequentially forming a first metal layer and a second metal layer on the oxide semiconductor film layer, and forming a drain electrode and a source electrode on the second metal layer, wherein the source electrode and the drain electrode are separated through a channel which exposes a part of the first metal layer; oxidizing the exposed part of first metal layer; forming an insulating passivation layer and setting a contact electrode. The manufacturing method of the oxide film transistor can protect the back channel of the oxide film transistor and meanwhile simplify the manufacturing process and save the cost.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

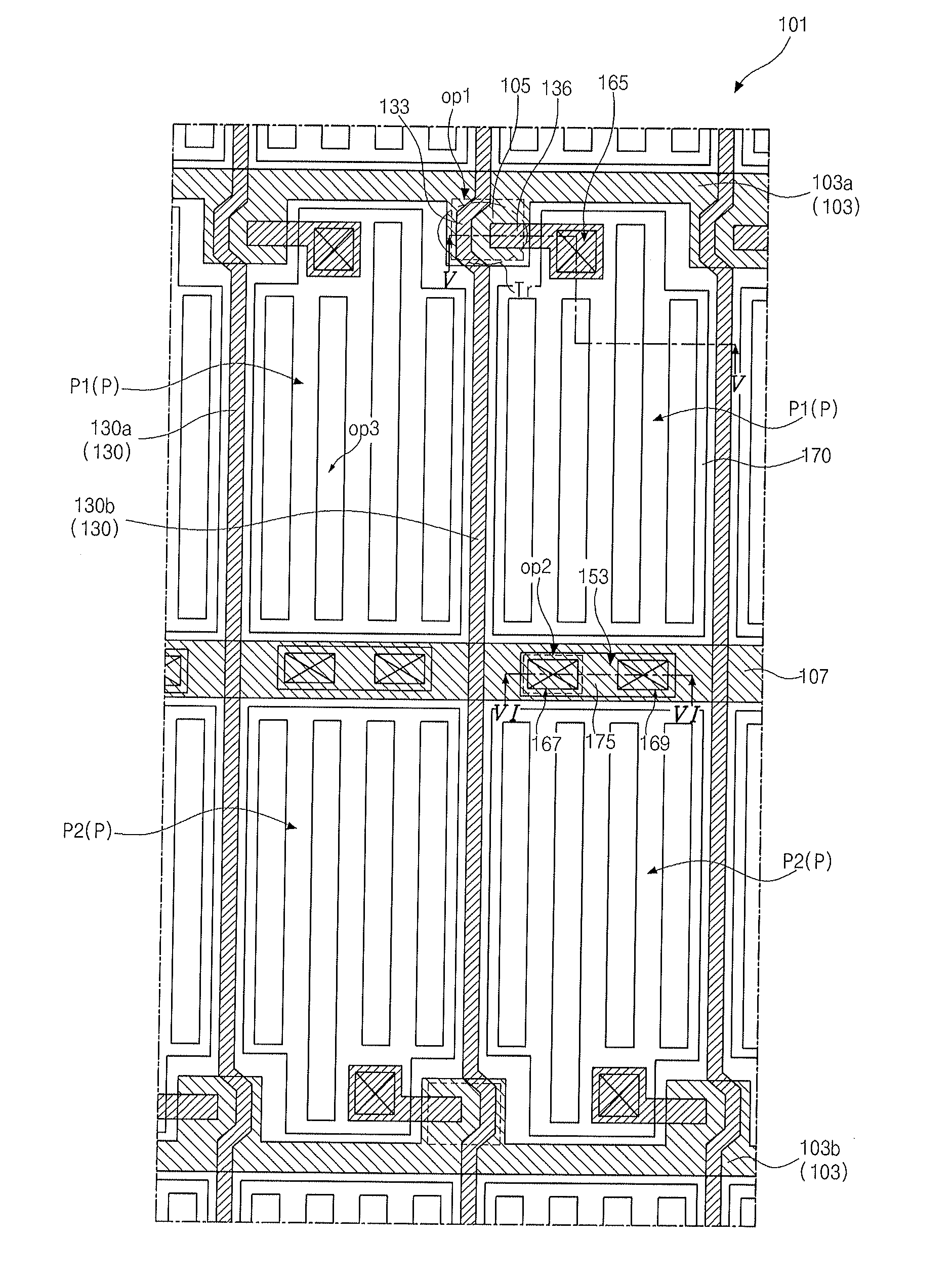

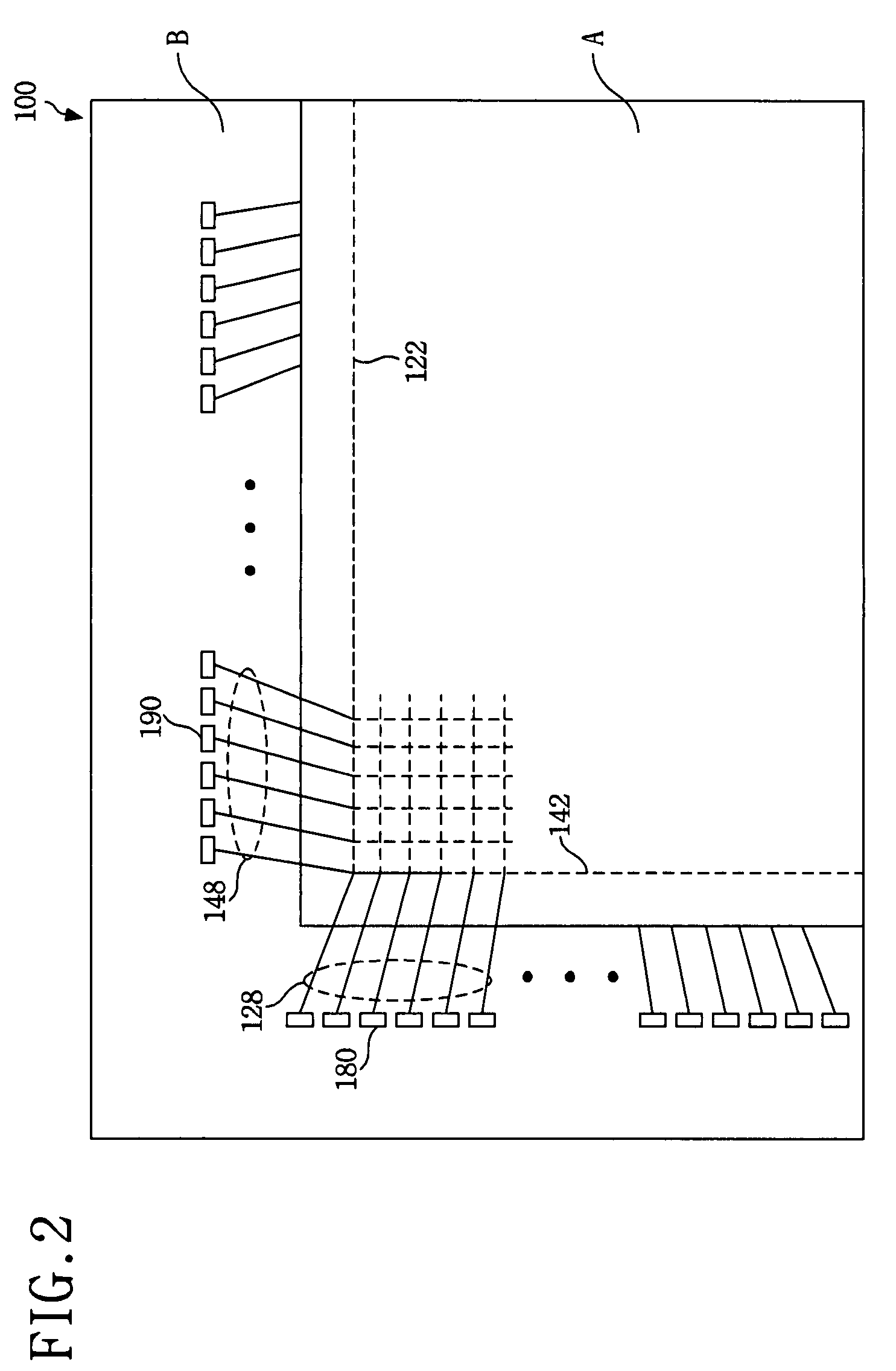

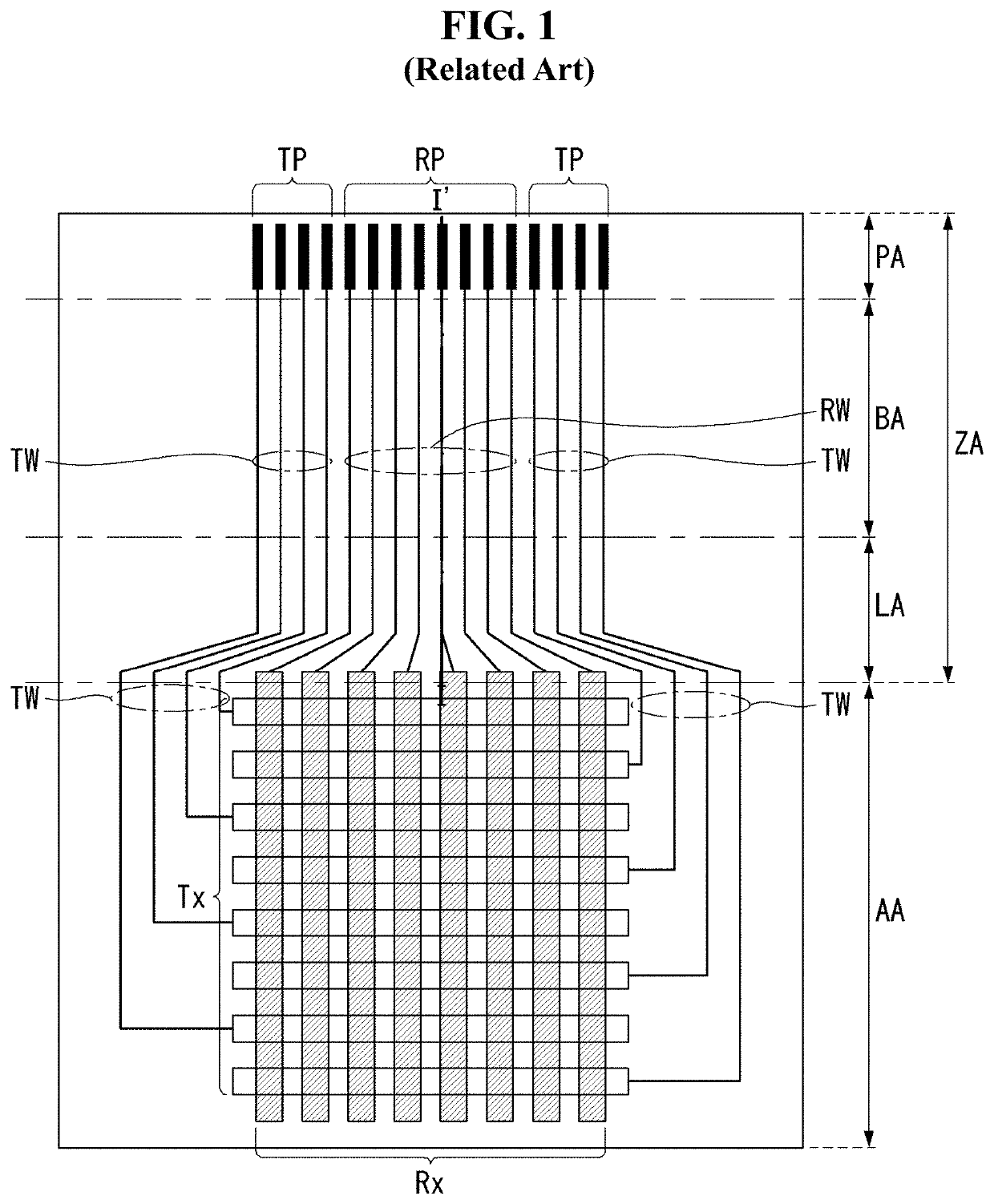

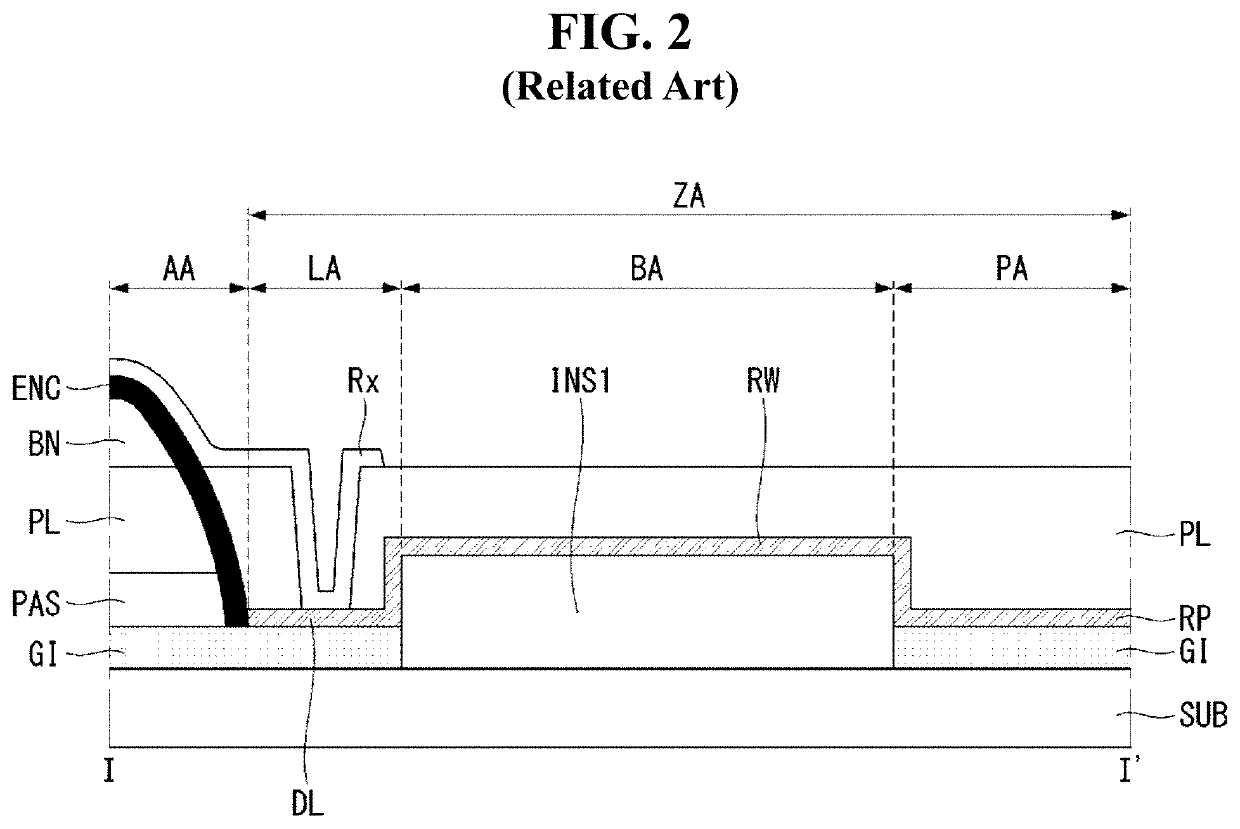

Array substrate for fringe field switching mode liquid crystal display device and method of fabricating the same

ActiveUS20140132875A1Increase the aperture ratioReduce decreaseSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayContact hole

An array substrate for a liquid crystal display (LCD) device includes a common line and gate lines. The array substrate includes a first, second, and third passivation layer and thin film transistors (TFTs). The second passivation layer includes first and second holes respectively corresponding to a drain electrode and the common line. A common electrode on the second passivation layer includes a first opening corresponding to the TFTs and a second opening in the second hole. A drain contact hole through the third and first passivation layers exposes the drain electrode. A first common contact hole through the third passivation layer exposes the common electrode in the second hole. A second common contact hole through the third and first passivation layers exposes the common line, and a pixel electrode includes a third opening and a connection pattern connecting the common electrode to the common line on the third passivation layer.

Owner:LG DISPLAY CO LTD

Thin film transistor, array substrate and manufacturing method thereof

ActiveCN111725324AReduce photomask processIncrease productivityTransistorSolid-state devicesThin membraneEngineering

The invention provides a manufacturing method of an array substrate, the array substrate and a thin film transistor. The thin film transistor includes a gate, an active layer which is arranged corresponding to a grid electrode, a source electrode and a drain electrode which are arranged at two ends of the active layer and are electrically connected with the active layer, and an interlayer insulating layer which is arranged among the active layer, the source electrode and the drain electrode, wherein a step-shaped contact hole is formed in the interlayer insulating layer, and the source electrode and the drain electrode are respectively filled in the contact hole and are electrically connected with the active layer.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Method for fabricating thin film transistor substrate

ActiveUS7977171B2Reduce photomask processSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTransistor

A method of fabricating a thin film transistor substrate for reducing a mask process and, at the same time removing a transparent electrode ITO which remains at a non-display area by a contact hole filling process is disclosed. In the method of fabricating the thin film transistor substrate having a display area and a non-display area, a gate pattern is formed at the exterior of the display area. A gate insulating film is formed on a substrate provided with a gate pattern, and then a data pattern is formed. And a protective film is formed on an entire substrate provided with a data pattern, and then a conductive pattern, and then a conductive pattern, which is comprised of a pixel electrode which is formed at a display area, and a lower gate pad electrode and a lower data pad electrode which are formed at a non-display area, is formed.

Owner:LG DISPLAY CO LTD

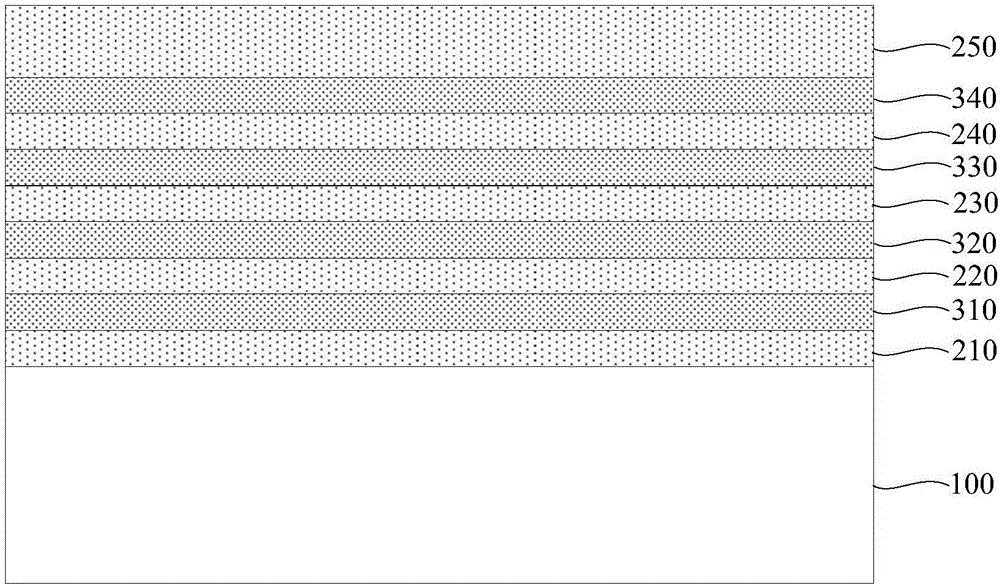

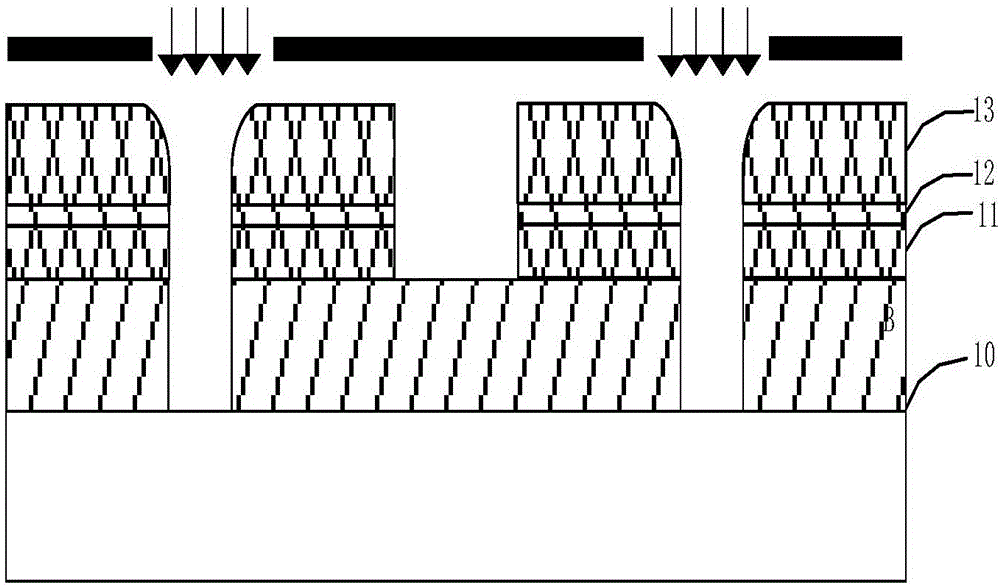

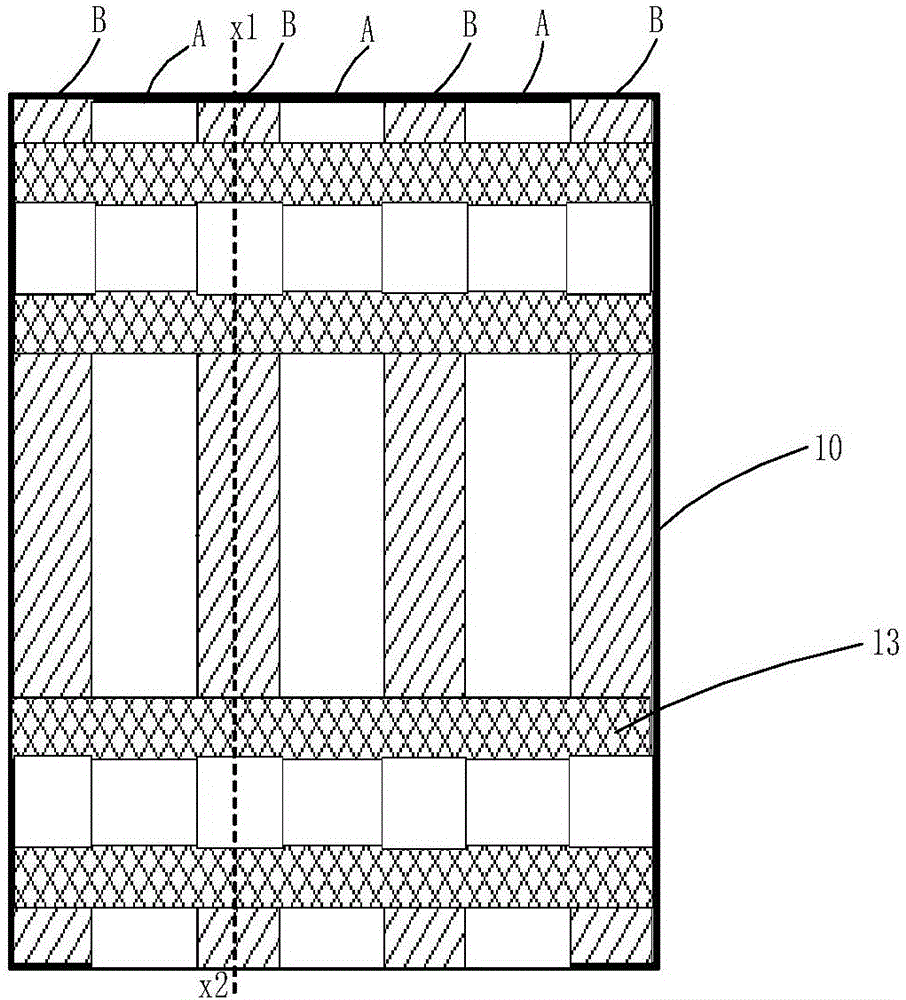

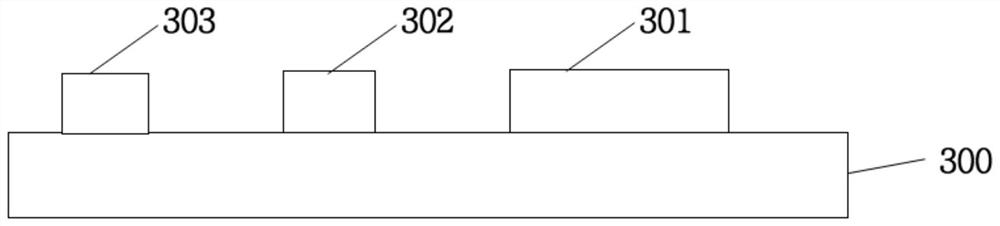

Storage structure and preparation method thereof

InactiveCN105742250AReduce overall heightShorten the timeSolid-state devicesSemiconductor/solid-state device manufacturingControllabilityMedia layer

The invention provides a storage structure and a preparation method thereof. The preparation method comprises the following steps of: providing a semiconductor substrate, wherein a plurality of interlay medium layers and virtual medium layers which are overlapped in a staggered manner are formed on the surface of the semiconductor substrate, and the virtual medium layers are formed between adjacent interlay medium layers; etching the interlay medium layers, the virtual medium layers and a part of the semiconductor substrate so as to form grooves; forming epitaxial layers at the bottoms of the grooves, wherein the upper surfaces of the epitaxial layers do not exceed the upper surfaces of the interlay medium layers; sequentially forming partitioning medium layers and polycrystalline silicon layers on side walls of the grooves. According to the storage structure, as the epitaxial layers are only formed at the bottoms of the grooves, the time for selective extension is shortened, and meanwhile a photomask process can be reduced. In addition, the upper surfaces of the epitaxial layers do not exceed the upper surfaces of the interlay medium layers, so that the total height of the interlay medium layers and the virtual medium layers on the semiconductor substrate can be reduced. The storage structure is relatively good in controllability of threshold voltage of a selecting grid in programming operation of a memory.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Thin film transistor and manufacturing method thereof

ActiveCN102881653AGood electrical propertiesQuality improvementTransistorSemiconductor/solid-state device manufacturingTitaniumCopper

The invention provides a thin film transistor and a manufacturing method thereof. The method includes following steps: step 1, providing a substrate; step 2, forming a first metal layer on the substrate, and forming a grid through photomask process; step 3, forming a grid insulating layer on the grid; step 4, forming an oxide semiconductor layer on the grid insulating layer, and forming a second metal layer on the oxide semiconductor layer, wherein the second metal layer comprises a titanium layer formed on the oxide semiconductor layer and a copper layer formed on the titanium layer, and forming a data line and a source / drain electrode through the photomask process; and step 5, forming a transparent conductive layer on the second metal layer, patterning the transparent conductive layer through the photomask process, and then obtaining the thin film transistor.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

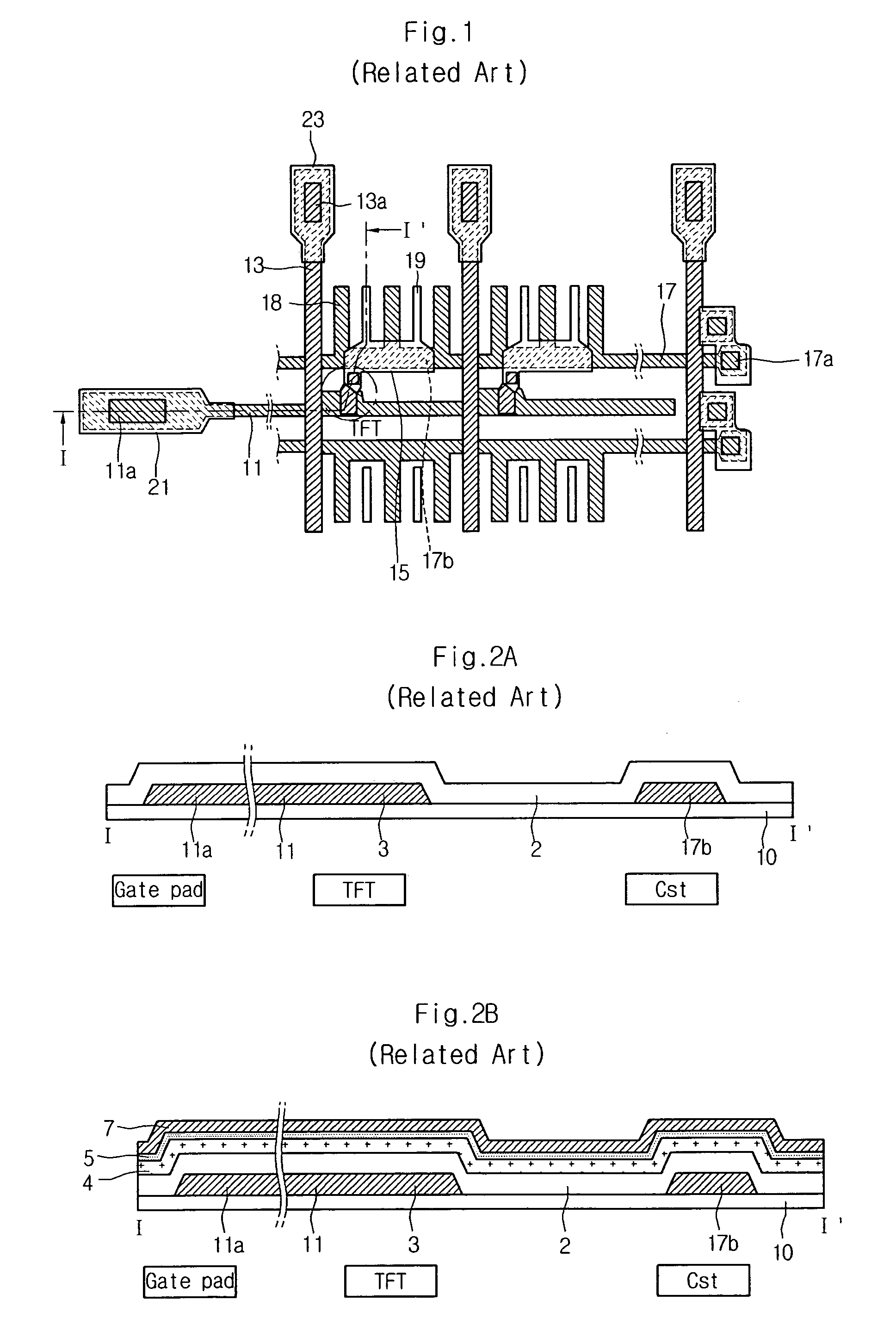

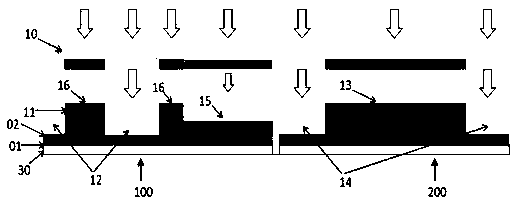

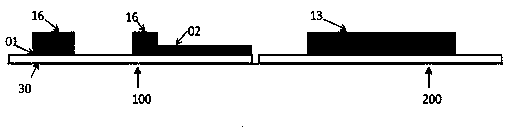

Method for fabricating thin film transistor substrate

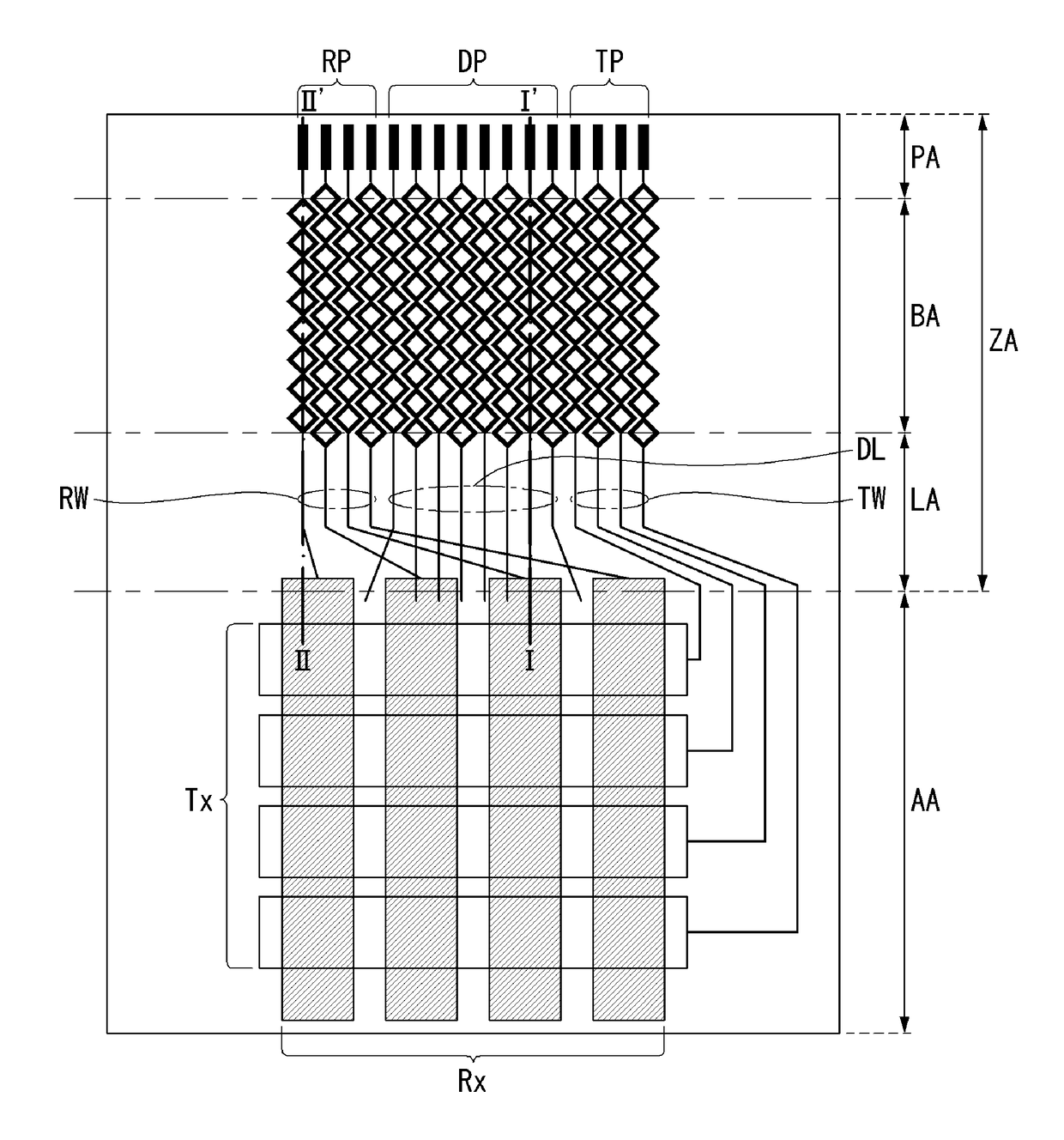

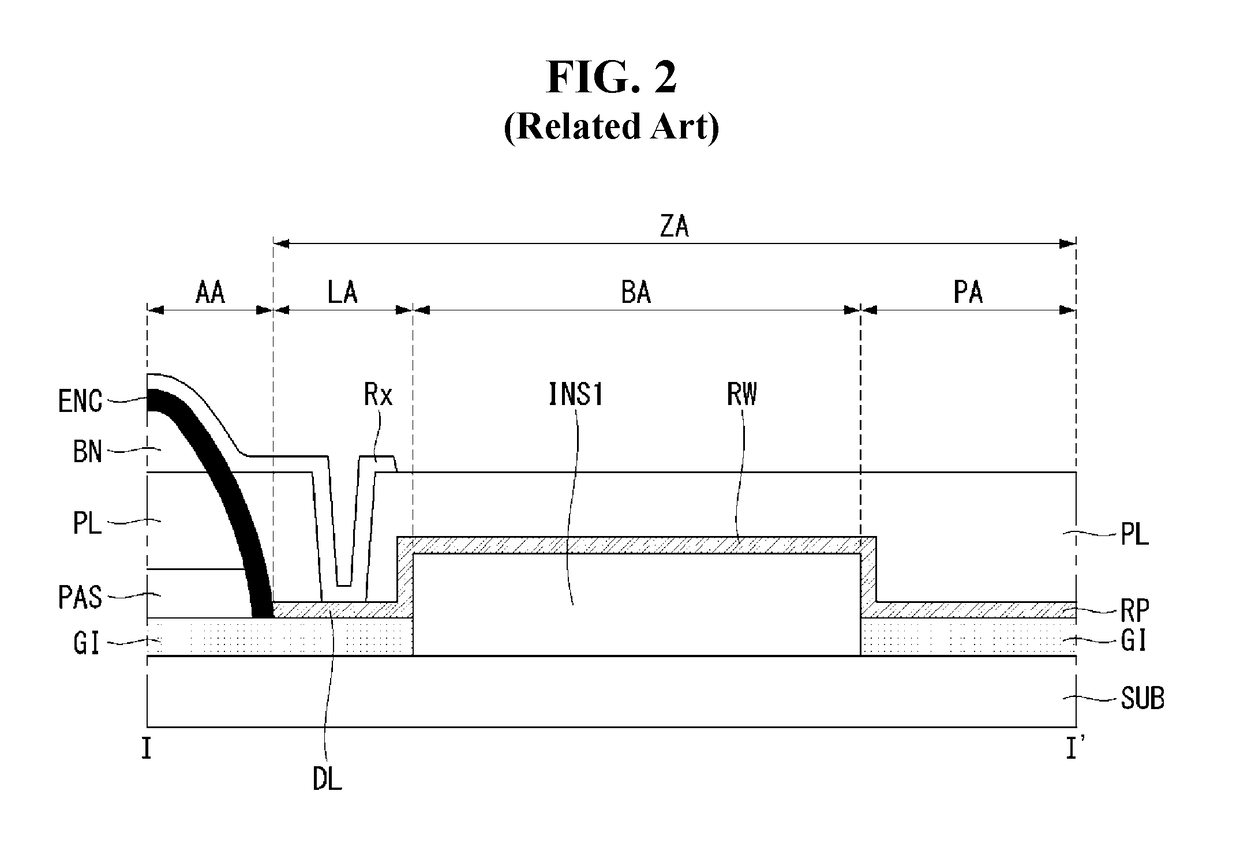

ActiveUS20080003723A1Reduce photomask processSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringData link

A method of fabricating a thin film transistor substrate for reducing a mask process and, at the same time removing a transparent electrode ITO which remains at a non-display area by a contact hole filling process is disclosed. In the method of fabricating the thin film transistor substrate having a display area and a non-display area where is located at the exterior of the display area, a gate pattern, which is comprised of a gate line which is formed at a display area, a gate electrode which is connected to a gate line, a gate link which is formed at a non-display area, and a lower gate pad electrode which is connected, via a gate link, to a gate line, is formed. A gate insulating film is formed on a substrate provided with a gate pattern, and then a data pattern, which is comprised of a data line which is formed at a display area and is crossed with a gate line, a source electrode and a drain electrode which are connected to a data line, a data link which is formed at a non-display area, and a lower data pad electrode which is connected, via a data link, to a data line, is formed. And a protective film is formed on an entire substrate provided with a data pattern, and then a conductive pattern, which is comprised of a pixel electrode which is formed at a display area by a contact hole filling process using a smoothing material, and a lower gate pad electrode and a lower data pad electrode which are formed at a non-display area, is formed.

Owner:LG DISPLAY CO LTD

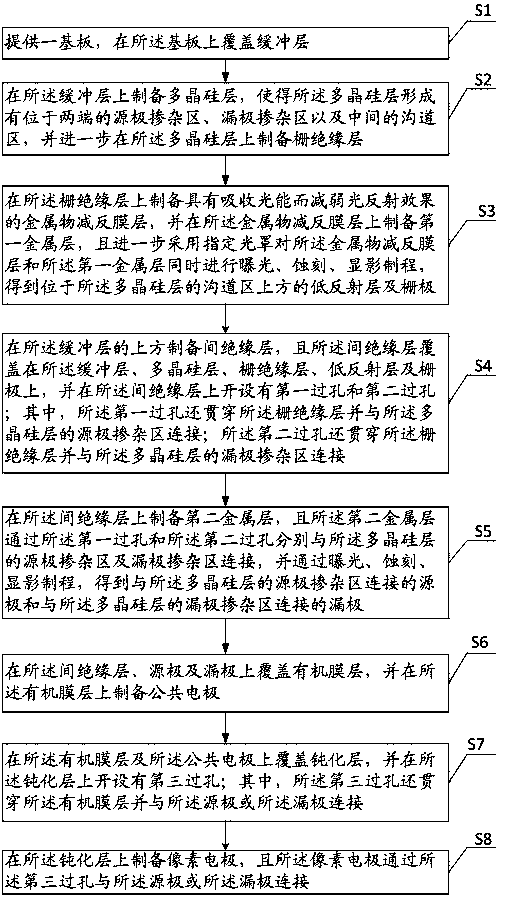

An array substrate and a preparation method thereof

ActiveCN109003943AReduce photogenerated leakage currentShorten the production cycleSolid-state devicesSemiconductor/solid-state device manufacturingOrganic filmLight energy

The invention provides an array substrate, comprising providing a substrate, and sequentially preparing a buffer layer, a polysilicon layer, a gate insulating layer, a low-reflection layer, a gate electrode, an inter-insulating layer, a source-drain electrode, an organic film layer, a common electrode, a passivation layer and a pixel electrode on the substrate; A low-reflective lay and a gate electrode are fabricated by that same mask, and the low-reflective lay has the effect of absorbing light energy and reducing light reflection, replaces the design of a traditional light-shielding metal plate, can also effectively reduce the problem of photogenerated leakage current of an LTPS array substrate structure, and simultaneously saves an original mask manufacture process of the traditional light-shielding metal plate. Therefore, the invention can not only effectively reduce the problem of photogenerated leakage current of the LTPS array substrate structure, but also reduce the number of masks required for manufacturing the array substrate, thereby reducing the production cycle and the cost.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

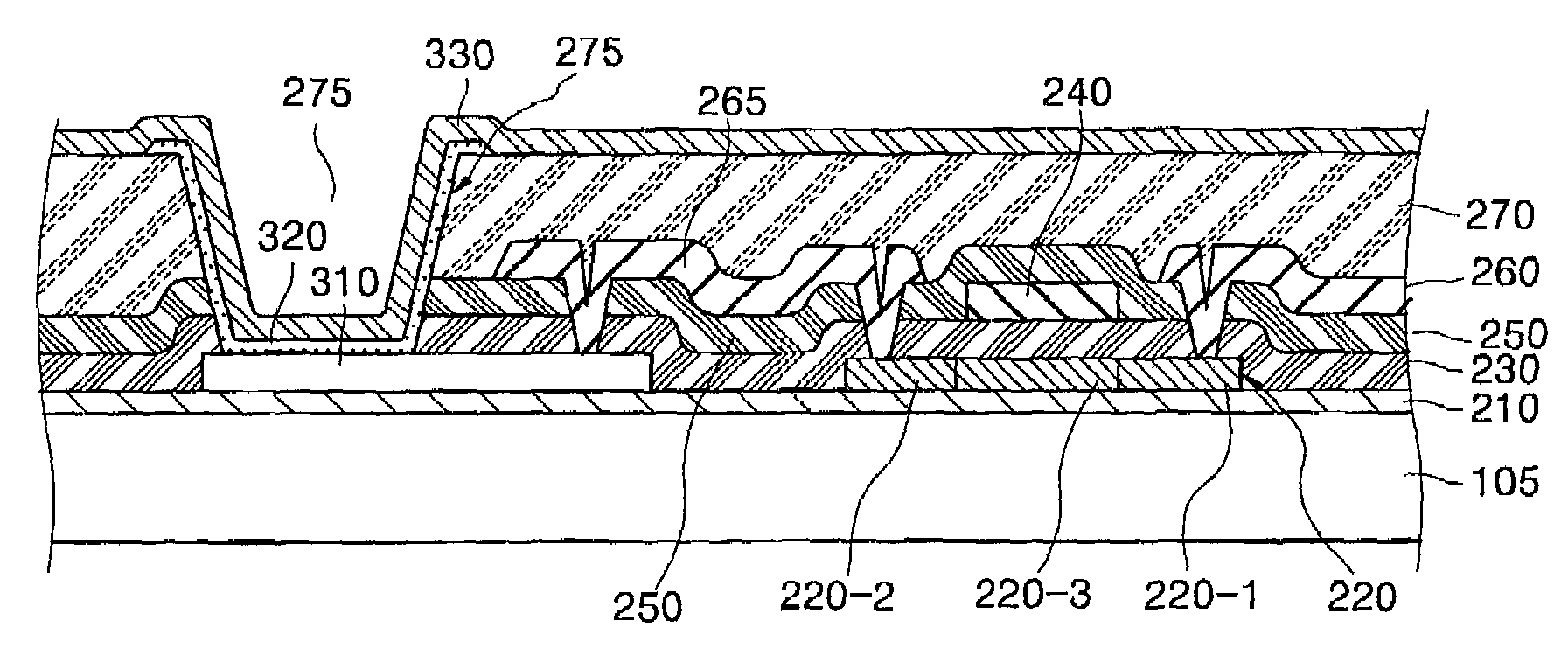

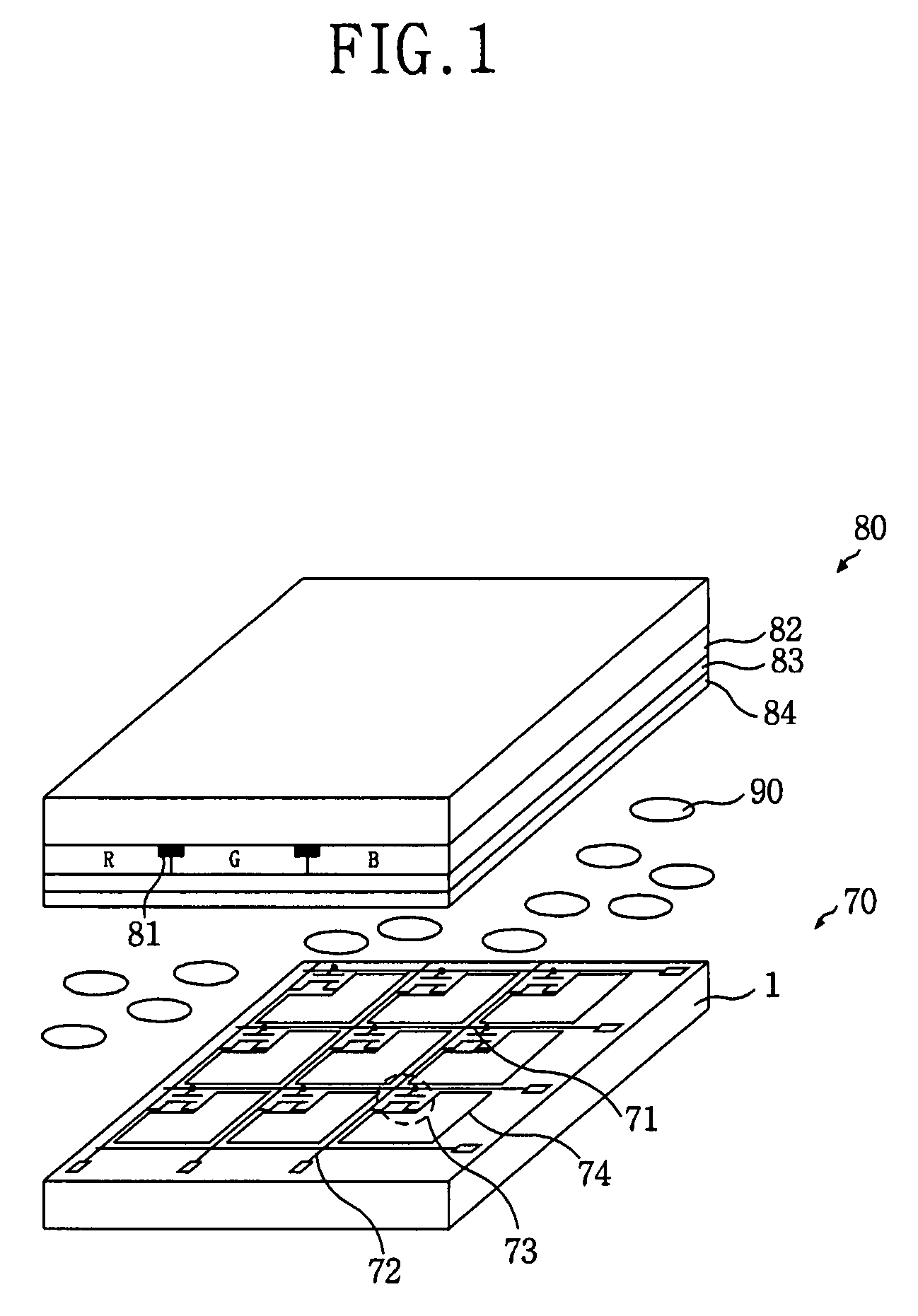

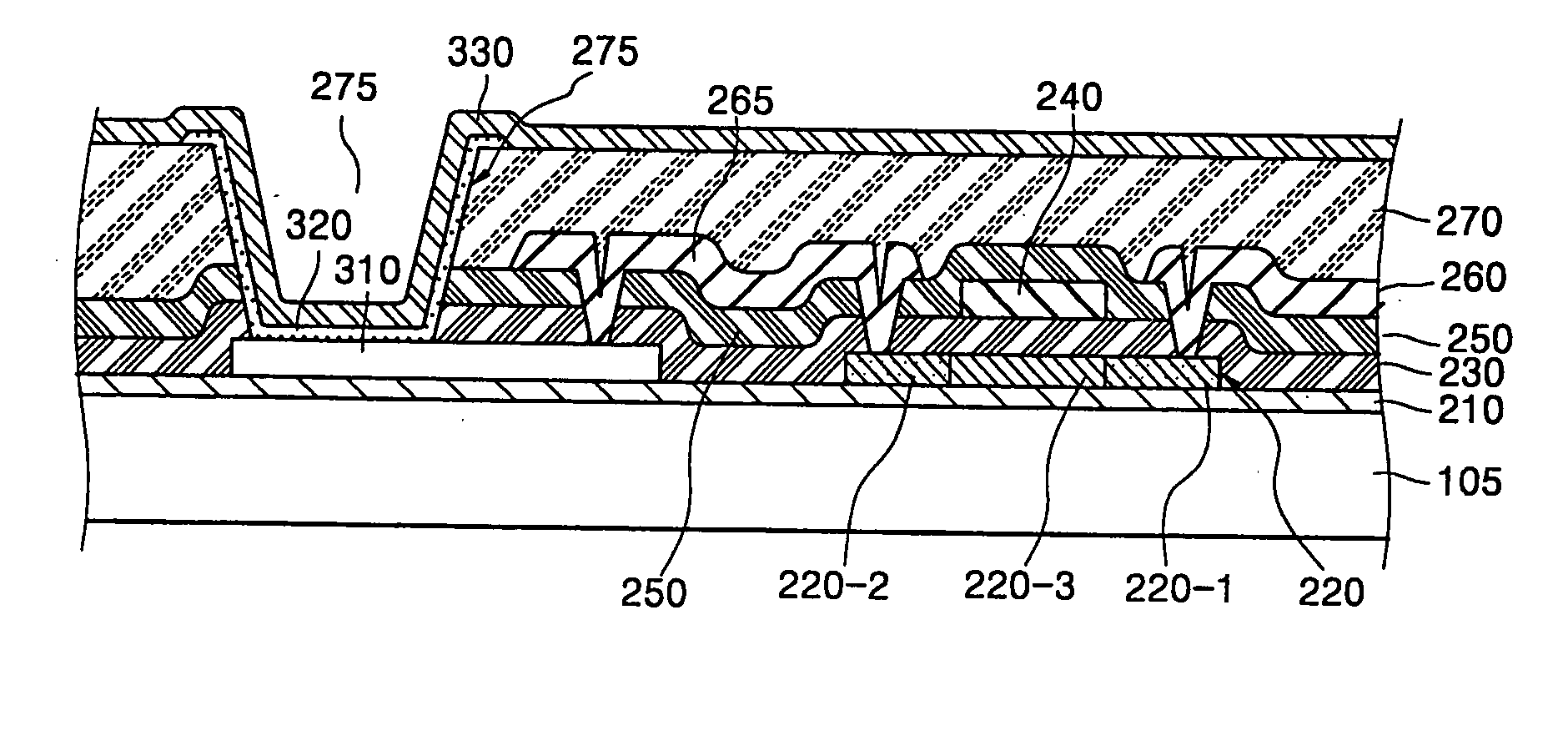

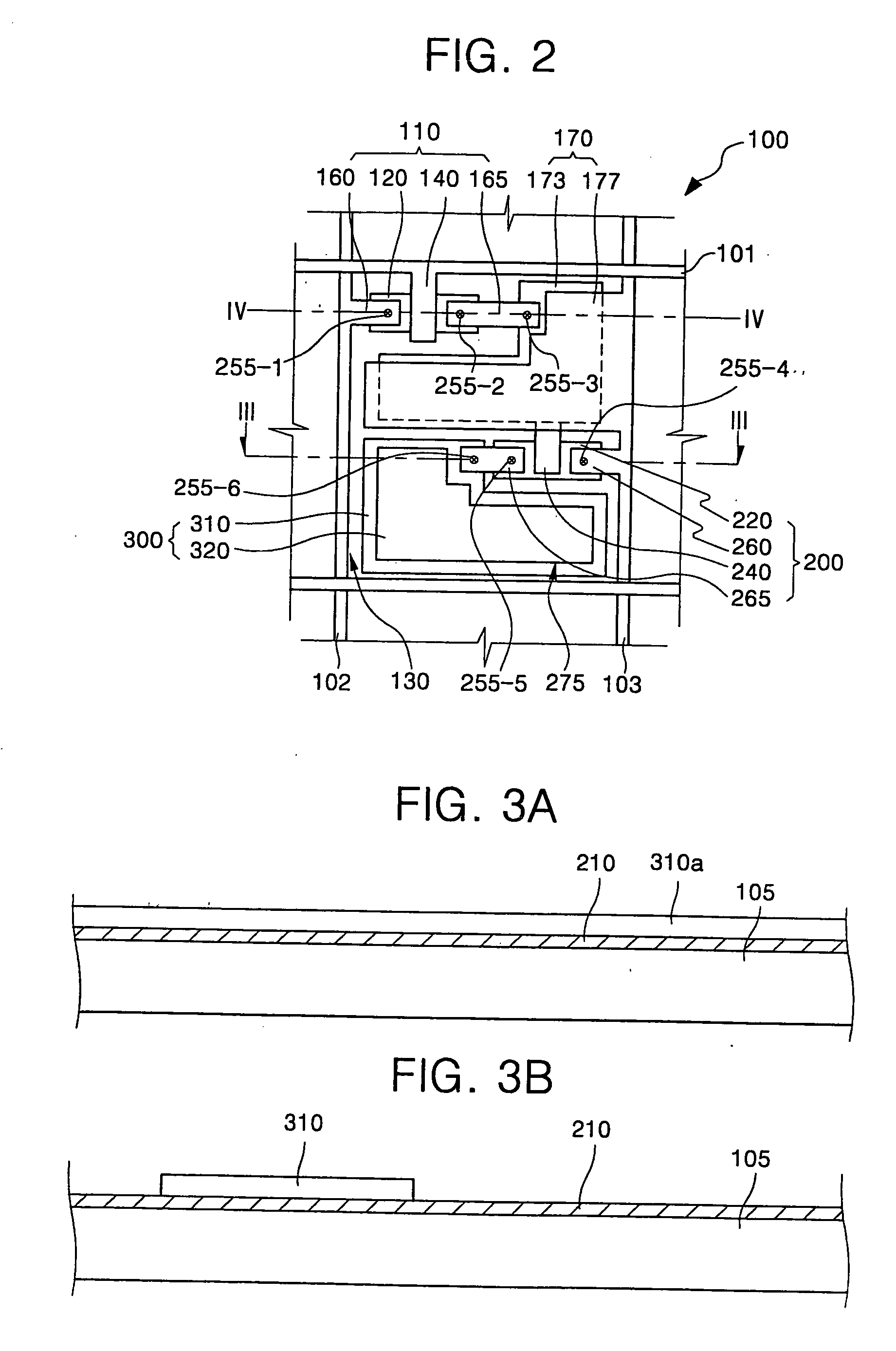

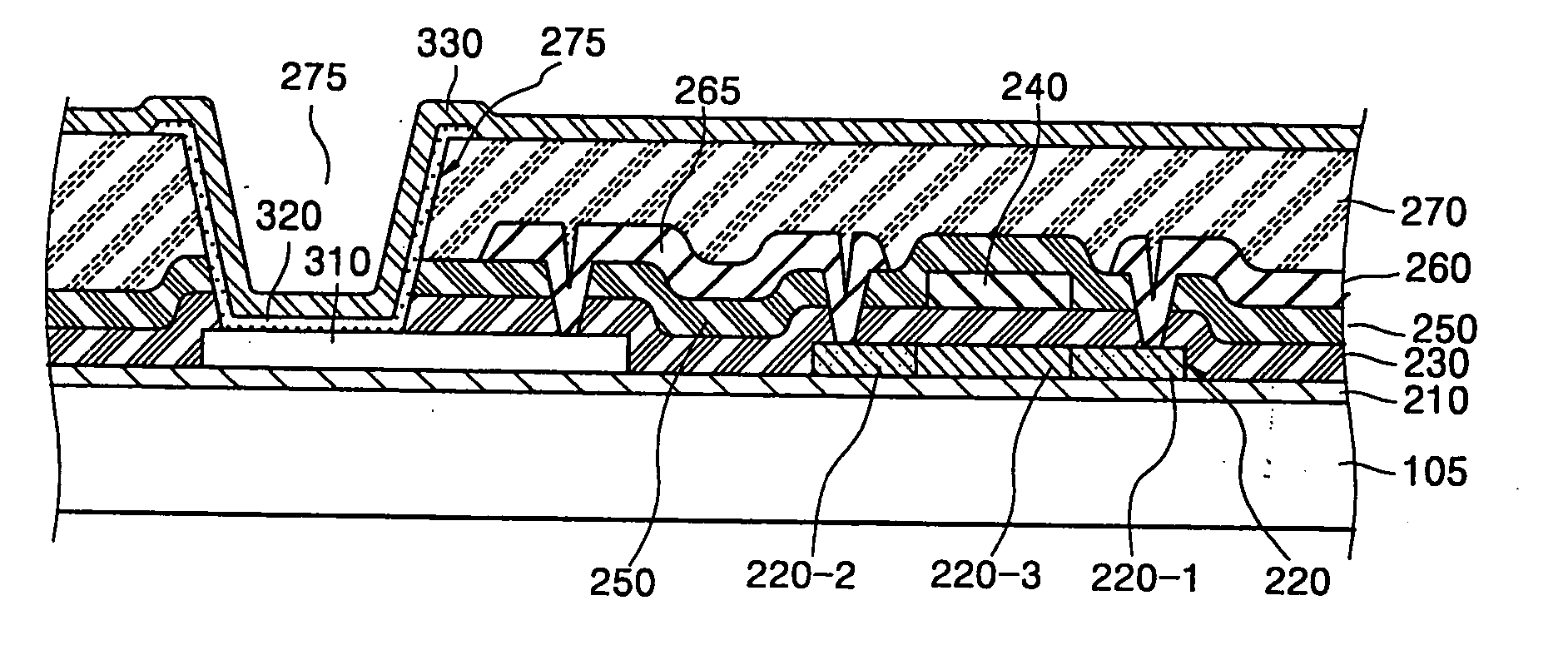

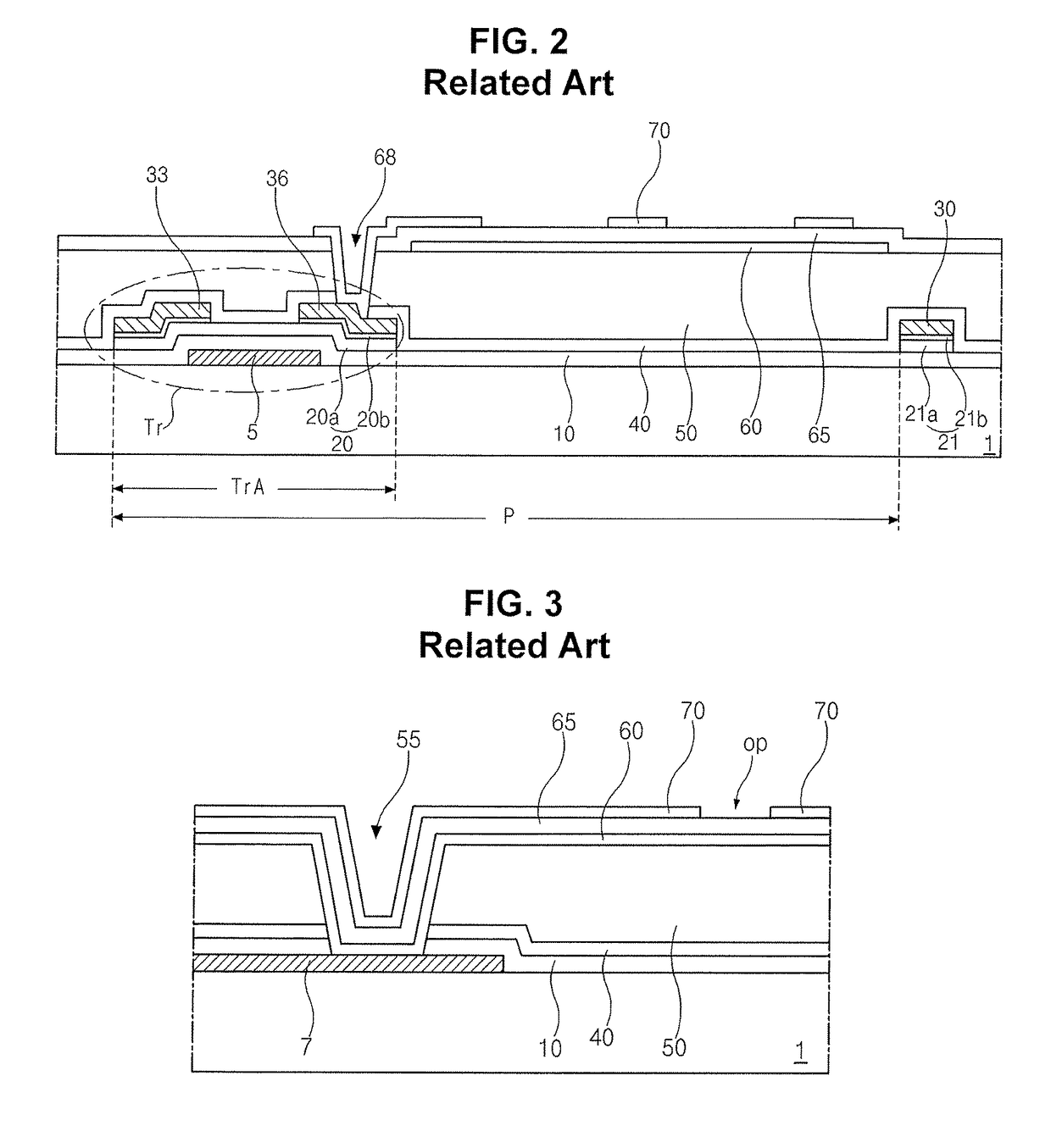

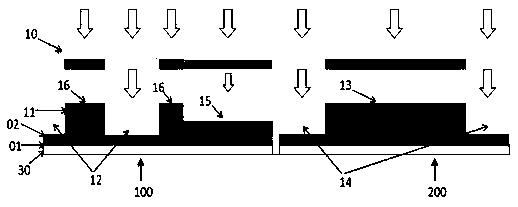

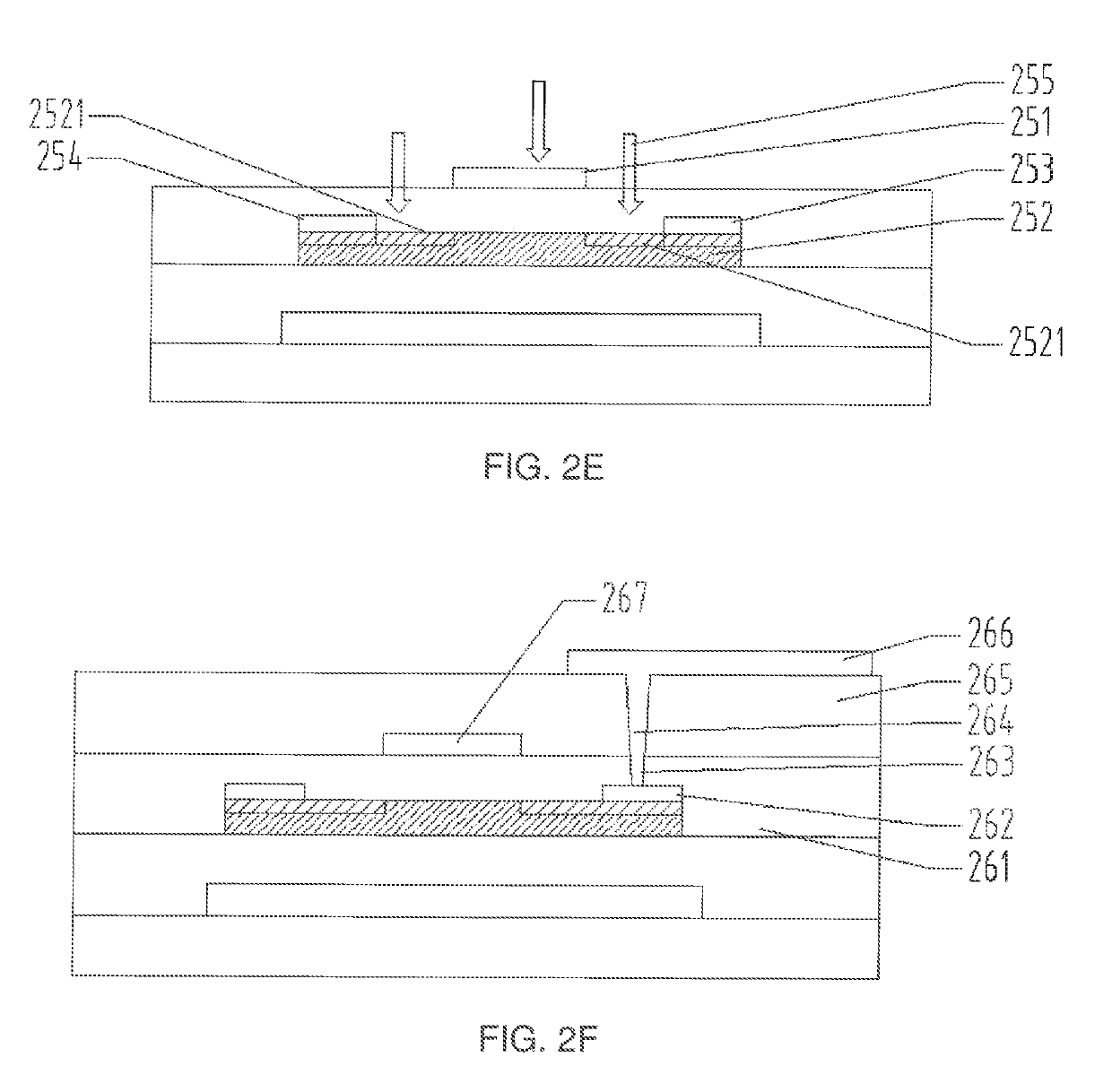

Flat panel display device and method of manufacturing the same

InactiveUS20060035397A1Improve production yieldReduce photomask processElectroluminescent light sourcesSolid-state devicesTransmittanceDisplay device

A flat panel display includes a pixel electrode having an opening portion formed on an insulating substrate, a semiconductor layer formed over a surface of the insulating substrate, spaced apart from the pixel electrode, having source and drain regions formed to both end portions thereof, a first insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode, a gate electrode formed on the first insulating layer over the semiconductor layer, and a second insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode. The present invention provides an organic EL display manufactured with reduced mask processes which has excellent electrical characteristics and improved light transmittance.

Owner:SAMSUNG DISPLAY CO LTD

Flexible electroluminescent display device

ActiveUS10475874B2Reduce stressReduce photomask processStatic indicating devicesSolid-state devicesElectricityInsulation layer

An electroluminescent display device includes: a substrate including: an active area, and bezel area outside the active area and including a bending area, a first organic insulation layer (OIL) in the active area, covering a first signal line extending from the active area to the bezel area, a second OIL in the bending area, the second OIL being in a same layer as the first organic insulation film, first and second touch electrodes crossing over each other and sealing the active area on an encapsulation layer above the first OIL with a third OIL therebetween, a first signal line link pattern connected to the first signal line, and on the second OIL in the bending area, and second and third signal lines respectively connected to the first and second touch electrodes, and on the second OIL in parallel with the first signal line link pattern.

Owner:LG DISPLAY CO LTD

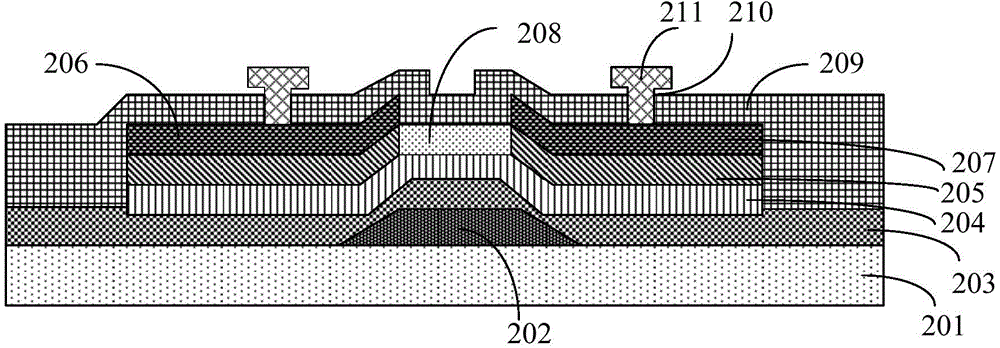

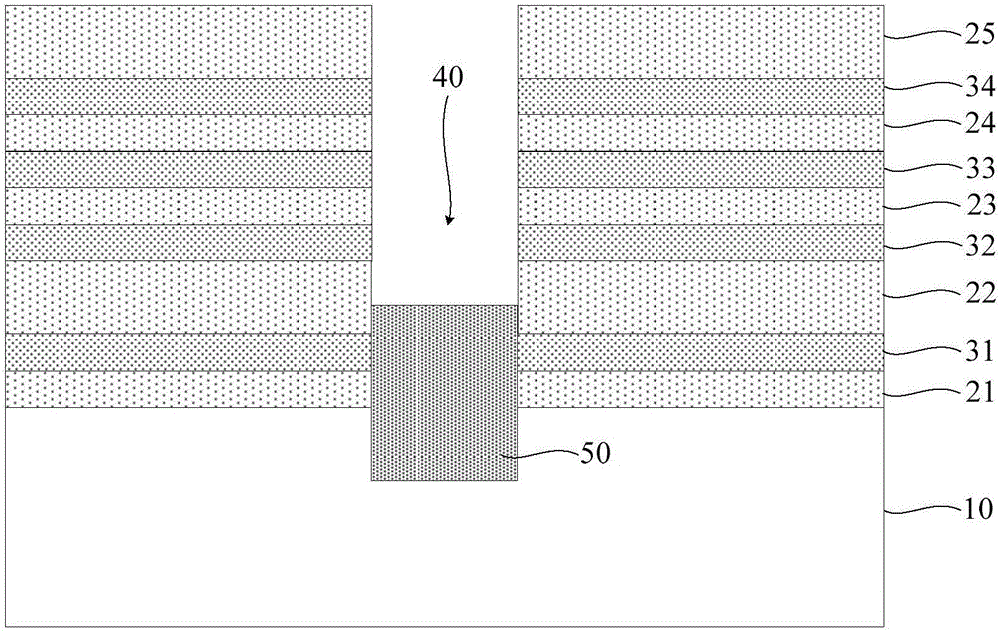

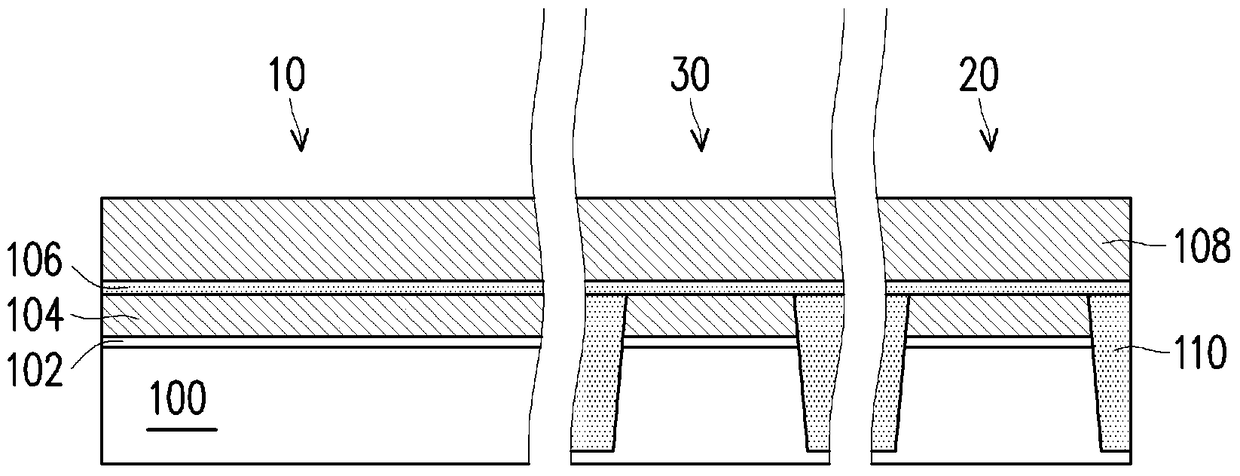

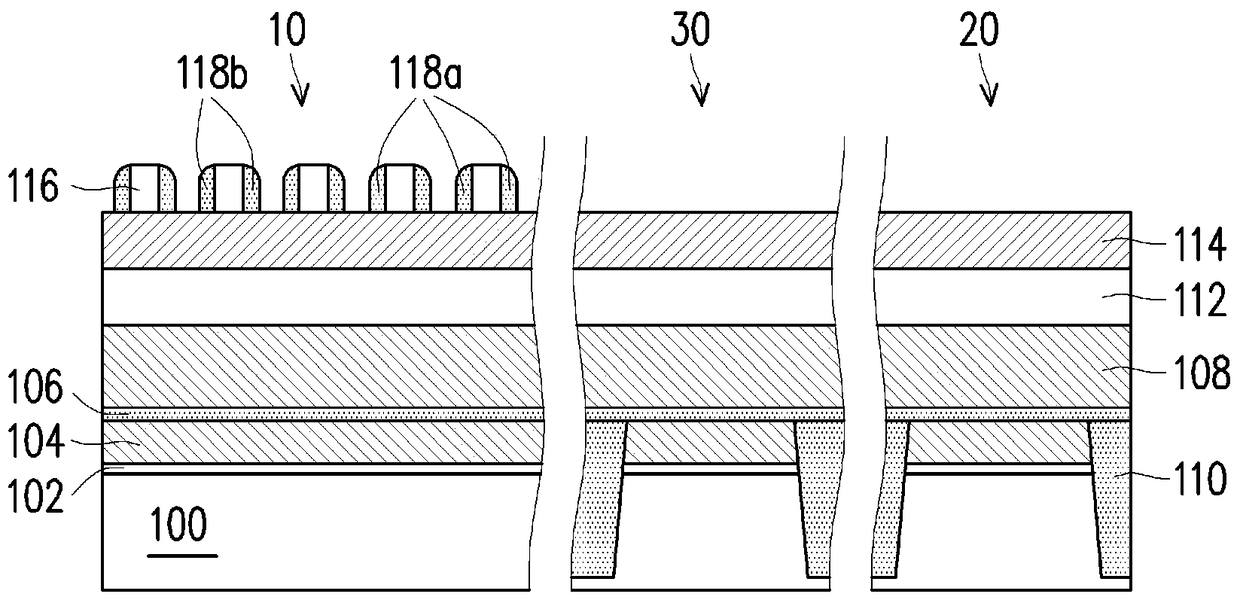

Display device and method for manufacturing the same

ActiveUS20210202653A1Improve luminous efficiencyImprove processing efficiencySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringContact hole

A display device and a method of the display device are provided. The display device includes a lower metal layer on a substrate, a buffer layer on the lower metal layer, a first semiconductor layer on the buffer layer, a gate insulating layer on the first semiconductor layer, a first gate electrode on the gate insulating layer, an interlayer insulating layer on the first gate electrode, a via layer on the interlayer insulating layer, a pixel electrode on the via layer and electrically connected to the first semiconductor layer, a light emitting layer on the pixel electrode, a common electrode on the light emitting layer, a first contact hole penetrating the buffer layer and the interlayer insulating layer and a second contact hole penetrating the interlayer insulating layer, and a first via hole and a second via hole each penetrating the via layer.

Owner:SAMSUNG DISPLAY CO LTD

Thin film transistor substrate and preparation method of thin film transistor substrate

ActiveCN111710726ASimple structureEasy to produceTransistorSolid-state devicesThin membraneMaterials science

The invention provides a thin film transistor substrate and a preparation method thereof. The thin film transistor substrate comprises a metal layer, a buffer layer, a switching thin film transistor and a driving thin film transistor. The metal layer comprises a source electrode of the switching thin film transistor, a first metal layer and a shading layer. The source electrode, the first metal layer and the shading layer are formed by patterning the same metal layer and are arranged in the same layer. According to the structure disclosed by the embodiment of the invention, a flat layer structure is omitted, and the structure of the thin film transistor substrate is effectively simplified. Meanwhile, the photomask template process in the preparation process is reduced, the photomask frequency is reduced, the production process is simplified, and the production cost is reduced.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Processing method for array substrate and display panel

InactiveCN109524357AGood etch stopReduce photomask processSolid-state devicesSemiconductor/solid-state device manufacturingPhotoresistSemiconductor

The invention discloses a processing method for an array substrate and a display panel. The method comprises a step of forming a gate metal layer and a gate insulating layer on a glass substrate, a step of forming a semiconductor layer on the gate insulating layer and forming an etching stop layer at a trench position of a thin film transistor, a step of forming a metal layer on the etching stop layer, depositing a photoresist on the metal layer, performing a light mask process on a light mask and exposing and developing to form a photoresist layer with a predetermined shape, a step of etchingto obtain a source electrode and a drain electrode, a step of performing post-baking on a photoresist layer remaining on the source electrode and the drain electrode such that the photoresist layer flows to the trench position, a step of etching a semiconductor layer and obtaining a predetermined pattern, a step of stripping the photoresist layer on the source electrode, the drain electrode and the trench position, and a step of forming a passivation layer and a conductive thin film layer on the source electrode, the drain electrode, and the channel locations. According to the invention, themask process can be reduced, and the production cost is effectively reduced.

Owner:HKC CORP LTD

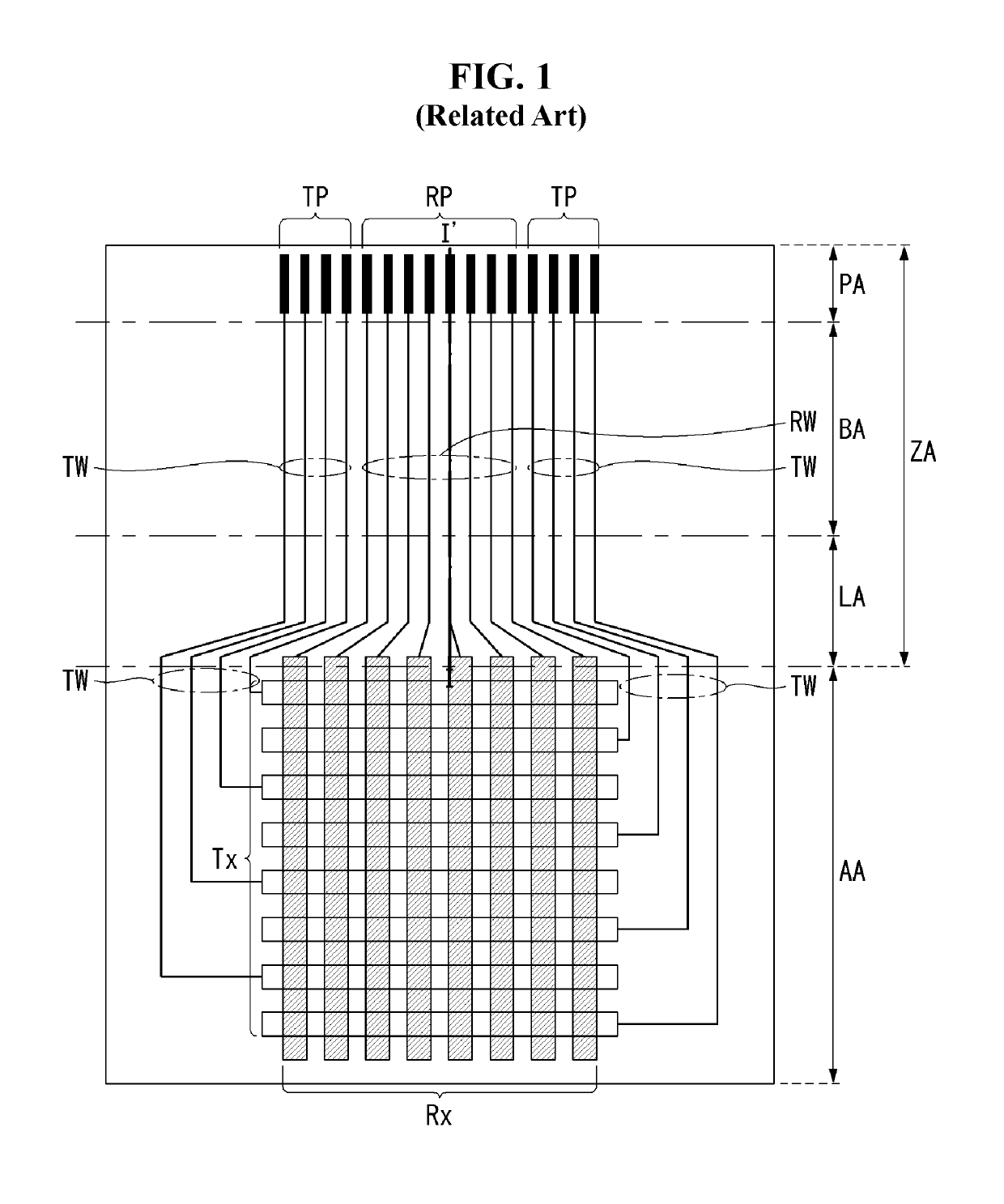

Liquid crystal display device and method of manufacturing the same

InactiveUS7719622B2Reduce in quantityObtaining adequateNon-linear opticsCapacitanceLiquid-crystal display

An LCD include a gate line, a first data line and a second data line arranged to cross each other, thereby defining a unit pixel region, a TFT disposed at a region where the gate line, the first data line and the second data line cross, and having a passivation layer on an exposed channel layer, a common line disposed in parallel to the gate line, a first storage electrode integrally formed with the common line for forming a storage capacitance in the unit pixel region, a second electrode disposed to overlap with the first storage electrode, common electrodes branched from the first storage electrode and disposed at the unit pixel region, and pixel electrodes branched from the second storage electrode and alternately disposed with the common electrodes.

Owner:LG DISPLAY CO LTD

Flash memory structure and manufacturing method thereof

ActiveCN106653759AImprove performanceReduce manufacturing costSolid-state devicesSemiconductor devicesEngineeringIon implantation

The invention discloses a flash memory structure and a manufacturing method thereof. Active areas are defined in a substrate, the active areas comprise a first active area and a second active area, and the first active area and the second active area are mutually vertically distributed; a gate structure is formed on the substrate, the gate structure is positioned on two parallel sides of the second active area, and a part of the first active area is covered with the gate structure; an ion implantation technology is carried out on the substrate by using the gate structure as a mask, and a source electrode is formed on one side of the gate structure in the active areas. The source electrode in the flash memory structure is formed through the manufacturing method, a photomask technology can be reduced, and harmful effects of the photomask technology on the gate structure can also be avoided. Therefore, according to the flash memory structure formed through the manufacturing method, the performance of the flash memory can be improved, the production cost is reduced, and the competitive force is improved.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Thin film transistor and manufacturing method thereof

ActiveCN109659372AReduce photomask processTransistorSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

The invention provides a thin film transistor and a manufacturing method thereof, and relates to the technical field of liquid crystal display. The manufacturing method of an oxide thin film transistor, in combination with a traditional 6Mask process (gate, semiconductor layer / source drain, organic insulating layer, common electrode, second insulating layer, pixel electrode), constructs the commonelectrode (Com electrode) on a bottom layer. The common electrode and the gate are completed at a time to reduce a mask process (achieved by semi-transparent mask multi-stage exposure), so as to forma bottom Com architecture. In addition, an organic insulating film is not required, and an FFS array substrate is manufactured in four mask processes. Further, an intermediate protective layer of thepixel electrode and the common electrode in the pixel region of the thin film transistor has a suitable thickness (2000 angstroms to 8000 angstroms) required to form a storage capacitor.

Owner:NANJING CEC PANDA LCD TECH

Flexible electroluminescent display device

ActiveUS20200066824A1Reduce stressReduce photomask processStatic indicating devicesSolid-state devicesInsulation layerMaterials science

An electroluminescent display device includes: a substrate including: an active area, and bezel area outside the active area and including a bending area, a first organic insulation layer (OIL) in the active area, covering a first signal line extending from the active area to the bezel area, a second OIL in the bending area, the second OIL being in a same layer as the first organic insulation film, first and second touch electrodes crossing over each other and sealing the active area on an encapsulation layer above the first OIL with a third OIL therebetween, a first signal line link pattern connected to the first signal line, and on the second OIL in the bending area, and second and third signal lines respectively connected to the first and second touch electrodes, and on the second OIL in parallel with the first signal line link pattern.

Owner:LG DISPLAY CO LTD

Liquid crystal display device

ActiveUS20100201898A1Reduce in quantityObtaining adequateNon-linear opticsCapacitanceLiquid-crystal display

An LCD include a gate line, a first data line and a second data line arranged to cross each other, thereby defining a unit pixel region, a TFT disposed at a region where the gate line, the first data line and the second data line cross, and having a passivation layer on an exposed channel layer, a common line disposed in parallel to the gate line, a first storage electrode integrally formed with the common line for forming a storage capacitance in the unit pixel region, a second storage electrode disposed to overlap with the first storage electrode, common electrodes branched from the first storage electrode and disposed at the unit pixel region, and pixel electrodes branched from the second storage electrode and alternately disposed with the common electrodes.

Owner:LG DISPLAY CO LTD

Flat panel display device and method of manufacturing the same

InactiveUS20060011918A1Improve production yieldReduce photomask processTransistorElectroluminescent light sourcesTransmittanceDisplay device

A flat panel display includes a pixel electrode having an opening portion formed on an insulating substrate, a semiconductor layer formed over a surface of the insulating substrate, spaced apart from the pixel electrode, having source and drain regions formed to both end portions thereof, a first insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode, a gate electrode formed on the first insulating layer over the semiconductor layer, and a second insulating layer formed over the surface of the insulating substrate excluding the opening portion of the pixel electrode. The present invention provides an organic EL display manufactured with reduced mask processes which has excellent electrical characteristics and improved light transmittance.

Owner:SAMSUNG DISPLAY CO LTD

Display panel, preparation method thereof, and display device

InactiveCN111223875AReduced lamellar structureReduce photomask processSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention provides a display panel, a preparation method thereof, and a display device. The display panel comprises an active layer, an insulating layer, a source electrode, a drain electrode, a grid electrode and a pixel electrode. The source electrode, the drain electrode and the grid electrode are arranged on the same layer on the insulating layer, and the pixel electrode is arranged on thesurface, away from the insulating layer, of the source electrode, the drain electrode and the grid electrode.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Display device and method for manufacturing the same

ActiveUS11411066B2Improve luminous efficiencyImprove processing efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceSemiconductor

A display device and a method of the display device are provided. The display device includes a lower metal layer on a substrate, a buffer layer on the lower metal layer, a first semiconductor layer on the buffer layer, a gate insulating layer on the first semiconductor layer, a first gate electrode on the gate insulating layer, an interlayer insulating layer on the first gate electrode, a via layer on the interlayer insulating layer, a pixel electrode on the via layer and electrically connected to the first semiconductor layer, a light emitting layer on the pixel electrode, a common electrode on the light emitting layer, a first contact hole penetrating the buffer layer and the interlayer insulating layer and a second contact hole penetrating the interlayer insulating layer, and a first via hole and a second via hole each penetrating the via layer.

Owner:SAMSUNG DISPLAY CO LTD

Array substrate for fringe field switching mode liquid crystal display device and method of fabricating the same

ActiveUS9768275B2Increase the aperture ratioReduce photomask processSolid-state devicesNon-linear opticsLiquid-crystal displayCommon line

An array substrate for a liquid crystal display (LCD) device includes a common line and gate lines. The array substrate includes a first, second, and third passivation layer and thin film transistors (TFTs). The second passivation layer includes first and second holes respectively corresponding to a drain electrode and the common line. A common electrode on the second passivation layer includes a first opening corresponding to the TFTs and a second opening in the second hole. A drain contact hole through the third and first passivation layers exposes the drain electrode. A first common contact hole through the third passivation layer exposes the common electrode in the second hole. A second common contact hole through the third and first passivation layers exposes the common line, and a pixel electrode includes a third opening and a connection pattern connecting the common electrode to the common line on the third passivation layer.

Owner:LG DISPLAY CO LTD

Thin film transistor array substrate, manufacturing method thereof, and liquid crystal display panel

ActiveCN109494231BImprove electrical reliabilityAvoid pollutionSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arraySemiconductor materials

Owner:KUSN INFOVISION OPTOELECTRONICS

Thin film transistor substrate and preparation method of thin film transistor substrate

ActiveCN111710726BSimple structureEasy to produceTransistorSolid-state devicesThin membraneMaterials science

The invention provides a thin film transistor substrate and a preparation method thereof. The thin film transistor substrate includes a metal layer, a buffer layer, a switching thin film transistor, and a driving thin film transistor. The metal layer includes the source of the switching thin film transistor, the first metal layer and the light-shielding layer, wherein the source, the first metal layer and the light-shielding layer are formed by patterning the same metal layer and arranged in the same layer. In the disclosed embodiment The structure omits the flat layer structure, effectively simplifies the structure of the thin film transistor substrate, reduces the mask mask process in the preparation process, reduces the number of masks, simplifies the production process, and reduces the production cost.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

A kind of thin film transistor and its manufacturing method

ActiveCN109659372BReduce photomask processTransistorSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

The invention provides a thin film transistor and a manufacturing method thereof, and relates to the technical field of liquid crystal display. The manufacturing method of an oxide thin film transistor, in combination with a traditional 6Mask process (gate, semiconductor layer / source drain, organic insulating layer, common electrode, second insulating layer, pixel electrode), constructs the commonelectrode (Com electrode) on a bottom layer. The common electrode and the gate are completed at a time to reduce a mask process (achieved by semi-transparent mask multi-stage exposure), so as to forma bottom Com architecture. In addition, an organic insulating film is not required, and an FFS array substrate is manufactured in four mask processes. Further, an intermediate protective layer of thepixel electrode and the common electrode in the pixel region of the thin film transistor has a suitable thickness (2000 angstroms to 8000 angstroms) required to form a storage capacitor.

Owner:NANJING CEC PANDA LCD TECH

Method for simultaneously fabricating semiconductor elements in unit cell region and surrounding region

ActiveCN106158745BAccurately control the amount of etchingReduce risk of damageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorGate dielectric

The invention provides a method for simultaneously manufacturing the semiconductor elements of a cell region and a surrounding region. The method comprises the steps of sequentially forming a gate oxide layer, a first conductor structure layer, an inter-gate dielectric layer and a second conductor structure layer on a substrate; forming a mask structure on the second conductor structure layer; adopting the mask structure as an etching mask to remove the second conductor structure layer in the cell region and in the surrounding region; adopting the inter-gate dielectric layer as an etching stop layer; covering the inter-gate dielectric layer in the surrounding region with a protection layer; etching the inter-gate dielectric layer and the first conductor structure layer both exposed out of the cell region; etching the inter-gate dielectric layer and the first conductor structure layer in the surrounding region; and adopting the gate oxide layer as the etching stop layer. According to the technical scheme of the invention, the damage risk of the oxide layer in the surrounding region is reduced.

Owner:WINBOND ELECTRONICS CORP

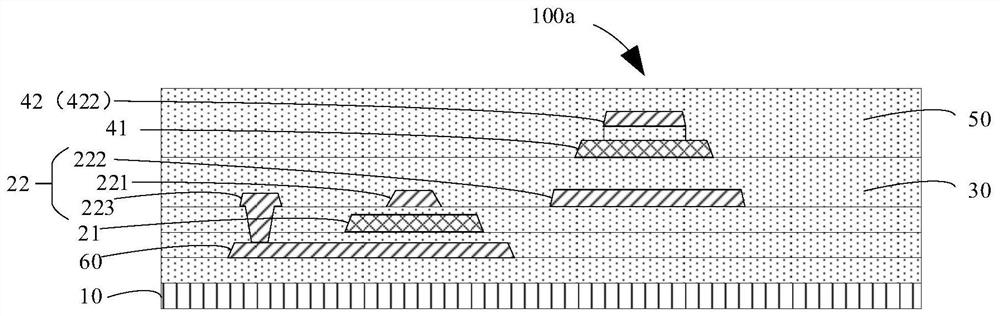

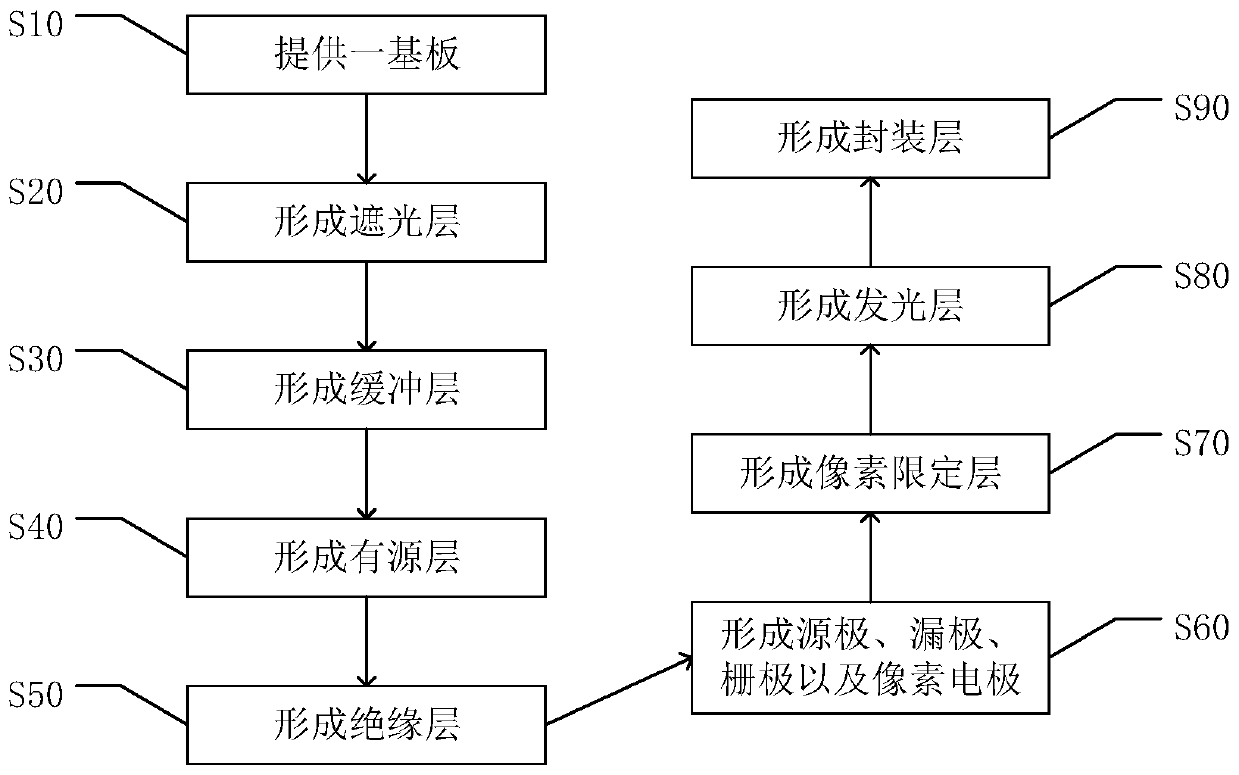

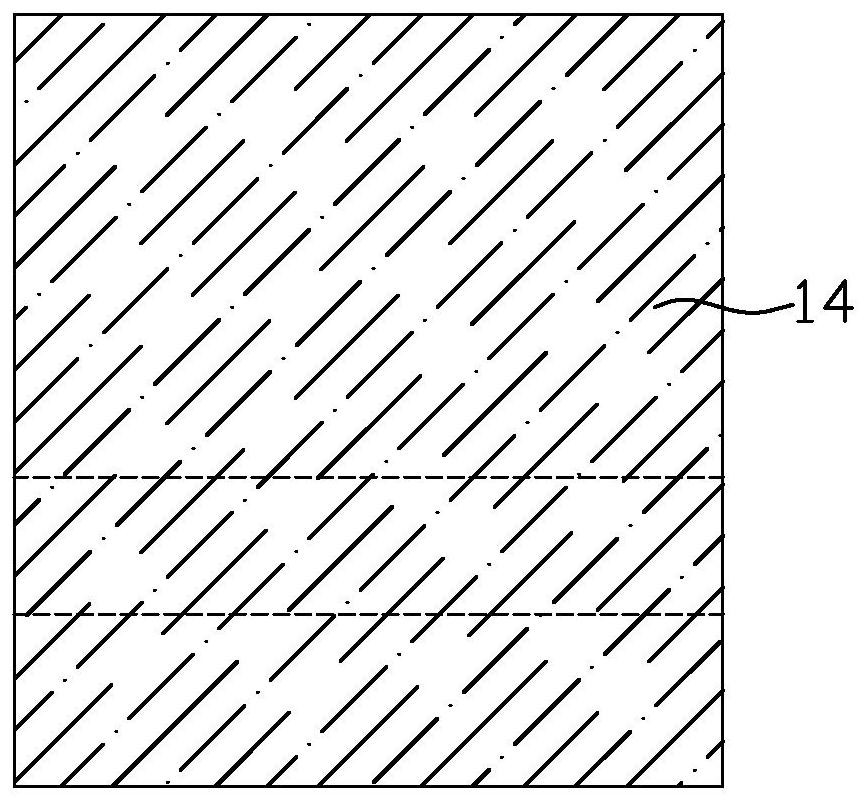

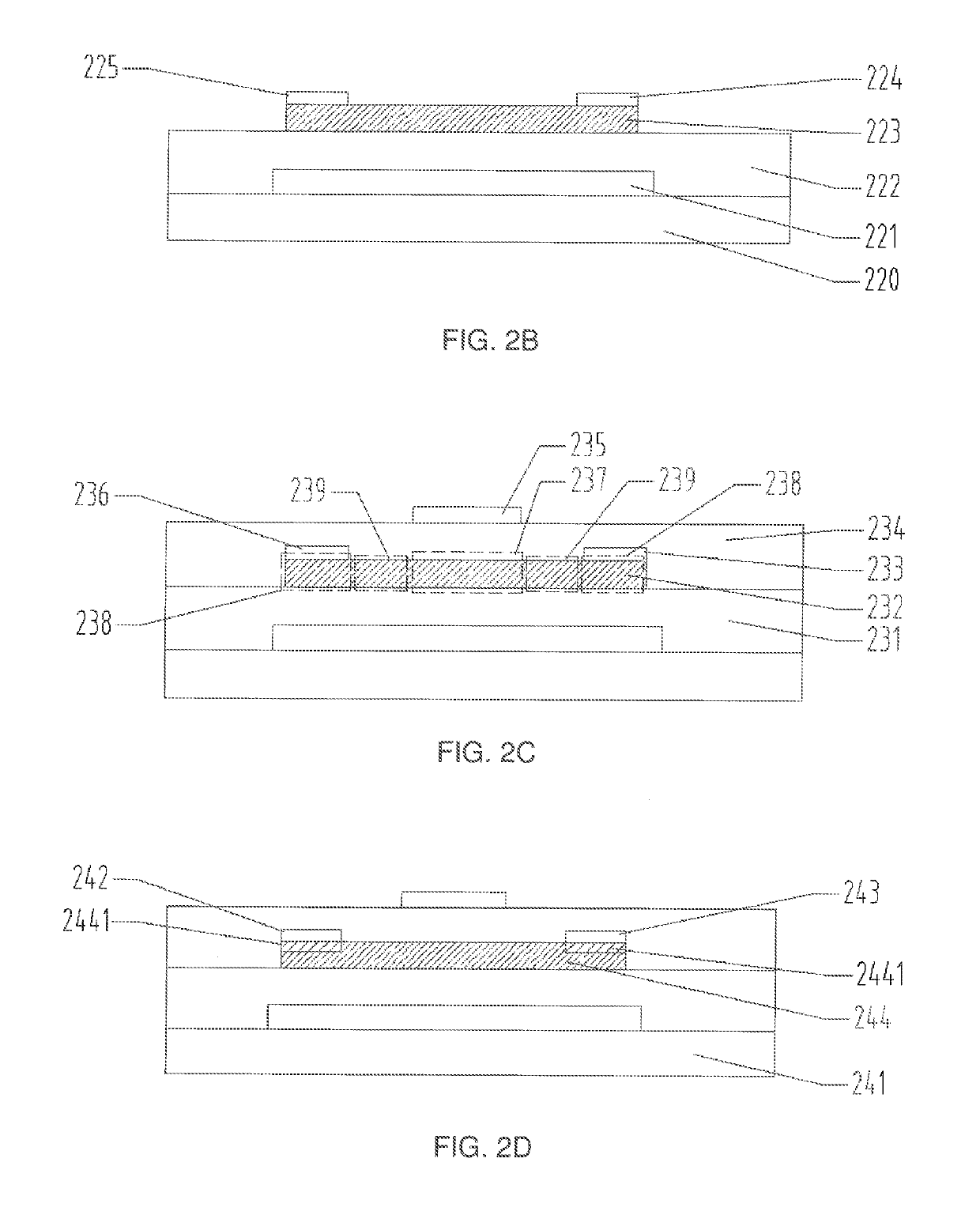

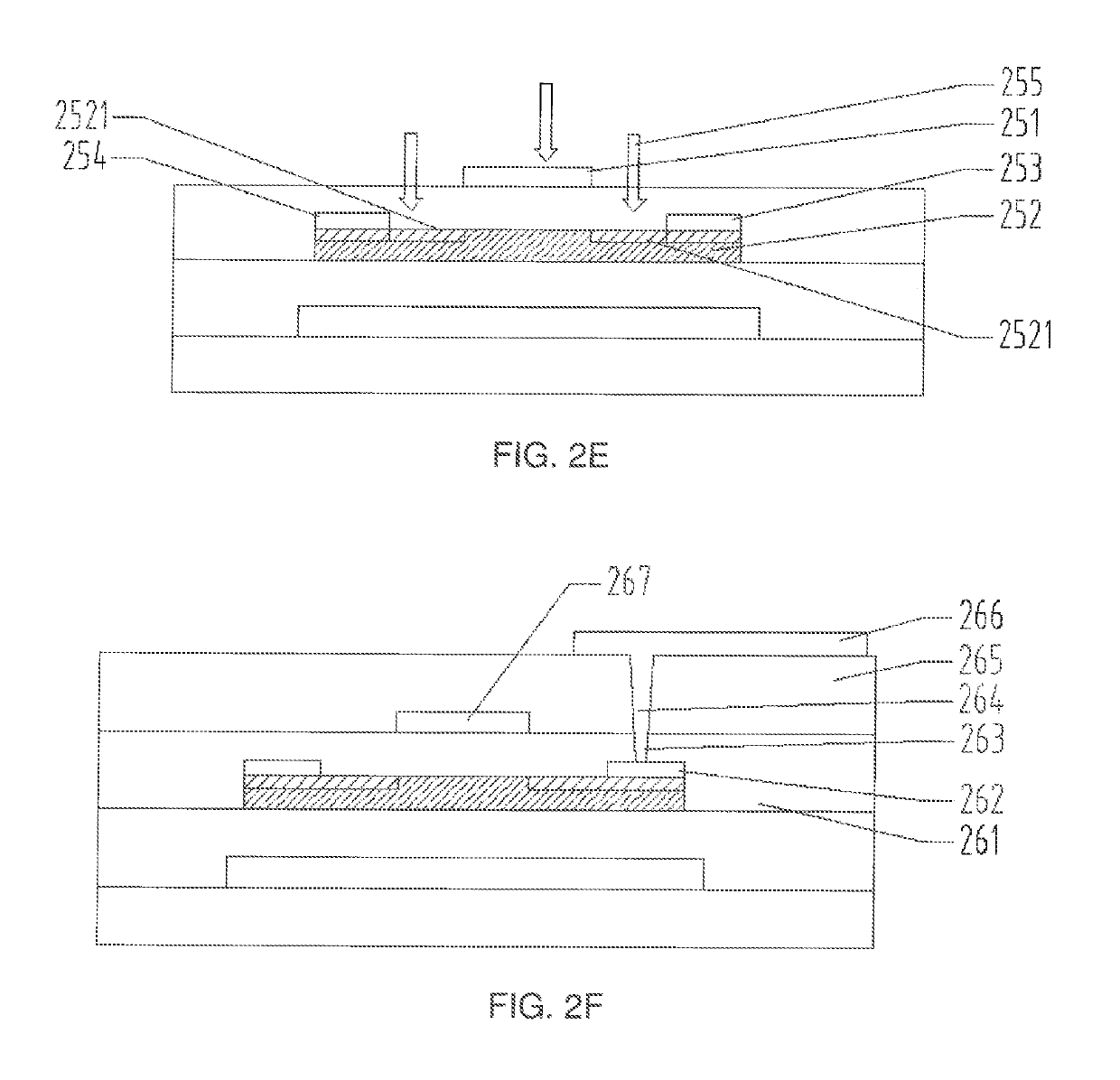

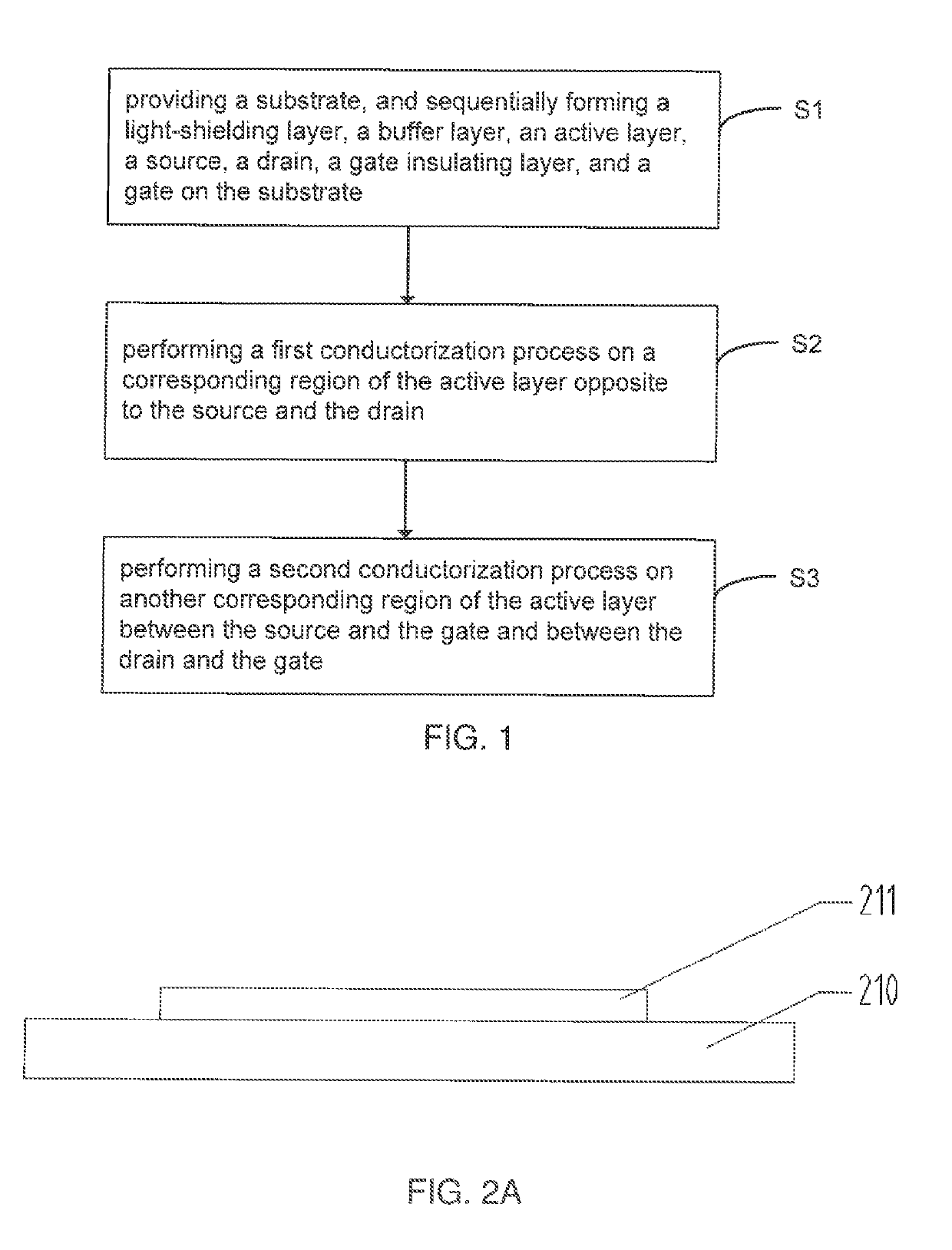

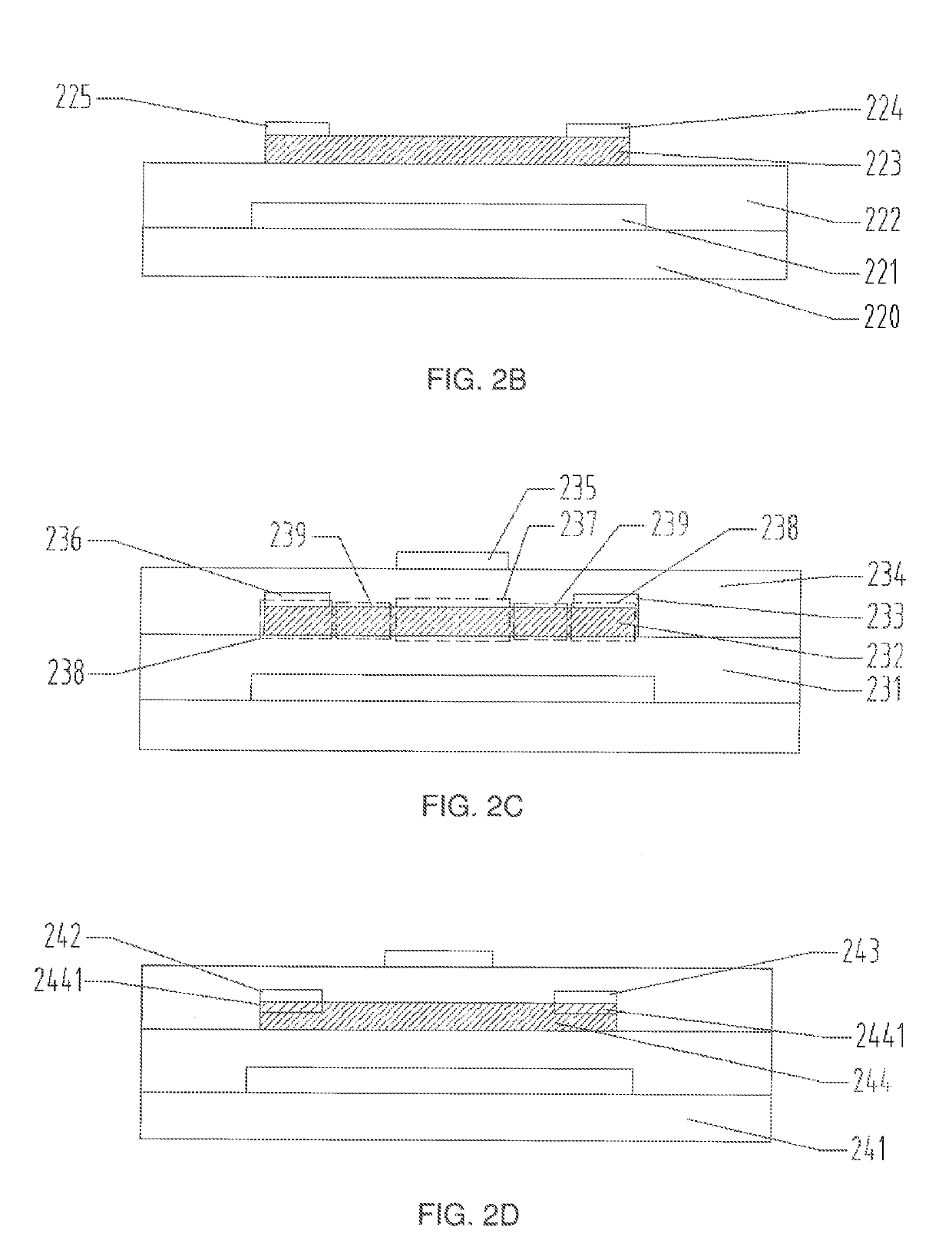

Array substrate and manufacturing method thereof

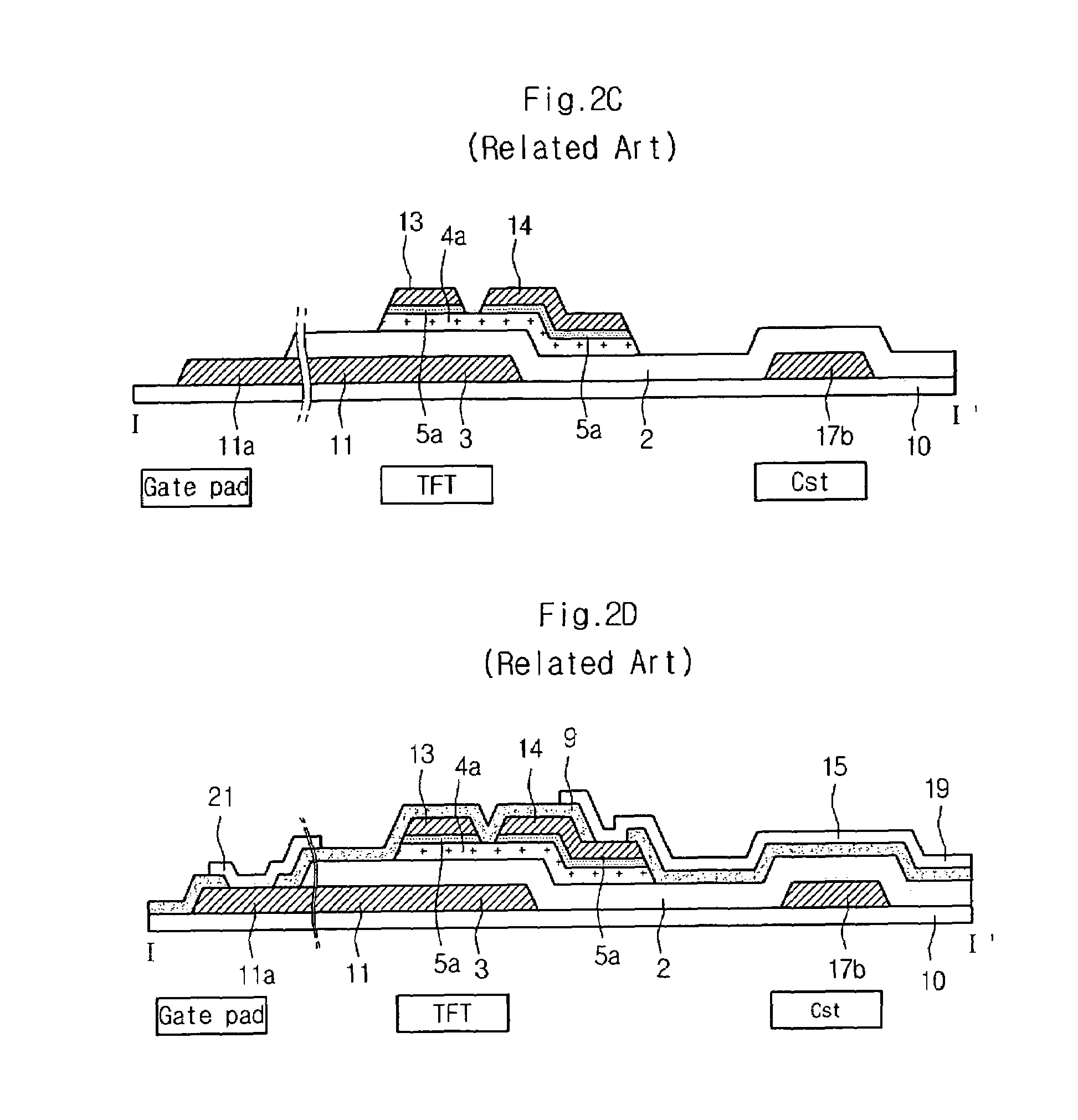

ActiveUS10367017B2Reduce photomask processLow costTransistorSolid-state devicesEngineeringActive layer

An array substrate and a method of manufacturing the array substrate are provided. The method includes providing a substrate, sequentially forming a light-shielding layer, a buffer layer, an active layer, a source, a drain, a gate insulating layer, and a gate on the substrate, performing a first conductorization process on a corresponding region of the active layer opposite to the source and the drain, and performing a second conductorization process on another corresponding region of the active layer between the source and the gate and between the drain and the gate.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Array substrate and manufacturing method thereof

ActiveUS20190157316A1Reduce photomask processLow costTransistorSolid-state devicesEngineeringActive layer

An array substrate and a method of manufacturing the array substrate are provided. The method includes providing a substrate, sequentially forming a light-shielding layer, a buffer layer, an active layer, a source, a drain, a gate insulating layer, and a gate on the substrate, performing a first conductorization process on a corresponding region of the active layer opposite to the source and the drain, and performing a second conductorization process on another corresponding region of the active layer between the source and the gate and between the drain and the gate.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com