Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

61results about How to "Reduce coupling noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

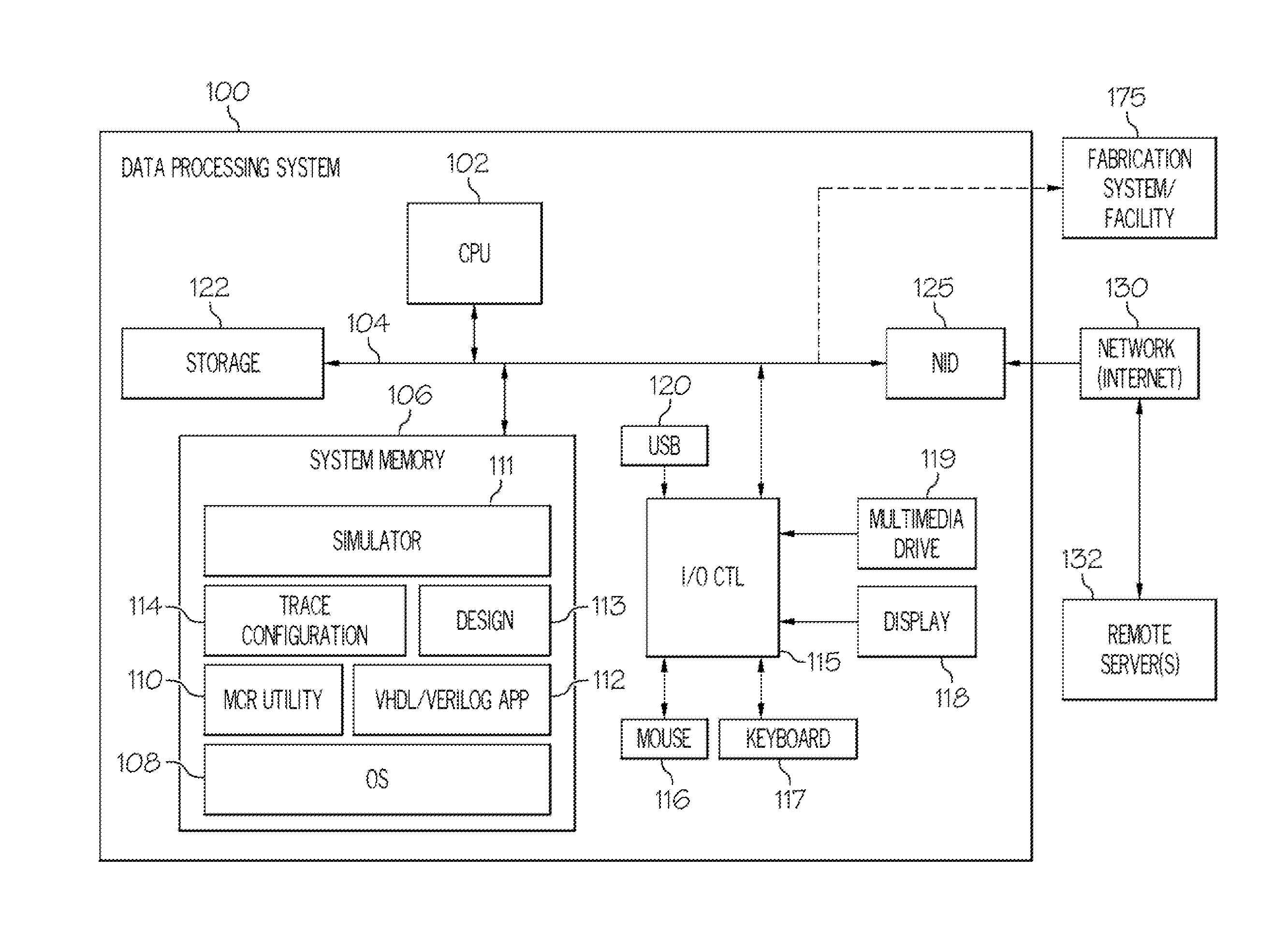

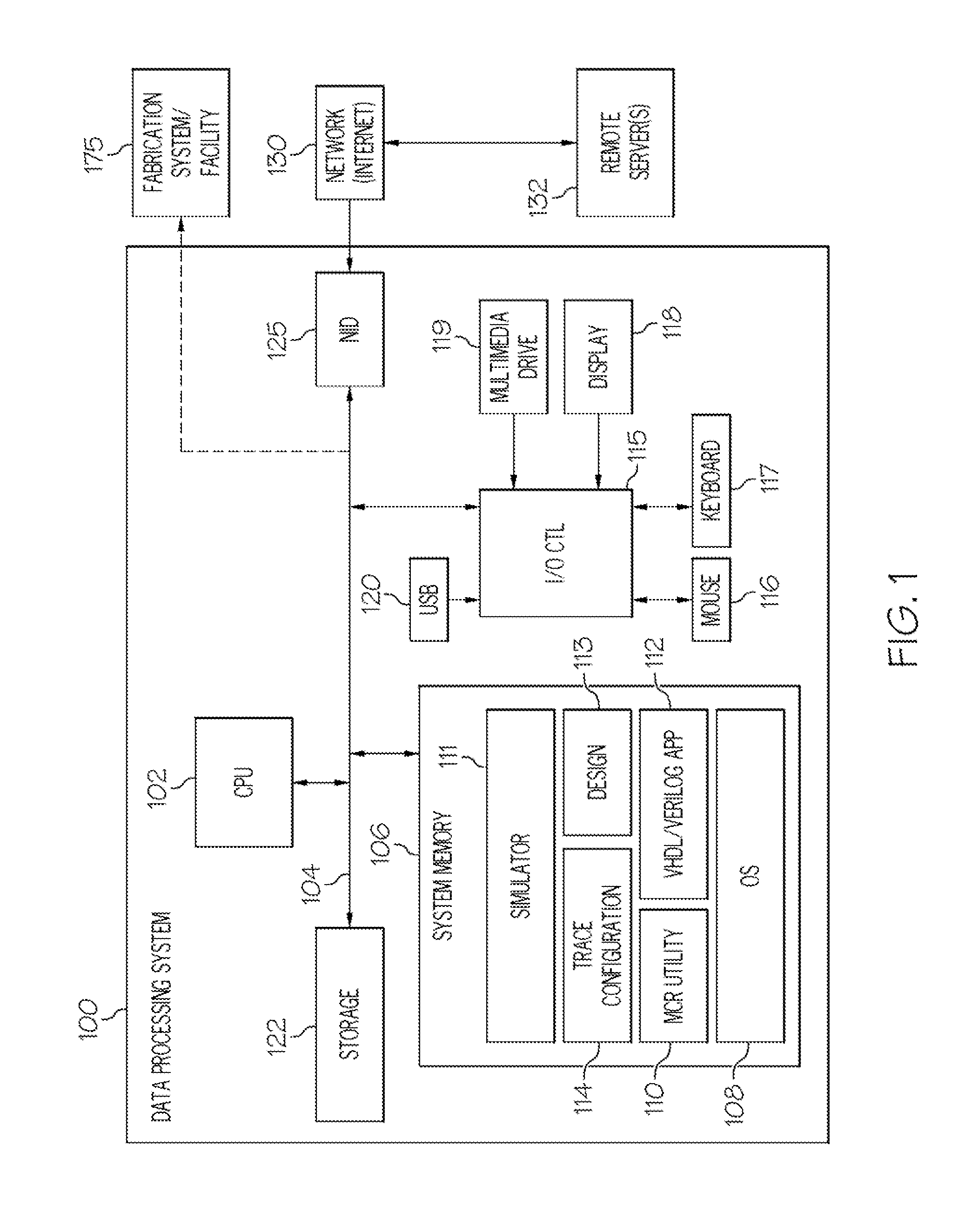

Method for improving wiring related yield and capacitance properties of integrated circuits by maze-routing

InactiveUS6305004B1Improved yieldGood yieldComputer aided designSoftware simulation/interpretation/emulationCapacitanceIntegrated circuit

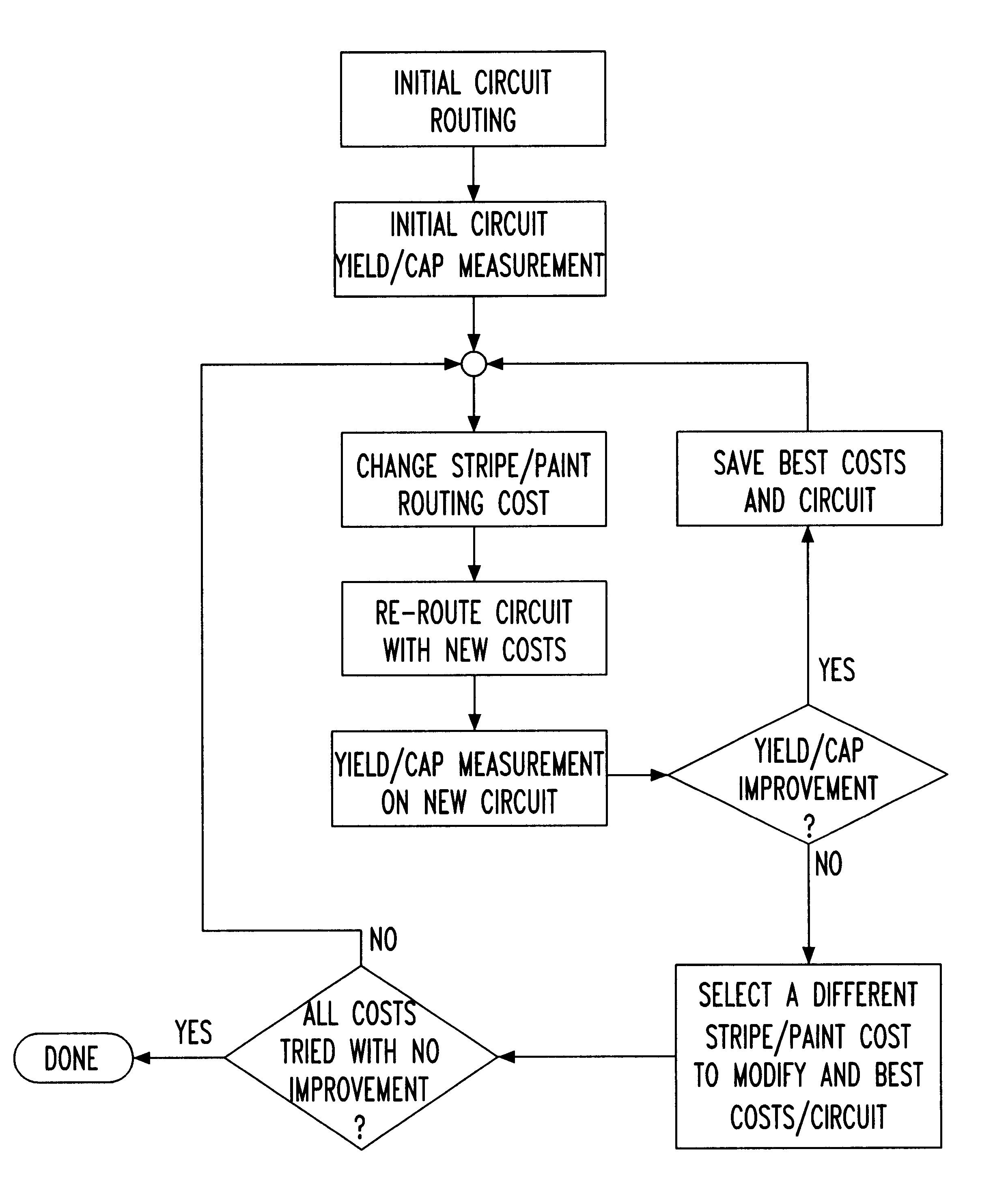

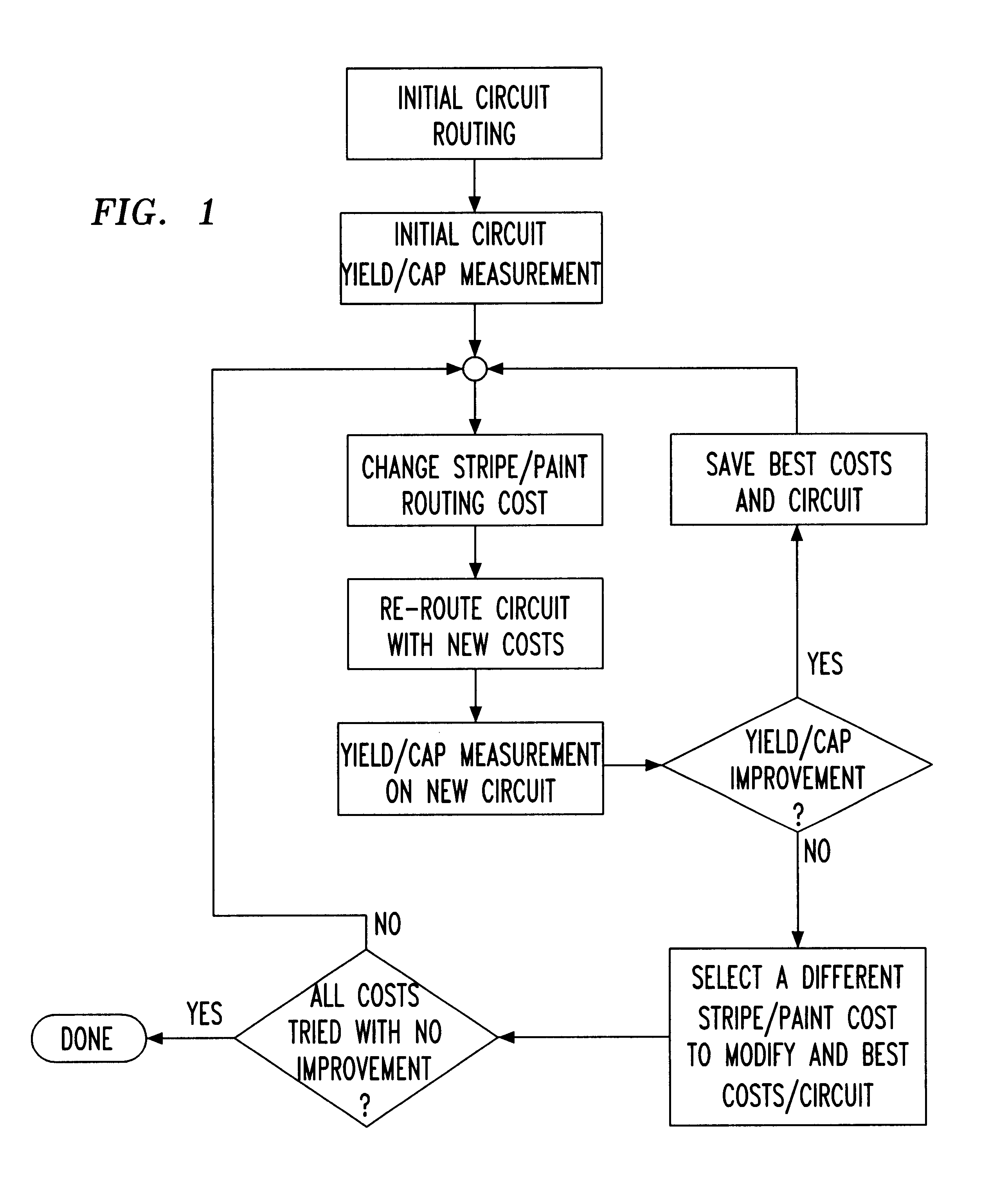

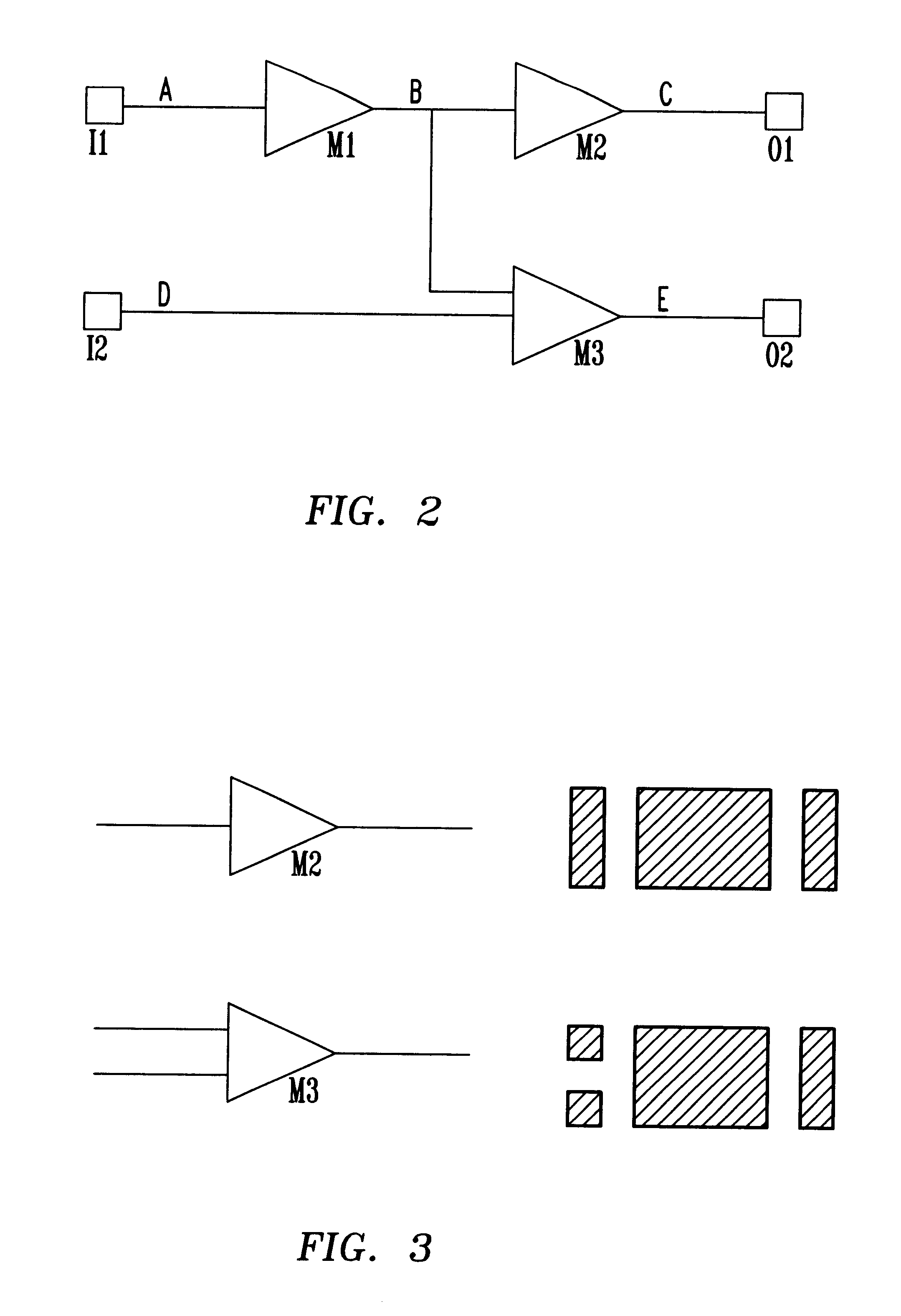

A method for automatically wiring (i.e., routing) an integrated circuit chip after completing the placement of cells on the chip is described. The method employs a maze routing such that the spacing between the routed wires is increased, while at the same time maintaining control over the total wiring length. The maze routing herein described is modified to improve chip yield, reduce wiring capacitance, limit power consumption and coupled signal noise, all of which are achieved by increasing wire-to-wire spacings.

Owner:IBM CORP

Practical method for hierarchical-preserving layout optimization of integrated circuit layout

InactiveUS6986109B2High yieldReduce coupling noiseCAD circuit designSoftware simulation/interpretation/emulationComputer architecturePartial solution

Owner:INT BUSINESS MASCH CORP

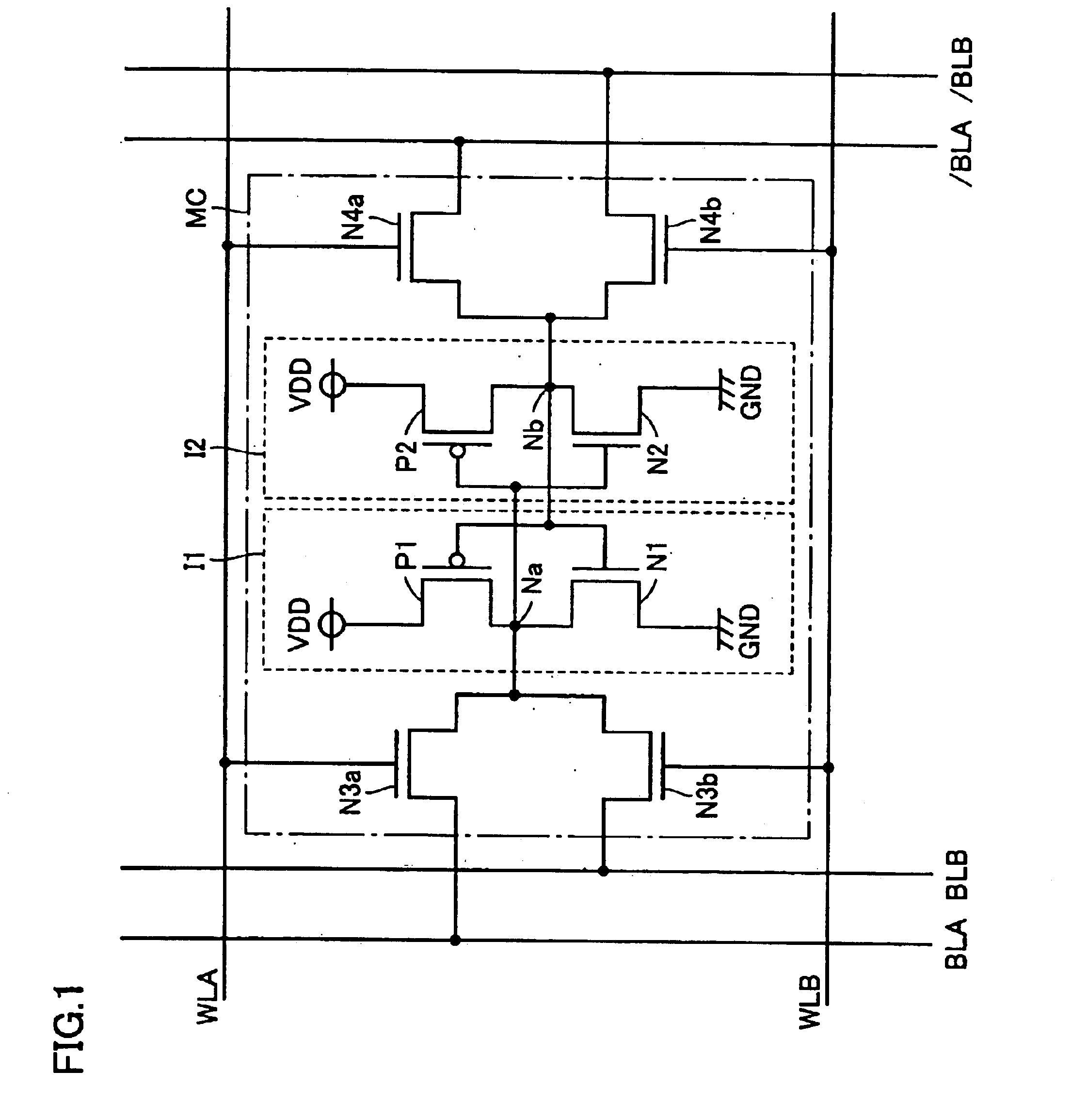

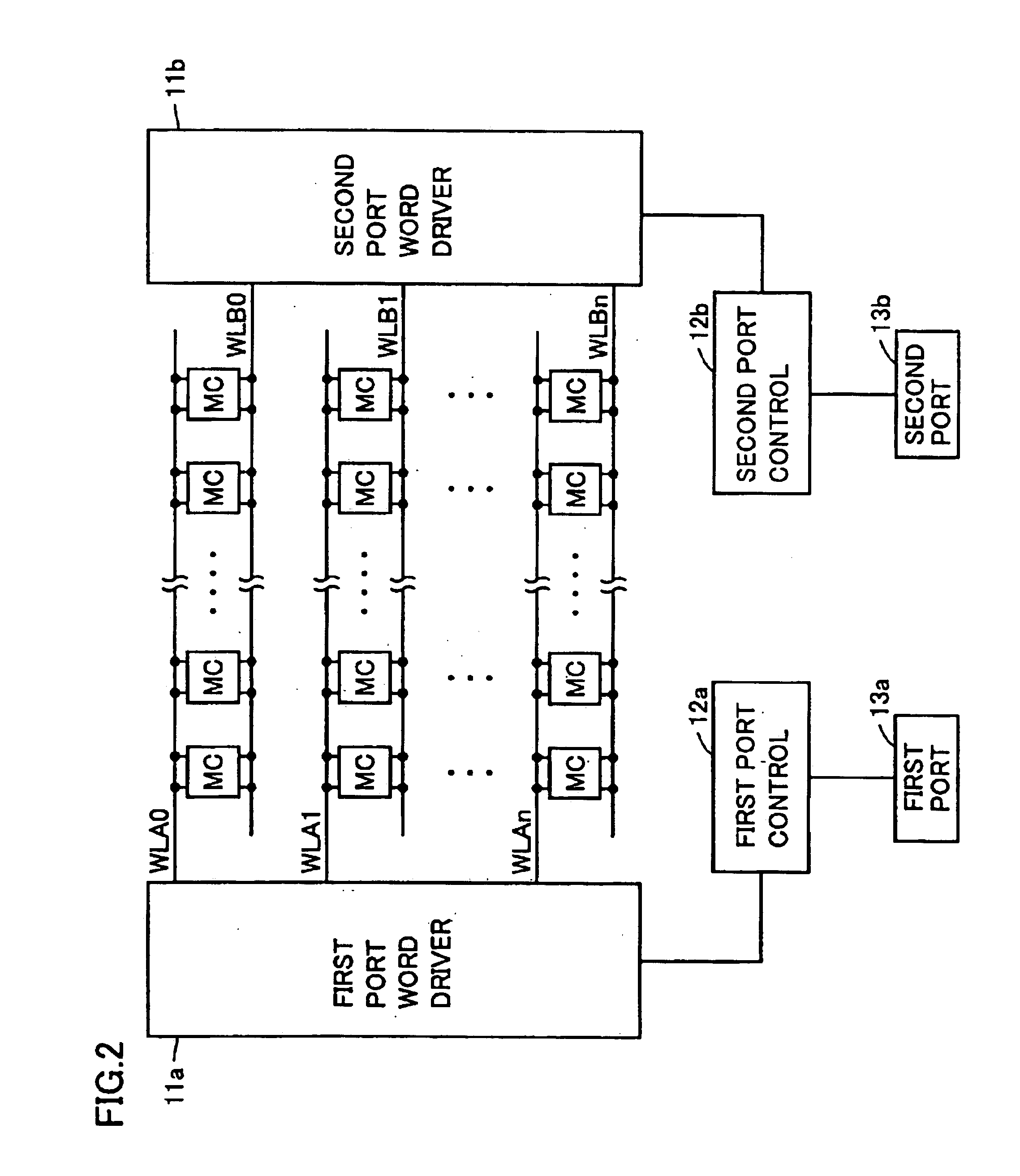

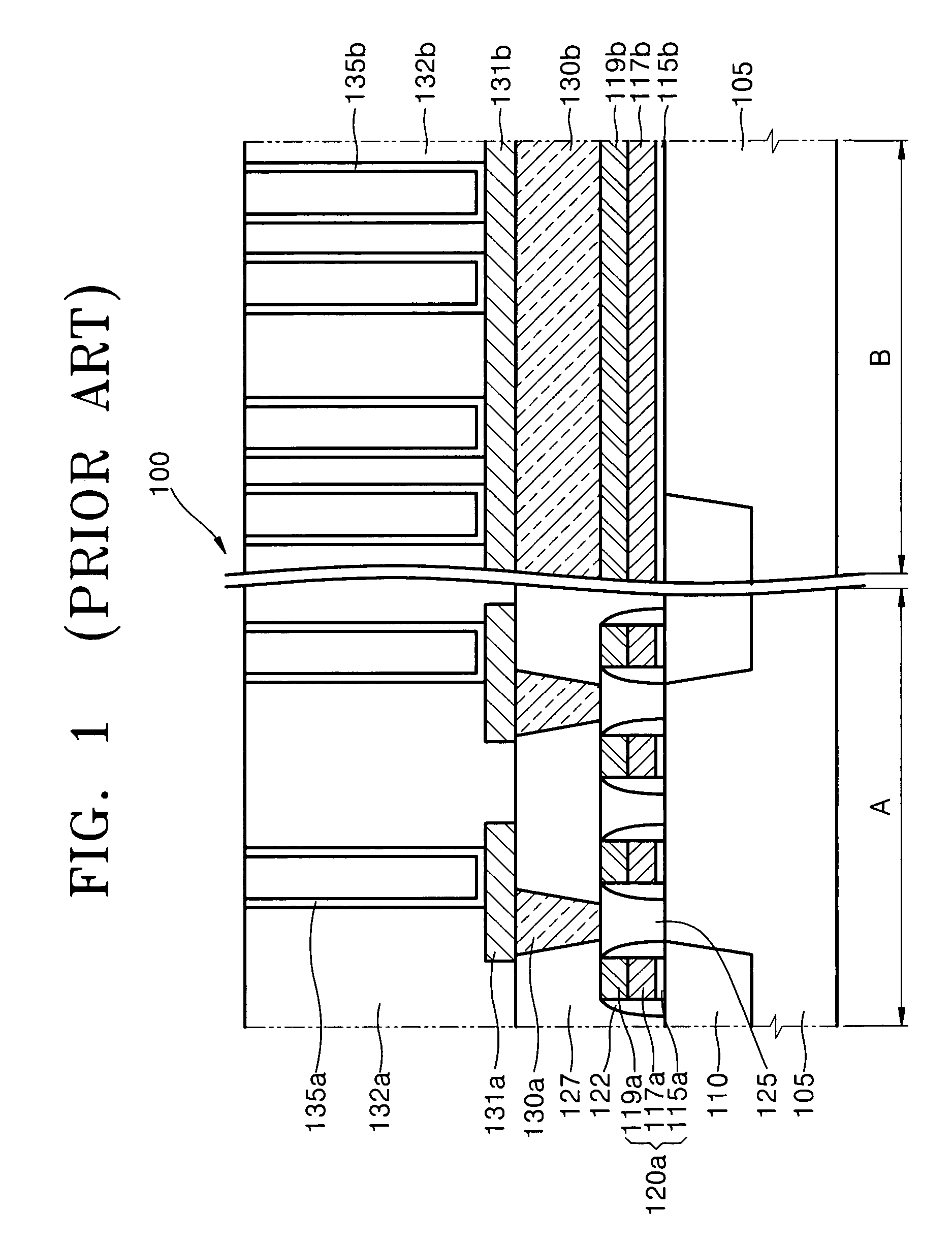

Reduction of capacitive effects in a semiconductor memory device

ActiveUS6917560B2Reduce coupling noiseIncrease the areaTransistorSolid-state devicesCapacitanceCapacitive effect

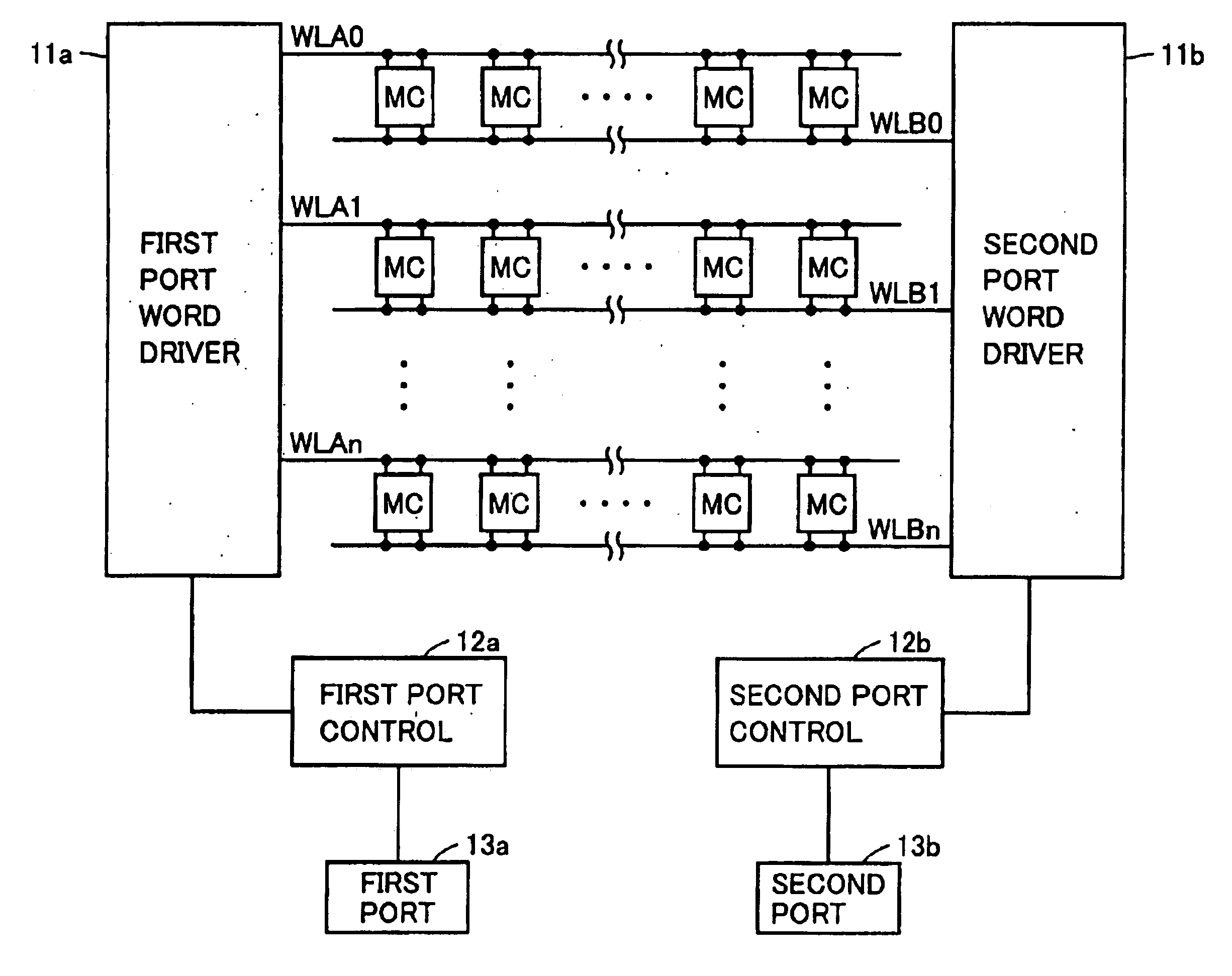

A semiconductor memory device having a multiport memory includes a plurality of memory cells MC arranged in columns and rows, a plurality of first word lines WLA0-WLAn connected to a first port 13a, and a plurality of second word lines WLB0-WLBn connected to a second port 13b. Each of a plurality of first word lines WLA0-WLAn and each of a plurality of second word lines WLB0-WLBn are arranged alternately in a planar layout. A semiconductor memory device is thus obtained that allows a coupling noise between interconnections to be reduced without an increase in memory cell area.

Owner:RENESAS ELECTRONICS CORP

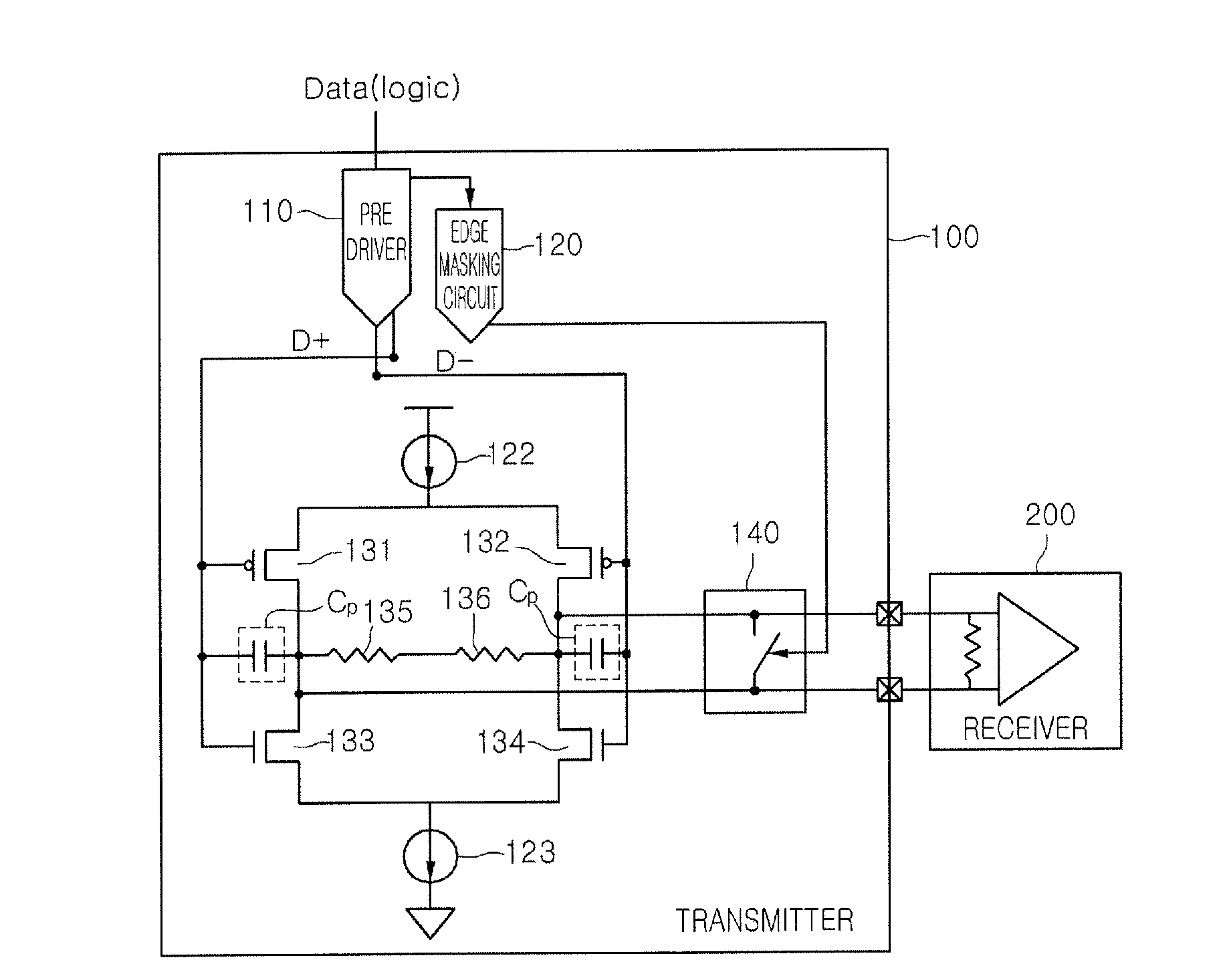

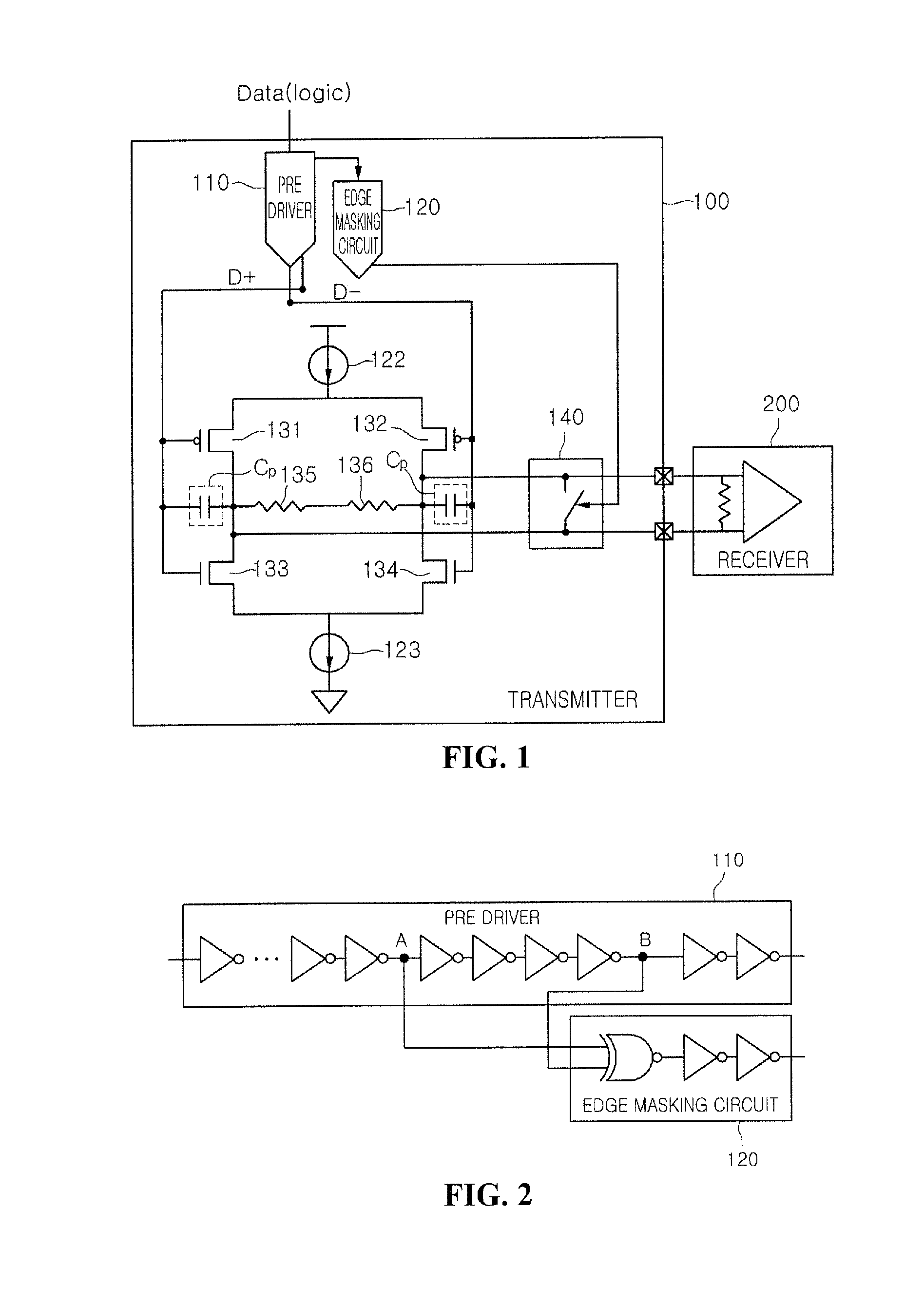

Data transmitting system

InactiveUS20100124298A1Short transition timeAvoid volatilityDigital storageSecret communicationEngineeringTransmitter

A data transmitting system is provided that includes a transmitter that suppresses coupling noise by being operated using a differential voltage driving scheme at the time of transmitting data and being operated using a common voltage driving scheme by equalizing potential of a pair of transmission lines during a transition interval; and a receiver that is connected to the transmitter through the pair of transmission lines and recovers the data by sensing the voltage difference in signals of the pair of transmission lines.

Owner:DONGBU HITEK CO LTD

Non-Volatile Memory Devices that Utilize Mirror-Image Programming Techniques to Inhibit Program Coupling Noise and Methods of Programming Same

ActiveUS20070195597A1Improve reliability of data storedReduce coupling noiseRead-only memoriesDigital storageMirror imageComputer science

Non-volatile memory devices have improved data storage reliability resulting from mirror-image programming techniques that operate to reduce coupling noise between adjacent memory cells within a memory array. The adjacent memory cells include a first pair of memory cells and a second pair of memory cells. A program control circuit is provided to support mirror-image programming of the first and second pairs of memory cells when the two pairs of memory cells are storing the same 3-bit data.

Owner:SAMSUNG ELECTRONICS CO LTD

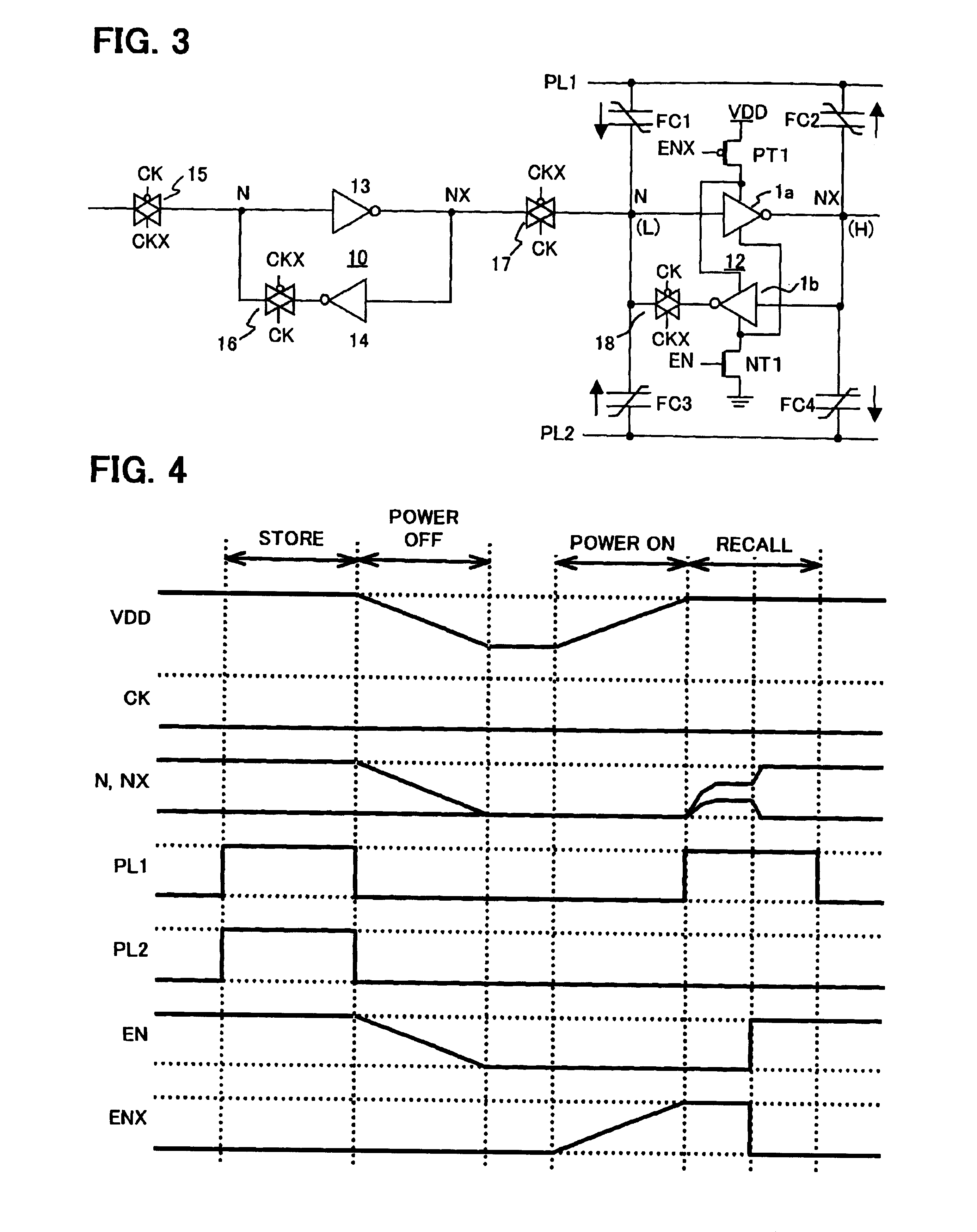

Nonvolatile data storage circuit using ferroelectric capacitors

InactiveUS6934178B2Avoid dataReduce coupling noiseSolid-state devicesSemiconductor/solid-state device manufacturingFerroelectric capacitorCoupling noise

A nonvolatile data storage circuit has a data holding circuit having a storage node, and a plurality of ferroelectric capacitors one electrodes of which are connected to the storage node. In this nonvolatile data storage circuit, in store operations to write data from the data holding circuit to the ferroelectric capacitors, the timing of at least the rising or the falling of plate signals supplied to the other electrodes of the plurality of ferroelectric capacitors, is made different. During store operation, the timing of the plate signals applied to the plurality of ferroelectric capacitors connected to the storage node is shifted, so that coupling noise between the ferroelectric capacitors is dispersed and can be reduced, and data inversion of the data holding circuit can be prevented.

Owner:FUJITSU SEMICON LTD

Non-volatile memory devices that utilize mirror-image programming techniques to inhibit program coupling noise and methods of programming same

ActiveUS7639529B2Improve reliability of data storedReduce coupling noiseRead-only memoriesDigital storageMirror imageComputer science

Non-volatile memory devices have improved data storage reliability resulting from mirror-image programming techniques that operate to reduce coupling noise between adjacent memory cells within a memory array. The adjacent memory cells include a first pair of memory cells and a second pair of memory cells. A program control circuit is provided to support mirror-image programming of the first and second pairs of memory cells when the two pairs of memory cells are storing the same 3-bit data.

Owner:SAMSUNG ELECTRONICS CO LTD

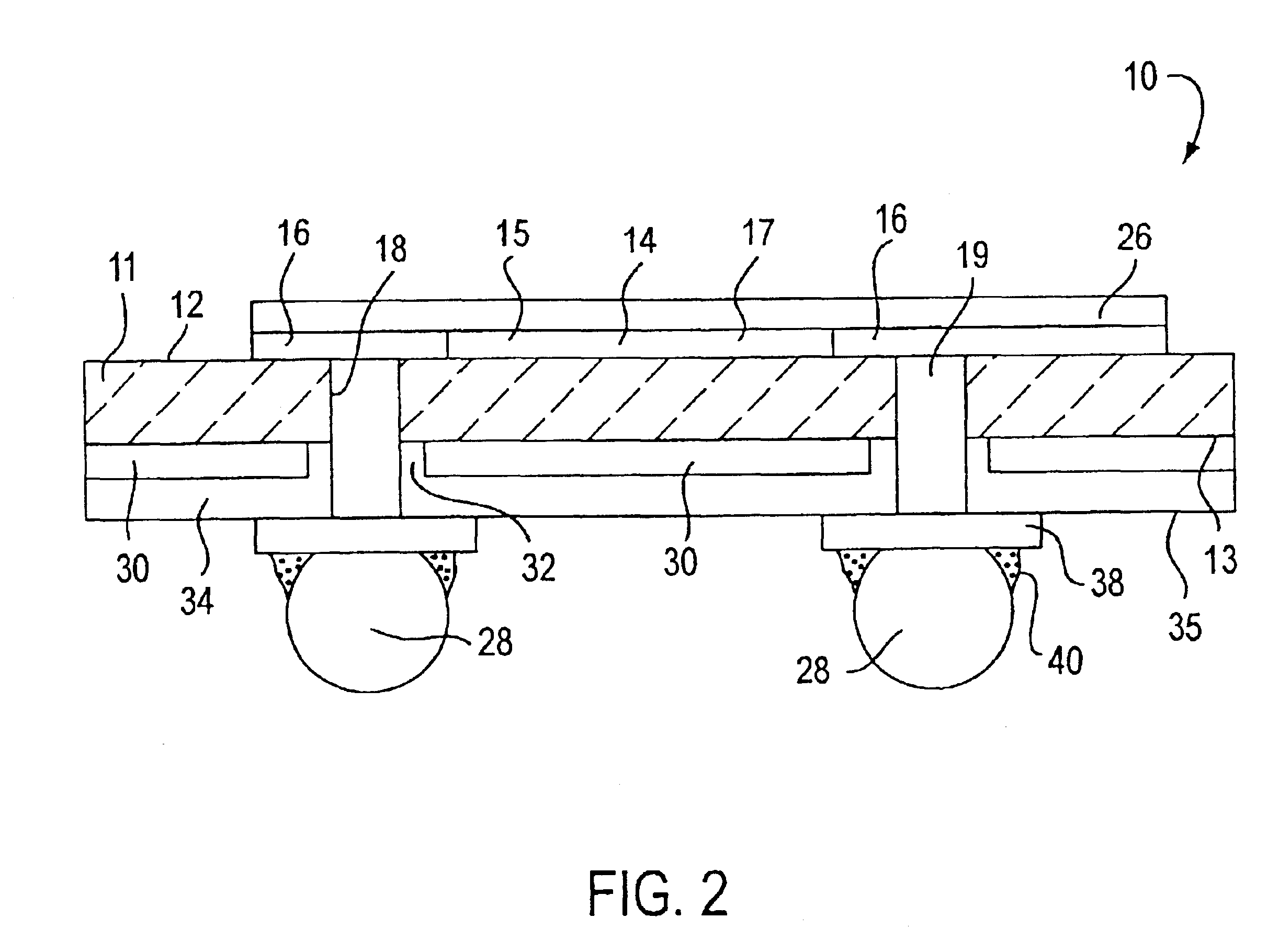

Ball grid array resistor network having a ground plane

InactiveUS6882266B2Reduce coupling noisePrinted circuit assemblingOther resistor networksElectrical conductorEngineering

A ball grid array resistor network that has a ground plane to reduce noise and improve signal integrity. The ball grid array resistor network includes a substrate having a first and a second surface and vias that extending through the substrate between the first and second surfaces. Resistors are located on the first surface between the vias. Conductors are located over the vias and are electrically connected to ends of the resistors. A cover coat covers the conductors and resistors. A ground plane is located on the second surface. An insulating layer is located over the ground plane. Ball pads are located over the vias. The ball pads are electrically connected to the vias. Solder spheres are attached to the ball pads.

Owner:CTS CORP ELKHART

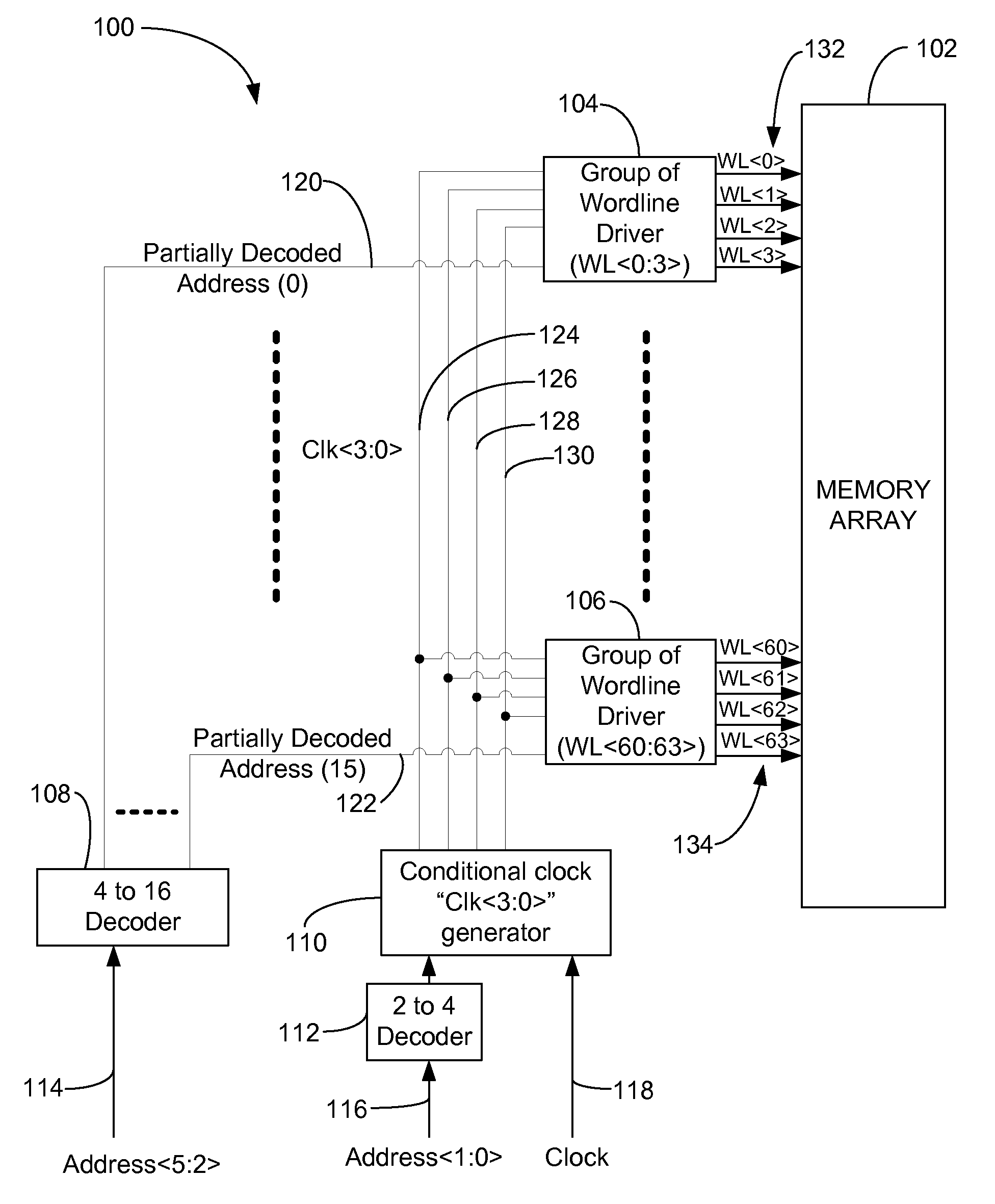

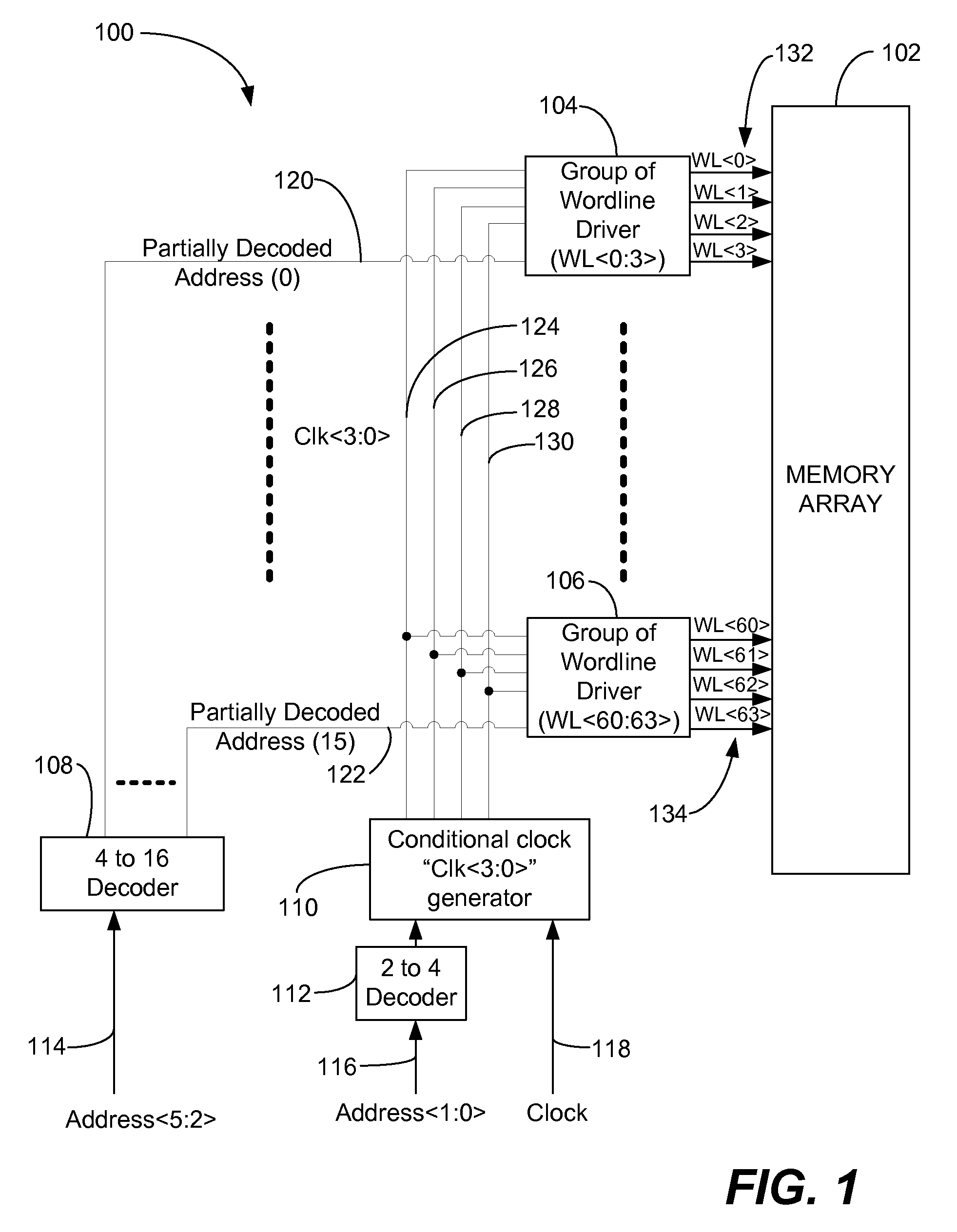

Dynamic word line drivers and decoders for memory arrays

In a particular illustrative embodiment, a circuit device that includes first logic and second logic is disclosed. The first logic receives a clock signal and a first portion of a memory address of a memory array, decodes the first portion of the memory address, and selectively applies the clock signal to a selected group of wordline drivers associated with the memory array. The second logic decodes a second portion of the memory address and selectively activates a particular wordline driver of the selected group of wordline drivers according to the second portion of the memory address.

Owner:QUALCOMM INC

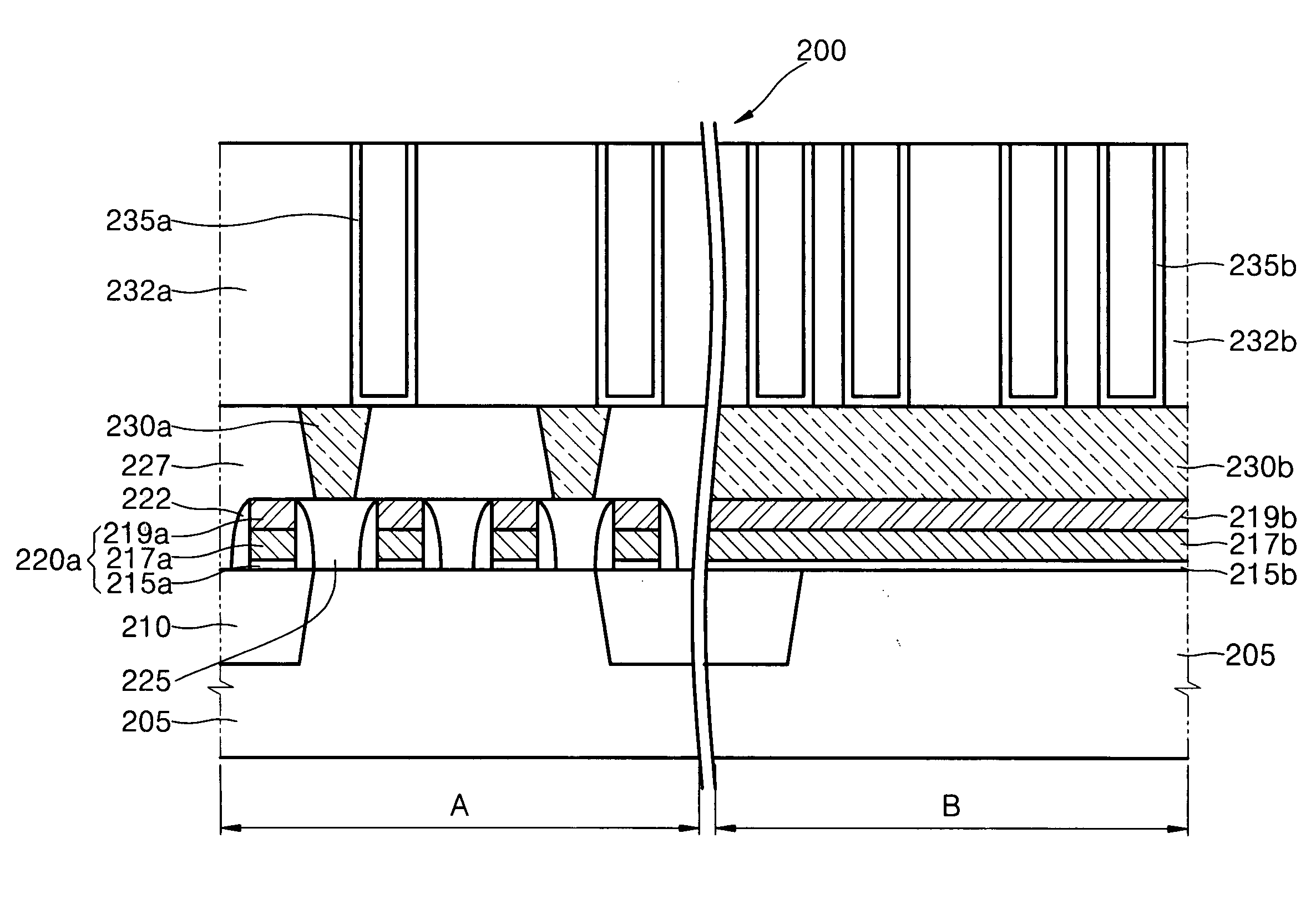

Semiconductor memory device having a decoupling capacitor

InactiveUS20060113633A1Reduce noiseReduce coupling noiseSolid-state devicesSemiconductor/solid-state device manufacturingCell regionDecoupling capacitor

A semiconductor memory device comprises a cell capacitor having a first buried contact connected with a semiconductor substrate of a cell region and a first storage node connected with the first buried contact, and a decoupling capacitor for reducing a coupling noise, having a plurality of second buried contacts formed on a semiconductor substrate portion adjacent in the cell region and extended in parallel with each other and a plurality of second storage nodes connected with the second buried contacts.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device

InactiveUS20050201185A1Increase the areaCoupling noiseTransistorSolid-state devicesInterconnectionComputer science

A semiconductor memory device having a multiport memory includes a plurality of memory cells MC arranged in columns and rows, a plurality of first word lines WLA0-WLAn connected to a first port 13a, and a plurality of second word lines WLB0-WLBn connected to a second port 13b. Each of a plurality of first word lines WLA0-WLAn and each of a plurality of second word lines WLB0-WLBn are arranged alternately in a planar layout. A semiconductor memory device is thus obtained that allows a coupling noise between interconnections to be reduced without an increase in memory cell area.

Owner:RENESAS ELECTRONICS CORP

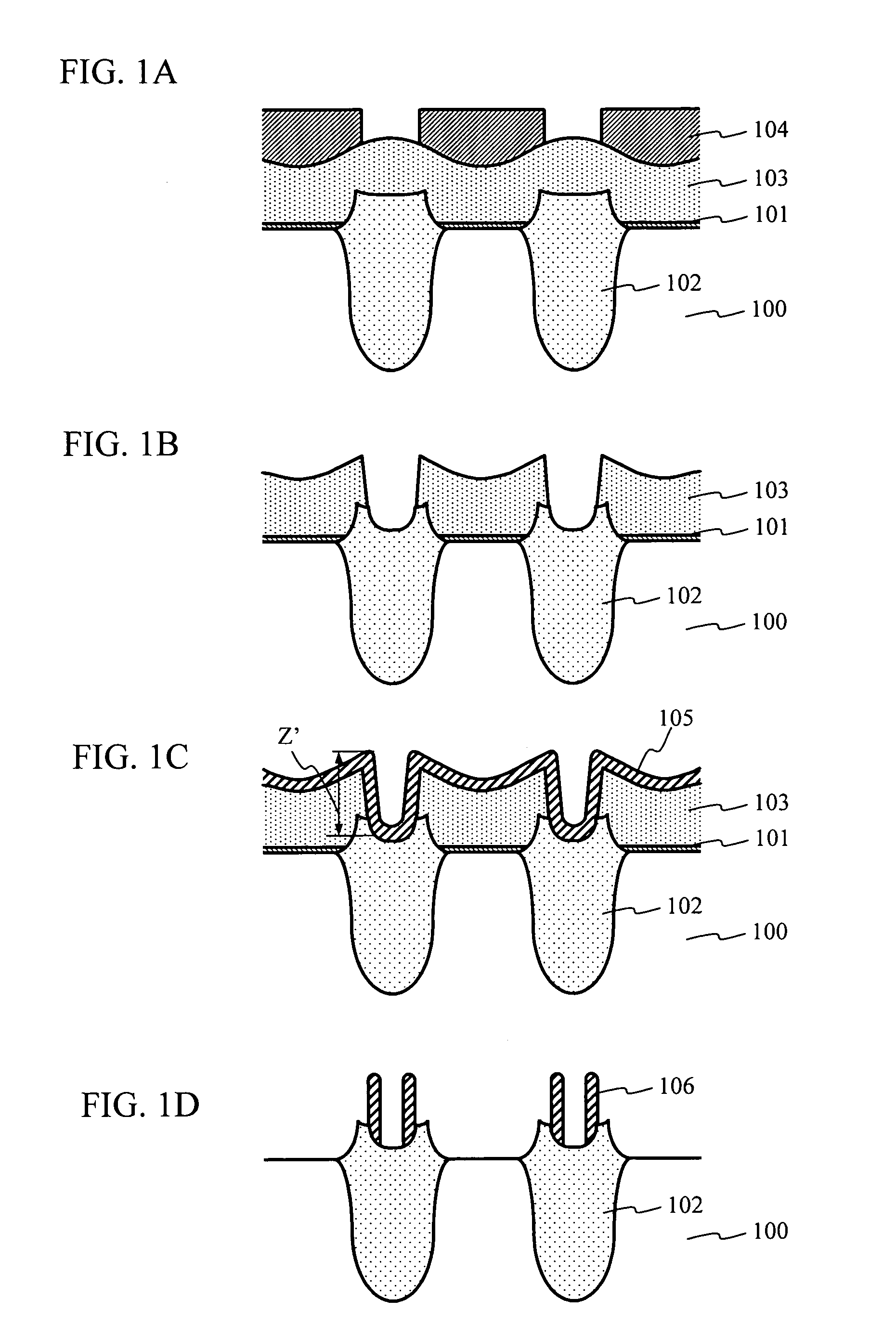

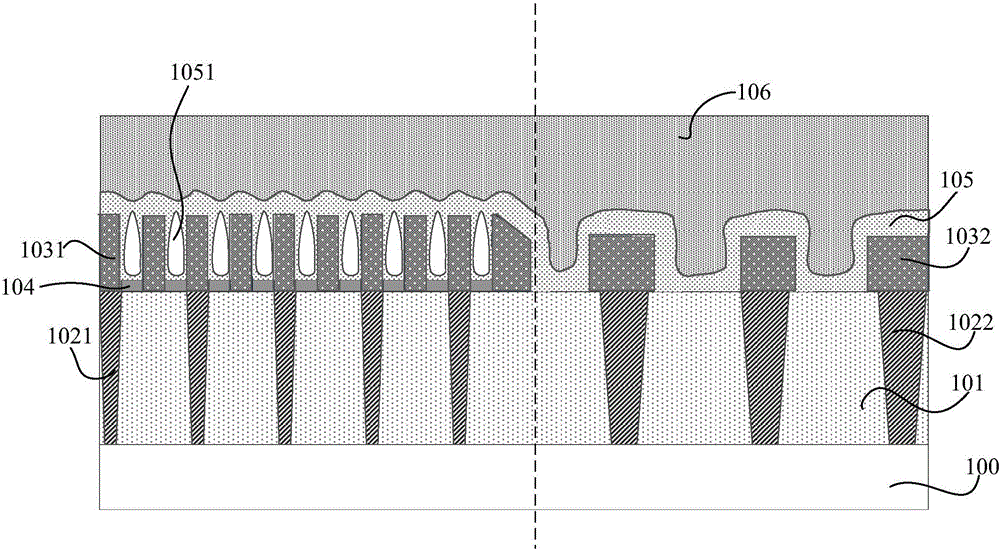

Semiconductor device and method for fabricating thereof

InactiveUS20060091445A1Residue can be suppressedSuppress generationSolid-state devicesSemiconductor devicesDevice materialSemiconductor

A silicon nitride film, which is a second hard mask, is dry etched to be removed completely. The silicon nitride film, which is formed on a sidewall of a silicon nitride film used as a first hard mask, has a relatively low etching rate. Therefore, if the silicon nitride film is continued etching until the corresponding portion thereof is removed, polysilicon is etched in a direction of depth in trench shape. Then, floating gates in adjacent cells are separated and a step portion of the polysilicon is formed. Consequently, a remaining portion of the silicon nitride film used as the first hard mask is removed, an ONO film is laminated on a whole surface of the poly silicon having the step portion on an edge that has been etched, and then, a polysilicon for a control gate is laminated on the ONO film.

Owner:MONTEREY RES LLC

Semiconductor memory device

A semiconductor memory device comprises. word lines; global bit lines intersecting with the word lines; local bit lines partitioned into N (N is an integer greater than or equal to two) sections along the global bit lines and aligned with a same pitch as the global bit lines; N memory cell arrays each including memory cells each having cylindrical capacitor structure formed at intersections of the word lines and the local bit lines and being arranged corresponding to the sections of the local bit lines; local sense amplifiers for amplifying a signal read out from a selected memory cell to the local bit line and for outputting the signal to the global bit line; and global sense amplifiers for coupling the signal transmitted from the local sense amplifier corresponding to the selected memory cell through the global bit line to an external data line.

Owner:LONGITUDE LICENSING LTD

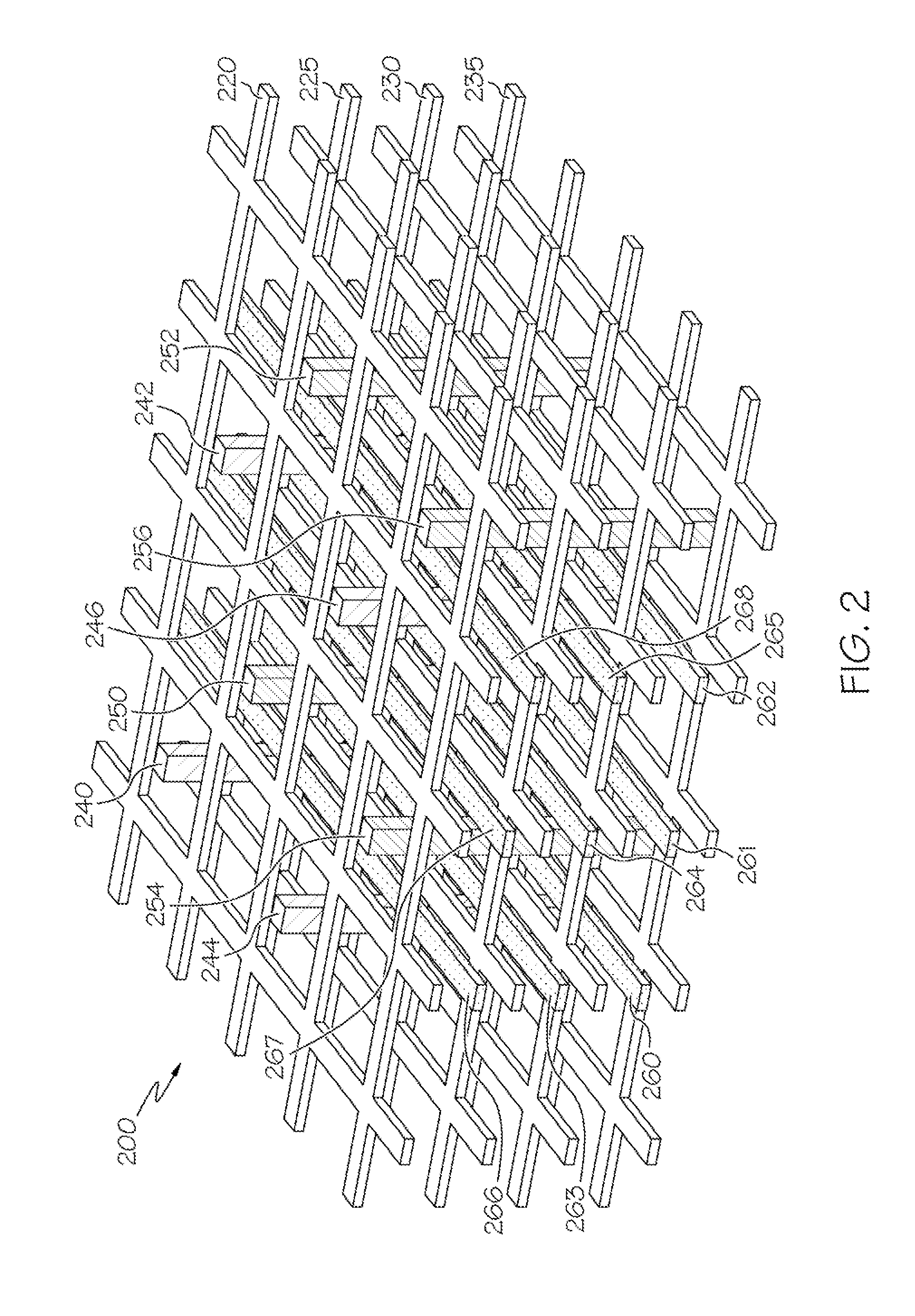

Noise Coupling Reduction and Impedance Discontinuity Control in High-Speed Ceramic Modules

ActiveUS20120204141A1Reduce discontinuityReduce noise couplingSemiconductor/solid-state device detailsCross-talk/noise/interference reductionMechanical engineeringSignal trace

A method reduces coupling noise and controls impedance discontinuity in ceramic packages by: providing at least one reference mesh layer; providing a plurality of signal trace layers, with each signal layer having one or more signal lines and the reference mesh layer being adjacent to one or more of the signal layers; disposing a plurality of vias through the at least one reference mesh layer, with each via providing a voltage (Vdd) power connection or a ground (Gnd) connection; selectively placing via-connected coplanar-type shield (VCS) lines relative to the signal lines, with a first VCS line extended along a first side of a first signal line and a second VCS line extended along a second, opposing side of said first signal line. Each of the VCS lines interconnect with and extend past one or more vias located within a directional path along which the VCS lines extends.

Owner:GLOBALFOUNDRIES U S INC

Array substrate and display device

ActiveCN109426041AIncrease capacitanceReduce coupling noiseStatic indicating devicesNon-linear opticsCapacitanceEngineering

Embodiments of the invention provide an array substrate and a display device, which belong to the technical field of displaying and can solve the problem that a GOA circuit occupies more wiring spacein order to increase the capacity of a bootstrap capacitor. The array substrate includes an effective display area and a non-display area located around the effective display area. The array substratefurther includes gate drive circuits and multiple rows of dummy sub-pixels located in the non-display area, and the dummy sub-pixels are disposed adjacent to the effective display area. Auxiliary capacitors are disposed in at least a portion of the dummy sub-pixels. Shift register units in the gate drive circuits are connected to the auxiliary capacitors, and the auxiliary capacitor at least constitutes a portion of bootstrap capacitors in the shift register units. The array substrate is used for forming the display device.

Owner:BOE TECH GRP CO LTD +1

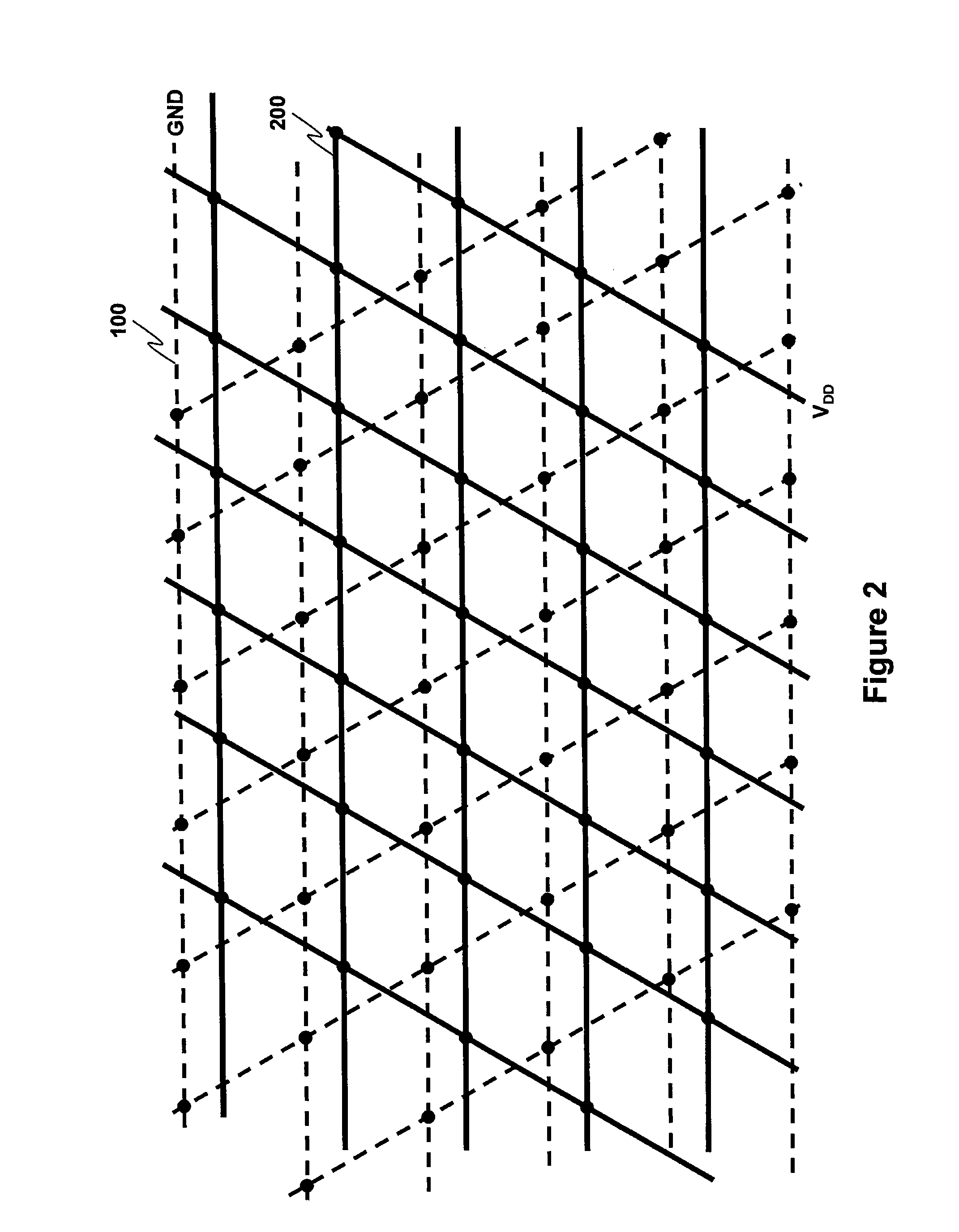

Ceramic substrate grid structure for the creation of virtual coax arrangement

InactiveUS7465882B2Reduce coupling noiseMinimizes problemMagnetic/electric field screeningCross-talk/noise/interference reductionCoaxial cableElectrical conductor

Signal line conductors passing through vertical vias in an insulative substrate for supporting and interconnecting integrated circuit chips are provided with shielding conductors in adjacent vias that link respective power and ground planes. The shielding conductors' presence in positions around a signal via is made possible through the employment of power plane and ground plane conductive grids that are laid out in rhomboid patterns. The power plane and ground plane grids possess a left-right mirror relation to one another and are displaced to place the rhomboid's corners to avoid overlapping any of the grid lines.

Owner:GLOBALFOUNDRIES INC

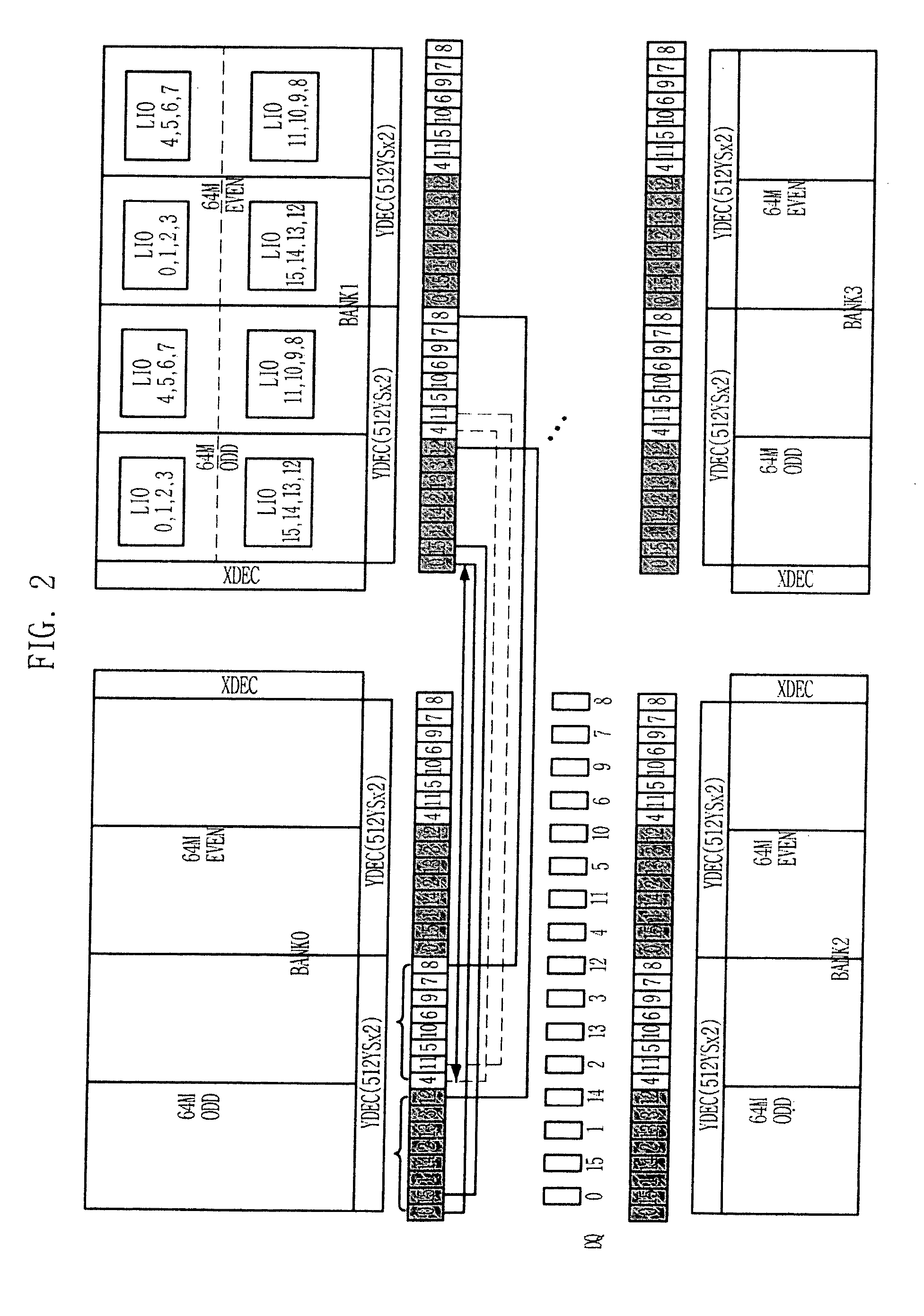

Semiconductor memory device having a global data bus

There is provided a semiconductor design technology, particularly, a bus line arrangement method of global data bus in the semiconductor memory device. According to the invention, skew by lines can be not occurred, or can be minimized upon an issuance thereof. Further, upon its issuance, it is easy to compensate it relying on the specific rule. The present invention proposes a scheme that classifies data transmission units corresponding to each bank into plural groups, each group having some continuous data transmission units, and makes bus lines of the global data bus to be arranged alternately for each group. In other words, the global data bus line arrangement scheme suggested by the present invention may be defined as grouped alternate arrangement scheme. In this case, the overlap interval between adjacent global data bus lines can be reduced largely and skew problem by lines can also be solved.

Owner:SK HYNIX INC

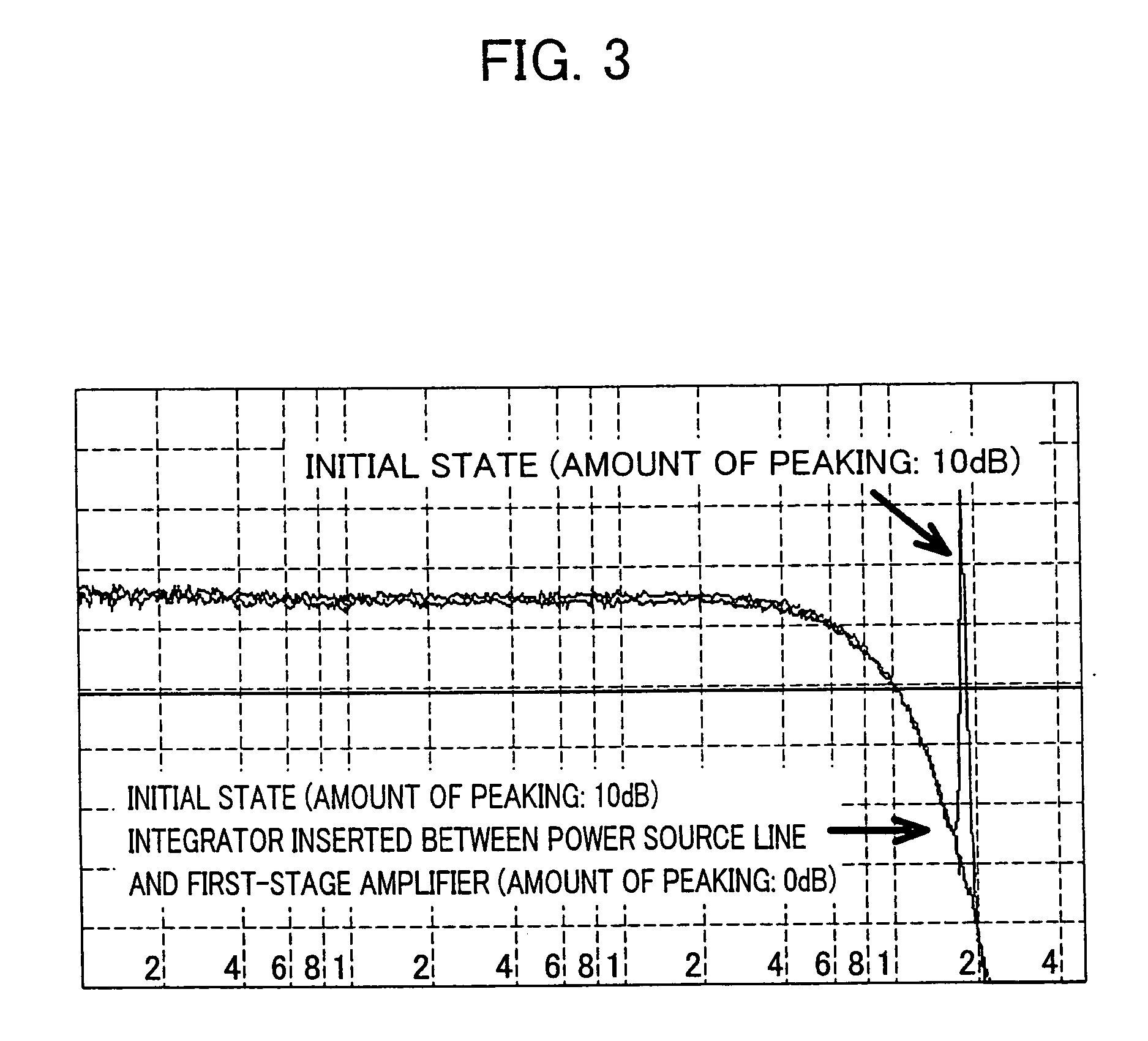

Integrated circuit and optical pickup device

InactiveUS20050062544A1Reduce couple noiseStabilize circuit operationAmplifier modifications to reduce noise influenceAmplifier combinationsIntegratorIntegrated circuit

An integrated circuit includes a first-stage amplifier circuit and a following-stage amplifier circuit connected in series, a common power source pad for supplying power to the amplifier circuits, and metal wires respectively connecting the common power source pad to the amplifier circuits. On the metal wire which connects the first-stage amplifier and the power source pad, an integrator is electrically connected. This arrangement decreases a coupling noise generated in the first-stage amplifier circuit, thereby stabilizing circuit operation of the following-stage amplifier circuit.

Owner:SHARP KK

Semiconductor memory device having a decoupling capacitor

InactiveUS7176552B2Reduce noiseReduce coupling noiseSolid-state devicesSemiconductor/solid-state device manufacturingCell regionEngineering

A semiconductor memory device comprises a cell capacitor having a first buried contact connected with a semiconductor substrate of a cell region and a first storage node connected with the first buried contact, and a decoupling capacitor for reducing a coupling noise, having a plurality of second buried contacts formed on a semiconductor substrate portion adjacent in the cell region and extended in parallel with each other and a plurality of second storage nodes connected with the second buried contacts.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory having dummy regions in memory cell array

A memory cell array is partitioned into a plurality of memory regions each of which includes a plurality of sense amplifiers and each of which is established as a unit of data input / output. Dummy regions each are formed between every two memory regions and include dummy bit lines that are set to a predetermined voltage at least during the operation of the memory cell array. Since the dummy bit lines are wired between the bit lines of the two adjacent memory regions, the voltage change in the bit lines in any of the memory regions can be prevented from affecting the bit lines in the other memory regions. As a result, malfunction of semiconductor memories can be prevented.

Owner:SOCIONEXT INC

Dynamic word line drivers and decoders for memory arrays

Owner:QUALCOMM INC

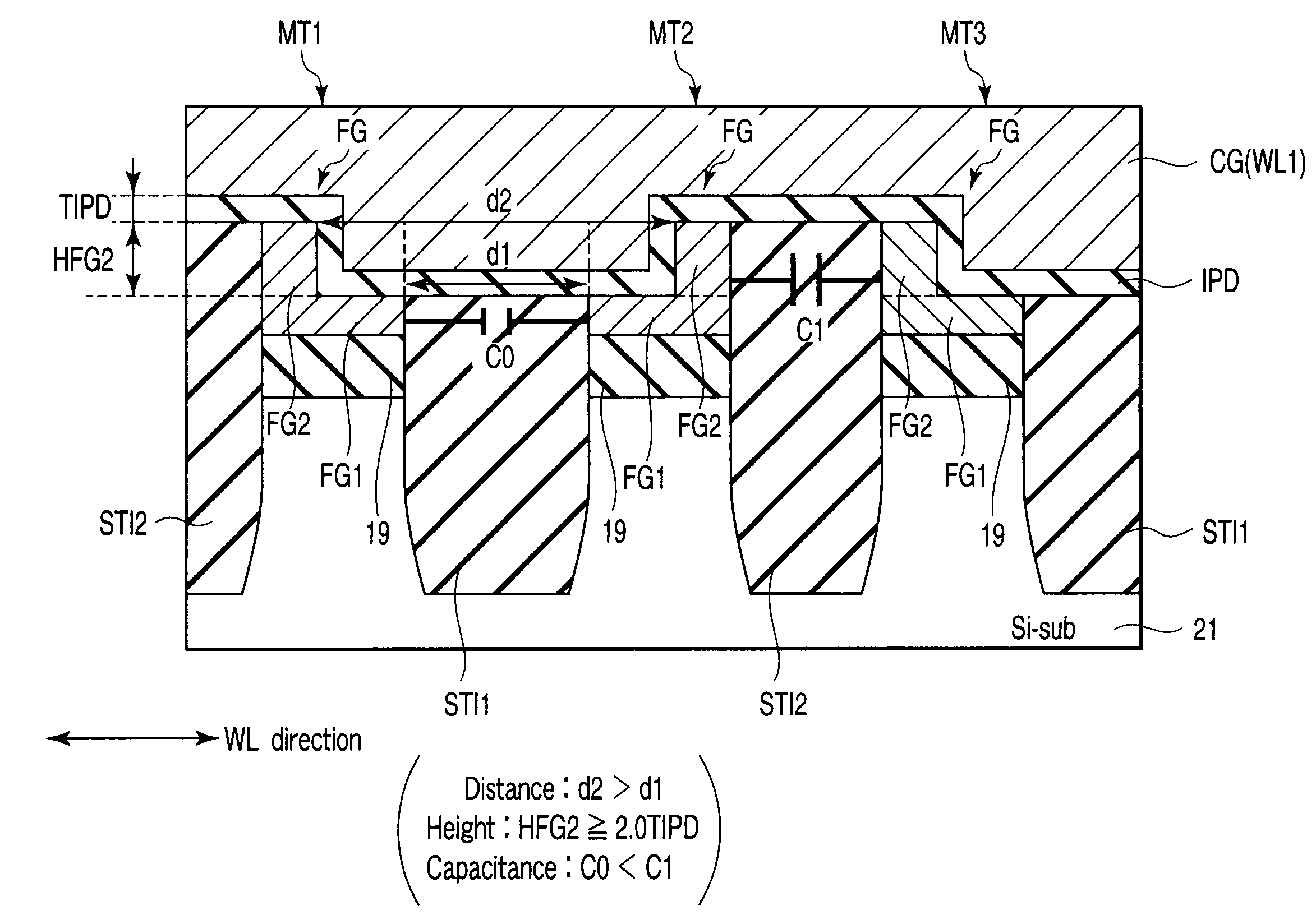

Semiconductor memory device and method of fabrication of the same

InactiveUS7884414B2Coupling noiseReduce coupling noiseTransistorSolid-state devicesEngineeringFloating electrode

A semiconductor memory device includes a first memory cell transistor. The first memory cell transistor includes a tunnel insulation film provided on a semiconductor substrate, a floating electrode provided on the tunnel insulation film, an inter-gate insulation film provided on the floating electrode, and a control electrode provided on the inter-gate insulation film. The floating electrode includes a first floating electrode provided on the tunnel insulation film and a second floating electrode provided on one end portion of the first floating electrode, the floating electrode having an L-shaped cross section in a wiring direction of the control electrode.

Owner:KK TOSHIBA

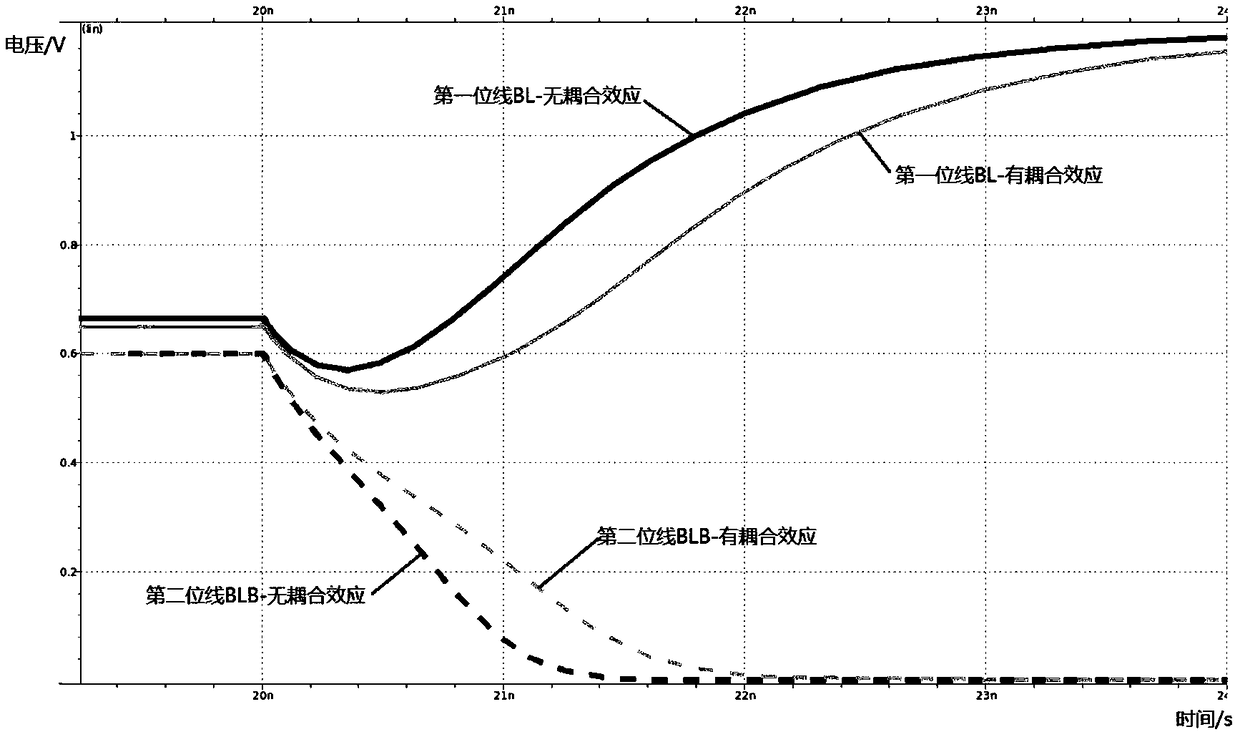

Sensitive amplifier circuit, memory and signal amplification method

PendingCN109166598AEnhanced Sensing CapabilitiesReduce coupling noiseDigital storageBit lineAudio power amplifier

The invention relates to a sensitive amplifier circuit, a memory and a signal amplification method. The sensitive amplifier circuit in the embodiment of the invention comprises: a sensitive amplifier,one end of which is connected with a first data line and the other end of which is connected with a second data line; a first semiconductor switching element having a first terminal connected to a first bit line, a second terminal connected to the first data line, and a control terminal receiving a first control signal, wherein the first semiconductor switching element changes the on degree according to the first control signal and the signal transmitted by the first bit line; and a second semiconductor switching element having a first terminal connected to a second bit line, a second terminal connected to a second data line, and a control terminal receiving a second control signal, wherein the second semiconductor switching element changes the opening degree according to the second control signal and the signal transmitted by the second data line. The sensitive amplifier circuit reduces bit line coupling noise and improves overall sensing efficiency.

Owner:CHANGXIN MEMORY TECH INC

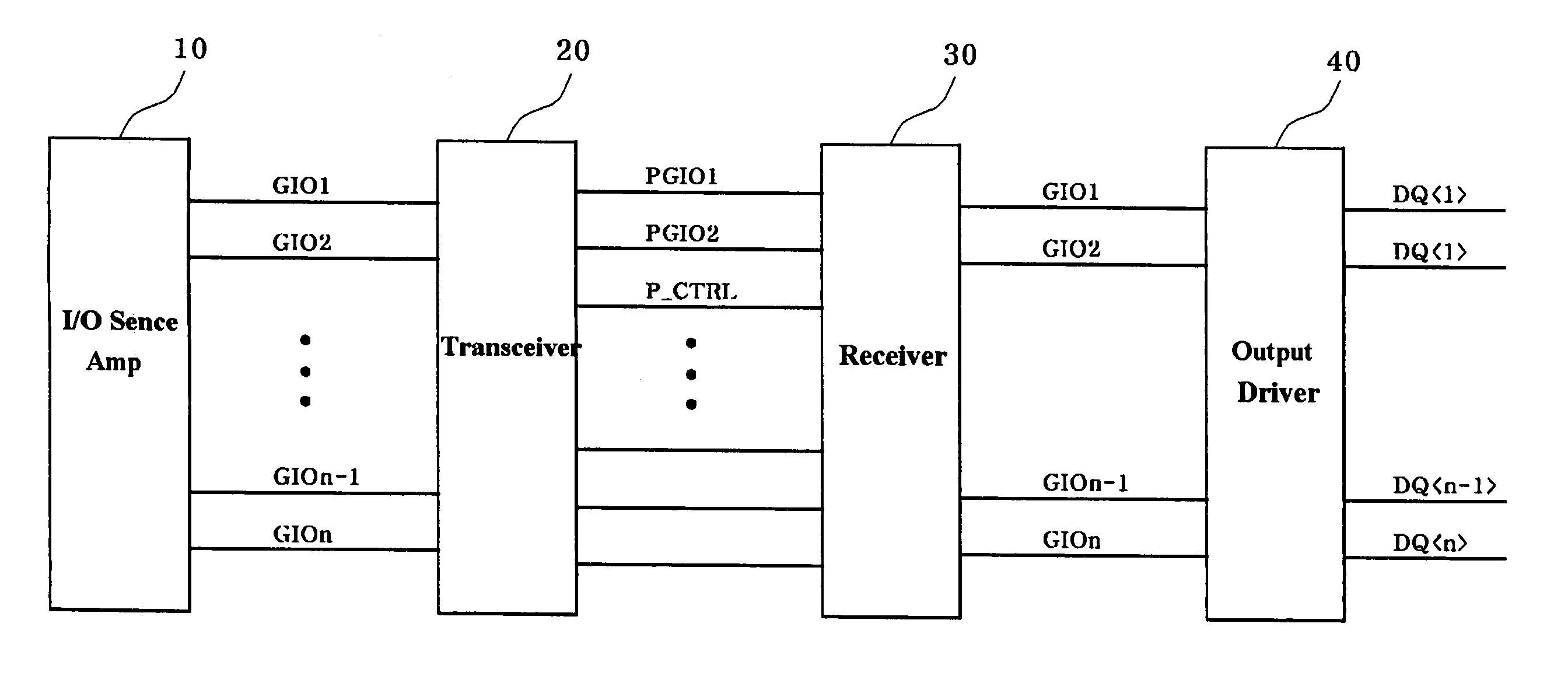

Data input/output (I/O) apparatus for use in memory device

InactiveUS20050226058A1Prevents memory failureSame polarityDigital storageFailure rateElectrical polarity

A data I / O apparatus for use in a memory device. The data I / O apparatus for use in the memory device performs data transmission using the same polarity when neighbor global I / O lines have opposite polarities to reduce coupling noise generated between global I / O lines acting as data I / O lines of a memory device, performs data recovery, and basically deletes the coupling noise, such that it reduces the failure rate of the memory device.

Owner:SK HYNIX INC

Semiconductor memory device for reducing bit line coupling noise

A semiconductor memory device including: first and second memory cell arrays each including at least one word line, at least three bit lines, and memory cells; and a sense amplifier area disposed between the first and second memory cell arrays and including a sense amplifier circuit for sensing and amplifying data of the memory cells, wherein the at least three bit lines of the first memory cell array and the at least three bit lines of the second memory cell array extend in a first direction and the at least three bit lines of the first and the second memory cell arrays are respectively connected to data lines disposed in a second direction, and wherein a bit line located between two of the at least three bit lines of each of the first and the second memory cell arrays is connected to an outermost data line of the data lines.

Owner:SAMSUNG ELECTRONICS CO LTD

Data transmitting system

InactiveUS7924055B2Short transition timeAvoid volatilityDigital storageSecret communicationEngineeringTransmitter

A data transmitting system is provided that includes a transmitter that suppresses coupling noise by being operated using a differential voltage driving scheme at the time of transmitting data and being operated using a common voltage driving scheme by equalizing potential of a pair of transmission lines during a transition interval; and a receiver that is connected to the transmitter through the pair of transmission lines and recovers the data by sensing the voltage difference in signals of the pair of transmission lines.

Owner:DONGBU HITEK CO LTD

Data input/output (I/O) apparatus for use in memory device

InactiveUS7161847B2Low failure rateReduce coupling noiseDigital storageFailure rateElectrical polarity

A data I / O apparatus for use in a memory device. The data I / O apparatus for use in the memory device performs data transmission using the same polarity when neighbor global I / O lines have opposite polarities to reduce coupling noise generated between global I / O lines acting as data I / O lines of a memory device, performs data recovery, and basically deletes the coupling noise, such that it reduces the failure rate of the memory device.

Owner:SK HYNIX INC

Solid-state image sensing device and method of operating the same

InactiveUS20070229690A1Reduce couple noiseReduce charge transfer errorTelevision system detailsTelevision system scanning detailsSolid-stateImage sensing

A charge coupled device is provided with; an output gate; a main CCD region operated in response to a set of clock signals; and an output region positioned between the output gate and the main CCD region and designed to transfer electric charges received from the main CCD region to the output gate. The main CCD region includes first and second transfer electrodes. The output region includes third and fourth transfer electrodes receiving clock signals which are phase-reversed from each other. The set of clock signals received by the main CCD region and the clock signals received by the output region are outputted from different driver circuits.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device, manufacturing method therefor, and electronic device

ActiveCN107527913AImprove performanceImprove RC delaySolid-state devicesSemiconductor devicesCapacitancePower semiconductor device

The invention provides a semiconductor device, a manufacturing method therefor and an electronic device, and relates to the technical field of semiconductors. The semiconductor substrate comprises a substrate which comprises a core region and is provided with an interlayer dielectric layer; a plurality of first bit lines which are disposed on the interlayer dielectric layer in the core region at intervals; a first dielectric layer which covers the first bit lines and the interlayer dielectric layer in the core region, wherein each part, between the adjacent first bit lines in the core region, of the first dielectric layer is provided with an air gap. According to the invention, the air gaps are disposed between the adjacent bit lines of the semiconductor devices, thereby reducing the capacitance of the bit lines, and reducing the coupling noise between the bit lines. Also, units with the uniform performances can be obtained, such as a unit with the uniform threshold voltage (Vt) and a unit with the uniform random telegraph noise. Moreover, the device improves the RC delay of the bit lines, and is enabled to have better performances.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Integrated circuit and optical pickup device

InactiveUS7199668B2Reduce coupling noiseGuaranteed uptimeAmplifier modifications to reduce noise influenceAmplifier combinationsOptical pickupIntegrator

An integrated circuit includes a first-stage amplifier circuit and a following-stage amplifier circuit connected in series, a common power source pad for supplying power to the amplifier circuits, and metal wires respectively connecting the common power source pad to the amplifier circuits. On the metal wire which connects the first-stage amplifier and the power source pad, an integrator is electrically connected. This arrangement decreases a coupling noise generated in the first-stage amplifier circuit, thereby stabilizing circuit operation of the following-stage amplifier circuit.

Owner:SHARP KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com