Semiconductor device, manufacturing method therefor, and electronic device

A manufacturing method and semiconductor technology, applied in semiconductor devices, electric solid state devices, circuits, etc., can solve the problem that it is difficult to form air gaps between bit lines, etc., to reduce bit line capacitance, reduce coupling noise, and improve RC delay Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

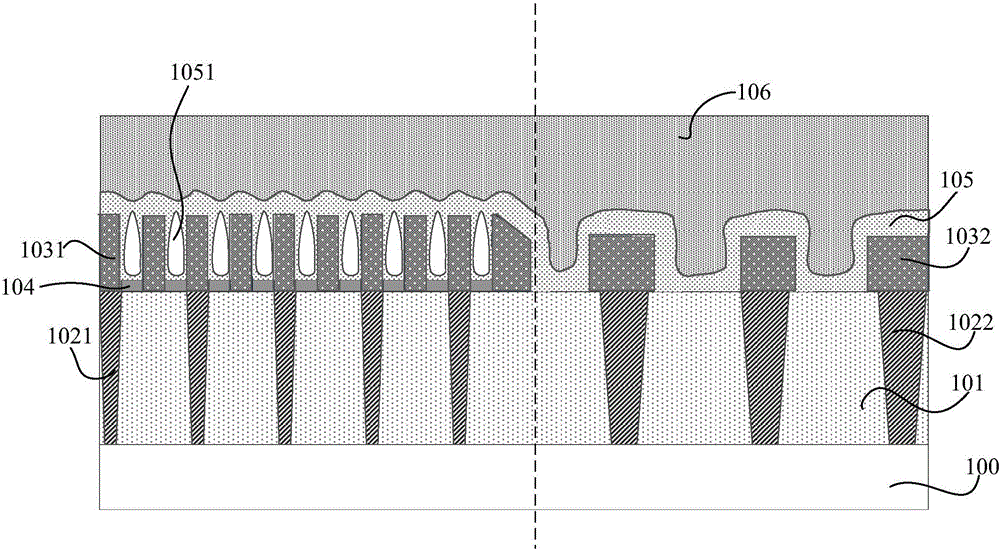

[0056] Refer below figure 1 The semiconductor device of the present invention is described in detail, wherein, figure 1 A cross-sectional view of a semiconductor device in a specific embodiment of the present invention is shown.

[0057] The semiconductor device of the present invention may be any semiconductor device known to those skilled in the art. As an example, the semiconductor device is a NAND flash memory.

[0058] The semiconductor device of the present invention includes the following main structures: a base, the base includes a core area, and an interlayer dielectric layer is arranged on the base; A plurality of first bit lines, wherein the first bit lines extend along a first direction; a first dielectric layer is arranged to cover the first bit lines and the interlayer dielectric layer in the core region, wherein, An air gap is formed in the first dielectric layer between adjacent first bit lines in the core region.

[0059] Specifically, as figure 1 As shown...

Embodiment 2

[0094] In view of the superior performance of the above-mentioned semiconductor device, the present invention also provides a manufacturing method of the semiconductor device, such as image 3 As shown, the semiconductor device mainly includes the following steps:

[0095] Step S301: providing a substrate, the substrate includes a core region and a peripheral region, an interlayer dielectric layer is formed on the substrate, and a patterned hard mask layer is formed on the interlayer dielectric layer in the core region , the patterned hard mask layer includes a plurality of openings, the openings corresponding to the predetermined pattern of the first bit line in the core region;

[0096] Step S302: forming a bit line material layer covering the patterned hard mask layer and the exposed interlayer dielectric layer of the core region and the peripheral region;

[0097] Step S303: forming a patterned photoresist layer on the bit line material layer in the peripheral area;

[0...

Embodiment 3

[0165] The present invention also provides an electronic device, including the semiconductor device described in Embodiment 1, and the semiconductor device is prepared according to the method described in Embodiment 2.

[0166] The electronic device of this embodiment can be any electronic device such as a mobile phone, a tablet computer, a notebook computer, a netbook, a game console, a TV set, a VCD, a DVD, a navigator, a digital photo frame, a camera, a video camera, a recording pen, MP3, MP4, PSP, etc. Product or equipment, but also any intermediate product including electrical circuits. The electronic device of the embodiment of the present invention has better performance due to the use of the above circuit.

[0167] in, Figure 4 An example of a mobile phone handset is shown. The mobile phone handset 400 is provided with a display portion 402 included in a housing 401, operation buttons 403, an external connection port 404, a speaker 405, a microphone 406, and the lik...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com