Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Reduce core size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

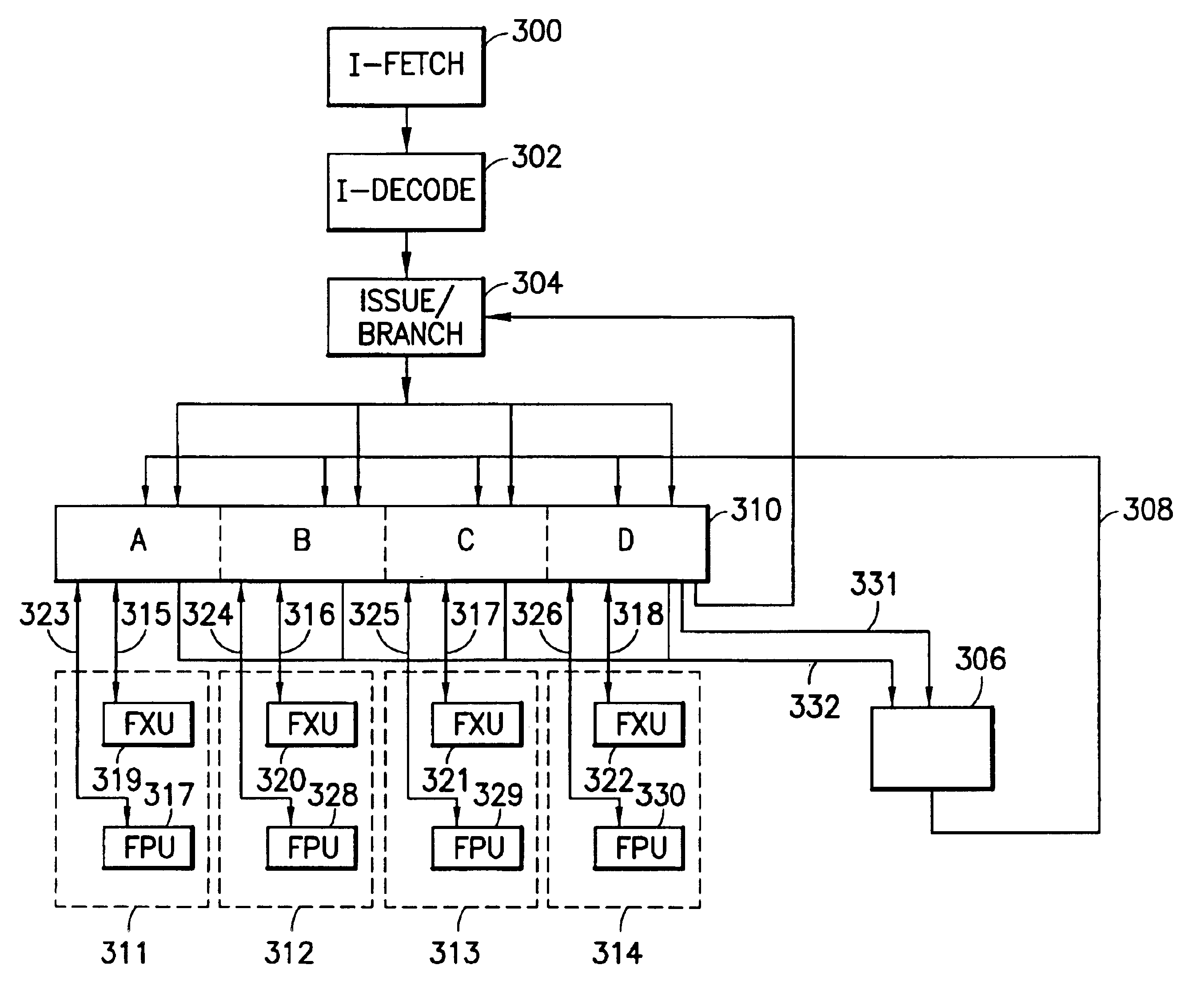

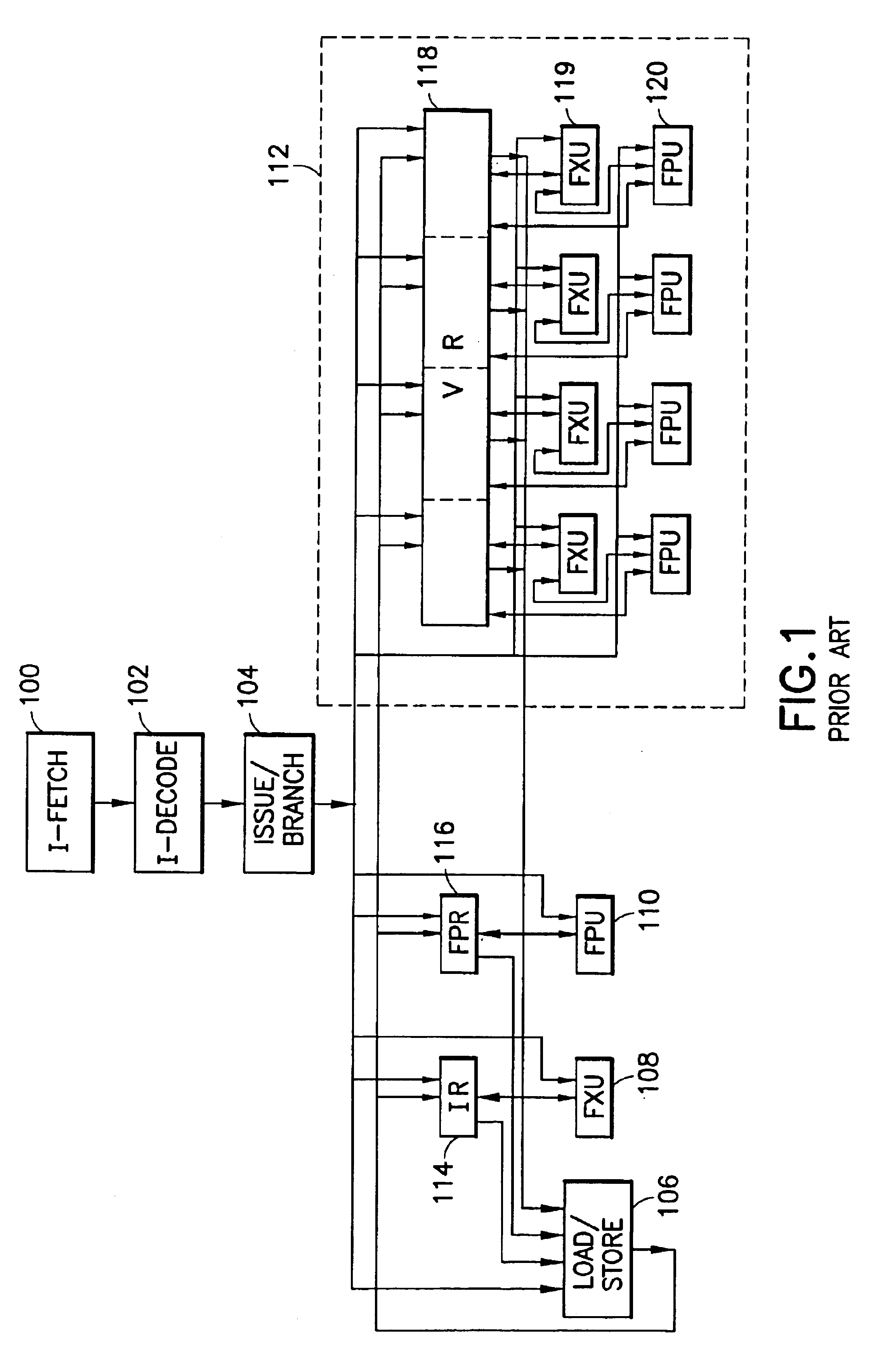

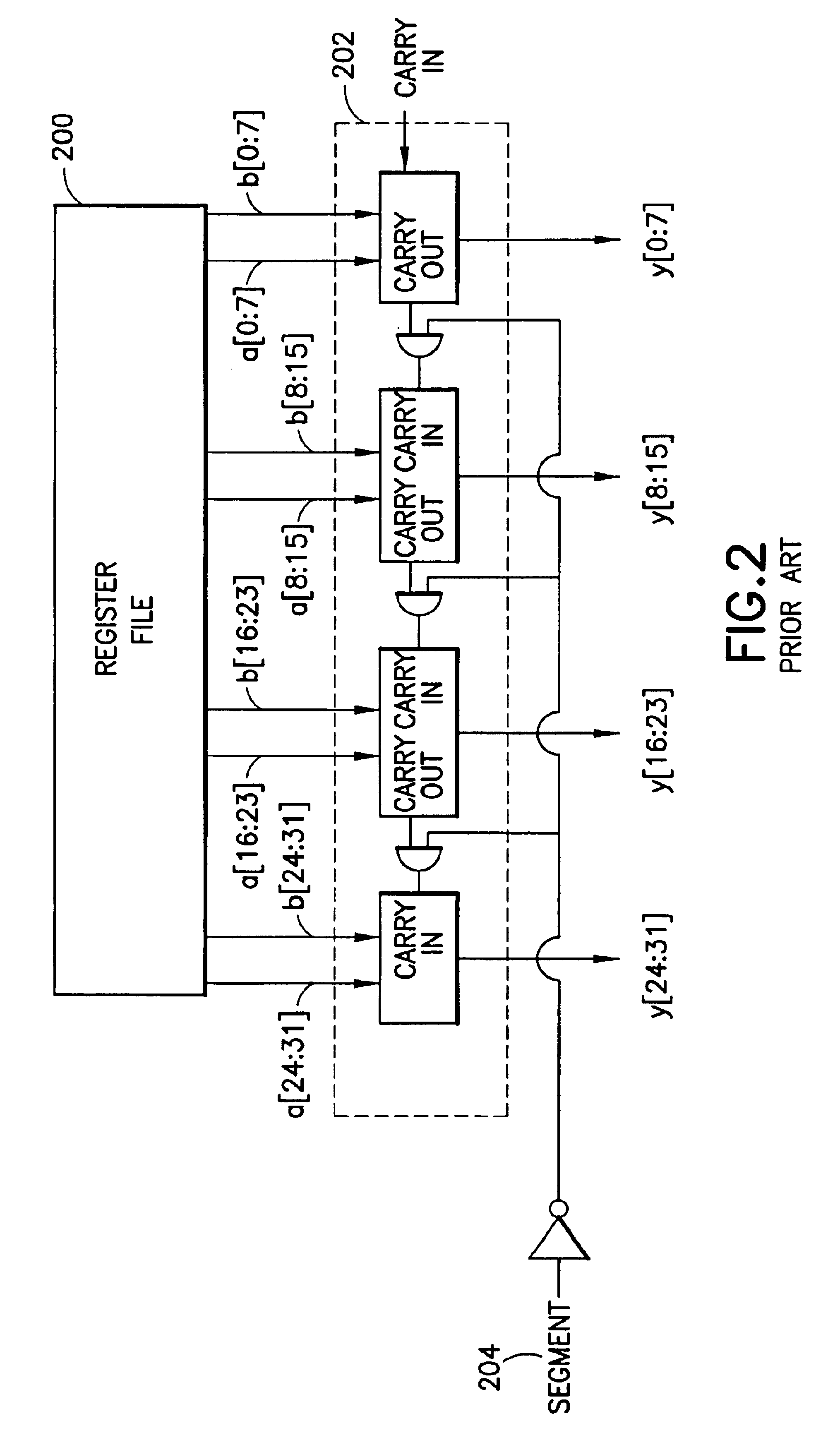

SIMD datapath coupled to scalar/vector/address/conditional data register file with selective subpath scalar processing mode

InactiveUS6839828B2Not compromise SIMD data processing performanceReduce consumptionRegister arrangementsDigital data processing detailsProcessor registerOperation mode

There is provided a processor designed to operate in a plurality of modes for processing vector and scalar instructions. Register files are each for storing scalar and vector data and address information. A parallel vector unit, coupled to the register files, includes functional units configurable to operate in a vector operation mode and a scalar operation mode. The vector unit includes an apparatus for tightly coupling the functional units to perform an operation specified by a current instruction. Under a vector operation mode, the vector unit performs, in parallel, a single vector operation on a plurality of data elements. The operations performed on the plurality of data elements are each performed by a different functional unit of the vector unit. Under a scalar operation mode, the vector unit performs a scalar operation on a data element received from the register files in a functional unit within the vector unit.

Owner:INTEL CORP

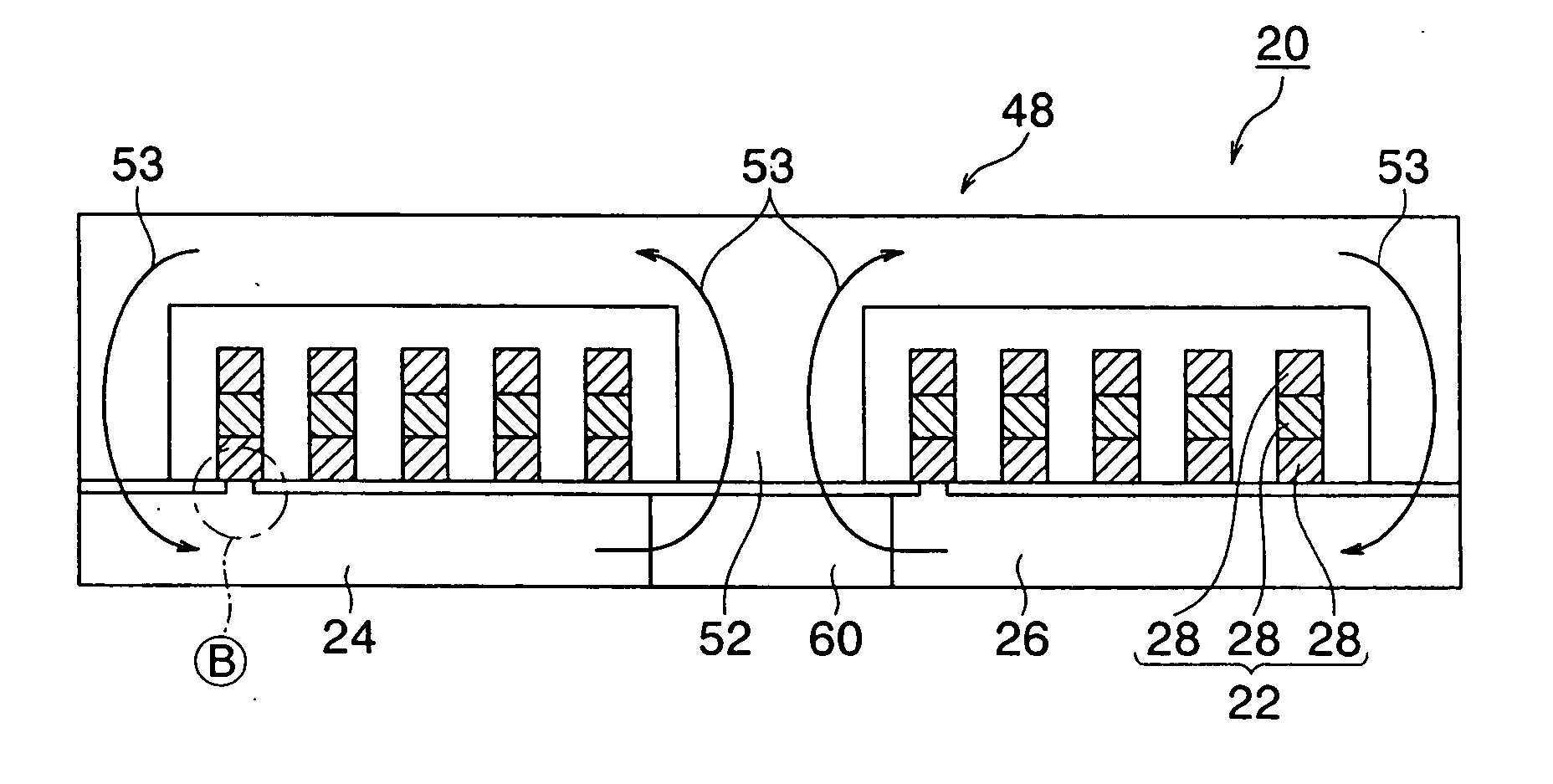

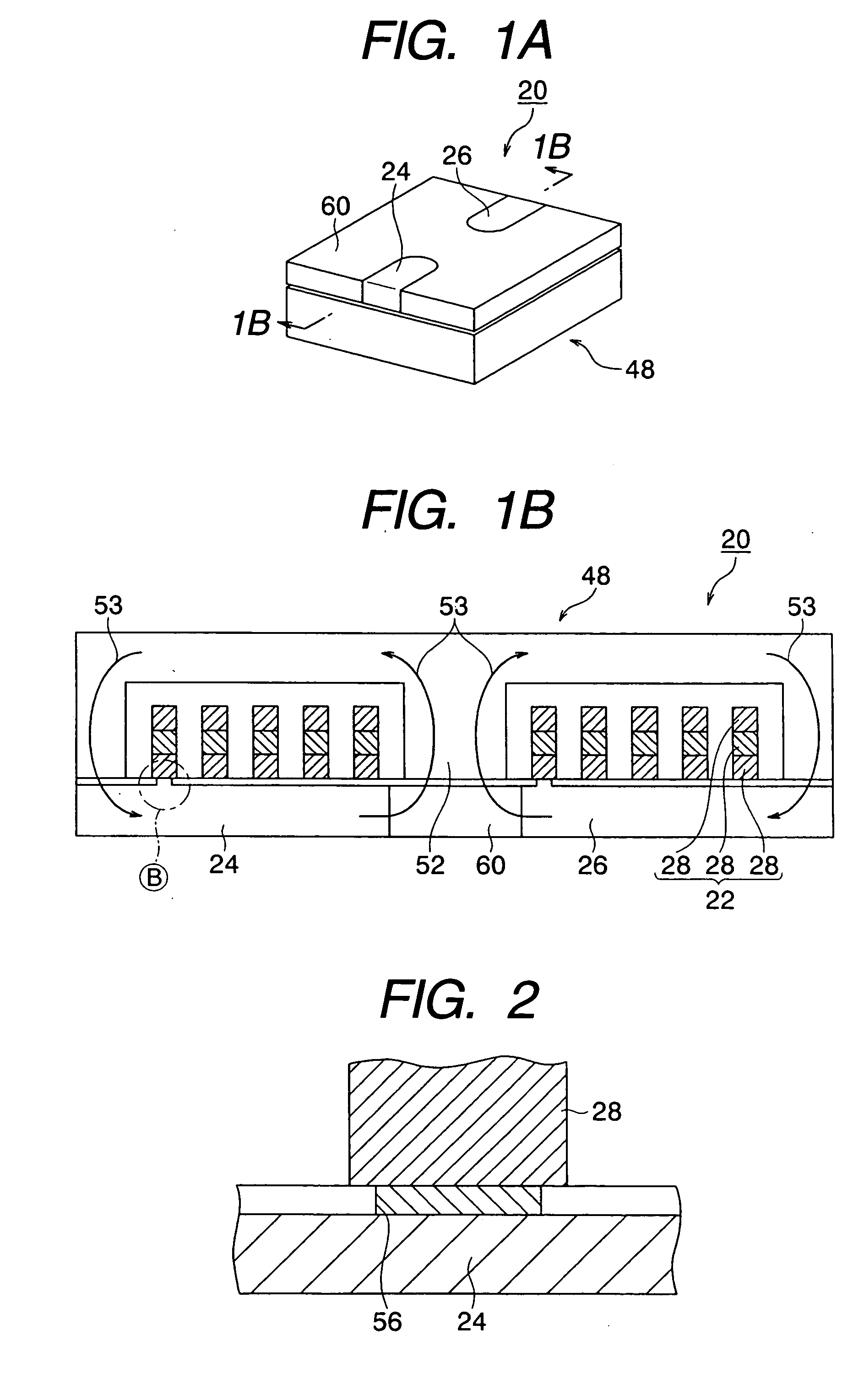

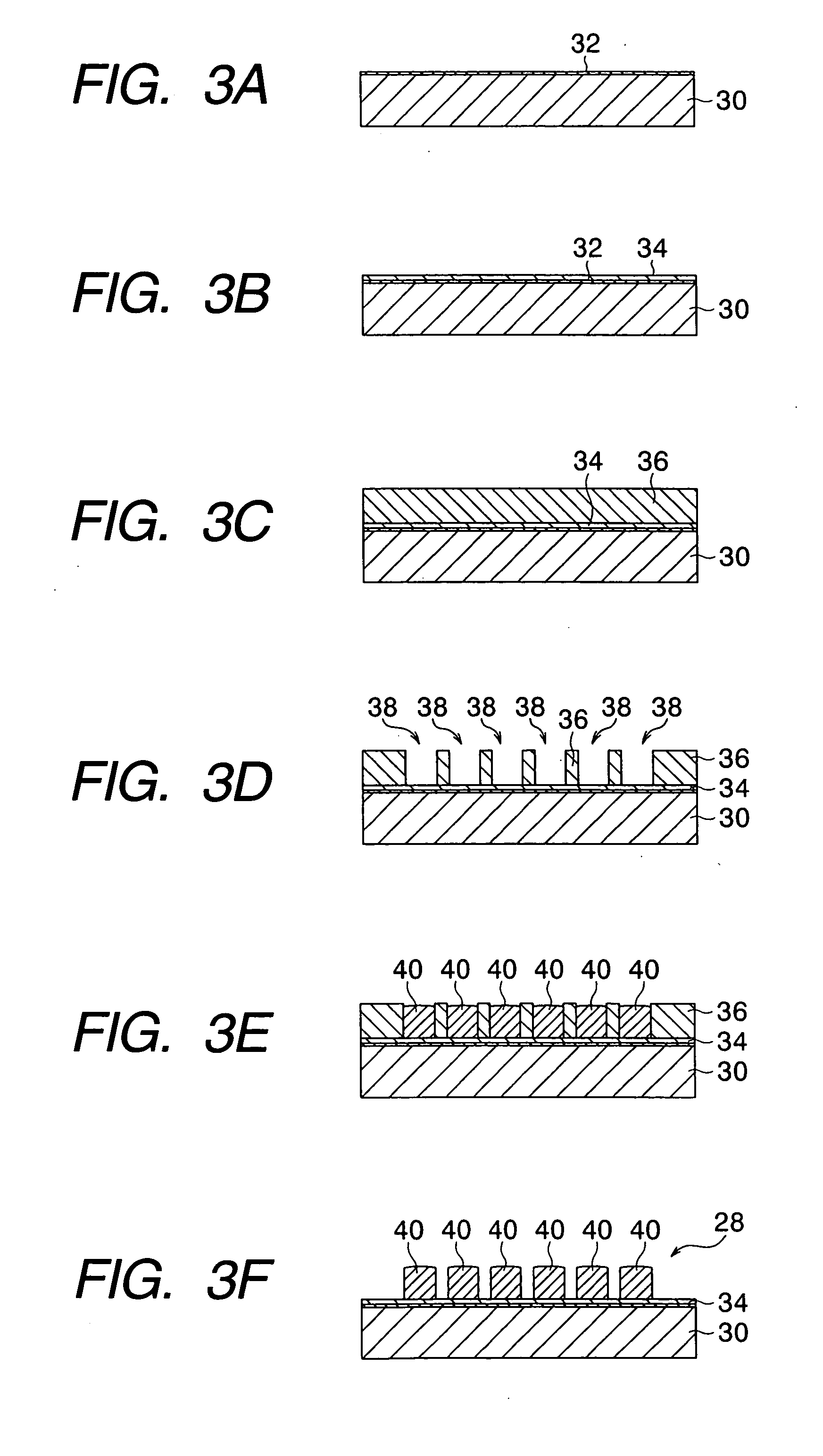

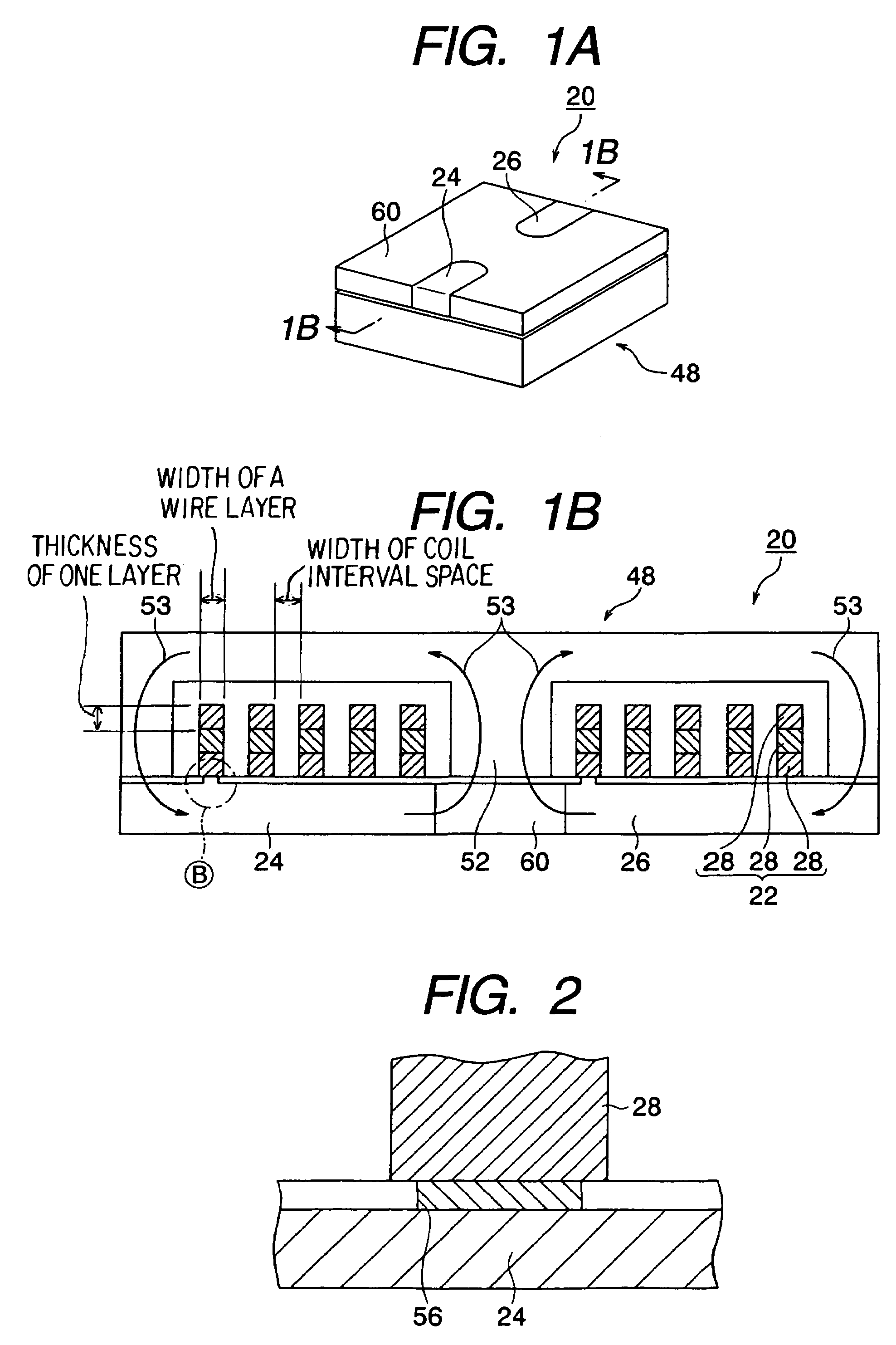

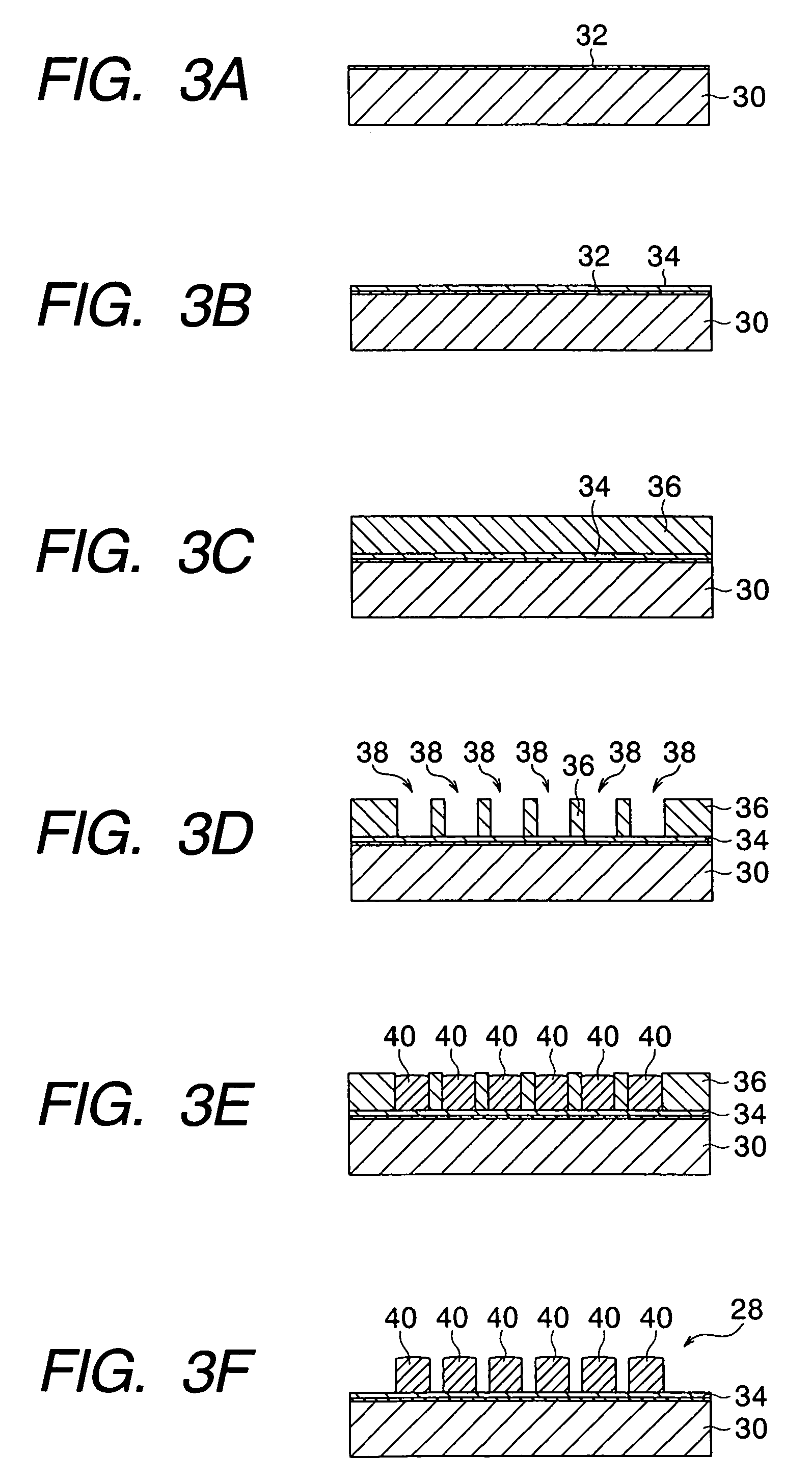

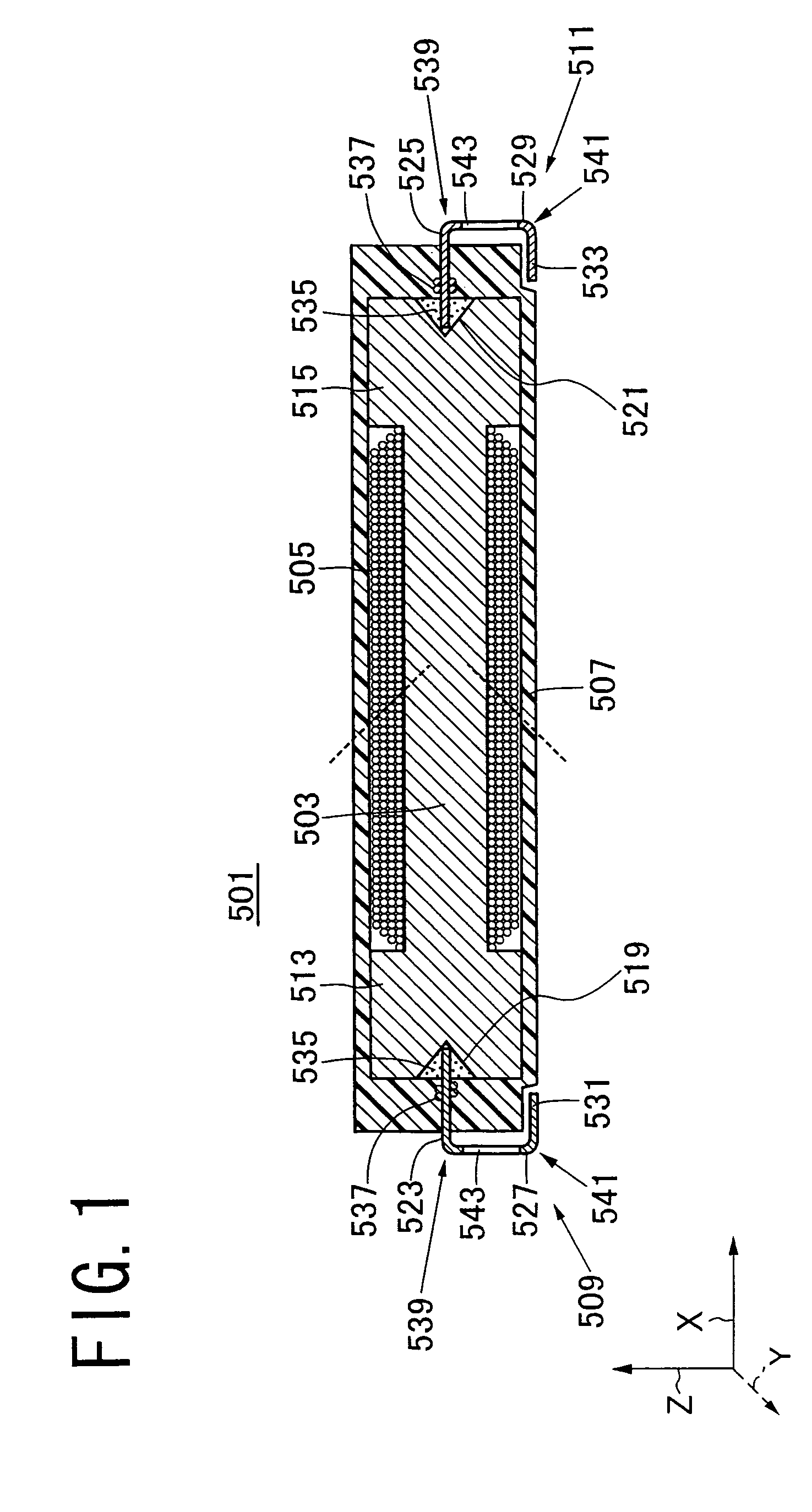

High density inductor and method for producing same

InactiveUS20040164835A1Reduce core sizeAccurate shapeTransformers/inductances coils/windings/connectionsSolid-state devicesHigh densityInductor

A method for producing a high density inductor includes the steps of forming a coil having a spiral shape, sealing the coil in the interior of a core member, and forming a terminal electrode for allowing electric conduction to said coil on the outside of said core member. In this method, the coil is formed by repeating a process of forming a wire layer by means of a thin film forming process and a process of forming an additional wire layer on top of the wire layer by means of the thin film forming process to pile up the wire layers. With this production method, it is possible to form a coil with a high aspect ratio. In addition, the inductor is designed in such a way that the core member envelopes only the coil. With that design, it is possible to make the inductor compact.

Owner:TDK CORPARATION

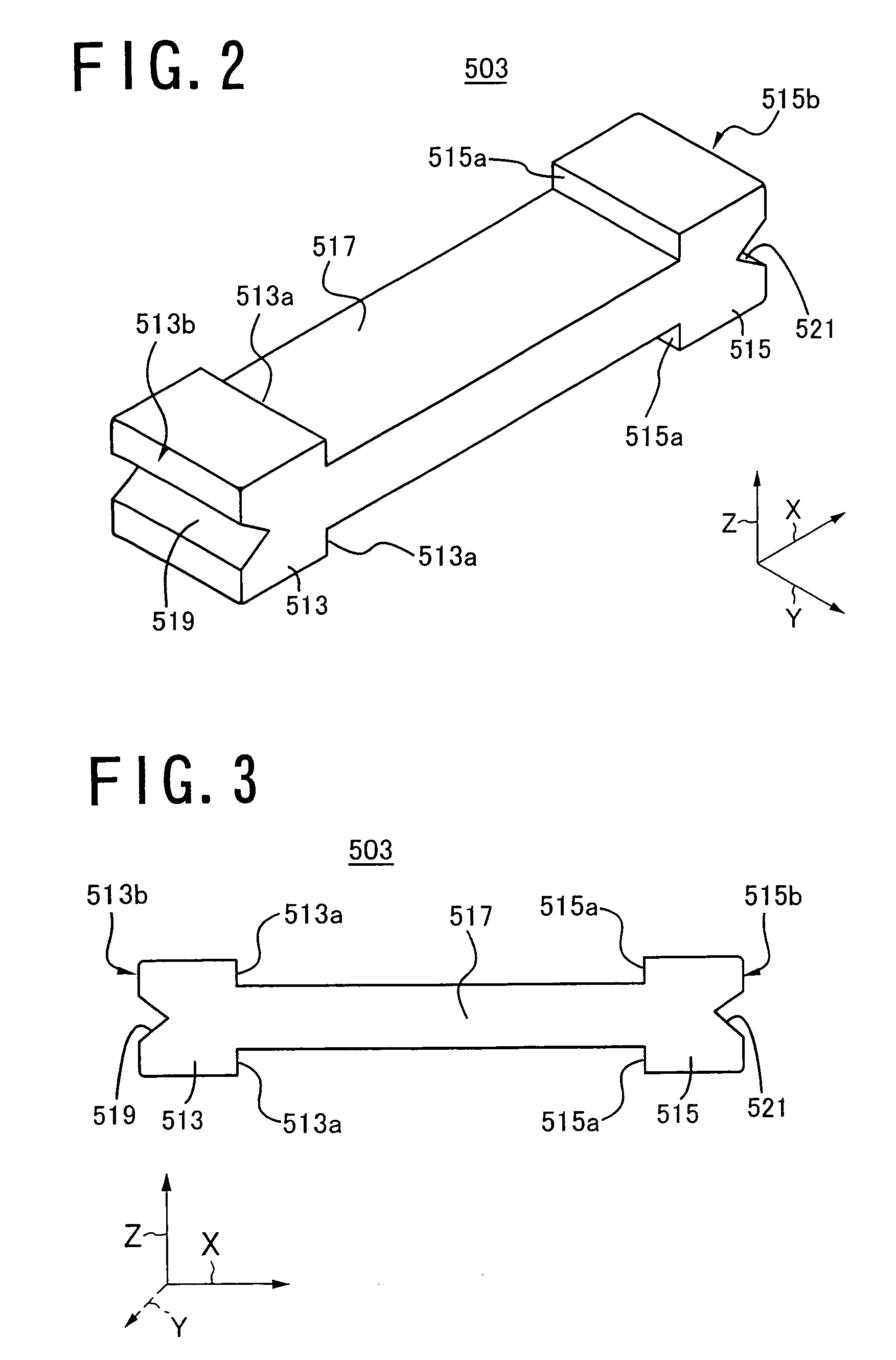

High density inductor and method for producing same

InactiveUS7176773B2Reduce core sizeAccurate shapeTransformers/inductances casingsTransformers/inductances coils/windings/connectionsHigh densityInductor

Owner:TDK CORPARATION

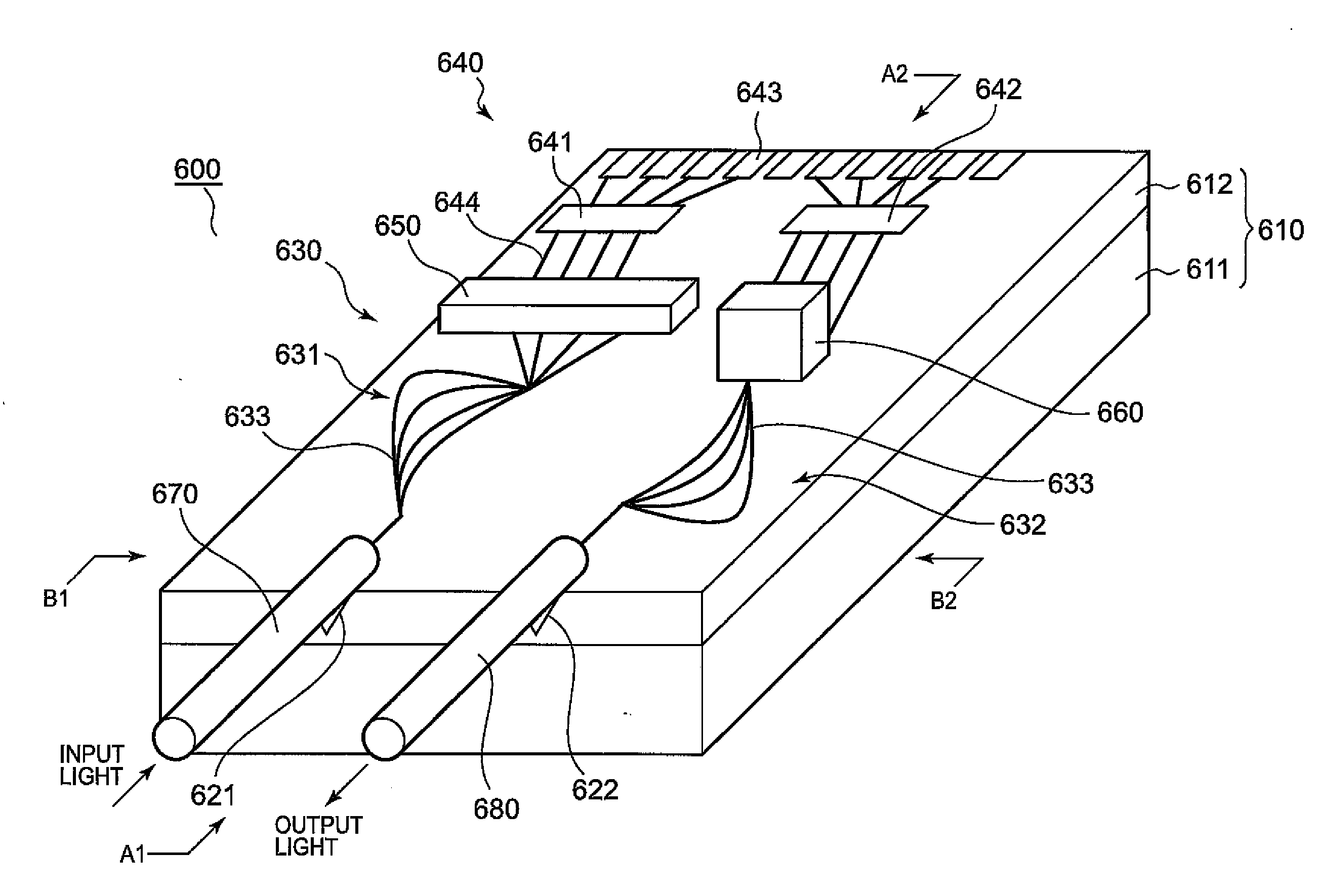

Method and apparatus for combining laser light

InactiveUS7460755B2Reduce core sizeIncrease in sizeLaser arrangementsCoupling light guidesFiberLaser light

A fiber optic apparatus formed by fusing together multiple optical fibers and stretching the fused optical fibers to form a tapered portion. The tapered portion is cleaved or cut and polished to form a facet at which an optical beam is received or transmitted.

Owner:HRL LAB

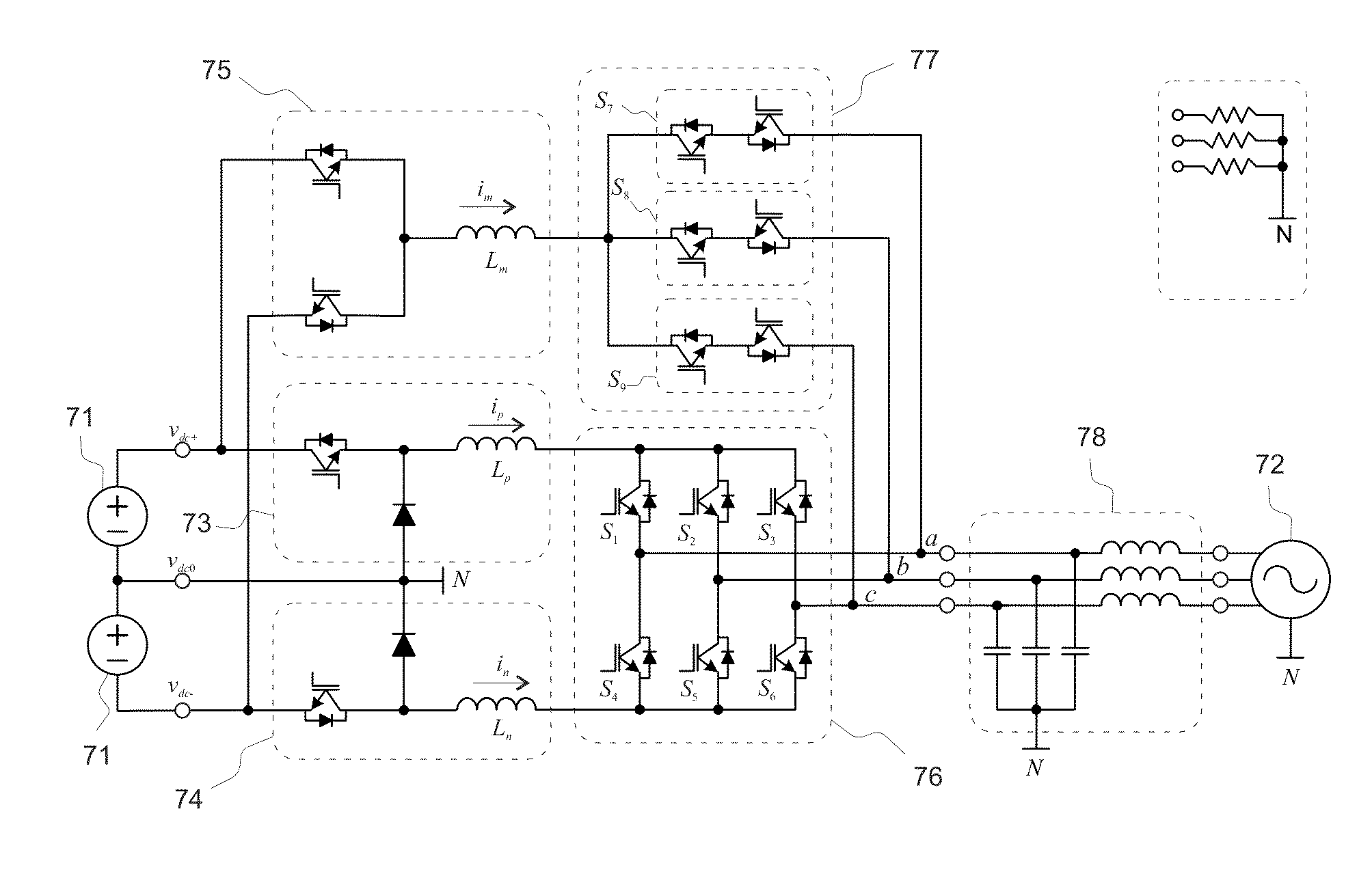

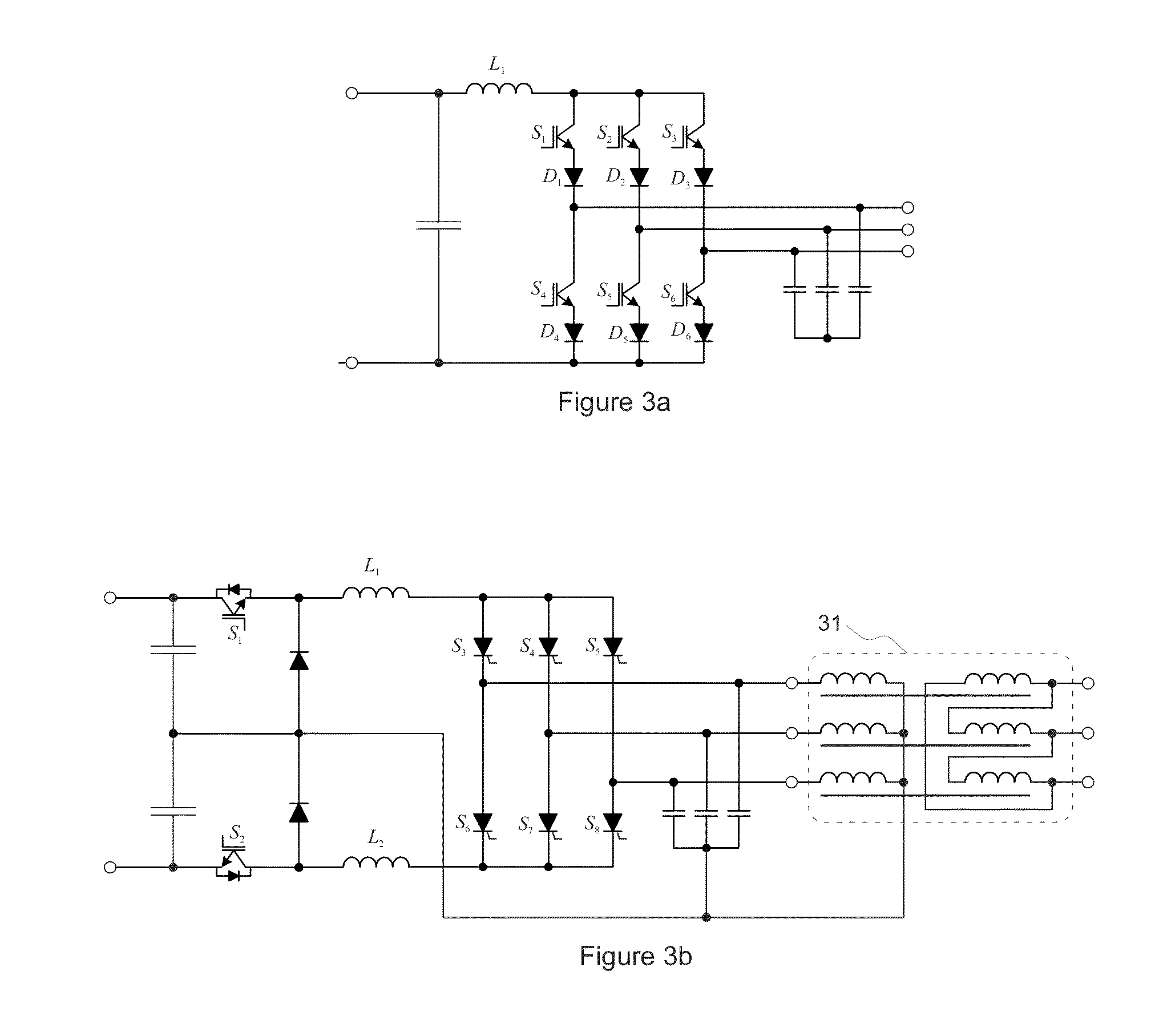

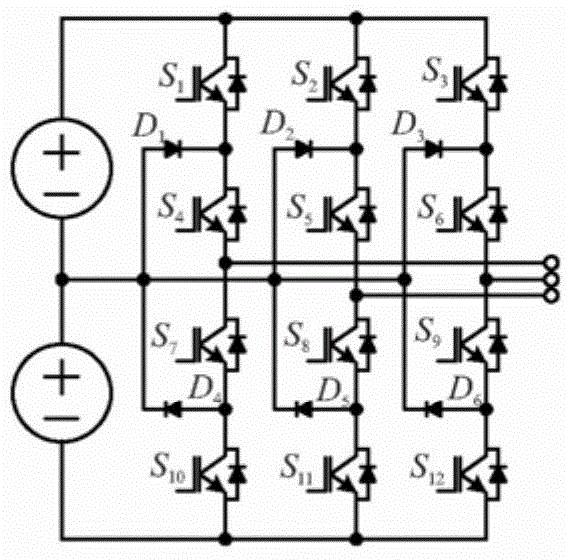

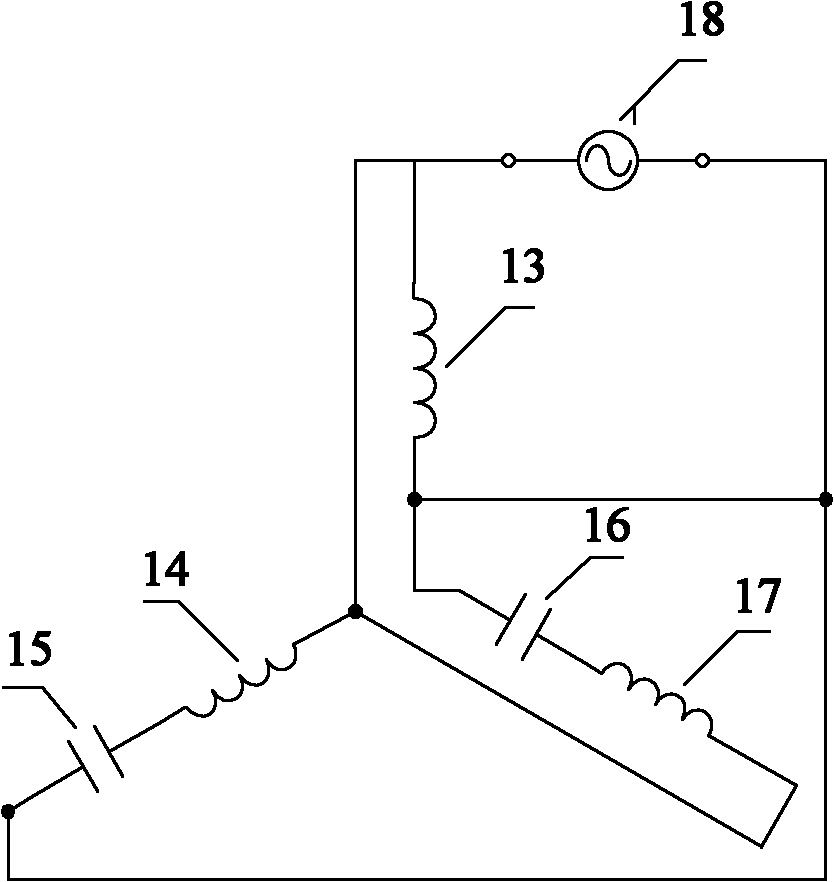

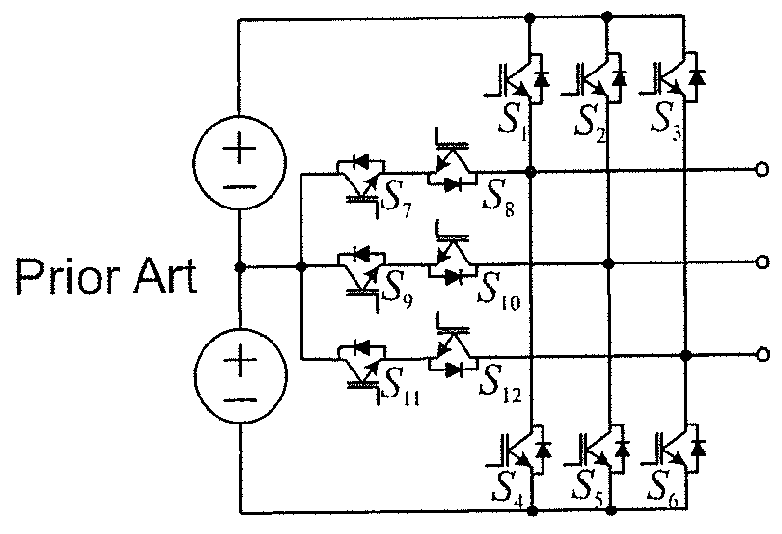

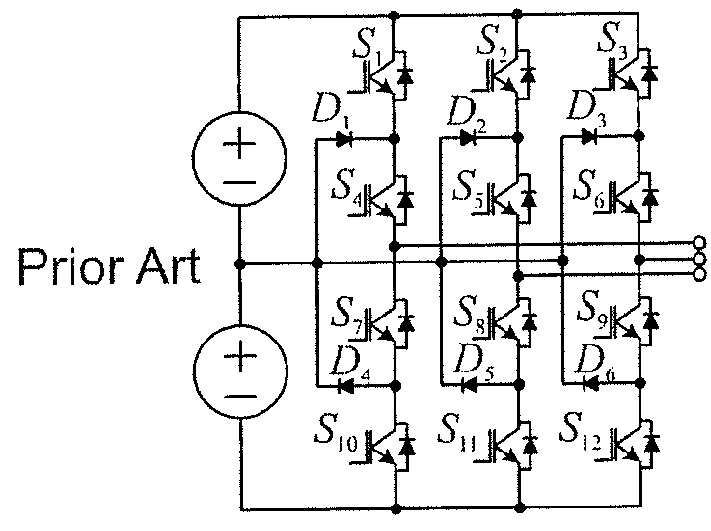

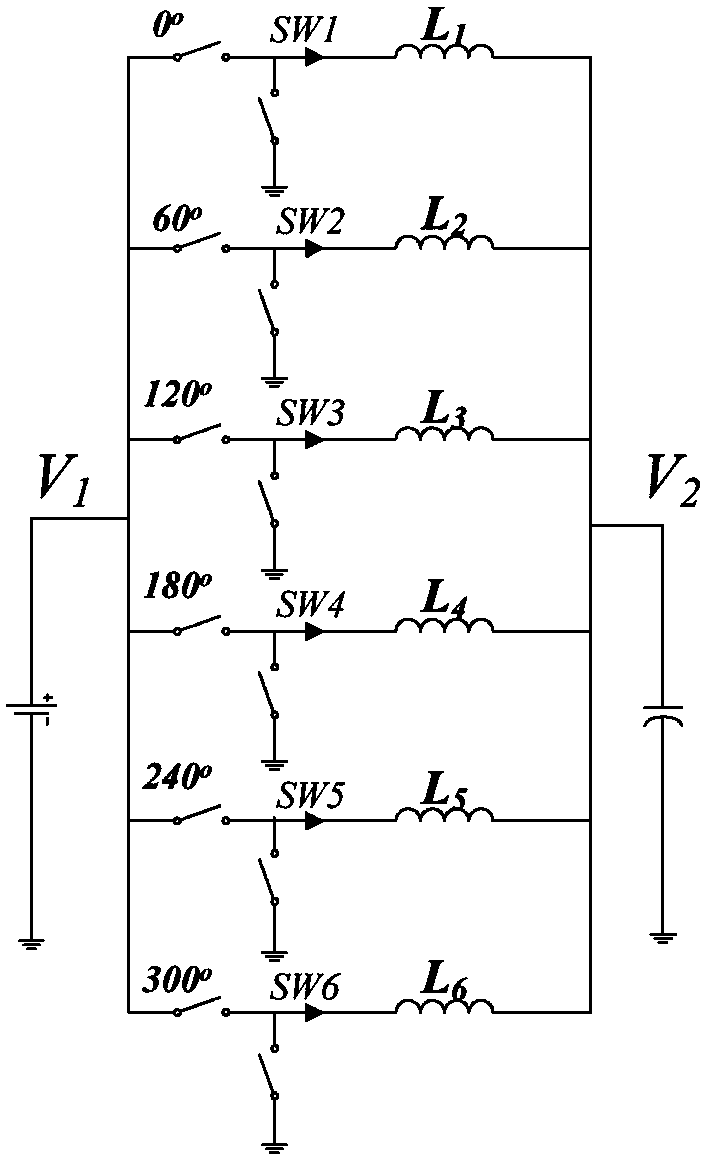

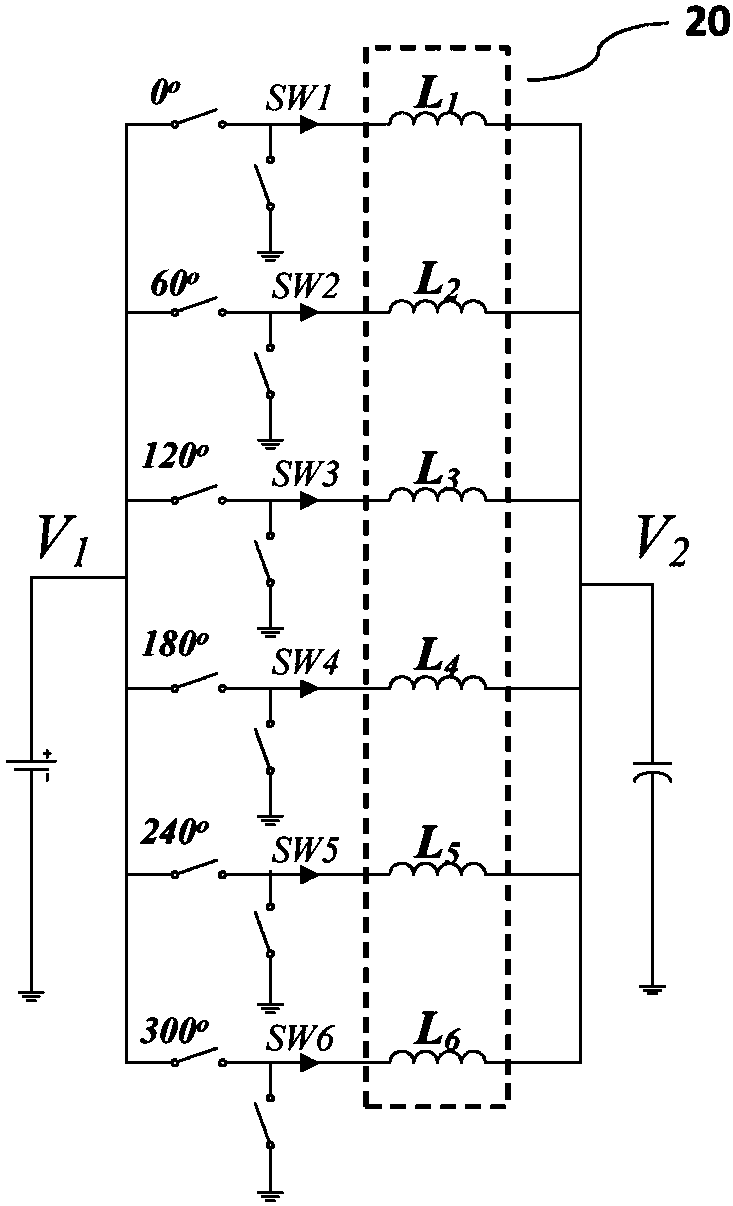

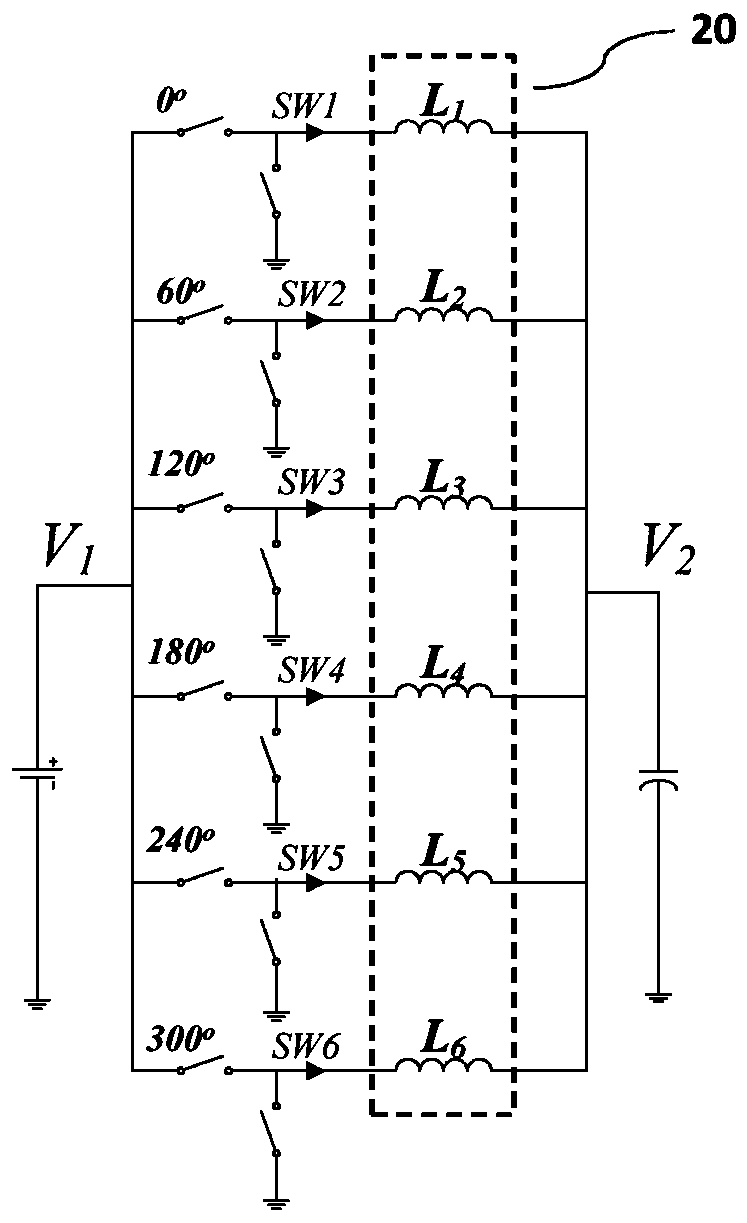

Method and apparatus for producing three-phase current

ActiveUS20140241016A1Current ratingIncrease chanceDc-dc conversionOscillations generatorsPhase currentsElectrical conductor

Exemplary embodiments are directed to methods and systems for producing a three-phase current to a three-phase output. Switching converters are used to generate a positive current, a negative current, and an intermediate current. The system is configured such that the produced positive current follows a path of a highest phase of a sinusoidal three-phase signal at a given time, the produced negative current follows a path of a lowest phase of the three-phase signal at the given time, and the produced intermediate current follows a path of a phase of the three-phase signal between the highest and the lowest phase at the given time. The produced currents are switched to each phase conductor of the three-phase output in sequence so that phase currents of the three-phase current are formed in the output conductors.

Owner:ABB (SCHWEIZ) AG

Coil device

ActiveUS20070046413A1High mechanical strengthSufficient propertyTransformers/inductances casingsTransformers/inductances coils/windings/connectionsConductor CoilFerrite core

A coil apparatus having a divided winding conformation and a manufacturing method of the coil apparatus which can prevent a winding from collapsing while achieving a reduction in size of a core and simplification of a structure. A coil apparatus includes a ferrite core and a coil provided around the core. The coil includes at least a first coil portion and a second coil portion, and a boundary end surface of the first coil portion on the second coil portion side is inclined in such a manner that its inner peripheral side is closer to the second coil portion than its outer peripheral side. Further, a boundary end surface of the second coil portion on the first coil portion side is inclined in such a manner that its outer peripheral side is closer to the first coil portion than its inner peripheral side.

Owner:TDK CORPARATION

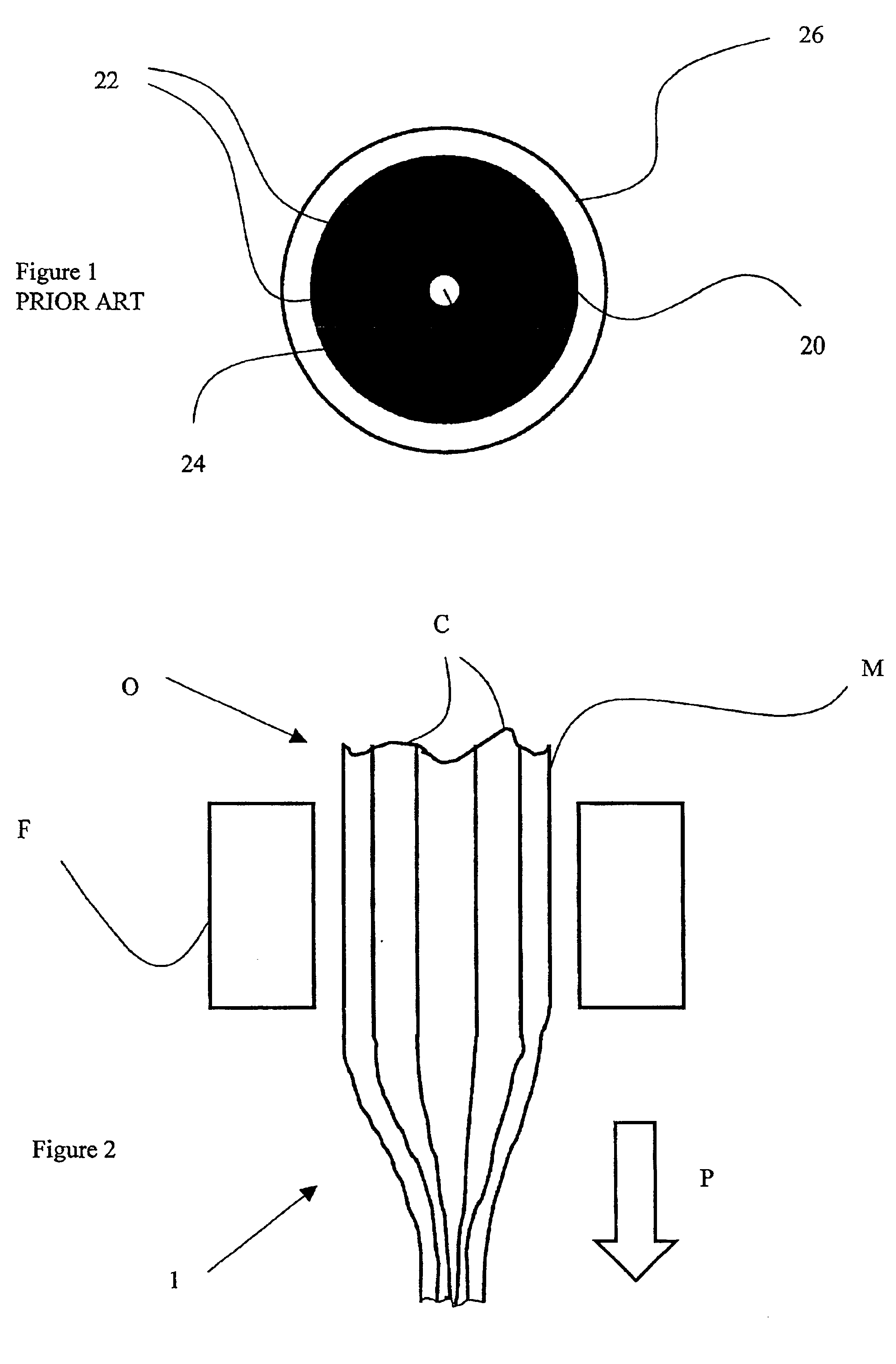

Magneto-optical recording apparatus having a magnetic head with a regulating member

InactiveUS6909673B2Reduce core sizeHigh-frequency recordingRecord information storageLight beam reproducingOptical pickupLight beam

The magneto-optical recording apparatus of the present invention comprises: a magnetic head of which one end is fixed and of which the other end is free and provided with a magnetic field generating portion for applying a magnetic field onto a magneto-optical recording medium; an optical pickup, provided opposite the magnetic head with the recording medium between them, for irradiating a portion applied with a magnetic field from the magnetic head with a light beam; and a member for regulating displacement of the magnetic head in a direction parallel to a magneto-optical recording medium surface.

Owner:CANON KK

Method and apparatus for producing three-phase current

ActiveCN104009666AReduce core sizeImprove power densityDc-dc conversionSingle network parallel feeding arrangementsPhase currentsElectrical conductor

The present disclosure discloses a method and an apparatus for implementing the method for producing a three-phase current to a three-phase output. The method comprises producing a positive current, a negative current, and an intermediate current by using switching converters. The produced positive current follows a path of a highest phase of a sinusoidal three-phase signal at a given time, the produced negative current follows a path of a lowest phase of the three-phase signal at the given time, and the produced intermediate current follows a path of a phase of the three-phase signal between the highest and the lowest phase at the given time. The produced currents are switched to each phase conductor of the three-phase output in sequence so that phase currents of the three-phase current are formed in the output conductors.

Owner:ABB (SCHWEIZ) AG

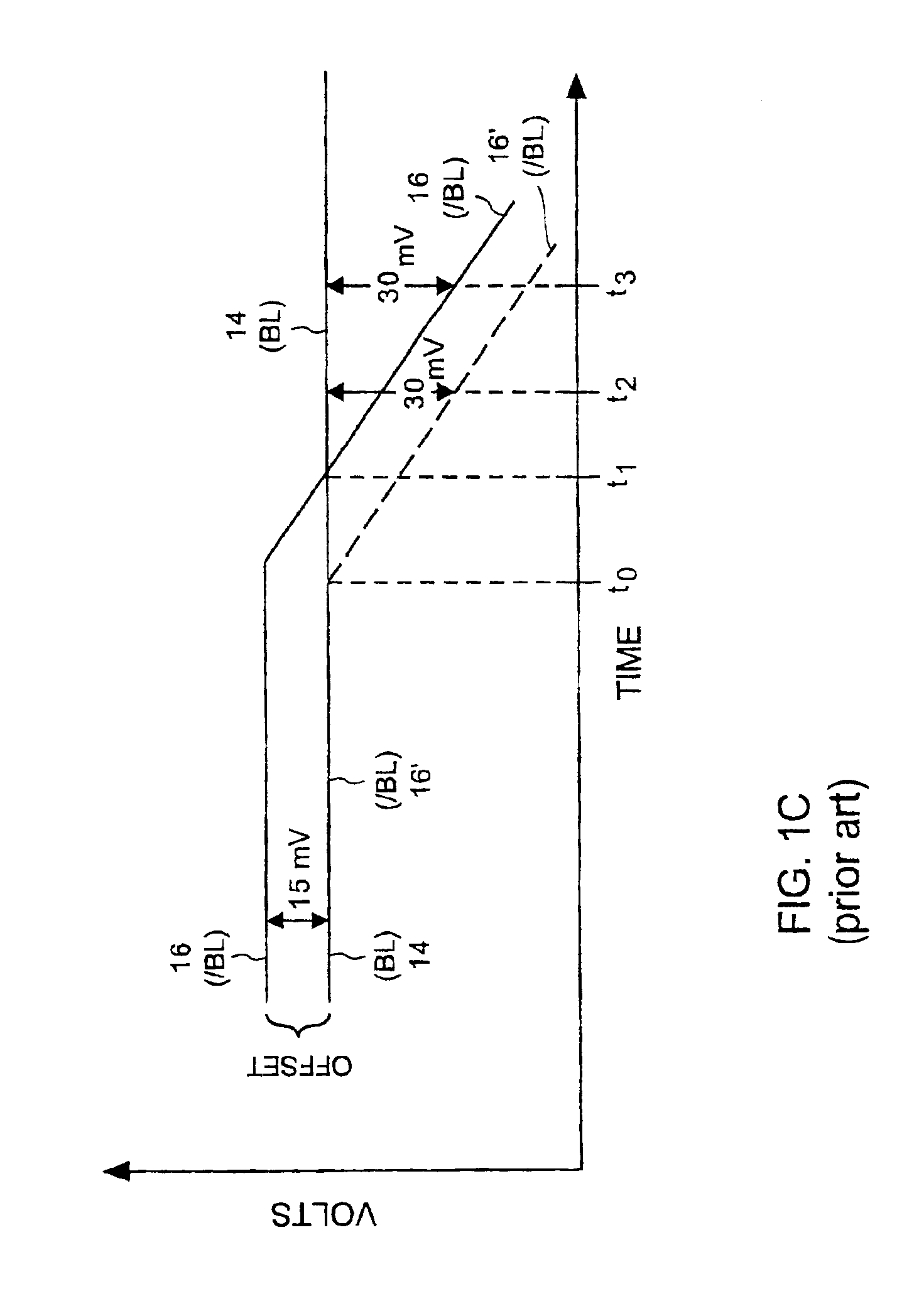

Methods for reducing bitline voltage offsets in memory devices

InactiveUS6944582B2Eliminate voltage offsetReduce areaTransistorSolid-state devicesComputer scienceVoltage

A method of designing a memory device that has substantially reduced bitline voltage offsets is provided. The method includes providing a memory core having a depth that defines a plurality of words, and a word width that is defined by multiple pairs of a global bitline and a global complementary bitline. The method also includes designing a core cell having a bitline and a complementary bitline, and designing a flipped core cell that has a flipped bitline and a flipped complementary bitline. Further, the method includes arranging a core cell followed by a flipped core cell along each of the multiple pairs of the global bitline and the global complementary bitline. Preferably, the bitline of the core cell is coupled with the flipped complementary bitline of the flipped core cell, and the complementary bitline of the core cell is coupled to the flipped bitline of the flipped core cell.

Owner:ARM INC

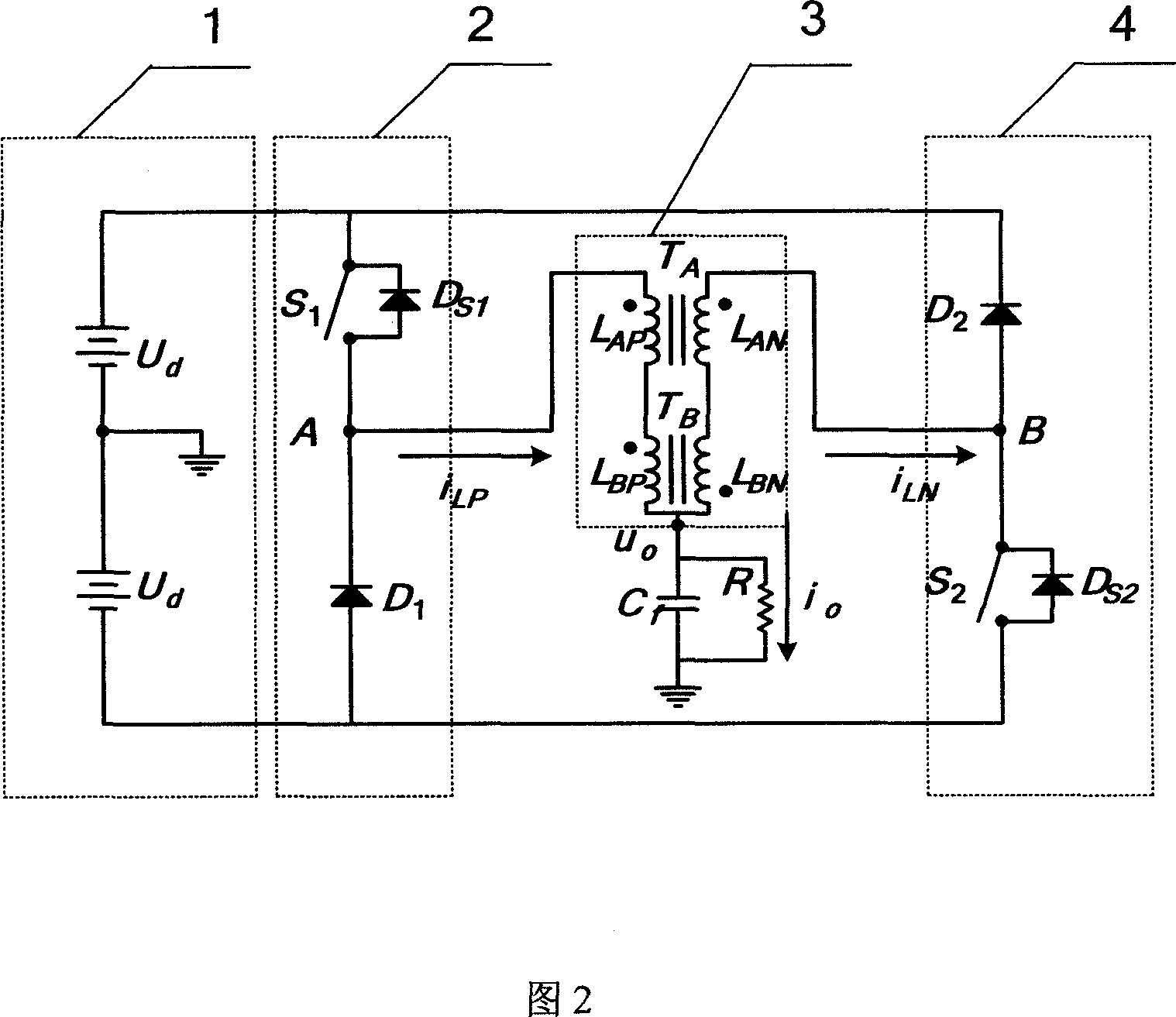

Magnetism-integrated double decompression semi-bridge converter

This invention provides one magnetic double lowering semi-bridge inverter, which comprises inverter first arm, second arm, and magnetic couple induction composed of first and second couple filter induction. This invention adopts magnetic integration technique to roll magnetic parts into one common core through couple means and parameters setting to reduce parts volume and consumption.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

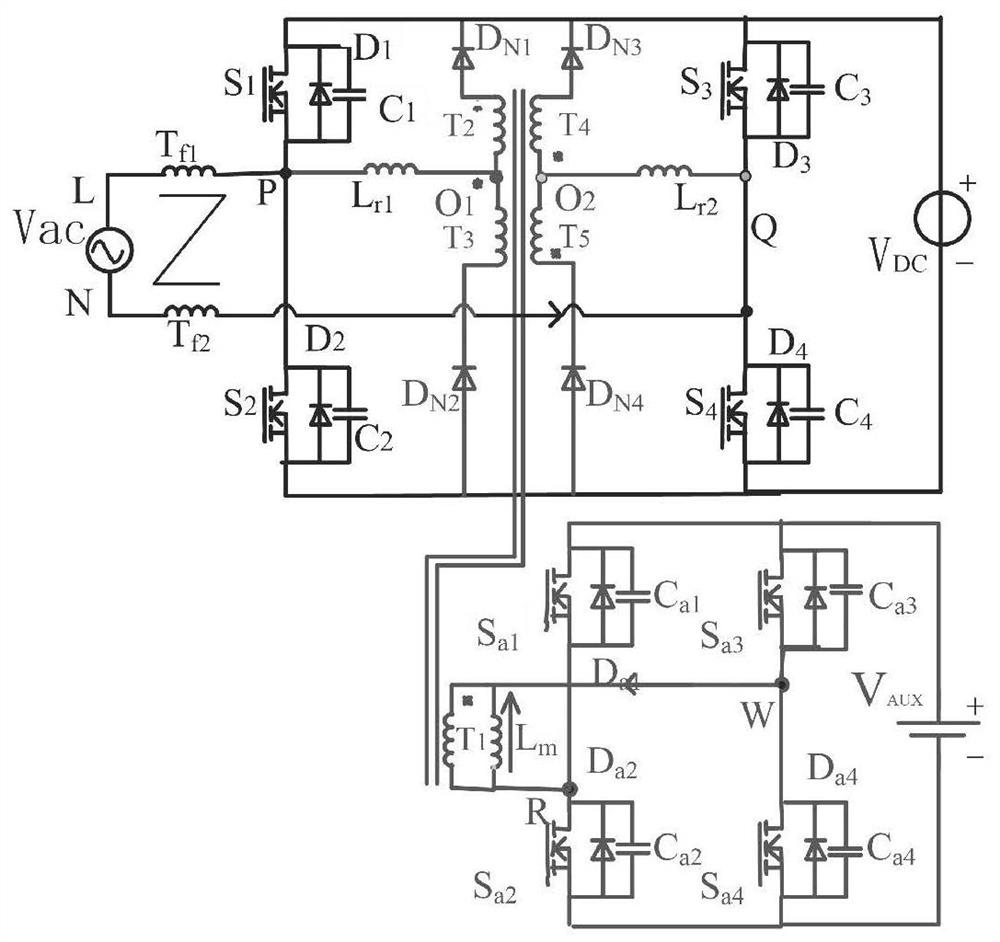

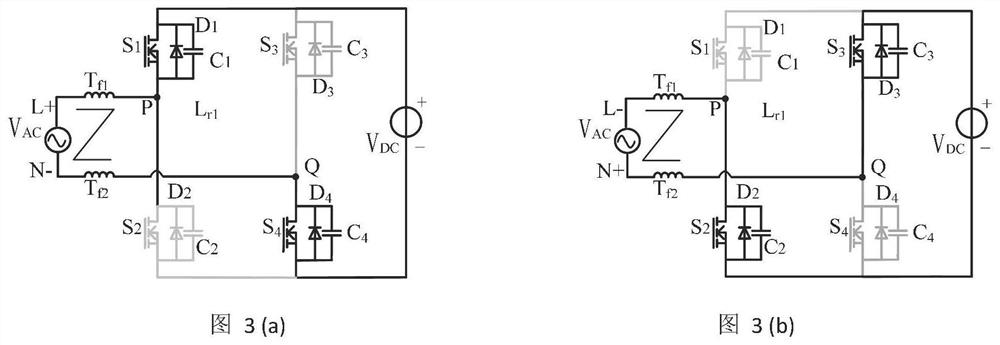

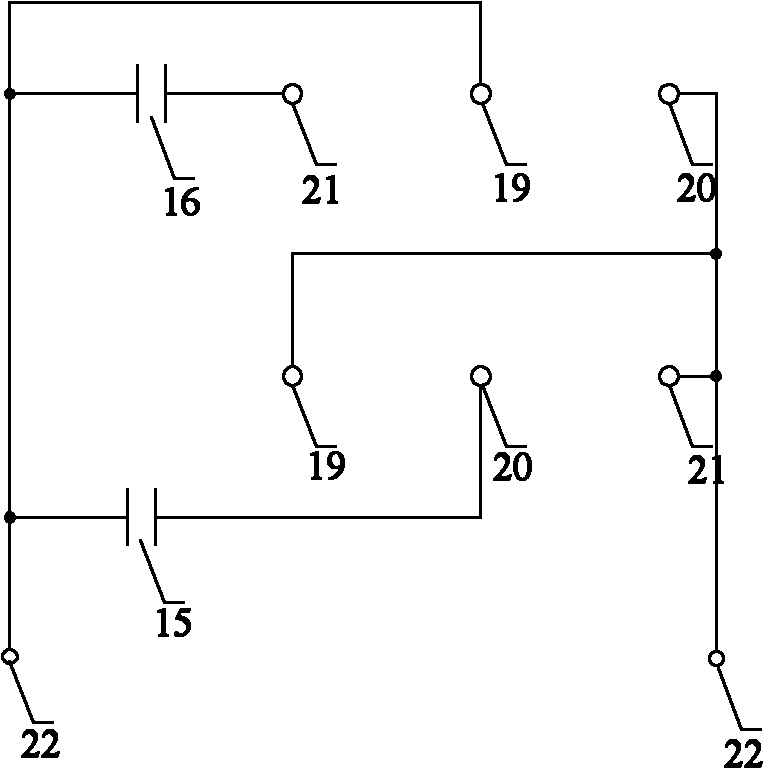

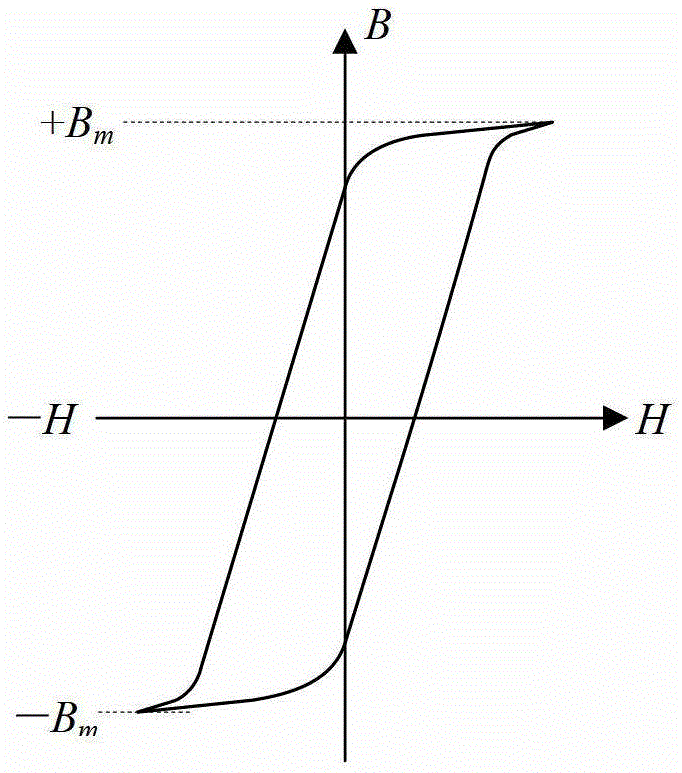

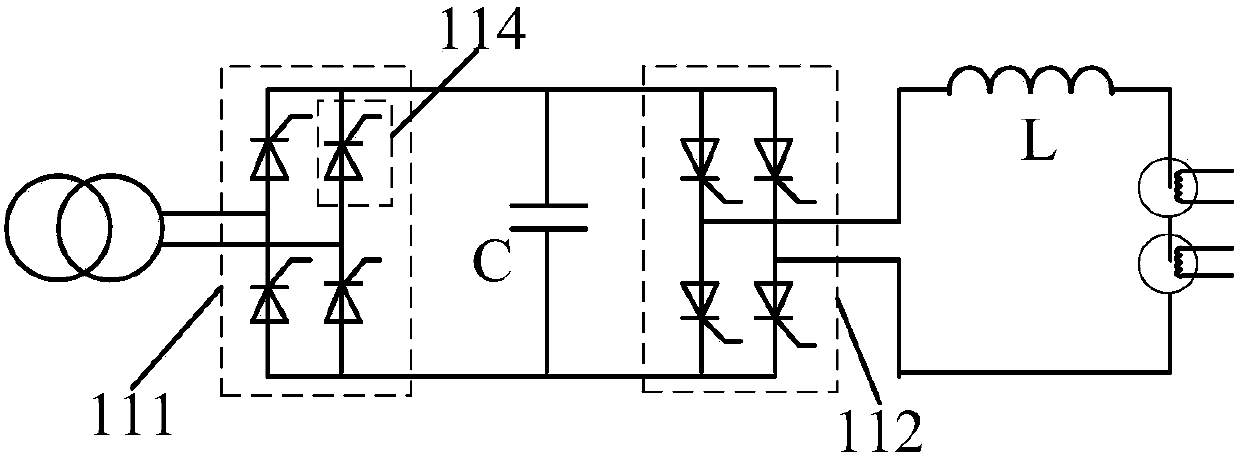

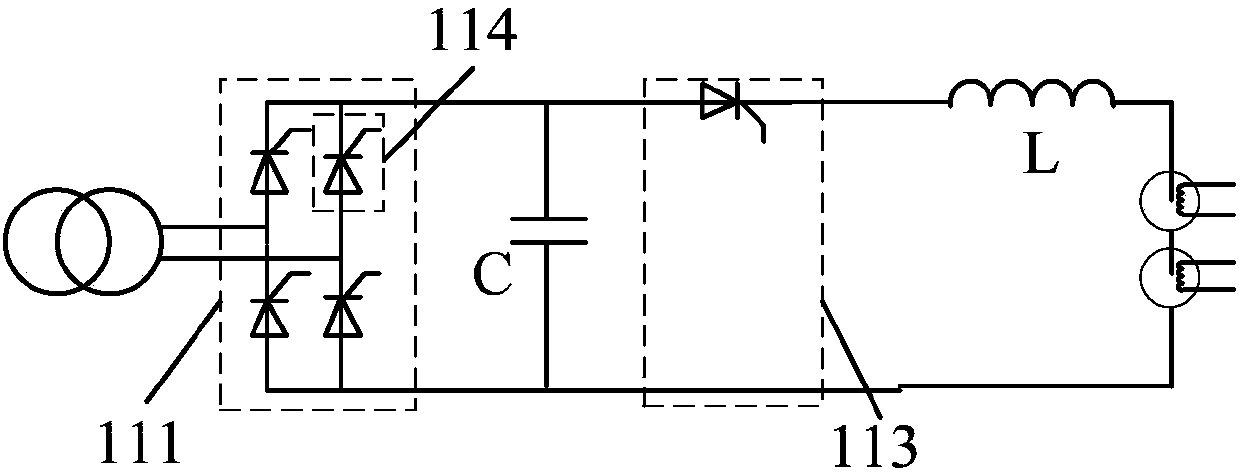

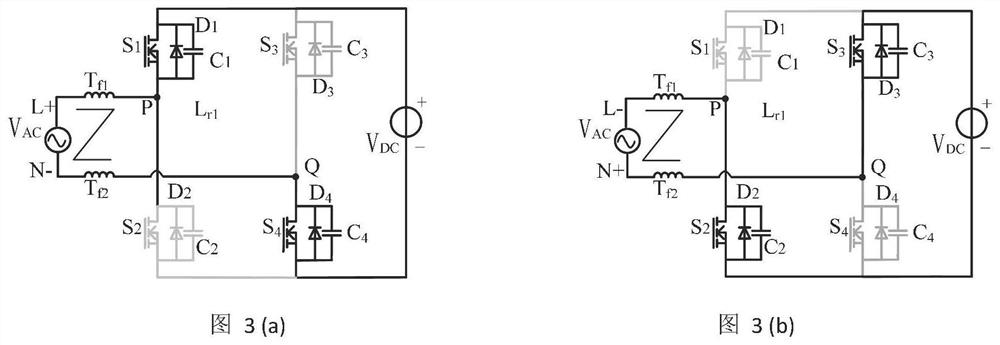

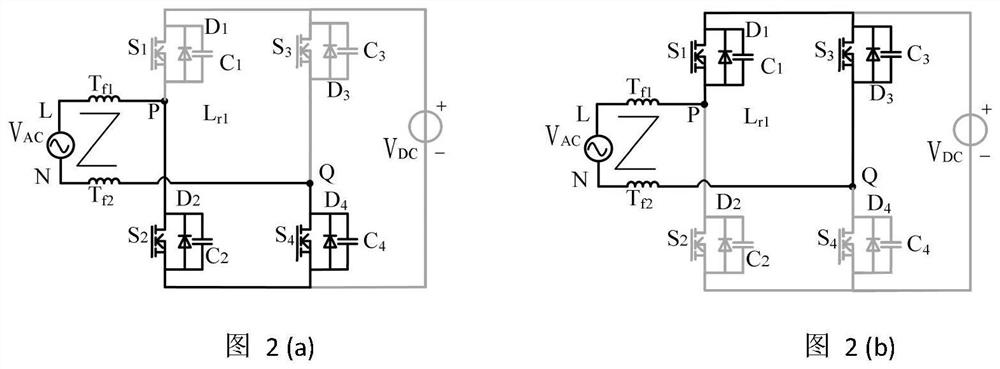

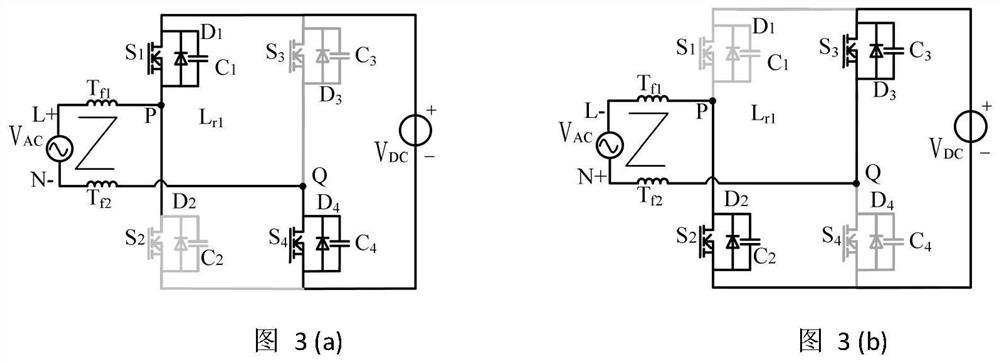

Bridgeless double-Boost power factor correction rectifier for left-right alternating auxiliary current conversion

ActiveCN111934567AReduce voltage stressReduce core sizeEfficient power electronics conversionAc-dc conversionHemt circuitsRectifier diodes

The invention discloses a bridgeless double-Boost power factor correction rectifier for left-right alternating auxiliary current conversion. ZVS conduction of a main loop switch and an auxiliary loopswitch can be realized. A fully-controlled switch replaces a rectifier diode of a basic bridgeless circuit, and a main loop has two charging states. Two-way reset of exciting current is achieved through the auxiliary loops working alternately, and therefore the size of a transformer magnetic core is reduced. Coupling of the secondary winding of the transformer reduces the voltage stress of the auxiliary converter diode.

Owner:SHANXI UNIV

Three-winding parallel single-phase induction motor

InactiveCN102005880AImprove efficiencyIncrease powerAsynchronous induction motorsCapacitancePower factor

The invention relates to a three-winding parallel single-phase induction motor. A stator winding of the single-phase induction motor adopts a three-winding parallel connection mode, so when the single-phase induction motor operates under a rated load, the single-phase induction motor has an approximately symmetrical air gap field, has the efficiency closer to that of a same-capacity three-phase induction motor and higher power factor and is small in volume and light in weight. The single-phase induction motor comprises a shell, wherein a stator is arranged inside the shell; a rotor is arranged on a rotating shaft; the stator winding is divided into three phases A, B and C which spatially form an angle of 120 degrees respectively in turn; the phase B and the phase C are respectively connected in series with a respective capacitor; and the phase A is connected in parallel with the phase C and is reversely connected in parallel with the phase B to form a composite parallel branch so as to be connected to a single-phase power supply.

Owner:SHANDONG UNIV

Method and apparatus for producing three-phase current

ActiveUS9344005B2Current ratingIncrease chanceAc-dc conversion without reversalDc-dc conversionPhase currentsElectrical conductor

Exemplary embodiments are directed to methods and systems for producing a three-phase current to a three-phase output. Switching converters are used to generate a positive current, a negative current, and an intermediate current. The system is configured such that the produced positive current follows a path of a highest phase of a sinusoidal three-phase signal at a given time, the produced negative current follows a path of a lowest phase of the three-phase signal at the given time, and the produced intermediate current follows a path of a phase of the three-phase signal between the highest and the lowest phase at the given time. The produced currents are switched to each phase conductor of the three-phase output in sequence so that phase currents of the three-phase current are formed in the output conductors.

Owner:ABB (SCHWEIZ) AG

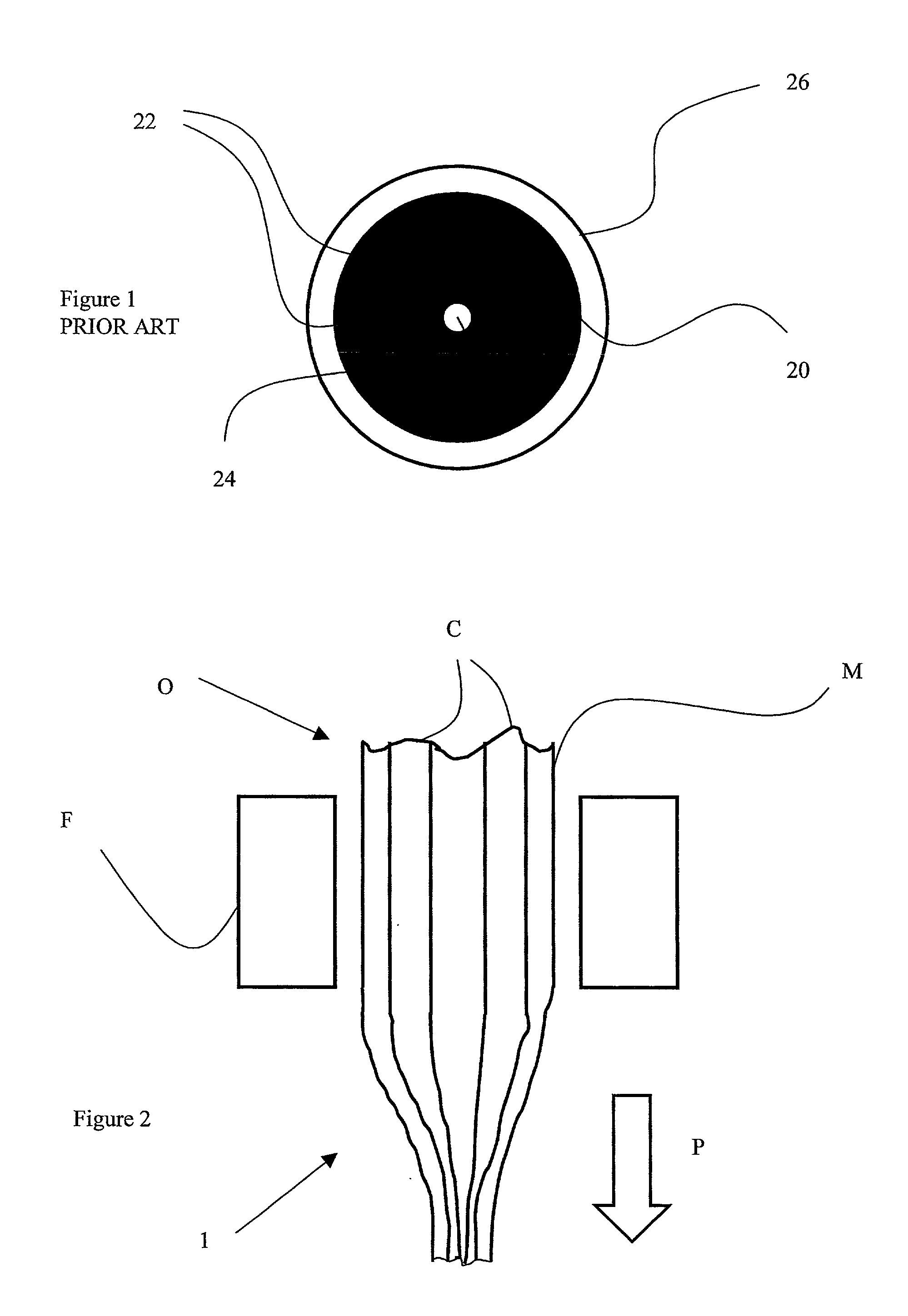

Micro-structured optical fibres

InactiveUS20030108316A1Reduce core sizeOvercome difficultiesGlass making apparatusOptical fibre with multilayer core/claddingOptoelectronicsPeriodic Interval

A micro-structured optical fibre precursor 1 is made by size reducing a multiple core optical fibre having solid multiple cores or a multiple core optical fibre preform O having multiple solid core preforms C. A fibre fuse is induced in at least one of the cores 2 of the precursor 1. The effect of the fibre fuse is to consume the core 2 along the whole length of the fibre or to consume periodically spaced lengths of core 2 along the whole length of the fibre.

Owner:NORTEL NETWORKS LTD

Micro-structured optical fibers

InactiveUS6775450B2Reduce core sizeGlass making apparatusOptical fibre with multilayer core/claddingPeriodic IntervalSolid core

A micro-structured optical fiber precursor 1 is made by size reducing a multiple core optical fiber having solid multiple cores or a multiple core optical fiber preform O having multiple solid core preforms C. A fiber fuse is induced in at least one of the cores 2 of the precursor 1. The effect of the fiber fuse is to consume the core 2 along the whole length of the fiber or to consume periodically spaced lengths of core 2 along the whole length of the fiber.

Owner:NORTEL NETWORKS LTD

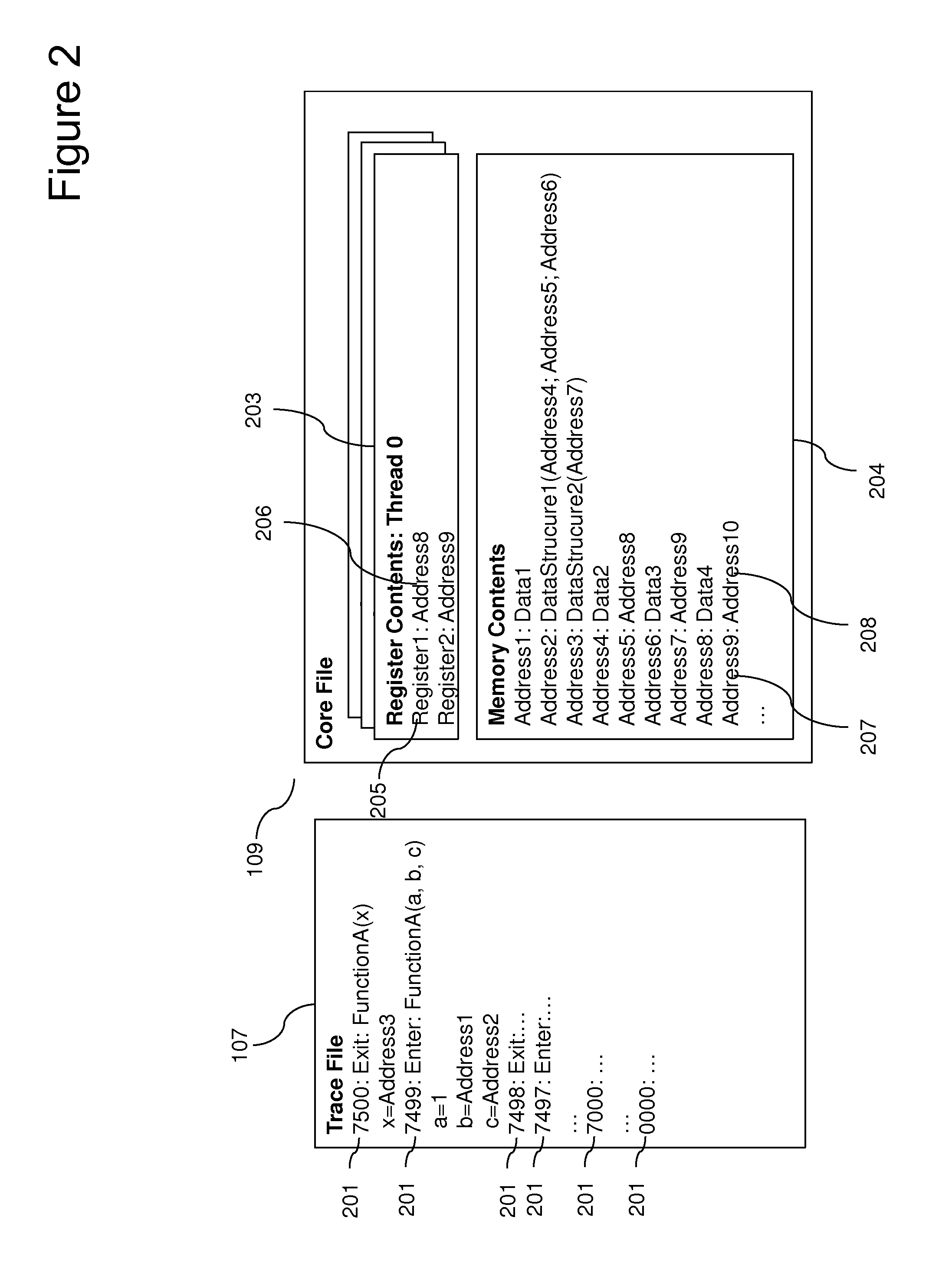

Processing core data produced by a computer process

InactiveUS20150100834A1Reduce core sizeSmall sizeSoftware testing/debuggingMemory addressProcessing core

A method, apparatus, computer program and computer program product for processing core data produced by a computer process to identify data relevant to the computer process, the method comprising the steps of: identifying core data for a computer process; identifying trace data comprising sequential trace entries for the computer process; selecting a predetermined number of most recent entries in the trace data; identifying any references to a memory address in each selected trace data entry; dereferencing each identified memory address in the core data; and extracting the data from the dereferenced memory location in the core data.

Owner:GLOBALFOUNDRIES INC

Power converter, inductor element and inductor cut-off control method

ActiveCN108809079AImprove light load efficiencyImprove power densityEfficient power electronics conversionTransformers/inductances coils/windings/connectionsCouplingInductor

The invention relates to an N-phase power converter, an inductor element, and an inductor cut-off control method, wherein the converter has input-parallel and output-parallel N phase. The converter includes: N switch units, wherein each phase of the N-phase power converter includes one of the N switch units; and an integrated inductor unit including M inductor subunits, M being a natural number greater than or equal to 2, each inductor subunit including i inductors, i being a natural number greater than or equal to 2, and N>M*i or N=M*i. The M*i inductors in the integrated inductor unit are respectively coupled to the M*i switch units in the N switch units, wherein the i inductors of each of the inductor subunits are inversely coupled to each other, and a coupling coefficient of the M inductor subunits is smaller than the coupling coefficient of the i inductors in each inductor subunit.

Owner:DELTA ELECTRONICS SHANGHAI CO LTD

ET type filter inductor

InactiveCN104715885AReduce core sizeSimple structureTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresInductorEngineering

The invention discloses an ET type filter inductor. The ET type filter inductor comprises a magnetic core, a framework, an enameled wire and pins. The two ends of the magnetic core and the two ends of the framework are connected through glue. The enameled wire is wound around the framework. The pins are arranged at the end of the framework. The magnetic core is made of ET24R10K. The framework is made of ET24PBT. The ET type filter inductor further comprises a base. The base is located at the end of the magnetic core and fixedly connected with the magnetic core. The pins are located at the lower end of the base. The maximum total length of the magnetic core is not larger than 34 mm. The ET type filter inductor is simple in structure, the size of the magnetic core is small, and the maximum resistance is not larger than 0.8 ohm. The maximum withstand voltage between coils and between the coils and the magnetic core is 1000 VAC / 1 min / 10 mA.

Owner:CHANGZHOU GALAXY INNOVATION MAGNETOELECTRICITY

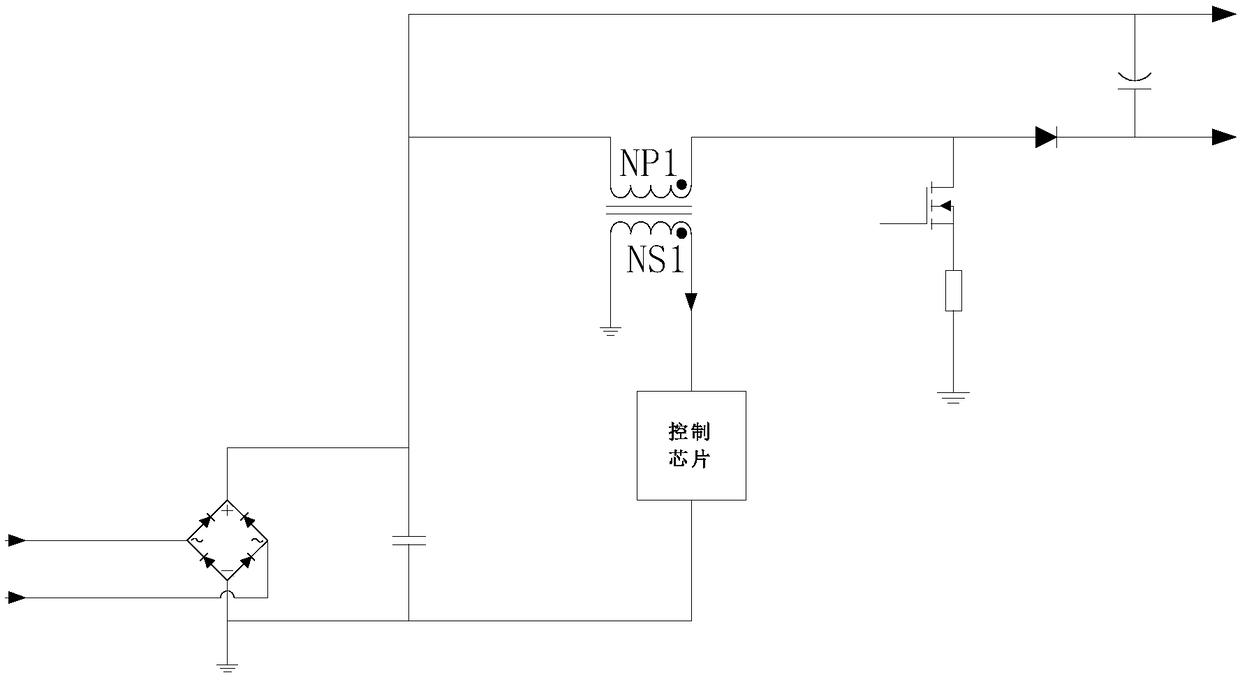

LED driver

PendingCN109451630AMeet power needsReduce core sizeElectrical apparatusElectroluminescent light sourcesLed driverMagnetic core

The invention relates to an LED driver. The LED driver comprises a first capacitor, a second capacitor, a transistor, a diode, an energy storage inductance unit and a control circuit board; two ends of the first capacitors are electrically connected with a power supply, two ends of the second capacitor are electrically connected with the load; a source electrode of the transistor is grounded through a resistor, a drain electrode is electrically connected with the first end of the second capacitor; the energy storage inductance unit comprises at least two energy storage inductors in series connection; a first connecting end of the energy storage induction unit is electrically connected with the second end of the first capacitor and the second end of the second capacitor, and a second connecting end of the energy storage induction unit is electrically connected with the drain electrode of the transistor; a control signal connecting end of the control circuit board is electrically connected with a grid electrode of the transistor. Through the LED driver disclosed by the invention, a magnetic core in each energy storage inductor of the energy storage induction unit is small, and the flattening arrangement can be realized, and then the height of the energy storage inductor can be reduced, and the height requirement of the flattened lamp is satisfied.

Owner:NINGBO FAREAST LIGHTING

A Method of Improving the Inductance Coefficient of Air Gap Magnetic Core

ActiveCN103137303BSimple winding processSave man hoursTransformers/inductances magnetic coresInductances/transformers/magnets manufactureTransformerInductor

The invention discloses a method for improving the inductance coefficient of an air gap magnetic core. The air gap magnetic core is formed by combining more than two magnetic cores. The combined surface which magnetic flow passes comprises lateral surfaces, the mirror surface process is adopted for the lateral surfaces, and accordingly the inductance coefficient of the whole magnetic core can reach above 80%. Well wound windings are arranged on the magnetic core in an interdigitation mode and then are baked at a high temperature or are electrified on two magnetic cores for fusion, and accordingly the inductance coefficient of the magnetic core can be further improved. After adopting the method, the volume of a transformer or an inductor which is made of the magnetic core is small, and the winding process of the transformer or the inductor is simple.

Owner:MORNSUN GUANGZHOU SCI & TECH

Coil device

ActiveUS7746207B2Reduce core sizeSimple structureTransformers/inductances casingsTransformers/inductances coils/windings/connectionsEngineeringConductor Coil

A coil apparatus having a divided winding conformation and a manufacturing method of the coil apparatus which can prevent a winding from collapsing while achieving a reduction in size of a core and simplification of a structure. A coil apparatus includes a ferrite core and a coil provided around the core. The coil includes at least a first coil portion and a second coil portion, and a boundary end surface of the first coil portion on the second coil portion side is inclined in such a manner that its inner peripheral side is closer to the second coil portion than its outer peripheral side. Further, a boundary end surface of the second coil portion on the first coil portion side is inclined in such a manner that its outer peripheral side is closer to the first coil portion than its inner peripheral side.

Owner:TDK CORPARATION

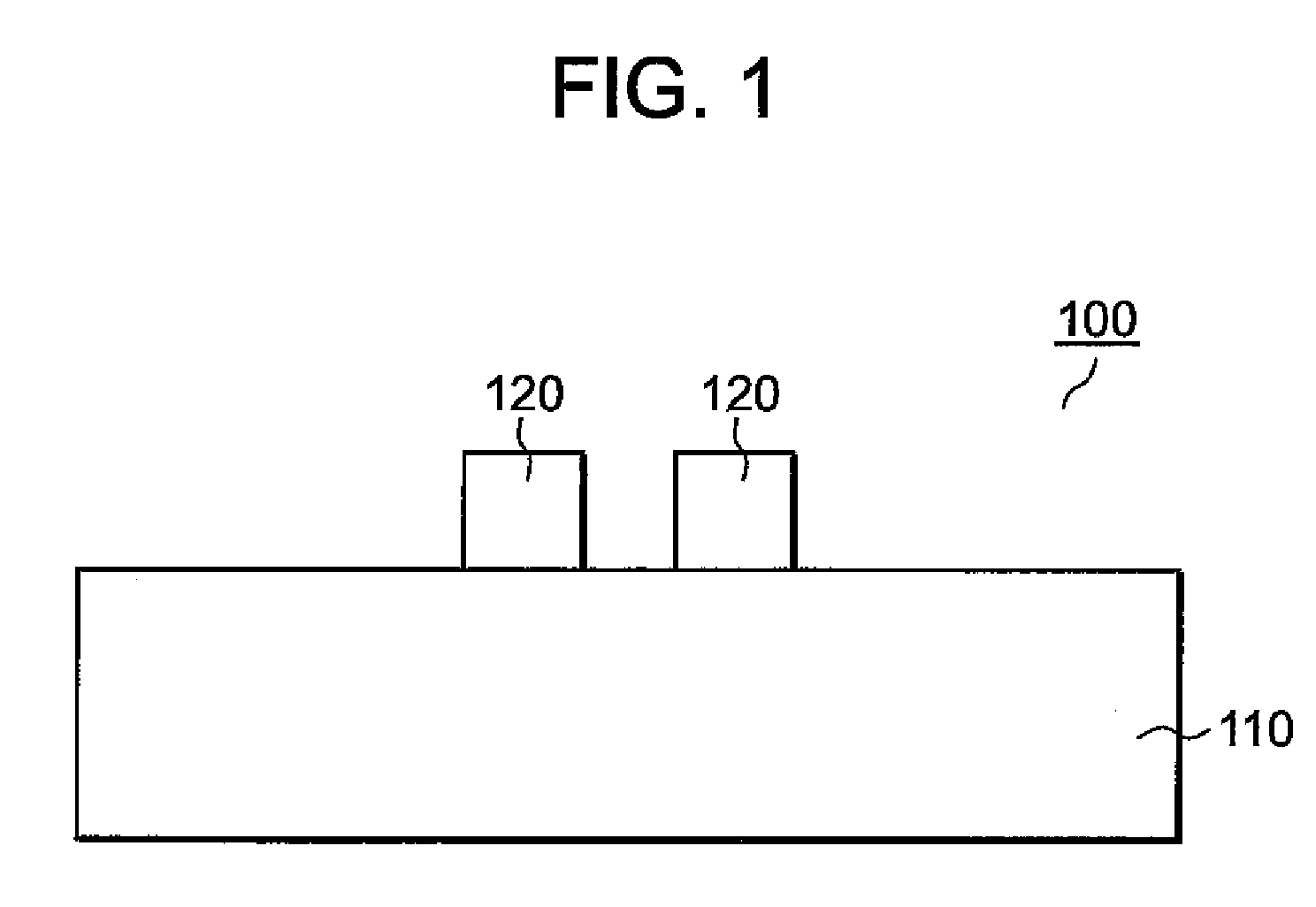

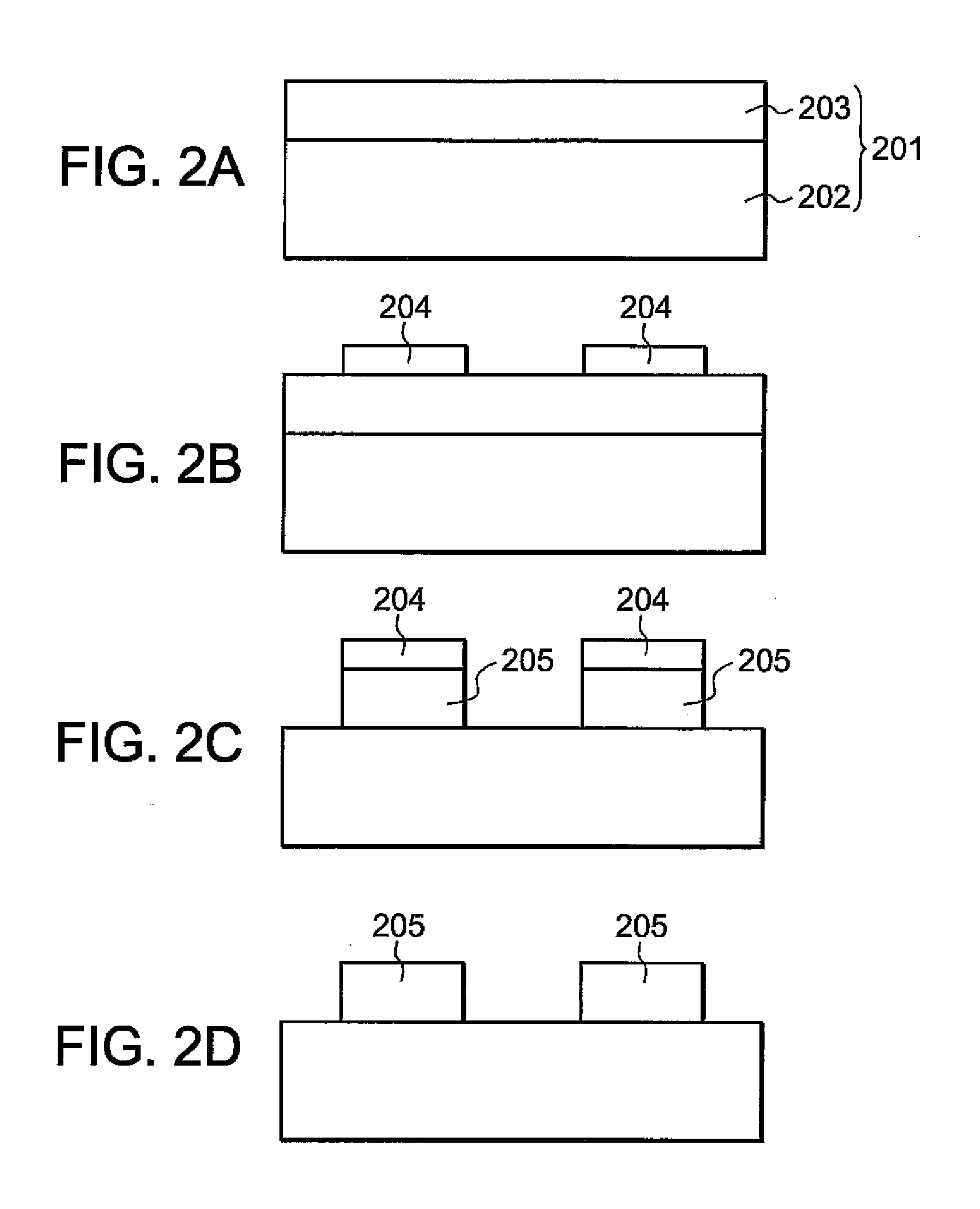

Optical Integrated Circuit, Opto-Electronic Integrated Circuit and Manufacturing Method Thereof

InactiveUS20090196546A1Refractive index differenceShorten timeOptical waveguide light guideOpto electronicLight wave

In the opto-electronic integrated circuit, an optical waveguide in which a sapphire substrate for an SOS substrate is formed as a lower clad and a silicon film is formed as a core, an electronic integrated circuit formed in the silicon film, and grooves for fixing optical fibers are formed monolithically. Further, a photodiode array and a laser diode array are mounted on a hybrid basis. Since the lower clad of the optical waveguide is used as the sapphire substrate and the core is used as the silicon film, a difference in refractive index can be made large sufficiently, thus resulting in thinning of the silicon film. It is therefore possible to shorten the time required to process the core and the like. Further, since the electronic integrated circuit is formed on the sapphire substrate, the high-frequency characteristics are enhanced.

Owner:NEOPHOTONICS SEMICON GK

High-voltage pancake winding of transformer

PendingCN112735774AReduce core sizeReduce no-load lossTransformers/inductances coils/windings/connectionsLoad lossPhysics

The application provides a high-voltage pancake winding of a transformer; the winding comprises a low-voltage coil 1, an insulating barrel 2, comb type supporting strips 3, filler strips 4 and high-voltage coils 5, the distance between the low-voltage coil 1 and the insulating barrel 2 is a, the insulating barrel 2 and the comb type supporting strips 3 are fixed, the high-voltage coils 5 are arranged on comb teeth of the comb type supporting strips 3, and one comb tooth is provided with a cake 51 of one high-voltage coil 5; multiple wire cakes 51 of the high-voltage coil 5 are arranged, the wire cakes 51 are connected in series to form the high-voltage coils 5, the distance between the high-voltage coil 5 and the insulating barrel 2 is b, filler strips 4 are added into the head wire cakes 51 and the tail wire cakes 51 of the high-voltage coils 5, andin a direction from the head end wire cake 51 to the middle wire cake 51 and a direction from the tail end wire cake 51 to the middle wire cake 51, the thicknesses of the added filler strips 4 are gradually reduced, so that the distance a between the low-voltage coil 1 and the insulating barrel 2 and the distance b between the high-voltage coil 5 and the insulating barrel 2 can be reduced, the size of an iron core of the transformer is reduced, and the no-load loss is reduced.

Owner:SIBERIAN MOTOR TECH SUZHOU CO LTD

DC circuit breaker energy supply system and control method and device thereof

InactiveCN108039693AReduce core sizeReduce volumeEmergency protection for supplying operative powerCapacitanceEngineering

The invention provides a DC circuit breaker energy supply system and a control method and device thereof. The energy supply system comprises a resonant capacitor of which the input end is connected with a low-frequency AC voltage source through a rectification circuit and the output end is connected with a resonant inductor through a switching circuit, wherein the resonant capacitor and the resonant inductor generate resonant current when the switching circuit is conducted and low-frequency alternating current is converted into high-frequency alternating current to be outputted; and an energytaking magnet ring which sleeves on an energy supply cable with the output end connected with a load for converting the high-frequency alternating current into the voltage meeting the load requirements to supply power to the load. Compared with the low-frequency energy supply mode, the low-frequency alternating current is converted into high-frequency alternating current to be outputted so that the size of the energy taking magnet ring can be reduced under the condition of meeting the same power supply requirement and then the size of the high voltage DC circuit breaker system and the cost ofthe system can be reduced.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Vascular endothelial growth factor/Anti-fibronectin antibody fusion proteins

ActiveUS20210163579A1Improve lymphatic clearanceFunction increasePeptide/protein ingredientsImmunoglobulins against growth factorsDiseaseAntiendomysial antibodies

The application relates to a fusion protein comprising an antibody molecule, or antigen-binding fragment thereof, and a member of the vascular endothelial growth factor family, such as VEGF-C or VEGF-D. The antibody molecule preferably binds an antigen associated with angiogenesis, such as the ED-A isoform of fibronectin. In particular, the application relates to the therapeutic use of such fusion protein in the treatment of an inflammatory disease or disorder.

Owner:PHILOGEN SRL LLC

A Bridgeless Double Boost Power Factor Correction Rectifier with Alternate Left and Right Auxiliary Commutation

ActiveCN111934567BReduce voltage stressReduce core sizeEfficient power electronics conversionAc-dc conversionExcitation currentHemt circuits

Owner:SHANXI UNIV

A Bridgeless Double Boost Power Factor Correction Rectifier with Alternate Up and Down Auxiliary Commutation

ActiveCN111934568BReduce voltage stressReduce core sizeEfficient power electronics conversionAc-dc conversionExcitation currentHemt circuits

The invention discloses a bridgeless double Boost power factor correcting rectifier with alternating up and down auxiliary commutation, which can realize ZVS conduction of a main circuit switch and an auxiliary circuit switch. The fully controlled switch replaces the rectifier diode of the basic bridgeless circuit, and the main circuit has two charging states. The alternately working auxiliary circuit realizes the bidirectional reset of the excitation current, thus reducing the volume of the transformer magnetic core. The secondary winding coupling of the transformer reduces the voltage stress of the auxiliary commutation diode.

Owner:SHANXI UNIV

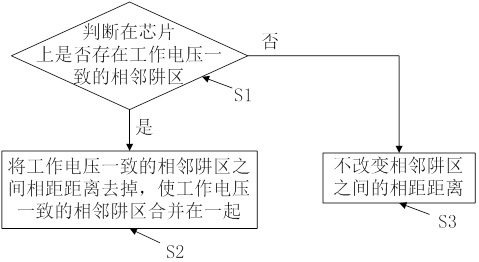

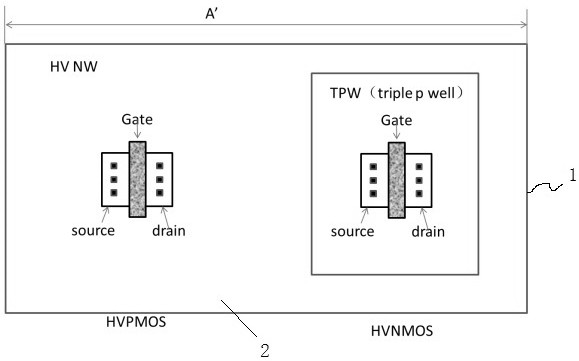

Method, device and chip for reducing core size of nonvolatile flash memory

ActiveCN111626015AReduce core sizeReduce overall areaSolid-state devicesComputer aided designEngineeringBreakdown voltage

The invention discloses a method, a device and a chip for reducing the core size of a nonvolatile flash memory. The method comprises the following steps: judging whether adjacent well regions with consistent working voltage exist on a chip or not, and removing the distance between the adjacent well regions with consistent working voltage if the adjacent well regions with consistent working voltageexist, so that the adjacent well regions with consistent working voltage are merged together; according to the technical scheme, the total area of a specific module region of the chip can be greatlyreduced, and the width-to-length ratio of the mos device does not need to be reduced, so that the problems of leakage current increase and breakdown voltage reduction caused by reduction of the width-to-length ratio of the mos device are avoided.

Owner:XTX TECH INC

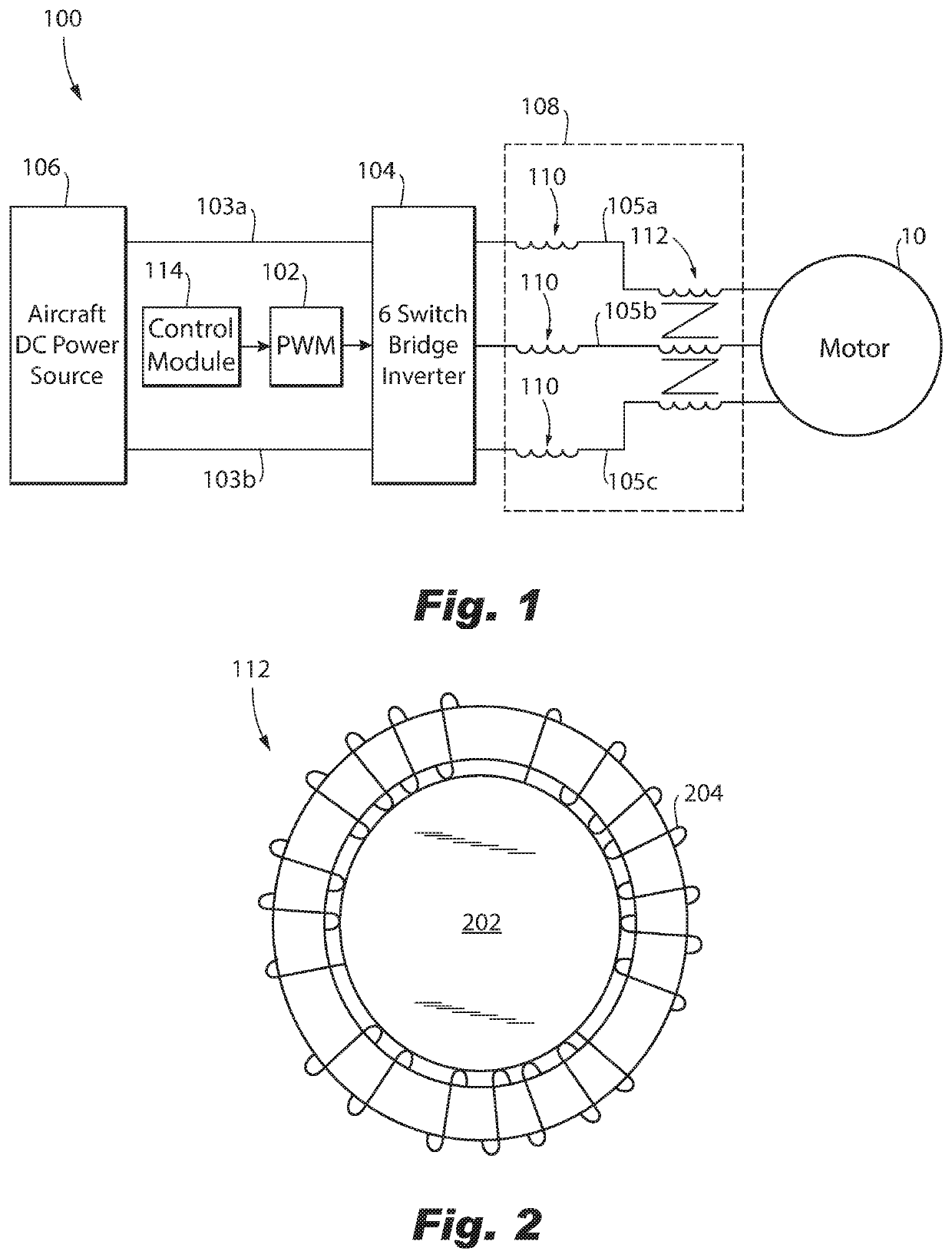

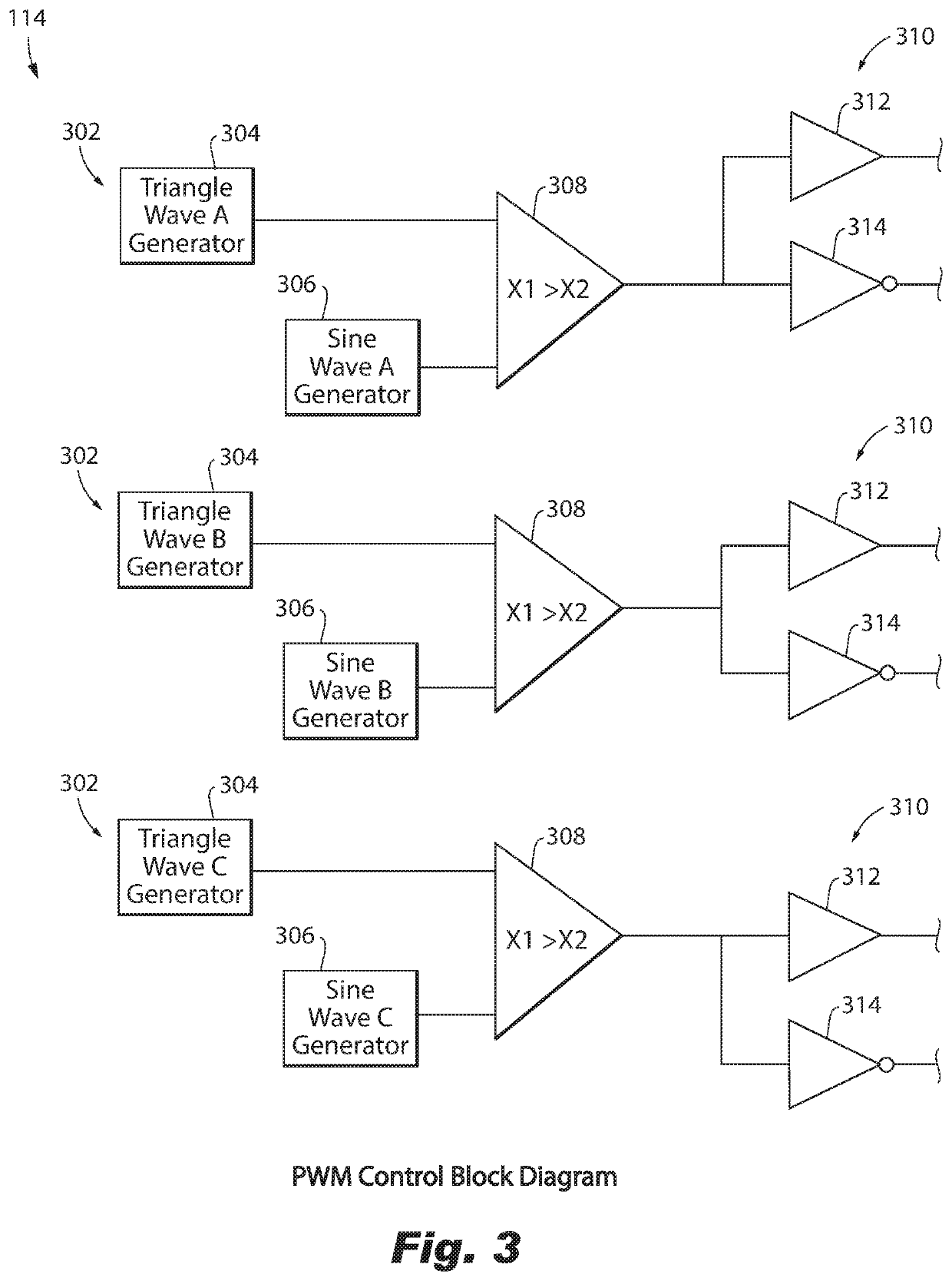

Power converter PWM

ActiveUS11368106B2Reduce core sizeSmall sizeAC motor controlAc-dc conversionConvertersControl signal

A pulse width modulator (PWM) of a multi-phase power converter is provided. The PWM includes a signal modulator that corresponds to each phase of the converter. Each signal modulator of the PWM is configured to receive a unique triangle carrier signal, receive a unique sine wave signal, compare the received triangle carrier signal and the received sine wave signal, and output at least one control signal based on a result of the comparison. The control signal controls an inverter that applies pulse width modulation to a DC power for converting the DC power to a multi-phase power, AC harmonics of the multi-phase power filtered by a common mode inductor.

Owner:HAMILTON SUNDSTRAND CORP

Power converter, inductance element and inductance cutting control method

ActiveCN108809079BImprove light load efficiencyImprove power densityEfficient power electronics conversionTransformers/inductances coils/windings/connectionsCouplingInductor

The present disclosure relates to an N-phase power converter, an inductance element, and an inductance cut-off control method, wherein the converter has N phases with parallel inputs and parallel outputs, and the converter includes: N switching units, wherein the N Each phase of the phase power converter includes one of the N switching units; and an integrated inductance unit, the integrated inductance unit includes M inductance subunits, M is a natural number greater than or equal to 2, and each inductance subunit includes i inductances, i is a natural number greater than or equal to 2, and N>M*i or N=M*i, the M*i inductances in the integrated inductance unit are respectively coupled to the inductances in the N switch units M*i switch units, wherein: the i inductances of each inductance subunit are inversely coupled to each other, and the coupling coefficient between the M inductance subunits is smaller than the i in each of the inductance subunits The coupling coefficient between the inductors.

Owner:DELTA ELECTRONICS (SHANGHAI) CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com