Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

163results about How to "Prevent voltage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

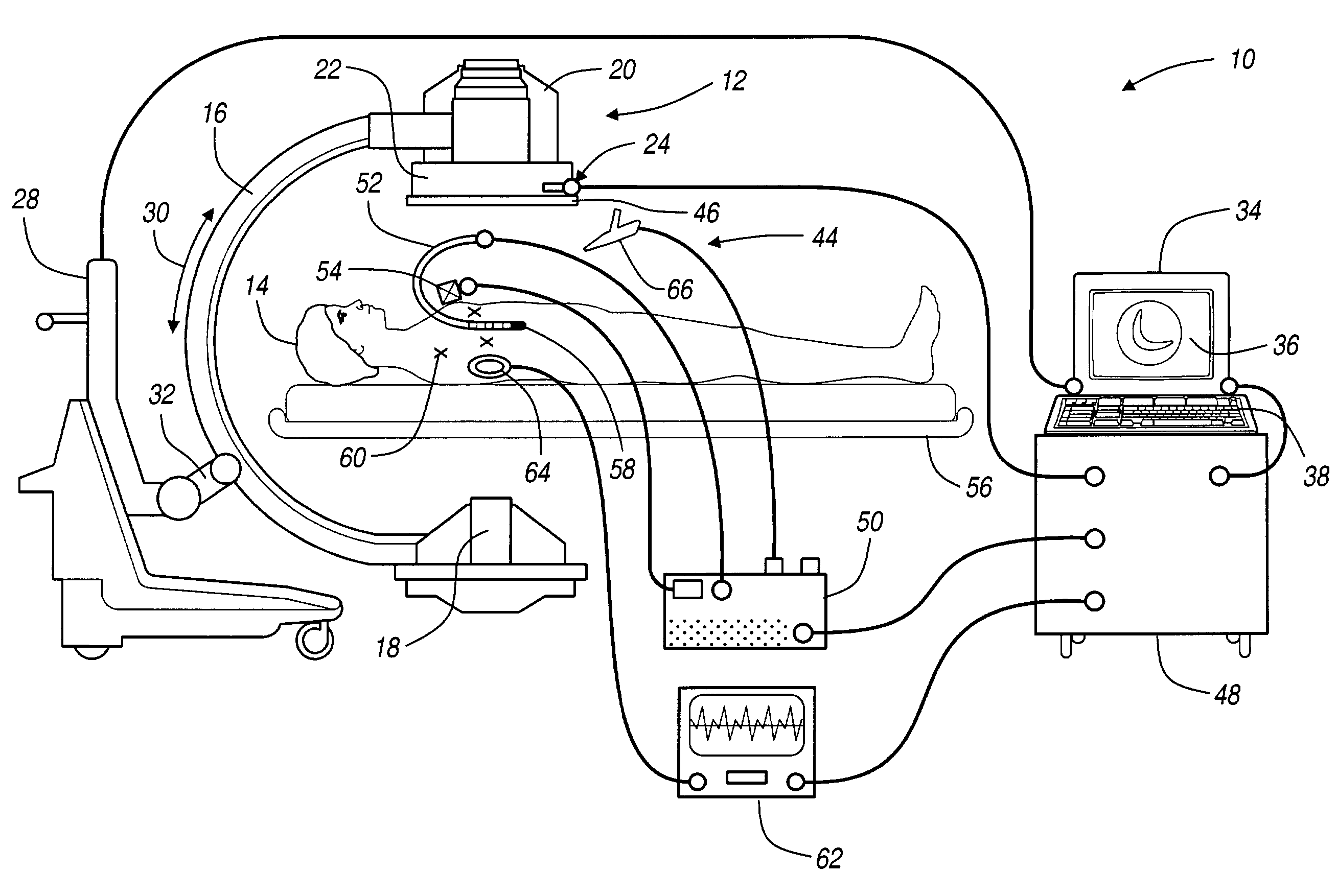

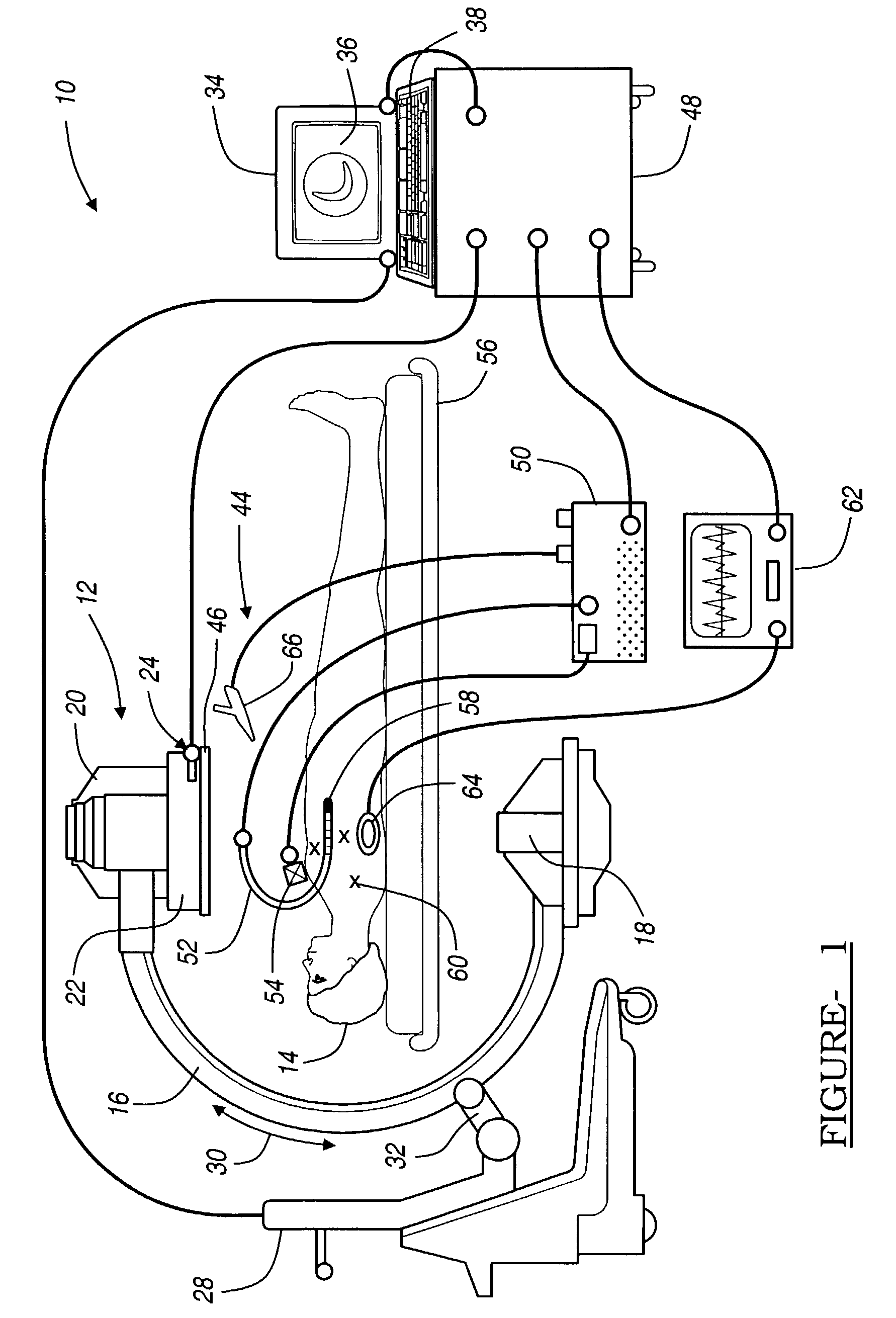

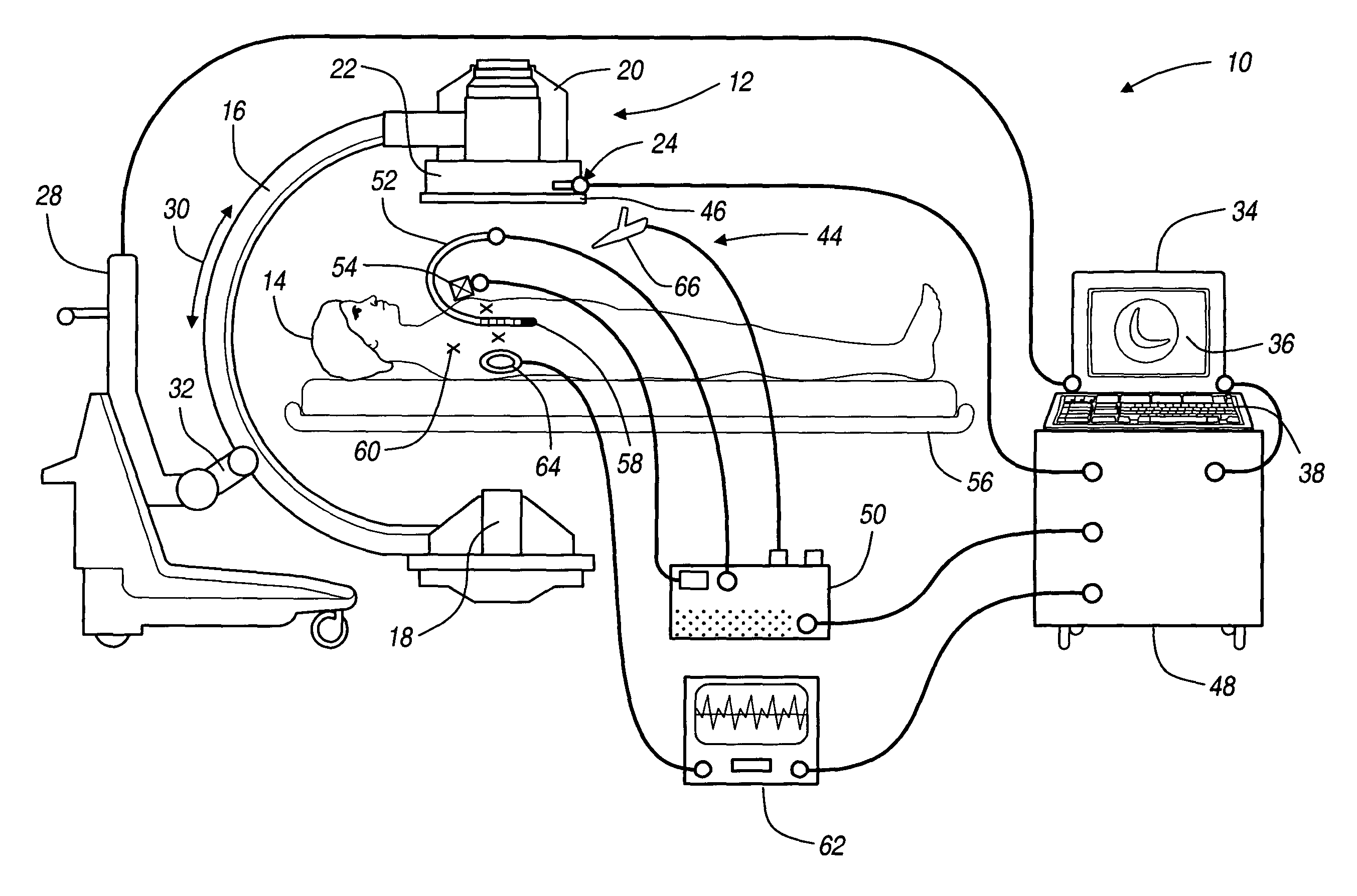

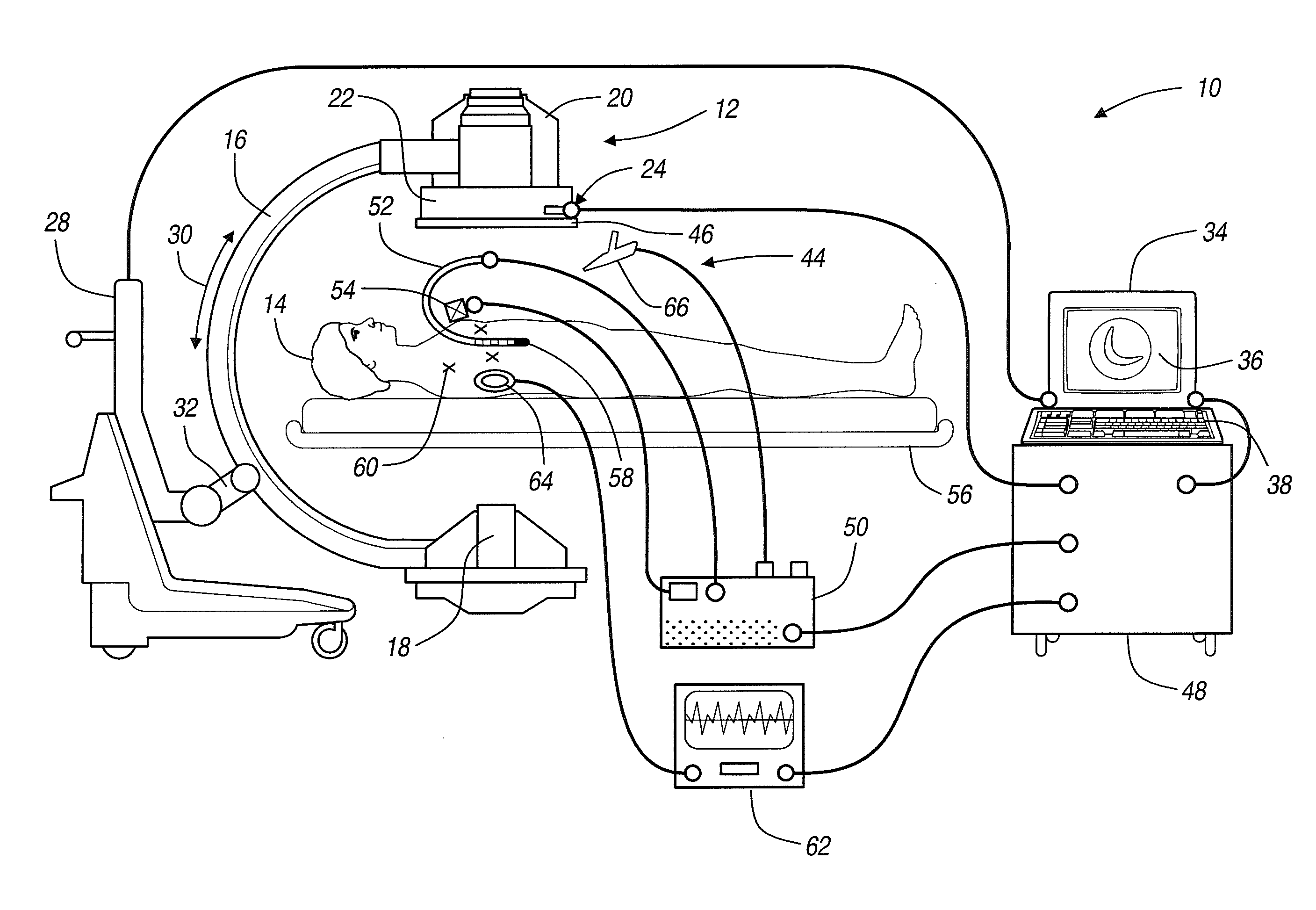

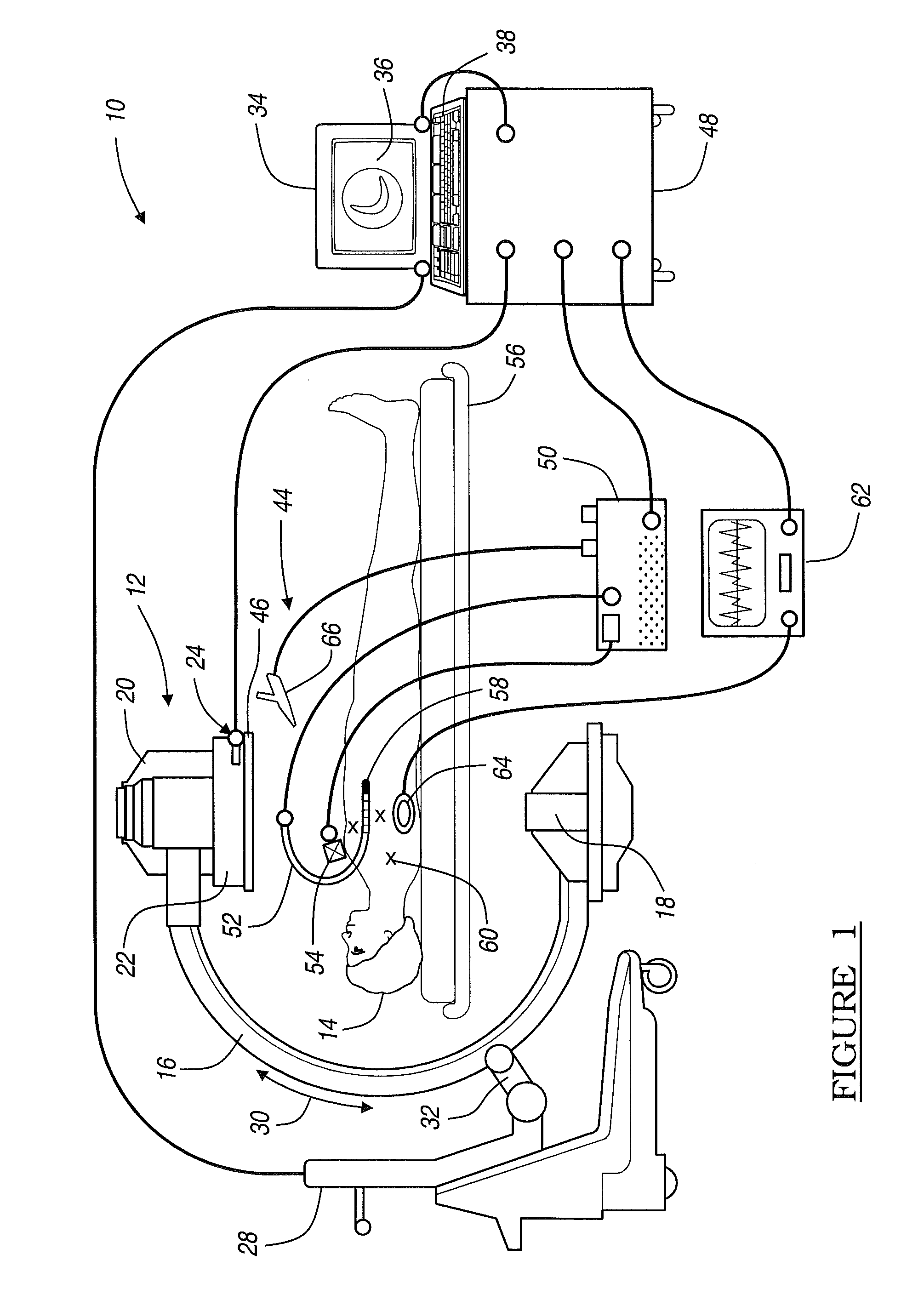

Navigation system for cardiac therapies

InactiveUS7599730B2Accurate identificationReduce exposureSurgical needlesSurgical navigation systemsDisplay deviceNavigation system

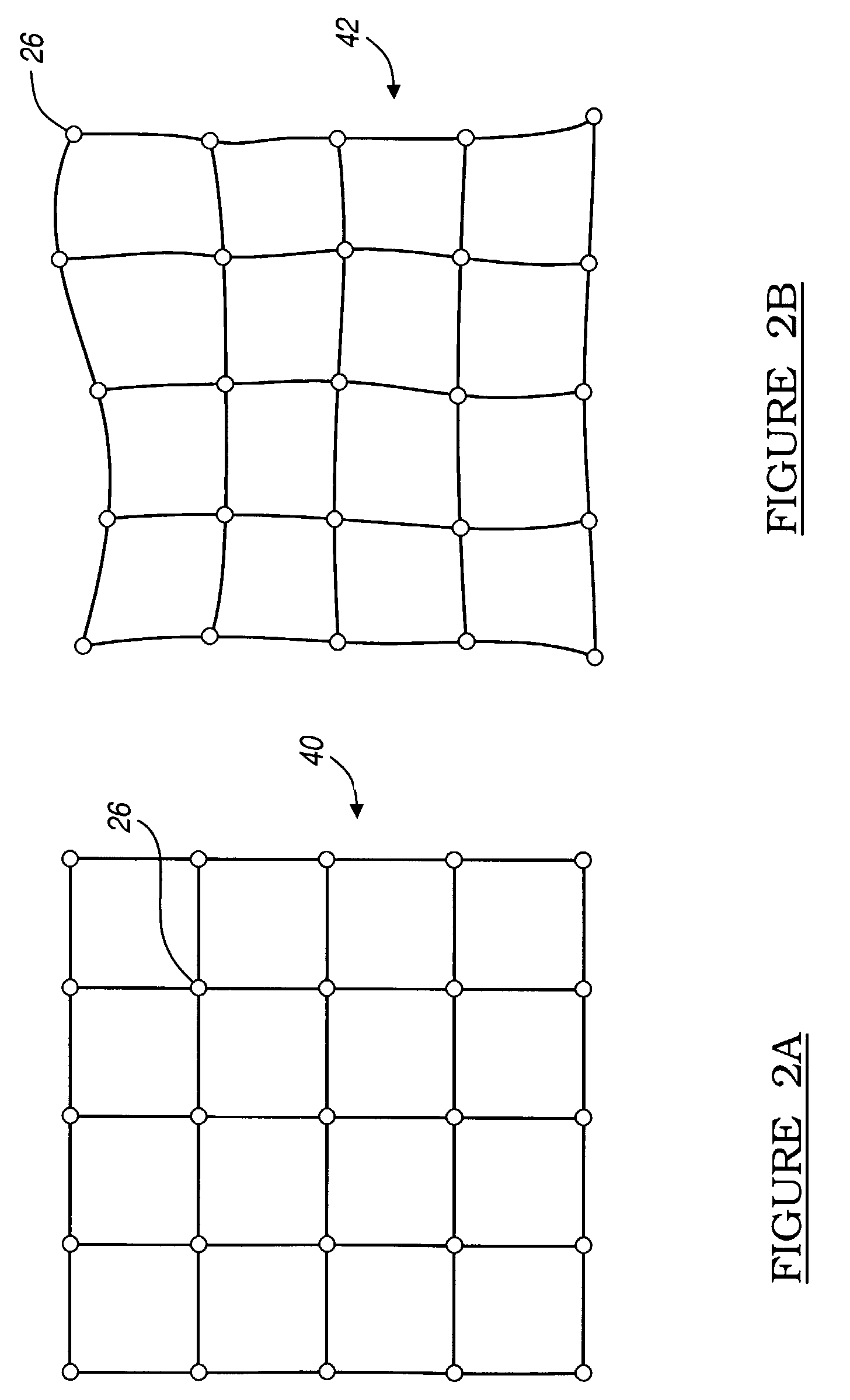

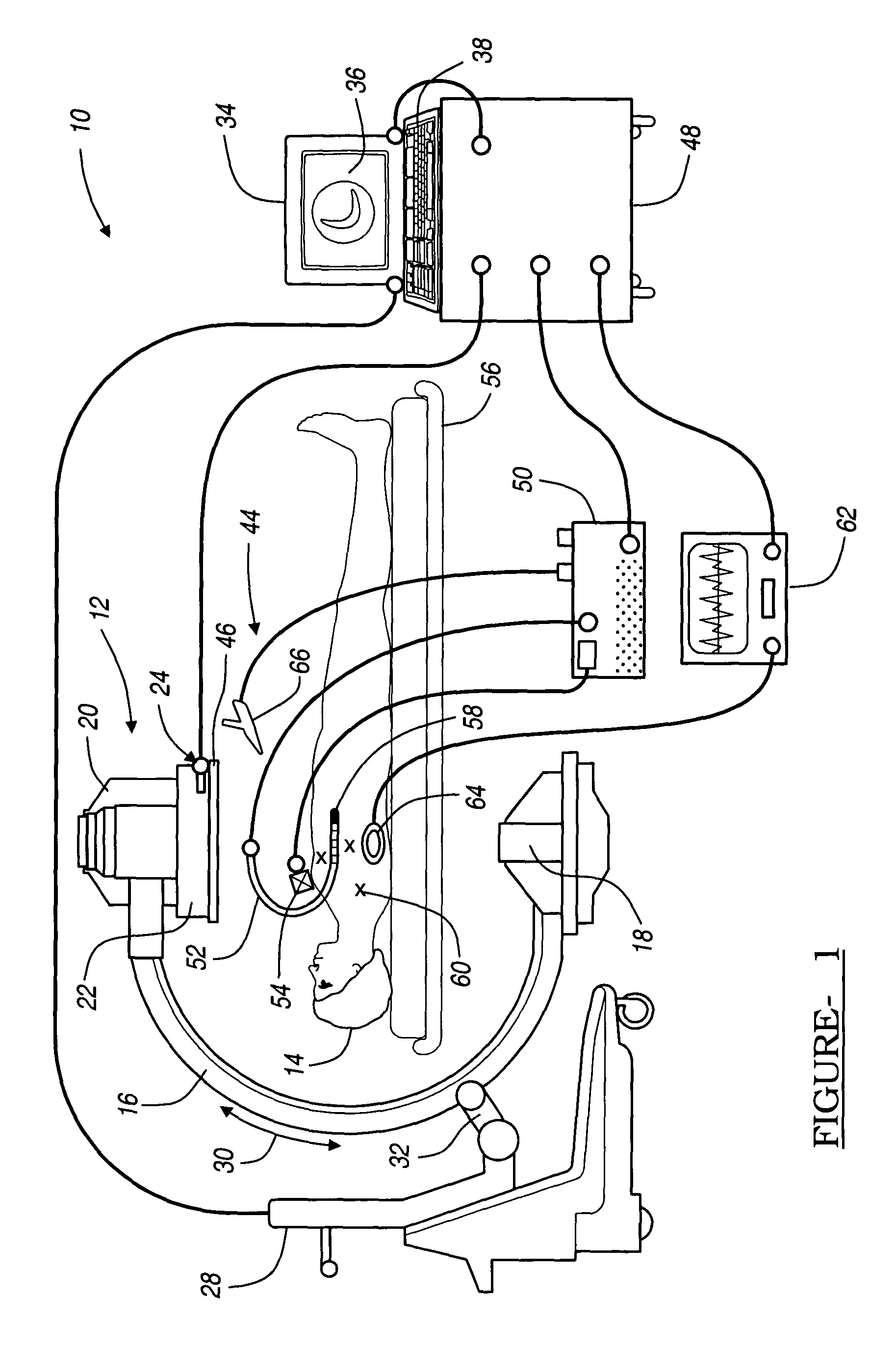

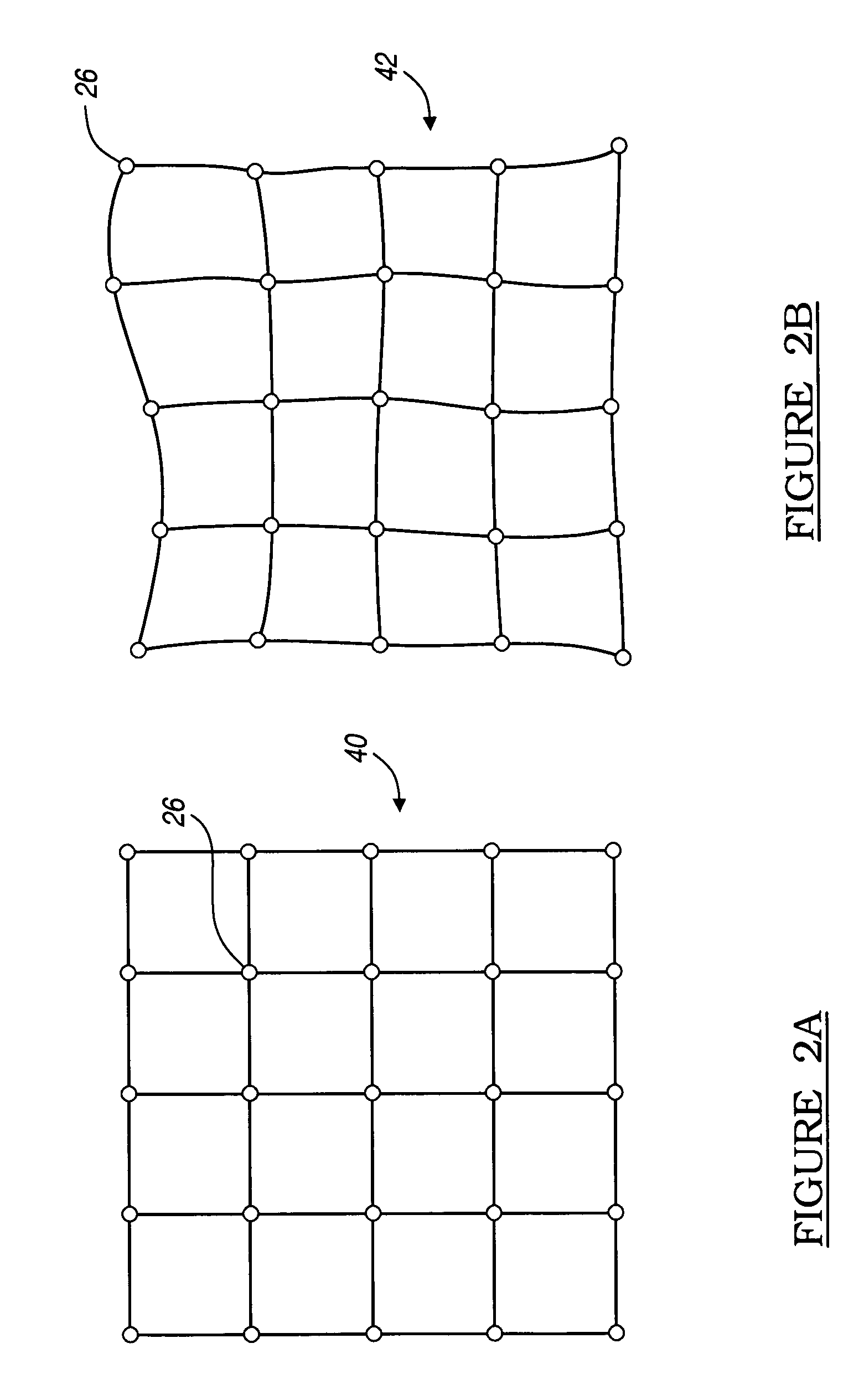

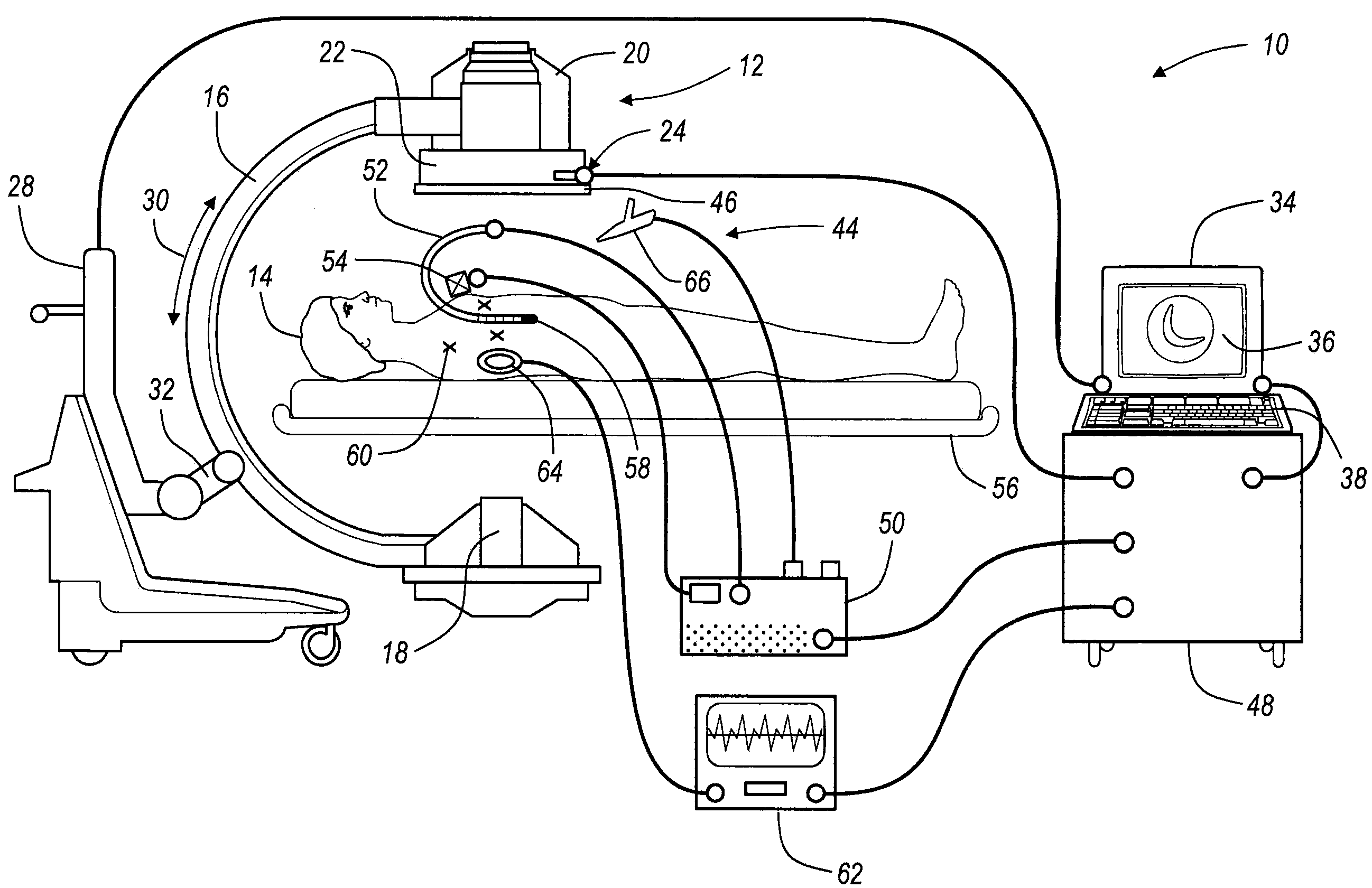

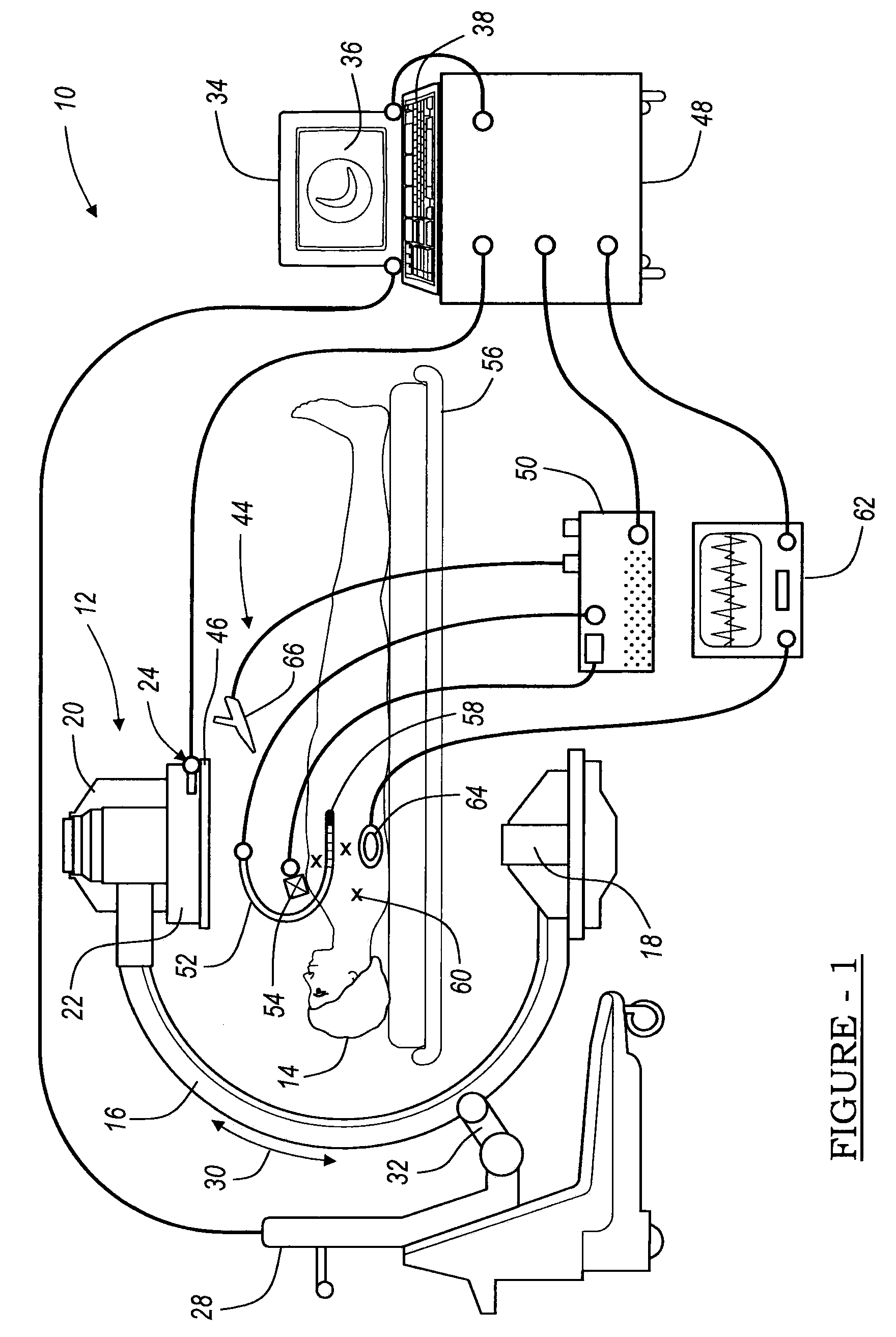

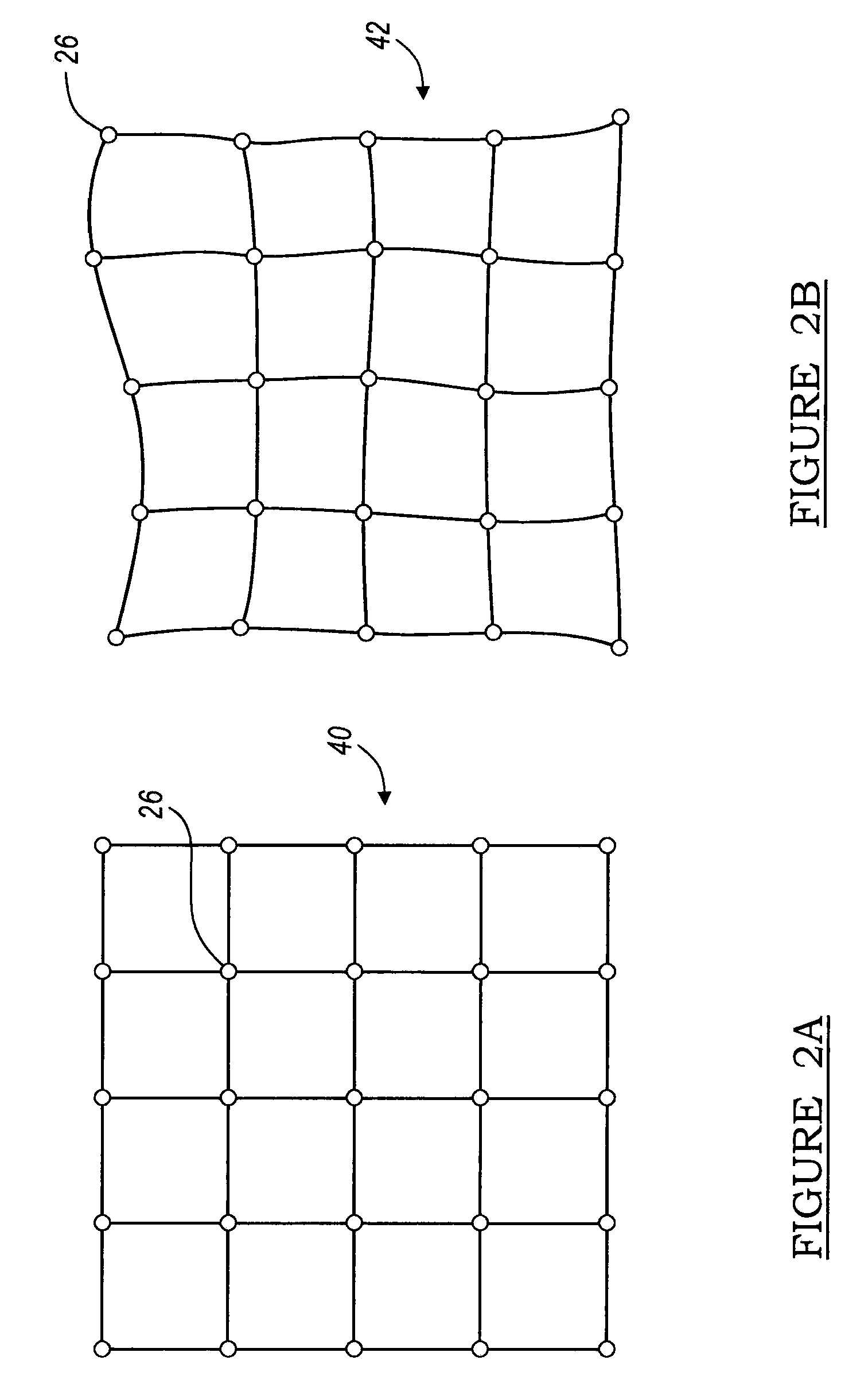

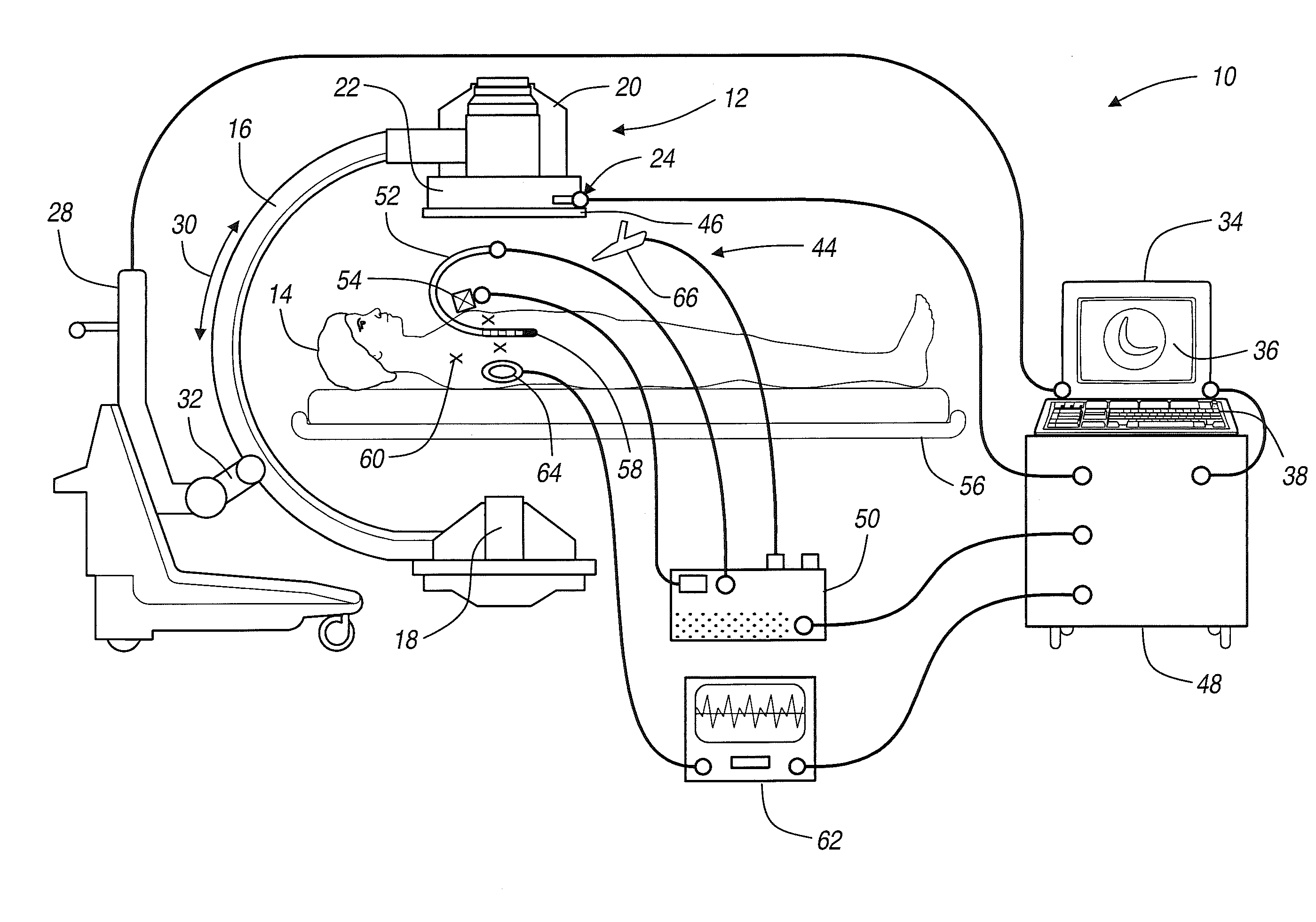

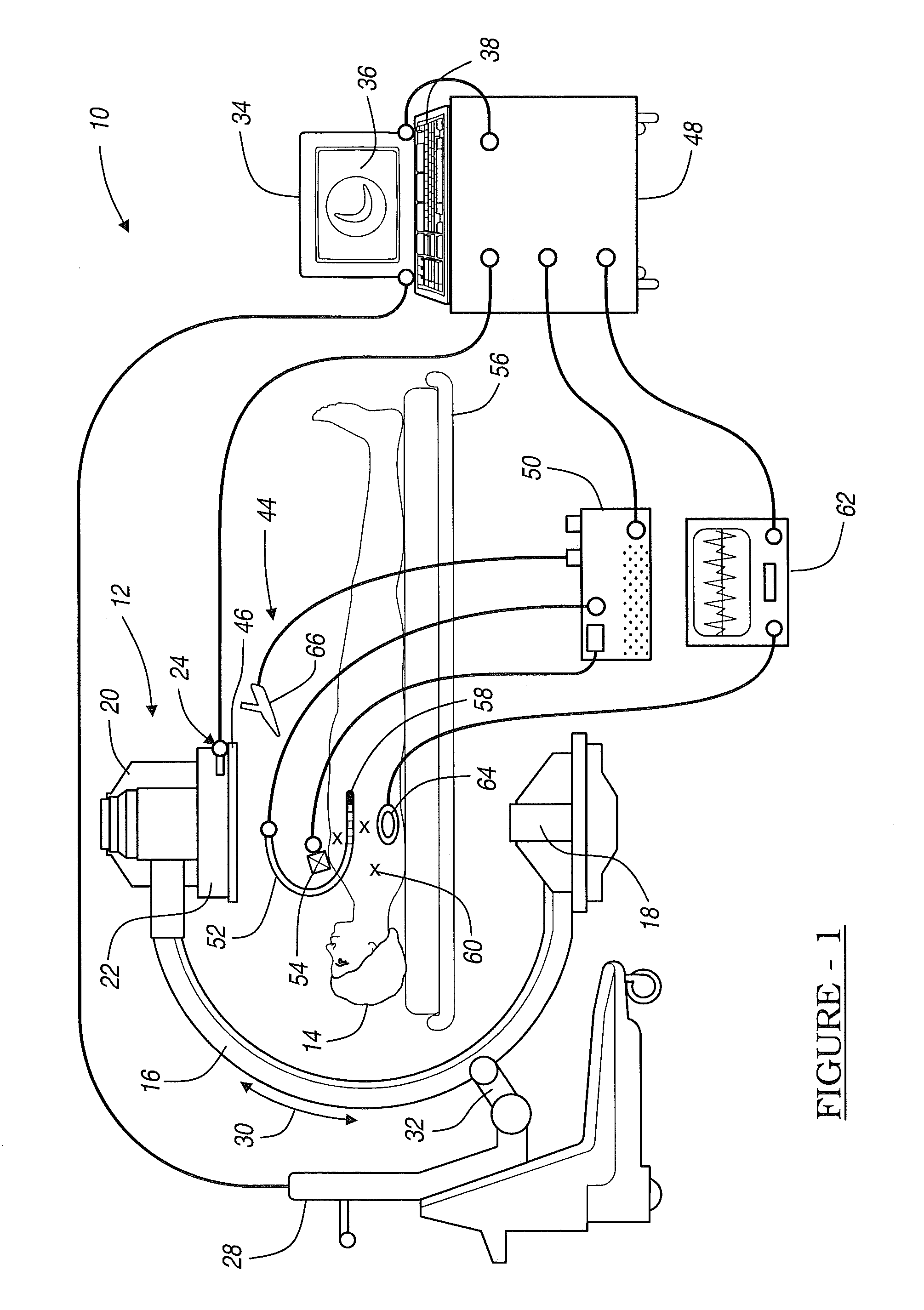

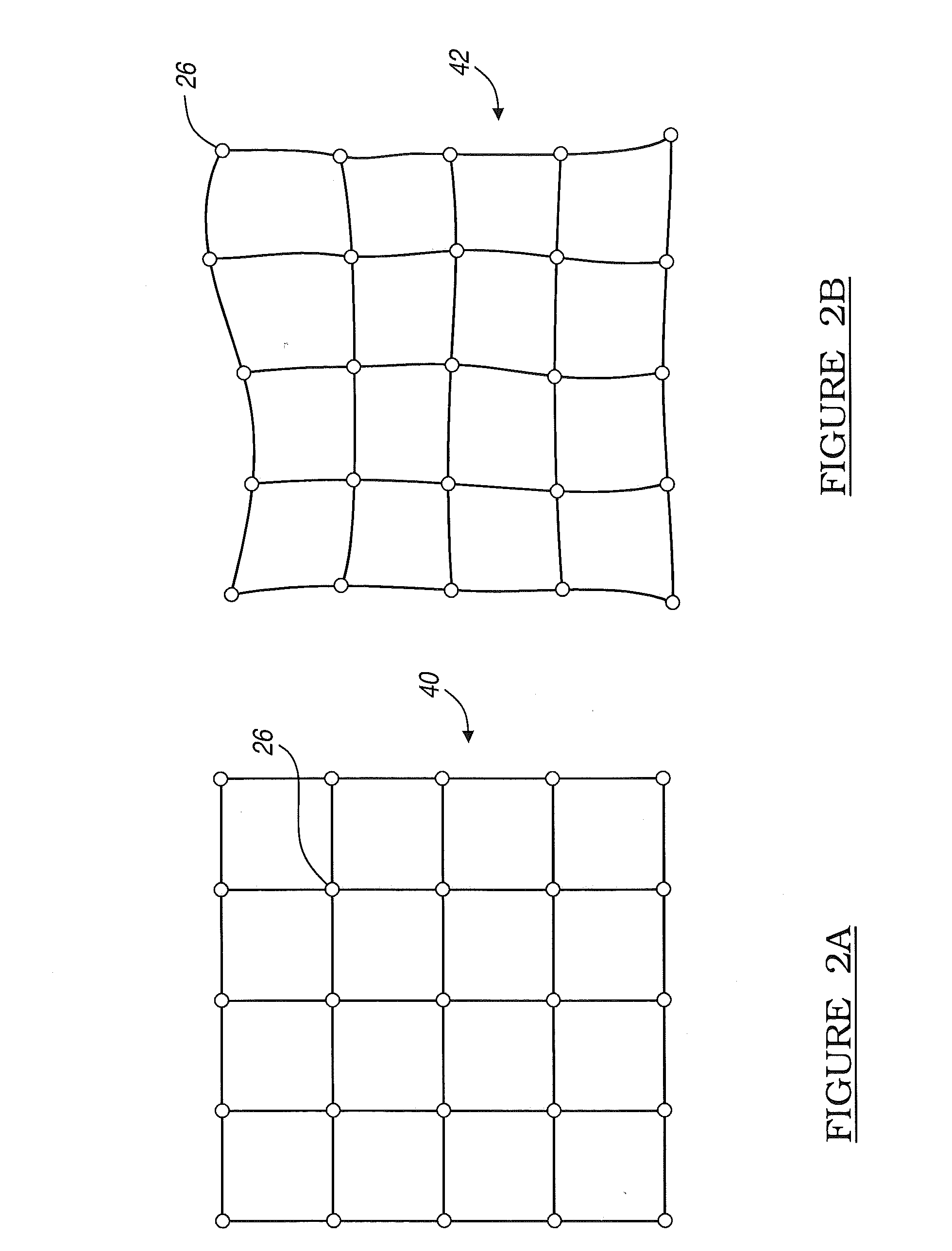

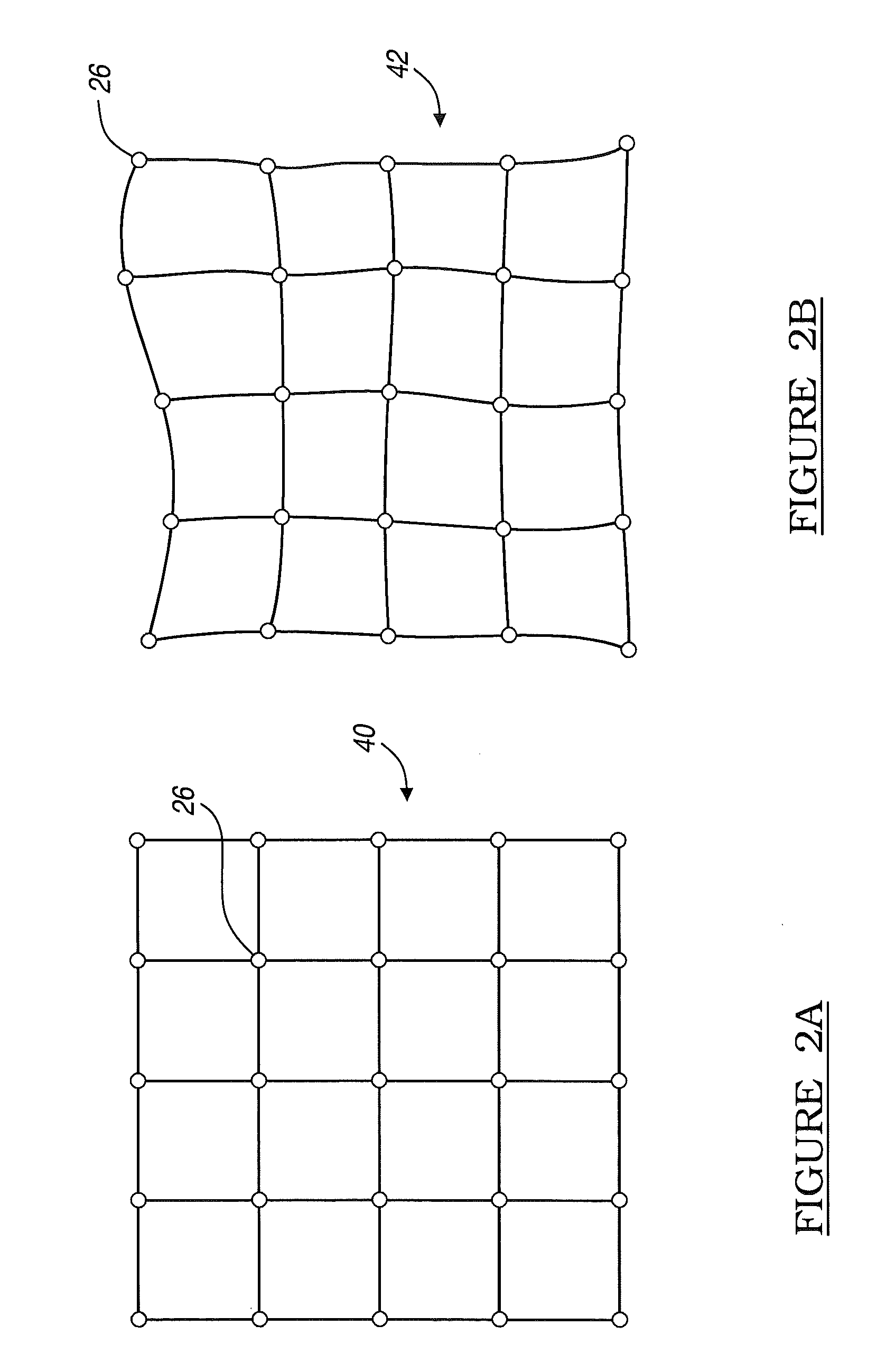

An image guided catheter navigation system for navigating a region of a patient includes an imaging device, a tracking device, a controller, and a display. The imaging device generates images of the region of the patient. The tracking device tracks the location of the catheter in the region of the patient. The controller superimposes an icon representing the catheter onto the images generated from the imaging device based upon the location of the catheter. The display displays the image of the region with the catheter superimposed onto the image at the current location of the catheter.

Owner:MEDTRONIC NAVIGATION INC

Navigation system for cardiac therapies

ActiveUS7697972B2Accurate identificationReduce exposureUltrasonic/sonic/infrasonic diagnosticsSurgical needlesRadiologyDisplay device

An image guided navigation system for navigating a region of a patient includes an imaging device, a tracking device, a controller, and a display. The imaging device generates images of the region of a patient. The tracking device tracks the location of the instrument in a region of the patient. The controller superimposes an icon representative of the instrument onto the images generated from the imaging device based upon the location of the instrument. The display displays the image with the superimposed instrument. The images and a registration process may be synchronized to a physiological event. The controller may also provide and automatically identify an optimized site to navigate the instrument to.

Owner:MEDTRONIC NAVIGATION

Navigation system for cardiac therapies using gating

InactiveUS20100030061A1Accurate identificationReduce exposureUltrasonic/sonic/infrasonic diagnosticsElectrotherapyEcg signalDisplay device

An image guided navigation system for navigating a region of a patient which is gated using ECG signals to confirm diastole. The navigation system includes an imaging device, a tracking device, a controller, and a display. The imaging device generates images of the region of a patient. The tracking device tracks the location of the instrument in a region of the patient. The controller superimposes an icon representative of the instrument onto the images generated from the imaging device based upon the location of the instrument. The display displays the image with the superimposed instrument. The images and a registration process may be synchronized to a physiological event.

Owner:MEDTRONIC INC

Navigation System for Cardiac Therapies

InactiveUS20100210938A1Accurate identificationReduce exposureUltrasonic/sonic/infrasonic diagnosticsSurgical needlesDisplay deviceComputer science

An image guided navigation system for navigating a region of a patient includes an imaging device, a tracking device, a controller, and a display. The imaging device generates images of the region of a patient. The tracking device tracks the location of the instrument in a region of the patient. The controller superimposes an icon representative of the instrument onto the images generated from the imaging device based upon the location of the instrument. The display displays the image with the superimposed instrument. The images and a registration process may be synchronized to a physiological event. The controller may also provide and automatically identify an optimized site to navigate the instrument to.

Owner:MEDTRONIC NAVIGATION INC

Navigation System for Cardiac Therapies

InactiveUS20100022873A1Accurate identificationReduce exposureSurgical needlesSurgical navigation systemsDisplay deviceNavigation system

An image guided catheter navigation system for navigating a region of a patient includes an imaging device, a tracking device, a controller, and a display. The imaging device generates images of the region of the patient. The tracking device tracks the location of the catheter in the region of the patient. The controller superimposes an icon representing the catheter onto the images generated from the imaging device based upon the location of the catheter. The display displays the image of the region with the catheter superimposed onto the image at the current location of the catheter.

Owner:MEDTRONIC NAVIGATION INC

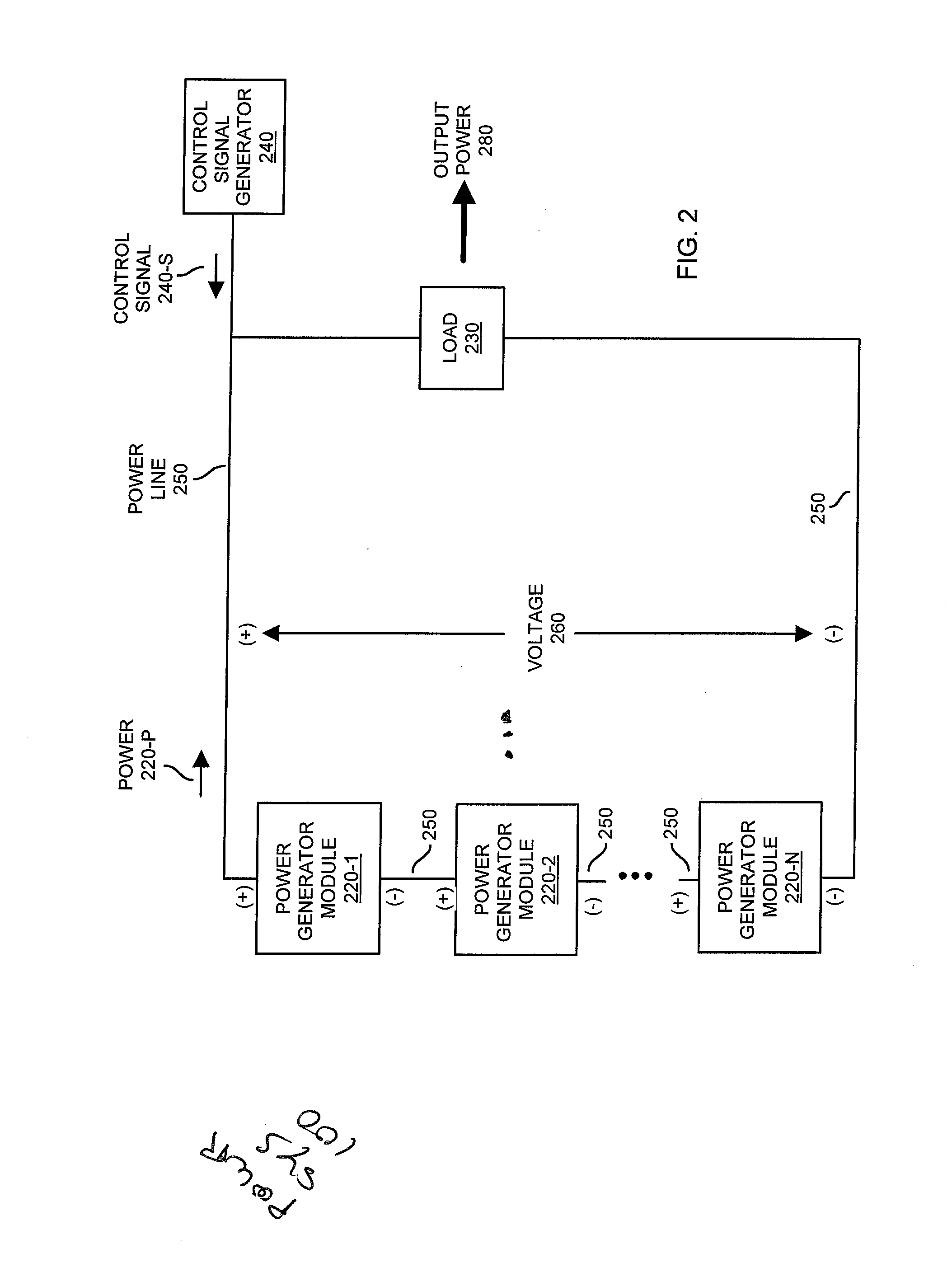

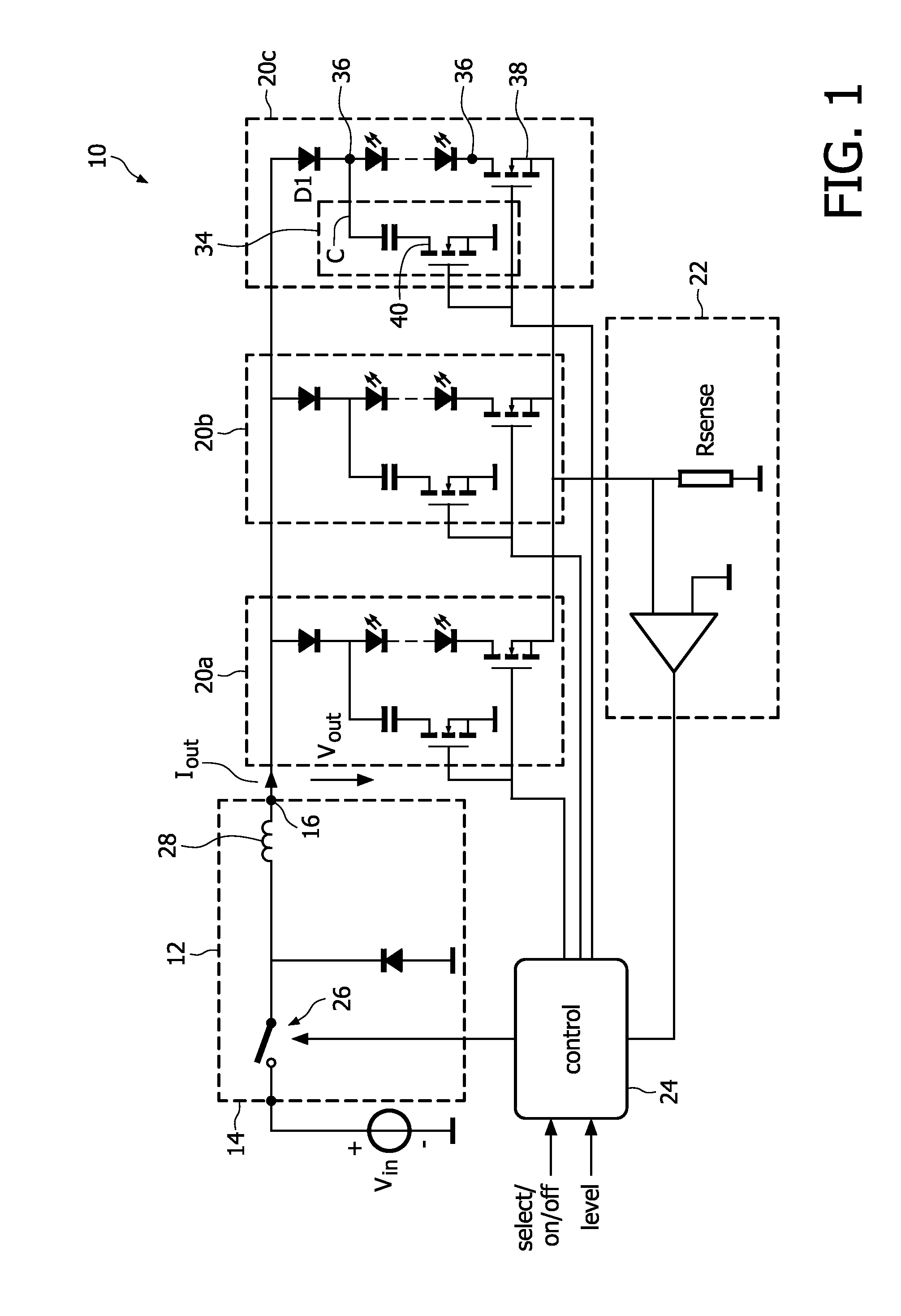

Power generator module connectivity control

InactiveUS20130009483A1Prevent voltageReduce voltageBatteries circuit arrangementsPhotovoltaic monitoringControl signalComputer module

A remote resource can be configured to control connectivity of the power generator modules in a string. For example, a respective power generator module can include a current sense circuit that monitors for presence of communication signal. The power generator module can monitor for a presence of a remotely generated control signal over power line that is used by the respective power generator module to convey power to the external load. If the control signal is present on the power line, as generated by the remote resource, the control circuit in the respective power generator module activates the switch to an ON state such that respective activated power generator module is connected in series with the other activated power generator modules. If no keep-alive control signal is detected within a timeout period, the controller deactivates the respective power generator module.

Owner:SENSATA TECHNOLOGIES INC

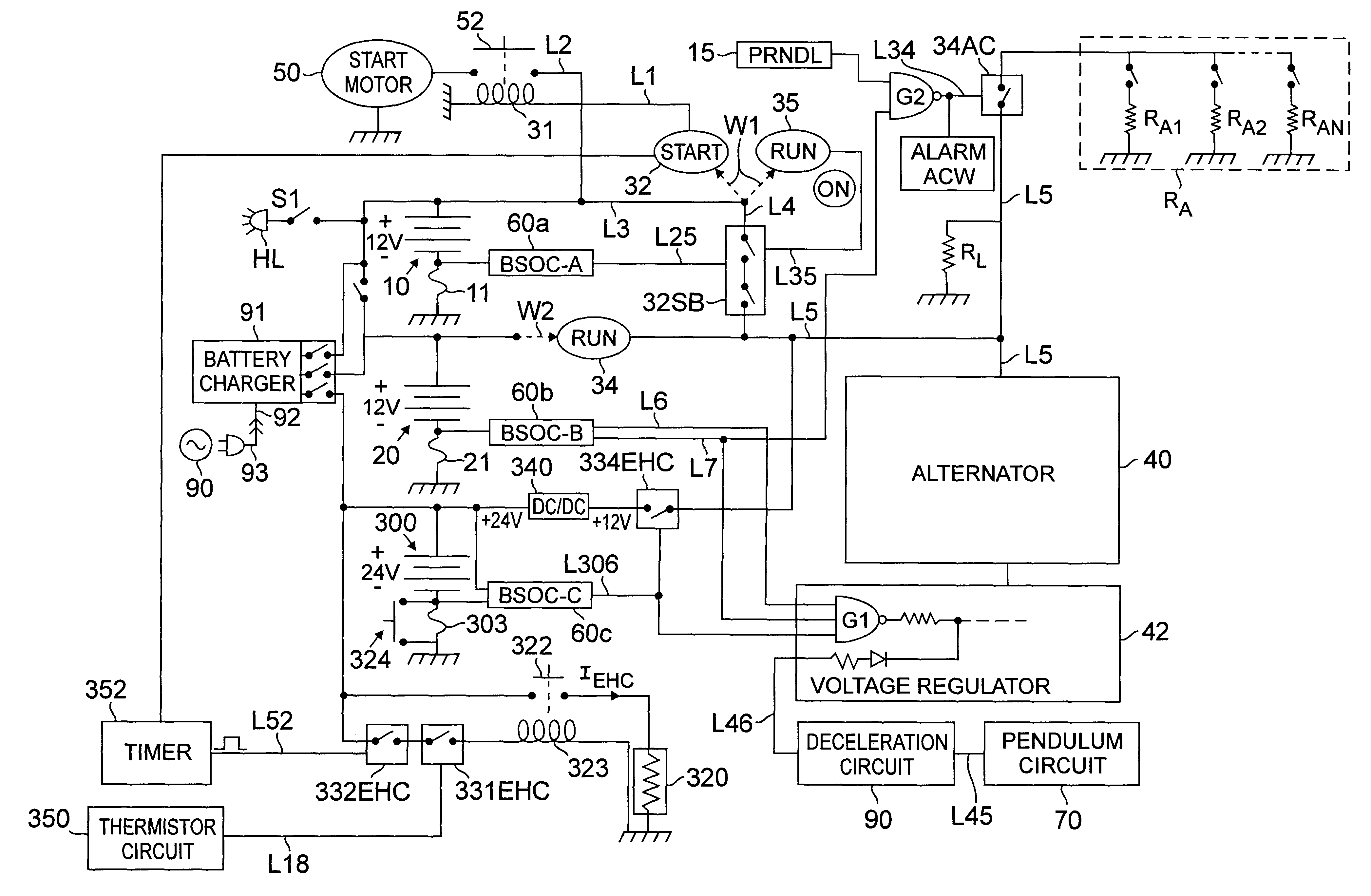

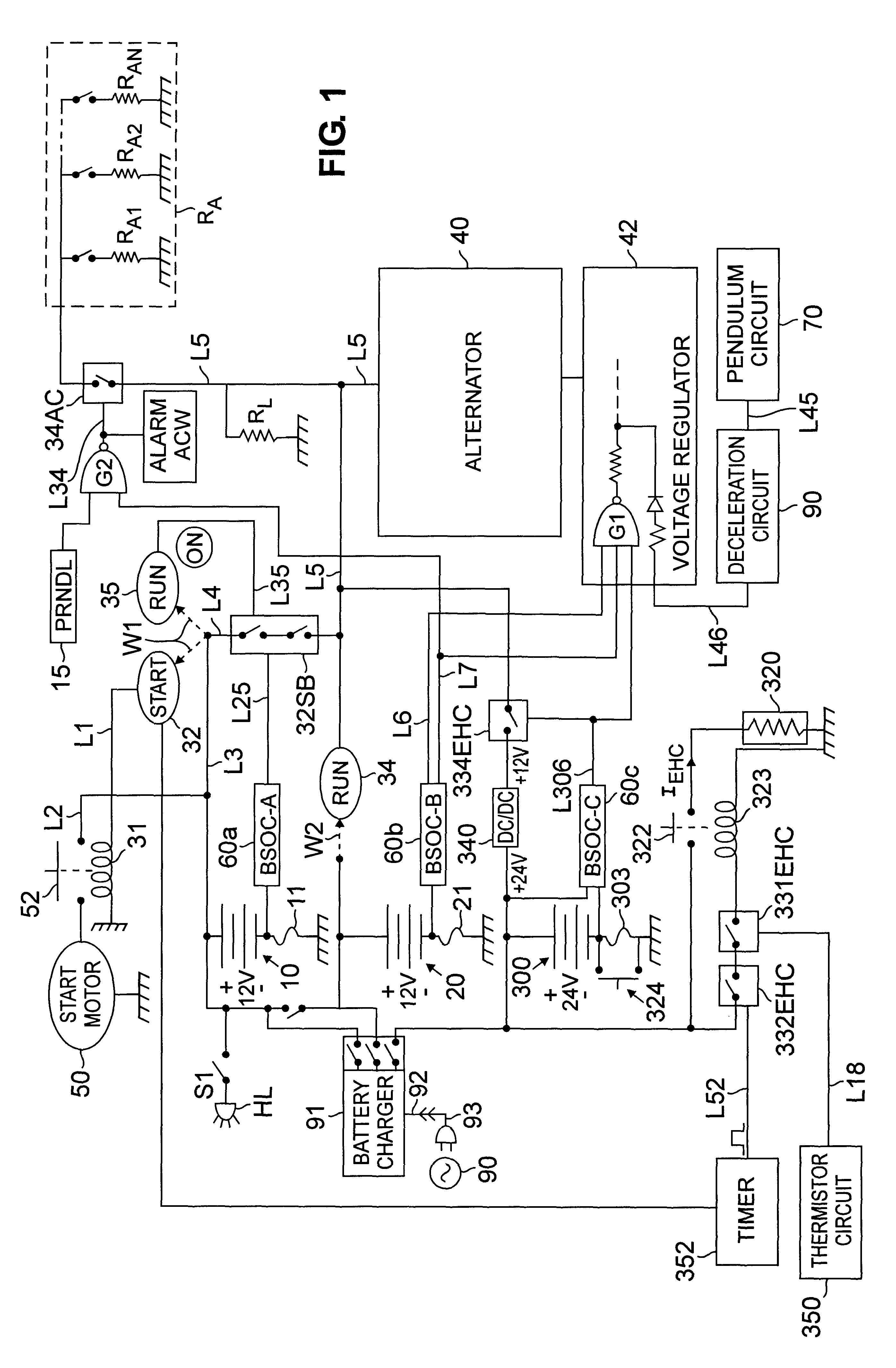

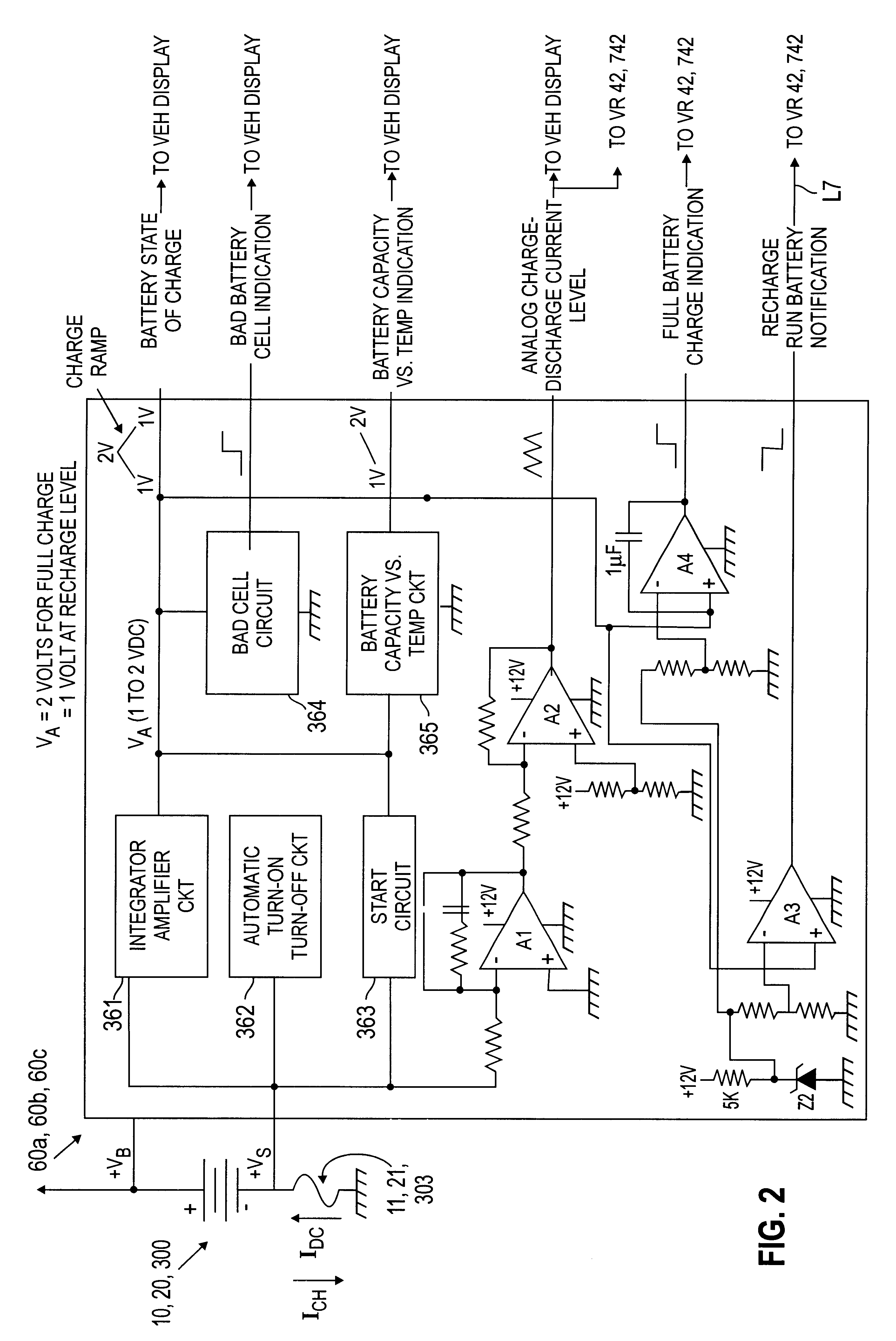

Multi-battery fuel saving and emission reduction system for automotive vehicles

InactiveUS6466024B1Easy to controlImprove the immunityCircuit monitoring/indicationExhaust apparatusAlternatorBattery charge

A multi-battery charging system for reduced fuel consumption and emissions for an automotive vehicle. The system starts the vehicle with a start battery in a fuel savings manner, removing electrical torque from the alternator shaft, and allows a second (run) battery to provide all or some of the current required by the vehicle loads as a fuel savings measure. The system also utilizes an electrically heated catalytic converter (EHC) and a third (EHC or storage) battery to provide a 3 to 15 second preheat and / or a 20 second current, during vehicle start, to the EHC heater coil, e.g., of a small EHC located in series with a standard catalytic converter for emissions reduction to reduce emissions during start. The start battery is recharged after start and switched out of the system fully charged for future vehicle starts. The run battery is recharged when its charge level drops below a predetermined level with an on board battery charging device powered from a 115 volt or 220 volt ac power line source external to the vehicle.

Owner:BRADLEY CHARLES W

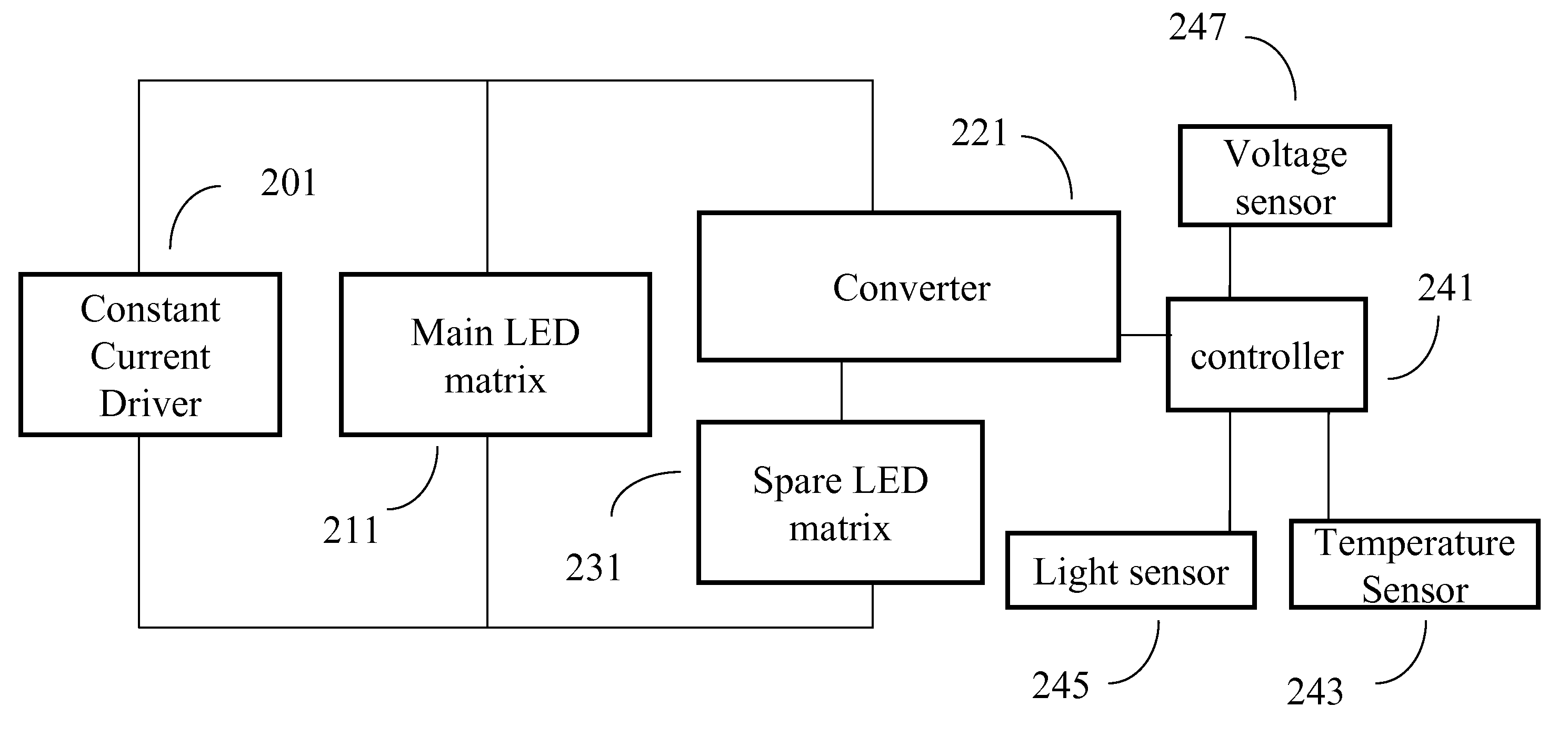

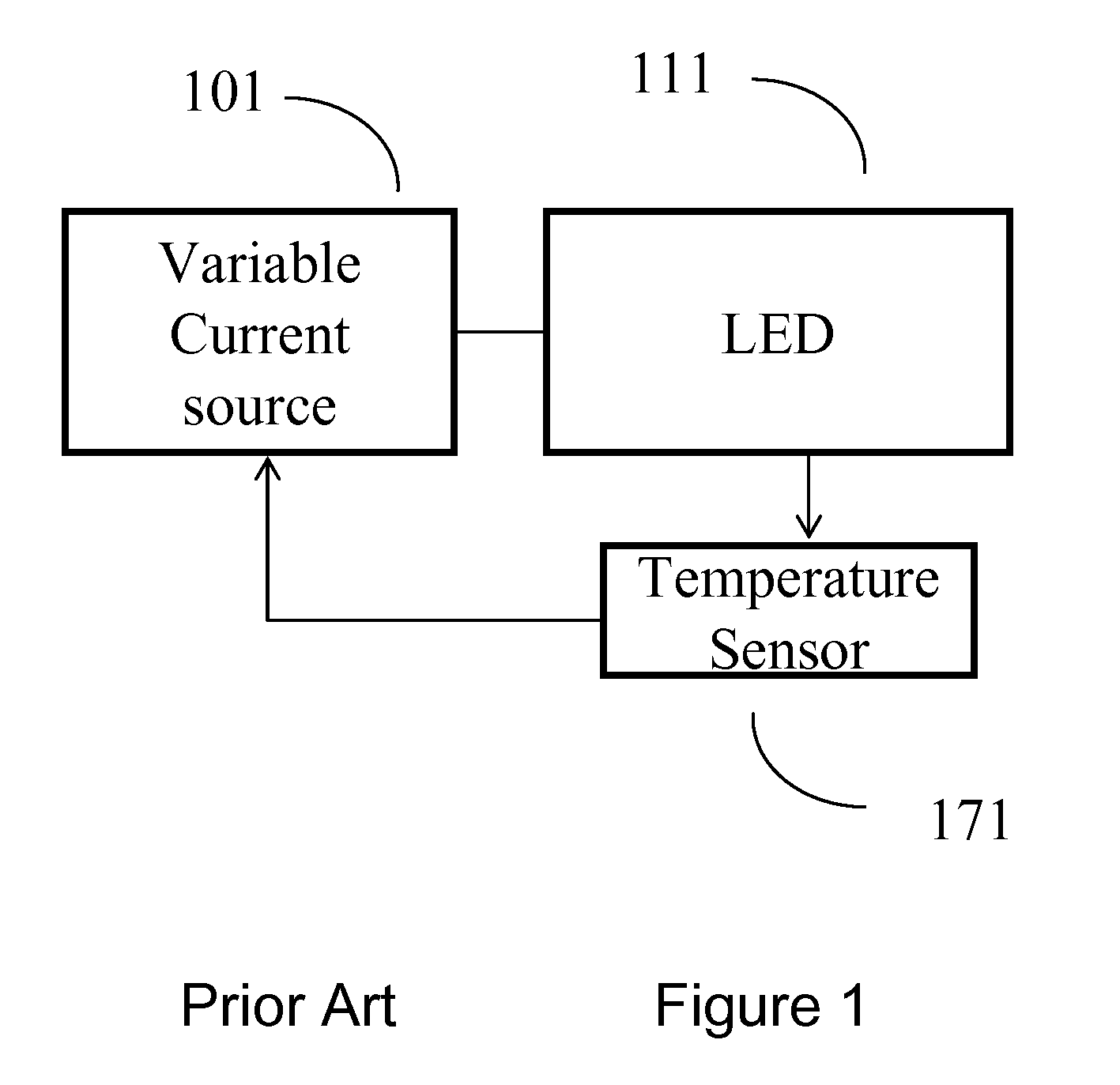

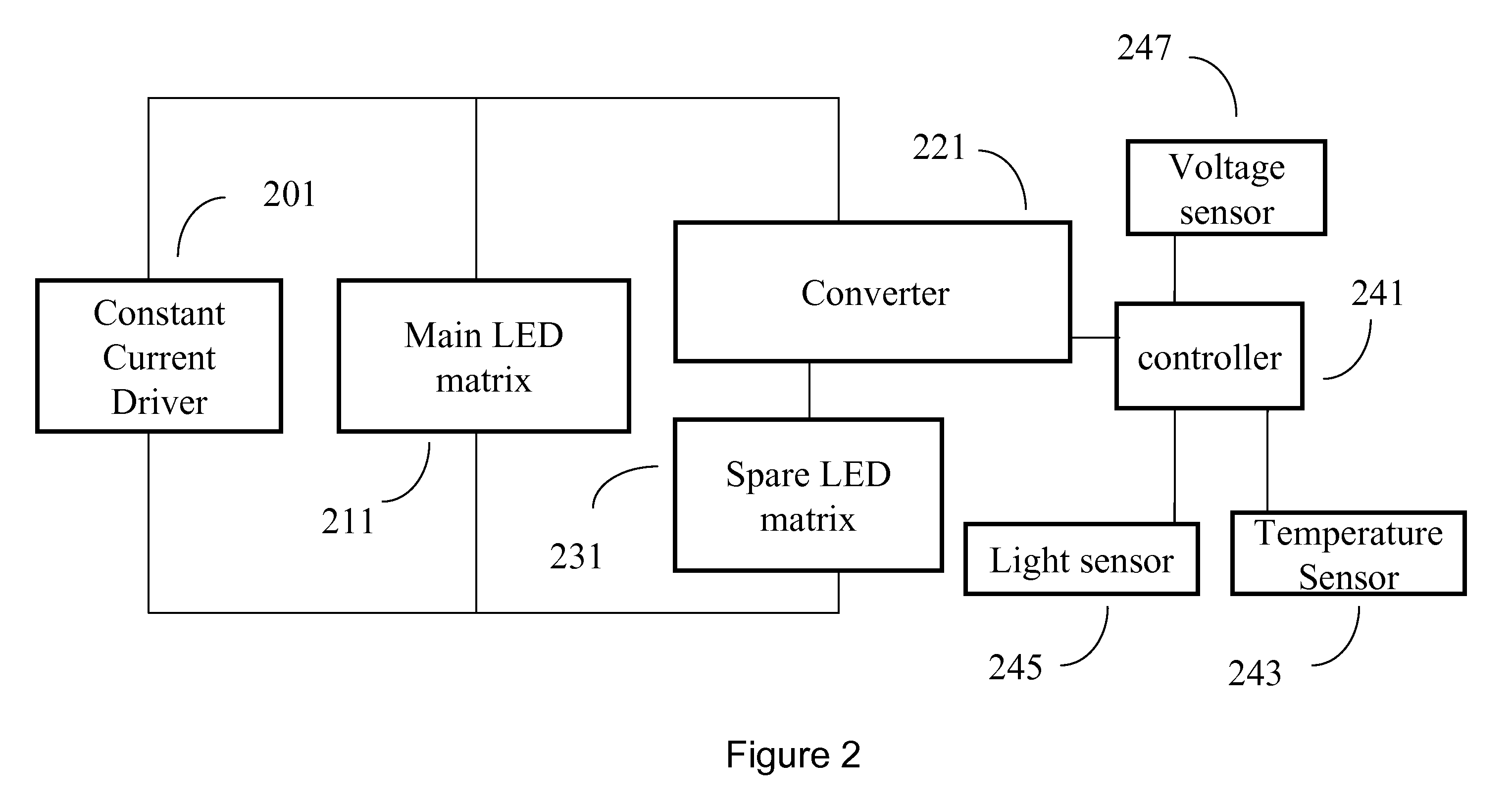

Apparatus and method to enhance the life of Light Emitting diode (LED) devices in an LED matrix

InactiveUS20100277077A1Prolong lifeLower junction temperatureElectrical apparatusElectroluminescent light sourcesDirect couplingEngineering

The present invention is an apparatus to enhance the Life of LED devices in an LED matrix for illumination. It comprises of a spare LED matrix in addition to a main LED matrix. It further comprises of a constant current source which is the power source. Such constant current source is coupled directly to said main LED matrix and powers it up accordingly. In adverse conditions, say when the ambient temperature is high, continuous operation of said main LED matrix at full power will deteriorate the LED life. A power converter coupled to said constant current source operates and draws current to power on said spare LED matrix. This relieves said main LED matrix from full power and the reduction in illumination is largely compensated by said spare LED matrix. This invention further comprises a controller which senses temperature and other parameters and operates said spare LED matrix intelligently. The present invention is also a method to operate said apparatus to maximize LED life or to maximize illumination.

Owner:PONG MAN HAY +1

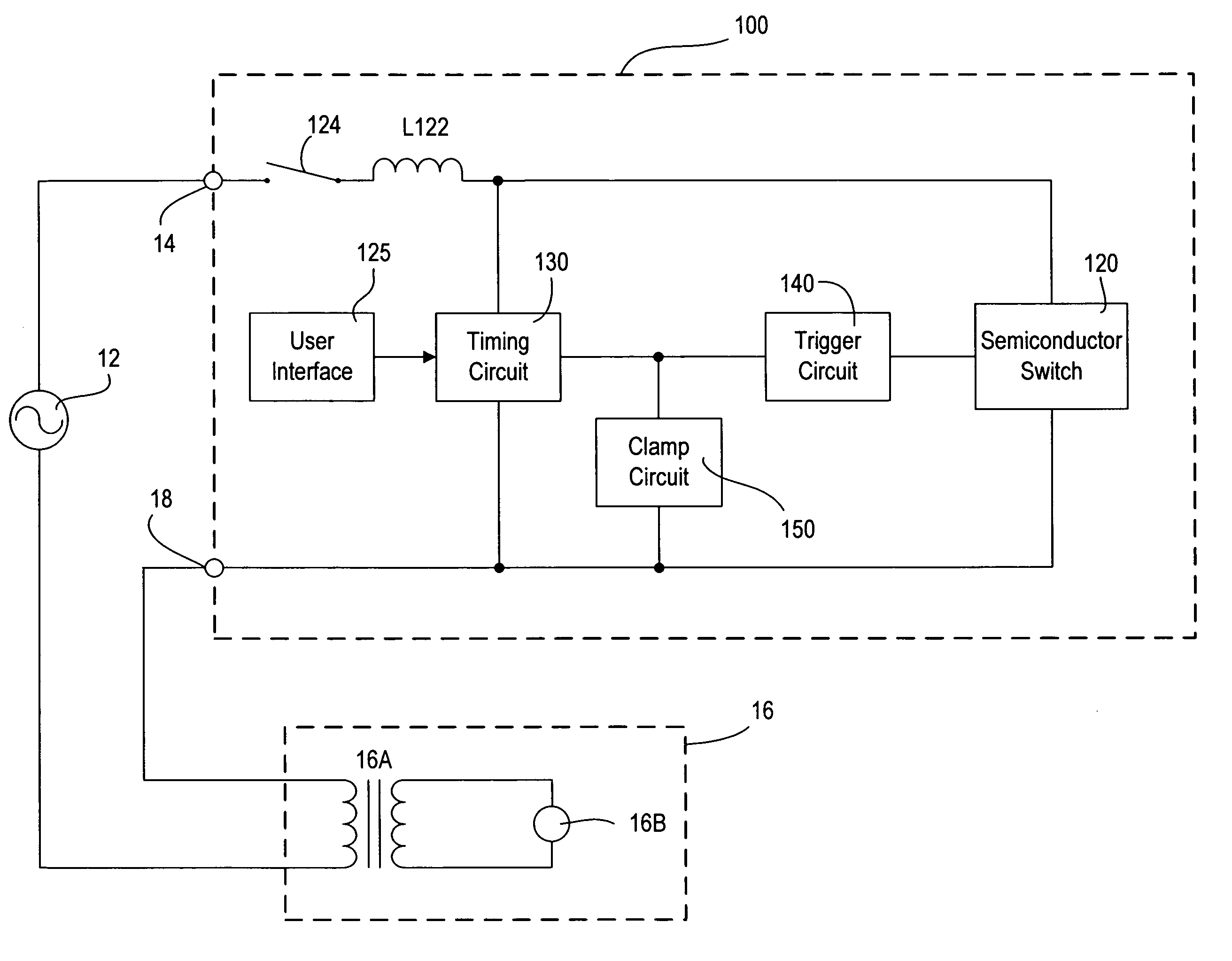

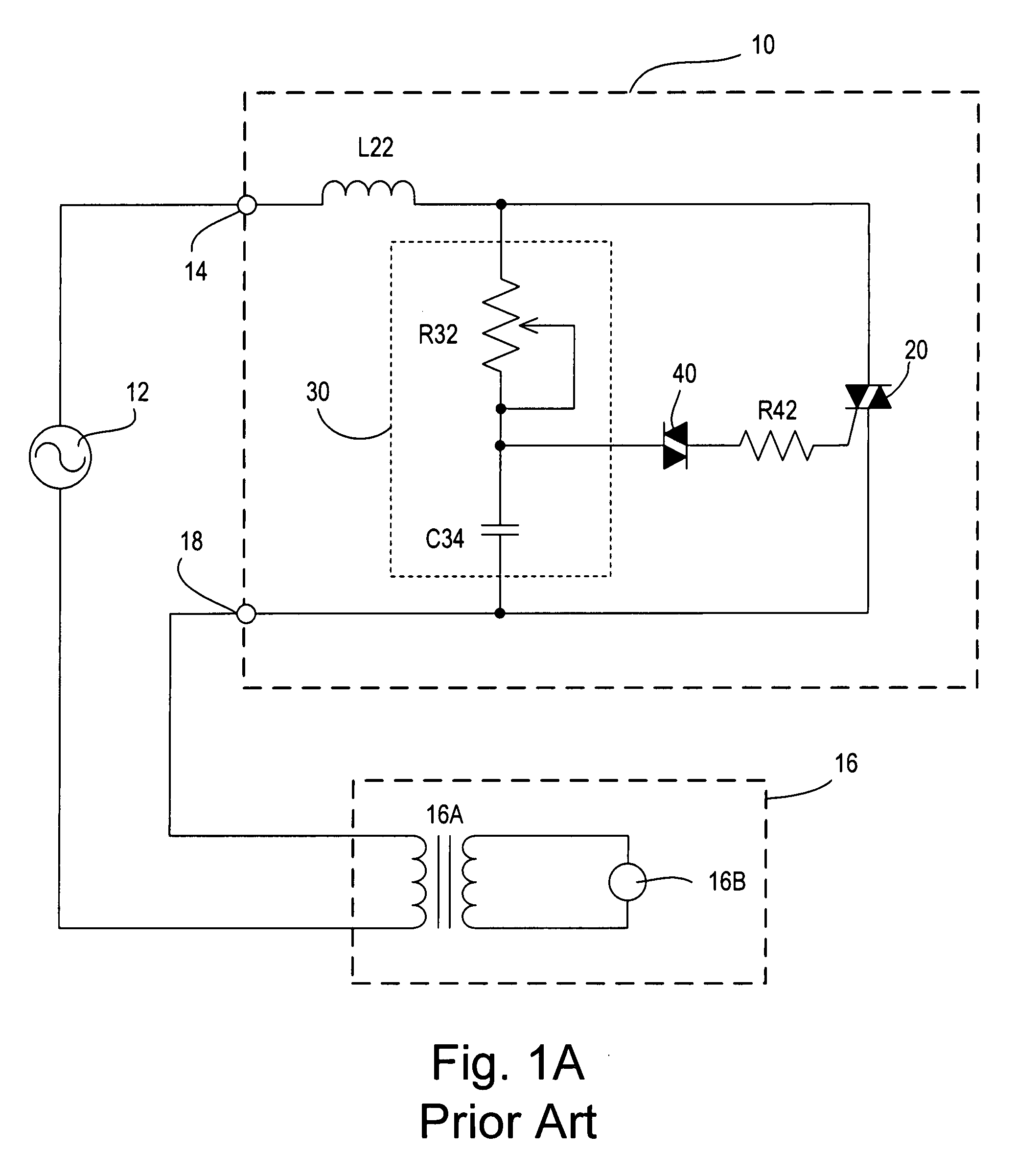

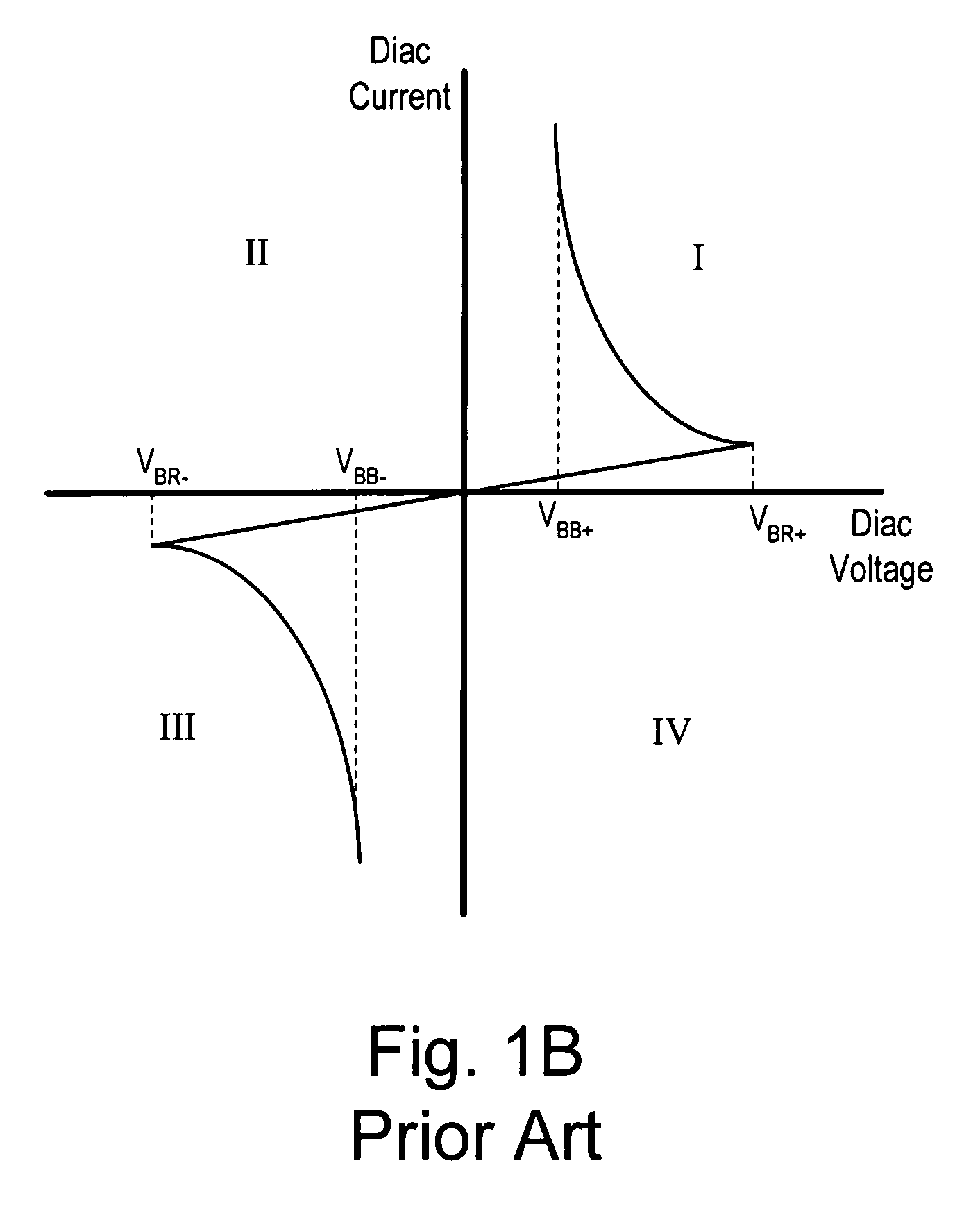

Dimmer for preventing asymmetric current flow through an unloaded magnetic low-voltage transformer

ActiveUS20070217237A1Limit magnitudePrevent voltageElectric lighting sourcesAc-dc conversionLow voltageTransformer

A two-wire dimmer is operable to control the amount of power delivered to a magnetic low-voltage (MLV) load and comprises a bidirectional semiconductor, a timing circuit, a trigger circuit having a variable voltage threshold, and a clamp circuit. When a timing voltage signal of the timing circuit exceeds an initial magnitude of the variable voltage threshold, the trigger circuit is operable to render the semiconductor switch conductive, reduce the timing voltage signal to a predetermined magnitude less than the initial magnitude, and to increase the variable voltage threshold to a second magnitude greater than the first magnitude. The clamp circuit limits the magnitude of the timing voltage signal to a clamp magnitude between the initial magnitude and the second magnitude, thereby preventing the timing voltage signal from exceeding the second magnitude. Accordingly, the MLV dimmer is prevented from conducting asymmetric current when an MLV transformer of the MLV load is unloaded.

Owner:LUTRON TECH CO LLC

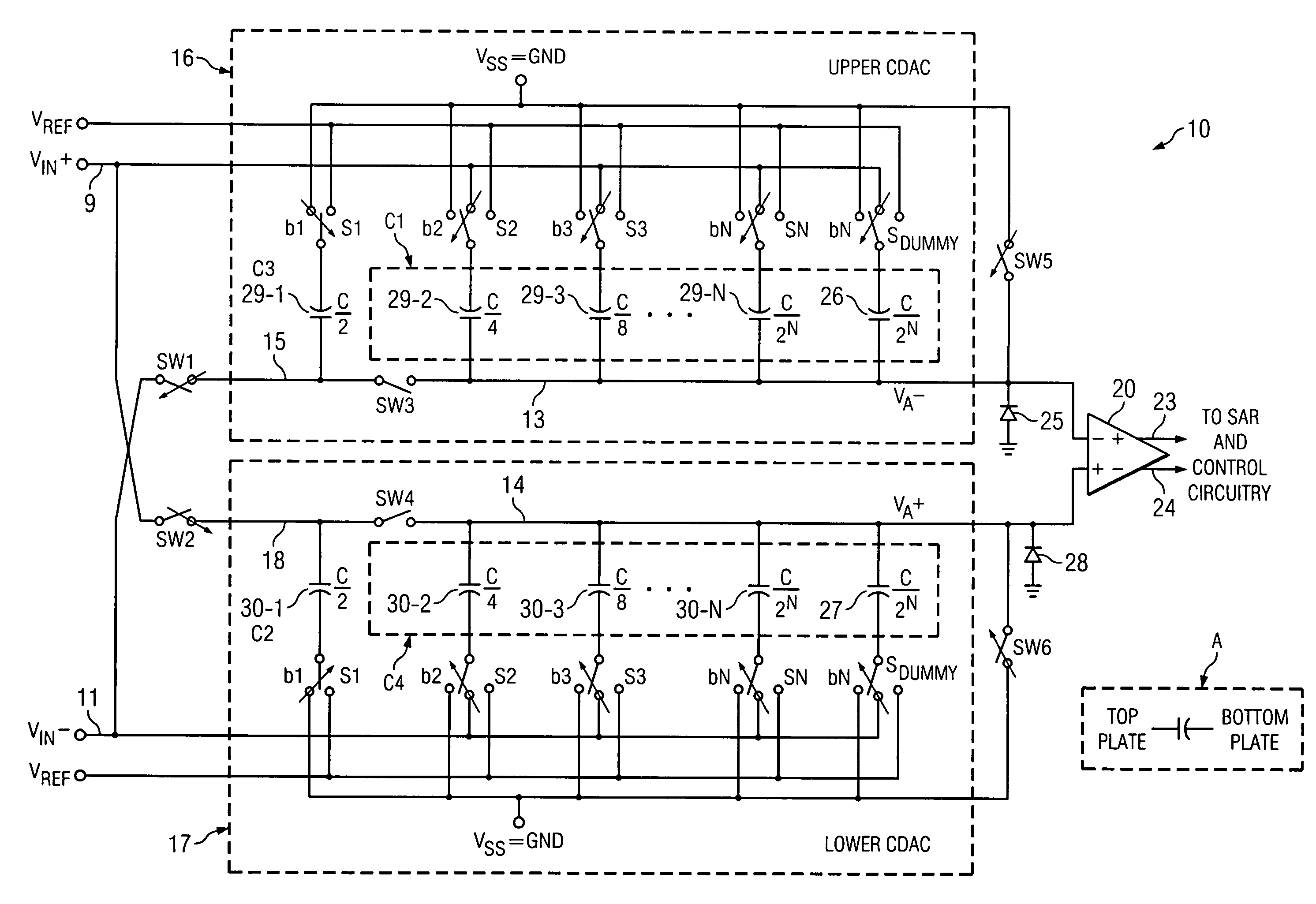

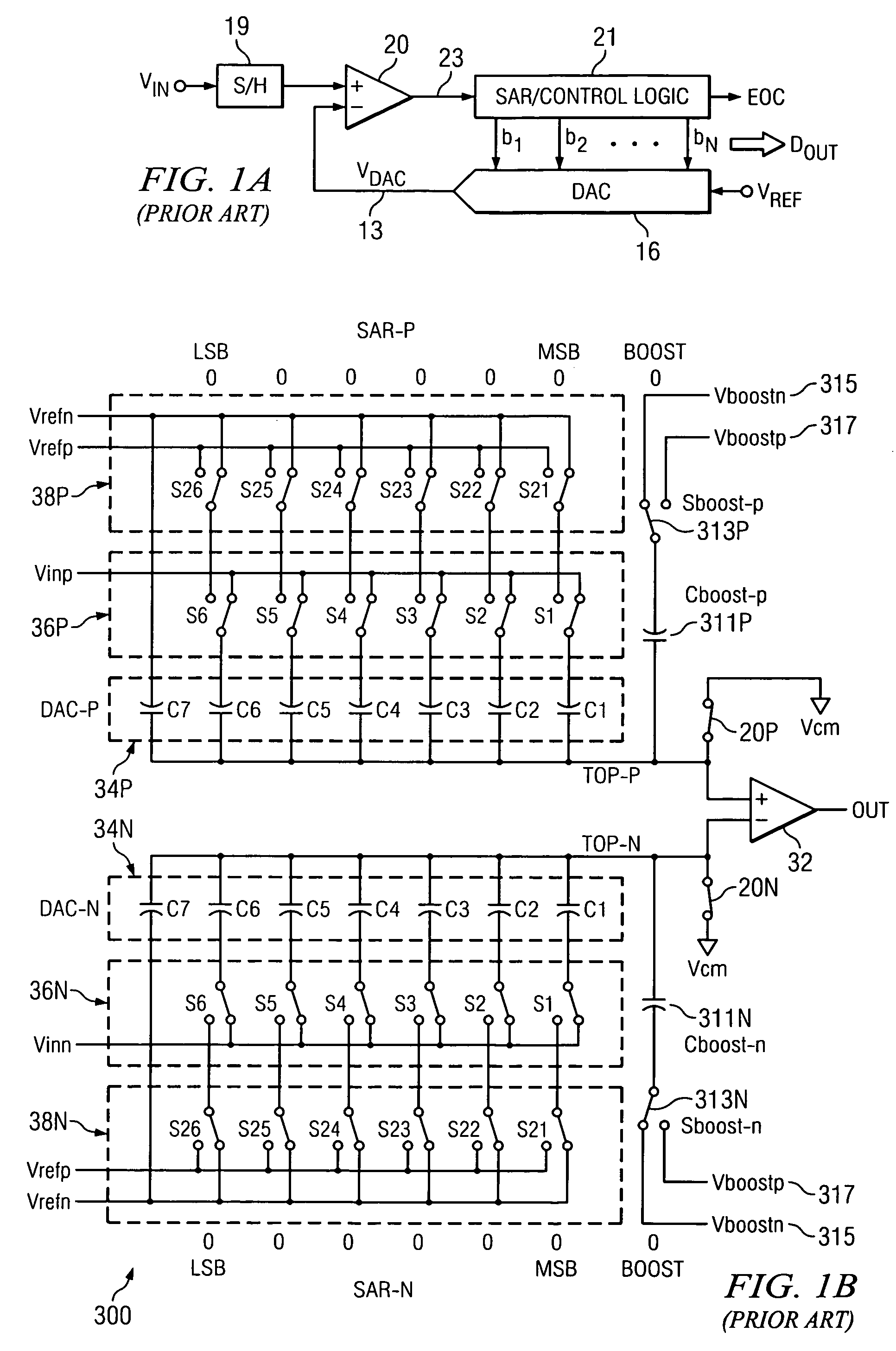

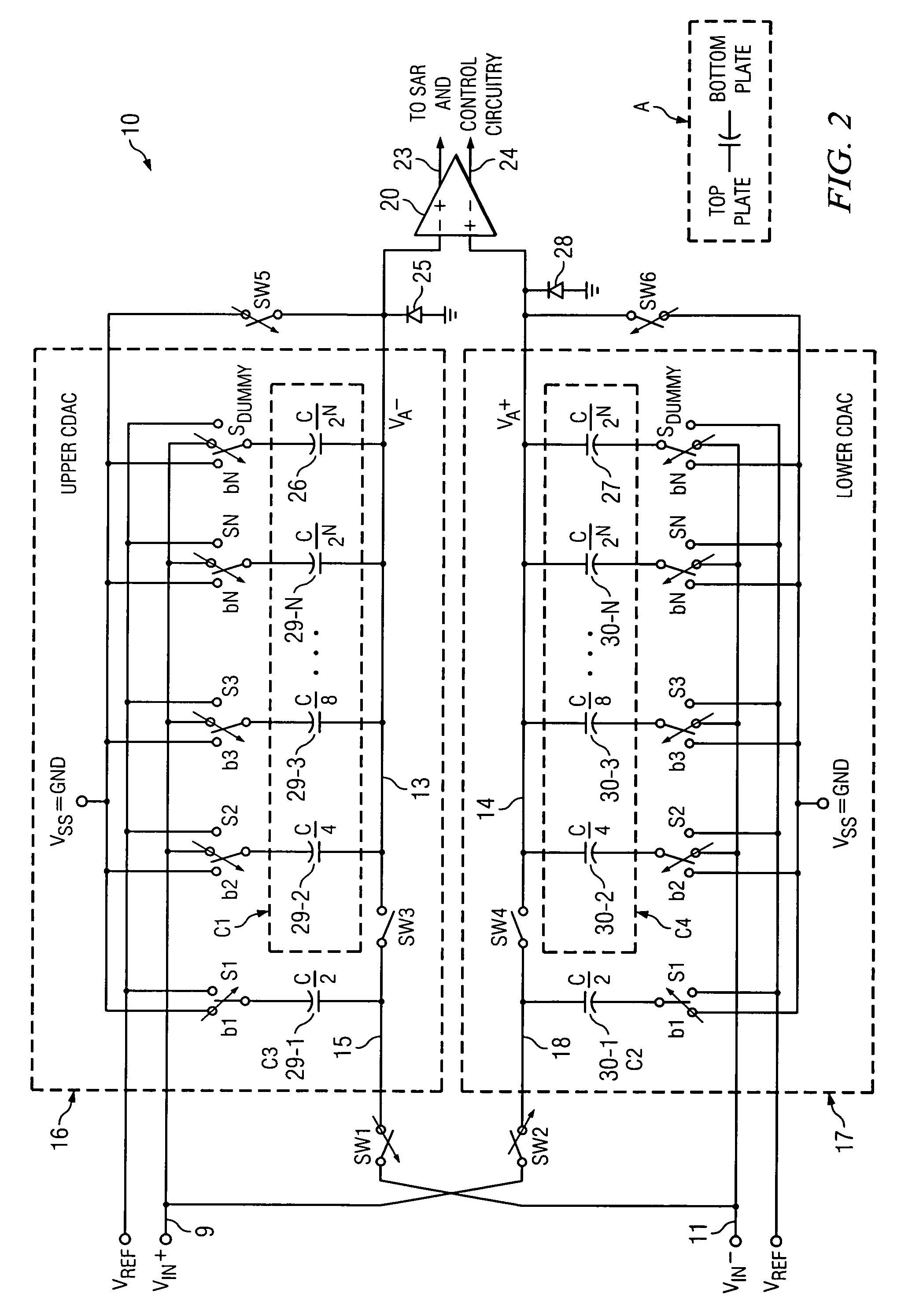

Zero-power sampling SAR ADC circuit and method

ActiveUS20120280841A1Prevent leakagePrevent voltageElectric signal transmission systemsAnalogue-digital convertersIntegratorVoltage reference

A switched-capacitor circuit (10, 32 or 32A) samples a first signal (VIN+) onto a first capacitor (C1 or CIN1) by switching a top plate thereof via a summing conductor (13) to a first reference voltage (VSS) and switching a bottom plate thereof to the first signal. A second signal (VIN−) is sampled onto a second capacitor (C3 or CIN3) by switching a top plate thereof to the second signal and switching a bottom plate thereof to the first reference voltage. After the sampling, the top plate of the second capacitor is coupled to the top plate of the first capacitor. The bottom plate of the second capacitor is coupled to the first reference voltage. The bottom plate of the first capacitor is coupled to a second reference voltage (VDD or VREF), to thereby cancel at least a portion of a common mode input voltage component from the first conductor (13), hold the sampled differential charge on the summing conductor and establish a predetermined common mode voltage thereon, and prevent the summing conductor from having a voltage which allows the leakage of charge therefrom. The switched-capacitor circuit may be a SAR, an integrator, or an amplifier.

Owner:TEXAS INSTR INC

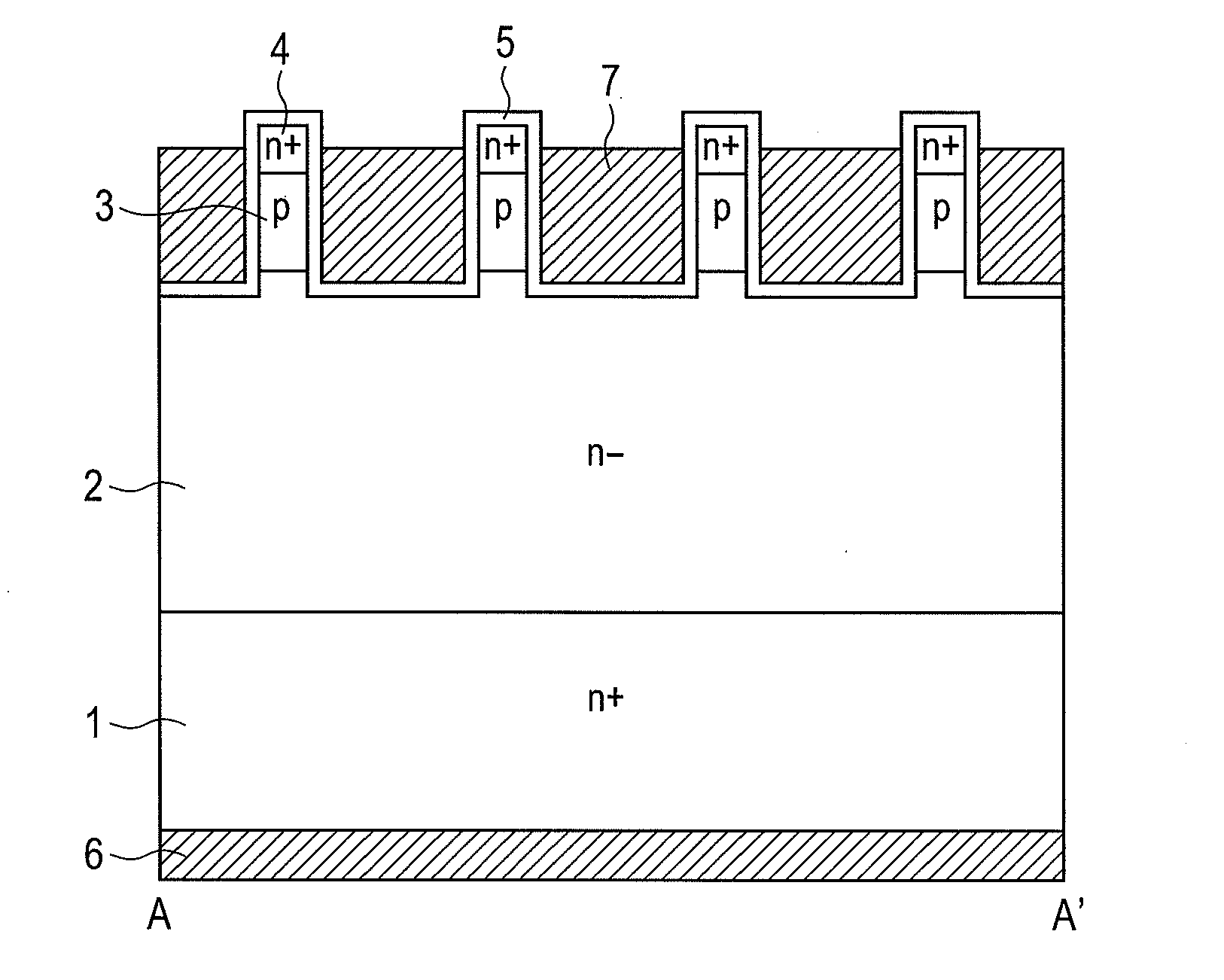

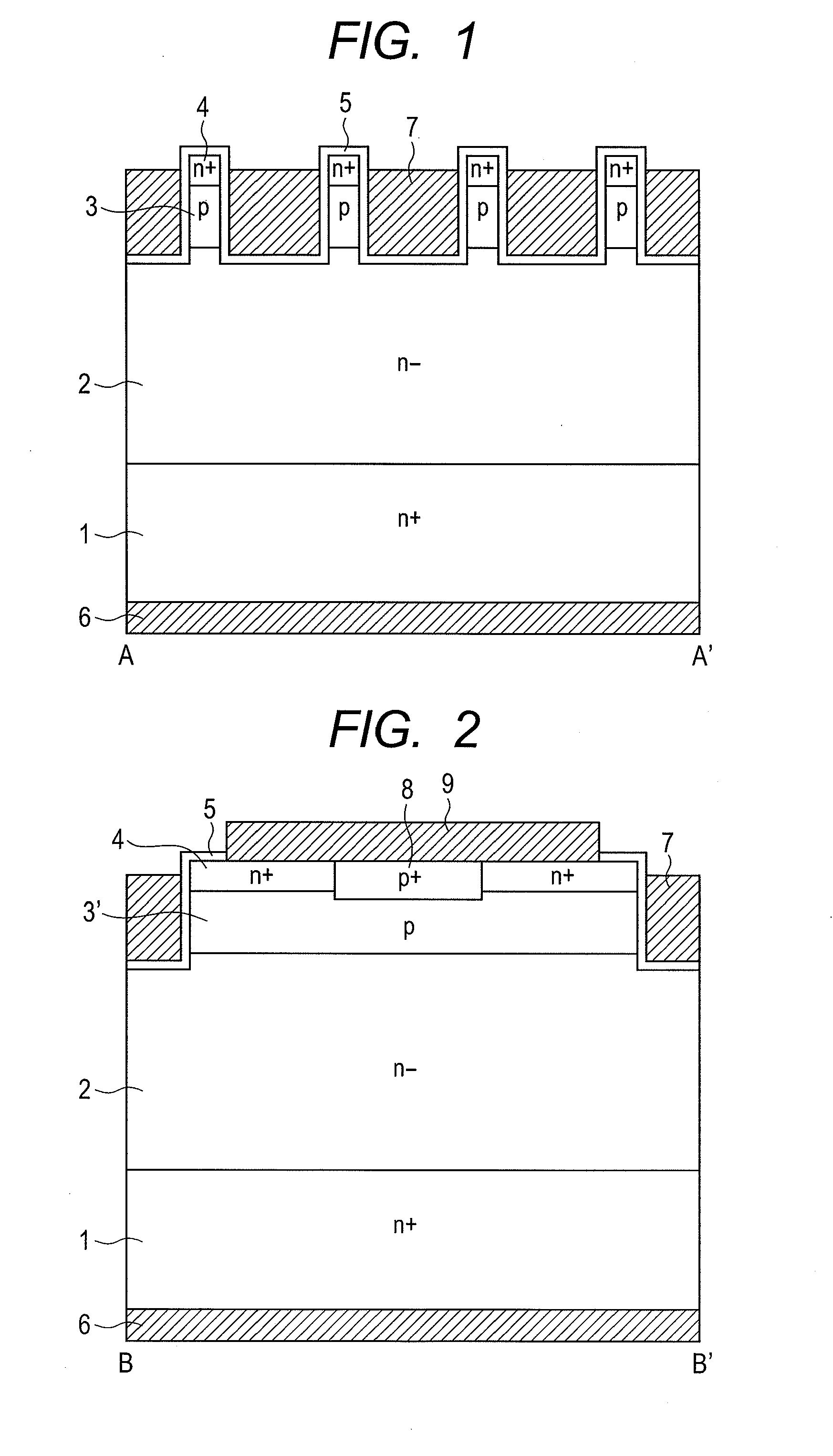

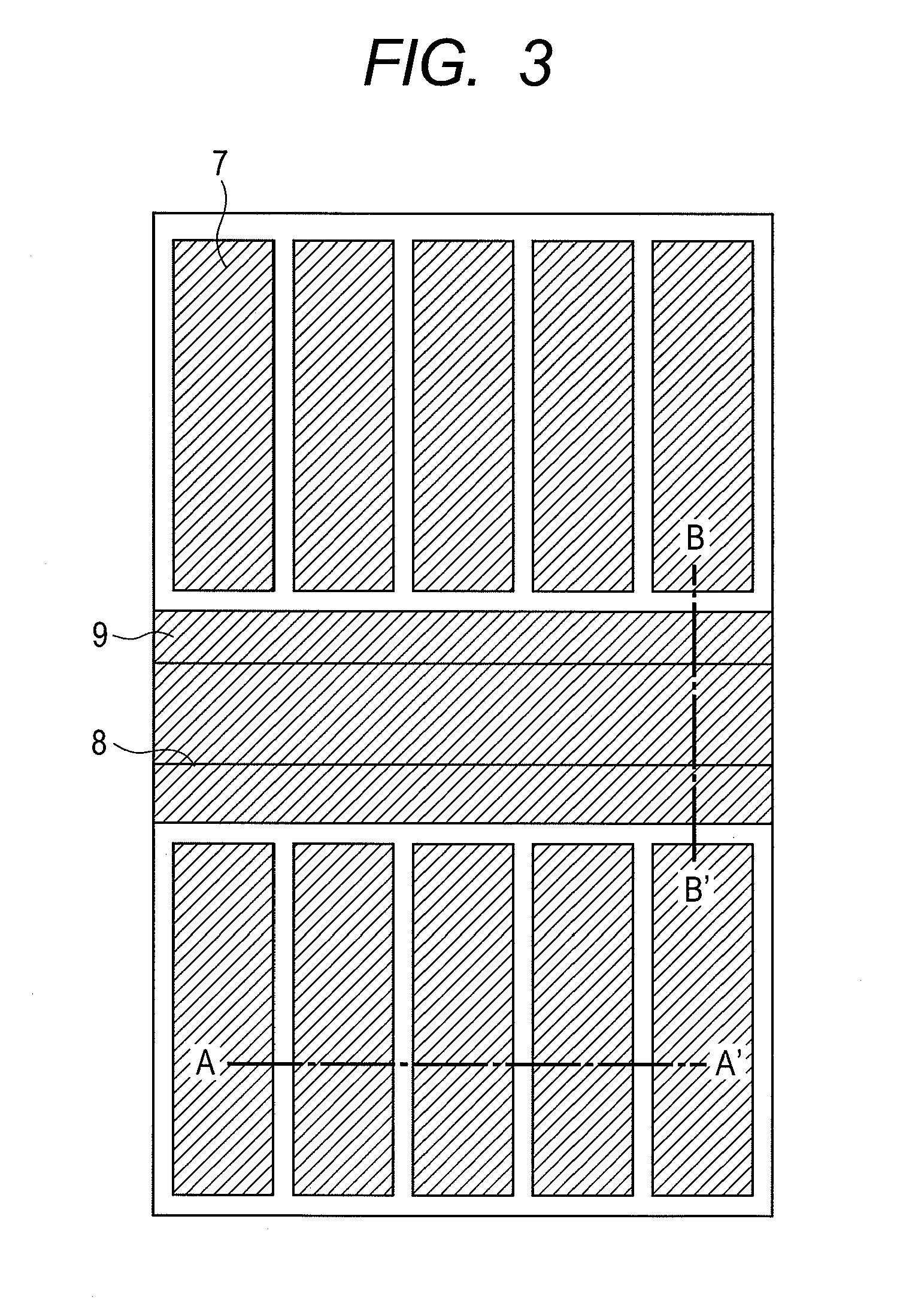

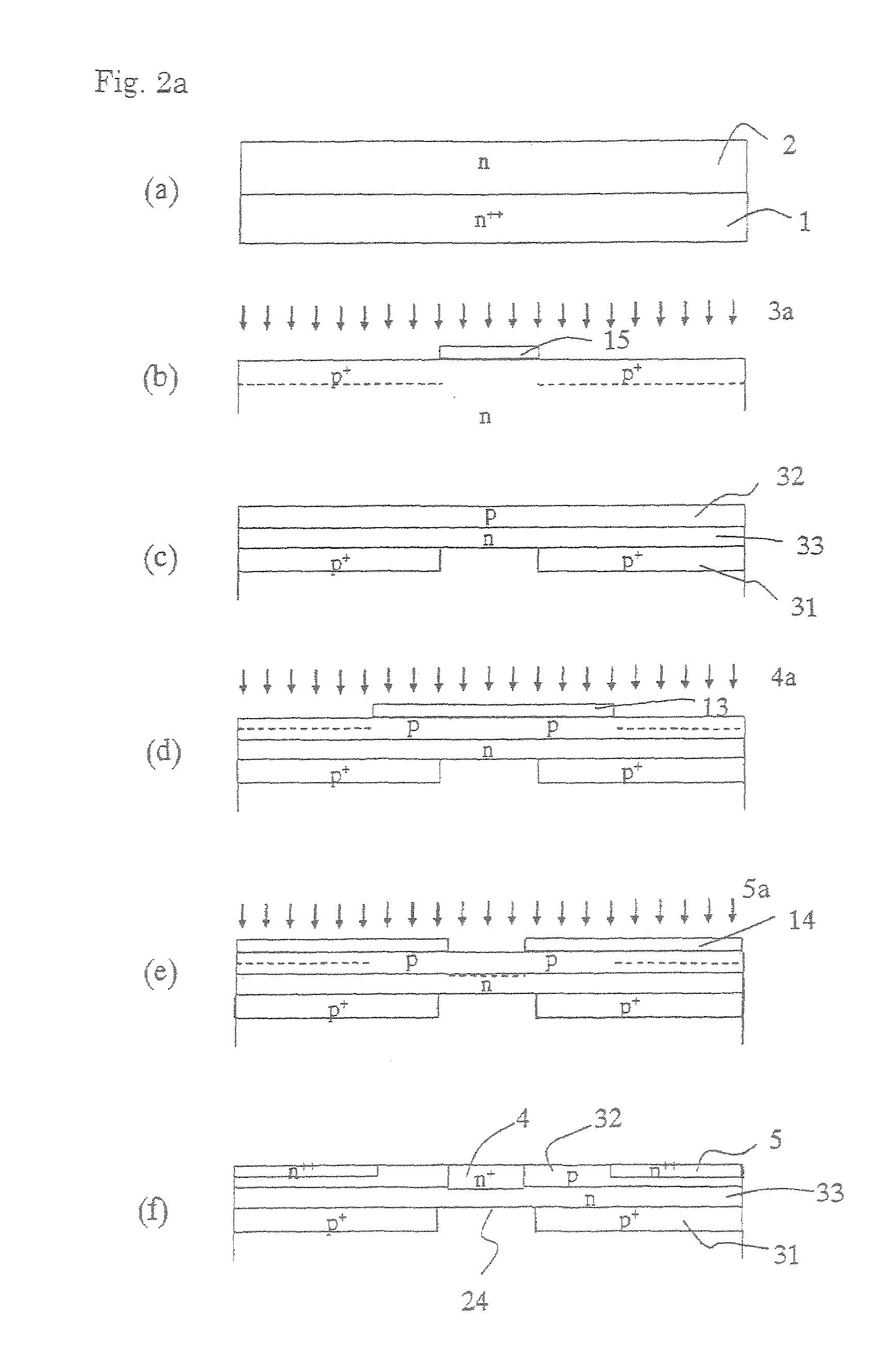

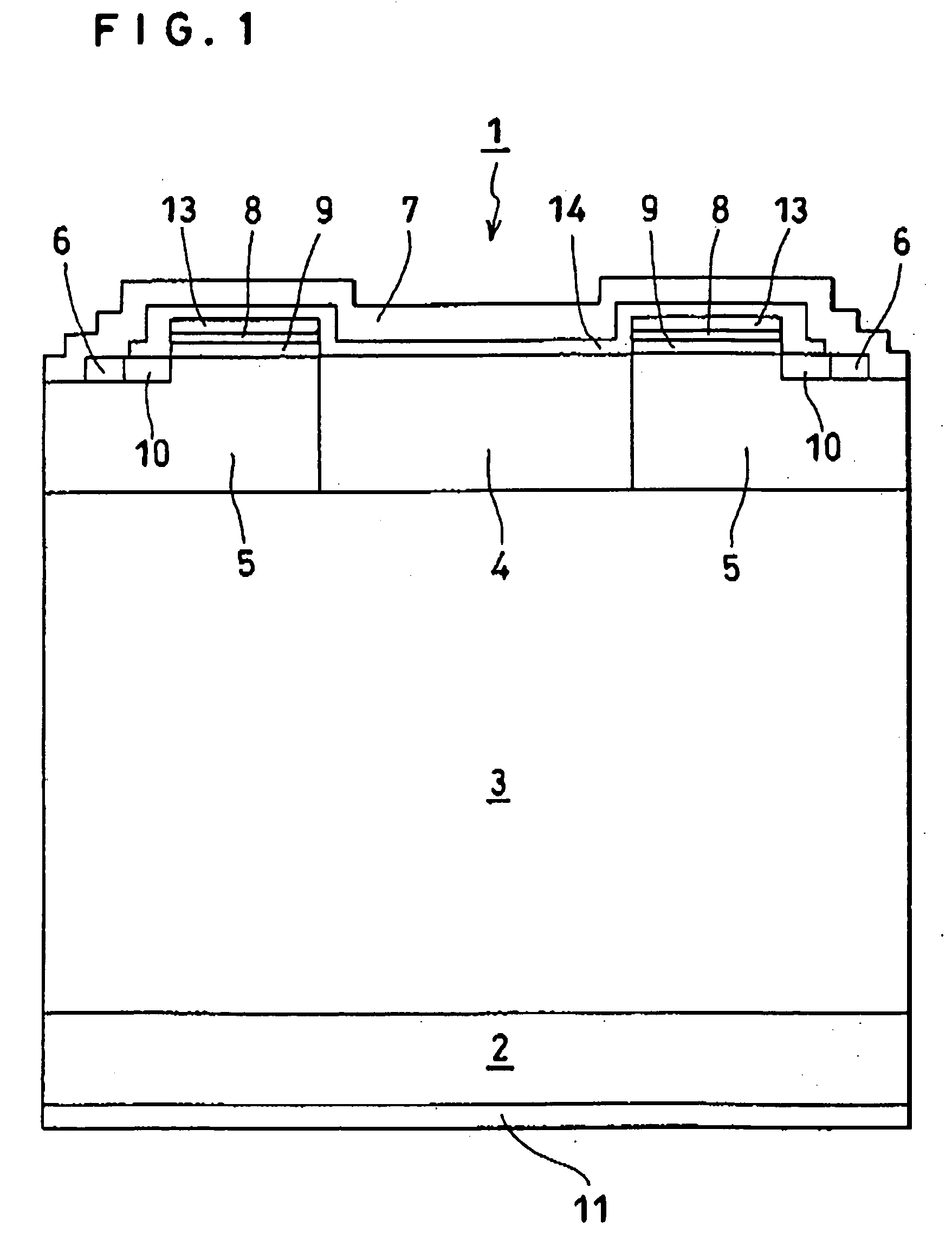

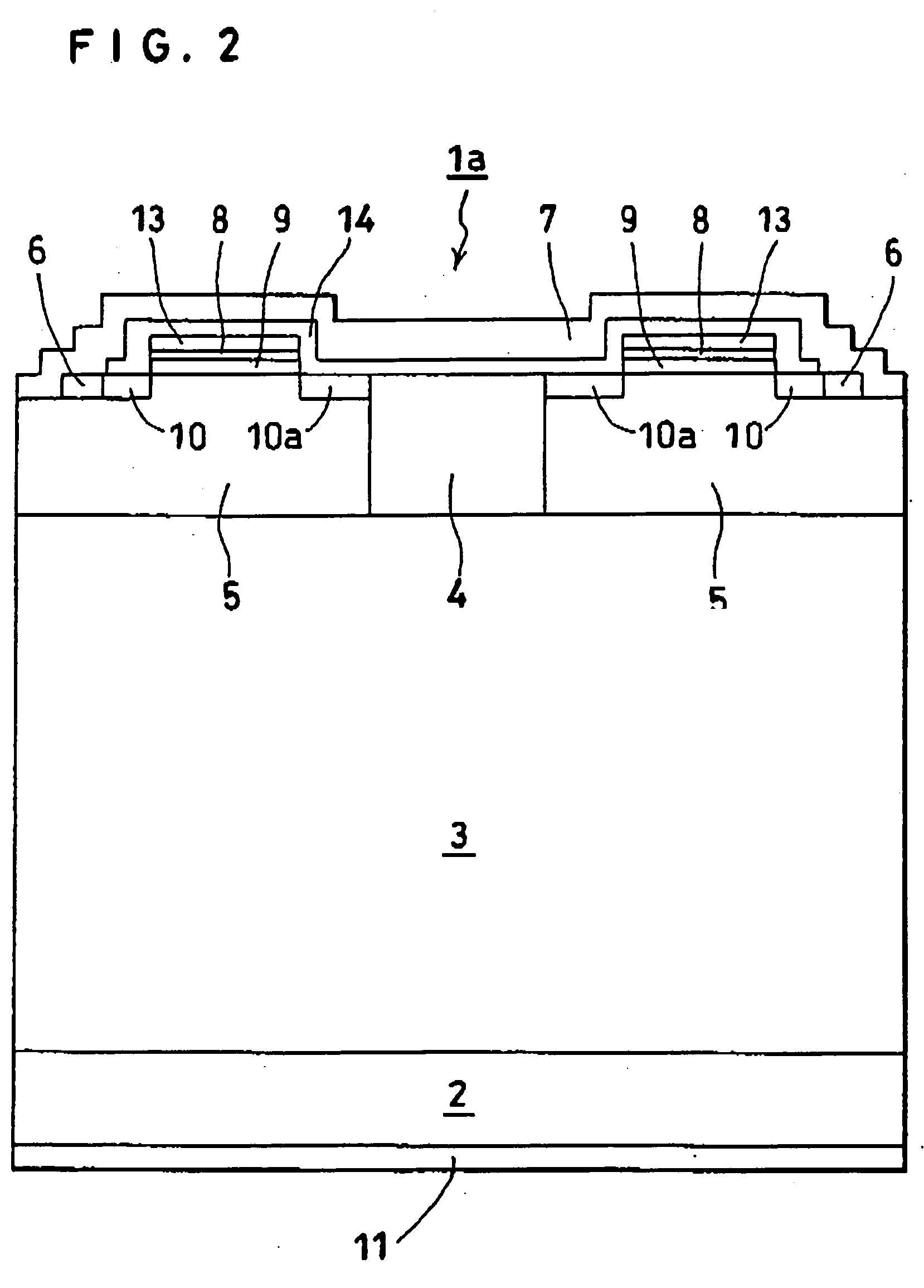

Semiconductor device with large blocking voltage and manufacturing method thereof

InactiveUS20110018004A1Lower threshold voltagePrevent voltageSemiconductor/solid-state device manufacturingSemiconductor devicesTrench mosfetDevice material

There is no effective method for fabricating a semiconductor power device containing UMOSFET possessing large channel mobility and whose threshold voltage can be lowered with no loss in blocking voltage. A semiconductor device with large blocking voltage is provided utilizing silicon carbide trench MOSFET possessing both narrow regions where the p body concentration is low, and wide regions where the p body concentration is high.

Owner:HITACHI LTD

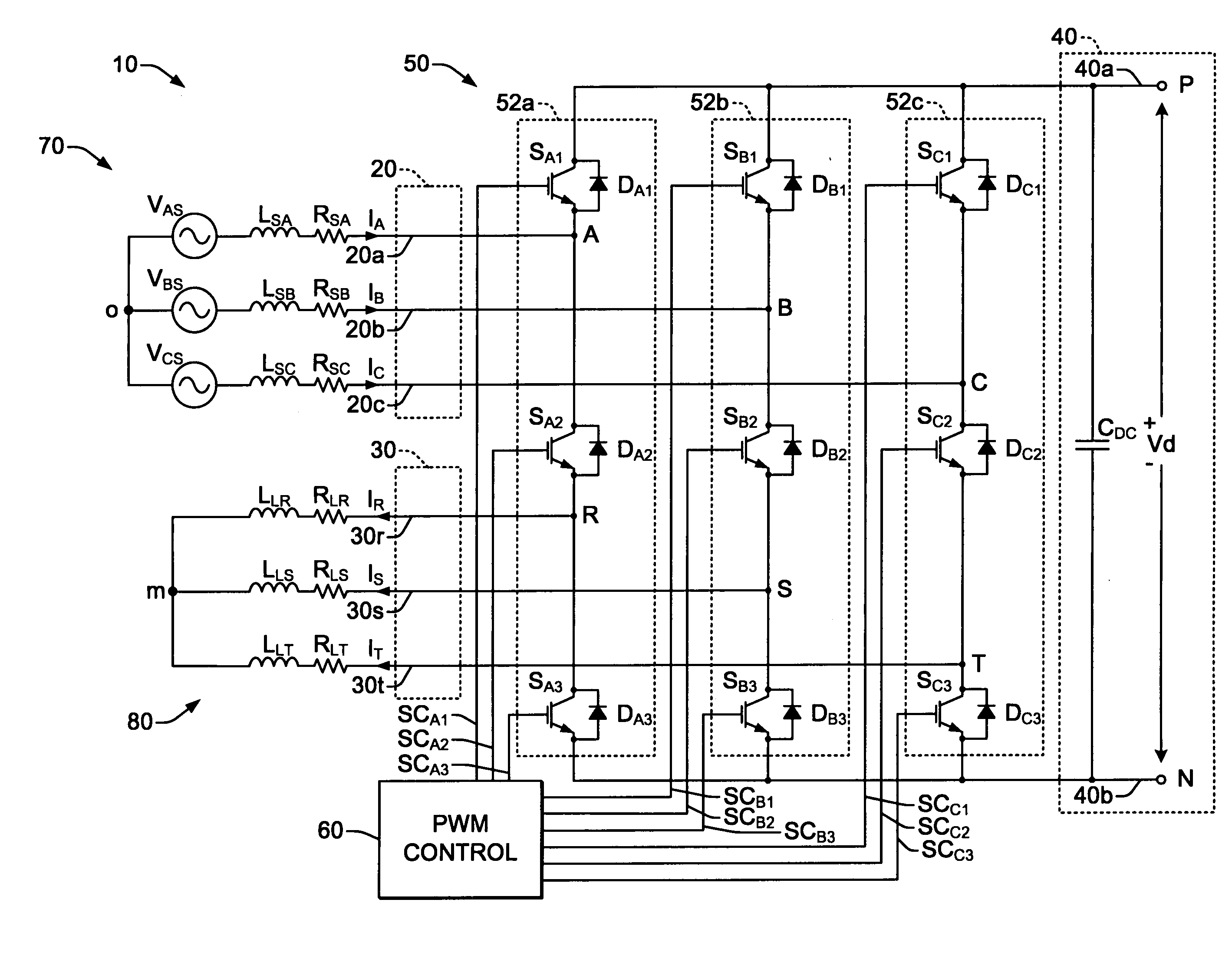

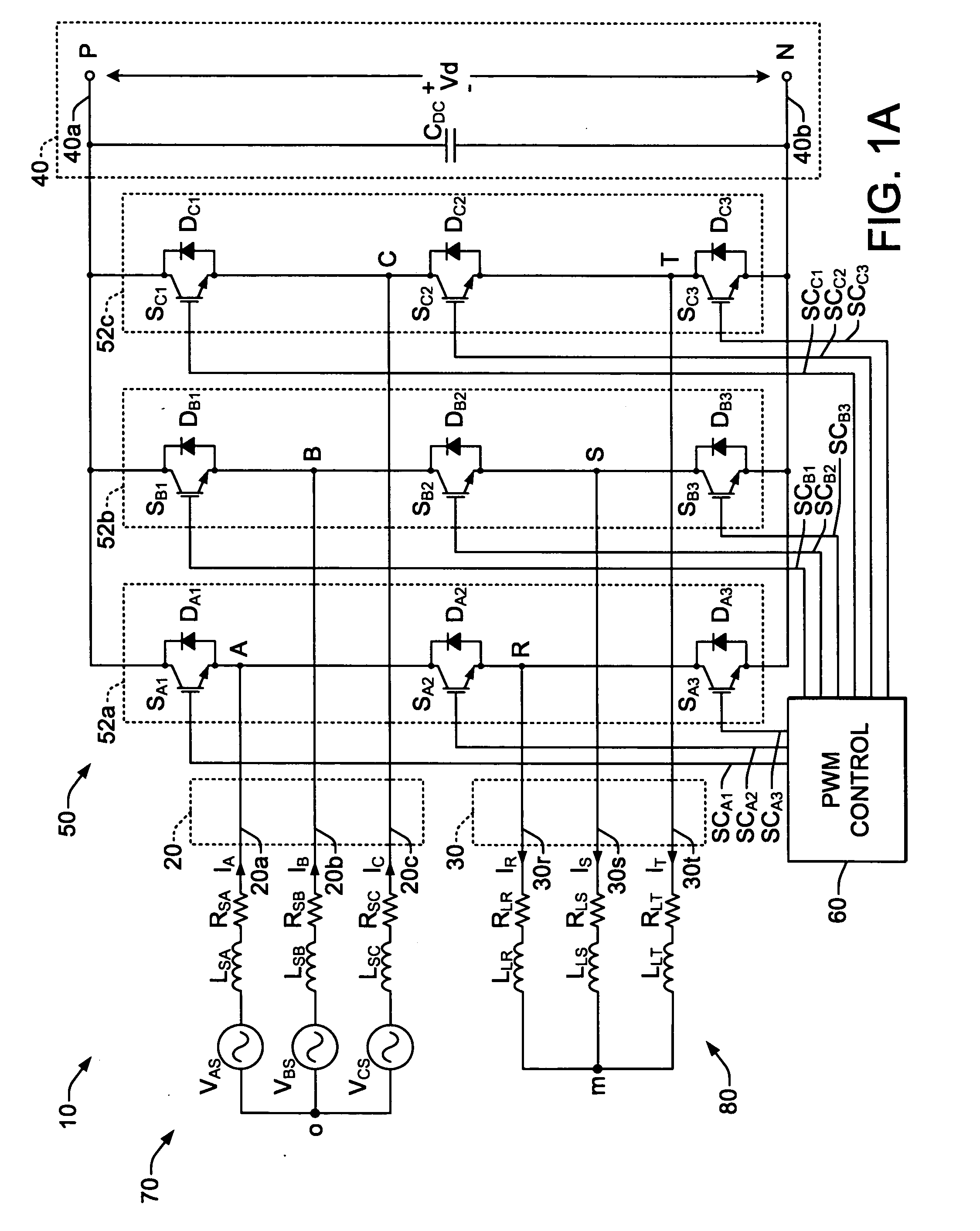

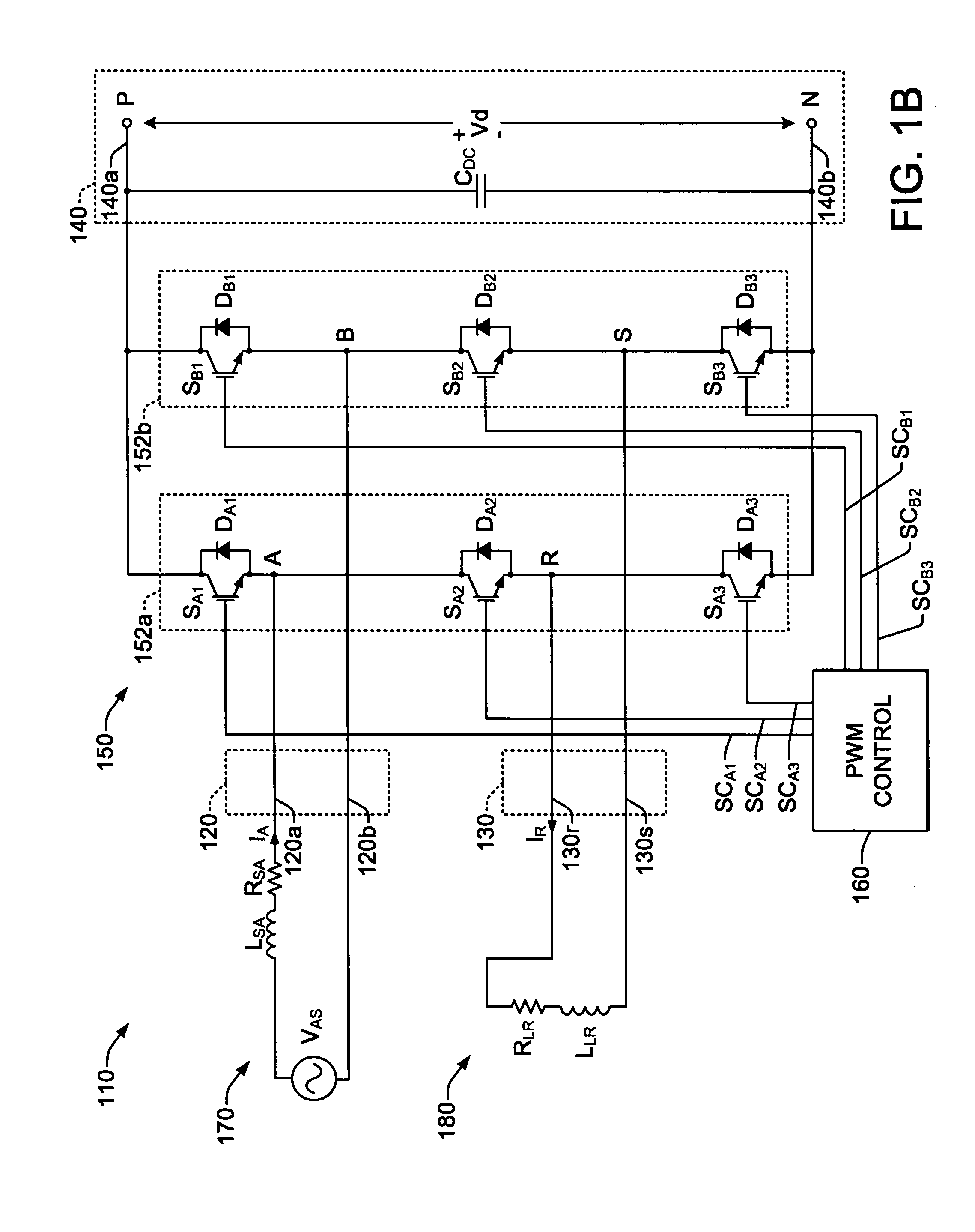

Nine device AC-to-AC converter

ActiveUS20070189044A1Easy to understandPrevent voltageConversion with intermediate conversion to dcAc network circuit arrangementsPower switchingEngineering

AC-to-AC power conversion systems and methods are presented, in which a small number of asymmetrical power switching devices are used to convert input AC power to output AC power of constant or variable frequency.

Owner:ROCKWELL AUTOMATION TECH

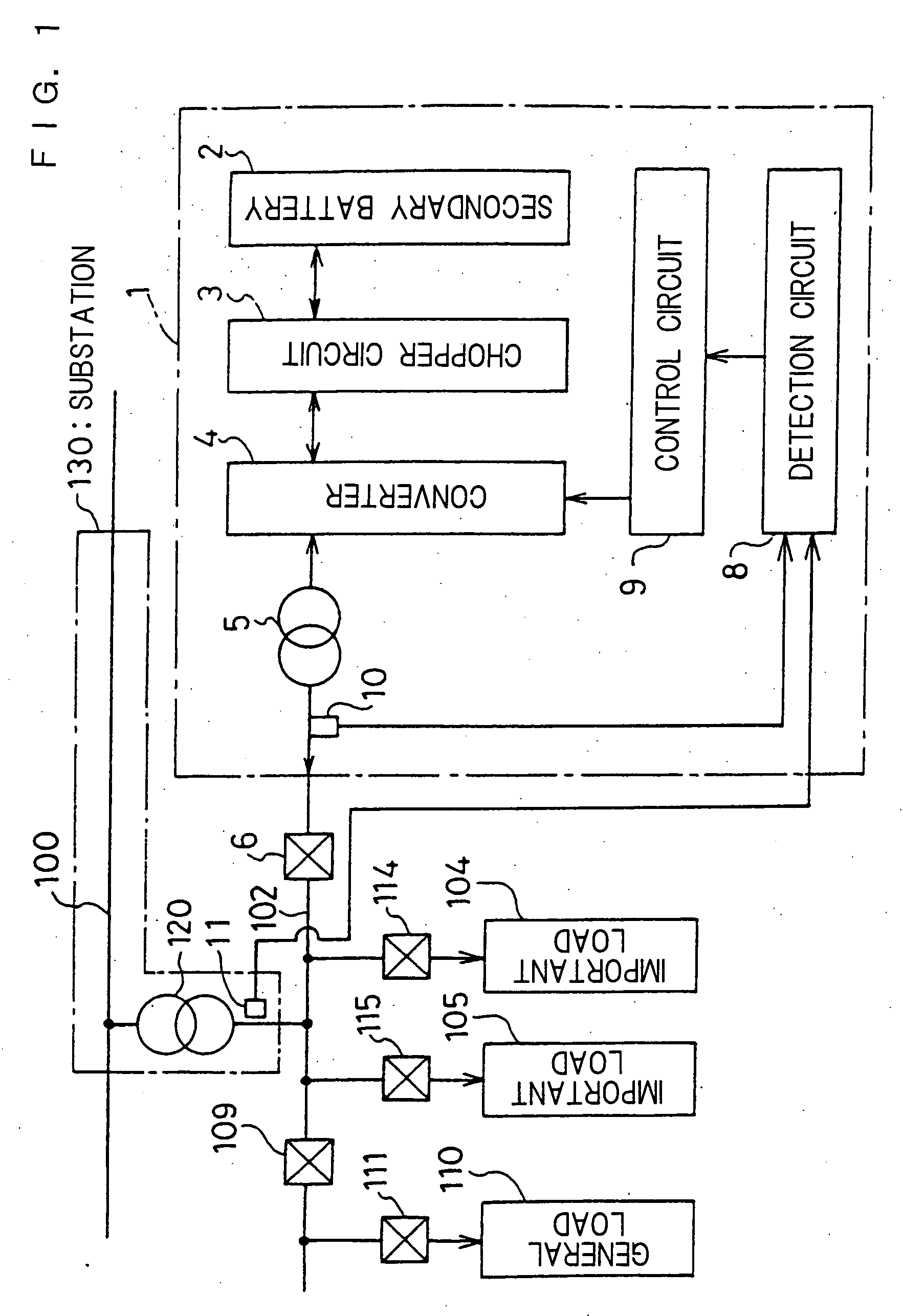

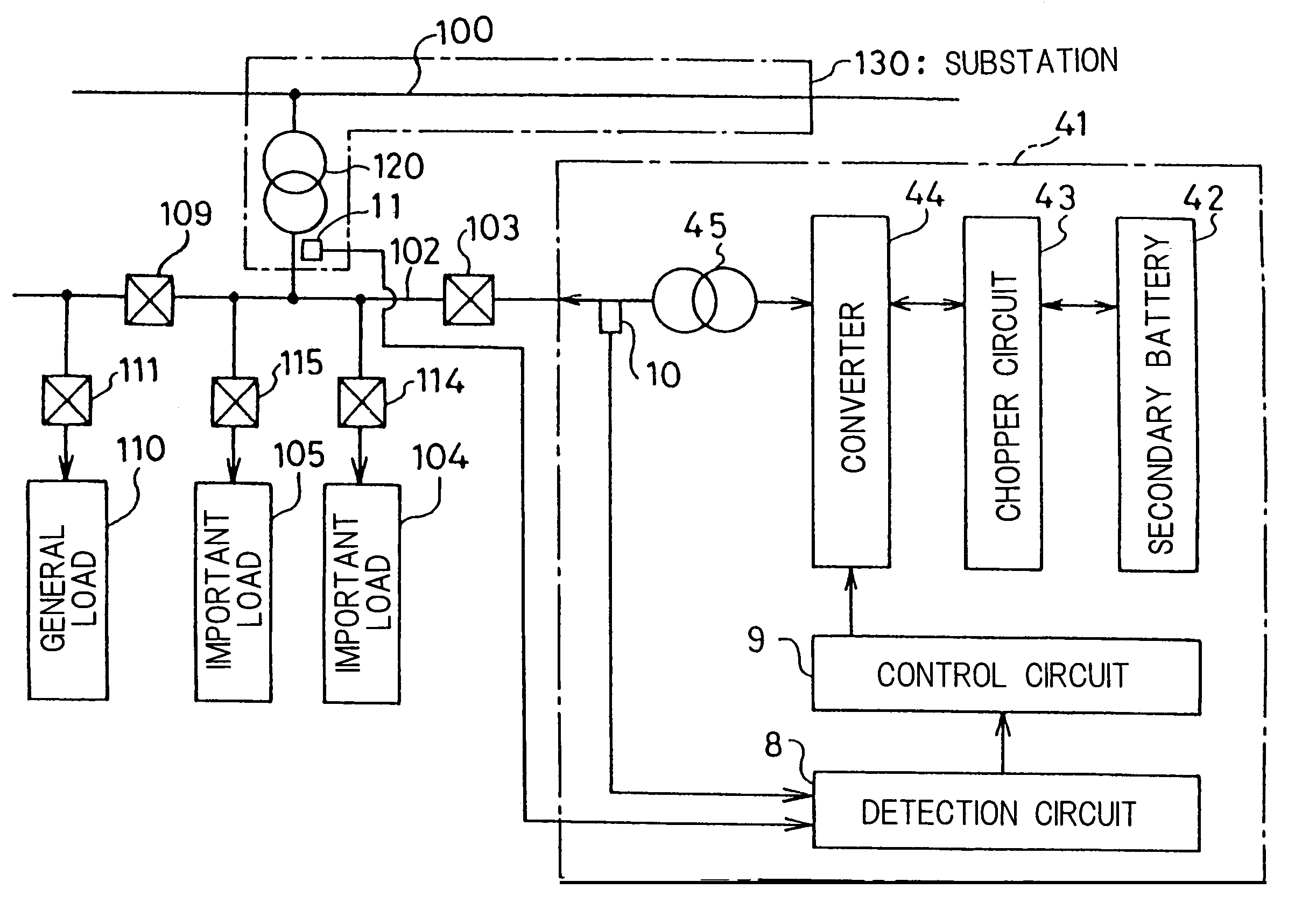

Stable power supplying apparatus

InactiveUS20060014054A1Small sizeLight weightBatteries circuit arrangementsCells structural combinationElectric forceDevice material

A stable power supply apparatus in accordance with the present invention comprises a secondary battery, a bidirectional chopper circuit and a bidirectional converter, wherein the secondary battery, the chopper circuit and the converter are connected in this order in the direction from the secondary battery side to a system bus line side. The converter is formed of a wide-gap semiconductor device, more particularly, a wide-gap bipolar semiconductor device, and the instantaneous large-power operation capability of the wide-gap bipolar semiconductor device and the instantaneous large-power supplying capability of the secondary battery are utilized. For a short time during which the influence of an instantaneous drop is prevented, the converter is operated as a converter having capability exceeding the instantaneous large-power supplying capability of the secondary battery and having power capacity several times or more the rating of the converter.

Owner:THE KANSAI ELECTRIC POWER CO

Safety drive for a flap or a valve

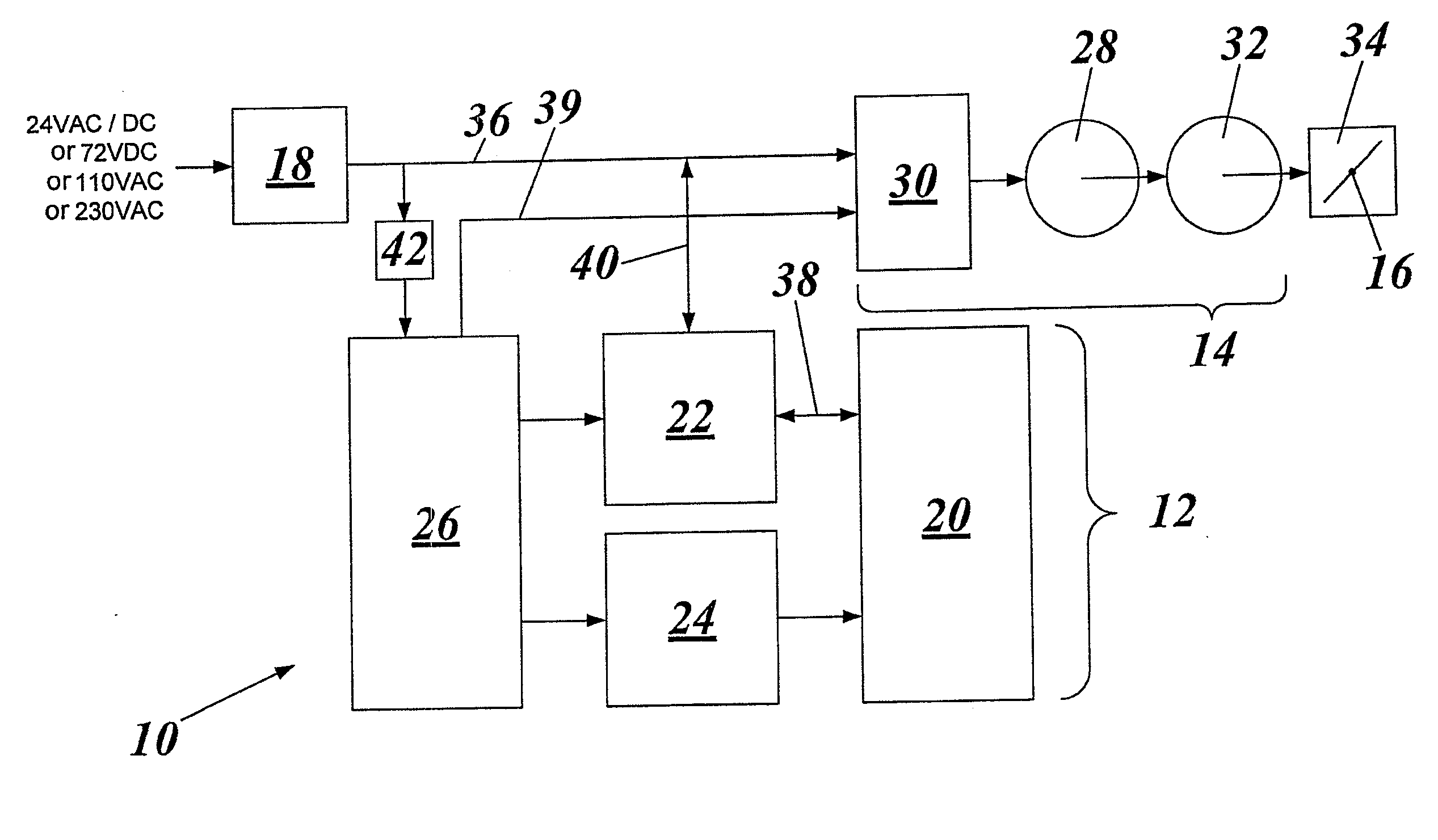

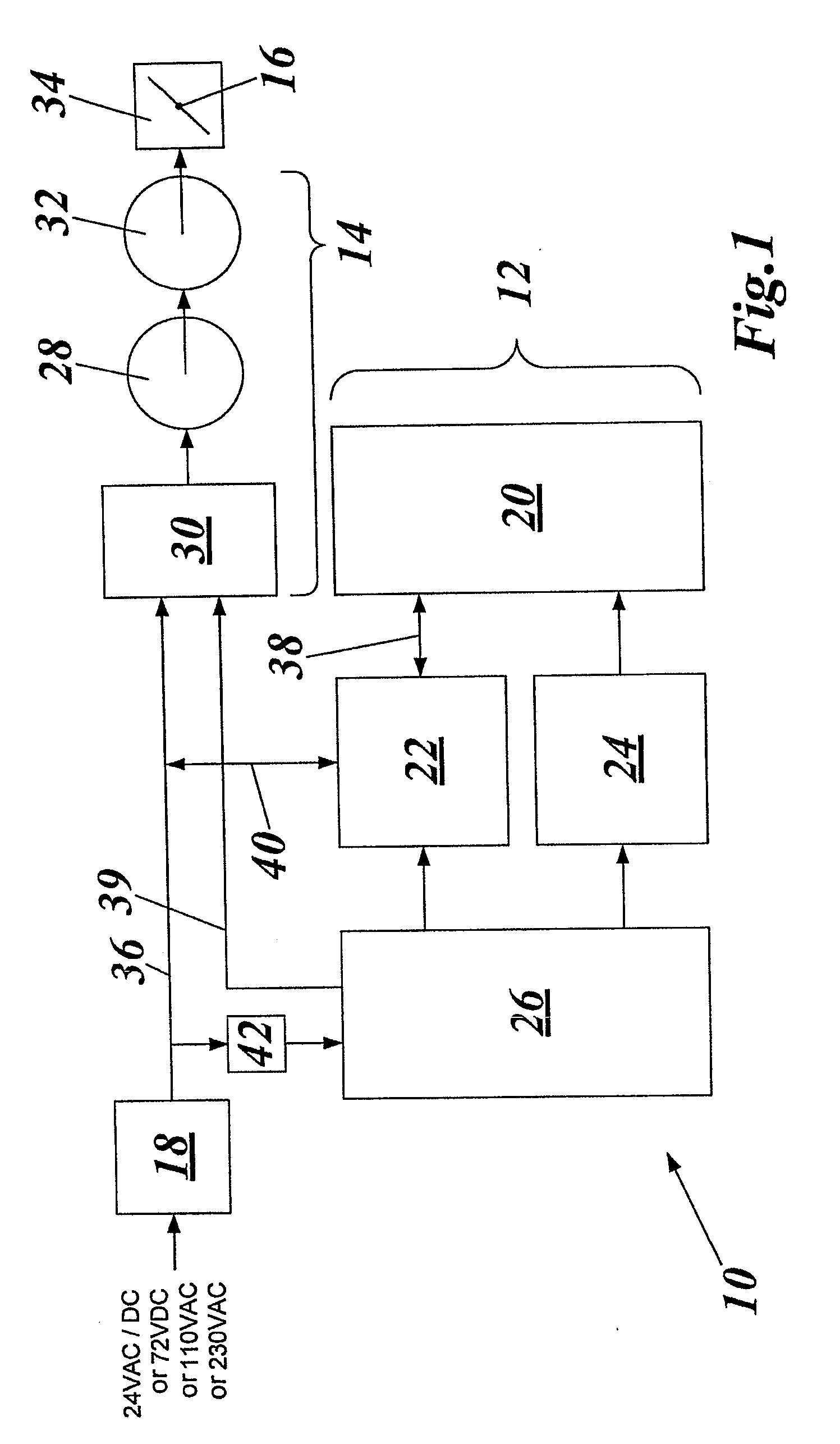

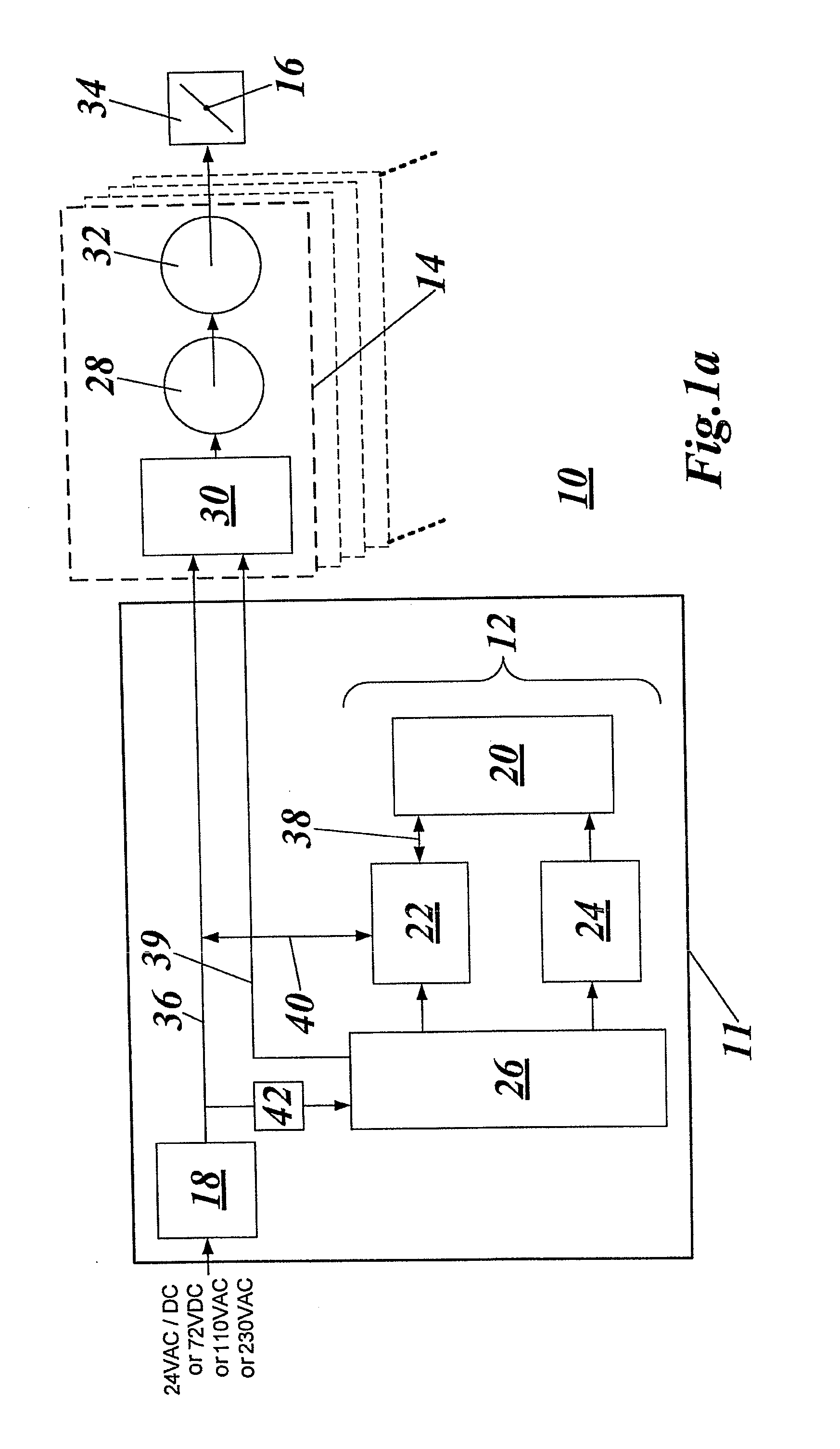

ActiveUS20100007301A1Simplified and improved safetySimple designSynchronous motors startersAC motor controlLow voltageEngineering

A safety drive unit (10) with a safety circuit (12) resets a flap or a valve into a specified safety position for controlling a gas or liquid volumetric flow, in particular in the field of heating, ventilation, and air conditioning (HVAC) fire protection and monitoring systems. The safety drive unit (10) essentially comprises an actuator (14) with a controllable electric motor (28), a capacitive energy storage unit (20), an energy converter (22) with a power module, and a power supply (18). During normal operation, the electric current in the power module of the energy converter (22) is converted to a lower voltage and stored in the capacitive energy storage unit (20) with at least one double-layer capacitor. If the voltage drops below a predetermined value or if there is a power failure, the stored electrical charge is converted back to a higher voltage by the same power module, and the electric motor (28) is activated until the specified safety position is reached.

Owner:BELIMO HOLDING AG

Stable power supplying apparatus

InactiveUS7554220B2Small sizeLight weightBatteries circuit arrangementsCells structural combinationWide gap semiconductorsEngineering

A stable power supply apparatus in accordance with the present invention comprises a secondary battery, a bidirectional chopper circuit and a bidirectional converter, wherein the secondary battery, the chopper circuit and the converter are connected in this order in the direction from the secondary battery side to a system bus line side. The converter is formed of a wide-gap semiconductor device, more particularly, a wide-gap bipolar semiconductor device, and the instantaneous large-power operation capability of the wide-gap bipolar semiconductor device and the instantaneous large-power supplying capability of the secondary battery are utilized. For a short time during which the influence of an instantaneous drop is prevented, the converter is operated as a converter having capability exceeding the instantaneous large-power supplying capability of the secondary battery and having power capacity several times or more the rating of the converter.

Owner:THE KANSAI ELECTRIC POWER CO

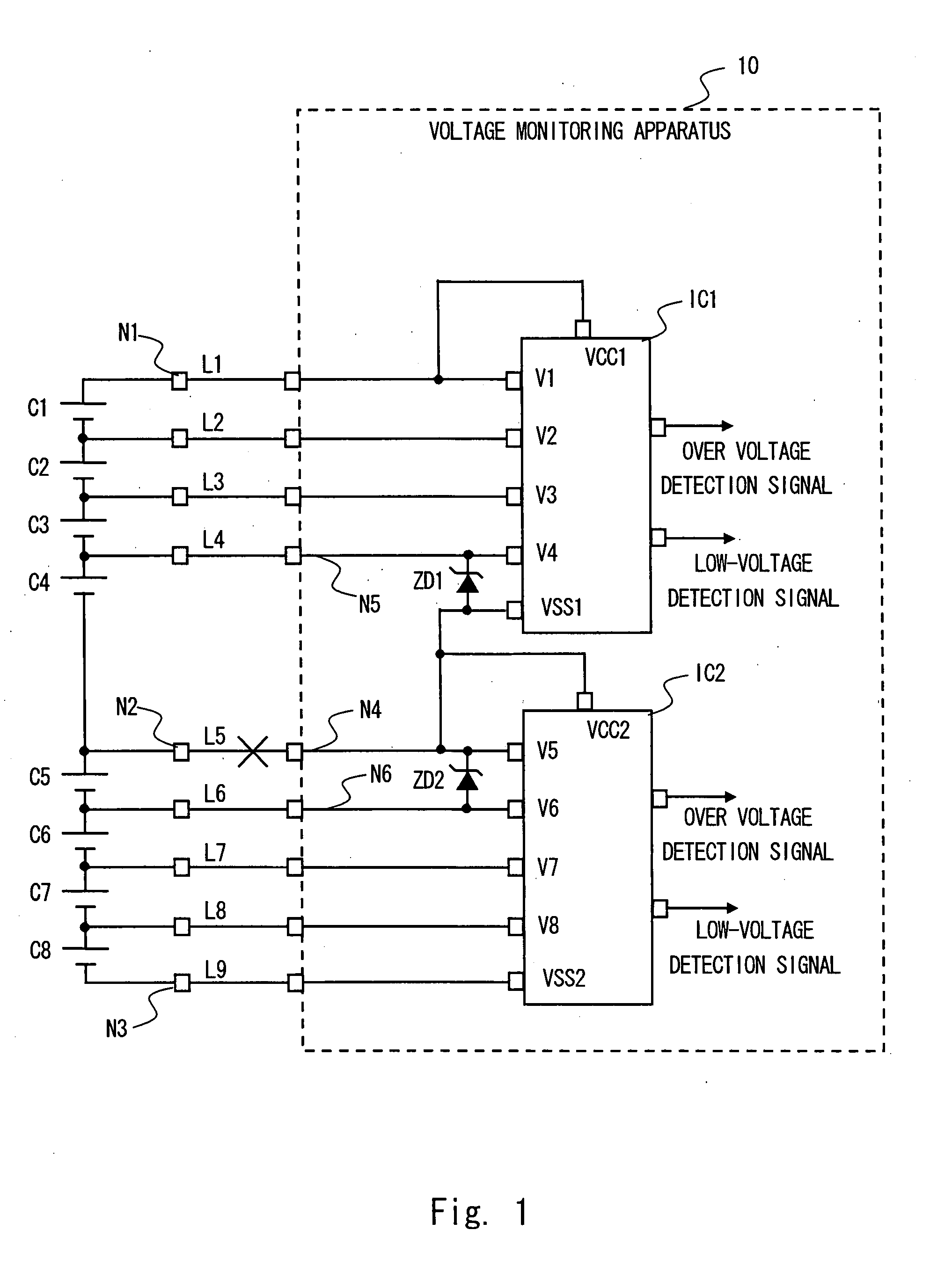

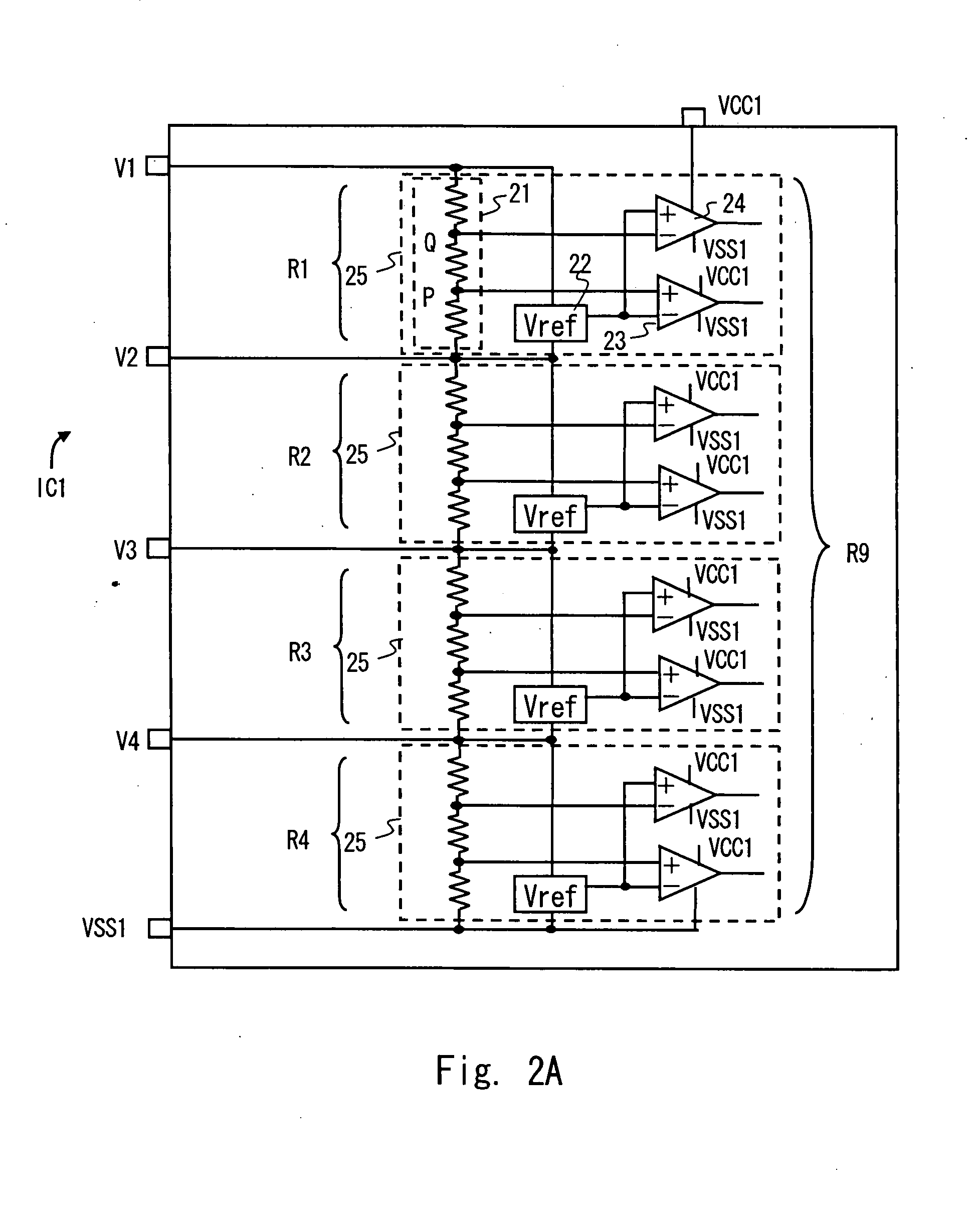

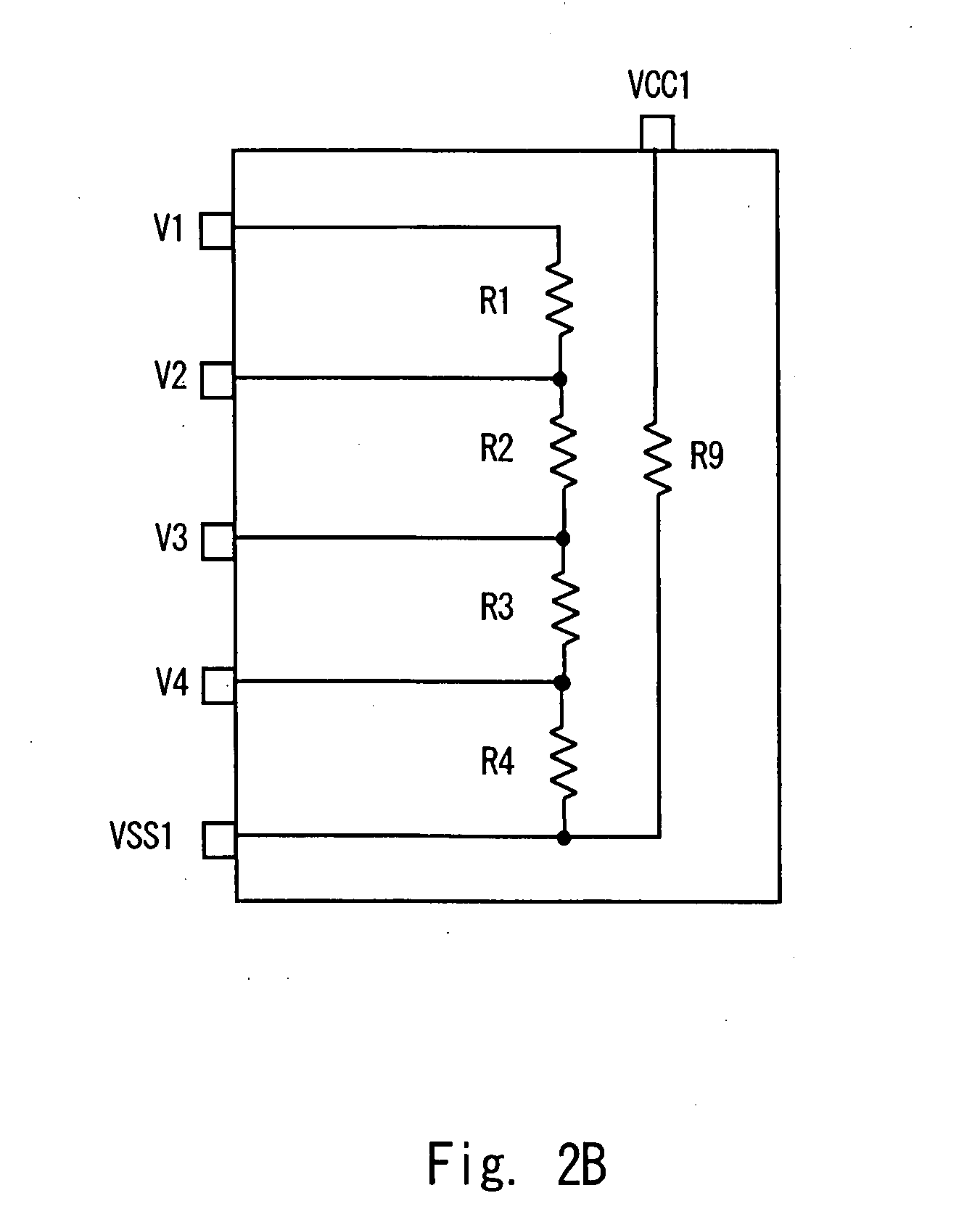

Battery voltage monitoring apparatus

InactiveUS20070188149A1Prevent voltageAvoid damageCharge equalisation circuitElectric powerVoltage sensorElectrical and Electronics engineering

A battery voltage monitoring apparatus to monitor a voltage of an assembled battery having a plurality of battery cells, the battery voltage monitoring apparatus comprises a first voltage sensor module having a voltage sensor and a first and a second module terminals connected to the voltage sensor, a second voltage sensor module having a voltage sensor different from the voltage sensor included in the first voltage sensor module and a third module terminal connected to the voltage sensor, a first terminal connected to the first and the third module terminals, a second terminal connected to the second module terminal, and a voltage clamp circuit to clamp a voltage between the first and the second terminals disposed between the first and the second terminals.

Owner:RENESAS ELECTRONICS CORP

Silicon carbide mos field-effect transistor and process for producing the same

InactiveUS20090134402A1Lower on-resistanceHigh blocking voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHigh concentration

In the SiC vertical MOSFET having a low-concentration p-type deposition film provided therein with a channel region and a base region resulting from reverse-implantation to n-type through ion implantation, dielectric breakdown of gate oxide film used to occur at the time of off, thereby preventing a further blocking voltage enhancement. This problem has been resolved by interposing of a low-concentration n-type deposition film between a low-concentration p-type deposition film and a high-concentration gate layer and selectively forming of a base region resulting from reverse-implantation to n-type through ion implantation in the low-concentration p-type deposition film so that the thickness of deposition film between the high-concentration gate layer and each of channel region and gate oxide layer is increased.

Owner:NAT INST OF ADVANCED IND SCI & TECH

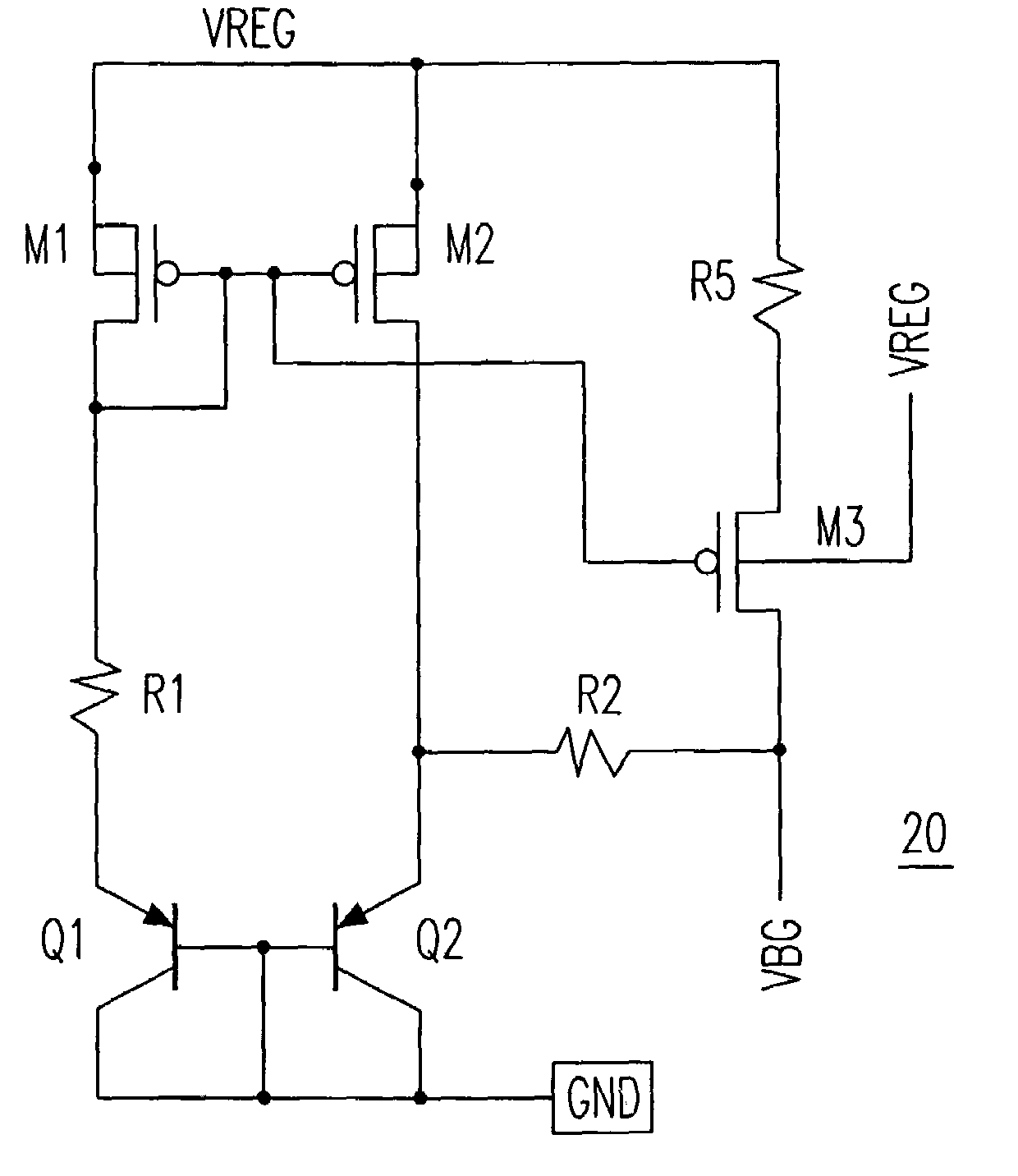

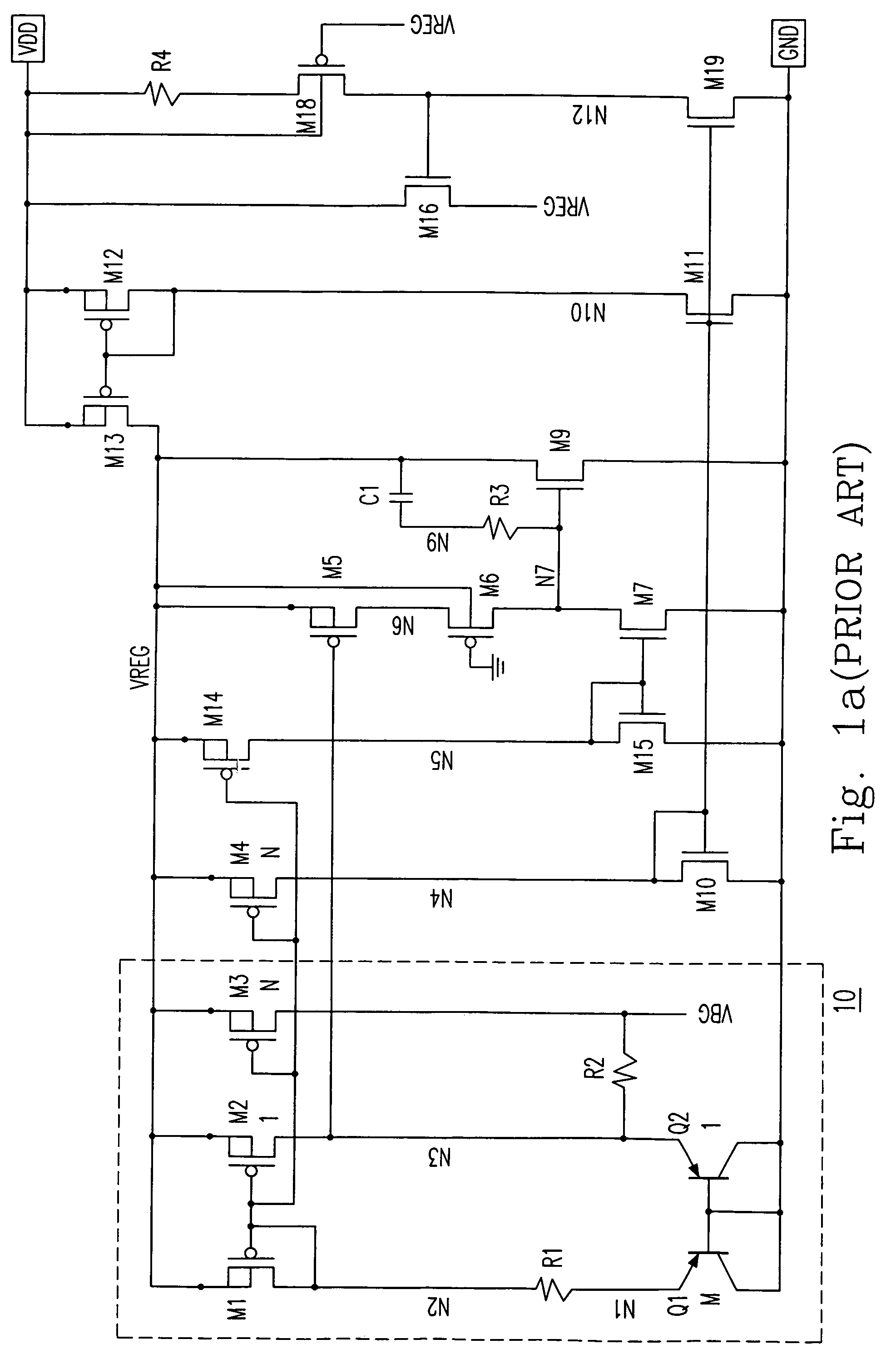

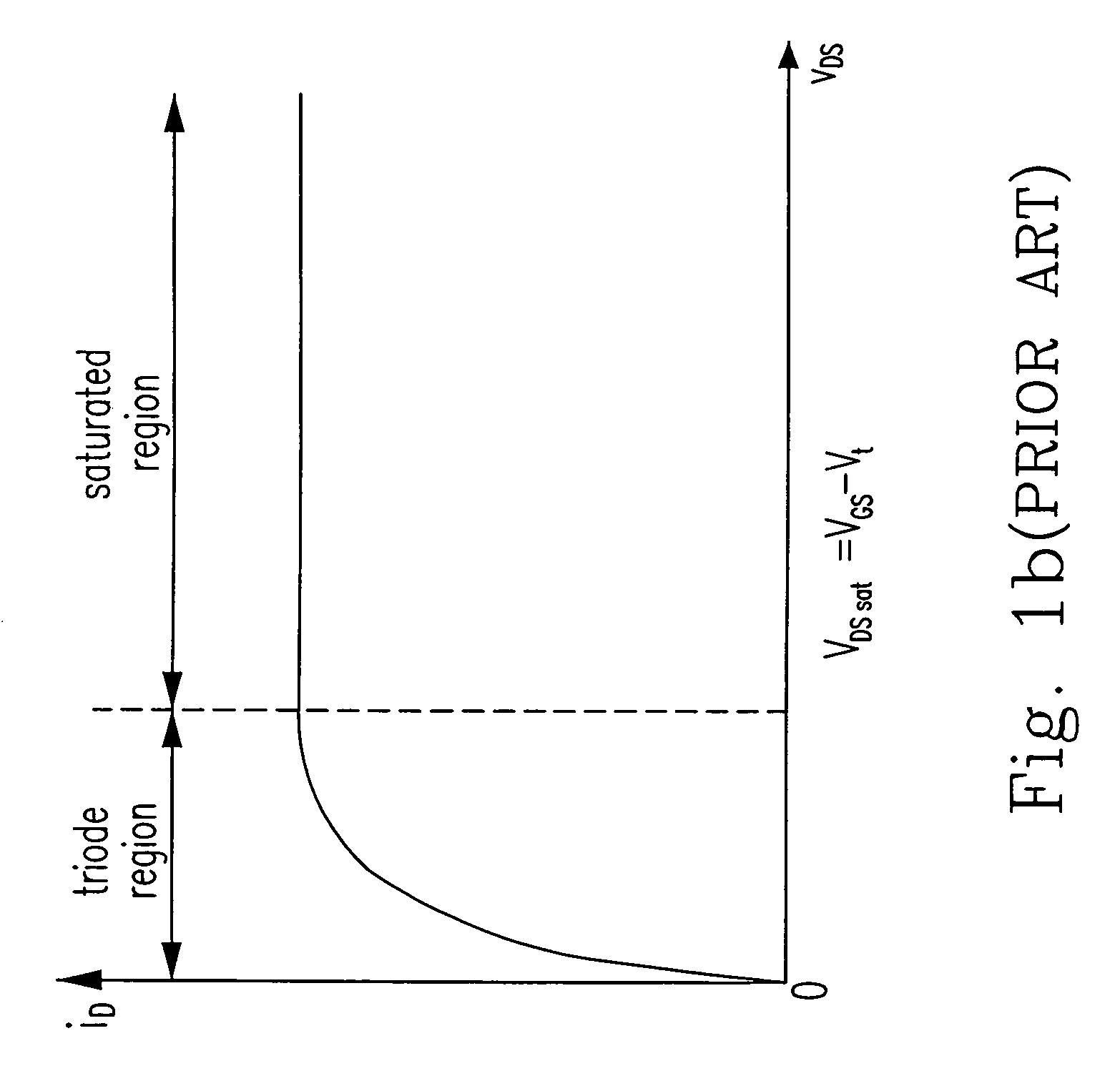

Bandgap reference voltage circuit

ActiveUS7193402B2Prevent voltagePower supply linesElectronic switchingCompensation effectEngineering

A bandgap reference voltage circuit is provided, in which an additional resistor as well as a transistor is utilized to prevent the source-drain voltage of a metal oxide semiconductor field effect transistor electrically connected to an output terminal of the bandgap reference voltage circuit from falling into the triode region. Through the provided bandgap reference voltage circuit, the temperature compensation effect is able to be normally executed, so as to supply a stable bandgap reference voltage.

Owner:ANALOG INTEGRATIONS CORP

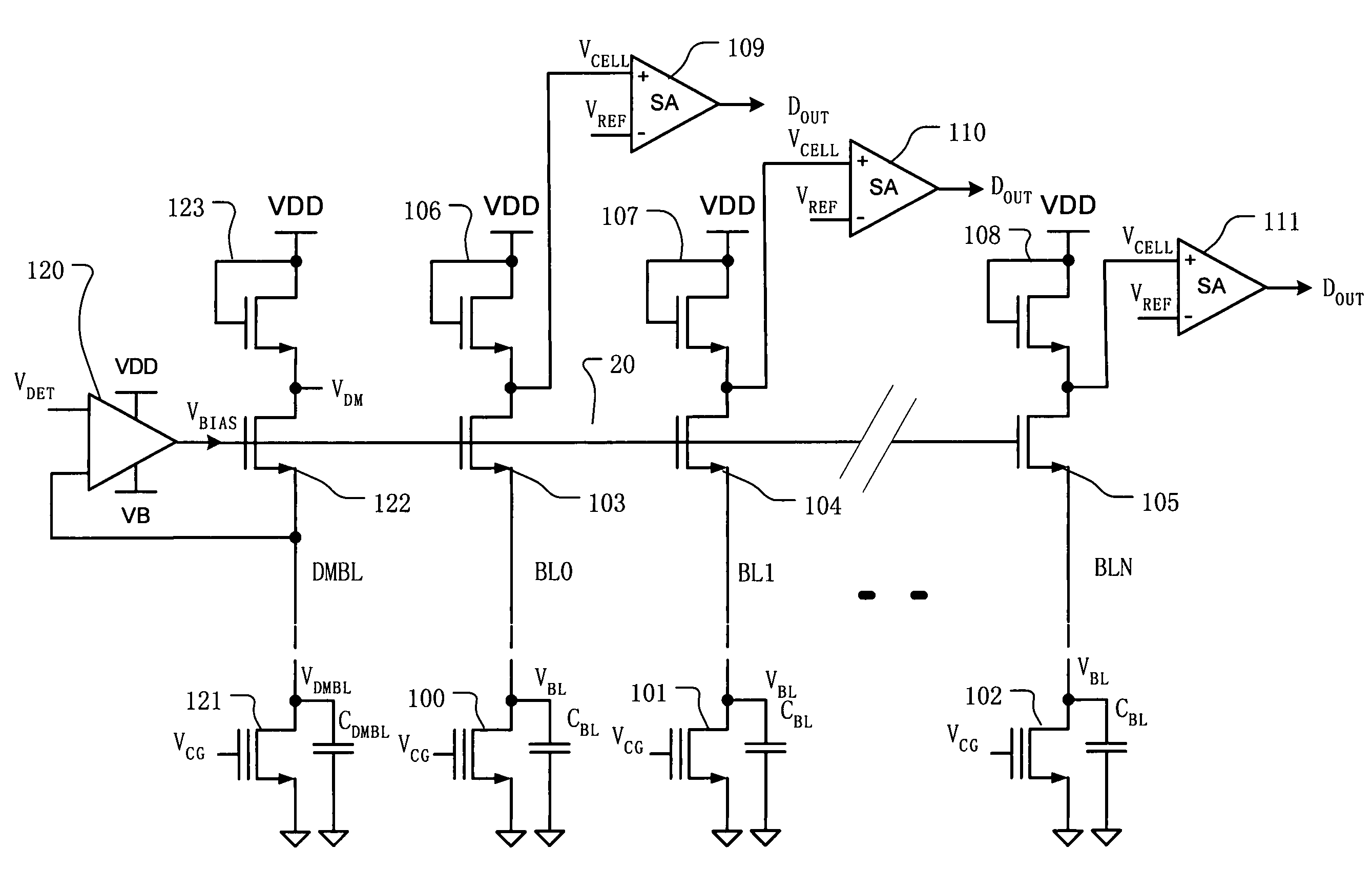

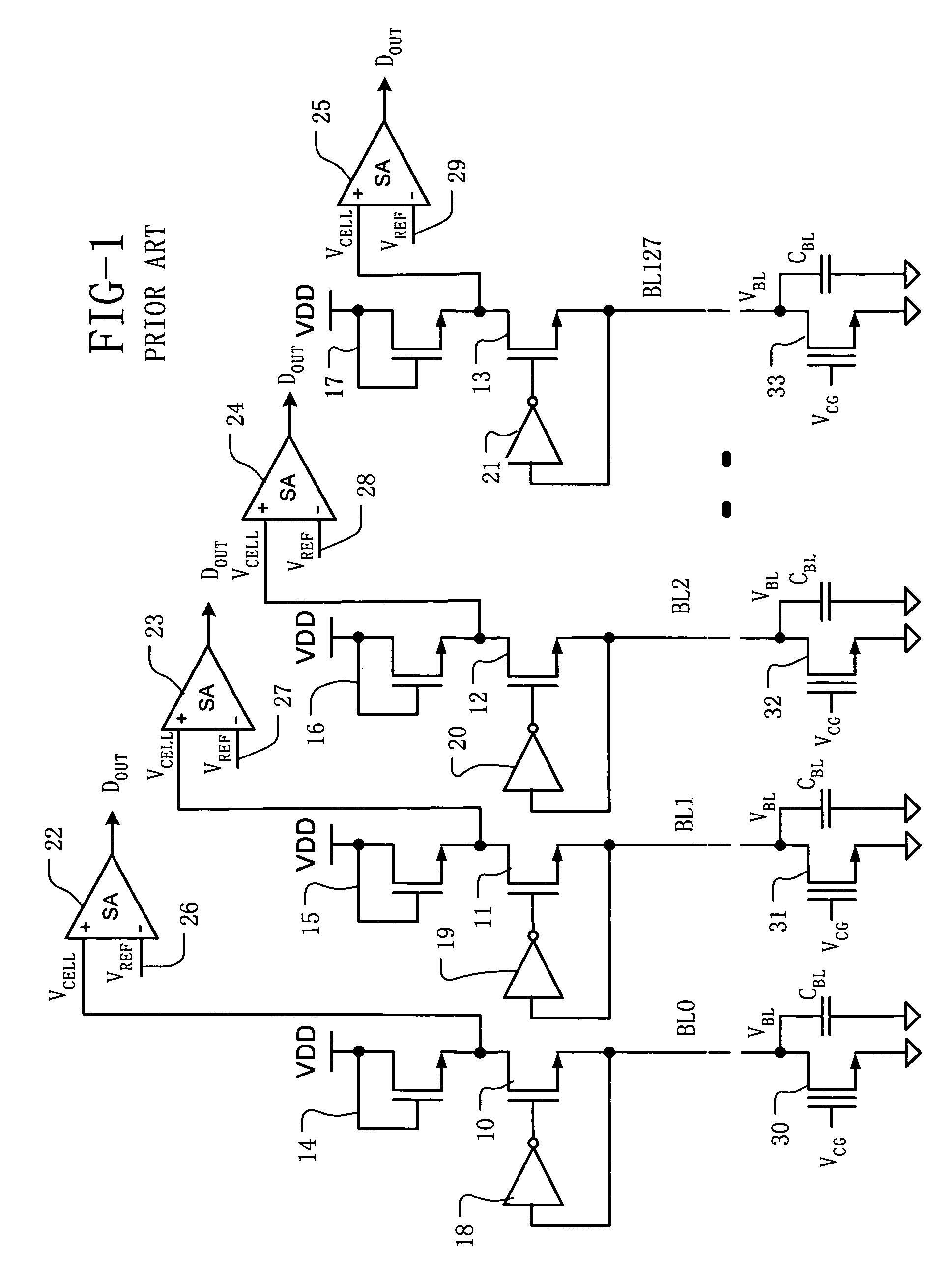

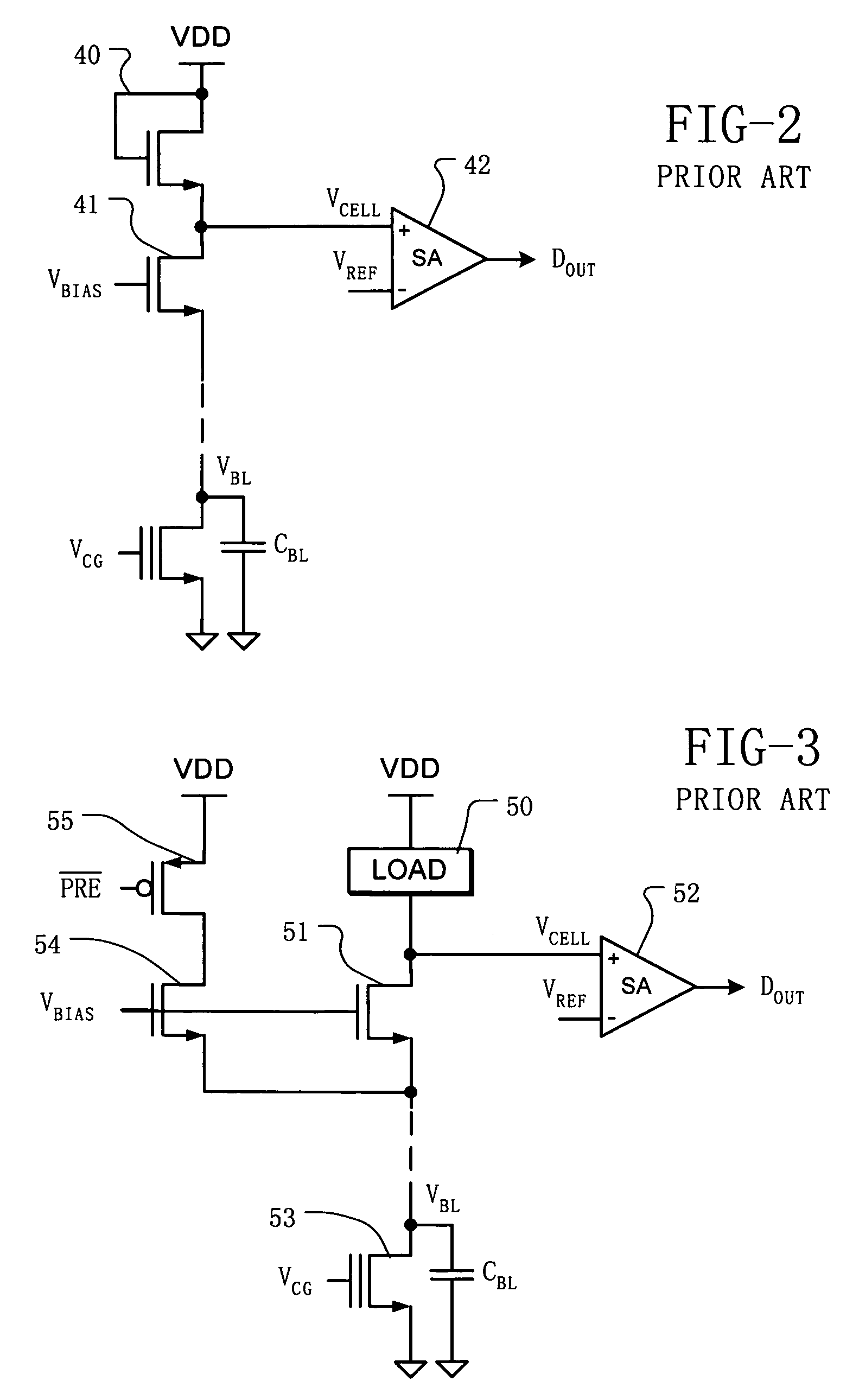

Memory array with low power bit line precharge

An integrated circuit memory array with an extra column of memory cells and a reference bit line is provided, in which the reference bit line acts as a reference for a shared precharging and clamping control on the bit lines in the array. Clamp transistors are coupled to respective bit lines in the array, and adapted to prevent voltage on the respective bit lines from exceeding a target level. A comparator has an input coupled to the reference bit line and an output coupled to the clamp transistors on the plurality of bit lines. The comparator generates a bias voltage which turns on the clamp transistors at a first bias level when the reference bit line has a voltage below the target level, and a second bias level, which is lower than the first bias level, when the reference bit line has a voltage near the target level.

Owner:MACRONIX INT CO LTD

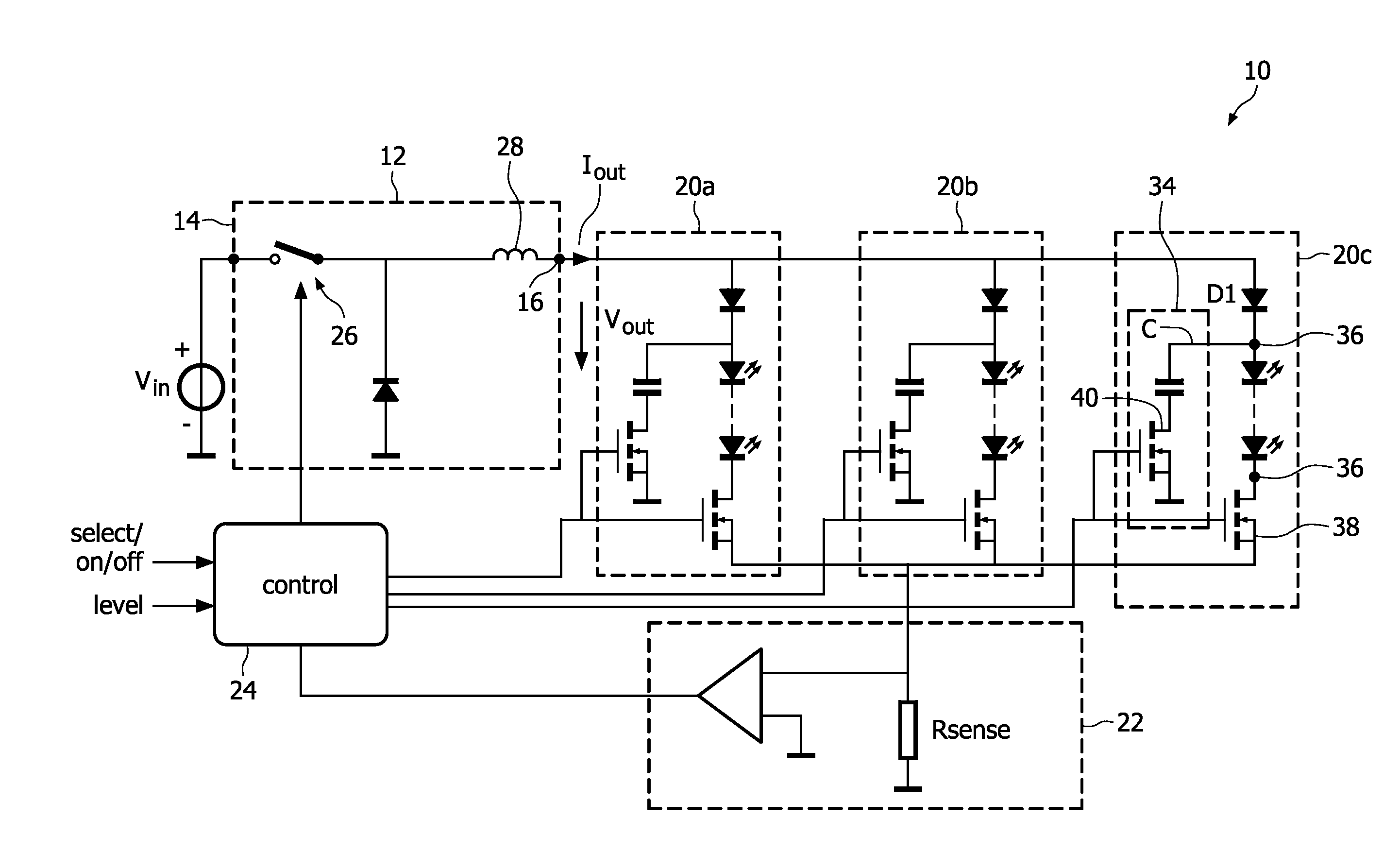

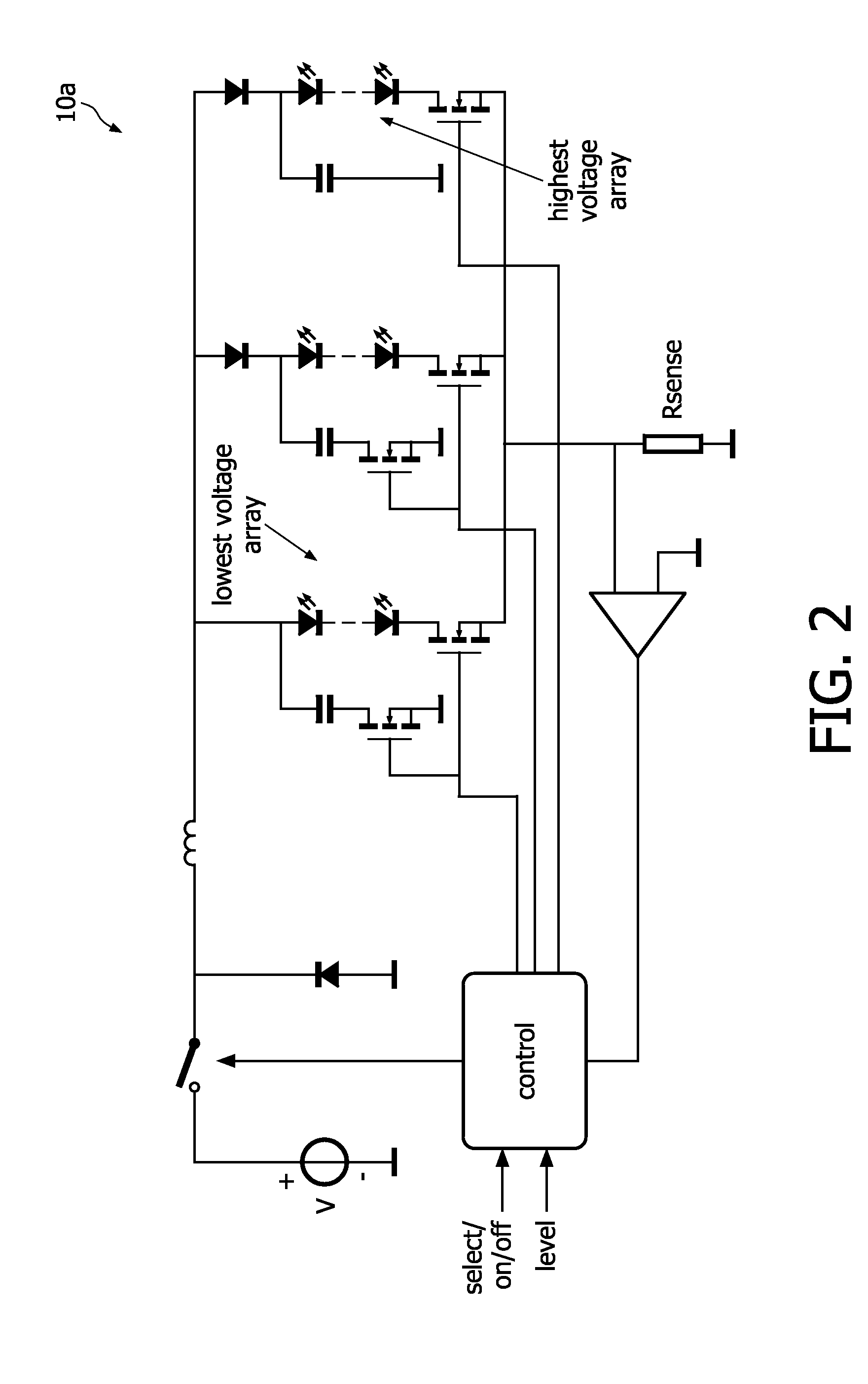

Power suppy circuit

InactiveUS20100253302A1Prevent voltageElectroluminescent light sourcesDc-dc conversionElectricitySwitched capacitor

The invention relates to a power supply circuit (10) and methods for supplying electrical power to at least one load output. The circuit comprises a main power supply unit (12) with a voltage input (14), a main switching element (26) and a reactive element (28). The switching element (26) is controllable to deliver an output voltage or current (I out). Output units (20a, 20b, 20c) with load outputs are connected to a main power supply unit (12). In order to drive loads connected to the load outputs, e.g. LEDs, OLEDs or laser diodes, with exact pulses, each output unit (20a, 20b, 20c) has a load switching element (38) to connect or disconnect the main power supply unit (12) to or from the load output. There are further provided switched capacitor units (34), each with a capacitor (C) and a capacitor switching element (40). The capacitor units may be operated such that the capacitors remain essentially charged at different voltage levels. According to a second aspect of the invention, each output unit (20a, 20b, 20c) has a switched capacitor unit (34) with a capacitor (C) and a capacitor switching element (40) connected to the load output. The load switching element (38) and the capacitor switching elements (40) are controlled synchronously.

Owner:SIGNIFY HLDG BV +1

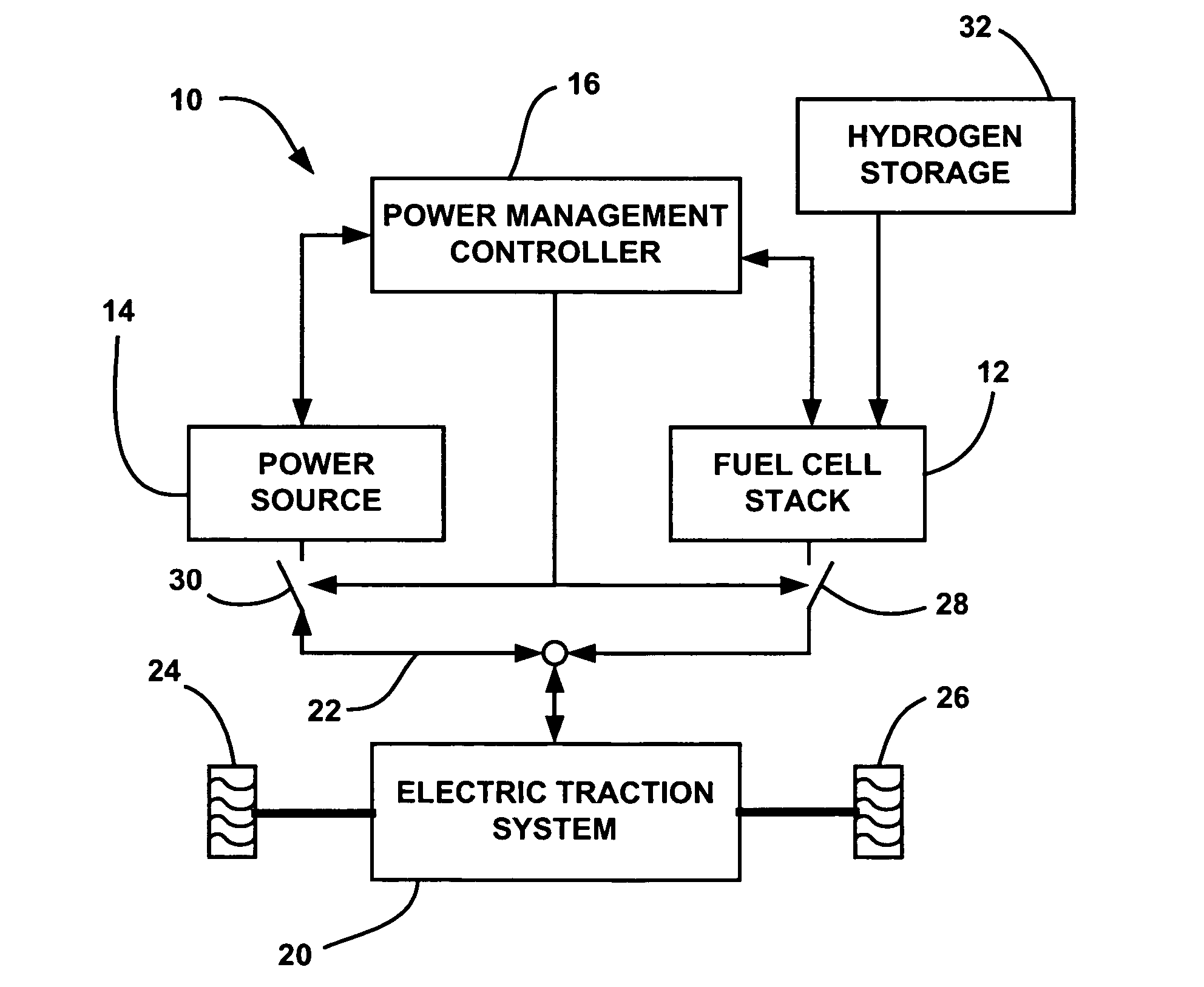

Reduction of voltage loss caused by voltage cycling by use of a rechargeable electric storage device

InactiveUS20060147770A1Easy loadingReduce voltageFuel cells groupingFuel cell auxillariesElectricityFuel cells

A fuel cell system that employs a fuel cell stack and a supplemental power source, such as a battery or an ultra-capacitor. The power source provides supplemental power in addition to the output power of a fuel cell stack for high load demands. The fuel cell system includes a power management controller that controls the power output from the supplemental power source and the fuel cell stack as the demand on the fuel cell stack changes. During low load demands, where the voltage across the fuel cell stack may increase above a potential that could cause oxidation of platinum catalyst particles within the fuel cells in the stack, the power management controller causes the fuel cell stack to charge the power source so as to decrease the voltage output on the stack.

Owner:GM GLOBAL TECH OPERATIONS LLC

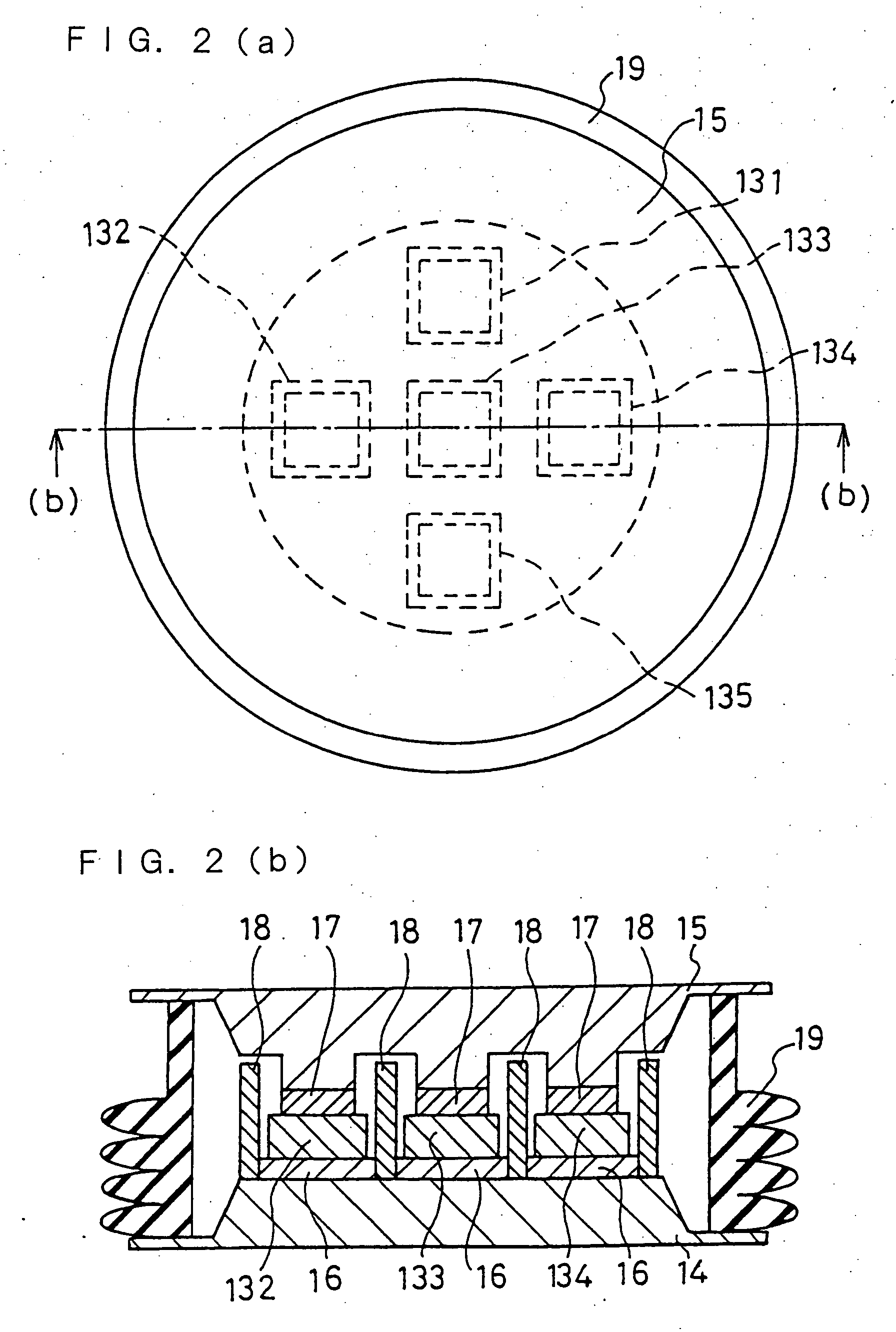

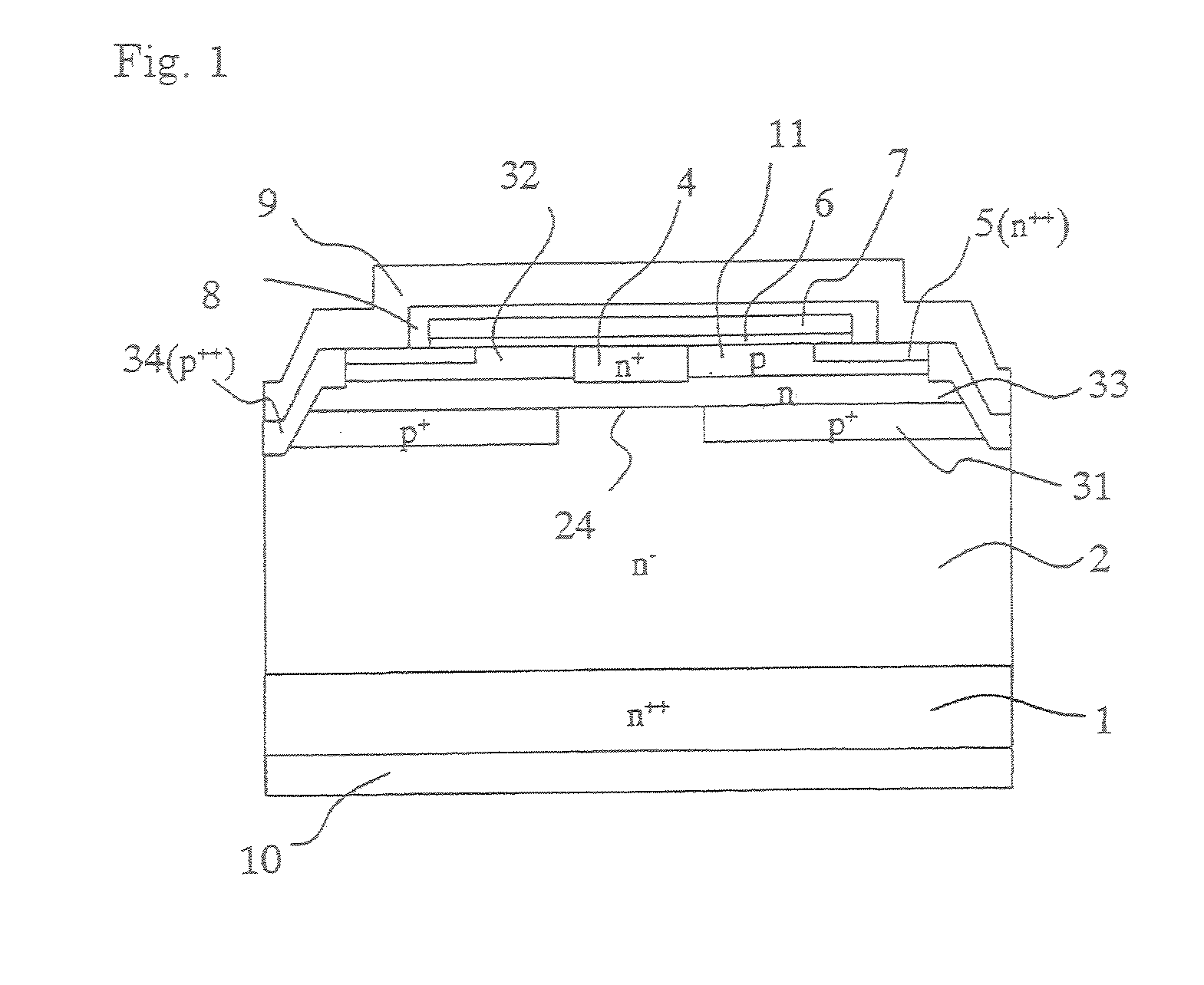

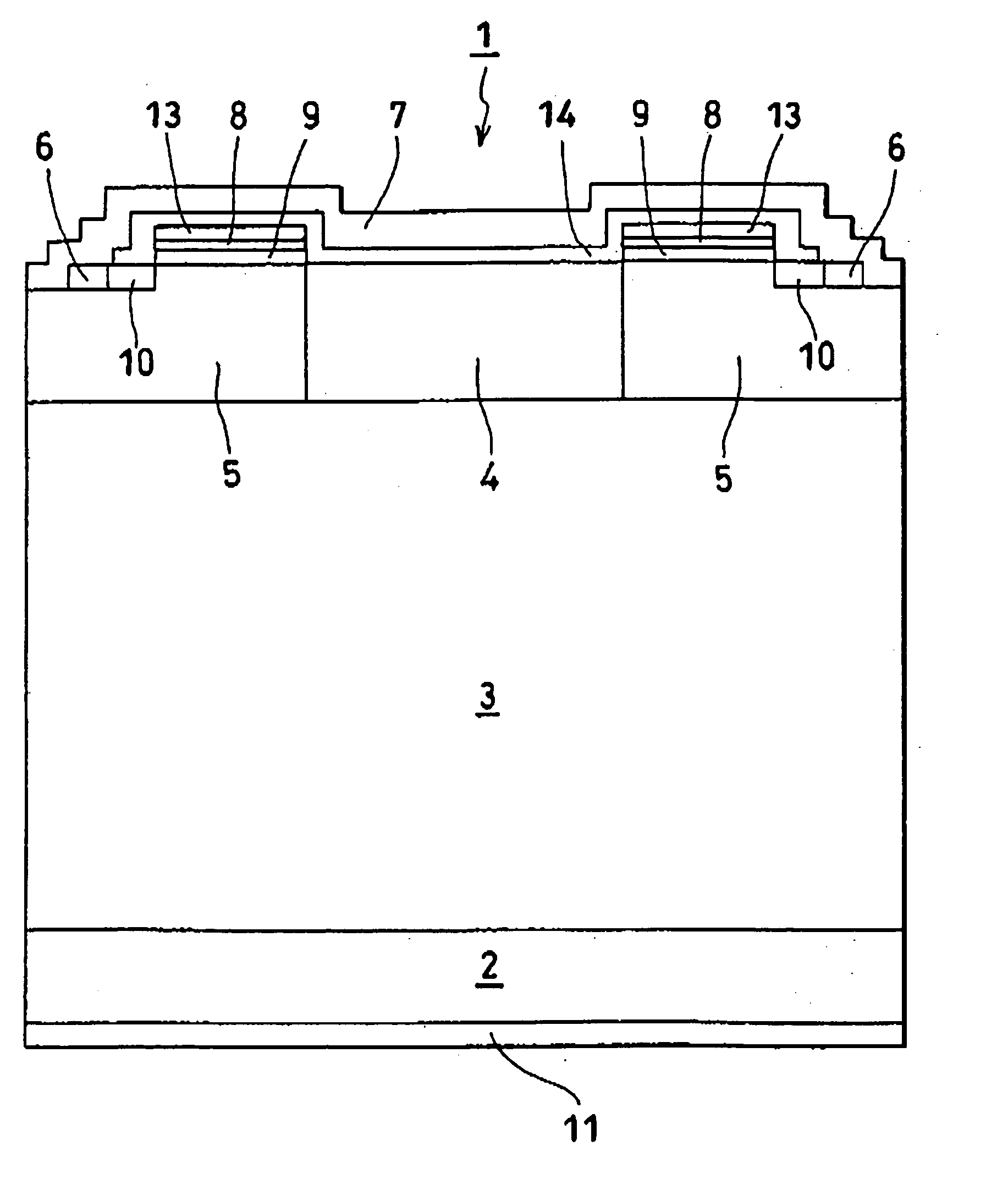

Semiconductor device

InactiveUS20060108589A1Improve channel mobilityPrevent voltageTransistorSemiconductor/solid-state device manufacturingDevice materialCarbide

A semiconductor device (1) includes an n-type silicon carbide substrate (2) of a high impurity concentration, an n-type silicon carbide layer (3) of a low impurity concentration disposed on the substrate, a first n-type silicon carbide region (4) of a first impurity concentration disposed on the surface of the n-type silicon carbide layer, first p-type silicon carbide regions (5) disposed as adjoined to the opposite sides of the first n-type silicon carbide region, a second n-type silicon carbide region (6) disposed selectively from the surface through the interior of the first p-type silicon carbide region, polycrystalline silicon (7) short-circuiting the first p-type silicon carbide region (5) to the second n-type silicon carbide region (6), a gate electrode (8) and a third n-type silicon carbide region (10), wherein the components thereof are individually constructed in a vertical DMOS structure. Since the polycrystalline silicon short-circuits the first p-type silicon carbide region to the second n-type silicon carbide region, the threshold voltage can be given a fixed value, and the device can be used as an actual MISFET.

Owner:NAT INST OF ADVANCED IND SCI & TECH

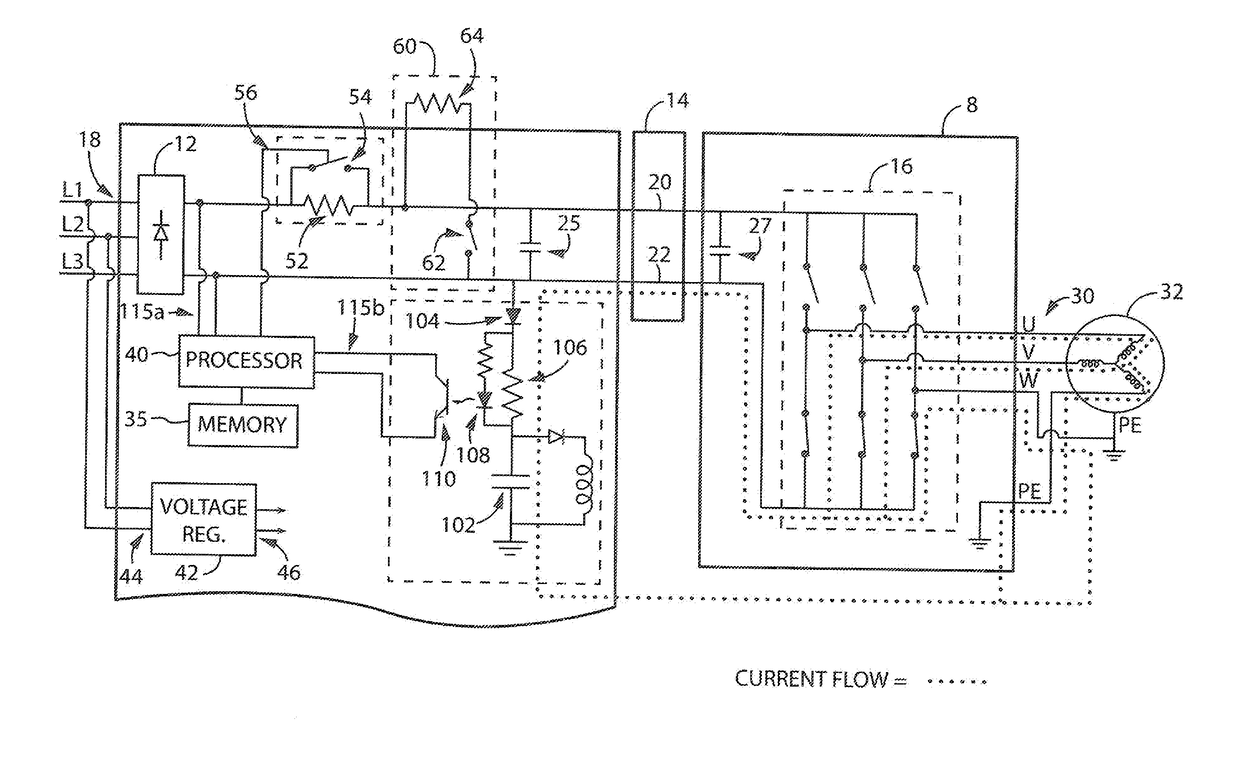

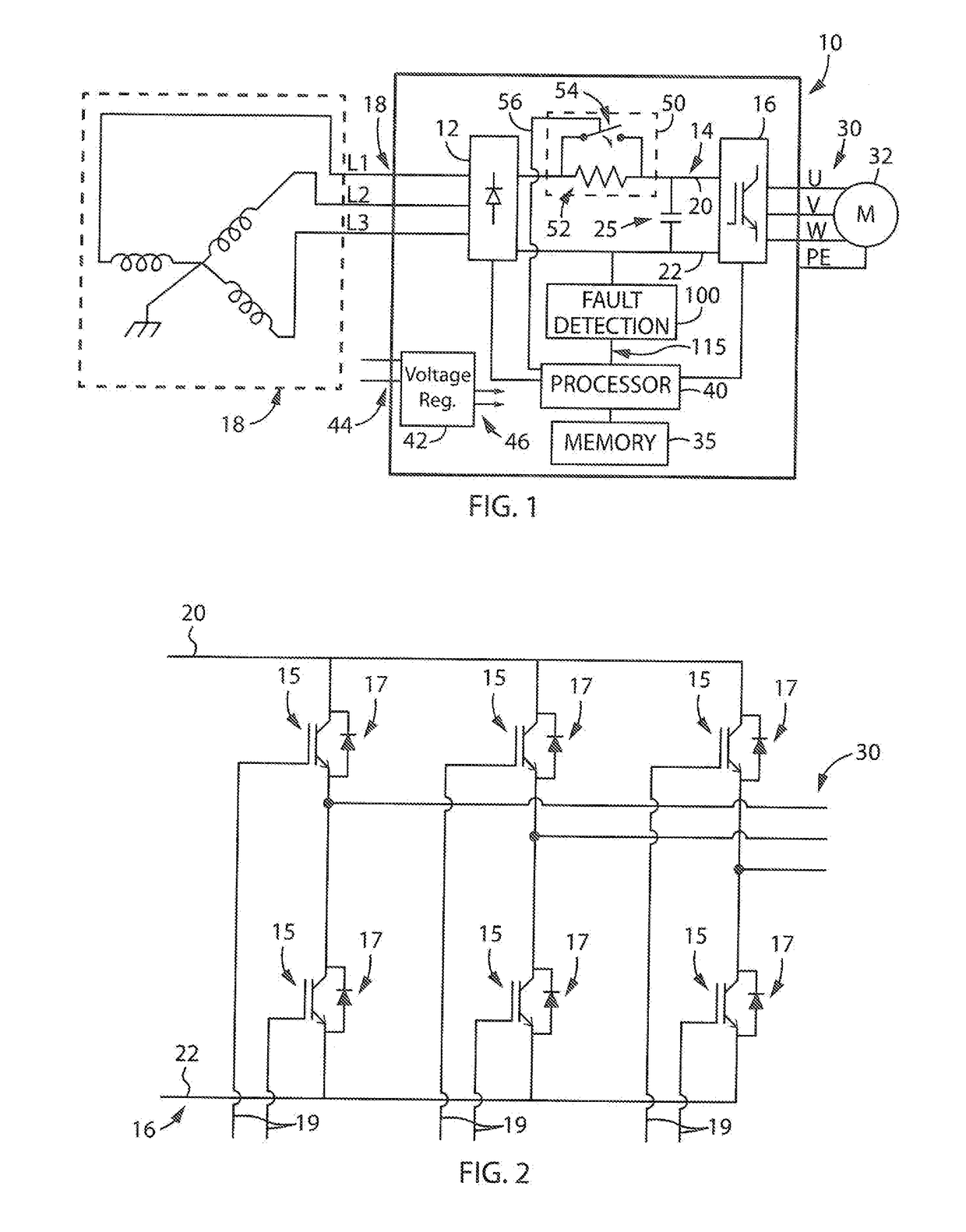

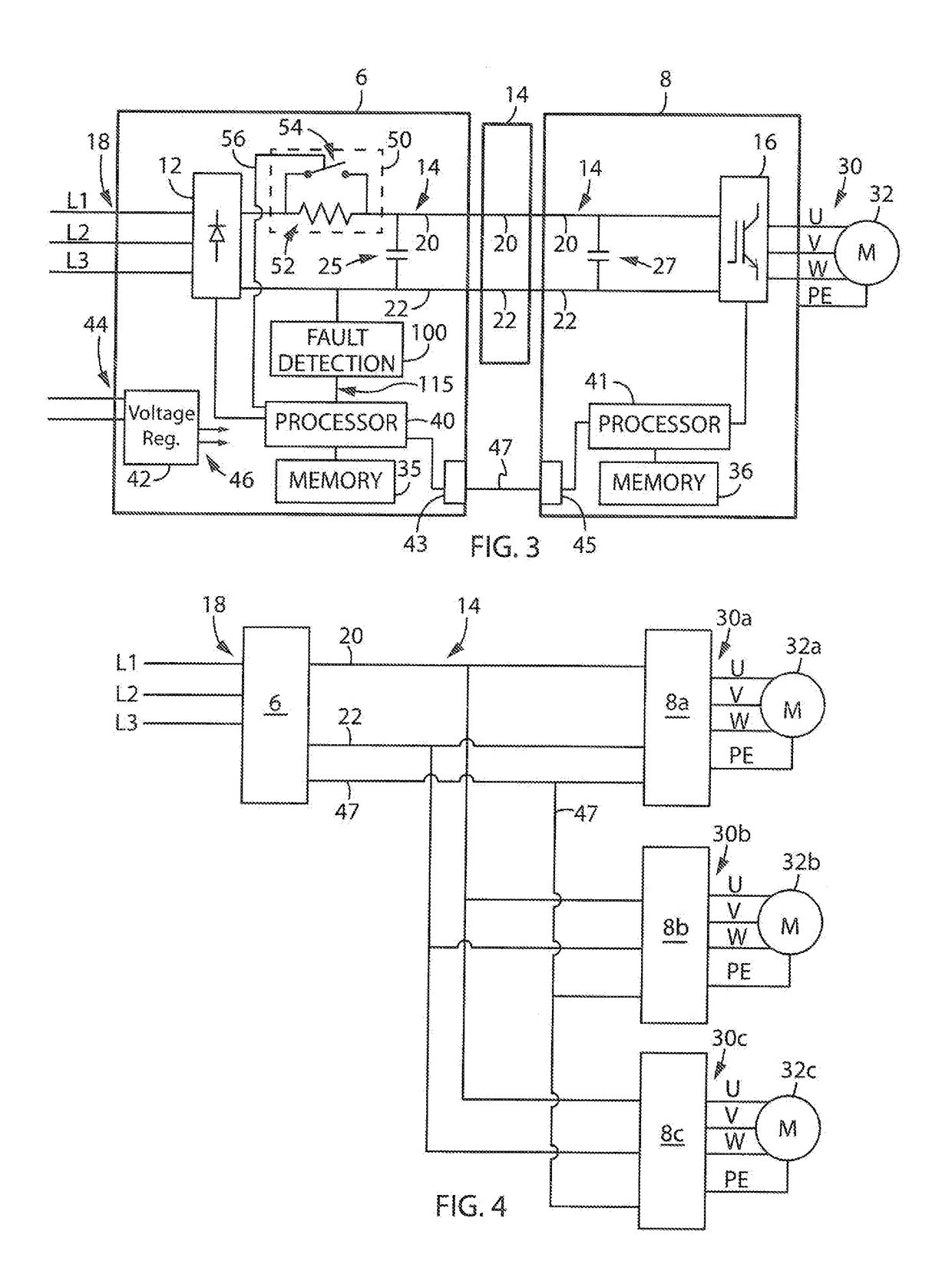

Method and apparatus for detecting ground faults in inverter outputs on a shared DC bus

ActiveUS20170373630A1Prevent voltageEase of applicationProgramme controlAC motor controlDC-BUSPower inverter

A system to detect a ground fault at the output of an inverter section prior to powering up a motor drive system is disclosed. A low voltage power supply is connected to the DC bus prior to connecting the input power source to the rectifier section. If a ground fault exists, the voltage potential on the DC bus causes conduction through one of the freewheeling diodes connected in parallel to the power switching device on the output of the inverter section. A fault detection circuit generates a signal corresponding to the presence of the low Voltage potential when the low voltage is applied to the DC bus. If a ground fault is present at the output of one of the inverter sections, the motor drive system prevents the AC voltage from being applied to the rectifier section.

Owner:ROCKWELL AUTOMATION TECH

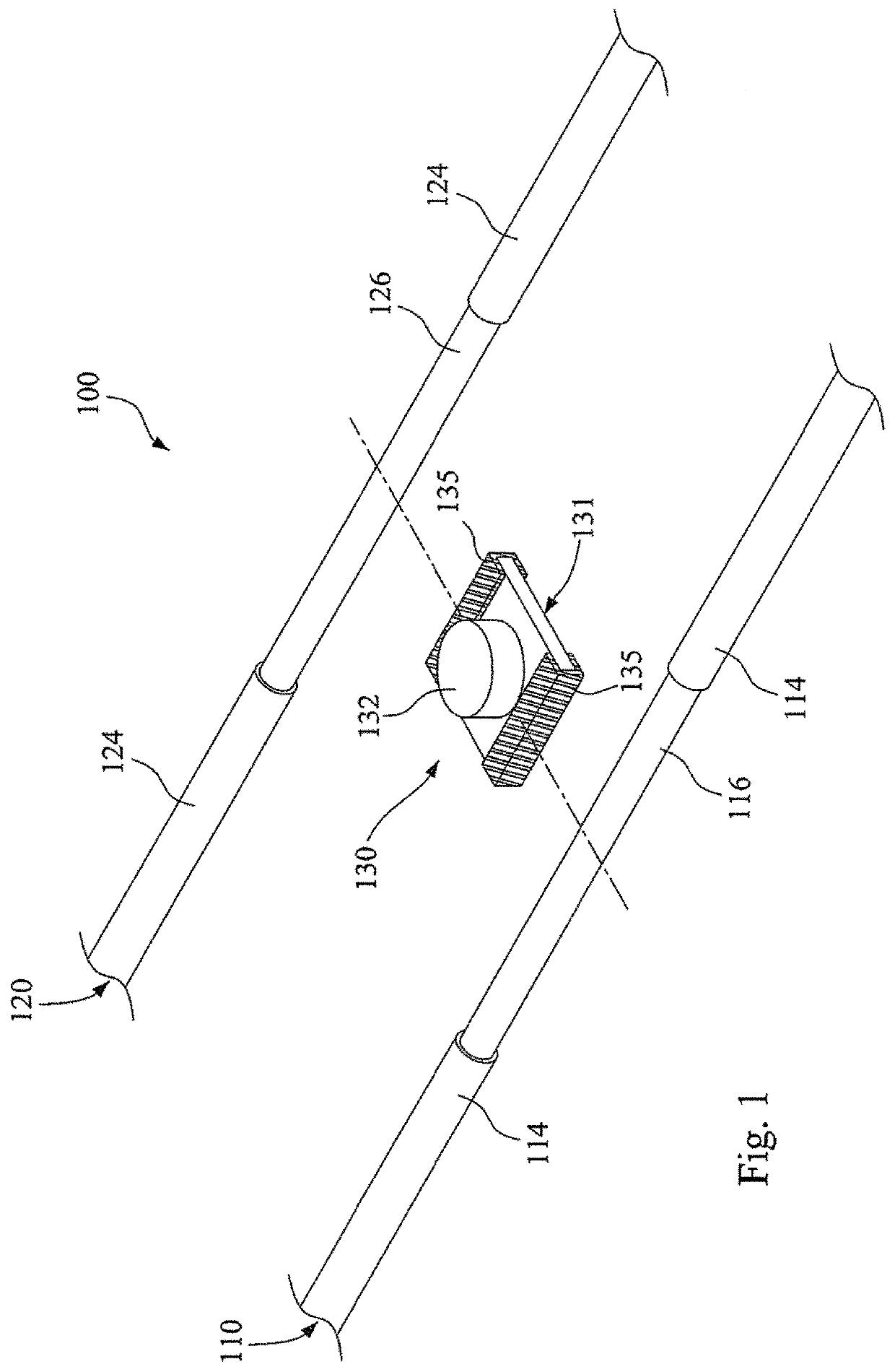

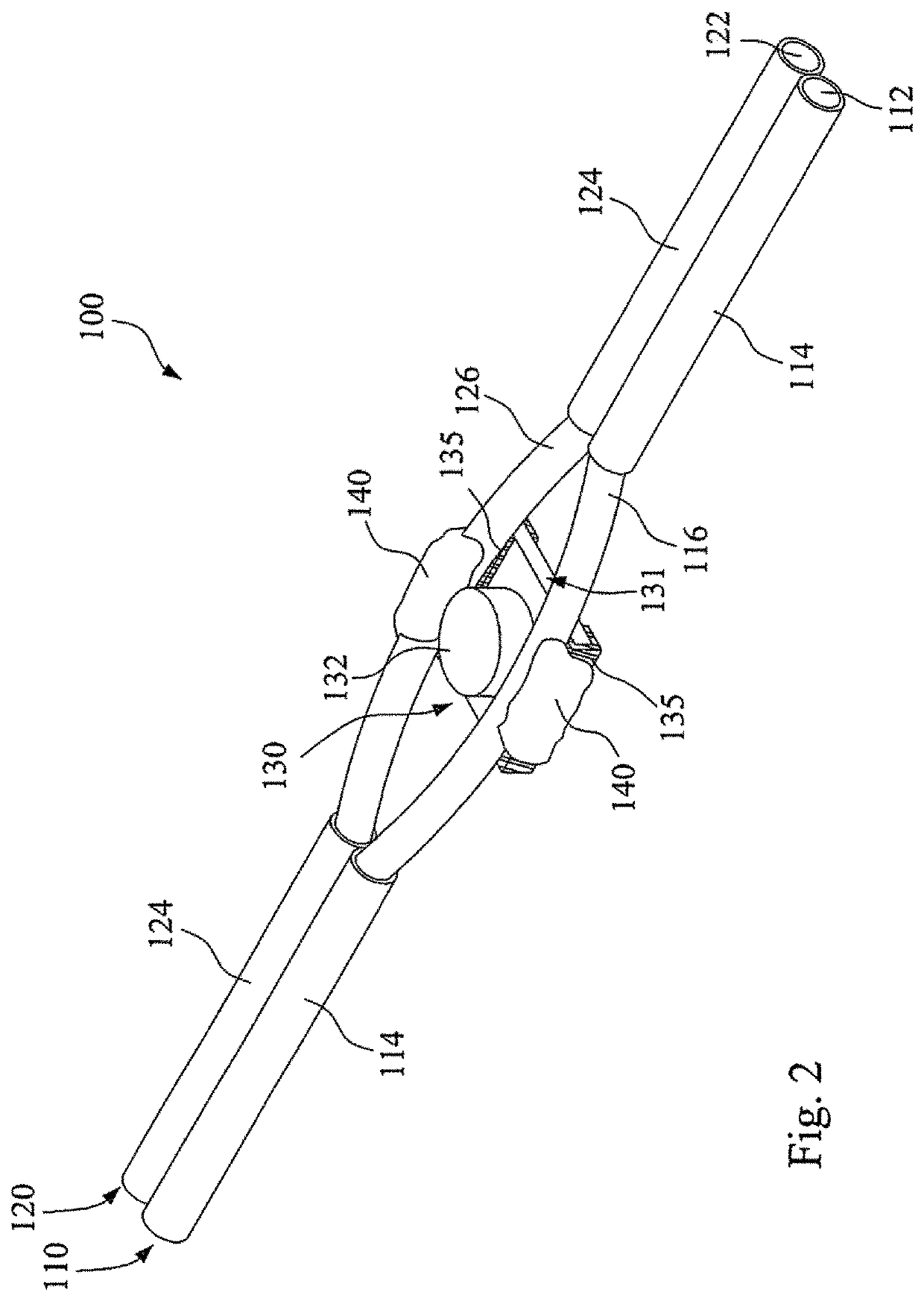

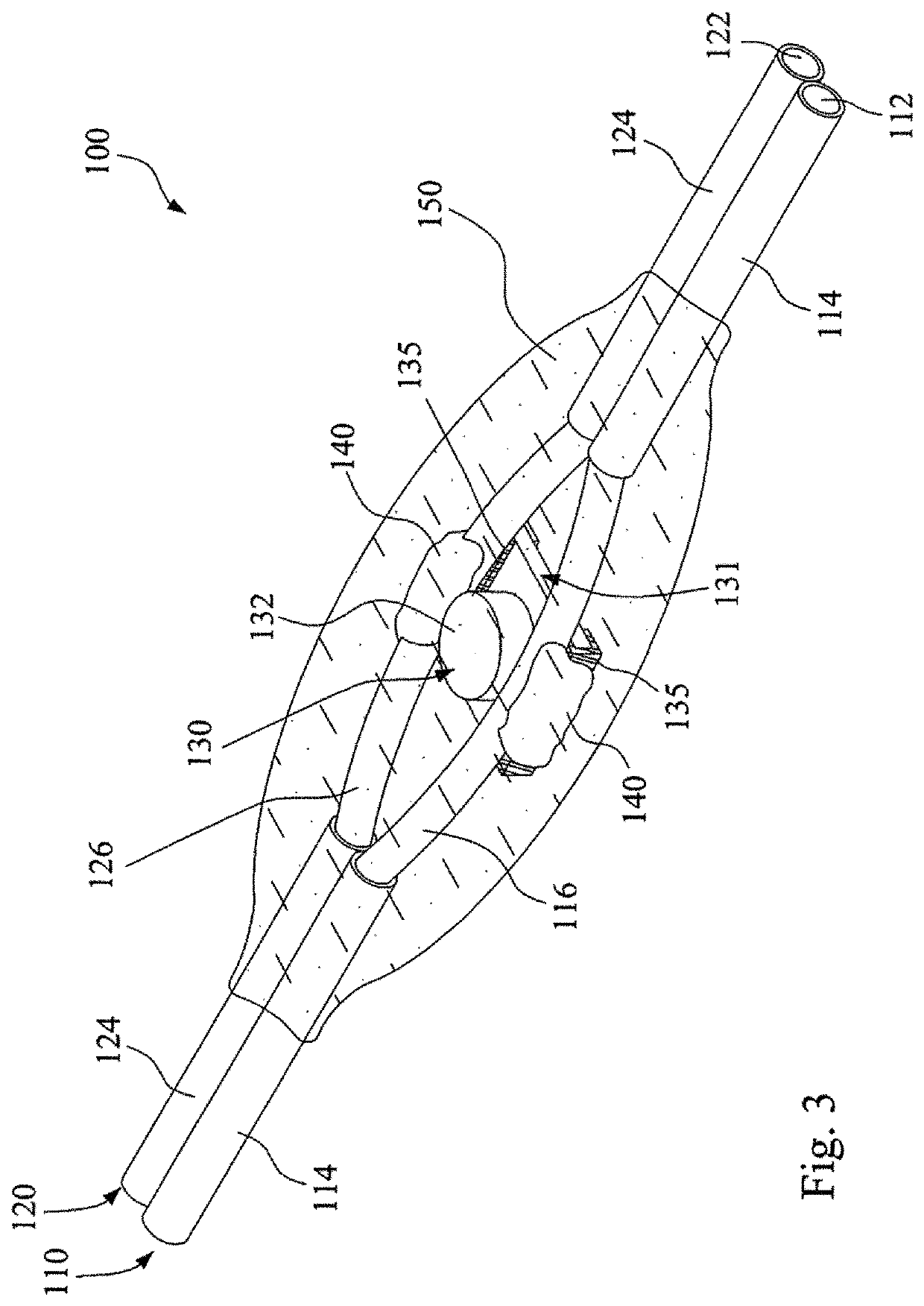

Light string and light string circuits

ActiveUS10697598B1Good illumination effectPrevent voltageElectric circuit arrangementsSolid-state devicesEngineeringAdhesive

A light string includes an illumination device, a first wire, a second wire, soldering material, and transparent adhesive. The illumination device includes two soldering portions. The conductors of the first wire and the second wire are partially exposed to form a first soldering section and a second soldering section. Soldering material is used to attach the first soldering section and the second soldering section to the two soldering portions. The transparent adhesive forms a layer over, and covers, the illumination device, the first soldering section and the second soldering section, and extends to partially cover other portions of the first wire and the second wire.

Owner:BLOOMING INT LTD

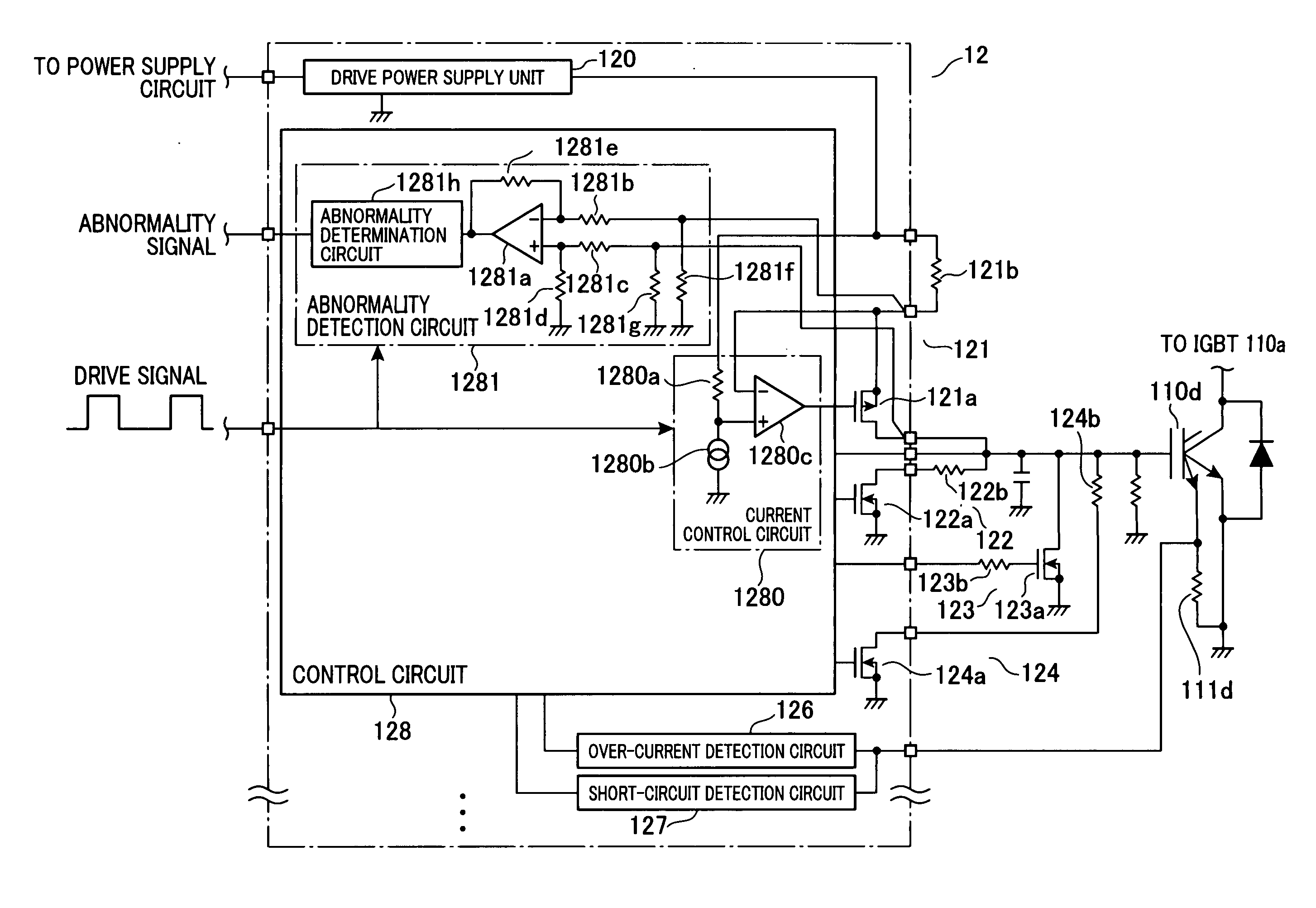

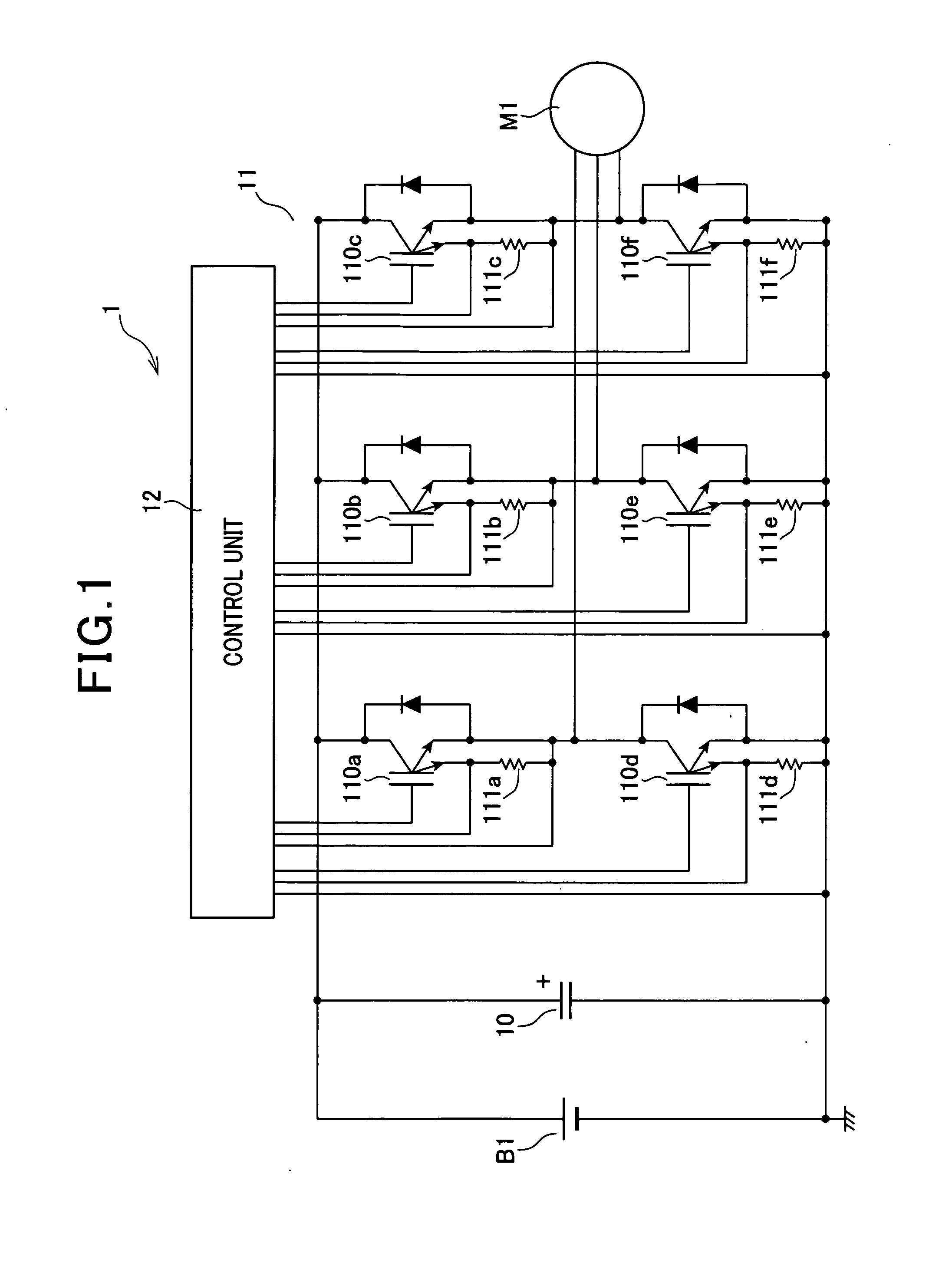

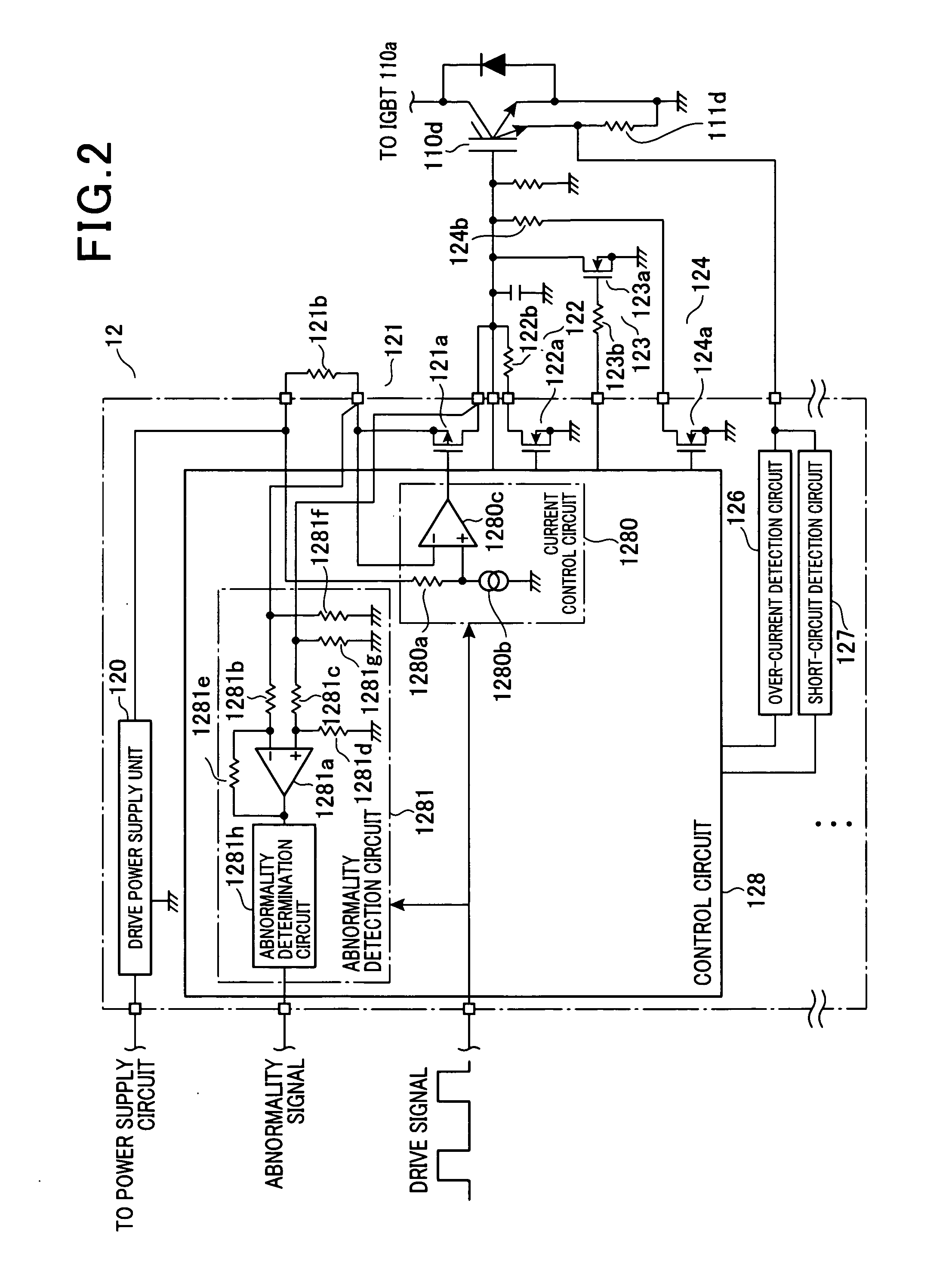

Electronic control apparatus having switching element and drive circuit

ActiveUS20120188001A1Prevent voltageElectric motor controlElectronic switchingDriver circuitControl switch

An electronic control apparatus includes a switching element having a control terminal; an ON-drive constant-current circuit for supplying a constant current to the control terminal, thereby charging the control terminal of the switching element with electrical charge; an OFF-drive switching element for discharging electrical charge from the control terminal of the switching element by being turned ON; and a control circuit adapted to control the ON-drive constant-current circuit and the OFF-drive switching element in response to a drive signal being inputted, thereby controlling the voltage of the control terminal of the switching element to drive the switching element. The ON-drive constant-current circuit includes a current control transistor and a current detection element. The control circuit controls the current control transistor based on the voltage of the current detection resistor and detects abnormality in the ON-drive constant-current circuit based on a source-drain voltage of the current control transistor.

Owner:DENSO CORP

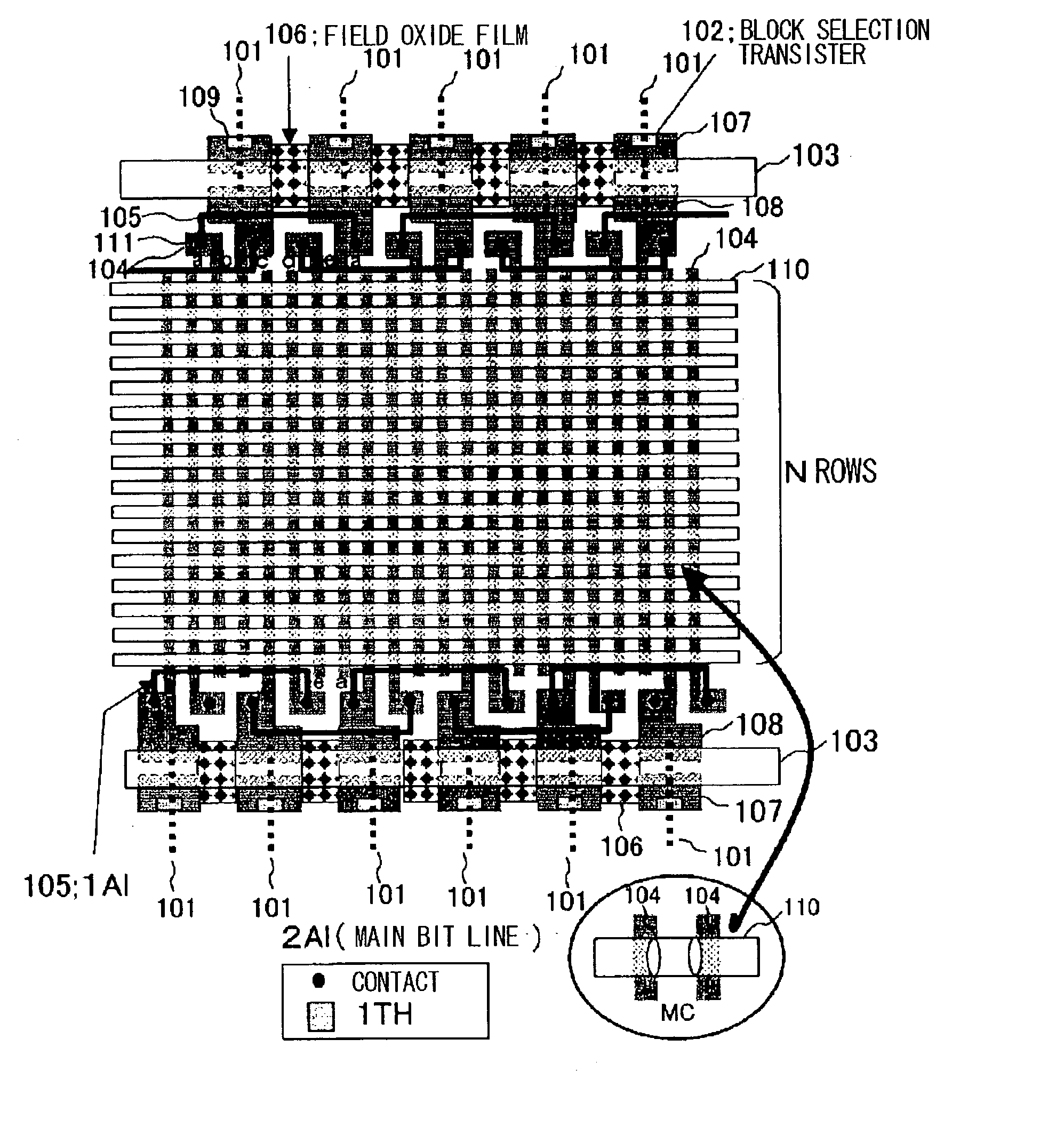

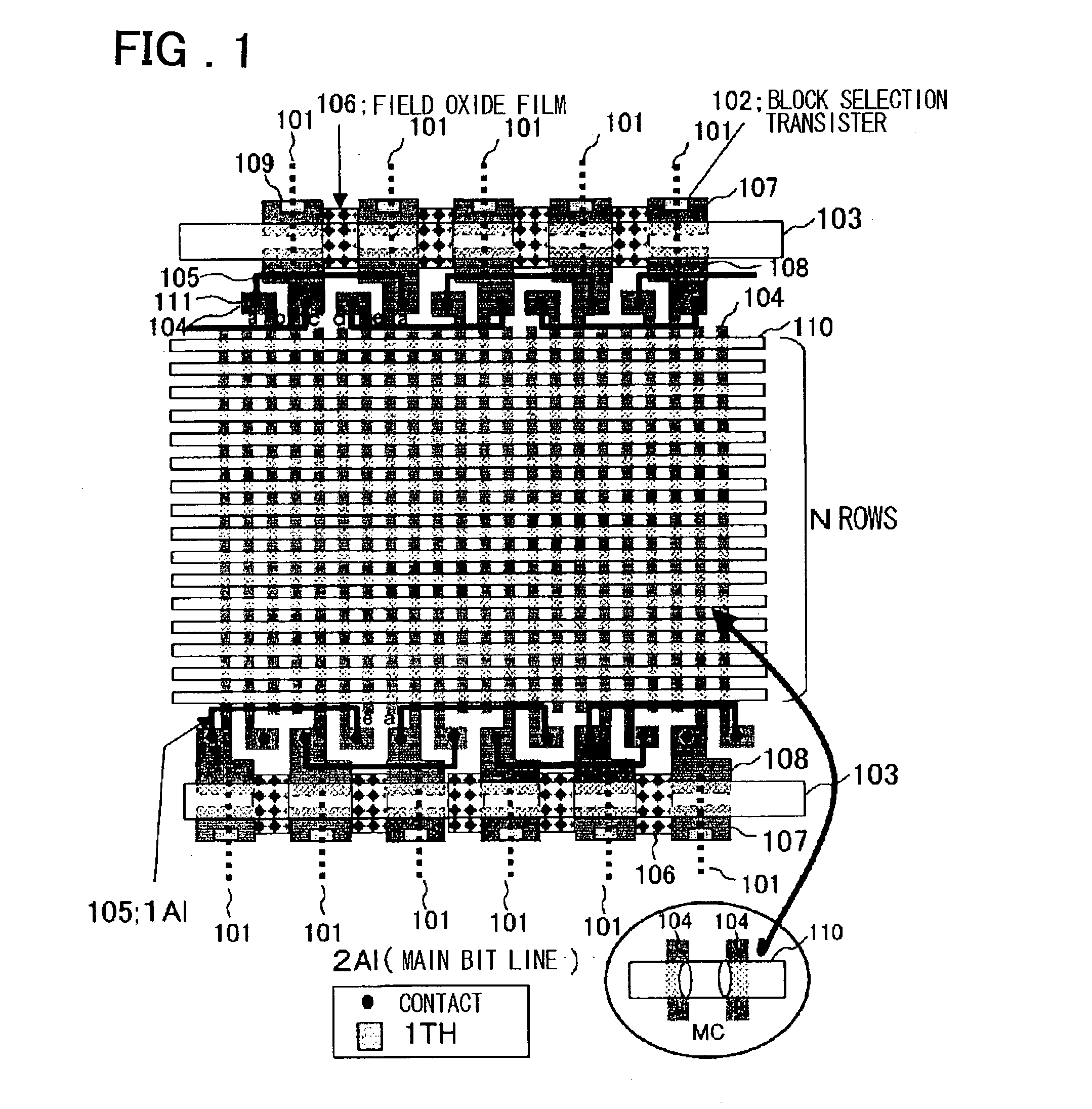

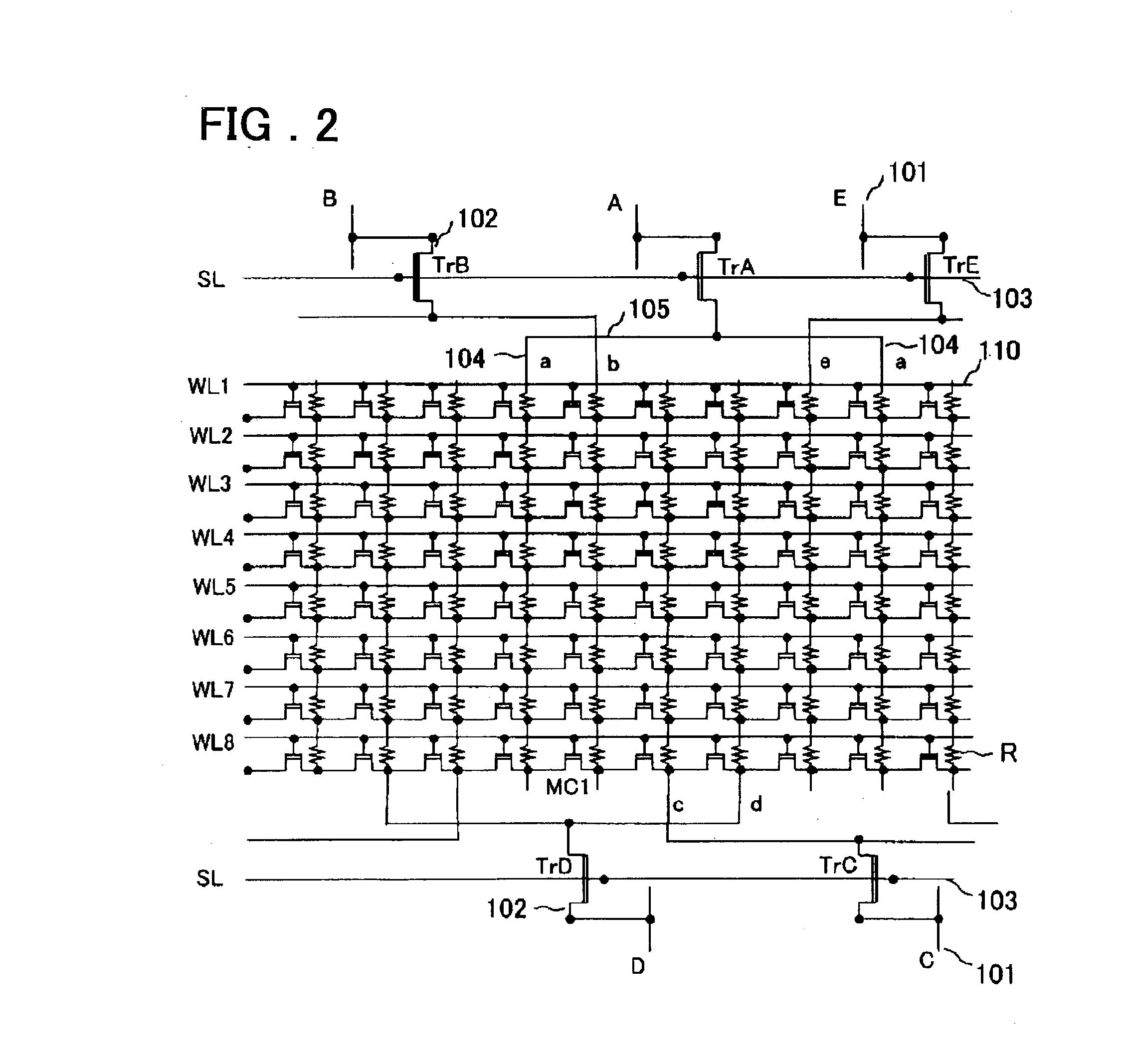

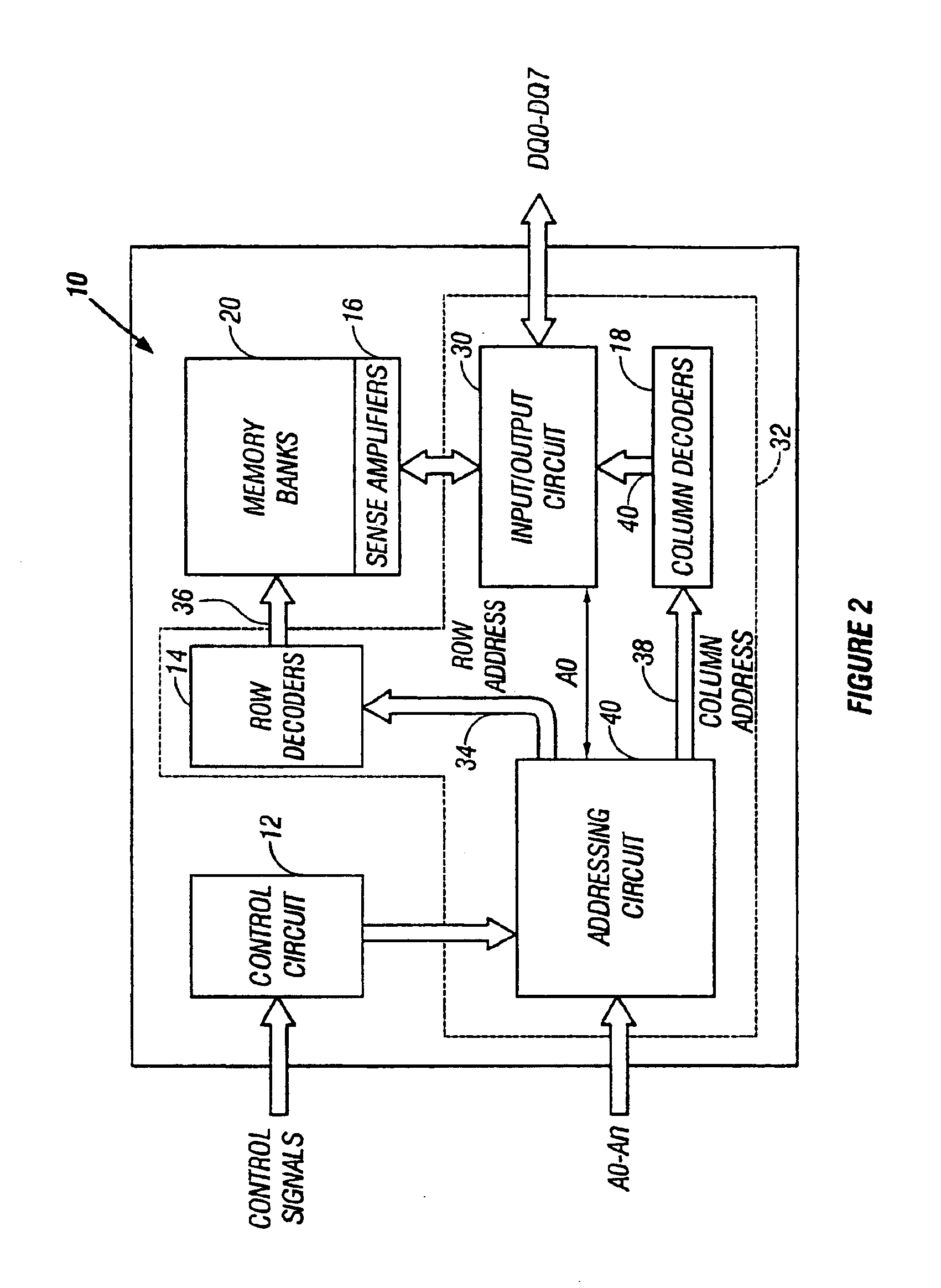

Semiconductor memory device and write/readout controlling method error correction code decoding device

Disclosed are device and method for enabling a programmable semiconductor memory device to provide a block selection transistor of a high voltage withstand type, to prevent the voltage from being decreased at the time of programming and to prevent the readout current from being decreased and to provide a constant sum resistance of the electrically conductive regions without dependency upon the memory cell locations. In a pair of two electrically conductive regions, provided for extending parallel to and in separation from each other on a substrate surface, one longitudinal end of one of the electrically conductive regions is diagonally connected to the other longitudinal end of the other electrically conductive region by a wiring to form a set of sub bit lines. On both ends of the memory cell array, there are provided selection transistors for interconnecting the sub bit lines and main bit lines. A plural number of the sets of the sub bit lines, connecting to the selection transistors on both ends of the memory cell array, are arranged, such that, in a region between paired electrically conductive regions (a, a) forming a set of the sub bit lines, there are provided one each (b, e) of two sets of paired electrically conductive regions forming two sets of sub bit lines connecting to two main bit lines on both sides of a given main bit line and each one (c, d) of two sets of paired electrically conductive regions forming two sets of sub bit lines connecting to the opposite longitudinal end selection transistors. The selection transistors are isolated from one another by a field oxide film.

Owner:RENESAS ELECTRONICS CORP

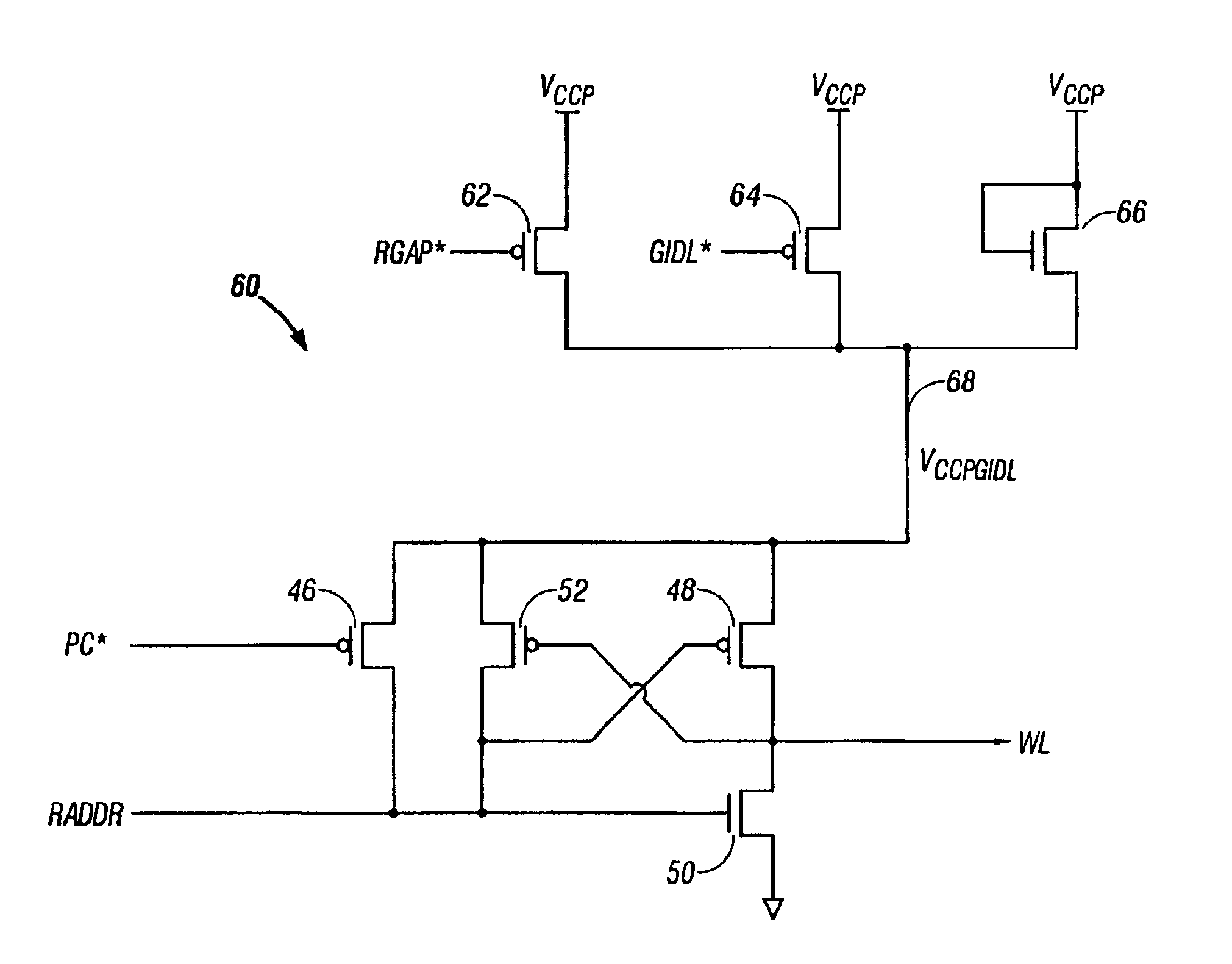

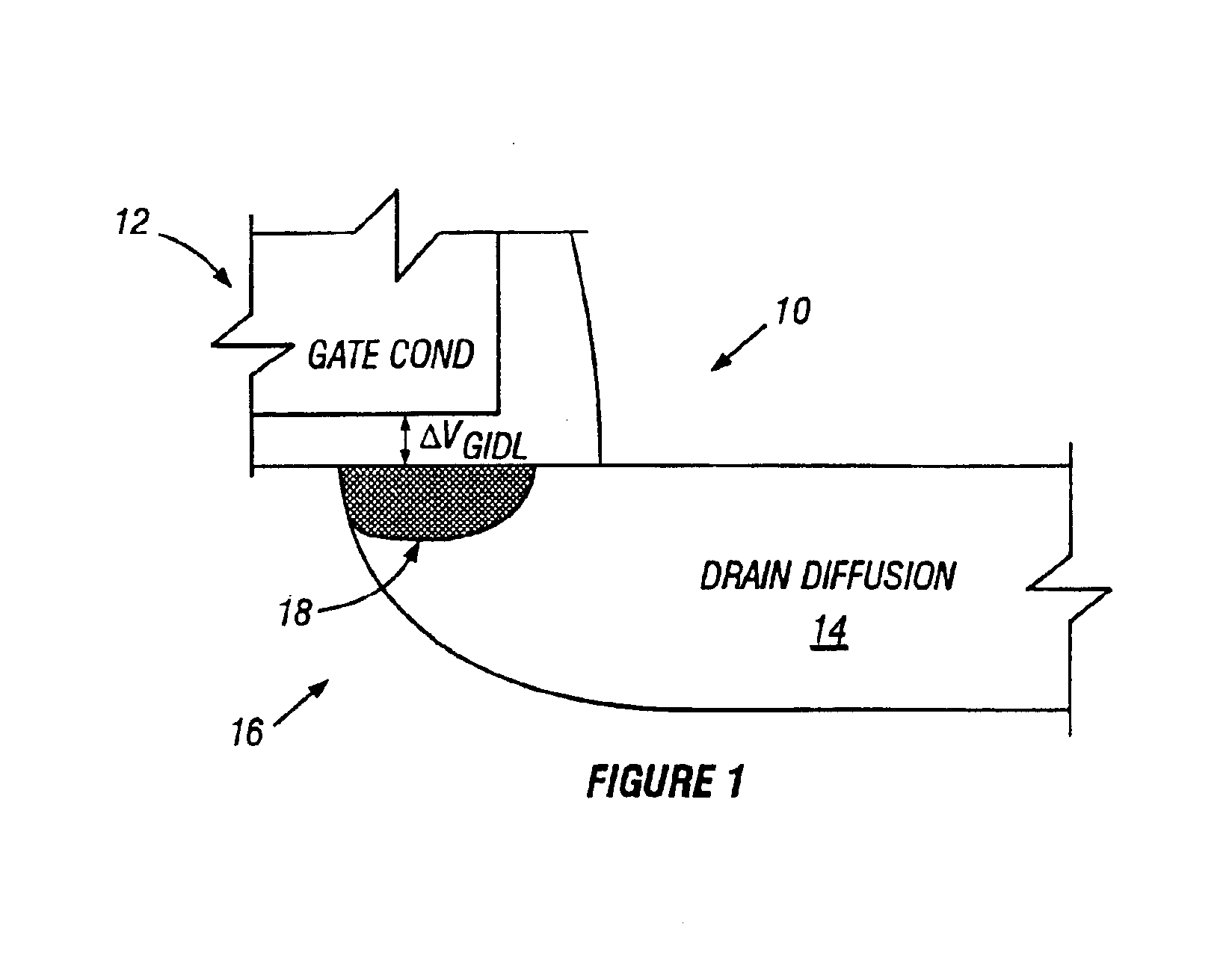

Method and apparatus for standby power reduction in semiconductor devices

InactiveUS6873562B2Reduce voltageVoltage on the local power supply node is preventedDigital storagePower semiconductor deviceDriver circuit

A word line driver circuit for a semiconductor memory device. One or more transistors in the driver circuit are fabricated such that they are susceptible, under certain conditions, to gate-induced diode leakage (GIDL). One terminal of the transistors are coupled to a local supply node, which during standby conditions when the word line driver circuit is not driving a word line, is maintained at a voltage less than that of a global power supply node. In one embodiment, the local power supply node is coupled to the global power supply node by means of at least one decoupling transistor receiving a control signal at its gate and by a vt-connected transistor, such that the voltage on the local power supply node is maintained at a level not exceeding one transistor threshold voltage less than the global power supply node voltage when the decoupling transistor is off. When the decoupling transistor(s) is / are switched on prior to word line driving operation, the voltage on the local power supply node rises to the voltage of the global power supply node. Preferably, the control signal(s) controlling the decoupling transistor(s) are, or are derived from, control signals generated for purposes other than controlling the decoupling transistor.

Owner:MICRON TECH INC

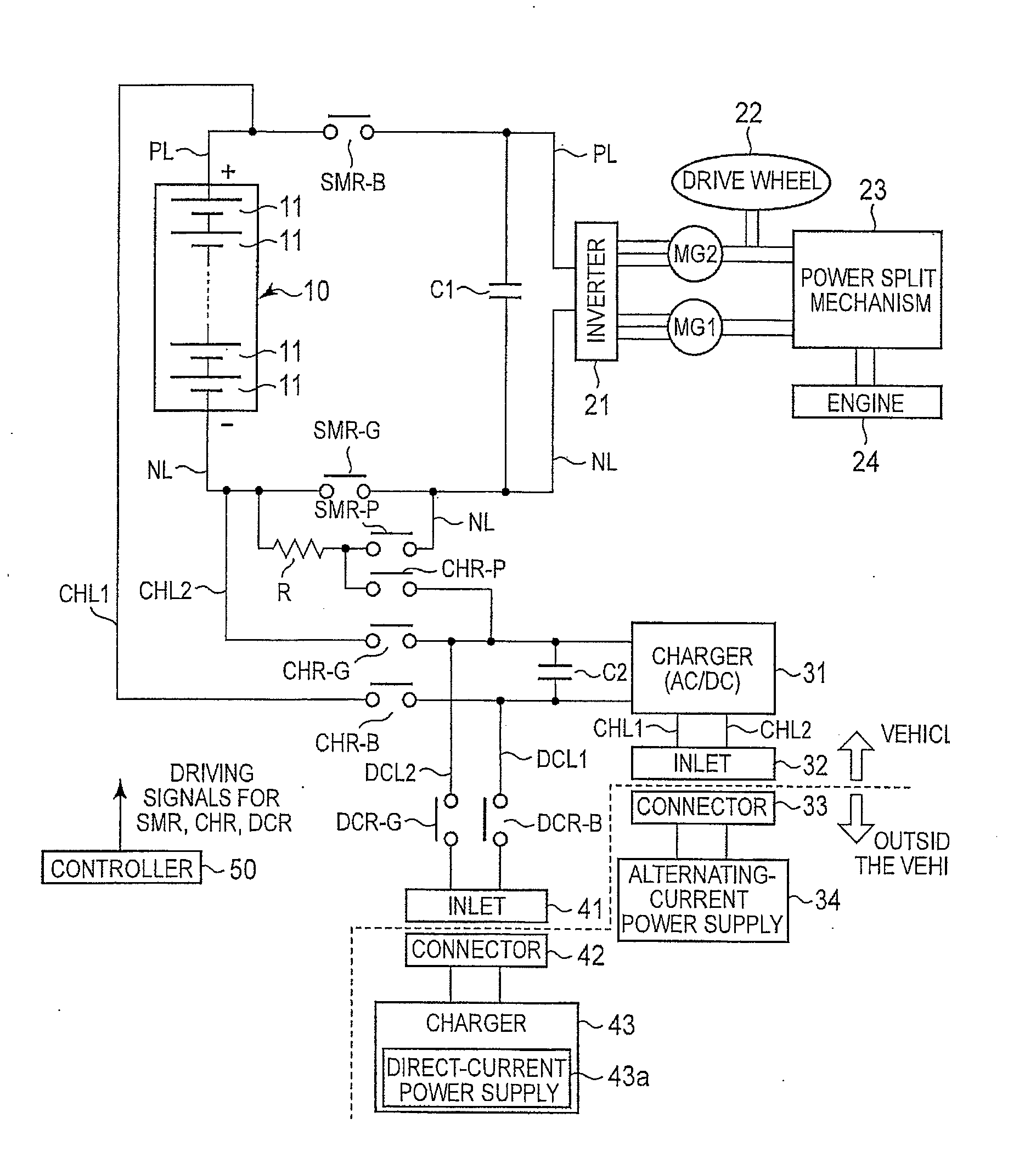

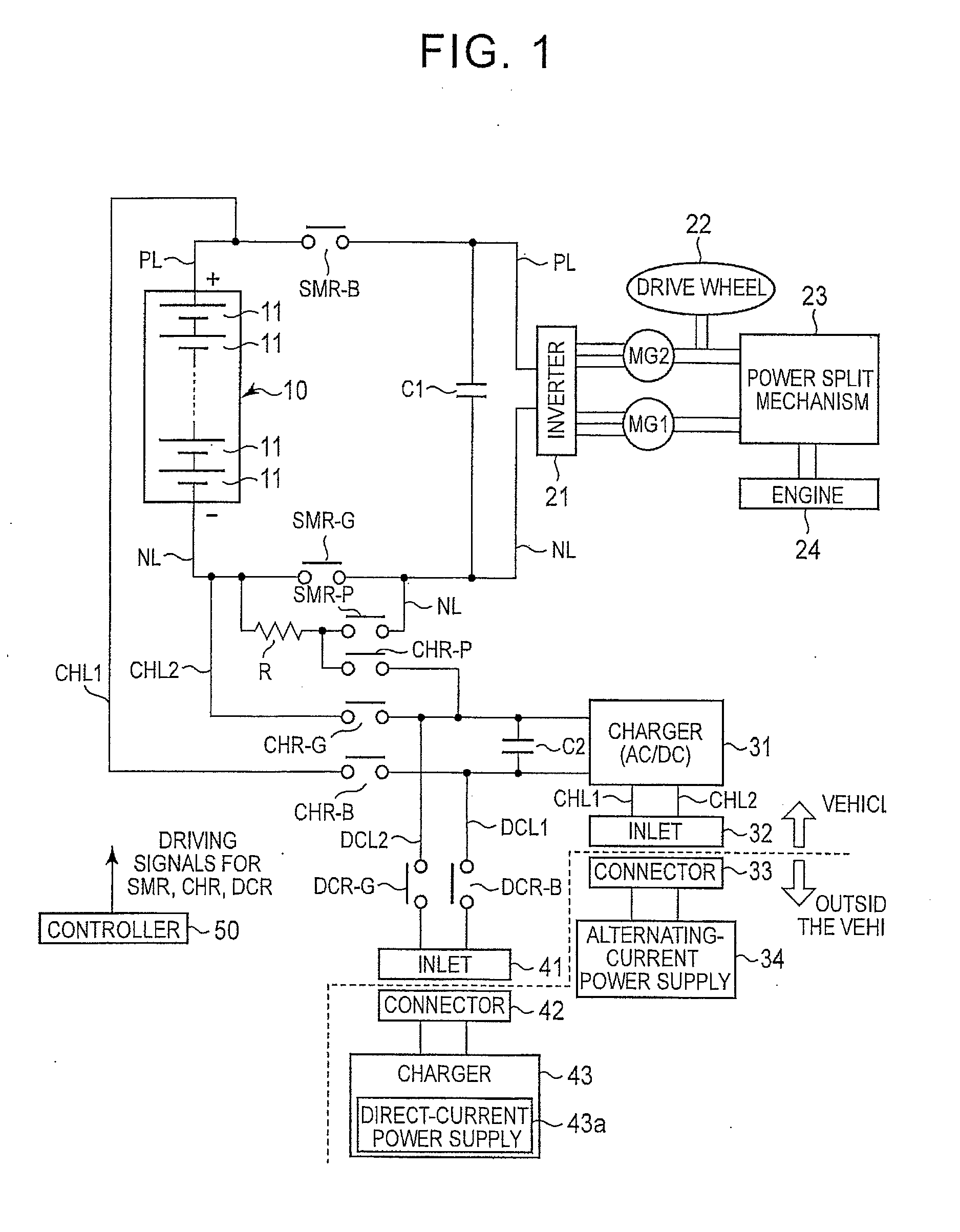

Electrical storage system

The electrical storage system includes an electrical storage device, a motor, a system main relay, a first charging line, a charger, a first charging relay, a second charging line, an inlet, a second charging relay and a controller. The controller is configured to control a energizing state and a non-energizing state of the system main relay, the first charging relay and the second charging relay. The controller is configured to cause the first charging relay to the non-energizing state when the second charging relay in the energizing state is subjected to adhesion.

Owner:TOYOTA JIDOSHA KK

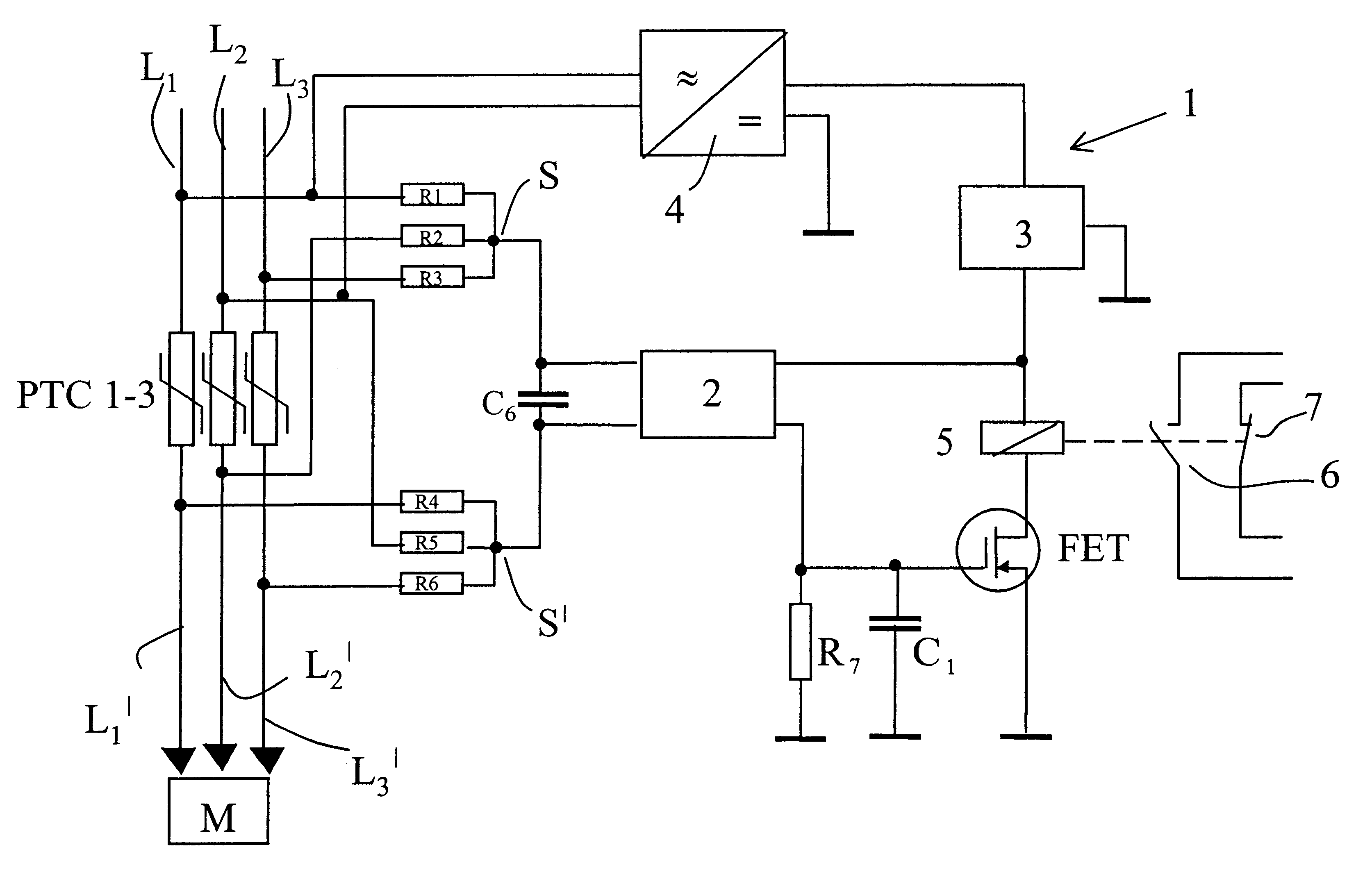

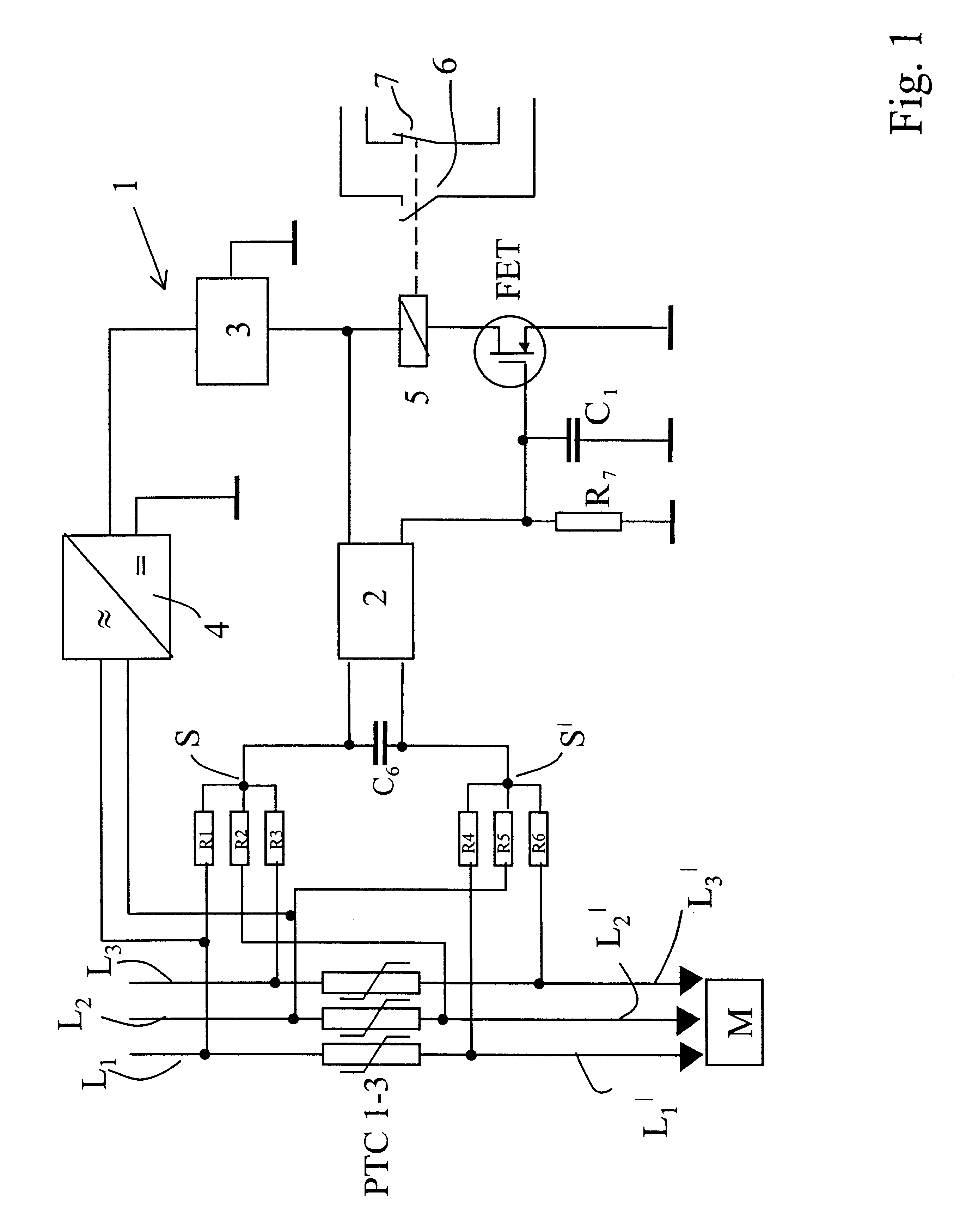

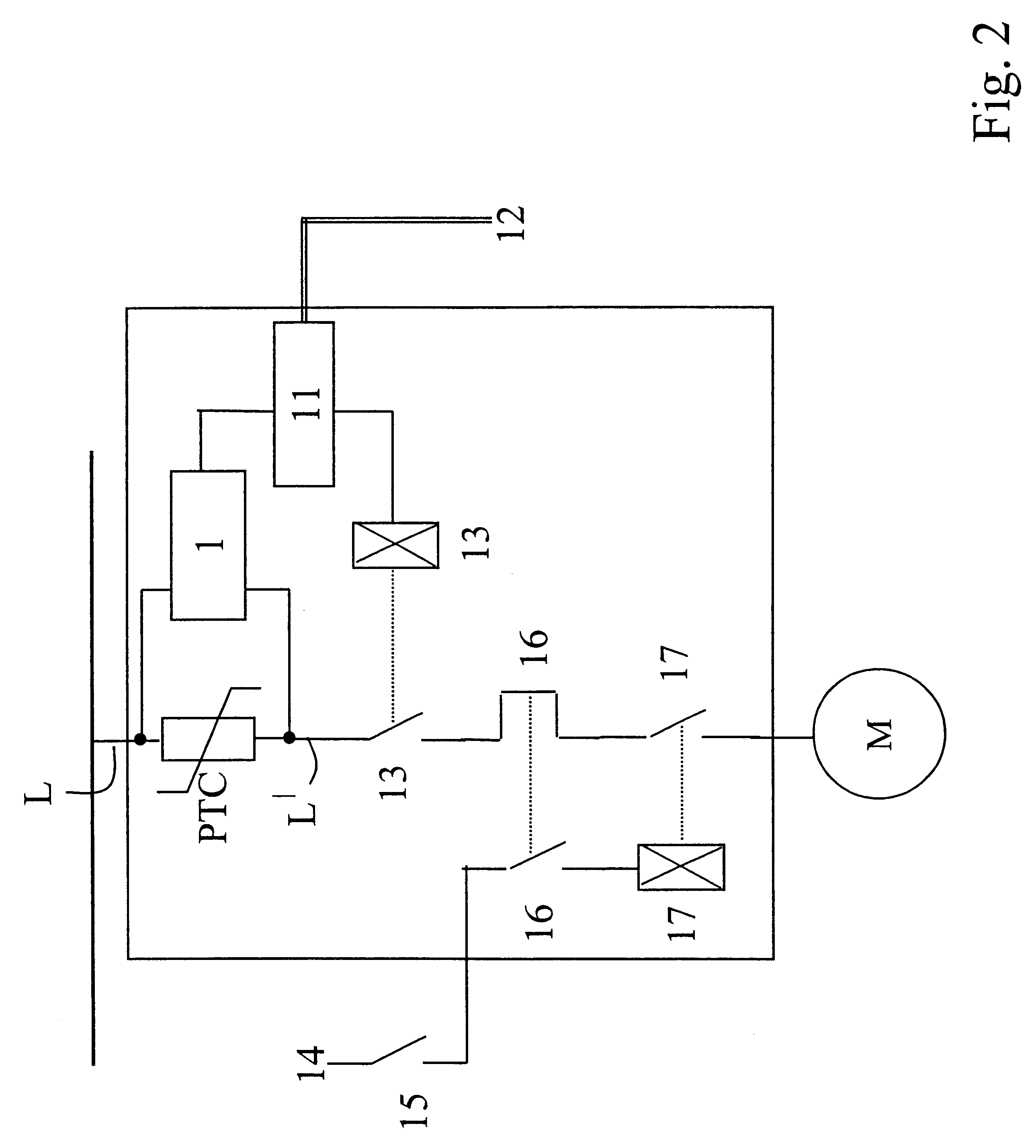

Monitor circuit for a current limiting device

InactiveUS6492799B1Simple circuit designAvoid triggerVoltage-current phase angleEmergency protective arrangements for automatic disconnectionCurrent limitingEngineering

An electrical monitor circuit in which star points of taps on a first and a second side of a three-phase current limiting device are voltage compared. Possible applications are combinations with electrical switches, especially for power supplying and protecting circuits for electrical motors.

Owner:ABB RES LTD

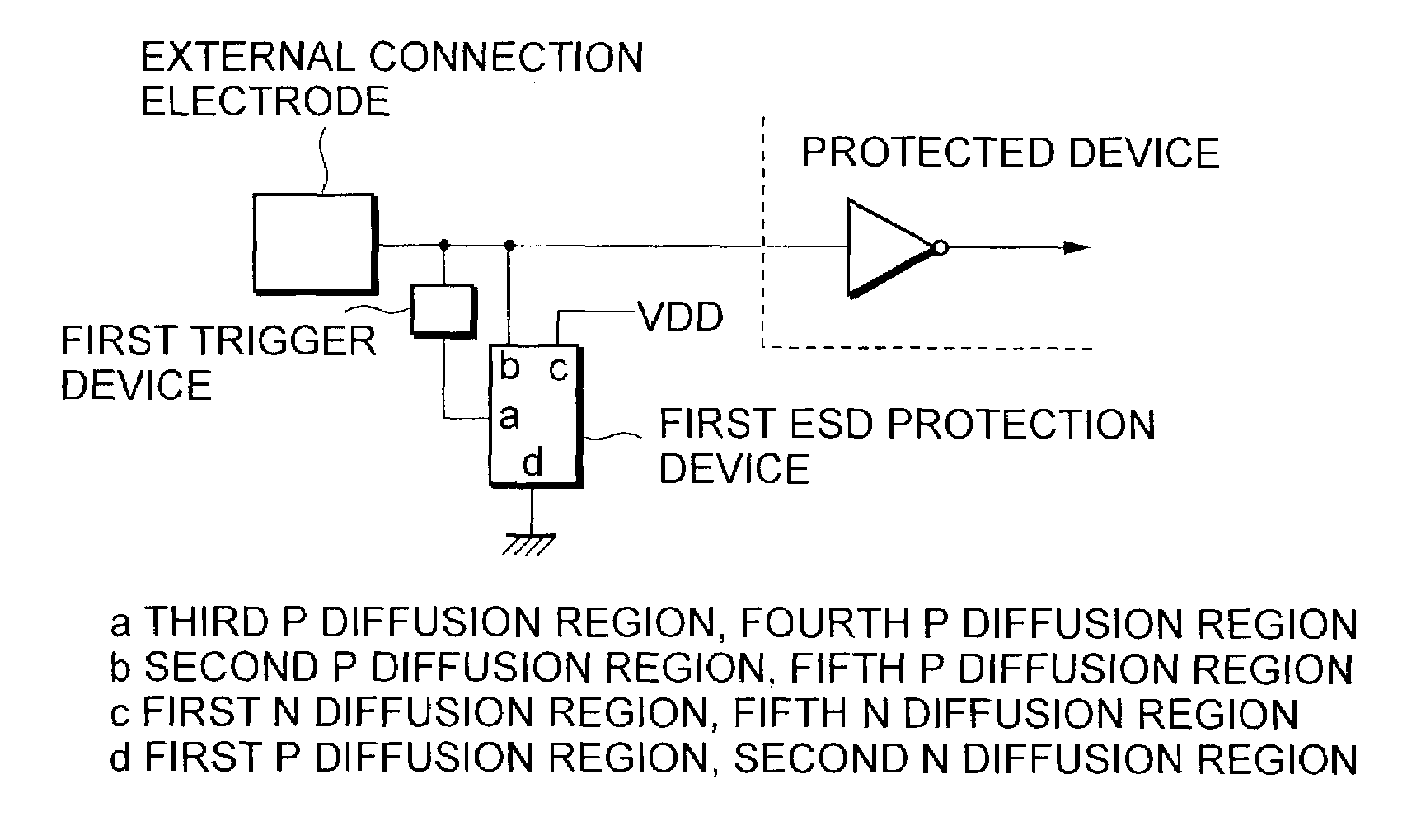

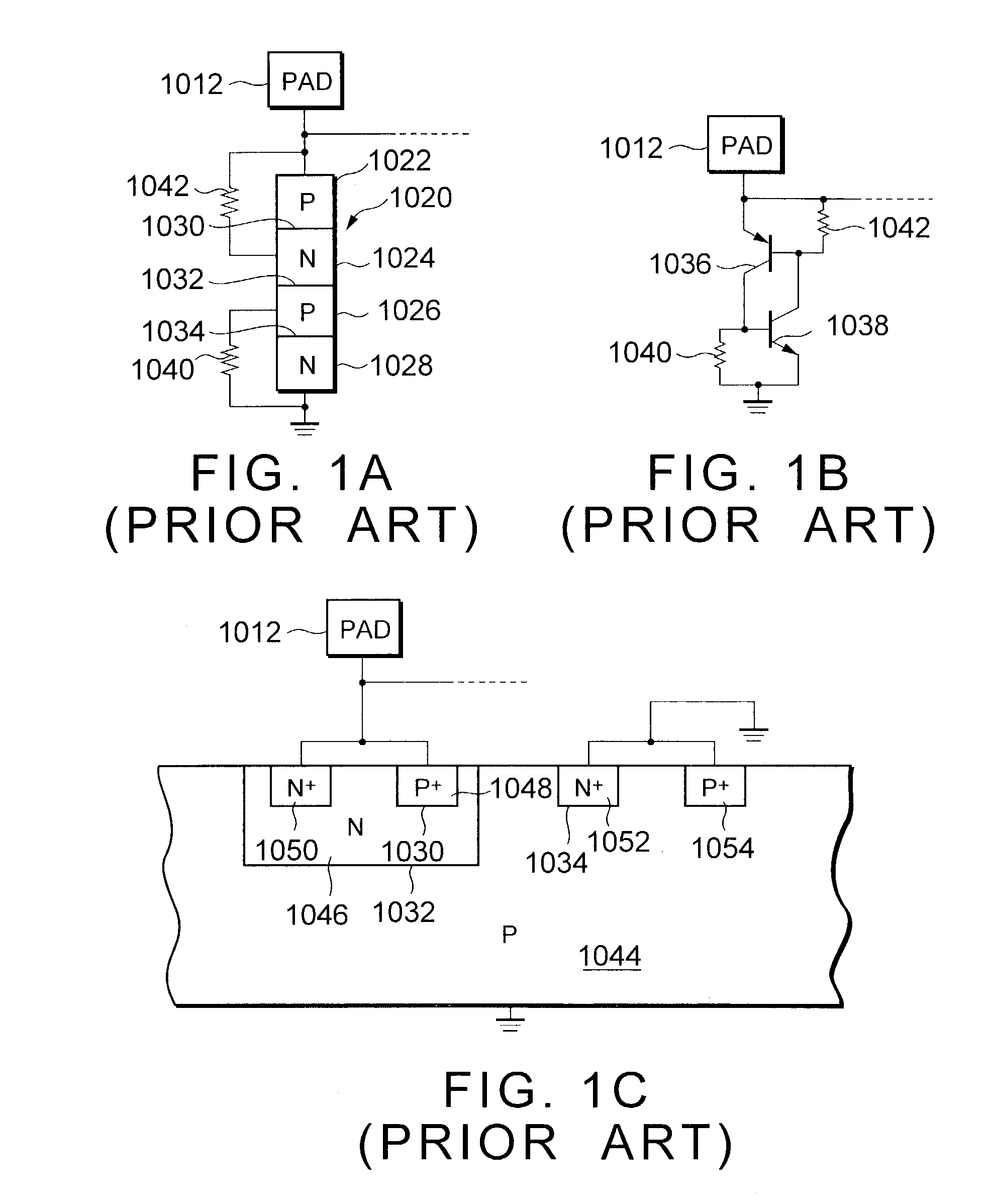

Electrostatic discharge protection device

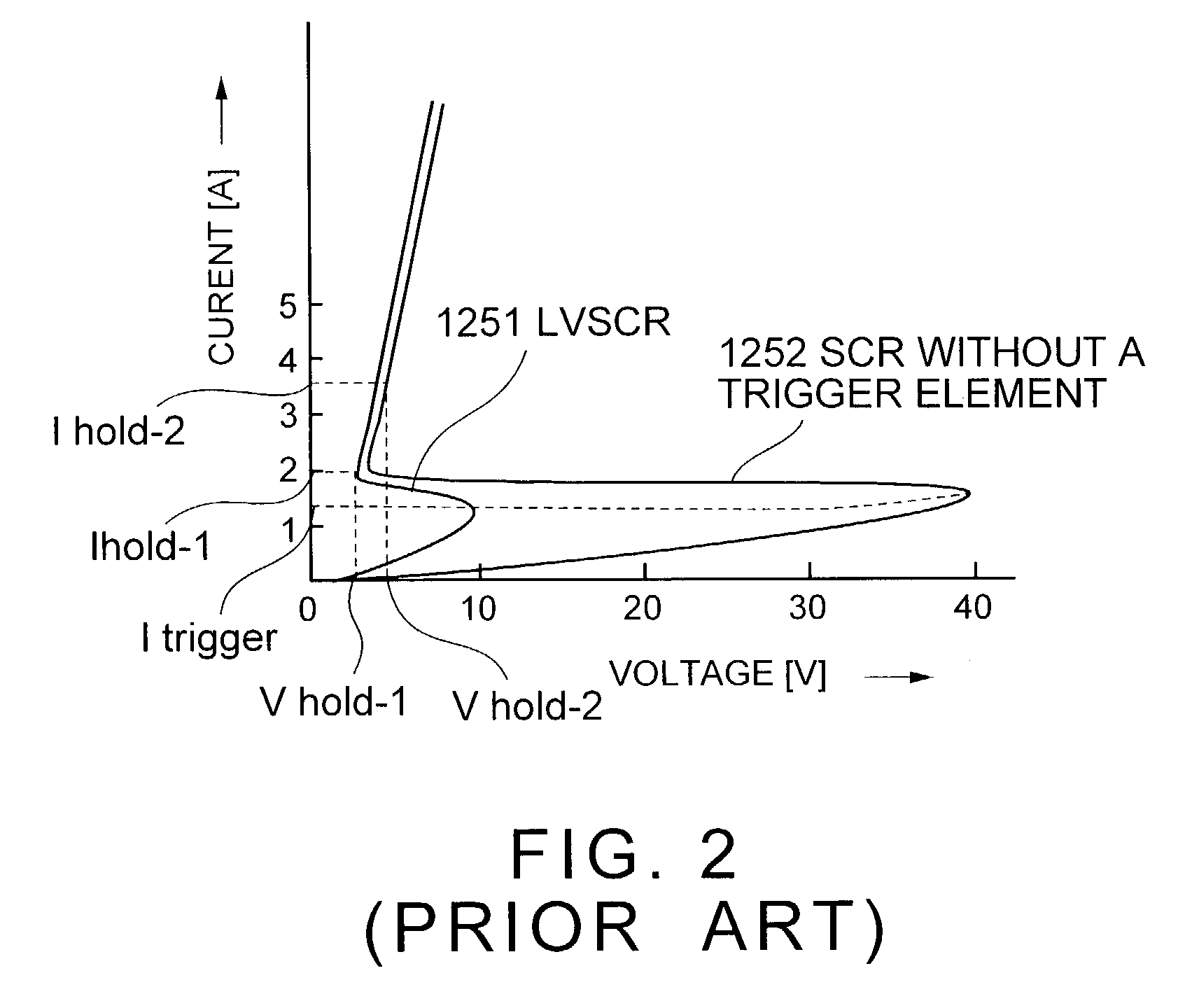

InactiveUS7109533B2Lower resistanceEasy to operateTransistorThyristorEngineeringElectrostatic discharge protection

There is provided an electrostatic discharge protection device comprising a P conductive type first P well region 101 formed in a P type epitaxial layer 31 being deposited on a surface of a P+ substrate 30 having a prescribed thickness, an N conductive type first N well 101 a periphery thereof being brought into direct contact with and surrounded by a first P well region 101, P conductive type first P diffusion regions 121a and 121b, a P conductive type third P diffusion region 125, and an N conductive type second N diffusion region 223 arranged within a first P well region 101, and a P conductive type second P diffusion region 123 and an N conductive type first N diffusion region 221 arranged within a first N well 201.

Owner:RENESAS ELECTRONICS CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com