Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

40results about How to "Good reset function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

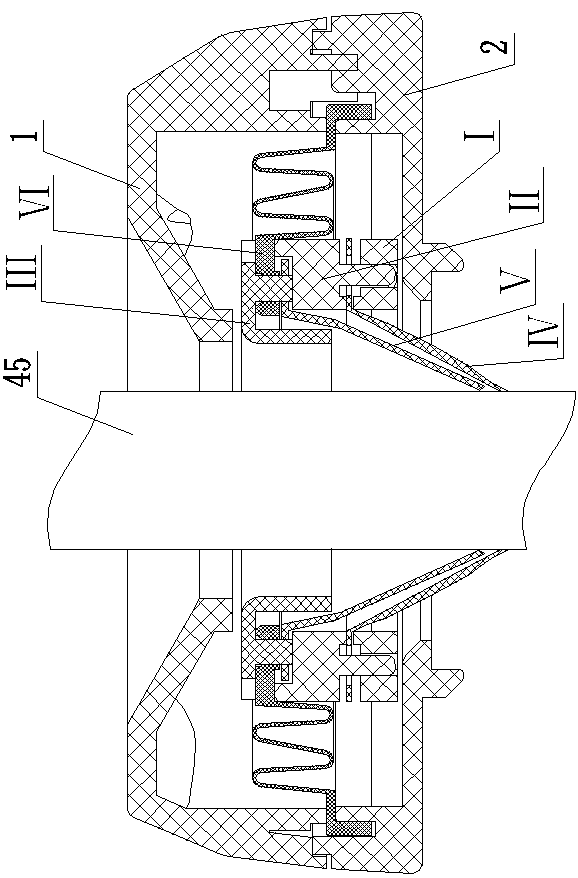

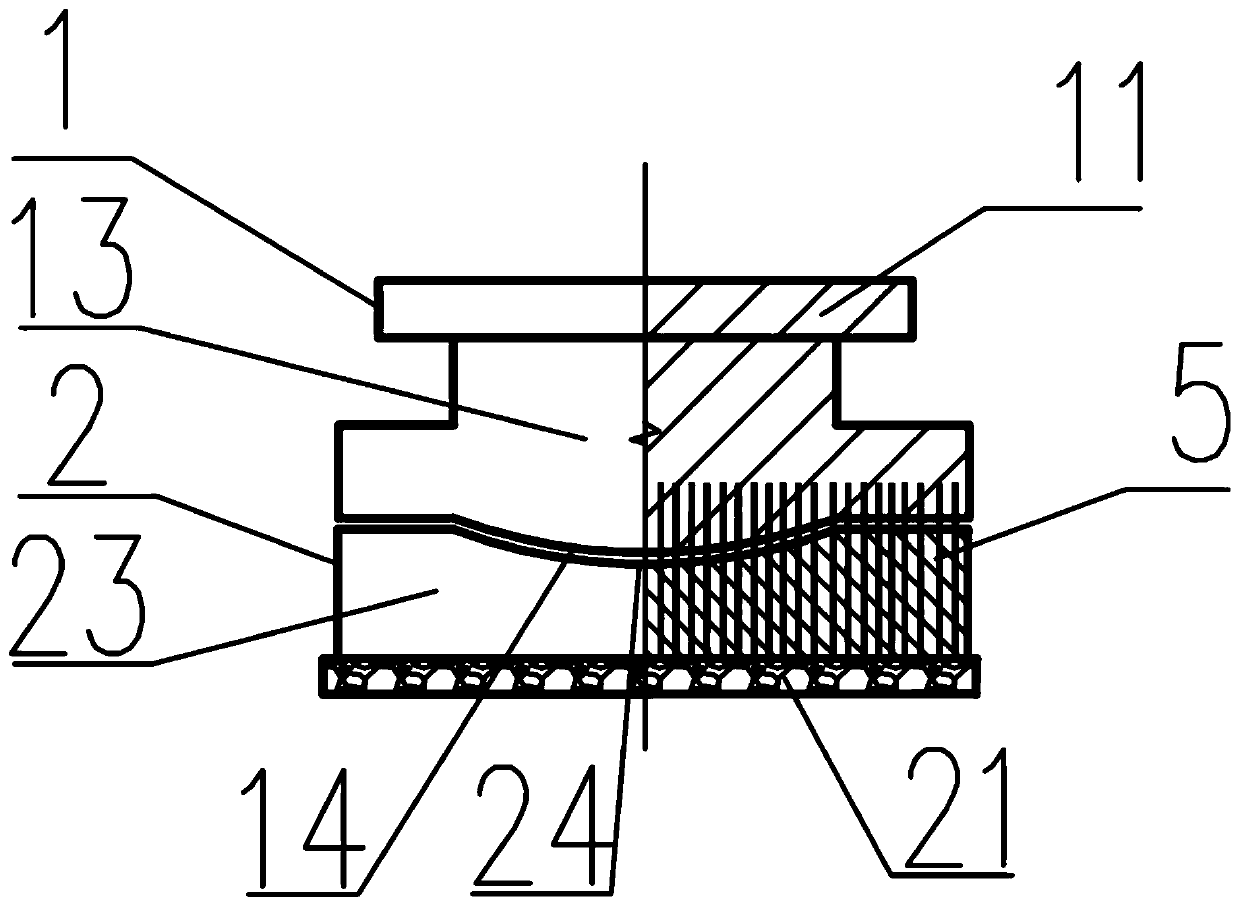

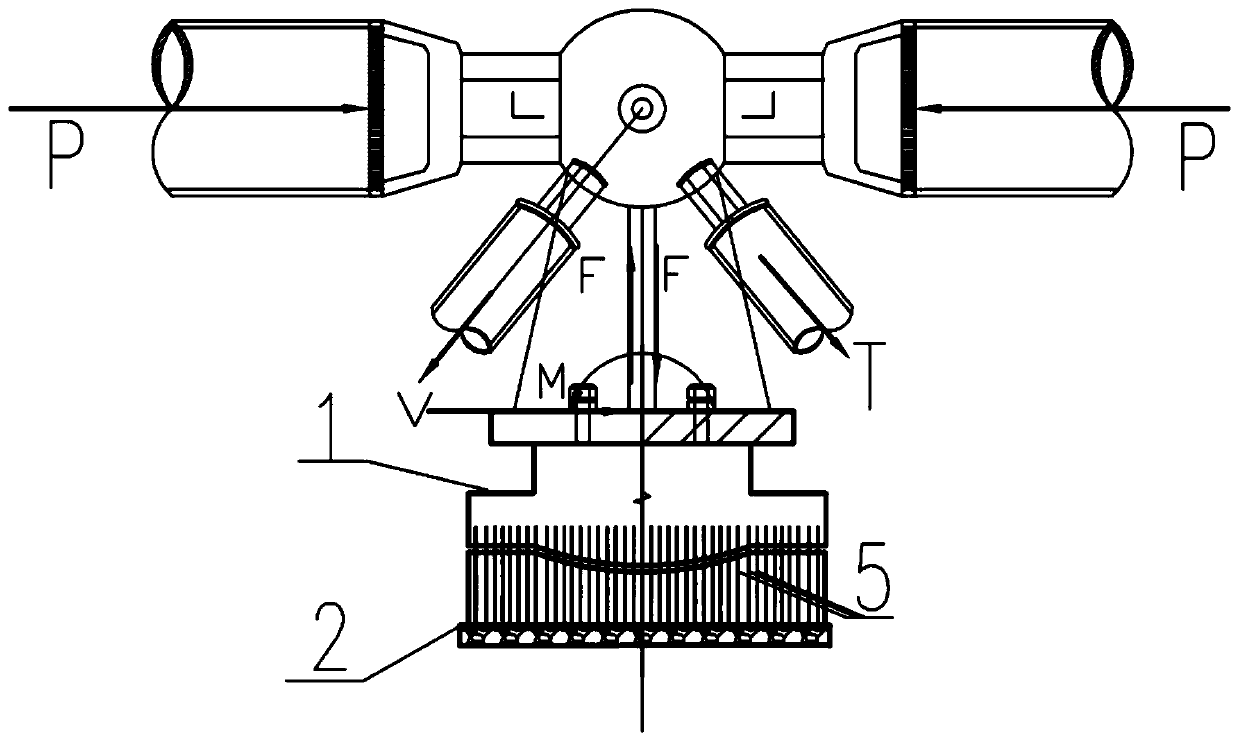

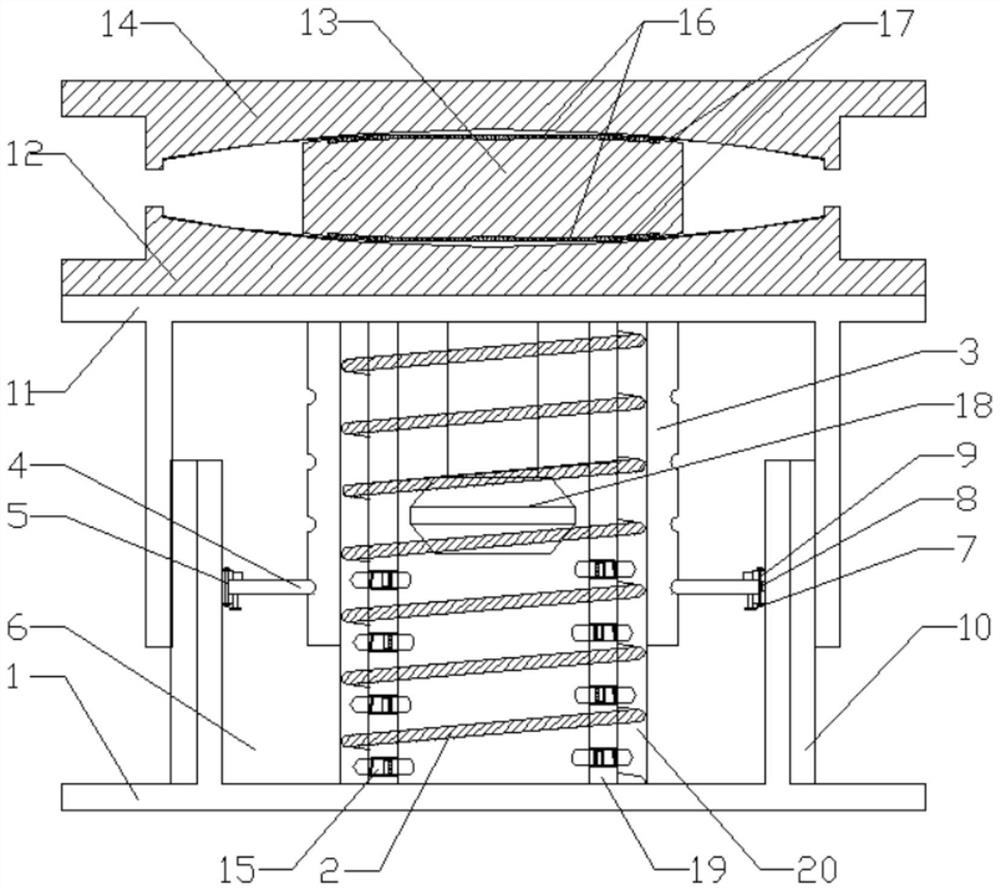

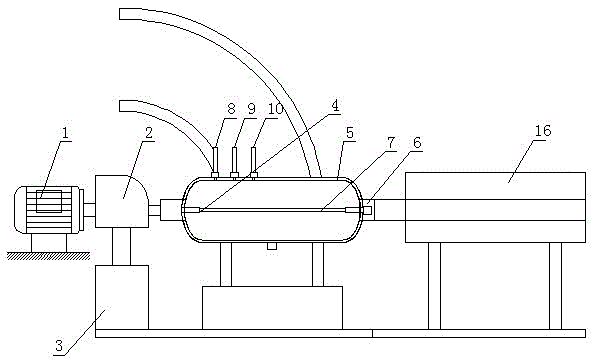

SMA spring-STF viscous damper

InactiveCN109404477AGood shock absorptionGood reset functionSprings/dampers functional characteristicsSprings/dampers design characteristicsControl theoryPiston rod

The invention provides an SMA spring-STF viscous damper which comprises a first connecting component, a piston rod, a left end cover, a first damping cavity, a damping cylinder, a piston, a second damping cavity, two SMA springs, a right end cover and a second connecting component, wherein the left end cover is arranged at one end of the damping cylinder; the right end cover is arranged at the other end of the damping cylinder; the interior of the damping cylinder is divided by the piston into the first damping cavity and the second damping cavity; the SMA springs which sleeve the piston rod are correspondingly arranged in the first damping cavity and the second damping cavity; the first damping cavity and the second damping cavity are filled with an STF shearing thickener; when the pistonmoves towards one side, the SMA spring on one side is compressed, and the SMA spring on the other side is restored towards the trend of the original length; and due to the different expansion and contraction degrees of the SMA springs on both sides, the resistance difference is produced, and the damping force is provided for the viscous damper. The SMA spring-STF viscous damper provided by the invention has the effects of improving the energy consumption under low-frequency loads and causing limiting resistance to the structural excessive displacement; furthermore, the self-resetting effect can be achieved after unloading; and the SMA spring-STF viscous damper has the advantages that the structure is simple and the space is saved.

Owner:SHENYANG JIANZHU UNIVERSITY

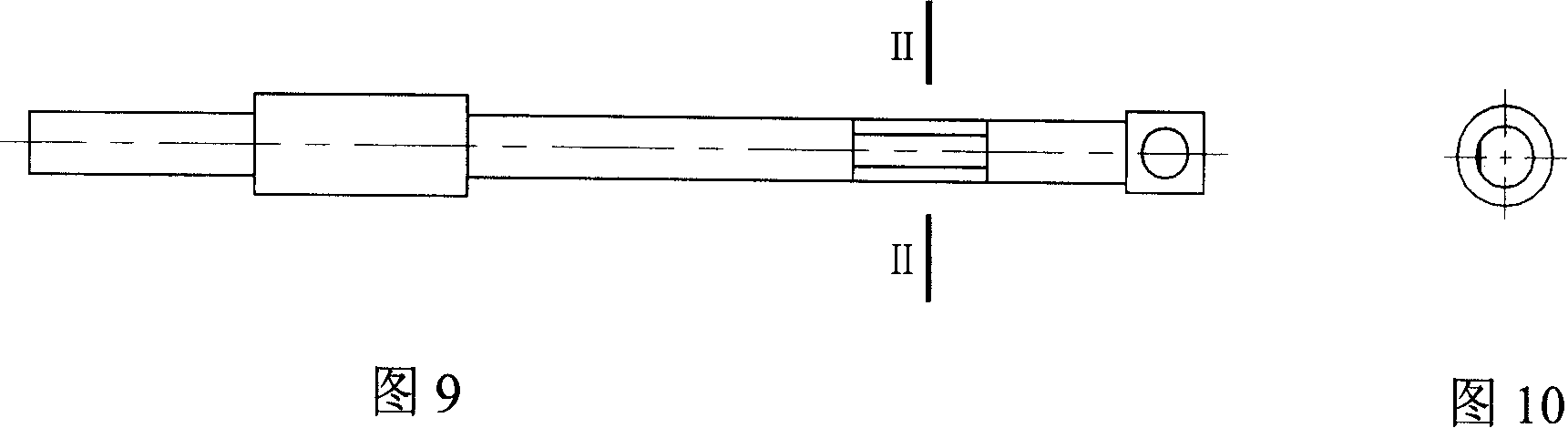

Self-resetting super-elastic shape memory alloy damper

InactiveCN101070716ASimple structureEasy to installShock proofingPre strainMechanical engineering technology

Automatic-resetting super elasticity shape memory alloy damper is a damping control device used in the areas of civil construction and mechanical engineering technique .It is characteristiced by its framework that consisted of a working piston , a fixing piston , a cylinder ,a cover and a joint rod .The machine uses its alloy wire to restrict the left and right pistons to the partition-wall of the cylinderand the spacing nut. when the pull bar works, piston in one side works follow it ,the piston in the other side is resisted by the partition-wall of the cylinder and keep the resetting alloy wire on running and produce a great anamorphosis restoration ability.The pre-strain resetting super elasticity shape memory alloy wires are divided into tow groups, one of which is used to connect the right fixing piston to the left coverand, the other is used to bind the left fixing piston to the right cover.the two groups doing a interchange push and pull in the pull bars in order to create a bigger energy consumption. The invention simultaneously has the functions of good energy consumption and resetting.It can reduce the vibration of fabrics, components or the remained deformation and has simple structure.

Owner:DALIAN UNIV OF TECH

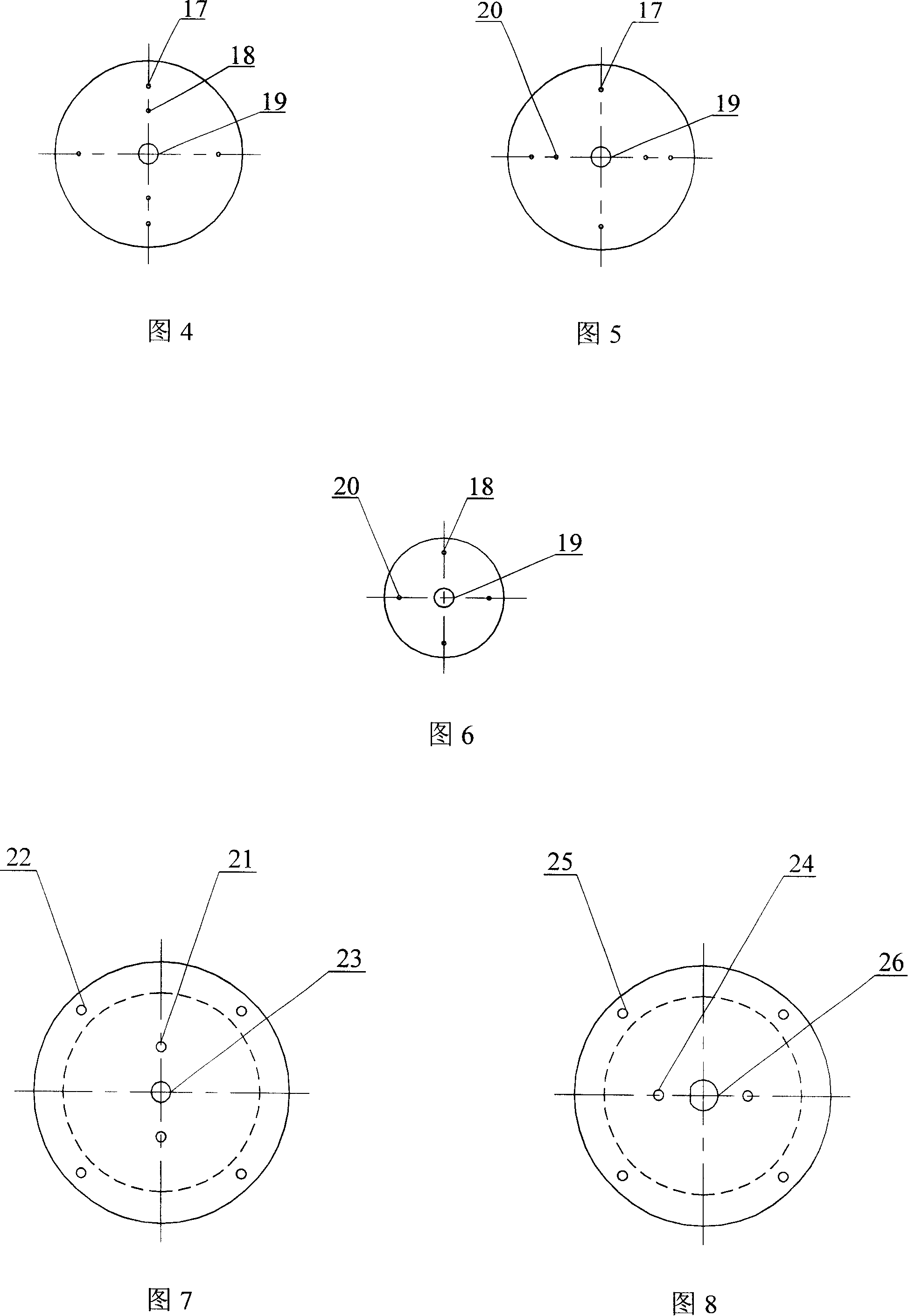

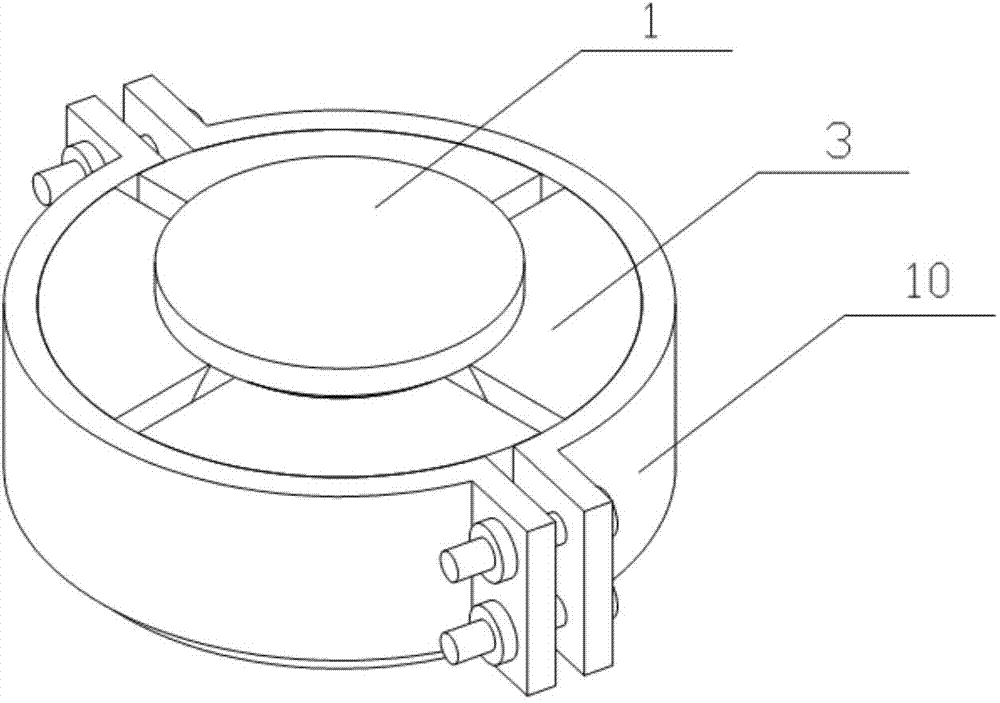

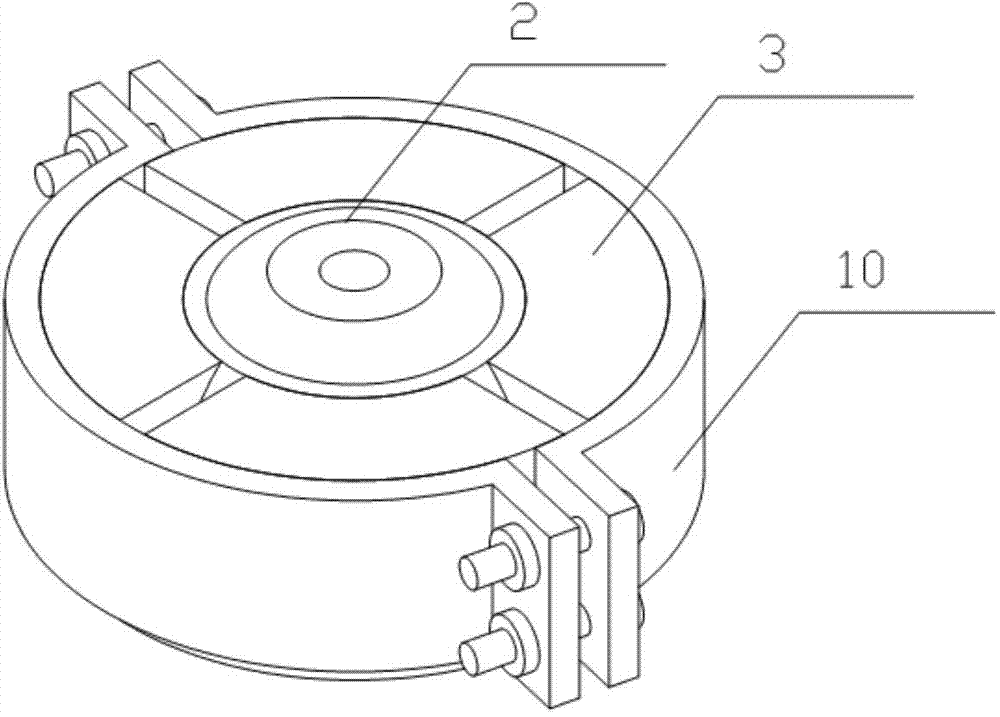

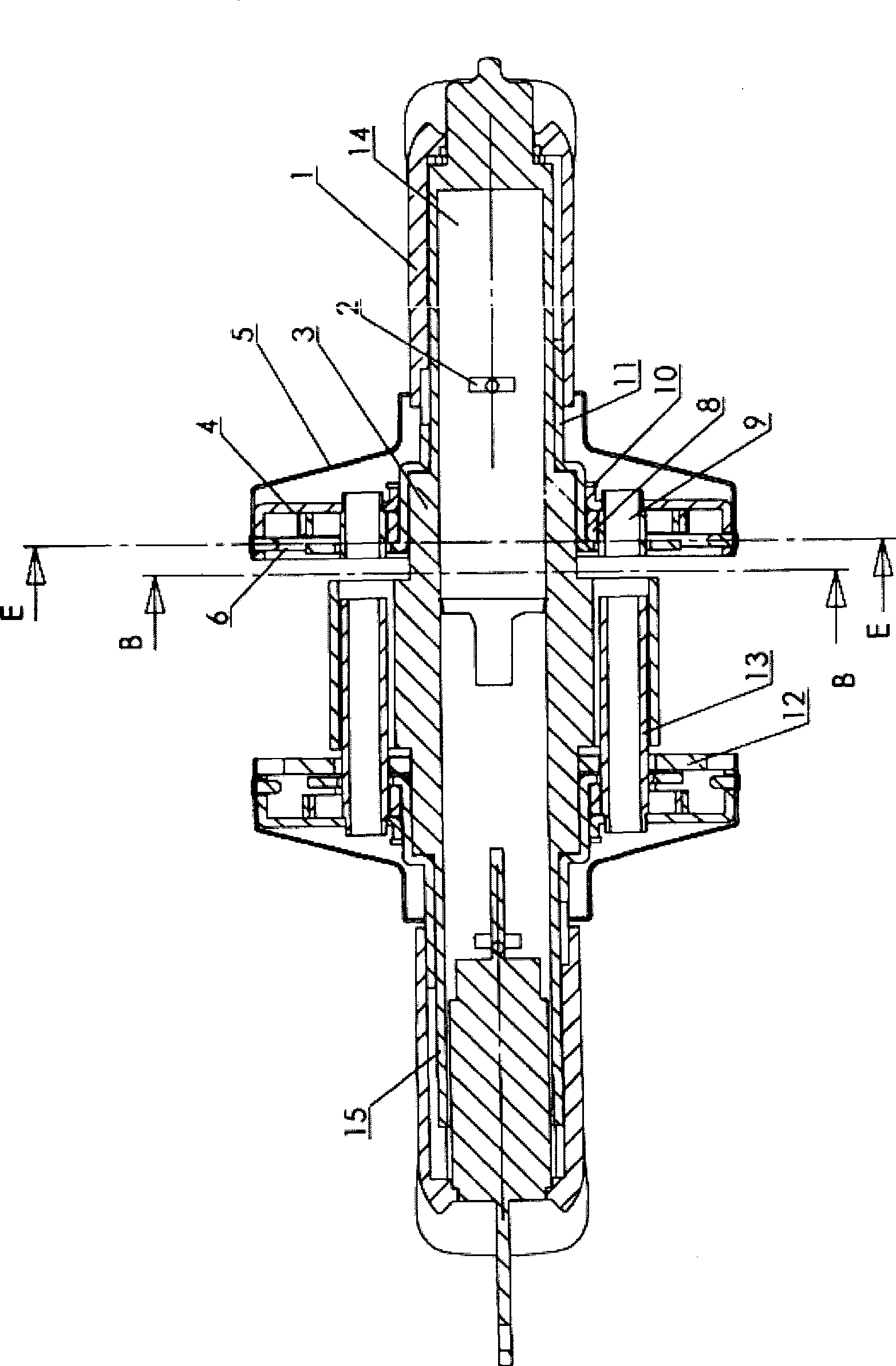

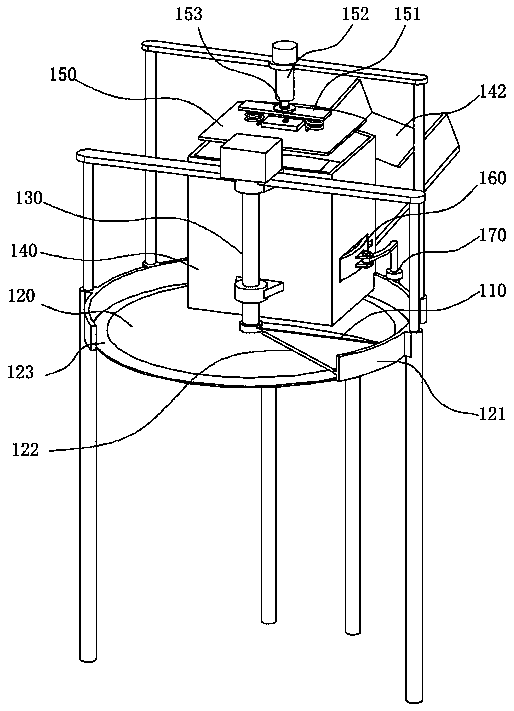

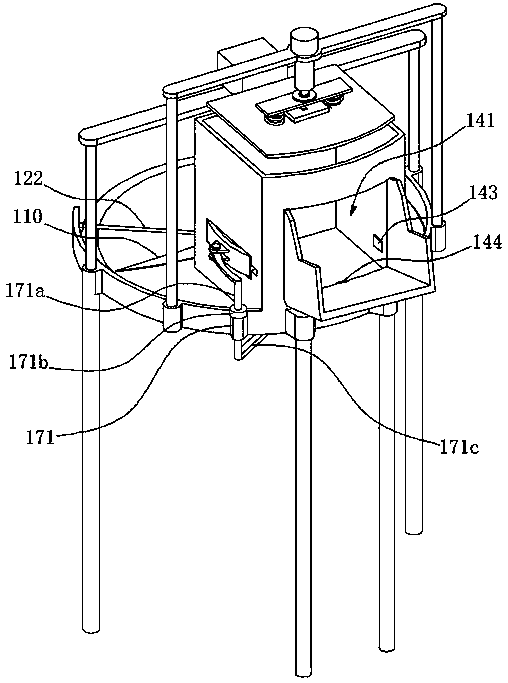

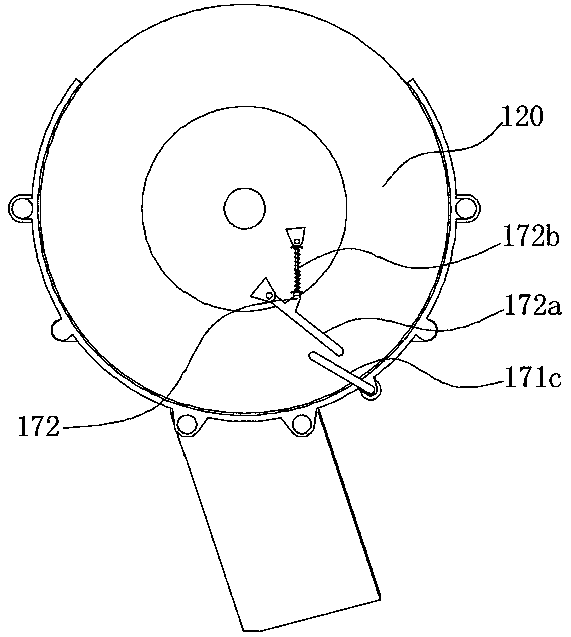

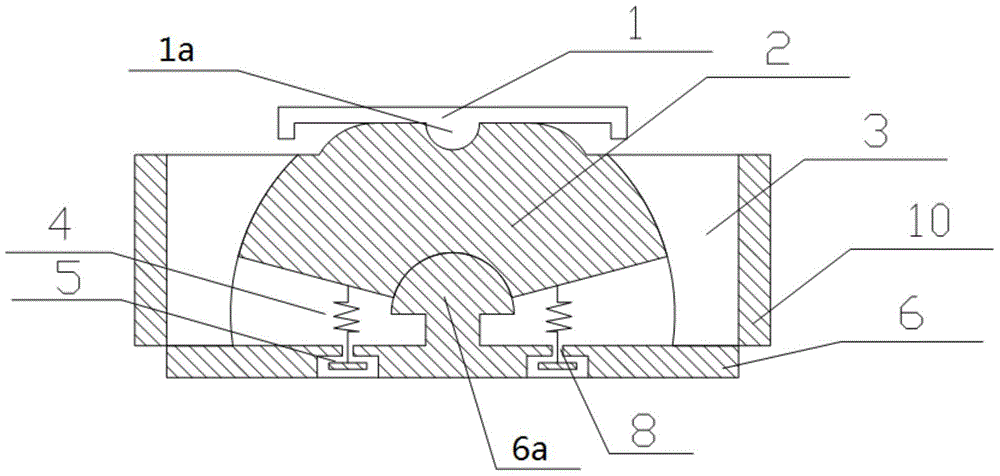

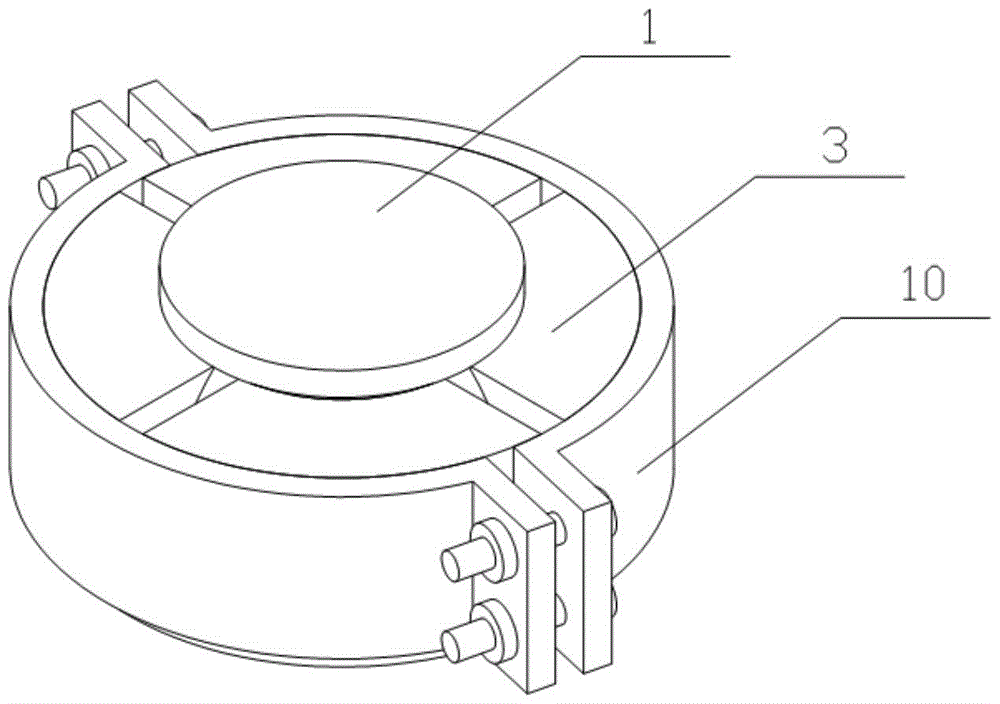

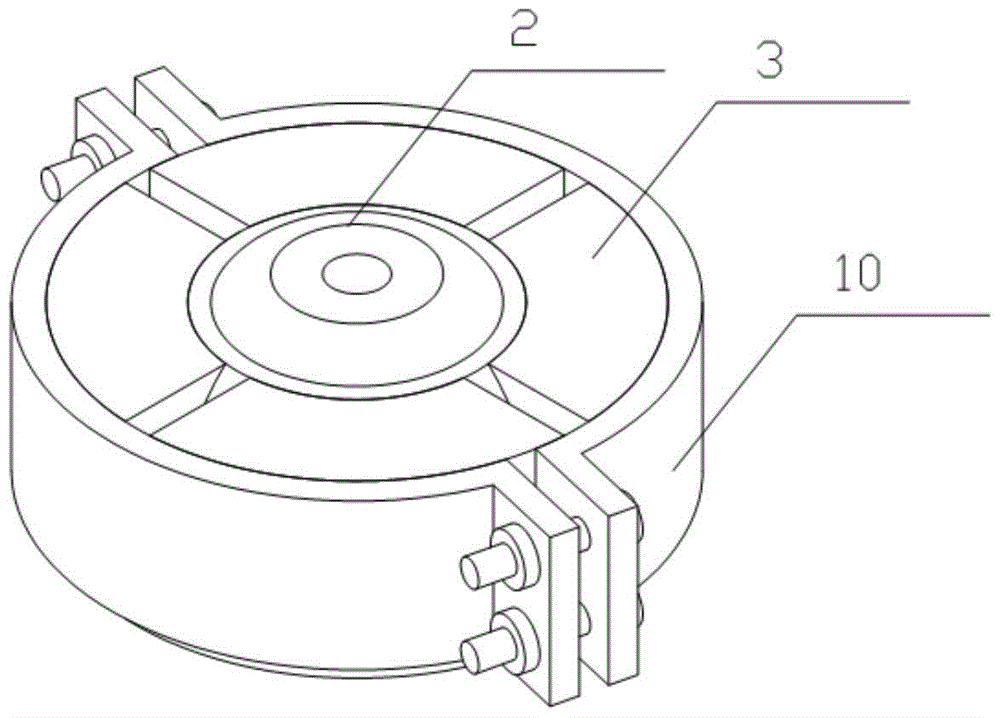

Annular frictional rotating shockproof supporting base

ActiveCN104763056AGuaranteed stabilityImprove shock absorptionBridge structural detailsShock proofingEngineeringRigid body

The invention relates to an annular frictional rotating shockproof supporting base. The annular frictional rotating shockproof supporting base comprises an upper cover plate, a rotating rigid body, an annular frictional wall, a buffer spring, a suspending steel block, and a base; the lower part of the upper cover plate is provided with a convex hemispheroid, the upper part of the rotating rigid body is provided with a groove, and the convex hemispheroid is meshed and contacted with the groove; the center of the lower part of the rotating rigid body is provided with a spherical groove, and the spherical groove is in supporting connection with the hemispheroid to form rotating contact in every direction; the overall side face of the rotating rigid body is provided with a spherical face and forms a frictional contact with the annular frictional wall; when the rotating rigid body is rotated, the rotating rigid body rubs the annular frictional wall to dissipate the earthquake energy; one ring at the bottom part of the rotating rigid body is provided with a vertical buffer spring, and the other end of the buffer spring is connected with the suspending steel block; the suspending steel block is placed in a block opening of the base, and the thickness of the suspending steel block is less than the height of the block opening; when the rotating rigid body is rotated to a certain position, the buffer spring can upwards raise up so as to drive the suspending steel block to upwards move; when the buffer spring is contacted with the block opening, the buffer spring is stretched to limit the movement of the rotating rigid body.

Owner:SHANGHAI BAOYE GRP CORP +1

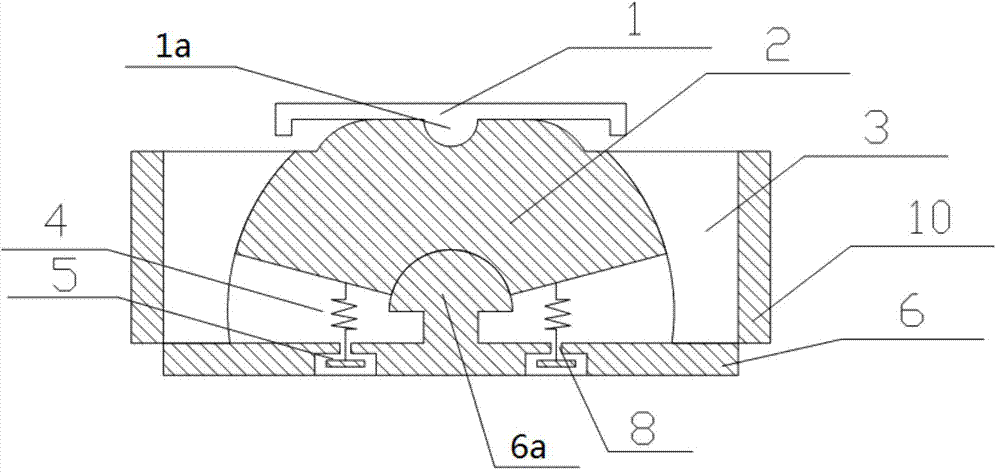

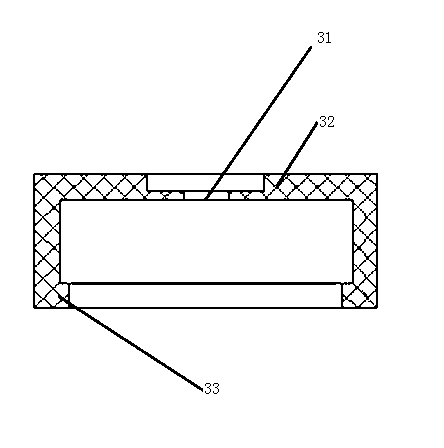

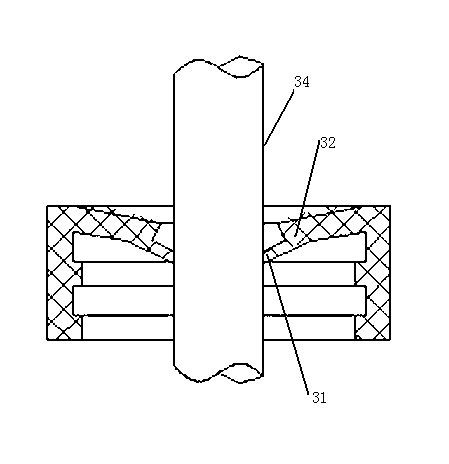

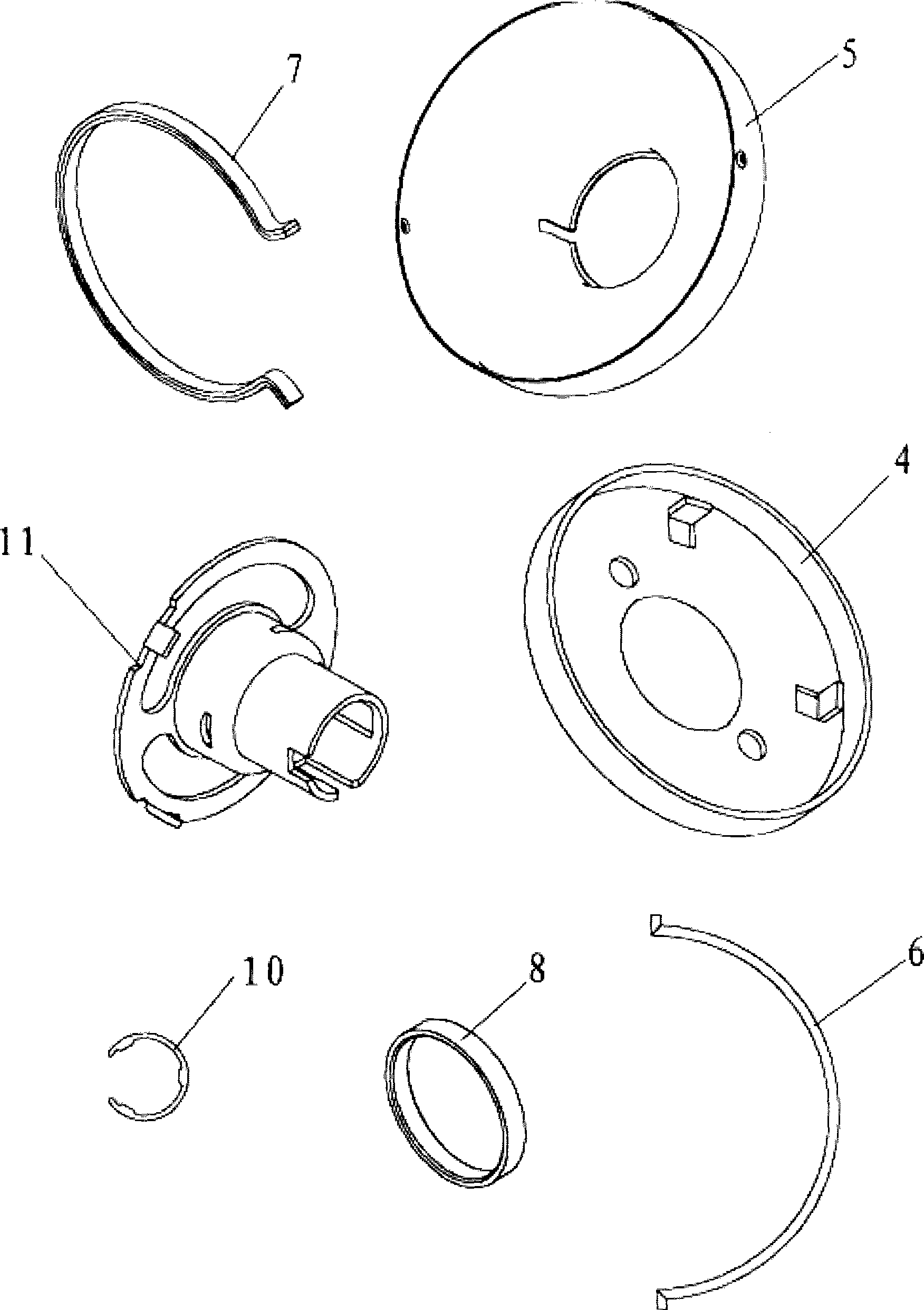

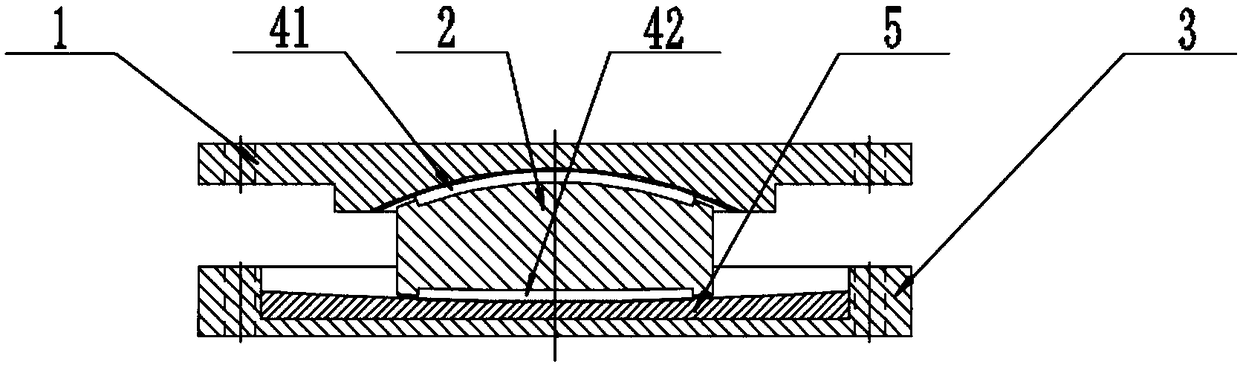

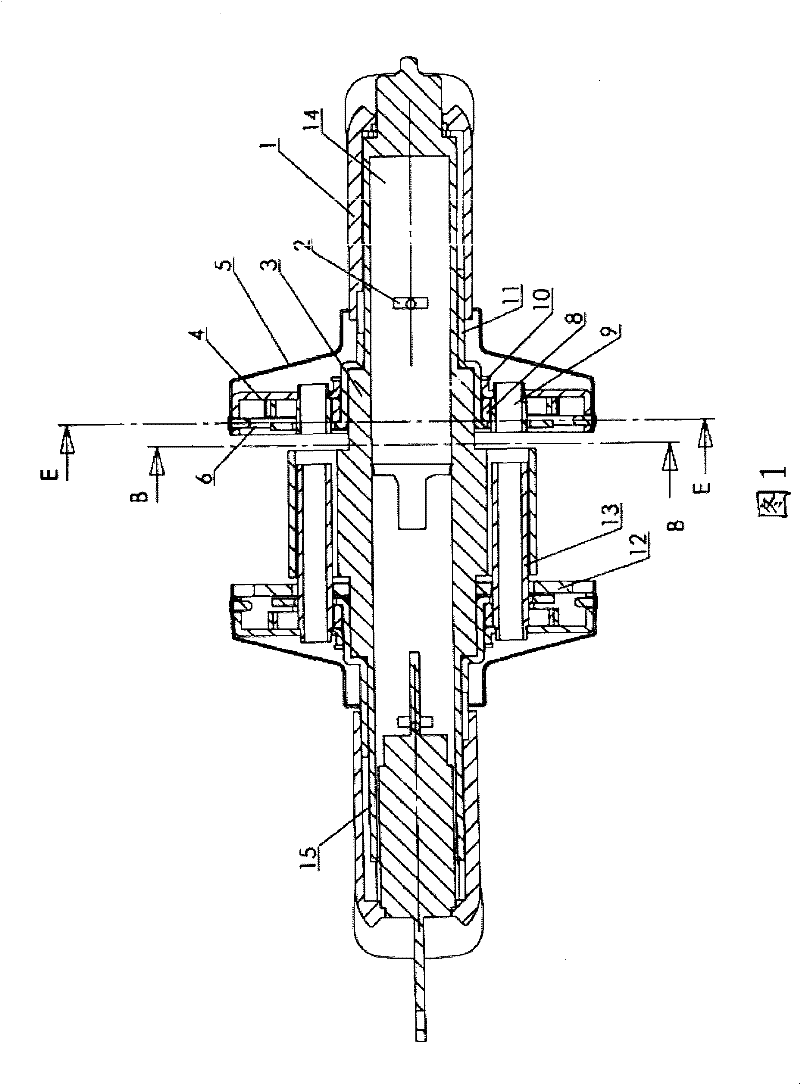

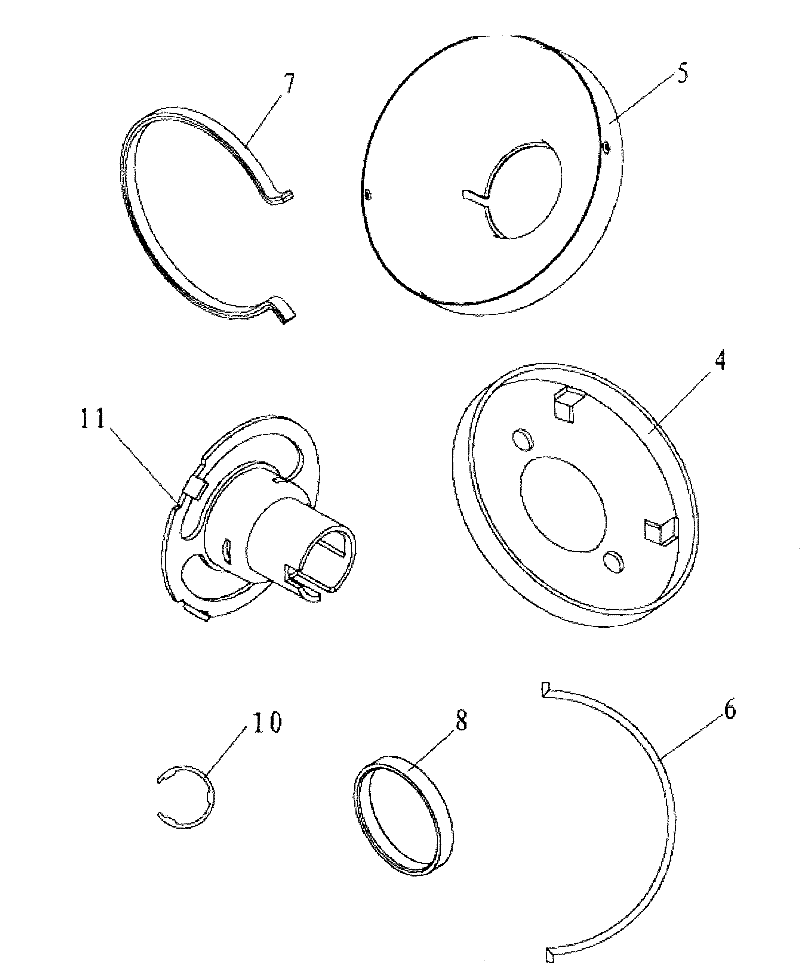

Multifunctional external sealing device for medical operation puncturing device

The invention relates to a multifunctional external sealing device for a medical operation puncturing device. The multifunctional external sealing device for the medical operation puncturing device comprises an upper pressing cover, a lower pressing cover, a base, a supporting base, a top base, a sealing film assembly, a supporting piece assembly and a sealing cushion assembly, wherein the upper pressing cover is fixed with the lower pressing cover, the sealing film assembly is installed between the base and the supporting base, the supporting piece assembly is installed between the supporting base and the sealing cushion assembly, the sealing cushion assembly is installed between the supporting piece assembly and the top base, the base, the supporting base, the top base, the sealing film assembly, the supporting piece assembly and the sealing cushion assembly are installed in the upper pressing cover and the lower pressing cover, and the sealing cushion assembly and the lower pressing cover are fixed. The multifunctional external sealing device for the medical operation puncturing device is reasonable in design, good in sealing effect, long in service life, and suitable for instruments with different external diameters and specifications, ensures that an operation is more conveniently and simply and faster conducted, and effectively shortens operation time.

Owner:HANGZHOU KANGJI MEDICAL INSTR

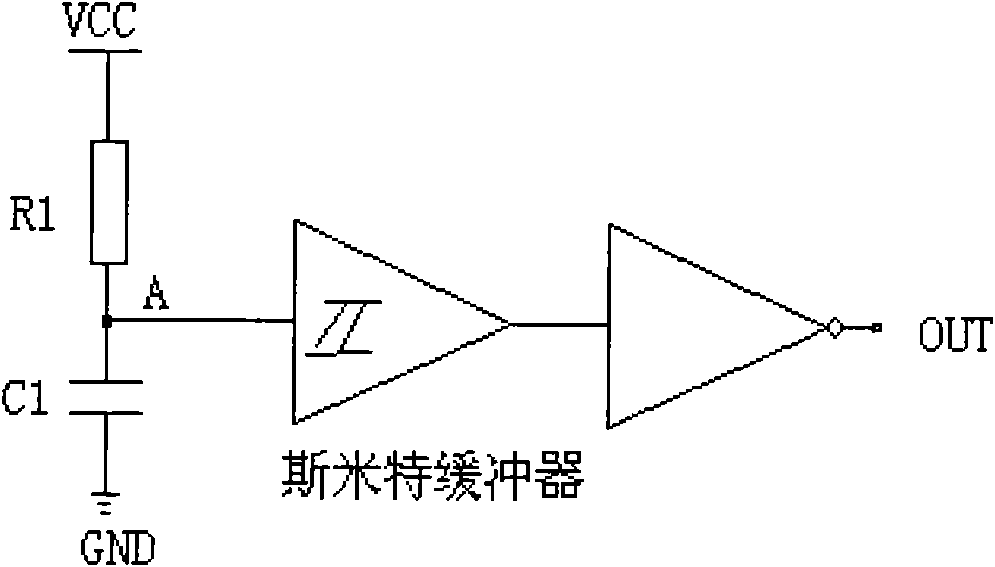

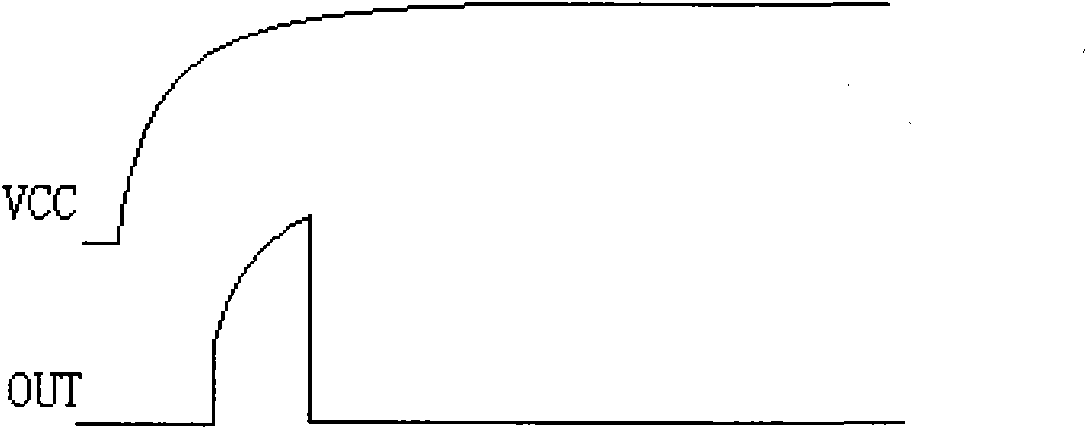

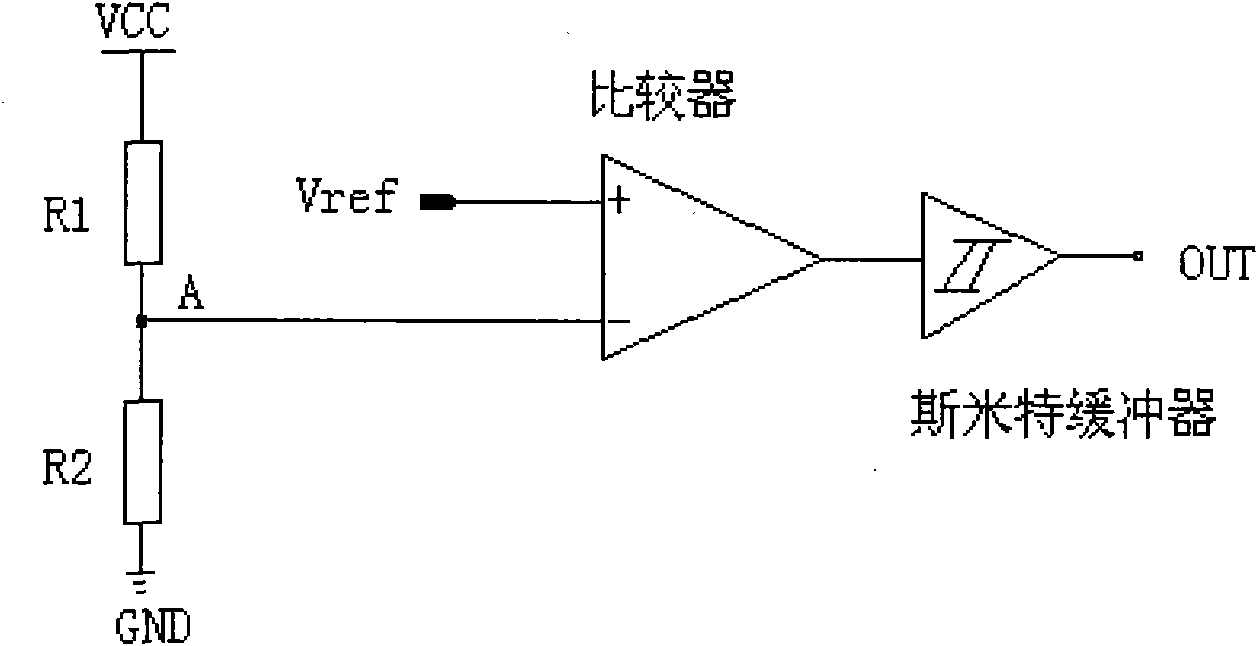

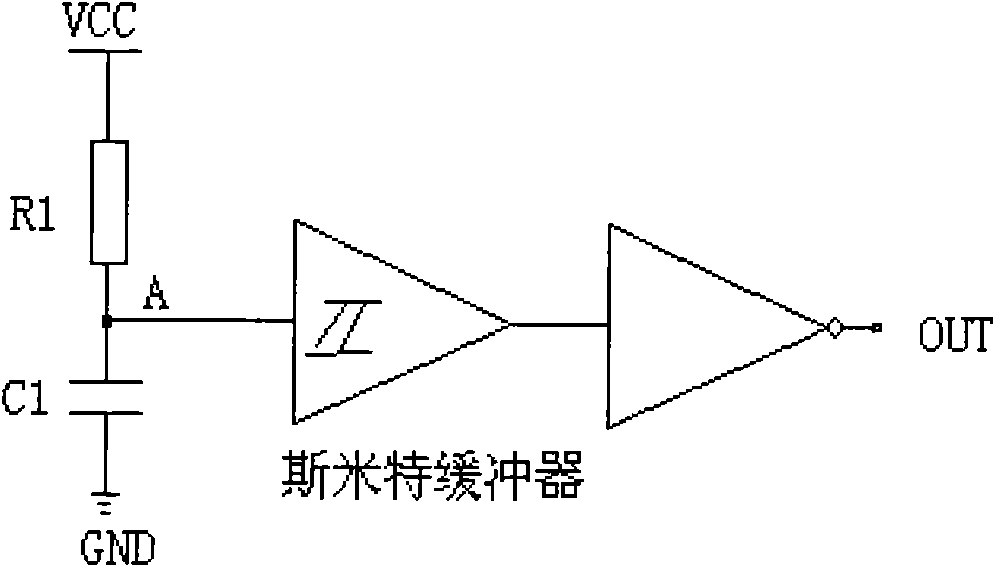

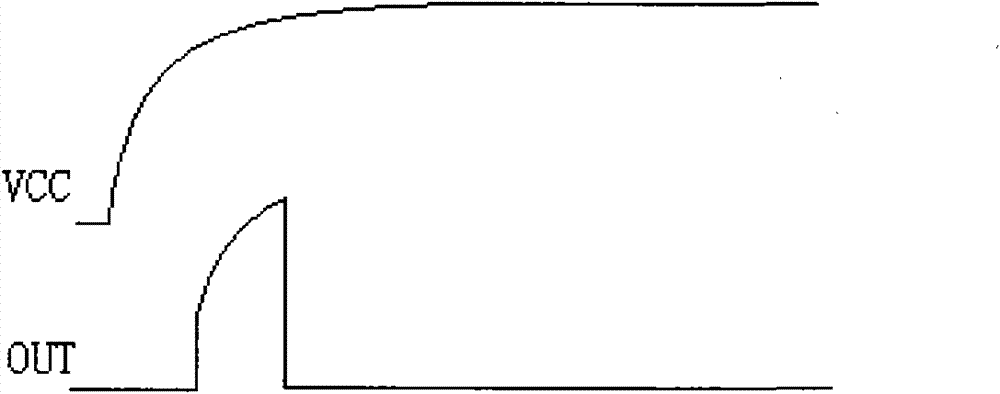

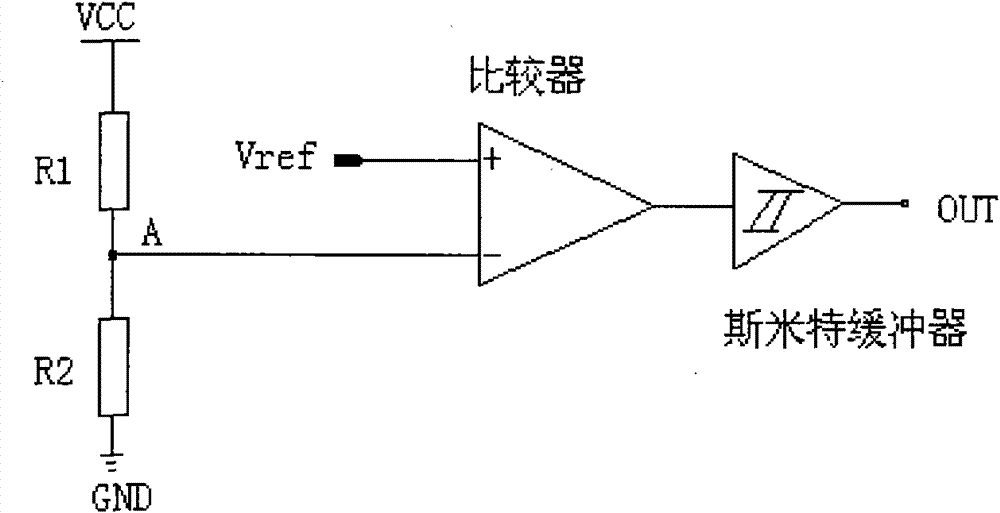

Reset circuit

ActiveCN102006039AGood reset functionReduce power consumptionElectronic switchingCapacitancePower-on reset

The invention relates to a reset circuit, which comprises a power-on reset circuit and a power-off reset circuit, wherein the power-on reset circuit comprises a first field-effect tube, a second field-effect tube, a third field-effect tube, a first two-input NAND gate, a second two-input NAND gate, a first NOT gate, a second NOT gate, a third NOT gate, a fourth NOT gate, an OR gate, a first capacitor, a second capacitor and a buffering delay module; and the power-off reset circuit comprises fourth to tenth field-effect tubes, a fifth NOT gate and a buffering module. The reset circuit can well execute a reset function, is simple, low in cost and high in electro magnetic compatibility (EMC), can be widely used in integrated circuits, particularly integrated circuits with strict requirements on cost control such as infrared circuits, as well as most microprogrammed control units (MCUs) and circuits with high requirements on anti-interference performance and EMC performance.

Owner:SUZHOU HUAXIN MICROELECTRONICS

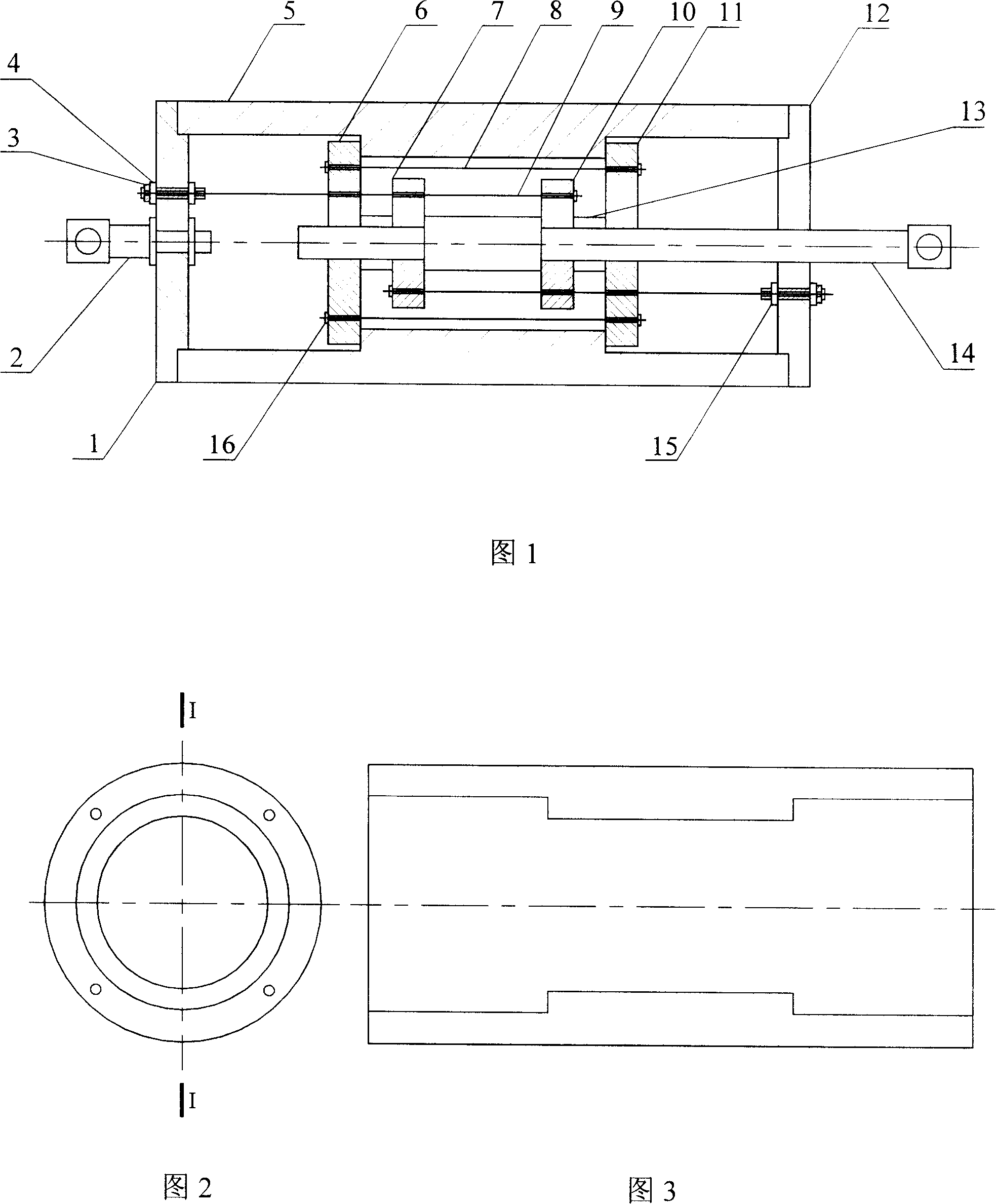

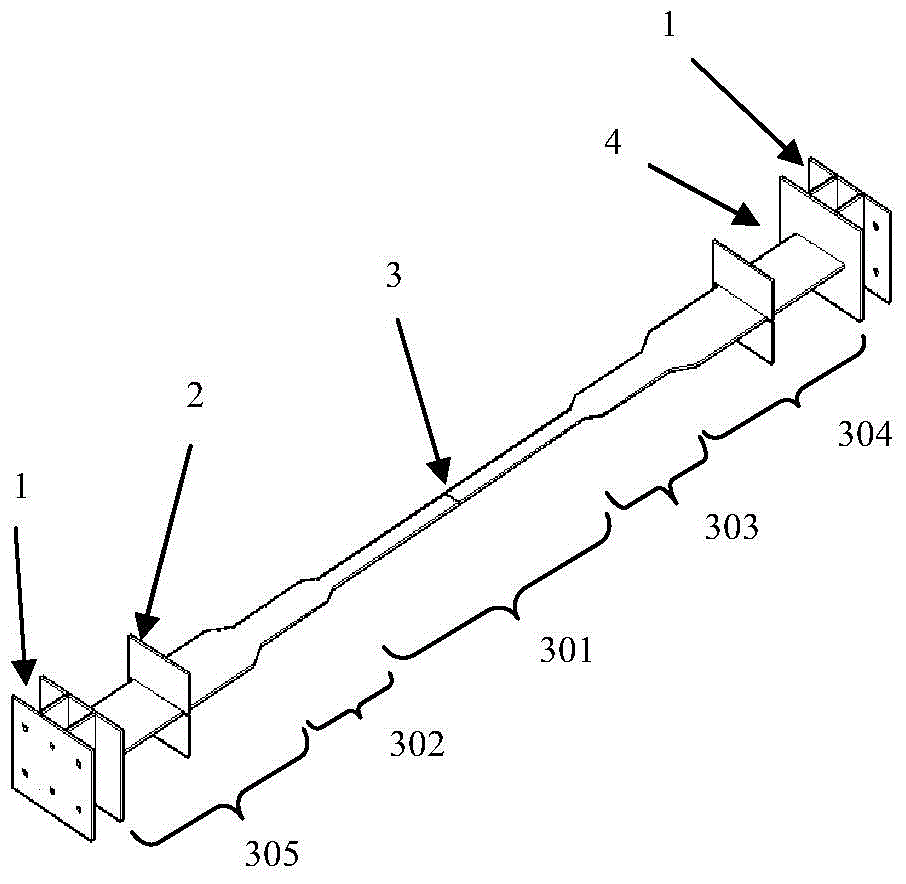

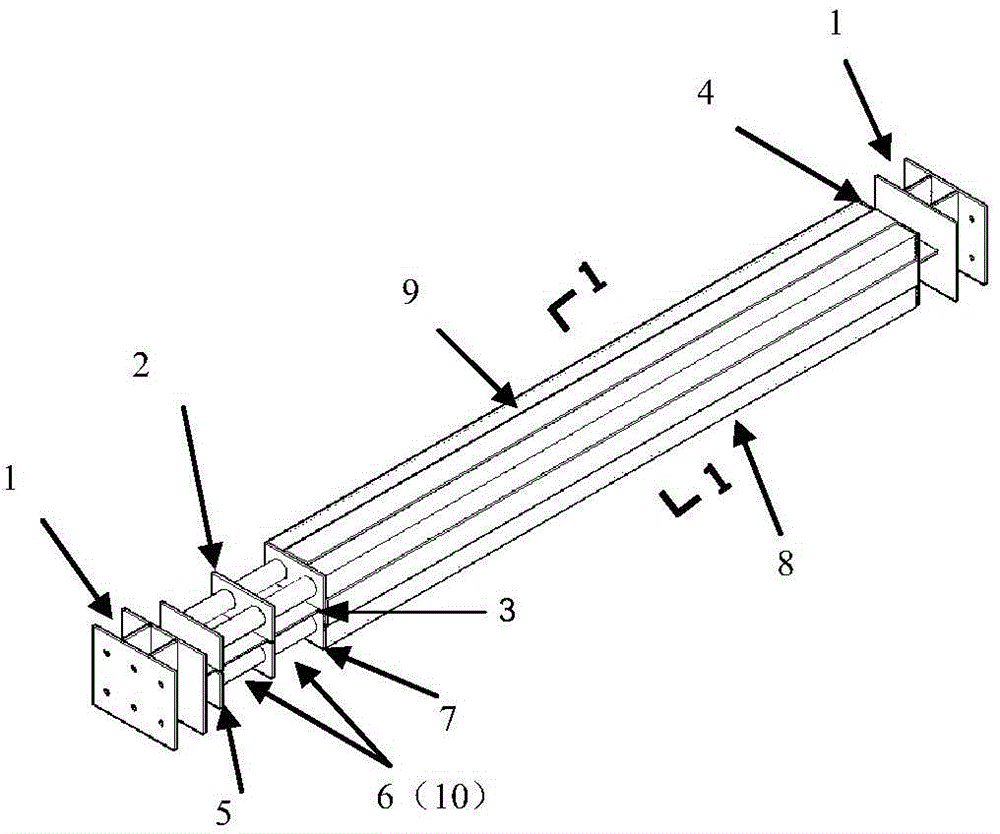

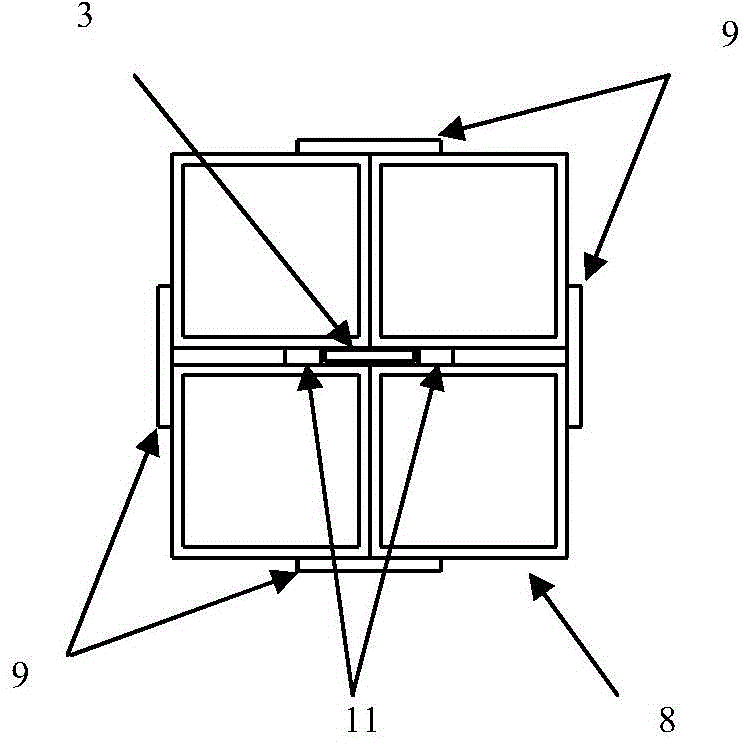

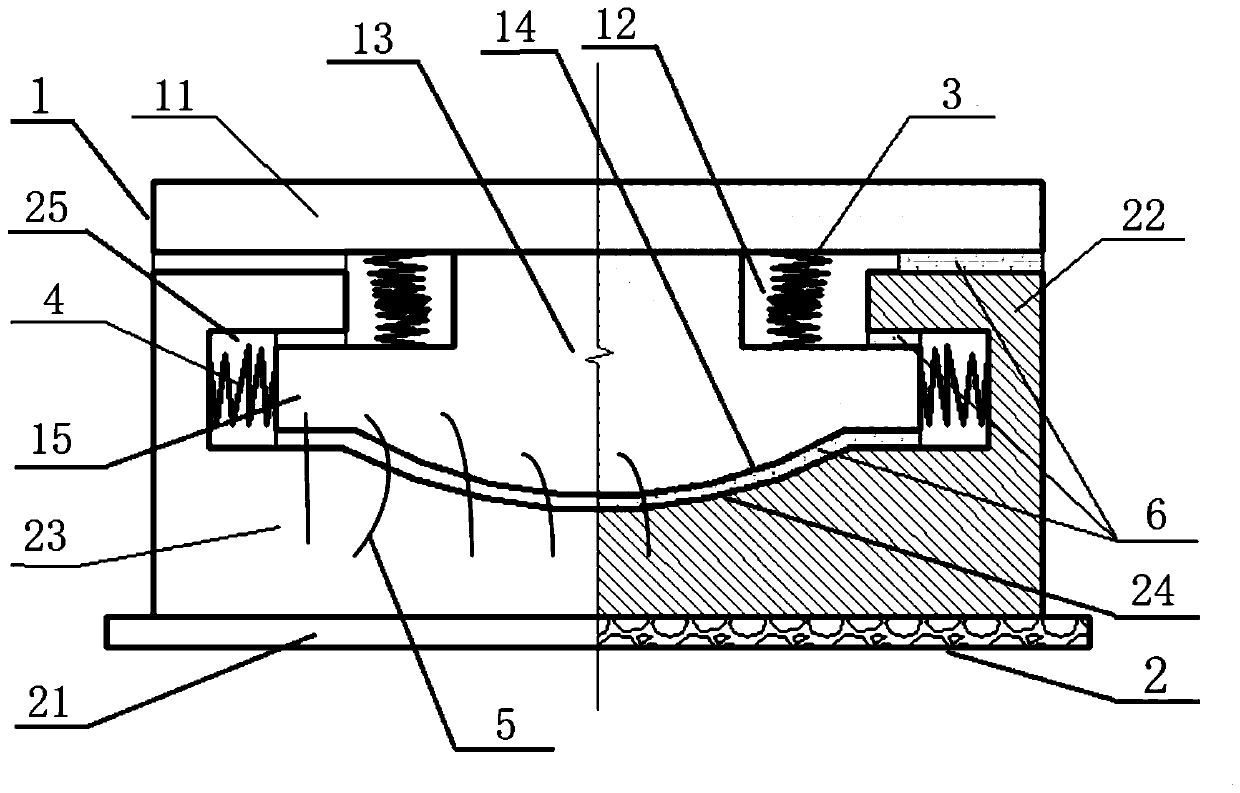

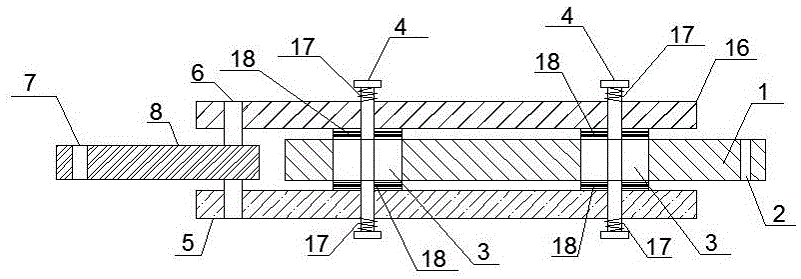

Spring type self-reset anti-buckling supporting device

The invention relates to a self-reset anti-buckling supporting device which comprises an external constraint unit, an inner core and a reset device. The reset device is a reset spring component. The external constraint unit is used for containing the bending deformation of the inner core. The reset spring component is used for recovering the stretch or compression deformation of the inner core. The reset spring component can generate reactive force to conduct resetting without exerting prestressing force after a spring bears force and deforms, the residual deformation of the device under great shock can be reduced while the good energy consumption capacity of anti-buckling supporting is ensured, and then the preset resetting effect is achieved. Compared with prestress type self-reset anti-buckling supporting, the resetting function during supporting pull and press can be more conveniently achieved. The self-reset anti-buckling supporting device is simple in structure, low in price, convenient to machine and manufacture and beneficial to engineering application and popularization.

Owner:HEILONGJIANG UNIVERSITY OF SCIENCE AND TECHNOLOGY

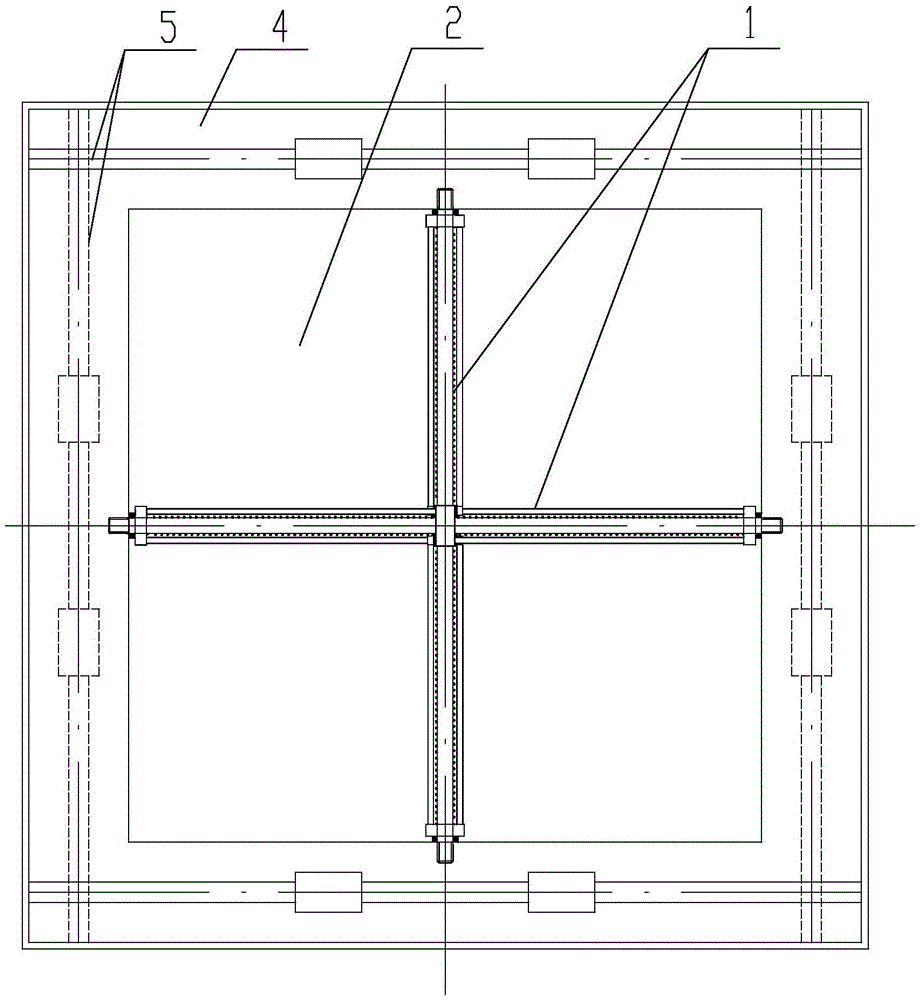

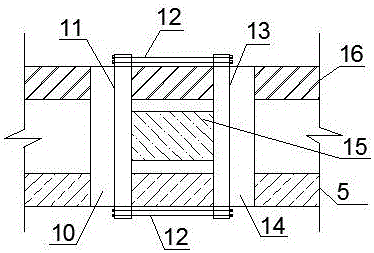

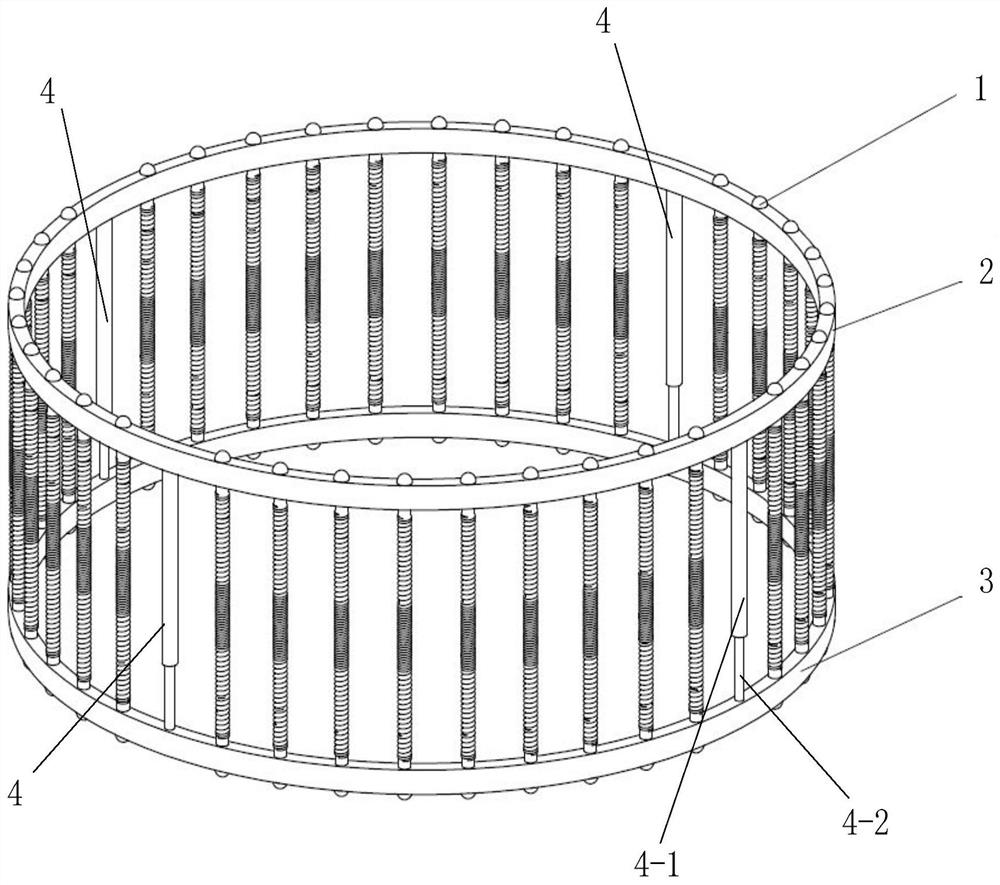

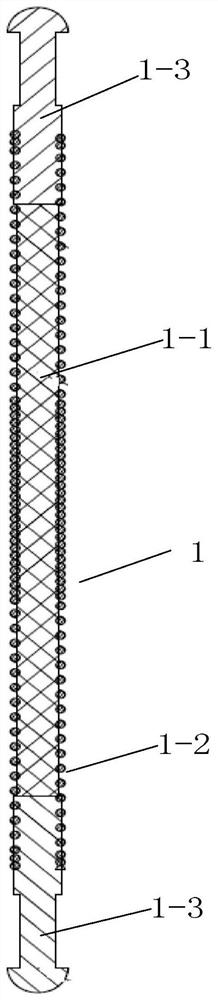

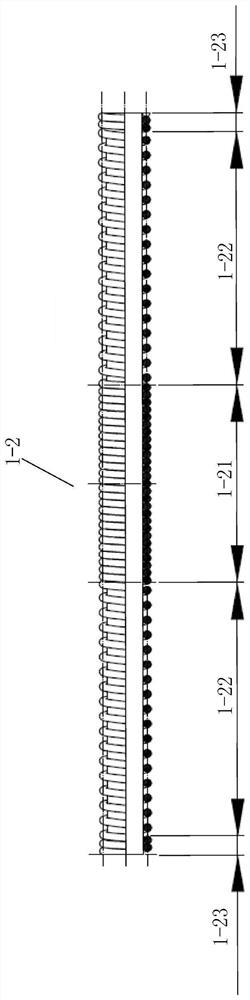

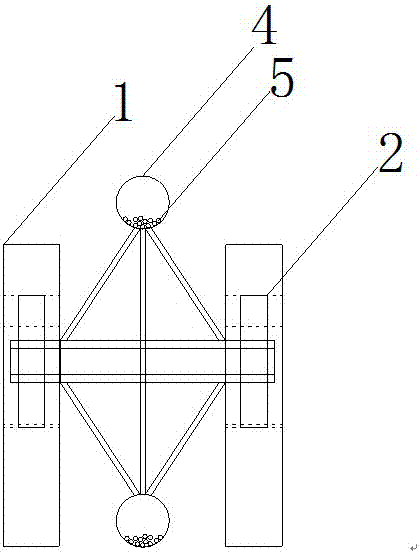

Large-span grid structure multidirectional bearing and anti-seismic spherical hinge support joint

PendingCN109750889AGood vertical bearing capacityGood reset functionProtective buildings/sheltersShock proofingHorizontal forceTemperature stress

The invention provides a large-span grid structure multidirectional bearing and anti-seismic spherical hinge support joint, comprising an upper support, a lower support and a flexible steel bar group.An upper support base is located at the lower end of the upper support, and a lower support supporting seat is located at the upper end of the lower support. The spherical convex face of the upper support base and the spherical concave face of the lower support supporting seat are connected in an embedded fit mode. The upper support and the lower support are connected through the flexible steel bar group. Micro vertical, horizontal and rotary displacements can be allowed, the stability of the structure out of the plane is limited, and the load effects of bearing vertical pressure, stirring force, horizontal force, bending moment, earthquake force, temperature stress and the like are achieved. The structure is used for absorbing and consuming loads caused by earthquakes, the form of support nodes is simplified, good anti-seismic and damping effects on the upper grid structure are achieved, the influence of complex loads on deformation of the lower structure is reduced, and the overallanti-seismic performance of the structure is improved. The manufacturing is simple, the development of an assembly type space structure is promoted, and engineering popularization and application arefacilitated.

Owner:JIYANG COLLEGE OF ZHEJIANG A & F UNIV

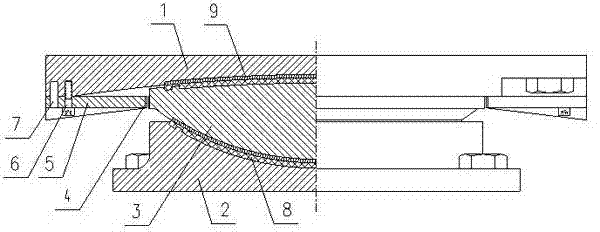

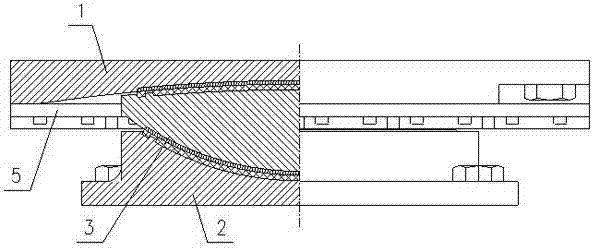

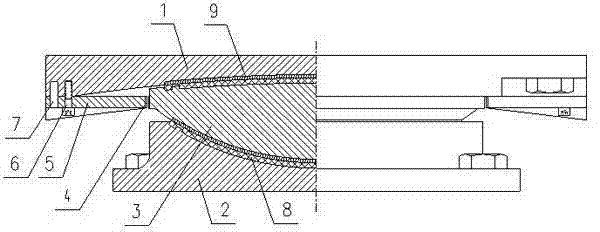

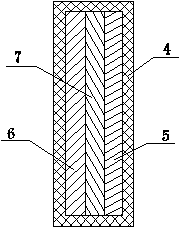

Run-through channel for track passenger trains

InactiveCN102120460AImprove fire performanceImprove sound insulation and noise reductionAxle-box lubricationRailway bodiesThermal insulationEngineering

The invention relates to a run-through channel for track passenger trains, which comprises a vestibule diaphragm body assembly, a gangway foot plate assembly, a pedal assembly and a reset plate spring assembly, wherein the vestibule diaphragm body assembly is provided with an external vestibule diaphragm body arched outwards and an internal vestibule diaphragm body arched inwards; and the end part of the internal vestibule diaphragm body is connected with a fabric inserted aluminum frame, the external vestibule diaphragm body is connected with an end-wall connecting frame, the fabric inserted aluminum frame is fixedly connected with the end-wall connecting frame, and a rubber sealing strip is embedded into the end-wall connecting frame. The internal vestibule diaphragm body is formed by connecting more than two pieces of double-layer U-shaped internal diaphragm fabric together, and the internal diaphragm fabric is made by an integral sulfidizing process with a forming die. The run-through channel provided by the invention is flexible to move, is safe and reliable and has high sound insulation, high thermal insulation and high air tightness, and can satisfy the high performance requirements of high speed track passenger trains.

Owner:CHANGZHOU HUBOLA JINCHUANG TRAFFIC EQUIP

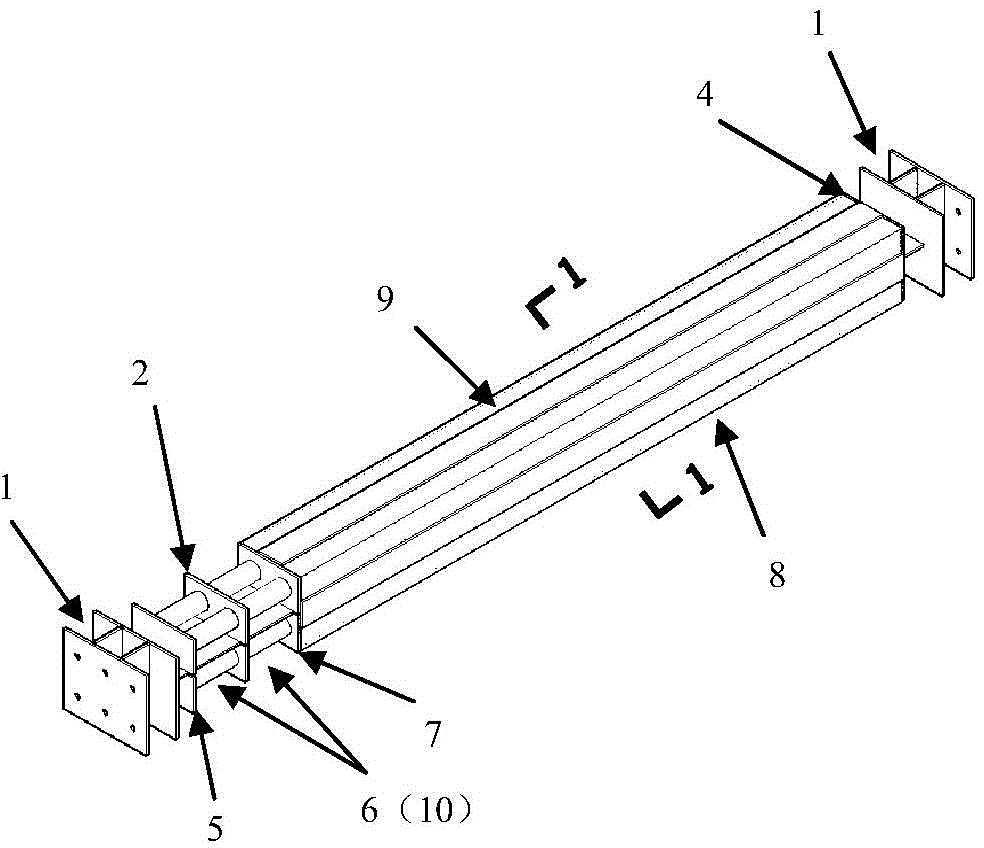

Self-reset buckling-restrained brace device

The invention relates to a self-reset buckling-restrained brace device. The self-reset buckling-restrained brace device comprises an outer portion constraint unit, an inner core and a reset device, wherein the reset device is a reset spring component, the outer portion constraint unit is used for constraining the bending deformation of the inner core, and the reset spring component is used for recovering the stretching or compression deformation of the inner core. The reset spring component adopted by the self-reset buckling-restrained brace device uses the reactive force generated after a spring is stressed and deformed to conduct reset, a pre-stressing force is not needed to be exerted, on the basis that the good energy-dissipating capacity of a buckling-restrained brace is guaranteed, the residual deformation of the buckling-restrained brace under a large earthquake can be reduced, and the predetermined reset effect is achieved. Compared with a pre-stressing force type self-reset buckling-restrained brace, by means of the self-reset buckling-restrained brace device, the reset functions in stretching and pressing of a brace can be achieved more conveniently. The self-reset buckling-restrained brace device is simple in structure, low in price, convenient to machine and manufacture and convenient for project popularization and application.

Owner:HEILONGJIANG UNIVERSITY OF SCIENCE AND TECHNOLOGY

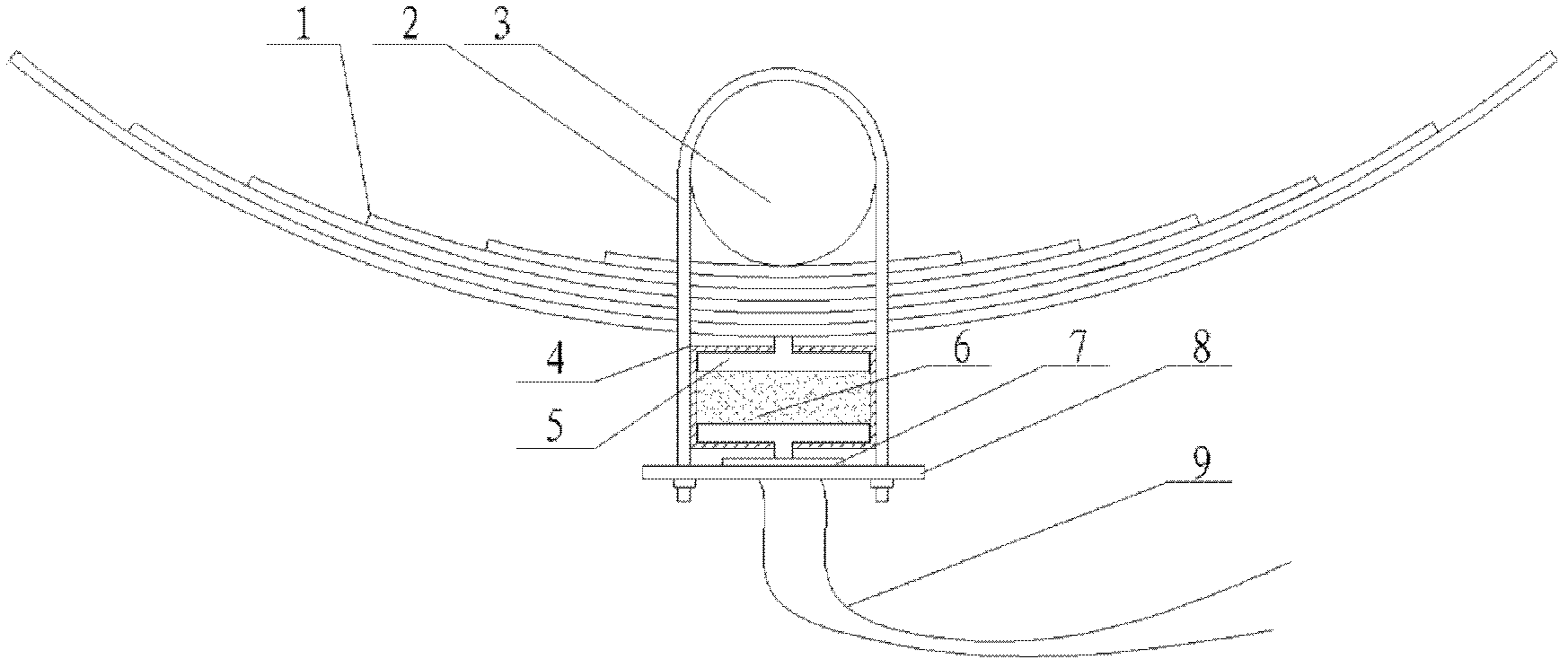

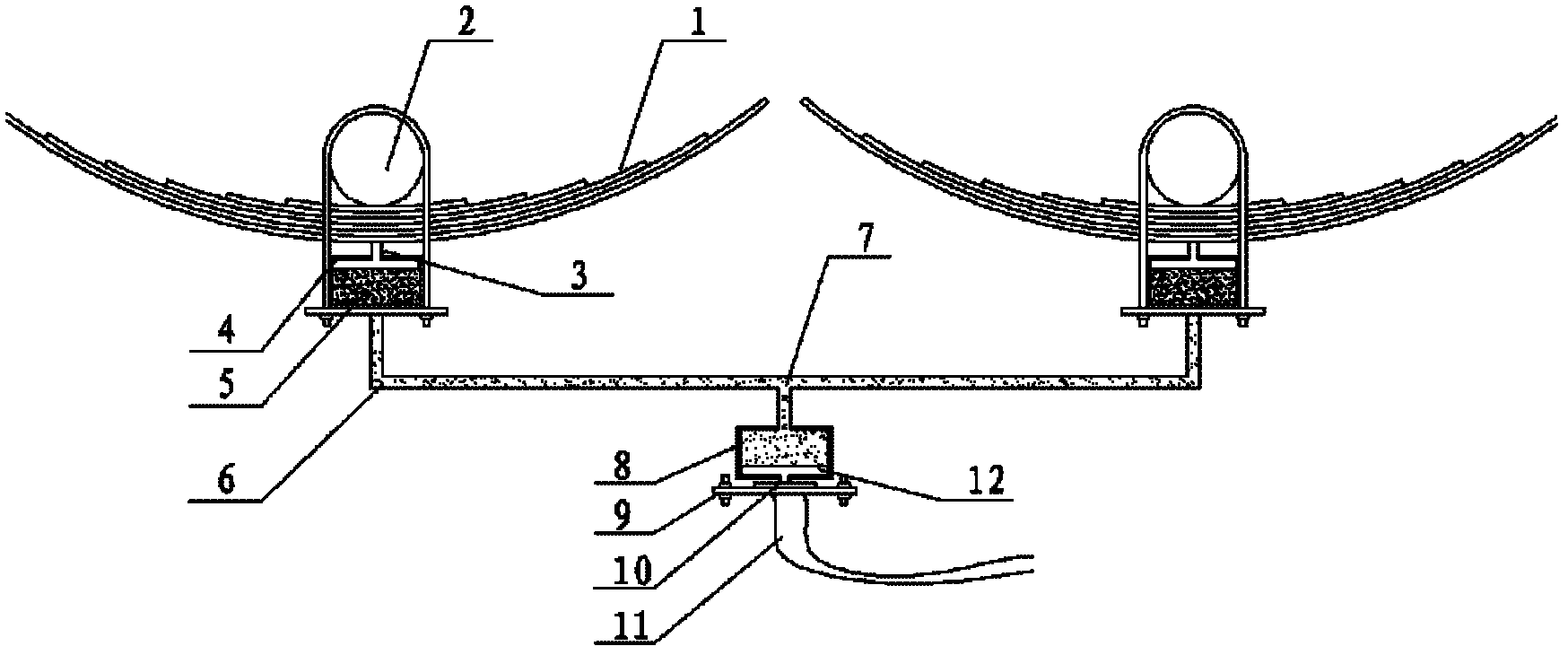

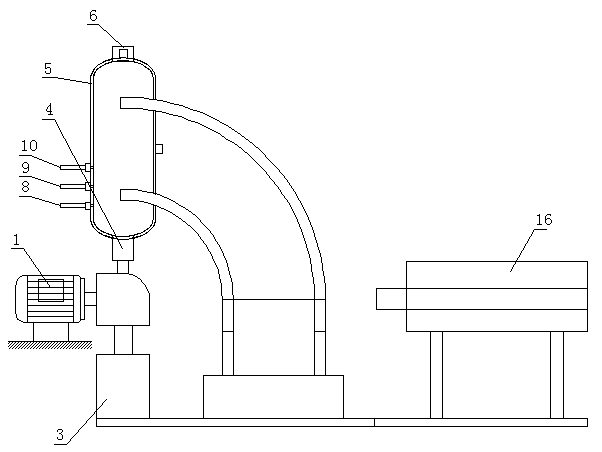

Load capacity self-measuring transducer of freight vehicle

InactiveCN103171481AEasy to passSimple structureSpecial purpose weighing apparatusTransducerEngineering

The invention discloses a load capacity self-measuring transducer of a freight vehicle. The transducer comprises a transducer shell body, hydraulic medium, a pressure transducer, a n-shaped fixed steel tube, a guide wire and a piston device, wherein the piston device is respectively formed by two piston rods and two piston plates and the upper portion and the lower portion of the piston device are symmetrical, the hydraulic medium is filled between the upper portion of the piston device and the lower portion of the piston device, the pressure transducer is installed on a fixed steel plate and converts a pressure value to an electrical signal, the middle section of the fixed steel tube bypasses an axle, the right end and the left end of the fixed steel tube penetrate through the fixed steel plate, the shape of the fixed steel tube is n-shaped, and the guide wire is used for transmitting the signal output by the pressure transducer to a cab and showing in a form of a weight numerical value finally. The transducer has the advantages of being simple in structure, stable in operation and accurate in measurement, and not damaging the structure of an original car body because the whole device is installed on the bottom portion of a steel plate spring of the original car body. Through the hydraulic medium, the pressure is distributed uniformly to be passed on conveniently and the device is also good in reset function and with the change of load weight, the piston device changes in real-time mode under an effect of the hydraulic medium and the steel plate spring.

Owner:陕西银星科技有限公司

Shock-insulating elastic returning mechanism with preset starting load and start-control shock insulating equipment with preset starting load

ActiveCN105605147ARealization of horizontal isolationFunction increaseNon-rotating vibration suppressionEngineeringMechanical engineering

Owner:FOSHAN BAJ ISO TECH

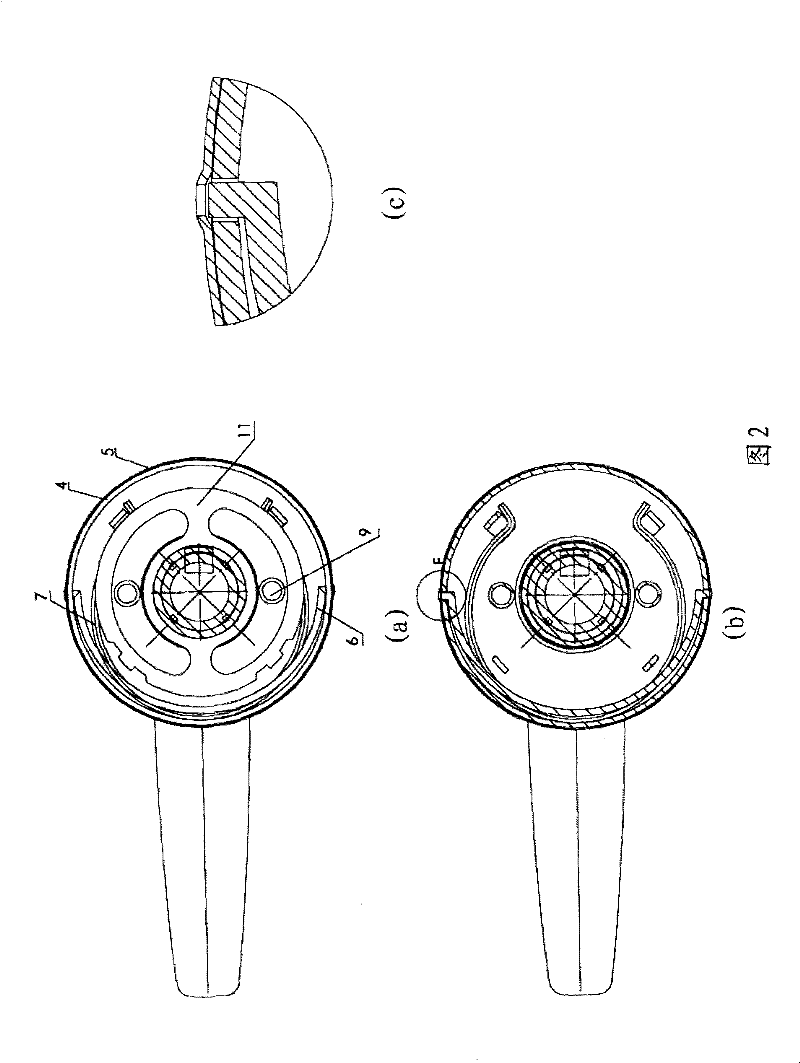

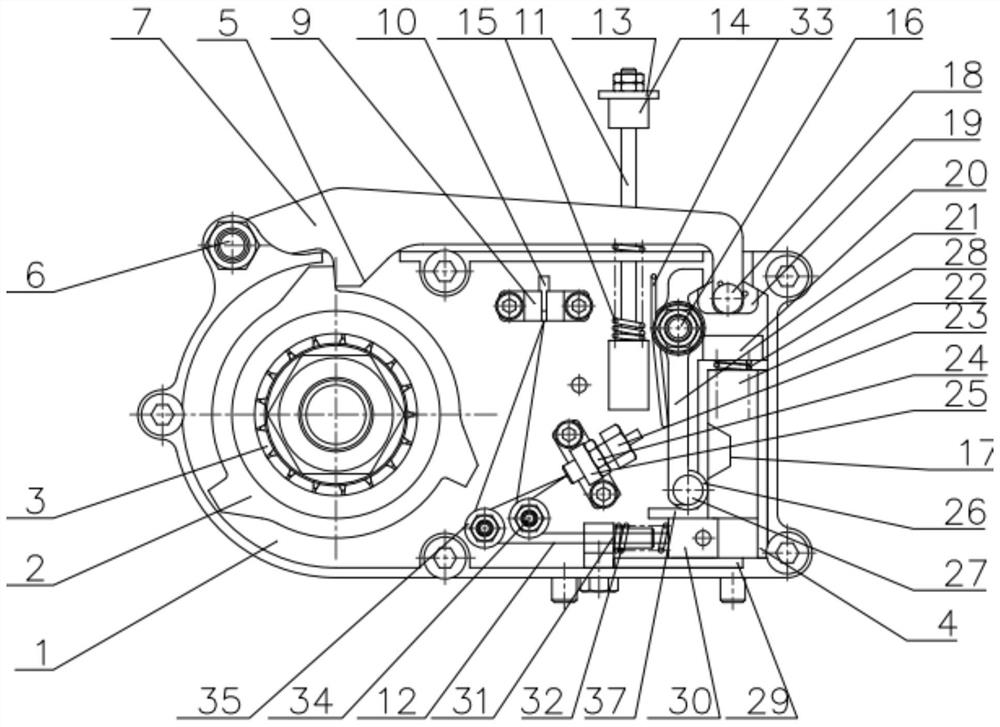

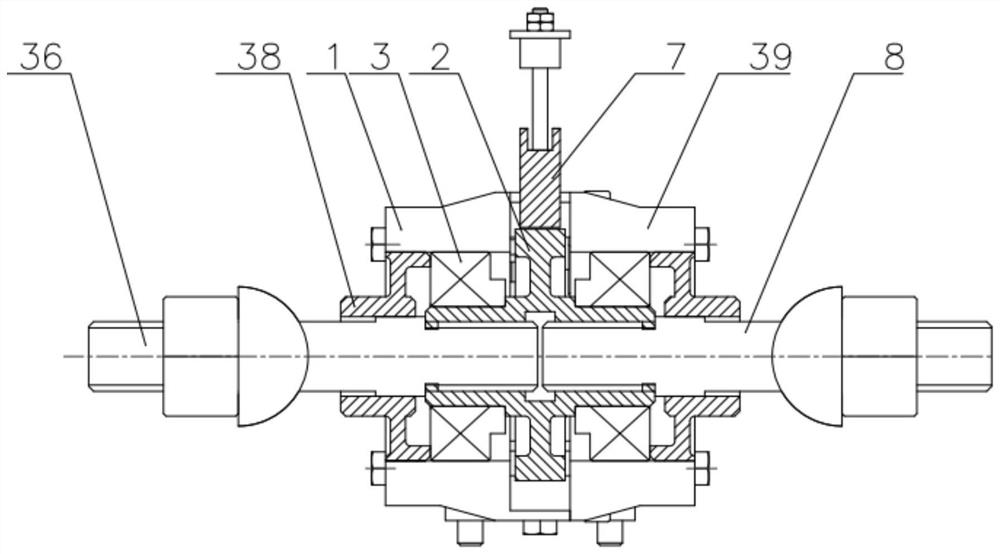

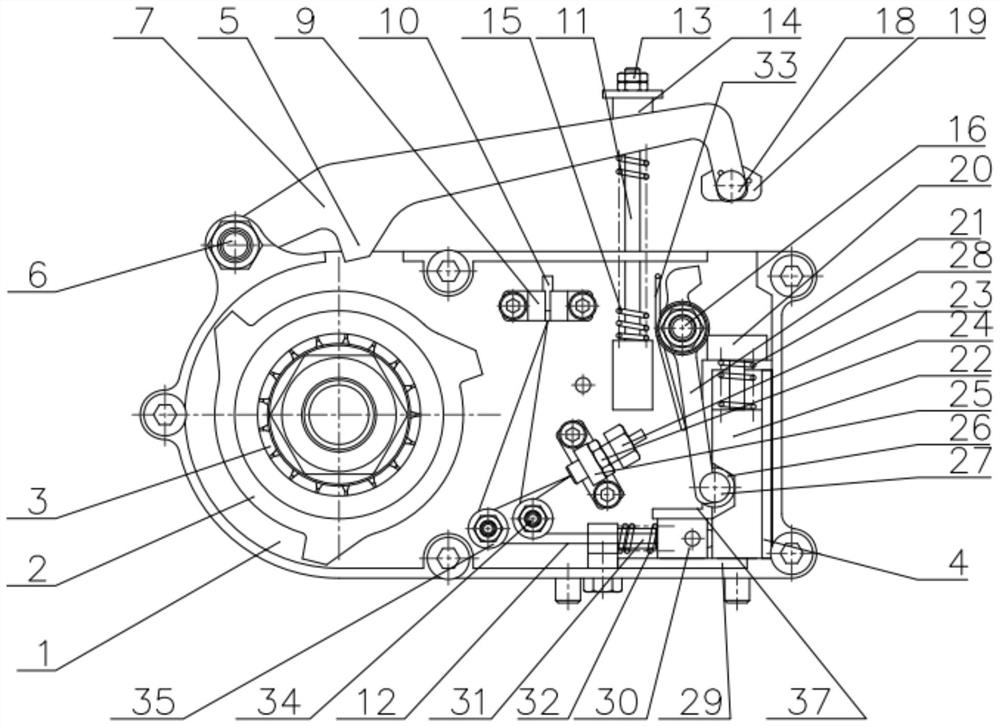

Barrel type handle lock

ActiveCN101487365AEasy to installEasy to disassembleLock casingsHandle fastenersEngineeringMechanical engineering

The invention relates to a cylinder handle lock, which comprises a lock body, a handle and a block cover component which comprises a front block cover component and a back block cover component. The back block cover component comprises a rotational frame which is sheathed on the lock body, a decorative cover which is sheathed on the rotational frame, a block cover which is sheathed outside the rotational frame and inside the decorative cover, a positioning spring which is arranged at the lower part of the block cover and is arranged on the decorative cover in a block way, a reset spring which is arranged inside the block cover and at the upper part of the positioning spring, a limiting sleeve which is sheathed outside the rotational frame, limiting columns which are arranged at the two sides of the limiting sleeve symmetrically and a block spring which is sheathed on the rotational frame and above the limiting sleeve. The application range of the handle lock is comparatively wide for door frames of different thicknesses, assembly and disassembly are convenient, and the use function of the lock cannot be affected when the lock endures larger torque.

Owner:李宝强

Load capacity self-measuring system of freight vehicle

InactiveCN103171482ASimple structureRun smoothlySpecial purpose weighing apparatusPistonSteel plates

The invention discloses a load capacity self-measuring system of a freight vehicle. The transducer comprises a self-measuring transducer device installed on the bottom portion of a steel plate spring of the freight vehicle, medium pipelines drawn forth from the bottom portion of the self-measuring transducer device, a pipeline connecting device used for enabling the tail ends of a plurality of the medium pipelines to be connected, a gathering device which is connected with the pipeline connecting device through a gathering pipeline and guide wires used for sending all signals sent by the gathering device to a cab and showing in a form of a weight numerical value finally. The load capacity self-measuring system has the advantages of being simple in structure, stable in operation and accurate in measurement, and avoiding damaging the structure of an original car body because the whole device is installed on the bottom portion of the steel plate spring of the original car body. Through hydraulic medium, not only is pressure transmitted in an even distributing mode conveniently, but also a good resetting function is achieved, and with the change of load capacities, a piston device changes in real time under the effects of the hydraulic medium and the steel plate spring.

Owner:陕西银星科技有限公司

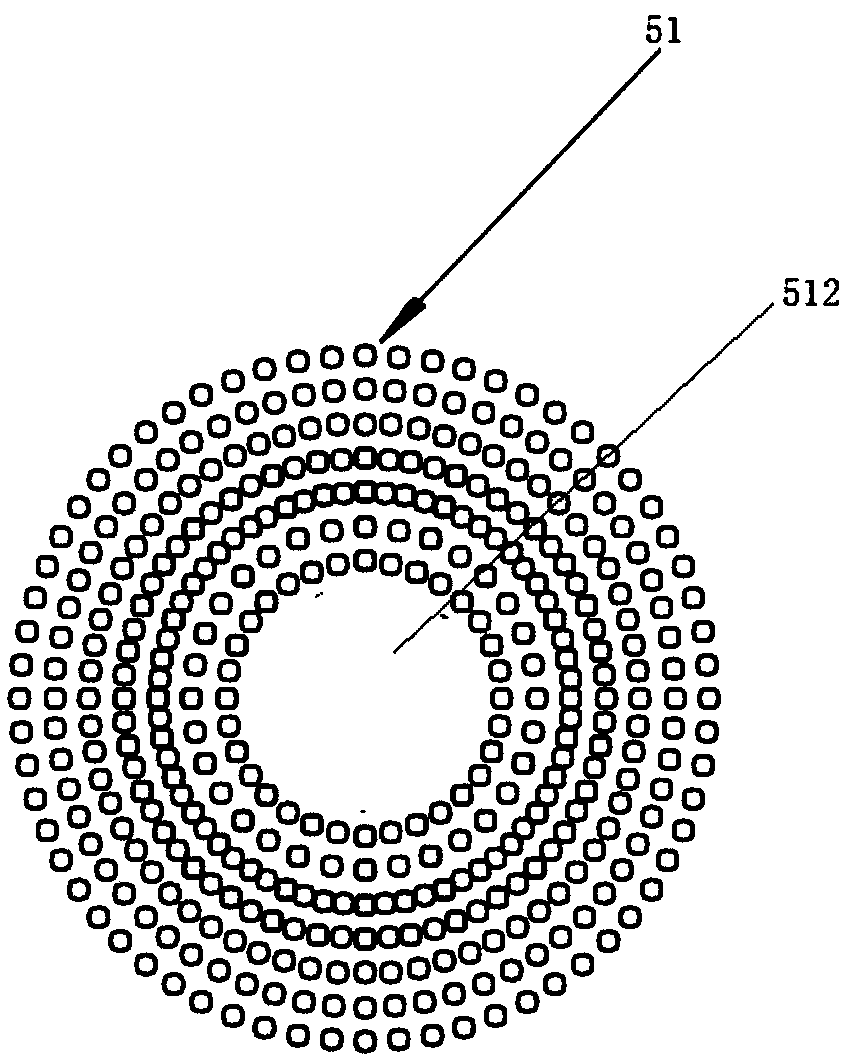

Friction pendulum type three-dimensional multi-stage vibration isolation device with inerter

PendingCN114165092AAchieve isolationGood vibration isolationProtective buildings/sheltersShock proofingVertical vibrationEarthquake resistance

The invention relates to the field of earthquake resistance and shock absorption of buildings, in particular to a friction pendulum type three-dimensional multi-stage vibration isolation device with an inerter, which comprises a decoupling system, a horizontal vibration isolation system and a vertical vibration isolation system, the horizontal vibration isolation system is a friction pendulum support mechanism, and the vertical center line of the vertical vibration isolation system and the vertical center line of the friction pendulum support mechanism are kept consistent; the friction pendulum support mechanism is connected with the upper structure; the vertical vibration isolation system is arranged below the friction pendulum support mechanism and connected with a foundation. The inerter vibration isolation system and the friction pendulum support are connected in a decoupling mode to achieve three-dimensional vibration isolation. Effective vertical vibration isolation can be achieved by connecting the spiral spring and the inerter system in parallel, the friction pendulum support can play a role in horizontal vibration isolation, due to the existence of the decoupling system, horizontal vibration isolation and vertical vibration isolation can play roles respectively, and three-dimensional vibration isolation is achieved.

Owner:NANCHANG UNIV

Friction pendulum type shock absorption and isolation support seat

InactiveCN102337725AConsume as soon as possibleSignificant frictional energy consumptionBridge structural detailsWear resistantEnergy consumption

The invention discloses a friction pendulum type shock absorption and isolation support seat, which comprises an upper seat plate, a lower seat plate, a double-spherical-surface rotating block and position limiting blocks, wherein the double-spherical-surface rotating block is arranged between the upper seat plate and the lower seat plate, the position limiting blocks are respectively and fixedly arranged on the lower surfaces of the left end part and the right end part of the upper seat plate in the transverse axial direction, one ends of the position limiting blocks are in contact with the side surface of the double-spherical-surface rotating block, the upper surface and the lower surface of the double-spherical-surface rotating block are respectively spherical surfaces, and the lower surface of the upper seat plate and the upper surface of the lower seat plate are provided with recessed spherical surfaces matched with the upper seat plate and the lower seat plate. The friction pendulum type shock absorption and isolation support seat has the beneficial effects that the friction energy consumption is obvious, the resetting function and the durability are good, the fireproof and wear-resistant functions are realized, the period is fixed, the structure is simple, the size is small, and the cost is low.

Owner:CHENGDU XINZHU ROAD & BRIDGE MASCH CO LTD

Connecting device of USB plug

InactiveCN104051924AFlexible swingWith reciprocating swing functionFlexible/turnable line connectorsUSBMechanical engineering

The invention discloses a connecting device of a USB plug. The connecting device of the USB plug comprises a support and a connecting device body. A first pin shaft and a second pin shaft are formed at the two ends of the connecting device body respectively and are rotatably mounted at the two ends of the support respectively, and a reset spring used for driving the connecting device body to reset is arranged between the support and the connecting device body. The connecting device has the function of reciprocating swing, the function of flexible contact is achieved when the connecting device is plugged or unplugged in a computer, damage caused by improper force exertion to welding pins of the connecting device is avoided, and an auxiliary circuit board on the connecting device is also protected. Furthermore, due to the fact that the connecting device has the automatic reset function, the alignment action can be more accurate and faster when the connecting device is plugged or unplugged.

Owner:钟国麟

Special type protection mask

InactiveCN103844407AGood reset functionFit tightlyProtective garmentSpecial outerwear garmentsActivated carbonParticulates

The invention discloses a special type protection mask, which comprises a mask body and a tying belt which is connected to the mask body, wherein a static filter cotton layer, an activated carbon layer, a visco-elastic layer and a medical absorbent gauze wrapping sleeve are contained in the mask body; the static filter cotton layer, the activated carbon layer and the visco-elastic layer are put in the medical absorbent gauze wrapping sleeve in sequence and are sewn and connected into a whole. The special type protection mask has the advantages that a plurality of protection layers are contained in the special type protection mask, the protection mask is tightly fitted to the face during use, can effectively filter particulate matter, toxic substances and dust, and the special type protection mask has an excellent protection effect for people who work and live under special environments and special weather.

Owner:NANHUA UNIV

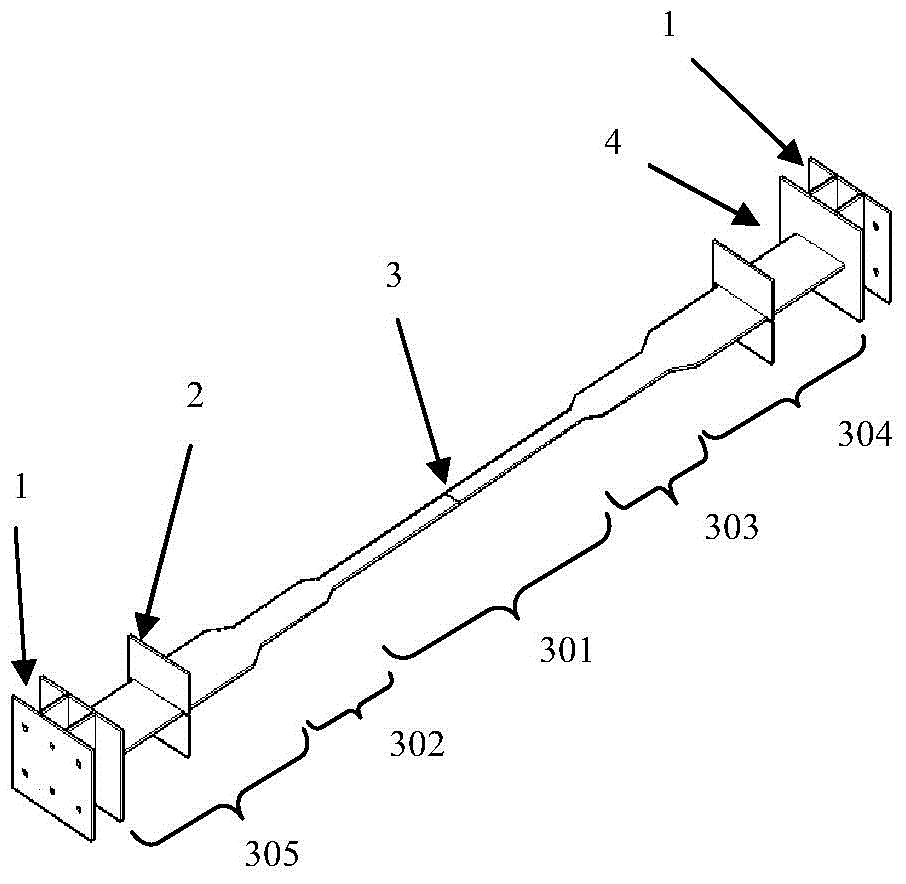

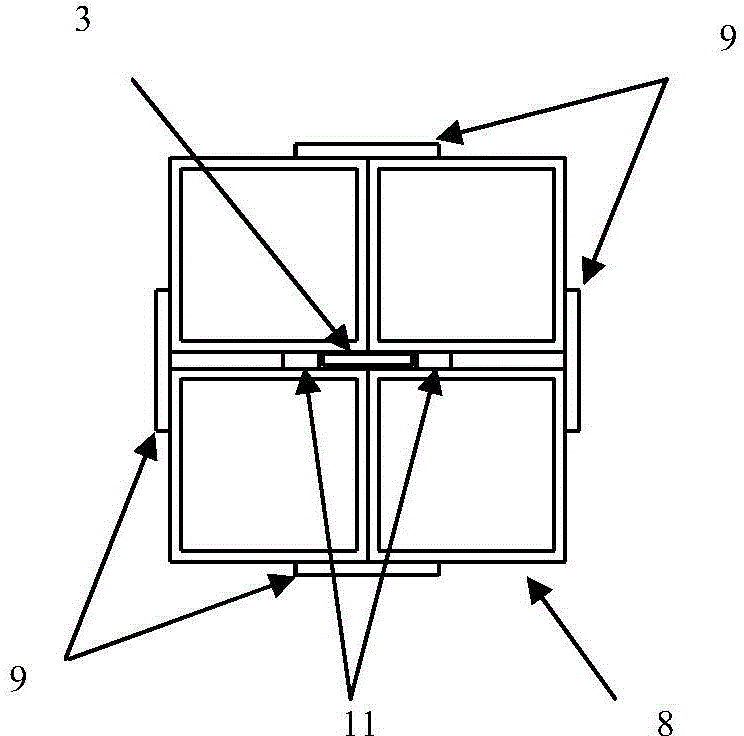

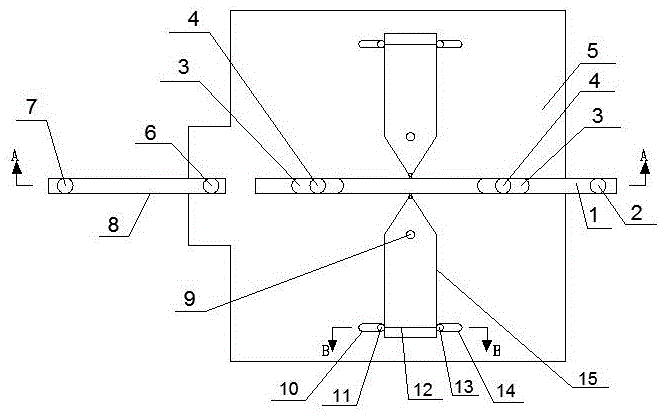

Multiple combination energy-dissipating damper

InactiveCN106760861AEasy to useReduce usageProtective buildings/sheltersShock proofingShape-memory alloyEngineering

The invention discloses a multiple combination energy-dissipating damper, comprising an auto-adjustable frictional energy-dissipating device and a shape memory alloy energy-dissipating self-restoring device; the auto-adjustable frictional energy-dissipating device comprises a main plate, an upper auxiliary plate and a lower auxiliary plate, the main plate is connected to the upper auxiliary plate and the lower auxiliary plate through high-strength bolts, and friction sheets are penetrated by the high-strength bolts and clamped between the main plate and the upper auxiliary plate as well as between the main plate and the lower auxiliary plate; the shape memory alloy energy-dissipating self-restoring device comprises a rocking plate, a left slide rod, a right slide rod and shape memory alloy wires, the head of the rocking plate is hinged to the main plate, the upper and lower auxiliary plates are each provided with a left slide hole and a right slide hole, the left slide rod and the right slide rod are arranged in the left slide hole and the right slide hole respectively, and the ends of the left and right slide rods are wound with the shape memory alloy wires. The shape memory alloy energy-dissipation and frictional energy-dissipation are combined in the multiple combination energy-dissipating damper; the multiple combination energy-dissipating damper has good energy-dissipating shock reduction and restoring functions; a displacement amplifier is provided, so that the shape memory alloy wires are more value in use and the cost is low.

Owner:HENAN POLYTECHNIC UNIV

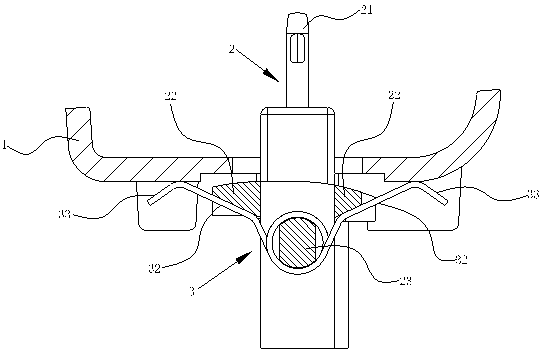

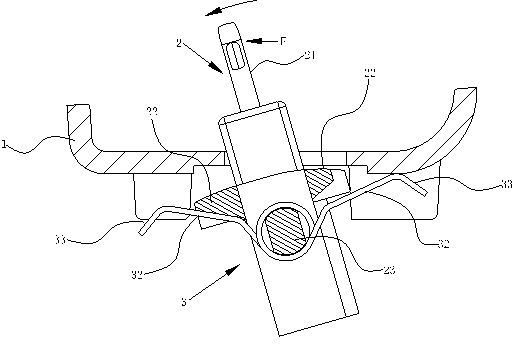

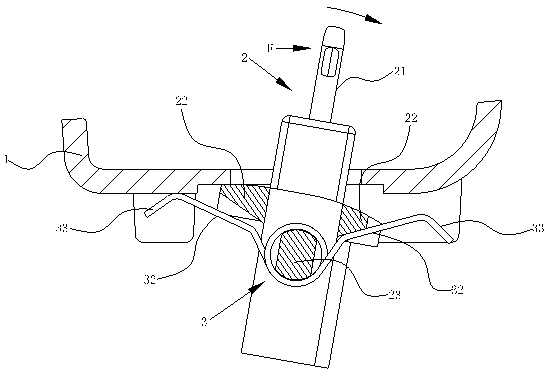

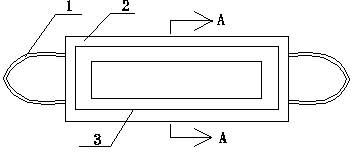

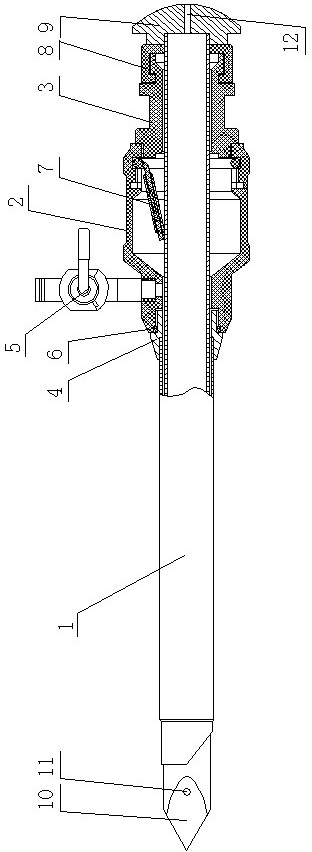

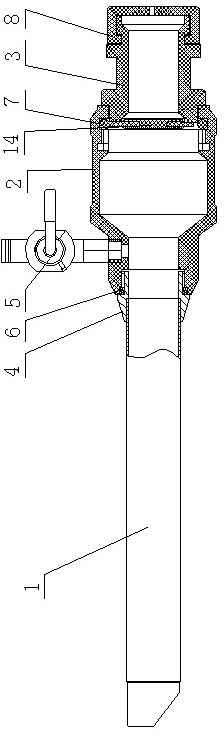

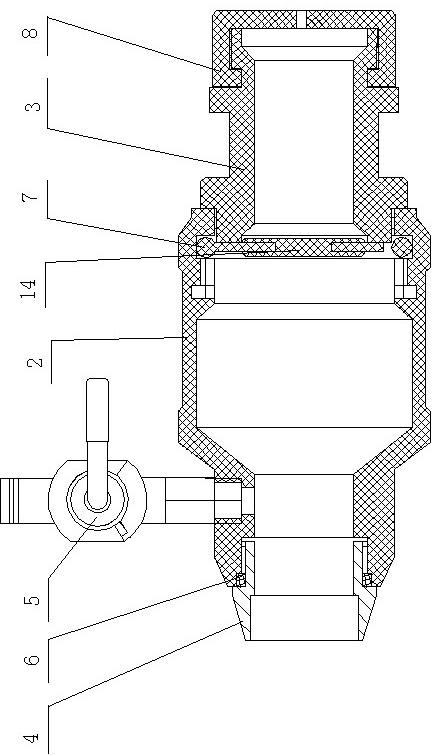

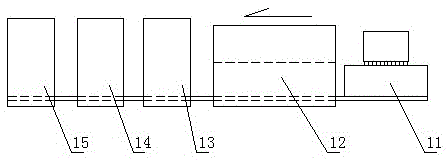

Flexible silica gel flip puncture outfit

InactiveCN102008343AGood reset functionHard textureSurgical needlesTrocarSilica gelBiomedical engineering

The invention relates to a flexible silica gel flip puncture outfit. At present, puncture outfits with good performance do not exist. The flexible silica gel flip puncture outfit comprises a puncture tube, a puncture base, a seal base, a puncture tube base, a seal ring, a flexible seal cap and a puncture needle, and is characterized by also comprising a silica gel flip seal base device, wherein the silica gel flip seal base device consists of a flexible silica gel pad and a ceramic anti-scratch base; the flexible silica gel pad consists of a flexible silica gel pad outer ring, a connecting block and a flexible silica gel pad inner ring; the flexible silica gel pad inner ring is connected with the flexible silica gel pad outer ring through the connecting block; the ceramic anti-scratch base is clamped in the flexible silica gel pad inner ring; the flexible silica gel pad outer ring is clamped in a clamping groove on the inner wall at the other end of the puncture base; the ceramic anti-scratch base is matched with one end of the seal base; the puncture needle is inserted in an operating channel; and a puncture cap is matched with the flexible seal cap. The flexible silica gel flip puncture outfit has a reasonable structural design, is easy to operate, has good sealing effect, long service life and safe and reliable performance, and is special for surgical equipment to insert into a human body.

Owner:申屠作本

Making method of carbon nanotube reinforced composite material nerve conduit

The invention provides a making method of a carbon nanotube reinforced composite material nerve conduit, and belongs to the medical technology field. The making method concretely comprises the following steps: modifying the surface of a carbon nanotube with different functional groups to make the surface of the carbon nanotube carry different charges and functional group molecules in order to improve the dispersibility and biocompatibility of the carbon nanotube; and adopting an ultrasonic dispersion process to fully mix the functionally modified carbon nanotube with an acid-soluble chitosan solution in order to make the carbon nanotube uniformly dispersed in the chitosan solution, mixing with collagen after uniform dispersion, and continuously carrying out ultrasonic dispersion until uniform dispersion. The functionally modified carbon nanotube is adopted by the making method of the carbon nanotube reinforced composite material nerve conduit to improve the physical, chemical and biologic performances of the chitosan / collagen composite material nerve conduit as an enhance component, and the functionally modified carbon nanotube reinforced composite material nerve conduit is used for restoring peripheral nerve defects.

Owner:SHANDONG PROVINCIAL HOSPITAL

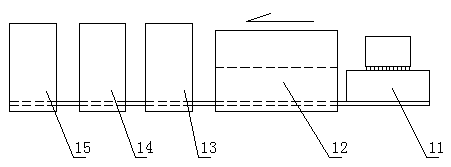

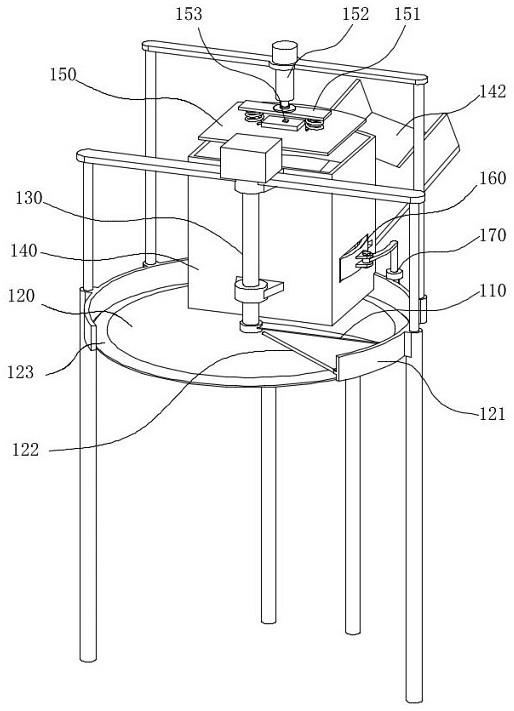

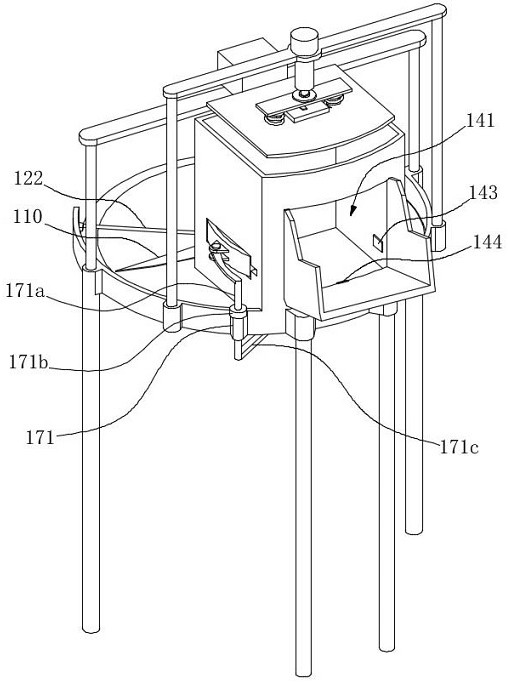

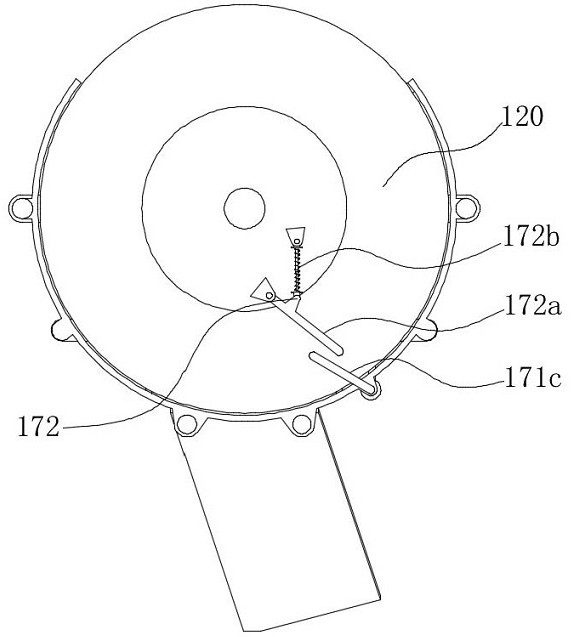

Traditional Chinese medicine raw material slicing device

InactiveCN110465979AStable structureRun smoothlyMetal working apparatusSlice thicknessChinese herbology

The invention relates to a traditional Chinese medicine raw material slicing device. The traditional Chinese medicine raw material slicing device comprises a rack. A conveying belt is arranged on therack. The feeding end of the conveying belt is provided with a hopper used for restraining medicinal materials to horizontally move. An opening allowing the medicinal materials to descend is formed inthe lower end of the hopper. A slicing knife and a material supporting surface which are arranged at intervals up and down are arranged at the lower end of the hopper and are horizontally arranged. The distance between the slicing knife and the material supporting surface is consistent with the slice thickness of the medicinal materials. The material supporting surface is used for supporting themedical materials. The slicing knife and the material supporting surface are connected with a driving mechanism. The driving mechanism is used for driving the slicing knife and the material supportingsurface to horizontally move. The slicing knife horizontally moves to slice the medicinal materials. The material supporting surface horizontally moves to transfer the sliced medicinal materials to the conveying belt. The traditional Chinese medicine raw material slicing device is stable in structure, reasonable in layout, stable in operation, high in slicing efficiency, low in slicing crushing rate and capable of realizing automatic slicing processing and meeting existing use requirements.

Owner:安徽亳药千草中药饮片有限公司

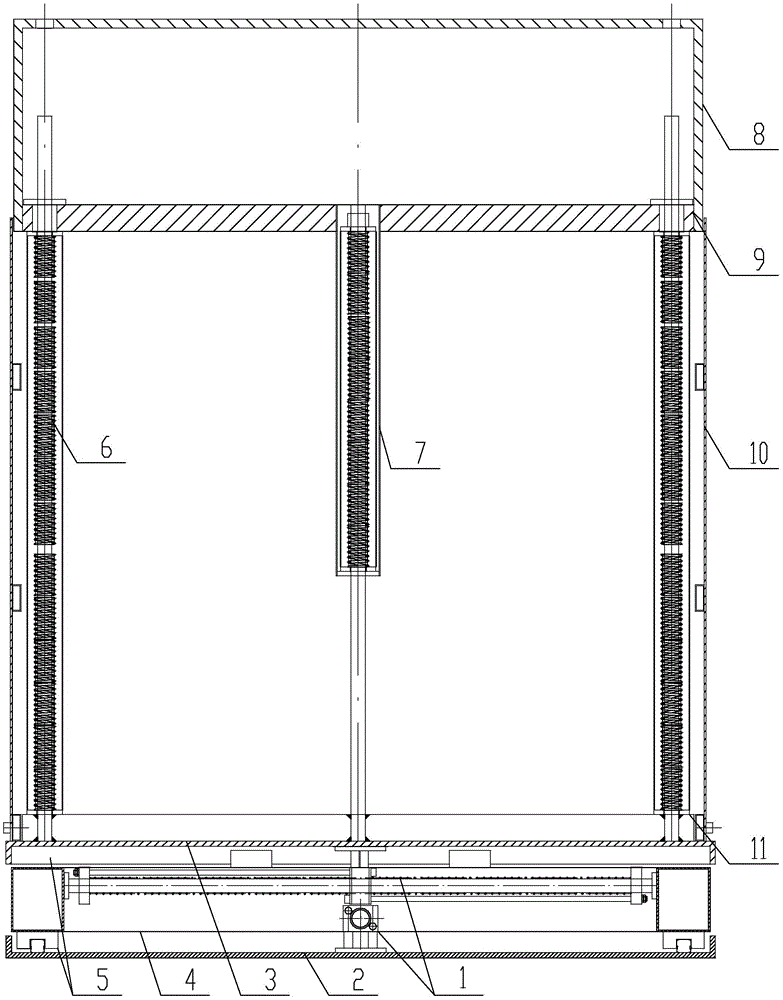

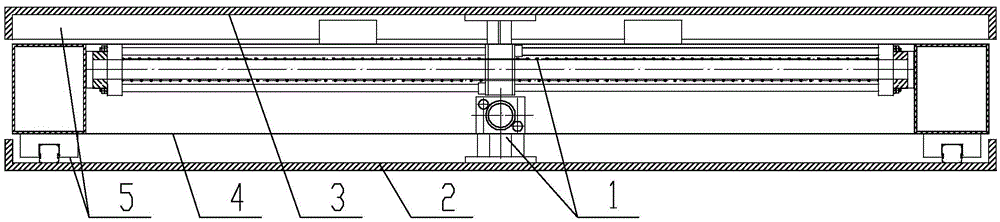

Framework type buffer device and setting method thereof

ActiveCN112228504AReduce impactGood corrosion resistanceNon-rotating vibration suppressionPhysicsCorrosion resistant

The invention provides a framework type buffer device and a setting method thereof. A plurality of height adjusting devices which are connected with an upper framework and can make the upper frameworkor a lower framework freely ascend and descend up and down are fixed to the lower framework; a plurality of combined type elastic buffer pieces are arranged between every two adjacent height adjusting devices; and the upper ends and the lower ends of the combined type elastic buffer pieces are fixedly connected with the upper framework and the lower framework respectively. Due to the fact that the plurality of height adjusting devices are arranged between the upper framework and the lower framework, the upper framework or the lower framework can ascend and descend freely up and down, and a guide basis is provided for downward movement under pressure and movement after pressure relief; and due to the fact that the plurality of combined type elastic buffer pieces are arranged between everytwo adjacent height adjusting devices, the device can achieve the function of quickly absorbing and slowly dissipating impact energy, effectively reduces the impact force to protect a moving body, hasa reset function, is good in corrosion resistance and fatigue resistance, can be repeatedly used to reduce the application cost, can adapt to application environments with different buffer space scales, and is wide in application range.

Owner:ZHONGBEI UNIV

A ring-shaped friction-rotation shock-isolation bearing

ActiveCN104763056BGuaranteed stabilityImprove shock absorptionBridge structural detailsShock proofingEngineeringRigid body

The invention relates to an annular frictional rotating shockproof supporting base. The annular frictional rotating shockproof supporting base comprises an upper cover plate, a rotating rigid body, an annular frictional wall, a buffer spring, a suspending steel block, and a base; the lower part of the upper cover plate is provided with a convex hemispheroid, the upper part of the rotating rigid body is provided with a groove, and the convex hemispheroid is meshed and contacted with the groove; the center of the lower part of the rotating rigid body is provided with a spherical groove, and the spherical groove is in supporting connection with the hemispheroid to form rotating contact in every direction; the overall side face of the rotating rigid body is provided with a spherical face and forms a frictional contact with the annular frictional wall; when the rotating rigid body is rotated, the rotating rigid body rubs the annular frictional wall to dissipate the earthquake energy; one ring at the bottom part of the rotating rigid body is provided with a vertical buffer spring, and the other end of the buffer spring is connected with the suspending steel block; the suspending steel block is placed in a block opening of the base, and the thickness of the suspending steel block is less than the height of the block opening; when the rotating rigid body is rotated to a certain position, the buffer spring can upwards raise up so as to drive the suspending steel block to upwards move; when the buffer spring is contacted with the block opening, the buffer spring is stretched to limit the movement of the rotating rigid body.

Owner:SHANGHAI BAOYE GRP CORP +1

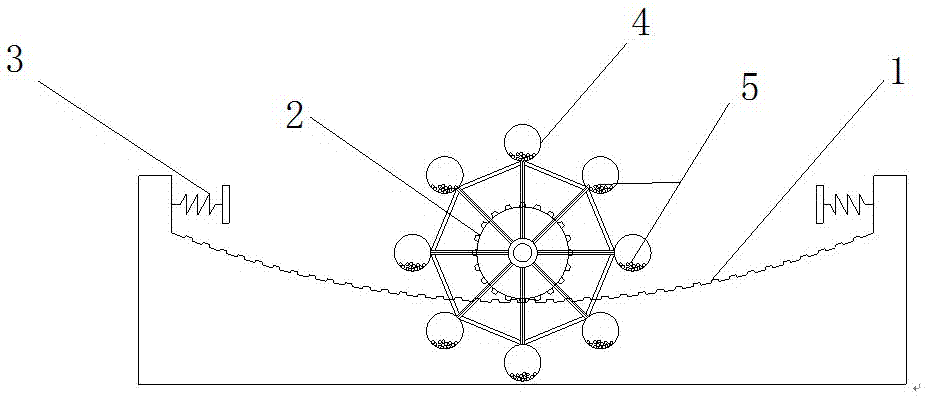

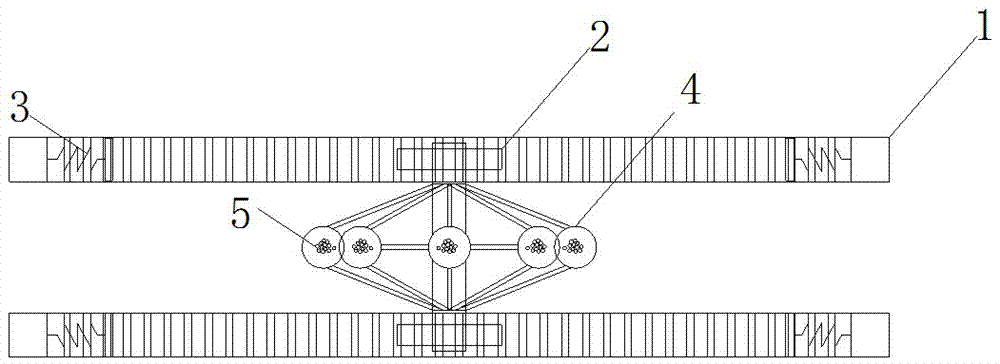

A Nonlinear Rail-Type Particle Damper

InactiveCN105239692BFull impact friction energy consumptionImprove energy efficiencyBridge structural detailsShock proofingEnergy particleEngineering

Owner:TONGJI UNIV

A device for slicing raw materials of traditional Chinese medicine

InactiveCN110465979BAvoid fragileRealize functionMetal working apparatusMedicinal herbsConveyor belt

The invention relates to a traditional Chinese medicine raw material slicing device, which includes a frame, on which a conveyor belt is installed, and a hopper for constraining the horizontal movement of the medicinal material is installed at the feeding end of the conveyor belt. There are slicing knives and supporting surfaces arranged at intervals up and down. The slicing knives and supporting surfaces are arranged horizontally. The distance between the slicing knives and the supporting surface is consistent with the slice thickness of the medicinal materials. The driving mechanism is connected with the supporting material surface, and the driving mechanism is used to drive the slicing knife and the supporting material surface to move horizontally. The slicing knife moves horizontally to slice the medicinal materials, and the supporting material surface moves horizontally to transfer the sliced medicinal materials to the conveyor belt. The structure of the invention is stable. , reasonable layout, stable operation, high slicing efficiency, low slicing breakage rate, automatic slicing processing can be realized, which meets the current use requirements.

Owner:安徽亳药千草中药饮片有限公司

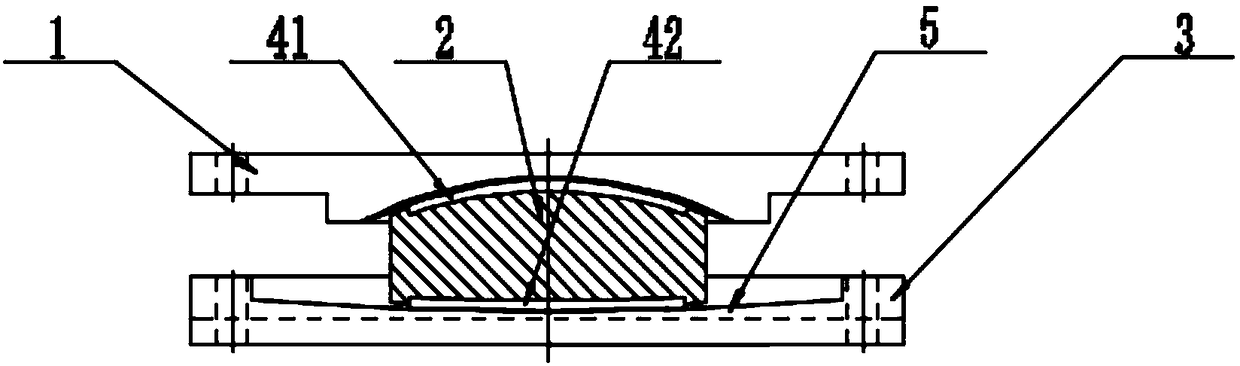

Unidirectional large damping friction pendulum supporting seat

PendingCN109440961AGood reset functionGuaranteed stable workBridge structural detailsProtective buildings/sheltersHysteresisWear particle

The invention belongs to the technical field of structural seismic safety, and provides an unidirectional large damping friction pendulum supporting seat. The unidirectional large damping friction pendulum supporting seat comprises an upper seat plate, an upper super-high pressure wear plate, a double convex curved surface ball core, a lower super-high pressure wear plate and a lower seat plate arranged from top to bottom in sequence; unidirectional point-like textured structures are arranged on the end surface of a unidirectional damping plate, the unidirectional point-like textured structures are concentrically and finely distributed, and are in the radial direction of a concentric circle, the point-like textured structures corresponding to the center of a circle are of symmetrical barbed structures, and tips of the barbed structures faces the center of the circle. According to the unidirectional large damping friction pendulum supporting seat, the function of unidirectional dampingis realized and excellent hysteresis performance is achieved; fine unidirectional point-like protruding textures are distributed on the unidirectional damping plate, large unidirectional friction coefficient in the single direction and small friction coefficient in the return direction can be realized, and the function of support resetting is facilitated; and the point-like texture protruding structures are finely distributed in a discontinuous concentric circle, so that fine wear particles generated under the action of friction can be cleaned out through intervals of the point-like texture protruding structures, and the smooth work of the supporting seat is ensured.

Owner:衡水市橡胶总厂有限公司

Preparation method of carbon nanotube reinforced composite nerve guide

The invention provides a making method of a carbon nanotube reinforced composite material nerve conduit, and belongs to the medical technology field. The making method concretely comprises the following steps: modifying the surface of a carbon nanotube with different functional groups to make the surface of the carbon nanotube carry different charges and functional group molecules in order to improve the dispersibility and biocompatibility of the carbon nanotube; and adopting an ultrasonic dispersion process to fully mix the functionally modified carbon nanotube with an acid-soluble chitosan solution in order to make the carbon nanotube uniformly dispersed in the chitosan solution, mixing with collagen after uniform dispersion, and continuously carrying out ultrasonic dispersion until uniform dispersion. The functionally modified carbon nanotube is adopted by the making method of the carbon nanotube reinforced composite material nerve conduit to improve the physical, chemical and biologic performances of the chitosan / collagen composite material nerve conduit as an enhance component, and the functionally modified carbon nanotube reinforced composite material nerve conduit is used for restoring peripheral nerve defects.

Owner:SHANDONG PROVINCIAL HOSPITAL

Barrel type handle lock

ActiveCN101487365BEasy to installEasy to disassembleLock casingsHandle fastenersEngineeringMechanical engineering

Owner:李宝强

A new type of high-load and low-impact line connection and separation mechanism for aerospace

ActiveCN110654578BReduce shockExtended load release timeCosmonautic vehiclesCosmonautic component separationEngineeringSpaceflight

The invention provides a novel line type connecting and separating mechanism with high bearing and low impact for an aerospace. The novel line type connecting and separating mechanism with the high bearing and the low impact comprises a shell body, an SMA triggering assembly, an unlocking and transmission assembly and a connecting and separating assembly, wherein the SMA triggering assembly is arranged between the connecting and separating assembly and the unlocking and transmission assembly; and the shell body comprises a outer shell and a shell cover, through holes are formed in the front side and the rear side of the shell body correspondingly, a limiting plate is arranged on the inner wall of the shell body, a vertical sliding groove is defined between the limiting plate and the rightside wall of the shell body, and a horizontal sliding groove is defined between the limiting plate and the bottom wall of the shell body. According to the novel line type connecting and separating mechanism with the high bearing and the low impact for the aerospace, the shape memory effect of SMA is used for triggering and acting, and the connecting and separating mechanism with high reliability,large bearing and low impact is provided so as to meet the actual requirement of the aerospace application at the present stage.

Owner:HARBIN INST OF TECH

Reset circuit

ActiveCN102006039BGood reset functionReduce power consumptionElectronic switchingCapacitancePower-on reset

The invention relates to a reset circuit, which comprises a power-on reset circuit and a power-off reset circuit, wherein the power-on reset circuit comprises a first field-effect tube, a second field-effect tube, a third field-effect tube, a first two-input NAND gate, a second two-input NAND gate, a first NOT gate, a second NOT gate, a third NOT gate, a fourth NOT gate, an OR gate, a first capacitor, a second capacitor and a buffering delay module; and the power-off reset circuit comprises fourth to tenth field-effect tubes, a fifth NOT gate and a buffering module. The reset circuit can well execute a reset function, is simple, low in cost and high in electro magnetic compatibility (EMC), can be widely used in integrated circuits, particularly integrated circuits with strict requirements on cost control such as infrared circuits, as well as most microprogrammed control units (MCUs) and circuits with high requirements on anti-interference performance and EMC performance.

Owner:SUZHOU HUAXIN MICROELECTRONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com