Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Delayed correction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

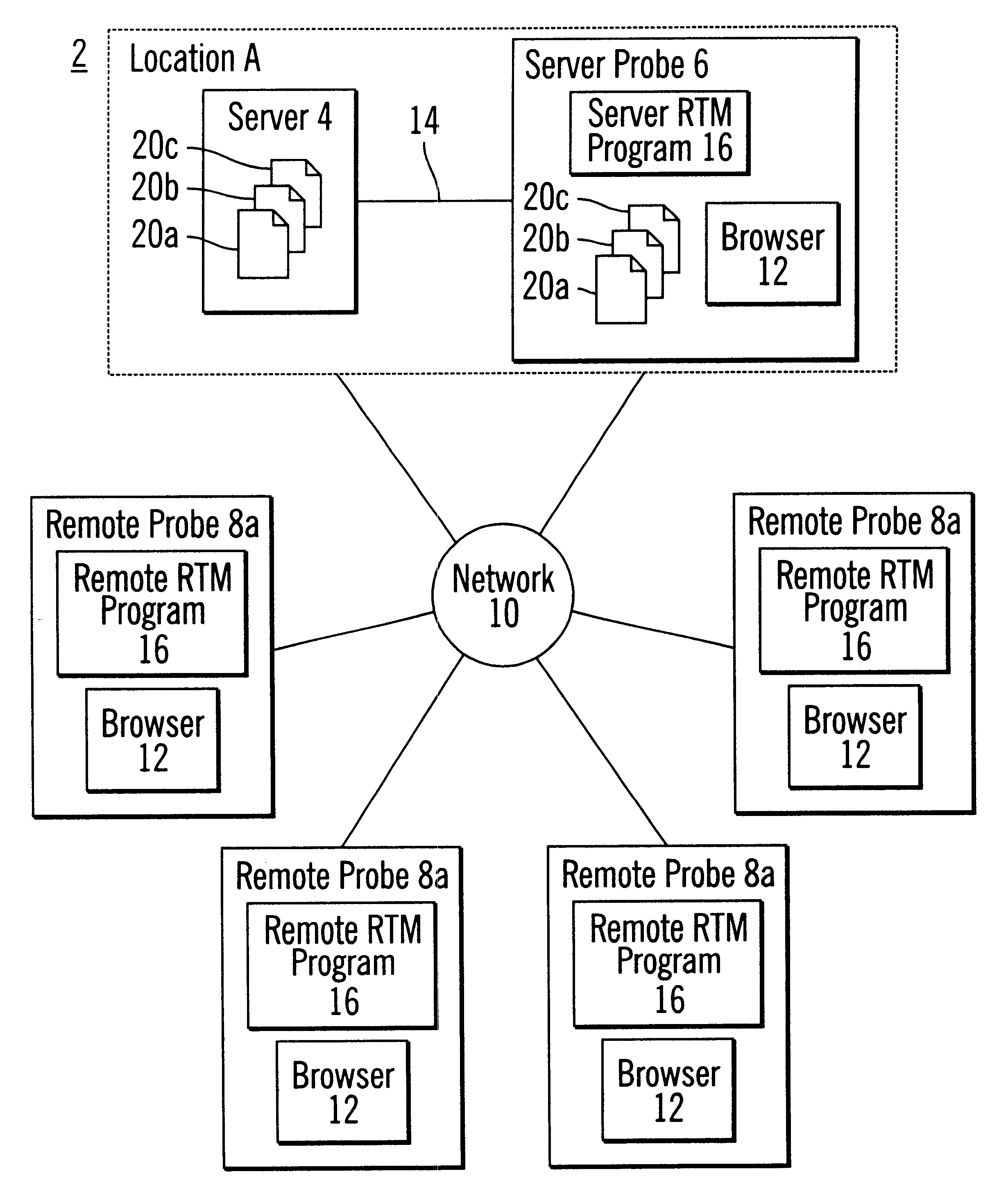

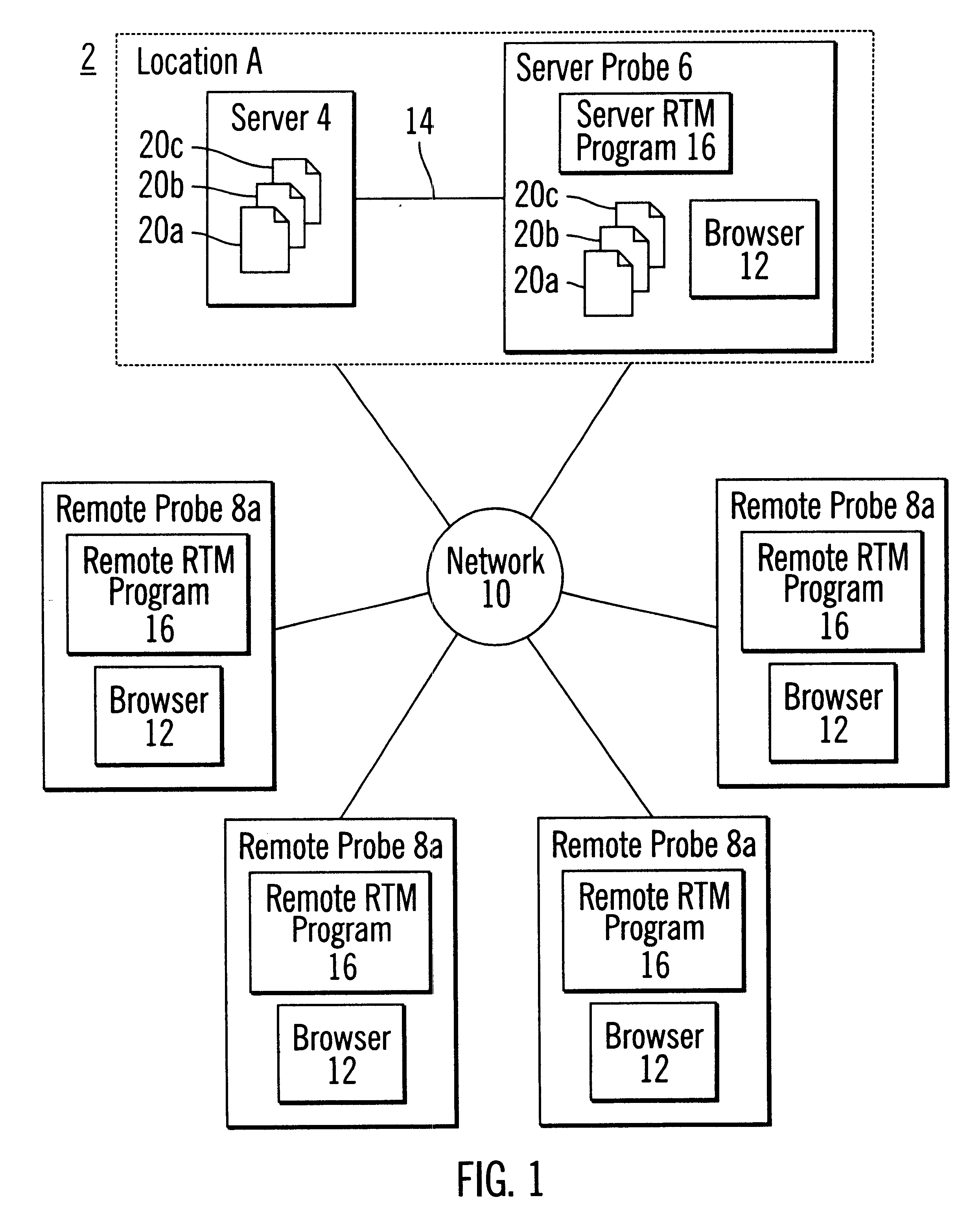

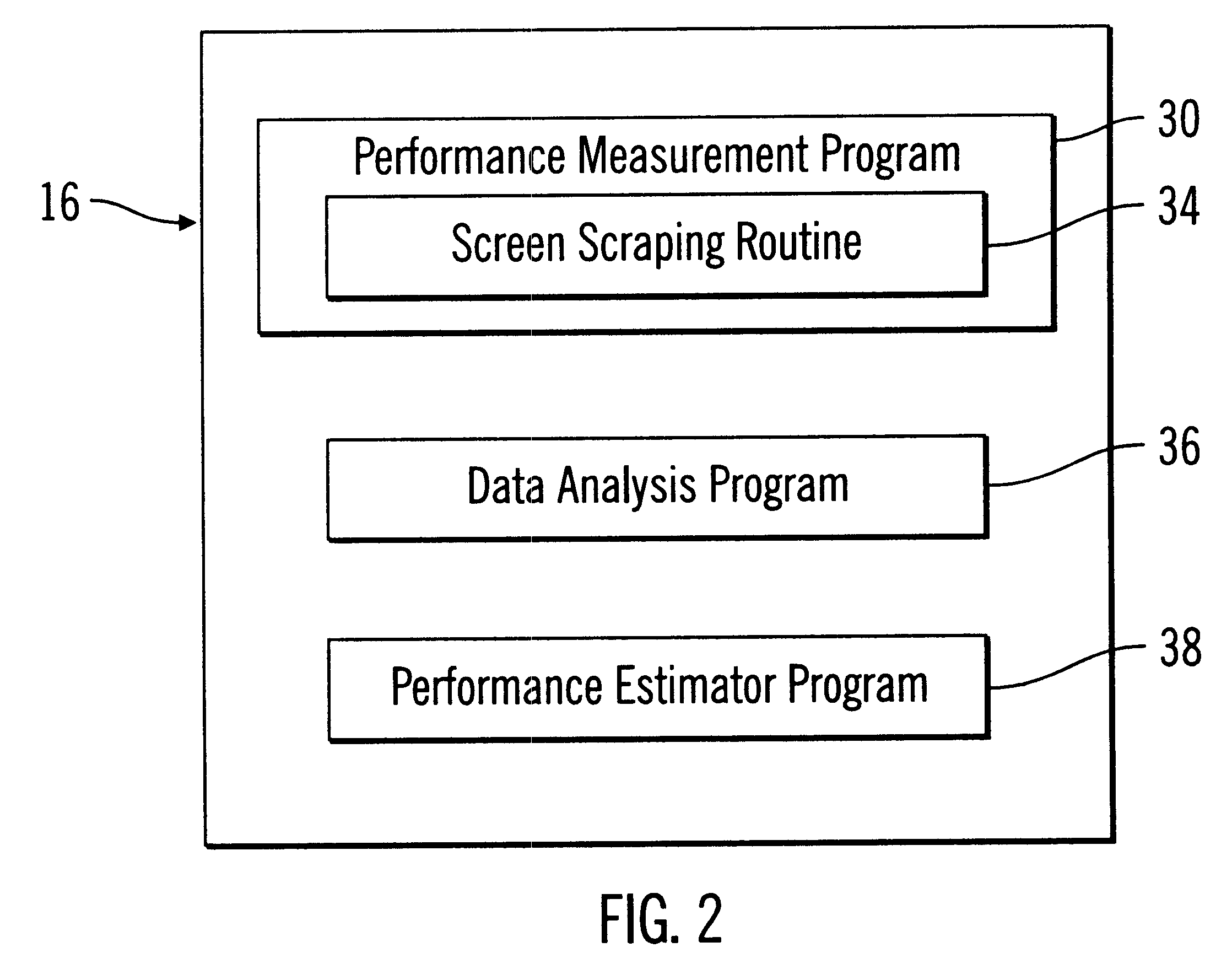

System, method, and program for measuring performance in a network system

InactiveUS6587878B1Unacceptable delayAvoid delayDigital computer detailsHardware monitoringApplication softwareReal-time computing

Disclosed is a method, system, and program for generating network performance data. Performance information including a performance time to download a page and execute the page within an application program is received. The received performance information is processed and then performance information output indicating network performance is generated in response to processing the performance information.

Owner:IBM CORP

System, method, and program for measuring performance in a network system

InactiveUS20030195960A1Unacceptable delayAvoid delayNuclear monitoringDigital computer detailsApplication softwareReal-time computing

Owner:IBM CORP

System, method and program for measuring performance time in a network system using a browser's "done" indicator message

InactiveUS7216168B2Unacceptable delayAvoid delayDigital computer detailsNuclear monitoringApplication softwareReal-time computing

Disclosed is a method, system, and program for generating network performance data. Performance information including a performance time to download a page and execute the page within an application program is received. The received performance information is processed and then performance information output indicating network performance is generated in response to processing the performance information.

Owner:INT BUSINESS MASCH CORP

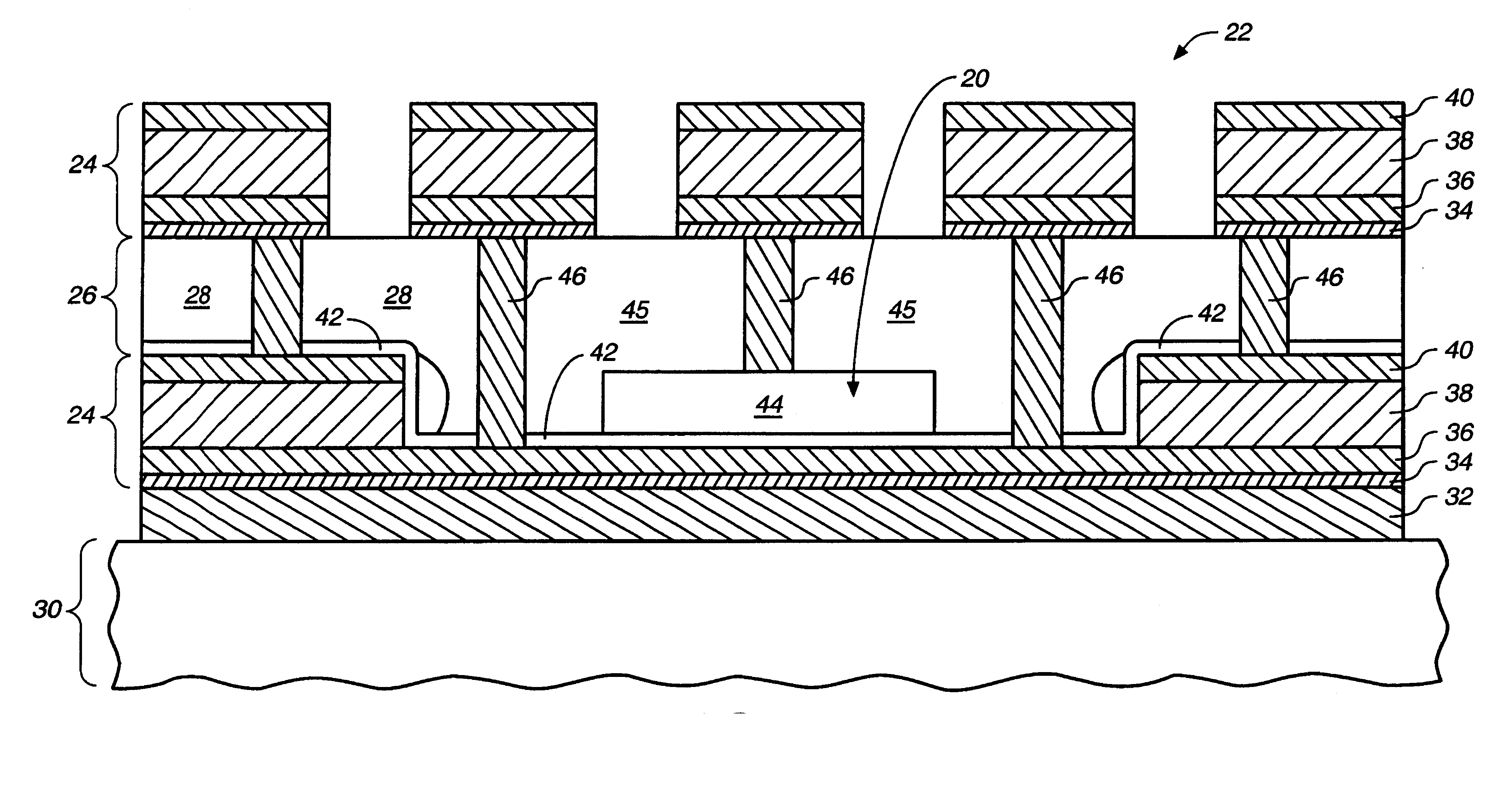

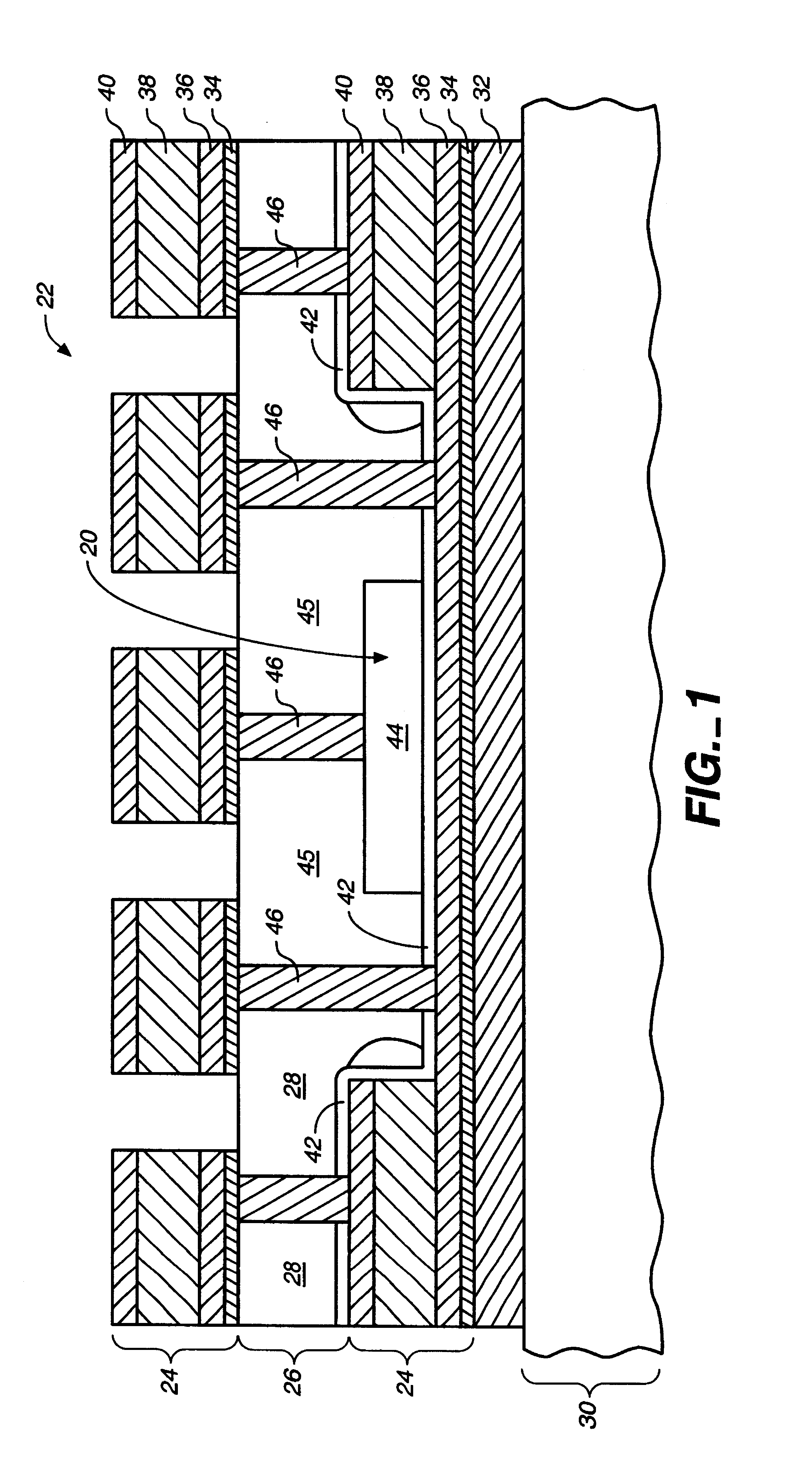

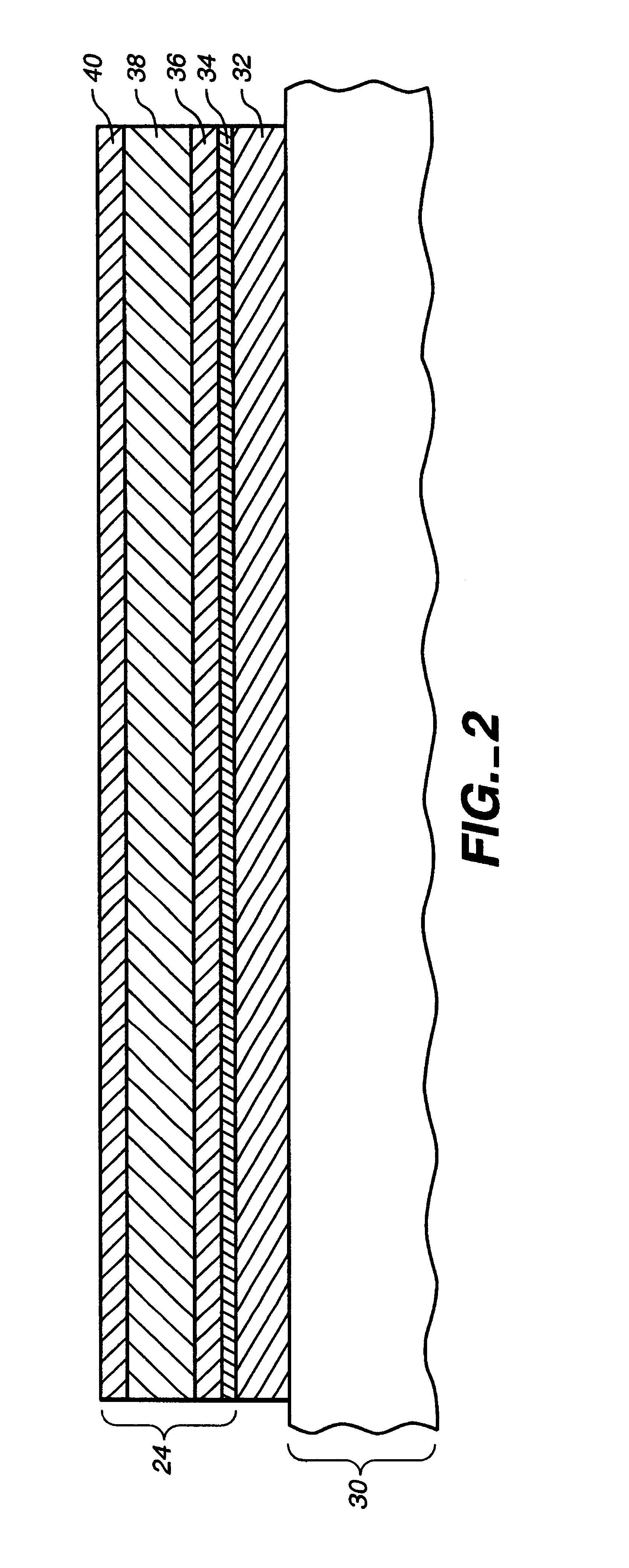

Method of forming a metal-insulator-metal capacitor in an interconnect cavity

InactiveUS7118985B2Reduce the amount requiredUniform thicknessSemiconductor/solid-state device detailsSolid-state devicesMetalIntegrated circuit

A metal-insulator-metal capacitor is embedded in an interconnect layer of an integrated circuit (IC). The interconnect layer has a cavity, and the capacitor is formed in the cavity with one of the plates of the capacitor integral with a conductive layer of the interconnect layer, so the capacitor plate electrically communicates with the interconnect layer. The interconnect layer has multiple conductive layers, including a layer, such as aluminum, that is subject to deformation at certain temperatures during fabrication of the IC, and the cavity extends through this layer. A remaining conductive layer of the interconnect layer defines one of the capacitor plates, and a dielectric layer and another capacitor plate are formed thereon within the cavity. Via interconnects of about the same length electrically connect to the top plate and through the interconnect layer to the bottom plate.

Owner:BELL SEMICON LLC

Communication system endpoint device with integrated call synthesis capability

ActiveUS7313098B2Delayed correctionImprove performanceError detection/prevention using signal quality detectorCorrect operation testingTraffic capacityCommunications system

Techniques are disclosed for improved monitoring and analysis of VoIP communications, multimedia communications or other types of network traffic in a network-based communication system. In accordance with one aspect of the invention, an endpoint device of the system includes an integrated call synthesis capability. More particularly, the endpoint device is configurable into at least a first mode of operation in which the device responds to one or more commands from a testing server of the system directing the device to participate in a synthetic call or other test communication within the system, and a second mode of operation in which the device is utilizable by a system user to establish an actual communication. Other aspects of the invention relating to kernel timestamping and timestamp post-processing provide improved accuracy for measurements such as jitter, loss and delay.

Owner:AVAYA INC

Base station transceiver to radio network controller synchronization filtering function

InactiveUS7068746B1Accurate synchronization in timeFiltered outTime-division multiplexRadio/inductive link selection arrangementsTransceiverRadio Network Controller

A method for synchronizing communications in a wireless communications network wherein time synchronization is performed between a clock master and a clock slave. To achieve synchronization between the clock master and the clock slave, several time synchronization passes are initiated by the clock slave to the clock master. For every pass, each clock slave component generates and transmits a first timing cell containing a transmission time based on the clock slave's component clock, to the clock master. Upon receipt of the first timing cell, the clock master generates and transmits to the clock slave component a second timing cell containing the time the clock master received the first timing cell and the time the clock master transmitted the second timing cell. Upon receipt of the second timing cell, the clock slave component will obtain its reception time and calculate a transmission delay based on the reception time and the timing information contained in the timing cells.

Owner:RPX CORP +1

Multiband Doherty amplifier

ActiveUS7602241B2Sufficient operation performanceSufficient gain and efficiencyAmplifier modifications to raise efficiencyAmplifier combinationsAudio power amplifierImpedance Converter

Owner:NTT DOCOMO INC

Pulse signal delay circuit and LED drive circuit

InactiveUS20090167398A1Avoid inconsistenciesLimited setStatic indicating devicesElectroluminescent light sourcesDelayed pulseLED circuit

A pulse signal delay circuit comprises: a first pulse edge delay circuit for generating a first delay timing signal for sequentially outputting a first edge detection delay timing gained by detecting the rising edge of an input pulse signal and delaying the detection timing by a constant delay time a predetermined number of times; a second pulse edge delay circuit for generating a second delay timing signal for sequentially outputting a second edge detection delay timing gained by detecting the falling edge of the input pulse signal and delaying the detection timing by the delay time the number of times; and a delay pulse signal generating circuit for generating and outputting delay pulse signals rising and falling according to the first and second edge detection delay timings, respectively, from the first and second delay timing signals, the first and second edge detection delay timings delayed the same number of times.

Owner:SHARP KK

Method and Apparatus for Mobile Cash Transportation

ActiveUS20140368345A1Maintain securityFew electrical connectionElectric signal transmission systemsDigital data processing detailsDocking stationDevice Monitor

A device designed to validate and transport paper currency in a protected fashion. While being transported, the device monitors for tampering or break-in attempts and subsequently generates warning notifications, or sounds an alarm depending on configuration and the type of tampering detected. The transport case provides end-to-end cash accountability from a location where a bill is inserted into the case, to the bank or cash destination, where the transport case is delivered. Additionally, a docking station accessory is described in which the transport case can be securely fixed while at a point of sale.

Owner:ELLENBY TECH

Multiband doherty amplifier

ActiveUS20080007331A1Sufficient operation performanceSufficient gain and efficiencyAmplifier modifications to raise efficiencyAmplifier combinationsAudio power amplifierImpedance Converter

A multiband Doherty amplifier having a configuration including a divider which divides an input signal into two, a carrier amplifier which amplifies one of the divided signals, a delay element which delays the other divided signal, a peak amplifier which amplifies the output signal of the delay element, an impedance converter which is connected to an output port of the carrier amplifier and performs predetermined impedance conversion and a combiner which combines the output signals of the peak amplifier and the impedance converter, wherein the electric length of the delay element is the same as the electric length of the impedance converter and the impedance converter has N (N≧2) cascade-connected impedance conversion transmission lines and performs substantially the same impedance conversion at each of the N frequencies.

Owner:NTT DOCOMO INC

Image processing device

ActiveUS20030016389A1Reduce the number of pixelsDelayed correctionTelevision system detailsPicture reproducers using cathode ray tubesImaging processingLow speed

The objective of the invention is to provide an image processing device that can operate at high speed even if input / output with respect to the outside is performed at low speed, and that can fully exploit processibility, by means of input line memory 23 and output line memory 24, which can store image data of one scan line, and are arranged in the input unit and output unit, respectively; the input image data are written in input line memory 23 at the speed of the input image data; the image data that have been written to the input line memory are read at a speed n times faster than the input image data and are sent to processing unit 25 or memory unit 26; processing unit 25 and memory unit 26 receive the image data of one scan line at a speed n times faster than the speed of the input image data, perform a prescribed processing, and then output the processing results at a speed n times faster than the speed of the input image data; the image data output from processing unit 25 or memory unit 26 are selected by selector 29 and written to output line memory 24 at a speed n times faster than the speed of the input image data; the output image data are read in units of one scan line from output line memory 24 at a prescribed speed.

Owner:TEXAS INSTR INC

Delay distribution calculation method, circuit evaluation method and false path extraction method

InactiveUS20070033554A1Delayed correctionAccurate calculationProgramme controlComputer controlRelevant informationFalse path

Delay distribution in an integrated circuit is calculated while taking into account a correlation of performance between interconnects or elements in the integrated circuit, thereby improving estimation accuracy. Circuit information, performance distribution information of the interconnects or elements in the integrated circuit, and correlation information of performance between the interconnects or elements are input. A vertex is selected for calculation, and a correlation between delay distribution at the selected vertex and delay distribution in a partial circuit including the selected vertex is calculated based on the performance distribution information and the correlation information.

Owner:PANASONIC CORP

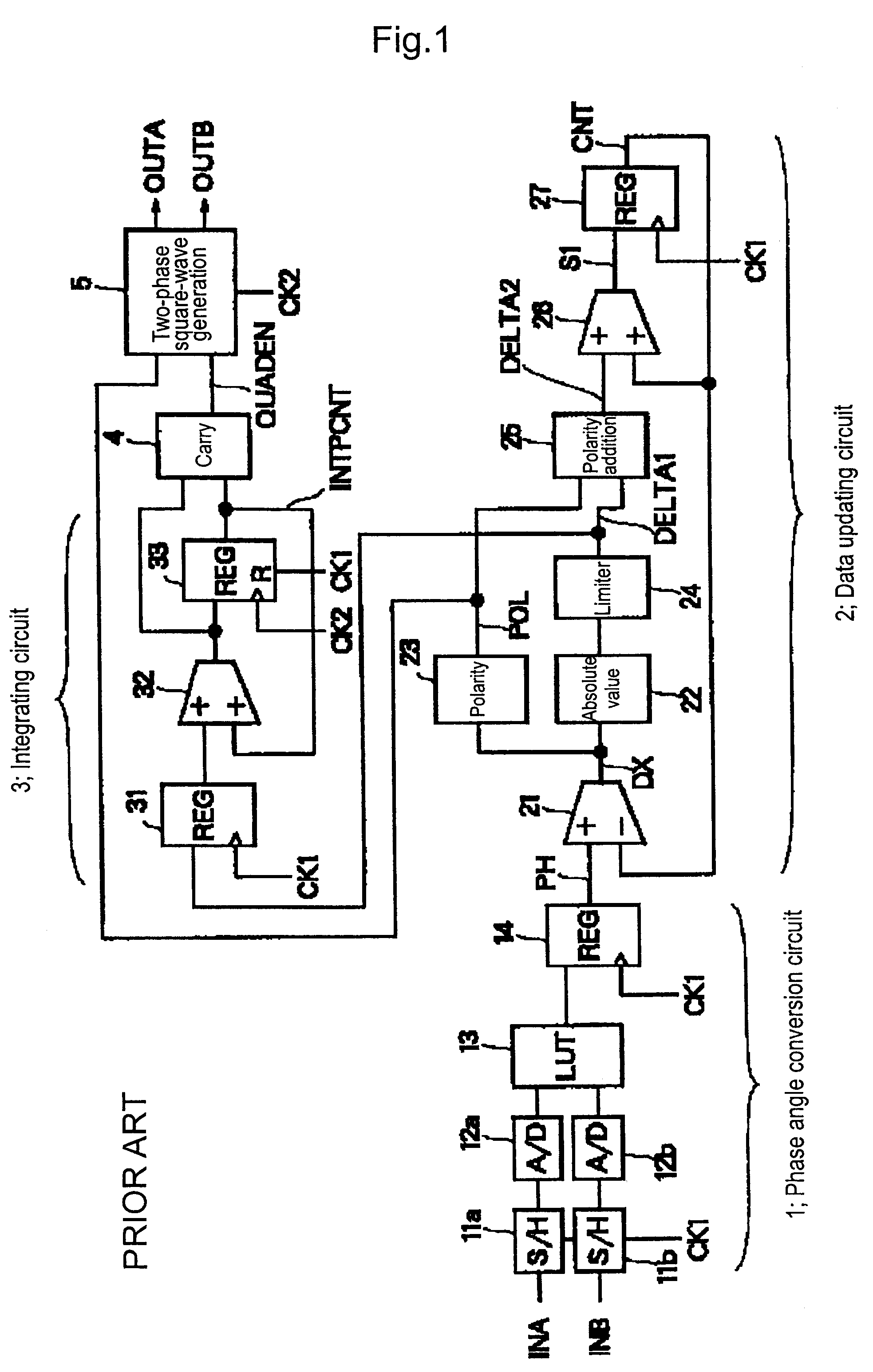

Method and circuit for interpolating encoder output

InactiveUS7352305B2Reduce synchronization errorHigh precisionAnalogue/digital conversionElectric signal transmission systemsComputer scienceSample and hold

Two-phase sinusoidal signals QA, QB output from an encoder are interpolated by sample-and-hold (S / H) circuits and A / D conversion (ADC) circuits, and data D is output in accordance with a data request signal RQ from exterior. For this interpolation of encoder output, a direction discrimination up / down counter is arranged near a two-phase square-wave uniform pulse generating circuit, and the data D is latched and output using a signal which is obtained by delaying the data request signal RQ. This can reduce synchronization errors between the data request signal RQ from exterior and the interpolated data, with an improvement in dynamic precision.

Owner:MITUTOYO CORP

Driving aid device

InactiveUS20060132600A1Optimal quality levelImprove night visionColor television detailsClosed circuit television systemsLuminous intensityDriver/operator

A driving aid device for a vehicle comprises a means for imaging and a means for projecting a virtual image in a field of vision of a driver, an opaque screen, arranged in the field of view of the driver, for the formation of a virtual image focused at infinity in the field of vision of the driver of the vehicle, and further comprises means for filtration of zones of high luminous intensity.

Owner:TIETRONIX OPTICS

Gradient aocv methodology enabling graph-based timing closure with aocv timing models

ActiveUS20140082576A1Accurate delay estimationReduce pessimismComputer aided designSoftware simulation/interpretation/emulationClock treeTiming closure

A method of manufacturing semiconductor circuits seeks timing closure on a preliminarily select, placed and routed set of cells using a delay for each cell as derated by a derate value obtained from a timing model table having a derate value corresponding to a circuit path depth in the netlist. The derate value for a predetermined number of circuit path depths below k are identical. The derate values are monotonically decreasing for increasing circuit depths in a range between 1.0 and 1.5. Separate timing model tables with differing identical values can be employed for standard and clock tree cells.

Owner:TEXAS INSTR INC

Phase delay line

InactiveUS20100123497A1Delayed correctionEasy to controlPulse automatic controlSingle output arrangementsBand gapPhase-locked loop

A phase delay line comprises a phase-locked loop, a duty-cycle adjusting ring and a voltage equal division to time equal division converter, wherein the phase-locked loop and the duty-cycle adjusting ring form a loop, and one output of the phase-locked loop is connected with the input of the voltage equal division to time equal division converter. The voltage can be precisely divided, and the number of the phases can be easily controlled and expanded. The band gap reference technology enables the working points not affected by the temperature. The negative feedback mechanism of the phase-locked loop determines the period, phase, duty-cycle of the sawtooth wave are same with the reference clock. The ascending and descending time of the sawtooth wave are precisely equal.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

Gradient AOCV methodology enabling graph-based timing closure with AOCV timing models

ActiveUS8806413B2Delayed correctionGood correlationComputer aided designSoftware simulation/interpretation/emulationGraphicsClock tree

A method of manufacturing semiconductor circuits seeks timing closure on a preliminarily select, placed and routed set of cells using a delay for each cell as derated by a derate value obtained from a timing model table having a derate value corresponding to a circuit path depth in the netlist. The derate value for a predetermined number of circuit path depths below k are identical. The derate values are monotonically decreasing for increasing circuit depths in a range between 1.0 and 1.5. Separate timing model tables with differing identical values can be employed for standard and clock tree cells.

Owner:TEXAS INSTR INC

Delay distribution calculation method, circuit evaluation method and false path extraction method

InactiveUS7131082B2Delayed correctionAccurate calculationProgramme controlComputer controlRelevant informationFalse path

Delay distribution in an integrated circuit is calculated while taking into account a correlation of performance between interconnects or elements in the integrated circuit, thereby improving estimation accuracy. Circuit information, performance distribution information of the interconnects or elements in the integrated circuit, and correlation information of performance between the interconnects or elements are input. A vertex is selected for calculation, and a correlation between delay distribution at the selected vertex and delay distribution in a partial circuit including the selected vertex is calculated based on the performance distribution information and the correlation information.

Owner:SOCIONEXT INC

Method and circuit for interpolating encoder output

InactiveUS20070035417A1Reduce synchronization errorImprove dynamic accuracyElectric signal transmission systemsAnalogue-digital convertersComputer scienceSample and hold

Two-phase sinusoidal signals QA, QB output from an encoder are interpolated by sample-and-hold (S / H) circuits and A / D conversion (ADC) circuits, and data D is output in accordance with a data request signal RQ from exterior. For this interpolation of encoder output, a direction discrimination up / down counter is arranged near a two-phase square-wave uniform pulse generating circuit, and the data D is latched and output using a signal which is obtained by delaying the data request signal RQ. This can reduce synchronization errors between the data request signal RQ from exterior and the interpolated data, with an improvement in dynamic precision.

Owner:MITUTOYO CORP

Dispersion compensating circuits for optical transmission system

InactiveUS7809282B2Delay time compensationDifferent fiber length can be easily compensatedLaser detailsElectromagnetic transmittersFixed capacitorLow-pass filter

Improved dispersion compensating circuits for optical transmission systems are disclosed. According to the improved method, there is provided a compensation circuit comprising a varactor diode network. The network is preferably inserted between a source of laser modulating signal and the laser. A low pass filter constructs the network. The network preferably includes an inductance and a combined circuit, which includes varactors. The network preferably provides an amplitude dependent delay of the modulating signal applied to the laser. In a first embodiment, a fixed capacitor is in series with a varactor and connected to a DC bias through inductor. In a second embodiment, second varactor is in series with varactor instead with an opposite polarity of a fixed capacitor as used in the first embodiment. In a third embodiment, two varactors 301 and 302 are used in place of the fixed capacitor in parallel.

Owner:GOOGLE TECH HLDG LLC

Method for detecting and powering off unused I/O slots in a computer system

ActiveUS7039820B2Delayed correctionEnergy efficient ICTVolume/mass flow measurementPower cycleComputer program

A method, apparatus and computer program product are provided for detecting and powering off unused I / O slots in a computer system. For each of the I / O slots, the current slot is checked to determine if the slot is powered on and unlocked. When the current slot is powered on and unlocked, the current slot is checked to determine if the current slot is a candidate for being powered off. When the current slot is determined to be a candidate for being powered off, then the current slot is powered off and the checking continues with a next one of the I / O slots. Recording the slot as a candidate for being powered off before the slot is actually powered off ensures a proper delay to avoid powering off a slot that is about to be locked, which could cause slot power cycles in quick succession.

Owner:TWITTER INC

Fault detection method, test circuit and semiconductor device

InactiveUS20080122471A1Delayed correctionOutput andError preventionTransmission systemsDelayed timeEngineering

A fault detection method for detects, within a semiconductor device, a fault in a delay chain that is provided within the semiconductor device and is made up of delay parts that are each formed by delay cells. The method judges if a fault exists in a first specific delay cell within a first delay part when testing the first specific delay cell, by detecting a first relative delay time between input and output signals of the first specific delay cell, and processing the first relative delay time at a timing based on an output of a delay cell within a second delay part that is provided at a stage preceding or subsequent to the first delay part. The method judges if a fault exists in a second specific delay cell within the second delay part exists when testing the second specific delay cell, by detecting a second relative delay time between input and output signals of the second specific delay cell, and processing the second relative delay time at a timing based on an output of a delay cell within the first delay part.

Owner:SOCIONEXT INC

Pulse signal delay circuit and LED drive circuit

InactiveUS8299988B2Avoid inconsistenciesLimited setStatic indicating devicesElectroluminescent light sourcesDelayed pulseEngineering

A pulse signal delay circuit comprises: a first pulse edge delay circuit for generating a first delay timing signal for sequentially outputting a first edge detection delay timing gained by detecting the rising edge of an input pulse signal and delaying the detection timing by a constant delay time a predetermined number of times; a second pulse edge delay circuit for generating a second delay timing signal for sequentially outputting a second edge detection delay timing gained by detecting the falling edge of the input pulse signal and delaying the detection timing by the delay time the number of times; and a delay pulse signal generating circuit for generating and outputting delay pulse signals rising and falling according to the first and second edge detection delay timings, respectively, from the first and second delay timing signals, the first and second edge detection delay timings delayed the same number of times.

Owner:SHARP KK

Image processing device with a processing unit that processes image data in units of one scan line

ActiveUS7015975B2Delayed correctionReduce the number of pixelsTelevision system detailsPicture reproducers using cathode ray tubesComputer hardwareImaging processing

Owner:TEXAS INSTR INC

Packet Delay Variation in a Packet Switched Network

ActiveUS20160065442A1Jitter value can be largeDelayed correctionError preventionTransmission systemsTimestampNetwork packet

A packet switched network tester for testing a network using a packet delay variation test profile that has a plurality of different delays for applying to timestamps of packets received at the tester, the tester being configured to: detect a packet; determine whether a test profile delay when applied to the packet would result in a packet delayed to a time after any preceding packet; if not, repeat the steps of detecting and determining with subsequent packets; if yes, apply the delay to the timestamp of the packet and identify the next test profile delay; and repeat for the next test profile delay the steps of detecting and determining.

Owner:CALNEX SOLUTIONS

Device and method for reproducing digital signal and device and method for recording digital signal

ActiveUS7978572B2Correction errorSave powerCombination recordingTelevision system detailsClock rateError correcting

A technique capable of realizing a power saving in a device for reproducing / recording digital signals by properly controlling a frequency of a clock. The device for reproducing / recording digital signals (device for reproducing an optical disk) includes: a difference comparing circuit for comparing a first parameter (demodulating block counter) updated each time a process for one correcting block is done in a demodulating circuit with a second parameter (error correcting block counter) updated each time a process of one correcting block is done in an error correcting circuit; and a circuit (clock controlling circuit etc.) for switching a frequency of a master clock (MCLK) depending on a comparison result of the difference comparing circuit. Thereby, the frequency of the clock can be switched both of when the demodulation for one correcting block is ended and when the correcting process for one correcting block is ended by using the switched master clock.

Owner:RENESAS ELECTRONICS CORP

Closure panel control apparatus

ActiveUS7952312B2InhibitionDelayed correctionEmergency protective circuit arrangementsAsynchronous induction motorsObject basedControl theory

A controller computes a pinching amount of an object caused by a window glass. The controller estimates a prior pinching amount of the object caused by the window glass before the controller computes the pinching amount of the object. The controller confirms occurrence of the pinching of the object based on the computed pinching amount and the estimated prior pinching amount of the object.

Owner:DENSO CORP

Method and device for synchronous control of image signal and audio signal in image apparatus

InactiveUS20080049139A1Delayed correctionTelevision system detailsDifferential synchronisation source lockingSynchronous controlDelayed time

When a certain signal processing is performed on each of an image signal and an audio signal, an object is to correct a delay of the signal so as to synchronize the signals. An image signal processing portion (12, 16) that performs signal processing on an input image signal and an input audio signal, an input signal detecting portion (NS) that stores a signal state of the input image signal or the input audio signal, an output signal detecting portion (SS) that stores a signal state of the image signal or the audio signal after the signal processing performed by the image signal processing portion (12, 16), an image delay detecting portion (25) and an sound delay detecting portion (26) that compare the image signal and the audio signal stored in the input signal detecting portion NS with those stored in the output signal detecting portion SS so as to determine delay time (n) and delay time (k), a delay correction amount detecting portion (27) that determines delay correction amount (HRV, HRA) with respect to the image signal or the audio signal based on a difference between the delay time (n) and the delay time (k), a delay correcting portion (13, 17) that corrects a delay of the image signal or the audio signal to be delivered based on the determined delay correction amount, an image output portion (14) that delivers an image, and a sound output portion (18) that delivers sound are provided.

Owner:FUJITSU LTD

Margin registration of a scan line in an electrophotographic printer

A method of aligning a print image of an electrophotographic machine, the method including the steps of determining a power level of a laser beam, sensing a synch position of the laser beam associated with the scan line and varying a delay time before starting the scan line dependent upon the power level and the synch position.

Owner:LEXMARK INT INC

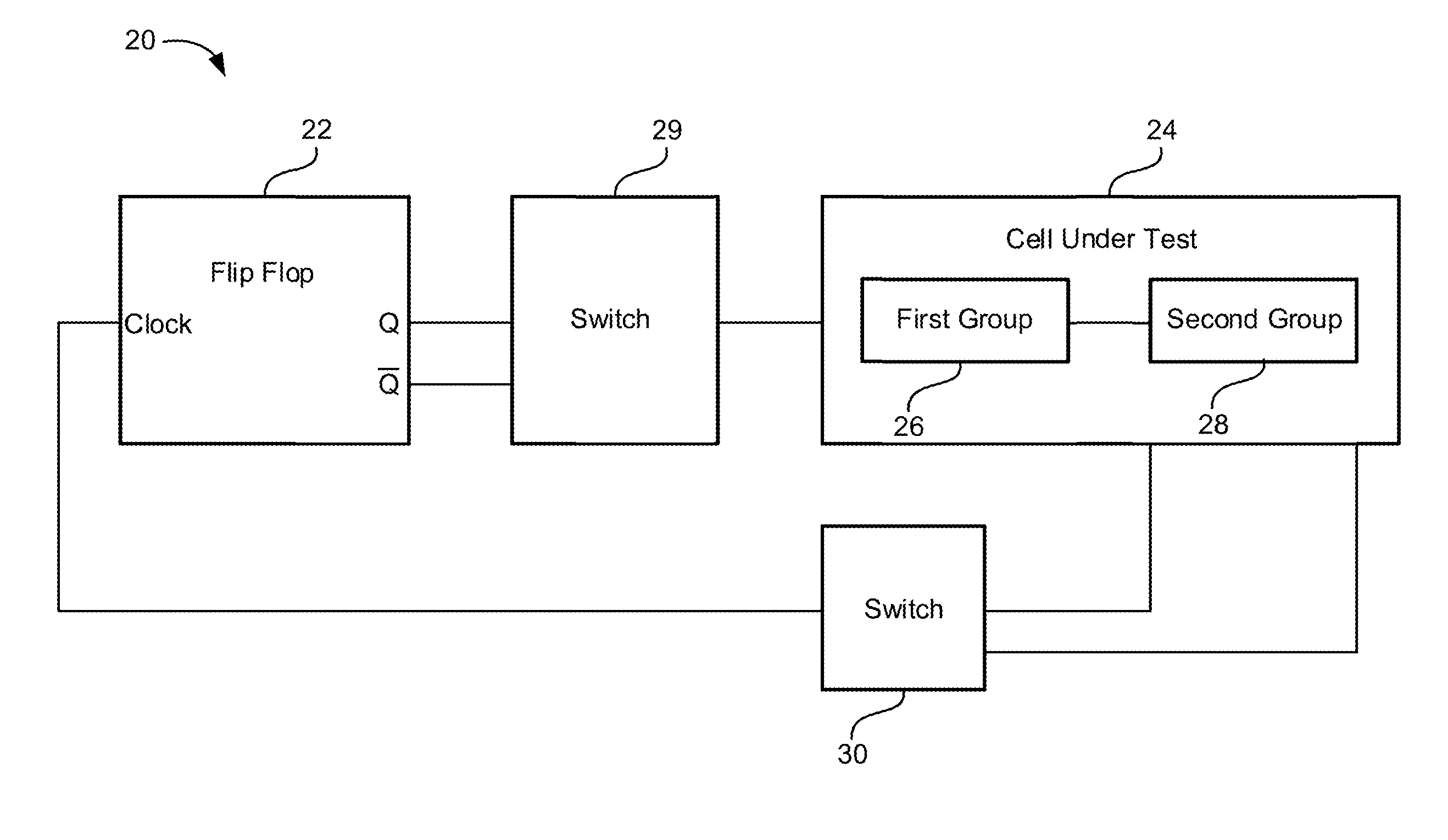

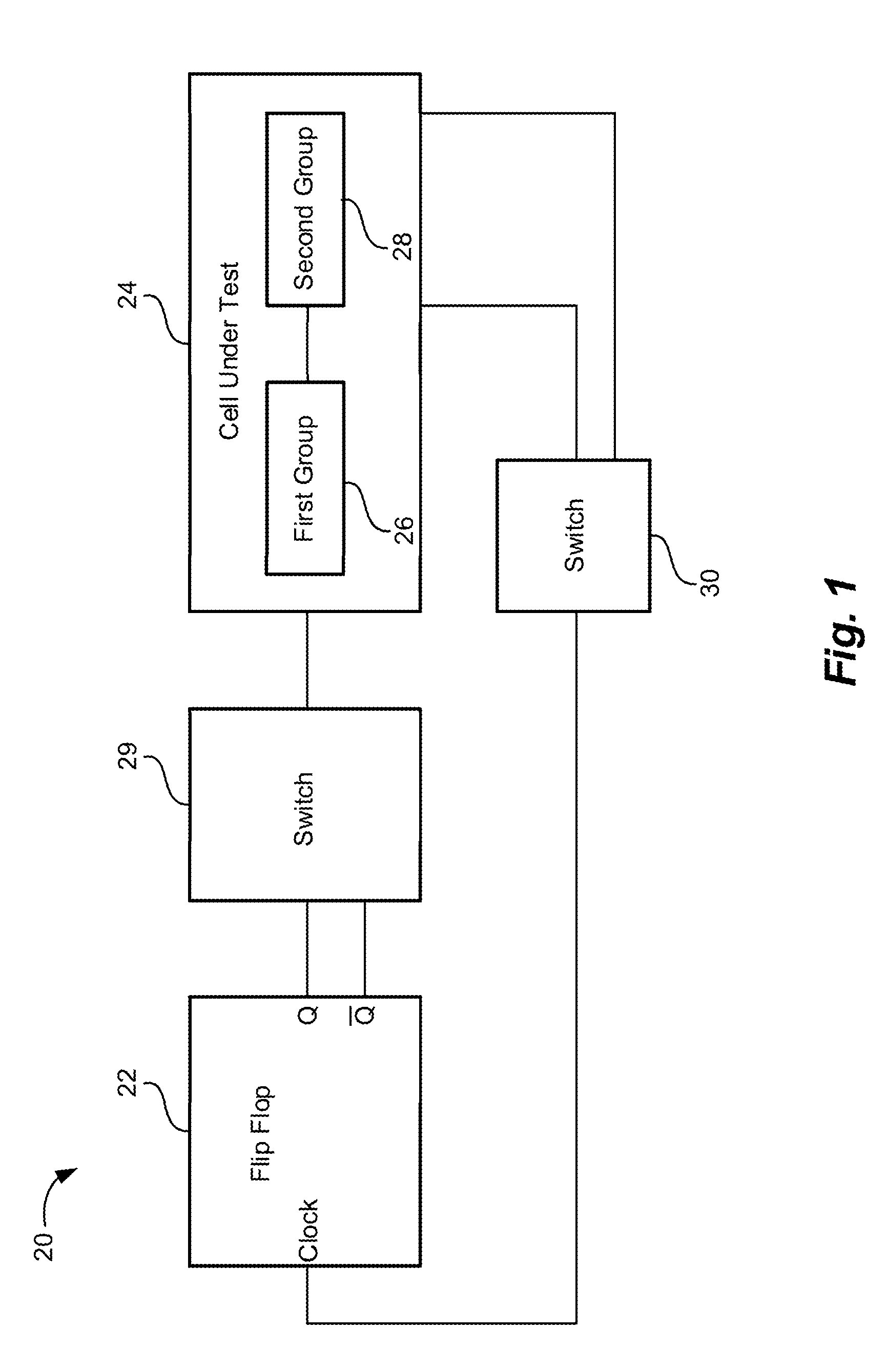

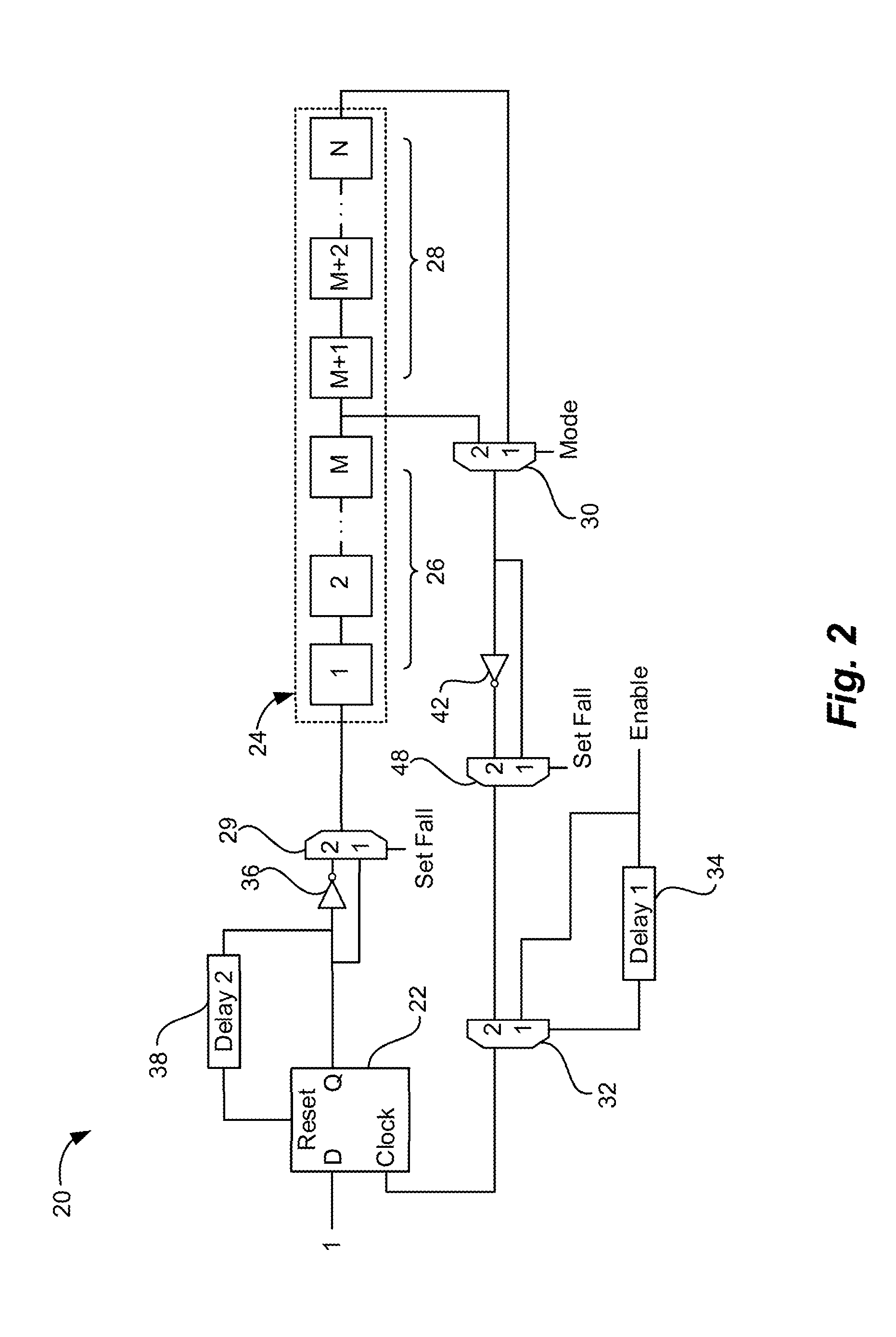

Scheme to measure individually rise and fall delays of non-inverting logic cells

A test circuit measures both the rising edge delay and the falling edge delay associated with a logic cell. The test circuit includes a flip-flop type ring oscillator with two groups of logic cells connected in series in the oscillation path. A first multiplexor switches the ring oscillator between a rising edge and a falling edge mode. A second multiplexer causes the second group of logic cells to be included or excluded from the oscillation path. By measuring the oscillation period in the various modes, the rising edge and falling edge delays can be individually calculated.

Owner:STMICROELECTRONICS INT NV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com