Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

239results about "Virtual memory details" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

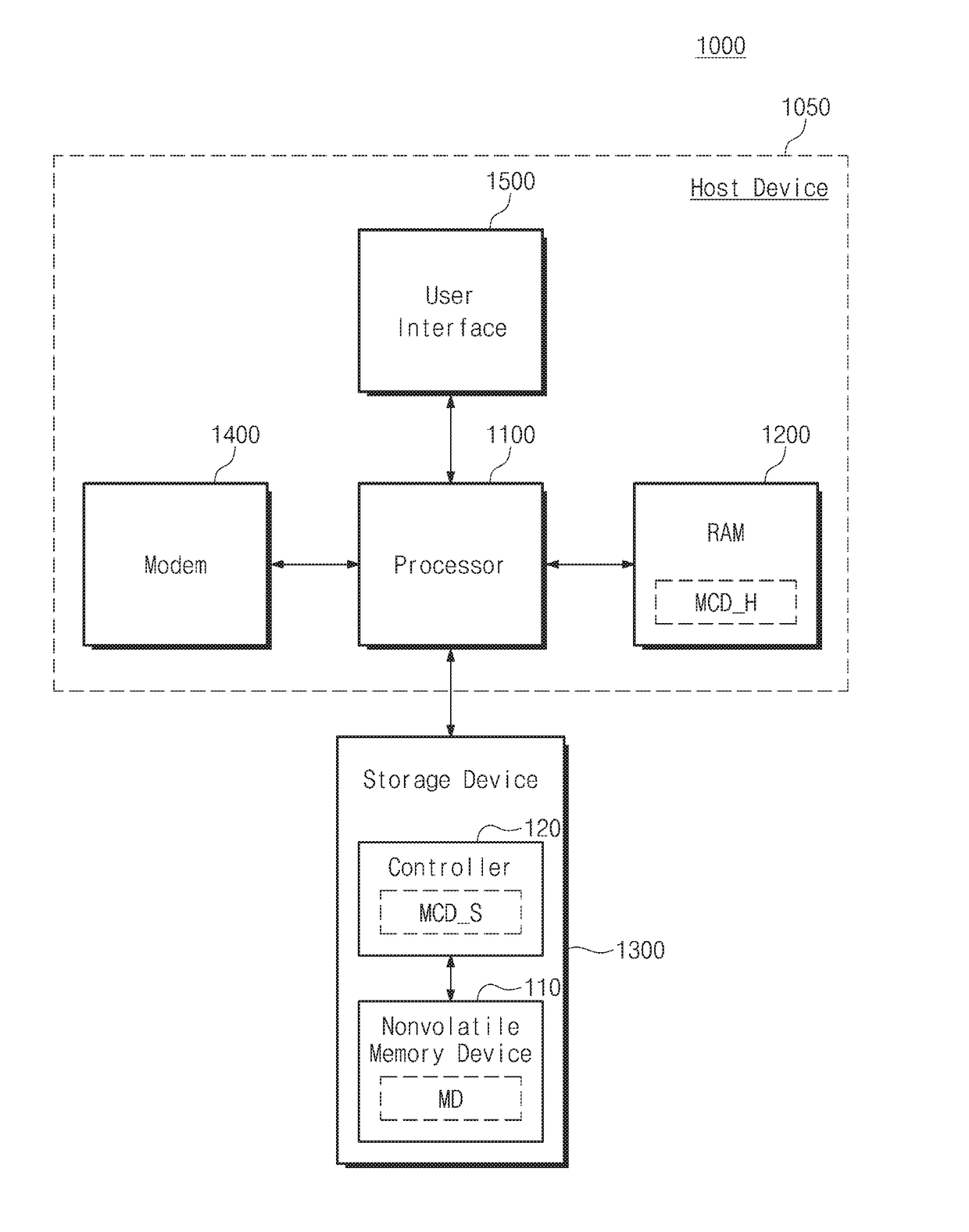

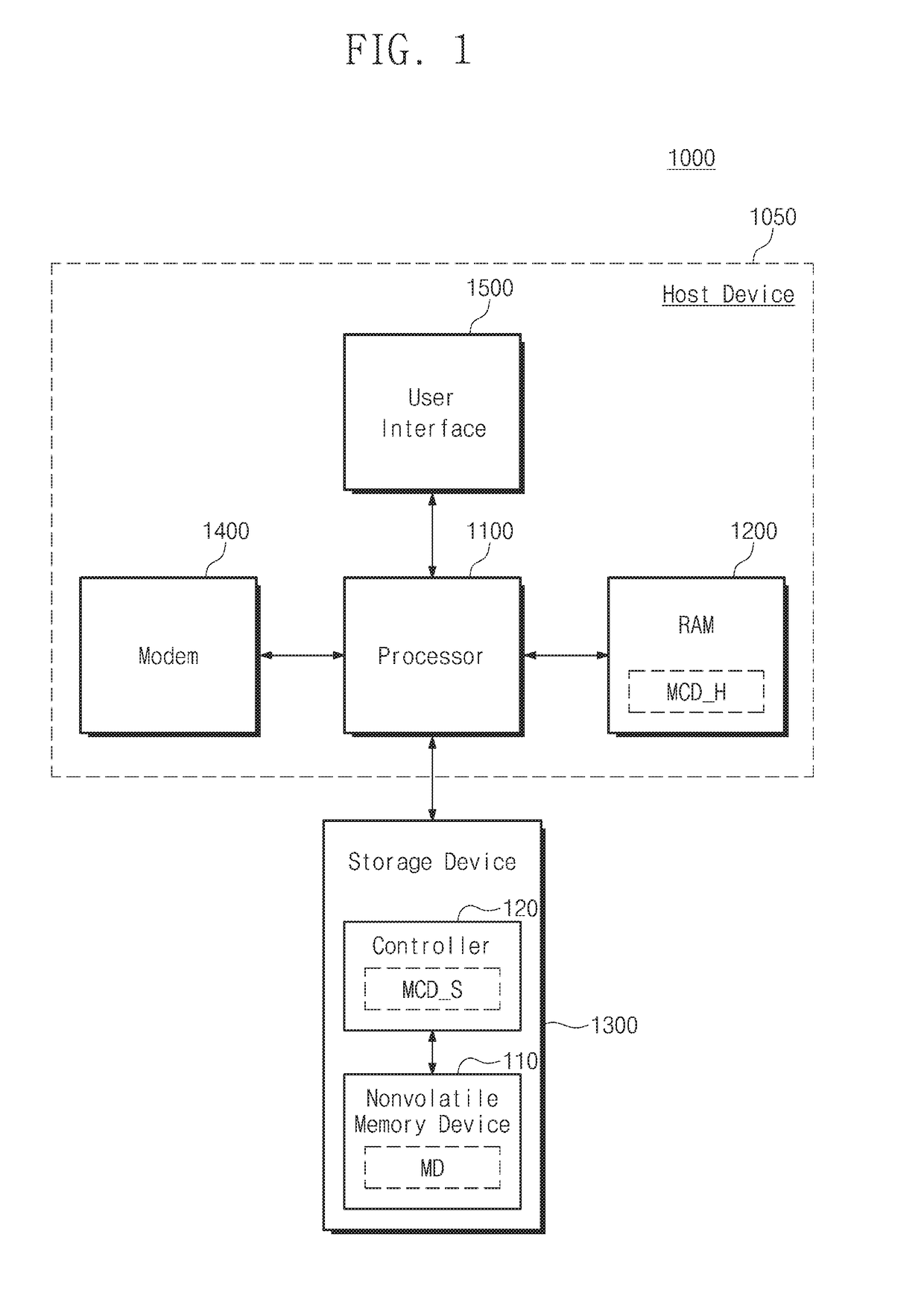

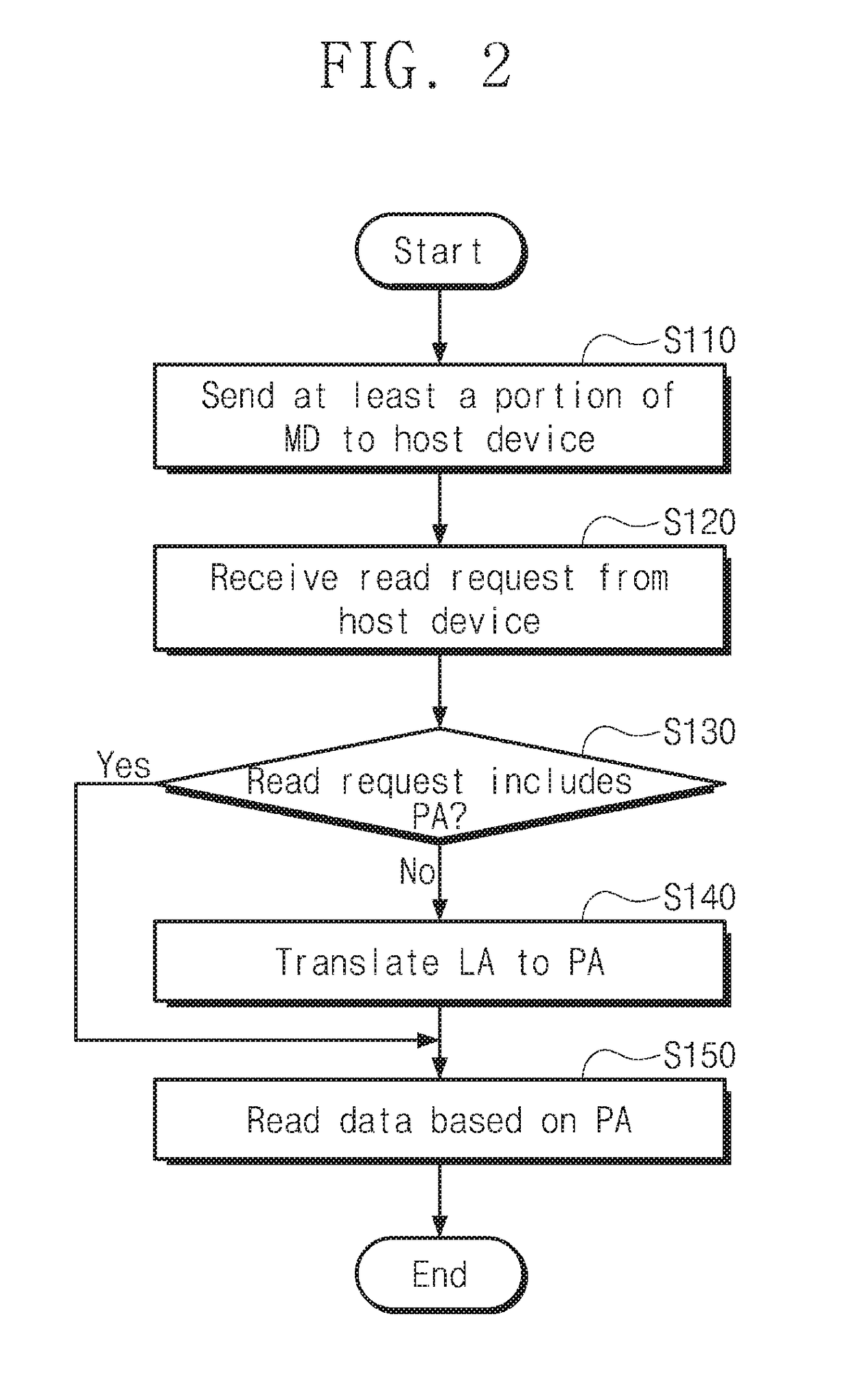

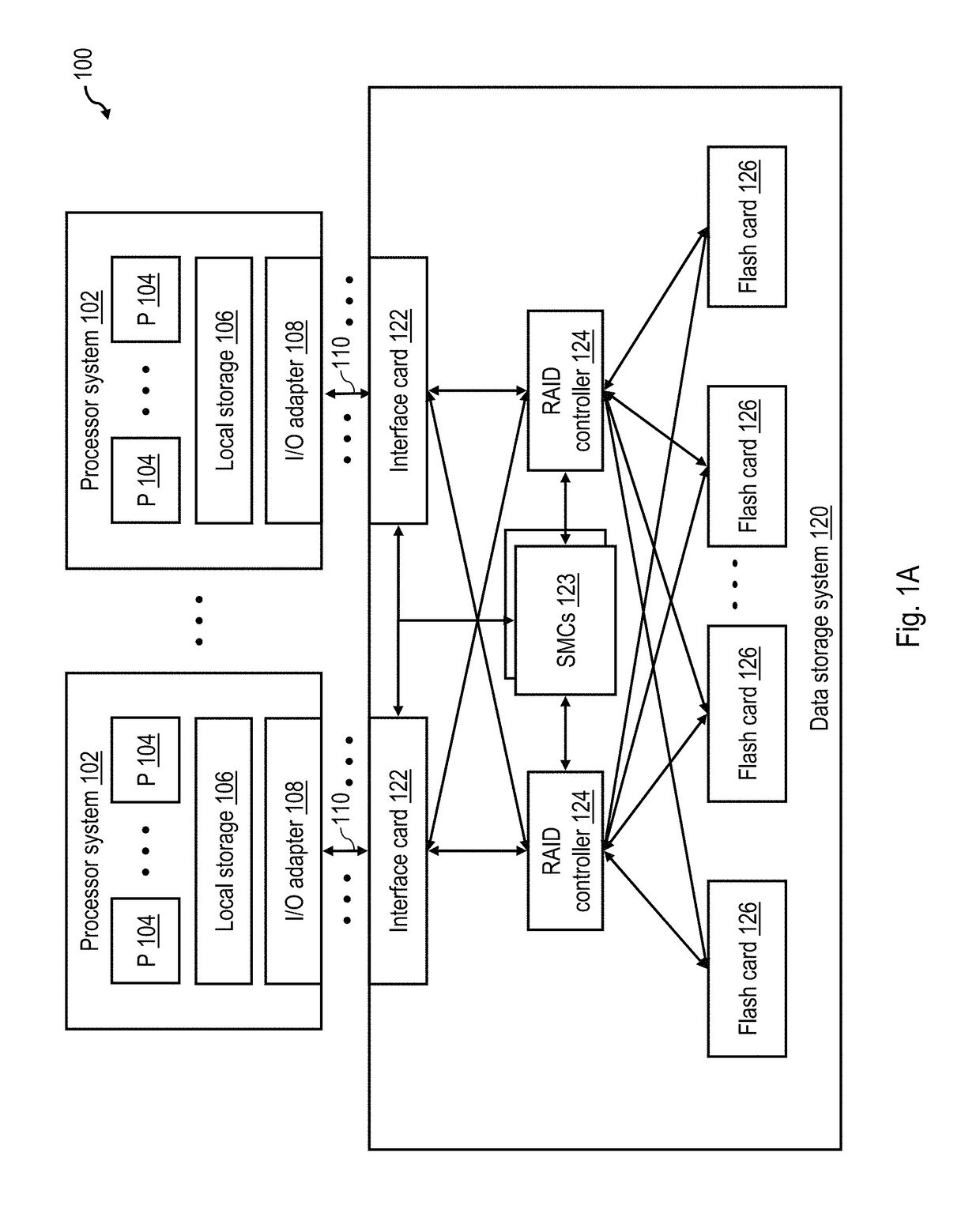

Storage device including nonvolatile memory device and controller, operating method of storage device, and method for accessing storage device

ActiveUS20170192902A1High speedMemory architecture accessing/allocationMemory adressing/allocation/relocationNon-volatile memoryHost machine

An operating method of a storage device that includes a nonvolatile memory device and a controller configured to control the nonvolatile memory device includes sending map data from the storage device to a host device, the map data mapping one or more of a plurality of physical addresses of the nonvolatile memory device to one or more of a plurality of logical addresses of the host device; receiving, at the storage device, a read request from the host device; if the read request includes a physical address, reading data from the nonvolatile memory device based on the included physical address; and if the read request does not include a physical address, translating a logical address of the read request into a first physical address, and reading data from the nonvolatile memory device based on the translated first physical address.

Owner:SAMSUNG ELECTRONICS CO LTD

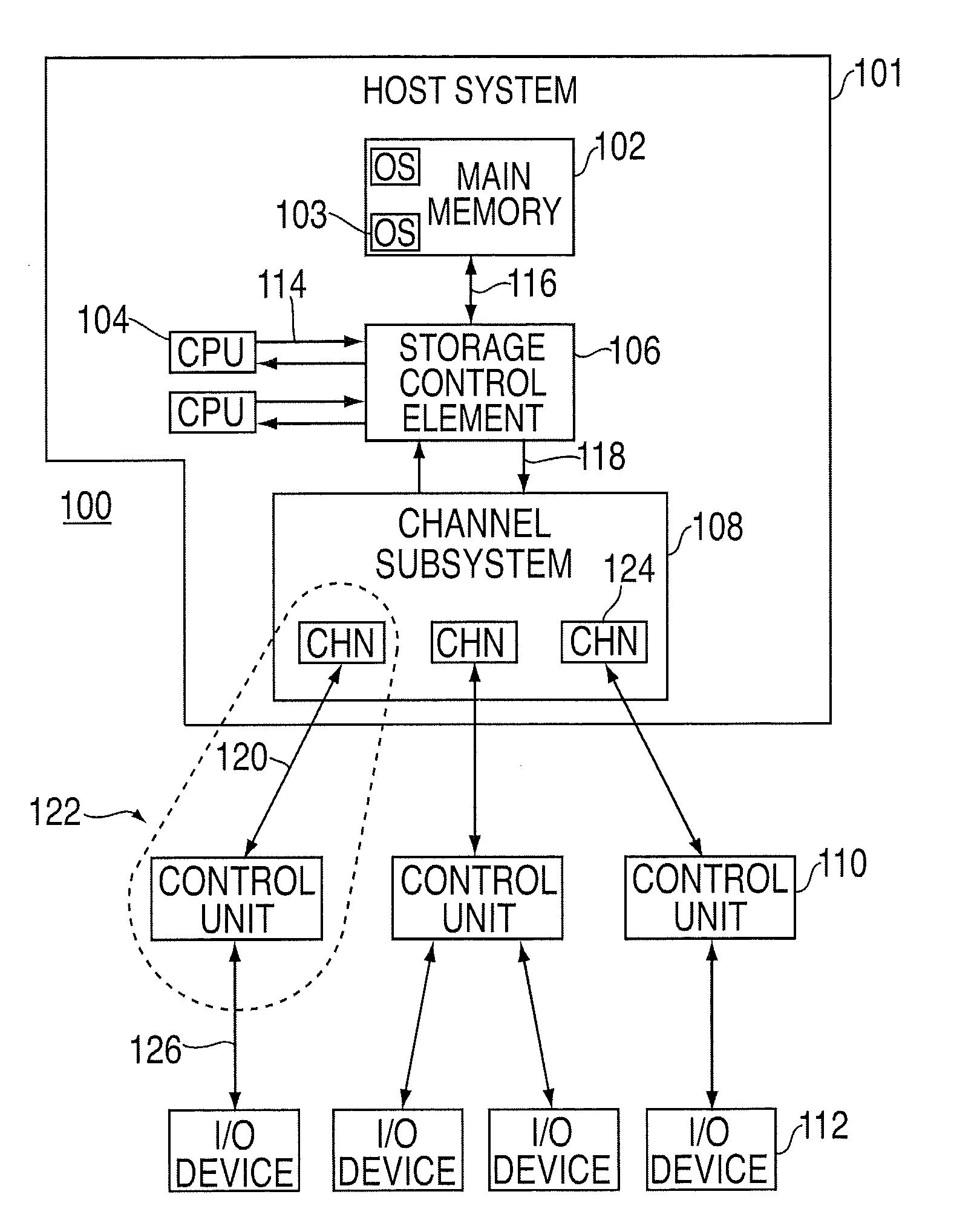

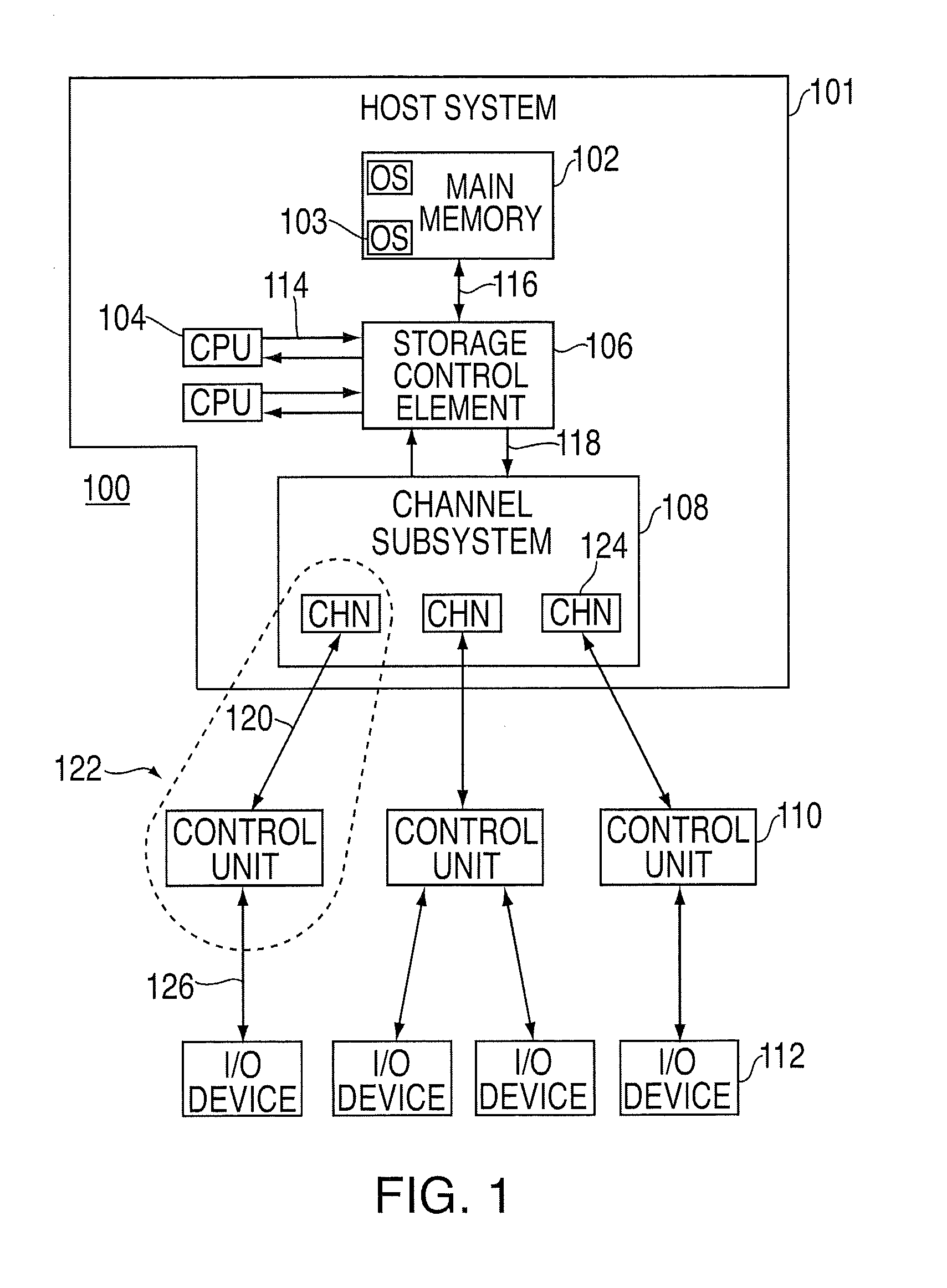

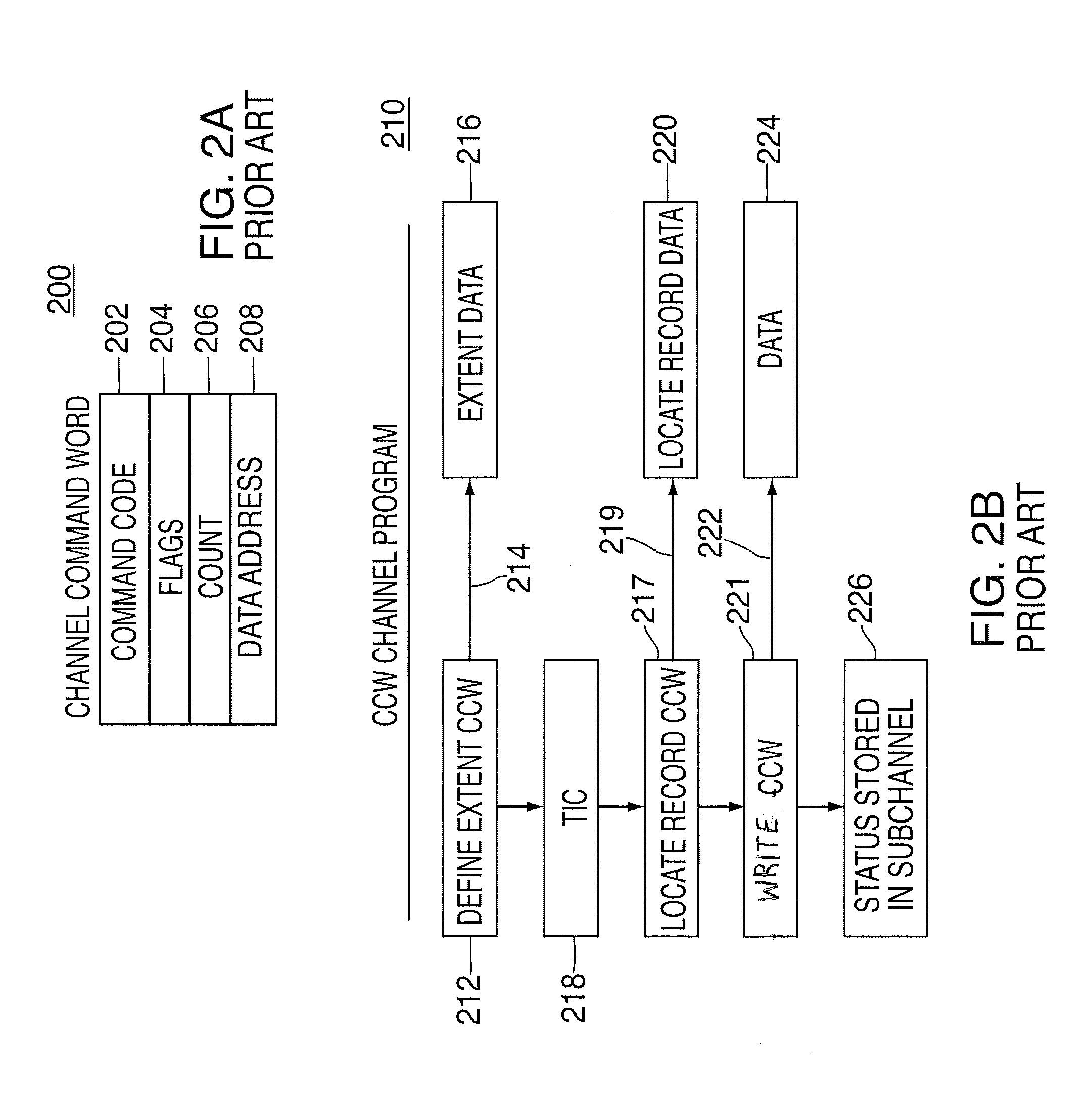

Providing indirect data addressing in an input/output processing system where the indirect data address list is non-contiguous

ActiveUS20090210576A1Memory adressing/allocation/relocationVirtual memory detailsHome positionInput/output

Systems, methods and computer program products for providing indirect data addressing at an I / O subsystem of an I / O processing system. The computer program product includes a tangible storage medium readable by a processing circuit and storing instructions for execution by the processing circuit for performing a method. The method includes receiving a control word for an I / O operation. The control word includes an indirect data address for data associated with the I / O operation. The indirect data address includes a starting location of a list of storage addresses that collectively specify the data, the list spans two or more non-contiguous storage locations. Data is gathered responsive to the list. The gathered data is transmitted to a control unit in the I / O processing system.

Owner:IBM CORP

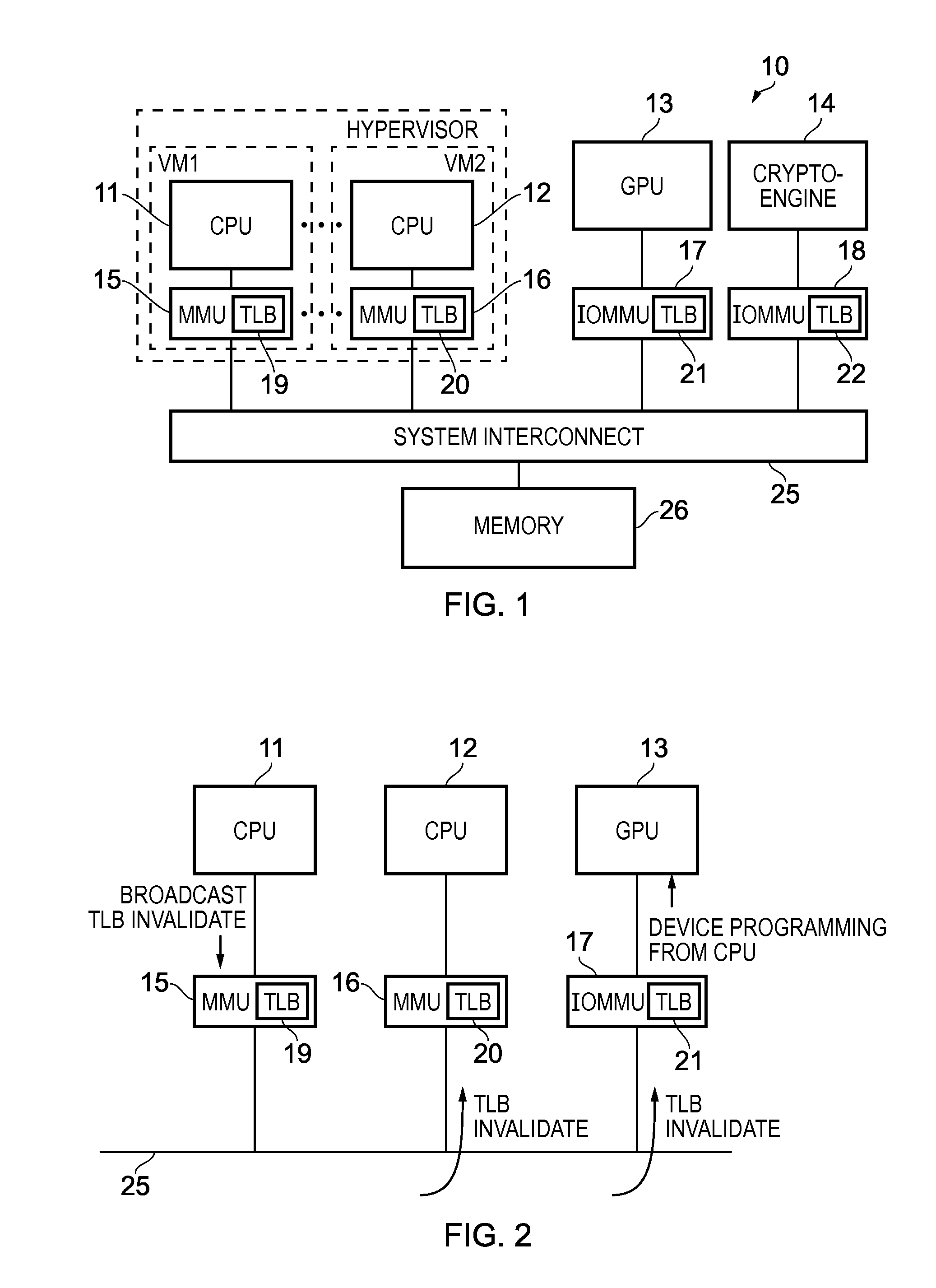

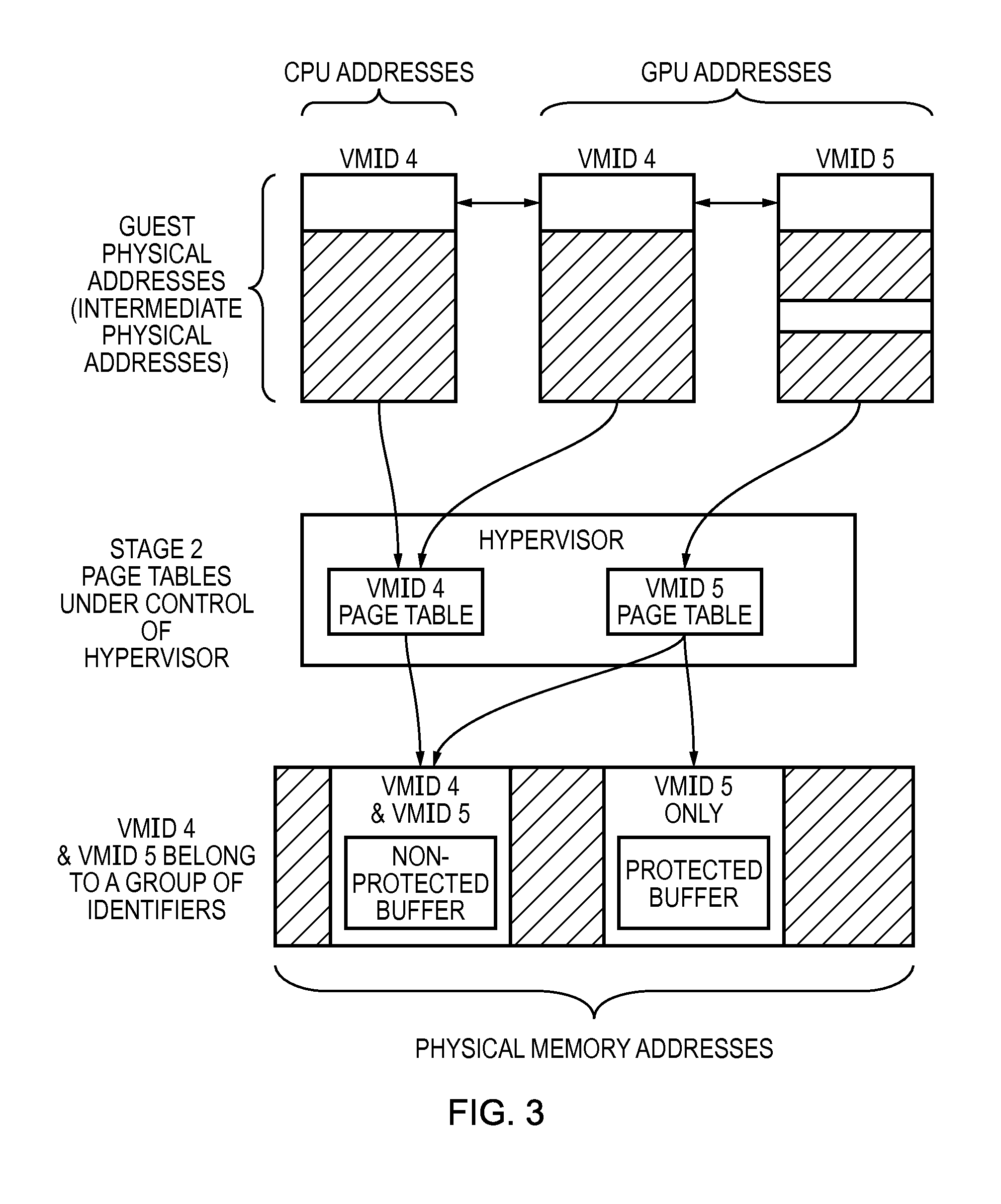

Invalidating stored address translations

ActiveUS20150242319A1Save storage spaceMemory architecture accessing/allocationMemory adressing/allocation/relocationData processing

A data processing apparatus and a method of processing data are disclosed, in which address translations between first addresses used in a first addressing system and second addresses used in a second addressing system are locally stored. Each stored address translation is stored with a corresponding identifier. In response to an invalidation command to perform an invalidation process on a selected stored address translation the selected stored address translation is invalidated, wherein the selected stored address translation is identified in the invalidation command by a specified first address and a specified identifier. The invalidation process is further configured by identifier grouping information which associates more than one identifier together as a group of identifiers, and the invalidation process is applied to all stored address translations which match the specified first address and which match any identifier in the group of identifiers to which the specified identifier belongs.

Owner:ARM LTD

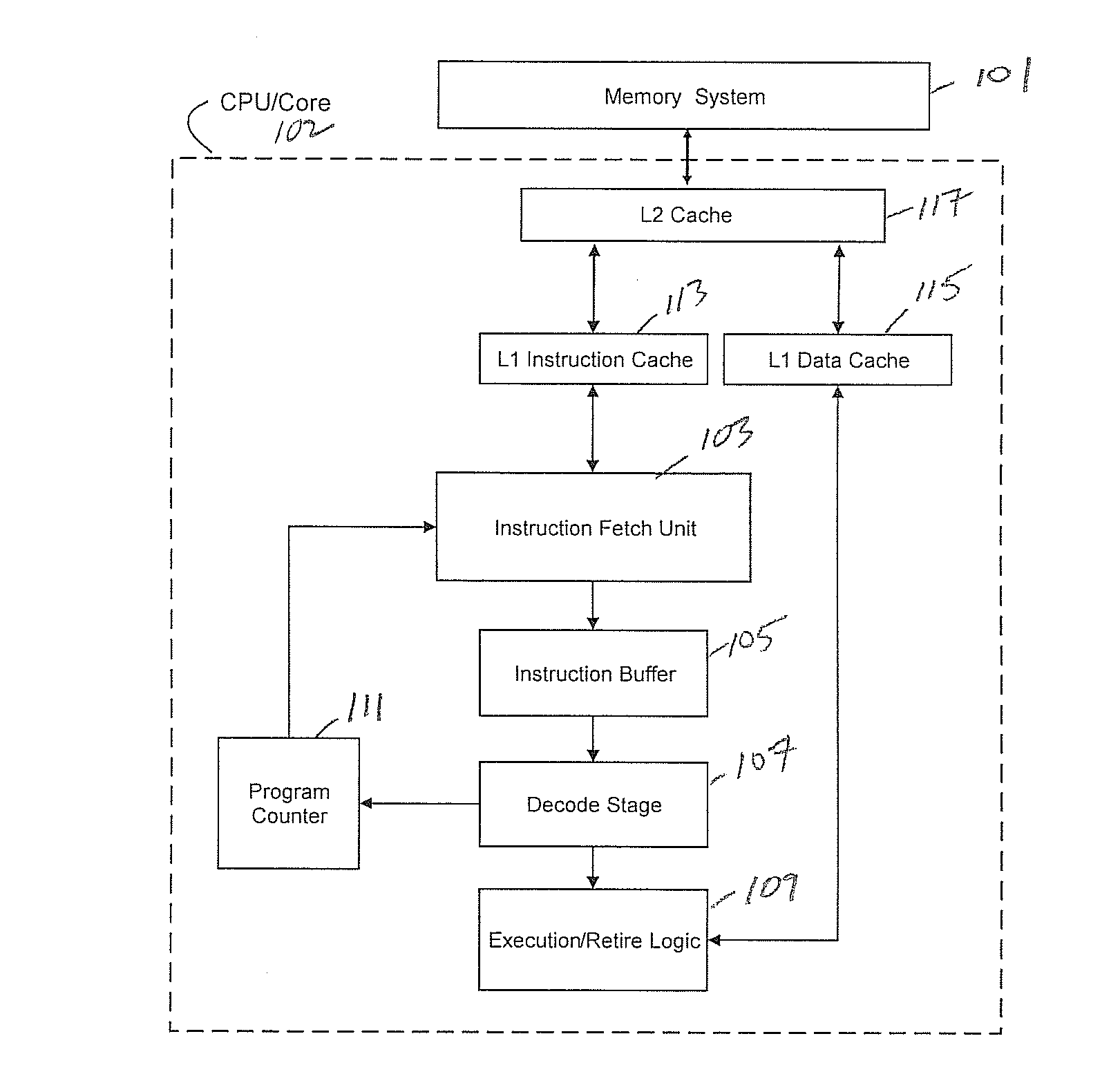

Apparatus and method for low-overhead synchronous page table updates

ActiveUS20170286300A1Memory architecture accessing/allocationMemory adressing/allocation/relocationPage tableTranslation lookaside buffer

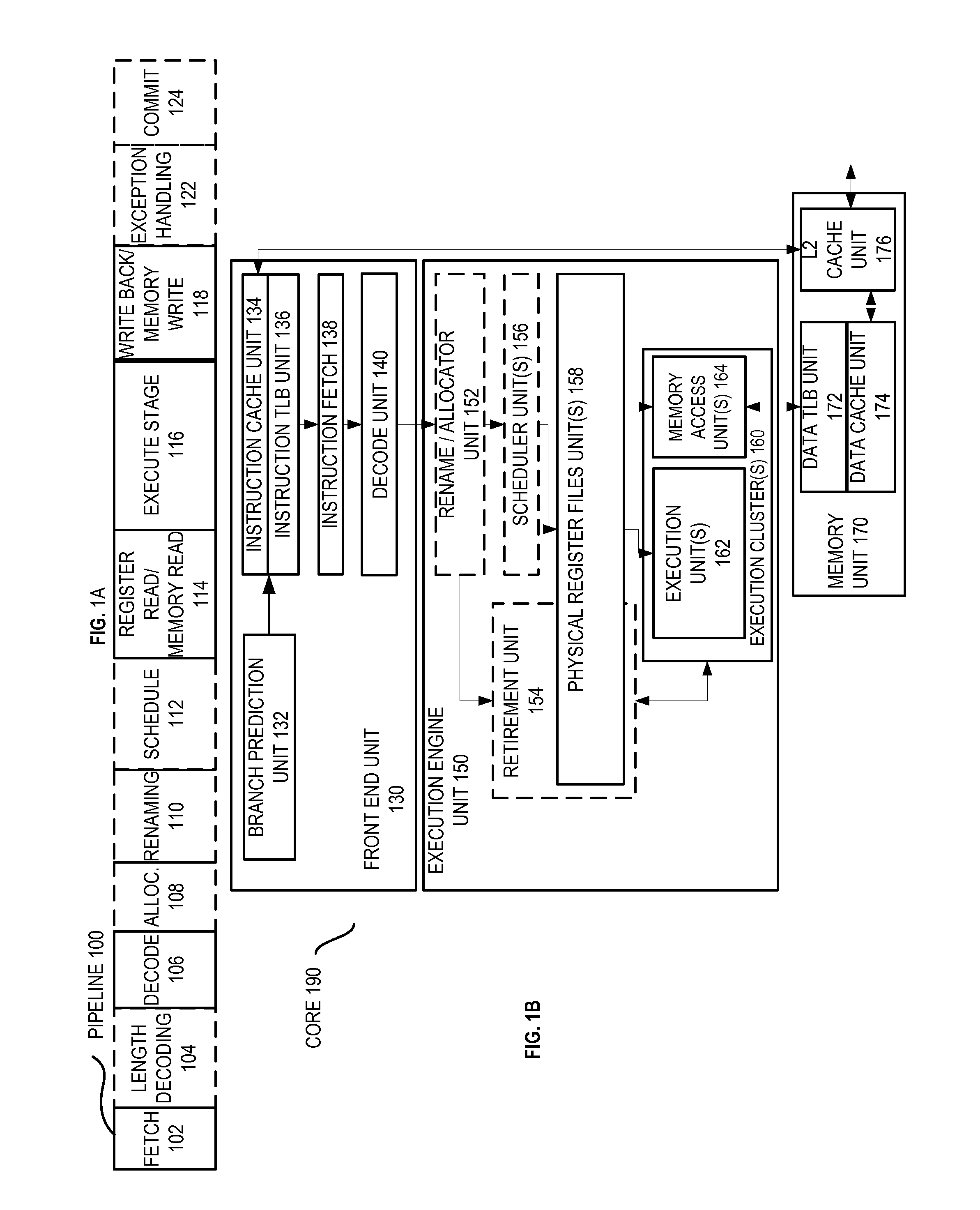

An apparatus and method are described for low overhead synchronous page table updates. For example, one embodiment of a processor comprises: a set of one or more cores to execute instructions and process data; a translation lookaside buffer (TLB) comprising a plurality of entries to cache virtual-to-physical address translations usable by the set of one or more cores when executing the instructions; locking circuitry to allow a thread to lock a first page table entry (PTE) in the TLB to ensure that only one thread can modify the first PTE at a time, wherein the TLB is to modify the first PTE upon the thread acquiring the lock; a PTE invalidation circuit to execute a PTE invalidate instruction on a first core to invalidate the first PTE in other TLBs of other cores, the PTE invalidation circuit, responsive to execution of the PTE invalidate instruction, to responsively determine a number of other TLBs of other cores which need to be notified of the PTE invalidation, transmit PTE invalidate messages to the other TLBs, and wait for responses; and the locking circuitry to release the lock on the first PTE responsive to receiving responses from all of the other TLBs.

Owner:INTEL CORP

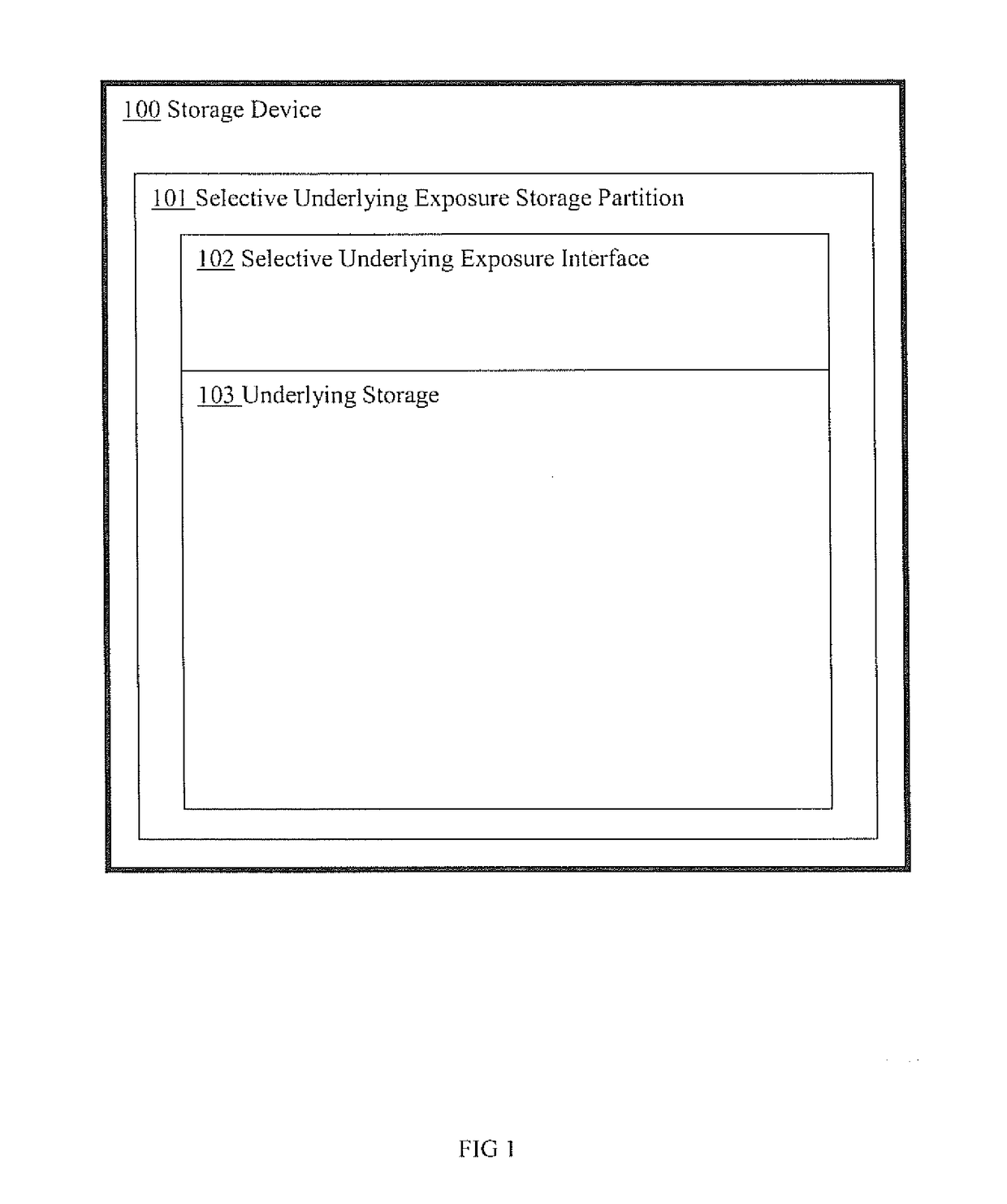

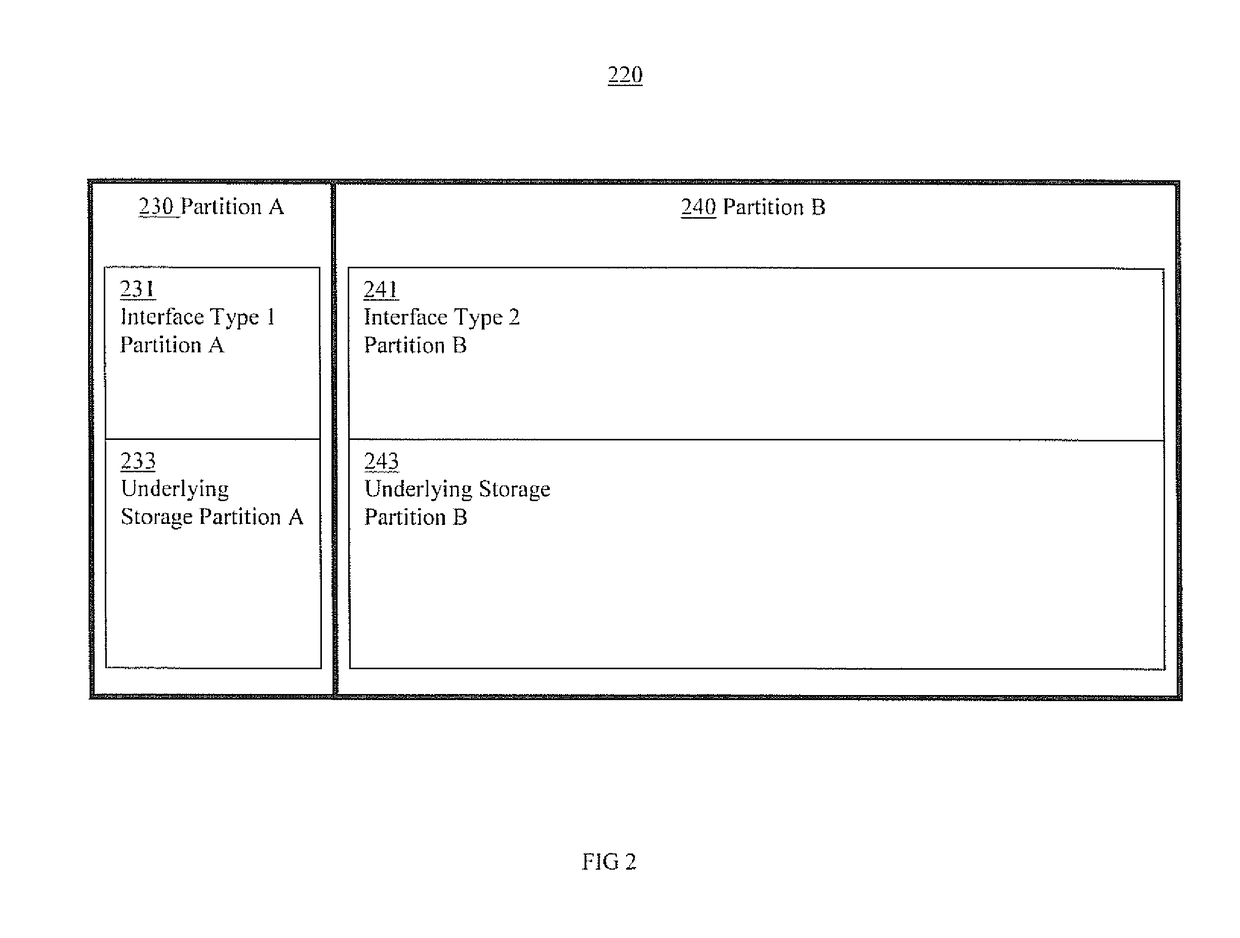

Selective underlying exposure storage mapping

ActiveUS20170139838A1Memory architecture accessing/allocationInput/output to record carriersMachine instructionJoint management

An apparatus for mapping user data into a selective underlying exposure address (SUE) space includes a memory that stores machine instructions and a processor that executes the instructions to combine first user data from a plurality of logically-addressed blocks to create a SUE page. The SUE page corresponds to a respective physical page of a respective physical block on each of a plurality of dies for which corresponding physical blocks of memory cells are jointly managed as a unit in a storage device. The processor further executes the instructions to store mapping information associating the first user data with the SUE page in a logical address space in the storage device.

Owner:SAMSUNG ELECTRONICS CO LTD

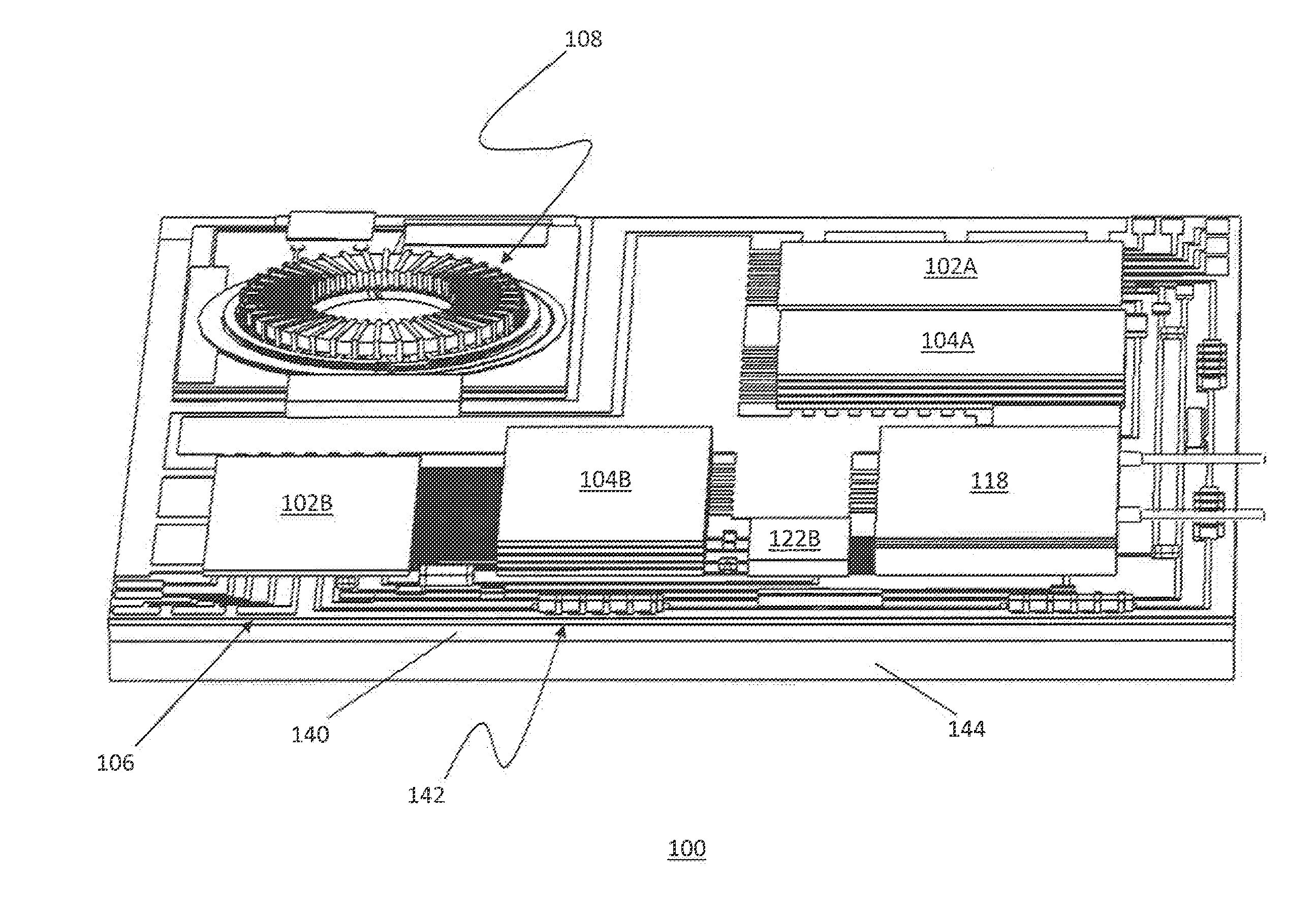

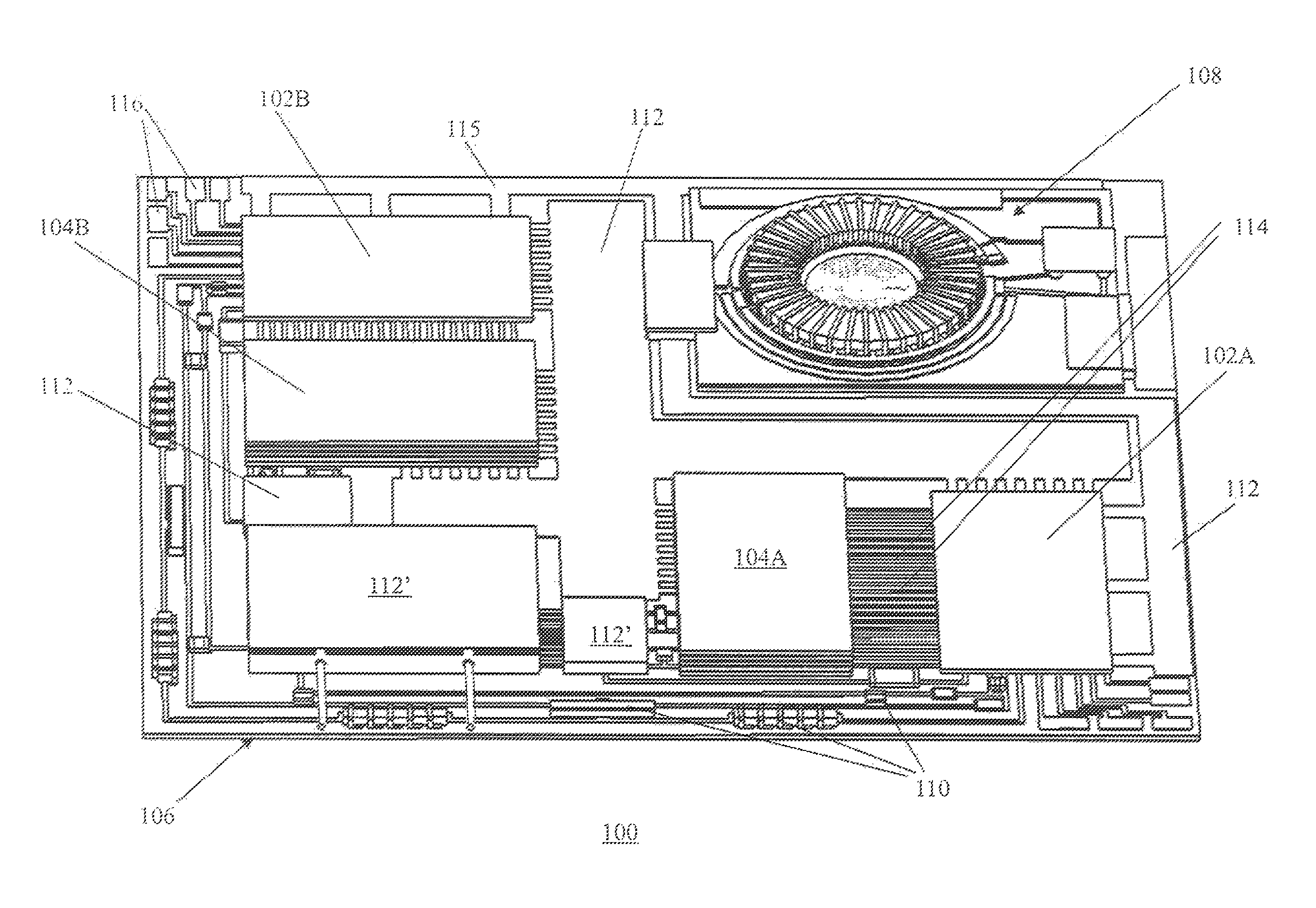

Hybrid computing module

ActiveUS20140013132A1Efficient transferSmall sizeMemory architecture accessing/allocationRegister arrangementsHybrid systemSemiconductor chip

A hybrid system-on-chip provides a plurality of memory and processor die mounted on a semiconductor carrier chip that contains a fully integrated power management system that switches DC power at speeds that match or approach processor core clock speeds, thereby allowing the efficient transfer of data between off-chip physical memory and processor die.

Owner:DEROCHEMONT L PIERRE

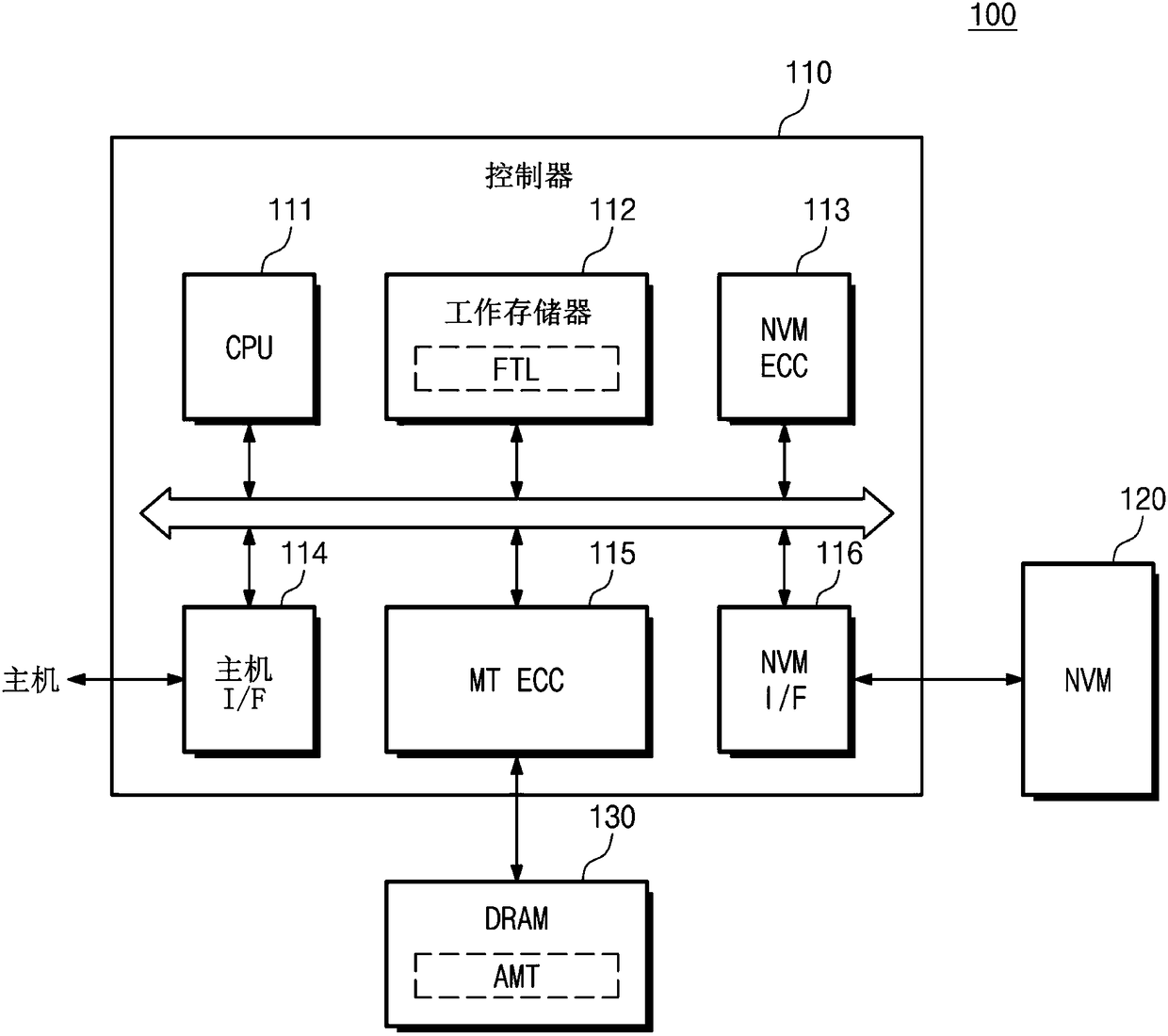

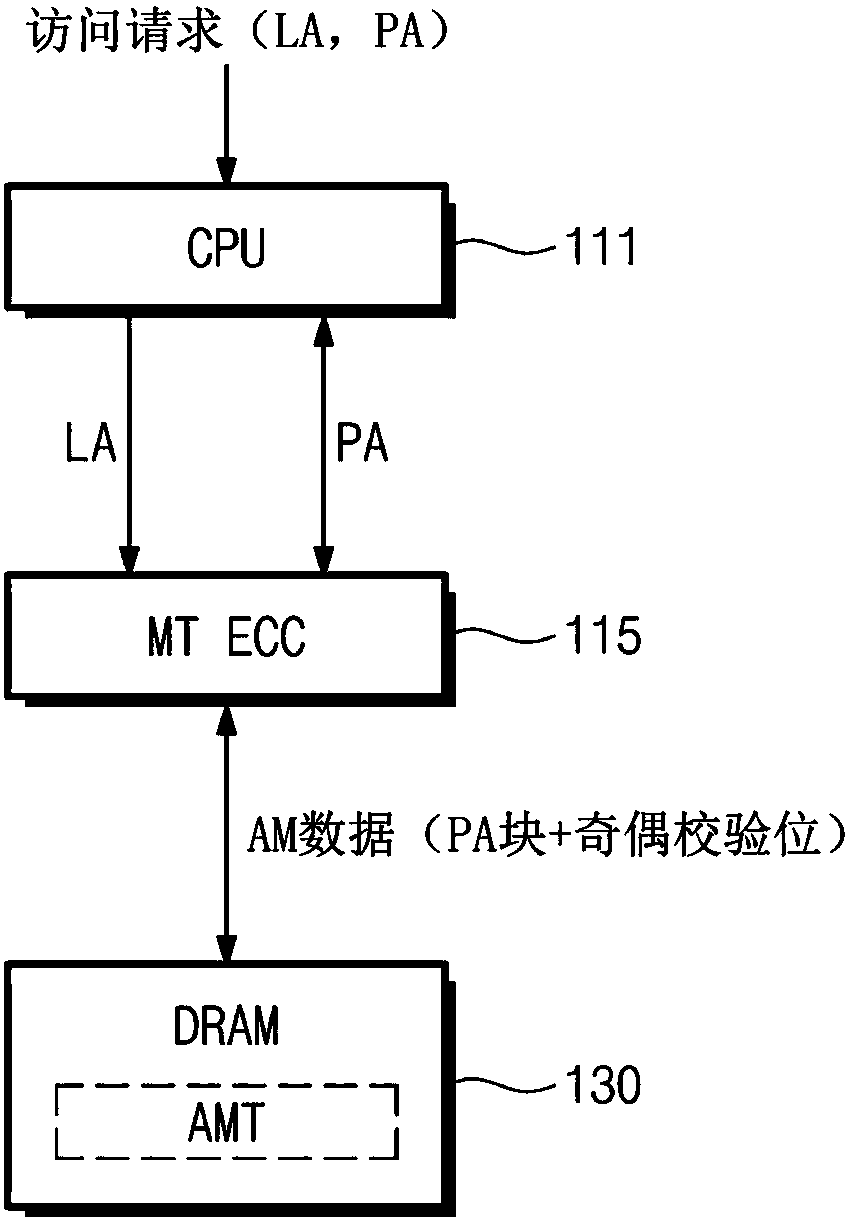

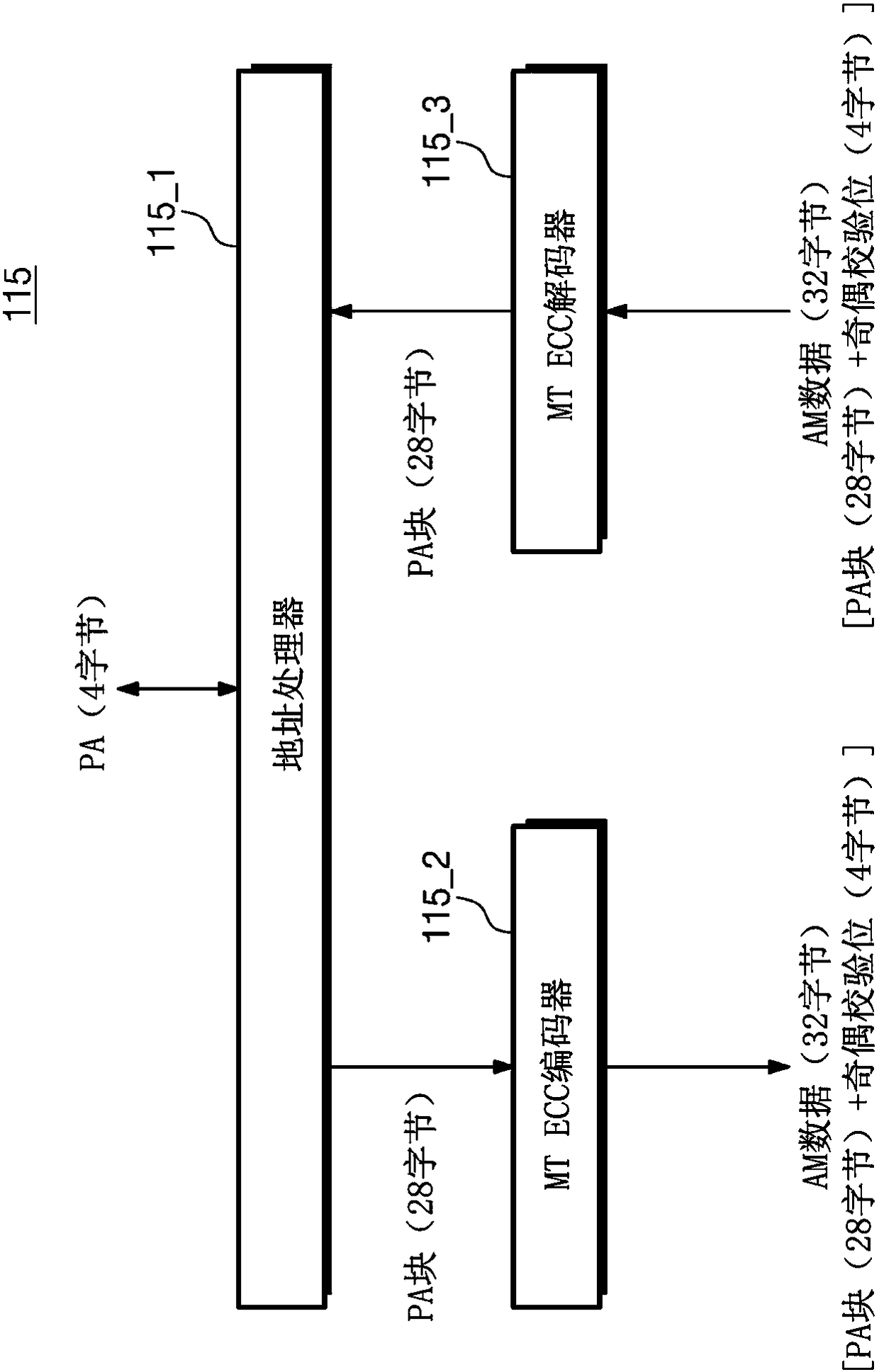

Memory system performing error correction of address mapping table and method of controlling same

ActiveCN108073470AMemory architecture accessing/allocationVirtual memory detailsAddress mappingNon-volatile memory

A memory system performing error correction of an address mapping table and a method of controlling the same are provided. A memory system includes a nonvolatile memory device, a dynamic random accessmemory (DRAM) configured to store an address mapping table for an access to the nonvolatile memory device, and a controller configured to store, in the DRAM, the address mapping table that is dividedin units of address mapping data, each of the units having a size of an interface of the DRAM, read, from the stored address mapping table, target address mapping data corresponding to a logical address that is received from a host, the target address mapping data including a target parity and physical addresses of the nonvolatile memory device, and perform an error correction on the read targetaddress mapping data, using the target parity.

Owner:SAMSUNG ELECTRONICS CO LTD

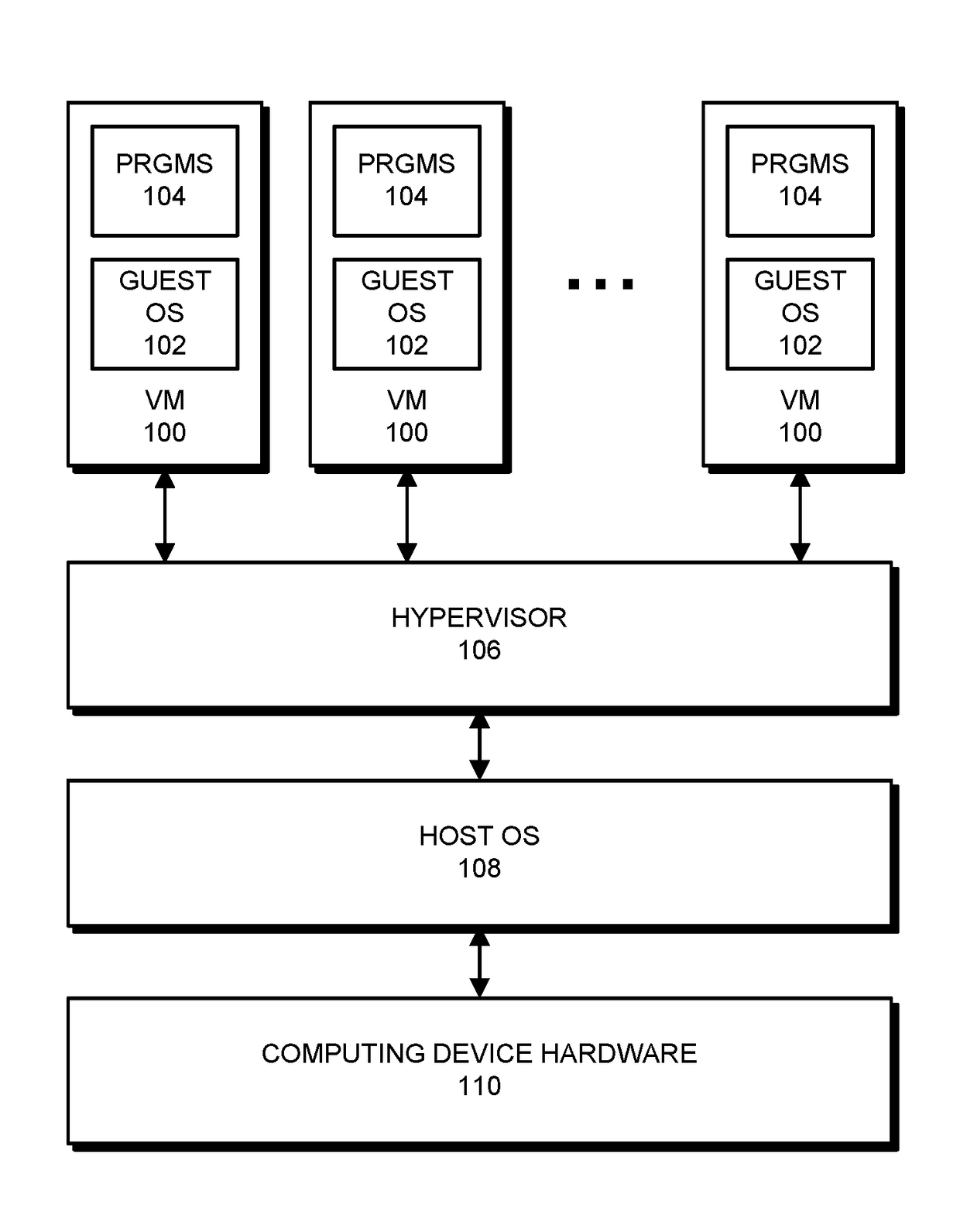

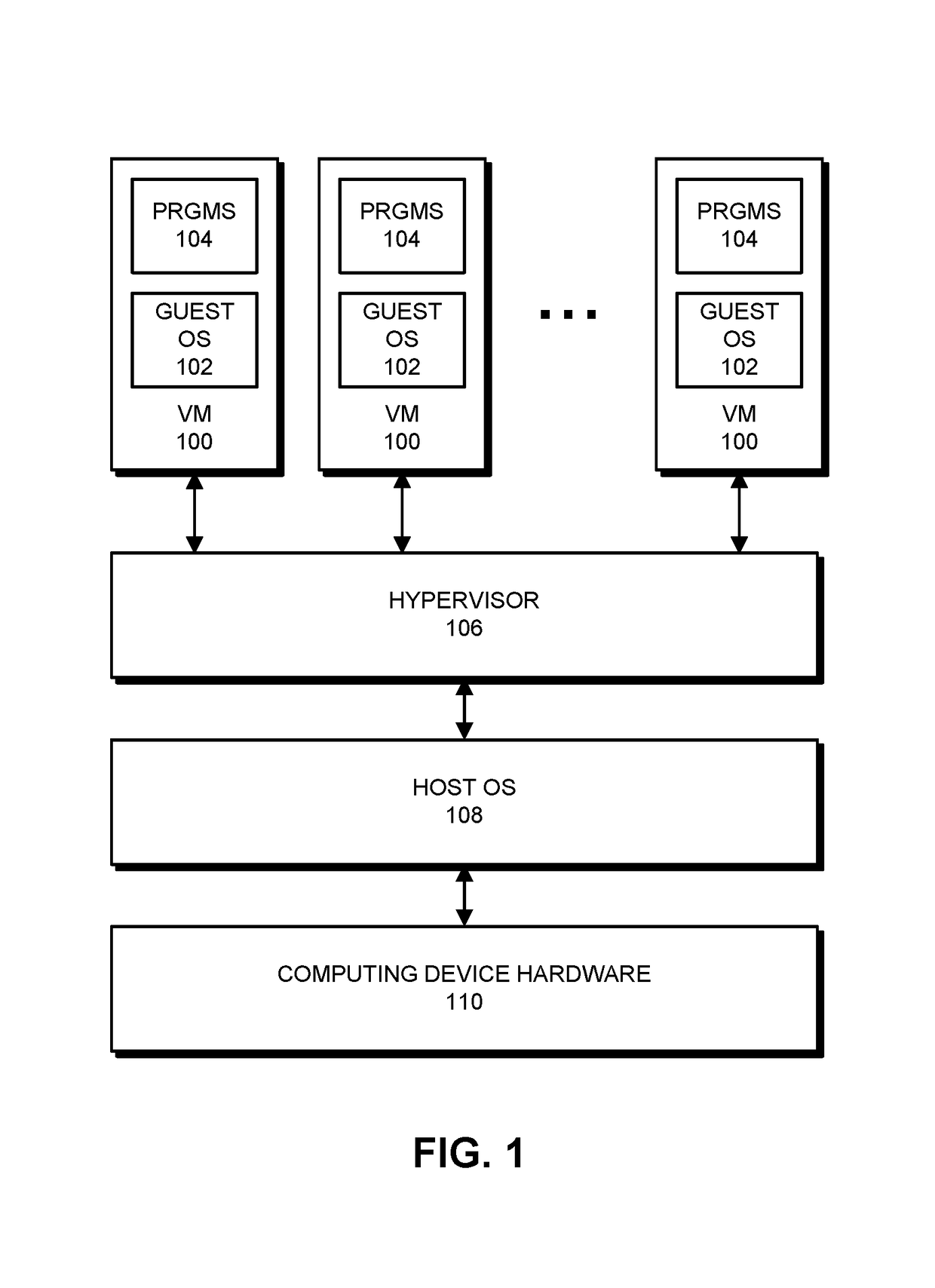

Controlling Access to Pages in a Memory in a Computing Device

ActiveUS20180032447A1Memory architecture accessing/allocationProgram synchronisationRemedial actionDatabase

A table walker receives, from a requesting entity, a request to translate a first address into a second address associated with a page of memory. During a corresponding table walk, when a lock indicator in an entry in a reverse map table (RMT) for the page is set to mark the entry in the RMT as locked, the table walker halts processing the request and performs a remedial action. In addition, when the request is associated with a write access of the page and an immutable indicator in the entry in the RMT is set to mark the page as immutable, the table walker halts processing the request and performs the remedial action. Otherwise, when the entry in the RMT is not locked and the page is not marked as immutable for a write access, the table walker continues processing the request.

Owner:ADVANCED MICRO DEVICES INC

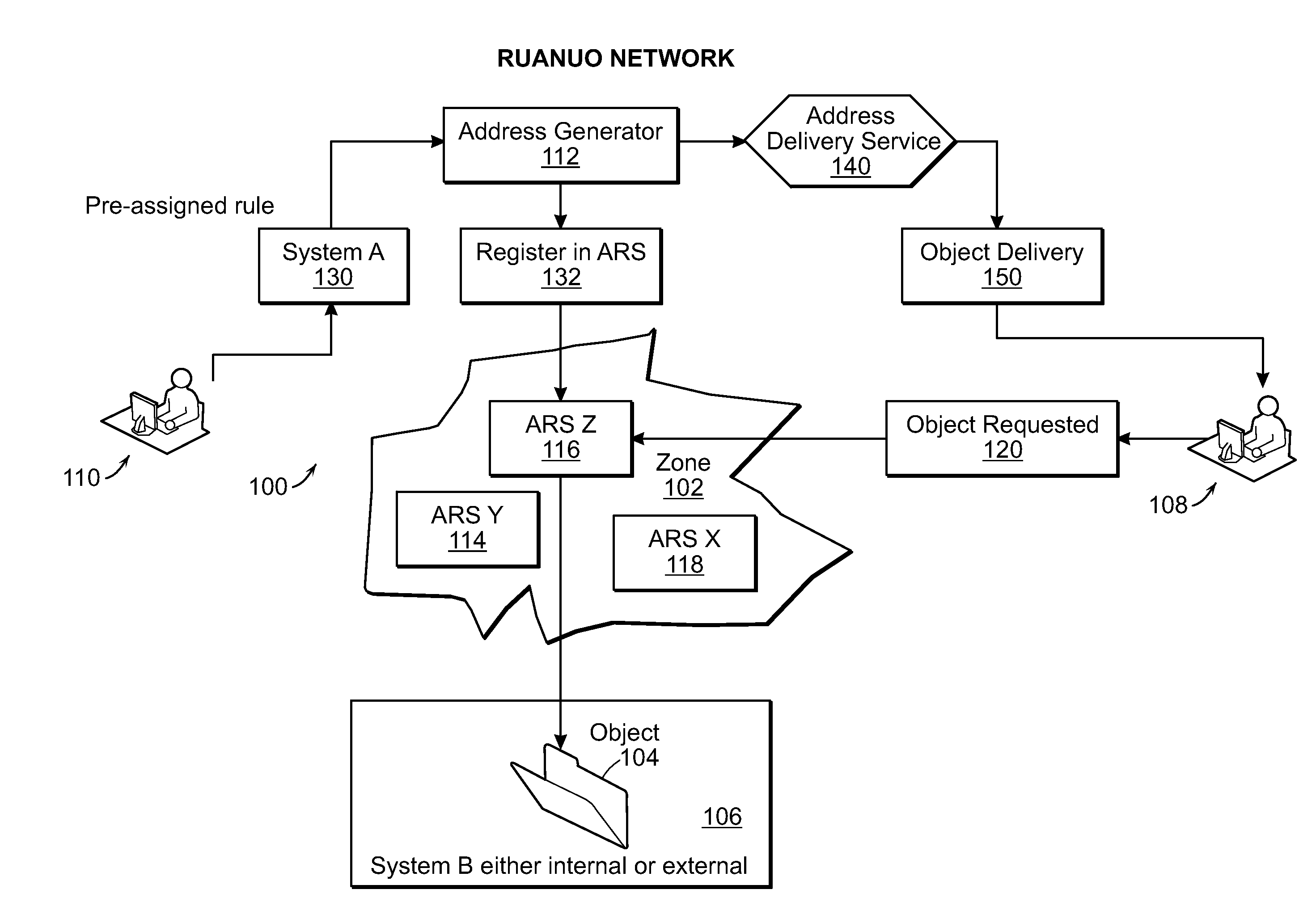

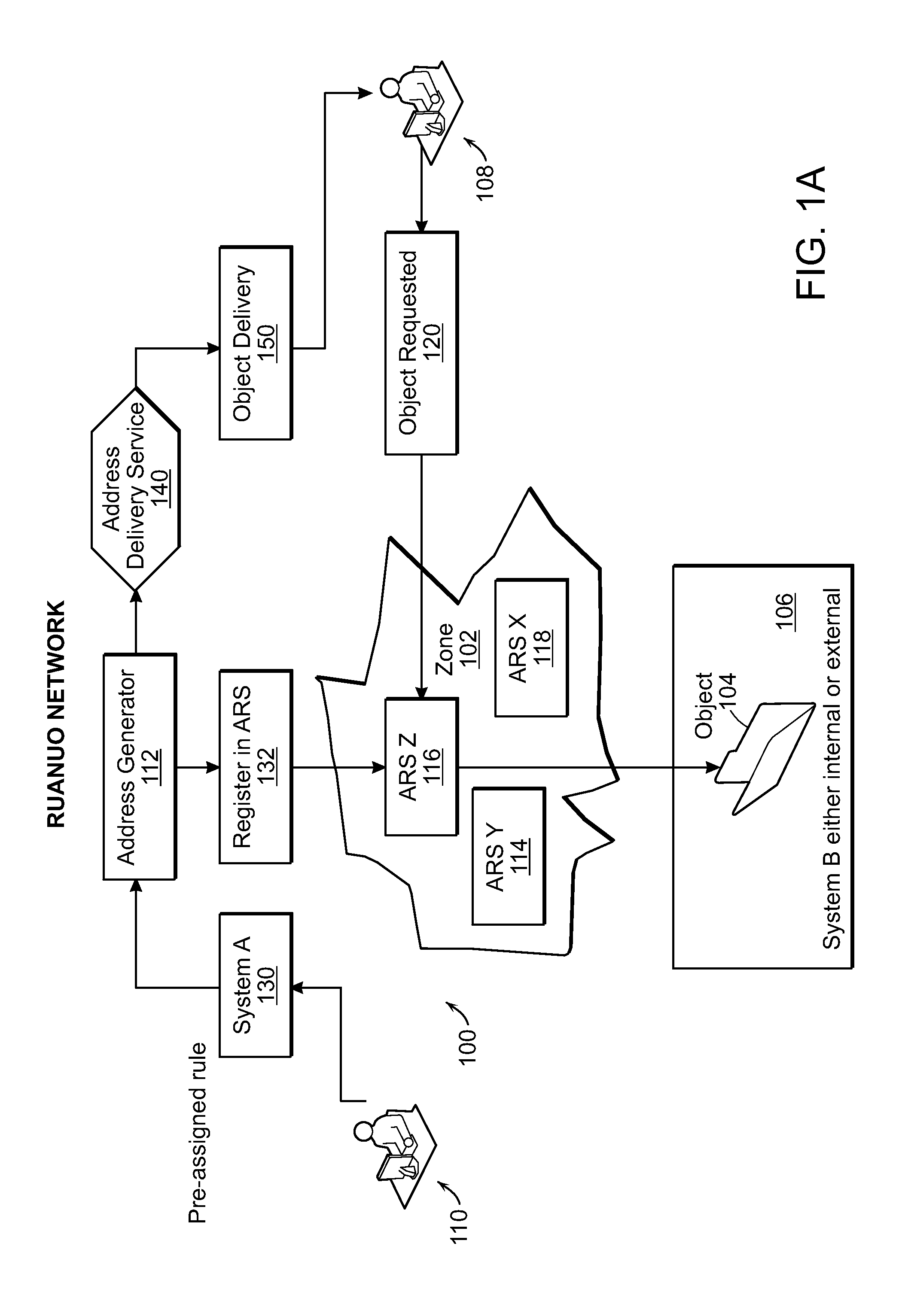

Apparatus and data processing systems for accessing an object

ActiveUS20140173706A1Memory architecture accessing/allocationDigital data processing detailsData processing systemAddress resolution

A system and method for providing access to an object over a network may comprise hosting an object on a distributed data processing system accessible over the network, the object contained within a cell; generating, by a cell access provider, a unique and random address for the cell containing the object, utilizing an address resolution module and providing, by the cell access provider, the unique and random address to a computing device of a unique consumer; and upon receipt of the unique and random address from the unique user, matching the unique and random address with the cell to facilitate access by the unique user to the object. The object may comprise a virtual object acting as a cell for facilitating access to one or more additional objects. The virtual object cell may contain one or more unique and random addresses facilitating access to one or more additional objects.

Owner:SERVMAX

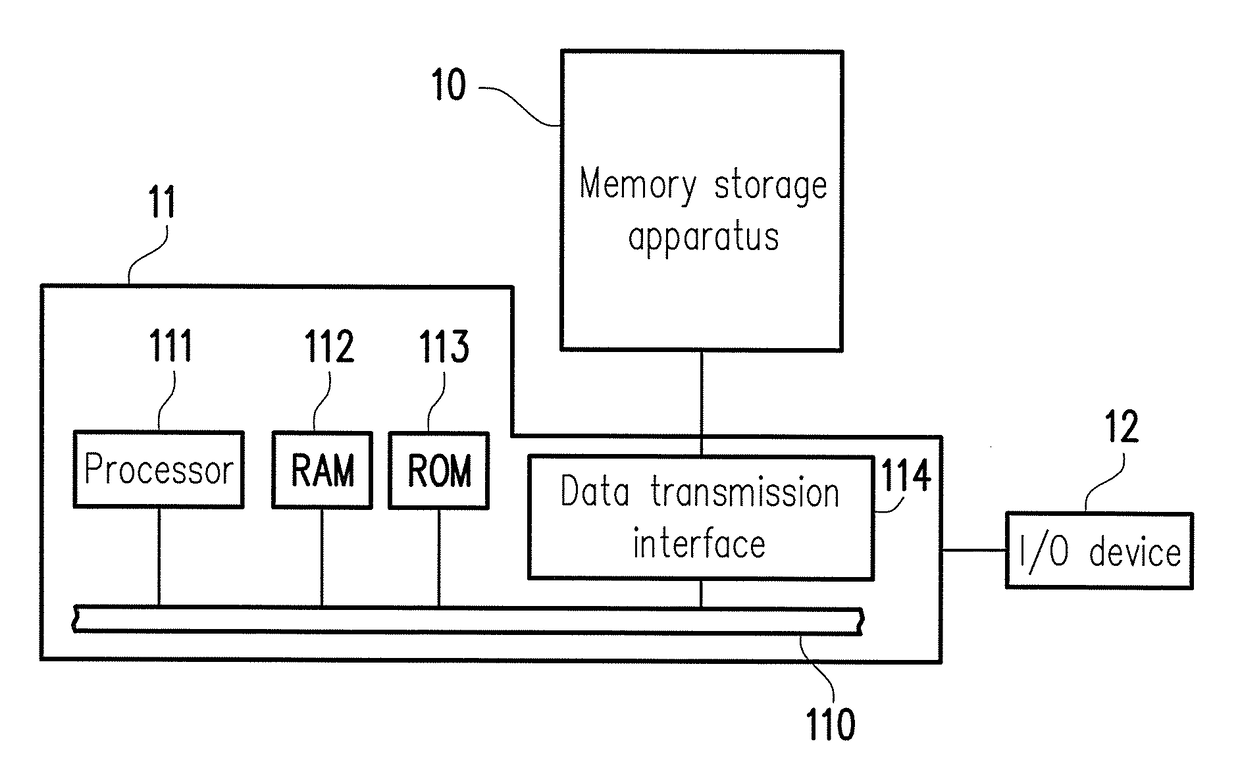

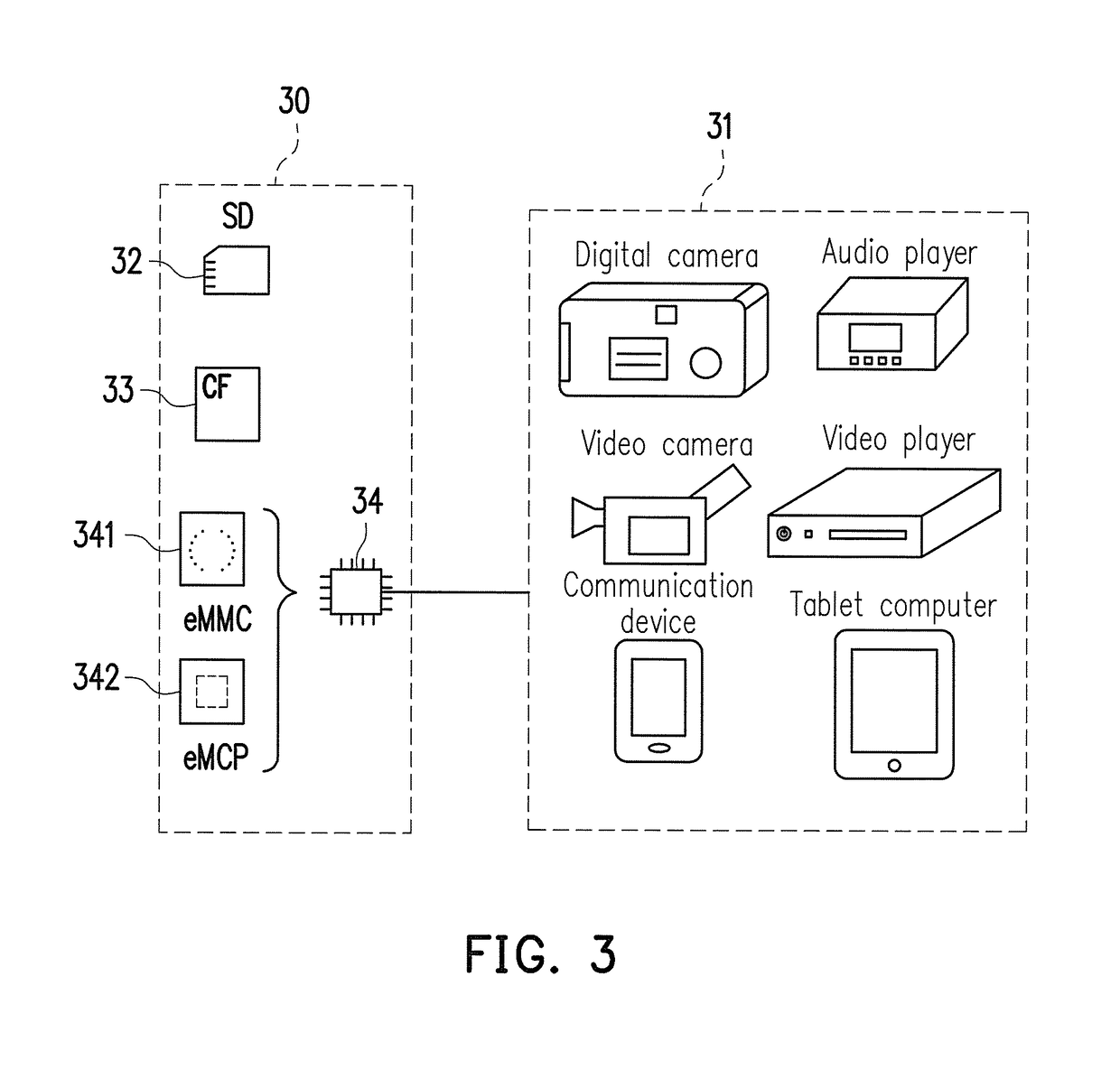

Mapping table loading method, memory control circuit unit and memory storage apparatus

ActiveUS20170315925A1Easy to useImprove performanceMemory architecture accessing/allocationVirtual memory detailsComputer moduleOperation mode

A mapping table loading method, a memory control circuit unit and a memory storage apparatus are provided. The method includes: receiving a first command; loading a first sub-logical address-physical address mapping table corresponding to the first command if an operating mode of a non-volatile rewritable memory module is a first operating mode; and loading a first logical address-physical address mapping table corresponding to the first command if the operating mode of the non-volatile rewritable memory module is a second operating mode, wherein the first logical address-physical address mapping table includes the first sub-logical address-physical address mapping table.

Owner:PHISON ELECTRONICS

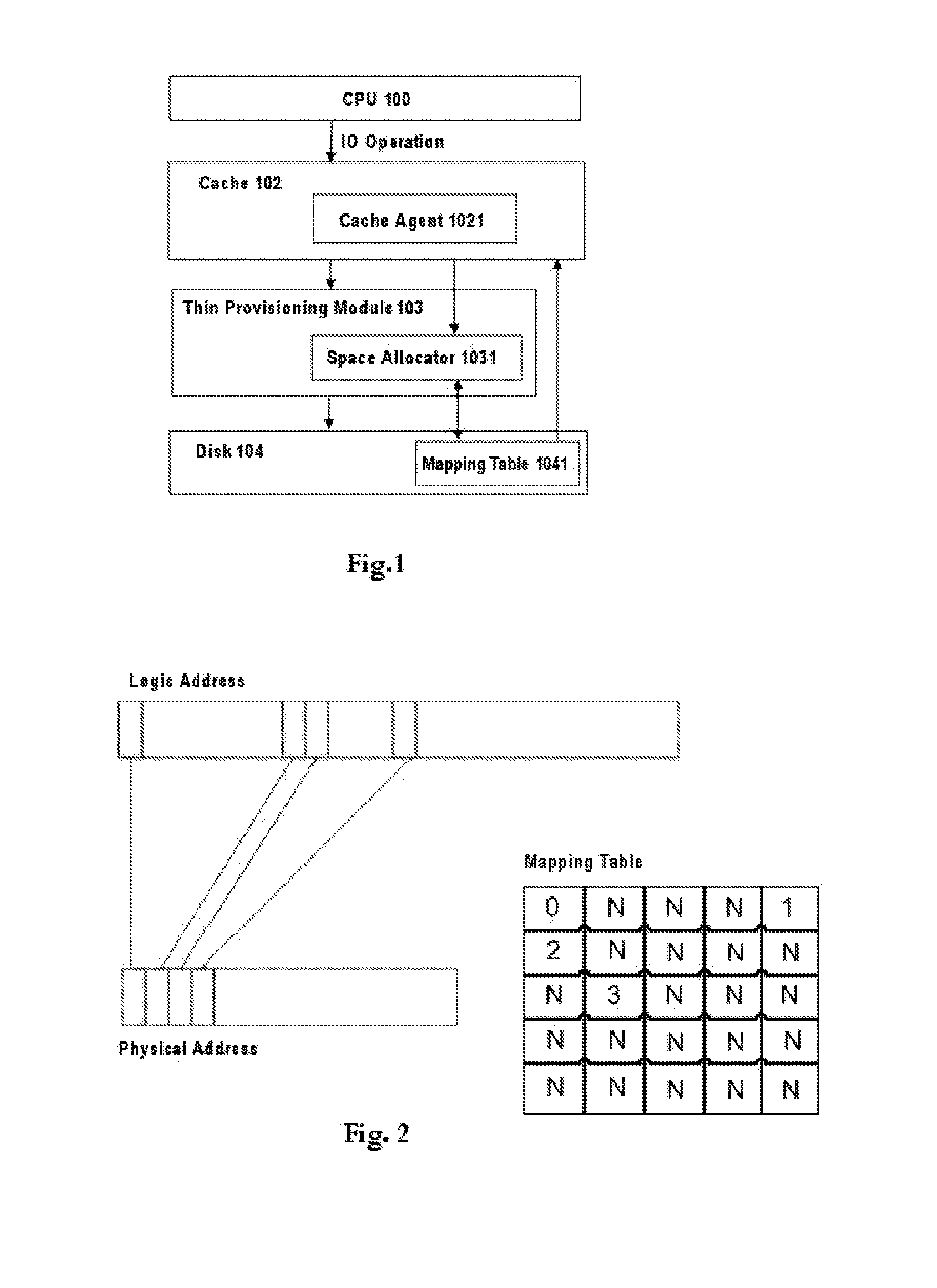

Retrieving data in a storage system using thin provisioning

InactiveUS20120221828A1Reduce IO access timeImprove IO access efficiencyMemory architecture accessing/allocationDigital data information retrievalThin provisioningDatabase

The invention relates to retrieving data from a storage system. One embodiment of the invention comprises receiving a write operation, establishing a correspondence relationship between a logic block address and a physical block address of the write operation, and determining whether a valid data percentage in a mapping table is greater than a predetermined threshold after the correspondence relationship is added in stored metadata. In response to the valid data percentage being less than the predetermined threshold, the embodiment adds the correspondence relationship to a B-tree data structure of stored metadata.

Owner:IBM CORP

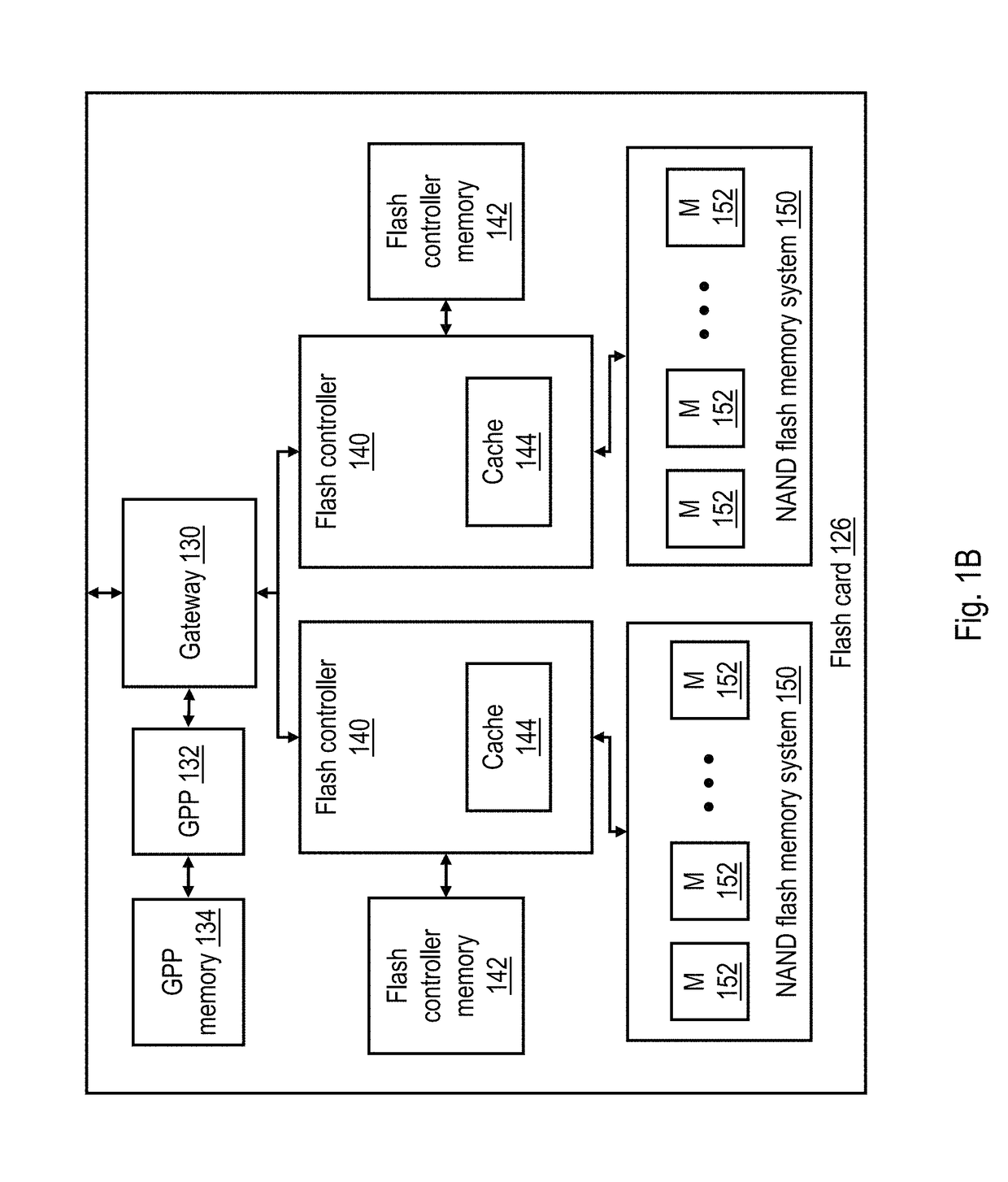

Mitigating read errors following programming in a multi-level non-volatile memory

ActiveUS10101931B1Increase the number ofReduce errorsMemory architecture accessing/allocationInput/output to record carriersOperating systemVoltage

Read errors following programming in a multi-level non-volatile memory are mitigated by a controller of the non-volatile memory. The controller temporarily buffers, in a cache, pages of data programmed into the non-volatile memory. In response to receiving a read request for a target page of data programmed into the non-volatile memory, where the read request is received during a delay time affecting the target page, the controller services the read request by accessing data of the target page in the cache in response to the read request hitting in the cache. The controller instead services the read request from the non-volatile memory in response to the read request missing in the cache. When servicing the read request from the non-volatile memory, the controller preferably reads the target page from the non-volatile memory utilizing a set of read voltage thresholds determined based on the read-after-write delay.

Owner:IBM CORP

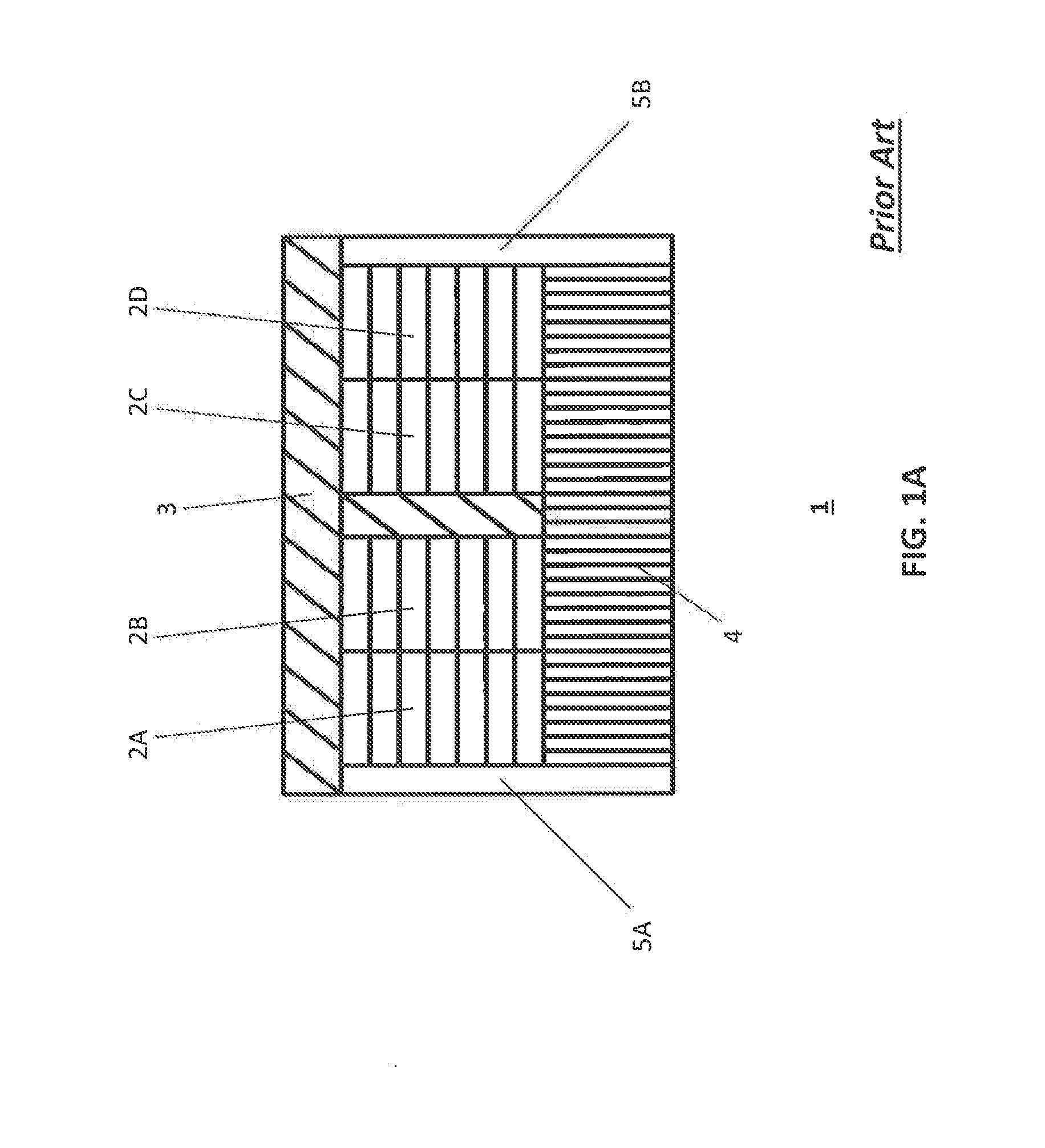

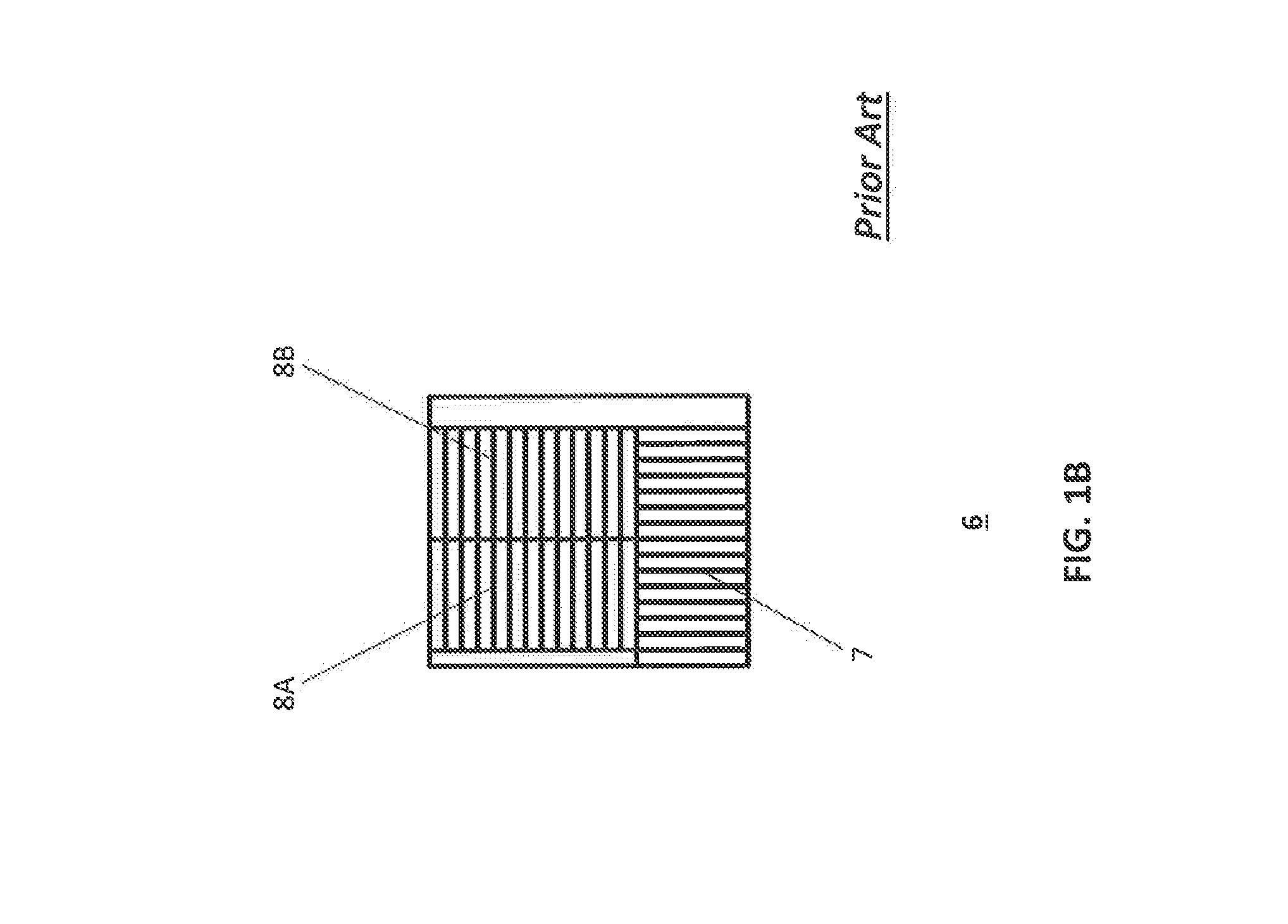

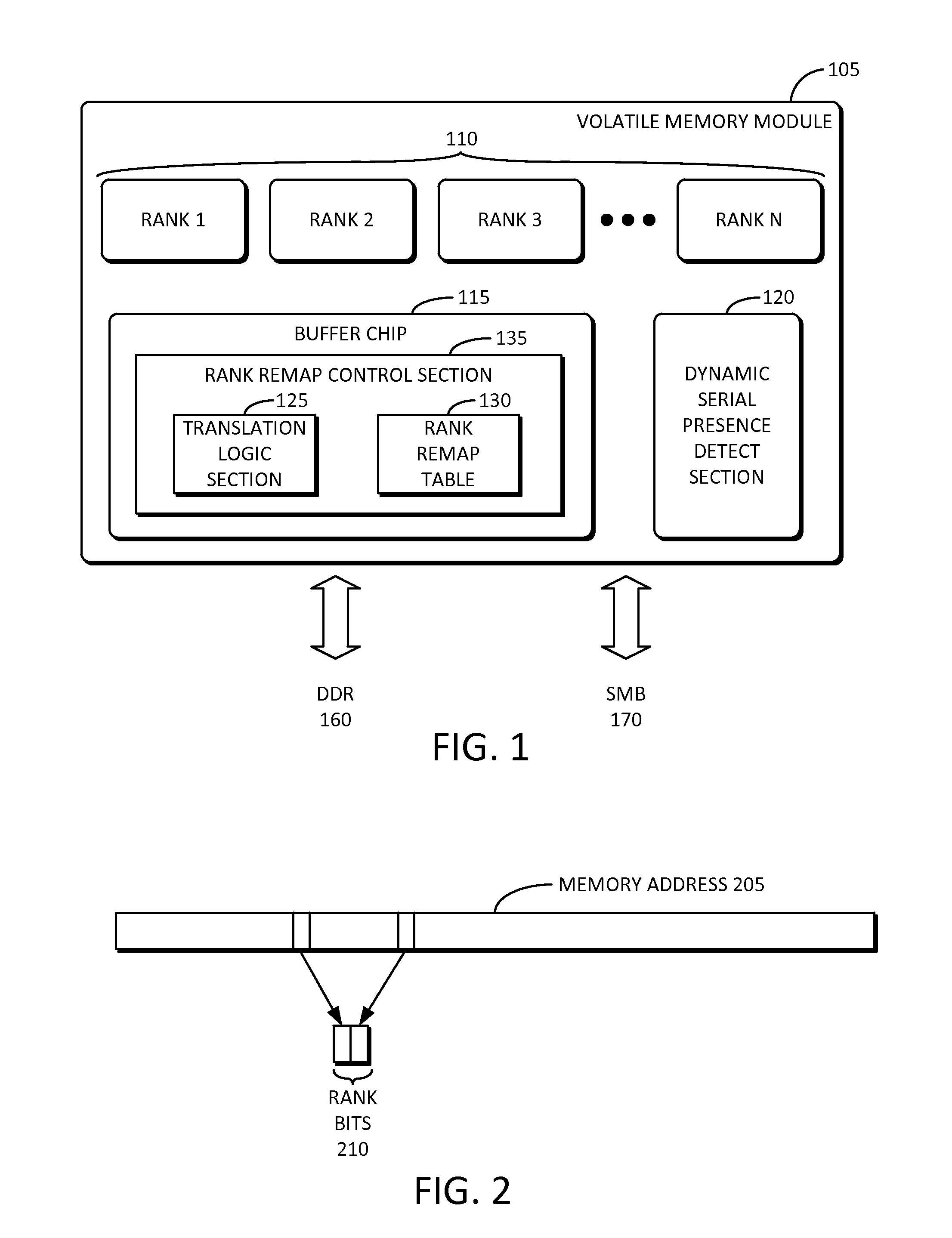

Rank and page remapping logic in a volatile memory

ActiveUS20160147623A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSerial presence detectMemory rank

Embodiments of the inventive concept include a plurality of memory ranks, a buffer chip including a rank remap control section configured to remap a rank from among the plurality of memory ranks of the volatile memory module responsive to a failure of the rank, and a dynamic serial presence detect section configured to dynamically update a stated total capacity of the volatile memory module based at least on the remapped rank. In some embodiments, a memory module includes a plurality of memory ranks, an extra rank in addition to the plurality of memory ranks, the extra rank being a spare rank configured to store a new page corresponding to a failed page from among the plurality of ranks, and a buffer chip including a page remap control section configured to remap the failed page from among the plurality of ranks to the new page in the extra rank.

Owner:SAMSUNG ELECTRONICS CO LTD

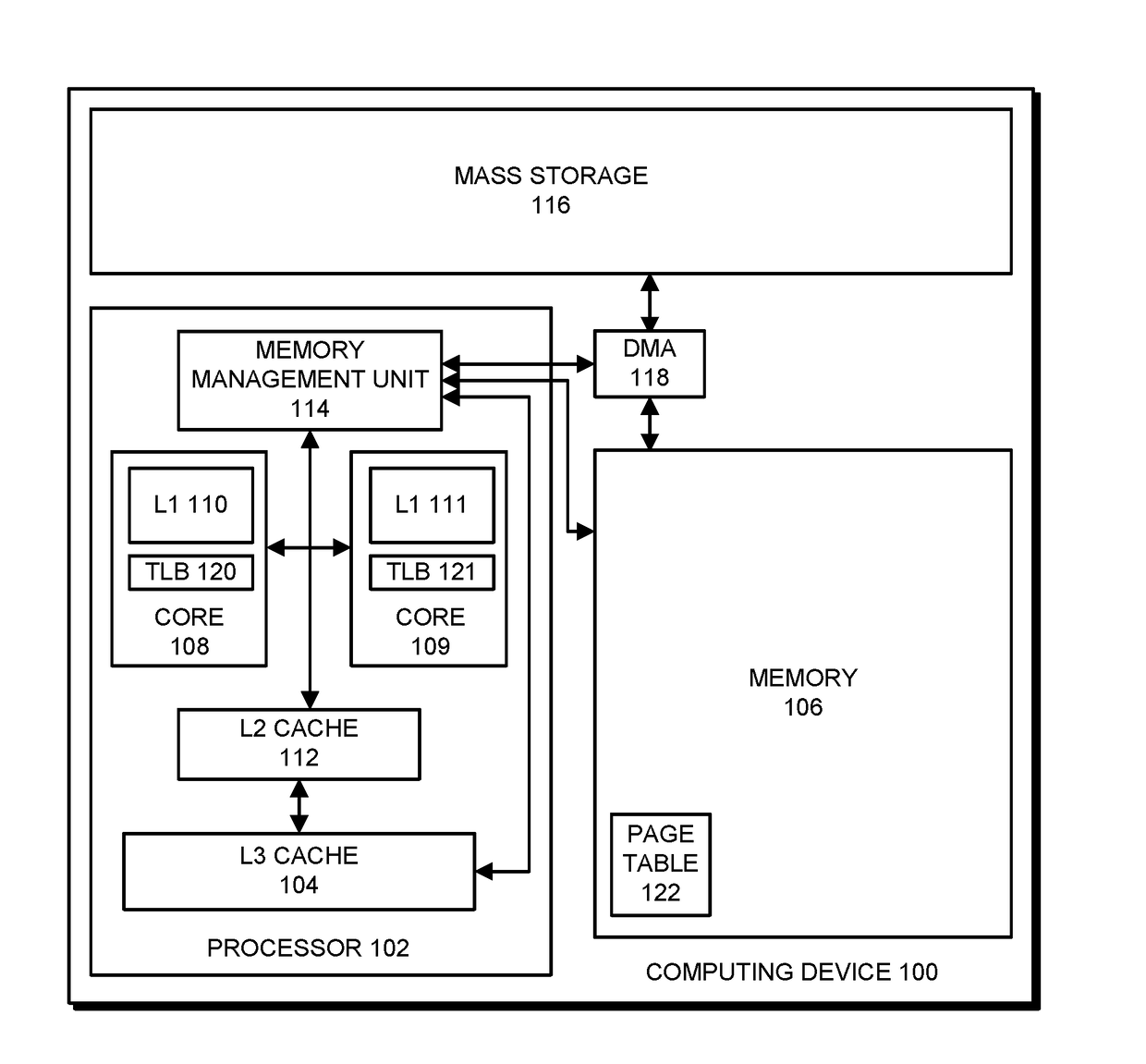

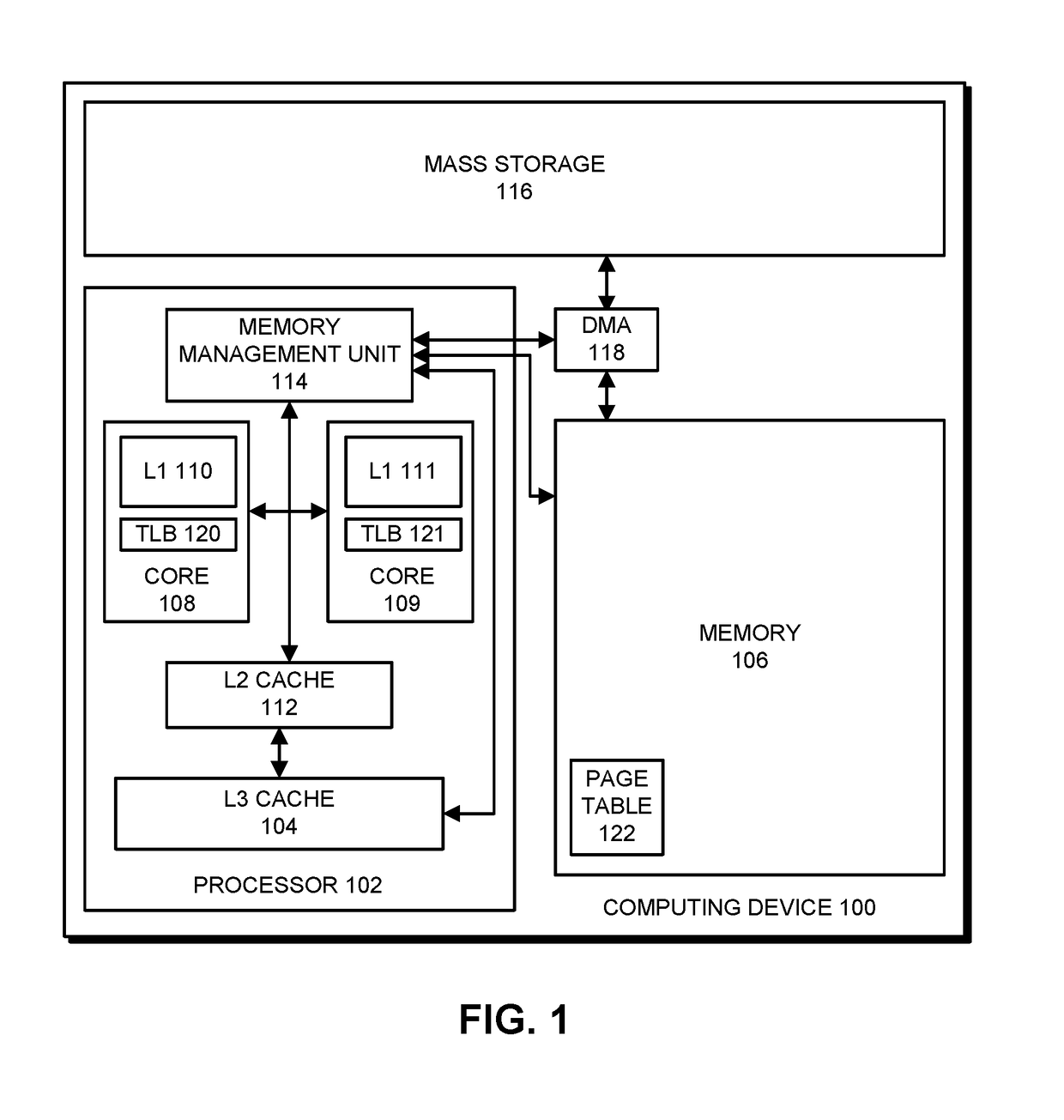

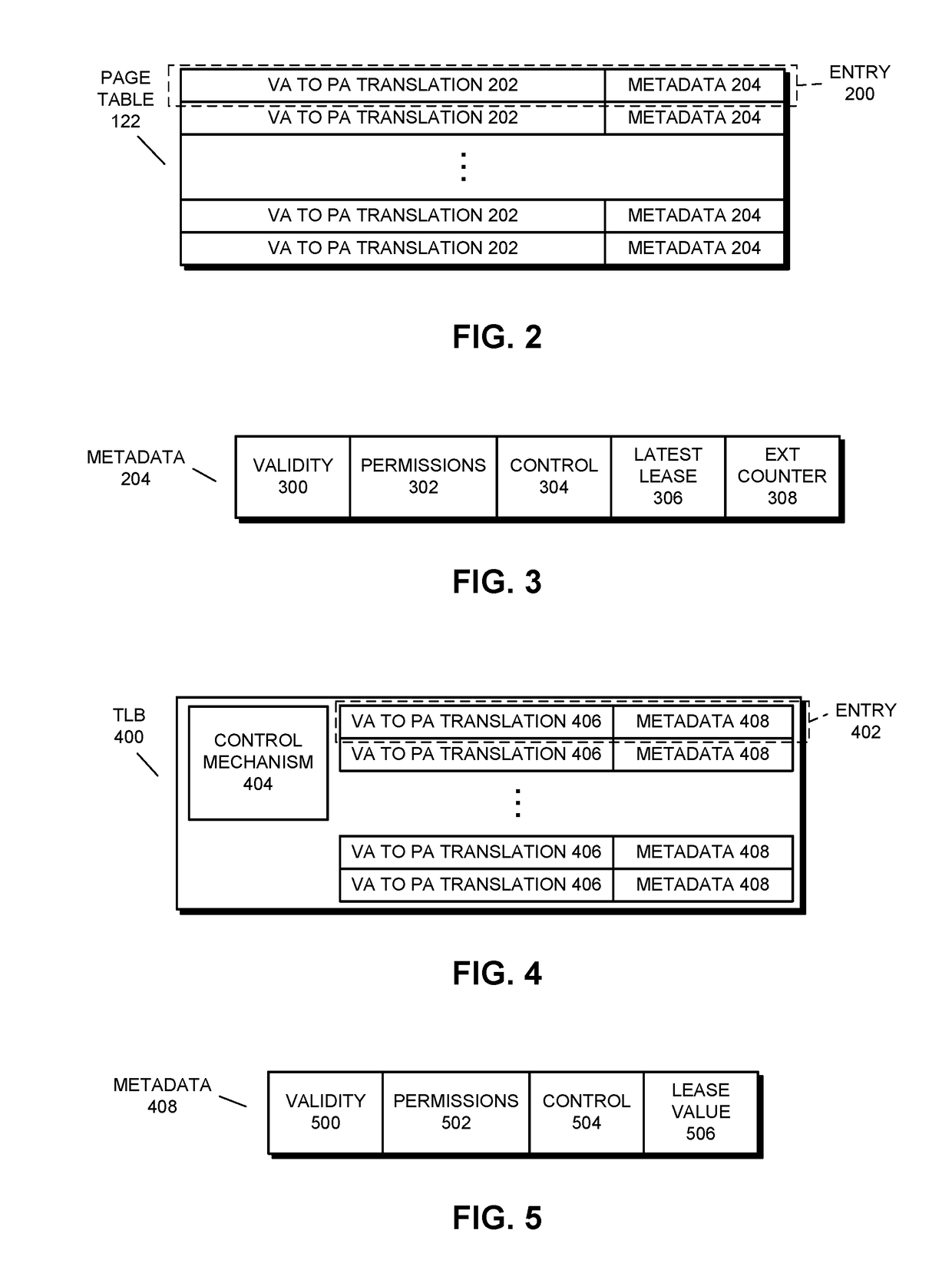

Adaptive Extension of Leases for Entries in a Translation Lookaside Buffer

ActiveUS20170277639A1Memory architecture accessing/allocationVirtual memory detailsPage tableTranslation lookaside buffer

The described embodiments include a computing device with two or more translation lookaside buffers (TLB). During operation, the computing device updates an entry in the TLB based on a virtual address to physical address translation and metadata from a page table entry that were acquired during a page table walk. The computing device then computes, based on a lease length expression, a lease length for the entry in the TLB. Next, the computing device sets, for the entry in the TLB, a lease value to the lease length, wherein the lease value represents a time until a lease for the entry in the TLB expires, wherein the entry in the TLB is invalid when the associated lease has expired. The computing device then uses the lease value to control operations that are allowed to be performed using information from the entry in the TLB.

Owner:ADVANCED MICRO DEVICES INC

Computer Processor Employing Cache Memory Storing Backless Cache Lines

ActiveUS20150106545A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingHandling system

A computer processing system with a hierarchical memory system having at least one cache and physical memory, and a processor having execution logic that generates memory requests that are supplied to the hierarchical memory system. The at least one cache stores a plurality of cache lines including at least one backless cache line.

Owner:MILL COMPUTING

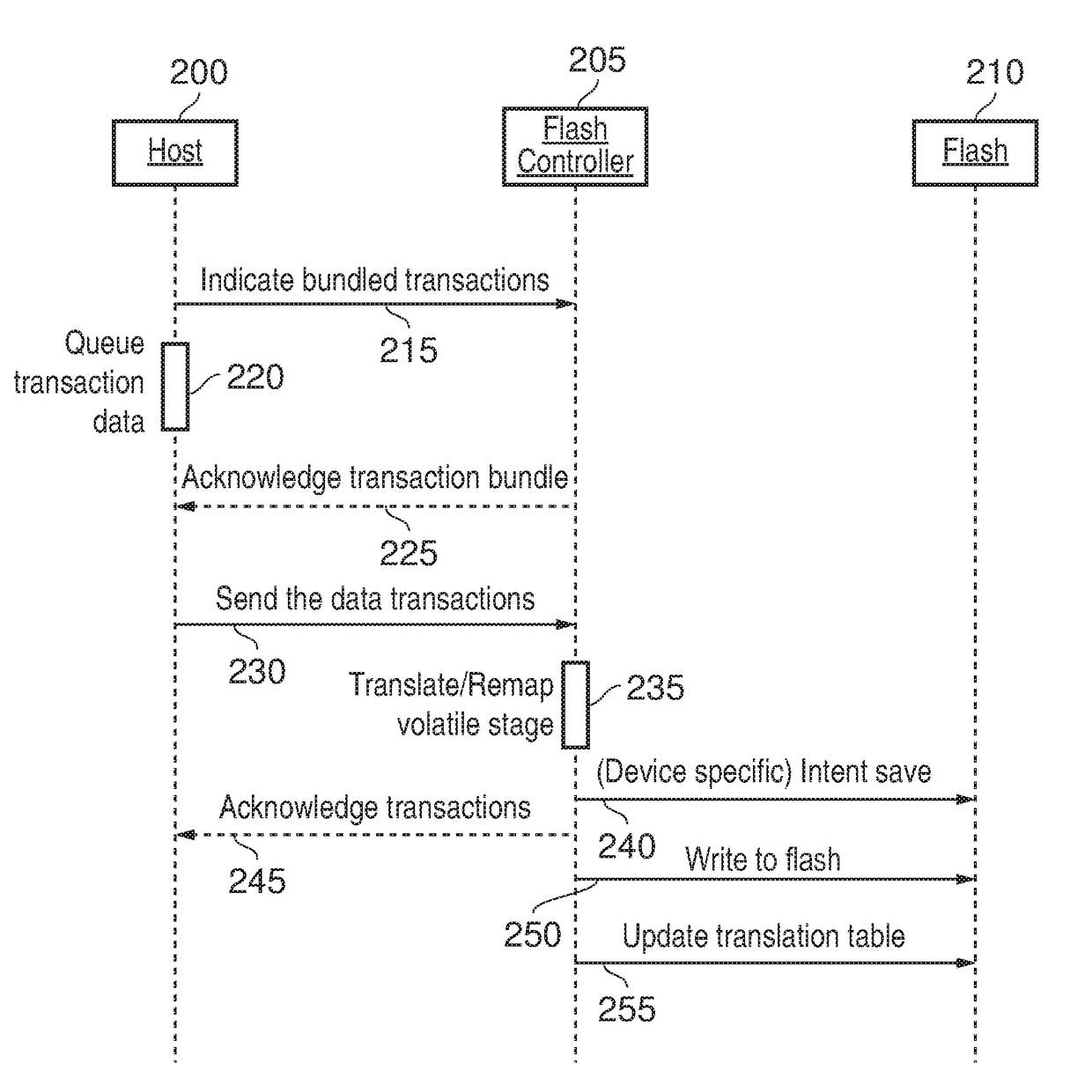

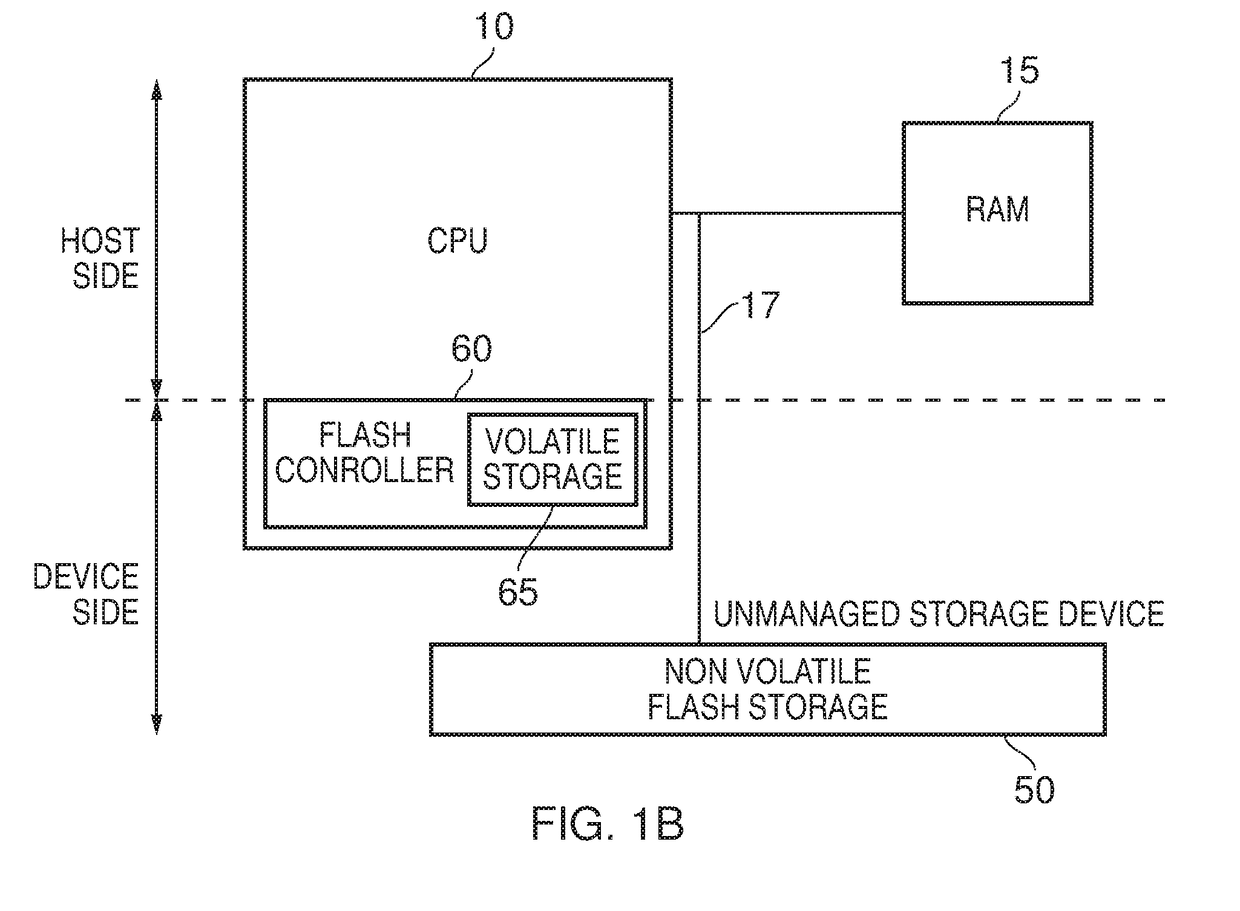

A device controller and method for performing a plurality of write transactions atomically within a nonvolatile data storage device

ActiveUS20170160933A1Avoid the needMemory architecture accessing/allocationInput/output to record carriersDisk controllerOperating system

A device controller and method are provided for performing a plurality of write transactions atomically within a non-volatile data storage device. Each transaction specifies a logical address and the method comprises creating an address translation map for the logical addresses specified by the plurality of write transactions, by referencing an address translation record within the non-volatile data storage device to determine for each logical address a corresponding physical address within the data storage device. Further, if the corresponding physical address indicated in the address translation record already contains valid data, the logical address is remapped to a new physical address in the address translation map. However, at this point the address translation record as stored in the data storage device is not updated. Instead, the plurality of write transactions are performed using the logical address to physical address mapping in the address translation map. Then, only once the plurality of write transactions have been performed is the address translation record updated in the non-volatile data storage device in order to identify the logical address to physical address mapping in the address translation map. Since, at the time of performing the write transactions, any new data that updates data already stored in the data storage device is written into a different physical address location, and hence the previous version of the data is still stored on the data storage device, and given that the address translation record is not updated unless the plurality of write transactions are actually performed atomically, then this enables the state held on the data storage device to be rolled back to the state that existed prior to performing the plurality of write transactions, if any event prevents that plurality of write transactions being performed atomically.

Owner:ARM LTD

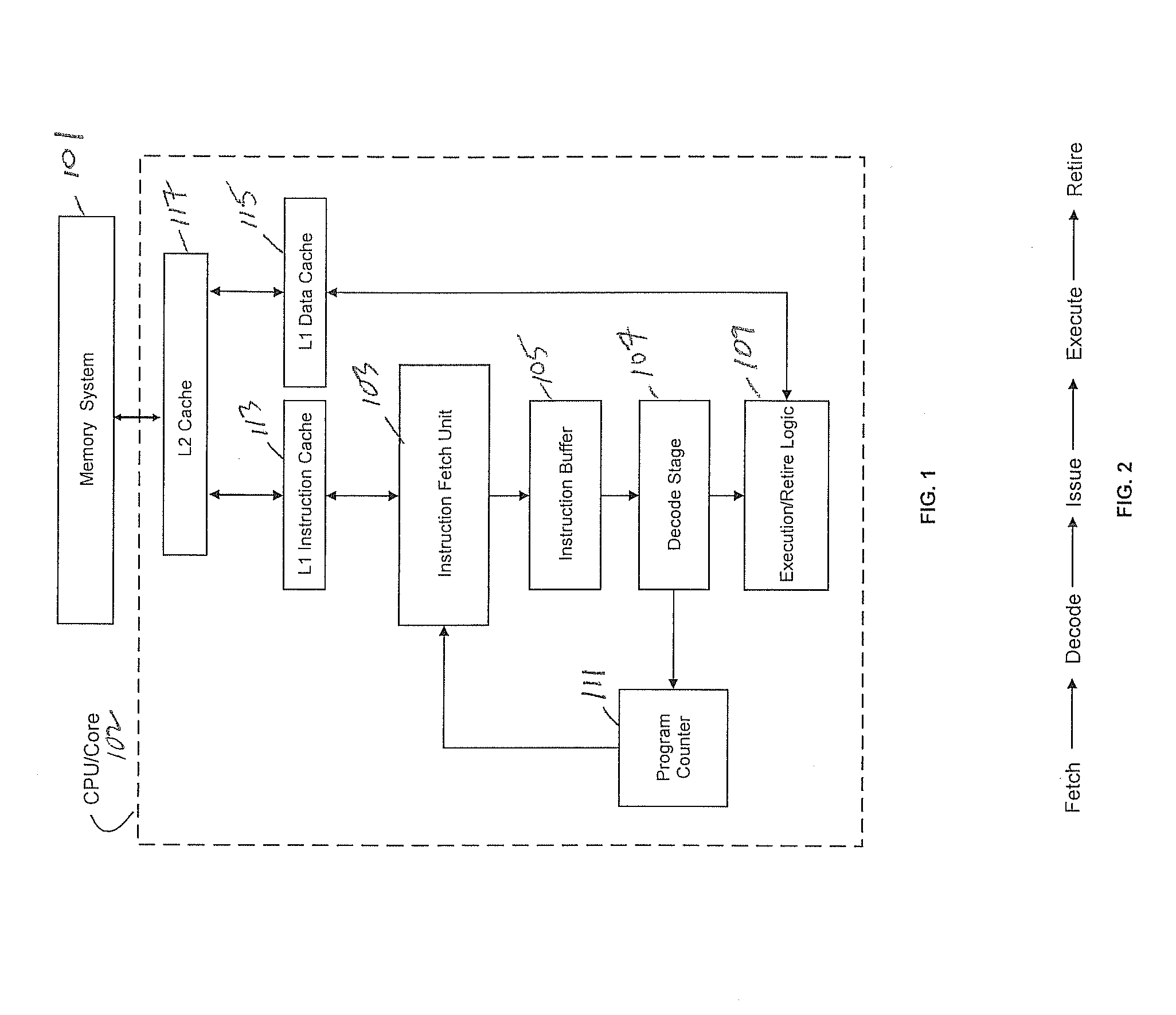

Linear to physical address translation with support for page attributes

ActiveUS20080301398A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressPhysical address

Embodiments of the invention are generally directed to systems, methods, and apparatuses for linear to physical address translation with support for page attributes. In some embodiments, a system receives an instruction to translate a memory pointer to a physical memory address for a memory location. The system may return the physical memory address and one or more page attributes. Other embodiments are described and claimed.

Owner:UNM RAINFOREST INNOVATIONS

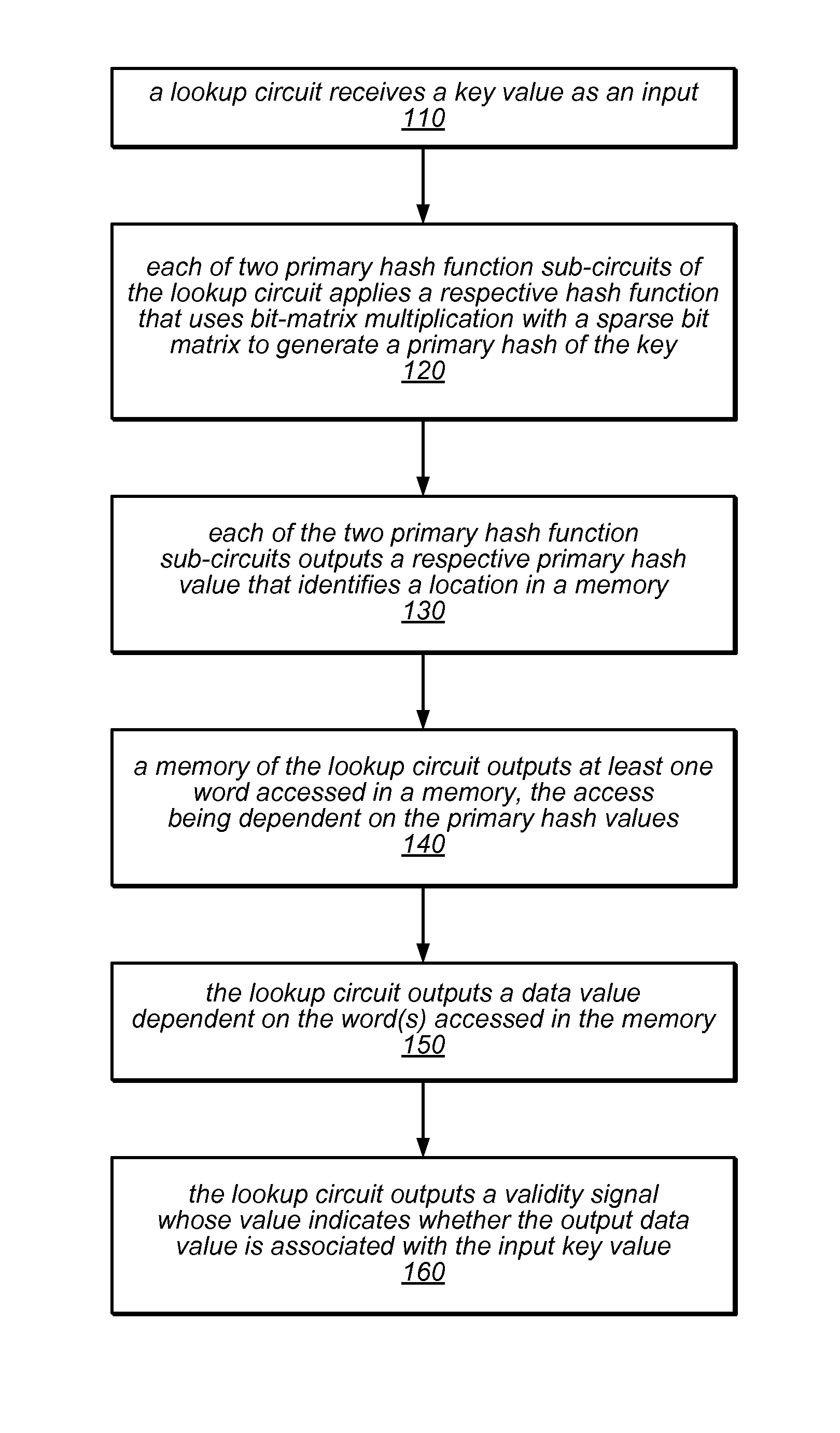

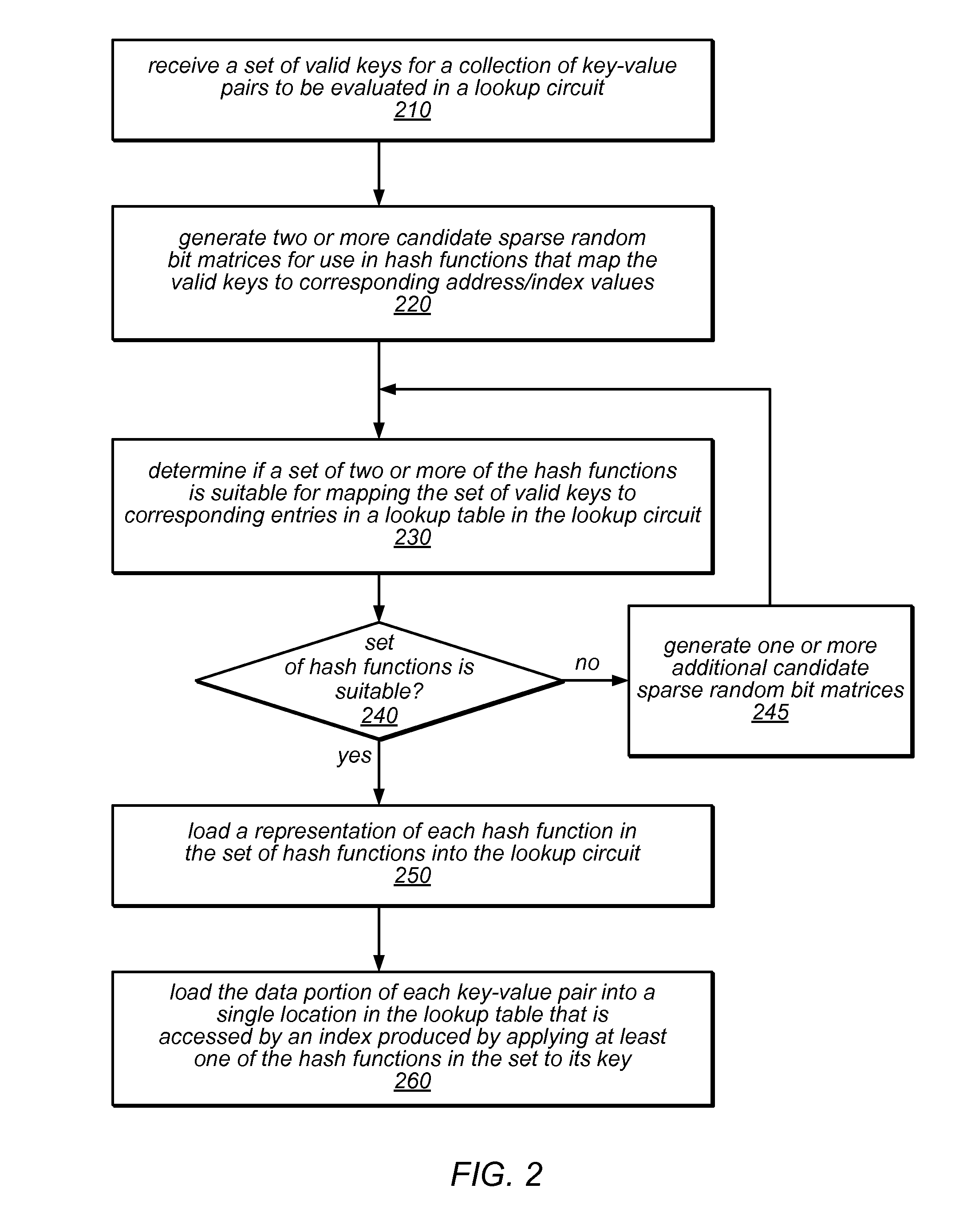

Systems and Methods for Implementing Low-Latency Lookup Circuits Using Sparse Hash Functions

ActiveUS20150121035A1Lower latencyMemory architecture accessing/allocationMemory adressing/allocation/relocationHash functionLatency (engineering)

A lookup circuit evaluates hash functions that map keys to addresses in lookup tables. The circuit may include multiple hash function sub-circuits, each of which applies a respective hash function to an input key value, producing a hash value. Each hash function sub-circuit may multiply bit vectors representing key values by a sparse bit matrix and may add a constant bit vector to the results. The hash function sub-circuits may be constructed using odd-parity circuits that accept as inputs subsets of the bits of the bit vectors representing the key values. The sparse bit matrices may be chosen or generated so that there are at least twice as many 0-bits per row as 1-bits or there is an upper bound on the number of 1-bits per row. Using sparse bit matrices in the hash function sub-circuits may allow the lookup circuit to perform lookup operations with very low latency.

Owner:ORACLE INT CORP

Managing de-duplication using estimated benefits

InactiveUS20160034201A1Memory architecture accessing/allocationInput/output to record carriersData setData deduplication

A protocol is employed to estimate duplication of data in a storage system. This estimate is employed as a factor of enabling de-duplication, and if de-duplication is enabled, the data sets which will be subject to the de-duplication. The protocol includes a measurement procedure and an execution procedure. The measurement procedure characterizes data duplication in part of the data on the storage system, and the execution procedure use the characterization to adjust selection of which data sets are subject to de-duplication.

Owner:IBM CORP

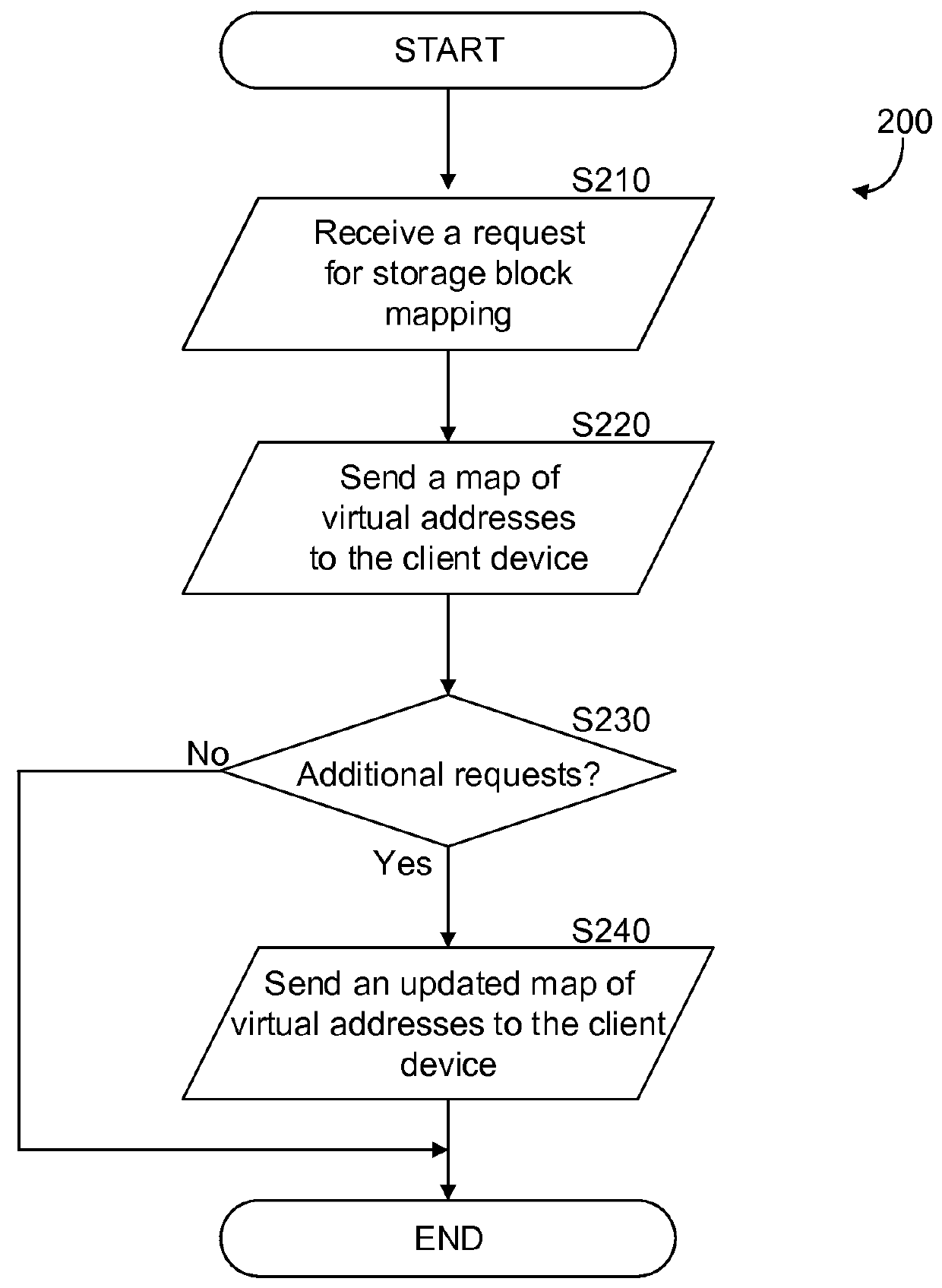

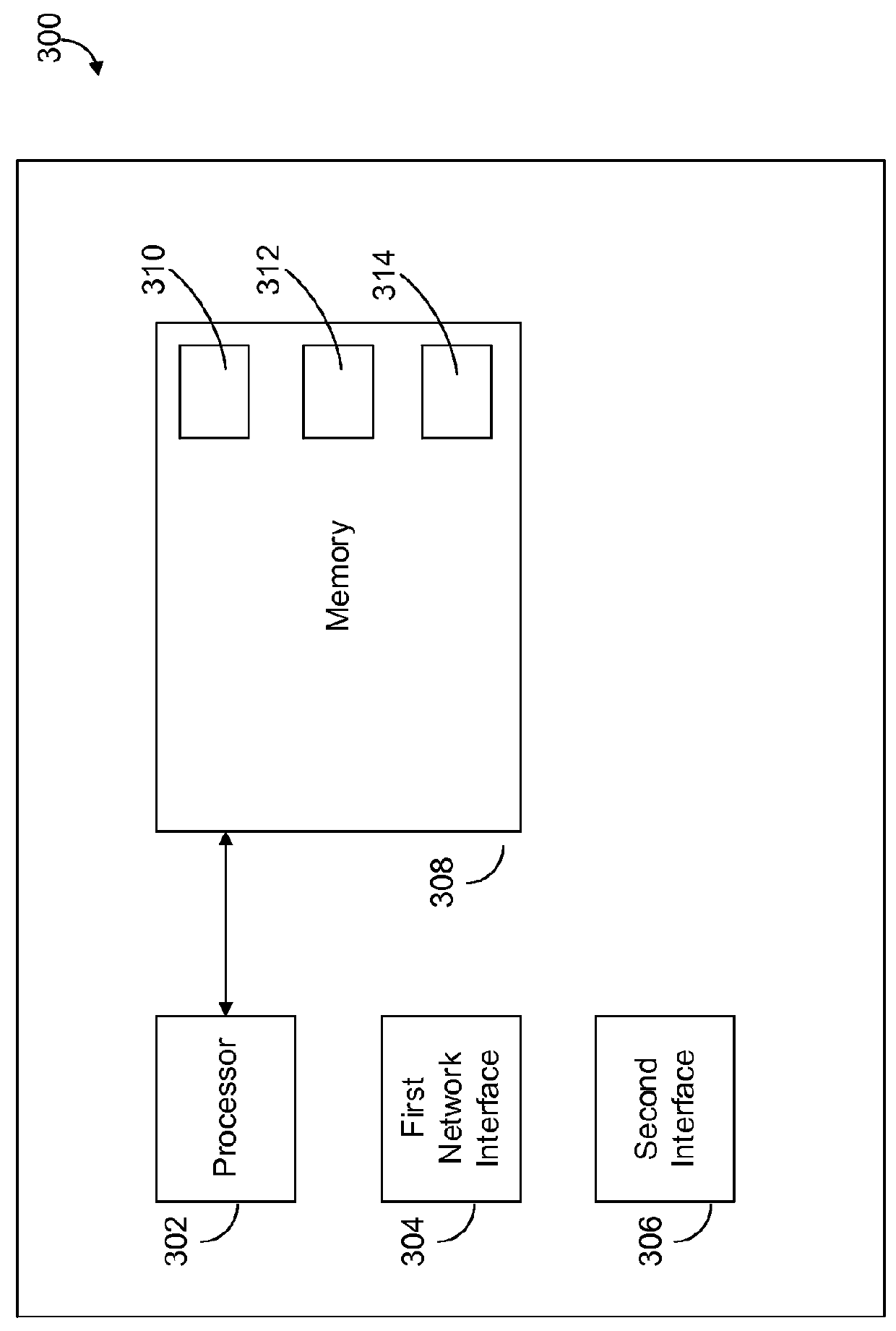

Method for providing a client device access to a plurality of remote storage devices

ActiveUS20160036913A1Input/output to record carriersMemory adressing/allocation/relocationClient-sideVirtual address space

A controller system allows direct access to a client device accessing remote data storage devices communicatively connected to the controller. A virtual block metadata (VBM) is generated by the controller system, the VBM including a plurality of maps. Each map includes a plurality of virtual addresses, each virtual address mapped to a physical address, each physical address on a remote storage device of the plurality of storage devices. The client device is sent a portion of the VBM, the portion including the map of the virtual addresses sent to the client. The controller receives, over a first network interface, read / write instructions from the client device for the a physical address corresponding to the virtual address allocated to the client device.

Owner:NVIDIA CORP

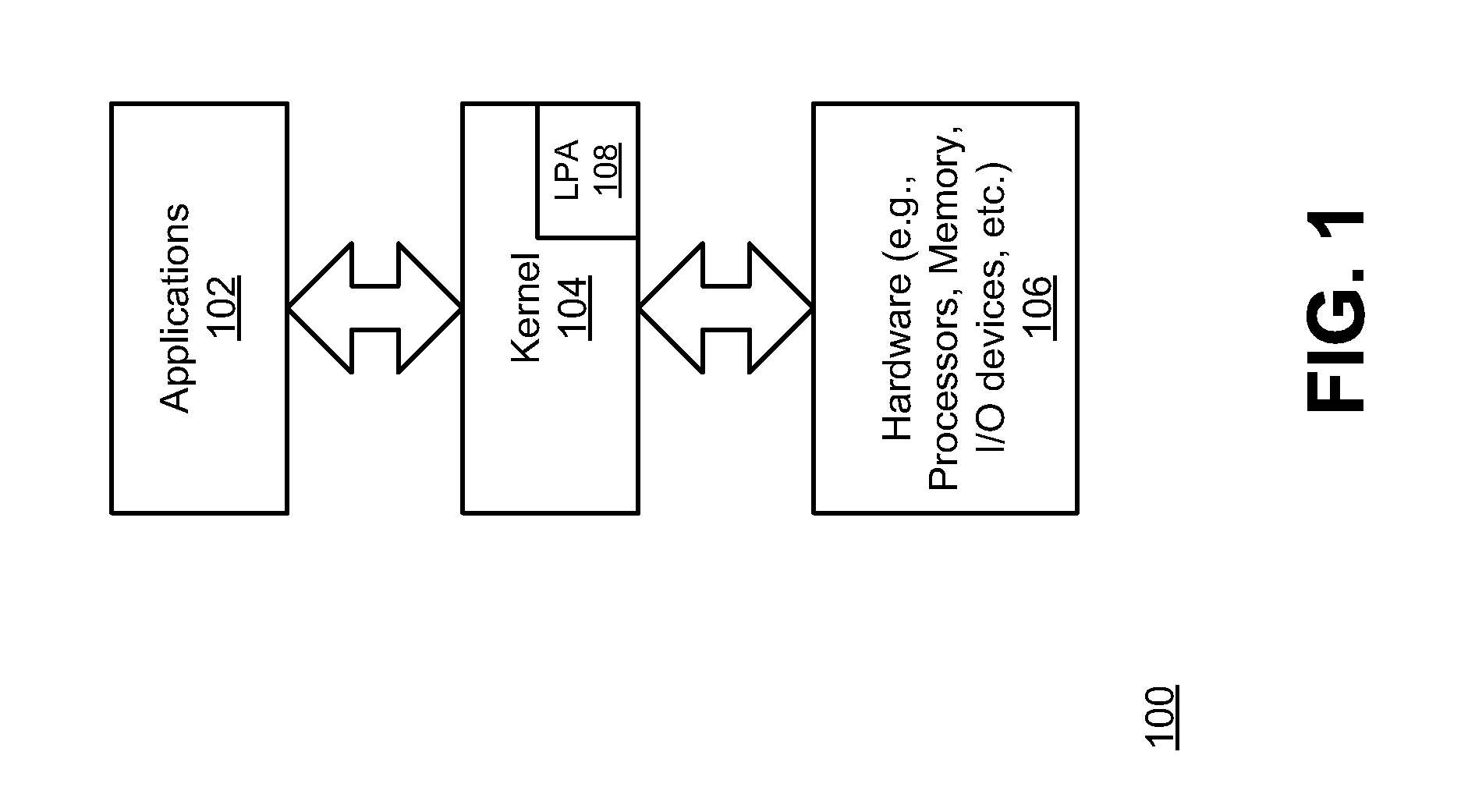

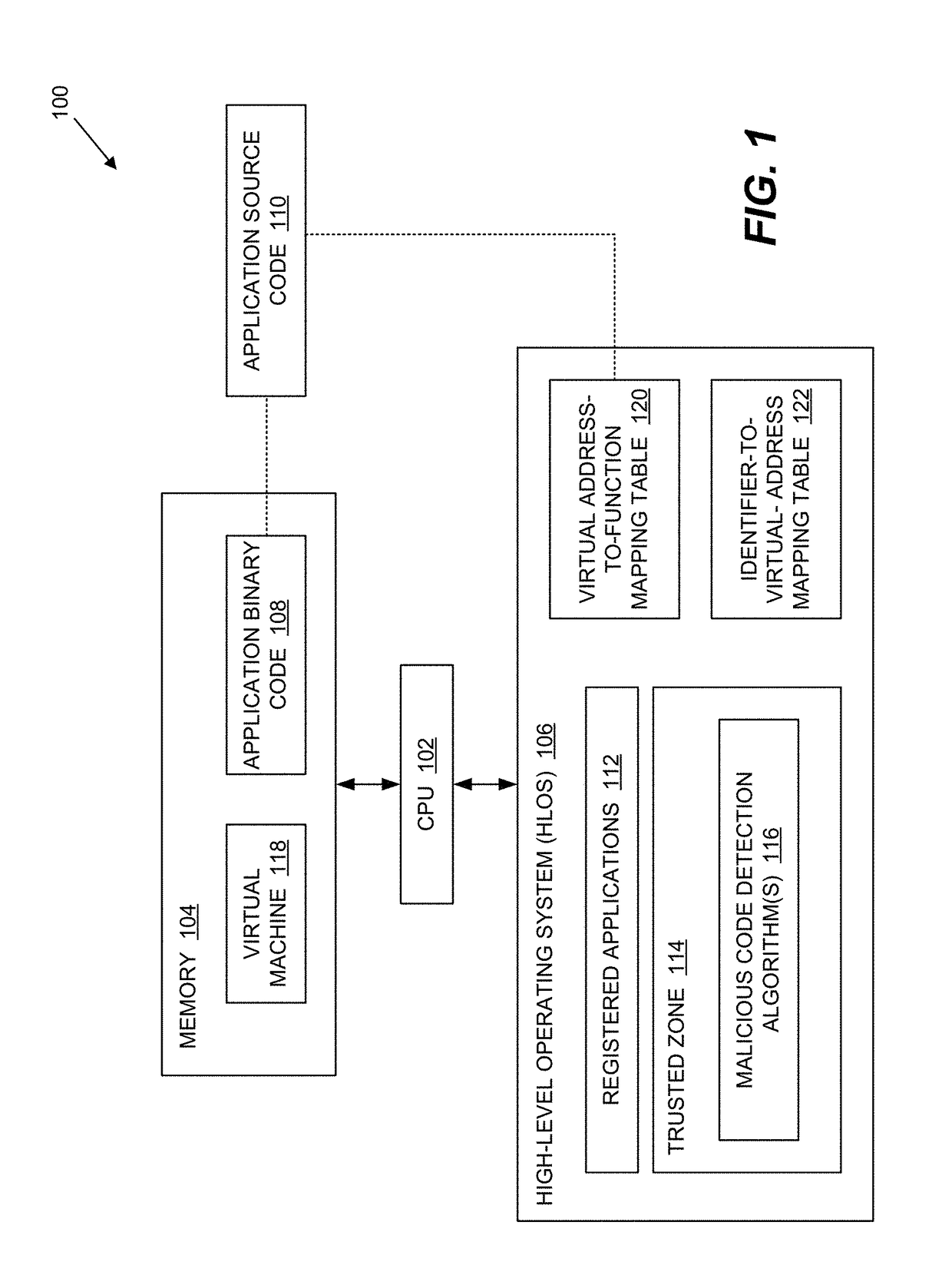

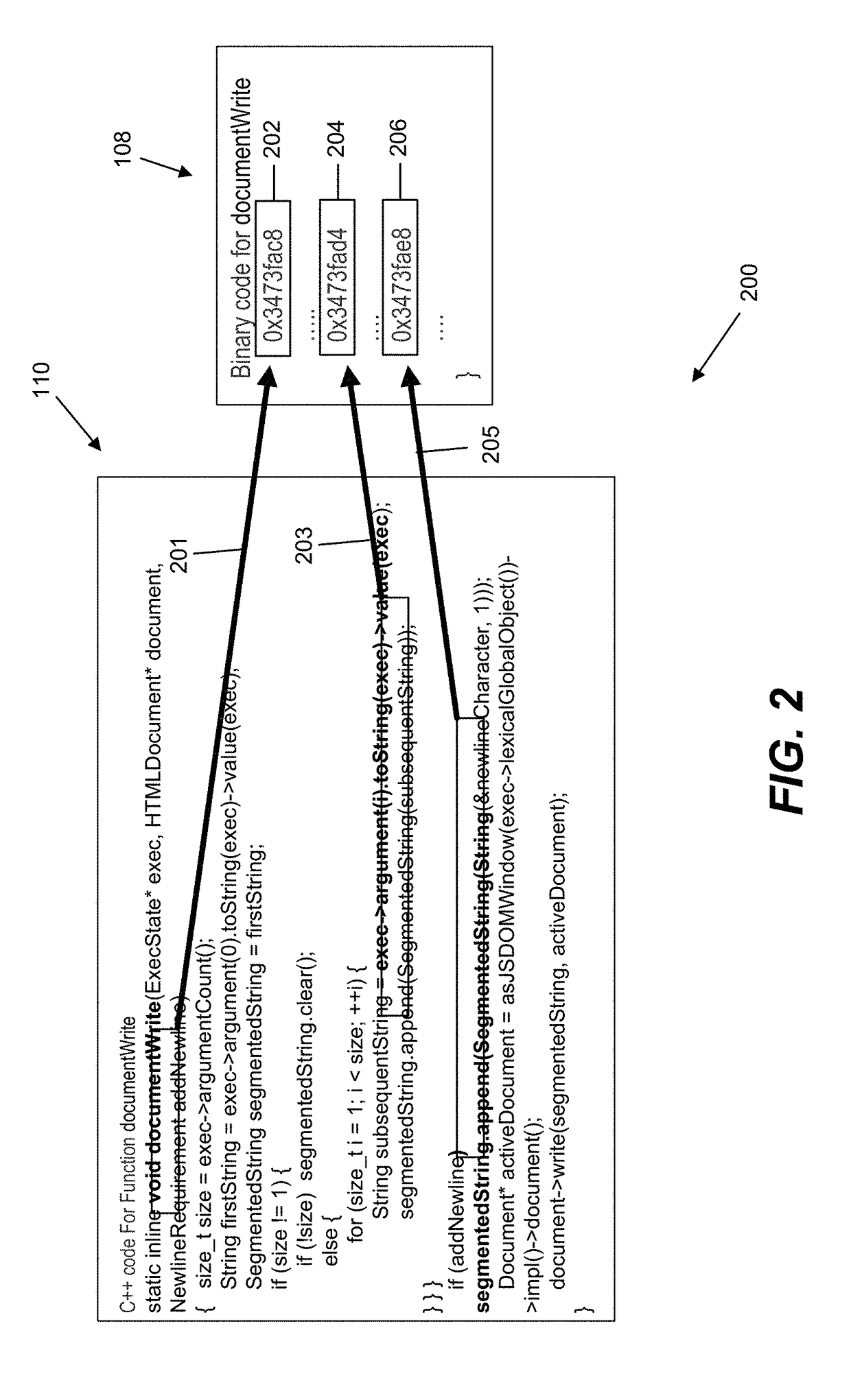

Kernel-based detection of target application functionality using virtual address mapping

ActiveUS20180032731A1Memory architecture accessing/allocationError detection/correctionOperational systemApplication software

Systems, methods, and computer programs are disclosed for detecting high-level functionality of an application executing on a computing device. One method comprises storing, in a secure memory on a computing device, a virtual address mapping table for an application. The virtual address mapping table comprises a plurality of virtual addresses in the application binary code mapped to corresponding target application functionalities. The application is registered with a high-level operating system (HLOS). During execution of the application binary code, the HLOS detects when one or more of the virtual addresses corresponding to the target application functionalities are executed based on the virtual address mapping table.

Owner:QUALCOMM INC

Data staging area

InactiveUS20130191610A1Memory architecture accessing/allocationMemory adressing/allocation/relocationCold areaReal-time computing

An illustrative embodiment of a computer-implemented process for managing a staging area creates the staging area for identified candidate cold objects, moves the identified candidate objects into the staging area, tracks application access to memory comprising the staging area and determines whether frequency of use information for a specific object exceeds a predetermined threshold. Responsive to a determination that the frequency of use information for the specific object exceeds a predetermined threshold, move the specific object into a regular area and determine whether a current time exceeds a predetermined threshold. Responsive to a determination that the current time exceeds a predetermined threshold, the computer-implemented process moves remaining objects from the staging area to a cold area.

Owner:IBM CORP

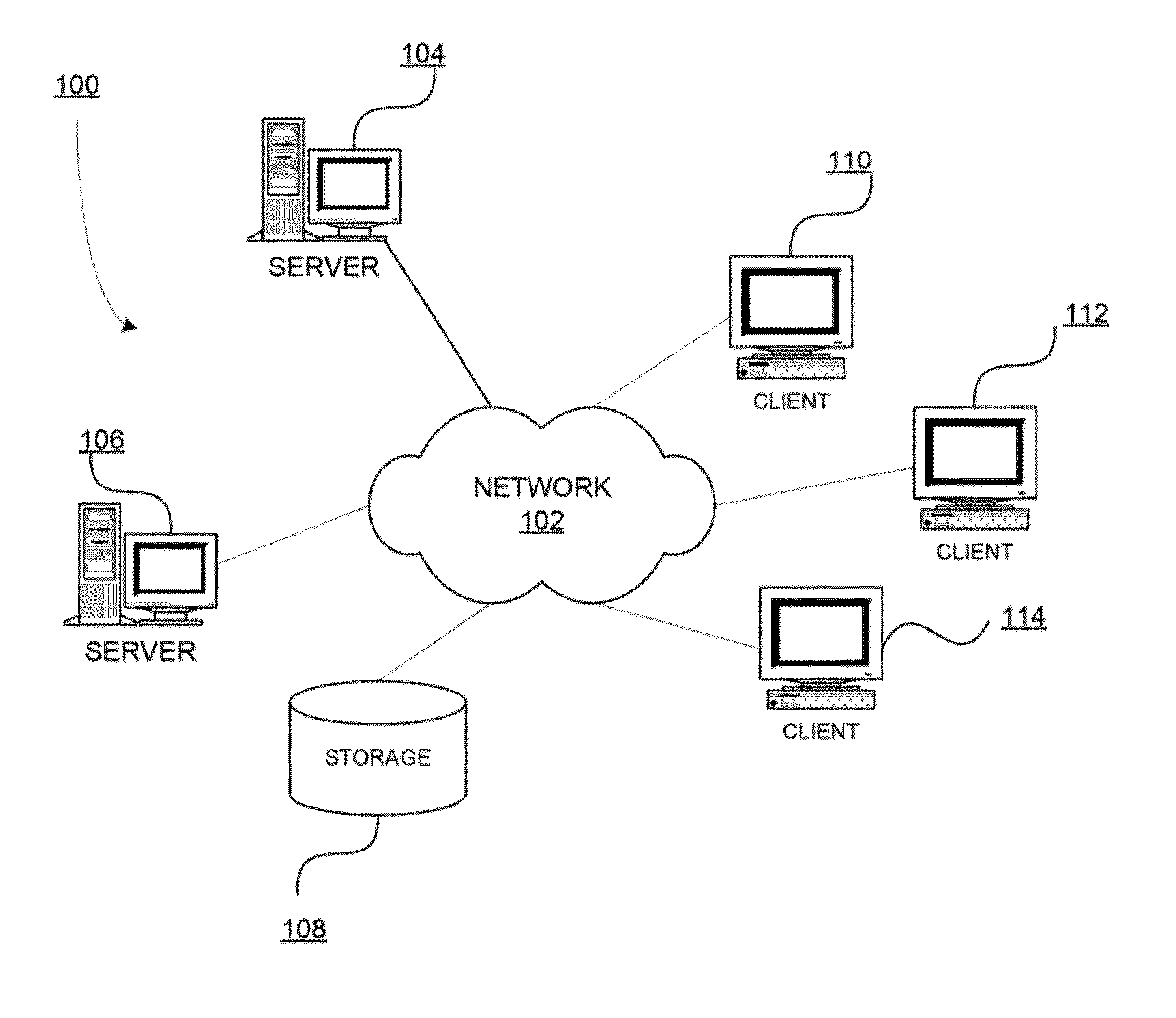

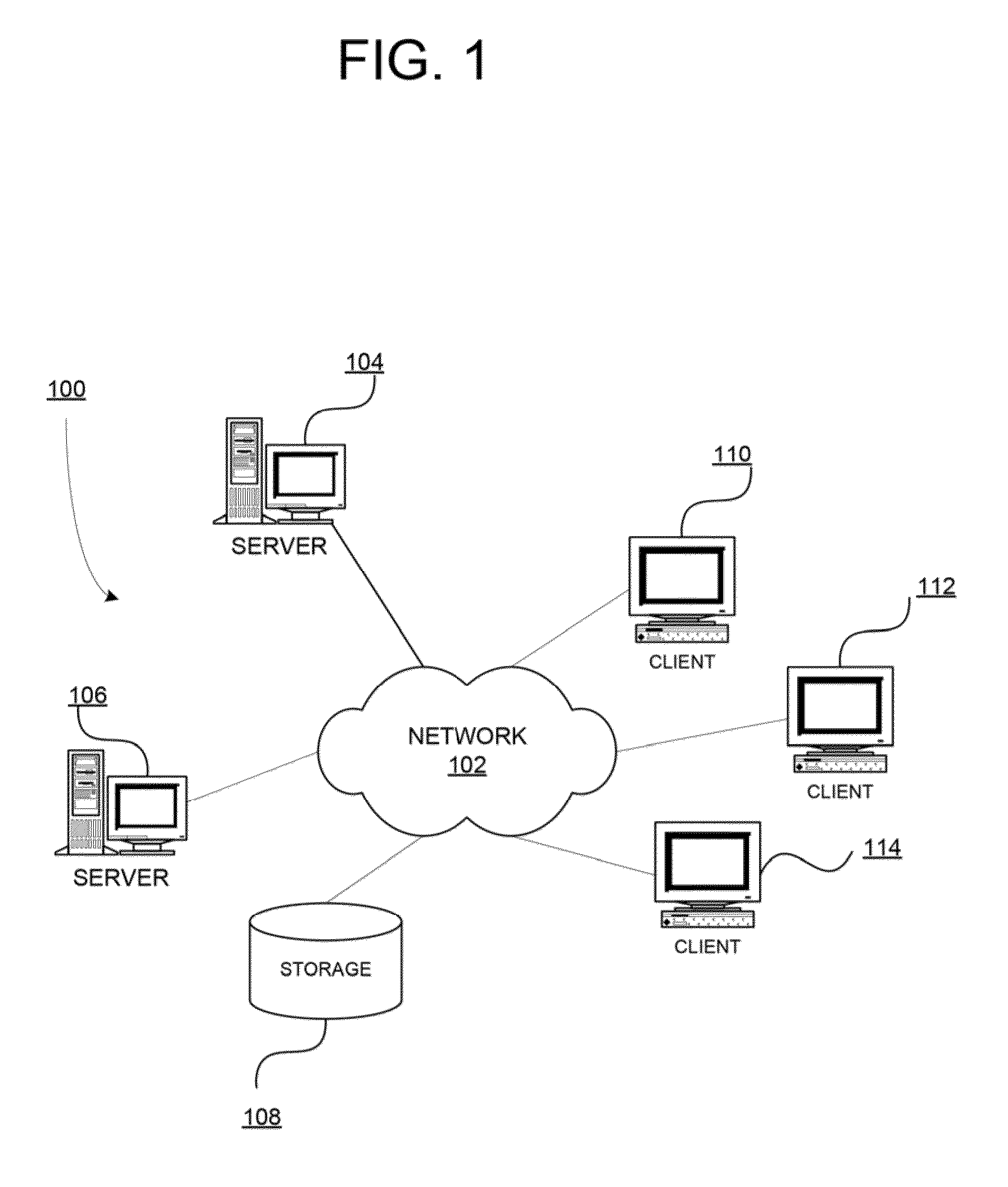

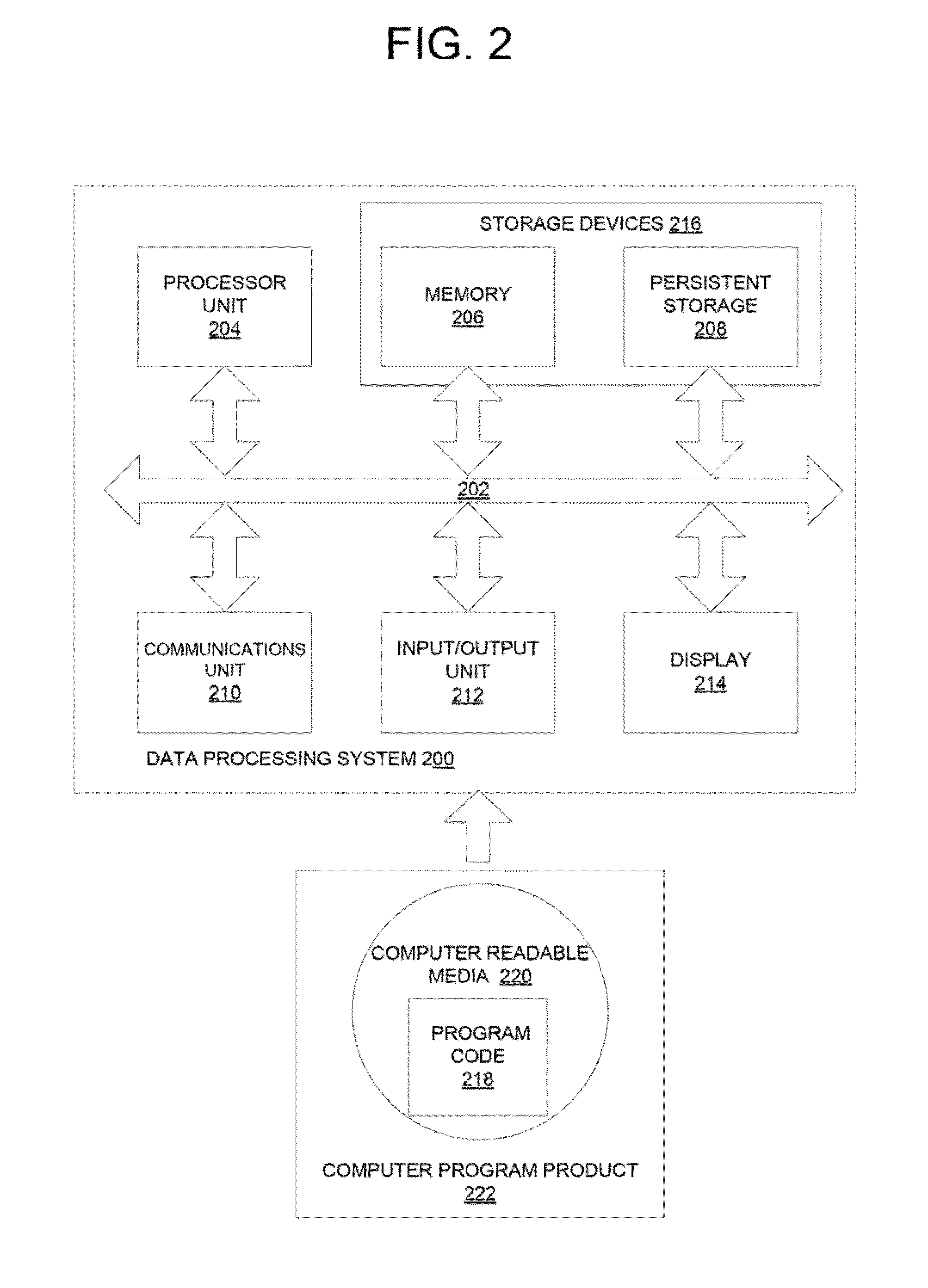

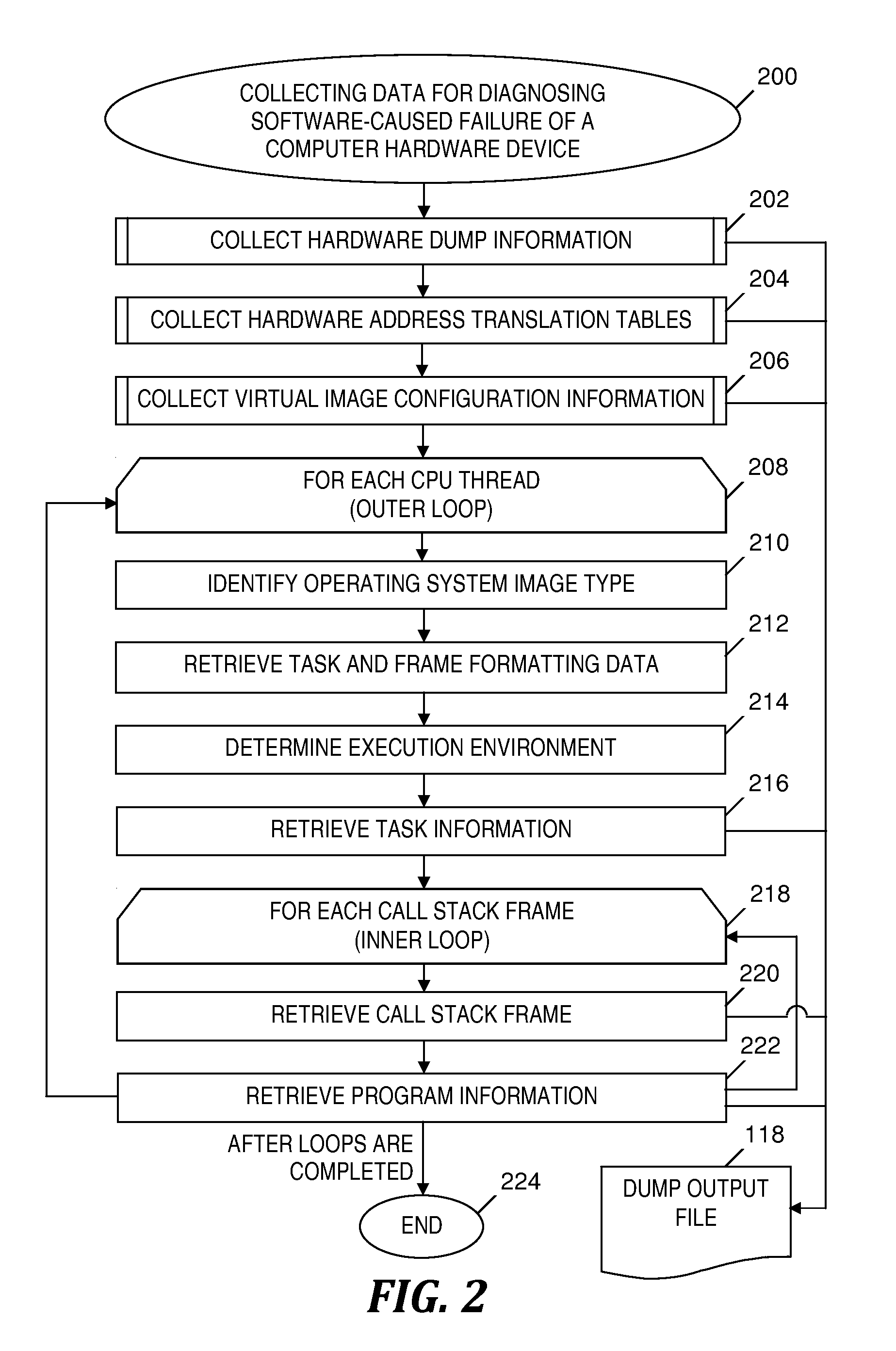

Enhanced dump data collection from hardware fail modes

InactiveUS20130061096A1Simple technologyMemory adressing/allocation/relocationHardware monitoringCall stackOperational system

A method and system for collecting data for diagnosing a failure of a computer hardware device. After an indication of the failure of the computer hardware device that results in a full system crash is received, an address translation table of a central processing unit (CPU) of the computer hardware device is collected. A format of call stack frames of an operating system (OS) image of the computer hardware device is retrieved. Based on the collected address translation table and the retrieved format of the plurality of call stack frames, the call stack frames are retrieved and output to a computer file.

Owner:KYNDRYL INC

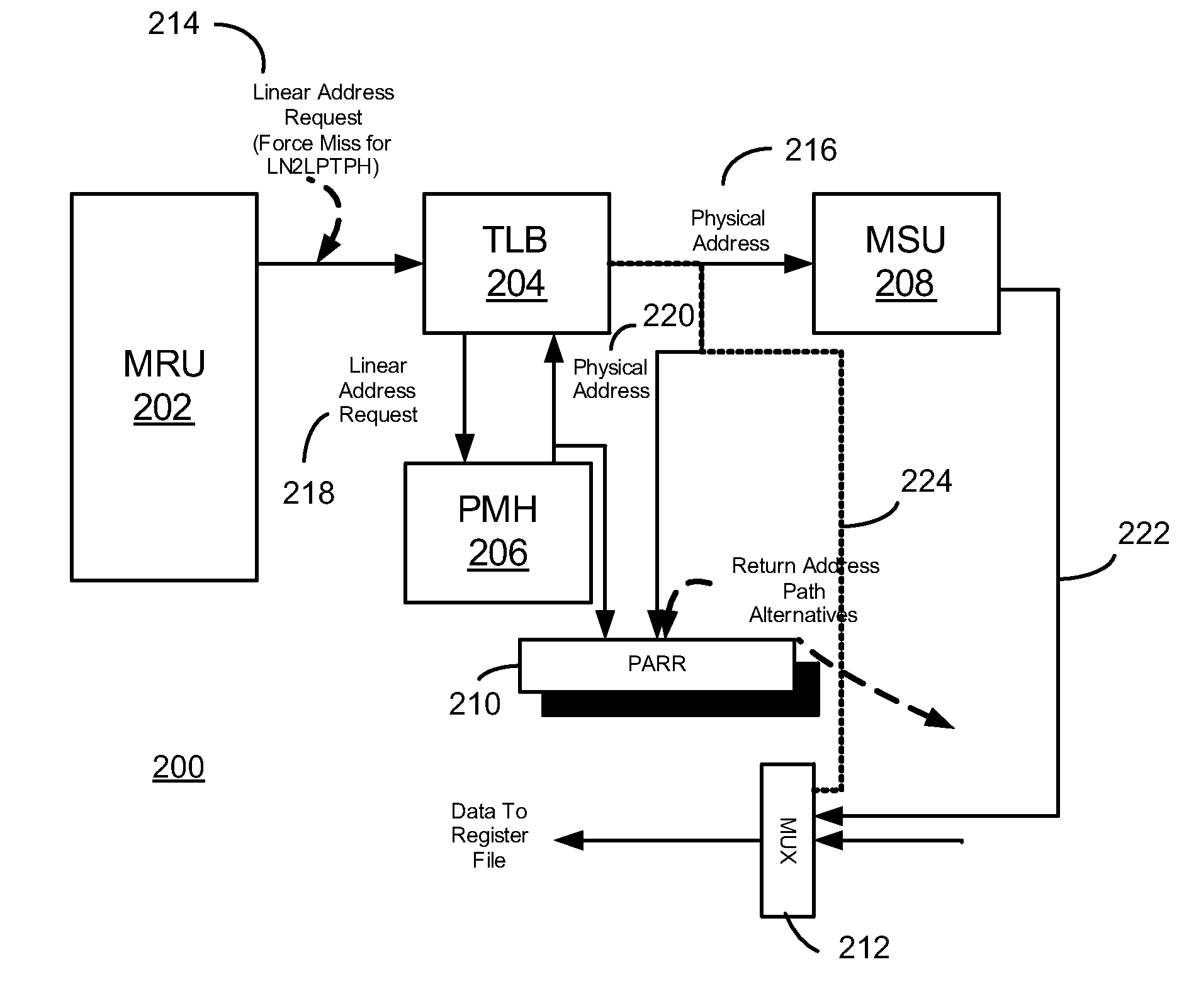

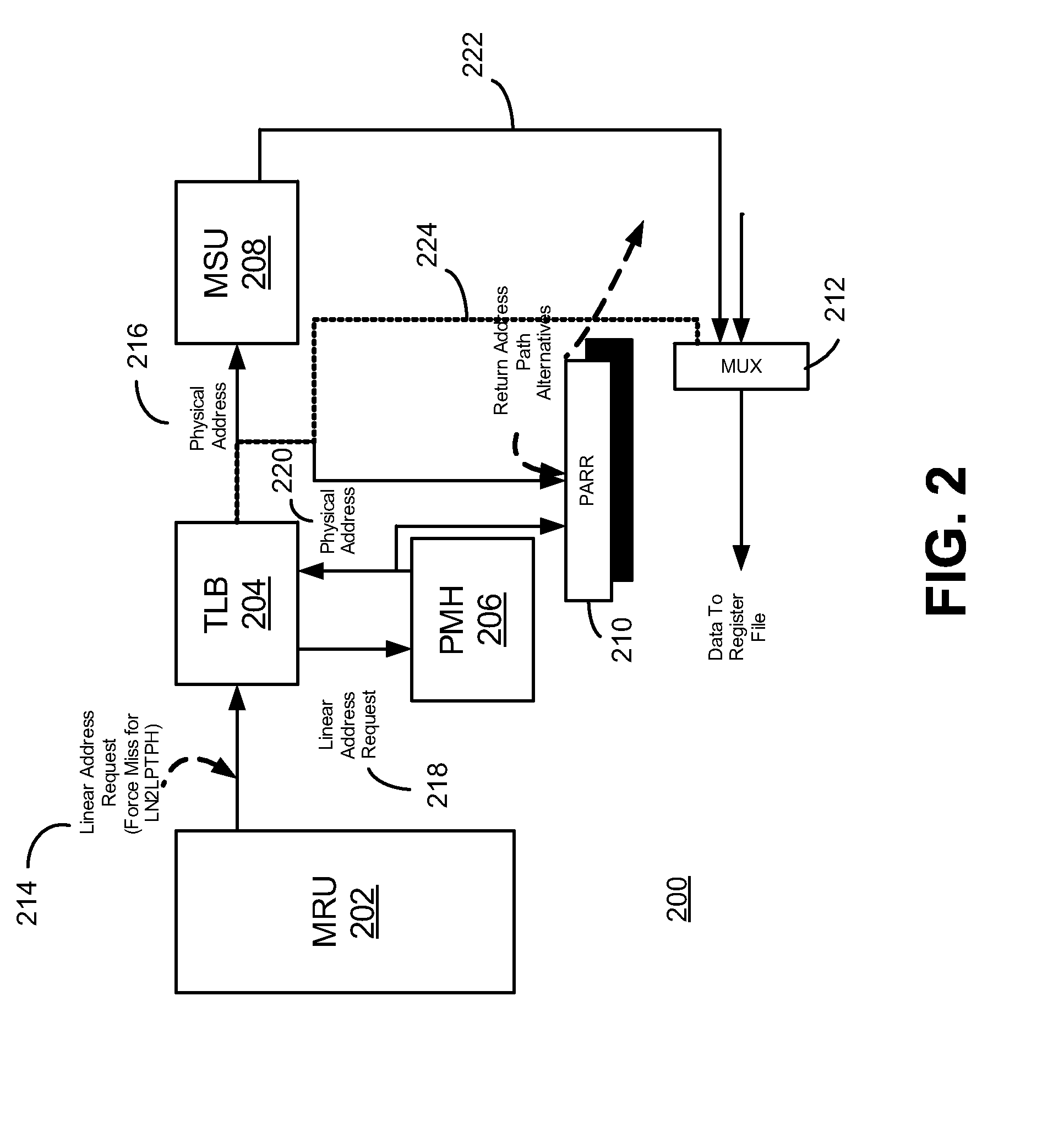

Method and Apparatus For Deterministic Translation Lookaside Buffer (TLB) Miss Handling

InactiveUS20160092371A1Memory architecture accessing/allocationMemory adressing/allocation/relocationPage tableTranslation lookaside buffer

An apparatus and method are described for translation lookaside buffer (TLB) miss handling. For example, one embodiment of a processor comprises: a translation lookaside buffer (TLB) to store virtual-to-physical address translations; a page miss handler (PMH) to process TLB misses when a desired virtual-to-physical address translation is not present in the TLB; and a compressed page table to be managed by the PMH, the compressed page table to store specified portions of page tables, wherein in response to a TLB miss for a first address translation, the PMH is to check the compressed page table to determine if a page table entry corresponding to the first address translation is stored therein and, if so, to provide the first address translation from the compressed page table.

Owner:INTEL CORP

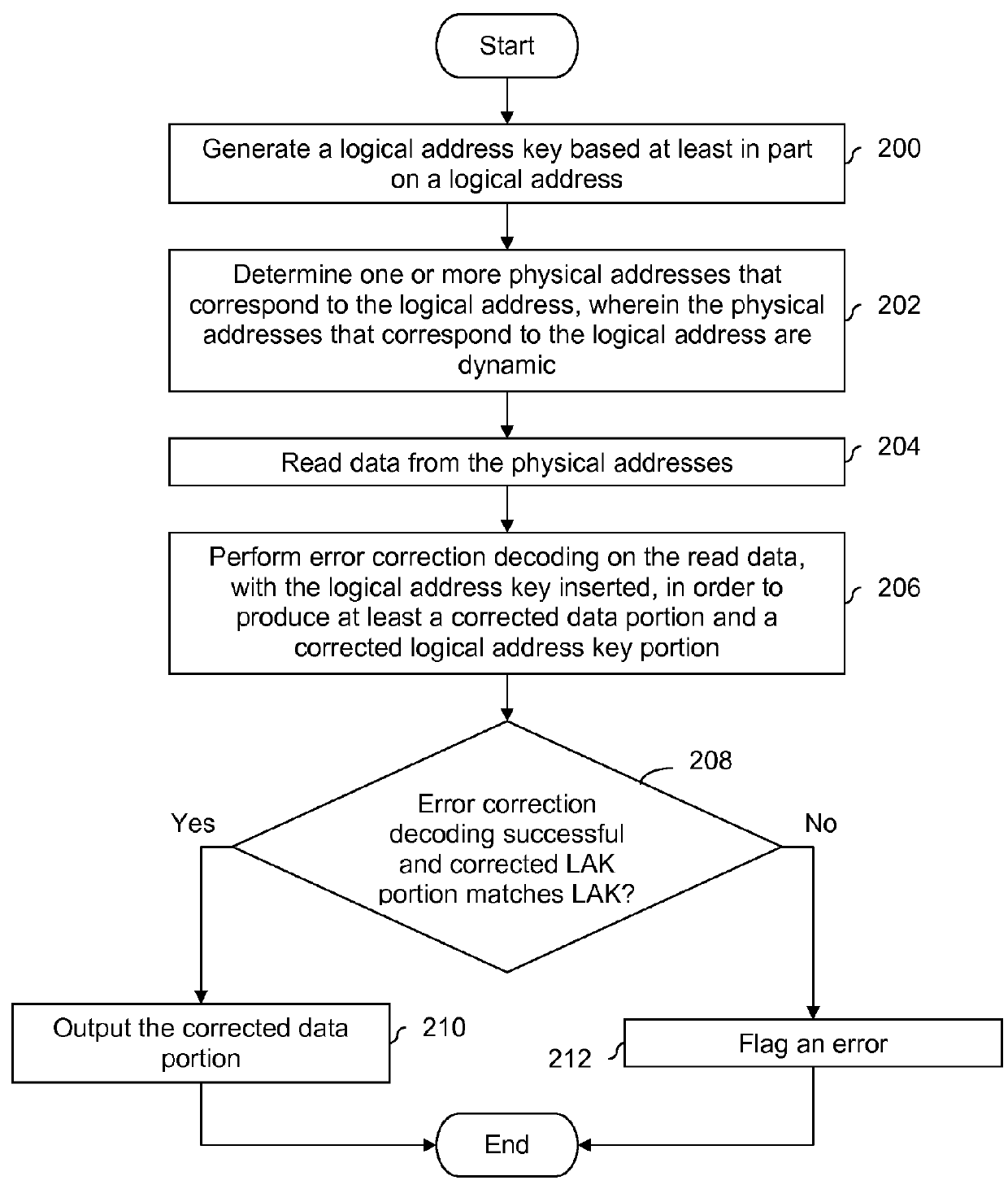

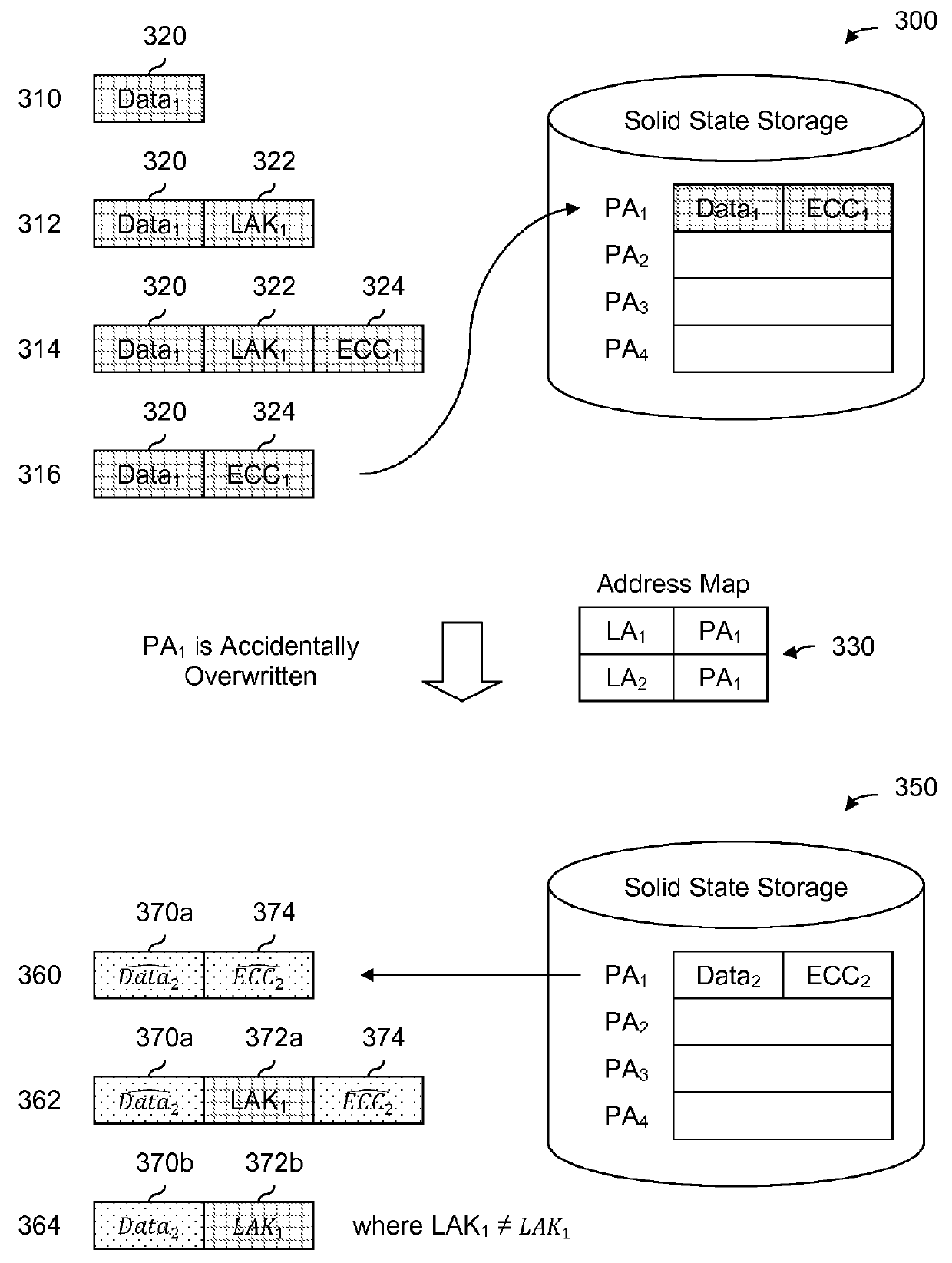

Error detection using a logical address key

ActiveUS9384144B1Memory architecture accessing/allocationMemory adressing/allocation/relocationComputer hardwareForward error correction

A logical address key is generated based at least in part on a logical address. Encoded data is generated by systematically error correction encoding the logical address key and write data. One or more physical addresses are determined that correspond to the logical address where the physical addresses that correspond to the logical address are dynamic. At the physical addresses, the encoded data is stored with the logical address key removed.

Owner:SK HYNIX INC

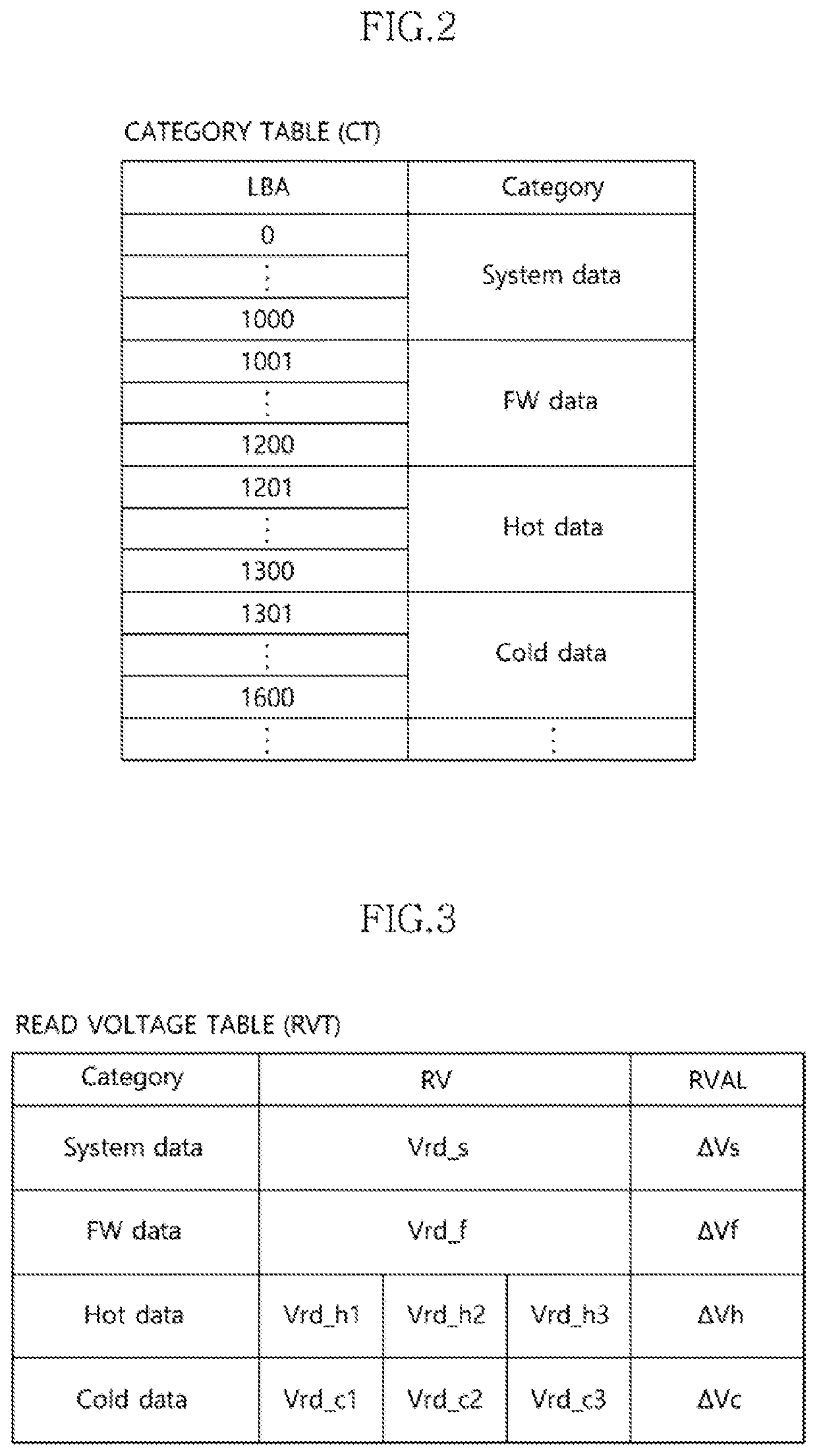

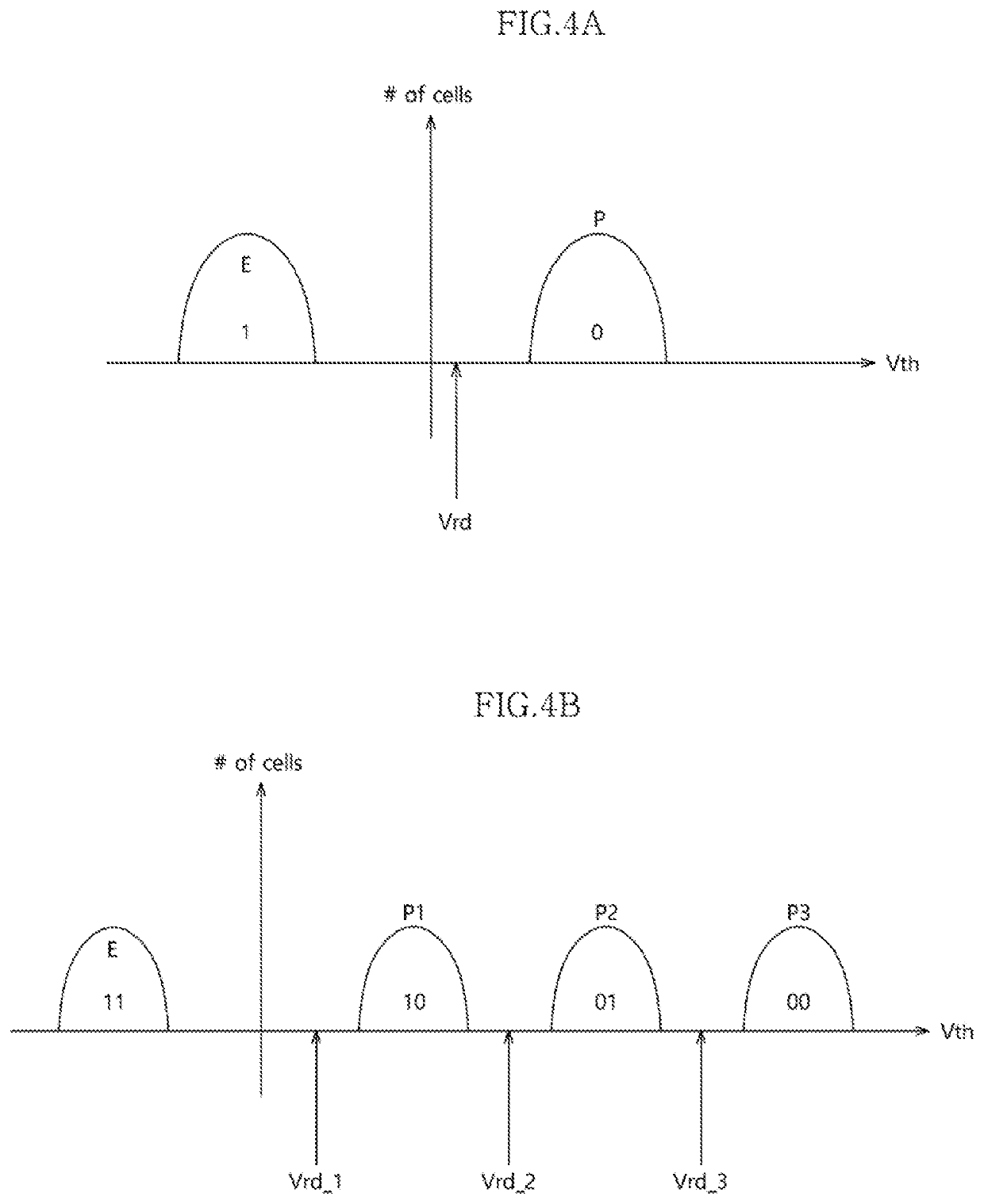

Data storage device and operating method thereof

ActiveUS10521353B2Improve methodIncrease successRead-only memoriesDigital storageComputer scienceOperating system

A data storage device includes a nonvolatile memory device and a controller configured to control an operation of the nonvolatile memory device. The controller includes an RAM in which a category table that categories with respect to LBAs are defined and a read voltage table that read voltages with respect to the categories are set are stored and a controller configured to, when a read request and an LBA to be read are received from a host apparatus, determine a category corresponding to the LBA with reference to the category table and perform a read operation on a read-requested memory cell of the nonvolatile memory device by applying a read voltage corresponding to the determined category to the memory cell with reference to the read voltage table.

Owner:SK HYNIX INC

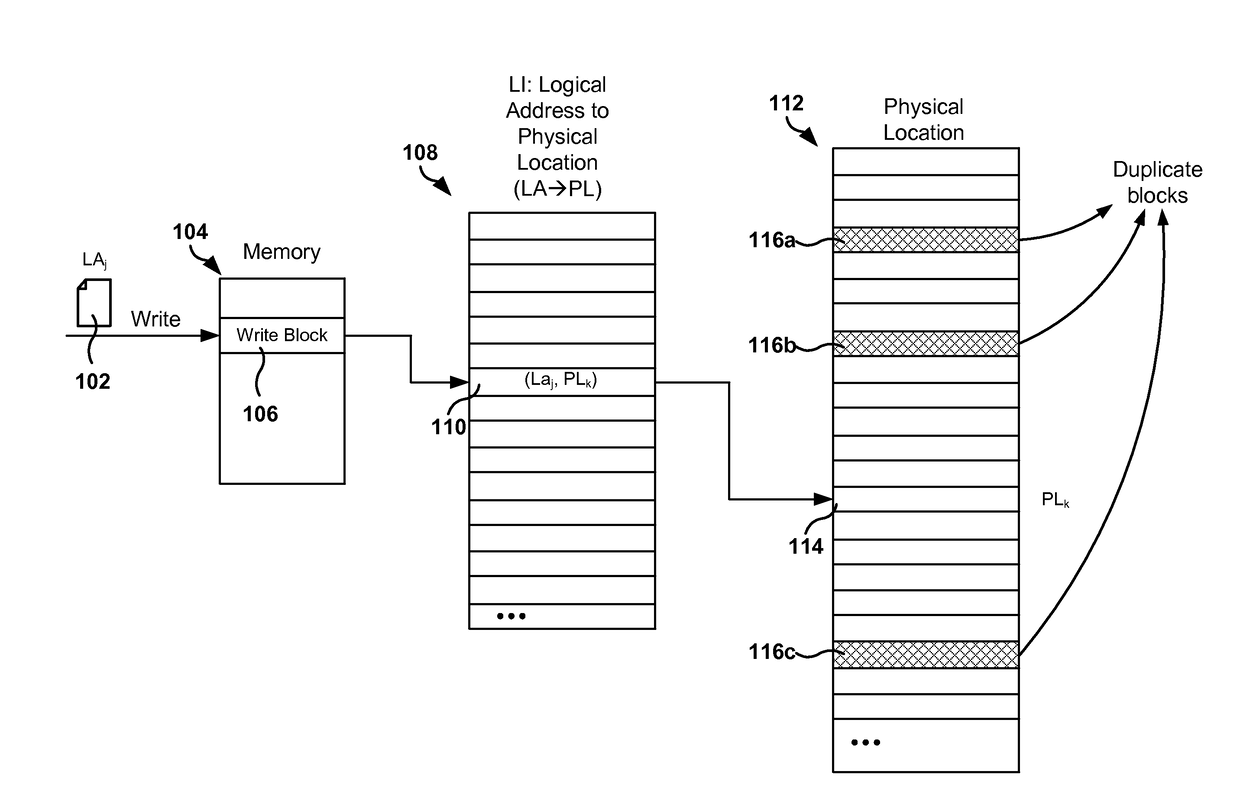

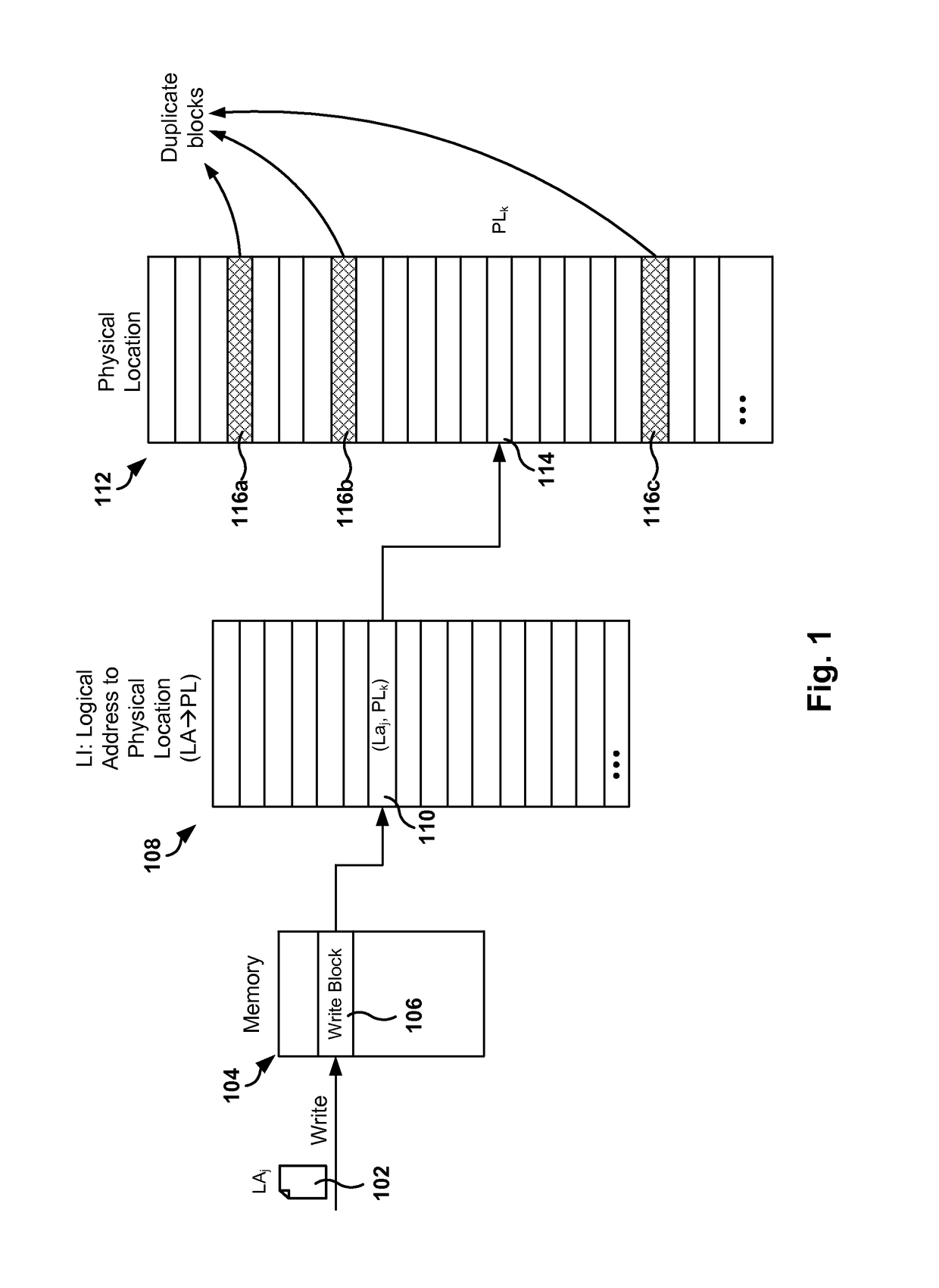

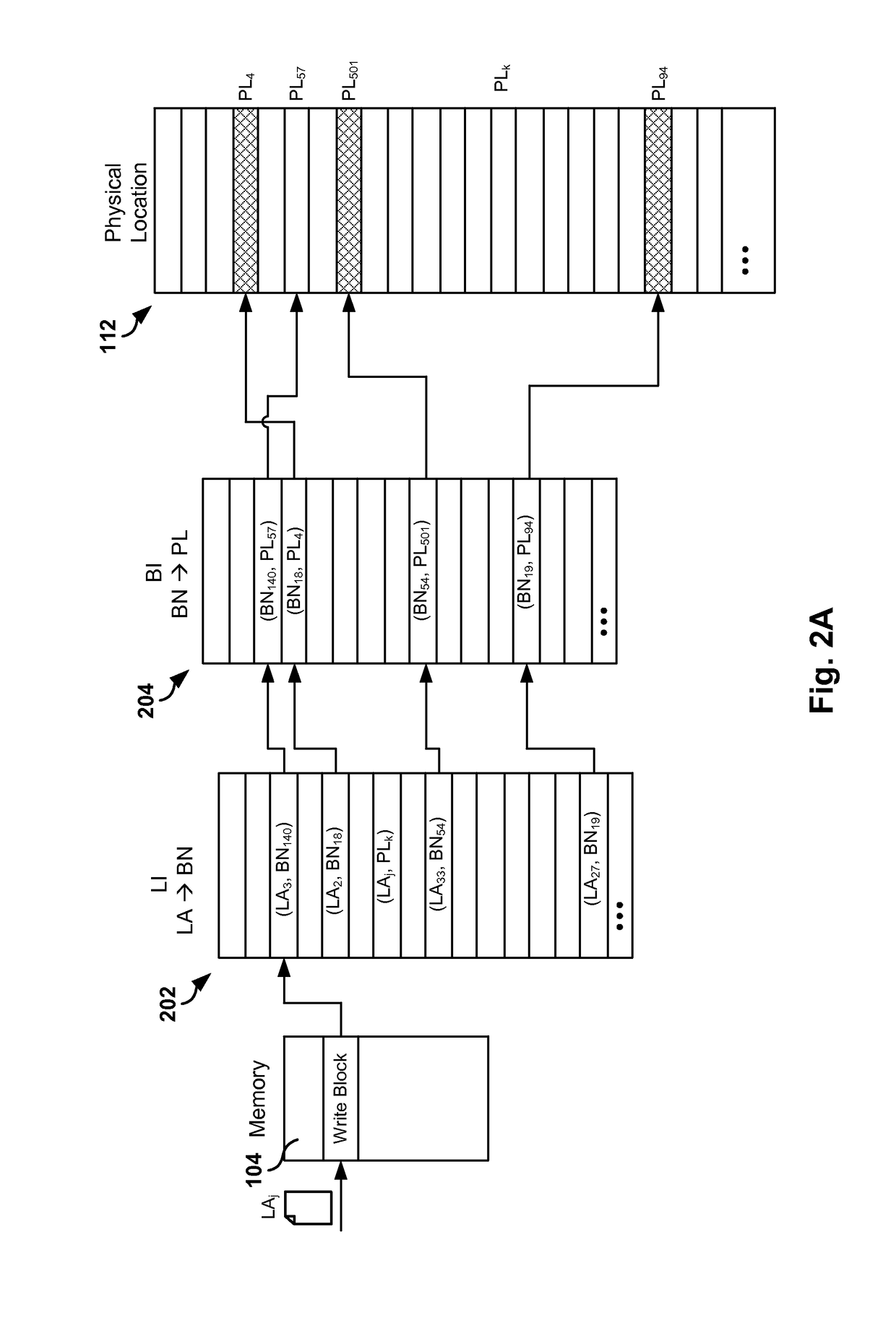

Processing of Incoming Blocks in Deduplicating Storage System

ActiveUS20170115883A1Memory architecture accessing/allocationInput/output to record carriersParallel computingBlock number

Methods, systems, and computer programs are presented for deduplicating data. One method includes an operation for receiving a data block having a logical address. The storage system includes a logical address mapping index for mapping logical addresses to block numbers, a block index for mapping block numbers to physical locations, and a fingerprint index for mapping fingerprints of data blocks to block numbers. Additionally, the method includes an operation for inline processing the data block. Inline processing the data block includes determining a fingerprint of the data block, examining the fingerprint index to determine if the fingerprint is already mapped to an existing data block in the storage system, if the fingerprint is already mapped then adding a mapping of the logical address to the existing data block in the logical address mapping index, and if the fingerprint is not already mapped then creating the corresponding entries in the indices.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

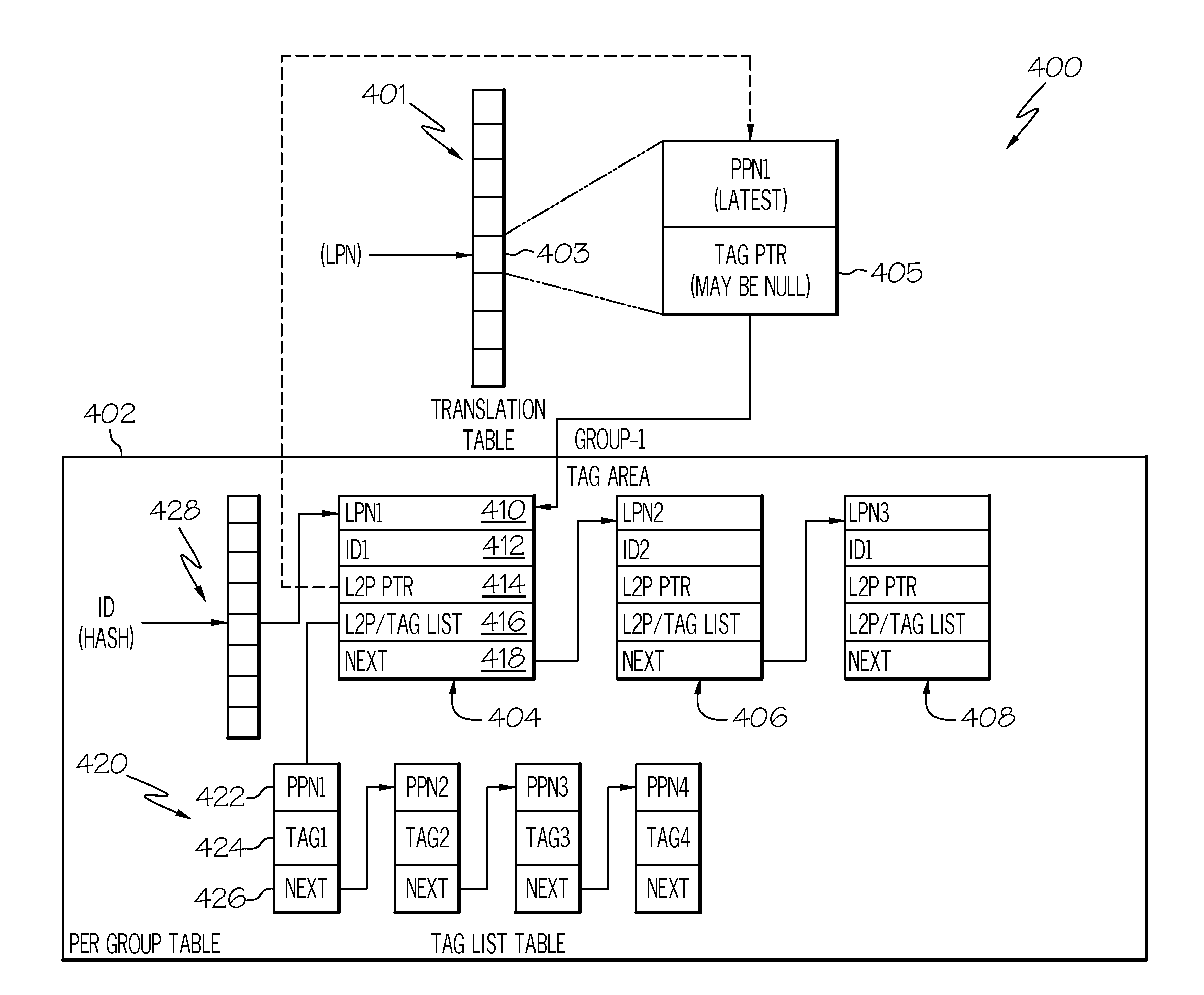

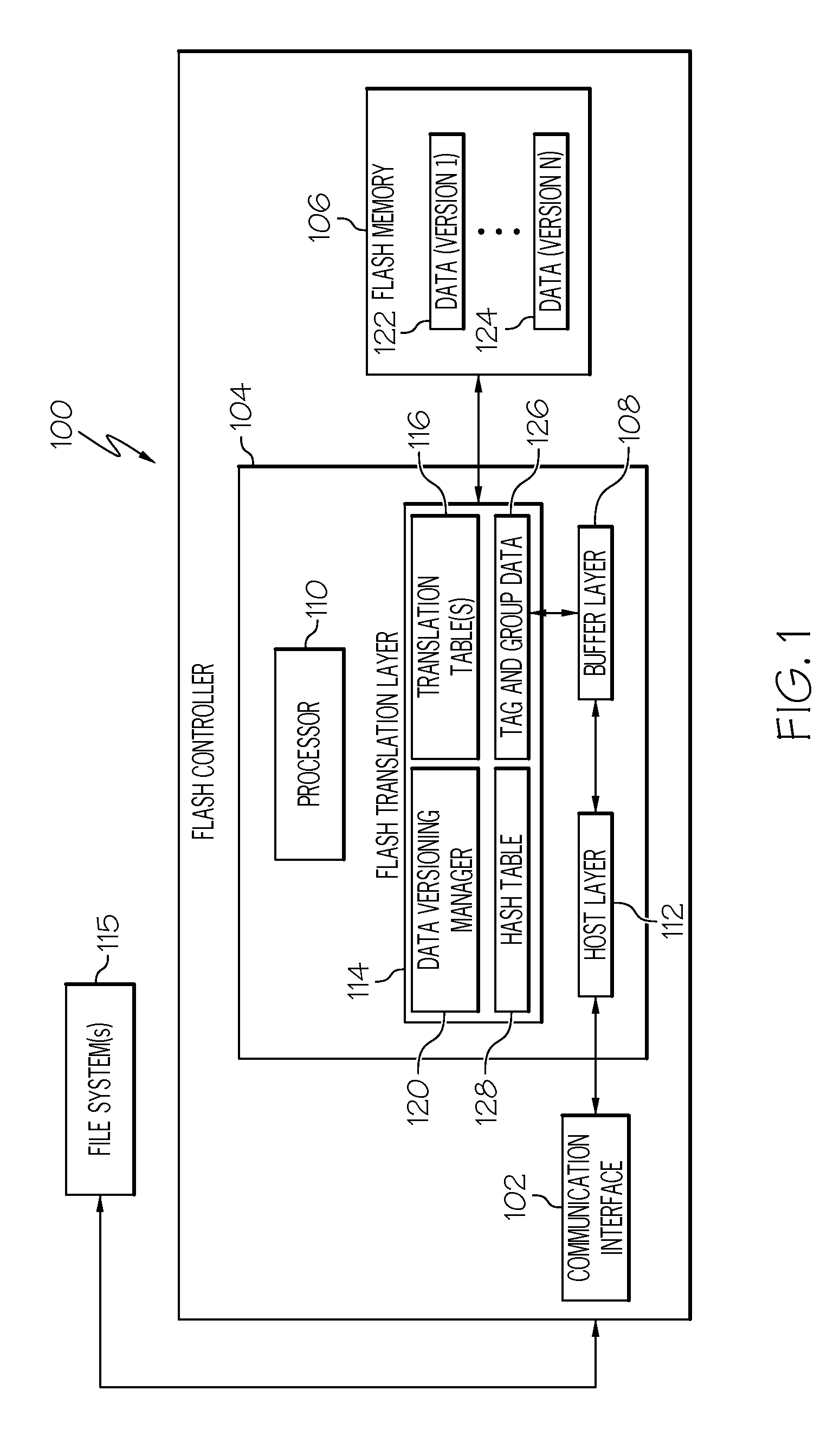

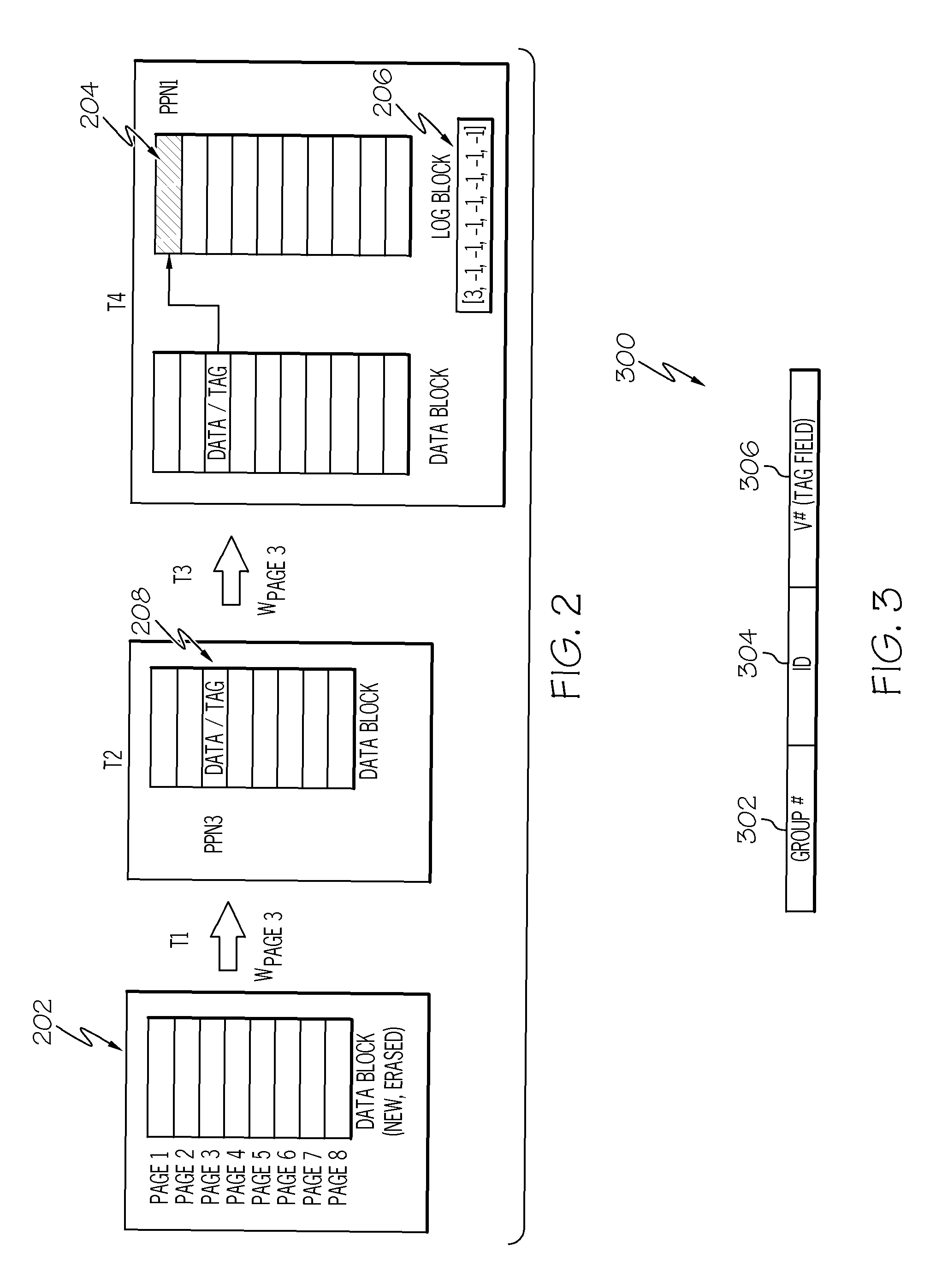

Maintaining versions of data in solid state memory

InactiveUS9116793B2Memory architecture accessing/allocationMemory adressing/allocation/relocationData setFile system

Various embodiments are directed to maintaining versions of data within a solid state memory. At least one request to write at least one dataset to a logical page of a solid state memory is received from a file system. At least one physical page in a data block of the solid state memory associated with the logical page is identified. A processor stores the dataset in the at least one physical page. At least one data versioning tag is associated with the at least one dataset in a data structure associated with the logical page. The data versioning tag identifies the at least one dataset as a given version of the logical page. The at least one dataset is maintained as accessible from the at least one physical page irrespective of subsequent write operations to the logical page in response to associating the at least one data versioning tag.

Owner:IBM CORP

Hybrid computing module

ActiveUS9348385B2Efficient transferSmall sizeMemory architecture accessing/allocationRegister arrangementsHybrid systemComputer module

A hybrid system-on-chip provides a plurality of memory and processor die mounted on a semiconductor carrier chip that contains a fully integrated power management system that switches DC power at speeds that match or approach processor core clock speeds, to enable transfer of data between off-chip physical memory and processor die.

Owner:DEROCHEMONT L PIERRE

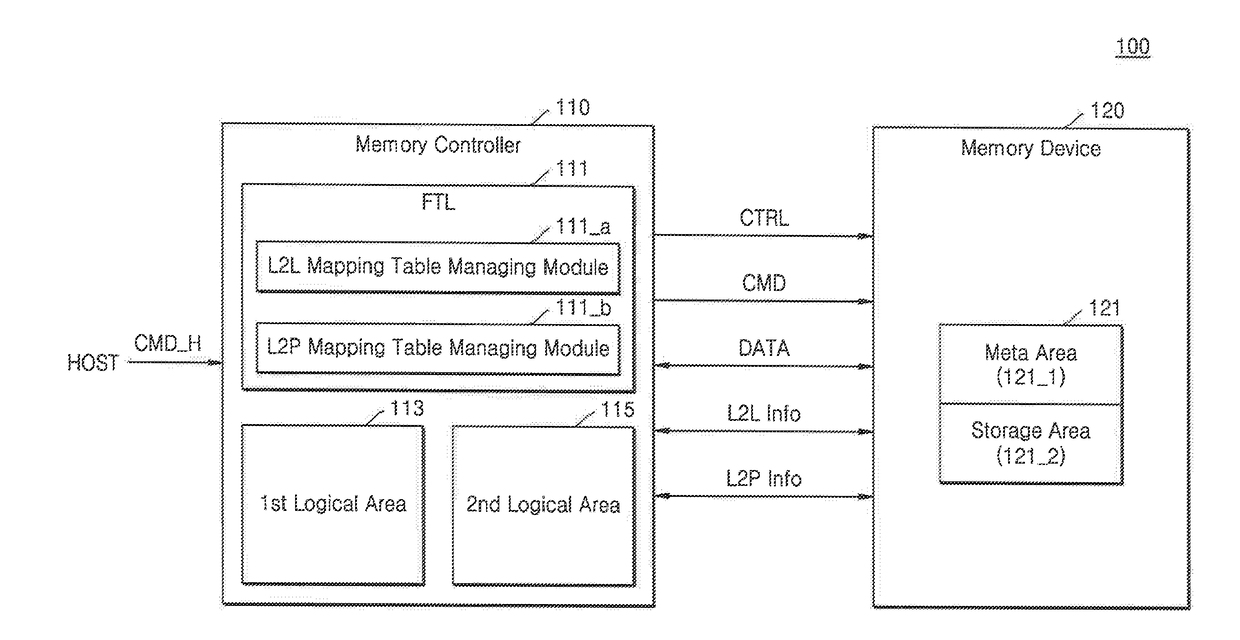

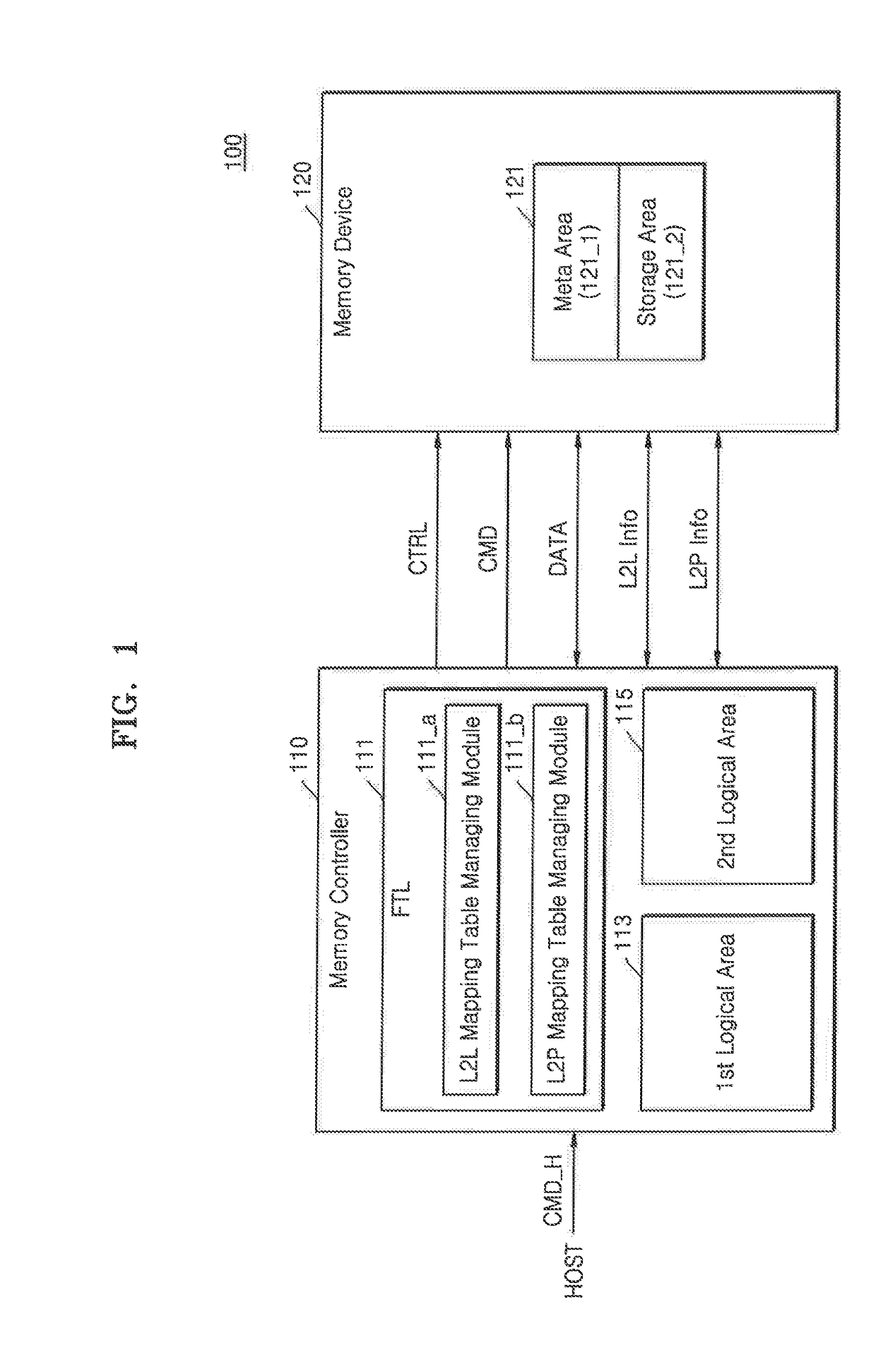

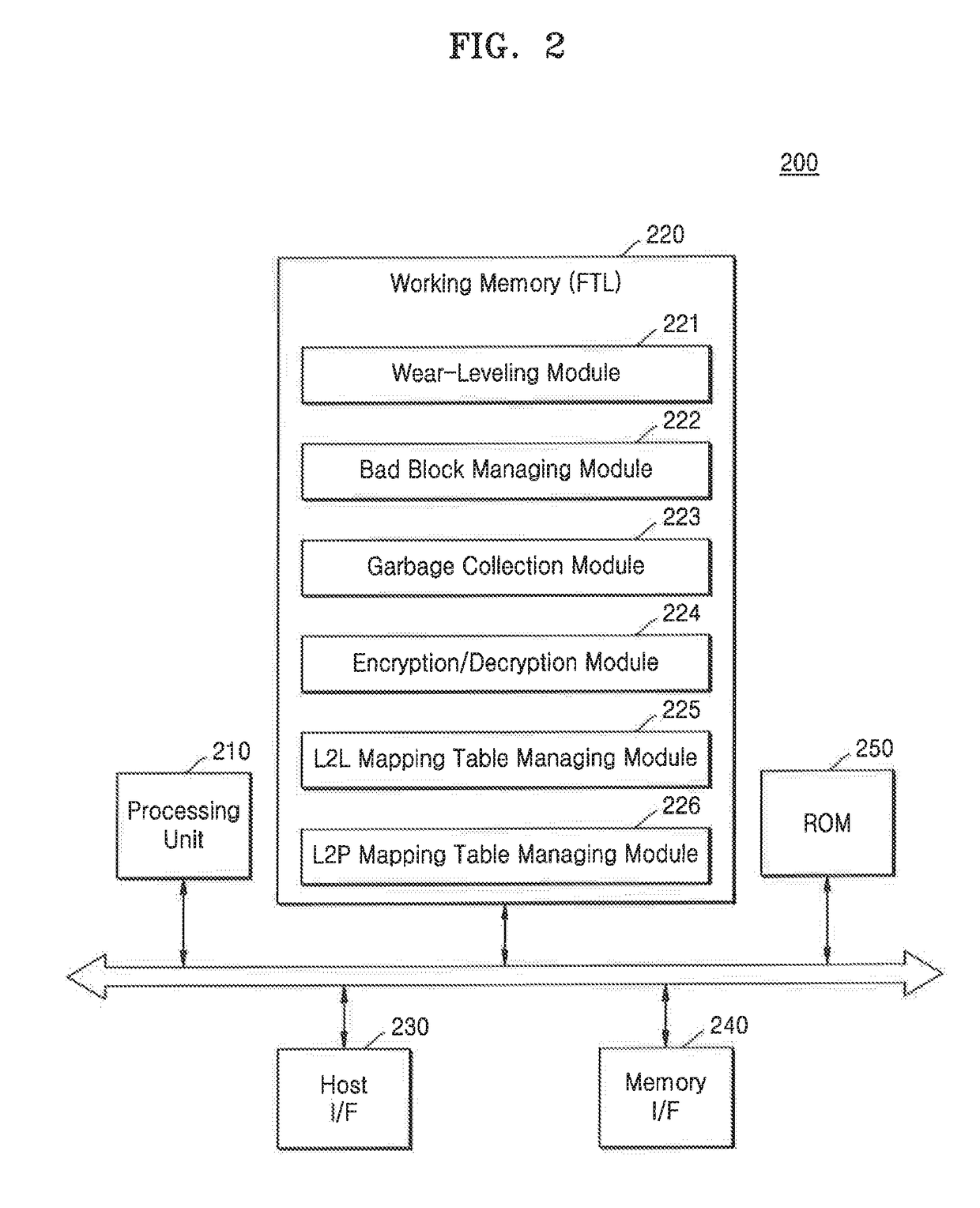

Memory controller, nonvolatile memory system, and operating method thereof

ActiveUS20180052768A1Memory architecture accessing/allocationMemory adressing/allocation/relocationControl storeMemory controller

In an operating method of a memory controller, the memory controller includes a logical-to-logical (L2L) mapping table including mapping information between a first logical area and a second logical area and a logical-to-physical (L2P) mapping table including mapping information between the second logical area and a physical area of a memory device. The operating method includes receiving a first logical address of the first logical area and a first command for changing the L2L mapping table to access first data stored in the memory device through the first logical address, detecting a second logical address of the second logical area mapped to a physical address of the physical area in which the first data is stored, in response to the first command, and changing the L2L mapping table to map the first logical address to the second logical address.

Owner:SAMSUNG ELECTRONICS CO LTD

Popular searches

Input/output processes for data processing Micro-instruction address formation Volume/mass flow measurement Solid-state devices Semiconductor/solid-state device manufacturing Power supply for data processing Energy efficient computing Architecture with multiple processing units Semiconductor devices Static storage

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com