Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

350results about "Electronic products manufacture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

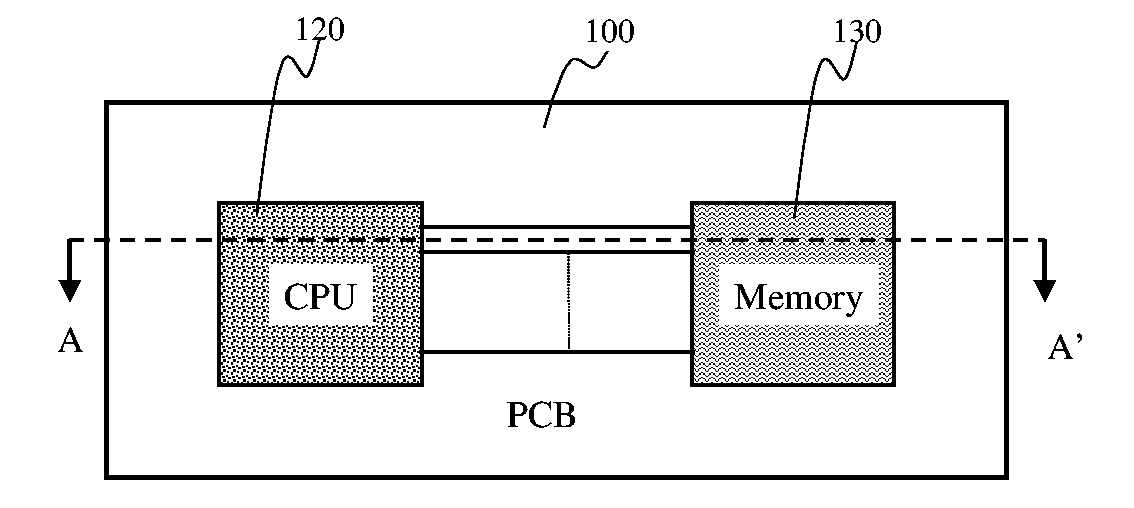

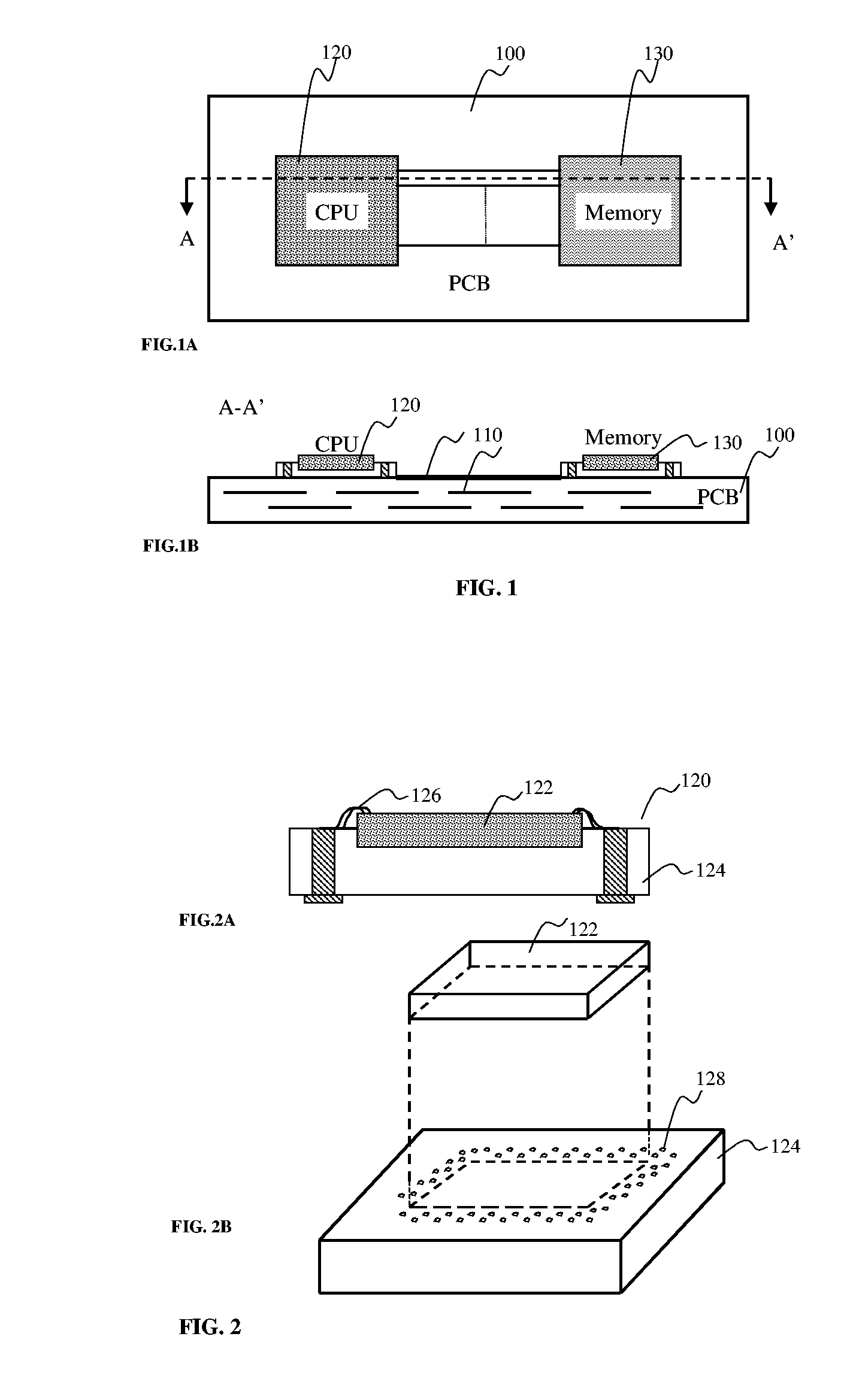

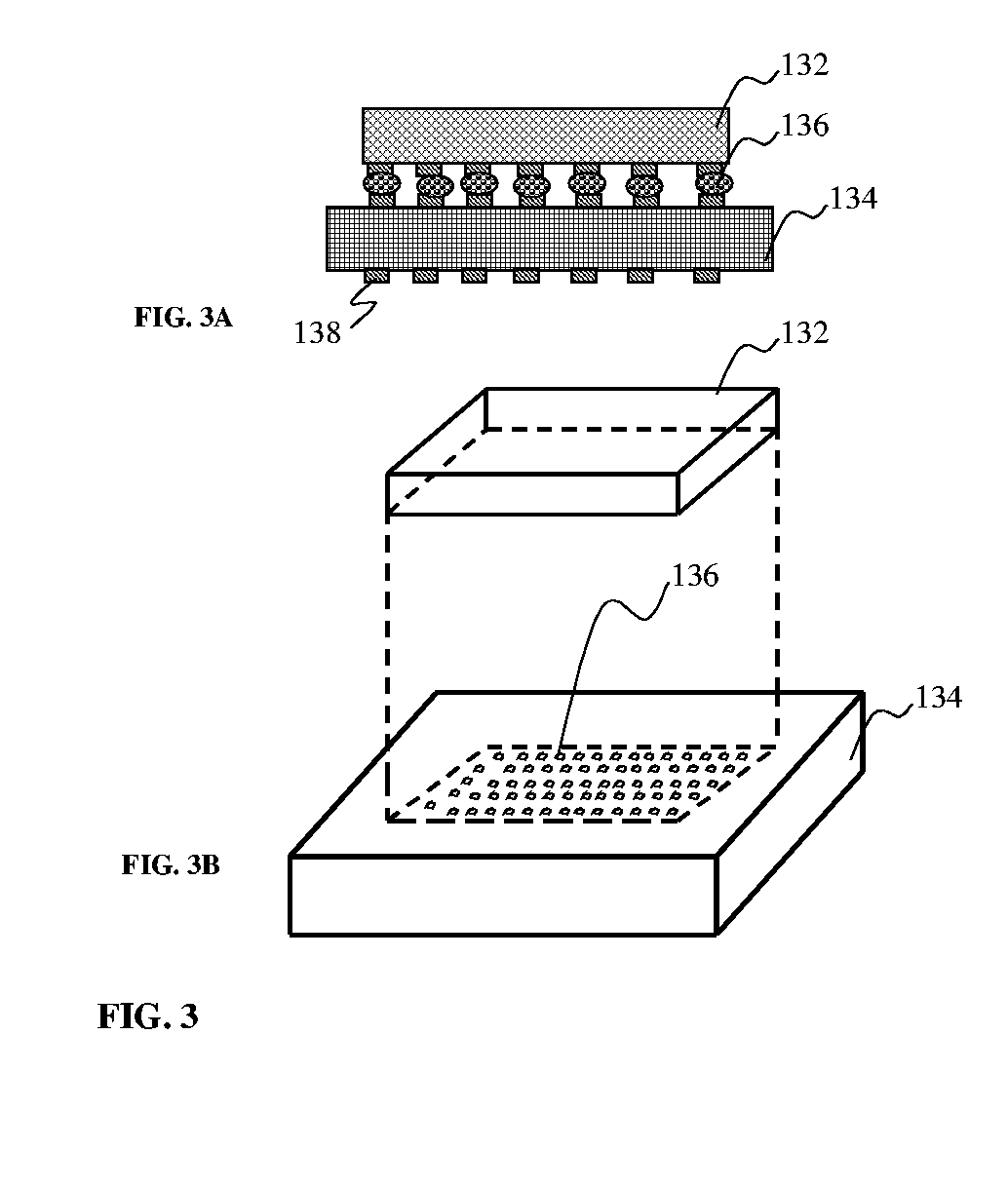

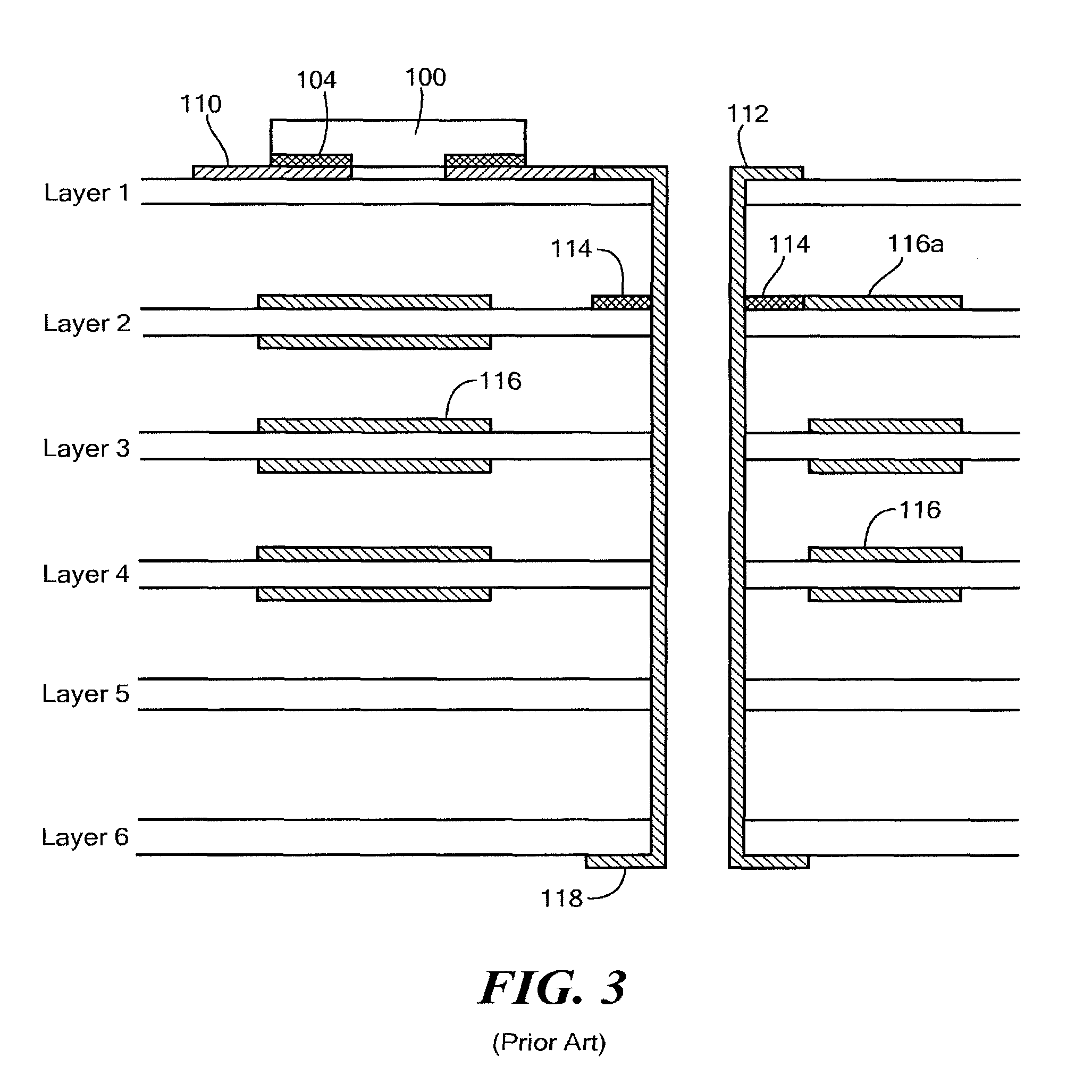

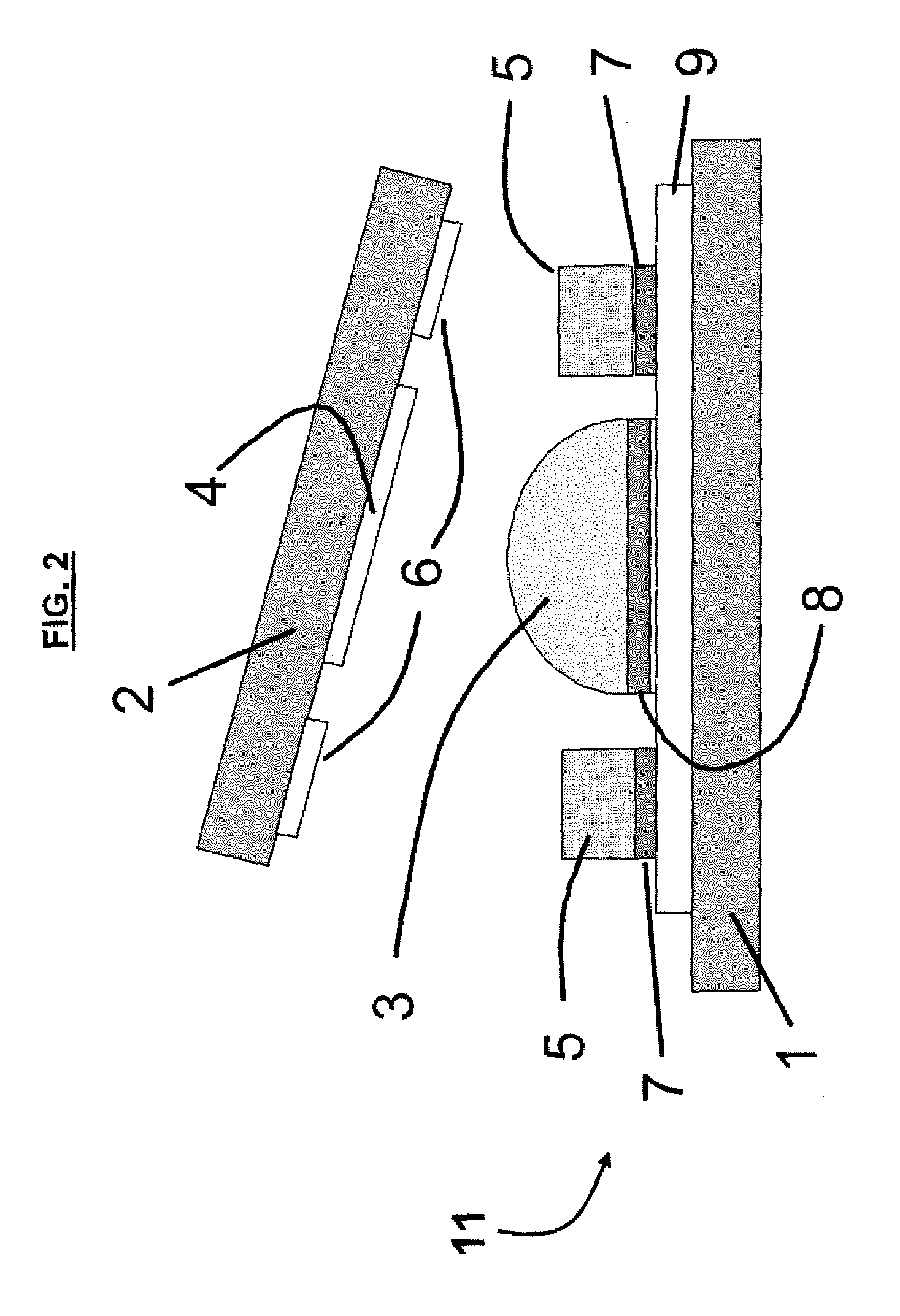

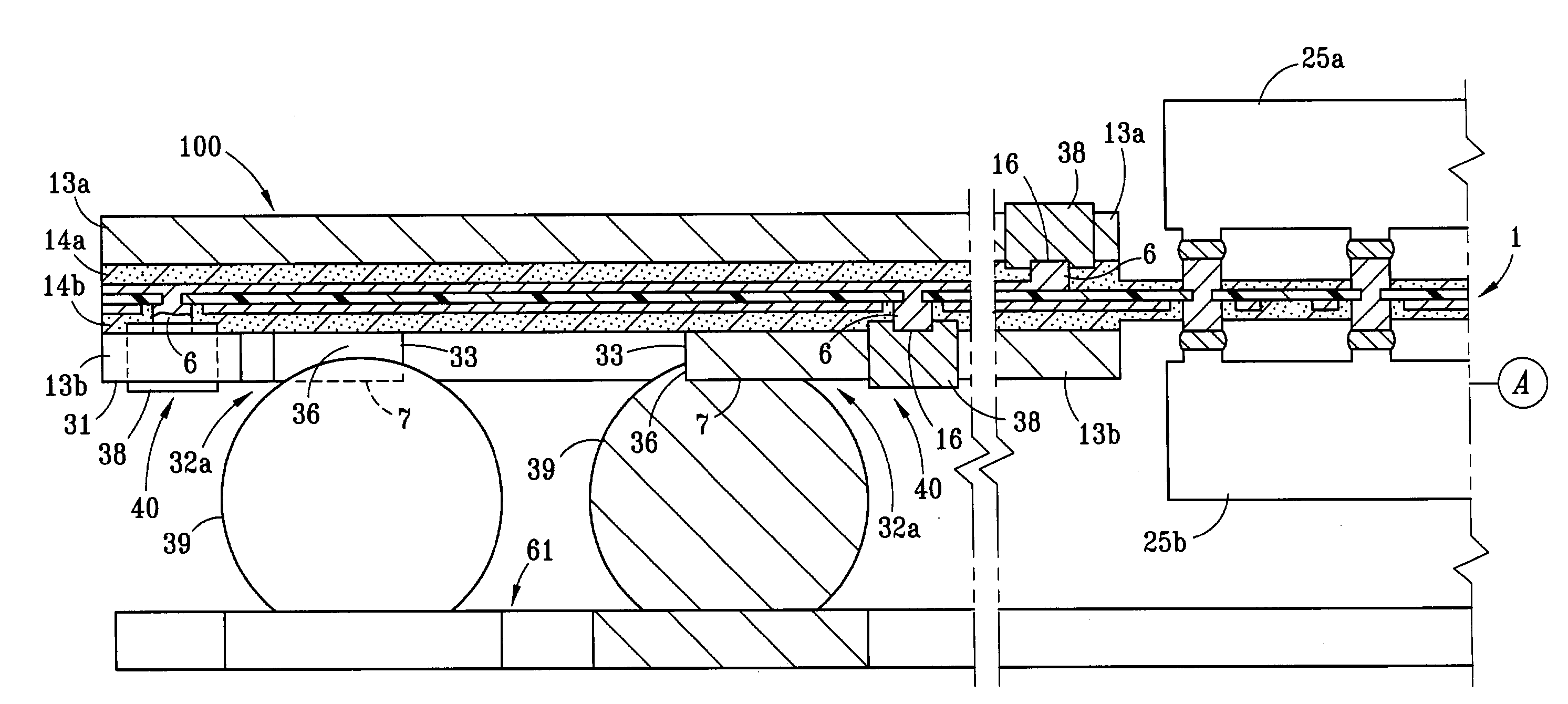

Stackable optoelectronics chip-to-chip interconnects and method of manufacturing

ActiveUS20050224946A1Minimize skewEasily stackable/mountableCircuit optical detailsSemiconductor/solid-state device detailsElectrical conductorEngineering

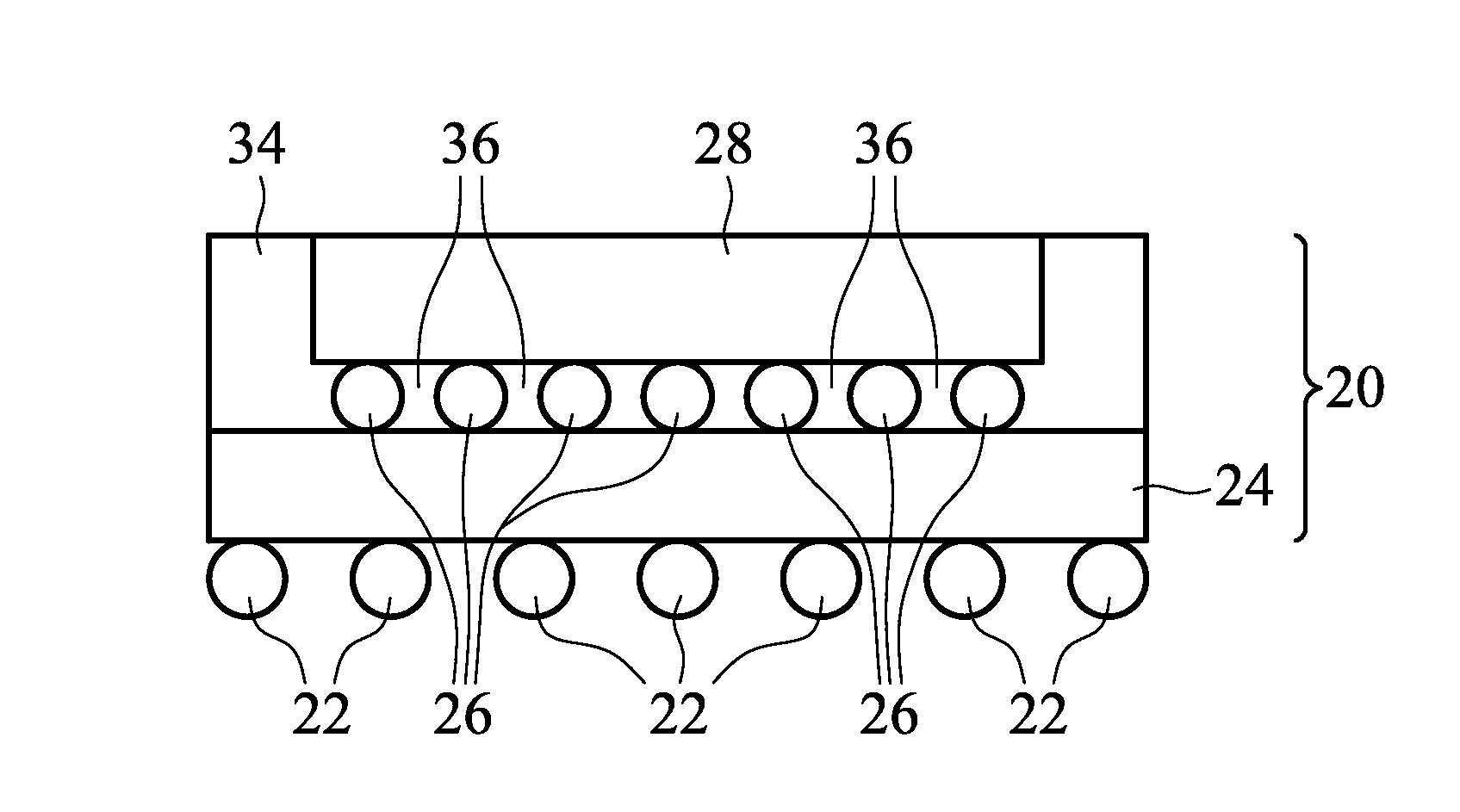

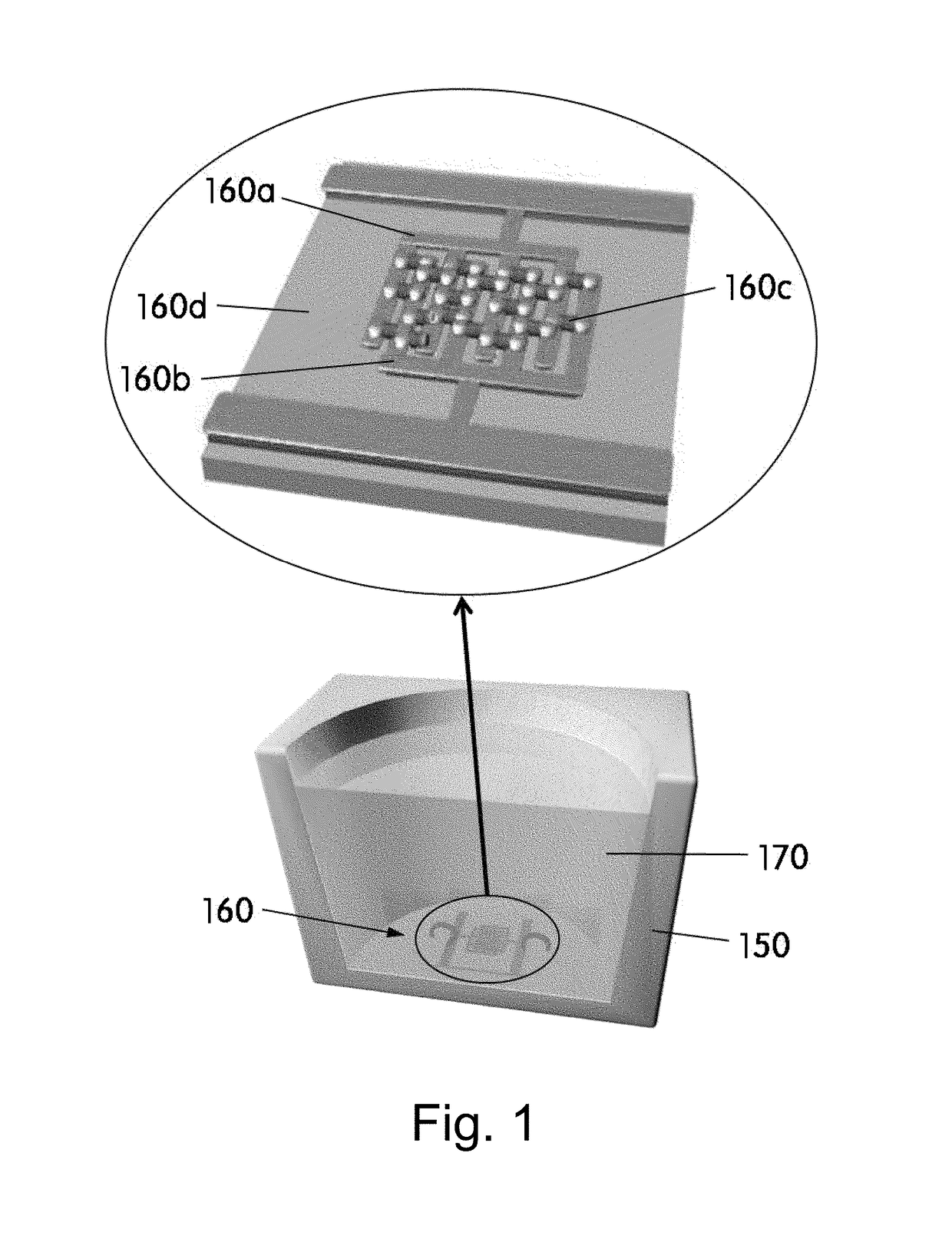

An optoelectronics chip-to-chip interconnects system is provided, including packaged chips to be connected on printed-circuit-board (PCB), multiple-packaged chip, optical-electrical(O-E) conversion means, waveguide-board, and PCB. Single to multiple chips interconnects can be possible using this technique. The packaged-chip includes semiconductor-die and its package based on the ball-grid array or chip-scale-package. The O-E board includes the optoelectronics components and multiple electrical contacts. The waveguide board includes electrical conductors transferring signal from O-E board to PCB and the flex optical waveguide easily stackable onto the PCB, to guide optical signal from one chip-to-other chip. The chip-to-chip interconnects system is pin-free and compatible with the PCB. The main advantages are that standard packaged-chip and conventional PCB technology can be used for low speed electrical signal connection. Also, the part of the heat from the packaged chip can be transmitted to PCB through conductors, so that complex cooling system can be avoided.

Owner:BANPIL PHOTONICS

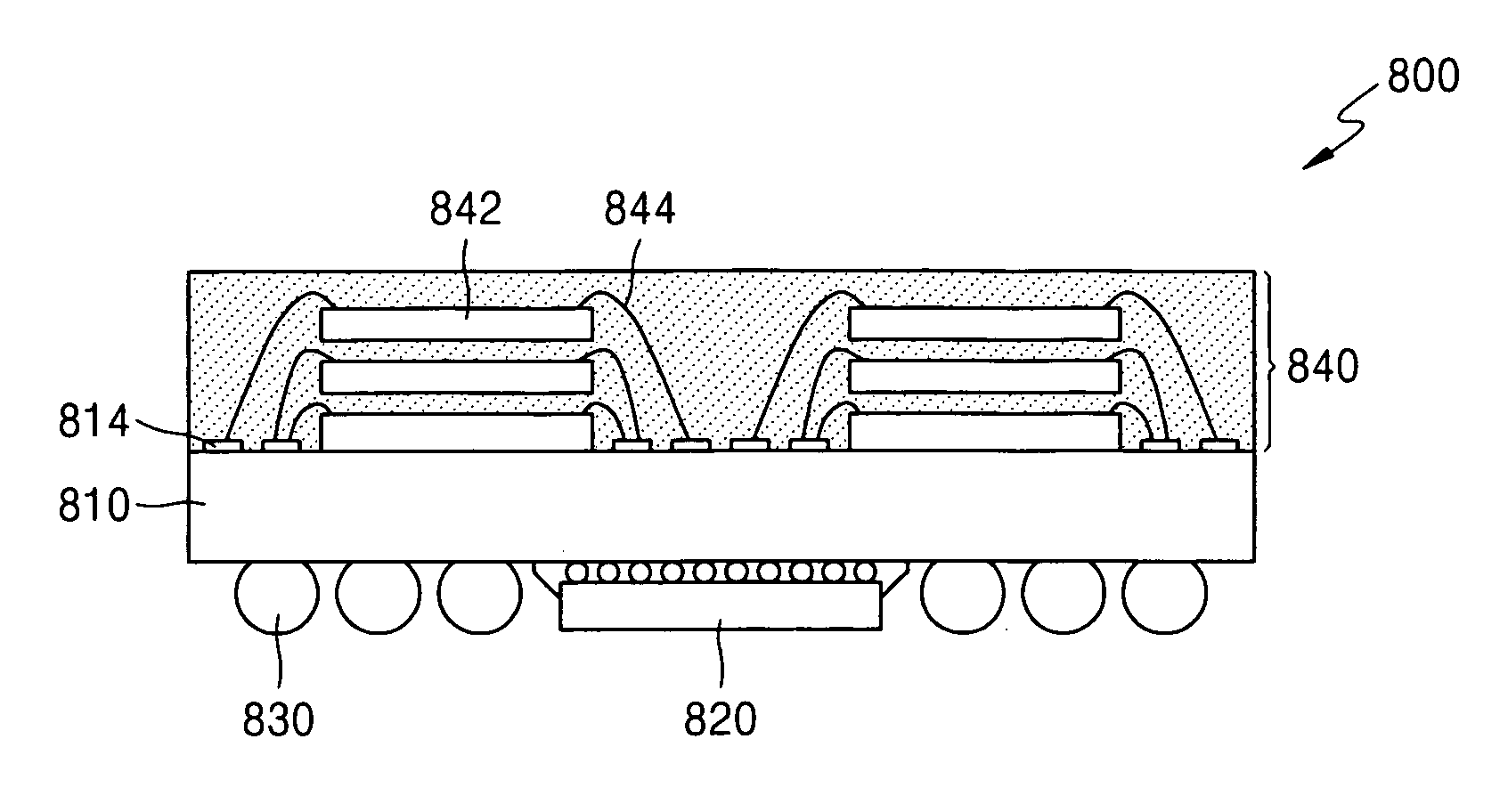

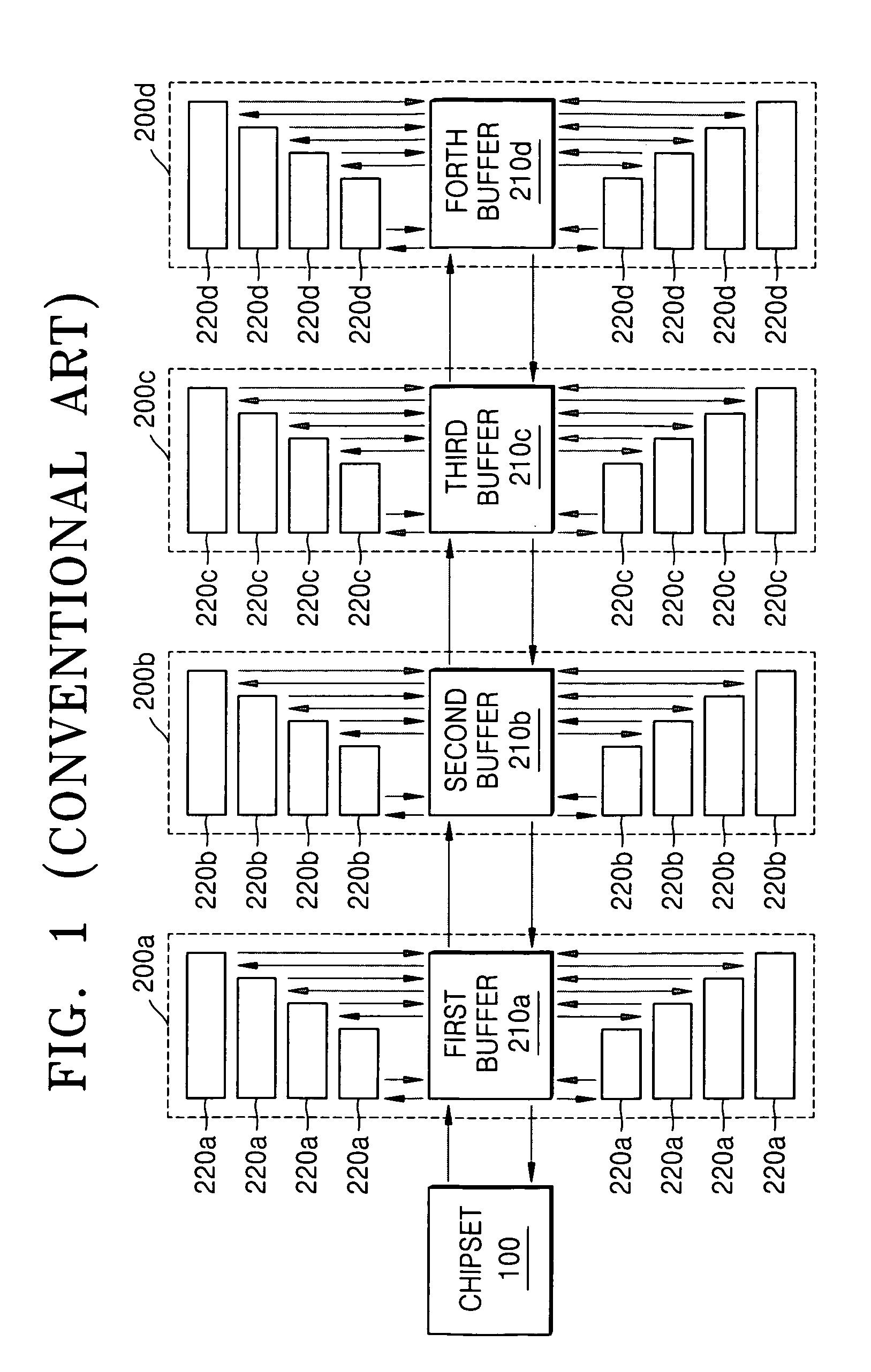

Semiconductor device package having buffered memory module and method thereof

ActiveUS20050224948A1Excellent electrical propertiesReduce distanceSemiconductor/solid-state device detailsPrinted circuit aspectsMemory chipDevice material

A method and apparatus of fabricating a semiconductor device are disclosed. The semiconductor device may include a buffer chip package having a buffer chip mounted on a buffer chip substrate and at least one memory package mounted on the buffer chip substrate, wherein the at least one memory package may include a plurality of memory chips. Further, the buffer chip package may have a plurality of external connection terminals.

Owner:SAMSUNG ELECTRONICS CO LTD

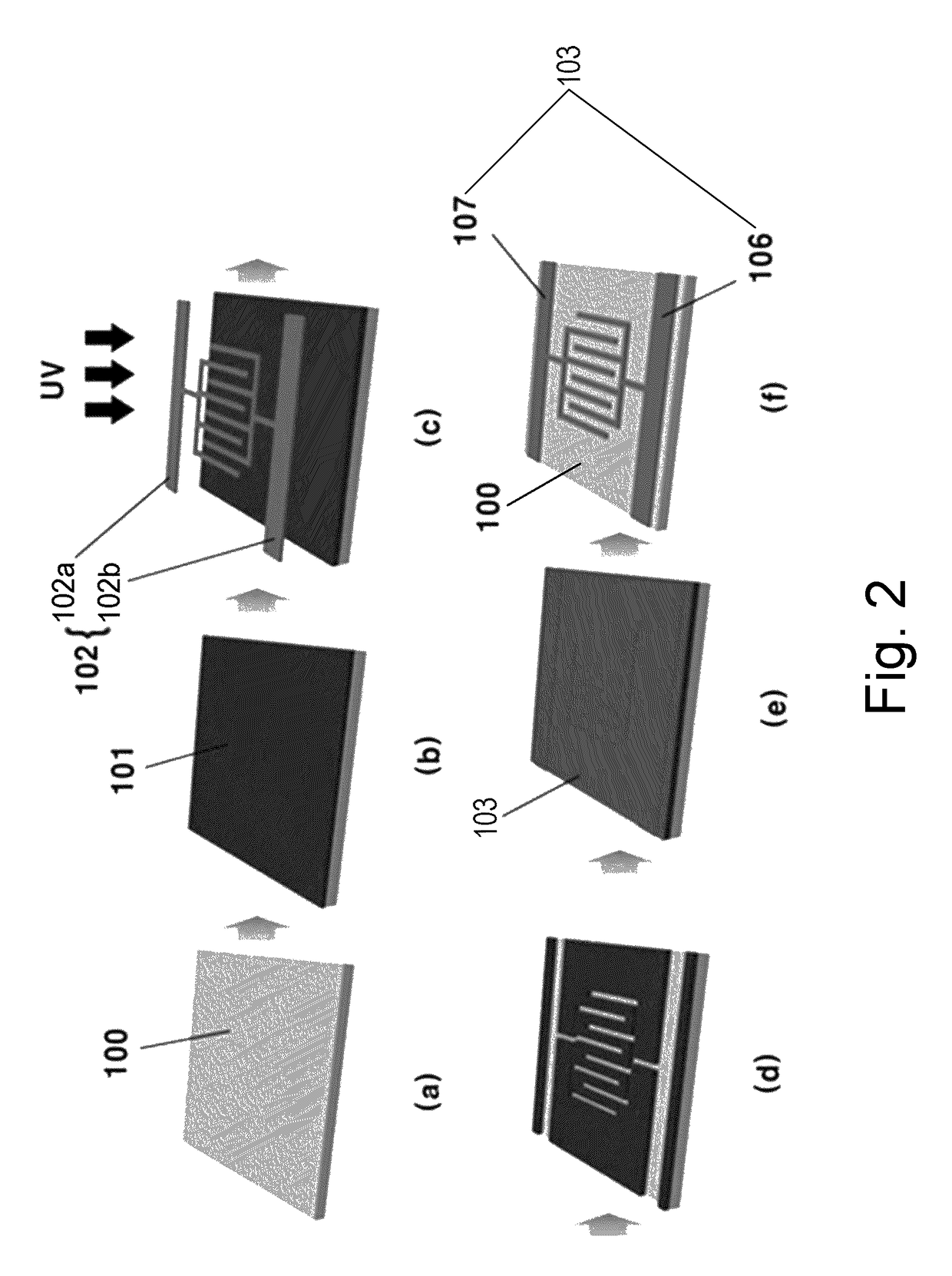

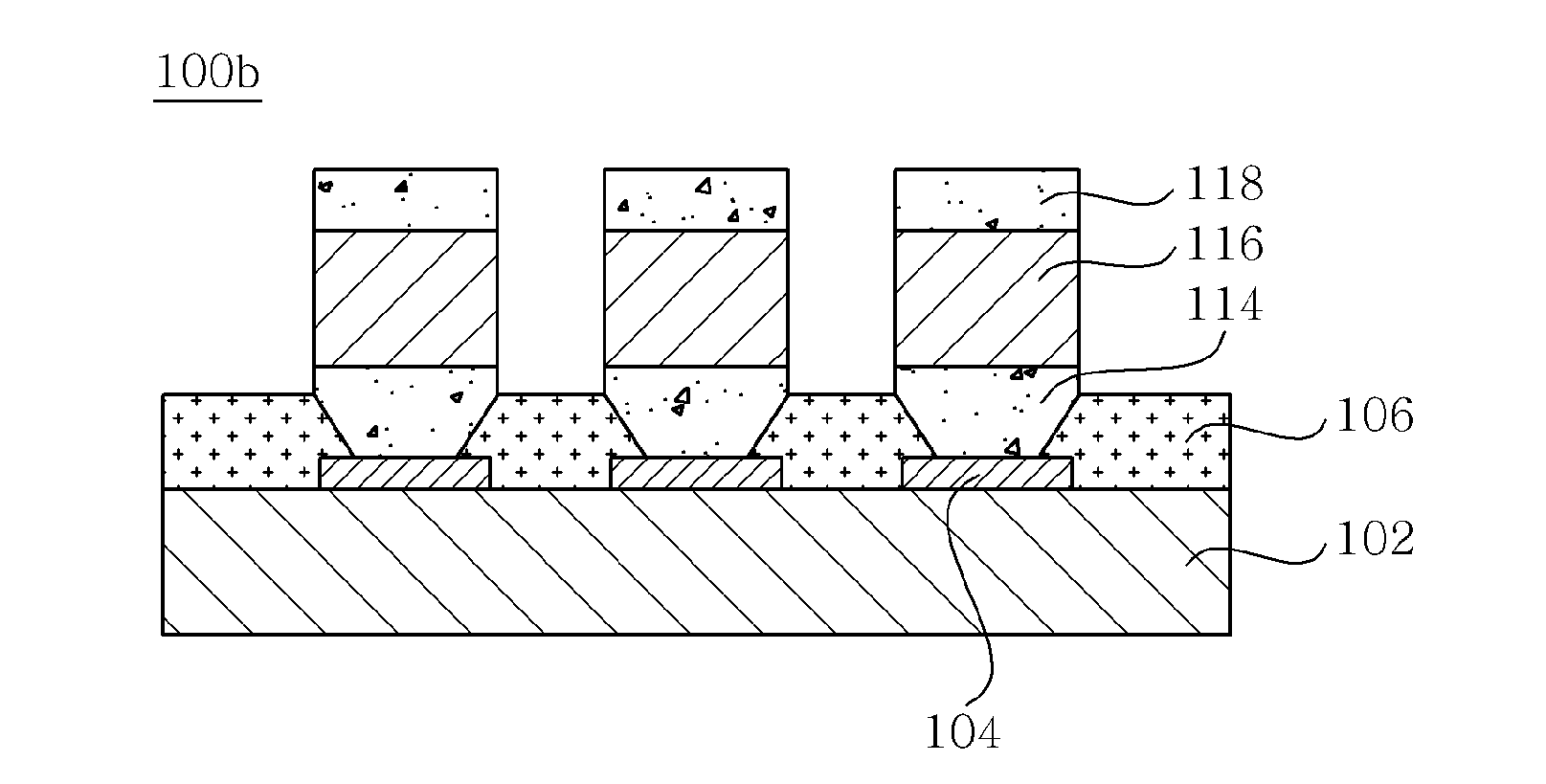

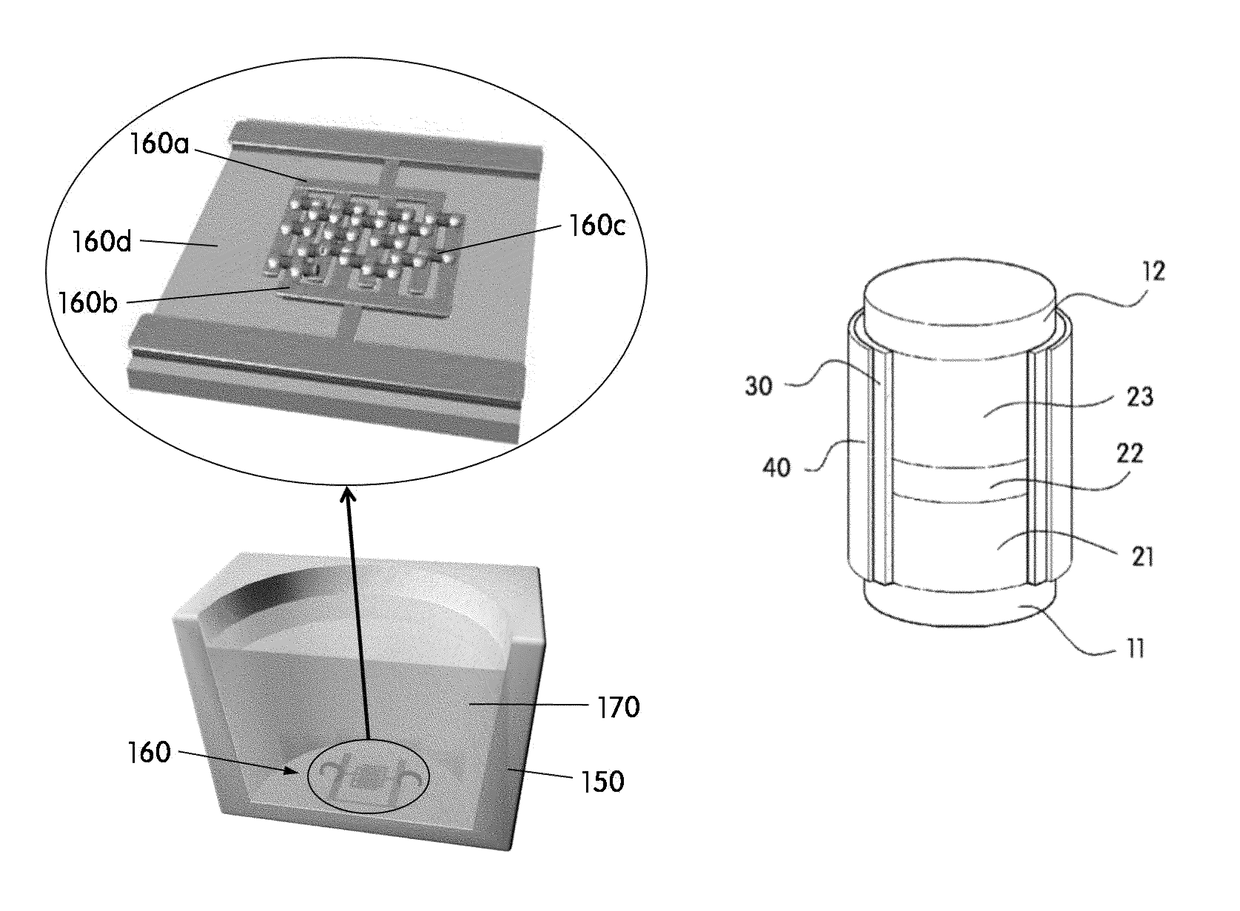

Ultra-small LED electrode assembly and method for manufacturing same

ActiveUS9773761B2Improve extraction efficiencyInhibit aggregationPrinted circuit assemblingPrinted circuit aspectsEngineeringNanometre

Owner:SAMSUNG DISPLAY CO LTD

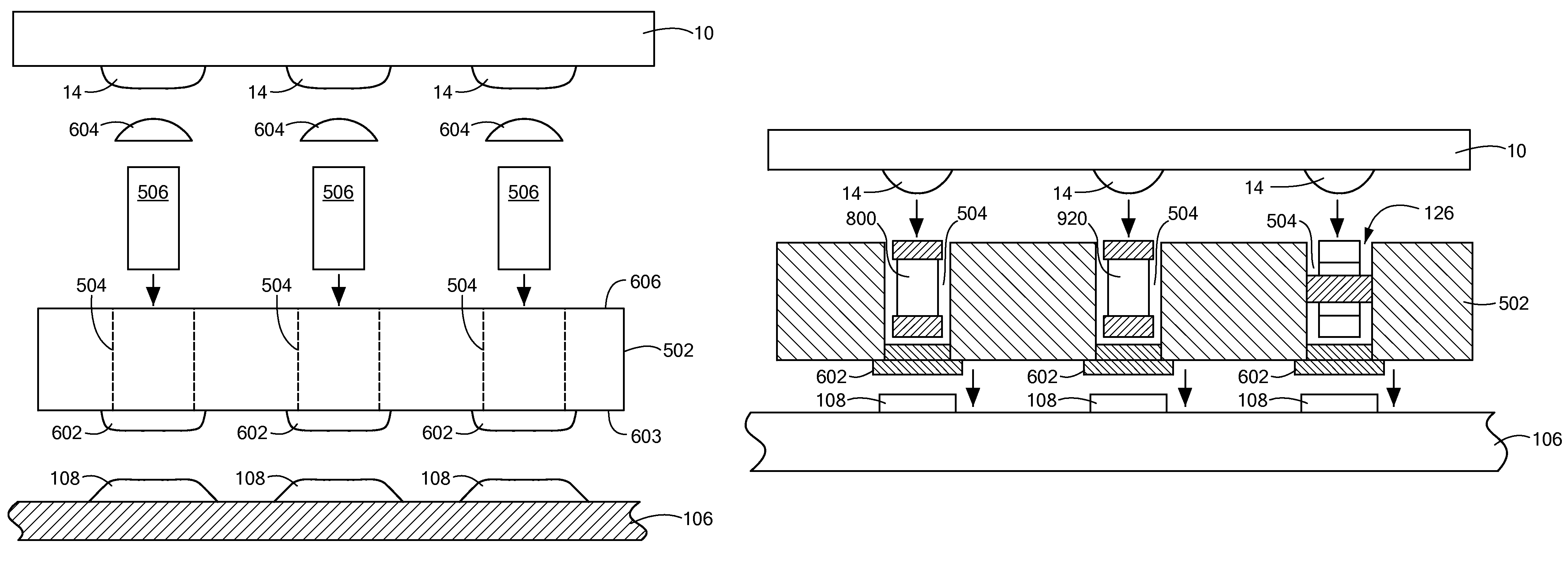

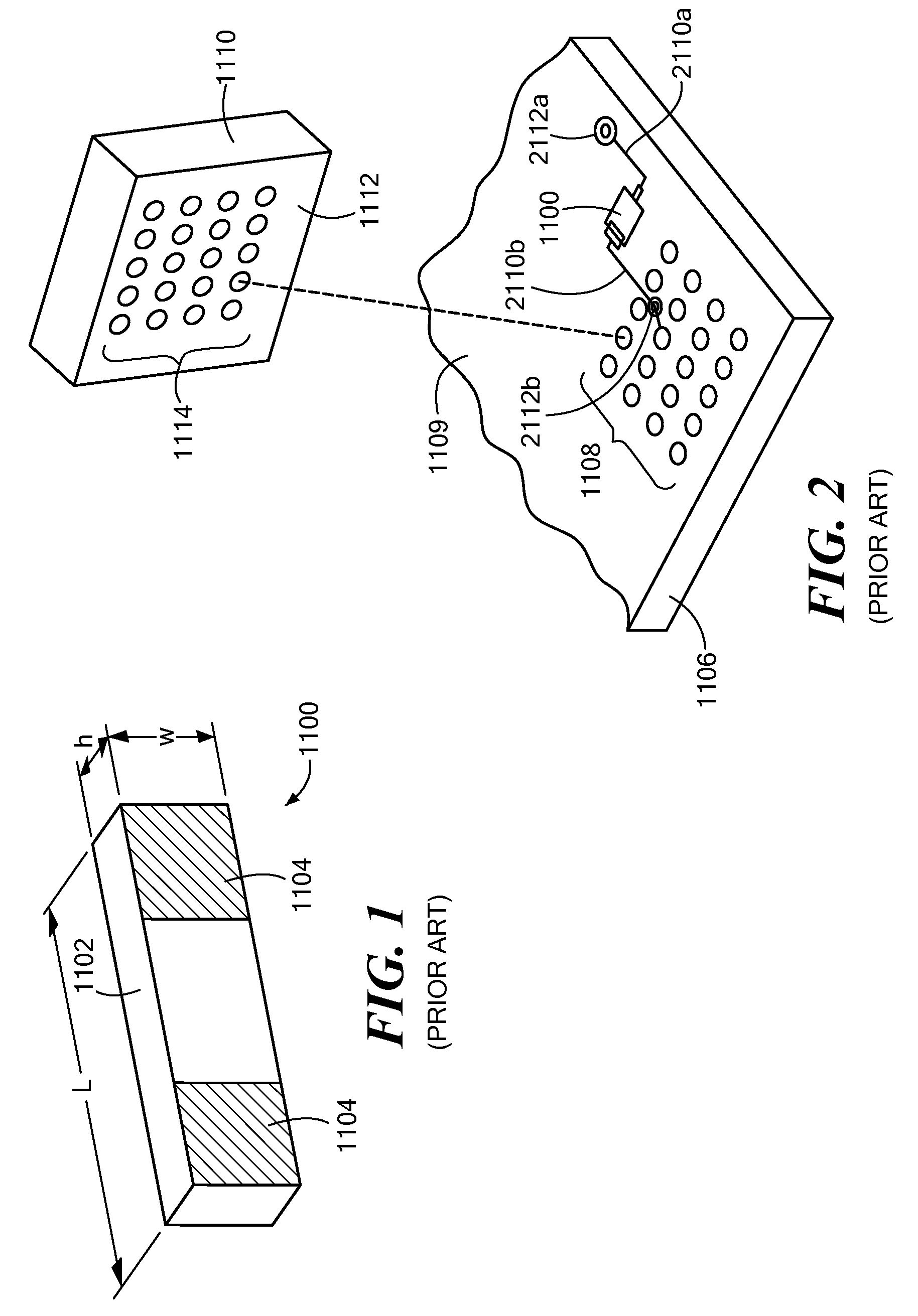

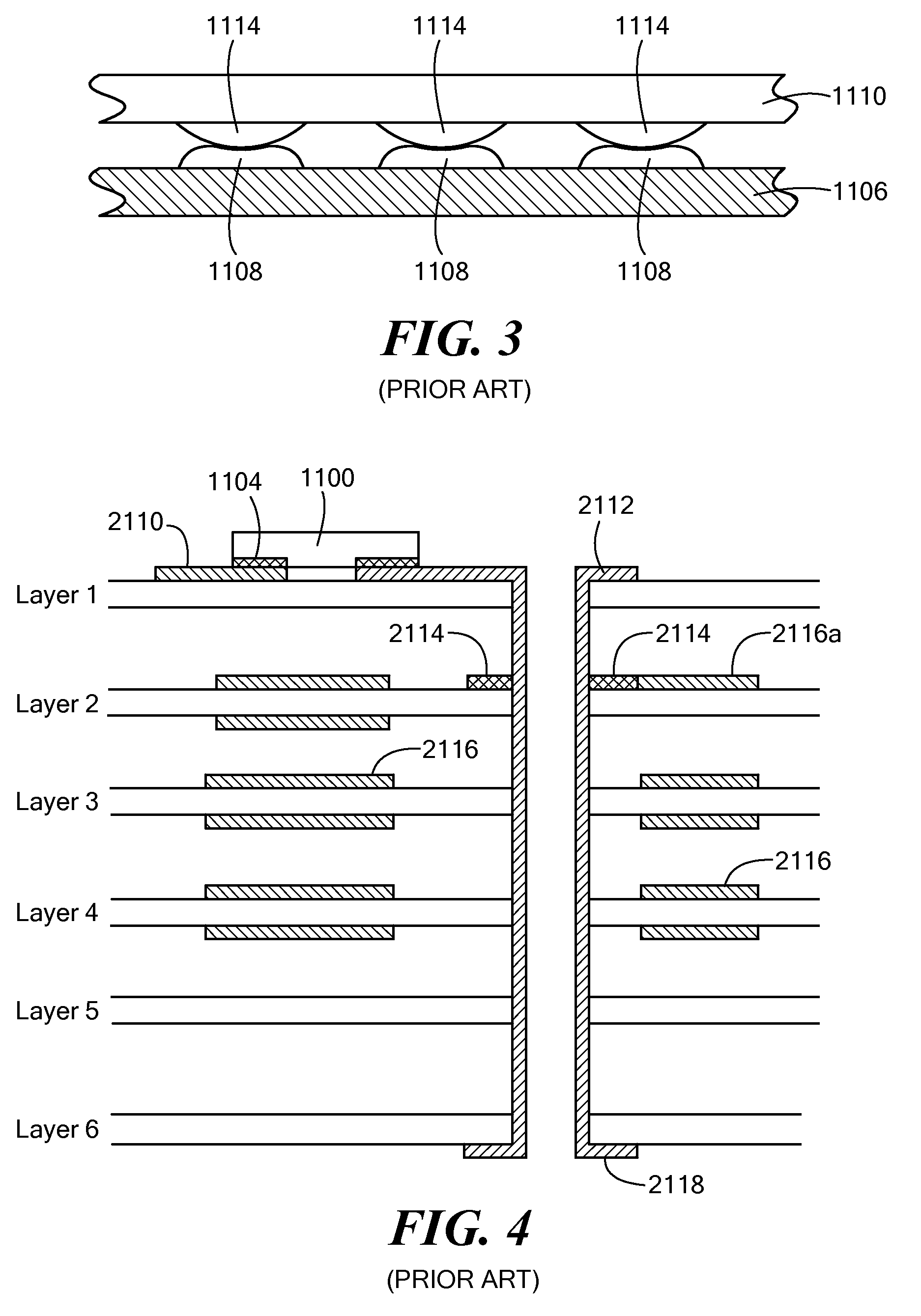

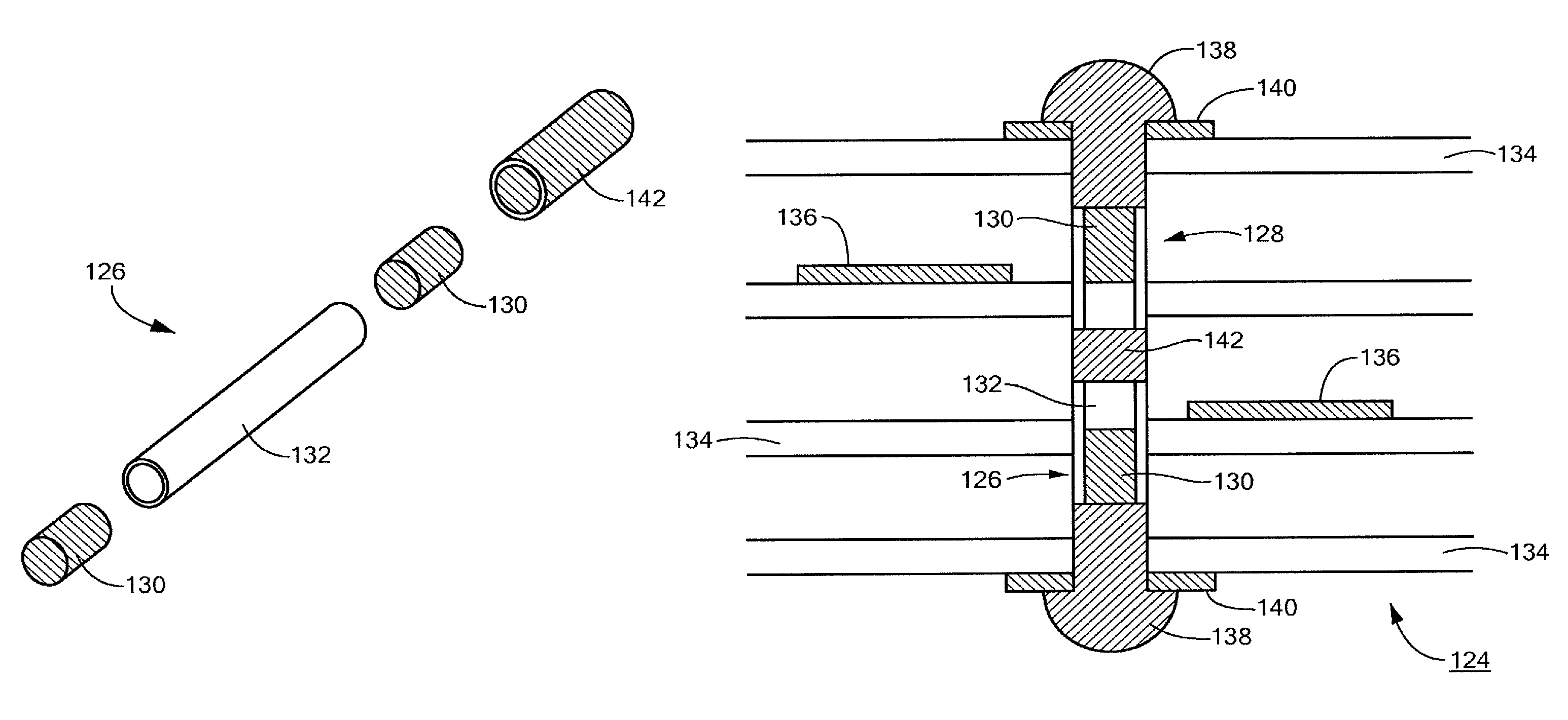

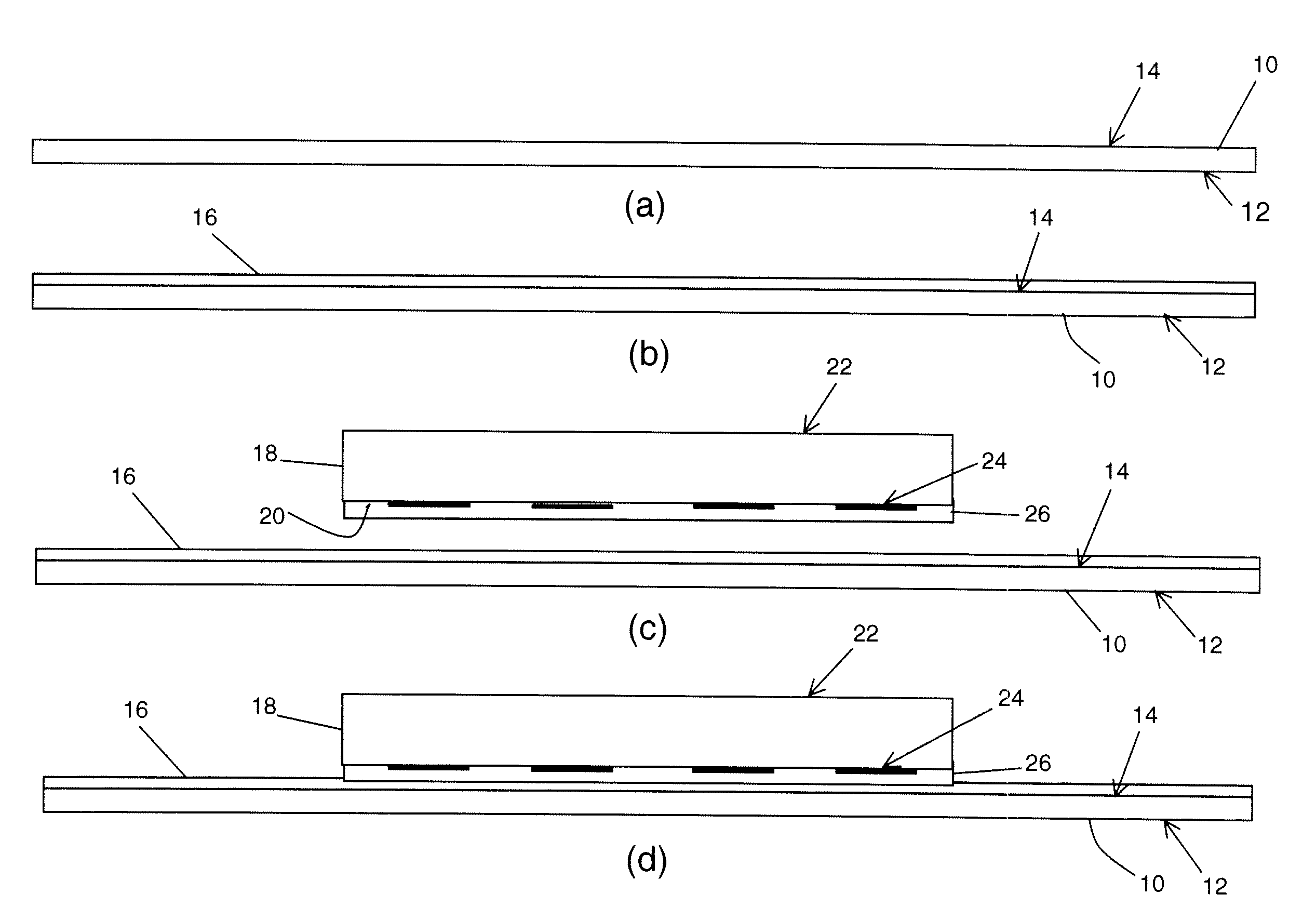

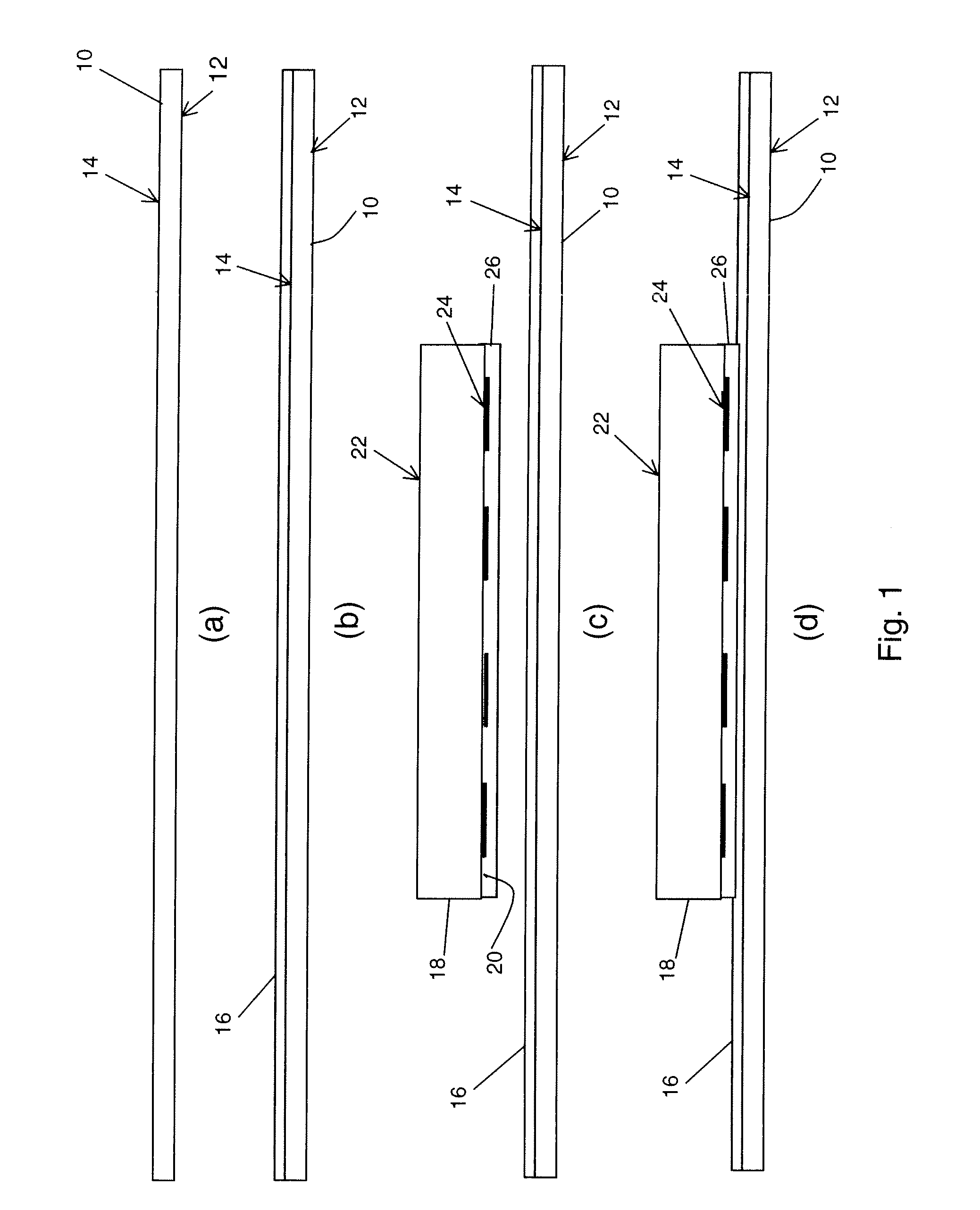

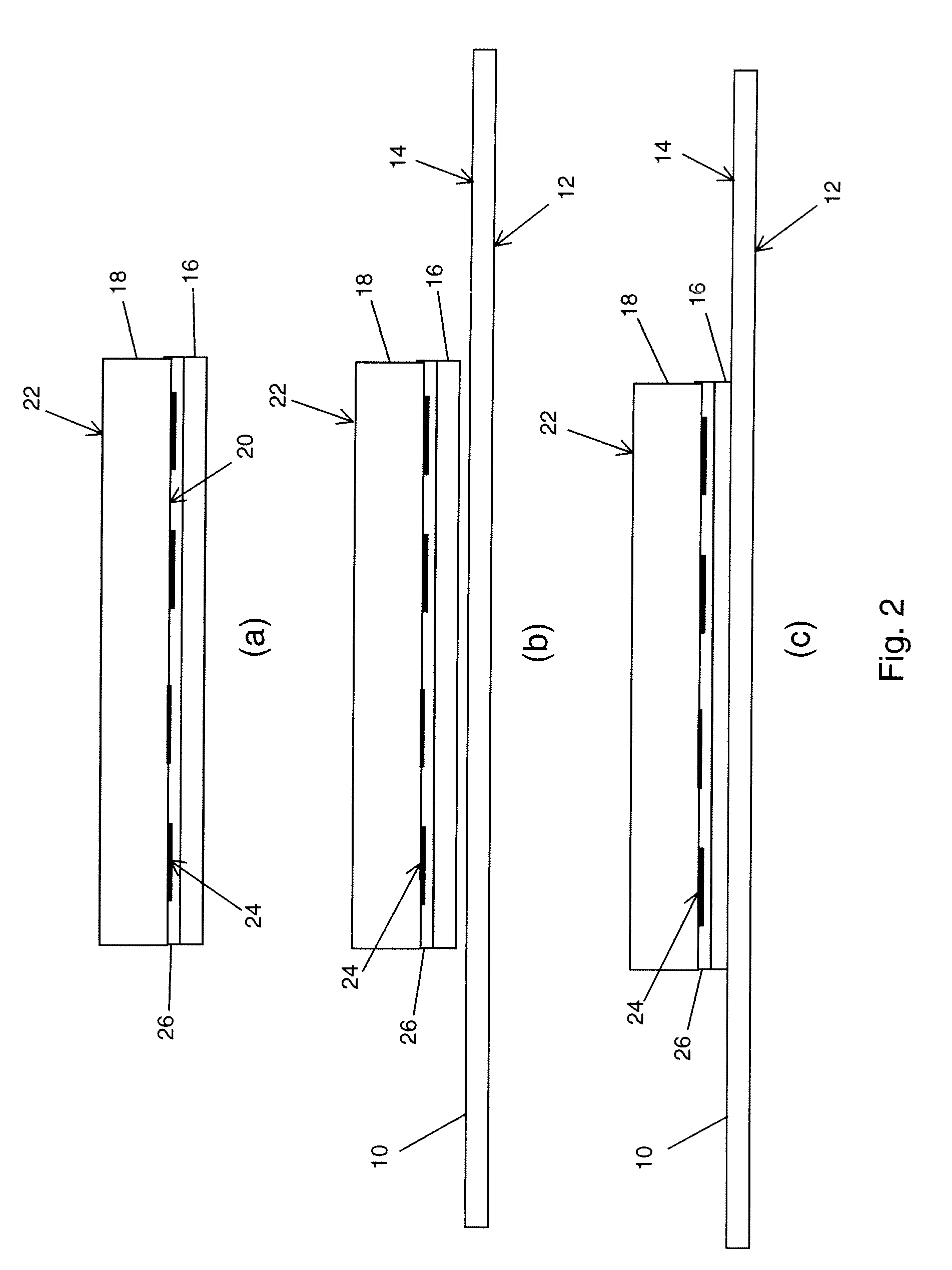

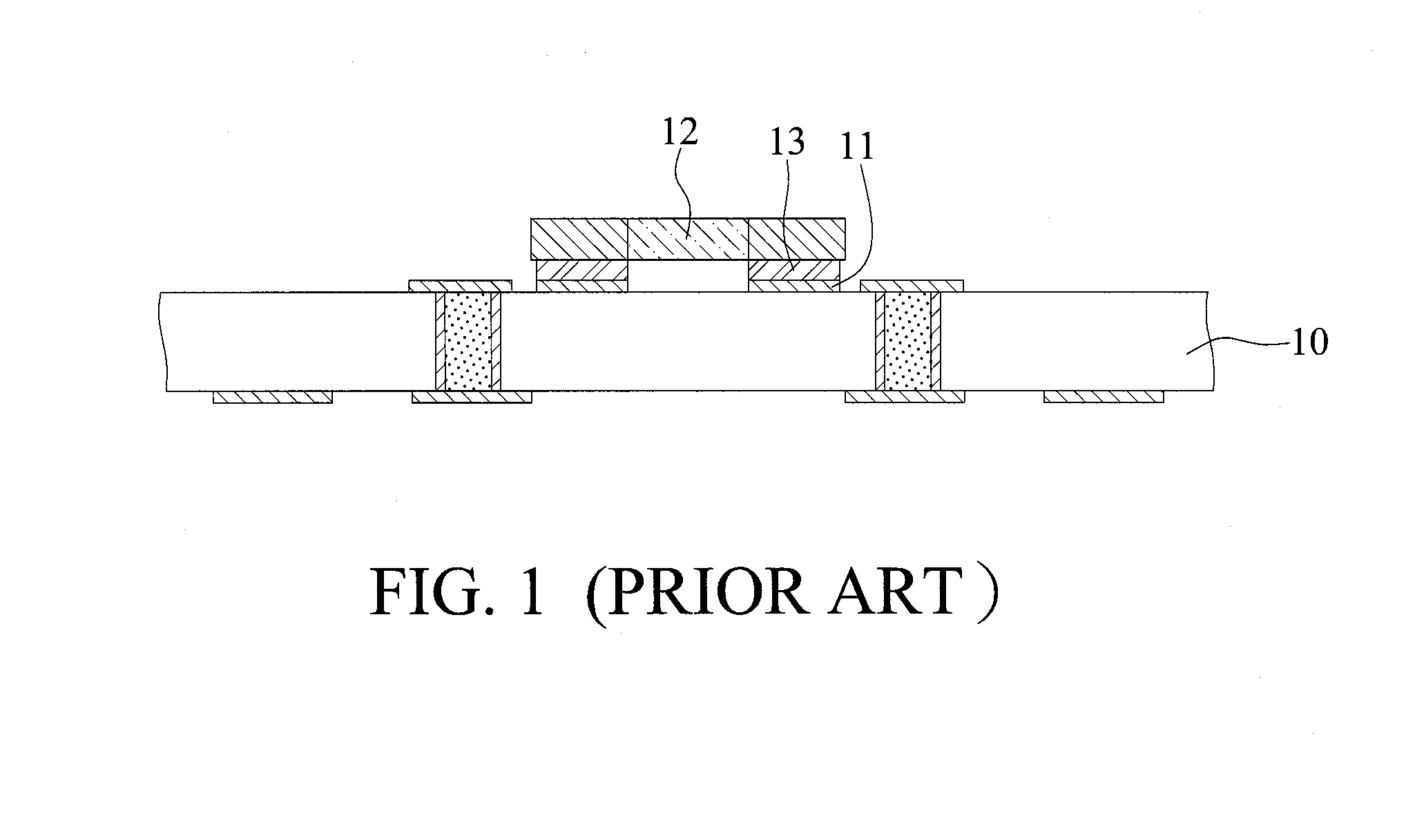

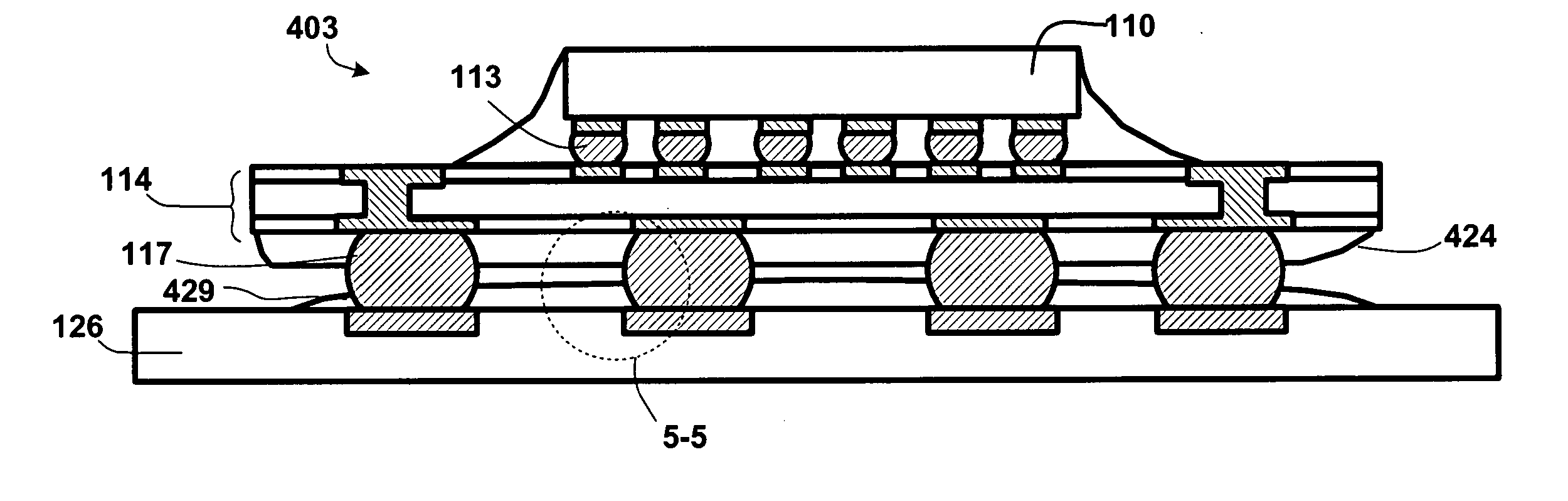

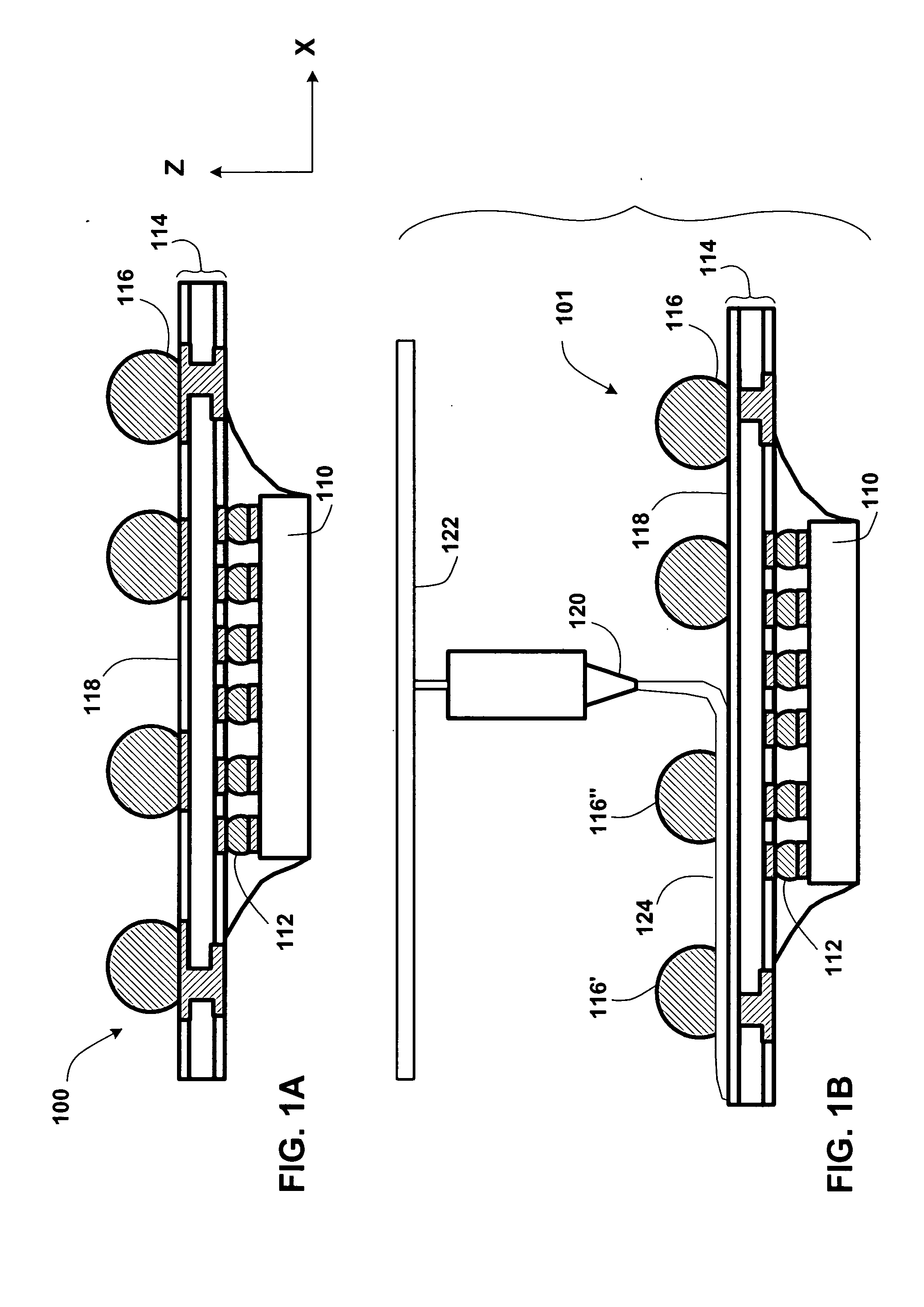

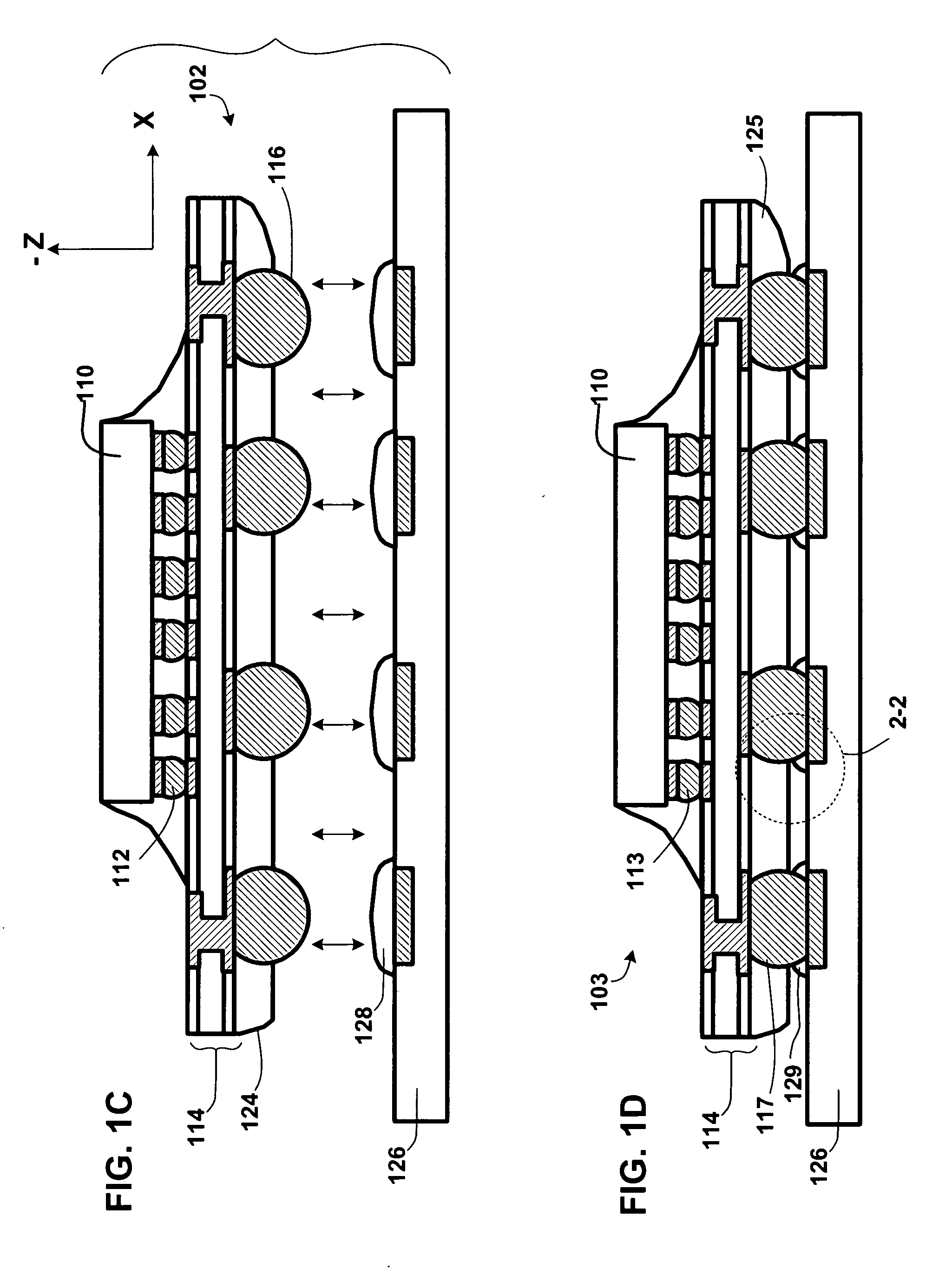

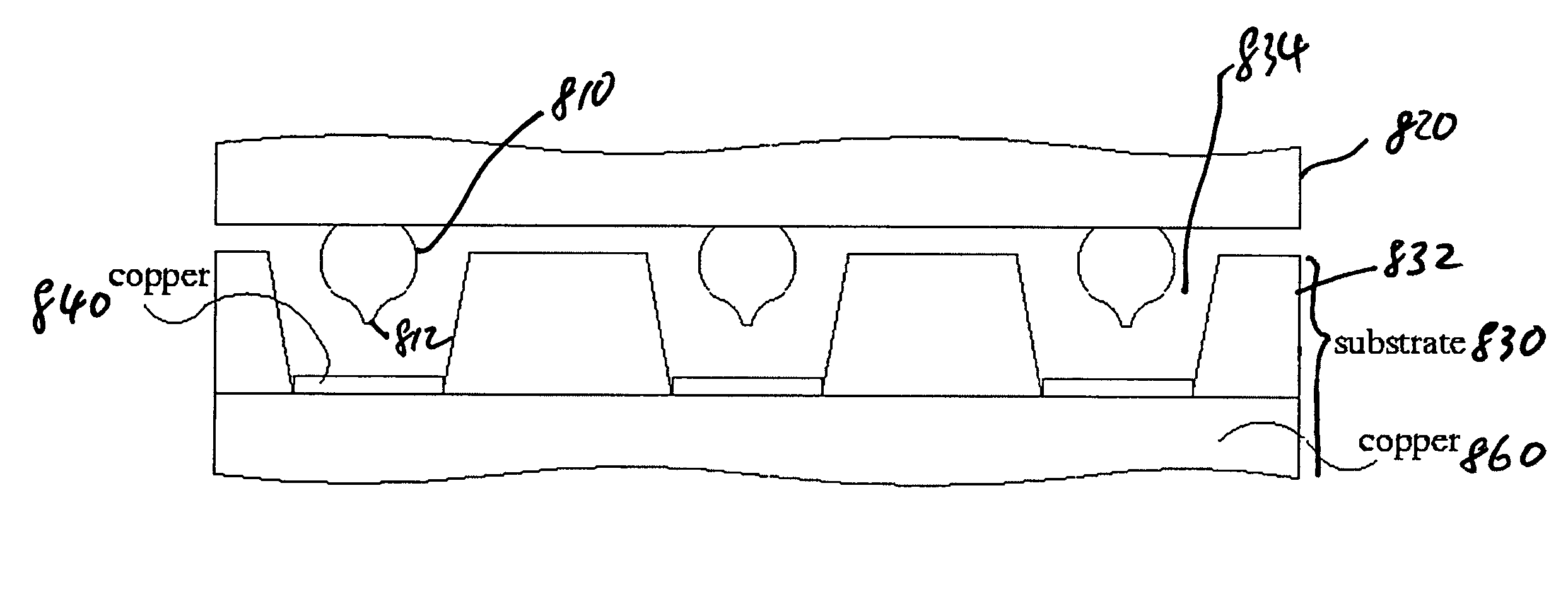

Interconnect device with discrete in-line components

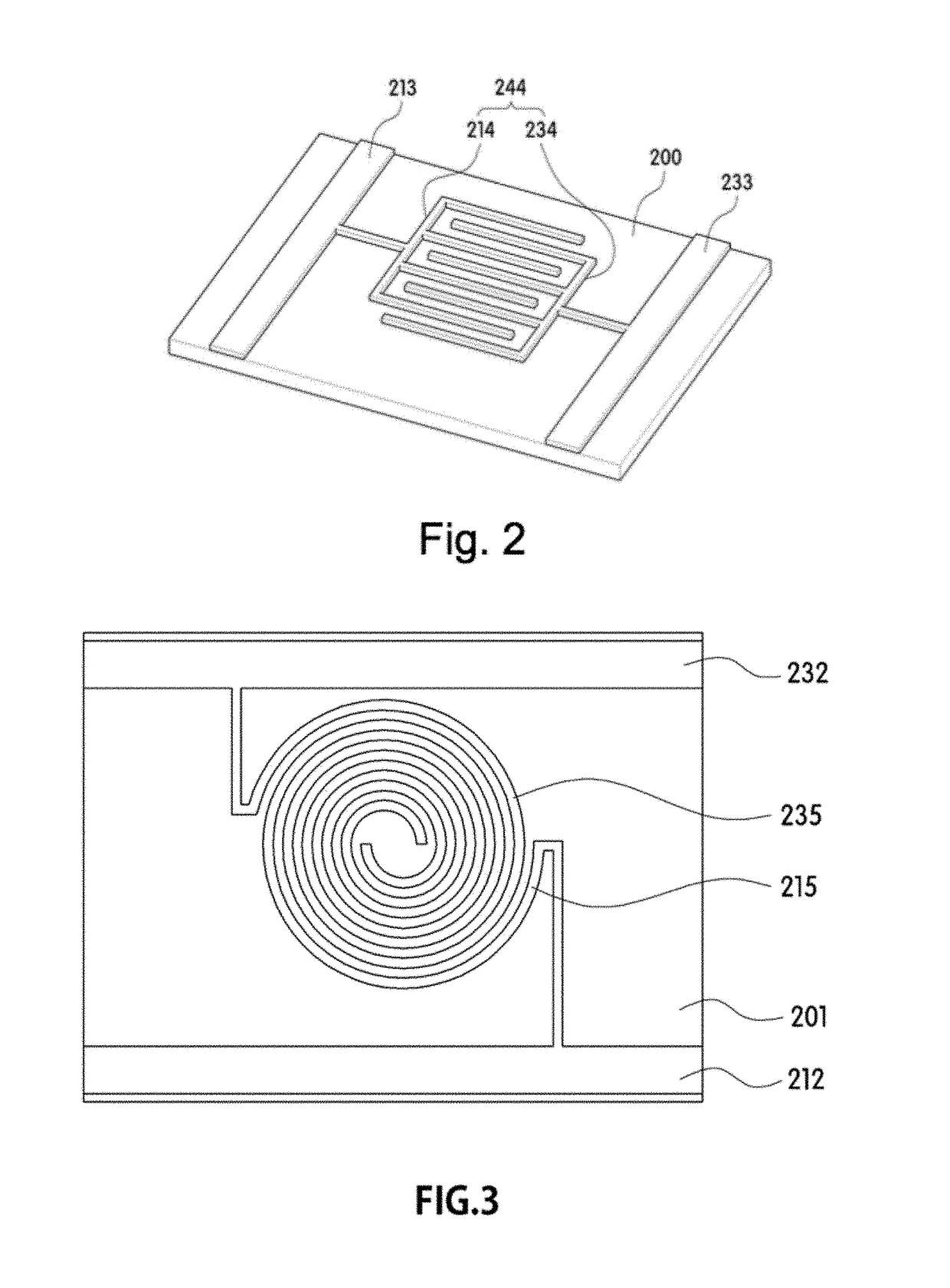

ActiveUS7891980B2Closely positionedCross-talk/noise/interference reductionPrinted circuit aspectsSolder ballBall grid array

An interconnect device is provided with a body through which a plurality of wells has been defined. At least one component having two terminals is provided in one or more of the wells. The component is sealed in its respective well such that the two terminals are accessible on opposite sides of the body. The body corresponds to a Ball Grid Array (BGA) device and is positioned between a BGA device and a printed circuit board (PCB). The component in the well is then inline with a solder ball on the BGA device and a corresponding pad on the PCB. Providing the component in the well frees up surface area on the PCB and also allows for positioning the component closer to a source of a signal. A component in the well is a discrete component having two terminals that may be solderable or made from a conductive pliable material. The terminals may be spring-mounted on the component.

Owner:SANGOMA US INC

Interconnect device with discrete in-line components

ActiveUS20100112826A1Closely positionedCross-talk/noise/interference reductionPrinted circuit aspectsSolder ballEngineering

An interconnect device is provided with a body through which a plurality of wells has been defined. At least one component having two terminals is provided in one or more of the wells. The component is sealed in its respective well such that the two terminals are accessible on opposite sides of the body. The body corresponds to a Ball Grid Array (BGA) device and is positioned between a BGA device and a printed circuit board (PCB). The component in the well is then inline with a solder ball on the BGA device and a corresponding pad on the PCB. Providing the component in the well frees up surface area on the PCB and also allows for positioning the component closer to a source of a signal. A component in the well is a discrete component having two terminals that may be solderable or made from a conductive pliable material. The terminals may be spring-mounted on the component.

Owner:SANGOMA US INC

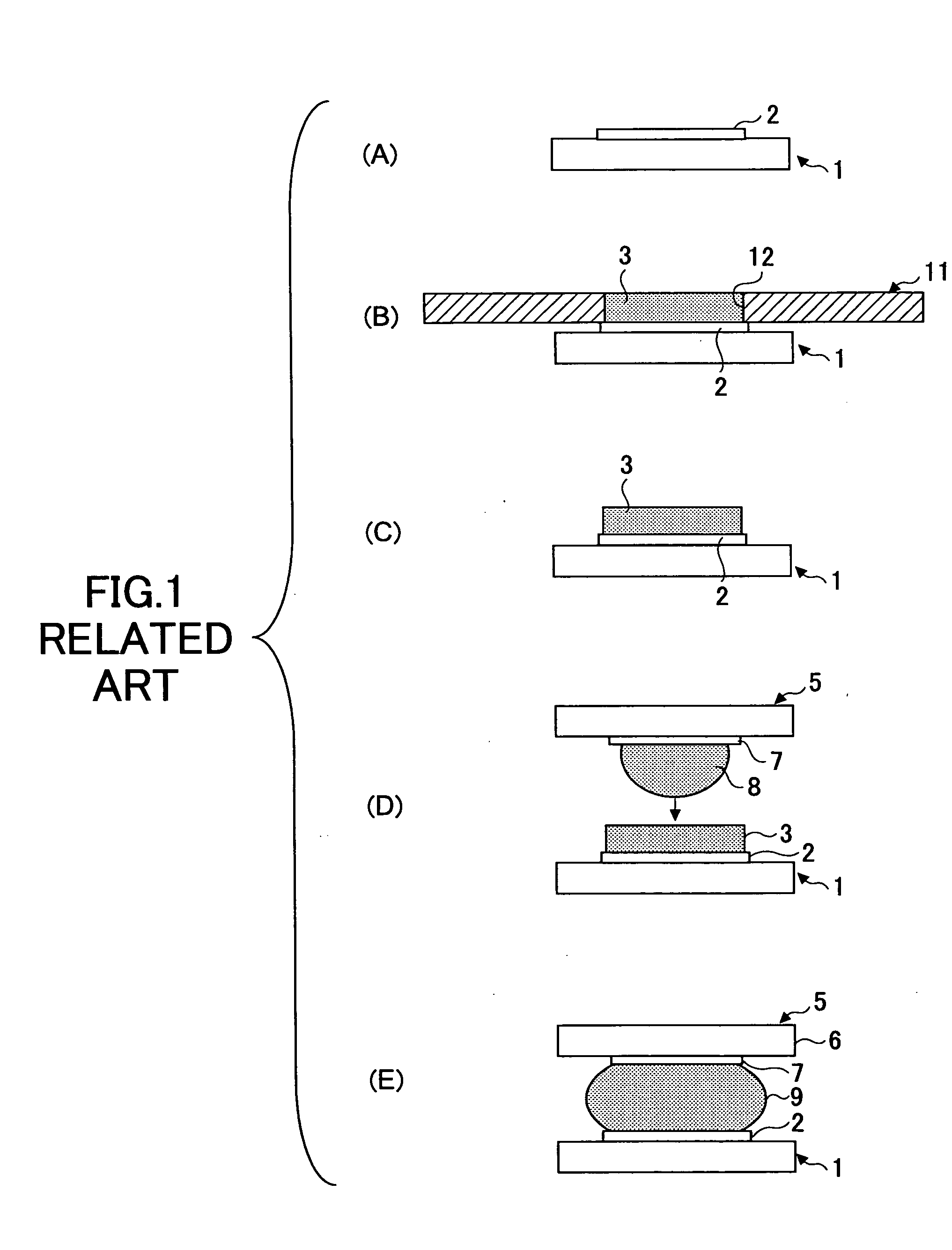

Flip chip with integrated flux and underfill

InactiveUS20010003058A1Printed circuit assemblingSemiconductor/solid-state device detailsEngineering physicsMechanical engineering

A flip chip having solder bumps and an integrated flux and underfill, as well as methods for making such a device, is described. The resulting device is well suited for a simple one-step application to a printed circuit board, thereby simplifying flip chip manufacturing processes which heretofore have required separate fluxing and underfilling steps.

Owner:FRY S METALS INC

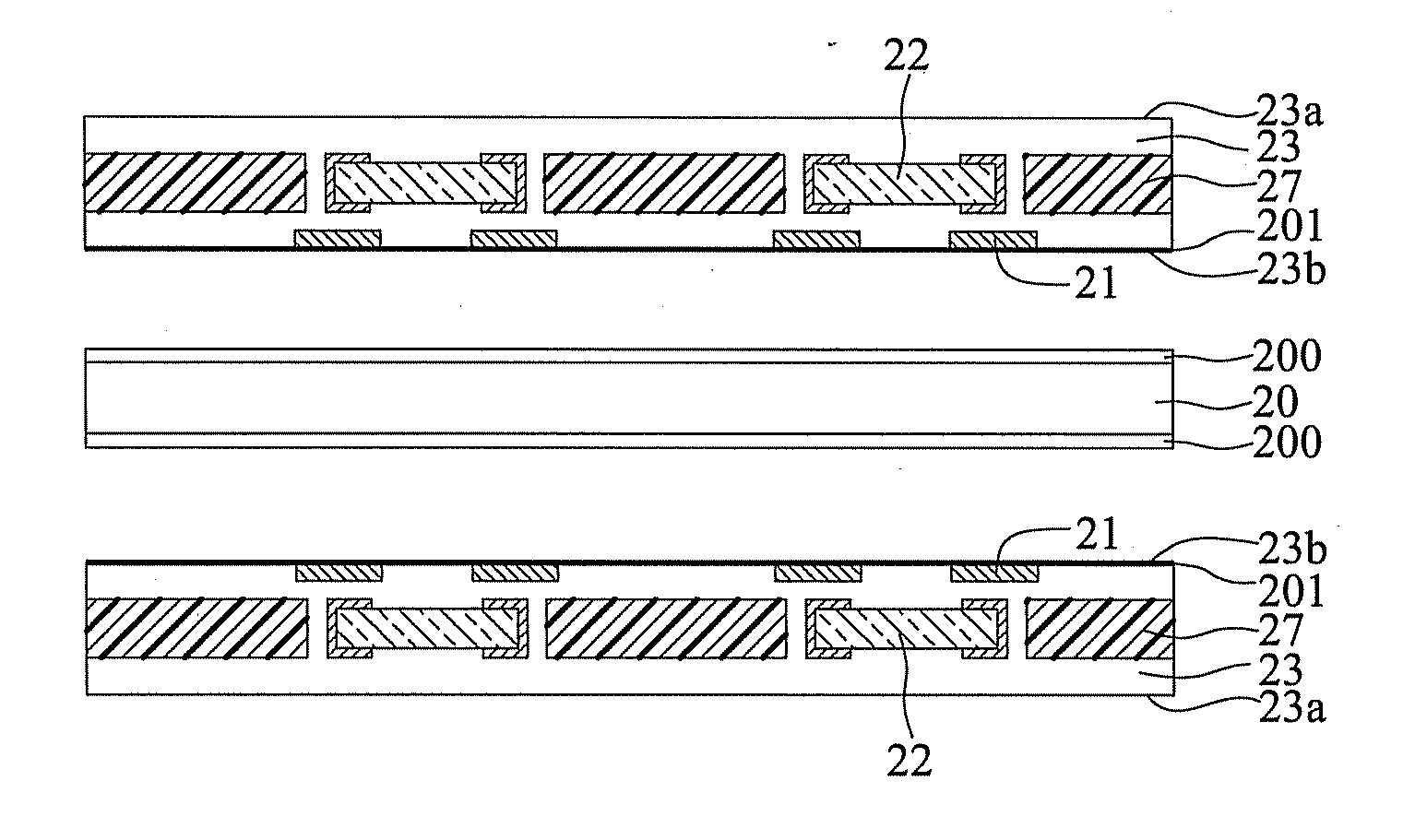

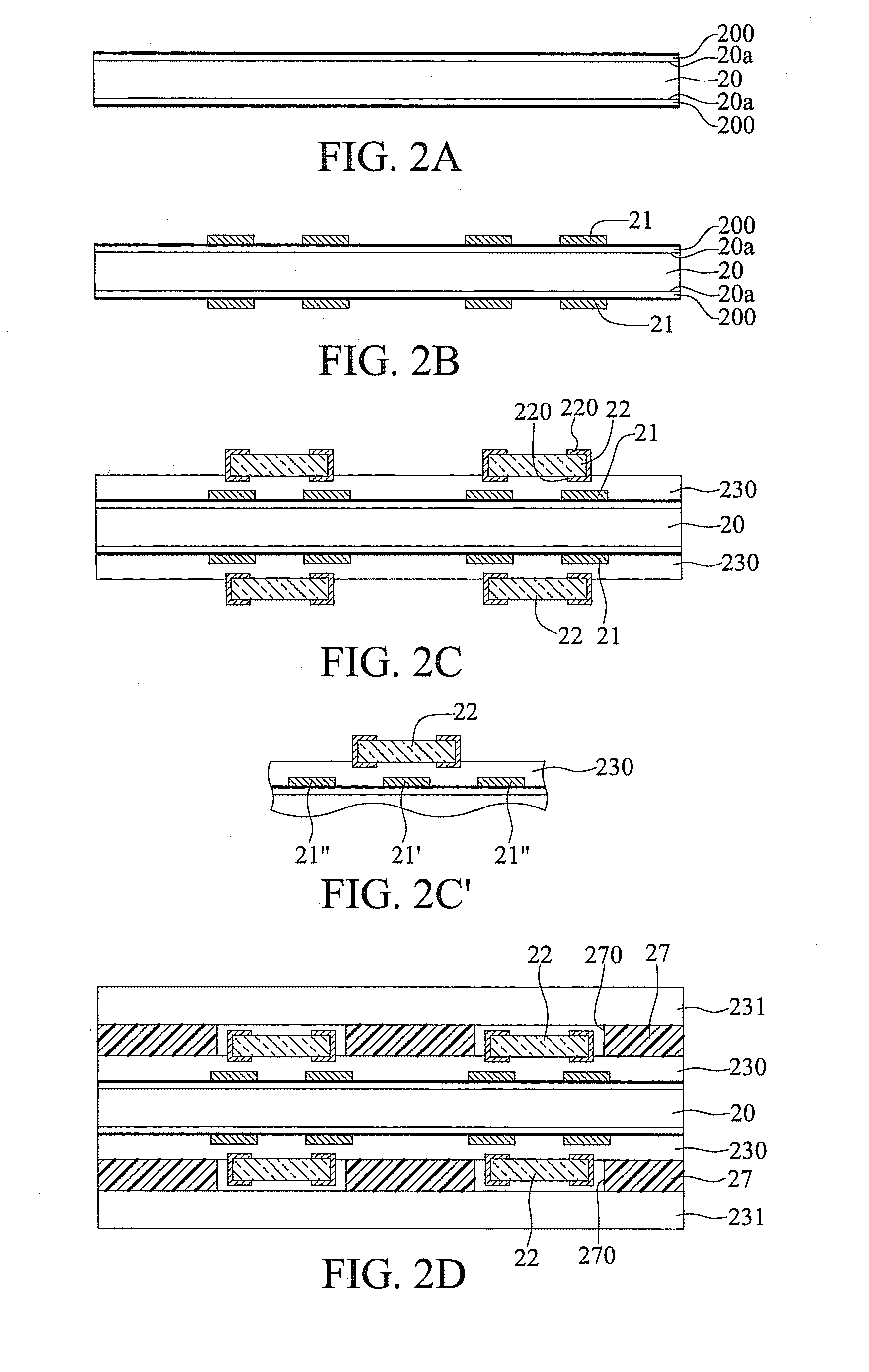

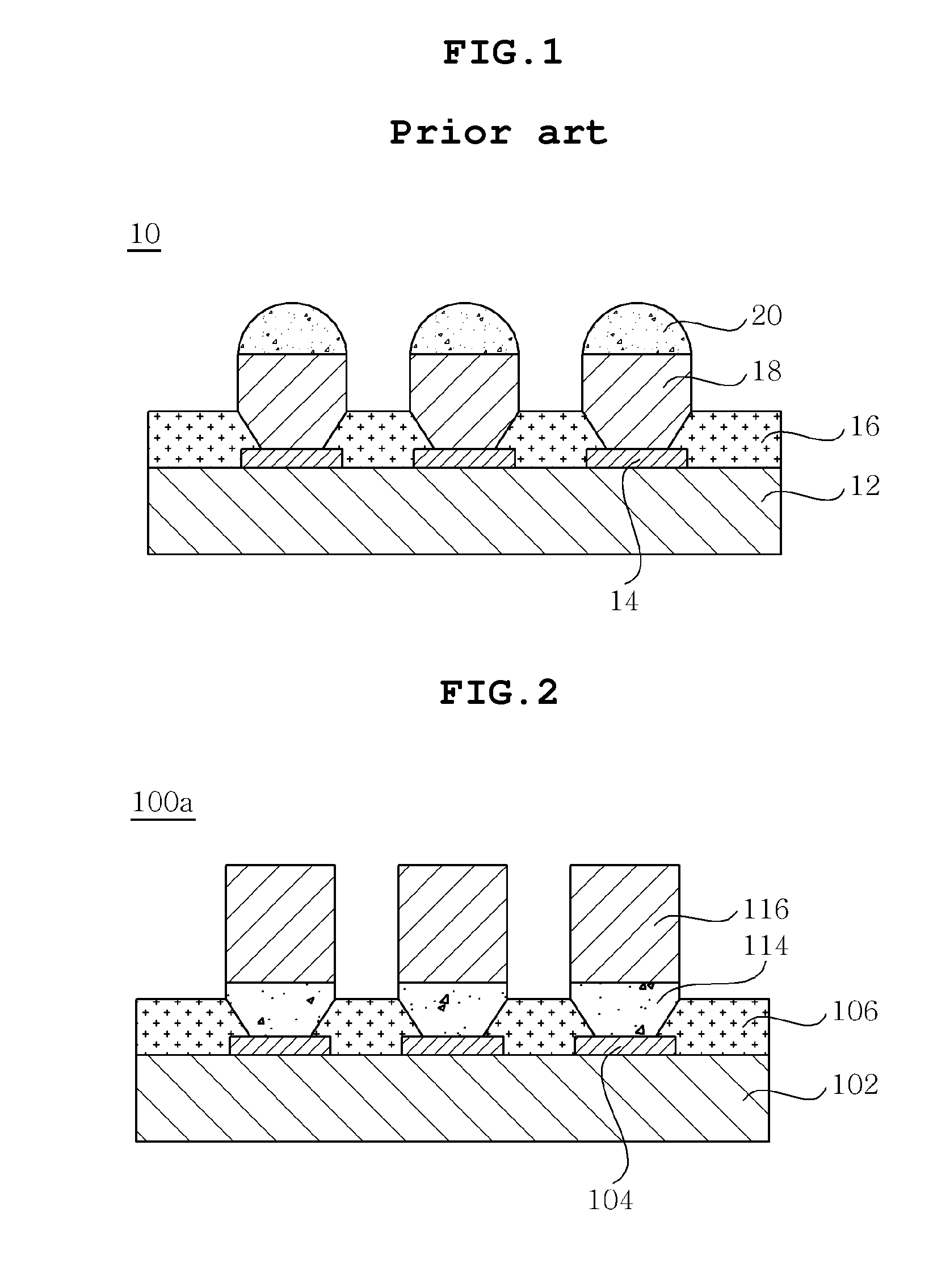

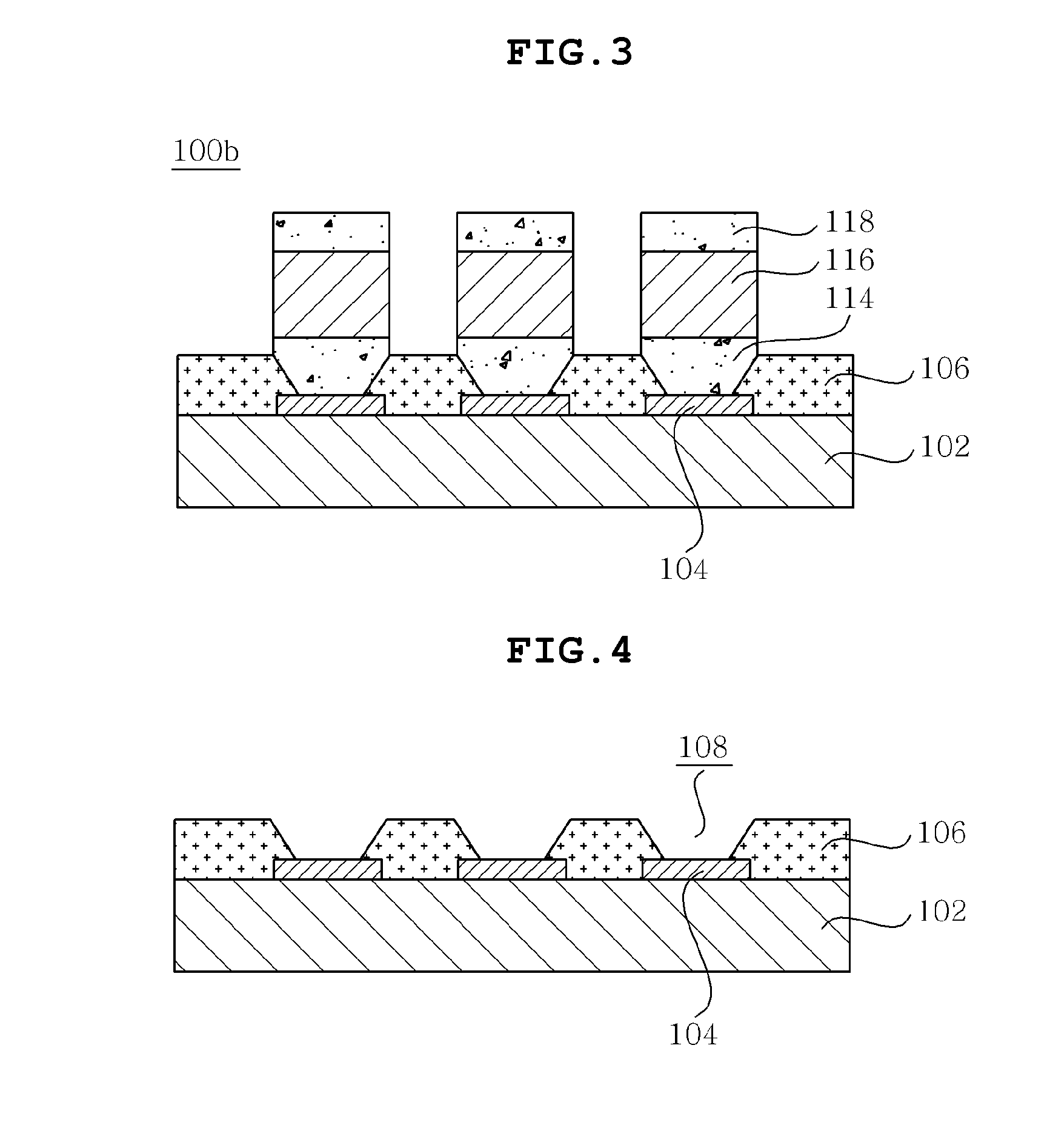

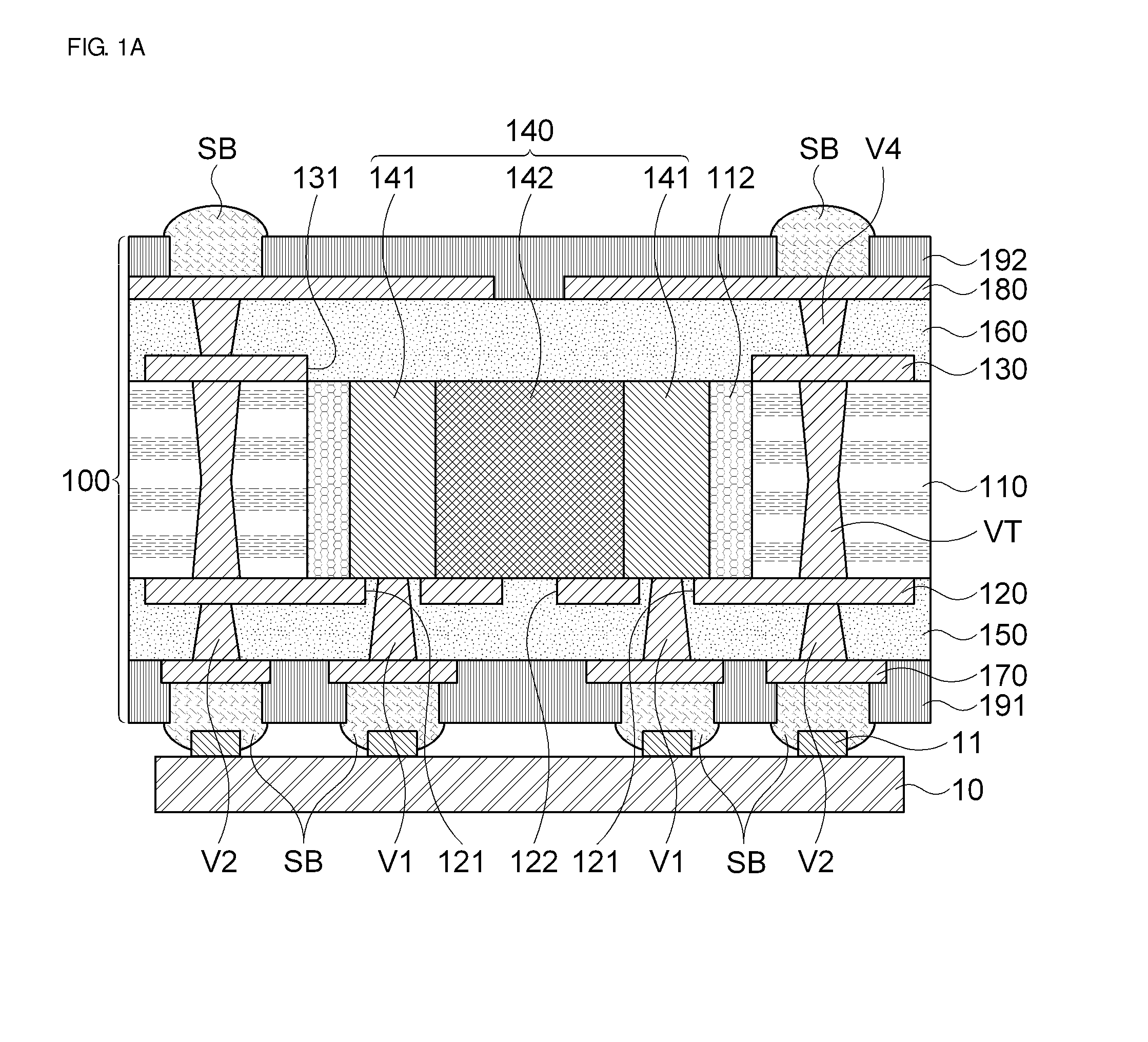

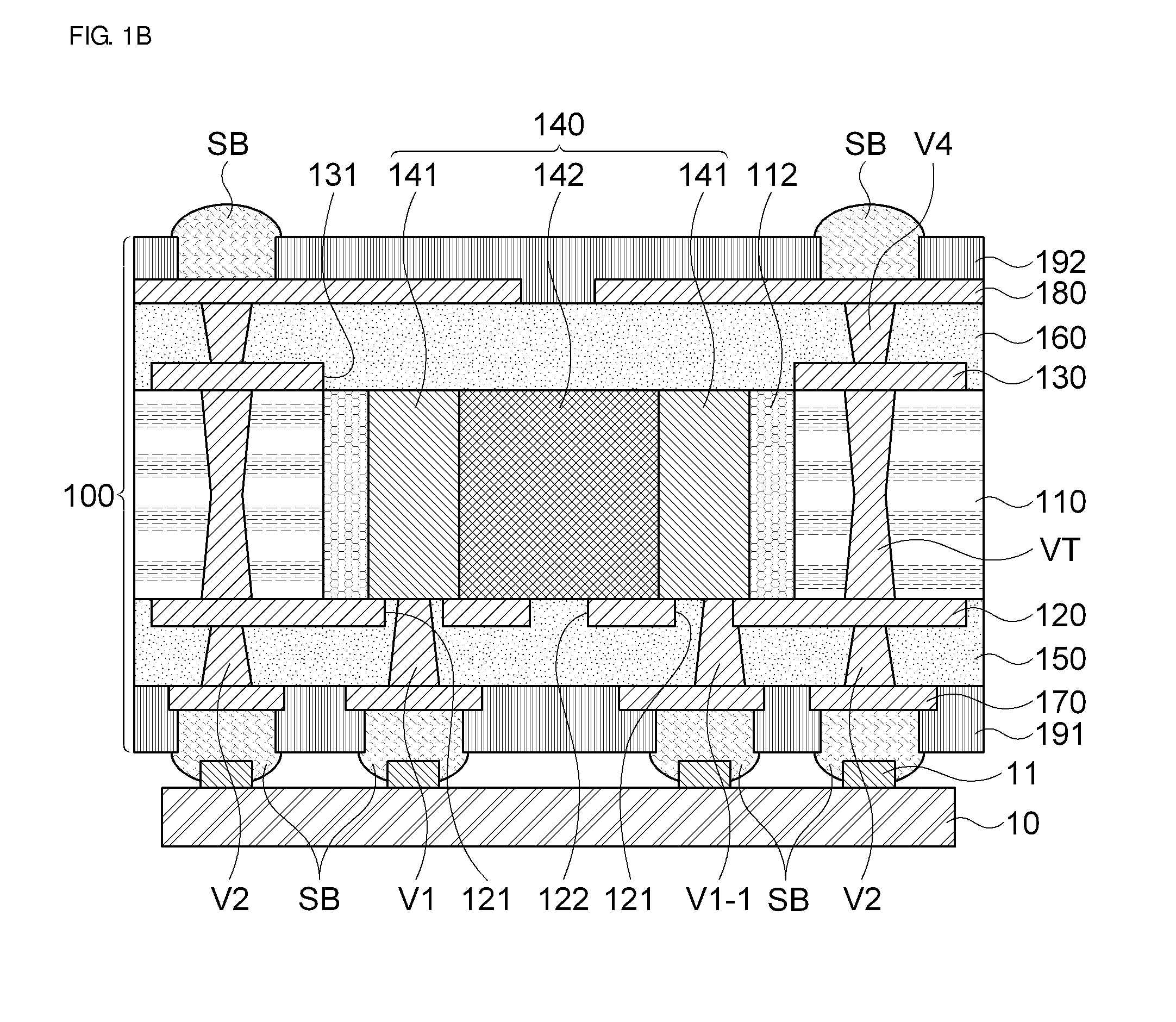

Packaging substrate having embedded passive component and fabrication method thereof

ActiveUS20120037411A1Reduce the overall heightShorten the signal transmission pathPrinted circuit assemblingPrinted electric component incorporationEngineeringDielectric layer

A packaging substrate includes: a core board with at least a cavity; a dielectric layer unit having upper and lower surfaces and encapsulating the core board and filling the cavity; a plurality of positioning pads embedded in the lower surface of the dielectric layer unit; at least a passive component having upper and lower surfaces with electrode pads disposed thereon and embedded in the dielectric layer unit so as to be received in the cavity of the core board at a position corresponding to the positioning pads; first and second wiring layers disposed on the upper and lower surfaces of the dielectric layer unit and electrically connected to the electrode pads of the upper and lower surfaces of the passive component through conductive vias, respectively. By embedding the passive component in the core board and the dielectric layer unit, the invention effectively reduces the height of the overall structure.

Owner:UNIMICRON TECH CORP

Press fit passive component

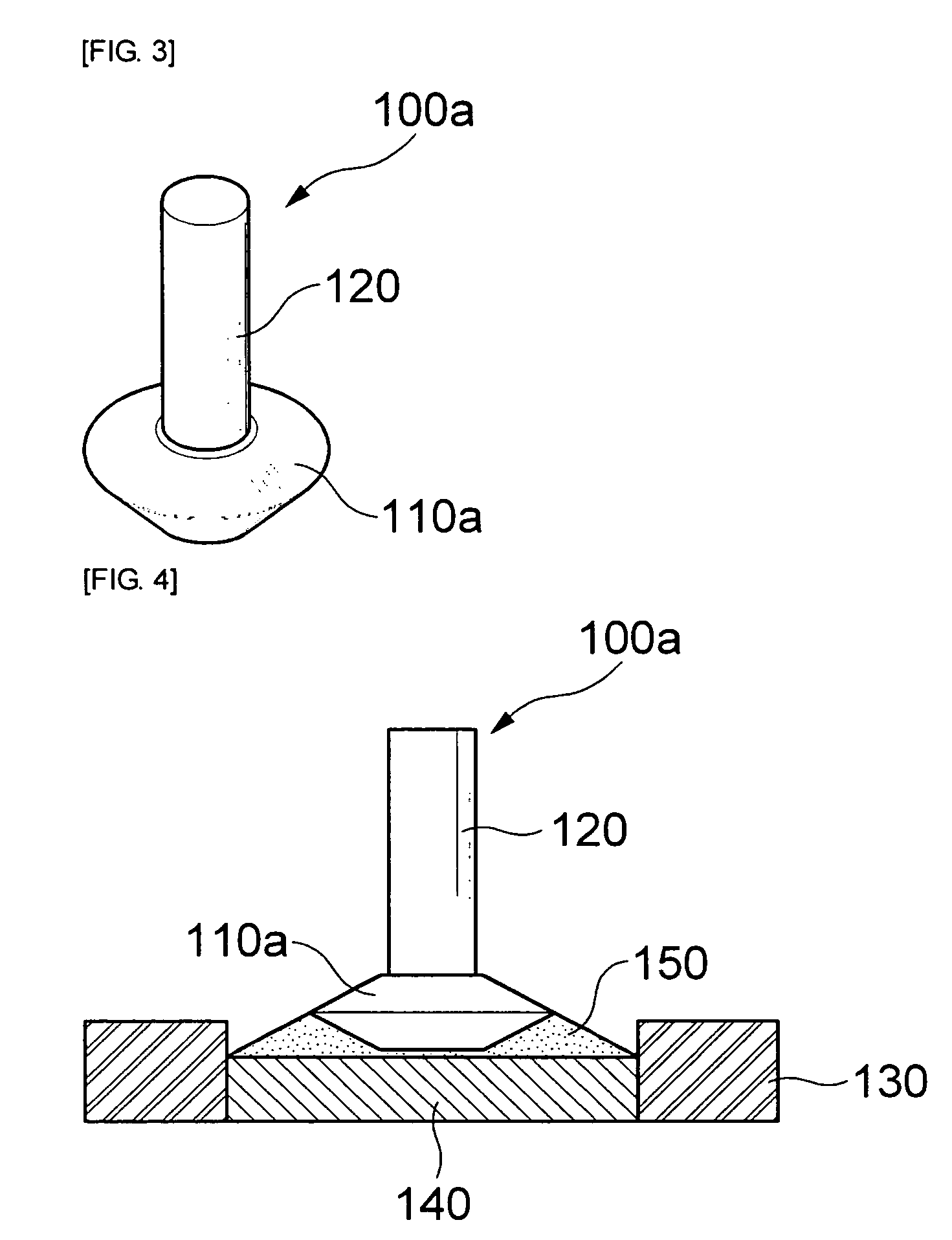

InactiveUS8064214B2Printed circuit assemblingPrinted electric component incorporationEngineeringPrinted circuit board

A press fit passive component, such as a resistor or capacitor, adapted to fit within, or partially within, a via of a printed circuit board. In one example, the press fit passive component has a cylindrically shaped body with solderable terminals at either end of the body, and a dielectric collar disposed at least partially about the cylindrically shaped body.

Owner:SANGOMA US INC

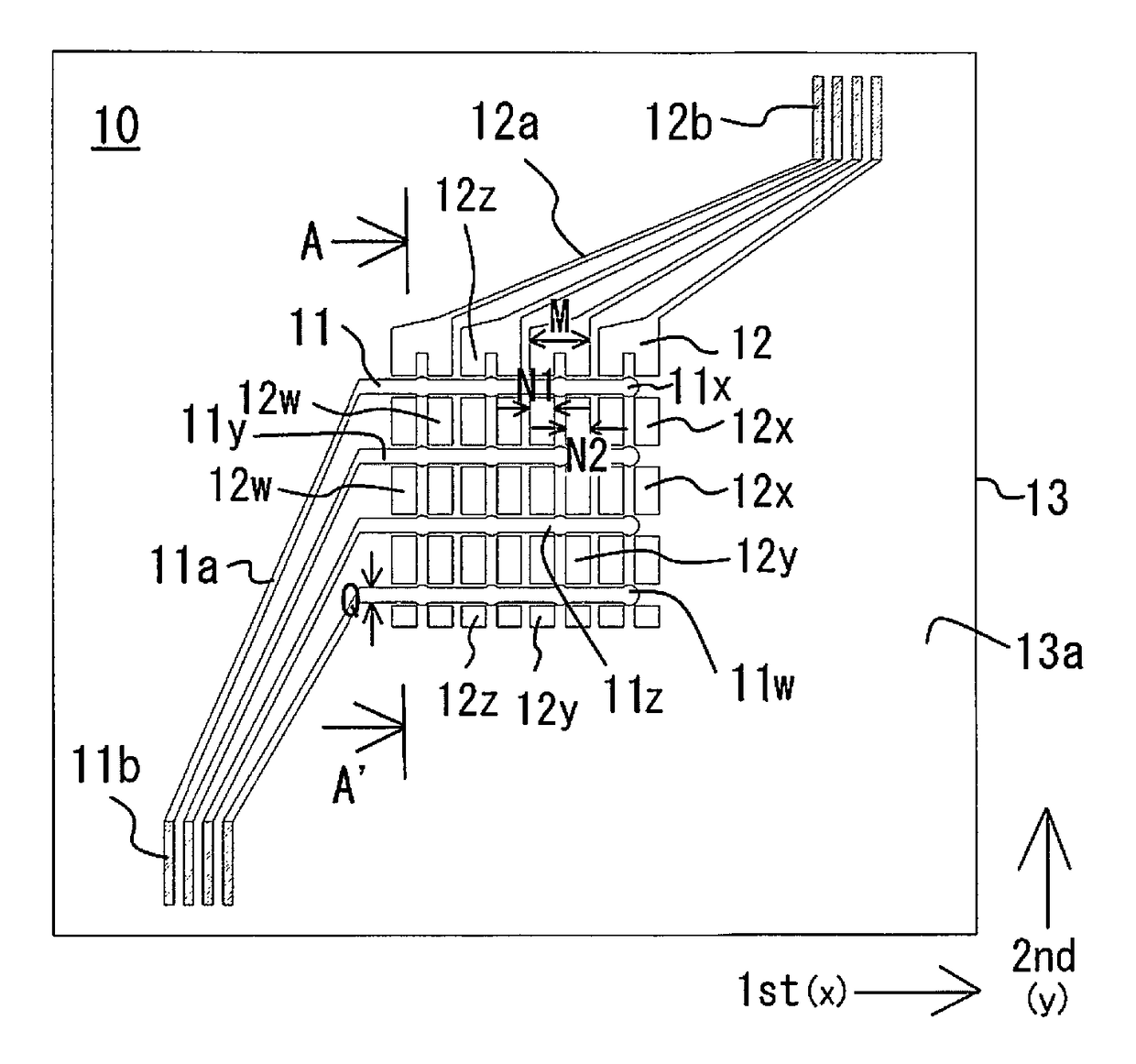

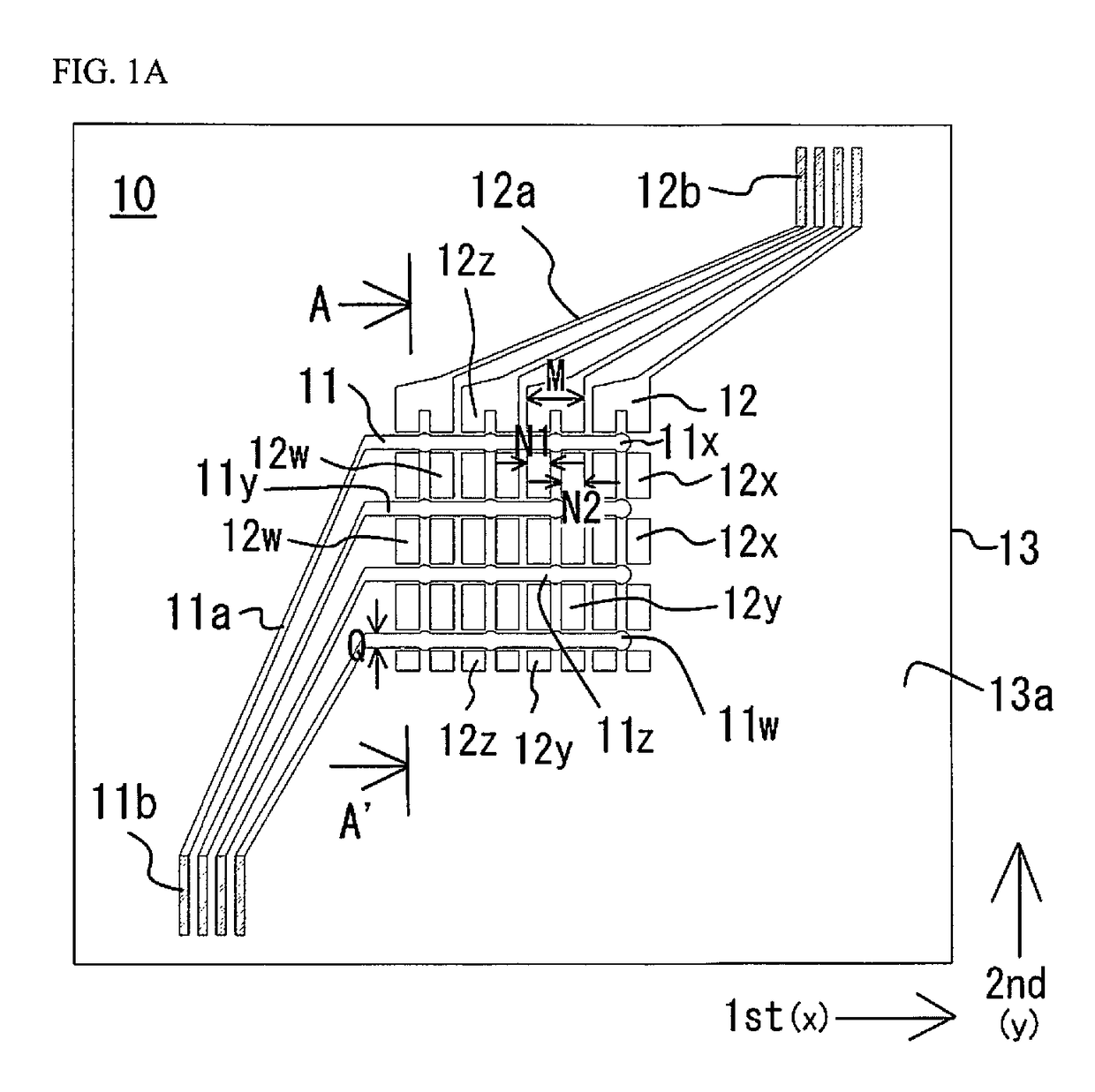

Light emitting device and adaptive driving beam headlamp system

ActiveUS9722160B2Small sizeSimple structurePlanar light sourcesVehicle headlampsLight beamEngineering

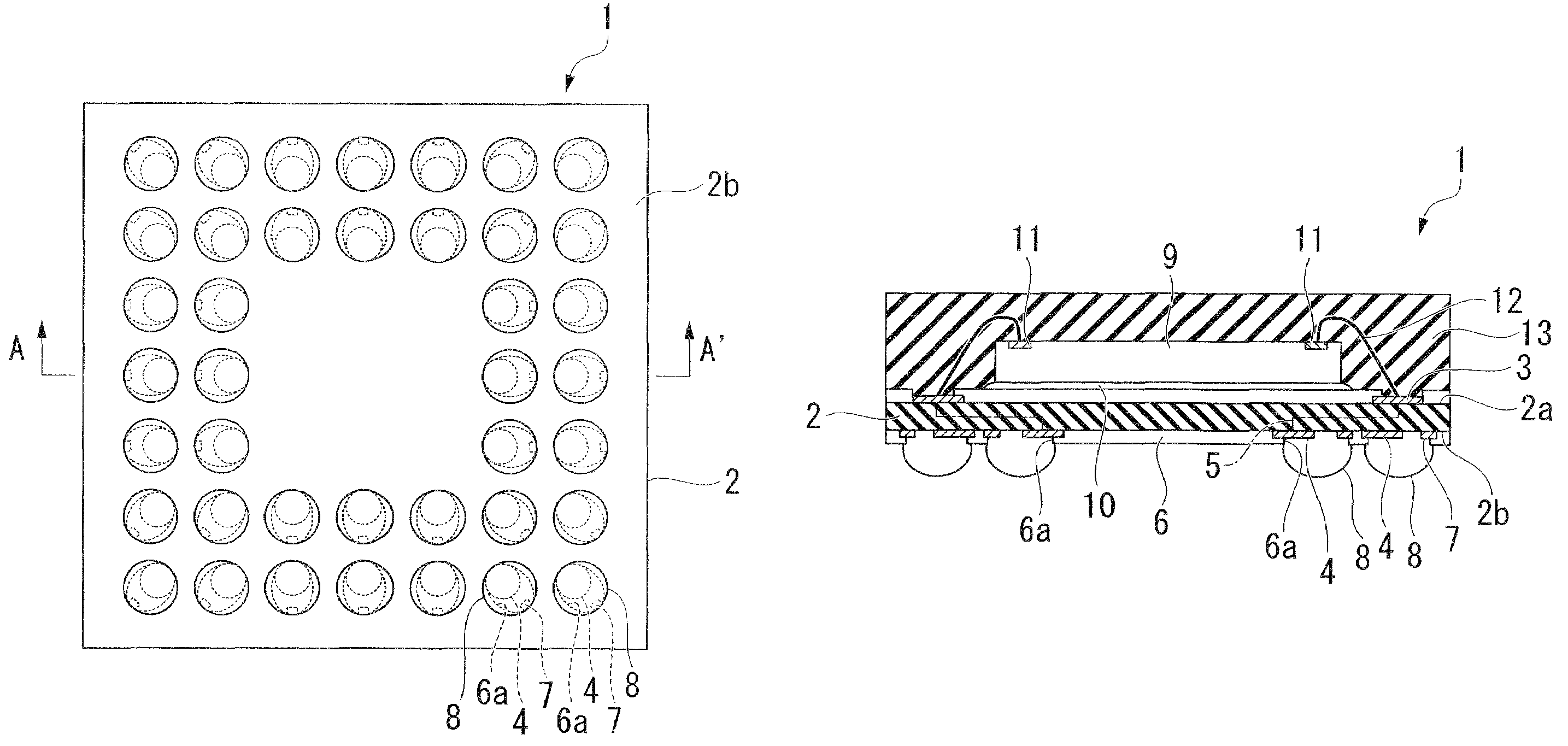

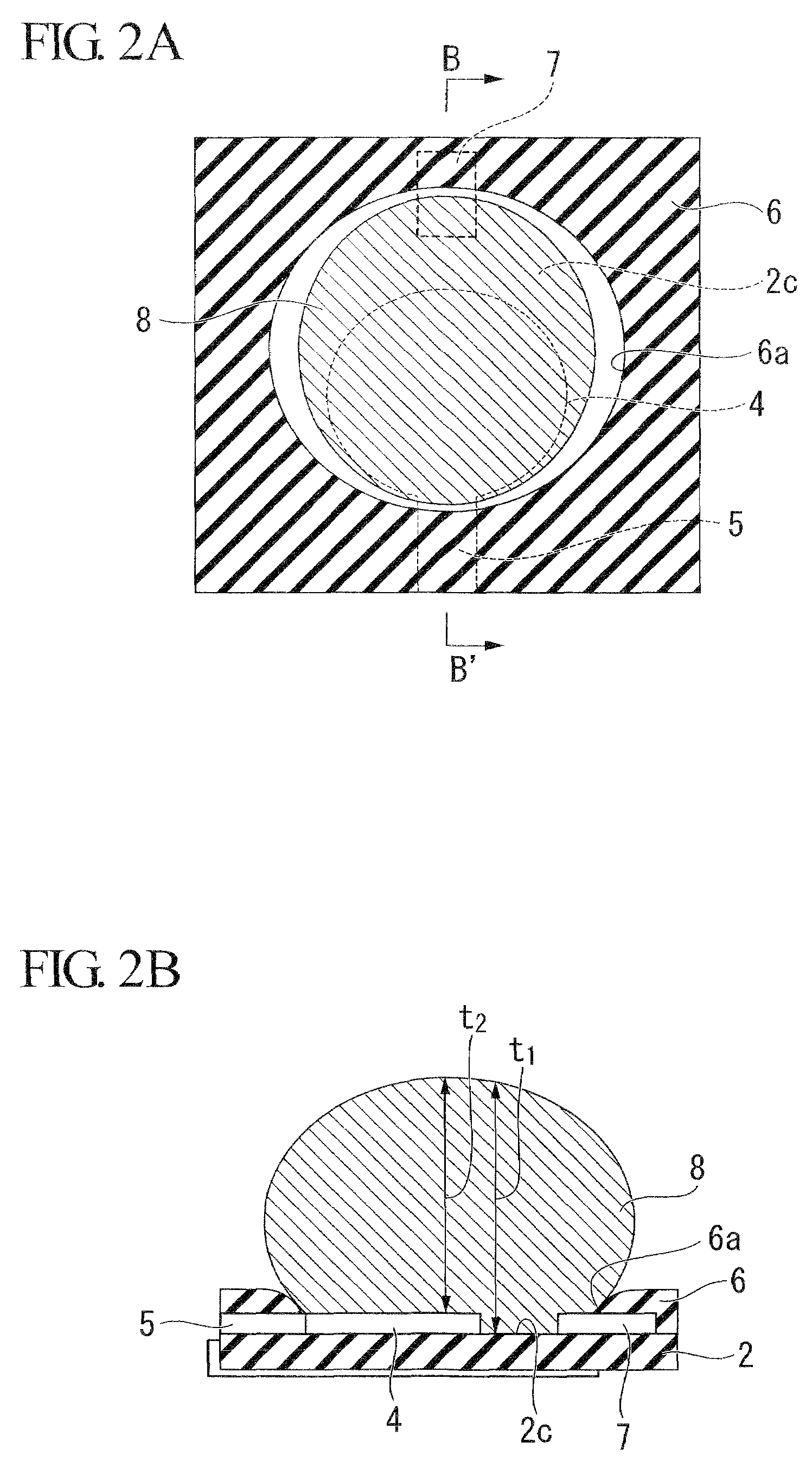

A light emitting device includes a substrate, a plurality of first wiring members, a plurality of second wiring members and a plurality of light emitting elements. The first wiring members extend in a first direction. The second wiring members extend in a second direction. Each of the second wiring members is segmented into a plurality of second wiring portions. The light emitting elements are disposed along the second direction. A first electrode of the light emitting element is connected to a corresponding one of the first wiring members. A second electrode of the light emitting element has a first connection part and a second connection part that is linked to the first connection part. The first connection part and the second connection part are connected to a corresponding one of the second wiring members and bridge at least two of the segmented second wiring portions in the second direction.

Owner:NICHIA CORP

Recoverable electronic component

InactiveUS20080318055A1Free from damageSemiconductor/solid-state device detailsSynthetic resin layered productsEngineeringElectronic component

An electronic component includes a base insulative layer having a first surface and a second surface; an electronic device having a first surface and a second surface, and the electronic device being secured to the base insulative layer; an adhesive layer disposed between the first surface of the electronic device and the second surface of the base insulative layer; and a removable layer disposed between the first surface of the electronic device and the second surface of the base insulative layer. The base insulative layer secures to the electronic device through the removable layer. The removable layer is capable of releasing the base insulative layer from the electronic device. The removal may be done without damage to a predetermined part of the electronic component.

Owner:GENERAL ELECTRIC CO

Packaging substrate having a passive element embedded therein and method of fabricating the same

ActiveUS20120037404A1Reduce the height of the structureShorten the signal transmission pathSemiconductor/solid-state device detailsSolid-state devicesDielectric layerElectrical and Electronics engineering

A packaging substrate includes: a dielectric layer unit having top and bottom surfaces; a positioning pad embedded in the bottom surface of the dielectric layer unit; at least a passive element having a plurality of electrode pads disposed on upper and lower surfaces thereof, the passive element being embedded in the dielectric layer unit and corresponding to the positioning pad; a first circuit layer disposed on the top surface of the dielectric layer unit, the first circuit layer having first conductive vias electrically connected to the electrode pads disposed on the upper surface of the passive element; and a second circuit layer disposed on the bottom surface of the dielectric layer unit, the second circuit layer having second conductive vias electrically connected to the electrode pads disposed on the lower surface of the passive element. Through the embedding of the passive element, the overall structure may have a reduced height.

Owner:UNIMICRON TECH CORP

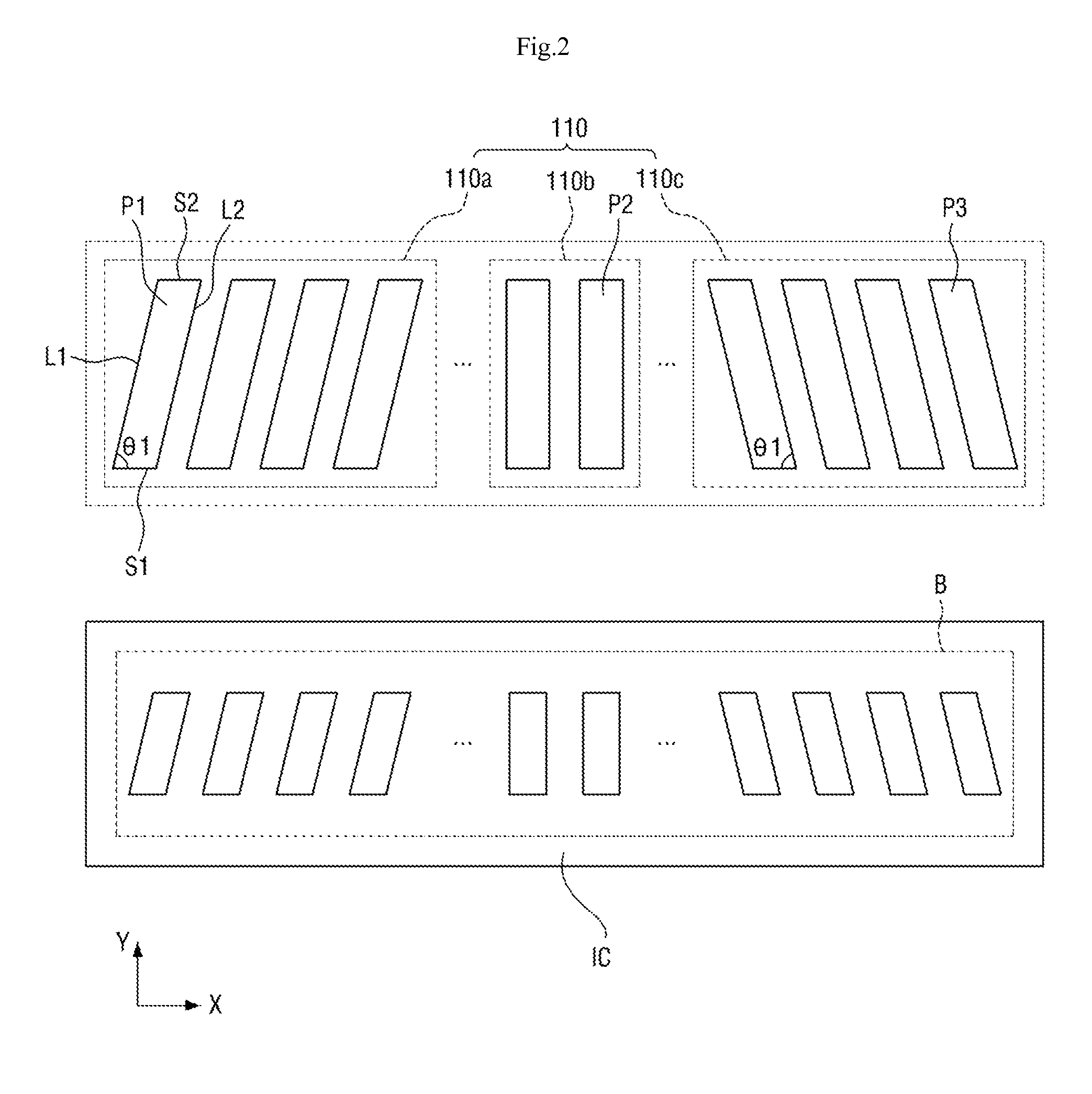

Array substrate and method of mounting integrated circuit using the same

ActiveUS9591754B2Avoid misalignmentSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringIntegrated circuit

An array substrate including a display area and a non-display area surrounding the display area. The non-display area includes a pad portion including one or more first pads that each have a parallelogram shape.

Owner:SAMSUNG DISPLAY CO LTD

Mounting substrate and mounting method of electronic part

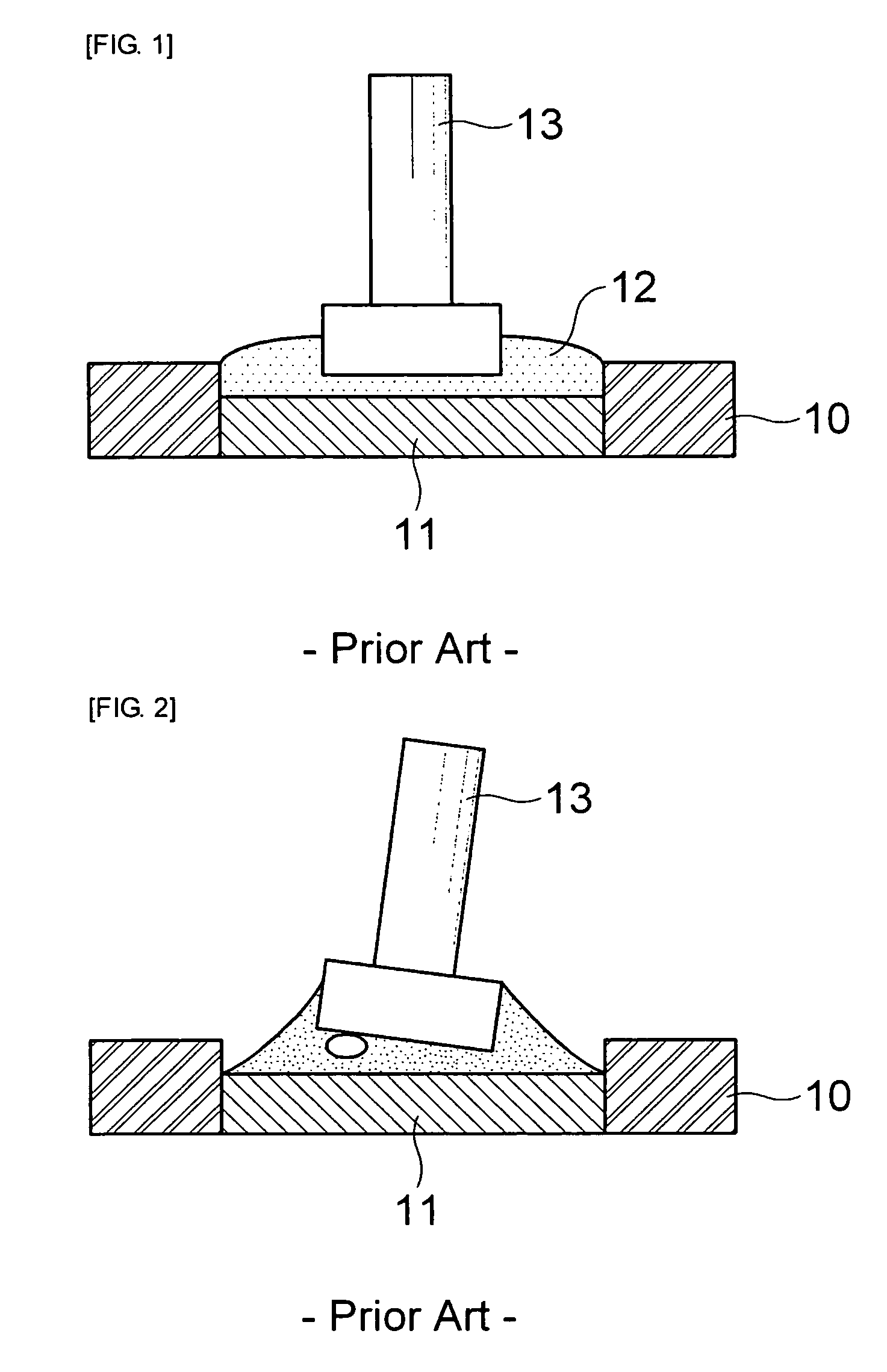

InactiveUS20050224560A1Improve connection reliabilityBalance can be obtainedSoldering apparatusSolid-state devicesEngineeringElectron

A mounting substrate includes a land connected to an electrode of an electronic part by a melt-capable connection member; and a connection member flow-generation part configured to generate a flow at the molten melt-capable connection member.

Owner:FUJITSU LTD

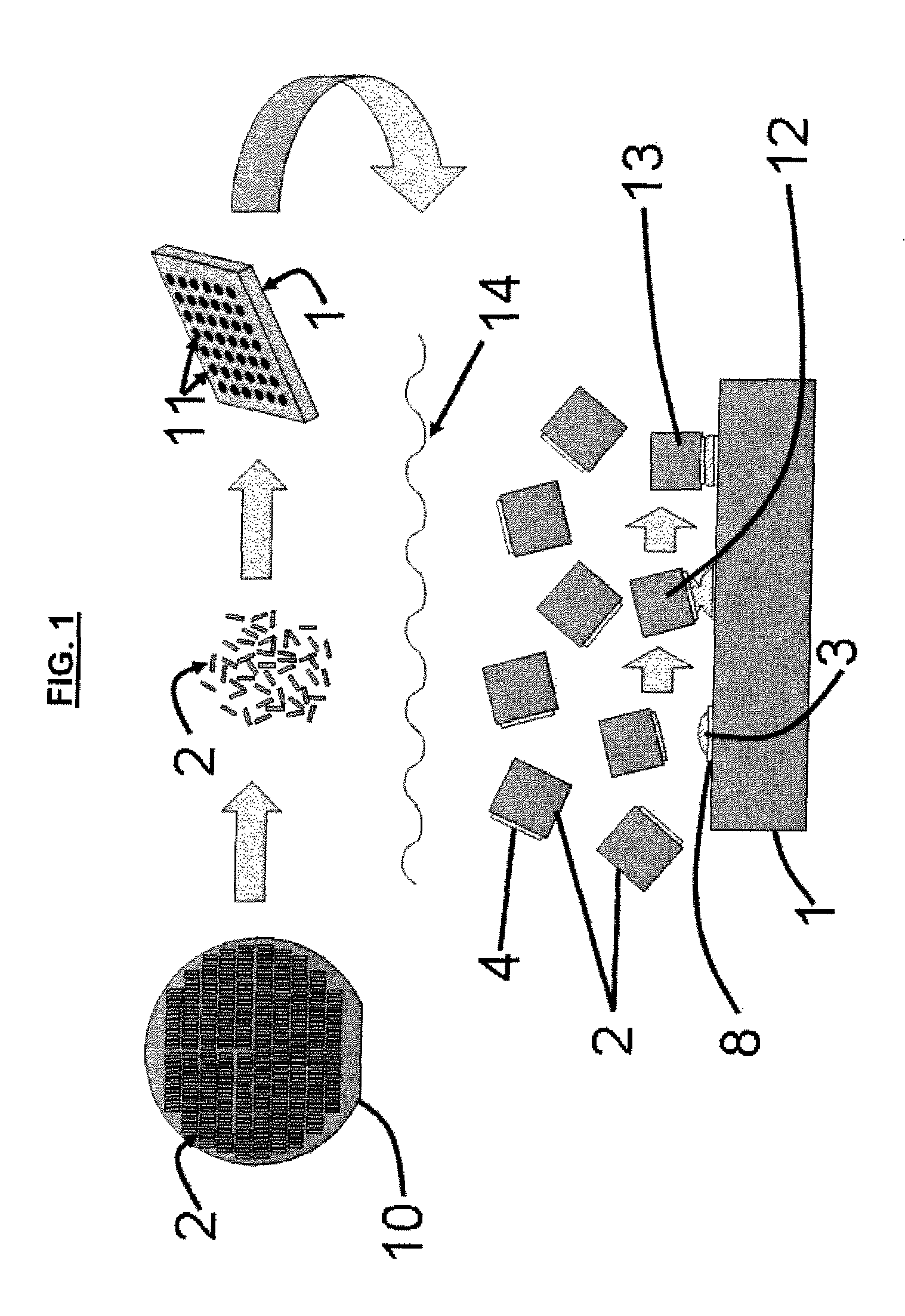

Self-assembled electrical contacts

InactiveUS8318595B2Solid-state devicesSemiconductor/solid-state device manufacturingElectrical conductorSelf-assembly

Self-assembling microscale electrical and mechanical connections includes a part binding site and a part electrical binding site; and a template binding site comprising a template electrical conductor layer; a metallization layer on the template electrical conductor layer; a bump structure comprising a solder alloy positioned on the metallization layer, wherein the solder alloy is liquefied to allow the bump structure to self-assemble and align with the part electrical binding site using capillary forces, and wherein the solder alloy only liquefies at a temperature above that at which the self-assembly and alignment is performed; and a fluid on the template electrical conductor layer, wherein the fluid comprises a melting point lower than that of the solder alloy, wherein the fluid binds with the part binding site.

Owner:UNITED STATES OF AMERICA THE AS REPRESENTED BY THE SEC OF THE ARMY

Substrate for flip chip bonding and method of fabricating the same

InactiveUS20100314161A1Improve impact resistanceImprove mounting reliabilitySemiconductor/solid-state device detailsSolid-state devicesMaterials scienceImpact resistance

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

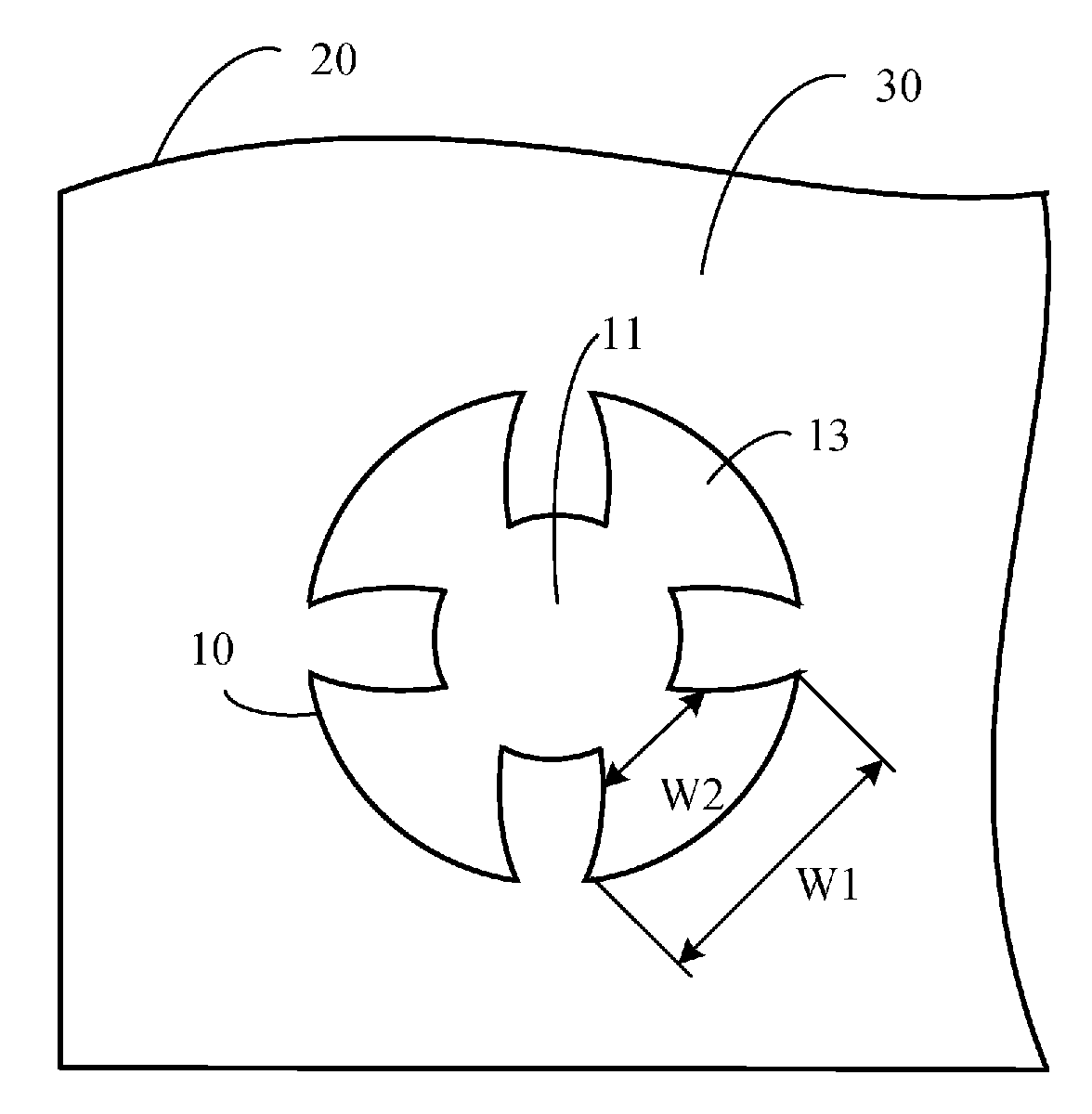

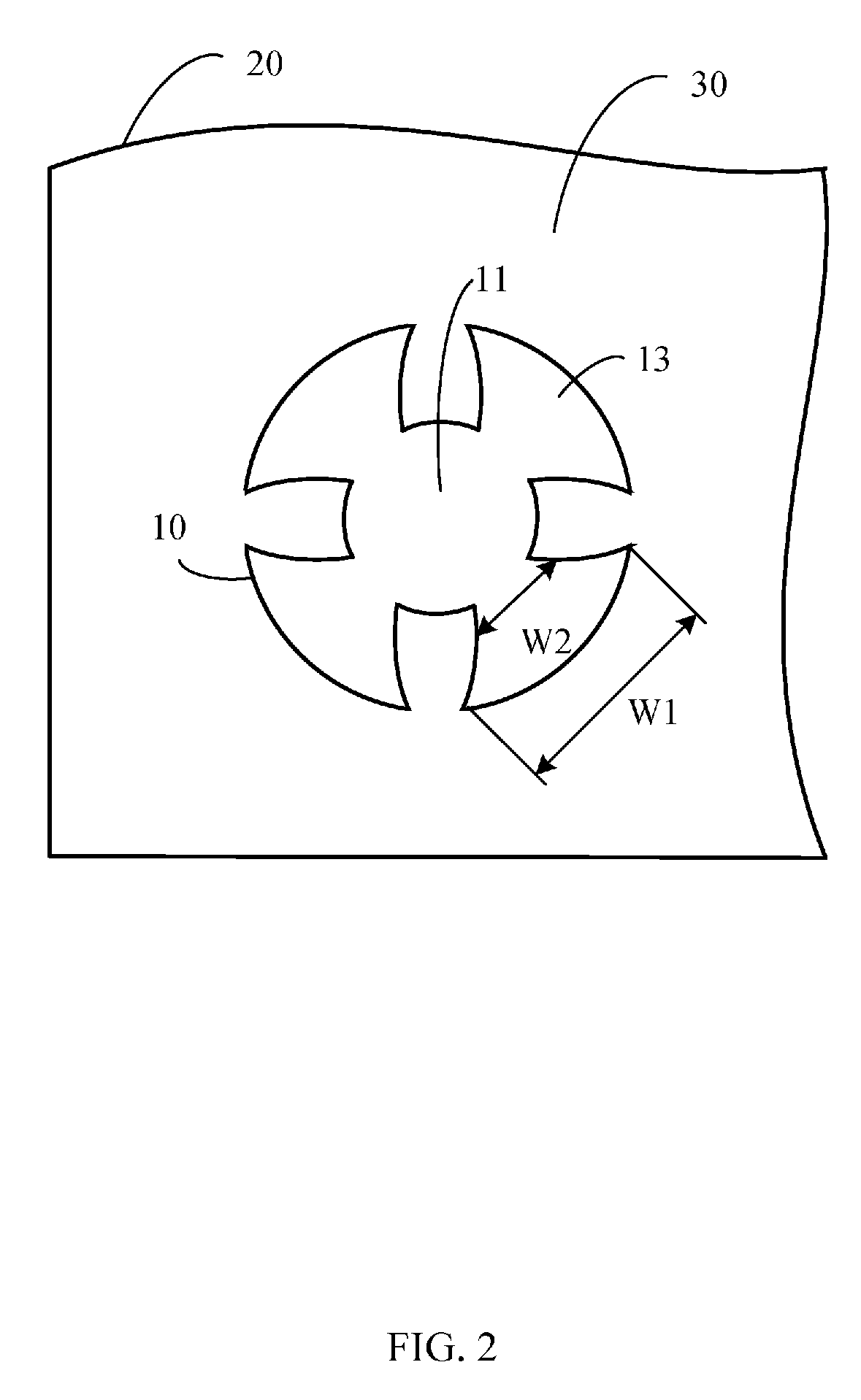

Pad and circuit board, electronic device using same

ActiveUS7723855B2Layered productsSemiconductor/solid-state device detailsSurface mountingBiomedical engineering

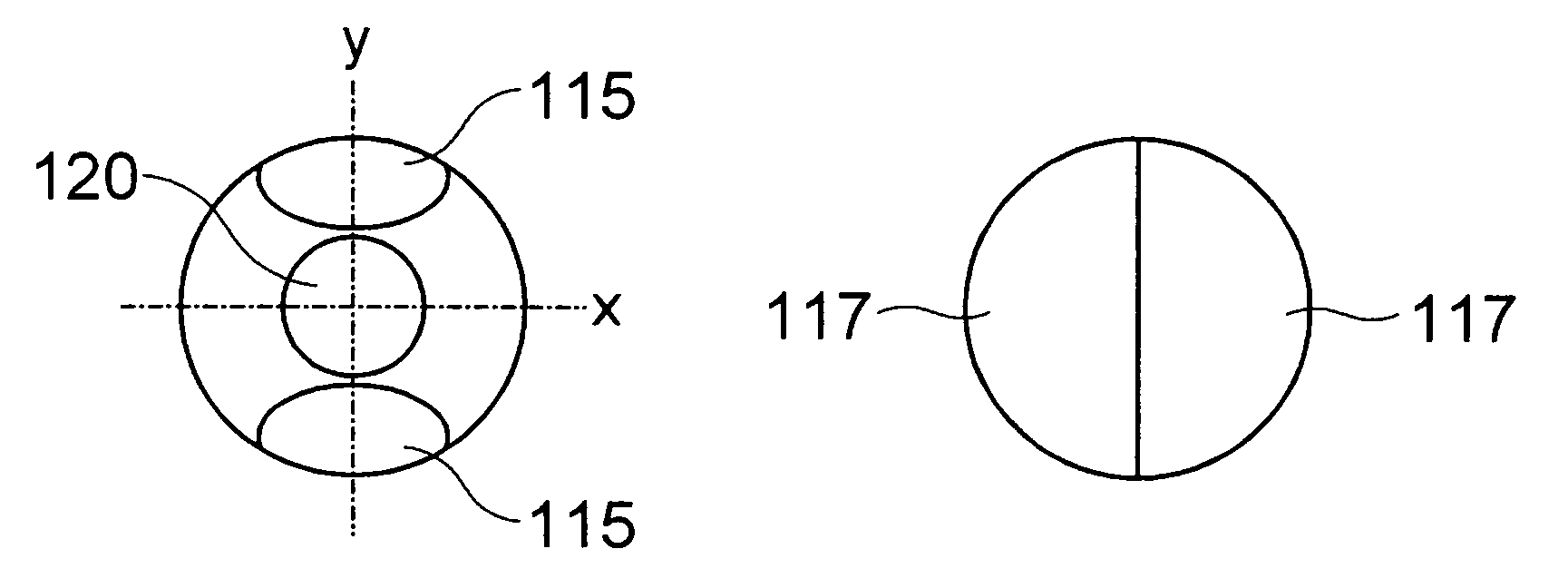

A pad for soldering a contact of a surface mounted component is provided herein. The pad includes a central portion and a plurality of separate extending portions extending from the central portion. All of the plurality of separate extending portions includes a free end and a connected end connected to the central portion. A width of the free end is larger than a width of the connected end. A circuit board and an electronic device are also provided.

Owner:HON HAI PRECISION IND CO LTD

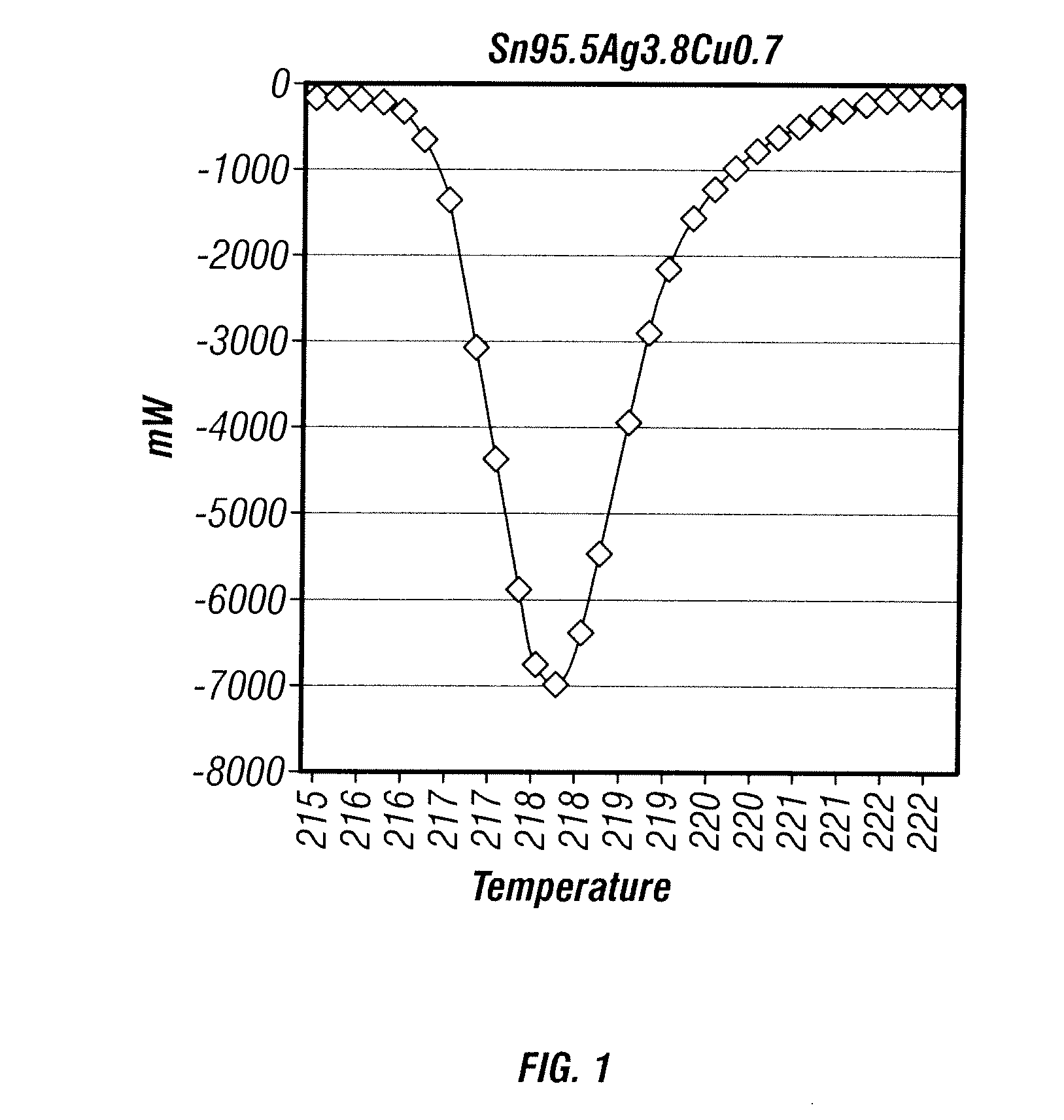

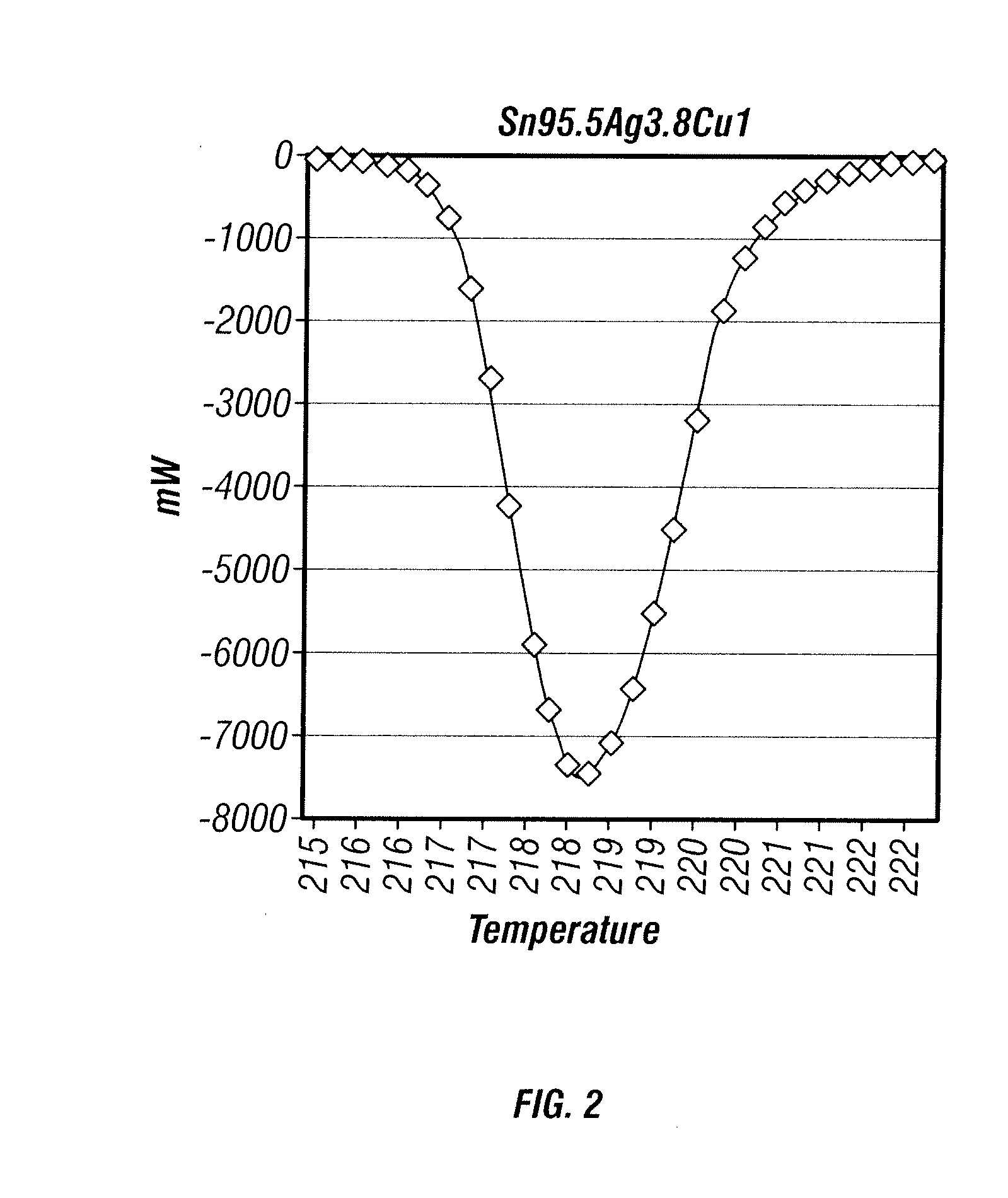

Ternary alloy column grid array

ActiveUS20070042211A1Good electrical contactSemiconductor/solid-state device detailsSolid-state devicesPolymer chemistryLiquidus

Techniques and structures have been developed for providing lead-free column grid array interconnect structures. An exemplary interconnect has a body, a first joint, and a second joint, all having compositions off the eutectic composition in a ternary alloy system, the first joint having a ternary composition distinct from the body composition, and the second joint having a ternary composition distinct from the body composition and the first joint composition. The interconnect may be formed by solidifying a solder, having a Sn-poor ternary composition in the Sn—Ag—Cu alloy system, in contact with a column, having a Ag-rich Cu-deficient composition in the same system, and a bonding pad or bare substrate. A second solder, having a Sn-rich ternary composition, may be solidified in contact with the column and a second bonding pad or bare substrate. In some embodiments joints may be severed and reformed by remelting and resolidifying the lower-liquidus solder.

Owner:ORACLE INT CORP

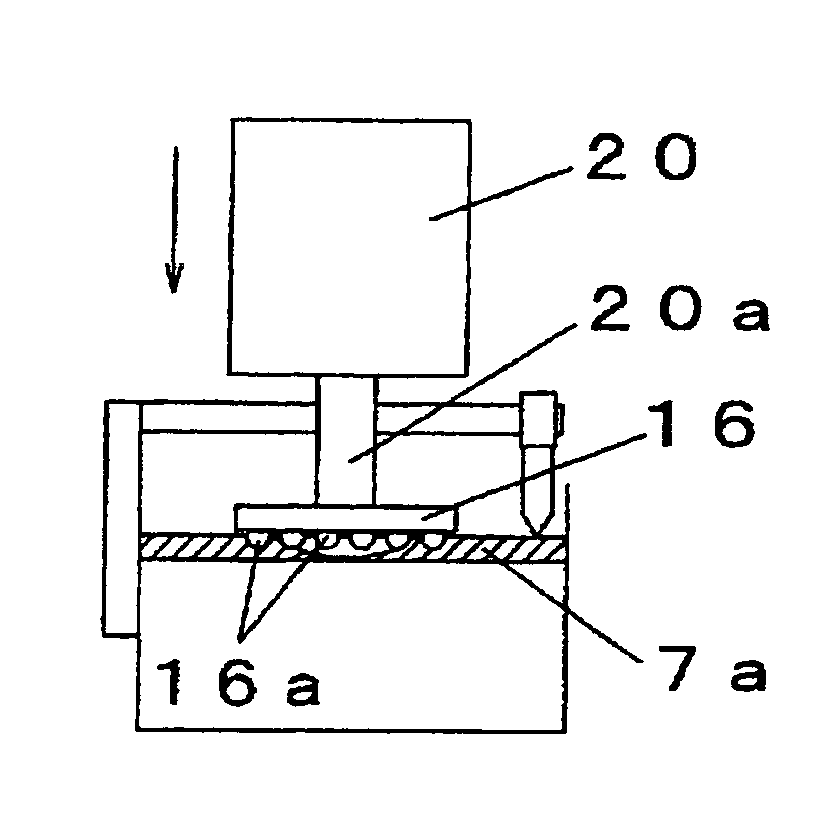

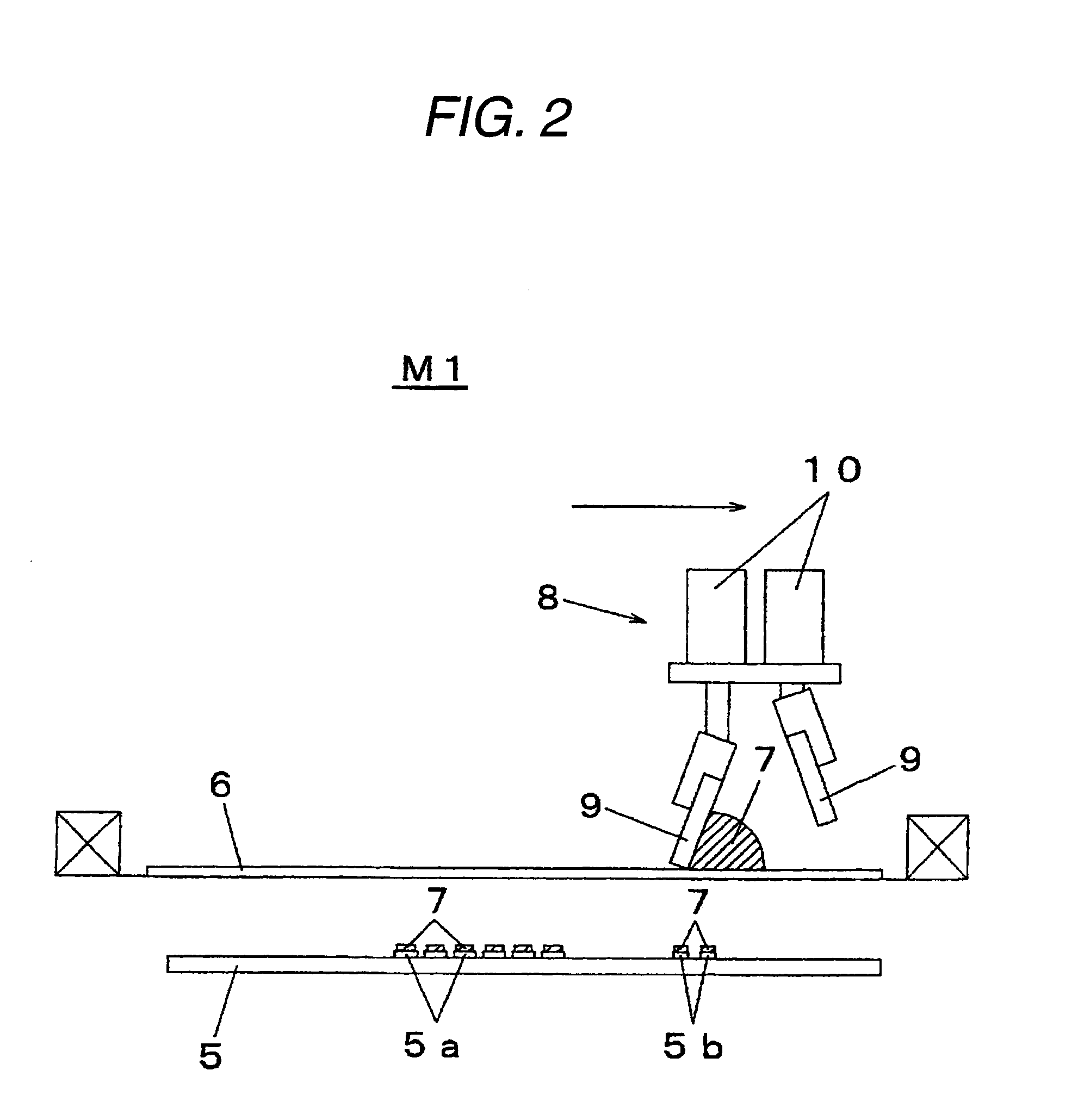

Electronic component placing apparatus and electronic component mounting method

To provide an electronic component placing apparatus and an electronic component mounting method that can prevent a cold joint from occurring when an electronic component likely to cause warp deformation is mounted by means of soldering.In the electronic component placing apparatus for placing the electronic component 16 with a plurality of solder bumps 16a formed on a lower surface on a board, a film 7a having a film thickness distribution for transferring a desired transfer amount of solder paste according to a state of warp deformation to each of the plurality of solder bumps is formed in a paste transfer unit 24, based on the component warp information indicating the state of warp deformation in a reflow process of the electronic component. Thereby, it is possible to prevent a cold joint from occurring when the electronic component likely to cause warp deformation is mounted by means of soldering by additionally supplying a just enough amount of solder to each solder bump 16a.

Owner:PANASONIC CORP

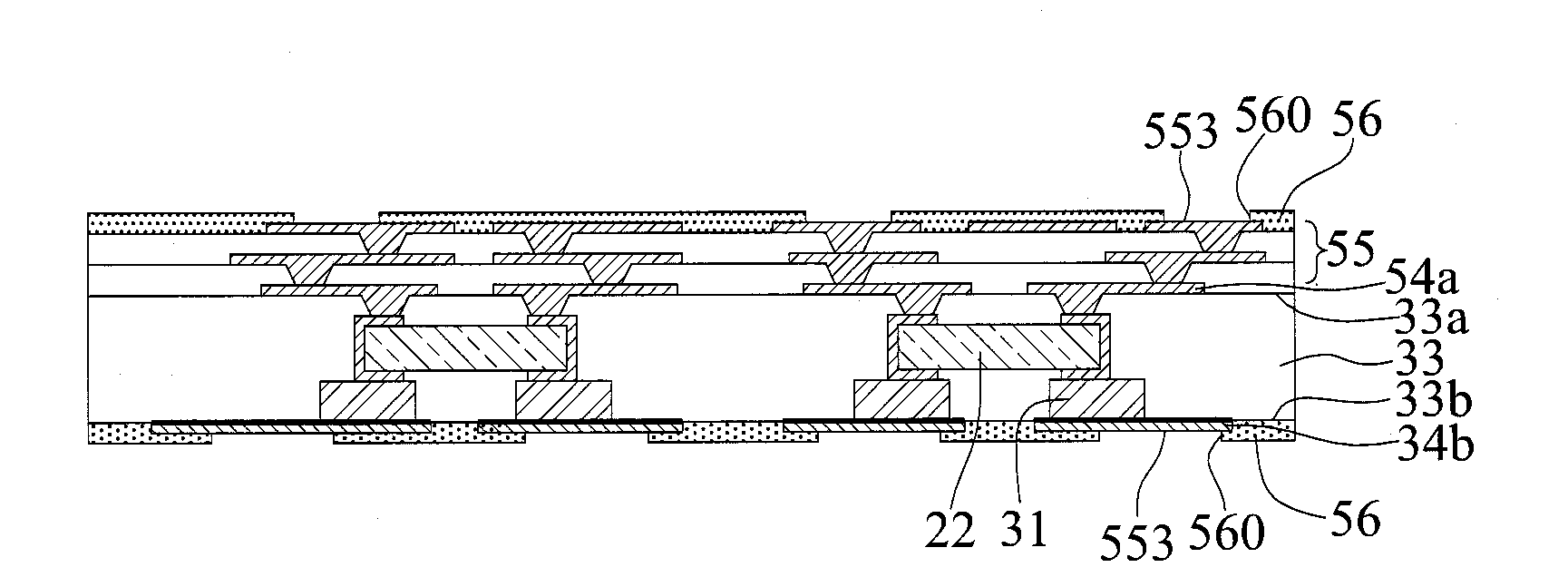

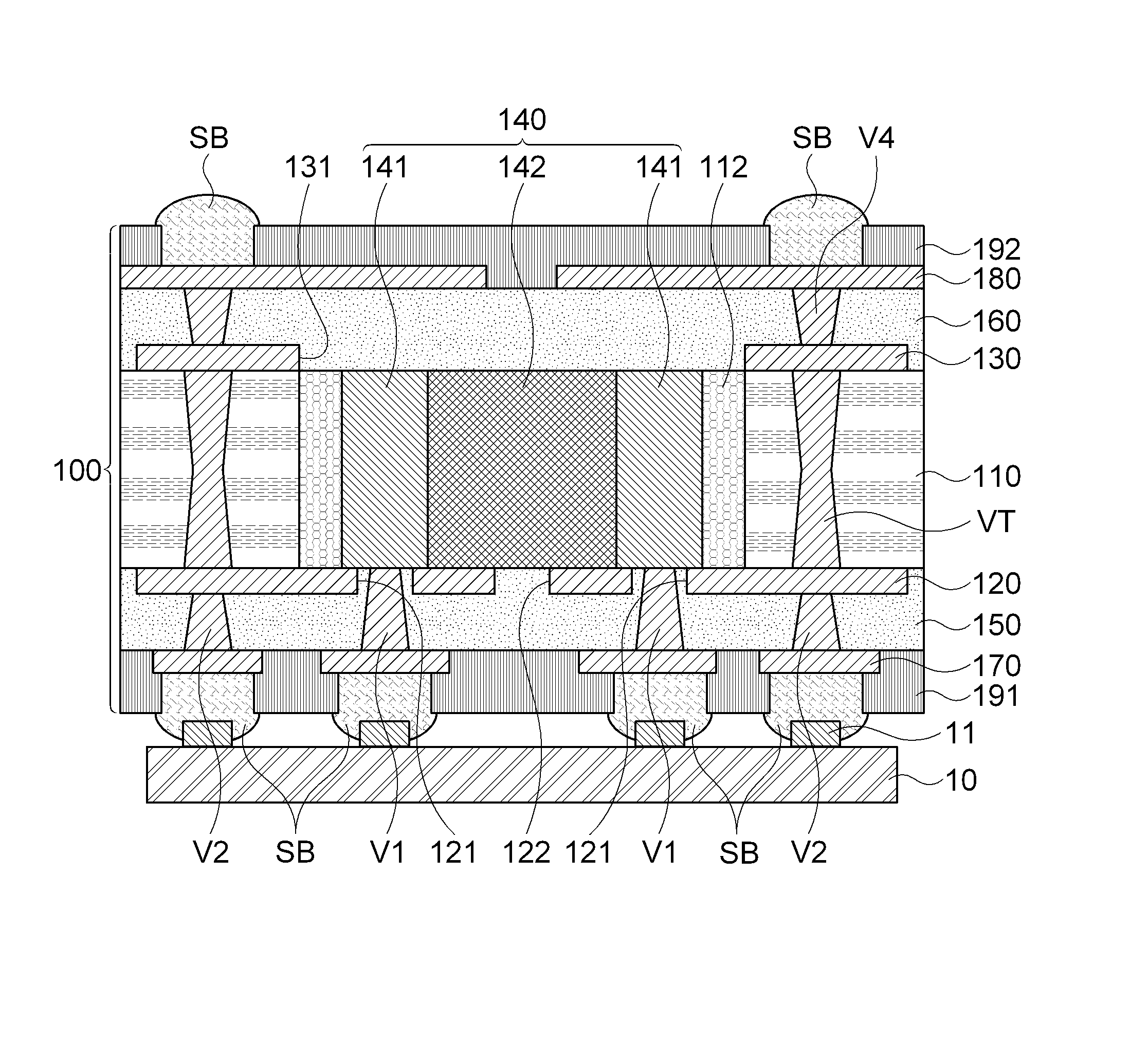

Electronic component embedded substrate and manufacturing method thereof

ActiveUS9462697B2Reliable electrical connectionImprove connectivityPrinted electric component incorporationPrinted circuit aspectsElectronic componentMetal

The present invention relates to an electronic component embedded substrate including: a first insulating layer including a cavity; an electronic component inserted in the cavity; a first metal pattern formed on a lower surface of the first insulating layer to mount the electronic component thereon and including at least one guide hole for exposing a portion of the external electrode; a second insulating layer formed on the lower surface of the first insulating layer to cover the first metal pattern; a first circuit pattern formed on a lower surface of the second insulating layer; and a first via for electrically connecting the first external electrode exposed through the guide hole and the first circuit pattern, and can improve electrical connectivity between the external electrode and the via even when the size of the external electrode of the electronic component is reduced than before.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Anti-tombstoning lead free alloys for surface mount reflow soldering

Owner:INDIUM CORP

Stress-relief layer and stress-compensation collar in contact arrays, and processes of making same

InactiveUS20050221534A1Printed circuit assemblingSemiconductor/solid-state device detailsMetallurgyStress relief

A stress-relief layer is formed by dispensing a polymer upon a substrate lower surface under conditions to partially embed a solder bump that is disposed upon the lower surface. The stress-relief layer flows against the solder bump. A stress-compensation collar is formed on a board to which the substrate is mated and the SCC partially embeds the solder bump. An article that exhibits a stress-relief layer and a stress-compensation collar is also included. A computing system that includes a stress-relief layer and a stress-compensation collar is also included.

Owner:INTEL CORP

Controlling Warpage in BGA Components in a Re-flow Process

ActiveUS20100302749A1Increase productionSpeed up the processPrinted circuit assemblingLine/current collector detailsAdhesiveBall grid array

A method of manufacturing an integrated circuit package includes providing a ball grid array (BGA) module including BGA balls on a side of the BGA module; providing a base substrate; and placing the BGA module on the base substrate. The BGA balls are placed between the BGA module and the base substrate. An adhesive is applied between and contacting the BGA module and the base substrate. The adhesive is then cured. The BGA balls are re-flowed after the step of curing the adhesive.

Owner:TAIWAN SEMICON MFG CO LTD +1

Lead pin for package boards

InactiveUS7893355B2Large caliberNon-insulated conductorsSemiconductor/solid-state device detailsEngineeringMechanical engineering

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Circuit assembly

ActiveUS20160234928A1Simple manufacturing processPrevent removalPrinted circuit assemblingPrinted circuit aspectsBusbarSoldering

Provided is a circuit assembly having a new structure in which a busbar circuit unit overlapped with a printed circuit board can reliably be fixed regardless of the heating temperature during soldering of an electrical component. In a circuit assembly in which a busbar circuit unit is overlapped with and fixed to a printed circuit board, the busbar circuit unit is configured as one piece by busbars being buried between insulator layers, and a section of the busbars is exposed via a through-hole of the insulator layer. The insulator layer of the busbar circuit unit is overlapped with the printed circuit board and is fixed thereto via fixing means, and terminal sections of an electrical component are soldered to and mounted on the exposed section of the busbar circuit unit and a printed wiring of the printed circuit board.

Owner:SUMITOMO WIRING SYST LTD

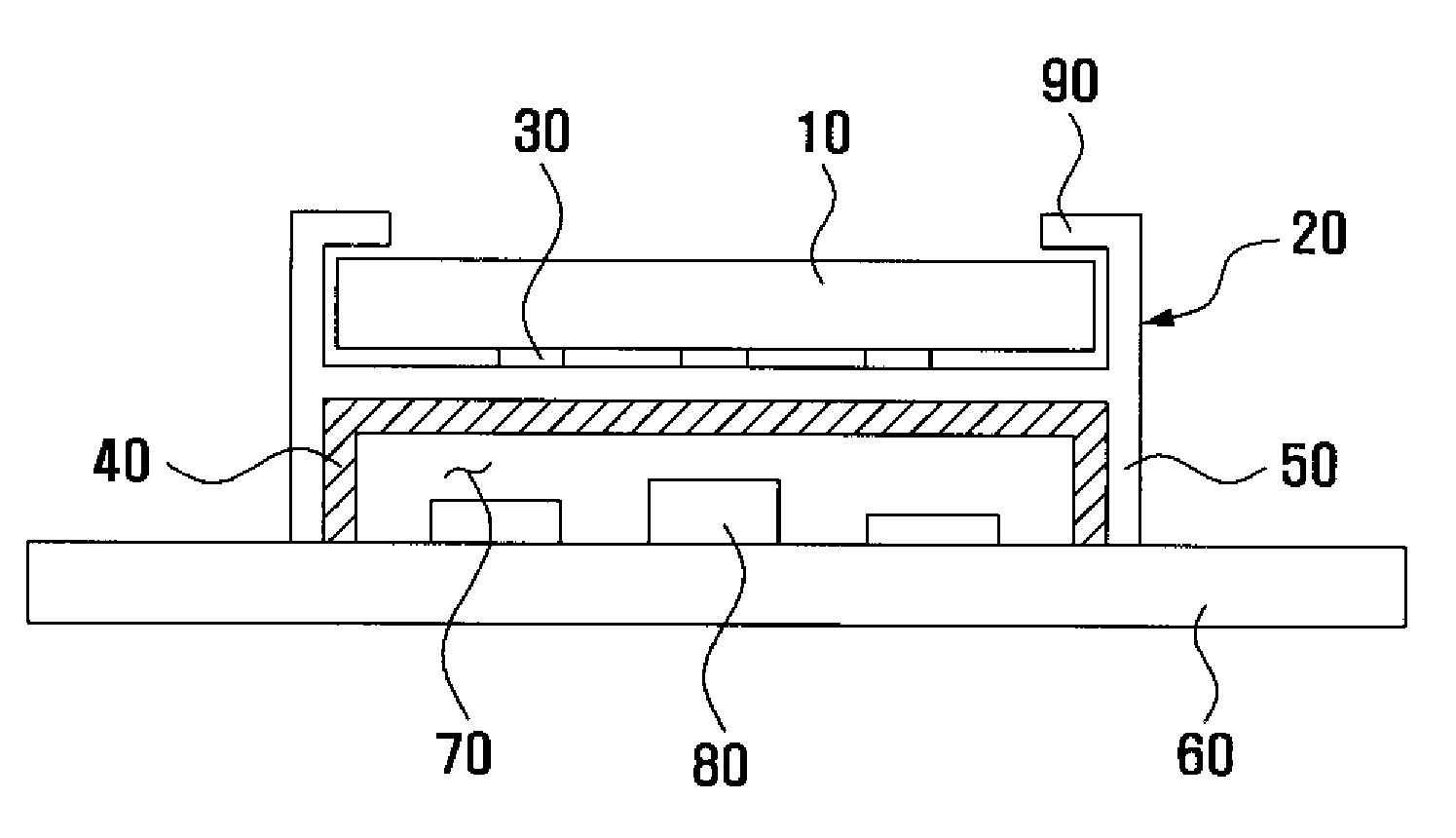

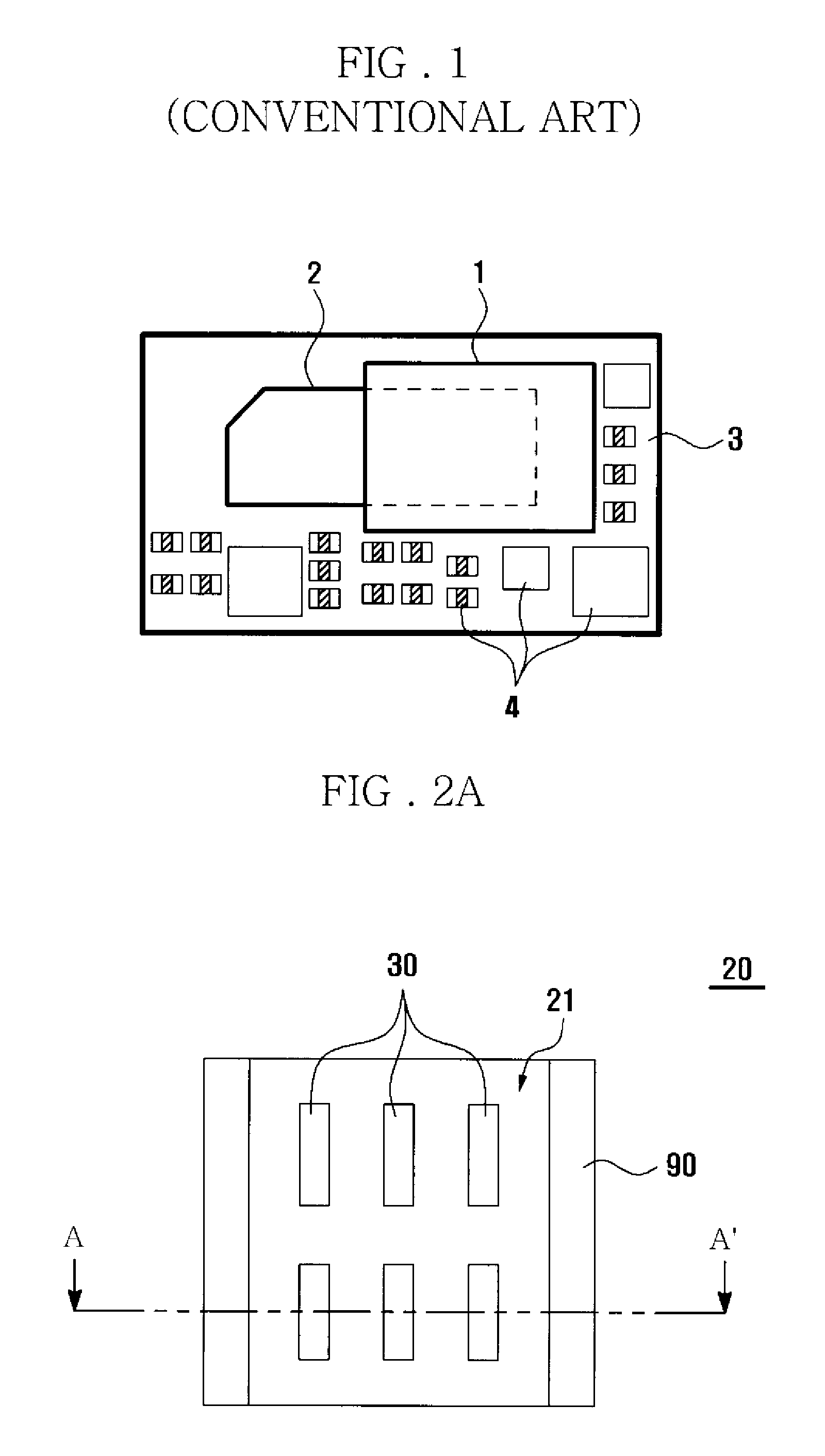

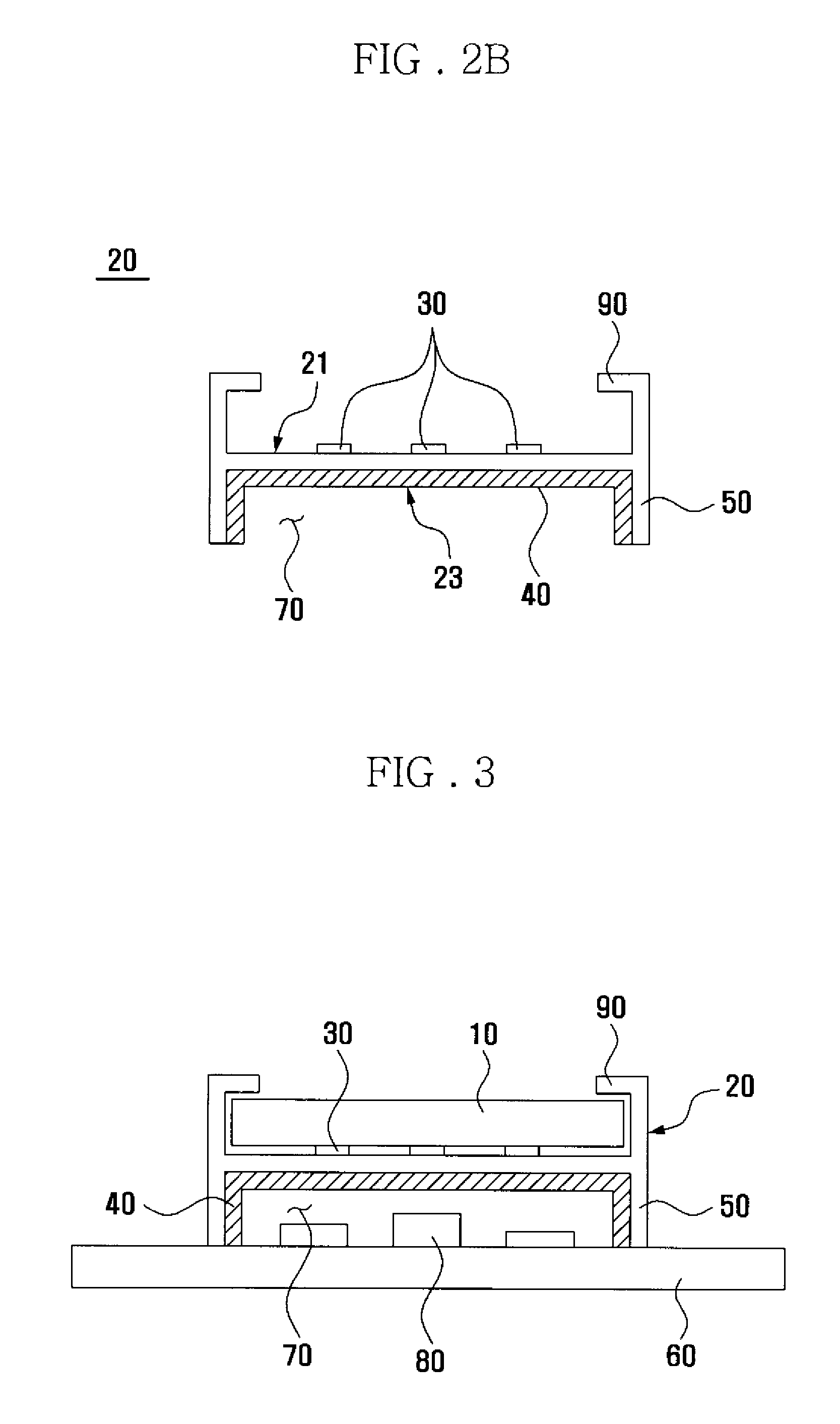

Sim card connector apparatus of portable wireless terminal

InactiveUS20090124126A1Secure spaceArrangement allowedPrinted circuit aspectsTwo-part coupling devicesEngineeringPrinted circuit board

A SIM card connector of a portable wireless terminal has a structure that forms a space thereunder using its lower edges to place electronic parts of a printed circuit board (PCB) within the space, so that the PCB can increase its space efficiency. The SIM card connector further forms an electromagnetic wave shield around the space, so that the electromagnetic wave shield can block electromagnetic waves generated from the electronic parts.

Owner:SAMSUNG ELECTRONICS CO LTD

Ball grid array package construction with raised solder ball pads

InactiveUS20040141298A1Semiconductor/solid-state device detailsSolid-state devicesSolder ballInterconnection

The present invention provides for a BGA solder ball interconnection to an outer conductive layer of a laminated circuit assembly having an underlying circuit layer. The invention includes a raised BGA solder ball pad substantially co-planar with the outer conductive layer, the raised pad having a raised face and a plurality of vertical conductive walls and a BGA solder ball having an average diameter of greater than the width of the raised face, the BGA solder ball being adhered to the raised face and to a substantial portion of the vertical conductive walls.

Owner:ULTRATECH INT INC

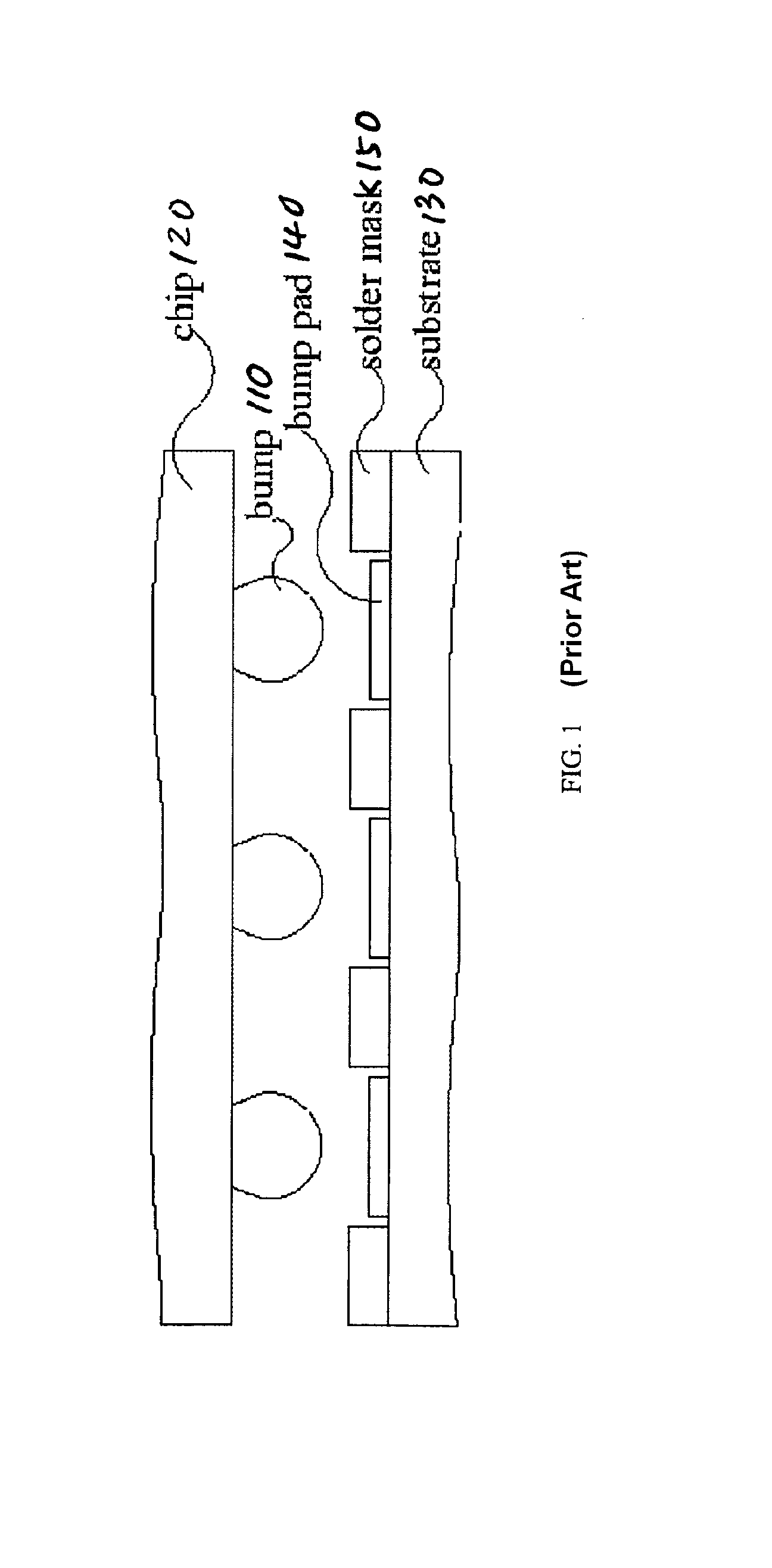

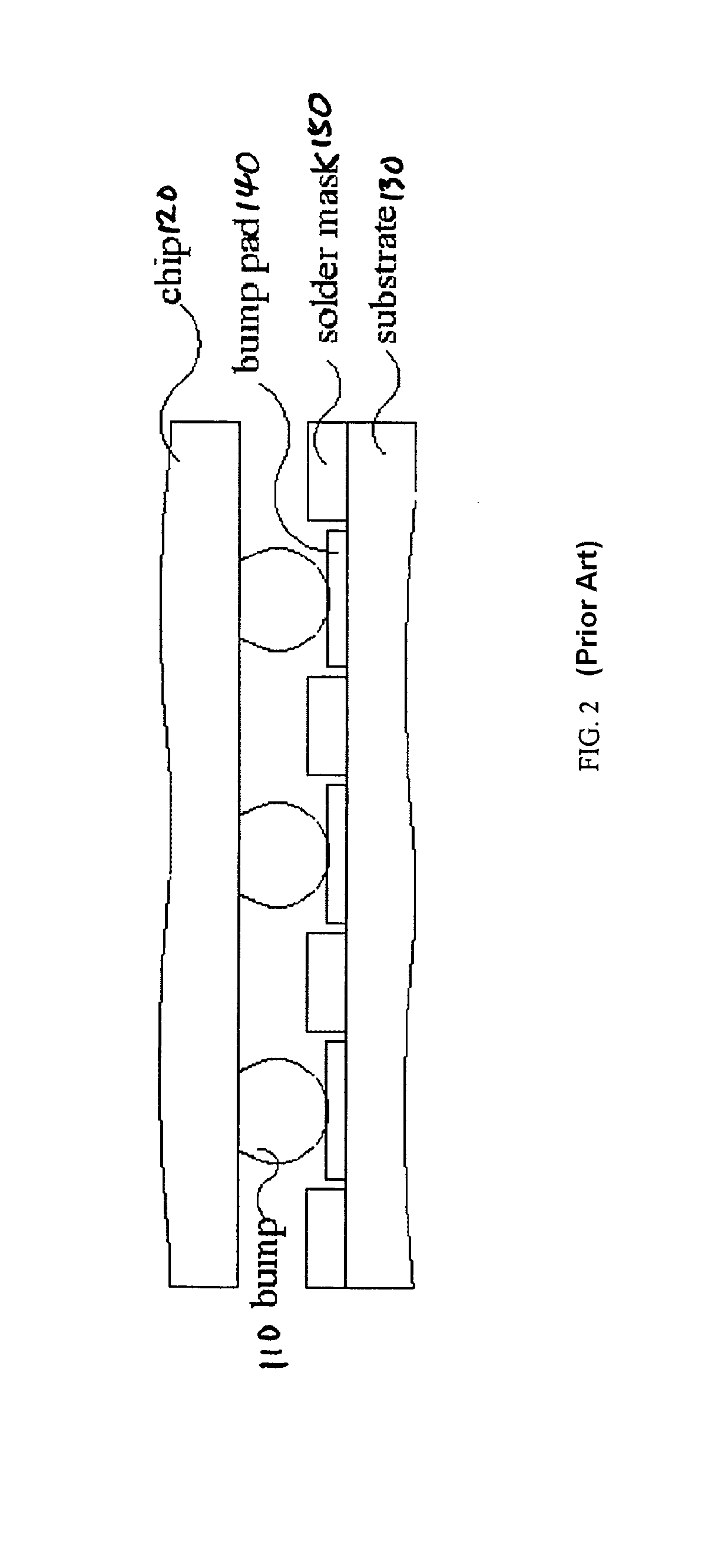

Substrate and process for semiconductor flip chip package

ActiveUS7652374B2Increase contact areaImprove solder joint reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical connectionSemiconductor package

A semiconductor package structure for flip chip package includes at least a patterned circuit layer and an insulating layer alternately stacking up each other. The patterned layer includes a plurality of bump pads, and the insulating layer includes a plurality of etching holes. The etching holes and the bump pads are aligned, such that the bump pads are exposed through the etching holes. A plurality of bumps is disposed on the active surface of the chip, which can be obtained by stud bumping. The etching holes are filled with solder paste, and the bumps of the chips penetrate into the solder filled etching holes. Vibration obtained by mechanical equipment, or ultrasonic equipment can be applied to assist the alignment of the bumps to the corresponding bump pads. A reflow process is applied to collapse the solder paste that fills the etching holes to form electrical connection between the bumps and bump pads.

Owner:INTELLECTUAL VENTURES FUND 27

LED lamp using ultra-small LED electrode assembly

ActiveUS9978725B2Improve extraction efficiencyFunctional deteriorationPrinted circuit assemblingPrinted circuit aspectsEngineeringLED lamp

Provided is an LED lamp using a nano-scale LED electrode assembly. The LED lamp using the nano-scale LED electrode assembly may solve limitations in which, when a nano-scale LED device according to the related art stands up and is three-dimensionally coupled to an electrode, it is difficult to allow the nano-scale LED device to stand up, and when the nano-scale LED devices are coupled to one-to-one correspond to electrodes different from each other, product quality is deteriorated. Thus, the nano-scale LED device having a nano unit may be connected to the two electrodes different from each other without causing defects, and light extraction efficiency may be improved due to the directivity of the nano-scale LED devices connected to the electrodes. Furthermore, deterioration in function of the LED lamp due to the defects of a portion of the nano-scale LEDs provided in the LED lamp may be minimized, and the LED lamp may have a flexible structure and shape by using the nano-scale LED electrode assembly of which a portion is deformable according to the used purpose or position of the LED lamp.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device

InactiveUS7660130B2Increase resistanceConnection strengthSemiconductor/solid-state device detailsPrinted circuit aspectsResistDevice material

Owner:LONGITUDE LICENSING LTD

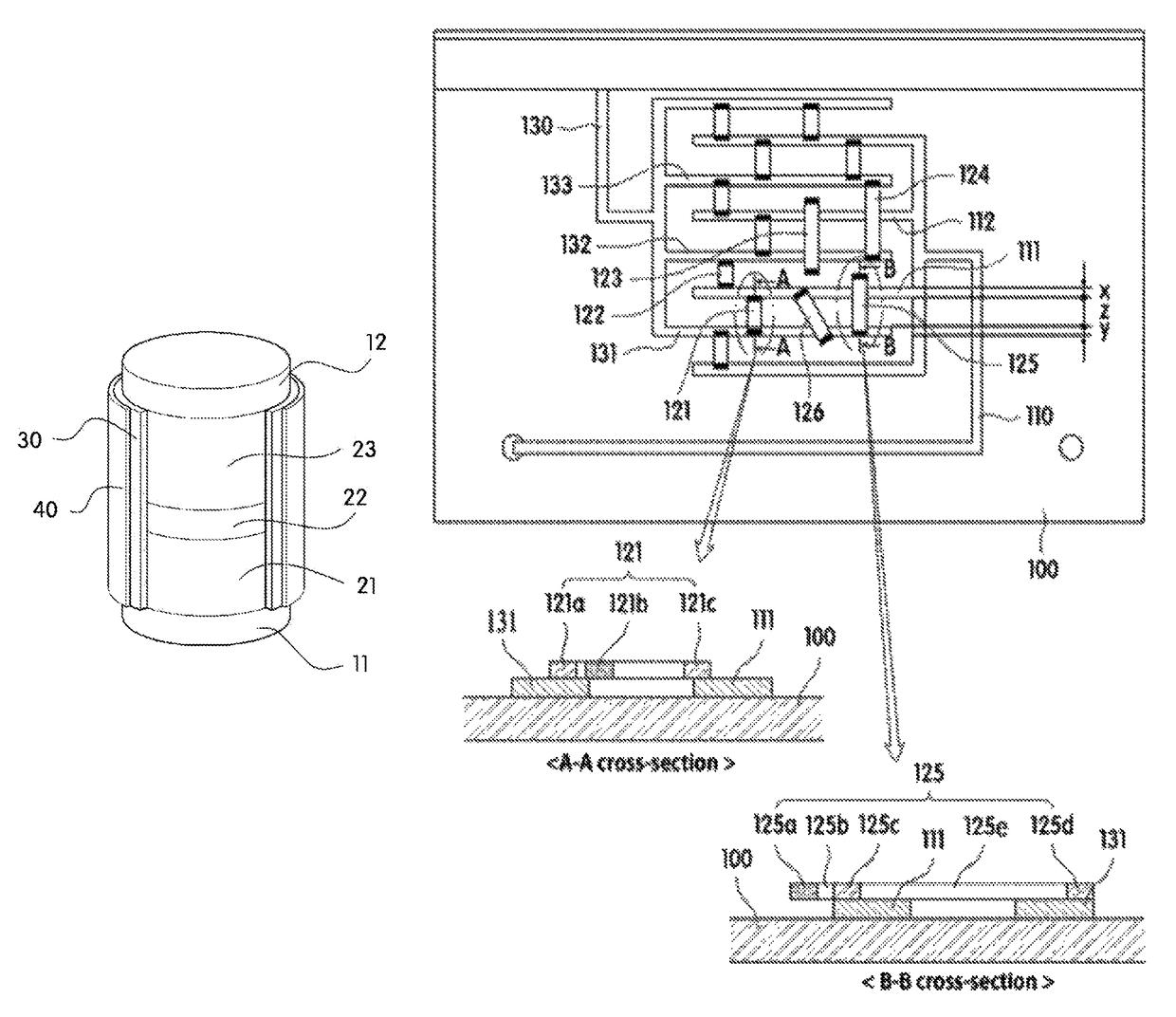

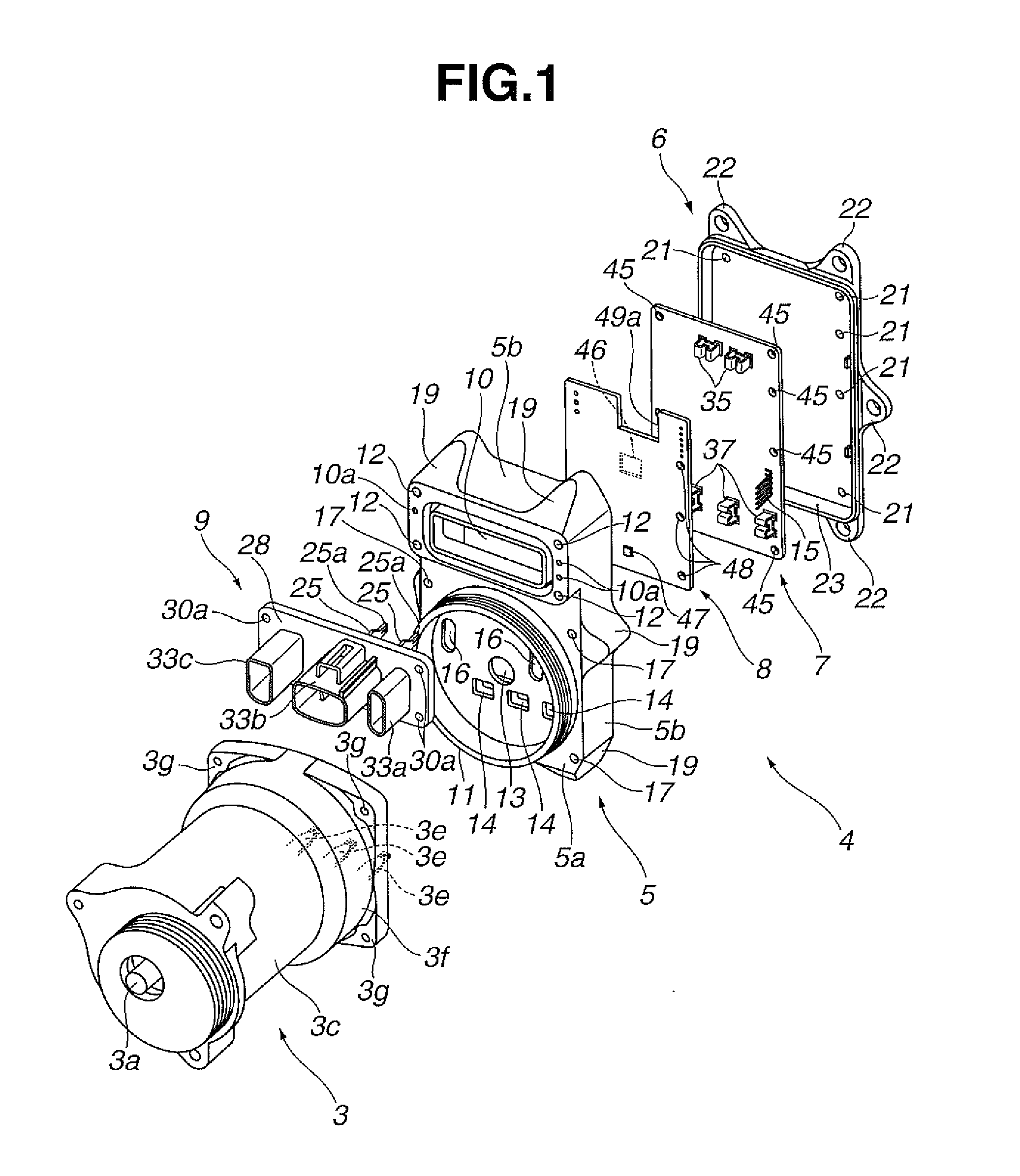

Electronic Control Device

ActiveUS20160244088A1Reduced connection reliabilityImprove connection reliabilityClosed casingsCasings with display/control unitsElectricityElectric power system

An electronic control unit includes a casing and a cover which are mutually bonded. A drive circuit board which drives a motor unit is fixed to the cover and, on the other hand, a control circuit board which controls the drive circuit board is fixed to the casing. An electrical connector which supplies an electric power to each board and a motor unit is attached on an opening section of the casing. First power supply terminals of this electrical connector and the motor unit and second power supply terminals of the drive circuit board are directly electrically connected by a bonding of both of casing and the cover.

Owner:HITACHI ASTEMO LTD

Popular searches

Coupling light guides Electronic products manufacture Printed circuits structural associations Semiconductor lasers Optical waveguide light guide Printed circuit non-printed electric components association Semiconductor devices Digital storage Printed circuit manufacture Electrical connection printed elements

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com