Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

138 results about "Voltage controlled ring oscillator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The voltage controlled ring oscillator (VCO) is a critical and necessary component in data communication systems and clock recovery circuits. It is basically an oscillator, whose output frequency is controlled by the input control voltage.

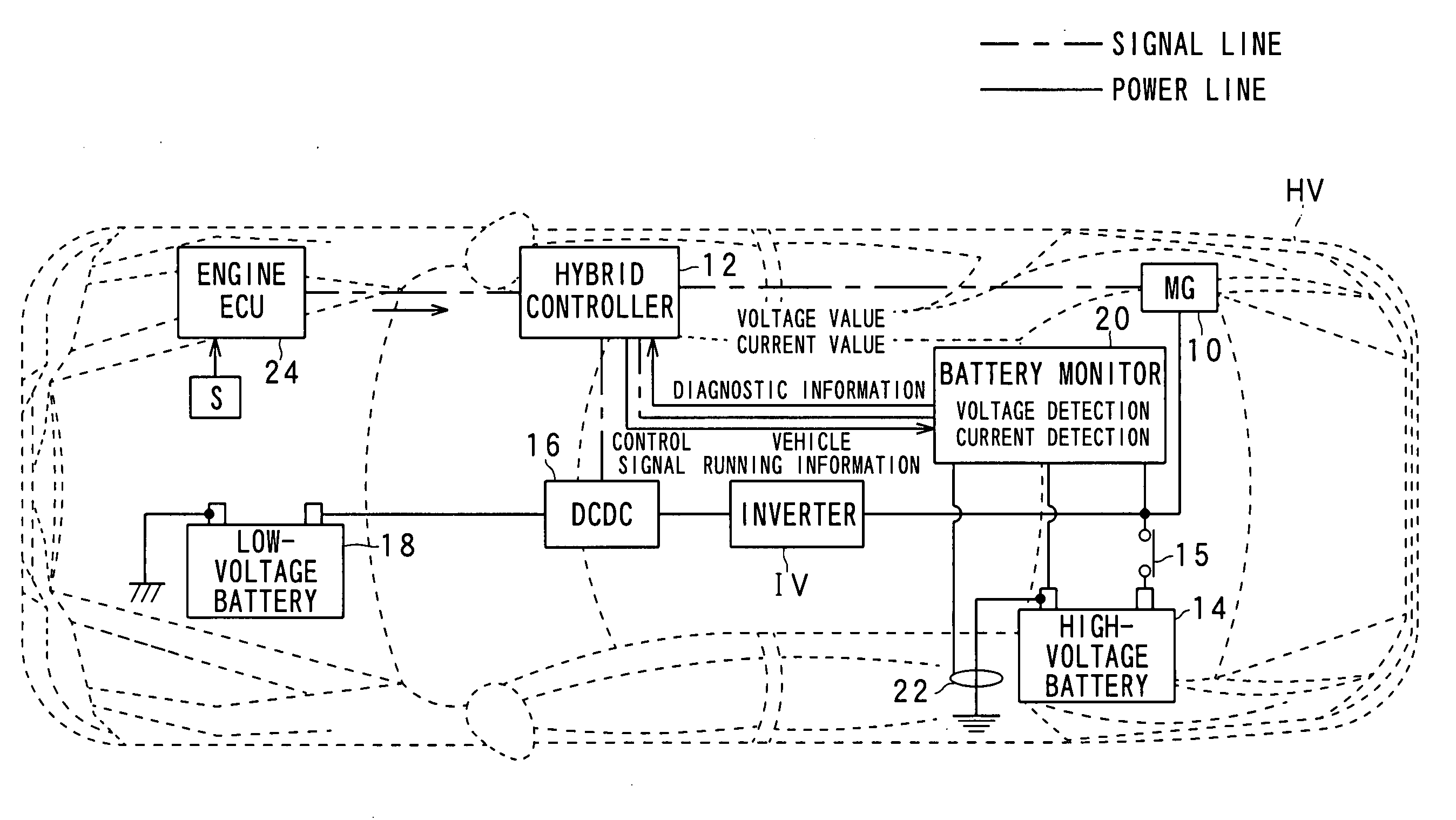

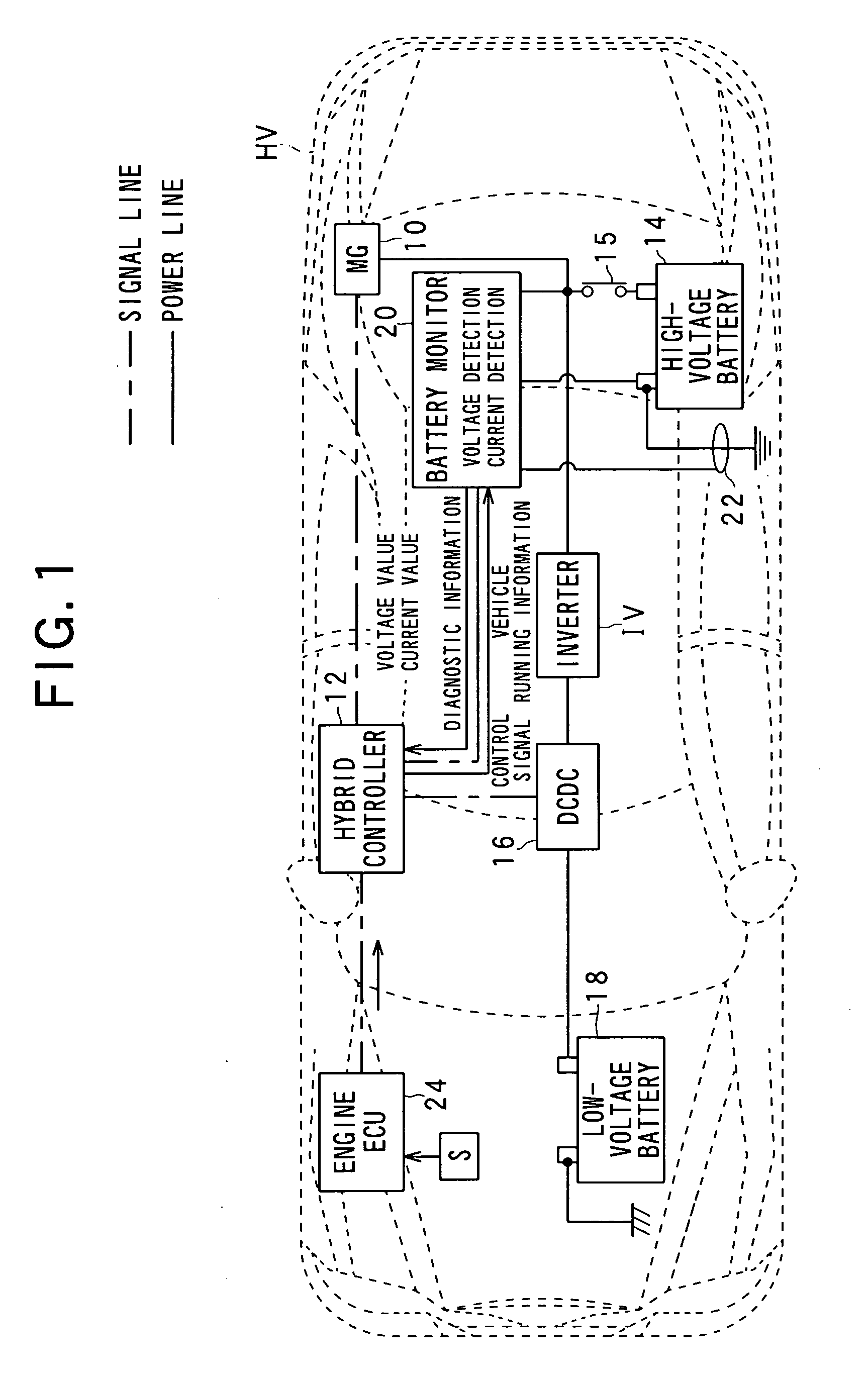

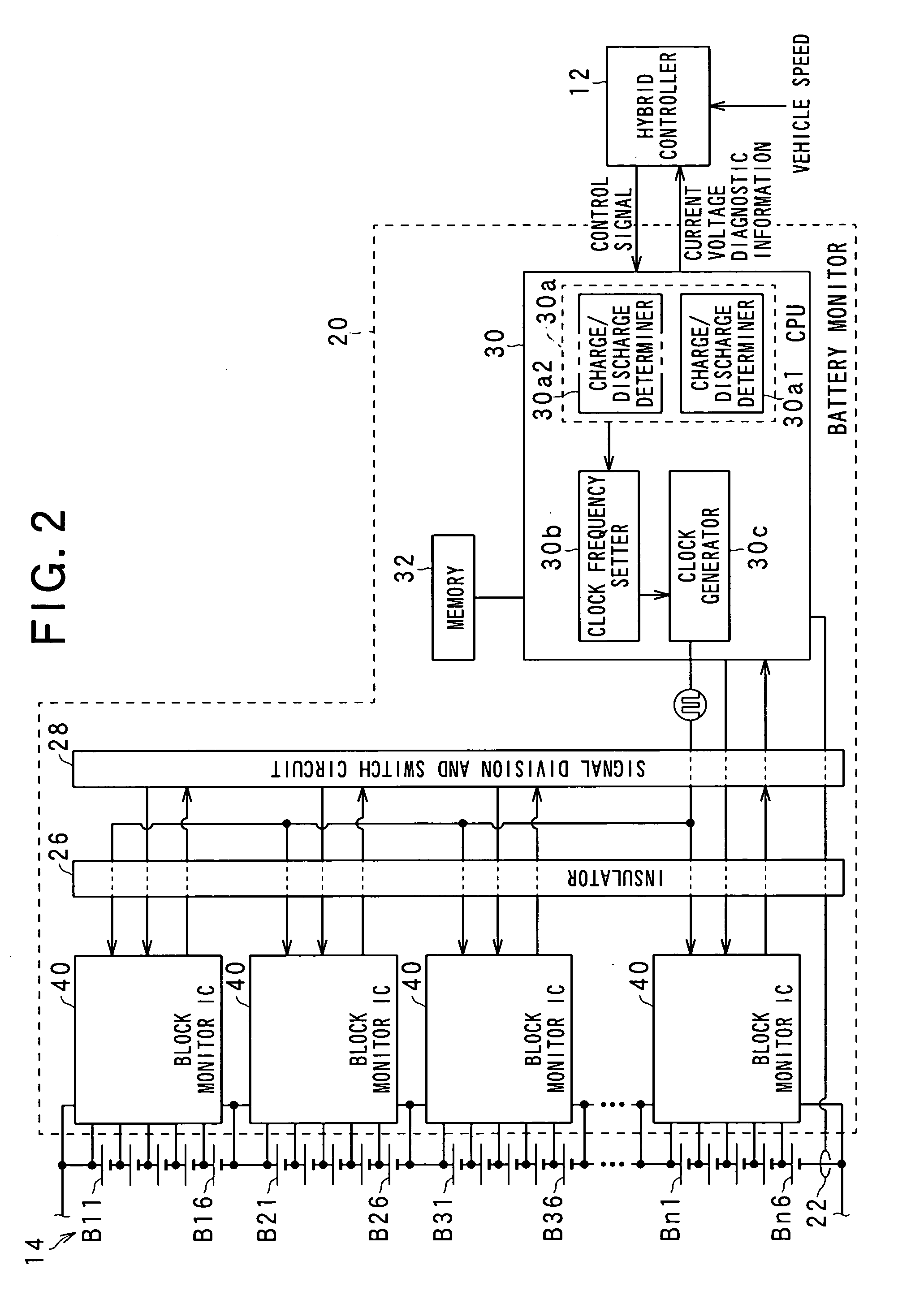

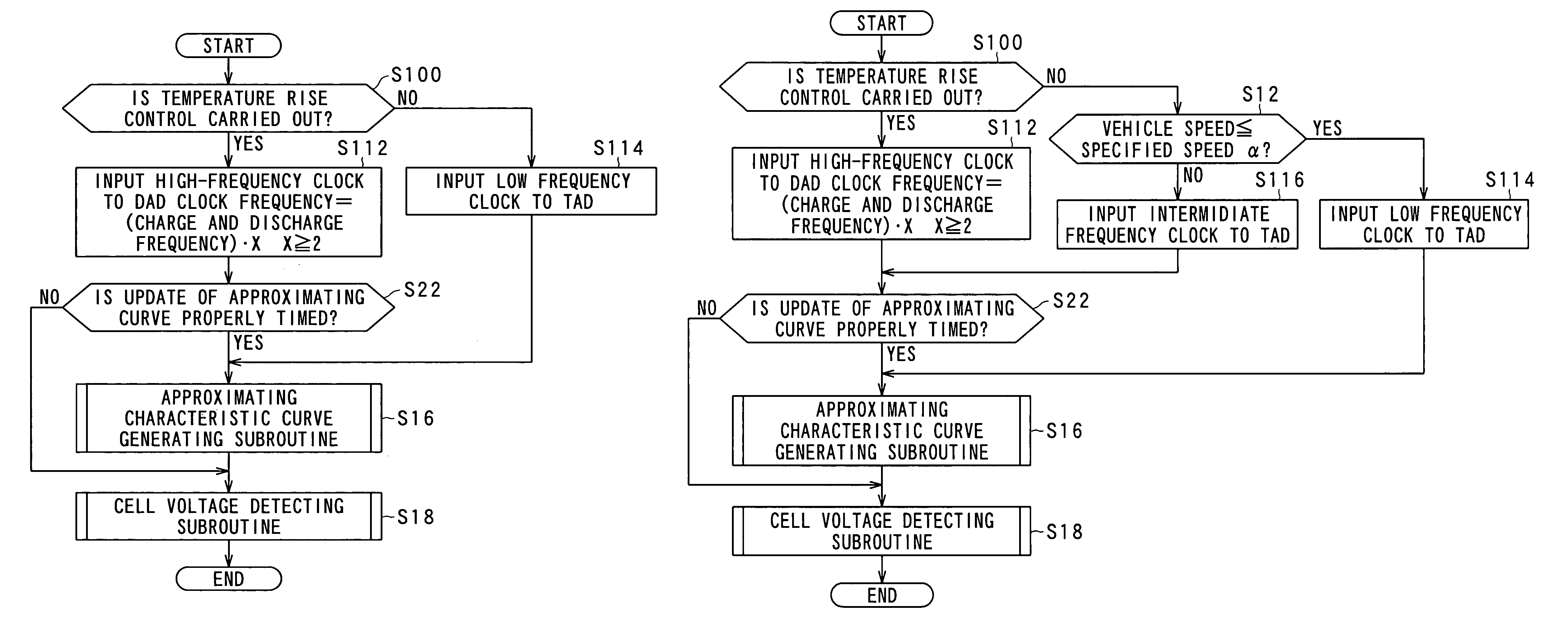

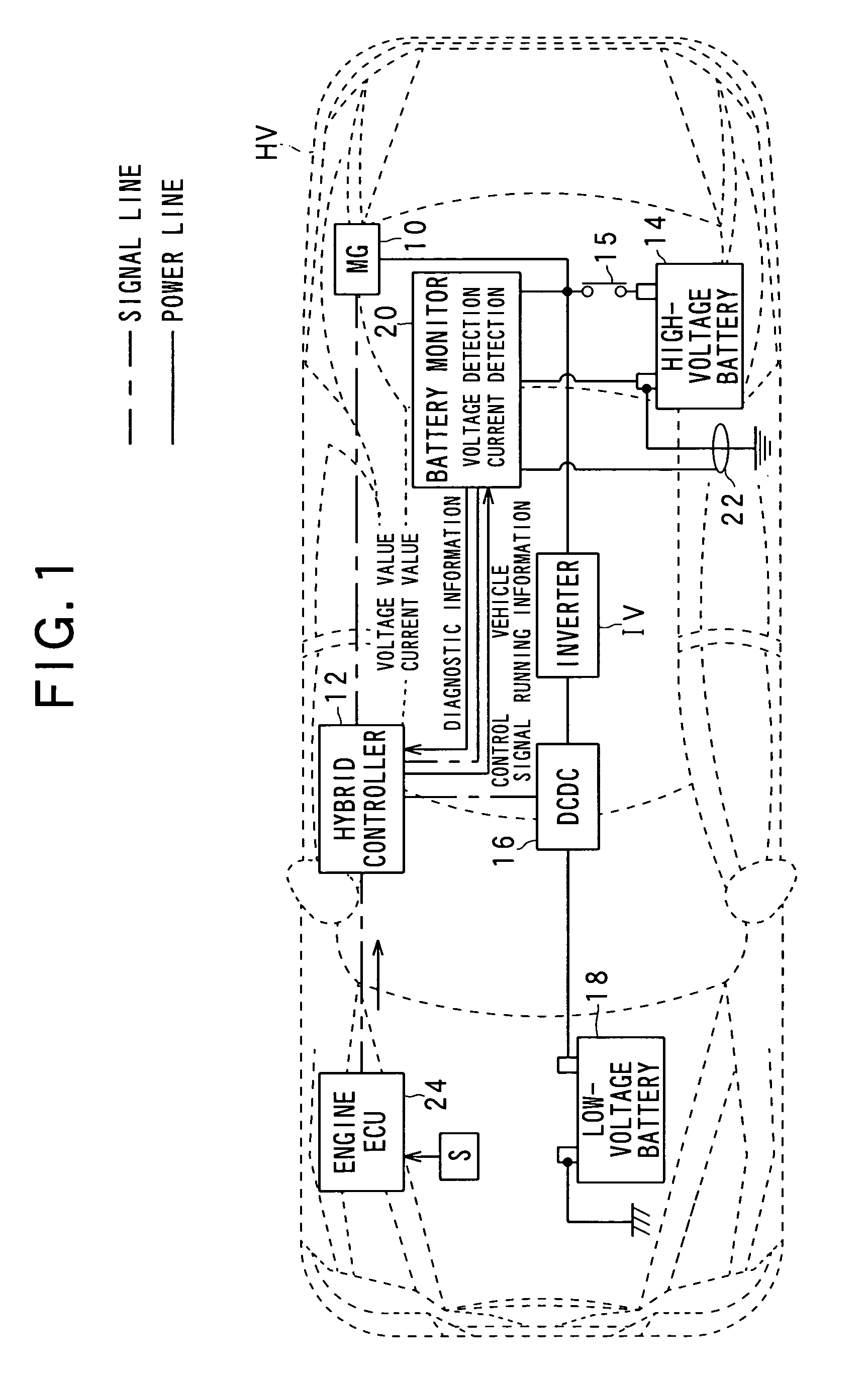

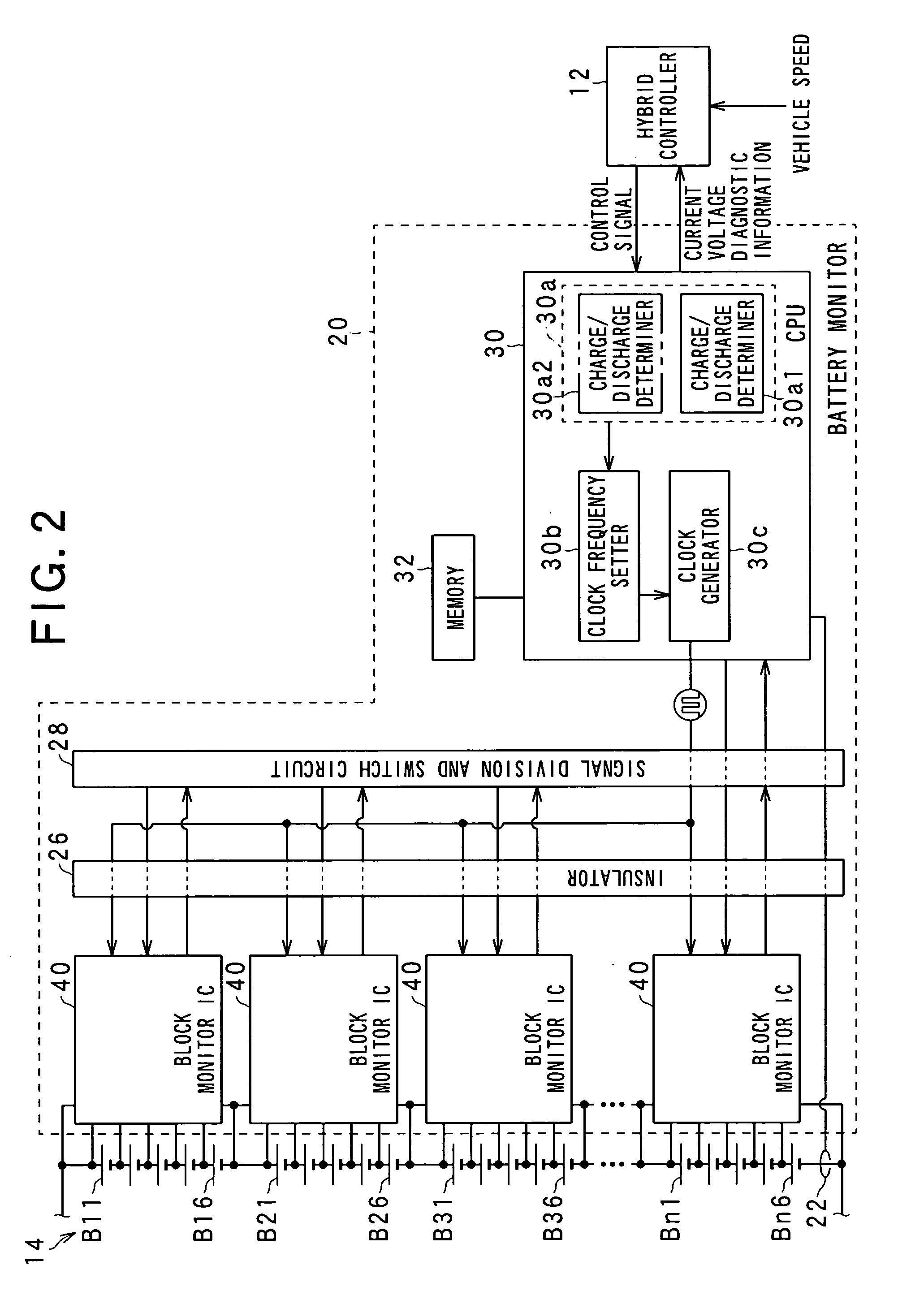

Voltage detecting apparatus with voltage controlled oscillator and battery state control system

ActiveUS20090251103A1Facilitating battery-pack longevityImprove accuracyBatteries circuit arrangementsMaterial analysis by electric/magnetic meansVIT signalsVoltage controlled ring oscillator

In a voltage detecting apparatus, a voltage controlled oscillator, when an input voltage is applied thereto, outputs a signal with a logical value that is periodically inverted. A detector counts a number of logical inversion of the output signal from the voltage controlled oscillator over an interval between edges of pulses of a pulse signal to thereby generate, based on the counted number of logical inversion, digital data as a detected result of the input voltage. A determiner determines whether a reduction of a time required to detect the input voltage is higher in priority than an increase of a resolution of detection of the input voltage. A variably setting unit variably sets a frequency of the pulse signal based on a result of the determination of whether the reduction of the time required to detect the input voltage is higher in priority than the increase of the resolution of detection of the input voltage.

Owner:DENSO CORP

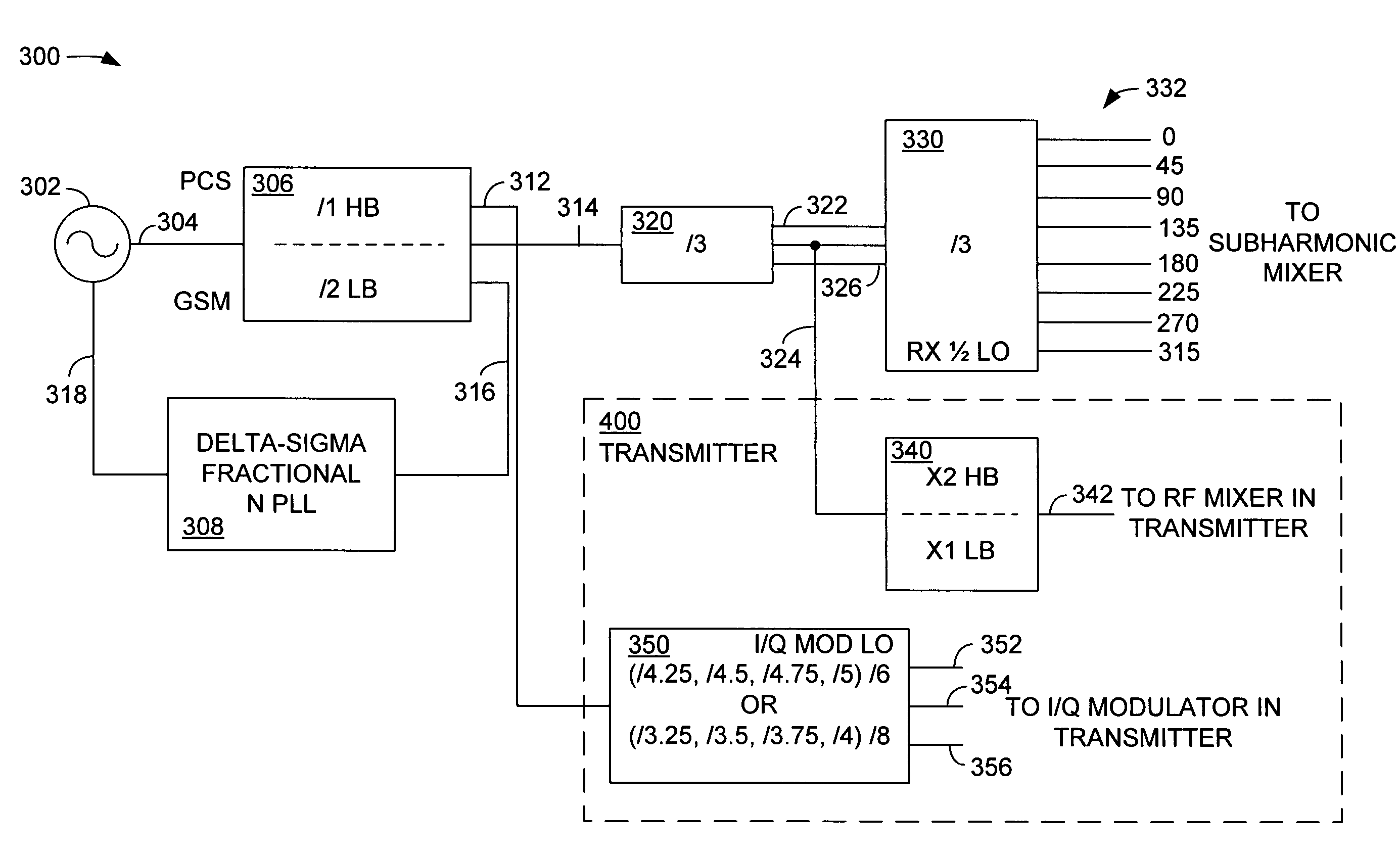

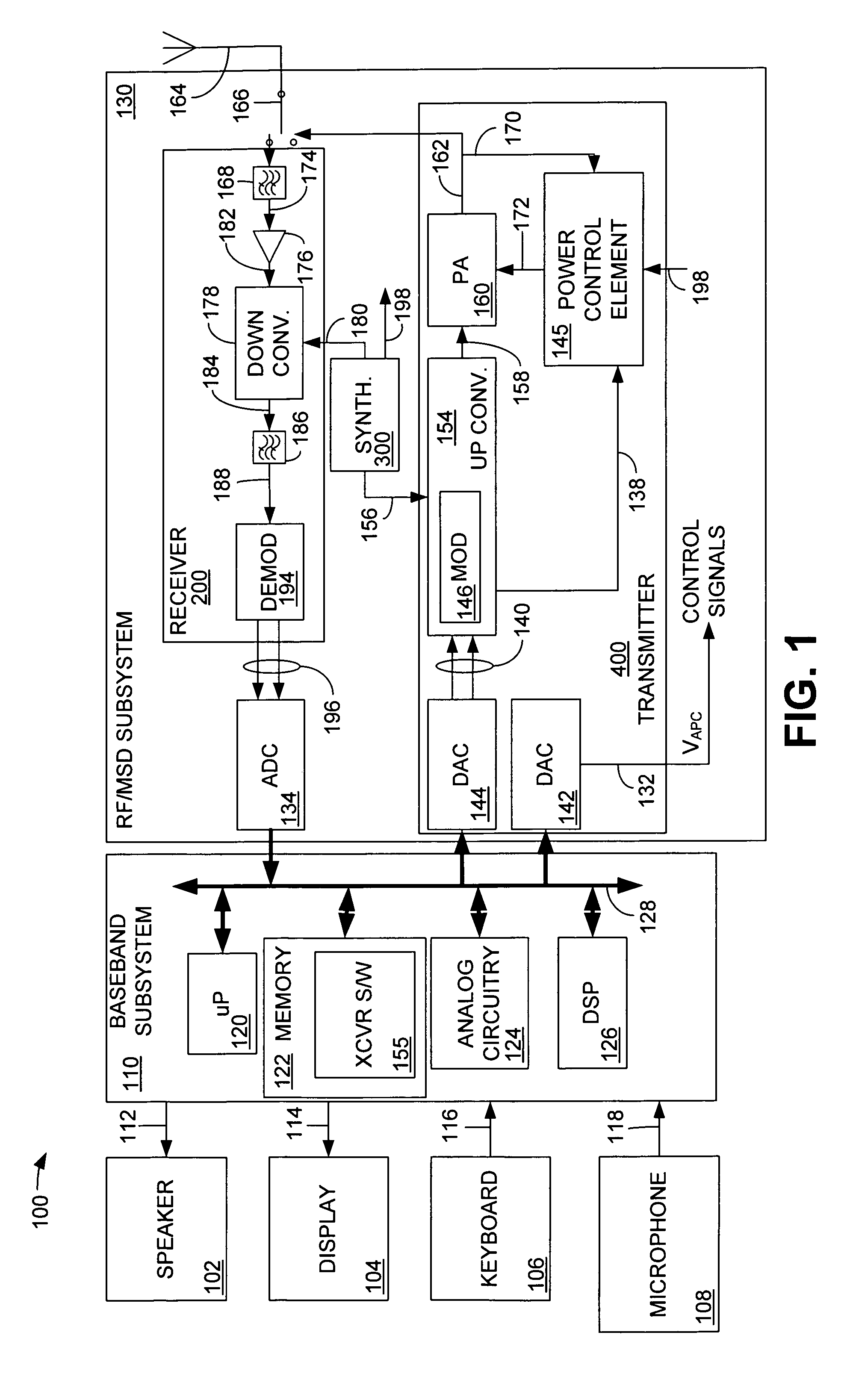

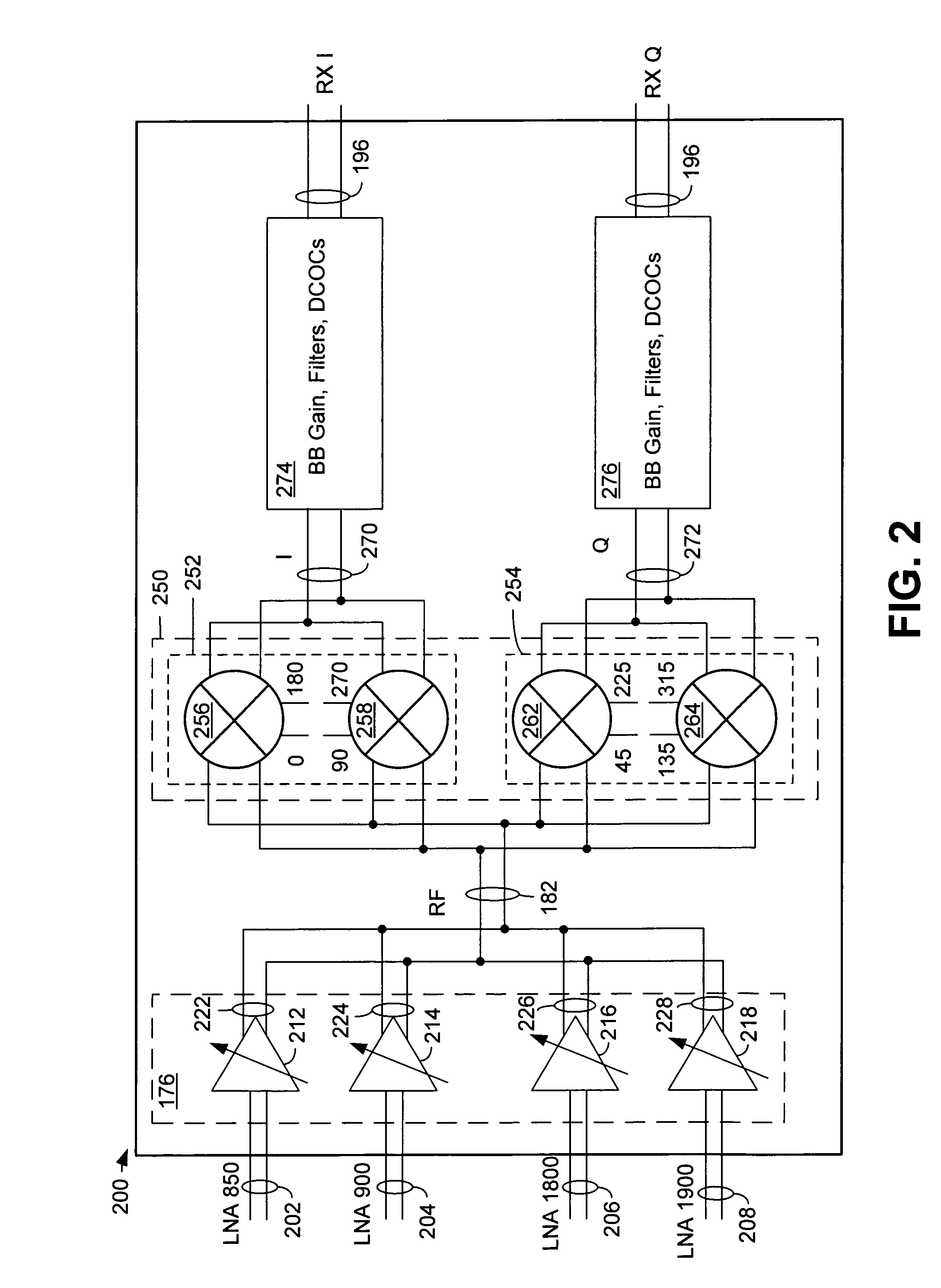

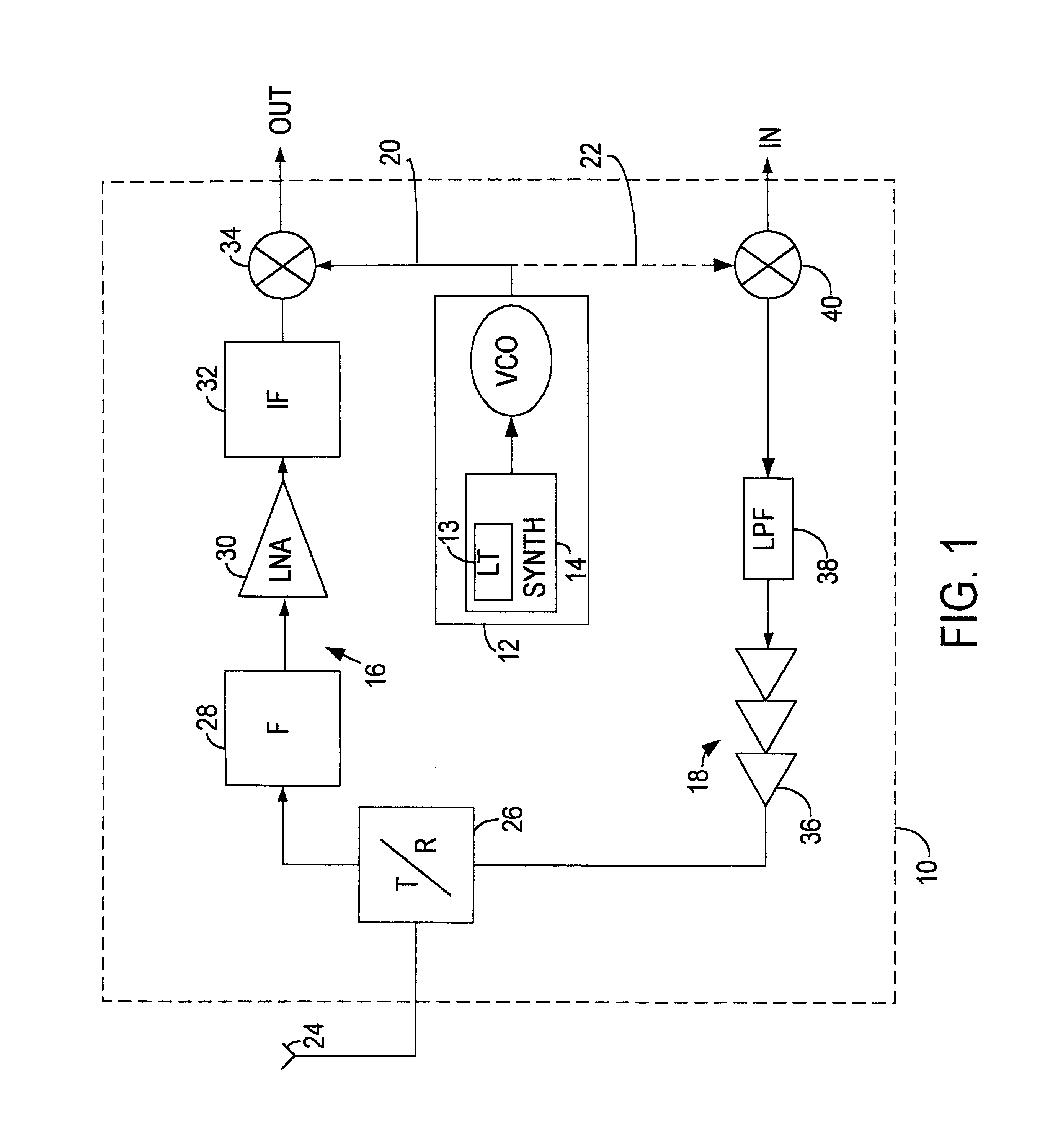

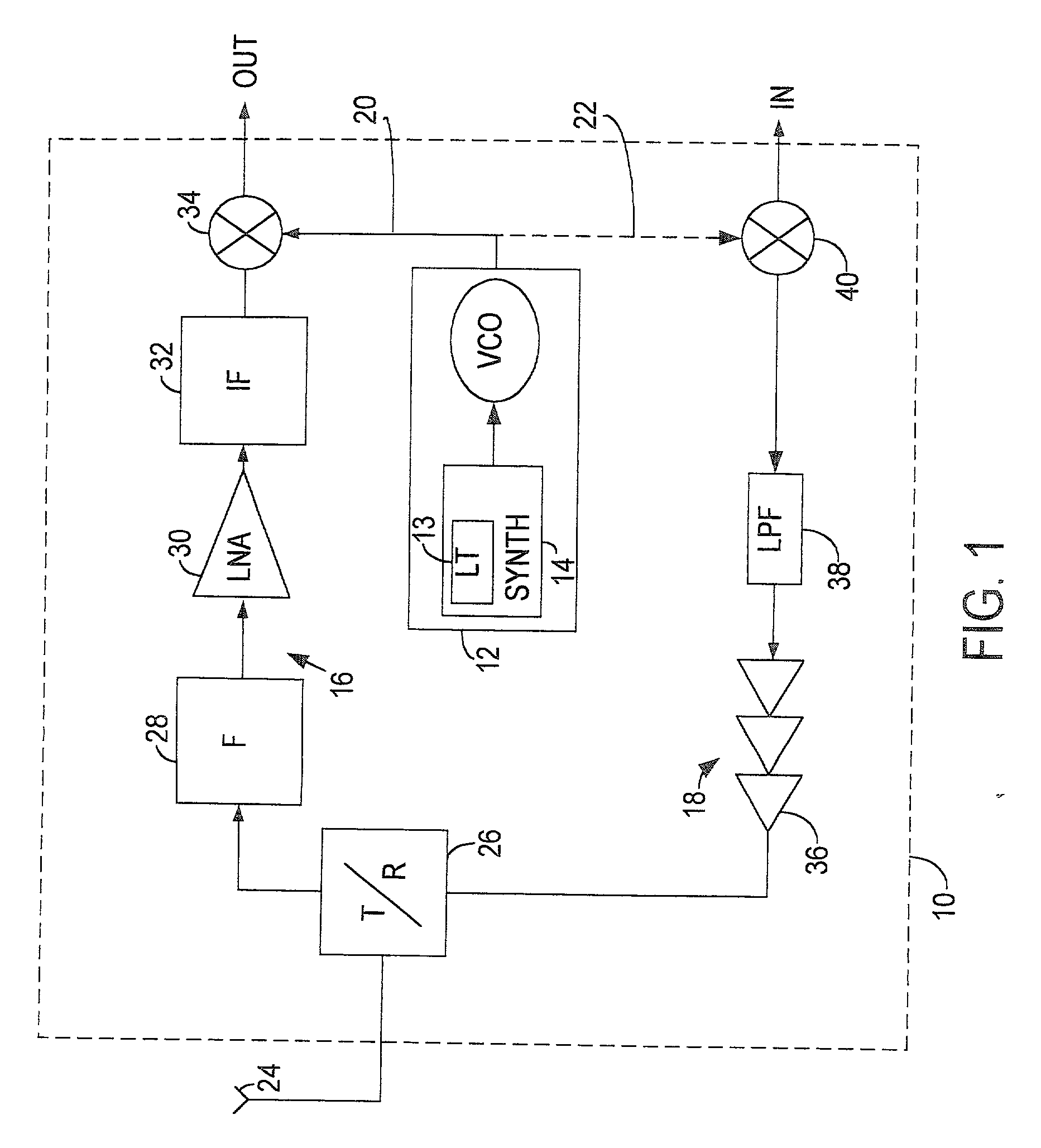

Single chip GSM/EDGE transceiver architecture with closed loop power control

InactiveUS7483678B2Resonant long antennasNegative-feedback-circuit arrangementsClosed loopFrequency multiplier

Owner:INTEL CORP

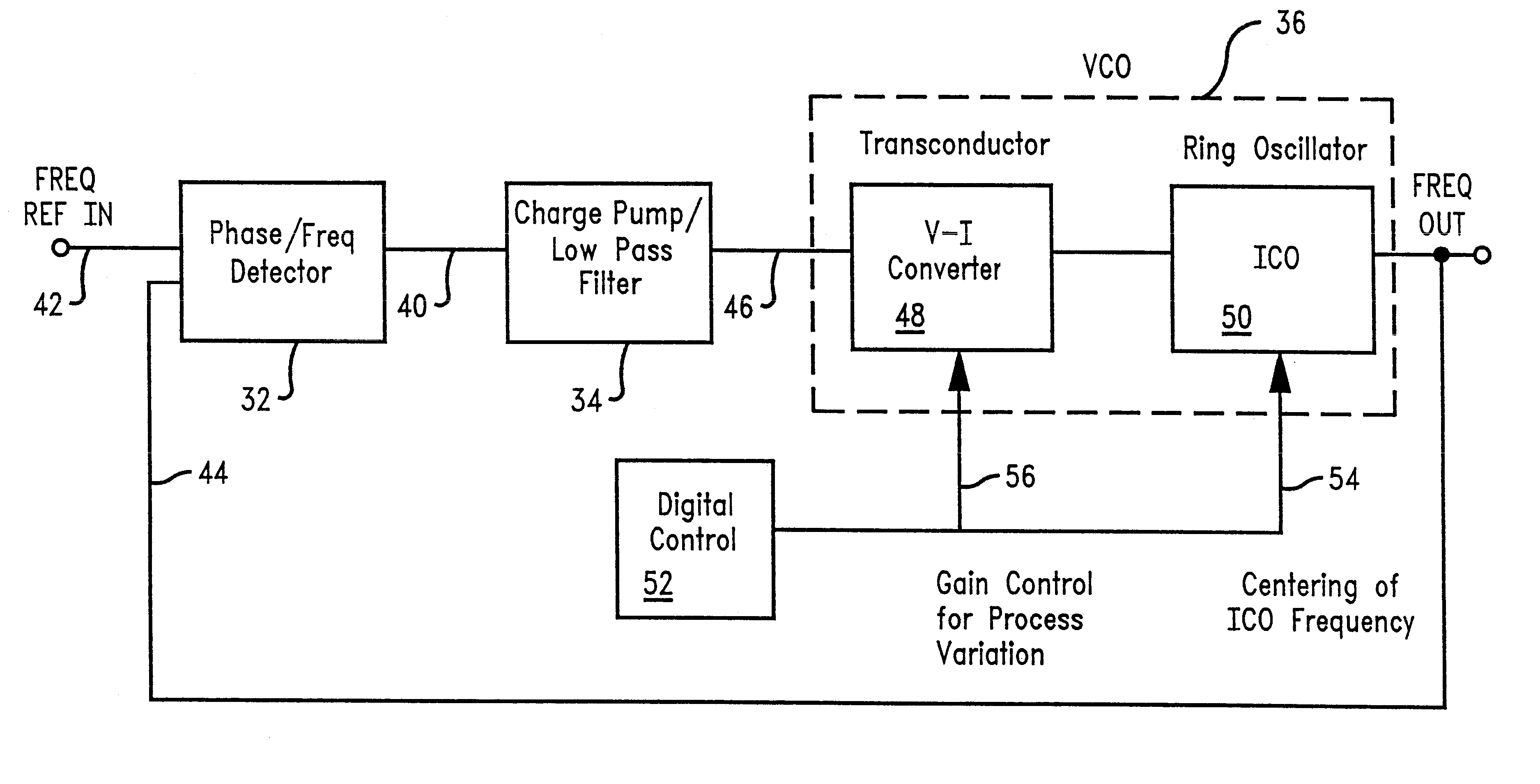

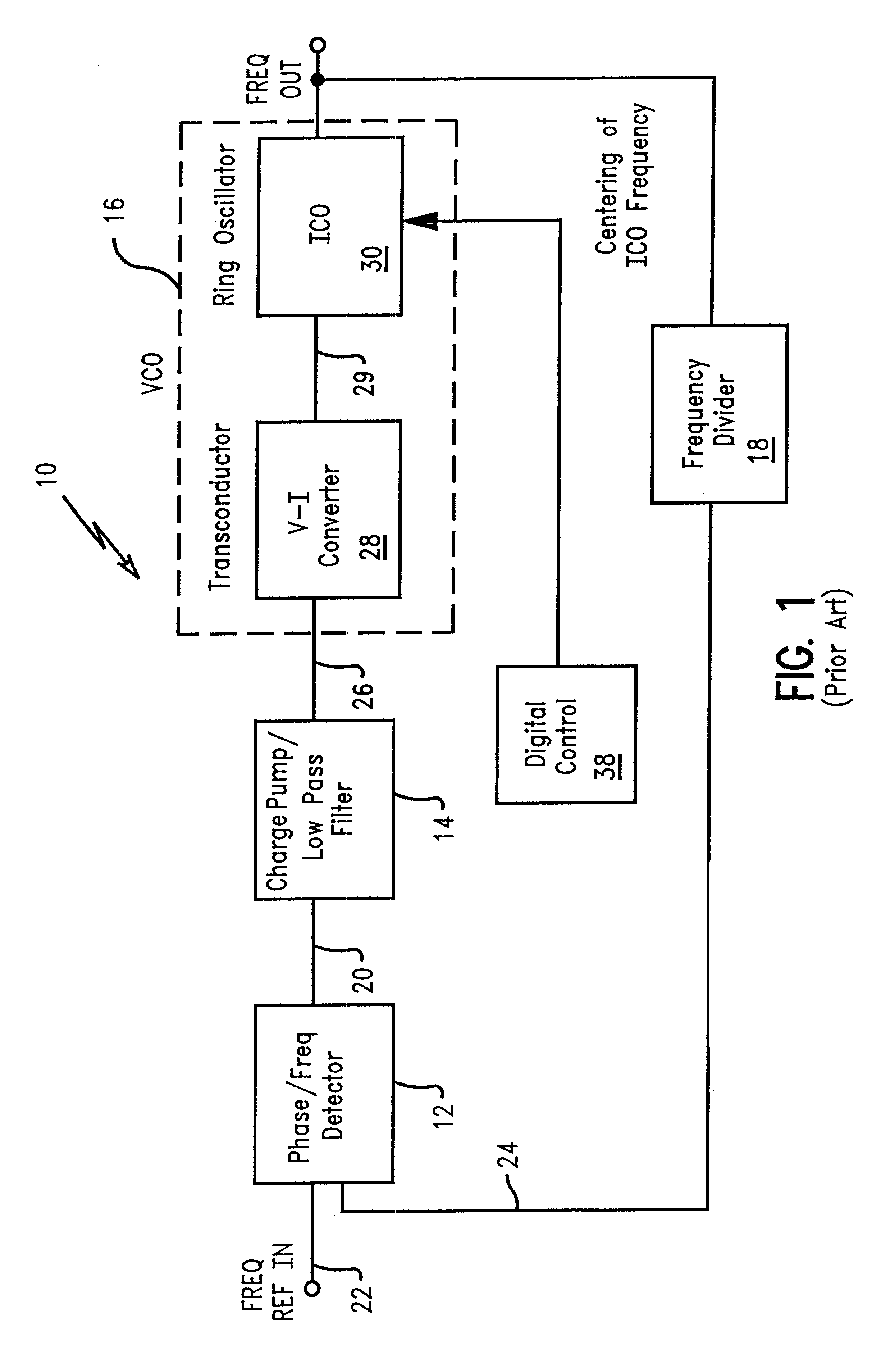

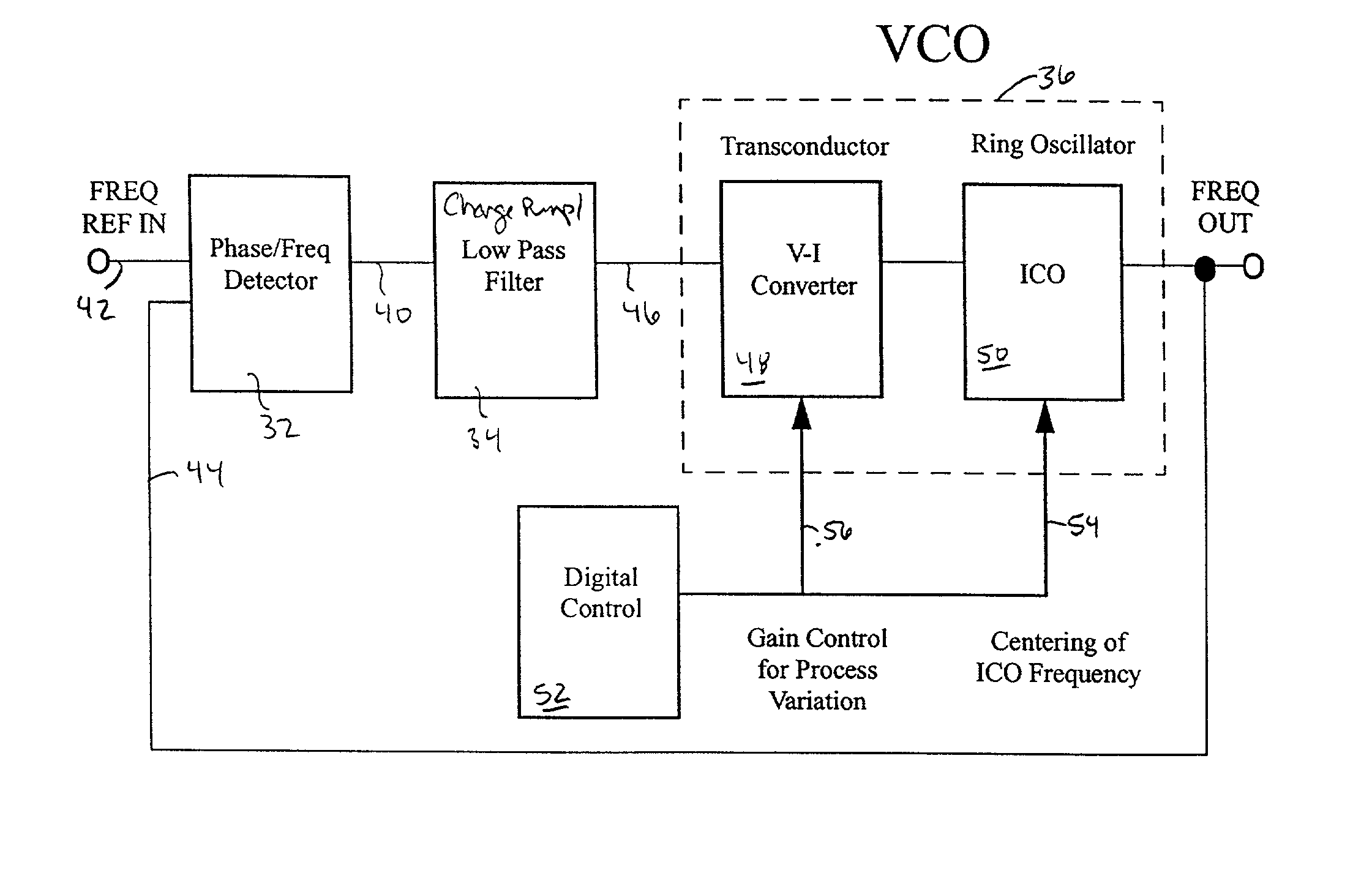

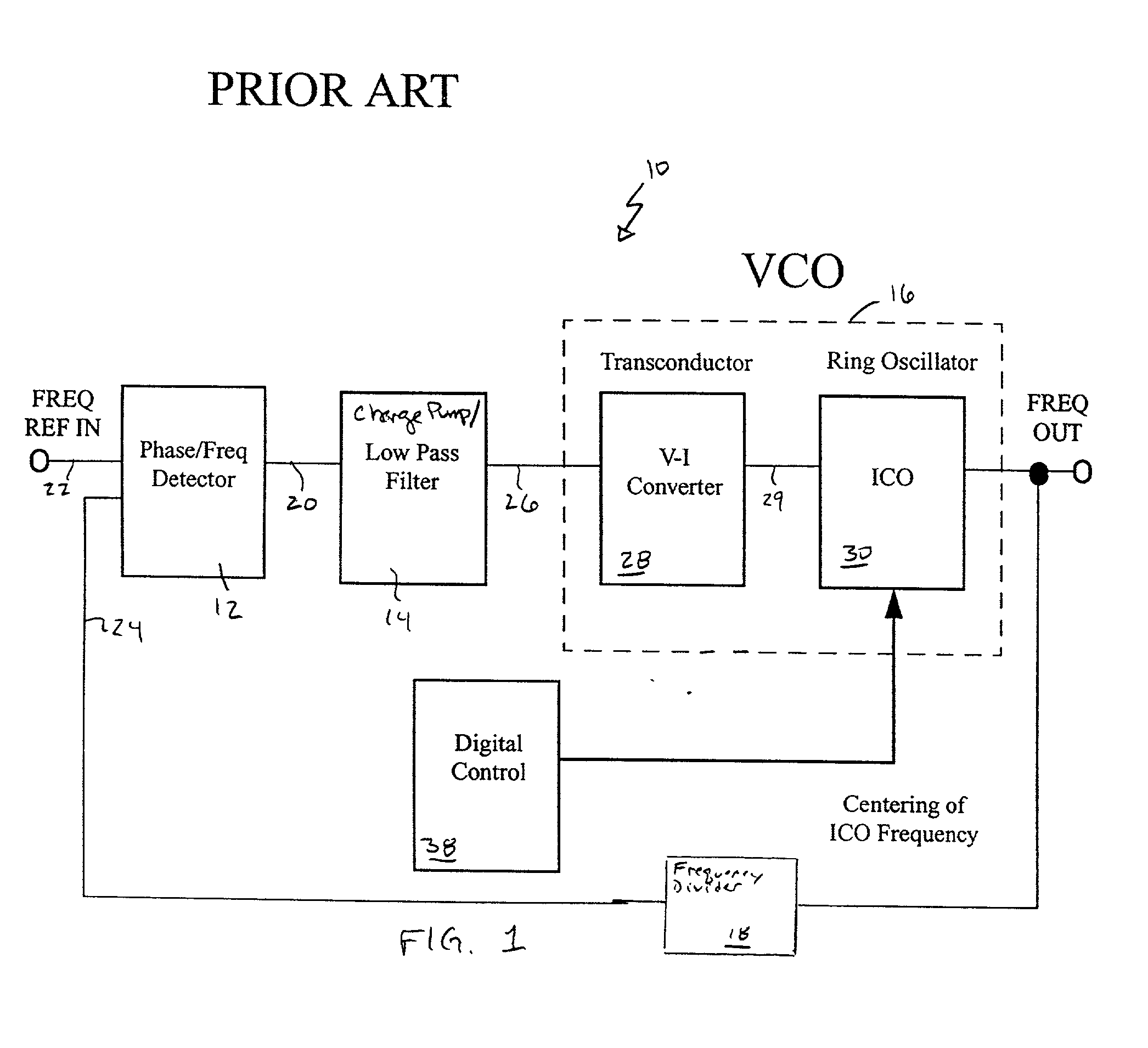

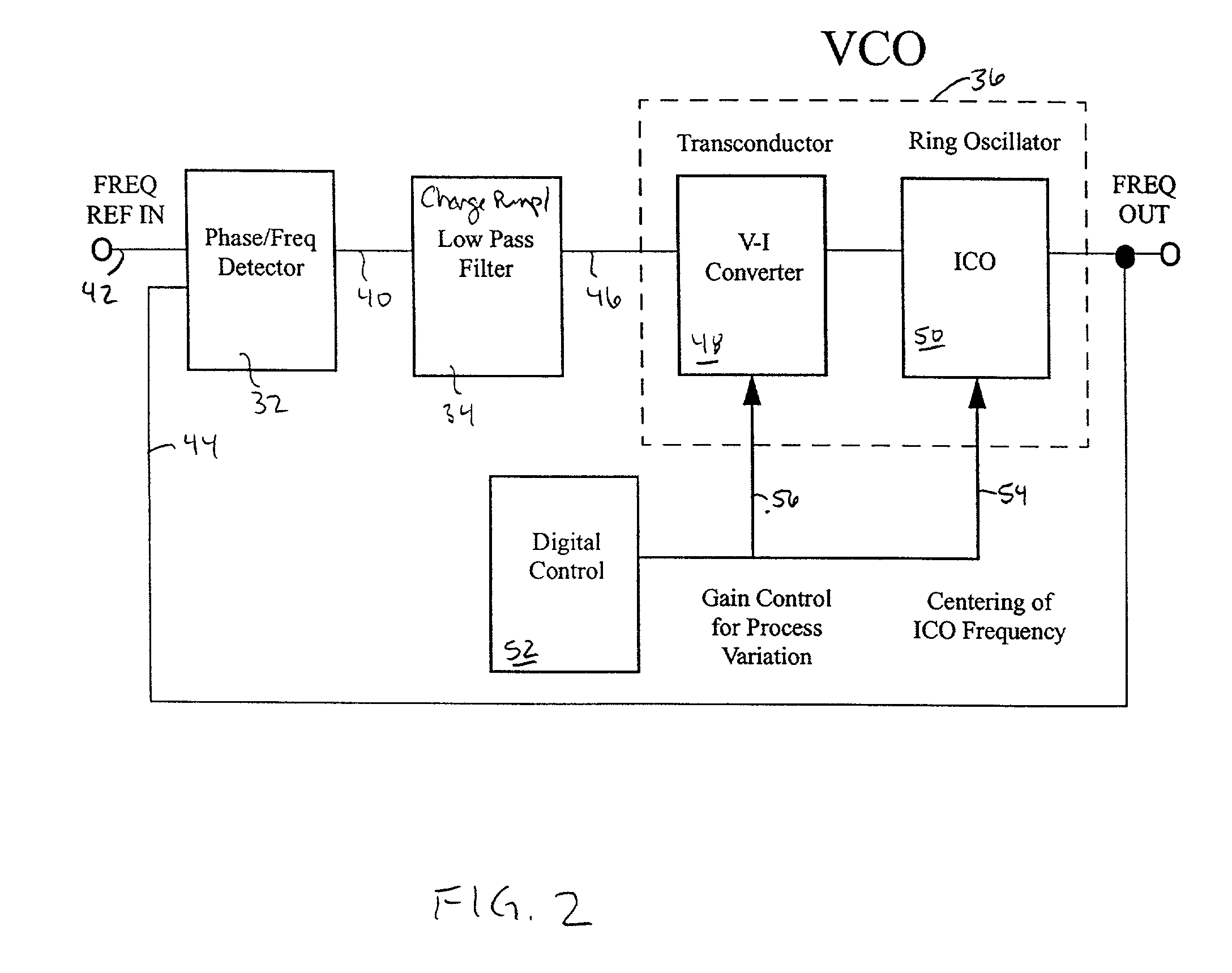

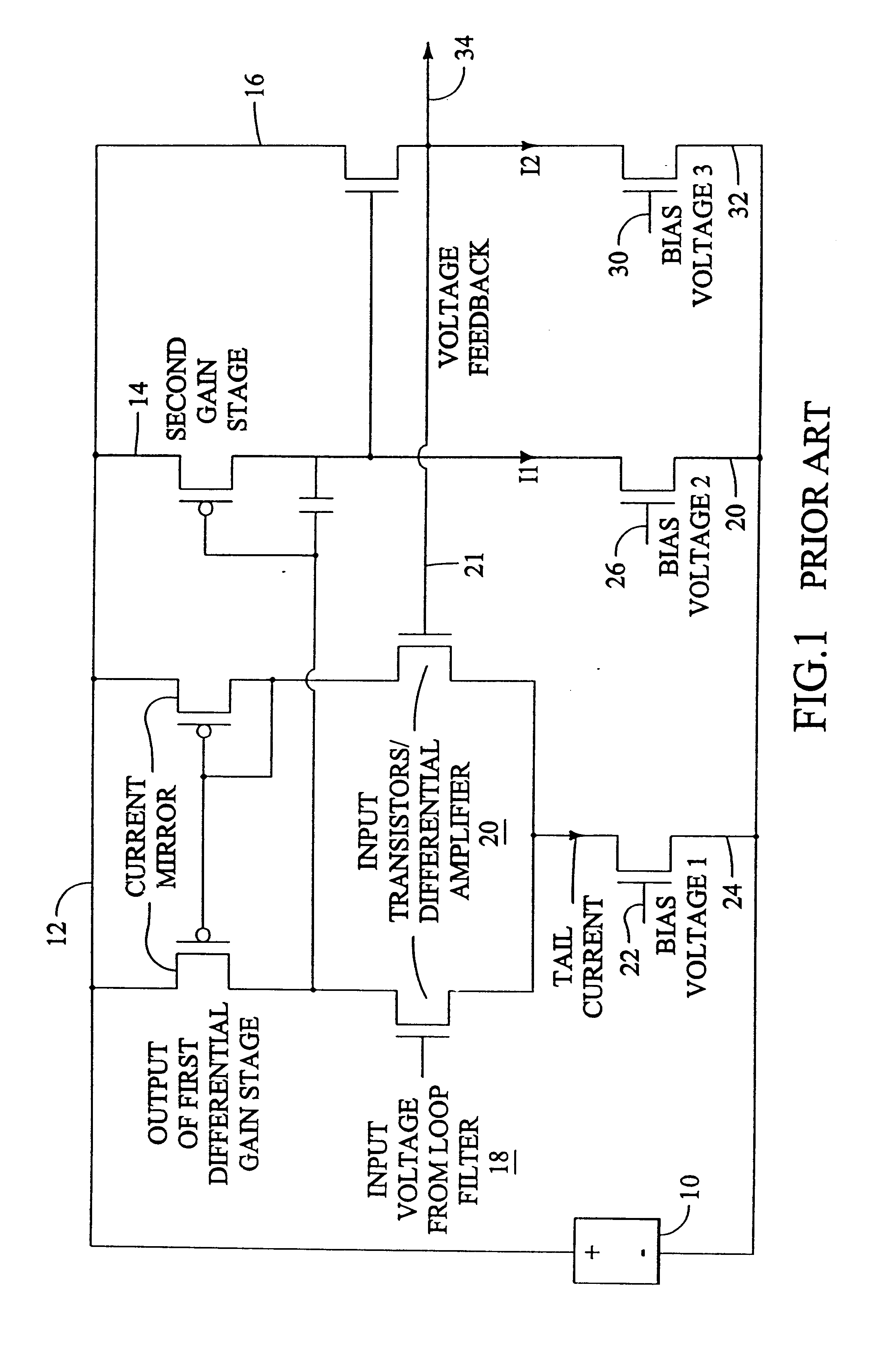

Linear voltage controlled oscillator transconductor with gain compensation

InactiveUS6466100B2More of the gainLess of the gainPulse automatic controlPulse generation by logic circuitsPhase locked loop circuitLow-pass filter

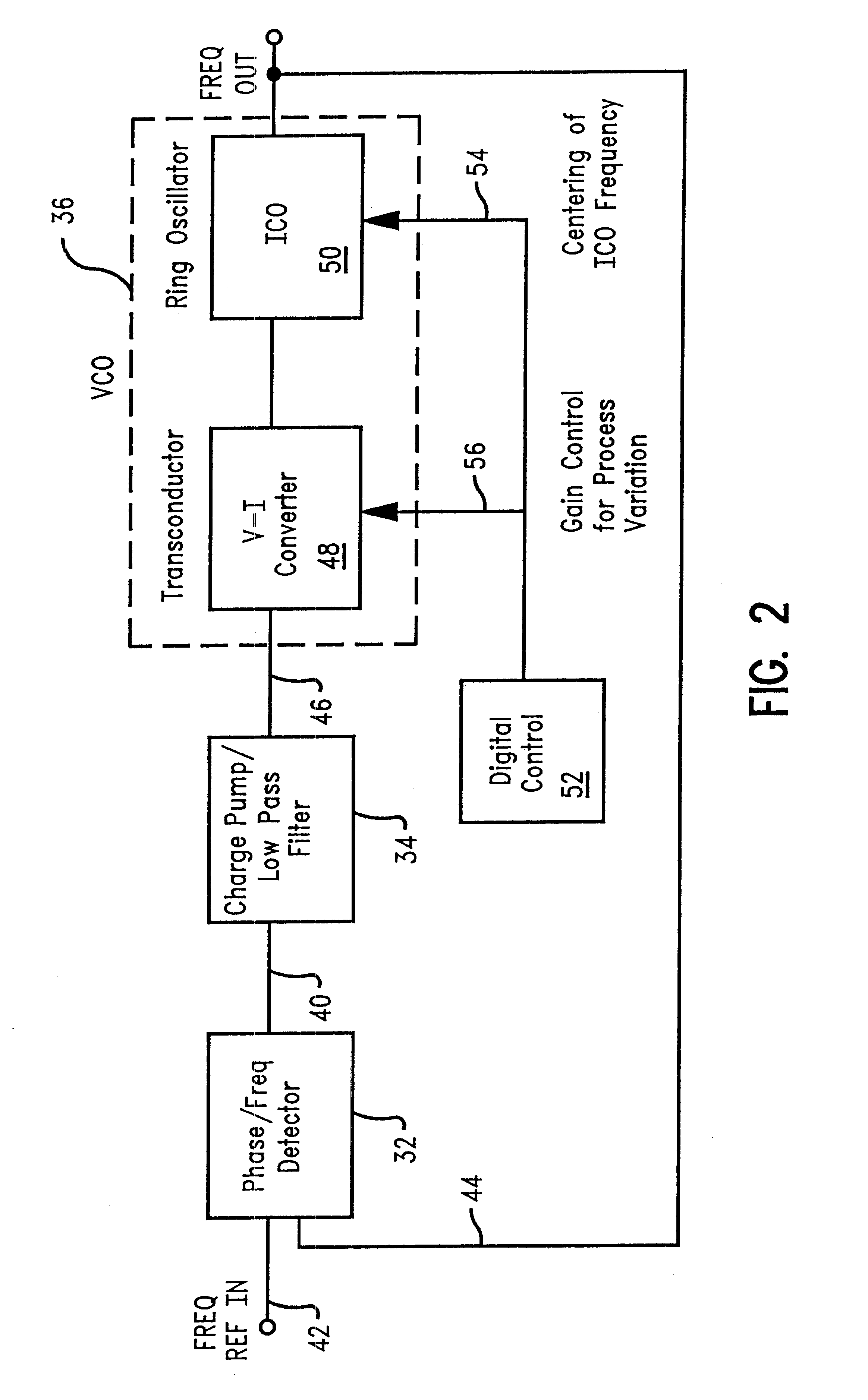

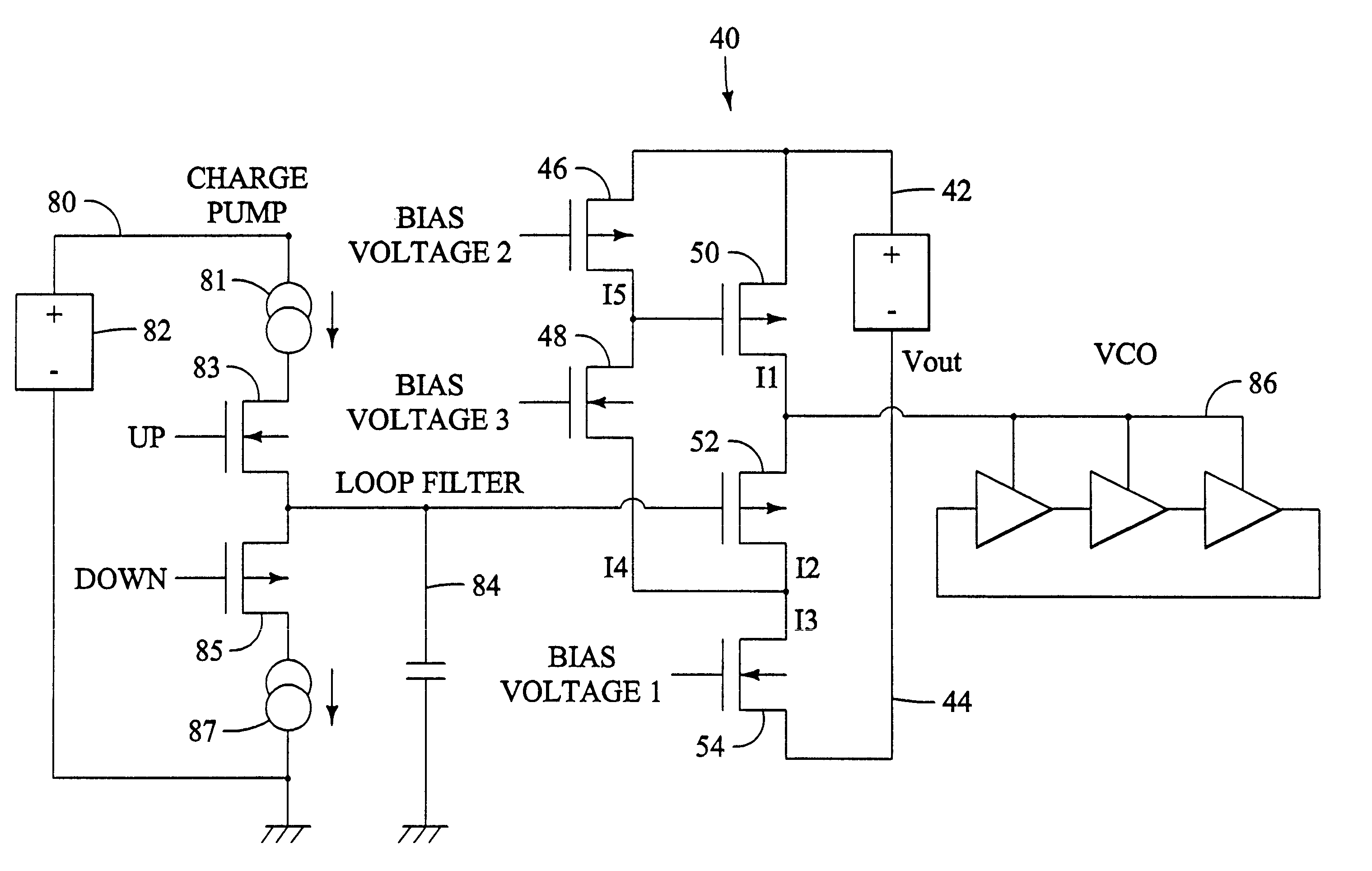

A voltage controlled oscillator of a phase locked loop circuit having digitally controlled gain compensation. The digital control circuitry provides binary logic input to the voltage controlled oscillator for a digitally controlled variable resistance circuit, a digitally controlled variable current transconductor circuit, or differential transistor pairs having mirrored circuitry for adjusting the V-I gain. The latter configuration requires the voltage controlled oscillator to incorporate a source-coupled differential pair which is driven by a low pass filter capacitor output voltage, and connected to load transistors; a current source and a current mirror for generating a tail current; individual banks of transistors to mirror the load transistor currents; a digital-to-analog converter with control lines outputted there from, the digital-to-analog converter used to increase the amount of current allowed to flow to the transconductor output, the current being digitally increased and decreased corresponding to an amount of current pulled from the current source, and mirroring the current through at least one transistor mirror circuit.

Owner:MARVELL ASIA PTE LTD

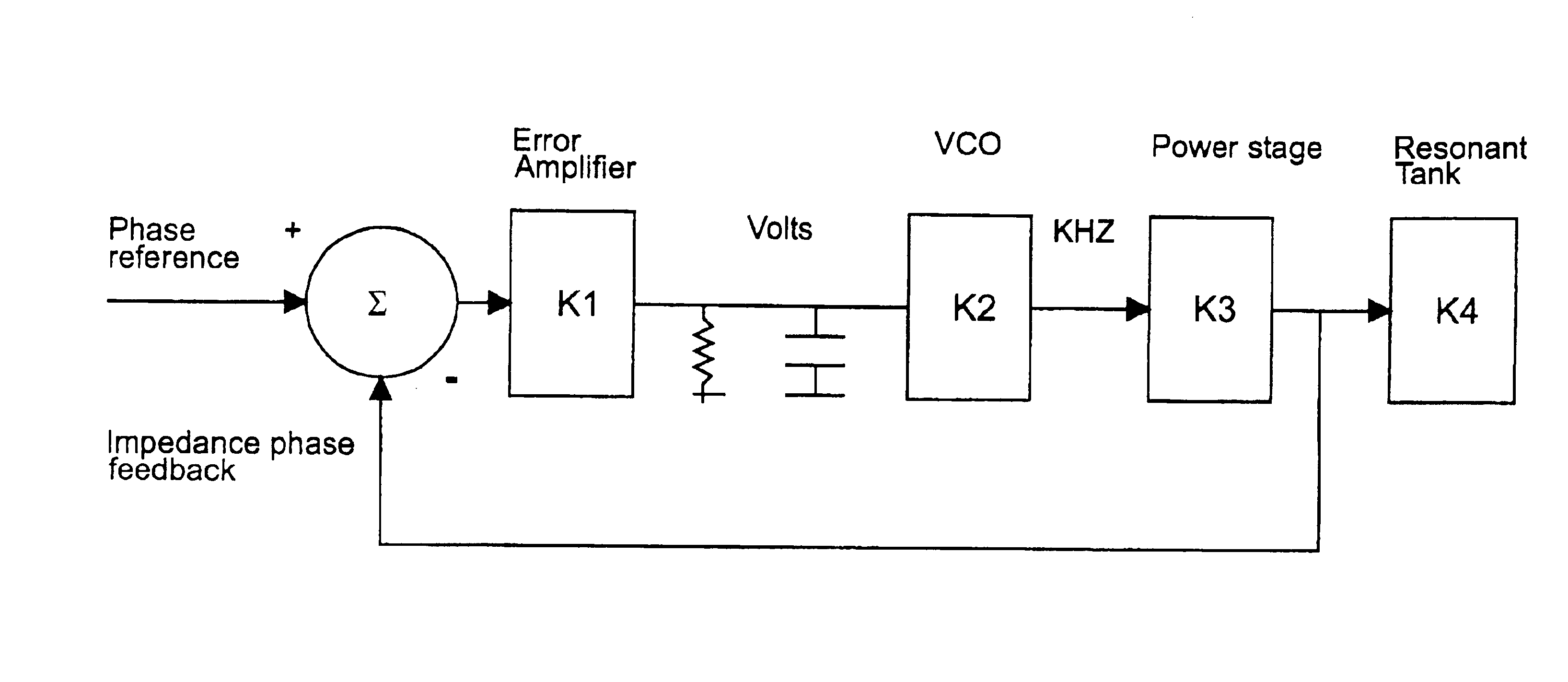

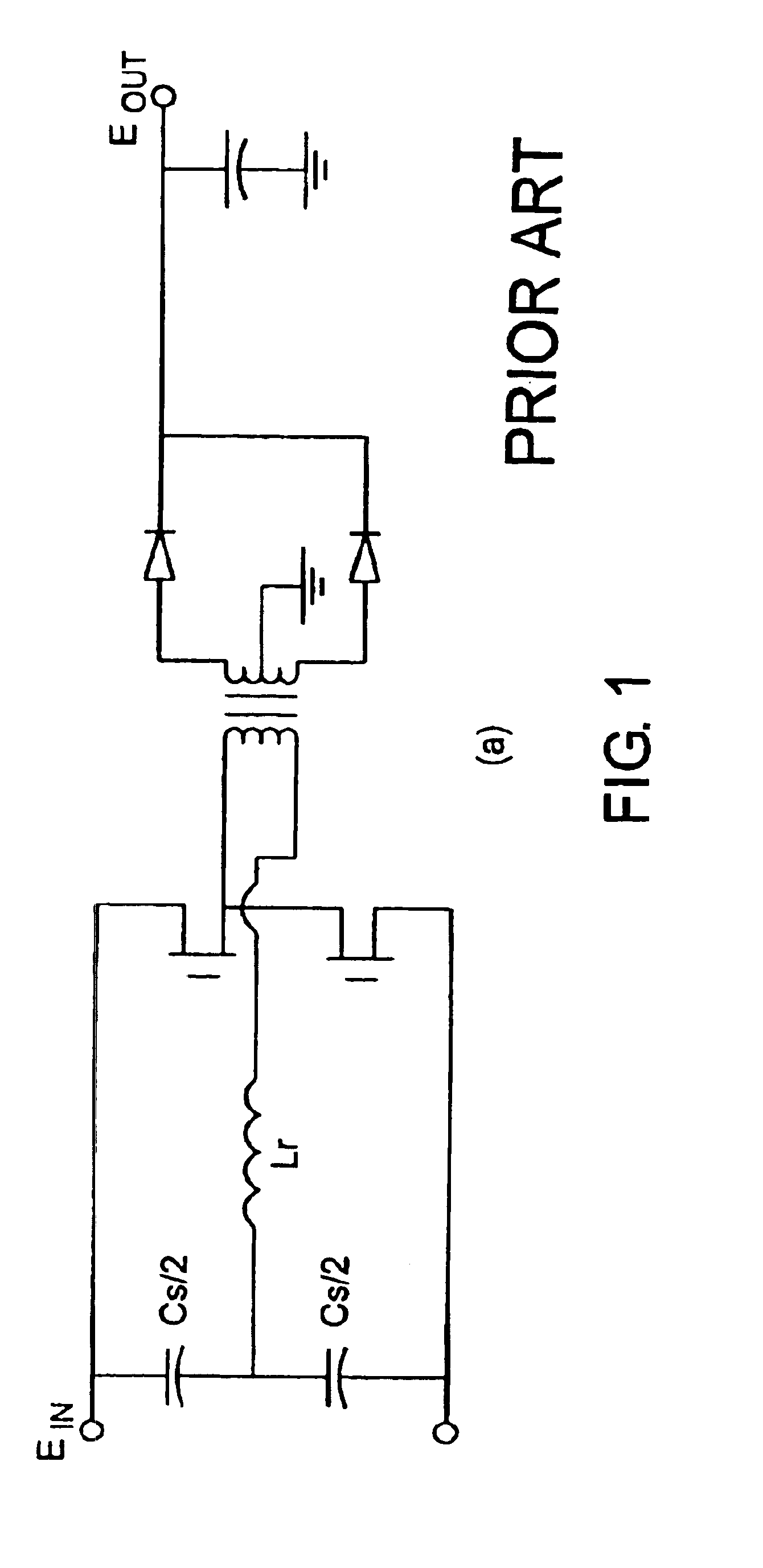

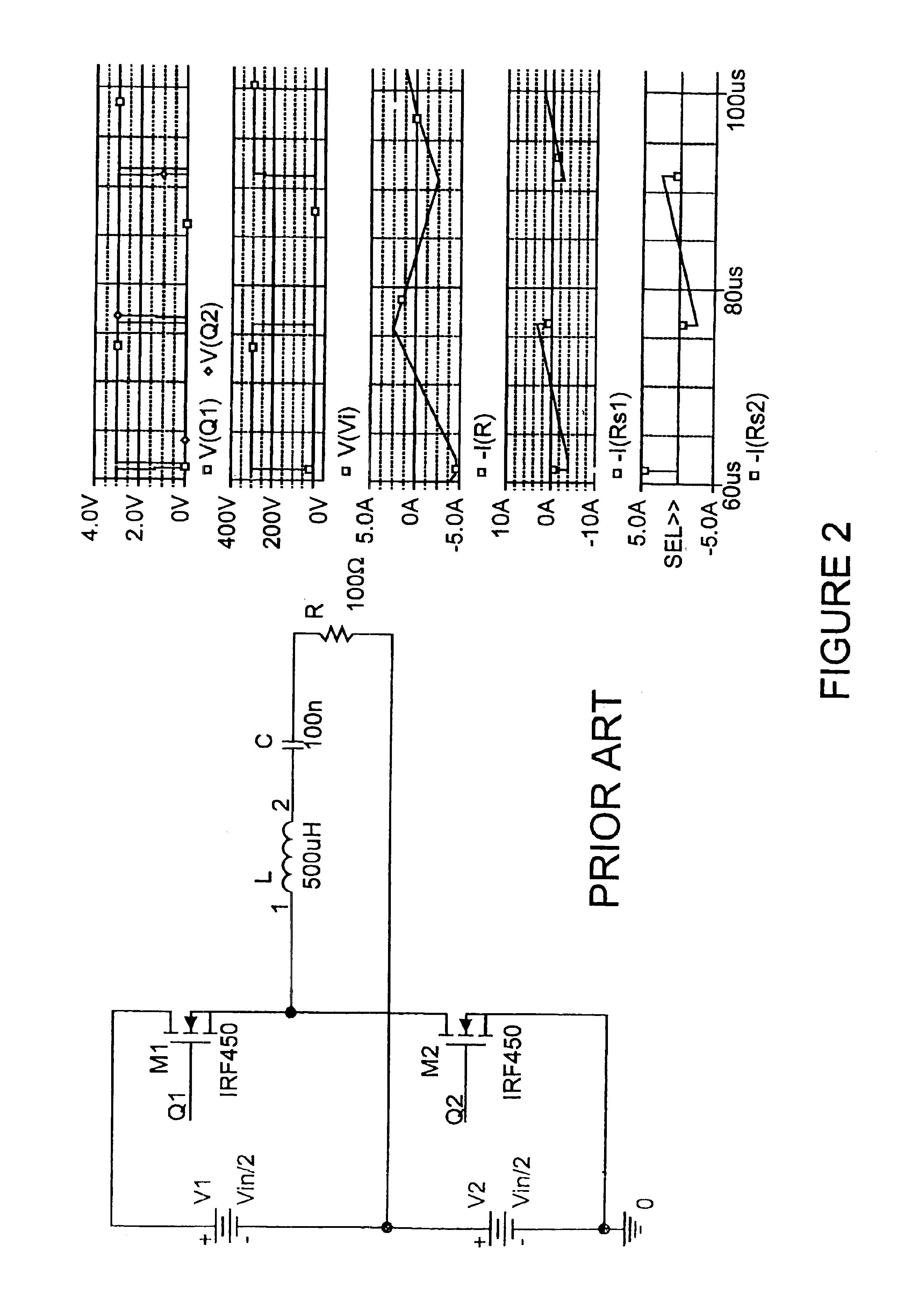

Resonant converter with phase delay control

InactiveUS6903949B2Easy Feedback ControlImprove efficiencyEfficient power electronics conversionConversion with intermediate conversion to dcTransverterResonant converter

A phase delay control for a power converter operates with a phase locked loop and current sense feedback to provide improved control stability and dynamic output range. The phase lock loop includes a voltage controlled oscillator that is controlled based on an error signal derived from a phase of the power converter output. The error signal applied to the voltage controlled oscillator produces a shift in switching frequency for the converter to drive the error to zero. The power converter includes an LCC resonant circuit to manipulate resonant electrical energy to improve switching speed and power density.

Owner:INFINEON TECH AMERICAS CORP

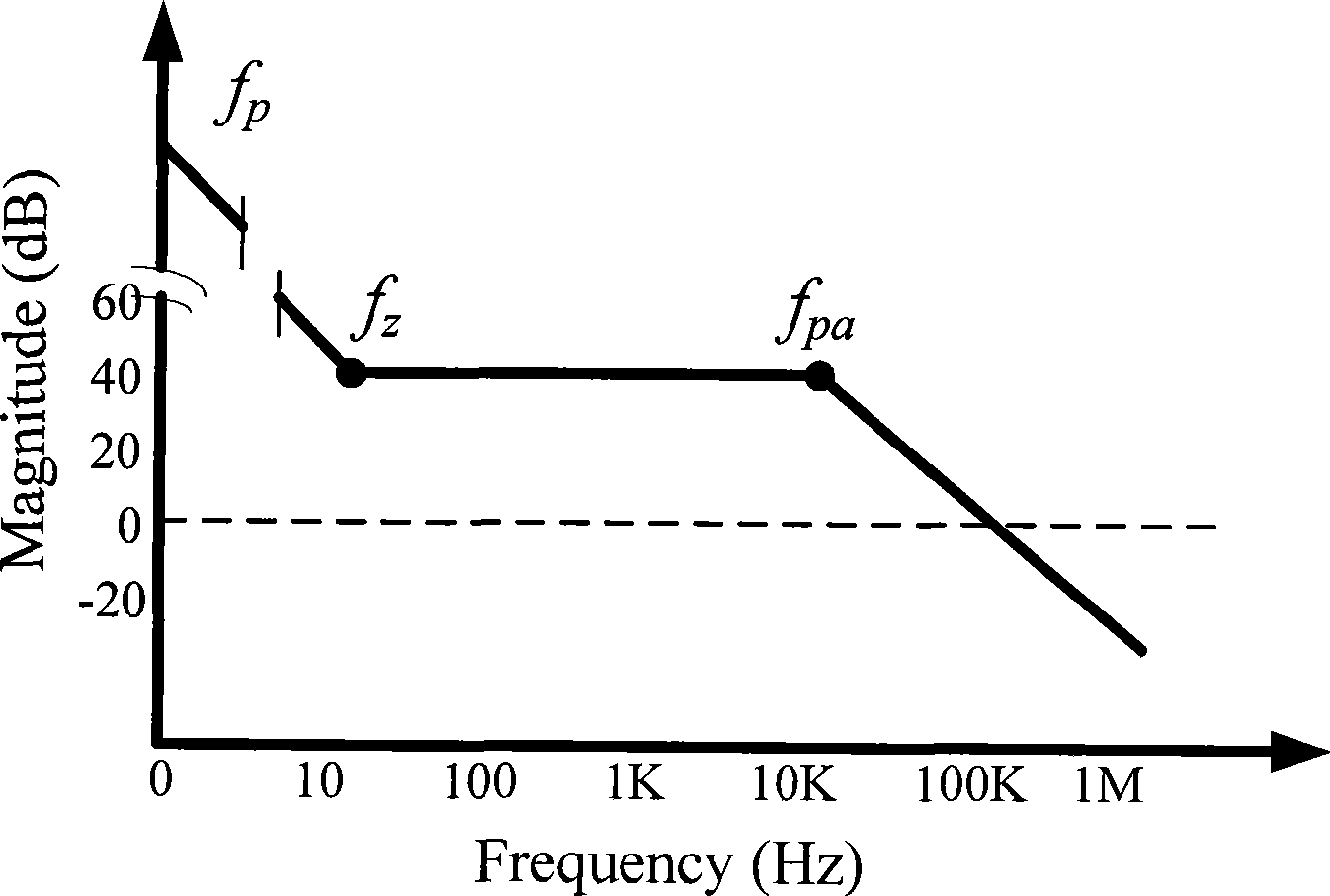

PLL loop filter with switched-capacitor resistor

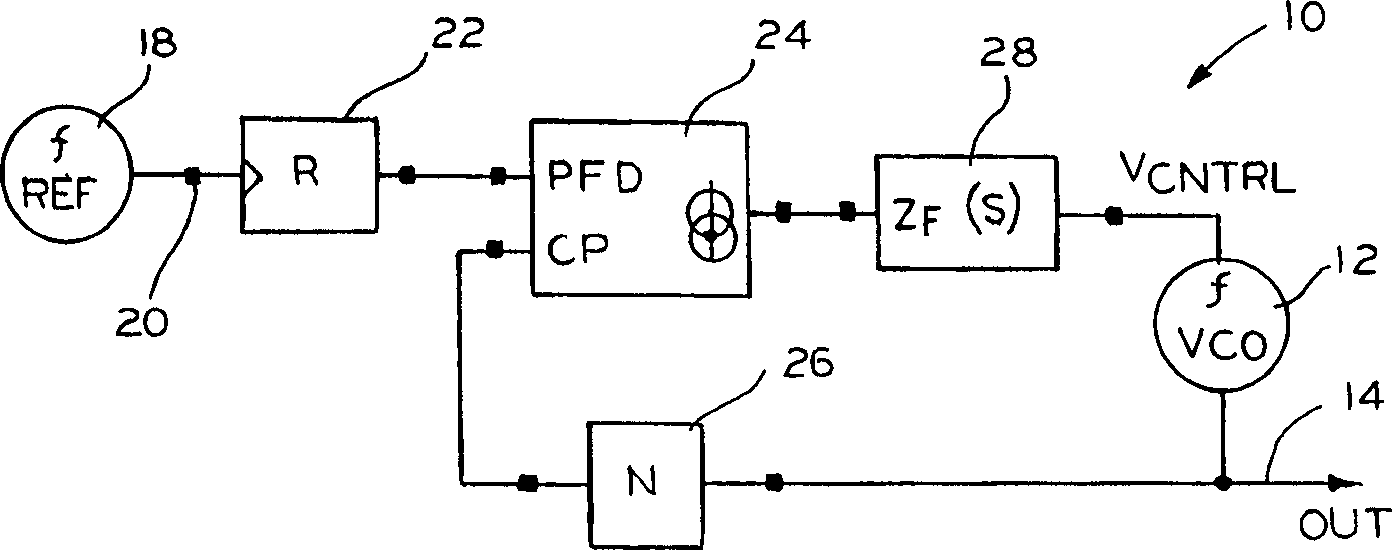

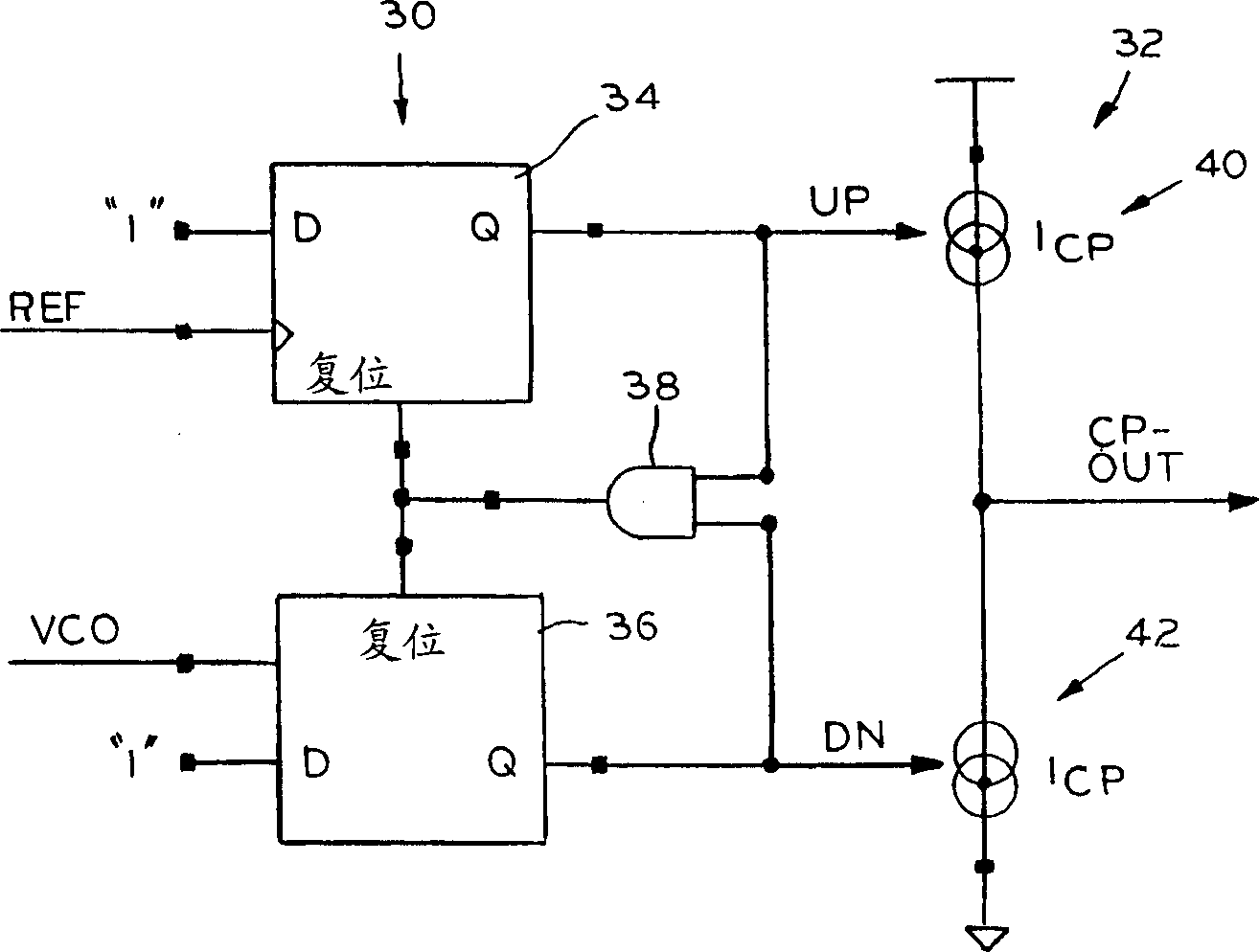

A phase locked loop circuit with improved noise characteristics includes a voltage controlled oscillator (12) that generates an oscillating output signal in response to a voltage controlled input. A reference source provides the reference frequency signal. A phase detector (30) is operatively connected to the voltage controlled oscillator and a reference source and produces an output proportional to the phase difference between the oscillation output signal and the reference signal. A loop filter (46) connects the phase detector output to the voltage control input. The loop filter consists of a switch-capacitor equivalent resistance (Q1, Q2, CR).

Owner:TELEFON AB LM ERICSSON (PUBL)

Single chip GSM/EDGE transceiver architecture with closed loop power control

InactiveUS20070072577A1Resonant long antennasNegative-feedback-circuit arrangementsClosed loopFrequency multiplier

A single chip GSM / EDGE transceiver comprises a fully differential receive chain, a subharmonic mixer in the receive chain, the subharmonic mixer configured to receive a radio frequency (RF) input signal and a local oscillator (LO) signal that is phase-shifted by a nominal 45 degrees, and a synthesizer having a voltage controlled oscillator and having at least one frequency divider to generate desired transmit and receive LO signals. The transceiver also comprises a transmitter having a closed power control loop, and a harmonic rejection modulator, the use thereof made possible by a frequency plan designed to allow the synthesizer to develop the transmit and receive LO signals without a frequency multiplier.

Owner:INTEL CORP

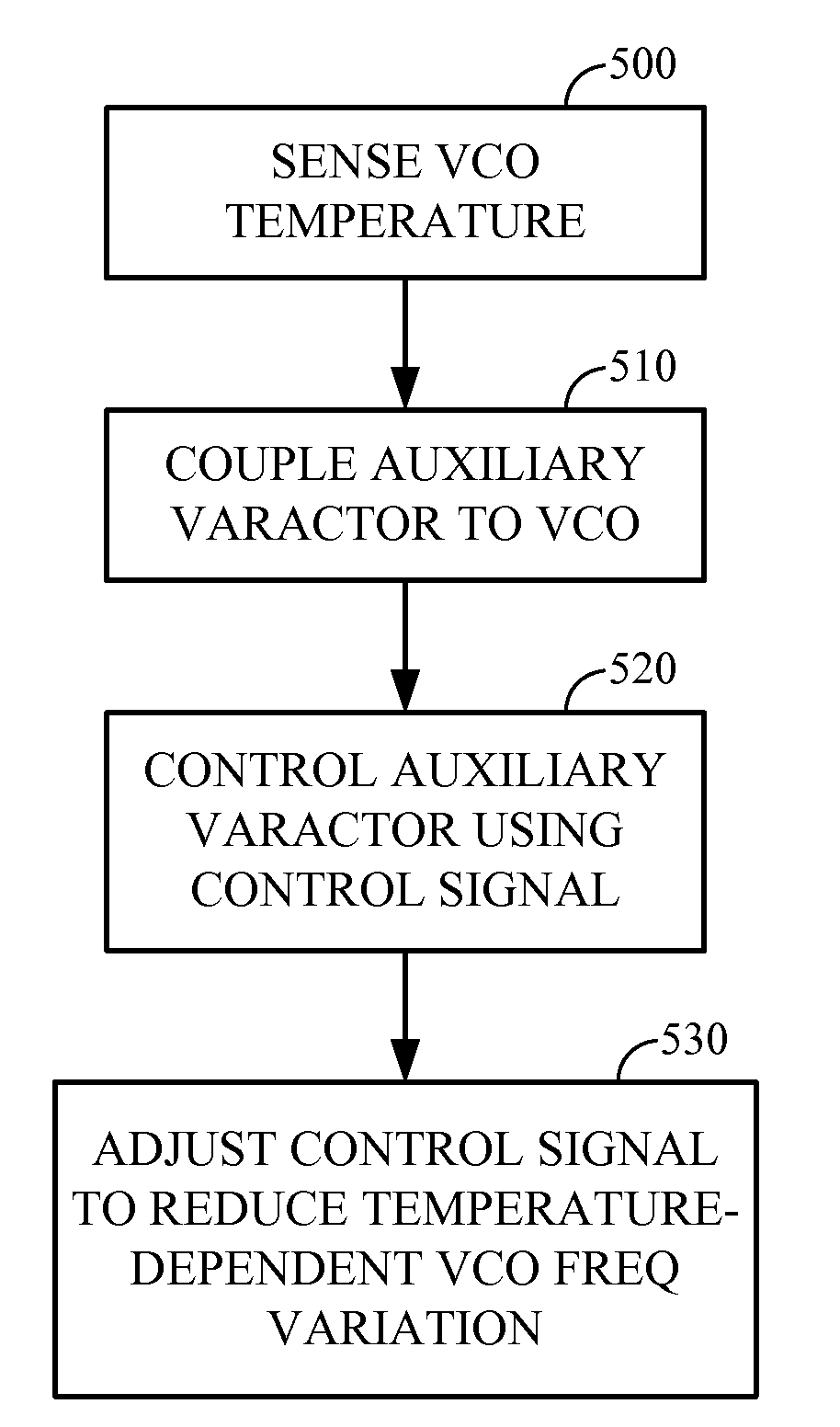

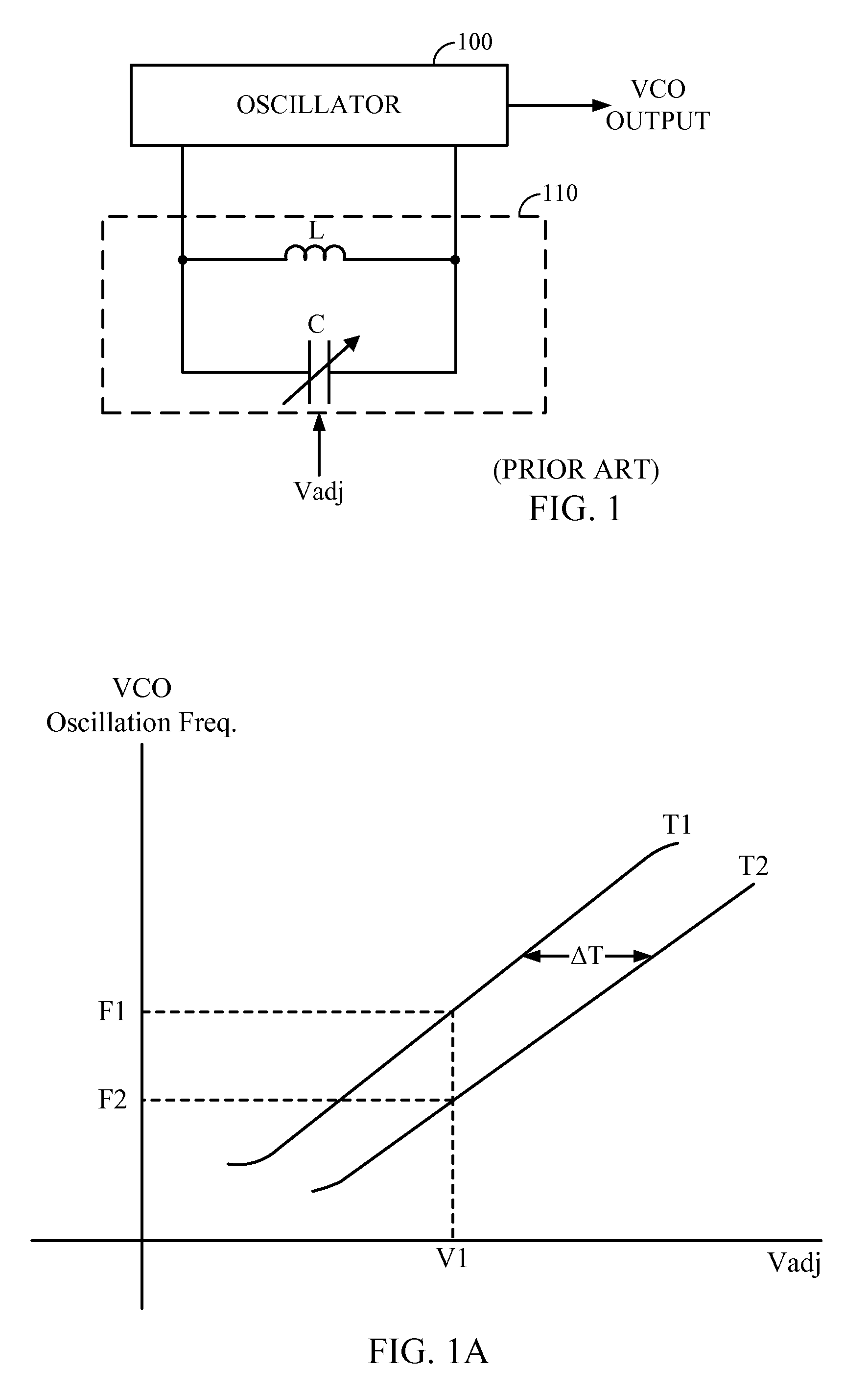

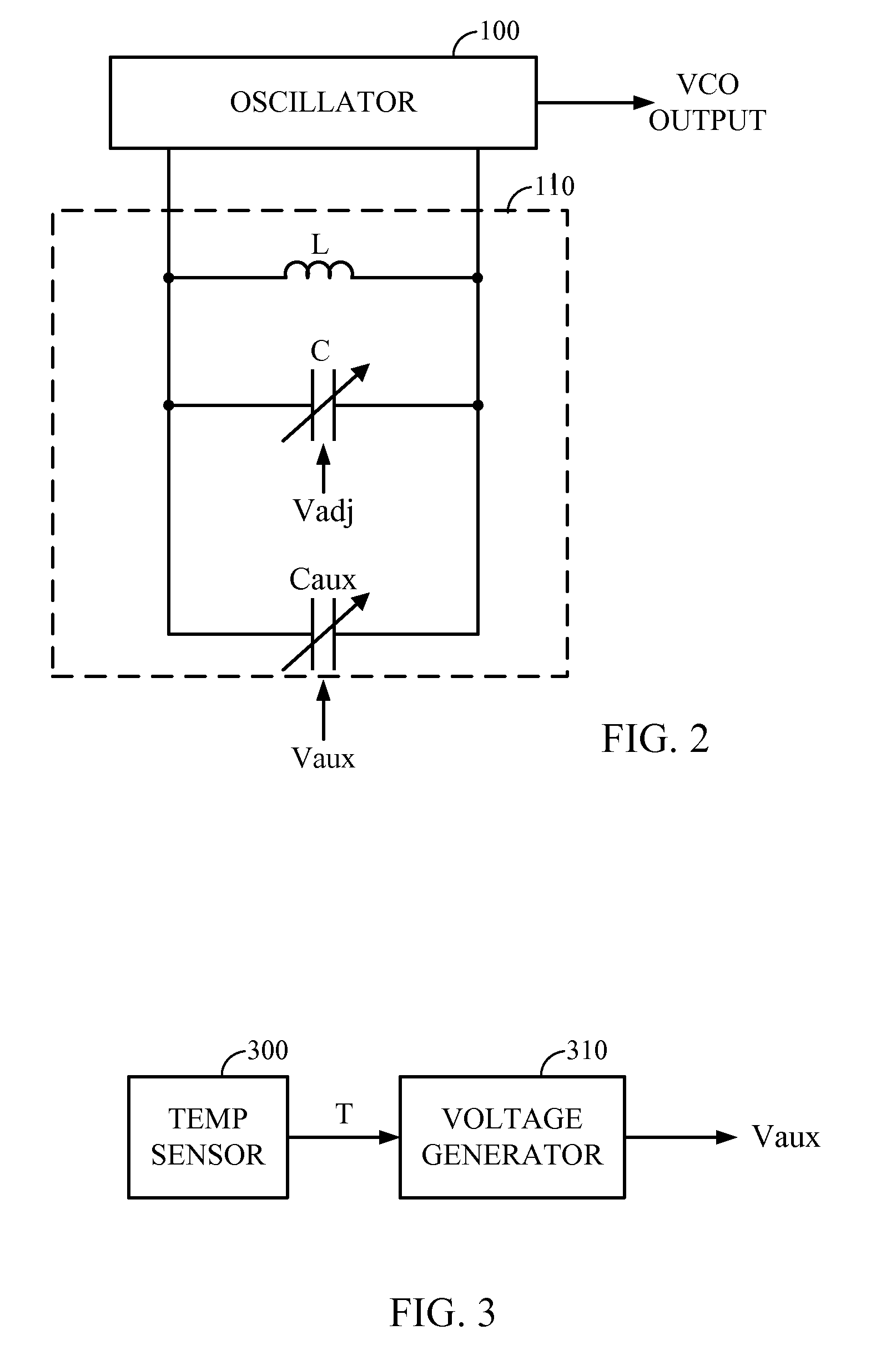

Auxiliary varactor for temperature compensation

InactiveUS20090261917A1Reduce variationAngle modulation detailsGenerator stabilizationVoltage controlVaricap

Techniques for compensating for the effects of temperature change on voltage controlled oscillator (VCO) frequency are disclosed. In an embodiment, an auxiliary varactor is coupled to an LC tank of the VCO. The auxiliary varactor has a capacitance controlled by a temperature-dependant control voltage to minimize the overall change in VCO frequency with temperature. Techniques for generating the control voltage using digital and analog means are further disclosed.

Owner:QUALCOMM INC

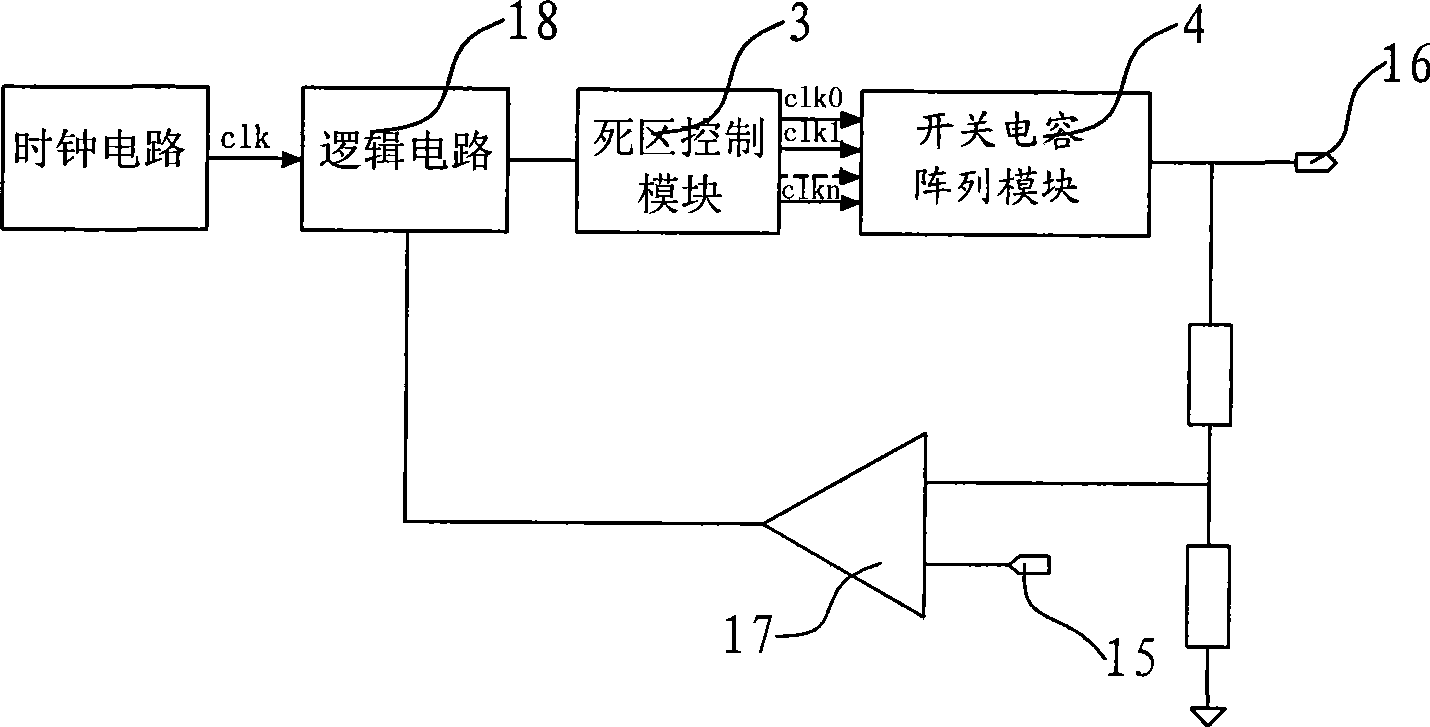

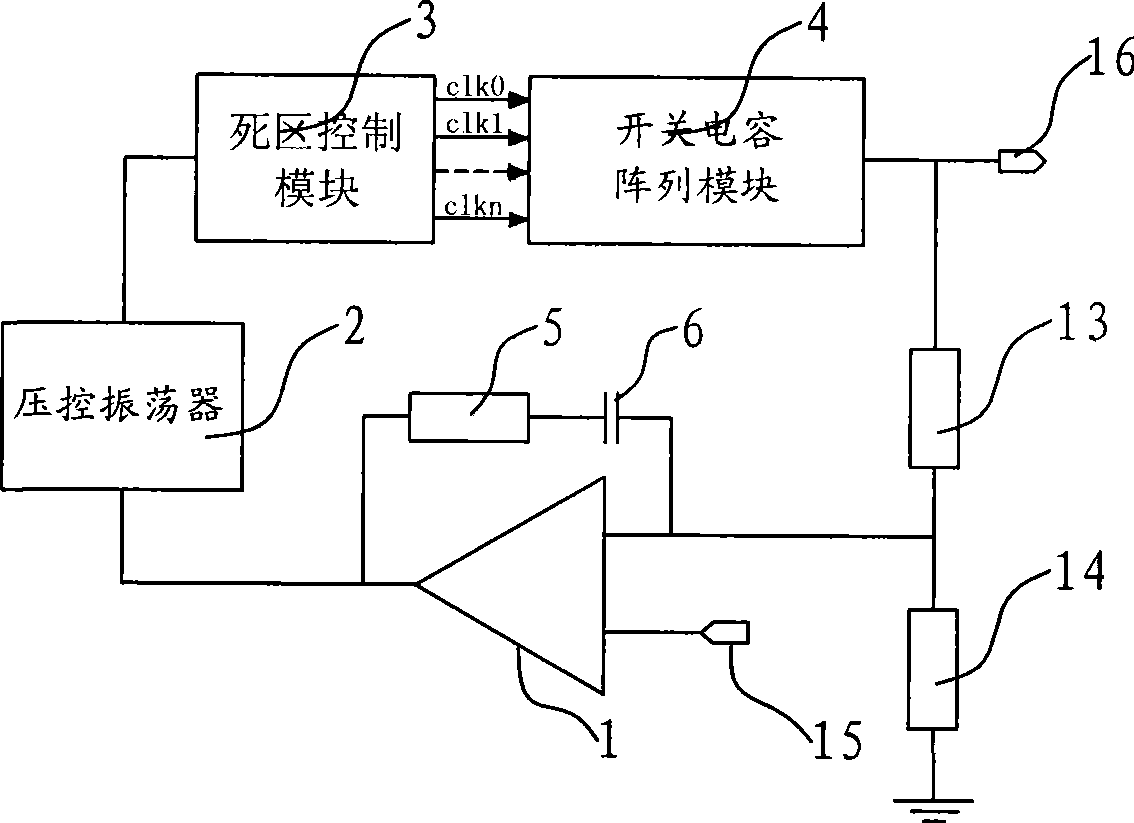

Switching capacitor type DC-DC converter

InactiveCN101478234AImprove efficiencySmall output rippleApparatus without intermediate ac conversionDc dc converterEngineering

The invention provides a switched capacitor DC-DC converter. The switched capacitor DC-DC converter comprises an output sampling branch, a dead area control module for generating the dead area and outputting multiunit clock signals which has the same frequency as the input clock, a switched capacitor array module for receiving multiunit clock signals which are not overlapped and sent by the dead area control module, an error amplifier for receiving the voltage signal from the output sampling branch and the reference voltage signals, and a voltage controlled oscillator for receiving the output voltage signals of the error amplifier and for outputting the clock signals with corresponding frequency. The voltage controlled oscillator sends the clock signals to the dead control module. The frequency variation of the clock signals is in proportion to the output voltage variation of the error amplifier. The converter has low output voltage ripple and high efficiency in full load range.

Owner:ZHEJIANG UNIV +1

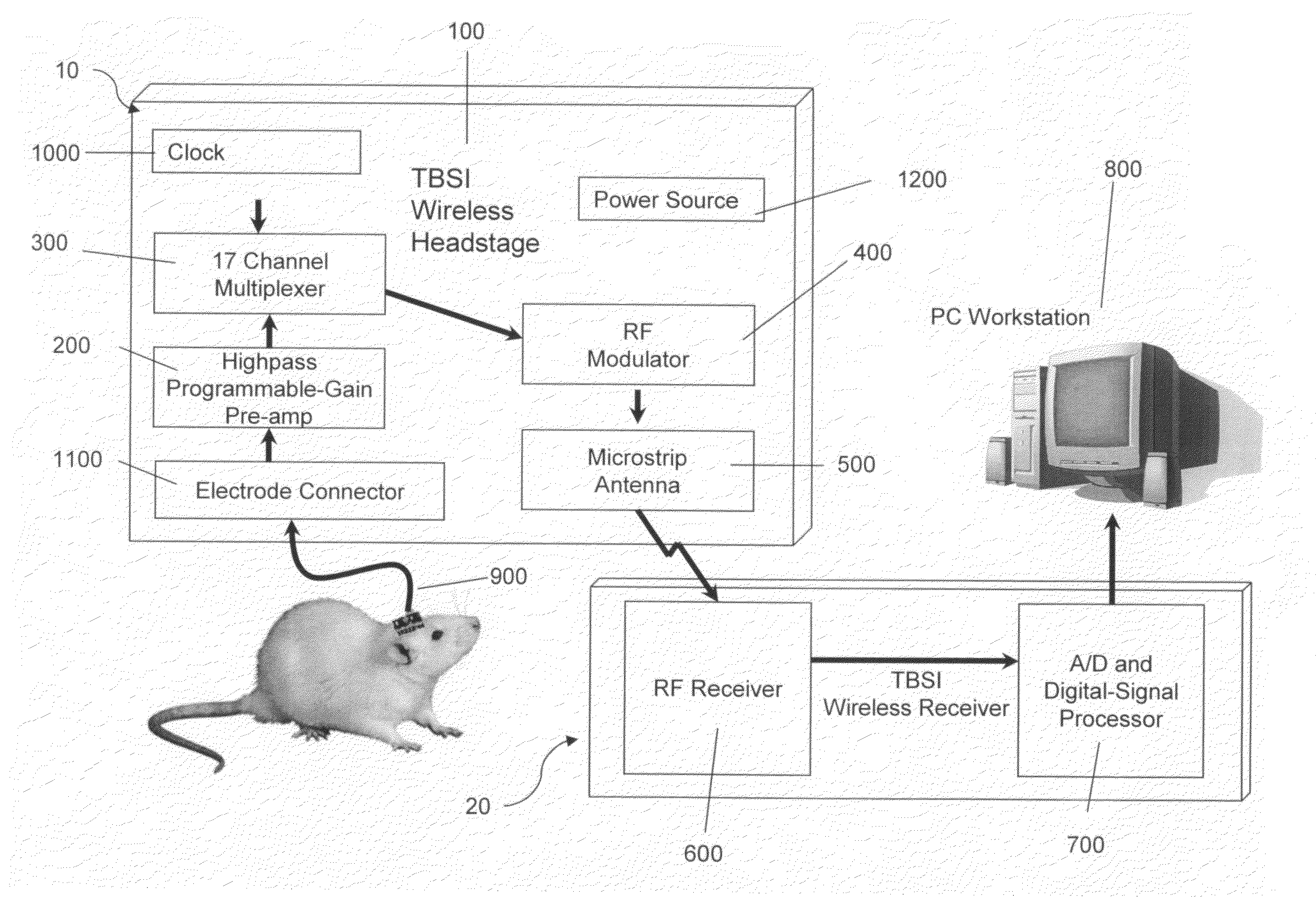

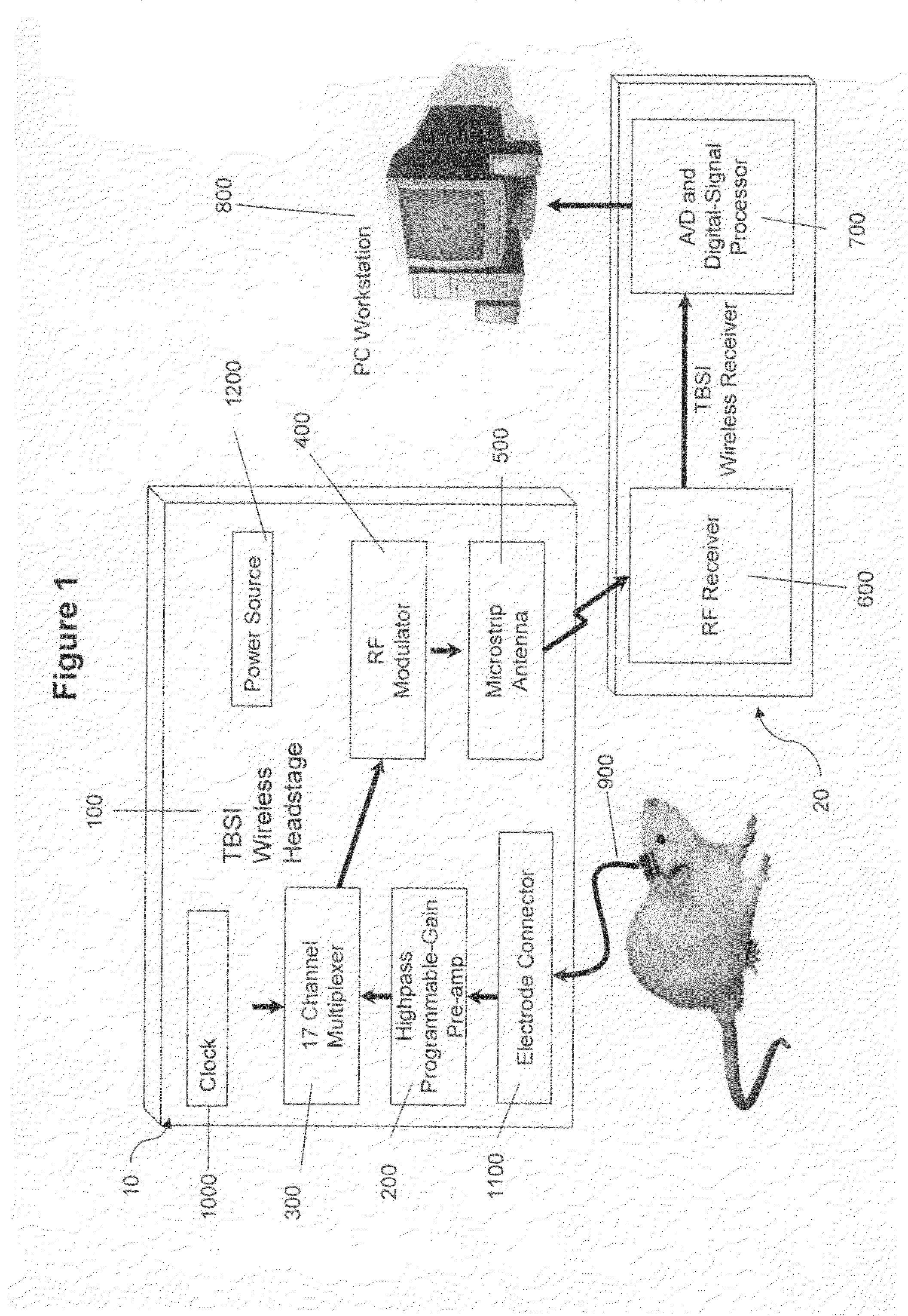

Wireless neural data acquisition system

InactiveUS7346312B2Accurate and reliable transmissionImprove power efficiencyElectroencephalographySimultaneous amplitude and angle demodulationDigital signal processingBandpass filtering

A Wireless Neural Data Acquisition System for increased power efficiency, compact size, robust signaling and reliable transmission is shown and described. In one embodiment, the system includes a headstage, an RF receiver, an analog-to-digital converter, a digital signal processor, and a communication interface. The headstage includes at least one input pre-amplifier high-pass filter and amplifier, a multiplexer (MUX), an RF Modulator comprising a voltage control oscillator (VCO), a transmitting antenna, and a power supply. The RF receiver includes at least one receiving antenna, at least one bandpass filter, at least one amplifier, at least one attenuator, and an FM Demodulator.

Owner:TRIANGLE BIOSYST

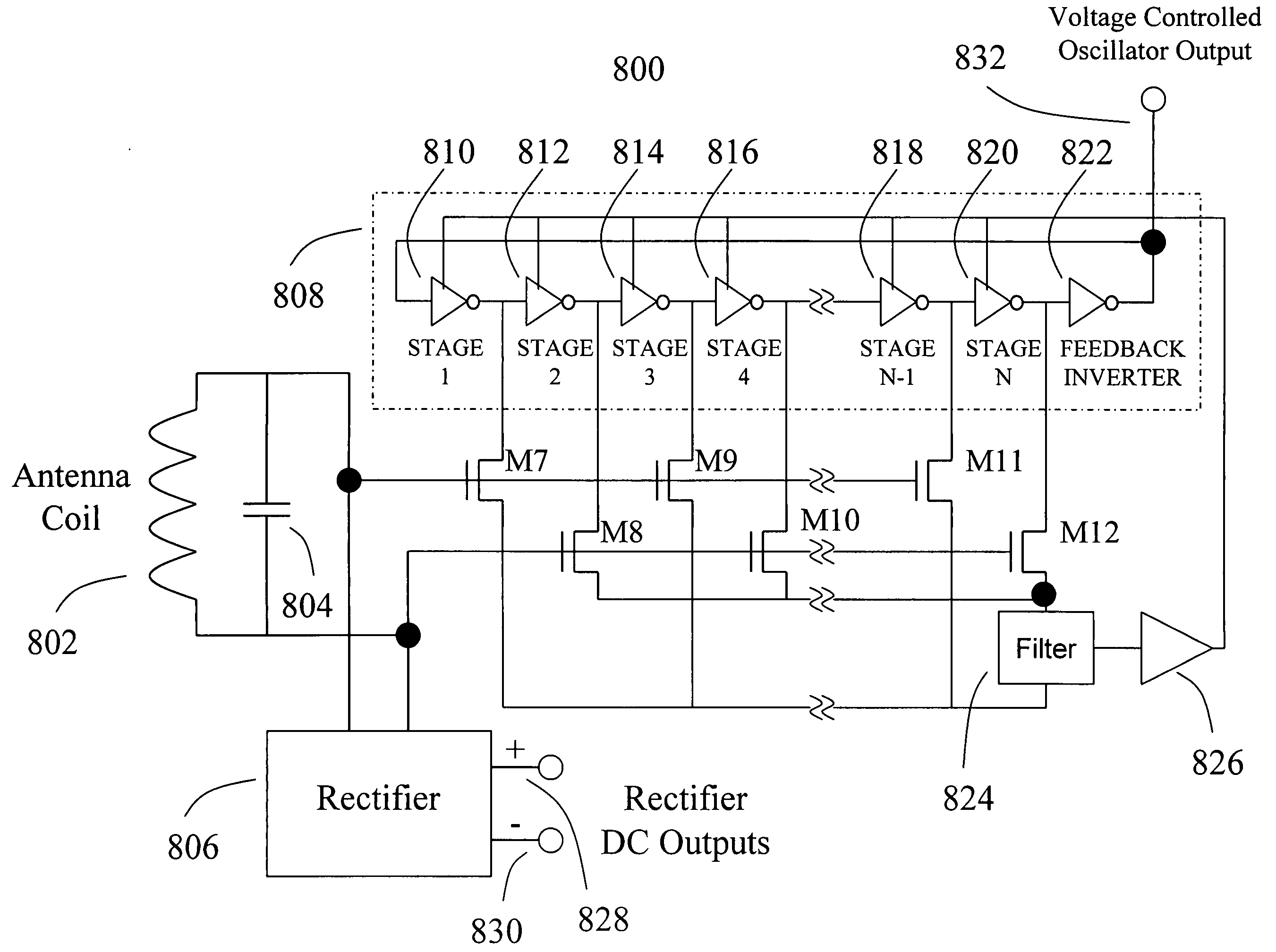

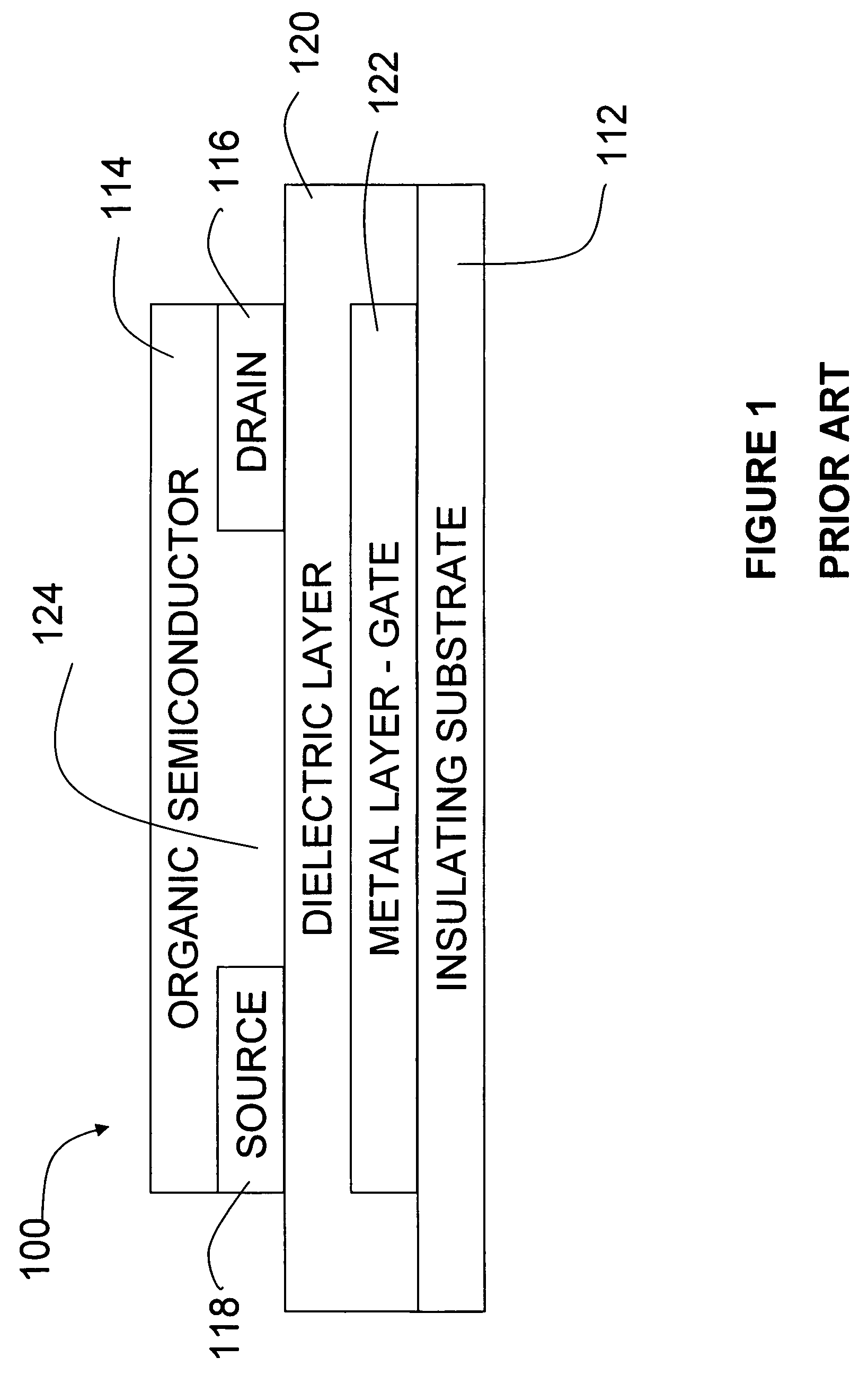

Non-quasistatic phase lock loop frequency divider circuit

ActiveUS20050156641A1Reduce output frequencyThe implementation process is simplePulse automatic controlPulse generation by logic circuitsCapacitancePhysics

A non-quasistatic MOS frequency divider circuit uses a phase lock loop configuration including an antenna coil to induce a differential input signal, an antenna resonating capacitor, a rectifier, a voltage controlled ring oscillator, a phase detector and a loop filter. All transistors used are organic MOS devices of PMOS, NMOS or both PMOS and NMOS varieties. The voltage-controlled oscillator includes a multiple delay stage ring oscillator. The phase detector includes transistors connected as sampling switches to sample the individual oscillator stage voltages into the loop filter. The sampling transistors have gates connected to the coil. The loop filter provides a substantially direct current to a loop amplifier and then to the voltage controlled oscillator delay control input. This configuration results in the voltage controlled oscillator frequency being synchronous to—and at a sub-multiple of the antenna signal frequency. The sampling transistor gates are all connected to the coil and thereby become part of the capacitance of the radio frequency parallel resonant network. The transistor gates are then efficiently switched at the rate of the radio frequency signal with no delay relative to the coil voltage. Operation of the phase detector organic transistors is based on non-quasistatic behavior of the transistor. Non-quasistatic operation results in phase detection at a frequency much higher than the quasistatic limit of transistor unity gain bandwidth.

Owner:GULA CONSULTING LLC

Frequency synthesizer

InactiveUS7317363B2Eliminate high frequency noiseAngle modulation by variable impedencePulse automatic controlCapacitancePhase locked loop circuit

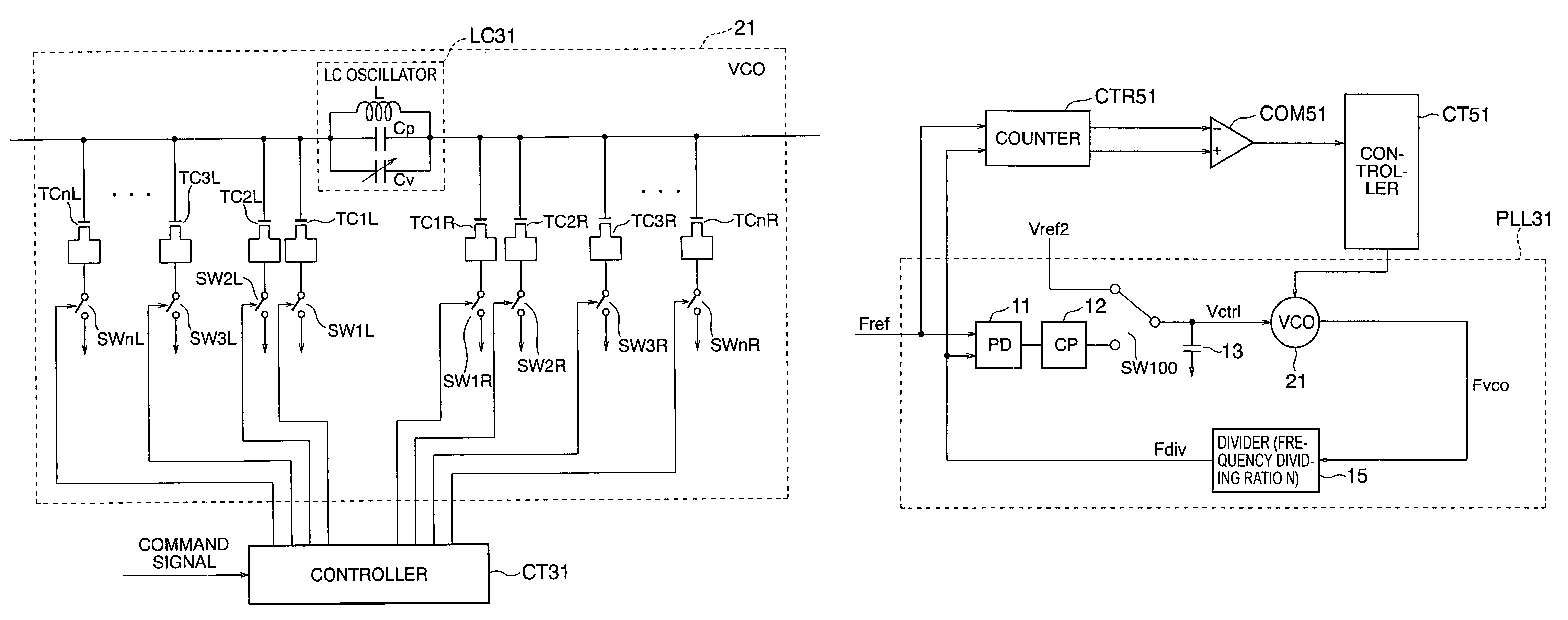

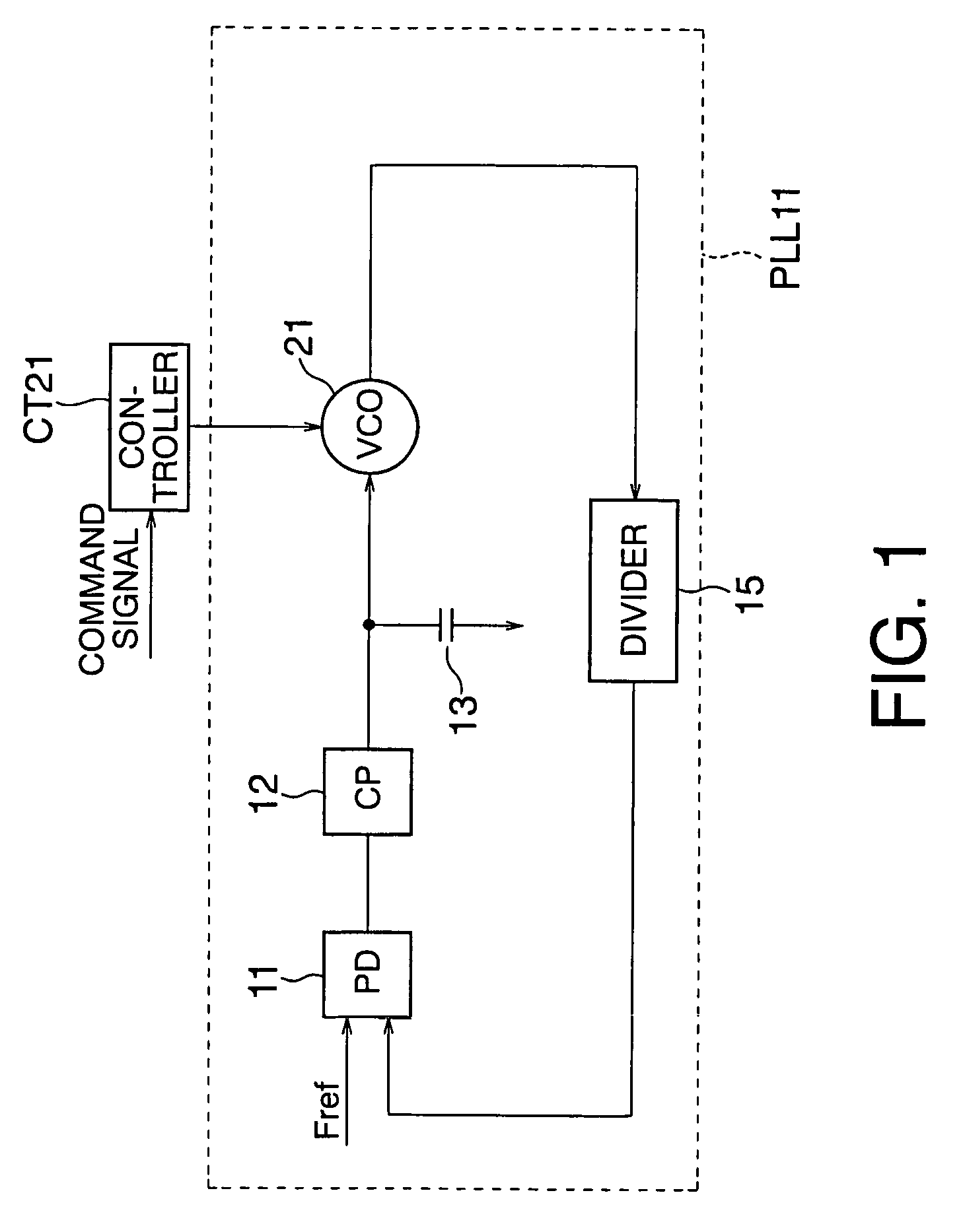

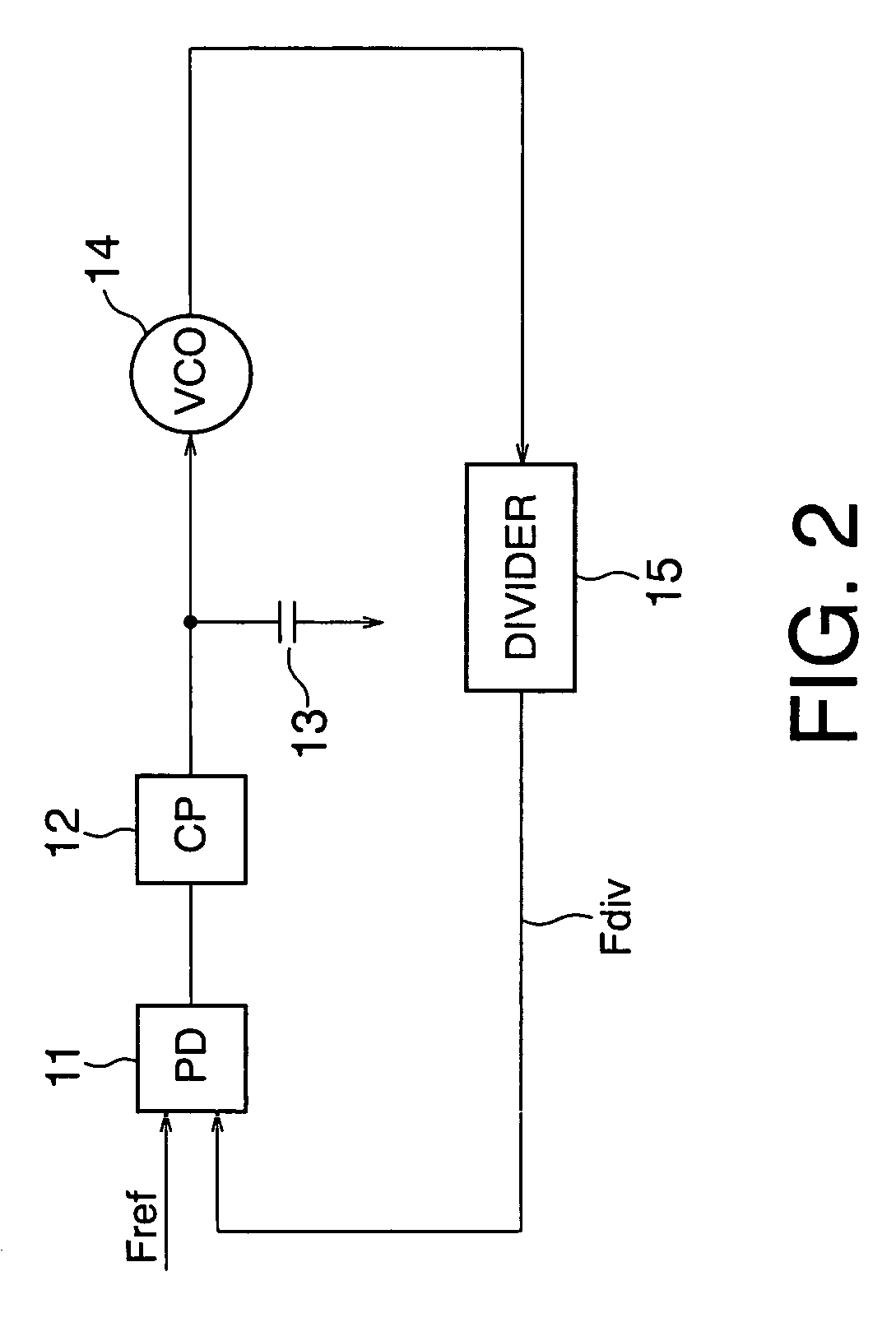

There is provided a phase locked loop circuit which receives a reference signal having a reference frequency and a first signal having a first frequency, compares phases of the reference signal and first signal, applies a control voltage based on a phase comparison result to an input terminal of a voltage controlled oscillator to generate a second signal having an oscillation frequency and output the second signal from an output terminal, and supplies the second signal to a divider to divide the frequency of the second signal and output the first signal; and a controller which generates and supplies a control signal to the voltage controlled oscillator, wherein the voltage controlled oscillator has an arrangement in which a coil and variable capacitance are connected in parallel between the input terminal and output terminal, and one of a plurality of capacitances is selectively connected between the input terminal and output terminal by a switch in parallel with the variable capacitance, and ON / OFF of the switch is controlled by the control signal.

Owner:KK TOSHIBA

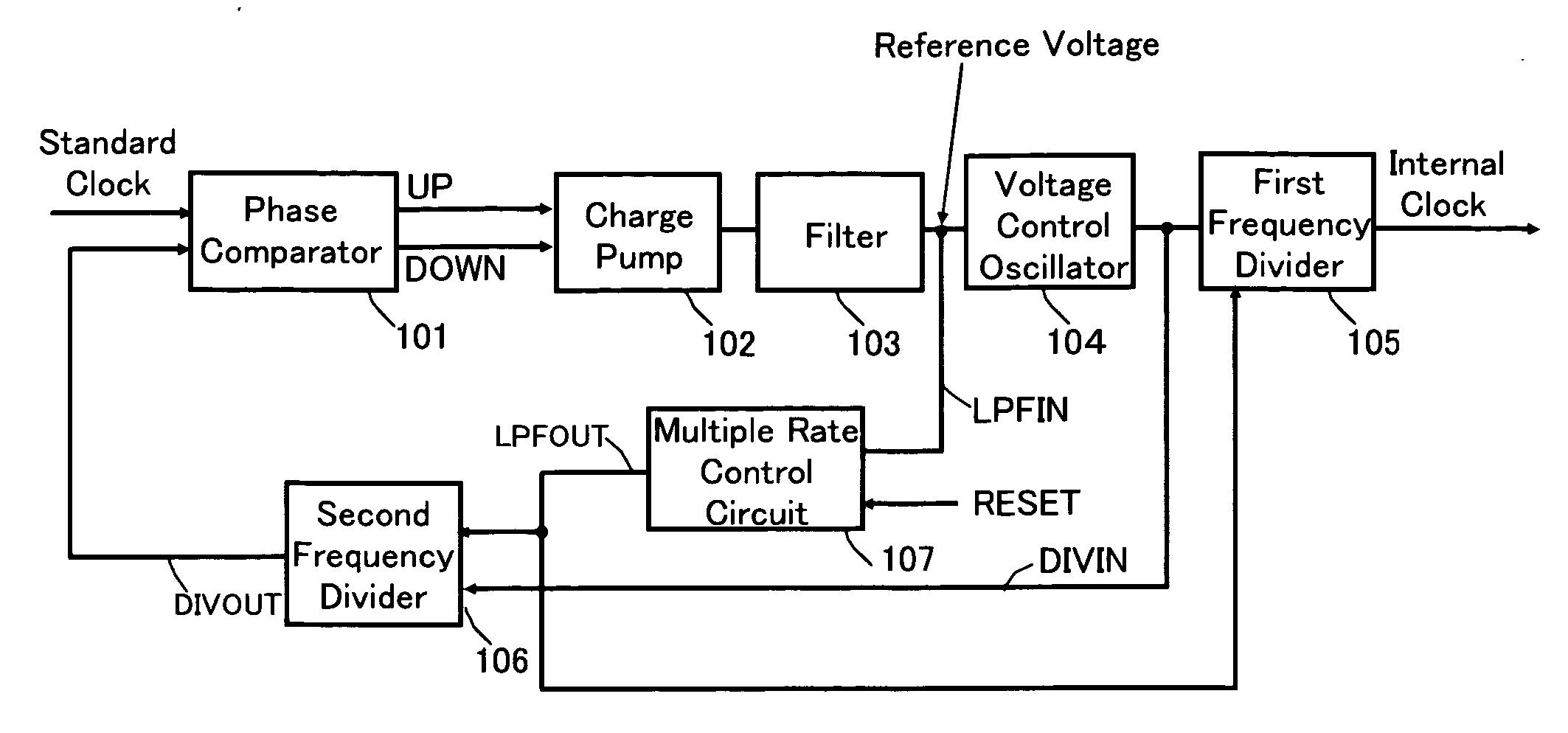

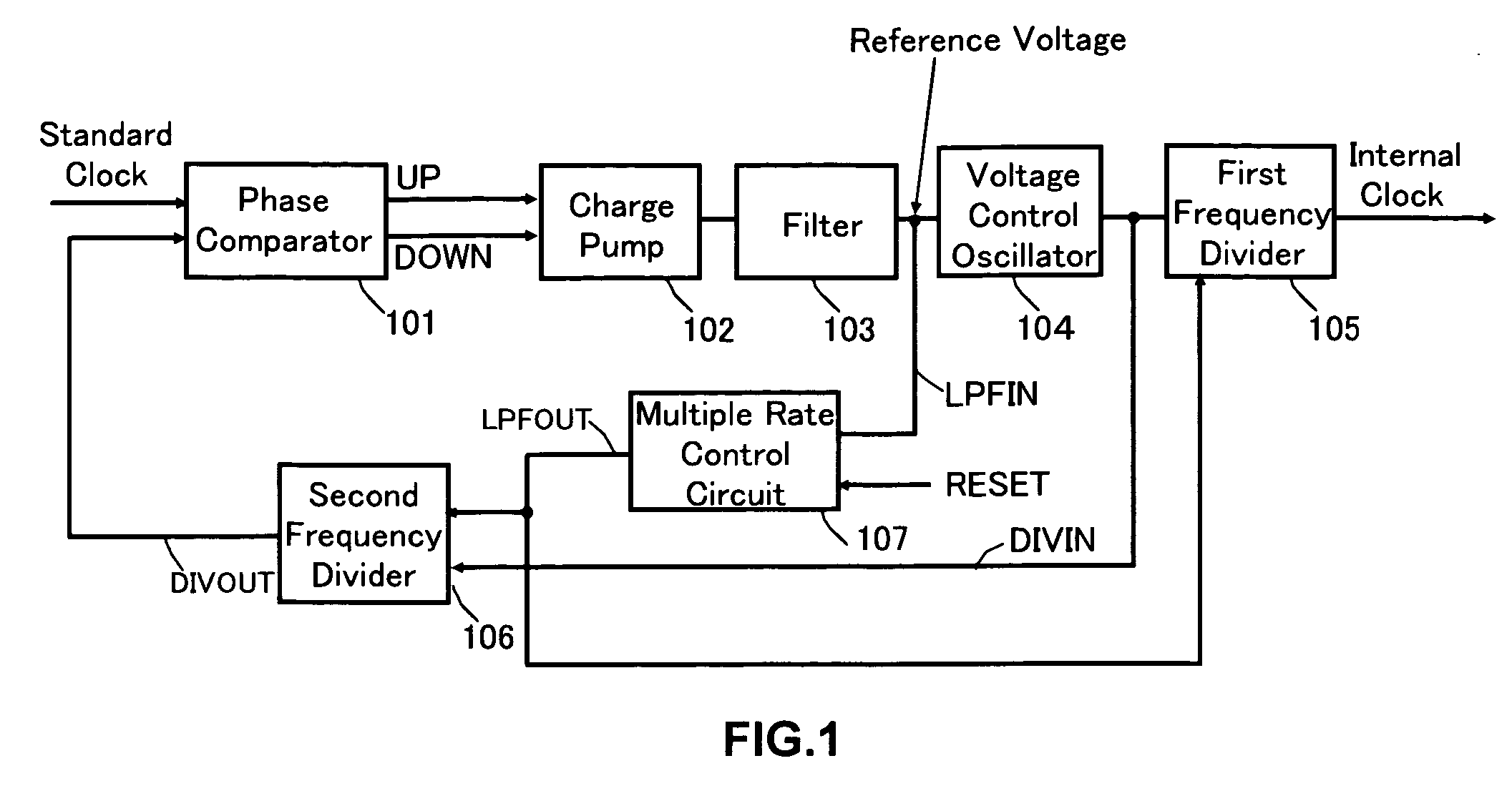

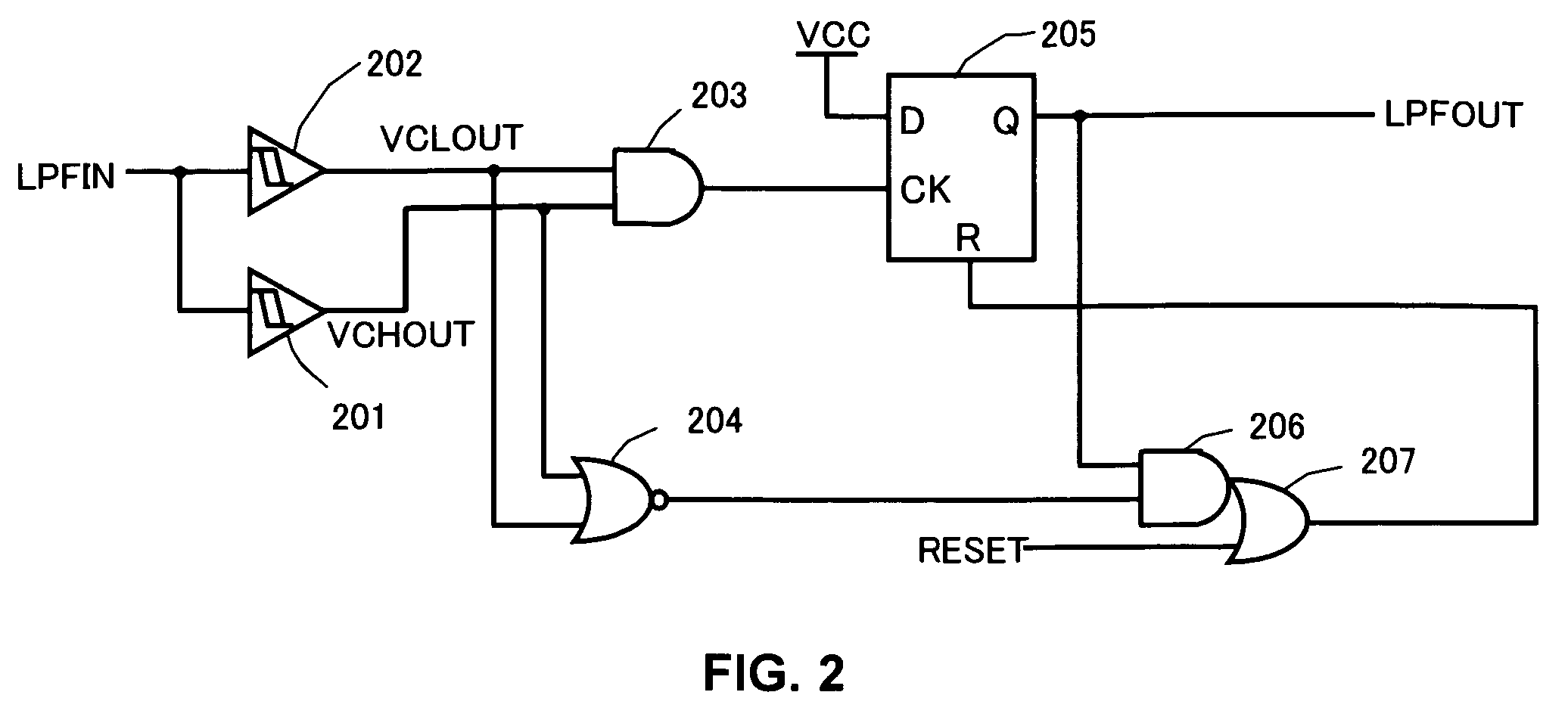

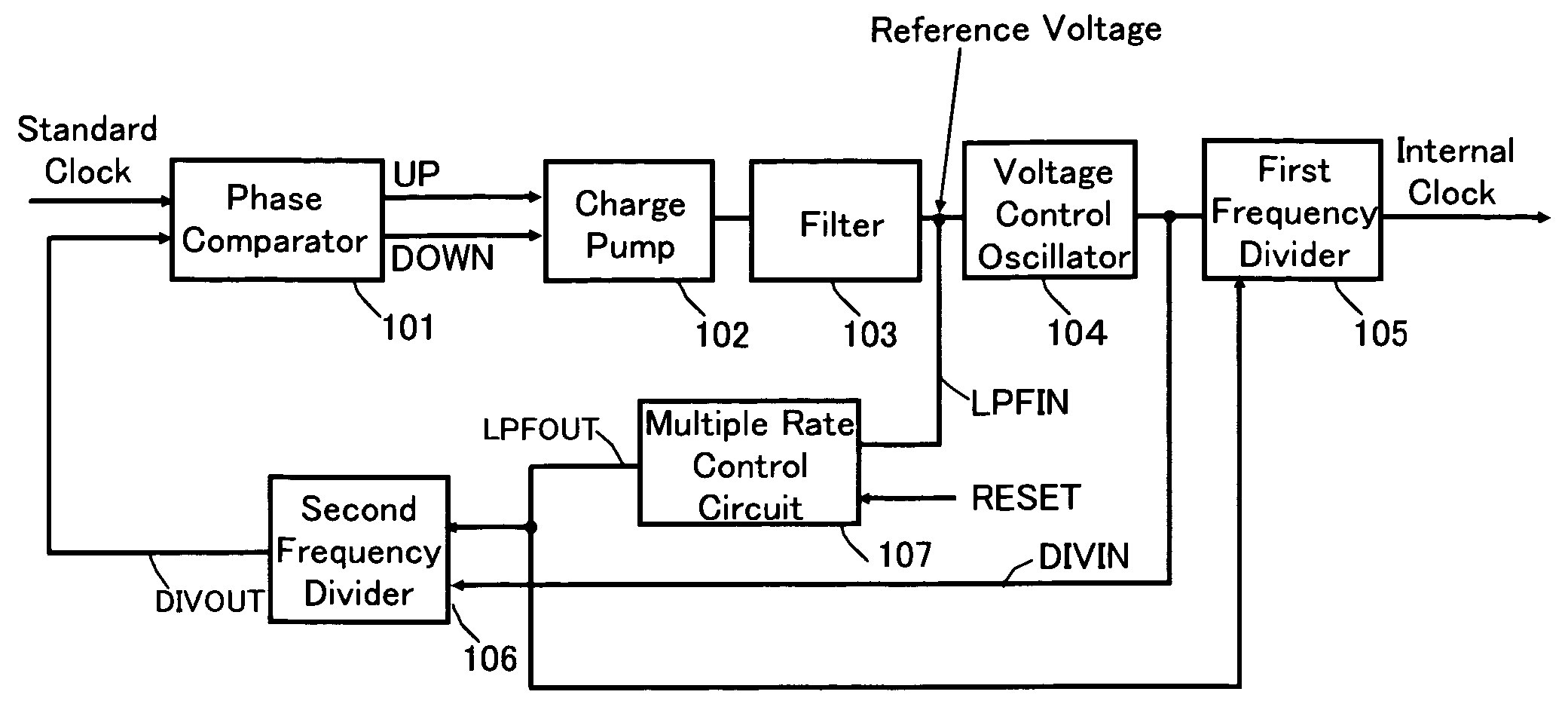

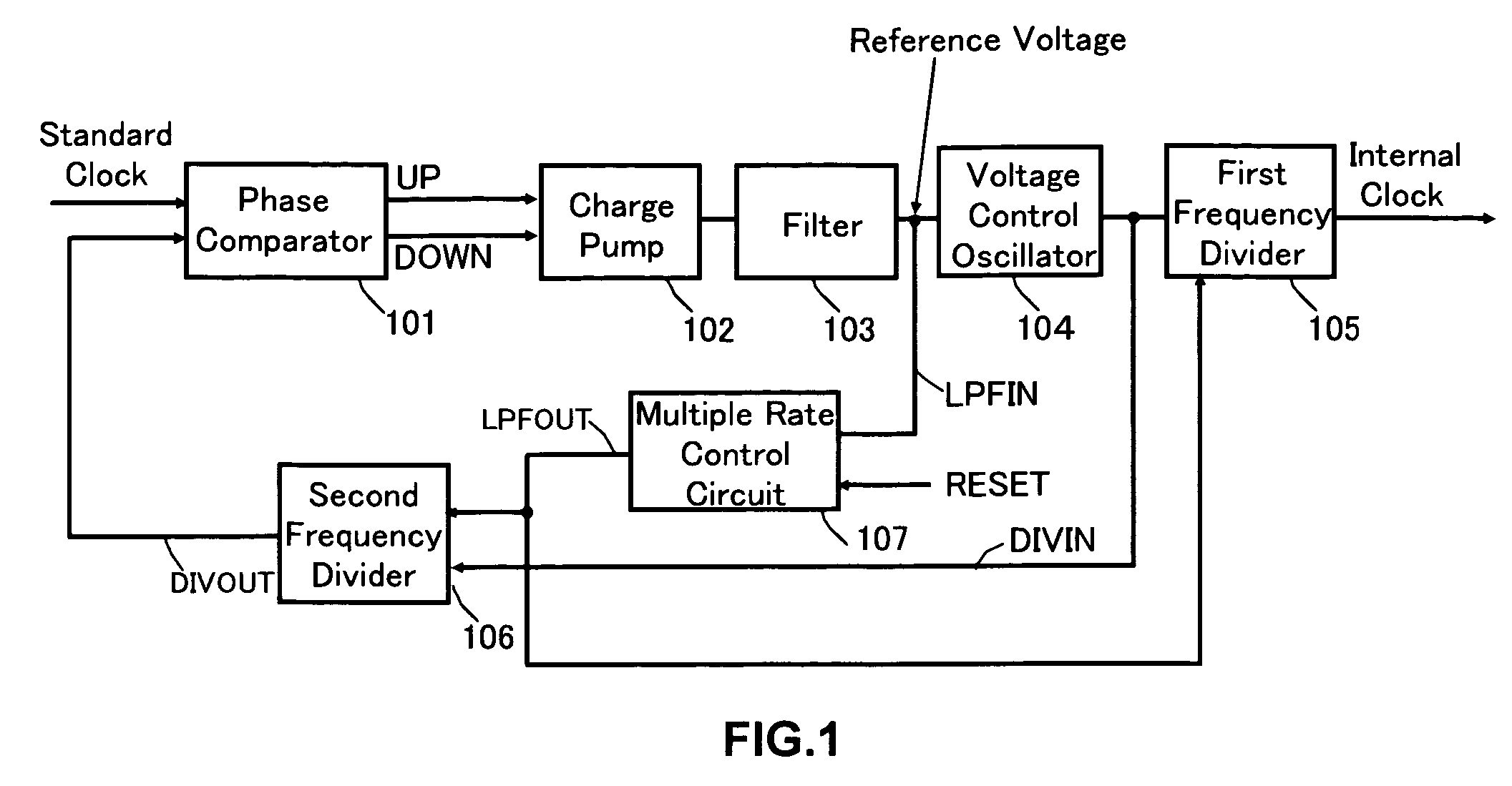

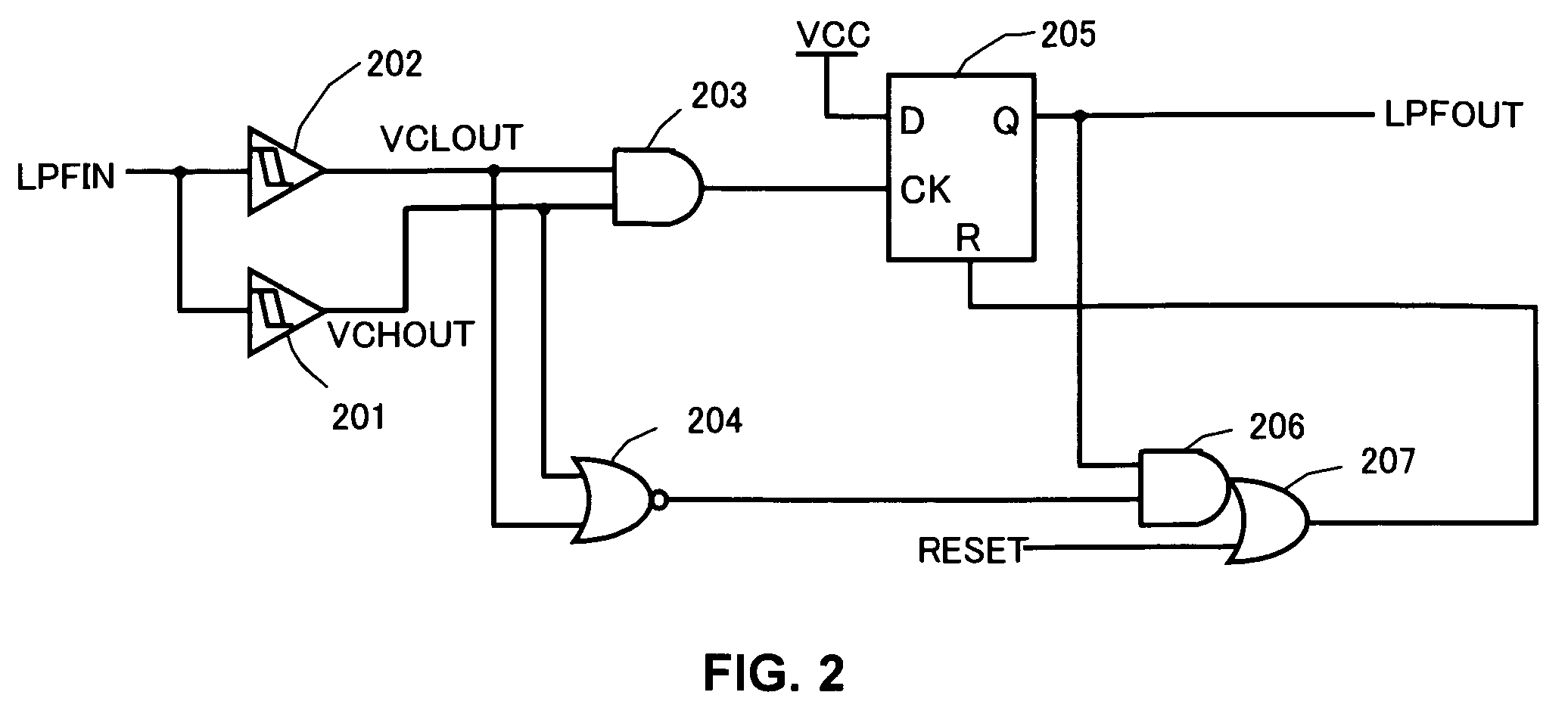

PLL clock signal generation circuit

InactiveUS20050099235A1Action performance is reliableRaise the ratioPulse automatic controlOscillator tubesControl signalVoltage reference

A PLL clock signal generation circuit comprising a phase comparator, a charge pump circuit, a filter circuit, a voltage control oscillator and a divider, wherein a multiple rate control circuit is further included which detects a state of the reference voltage (output from a filter circuit) and controls a change of a multiple rate of a divider according to a state of the detected reference voltage. The multiple rate control circuit further outputs control signal LPFOUT for changing a multiple rate so that the PLL clock signal generation circuit does not deviate from a region capable of locking when being detected of deviation from the region capable of locking by detecting the state of reference voltage.

Owner:III HLDG 12 LLC

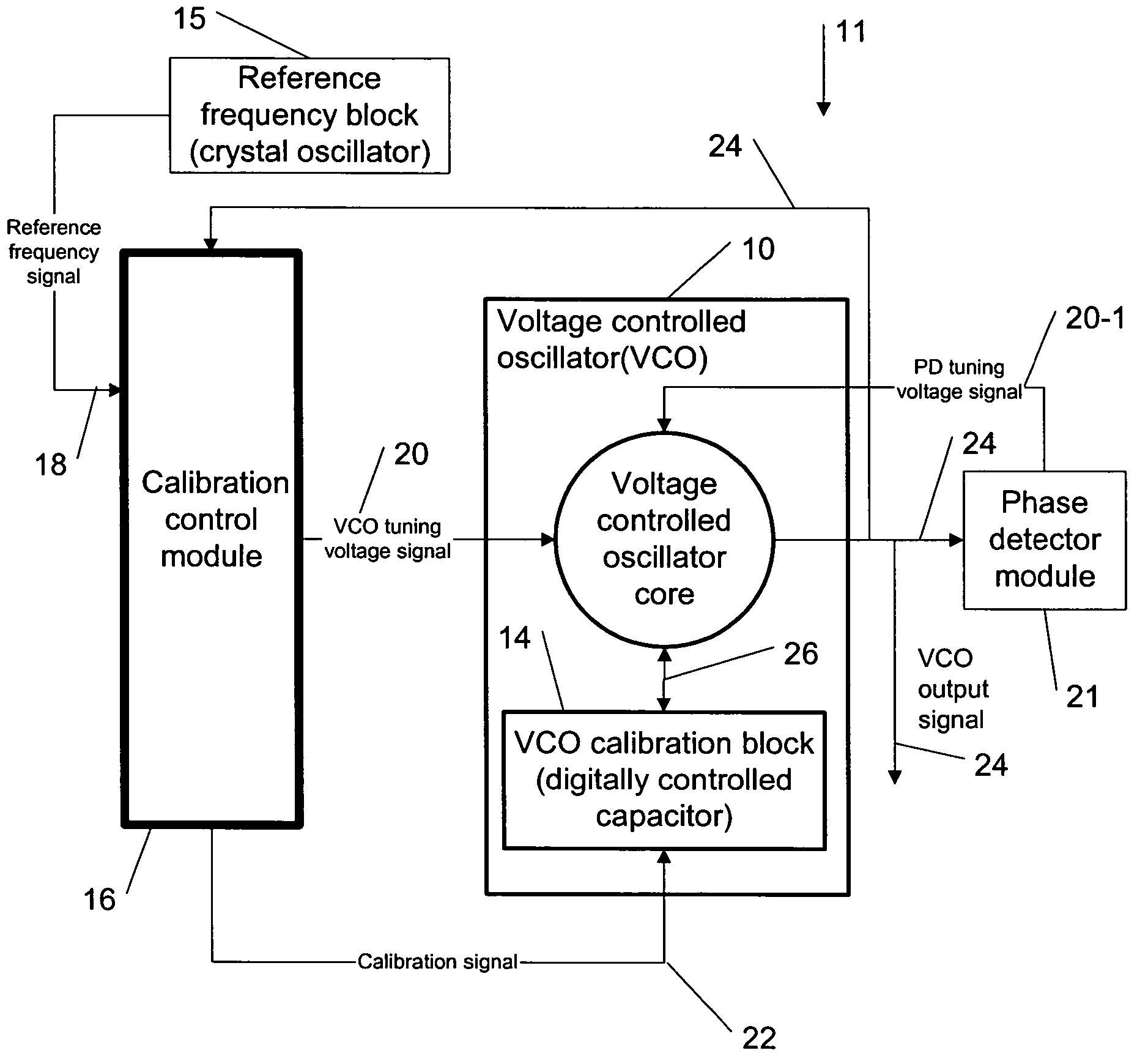

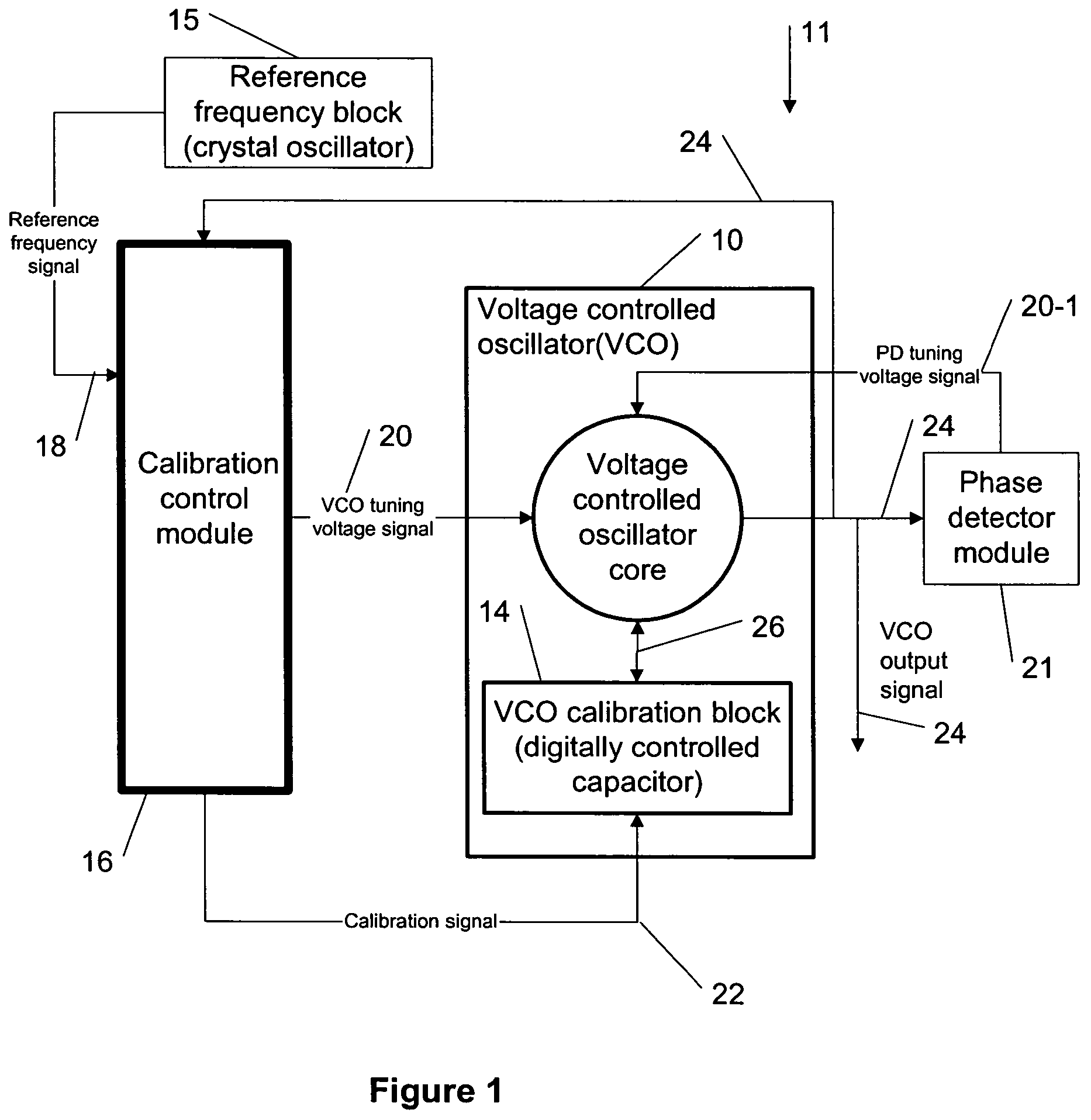

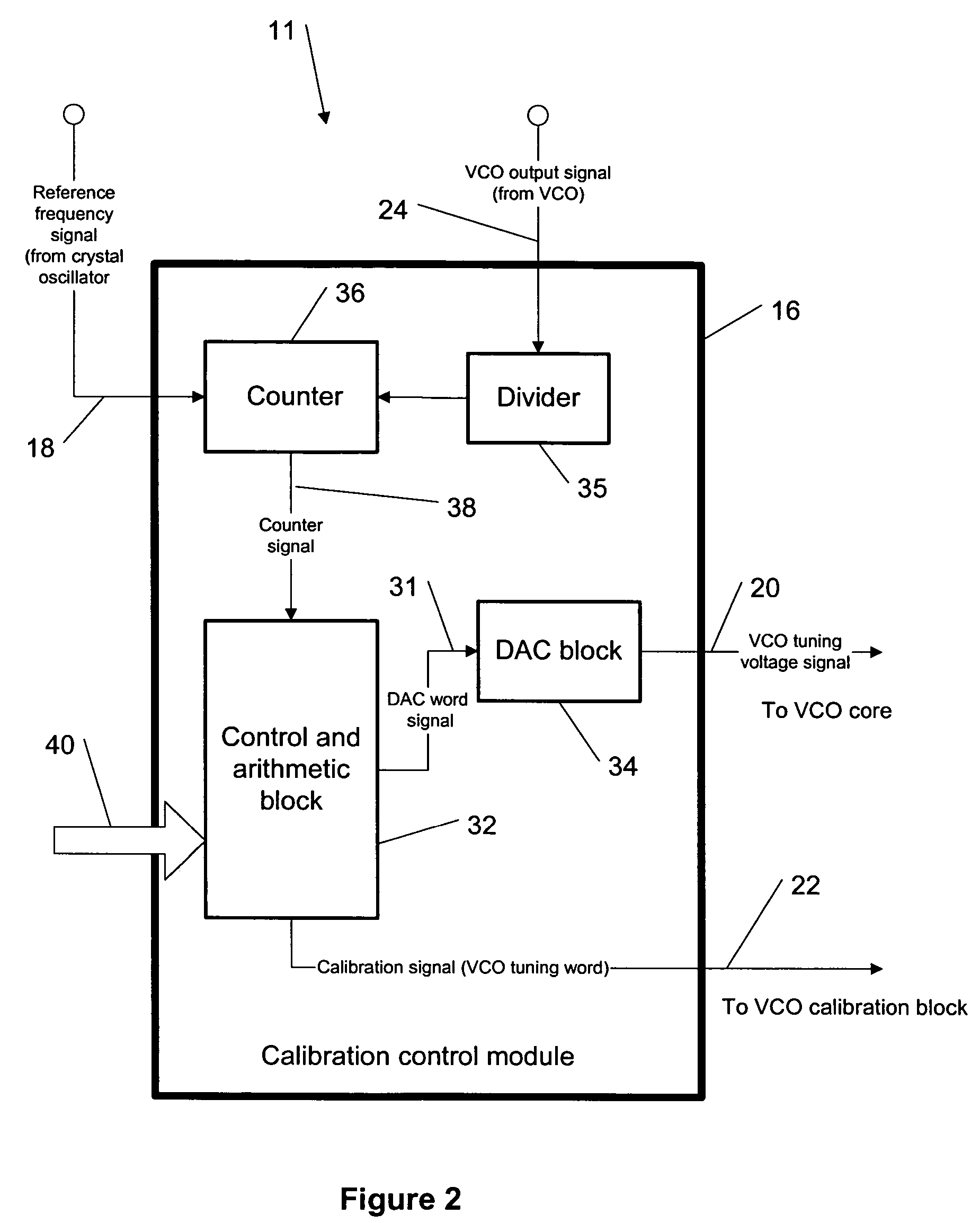

VCO center frequency tuning and limiting gain variation

ActiveUS7142062B2Fast on-chipExternal control can be minimizedPulse automatic controlRadio transmissionFrequency measurementsEngineering

This invention describes a method for simultaneous precise center frequency tuning and limiting a gain variation of a voltage controlled oscillator (VCO) of a phase locked loop (PLL) of an electronic device (e.g., a communication device, a mobile electronic device, a mobile phone, etc.). The invention utilizes frequency measurements and arithmetical optimizations. More specifically, the invention implementation is based on an analysis which includes measuring a frequency of a VCO and calculating a gain of the voltage controlled oscillator (VCO) using a predetermined criterion. The key element for implementing said analysis is a control and arithmetic block. The present invention can be used in any radio architecture that requires limiting of the VCO gain variation and tuning its center frequency.

Owner:NOKIA TECH OY

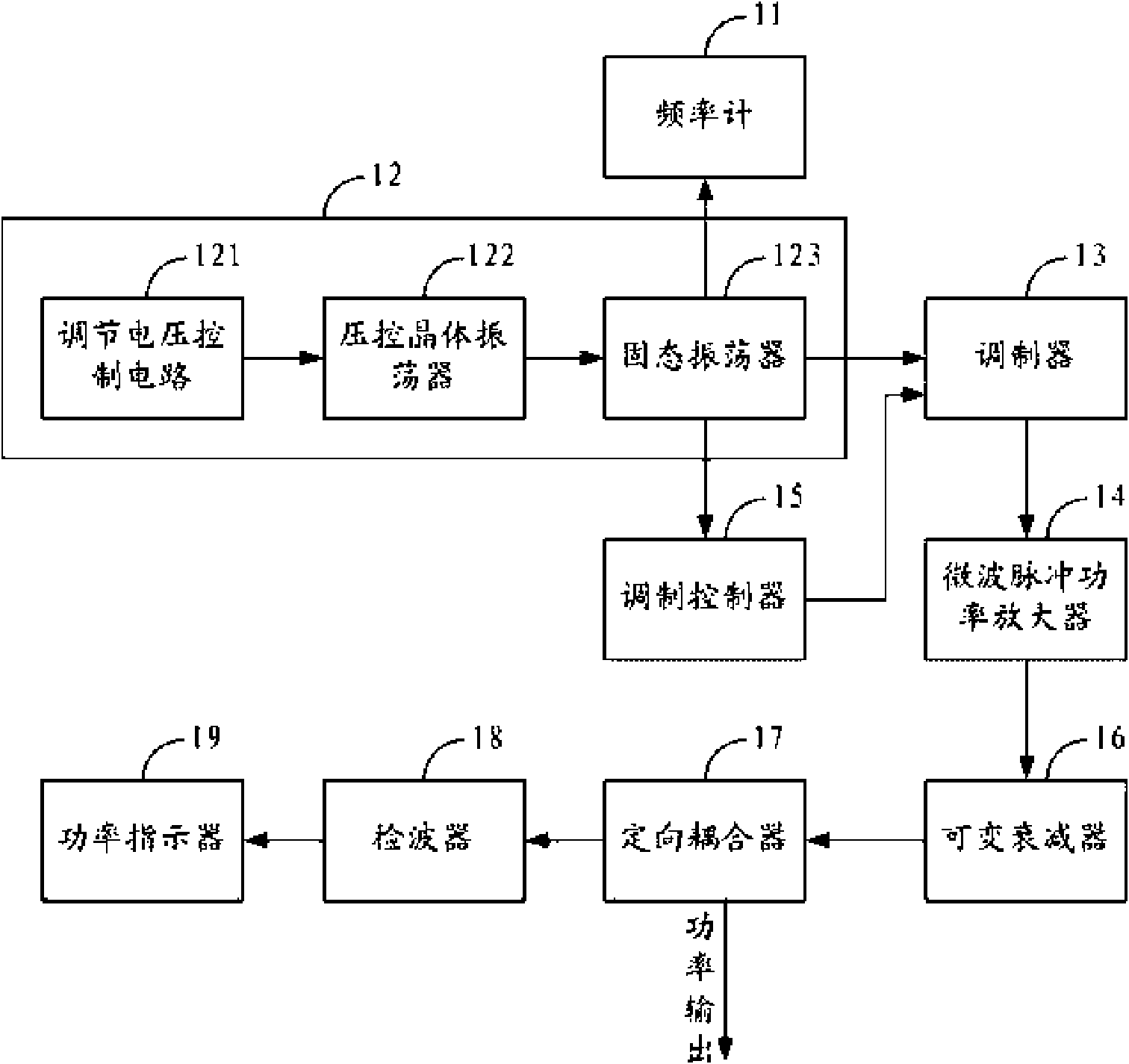

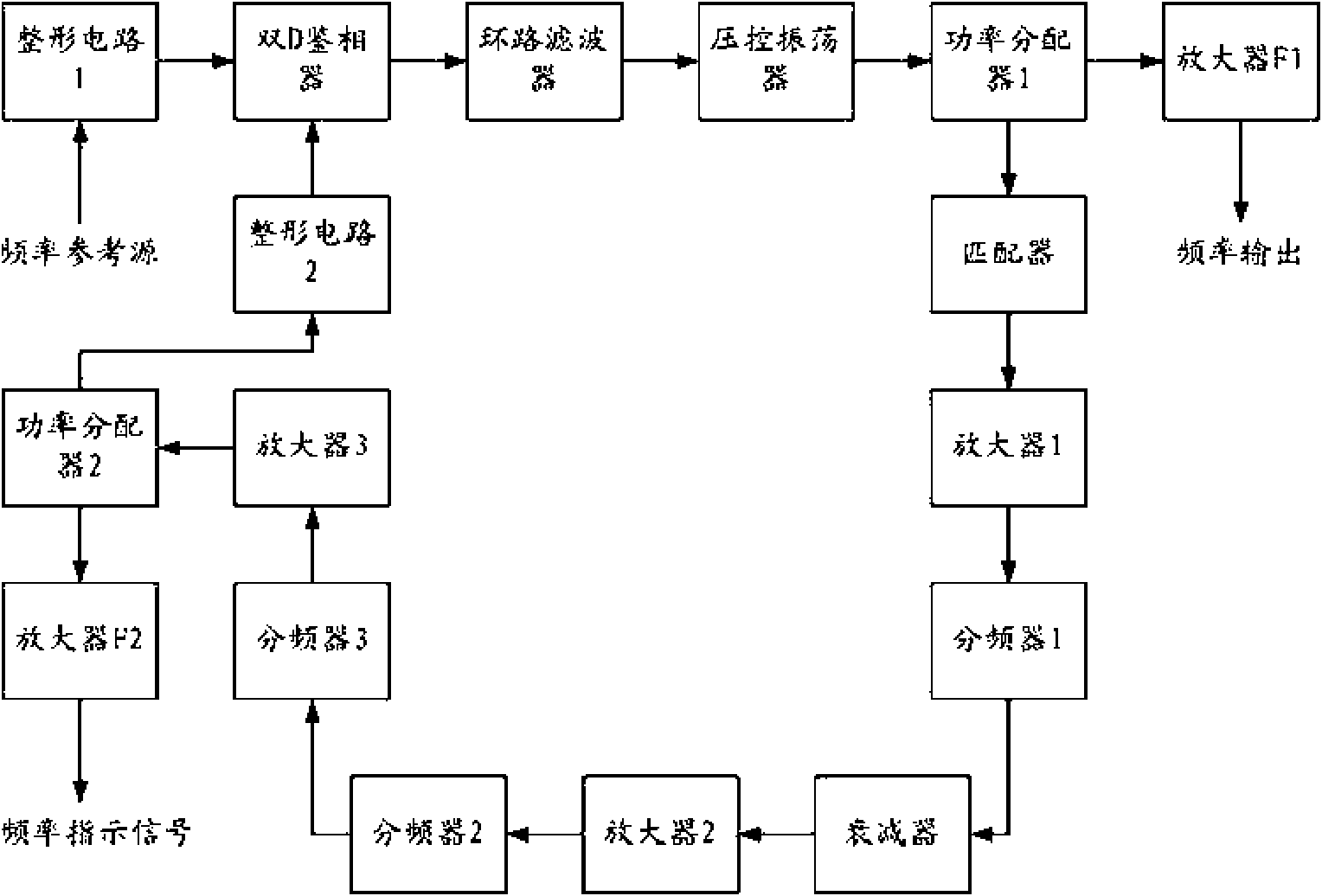

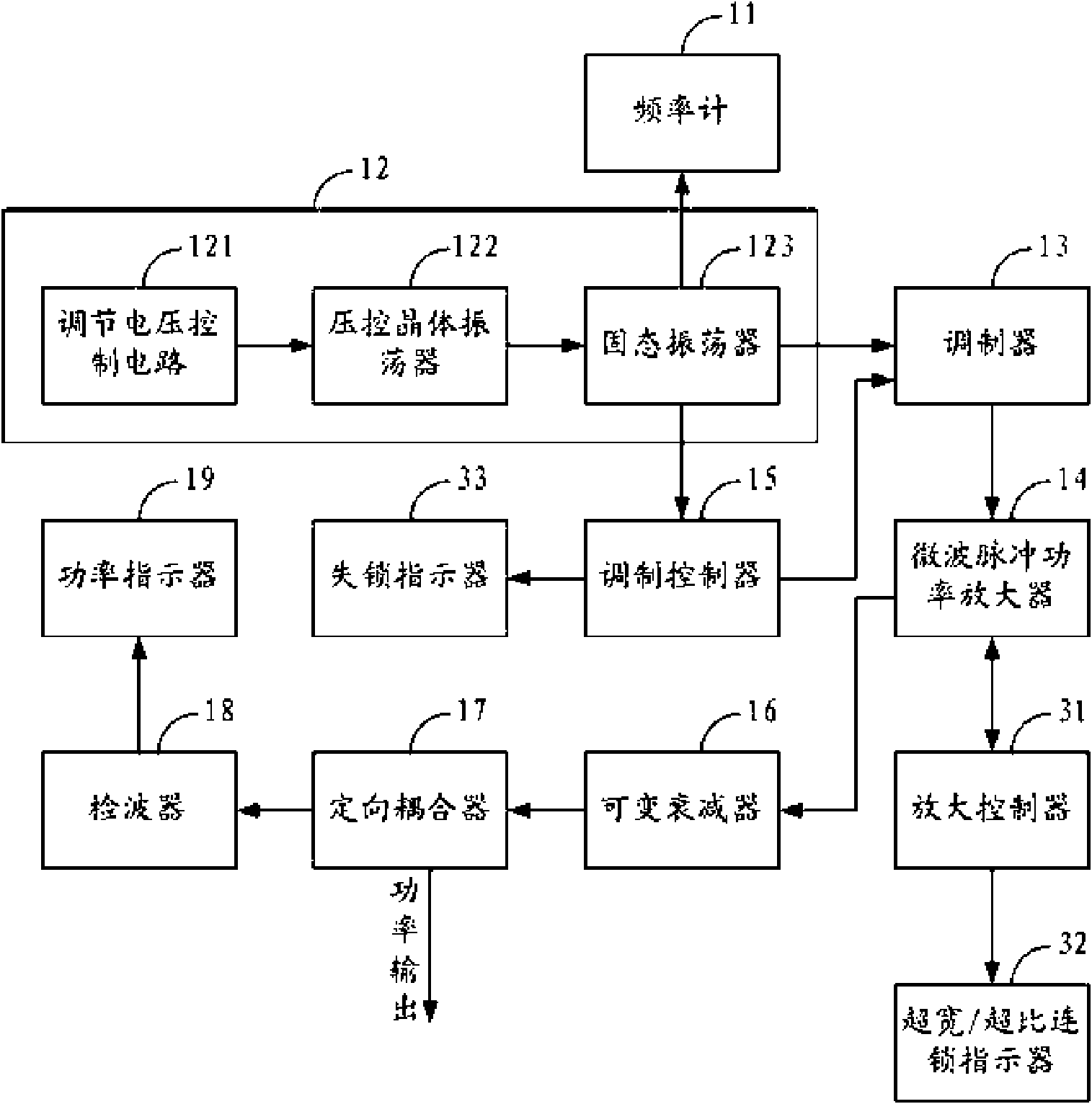

Microwave driving source

ActiveCN101582684AReduce phase noiseImproved clutter suppression performancePulse automatic controlSingle pulse train generatorFrequency stabilizationEngineering

The invention is applied to the technical field of microwave and provides a microwave driving source mainly comprising a frequency synthesizer composed of a voltage adjusting control circuit, a voltage controlled crystal oscillator and a solid state oscillator, a cymometer, a modulator, a tuning controller, a microwave pulse power amplifier, a variable attenuator, a directional coupler, a detector, a power indicator and the like. The invention is characterized in that the output frequencies in the range from 40W to 200W are respectively and continuously adjusted, the frequency stability of output signals reaches to 5 multiplied by 10(-6), the frequency adjustment rang of output signals is larger than or equal to 4MHz, the driving source automatically indicate output frequency and output power in real time, the phase noise is low, and the clutter suppression ability is high.

Owner:成都利尼科医学技术发展有限公司

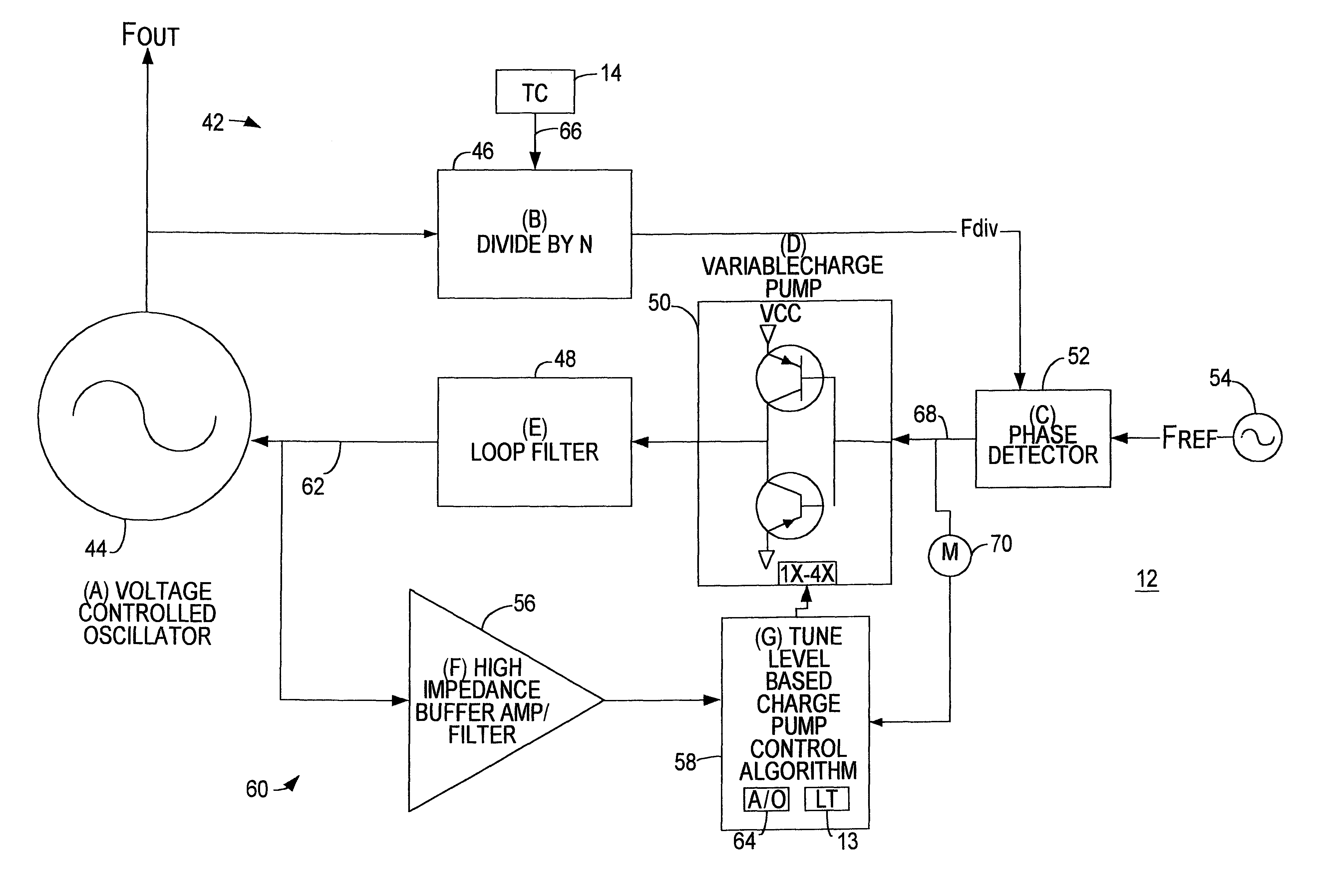

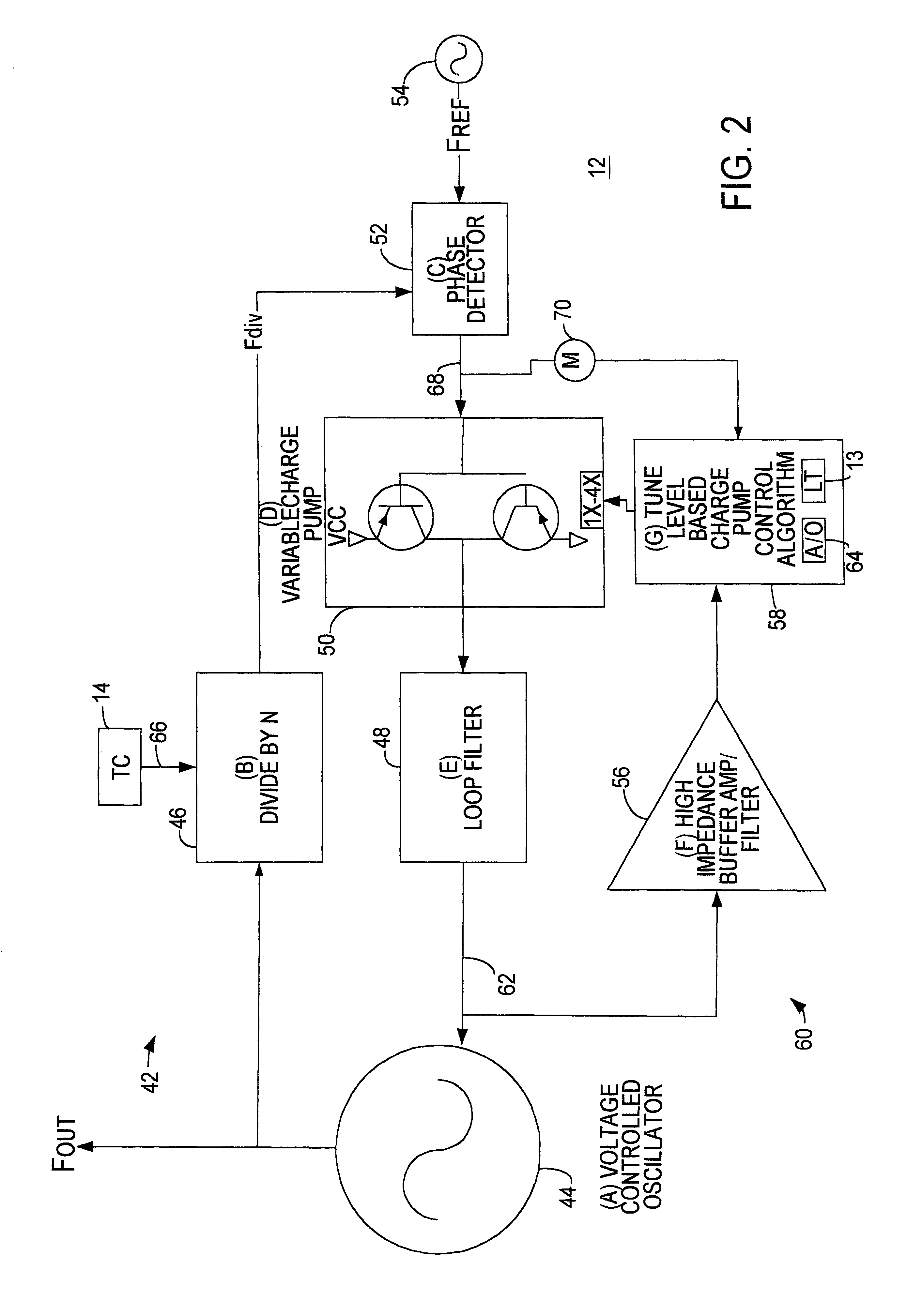

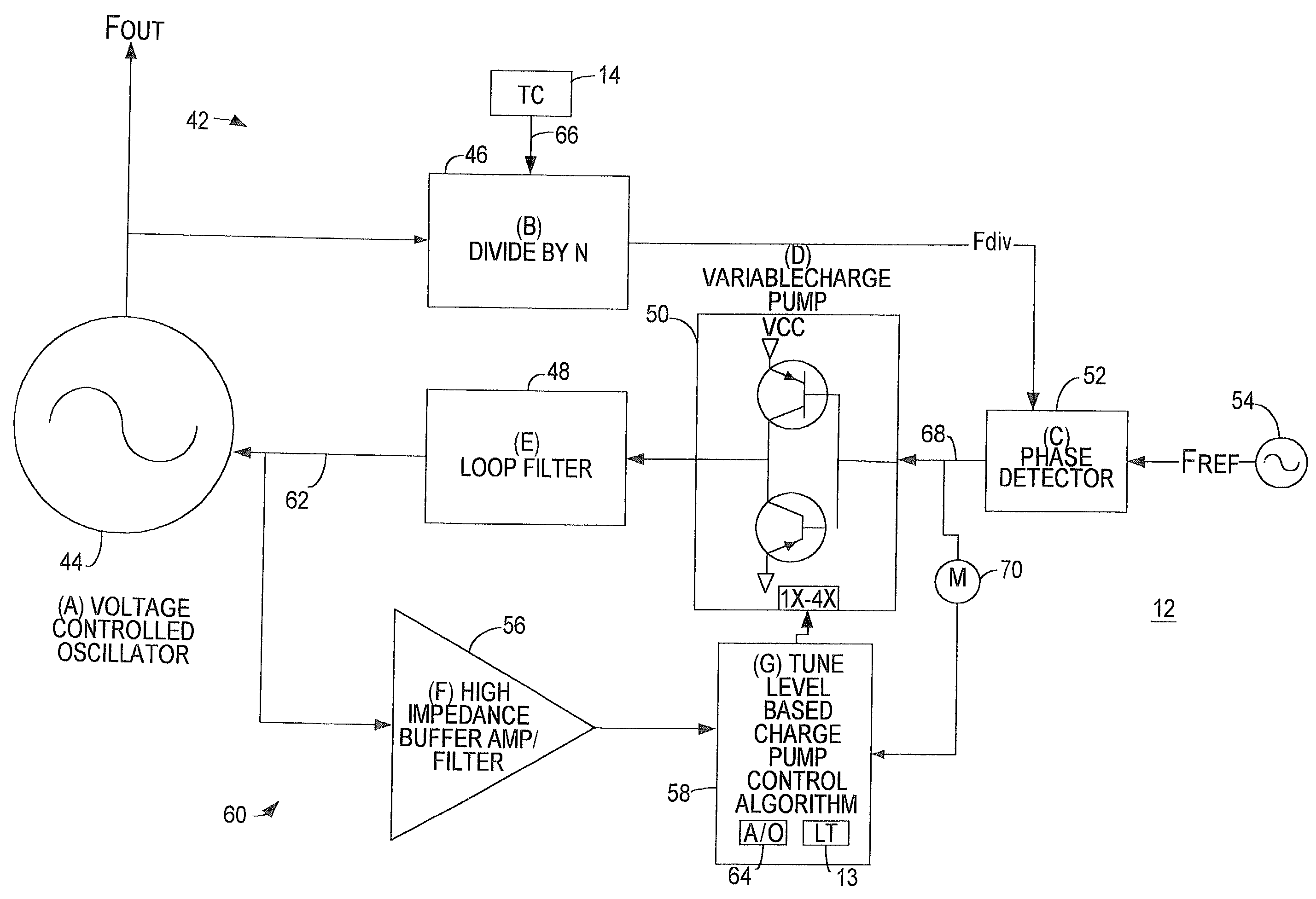

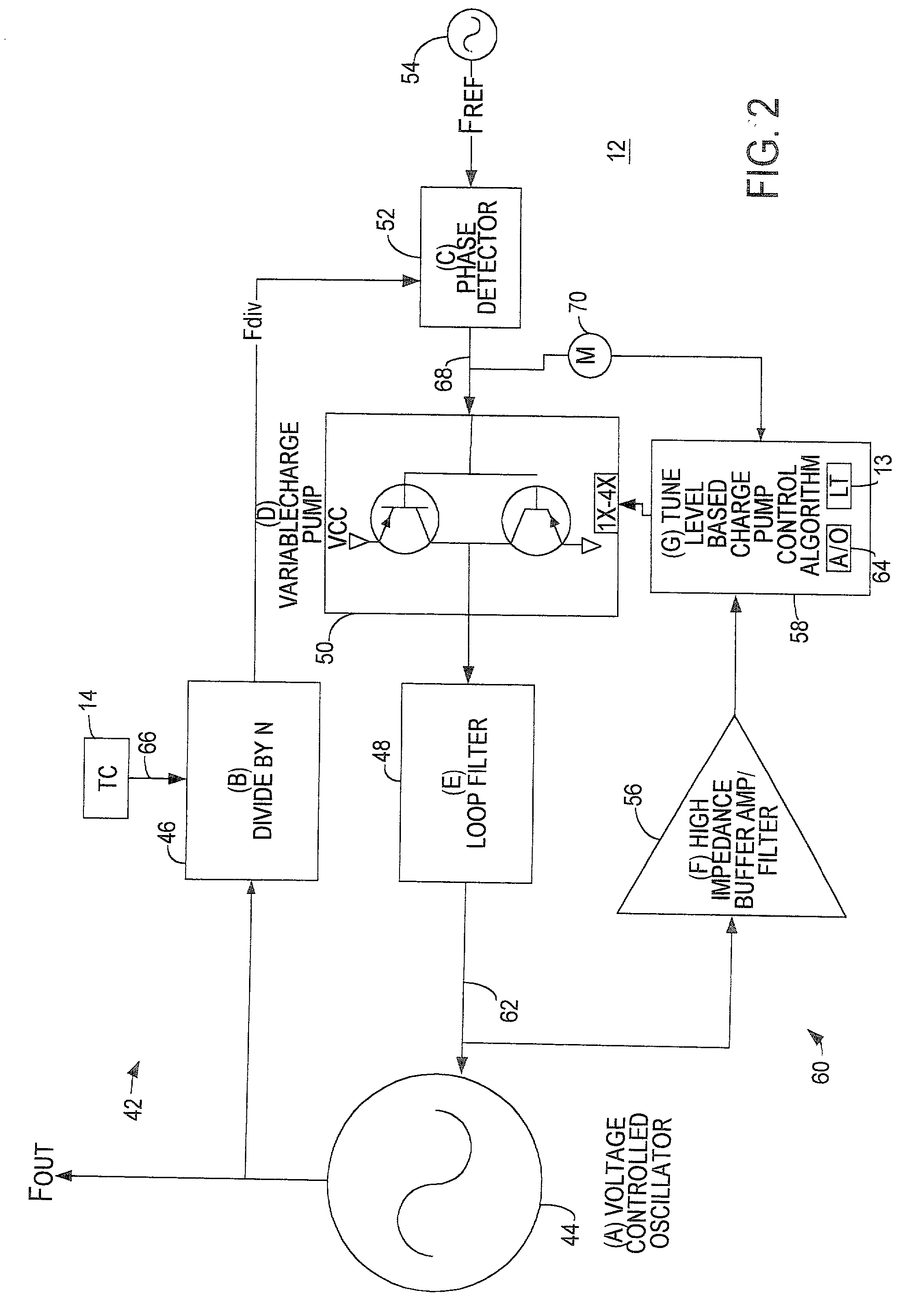

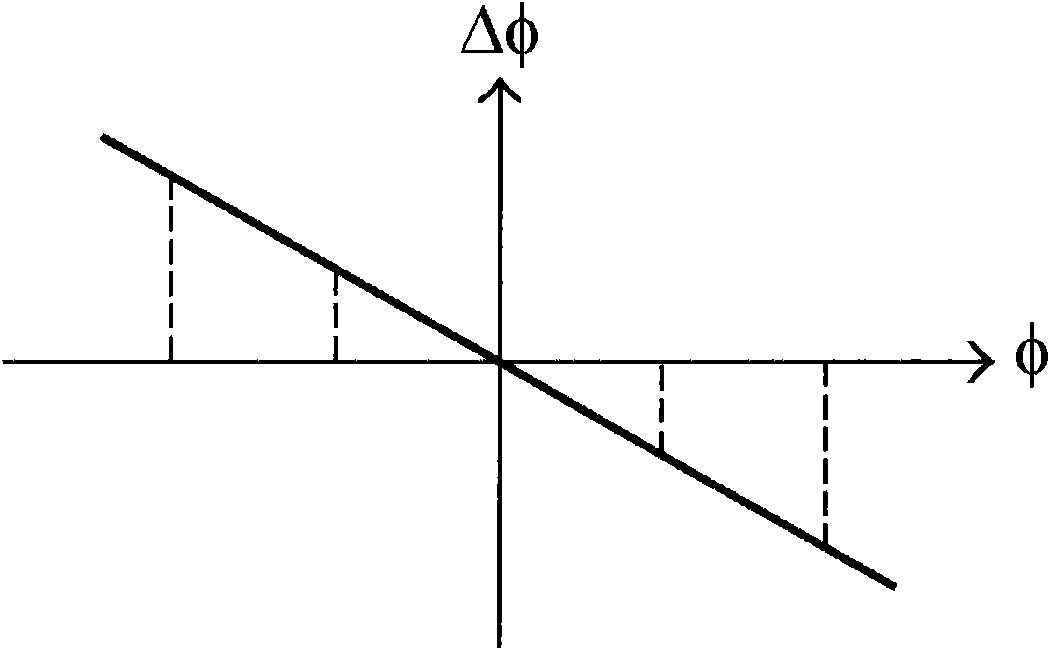

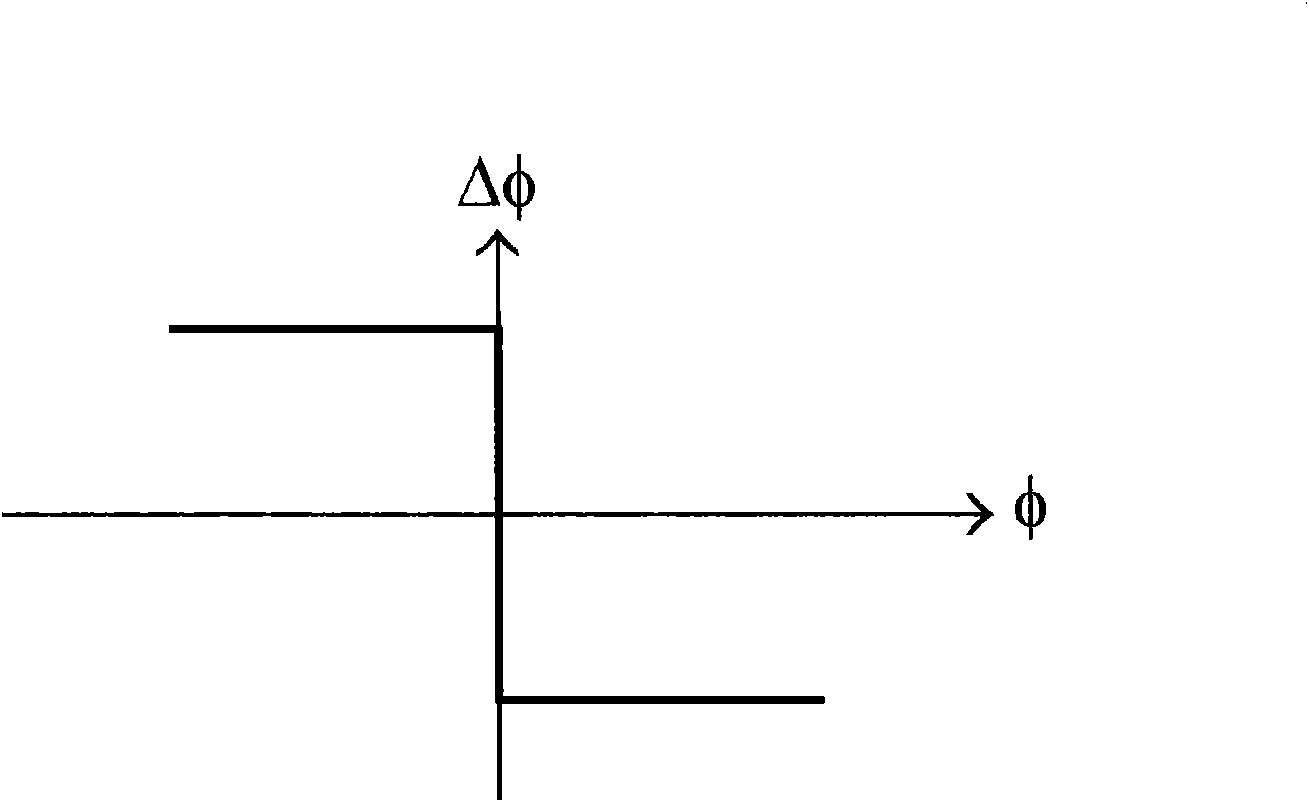

VCO tuning curve compensated charge pump current synthesizer

A system provided for controlling an output frequency of a voltage controlled oscillator relative to a reference frequency. A method includes the steps of detecting a phase error between a divided output of the voltage controlled oscillator and the reference frequency, pumping a frequency control input of the voltage controlled oscillator with the phase error and adjusting a pumping gain based upon a magnitude of the frequency control input to the voltage controlled oscillator.This apparatus includes a phase detector adapted to detect the phase error between the divided output of the voltage controlled oscilator and the reference frequency and a charge pump adapted to pump the frequency control input of the voltage controlled oscillator with the phase error. The apparatus also includes a gain controller adapted to adjust the pumping gain based upon the magnitude of the frequency control input to the voltage controlled oscillator.

Owner:SKYWORKS SOLUTIONS INC

VCO tuning curve compensated charge pump current synthesizer

InactiveUS20020039050A1Modulated-carrier systemsPulse automatic controlPhase detectorVoltage control

A system provided for controlling an output frequency of a voltage controlled oscillator relative to a reference frequency. A method includes the steps of detecting a phase error between a divided output of the voltage controlled oscillator and the reference frequency, pumping a frequency control input of the voltage controlled oscillator with the phase error and adjusting a pumping gain based upon a magnitude of the frequency control input to the voltage controlled oscillator. The apparatus includes a phase detector adapted to detect the phase error between the divided output of the voltage controlled oscilator and the reference frequency and a charge pump adapted to pump the frequency control input of the voltage controlled oscillator with the phase error. The apparatus also includes a gain controller adapted to adjust the pumping gain based upon the magnitude of the frequency control input to the voltage controlled oscillator.

Owner:SKYWORKS SOLUTIONS INC

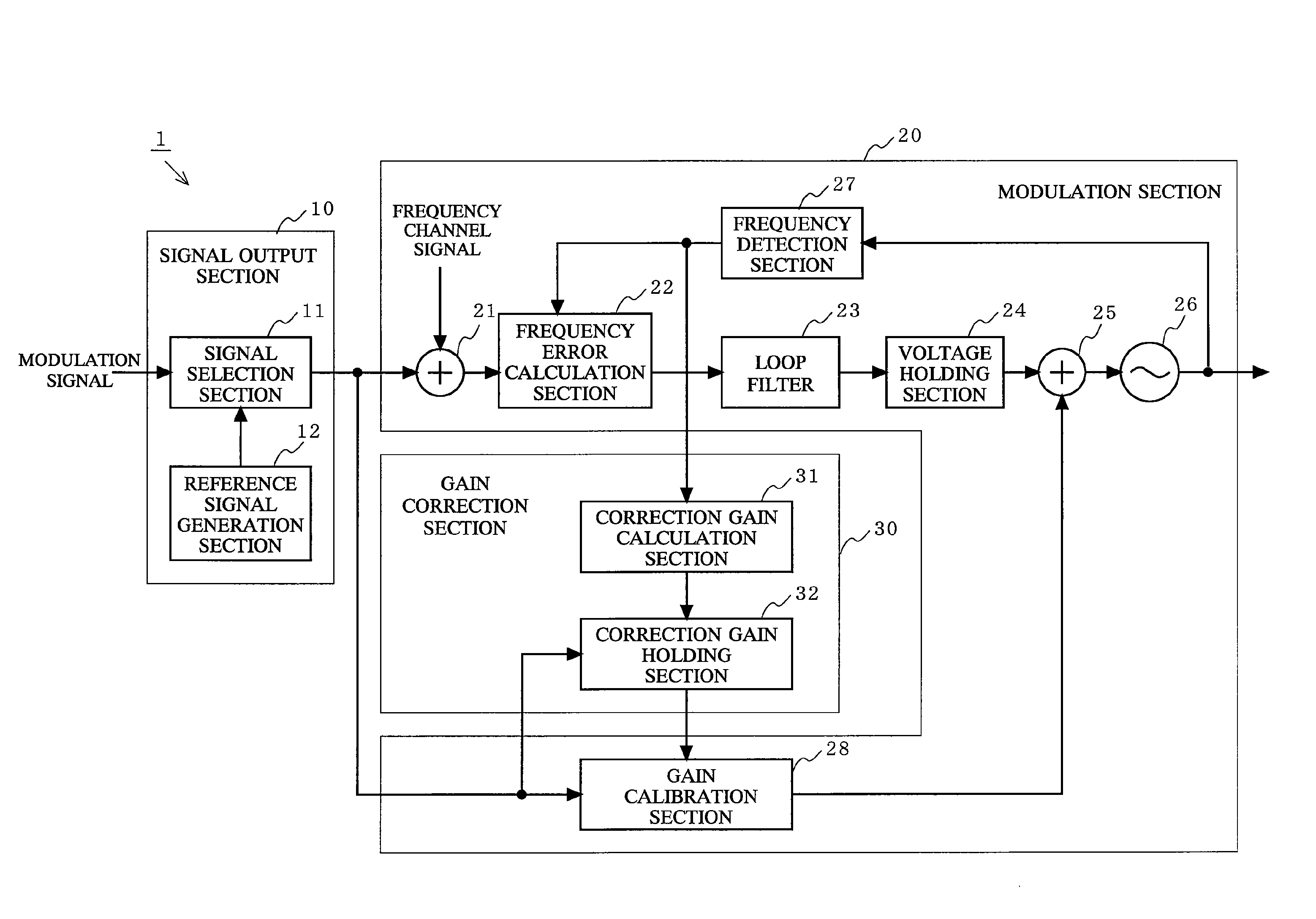

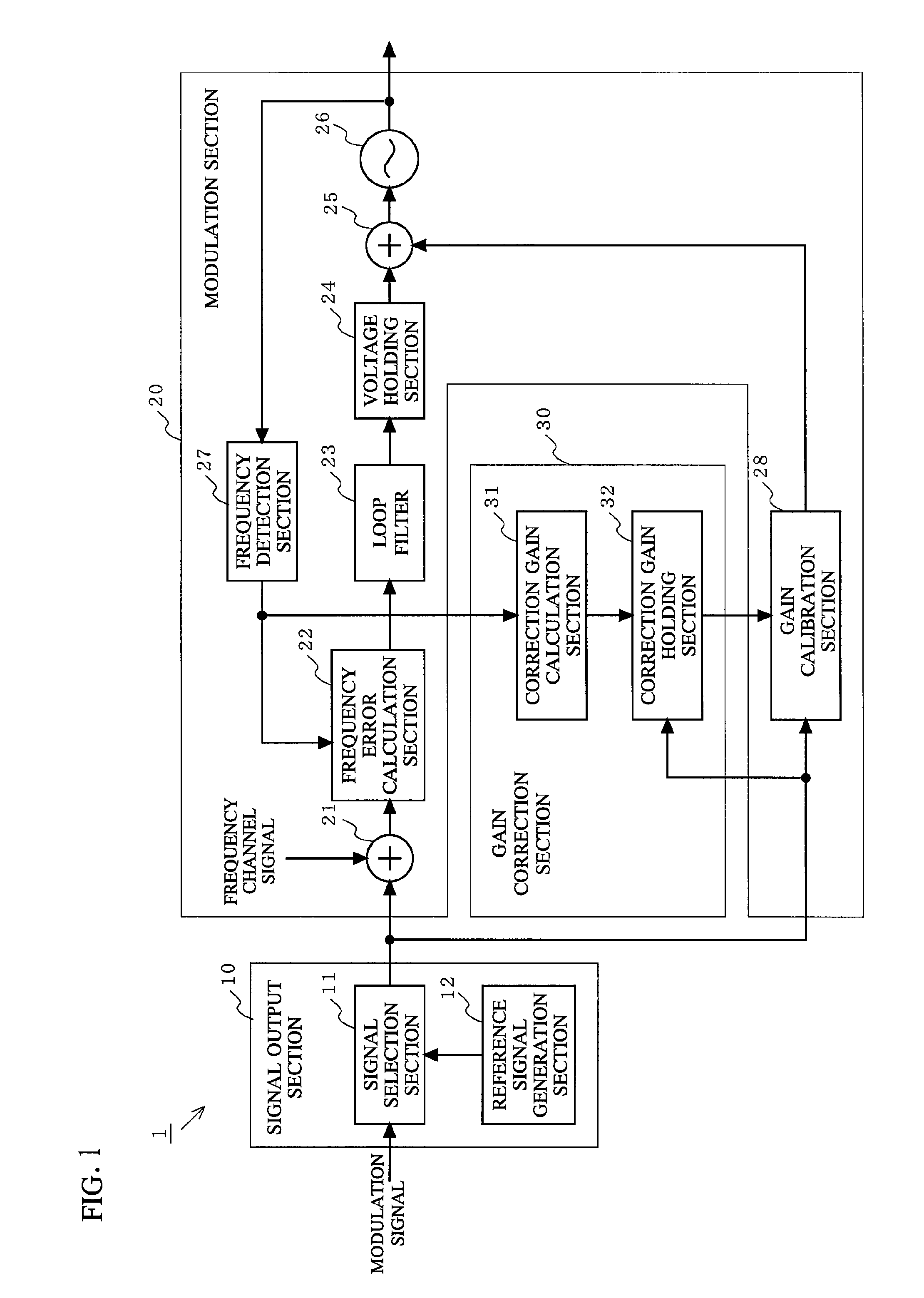

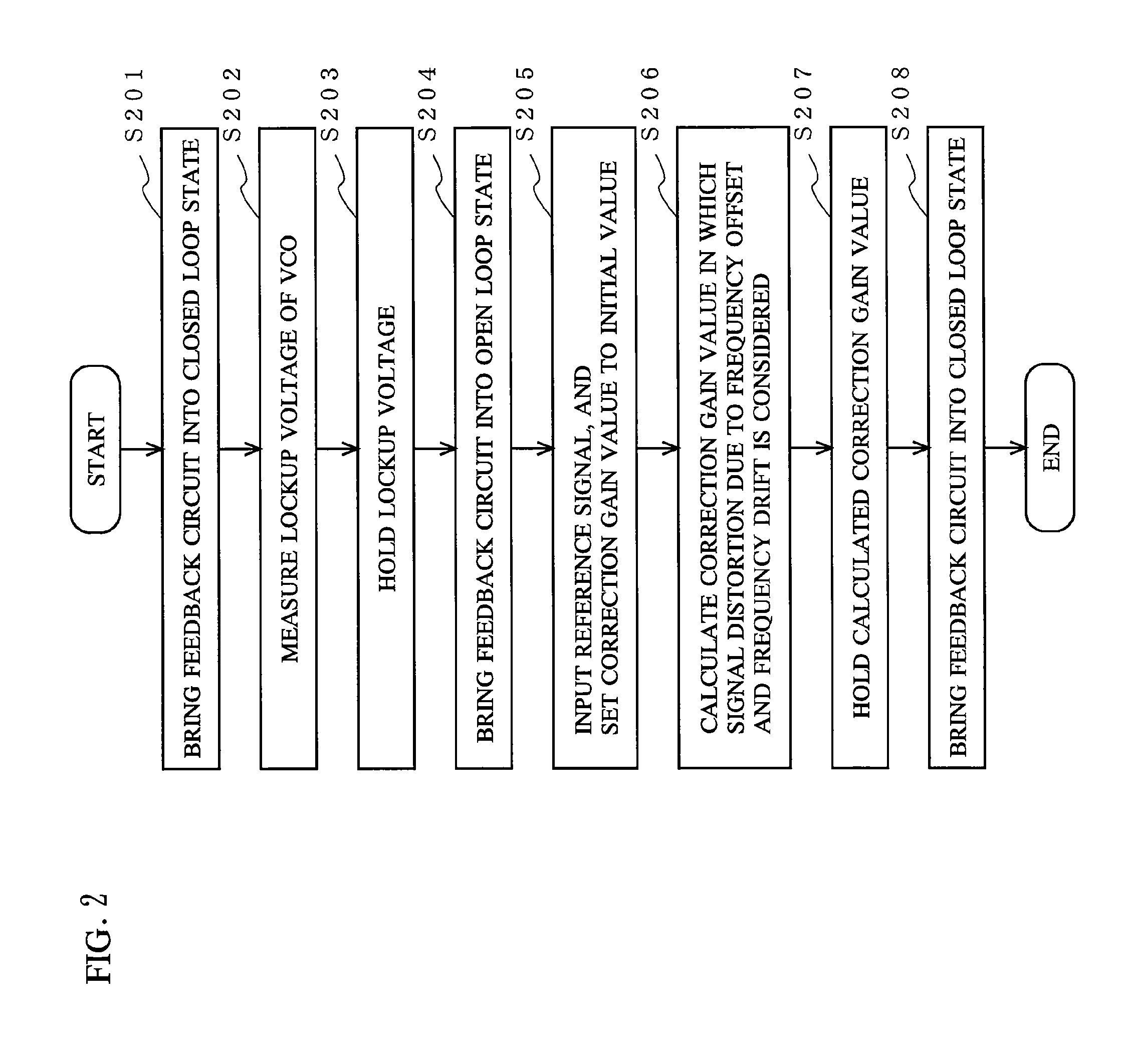

Two point modulator using voltage control oscillator and calibration processing method

InactiveUS7902891B1Short timeAdd nonlinearityPulse automatic controlAngle modulationEngineeringFeedback circuits

A two-point modulator using a voltage control oscillator includes: a modulation section including a feedback circuit for performing feedback control of a signal outputted from the voltage control oscillator based on an inputted modulated signal, and a feedforward circuit for calibrating the modulated signal and outputting the calibrated modulated signal to the voltage control oscillator; a signal output section for, upon calibration processing, outputting a predetermined reference signal in place of the modulated signal, to the modulation section; and a gain correction section for, in a state where the feedback circuit is in an open loop state, calculating a frequency transition amount of the reference signal outputted from the voltage control oscillator, and correcting a gain used for calibration of the modulated signal performed by the feedforward circuit, based on the calculated frequency transition amount.

Owner:PANASONIC CORP

Linear voltage controlled oscillator transconductor with gain compensation

InactiveUS20020089381A1Decrease resistance of variable resistanceMore of the gainPulse automatic controlPulse generation by logic circuitsPhase locked loop circuitLow-pass filter

A voltage controlled oscillator of a phase locked loop circuit having digitally controlled gain compensation. The digital control circuitry provides binary logic input to the voltage controlled oscillator for a digitally controlled variable resistance circuit, a digitally controlled variable current transconductor circuit, or differential transistor pairs having mirrored circuitry for adjusting the V-I gain. The latter configuration requires the voltage controlled oscillator to incorporate a source-coupled differential pair which is driven by a low pass filter capacitor output voltage, and connected to load transistors; a current source and a current mirror for generating a tail current; individual banks of transistors to mirror the load transistor currents; a digital-to-analog converter with control lines outputted there from, the digital-to-analog converter used to increase the amount of current allowed to flow to the transconductor output, the current being digitally increased and decreased corresponding to an amount of current pulled from the current source, and mirroring the current through at least one transistor mirror circuit.

Owner:MARVELL ASIA PTE LTD

Voltage detecting apparatus with voltage controlled oscillator and battery state control system

ActiveUS8305043B2Low reliabilityProcessing speedBatteries circuit arrangementsMaterial analysis by electric/magnetic meansDigital dataImage resolution

In a voltage detecting apparatus, a voltage controlled oscillator, when an input voltage is applied thereto, outputs a signal with a logical value that is periodically inverted. A detector counts a number of logical inversion of the output signal from the voltage controlled oscillator over an interval between edges of pulses of a pulse signal to thereby generate, based on the counted number of logical inversion, digital data as a detected result of the input voltage. A determiner determines whether a reduction of a time required to detect the input voltage is higher in priority than an increase of a resolution of detection of the input voltage. A variably setting unit variably sets a frequency of the pulse signal based on a result of the determination of whether the reduction of the time required to detect the input voltage is higher in priority than the increase of the resolution of detection of the input voltage.

Owner:DENSO CORP

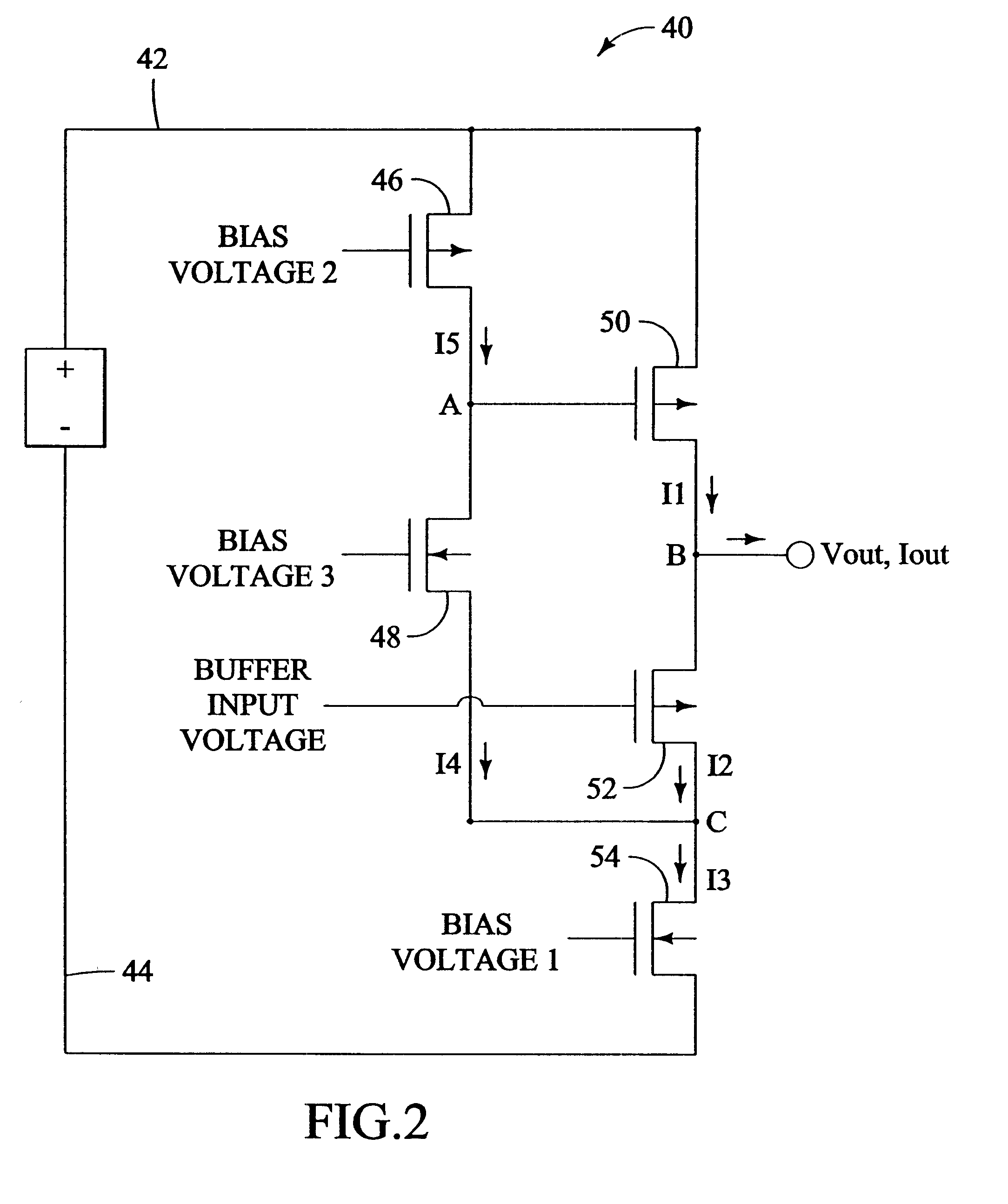

Efficient current feedback buffer

InactiveUS6525613B2Optimization rangeLimit its operationPulse automatic controlPulse generation by logic circuitsDelay-locked loopFrequency synthesizer

An efficient current feedback buffer is revealed. The buffer is useful in power supplies for a number of analog and digital devices, including CMOS voltage controlled ring oscillators, frequency synthesizers, delay locked loops, phase accumulators, and phase locked loops. The power supply and buffer maintains a low impedance output to the load, regulates the voltage output of the supply, and rejects power line noise.

Owner:INFINEON TECH AG

PLL clock signal generation circuit

InactiveUS7109764B2Raise the ratioSafer designPulse automatic controlOscillator tubesControl signalVoltage reference

A PLL clock signal generation circuit comprising a phase comparator, a charge pump circuit, a filter circuit, a voltage control oscillator and a divider, wherein a multiple rate control circuit is further included which detects a state of the reference voltage (output from a filter circuit) and controls a change of a multiple rate of a divider according to a state of the detected reference voltage. The multiple rate control circuit further outputs control signal LPFOUT for changing a multiple rate so that the PLL clock signal generation circuit does not deviate from a region capable of locking when being detected of deviation from the region capable of locking by detecting the state of reference voltage.

Owner:III HLDG 12 LLC

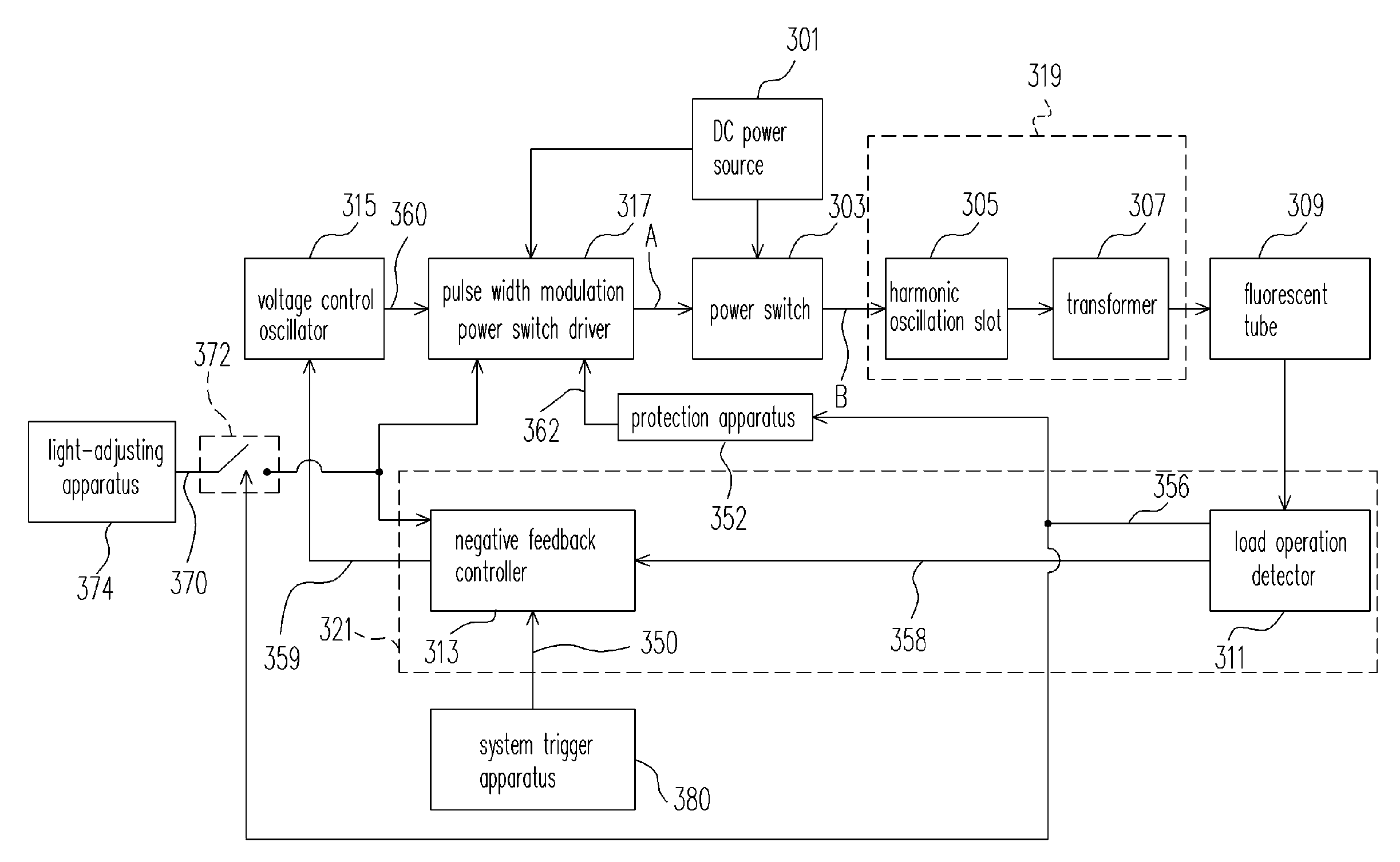

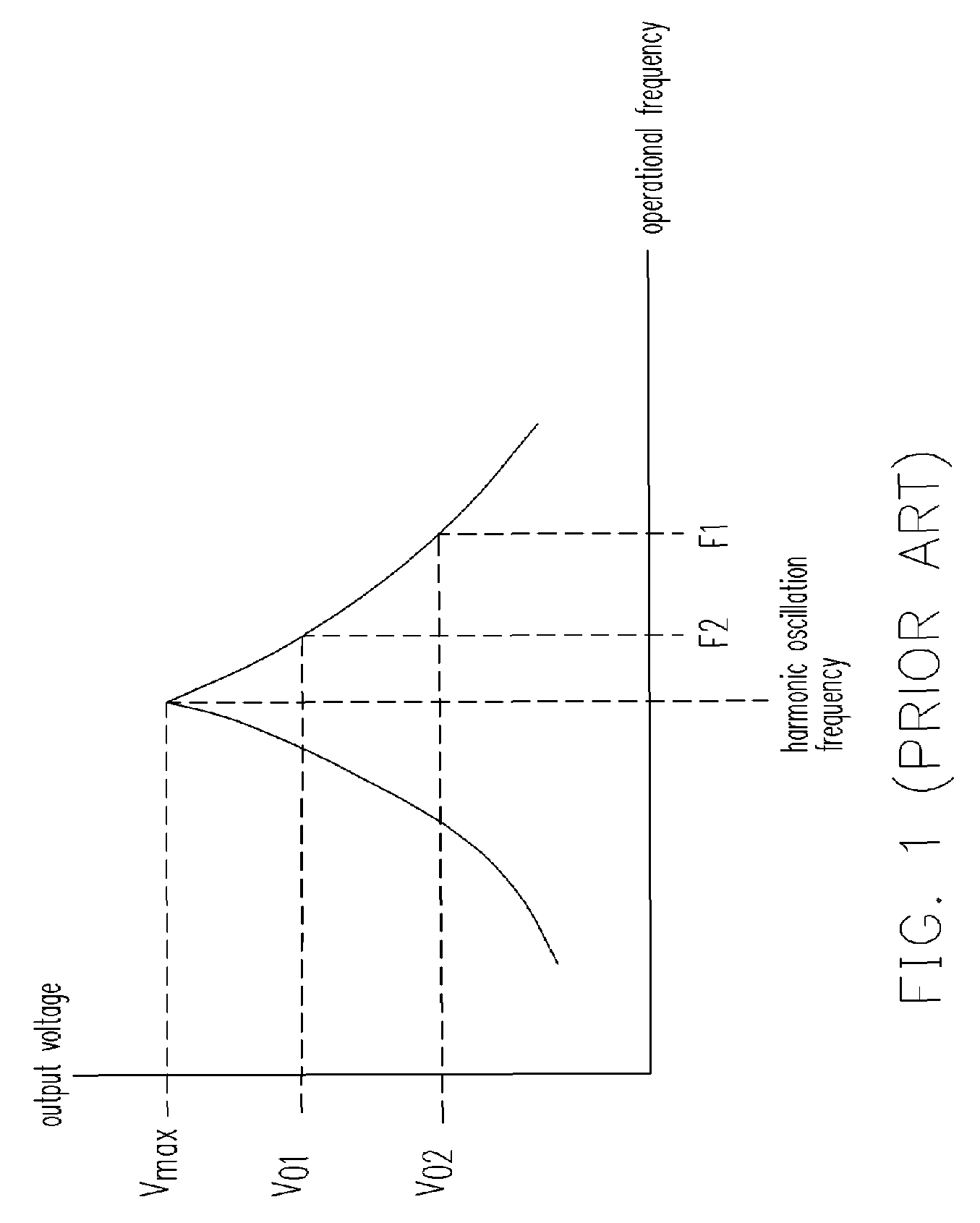

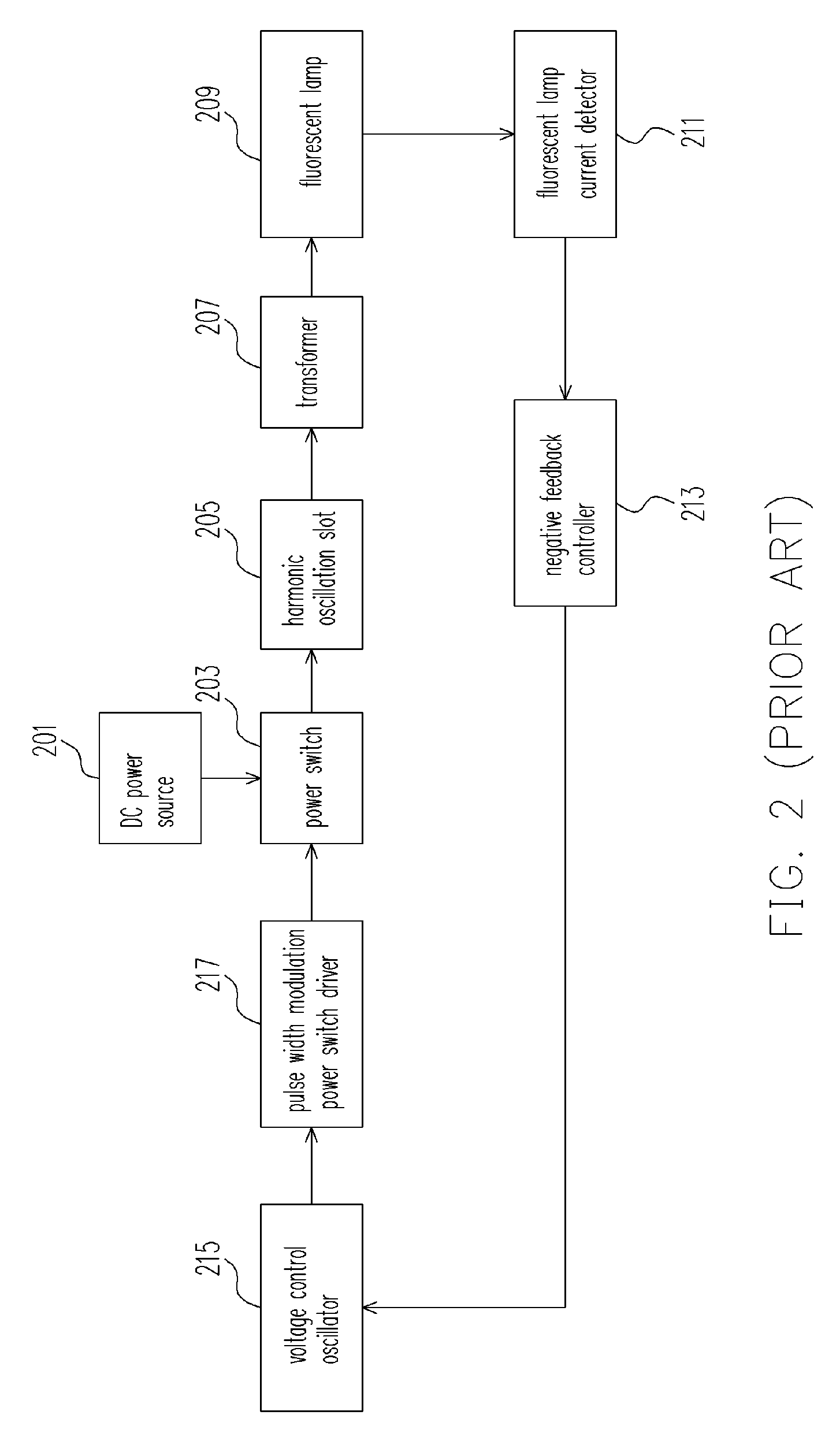

Pulse width modulation inverter circuit and control method thereof

InactiveUS7242153B2Avoid high input voltageLow efficiencyStatic indicating devicesColor television signals processingElectricityEngineering

A pulse width modulation inverter circuit is provided. The circuit includes a power switch driver, a power switch, a transformer unit, a feedback detector unit, and a voltage control oscillator. The circuit is electrically coupled to the DC power source to drive a load. The circuit adjusts the pulse width of the signal outputted from the power switch driver according to the voltage inputted to the DC power source. Accordingly, the circuit can maintain a fixed input voltage received by the fluorescent tube. Thus, the high input voltage but low output phenomenon can be avoided.

Owner:BEYOND INNOVATION TECH

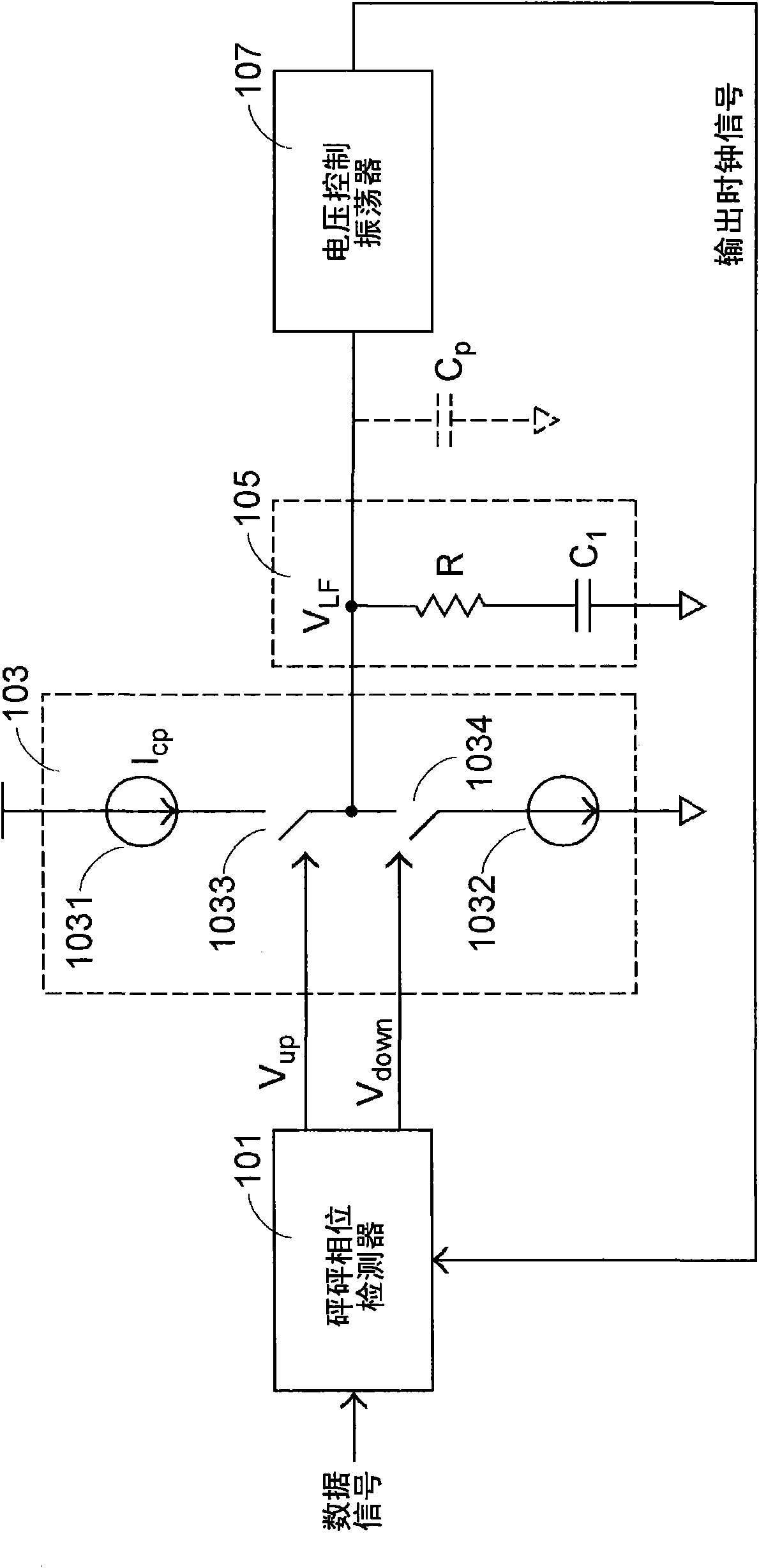

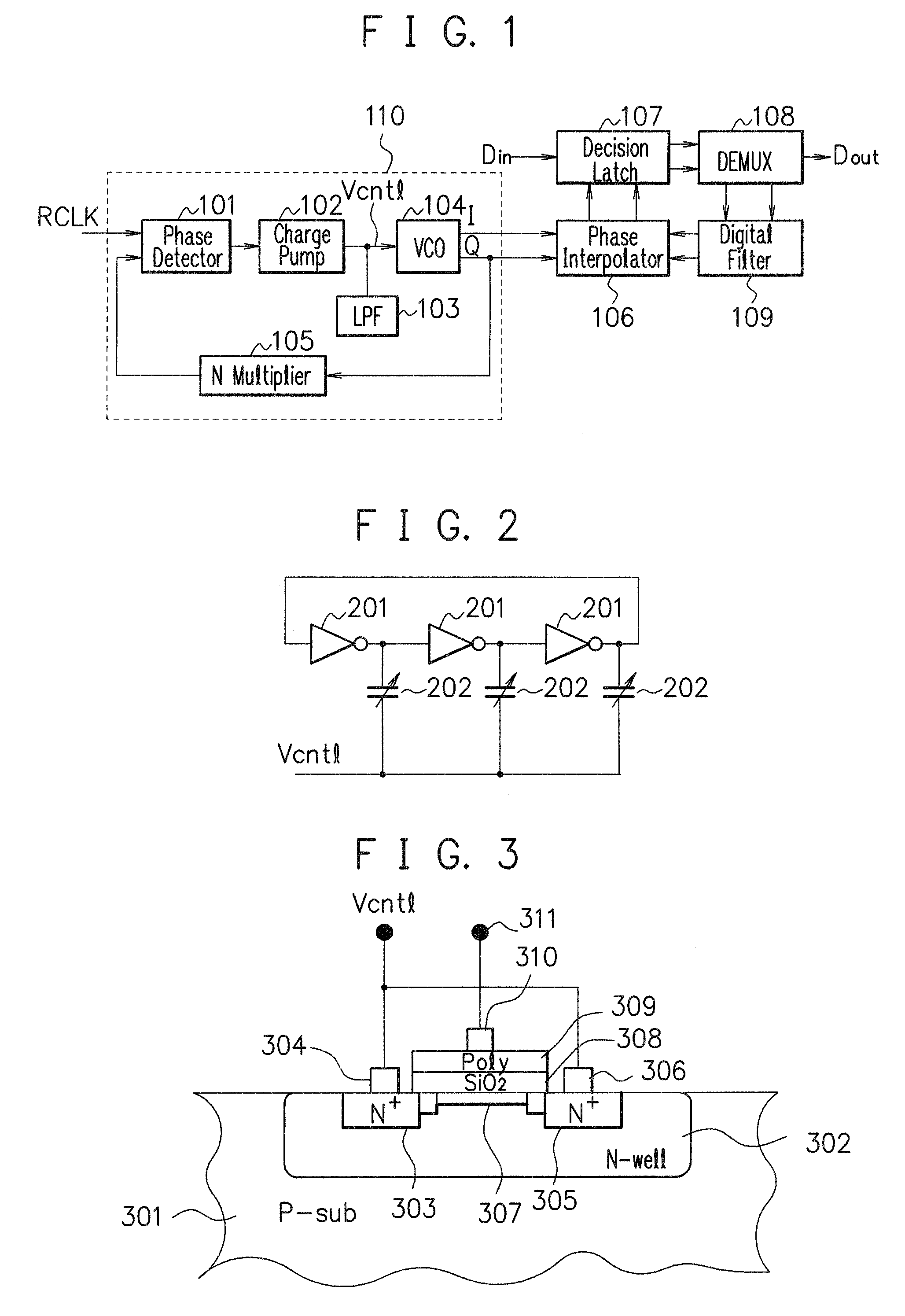

Clock data restorer

The invention discloses a clock data restorer, which comprises a phase detector, an electric charge charging pump, a loop filter, a voltage control oscillator, a current adjusting module, a current control oscillator and a frequency eliminator, wherein the phase detector compares a data signal with a first output clock signal and then generates a judgment signal; the electric charge charging pump converts the judgment signal into a switching signal; the loop filter converts the switching signal into a control voltage; the voltage control oscillator adjusts a generated second output clock signal according to the control voltage, and comprises a current mirror which is provided with a current control path and a current output path between which currents are in a proportional relation, and a control circuit which changes the current of the current control path according to the control voltage; the current adjusting module outputs difference current according to the judgment signal; the current control oscillator adjusts the phase of the second output clock signal according to the sum of the difference current and the current of the current output path; and the frequency eliminator converts the second output clock signal into the first output clock signal. The clock data restorer of the invention does not become a three-order system due to the influence of a parasitic capacitor or a decoupling capacitor.

Owner:FARADAY TECH CORP

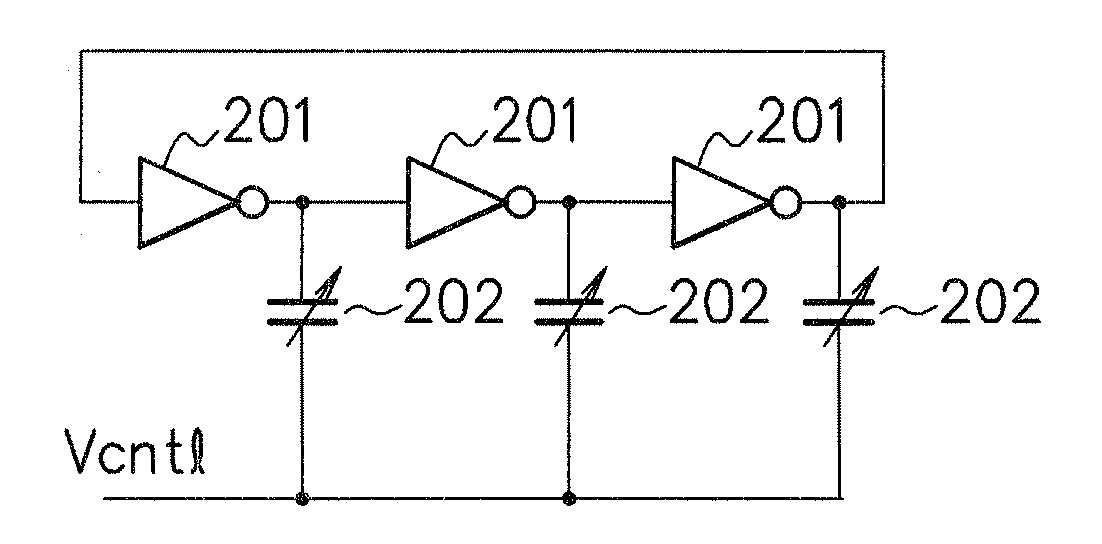

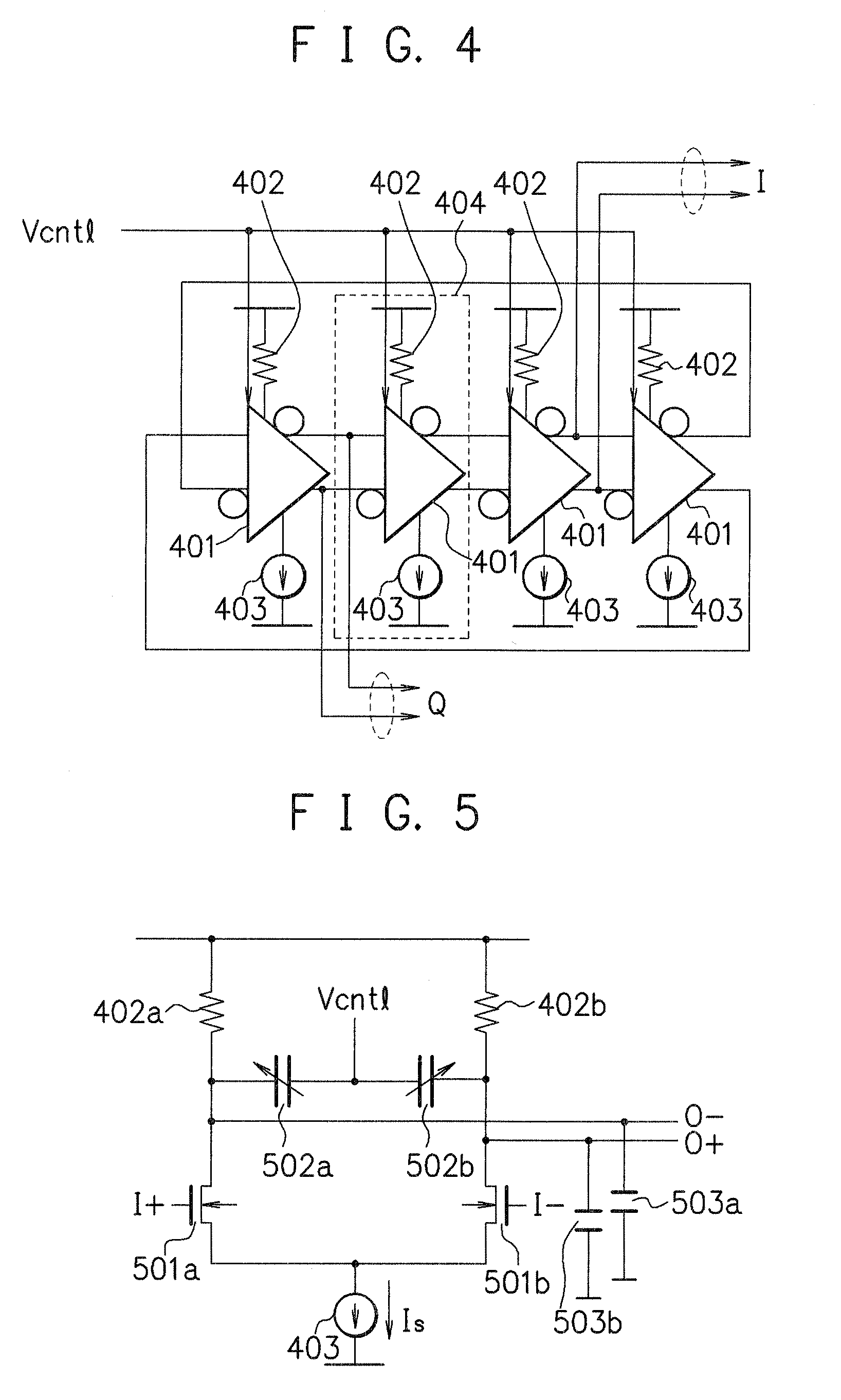

Voltage controlled ring oscillator

InactiveUS20090167446A1Capacitance varyPulse automatic controlPulse generation by logic circuitsCapacitanceAudio power amplifier

There is provided a voltage controlled ring oscillator having a plurality of ring-connected amplifiers (401), and a plurality of variable capacitance elements (502a, 502b) being respectively connected to the plurality of amplifiers and having capacitances varied by a voltage control. A plurality of load resistors (402) and a plurality of tail current sources (403) are respectively connected to the plurality of amplifiers.

Owner:FUJITSU LTD

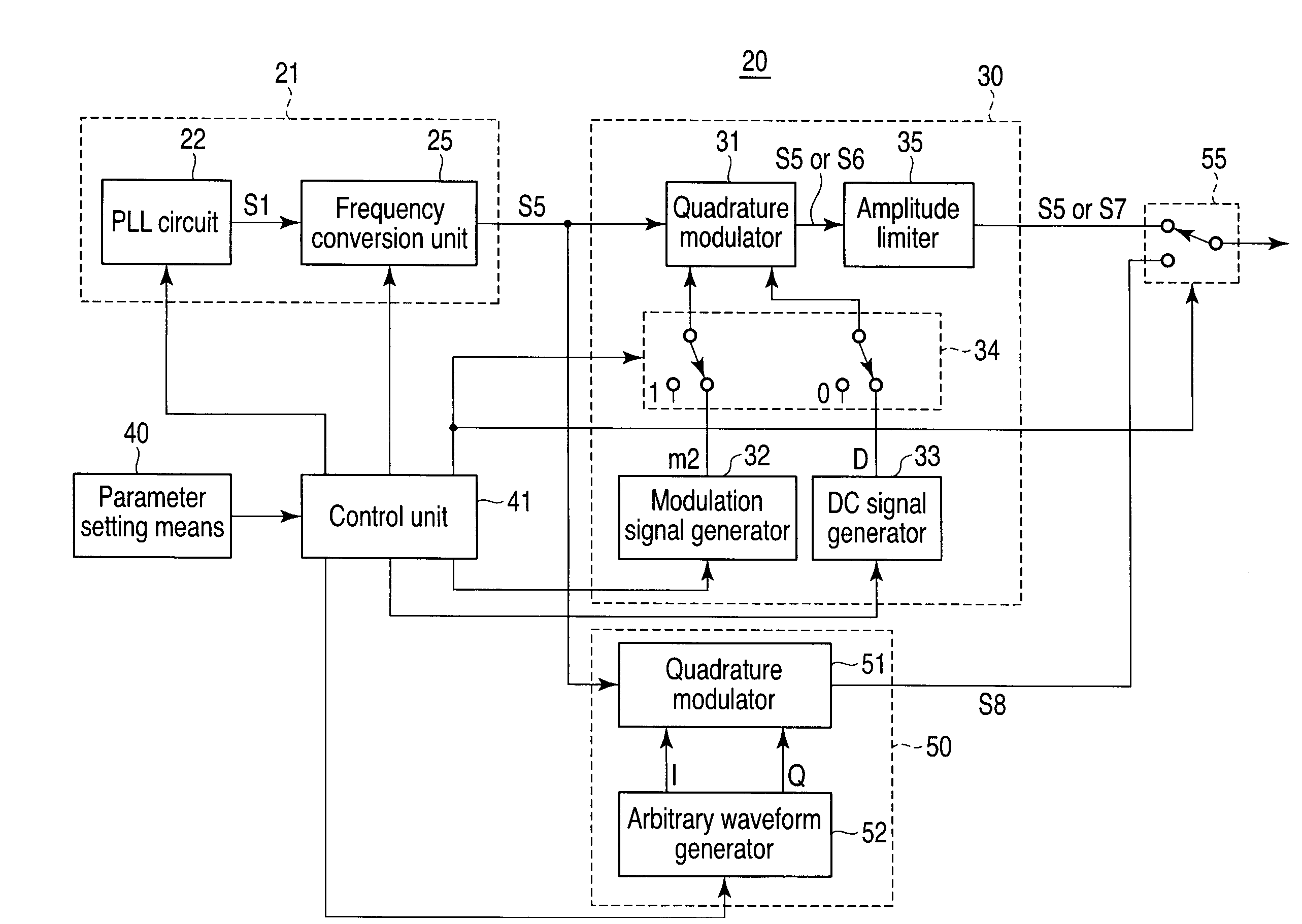

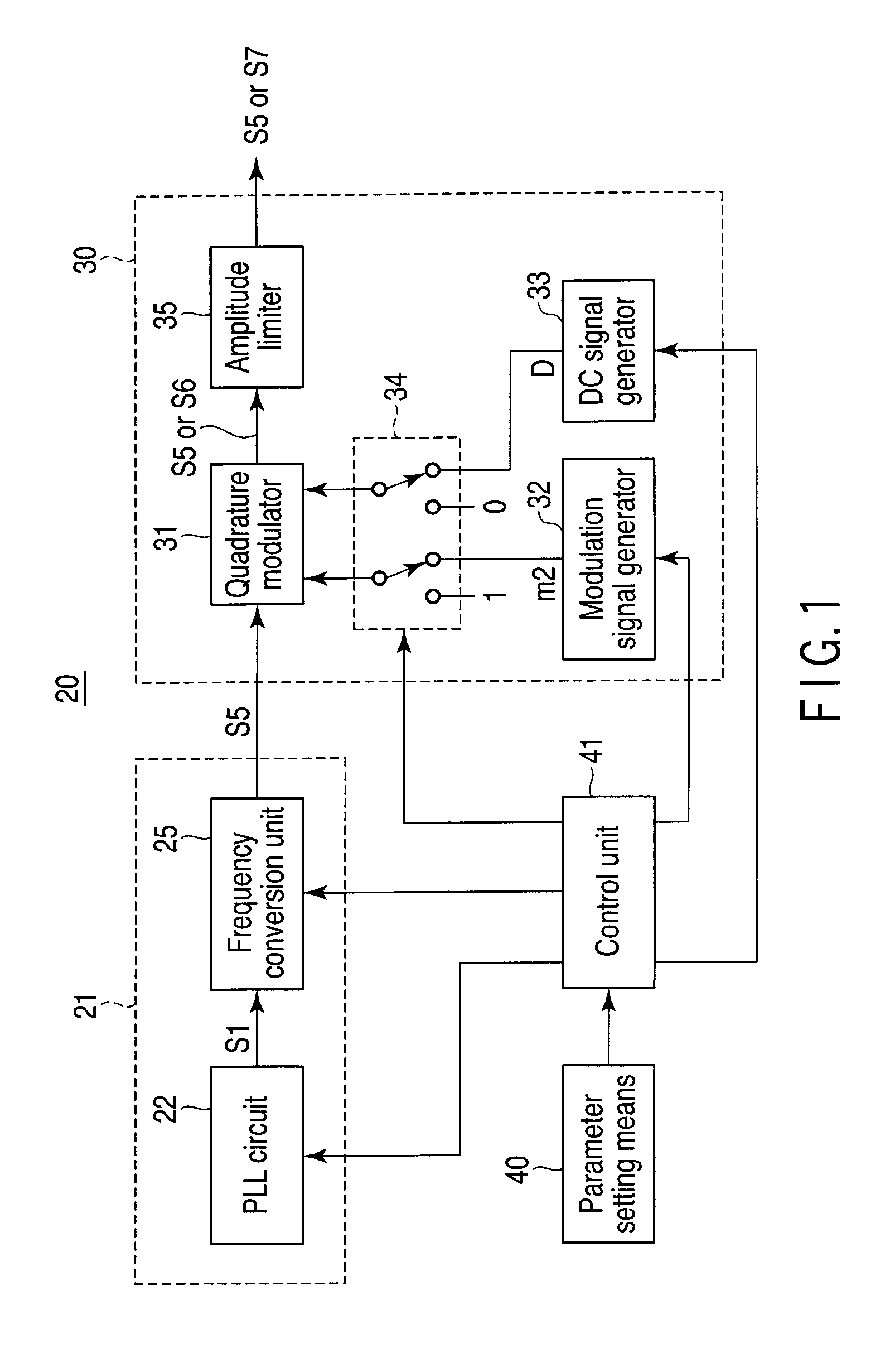

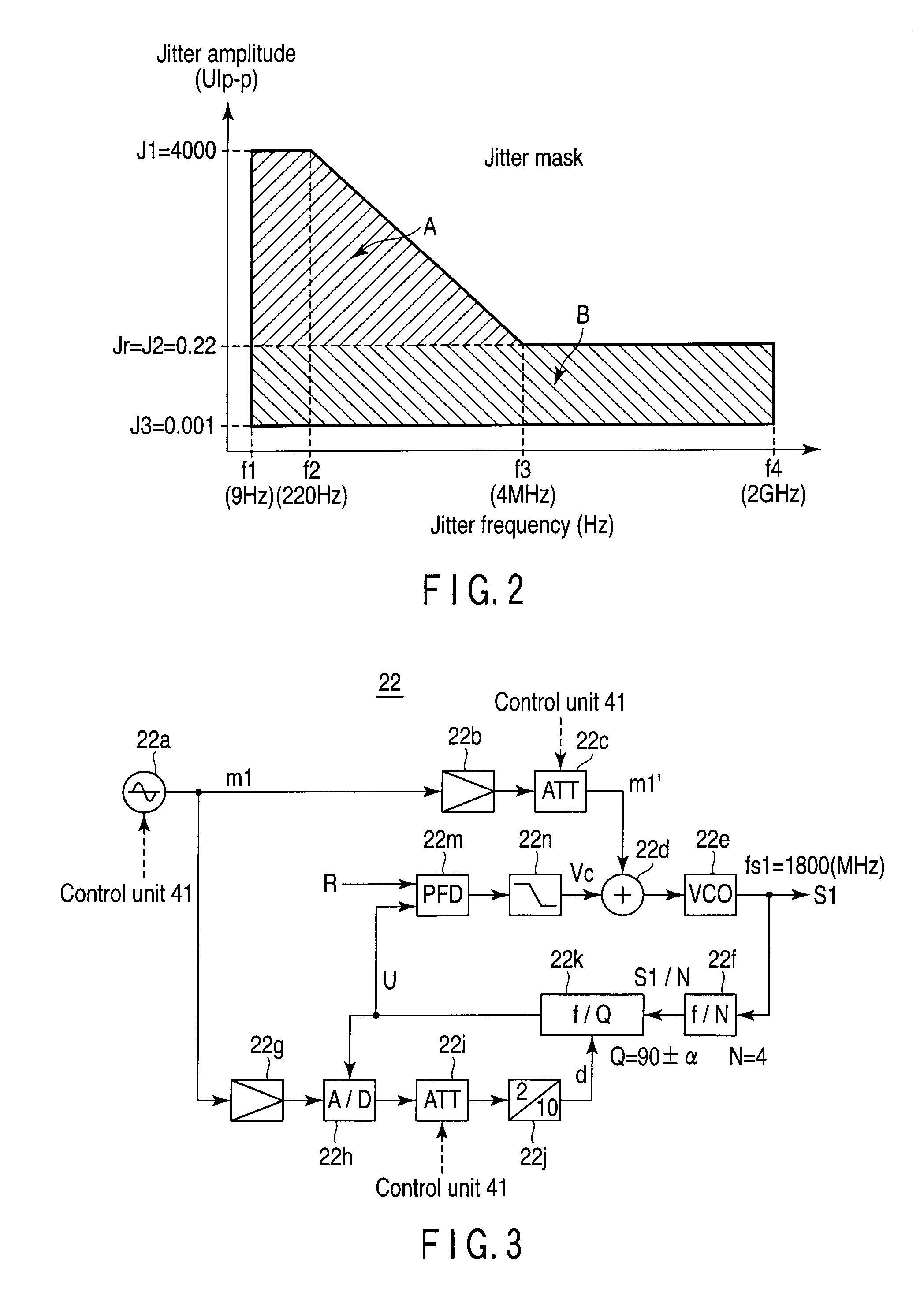

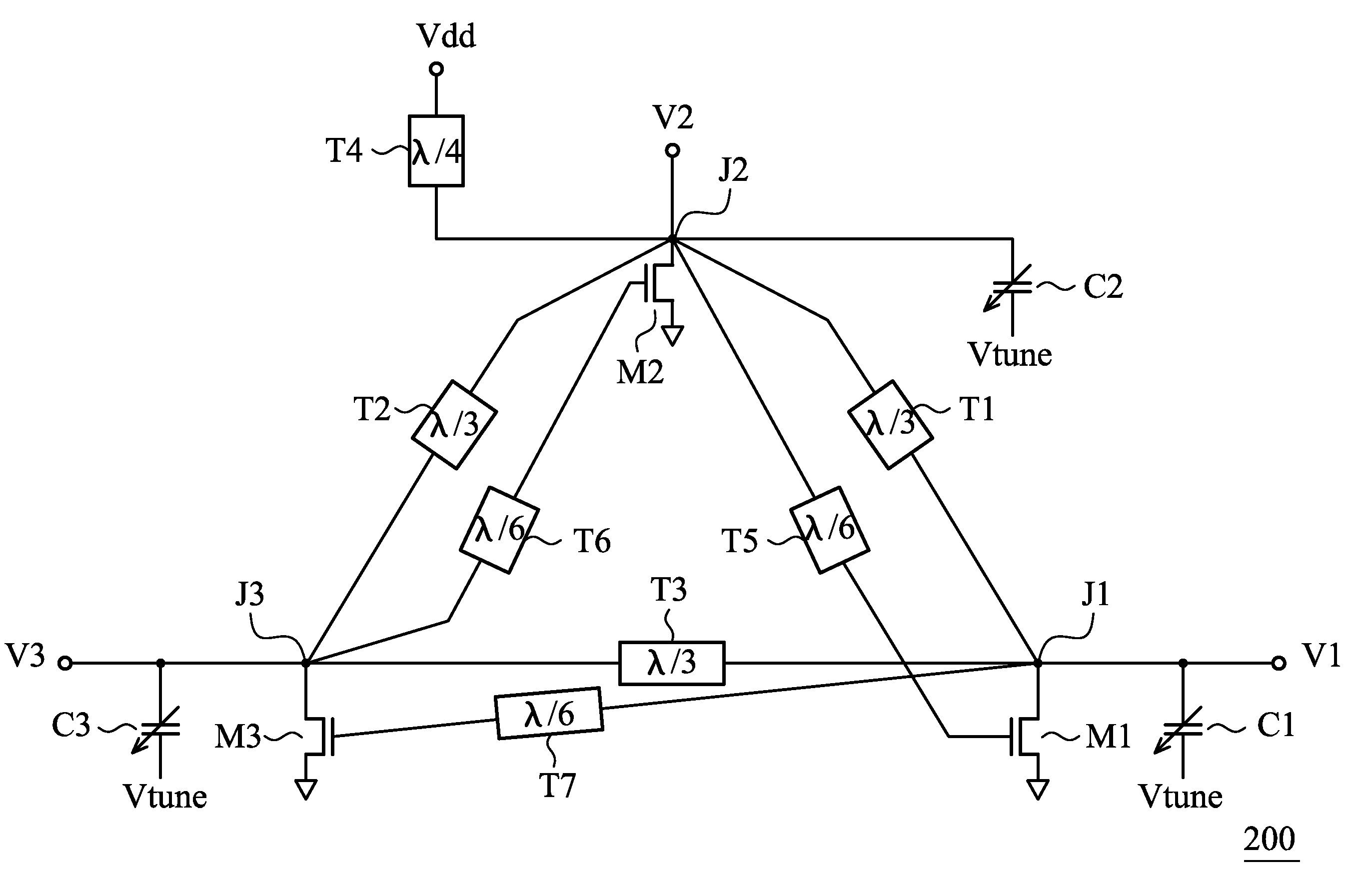

Jitter generation apparatus, device test system using the same, and jitter generation method

InactiveUS20100150218A1Reduce jitterKeep for a long timeElectrical testingAngle modulationQuadrature modulatorQuadrature modulation

A jitter generation apparatus for applying a phase modulation to a PLL is controlled by a control unit so as to output a signal with the desired jitter based on a parameters. When a switching unit is switched to a first state, the control unit controls first and second level control units so that the desired jitter in which an amplitude of a first modulation signal matches the parameter is added to an output signal from a voltage controlled oscillator unit, and passes through a quadrature modulator. When the switching unit is switched to the second state, the control unit controls the first and second level control units so that a quadrature modulation is applied to a local signal, which is input to the quadrature modulator without adding any jitter to an output signal from the voltage controlled oscillator unit, and a quadrature-modulated local signal is output.

Owner:ANRITSU CORP

Ring-shaped voltage control oscillator

InactiveUS8115560B2Angle modulation by variable impedencePulse automatic controlInjection lockedEngineering

Owner:TAIWAN SEMICON MFG CO LTD

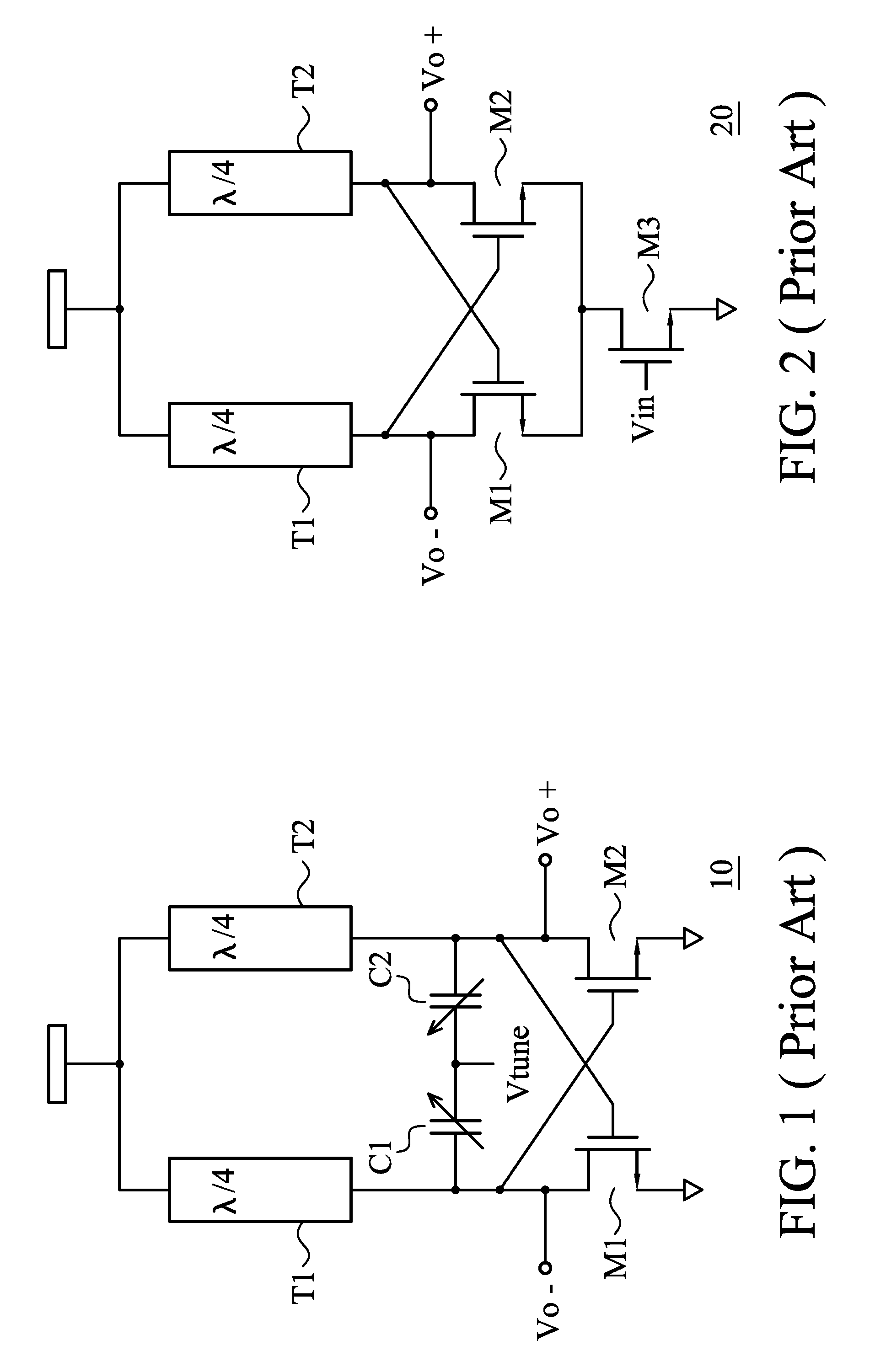

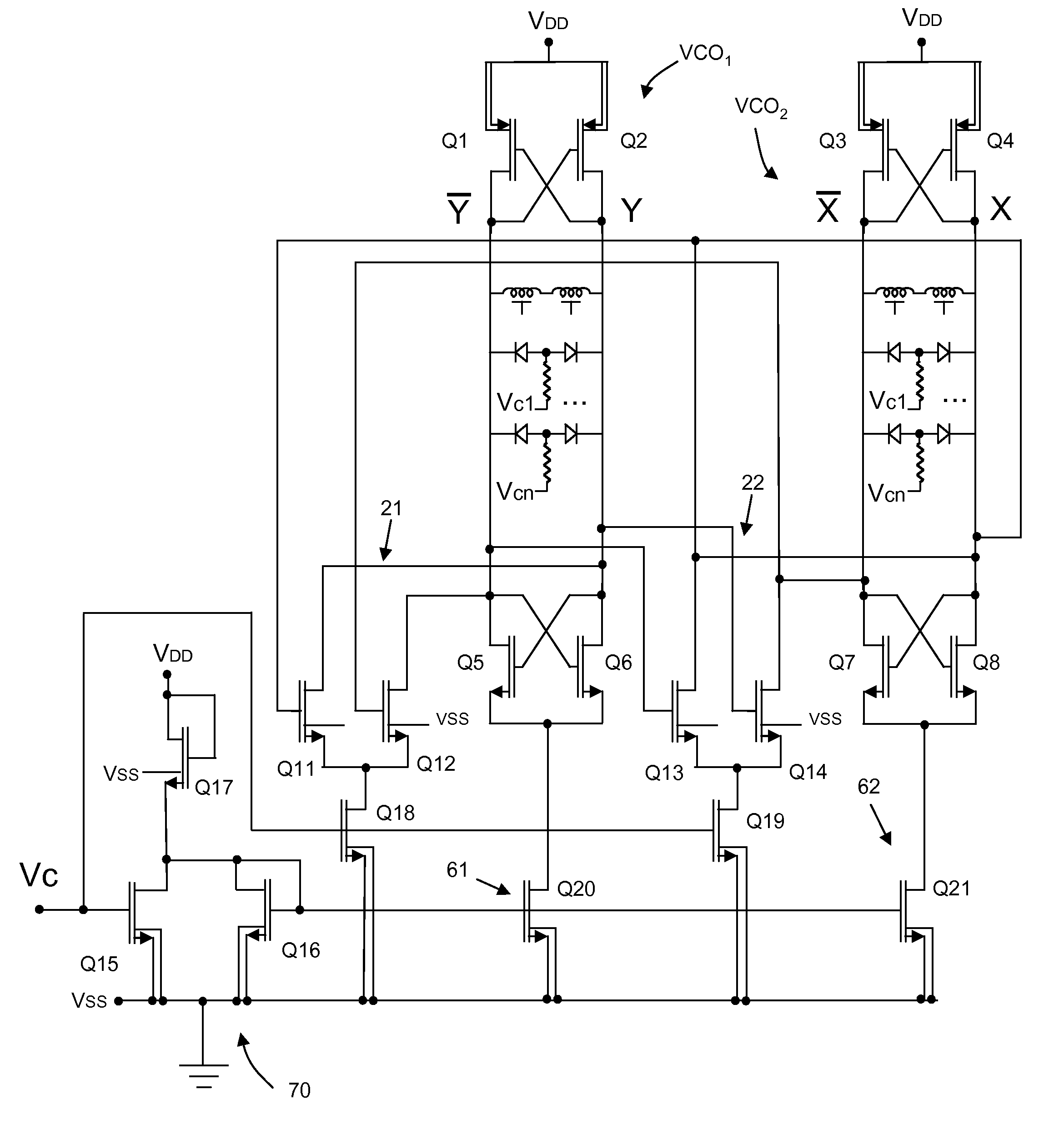

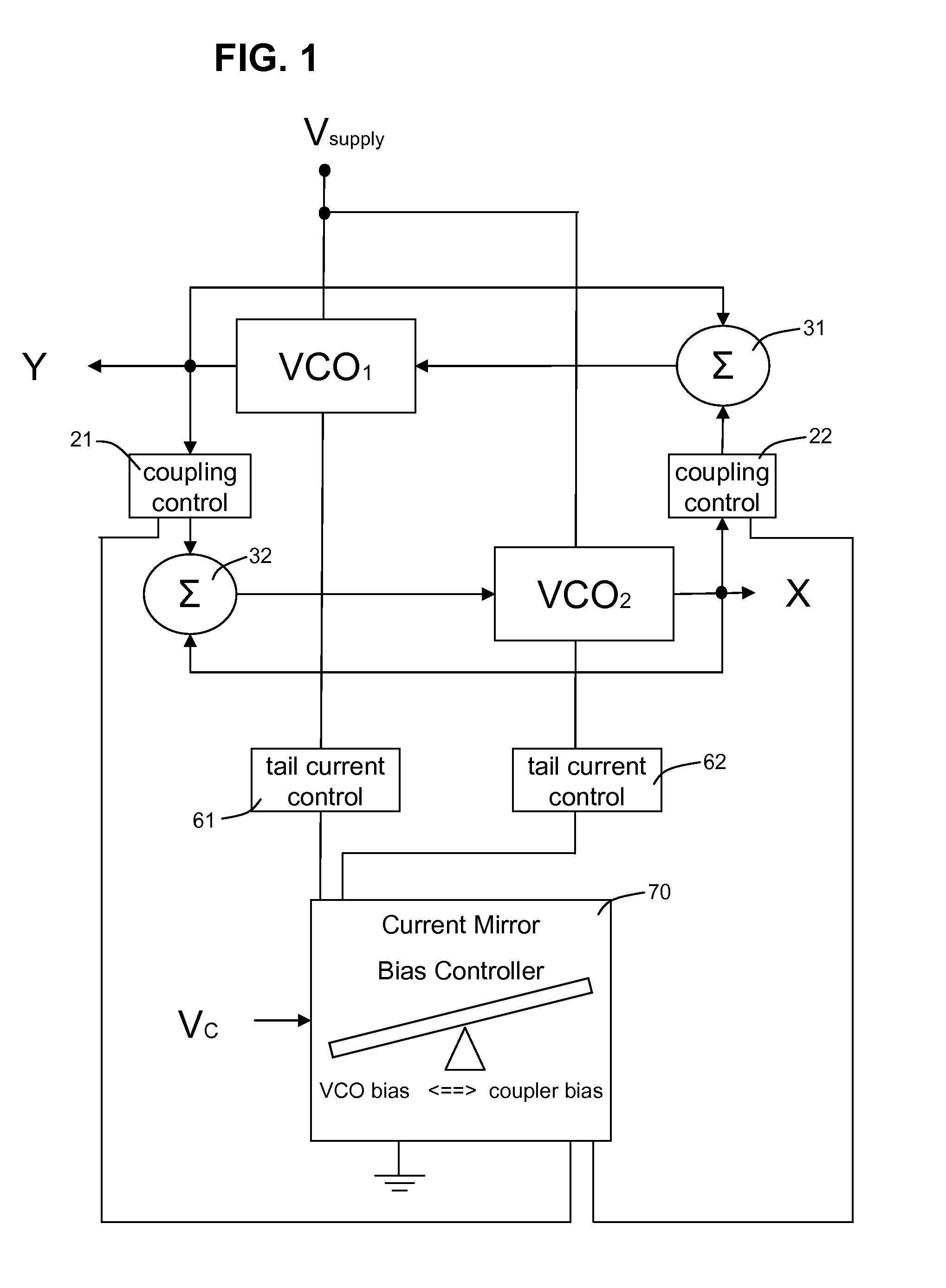

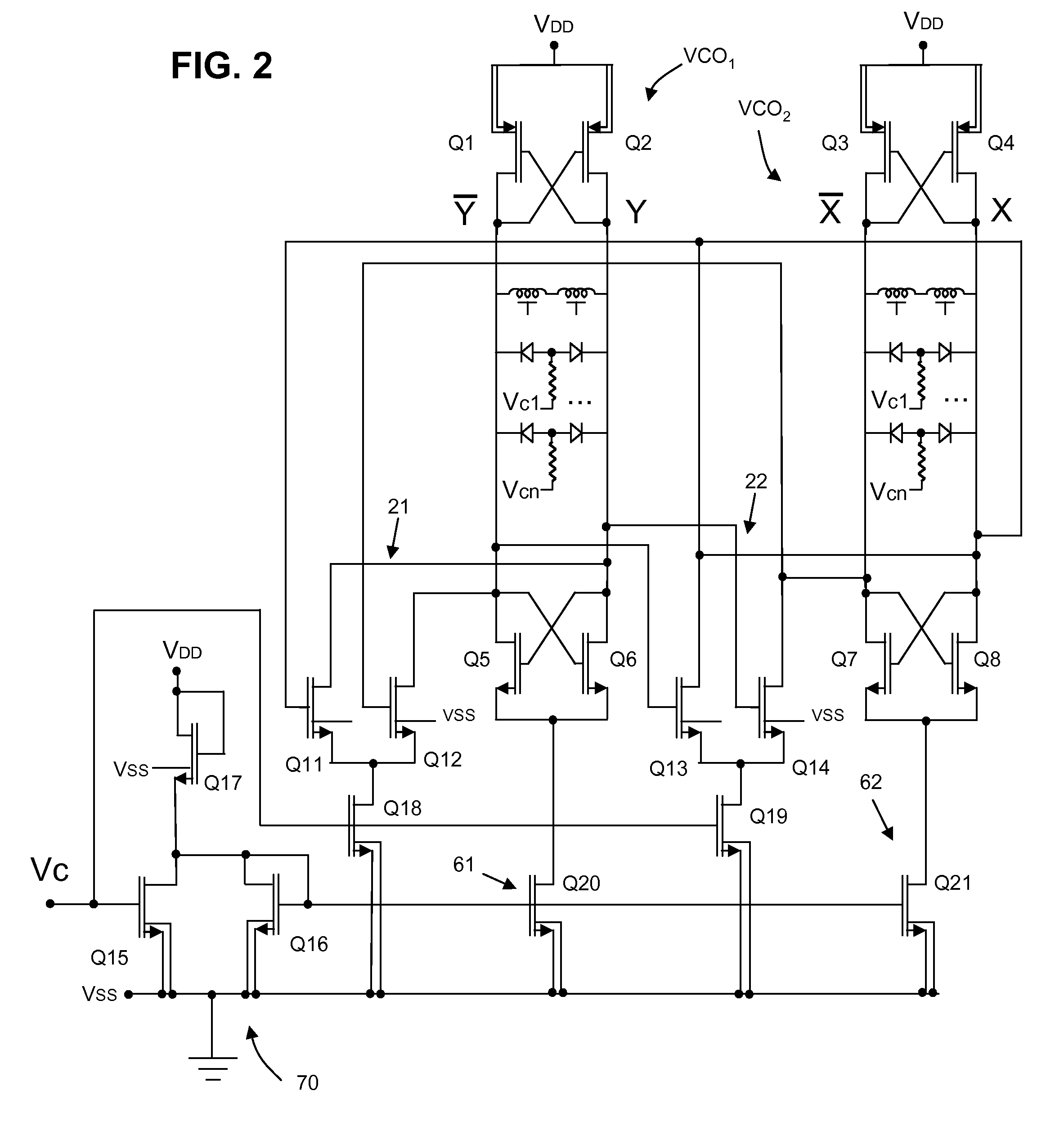

Quadrature LC voltage controlled oscillator with opposed bias and coupling control stages

InactiveUS7342462B1Improve the level ofTotal current dropAngle modulation by variable impedencePulse automatic controlCouplingEngineering

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

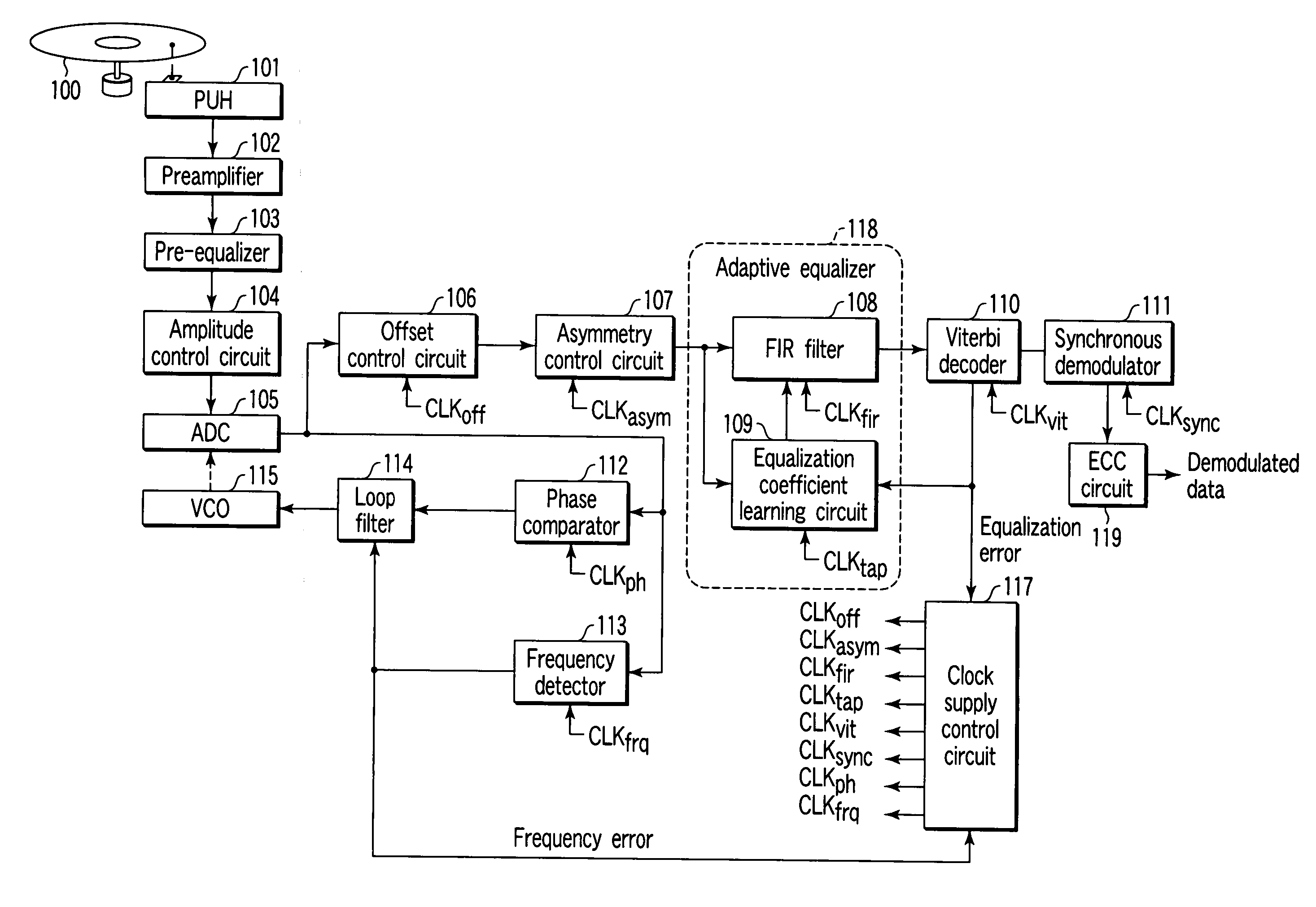

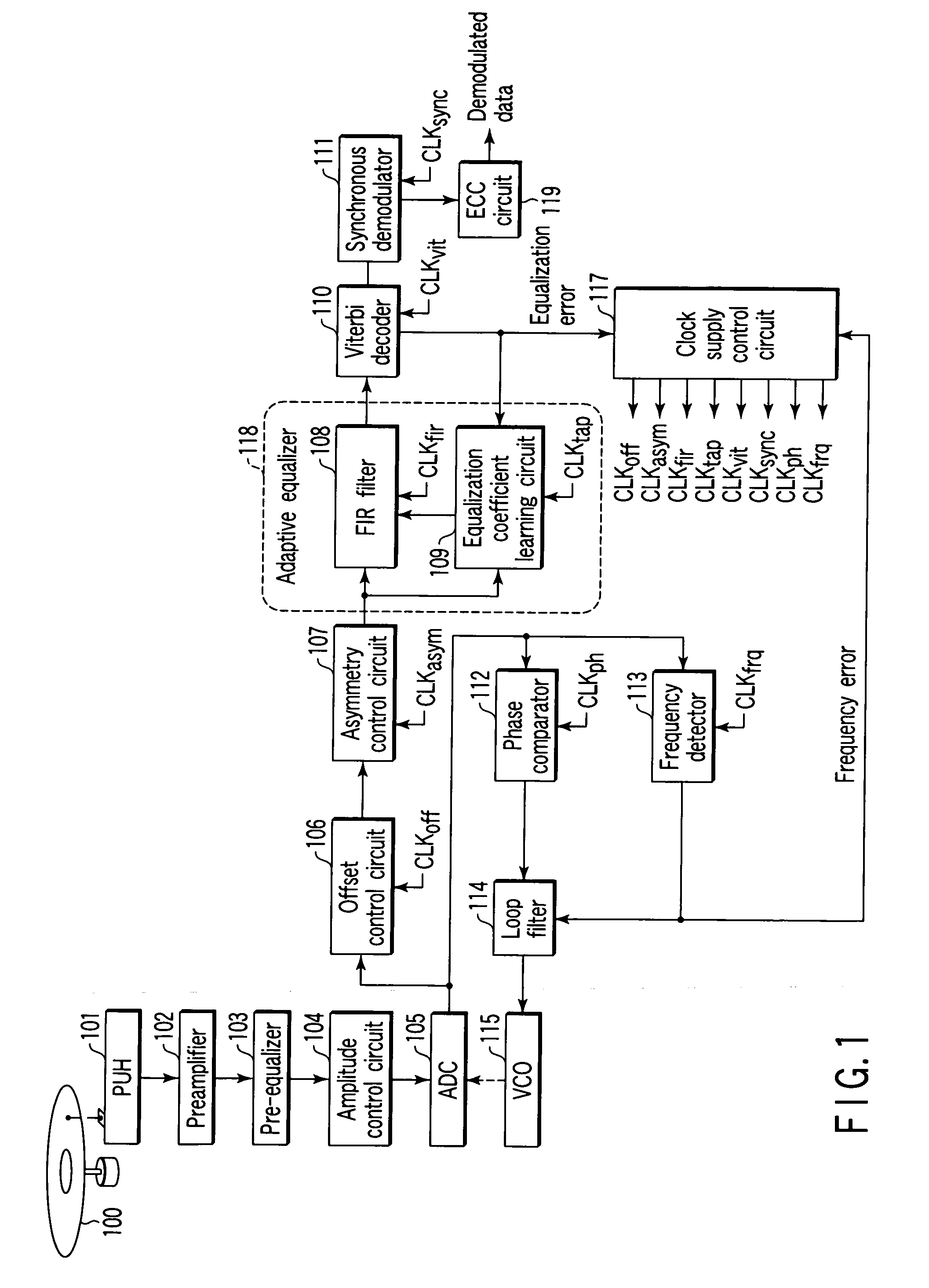

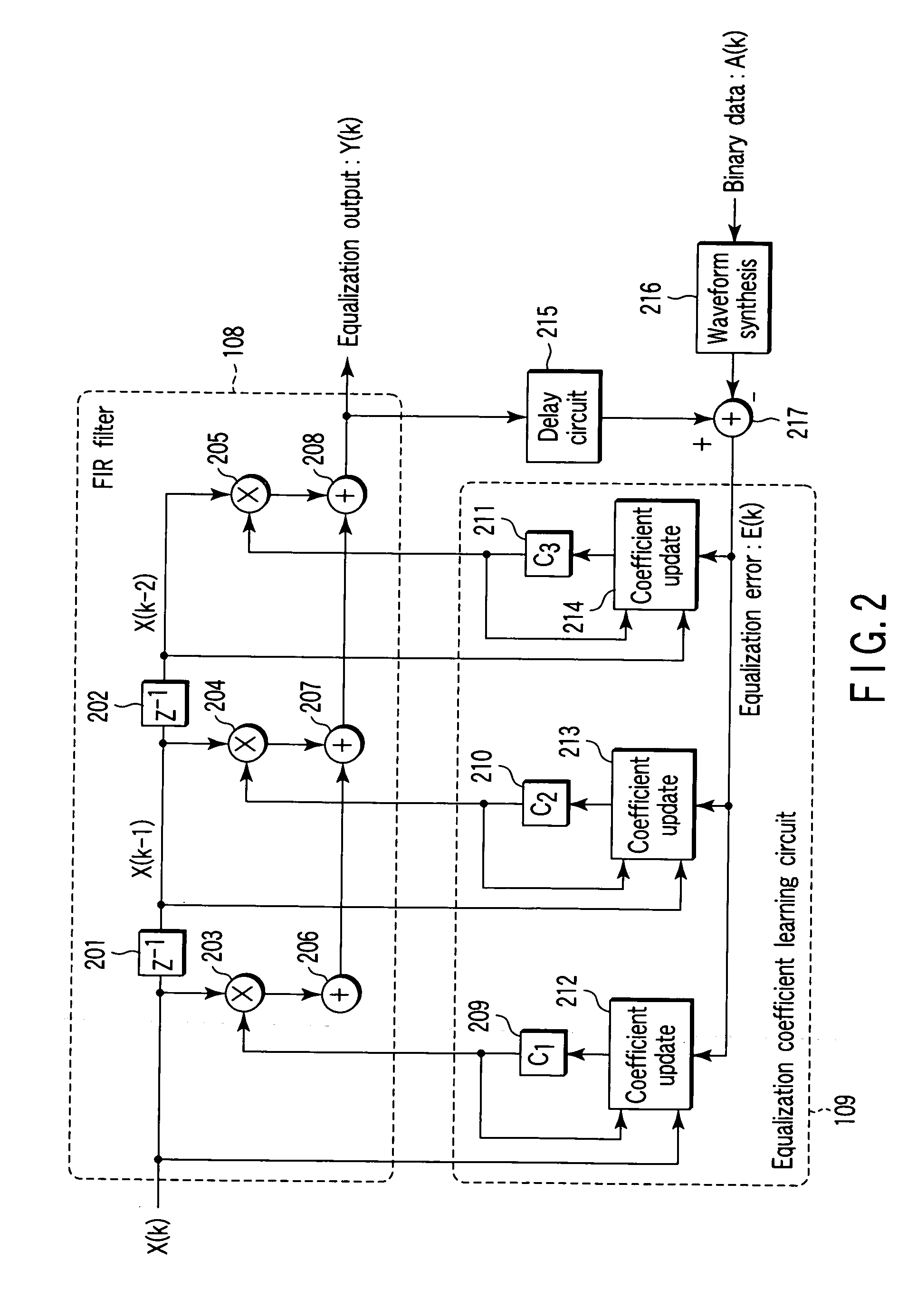

Optical disk drive

InactiveUS20070025224A1Television system detailsModification of read/write signalsViterbi decoderLoop filter

According to one embodiment, a frequency detector detects a frequency error between a frequency of a reproduction signal supplied from an analog to digital converter and a frequency of a clock for conversion. A loop filter controls an oscillation frequency of a voltage control oscillator based on the frequency error and a phase error detected by a phase comparator. An adaptive equalizer equalizes a waveform of the reproduction signal supplied from the analog to digital converter to obtain a response of a predetermined PR class. A Viterbi decoder decodes the waveform equalized signal into binary data by maximum likelihood sequence estimation. A clock supply control circuit stops supply of a clock to at least the phase comparator, the adaptive equalizer and the Viterbi decoder in a case where the frequency error is larger than a designated error.

Owner:KK TOSHIBA

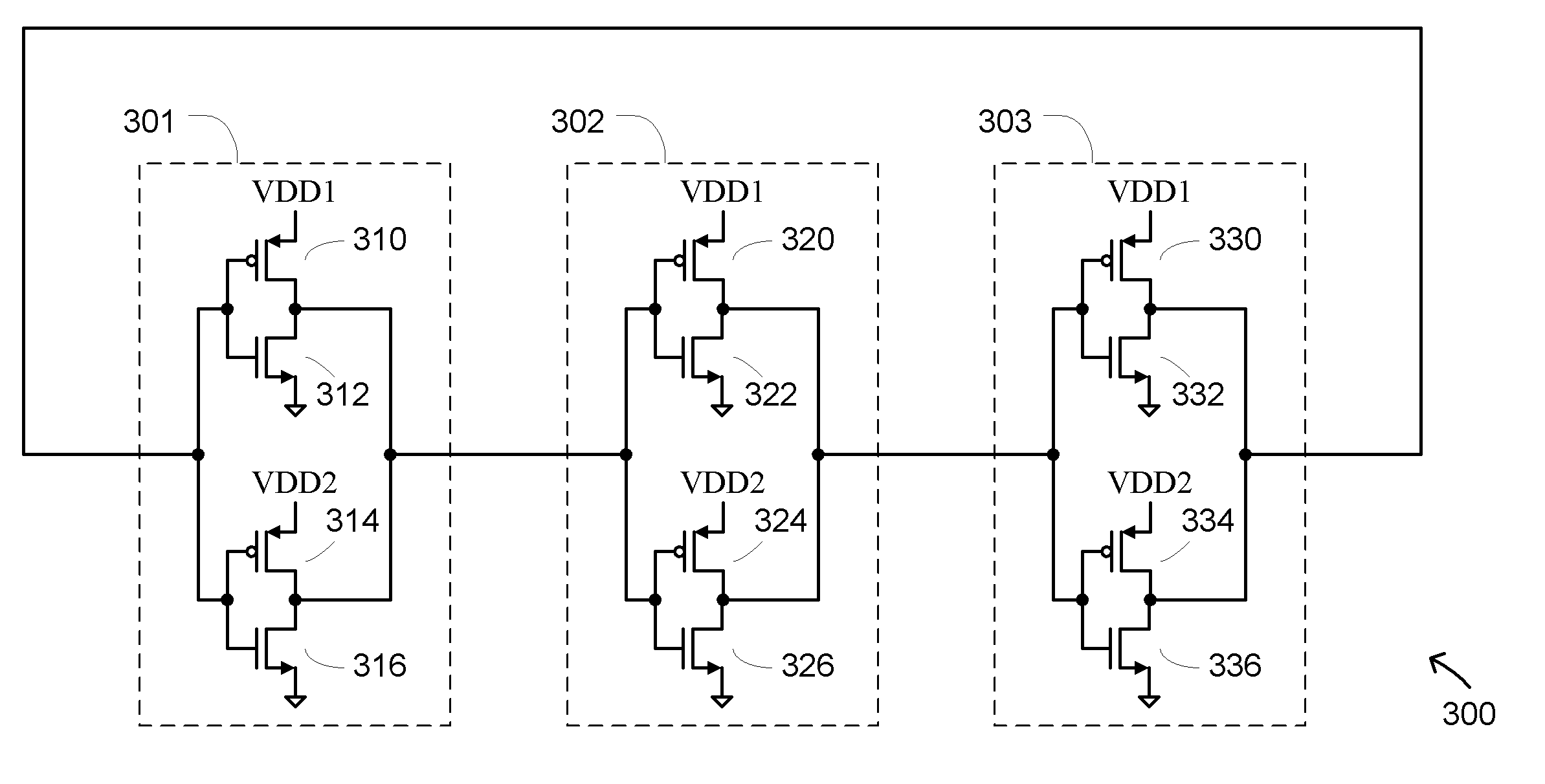

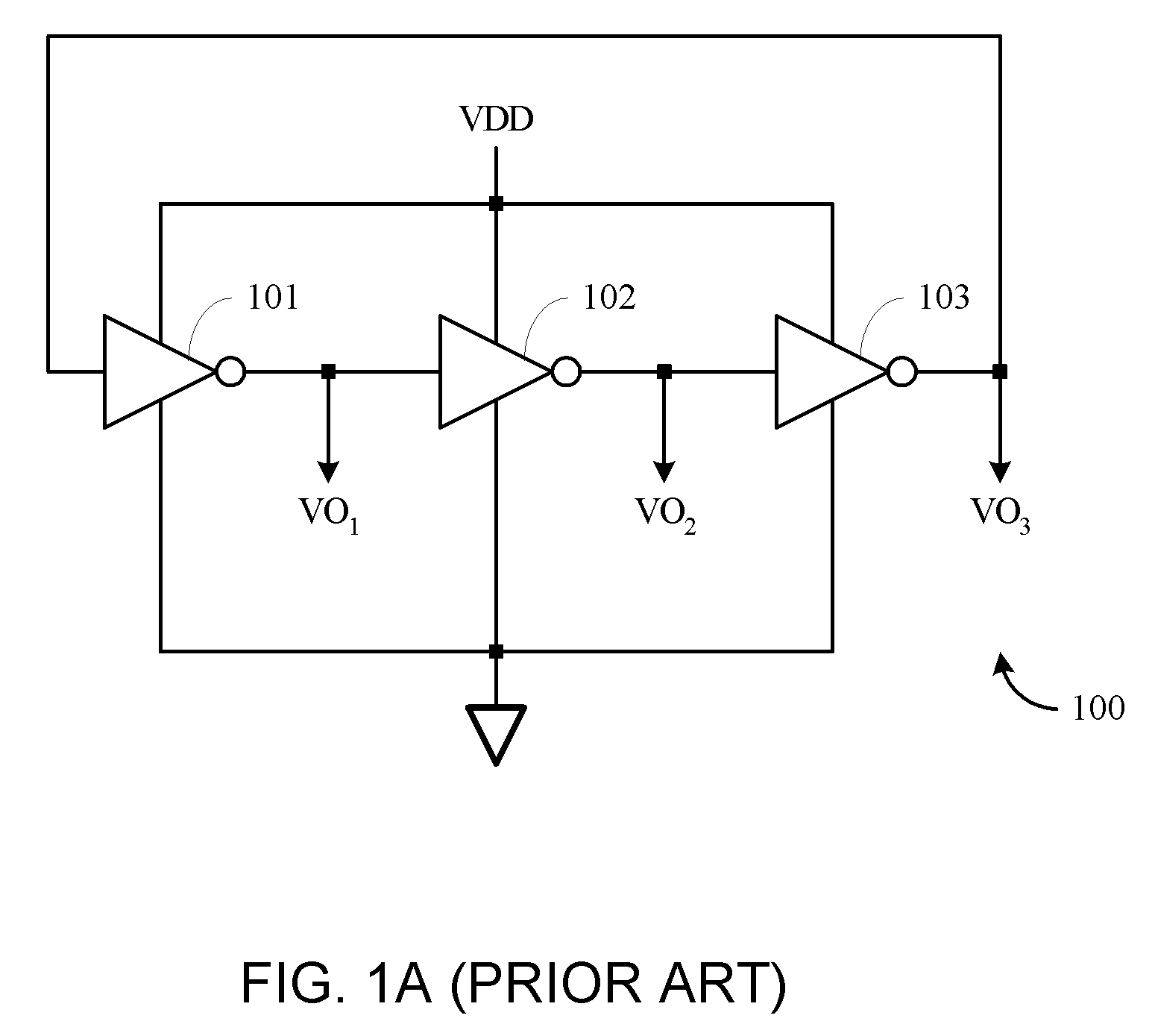

Dual supply inverter for voltage controlled ring oscillator

A voltage controlled ring oscillator reduces sensitivity of an oscillation frequency to a control voltage by using a dual supply inverter logic circuit. The dual supply inverter logic circuit includes two inverter circuits coupled in parallel between an input terminal and an output terminal. The first inverter circuit is powered by a variable supply voltage while the second inverter circuit is powered by a substantially fixed supply voltage. The variable supply voltage serves as the control voltage for the voltage controlled ring oscillator and sets the oscillation frequency. The sensitivity of the oscillation frequency to changes in the variable supply voltage is reduced due to the parallel connection of the second inverter circuit powered by a different supply voltage.

Owner:REALTEK SEMICON CORP

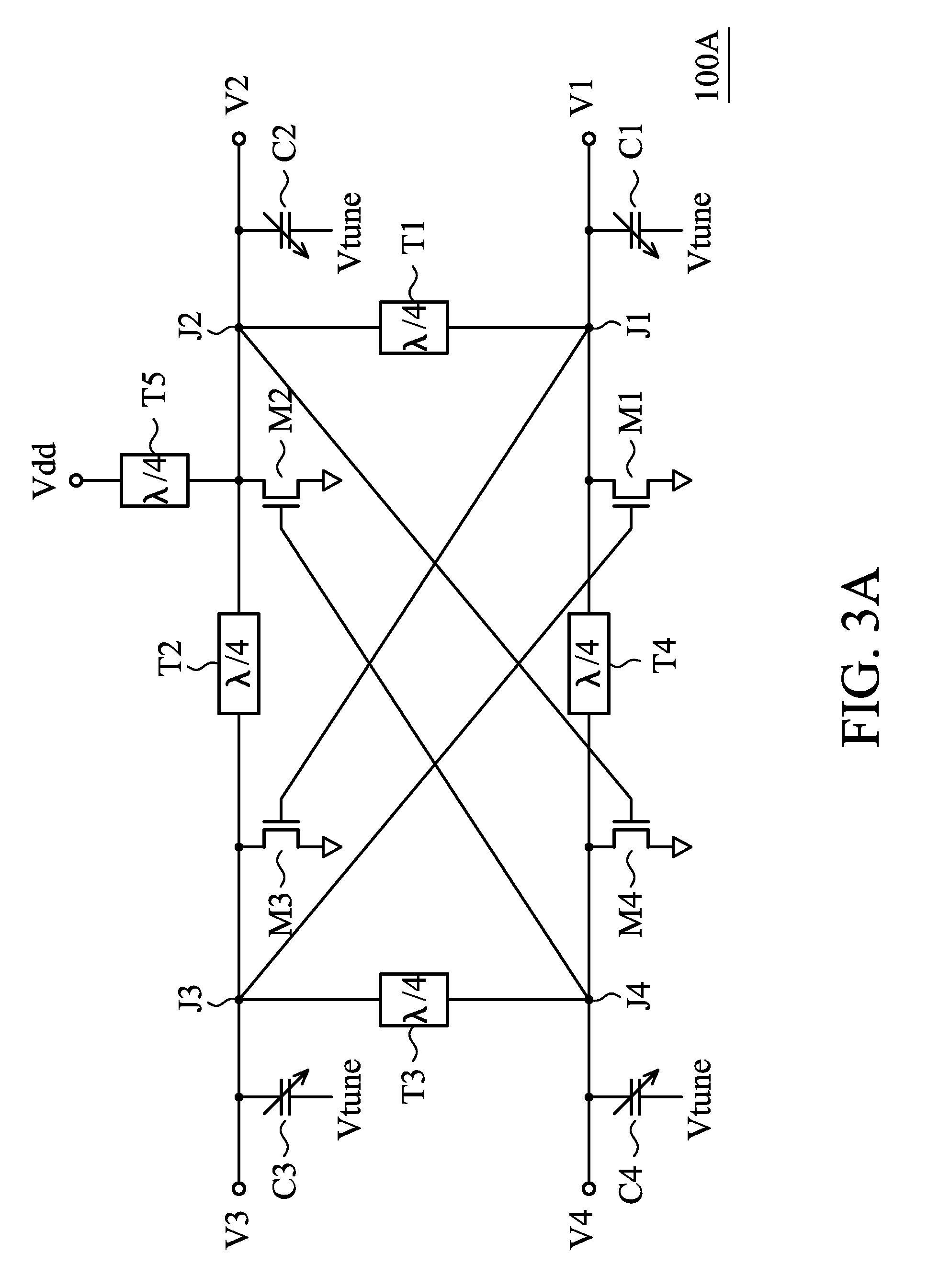

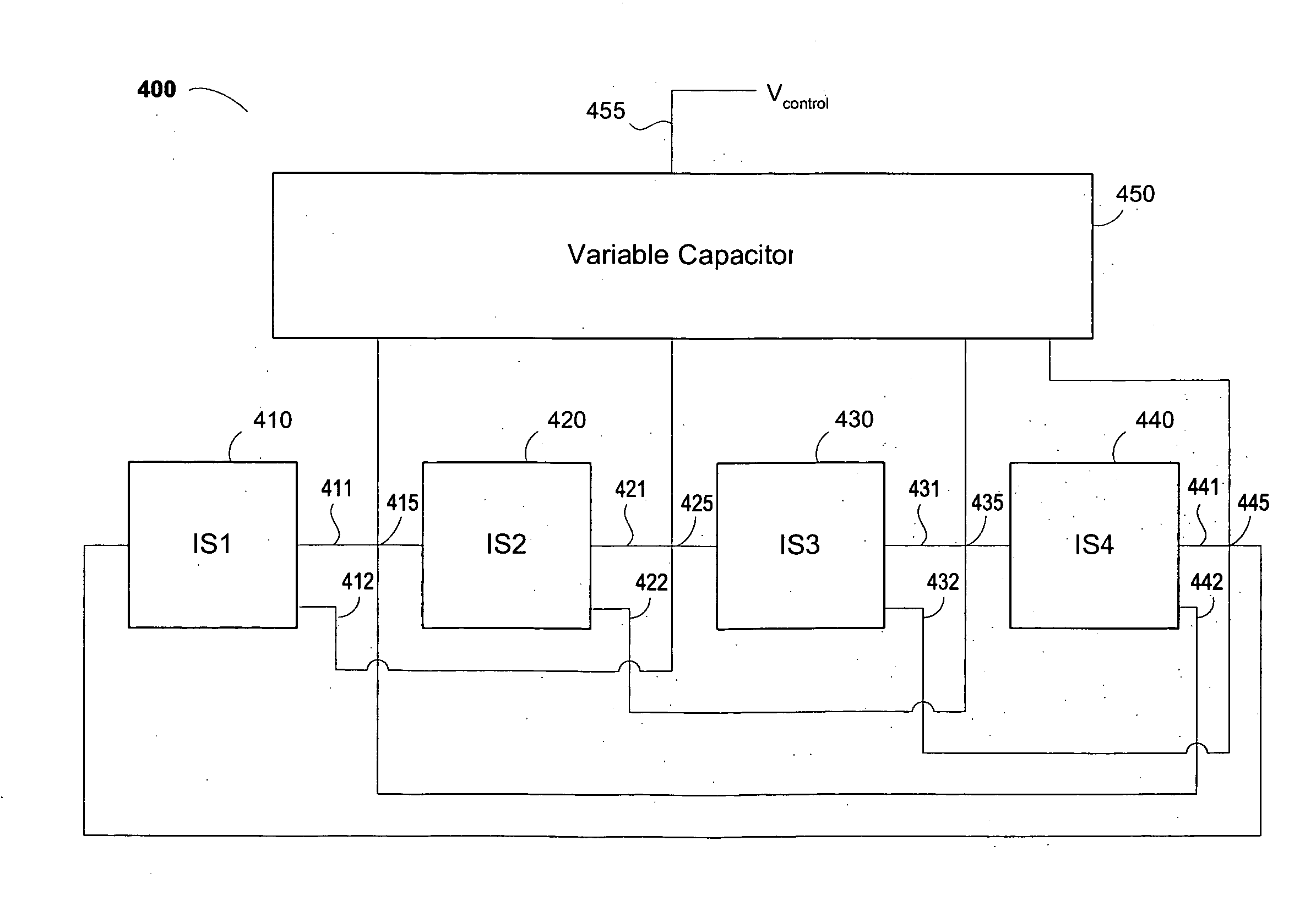

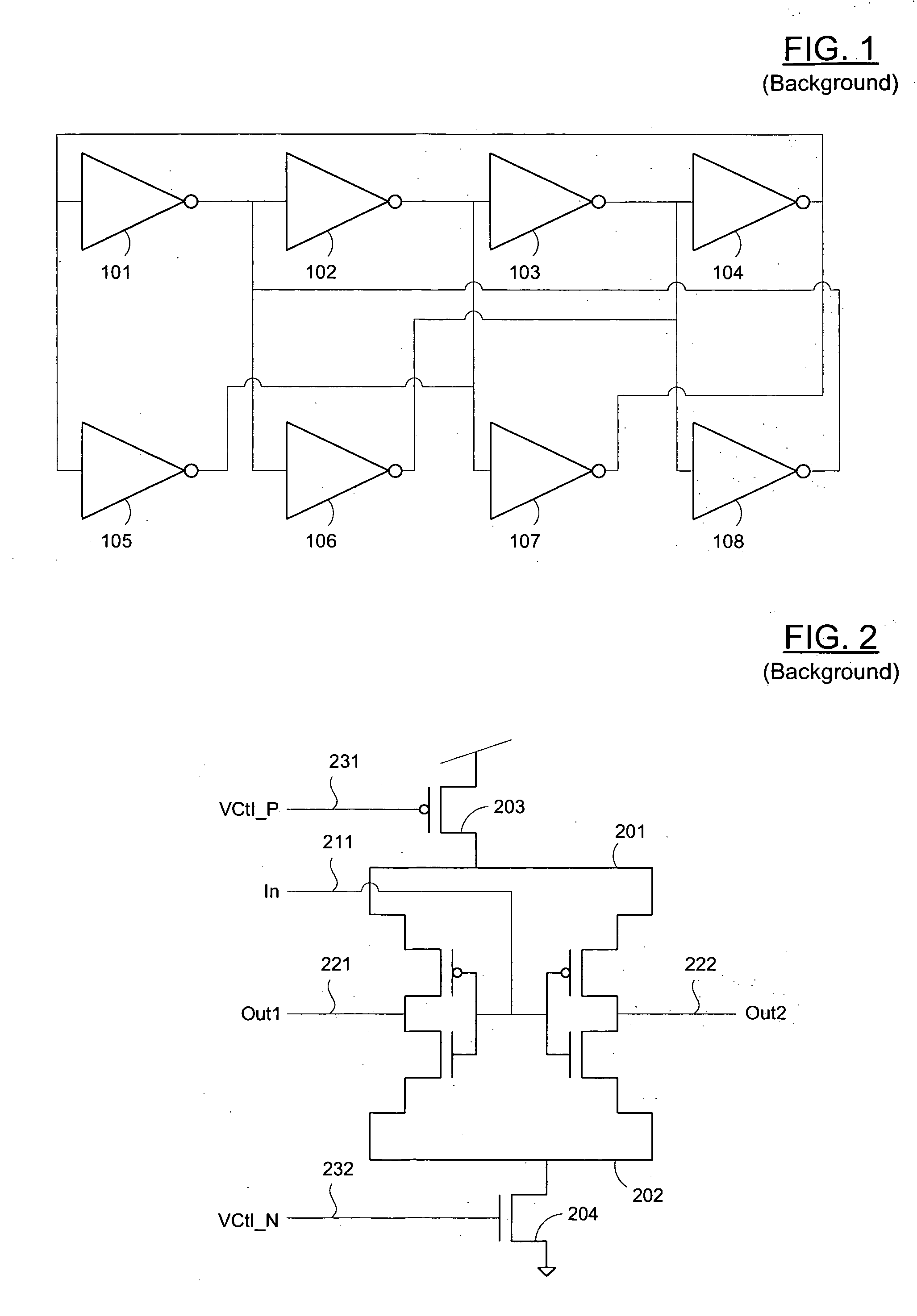

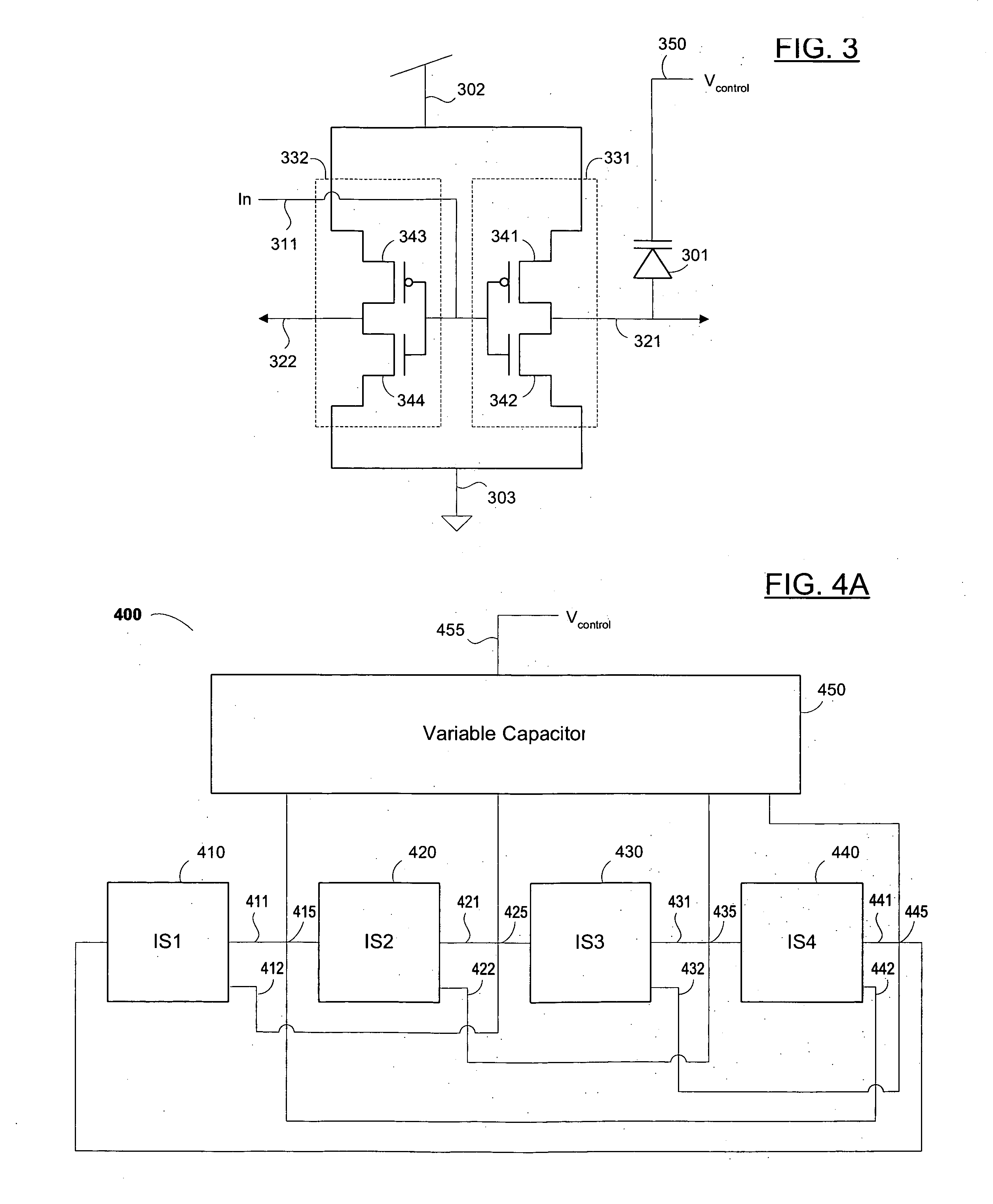

Circuits for voltage-controlled ring oscillators and method of generating a periodic signal

InactiveUS20060244543A1Easy to implementPulse generation by logic circuitsQuadrature oscillatorSoi cmos technology

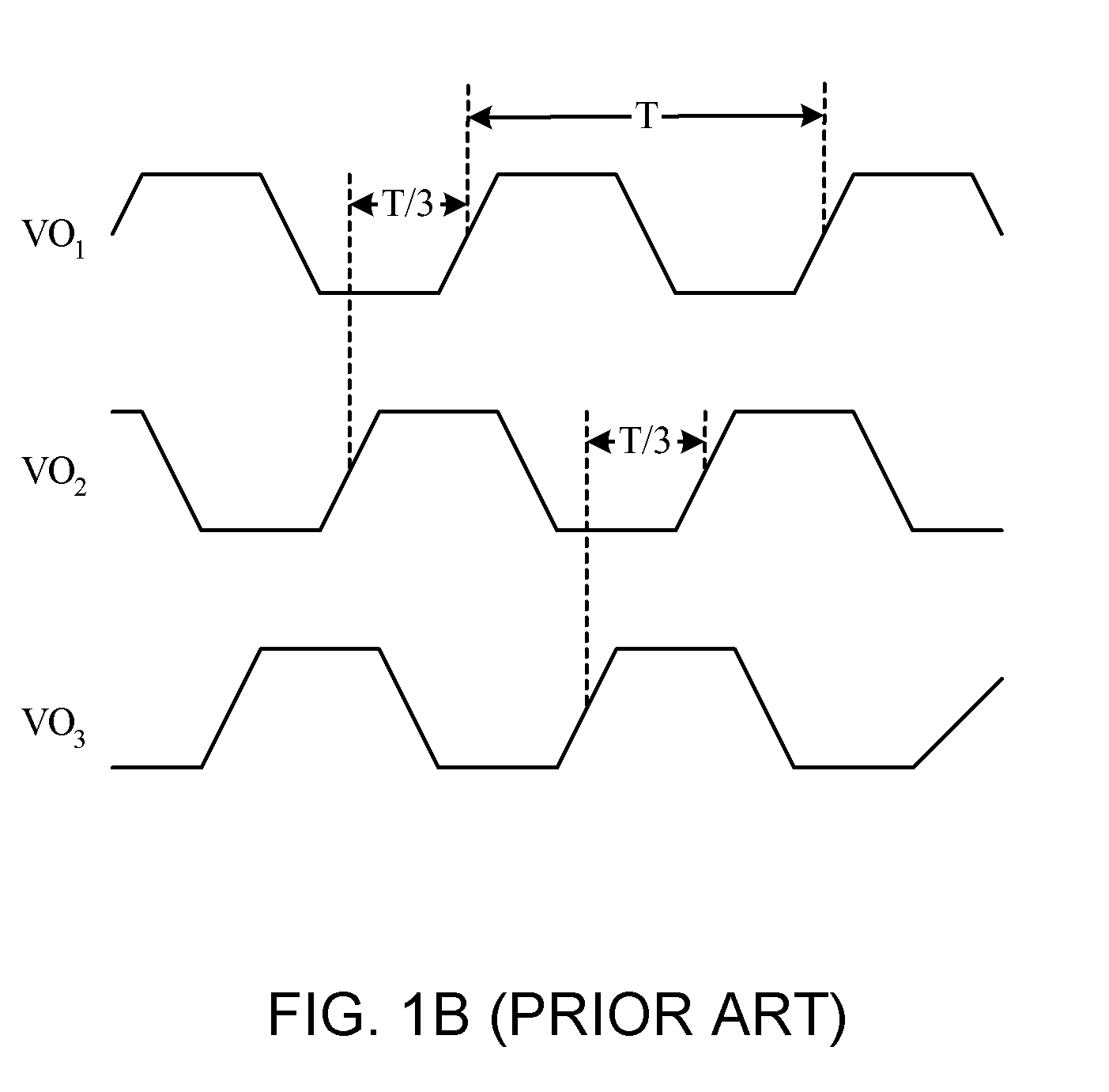

Circuits and methods and for generating oscillator outputs using standard integrated circuit components. The basic circuit generally includes two inverters and a variable capacitor to configure a delay of the circuit input and / or output. The oscillator circuit generally includes a plurality of inverter circuits, at least one of which uses a variable capacitor to adjust a delay between stages, and thereby adjust a frequency of oscillation. Thus, the oscillator outputs may be tuned using a single control voltage. The method generally includes the steps of (1) applying an operating voltage to a ring oscillator comprising a plurality of stages; and (2) applying a control voltage to a variable capacitor coupled to a node between at least two of those stages. The circuits have particular advantage in quadrature oscillators, and may be easily implemented using widely available CMOS technology.

Owner:SEIKO EPSON CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com