Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

30 results about "Verilog hardware description language" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

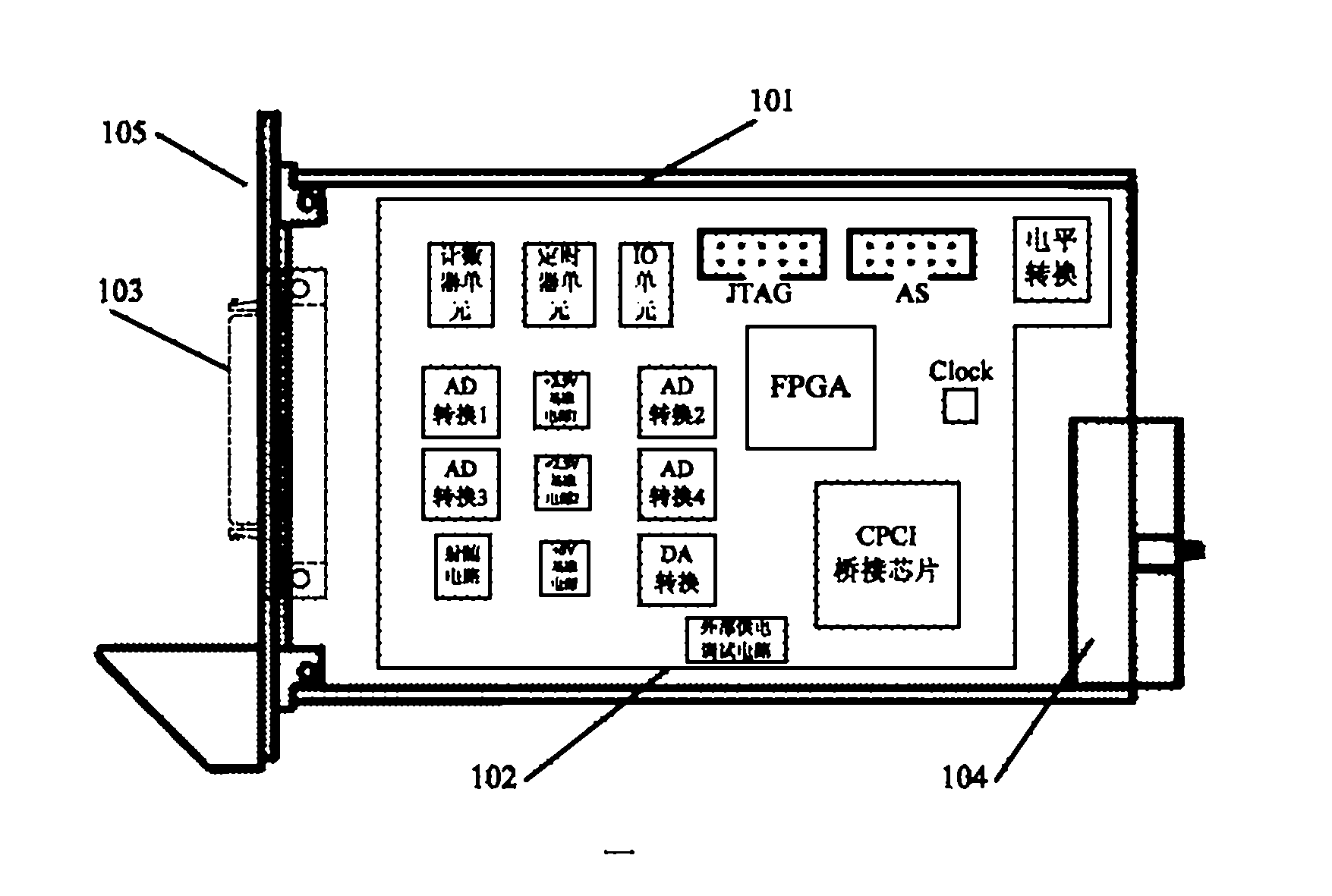

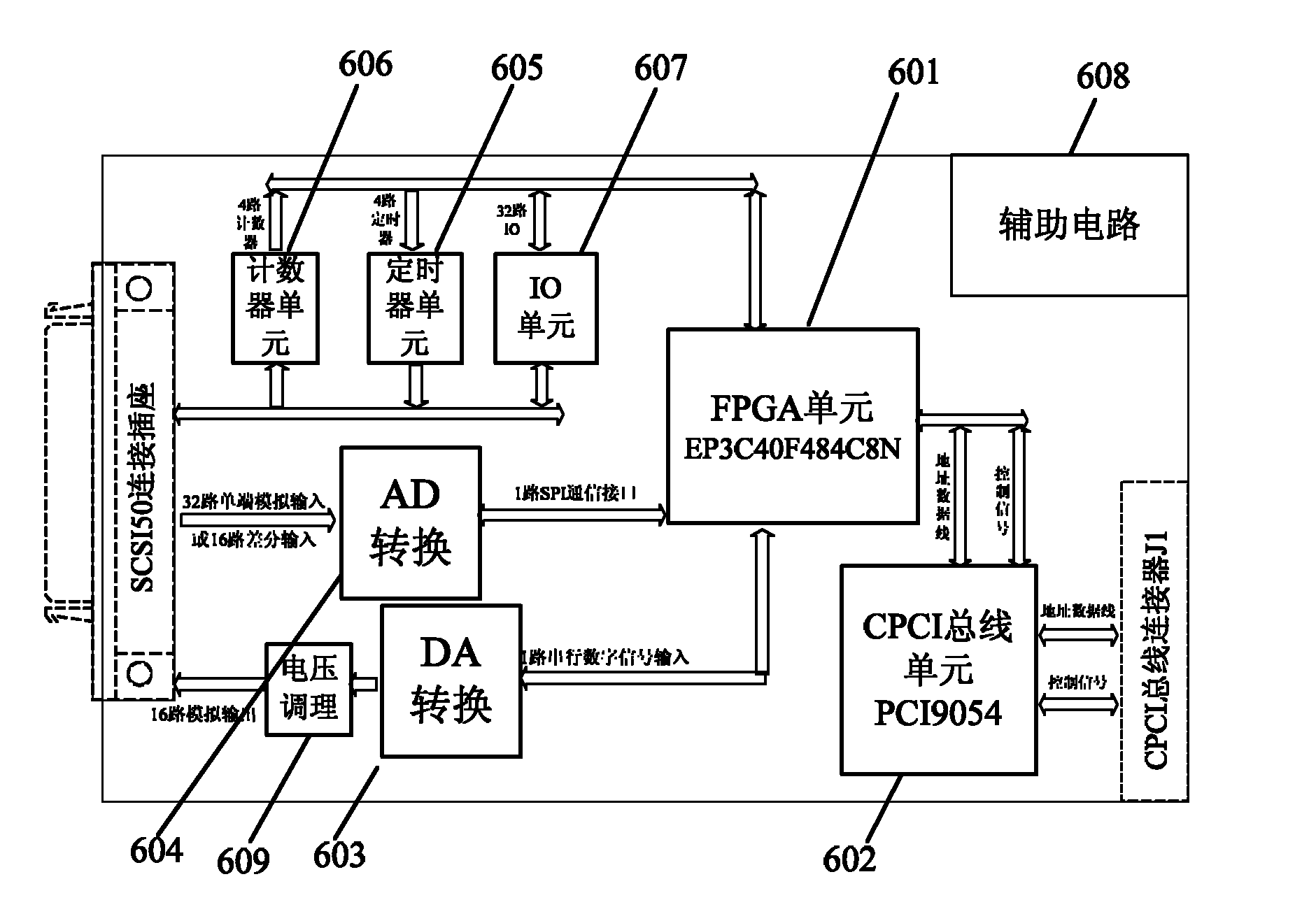

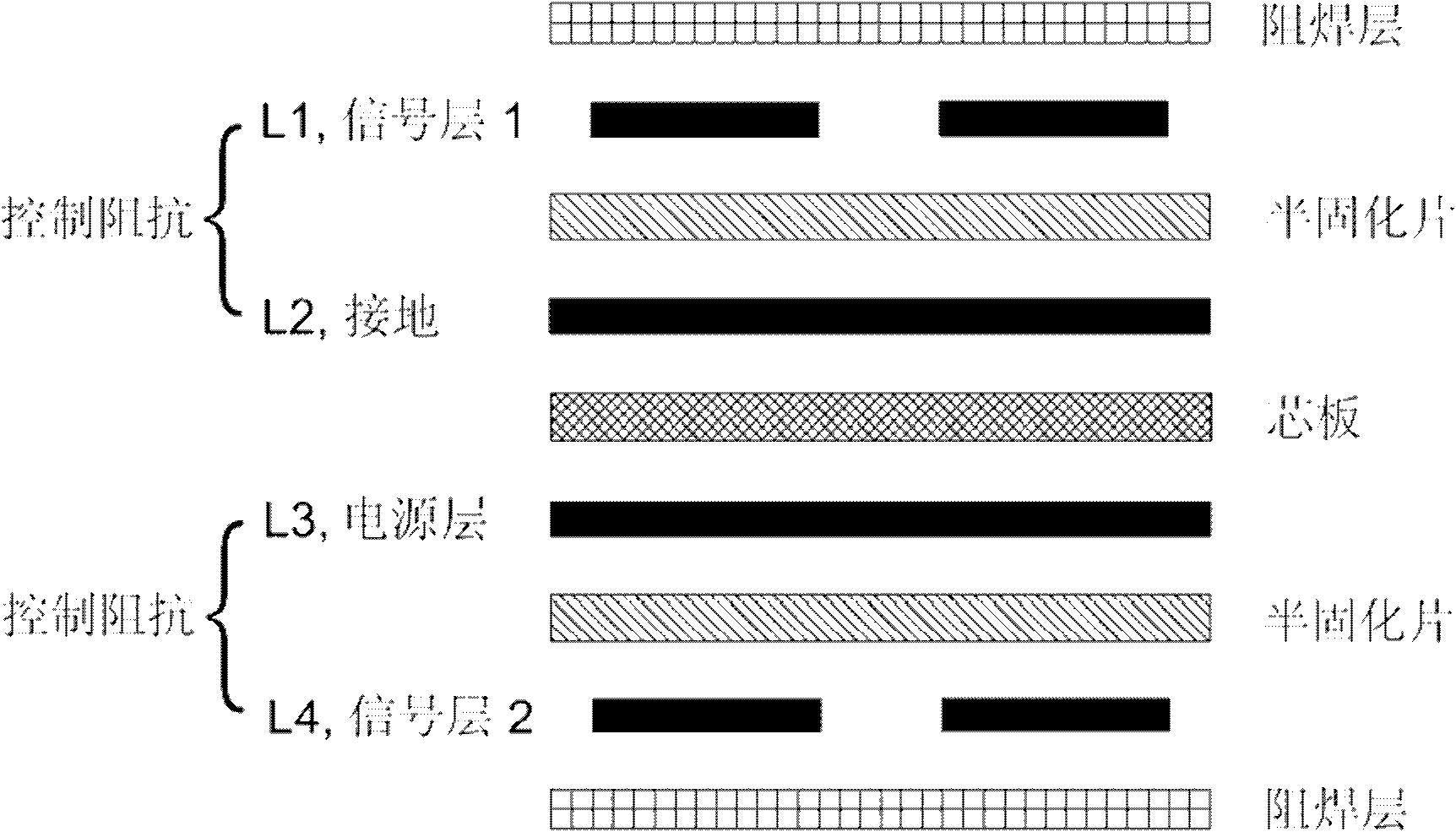

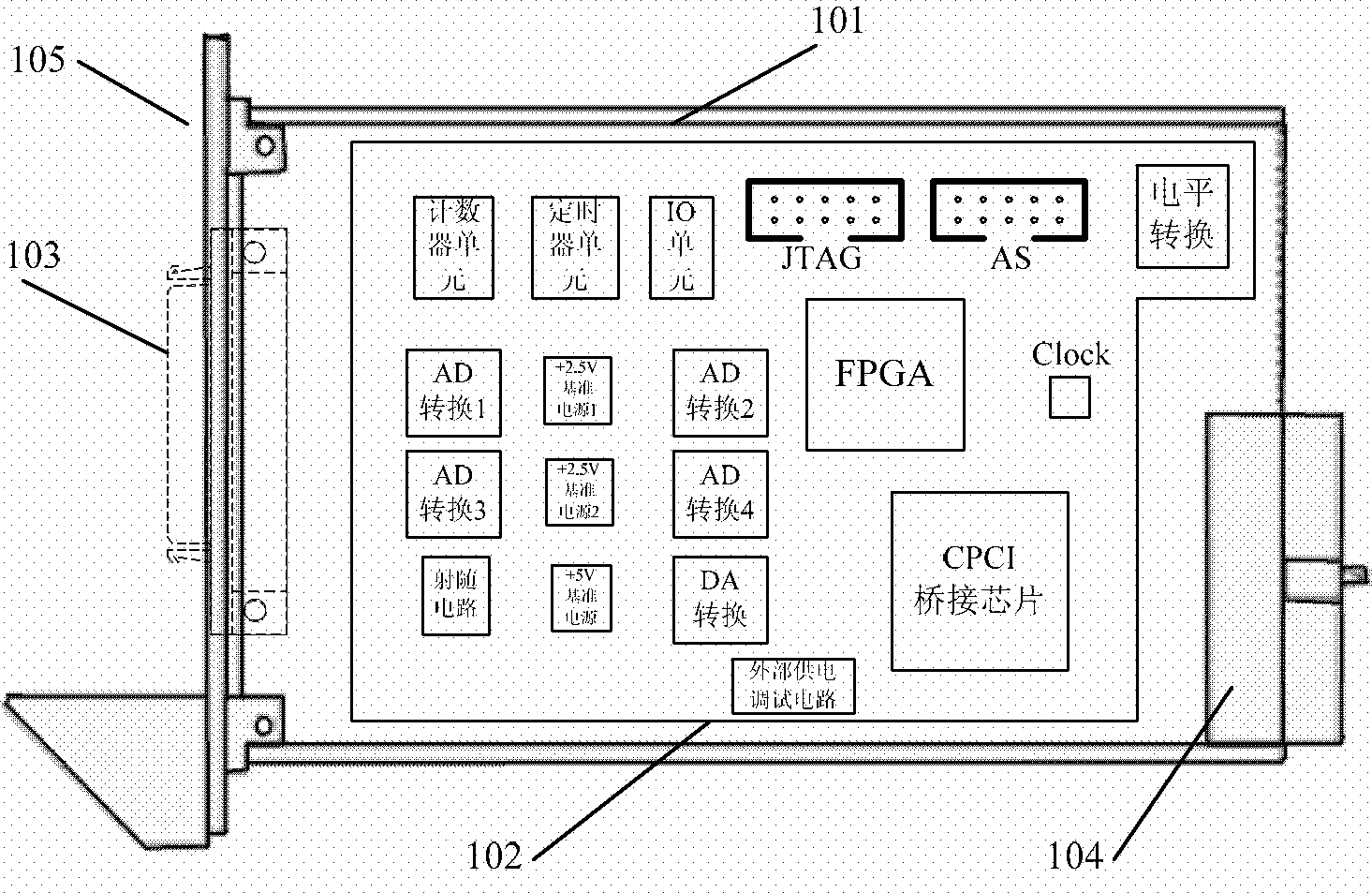

Multifunctional data acquisition module based on cpci bus

InactiveCN102279830AEasy to debugThe program is clearer and more stableElectric signal transmission systemsElectric digital data processingData acquisitionAuxiliary circuit

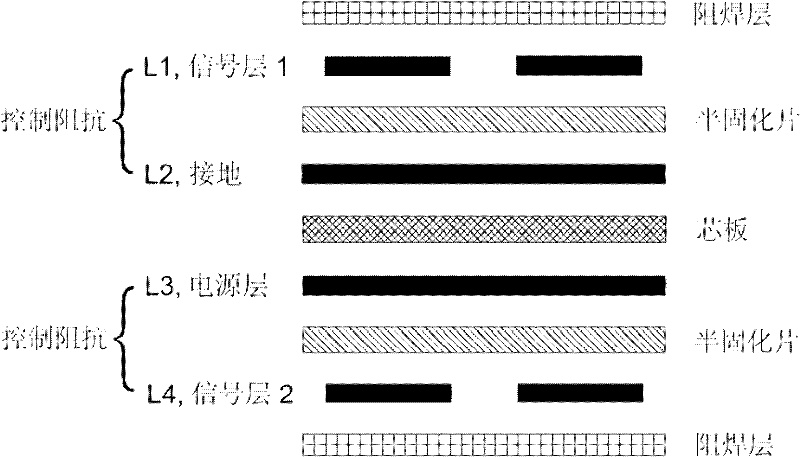

The invention relates to a multifunctional data acquisition module based on a compact peripheral component interconnect (CPCI) bus. The multifunctional data acquisition module comprises a hardware module and a field-programmable gate array (FPGA) program. The hardware module comprises an impedance control circuit board, an electronic component, a small computer system interface (SCSI100) signal connection socket, a standard CPCI bus connector, and a standard 3UEurocard front panel. The impedance control circuit board and the electronic component are the core functional carriers of the invention and are divided into eight functional units such as an analogue-digital (AD) conversion module, a digital-analogue (DA) conversion unit, a timer unit, a counter unit, a universal input-output (IO) unit and an auxiliary circuit unit. The FPGA program comprises an AD conversion module, a DA conversion module, a timer module, a counter module and a universal IO module and is programmed and developed by Verilog hardware description language (HDL). The multifunctional data acquisition module has steady performance, high reliability, high bus signal driving capability, far transmission distance, simple structure, powerful function, high cost performance, is convenient to use, and can perform long-term and continuous mass data transmission.

Owner:BEIHANG UNIV

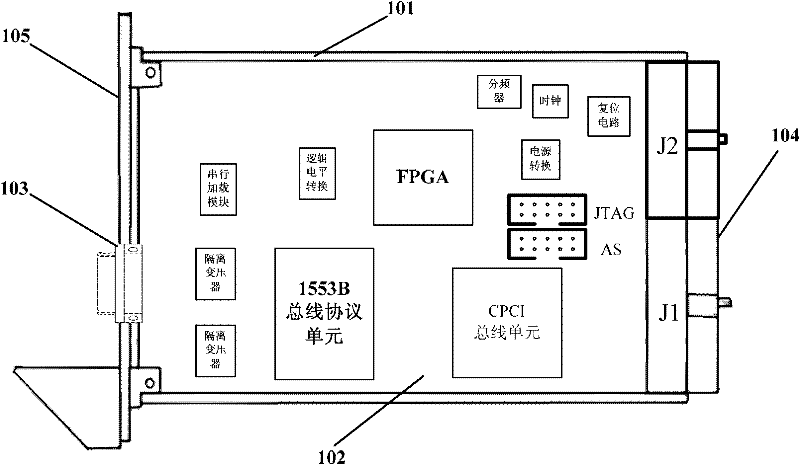

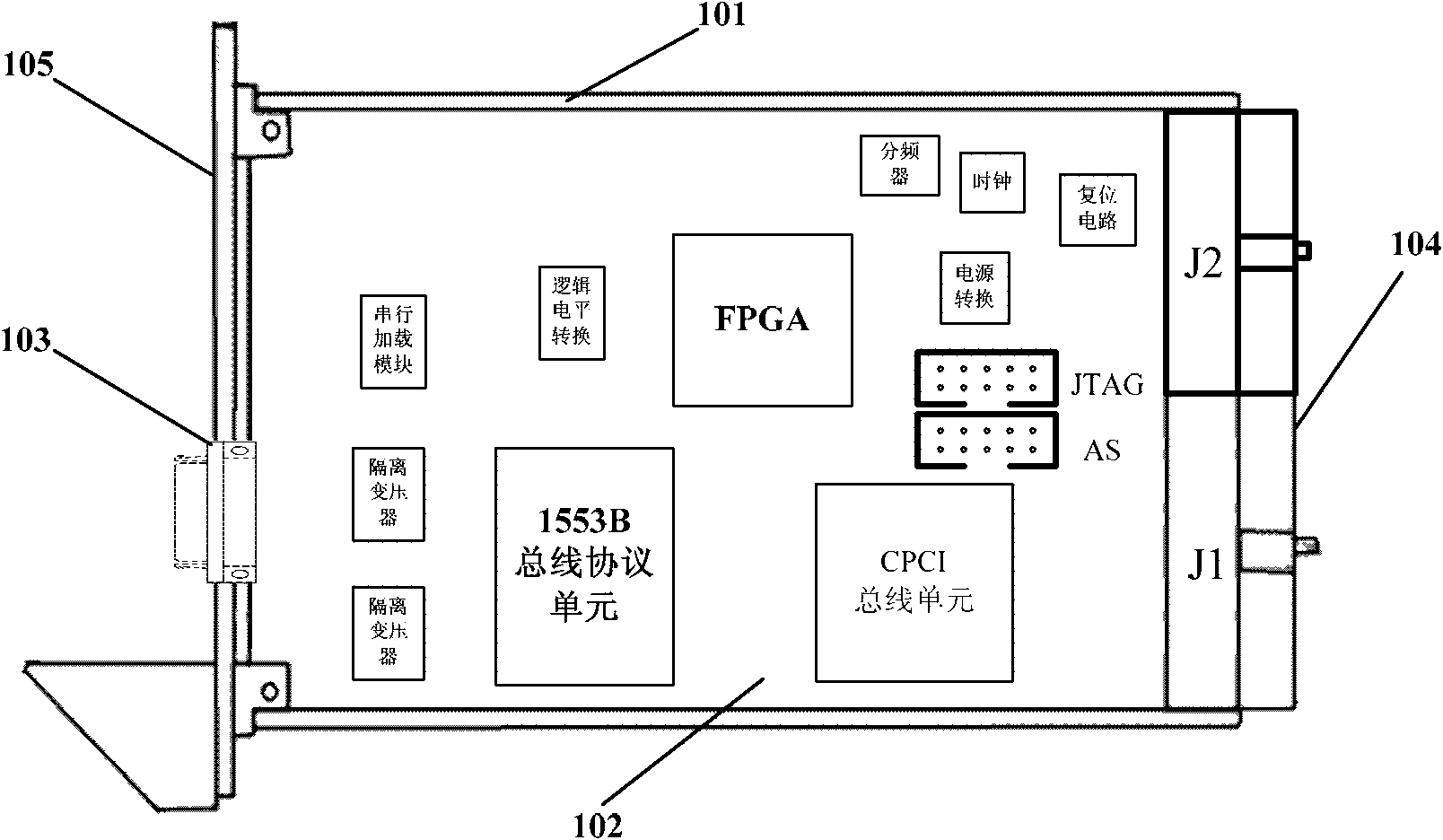

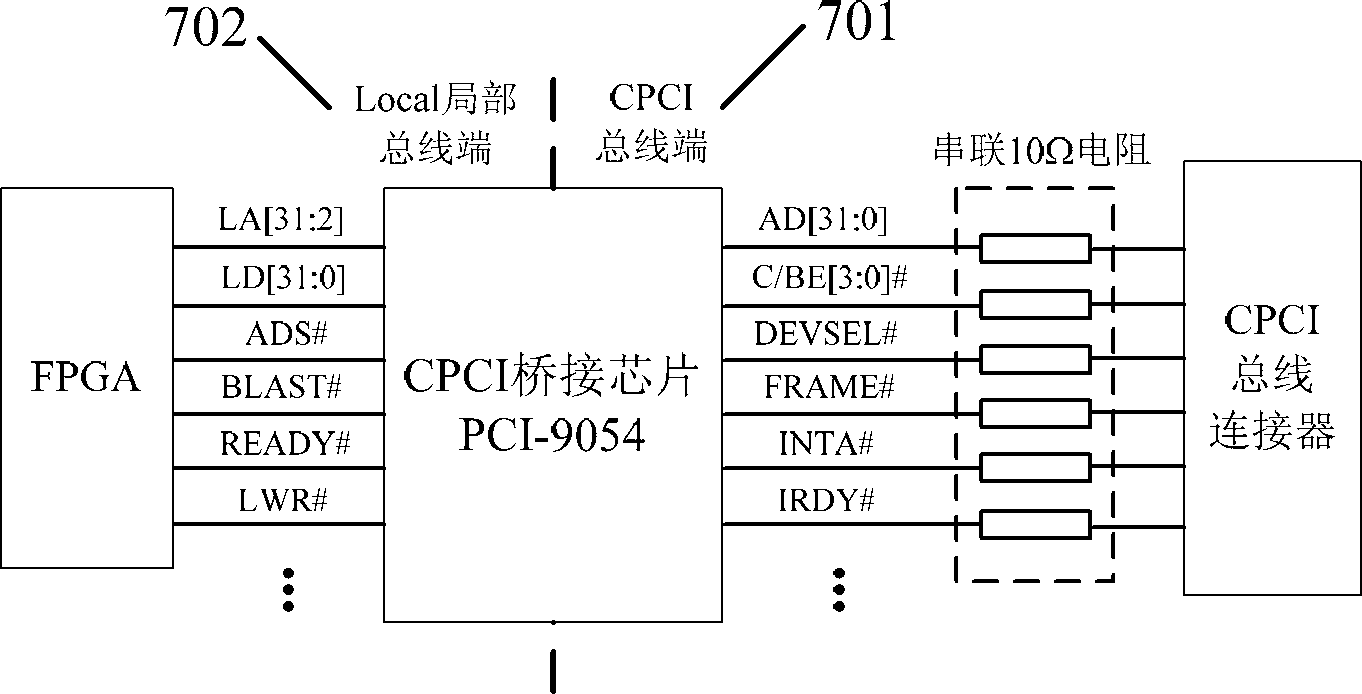

Compact peripheral components interconnect (CPCI)-bus-based 1553B protocol data communication and serial loading module

InactiveCN102411553AImprove performanceImprove reliabilityElectric digital data processingDirect memory accessHardware modules

The invention relates to a compact peripheral components interconnect (CPCI)-bus-based 1553B protocol data communication and serial loading module, which comprises a hardware module and a field programmable gate array (FPGA) program. The hardware module comprises an impedance control circuit board, a signal connection socket, a standard CPCI bus connector and a standard 3UEurocard board card front panel, wherein the impedance control circuit board is the core of the module, and is divided into an FPGA unit, a CPCI bus unit, an isolating transformer unit, a logic level translation unit, a 1553B bus protocol chip unit, a serial loading unit and an auxiliary circuit unit. The FPGA program comprises a 1553B bus communication bus controller (BC) module, a remote terminal (RT) module, a monitor terminal (MT) module, and a serial loading module, and is developed by Verilog hardware description language (HDL) programming. The module has stable performance and high reliability, can perform 1553B communication for long and can be randomly set as a BC, an RT or an MT in the 1553B communication; an RT address of external equipment suspended under a 1553B bus together with the module can be serially loaded and flexibly set; the data transmission of a CPCI bus has a direct memory access (DMA) function, the actual transmission rate of the bus is 1MB / s and continuous transmission can be realized without frame loss.

Owner:BEIHANG UNIV

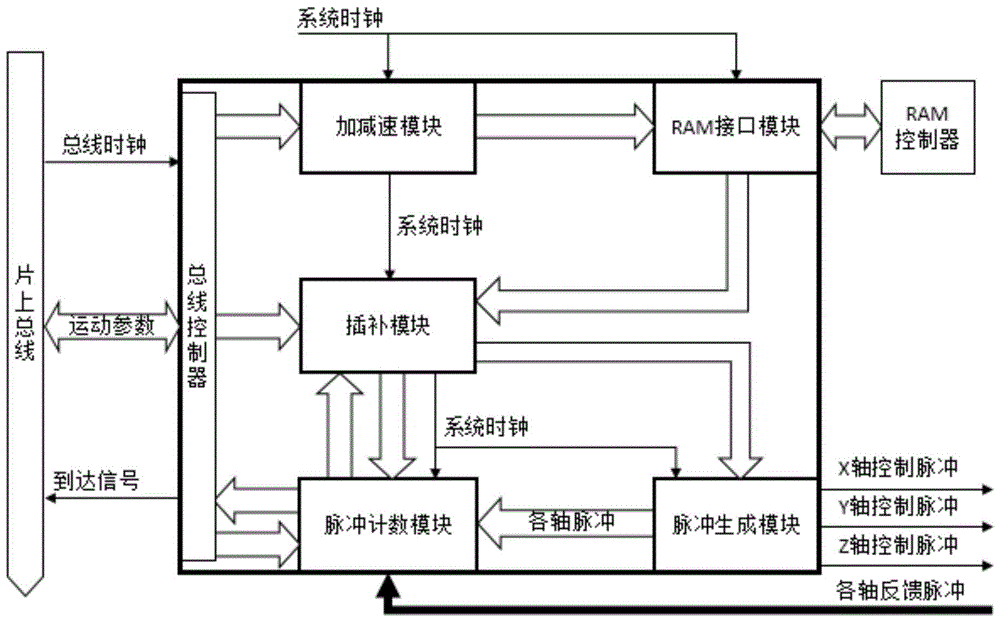

Flexibility motion control IP (Intellectual Property) core and implementation method thereof

ActiveCN104135212AFast operationShorten the control cycleElectric motor controlIntellectual propertyOperating frequency

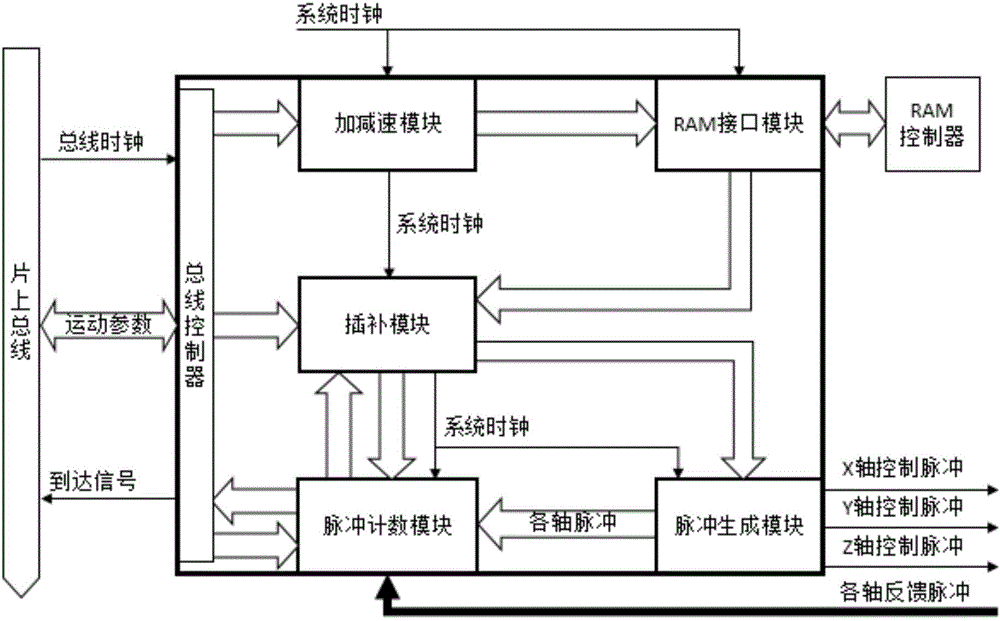

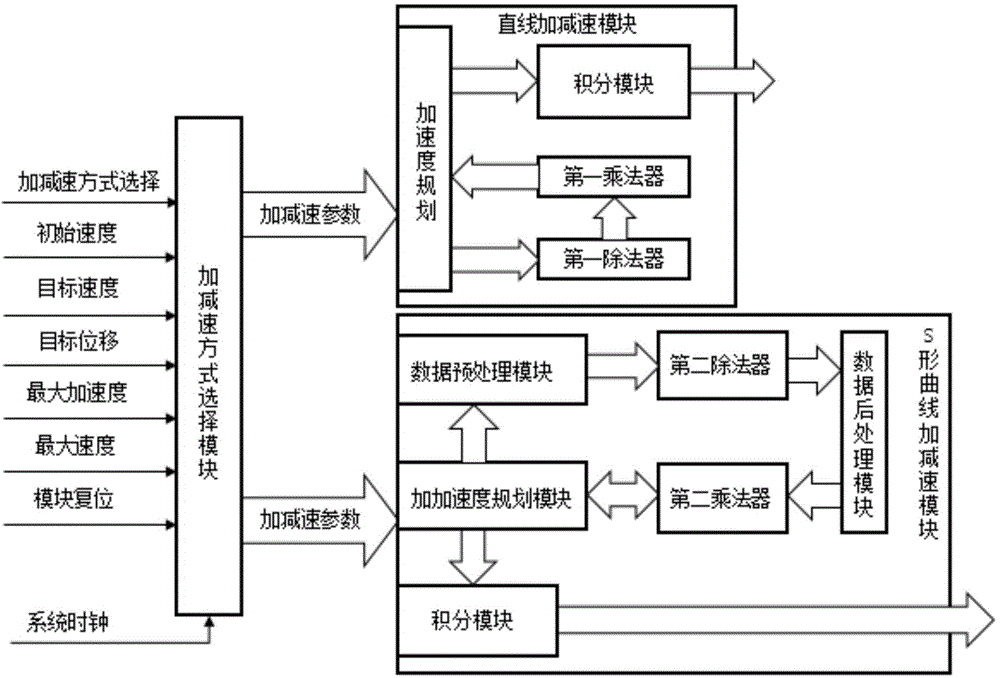

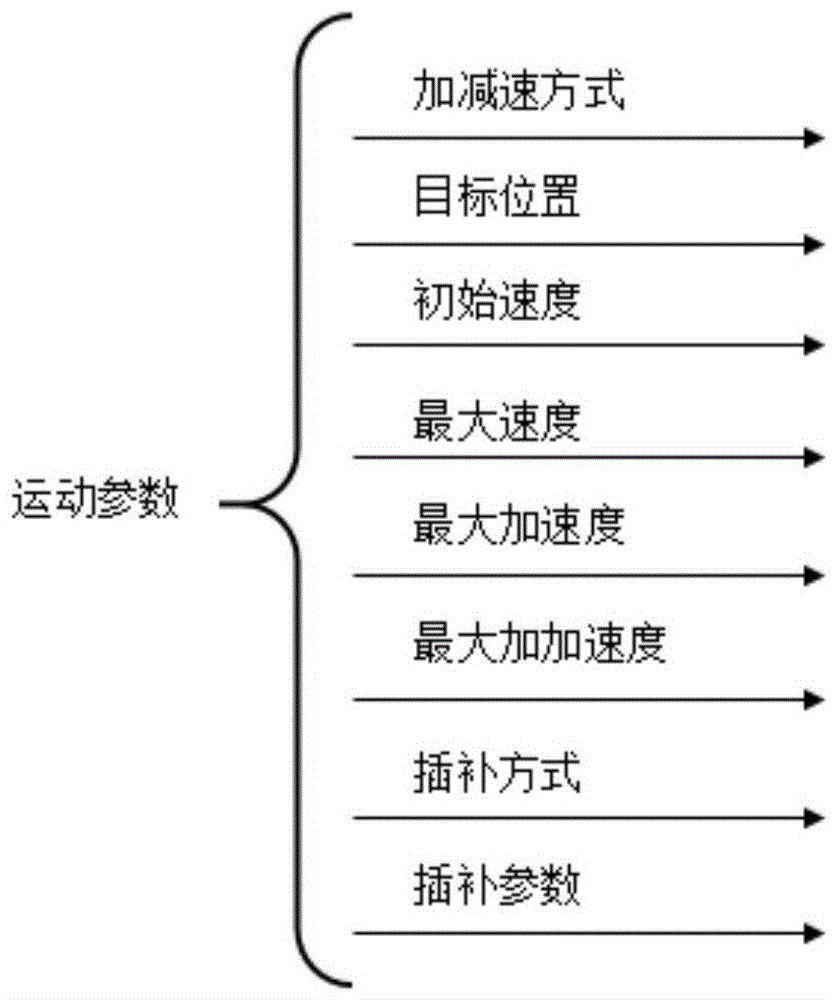

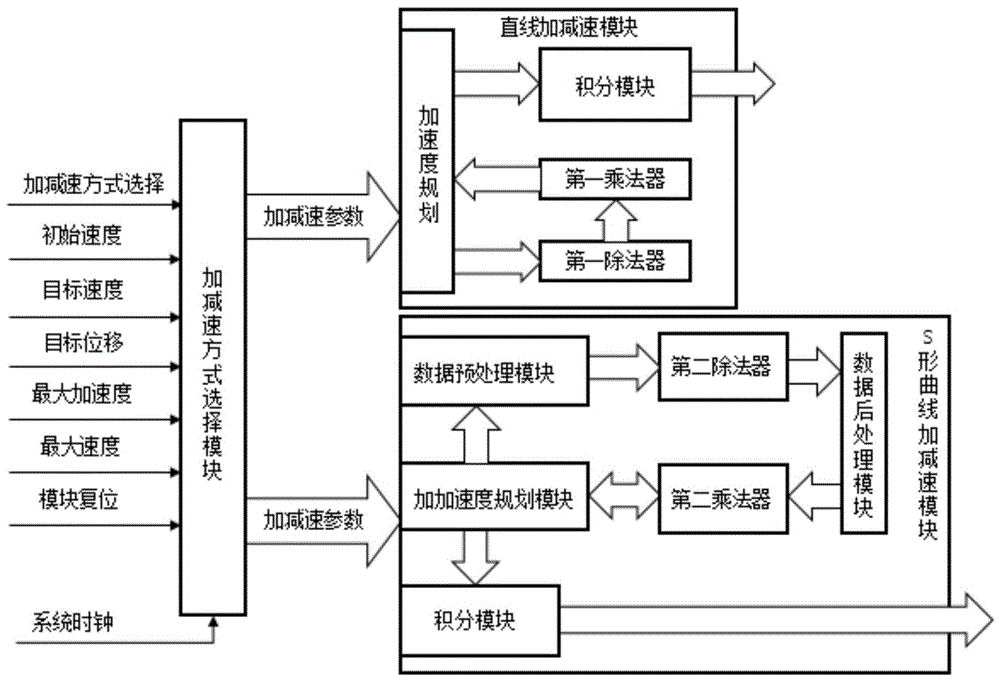

The invention discloses a flexibility motion control IP (Intellectual Property) core and an implementation method thereof, belonging to the field of motion control. The IP core comprises a acceleration / deceleration module, an interpolation module, a pulse counting module, a pulse generation module, a bus controller and an RAM (Random Access Memory) interface module. The flexibility motion control IP core and the implementation method thereof aim to solve the problems that high speed and high precision cannot be achieved due to incapability of further reducing a control period since a motion control algorithm has a long running period in a general MCU (Micro Controller Unit) or DSP (Digital Signal Processor). The IP core has the characteristics of short control period and high output pulse precision, non-symmetrical linear acceleration and deceleration can be achieved, non-symmetrical S-shaped curve acceleration and deceleration can be achieved, two-axis or three-axis linear interpolation with the linear or the S-shaped curve acceleration and deceleration can be achieved, and two-axis arc interpolation at an uniform speed also can be achieved. Through the adoption of the IP core, motion control relevant algorithm is realized in a Verilog hardware description language soft core mode, the motion control relevant algorithm can be implemented in an FPGA (Field Programmable Gate Array), can be implemented in an ASIC (Application Specific Integrated Circuit) mode, and can be integrated into SoC (System On Chip), the typical working frequency is 100MHz, and feasibility is provided for building a flexibility motion control system.

Owner:SOUTH CHINA UNIV OF TECH

Design and implementation of programmable data plane exchange prototype based on P4

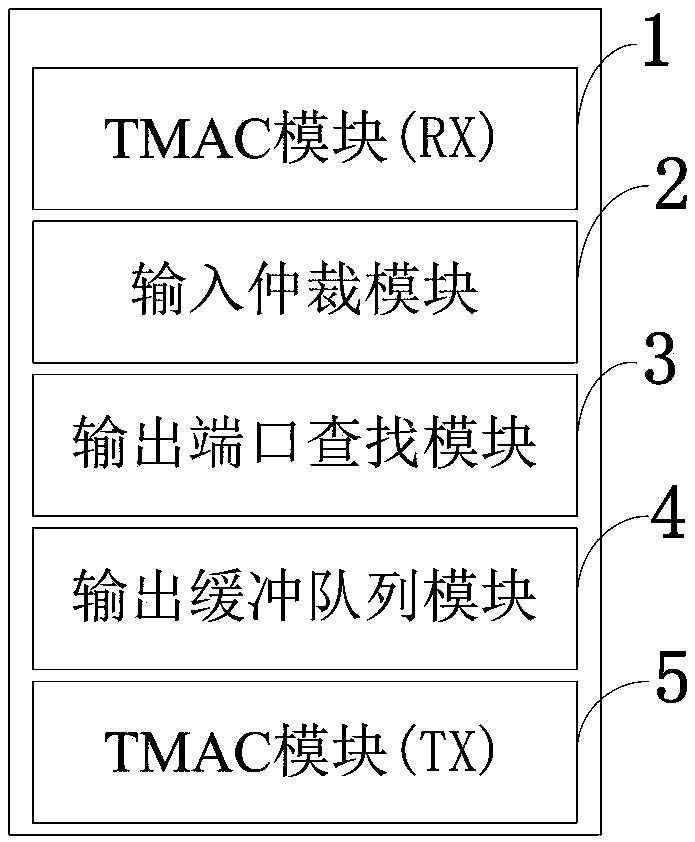

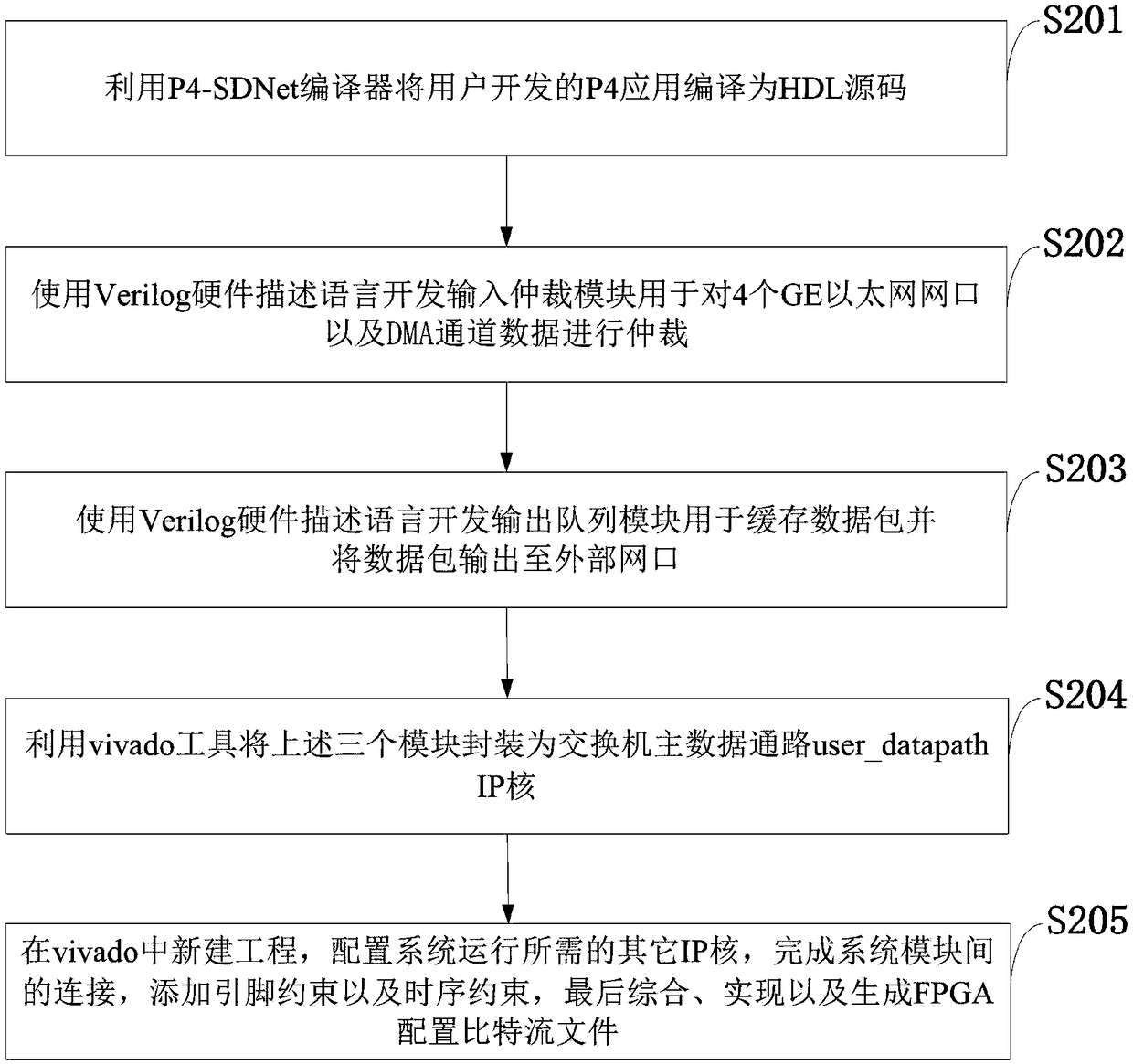

InactiveCN108768892AEnable Programmable PerformanceRealize irrelevant forwarding functionData switching networksChannel dataNetwork packet

The present invention belongs to the field of data plane exchanges, and discloses a design and an implementation of a programmable data plane exchange prototype based on a P4. A data plane employs anAXI4-Stream bus to achieve a pipeline architecture, perform sublevel processing for data entering a data passage, and each level on the pipeline is an independent IP core; a Verilog hardware description language development input arbitration module is employed to perform arbitration for 4 GE ethernet ports and a DMA channel data; P4-SDNet compiler is employed to a P4 appliance developed by the user to be compiled to an HDL model to achieve processing and forward of a data packet; and a Verilog hardware description language development output buffer queue module is employed to output the data packet to an external port. The user only needs to compile the compiled P4 appliance and to load the compiled P4 appliance to the system to achieve the network function described by the P4. Several development boards are employed to deploy a mini-type 4G network test system to have a certain practical value for teaching demonstration and scientific research usage of the P4.

Owner:XIDIAN UNIV

Flight Gear general three-dimensional scene data displaying method based on field programmable gate array (FPGA)

InactiveCN103235852ARealize the designRealize simulationSpecial data processing applicationsAviationSpace vehicle control

Provided is a Flight Gear general three-dimensional scene data displaying method based on a field programmable gate array (FPGA). The method includes that an FPGA chip is adopted, coding of Verilog hardware description language (HDL) language is conducted on the FPGA chip, and a data transmission protocol 1 is self-defined so as to enable the FPGA chip to finish receiving of serial data of specific frame format and with the baud rate of 115200 bps, analysis of data of a self-definition communication protocol 1 is finished in the FPGA, and the data is processed through corresponding algorithms. Then, the processed data is coded and packaged through another self-definition communication protocol 2 and transmitted to a Simulink project operated on a personal computer (PC) with the baud rate as 115200 bps, a series of data processing is conducted in the Simulink. Finally, corresponding gesture data is transmitted to Flight Gear software through a user datagram protocol (UDP) network transmission module to be displayed in real time in a three-dimensional (3D) mode. The Flight Gear general three-dimensional scene data displaying method has the advantage that design and simulation of an aerospace vehicle controller, simulation of an unmanned aerial vehicle controller, simulation of guided missile control, simulation of vehicle and ship controllers and 3D visual reproduction of actual aircraft test flight data and the like can be well achieved, and a use range is wide.

Owner:NANCHANG HANGKONG UNIVERSITY

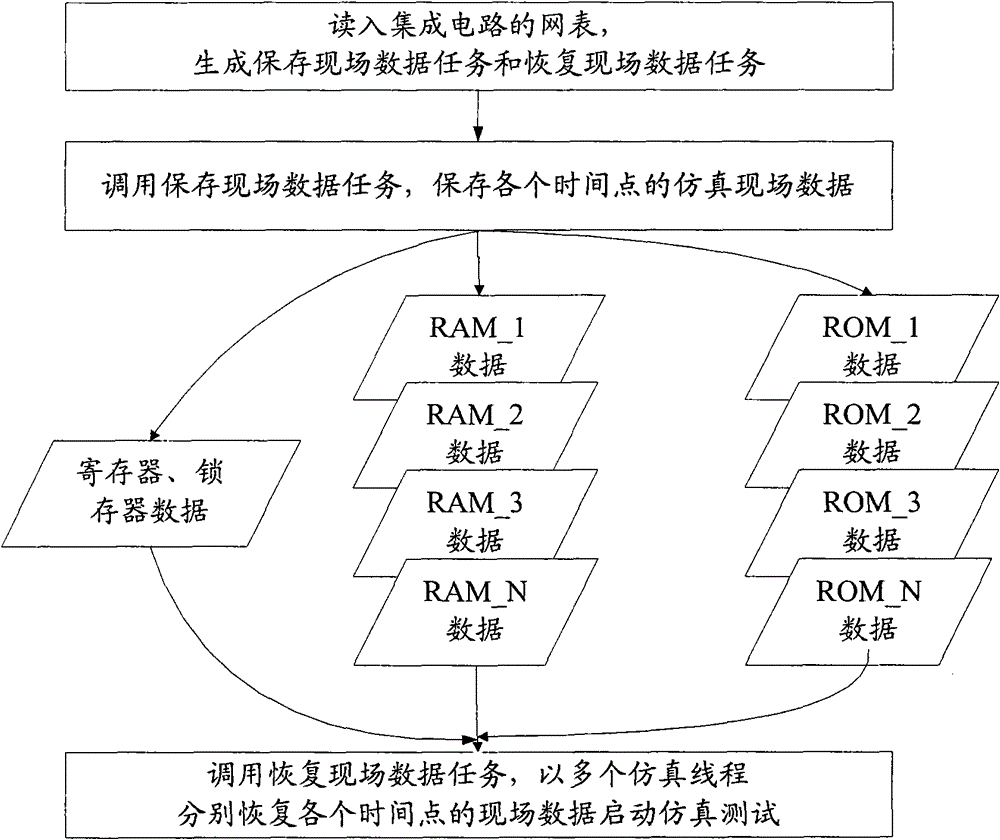

Simulation test method of integrated circuits

ActiveCN101719170AShorten the timeSpecial data processing applicationsIntegrated circuit layoutField data

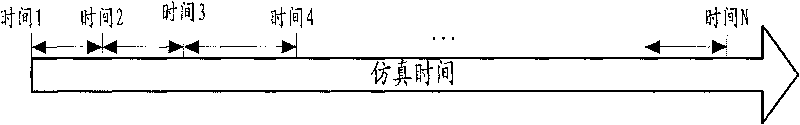

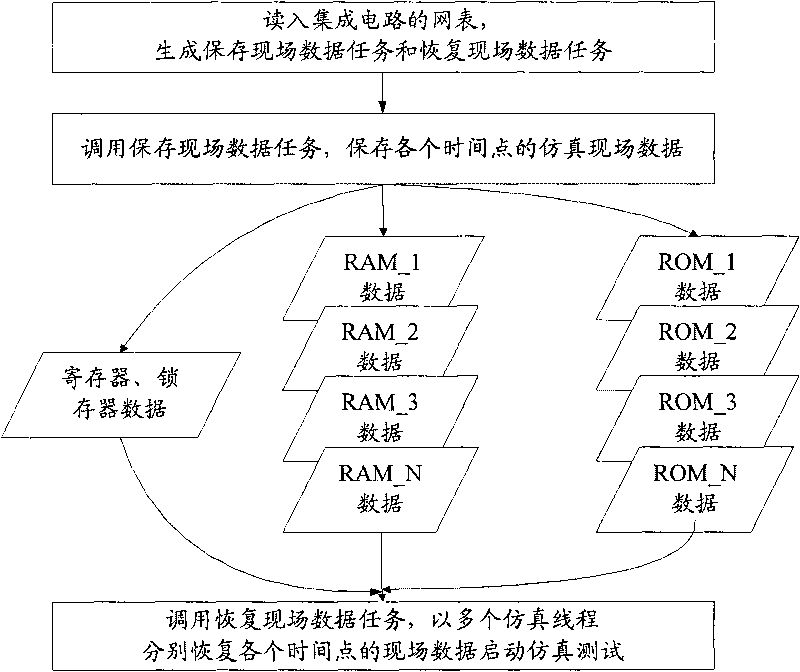

The invention relates to a simulation test method of integrated circuits, which comprises the following steps of: reading in a netlist of the integrated circuits; generating corresponding list files according to data of a register, a latch, an RAM and an ROM; generating a field data preservation task and a field data recovery task according to a verilog hardware description language by the list files; transferring the field data preservation task at different simulation time points to preserve simulation field data at different appointed simulation time points; generating a plurality of mutually independent simulation threads, wherein every simulation thread starts simulation software; transferring the field data recovery task for initializing the integrated circuit which is in simulation correspondence with each simulation software into the field data preserved at different simulation time points, and starting up all the simulation threads for simulation verification. The invention greatly shortens the simulation time and improves the simulation efficiency.

Owner:SHENZHEN STATE MICRO TECH CO LTD

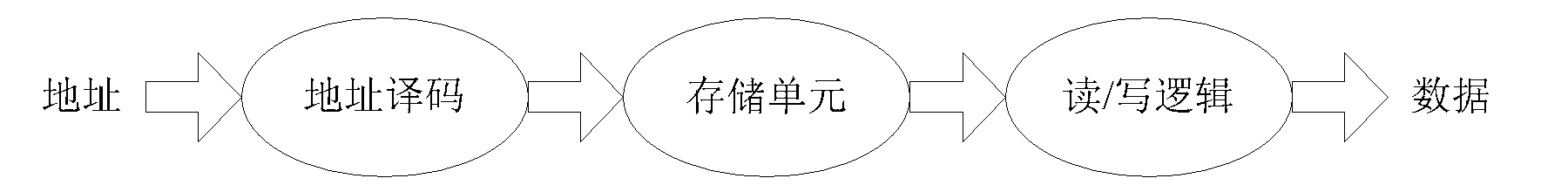

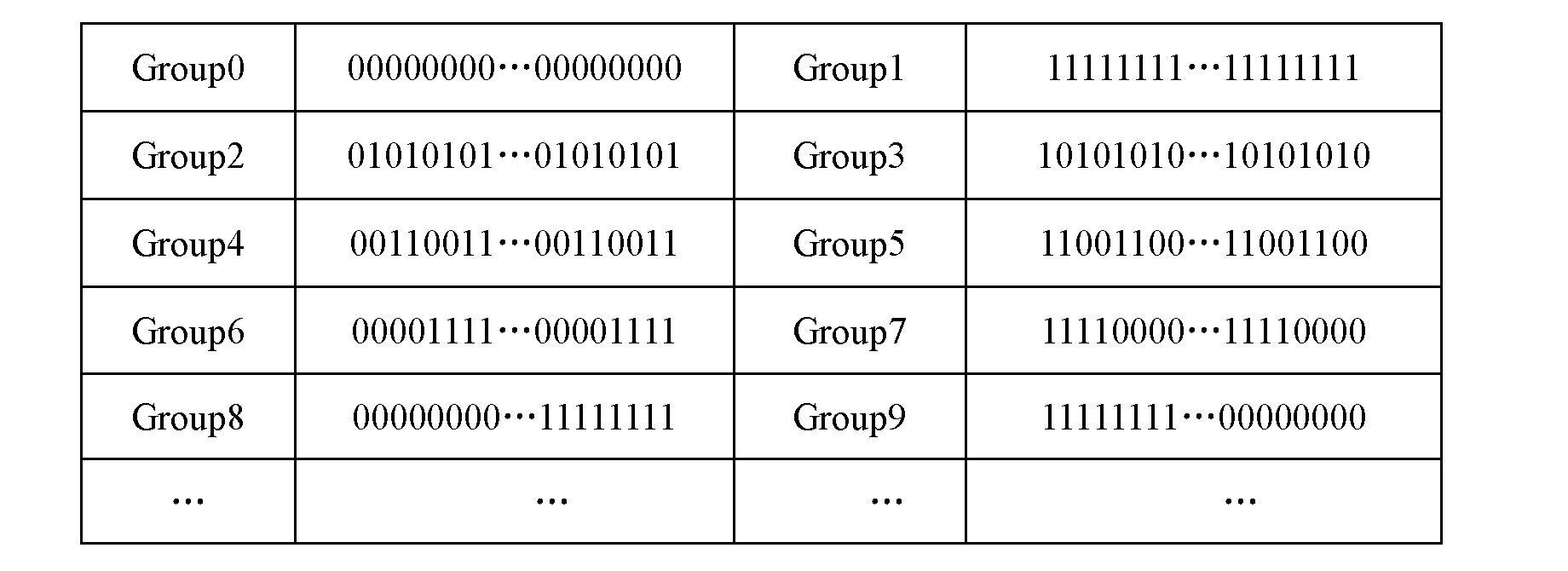

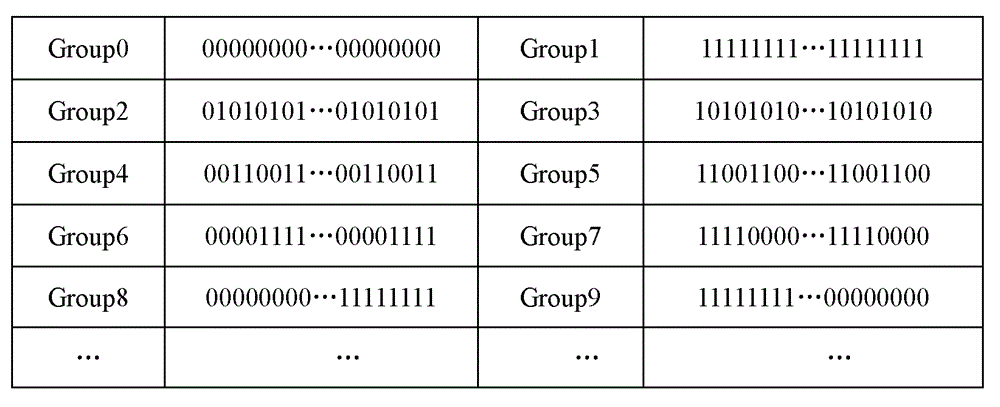

Method for testing fault of multiposition memorizer inlaid in FPGA

InactiveCN102157205AIncrease excessive consumptionImprove fault coverageStatic storageGraphicsWave form

The invention relates to a method for testing the fault of a multiposition memorizer inlaid in FPGA. The method comprises the following six steps of: firstly, increasing the quantity of test patterns through the formula: two multiplied by (one plus log2n) by the March C-algorithm; secondly, introducing the test patterns, the quantity of which is expressed by the formula: two multiplied by (one plus log2n) into six March units of the March C-algorithm so as to obtain the March C-algorithm for testing the memorizer based on memory cells and has the bit wide of n bit; thirdly, establishing a BIST structure in FPGA by utilizing the Verilog hardware description language; fourthly, using a control unit to control the test patterns of the tested memorizer, the state of a state controller as well as the start and stop of an internal response analyzer which are input under different states at the BIST platform, and generating the sequence of March element test patterns needed for different fault models of the memorizer by a test pattern generator; fifthly, testing the memorizer according to the generated test patterns; and sixthly, observing test wave forms, and determining the fault type of the memorizer. The method achieves simplicity and easiness for implementation, and has considerably broad application prospect in the field of testing the multiposition memorizer inlaid in FPGA.

Owner:BEIHANG UNIV

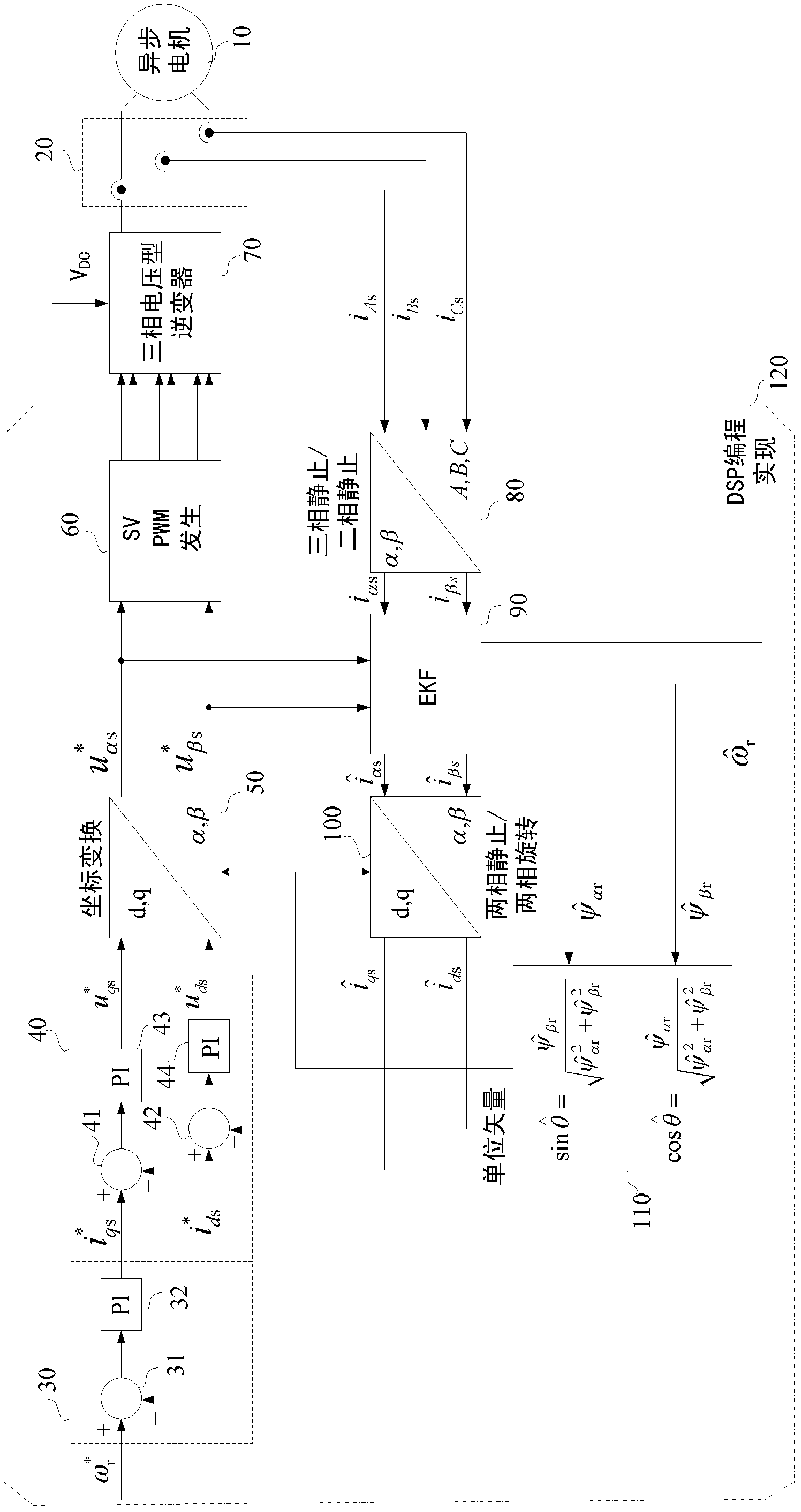

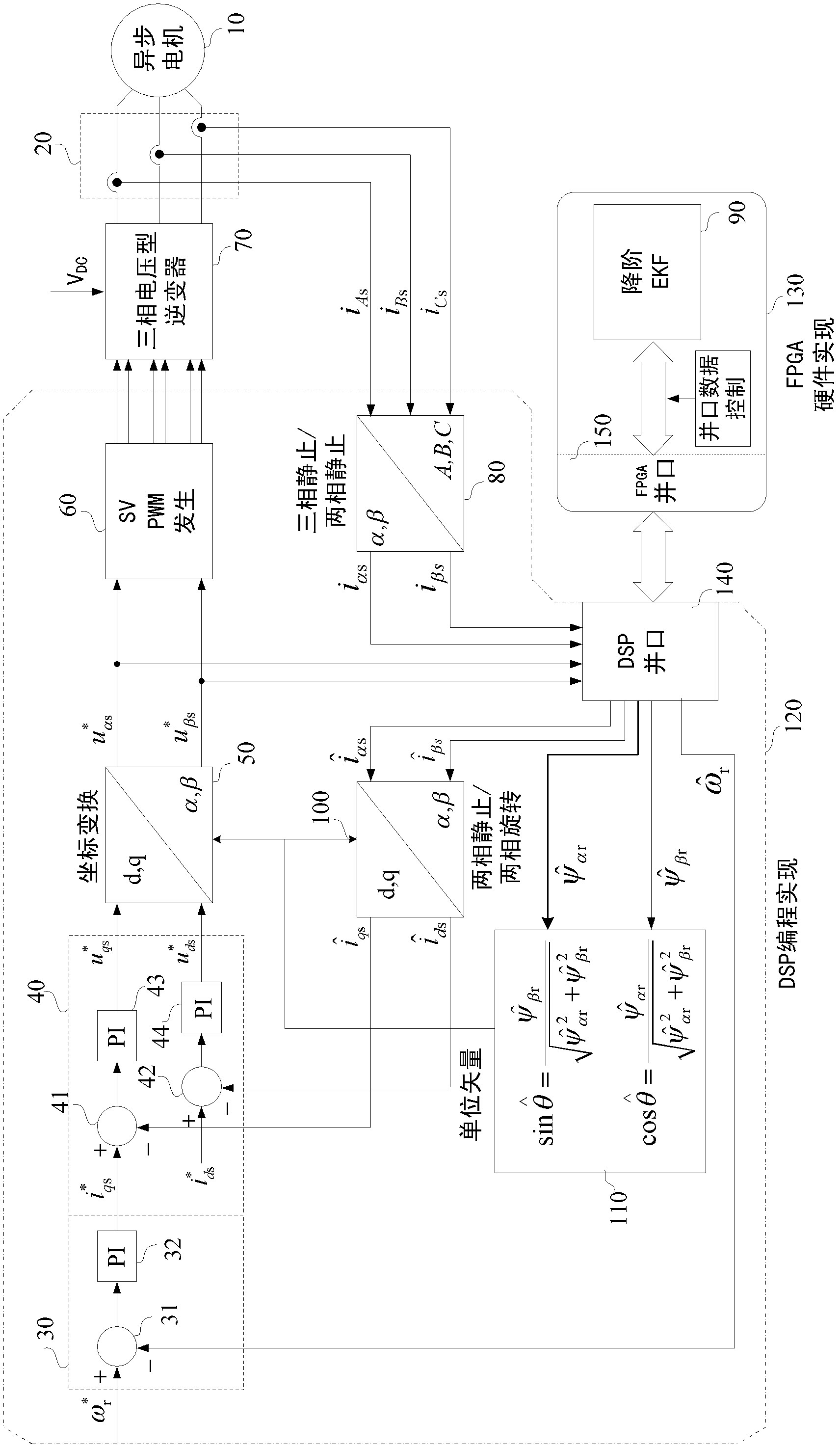

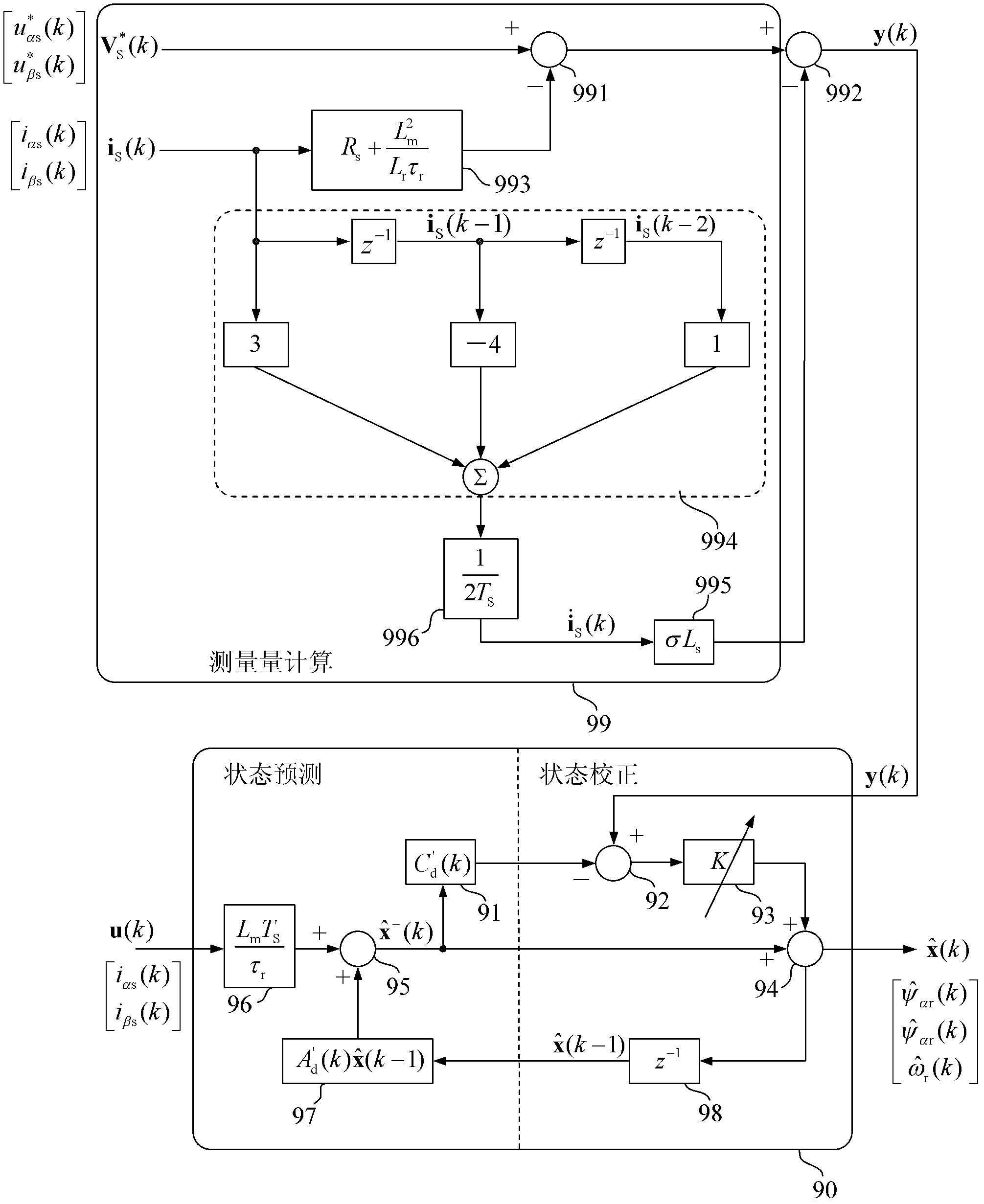

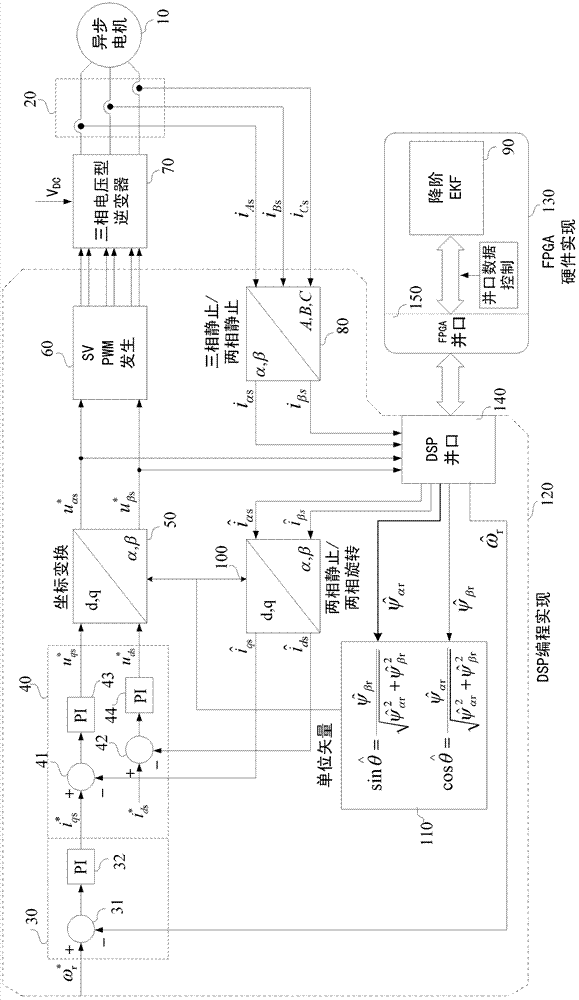

Asynchronous motor pure electronic speed feedback method

InactiveCN102629847ARelieve pressureMultiple storage spacesElectronic commutation motor controlVector control systemsMathematical modelFpga implementations

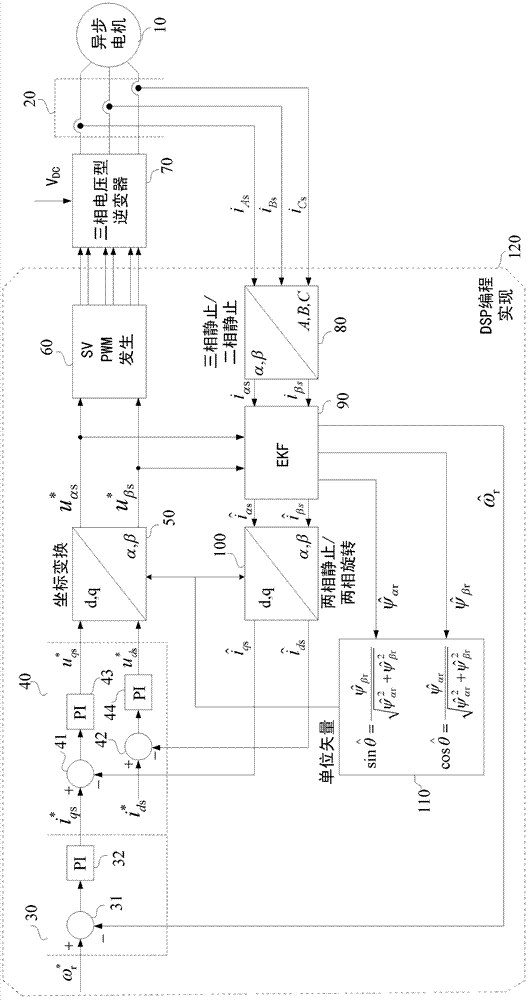

The invention provides an asynchronous motor pure electronic speed feedback method, which specifically comprises the following operation steps of: firstly obtaining a discrete time form expression of an asynchronous motor mathematical model, obtaining an asynchronous motor reduced order EKF (Extended Kalman Filter) speed estimation algorithm according to an extended Kalman filter algorithm, designing a FPGA (Field Programmable Gate Array) to realize a reduced order EKF speed estimation algorithm structure and carrying out hardware language VHDL (Verilog Hardware Description Language) description on the FPGA based on the described algorithm structure to obtain, send and transmit back state estimated values i alpha s, i beta s, Psi alpha r, Psi beta r and omega r to a main control DSP (Digital Signal Processor) through a port. The asynchronous motor pure electronic speed feedback method has the beneficial effects that the pressure of the main control DSP on real-time operation amount is greatly reduced, so that more storage spaces and more operation spaces are left for speed and current control; the EKF speed estimation algorithm realized by the FPGA in parallel is used for finishing within 1 microsecond, so that a less sampling period can be selected by using the speed estimation algorithm, therefore, the speed estimation precision is greatly improved.

Owner:XIAN UNIV OF TECH

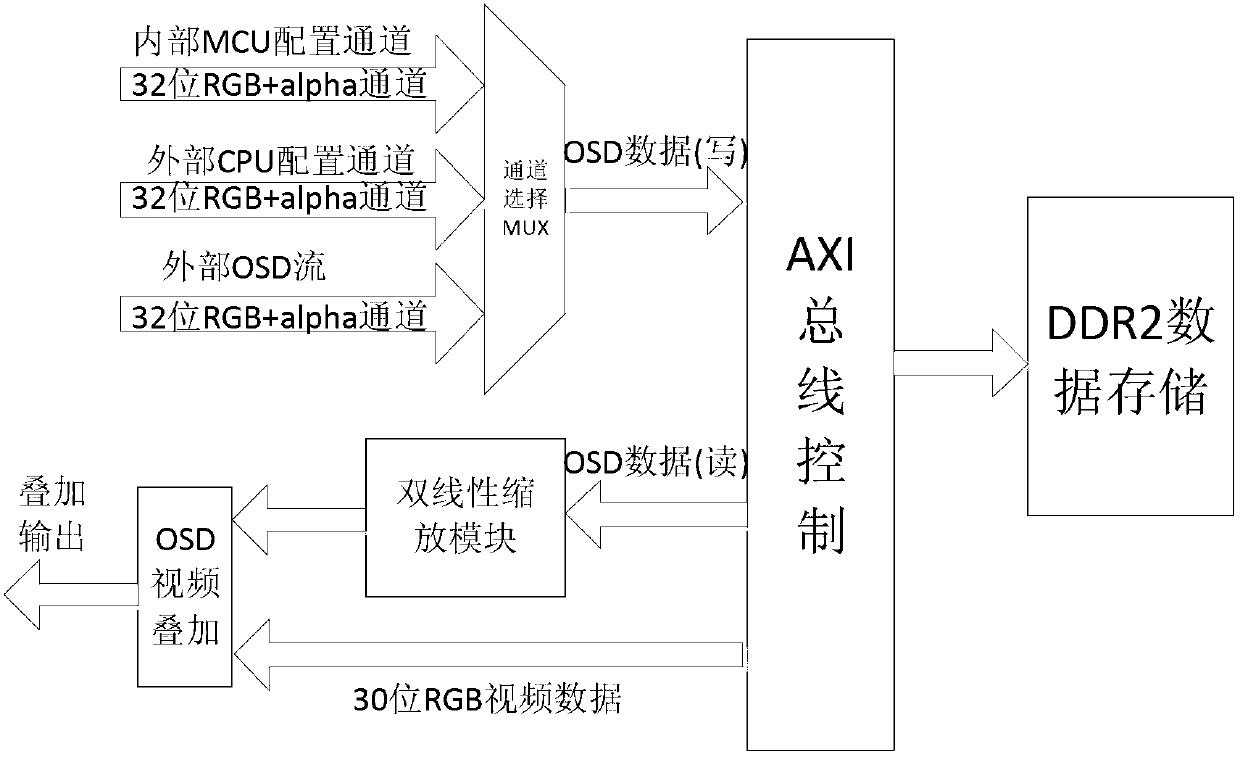

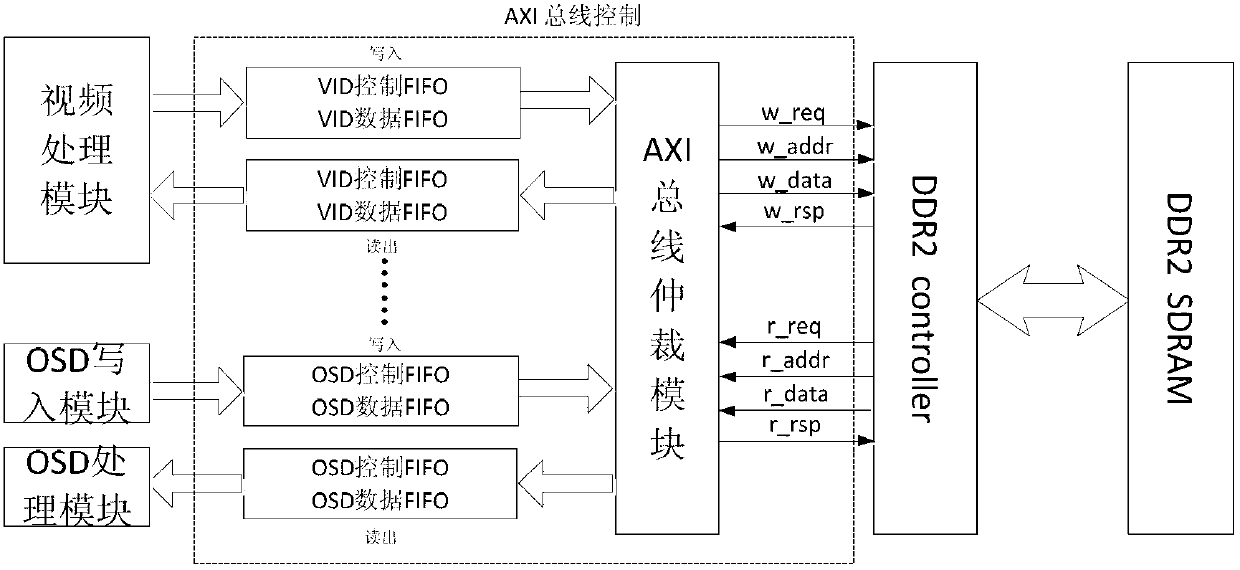

On screen display (OSD) control display method and device based on advanced extensible interface (AXI) bus protocol

InactiveCN103139509AReduce volumeLow costTelevision system detailsColor television detailsVideo memoryVery-large-scale integration

The invention discloses an on screen display (OSD) control display method and a device based on an advanced extensible interface (AXI) bus protocol. After OSD data is selected through an OSD data channel, flexible modification and display on an OSD map layer can be achieved by utilizing of read-write cache first input, first output (FIFO) and an advanced extensible interface (AXI) bus arbitration module, wherein video memory is shared by the OSD data, and at the same time, a path of video interfaces is arranged on the exterior so as to achieve the picture-in-picture effect. A bilinearity Scaler zoom module is used for carrying out zoom process on an OSD image with random proportions, and at last an OSD and video overlap module is utilized to achieve abundant and diversified display modes of the OSD. According to the OSD control display method and the device based on an AXI bus protocol, the design of very large scale integration (VLSI) is achieved, intensive study is carried out on key points in the VLSI, and code compiling and the function of the code compiling of a Verilog-hardware description language (HDL) are achieved on the basis of the intensive study on the key points in the VLSI.

Owner:西安创芯科技有限责任公司

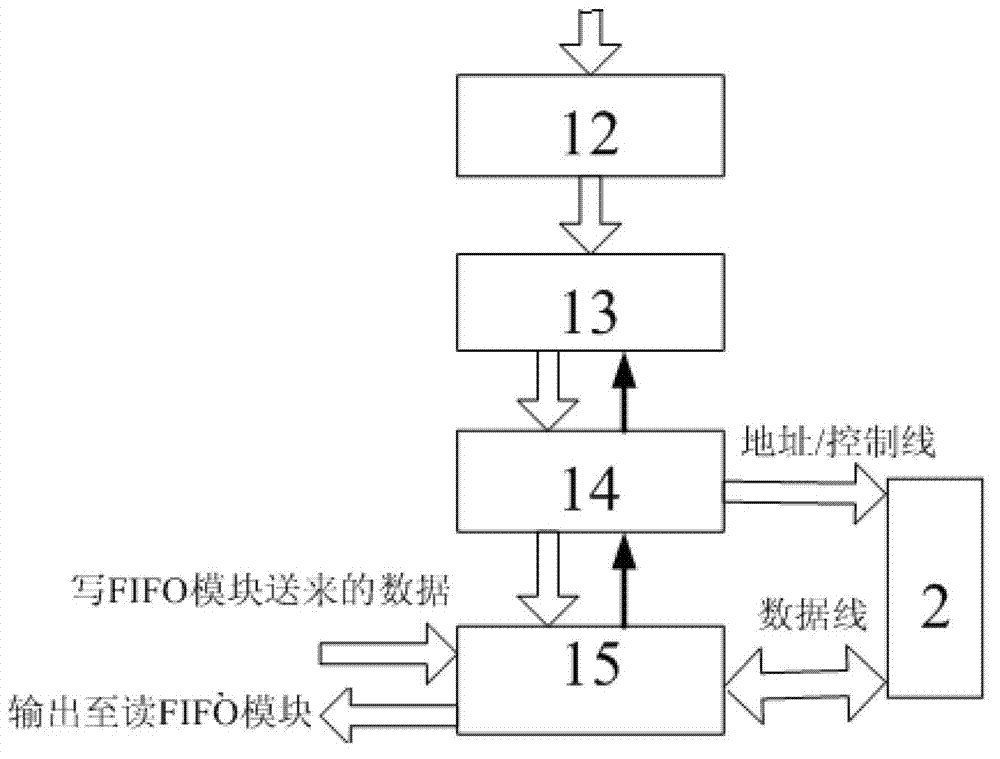

Field programmable gate array-based (FPGA-based) realization method for converting liquid crystal display (LCD) signal to video graphics array (VGA) signal

InactiveCN102831872ALow costReduce development riskCathode-ray tube indicatorsConfidentialityFpga design

The invention relates to a field programmable gate array-based (FPGA-based) realization method for converting a liquid crystal display (LCD) signal to a video graphics array (VGA) signal, which belongs to the technical field of the FPGA design, and a system is mainly established by an FPGA module, a synchronous dynamic random access memory (SDRAM) module and a register-packs network module. The FPGA module is used as a core of a conversion system, consists of a clock management module, a resetting module, an LCD signal receiving module, a writing first-in first-out (FIFO) module, an SDRAM controller module, a reading FIFO module, an FIFO controller module and a VGA display module and is realized through a Verilog hardware description language (HDL) code; the SDRAM module is a cache for processing the data of the FPGA module, and a controller of the SDRAM module is realized inside the FPGA module; and the exclusion network module is formed by register packs and used for converting a digital signal to an analog signal. The FPGA-based realization method has the advantages of low cost, short development period, low development risk, convenience in modification design and good confidentiality.

Owner:SHANDONG UNIV

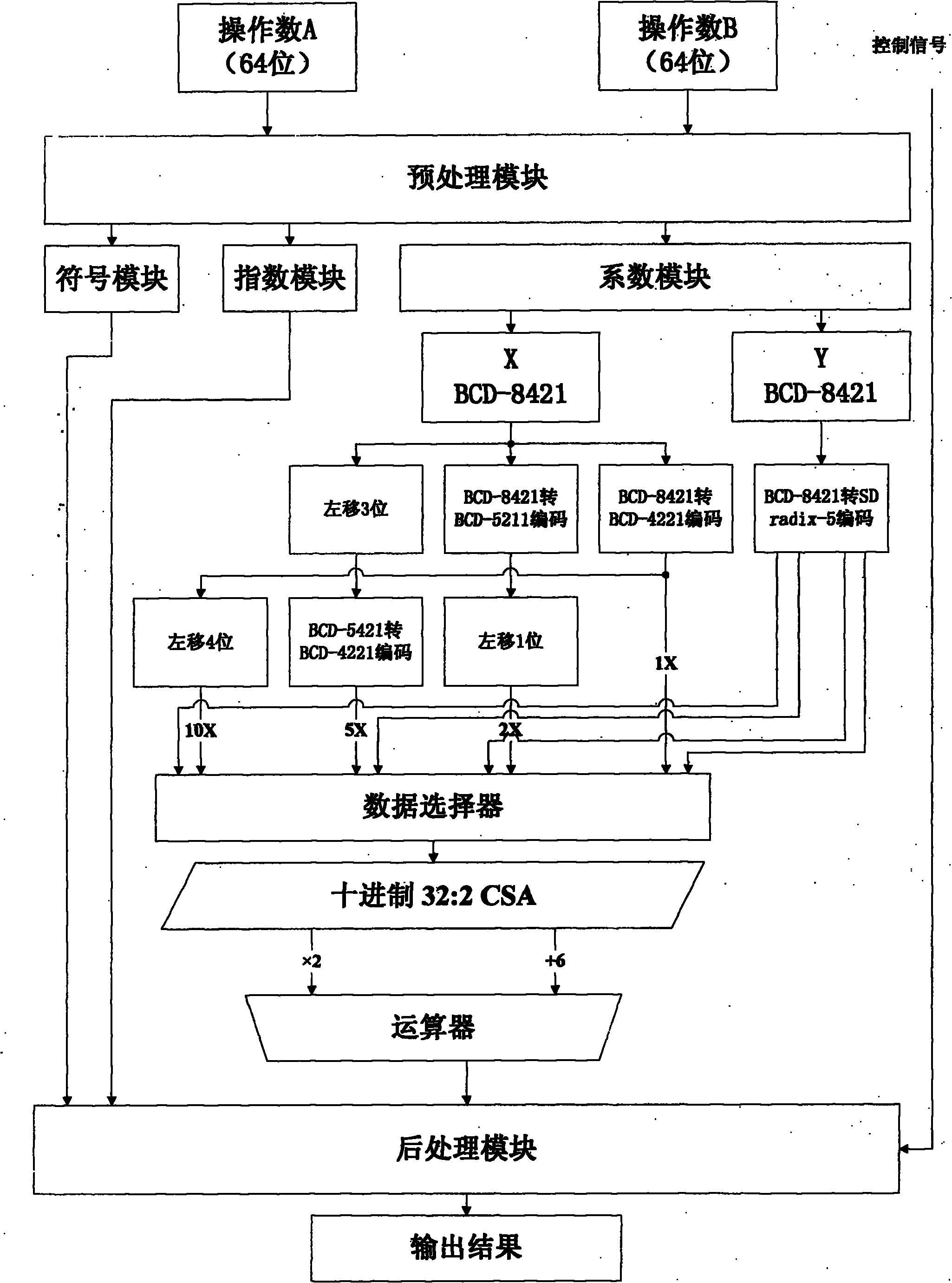

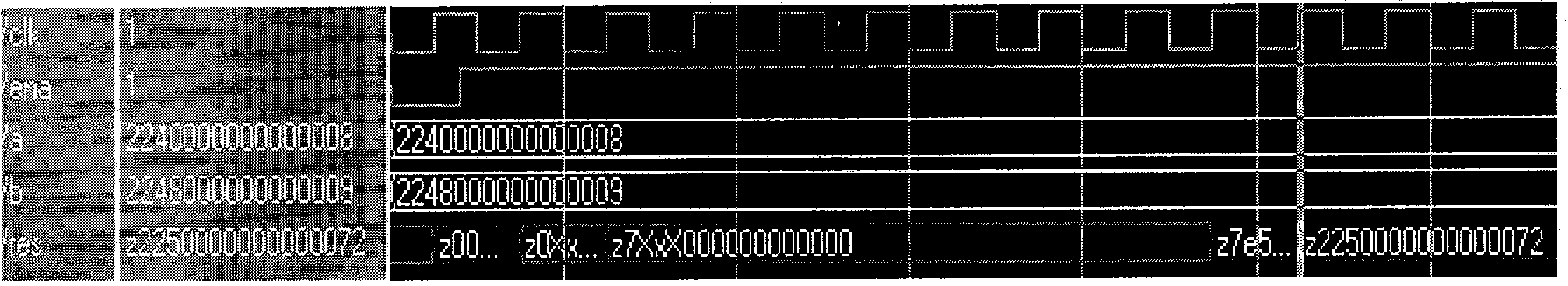

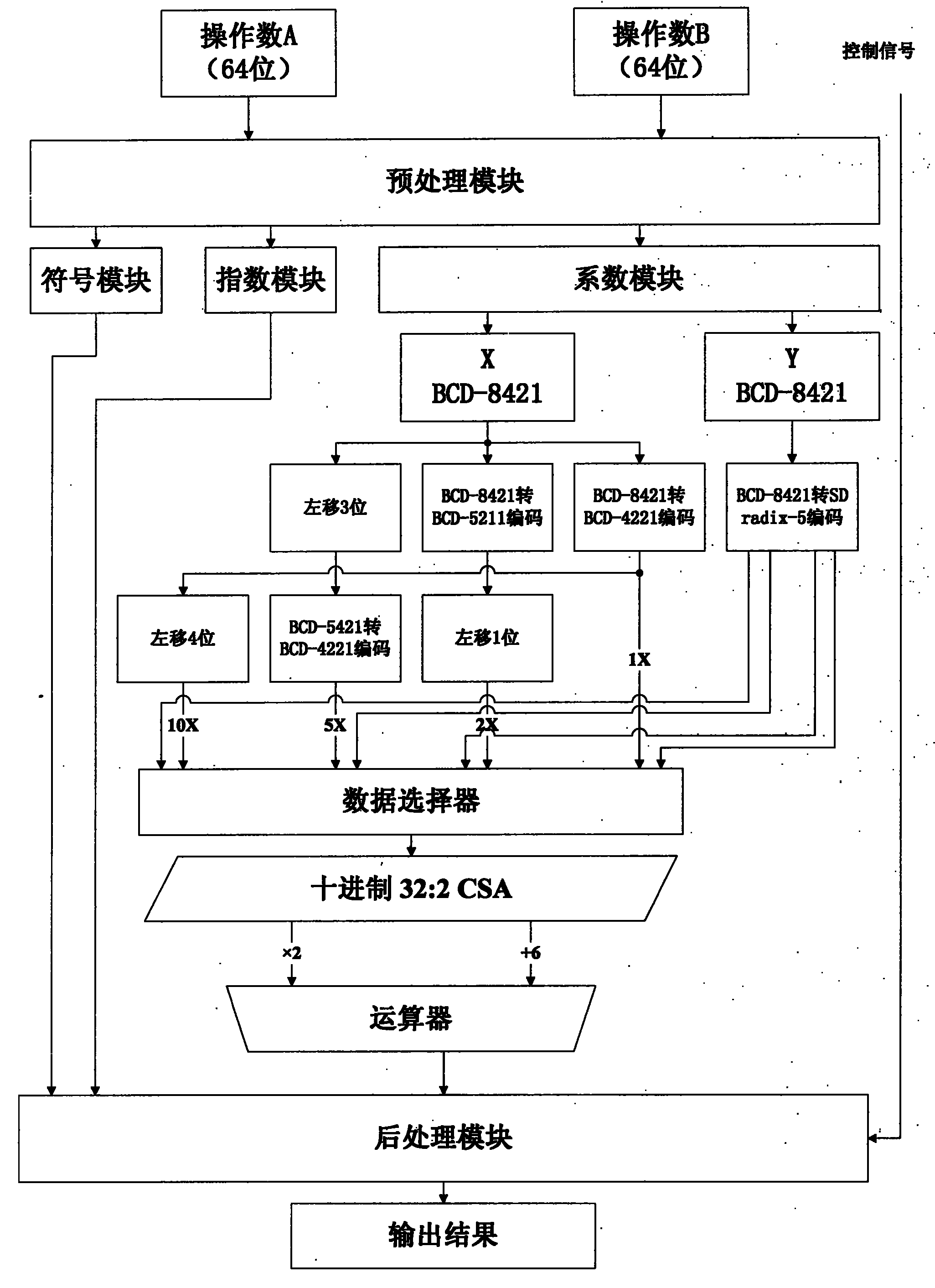

Field programmable gata array (FPGA)-based metric floating-point multiplier design

InactiveCN102073473ASave resourcesFix conversion precision issuesDigital data processing detailsImaging processingDensely packed decimal

The invention discloses a field programmable gata array (FPGA)-based metric floating-point multiplier design. The design adopts advanced and quick algorithms such as densely-packed decimal (DPD) coding, novel binary-coded decimal (BCD) coding, signed-digit radix-5, decimal 32:2 carry-save adder (CSA) and the like, is realized by programming through a Verilog hardware description language and can perform multiplication of 64-digit decimal floating-point numbers in accordance with the Institute of Electrical and Electronic Engineers (IEEE) 754-2008 new standard. The design effectively solves the problem of conversion accuracy existing in binary / decimal operation on the conventional hardware platform and the time problem of the realization of decimal floating-point multiplication by using software, consumes a small number of hardware resources and has high operation speed and a simple structure; moreover, according to the performance and characteristic of the FPGA, a system can be developed repeatedly, and a decimal floating-point unit which is accordant with the IEEE 754-2008 standard specification can be further developed and designed. The design is mainly applied to industries such as bank finance, image processing, medical treatment and the like.

Owner:YUNNAN UNIV

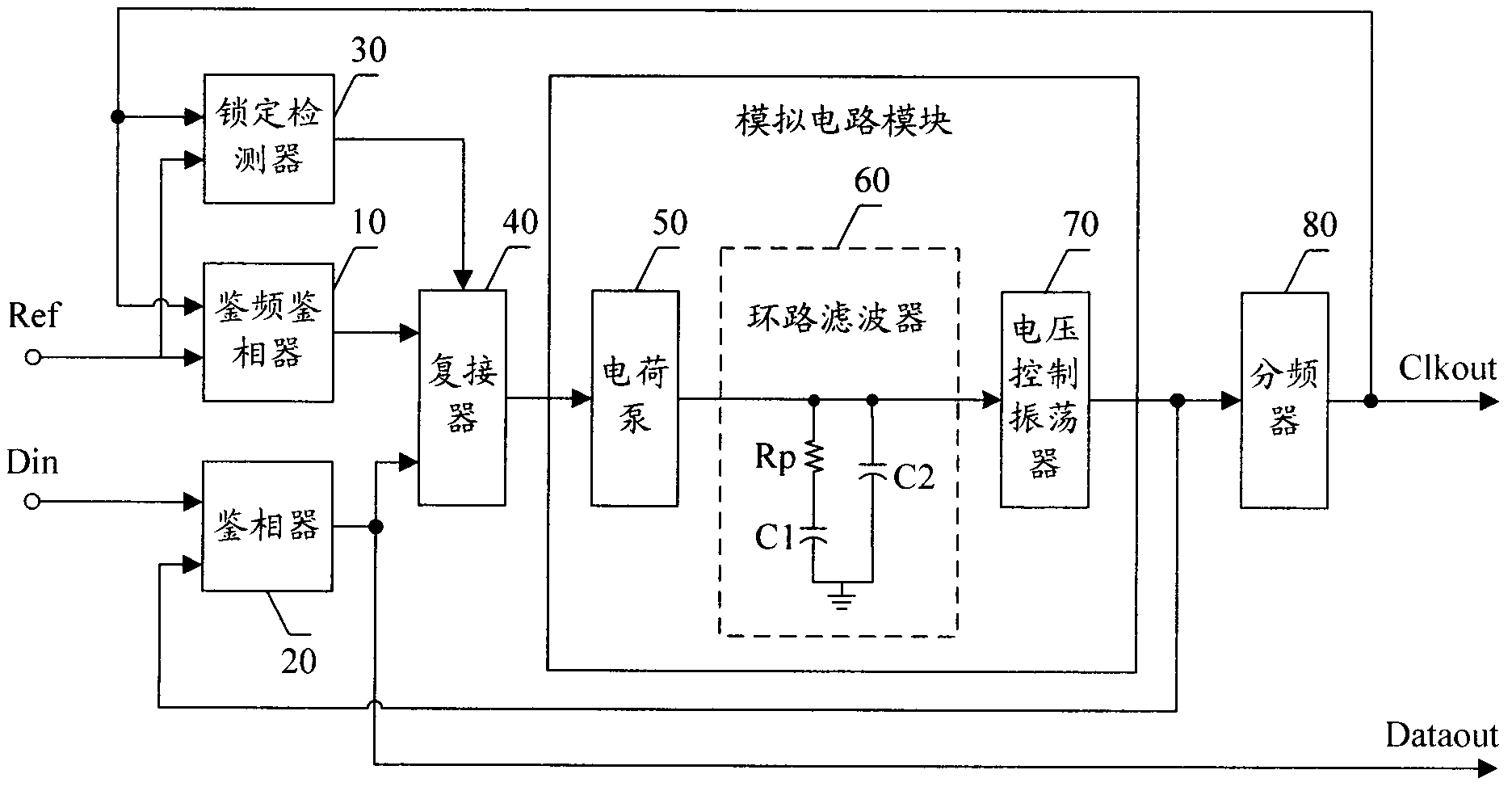

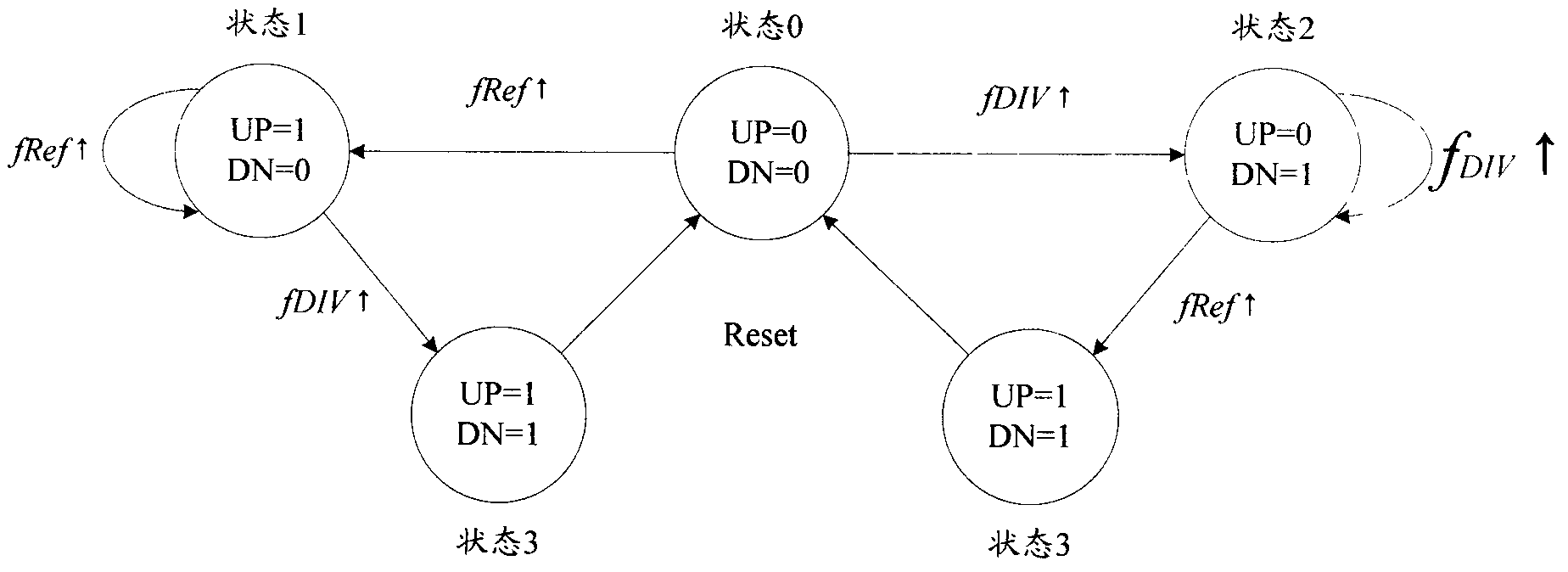

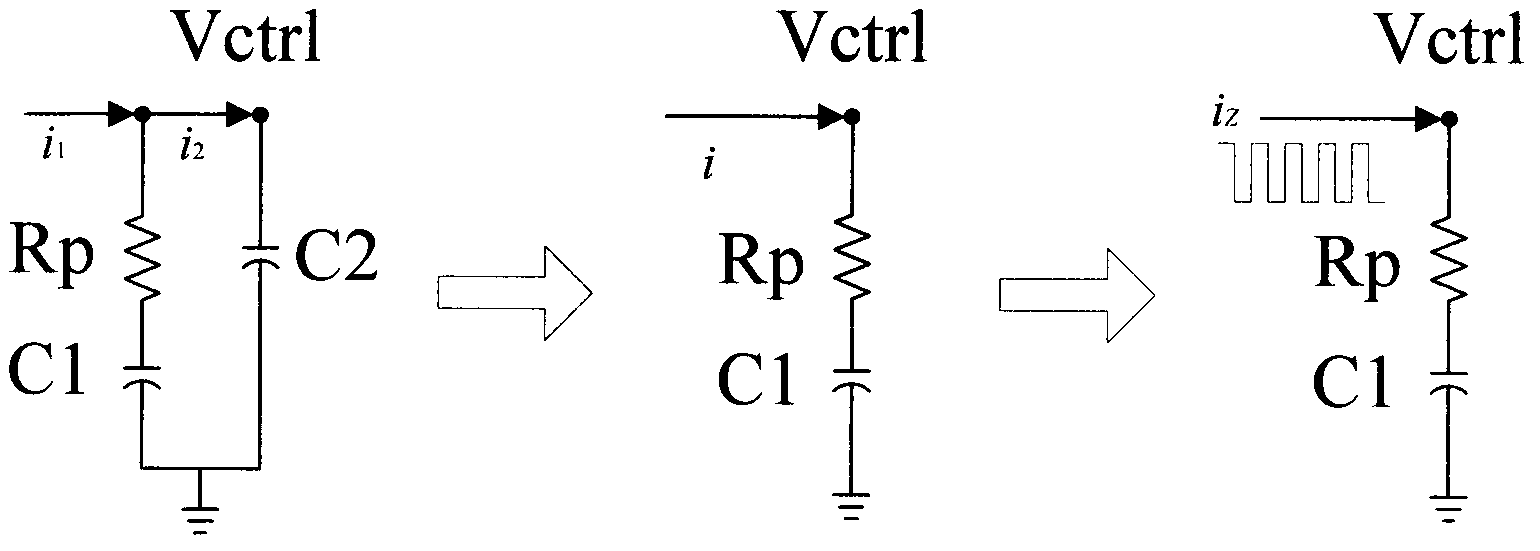

Behavioral modeling methods for clock and data recovery circuit and analog circuits

InactiveCN103425810AImprove verification efficiencyAvoid difficultiesSpecial data processing applicationsModel validationHuman language

The invention provides a behavioral modeling method for a clock and data recovery circuit. The behavioral modeling method includes steps of 1, dividing a circuit module in the clock and data recovery circuit into a digital circuit module and an analog circuit module; 2, respectively describing the circuit modules by a Verilog language according to the divided circuit modules. The invention further provides a behavioral modeling method for analog circuits. The behavioral modeling methods for the clock and data recovery circuit and the analog circuits have the advantages that the clock and data recovery circuit can be behaviorally modeled by the aid of the Verilog hardware description language, all the analog circuits can be modeled in the corresponding module, problems that the Verilog language does not support analog voltage and current modeling and simulation is difficult are solved, logic verification engineers can verify models in a top-level manner by the aid of digital simulators, and the model verification efficiency is improved.

Owner:SANECHIPS TECH CO LTD

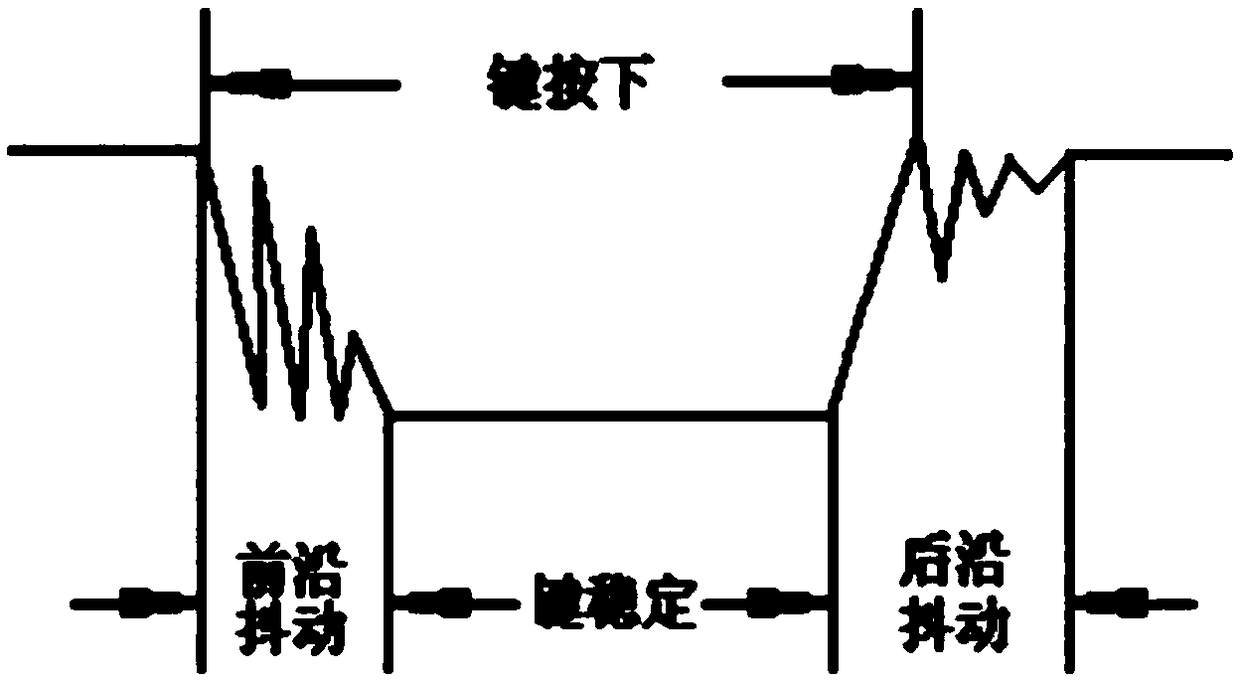

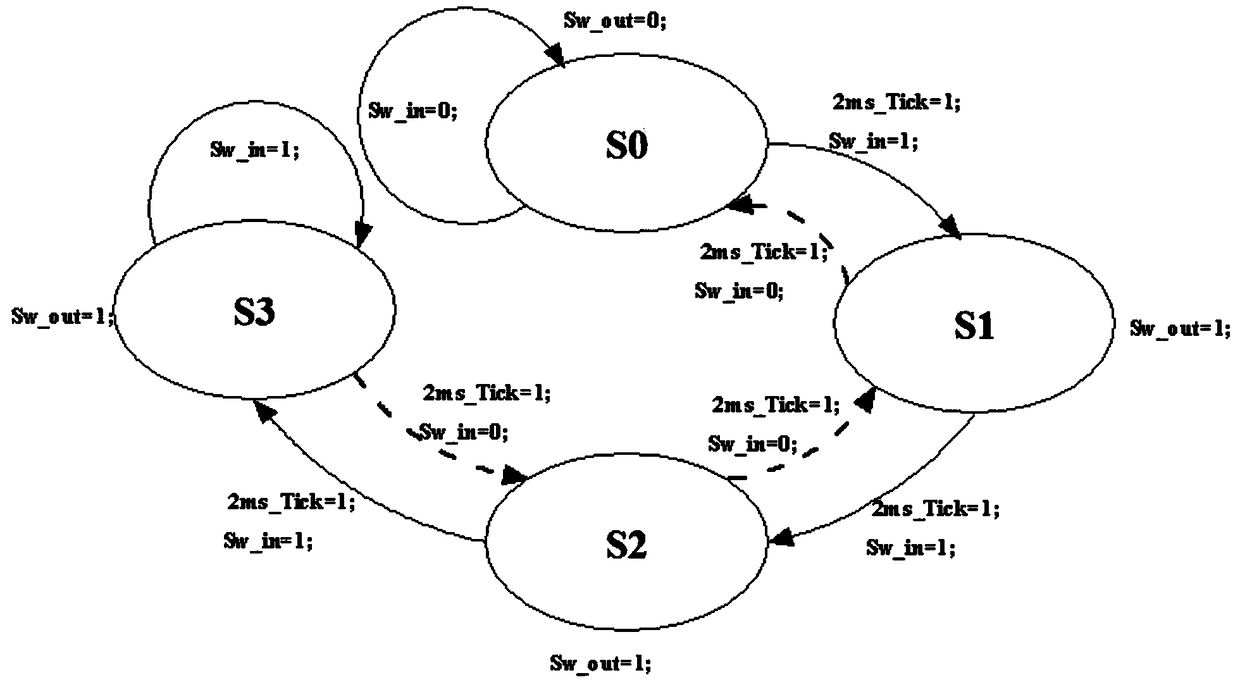

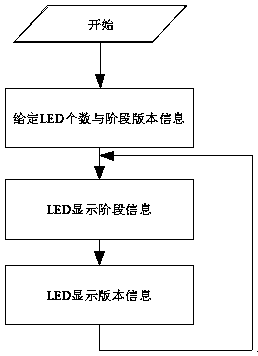

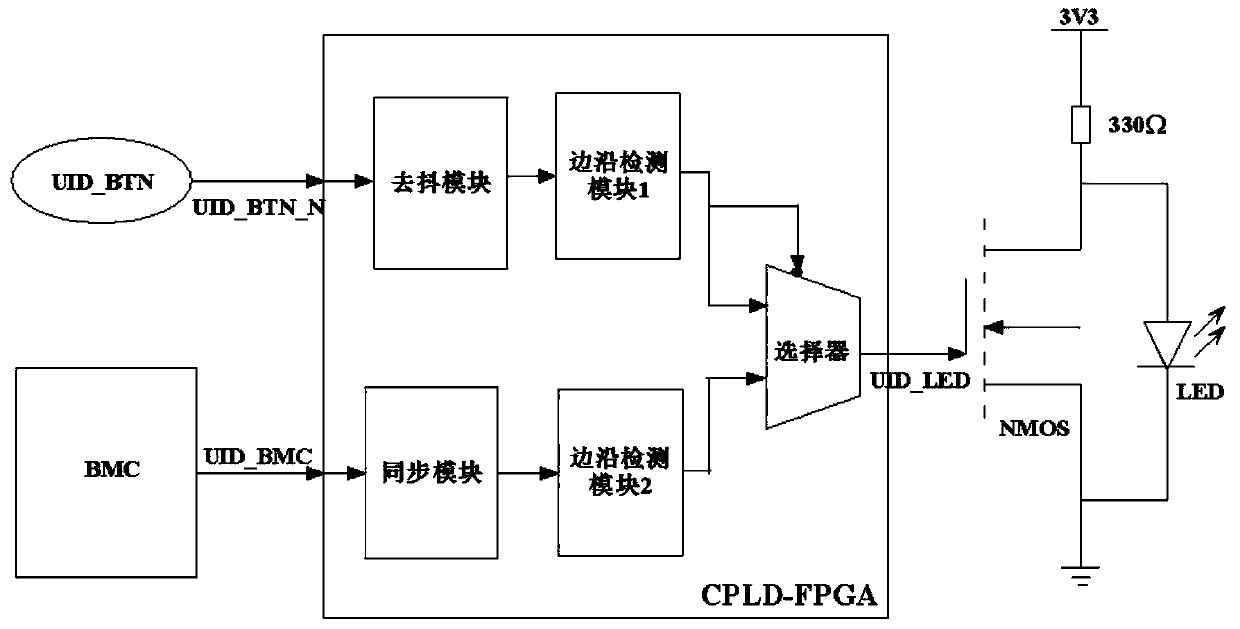

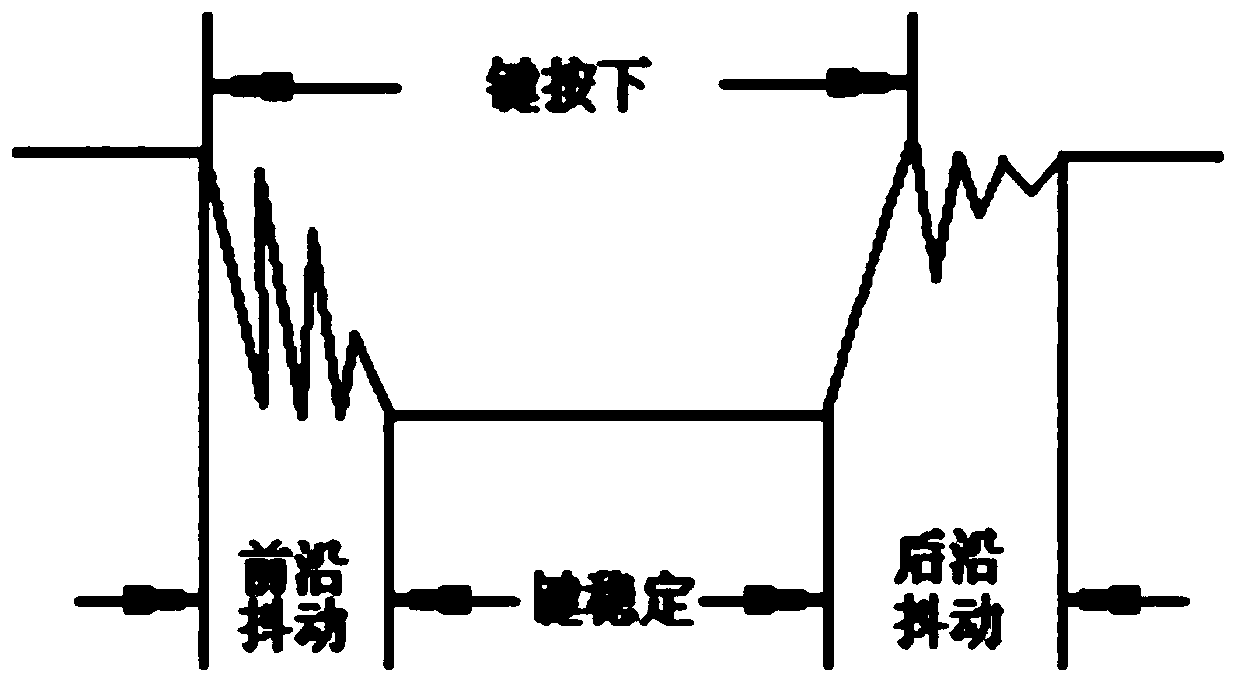

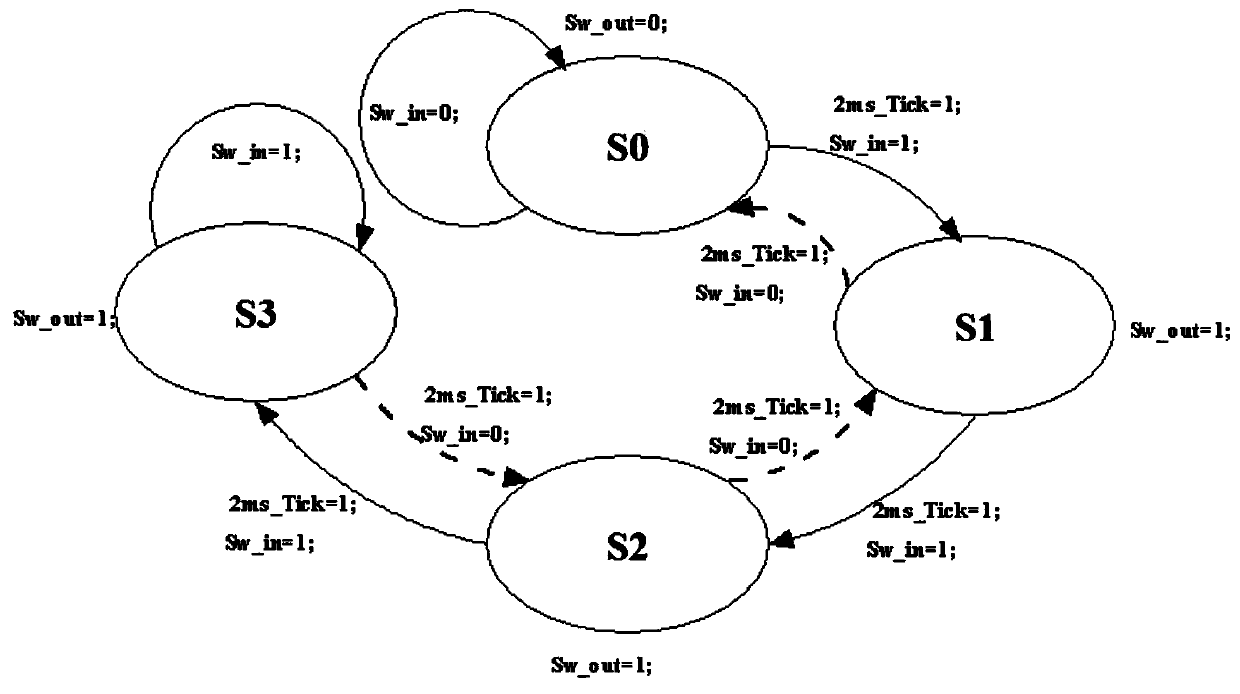

Method capable of achieving UID-LED multistate control

ActiveCN108919696AAdjust the blinking frequencyEffective way to distinguishProgramme controlComputer controlComputer modulePaper document

The invention relates to a method capable of achieving UID-LED multistate control and belongs to the technical field of server design and application. The method comprises the following steps that (1)peripheral circuit design is completed; (2) a UID-LED multistate controlled module is achieved through the Verilog hardware description language; (3) a mirror image document is downloaded into a CPLD / FPGA chip of a server to achieve UID-LED multistate control; (4) key shake removing module design and key detection are conducted on a UID key by a CPLD in real time; (5) IPMI signals input by a BMCare subjected to synchronous module design and signal detection by the CPLD in real time; and (6) the signals coming from the UID key and the BMC are judged and selected. The UID signals can be preprocessed, judged, selected and controlled on the basis of CPLD-FPGA, when UID-LED effective indication signals are detected, the signal source can be judged in real time, finally, UID-LED adopts different indication modes, and then UID-LED lightening modes are effectively distinguished.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

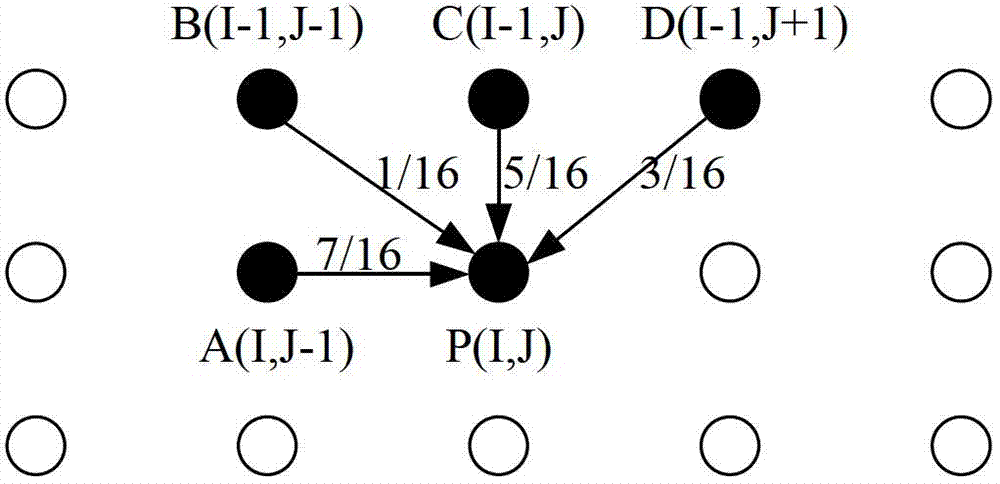

Low voltage differential signaling (LVDS) interface integrated circuit realizing method based on error diffusion algorithm

InactiveCN103200379AReduce the number of input portsReduce complexityTelevision system detailsCathode-ray tube indicatorsCode writingImaging quality

The invention provides a low voltage differential signaling (LVDS) interface integrated circuit realizing method based on the error diffusion algorithm. The method comprises the steps of educing the error diffusion algorithm to each path of RGB (red, green and blue) image data before input of LVDS, and reducing image quality reduction due to direct elimination of low-position signals. Line storage used at time of the error diffusion algorithm is designed by utilization of first in first out (FIFO), and a one-in four-out random-access memory (RAM) is set up at time of coding the LVDS interface, and therefore the condition that four RAMs (one in one out) are needed in the prior art is avoided. The LVDS interface integrated circuit realizing method finishes the very large scale integrated circuit (VLSI) design for a raised method, and conducts deep research on key points of the VLSI, and finishes code writing of Verilog-hardware description language (HDL) and function achievement.

Owner:西安创芯科技有限责任公司

Version displaying system and method based on CPLD_FPGA (Complex Programmable Logic Device_Field Programmable Gate Array)

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

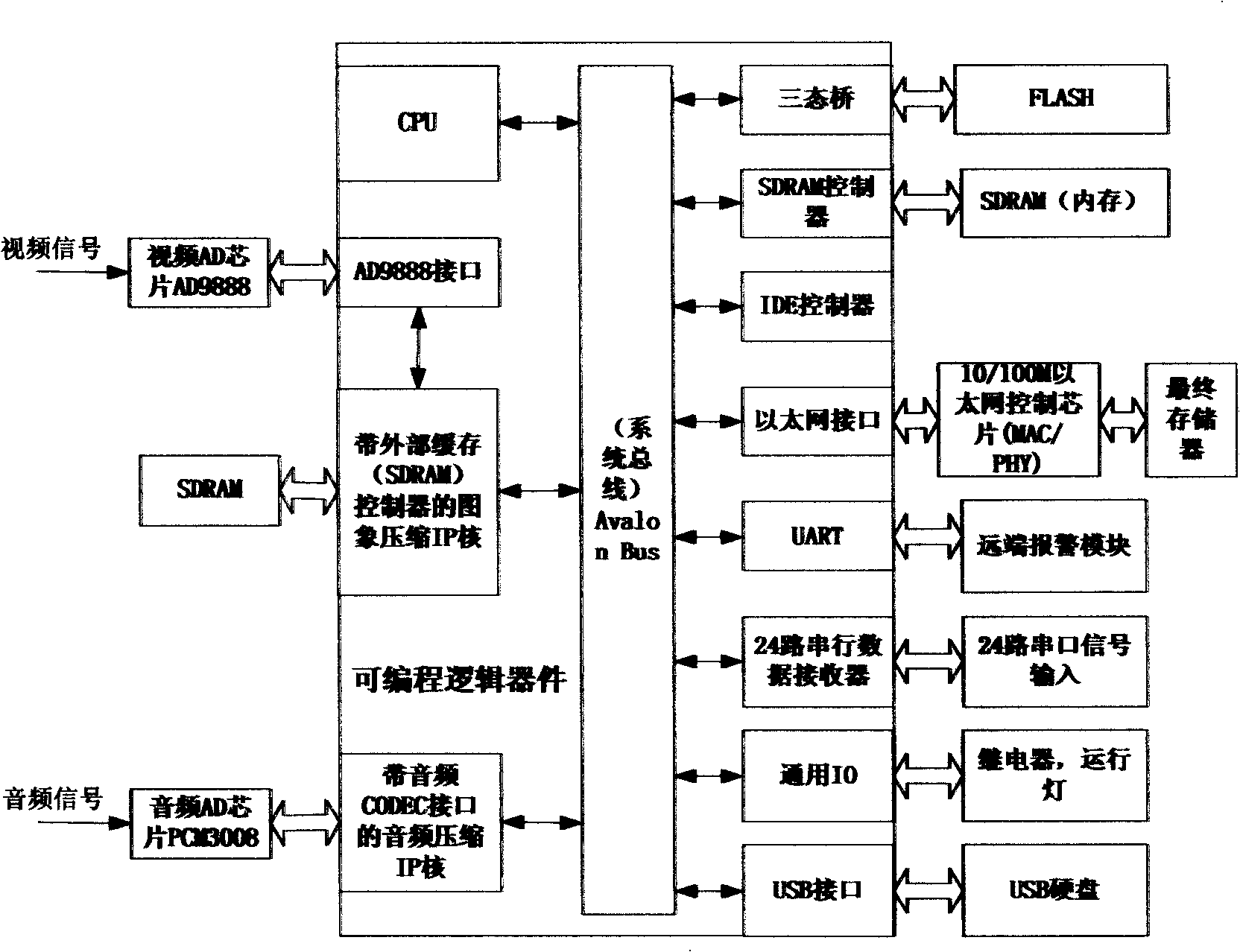

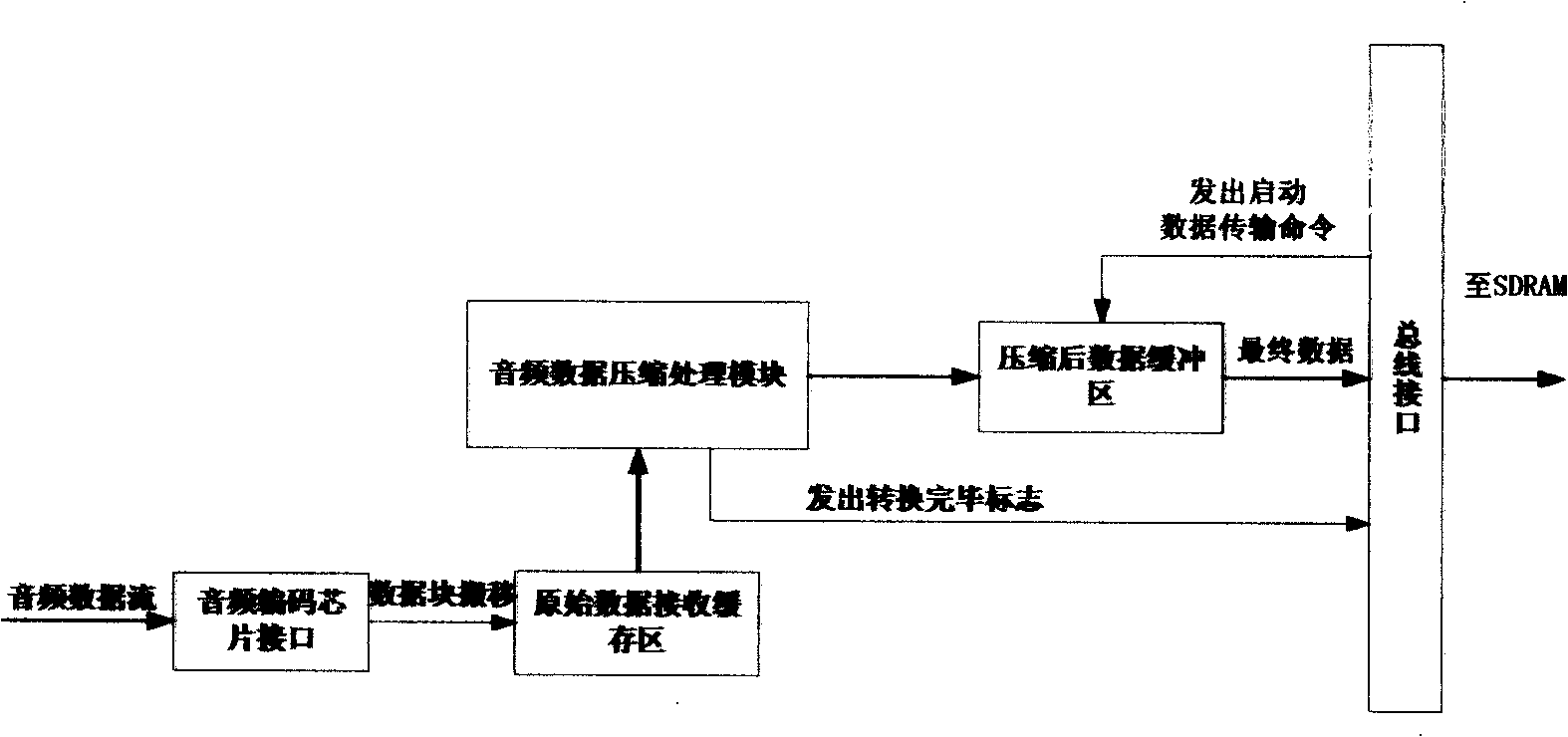

Single slice shipborne sailing data recording method and device based on SoC

InactiveCN101315707AImprove real-time performanceImprove reliabilityRegistering/indicating working of vehiclesData compressionData acquisition

The invention relates to a method and a device for recording single-chip ship-borne voyage data based on SoC; the method comprises the following steps: the whole system is established on a programmable chip and adopts a modular design; a CPU module of the system, an audio-image collecting interface module, a digital signal operation processing module and a memory control module all adopt an IP core mode, use Verilog hardware to describe language implementation, then carry out the simulation of function and time sequence by a simulation testing tool on the basis of introducing testing vector and finally integrate into a whole so as to form a complete device for collecting and recording single-chip ship-borne voyage data. The device comprises a 32-bit embedded microprocessor CPU module, a peripheral interface module, an image-audio data compression processing module containing an interface controller, which are arranged on the programmable chip. As the invention adopts the technical proposal, the real time performance, reliability and reusability of the system are improved and the volume and the cost of the system are reduced.

Owner:WUHAN UNIV OF TECH

A flexible motion control ip core and its implementation method

ActiveCN104135212BFast operationShorten the control cycleElectric motor controlIntellectual propertyOperating frequency

The invention discloses a flexibility motion control IP (Intellectual Property) core and an implementation method thereof, belonging to the field of motion control. The IP core comprises a acceleration / deceleration module, an interpolation module, a pulse counting module, a pulse generation module, a bus controller and an RAM (Random Access Memory) interface module. The flexibility motion control IP core and the implementation method thereof aim to solve the problems that high speed and high precision cannot be achieved due to incapability of further reducing a control period since a motion control algorithm has a long running period in a general MCU (Micro Controller Unit) or DSP (Digital Signal Processor). The IP core has the characteristics of short control period and high output pulse precision, non-symmetrical linear acceleration and deceleration can be achieved, non-symmetrical S-shaped curve acceleration and deceleration can be achieved, two-axis or three-axis linear interpolation with the linear or the S-shaped curve acceleration and deceleration can be achieved, and two-axis arc interpolation at an uniform speed also can be achieved. Through the adoption of the IP core, motion control relevant algorithm is realized in a Verilog hardware description language soft core mode, the motion control relevant algorithm can be implemented in an FPGA (Field Programmable Gate Array), can be implemented in an ASIC (Application Specific Integrated Circuit) mode, and can be integrated into SoC (System On Chip), the typical working frequency is 100MHz, and feasibility is provided for building a flexibility motion control system.

Owner:SOUTH CHINA UNIV OF TECH

High speed video data acquisition display system and display method

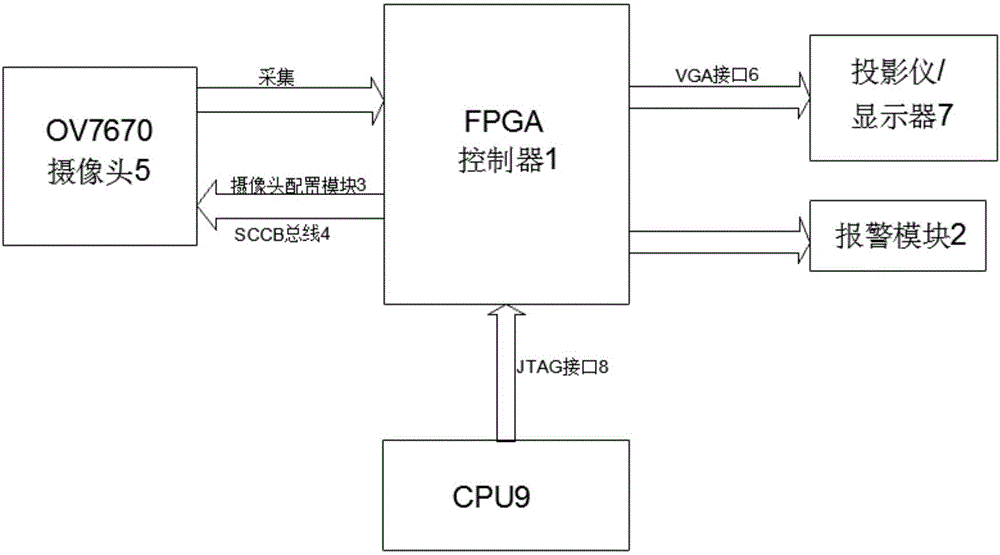

PendingCN106454215AImprove match compatibilityHigh acquisition rateClosed circuit television systemsAlarmsTime informationFpga implementations

The invention discloses a high speed video data acquisition display system and a display method. The high speed video data acquisition display system comprises an FPGA controller and an alarming module connected with the FPGA controller, and the FPGA controller is connected with an OV7607camera by a camera configuration module and an SCCB bus. The OV7607 camera is used to transmit the acquired data information to the FPGA controller, which is connected with a projector / display by a VGA interface, and is connected with a CPU by a JTAG interface. The front segment camera (OV7670) is used for data acquisition, and is used to store the data in the internal RAM of the FPGA. The FPGA is used to realize fast reading / writing and transceiving control, and under control of a Nios II, the CPU is used to control the acquired data on the VGA display screen. A verilog hardware description language is used to initialize the SCCB bus, and the data acquired by the camera is stored in the internal RAM of the FPGA, and under excitation of clock pulses, the real-time data information is stored constantly, and high matching compatibility is achieved, and then a high efficiency and high speed data acquisition function is realized.

Owner:ANHUI NORMAL UNIV

Asynchronous motor pure electronic speed feedback method

InactiveCN102629847BRelieve pressureMultiple storage spacesElectronic commutation motor controlVector control systemsFpga implementationsMathematical model

The invention provides a pure electronic speed feedback method for an asynchronous motor. The specific operation steps are as follows: first obtain the discrete-time form expression of the mathematical model of the asynchronous motor, and then obtain the reduced-order EKF speed estimation algorithm for the asynchronous motor according to the extended Kalman filter algorithm, and then Design the algorithm structure of FPGA to realize the reduced-order EKF speed estimation. Based on the algorithm structure described above, the FPGA is described in hardware language VHDL, and the state estimated values iαs, iβs, Ψαr, Ψβr, ωr are sent to the parallel port and sent back to the main control DSP. The present invention greatly reduces the pressure on the real-time calculation amount of the main control DSP, leaving more storage space and calculation space for speed and current control; and the EKF speed estimation algorithm implemented in parallel by FPGA can be implemented within 1 μs level Complete, so that the speed estimation algorithm can choose a smaller sampling period, so the speed estimation accuracy is greatly improved.

Owner:XIAN UNIV OF TECH

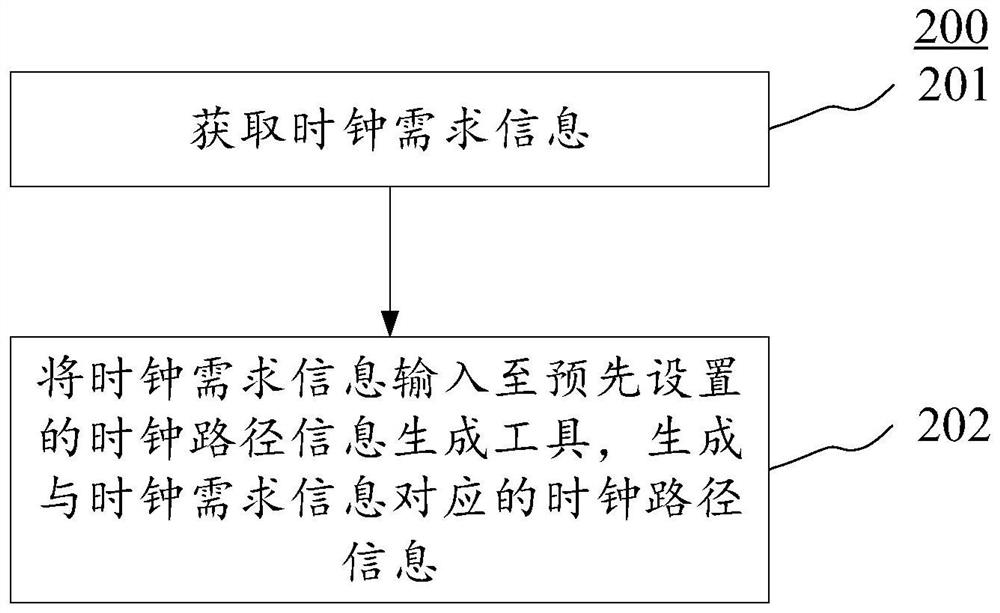

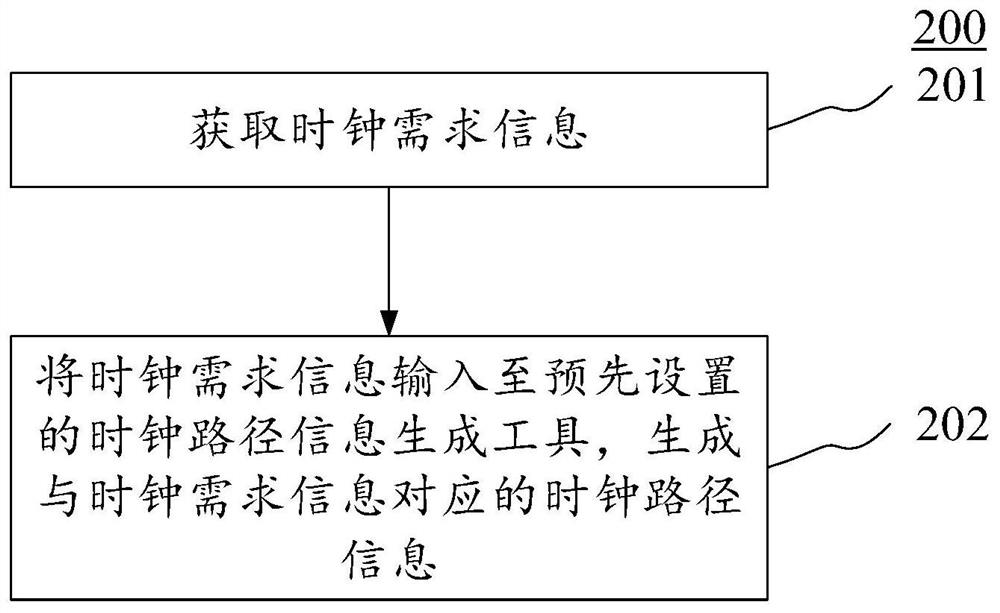

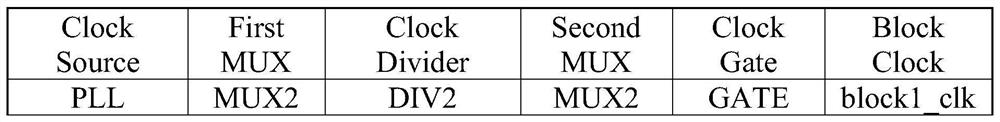

Clock path information generation method and device, electronic equipment and medium

PendingCN114297972ASolve rapid development problemsShorten development timeCAD circuit designSpecial data processing applicationsComputer hardwarePathPing

The invention provides a clock path information generation method and device, electronic equipment and a medium. Through a preset clock path information generation tool, the problem of rapid development of clock network circuits for different large-scale SoC chips is solved. Specifically, clock network information is imported into a clock path information generation tool (an implementation carrier is a script language, such as a Perl language), and clock path code information (such as a Verilog hardware description language) and clock path block diagram information are automatically generated by utilizing the clock path information generation tool, so that an efficient and error-free SoC chip clock network is quickly realized. The SoC chip development time can be greatly shortened, and the design efficiency is improved.

Owner:井芯微电子技术(天津)有限公司

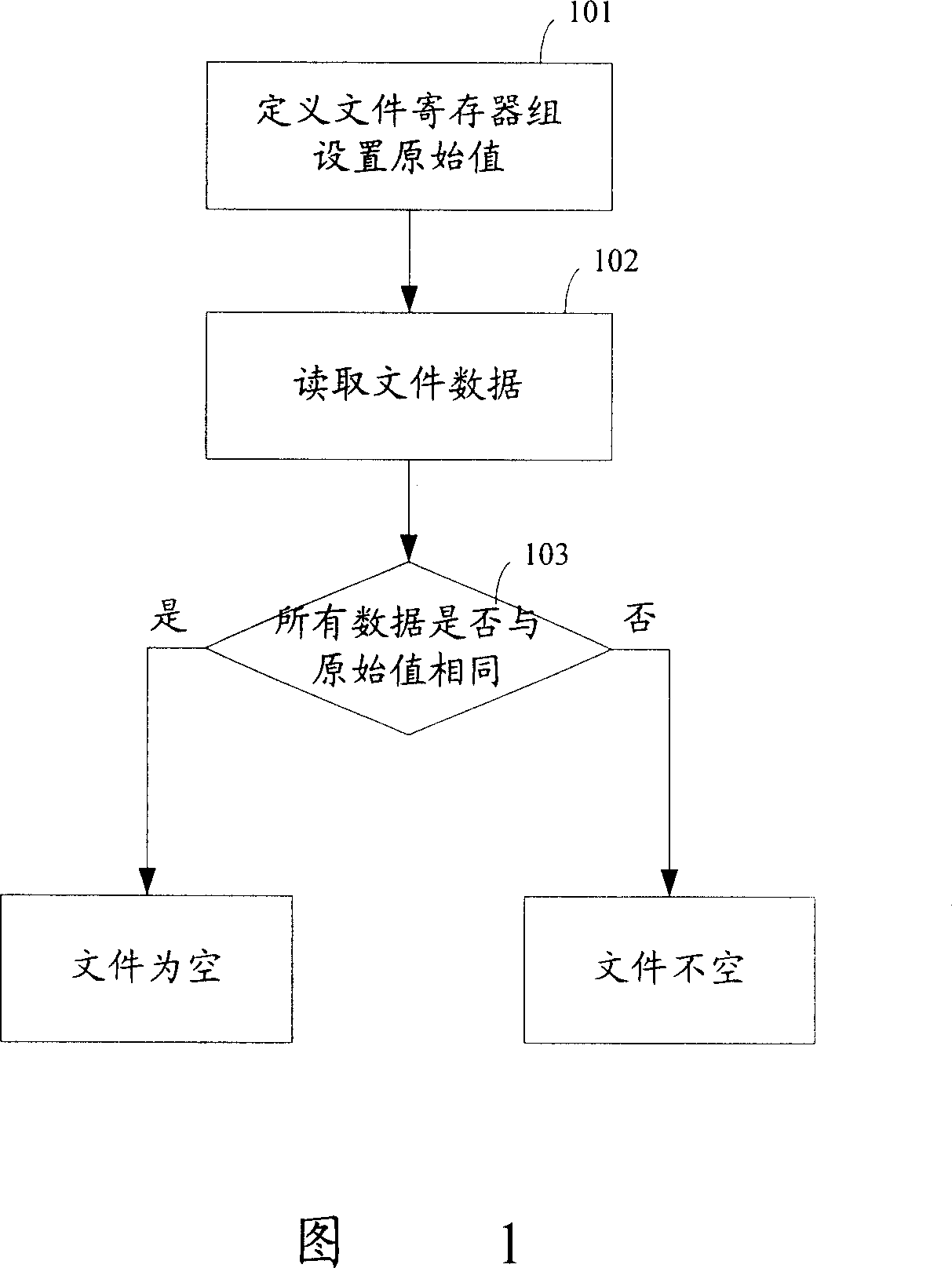

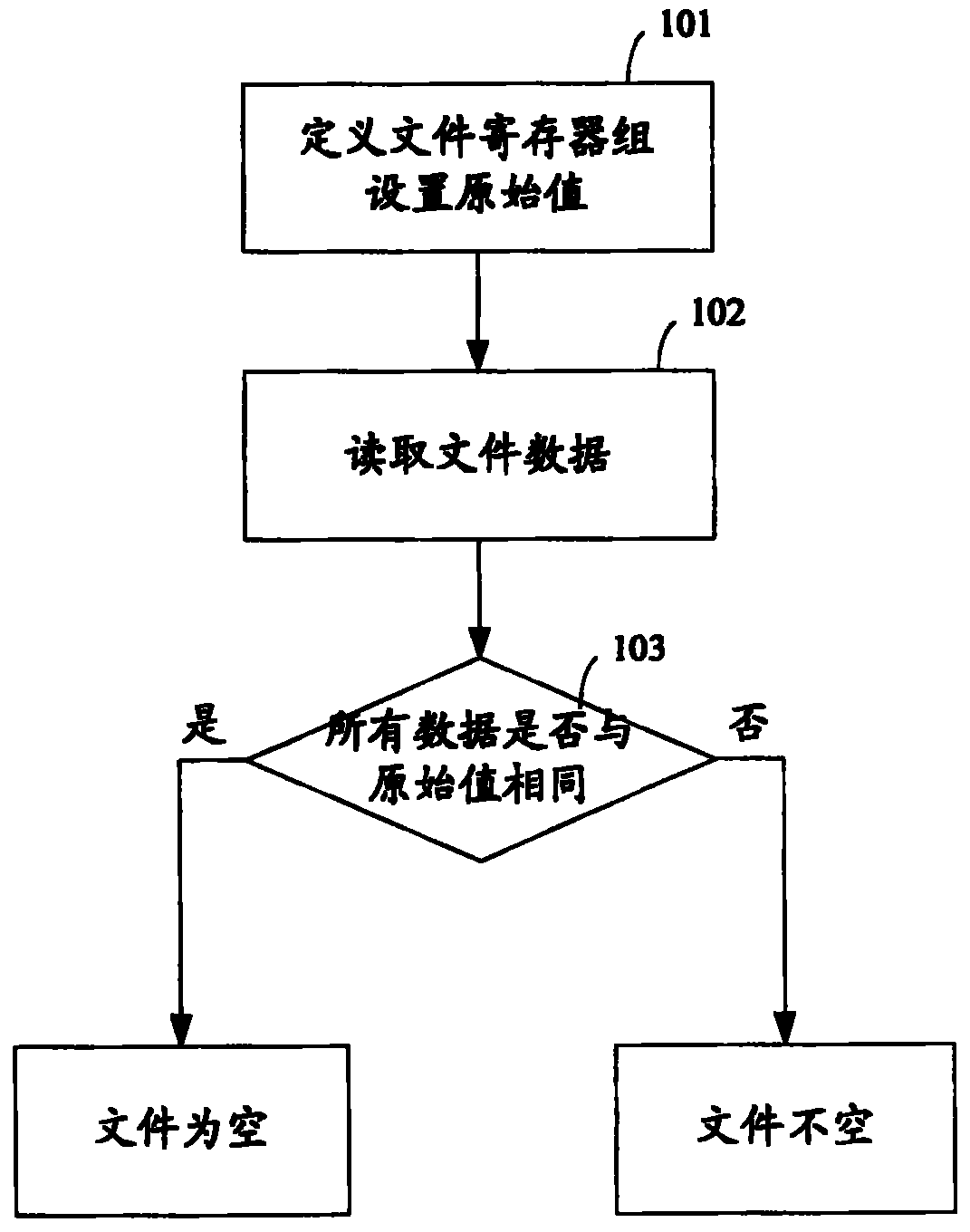

Method for acquiring file status by using Verilog hardware description language

InactiveCN1306398CRealize dynamic read and write exchangeIncrease operation functionProgram controlMemory systemsDocument StatusProcessor register

The invention relates to a file status acquisition method using the Verilog hardware description language. It is composed of the following steps. Setup a file register group composed of more than one register, and stores the file data in the file register group when handling the files. Determine whether the data in the register group is the original value of the corresponding data stored register. If it is, the register is empty. Otherwise the register is not empty, and the file status is determined according to the register status of the mentioned file register group. The invention implements the file status determination based on the Verilog language without involving the other languages. By this means, the file dynamically read-write exchanging can be implemented in the disk.

Owner:HUAWEI TECH CO LTD

A method for testing the fault of embedded multi-bit memory in fpga

InactiveCN102157205BIncrease excessive consumptionImprove fault coverageStatic storageMemory cellControl cell

The invention relates to a method for testing the fault of a multiposition memorizer inlaid in FPGA. The method comprises the following six steps of: firstly, increasing the quantity of test patterns through the formula: two multiplied by (one plus log2n) by the March C-algorithm; secondly, introducing the test patterns, the quantity of which is expressed by the formula: two multiplied by (one plus log2n) into six March units of the March C-algorithm so as to obtain the March C-algorithm for testing the memorizer based on memory cells and has the bit wide of n bit; thirdly, establishing a BIST structure in FPGA by utilizing the Verilog hardware description language; fourthly, using a control unit to control the test patterns of the tested memorizer, the state of a state controller as well as the start and stop of an internal response analyzer which are input under different states at the BIST platform, and generating the sequence of March element test patterns needed for different fault models of the memorizer by a test pattern generator; fifthly, testing the memorizer according to the generated test patterns; and sixthly, observing test wave forms, and determining the fault type of the memorizer. The method achieves simplicity and easiness for implementation, and has considerably broad application prospect in the field of testing the multiposition memorizer inlaid in FPGA.

Owner:BEIHANG UNIV

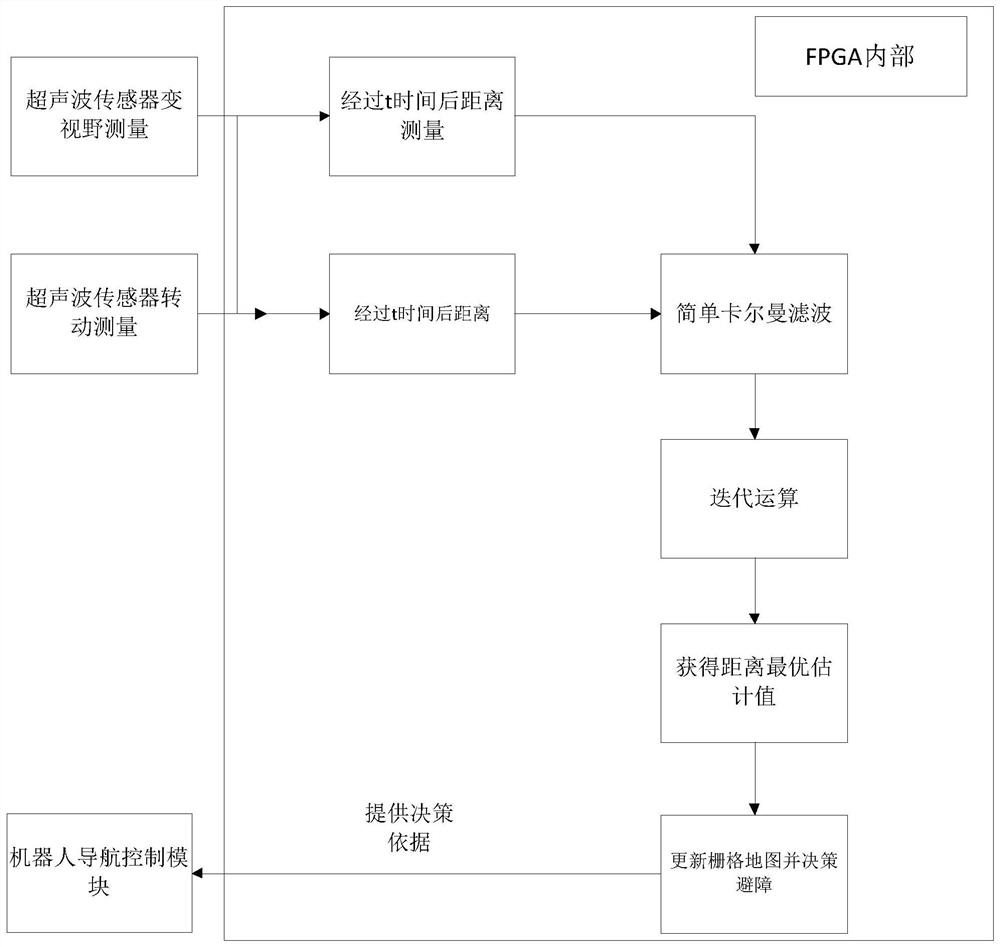

Robot ultrasonic sensor obstacle detection method and system

ActiveCN112782706BAccurate distance dataAccurate obstacle avoidanceAcoustic wave reradiationSimulationObstacle avoidance

The invention discloses a robot ultrasonic sensor obstacle detection method and system, which belong to the field of robots and embedded systems. The technical problem to be solved in the invention is how to make the robot avoid obstacles more accurately. The technical solution adopted is: The FPGA processor platform of the robot performs real-time calculation and processing of data, and the Verilog hardware description language is used in the FPGA for digital logic design; the details are as follows: ultrasonic sensor variable field of view measurement and ultrasonic sensor rotation measurement; distance measurement after t time; Record the real-time distance value after time; calculate the optimal estimate of the current distance value according to the Kalman filter algorithm; iteratively calculate the optimal estimate of the distance; update the grid map and make decisions to avoid obstacles; the FPGA processor platform controls the robot navigation The module provides decision-making basis to realize precise obstacle avoidance of the robot.

Owner:山东新一代信息产业技术研究院有限公司

Compact peripheral components interconnect (CPCI)-bus-based 1553B protocol data communication and serial loading module

InactiveCN102411553BImprove performanceImprove reliabilityElectric digital data processingField-programmable gate arrayAuxiliary circuit

The invention relates to a compact peripheral components interconnect (CPCI)-bus-based 1553B protocol data communication and serial loading module, which comprises a hardware module and a field programmable gate array (FPGA) program. The hardware module comprises an impedance control circuit board, a signal connection socket, a standard CPCI bus connector and a standard 3UEurocard board card front panel, wherein the impedance control circuit board is the core of the module, and is divided into an FPGA unit, a CPCI bus unit, an isolating transformer unit, a logic level translation unit, a 1553B bus protocol chip unit, a serial loading unit and an auxiliary circuit unit. The FPGA program comprises a 1553B bus communication bus controller (BC) module, a remote terminal (RT) module, a monitor terminal (MT) module, and a serial loading module, and is developed by Verilog hardware description language (HDL) programming. The module has stable performance and high reliability, can perform 1553B communication for long and can be randomly set as a BC, an RT or an MT in the 1553B communication; an RT address of external equipment suspended under a 1553B bus together with the module can be serially loaded and flexibly set; the data transmission of a CPCI bus has a direct memory access (DMA) function, the actual transmission rate of the bus is 1MB / s and continuous transmission can be realized without frame loss.

Owner:BEIHANG UNIV

Simulation test method of integrated circuits

ActiveCN101719170BShorten the timeSpecial data processing applicationsParallel computingIntegrated circuit layout

The invention relates to a simulation test method of integrated circuits, which comprises the following steps of: reading in a netlist of the integrated circuits; generating corresponding list files according to data of a register, a latch, an RAM and an ROM; generating a field data preservation task and a field data recovery task according to a verilog hardware description language by the list files; transferring the field data preservation task at different simulation time points to preserve simulation field data at different appointed simulation time points; generating a plurality of mutually independent simulation threads, wherein every simulation thread starts simulation software; transferring the field data recovery task for initializing the integrated circuit which is in simulationcorrespondence with each simulation software into the field data preserved at different simulation time points, and starting up all the simulation threads for simulation verification. The invention greatly shortens the simulation time and improves the simulation efficiency.

Owner:SHENZHEN STATE MICRO TECH CO LTD

Multifunctional data acquisition module based on compact peripheral component interconnect (CPCI) bus

InactiveCN102279830BHigh data acquisition accuracyImprove reliabilityElectric signal transmission systemsElectric digital data processingData acquisitionField-programmable gate array

The invention relates to a multifunctional data acquisition module based on a compact peripheral component interconnect (CPCI) bus. The multifunctional data acquisition module comprises a hardware module and a field-programmable gate array (FPGA) program. The hardware module comprises an impedance control circuit board, an electronic component, a small computer system interface (SCSI100) signal connection socket, a standard CPCI bus connector, and a standard 3UEurocard front panel. The impedance control circuit board and the electronic component are the core functional carriers of the invention and are divided into eight functional units such as an analogue-digital (AD) conversion module, a digital-analogue (DA) conversion unit, a timer unit, a counter unit, a universal input-output (IO) unit and an auxiliary circuit unit. The FPGA program comprises an AD conversion module, a DA conversion module, a timer module, a counter module and a universal IO module and is programmed and developed by Verilog hardware description language (HDL). The multifunctional data acquisition module has steady performance, high reliability, high bus signal driving capability, far transmission distance, simple structure, powerful function, high cost performance, is convenient to use, and can perform long-term and continuous mass data transmission.

Owner:BEIHANG UNIV

Robot ultrasonic sensor obstacle detection method and system

ActiveCN112782706AAccurate distance dataAccurate obstacle avoidanceAcoustic wave reradiationEngineeringComputer vision

The invention discloses a robot ultrasonic sensor obstacle detection method and system, belongs to the field of robots and embedded systems, and aims to solve the technical problem of how to enable a robot to more accurately avoid obstacles. The robot ultrasonic sensor obstacle detection method is characterized in that an FPGA processor platform of a robot is adopted for real-time calculation and processing of data, and a Verilog hardware description language is adopted in an FPGA for digital logic design. The robot ultrasonic sensor obstacle detection method specifically comprises the following steps of: ultrasonic sensor variable-view measurement and ultrasonic sensor rotation measurement; carrying out distance measurement after t time; recording a real-time distance value after t time; according to a Kalman filtering algorithm, calculating to obtain the optimal estimation of the current distance value; performing iterative operation to obtain an optimal distance estimation value; and updating a grid map and deciding obstacle avoidance. The FPGA processor platform provides a decision basis for the robot navigation control module to realize precise obstacle avoidance of the robot.

Owner:山东新一代信息产业技术研究院有限公司

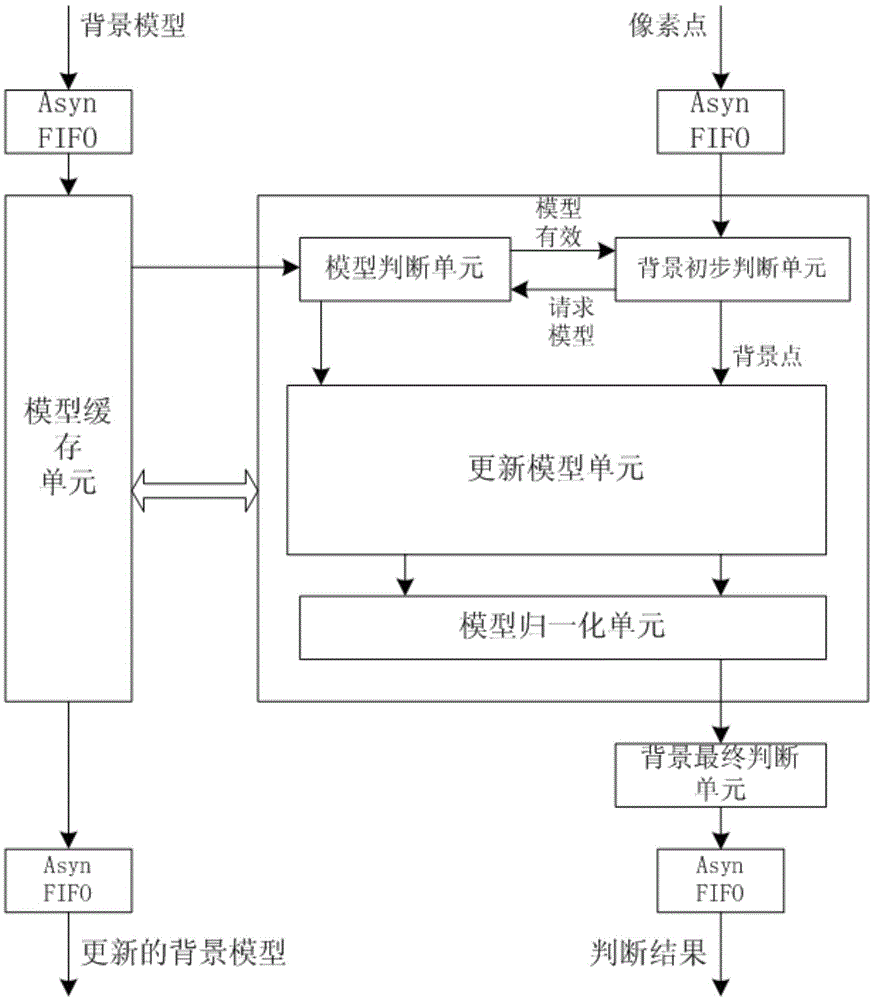

Adaptive real-time image background removing method and system

InactiveCN105631800AImprove portabilityEasy to useImage enhancementImage analysisComputer hardwareSystems design

The invention discloses an adaptive real-time image background removing method and system, and the system comprises a data storage module which is used for storing image data or a background model; an image reading and writing module which is used for receiving image data and storing the received image data in the data storage module; and a background removing module which reads the image data and the corresponding background module from the data storage module, and carries out the background discrimination of the image data according to the background model. The background removing module generates a mask code corresponding to the image data according to a discrimination result, and the image data with the background being removed, and enables the image data with the background being removed and / or the mask code to be stored in the data storage module. The system designs a hardware circuit through employing a Verilog hardware description language, is implemented on an FPGA, and is high in transplantability. Moreover, the background removing module can serve as an IP core to be used in other systems, thereby meeting more demands.

Owner:SHANGHAI HANTK INFORMATION TECH CO LTD

Clock path information generation method and device, electronic equipment and medium

InactiveCN113128162ASolve rapid development problemsShorten development timeCAD circuit designSpecial data processing applicationsComputer hardwarePathPing

The invention provides a clock path information generation method and device, electronic equipment and a medium. Through a preset clock path information generation tool, the problem of rapid development of clock network circuits for different large-scale SoC chips is solved. Specifically, clock network information is imported into a clock path information generation tool (an implementation carrier is a script language, such as a Perl language), and clock path code information (such as a Verilog hardware description language) and clock path block diagram information are automatically generated by utilizing the clock path information generation tool, so that an efficient and error-free SoC chip clock network is quickly realized. The SoC chip development time can be greatly shortened, and the design efficiency is improved.

Owner:井芯微电子技术(天津)有限公司

A method capable of realizing uid-led multi-state control

ActiveCN108919696BAdjust the blinking frequencyEffective way to distinguishProgramme controlComputer controlComputer hardwareFpga chip

The invention relates to a method capable of achieving UID-LED multistate control and belongs to the technical field of server design and application. The method comprises the following steps that (1)peripheral circuit design is completed; (2) a UID-LED multistate controlled module is achieved through the Verilog hardware description language; (3) a mirror image document is downloaded into a CPLD / FPGA chip of a server to achieve UID-LED multistate control; (4) key shake removing module design and key detection are conducted on a UID key by a CPLD in real time; (5) IPMI signals input by a BMCare subjected to synchronous module design and signal detection by the CPLD in real time; and (6) the signals coming from the UID key and the BMC are judged and selected. The UID signals can be preprocessed, judged, selected and controlled on the basis of CPLD-FPGA, when UID-LED effective indication signals are detected, the signal source can be judged in real time, finally, UID-LED adopts different indication modes, and then UID-LED lightening modes are effectively distinguished.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com