Design and implementation of programmable data plane exchange prototype based on P4

A programming data and plane technology, applied in the field of programmable data plane switches, can solve the problems of high power consumption, inconvenient teaching demonstration and scientific research, and inconvenient network system, and achieve the effect of simplifying the difficulty of development work

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0043] The design and implementation of the P4-based programmable data plane prototype system invented in this paper is based on the all-programmable chip zynq-7000 device, which has high-speed programmable logic resources and processor interconnection interfaces. The invention develops a test platform for configuring P4 application by using the fully programmable SOC as a target switch, and realizes the configuration and operation of P4 application on the programmable logic chip FPGA.

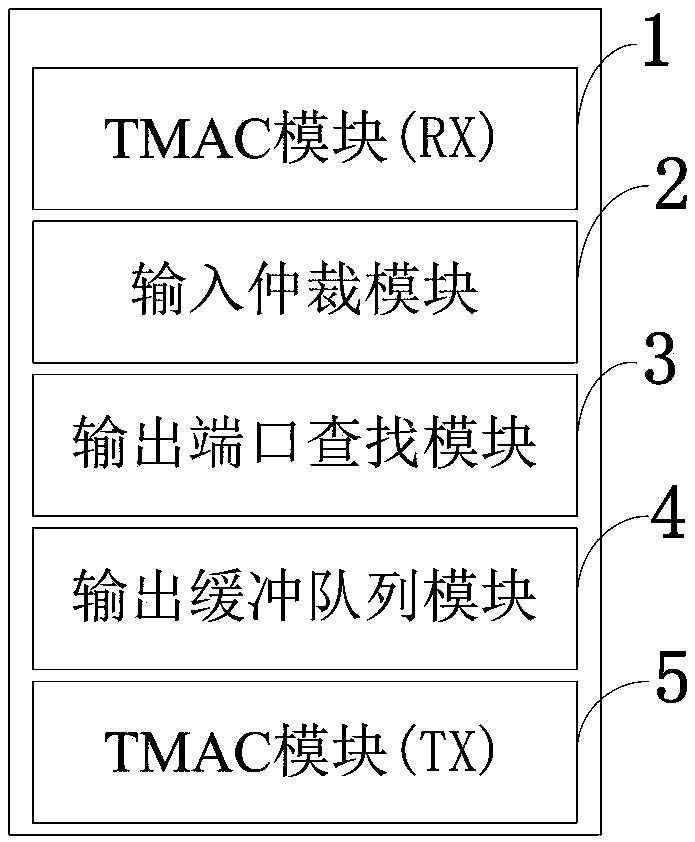

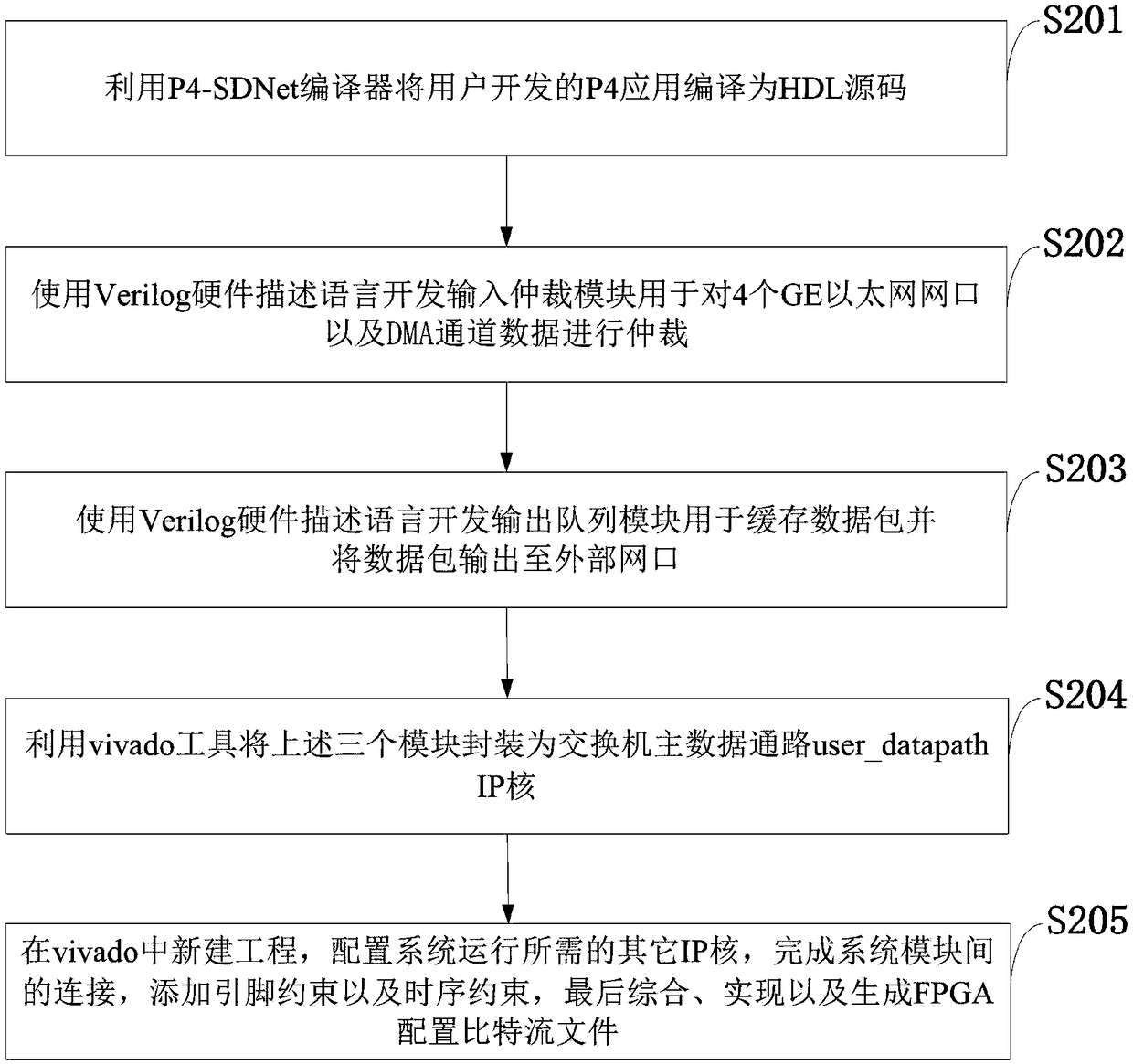

[0044] Such as figure 1 As shown, the P4-based programmable data plane switching prototype system provided by the embodiment of the pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com