Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53 results about "Sample and hold amplifier" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

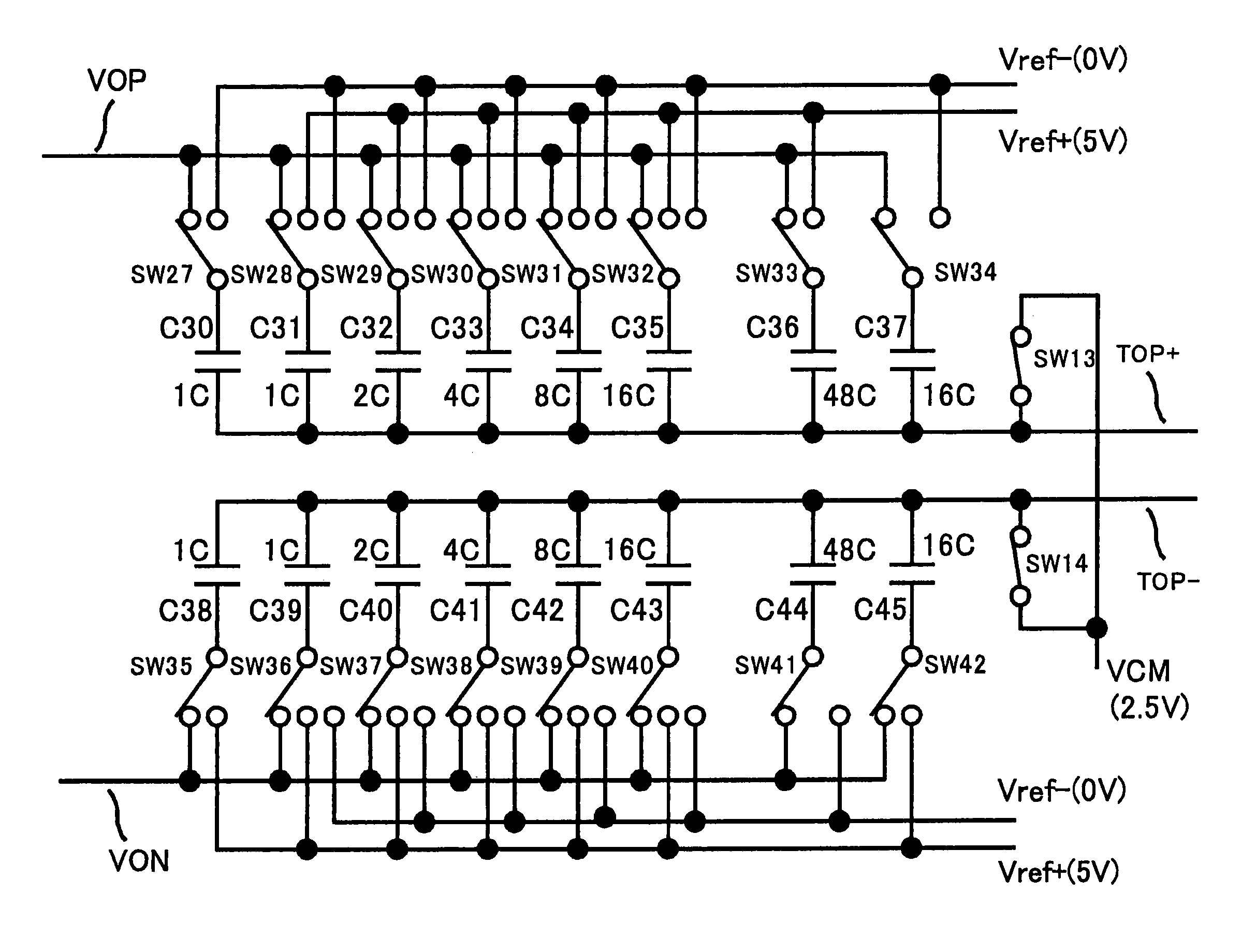

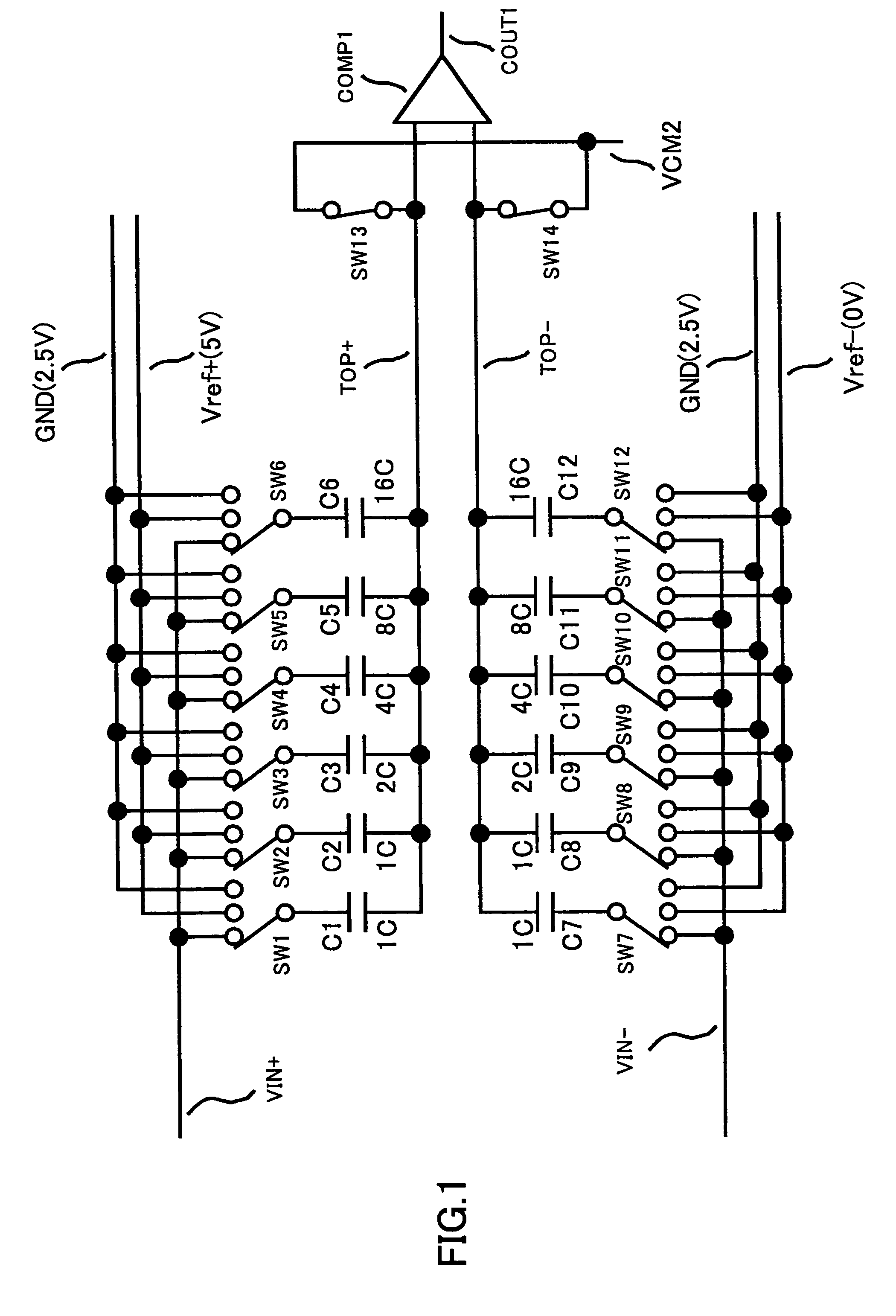

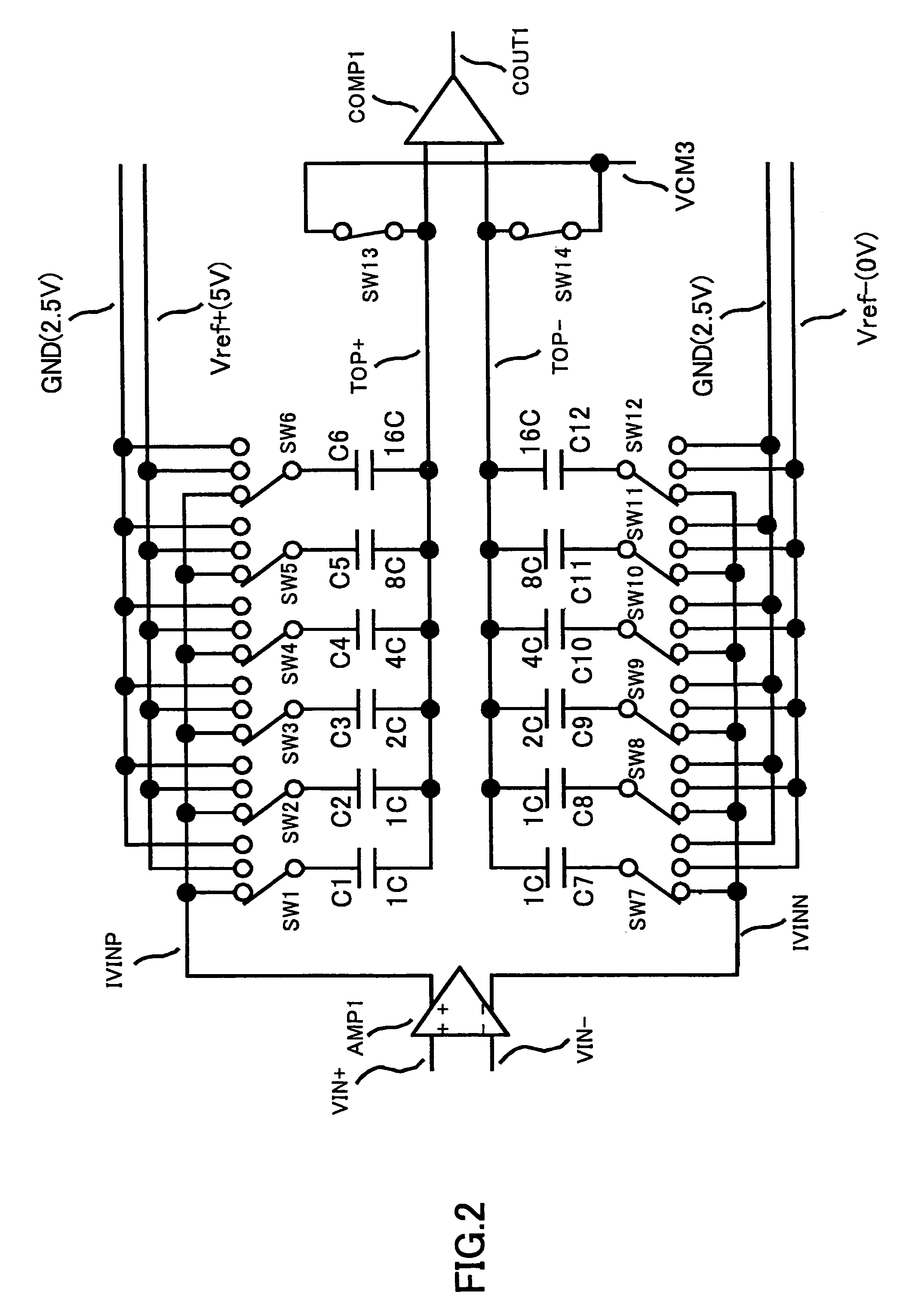

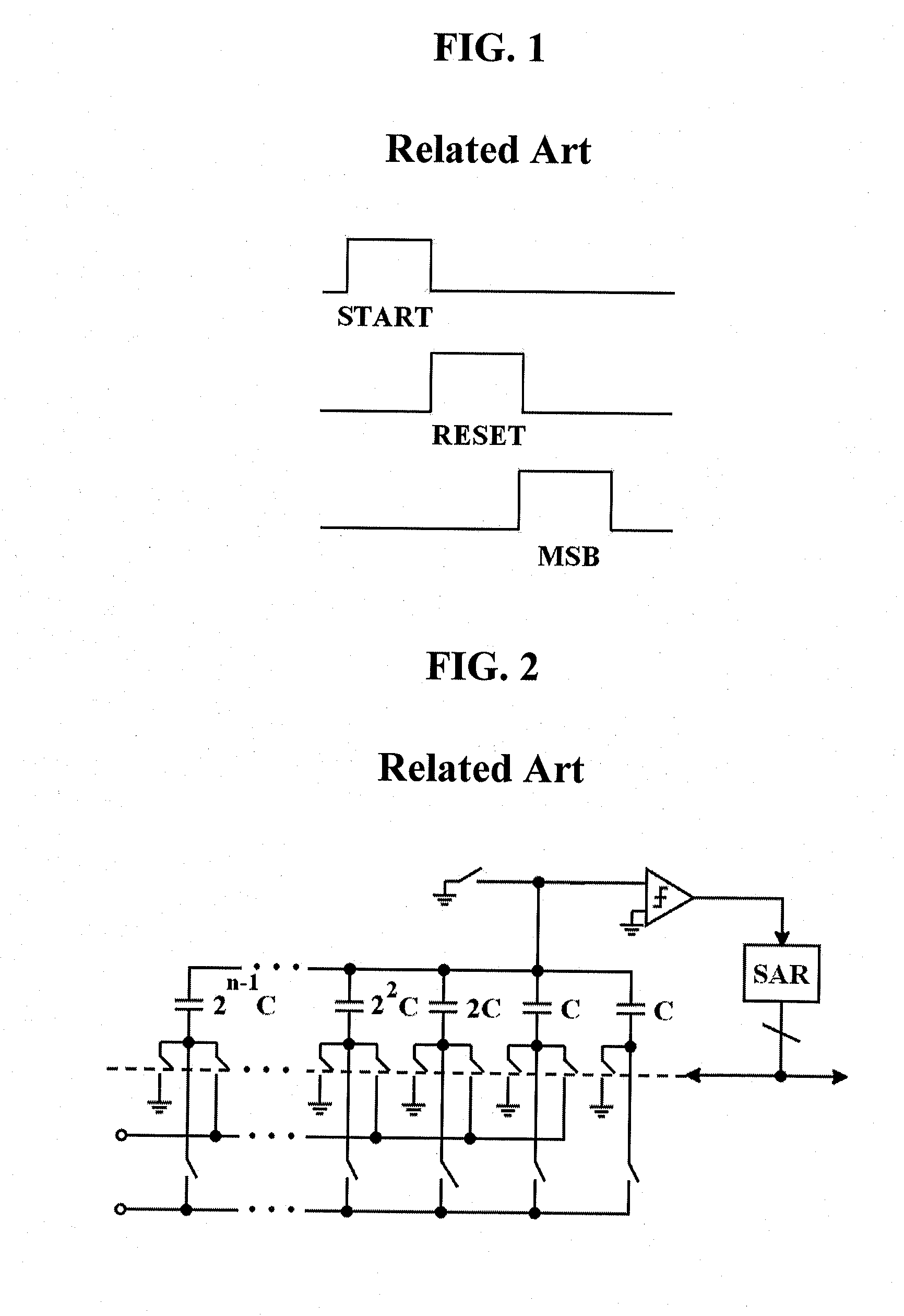

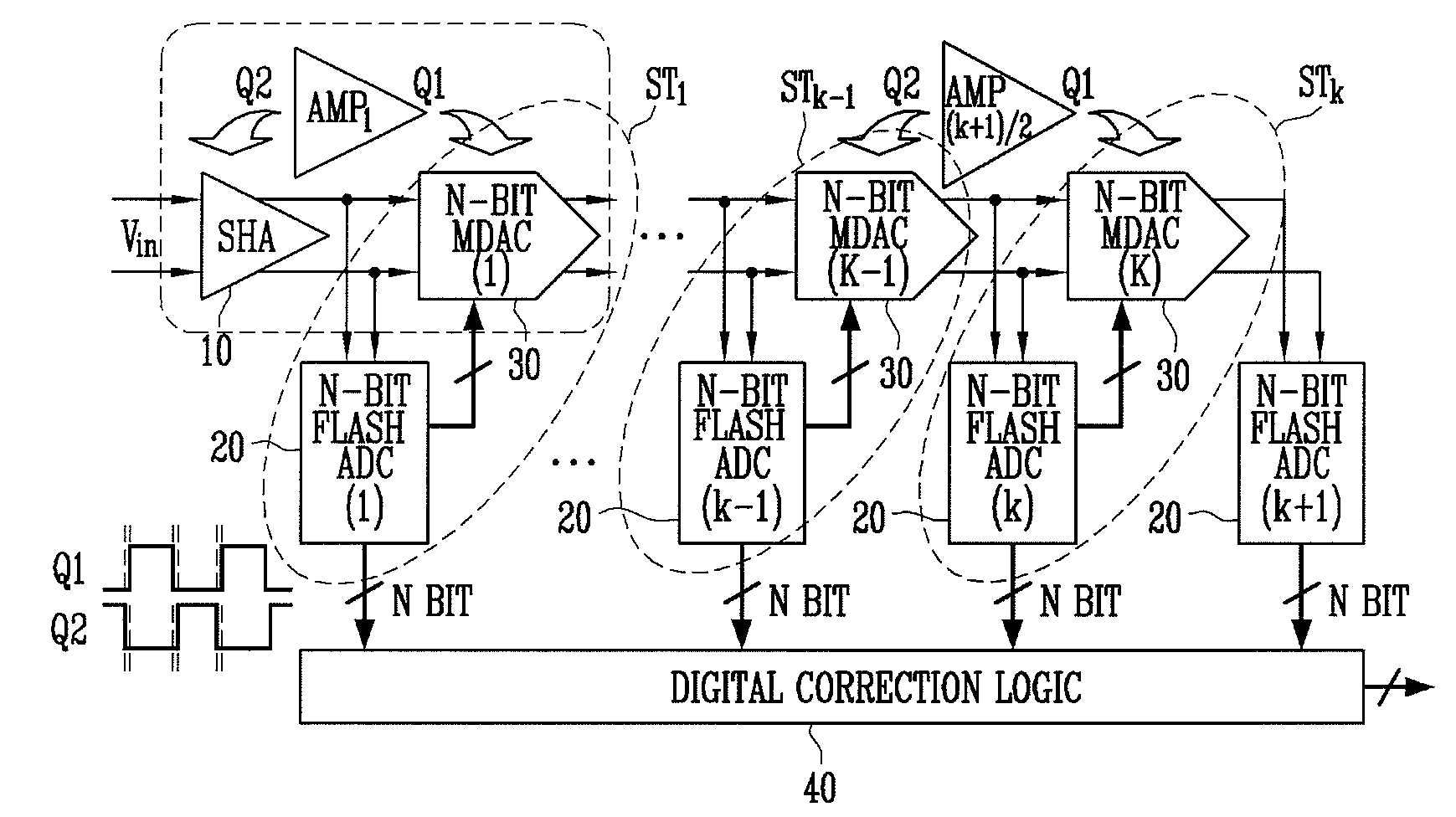

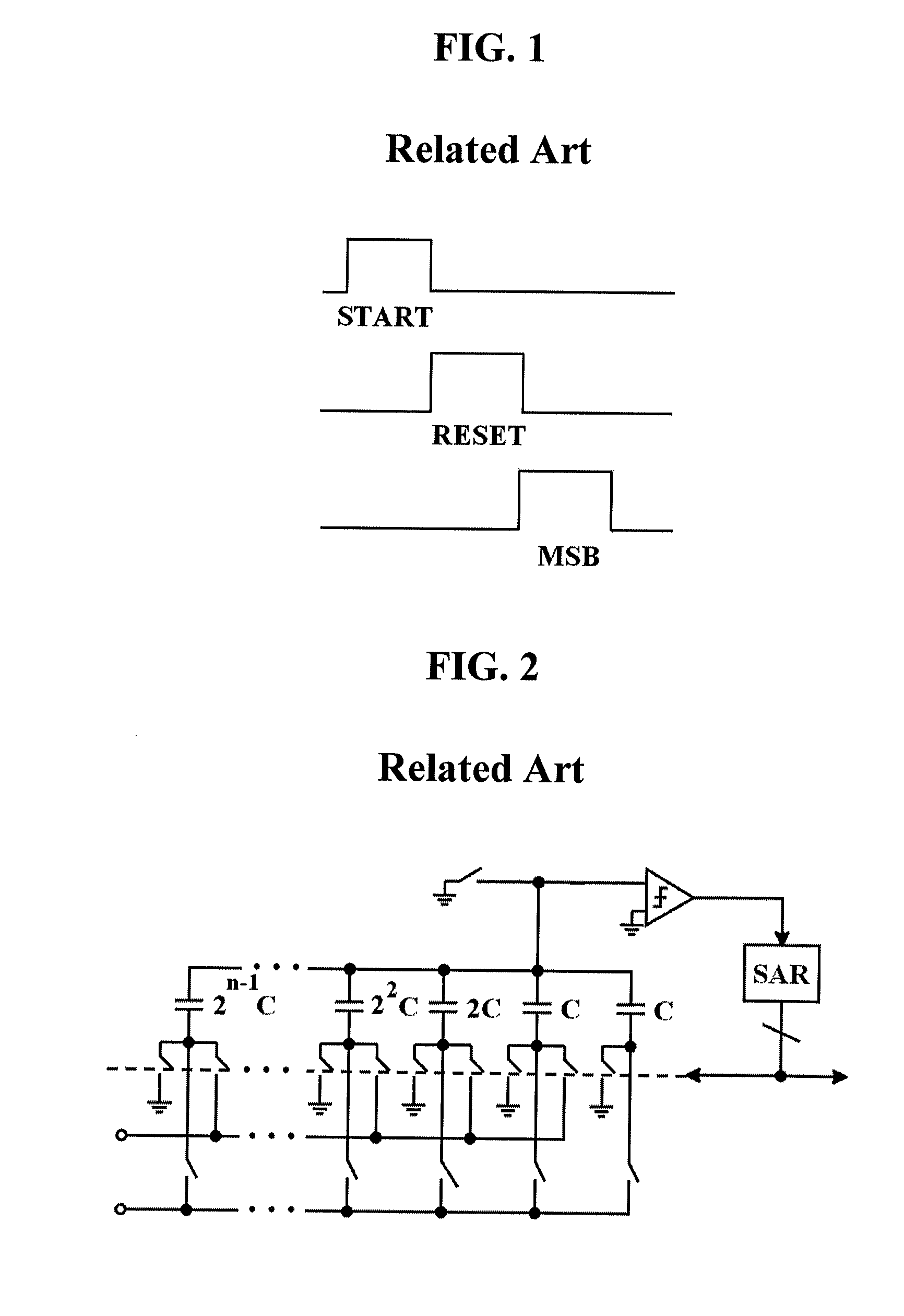

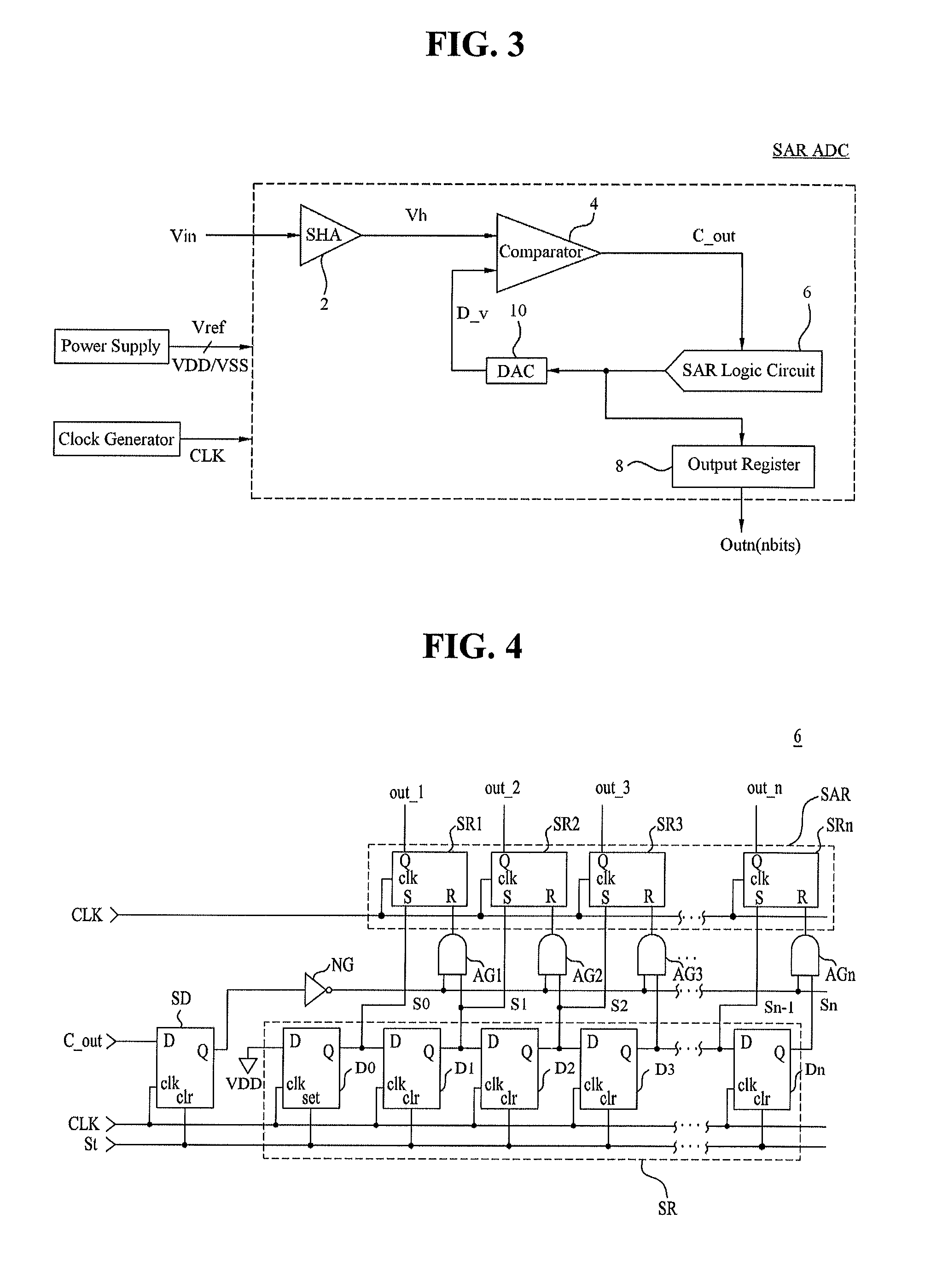

Successive approximation A/D converter

ActiveUS20070035434A1Increase speedElectric signal transmission systemsAnalogue-digital convertersControl signalĆuk converter

A successive approximation. A / D converter includes a sample-hold amplifier circuit configured to sample and hold an input analog voltage to produce an internal analog voltage proportional to the input analog voltage with a voltage gain being smaller than 1, a switched capacitor D / A converter coupled to the sample-hold amplifier circuit and including a plurality of capacitors for storing electric charge responsive to the internal analog voltage, the switched capacitor D / A converter configured to switch couplings of the capacitors in response to a control signal to produce a comparison analog voltage responsive to the internal analog voltage and the control signal, a comparator coupled to the switched capacitor D / A converter to produce a comparison result signal responsive to the comparison analog voltage, and a control circuit coupled to the comparator to supply the control signal responsive to the comparison result signal to the switched capacitor D / A converter.

Owner:CYPRESS SEMICON CORP

Successive approximation A/D converter provided with a sample-hold amplifier

ActiveUS7199745B2Increase speedElectric signal transmission systemsAnalogue-digital convertersControl signalĆuk converter

Owner:CYPRESS SEMICON CORP

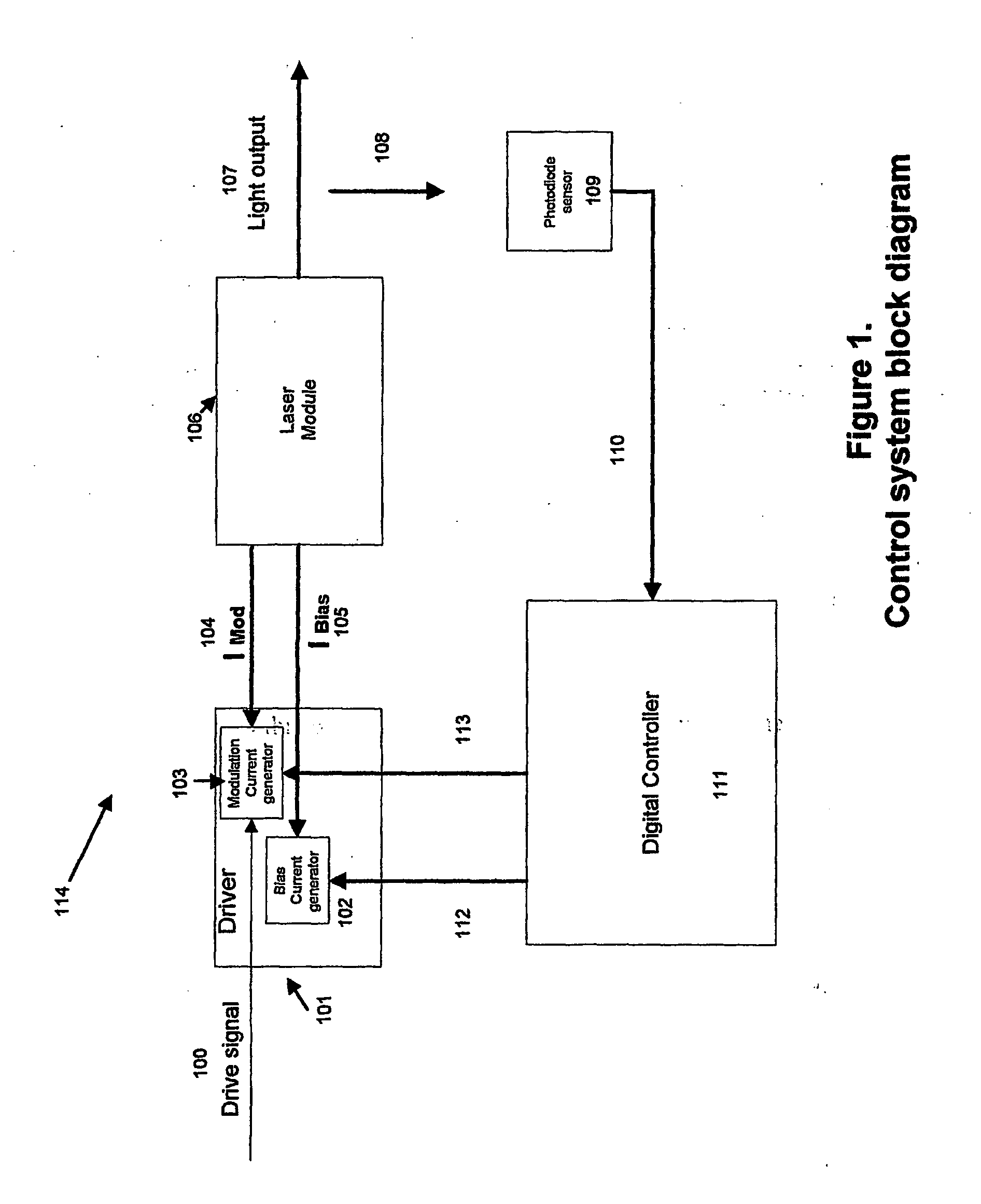

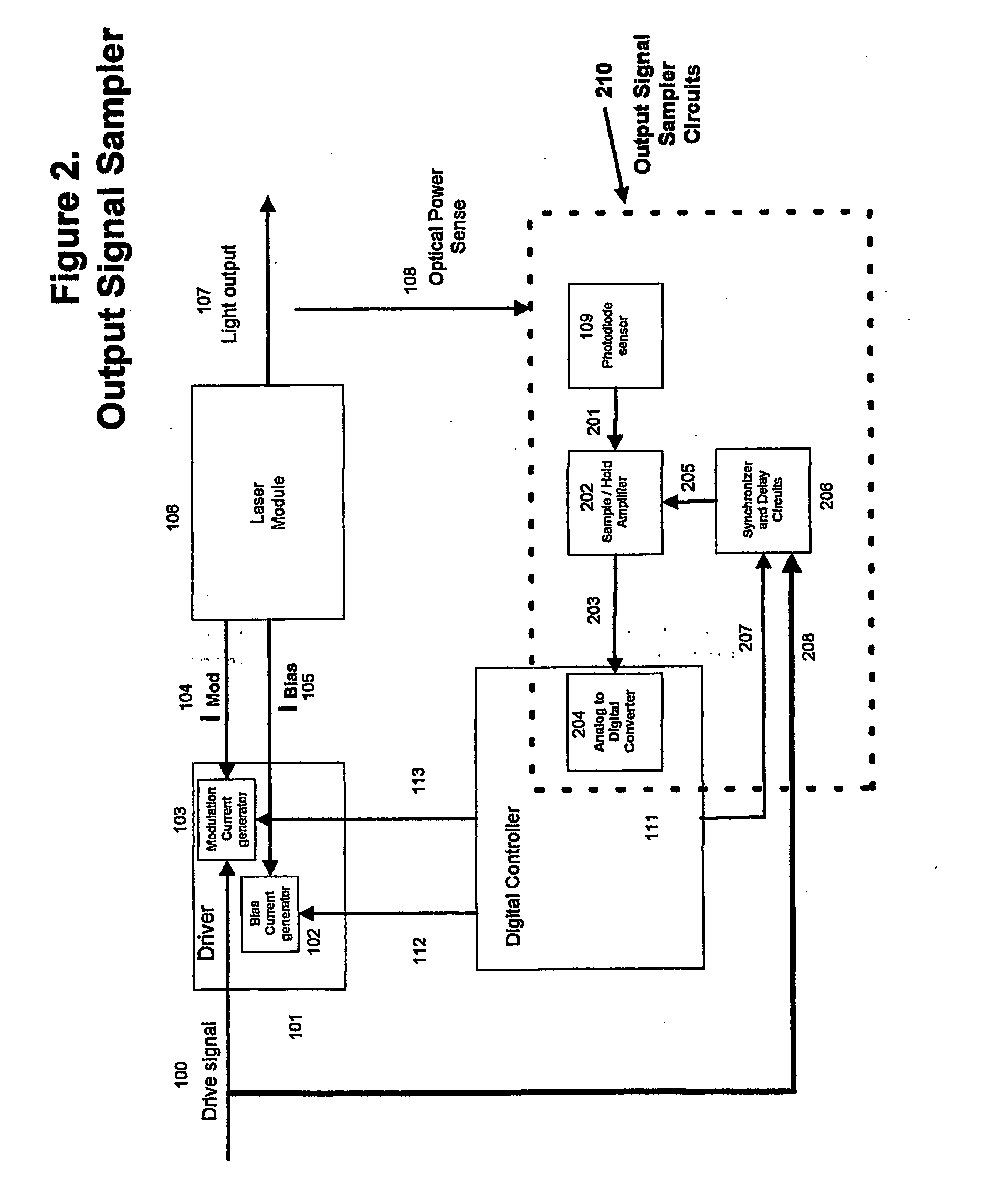

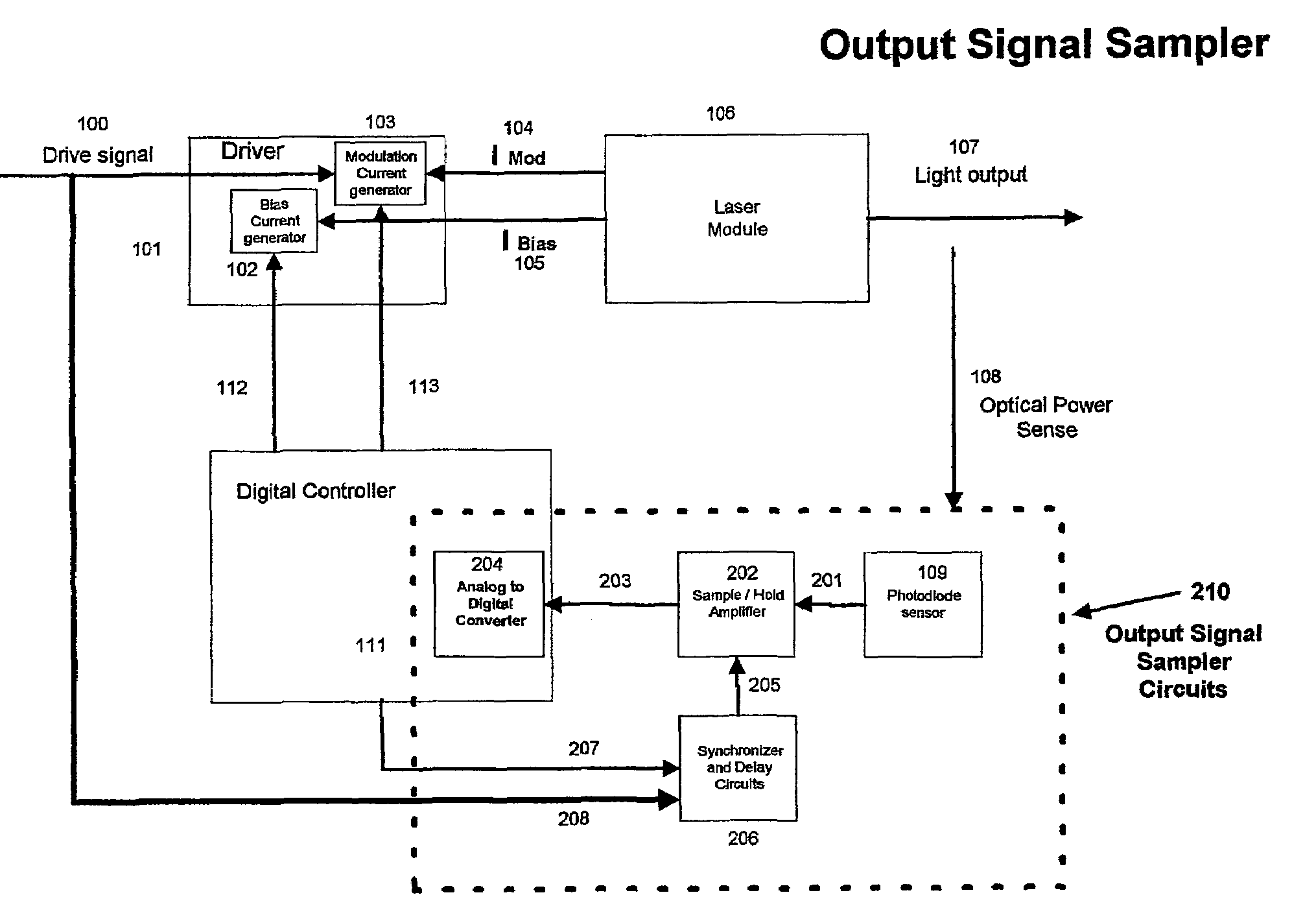

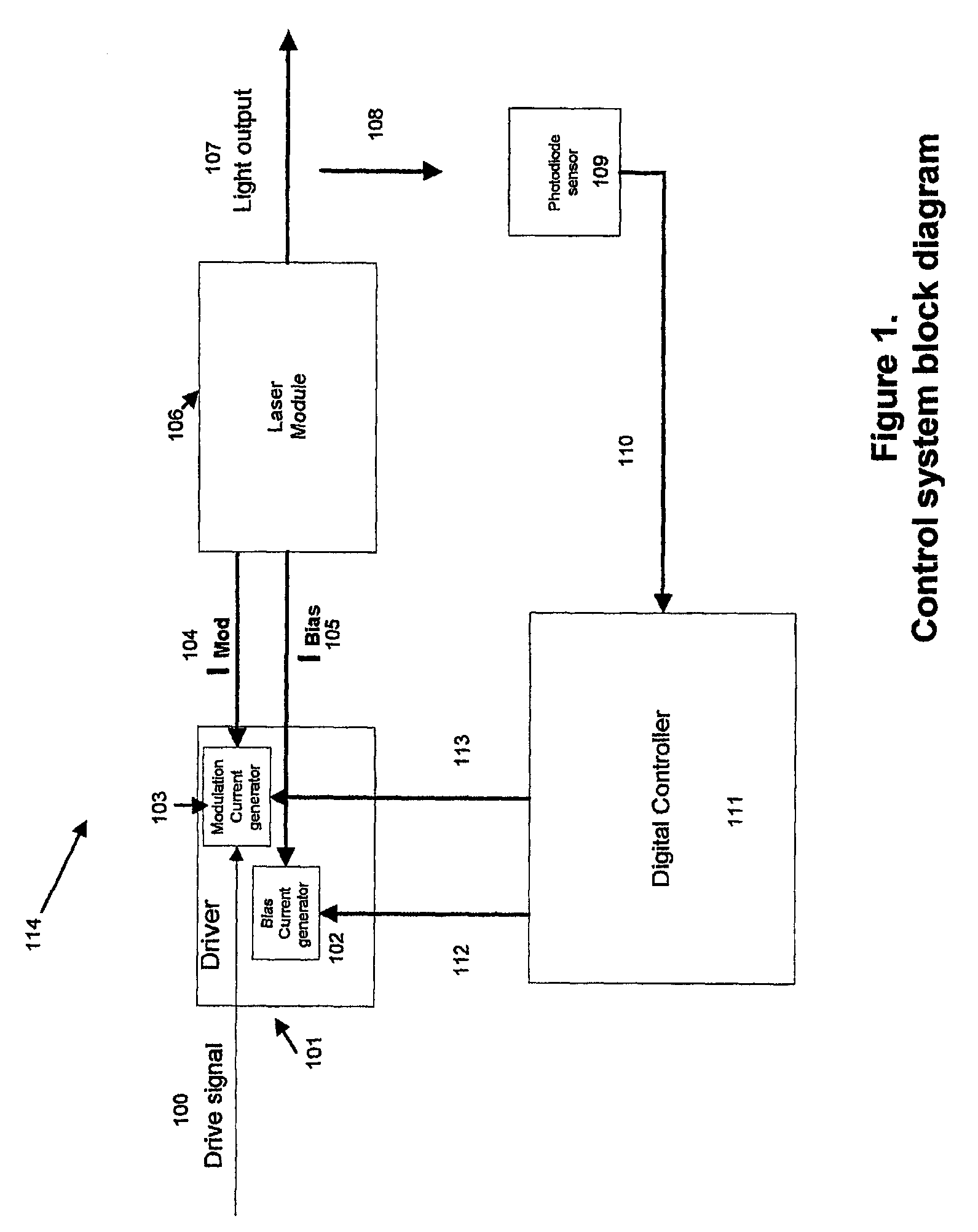

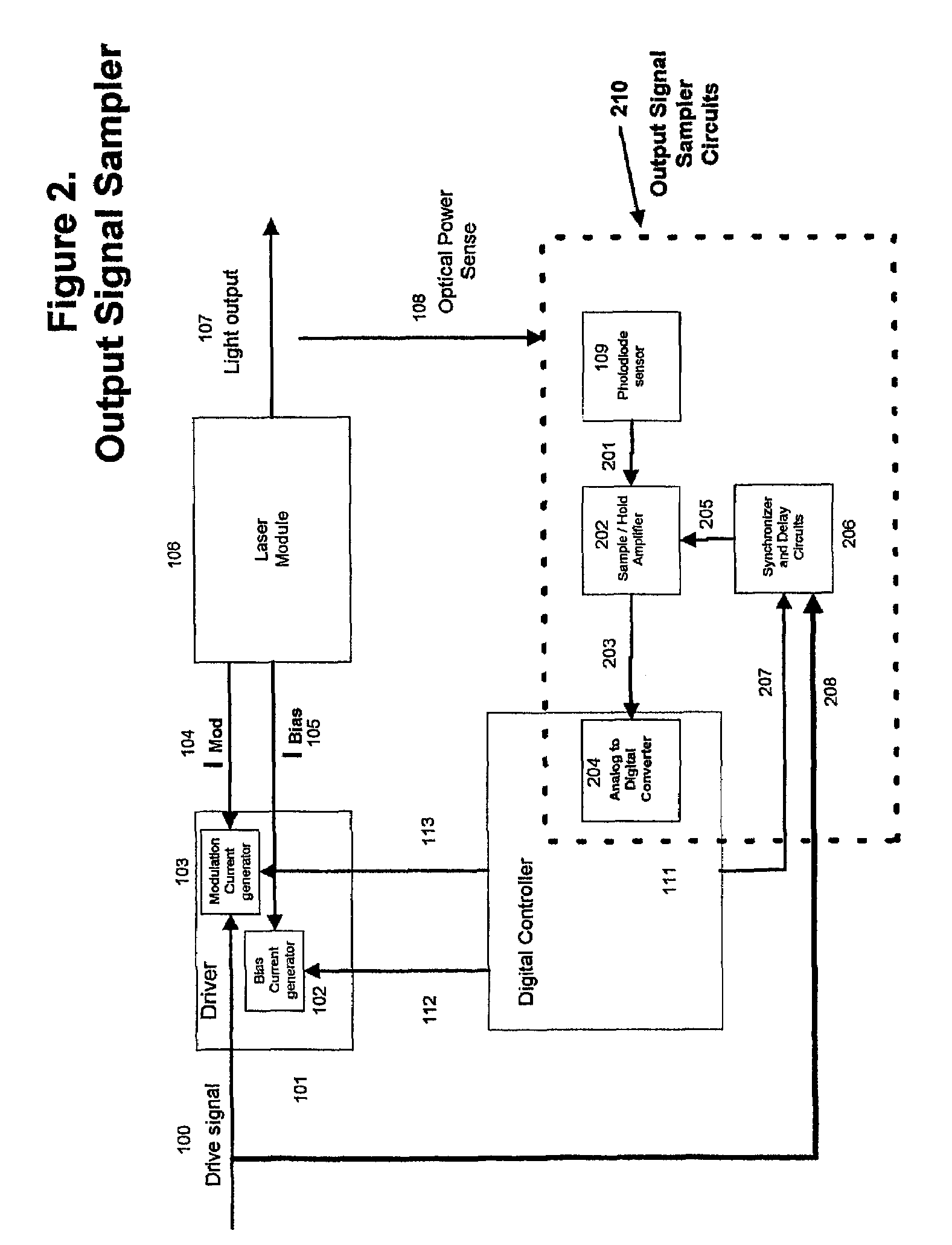

Apparatus and method for measurement for dynamic laser signals

InactiveUS20060165139A1No disruption of signal transmissionAccurate measurementLaser detailsElectromagnetic transmissionAudio power amplifierControl system

A system contains a laser output measurement circuit used in a laser control system (210). The circuits contain a photodiode (109), sample and hold amplifier (202), IC with synchronizer and delay circuits (206), and an analog to digital converter (204). The circuits measure the laser light output (107) while the laser Module (106) transmits signals. The measurement circuit tracks and stores the laser light output (107) signal using a Photodiode Sensor (109) and with a Sample / hold (202). The methods calculate the value of the laser light output (107) from mathematical relationships, which correlate the light output (107) of the laser Module (106) to the current value of the drive signal (100). Some of the distinguishing features in the present invention are 1) feedback information from the photodiode is obtained in a synchronous manner as a snapshot of the laser performance, and 2) the measurements are precise and calibrated, and 3) no disruption of the signal transmission occurs.

Owner:OL SECURITY LIABILITY CO +1

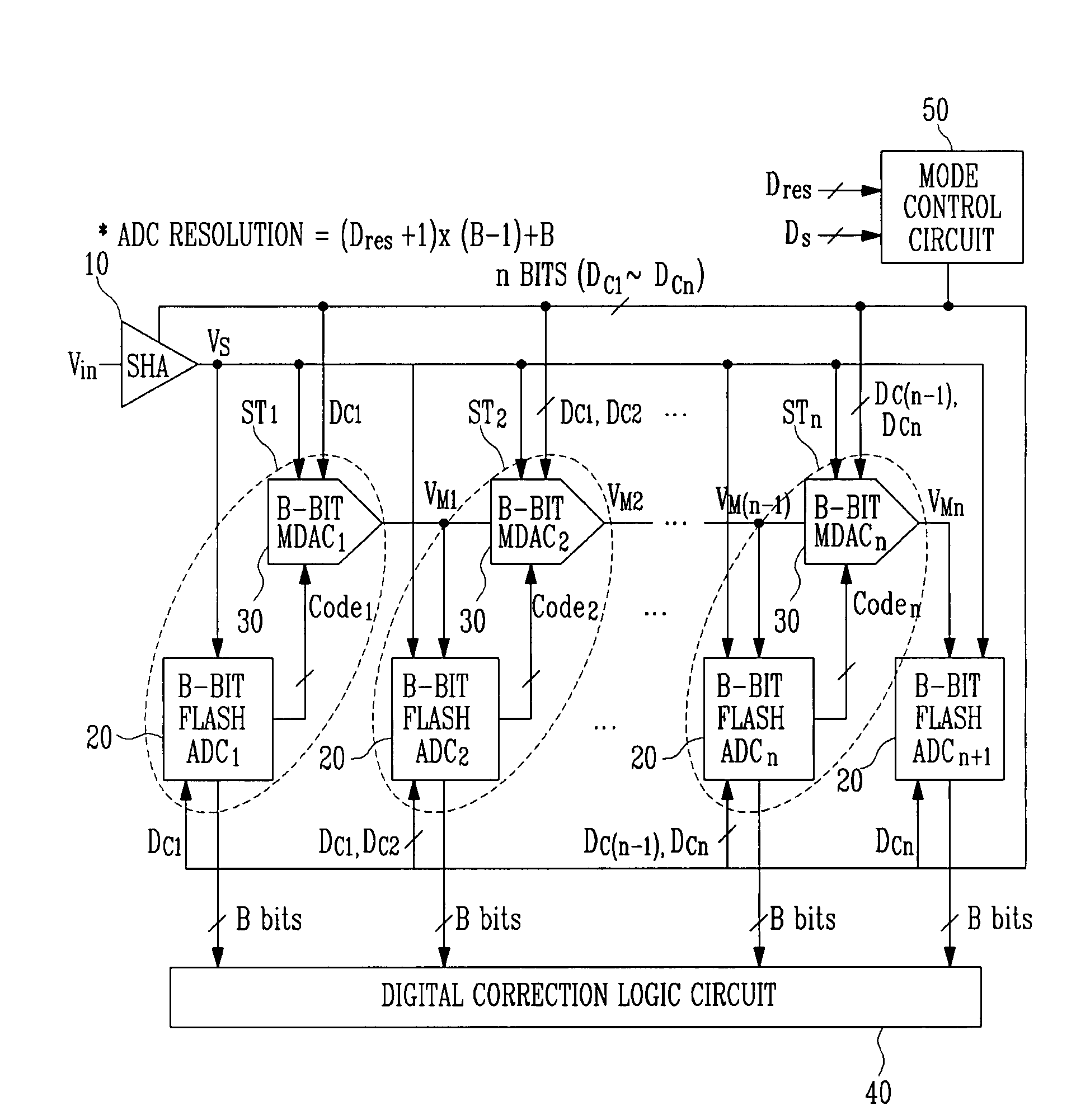

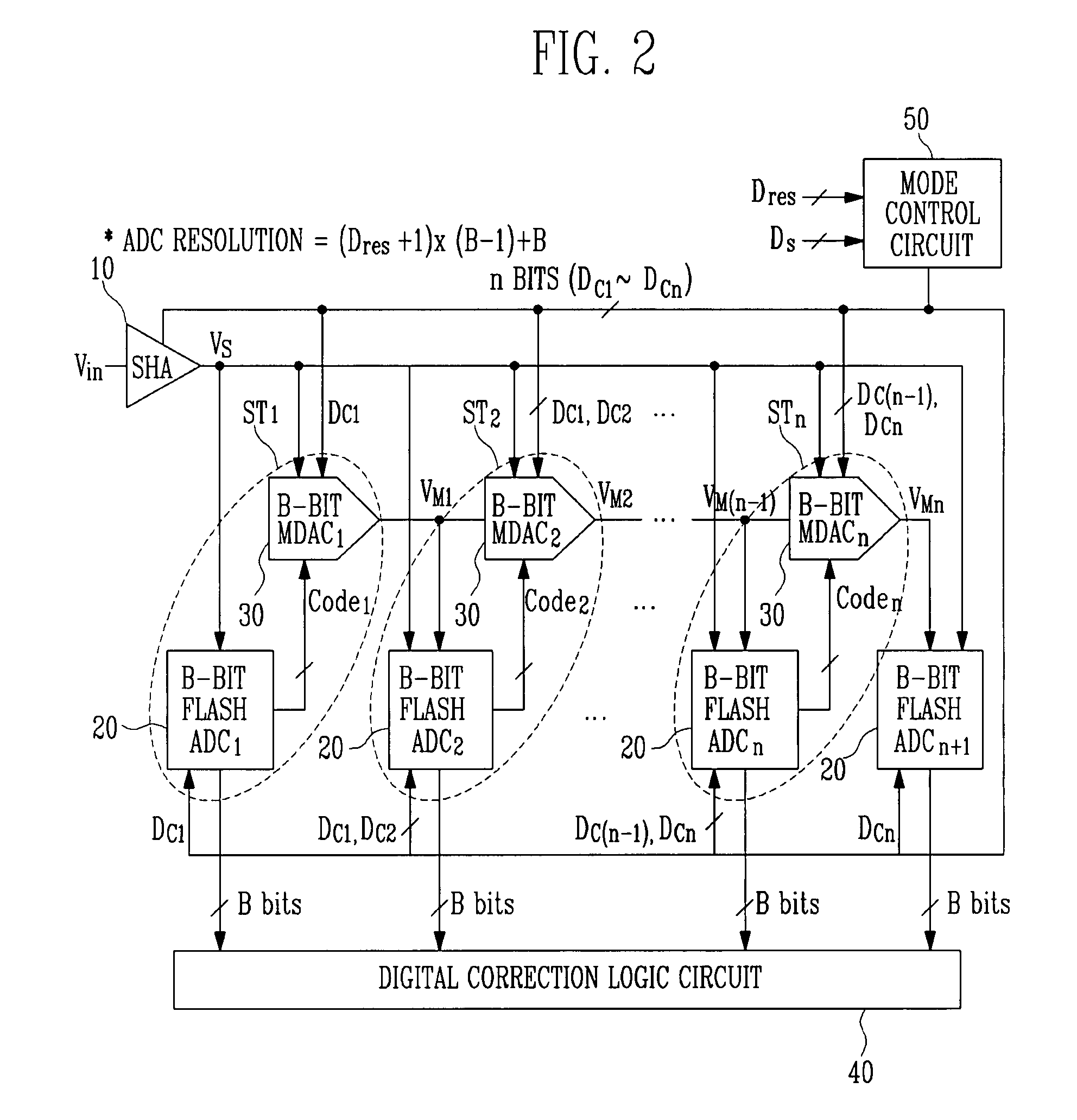

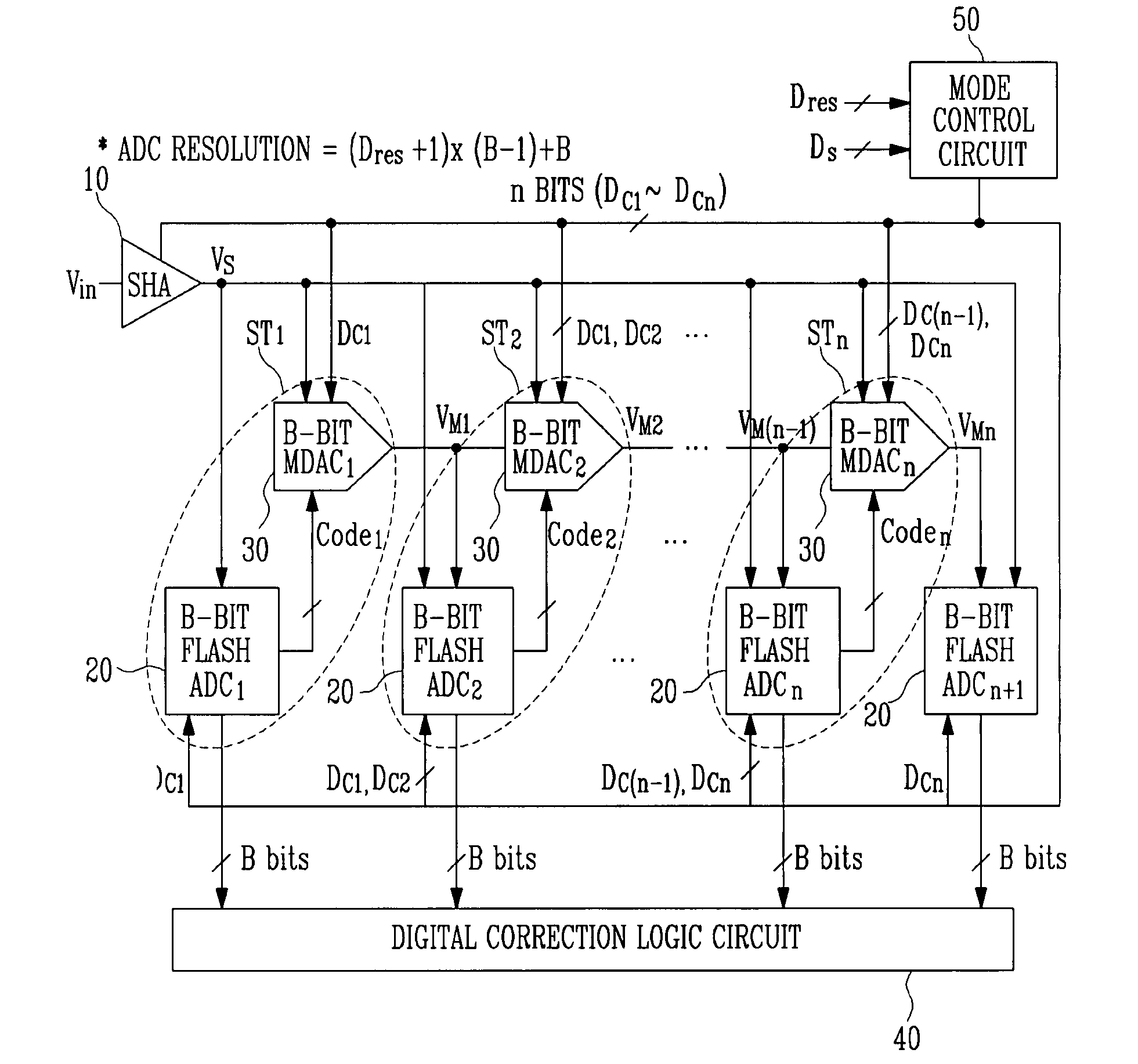

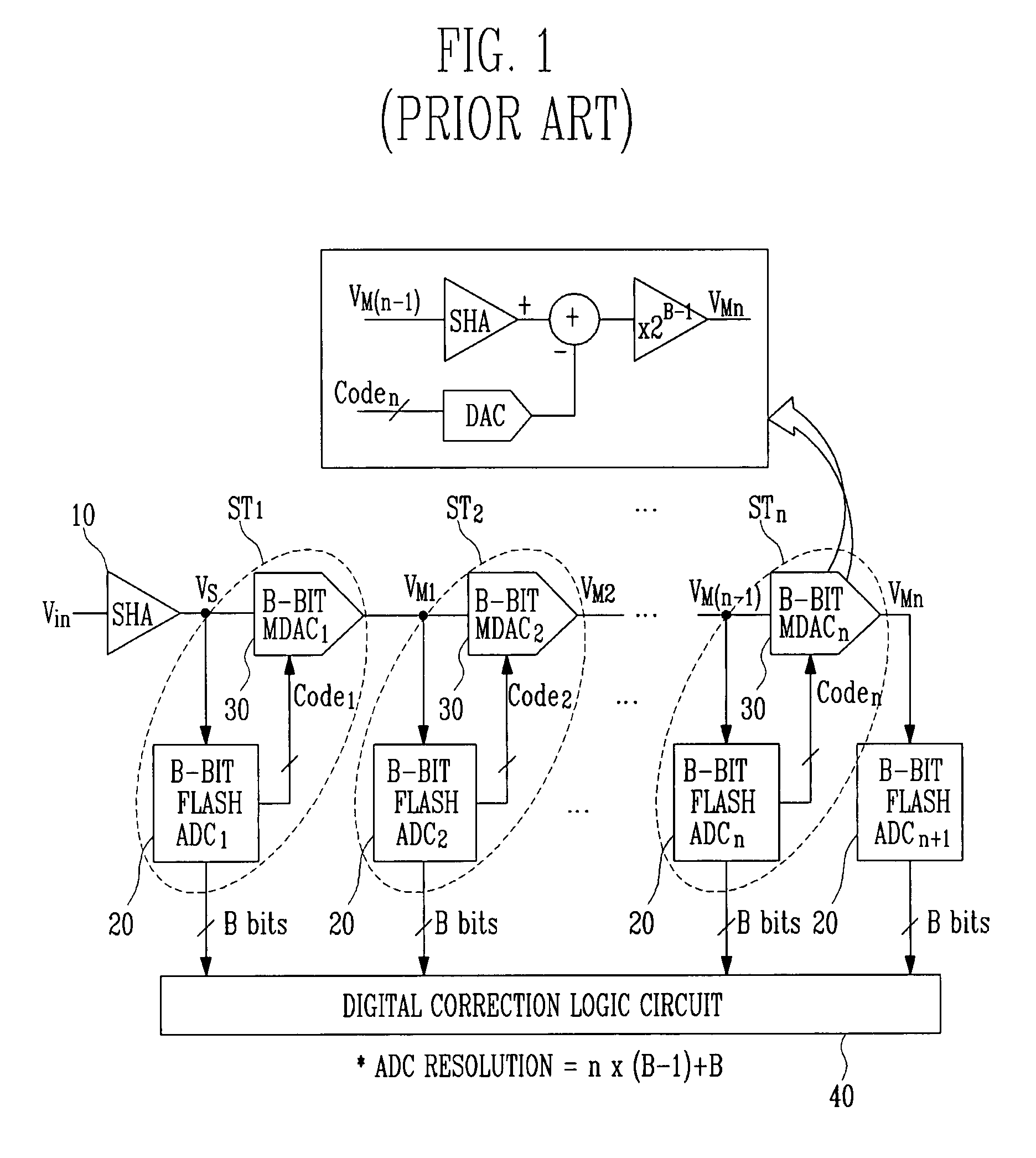

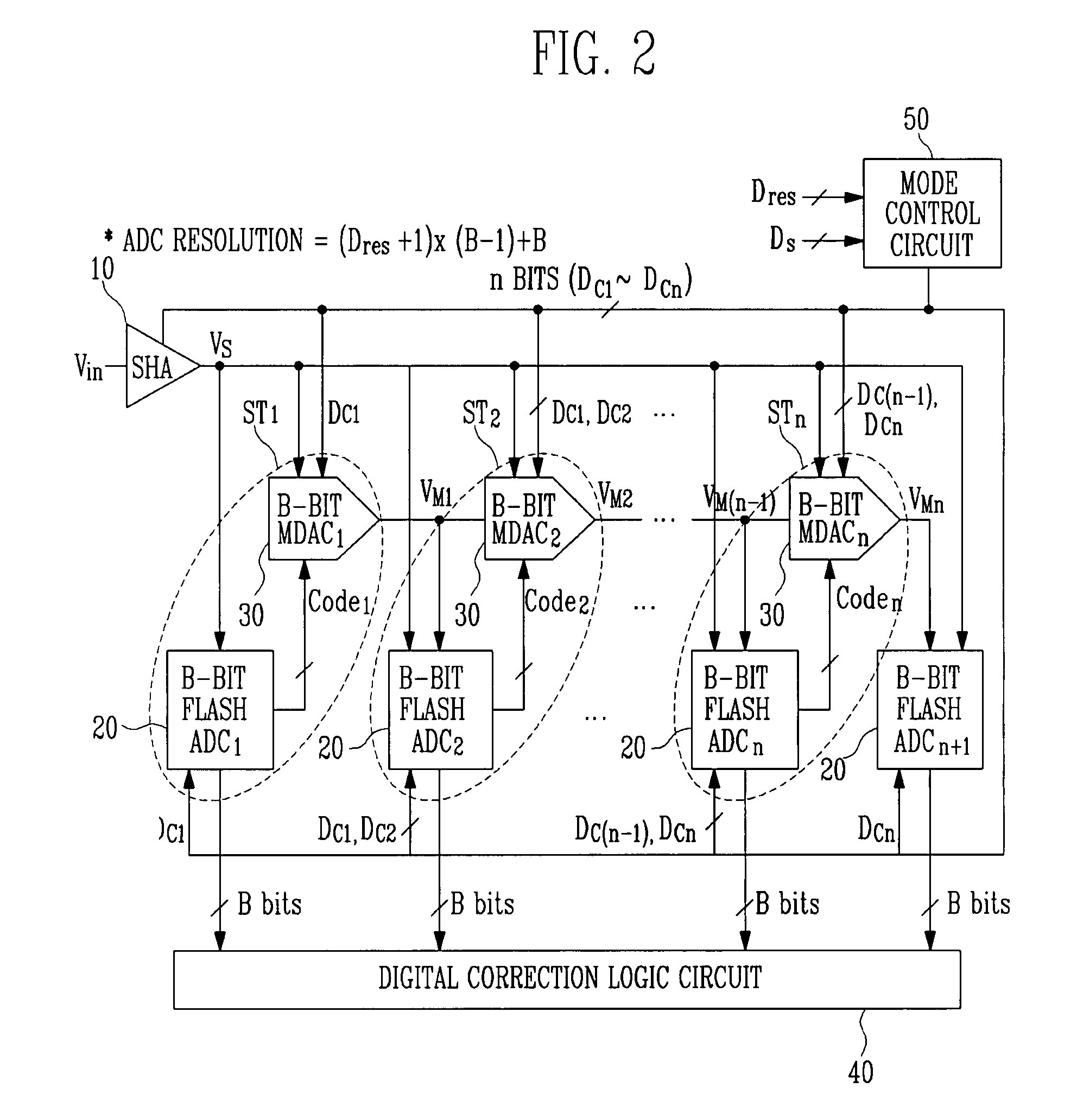

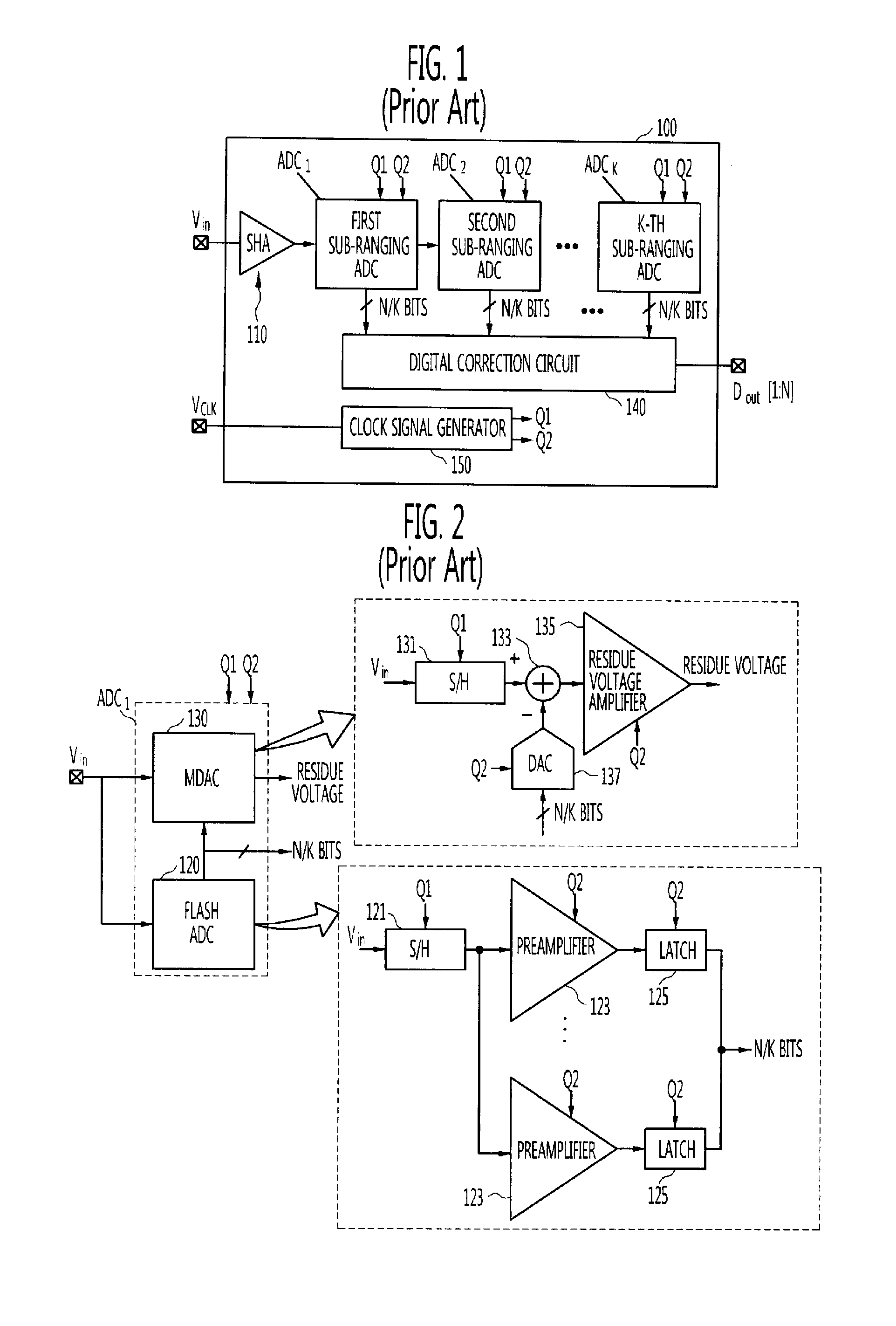

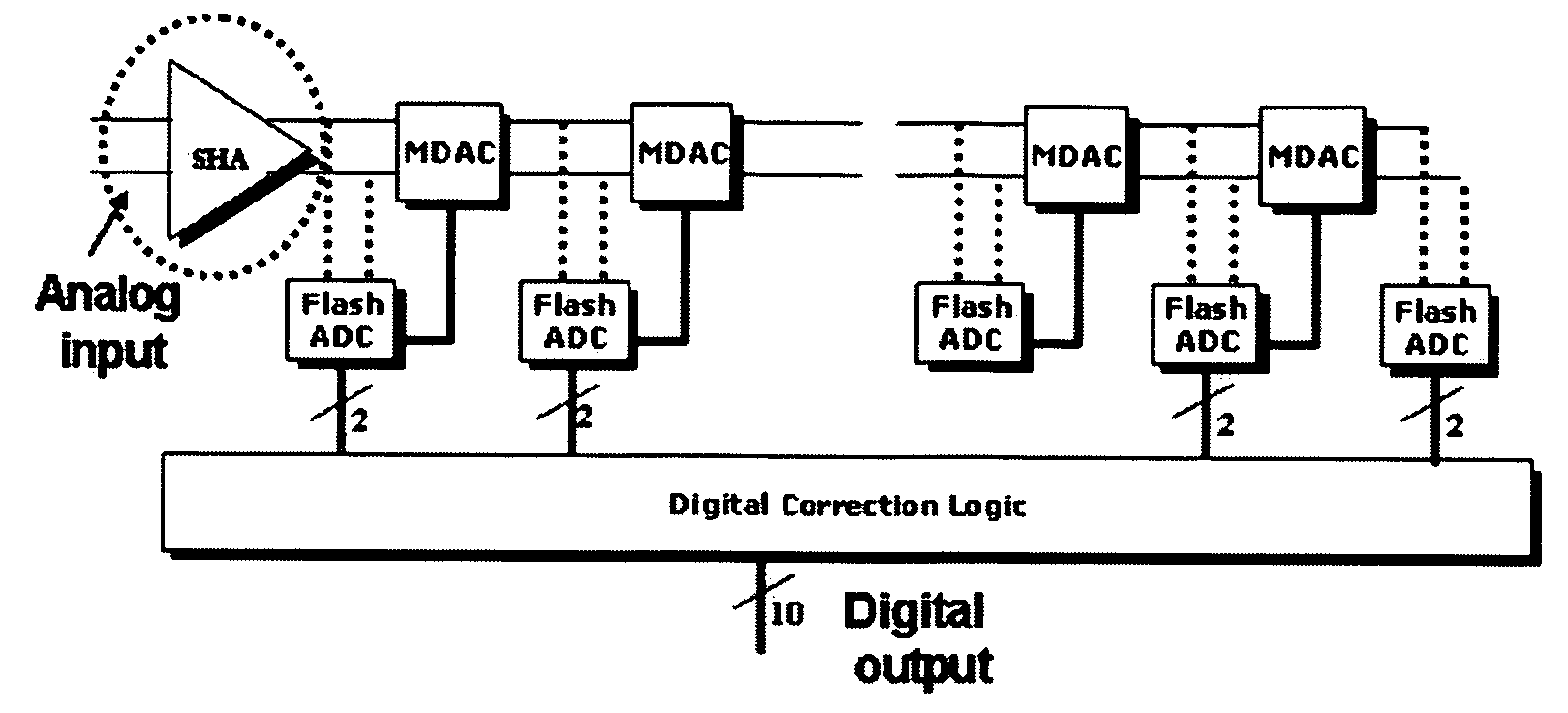

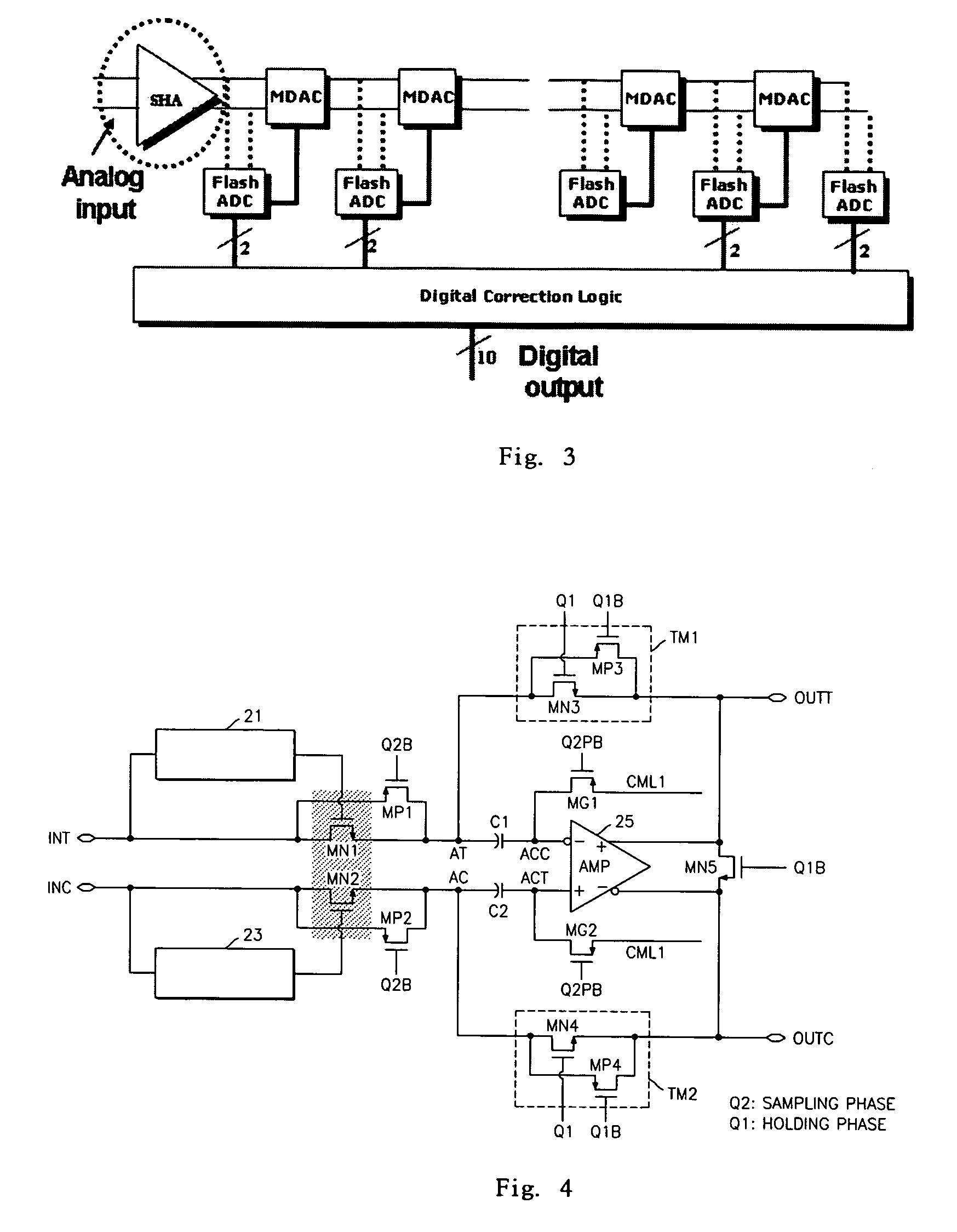

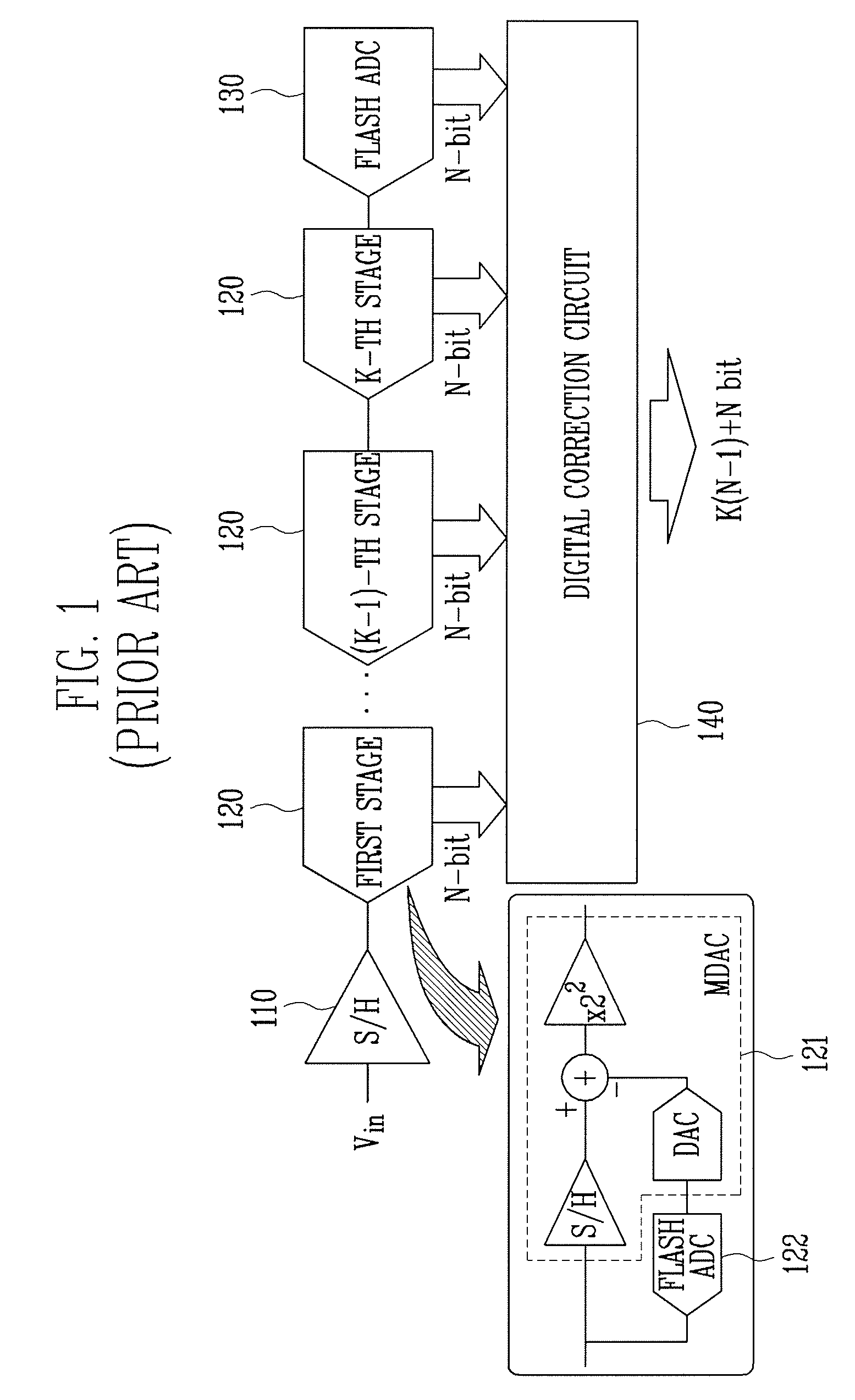

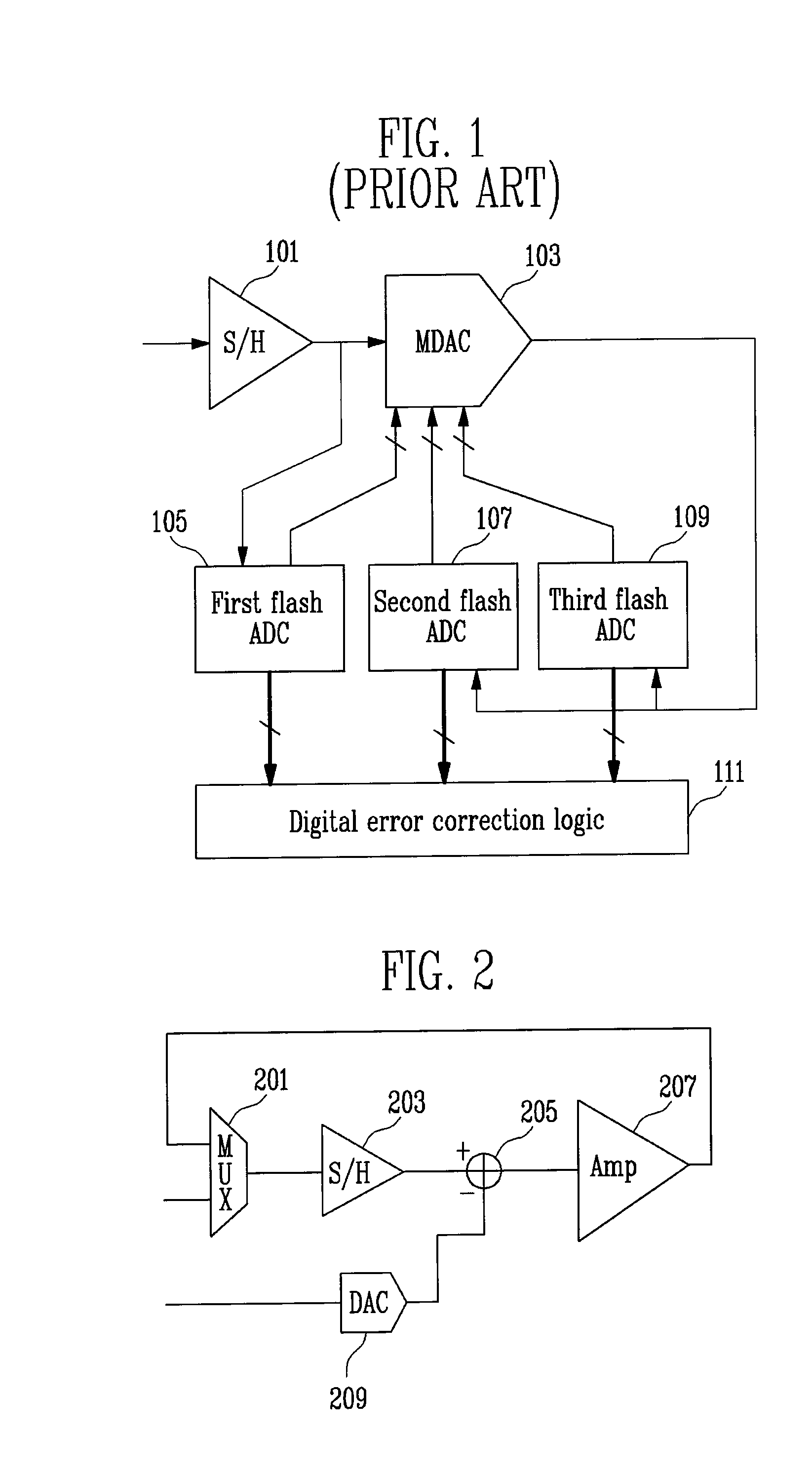

Multi-bit pipeline analog-to-digital converter capable of altering operating mode

InactiveUS20080129567A1Minimize power consumptionPower saving provisionsElectric signal transmission systemsControl signalMode control

Provided is a multi-bit pipeline analog-to-digital converter (ADC) capable of altering an operating mode. The ADC includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage; an n+1 number of B-bit flash ADCs for receiving an analog signal and converting the analog signal into a digital signal to output the digital signal; an n number of B-bit multiplying digital-to-analog converters (MDACs) for converting a difference between the digital signal output from the B-bit flash ADC and the front-stage output signal into an analog signal to output the analog signal to the next stage; and a mode control circuit for generating n-bit control signals to control the B-bit flash ADC and the B-bit MDAC according to required resolution and operating frequency. In the multi-bit pipeline ADC, an operating mode is altered by controlling the number of stages in a pipeline and a signal path according to required resolution and operating frequency, so that power consumption can be minimized under the corresponding operating condition and signals can be processed in a variety of ways.

Owner:ELECTRONICS & TELECOMM RES INST

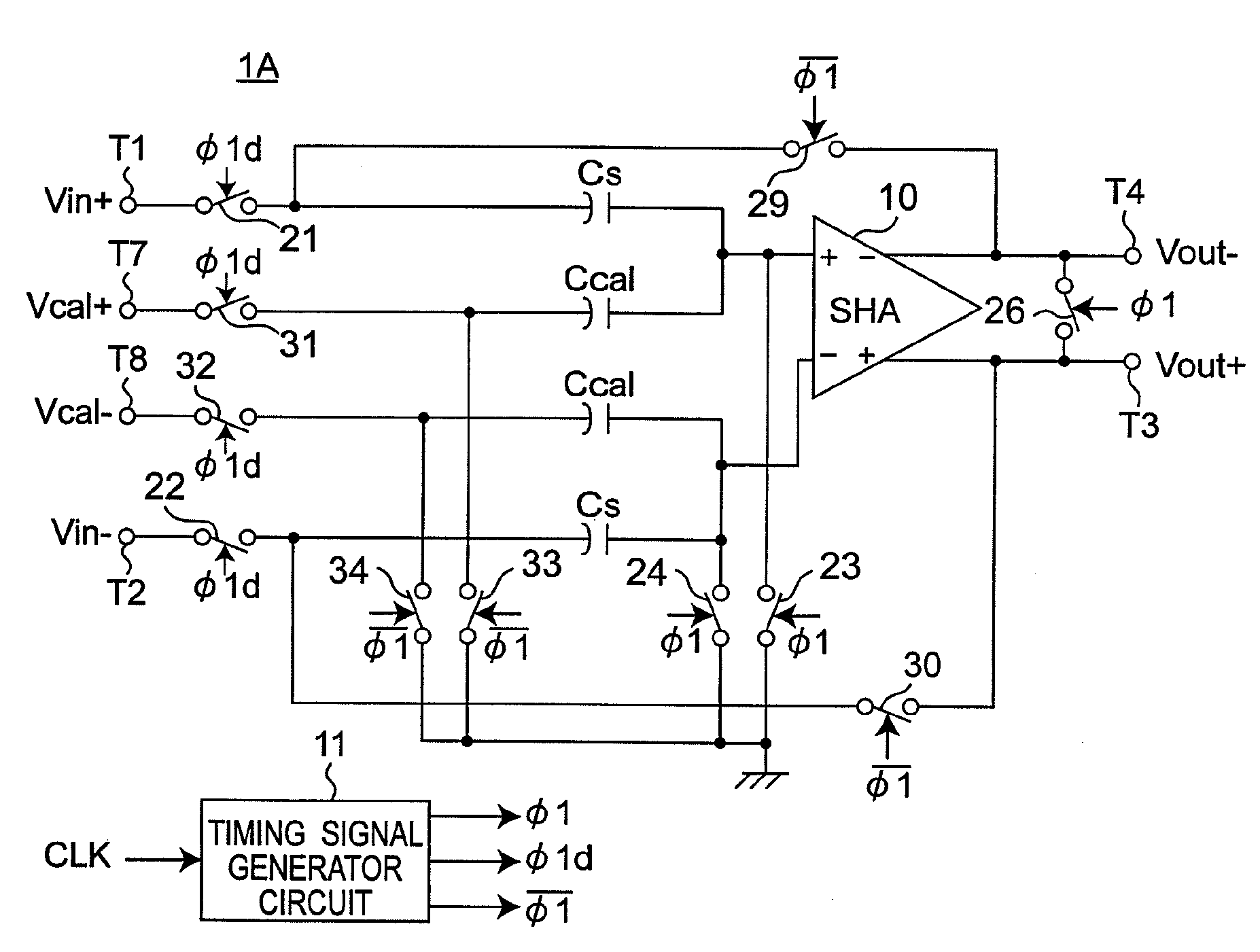

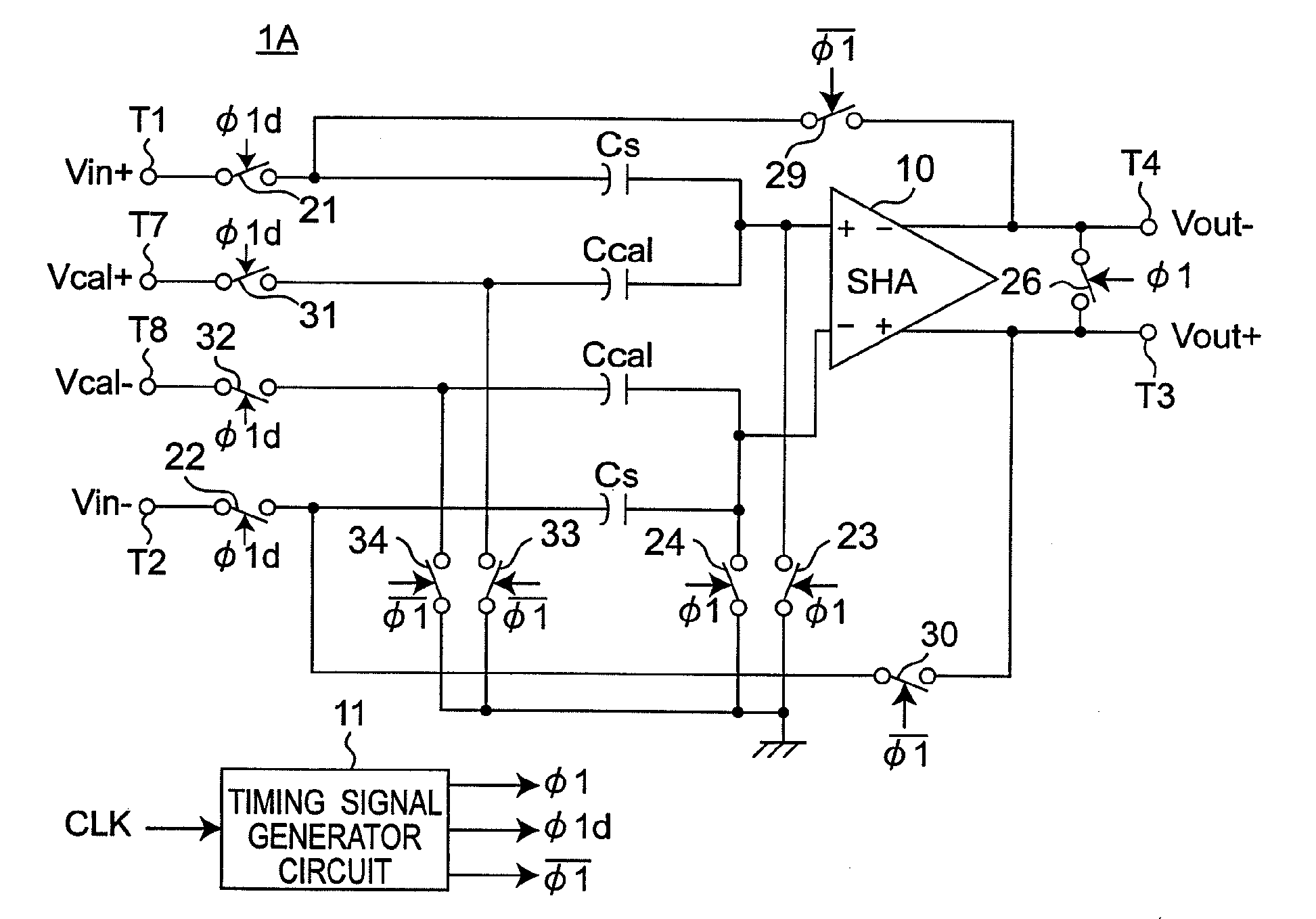

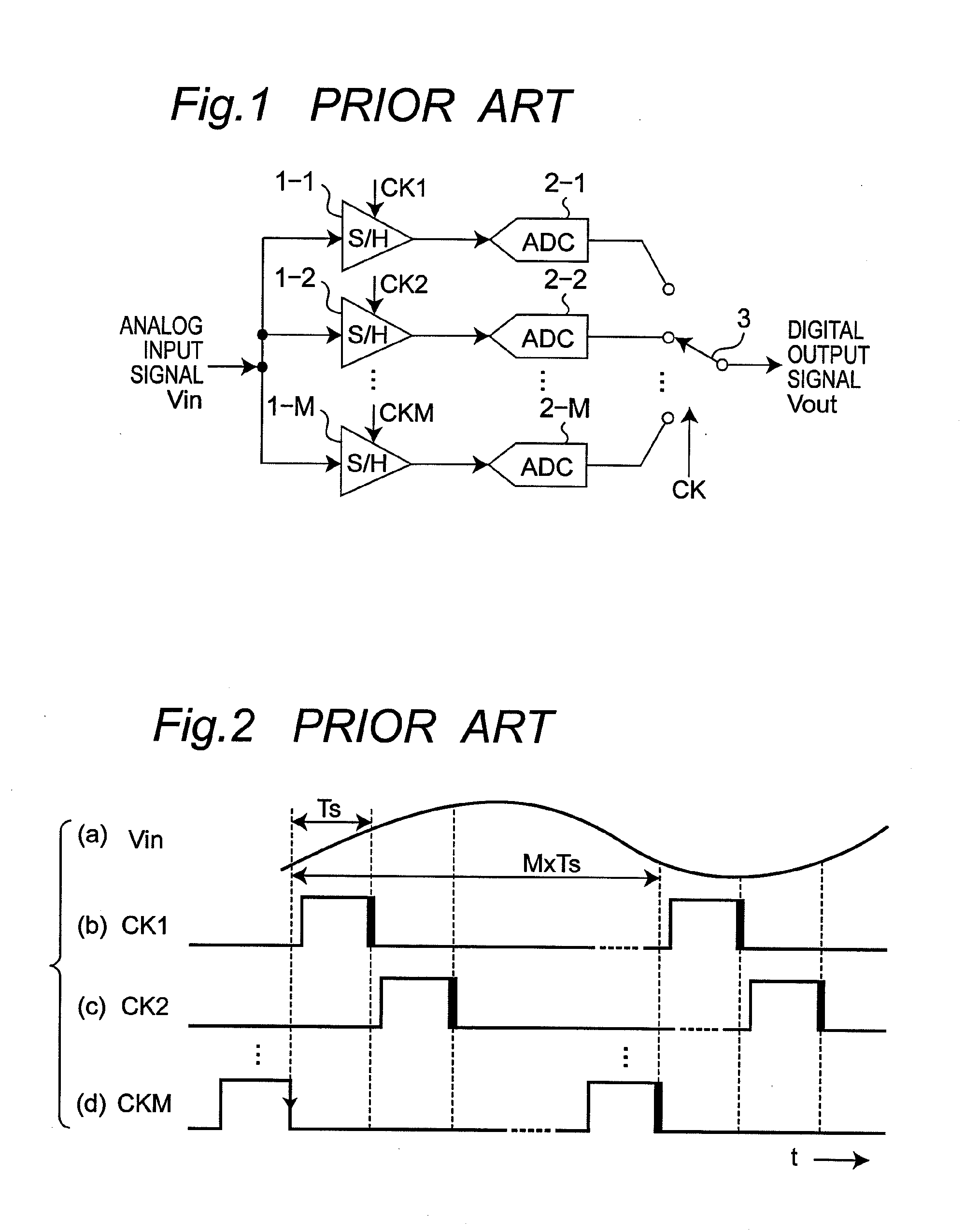

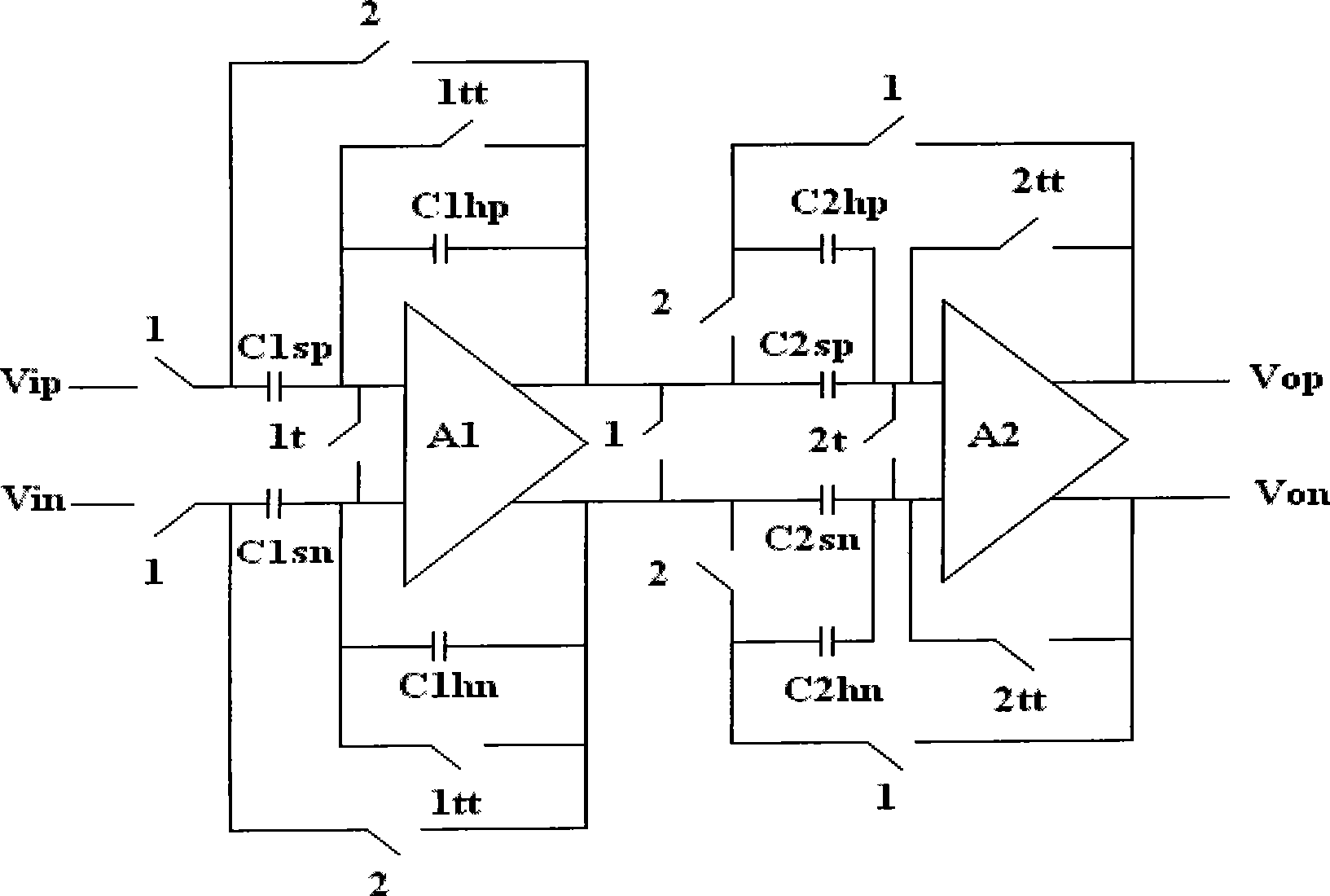

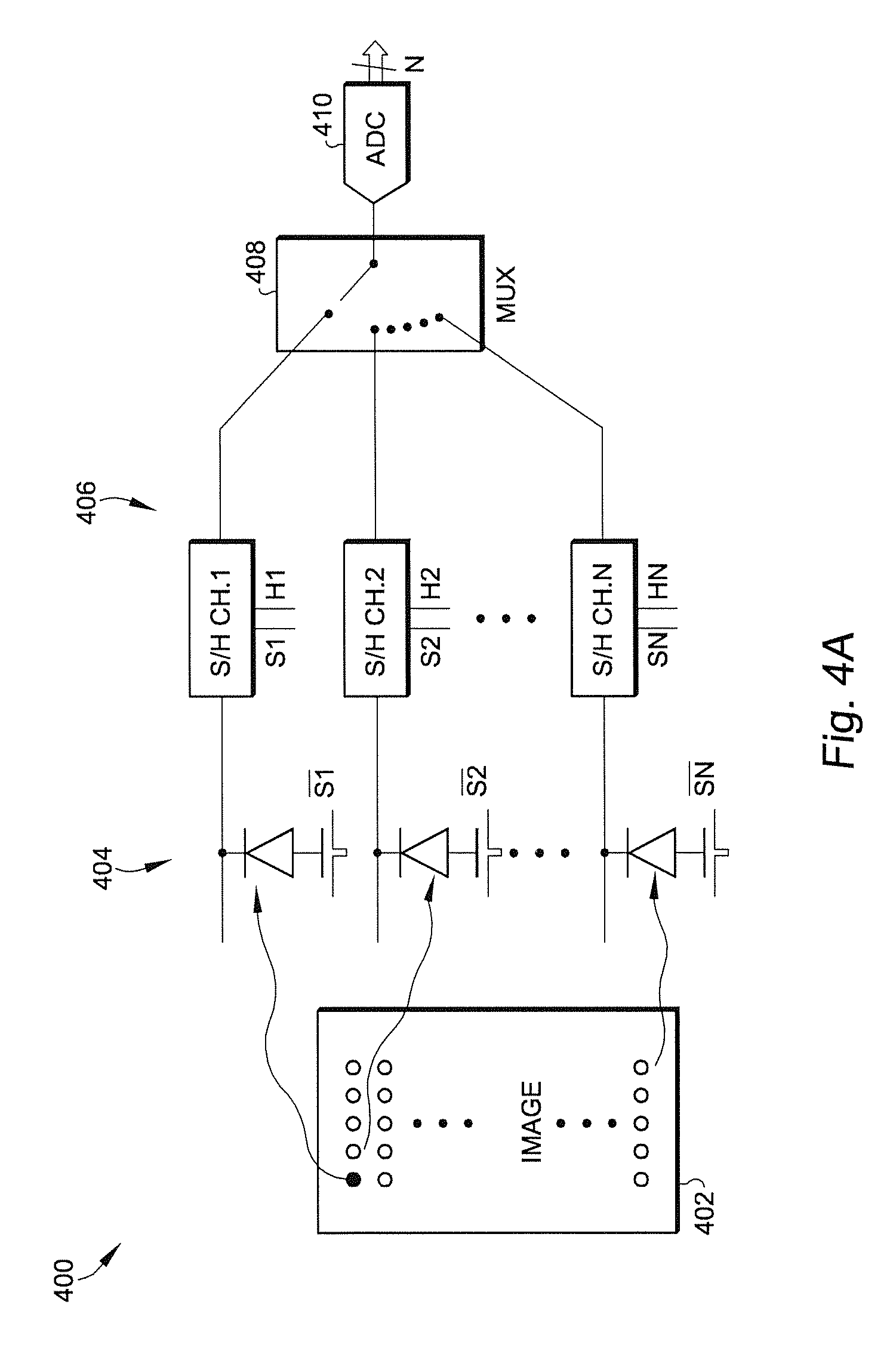

Sample hold circuit for use in time-interleaved A/D converter apparatus including paralleled low-speed pipeline A/D converters

InactiveUS7834786B2Reduce areaMinimize the clock skewElectric signal transmission systemsElectric analogue storesCapacitanceLow speed

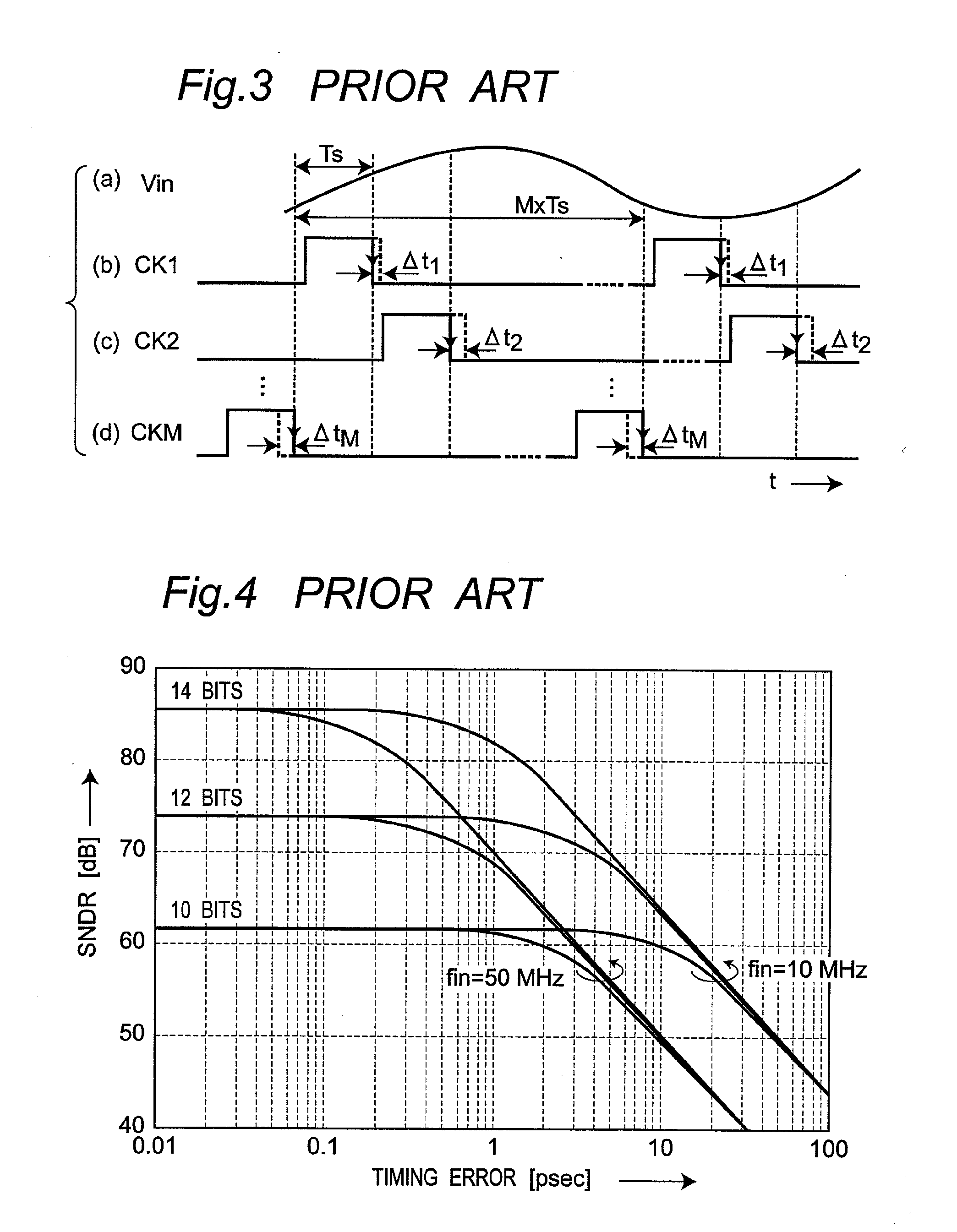

A sample hold circuit is provided for use in a time-interleaved A / D converter apparatus including a plurality of low-speed pipeline A / D converters which are parallelized. The sample hold circuit includes a sampling capacitor and a sample hold amplifier, and operates to sample and hold an input signal by using a switched capacitor. An adder circuit of the sample hold circuit adds a ramp calibration signal to the input signal, by inputting the ramp calibration signal generated to have a frequency identical to that of a sampling clock signal and a predetermined slope based on the sampling clock signal, into a sample hold amplifier via a calibration capacitor having a capacitance smaller than that of the sampling capacitor.

Owner:SEMICON TECH ACADEMIC RES CENT

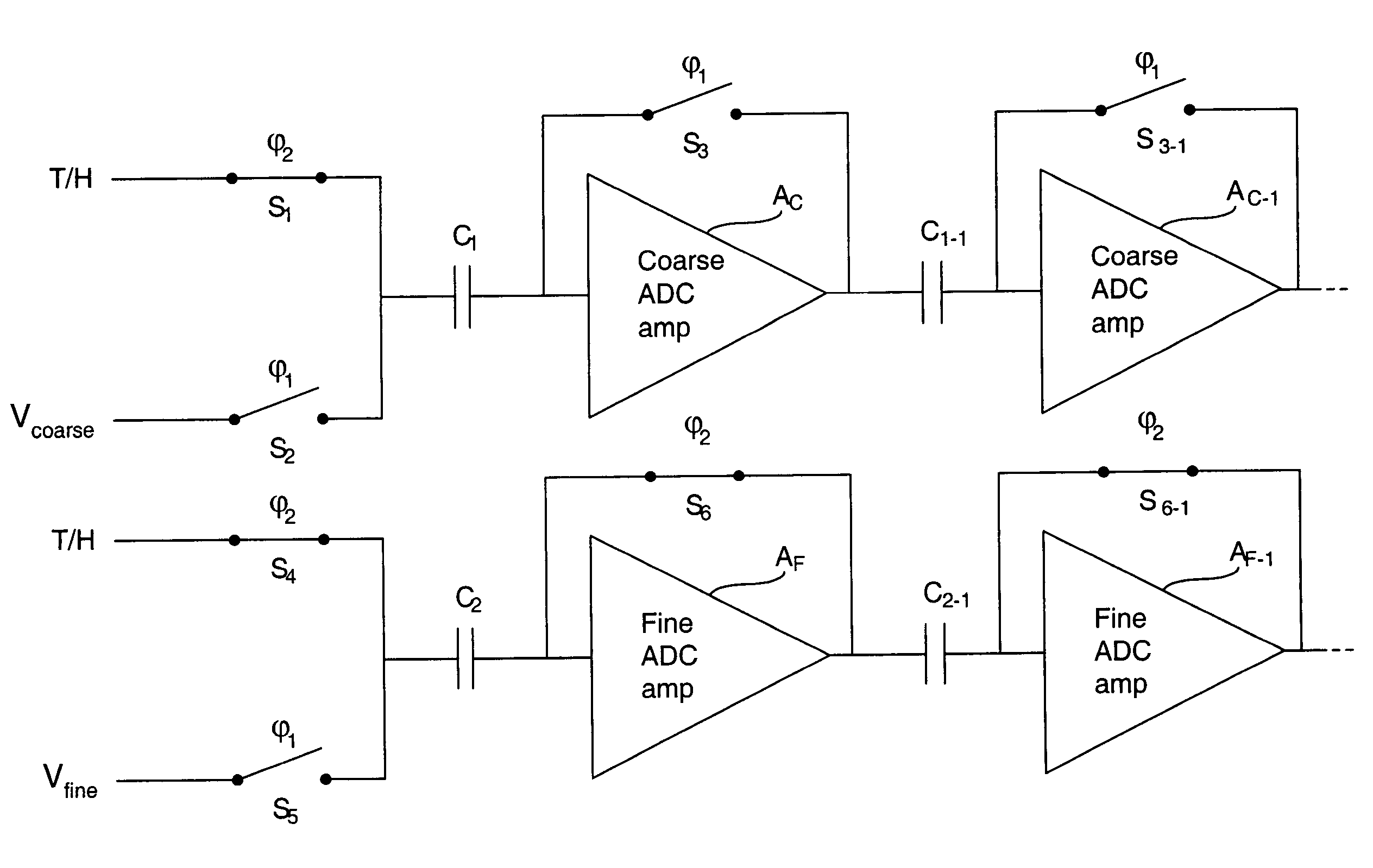

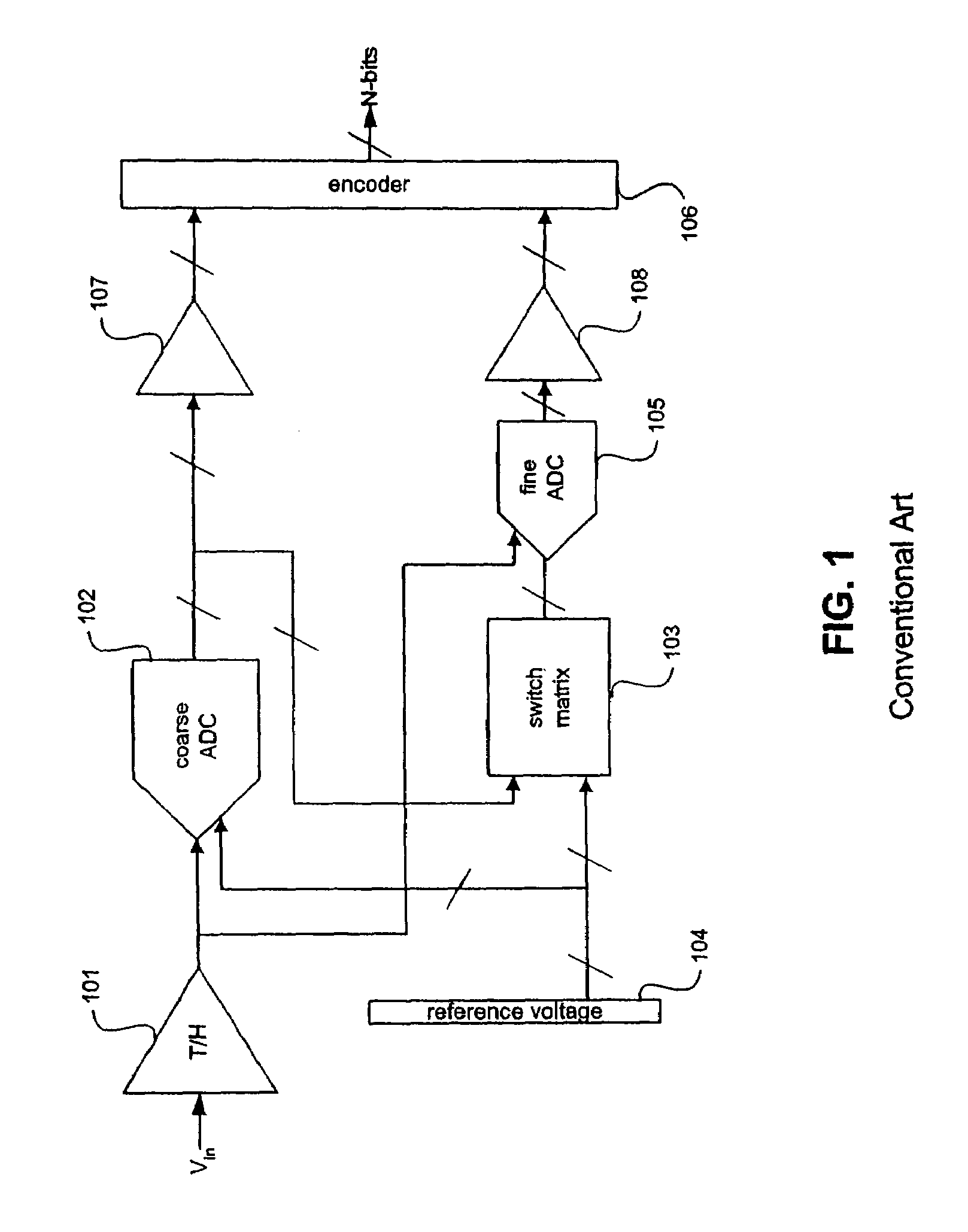

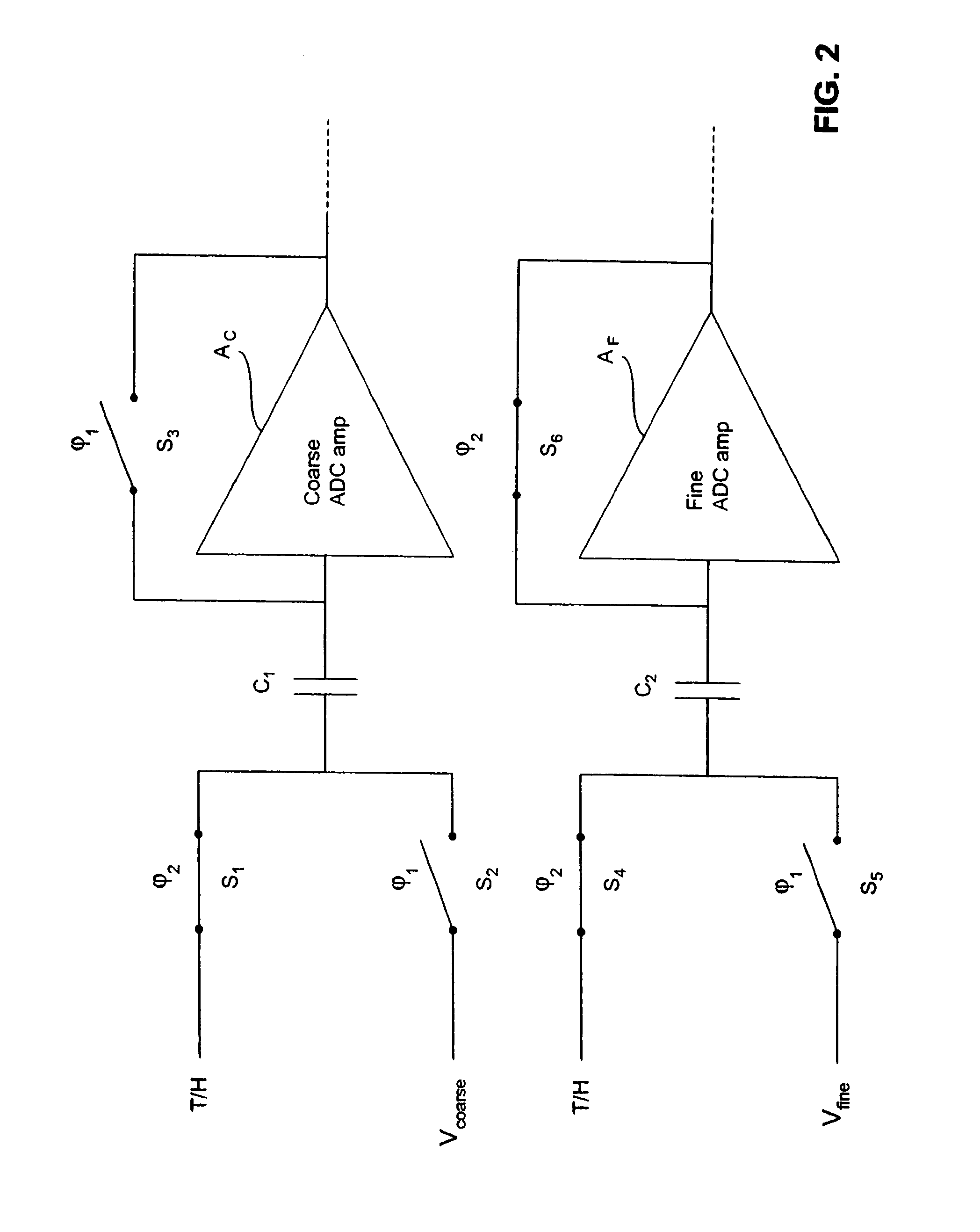

Subranging analog to digital converter with multi-phase clock timing

An N-bit analog to digital converter includes a reference ladder, a track-and-hold amplifier connected to an input voltage, a coarse ADC amplifier connected to a coarse capacitor at its input and having a coarse ADC reset switch controlled by a first clock phase of a two-phase clock, a fine ADC amplifier connected to a fine capacitor at its input and having a fine ADC reset switch controlled by a second clock phase of the two-phase clock, a switch matrix that selects a voltage subrange from the reference ladder for use by the fine ADC amplifier based on an output of the coarse ADC amplifier, and wherein the coarse capacitor is charged to a coarse reference ladder voltage during the first clock phase and connected to the T / H output during the second clock phase, wherein the fine capacitor is connected to a voltage subrange during the first clock phase and to the T / H output during the second clock phase, and an encoder that converts outputs of the coarse and fine ADC amplifiers to an N-bit output.

Owner:AVAGO TECH INT SALES PTE LTD

Sample hold circuit for use in time-interleaved a/d converter apparatus including paralleled low-speed pipeline a/d converters

InactiveUS20090278716A1Minimize clock skewIncrease chip areaElectric signal transmission systemsElectric analogue storesCapacitanceAudio power amplifier

A sample hold circuit is provided for use in a time-interleaved A / D converter apparatus including a plurality of low-speed pipeline A / D converters which are parallelized. The sample hold circuit includes a sampling capacitor and a sample hold amplifier, and operates to sample and hold an input signal by using a switched capacitor. An adder circuit of the sample hold circuit adds a ramp calibration signal to the input signal, by inputting the ramp calibration signal generated to have a frequency identical to that of a sampling clock signal and a predetermined slope based on the sampling clock signal, into a sample hold amplifier via a calibration capacitor having a capacitance smaller than that of the sampling capacitor.

Owner:SEMICON TECH ACADEMIC RES CENT

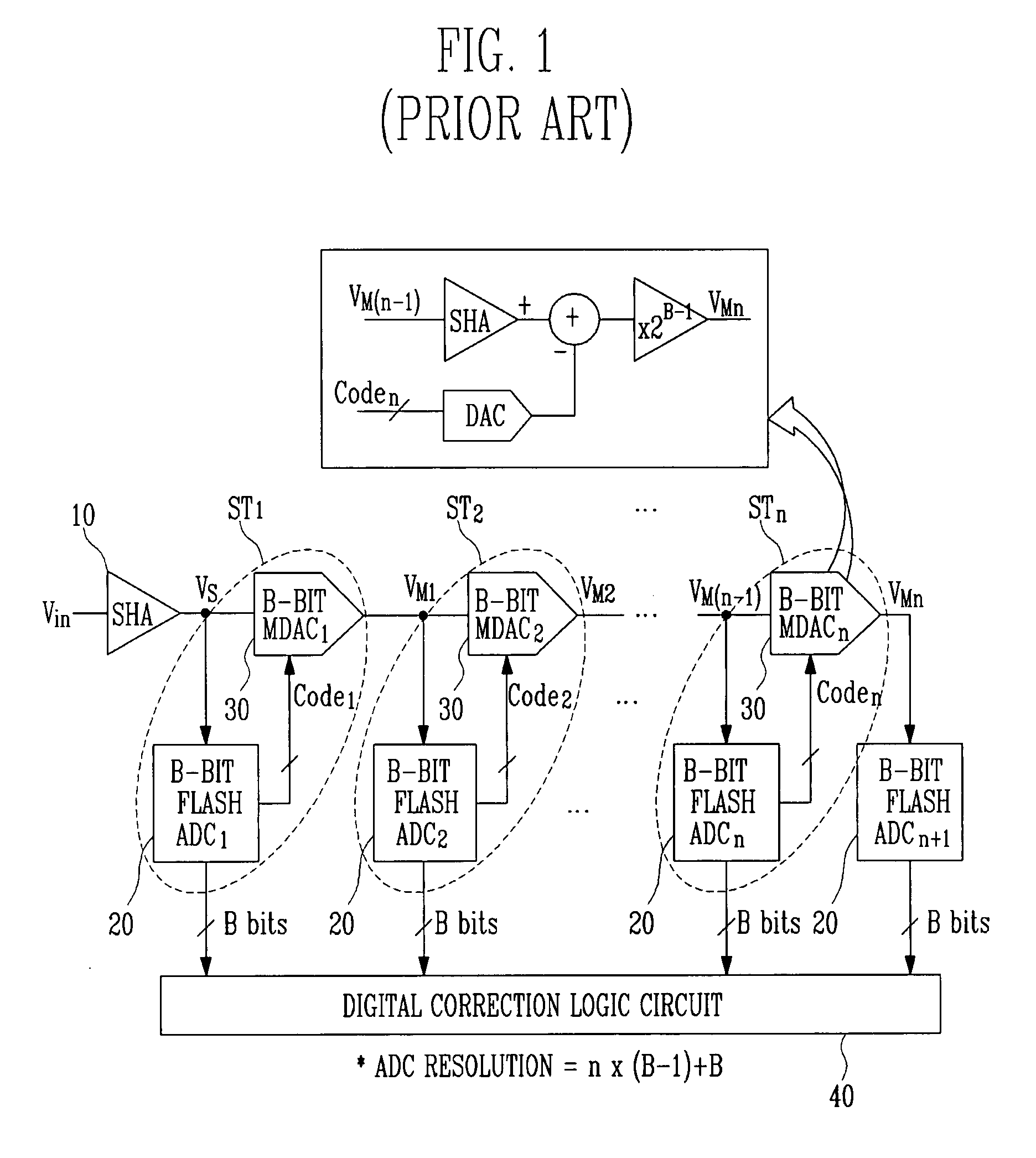

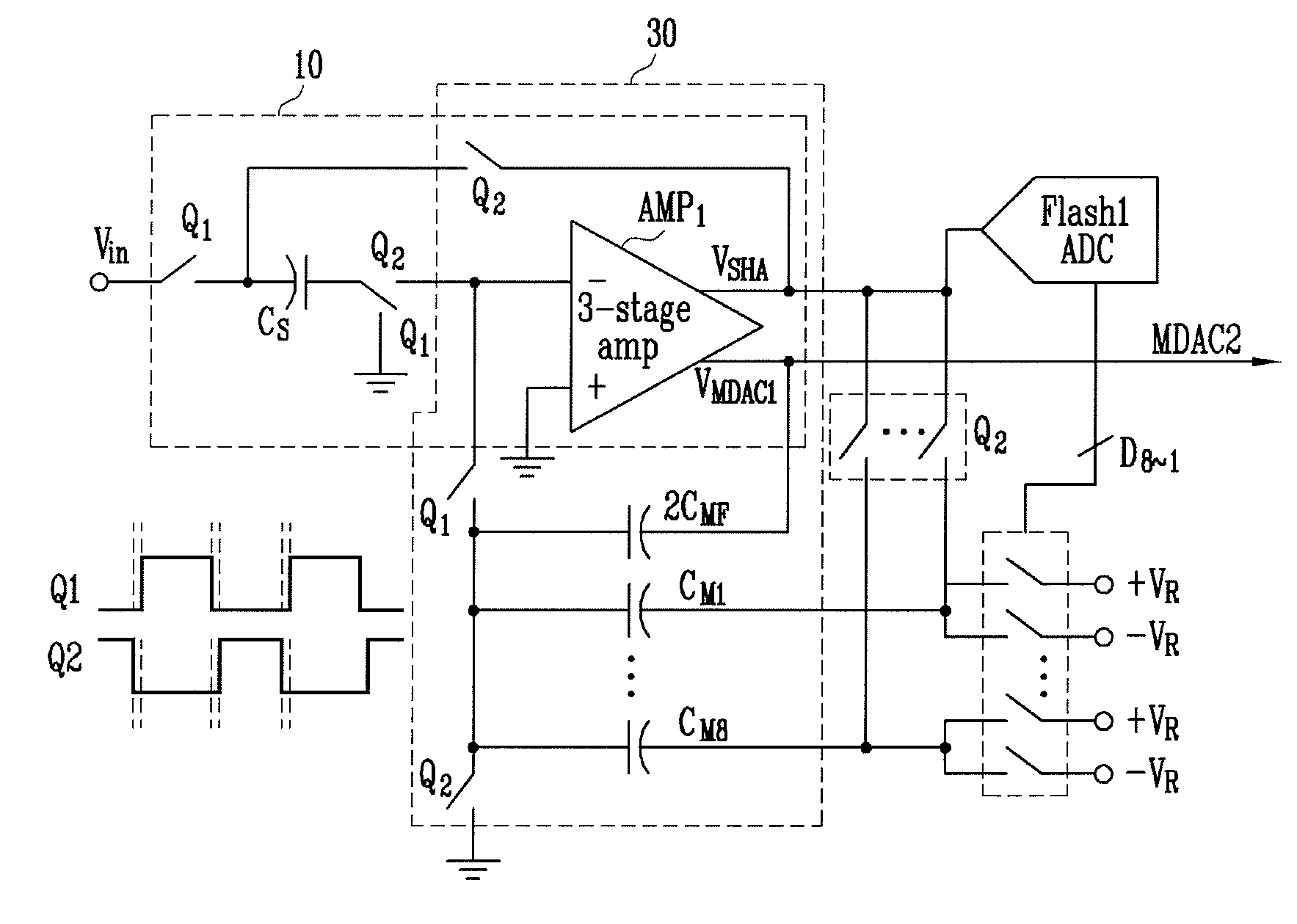

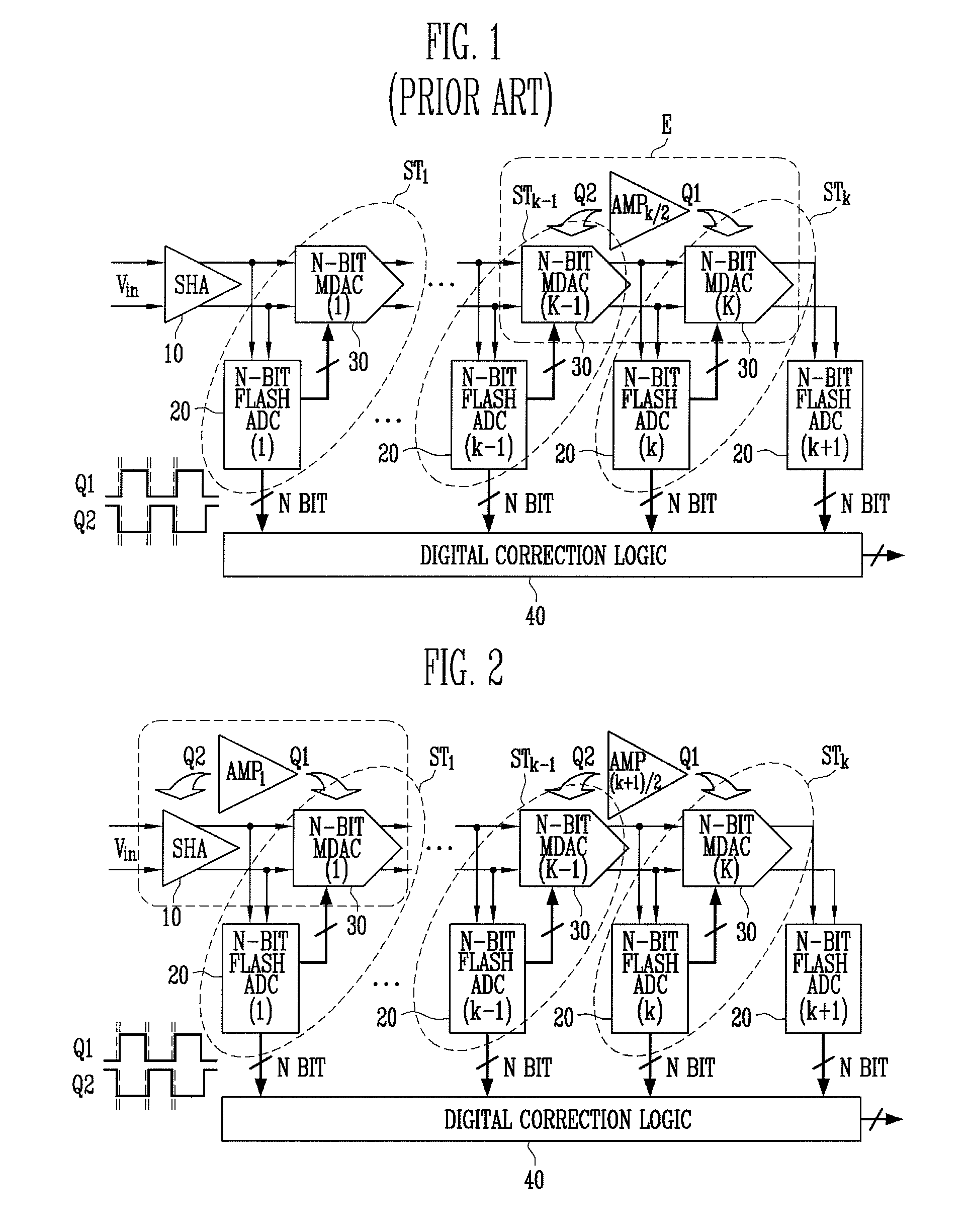

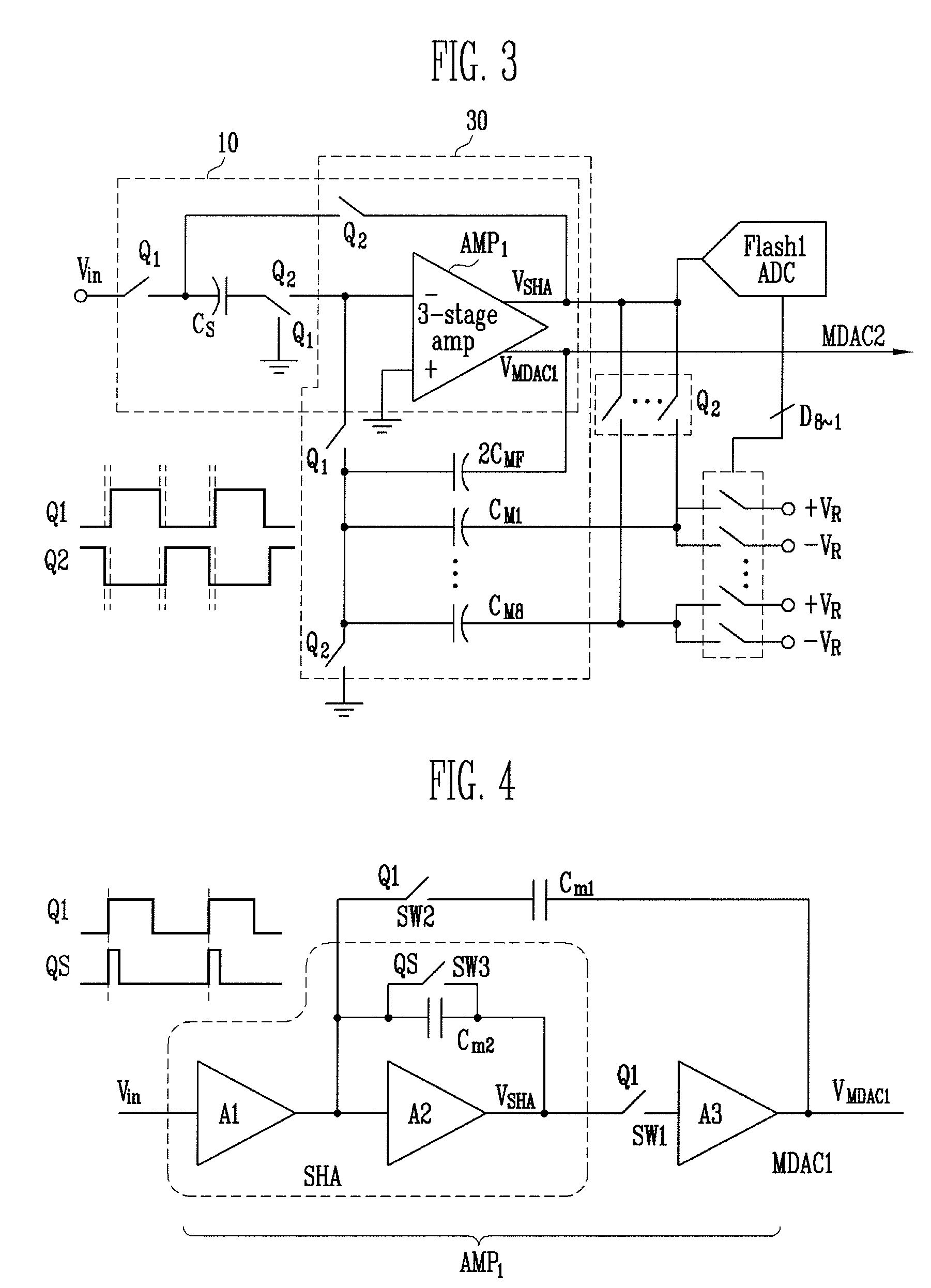

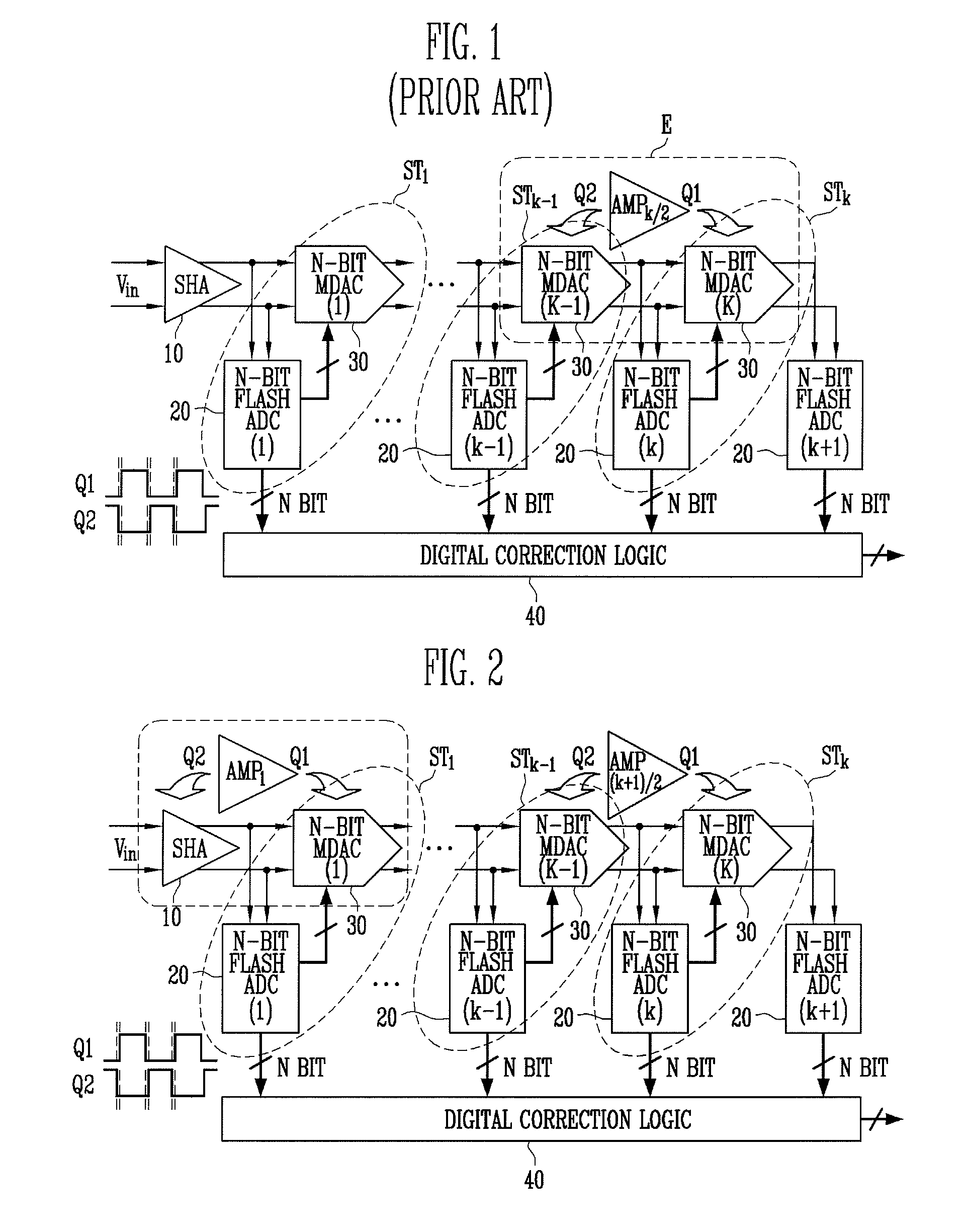

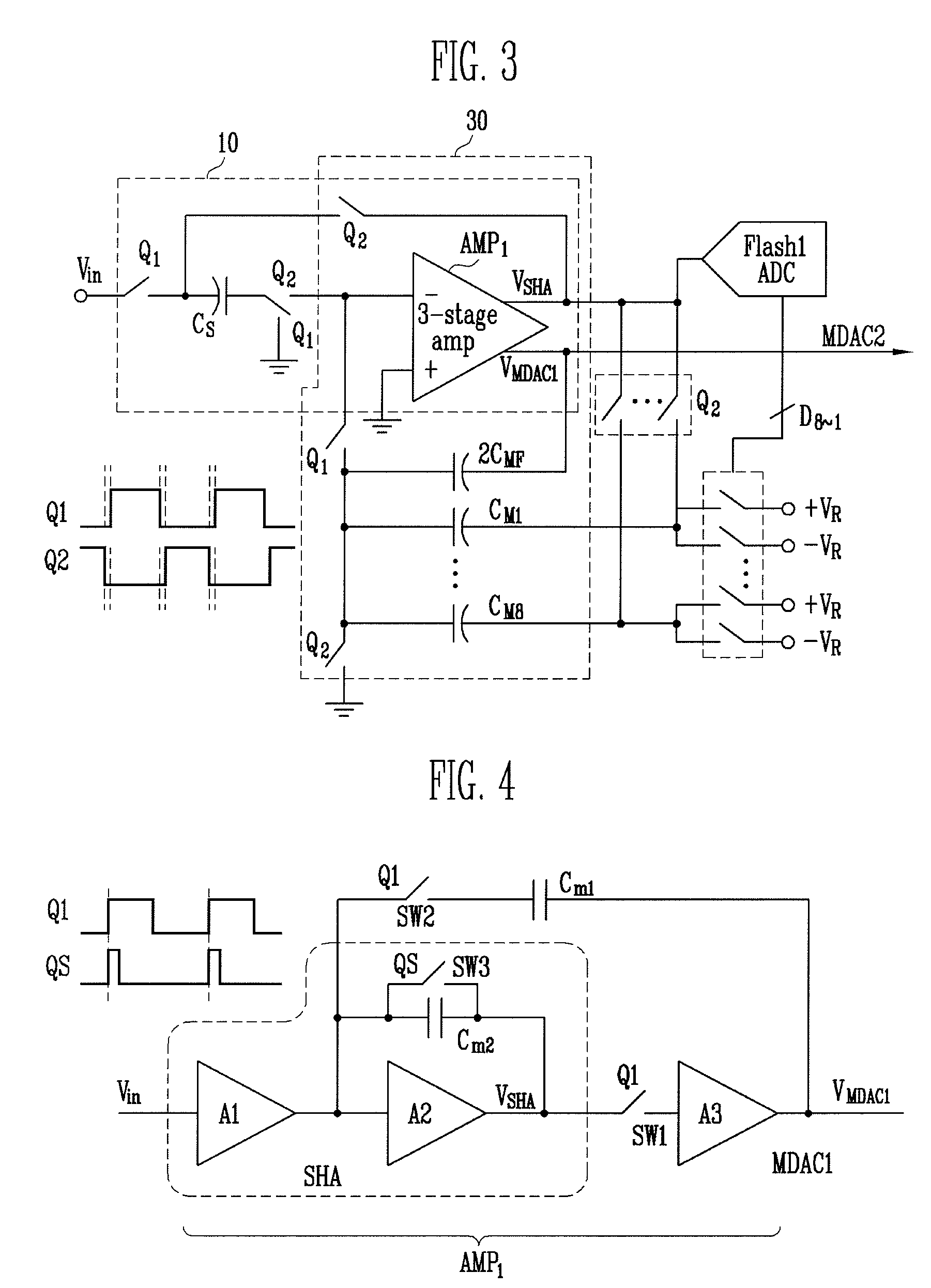

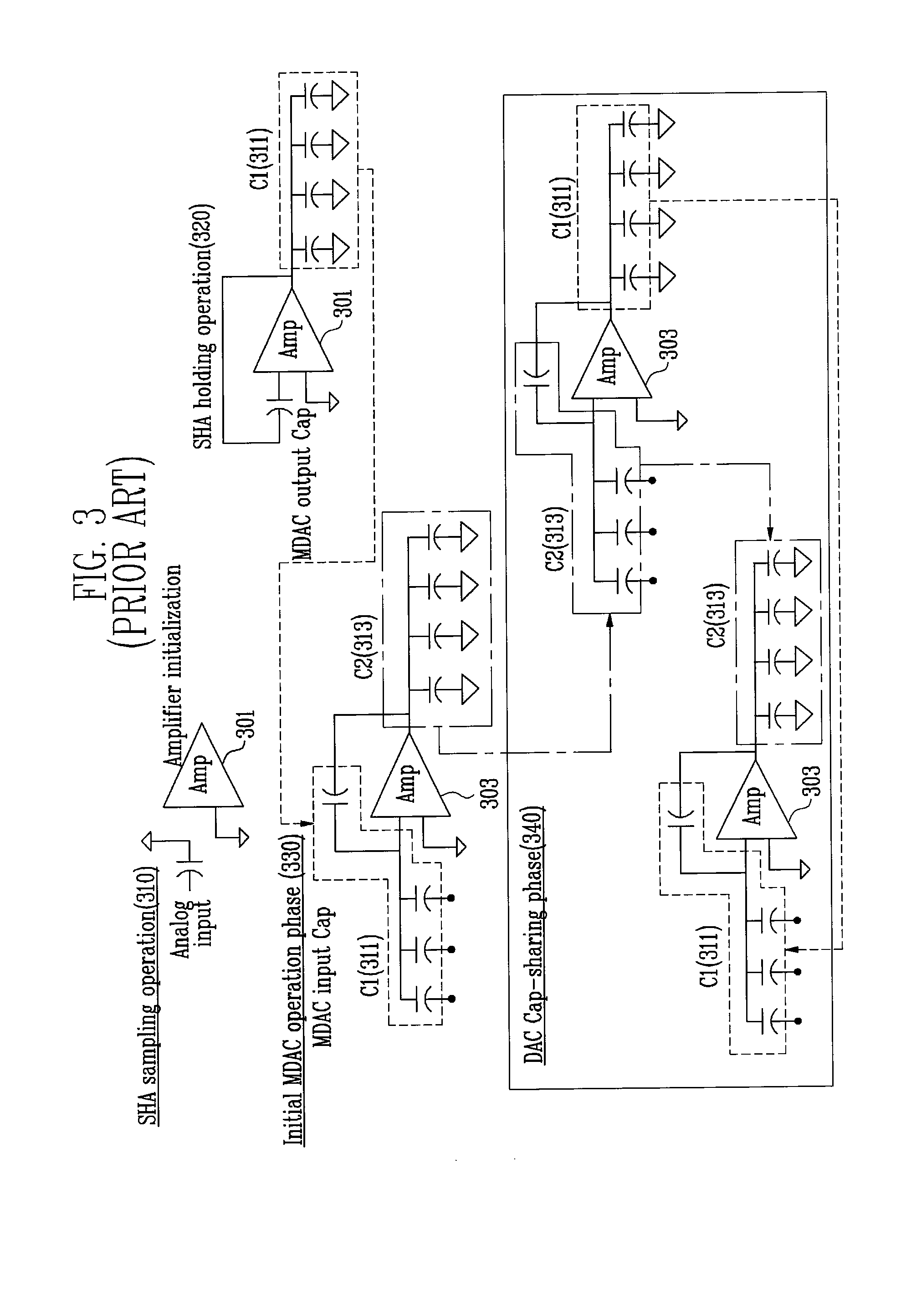

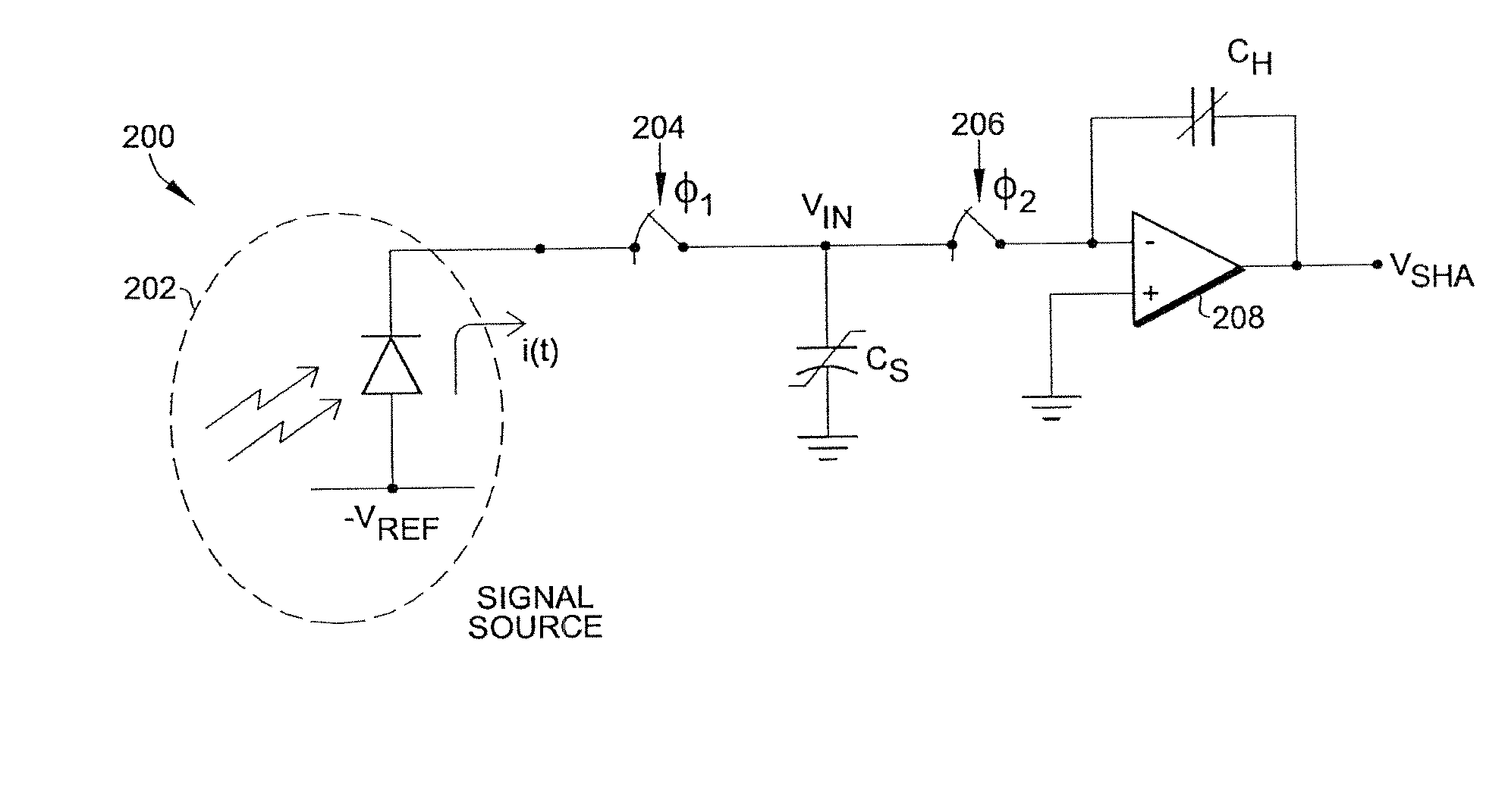

Multi-bit pipeline analog-to-digital converter having shared amplifier structure

ActiveUS7397409B2Reduce consumptionSmall sizeElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

A multi-bit pipeline analog-to-digital converter (ADC) having a shared amplifier structure includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage and removing a sampling error of the input voltage; N-bit flash ADCs of first to K-th stages receiving analog signals, converting them into digital signals and outputting the digital signals; N-bit multiplying digital-to-analog converters (MDACs) of first to K-th stages converting differences between the digital signals output from the N-bit flash ADCs and output signals of preceding stages back into analog signals and outputting the analog signals; and a three-stage amplifier connected to an output of the N-bit MDAC of the first stage at a first clock and an output of the SHA at a second clock, wherein intergers N>= and K>=2. An amplifier can be shared between an SHA and an MDAC of a first stage, thereby reducing power consumption and chip size.In the multi-bit pipeline ADC, an amplifier can be shared between an SHA consuming much power and an MDAC of a first stage, so that power consumption and chip size can be reduced.

Owner:ELECTRONICS & TELECOMM RES INST

Apparatus and method for measurement for dynamic laser signals

InactiveUS7505498B2Prolong lifeLaser detailsElectromagnetic transmissionAudio power amplifierControl system

Owner:OL SECURITY LIABILITY CO +1

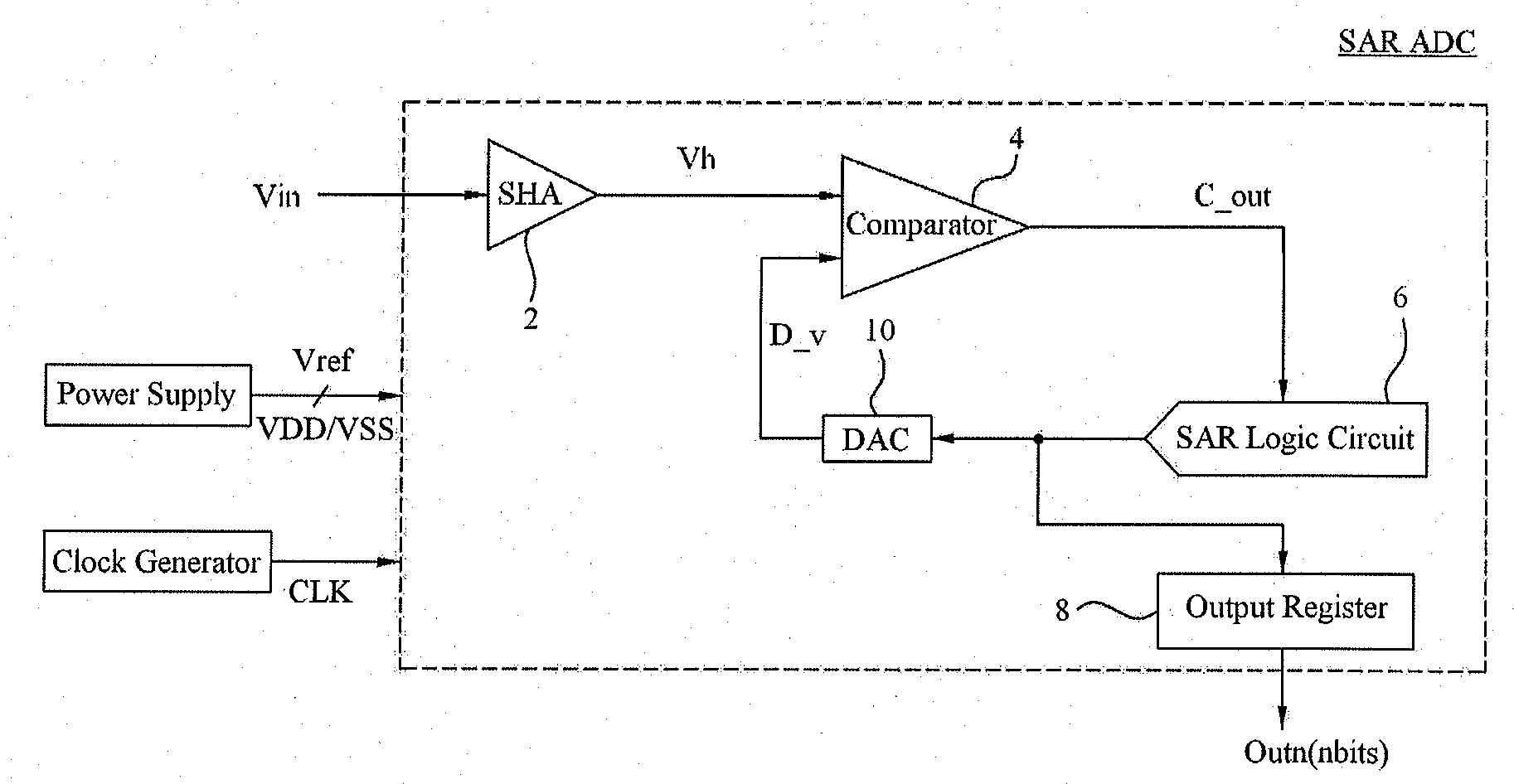

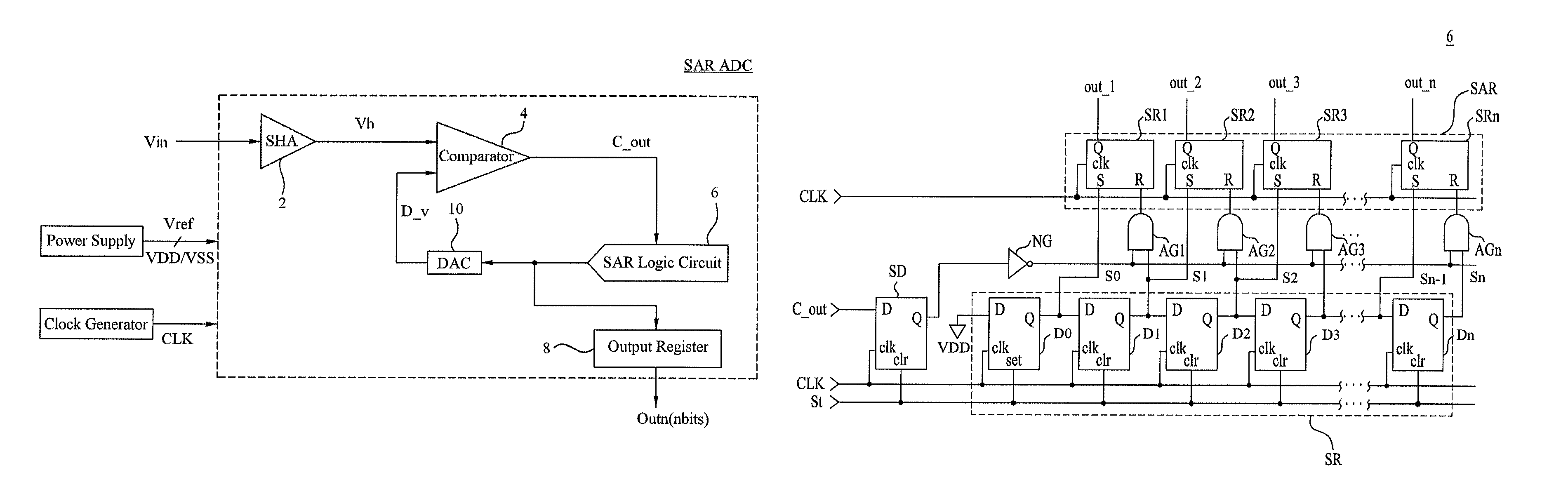

Successive approximation register analog-to-digital converter and analog-to-digital conversion method using the same

ActiveUS20120146822A1Optimize operating timeImprove stabilityElectric signal transmission systemsPhysical parameters compensation/preventionDigital down converterEngineering

A Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) includes a Sample-and-Hold Amplifier (SHA) for sampling and holding an externally input analog voltage, a comparator for comparing a level of the sampled and held analog voltage with a level of an analog signal corresponding to n bits and generating a comparison signal according to result of comparison, an SAR logic circuit for sequentially generating a digital signal from a Most significant Bit (MSB) to a Least Significant Bit (LSB) in response to the comparison signal, a Digital-to-Analog Converter (DAC) for providing the analog signal to the comparator, and an output register for holding the sequentially generated digital signal from the MSB to the LSB to generate an n-bit digital signal, wherein, upon externally receiving a start signal, the SAR logic circuit generates a digital signal of a MSB having a one-bit phase delay compared with the start signal.

Owner:LG DISPLAY CO LTD

Multi-bit pipeline analog-to-digital converter having shared amplifier structure

ActiveUS20080068237A1Reduce consumptionSmall sizeElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

Provided is a multi-bit pipeline analog-to-digital converter (ADC) having a shared amplifier structure. The multi-bit pipeline ADC includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage and removing a sampling error of the input voltage; N-bit flash ADCs of first to K-th stages receiving analog signals, converting them into digital signals and outputting the digital signals; N-bit multiplying digital-to-analog converters (MDACs) of first to K-th stages converting differences between the digital signals output from the N-bit flash ADCs and output signals of preceding stages back into analog signals and outputting the analog signals; and a three-stage amplifier connected with an output of the N-bit MDAC of the first stage at a first clock and an output of the SHA at a second clock, wherein N is an integer greater than or equal to 1 and K is an integer greater than or equal to 2.In the multi-bit pipeline ADC, an amplifier can be shared between an SHA consuming much power and an MDAC of a first stage, so that power consumption and chip size can be reduced.

Owner:ELECTRONICS & TELECOMM RES INST

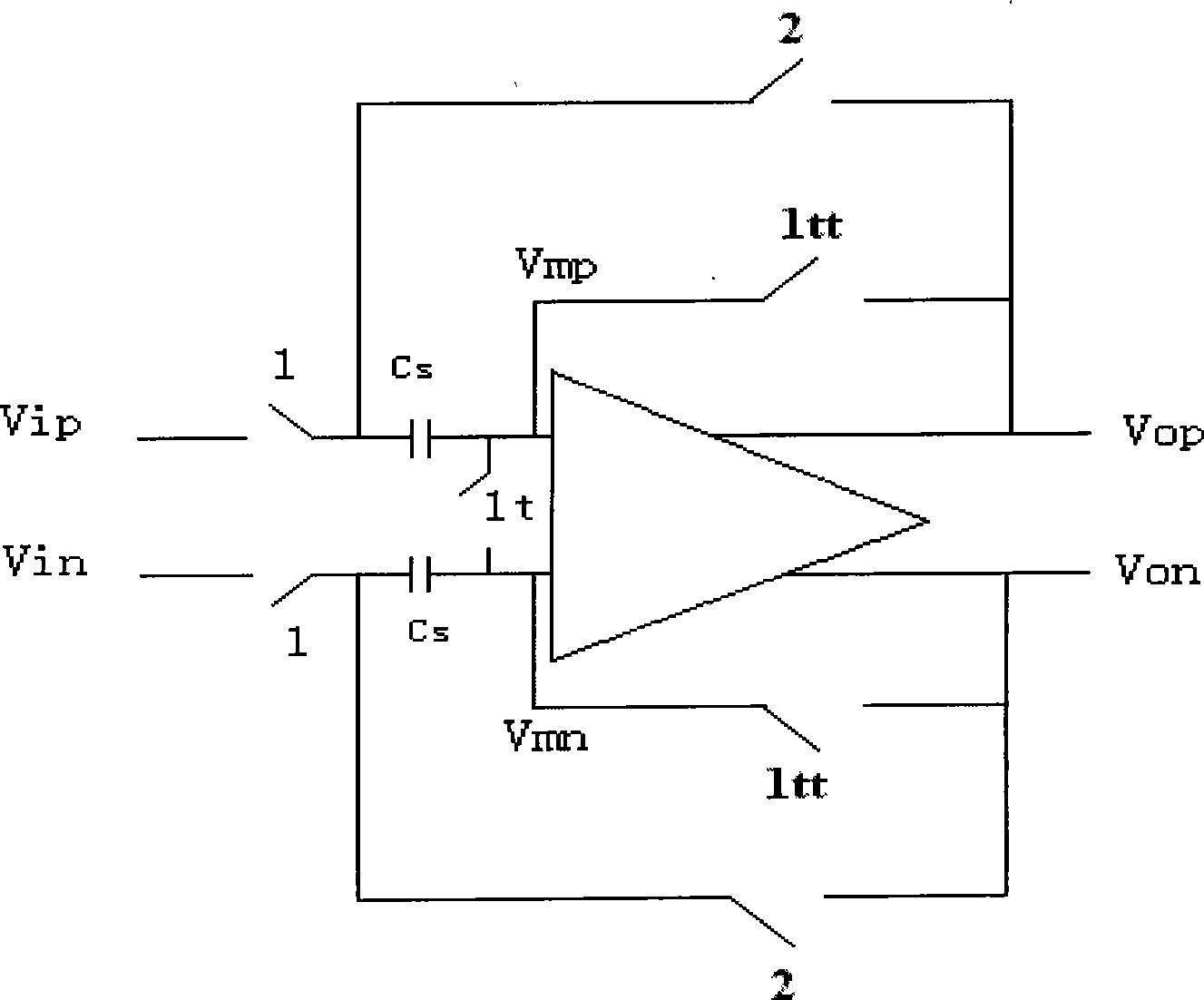

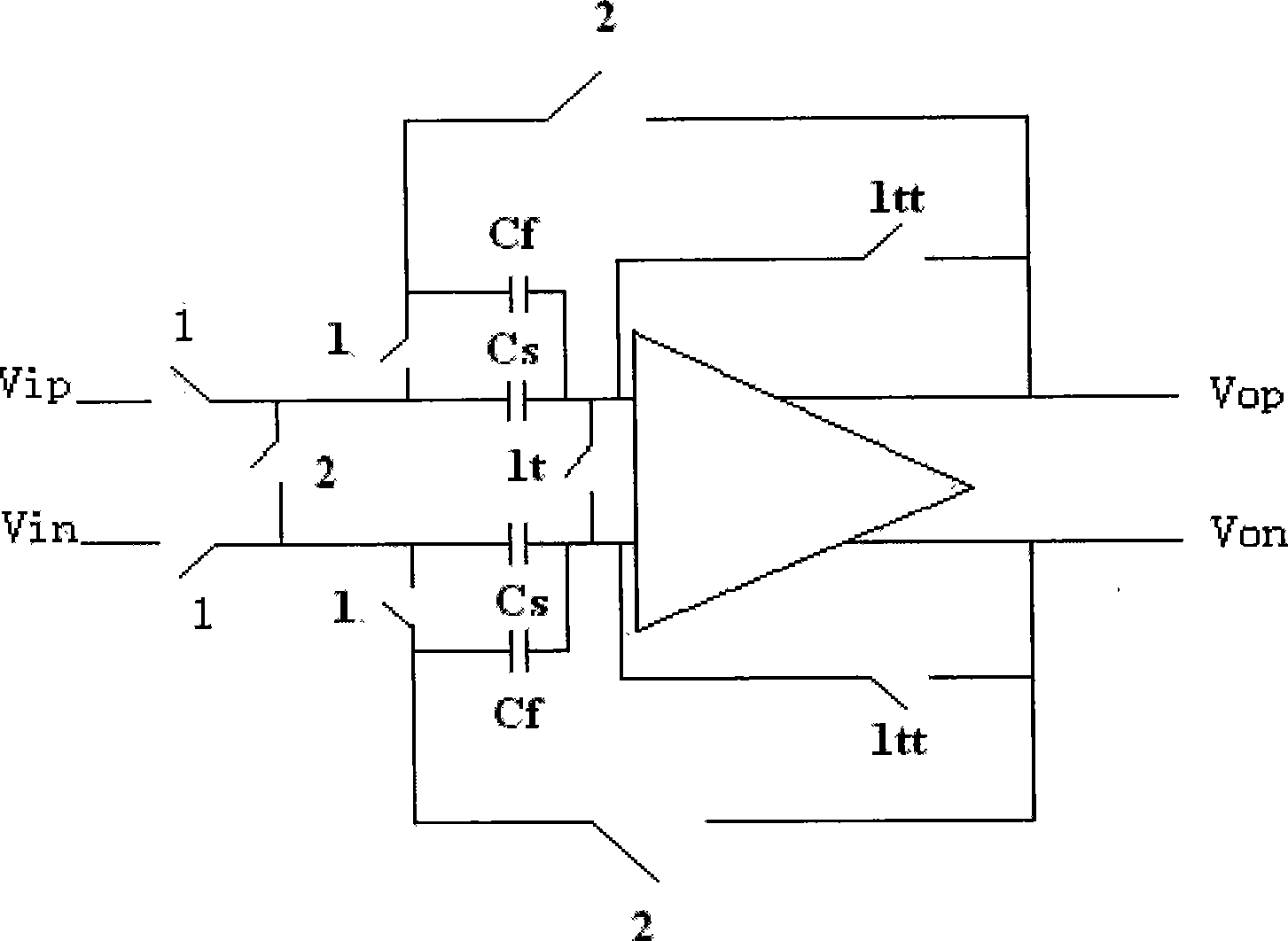

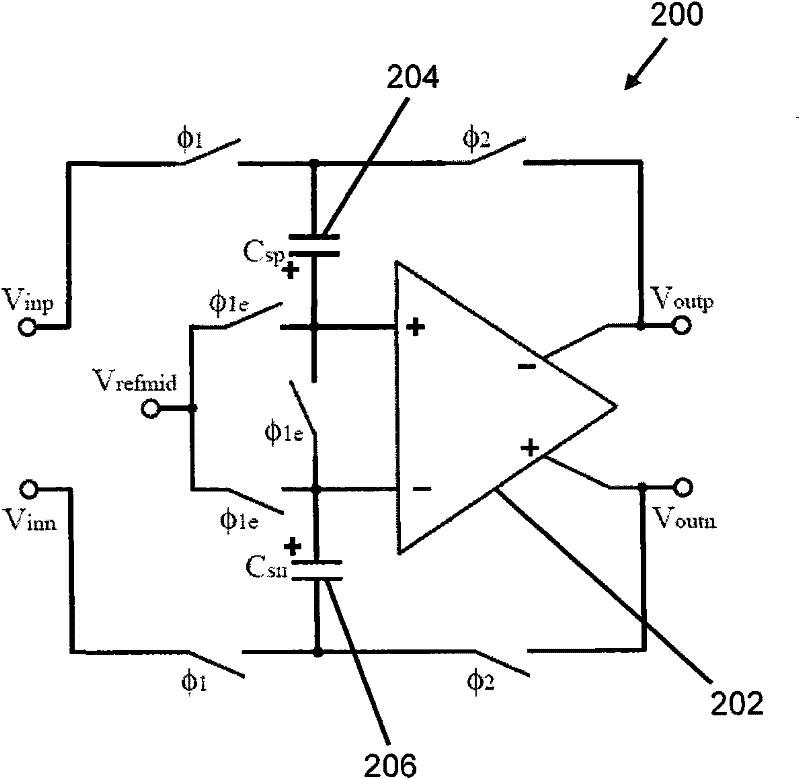

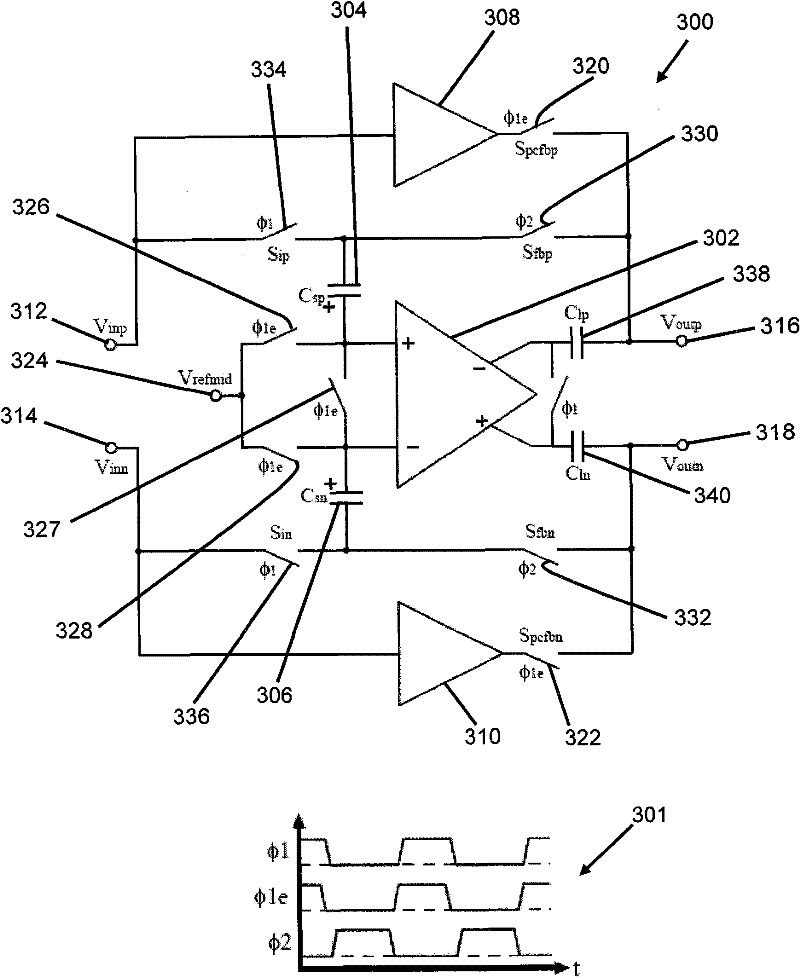

Device and method for holding sampling

InactiveCN101414487AImprove reliabilityAvoid designElectric analogue storesAnalogue-digital convertersAudio power amplifierSignal processing

The invention discloses a sample-and-hold amplifier which comprises a primary sample-and-hold circuit and a secondary sample-and-hold circuit. The input positive terminal and the input negative terminal of the primary sample-and-hold circuit receive an external signal, the output positive terminal and the output negative terminal of the primary sample-and-hold circuit are coupled to the input positive terminal and the input negative terminal of the secondary sample-and-hold circuit, the primary sample-and-hold circuit is provided with a primary operational amplifier with the amplification being less than a multiple, and the secondary sample-and-hold circuit is provided with a secondary operational amplifier which realizes the amplification more than the multiple; after the external signal is sampled, held and amplified, by the primary sample-and-hold circuit and the secondary sample-and-hold circuit, the external signal is output from the output positive terminal and the output negative terminal of the secondary sample-and-hold circuit. Meanwhile, the invention discloses a sample-and-hold method. The sample-and-hold amplifier, as a basic signal processing module, is used for front end processing of the external input signal; and the sample-and-hold amplifier ensures the speed and the precision of the signal conversion with the simple structure on the premise of realizing high reliability.

Owner:北京安策恒兴投资有限公司

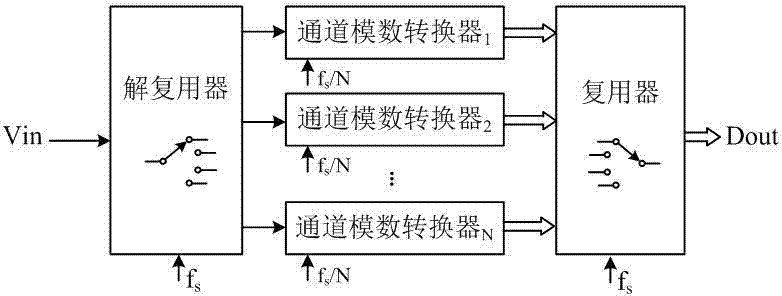

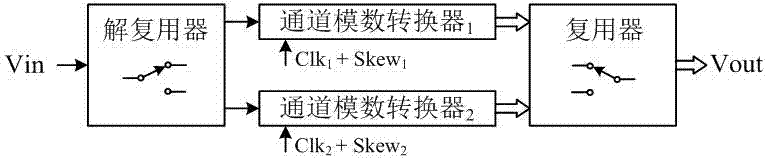

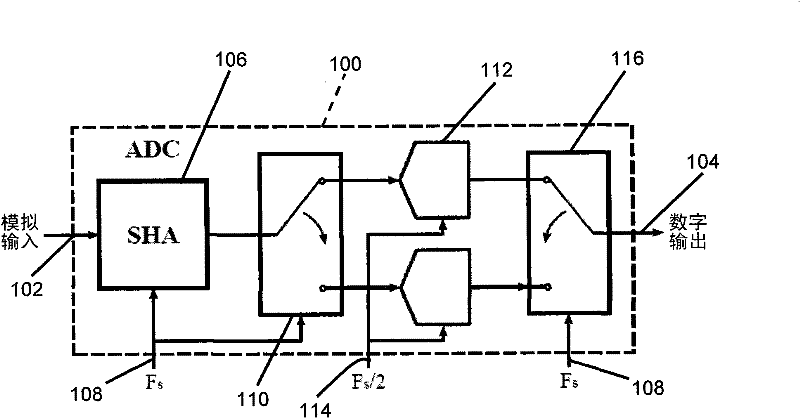

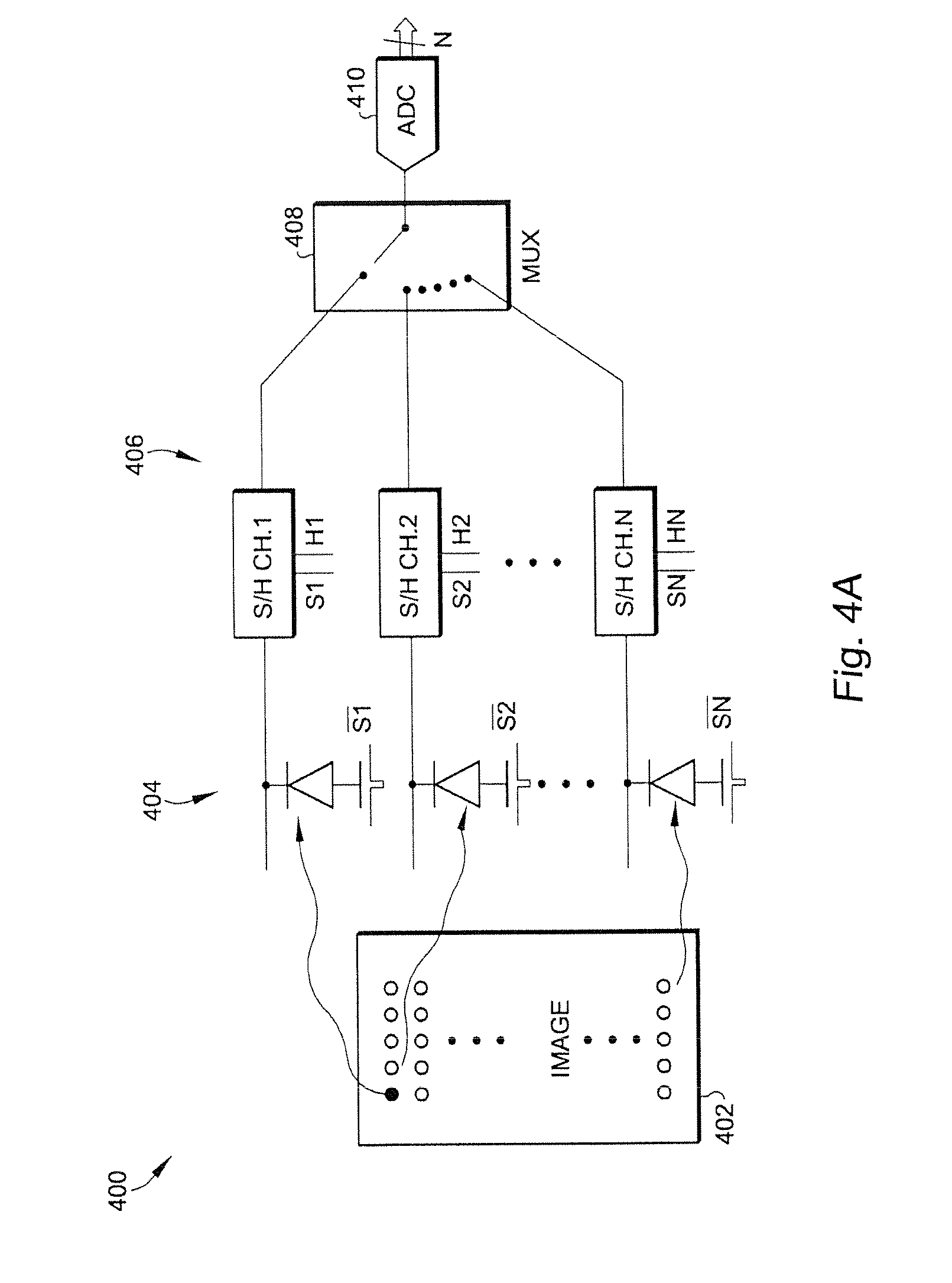

Time interweaving stream-line type analog-digital converter structure

ActiveCN102769468AGuaranteed and improved accuracyImprove accuracyAnalogue-digital convertersAudio power amplifierAnalog-to-digital converter

The invention belongs to the technical field of integrated circuits and particularly relates to a time interweaving stream-line type analog-digital converter structure which adopts a share front terminal analog-digital converter. A front end sampling maintaining amplification circuit of a channel analog-digital converter of a stream-line structure is removed. Sampling time errors in different types exist in both the stream-line structure analog-digital converter omitting the sampling maintaining amplification circuit and the time interweaving structure analog-digital converter. Compared with the existing method and structure, the structure of the share front terminal analog-digital converter is adopted at the front end of the stream-line type channel analog-digital converter omitting the sampling maintaining amplifier. The structure unifies sampling time errors in the two types, simplifies complexity of sampling time error calibration algorithm and circuit structure to the largest extent and finally effectively reduces power consumption and area of chips.

Owner:FUDAN UNIV

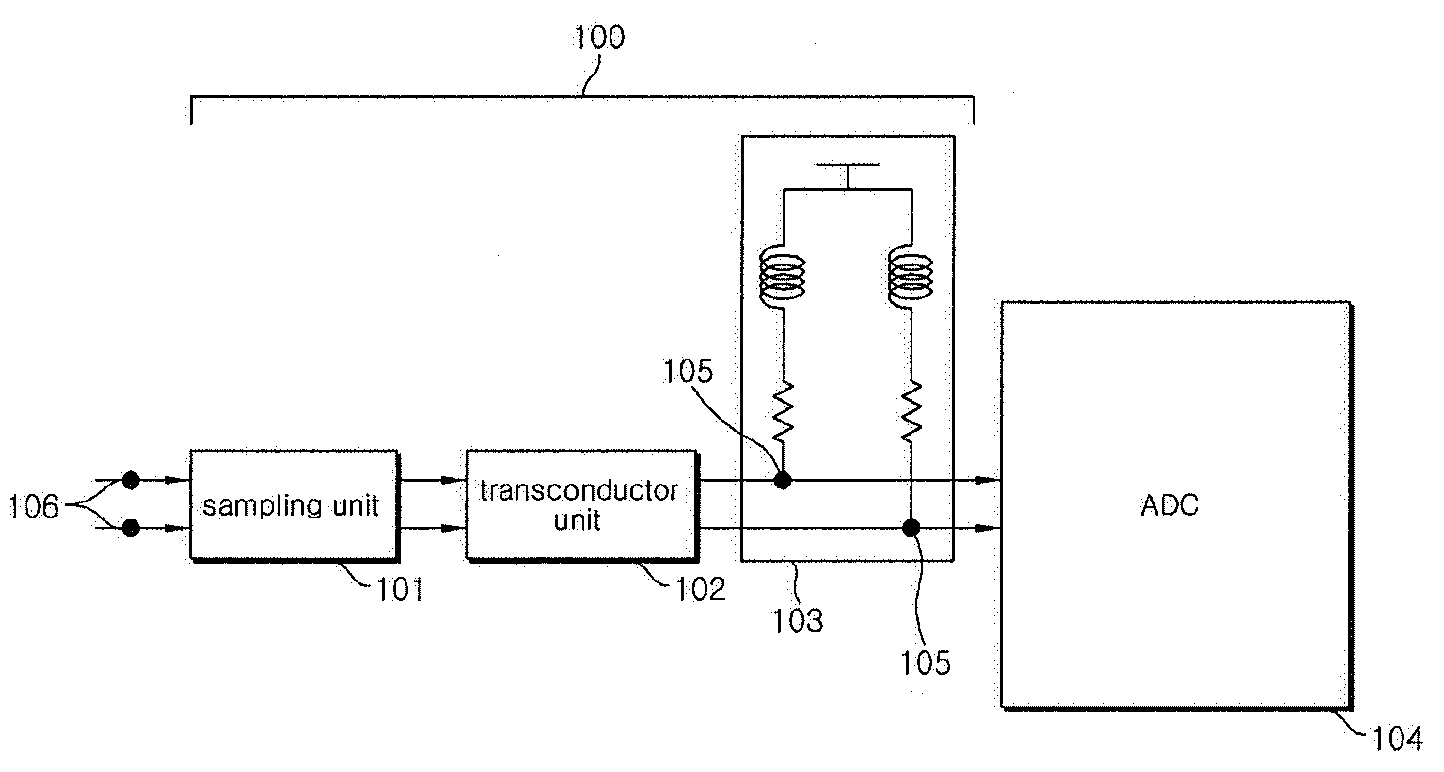

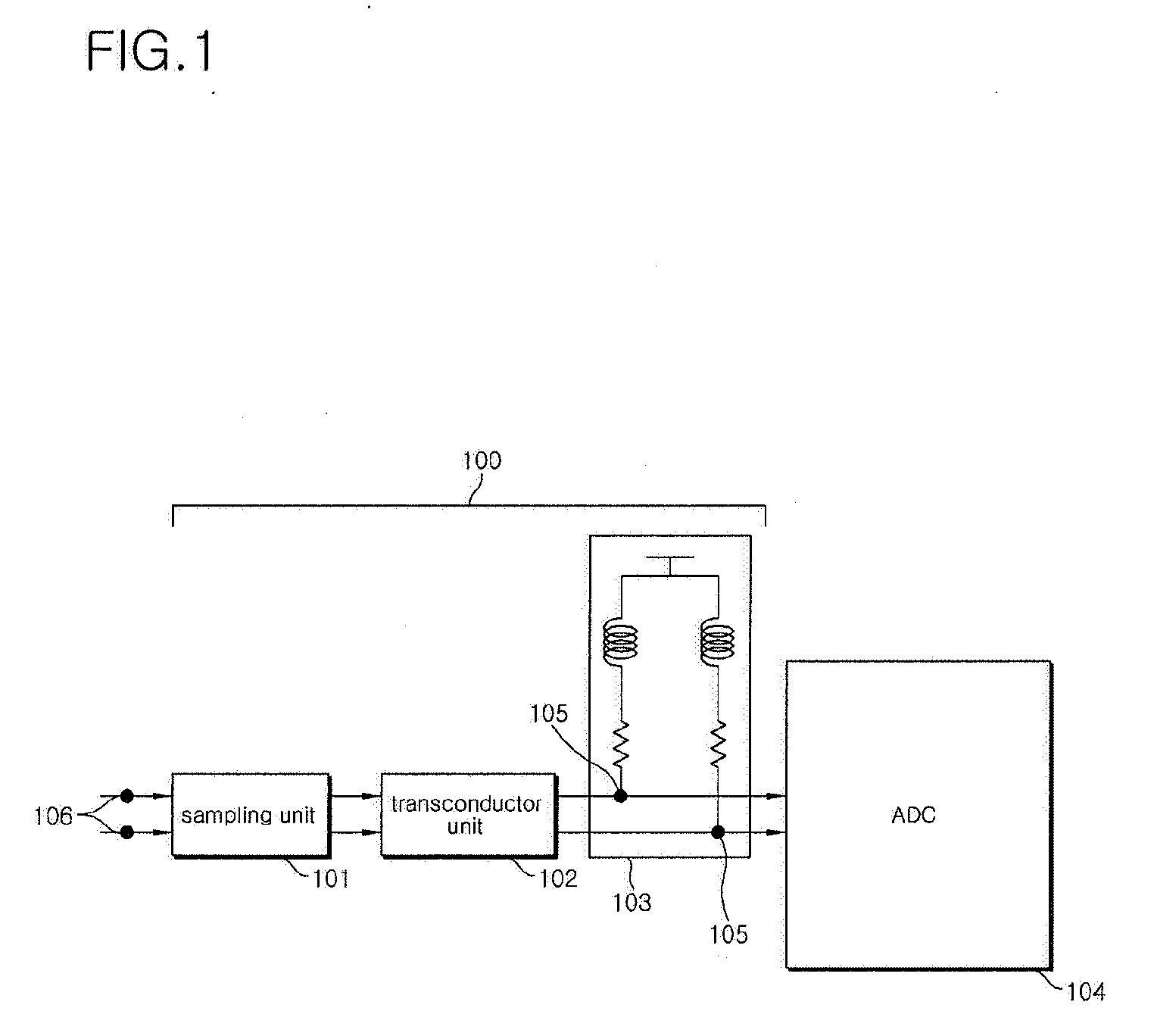

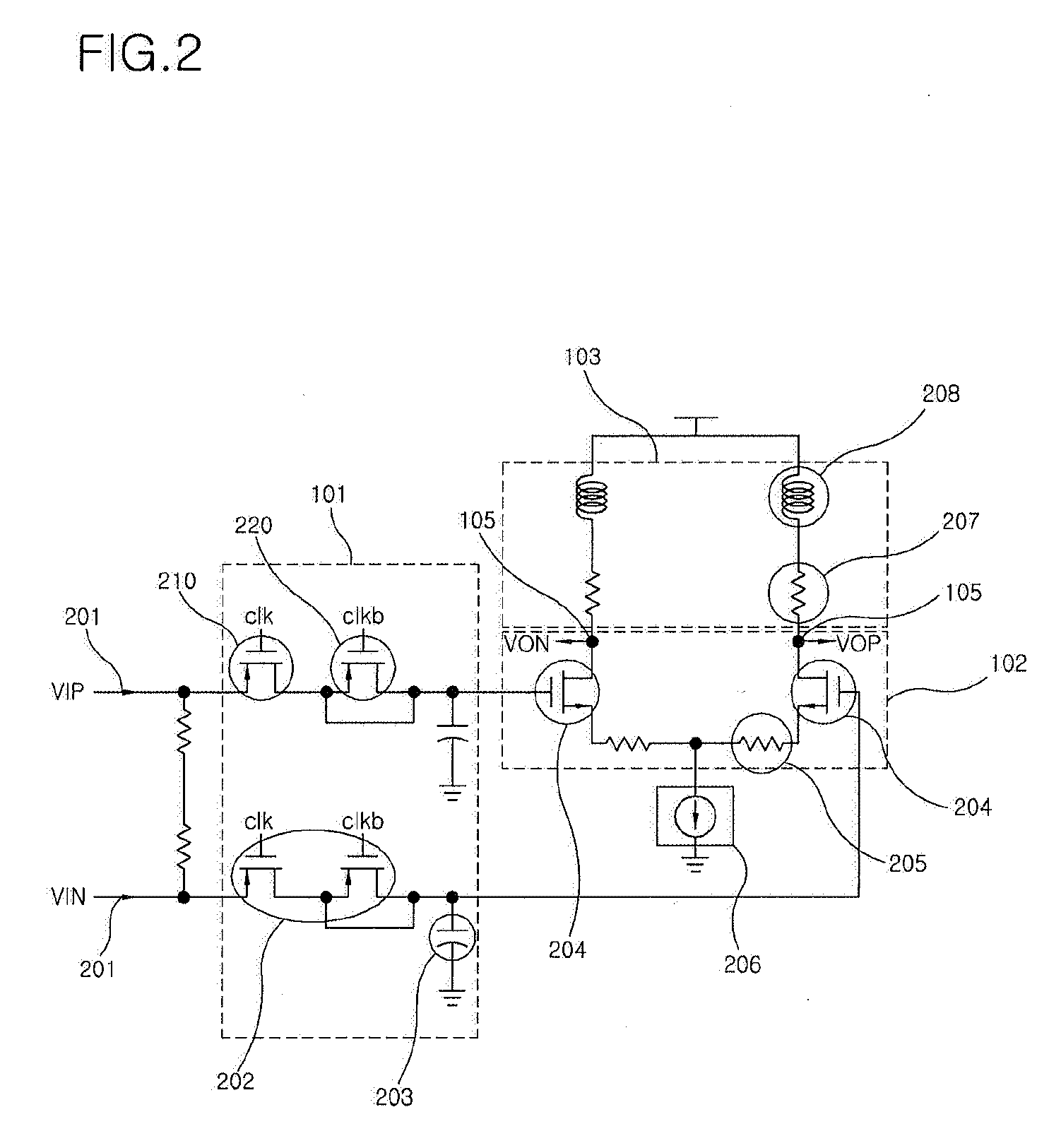

Wideband track-and-hold amplifier

InactiveUS20090072868A1Satisfactory linearityHigh speed machiningElectric analogue storesElectronic switchingCapacitanceAudio power amplifier

A wideband track-and-hold amplifier is provided. The wideband track-and-hold amplifier is provided in front of an analog-to-digital converter, receives and samples an analog signal, and transfers the sampled signal to the analog-to-digital converter, wherein an output load unit having an inductance component is connected to an input terminal of the analog-to-digital converter. Therefore, it is possible to compensate for a high capacitance component of an analog-to-digital converter, to increase the bandwidth of an output signal, and to improve system linearity.

Owner:SAMSUNG ELECTRONICS CO LTD

Multi-bit pipeline analog-to-digital converter capable of altering operating mode

InactiveUS7486216B2Minimize power consumptionPower saving provisionsElectric signal transmission systemsControl signalMode control

Provided is a multi-bit pipeline analog-to-digital converter (ADC) capable of altering an operating mode. The ADC includes: a sample-and-hold amplifier (SHA) for sampling and holding an input analog voltage; an n+1 number of B-bit flash ADCs for receiving an analog signal and converting the analog signal into a digital signal to output the digital signal; an n number of B-bit multiplying digital-to-analog converters (MDACs) for converting a difference between the digital signal output from the B-bit flash ADC and the front-stage output signal into an analog signal to output the analog signal to the next stage; and a mode control circuit for generating n-bit control signals to control the B-bit flash ADC and the B-bit MDAC according to required resolution and operating frequency. In the multi-bit pipeline ADC, an operating mode is altered by controlling the number of stages in a pipeline and a signal path according to required resolution and operating frequency, so that power consumption can be minimized under the corresponding operating condition and signals can be processed in a variety of ways.

Owner:ELECTRONICS & TELECOMM RES INST

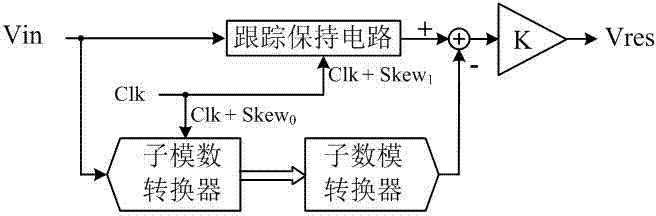

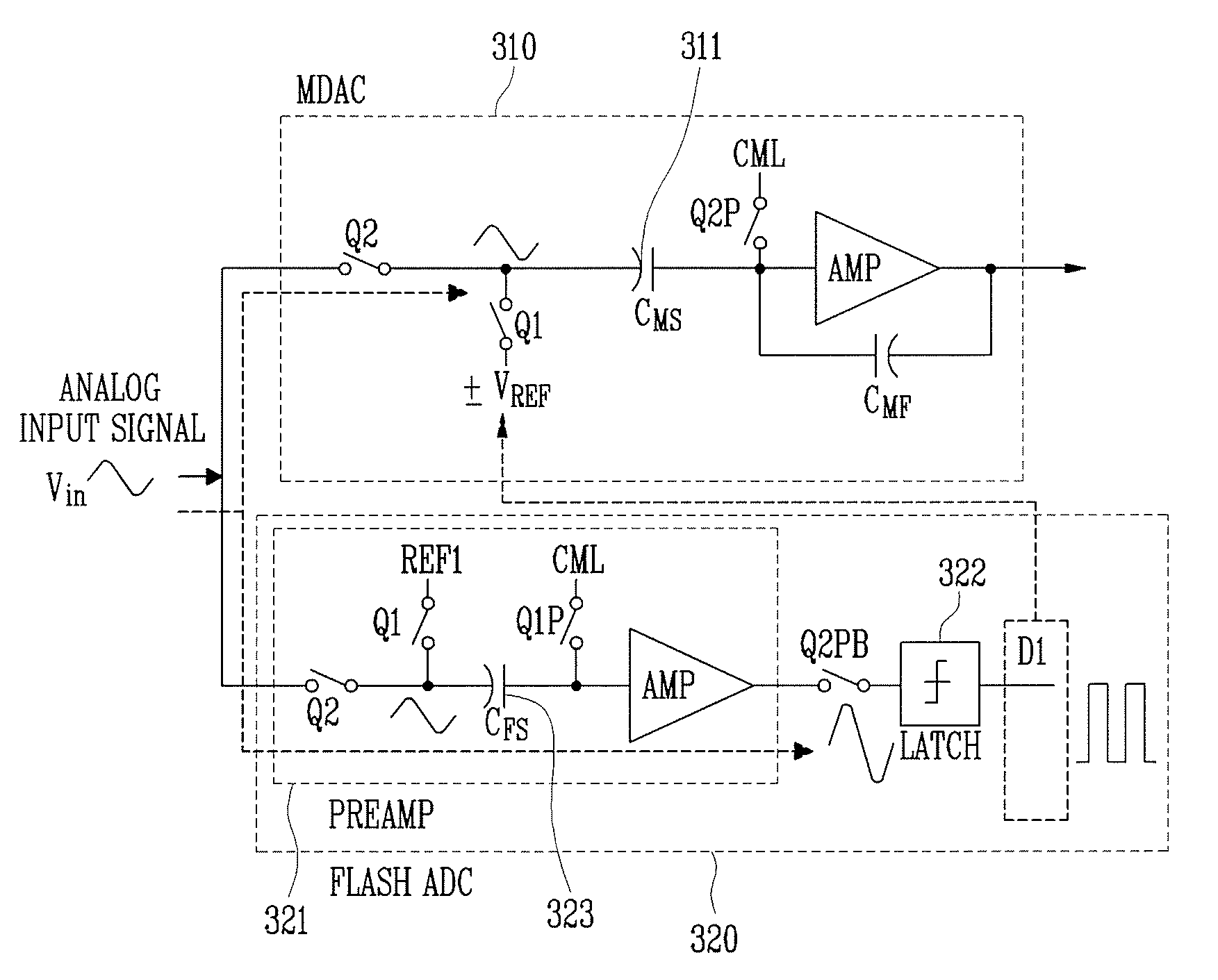

Pipeline analog-to-digital converter

ActiveUS20110102220A1Error minimizationReduce errorsElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

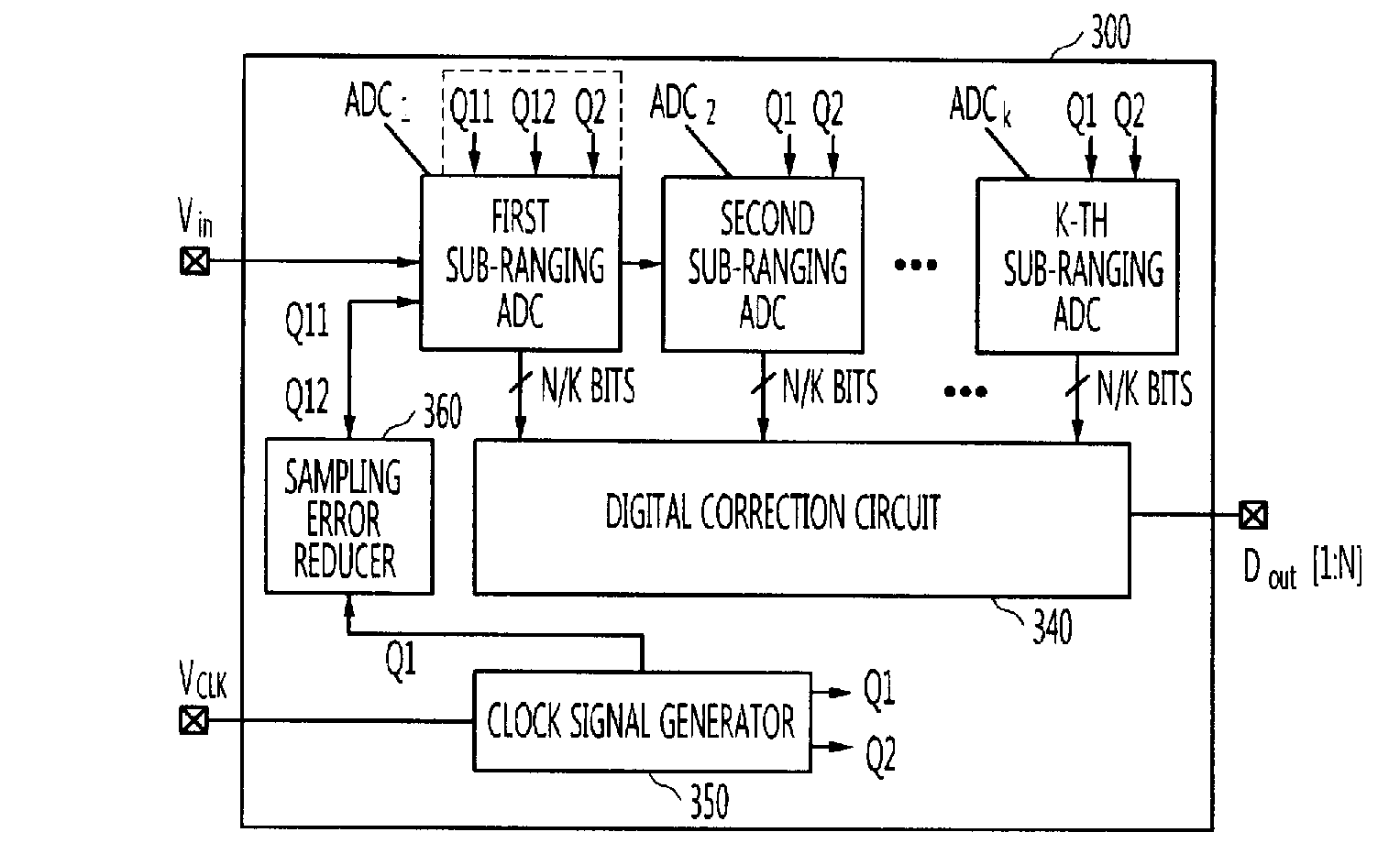

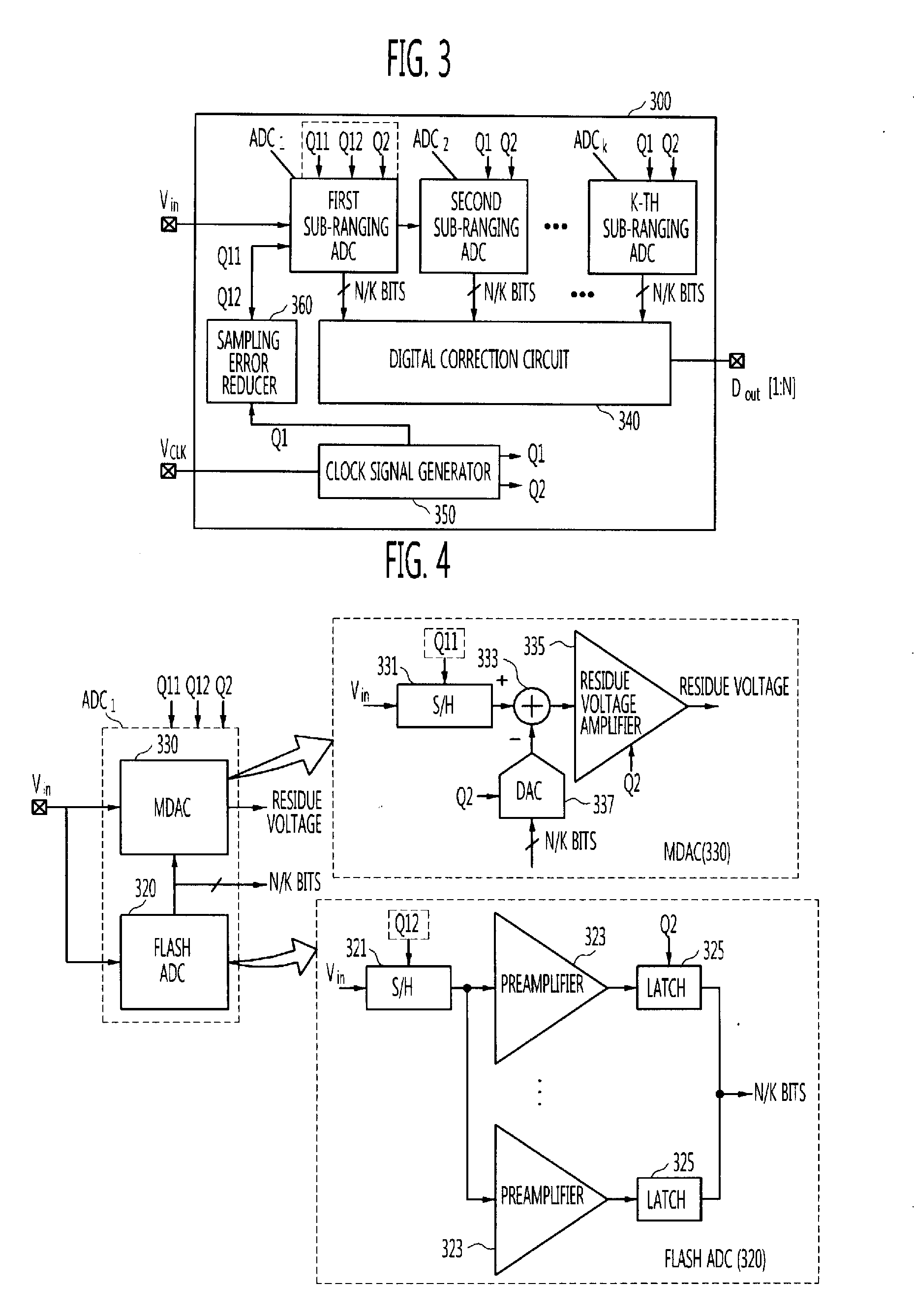

Provided is a pipeline analog-to-digital converter (ADC) without a front-end sample-and-hold amplifier (SHA). To minimize a sampling error occurring between a flash ADC and a multiplying digital-to-analog converter (MDAC) of a first sub-ranging ADC due to removal of a front-end SHA, a delay time of a preamplifier included in the flash ADC is calculated, and the flash ADC samples an analog input signal later by the delay time than the MDAC. Accordingly, the pipeline ADC can minimize a sampling error without using a front-end SHA, and its chip area and power consumption can be reduced.

Owner:ELECTRONICS & TELECOMM RES INST

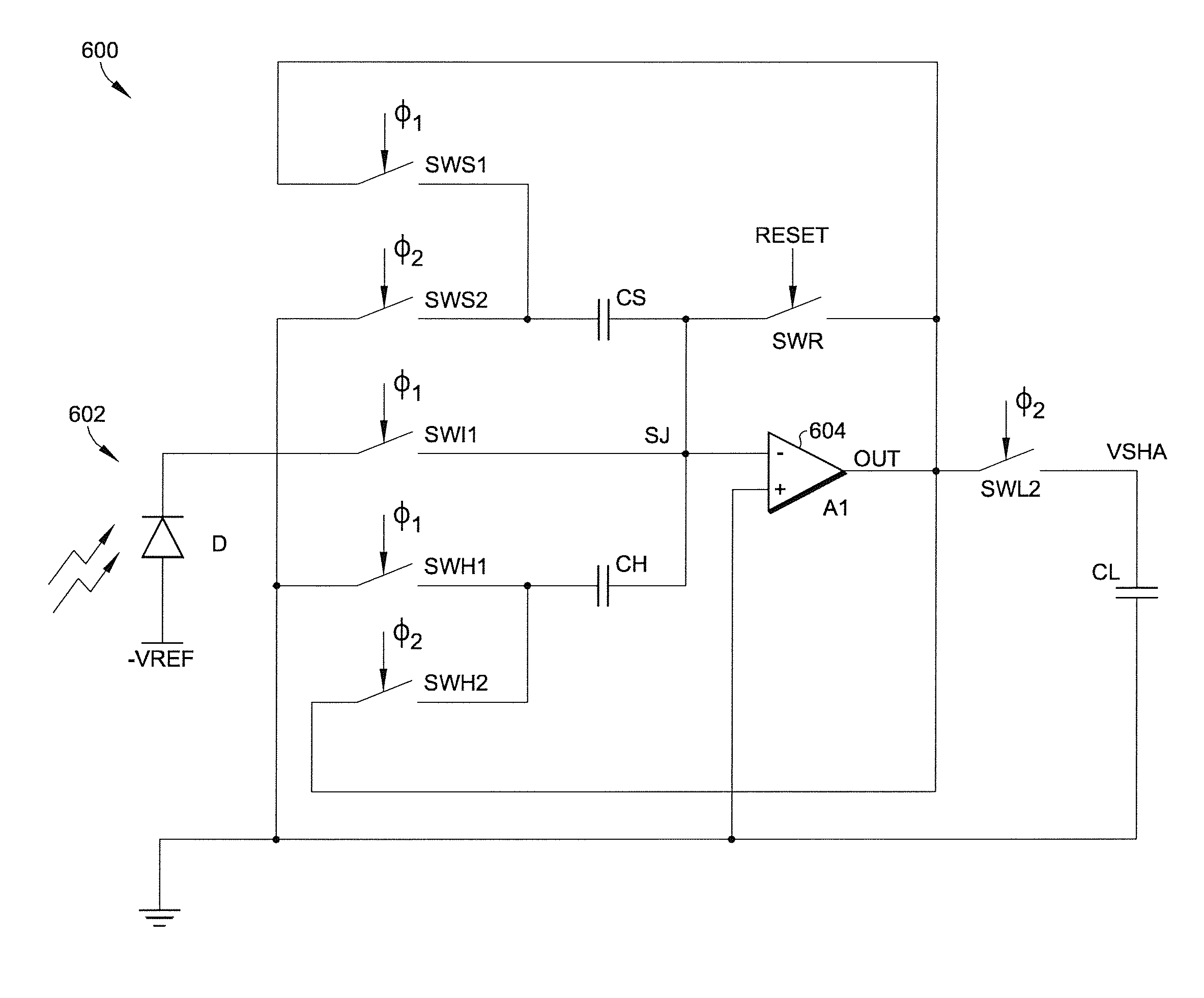

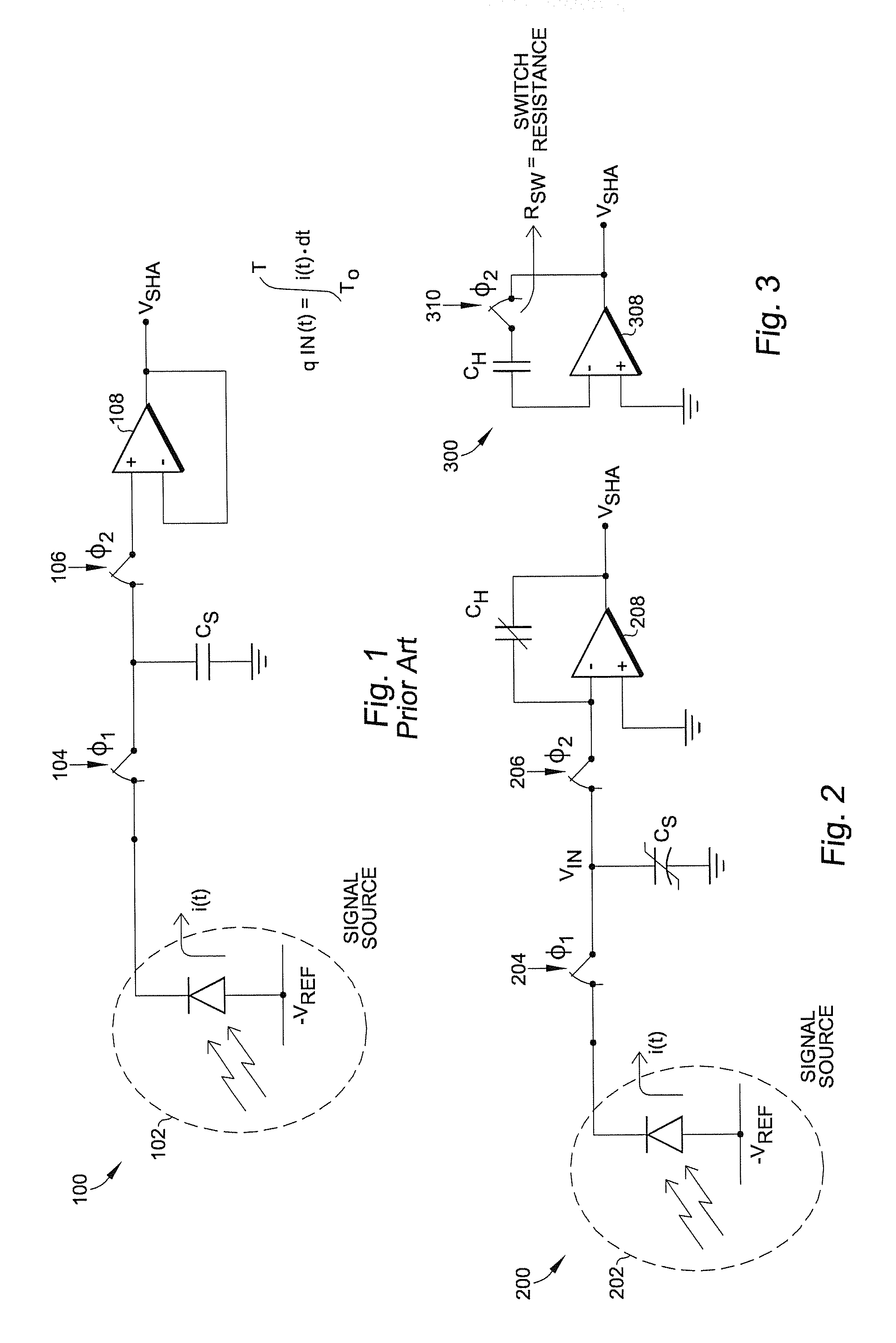

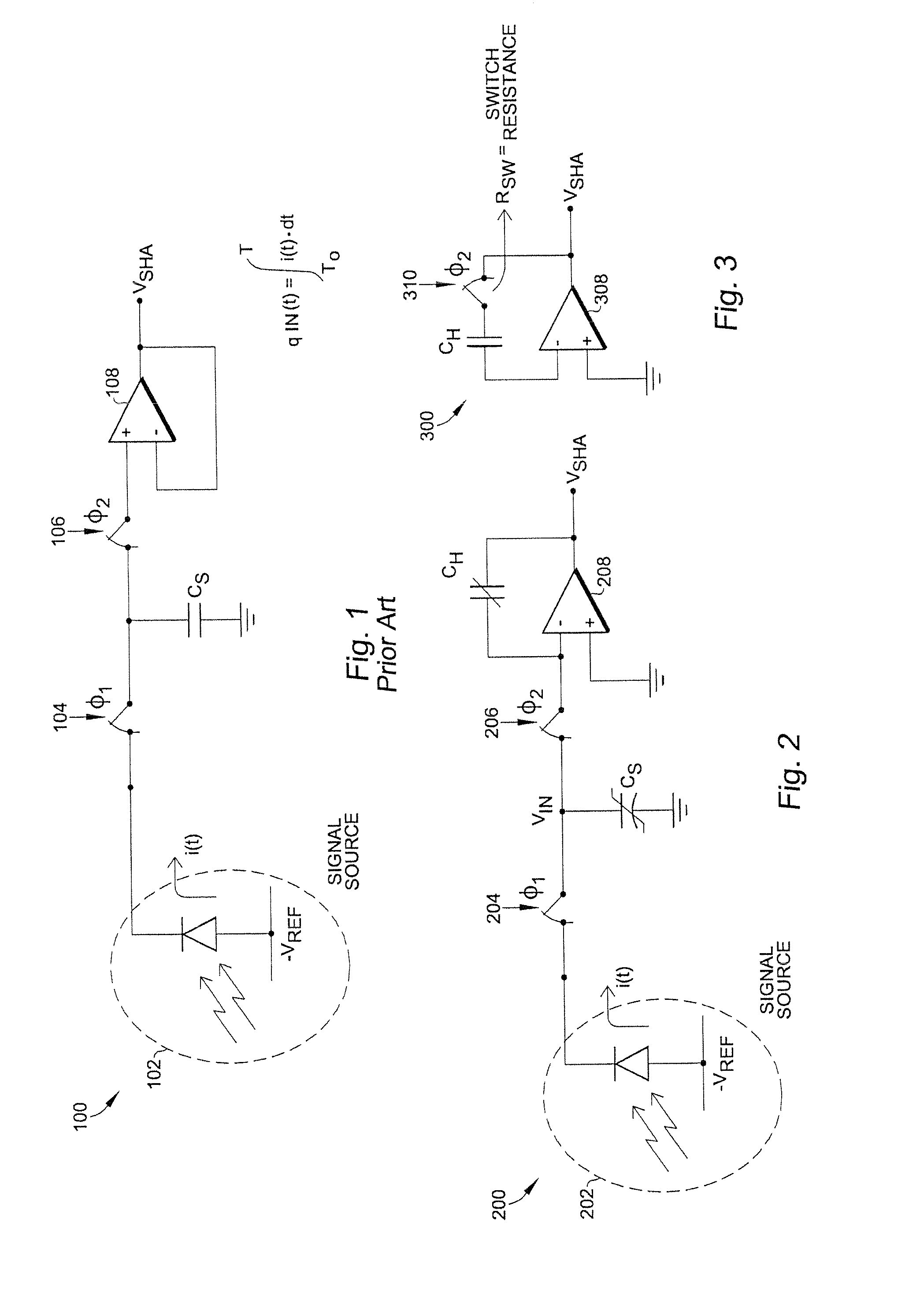

Low-noise low-distortion signal acquisition circuit and method with reduced area utilization

ActiveUS9076554B1Analogue/digital conversionElectric signal transmission systemsLow noiseLow distortion

A sample and hold amplifier includes an input node for receiving an input current signal, a non-linear sampling capacitor circuit having an input coupled to the input node, an operational amplifier having a negative input coupled to an output of the non-linear sampling capacitor circuit, a positive input coupled to ground, and an output for providing a sample and hold voltage signal, and a linear capacitor coupled between the negative input and the output of the operational amplifier. The non-linear sampling capacitor includes a non-linear capacitor coupled between an intermediate node and ground, a first switch coupled between the input and the intermediate node configured to switch according to a first phase signal, and a second switch coupled between the output and the intermediate node configured to switch according to a second phase signal.

Owner:CAES COLORADO SPRINGS LLC

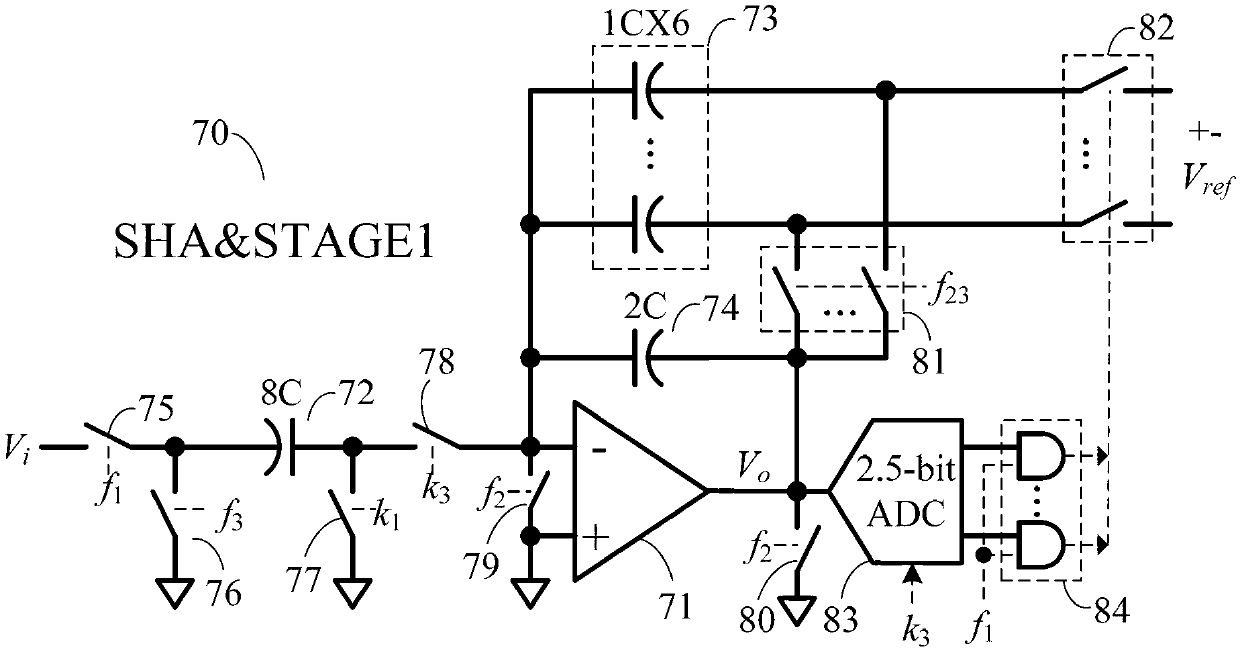

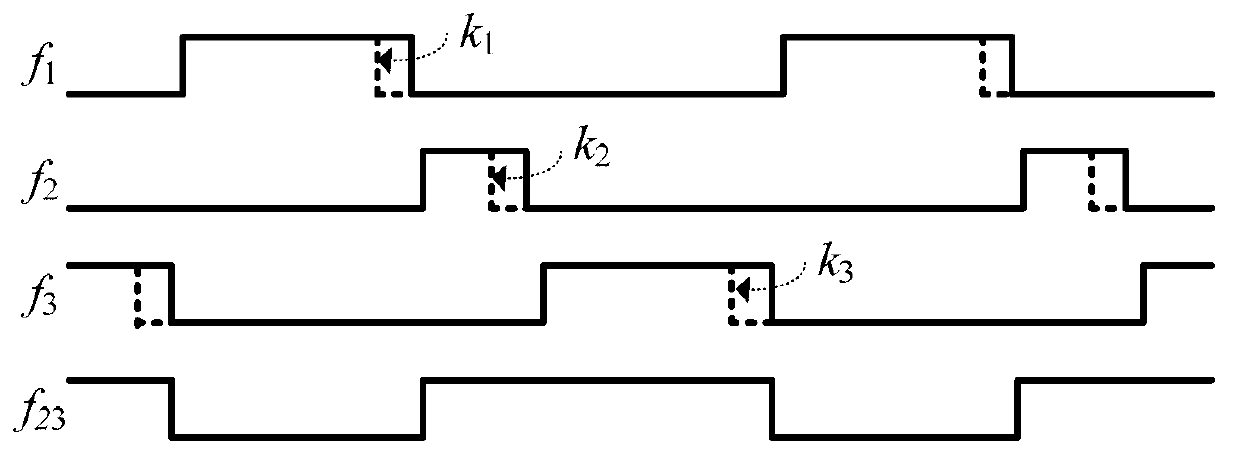

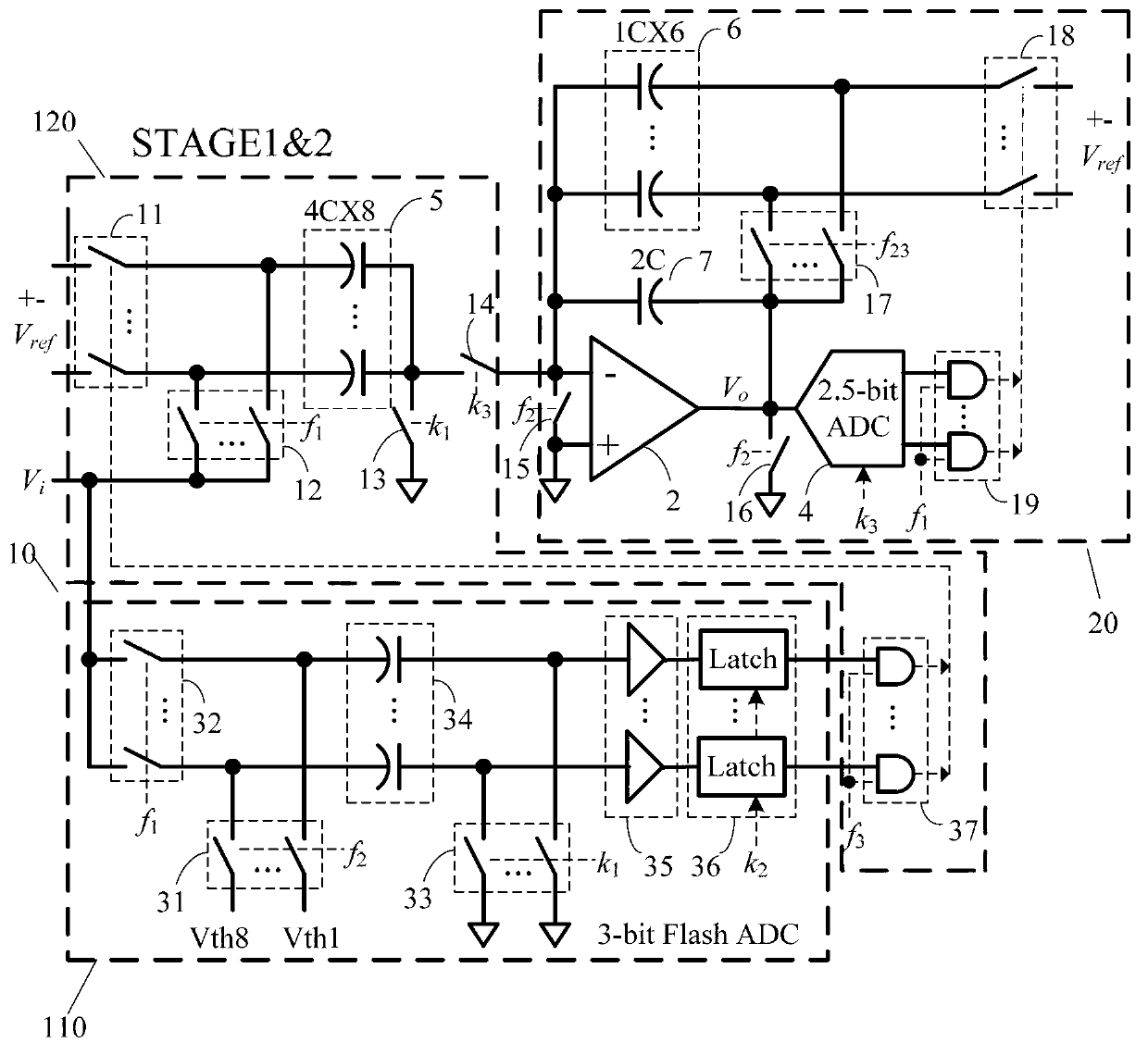

Front-end circuit for analogue-to-digital converter with pipeline structure and time sequence control method for front-end circuit

ActiveCN103281080AIncrease power consumptionImprove noiseElectric signal transmission systemsAnalogue-digital convertersDigital down converterAudio power amplifier

The invention discloses a front-end circuit for an analogue-to-digital converter with a pipeline structure and a time sequence control method for the front-end circuit, and aims to eliminate a sampling and holding amplifier, improve power consumption and noise indexes and reduce conversion delay. The front-end circuit is used for realizing the analogue-to-digital conversion of M1+M2 bits, and acquiring a second analogue residual error signal, wherein the second analogue residual error signal is used for the sampling of the next conversion stage of the front-end circuit in the analogue-to-digital converter with the pipeline structure. The front-end circuit comprises a first conversion stage and a second conversion stage, wherein the first conversion stage is used for directly sampling an input signal to finish the analogue-to-digital conversion of M1 bits, and acquiring a first analogue residual error signal; and the second conversion stage is used for receiving and sampling the first analogue residual error signal to finish the analogue-to-digital conversion of M2 bits, and acquiring the second analogue residual error signal.

Owner:TSINGHUA UNIV +1

Successive approximation register analog-to-digital converter and analog-to-digital conversion method using the same

ActiveUS8659462B2Optimize operating timeImprove stabilityElectric signal transmission systemsAnalogue-digital convertersDigital down converterEngineering

A Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) includes a Sample-and-Hold Amplifier (SHA) for sampling and holding an externally input analog voltage, a comparator for comparing a level of the sampled and held analog voltage with a level of an analog signal corresponding to n bits and generating a comparison signal according to result of comparison, an SAR logic circuit for sequentially generating a digital signal from a Most significant Bit (MSB) to a Least Significant Bit (LSB) in response to the comparison signal, a Digital-to-Analog Converter (DAC) for providing the analog signal to the comparator, and an output register for holding the sequentially generated digital signal from the MSB to the LSB to generate an n-bit digital signal, wherein, upon externally receiving a start signal, the SAR logic circuit generates a digital signal of a MSB having a one-bit phase delay compared with the start signal.

Owner:LG DISPLAY CO LTD

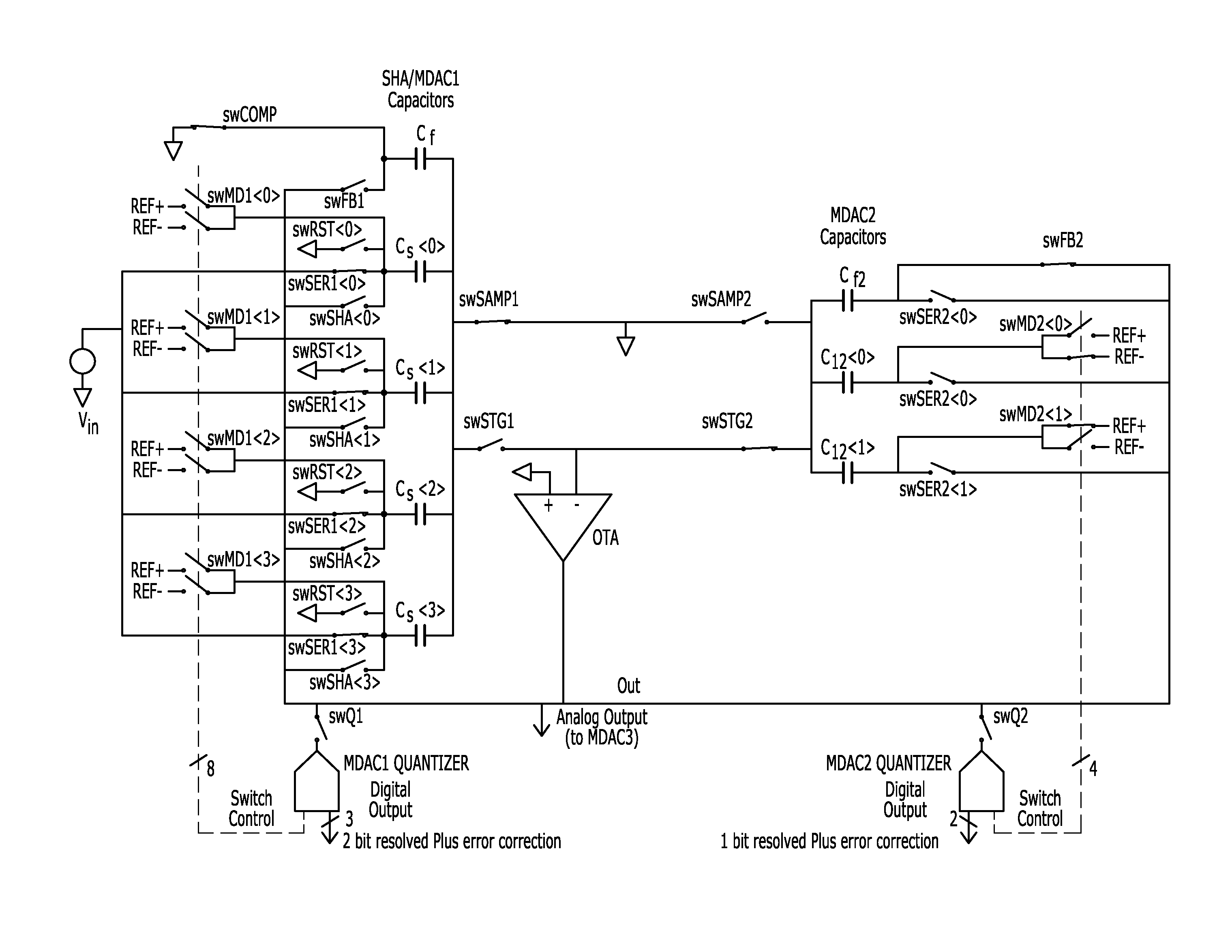

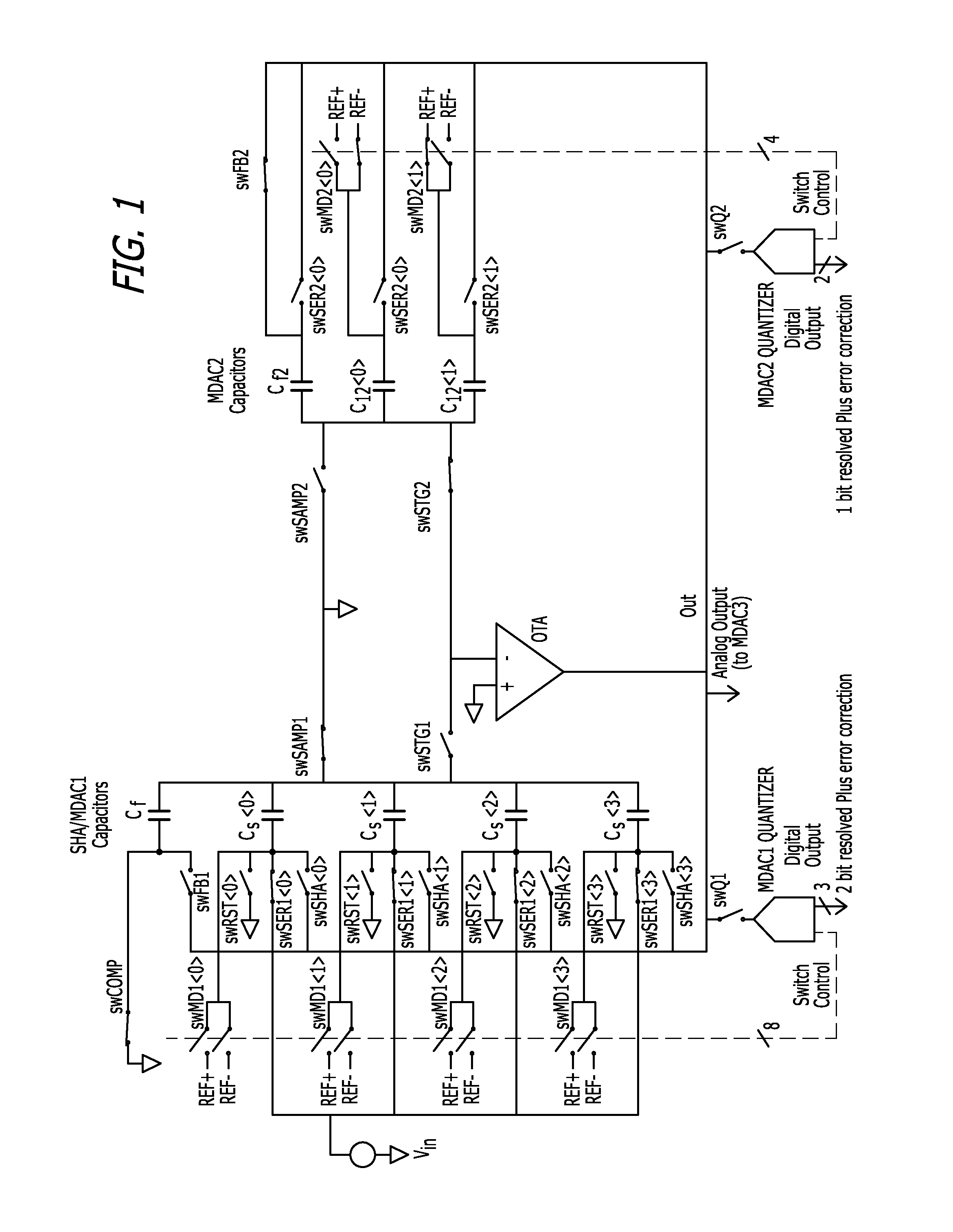

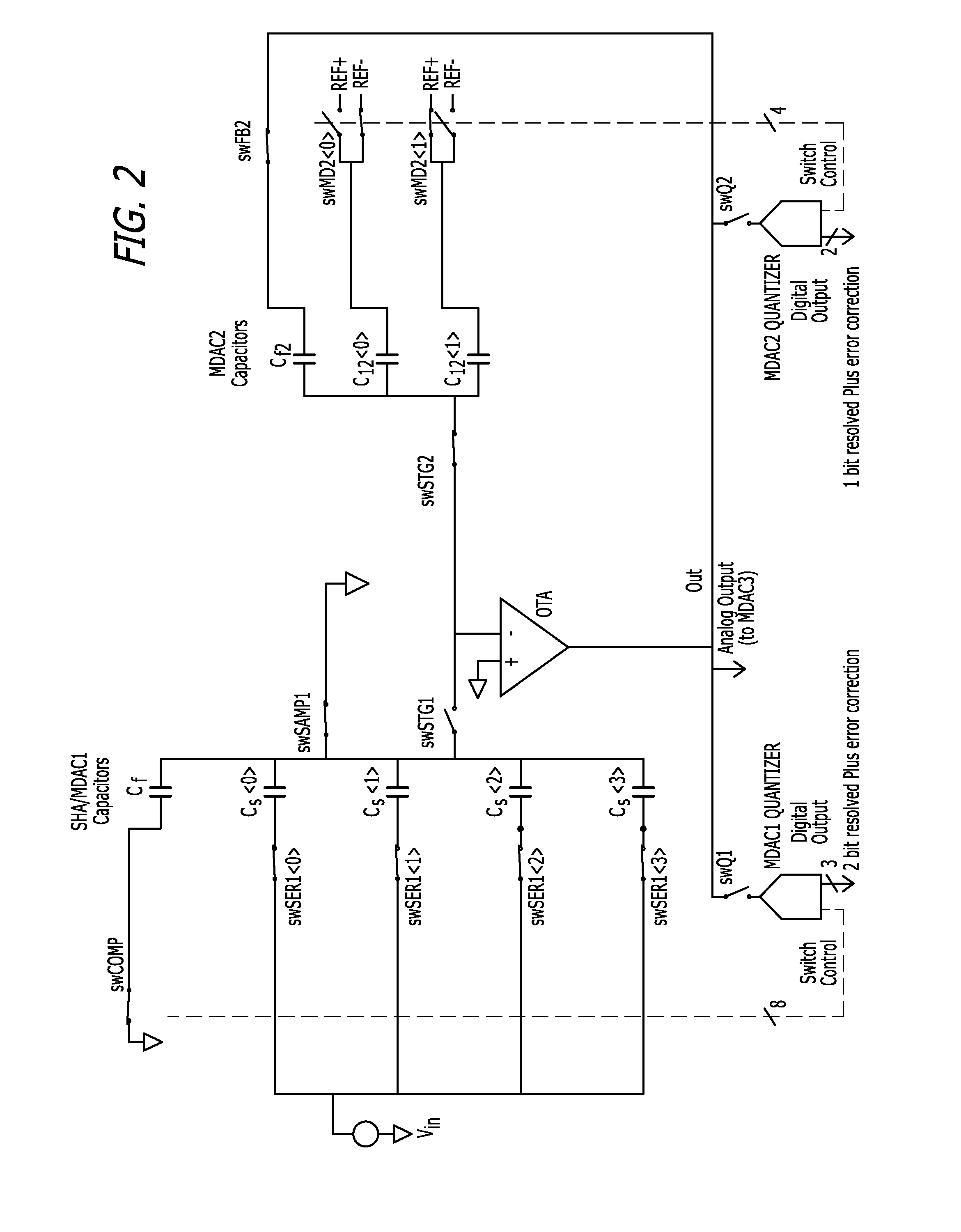

Shared Operational Transconductance Amplifier Pipelined ADC Incorporating a Sample/Hold Amplifier and Multiple MDAC Stages

ActiveUS20110298645A1Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierEngineering

A single operational transconductance pipelined ADC incorporating a sample / hold amplifier and multiple MDAC stages. An input signal is sampled on input signal sampling capacitors, and then coupled around an operational transconductance amplifier (OTA) so that the output of the OTA is equal to the sampled voltage. There is no net charge transfer in this operation, so the noise and power dissipation normally associated with an input sample and hold circuitry (SHA) in a pipelined ADC is substantially eliminated. A pipelined ADC using a shared OTA for sample / hold and two MDACs is disclosed.

Owner:MAXIM INTEGRATED PROD INC

A sample-and-hold amplifier

InactiveCN102195652AAnalogue/digital conversionElectric signal transmission systemsAudio power amplifierPre-charge

A sample-and-hold amplifier (400) having a sample phase of operation and a hold phase of operation. The sample,and-hold amplifier comprising one or more sampling components (404, 406) configured to sample input signals during the sample phase of operation, and provide sampled input signals during the hold phase of operation, and an amplifier (402) configured to pre-charge the output (416, 418) of the sample-and-hold amplifier (400) during the sample phase of operation, and buffer the sampled input signal during the hold phase of operation.

Owner:NXP BV

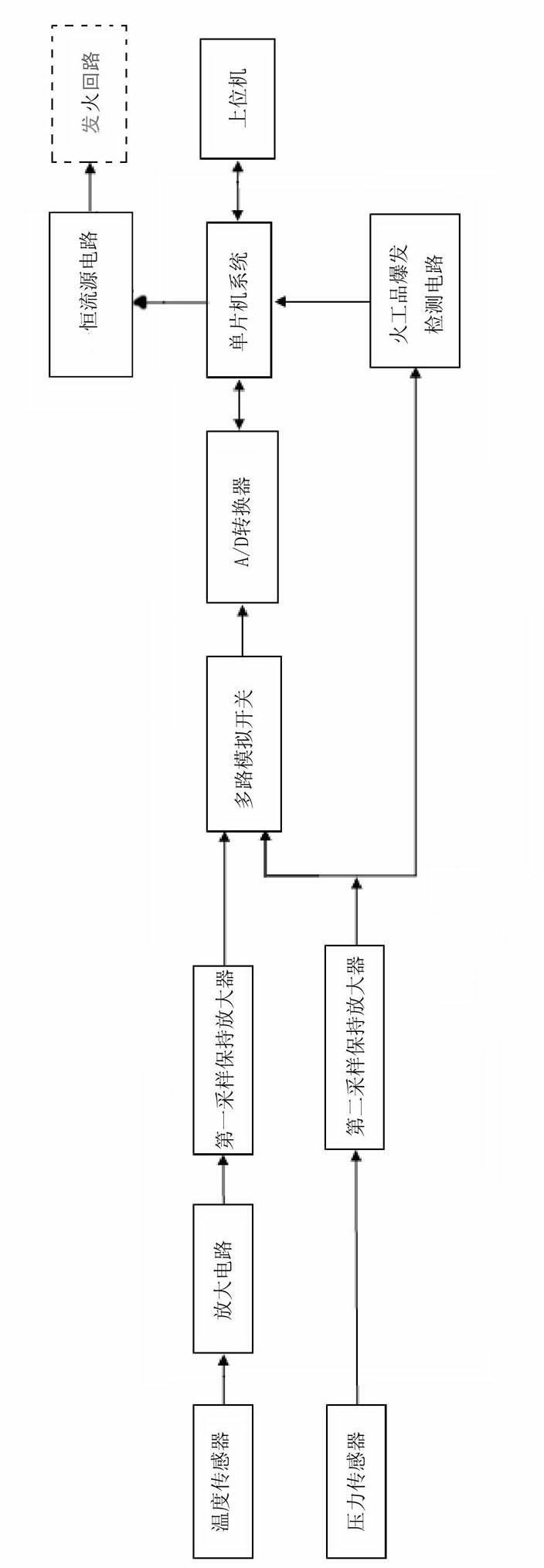

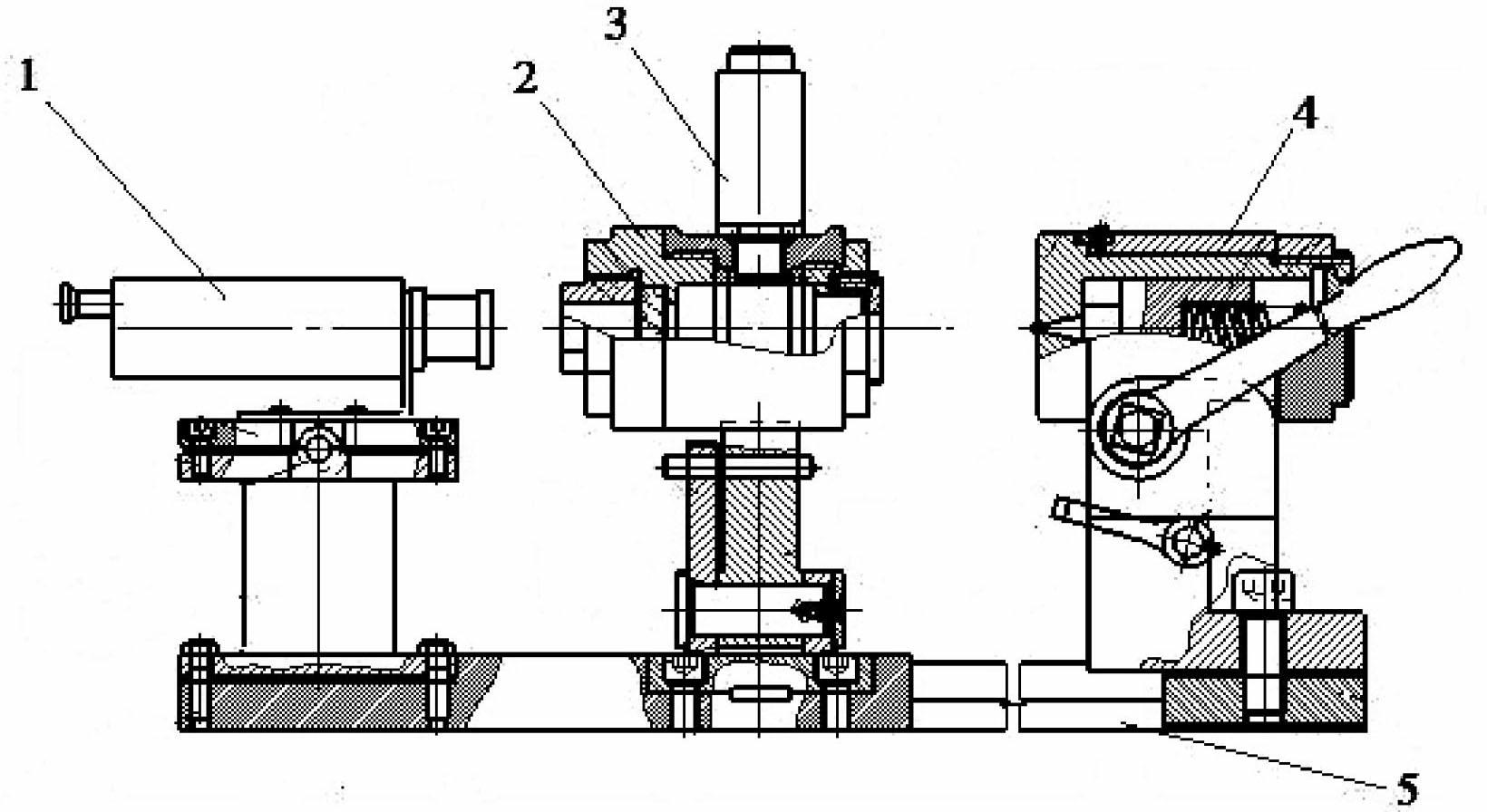

Initiating explosive device acting pressure-temperature tester

InactiveCN102183273AOvercome the shortcoming of a single test parameterHigh speed acquisitionRadiation pyrometryRapid change measurementAudio power amplifierTester device

The invention relates to an initiating explosive device acting pressure-temperature tester. The tester comprises a temperature sensor, a pressure sensor, an amplifying circuit, first and second sampling and holding amplifiers, a multi-channel analog switch, an analog / digital (A / D) converter, a singlechip system, an initiating explosive device explosion detection circuit and a constant current source circuit. The tester can simultaneously test two parameters, namely output pressure and temperature, and can provide two channels of accurate steady current so as to test the safe current and the firing current of an electric initiating explosive device.

Owner:ORDNANCE TECH RES INST OF THE GENERAL ARMAMENT DEPT PLA

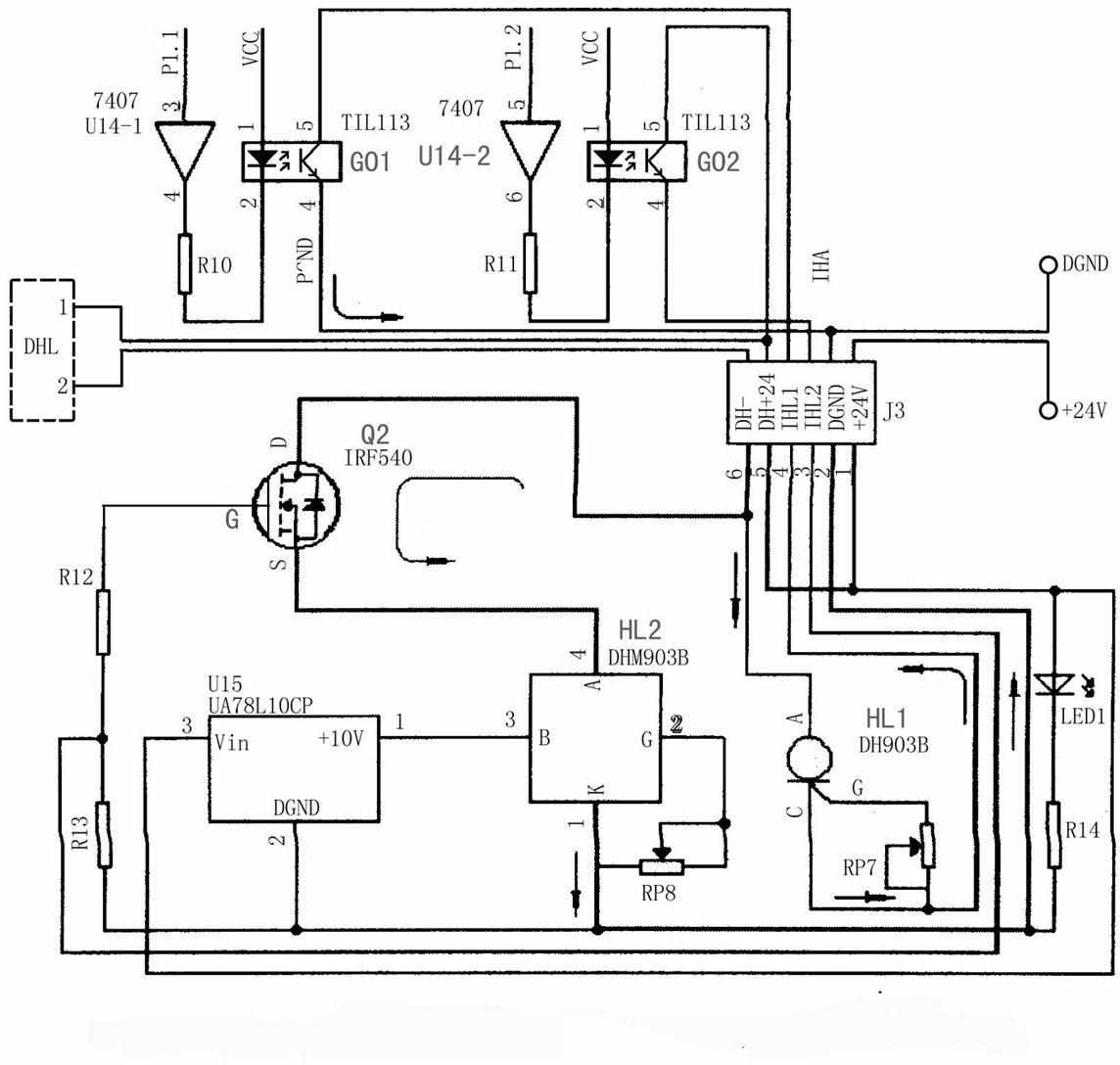

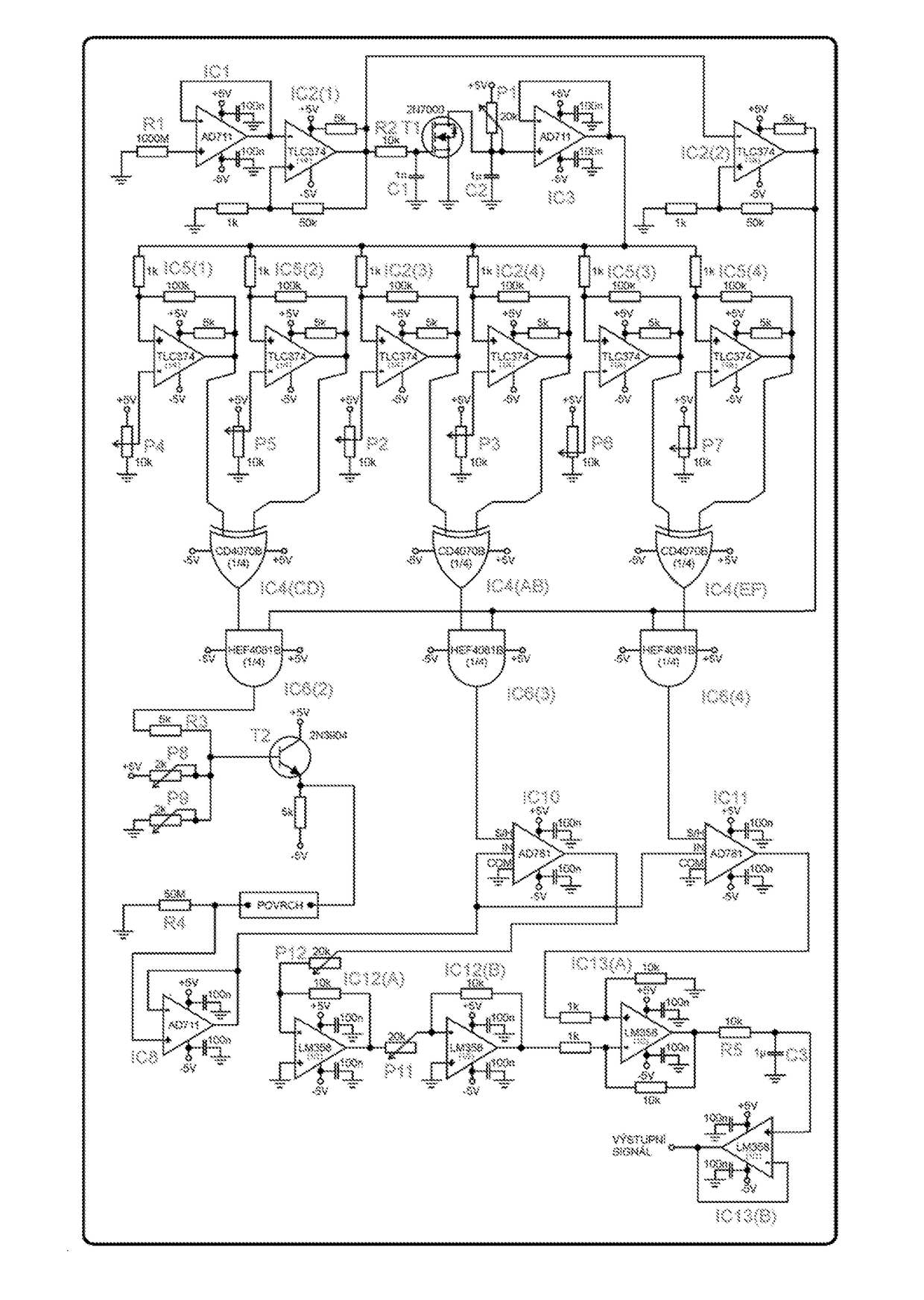

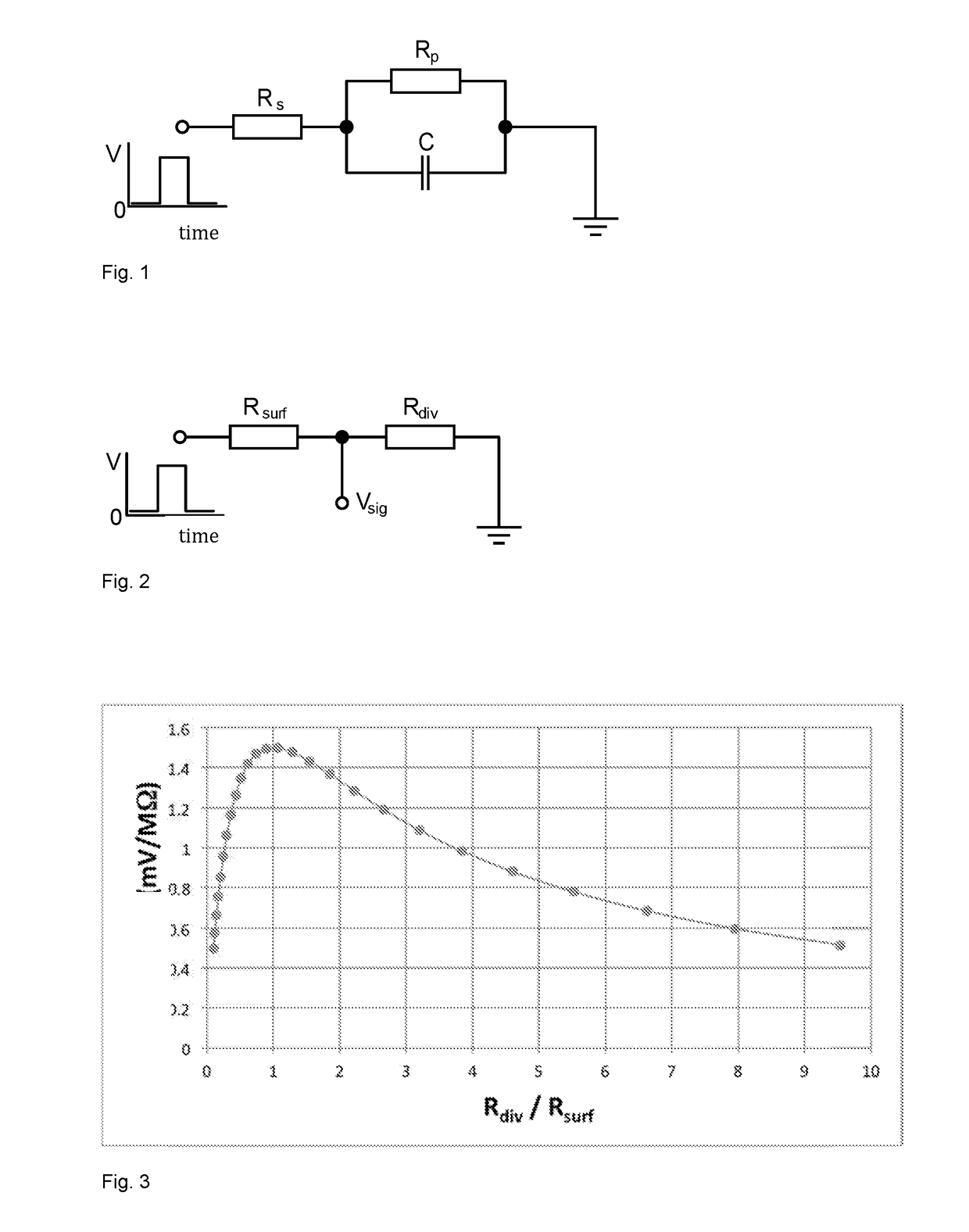

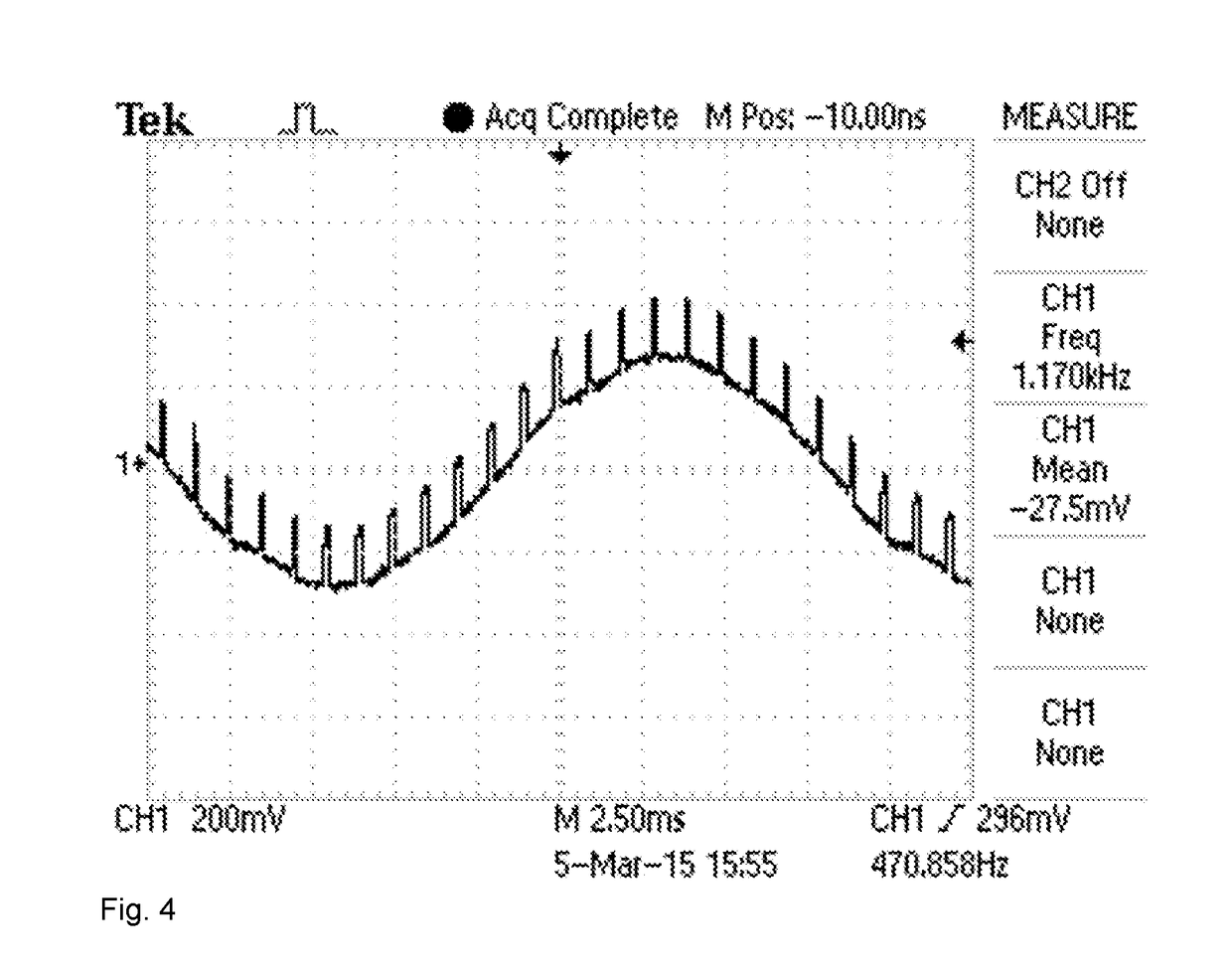

Method for measuring quick changes in low surface conductivity of dielectrics under electromagnetic interference of line voltage and equipment to perform this type of measurement

InactiveUS20180003758A1Eliminate fluctuationsDielectric property measurementsVery high resistance measurementsPulse parameterVoltage divider

Owner:PALACKY UNIV OLOMOUC

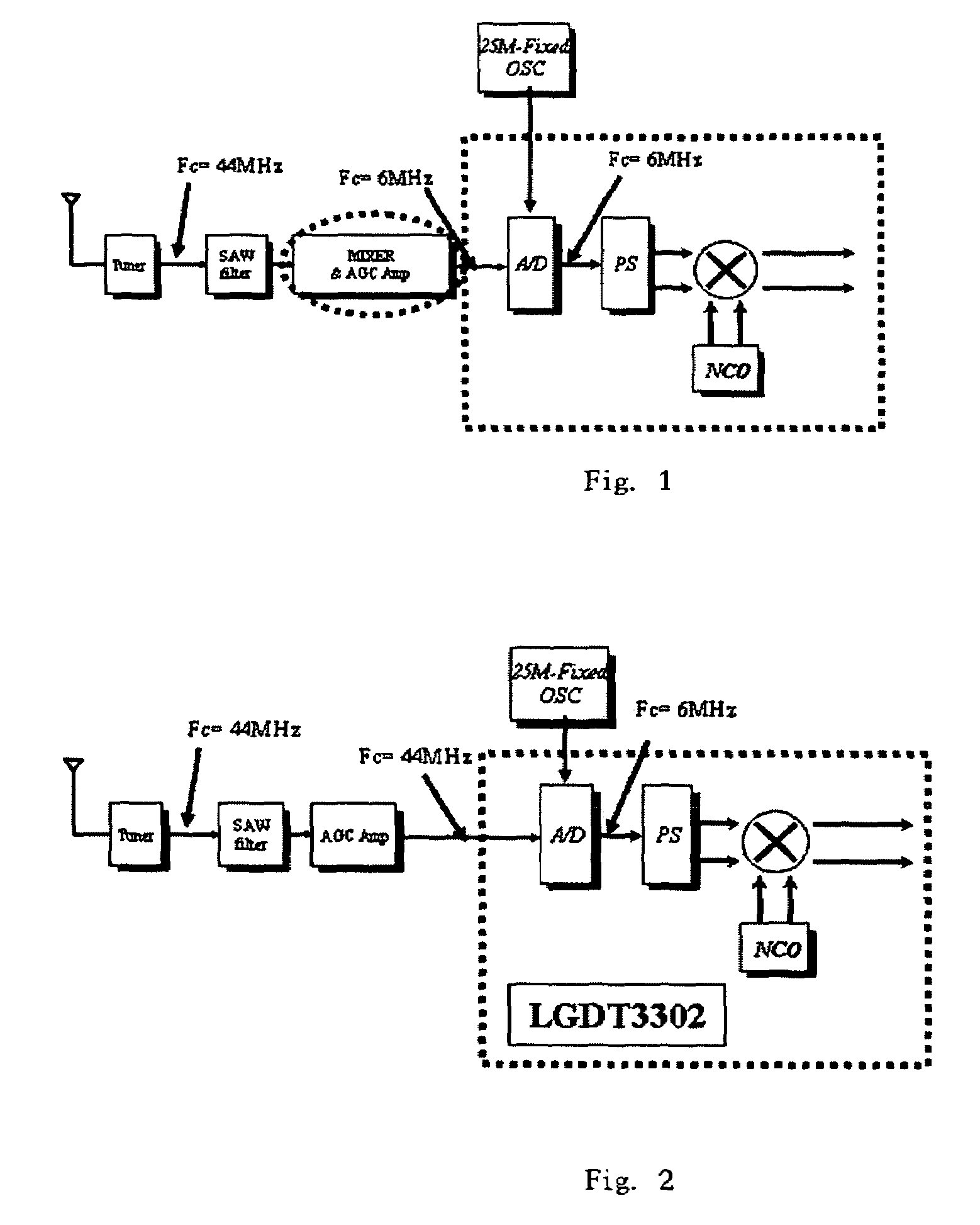

Analog-digital converter using clock boosting

InactiveUS7126507B2Improve featuresUnnecessary useElectric signal transmission systemsAnalogue-digital convertersAudio power amplifierDigital analog converter

Disclosed herein is an analog-digital converter. The analog-digital converter includes a sample-and-hold amplifier, a first analog-digital converter, a multiple digital-analog converter, a second analog-digital converter, and a digital correction logic. The sample-and-hold amplifier samples an analog input signal using clock boosting. The first analog-digital converter receives a sampled signal, and converts the sampled signal into a plurality of bits of first digital output code. The multiple digital-analog converter receives and stores the sampled signal, and amplifies and outputs the difference between the stored signal and an analog signal corresponding to the first digital output code. The second analog-digital converter receives the output signal of the multiple digital-analog converter, and converts the output signal into a plurality of bits of second digital output code. The digital correction logic receives the first digital output code and the second digital output code, overlaps certain bits of the first digital output code with certain bits of the second digital output code, and outputs remaining bits, exclusive of overlapping bits, as final digital output code.

Owner:LG ELECTRONICS INC

Method of controlling pipeline analog-to-digital converter and pipeline analog-to-digital converter implementing the same

ActiveUS7583219B2Minimizing sampling mismatchPower saving provisionsElectric signal transmission systemsDigital down converterAudio power amplifier

Provided are a pipeline Analog-to-Digital Converter (ADC) without a front-end Sample-and-Hold Amplifier (SHA) and a method of controlling the same. The method includes the steps of: simultaneously sampling, at an ADC and a residual signal generator included in a first stage, an analog input signal and respectively generating a first sampling value and a second sampling value; holding, at the residual signal generator, the second sampling value, and simultaneously amplifying and converting, at the ADC, the first sampling value into a corresponding digital code; and generating, at the residual signal generator, a residual signal using the digital code. The pipeline ADC and method of controlling the same minimize sampling mismatch caused by removing a front-end SHA, thereby ensuring stable performance without a front-end SHA. Since a front-end SHA is not used, it is possible to reduce chip size and power consumption, and improve the performance of the ADC.

Owner:ELECTRONICS & TELECOMM RES INST

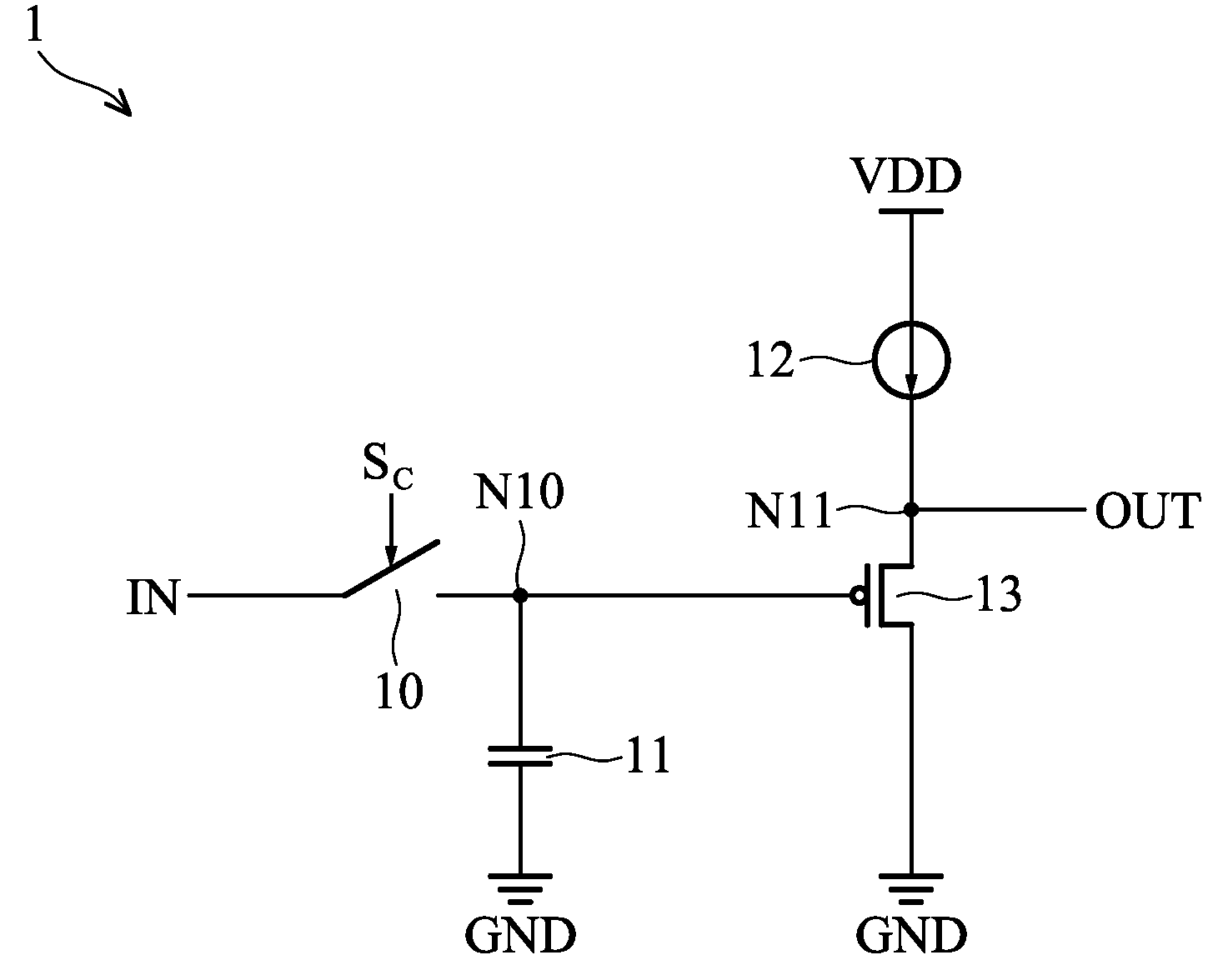

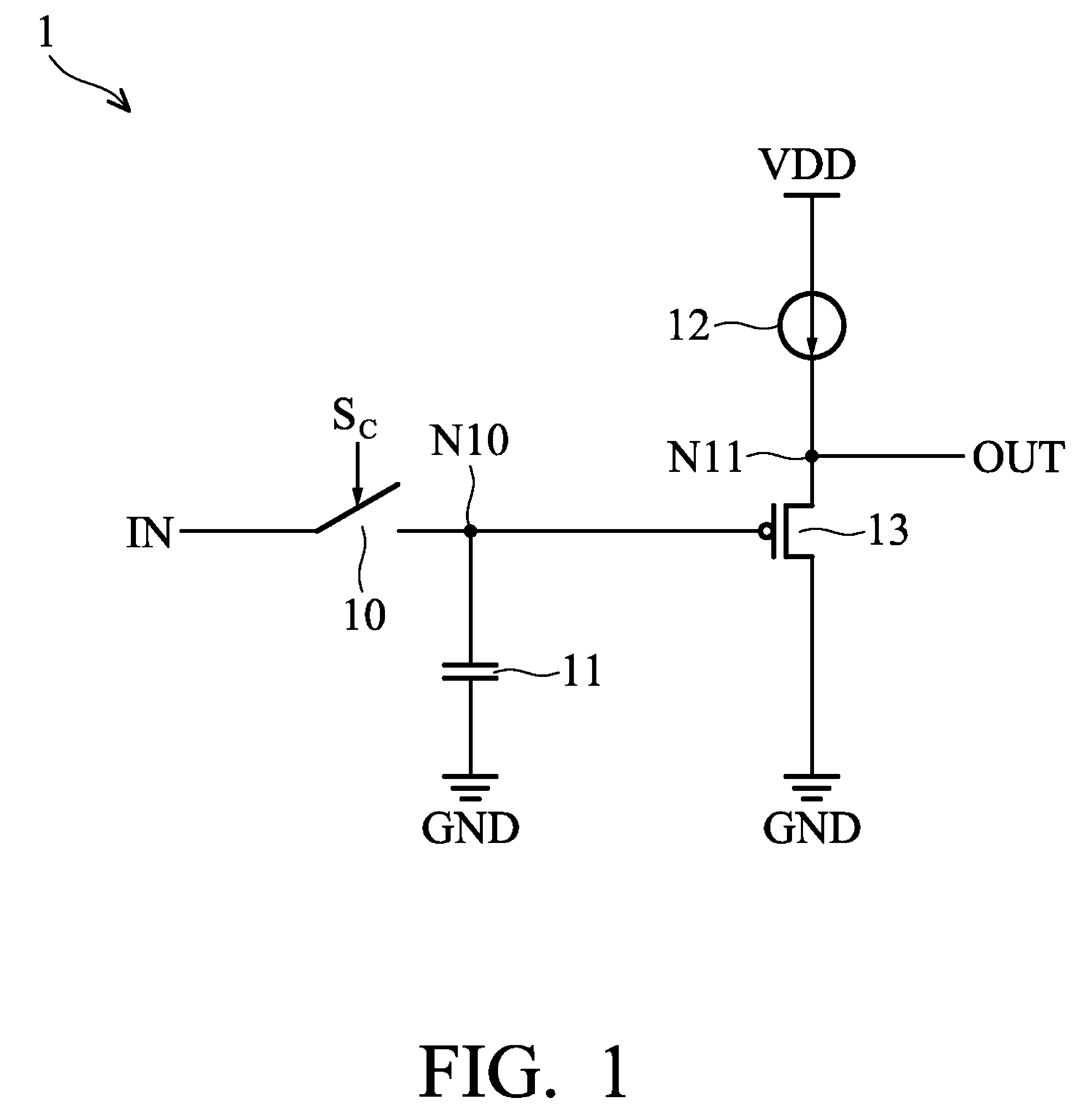

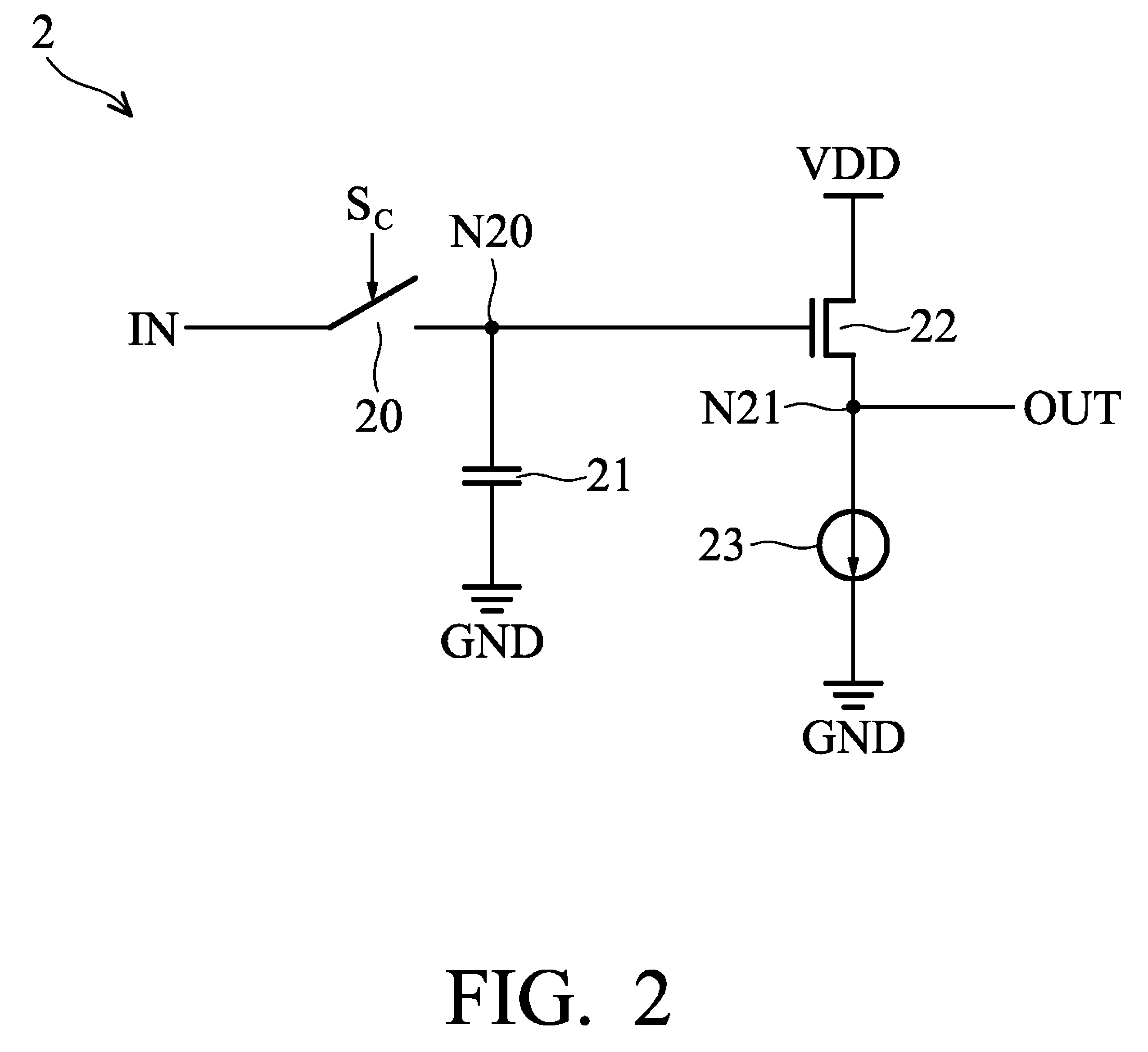

Sample-and-hold amplifiers

ActiveUS7847629B2Reduce power consumptionSmall sizeAmplifier modifications to raise efficiencyElectric analogue storesAudio power amplifierControl signal

A sample-and-hold amplifier is provided. The sample-and-hold amplifier comprises a sample-and-hold circuit and a buffer circuit. The sample-and-hold circuit receives an input signal and transmits the input signal to a first node according to a control signal. The buffer circuit is coupled between a supply voltage source and a ground and controlled by the first node to provide an output signal at an output node. The buffer circuit comprises a native MOS transistor coupled to the output node.

Owner:MEDIATEK INC

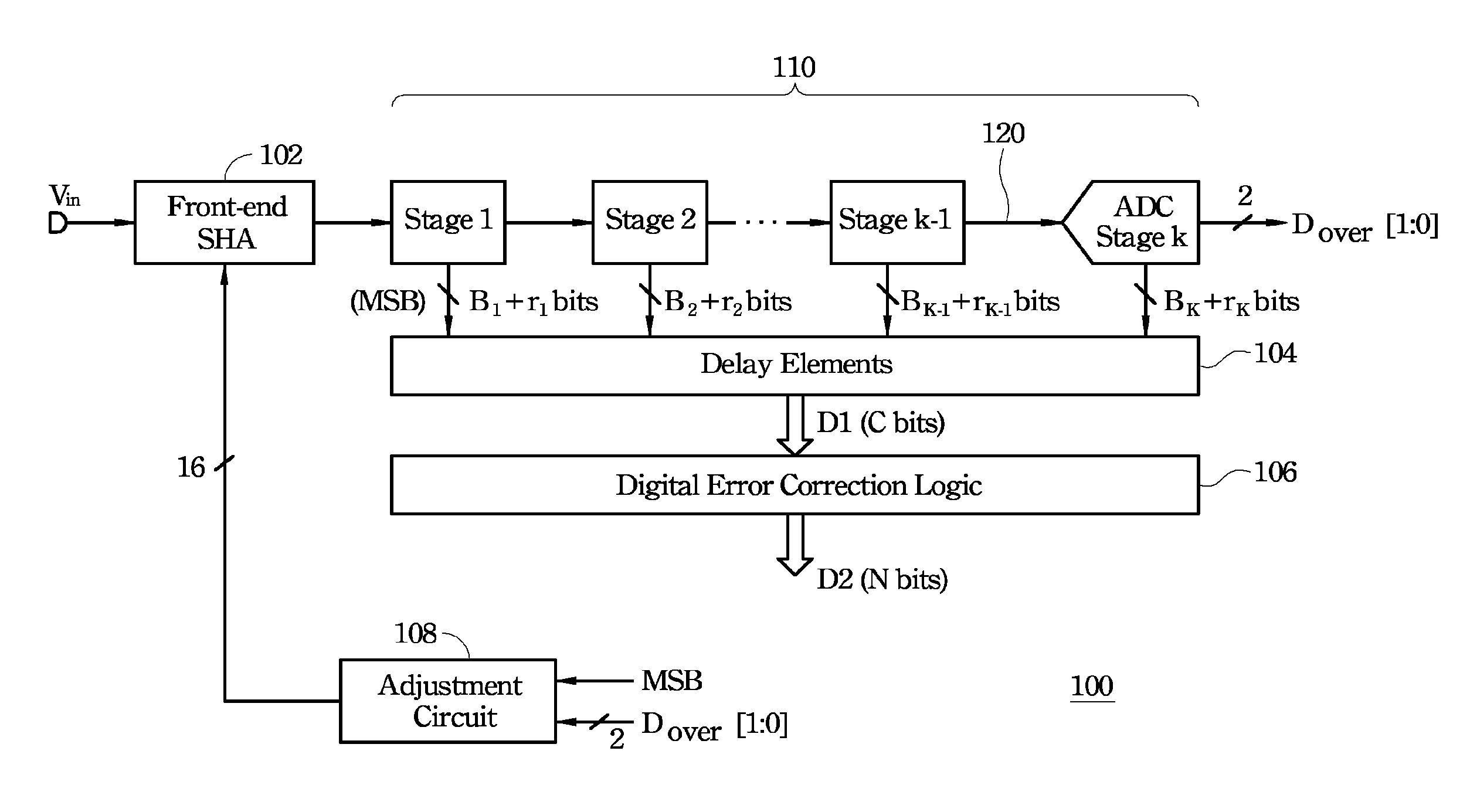

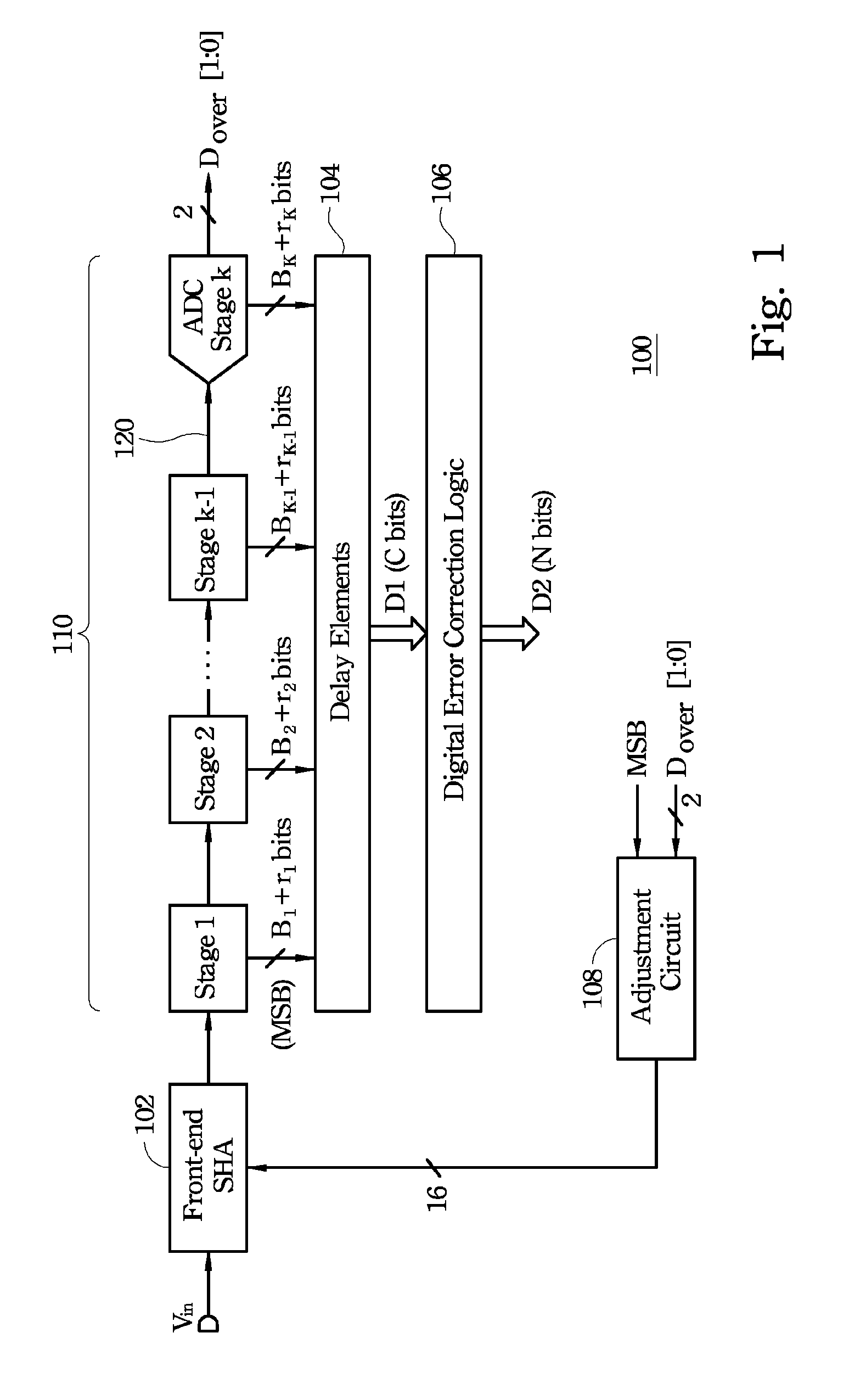

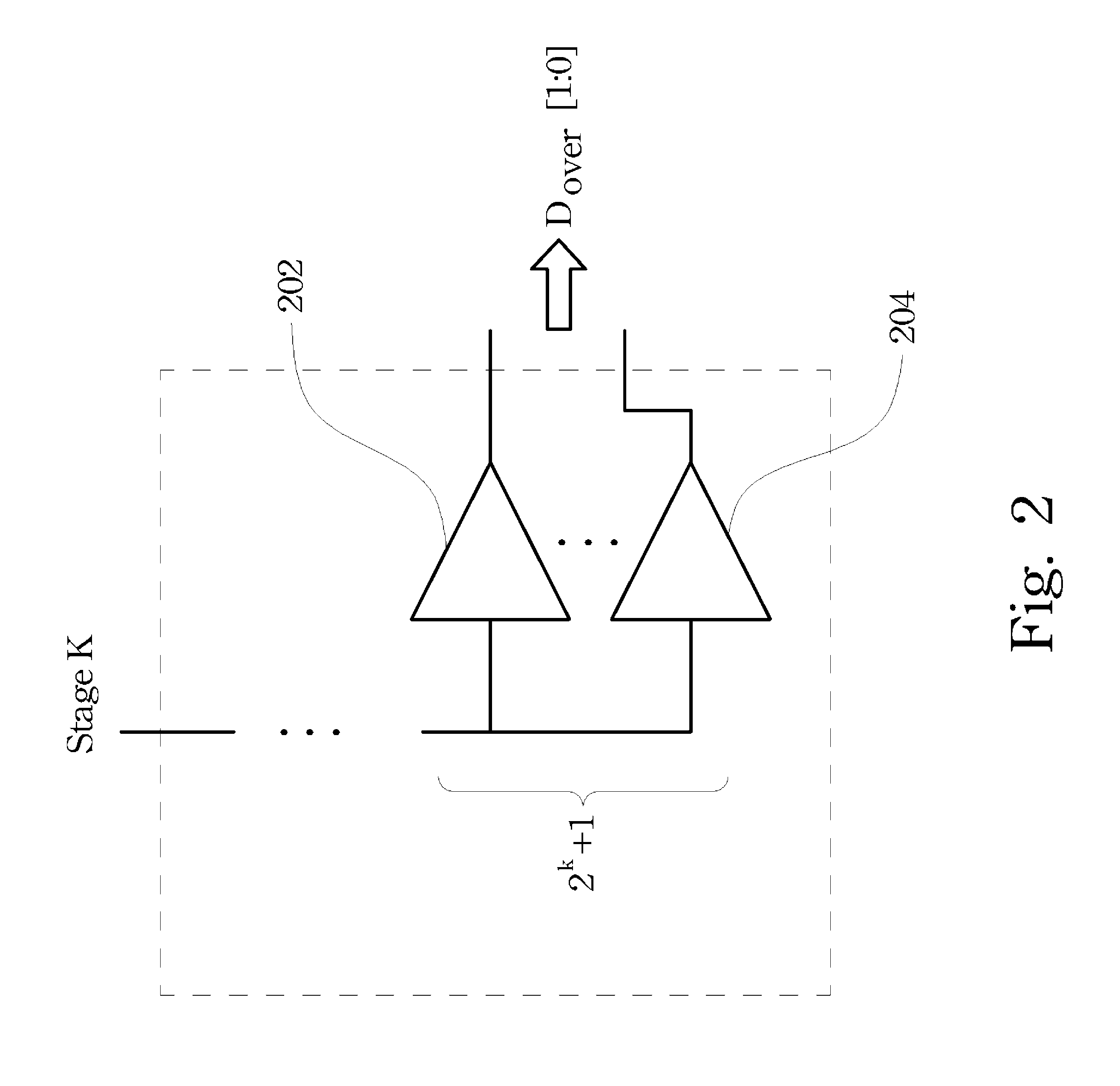

A/D converter, method for adjusting analog signal therein, and method for converting analog signal into digital signal

ActiveUS7746255B1Electric signal transmission systemsAnalogue-digital convertersAudio power amplifierBuck converter

An analog-to-digital converter includes a sample-and-hold amplifier (SHA), a plurality of stages of analog-to-digital converting (ADC) units and an adjustment circuit. The SHA samples an analog input signal. The ADC units serially converts the analog input signal sampled by the SHA into corresponding digital values, in which a first stage of the ADC units generates the digital value including most significant bits. The adjustment circuit controls the SHA by checking the most significant bits from the first stage of the ADC units to modify offsets of the analog input signal with respect to a reference value. A method for adjusting an analog input signal in an analog-to-digital converter and a method for converting an analog input signal into a digital signal are also disclosed herein.

Owner:HIMAX TECH LTD

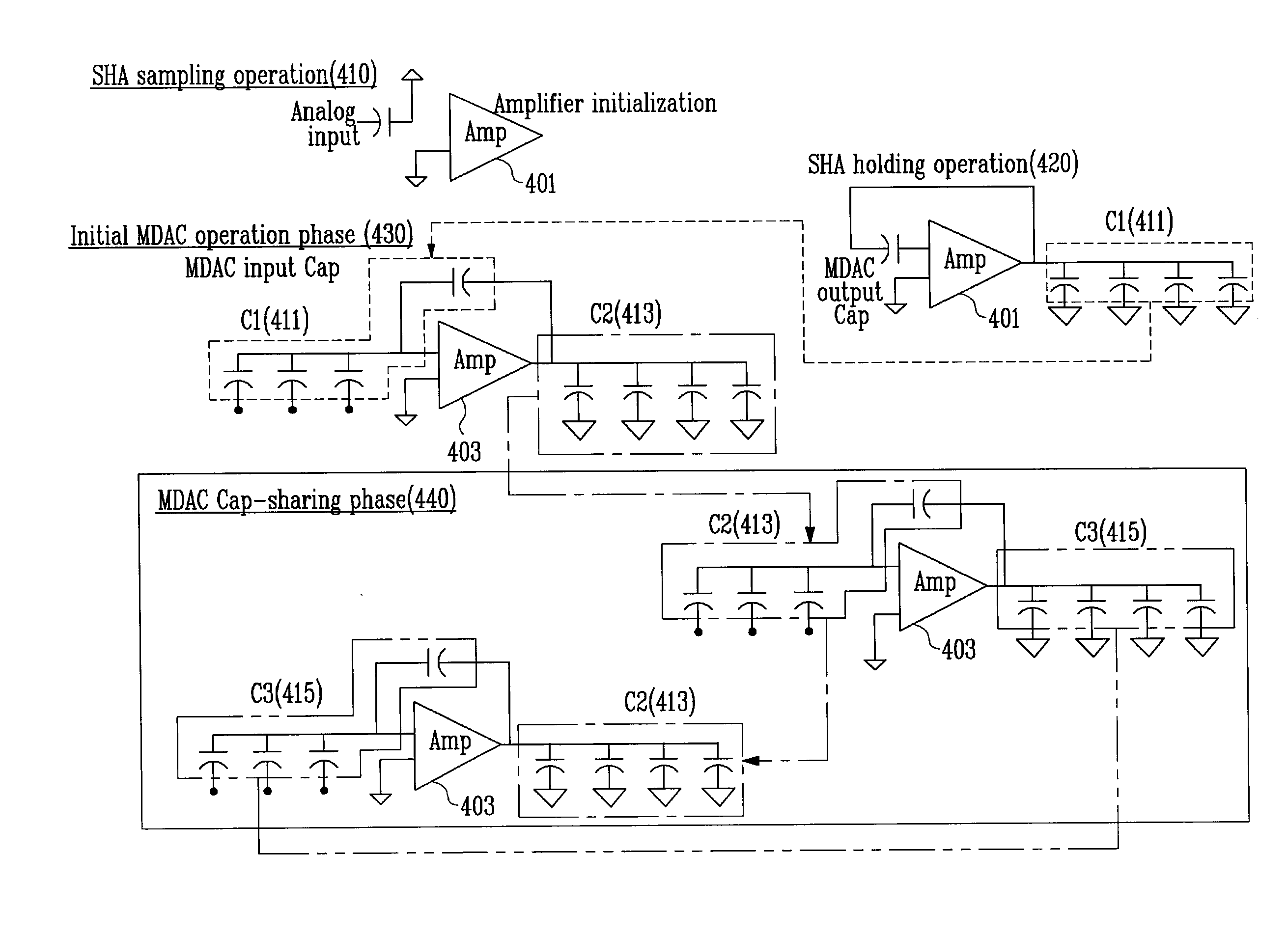

Method of algorithmic analog-to-digital conversion and algorithmic analog-to-digital converter

InactiveUS20090096646A1Freeing bandwidthEfficient executionElectric signal transmission systemsAnalogue conversionAudio power amplifierDigital analog converter

Provided are a method of algorithmic analog-to-digital conversion and an algorithmic Analog-to-Digital Converter (ADC). The algorithmic ADC includes a Multiplying Digital-to-Analog Converter (MDAC). The MDAC includes a Digital-to-Analog Converter (DAC) for converting a first digital signal into an analog signal, a subtractor for calculating a difference between the signal output from the DAC and an analog signal input from a first Sample and Hold Amplifier (SHA), an amplifier for amplifying the difference, a first capacitor unit connected with an output end of the first SHA and an input end of the amplifier through a first switching unit, a second capacitor unit connected with the input end and an output end of the amplifier through a second switching unit, and a third capacitor unit connected with the input end and the output end of the amplifier through a third switching unit.

Owner:ELECTRONICS & TELECOMM RES INST

Low-noise low-distortion signal acquisition circuit and method with reduced area utilization

A sample and hold amplifier includes an input node for receiving an input current signal, a non-linear sampling capacitor circuit having an input coupled to the input node, an operational amplifier having a negative input coupled to an output of the non-linear sampling capacitor circuit, a positive input coupled to ground, and an output for providing a sample and hold voltage signal, and a linear capacitor coupled between the negative input and the output of the operational amplifier. The non-linear sampling capacitor includes a non-linear capacitor coupled between an intermediate node and ground, a first switch coupled between the input and the intermediate node configured to switch according to a first phase signal, and a second switch coupled between the output and the intermediate node configured to switch according to a second phase signal.

Owner:CAES COLORADO SPRINGS LLC

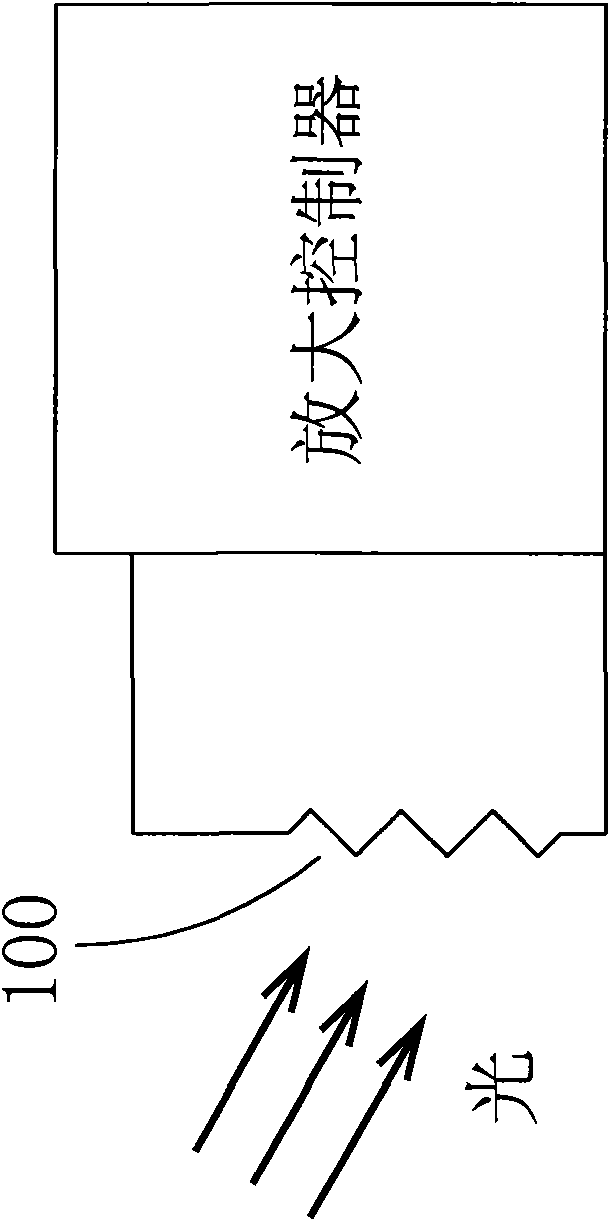

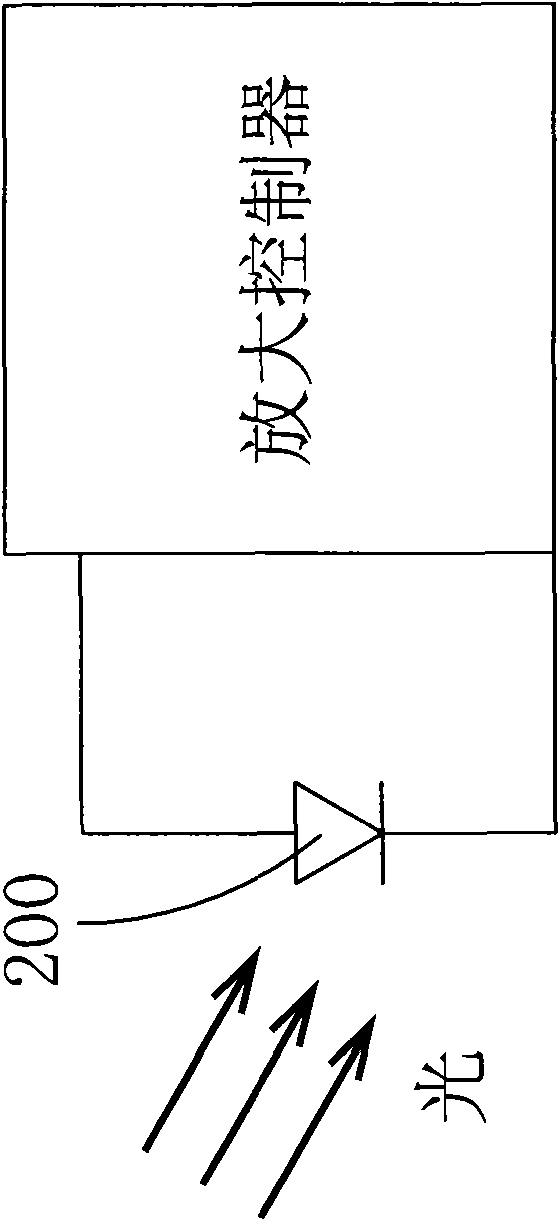

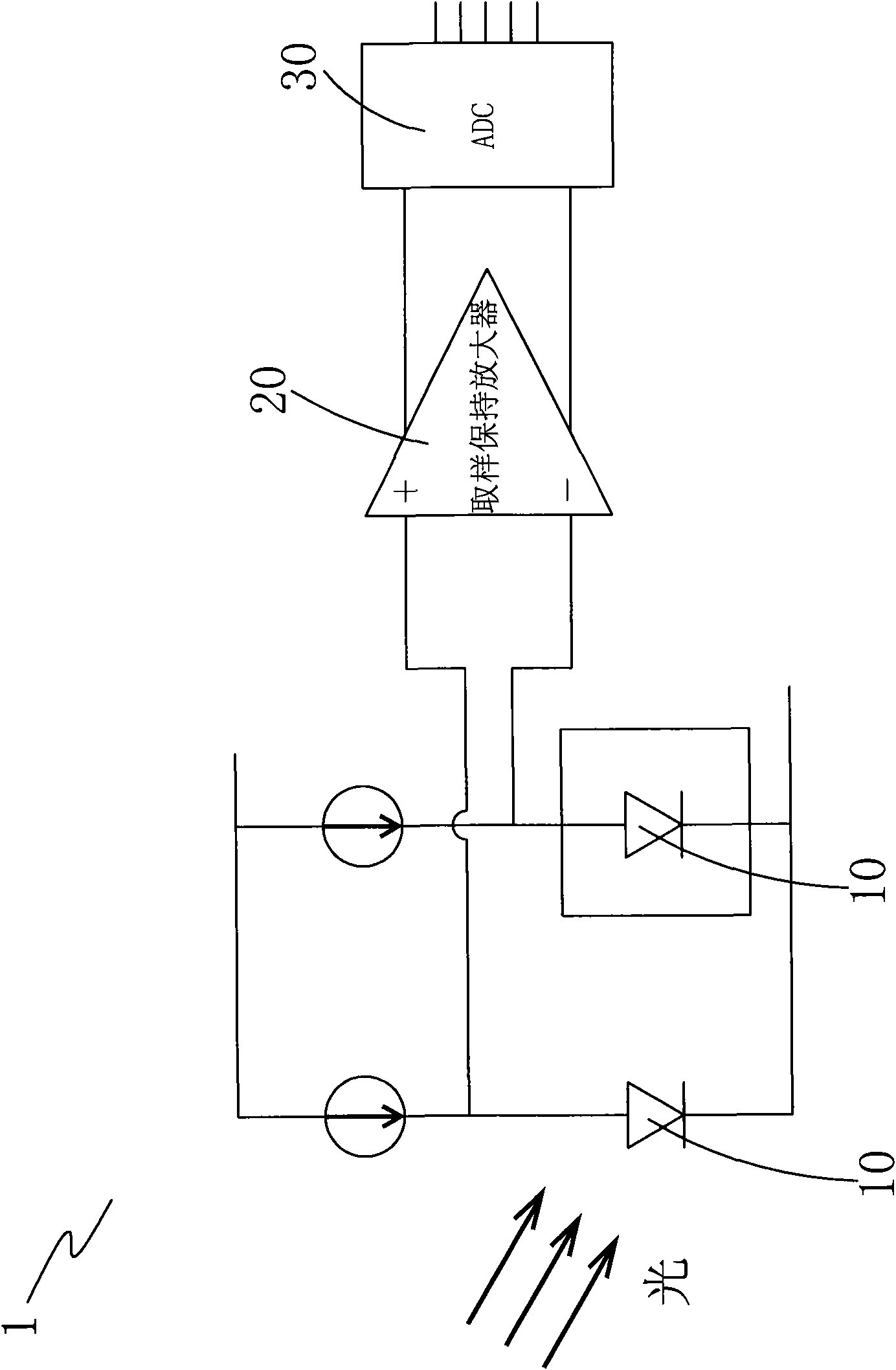

Digital photo induction device

InactiveCN101776479ANot easily affected by temperatureNot easily disturbedPhotometry electrical circuitsAudio power amplifierDigital down converter

The invention relates to a digital photo induction device, which comprises a sample-and-hold amplifier and an analog-digital converter (ADC). A non-inverting input end and an inverting input end of the sample-and-hold amplifier are respectively connected with a photo induction diode; an output end of the sample-and-hold amplifier is connected with the analog-digital converter (ADC); a digital signal can be output by the analog-digital converter (ADC) to fulfill the aim of detecting a light source; and the output of the digital signal is generated along with the change of the light source.

Owner:DIODES INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com