A sample-and-hold amplifier

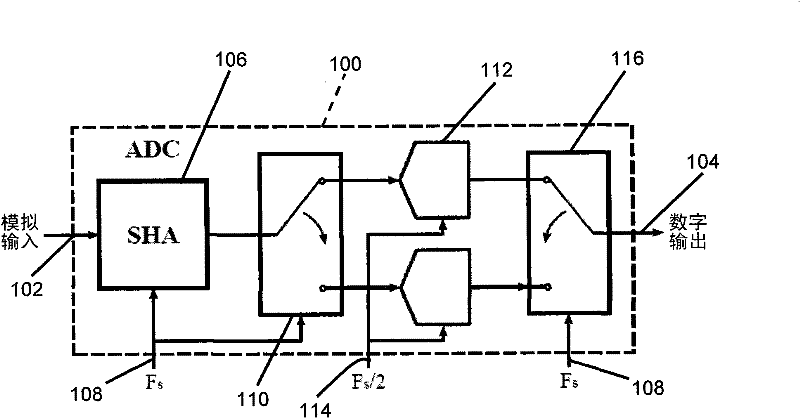

A sample-and-hold, amplifier technology, used in amplifiers, amplifiers using switched capacitors, amplifiers with semiconductor devices/discharge tubes, etc., can solve problems such as unrealistic time interleaving of front-end sample-and-hold amplifiers

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

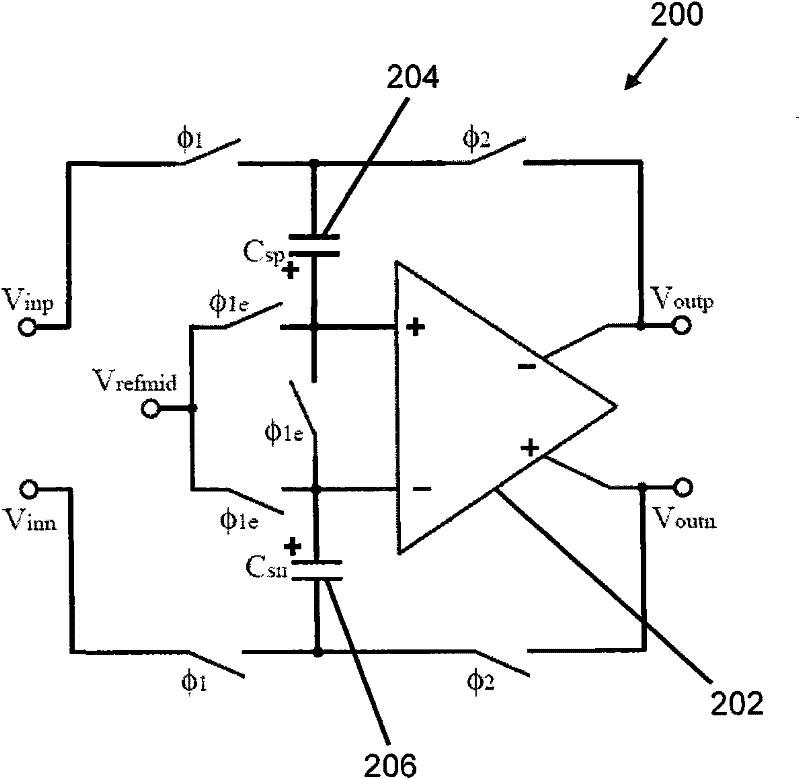

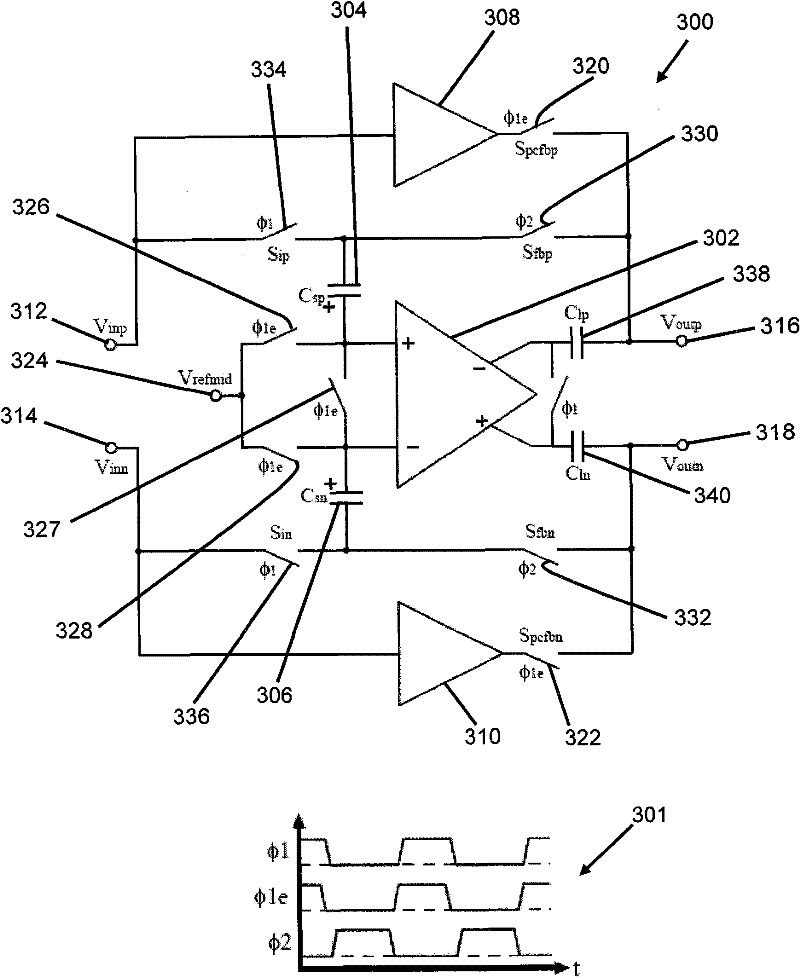

[0037] One or more embodiments described herein relate to a sample-and-hold amplifier that operates according to a sample phase of operation and a hold phase of operation. Track-and-hold amplifiers include amplifiers such as operational transconductance amplifiers (OTAs), which in conventional approaches can be used to buffer the input signal during the hold phase of operation and can also be used to precharge the output of the track-and-hold amplifier during the sample phase of operation. Such an embodiment may eliminate the need for an additional buffer to precharge the output during the sample phase of operation by utilizing OTA that would otherwise not be used during the sample phase of operation. This will result in a more efficient track-and-hold amplifier, since fewer components are required and / or the power consumption of the track-and-hold amplifier can be reduced.

[0038] In some embodiments, a Miller topology amplifier can be used as part of a sample-and-hold ampli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com