Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

60 results about "Domino logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

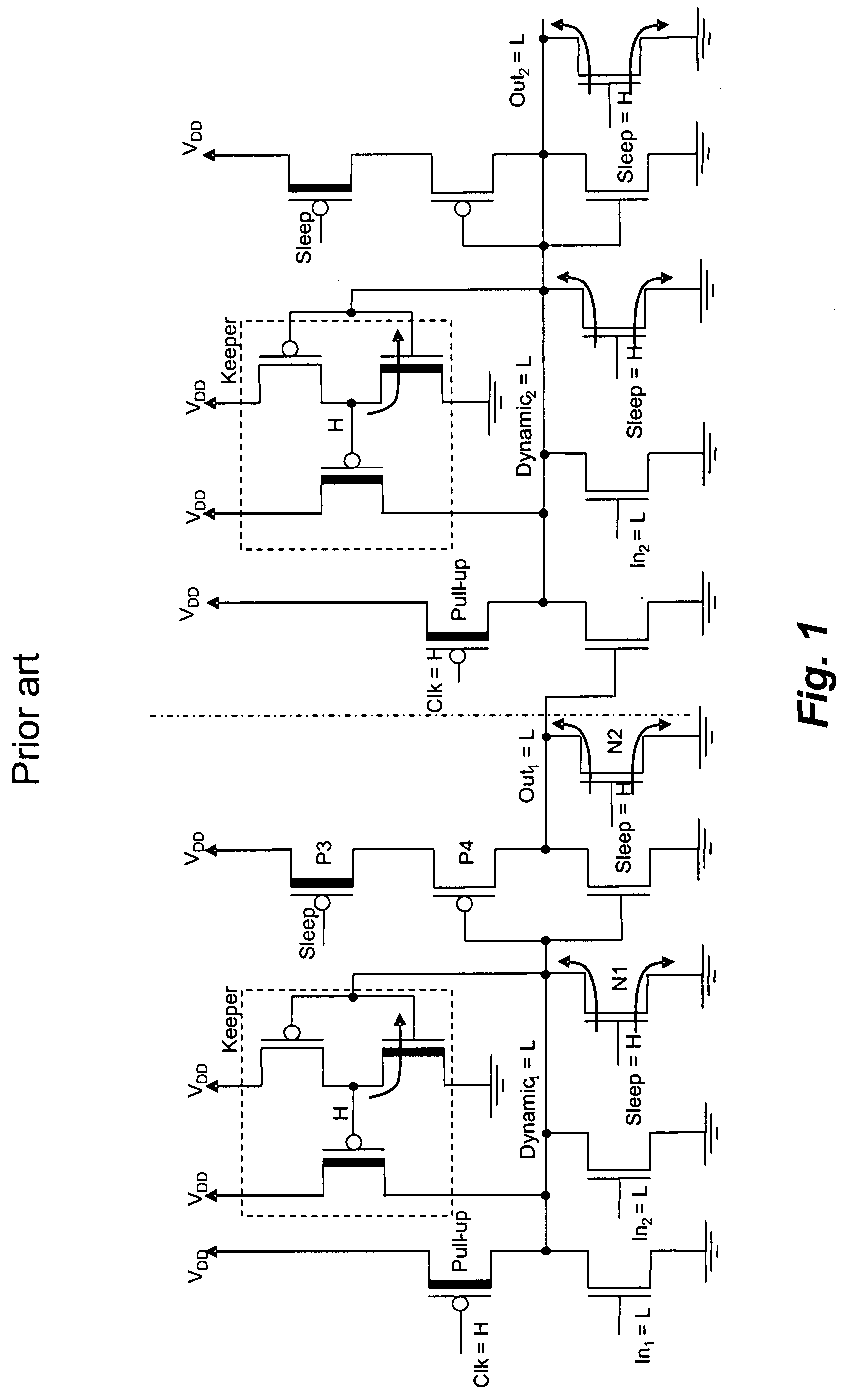

Domino logic is a CMOS-based evolution of the dynamic logic techniques based on either PMOS or NMOS transistors. It allows a rail-to-rail logic swing. It was developed to speed up circuits.

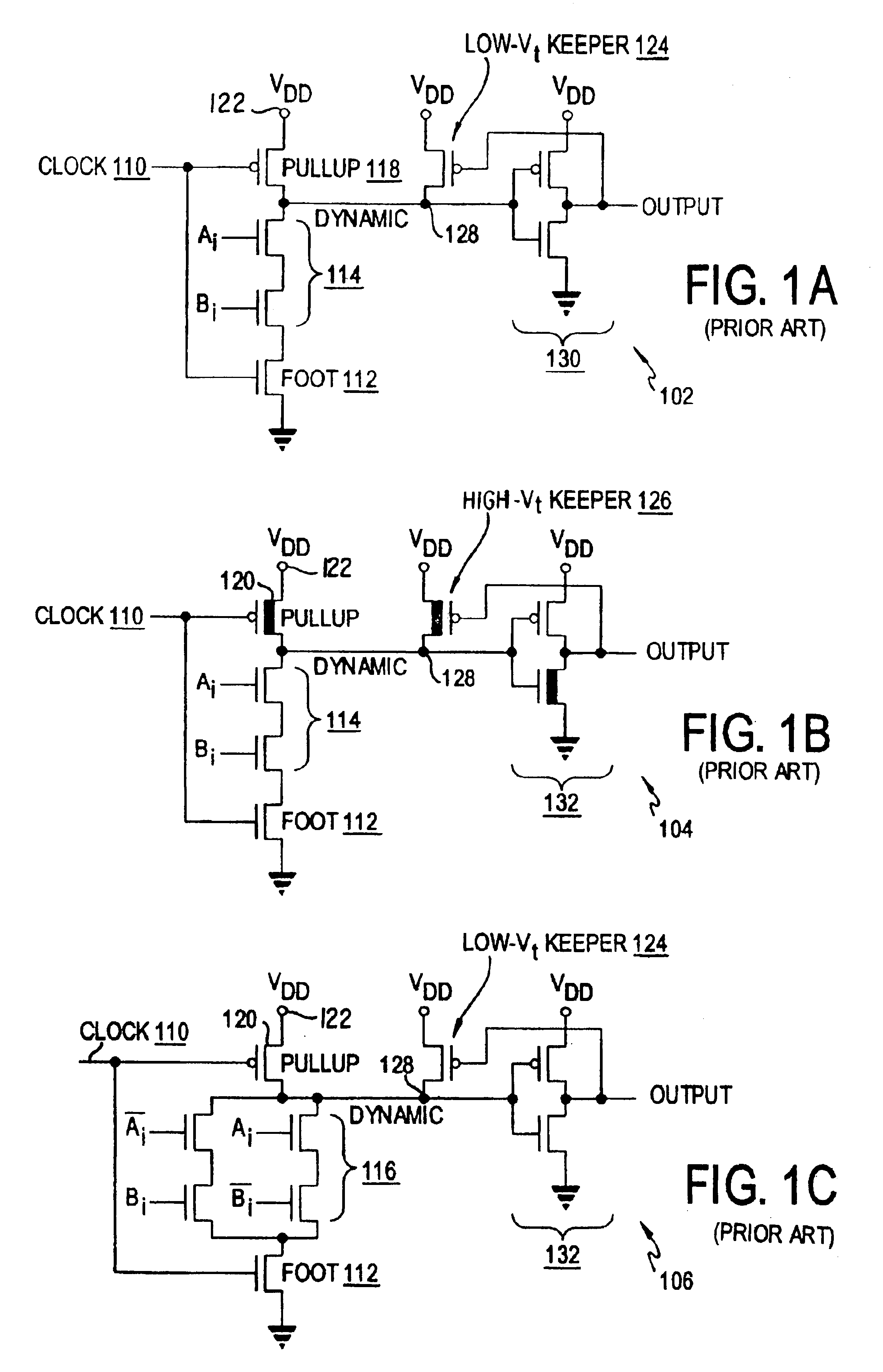

Dual threshold voltage and low swing domino logic circuits

InactiveUS6900666B2Lowering standby leakage energyReducing leakage energyPower reduction in field effect transistorsPower reduction by control/clock signalDomino logicGate voltage

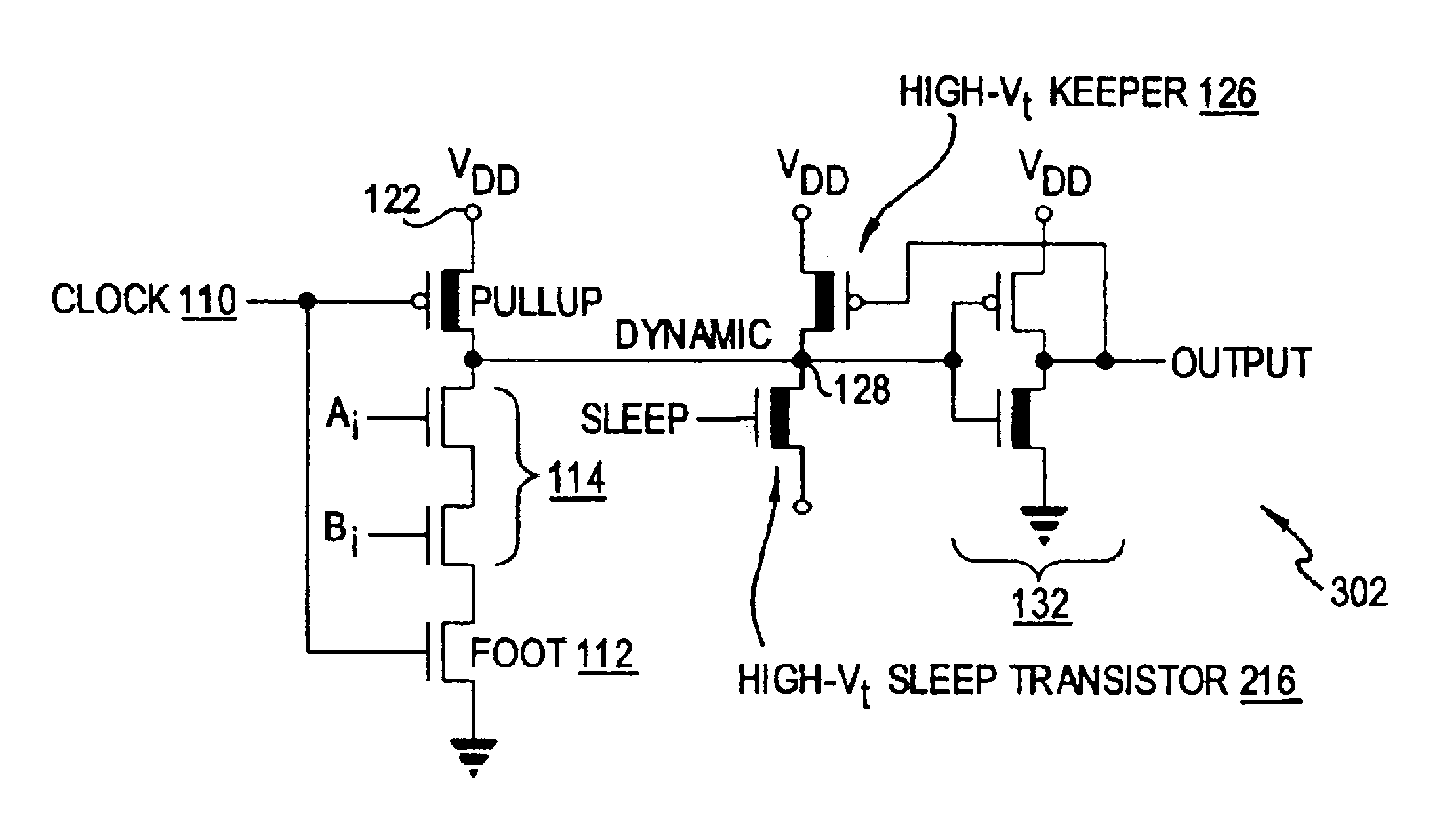

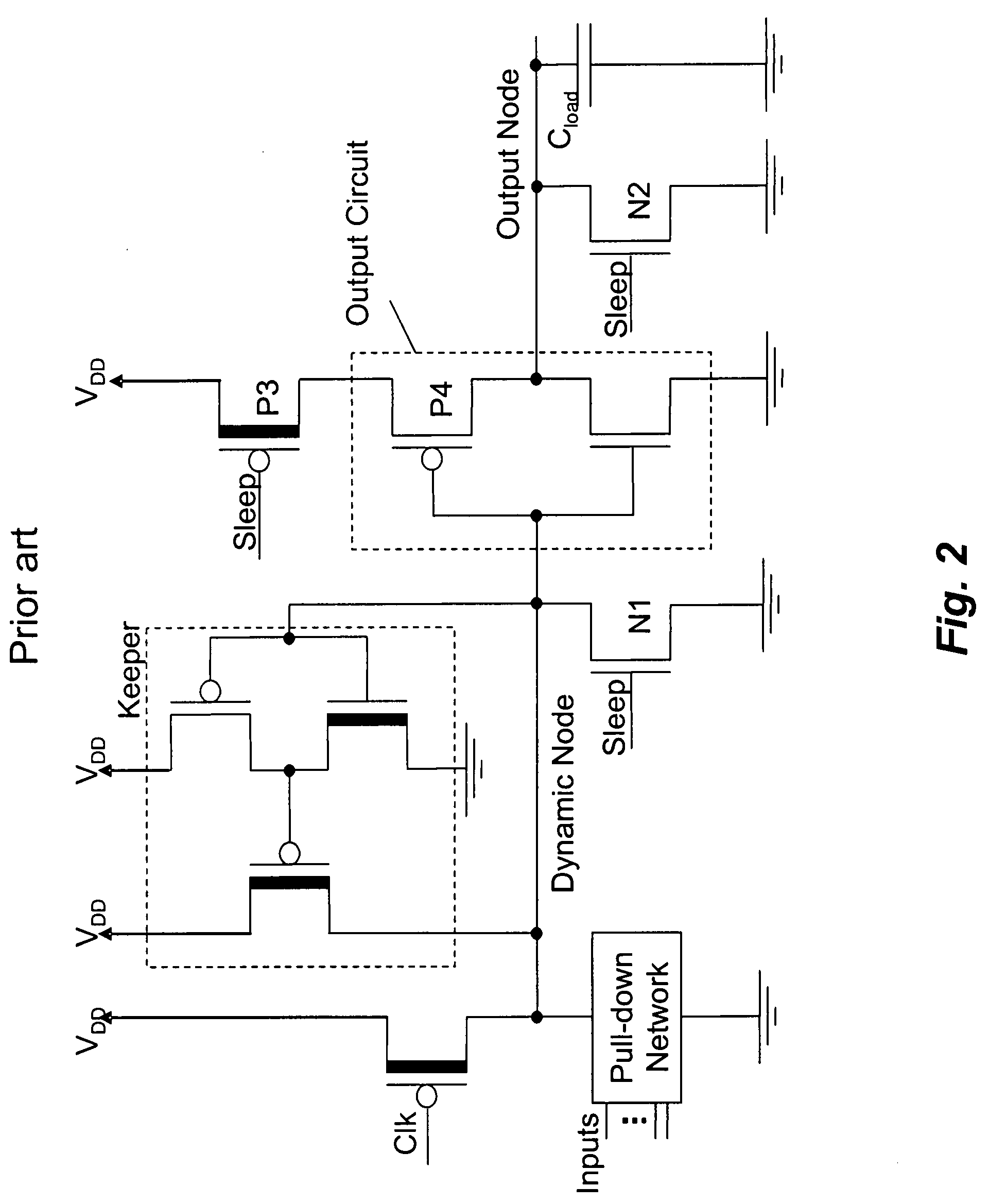

A domino logic circuit is configured to reduce power consumption. In a first embodiment, a sleep switch grounds the dynamic node during sleep mode. In a second embodiment, a low-swing circuit at the output reduces the output and keeper transistor gate voltage swings. A third embodiment combines those two techniques.

Owner:UNIVERSITY OF ROCHESTER

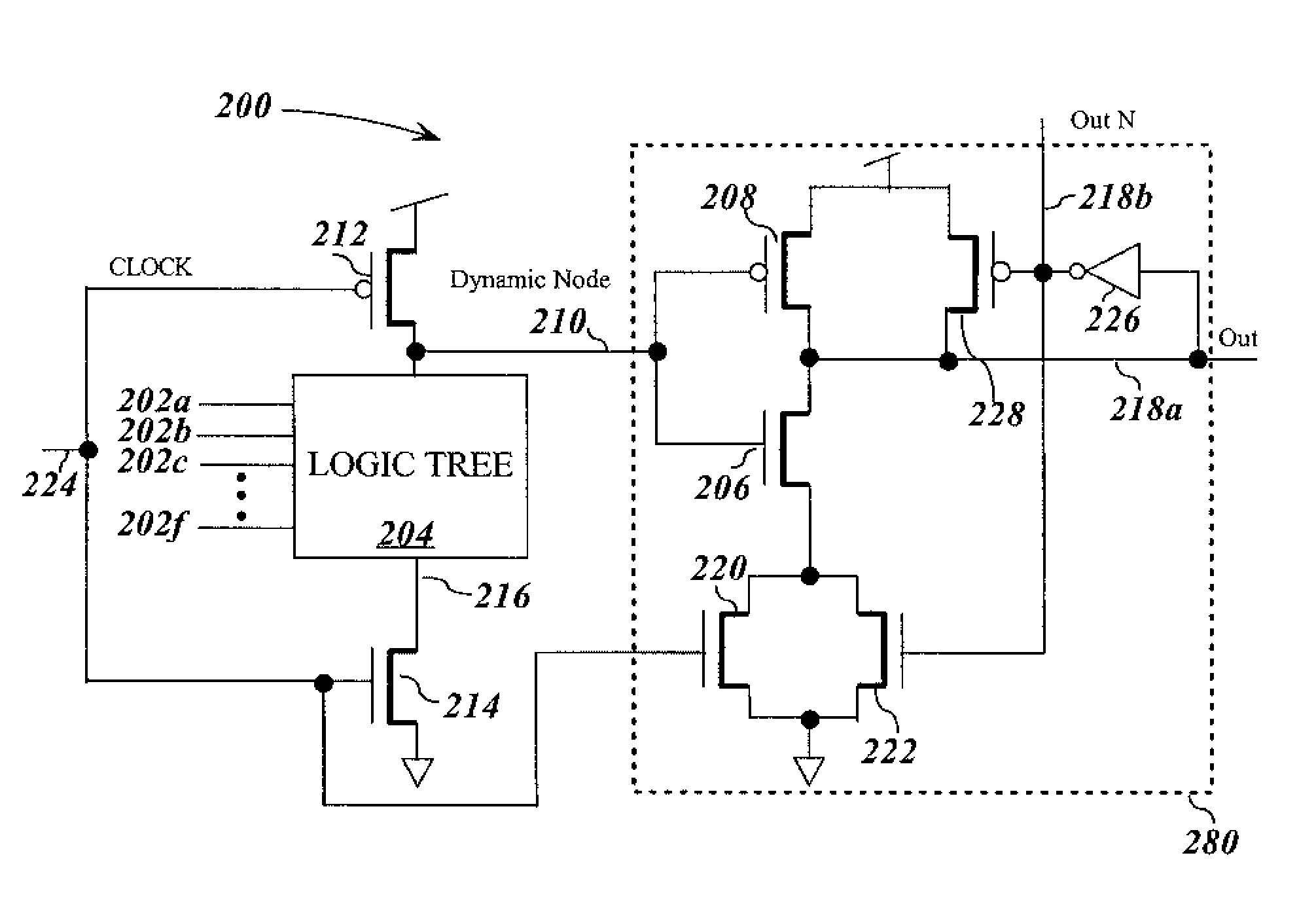

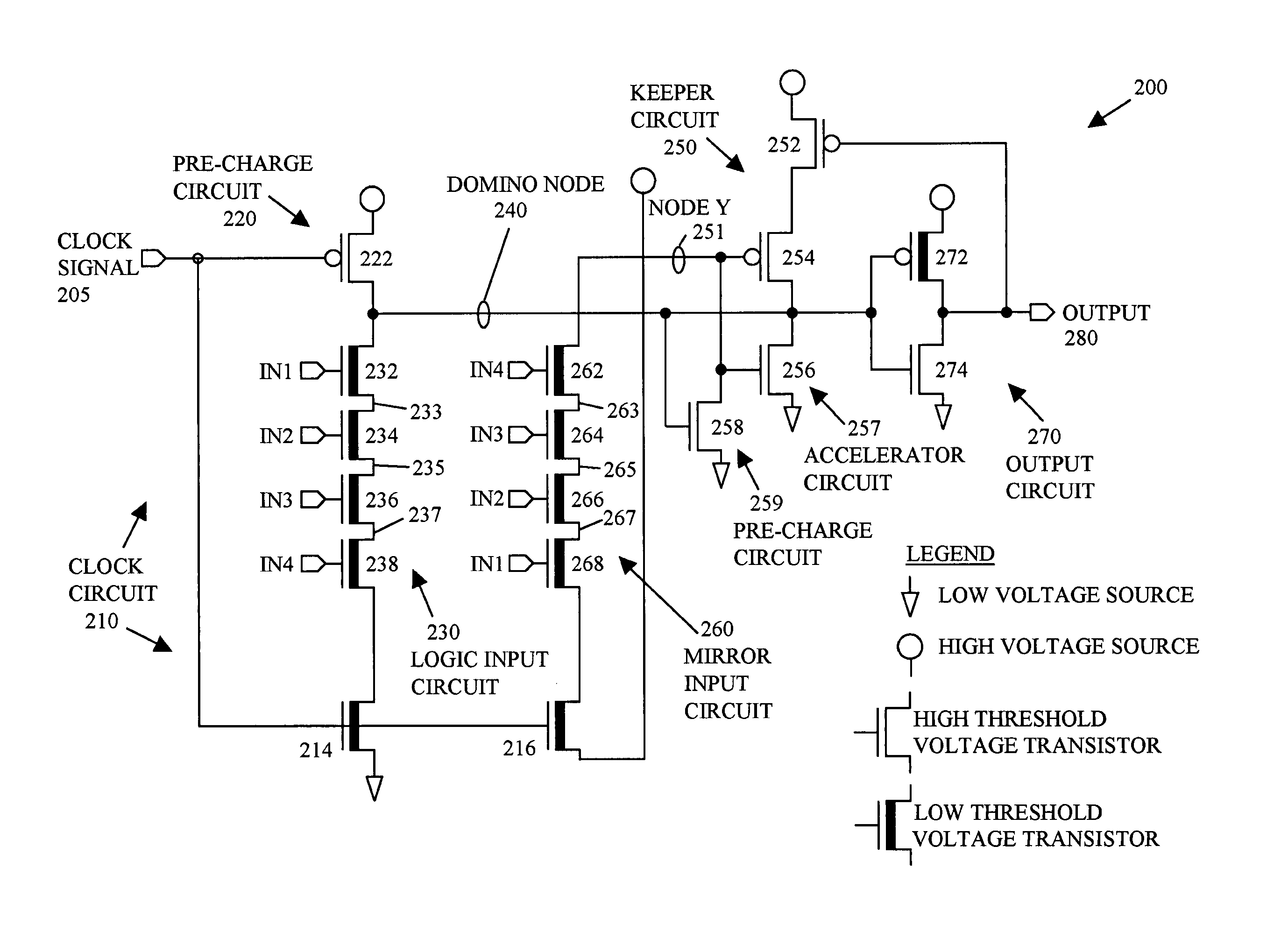

Methods and arrangements for enhancing domino logic

Methods and arrangements for enhancing domino logic are disclosed. Embodiments include a keeper circuit to pull up a domino node in response an output of an output circuit when the domino node is at a high voltage and to stop pulling up the domino node before the output changes to a first logical output. Further embodiments include an accelerator circuit to pull down the domino node when the keeper circuit stops pulling up the domino node. The domino node may couple with a pre-charge circuit and be pre-charged to a high voltage during a first portion of a clock cycle. The domino node may also couple with a logic input circuit to pull down the domino node during a second portion of the clock cycle, causing the output circuit to change the output from low to high in response to logic signals.

Owner:INT BUSINESS MASCH CORP

Techniques to improve the operations of a memory device

A method and system to improve the operations of a memory device by reducing its bit line leakage, power consumption, and read access time. The memory device has a static read word line for each of its bit cells and domino logic for each of its bit line. Each bit line of the memory device is coupled with a gating logic that is activated using a clocked signal. This eases the timing requirement of the read word lines of the memory device and the read word lines do not form the critical path of the access time of the memory device. The leakage current of the memory device in inactive mode is reduced by switching off the pre-charge circuit and / or the keeper circuit of each bit line. Each bit line is pre-charged on demand prior to the evaluation of each bit line.

Owner:TAHOE RES LTD

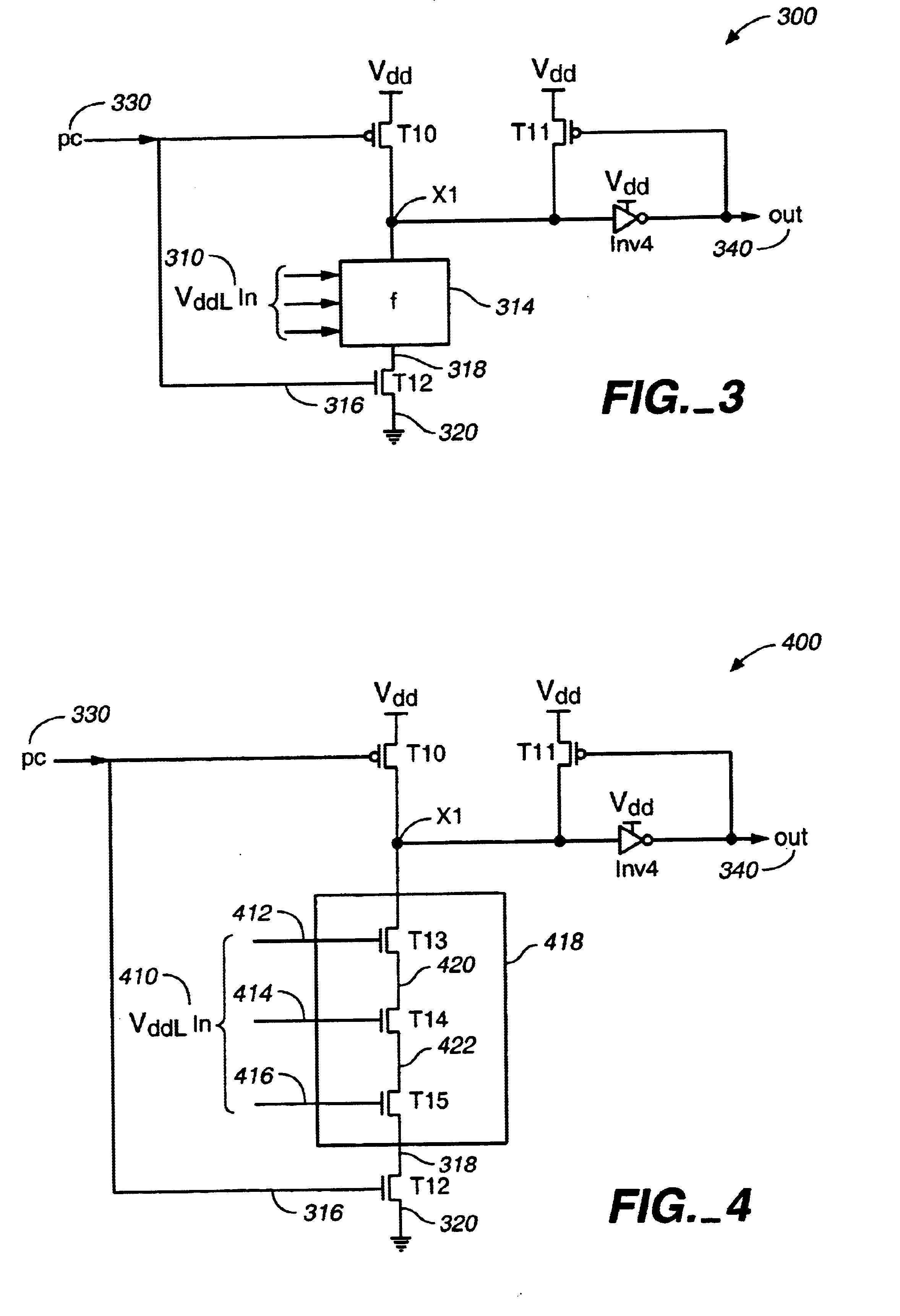

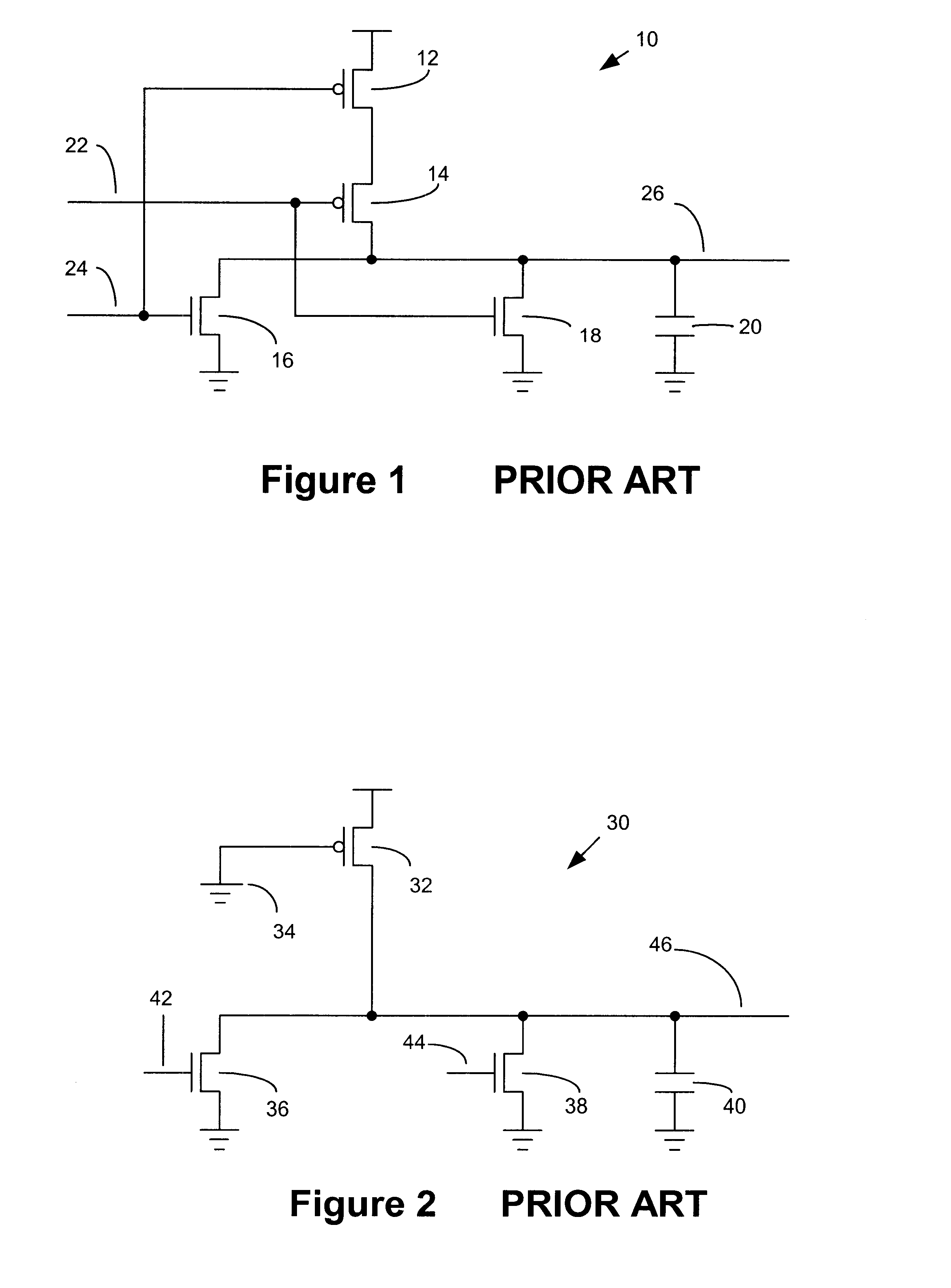

Low-to-high voltage conversion method and system

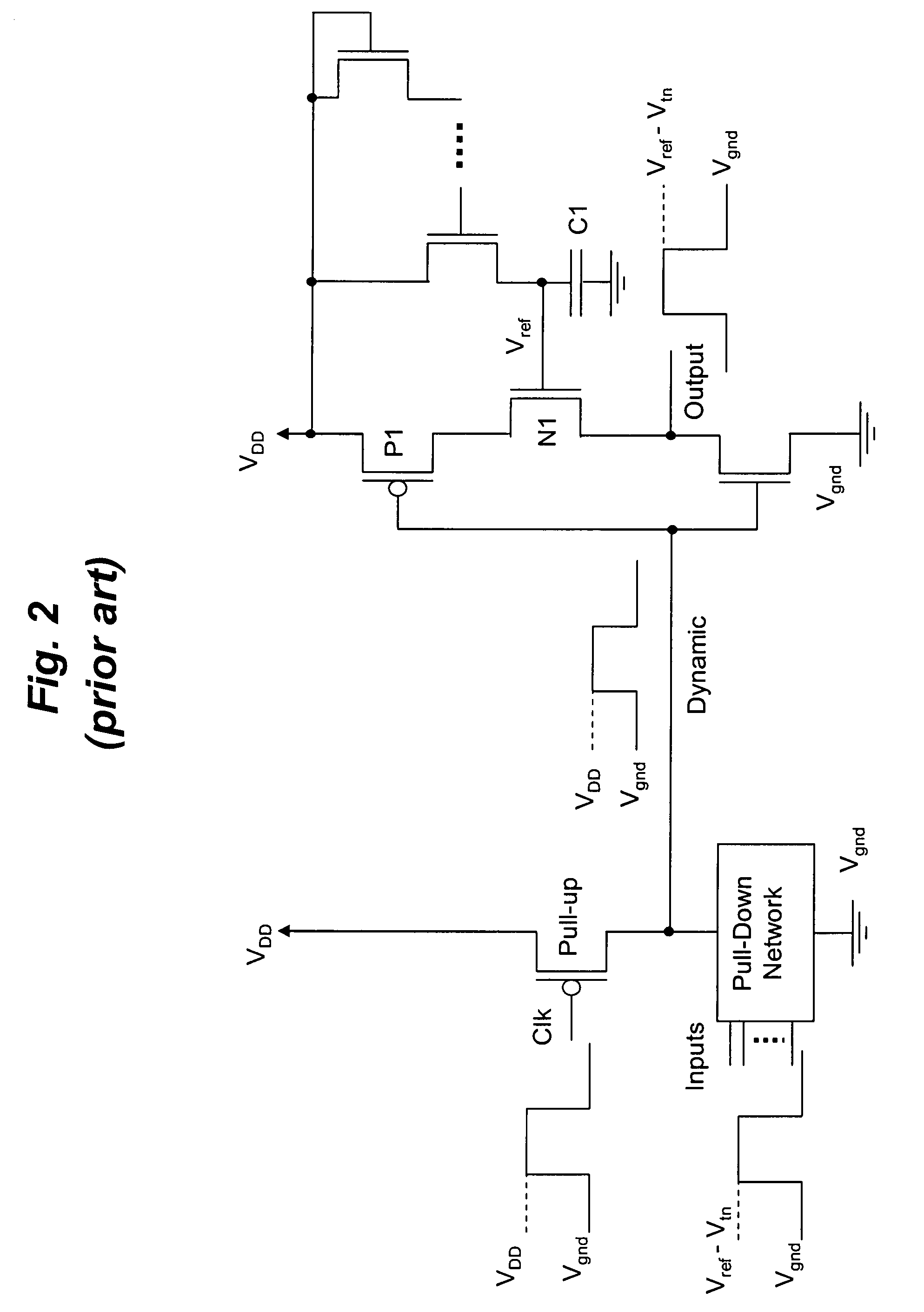

InactiveUS6842046B2Avoid excessive delayReduce power consumptionLogic circuits coupling/interface using field-effect transistorsDomino logicLow voltage

A system and method, for converting a voltage input from a low voltage source to a voltage output at a high voltage source using a domino logic circuit design. An embodiment provides a low to high voltage conversion system. The system includes: a pull-up transistor coupled to a high voltage source for charging a node, when a precharge signal is received; a low voltage source used for setting an input voltage; a pull-down network for discharging the node depending, at least in part, on the input voltage; and an output voltage determined from the node.

Owner:FUJITSU LTD

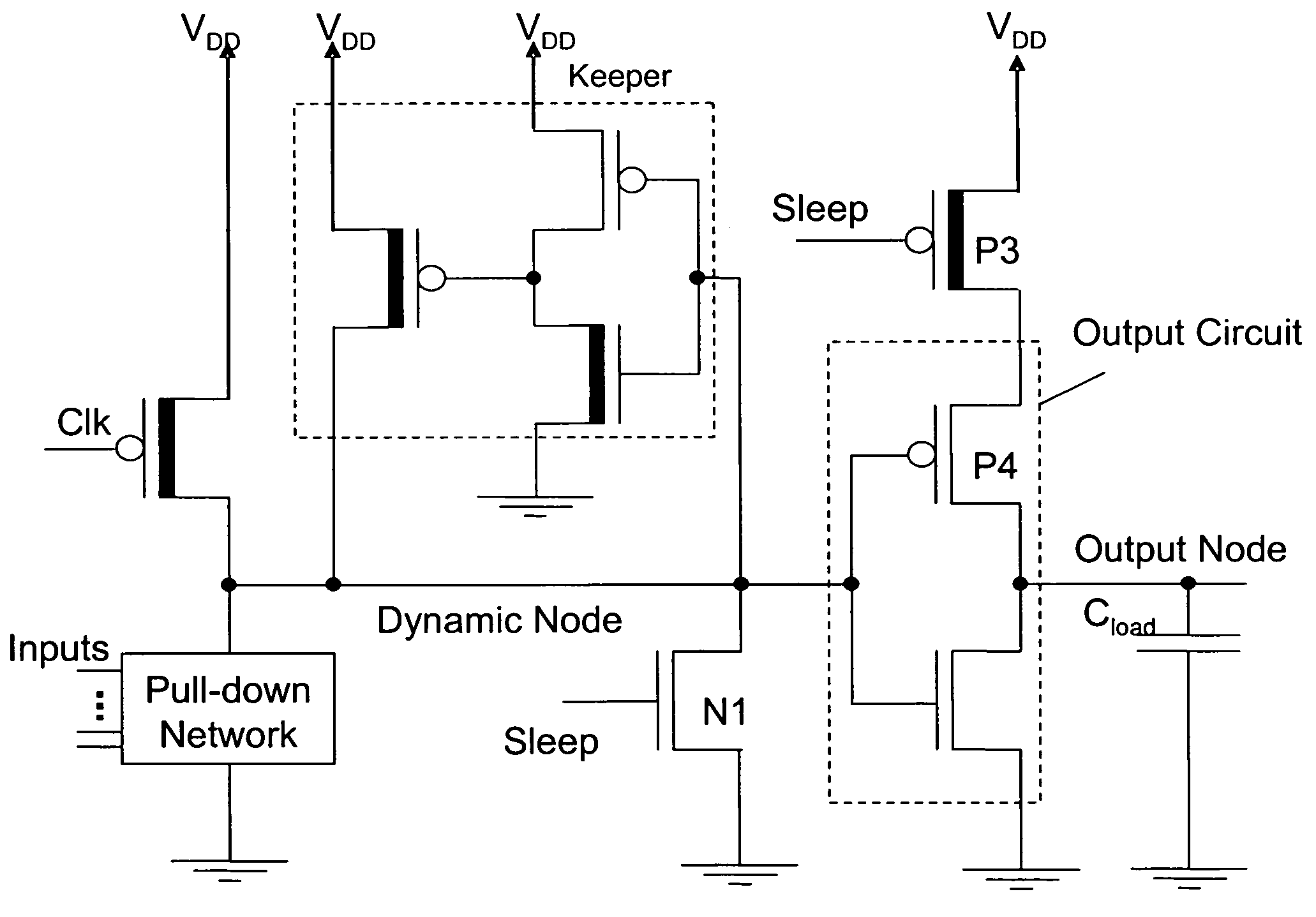

Domino logic circuit techniques for suppressing subthreshold and gate oxide leakage

ActiveUS20070176642A1Reduces subthresholdReduces gate oxide leakage power consumptionLogic circuitsDomino logicSoi cmos technology

Circuits are provided for simultaneously reducing the subthreshold and gate oxide leakage power consumption in domino logic circuits. Sleep transistors and a dual threshold voltage CMOS technology may be utilized to place idle domino logic circuits into a low leakage state. The circuits may significantly lower the total leakage power as compared to the standard dual threshold voltage domino logic circuits at both the high and low die temperatures. The energy overheads of the circuit techniques may be low, justifying the activation of the proposed sleep schemes by providing net savings in total power consumption during short idle periods.

Owner:WISCONSIN ALUMNI RES FOUND

Clock-delayed pseudo-NMOS domino logic

A logic gate includes a logic circuit having an input node and an output node, an enabling transistor coupled between a first power supply node and the output node, the enabling transistor adapted to couple the output node to the first power supply node during an evaluation phase in the logic gate, and a pre-charge transistor coupled between the output node and a second power supply node, the pre-charge transistor adapted to couple the output node to the second power supply node during a pre-charge phase in the logic gate.

Owner:NAN YA TECH

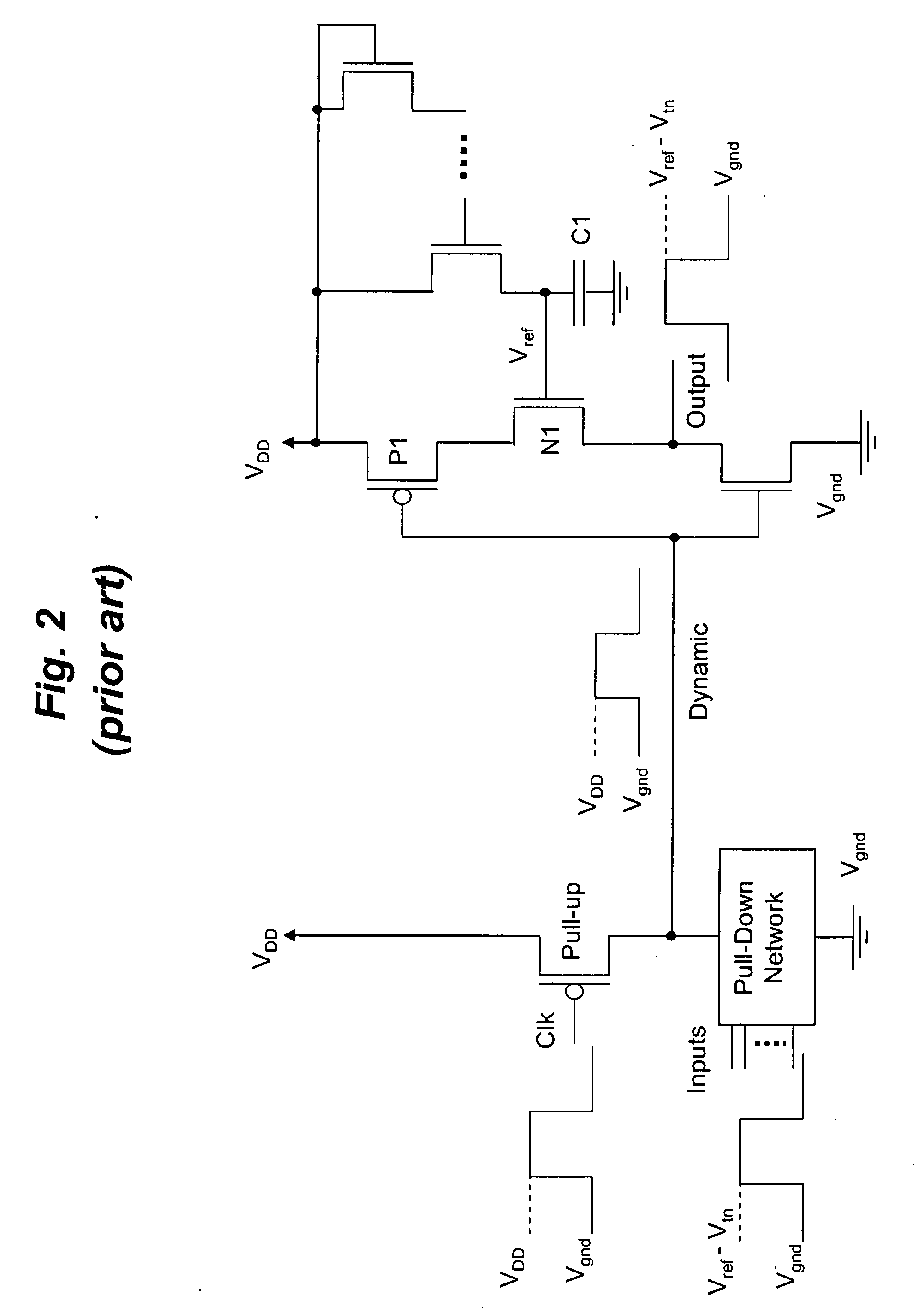

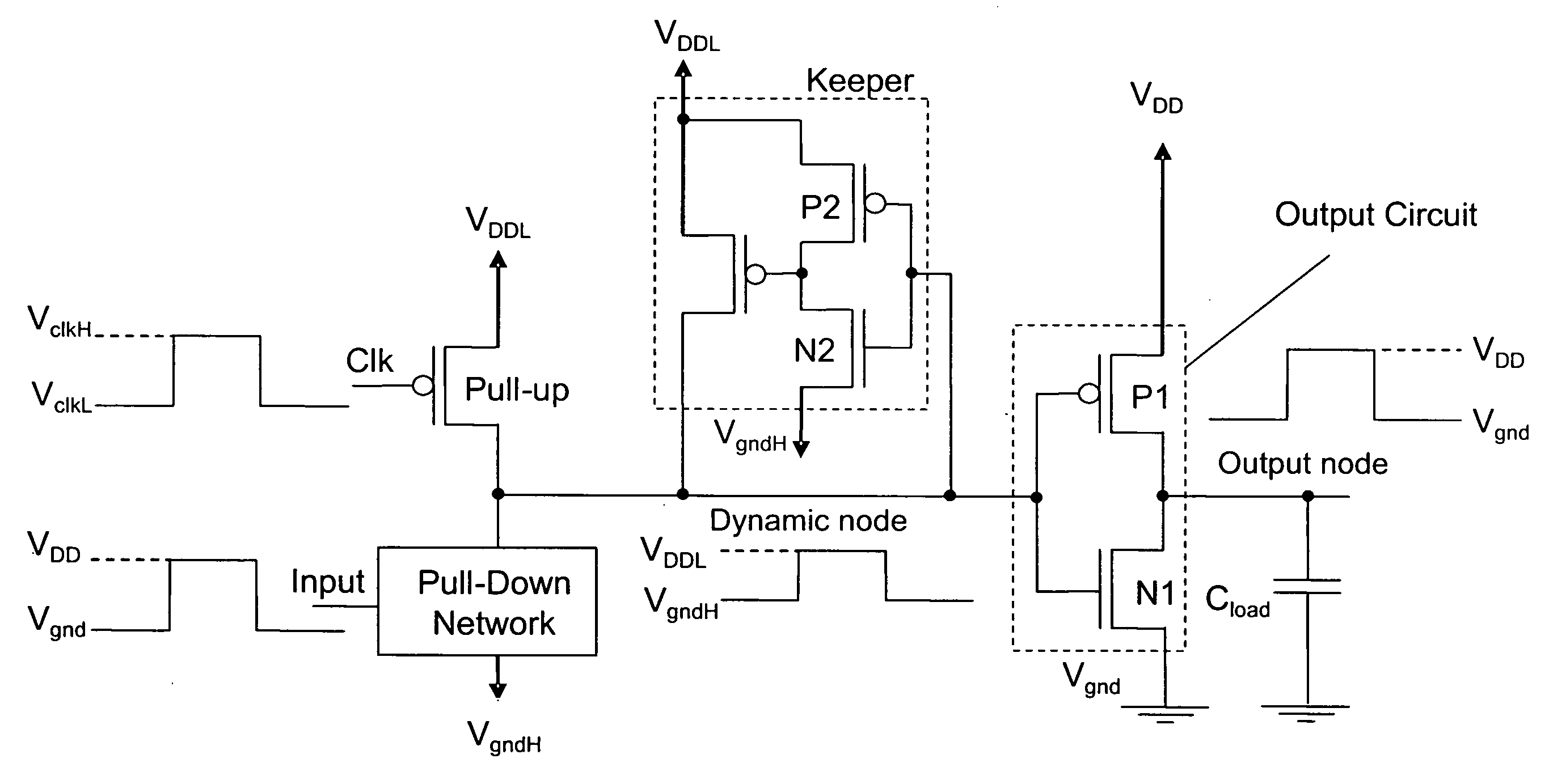

Low swing domino logic circuits

ActiveUS20070176641A1Reduce upper boundary of voltage swingMinimizing PDPLogic circuits characterised by logic functionLogic circuitsDomino logicLogic circuitry

Low voltage swing techniques are provided for simultaneously reducing the active and standby mode power consumption and enhancing the noise immunity in domino logic circuits. One or both the upper and lower boundaries of the voltage swing at the dynamic node may be different from the upper and lower boundaries of the voltage swing at the output node. For example, the voltage swing at the dynamic node may be less than the voltage swing at the output node, optimized for speed or power consumption. As another example, the voltage swing at the dynamic node may be greater than the voltage swing at the output node, optimized for speed or power consumption. Further, the domino logic circuit may use dual Vt thereby reducing the short-circuit current during operation.Meanwhile, full voltage swing signals may be maintained at the inputs and outputs for high speed operation. The low swing circuit techniques are provided that modify the output voltage swing of a domino gate, thereby reducing the active mode power consumption.

Owner:WISCONSIN ALUMNI RES FOUND

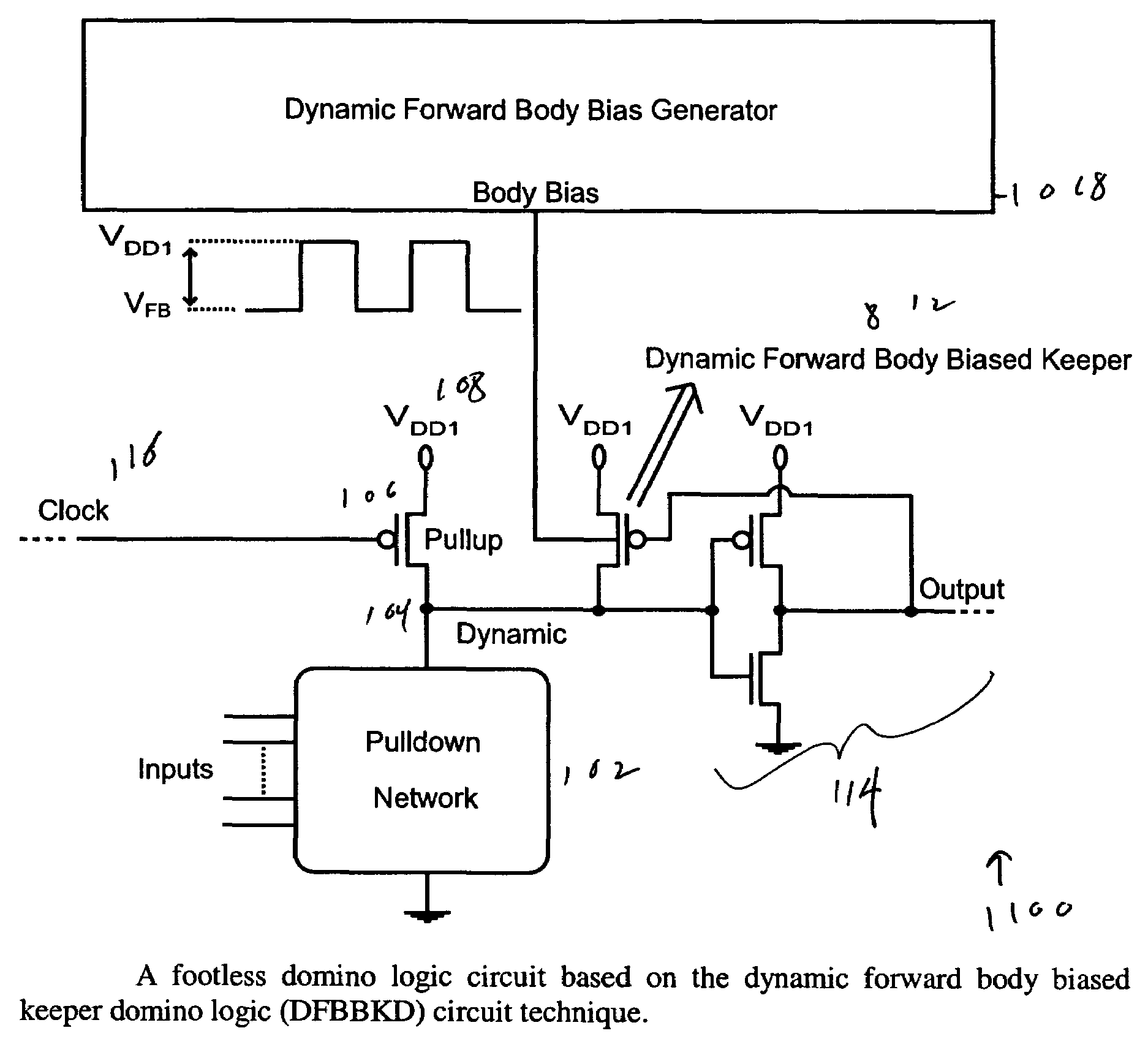

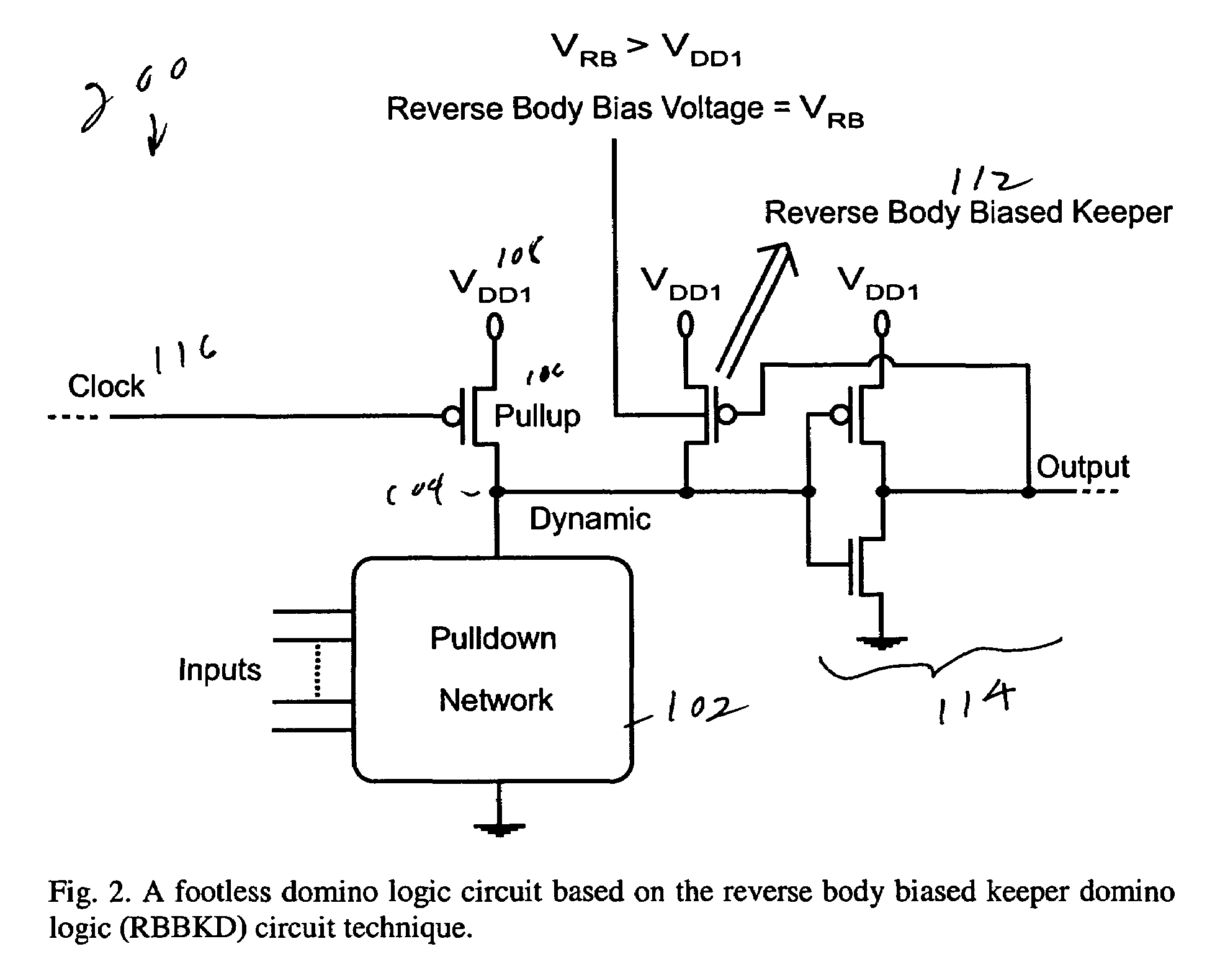

Domino logic with variable threshold voltage keeper

A variable threshold voltage keeper circuit technique is proposed for simultaneous power reduction and speed enhancement of domino logic circuits. The threshold voltage of the keeper transistor is dynamically modified during circuit operation to reduce the contention current without sacrificing noise immunity. The threshold voltage of the keeper transistor is controlled by a body bias generator which switches between two voltages in accordance with the clock signal.

Owner:UNIVERSITY OF ROCHESTER

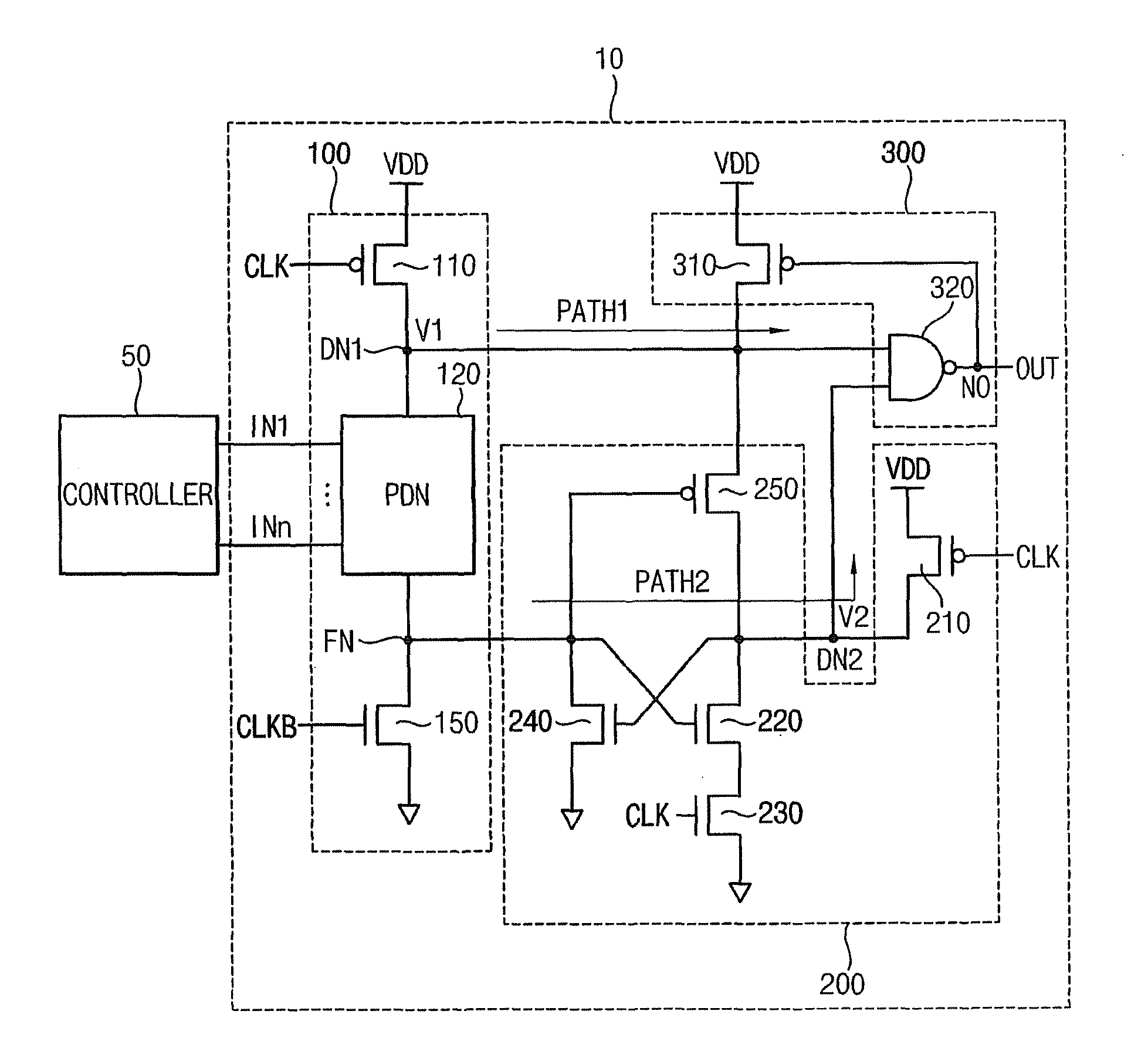

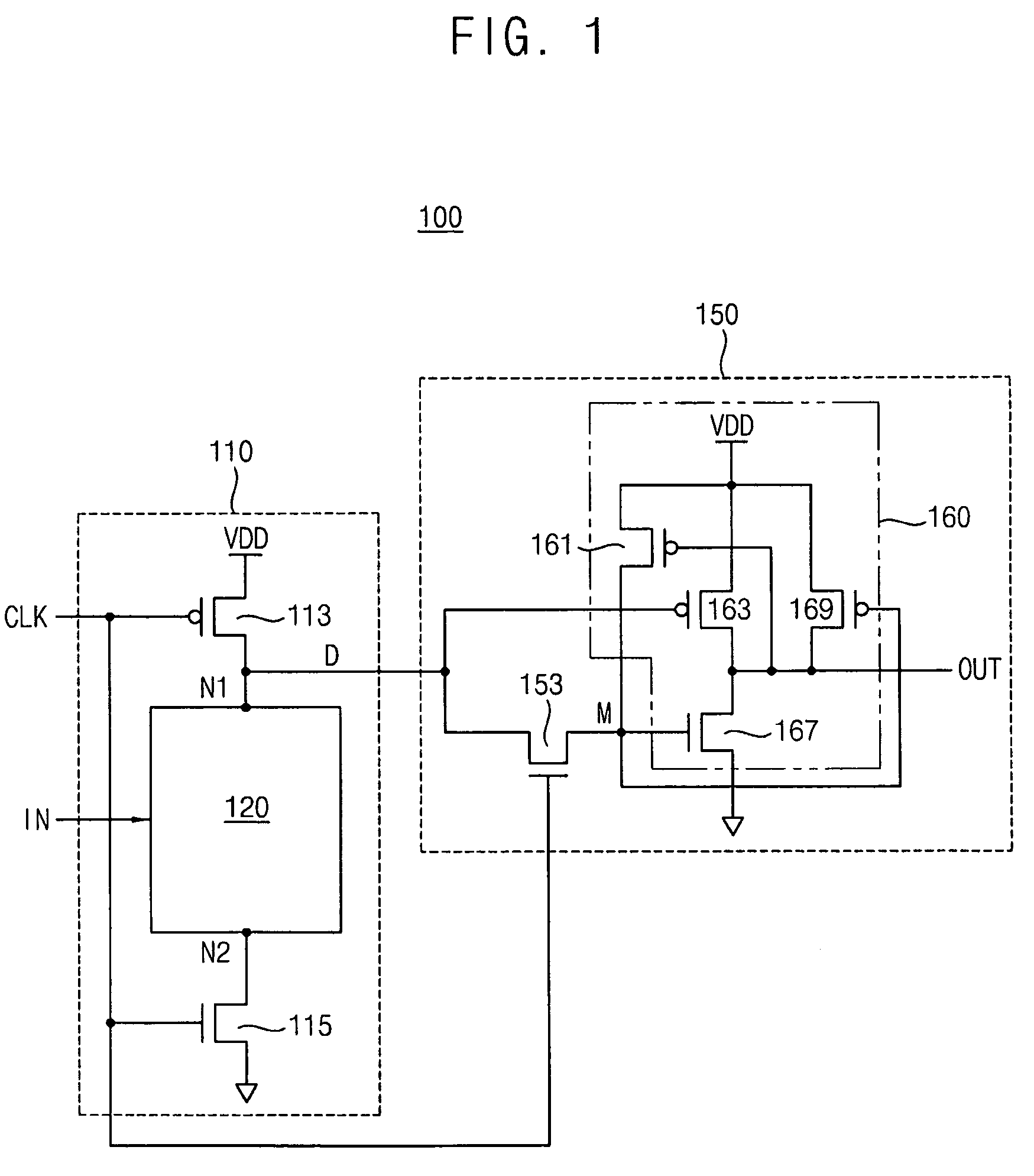

Domino logic circuits and pipelined domino logic circuits

ActiveUS8542033B2Improve noise immunityReduce power consumptionLogic circuitsDomino logicComputer science

A domino logic circuit includes a first evaluation unit, a second evaluation unit and an output unit. The first evaluation unit precharges a first dynamic node, discharges a footer node in a first phase of a clock signal, and evaluates a plurality of input signals to determine a logic level of the first dynamic node in a second phase of the clock signal. The second evaluation unit precharges a second dynamic node in the first phase of the clock signal, and determines a logic level of the second dynamic node in response to a logic level of the footer node in the second phase of the clock signal. The output unit provides an output signal having a logic level according to levels of a first voltage of the first dynamic node and a second voltage of the second dynamic node.

Owner:SAMSUNG ELECTRONICS CO LTD +1

Pseudo-dynamic latch deracer

ActiveUS6879186B2Electric pulse generatorLogic circuits using elementary logic circuit componentsDomino logicData signal

An apparatus and method for a pseudo-dynamic latch are disclosed. A deracer circuit includes a first logic gate configured to receive a data signal from a domino logic circuit and to invert the data signal. A second logic gate is configured to receive the inverted data signal and an inverted select signal and to generate a select signal. Thus, the deracer circuit is configured to prevent the select signal from being high when a precharge edge of a data signal arrives.

Owner:TAHOE RES LTD

Low swing domino logic circuits

ActiveUS7764087B2Reduce upper boundary of voltage swingMinimizing PDPLogic circuits characterised by logic functionDomino logicLogic circuitry

Low voltage swing techniques are provided for simultaneously reducing the active and standby mode power consumption and enhancing the noise immunity in domino logic circuits. One or both the upper and lower boundaries of the voltage swing at the dynamic node may be different from the upper and lower boundaries of the voltage swing at the output node. Further, the domino logic circuit may use dual Vt thereby reducing the short-circuit current during operation. Meanwhile, full voltage swing signals may be maintained at the inputs and outputs for high speed operation. The low swing circuit techniques are provided that modify the output voltage swing of a domino gate, thereby reducing the active mode power consumption.

Owner:WISCONSIN ALUMNI RES FOUND

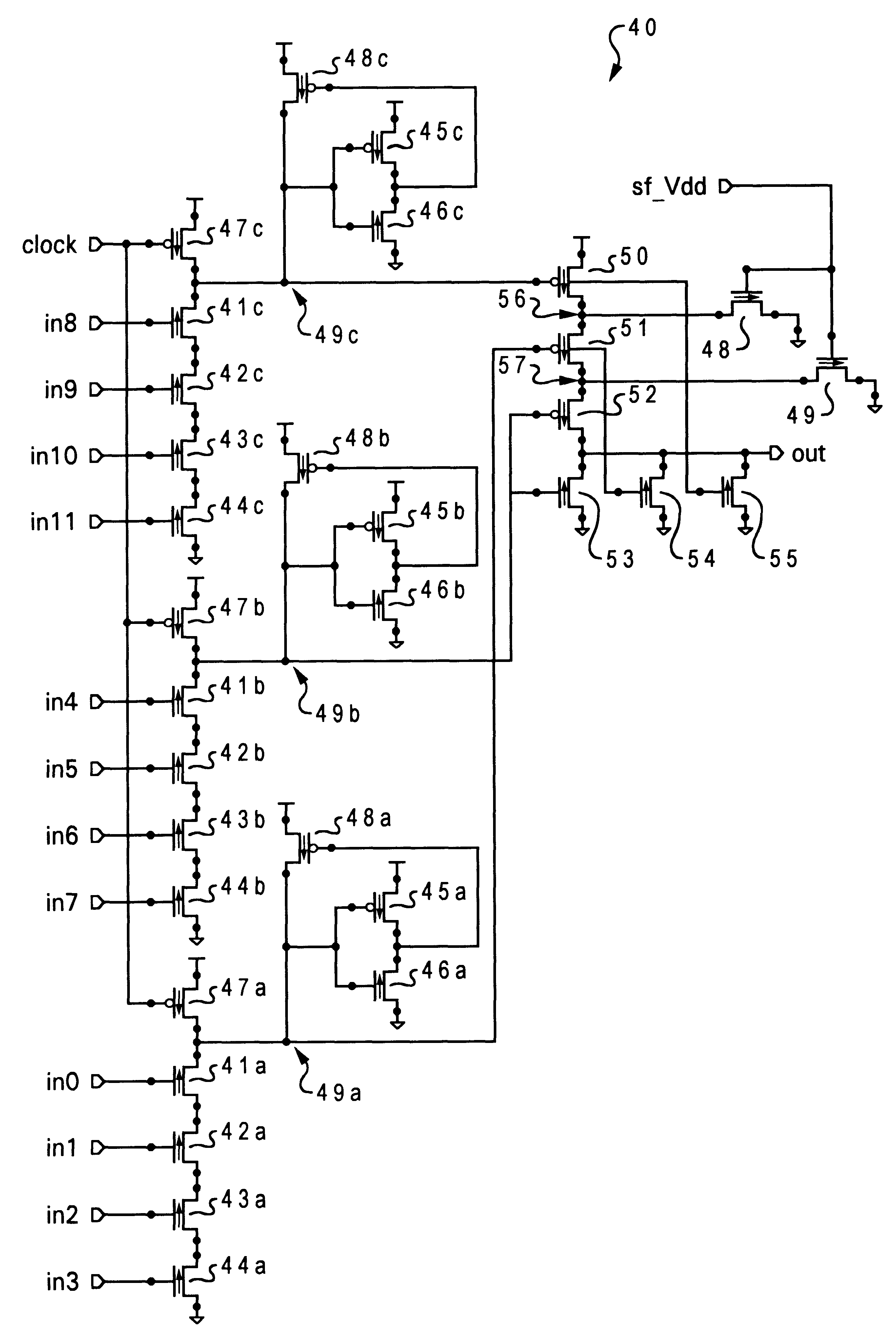

Ultra high-speed Nor-type LSDL/Domino combined address decoder

An ultra high speed address decoder uses a combination of Domino logic circuits and LSDL logic circuits. N address bits are converted into N logic true address bits and N complementary address bits. A partial address decoder generates two bit groups using selected of the N logic true address bits and N complementary address bits in NOR logic structures such only two cascaded NFETS are used in a logic tree. The bit groups are partitioned to optimize the layout of the parallel bit lines in the address decoder.

Owner:GOOGLE LLC

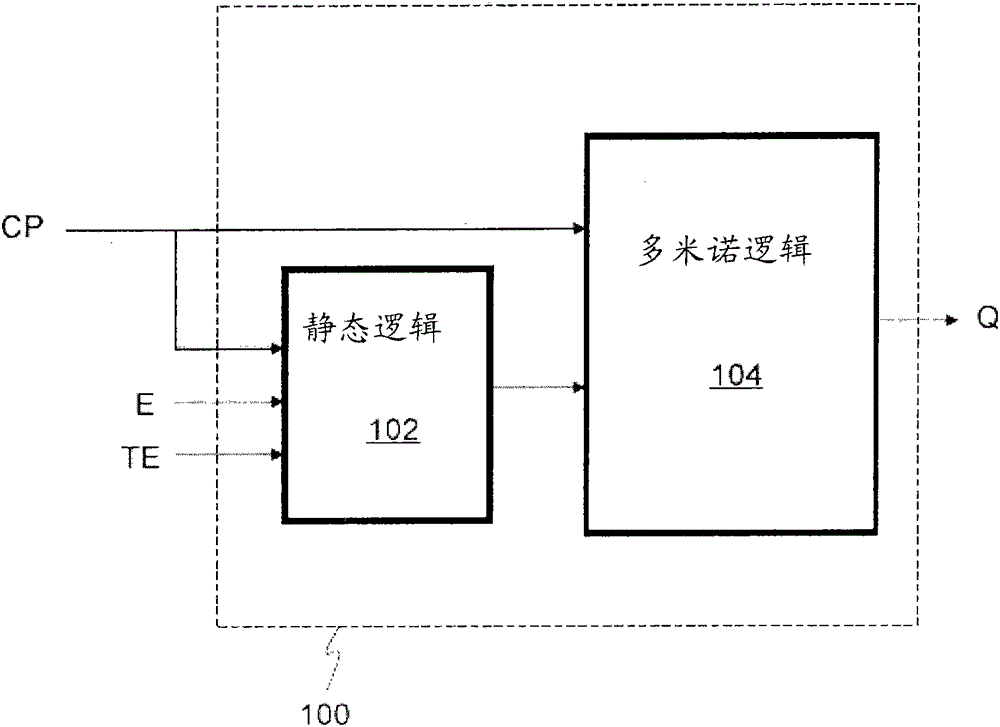

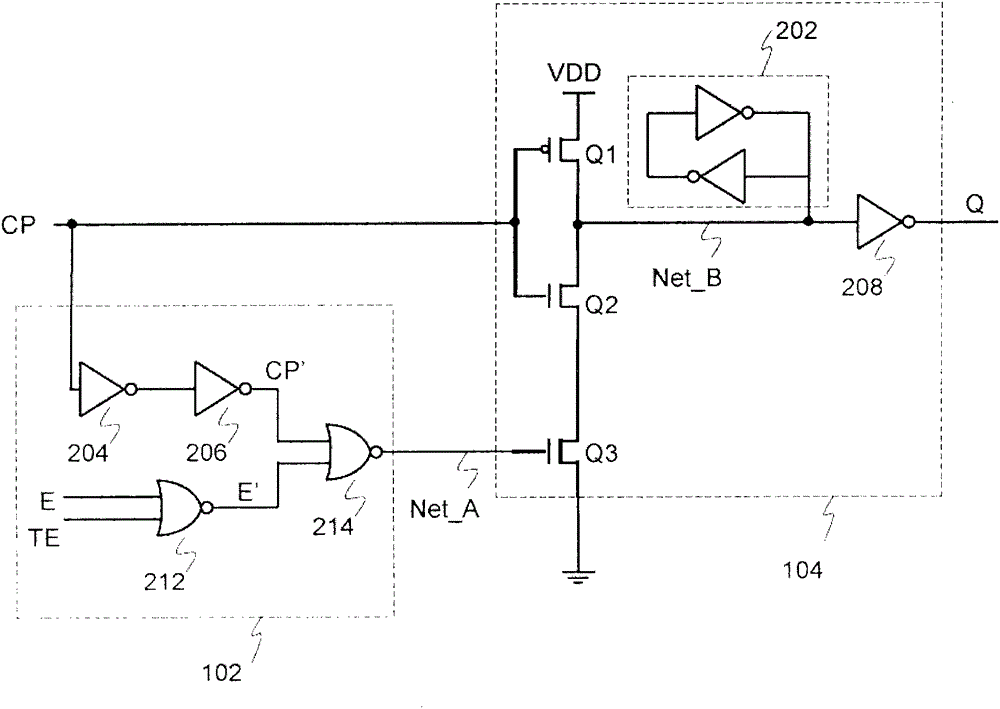

Internal clock gating apparatus

ActiveCN102799211AGenerating/distributing signalsEnergy efficient computingDomino logicControl signal

An internal clock gating apparatus comprises a static logic block and a domino logic block. The static logic block is configured to receive a clock signal and a clock enable signal. The domino logic block is configured to receive the clock signal and a control signal from an output of the static logic block. The static logic block and the domino logic block are further configured such that an output of the domino logic block generates a signal similar to the clock signal in phase when the clock enable signal has a logic high state. On the other hand, the output of the domino logic block generates a logic low signal when the clock enable signal has a logic low state. Furthermore, the static logic block and the domino logic block can reduce the setup time and delay time of the internal clock gating apparatus respectively.

Owner:TAIWAN SEMICON MFG CO LTD

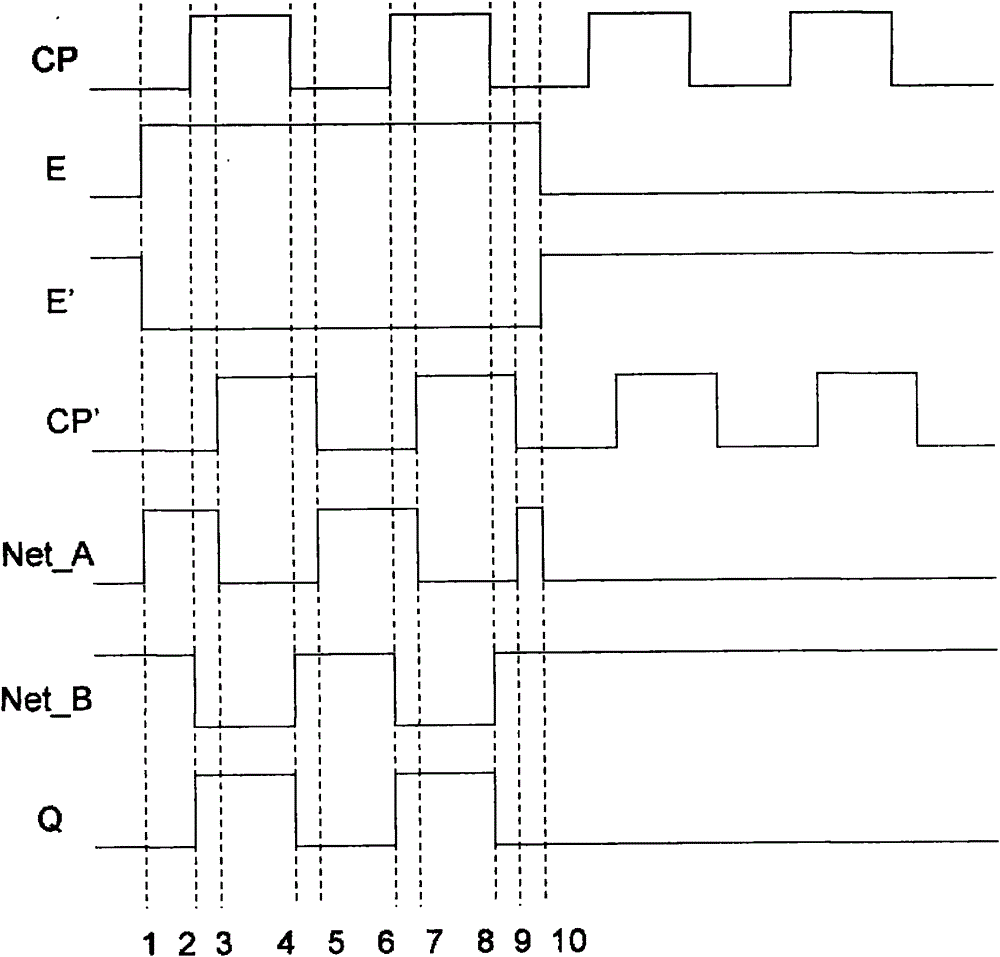

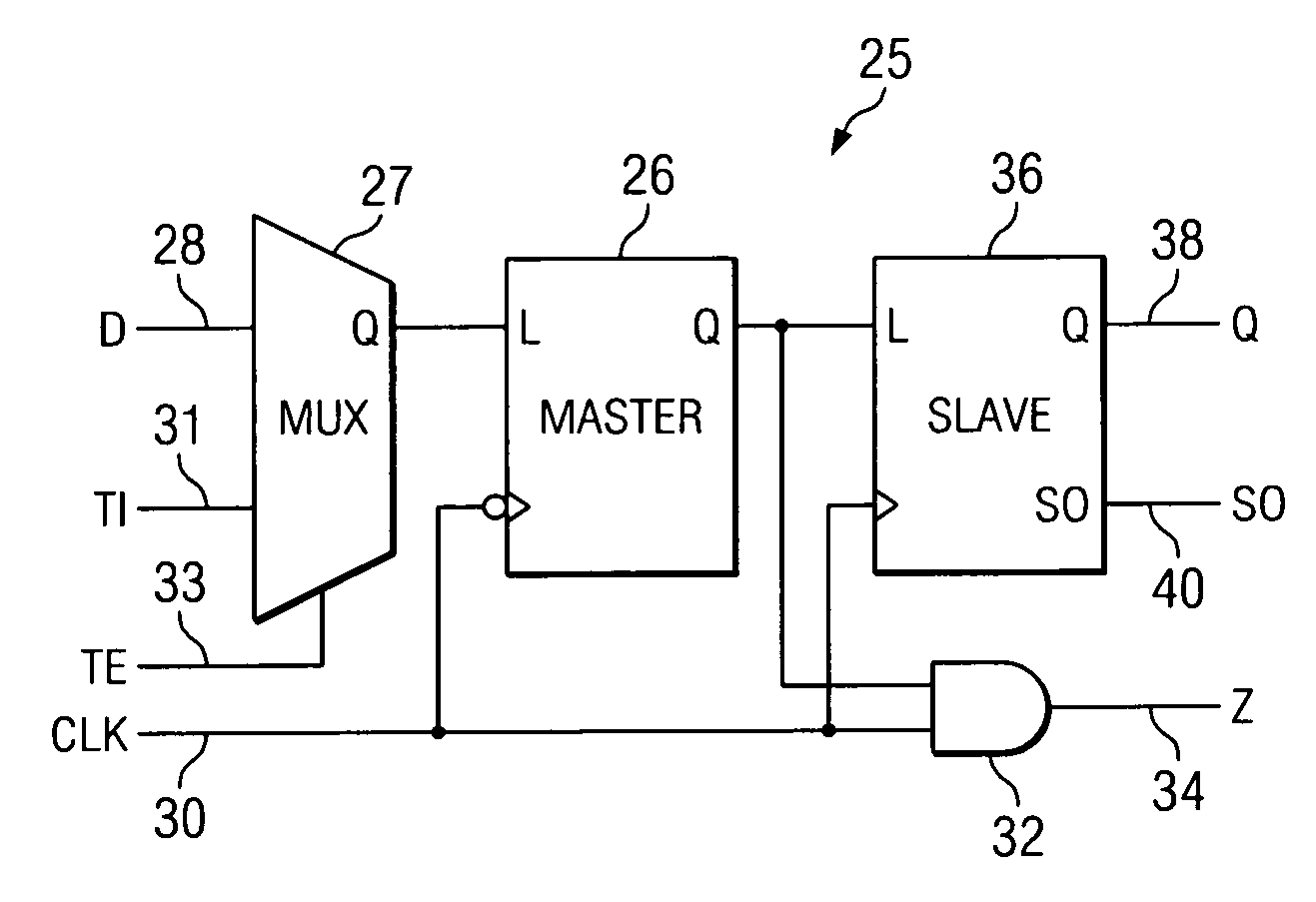

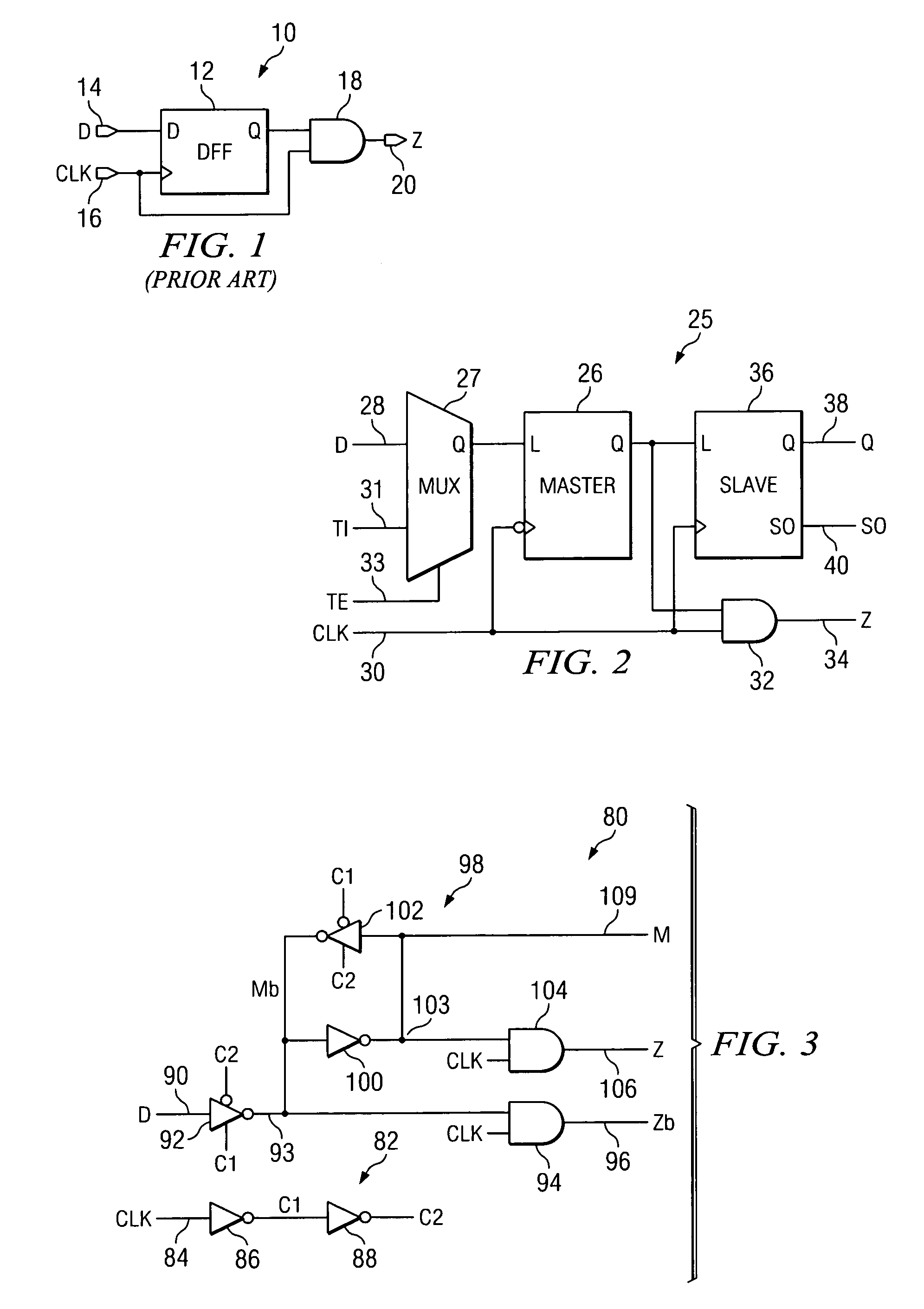

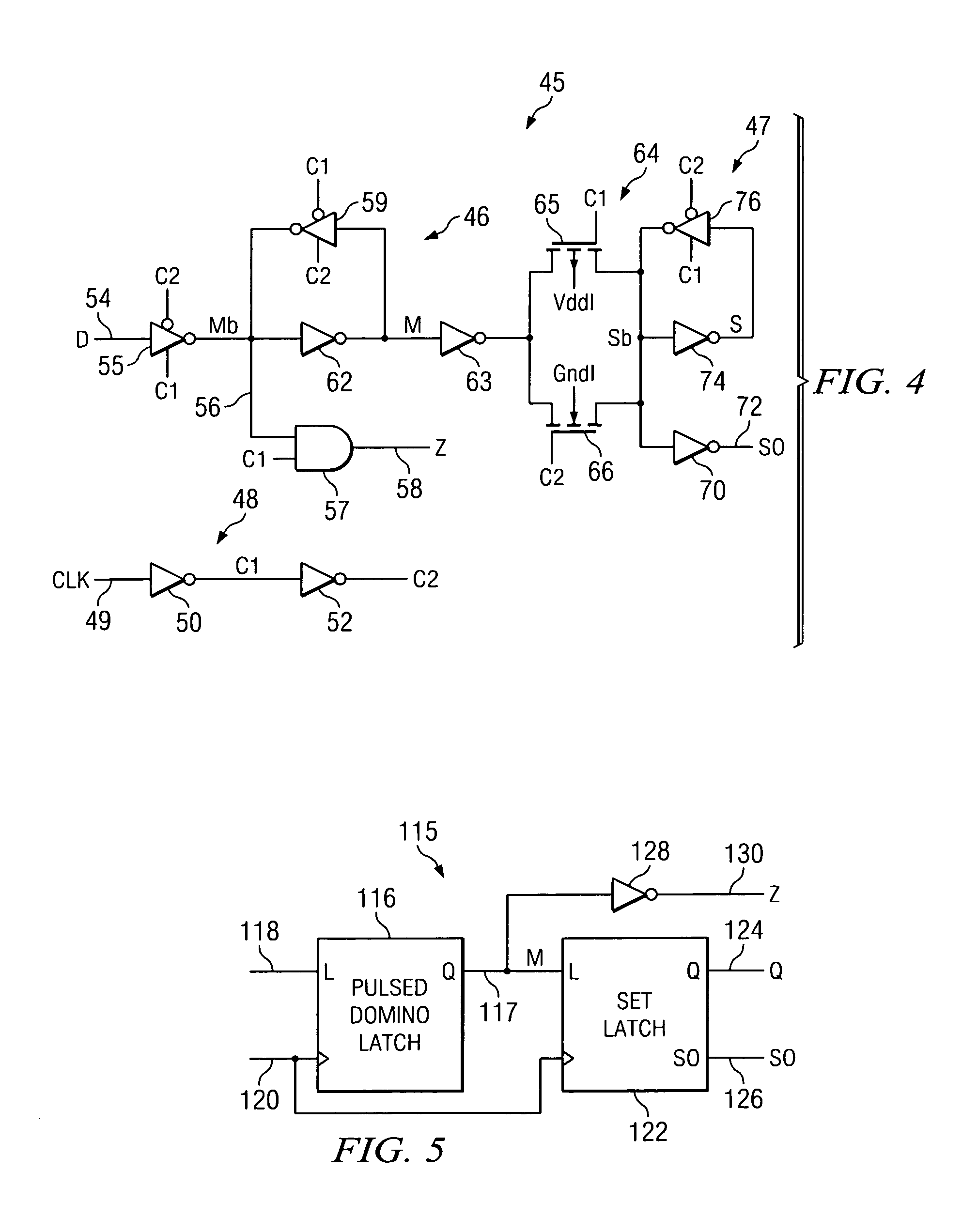

Domino logic compatible scannable flip-flop

InactiveUS7002374B2Electrical testingLogic circuits using elementary logic circuit componentsMultiplexingState variation

A testable, prechargeable circuit has a driving circuit for producing a driving circuit output signal. A timing circuit receives a clock signal and the driving circuit output signal to cause an output of the testable, prechargeable circuit to be in a low state when the clock signal is low. The timing circuit also causes the output of the circuit to be timed with a state change in the clock signal to provide a domino logic output signal. Either a data signal or a test signal are multiplexed to the input of the driving circuit to produce respectively the domino logic output signal or a test output signal. A static logic circuit receives the test output signal to produce a test signal output.

Owner:STMICROELECTRONICS SRL

Silicon on insulator domino logic circuits

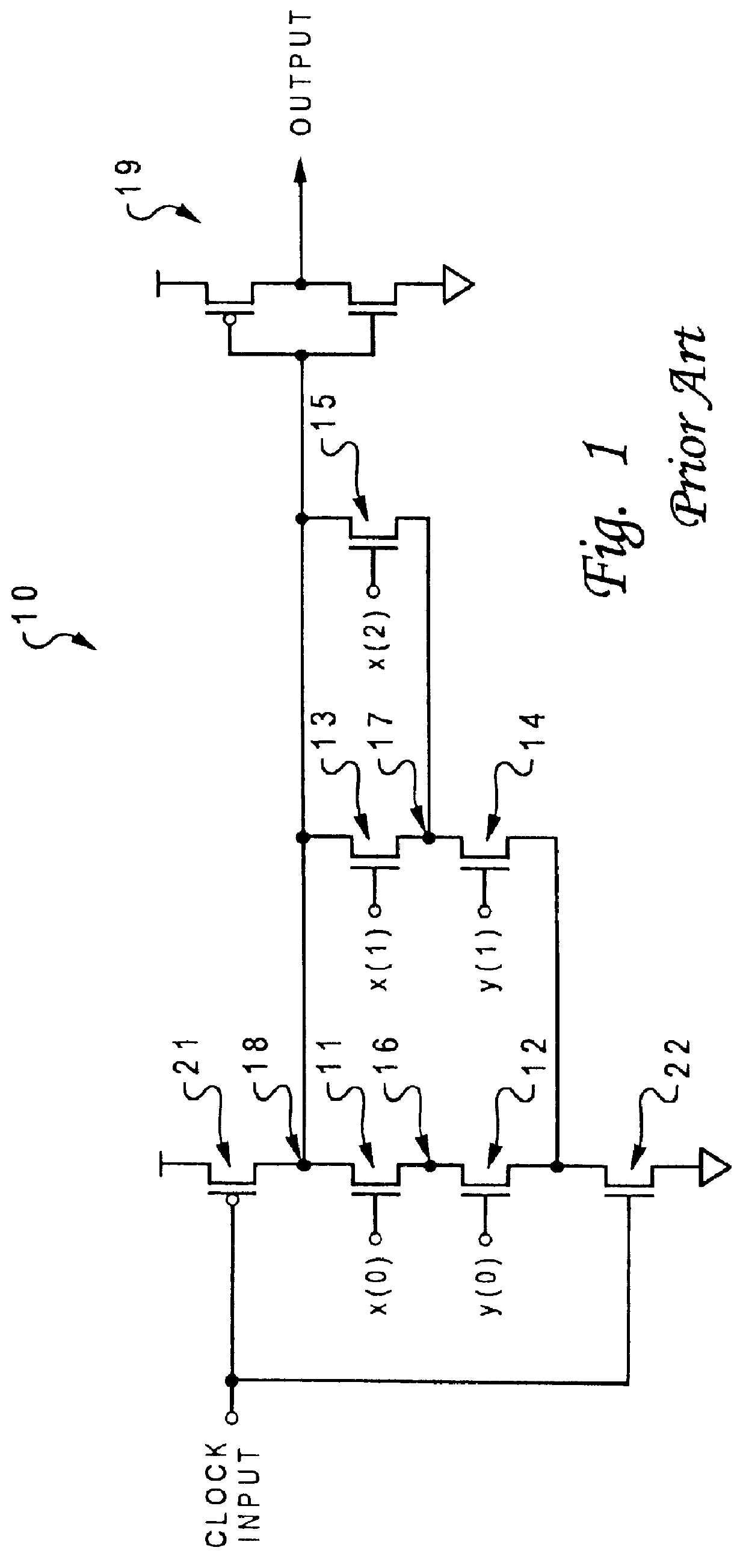

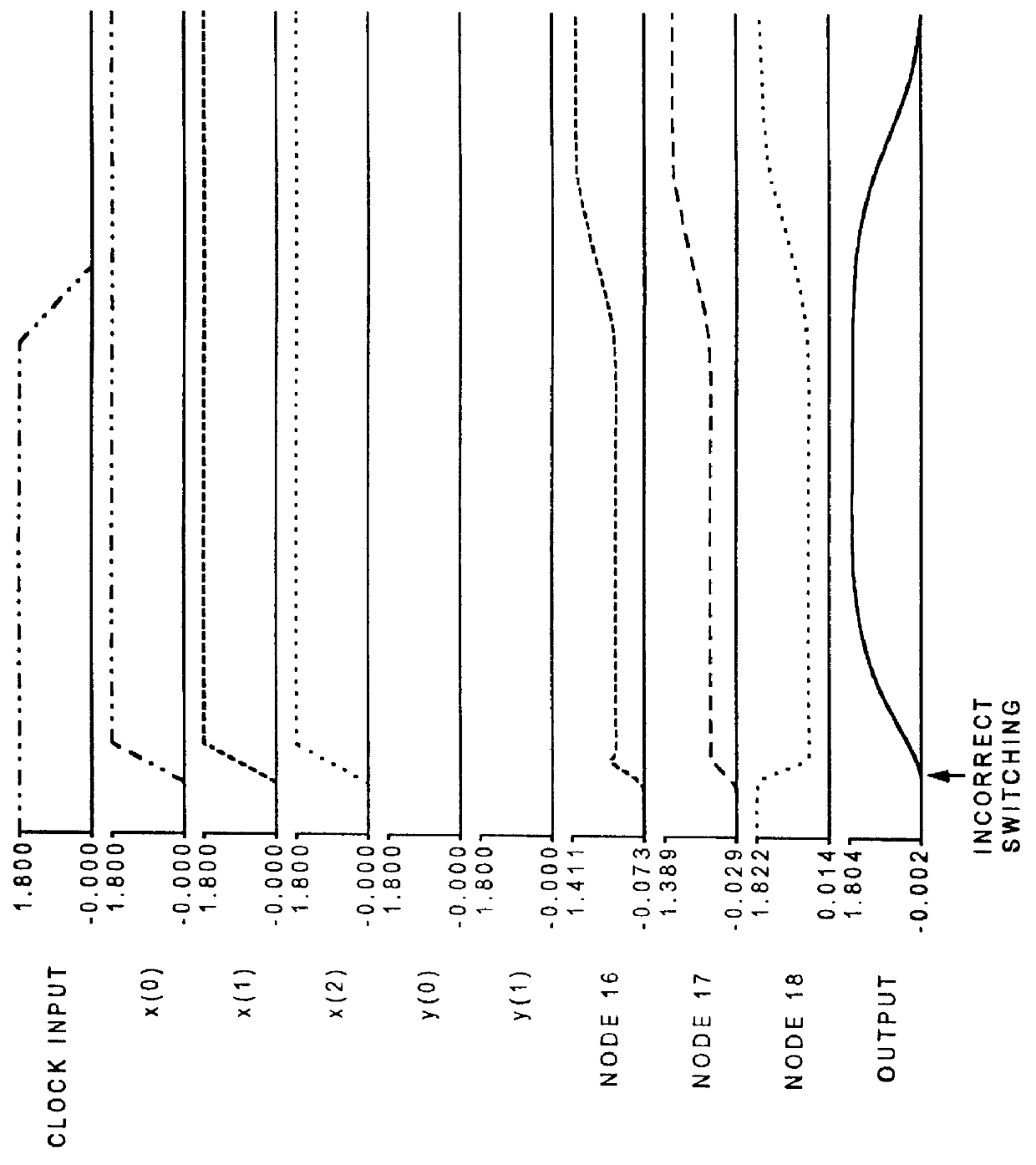

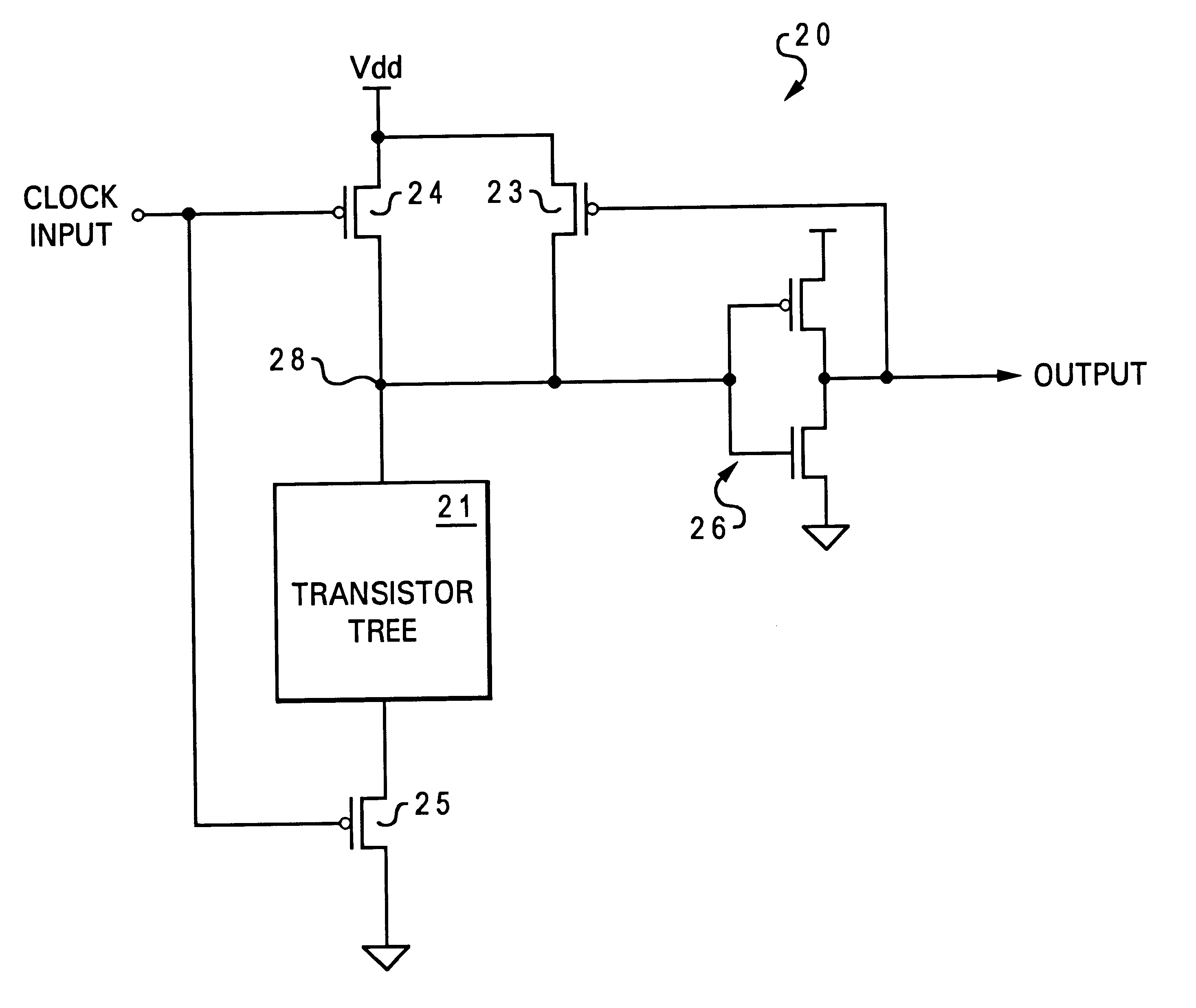

InactiveUS6049230ALogic circuits characterised by logic functionElectric pulse generator detailsDomino logicMultiple input

A domino logic circuit having a clocked precharge is disclosed. The domino logic circuit includes a precharge transistor, a discharge transistor, multiple input transistors, and a supplemental precharge transistor. Connected to a power supply, the precharge transistor receives a clock input. The discharge transistor is connected to ground and also receives the clock input. The input transistors, which are coupled between the precharge transistor and the discharge transistor, each receives a signal input. The supplemental precharge transistor is connected to the power supply and to a body of each of the input transistors. The supplemental precharge transistor also receives the same clock input as the precharge transistor.

Owner:IBM CORP

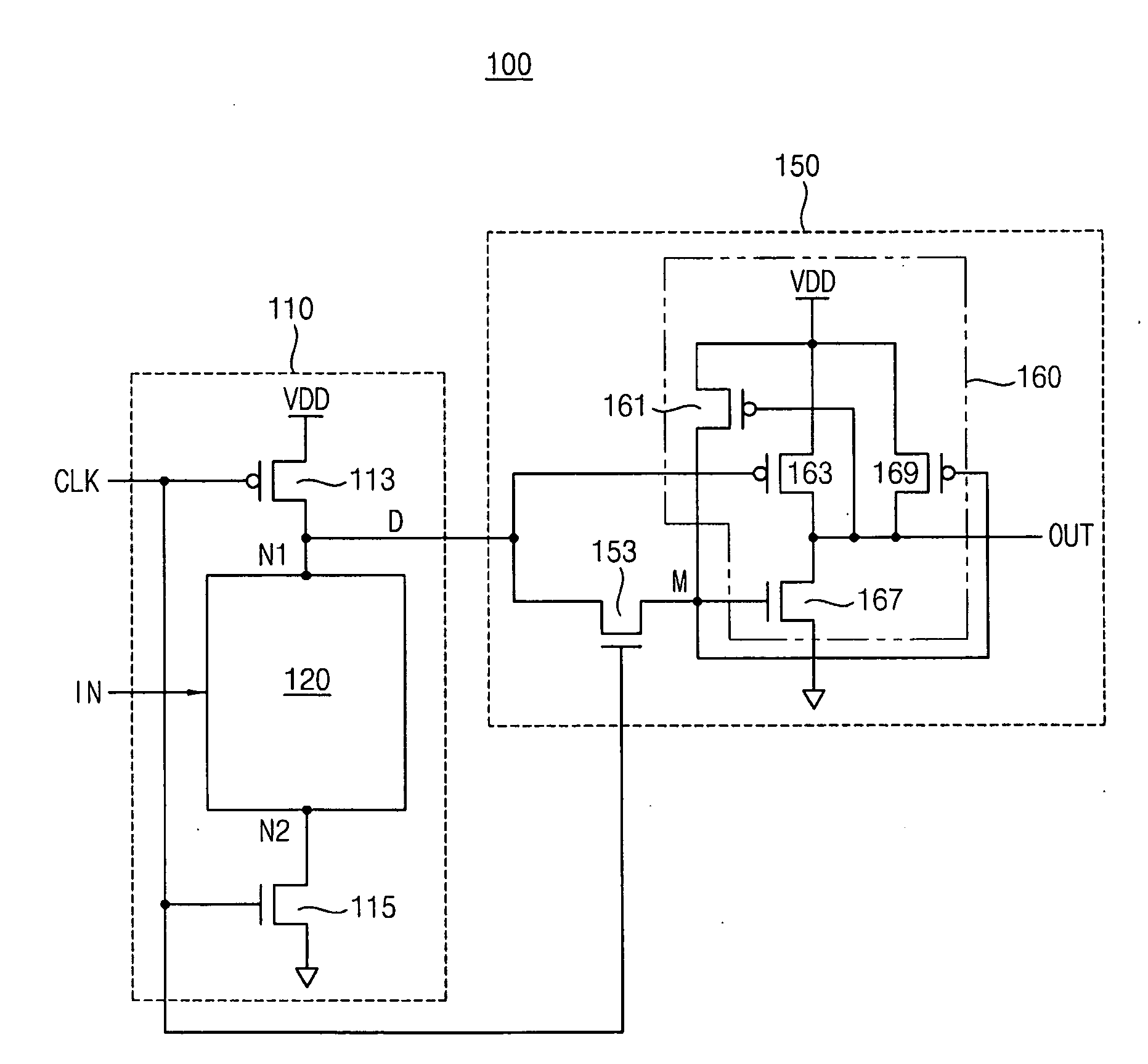

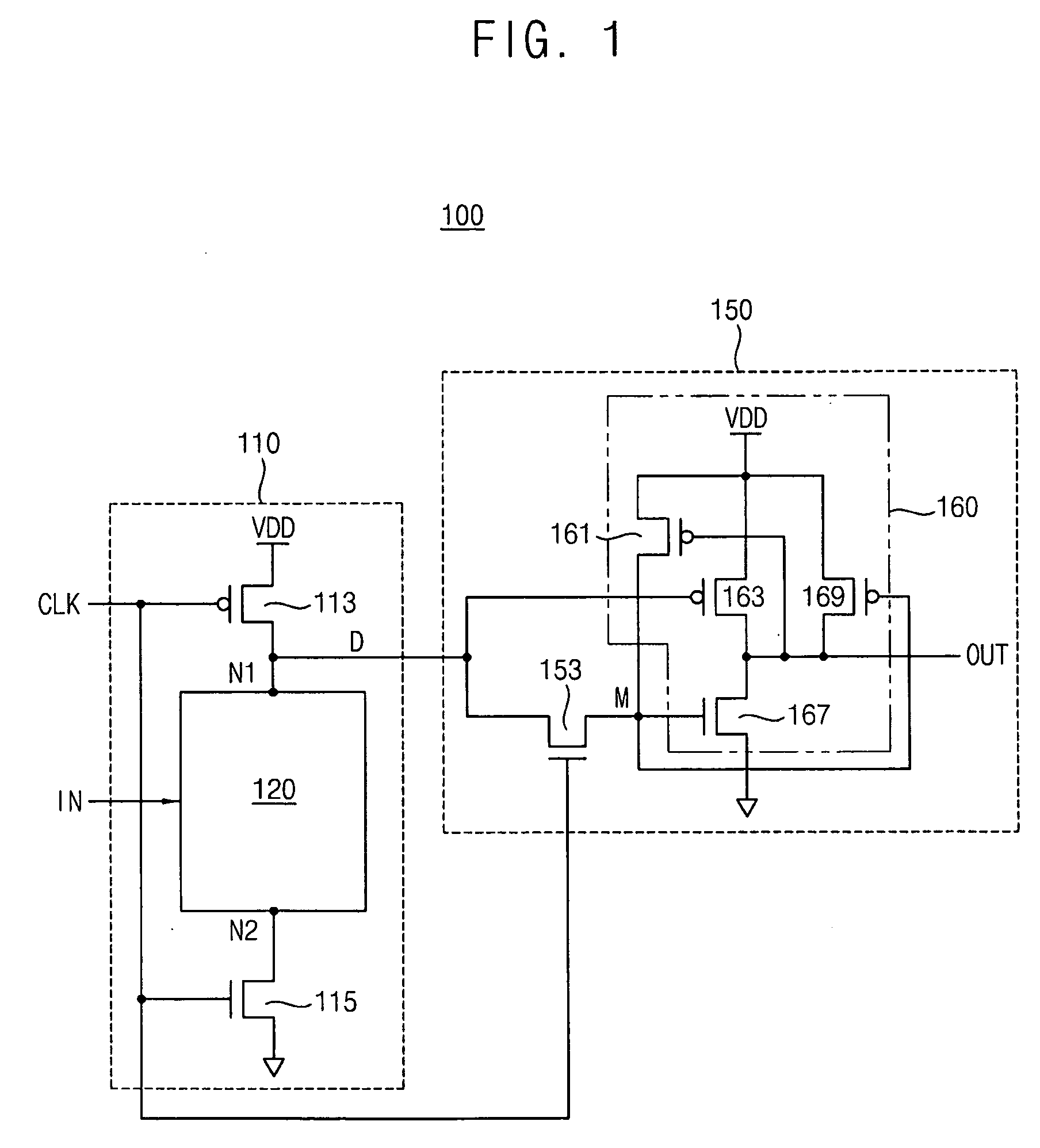

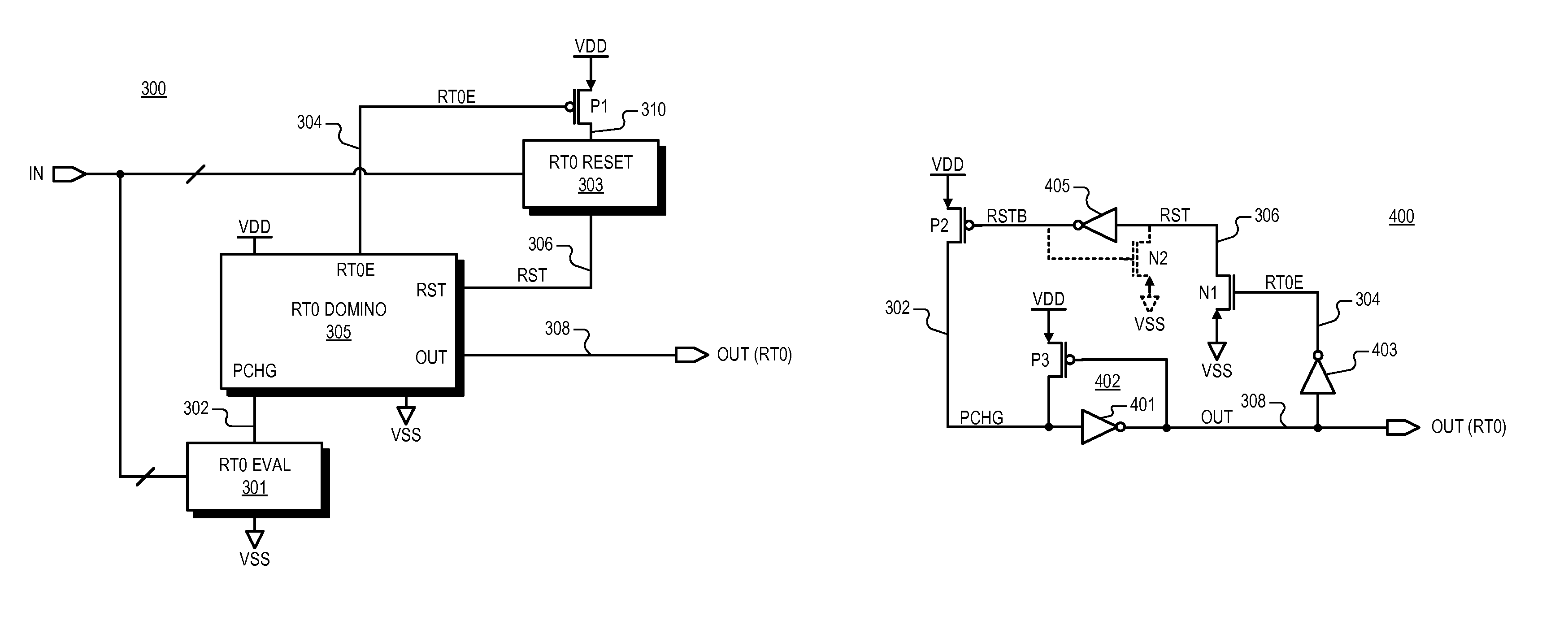

Domino logic circuit and pipelined domino logic circuit

ActiveUS20090230994A1Reduce switching currentReduce current consumptionSolid-state devicesDigital storageDomino logicComputer science

A domino logic circuit includes an input circuit and an output circuit. The input circuit precharges a dynamic node at a first phase of a clock signal. The input circuit determines a logic level of the dynamic node by performing a logic evaluation of input data at a second phase of the clock signal. The output circuit is coupled between an output node and the dynamic node. The output circuit determines a logic level of the output node in response to the clock signal and the logic level of the dynamic node. The output circuit maintains the logic level of the output node while the logic evaluation is performed.

Owner:SAMSUNG ELECTRONICS CO LTD

Domino logic circuit having multiplicity of gate dielectric thicknesses

A domino logic circuit having a clocked precharge is disclosed. The domino logic circuit includes a precharge transistor, an isolation transistor, and multiple evaluate transistors. Connected to a power supply, the precharge transistor receives a clock input. The isolation transistor is connected to ground and also receives the clock input. Each of the input transistors, which are coupled between the precharge transistor and the isolation transistor, receives a signal input. The gate dielectric thickness of the evaluate transistors is less than the gate dielectric thickness of the precharge transistor.

Owner:IBM CORP

Methods and arrangements for enhancing domino logic

Methods and arrangements for enhancing domino logic are disclosed. Embodiments include a keeper circuit to pull up a domino node in response an output of an output circuit when the domino node is at a high voltage and to stop pulling up the domino node before the output changes to a first logical output. Further embodiments include an accelerator circuit to pull down the domino node when the keeper circuit stops pulling up the domino node. The domino node may couple with a pre-charge circuit and be pre-charged to a high voltage during a first portion of a clock cycle. The domino node may also couple with a logic input circuit to pull down the domino node during a second portion of the clock cycle, causing the output circuit to change the output from low to high in response to logic signals.

Owner:IBM CORP

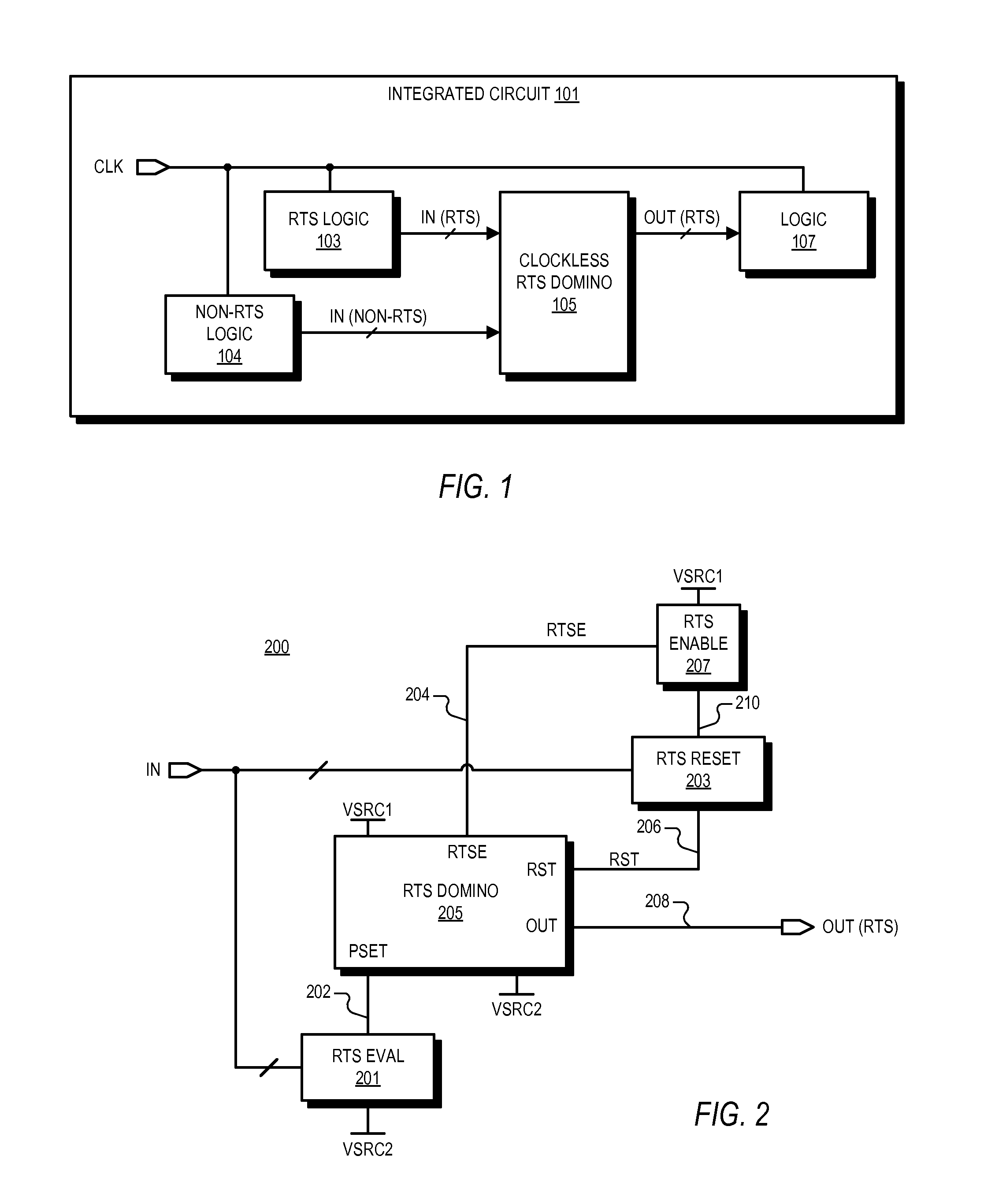

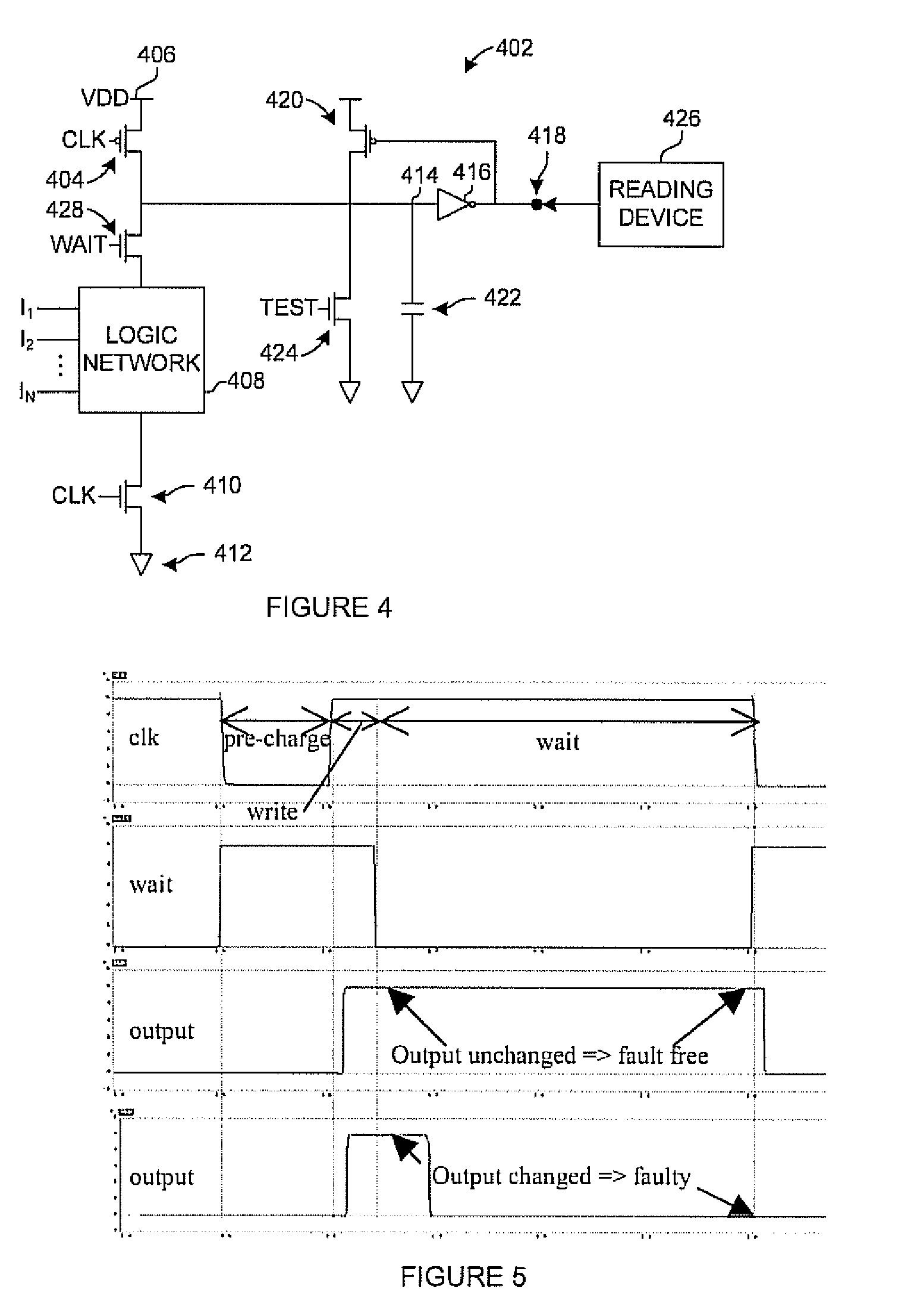

Clockless return to state domino logic gate

A clockless return to state domino logic gate is disclosed responsive to multiple return to state input nodes. A domino circuit has a preset state in which it presets a preset node to a second state. The domino circuit switches to a latch state and switches an output node when the preset node is pulled to a first state. The domino circuit resets back to the preset state and switches the output node back to its default state when a reset node is pulled to the second state. An evaluation circuit pulls the preset node to the second state when the input nodes are in an evaluation state. An enable circuit enables a reset condition when the domino circuit is in its latch state. A reset circuit pulls the reset node to the first state after an evaluation event when the input nodes are no longer in the evaluation state.

Owner:VIA TECH INC

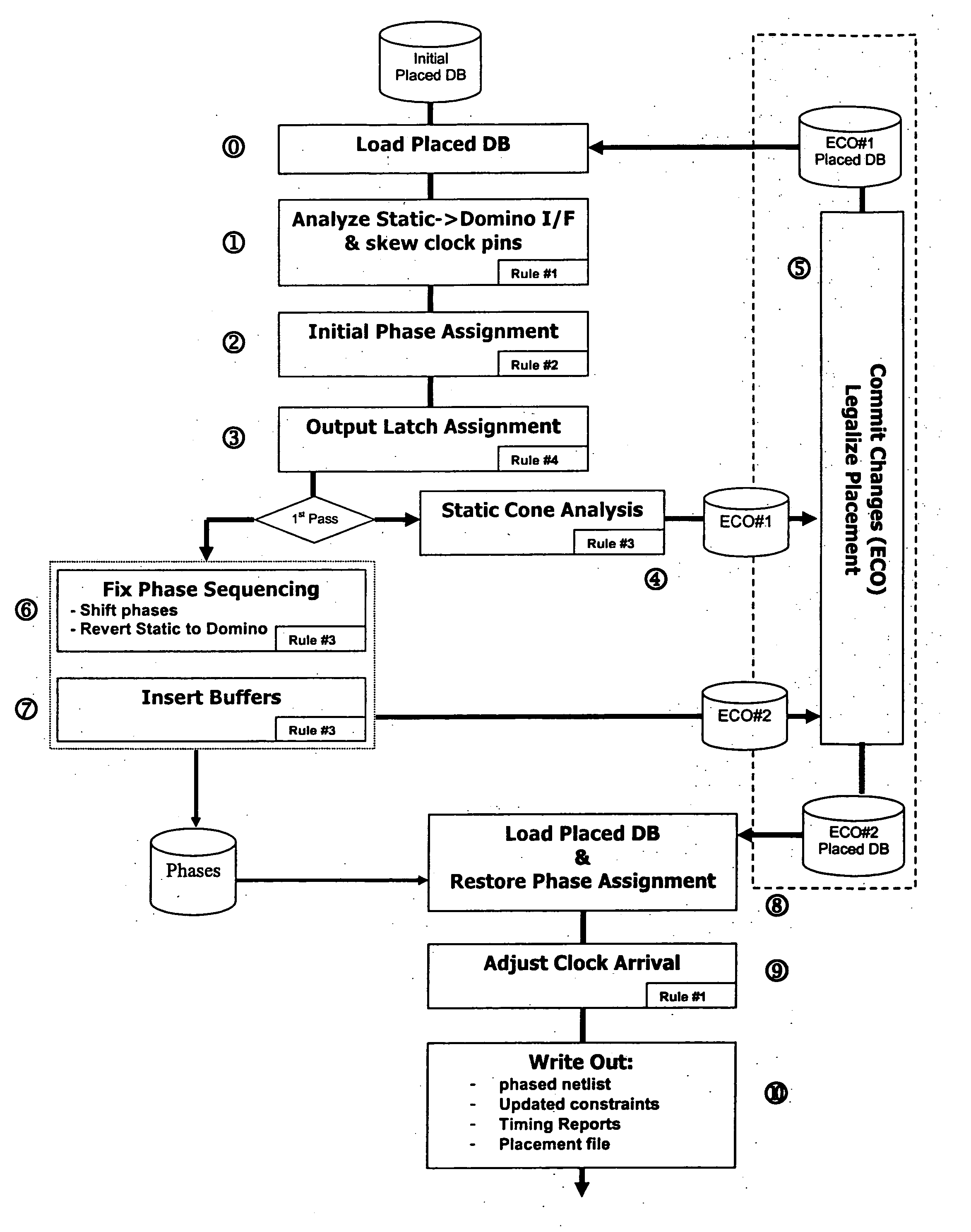

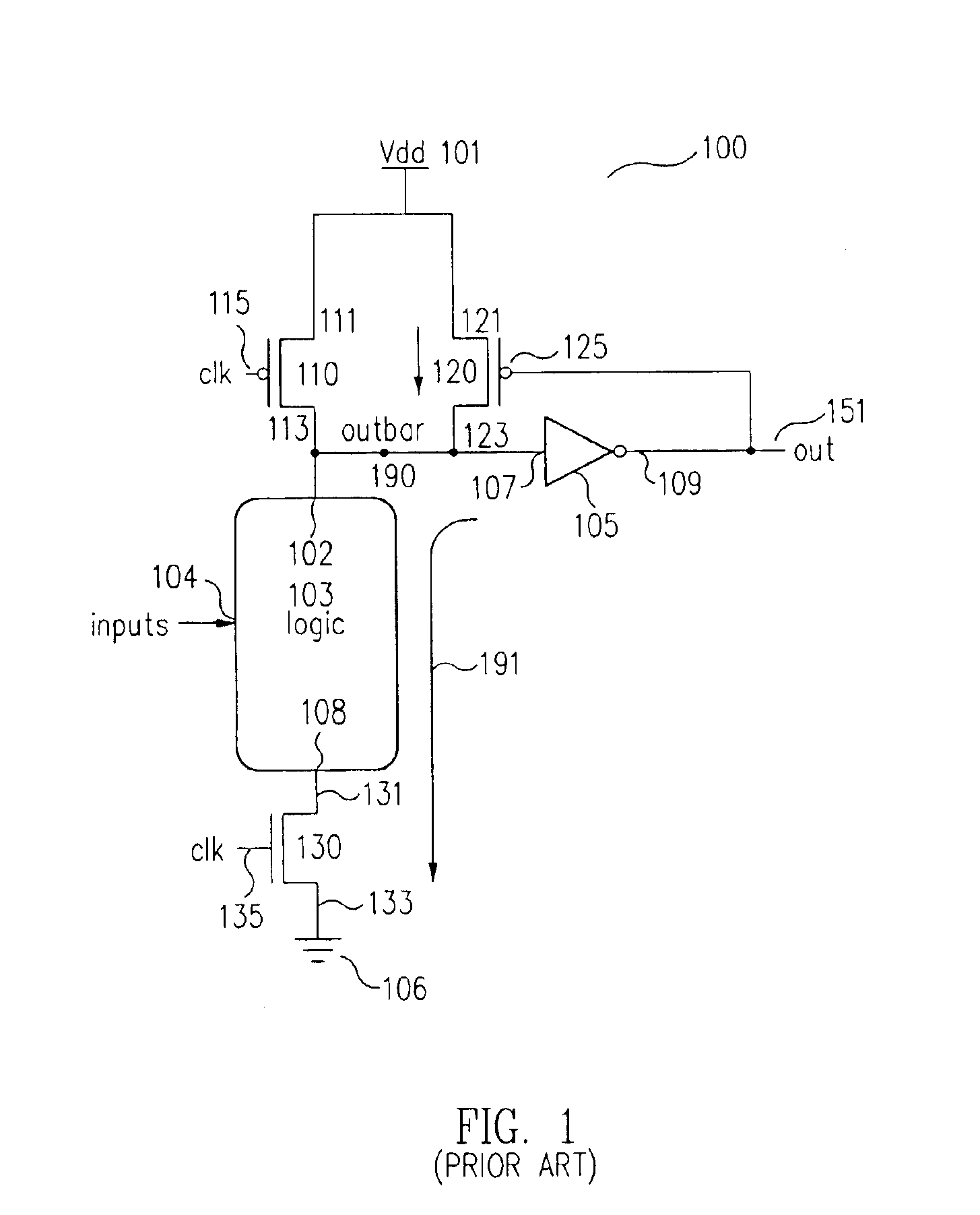

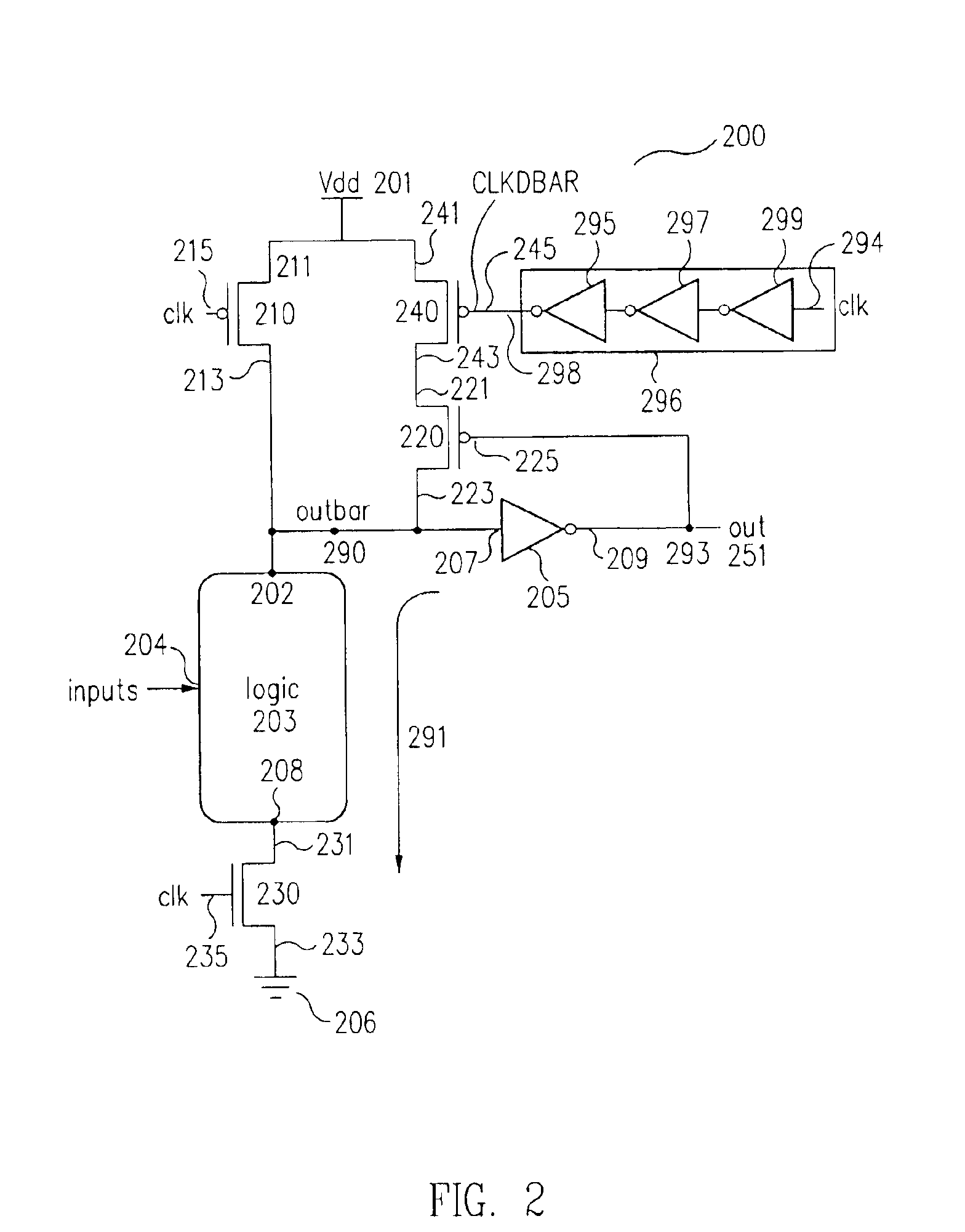

Method and apparatus for mixing static logic with domino logic

InactiveUS20060136852A1Efficient disseminationCost-effectiveCAD circuit designProgram controlDomino logicTheoretical computer science

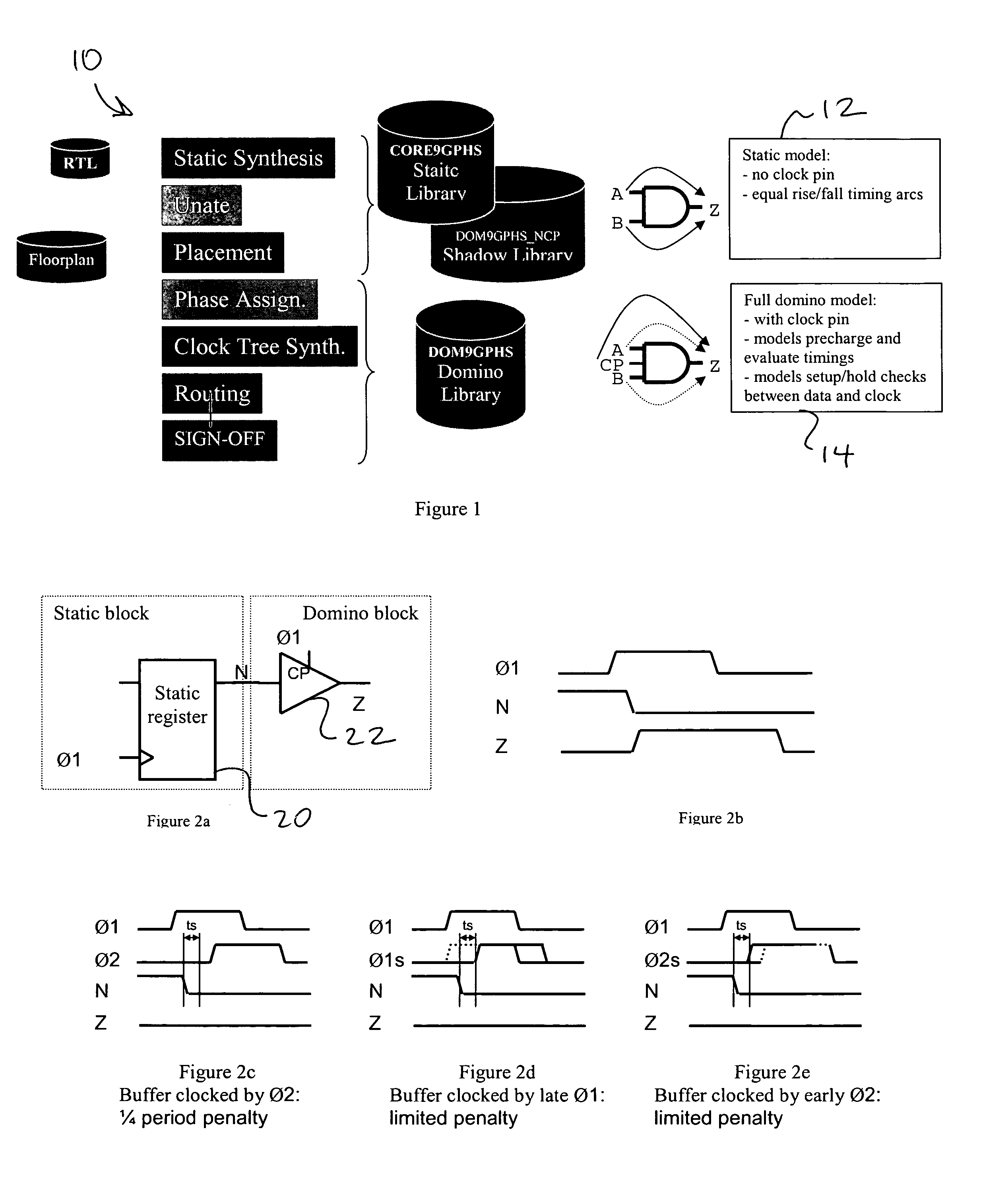

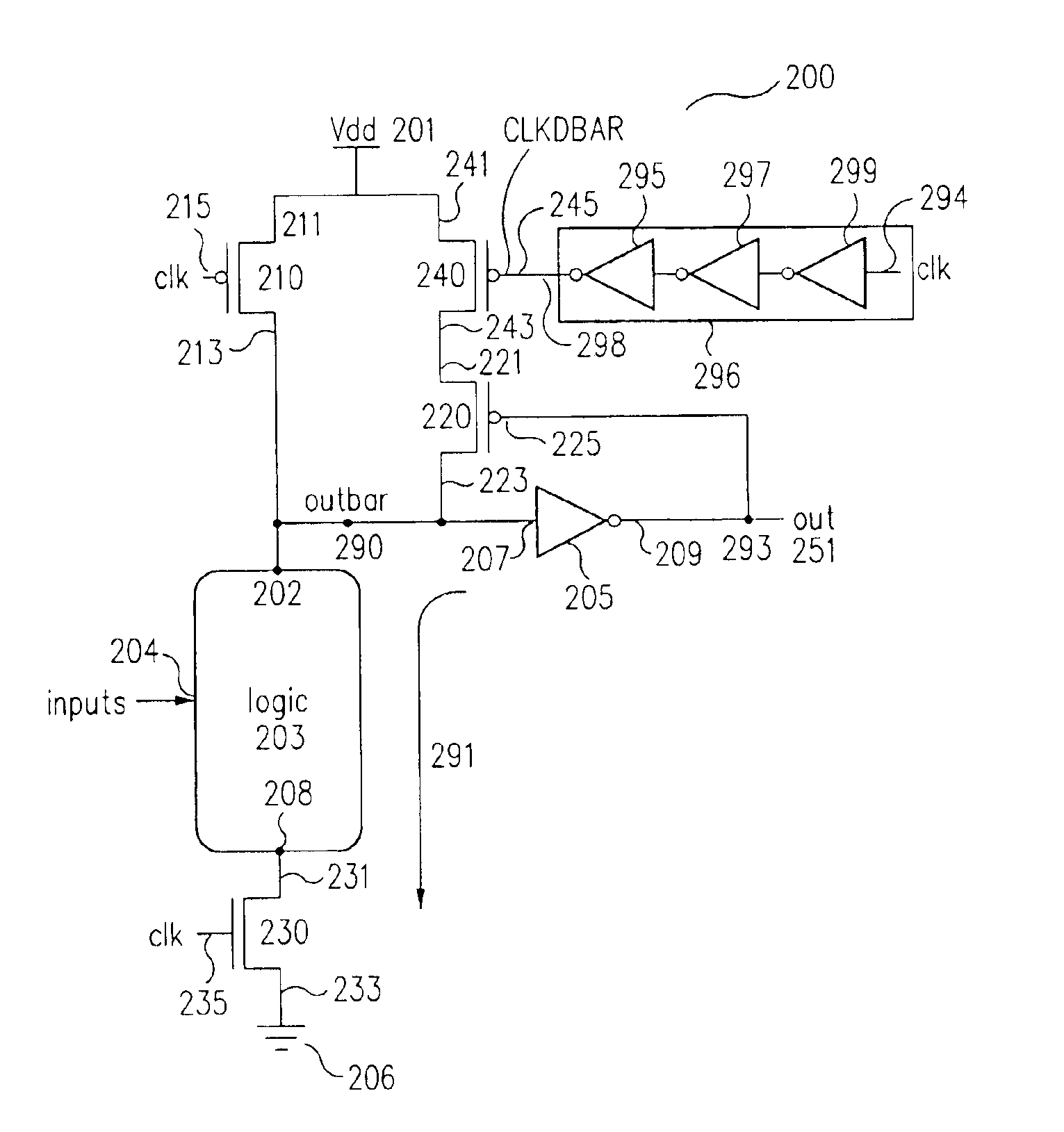

An automatic method for assigning the clock phases on a domino datapath embedding static gates includes replacing domino cells on non-critical paths by a static equivalent cell, delaying the clock arrival on domino gates driven by static signals, ensuring that critical data never waits for the clock in the domino pipeline, ensuring that a domino data never goes to precharge, and therefore is lost before it is consumed, ensuring that the domino datapath operates at any speed below the maximum operating speed, ensuring that domino signals leaving the design through primary outputs of a static block are latched to prevent the precharge to overwrite the evaluated results, providing an optimal solution in terms of performance, area and power, defining some constraints that are checked and enforced by the downstream tools in order to guaranty the proper functionality of the design.

Owner:STMICROELECTRONICS SRL

High-speed domino logic with improved cascode keeper

A high-speed domino logic with improved cascode keeper circuit uses an inverter delay element and an additional transistor to introduce a transition delay time and node isolation time to avoid the contest or “fight” between a first node and the keeper transistor in the event of a path to ground being created through the logic block portion of high-speed domino logic with improved cascode keeper circuit. The high-speed domino logic with improved cascode keeper circuits of the invention, in contrast to prior art domino logic circuits, can be designed to have high noise immunity and increased speed. In addition, since according to the invention, only a minimum of one new inverter and one new are required, the modification of the invention is space efficient and readily incorporated into existing designs.

Owner:SUN MICROSYSTEMS INC

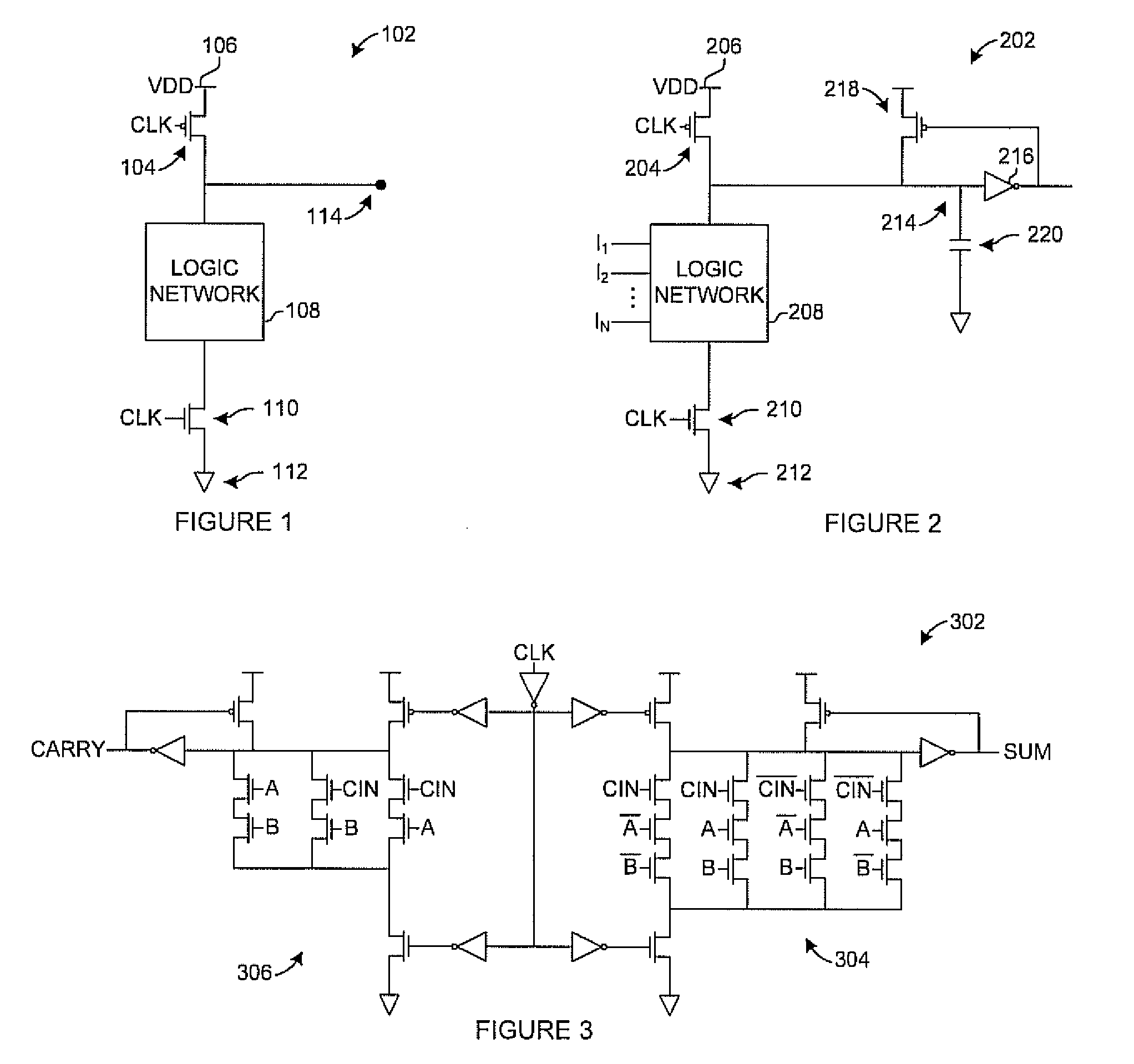

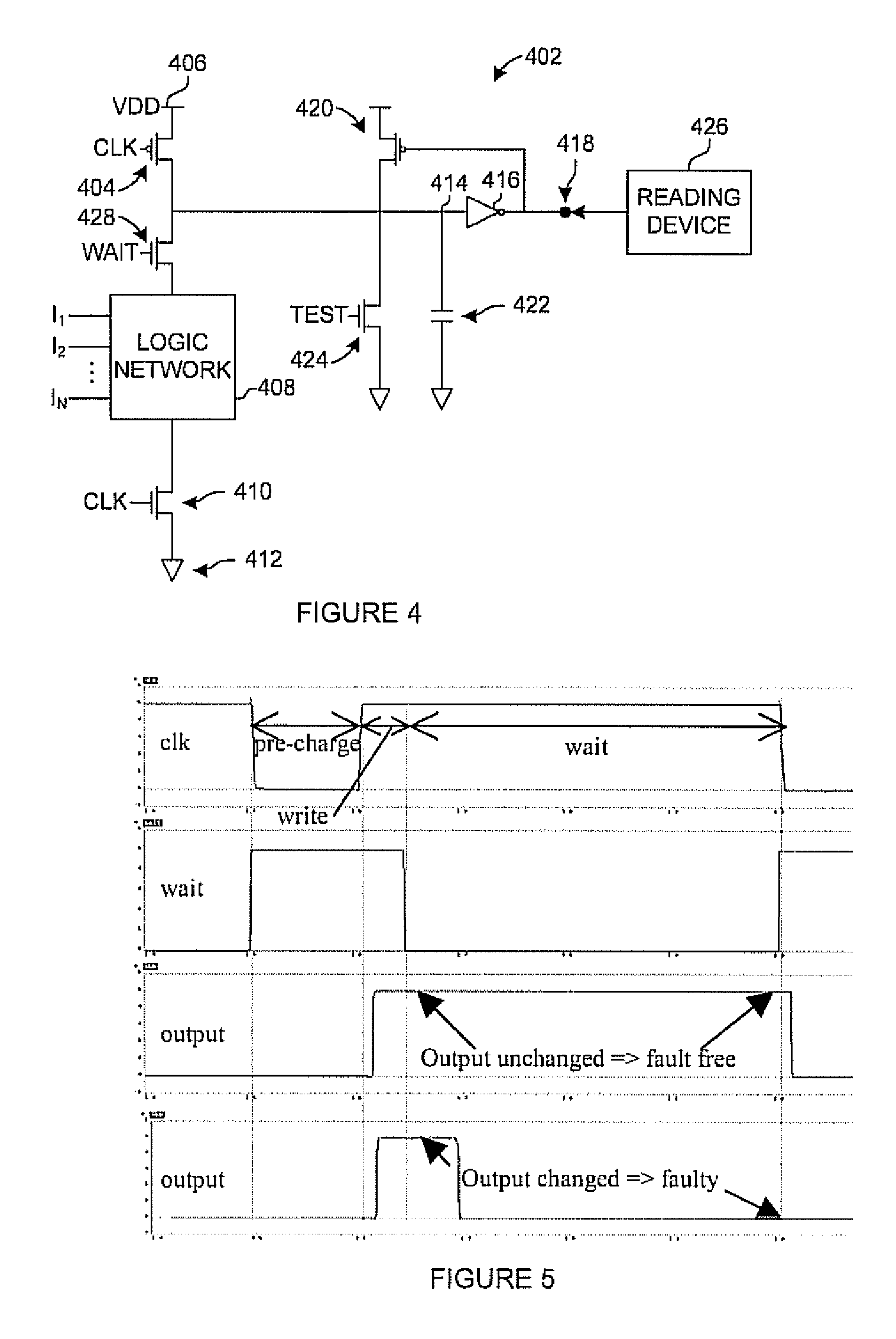

Domino logic testing systems and methods

InactiveUS20070296465A1Logic circuits characterised by logic functionDigital circuit testingDomino logicLogic network

A domino logic test circuit includes a dynamic node, a precharge device for charging the dynamic node, and an output inverter for inverting an output of the dynamic node. A logic network is coupled to the dynamic node for discharging the dynamic node in accordance with logic. A footer device enables and disables the logic network. A keeper device is coupled to the dynamic node for retaining a charge state of the dynamic node while awaiting the logic network to operate in accordance with the logic. A test mode selection device is coupled to the dynamic node and is configured to enable a latch in the test mode. A phase selection device is configured to receive at least a wait signal and to enable selection of at least a precharge phase for charging the dynamic node to a voltage level, a write phase for generating a value to the latch based on the logic and the voltage level of the dynamic node, and a wait phase for enabling reading the value. The selection is based, at least partially, on the wait signal state.

Owner:UNIVERSITY OF MISSOURI

Clockless return to state domino logic gate

A clockless return to state domino logic gate including a domino circuit and an input circuit. The domino circuit asserts s preset node and an enable node to a first logic state and asserts an output node and a reset node to a second logic state in a preset state, and switches to a latch state when the preset node is pulled to the second state. In the latch state, the domino circuit pulls the output node to the first logic state and pulls the enable node to the second logic state. The domino circuit resets back to the preset state when the first reset node is pulled to the first logic state. The input circuit controls the domino circuit based on collective state of input signals, and is configured to perform a selected logic function using at least one return to state signal without use of a clock signal.

Owner:VIA TECH INC

Domino logic circuit and pipelined domino logic circuit

ActiveUS7852121B2Total current dropReduce circuit sizeSolid-state devicesDigital storageDomino logicComputer science

A domino logic circuit includes an input circuit and an output circuit. The input circuit precharges a dynamic node at a first phase of a clock signal. The input circuit determines a logic level of the dynamic node by performing a logic evaluation of input data at a second phase of the clock signal. The output circuit is coupled between an output node and the dynamic node. The output circuit determines a logic level of the output node in response to the clock signal and the logic level of the dynamic node. The output circuit maintains the logic level of the output node while the logic evaluation is performed.

Owner:SAMSUNG ELECTRONICS CO LTD

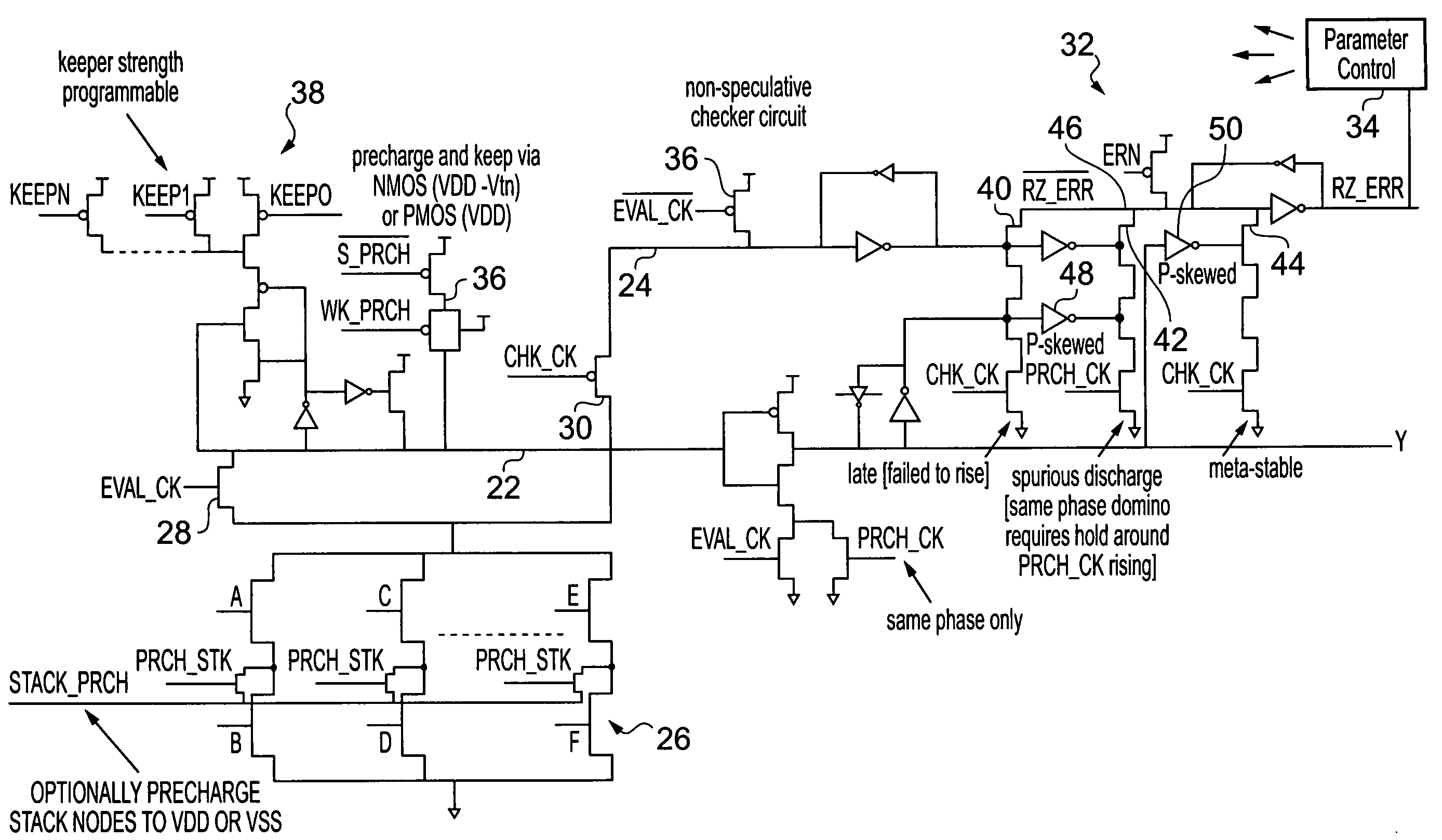

Error detection in precharged logic

ActiveUS20100235697A1Increases magnitudeEasy to operateElectronic circuit testingLogical operation testingDomino logicLogic circuitry

An integrated circuit 2 is provided with domino logic including a speculative node 22 and a checker node 24. Precharged circuitry 36 precharges both the speculative node and the checker node. Logic circuitry 26 provides a discharge path for the speculative node and the checker node in dependence upon input signal values. Evaluation control circuitry 28, 30 first couples the speculative node to the logic circuitry and then subsequently couples the checker node to the logic circuitry such that these can be discharged if the input signals to the logic circuitry 26 have appropriate values. Error detection circuitry 32 detects an error when the speculative node and the checker node are not one of both discharged or both undischarged.

Owner:RGT UNIV OF MICHIGAN +1

Clock logic domino circuits for high-speed and energy efficient microprocessor pipelines

ActiveUS7123056B2Reduce power consumptionGuaranteed high speed operationLogic circuitsNon-monotonic logicDomino logic

A systematic method for single-rail domino logic circuits is provided, in which inverting and non-monotonic logic functions can be integrated into a pipelined system with almost zero overhead. This logic family, called Clock Logic (CL)-domino is functionally complete while tolerating skew and minimizing the number of clock phases that must be distributed. Simulation results for a CL-domino ALU at 1-GHz under high skew (1-FO4) conditions, shows a power reduction of 41% over the same ALU implemented in dual-rail skew-tolerant domino logic. This power reduction incurs no performance penalty over dual-rail techniques, although in some cases additional design effort is required.

Owner:CONVERSANT INTPROP MANAGEMENT INC

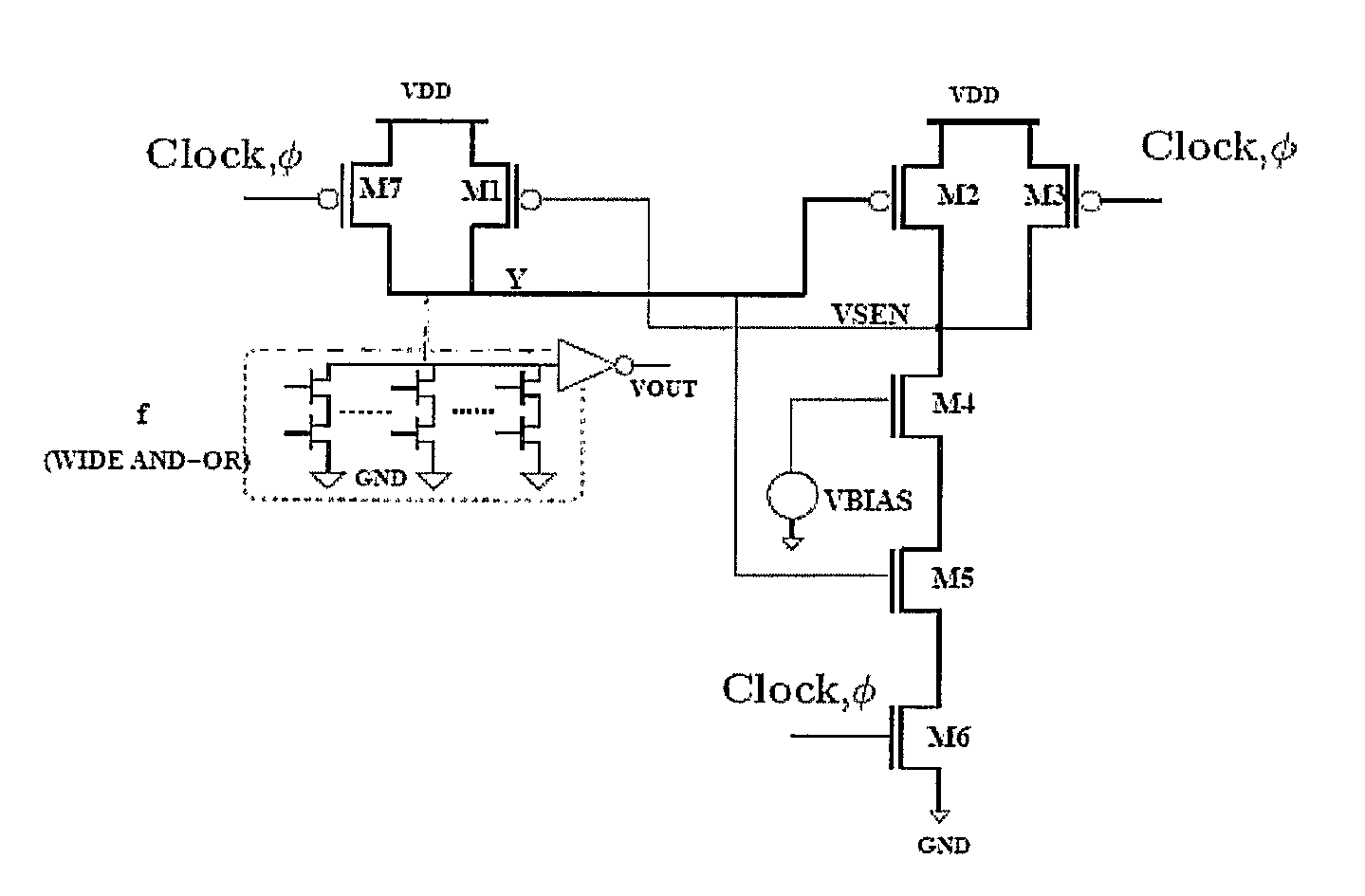

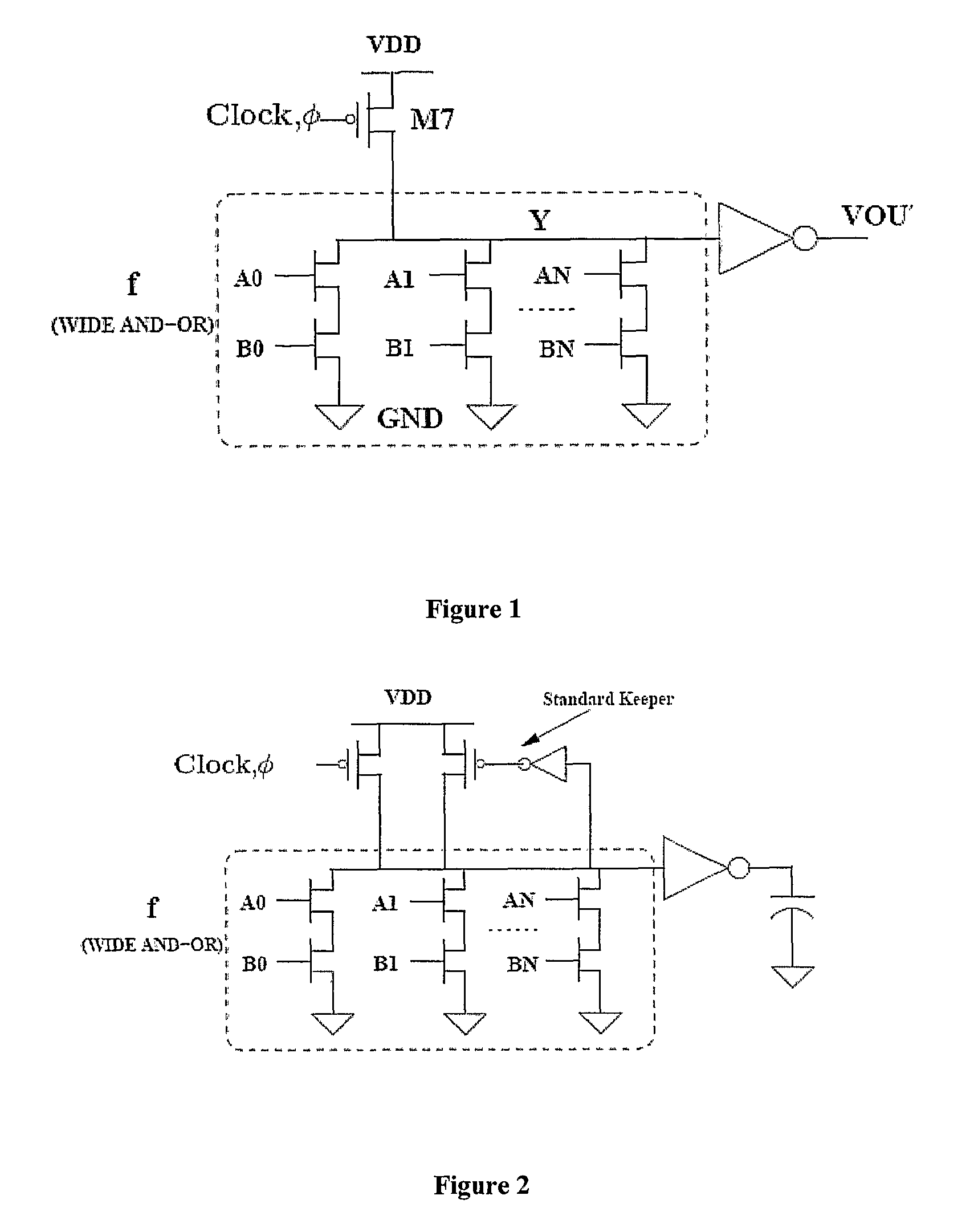

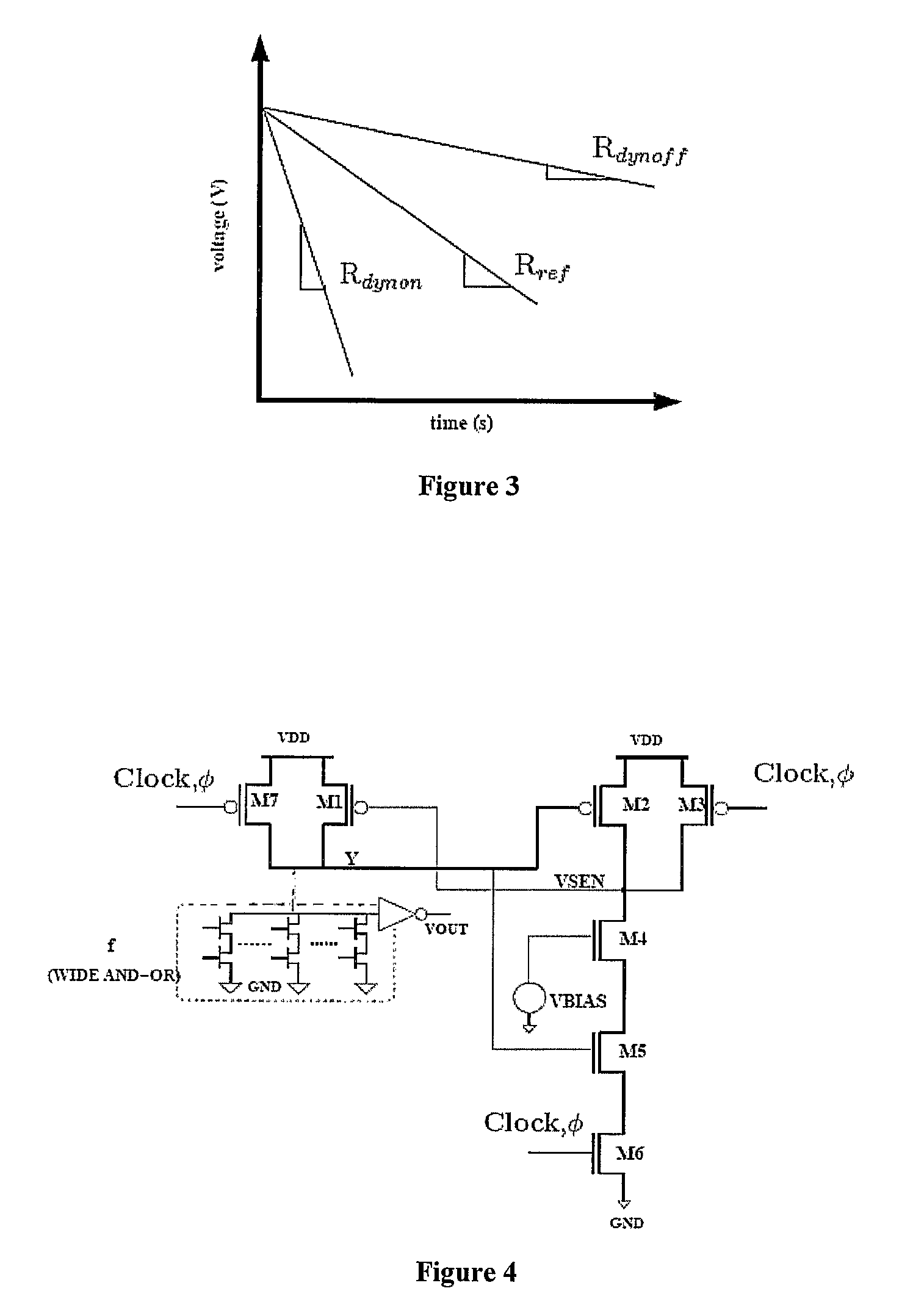

Adaptive keeper circuit to control domino logic dynamic circuits using rate sensing technique

InactiveUS7804330B2Reduce contentionEffective trackingPower reduction by control/clock signalLogic circuits characterised by logic functionDomino logicReference rate

The present invention provides an adaptive keeper circuit to control Domino Logic Dynamic Circuits using Rate Sensing Technique to provide reduced contention and efficient process tracking at given noise robustness with less overhead in area, power and delay, said adaptive keeper comprising, keeper PMOS transistor (M1), wherein the drain of M1 is connected to wide AND-OR logic circuit; the rate controller consisting of reference rate transistor (M4), feedback PMOS transistor (M2), feedback shutoff transistor (M5), clock shutoff transistor (M6), pre-charge PMOS transistor (M3), wherein the input of the rate controller is directly connected to drain of the keeper PMOS (M1) and the output of the rate controller is directly connected to the gate of the PMOS keeper (M1).

Owner:INDIAN INSTITUTE OF SCIENCE

Compound domino logic circuit having output noise elimination

InactiveUS6172529B1Reliability increasing modificationsLogic circuits characterised by logic functionDomino logicLogic gate

A domino logic circuit having output noise elimination is disclosed. A compound domino logic circuit includes at least two trees of logic devices arranged in parallel, with each tree having a precharge transistor connected to a power supply, and one or more input transistors coupled between the precharge transistor and ground. The precharge transistor receives a clock input while each of the one or more input transistors receives a signal input. The compound domino logic circuit also includes a logic gate coupled to the precharge transistor to produce a signal output. The logic gate includes at least two transistors connected in series. Further, an adjustment transistor is coupled to a node between the two transistors to ground.

Owner:IBM CORP +1

Domino logic testing systems and methods

InactiveUS7332938B2Digital circuit testingLogic circuits characterised by logic functionDomino logicEngineering

A domino logic test circuit includes a dynamic node, a precharge device for charging the dynamic node, and an output inverter for inverting an output of the dynamic node. A logic network is coupled to the dynamic node for discharging the dynamic node in accordance with logic. A footer device enables and disables the logic network. A keeper device is coupled to the dynamic node for retaining a charge state of the dynamic node while awaiting the logic network to operate in accordance with the logic. A test mode selection device is coupled to the dynamic node and is configured to enable a latch in the test mode. A phase selection device is configured to receive at least a wait signal and to enable selection of at least a precharge phase for charging the dynamic node to a voltage level, a write phase for generating a value to the latch based on the logic and the voltage level of the dynamic node, and a wait phase for enabling reading the value. The selection is based, at least partially, on the wait signal state.

Owner:UNIVERSITY OF MISSOURI

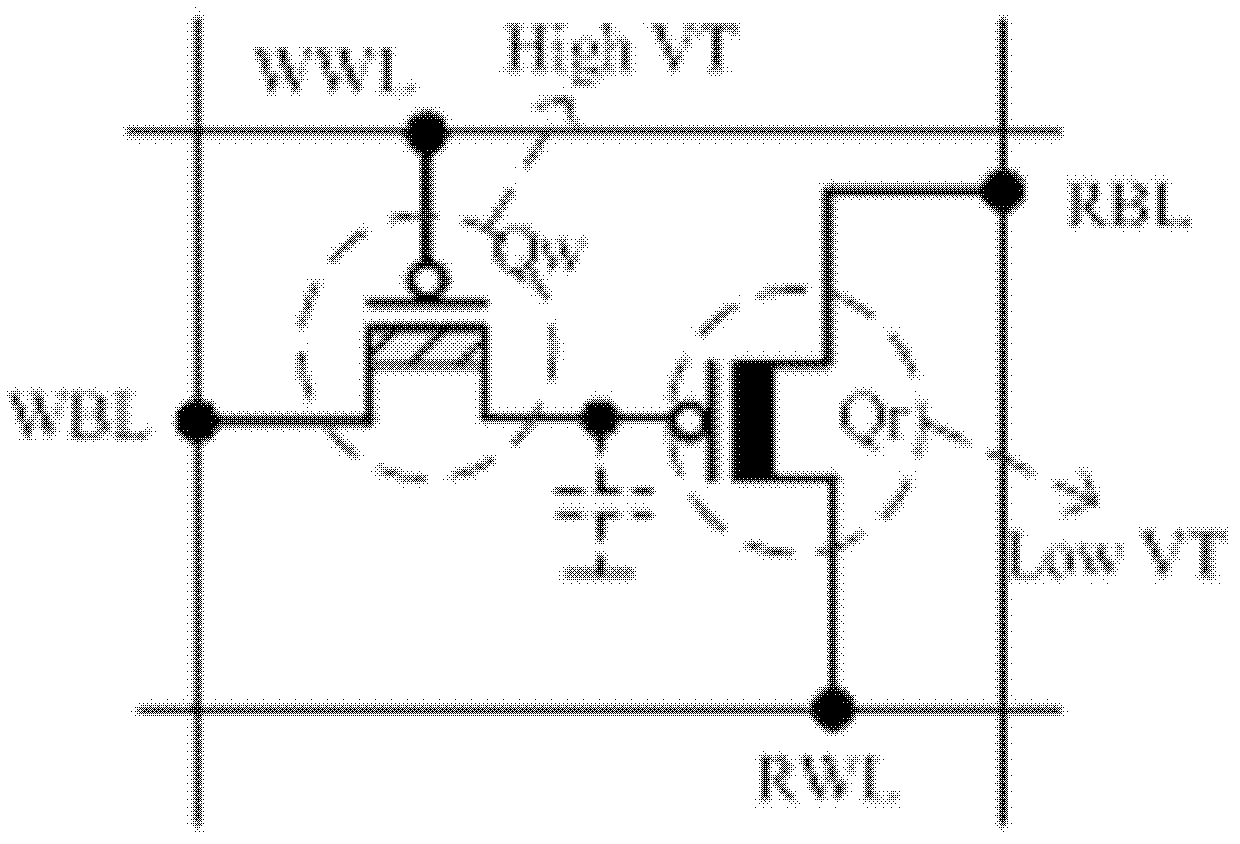

Method for high-speed writing operation of dynamic random access memory (DRAM)

The invention relates to the technical field of memories and particularly relates to a method for high-speed writing operation of a dynamic random access memory (DRAM). According to the method, a DRAM cell adopting a logical process is of a 2T gain cell structure and comprises a write-in tube Qw and a readout tube Qr, and an active area capacitor of the write-in tube Qw and a gate capacitor of the readout tube Qr constitute the storage capacitor of the cell. According to the method, in a writing circuit, a domino logic part is a drive circuit which executes the write-in operation of the cell, and evaluation tube sets M1-M4 of the domino logic part receive a cell read-out small signal and an outside write-in signal which are amplified by a sense amplifier respectively. When a writing drive enable signal (WPCH) is opened, the level of a domino logic prenode changes according to whether the evaluation tube sets M1-M4 are connected or not to enable the level of a wideband laser (WBL) of an output terminal of an inverter (INV) to swing, so that the write-in to the cell is completed. According to the method disclosed by the invention, the technical problems that as a non-logic process is adopted to produce capacitors of the traditional 1T1C DRAM, the application of the DRAM in embedded equipment is difficult, and the like can be solved.

Owner:FUDAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com