Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

81 results about "Clock power" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Clock reproduction circuit that can reproduce internal clock signal correctly in synchronization with external clock signal

InactiveUS6166990ASolid-state devicesSemiconductor/solid-state device manufacturingFrequency determinationPhase synchronization

A frequency determination circuit generating a clock signal phase-locking with an external clock signal at a coarse precision and a fine adjust circuit generating an internal synchronizing signal phase-locking with the external clock signal at a fine precision are provided. The fine adjust circuit has a function of adjusting the phase of the frequency determination circuit when phase synchronization is to be carried out exceeding the adjust range thereof. The frequency determination circuit and the fine adjust circuit receive a clock power supply voltage. A clock reproduction circuit is provided which generates an internal clock signal phase-locking with an external clock signal or a reference clock signal stably even when the operating environment changes.

Owner:HITACHI LTD +2

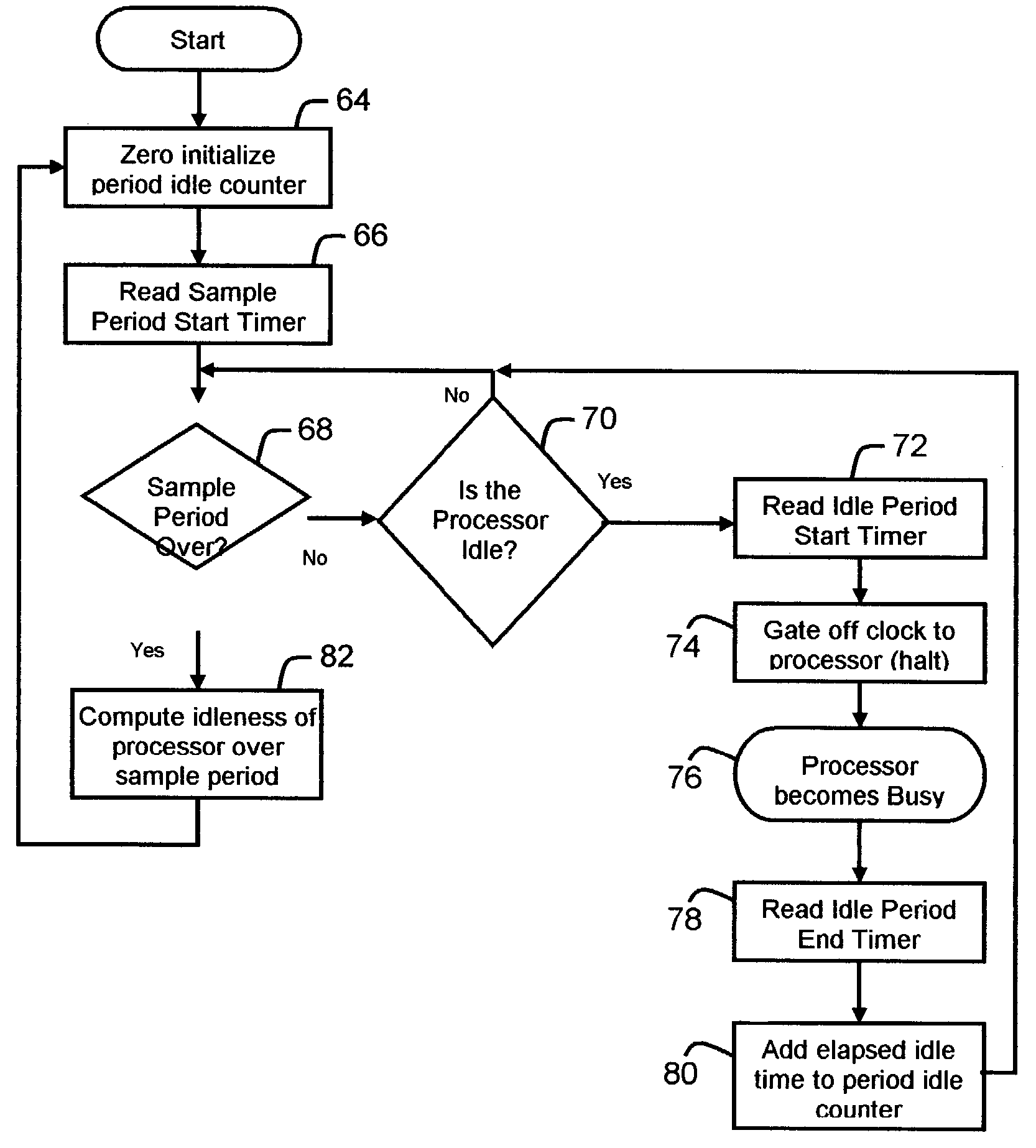

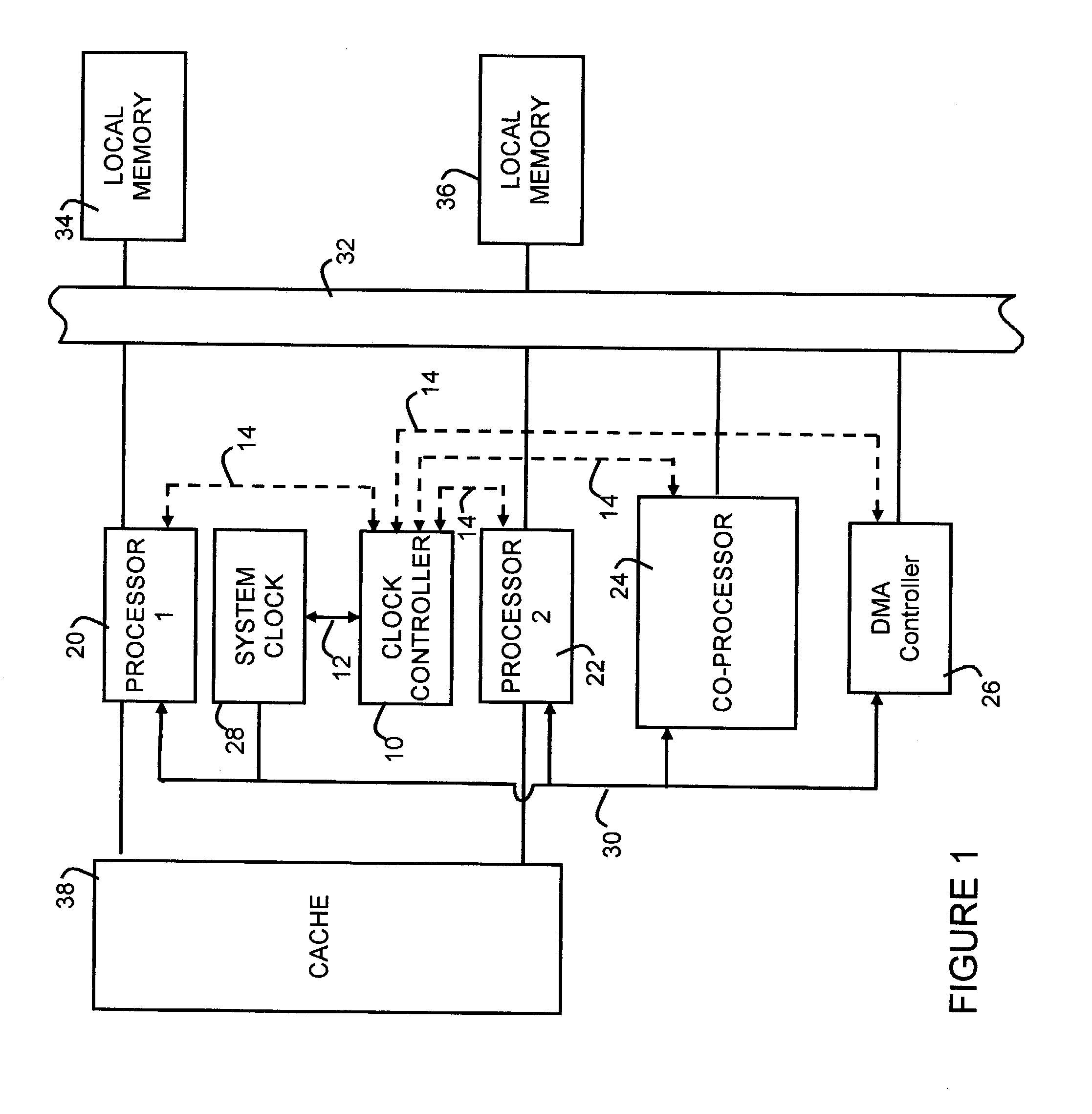

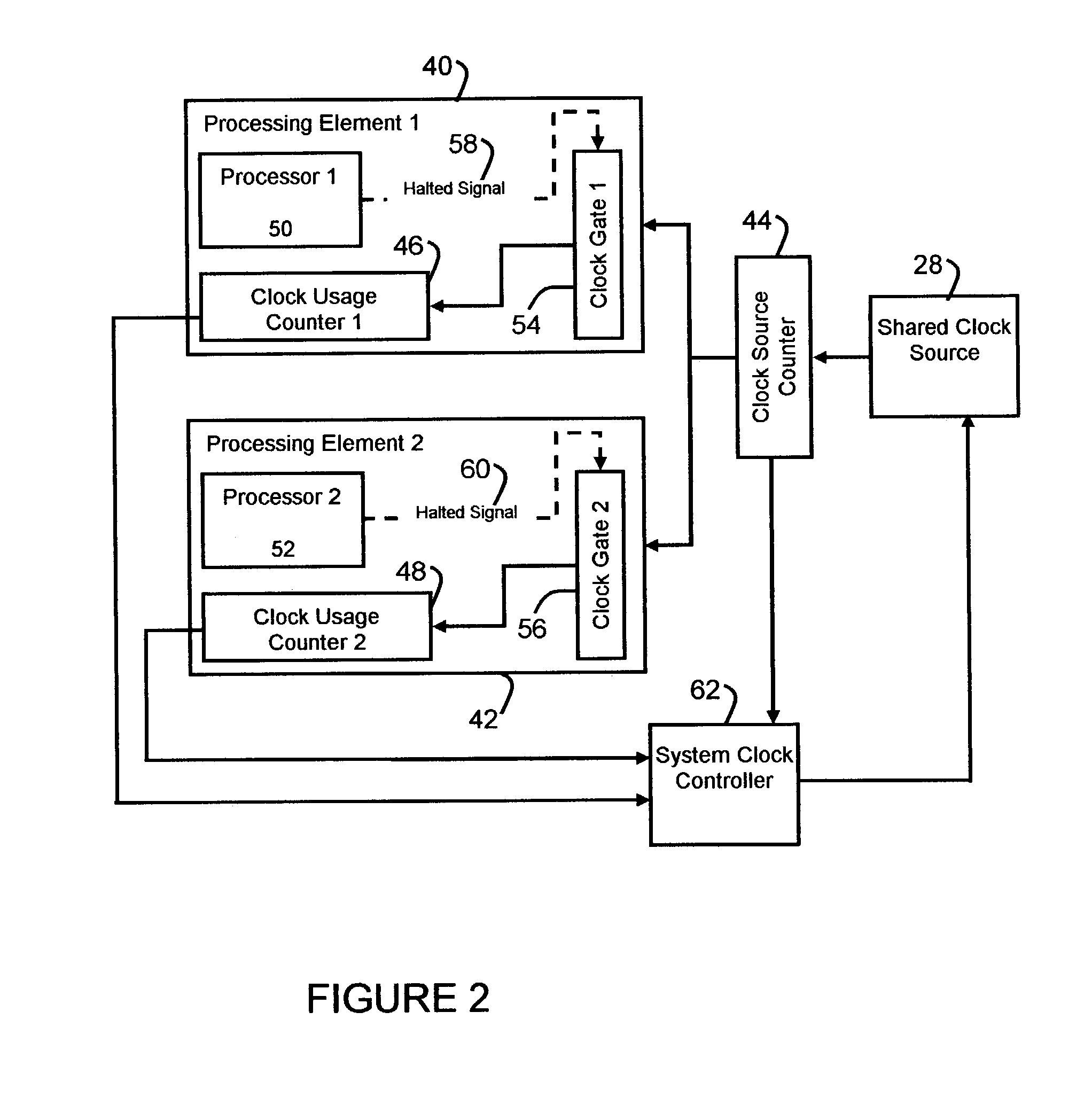

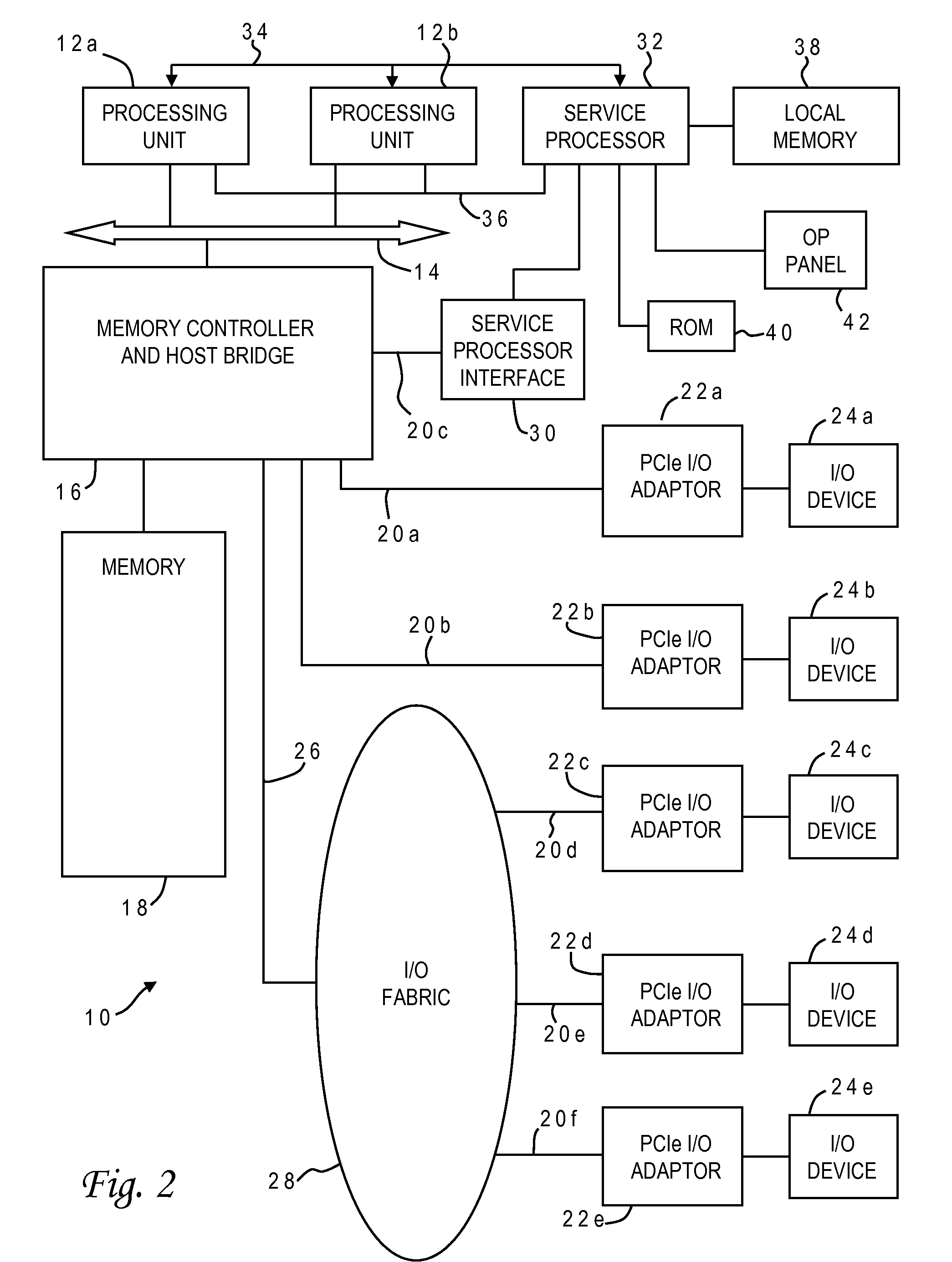

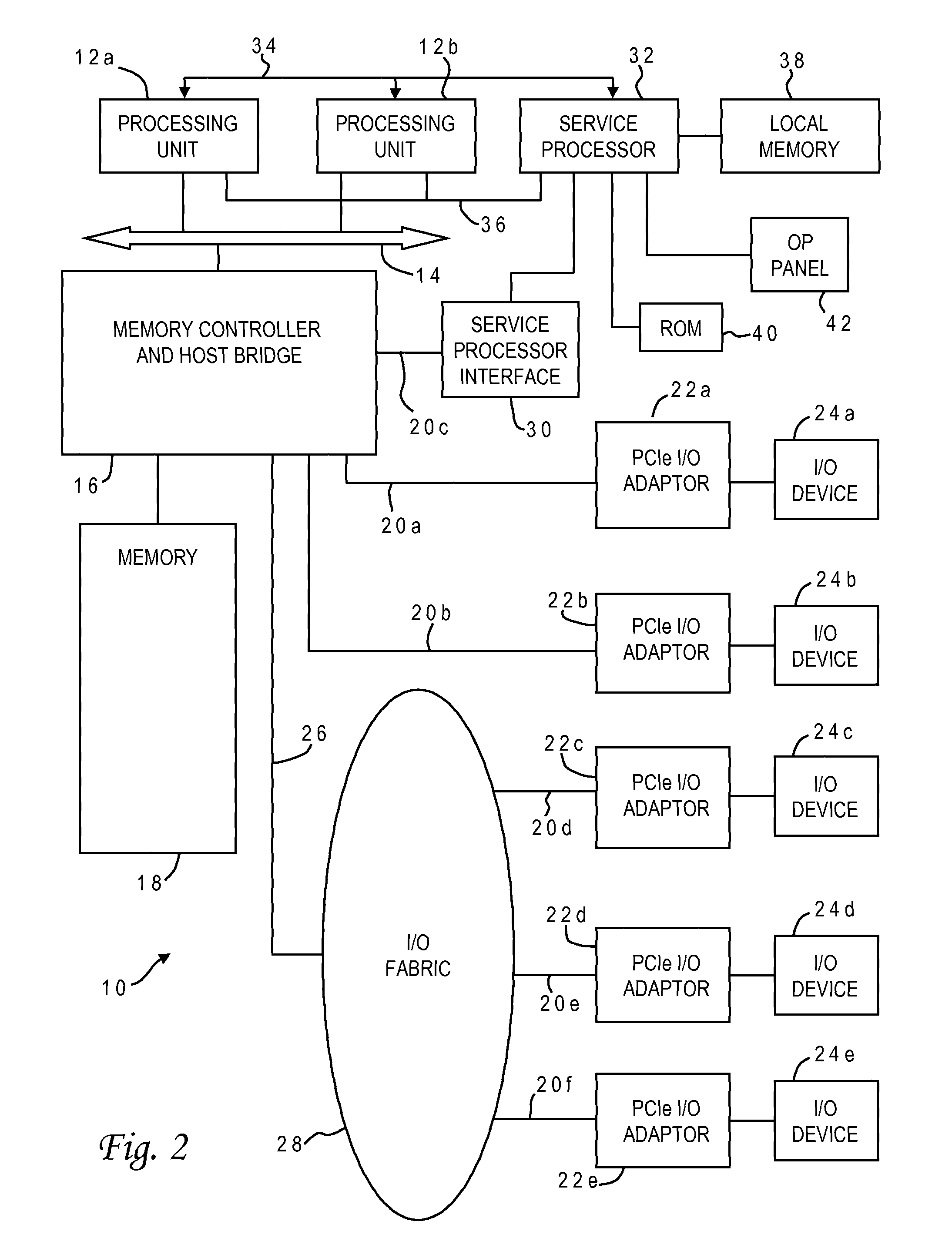

System clock power management for chips with multiple processing modules

ActiveUS7043649B2Reduce power consumptionEasy to operateEnergy efficient ICTPower supply for data processingProcessing elementComputer science

A system and method are disclosed for controlling the frequency of a common clock which is shared by a plurality of processing elements. The usage of the common clock by each of the plurality of processing elements is measured, and the common clock is controlled to have a frequency determined as a function of the measured common clock usage by the plurality of processing elements.

Owner:NVIDIA CORP

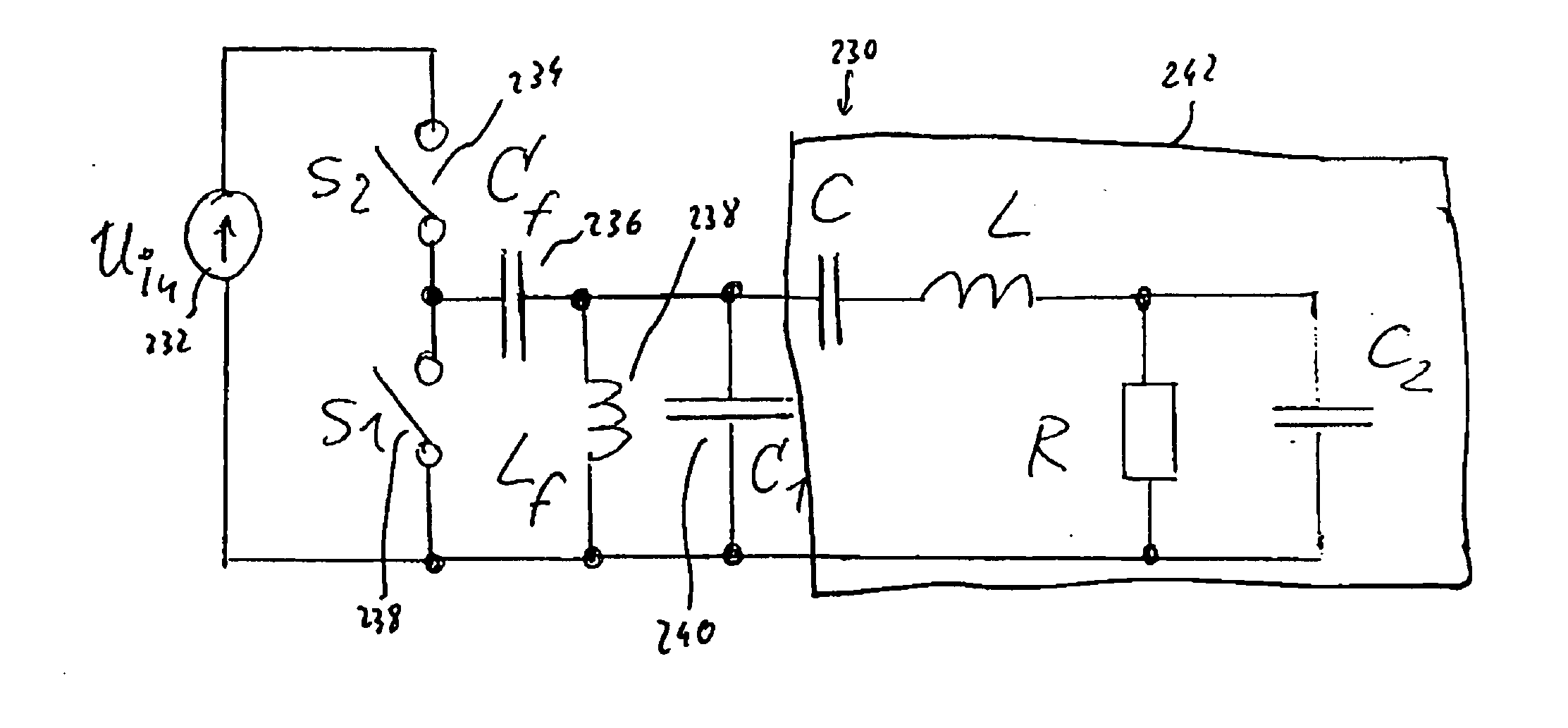

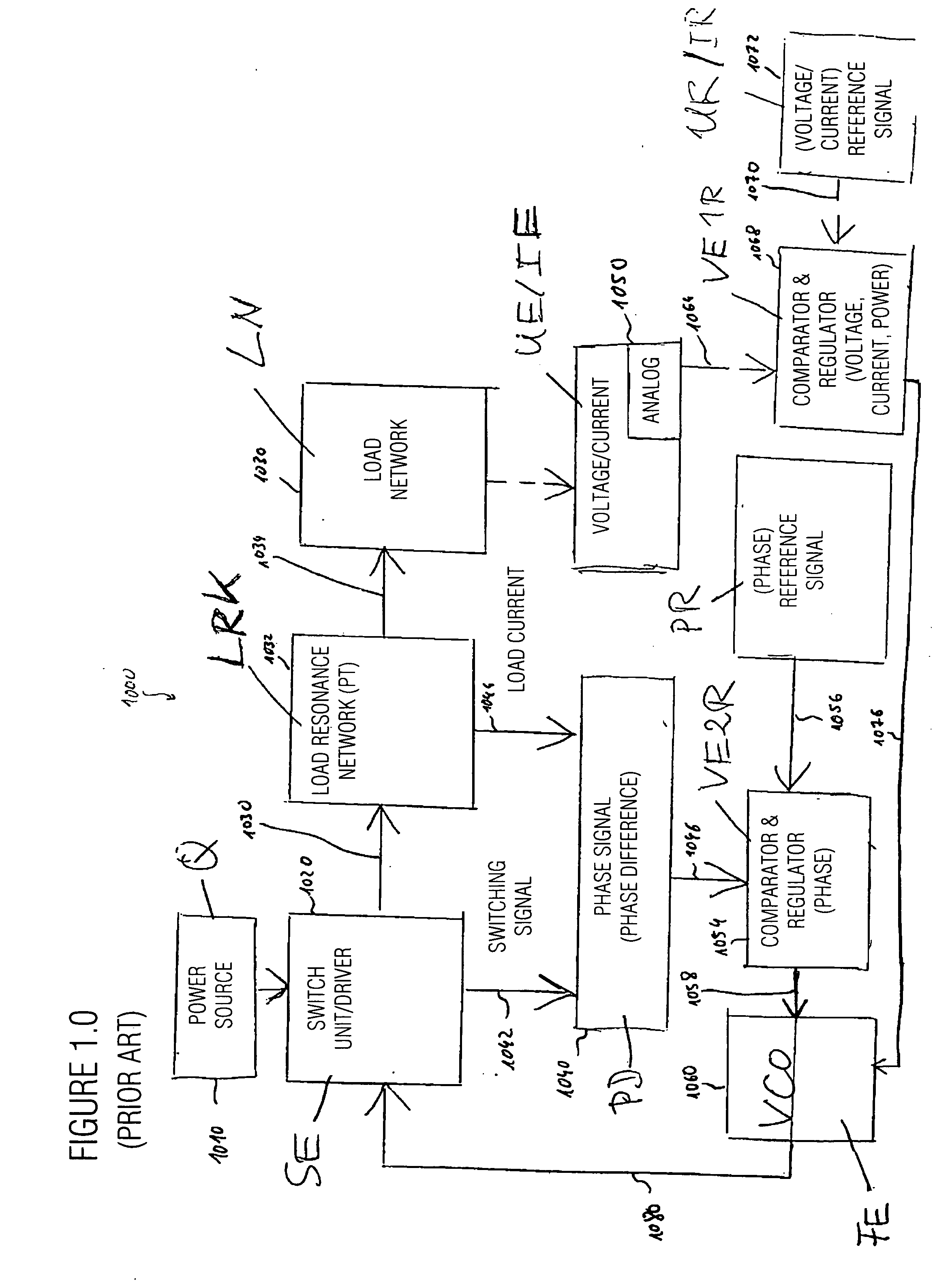

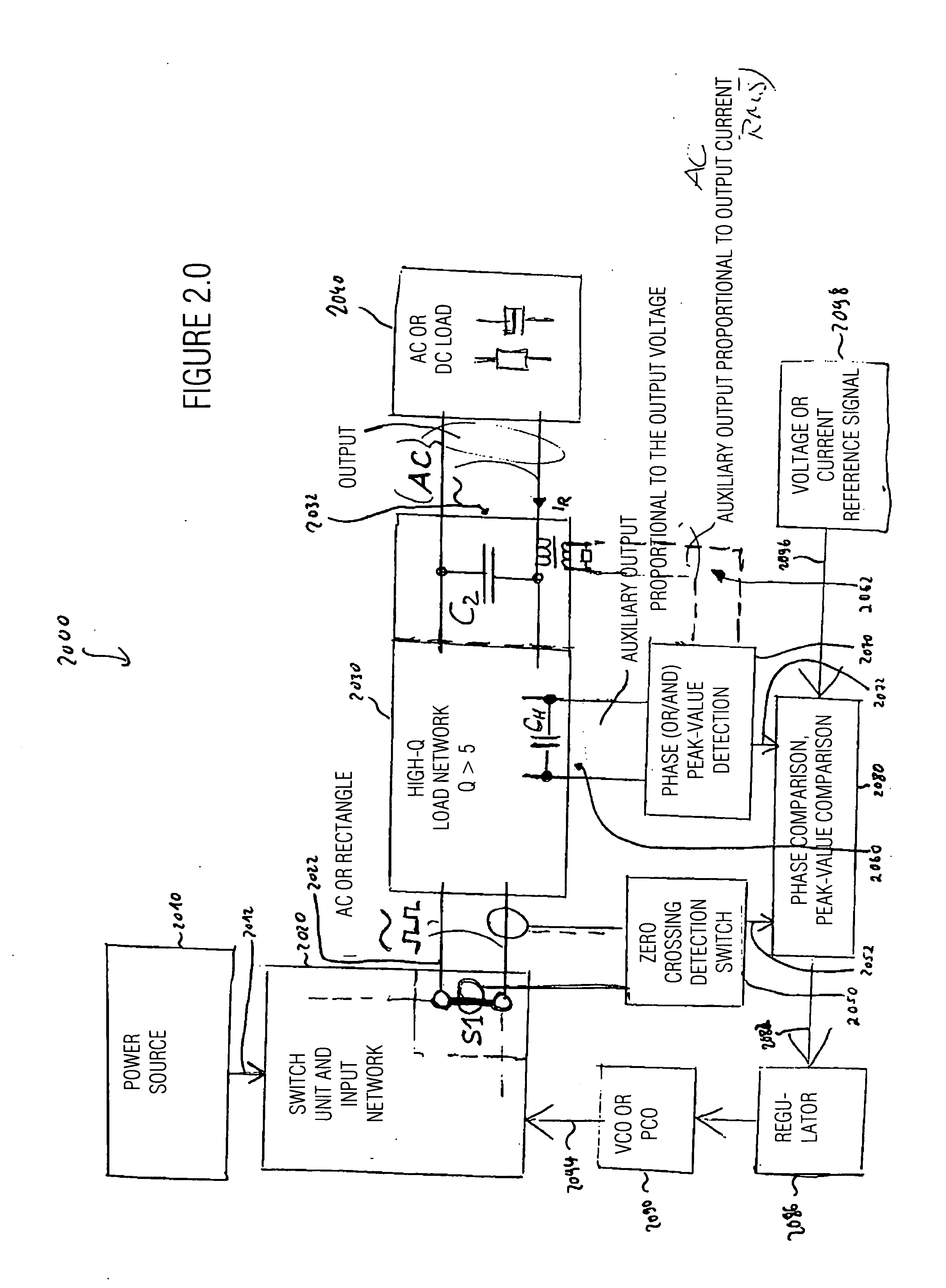

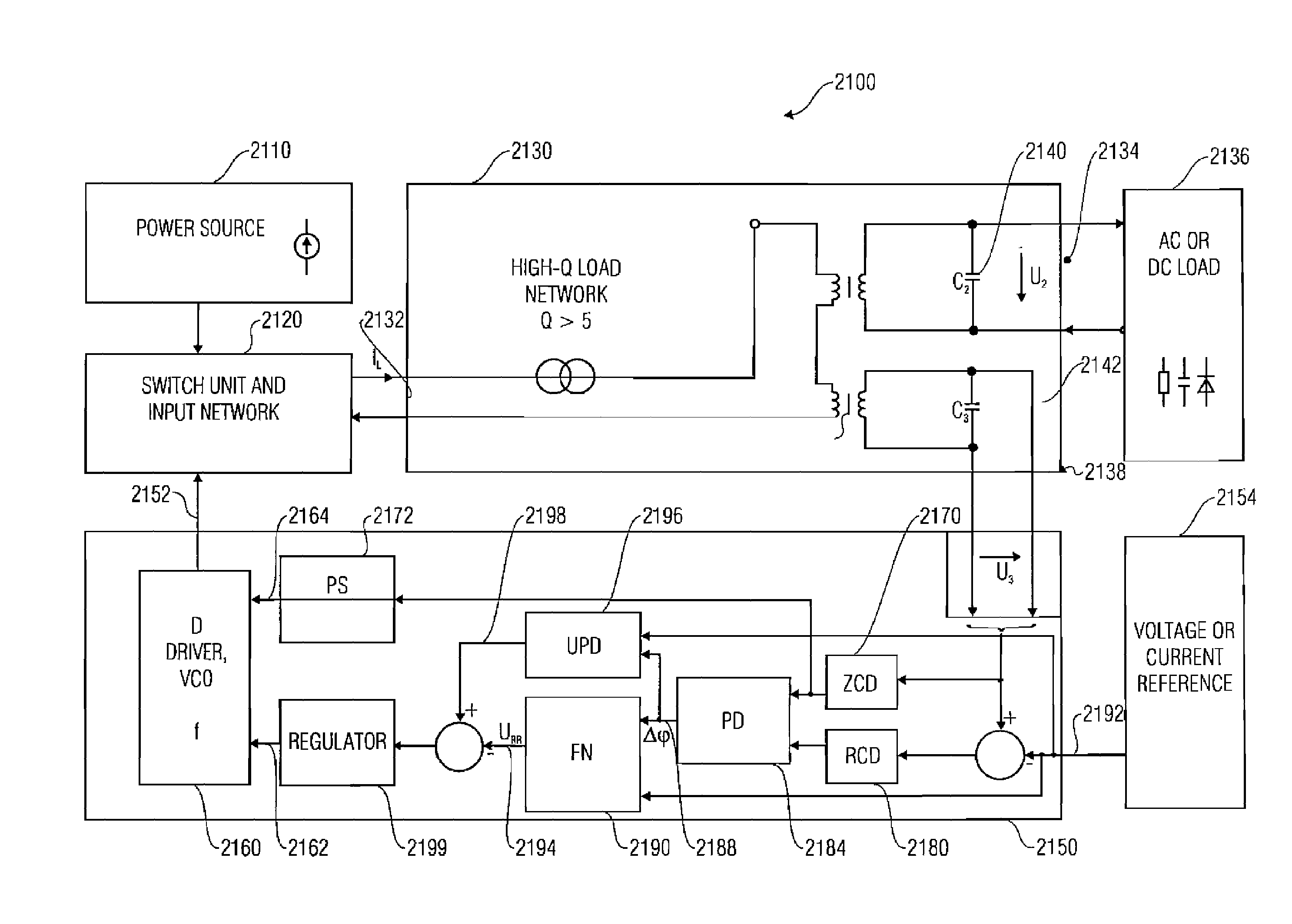

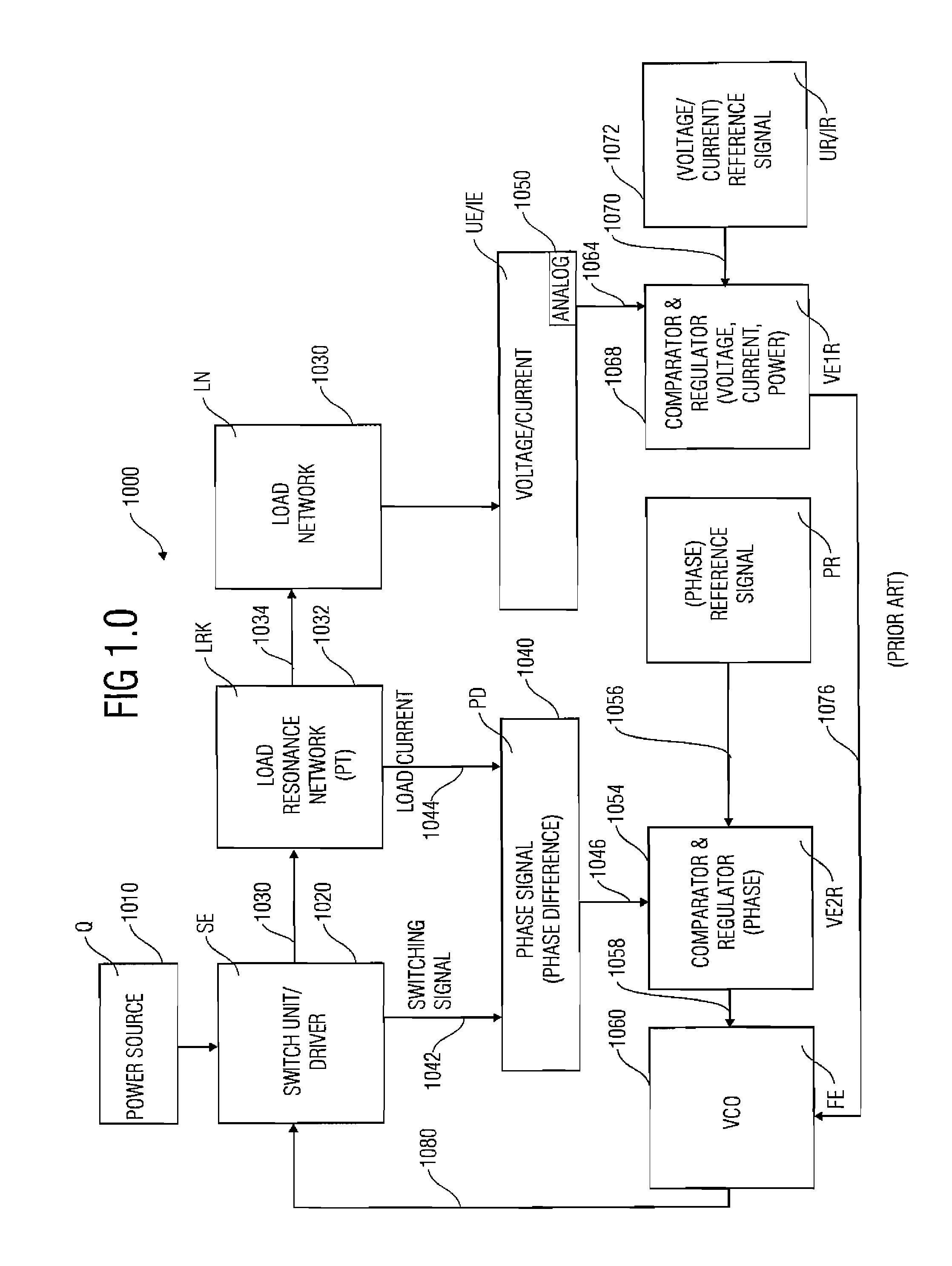

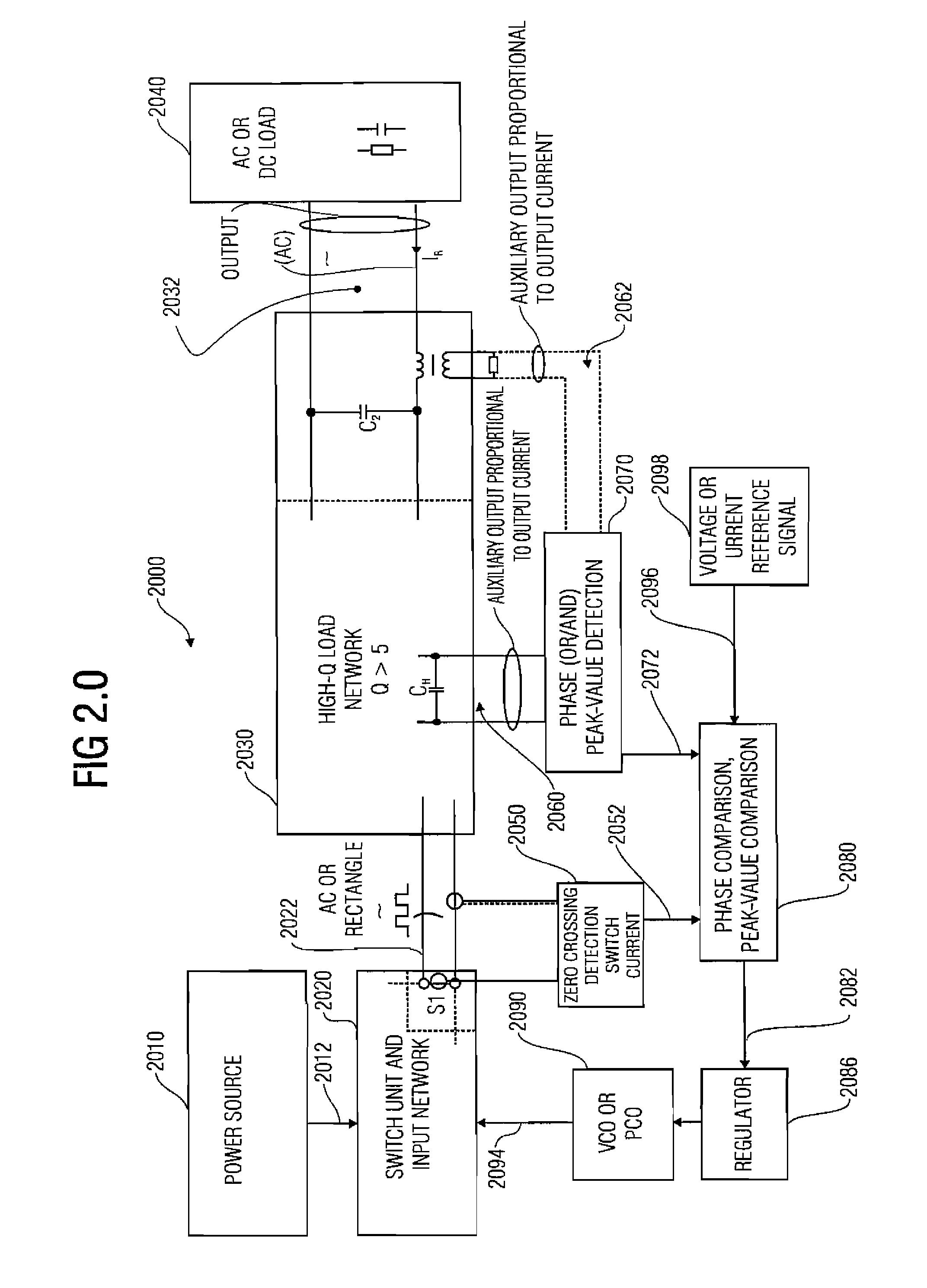

Control circuit for a switch unit of a clocked power supply circuit, and resonance converter

InactiveUS20060285366A1Low costLoss in of of efficiencyEfficient power electronics conversionAc-dc conversionDriver/operatorResonant converter

A control circuit for a switch unit of a clocked power supply circuit, the switch unit being designed to effect input-side excitation of a resonant transformer arrangement, comprises an input for receiving an auxiliary signal from the resonant transformer arrangement. The auxiliary signal exhibits an essentially fixed phase relation to a load alternating current flowing through a resonant circuit of the transformer arrangement. The control circuit further comprises a phase detector designed to detect reference crossing moments when the auxiliary signal crosses a predefined reference value, a driver controllable to switch the switch unit, and a synchronizer designed to synchronize a turn-on of the switch unit by the driver with regard to a phase position with the auxiliary signal so as to achieve a turn-on of the switch unit within a predetermined time interval around a zero crossing of a voltage present across the switch unit, or of a current flowing through the switch unit. The synchronizer is further designed to receive information about the reference crossing moments from the phase detector, and to provide a turn-on signal to the driver with a fixed phase delay at the reference crossing moments, so as to define turn-on moments at which the driver is to turn on the switch unit. The control circuit further comprises a detector designed to determine an amplitude information which depends on an amplitude or a mean value of the auxiliary signal, and a regulator designed to change an operating frequency in dependence on the amplitude information supplied by the detector, and to determine a period duration between turn-off moments at which the driver is to turn off the switch unit as a reciprocal of the operating frequency. An inventive resonance converter enables independent control of frequency and turn-on moments, or duty cycle, and thus enables a particularly efficient operation of the resonance converter, and a particularly precise regulation.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

Control circuit for a switch unit of a clocked power supply circuit, and resonance converter

InactiveUS7746671B2Low costLoss in of of efficiencyEfficient power electronics conversionAc-dc conversionResonanceEngineering

The invention involves a control circuit for a switch unit of a clocked power supply circuit, the switch unit being designed to effect input-side excitation of a resonant transformer arrangement, and comprises an input for receiving an auxiliary signal from the resonant transformer arrangement. The invention also includes a resonance converter that enables independent control of frequency and turn-on moments, or duty cycle, and thus enables a particularly efficient operation of the resonance converter, and a particularly precise regulation.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

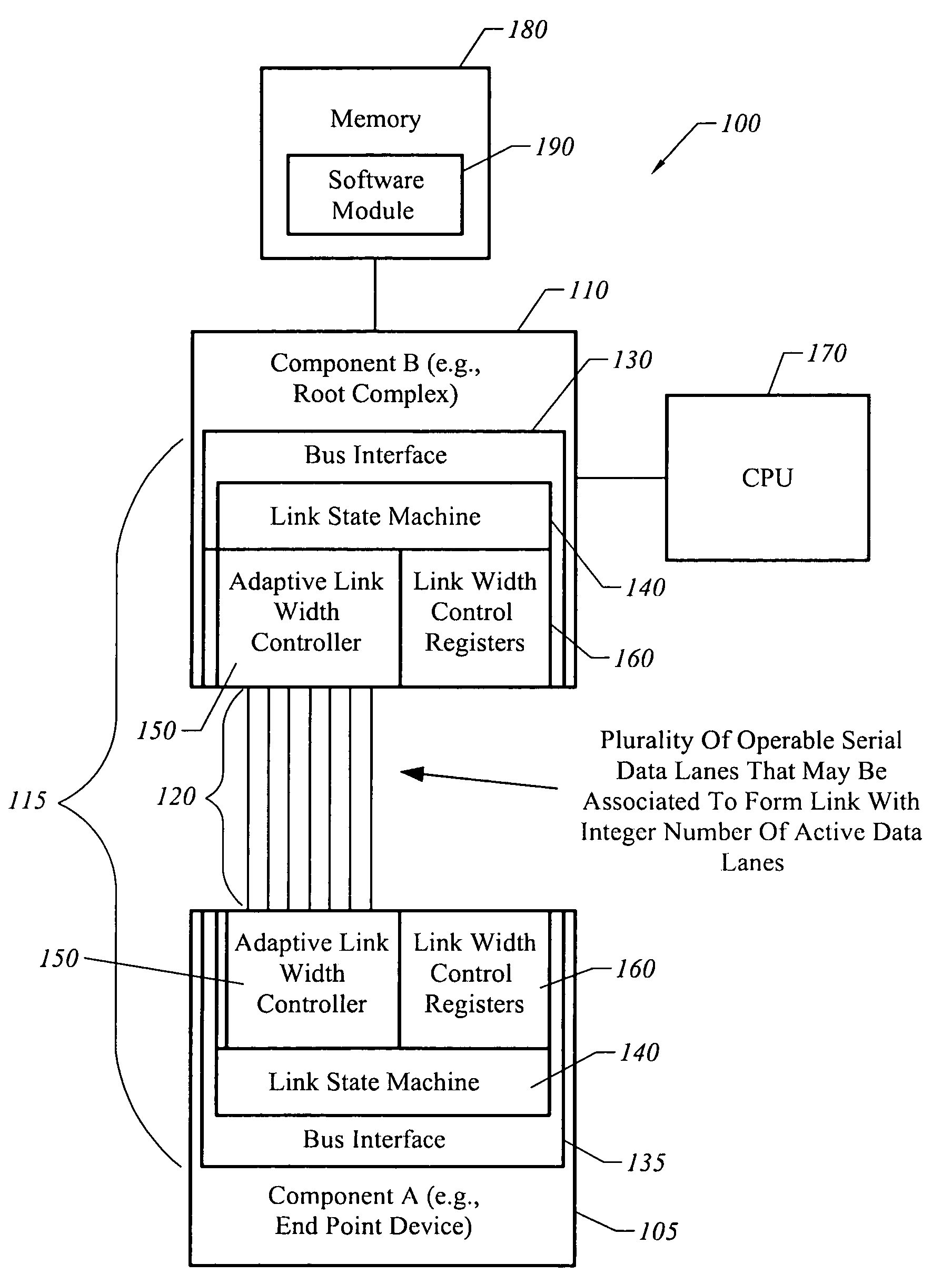

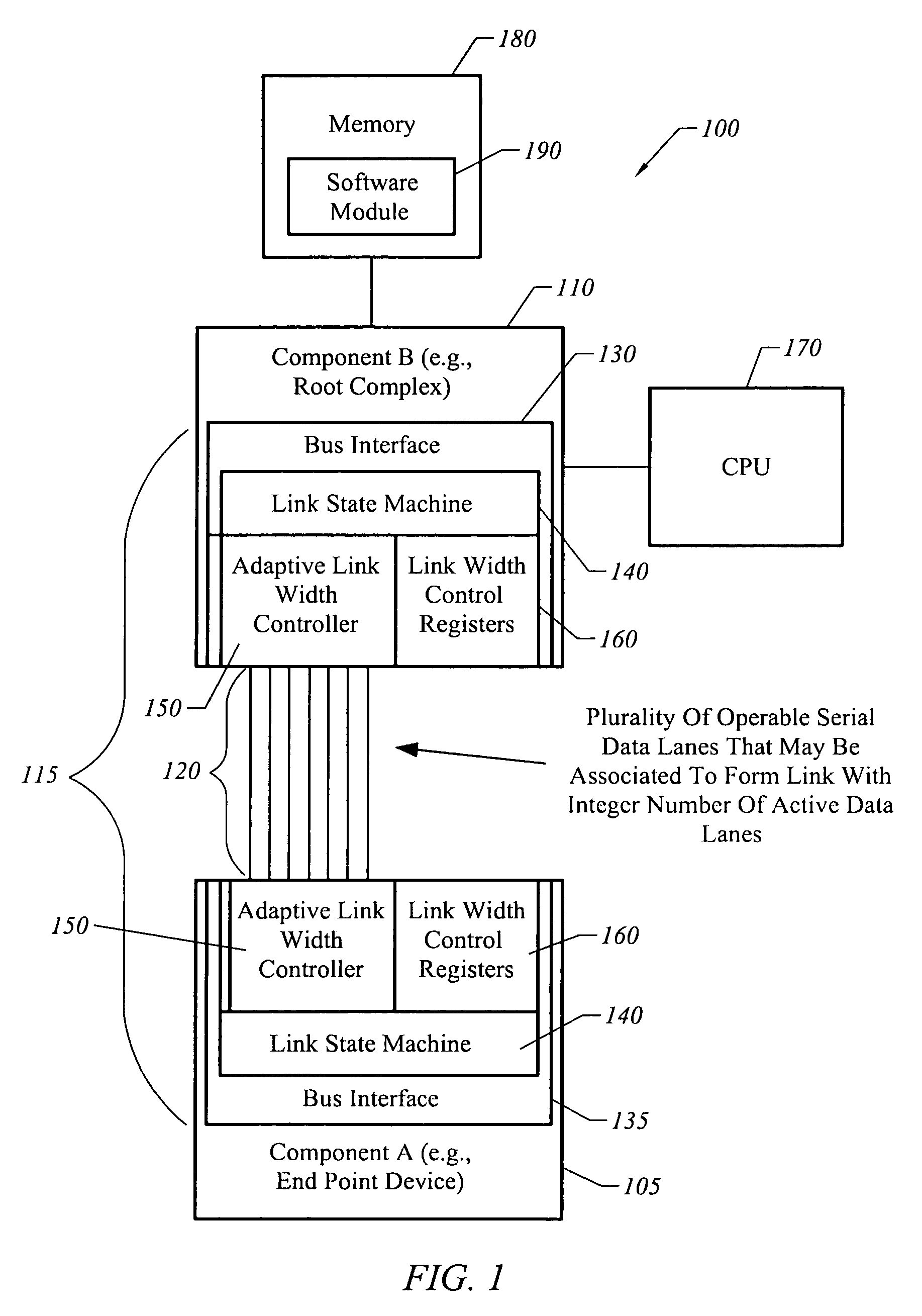

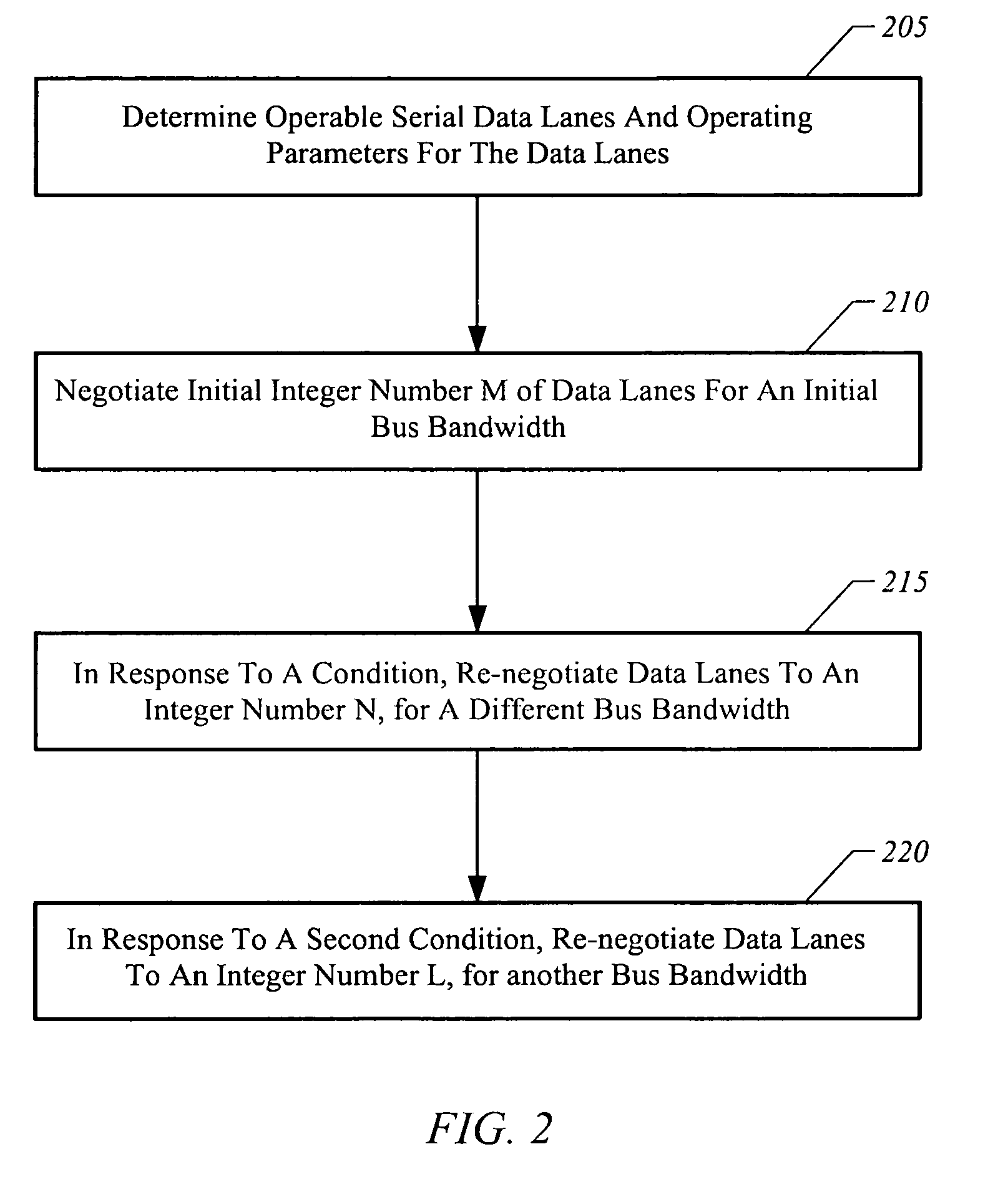

Logical-to-physical lane assignment to reduce clock power dissipation in a bus having a variable link width

InactiveUS7370132B1Reducing bus powerEnergy efficient ICTStatic indicating devicesBandwidth requirementEmbedded system

Owner:NVIDIA CORP

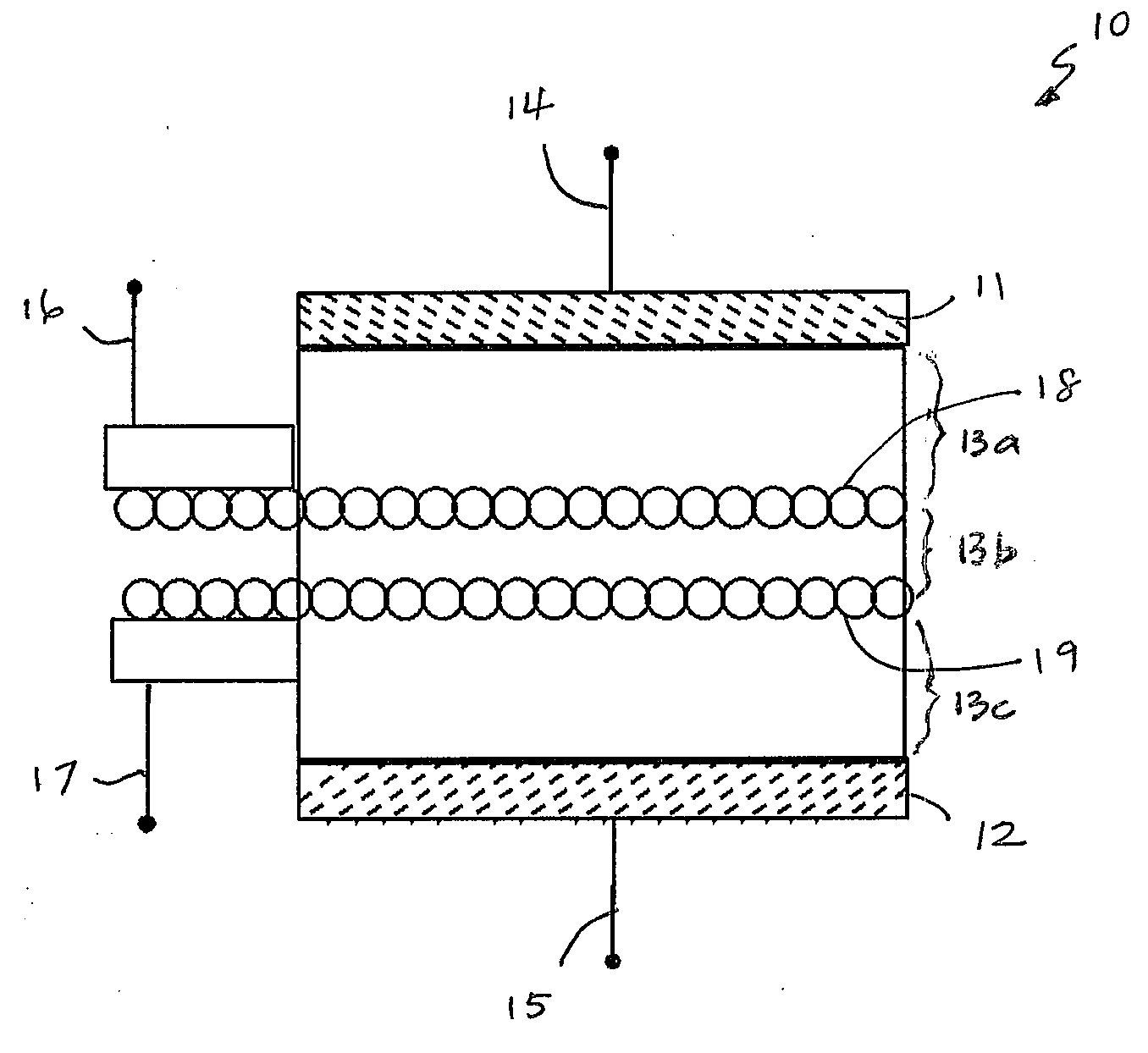

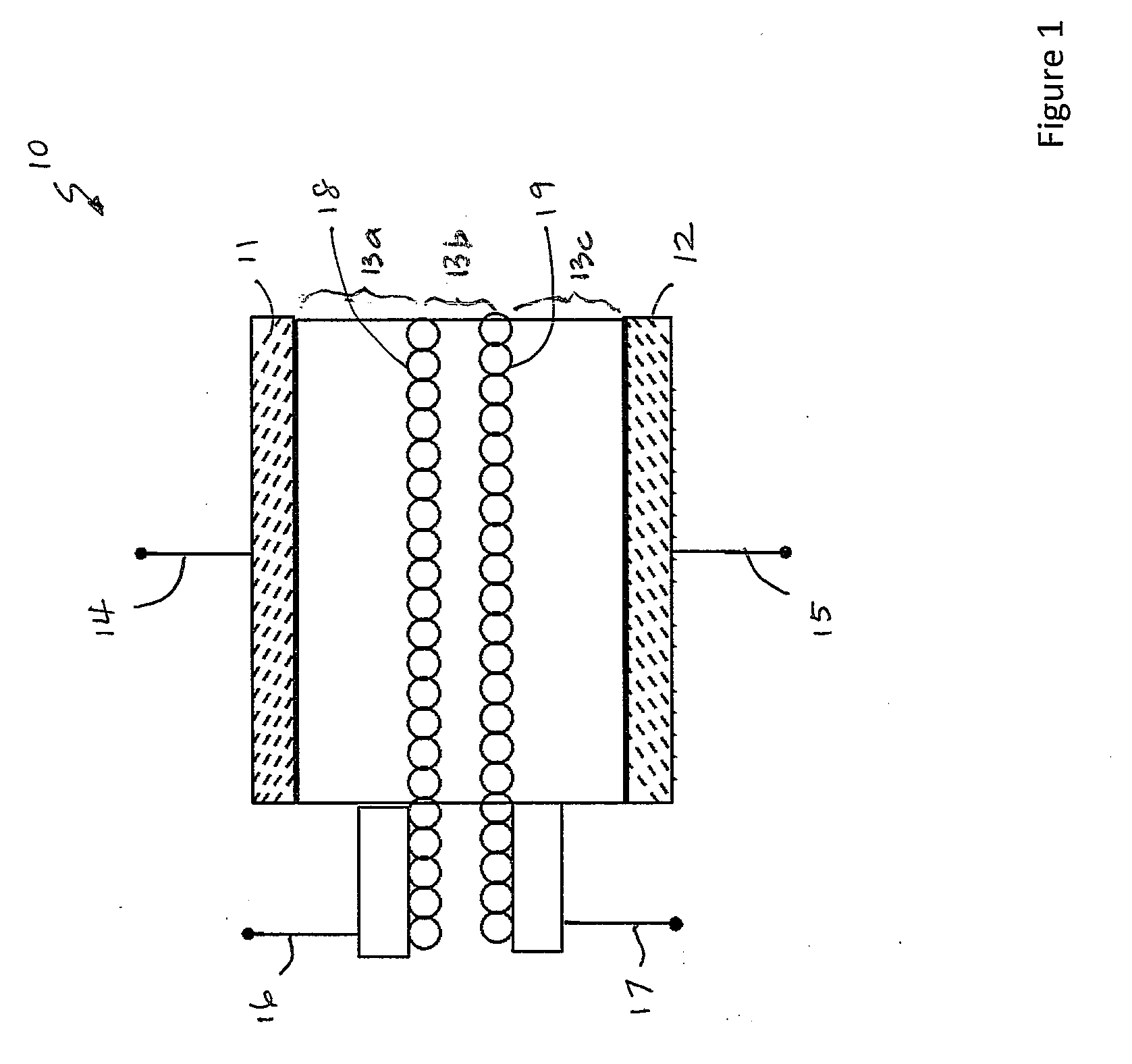

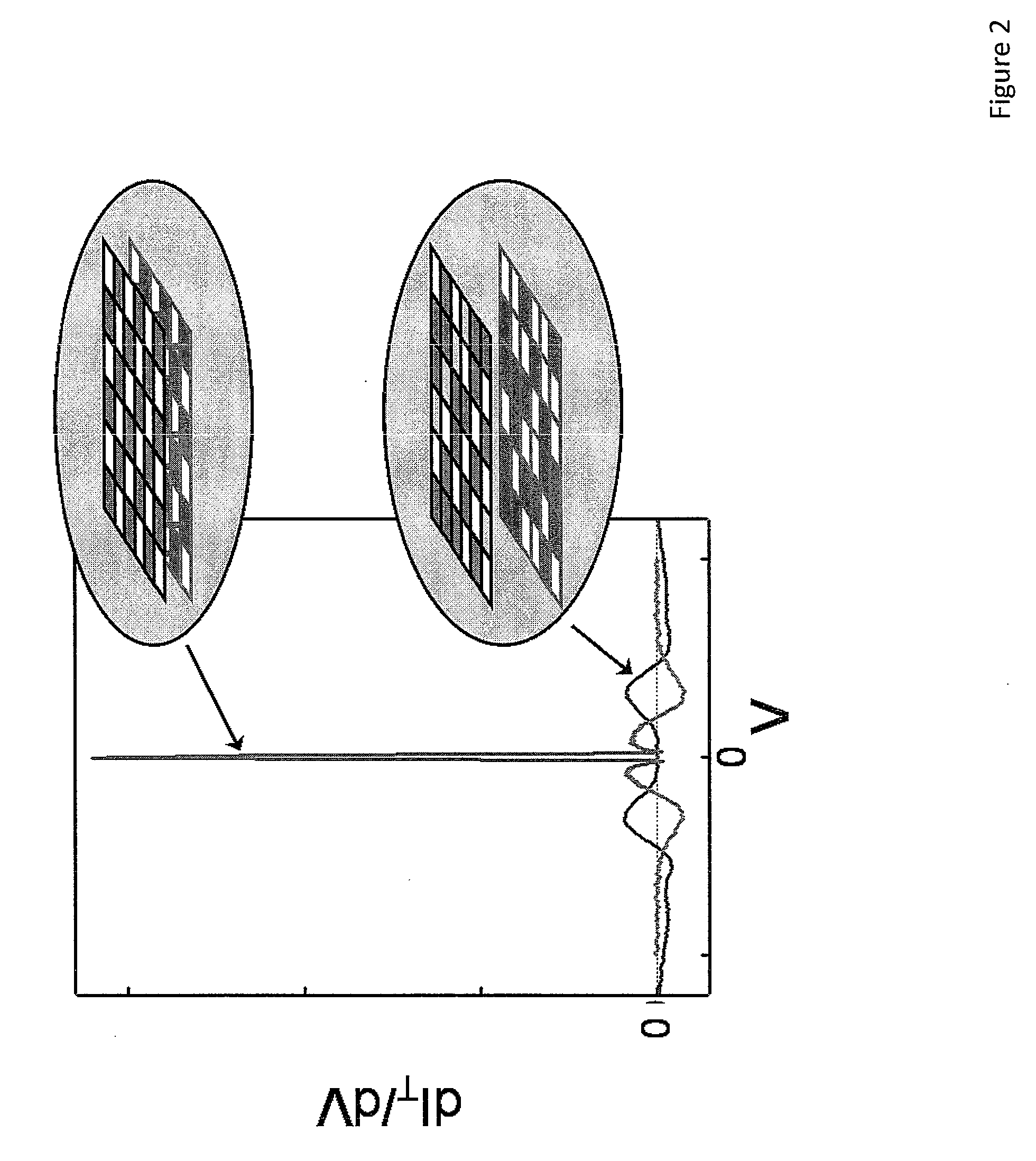

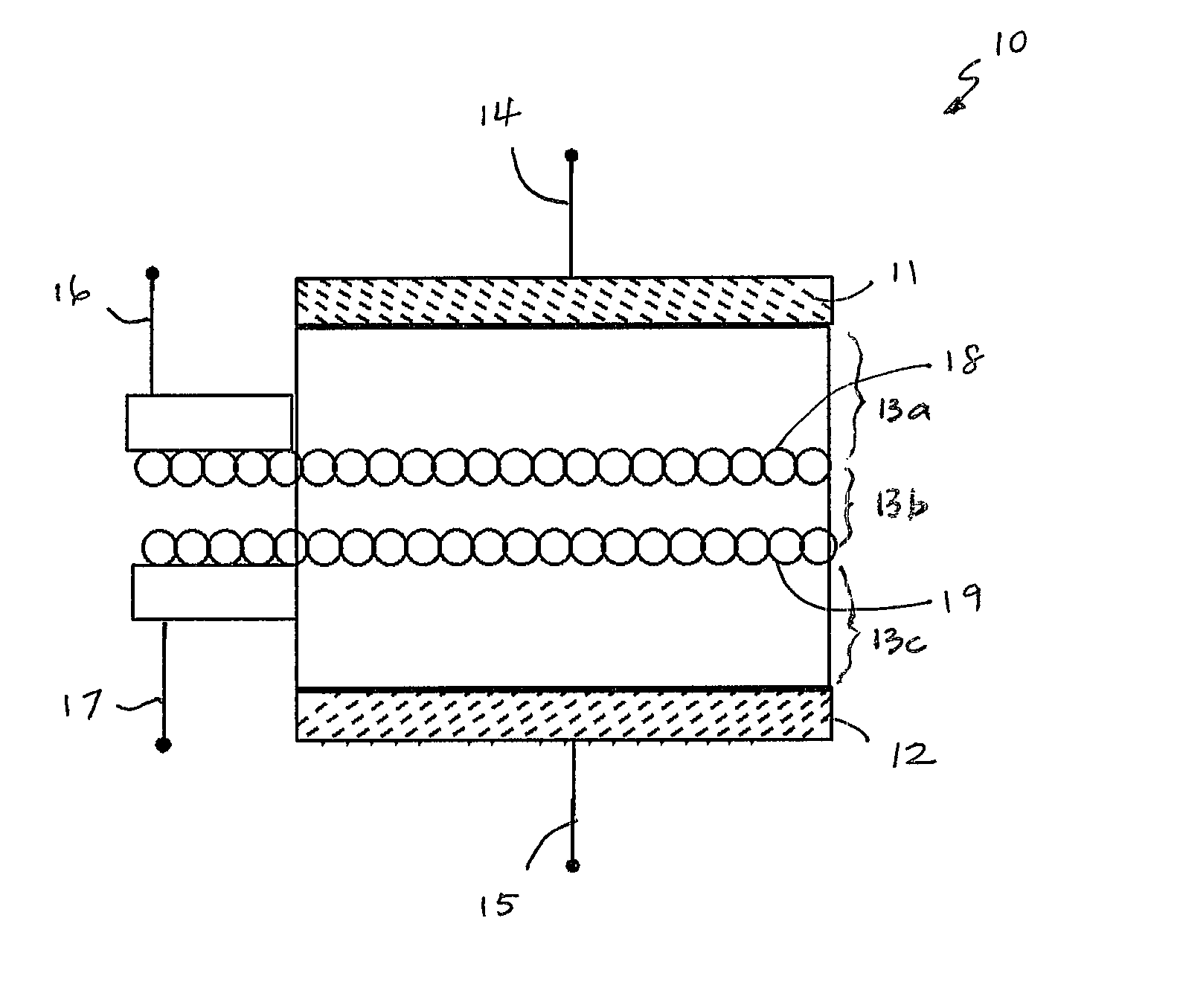

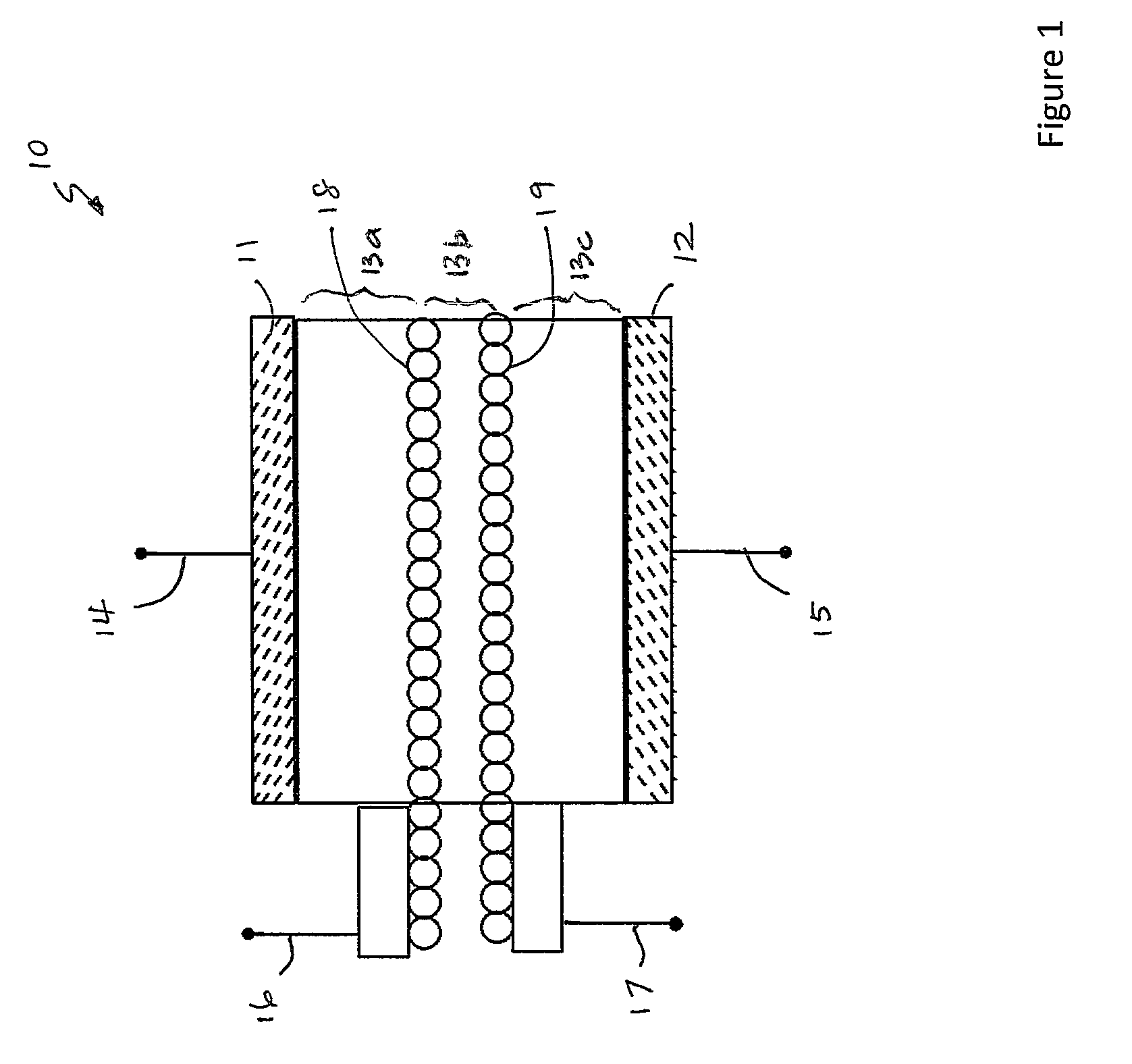

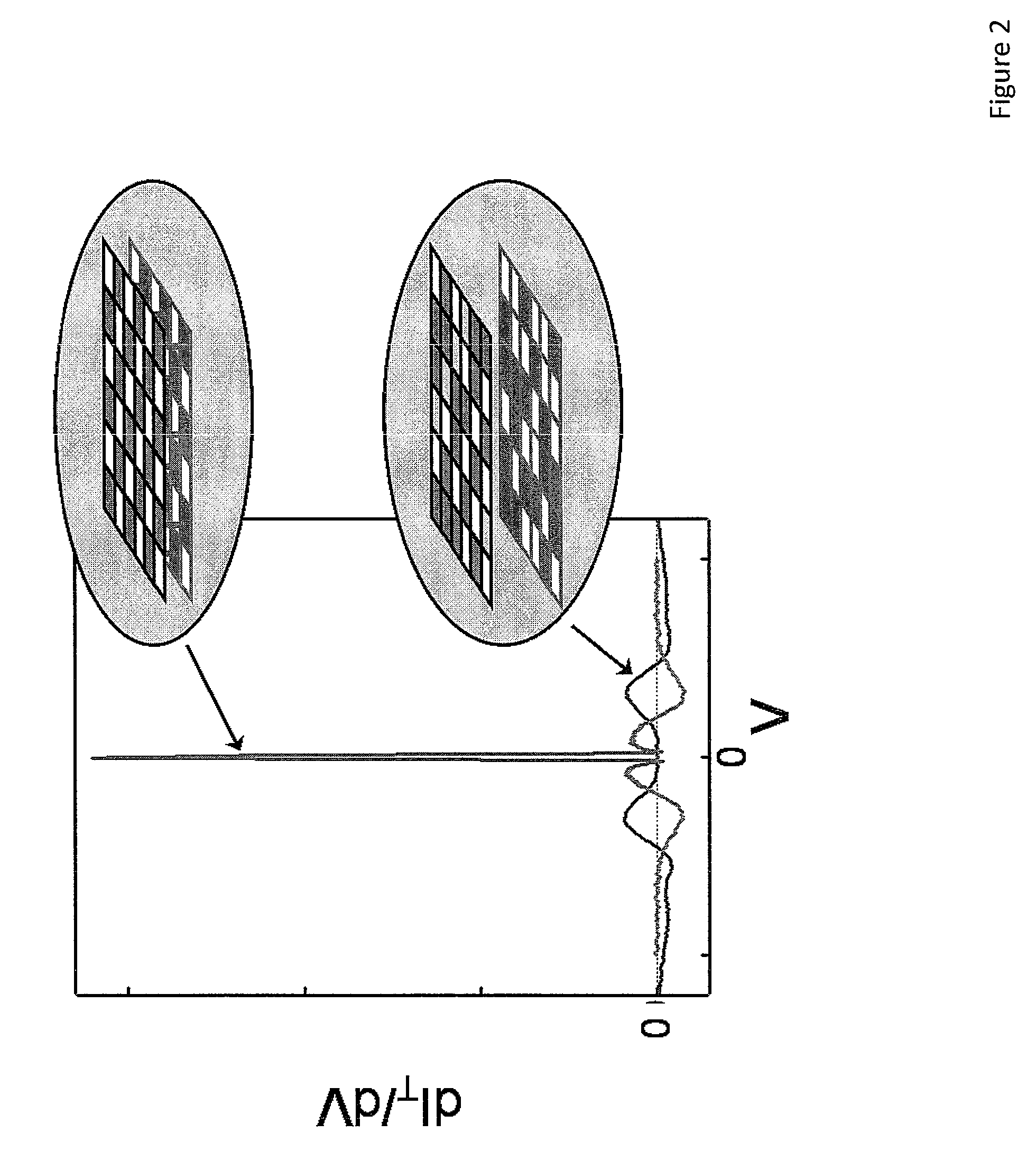

Bi-layer pseudo-spin field-effect transistor

InactiveUS20100127243A1Low gate and interlayer biasesNanoinformaticsSemiconductor/solid-state device manufacturingEngineeringPeak value

A bi-layer pseudo-spin field-effect transistor (BiSFET) is disclosed. The BiSFET includes a first and second conduction layers separated by a tunnel dielectric. The BiSFET transistor also includes a first gate separated from the first conduction layer by an insulating dielectric layer, and a second gate separated from the second conduction layer by an insulating layer. These conduction layers may be composed of graphene. The voltages applied to the first and / or second gates can control the peak current and associated voltage value for current flow between top and bottom conduction channels, and interlayer current voltage characteristic exhibiting negative differential resistance. BiSFETs may be used to make a variety of logic gates. A clocked power supply scheme may be used to facilitate BiSFET-based logic.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

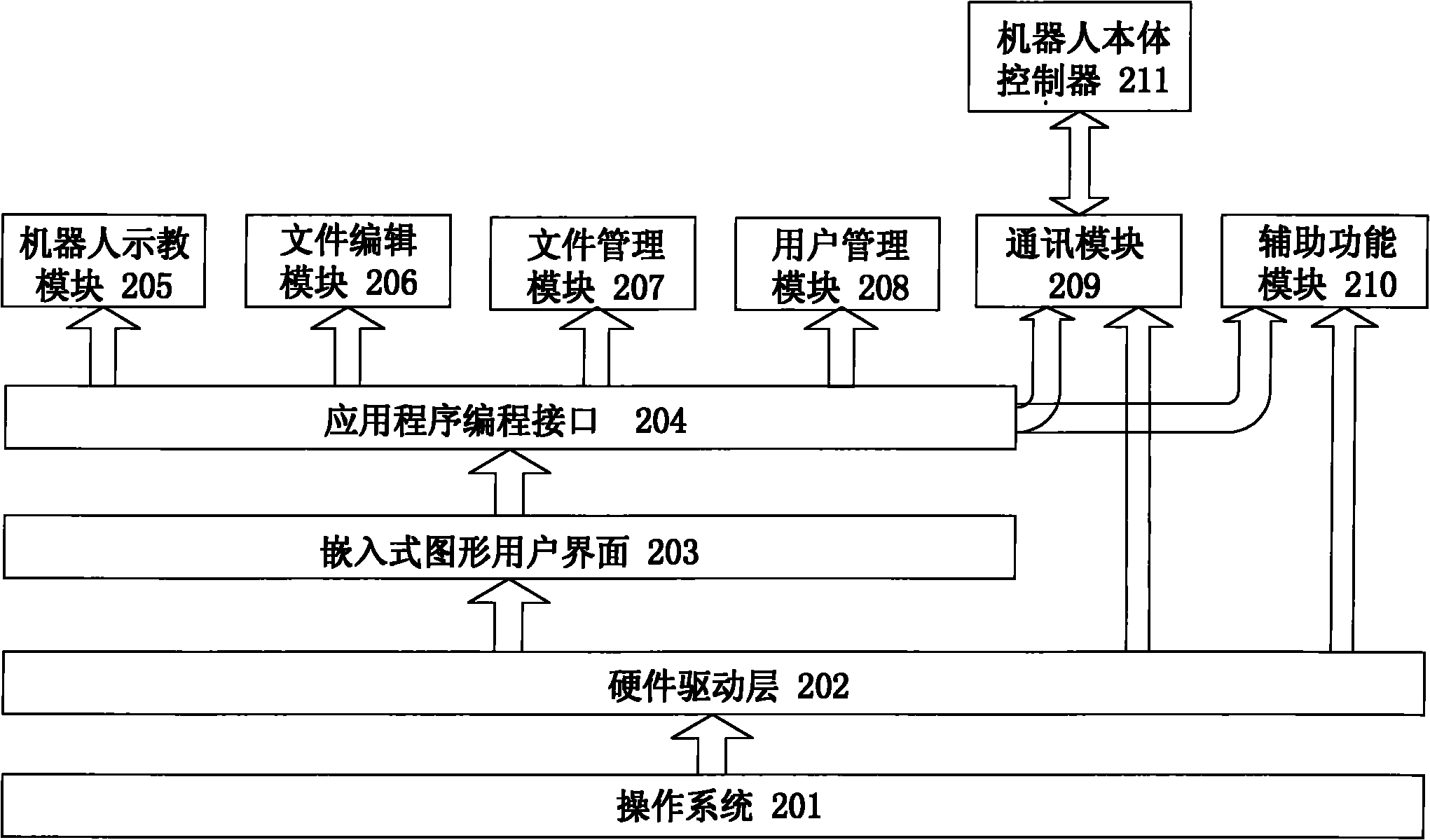

Embedded type teaching programming device and method for welding robot

The invention discloses embedded type teaching programming device and method for a welding robot. The device comprises a core board and an interface board, wherein the core board consists of a central processing unit, an ex-patulous memorizer and a clock power fail protection circuit; the interface board consists of an Ethernet interface, an RS-485 serial bus interface, an RS-232 interface, a USB interface, a liquid crystal display interface, a touch screen interface, a matrix keyboard interface, a JTAG interface, a power supply, a reset circuit and a safety control circuit; and a robot teaching module, a file editing module, a file management module, a user management module, a communication module and an auxiliary functional module are provided in the method. The invention has the advantages of high integrated level, strong antijamming capability, favorable human-machine interaction, convenient expansion and the like, can configure the two communication modes of an RS-485 bus and the Ethernet, and can meet the requirement for teaching programming of the welding robot.

Owner:SOUTHEAST UNIV

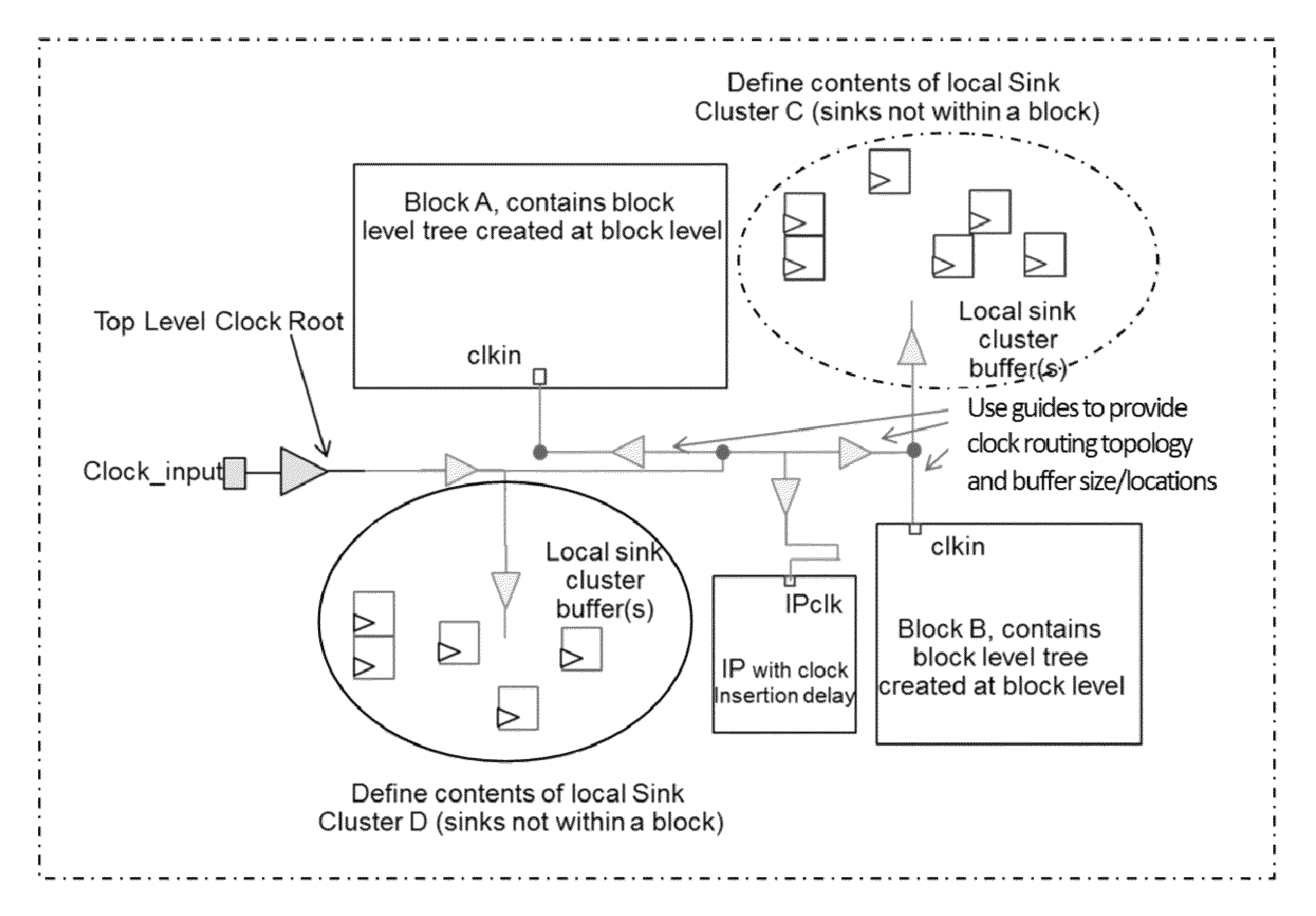

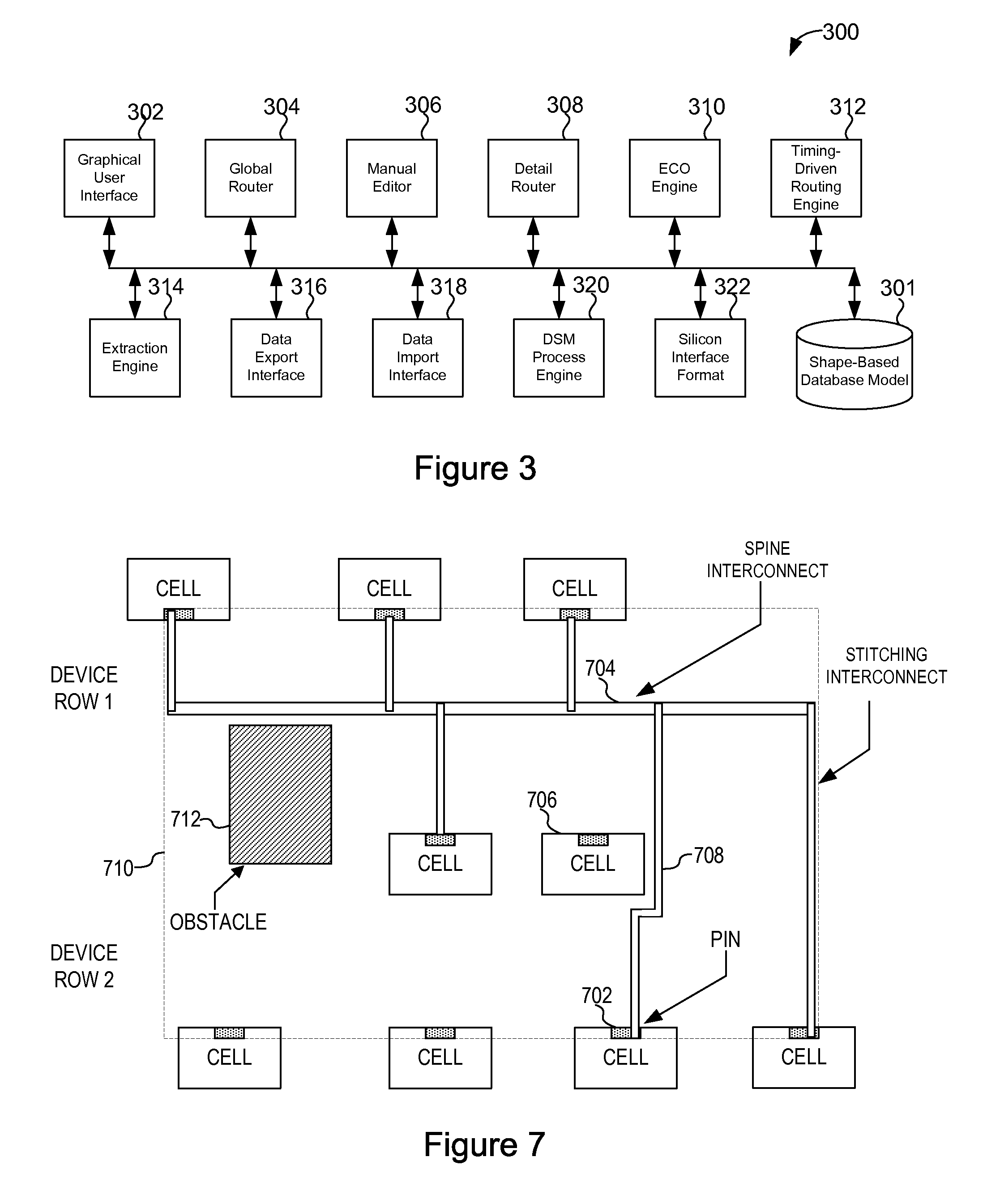

Clock tree generation and routing

ActiveUS8966425B1Ample structureAmple controlComputer aided designSpecial data processing applicationsClock treeMajorization minimization

A technique generates small scale clock trees using a spine-based architecture (using spine routing) while also using clustered placement. Techniques are used to control clock sink cluster contents in order to minimize clock skew, minimize clock buffer count, and minimize use of routing resources. This approach also provides the user with ample structure and control to customize small efficient clock trees, and can also reduce clock power consumption.

Owner:PULSIC

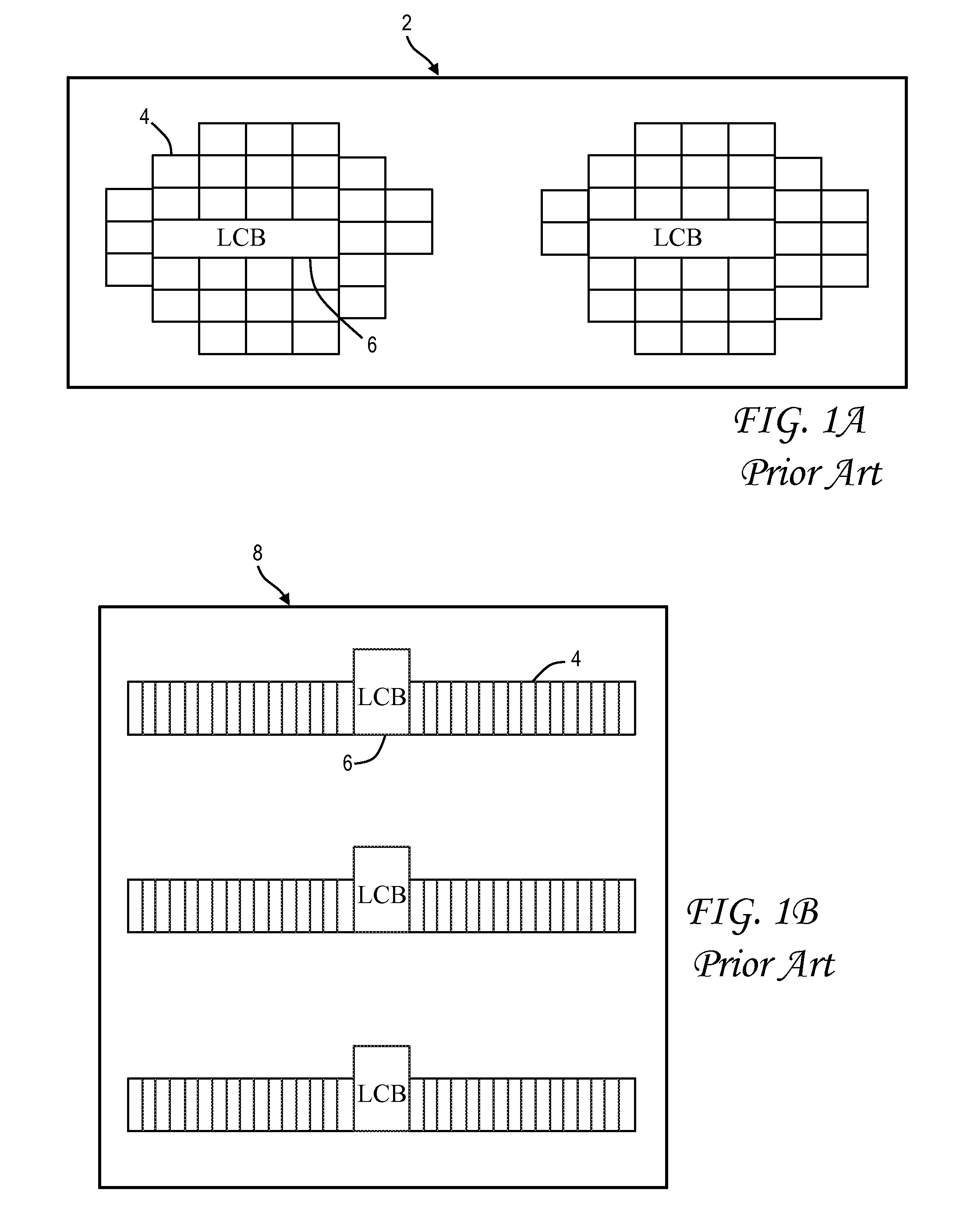

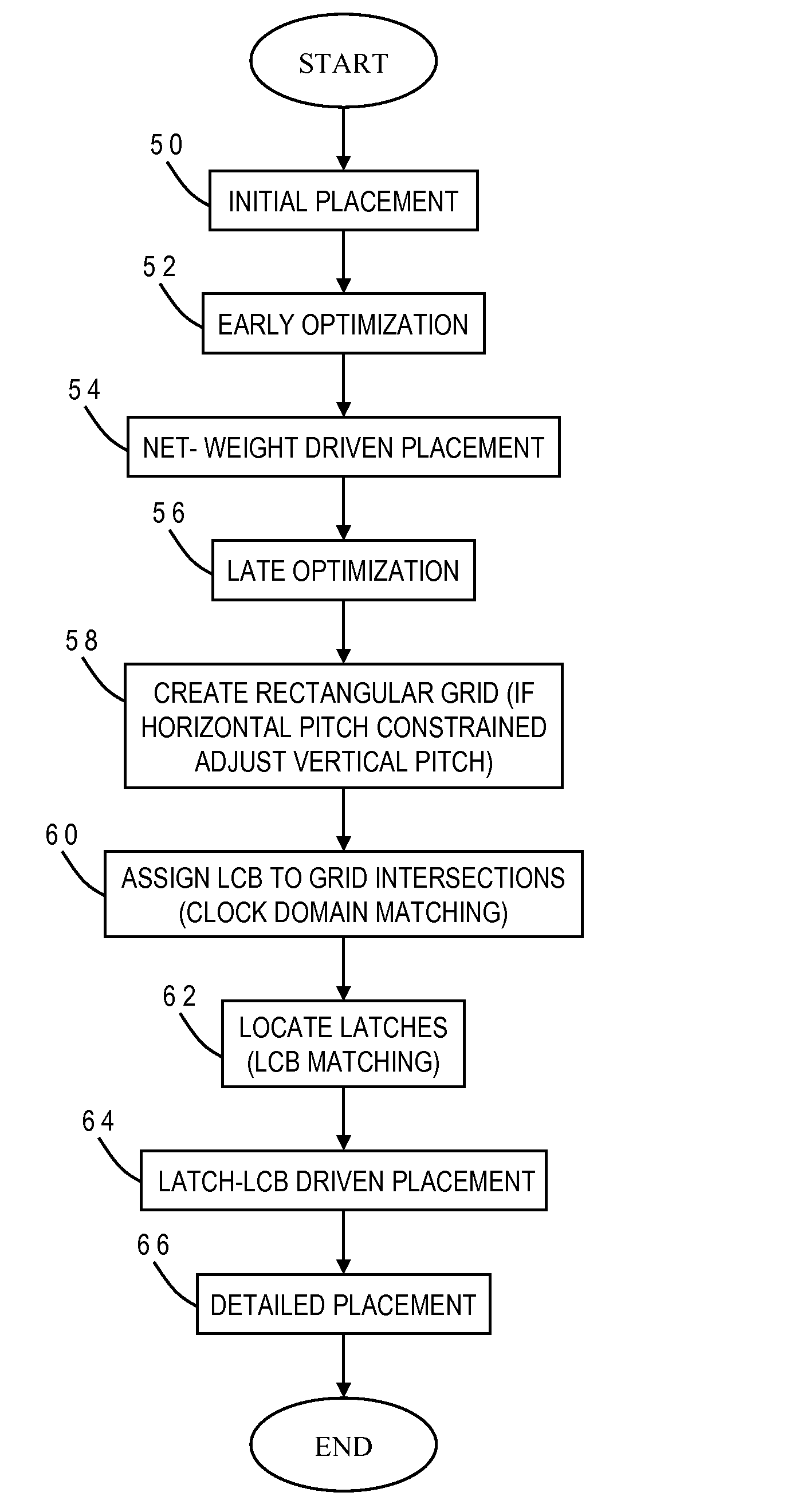

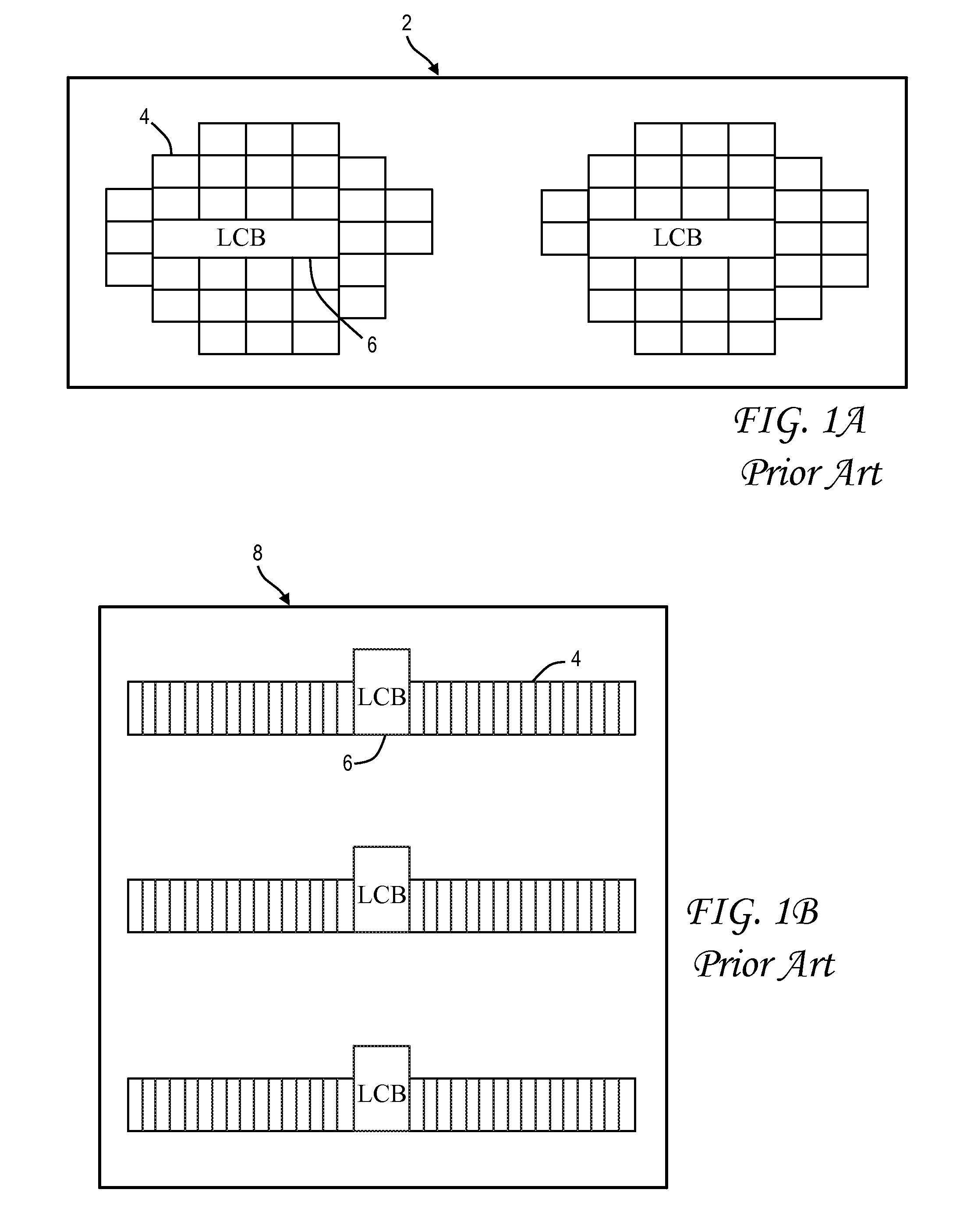

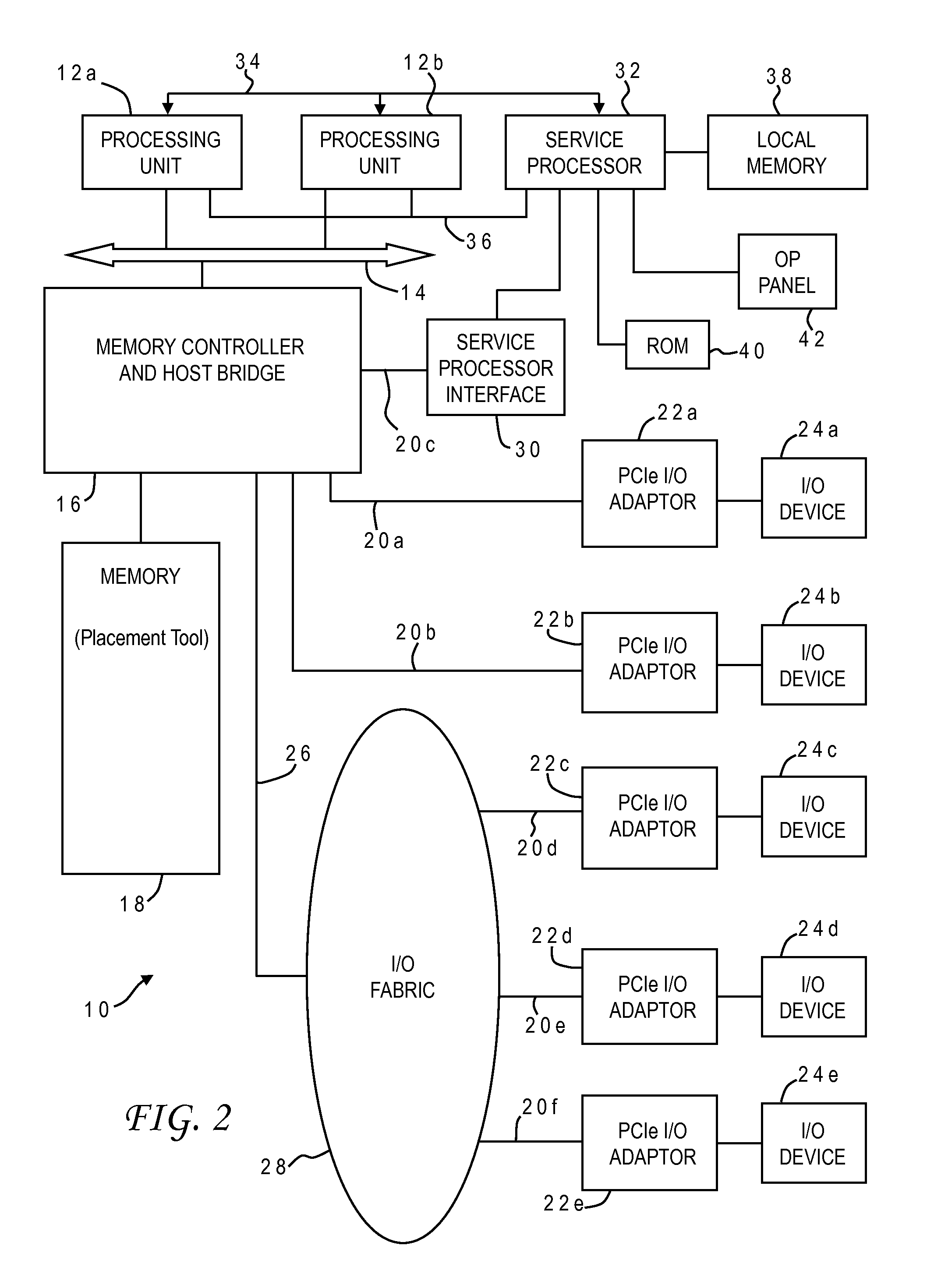

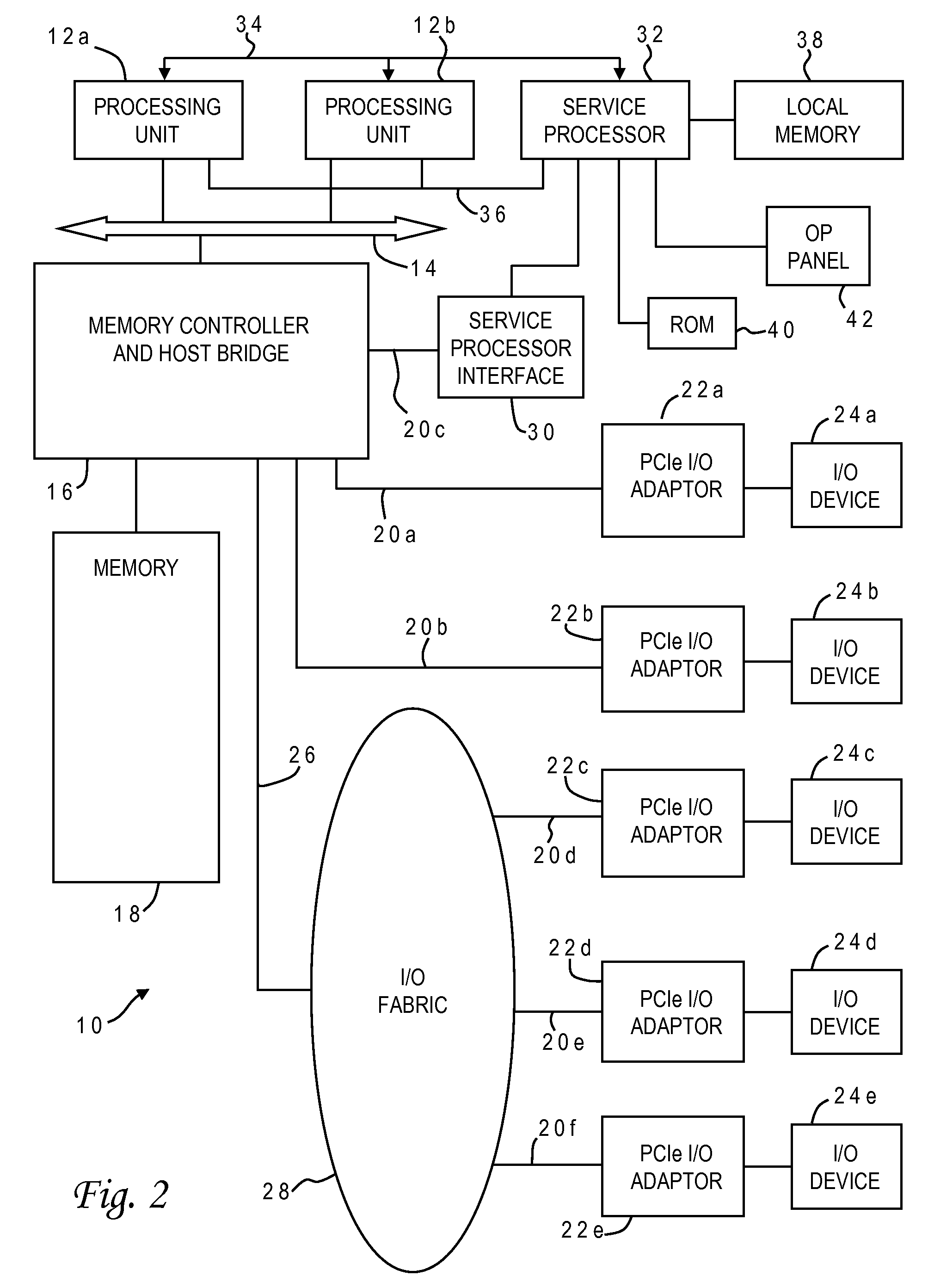

Clock power minimization with regular physical placement of clock repeater components

InactiveUS20090193376A1Improves clock powerReducing clock skewComputer aided designSpecial data processing applicationsCapacitanceModem device

Power, routability and electromigration have become crucial issues in modem microprocessor designs. In high performance designs, clocks are the highest consumer of power. Arranging clocking components with regularity so as to minimize the capacitance on the clock nets can help reduce clock power, however, it may hurt performance due to some loss of flexibility in physically placing those components. The present invention provides techniques to optimally place clock components in a regular fashion so as to minimize clock power within a performance constraint. A rectangular grid is created and clock distribution structures are assigned to the grid intersection points. Latches are then located around the clock distribution structures to minimize an overall distance for connections between the latches and respective clock distribution structures. The horizontal and vertical pitches of the grid may be independently adjusted to achieve a more uniform spread of the clock distribution structures.

Owner:IBM CORP

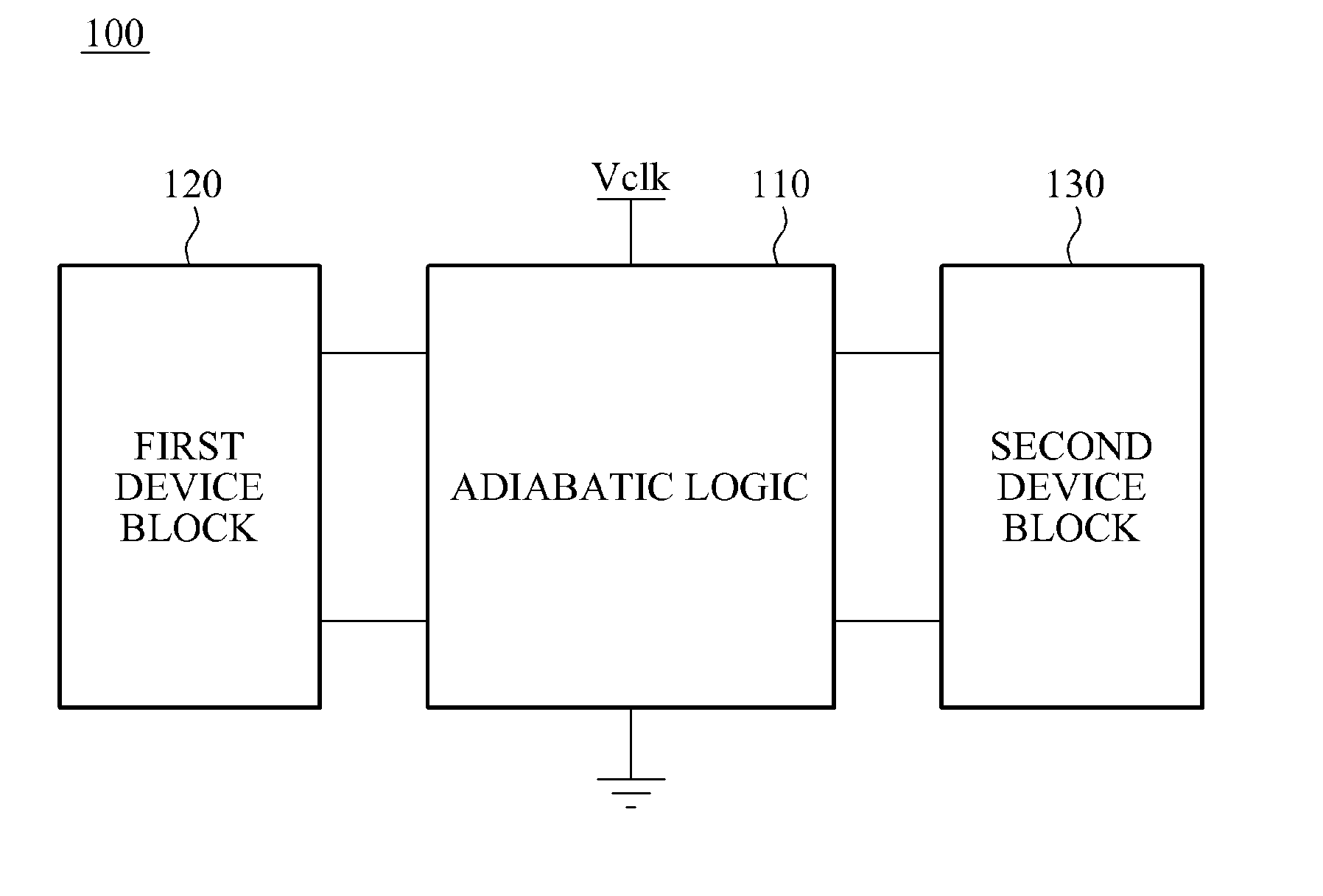

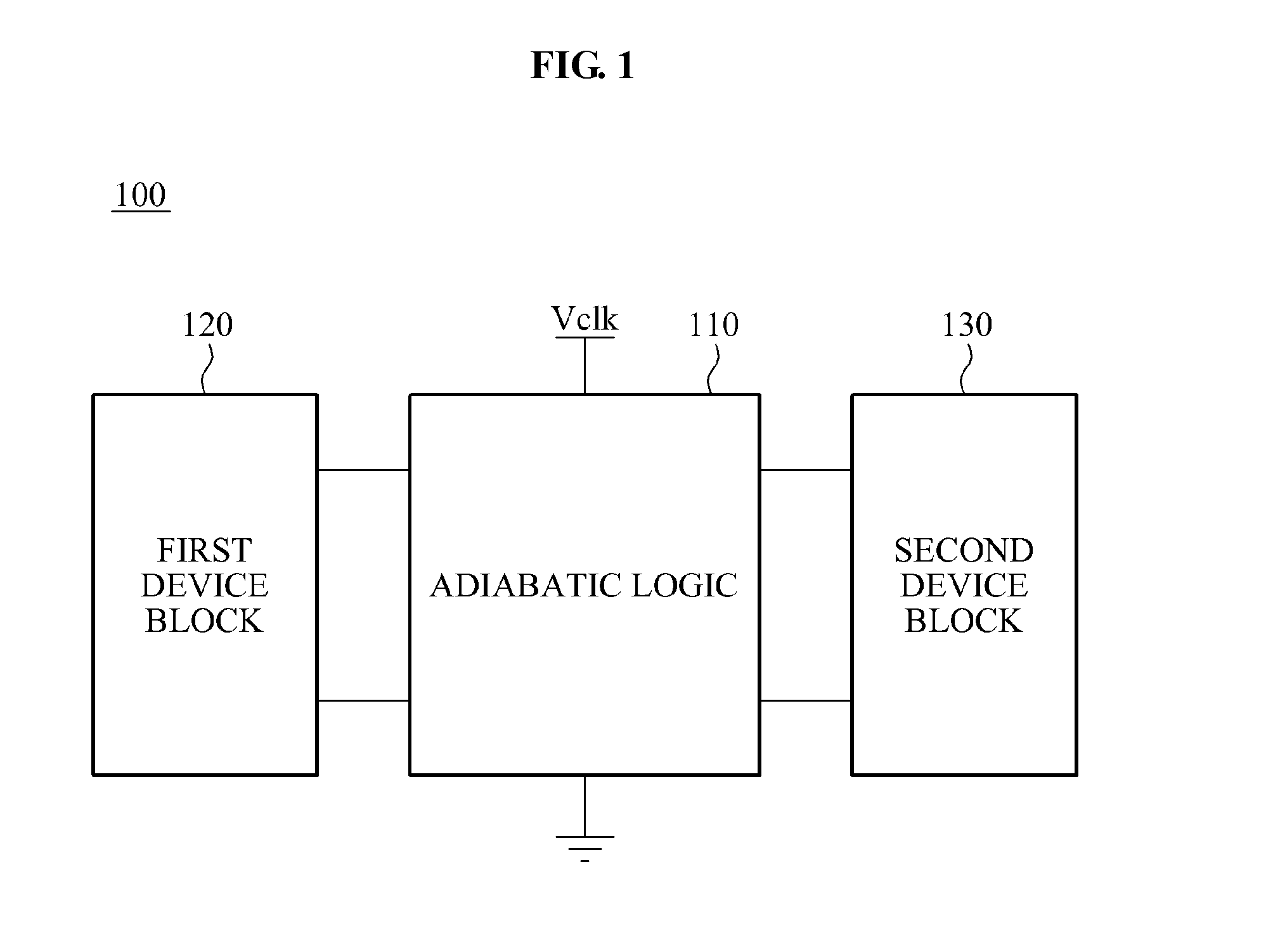

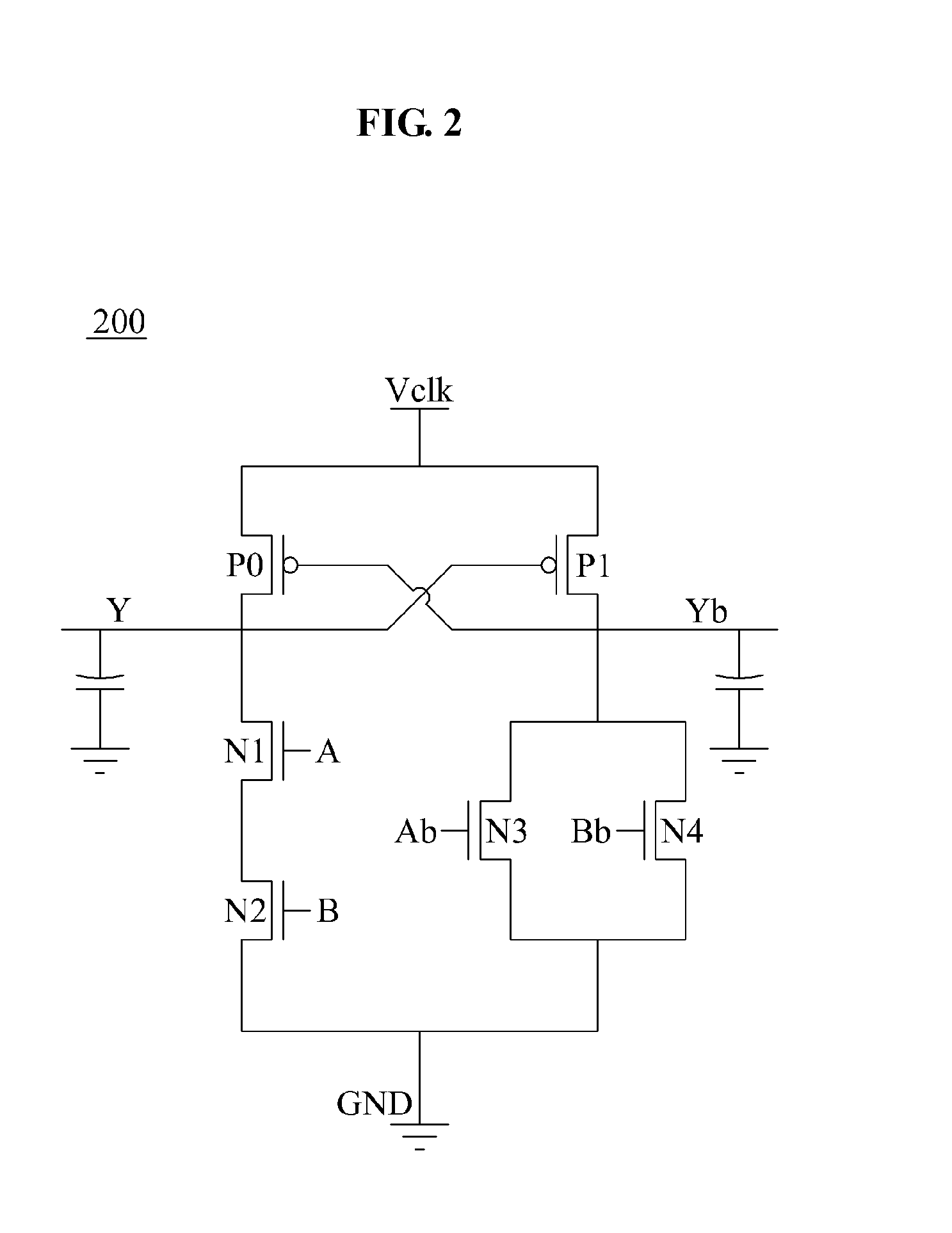

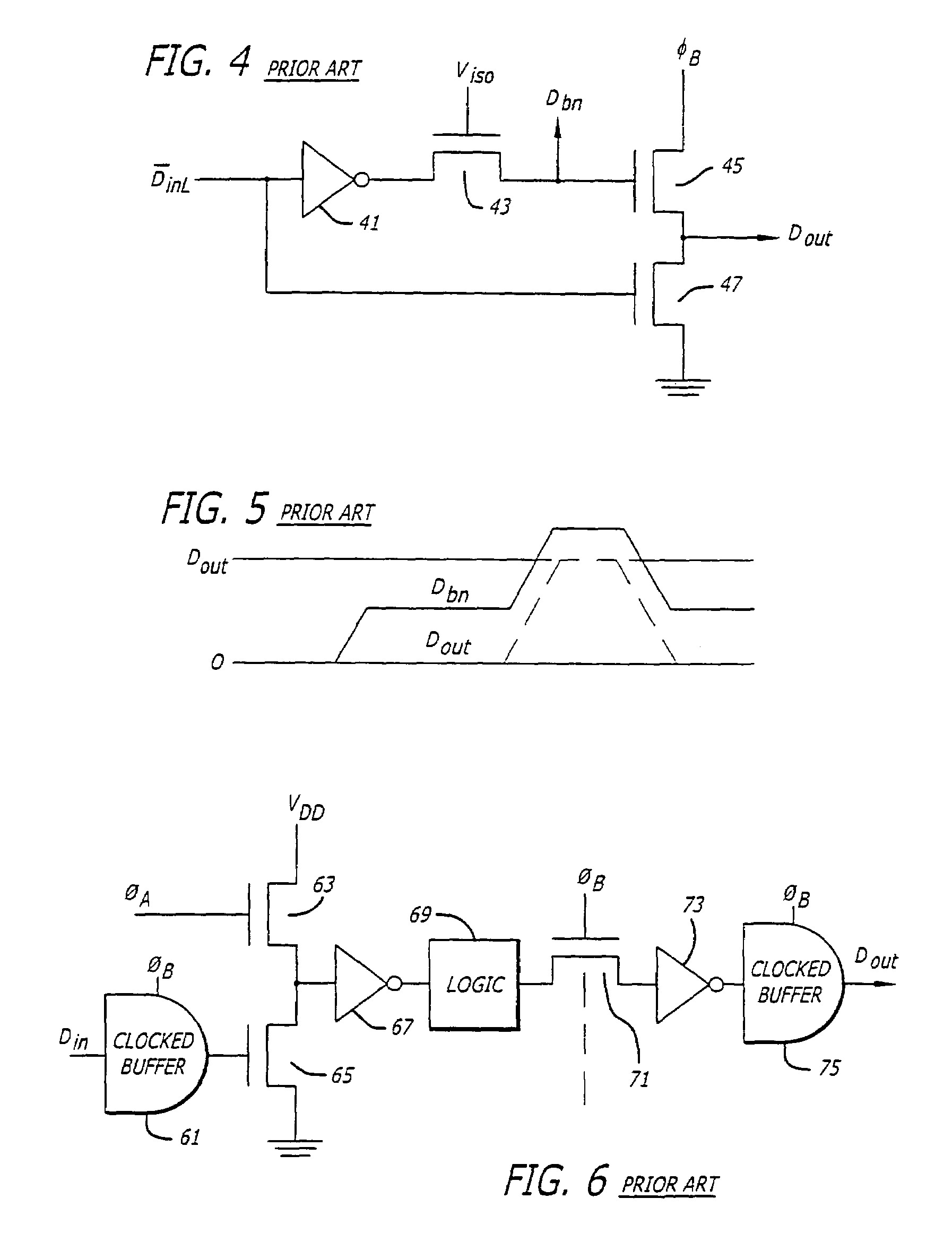

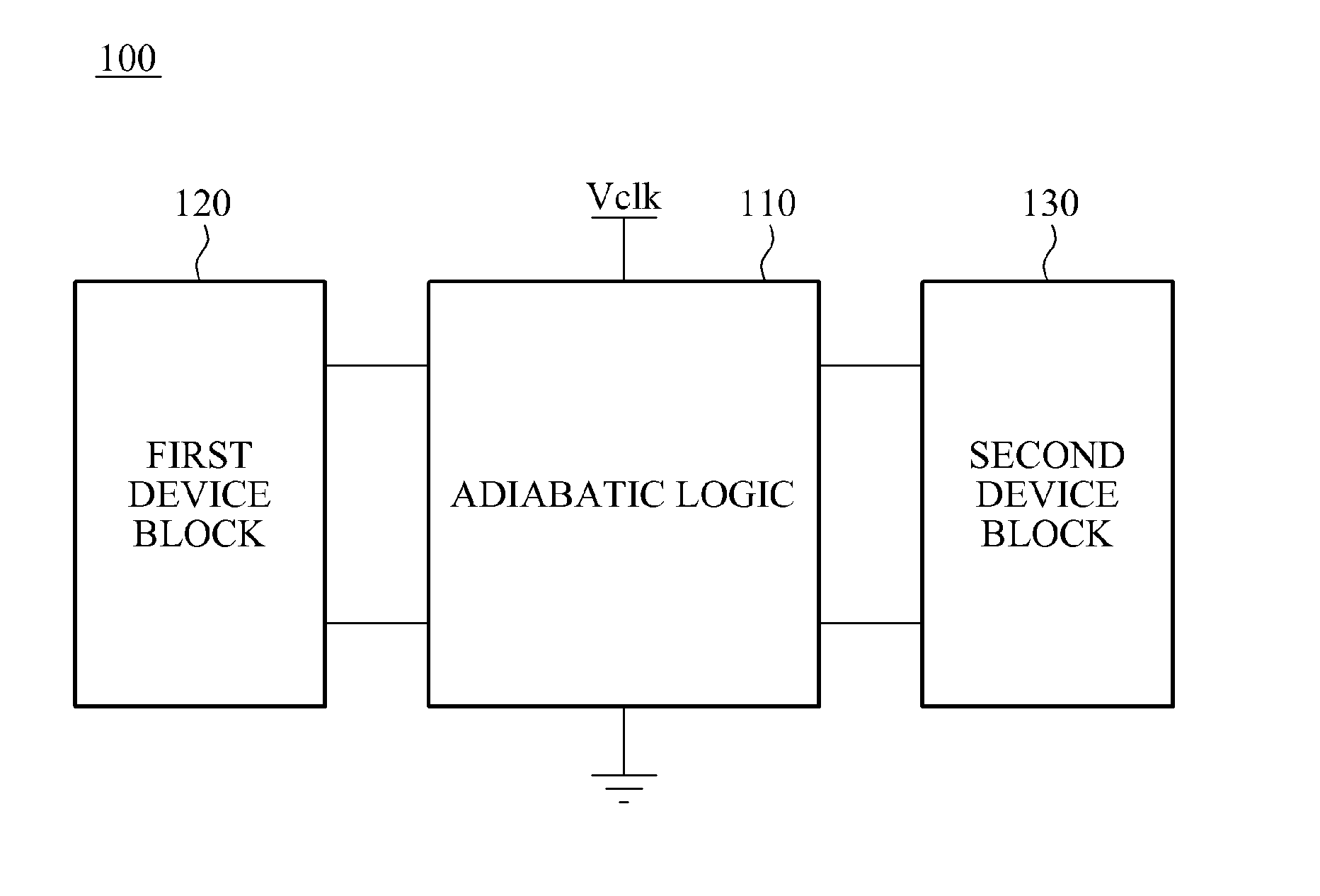

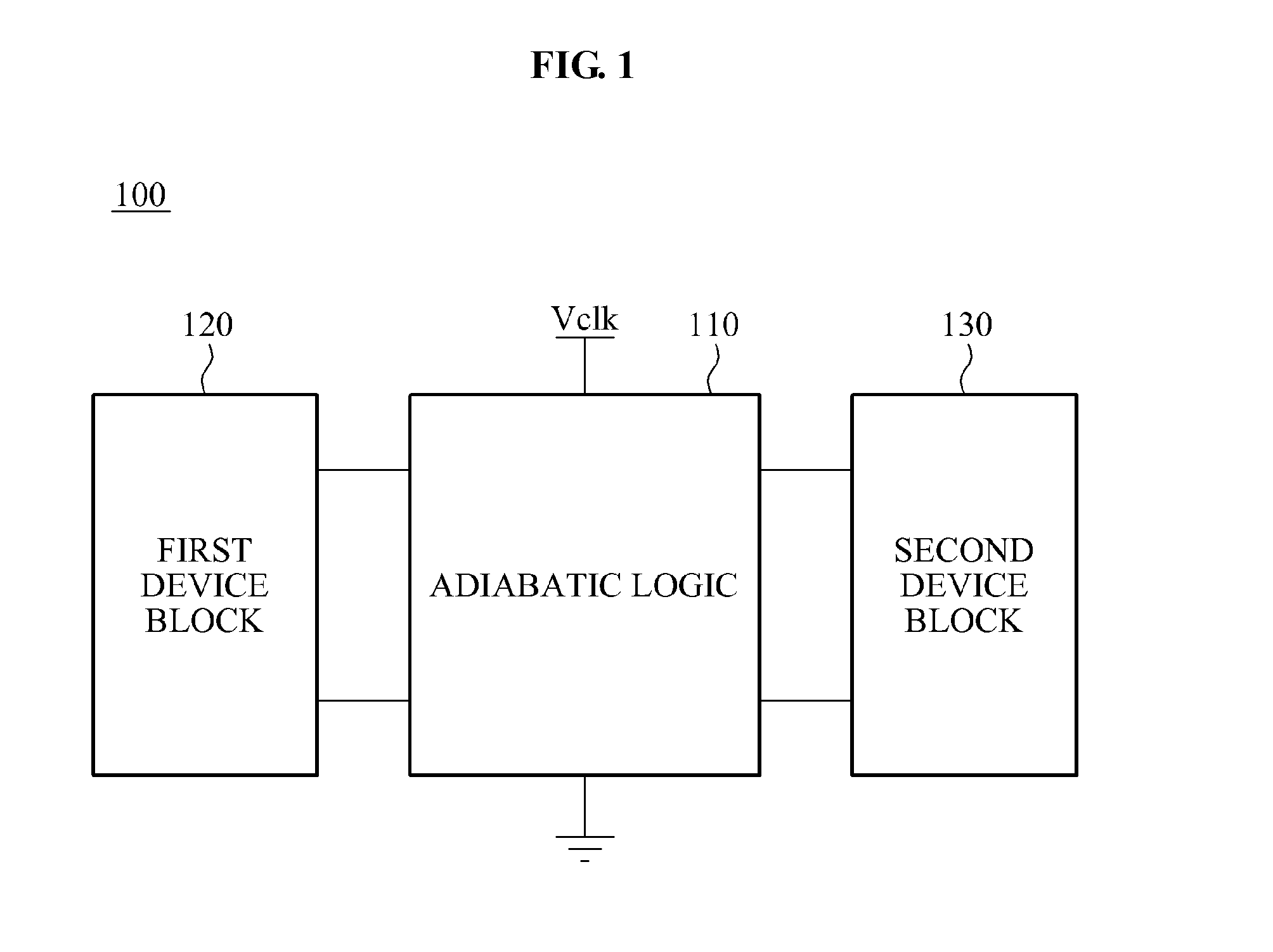

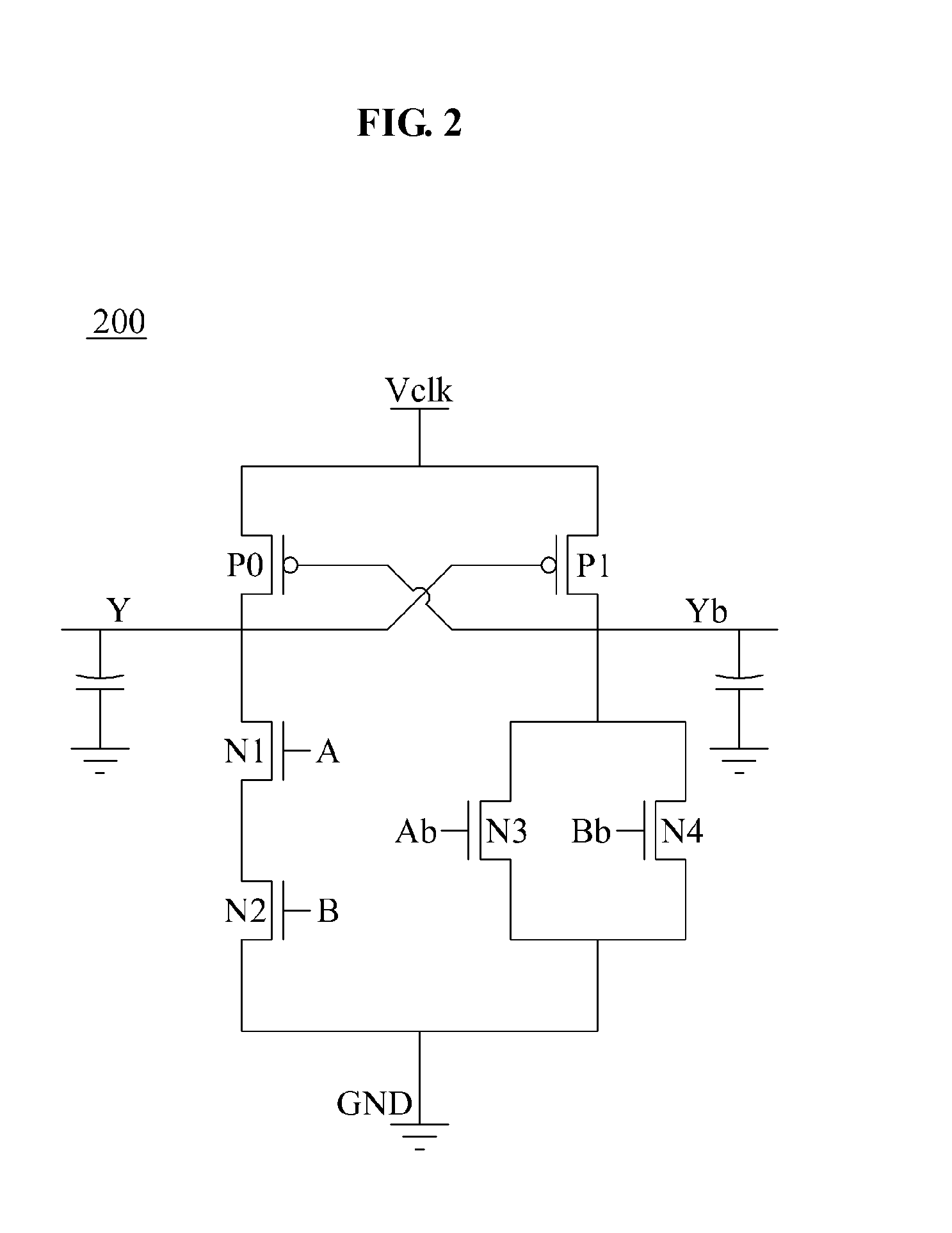

Apparatus for clocked power logic against power analysis attack

ActiveUS20120200313A1Avoid attackEliminate differencesReliability increasing modificationsPower reduction by energy recoveryPower analysisParasitic capacitance

A logic apparatus secure against a power analysis attack is disclosed. The logic apparatus may include a clocked power logic to recover and reuse at least a part of charges supplied during a single clock operation; a first device block connected to the clocked power logic to remove a parasitic capacitance difference in the clocked power logic, and a second device block to readjust remaining charges in each node of the clocked power logic after a single clock operation.

Owner:IUCF HYU (IND UNIV COOP FOUNDATION HANYANG UNIV)

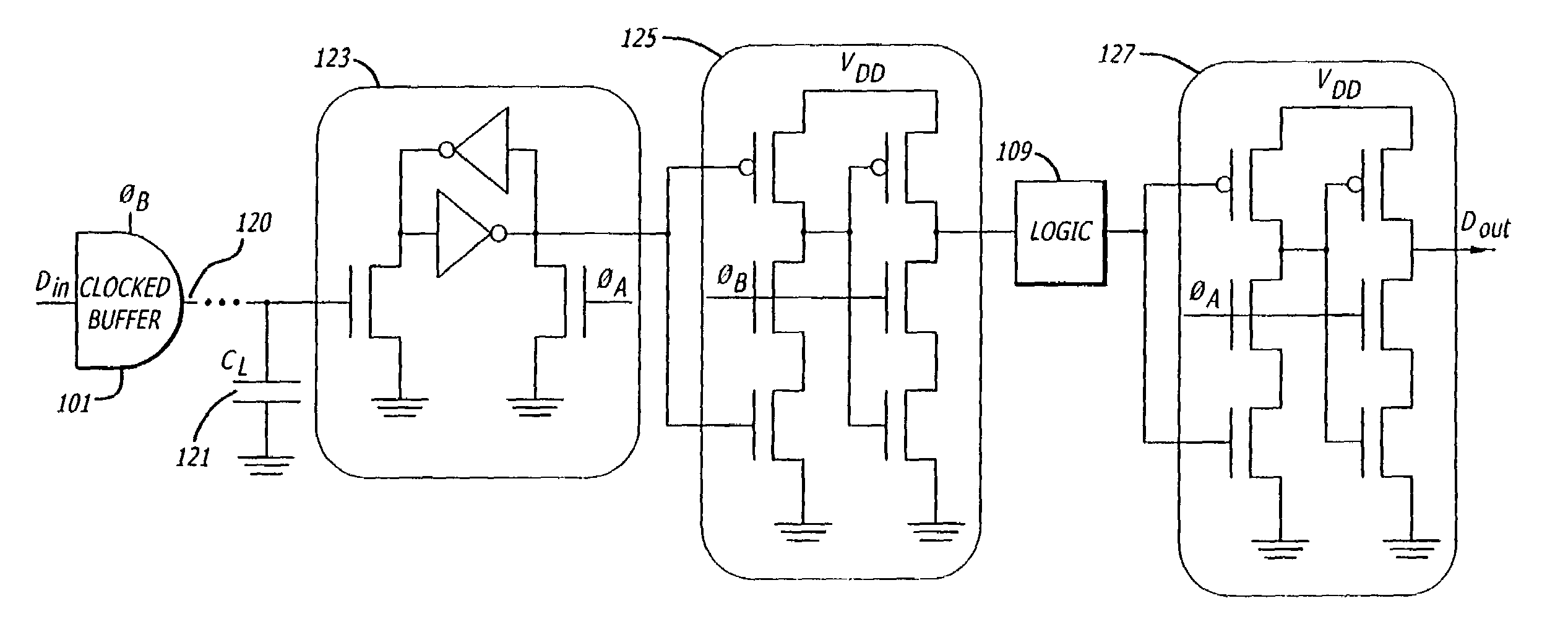

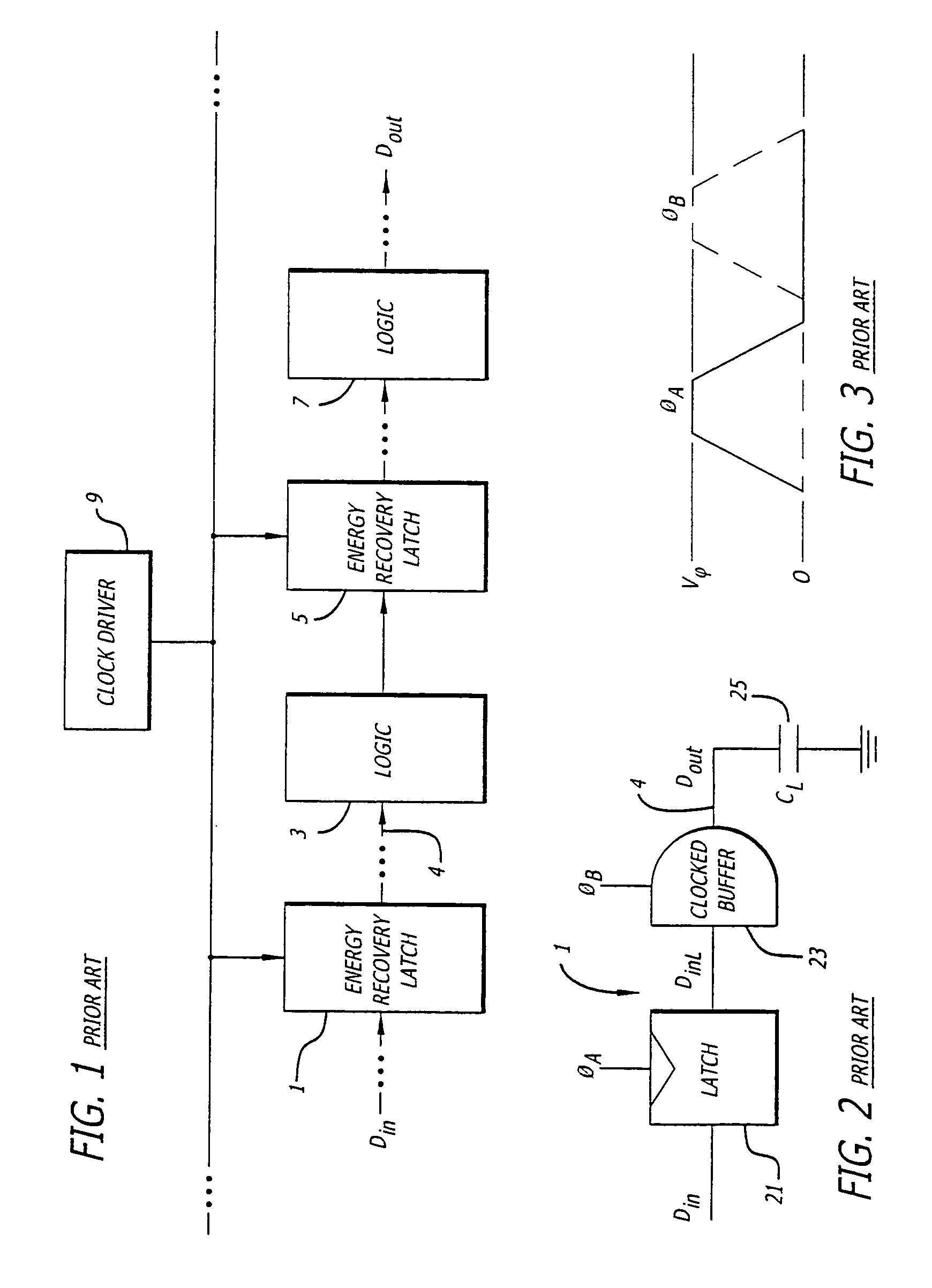

High-performance clock-powered logic

InactiveUS7005893B1Reduce energy consumptionIncrease speedReliability increasing modificationsPower reduction by energy recoveryEngineeringLogic circuitry

High performance clock-powered logic runs at below supply levels and reduces the need for faster digital logic circuitry. In a preferred embodiment, a clocked buffer (101) is used to drive the signal line. The receiving end of the line is connected to a jam latch (123), preferably followed by an n-latch (125), followed by the digital logic (109), and followed by a second n-latch (127). The first n-latch is eliminated in an alternative embodiment, preferably one that uses complementary data signals.

Owner:UNIV OF SOUTHERN CALIFORNIA

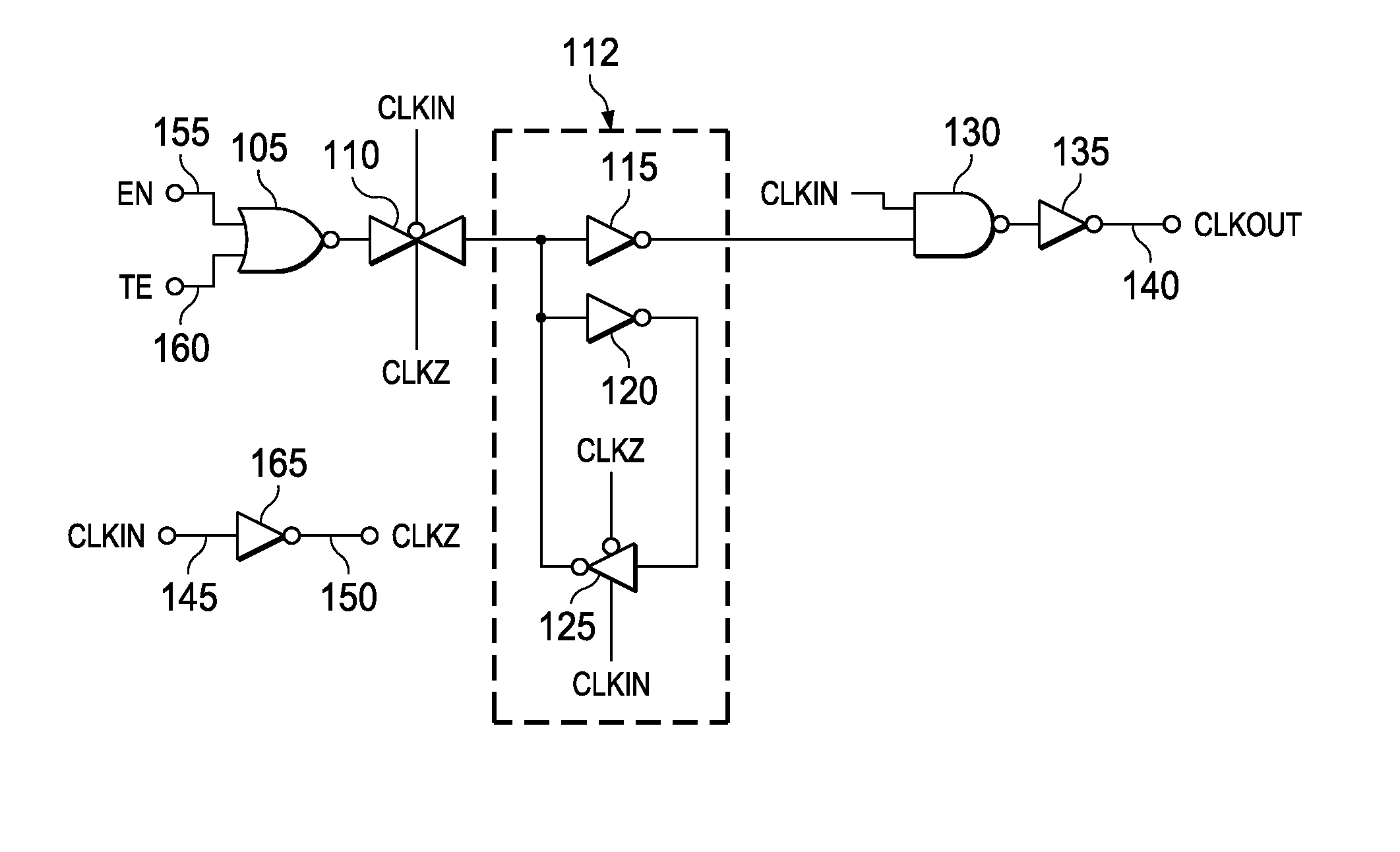

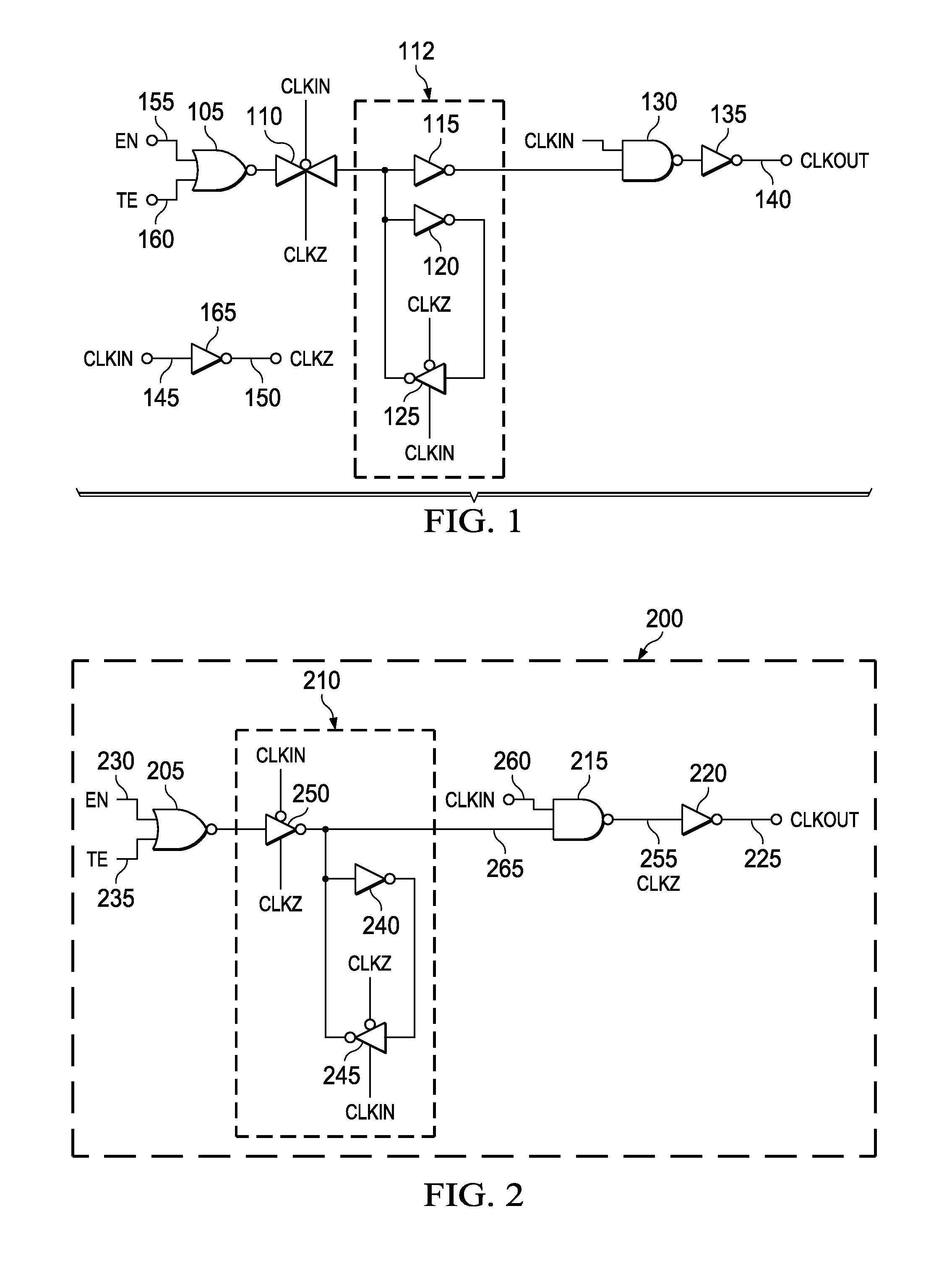

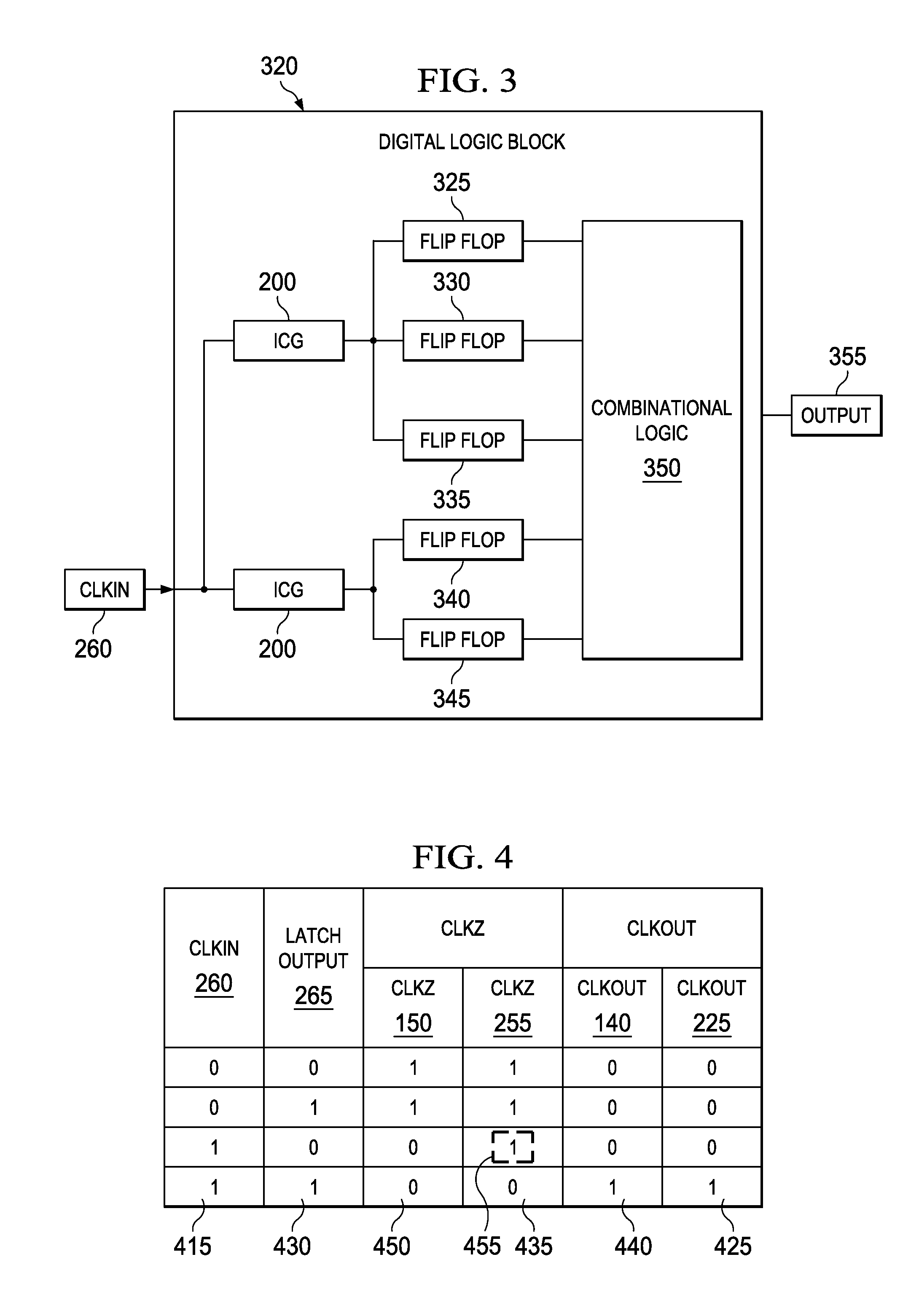

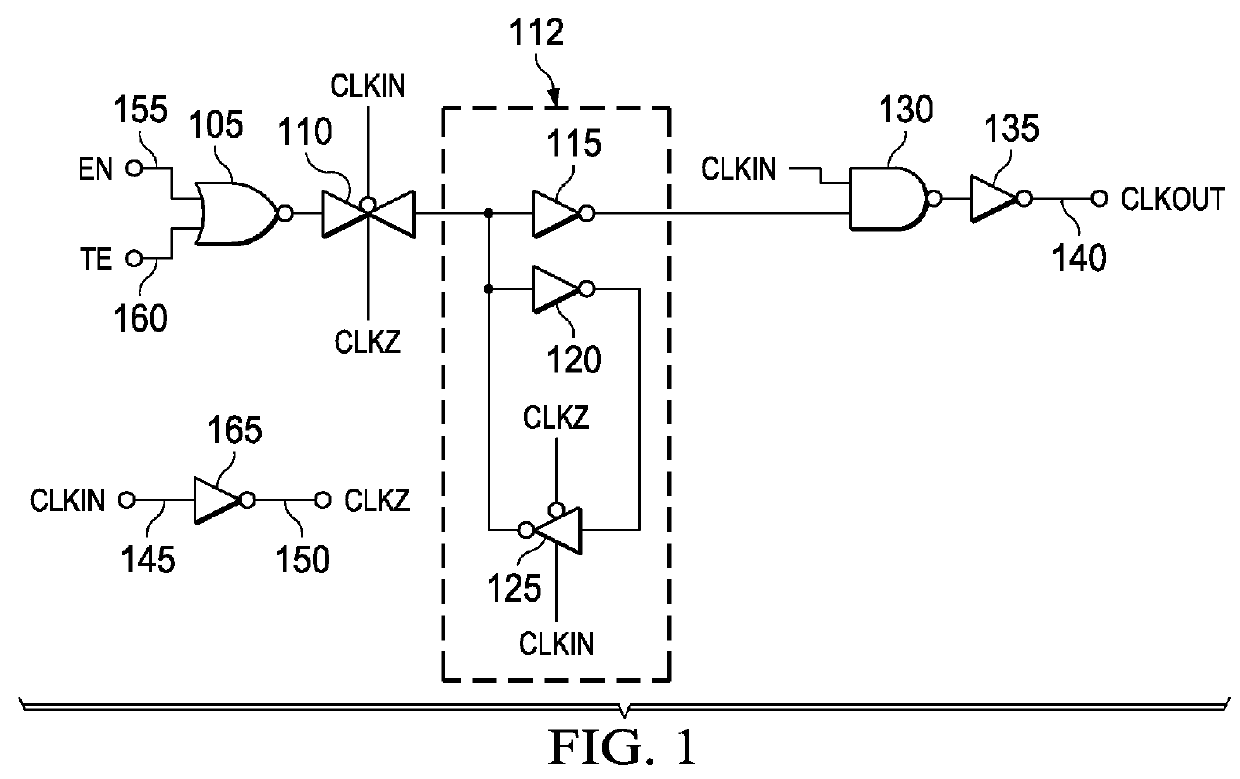

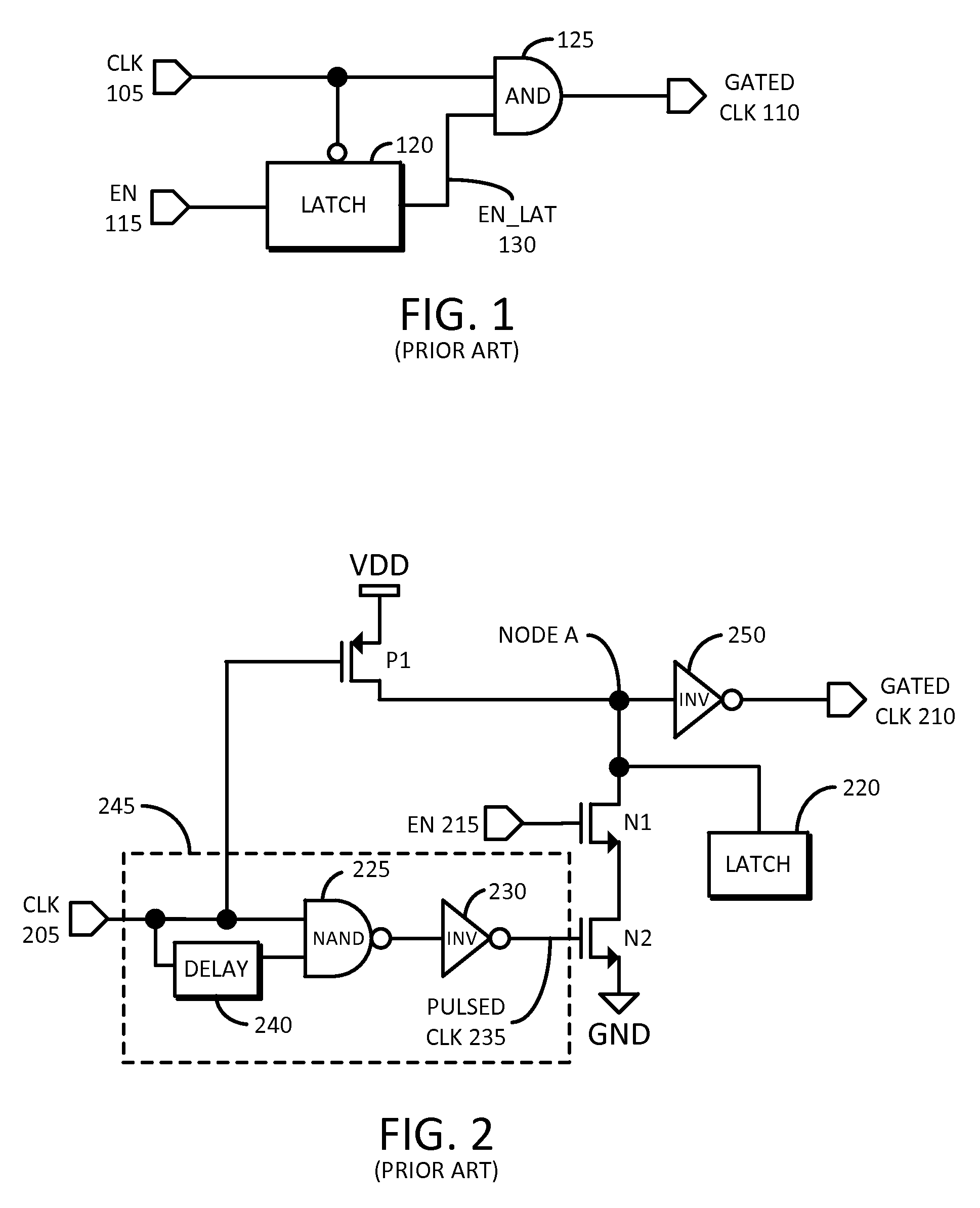

Low clock-power integrated clock gating cell

In an integrated clock gating (ICG) cell a latch is coupled to a NOR gate. The NOR gate receives an enable signal. The latch is configured to generate a latch output in response to the state of the enable signal. The latch includes a tri-state inverter. A NAND gate is coupled to the latch and the NAND gate is configured to generate an inverted clock signal in response to the latch output and a clock input.

Owner:TEXAS INSTR INC

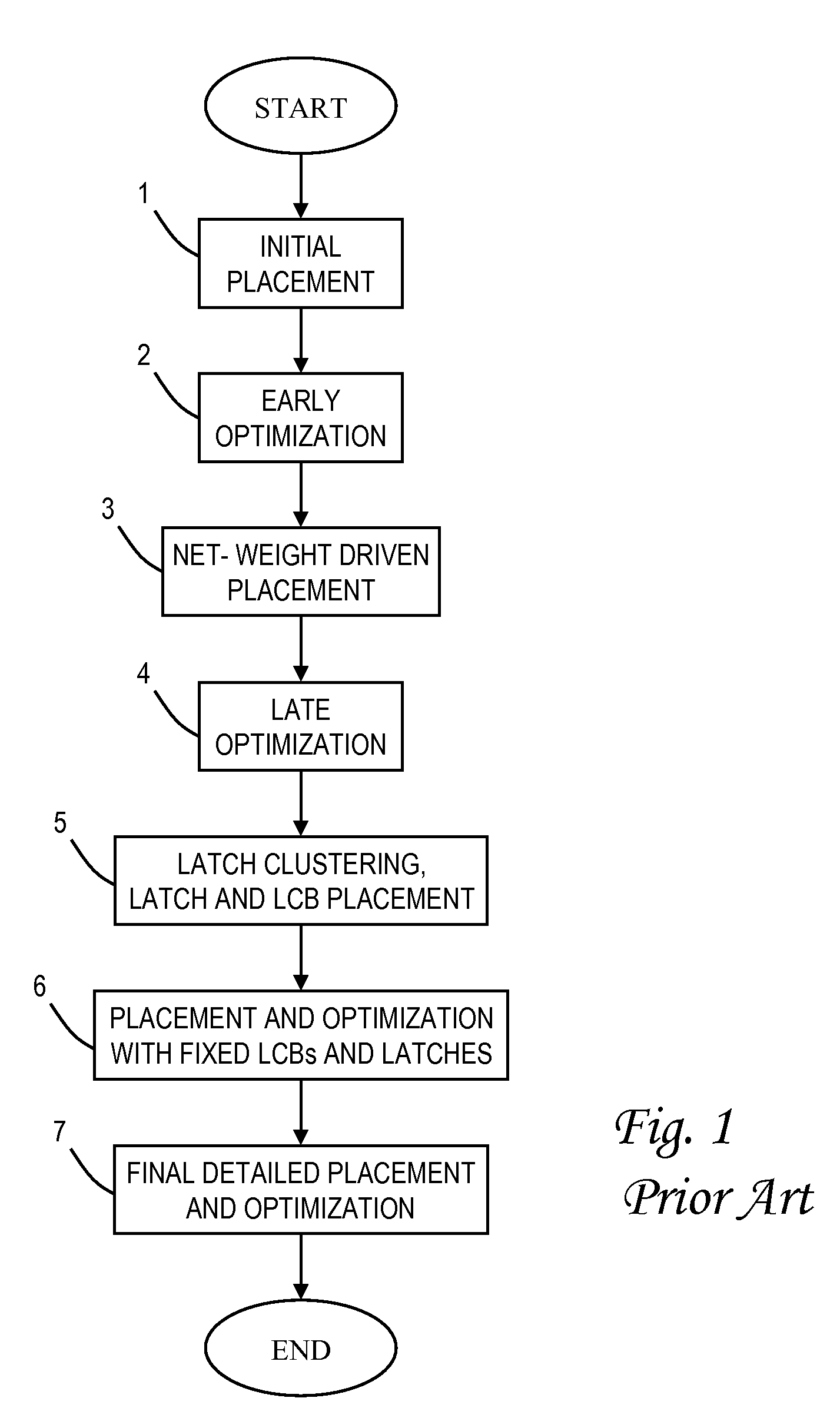

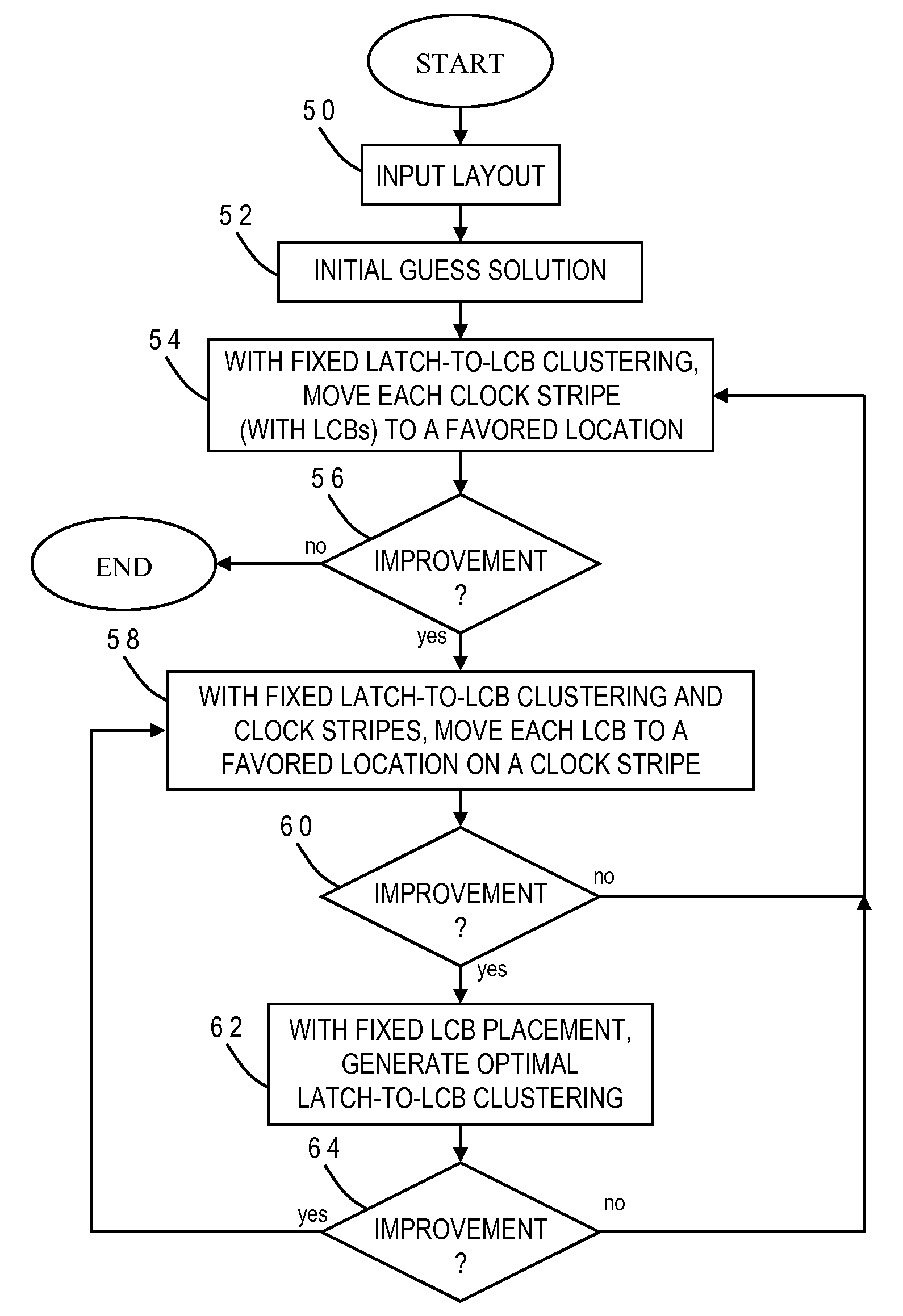

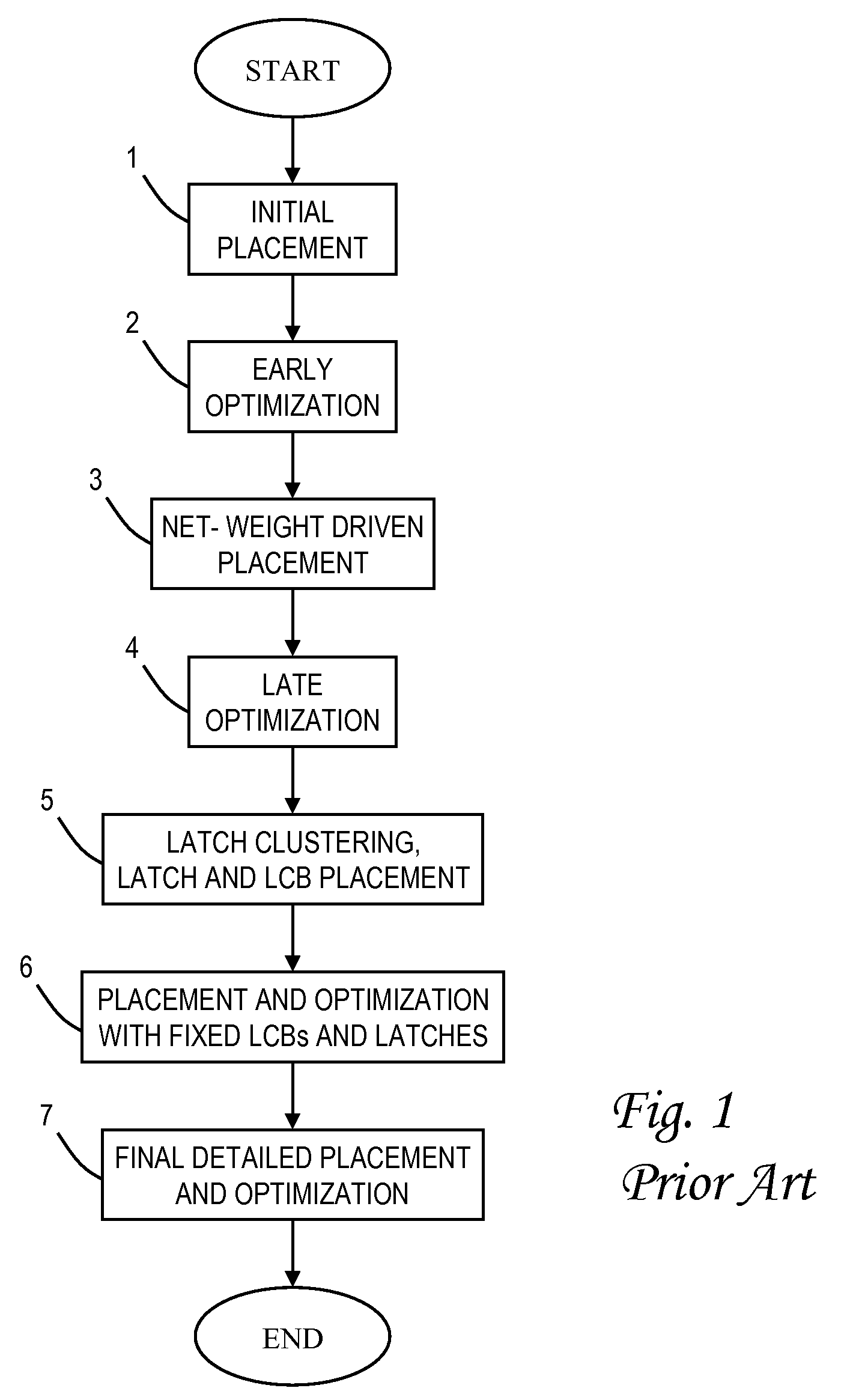

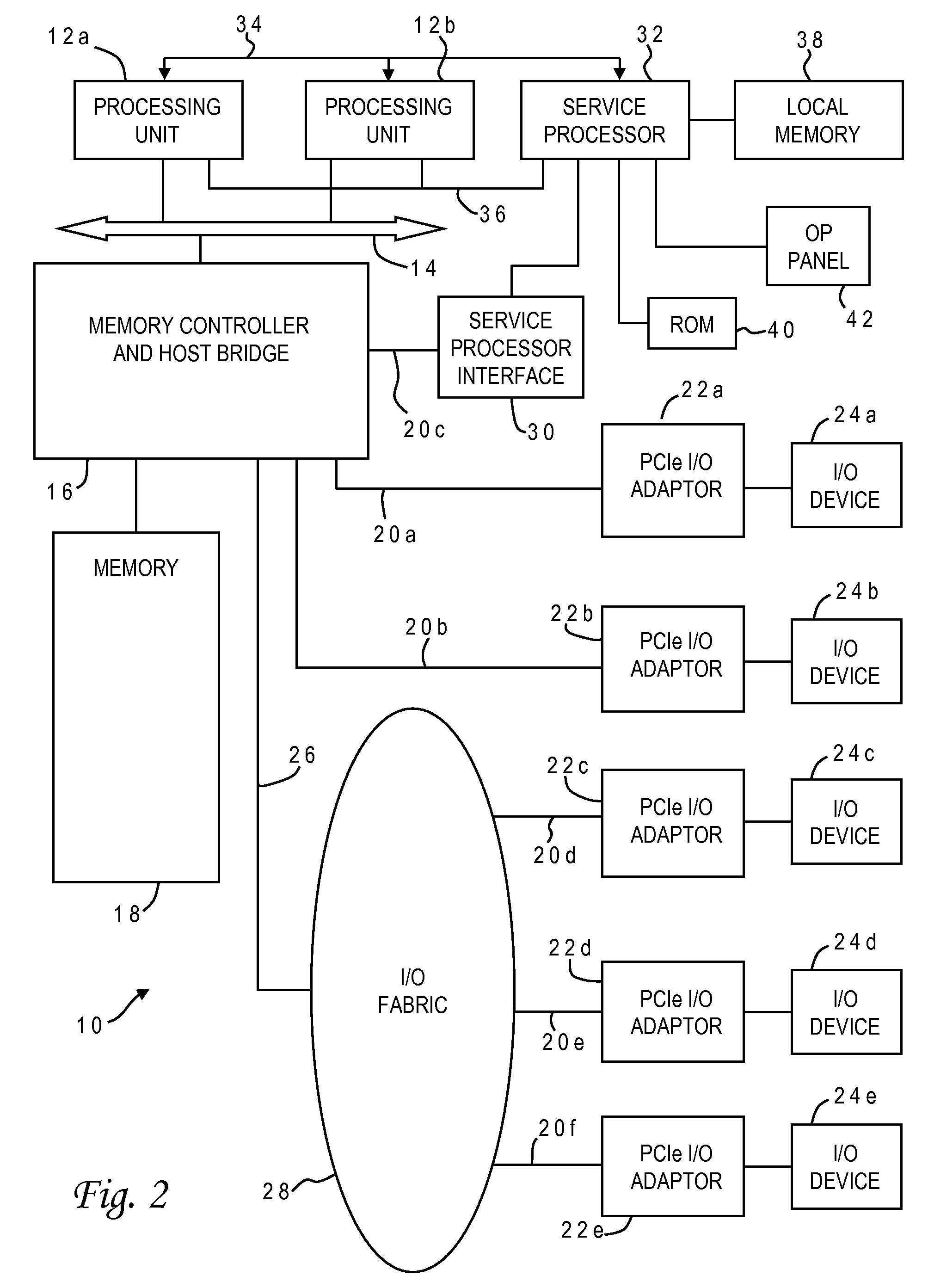

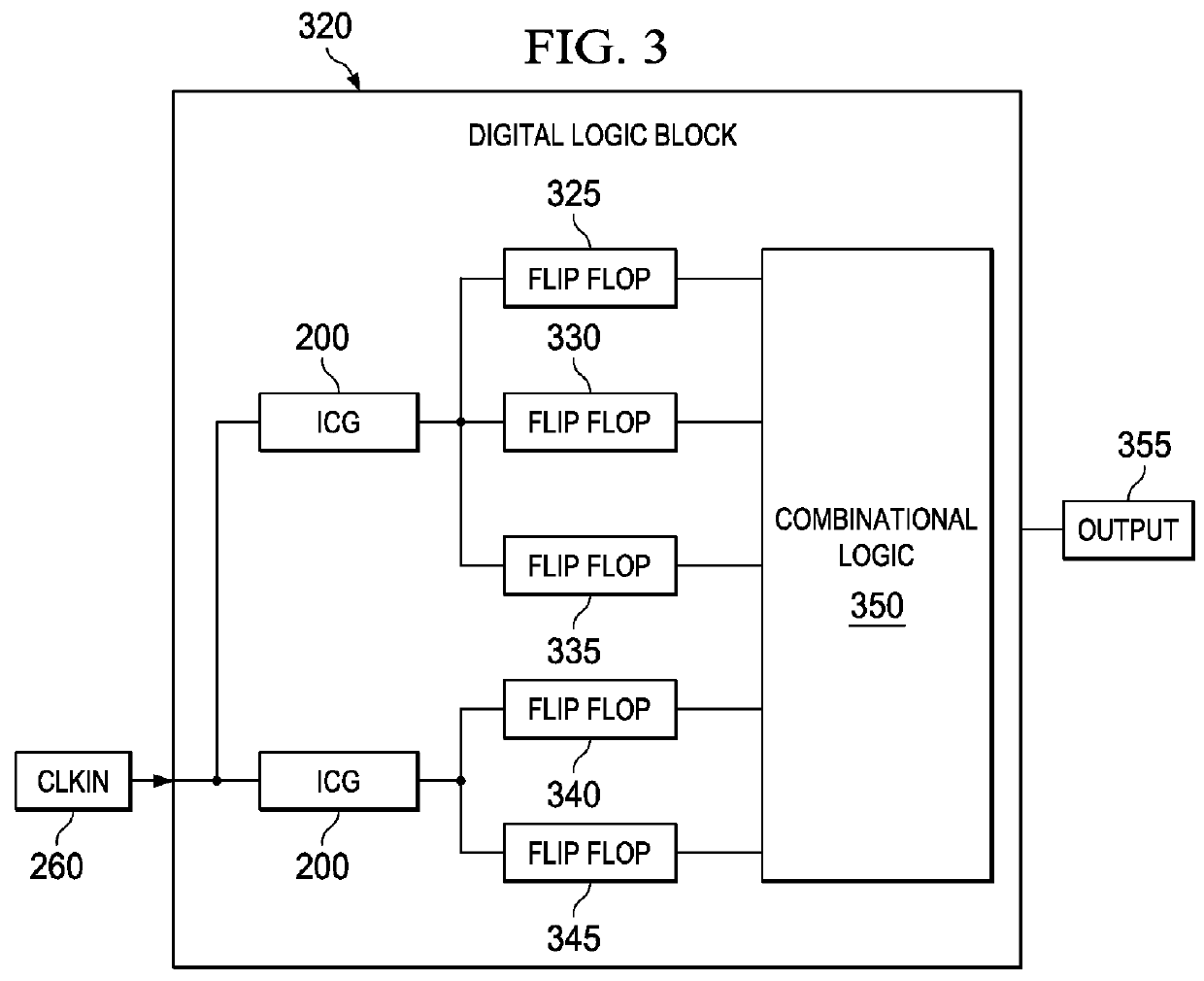

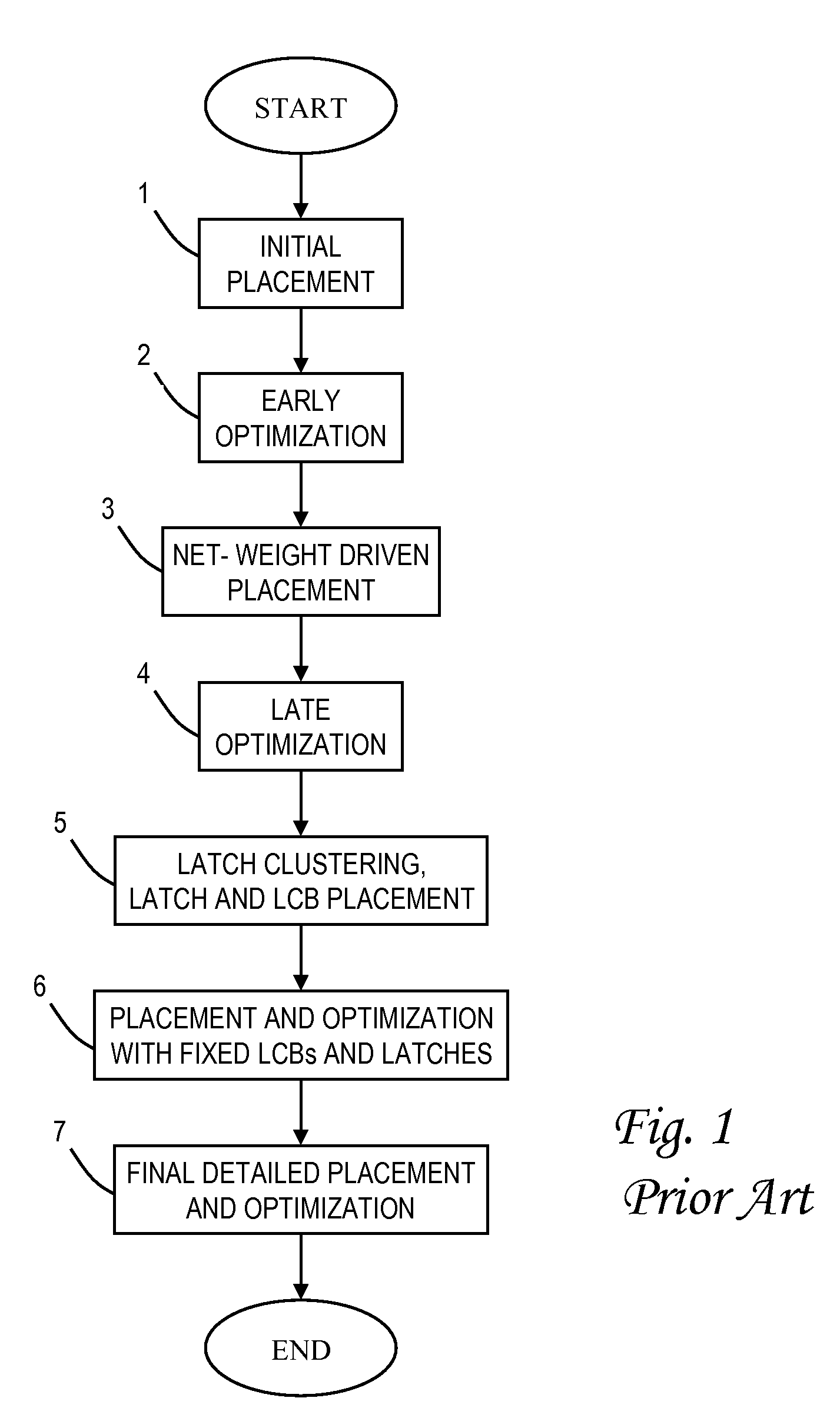

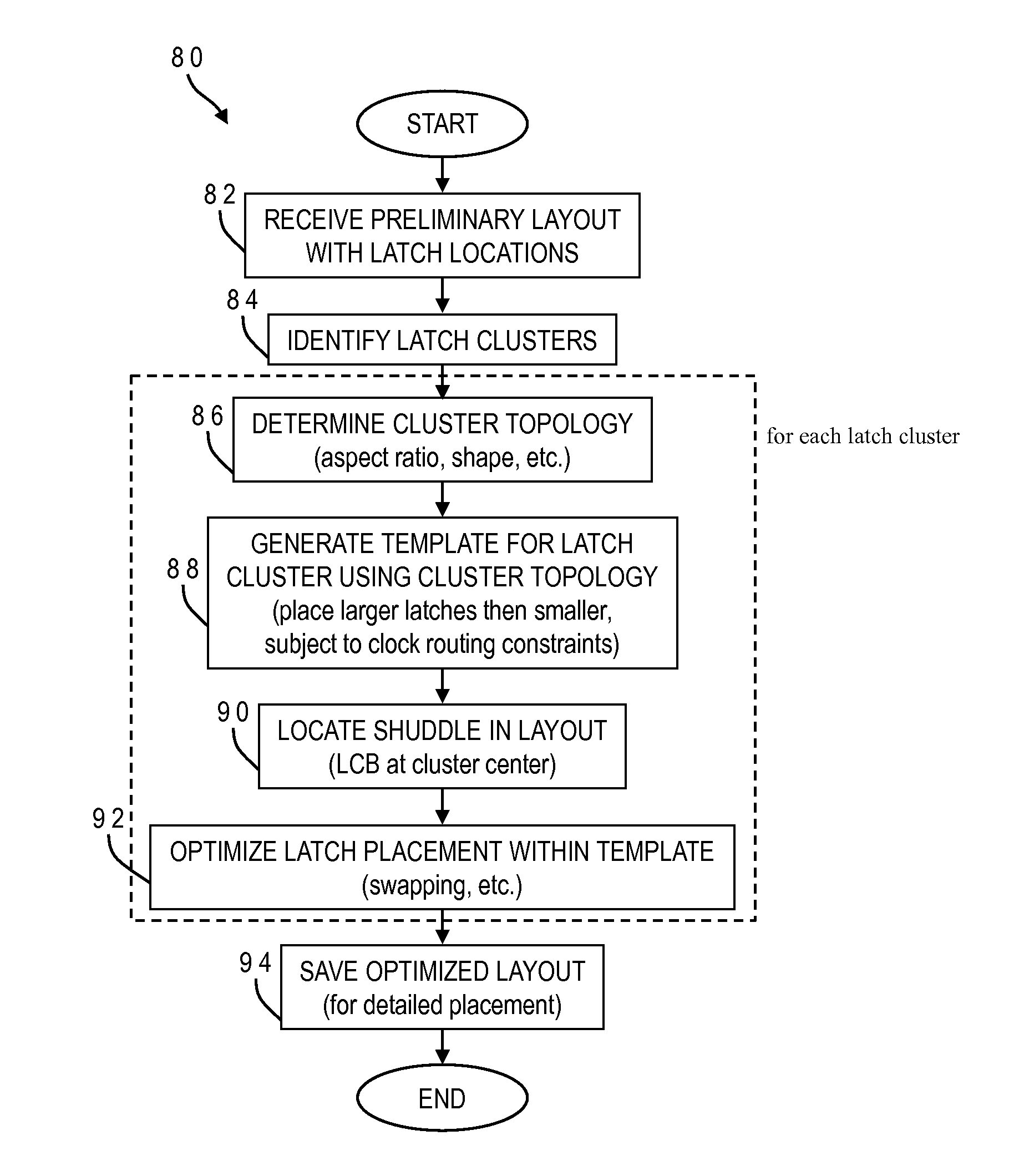

Regular local clock buffer placement and latch clustering by iterative optimization

InactiveUS20090193377A1Simple methodMore flexibility in the location of clock componentsComputer aided designSpecial data processing applicationsCapacitanceClock network

Power, routability and electromigration have become crucial issues in modem microprocessor designs. In high performance designs, clocks are the highest consumer of power. Arranging clocking components with regularity so as to minimize the capacitance of the clock nets can help reduce clock power, however, it may hurt performance due to some loss of flexibility in physically placing those components. The present invention provides techniques to optimally design a clock network by logically assigning clusters of the latches to respective clock distribution structures, placing clock pins at favored pin locations, and placing clock distribution structures directly underneath the clock pins. The clock distribution structures may be moved to favored distribution locations along the clock stripes, and new optimal clustering generated between the latches and the clock distribution structures. These three optimizations are preferably repeated iteratively to derive a local optimal solution for the clock network.

Owner:GLOBALFOUNDRIES INC

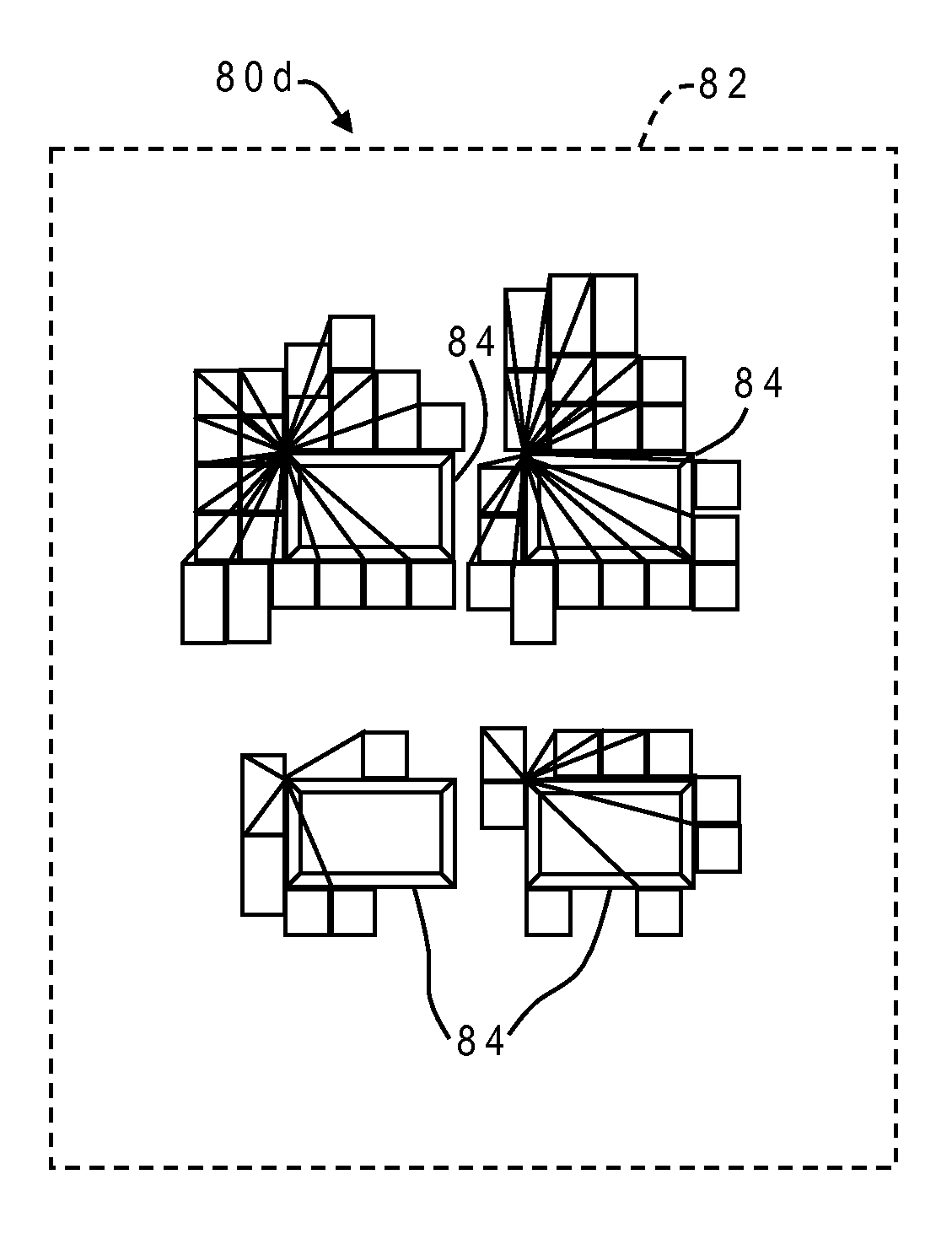

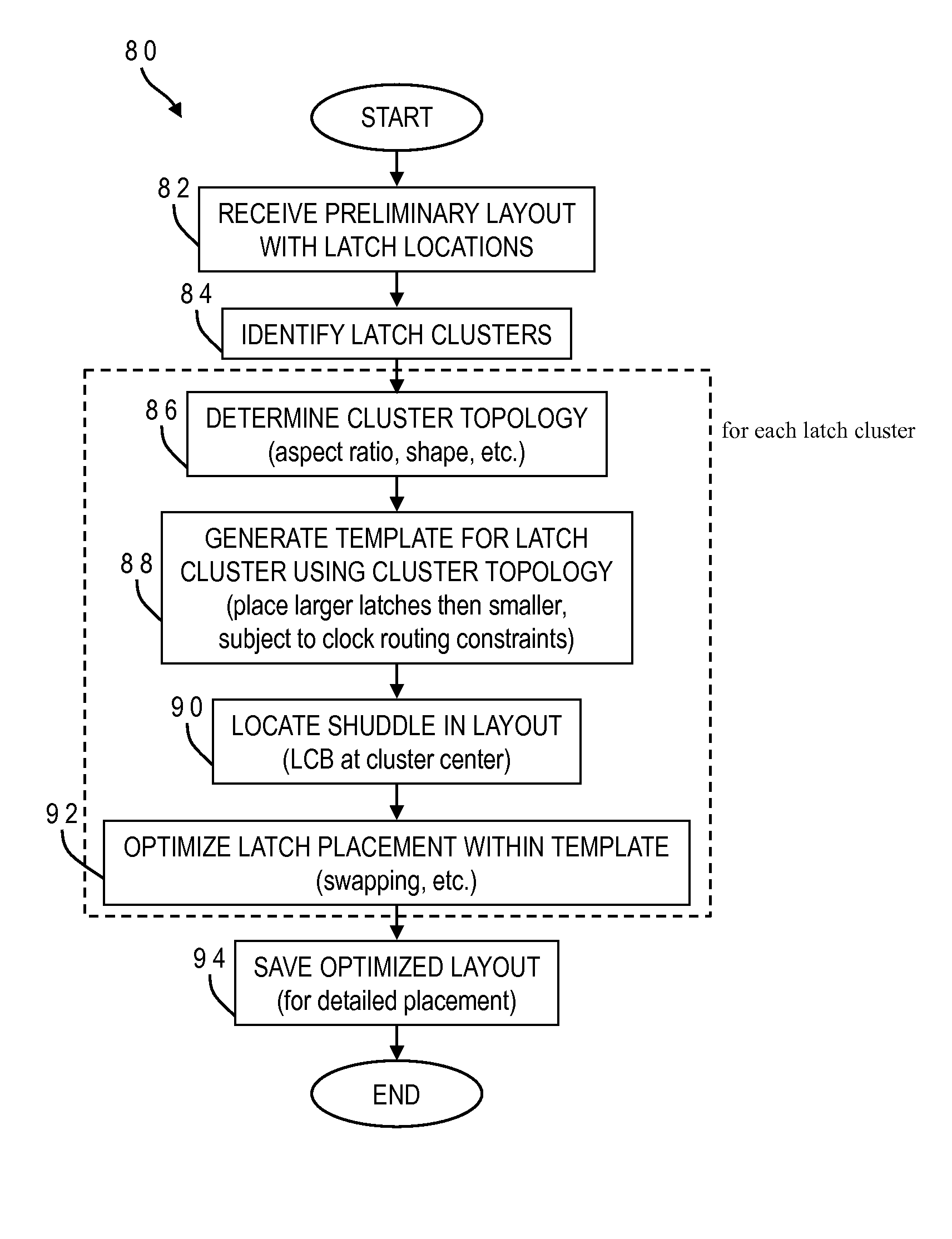

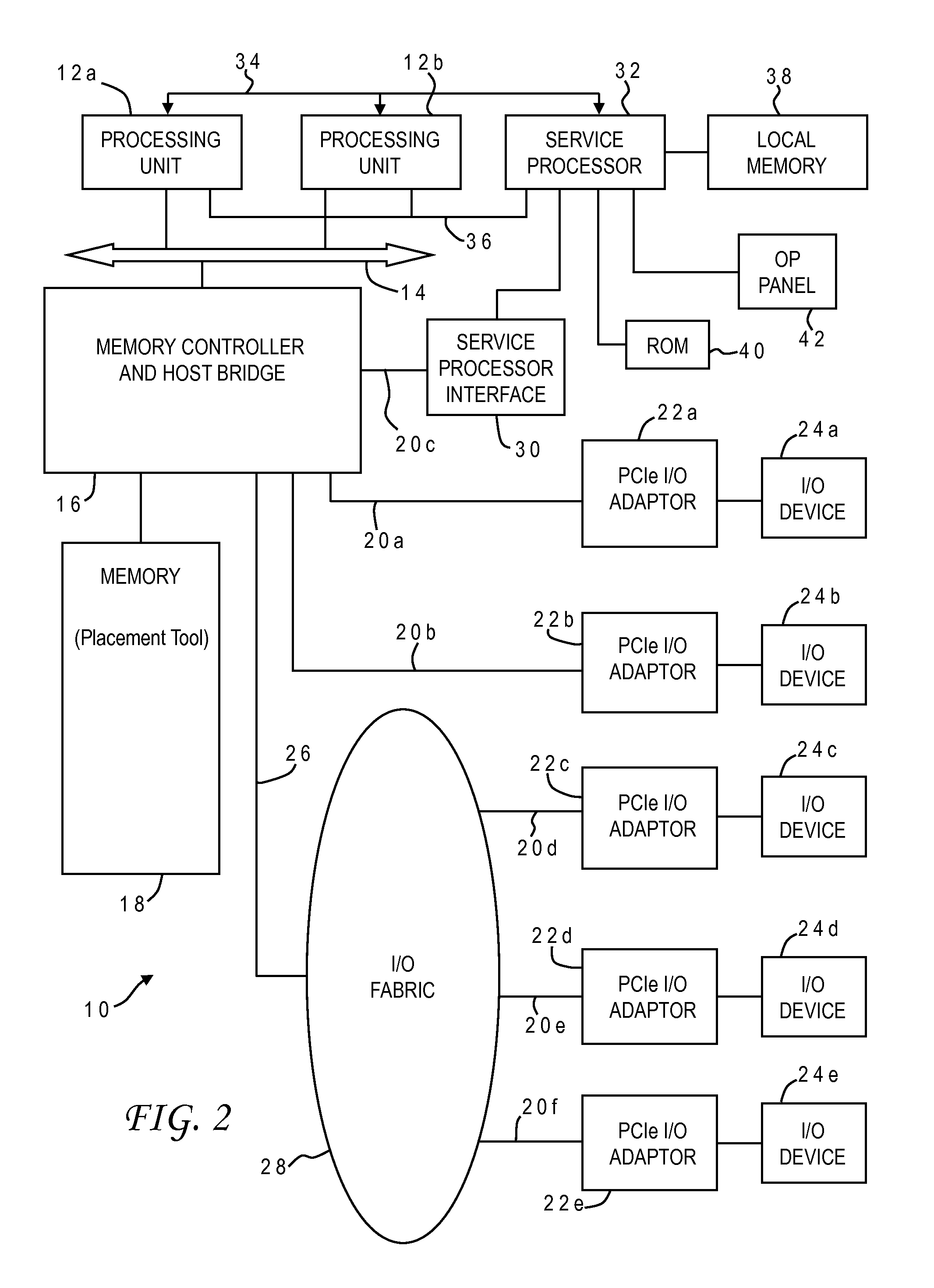

Structured placement of latches/flip-flops to minimize clock power in high-performance designs

InactiveUS8954912B2Minimize wirelengthEasy to placeComputer aided designSpecial data processing applicationsEngineeringNetlist

A latch placement tool determines a shape for a cluster of latches from a preliminary layout (or based on a netlist), including an aspect ratio of the shape, and generates a template for placement of the latches in conformity with the shape. Latches are placed around a local clock buffer (LCB) based on latch size, from largest latch first to smallest latch last, and based on their ideal locations given the target aspect ratio. The ideal locations may be further based on the clock driver pin configuration of the LCB. The final template preferably has an aspect ratio that is approximately equal to the aspect ratio of the shape of the cluster, but the latch placement may be constrained by clock routing topology. Latch placement within a cluster can be further optimized by swapping one of the latches with another to minimize total wirelength of the design.

Owner:GLOBALFOUNDRIES INC

Low clock-power integrated clock gating cell

In an integrated clock gating (ICG) cell a latch is coupled to a NOR gate. The NOR gate receives an enable signal. The latch is configured to generate a latch output in response to the state of the enable signal. The latch includes a tri-state inverter. A NAND gate is coupled to the latch and the NAND gate is configured to generate an inverted clock signal in response to the latch output and a clock input.

Owner:TEXAS INSTR INC

Clock power minimization with regular physical placement of clock repeater components

InactiveUS8010926B2Increase powerReducing clock skewComputer aided designSpecial data processing applicationsCapacitanceControl theory

Power, routability and electromigration have become crucial issues in modern microprocessor designs. In high performance designs, clocks are the highest consumer of power. Arranging clocking components with regularity so as to minimize the capacitance on the clock nets can help reduce clock power, however, it may hurt performance due to some loss of flexibility in physically placing those components. The present invention provides techniques to optimally place clock components in a regular fashion so as to minimize clock power within a performance constraint. A rectangular grid is created and clock distribution structures are assigned to the grid intersection points. Latches are then located around the clock distribution structures to minimize an overall distance for connections between the latches and respective clock distribution structures. The horizontal and vertical pitches of the grid may be independently adjusted to achieve a more uniform spread of the clock distribution structures.

Owner:IBM CORP

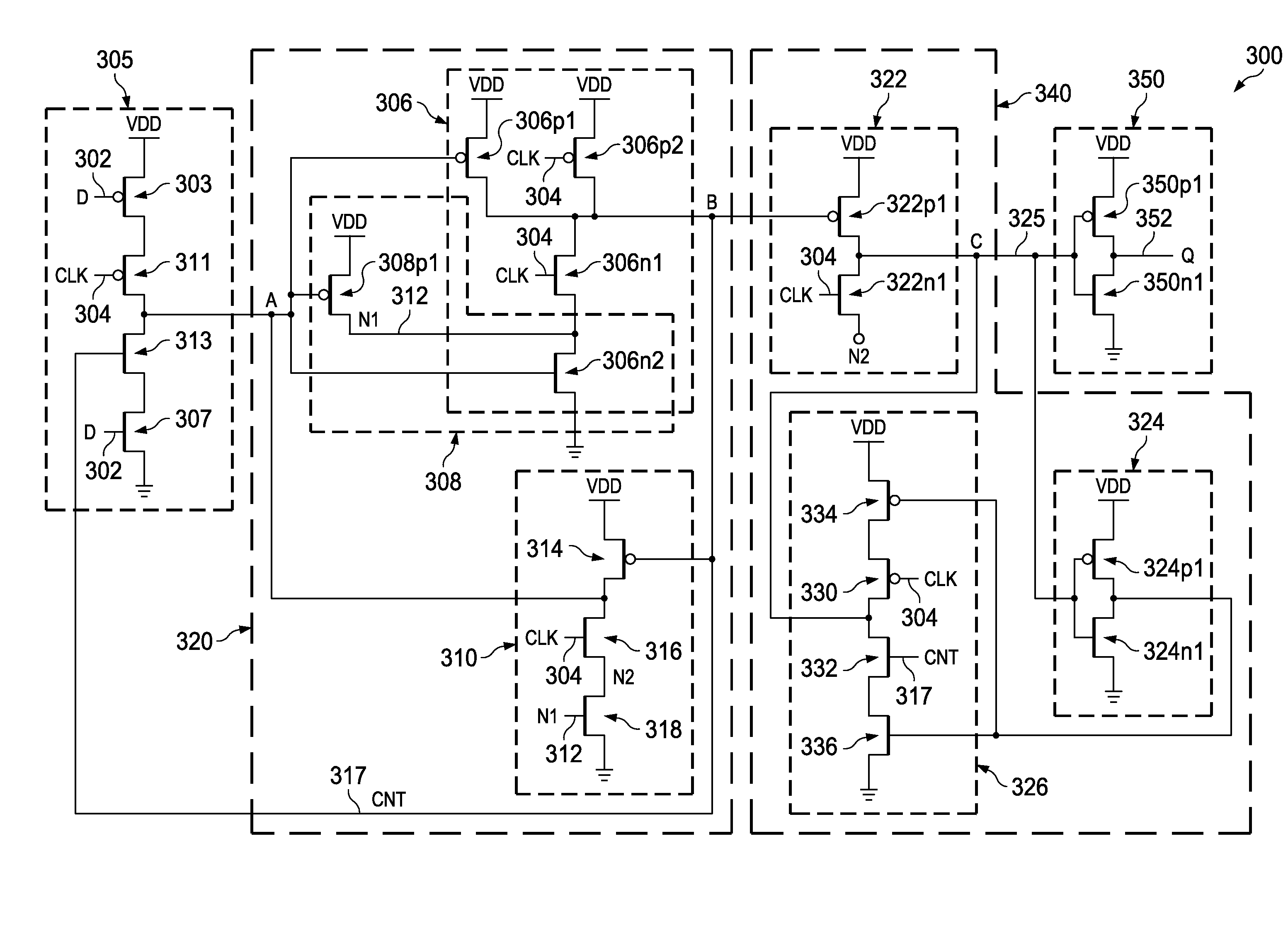

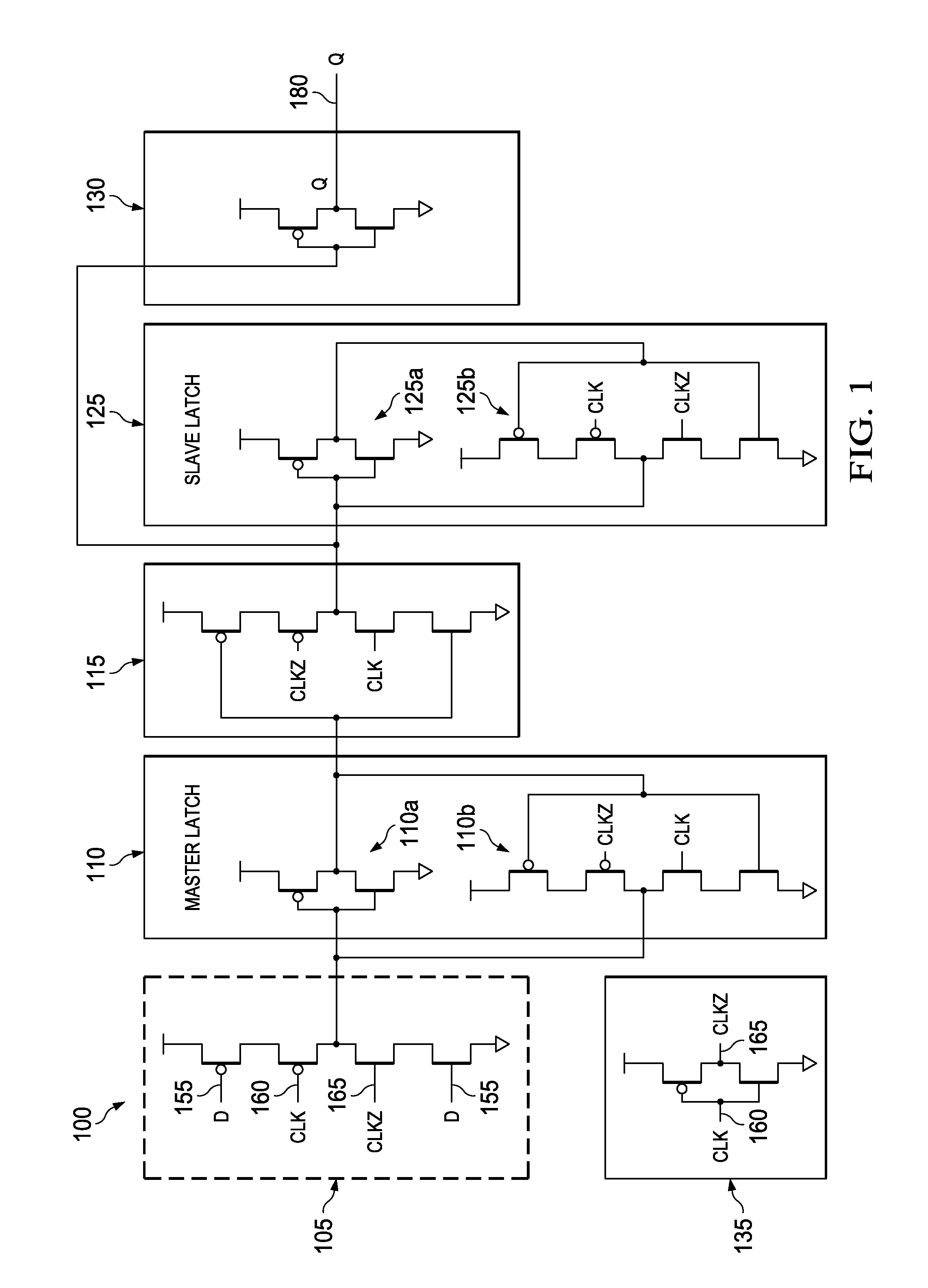

Flip-flops with low clock power

The disclosure provides a flip-flop that utilizes low power as a result of reduced transistor count. The flip-flop includes a tri-state inverter that receives a flip-flop input and a clock input. A master latch is coupled to an output of the tri-state inverter and provides a control signal to the tri-state inverter. The control signal activates the tri-state inverter. A slave latch receives an output of the master latch and the control signal. An output inverter is coupled to an output of the slave latch and generates a flip-flop output.

Owner:TEXAS INSTR INC

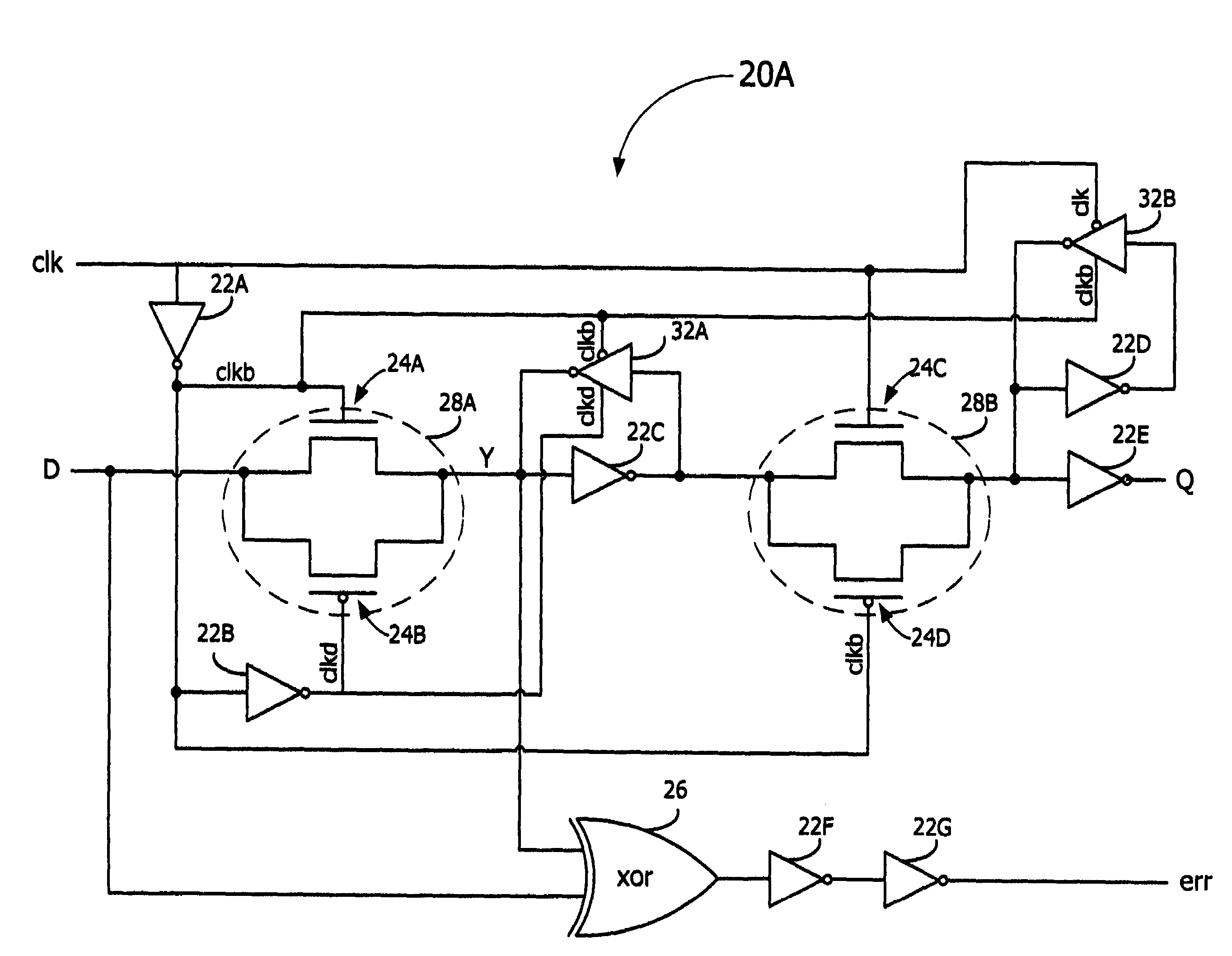

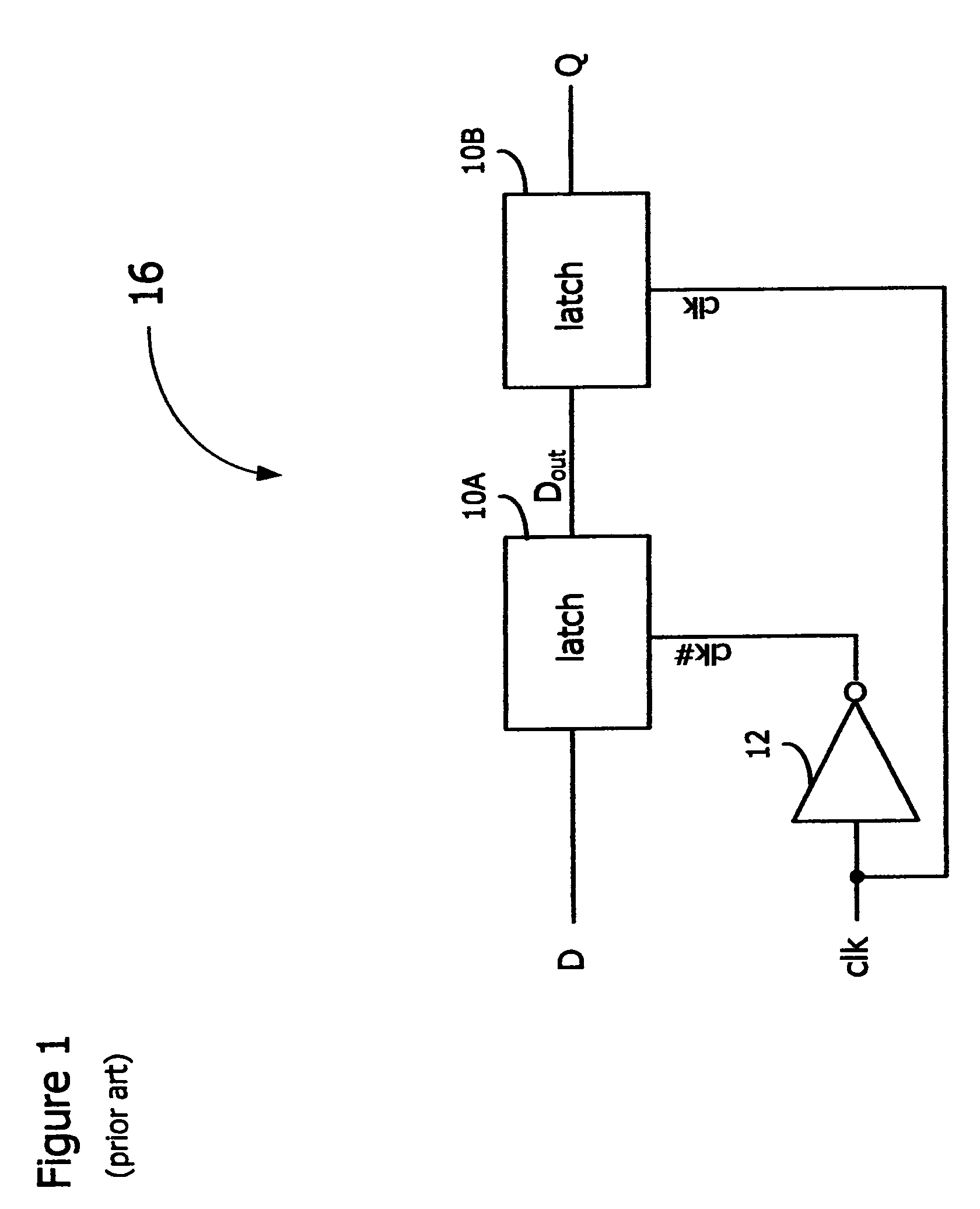

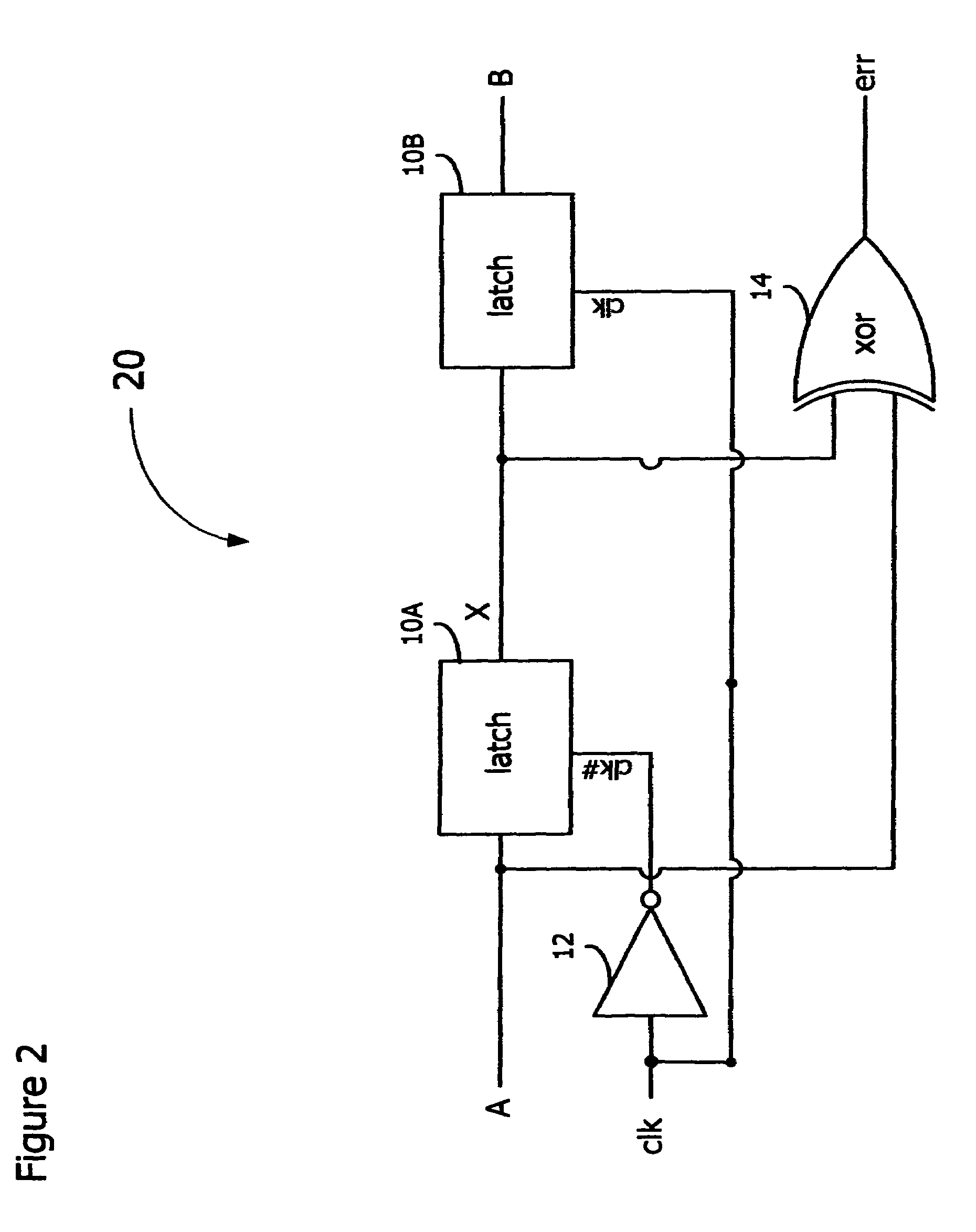

Error-detection flip-flop

An error-detection flip-flop is disclosed for identifying timing errors in digital circuits. The error-detection flip-flop is a master-slave flip-flop including logic to determine whether an input signal is received during a predetermined clock period, signifying a timing error. The error-detection flip-flop produces a variable-length error pulse, which may be combined with other error pulses and converted to a stable signal for sampling by error-correction circuitry. The error-detection flip-flop does not increase the clocking power of the digital circuit and consumes little additional circuit area.

Owner:TAHOE RES LTD

Structured placement of latches/flip-flops to minimize clock power in high-performance designs

InactiveUS20140149957A1Minimize wirelengthEasy to placeSpecial data processing applicationsEngineeringNetlist

A latch placement tool determines a shape for a cluster of latches from a preliminary layout (or based on a netlist), including an aspect ratio of the shape, and generates a template for placement of the latches in conformity with the shape. Latches are placed around a local clock buffer (LCB) based on latch size, from largest latch first to smallest latch last, and based on their ideal locations given the target aspect ratio. The ideal locations may be further based on the clock driver pin configuration of the LCB. The final template preferably has an aspect ratio that is approximately equal to the aspect ratio of the shape of the cluster, but the latch placement may be constrained by clock routing topology. Latch placement within a cluster can be further optimized by swapping one of the latches with another to minimize total wirelength of the design.

Owner:GLOBALFOUNDRIES INC

Regular local clock buffer placement and latch clustering by iterative optimization

InactiveUS8104014B2More flexibility in the location of clock componentsIncrease powerComputer aided designSoftware simulation/interpretation/emulationCapacitanceModem device

Owner:GLOBALFOUNDRIES INC

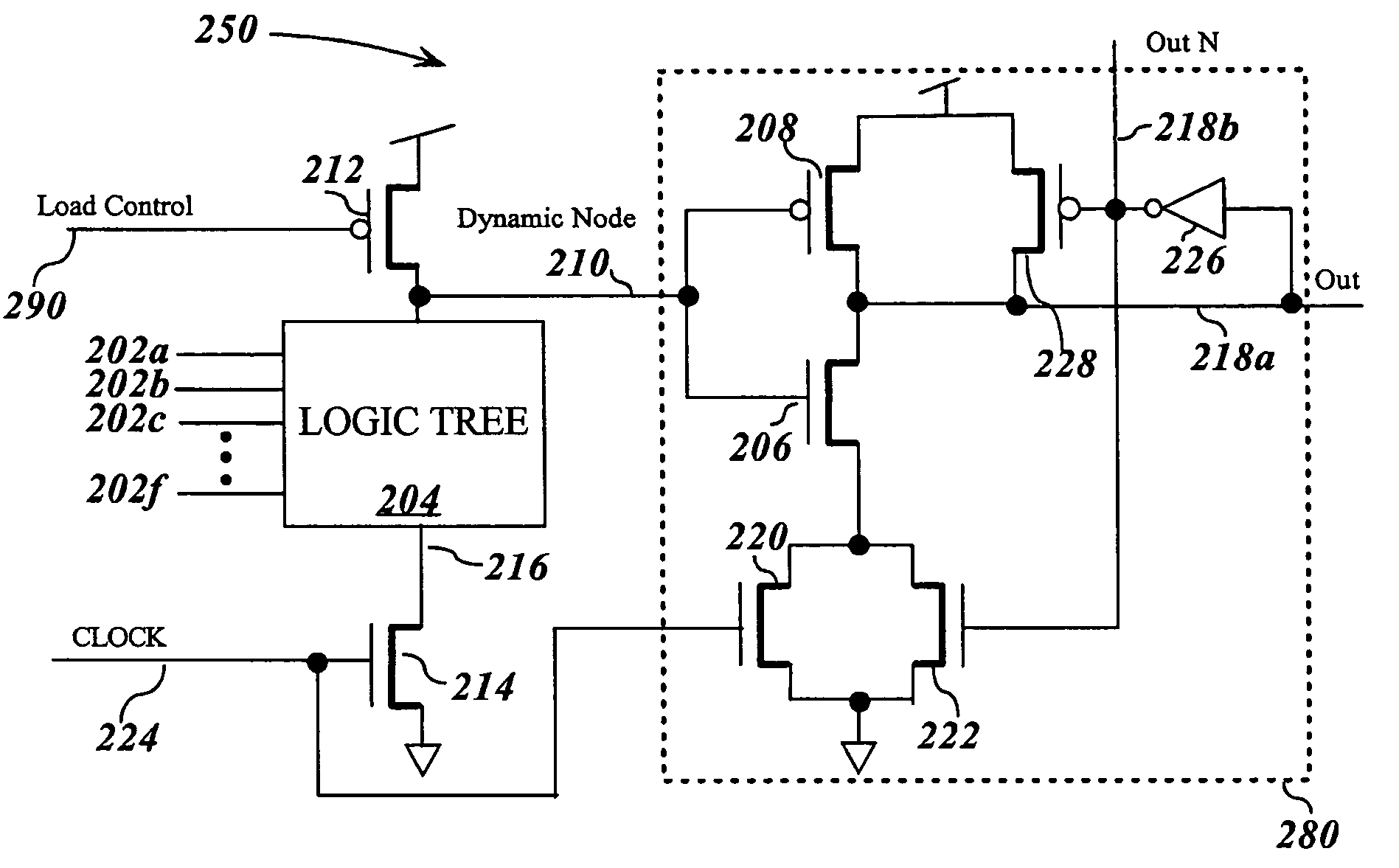

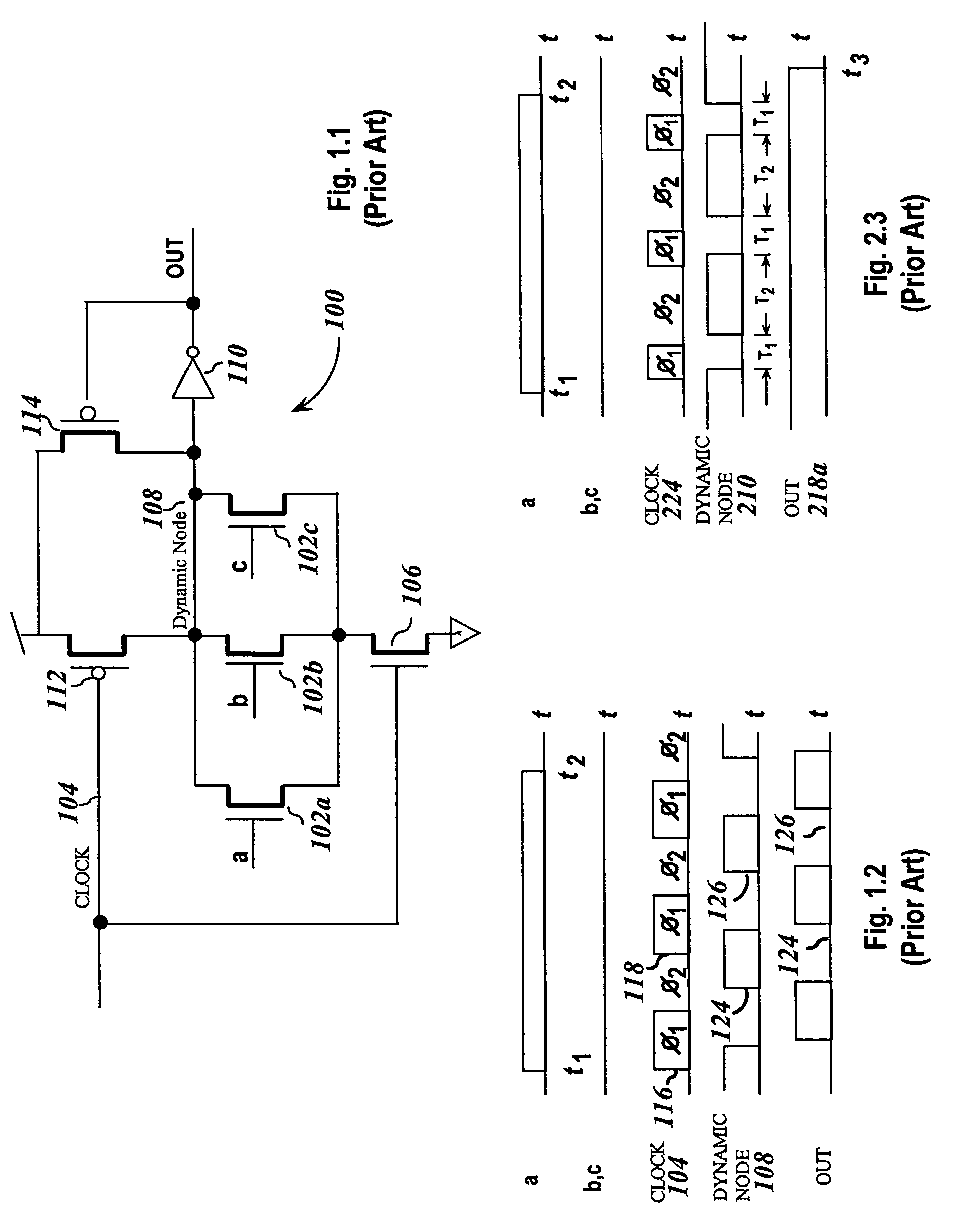

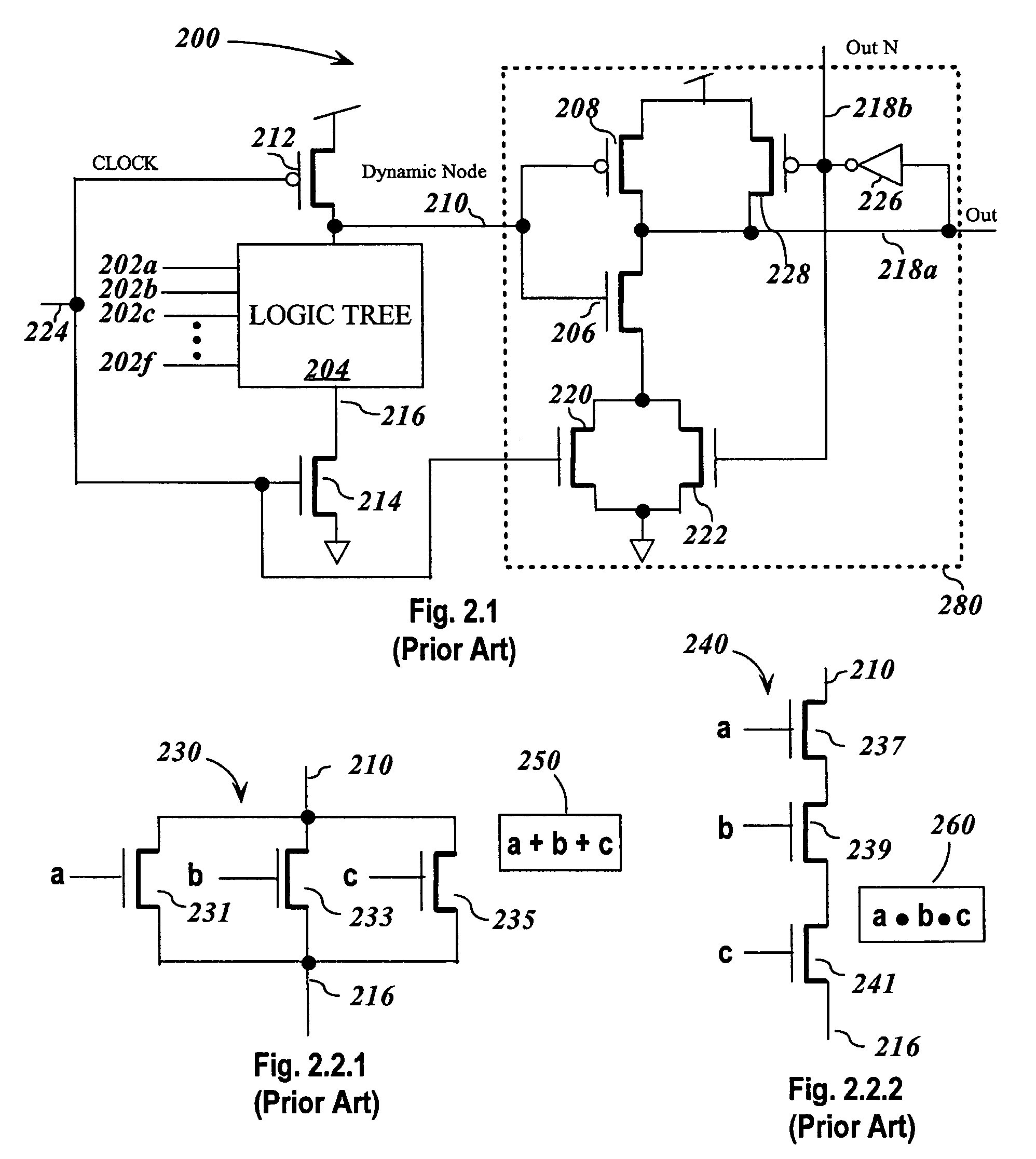

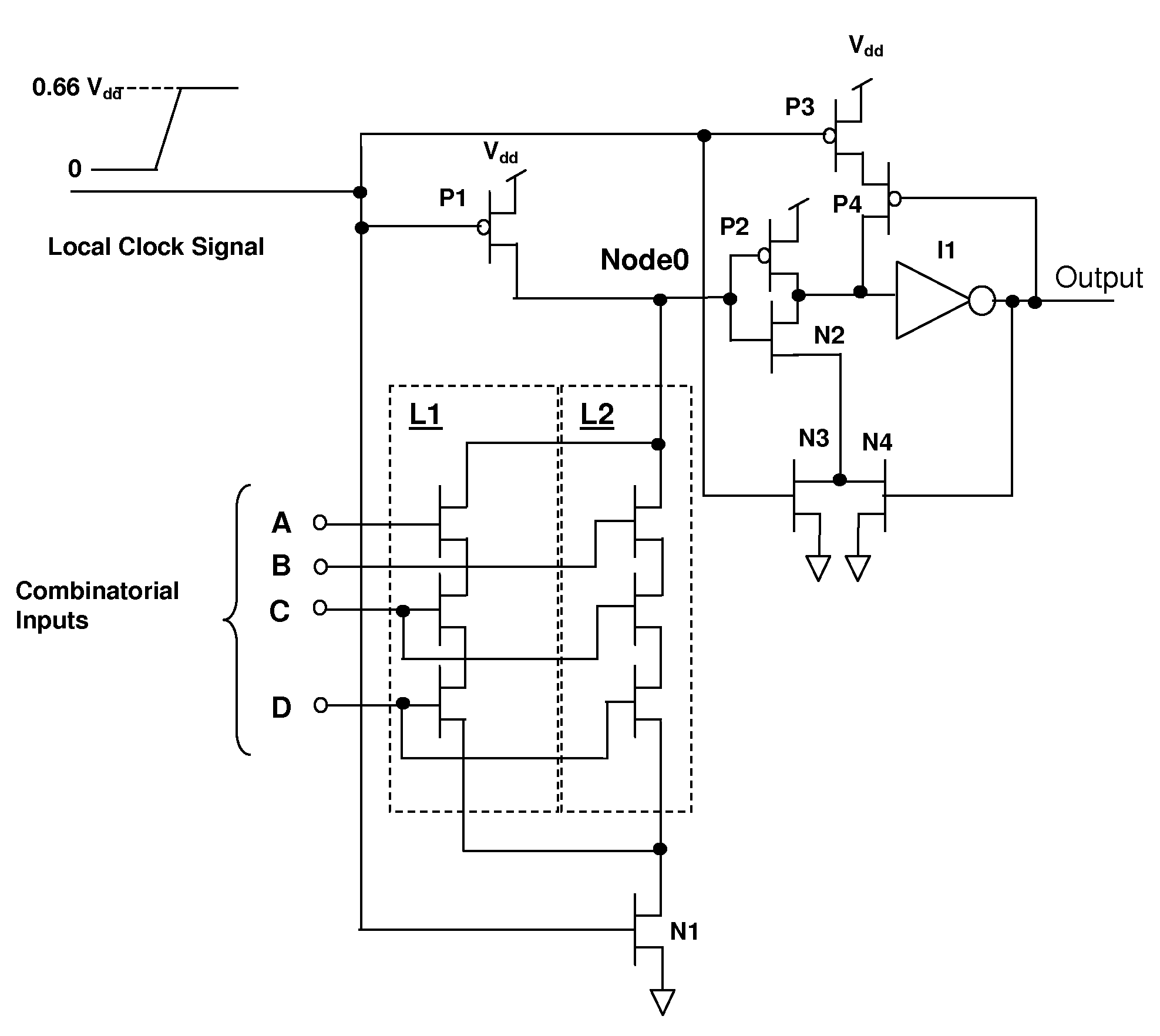

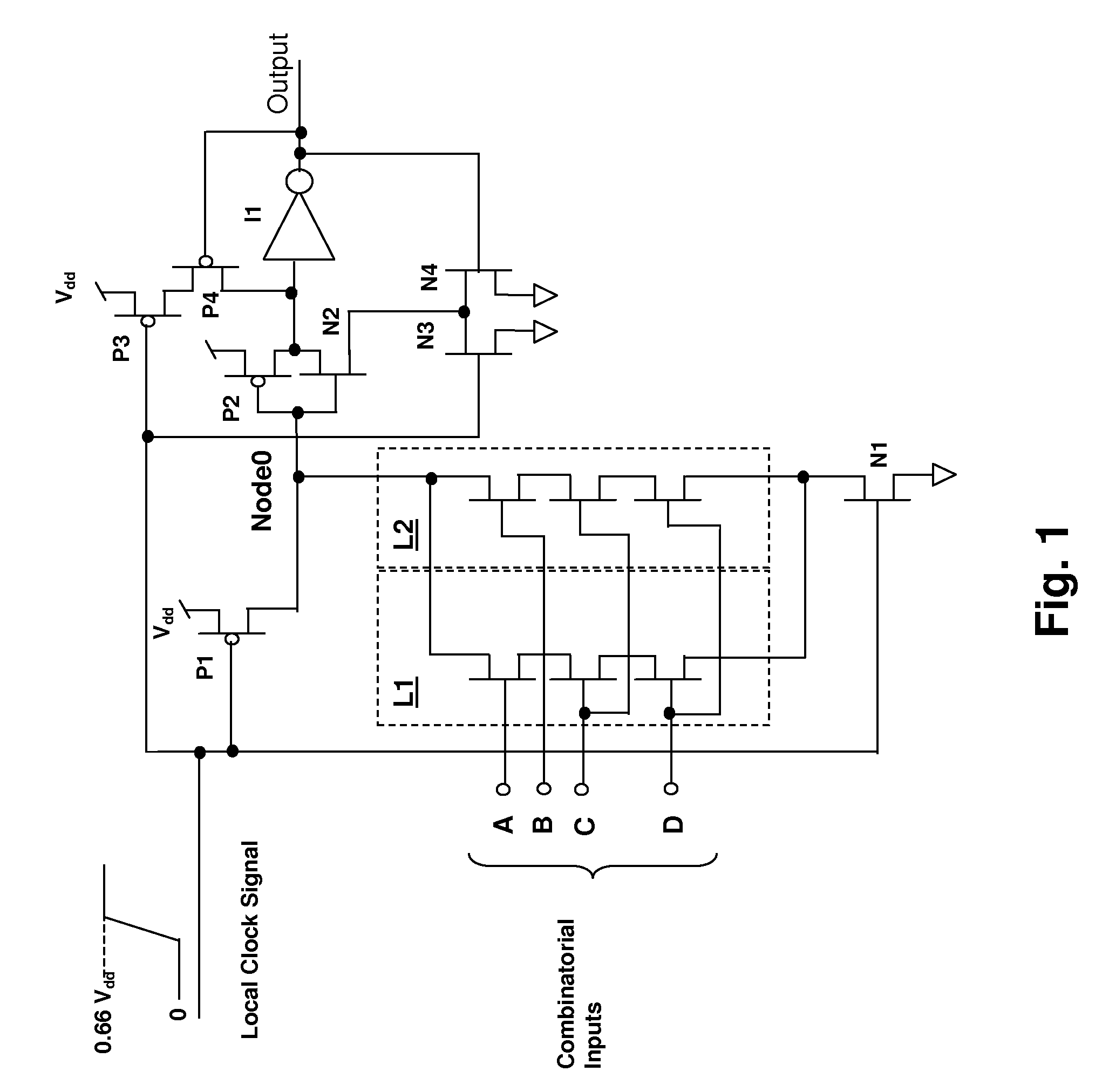

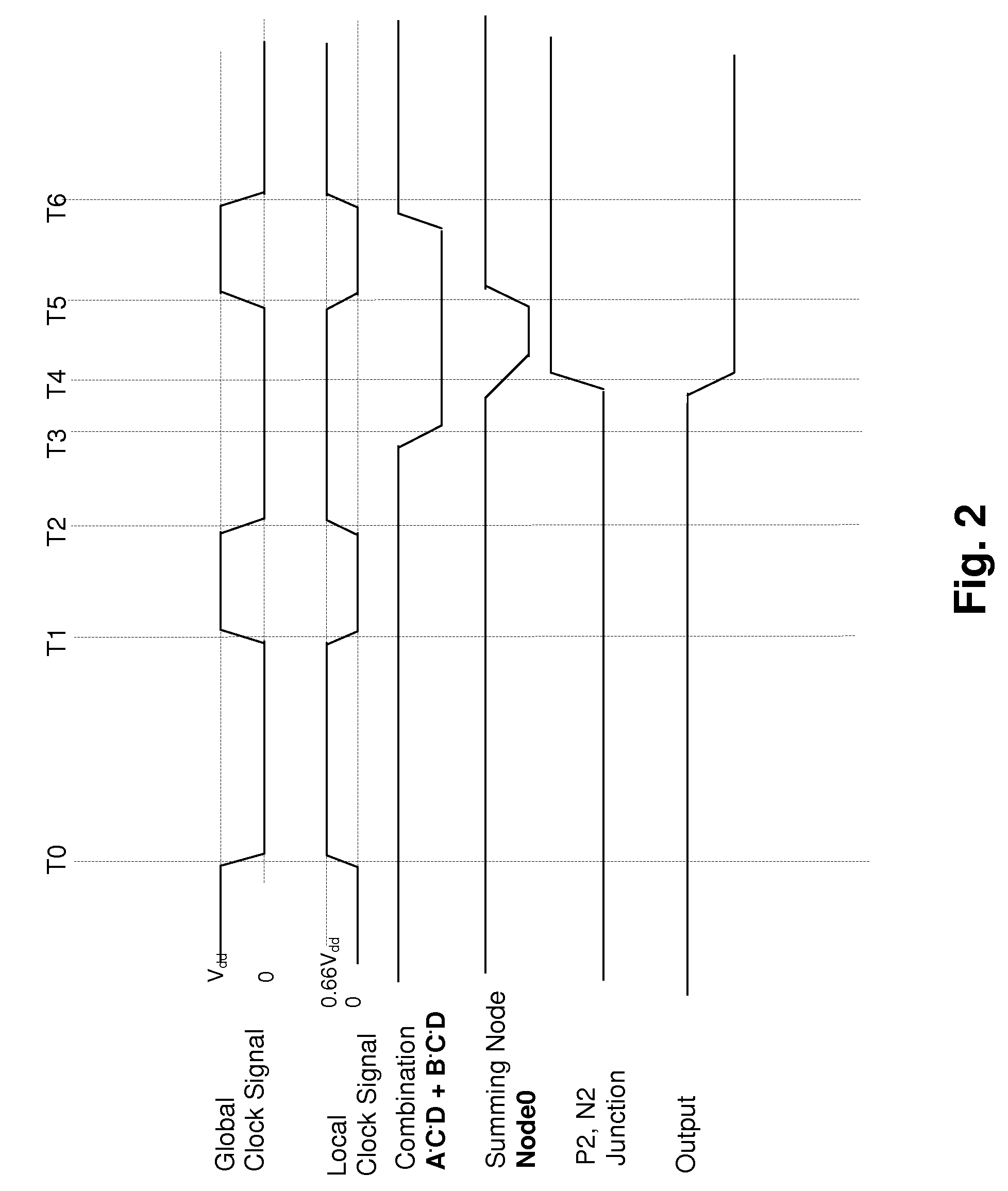

Controlled load limited switch dynamic logic circuitry

Owner:INT BUSINESS MASCH CORP

Method for power consumption reduction in a limited-switch dynamic logic (LSDL) circuit

ActiveUS7411425B2Reduce power consumptionReduce swingPower reduction by control/clock signalLogic circuits characterised by logic functionEngineeringClock power

A method for power consumption reduction in a limited-switch dynamic logic (LSDL) circuit provides reduced power consumption by reducing clock power dissipation. By clocking LSDL gates with a clock signal having a reduced voltage swing in the evaluation phase, the LSDL gates are permitted to operate, while reducing the clock power consumption dramatically. Since clock power consumption dominates in LSDL circuits, the reduction in clock power dissipation results in a significant reduction in overall circuit power consumption. The reduced swing clock is produced at a plurality of local clock buffers by supplying the local clock buffers with an extra power supply rail that is switched onto the clock distribution lines by the local clock buffers in response to the full-swing evaluate phase clock received from the global clock distribution network by the local clock buffers.

Owner:MARVELL ASIA PTE LTD

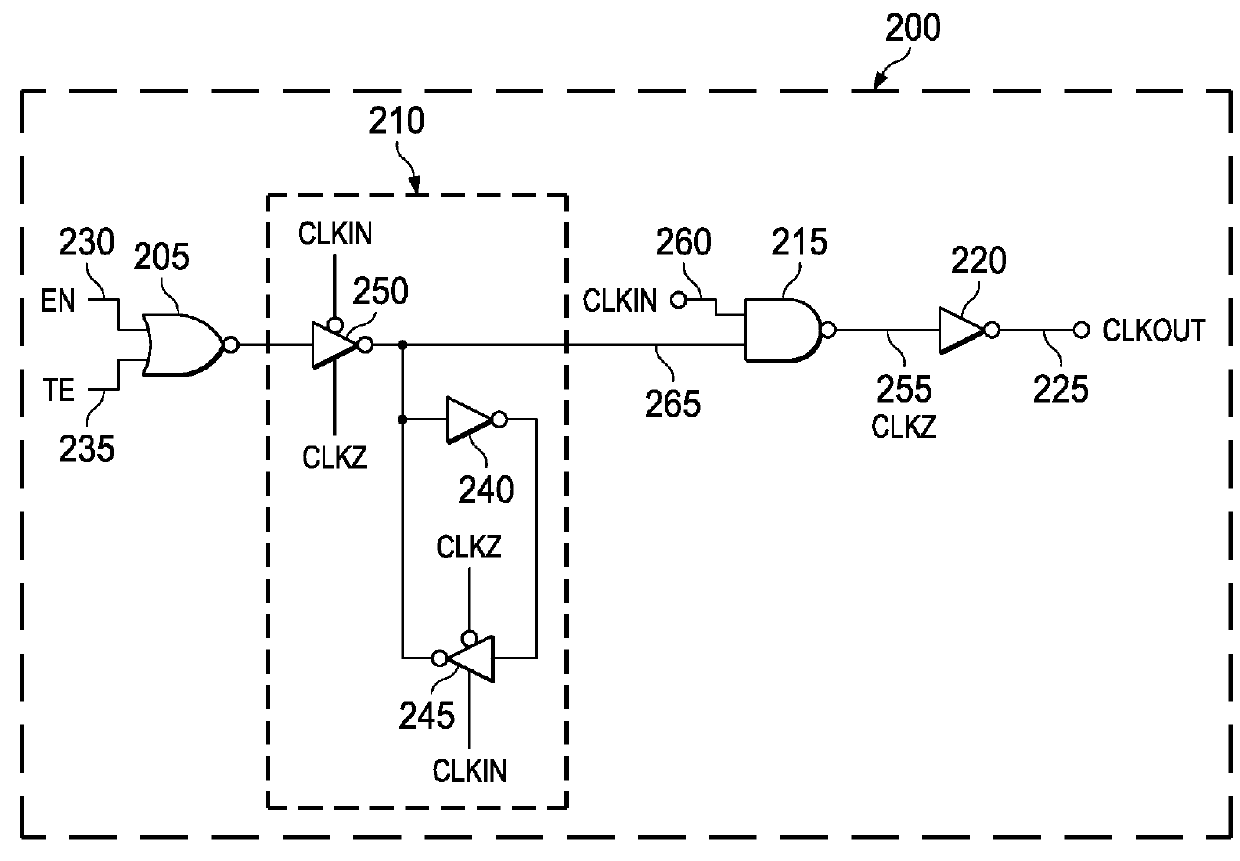

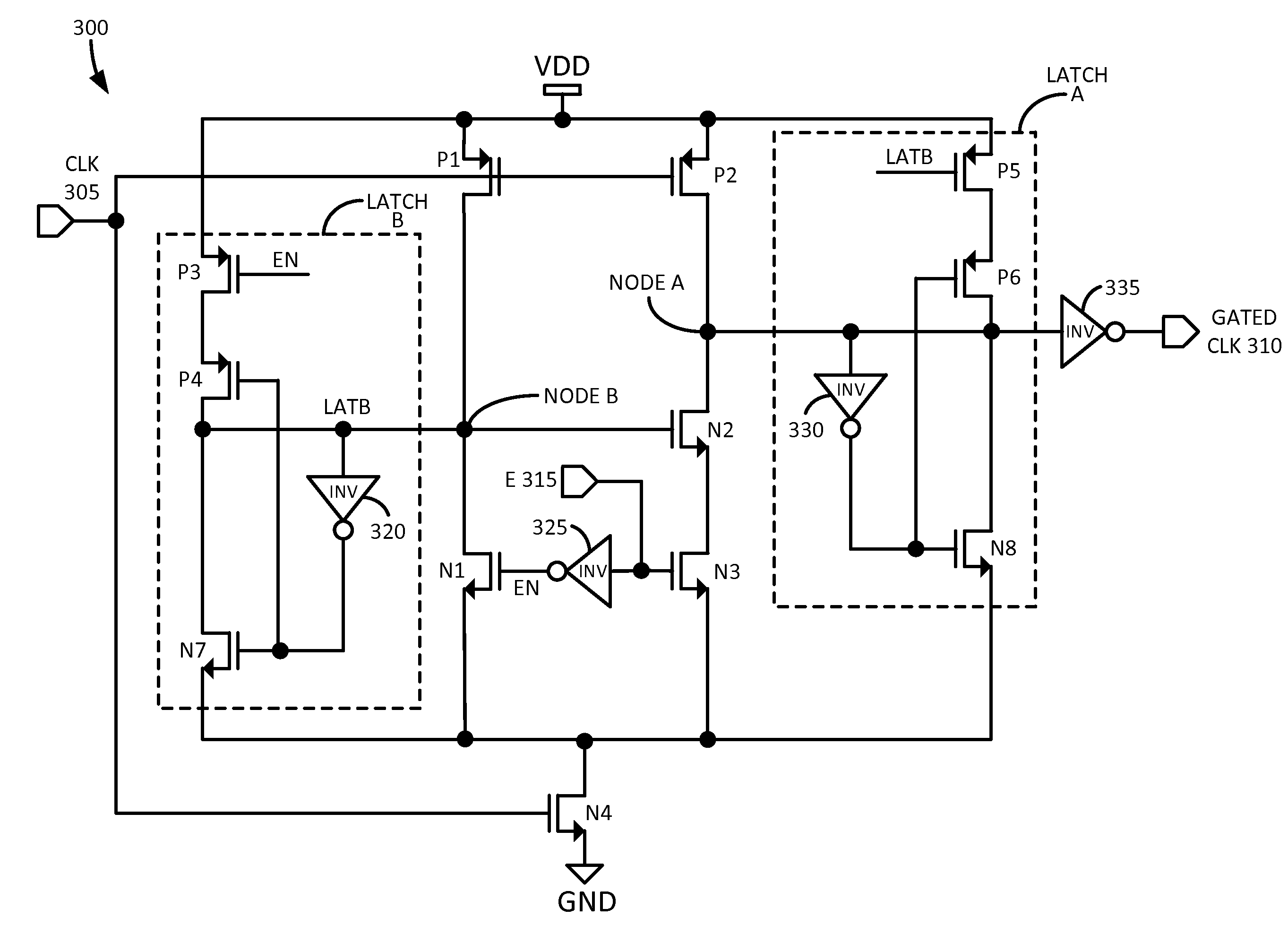

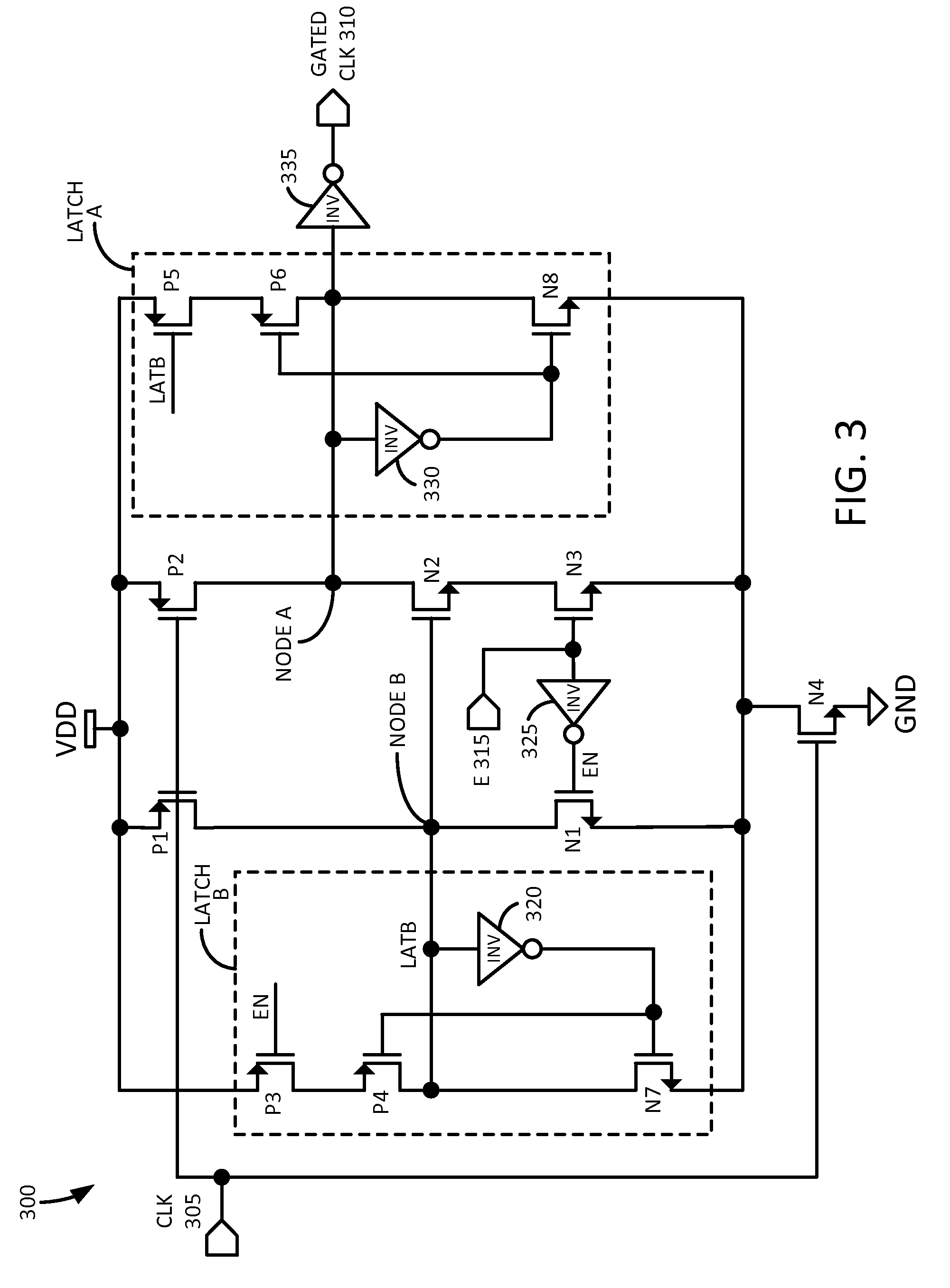

Integrated clock gater (ICG) using clock cascode complimentary switch logic

InactiveUS8975949B2Reduce power consumptionImprove performancePower reduction by control/clock signalElectronic switchingCascodeClock power

Inventive aspects include an integrated clock gater (ICG) circuit having clocked complimentary voltage switched logic (CICG) that delivers high performance while maintaining low power consumption characteristics. The CICG circuit provides a small enable setup time and a small clock-to-enabled-clock delay. A significant reduction in clock power consumption is achieved in both enabled and disabled modes, but particularly in the disabled mode. Complimentary latches work in tandem to latch different voltage levels at different nodes depending on the voltage level of the received clock signal and whether or not an enable signal is asserted. An inverter takes the voltage level from one of the nodes, inverts it, and outputs a gated clock signal. The gated clock signal may be active or quiescent depending on the various voltage levels. Time is “borrowed” from an evaluation window and added to a setup time to provide greater tolerances for receiving the enable signal.

Owner:SAMSUNG ELECTRONICS CO LTD

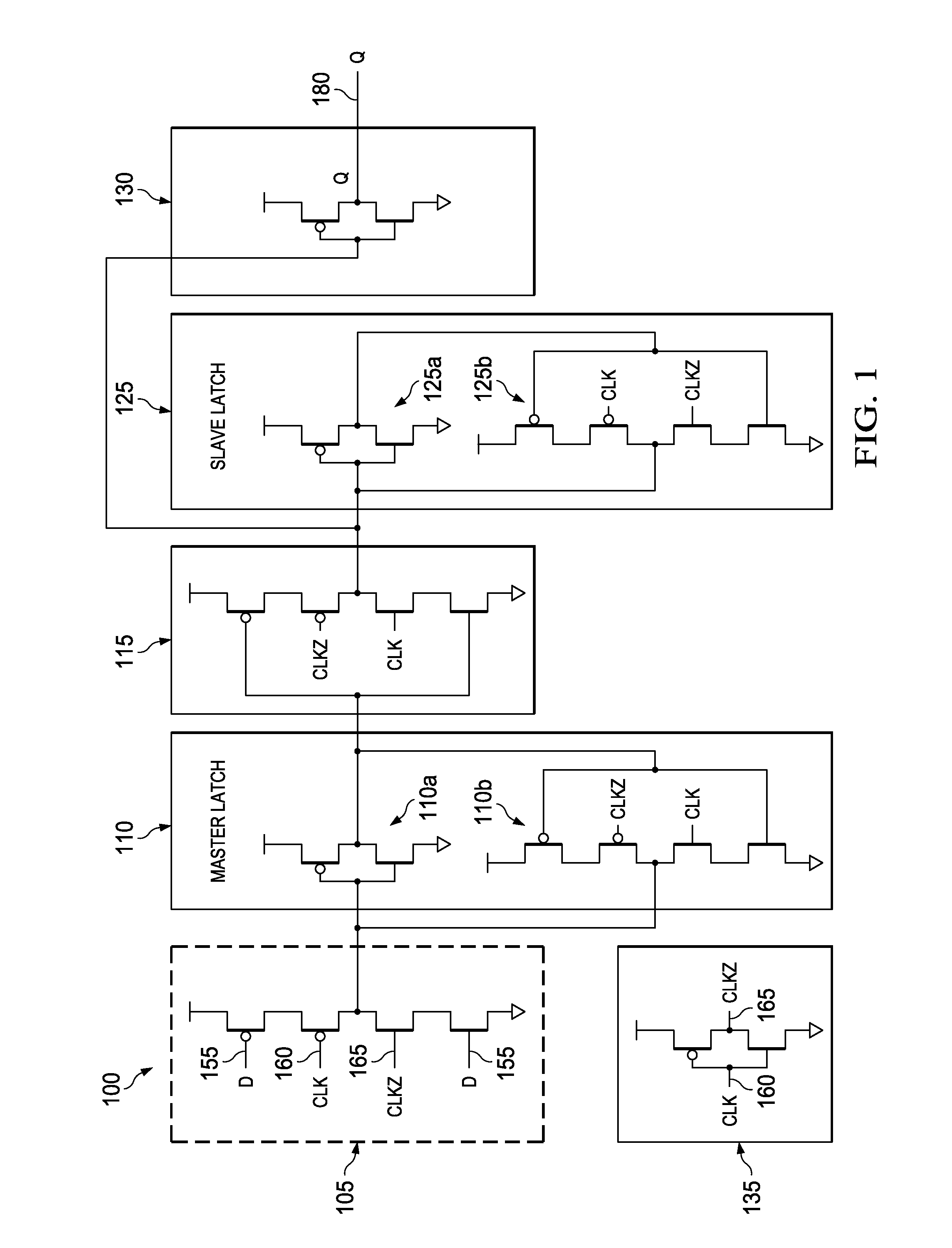

Flip-flops with low clock power

The disclosure provides a flip-flop that utilizes low power as a result of reduced transistor count. The flip-flop includes a tri-state inverter that receives a flip-flop input and a clock input. A master latch is coupled to an output of the tri-state inverter and provides a control signal to the tri-state inverter. The control signal activates the tri-state inverter. A slave latch receives an output of the master latch and the control signal. An output inverter is coupled to an output of the slave latch and generates a flip-flop output.

Owner:TEXAS INSTR INC

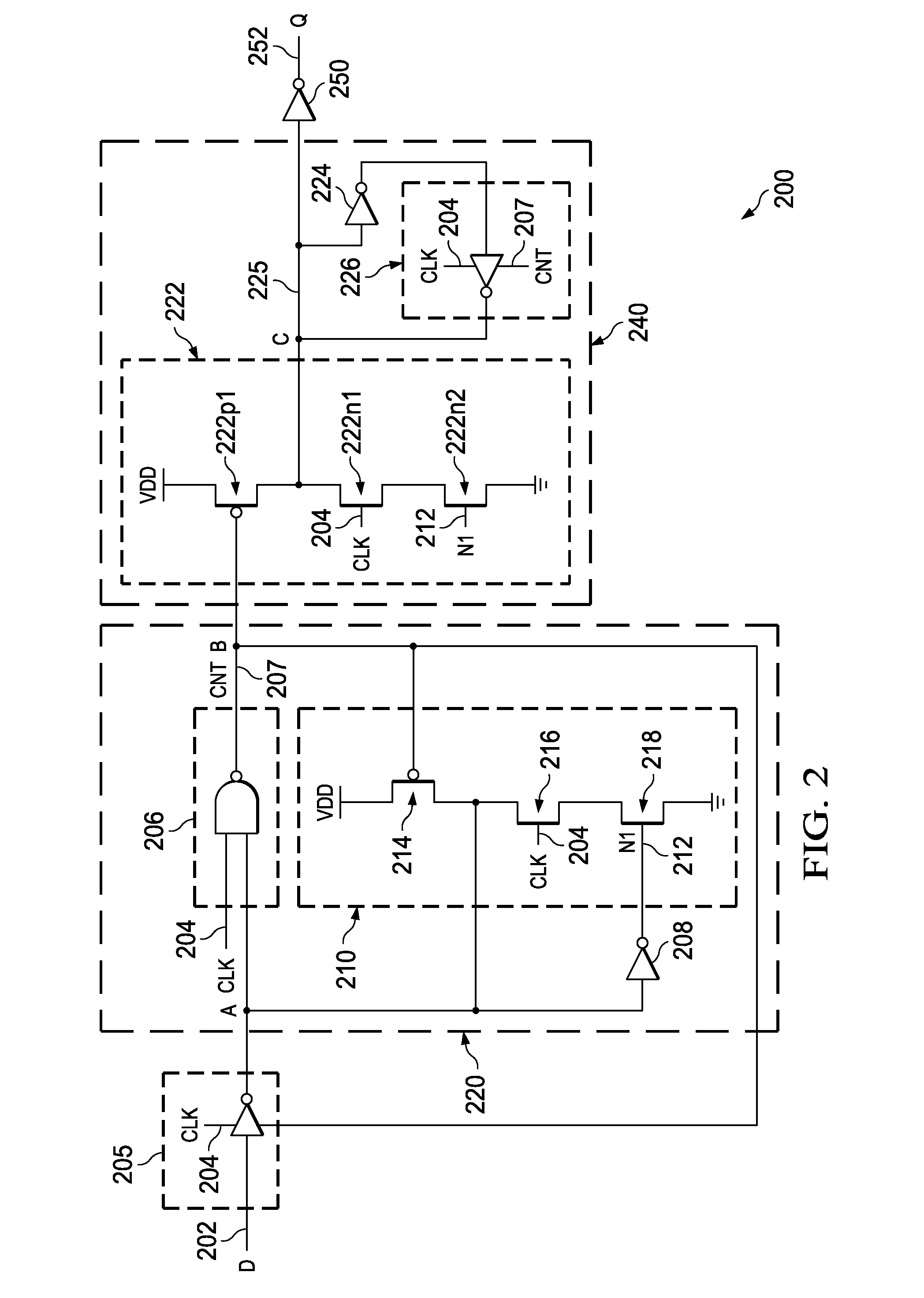

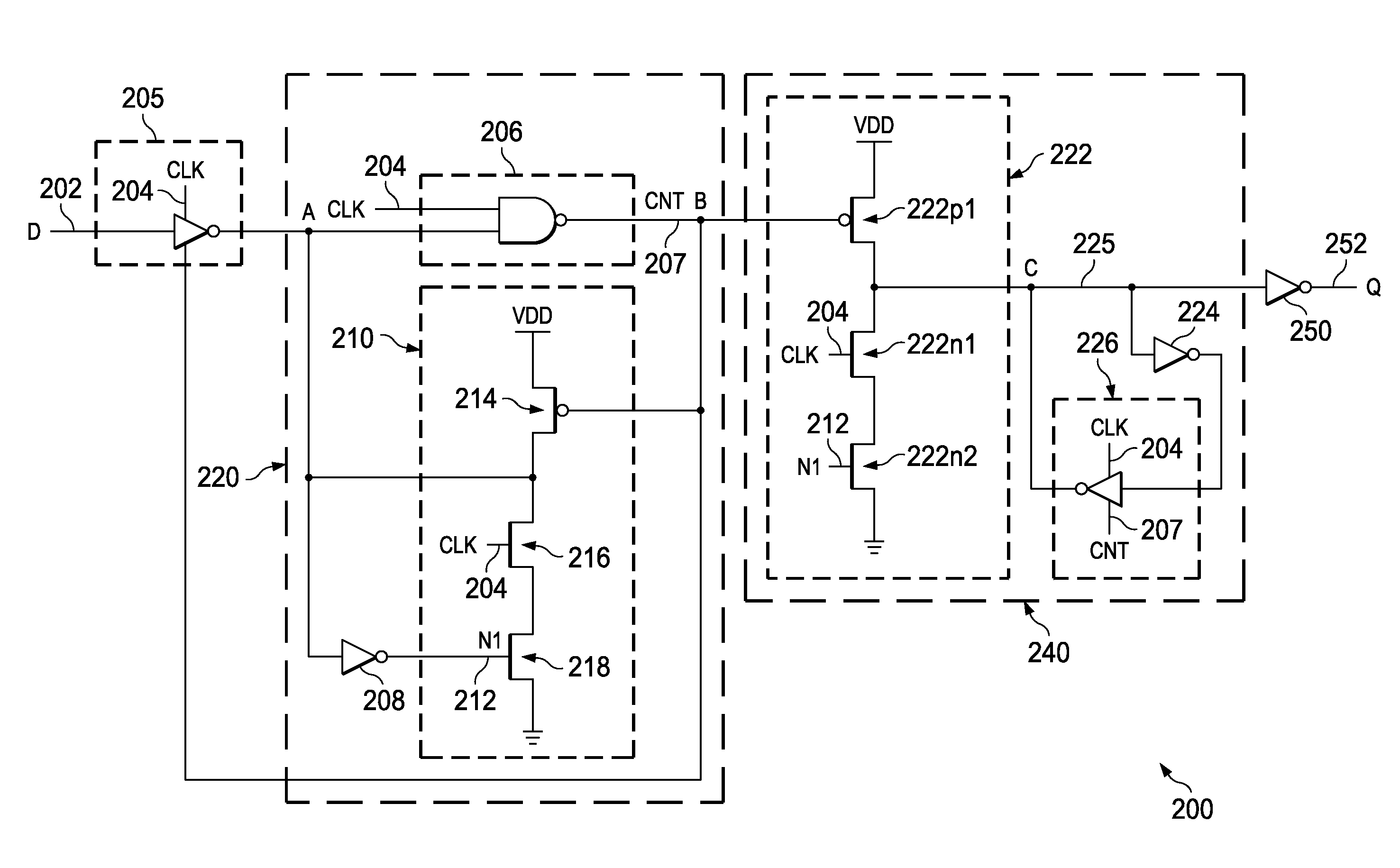

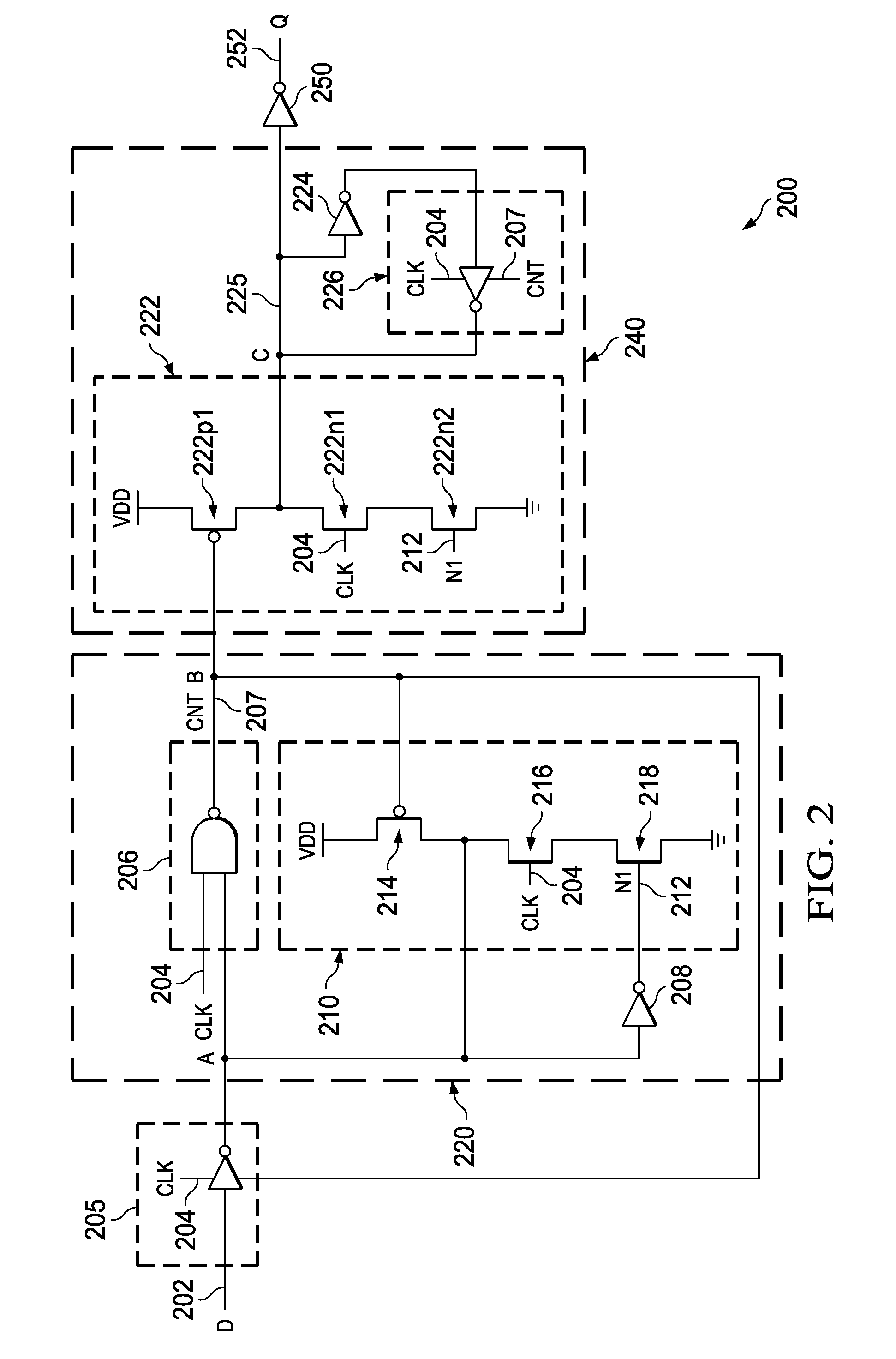

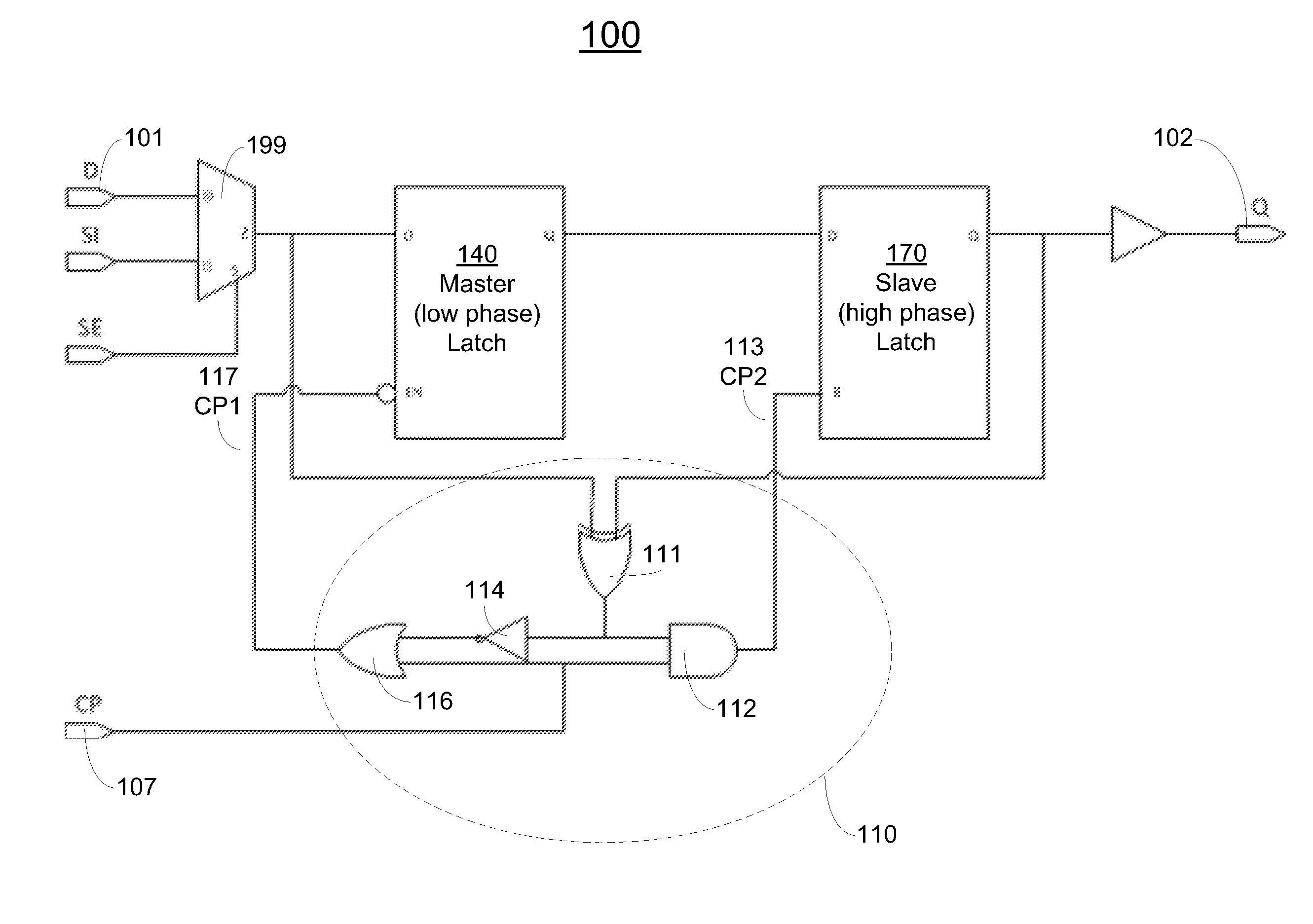

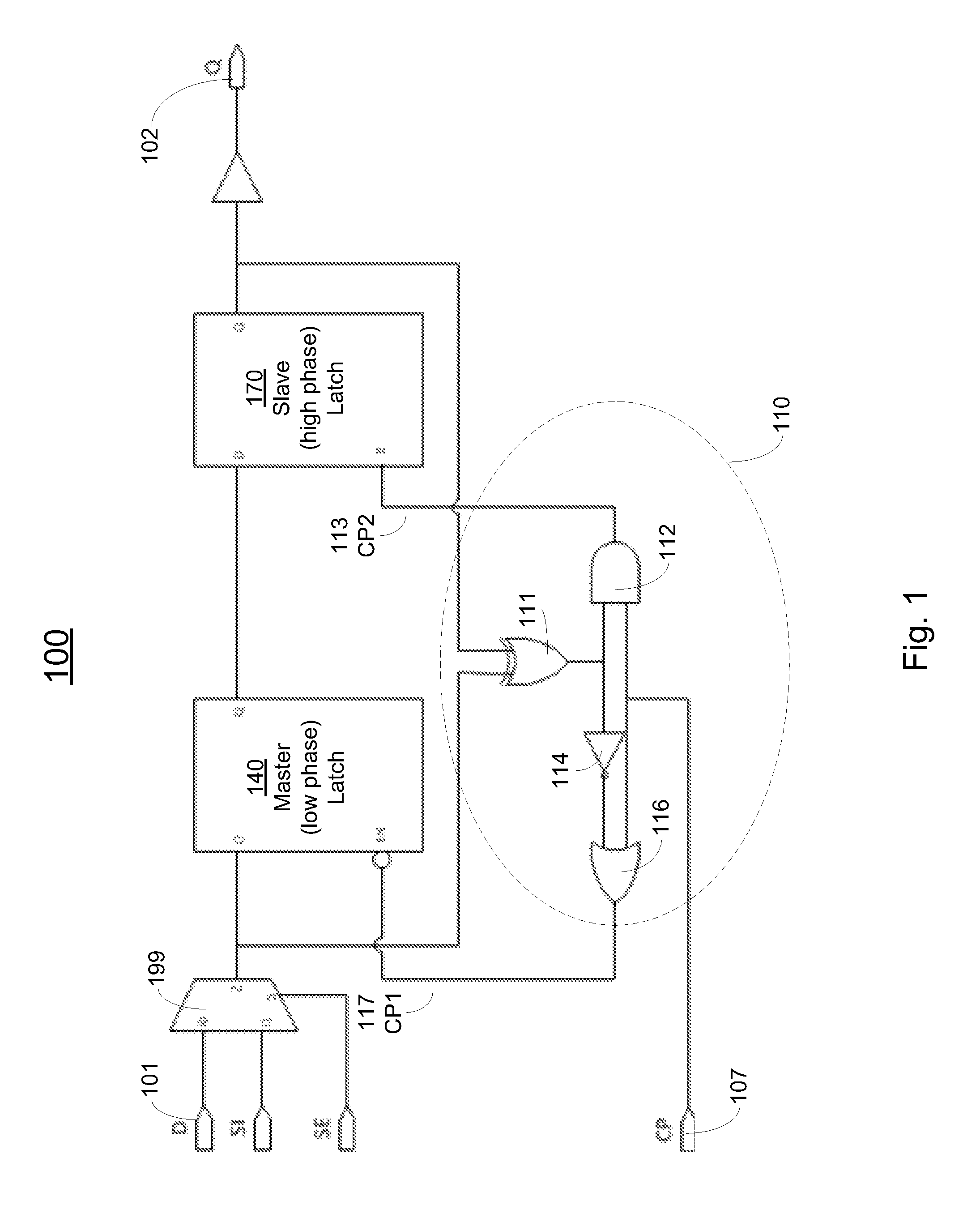

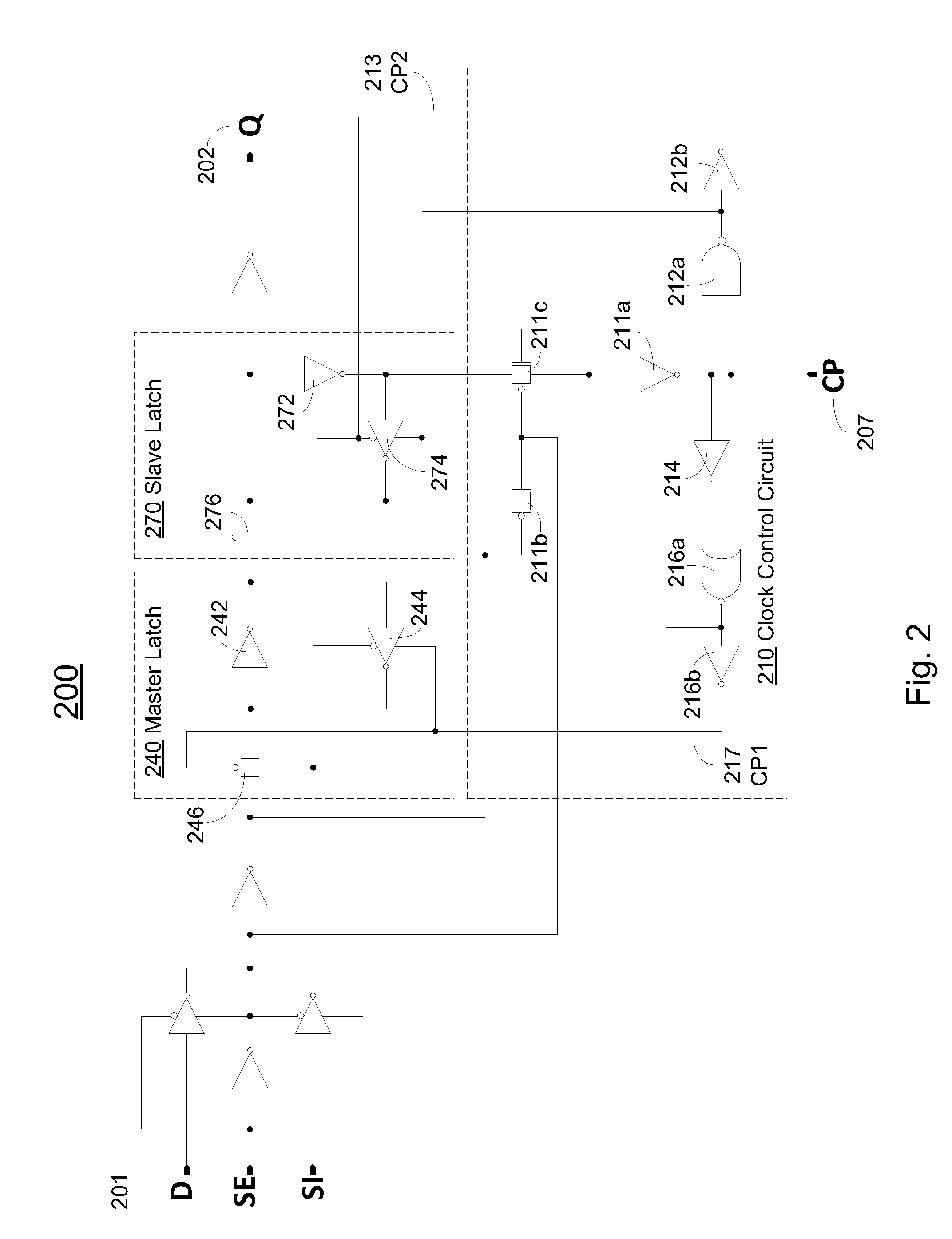

Low clocking power flip-flop

ActiveUS20160269002A1Reduce in quantityReduce gate capacitanceExclusive-OR circuitsElectrical testingFlip-flopClock power

Low clocking power flip-flop. In accordance with a first embodiment of the present invention, a flip-flop electronic circuit includes a master latch coupled to a slave latch in a flip-flop configuration. The flip-flop electronic circuit also includes a clock control circuit for comparing an input to the master latch with an output of the slave latch, and responsive to the comparing, blocking a clock signal to the master latch and the slave latch when the flip-flop electronic circuit is in a quiescent condition.

Owner:NVIDIA CORP

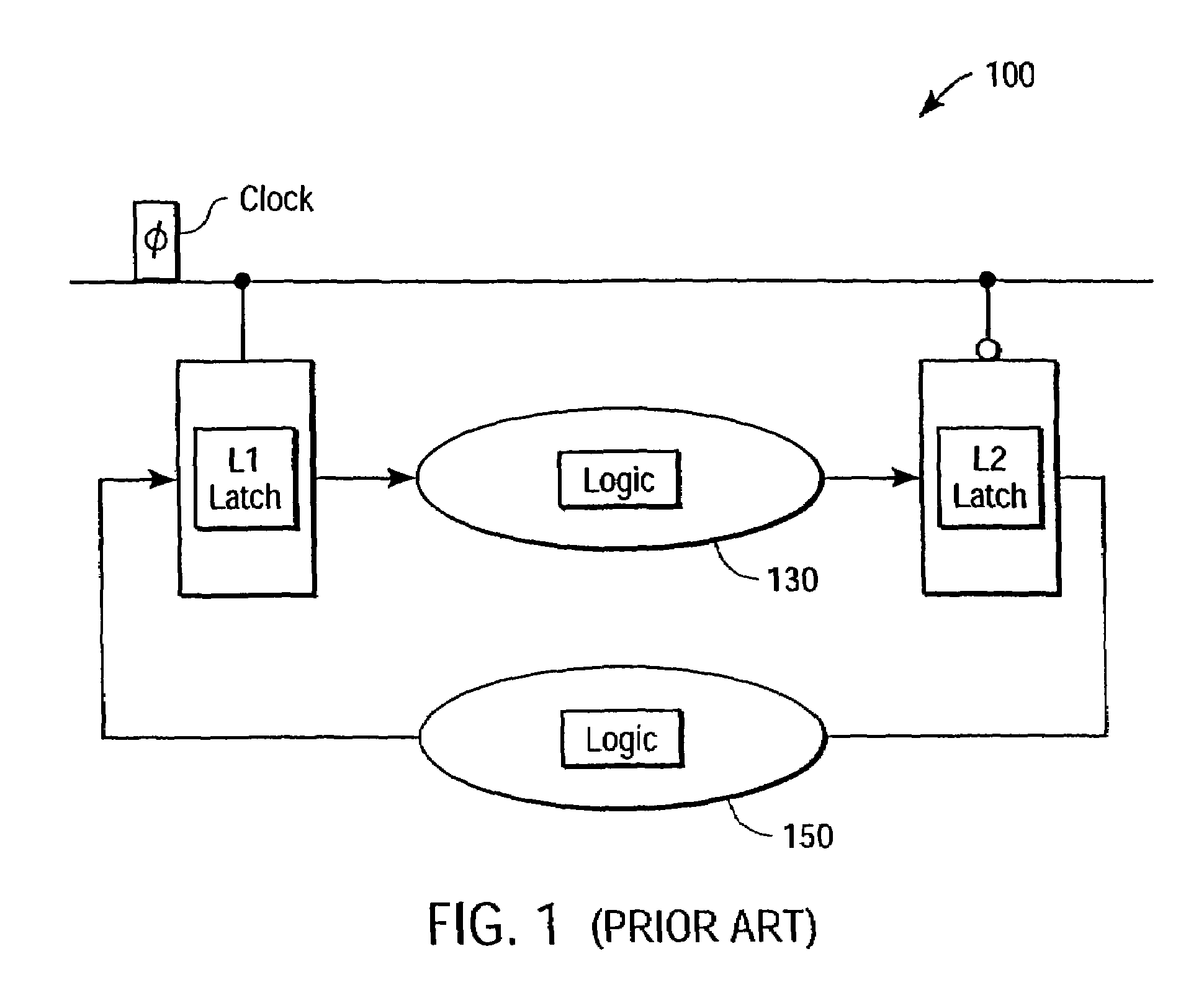

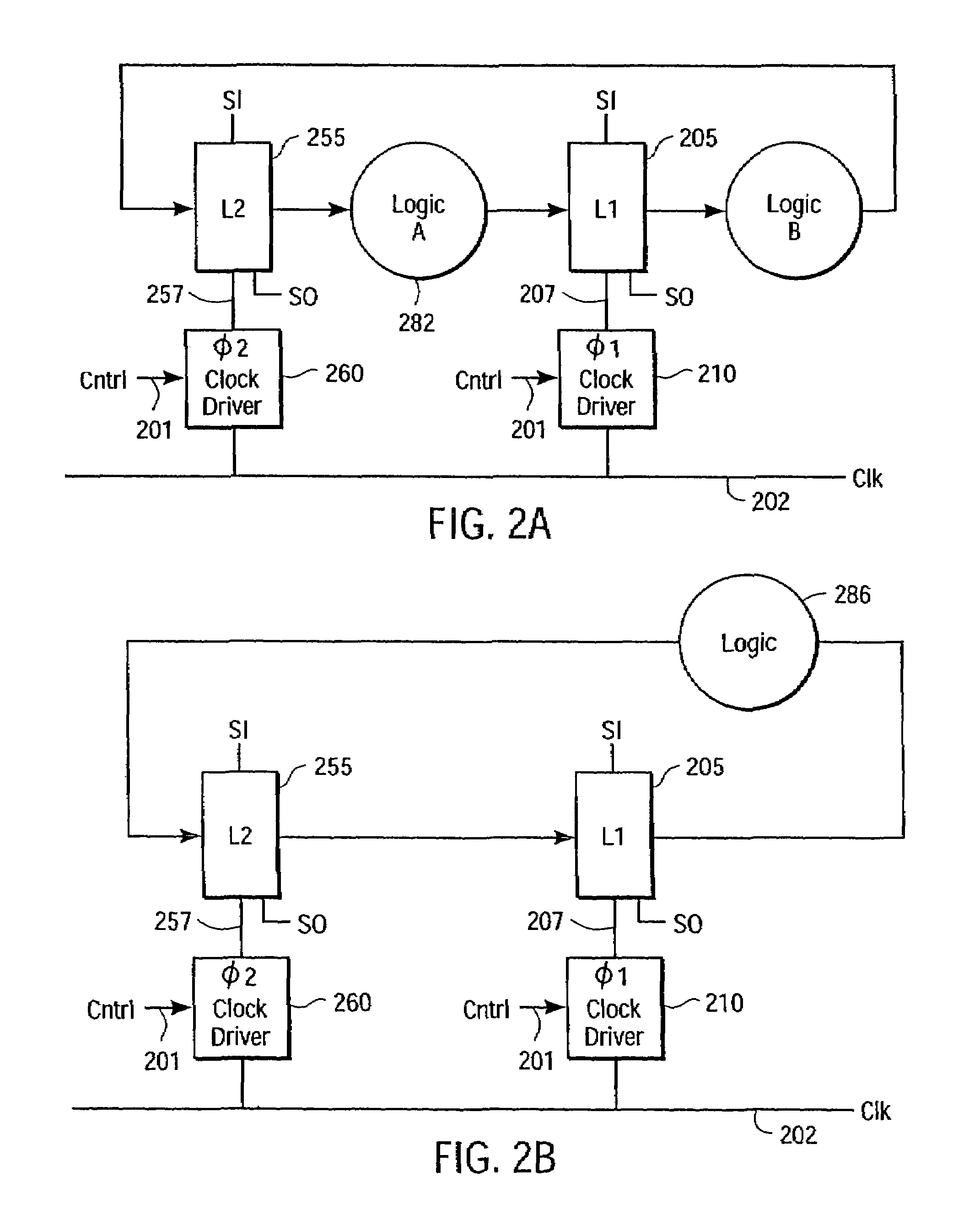

Cold clock power reduction

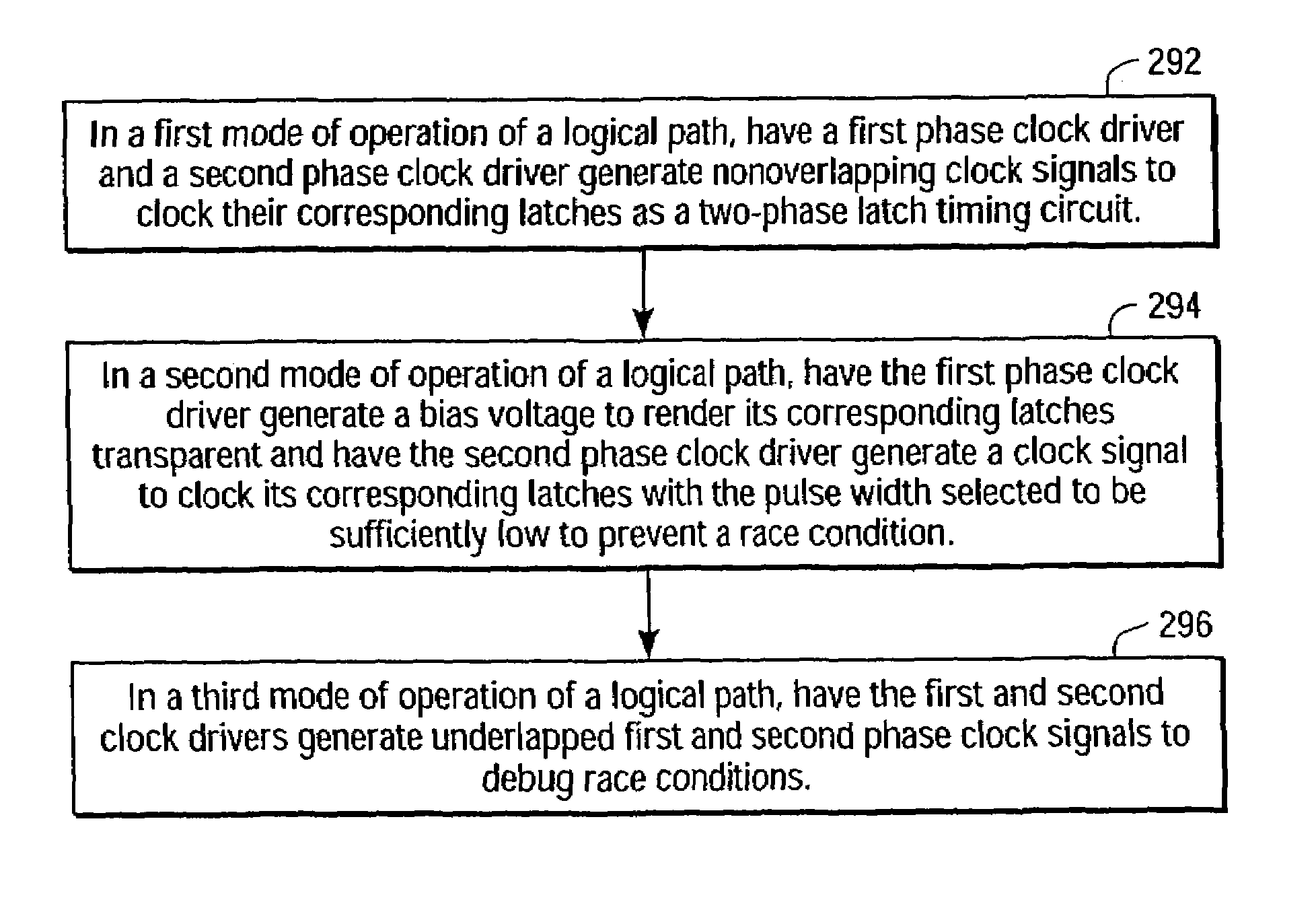

InactiveUS7051294B2Reduced clock powerReduce clock power consumptionEnergy efficient ICTVolume/mass flow measurementOperation modeComputer science

A multi-mode latch timing circuit has a first set of latches and a second set of latches in each logical path. In a first mode of operation, first and second phase clock signals are provided so that the latch timing circuit functions as a two-phase non-overlapping transparent latch timing circuit. In a second mode of operation, the first set of latches is held in a transparent state in some or all of the logical paths, thereby reducing clock power. In one embodiment, the first set of latches in each long path is held in a transparent state while the second phase clock signal is supplied to the second set of latches. In one embodiment, the first set of latches in each short path is held in a transparent state while a second phase clock signal comprised of shortened duty cycle pulses is supplied to the second set of latches.

Owner:FUJITSU LTD

Apparatus for clocked power logic against power analysis attack

ActiveUS8390311B2Reliability increasing modificationsPower reduction by energy recoveryPower analysisParasitic capacitance

Owner:IUCF HYU (IND UNIV COOP FOUND HANYANG UNIV)

Bi-layer pseudo-spin field-effect transistor

InactiveUS8188460B2Low gate and interlayer biasesNanoinformaticsSemiconductor/solid-state device manufacturingPower flowSpins

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

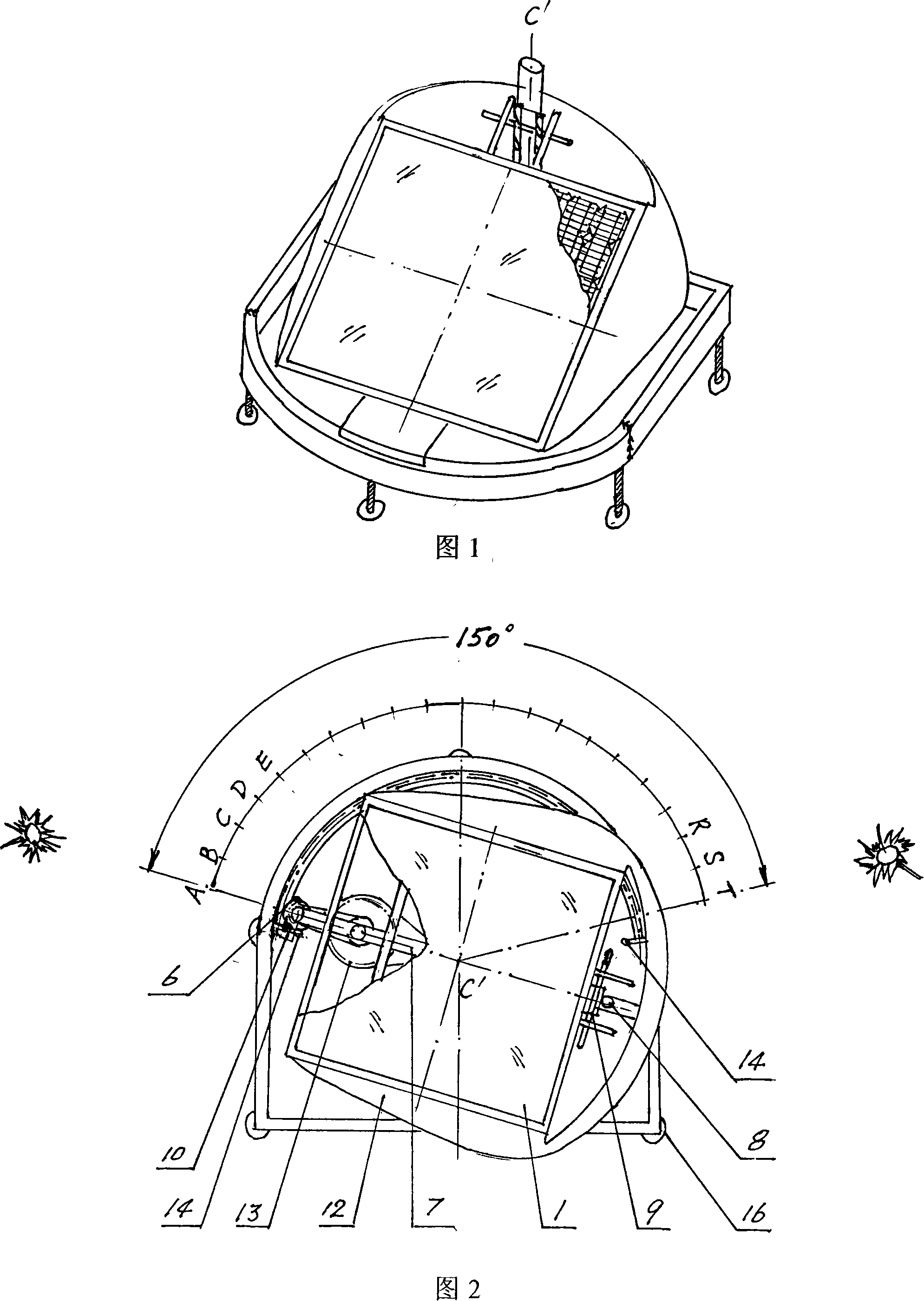

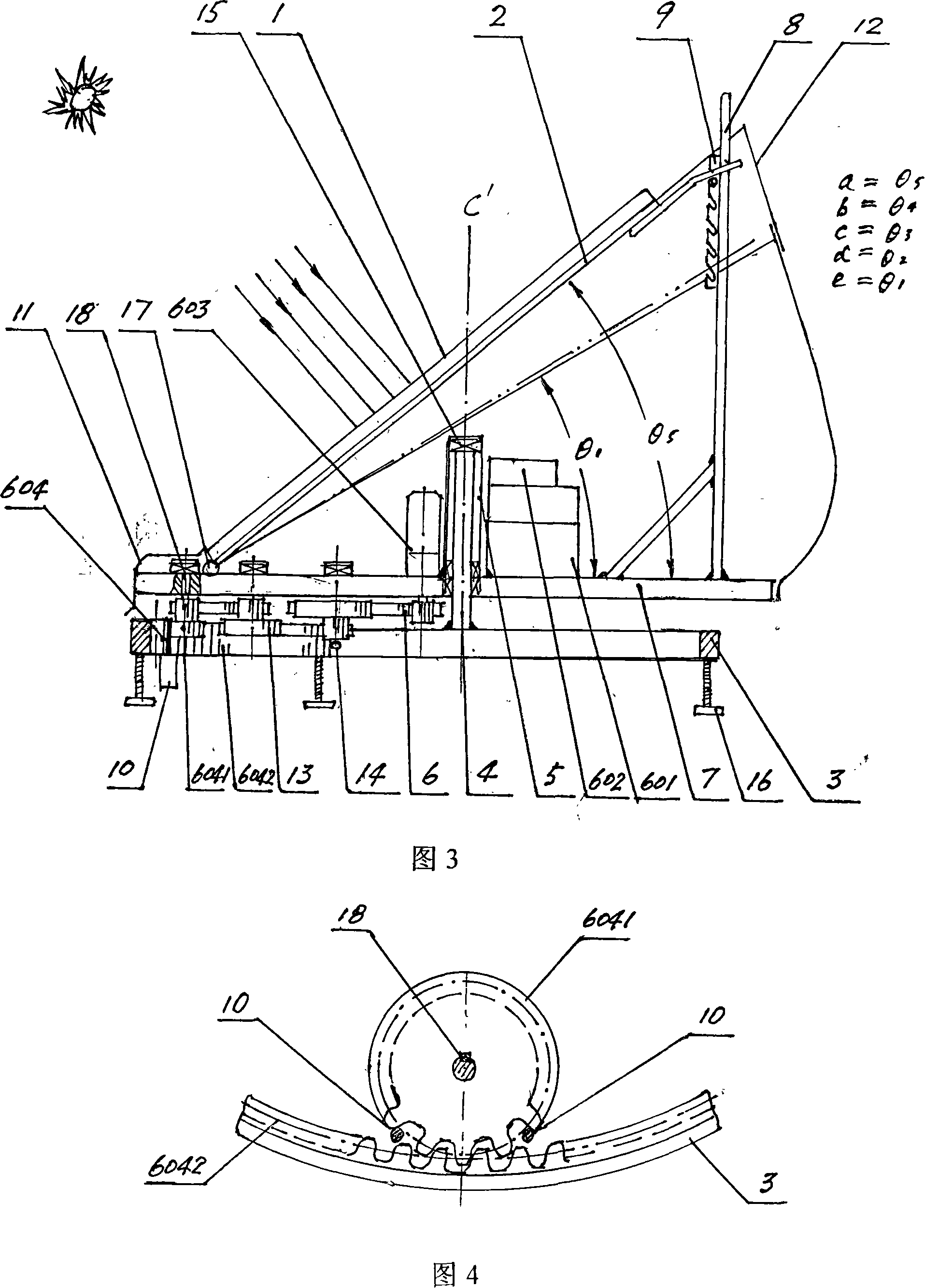

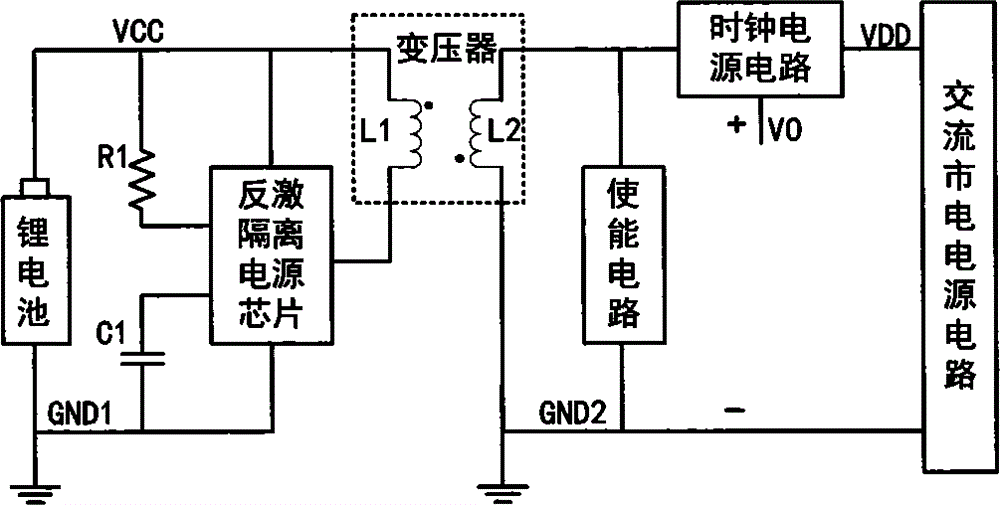

Clock type solar simple tracking apparatus

InactiveCN101131260ALower center of gravityImprove wind resistancePhotovoltaic supportsSolar heating energyElectric machineClock power

This invention relates to a clock type solar energy simple tracking rotation device. It includes solar energy heat collecting board, moving support for assembling the solar energy heat collecting board, base, vertical shaft connecting to the base, rotating spigot shaft matching the vertical shaft and clock mechanism which undertakes solar energy hour angle tracking control. Transmissions are respectively arranged on the moved rotating arm and fixed base. They control electric engine to output torque through clock power source and controlling element. The torque drives moving support and solar energy heat collecting board to carry out solar energy hour angle reciprocating tracking rotation along the vertical shaft. It makes the moment of resistance and driving power dissipation lowest. This invention is lighter and smaller. It is adequate for portable and movable equipments.

Owner:潘戈

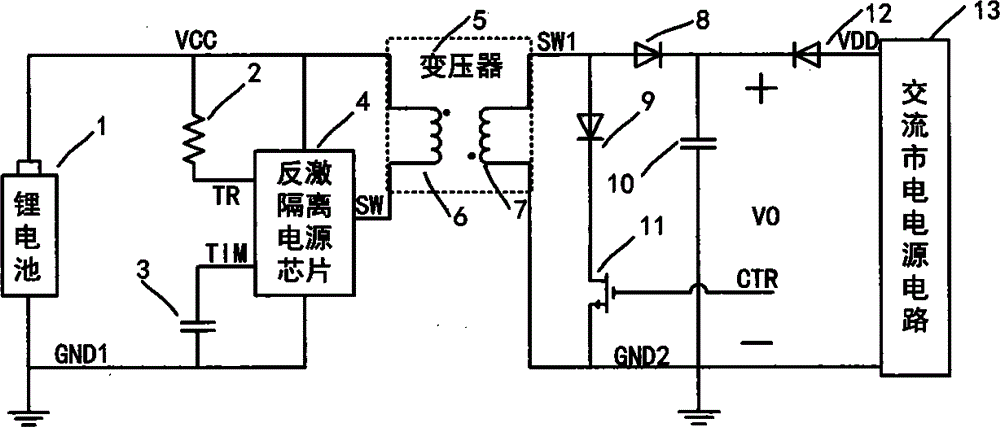

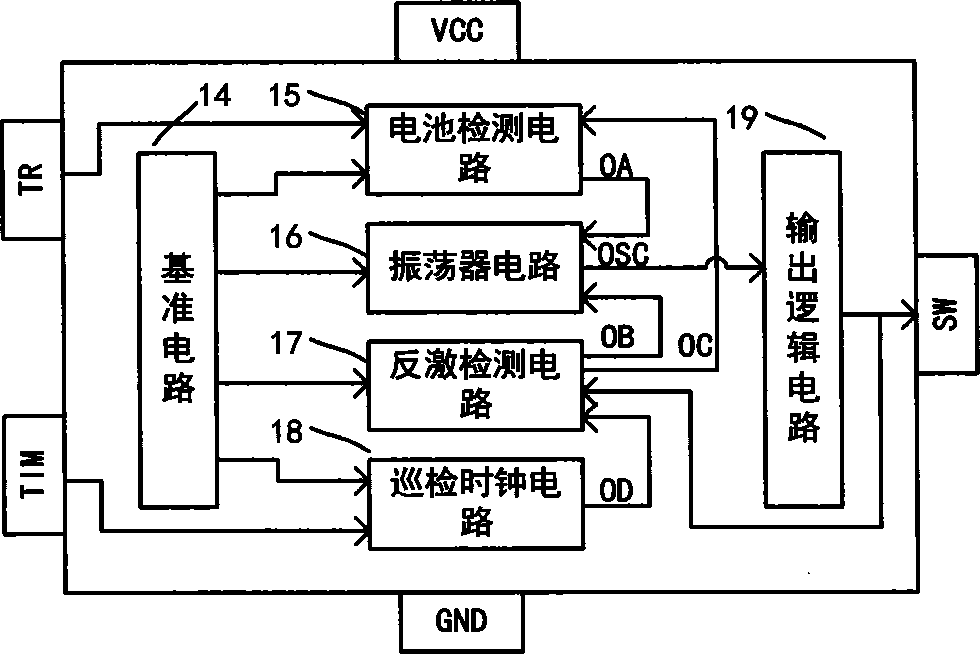

Isolation type battery power supply scheme

ActiveCN104953701AAvoid the risk of electric shockAchieve isolationElectrical testingApparatus with intermediate ac conversionTransformerElectrical battery

The invention provides an isolation type battery power supply scheme. A lithium battery, a resistor R1, a capacitor C1, a flyback isolation power supply chip, a transformer, an enable circuit, a clock power circuit and an alternating current mains supply circuit are adopted in the scheme. The scheme is characterized in that under the alternating current supply condition, the working voltage of the clock power circuit is provided by the alternating current mains supply circuit while the lithium battery only provides quiescent current for the flyback isolation power supply chip; under the alternating current outage condition, the lithium battery is used as a standby power supply by a system and provides the working voltage for the clock power circuit. Meanwhile, the power supply scheme has a lithium battery capacity detection function and sends out a battery replacement notice when the battery capacity is lower. With the adoption of the scheme, a lithium battery power supply system and a circuit of an alternating current mains supply system are isolated, that is, battery replacement electric shock hazards due to the fact that the battery power supply system is common-grounded with the alternating current mains supply system are avoided, and impact damage caused by direct connection of the battery with an MCU (micro controller unit) to MCU pins is also effectively avoided.

Owner:QINGDAO TOPSCOMM COMM

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com