Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31 results about "Adaptive routing algorithm" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Adaptive routing algorithms are the algorithms that base its decisions on data which reflects the current traffic conditions. Non adaptive routing algorithms are the algorithms that consult static tables to determine which node to send the packet.

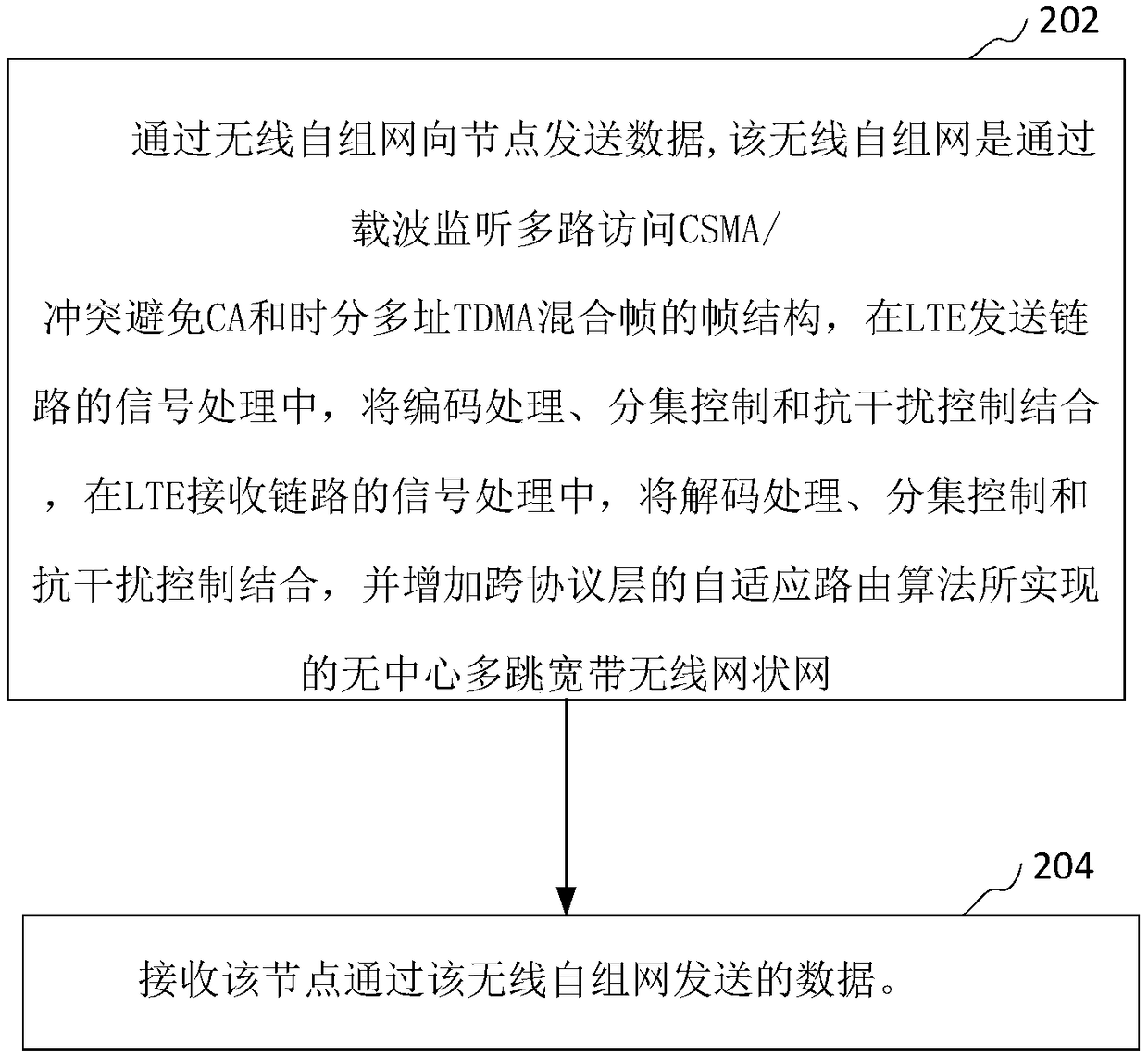

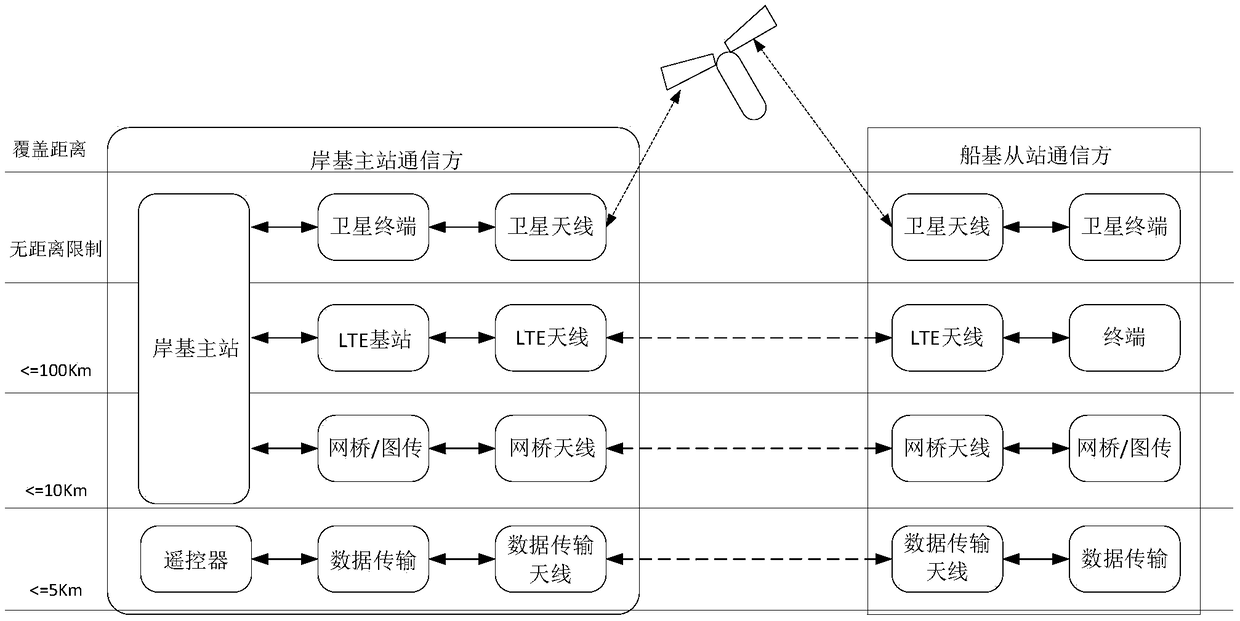

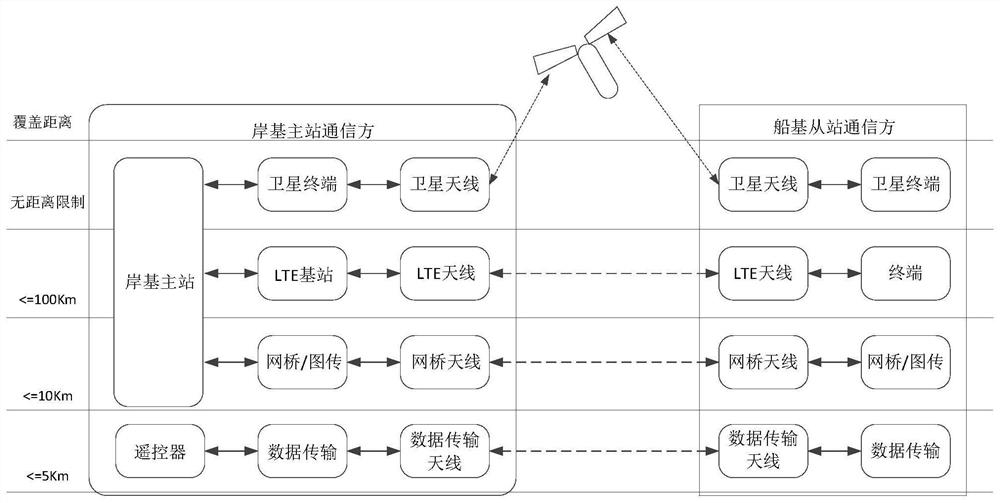

Wireless ad hoc network communication method and device

ActiveCN109275171AWill not affect operationImprove survivabilityError preventionNetwork topologiesAnti jammingWireless mesh network

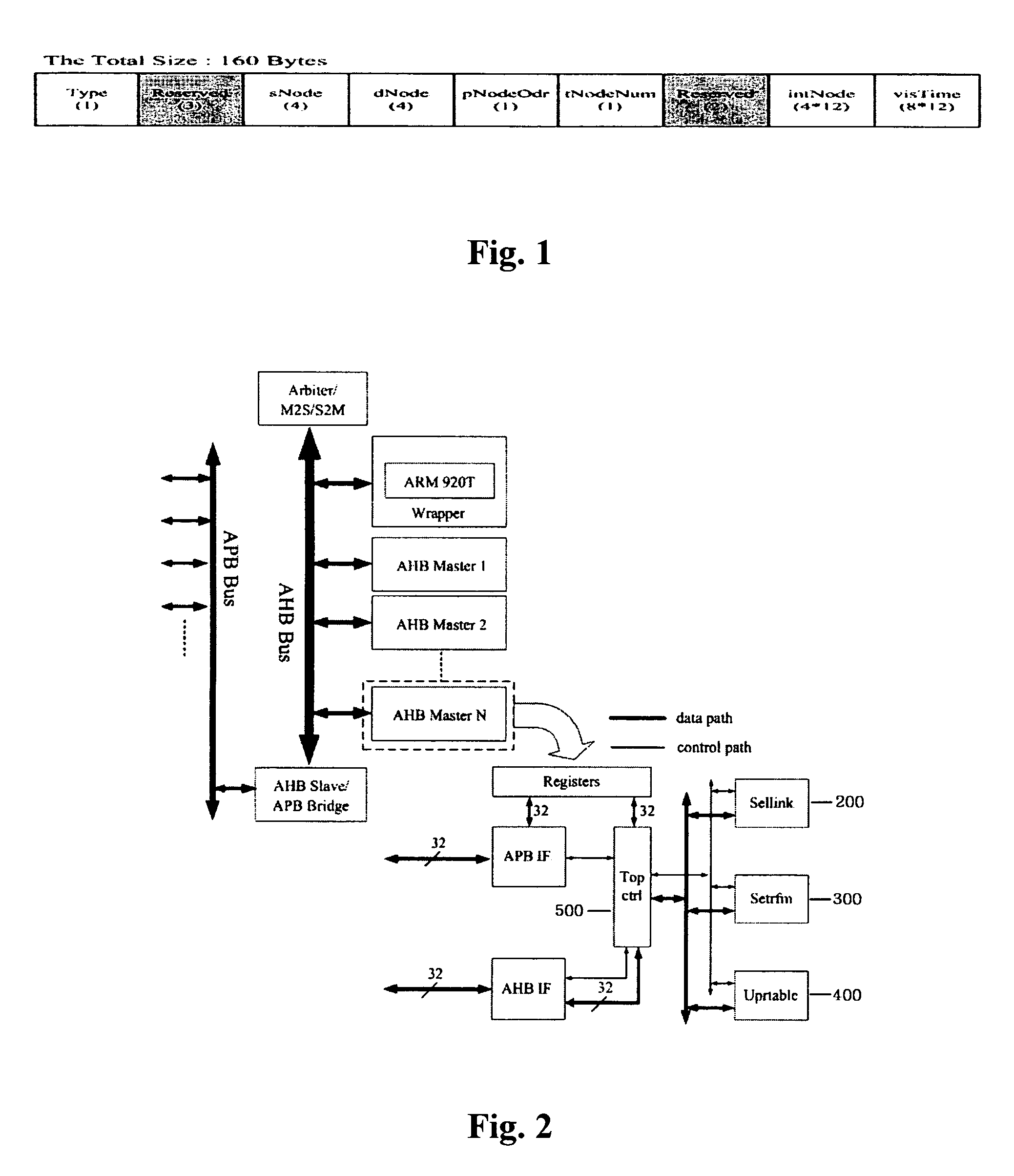

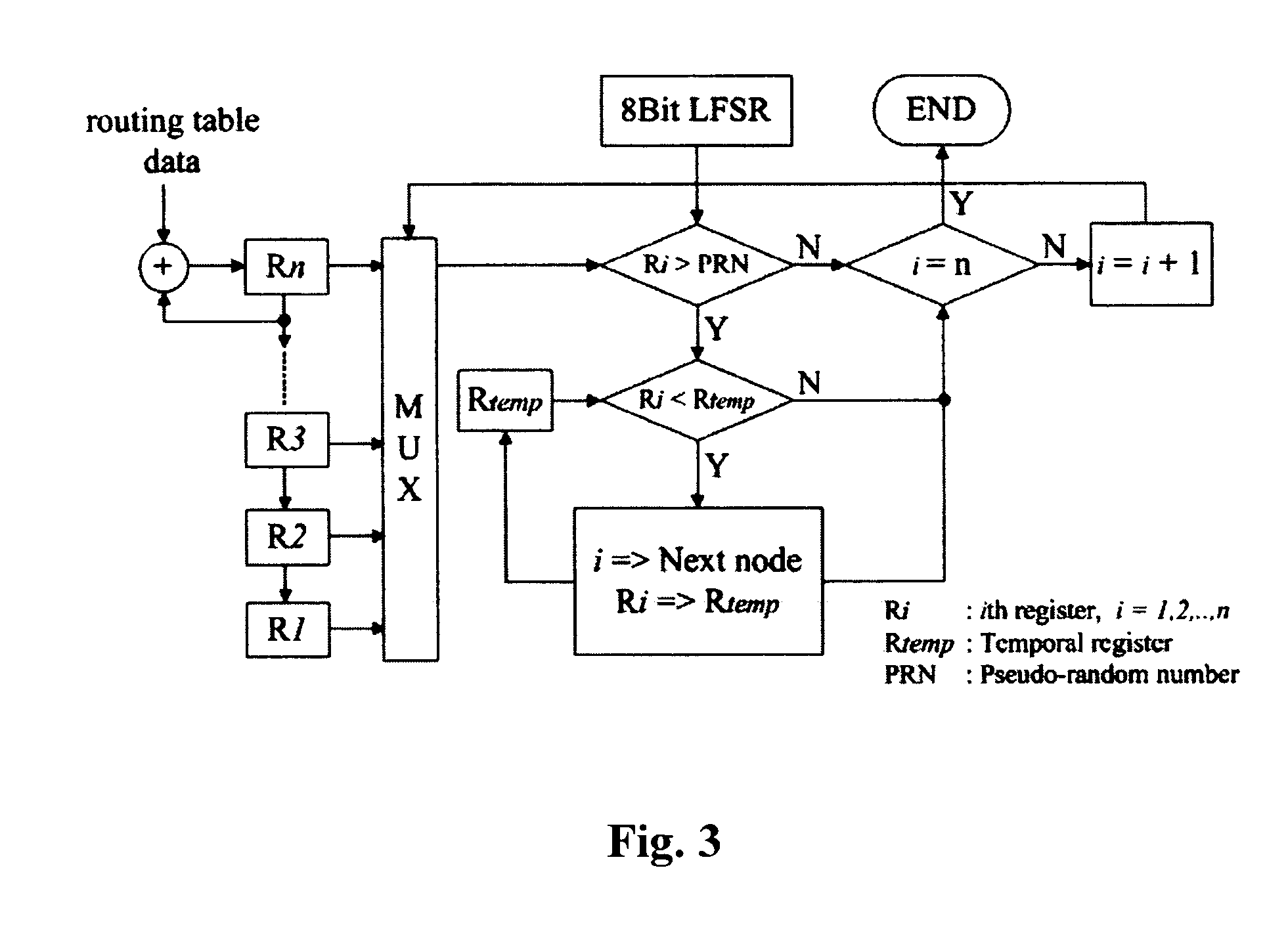

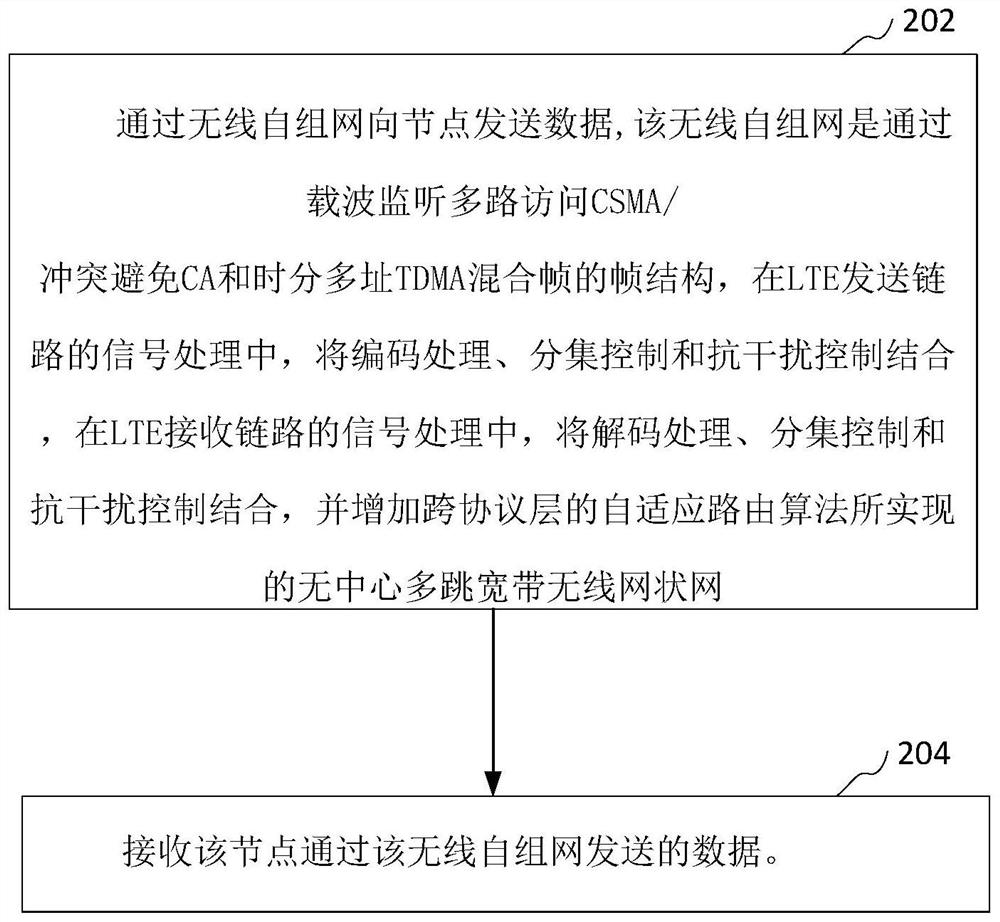

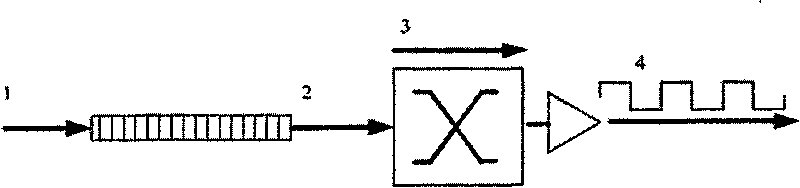

The invention relates to a wireless ad hoc network communication method and device. The method sends data to a node through a wireless ad hoc network and receives the data sent by the node through thewireless ad hoc network. Wherein the wireless ad hoc network is a frame structure of a mixed frame of a CSMA / collision avoidance CA and a time division multiple access TDMA through a carrier sense multiple access, In signal processing of LTE transmission link, encoding, diversity control and anti-jamming control are combined. In signal processing of LTE reception link, decoding, diversity controland anti-jamming control are combined, andAdaptive routing algorithm across protocol layer is added to realize centerless multi-hop wideband wireless mesh network. The wireless ad hoc network is a peer-to-peer network, all nodes in the network are equal in status, nodes can join and leave the network at any time, the failure of any node will not affect the operation of the whole network, and theinvulnerability of the network is improved.

Owner:ZHUHAI YUNZHOU INTELLIGENCE TECH COMPANY

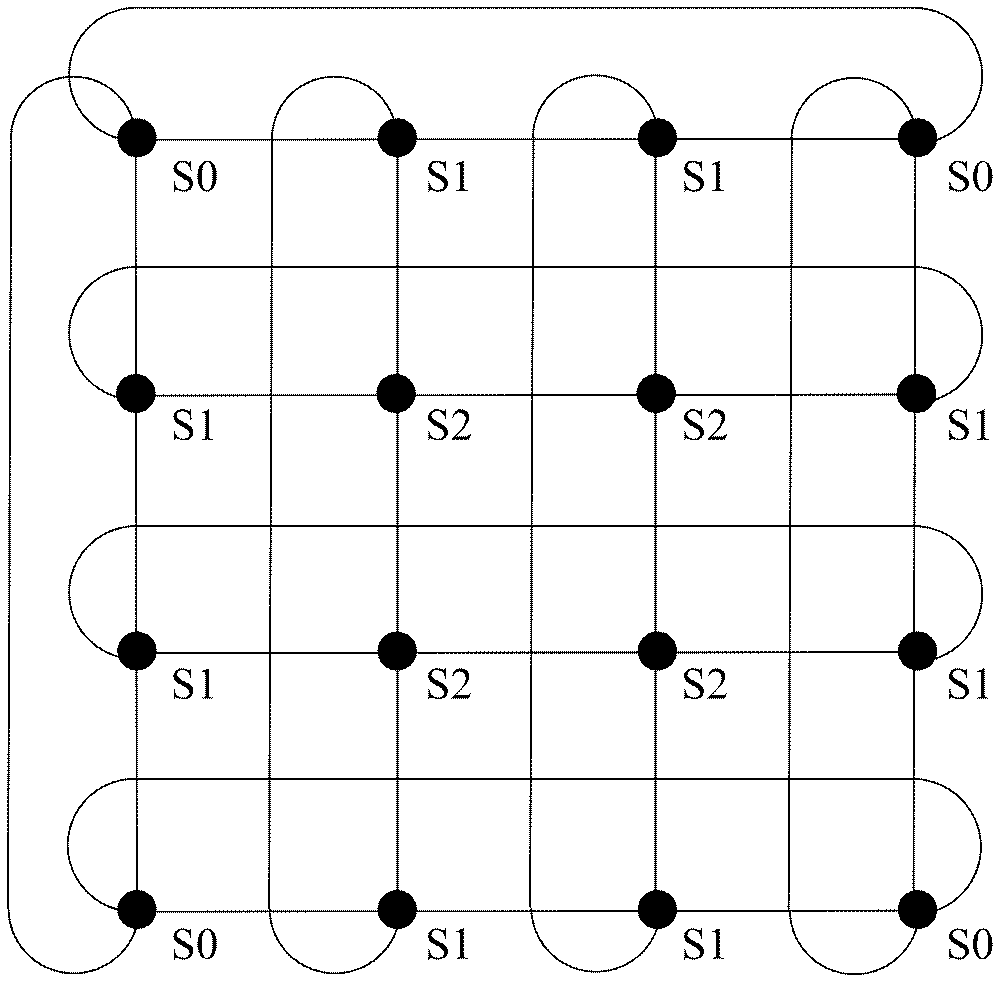

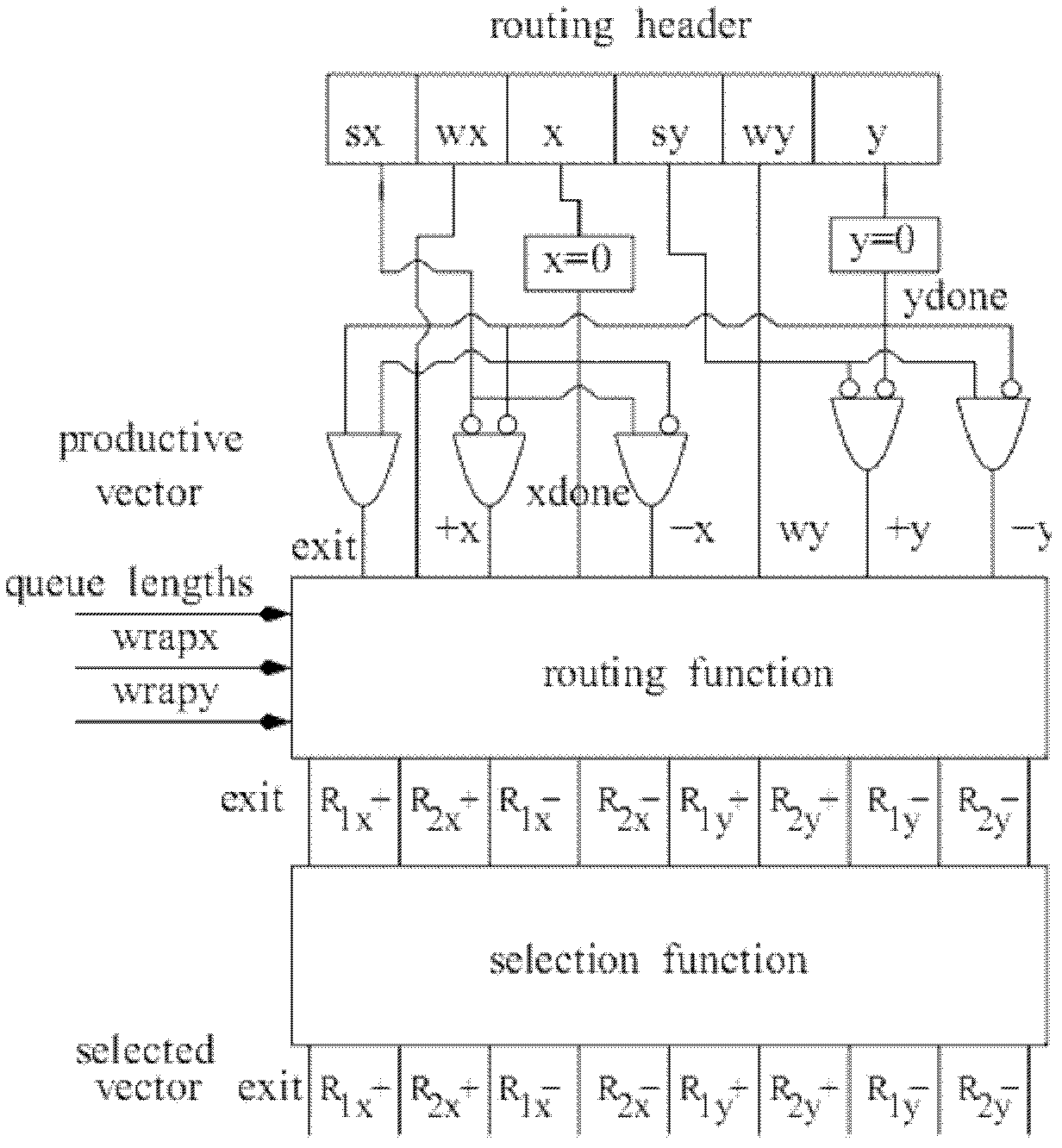

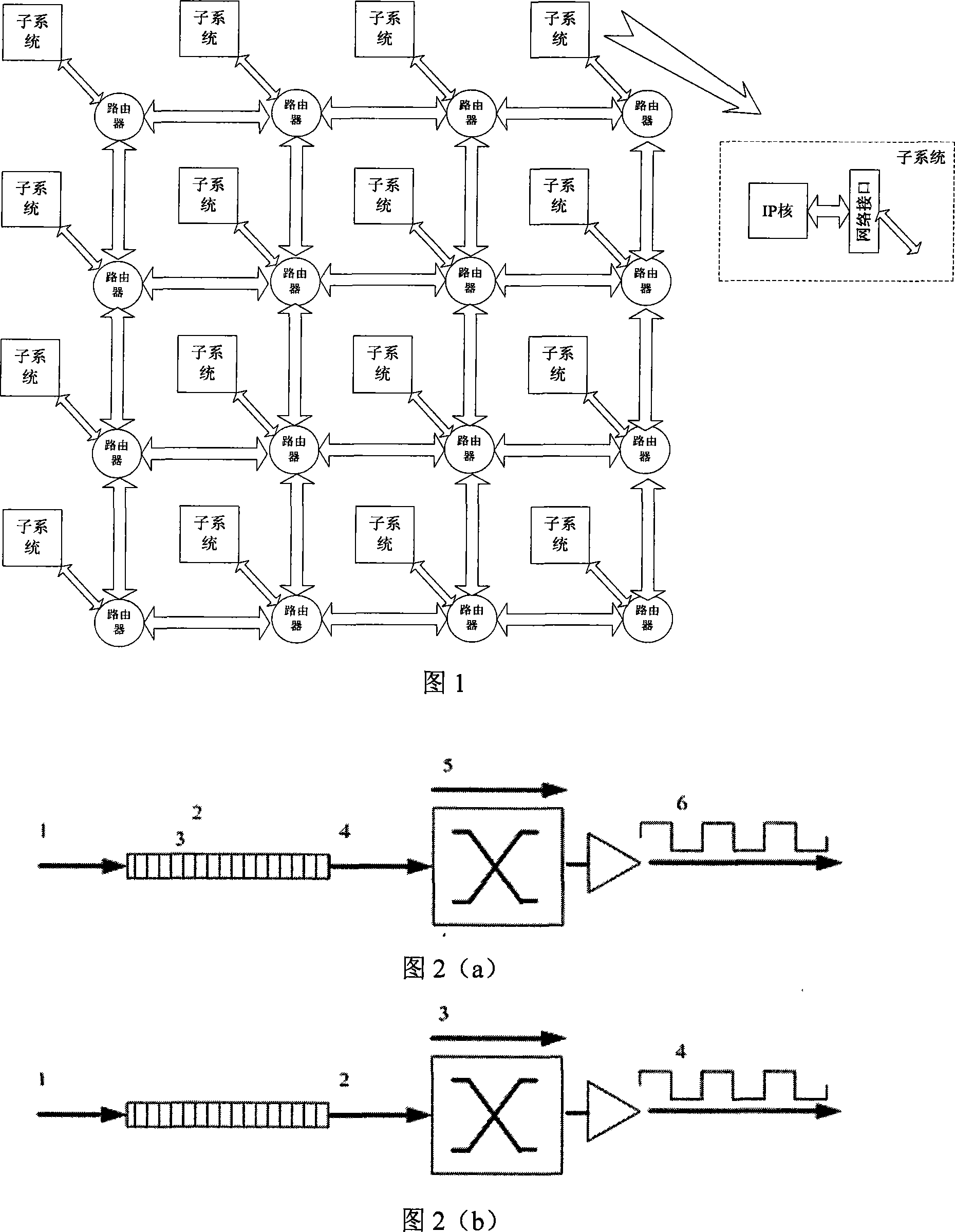

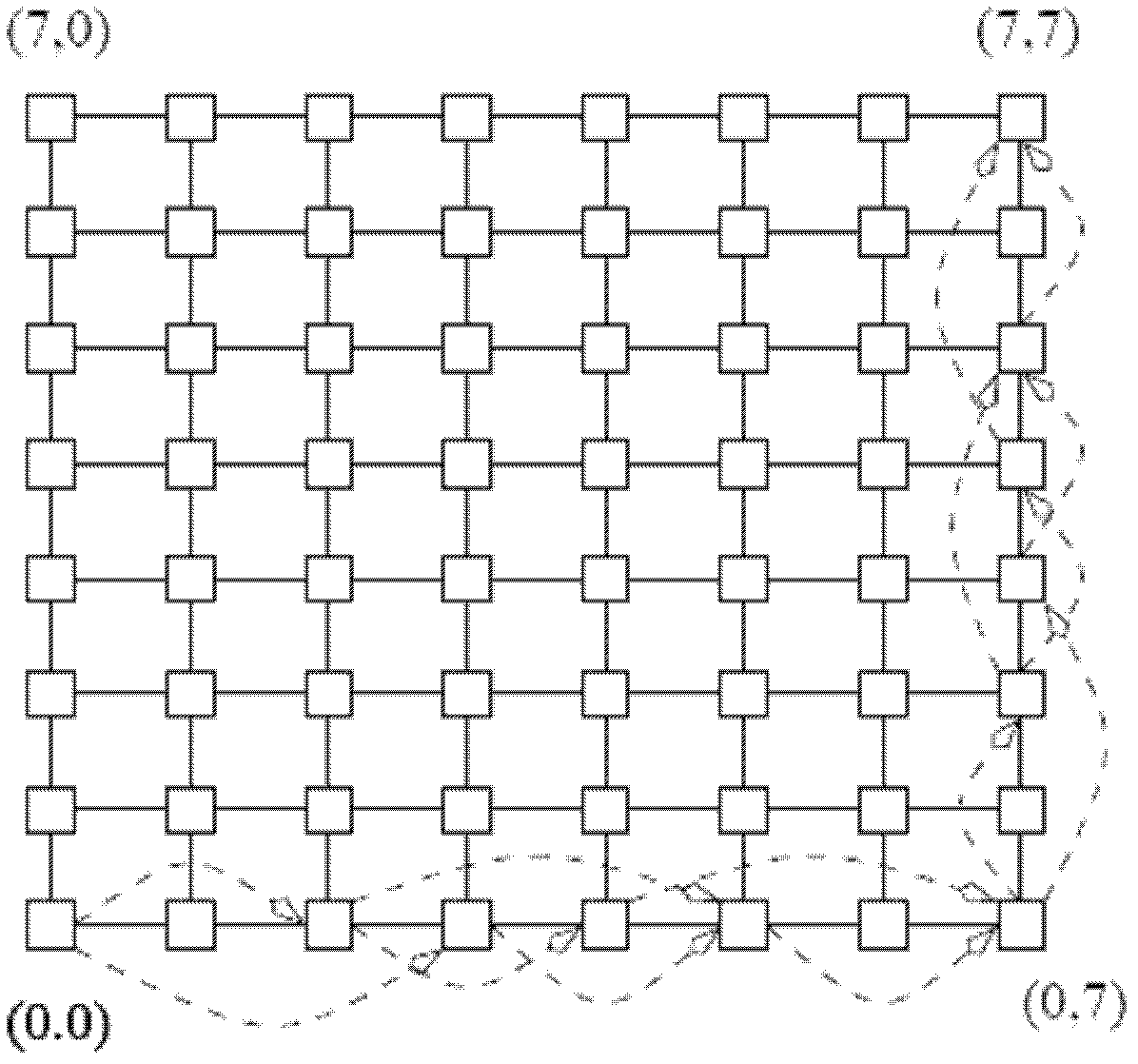

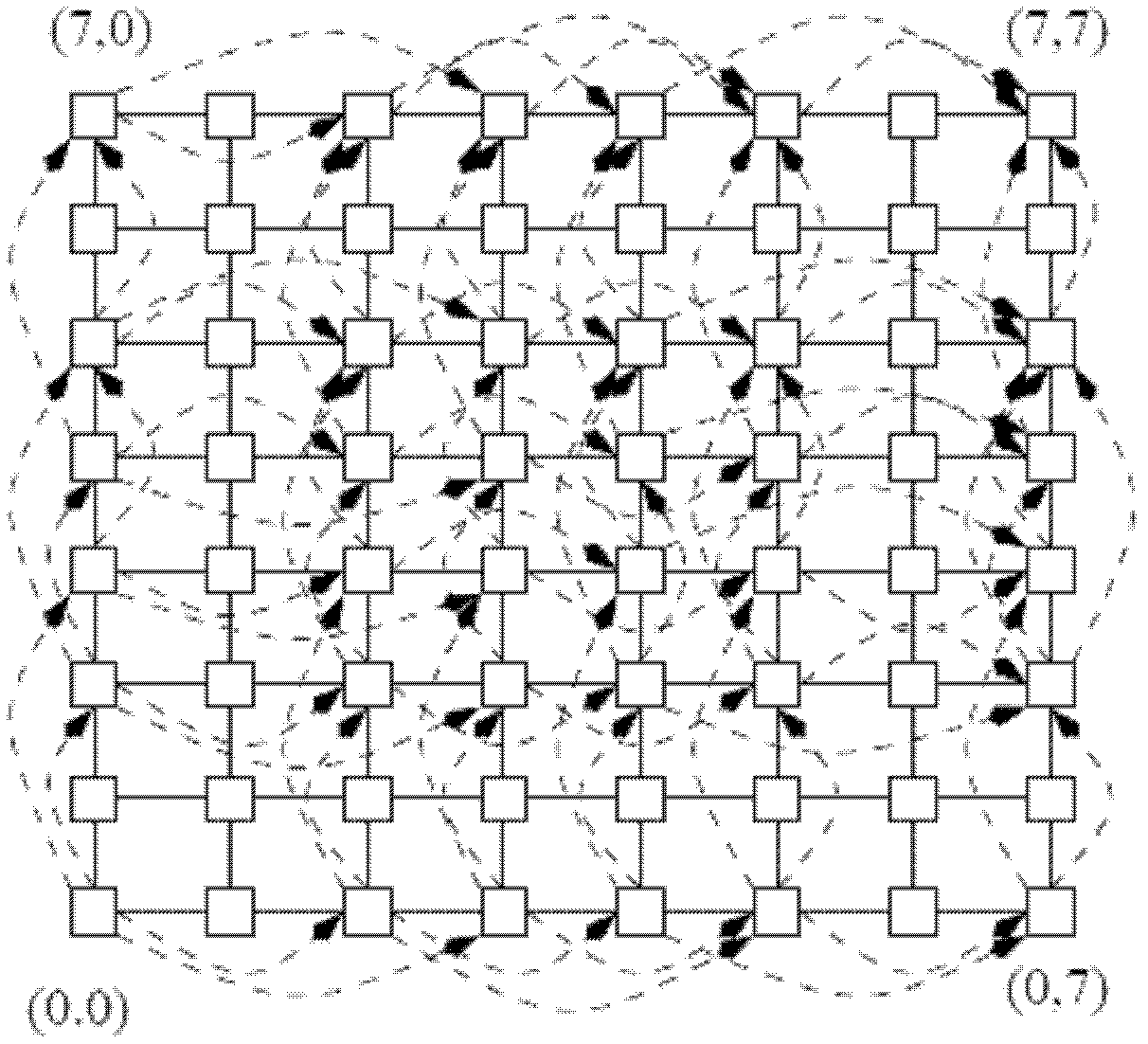

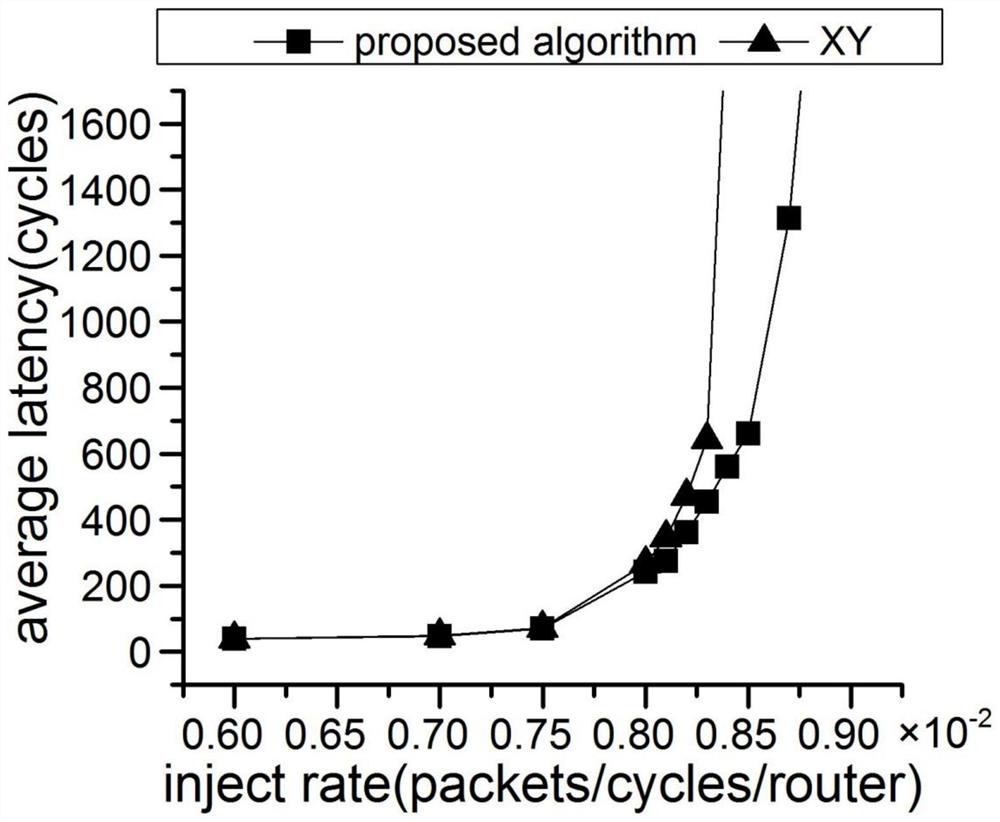

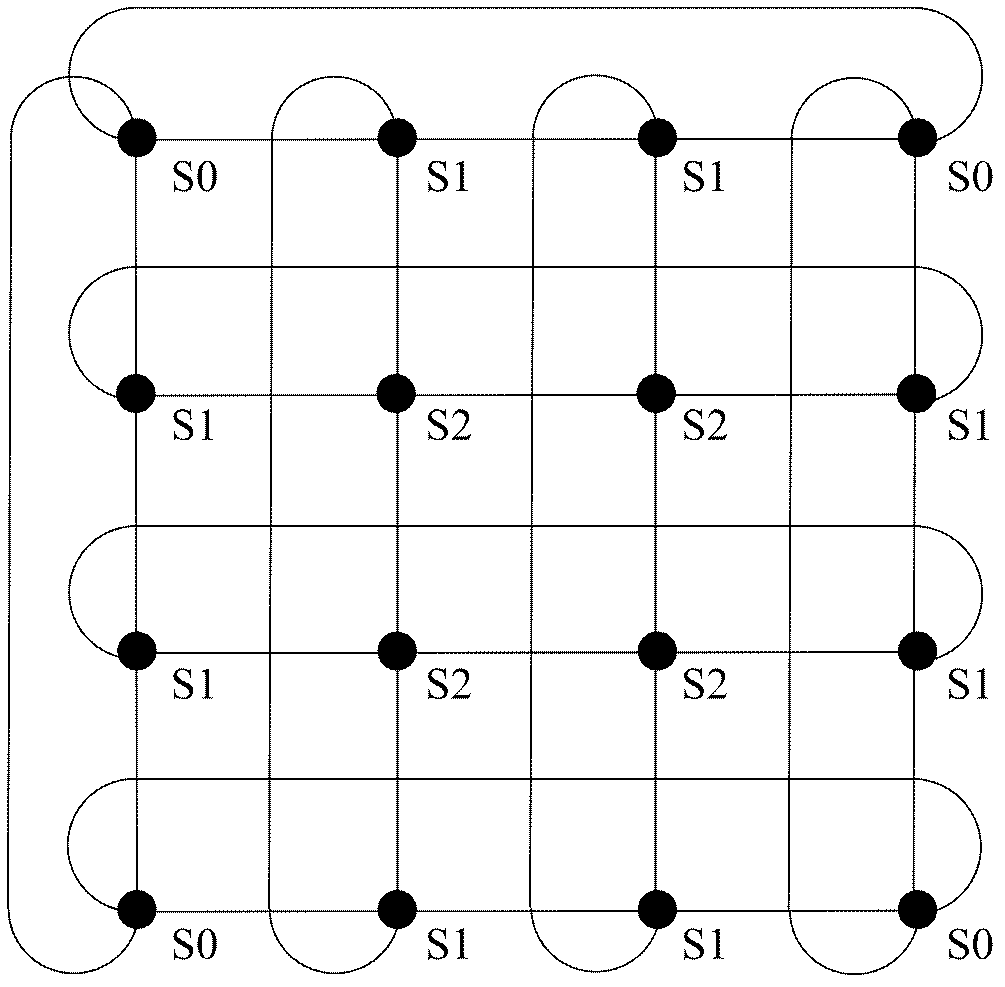

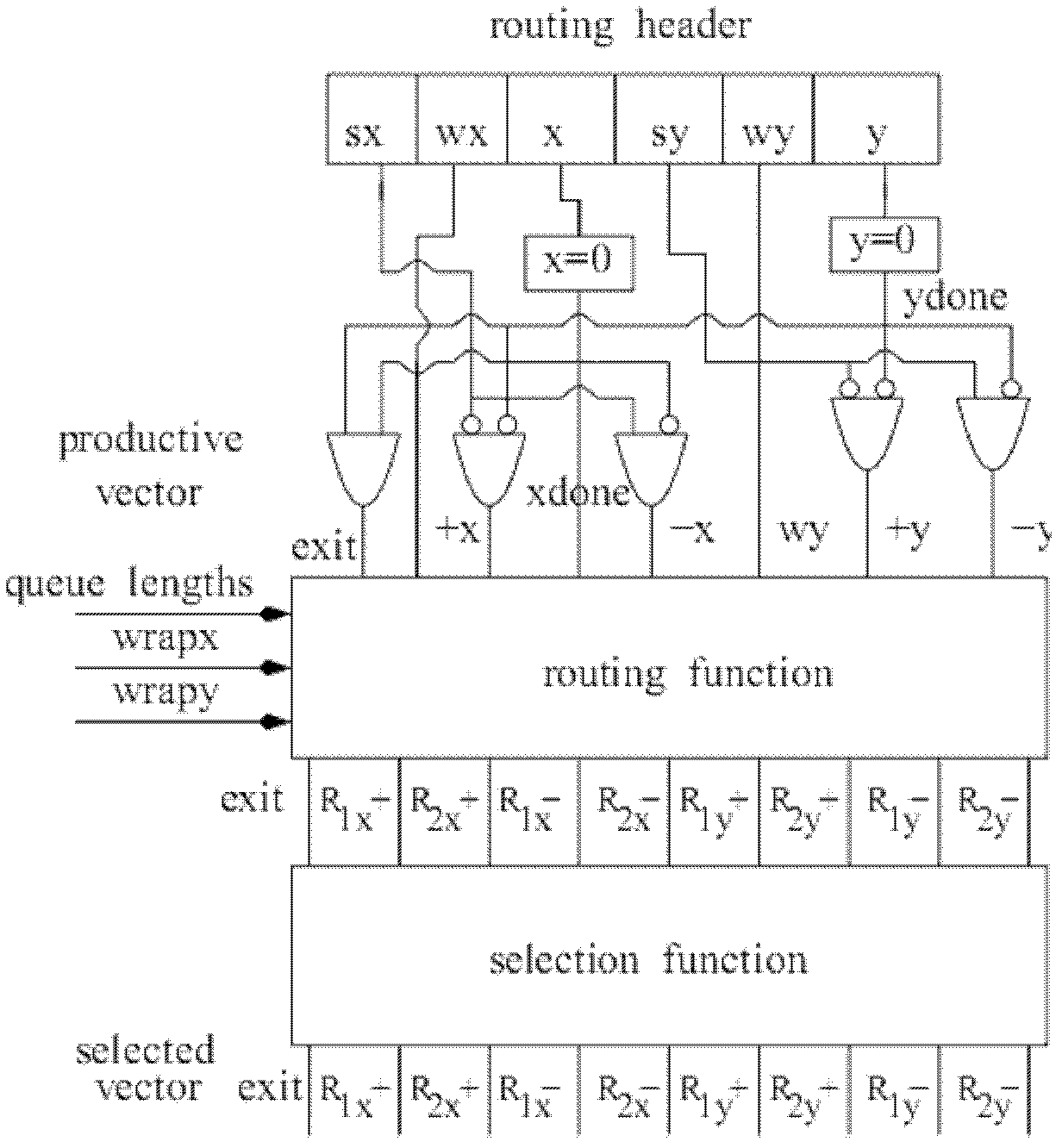

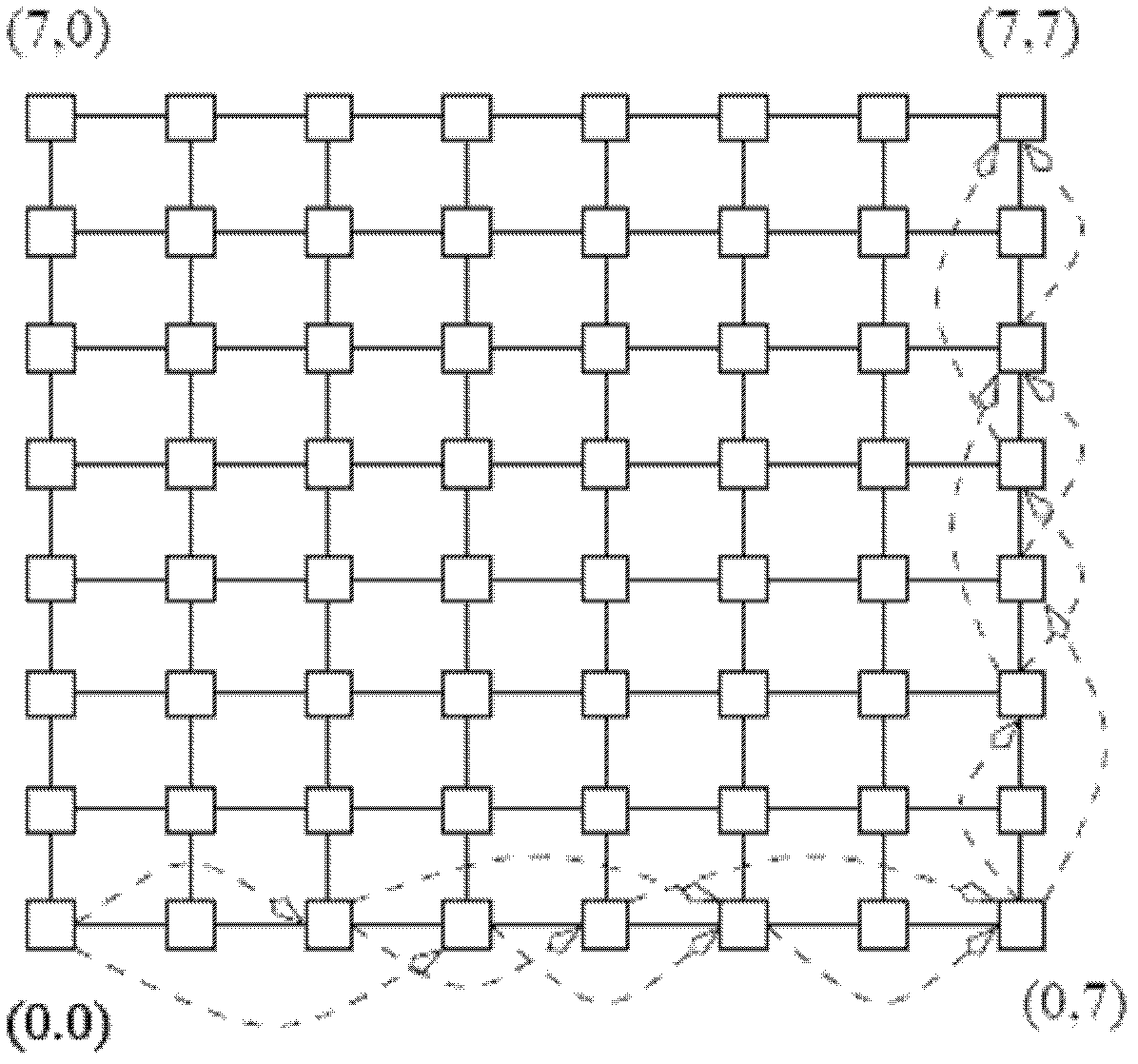

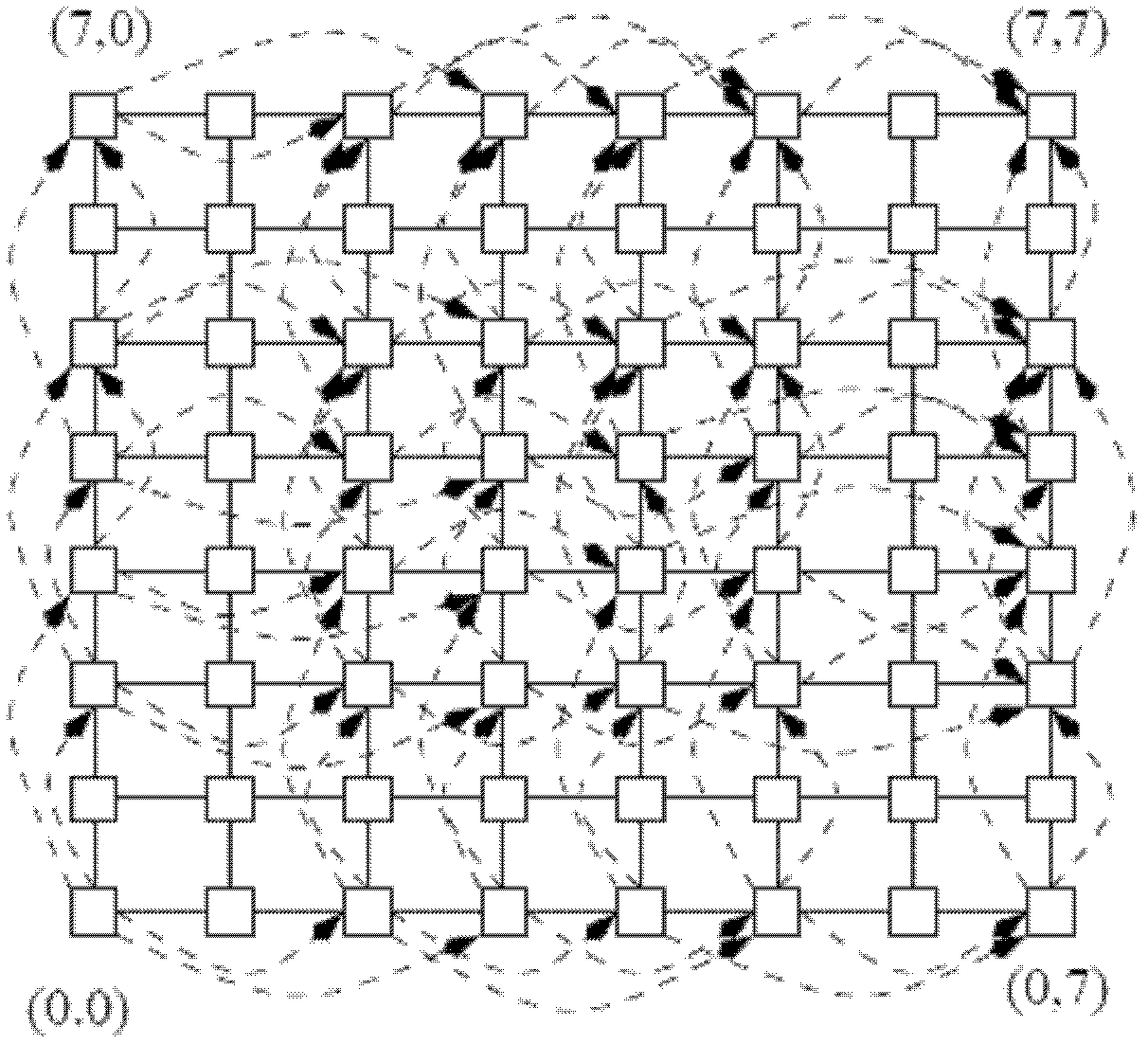

A deadlock-free adaptive routing algorithm in a Torus network

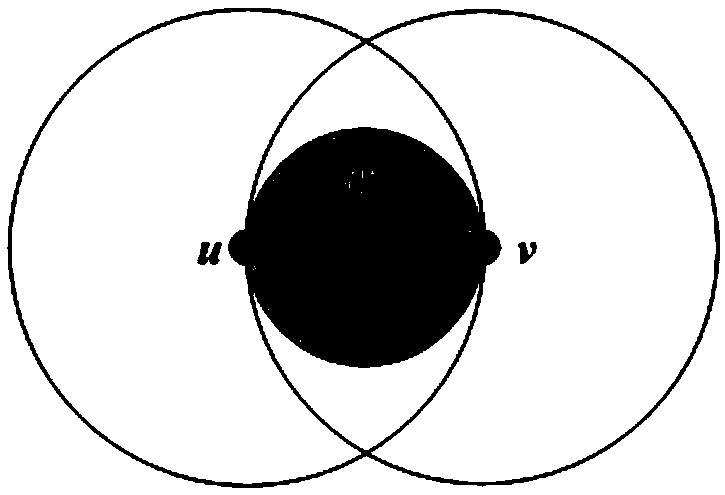

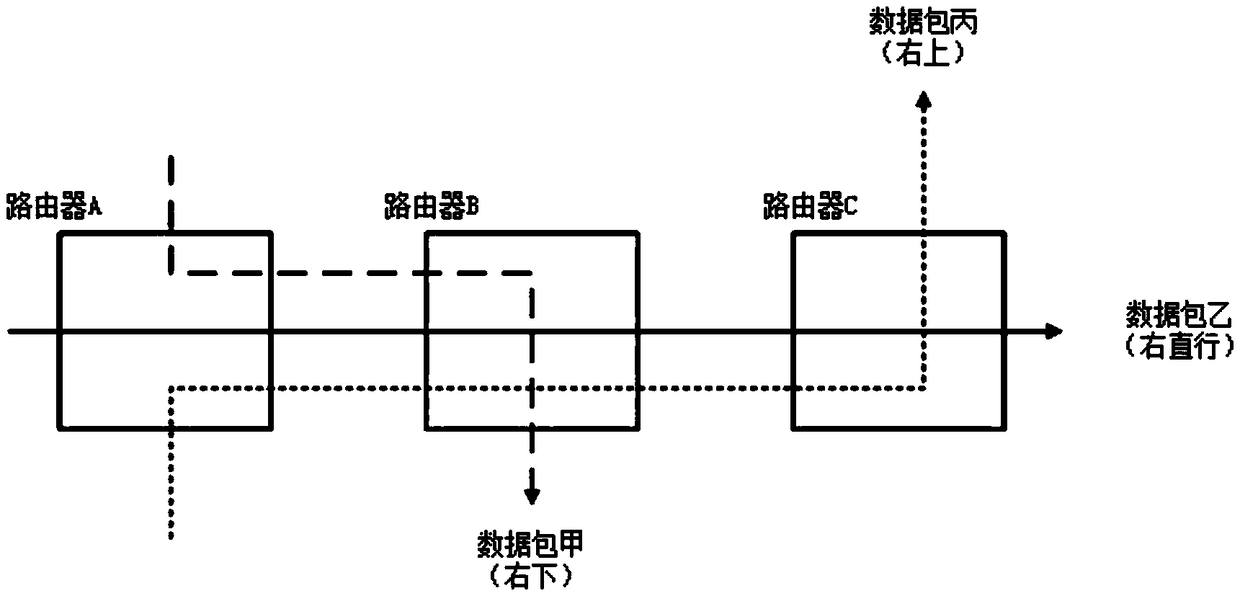

The invention belongs to the distributed network technology field, and relates to a deadlock-free adaptive routing algorithm in a Torus network. The deadlock-free adaptive routing algorithm in the Torus network is applied to a virtual cut-through switch mode or a wormhole switch mode, and is characterized by utilizing two virtual channels R1 and R2, wherein, the R1 is an adaptive channel that a data package can visit at any time, and the R2 applies a deadlock-free routing algorithm in a Mesh network. The novelty of the combination is that the first channel does not provide path for any pair of a source node and a destination node; in the Torus network based on the virtual cut-through switch technology, the deadlock-free adaptive routing algorithm is fully adaptive, and based on the wormhole switch, the deadlock-free adaptive routing algorithm is partially adaptive; when the deadlock-free adaptive routing algorithm is combined with a flow control system, under the virtual cut-through switch technology, the design of a router can be simplified substantially, and the performances can be advanced greatly. The simulation result shows that the performances of the algorithm all are better than those of the conventional algorithm based either on the virtual cut-through switch technology or on the wormhole switch technology.

Owner:TSINGHUA UNIV

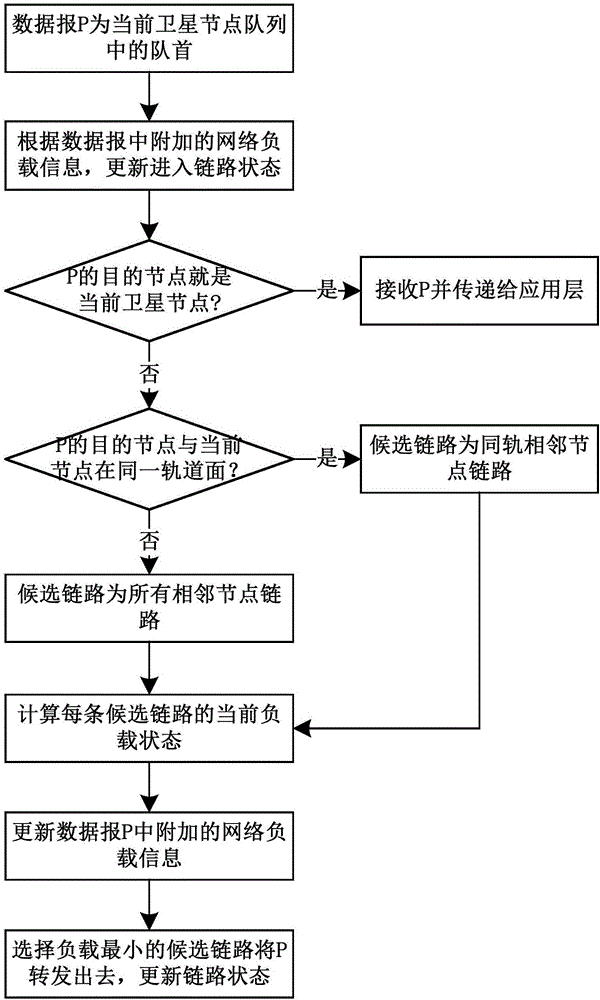

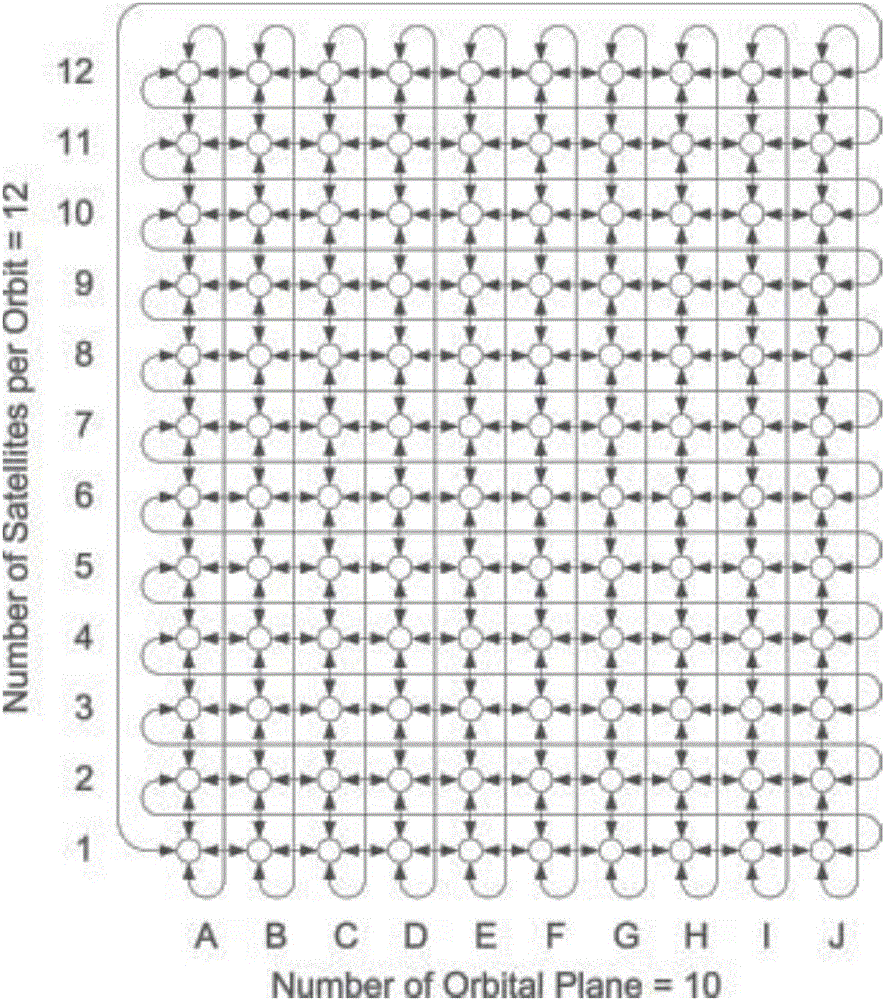

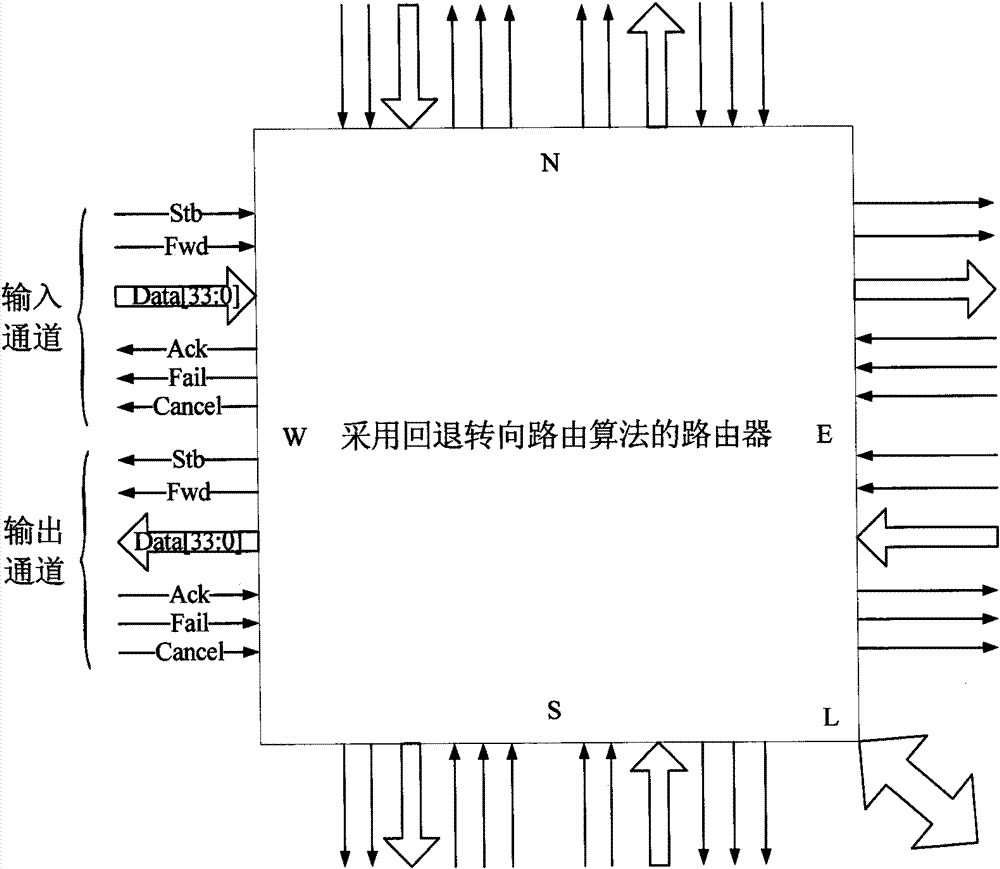

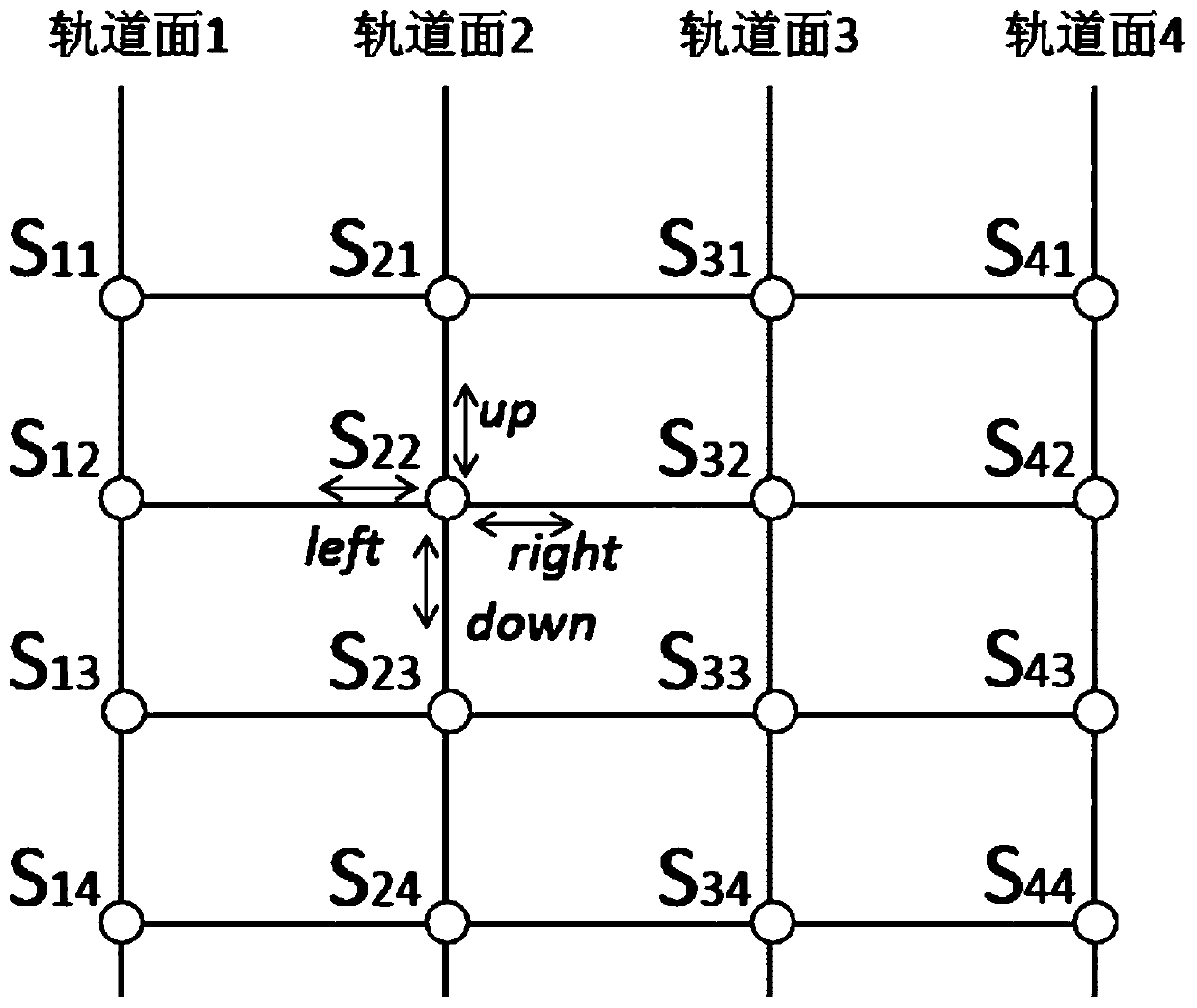

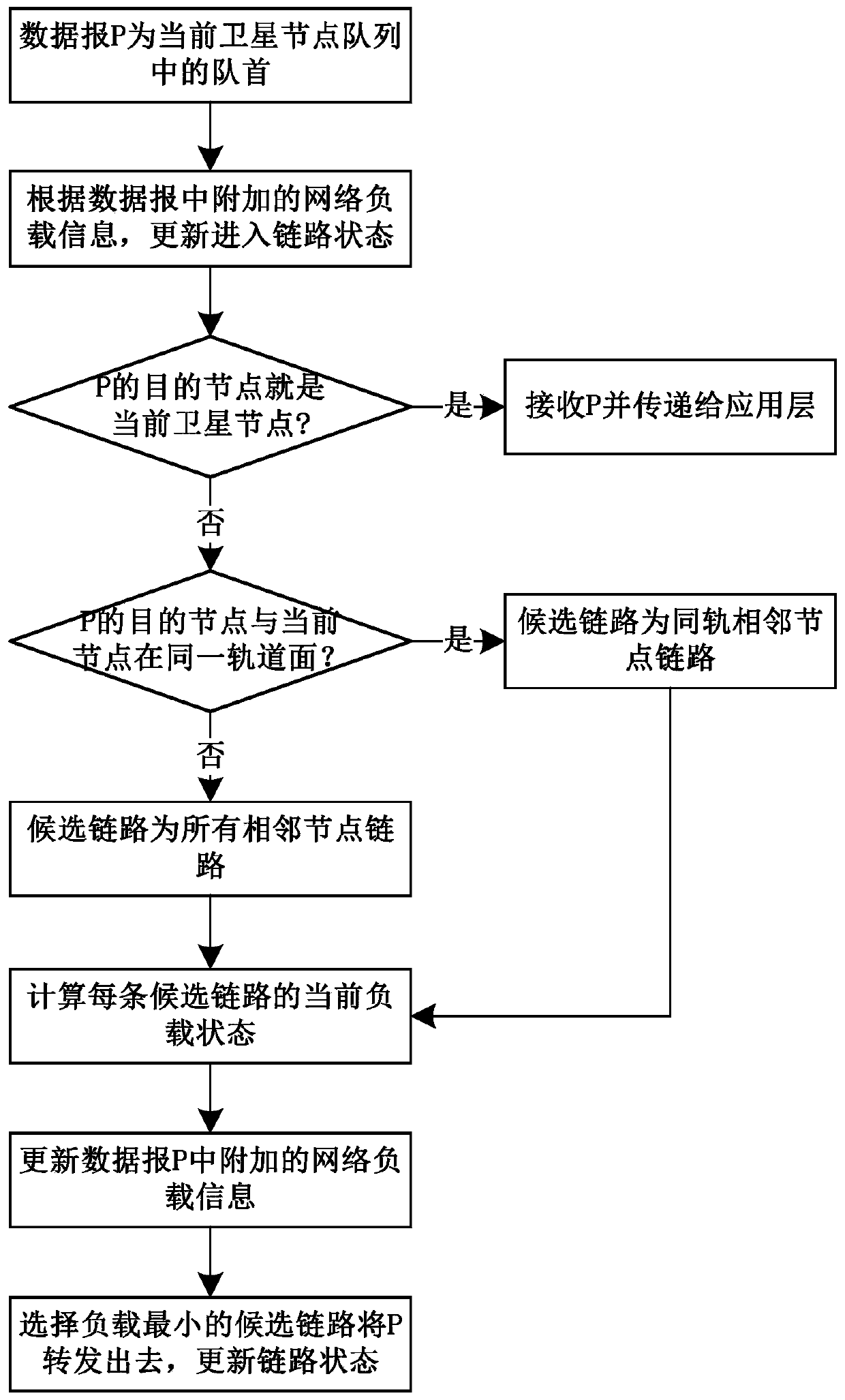

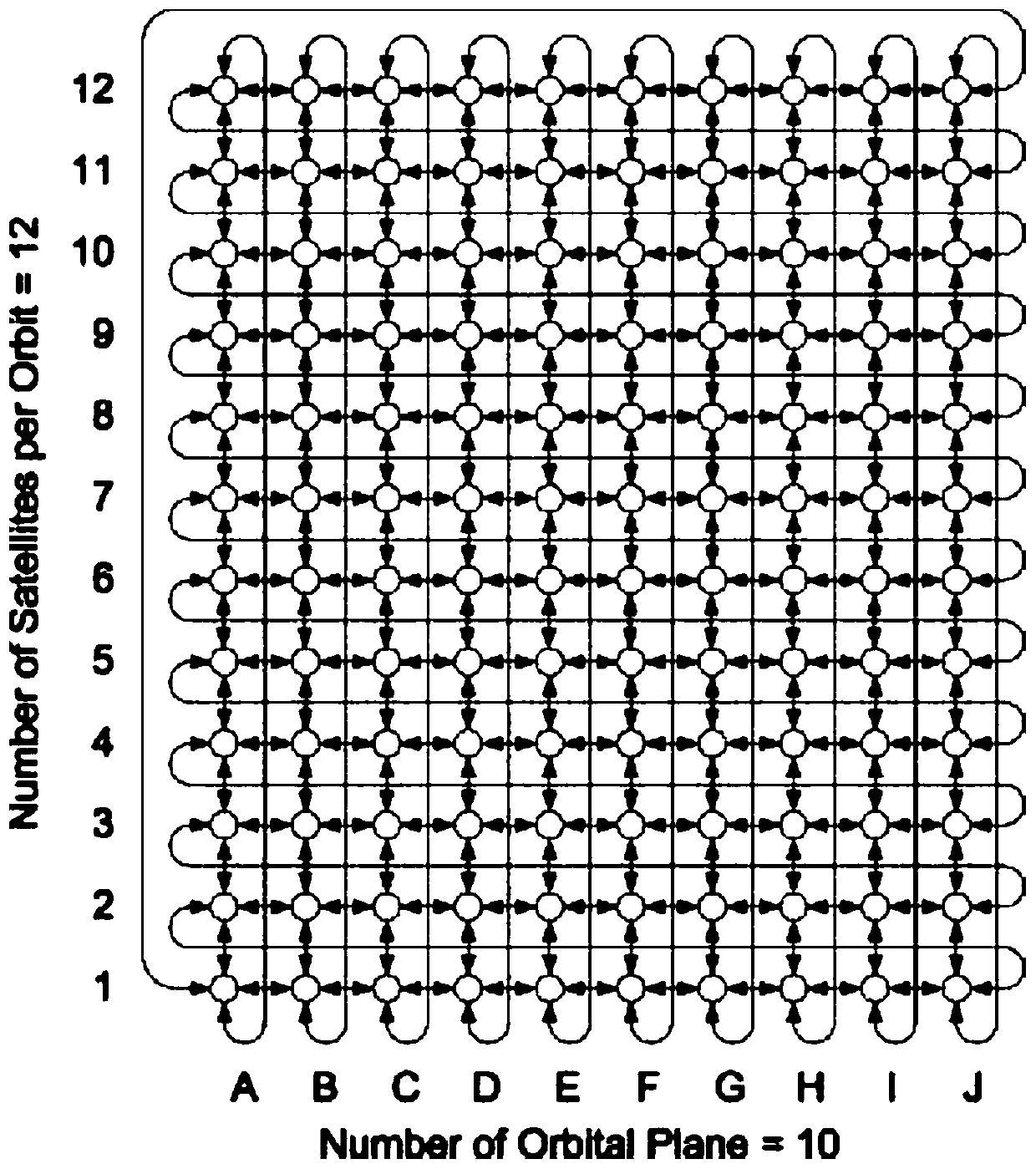

Distributed node self-adaptive routing algorithm for LEO satellite network

ActiveCN106656302ALittle impact on performanceAvoid route discoveryRadio transmissionData switching networksAdaptive routing algorithmLongitude

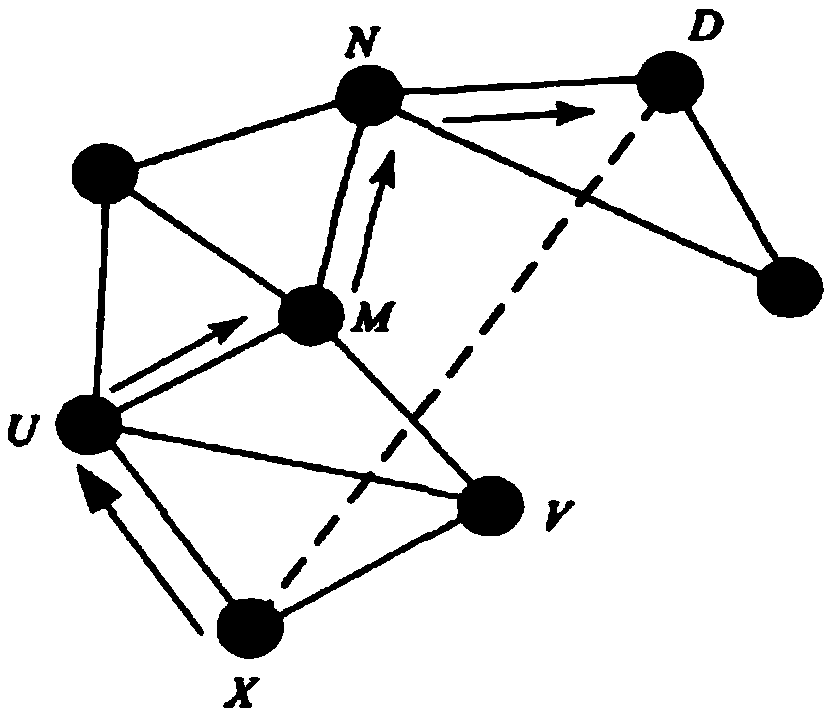

The invention discloses a distributed node self-adaptive routing algorithm for an LEO satellite network. The technical characteristics are that the algorithm includes the following steps: a latticed LEO satellite communication system similar to an Iridium constellation is constructed; according to an interstar link design in a longitude and latitude direction, each satellite node is independently responsible for forwarding datagrams in a queue through a netted topological structure of a satellite constellation; and through increases and transmission of additional network state information in the datagrams, the satellite nodes sense and predict network states in different routing directions, and then the datagrams are guided to select forwarding links. The distributed node self-adaptive routing algorithm is reasonable in design. The determined self-adaptive routing mechanism balances traffic to prevent congestion through a load balancing means, and is applied to a low earth orbit Iridium-like constellation satellite network system. The network performance index of the algorithm is better than network performance indexes of other conventional algorithms. Particularly in a condition that a few routing hops is increased, the network load balancing degree is substantially increased, and the performance of the algorithm is more excellent than the conventional algorithms.

Owner:NANJING UNIV OF SCI & TECH

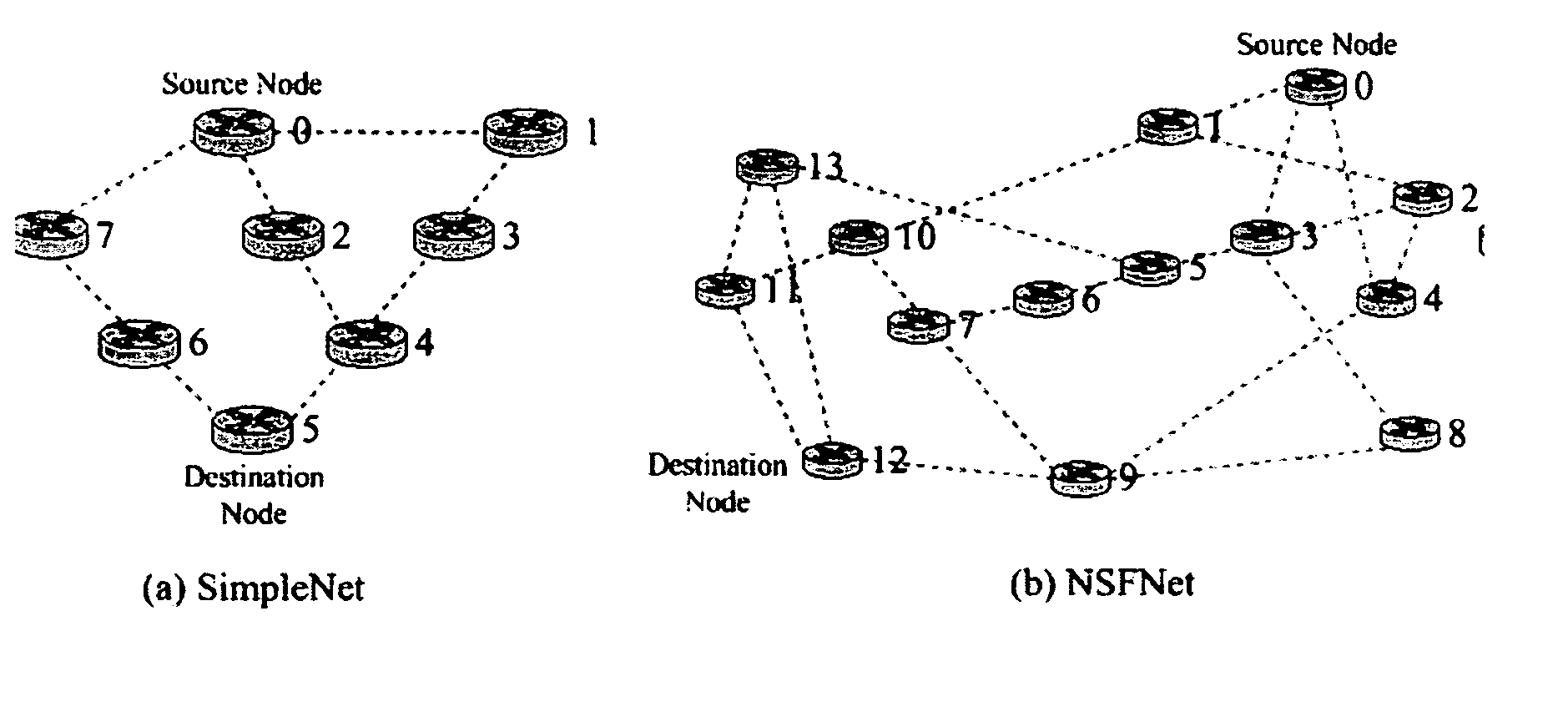

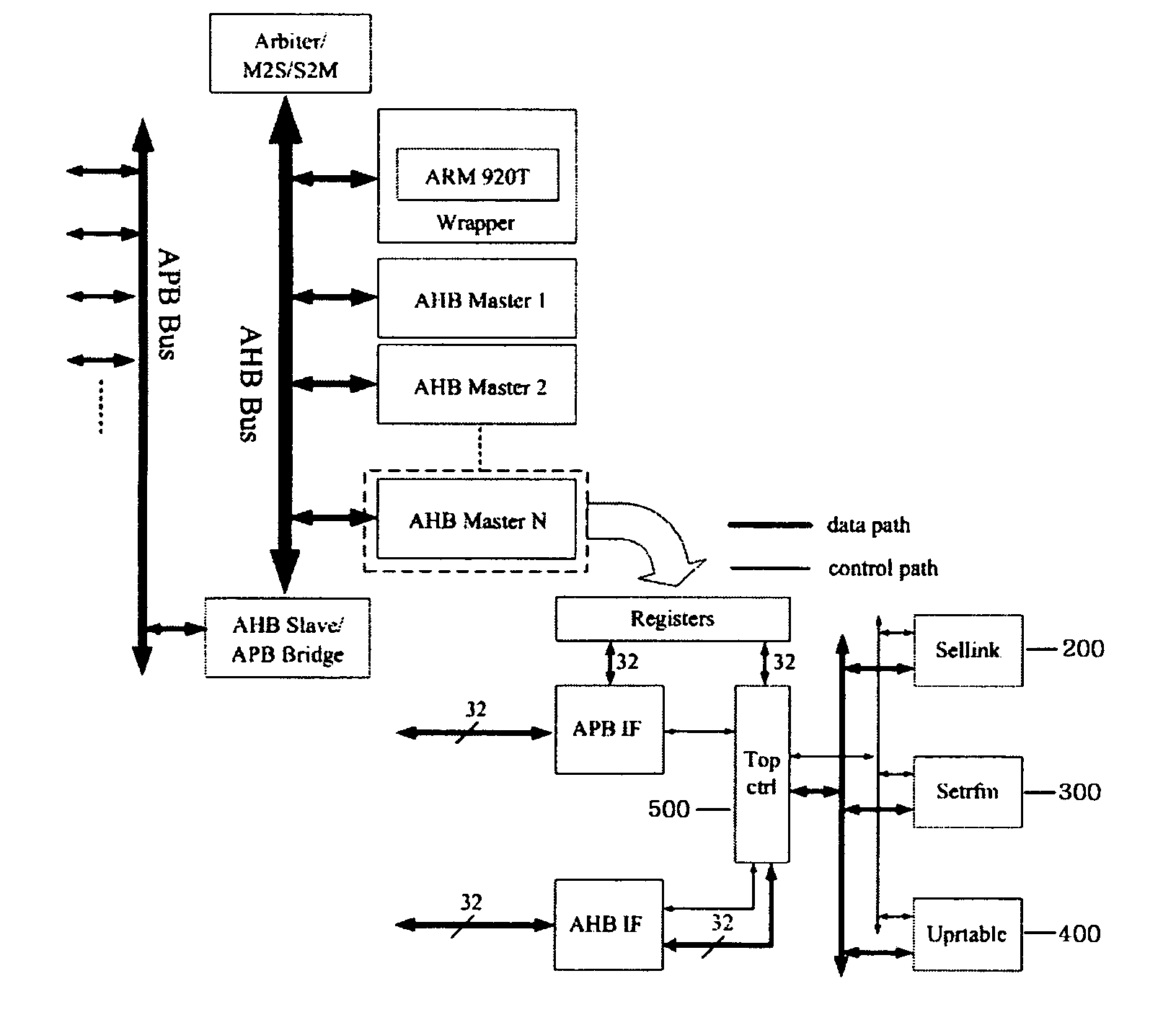

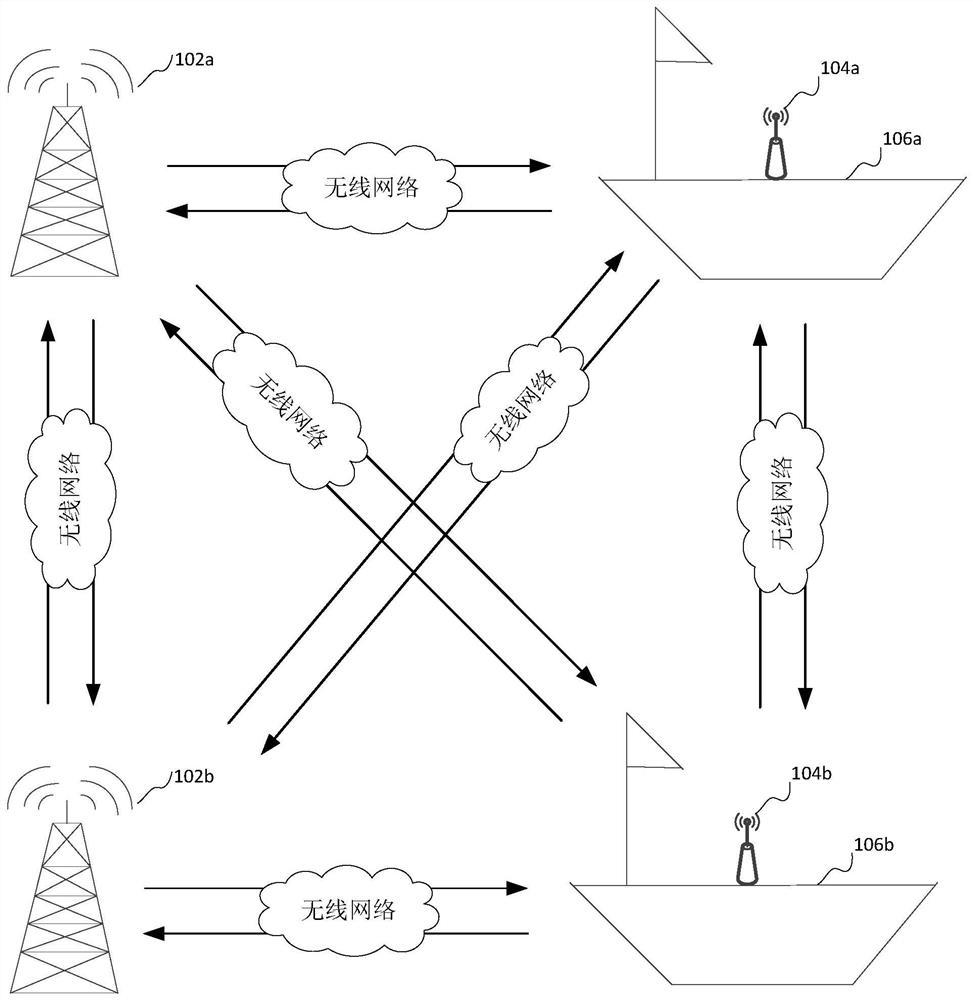

Apparatus for implementation of adaptive routing in packet switched networks

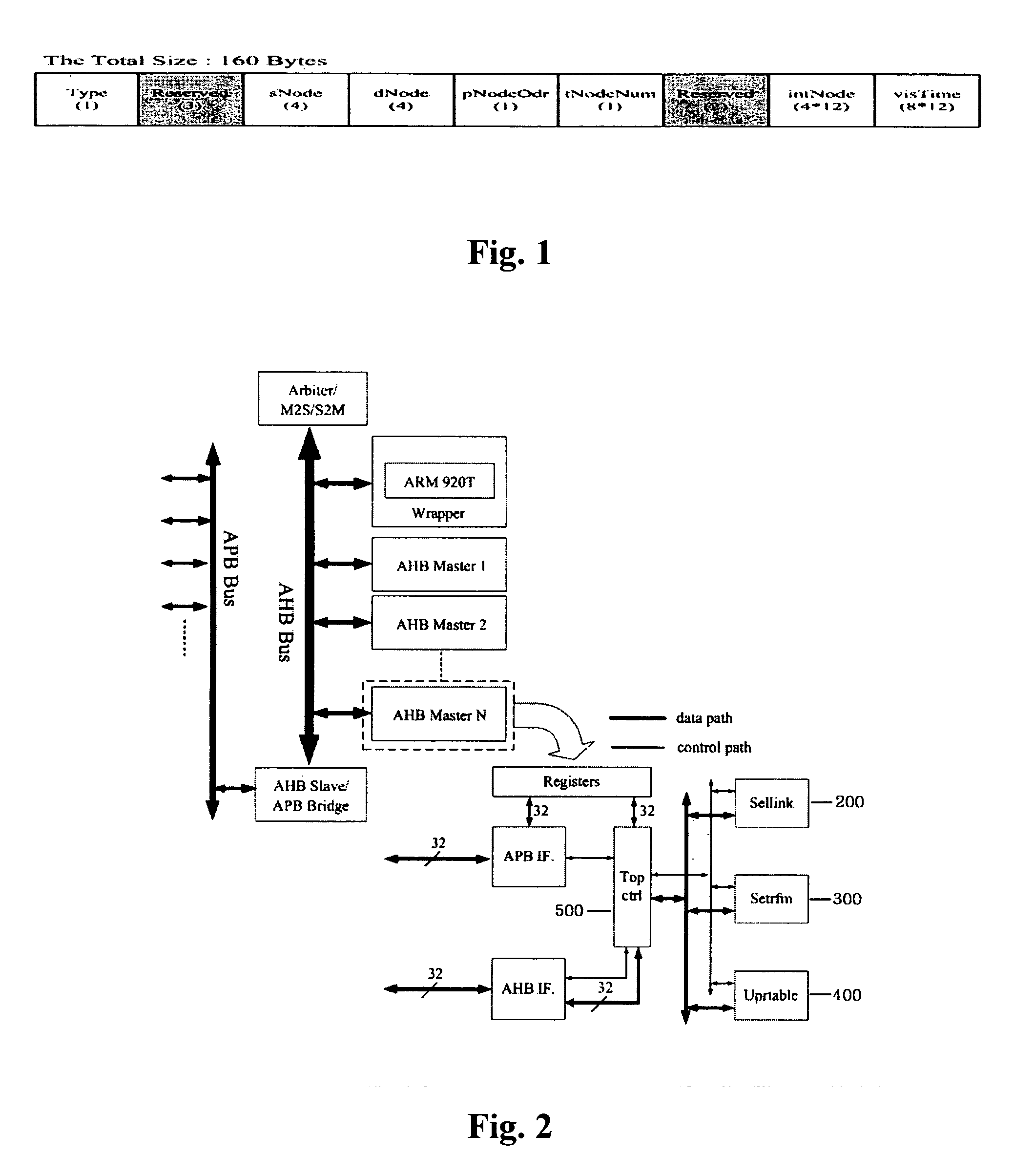

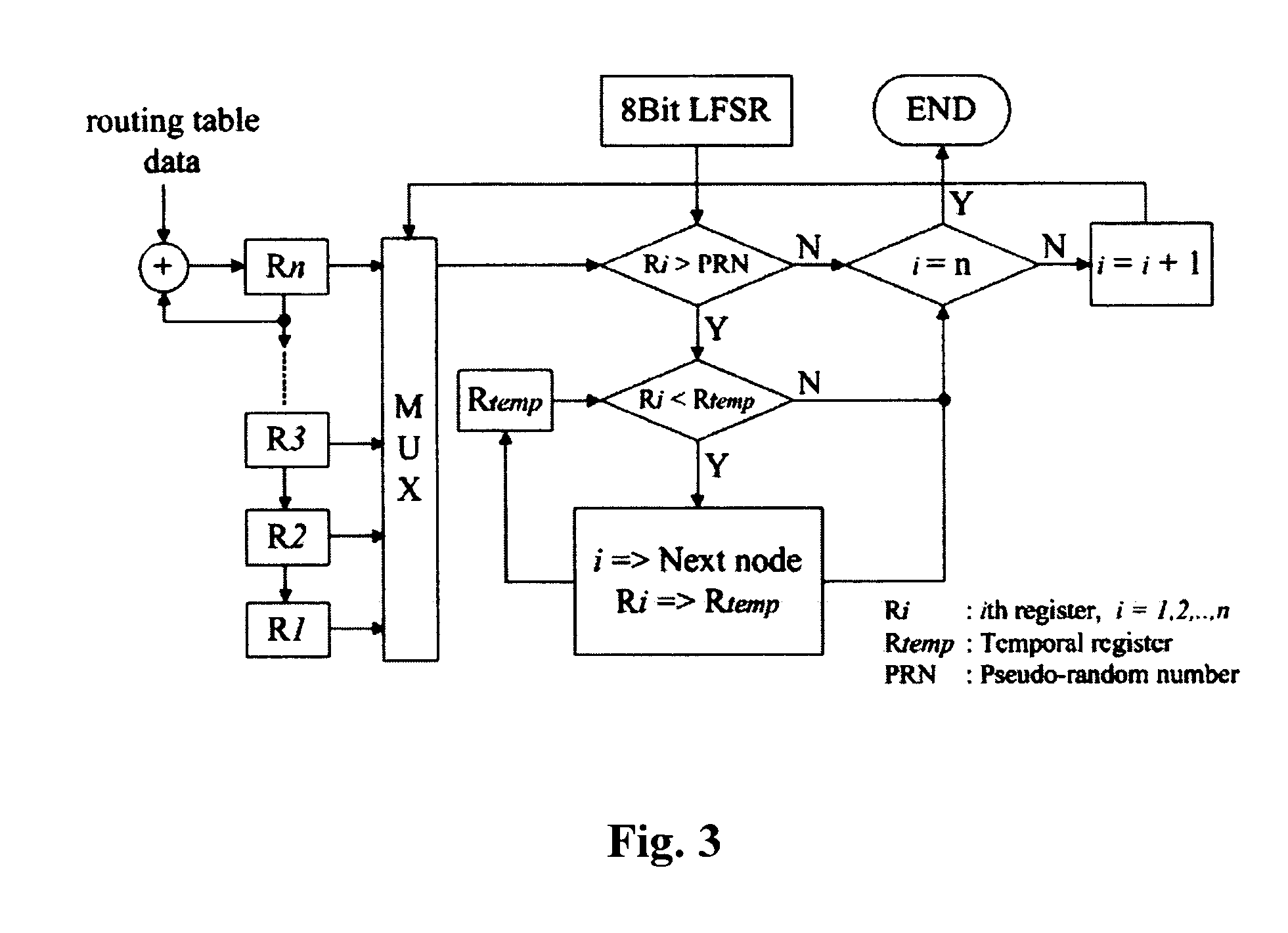

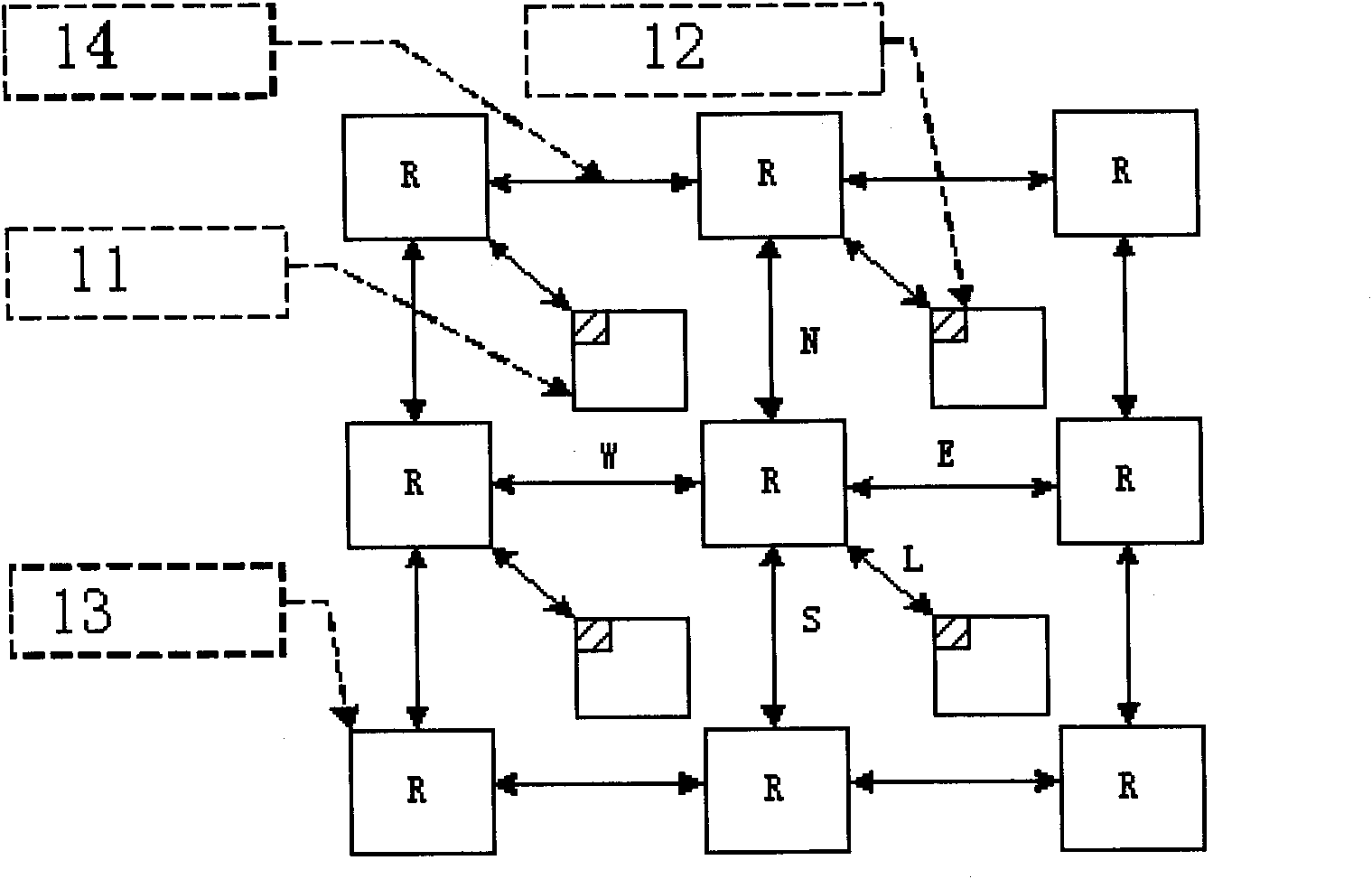

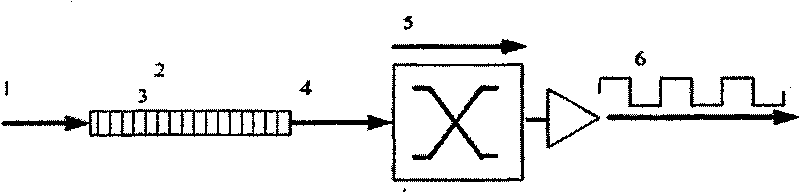

InactiveUS20060056302A1Minimizing and equalizing Ant processing timeMinimize timeError preventionTransmission systemsHardware structureAdaptive routing algorithm

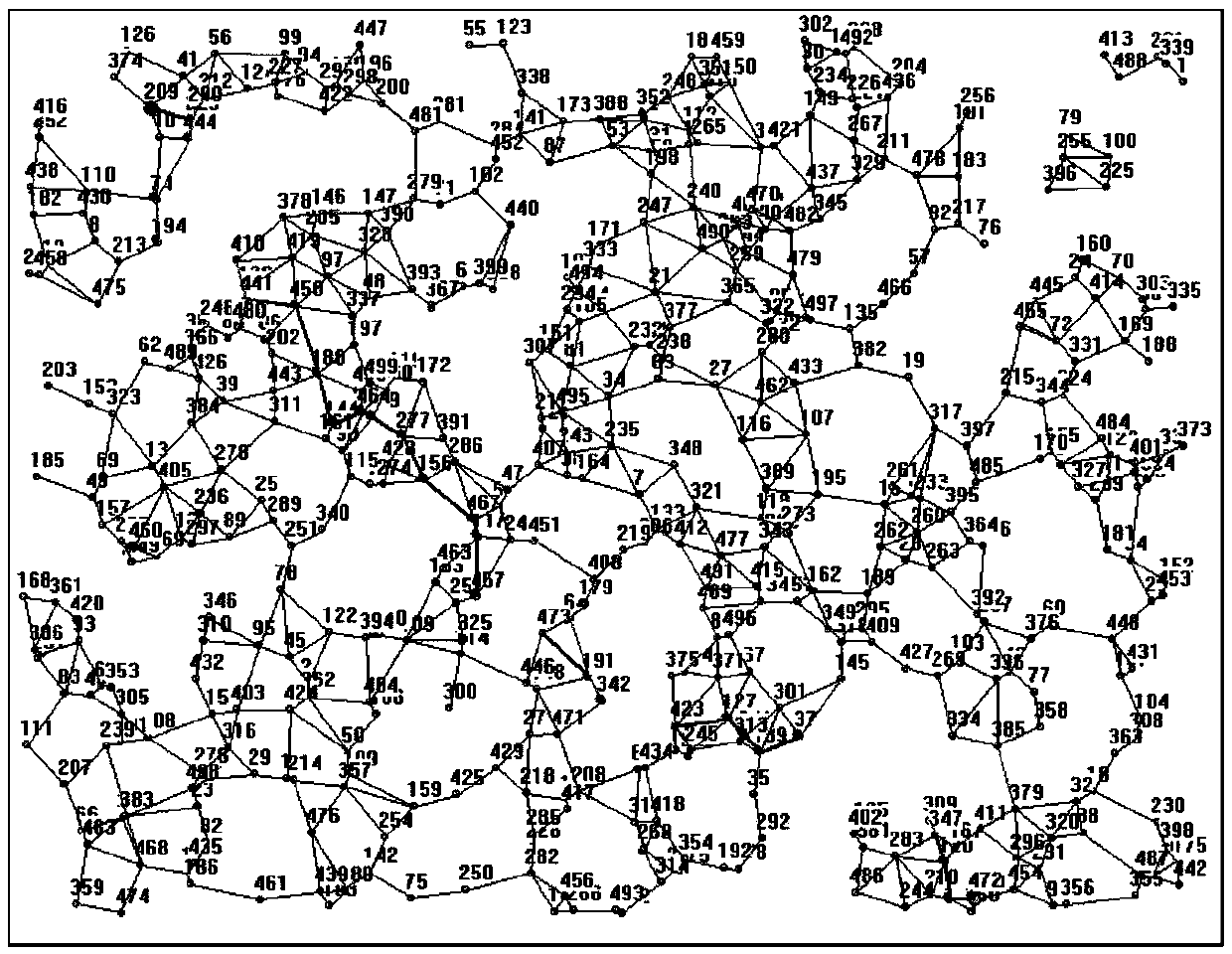

An apparatus is invented for implementing adaptive routing in packet switched networks. The hardware structure of the apparatus is based on the AntNet, which is an adaptive routing algorithm for selecting an optimized network route using a mobile agent that simulates an ant. The AntNet-based hardware structure can be applied to a system-on-chip system. The original AntNet algorithm is adapted for hardware implementation. Performance of the modified algorithm of the invention was verified by comparing the modified algorithm with the original AntNet algorithm in a virtual network structure. The hardware structure of the invention is effective for AntNet-based routing.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

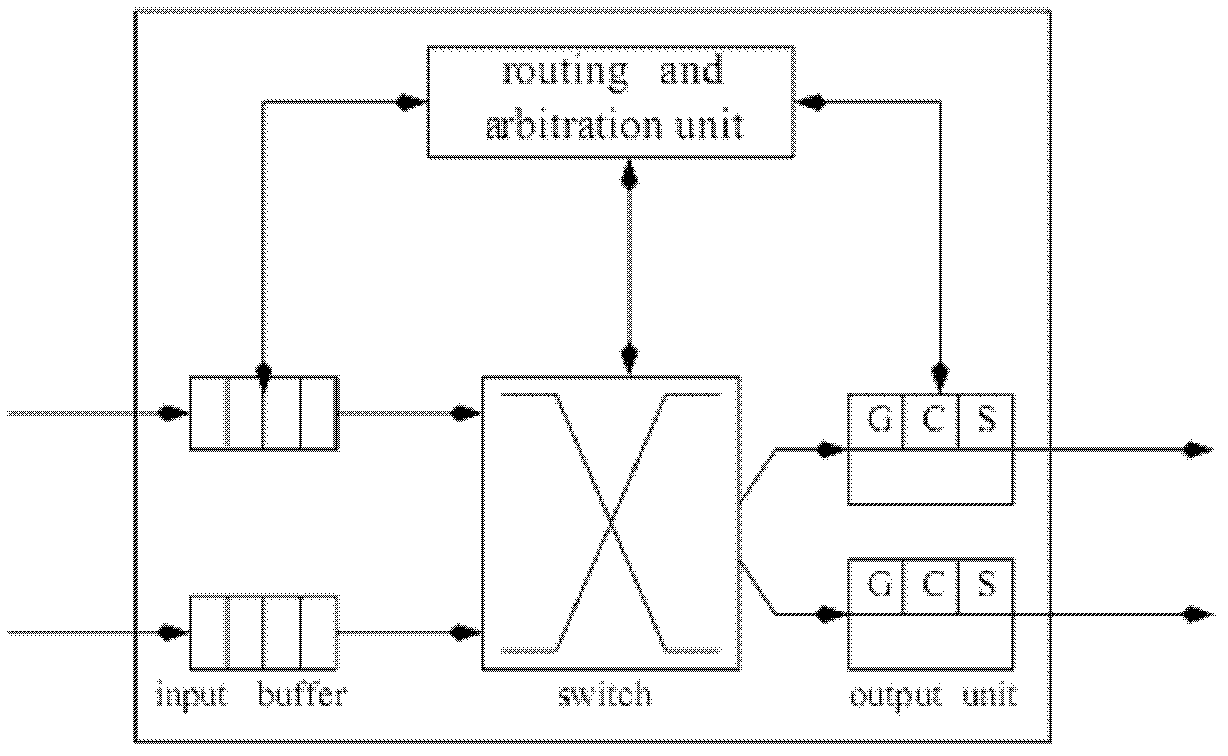

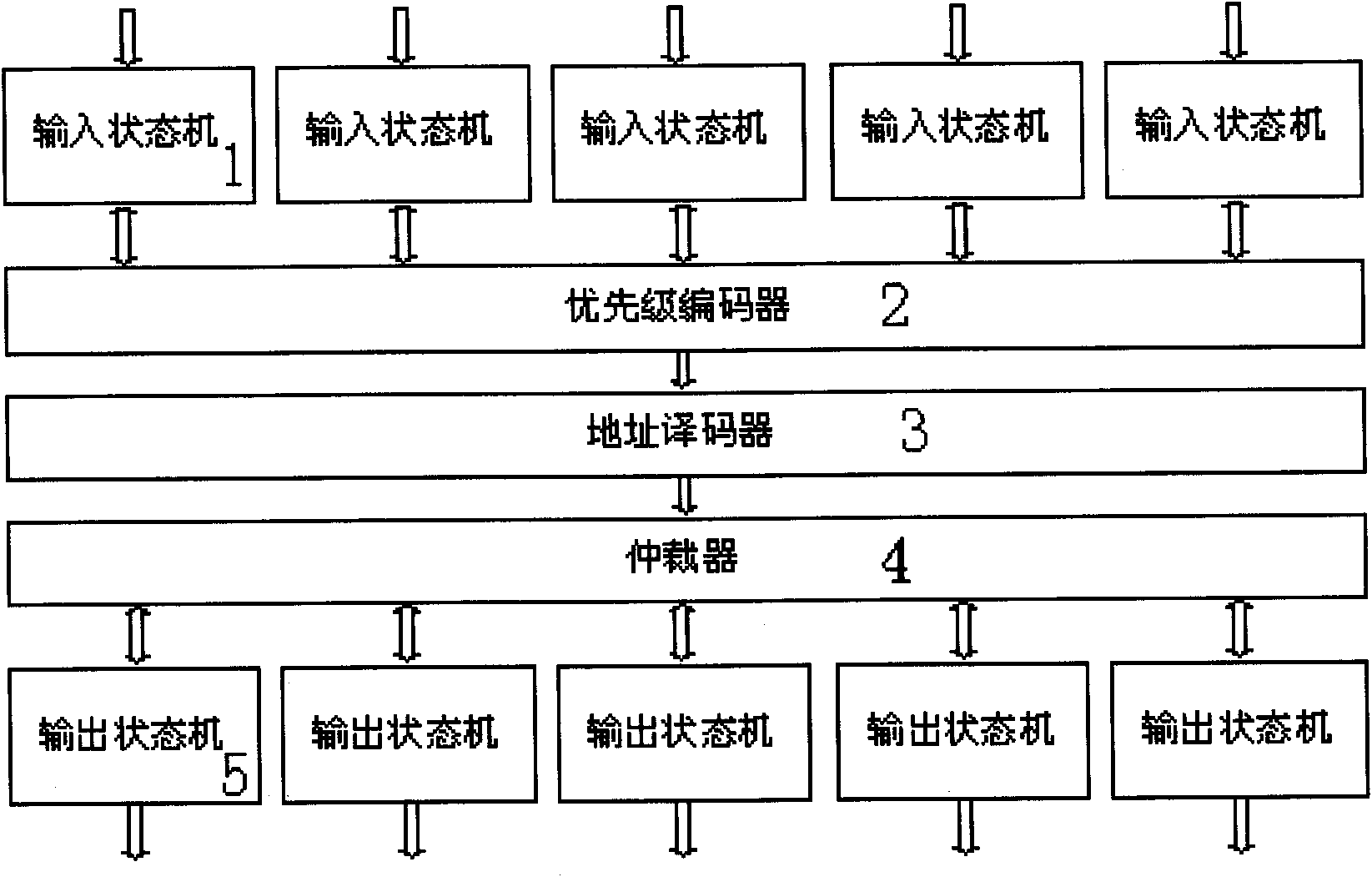

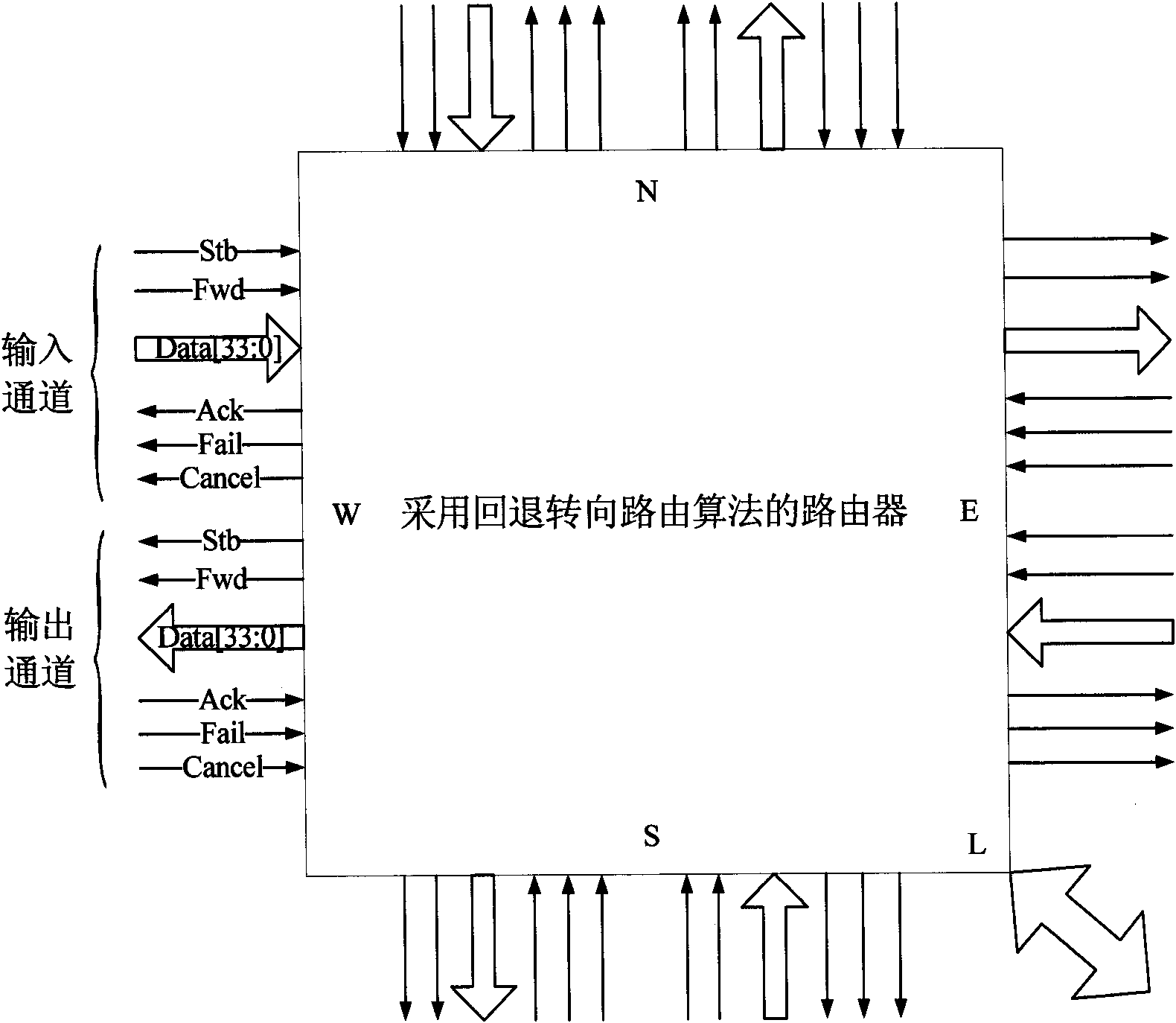

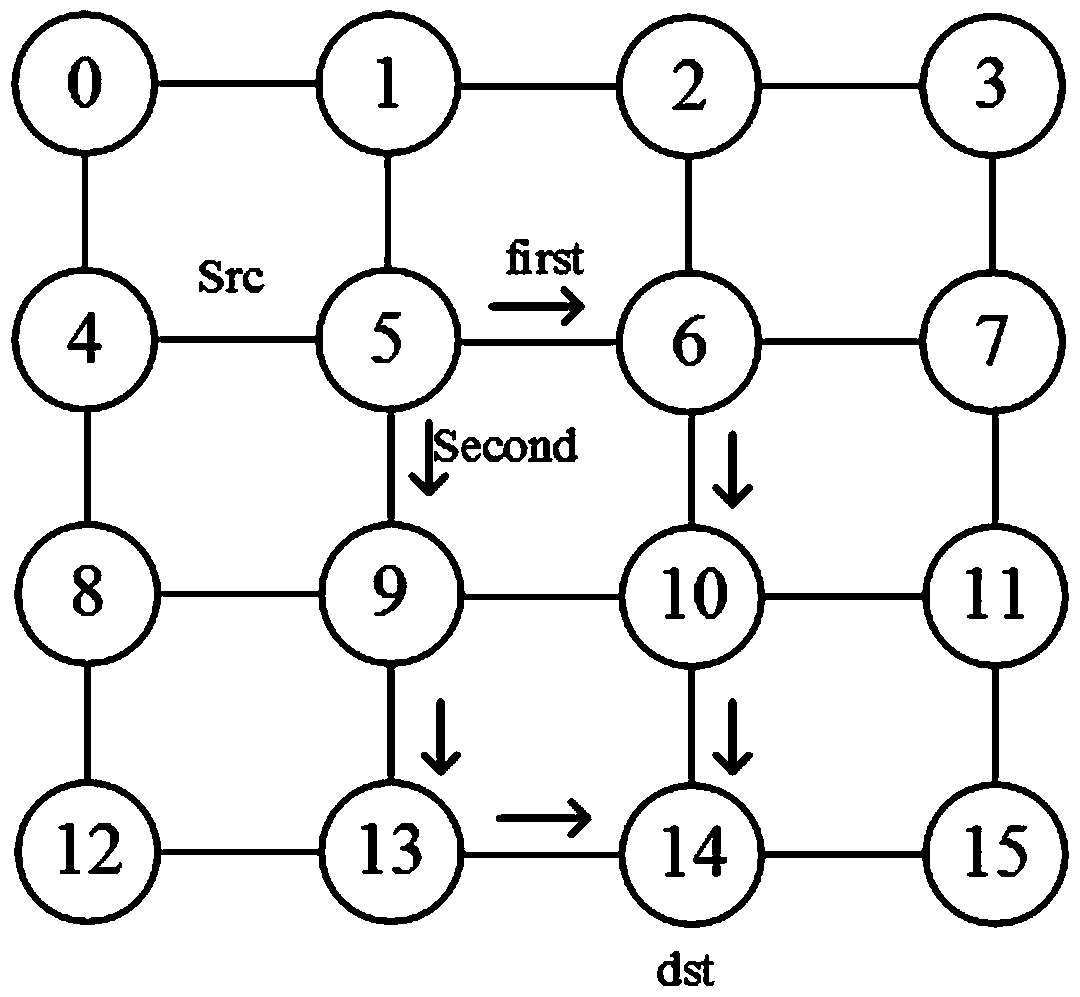

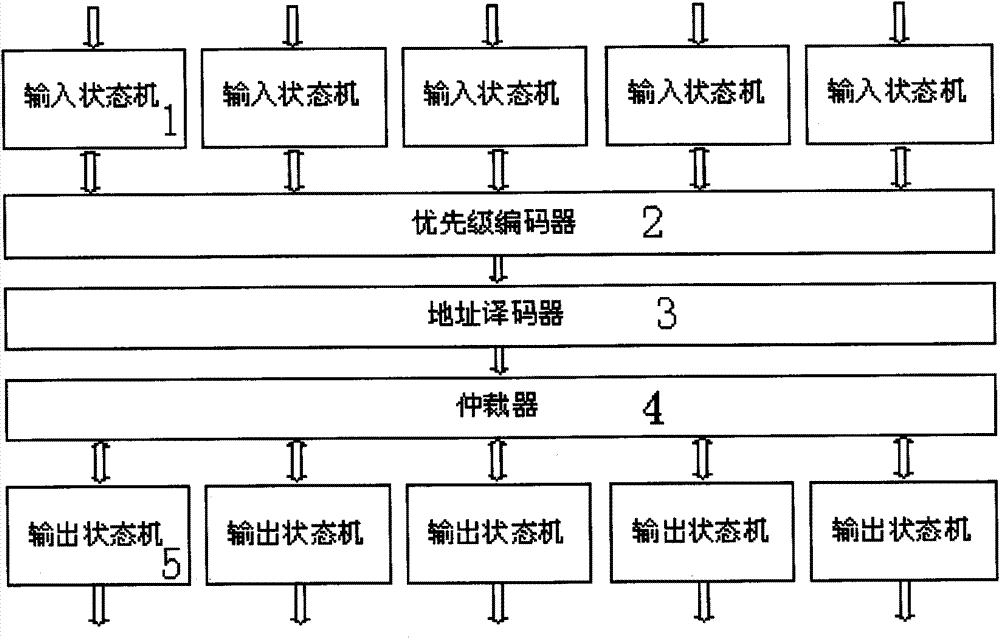

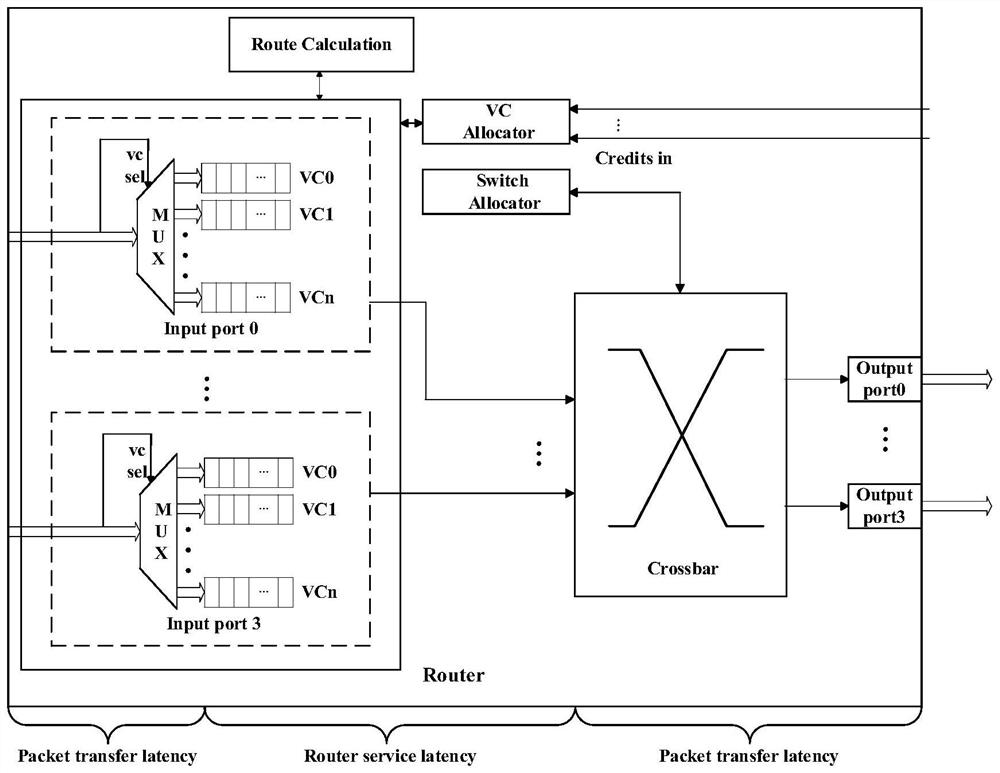

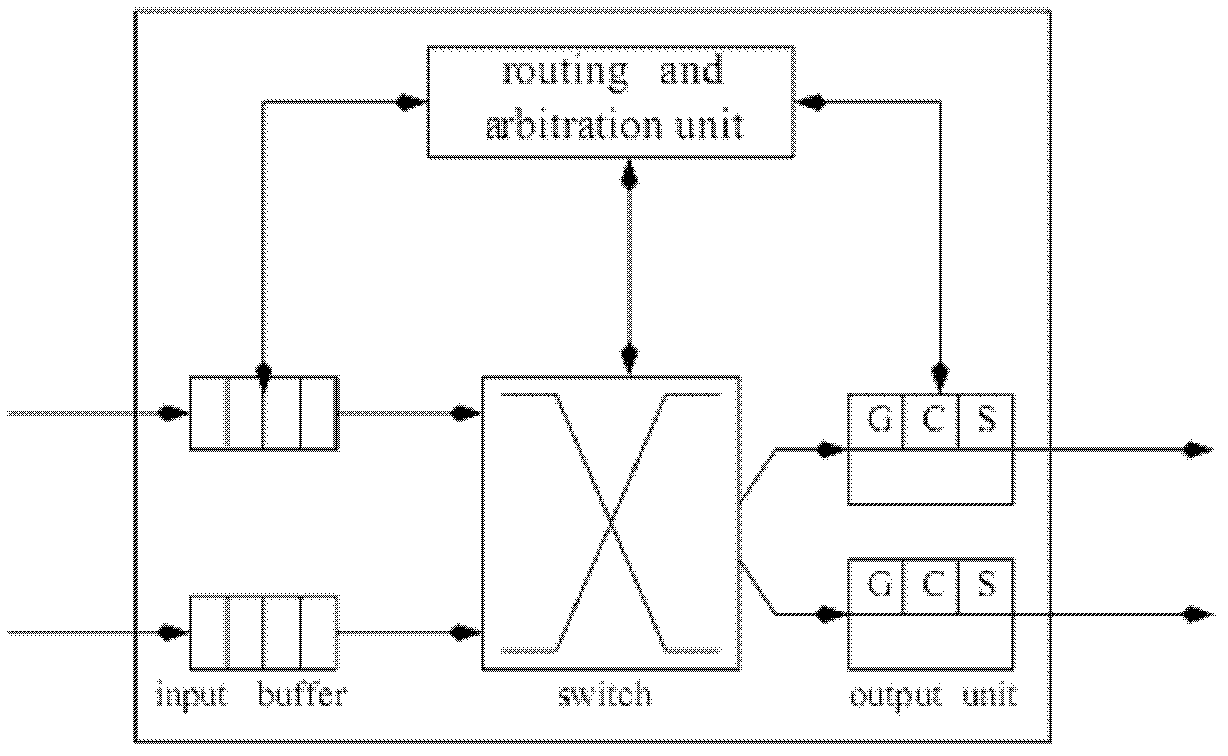

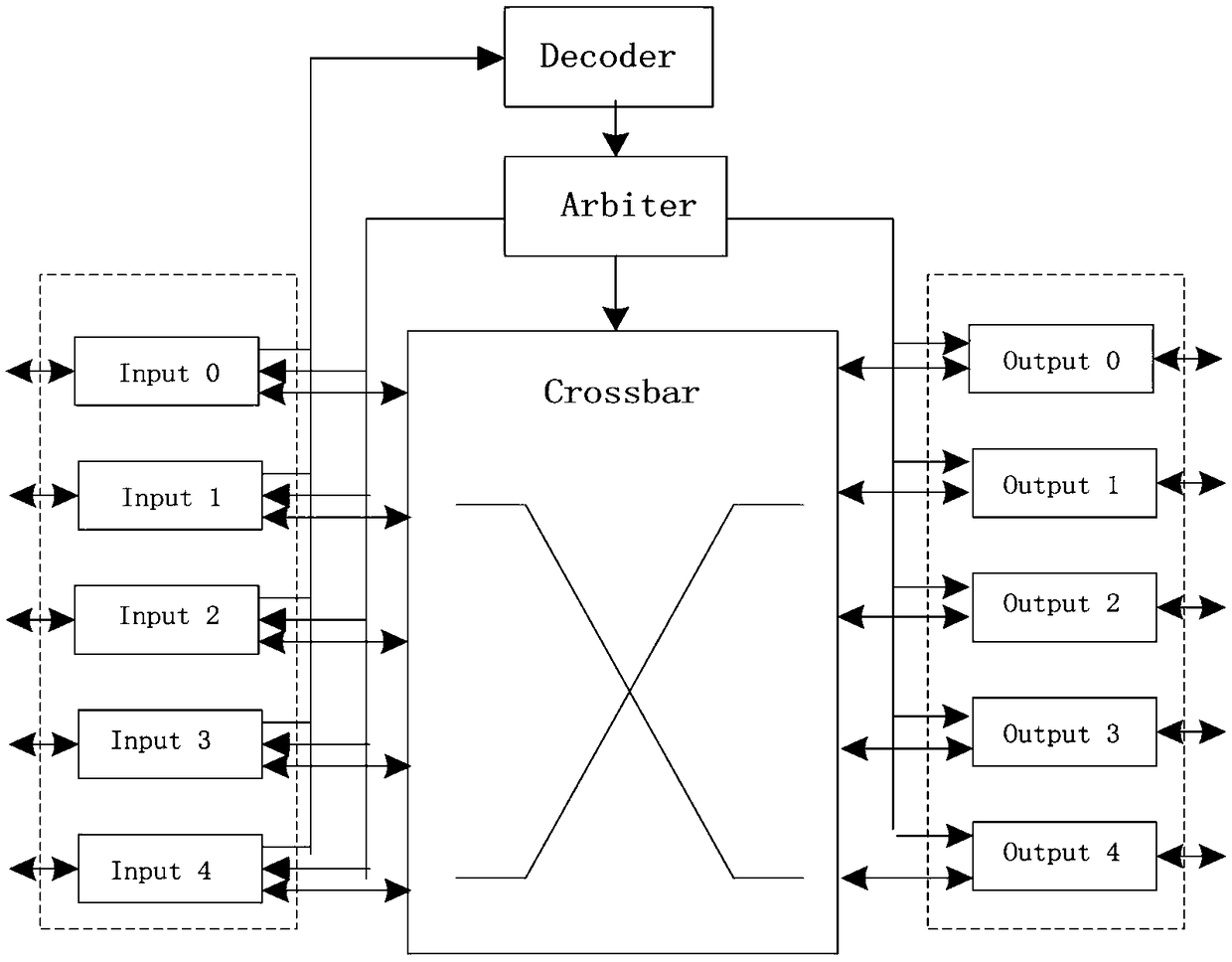

Packet-circuit exchanging on-chip router oriented rollback steering routing algorithm and router used thereby

InactiveCN101834789AAvoid congestionMaximize Communication EfficiencyData switching networksPathPingAlgorithm

The invention discloses a packet-circuit exchanging on-chip router oriented rollback steering routing algorithm and a router used thereby. The algorithm is an adaptive routing algorithm, which performs routing arbitrage according to an on-chip network congestion condition and dynamically changes a routing path according to the occupation situation of a link resource. The algorithm records output ports meeting a routing condition, reselects an output port after meeting congestion and realizes rollback routing so as to fully use network resources, effectively avoids congestion, improves average throughput and reduces average packet delay. The router comprises an input state machine, a priority encoder, an address decoder, an arbiter and an output state machine, which are sequentially connected. When selecting the routing path, the router does not retrace to route in a 180-degree direction and does not route in a direction far away from a target node, so the router does not cause the problem of dead locking or active locking. The algorithm and the router of the invention are low in cost and high in performance and are suitable for realizing an on-chip network system with high performance.

Owner:NANJING UNIV

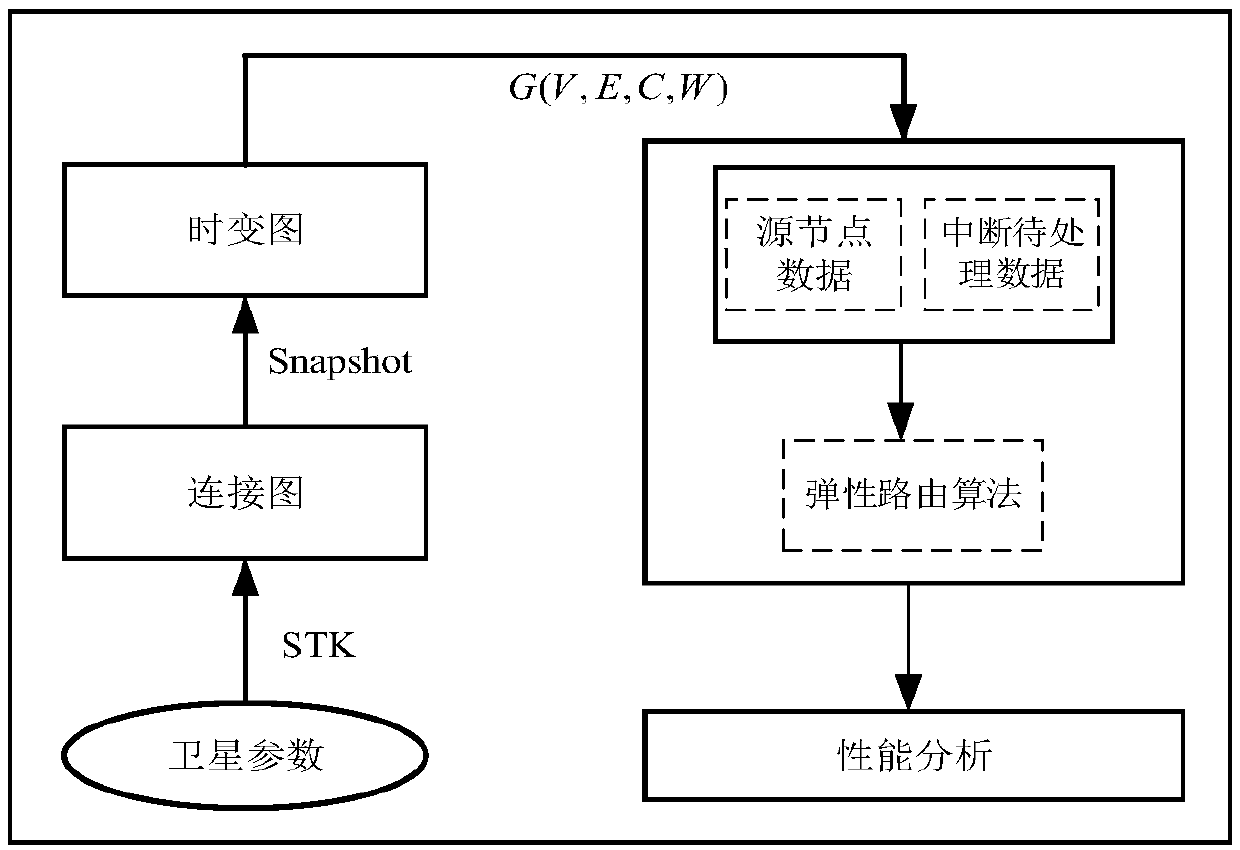

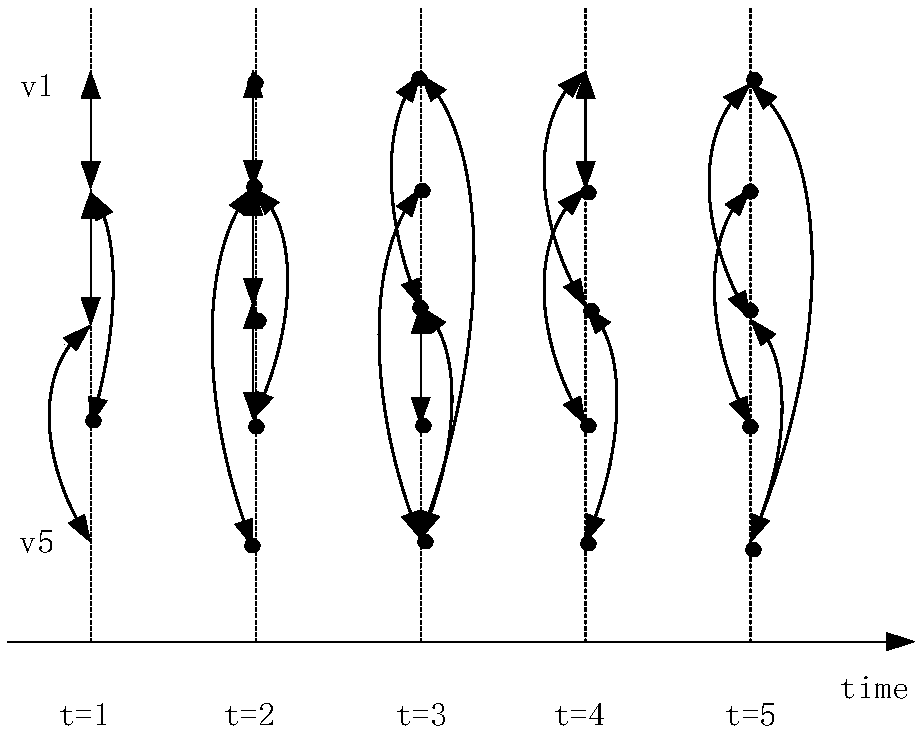

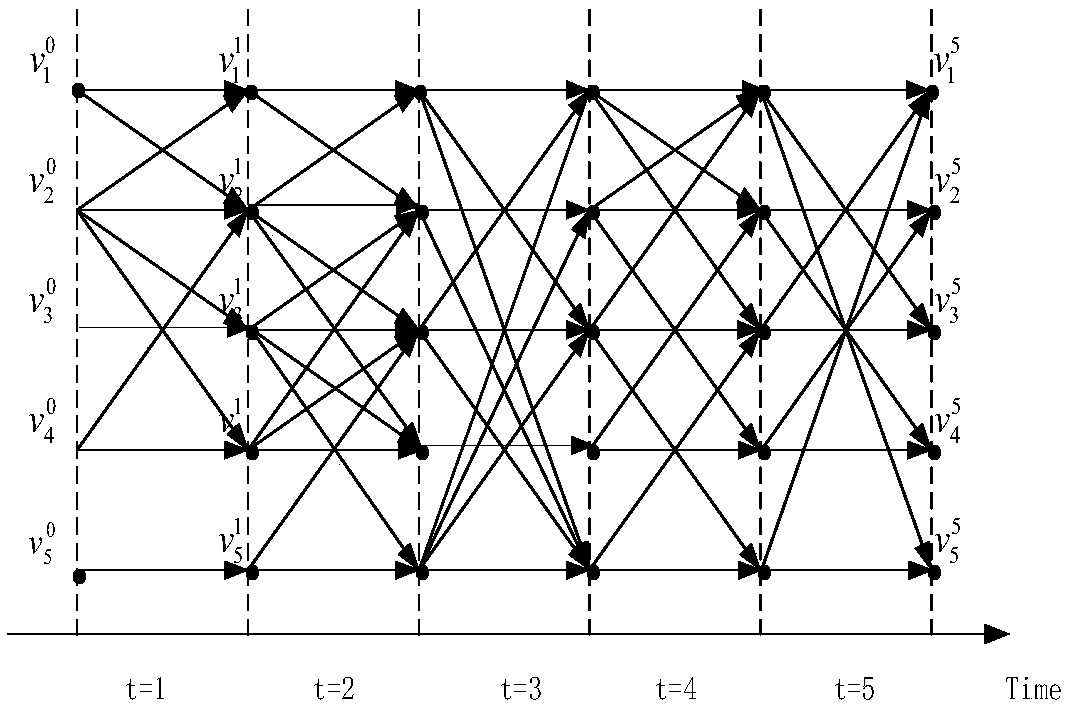

Resilient routing algorithm for unpredictable interrupts in satellite DTN networks based on spatiotemporal graph model

InactiveCN109067453ASolving Unpredictable OutagesGuaranteed normal transmissionRadio transmissionData switching networksMathematical modelAdaptive routing algorithm

The invention provides a satellite DTN network unpredictable interrupt elastic routing algorithm algorithm based on spatiotemporal graph model, which is applied to the spatial information network, theparameters of the satellite network and the mathematical models of the spatio-temporal graph model construction algorithm and routing algorithm are given, and the capacity and energy cost of the inter-satellite links in the satellite network are calculated, which provides a practical and feasible scheme for the data transmission problem of the satellite network in the event of unpredictable interruption. Through a specific algorithm generation example, the algorithm proposed by the invention is proved to be effective. The unpredictable interrupt elastic routing algorithm of the invention cansolve the problem that after the unpredictable interrupt occurs in the satellite network, the normal transmission of the data is guaranteed and the energy expenditure thereof is minimized; and the unpredictable interrupt elastic routing algorithm of the invention can solve the problem that the unpredictable interrupt occurs in the satellite network and the normal transmission of the data is guaranteed and the energy expenditure thereof is minimized. Therefore, compared with other traditional routing algorithms, the elastic routing algorithm designed by the invention can effectively solve the problem of unpredictable interruption in the satellite network.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

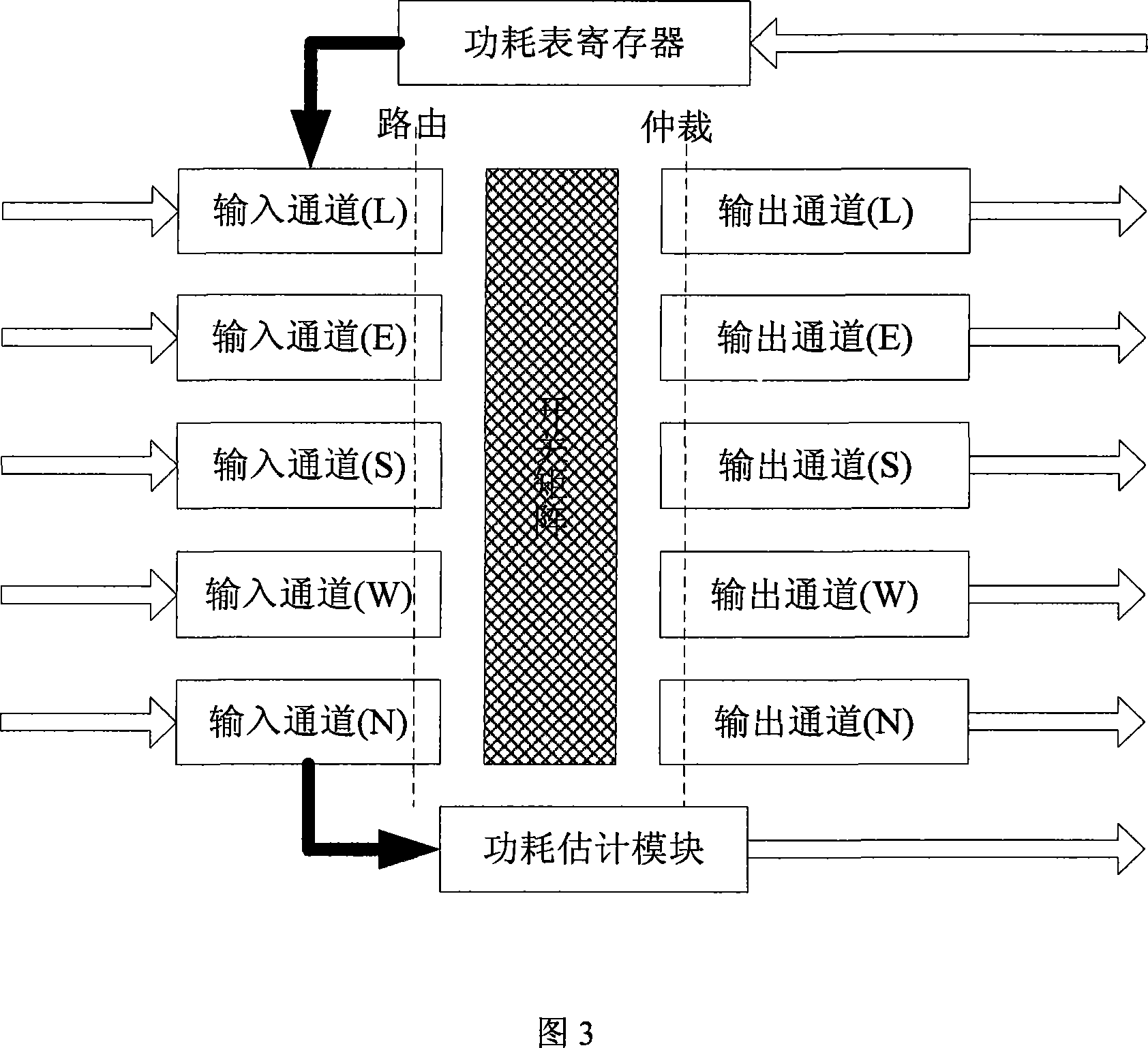

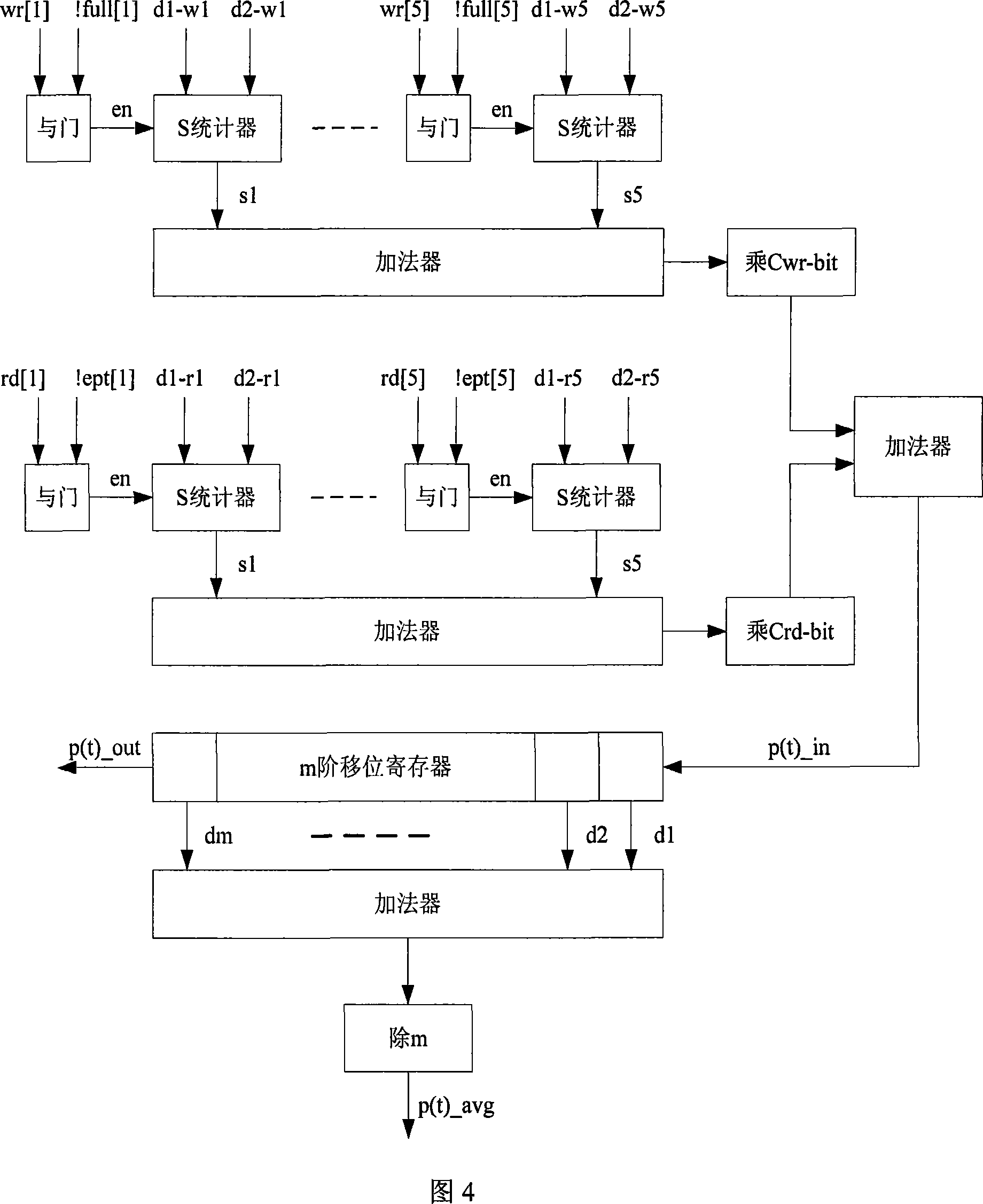

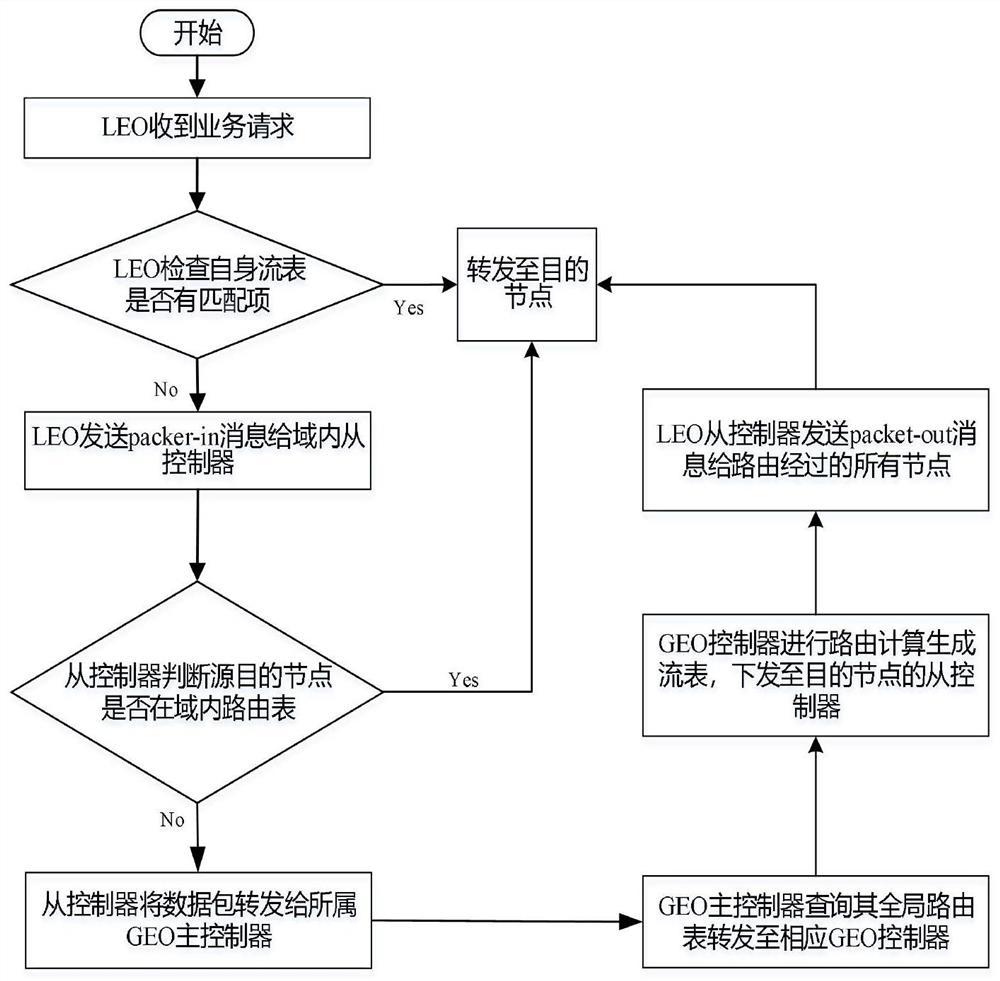

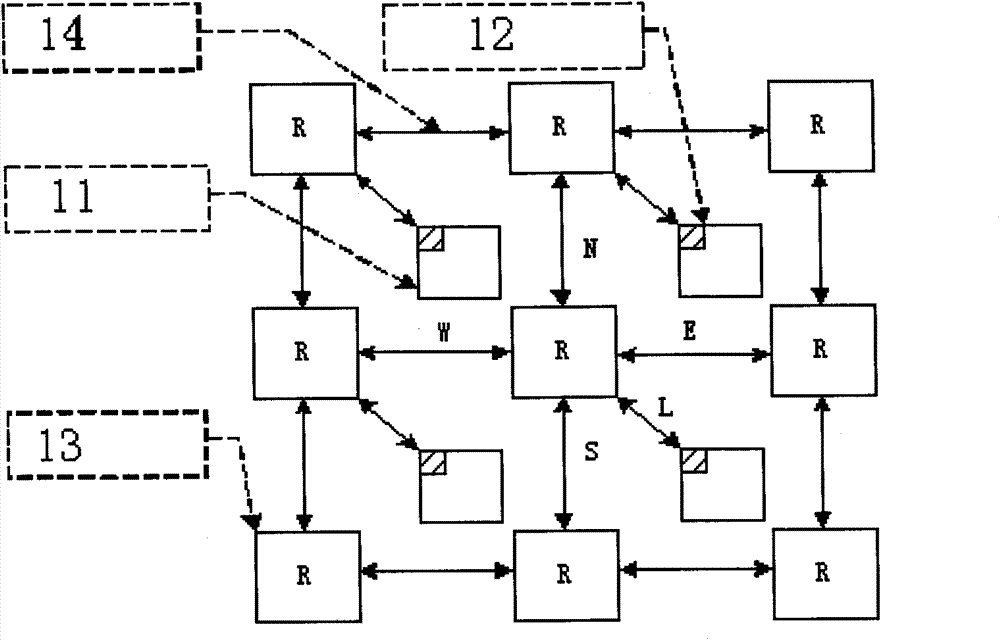

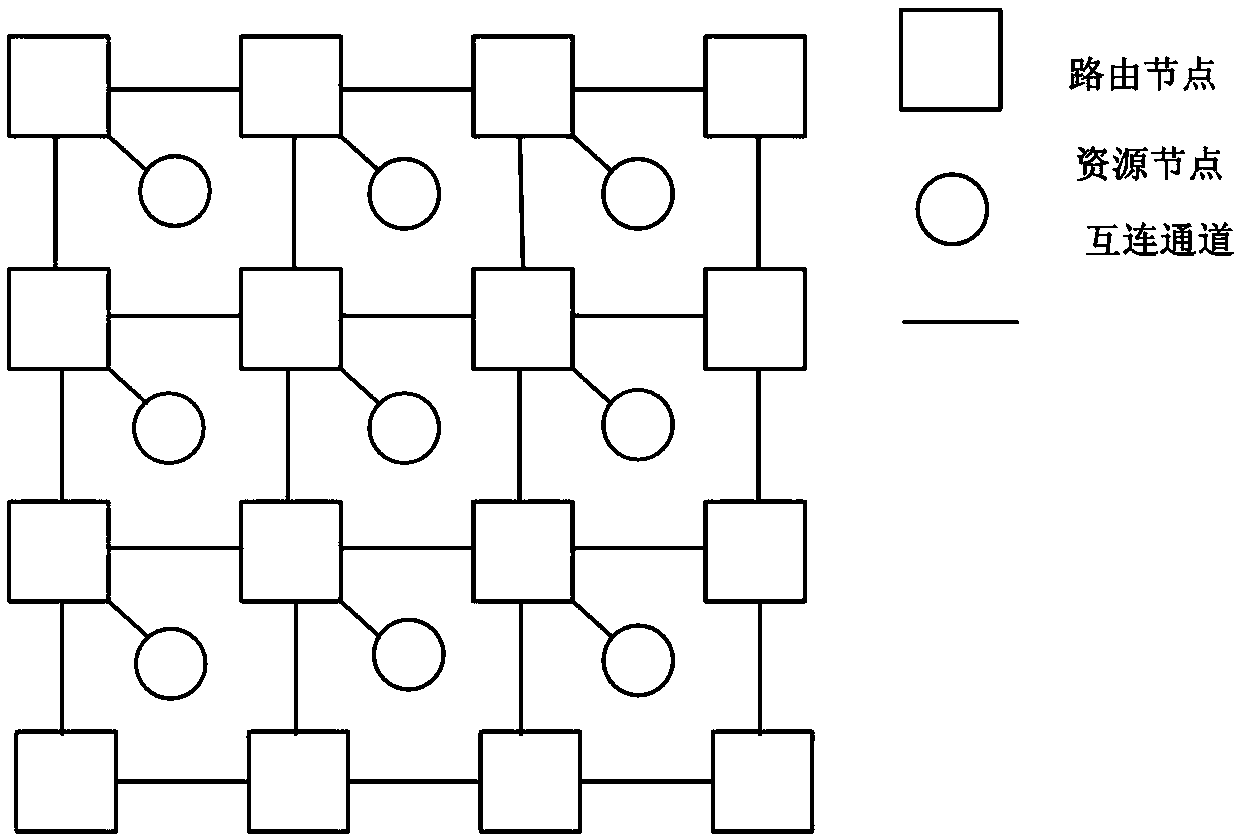

Router power consumption model based on network on chip

The invention discloses a router power model on the basis of a network-on-chip, which simplifies router operations into four power dissipation links namely write-cache, read-cache, a bestride switch and a bestride link according to the power dissipation specific weight and attributes dynamic power dissipation to bit flipping activities which are triggered when a present data film arrives, and numbers the power dissipation by the bit flipping activities to obtain the router power model. Considering that the implementation complexity which is required by the network-on-chip requirements to the power model is as low as possible, the invention can adopt the statistical average in stead of the instantaneous sampled value to obtain a power dissipation simplified model. Hardware implementation methods of two power dissipation models are given out aiming at a five-channel rooter structure, the simplified model is introduced to a self-adaptive routing algorithm, which realizes the power dissipation distribution optimization of the network-on-chip. The router power model which is proposed by the invention has low algorithm complexity and simple realization, is suitable for network-on-chip, and can be used in research and application in the aspects of power dissipation performance statistics, the power dissipation distribution optimization, thermal protection and the like.

Owner:NANJING UNIV

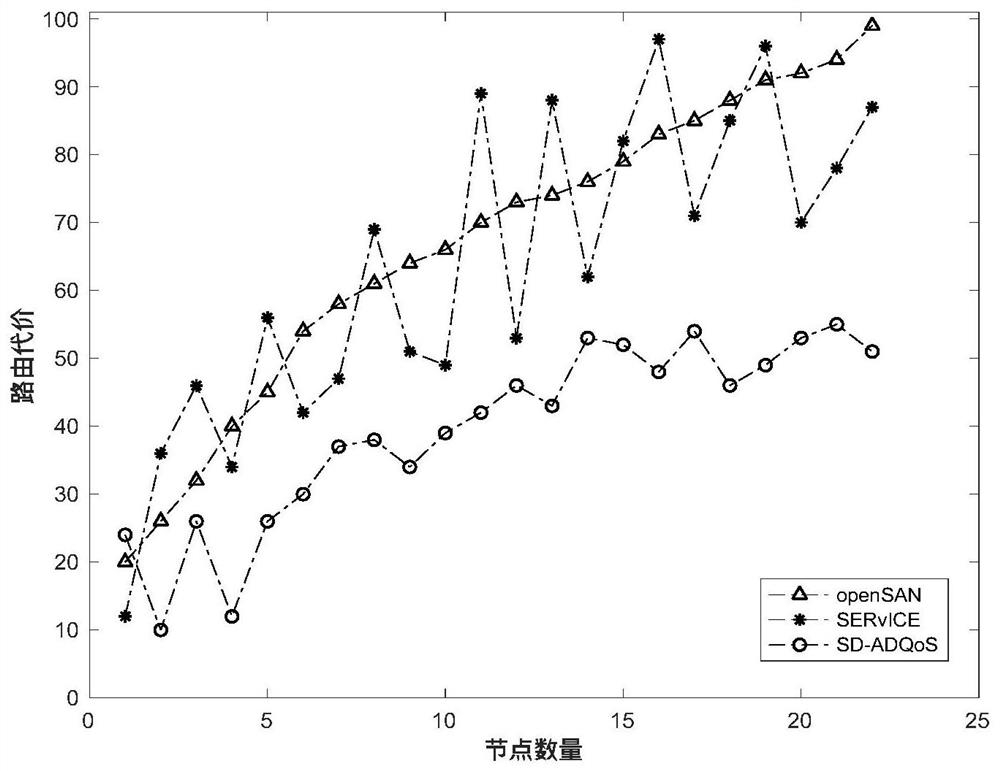

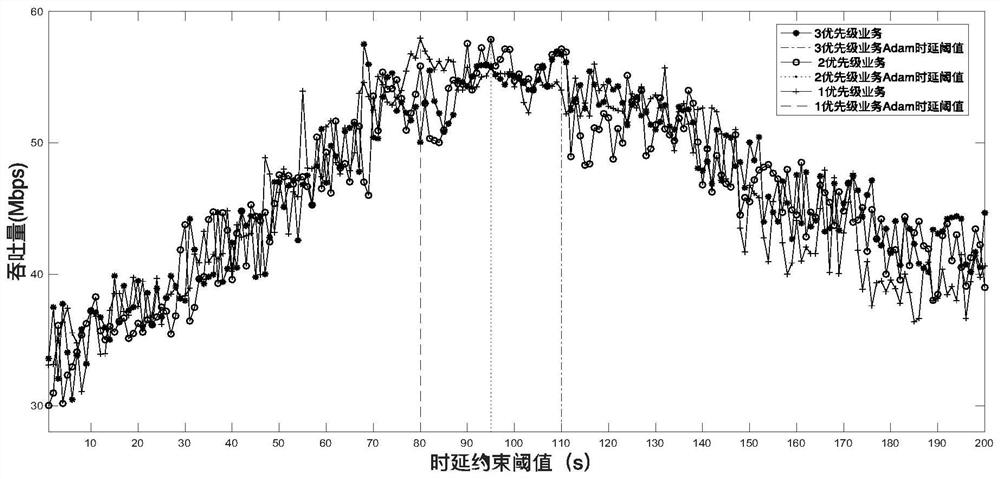

SDN (Software Defined Network)-based space-ground integrated adaptive dynamic QoS (Quality of Service) routing method

ActiveCN113572686AReduce long-distance transmissionReduce control overheadRadio transmissionData switching networksQos quality of serviceAdaptive routing algorithm

The invention discloses an SDN (Software Defined Network)-based space-ground integrated adaptive dynamic QoS (Quality of Service) routing method. The method comprises the following steps of: establishing an SDN-based hierarchical clustering network model; establishing network resource mapping; and establishing a multi-constraint QOS adaptive routing algorithm SDN-AD. According to the method, the control overhead can be effectively reduced by reducing long-distance transmission and shortest distance clustering of the control packet, and the transmission efficiency is improved. According to the method, the multi-constraint QoS problem is formulated into the optimization problem with the minimum transmission cost as the target, the transmission cost of links of different types can be effectively calculated, and the difference between satellites of different levels and a ground network is shielded. The method can better adapt to network changes, so that services meeting different service quality requirements are provided. According to the invention, the optimization problem is solved, and self-adaptive routing is realized. The method provided by the invention has better performance in the aspects of overhead control, network service quality and algorithm convergence speed.

Owner:DALIAN UNIV

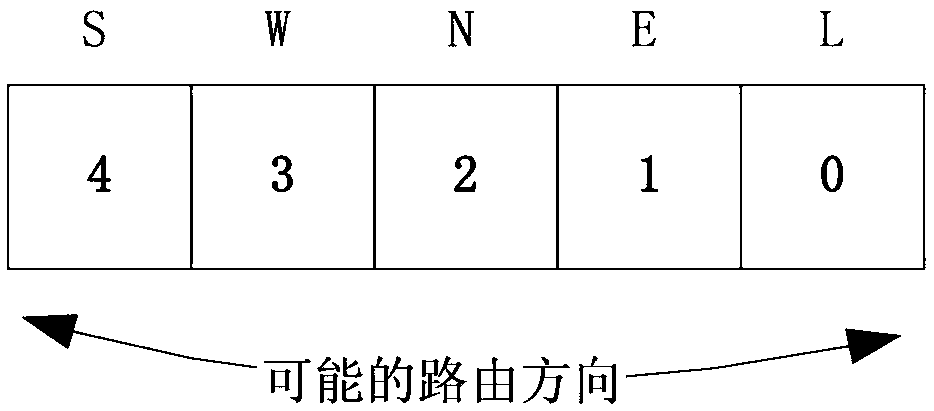

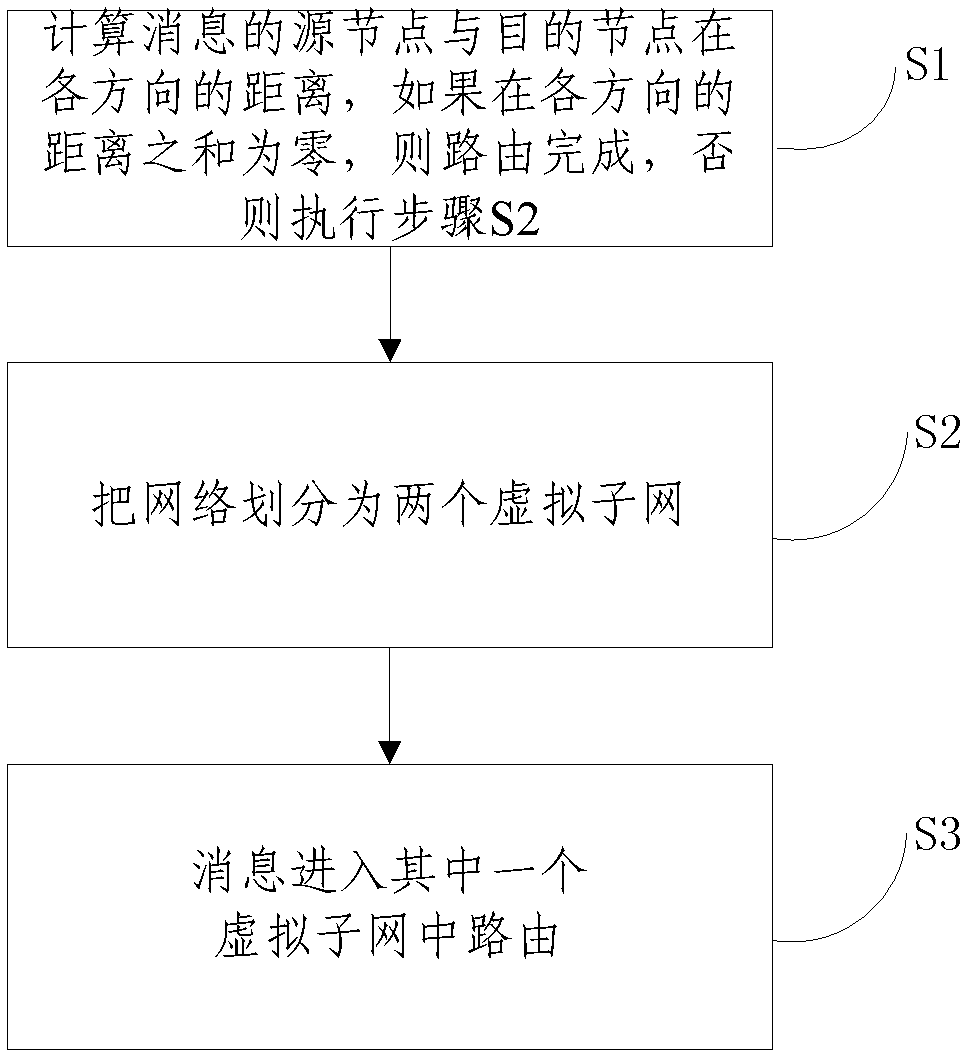

Low-power-consumption adaptive routing method in network on chip

ActiveCN102437953AImprove performanceReduce power consumptionData switching networksAdaptive routing algorithmNetworks on chip

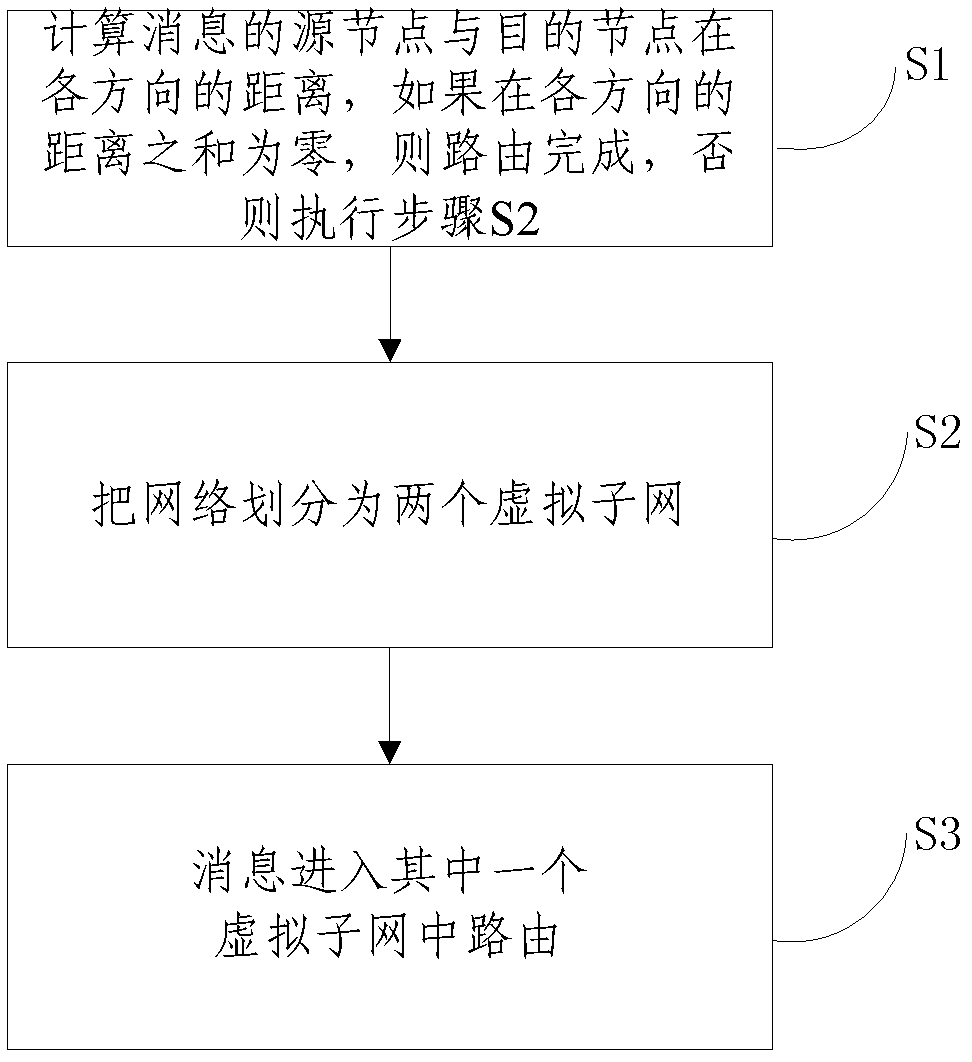

The invention relates to the technical field of networks on chip, and discloses a low-power-consumption adaptive routing method in a network on chip. The method comprises the following steps that: S1, distances between a source node and a destination node of a message in an x dimension direction and a y dimension direction are calculated respectively, if the sum of the distances is zero, routing is finished, otherwise, a step S2 is executed; S2, the network is divided into two virtual sub-networks x+y* and x-y*; and S3, the message enters into the virtual sub-network x+y* or x-y* for routing. In the method, the physical network is divided into two virtual sub-networks x+y* and x-y*, the interiors of the virtual sub-networks x+y* and x-y* both use a fully adaptive routing algorithm of the shortest path and a new EVC (Express Virtual Channel) flow control technology, data packets are injected into a corresponding virtual network according to the offset value of the destination node of the data packets relative to the source node, and the data packets are routed to the destination in a manner of adaptive routing. In the routing process of the data packets, an EVC is selected preferably, and an NVC (Normal Virtual Channel) is used when no idle EVC exists, so that the routing goes forward according to normal pipeline stages, the performance is improved and the power consumption is reduced.

Owner:TSINGHUA UNIV

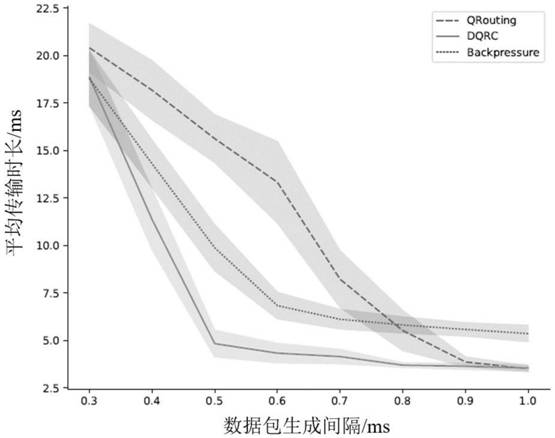

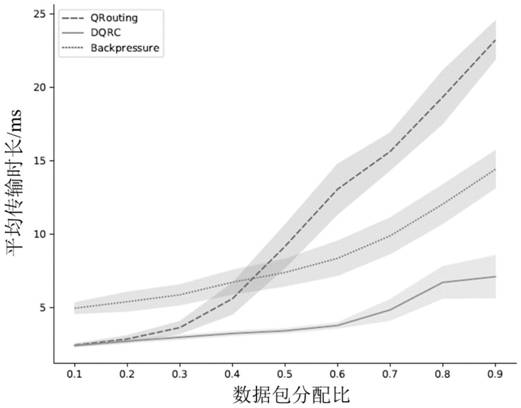

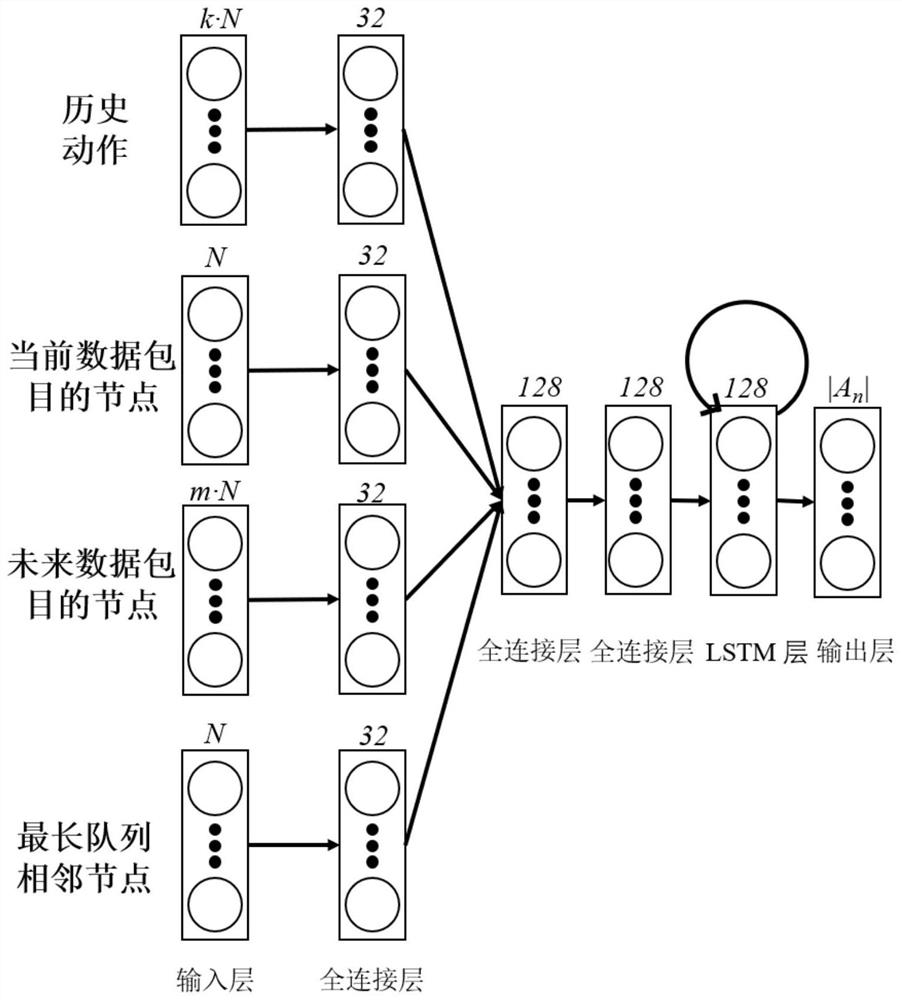

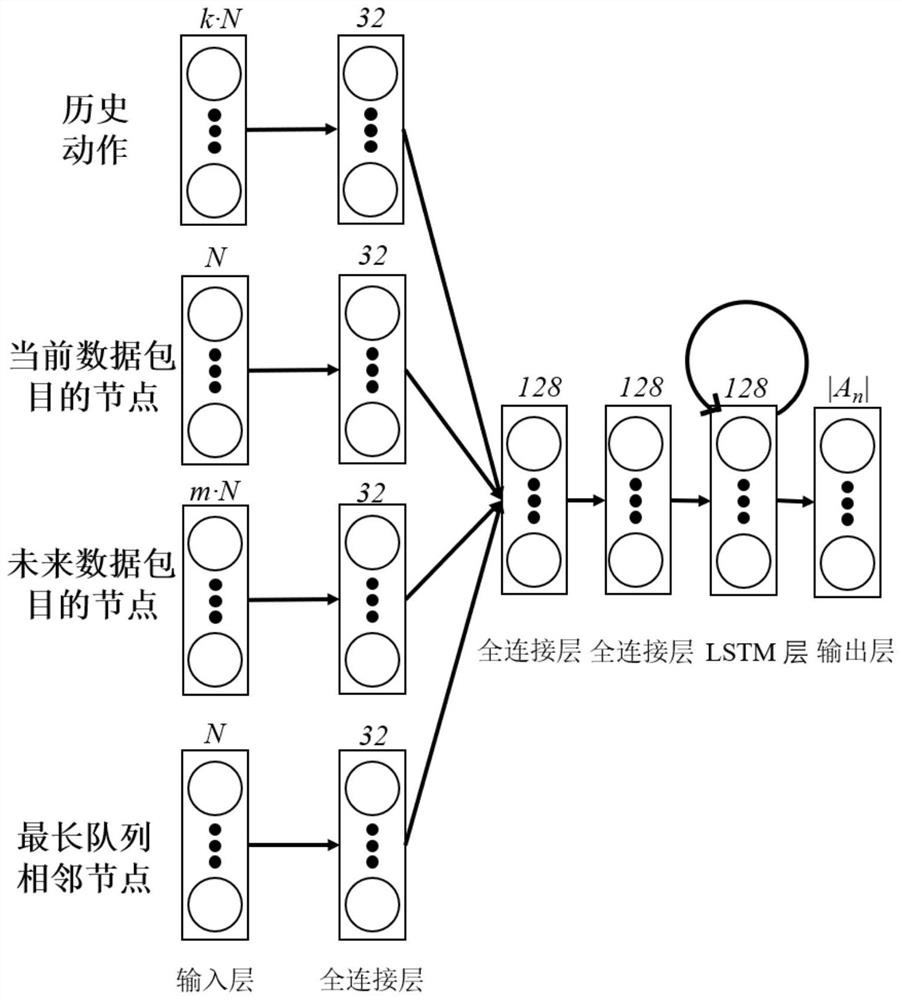

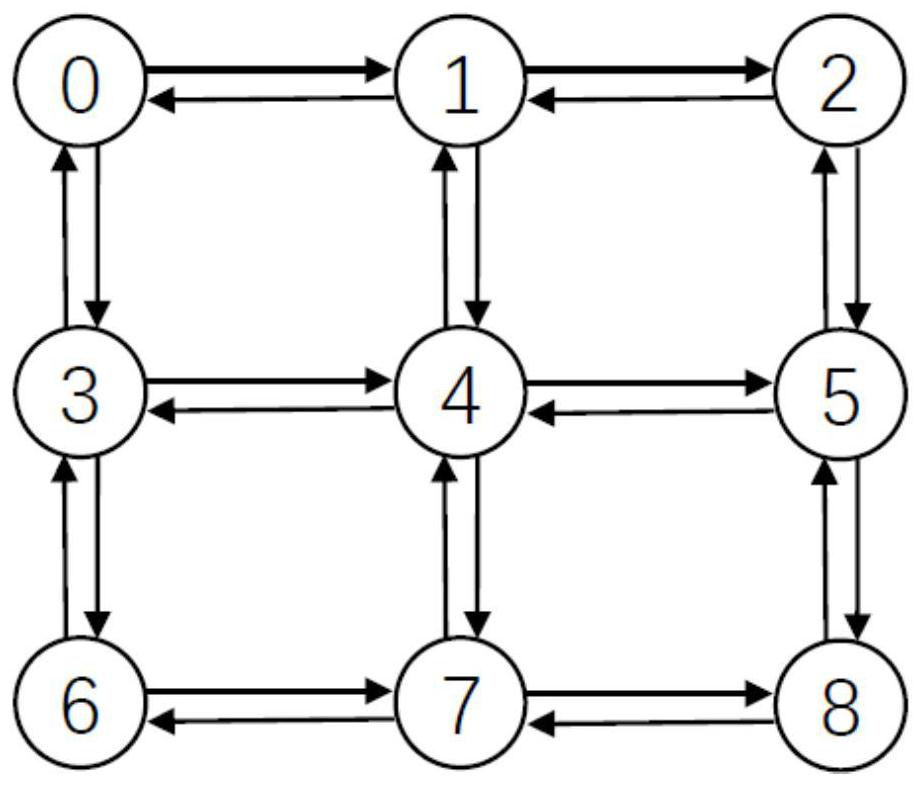

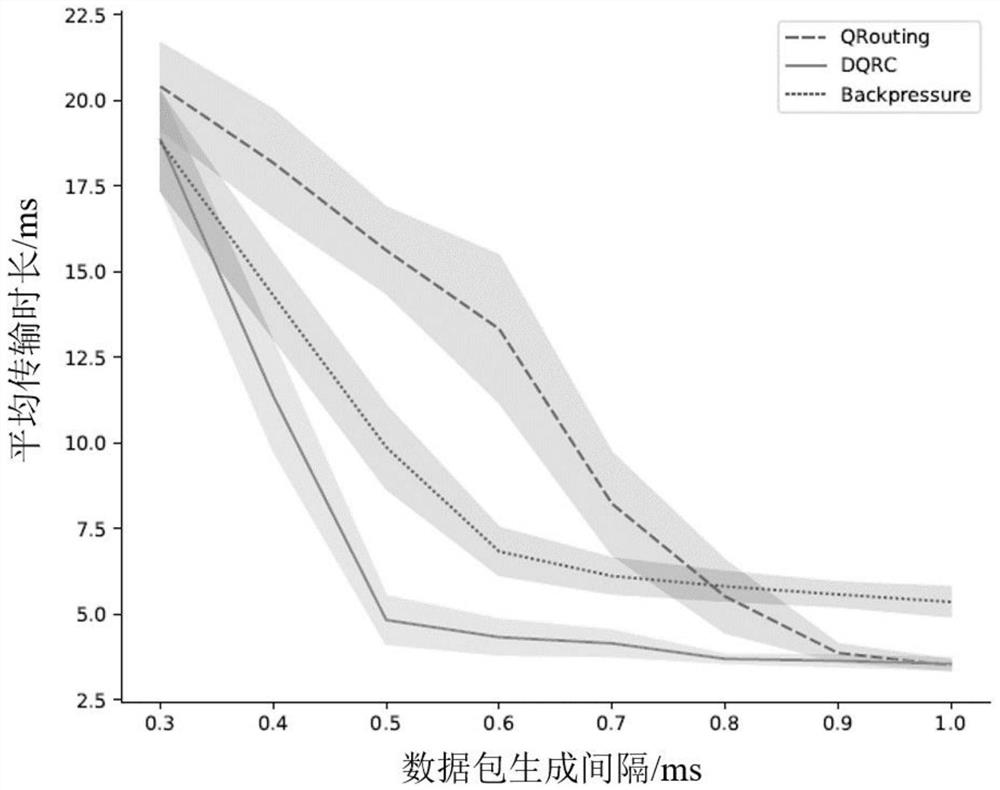

Data packet routing algorithm based on multi-agent deep reinforcement learning

ActiveCN112491712AShort transmission delayImprove performanceNeural architecturesData switching networksPathPingData pack

The invention belongs to the technical field of distributed routing, and particularly relates to a data packet routing algorithm based on multi-agent deep reinforcement learning. In order to relieve the congestion condition in a computer network, an end-to-end adaptive routing algorithm is designed by using a multi-agent deep reinforcement learning technology, and each router completes data packetscheduling according to local information, so that the transmission delay of data packets is reduced. According to the method, firstly, a mathematical model of distributed routing is constructed, specific meanings of all elements in reinforcement learning are defined, then a neural network is trained, and finally algorithm performance testing is carried out in a simulation environment. Simulationexperiment results show that introduction of the deep neural network can mine feature information in an input network state, balance between an unblocked path and a shortest path is achieved, and compared with other common routing algorithms, shorter data packet transmission time delay is achieved.

Owner:FUDAN UNIV +1

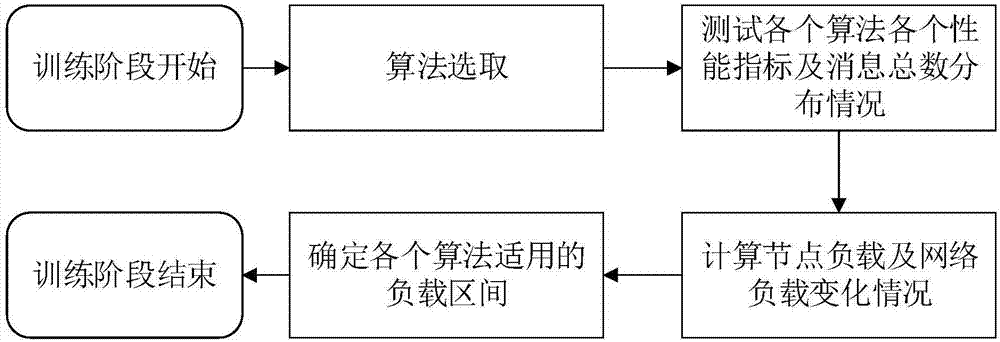

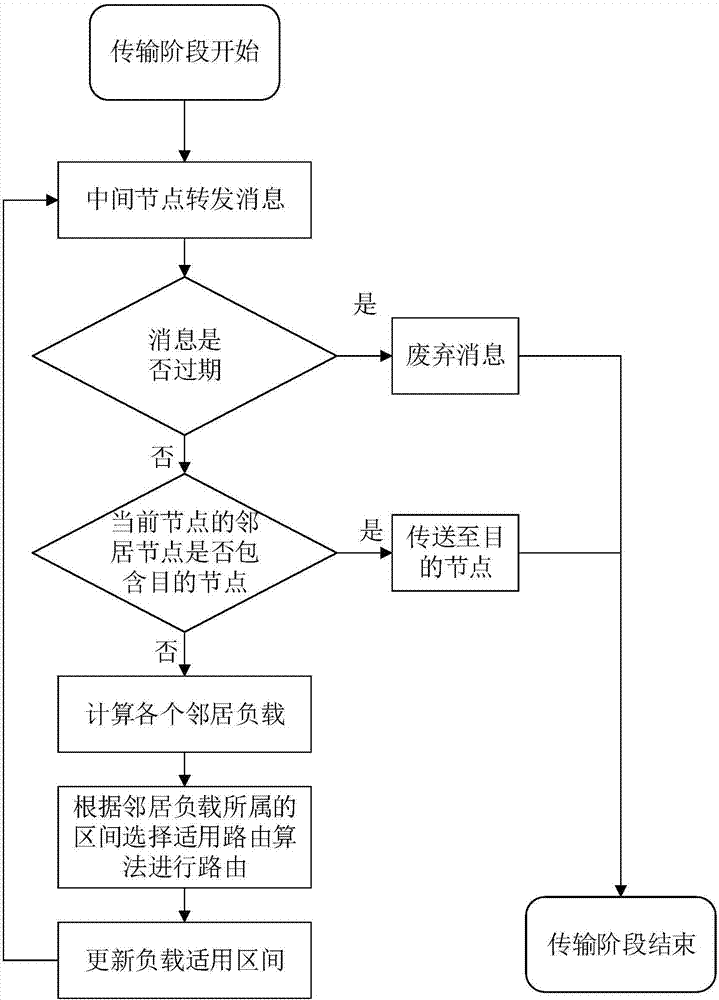

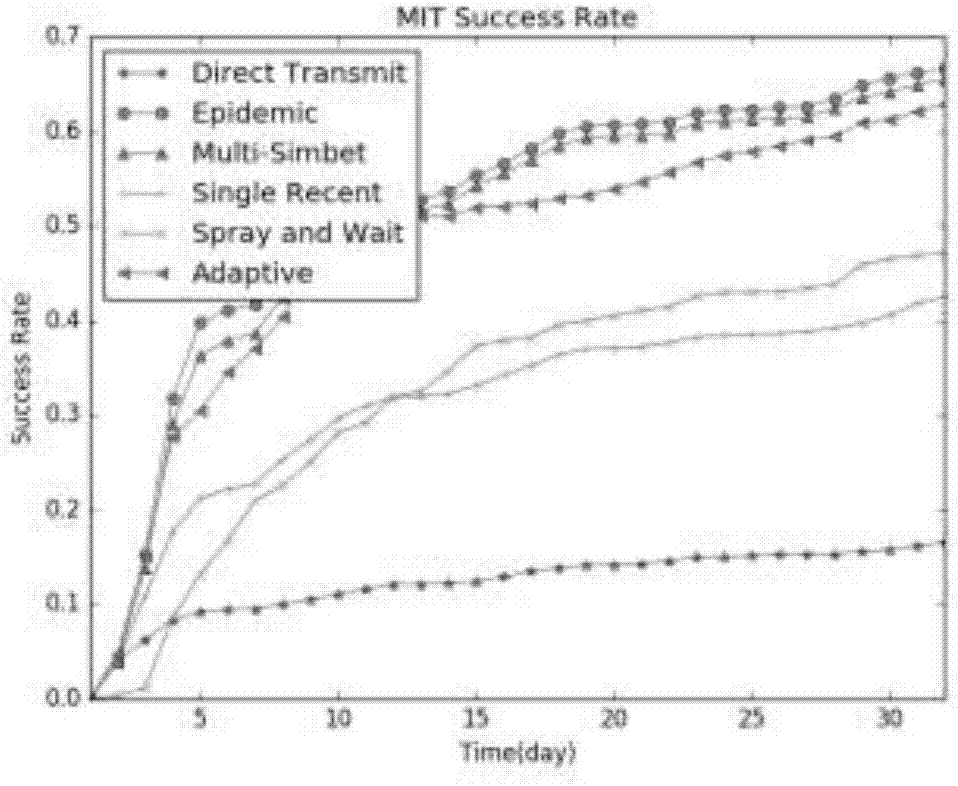

Adaptive DTN (Delay Tolerant Network) routing algorithm based on resource-constrained condition

ActiveCN107171957AAvoid congestionReduce consumptionData switching networksCurrent loadAdaptive routing algorithm

The invention provides an adaptive DTN (Delay Tolerant Network) routing algorithm based on a resource-constrained condition. That is, an applicable routing algorithm is selected according to the current load of a node based on an adaptive routing algorithm of a node load by using a forward routing algorithm with a high transmission success rate and a flooding routing algorithm with low resource consumption; the algorithm is divided into two stages: a training stage and a transmission stage; 1), the training stage: the main task is to determine the node load and network load calculation parameters according to the selected routing algorithm, and determine a load interval applicable to each algorithm; and 2), the transmission stage: the main task is to calculate unexpired data according to a node load calculation formula defined in the training stage to obtain the node load, judge the load interval of the node load and the routing algorithm corresponding to the node interval; perform routing according to the routing algorithm; and meanwhile, update parameters required for calculating the node load defined in the training stage according to the routing condition of the hop, and update the corresponding load interval.

Owner:NANJING UNIV

Dynamic steering routing algorithm based on ''package-circuit'' switching technology

ActiveCN106209518AReduce congestionEvenly distributedData switching networksData streamAdaptive routing algorithm

This invention discloses a dynamic steering routing algorithm based on ''package-circuit'' switching technology. The dynamic steering routing algorithm is characterized in being applied to the link establishment stage of the ''package-circuit'' switching technology, can select a proper route to transmit data according to information, such as traffic distribution, congestion situation and the like, in a network-on-chip, and is a self-adaptive algorithm. According to the port usage of a current routing node and a downstream routing node, the algorithm selects a congestion-free routing node to realize dynamic steering route; thus, the probability of network congestion can be reduced; the data stream can be distributed in the network evenly; and then, the network resource can be utilized adequately, and the performance of the system can be improved. At the same time, the success rate for establishing the link can be improved, so that the link is prevented to be established and cancelled for many times during the link establishing process; and thus, the power consumption of the network and the system can be reduced.

Owner:HEFEI UNIV OF TECH

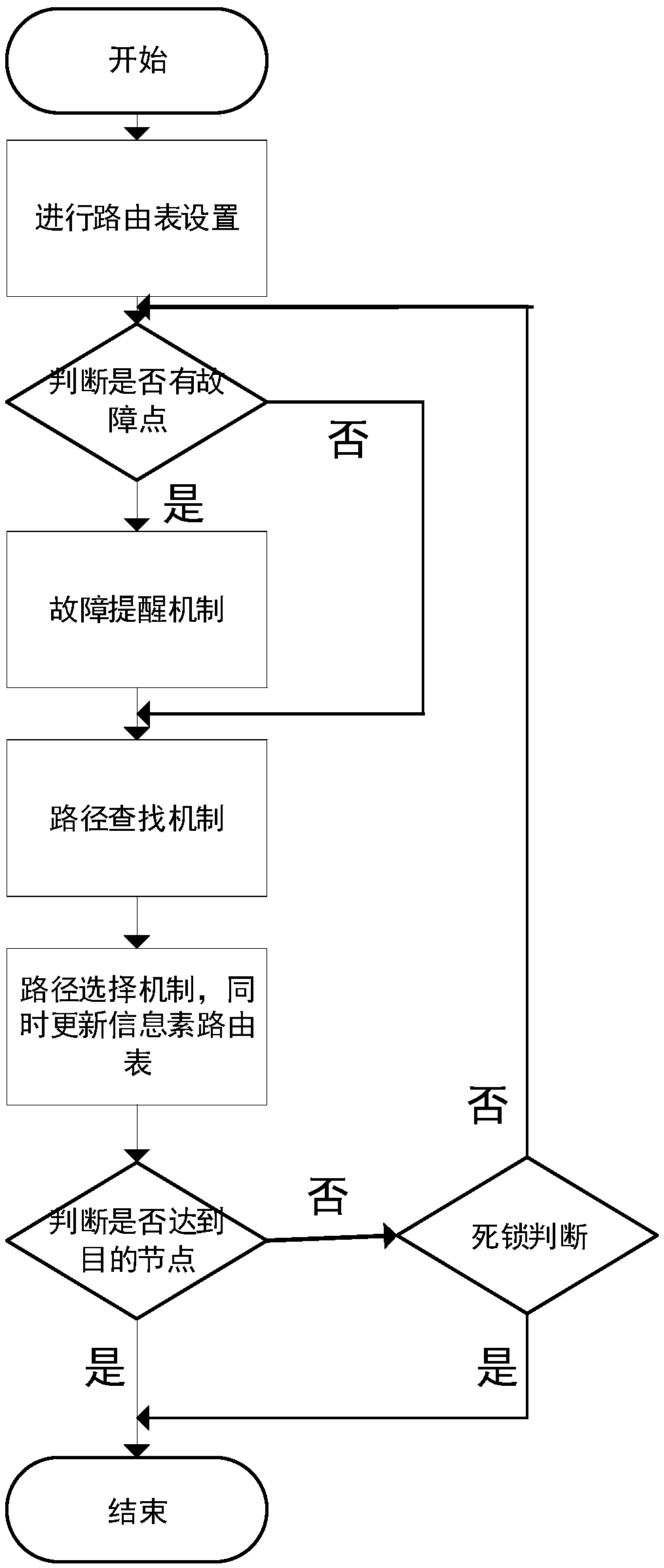

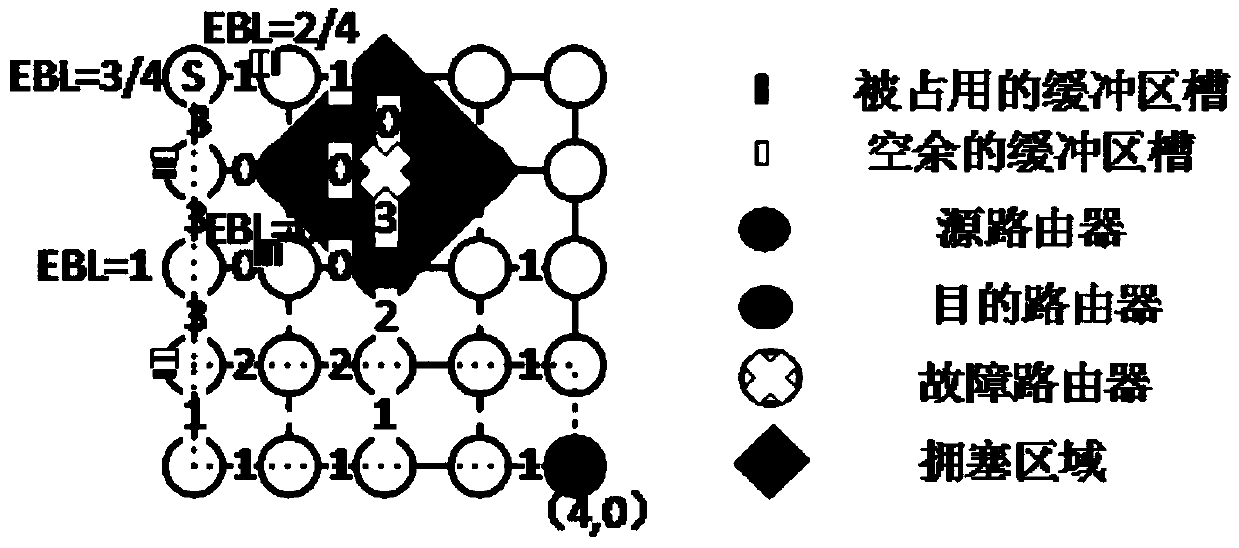

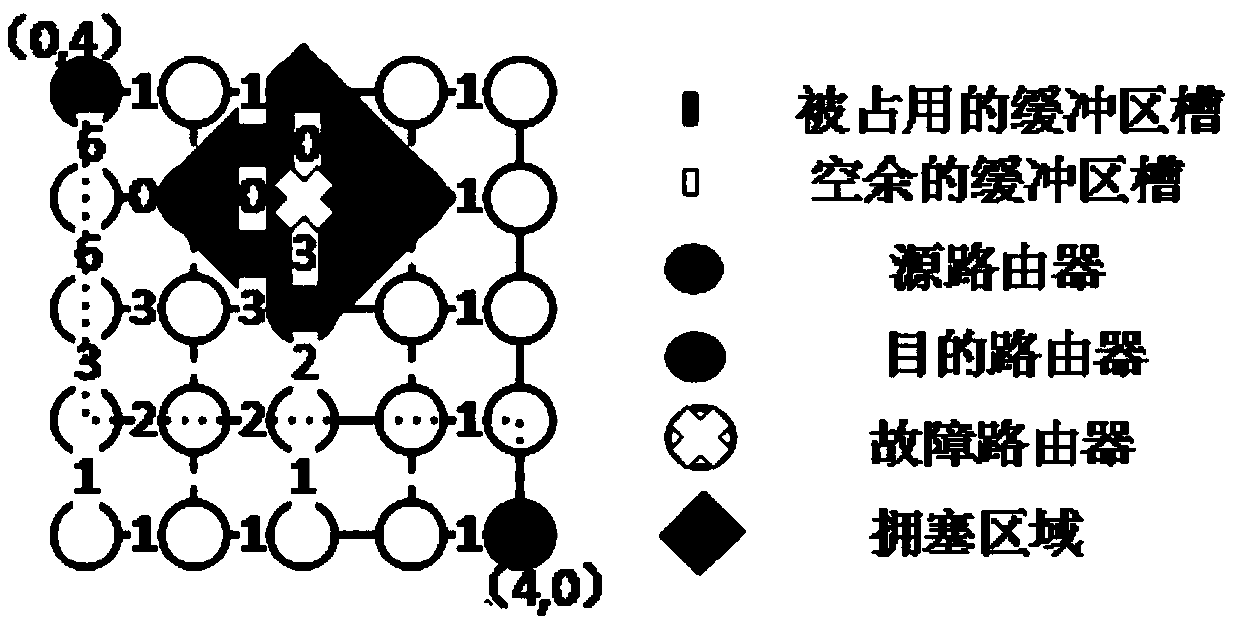

Fault-tolerant adaptive routing method based on ant colony algorithm

ActiveCN109660456AReduce Data Transfer LatencyLoad balancingArtificial lifeData switching networksRouting tableAdaptive routing algorithm

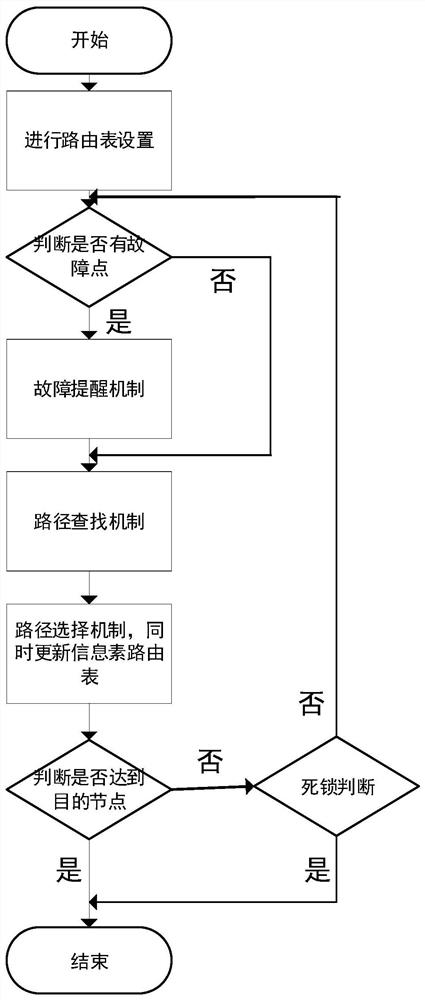

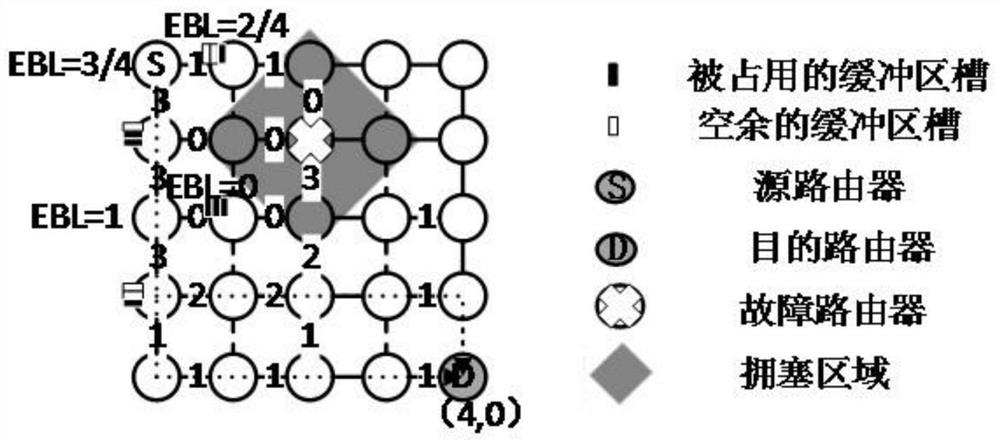

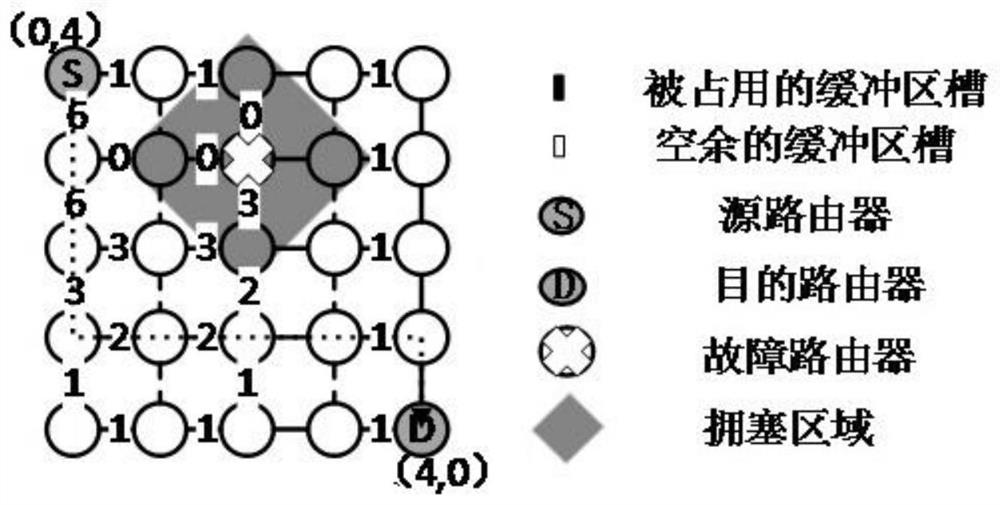

The invention discloses a fault-tolerant adaptive routing method based on an ant colony algorithm. The method comprises the steps of marking a position of each node in a two-dimensional network and setting a routing table; detecting a fault node, and computing a fault value and effective buffer length of an adjacent node of the fault node if the fault node exists; searching and obtaining one or more to-be-selected routing paths through utilization of an adaptive routing algorithm if the fault node does not exist; selecting the optimum routing path from the to-be-selected routing paths according to an assessment scale, and updating a pheromone routing table according to an ant colony routing algorithm; detecting whether a destination node arrives or not, and finishing routing if the destination node arrives; judging whether deadlock occurs in the routing path or not if the destination node does not arrive, and finishing routing if the deadlock occurs; and detecting the fault node againif the deadlock does not occur. On the basis of the ant colony algorithm, a path selection mechanism in the fault-tolerant adaptive routing method is optimized and the pheromone routing table is updated, under the condition that the fault node exists, data transmission delay of a whole network-on-chip is reduced, and network load balance is realized.

Owner:SOUTHEAST UNIV

Adaptive routing algorithm for heterogeneous network-on-chip

InactiveCN109587056AReduce error rateData switching networksAdaptive routing algorithmNetwork structure

In view of the diversity of running applications of the network-on-chip, a heterogeneous network as a relatively flexible network structure can reduce the transmission delay of the network and improvethe system performance. An adaptive routing algorithm for a heterogeneous network-on-chip is invented, and a static routing algorithm and a dynamic adaptive routing algorithm are used in a matching manner to transmit data packets. Meanwhile, an optimization algorithm for the adaptive routing algorithm is also invented. According to the algorithm, improvement is made on the bufferless routing partadded to the adaptive routing algorithm, and second competition arbitration of a data microchip is used to reduce the misinformation probability of data microchip deflection. Therefore, the transmission delay of a data microchip in the network is reduced, and the network performance is improved.

Owner:魏莹

Packet-circuit exchanging on-chip router oriented rollback steering routing algorithm and router used thereby

InactiveCN101834789BAvoid congestionMaximize Communication EfficiencyData switching networksAddress decoderAdaptive routing algorithm

The invention discloses a packet-circuit exchanging on-chip router oriented rollback steering routing algorithm and a router used thereby. The algorithm is an adaptive routing algorithm, which performs routing arbitrage according to an on-chip network congestion condition and dynamically changes a routing path according to the occupation situation of a link resource. The algorithm records output ports meeting a routing condition, reselects an output port after meeting congestion and realizes rollback routing so as to fully use network resources, effectively avoids congestion, improves averagethroughput and reduces average packet delay. The router comprises an input state machine, a priority encoder, an address decoder, an arbiter and an output state machine, which are sequentially connected. When selecting the routing path, the router does not retrace to route in a 180-degree direction and does not route in a direction far away from a target node, so the router does not cause the problem of dead locking or active locking. The algorithm and the router of the invention are low in cost and high in performance and are suitable for realizing an on-chip network system with high performance.

Owner:NANJING UNIV

An Adaptive Routing Algorithm for Distributed Nodes in Leo Satellite Networks

ActiveCN106656302BAvoid route discoveryAvoid synergyRadio transmissionData switching networksAdaptive routing algorithmNetworked system

The invention discloses a distributed node self-adaptive routing algorithm for LEO satellite network. Its technical characteristics are: constructing a grid-like LEO satellite communication system similar to the Iridium constellation; , using the mesh topology of the satellite constellation, each satellite node is independently responsible for forwarding the data packets in the queue; by adding and transmitting additional network status information in the datagram, the satellite nodes can realize the awareness of the network status in different routing directions And predict, and then guide the selection of data reported to the link. The present invention is reasonable in design, and its determined self-adaptive multi-path routing mechanism balances flow through load balancing means to avoid congestion, and is applied to low-orbit Iridium constellation satellite network systems, and the network performance index is superior to other traditional routing algorithms; especially in Under the premise of a small increase in the number of routing hops, the network load balance can be significantly improved, and the performance of the algorithm is better than that of the traditional algorithm.

Owner:NANJING UNIV OF SCI & TECH

Router delay model, establishment method and network-on-chip routing algorithm based on router delay model

As the scale of an integrated circuit is increased, the communication complexity of a network-on-chip is continuously improved, and the network performance is seriously influenced by the congestion problem caused by network hotspots and the like. How to measure the network congestion degree to avoid congestion nodes is a key problem in a network-on-chip adaptive routing algorithm. The invention provides a router time delay model, a building method and an on-chip network routing algorithm based on the router time delay model, the total time delay value of data from entering into a router node to leaving from the router node is evaluated, the router time delay model is built on the basis and serves as a standard for measuring node congestion, and a Q-learning reinforcement learning routing algorithm based on the router time delay model is provided. According to the routing algorithm provided by the invention, the latest global network state can be obtained in real time, the data can avoid a network congestion area, and the network performance is improved.

Owner:XIDIAN UNIV

Apparatus for implementation of adaptive routing in packet switched networks

InactiveUS7327685B2Minimize timeError preventionFrequency-division multiplex detailsHardware structureAdaptive routing algorithm

An apparatus is invented for implementing adaptive routing in packet switched networks. The hardware structure of the apparatus is based on the AntNet, which is an adaptive routing algorithm for selecting an optimized network route using a mobile agent that simulates an ant. The AntNet-based hardware structure can be applied to a system-on-chip system. The original AntNet algorithm is adapted for hardware implementation. Performance of the modified algorithm of the invention was verified by comparing the modified algorithm with the original AntNet algorithm in a virtual network structure. The hardware structure of the invention is effective for AntNet-based routing.

Owner:IND ACADEMIC CORP FOUND YONSEI UNIV

Wireless ad hoc network communication method and device

ActiveCN109275171BWill not affect operationImprove survivabilityError preventionNetwork topologiesWireless mesh networkAdaptive routing algorithm

The present application relates to a wireless ad hoc network communication method and device. The method sends data to a node through a wireless ad hoc network, and receives data sent by the node through the wireless ad hoc network; wherein, the wireless ad hoc network uses carrier sense multiple access CSMA / collision avoidance CA and time division The frame structure of the multiple-access TDMA hybrid frame, in the signal processing of the LTE transmission link, combines coding processing, diversity control and anti-interference control, and in the signal processing of the LTE receive link, the decoding processing, diversity control and anti-interference control are combined. Control the combination and increase the centerless multi-hop broadband wireless mesh network realized by the adaptive routing algorithm across the protocol layers. The wireless ad hoc network is a peer-to-peer network, in which all nodes have equal status, and nodes can join and leave the network at any time. The failure of any node will not affect the operation of the entire network, which improves the invulnerability of the network.

Owner:ZHUHAI YUNZHOU INTELLIGENCE TECH COMPANY

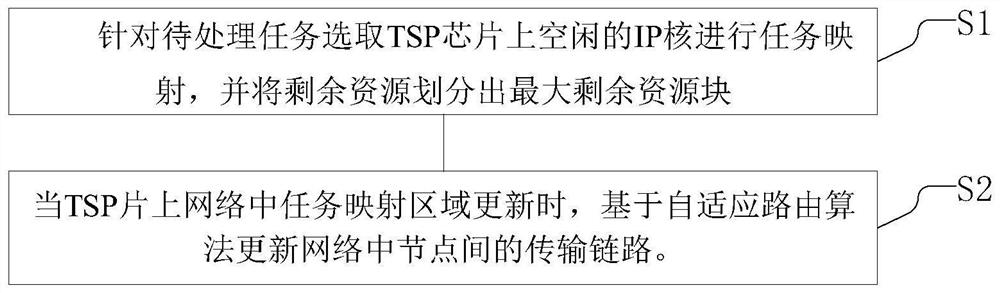

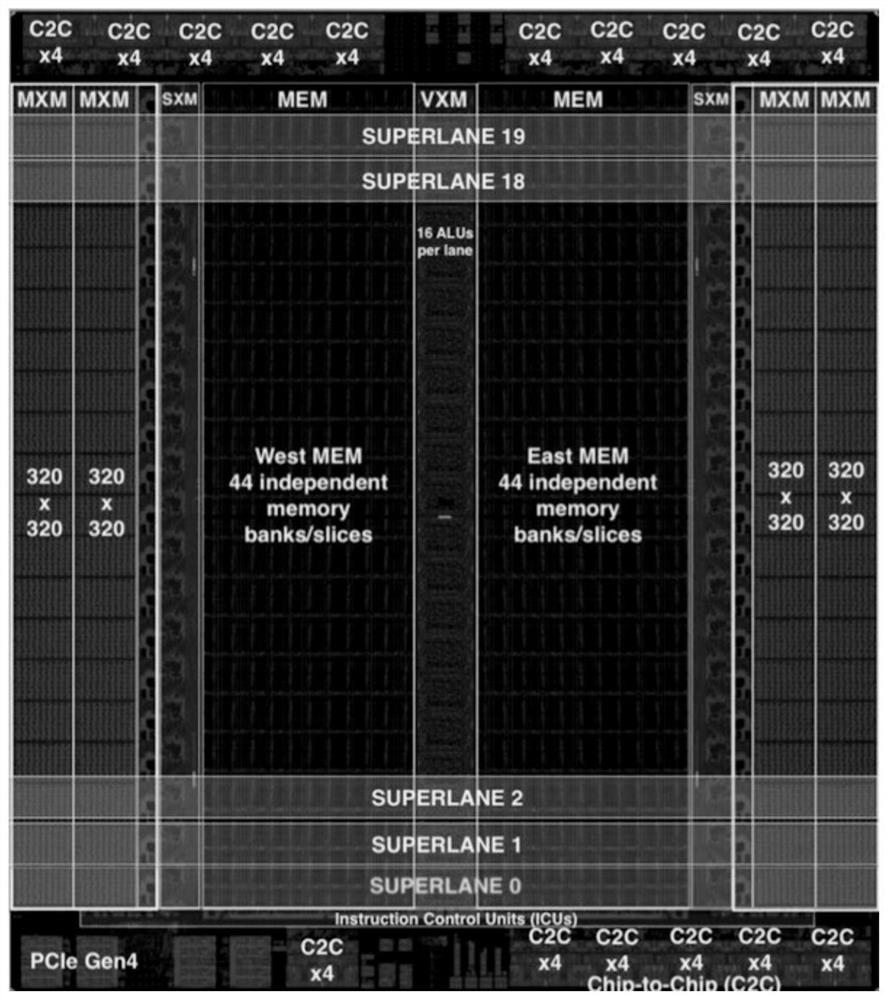

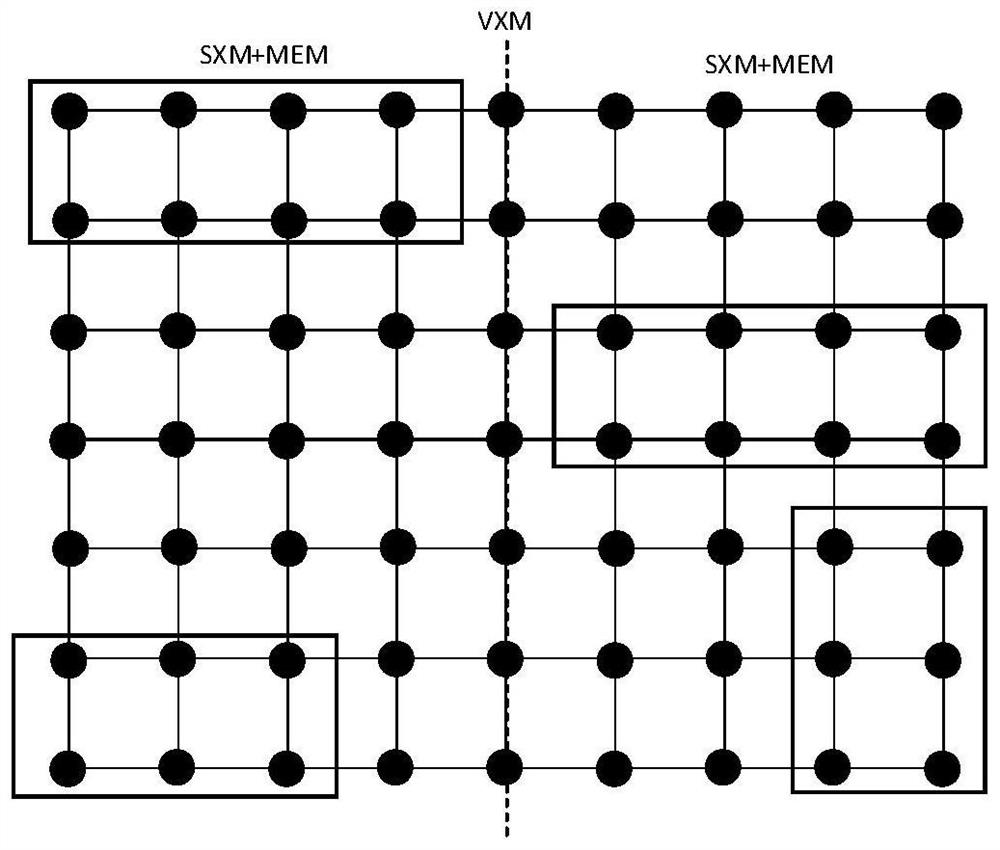

Software defined hardware control method and controller

PendingCN114356837ASave storage resourcesImprove performanceDigital computer detailsElectric digital data processingComputer hardwareAdaptive routing algorithm

The invention provides a software-defined hardware control method and a controller, which are applied to a TSP architecture chip, and the control method comprises the following steps: S1, selecting an idle IP core on a TSP chip for a task to be processed to carry out task mapping, and dividing residual resources into a maximum residual resource block as an area for next task mapping; and S2, when the task mapping area in the TSP network-on-chip is updated, updating a transmission link between nodes in the network based on an adaptive routing algorithm. Through the task mapping and adaptive routing control scheme design provided by the invention, the resource utilization rate of the TSP chip can be improved.

Owner:西安电子科技大学广州研究院

A fault-tolerant adaptive routing method based on ant colony algorithm

ActiveCN109660456BReduce Data Transfer LatencyLoad balancingArtificial lifeData switching networksPathPingRouting table

The invention discloses a fault-tolerant self-adaptive routing method based on ant colony algorithm, which includes: marking the position of each node in a two-dimensional network and setting the routing table; detecting a faulty node, if there is a faulty node, calculating the number of nodes adjacent to the faulty node The fault value of the node and the effective buffer length; if there is no faulty node, use the adaptive routing algorithm to find and obtain one or more routing paths to be selected; select an optimal routing path from the routing paths to be selected according to the evaluation scale, Update the pheromone routing table according to the ant colony routing algorithm; check whether the destination node is reached, and if so, end the routing; otherwise, judge whether there is a deadlock in the routing path, and end if there is a deadlock; otherwise, re-detect the faulty node. Based on the ant colony algorithm, the path selection mechanism in the fault-tolerant adaptive routing algorithm is optimized and the pheromone routing table is updated. In the case of faulty nodes, the data transmission delay of the entire network on chip is reduced, and the network load is balanced.

Owner:SOUTHEAST UNIV

Router power consumption determination method based on network on chip

The invention discloses a router power model on the basis of a network-on-chip, which simplifies router operations into four power dissipation links namely write-cache, read-cache, a bestride switch and a bestride link according to the power dissipation specific weight and attributes dynamic power dissipation to bit flipping activities which are triggered when a present data film arrives, and numbers the power dissipation by the bit flipping activities to obtain the router power model. Considering that the implementation complexity which is required by the network-on-chip requirements to the power model is as low as possible, the invention can adopt the statistical average in stead of the instantaneous sampled value to obtain a power dissipation simplified model. Hardware implementation methods of two power dissipation models are given out aiming at a five-channel rooter structure, the simplified model is introduced to a self-adaptive routing algorithm, which realizes the power dissipation distribution optimization of the network-on-chip. The router power model which is proposed by the invention has low algorithm complexity and simple realization, is suitable for network-on-chip, and can be used in research and application in the aspects of power dissipation performance statistics, the power dissipation distribution optimization, thermal protection and the like.

Owner:NANJING UNIV

A Routing Method for Tangent Handoff Hole Handling in Greedy Georouting Protocols

ActiveCN105933947BReduce routing hopsImprove transmission success rateWireless communicationMobile wireless sensor networkRight-hand rule

Owner:JIANGXI UNIV OF SCI & TECH

A deadlock-free adaptive routing algorithm in a Torus network

ActiveCN102170402BImprove data transfer efficiencyData switching networksAdaptive routing algorithmControl system

Owner:TSINGHUA UNIV

A Dynamic Steering Routing Algorithm Based on "Packet-Circuit" Switching Technology

ActiveCN106209518BReduce congestionEvenly distributedData switching networksTraffic capacityData stream

This invention discloses a dynamic steering routing algorithm based on ''package-circuit'' switching technology. The dynamic steering routing algorithm is characterized in being applied to the link establishment stage of the ''package-circuit'' switching technology, can select a proper route to transmit data according to information, such as traffic distribution, congestion situation and the like, in a network-on-chip, and is a self-adaptive algorithm. According to the port usage of a current routing node and a downstream routing node, the algorithm selects a congestion-free routing node to realize dynamic steering route; thus, the probability of network congestion can be reduced; the data stream can be distributed in the network evenly; and then, the network resource can be utilized adequately, and the performance of the system can be improved. At the same time, the success rate for establishing the link can be improved, so that the link is prevented to be established and cancelled for many times during the link establishing process; and thus, the power consumption of the network and the system can be reduced.

Owner:HEFEI UNIV OF TECH

Low-power-consumption adaptive routing method in network on chip

ActiveCN102437953BImprove performanceReduce power consumptionData switching networksAdaptive routing algorithmNetworks on chip

The present invention relates to the field of on-chip network technology, and discloses a low-power adaptive routing method in an on-chip network, including the following steps: S1. Calculate the distance between the source node and the destination node of the message in the two directions of x-dimension and y-dimension, if If the sum of the distances is zero, the routing is completed, otherwise step S2 is executed; S2, the network is divided into two virtual subnets x+y* and x-y*; S3, the message enters the virtual subnet x+y* or x-y* for routing . The present invention divides the physical network into two virtual subnets x+y* and x-y*, and the virtual subnets x+y* and x-y* all adopt the complete adaptive routing algorithm of the shortest path and the new EVC flow control technology, According to the offset value of the destination node of the data packet relative to the source node, it is injected into the corresponding virtual network, and adaptively routed to the destination in the virtual network. The EVC channel is used first when the data packet is routed, and the NVC channel is used only when there is no free EVC channel available. It proceeds according to the normal pipeline stage, which effectively improves performance and reduces power consumption.

Owner:TSINGHUA UNIV

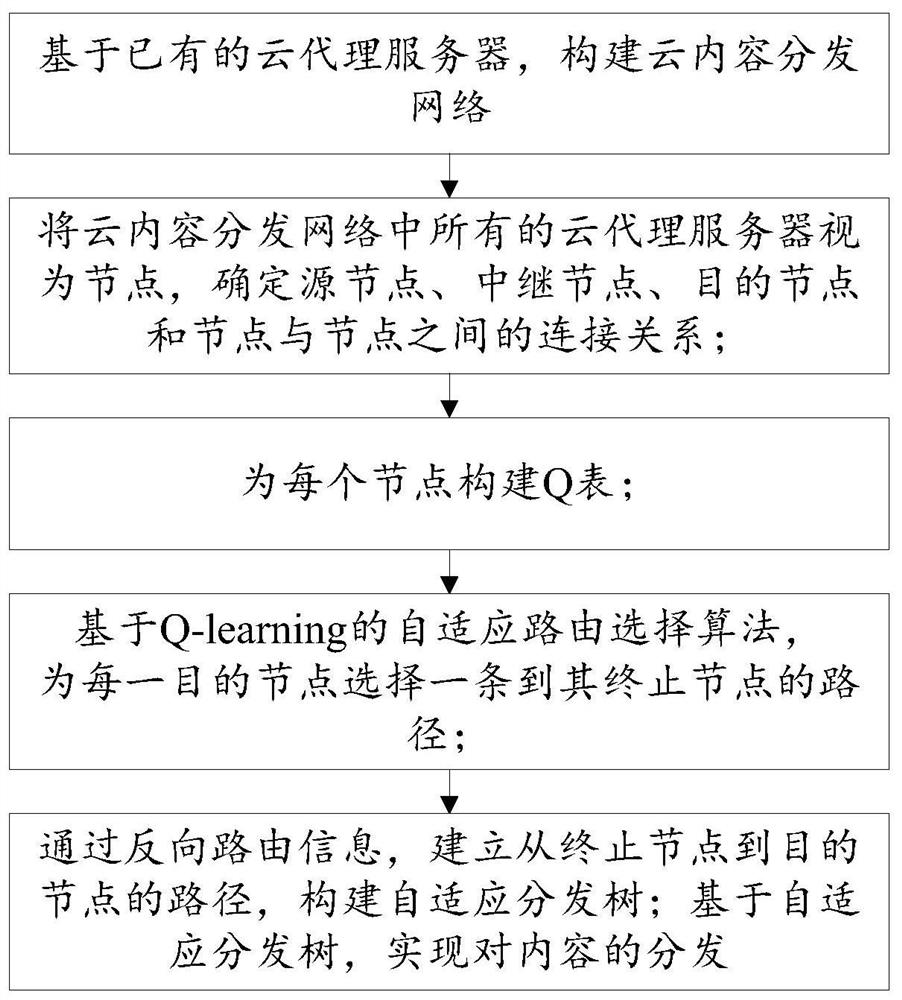

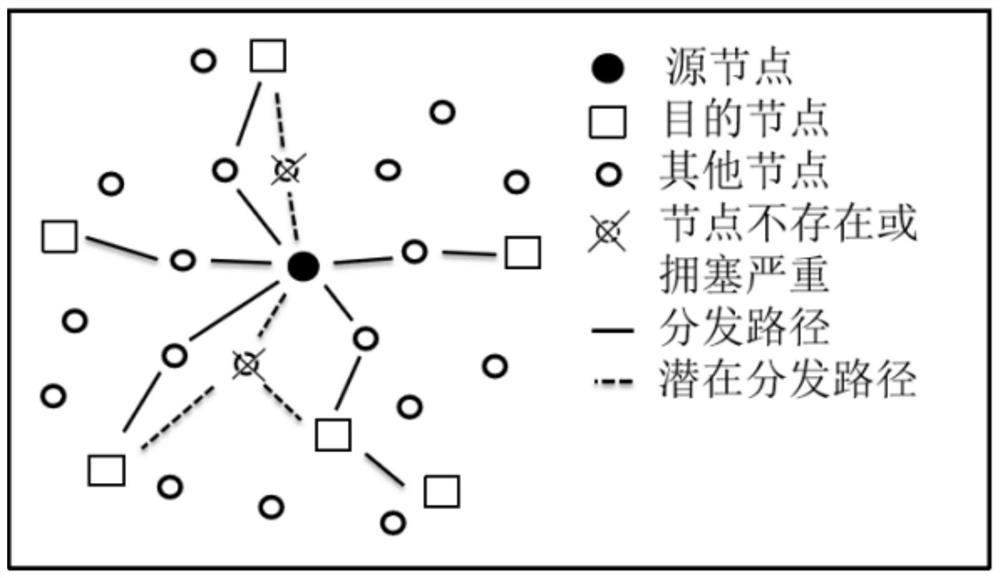

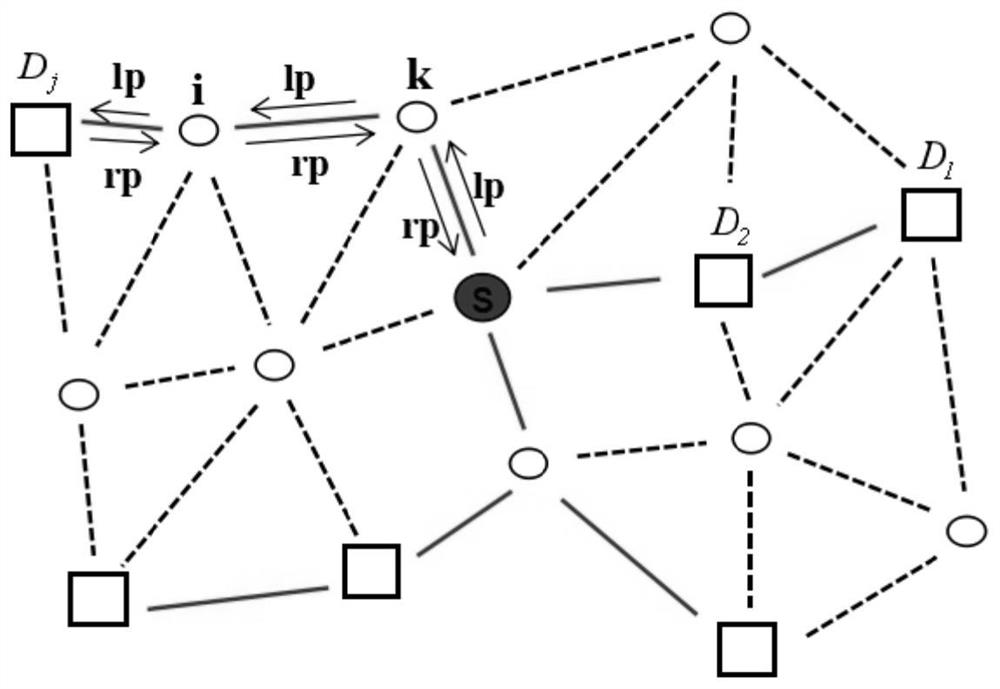

Content distribution method, system, device and medium of dynamic cloud content distribution network

ActiveCN109922161BAchieve distributionLow congestion costData switching networksContent distributionDistribution tree

The invention discloses a content distribution method, system, device and medium of a dynamic cloud content distribution network, and constructs a cloud content distribution network based on an existing cloud proxy server; regards all cloud proxy servers in the cloud content distribution network as nodes, and determines Source node, relay node, destination node and the connection relationship between nodes; construct Q table for each node; based on Q-learning adaptive routing selection algorithm, select a route to its termination node for each destination node path; establish a path from the terminal node to the destination node through reverse routing information, and construct an adaptive distribution tree; based on the adaptive distribution tree, the distribution of content is realized. The algorithm propagates local and non-local congestion information through network learning packets. Choose a path with low congestion cost and be able to adapt to the dynamic cloud distribution environment.

Owner:SHANDONG NORMAL UNIV

A Packet Routing Algorithm Based on Multi-Agent Deep Reinforcement Learning

ActiveCN112491712BShort transmission delayImprove performanceNeural architecturesData switching networksPathPingData pack

The invention belongs to the technical field of distributed routing, and specifically relates to a data packet routing algorithm based on multi-agent deep reinforcement learning. In order to alleviate the congestion in the computer network, the present invention uses multi-agent deep reinforcement learning technology to design an end-to-end adaptive routing algorithm, and each router completes data packet scheduling according to local information, reducing the transmission delay of data packets . The invention first constructs a mathematical model of distributed routing, defines the specific meaning of each element in reinforcement learning, then trains a neural network, and finally performs algorithm performance testing in a simulation environment. The simulation experiment results show that the introduction of the deep neural network can mine the characteristic information in the input network state and realize the trade-off between the smooth path and the shortest path. Compared with other commonly used routing algorithms, the present invention achieves a shorter data packet transmission time delay.

Owner:FUDAN UNIV +1

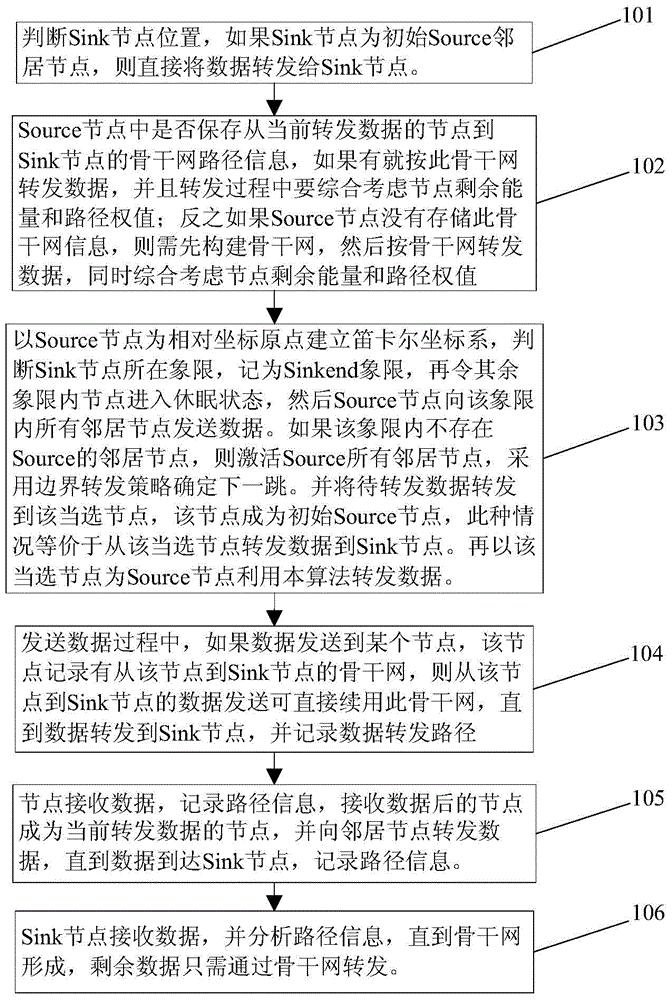

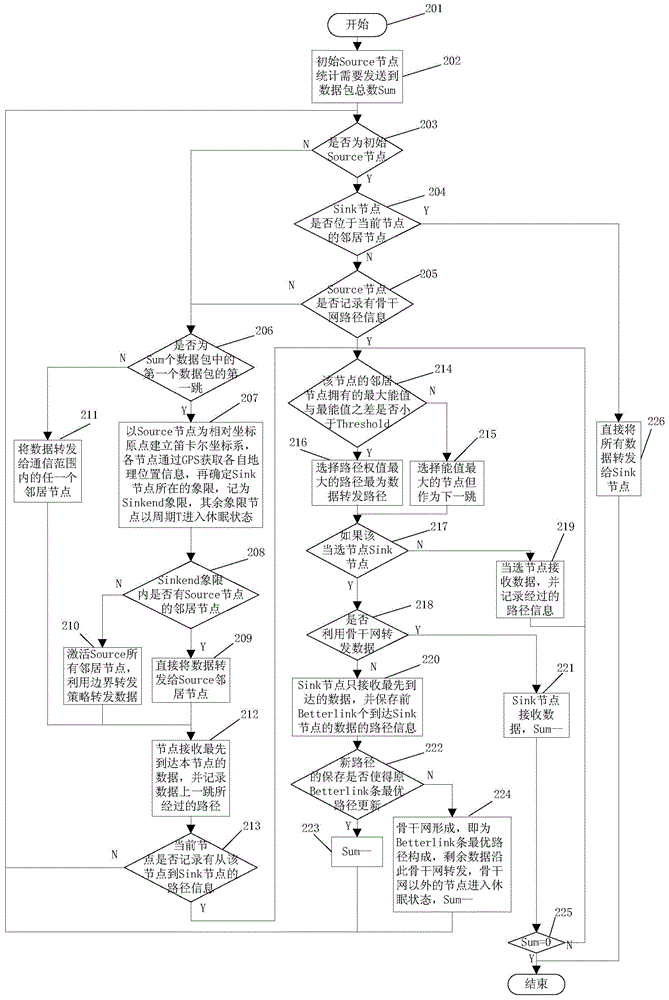

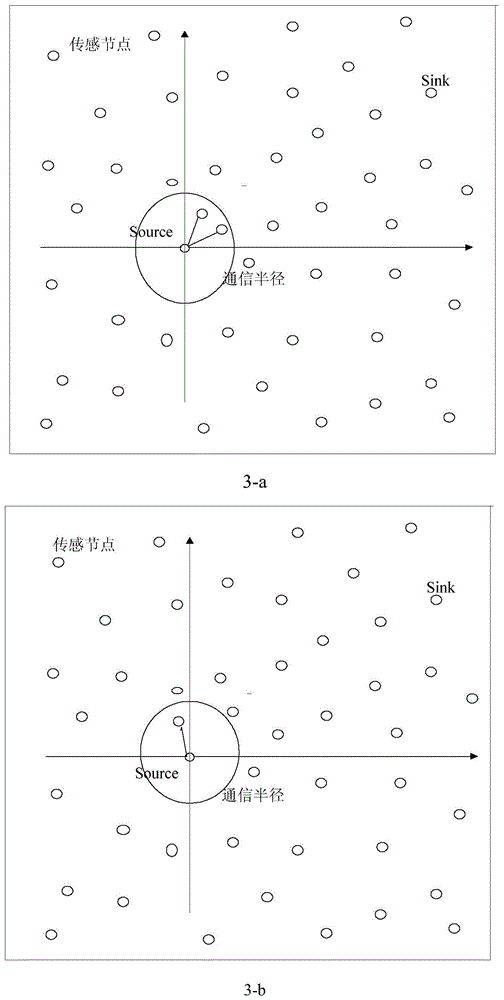

A Biologically Inspired Adaptive WSN Routing Algorithm

ActiveCN103686919BRobustImprove transmission efficiencyNetwork topologiesHigh level techniquesAdaptive routing algorithmGeolocation

The invention discloses a self-adaptive WSN (wireless sensor network) routing algorithm based on biological inspiring, and belongs to the technical field of WSN. The self-adaptive WSN routing algorithm based on the biological inspiring solves the problems of local optimizing and routing void easily caused by the greedy method which is relied by the existing GPSR (greedy perimeter stateless routing) algorithm. The method comprises the two basic steps of (1) sending data in the quadrant of Sink nodes in a flooding way to find a backbone network; (2) utilizing the found backbone network to send data. In the establishing process of the backbone network, the forming strategy of the physarum polycephalum feeding path is simulated, namely utilizing the geological location information and embodying the path weights to establish the route main network. In the process of sending data by nodes, the non-related nodes enter the sleeping state, the energy difference of all adjacent nodes should not be greater than Threshold, then the balance of energy consumption is realized, and the robustness of the network system is further improved. After the data is sent, the path information of the backbone network is remained. When the node sends the data next time, the backbone network can be continuously used, the time of researching the path is saved, the data transmission efficiency is improved, and the energy consumption is reduced.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

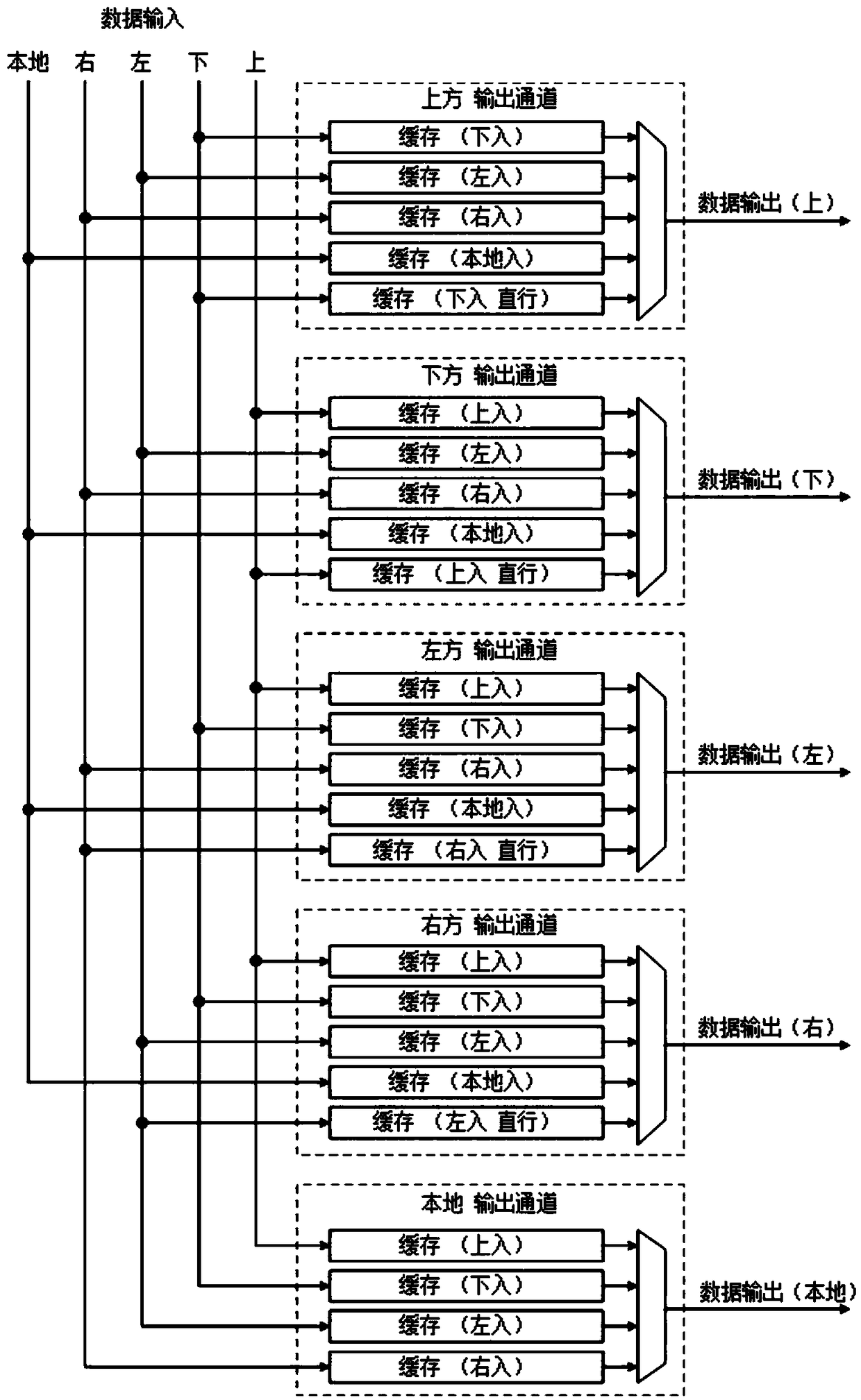

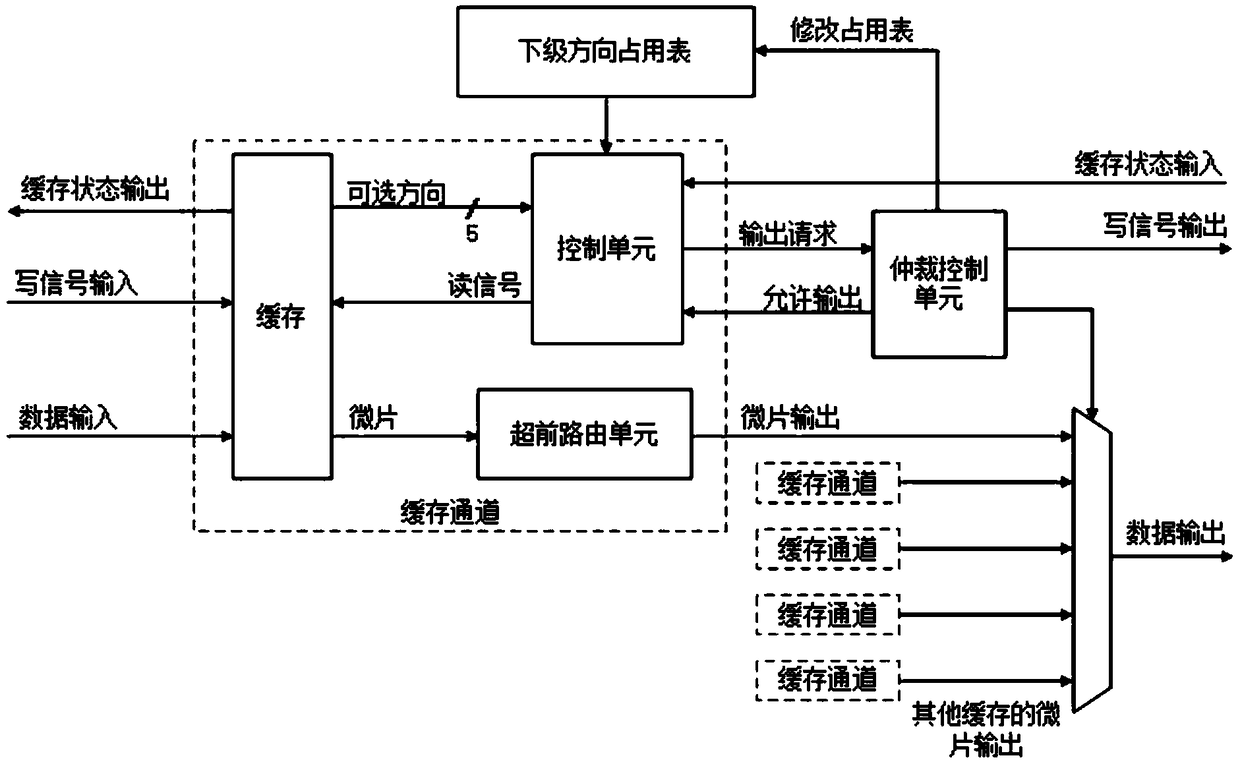

Self-adaptive routing single-cycle on-chip network router

InactiveCN108696441AImprove performanceReduce areaData switching networksAdaptive routing algorithmInterconnection

An on-chip network is an on-chip interconnection way applied to a multi-core or many-core chip, and has the features of being high in bandwidth and high in expansibility. The invention provides a single-cycle on-chip network router design using the self-adaptive routing algorithm. The router only needs one cycle to forward a data packet, and the network load can be distributed more averagely through the self-adaptive routing at the same time. A straight channel on each direction avoids the deadlock problem caused by the self-adaptive routing. Through the design disclosed by the invention, therouter network acquires ultra-low transmission delay and extremely high throughput.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com