Low-power-consumption adaptive routing method in network on chip

A network-on-chip, low-power technology, used in data exchange networks, digital transmission systems, electrical components, etc., to solve problems such as the lack of measuring the peak power consumption of on-chip networks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0066] A low-power adaptive routing method in a network-on-chip proposed by the present invention will be described in detail below with reference to the drawings and embodiments.

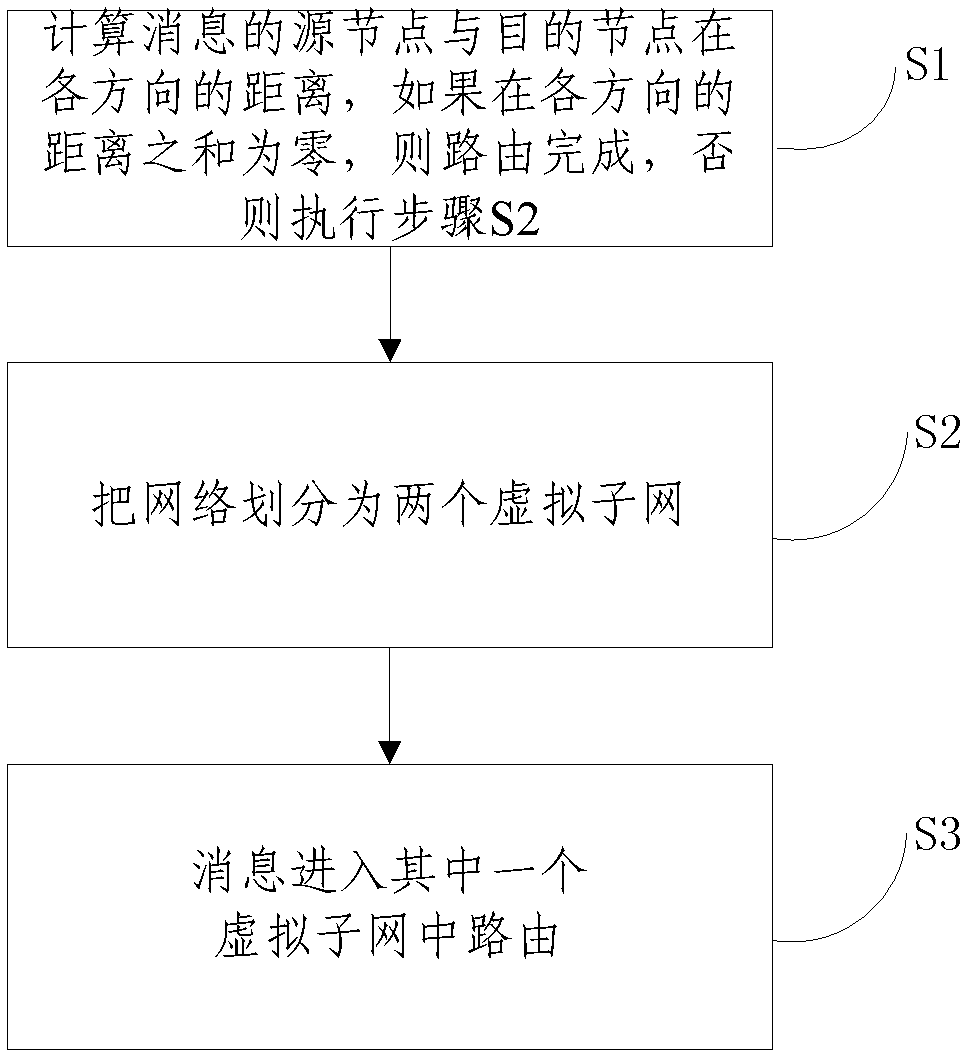

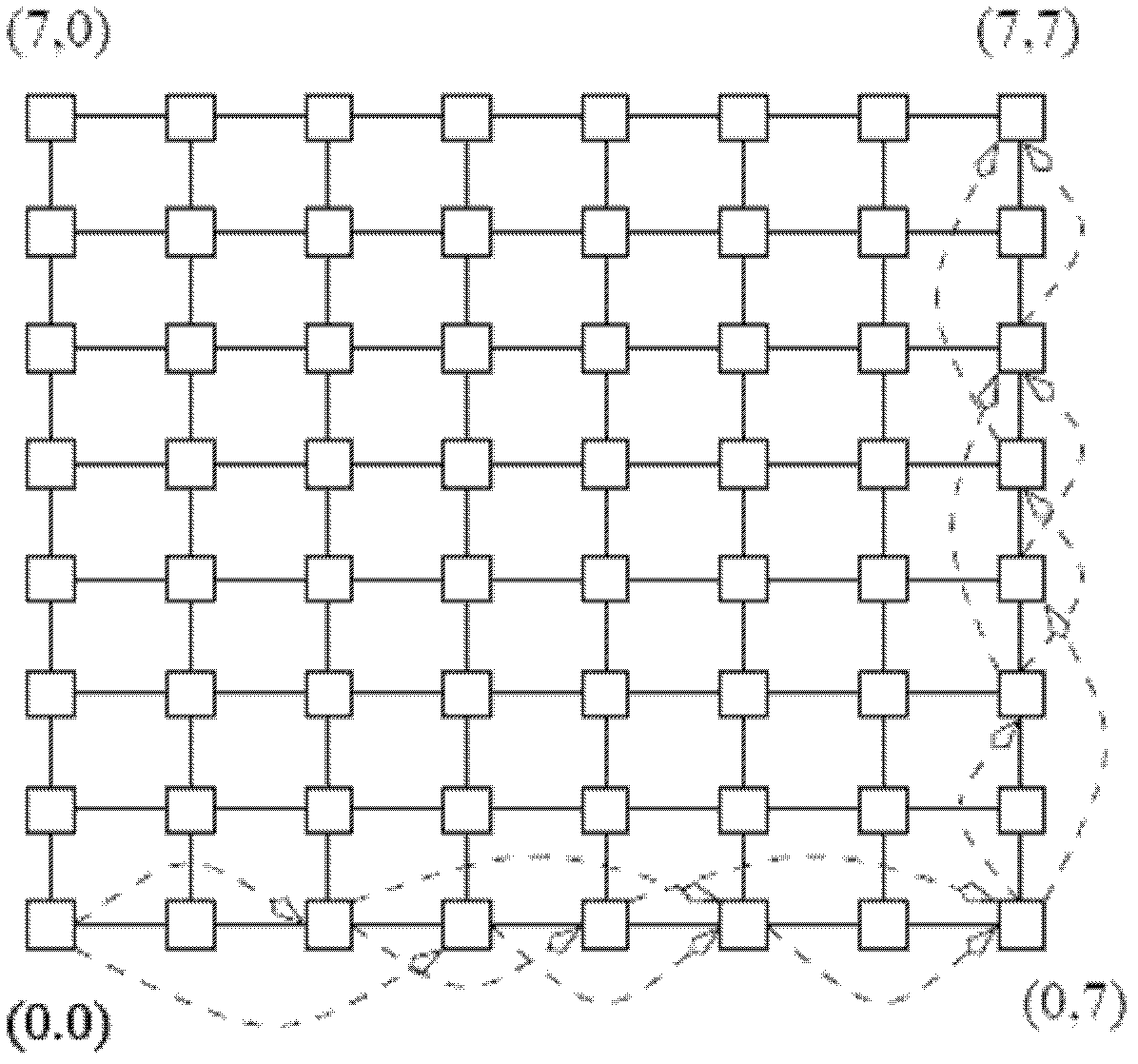

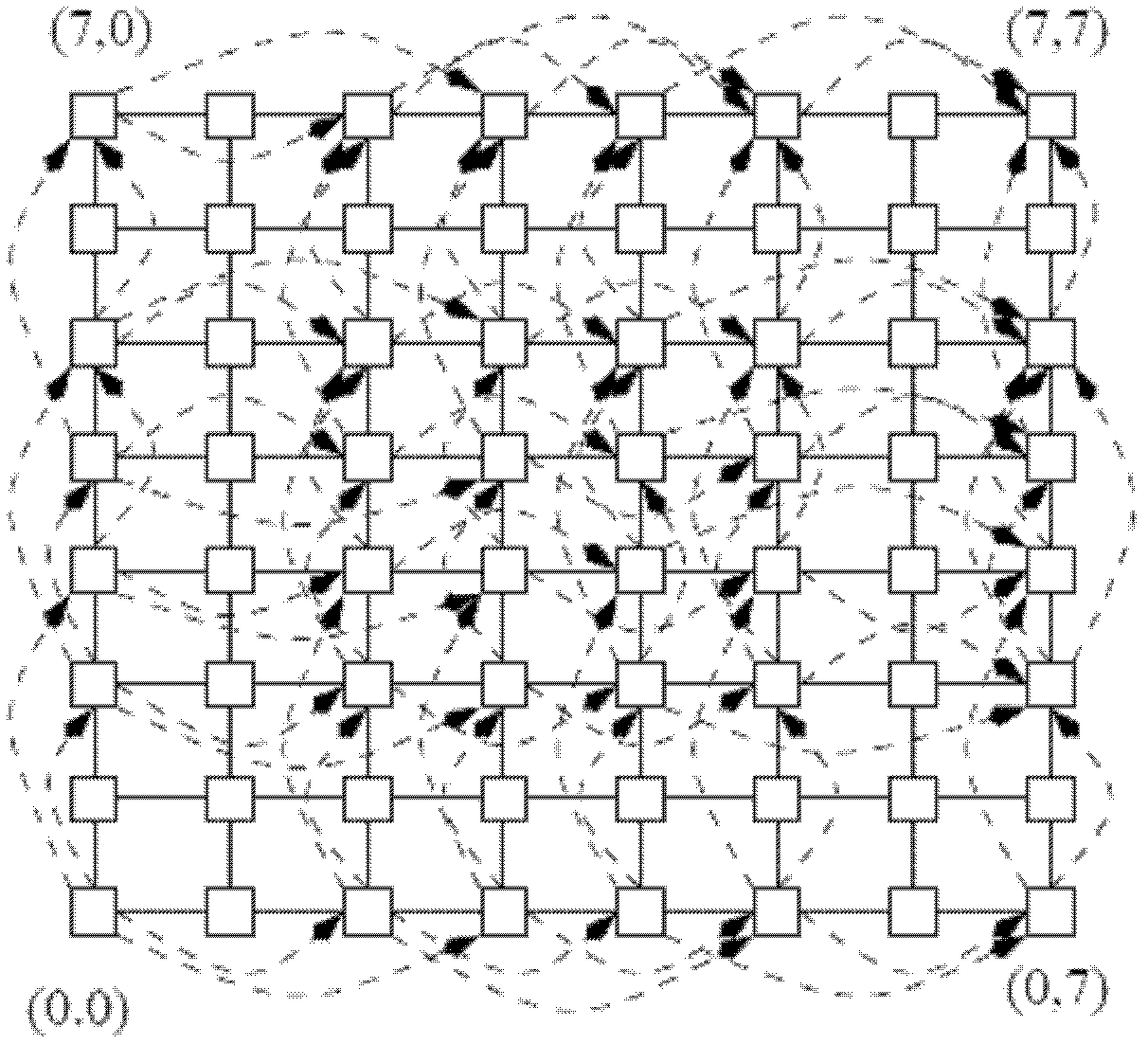

[0067] The embodiment of the present invention is proposed based on a two-dimensional mesh network, and its main idea is: divide the physical network into two virtual subnets x+y* and x-y*, and use the shortest path inside the virtual subnets x+y* and x-y* The fully adaptive routing algorithm and the new EVC flow control technology inject data packets into the corresponding virtual network according to the offset value of the destination node relative to the source node, and adaptively route to the destination in the virtual network. The data packet is preferentially used in the EVC channel when routing. In this way, when the microchip of the data packet passes through the intermediate node on the EVC channel, it is transmitted to the EVC latch, directly skipping the unnecessary intermediate pipelin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com