Adaptive routing algorithm for heterogeneous network-on-chip

A heterogeneous on-chip, self-adaptive technology, used in data exchange networks, digital transmission systems, electrical components, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

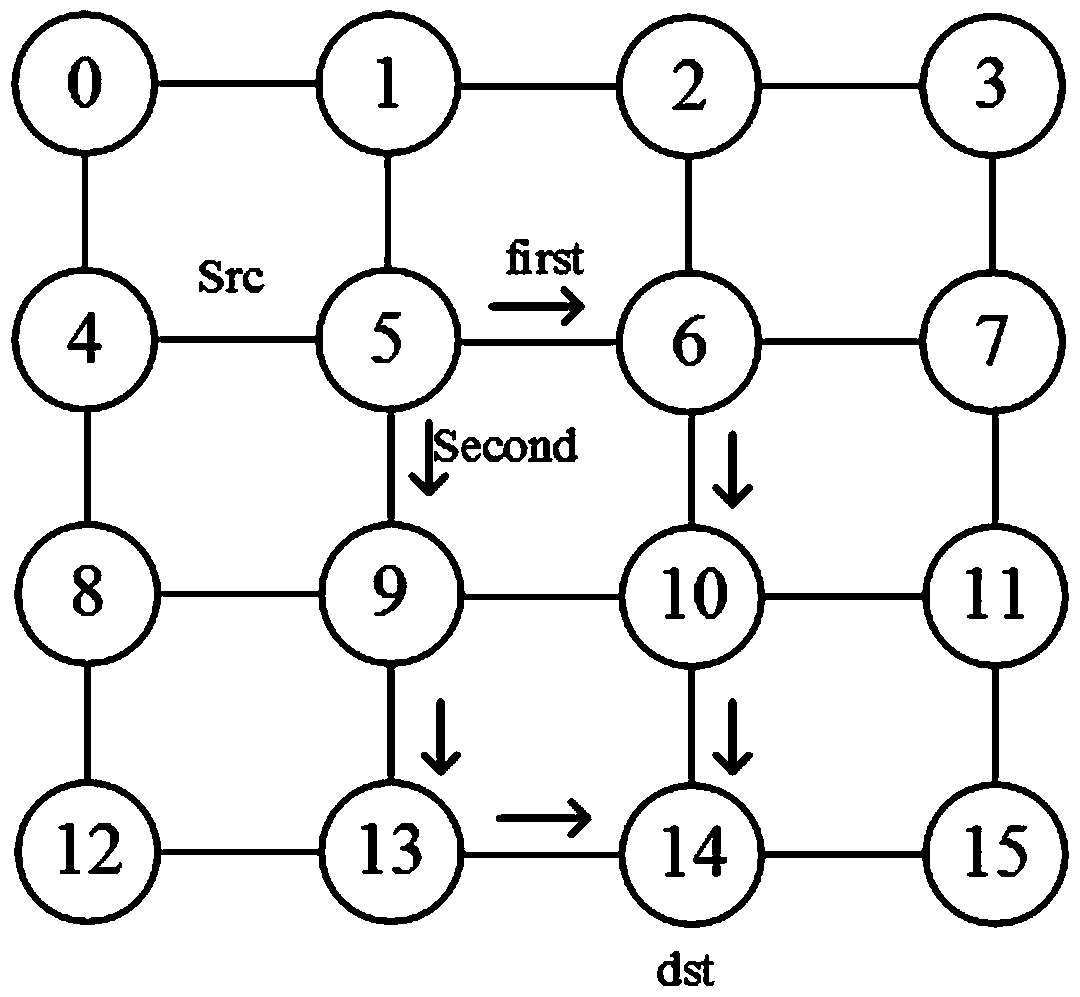

[0012] figure 1 The schematic diagram of the optimization strategy for the selection of the output port is shown, and the data flake selects a sub-optimal output port to perform the second competition arbitration, so that the probability of misinformation of the data flake is reduced. When the data flake arrives at the routing node, the effective output port and the suboptimal output port of the data flake must be calculated first. Assume that the current routing node coordinates are (Xc, Yc), and the destination node coordinates are (Xd, Yd). Set a flit_info structure for each data flit, including timestamp, effective output port first and suboptimal output port second. When Xd>Xc, if Yd>Yc), then set the first of the data slice to be down, and second to be right; if YdYc), then set first to be down, and second to be left; if YdYc), then set first to be down, and second to be -1; if Yd<Yc), then set first to be up, and second to be -1; otherwise, the output port is local.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com