Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

67results about How to "Reduce pause" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

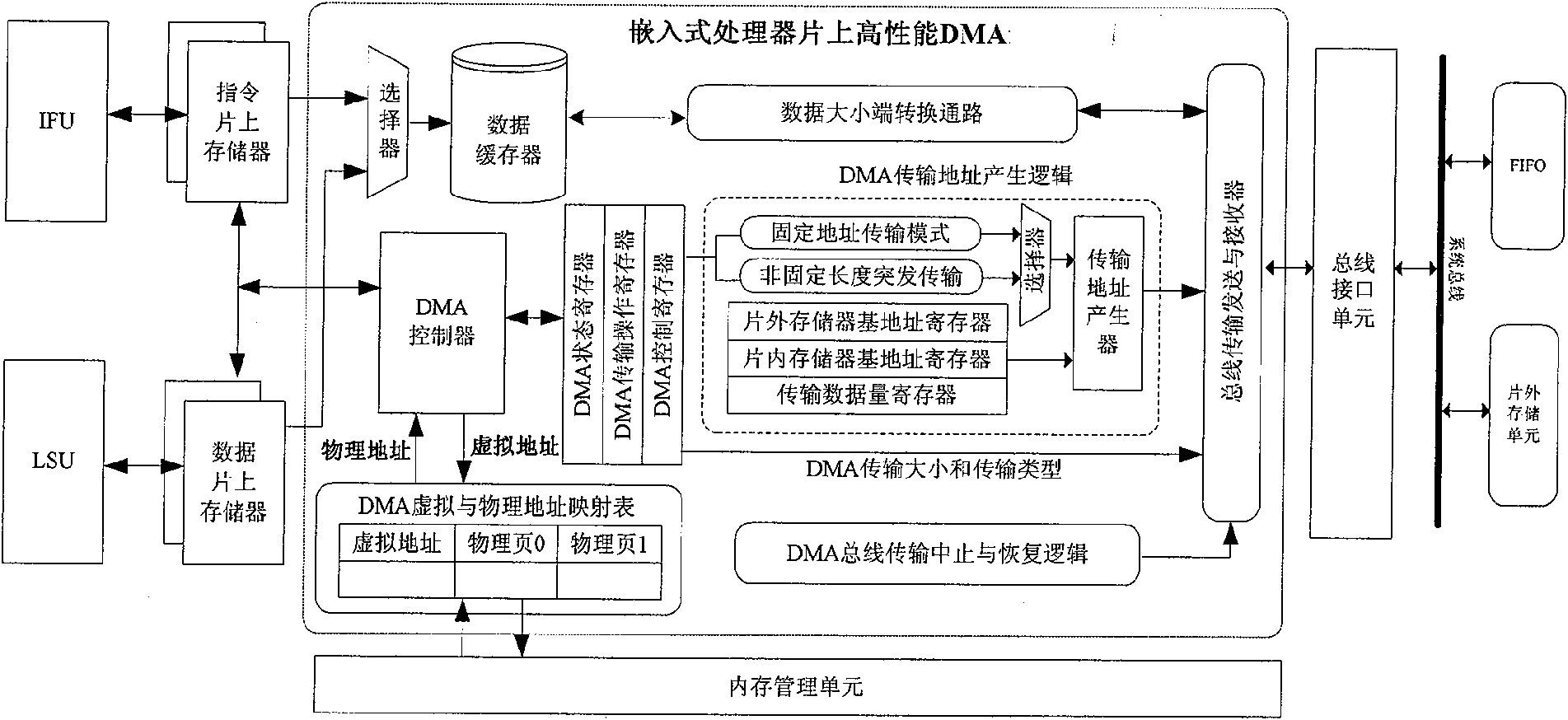

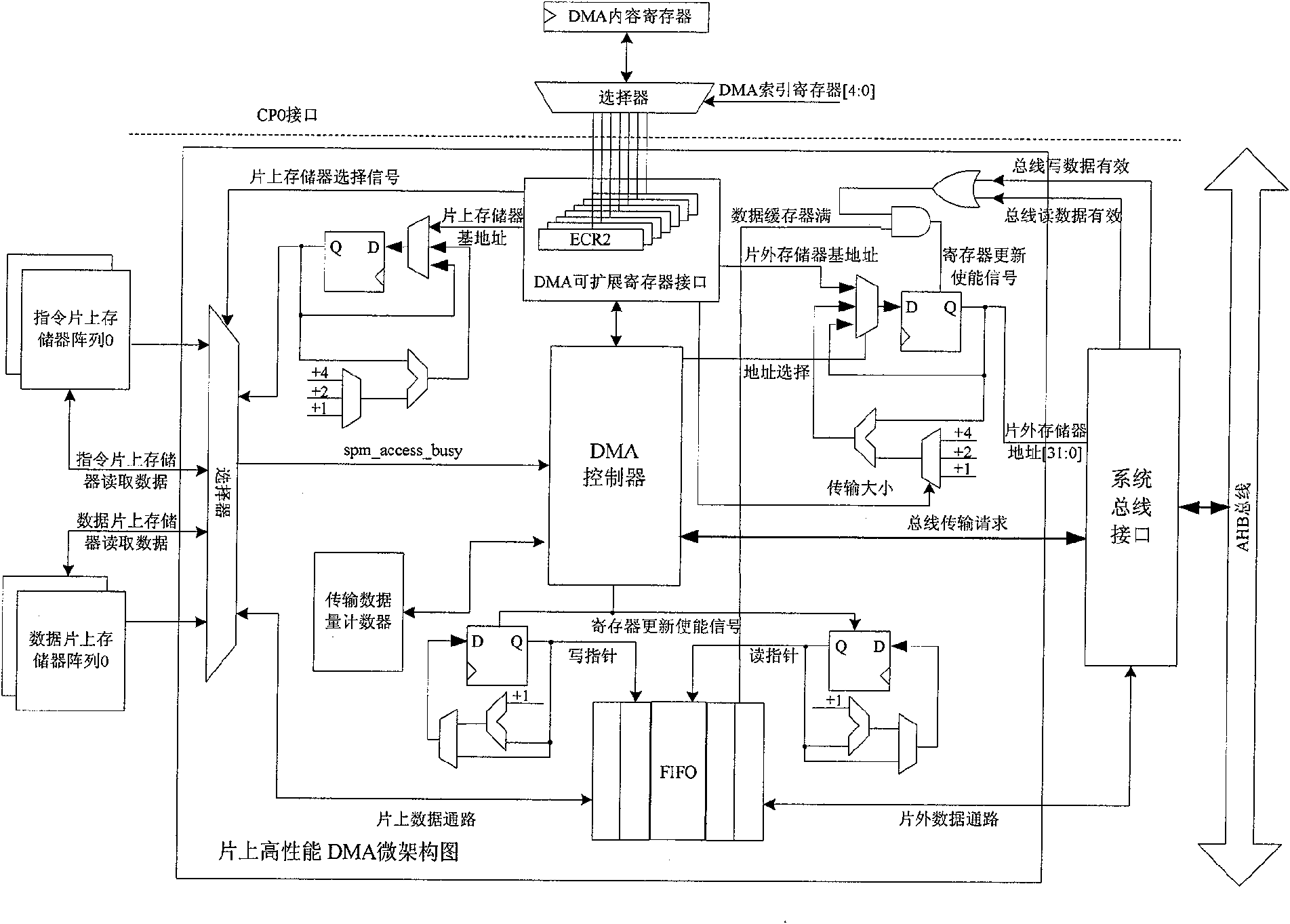

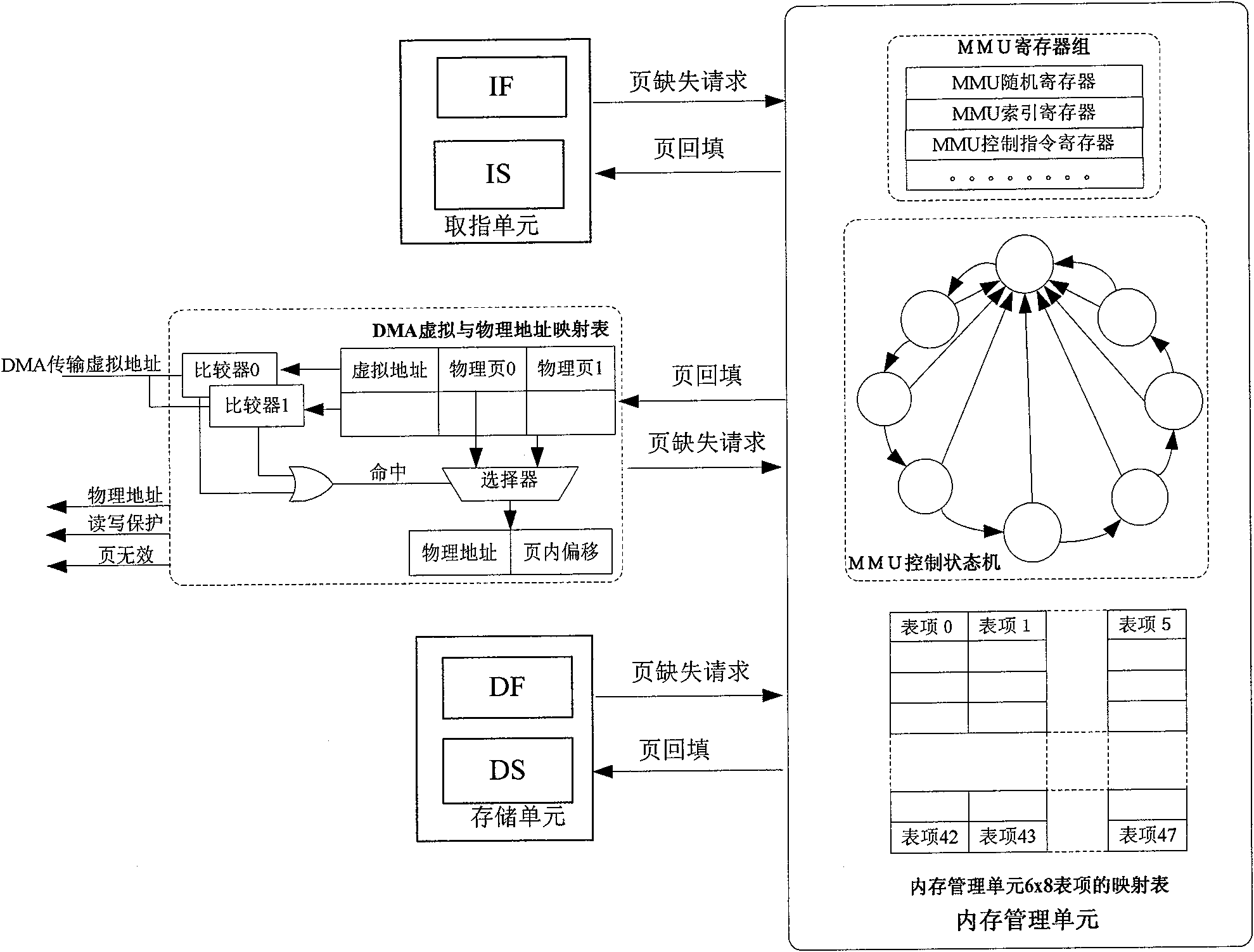

High performance DMA on embedded type processor chip

ActiveCN101556565AImprove performanceIncrease independenceElectric digital data processingPage address registerIp address

The invention relates to a high performance DMA on an embedded type processor chip. The high performance DMA comprises a data buffer used for caching the data read from an on-chip memory, the data sent to a bus interface unit, the data received from the bus interface unit, and the data written into the on-chip memory; a data big-endian and little-endian convertor; a DMA controller used for initializing a state register, a control register, an initial address register and a data size register; a DMA transmission address generating logic module used for automatically calculating the transmission address of the next data on an on-chip external memory and generating chip selection and read and write signals of the on-chip memory according to the on-chip address, and simultaneously updating a data size counter till the counter changes to zero; and a bus transmission transmitter and receiver. The high performance DMA has the advantages that the development difficulty is low, the cost of the hardware is low, the transplantation is convenient, the expansibility is flexible, the data transmission speed is high, and the performance of the processor is greatly enhanced.

Owner:C SKY MICROSYST CO LTD

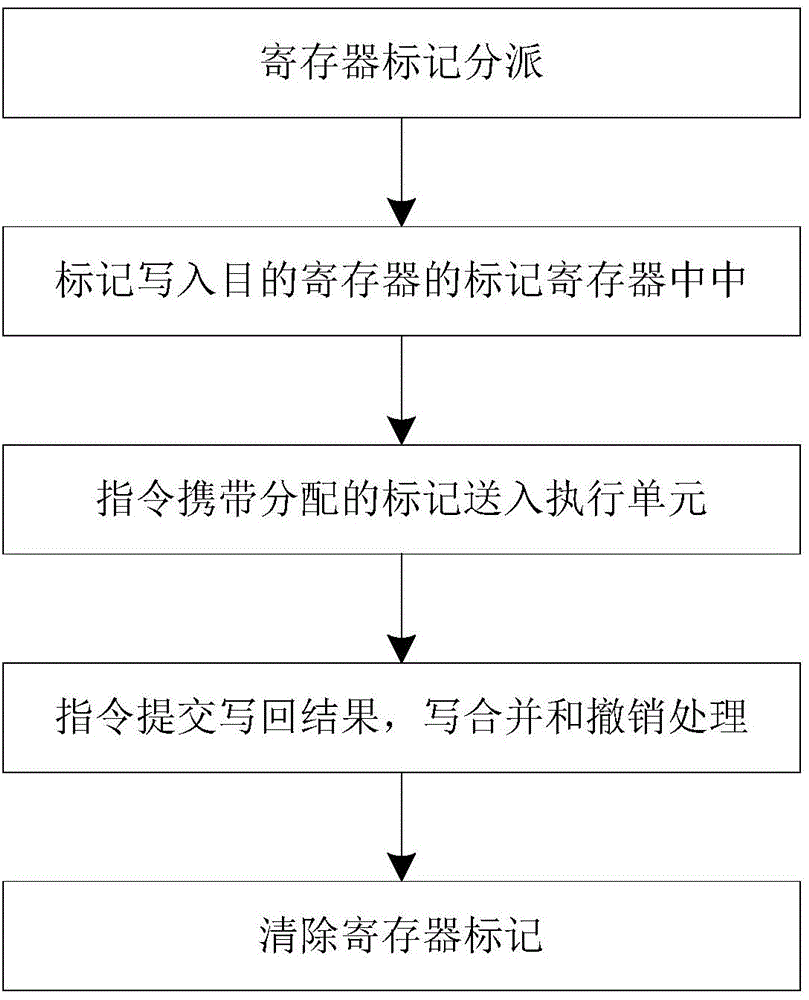

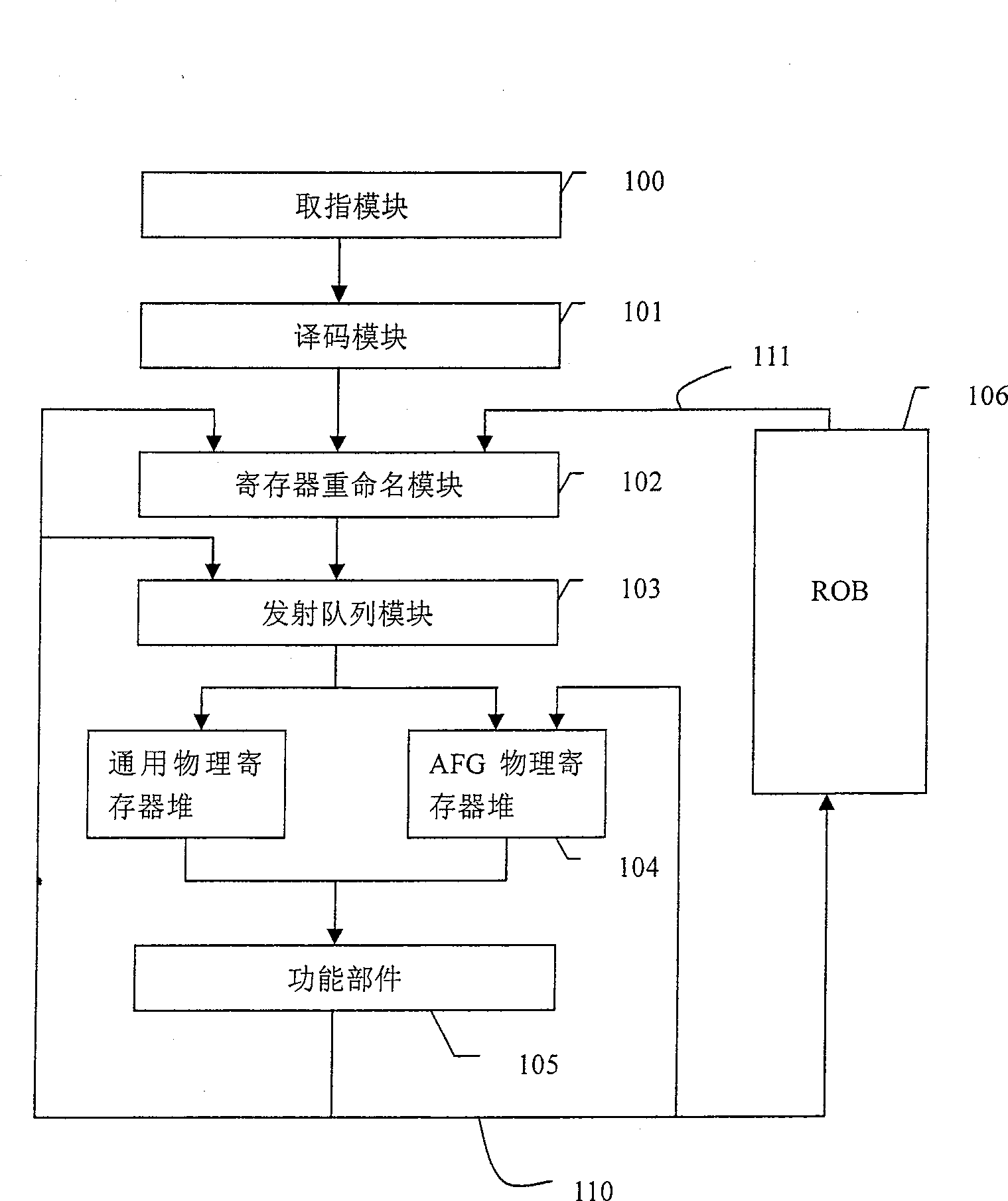

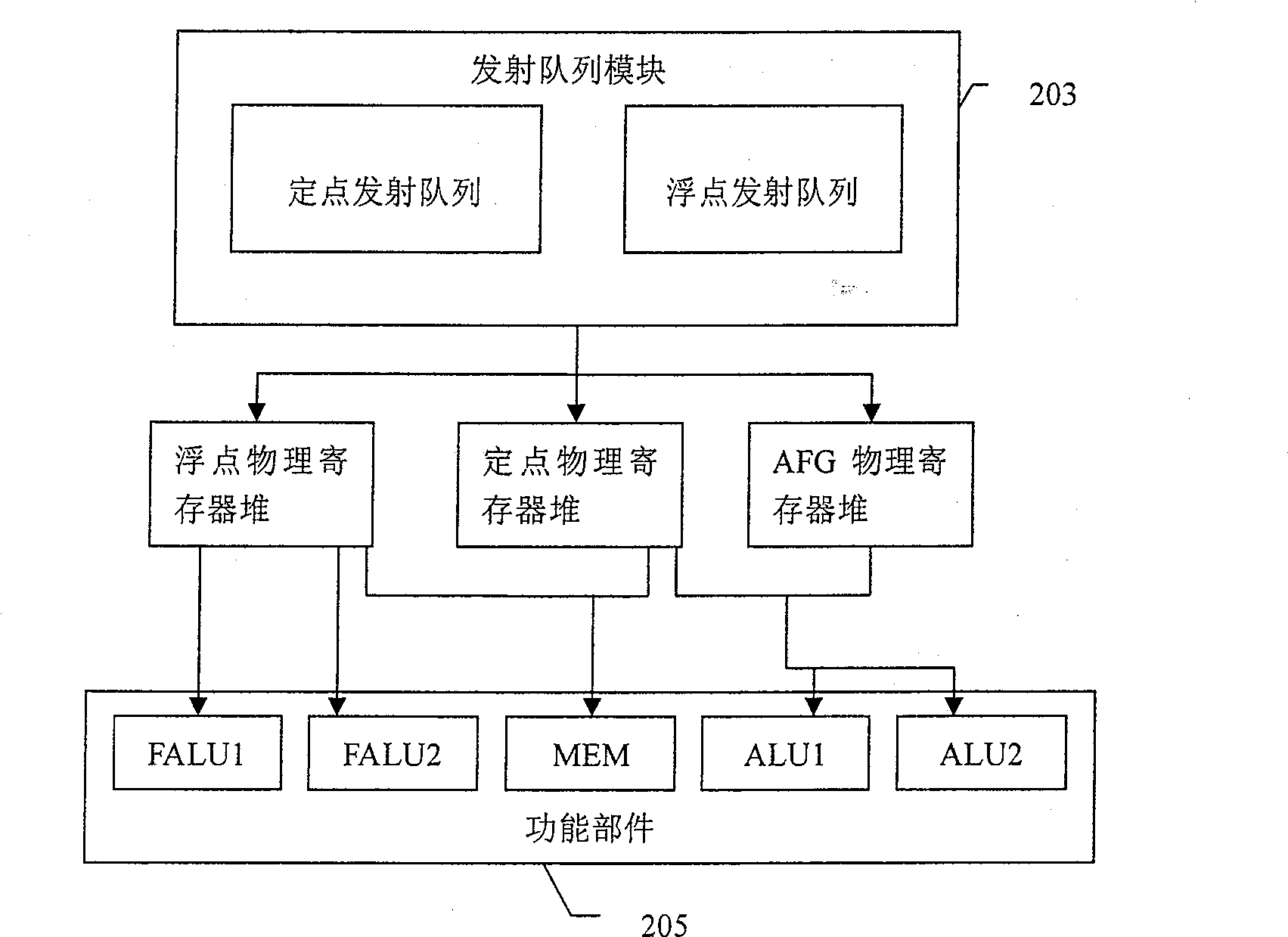

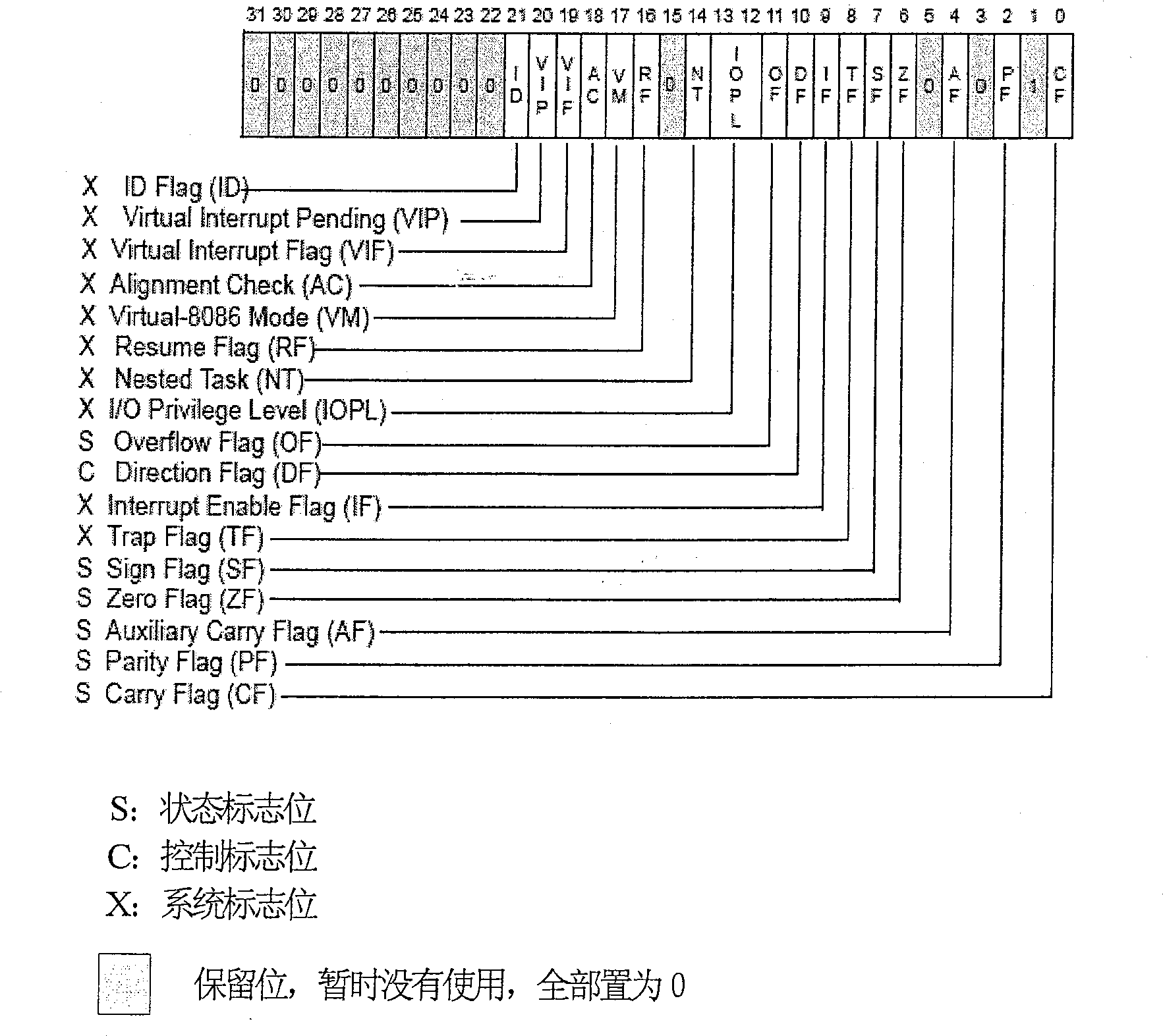

Method for renaming state register and processor using the method

ActiveCN101169710AReduce pauseReduce congestionConcurrent instruction executionComputer scienceFLAGS register

The invention provides a method for renaming a status register in a superscalar processor with a pipeline structure, wherein the status register is a register composed of a plurality of flag bits selected from all flag bits of a flag register. The method comprises determining whether a microcode will read the status register when the microcode coded by a command reaches a register renaming module of the processor; if determining that the microcode will read the status register, allocating a nearest mapping physical register for the status register; otherwise, not allocating the physical register for the status register; determining whether the microcode will be written to the status register; if determining that the microcode will be written into the status register, allocating a new physical register with empty status to the status register; and otherwise, not allocating the physical register for the status register.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Method for normal temperature high voltage continuous extracting natural product effective ingredient and equipment thereof

InactiveCN101249315AImprove dissolution efficiencyHigh extraction rateSolid solvent extractionNatural productAdditive ingredient

The invention discloses a normal temperature high pressure continuous extraction method of active ingredients of natural products, including five steps of crushing, soaking, ultra-fine smashing, high pressure extraction and solid-liquid separation, wherein the material liquid after the ultra-fine smashing is continuously pumped into a high pressure extractor by an underflow pump in the high pressure extraction, the material liquid achieves the pressure of 1 to 90MPa via a high pressure pump, the material liquid is impacted on a collision ring in the high pressure extractor by an annular working gap in the high pressure extractor being subject to the high pressure, and the cells of the natural products in the material liquid is crushed; the five steps are carried out at normal temperature, the normal temperature refers to the temperature ranged from 10 to 45 DEG C, the better temperature ranges from 15 to 40 DEG C, and the best temperature ranges from 15 to 30 DEG C. The invention also discloses a device to realize the method.

Owner:中山装备制造工业研究院 +1

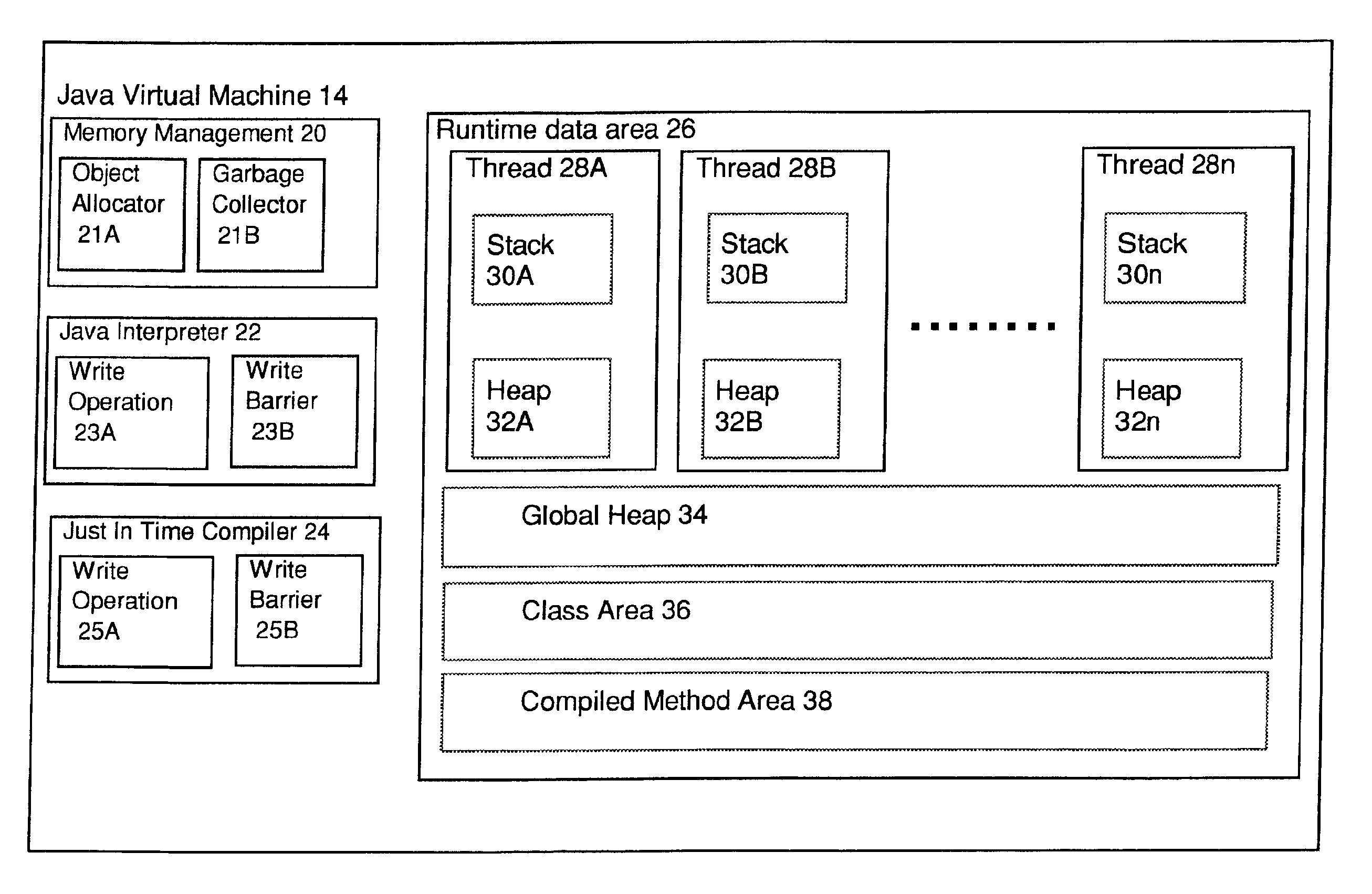

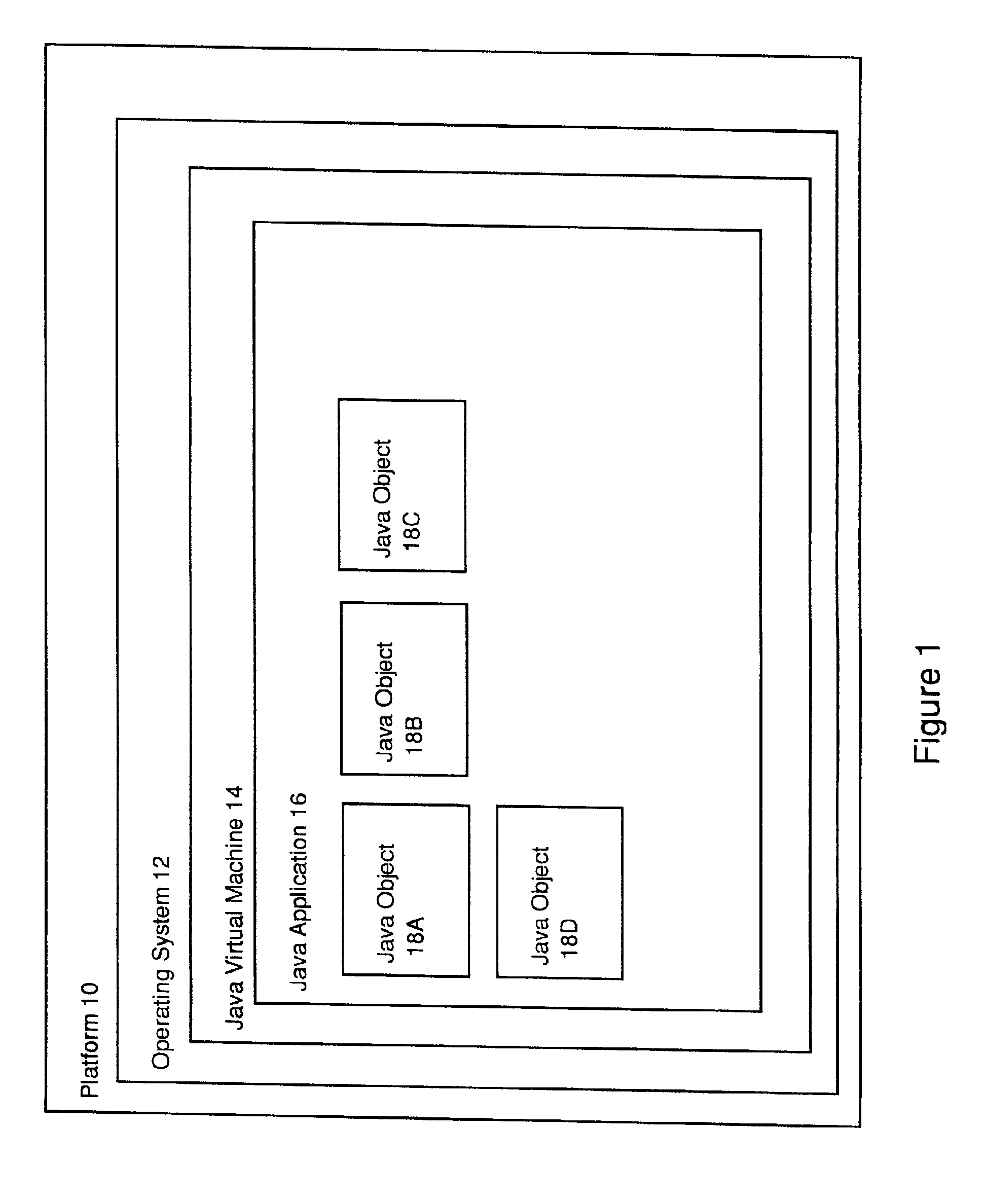

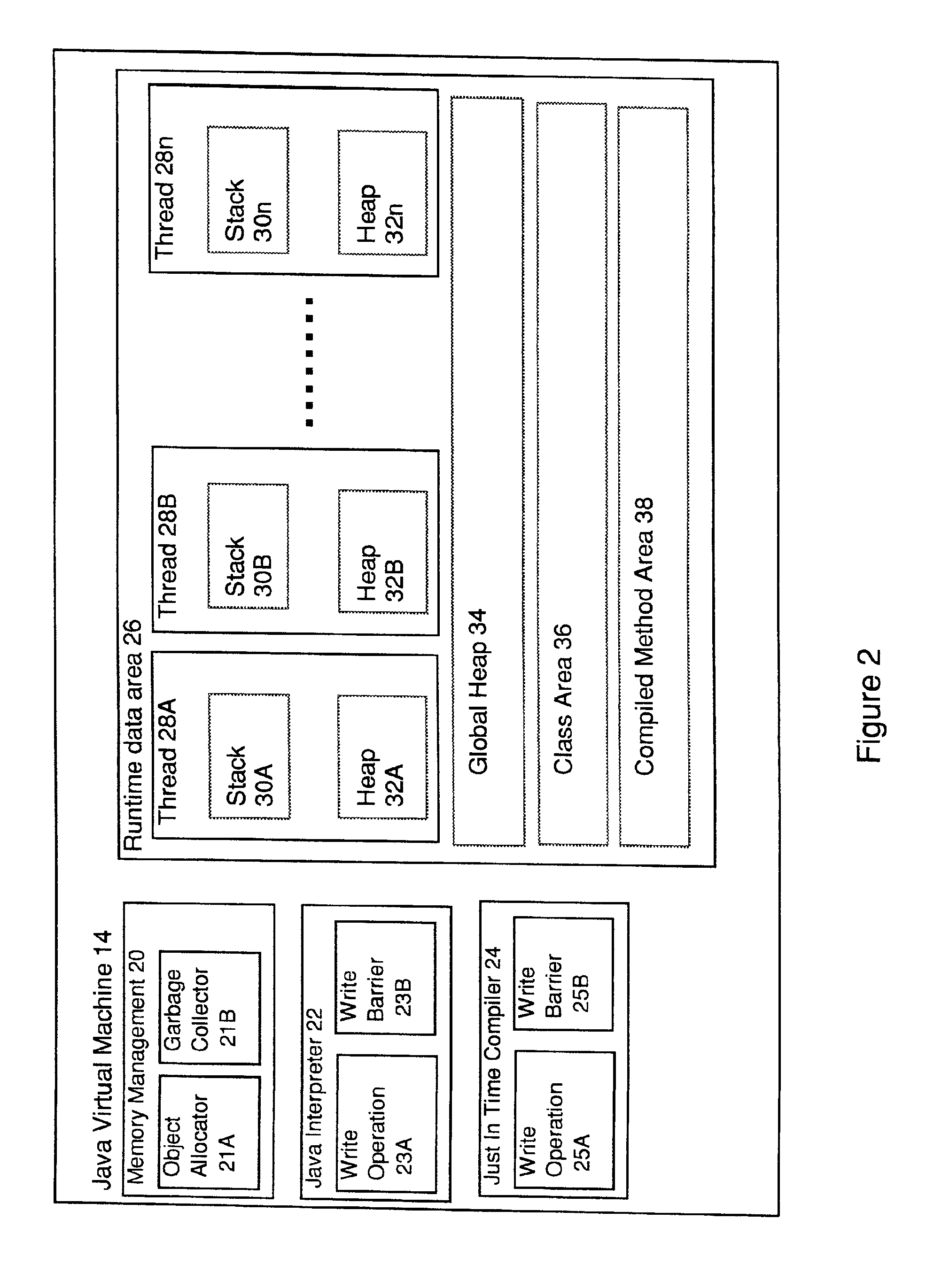

Virtual machine memory management

InactiveUS6904589B1Little effectHighly efficient compactionMemory adressing/allocation/relocationSpecific program execution arrangementsOperational systemWaste collection

This invention relates to memory management in a virtual machine or operating system and in particular to object creation and garbage collection. There is described a method and system of managing memory in a multi-threaded processing environment such as a java virtual machine comprising: creating an object in a thread heap; associating a status with the object and setting the status as local; using write barriers to change the status to global if the object is assigned to a static variable or if the object is assigned to a field in any other object; and performing garbage collection by deleting from the thread heap, when memory space in the thread heap is required, one or more local objects which can not be traced to the thread stack.

Owner:IBM CORP

Method for improving audio playing quality, audio data acquisition method and audio data acquisition system

ActiveCN101763238AImprove audio playback qualityAvoid pauses or delaysSound input/outputSpeech recognitionAudio frequency

The invention provides a method for improving the audio playing quality, an audio data acquisition method and an audio data acquisition system, wherein the method for improving the audio playing quality comprises the following steps: according to the preset time, acquiring and caching the audio data to be played of the guest operation system, wherein the quantity of the acquired audio data is larger than the quantity demanded of the audio data of the physical audio card; and according to the audio playing parameters of the physical audio card, sending the cached audio data to the physical audio card to play. The invention can improve the sound playing performance of the guest operation system, and improve the user experience.

Owner:LENOVO SOFTWARE

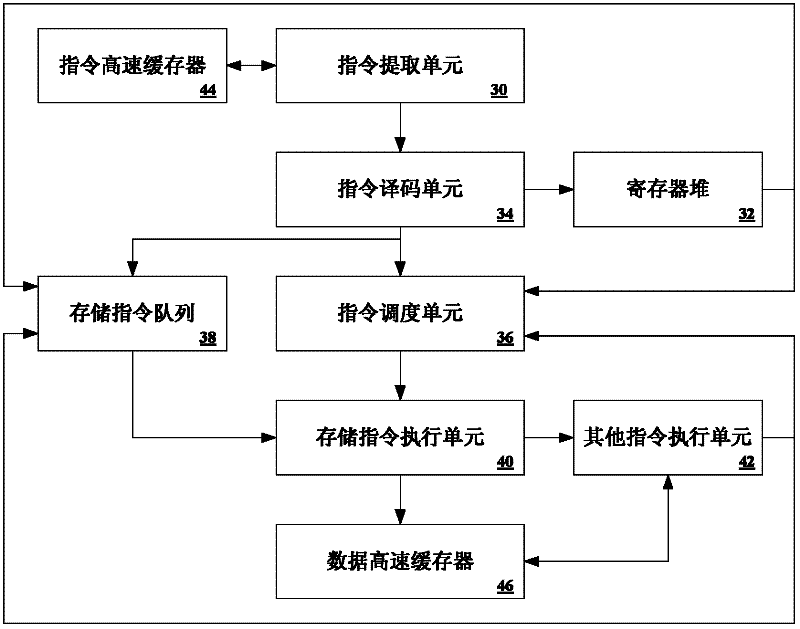

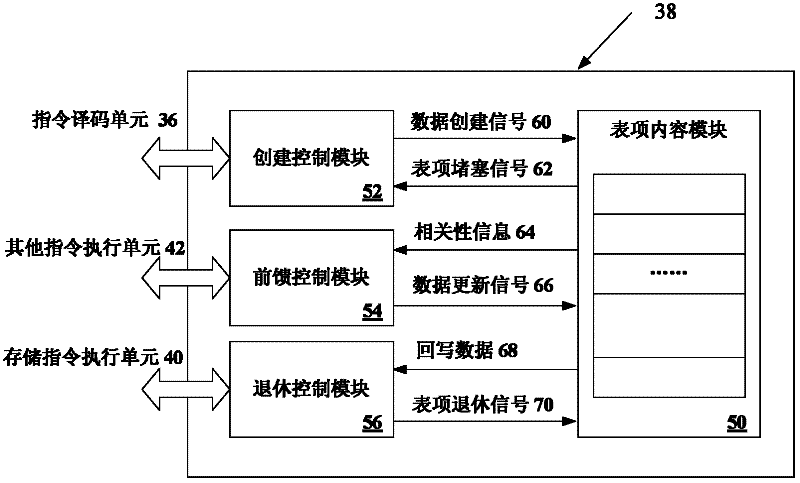

Data processor for improving storage instruction execution efficiency

InactiveCN102495724AReduce pauseImprove execution efficiencyProgram initiation/switchingConcurrent instruction executionScalar processorScheduling instructions

A data processor for improving the storage instruction execution efficiency comprises a register file, an instruction decoding unit, an instruction scheduling unit, a storage instruction queue and instruction execution units, wherein the instruction scheduling unit is used for completing feedforward of the address operand of a stored instruction and feedforward of all operands of other instructions according to related information of instruction operands, and transmitting the instructions completed by operand feedforward to the corresponding instruction execution unit; the storage instruction queue is used for receiving storage instructions from the instruction decoding unit, storing write-back data and related information of the stored instruction, monitoring outlet data of all the execution units and completing feedforward of the write-back data of the stored instruction according to the related information of the stored instruction data operand; and the instruction execution units are used for receiving instructions transmitted by the instruction scheduling unit and are divided into different execution units according to the instruction types. The data processor provided by the invention effectively reduces breakdown of assembly lines due to genuine correlation of data write after read, improves the execution efficiency of storage instructions and has promoted performance.

Owner:C SKY MICROSYST CO LTD

Method and device for displaying list on mobile terminal

ActiveCN102999568AReduce pausesAccelerateSpecial data processing applicationsInput/output processes for data processingHuman–machine interfaceMobile internet

The invention provides a method and a device for displaying a list on a mobile terminal, and the method and the device can be used for reducing the stopping phenomenon in the displaying process when a user operates a scroll bar of a human-computer interface of the mobile terminal. The method comprises the following steps of: in the rolling process of the list, outputting texts positioned in the display range in the list on the human-computer interface, wherein the list is from a mobile internet; and when the list stops rolling, outputting preformatted files positioned in the current display range in the list on the human-computer interface.

Owner:BEIJING JINGDONG CENTURY TRADING CO LTD

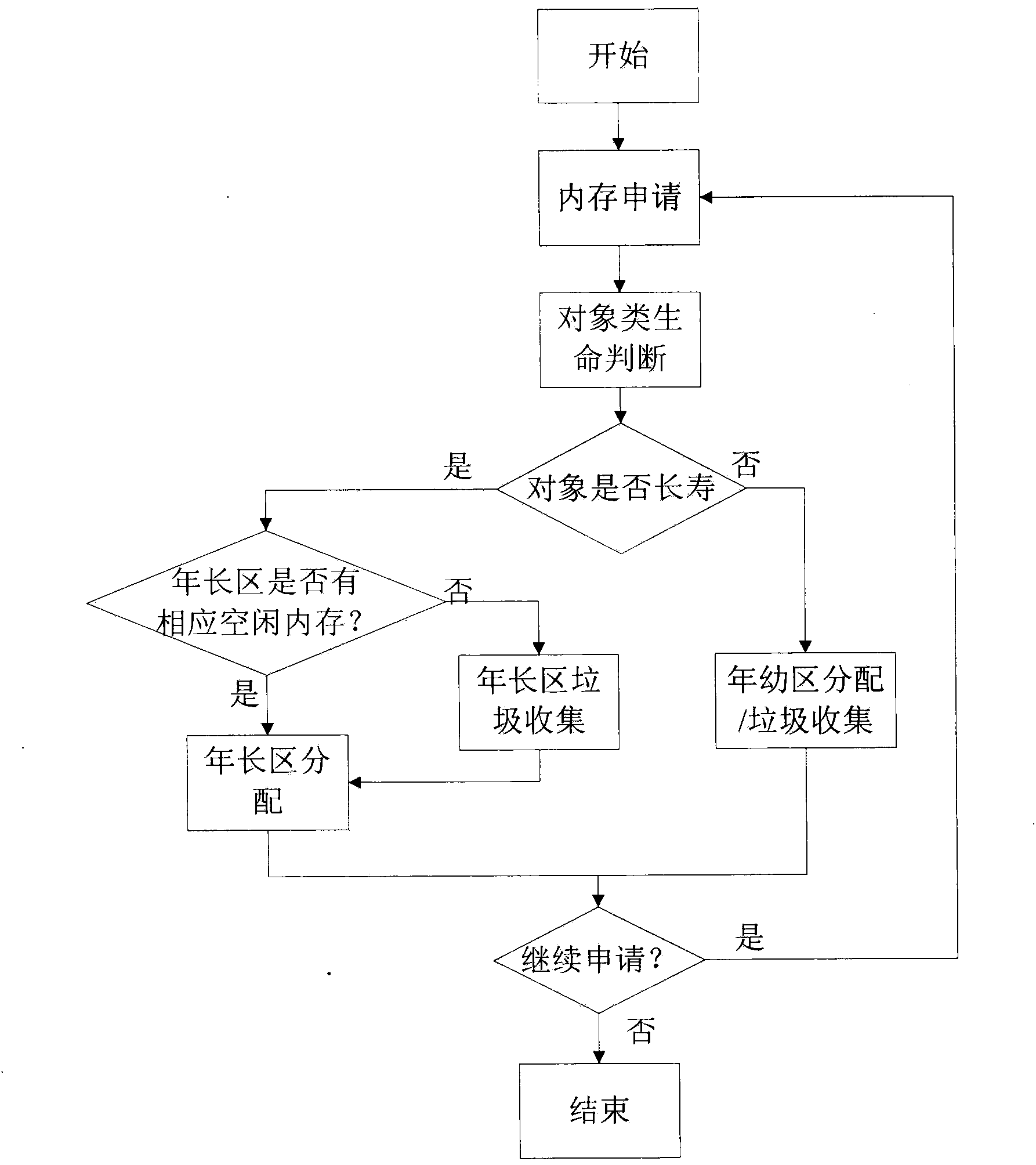

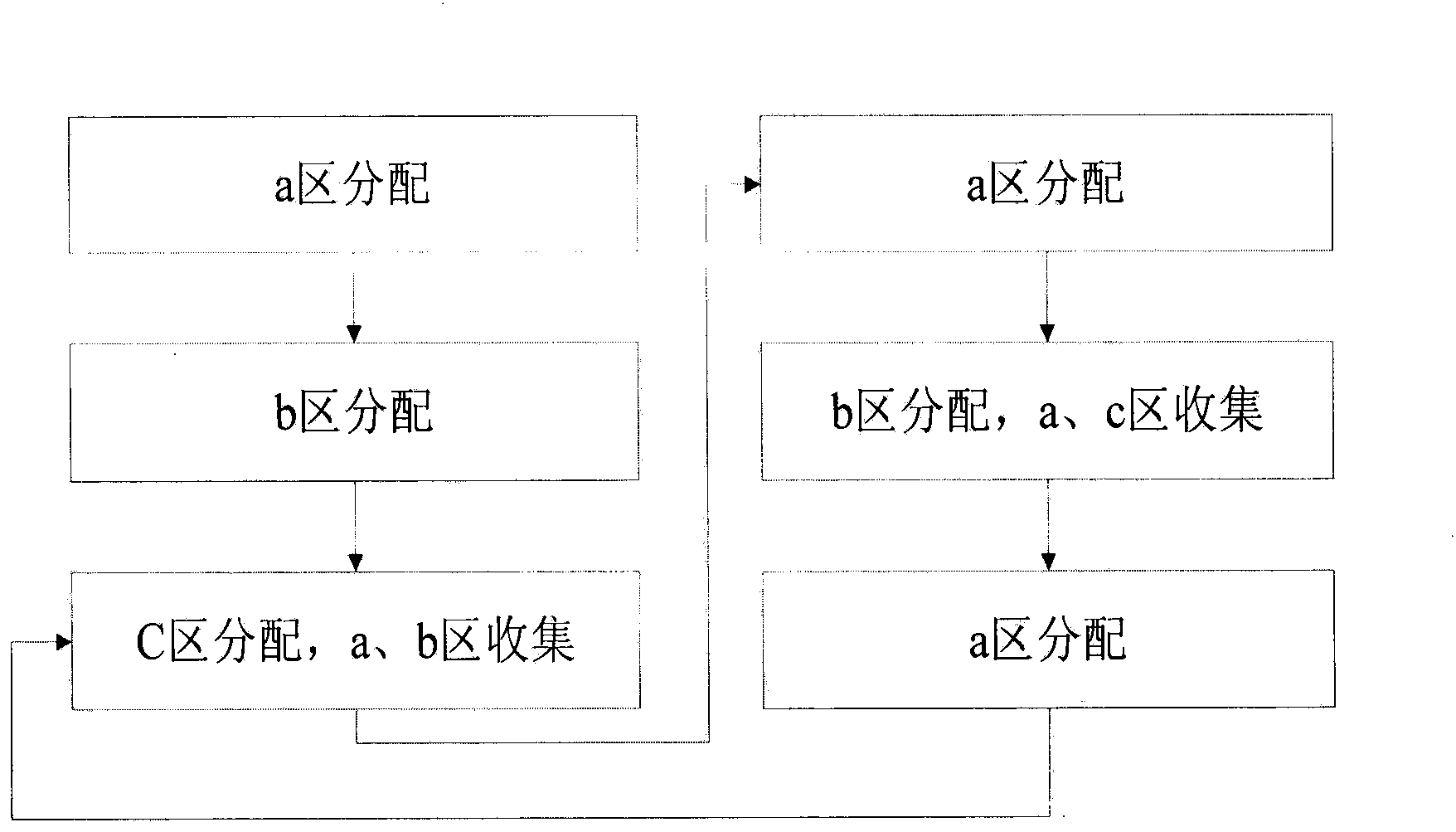

Memory allocation and garbage collection method based on life-period prediction

InactiveCN104035879AReduce collection execution timeAvoid copyingMemory adressing/allocation/relocationWaste collectionPeriod length

The invention discloses a memory allocation and garbage collection method based on life-period prediction. The method comprises the following steps that objects with long life-periods are directly allocated to an older area by predicting life-period lengths of the objects to be allocated, and the copied number from a young area to the older area is reduced to lower the execution time of garbage collection; in the young area, the young area is further effectively divided to achieve a non-pause mode of simultaneously allocating the objects and collecting garbage so as to reduce the pause times in a procedure operation process; a lazy-buddy mode is adopted in the older area to carry out memory allocation, so that the memory allocation speed is ensured, and a Mark-sweep method is combined to collect the garbage, so that copy operations of large objects is avoided, and the number of memory fragments is controlled.

Owner:JIANGNAN UNIV

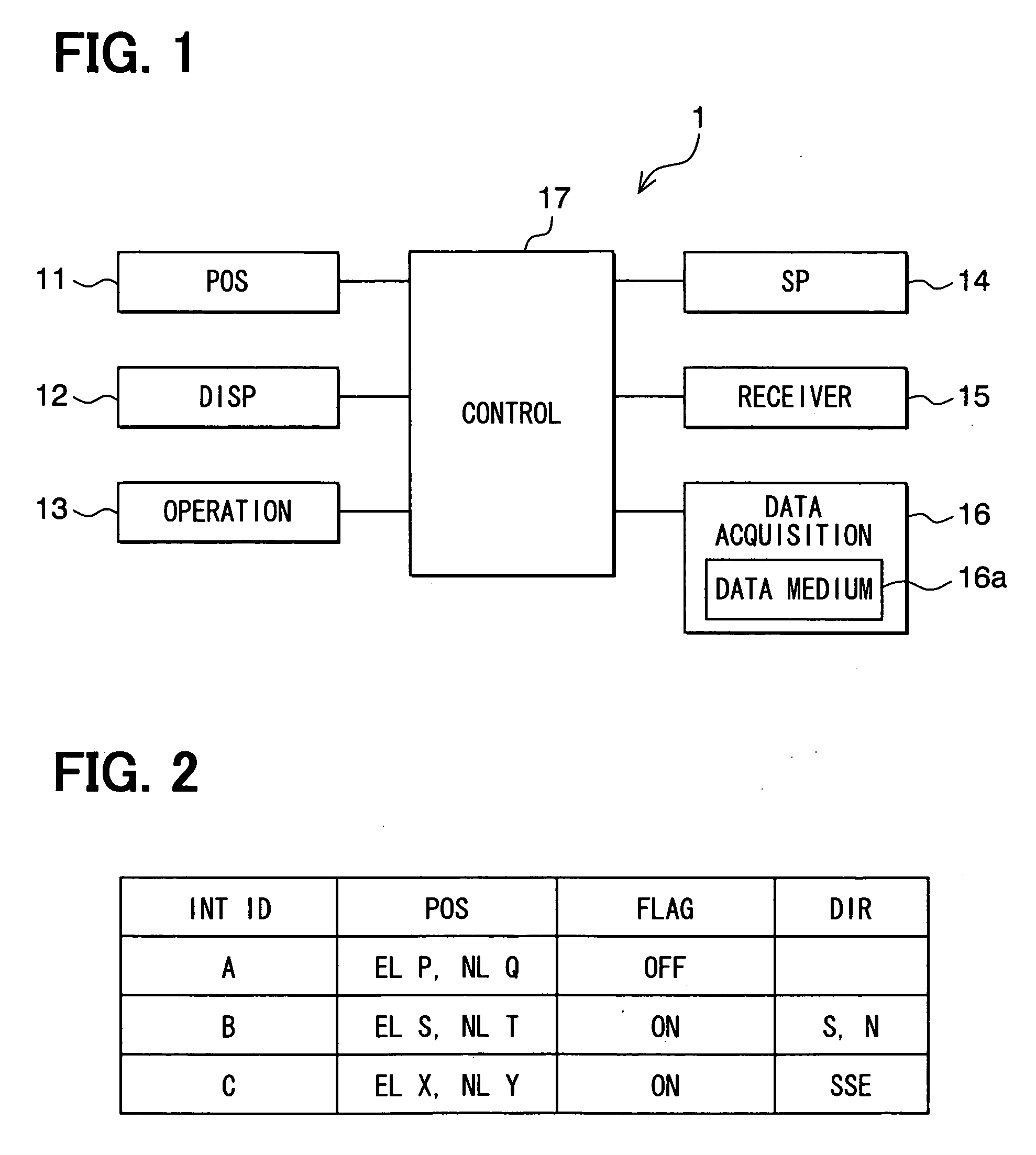

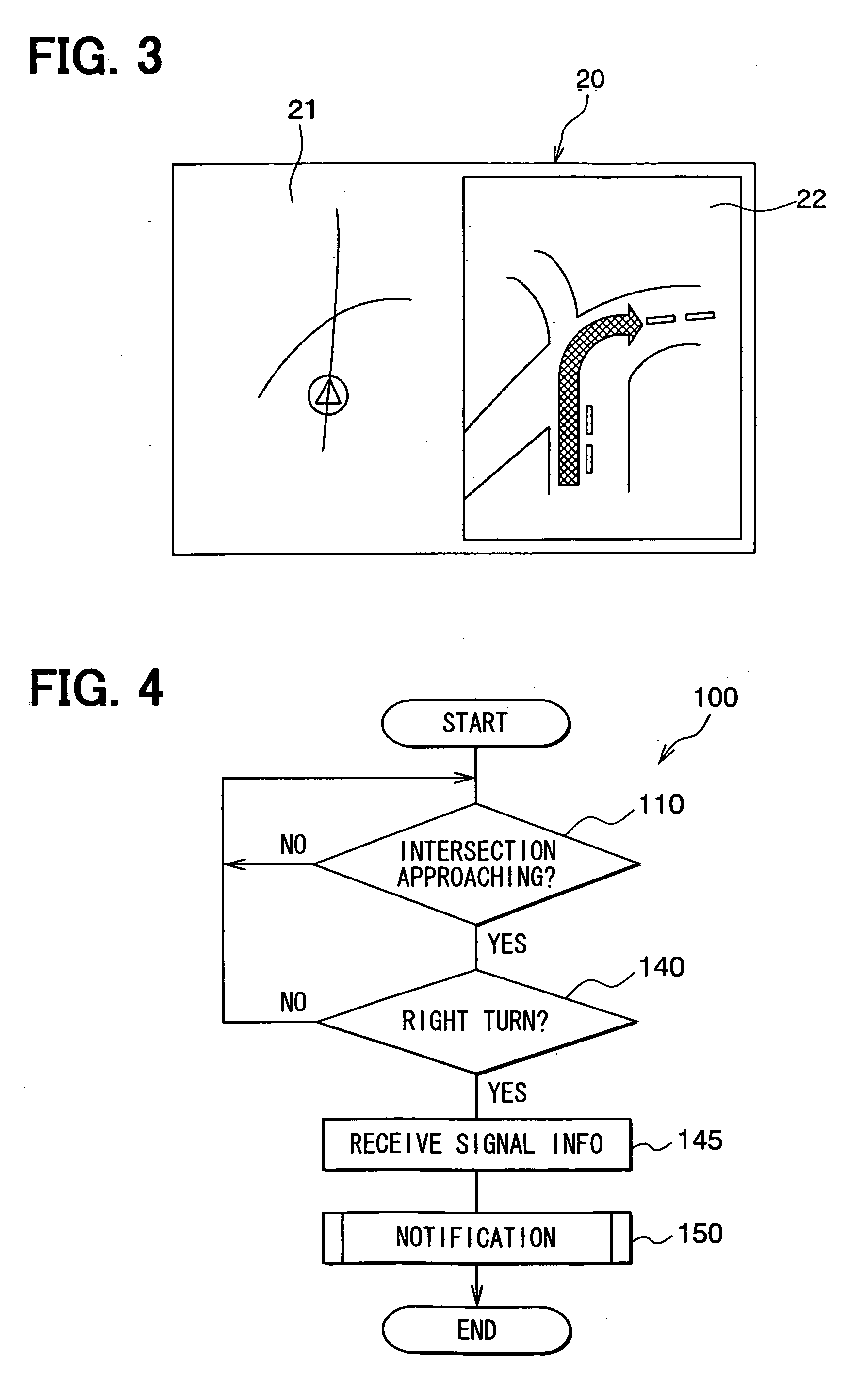

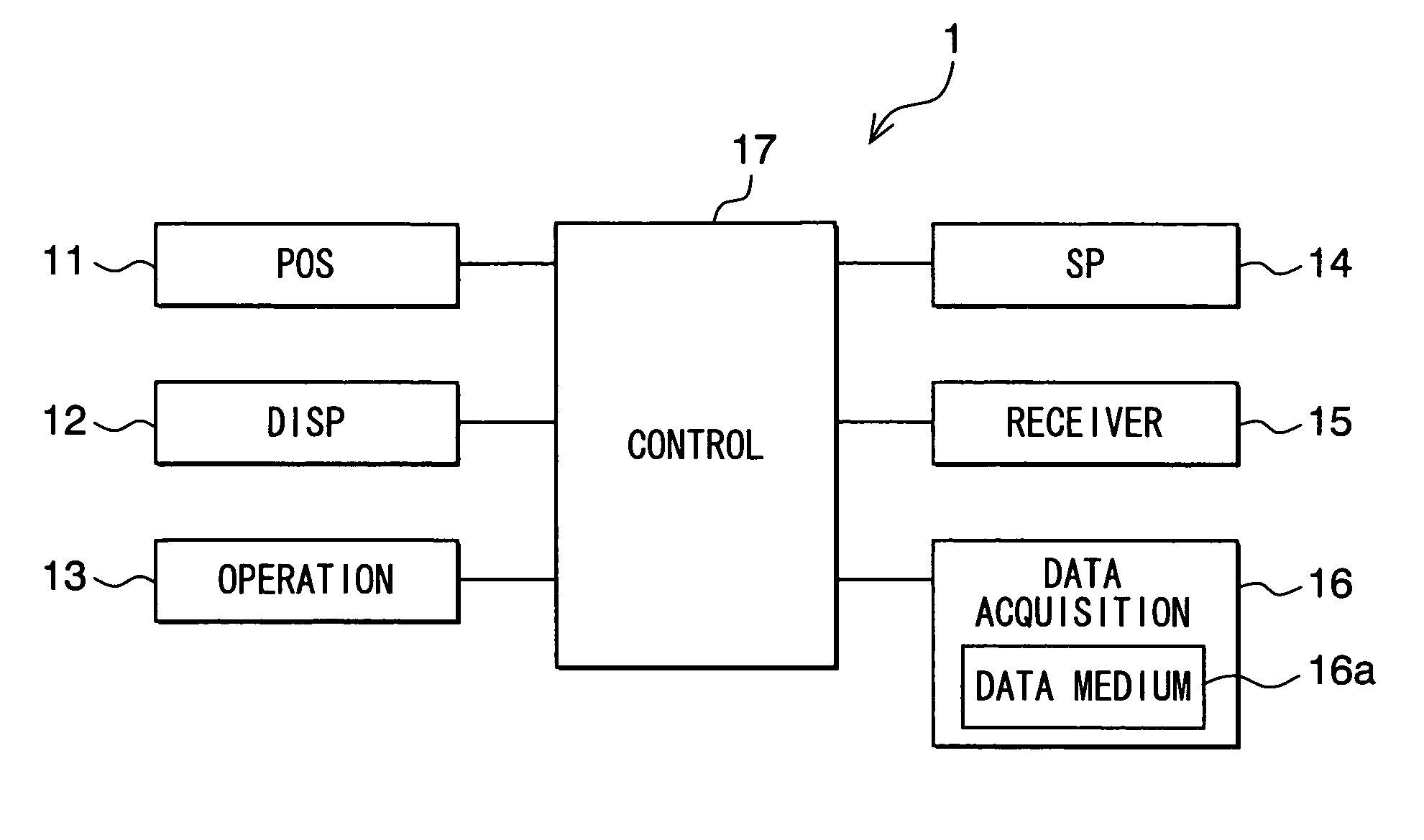

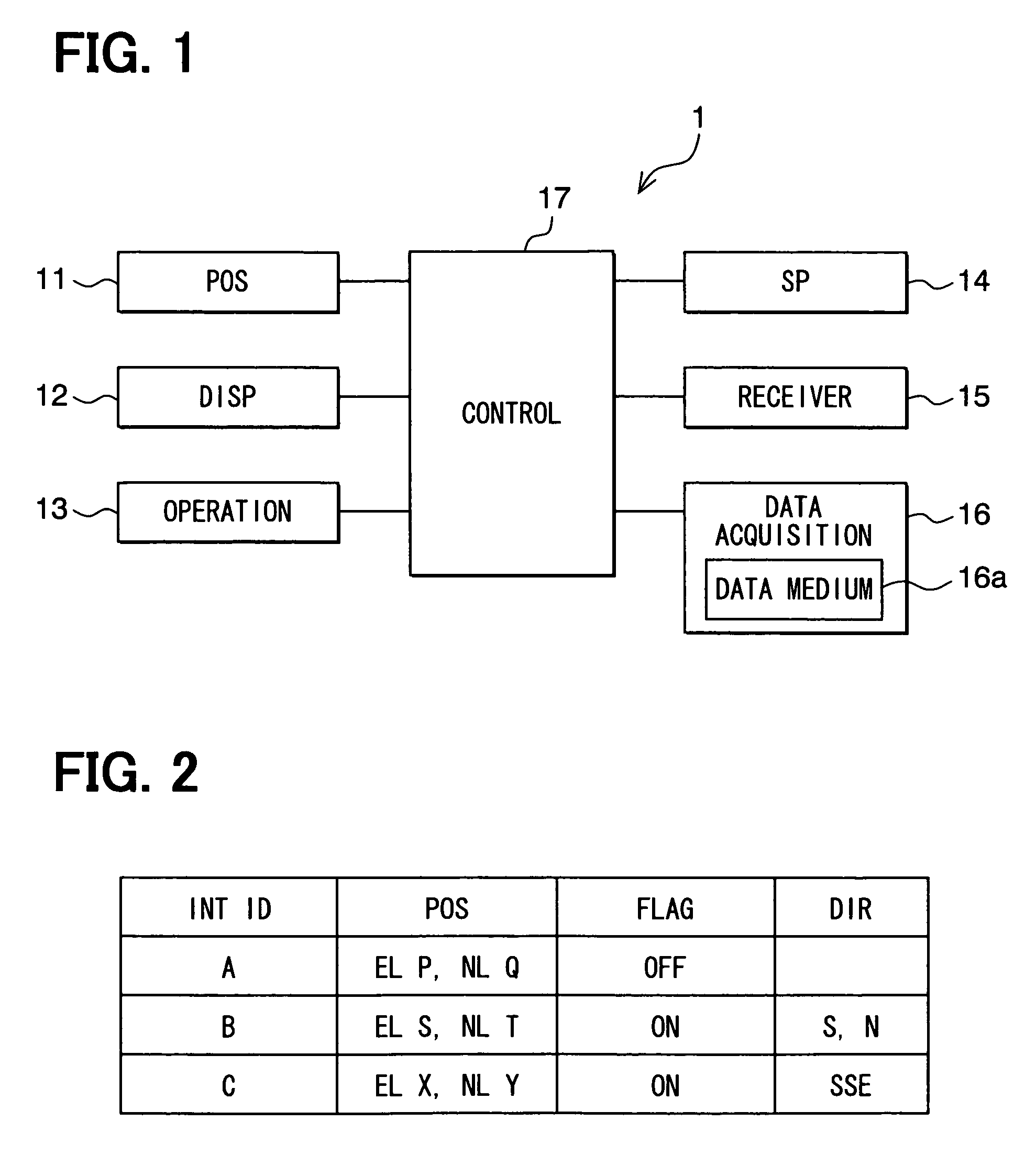

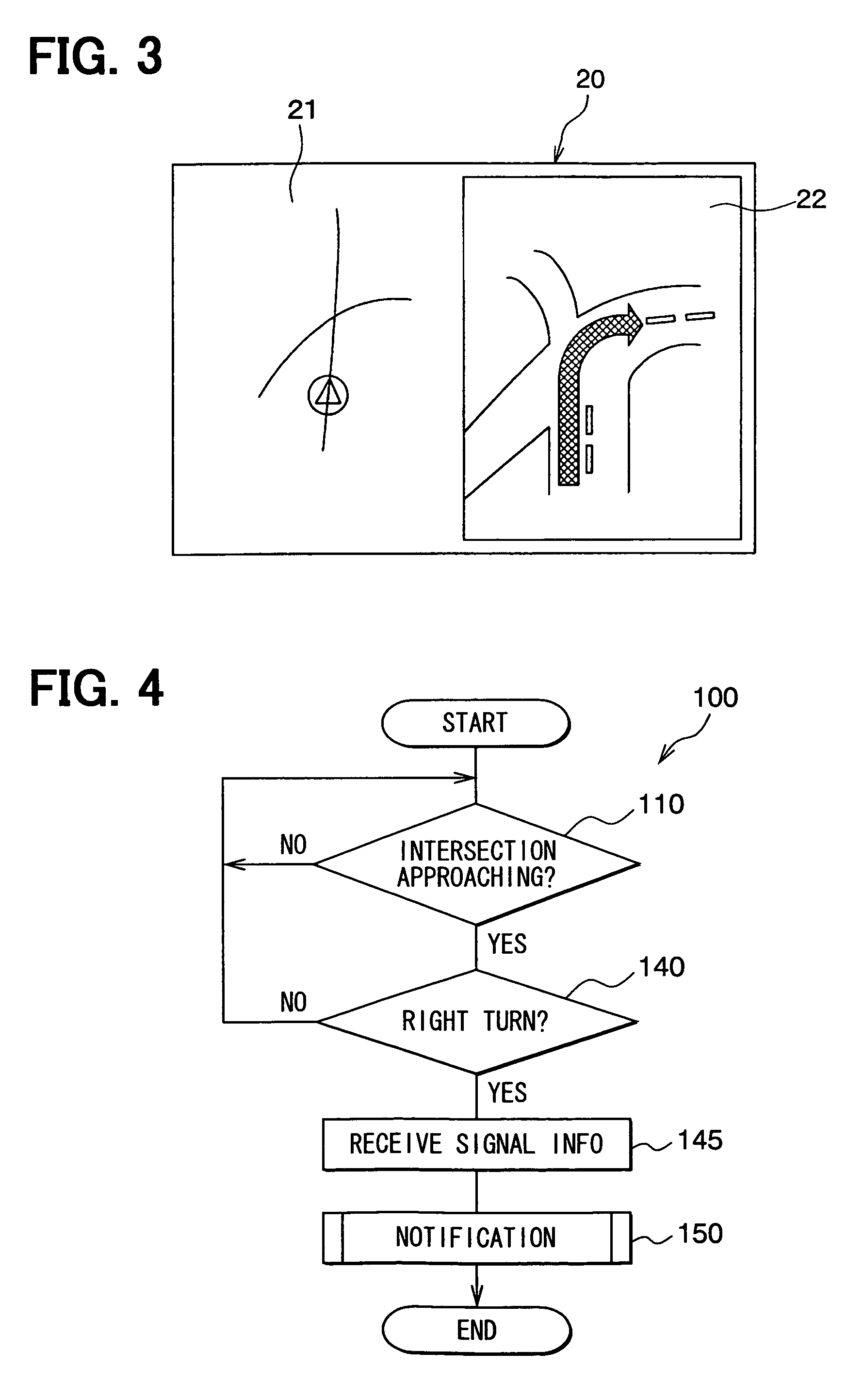

Apparatus, program and storage medium for notifying intersection information

ActiveUS20090212973A1Reduce the possibilityReduce pauseControlling traffic signalsBoardsTraffic signalDriver/operator

A signal sequence of a traffic signal is notified for a driver of a vehicle that is heading for an intersection by using a signal sequence notification apparatus. If the apparatus determines, based on received signal sequence information, that the information indicates that the traffic signal is currently allowing an entrance into the intersection having the next signal sequence indicating that entrance is not allowed with no right turning permission, the driver receives warning about the entrance into the intersection. The warning thus decreases the possibility of the vehicle to be brought to a standstill in the intersection due to the traffic signal that has a signal sequence of no right / left turn by the right / left turn light after a signal change from GO to STOP regarding the straight traffic.

Owner:DENSO CORP

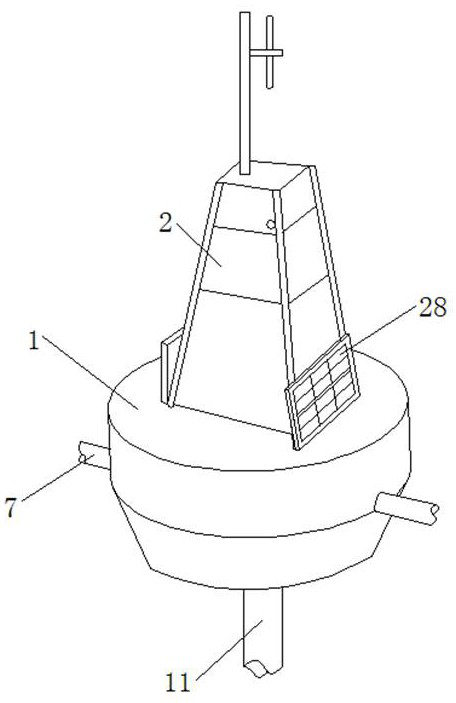

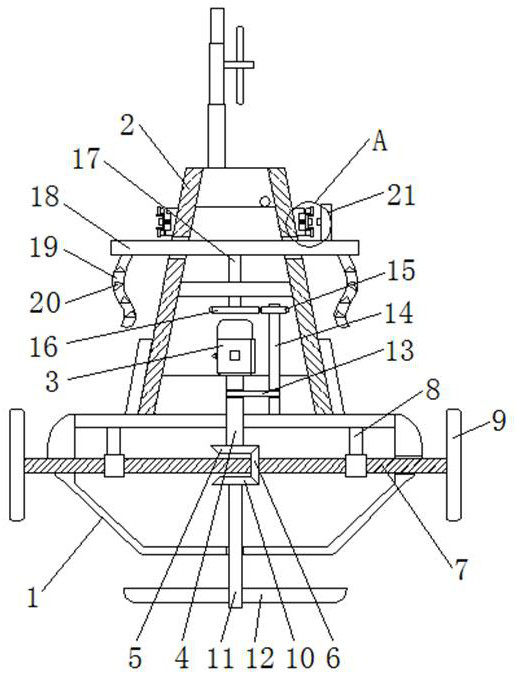

Environment-friendly stable floating device for marine environment monitoring

InactiveCN112246360ATo prevent the phenomenon of winding the deviceSmash in timeWaterborne vesselsTesting waterImpellerGear wheel

The invention discloses an environment-friendly stable floating device for marine environment monitoring. The device comprises a floating plate, a motor, a third bevel gear, connecting parts and solarpanels, wherein a fixing frame is welded to the upper portion of the floating plate, the motor is arranged in the floating plate, and a second rotating shaft penetrates into a second bevel gear; andsupporting rods are installed on the outer wall of the second rotating shaft, the left end and the right end of the second rotating shaft penetrate through the floating plate to be connected with impellers, ribbons are arranged on the periphery of the bottom of a fixing plate, reflectors are connected to the ribbons, the connecting parts are connected to the fixing plate through bolts, and secondneodymium magnets are arranged on the inner walls of the connecting parts. According to the environment-friendly stable floating device for marine environment monitoring, smashing blades are arrangedand can rotate along with a third rotating shaft so that algae can be smashed in time, the phenomenon that the device is wound by the algae is effectively avoided, and the device can normally walk andmove.

Owner:陈海艳

Apparatus, program and storage medium for notifying intersection information

InactiveUS8040252B2Reduce the possibilityReduce pauseControlling traffic signalsTraffic signalsTraffic signalComputer science

A signal sequence of a traffic signal is notified for a driver of a vehicle that is heading for an intersection by using a signal sequence notification apparatus. If the apparatus determines, based on received signal sequence information, that the information indicates that the traffic signal is currently allowing an entrance into the intersection having the next signal sequence indicating that entrance is not allowed with no right turning permission, the driver receives warning about the entrance into the intersection. The warning thus decreases the possibility of the vehicle to be brought to a standstill in the intersection due to the traffic signal that has a signal sequence of no right / left turn by the right / left turn light after a signal change from GO to STOP regarding the straight traffic.

Owner:DENSO CORP

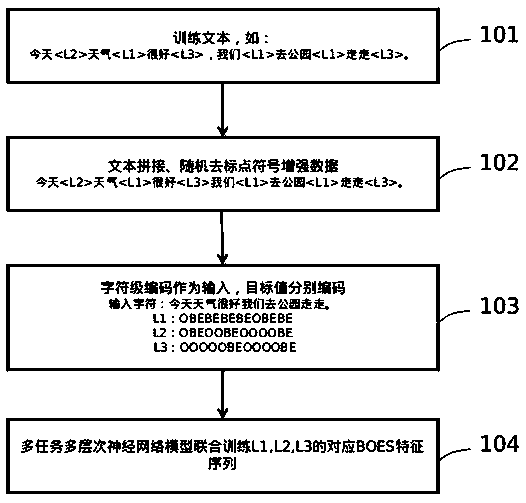

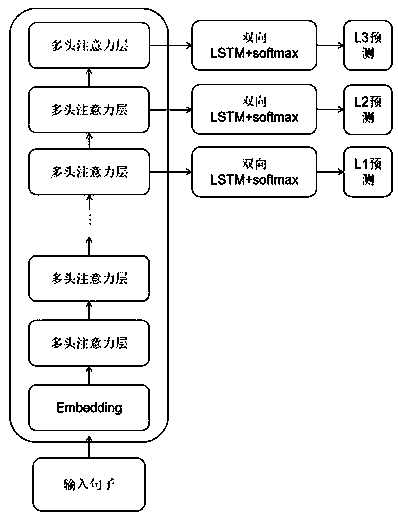

Text rhythm prediction method based on multi-task multi-level model

ActiveCN111339771AReduce errorsImprove utilizationSemantic analysisNeural architecturesSequence predictionPredictive text

The invention discloses a text rhythm prediction method based on a multi-task multi-level model, and the method is characterized in that the method comprises the following steps: 401, obtaining a prediction text; 402, performing character-level coding on the text to be predicted for the word table; step 403, performing sequence prediction by using a multi-task model; step 404, judging whether thesentences have long sentences without L2 and L3 or not; and step 405, combining output results of the L1, the L2 and the L3, overlapping boundary positions, performing selective combination accordingto priorities of the L3, the L2 and the L1, and returning an output result. The invention relates to the technical field of text rhythm prediction. The problems that rhythm information generation errors exist, information cannot be shared mutually, training and parameter adjustment are troublesome, boundary prediction of rhythm phrases and intonation phrases is not accurate enough, and long sentences have no rhythm phrase boundary or intonation phrase boundary easily are solved.

Owner:广州深声科技有限公司

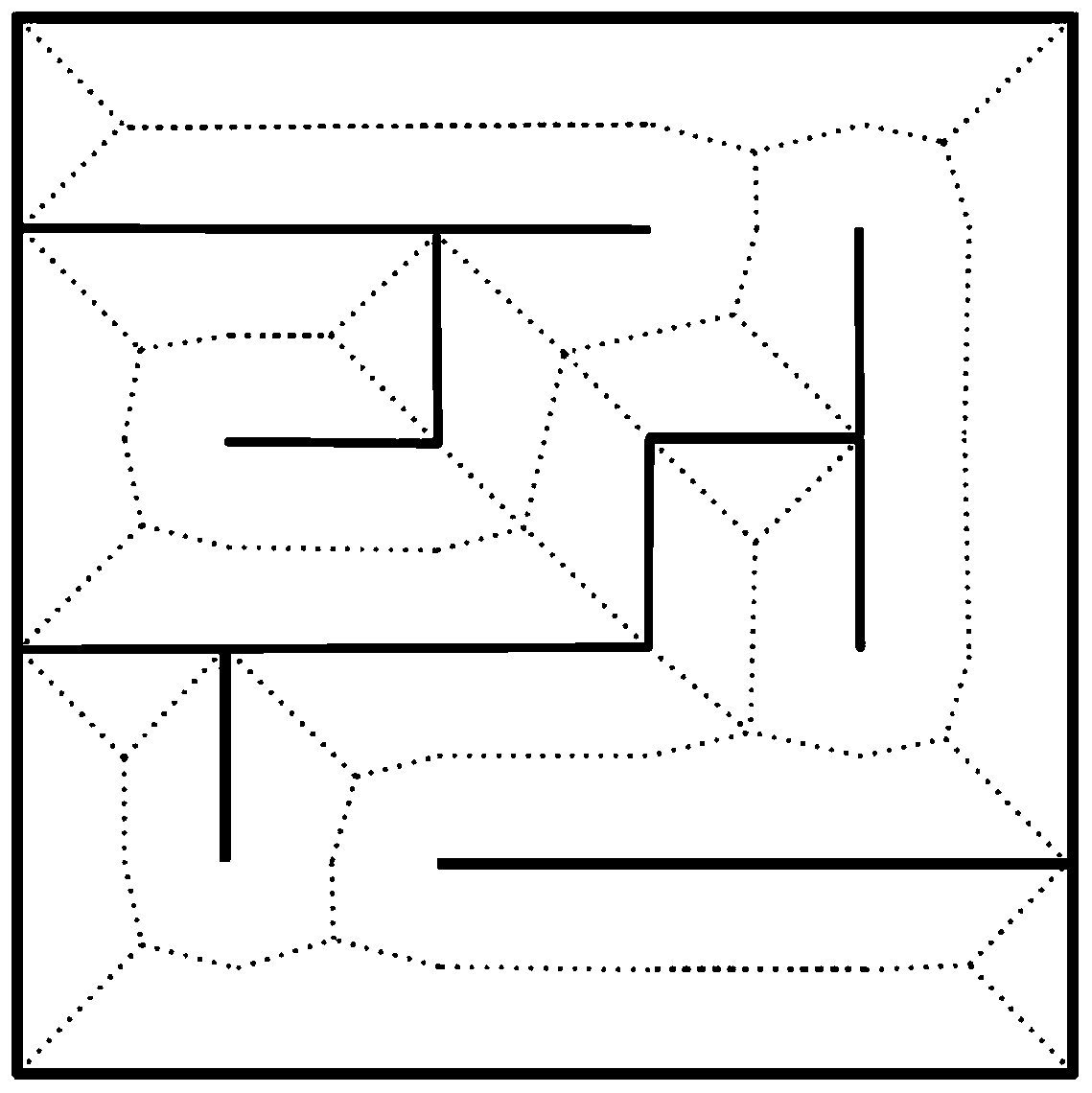

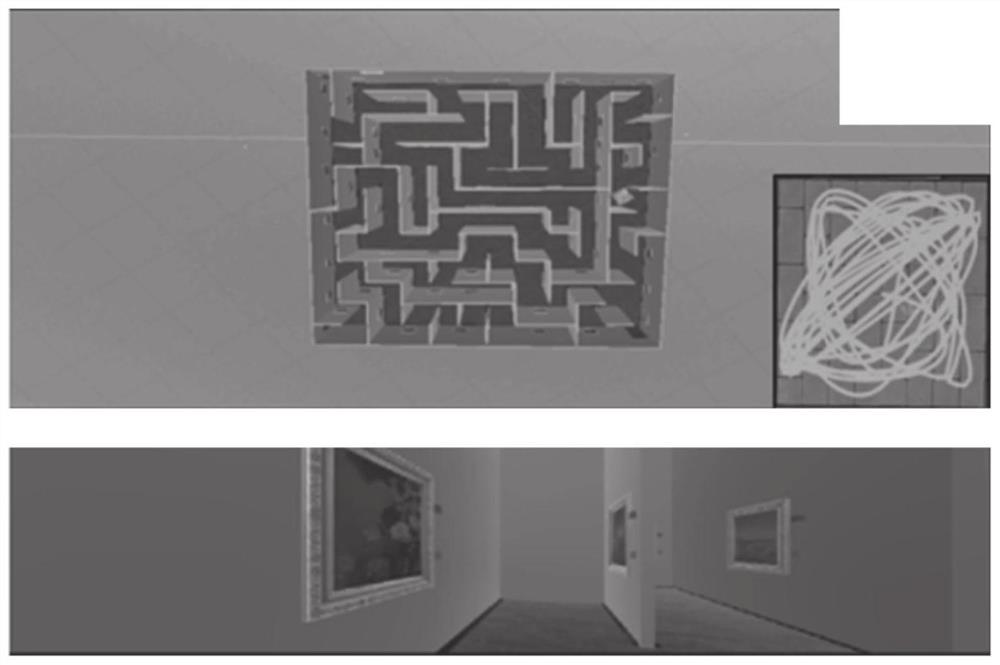

Actual and virtual space mapping method and system suitable for virtual roaming system

ActiveCN110853150AReduce the number of resetsShorten roaming timeImage data processingEnergy efficient computingPhysical spaceComputer graphics (images)

The invention provides an actual and virtual space mapping method and system suitable for a virtual roaming system, and the method comprises the steps: extracting a two-dimensional plane graph of a given virtual roaming scene, and building a Voronoi graph for the two-dimensional plane graph; establishing a skeleton path according to the established Voronoi diagram; generating a corresponding skeleton roaming path according to the input starting point of the roaming path, and merging the paths to obtain the roaming path; mapping the roaming path in the virtual scene into an actual walking pathin an actual space; obtaining the spatial position and direction, tracked in real time, of the user in the physical space in the walking process along the actual walking path, and calculating the corresponding spatial position and direction of the user in the virtual space in real time through a position inverse mapping algorithm for image rendering. The user can be effectively guided to be away from the boundary of the tracking area, the user resetting frequency of the system is greatly reduced, pause feeling is reduced, and immersion of the user is enhanced.

Owner:SHANDONG NORMAL UNIV

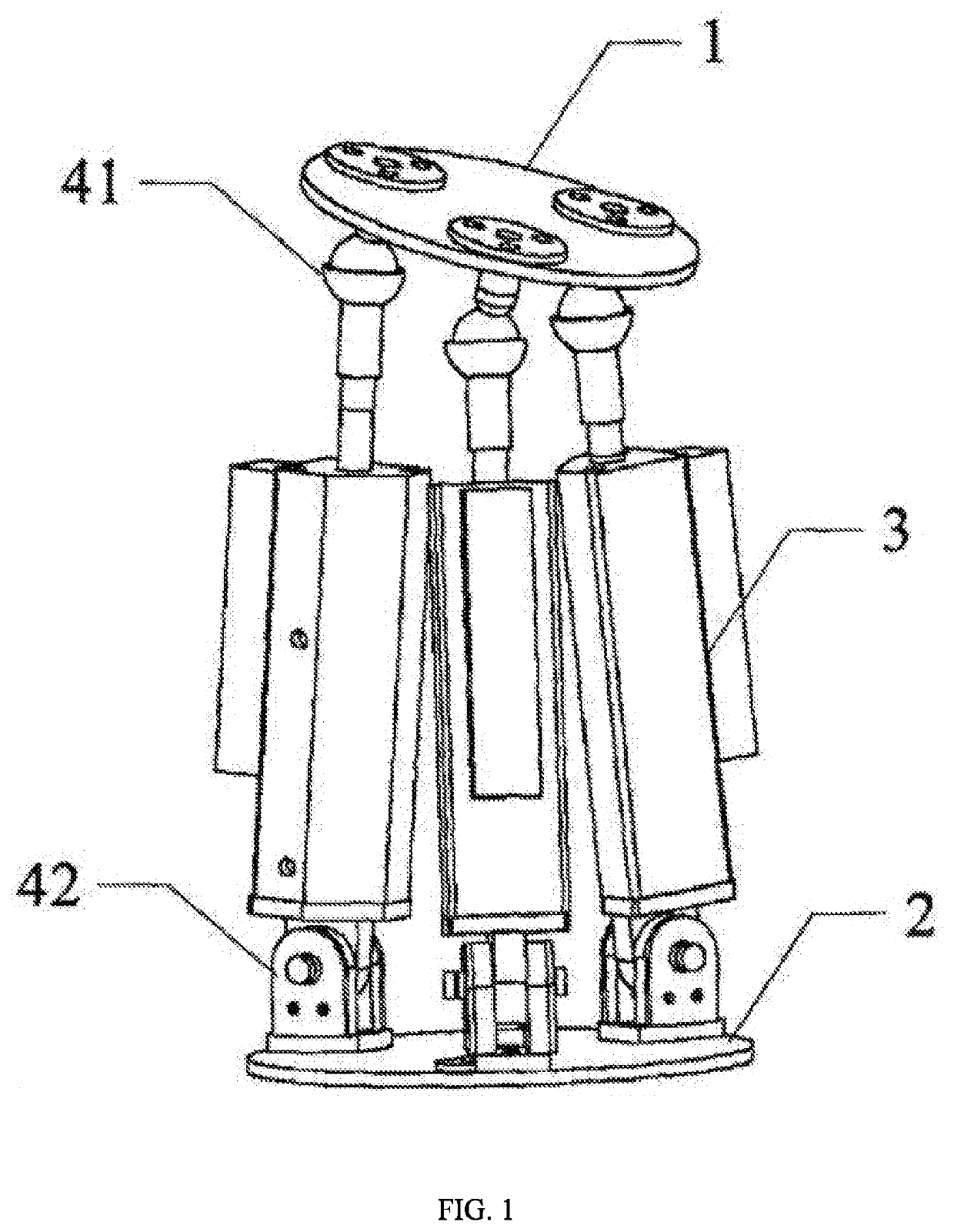

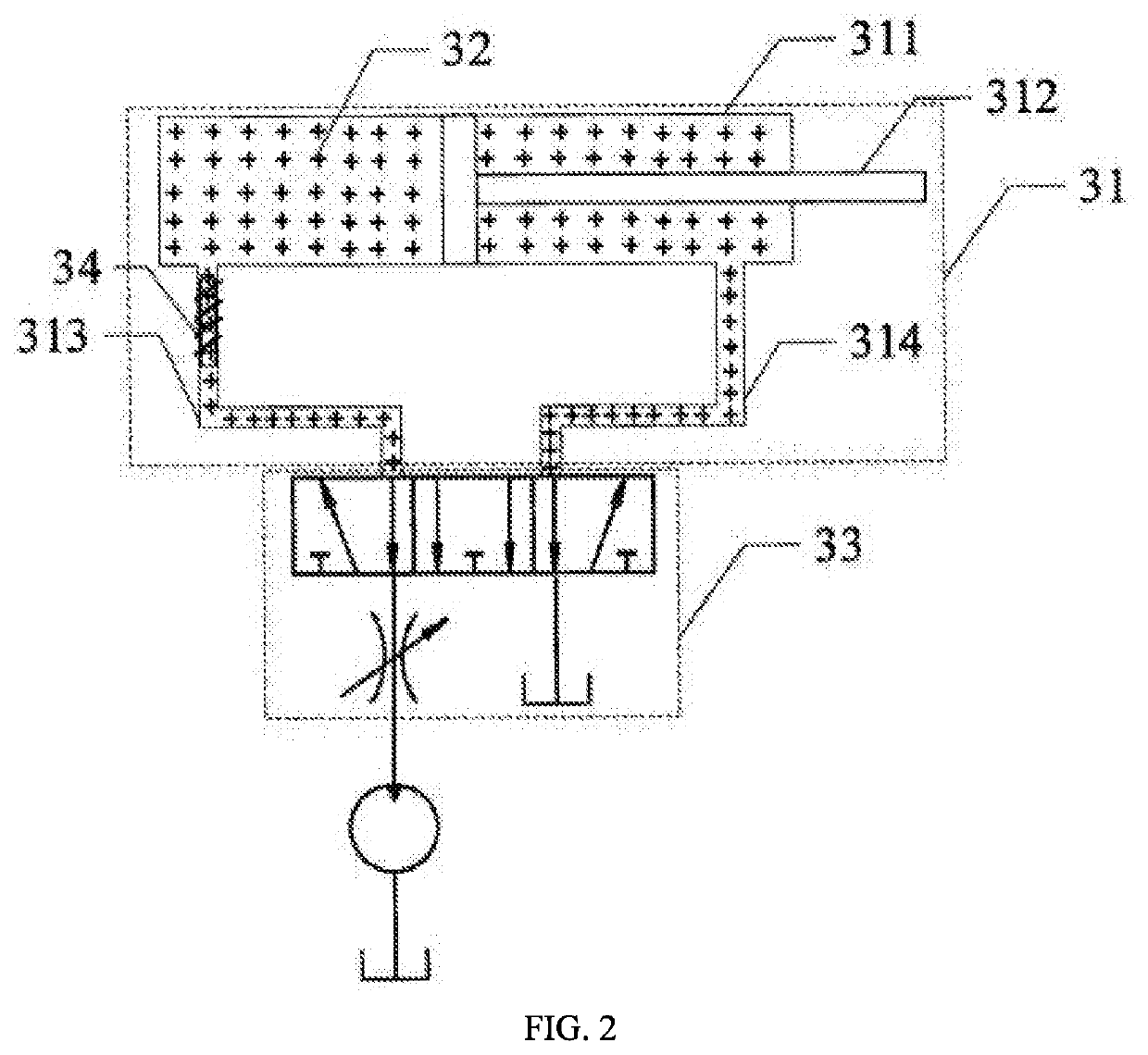

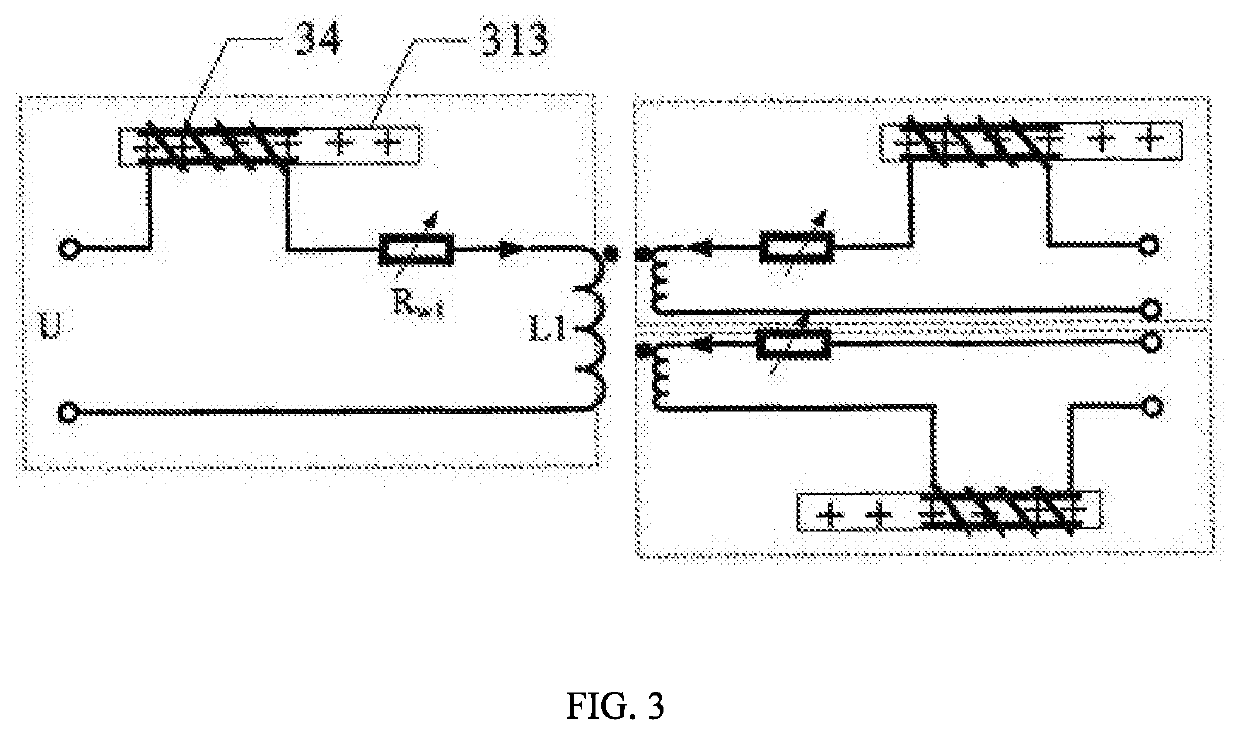

Bionic robot and spine apparatus thereof

ActiveUS20190351543A1Reduce pauseDelay transitionProgramme-controlled manipulatorJointsPower flowBionics

A bionic robot and a spine apparatus thereof. Magnetorheological fluids are filled in the cavity, the first tube and the second tube to actuate the first end of the piston rod, so that the piston rod is actuated to move along the axial direction of the cavity. The excitation coil is wound around the first tube. When the controller provides a variable current for the excitation coil, the excitation coil produces a variable magnetic field at the first tube, thereby causing a magnetorheological effect that the magnetorheological fluid is in low liquidity and high viscosity. Then, the transmission speed of the piston rod is changed, which is presented as a damping characteristic, reducing the pause and transition in the spine apparatus, and improving the flexibility and the bionic performance of the robot.

Owner:CHINA JILIANG UNIV

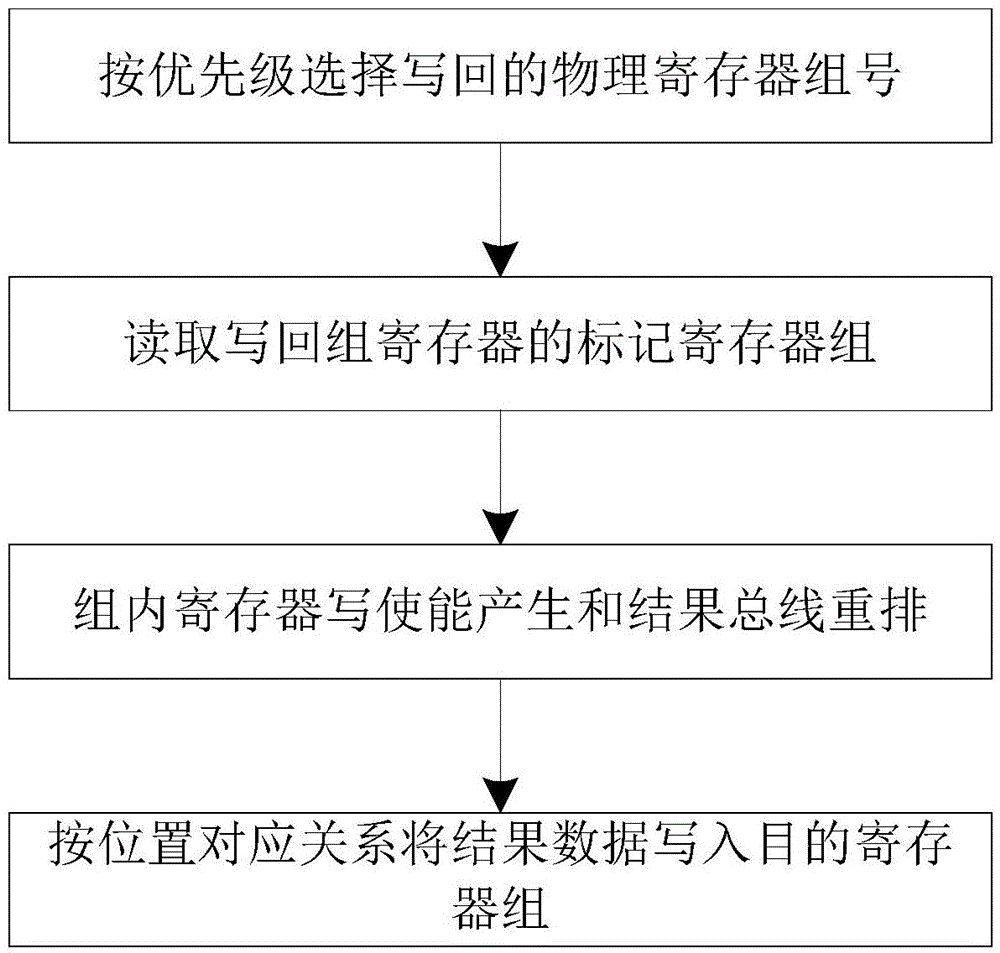

Writing merging and writing undo processing device and method in SIMD (single instruction multiple data) processor

ActiveCN104317555AReduce pauseIncrease concurrencyConcurrent instruction executionProcessor registerSingle instruction single data

The invention provides a writing merging and writing undo processing device and method in an SIMD (single instruction multiple data0 processor. The processing device is characterized in that a system structure register file is used as an operating code storage part of an instruction and connected to an execution unit of the processor; the output of a mark table is connected to a mark allocation unit; the mark allocation unit allocates a mark to the instruction which needs to be written back to a register from the mark table, the mark is different from the mark which is allocated by the instruction and already enters an assembly line and outputted and connected to a mark register file; a writing signal of a target register generated by a decoding logic controls the mark allocated by the mark allocation unit to be written into the mark register file. By adopting the processing device and method, the execution efficiency of the SIMD structure processor can be improved, and the complexity for designing a compiler is alleviated or hardly increased.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

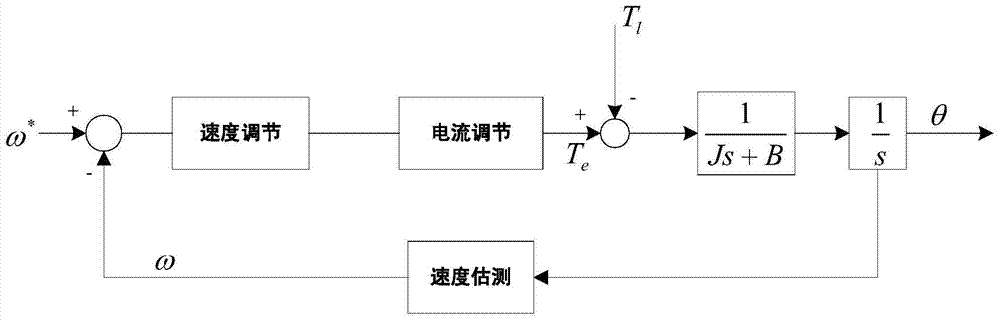

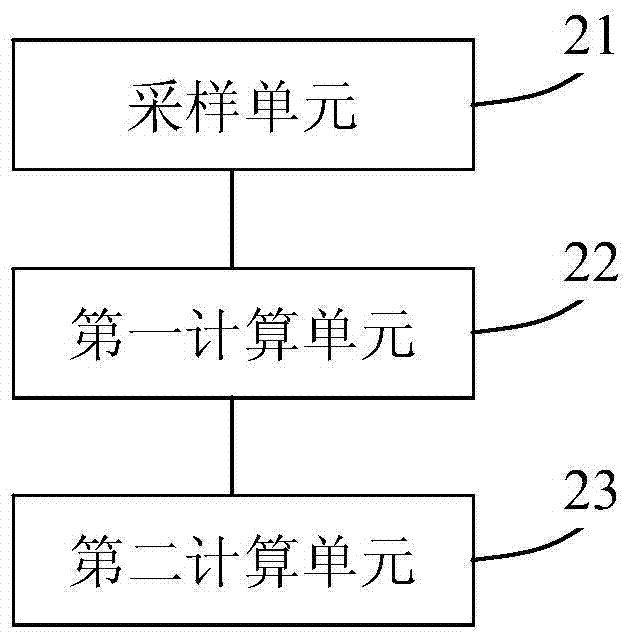

Inertia ratio on-line identifying system and method

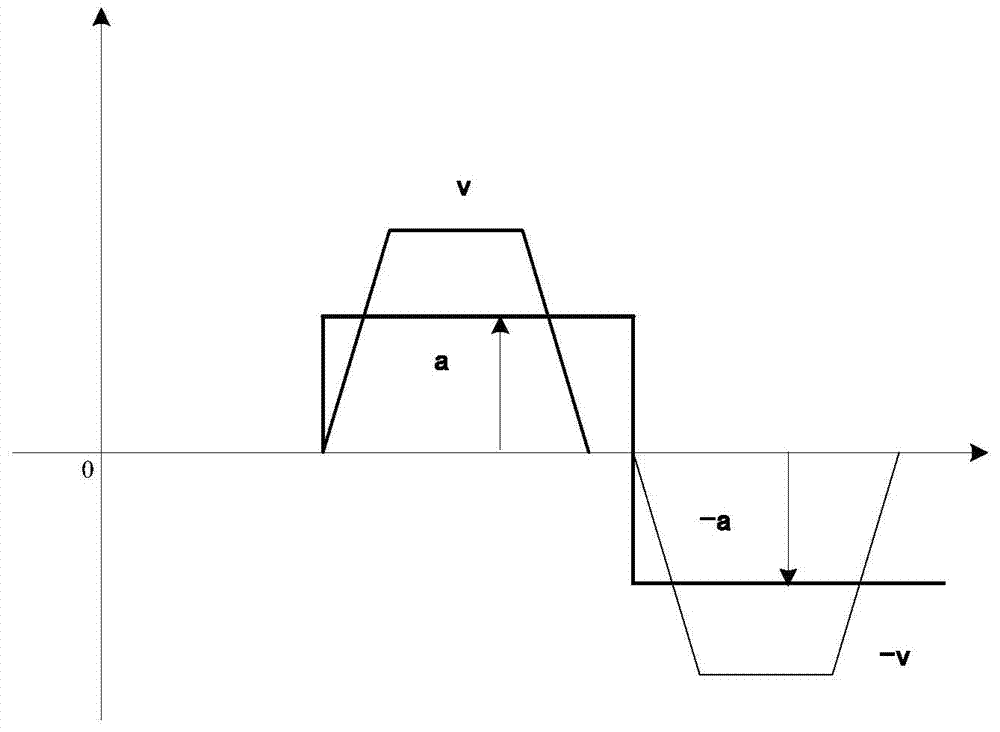

ActiveCN104124908AReduce pauseEasy to operateElectronic commutation motor controlVector control systemsControl theoryElectromagnetic torque

The invention provides an inertia ratio on-line identifying system and method. The inertia ratio on-line identifying system comprises a sampling unit, a first computing unit and a second computing unit, wherein the sampling unit is used for collecting rotation speeds and corresponding current of a plurality of servo motors in fixed sampling time when the servo motors are started or reversed; the first computing unit is used for calculating electromagnetic torque according to the current, and subjecting the collected rotation speeds and the calculated electromagnetic torque to iterative computation to obtain an identification vector; the second computing unit is used for calculating an inertia ratio according to the identification vector. According to the inertia ratio on-line identifying system and method, iterative computation of the identification vector from the sampled rotation speeds is performed, and the inertia ratio is calculated according to the identification vector, so that inertia ratio parameters of the servo motors can be obtained without off-line operation, and user's operation is simplified.

Owner:SHENZHEN INOVANCE TECH

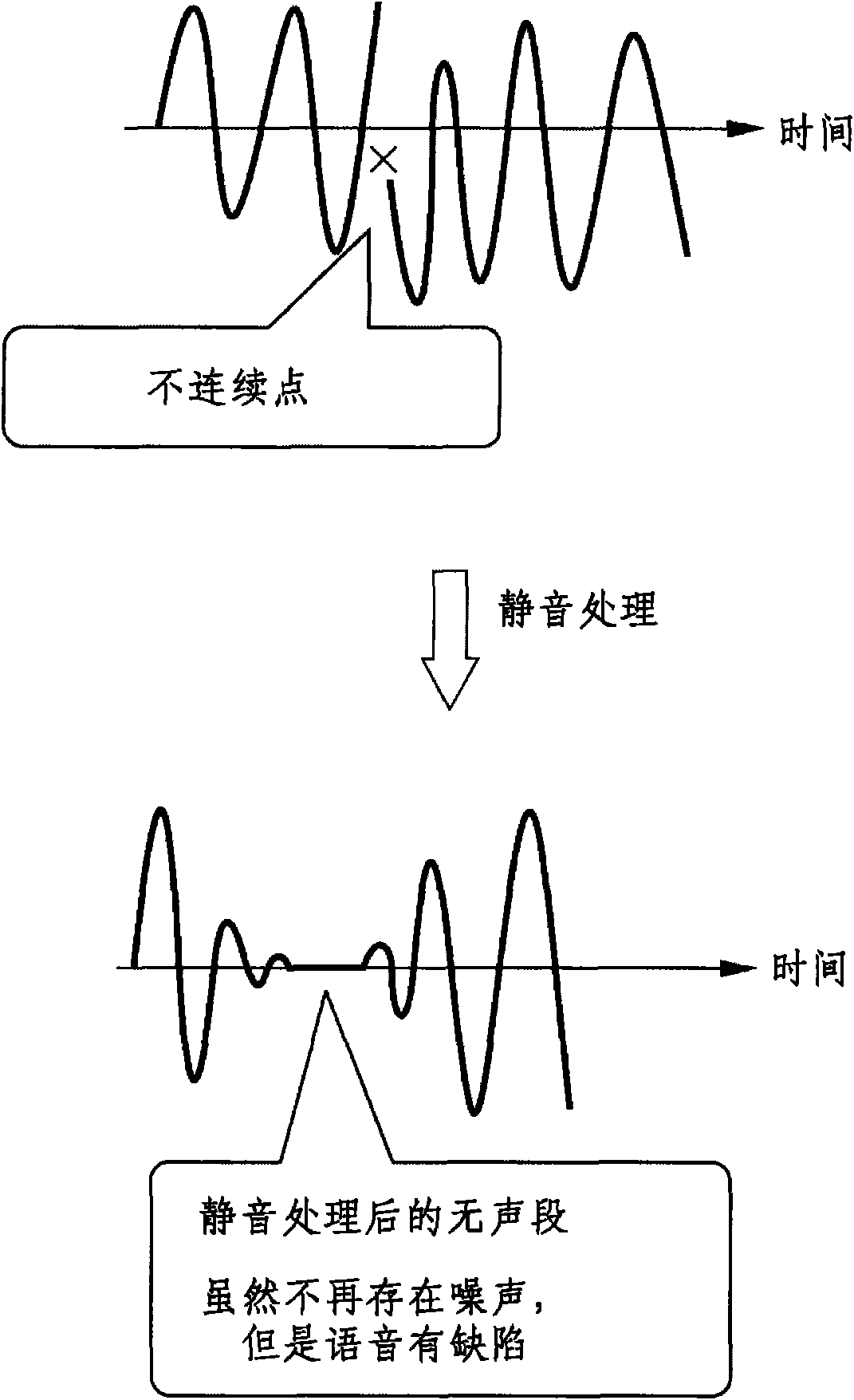

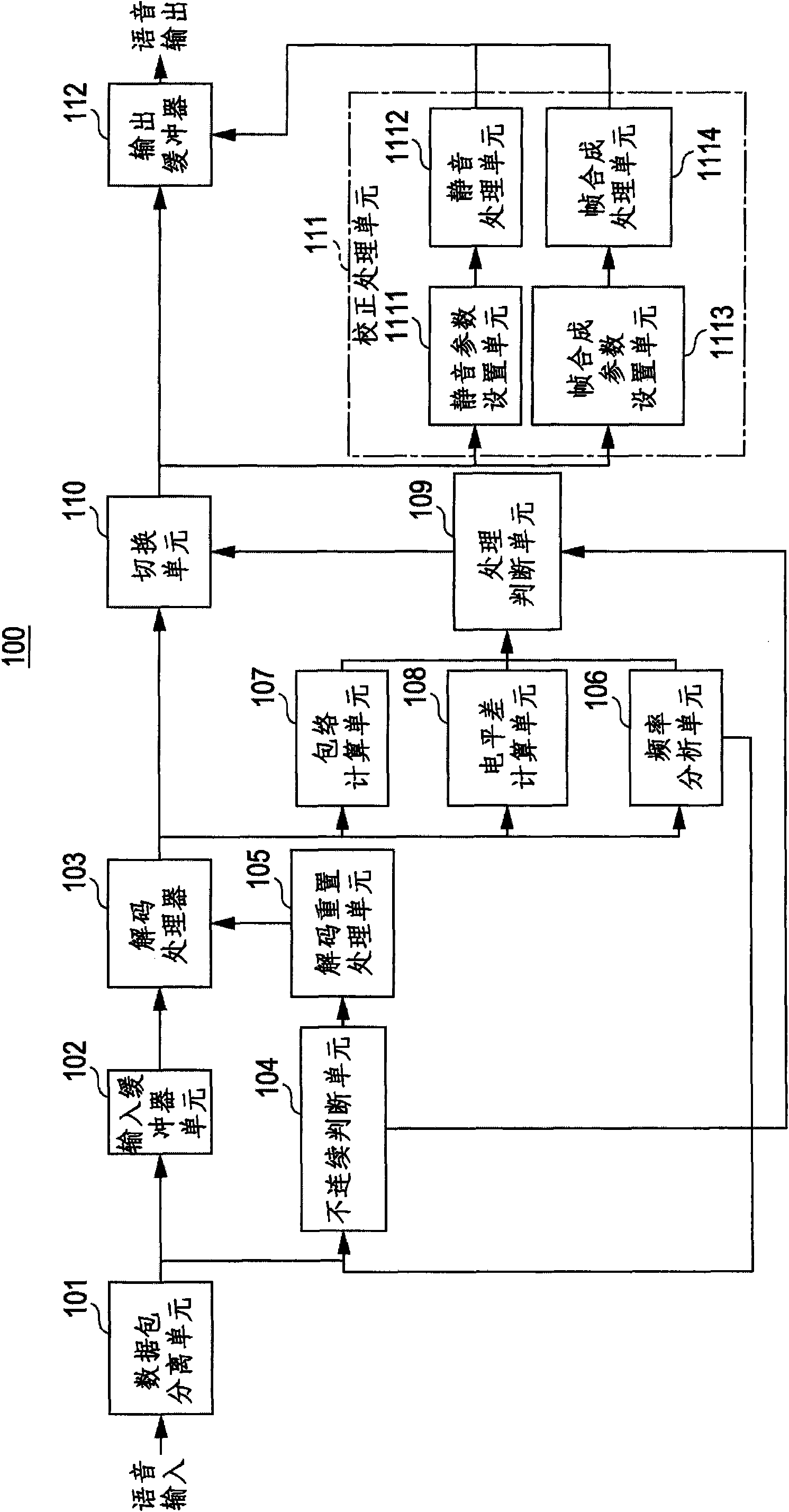

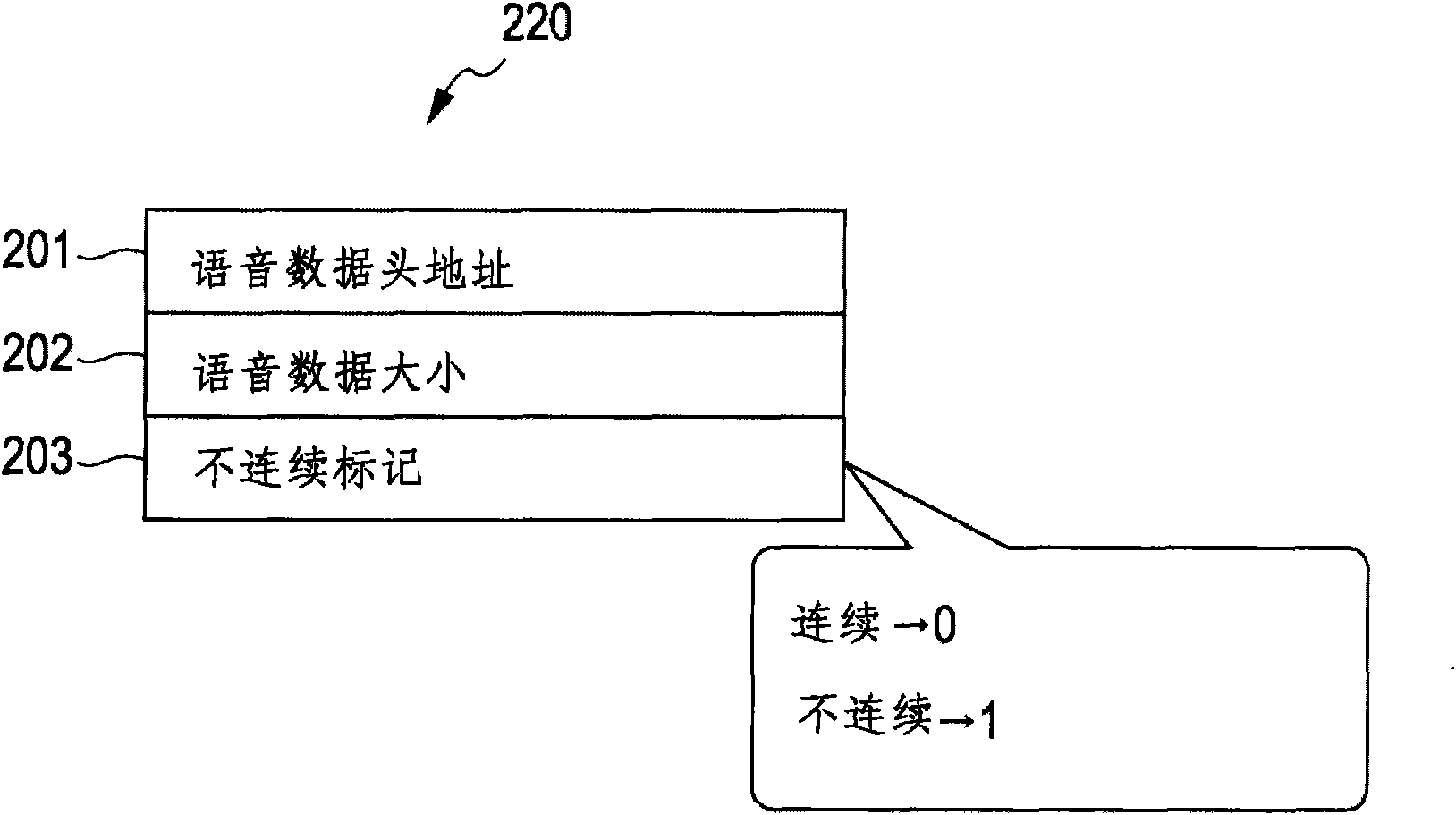

Audio reproduction device, information reproduction system, audio reproduction method

InactiveCN101789252AReduce pauseReproduce comfortableSpeech analysisRecord information storageNetwork packetSpeech sound

The invention provides an audio reproduction device, information reproduction system, audio reproduction method. The audio reproduction device includes a decoding processor to decode input voice data, a discontinuousness determination unit to determine whether or not a packet is discontinuous with a preceding packet, a reset processing unit to reset decode information, a frequency analysis unit to perform frequency analysis on the decoded data, an envelope calculation unit to calculate an envelope of the decoded data, a level difference calculation unit to calculate a level difference of the decoded data, a correction processing unit to apply a specific correction process to the decoded data if the correction process is necessary, and a processing determination unit to determine whether or not the correction process is to be performed, to determine whether or not the packet data is discontinuous, to determine which correction process is to be applied, and to output an instruction to perform the correction process. The invention can reduce the pause in the audio reproduction due to the mute and make the reproduced audio sounded more comfatable.

Owner:SONY CORP

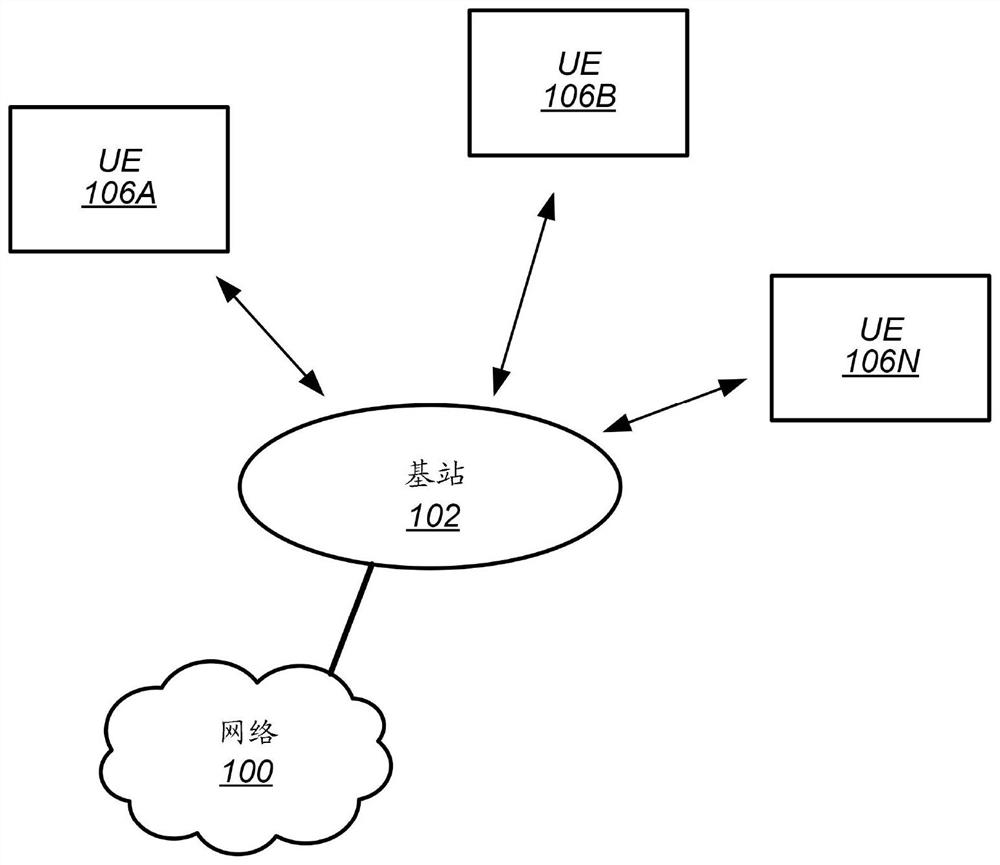

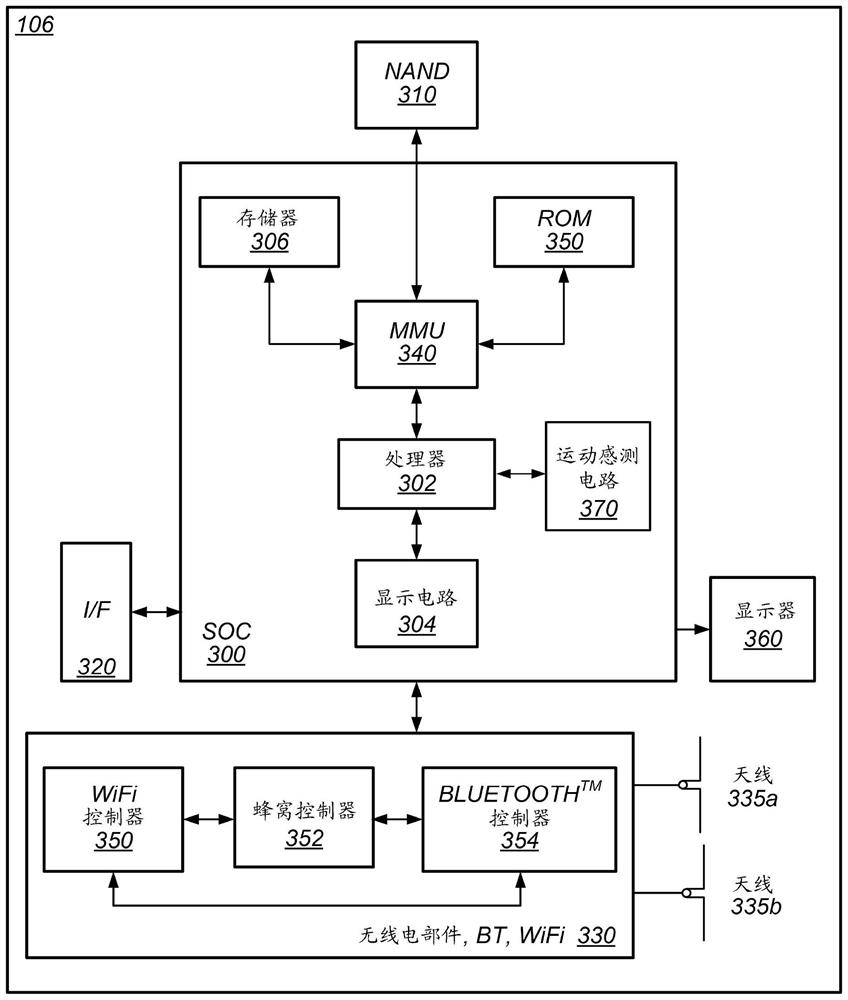

Continuous conditional switching

The invention relates to continuous conditional switching. The disclosure relates to techniques for performing continuous conditional switching. The cellular base station can provide the conditional switching information for a plurality of conditional switches to the wireless device. The conditional handover information can include the information for performing conditional handover from a cell provided by the cellular base station to at least one cell and the information for performing conditional handover from one or more of the cells to at least one cell. The wireless device may perform a plurality of consecutive conditional handoffs using the conditional handoff information.

Owner:APPLE INC

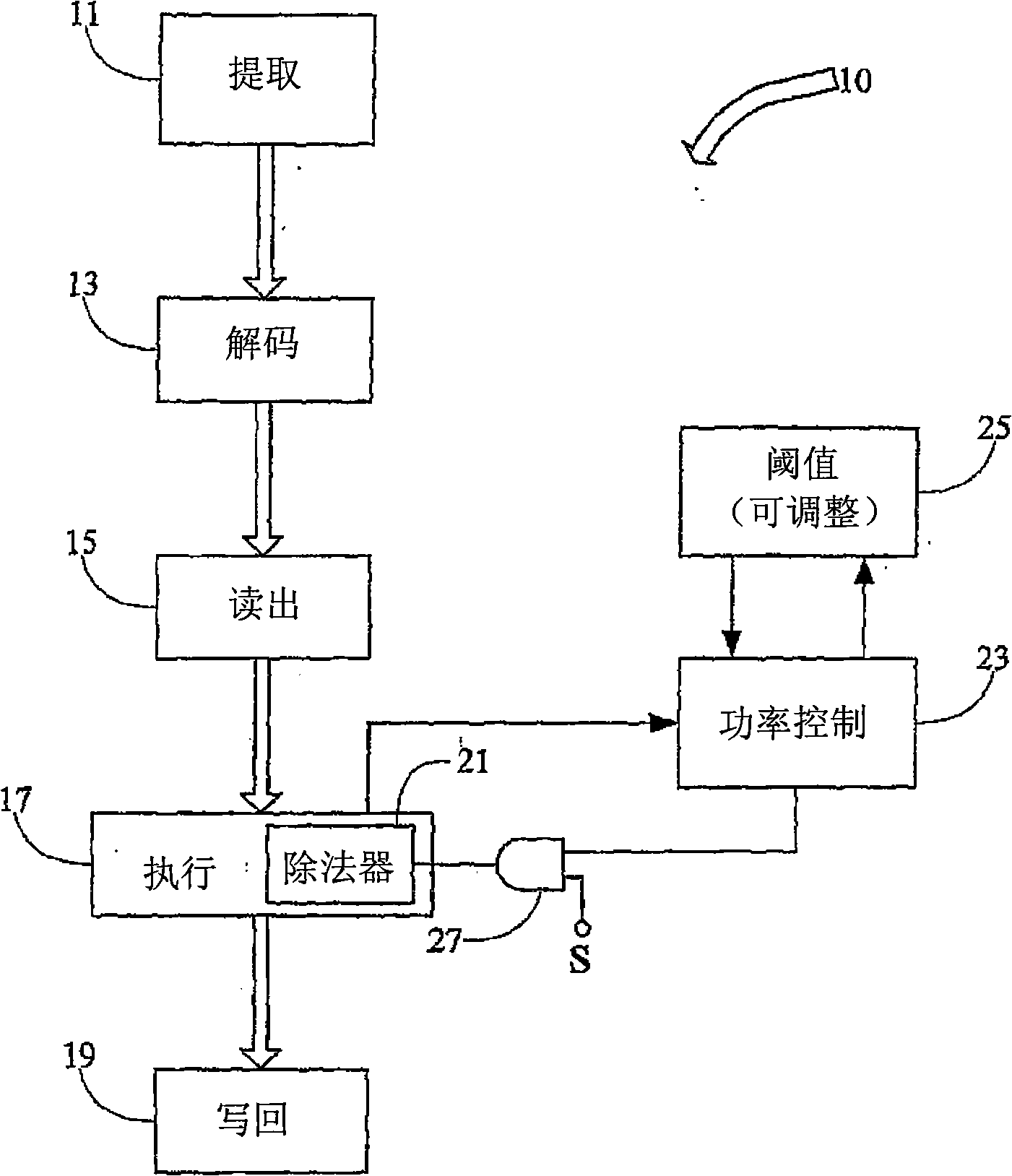

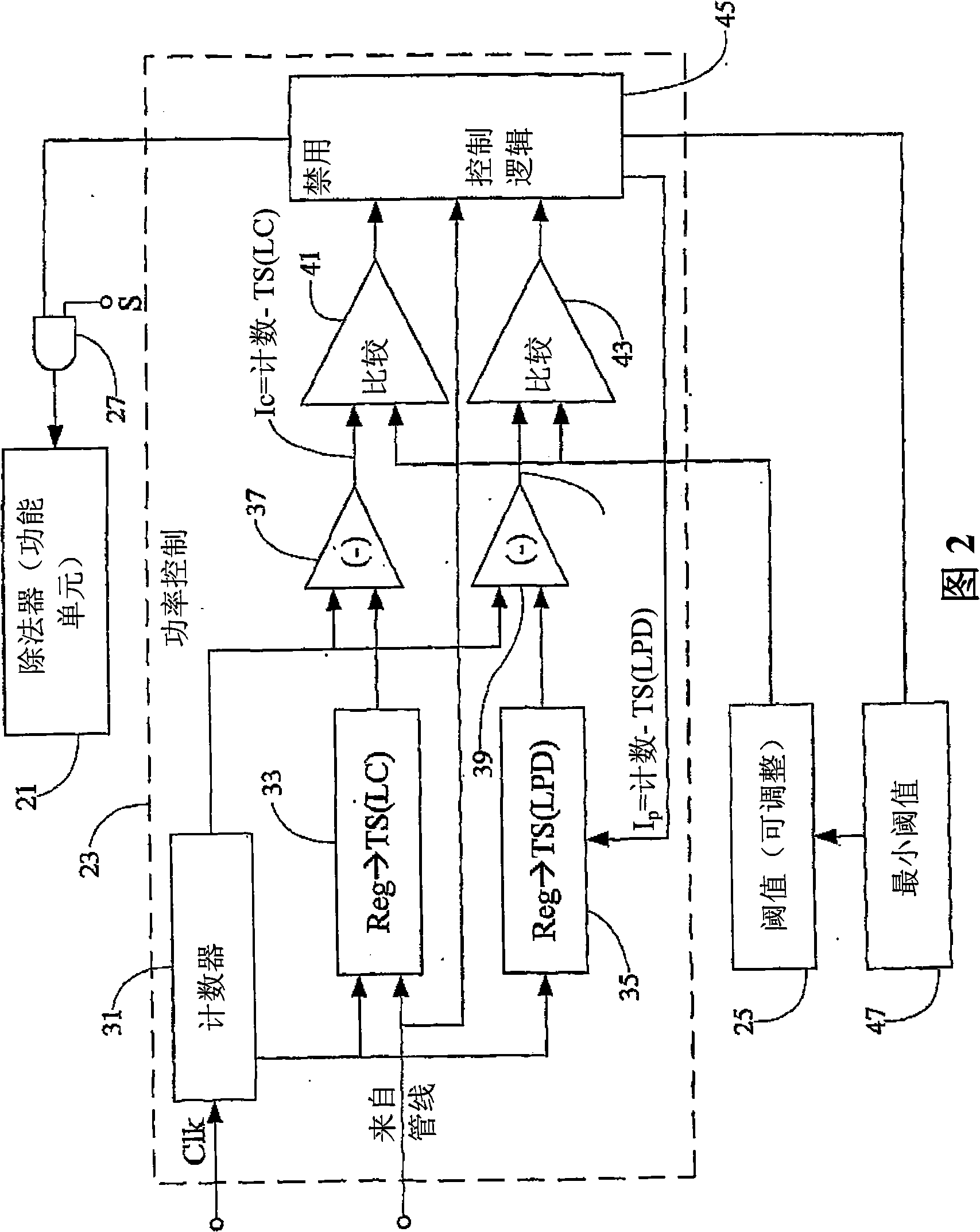

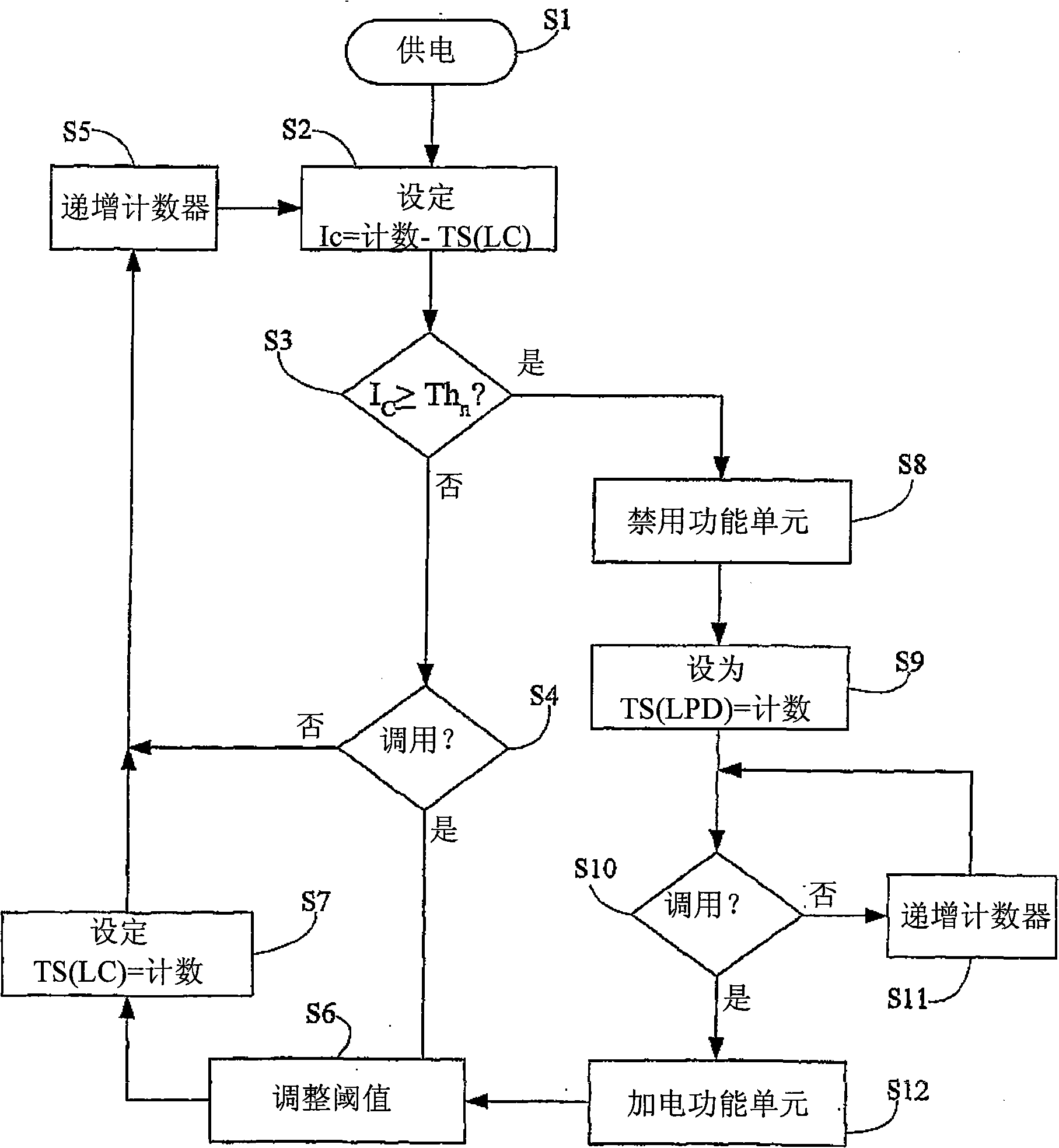

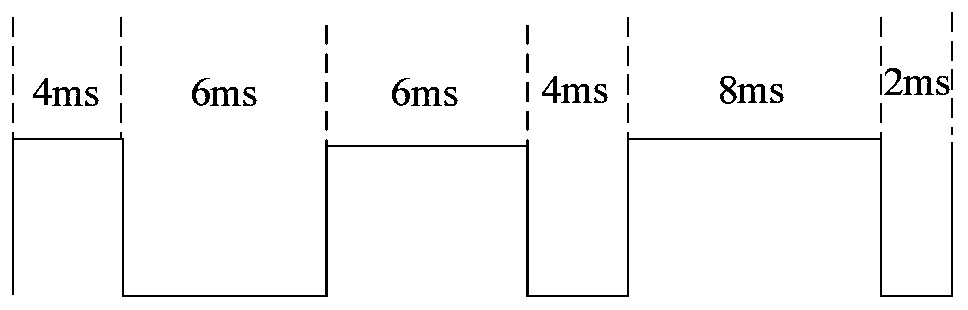

Idle-element prediction circuitry and anti-thrashing logic

ActiveCN101288039AReduce pauseReduce power consumptionEnergy efficient ICTVolume/mass flow measurementEngineeringControl logic

Control logic monitors use of a particular functional element (e.g., a divider, or multiplier or the like) in a programmable processor, and the control logic powers the unit down when it has not been used for a specified time period. A counter (local or central) and time threshold determine when the period has elapsed without use of the element. The control logic also monitors how soon the functional unit is woken up again, to determine if power control is causing thrashing. Upon the determination of such thrashing, the unit automatically adjusts its threshold period, to minimize thrashing. In an example of the logic, when it determines that it is being too conservative, it lowers the threshold. Mode bits may allow the programmer to override the power-down logic to either keep the logic always powered-up, or always powered-down.

Owner:QUALCOMM INC

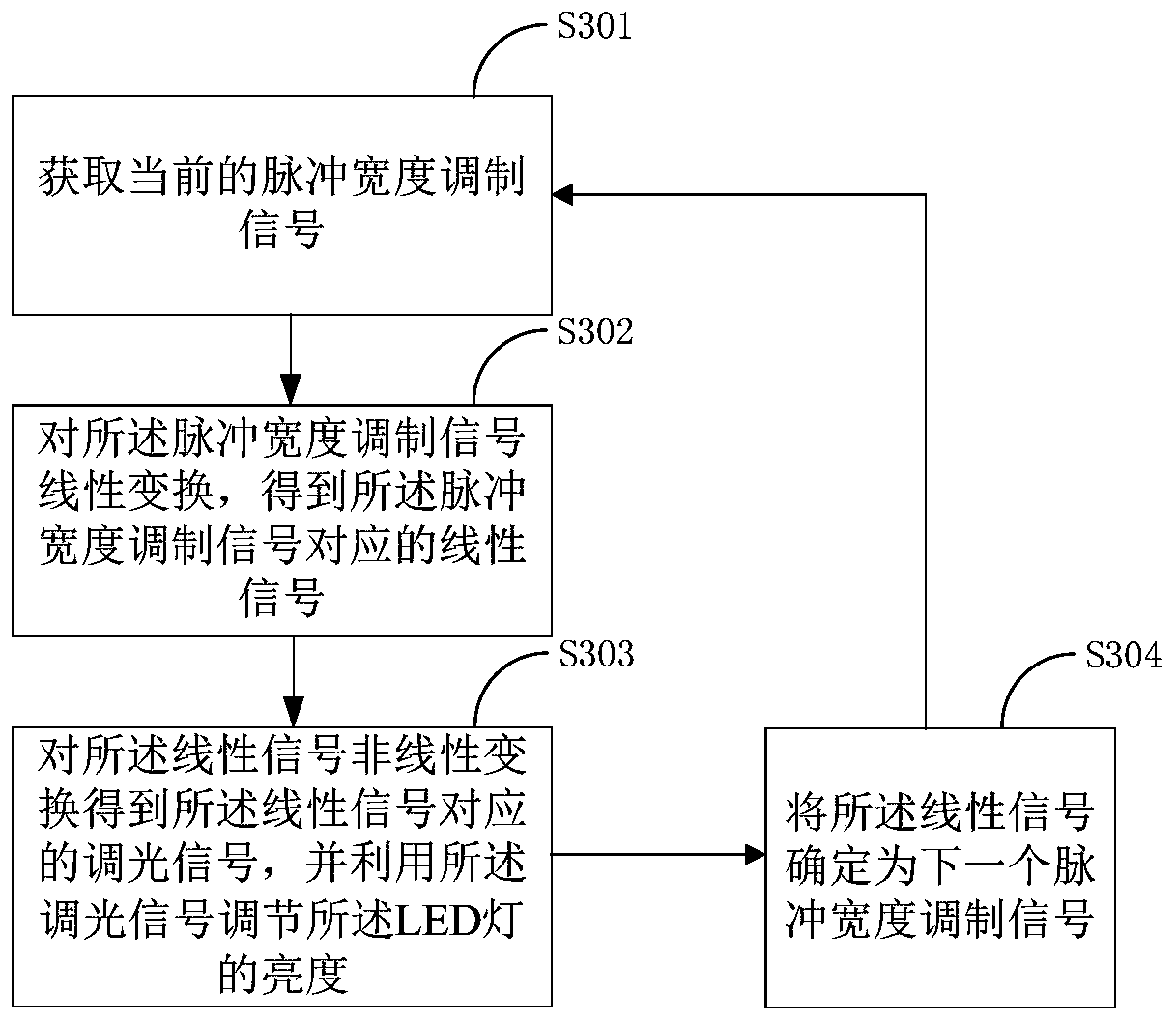

Light adjustment method, light adjustment device, and terminal device

The present application belongs to the technical field of circuits and provides a light adjustment method, a light adjustment device, and a terminal device. The light adjustment method comprises: obtaining a current pulse width modulation signal; obtaining a current pulse width modulation signal; linearly transforming the pulse width modulation signal to obtain a linear signal corresponding to thepulse width modulation signal; nonlinearly transforming the linear signal to obtain a dimming signal corresponding to the linear signal, and adjusting the brightness of an LED lamp by using the dimming signal. The method can effectively reduce the pause of light changes during a PWM dimming process, and effectively improve the softness of the light changes.

Owner:天一照明(深圳)有限公司

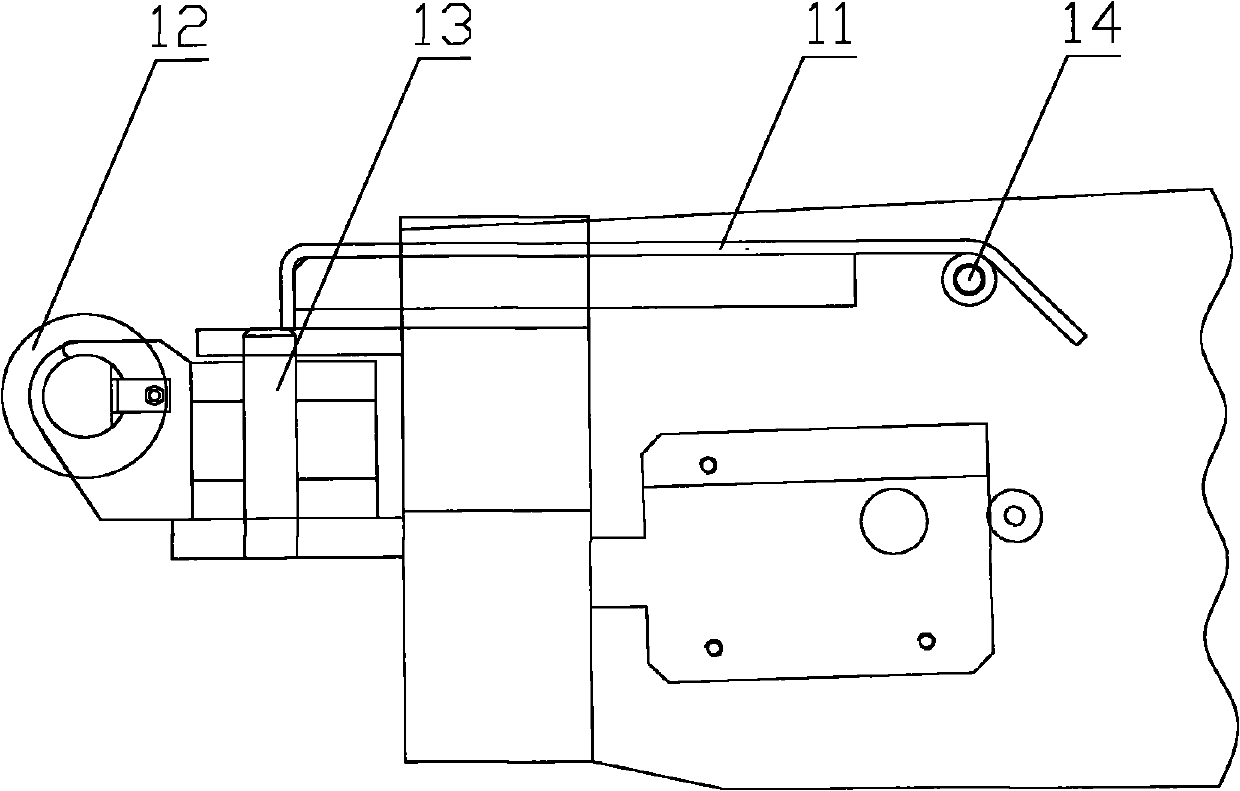

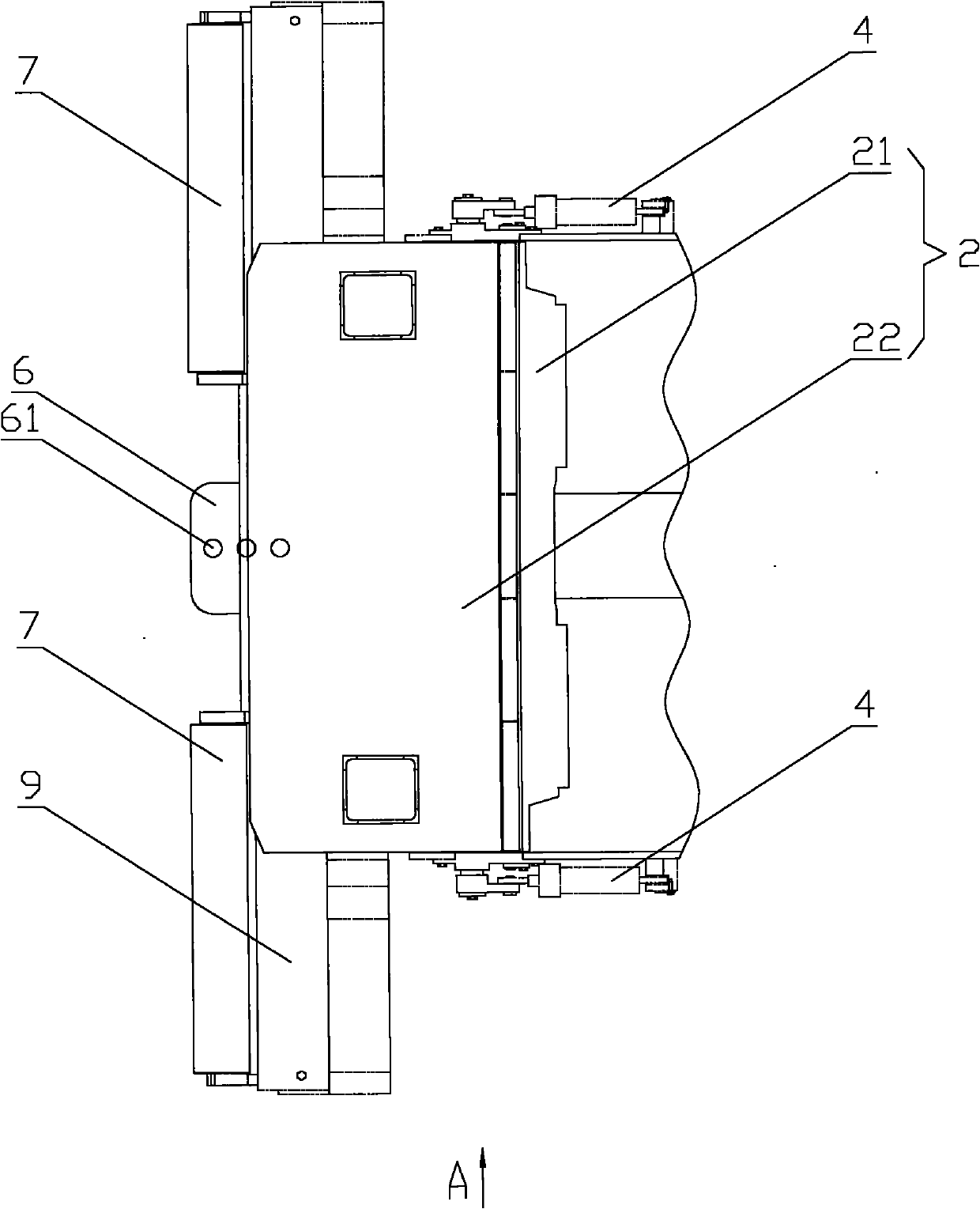

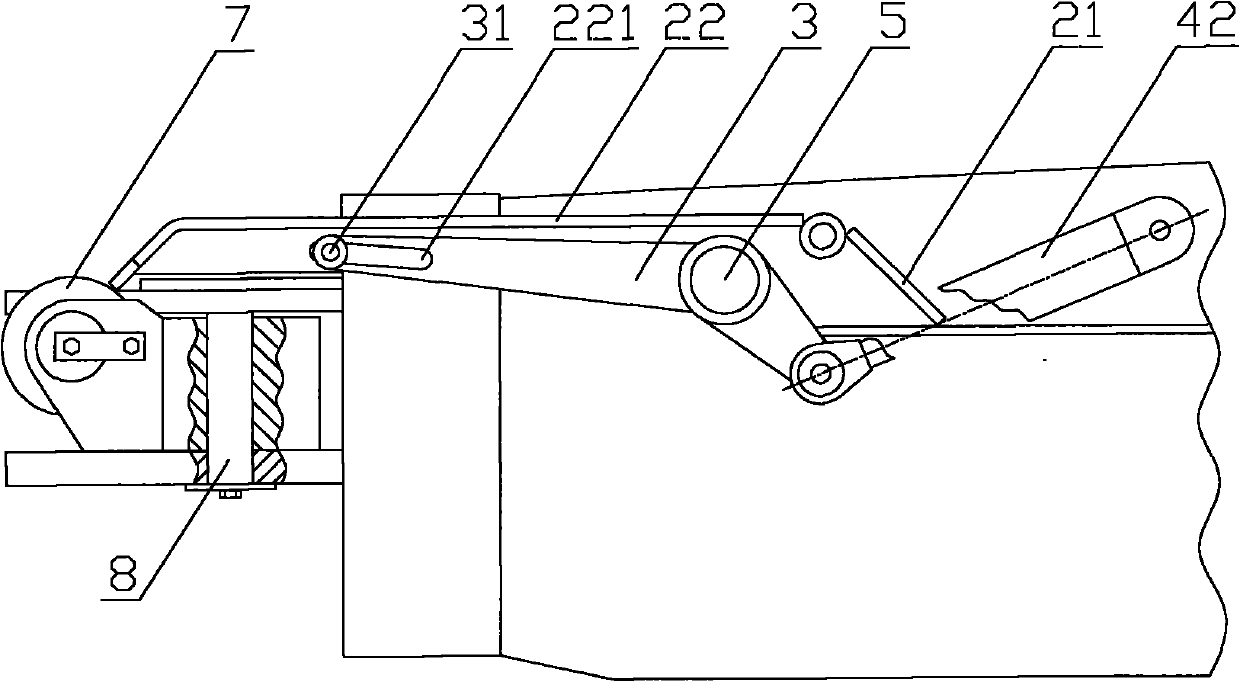

Spreading machine and material receiving device thereof

ActiveCN101768913AAvoid accumulationAvoid spillingRoads maintainenceEngineeringMechanical engineering

The invention discloses a material receiving device for a spreading machine, which comprises a hopper for receiving a spreading material, a baffle plate (2) matched with the hopper and a power part for driving the baffle plate (2), wherein the baffle plate (2) comprises a fixed baffle plate (21) and a movable baffle plate (22); the fixed baffle plate (21) is fixedly connected with a machine body; and the rear part of the movable baffle plate (22) is hinged to the fixed baffle plate (21), while the front part is in sliding connection with the power part, so that the spreading material on the movable baffle plate (22) is gathered to the inside and backside of the hopper. The material receiving device has good adaptability, can effectively reduce material spills of a small spreading machine, and simultaneously reduces phenomenon of clamping stagnation during material transportation. The invention also provides a spreading machine comprising the material receiving device. The stability of the spreading machine is obviously improved, and simultaneously the quality of roads spread by using the spreading machine also can be improved.

Owner:XCMG CONSTR MACHINERY

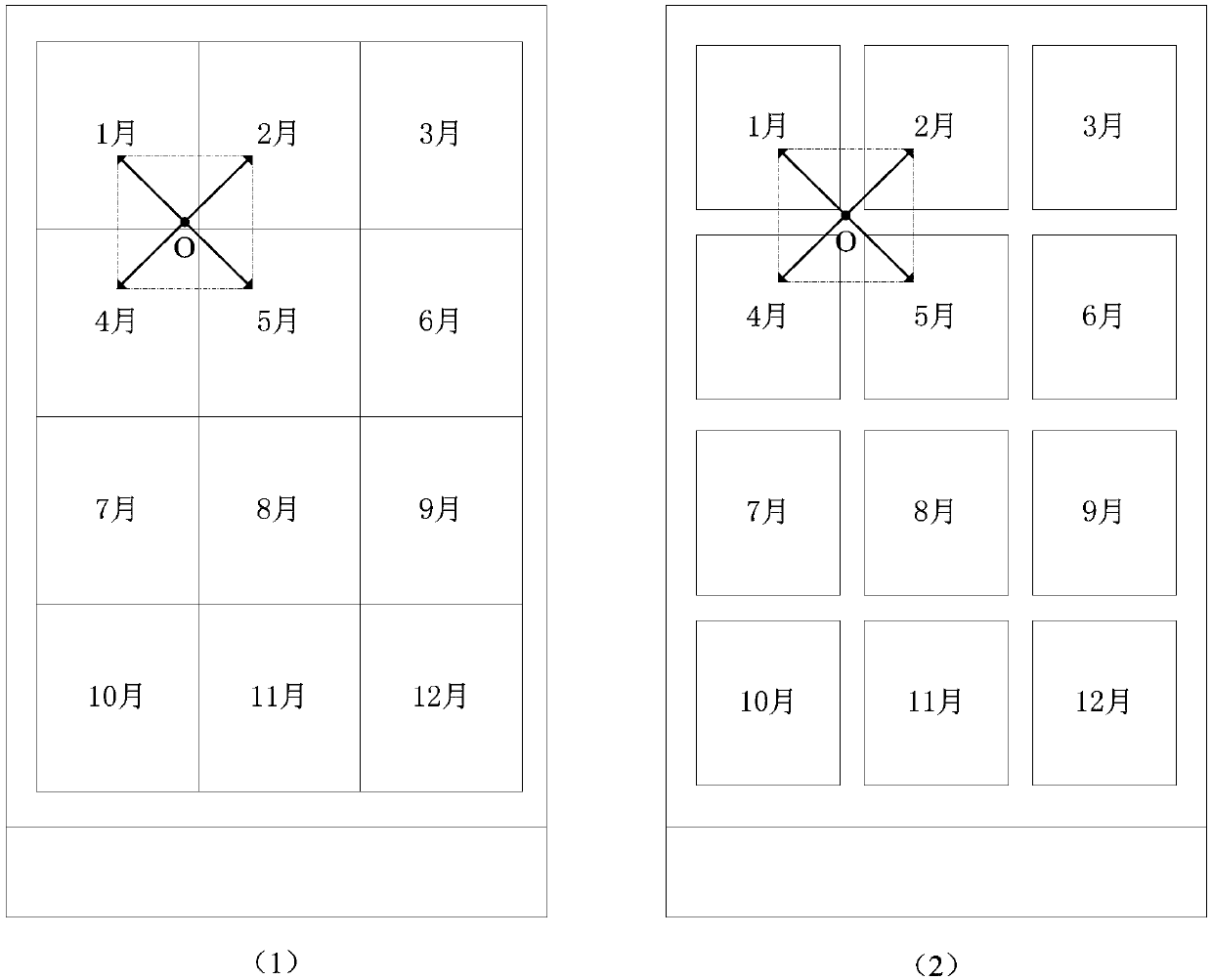

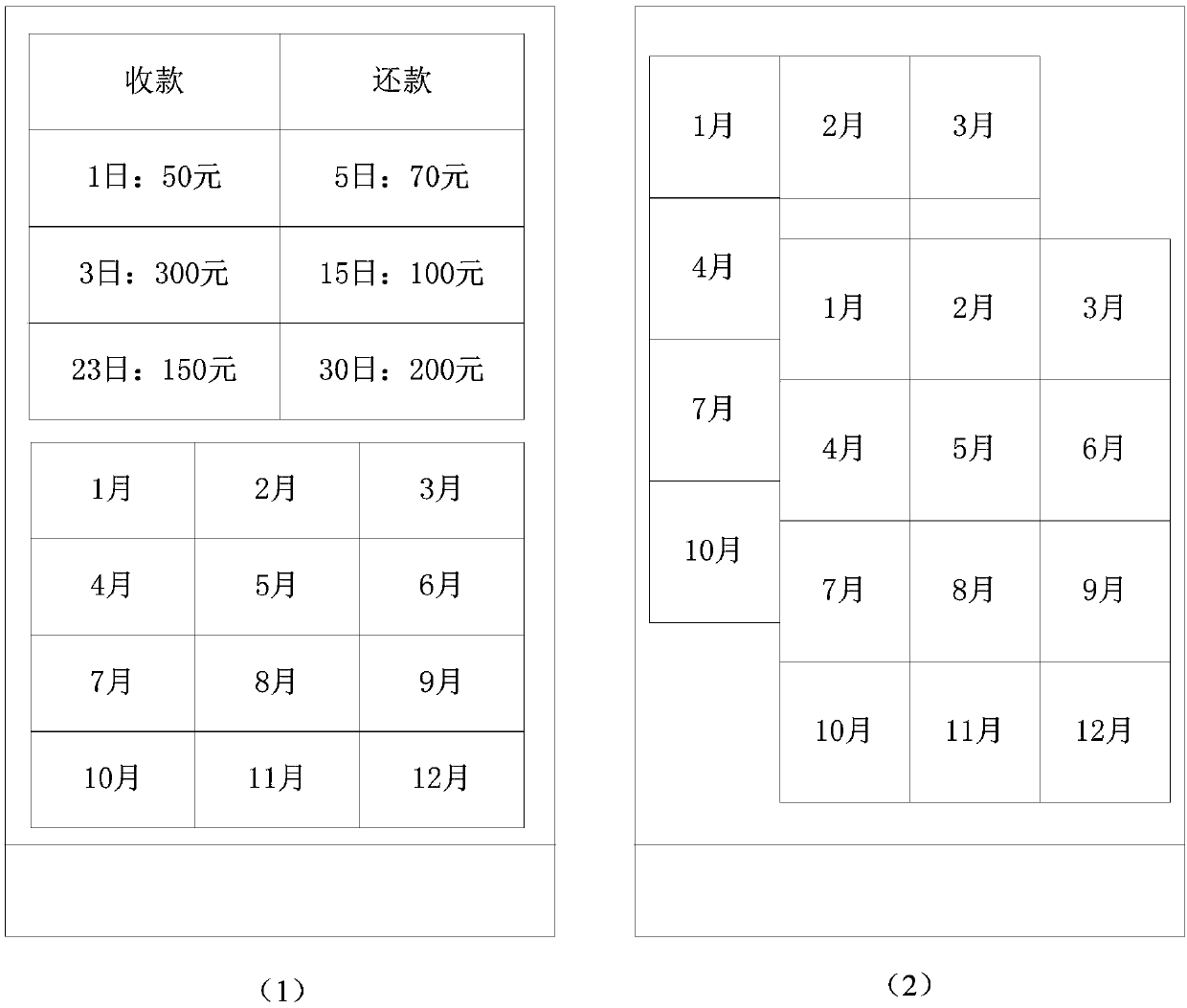

Bill query method, operation device and computer readable storage medium

ActiveCN107918635AEasy to operateQuick switchFinanceSpecial data processing applicationsComputer engineeringTime sequence

The invention discloses a bill query method, an operation device and a computer readable storage medium. The bill query method comprises the following steps of: ranking time points of all the pieces of bill information by taking a preset time unit as basis, so as to obtain a bill time sequence interface, and displaying the bill time sequence interface; when a zooming operation is received, determining a target time point on the bill time sequence interface according to an operation area of the zooming operation; when the operation category of the zooming operation is an amplification operation, determining an inferior time unit of the preset time unit as a basic unit of the target time point; when the operation category of the zooming operation is a shrinkage operation, determining a superior time unit of the preset time unit as the basic unit of the target time point; and carrying out classified statistic on all the pieces of bill information mapped by the target time point accordingto a preset bill type on the basis of the basic unit, and displaying the bill information. According to the method, the operation device and the computer readable storage medium, the bill function query process is simplified, bills at different time points can be compared conveniently and then the using experience of the users is enhanced.

Owner:WEIKUN (SHANGHAI) TECH SERVICE CO LTD

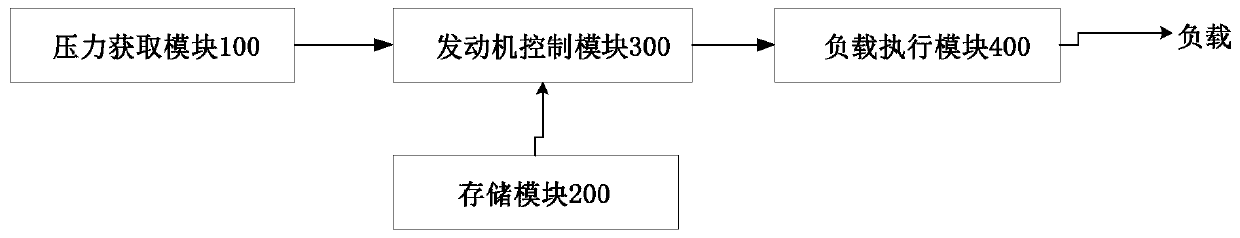

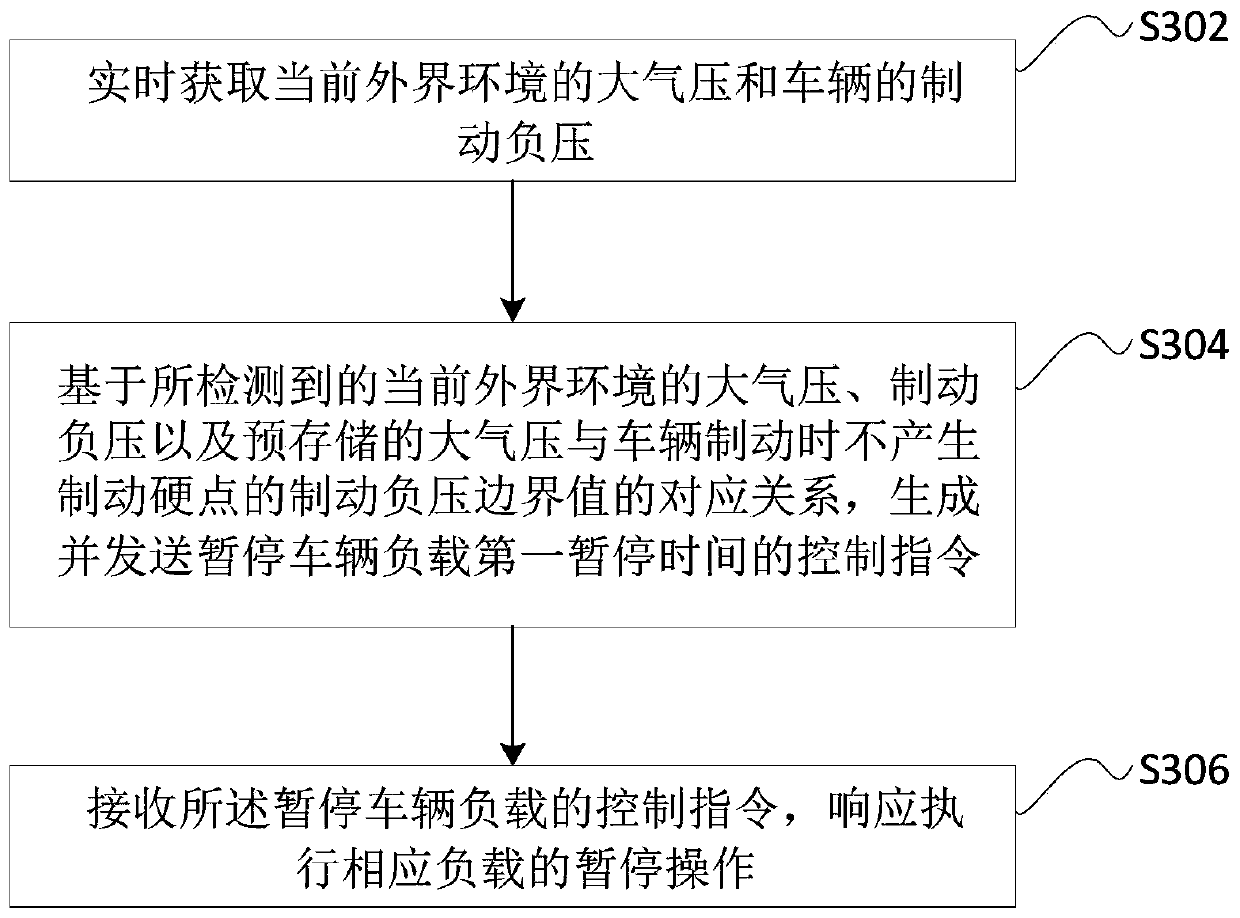

Vehicle control system and vehicle

ActiveCN109733362AImproved brake perceived qualityImprove braking effectBraking action transmissionControl systemBoundary values

The invention discloses a vehicle control system and a vehicle. The vehicle control system comprises an engine control module as well as a pressure acquisition module, a storage module and a load execution module which are electrically connected with the engine control module respectively. The engine control module is configured to generate and send a control instruction for pausing the vehicle load for a first pause time to the load execution module based on the atmospheric pressure of the current external environment detected by the pressure acquisition module, the brake negative pressure ofthe vehicle and the corresponding relation between the atmospheric pressure stored in the storage module and the brake negative pressure boundary value which does not generate the brake hard points during vehicle brake. By the adoption of the vehicle control system and the vehicle, the brake sensing quality of the brake system can be improved by pausing the corresponding load, in addition, the effect of the corresponding load is considered, and optimization of the vehicle brake performance and the load performance is achieved.

Owner:ZHEJIANG GEELY AUTOMOBILE RES INST CO LTD +1

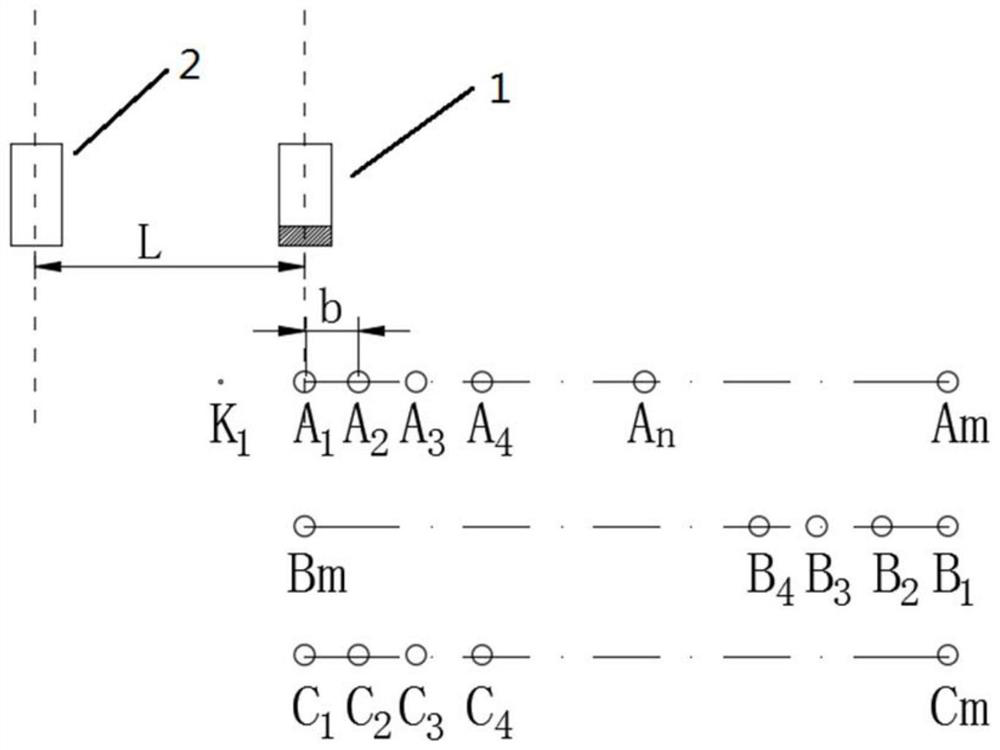

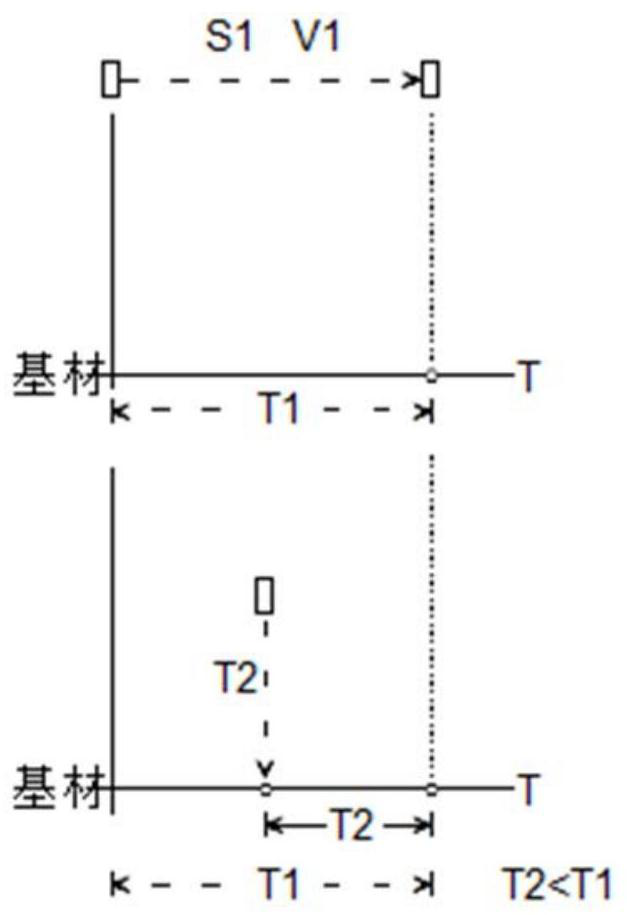

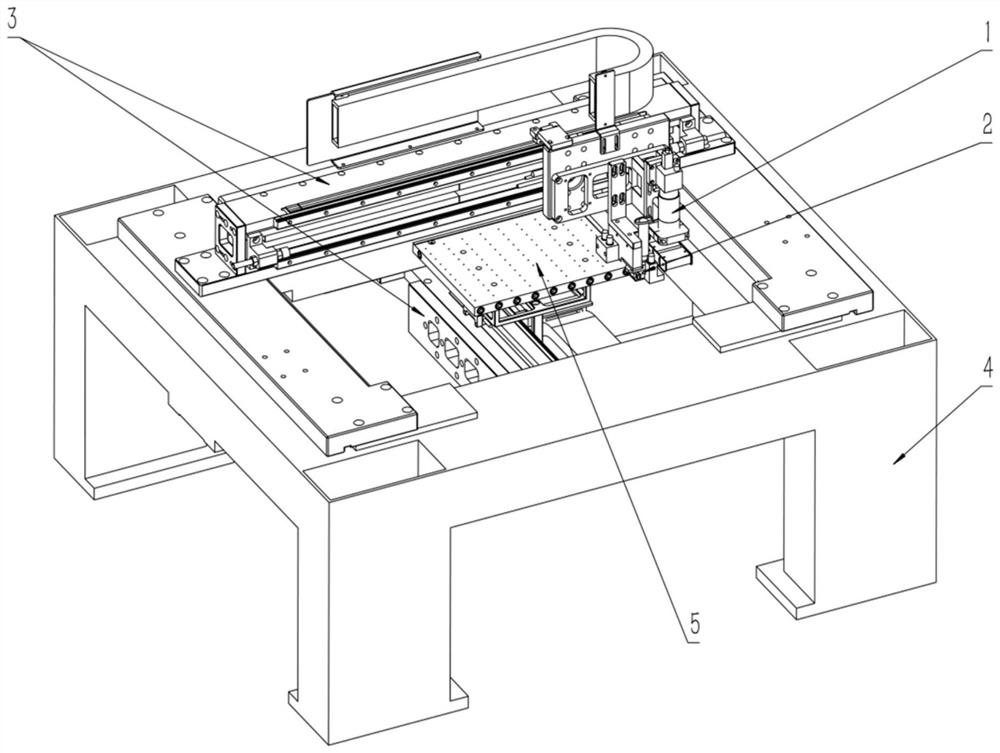

Flying dispensing method and flying dispensing equipment

InactiveCN112387553AReduce pauseIncrease productivityLiquid surface applicatorsCoatingsAdhesive glueMechanical engineering

Owner:BEIJING GOLDEN SPRING TECH DEV

Method for renaming state register and processor using the method

ActiveCN100524208CReduce pauseReduce congestionConcurrent instruction executionFLAGS registerEmbedded system

According to the present invention, a method for renaming a status register in a processor with a superscalar pipeline structure is proposed, wherein the status register is composed of a plurality of flag bits selected from all flag bits of the flag register Register, the method includes the following steps: when the microcode after instruction decoding arrives at the register renaming module of the processor, determine whether the microcode will read the status register; if it is determined that the microcode will read the status register register, then allocate the latest mapped physical register for the status register; otherwise, do not allocate a physical register for the status register; determine whether the microcode will write the status register; if it is determined that the microcode will write the status register , a new physical register whose state is empty is allocated to the state register; otherwise, no physical register is allocated to the state register.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

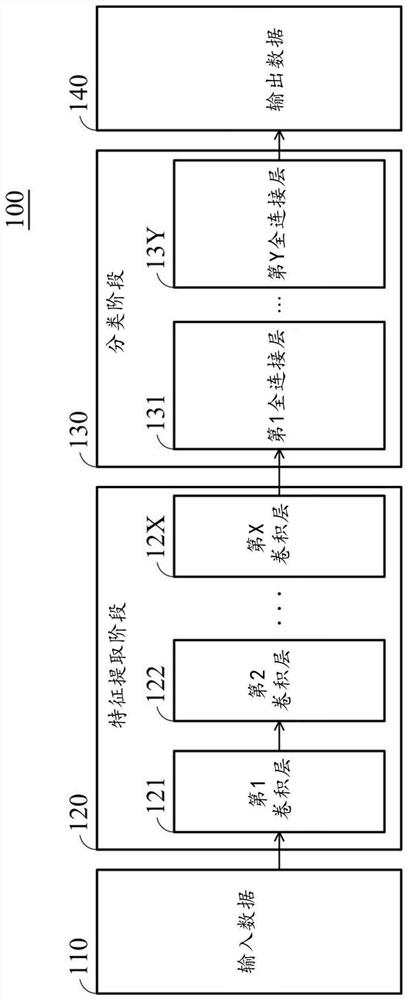

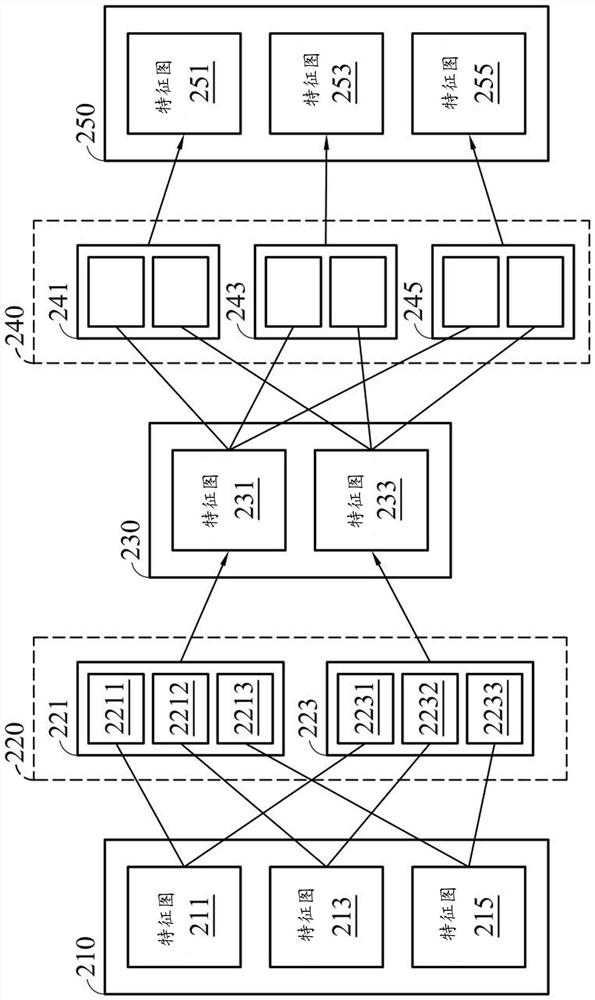

Convolution operation method and convolution operation device

PendingCN111898081AReduce pauseImprove computing efficiencyNeural architecturesComplex mathematical operationsComputer hardwareParallel computing

The invention provides a convolution operation method and a convolution operation device. The convolution operation method is used for executing convolution operation on an input feature map to generate a corresponding output feature map, and comprises the steps of dividing each input data block in a plurality of input data blocks into a plurality of non-overlapping areas, and wherein an overlapping area exists between any two adjacent input data blocks; storing a plurality of non-overlapping regions of each input data block into corresponding non-overlapping storage spaces in a cache; generating each input data block according to an area which is stored in the non-overlapped storage space and corresponds to the input data block; and performing convolution operation on the plurality of generated input data blocks to generate the output feature map.

Owner:VIA ALLIANCE SEMICON CO LTD

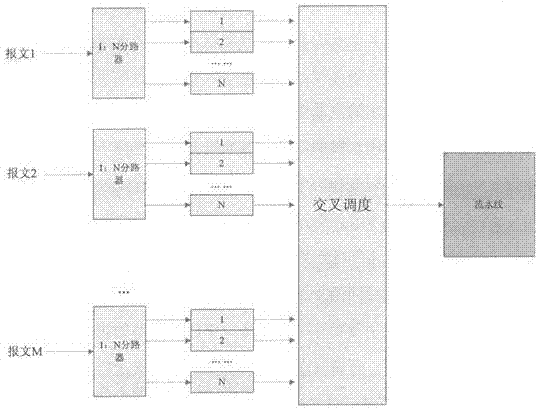

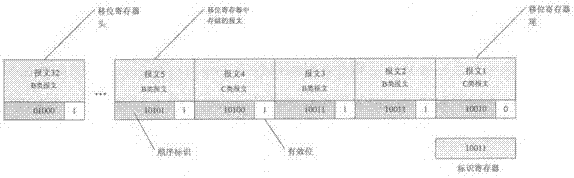

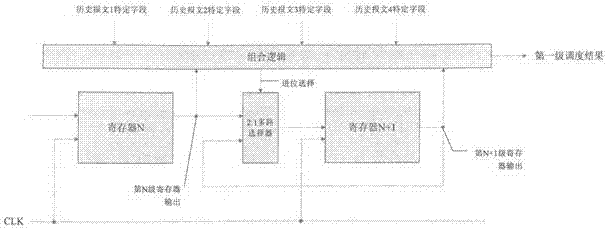

Message scheduling method based on shift register

InactiveCN107483362AReliable design principleSimple structureData switching networksShift registerStructure of Management Information

The invention relates to a message scheduling method based on a shift register. The message scheduling method is characterized by comprising the following steps: step S1, determining specific message fields that need to be compared according to a message processing requirement; step S2, determining the number L of historical messages that need to be compared according to a message processing pipeline structure; step S3, determining the series M of the shift register according to the specific fields and storage resources; step S4, according to an order-preserving requirement in pipeline processing, dividing the messages without the order-preserving requirement between each other into N classes, wherein each class of messages correspondingly realize one shift register to store messages to be scheduled; placing the messages with the order-preserving requirement in a same shift register; and executing a specific field comparison function through an additional combinatorial logic, and finishing first-level scheduling; and step 5, performing second-level scheduling in a first-level scheduling result, and selecting one message and sending the message to a message processing pipeline.

Owner:ZHENGZHOU YUNHAI INFORMATION TECH CO LTD

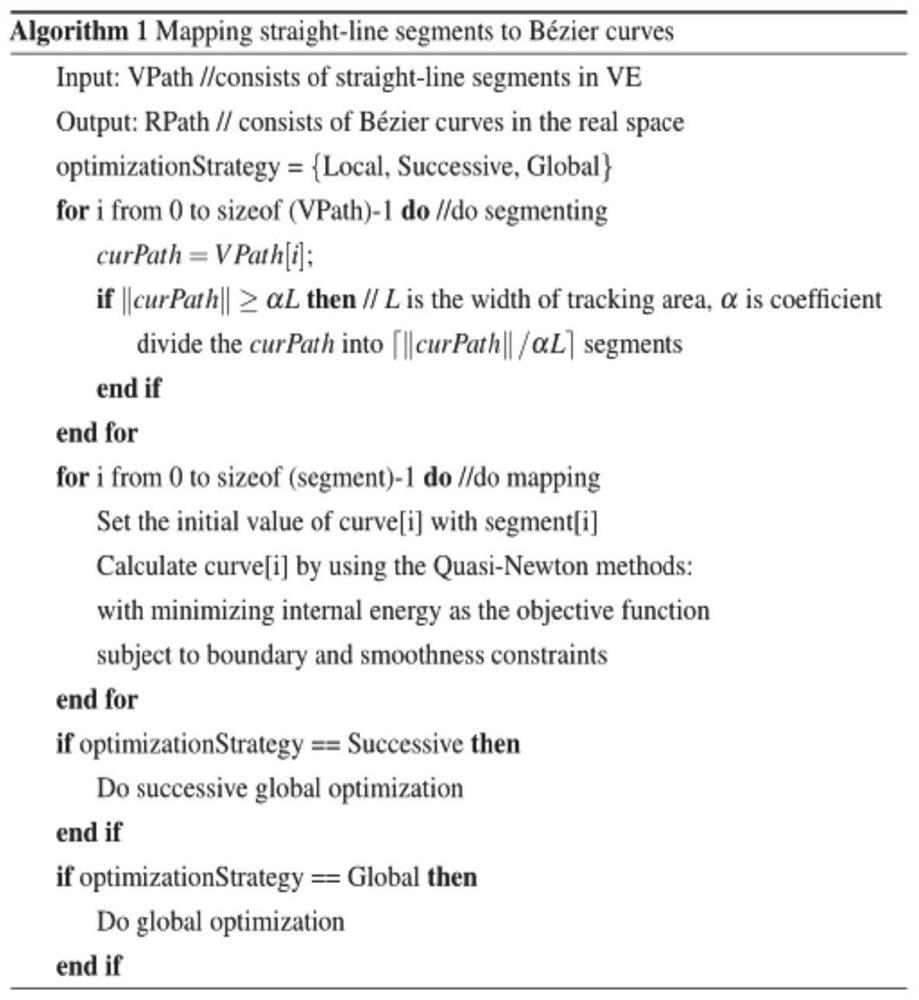

Mapping method and system suitable for large-scale virtual reality redirection walking

PendingCN114089828AReduce the number of times users are resetImprove navigation speed and smoothnessInput/output for user-computer interactionGraph readingComputer visionVirtual tour

The invention provides a mapping method and system suitable for large-scale virtual reality redirection walking. The mapping method comprises the following steps of acquiring virtual roaming scene data, obtaining a roaming path according to the obtained virtual roaming scene data, decomposing a roaming path in the virtual scene into a plurality of segments, sequentially mapping the segmented virtual paths into Bezier curves by taking minimization of internal energy as a target, according to a preset smooth constraint condition, connecting adjacent curves into a continuous smooth curve, and obtaining a walking path in an actual space. According to the method, the user can be effectively guided to be far away from the boundary of the tracking area, the number of times of resetting the user by the system is greatly reduced, the navigation speed and smoothness are effectively improved, the pause feeling and perception distortion are reduced, and the immersion feeling of the user is enhanced.

Owner:SHANDONG NORMAL UNIV

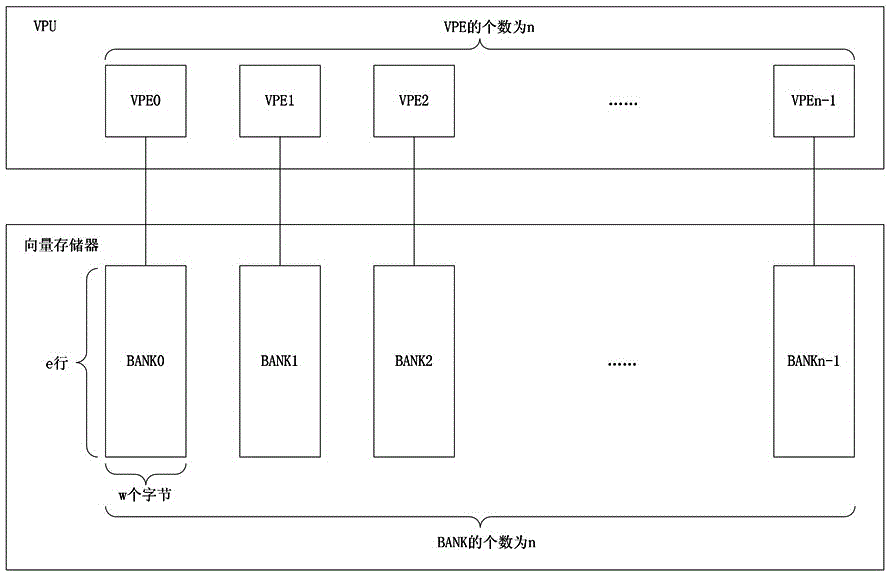

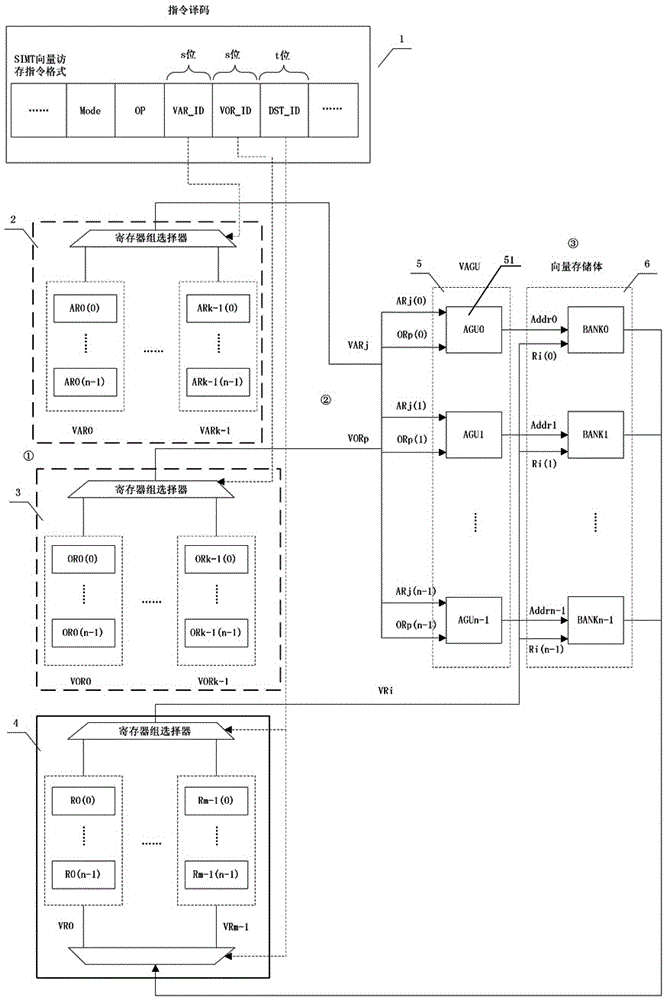

SIMT-supported vector memory access device and control method in vector processor

ActiveCN104699465BIncrease flexibilityImprove parallelismResource allocationConcurrent instruction executionMemory bankEngineering

Owner:NAT UNIV OF DEFENSE TECH

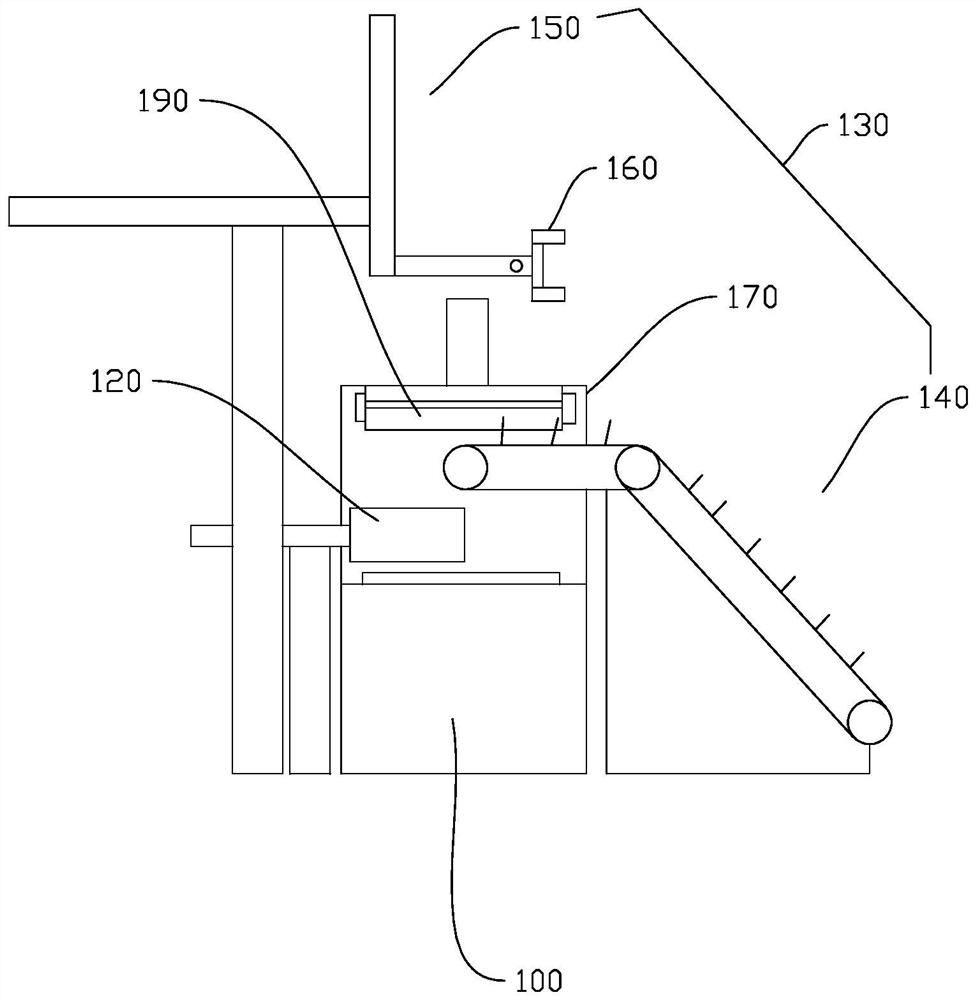

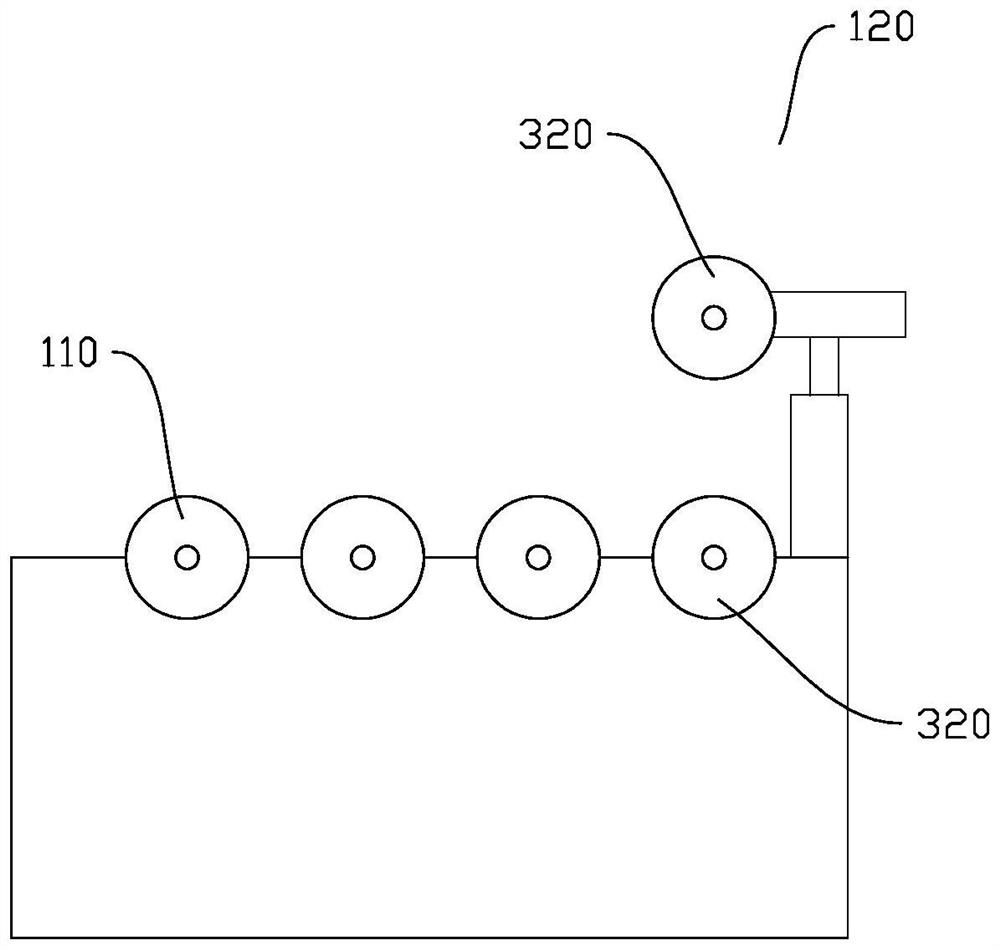

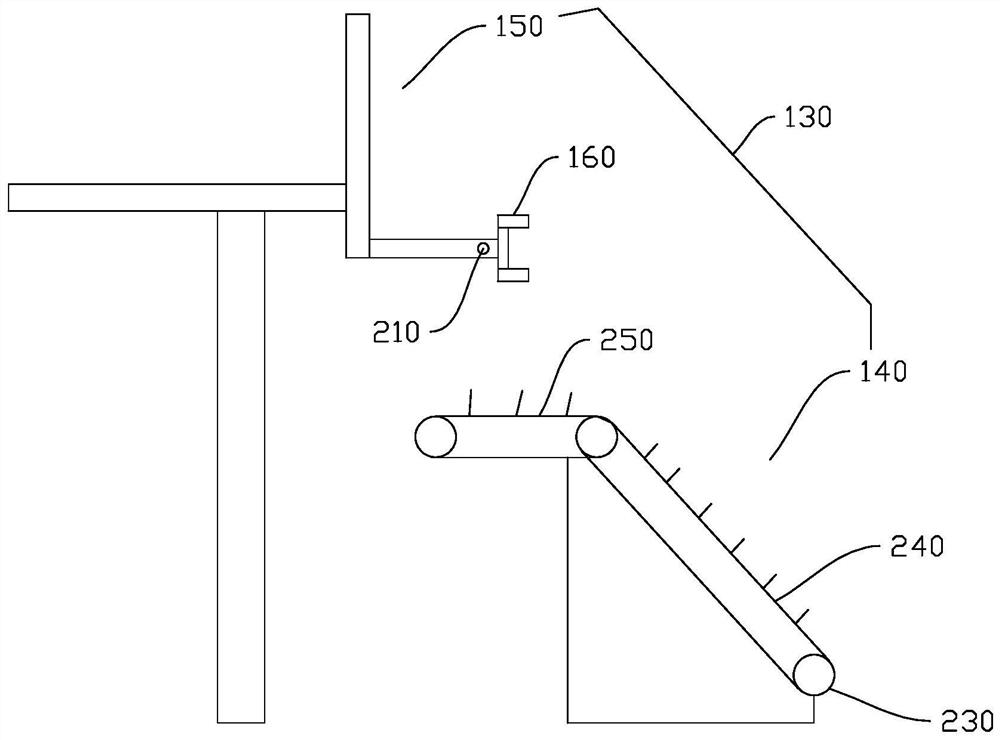

Production line and production method of energy-saving profile

InactiveCN114852670AEasy to placeAccurate placementConveyorsPassive housesProduction lineProcess engineering

The invention discloses a production line of an energy-saving profile and a production method comprising the production line, the energy-saving profile comprises a heat insulation strip and two aluminum profiles, the production line comprises an aluminum profile supply device which conveys the aluminum profiles in the length direction of the aluminum profiles and comprises a supporting mechanism and a power mechanism driving the aluminum profiles to move horizontally, the side, provided with the heat insulation strip, of the aluminum profile faces upwards. The heat insulation strip supply device is located on one side or two sides of the aluminum profile supply device and comprises a conveying mechanism, the conveying direction of the conveying mechanism is perpendicular to the length direction of the aluminum profiles, the heat insulation strip supply device further comprises a transferring mechanism, the transferring mechanism comprises a mechanical arm, and the mechanical arm places heat insulation strips on the aluminum profiles; and the compounding device is arranged on the discharging side of the aluminum profile supply device and comprises a compounding mechanism, and the compounding mechanism comprises an upper compounding roller and a lower compounding roller. According to the production line and the production method of the energy-saving sectional material, the production efficiency can be improved.

Owner:JINZHONG XIN MING GE ADVANCED MATERIAL SCI & TECH CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com