Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

91results about How to "Reduce output signal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

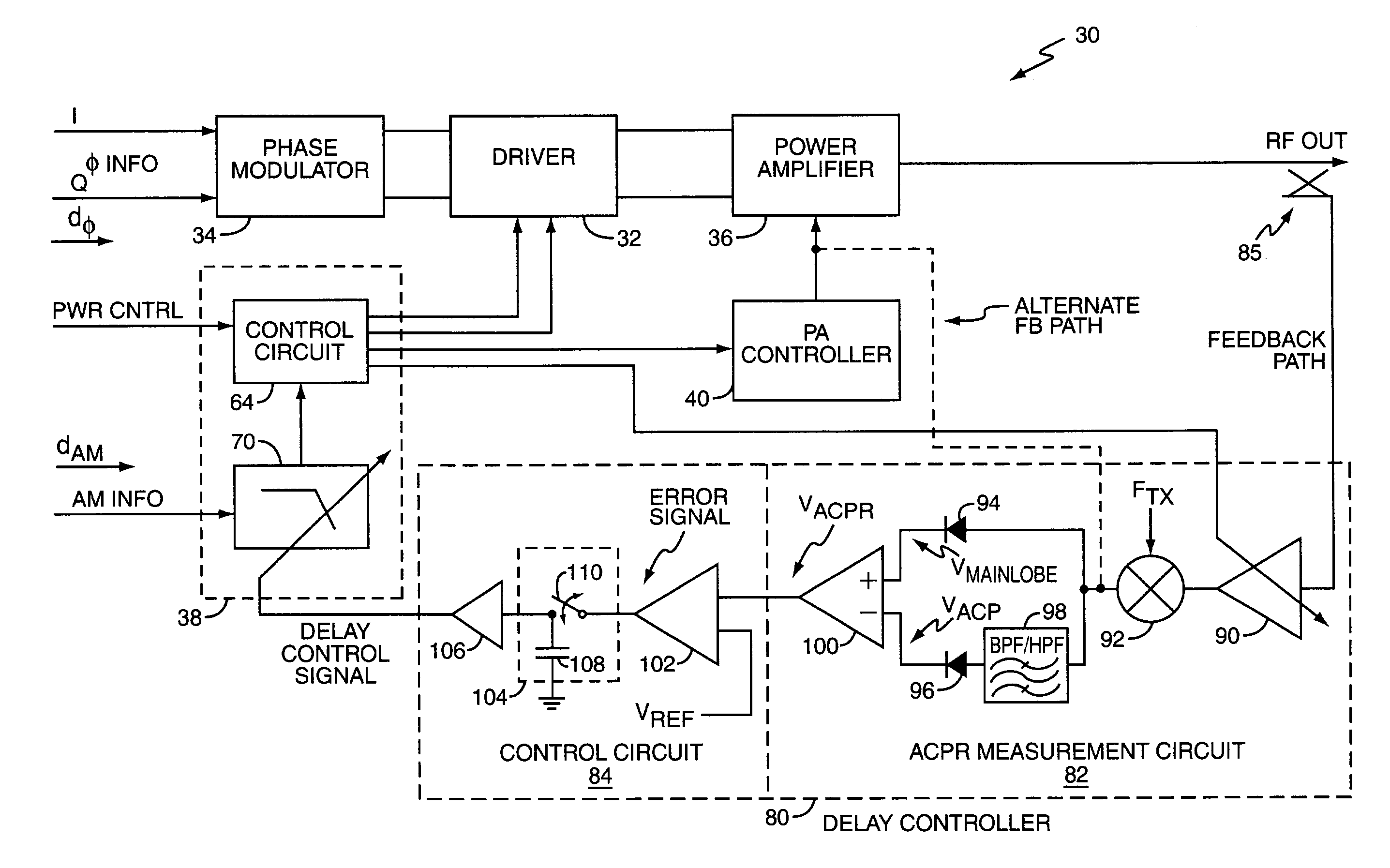

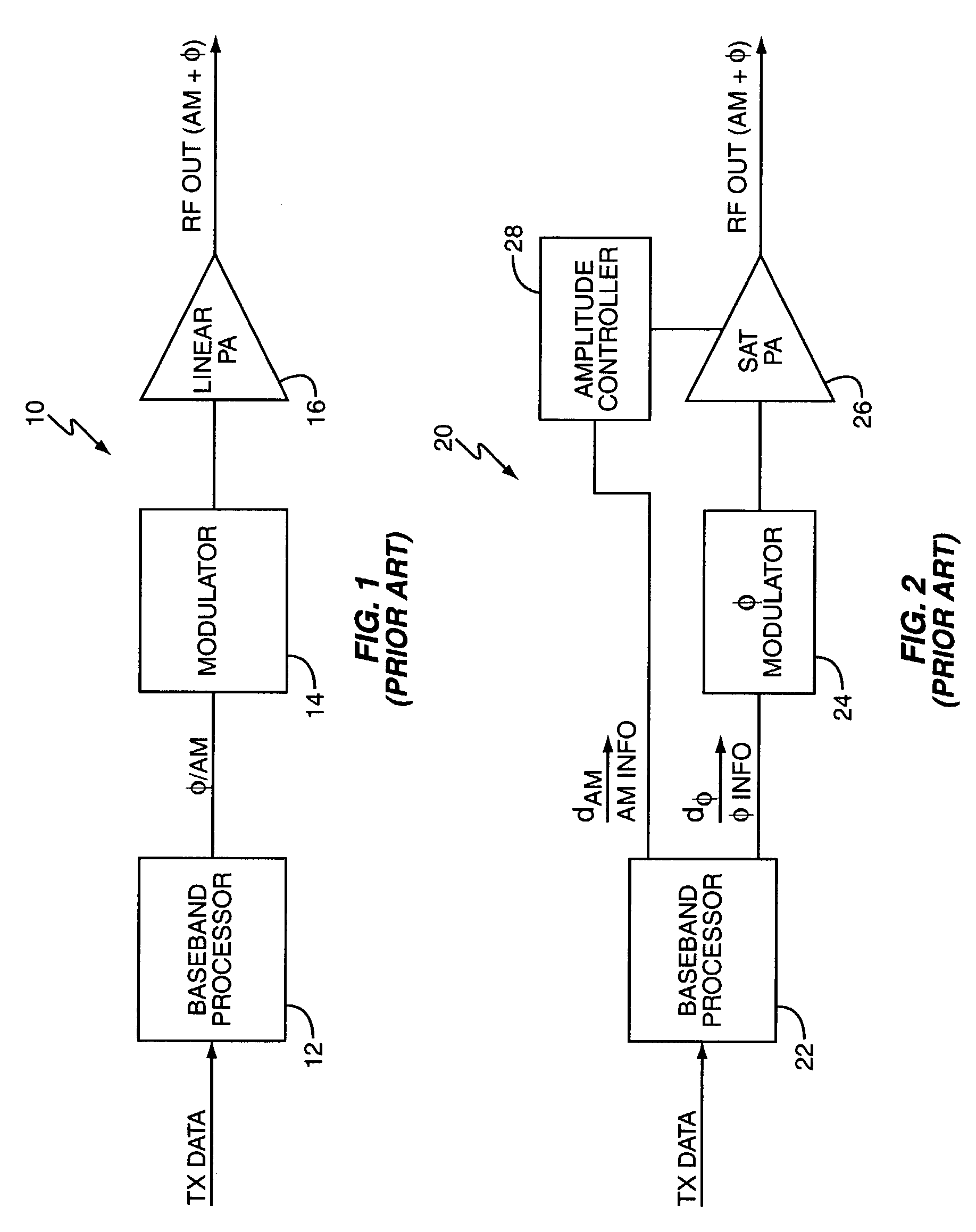

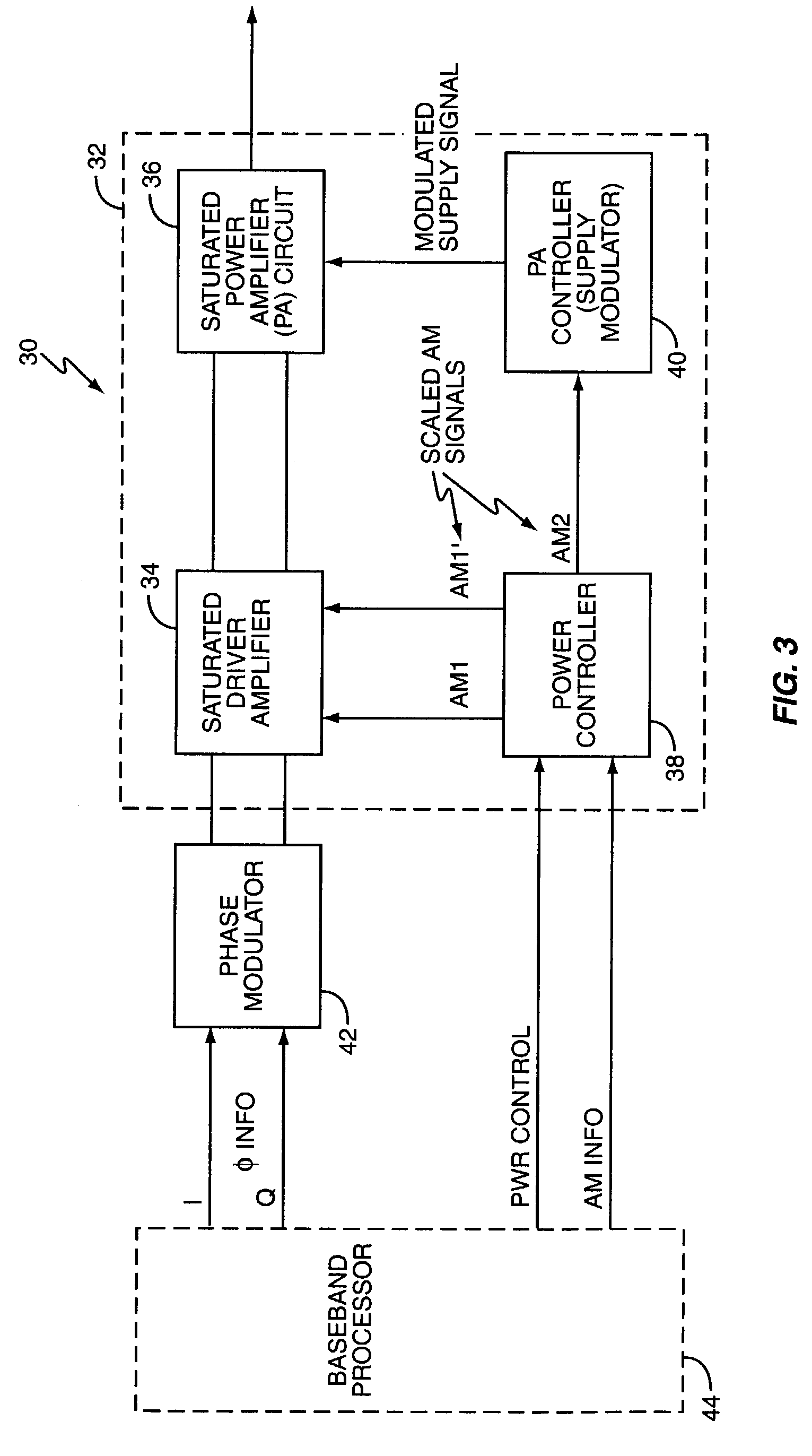

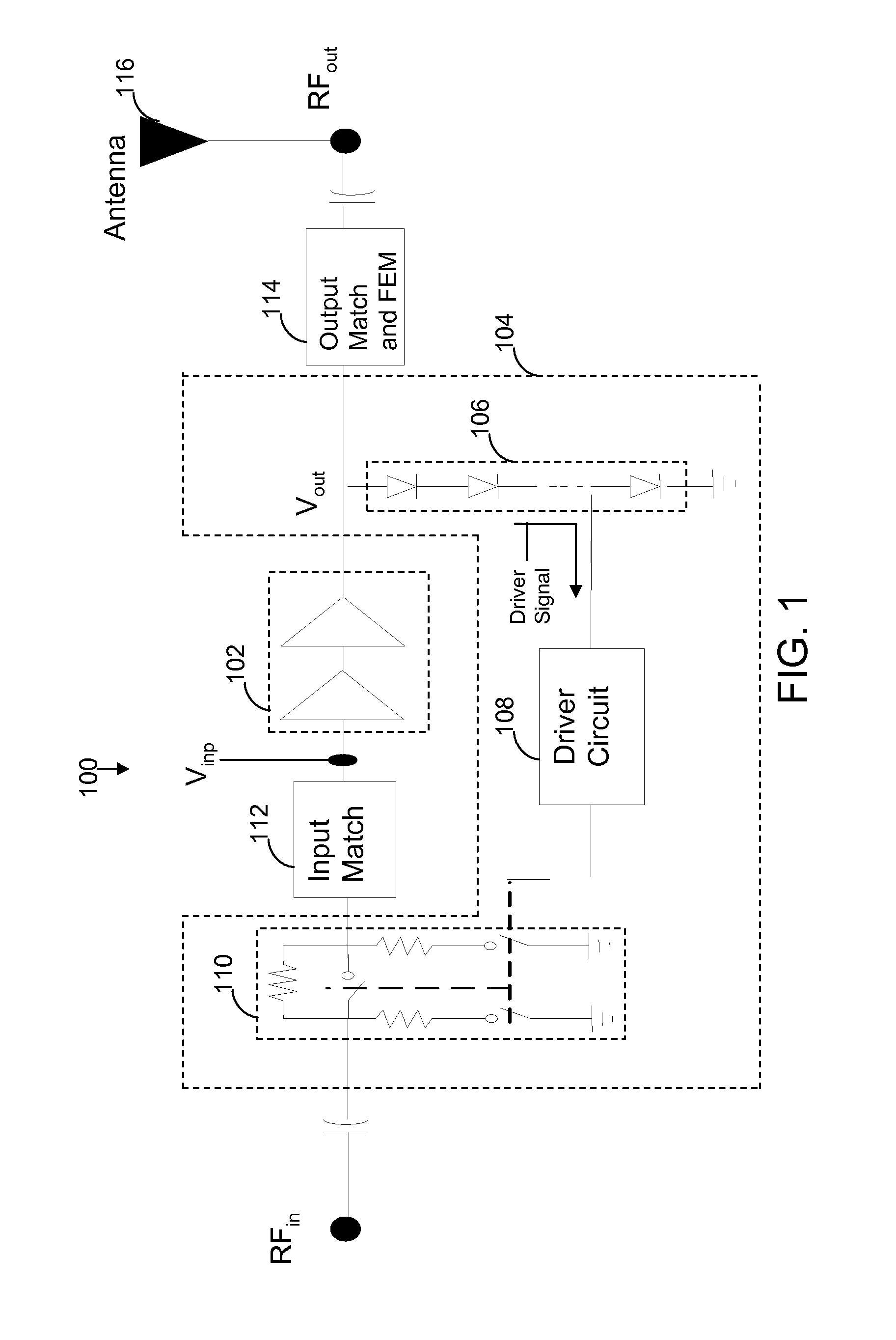

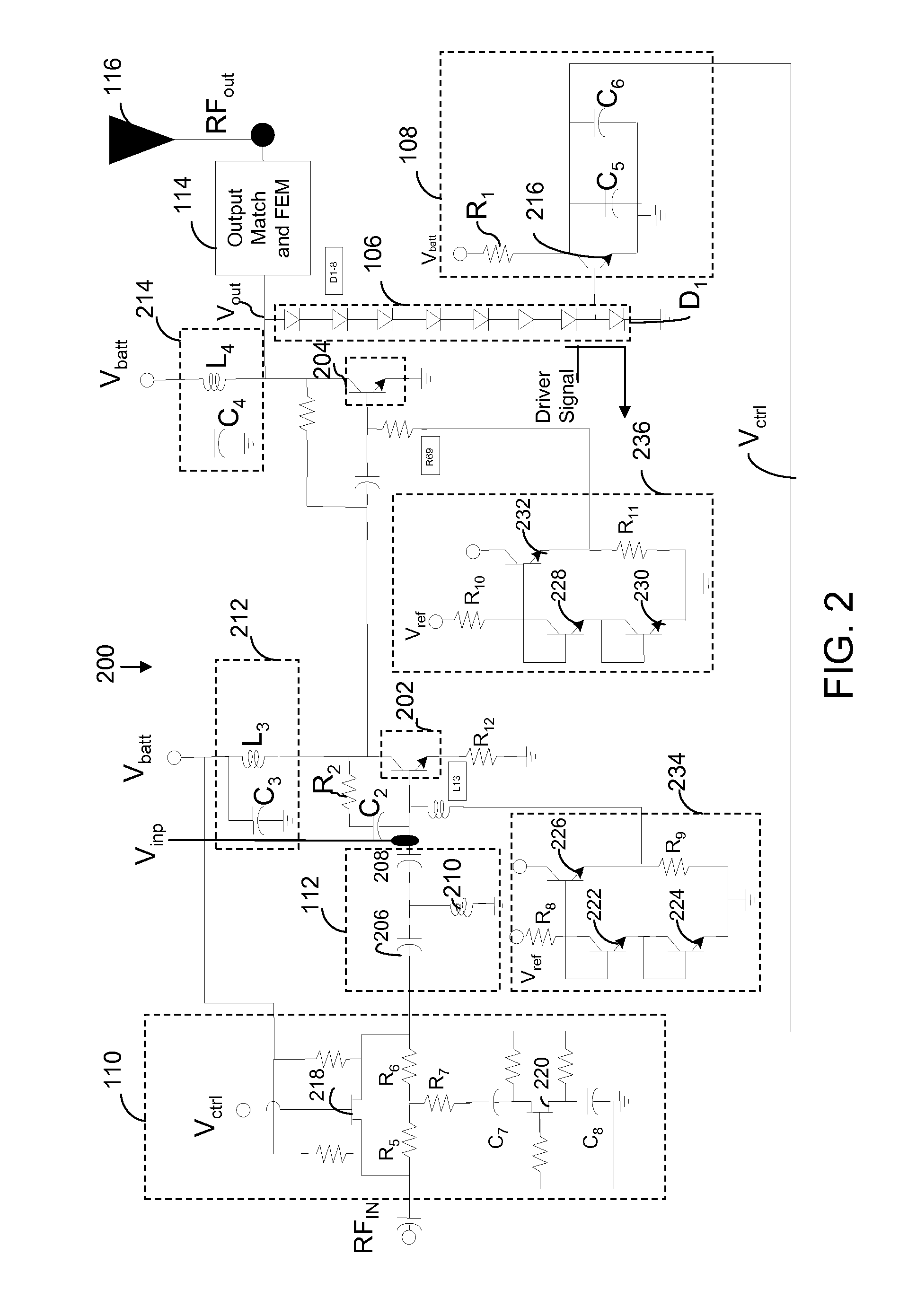

Polar modulation transmitter

ActiveUS7072626B2Improve performanceReduce ratio of average powerResonant long antennasPower amplifiersTransceiverAudio power amplifier

A polar modulation transmitter circuit provides reduced ACPR in its output signal by controlling the relative delay between its envelope and phase modulation operations based on direct or indirect feedback measurement the output signal's ACPR. Such measurement and associated control may be based on a delay controller that includes an ACPR measurement circuit and a delay control circuit. Additionally, or alternatively, the polar modulation transmitter circuit provides a greatly extended transmit power control range by using a staged amplifier circuit that includes a driver amplifier circuit operating in combination with a power amplifier circuit to impart desired envelope modulation. In an exemplary embodiment, the driver amplifier circuit is implemented as differential transistor pairs responsive to tail current modulation. As such, the driver amplifier circuit is suited in particular for economical and space saving integration within a transmitter or transceiver integrated circuit (IC).

Owner:UNWIRED PLANET

Method and system for non-destructive evaluation of conducting structures

InactiveUS20050270037A1Low costEasily separateResistance/reactance/impedenceFault locationTest inputNon destructive

Method and system for non-destructive evaluation for a conducting structure by measuring the electrical impulse response thereof including applying a PRBS test input signal to the conducting structure, detecting an output signal from the conducting structure and processing the data to assess the condition of the conducting structure via changes in the electrical impulse response and to locate any defects along the conducting structure.

Owner:INTELLIGENT AUTOMATION

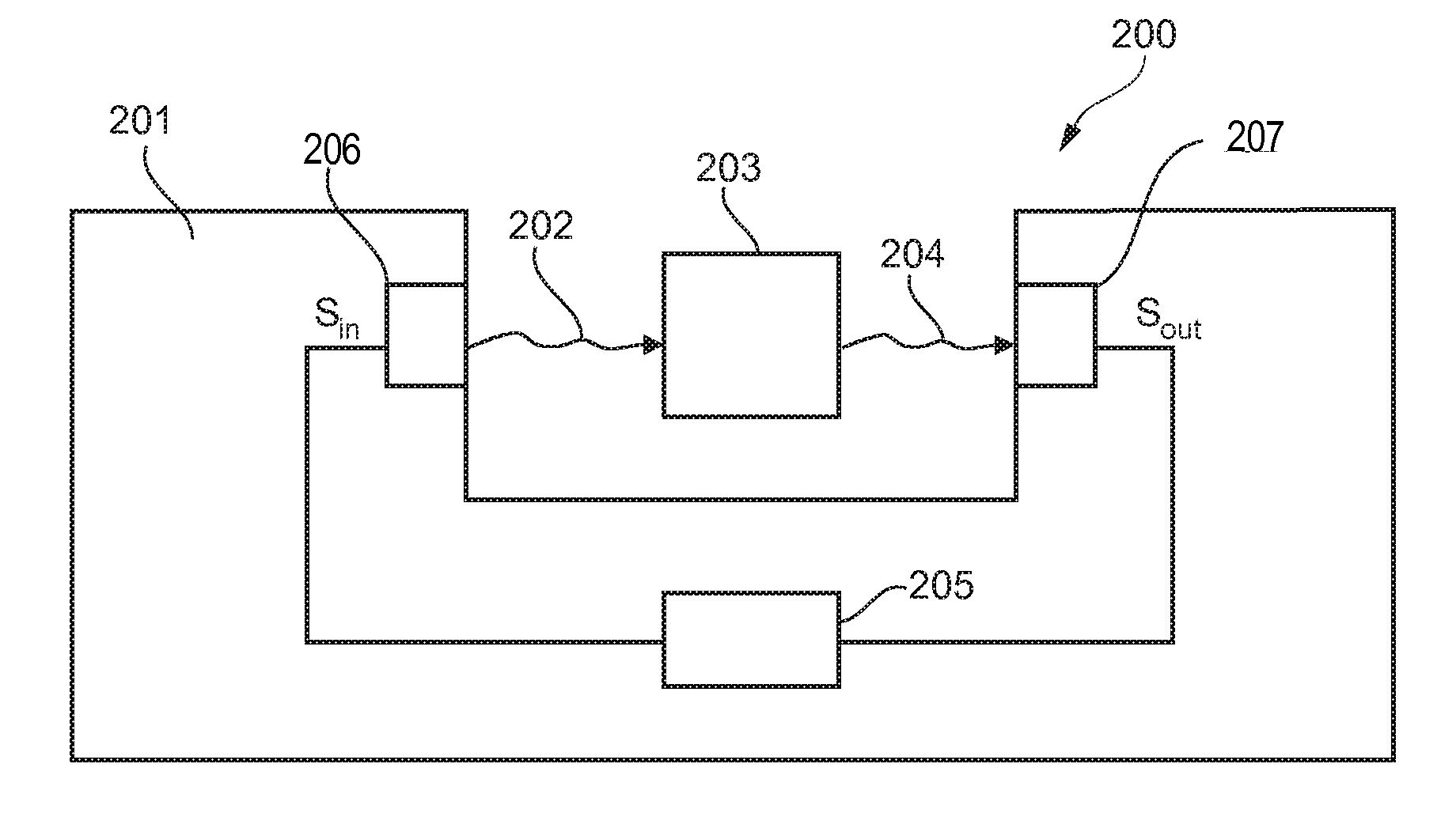

Signal transmission system

ActiveUS20100246707A1Inhibition is effectiveReduce output signalElectric signal transmission systemsElectric controllersEngineeringTransmitter

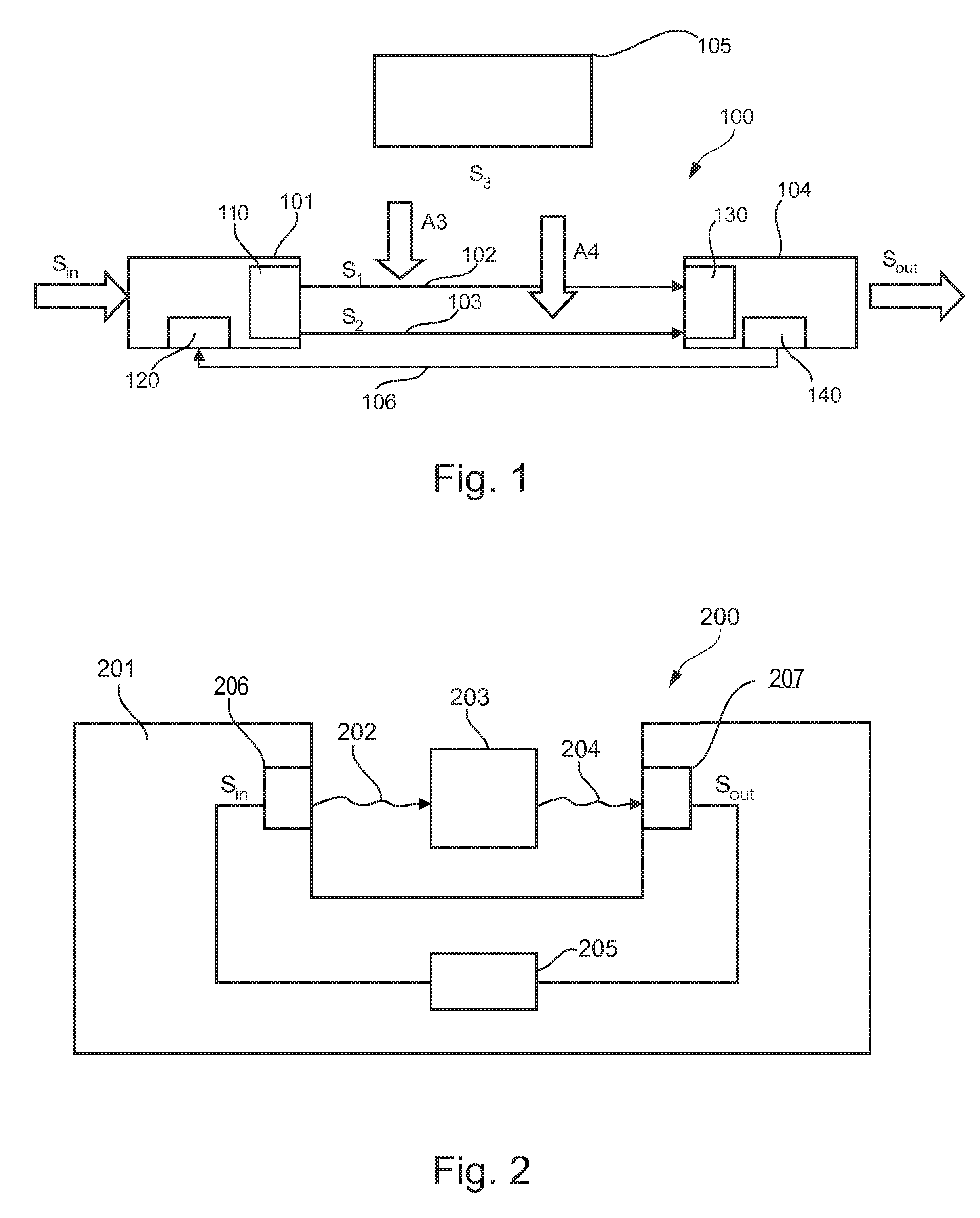

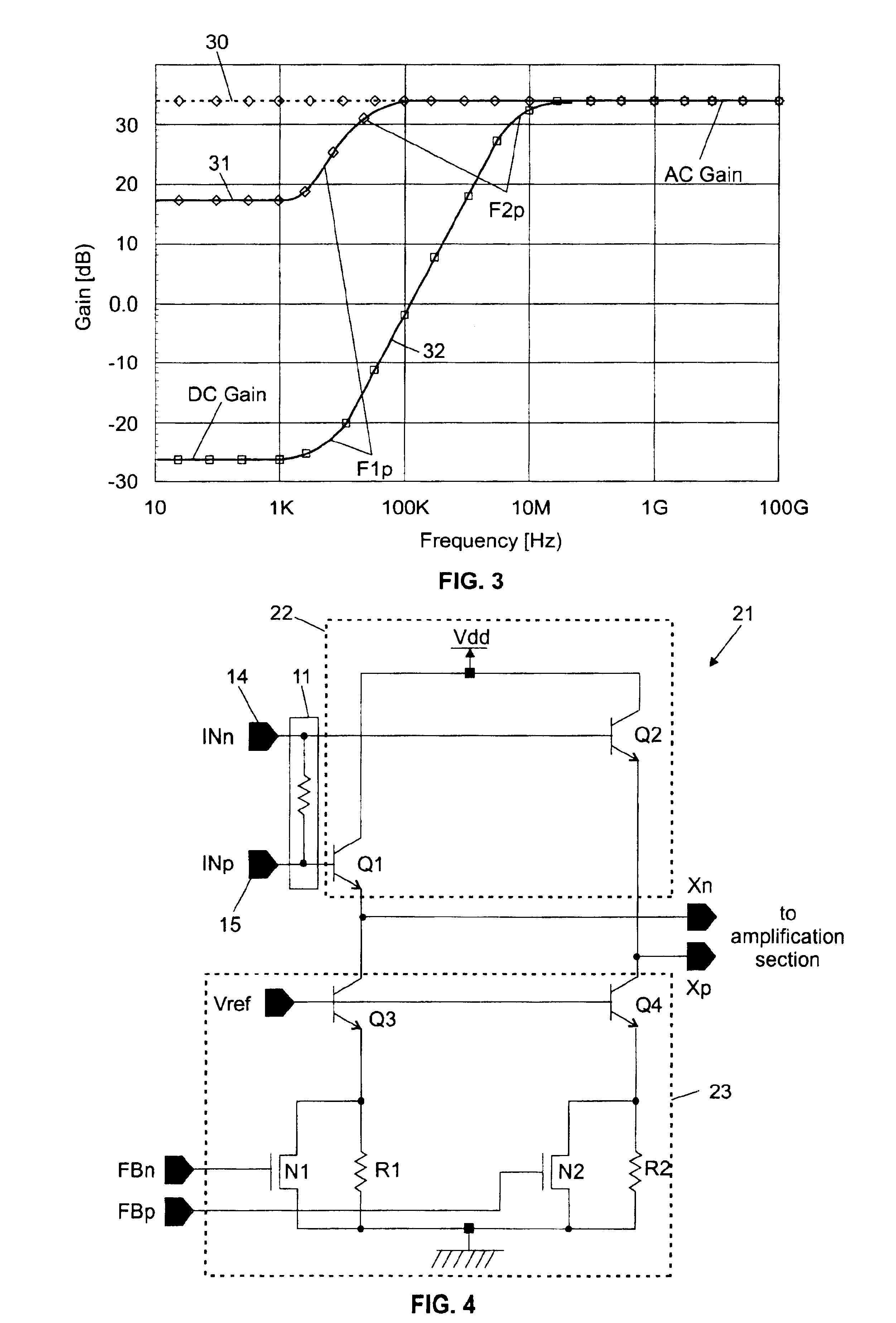

A method of operating a system (100, 200) for transmitting signals (si, S2, 202) from a transmitter (101, 206) to a receiver (104, 207), the method comprising the step of muting the transmitter (101, 206), adjusting a receiver transfer function of the receiver (104, 207) so that an output signal (sout) of the receiver (104, 207) is minimized, and setting a transmitter transfer function of the transmitter (101, 206) to be inverse to the adjusted receiver transfer function.

Owner:III HLDG 6

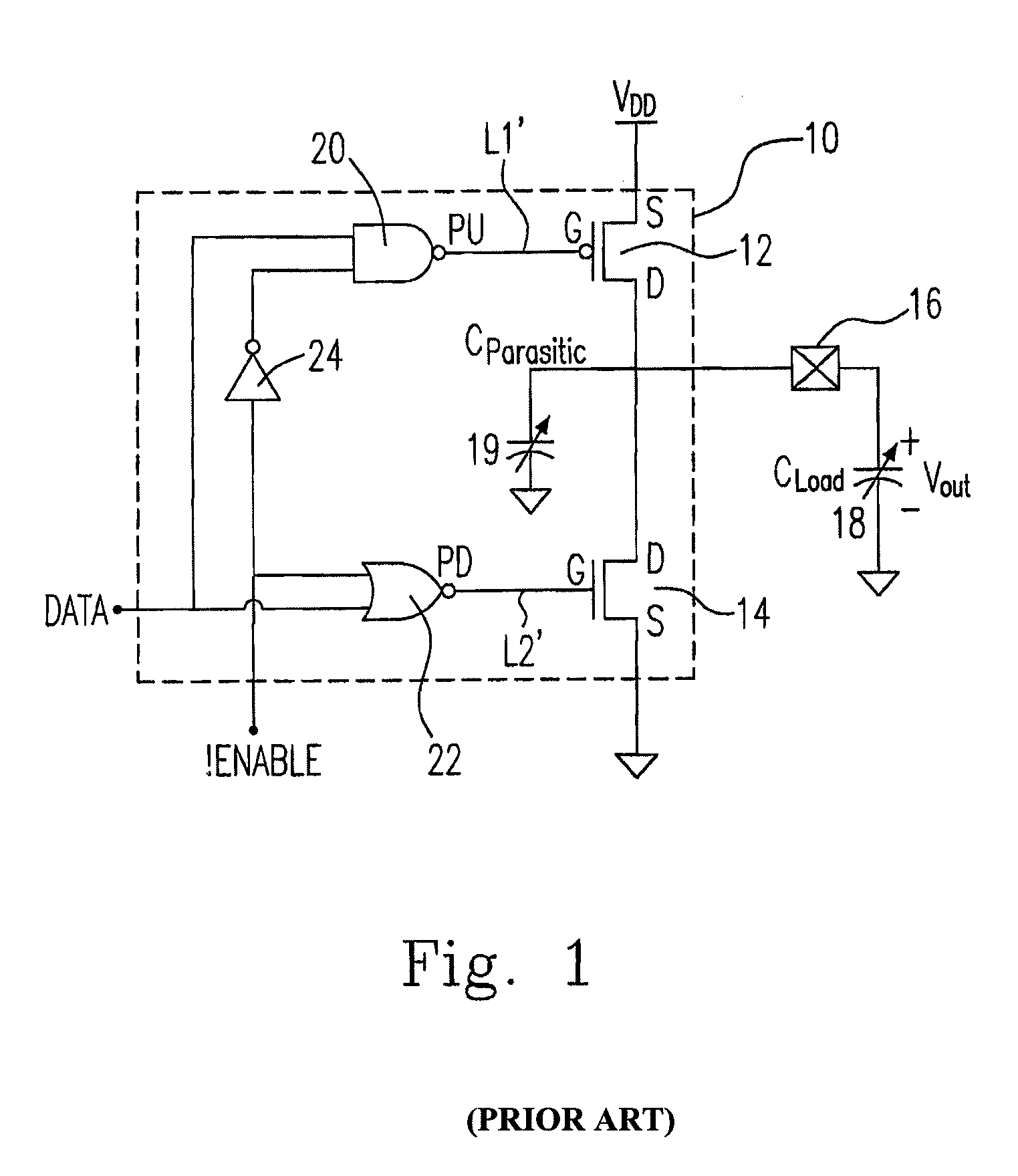

Differential amplifier with DC offset cancellation

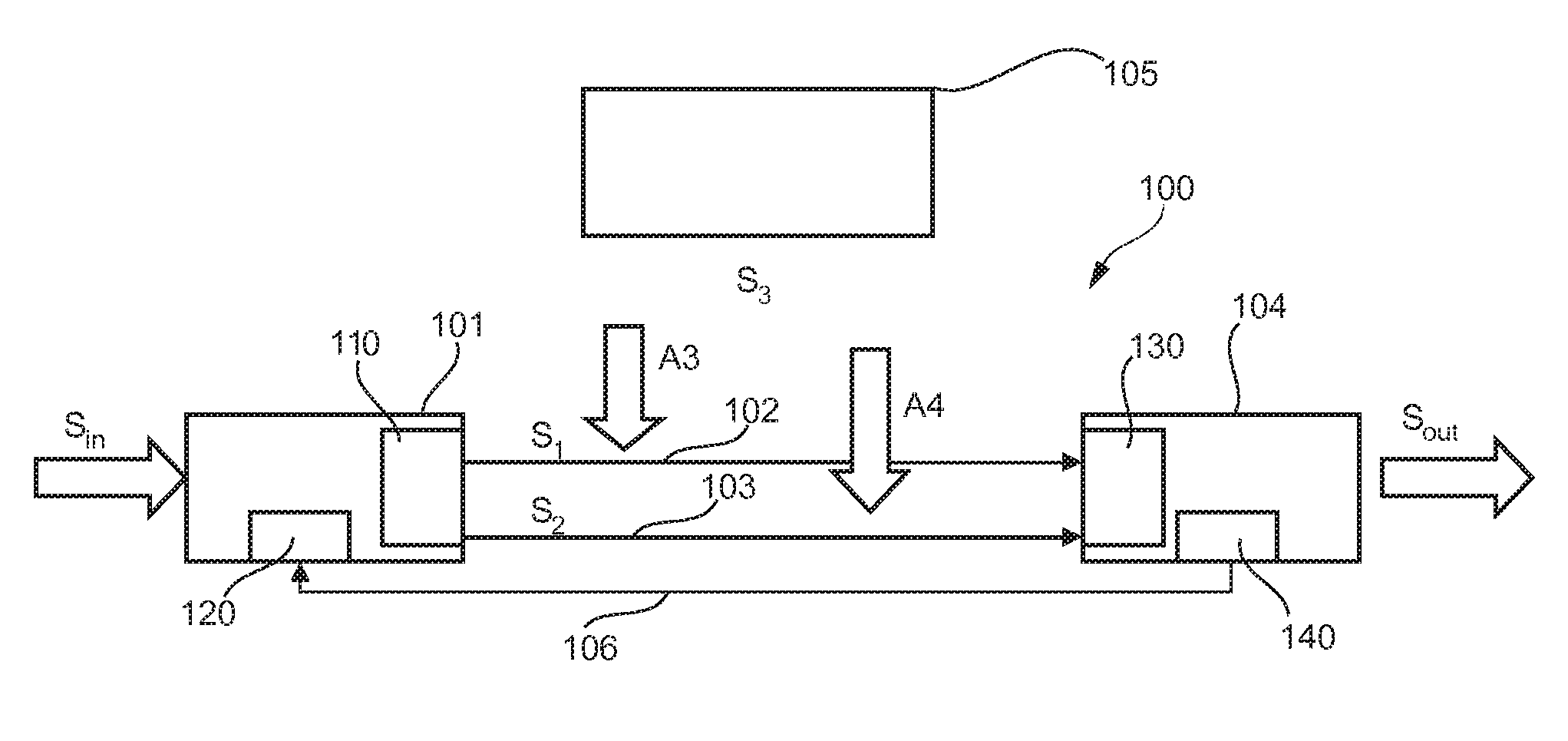

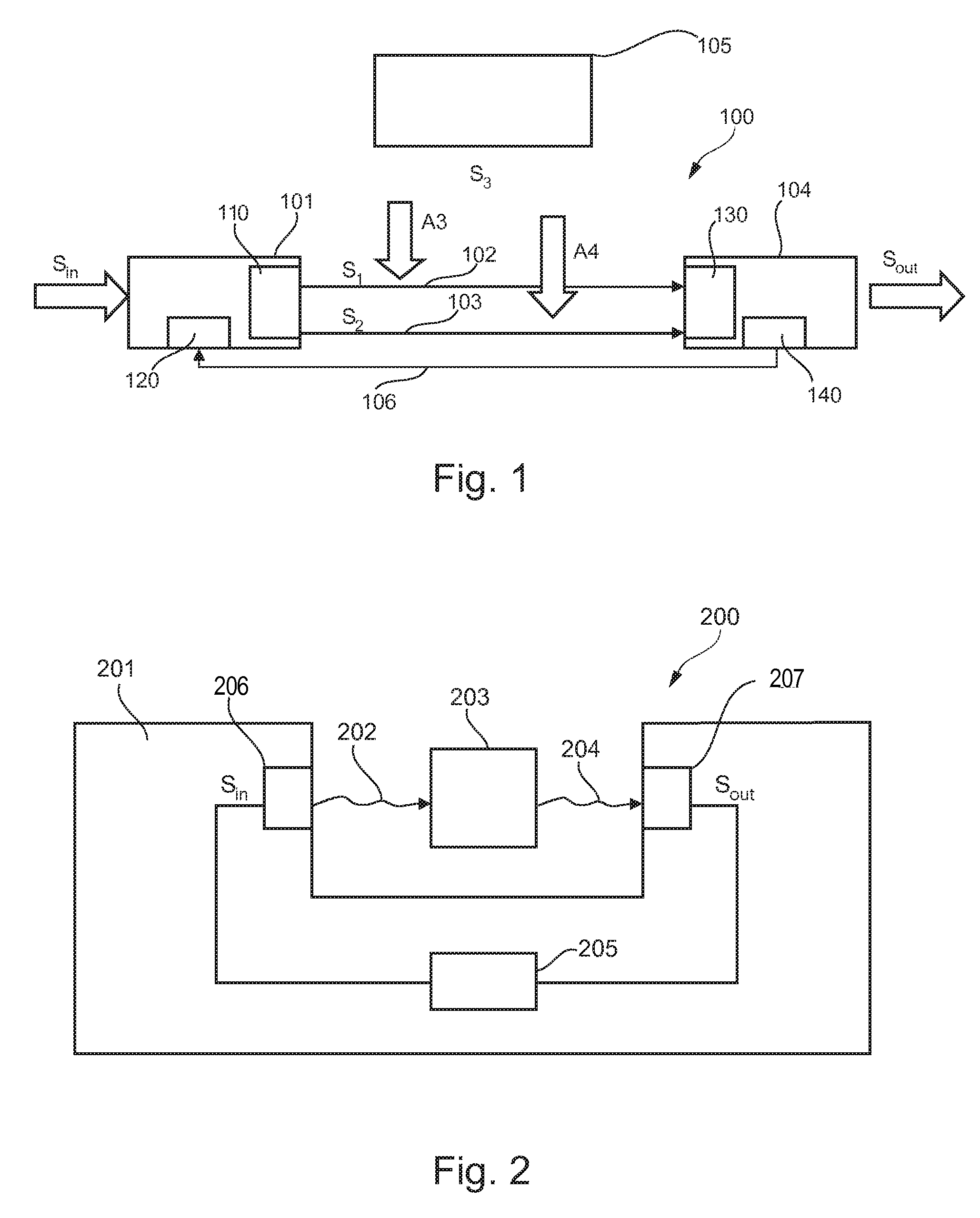

InactiveUS6914479B1Excellent input impedance matchingLow eye-diagram closureDifferential amplifiersDc-amplifiers with dc-coupled stagesAudio power amplifierOffset cancellation

There is disclosed an improved differential amplifier (20) having a feedback loop that generates an amplified output signal (Vout) from an input signal (Vin) supplied by a preceding stage. It comprises an input matching circuit (11) connected to said preceding stage, a buffer (22) and an amplification section (12) connected in series in the direct amplification line, a first amplifier (16), a RC network (17′) and a second amplifier (23) connected in series in a parallel loop between the outputs and the inputs of the amplification section that generate the feedback signal. The role of said buffer and second amplifier associated in a dedicated direct and feedback signal combining block (21) is to respectively isolate the input signal and the feedback signal from the summing nodes (A′,B′) at the amplification section inputs. As a result, the summation of the input signal and the feedback signal is improved, the DC component of the output signal is filtered out in order to significantly reduce the DC offset. In addition, the input impedance matching represented by parameter S11 is considerably improved.

Owner:IBM CORP

Signal transmission system

ActiveUS8509340B2Reduce output signalInhibition is effectiveElectric signal transmission systemsElectric controllersEngineeringTransmitter

Owner:III HLDG 6

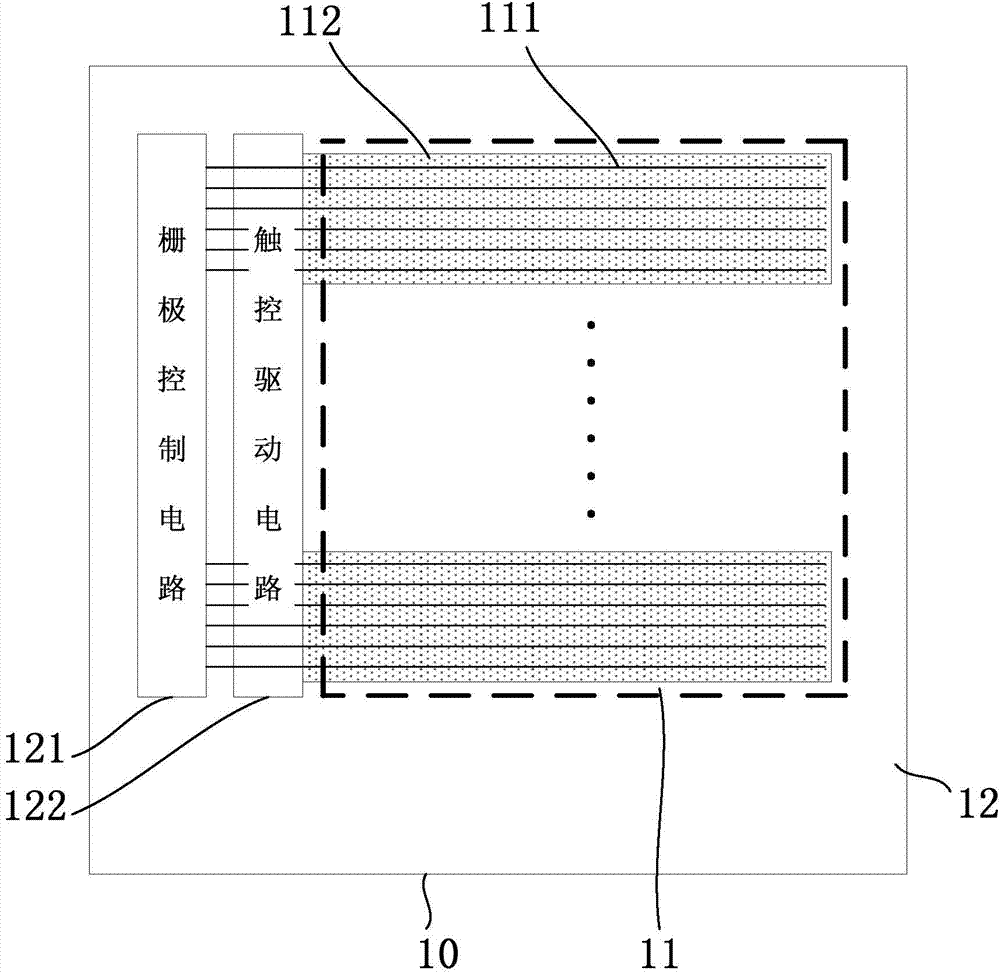

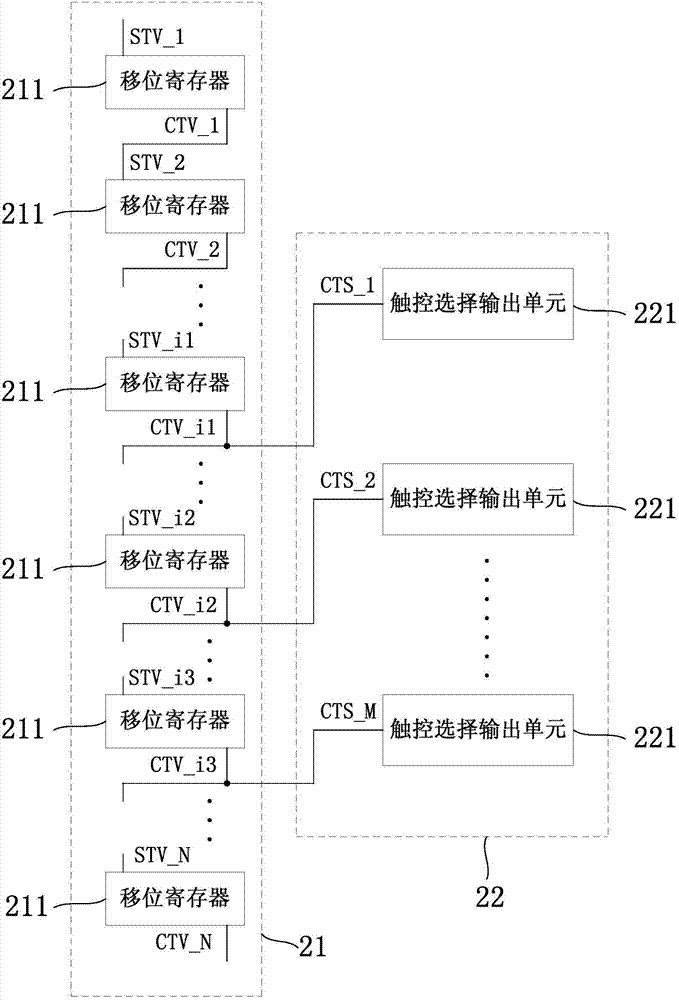

Drive circuit, array substrate and touch display device as well as drive method thereof

ActiveCN104505014ASimple touch drive circuitReduce output signalStatic indicating devicesInput/output processes for data processingElectricityEngineering

The invention discloses a drive circuit, an array substrate and a touch display device as well as a drive method thereof. A first gate electrode drive circuit and a touch drive circuit electrically connected with the first gate electrode drive circuit are arranged in the drive circuit; a secondary trigger signal output by a shifting register in the first gate electrode drive circuit is used as a grating signal of a touch selecting output unit in the corresponding touch drive circuit; correspondingly, the touch drive circuit is not needed to be equipped with a scanning unit for providing the grating signal for the touch selecting output unit, so that the touch drive circuit is relatively simple, not only can the touch display device easily realize narrow side frame, but also the output signal of IC and the cost of the IC can be reduced.

Owner:XIAMEN TIANMA MICRO ELECTRONICS +1

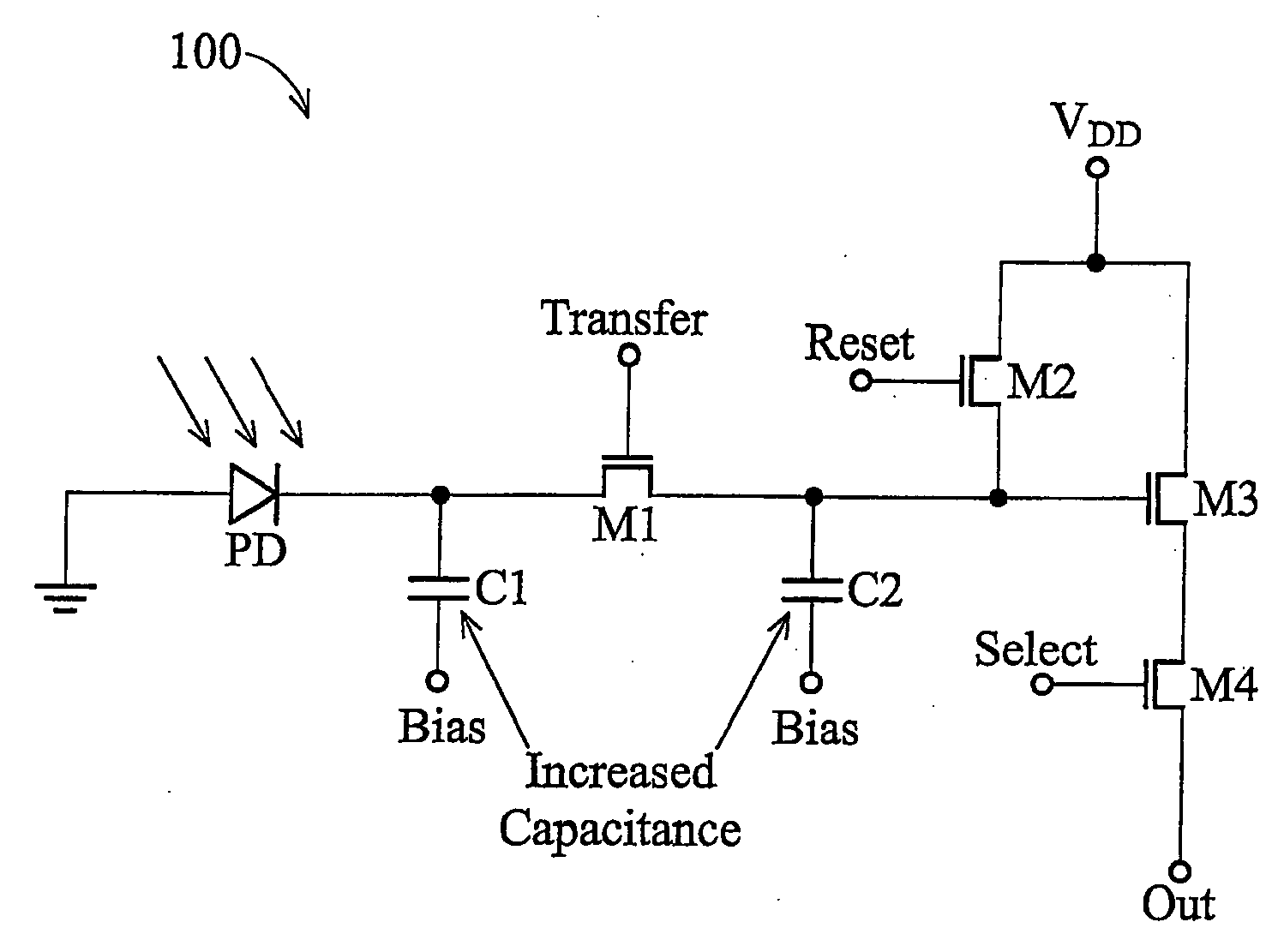

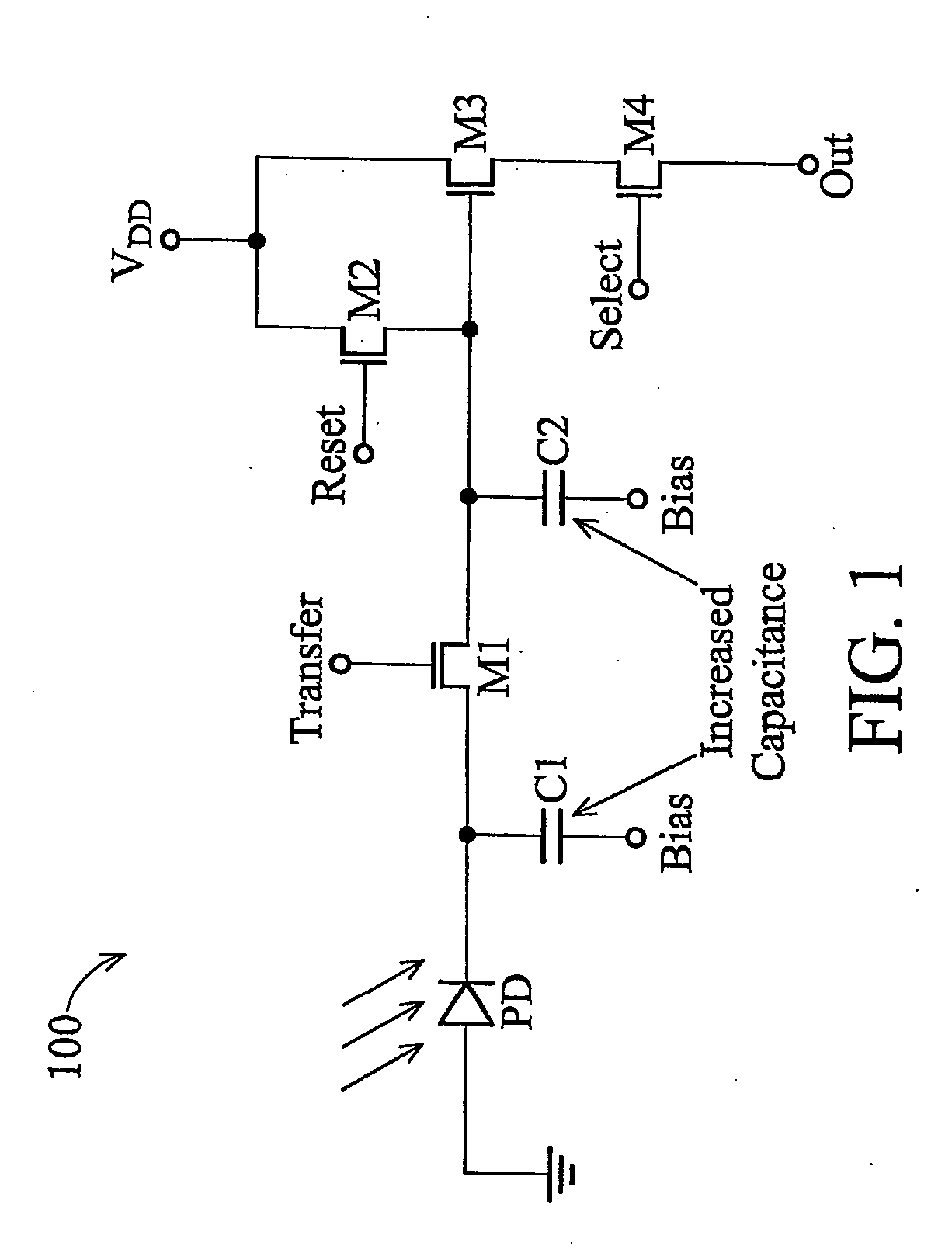

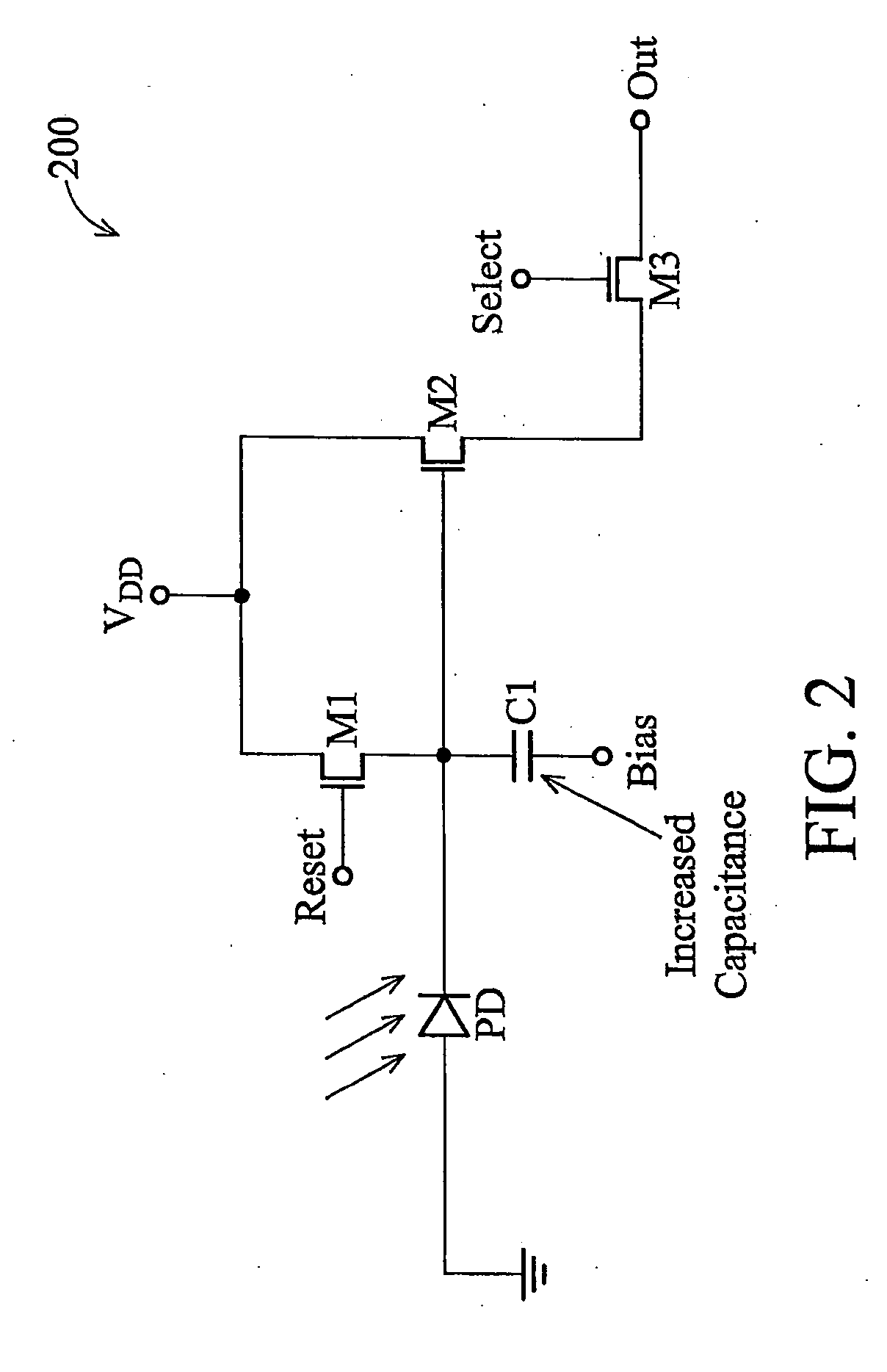

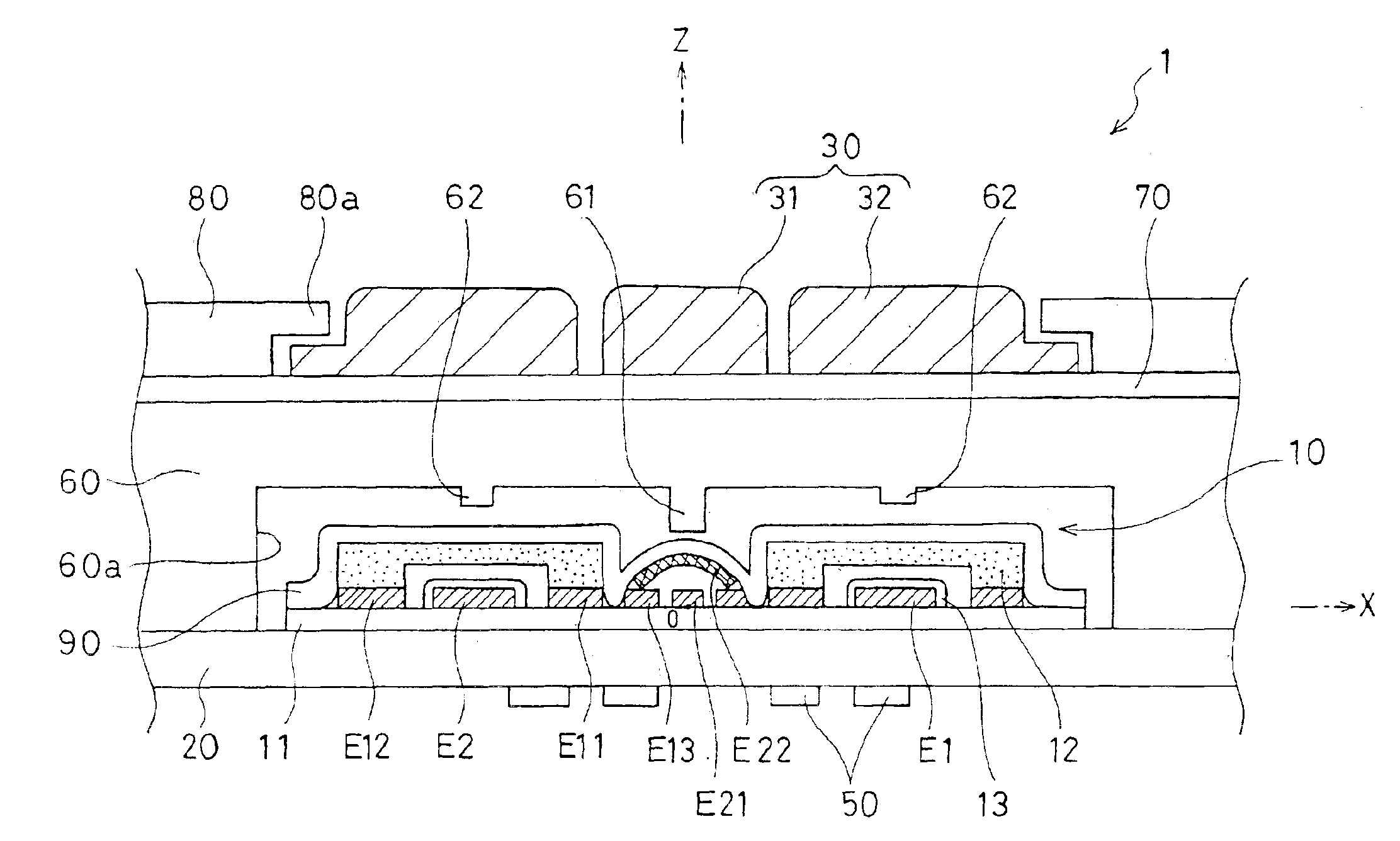

Structure for CMOS image sensor

ActiveUS20060164531A1Susceptibility to noiseReduce output signalTelevision system detailsTelevision system scanning detailsCapacitanceCMOS

A CMOS image sensor having increased capacitance that allows a photo-diode to generate a larger current is provided. The increased capacitance reduces noise and the dark signal. The image sensor utilizes a transistor having nitride spacers formed on a buffer oxide layer. Additional capacitance may be provided by various capacitor structures, such as a stacked capacitor, a planar capacitor, a trench capacitor, a MOS capacitor, a MIM / PIP capacitor, or the like. Embodiments of the present invention may be utilized in a 4-transistor pixel or a 3-transistor pixel configuration.

Owner:TAIWAN SEMICON MFG CO LTD

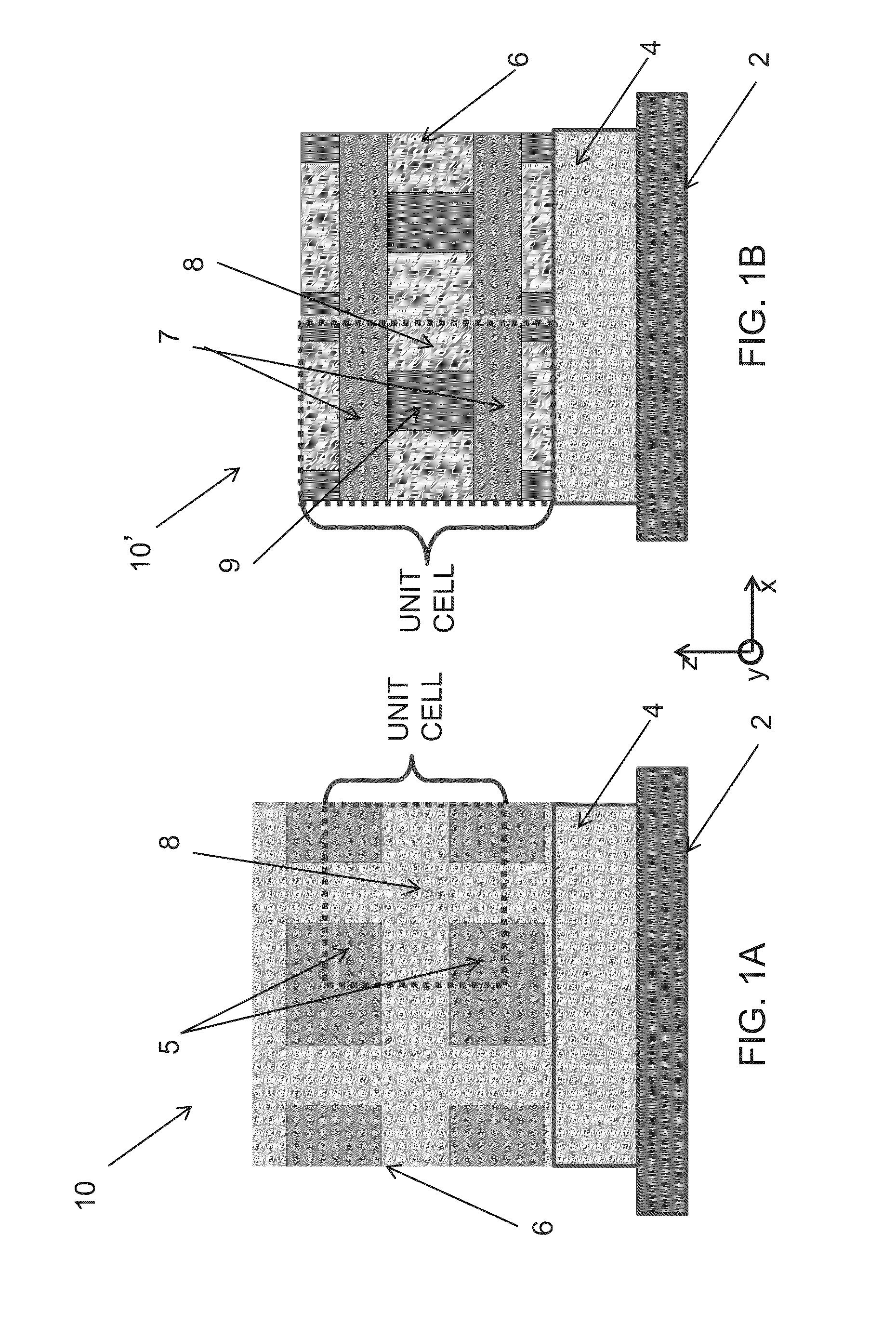

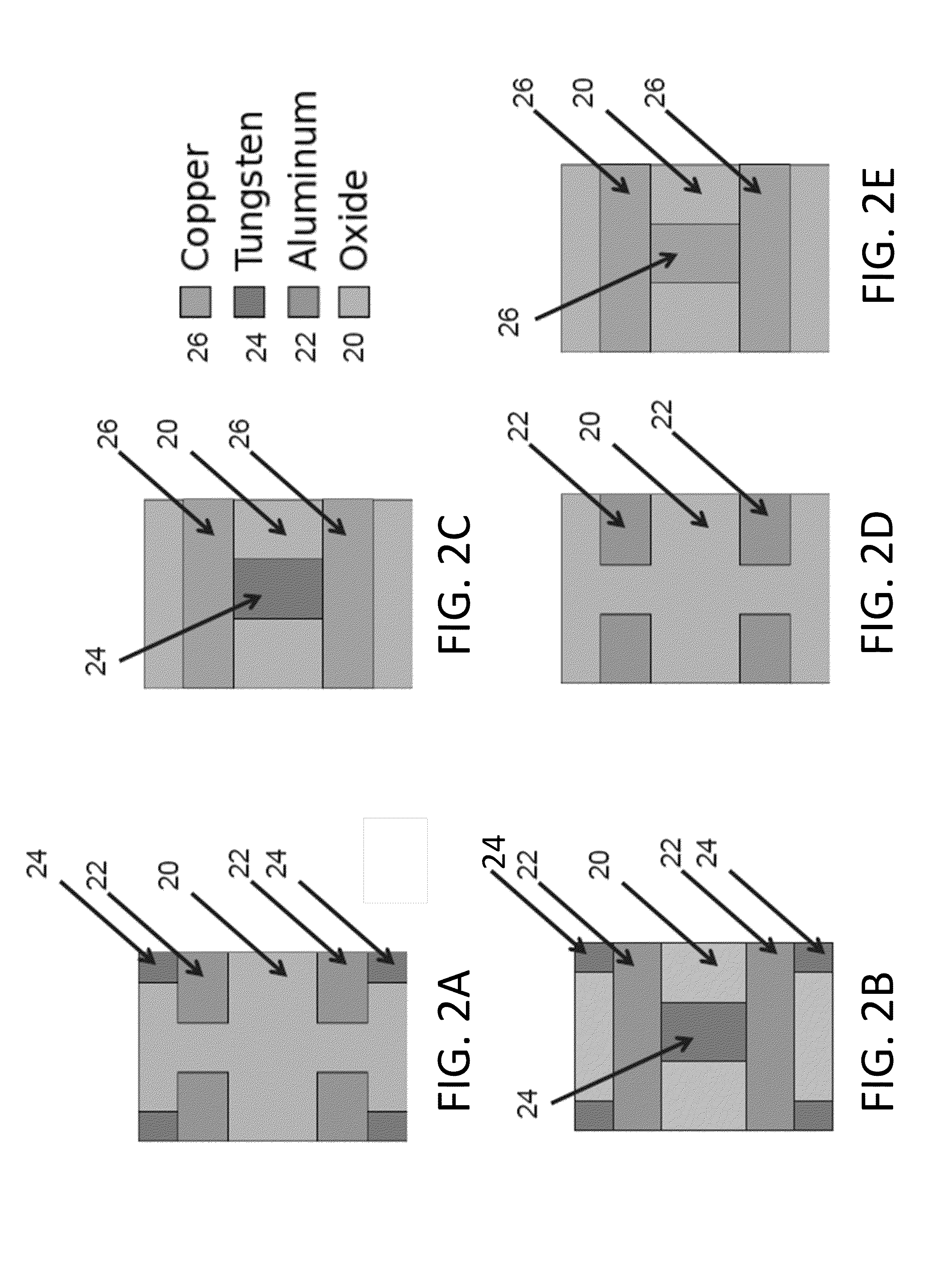

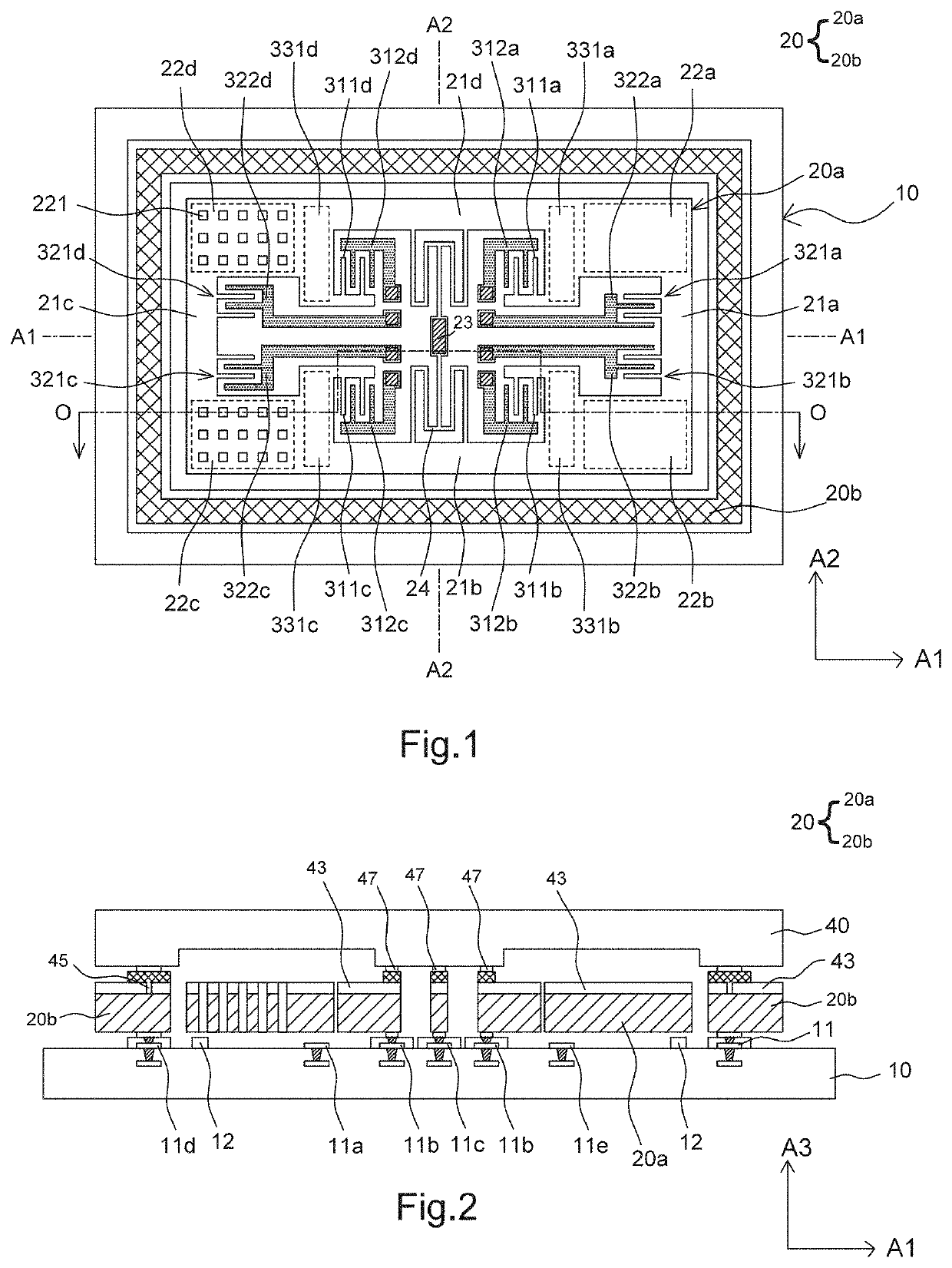

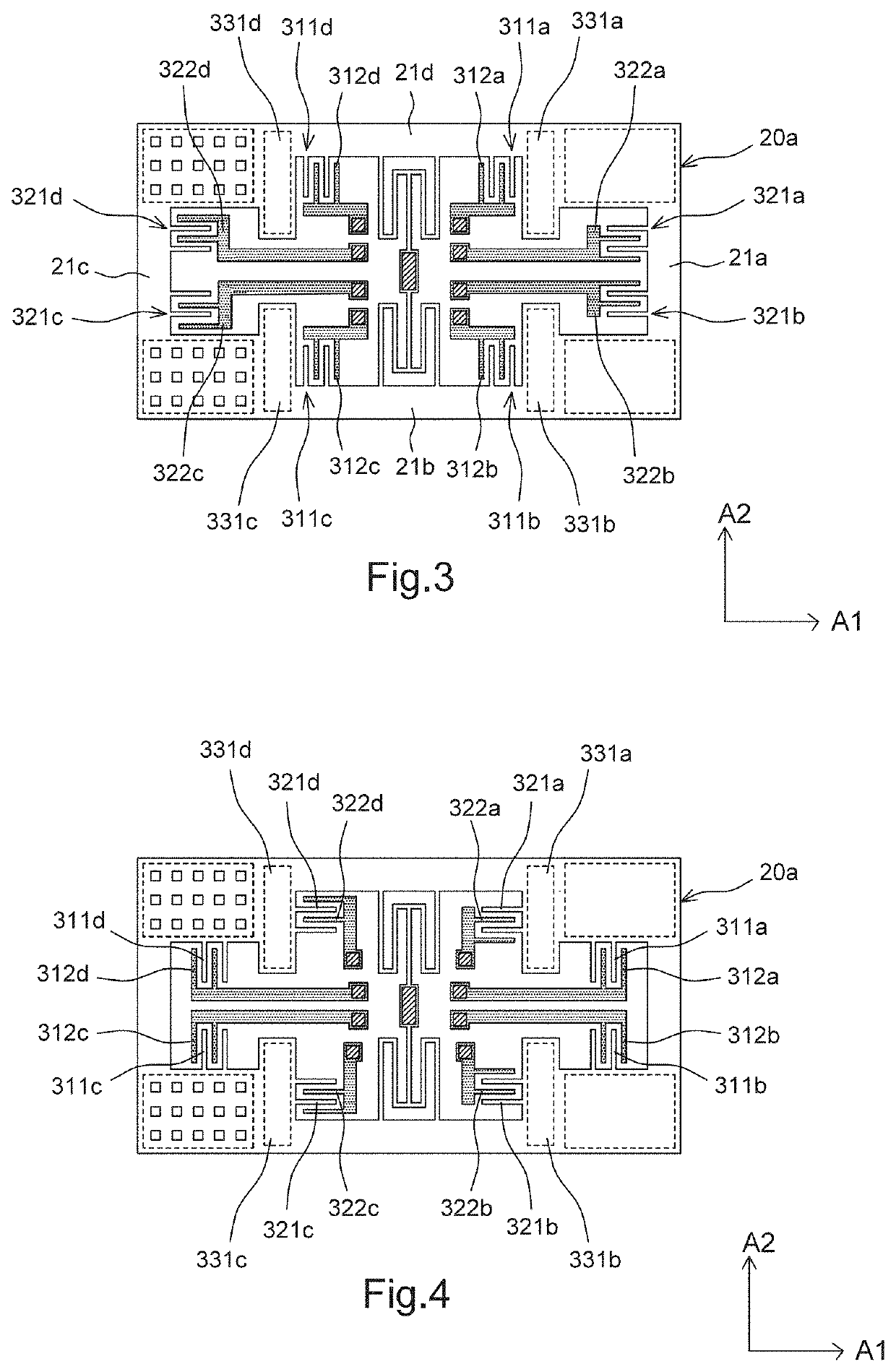

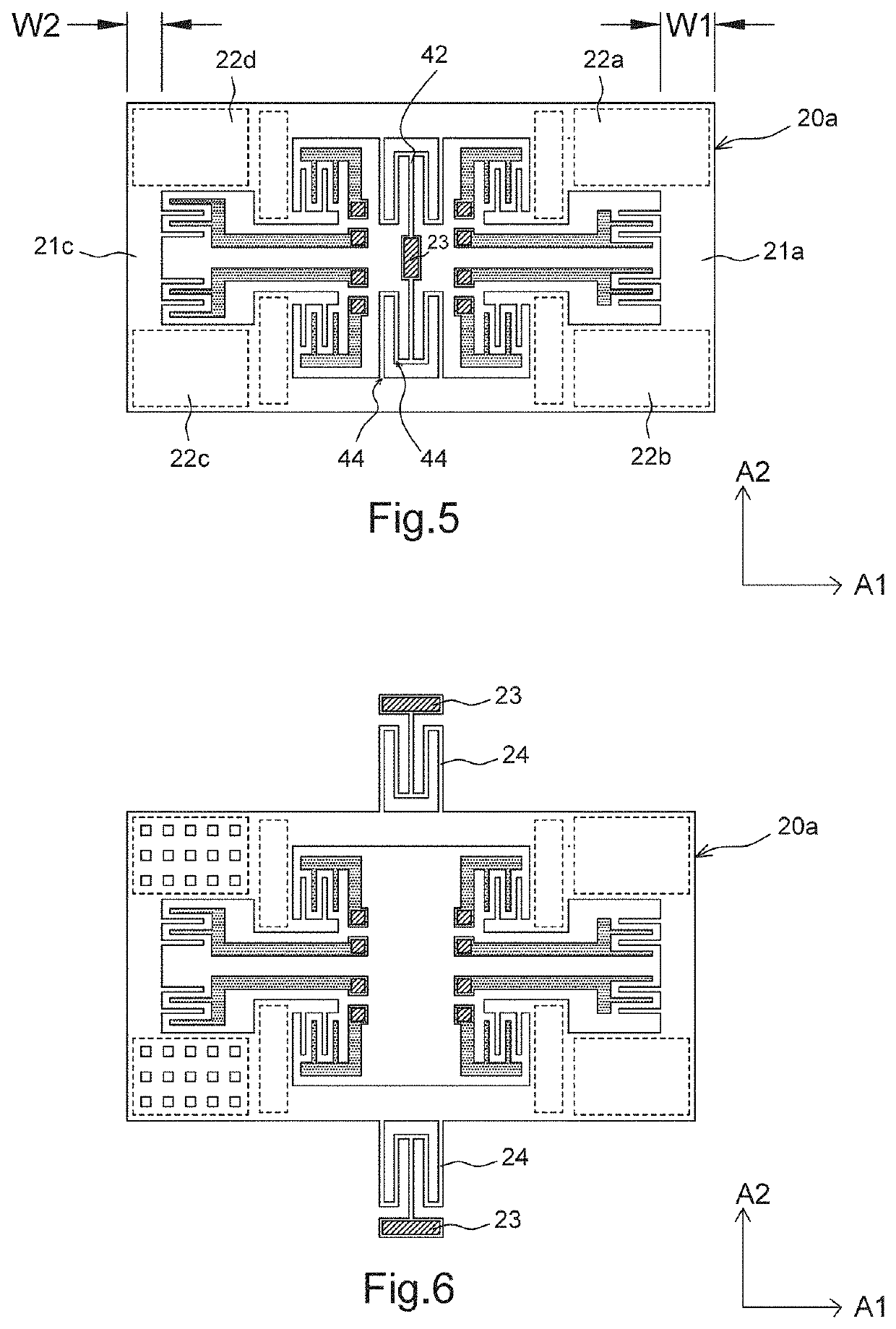

Acoustic bandgap structures for integration of MEMS resonators

ActiveUS20150237423A1Reduce constraintsReduce parasitismMicrophonesTransducer detailsResonant cavityAcoustics

Example acoustic bandgap devices provided that can be fabricated in a semiconductor fabrication tool based on design check rules. An example device includes a substrate lying in an x-y plane and defining an x-direction and a y-direction, an acoustic resonant cavity over the substrate, and a phononic crystal disposed over the acoustic resonant cavity by generating the phononic crystal as a plurality of unit cells disposed in a periodic arrangement. Each unit cell include: (a) at least one higher acoustic impedance structure having a longitudinal axis oriented in the y-direction and a thickness in the x-direction greater than or about equal to a minimal feature thickness of the semiconductor fabrication tool, and (b) at least one lower acoustic impedance material bordering at least a portion of the at least one higher acoustic impedance structure and forming at least a portion of a remainder of the respective unit cell.

Owner:MASSACHUSETTS INST OF TECH

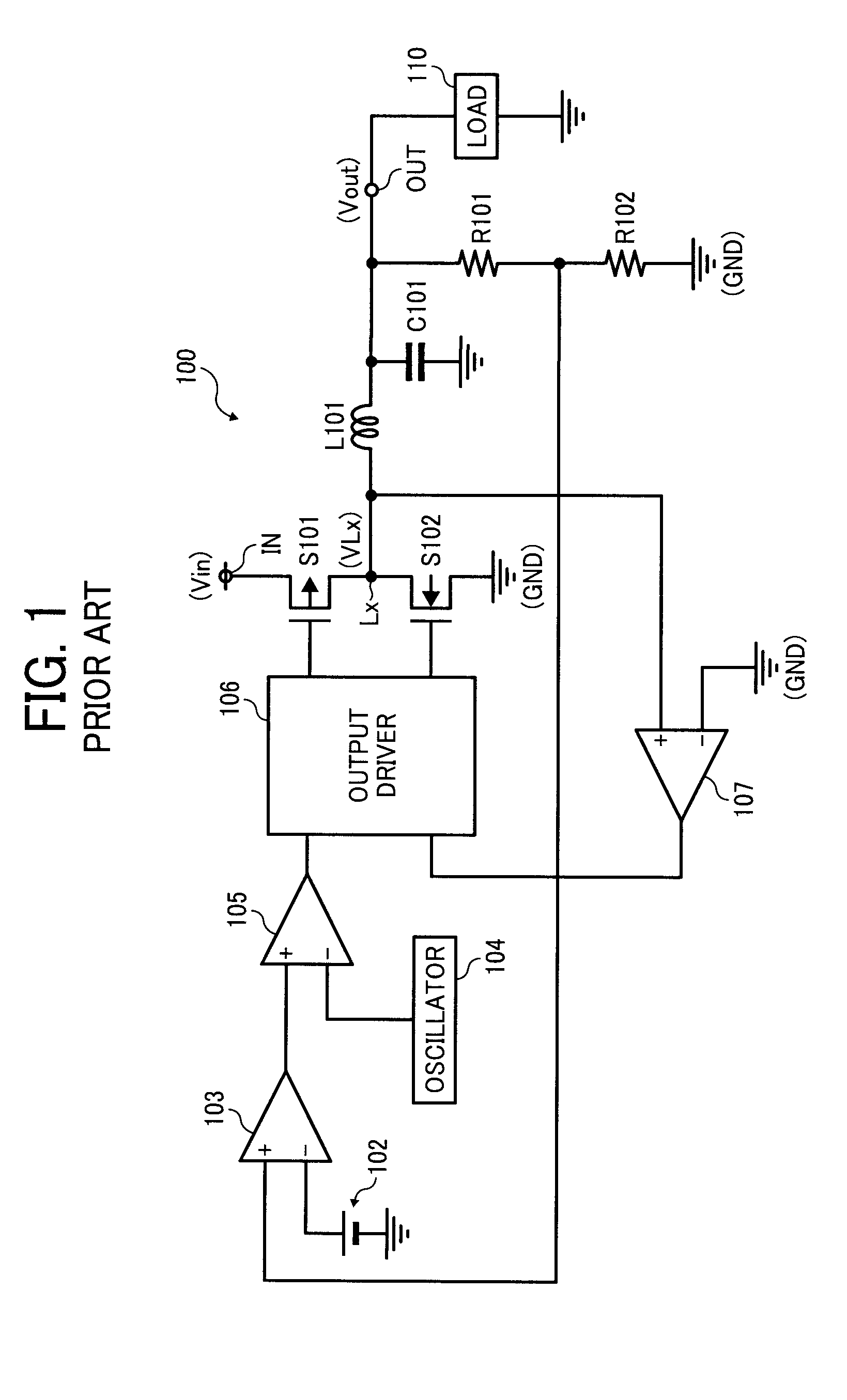

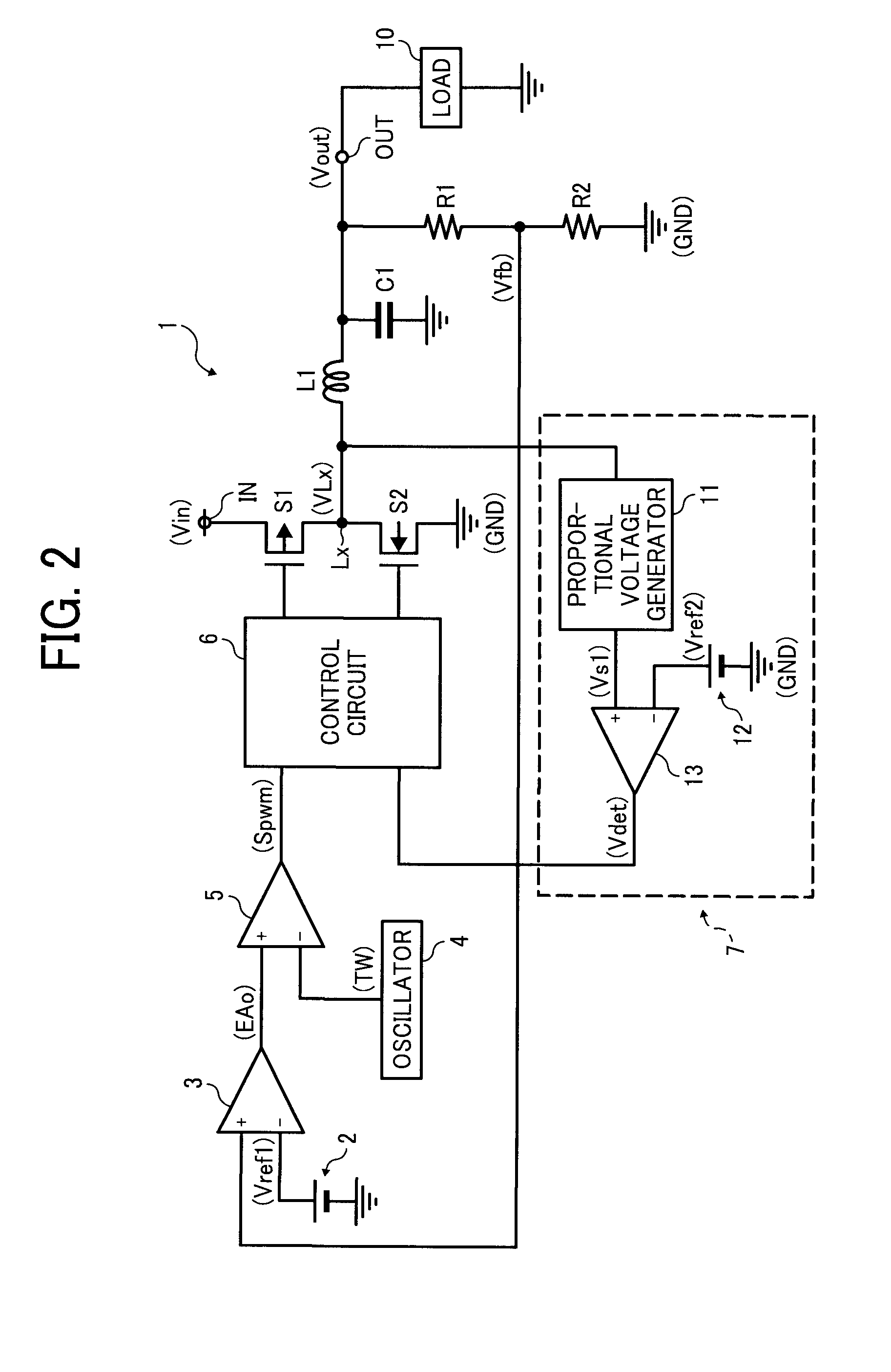

Switching regulator

InactiveUS20090066305A1Reduce output voltageReduce output signalEfficient power electronics conversionDc-dc conversionReverse currentInductor

A switching regulator includes a first switch, an inductor, a second switch, a controller to control a switching operation by switching the first switch and switching the second switch complementally to the first switch, and a reverse current detector to detect a reverse current that flows from an output terminal toward the second switch. The reverse current detector generates a proportional voltage that is proportional to a voltage at a junction node between the second switch and the inductor, and detects a generation or an indication of the reverse current based on the proportional voltage. The controller turns the second switch off to create a shutdown state when the reverse current detector detects the generation or the indication of the reverse current.

Owner:RICOH ELECTRONIC DEVICES CO LTD

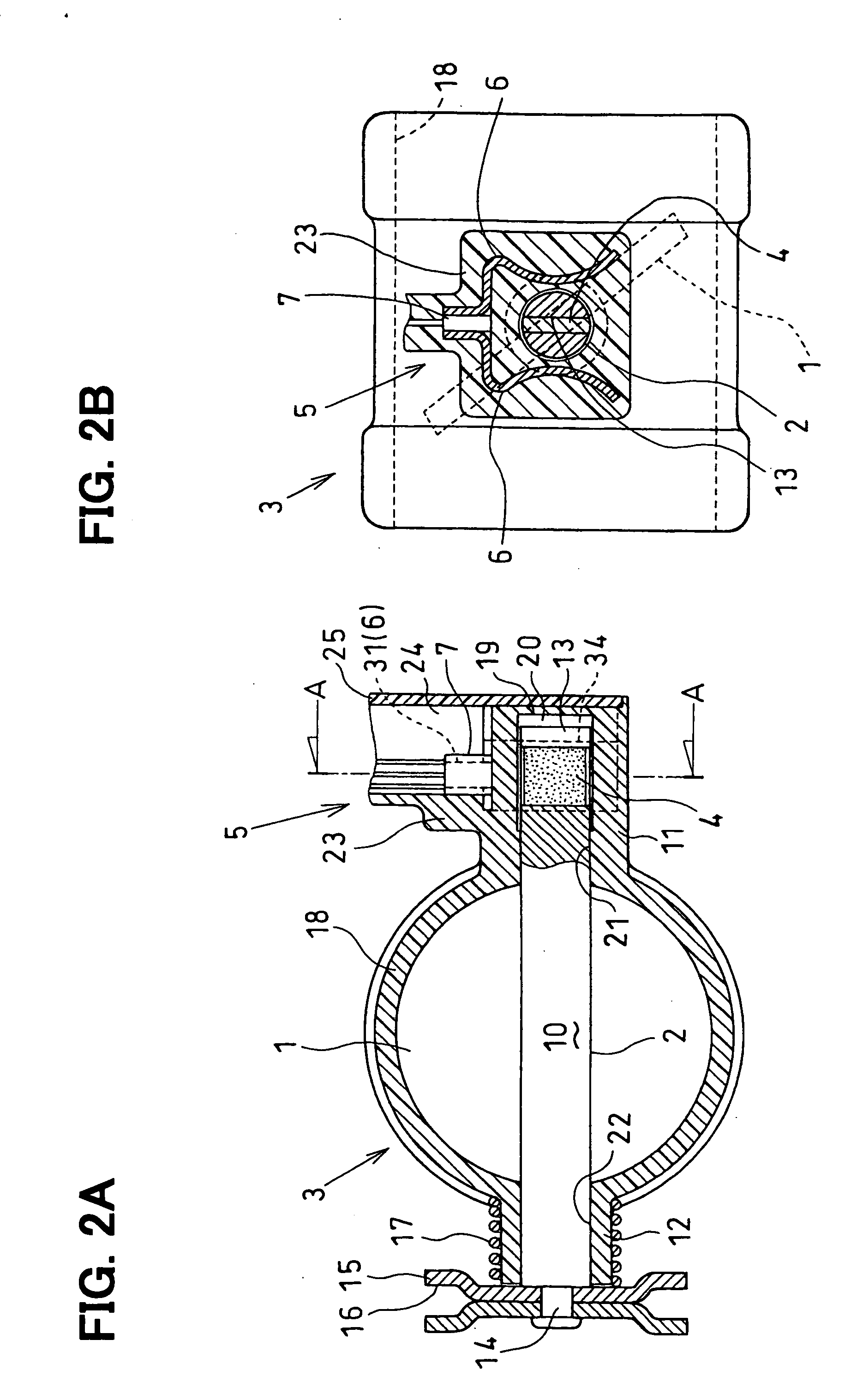

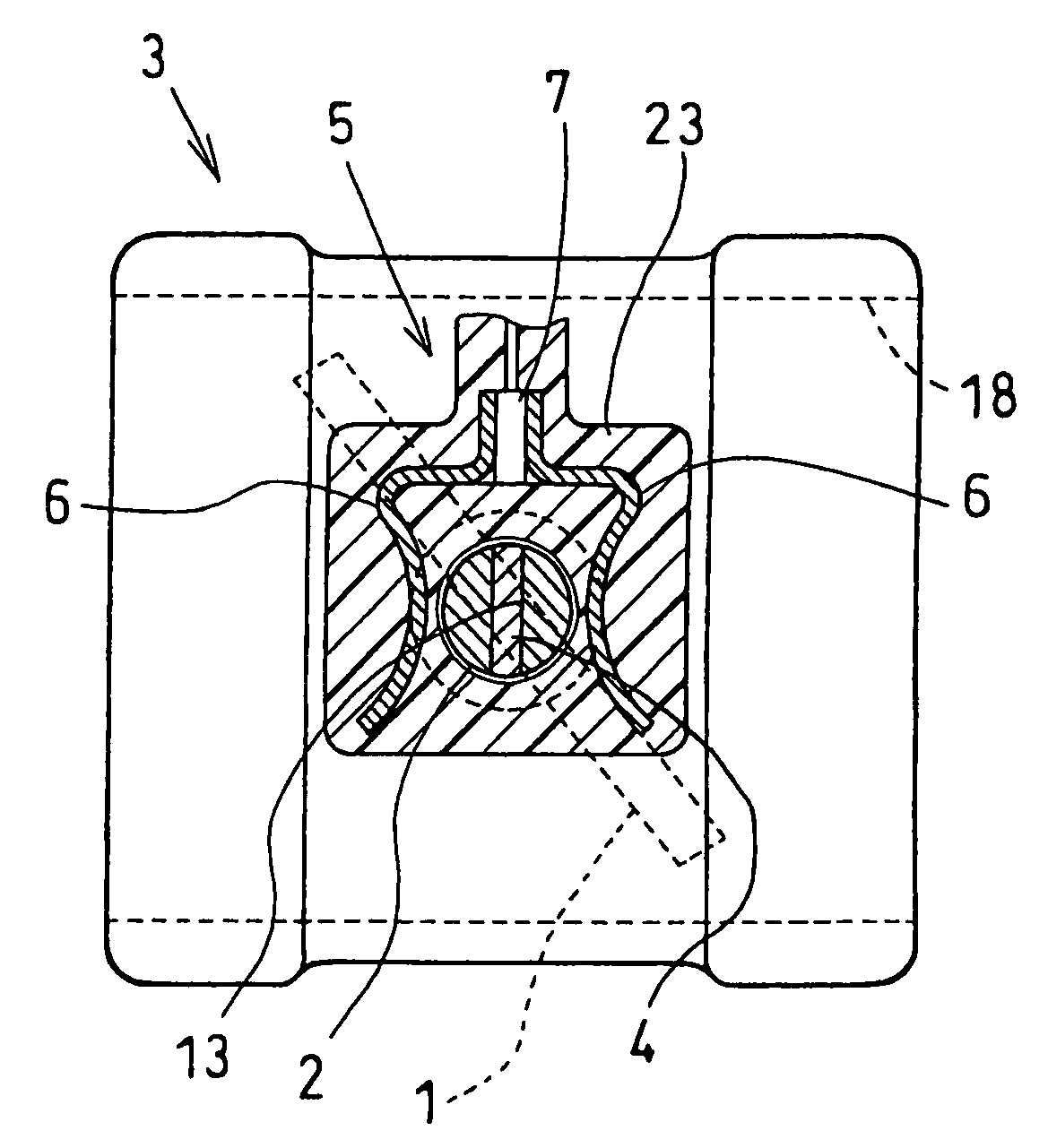

Rotation angle detecting device

InactiveUS20060119353A1Easy to detectImprove output linearityUsing electrical meansConverting sensor output electrically/magneticallyVertical planeElectrical polarity

A rotation angle detecting device includes a magnet (4), a magnetic substance unit (5), and a non-contact magnetic detection element (7). The magnet (4) rotates with an object to be measured and includes two ends magnetized so as to have opposite polarities. The magnetic substance unit (5) forms a predetermined air gap with the two ends of the magnet (4) and is divided into magnetic members (6) so as to provide plane symmetry with respect to a vertical plane perpendicularly crossing a rotational center axis of the magnet (4) to form a magnetic detection gap (9) by the division. The non-contact magnetic detection element (7) is provided in the magnetic detection gap (9) between the magnetic members (6) so as to output a signal corresponding to a density of a magnetic flux passing through the magnetic detection gap (9). The rotation angle of the object to be measured is detected based on the output signal from the magnetic detection element (7). The magnetic members (6) include reverse warp parts (34) so that the air gap suddenly increases when the magnet (4) rotates at a predetermined rotation angle from a state where the air gap is minimum in a direction in which the air gap increases.

Owner:DENSO CORP

Power amplifier protection circuit

ActiveUS8258876B1Maintain stabilityProtect powerNegative-feedback-circuit arrangementsGain controlDriver circuitNegative feedback

A protection circuit for a power amplifier connected as a negative feedback loop around the power amplifier. The negative feedback loop comprises a detector circuit, a driver circuit and an attenuator circuit. The detector circuit receives output voltage from the power amplifier and generates a signal when the output voltage exceeds a predefined threshold. The driver circuit filters the signal received from the detector circuit to maintain feedback loop stability and adjusts the feedback loop bandwidth and gain to provide a filtered signal. The attenuator circuit receives the filtered signal and attenuates the input voltage of the power amplifier to reduce the output voltage of the power amplifier to a level below the predefined threshold.

Owner:SKYWORKS SOLUTIONS INC

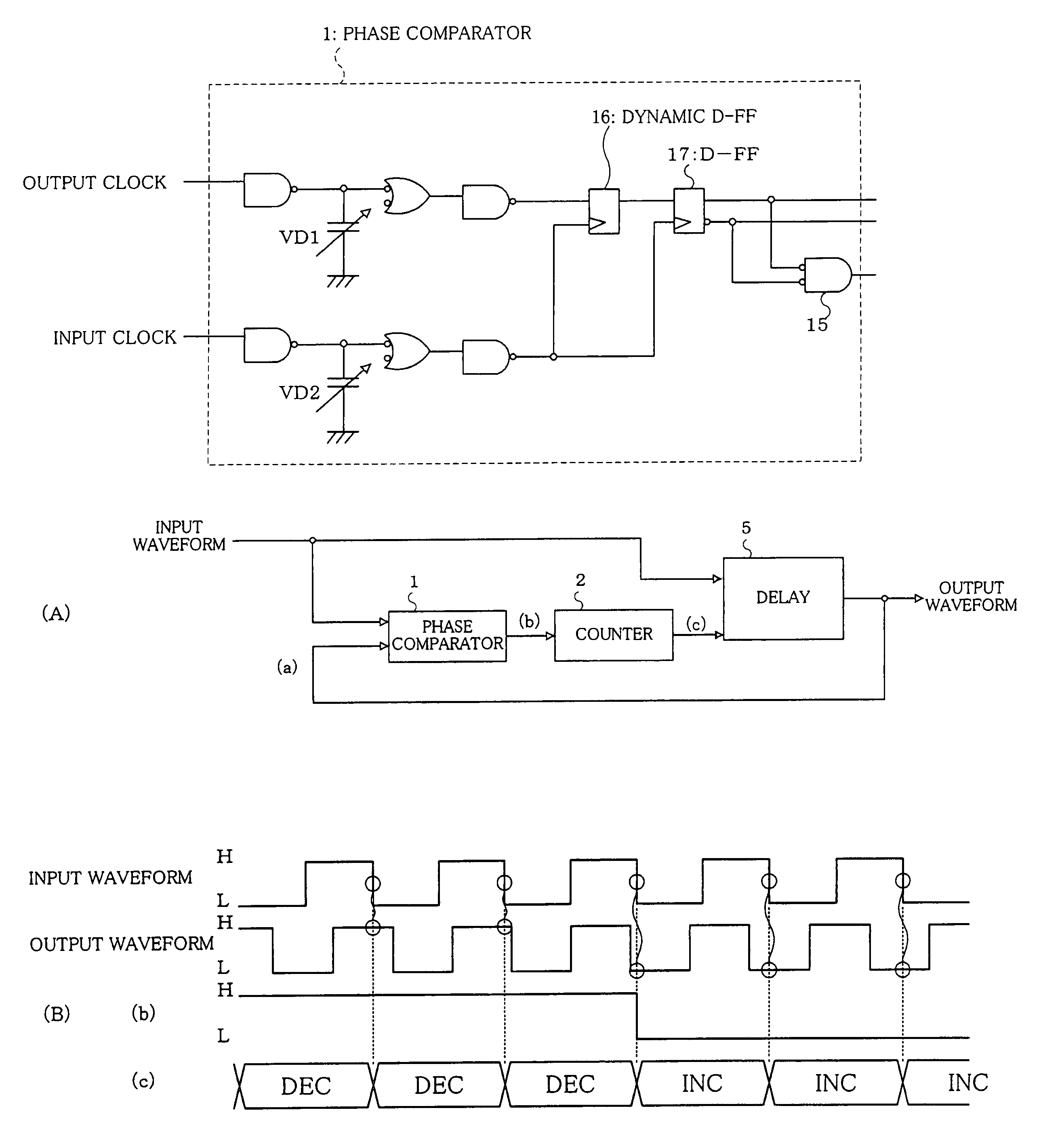

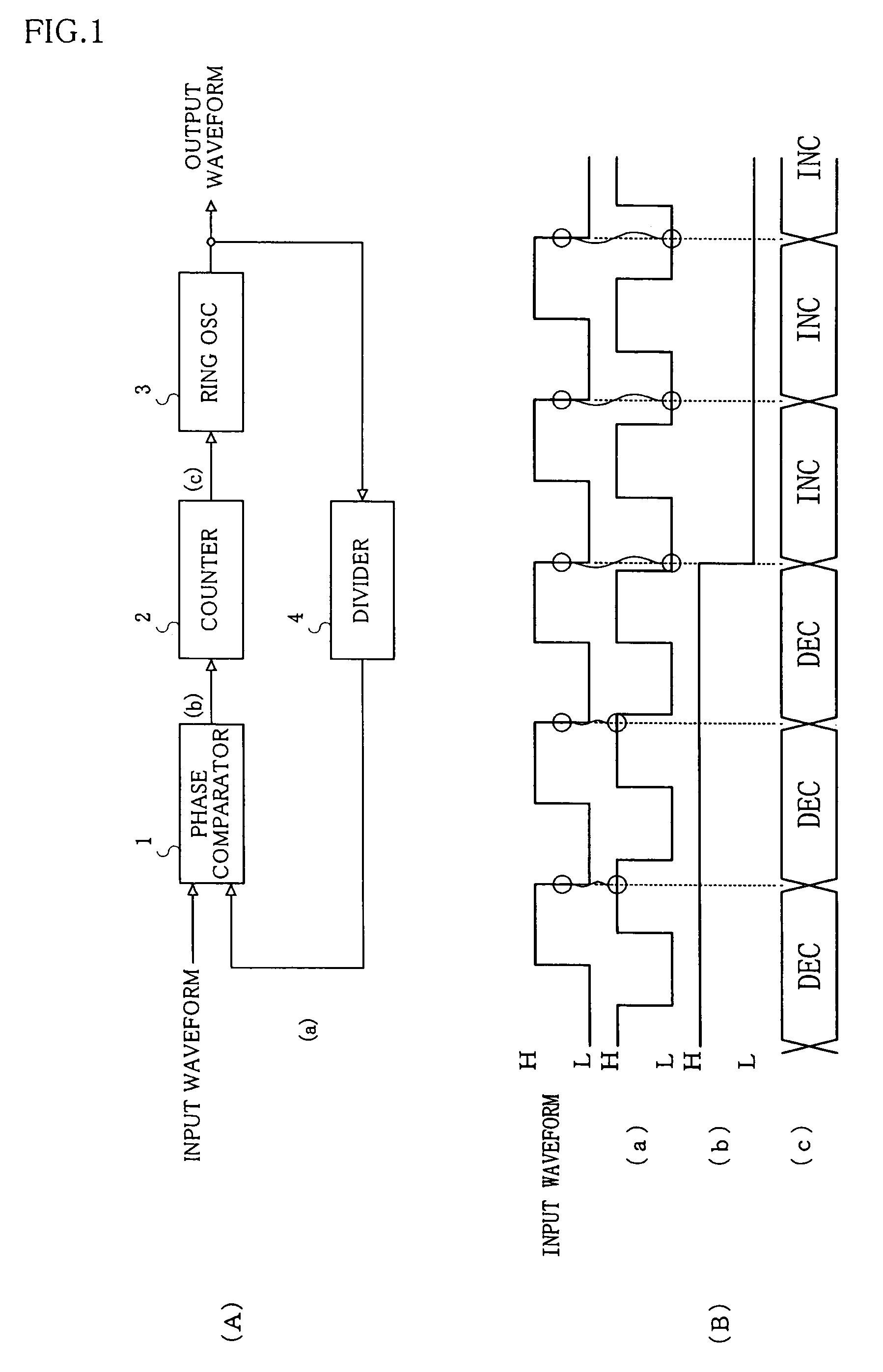

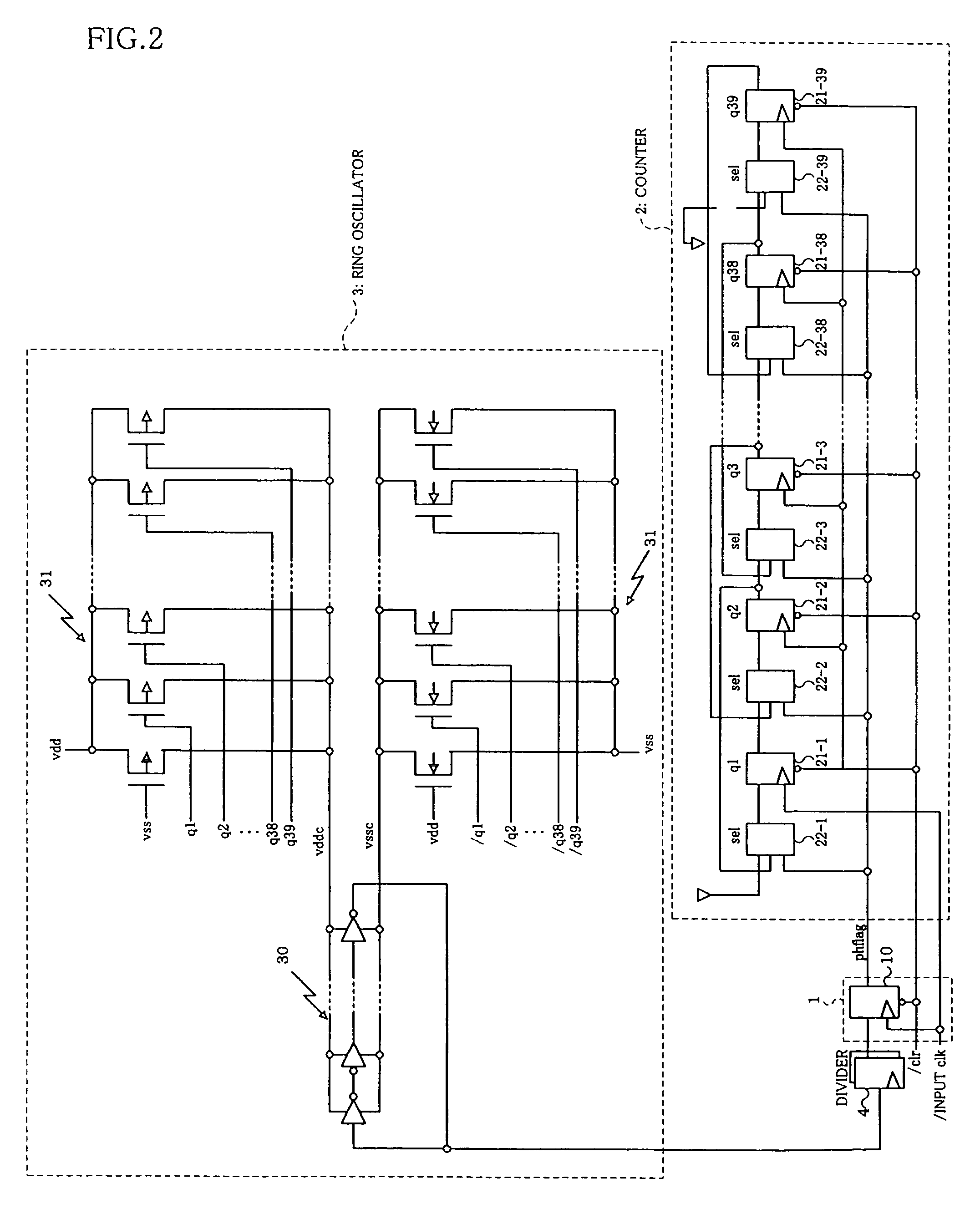

Phase-locked loop circuit, delay locked loop circuit, timing generator, semiconductor test instrument, and semiconductor integrated circuit

InactiveUS7492198B2Enhanced output signalReduce output signalPulse automatic controlVoltage-current phase anglePhase locked loop circuitControl signal

A PLL and DLL are designed such that the power consumption is reduced, the size is reduced, the band width of the locked loop is increased, and the reliability is improved. There are provided a phase comparator for measuring the value of a feedback signal in synchronism with an input signal and outputting a phase signal representing the lead or lag of the phase of the feedback signal, a counter for increasing by one the number of bits representing “H” in a control signal when the phase signal represents the lead of the phase or decreasing by one the number of bits representing “H” in the control signal when the phase signal represents the lag of the phase, and a ring oscillator for increasing the oscillation period when the number of bits representing “H” in the control signal increases or decreasing the oscillation period when the number of bits representing “H” decreases.

Owner:ADVANTEST CORP

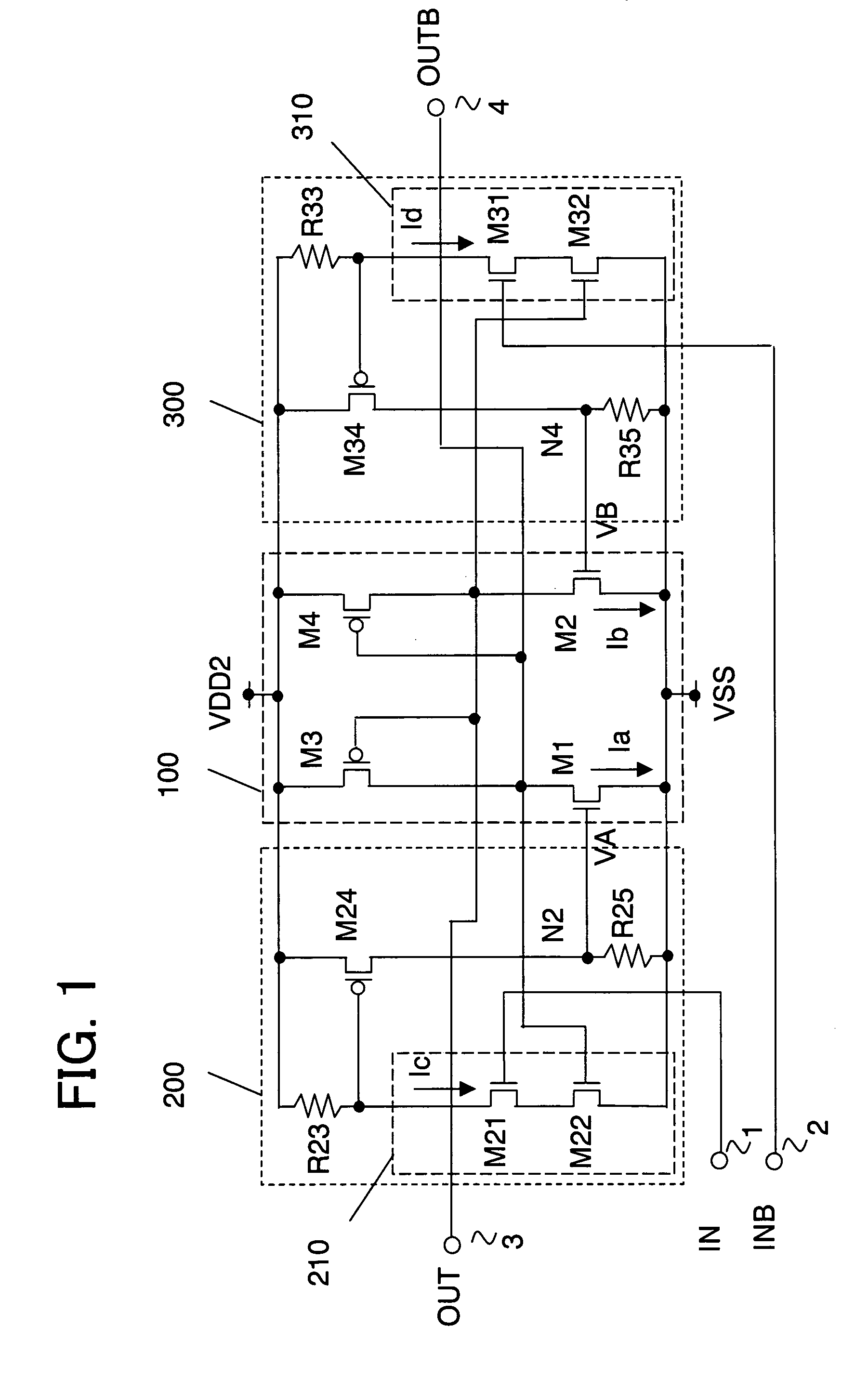

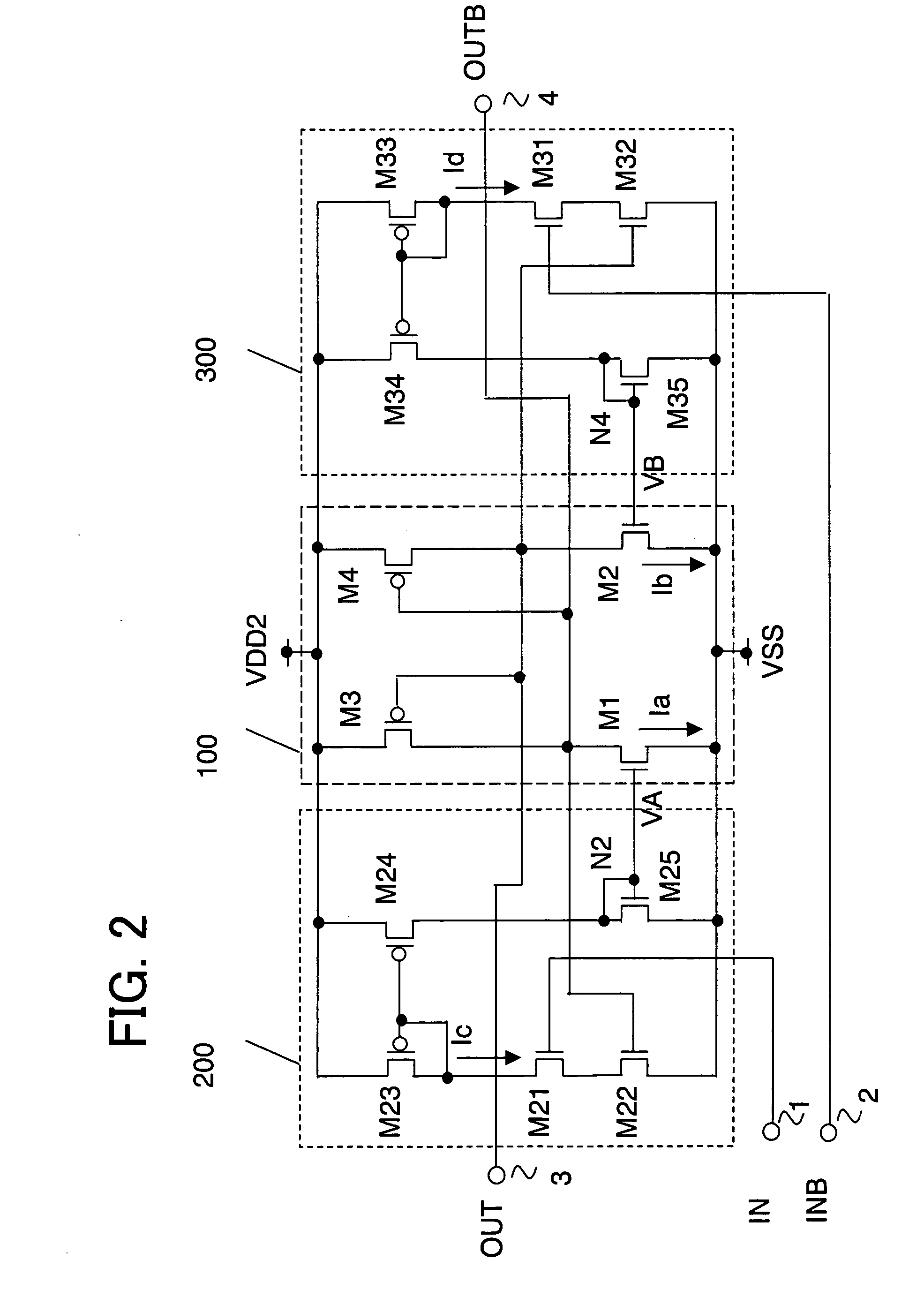

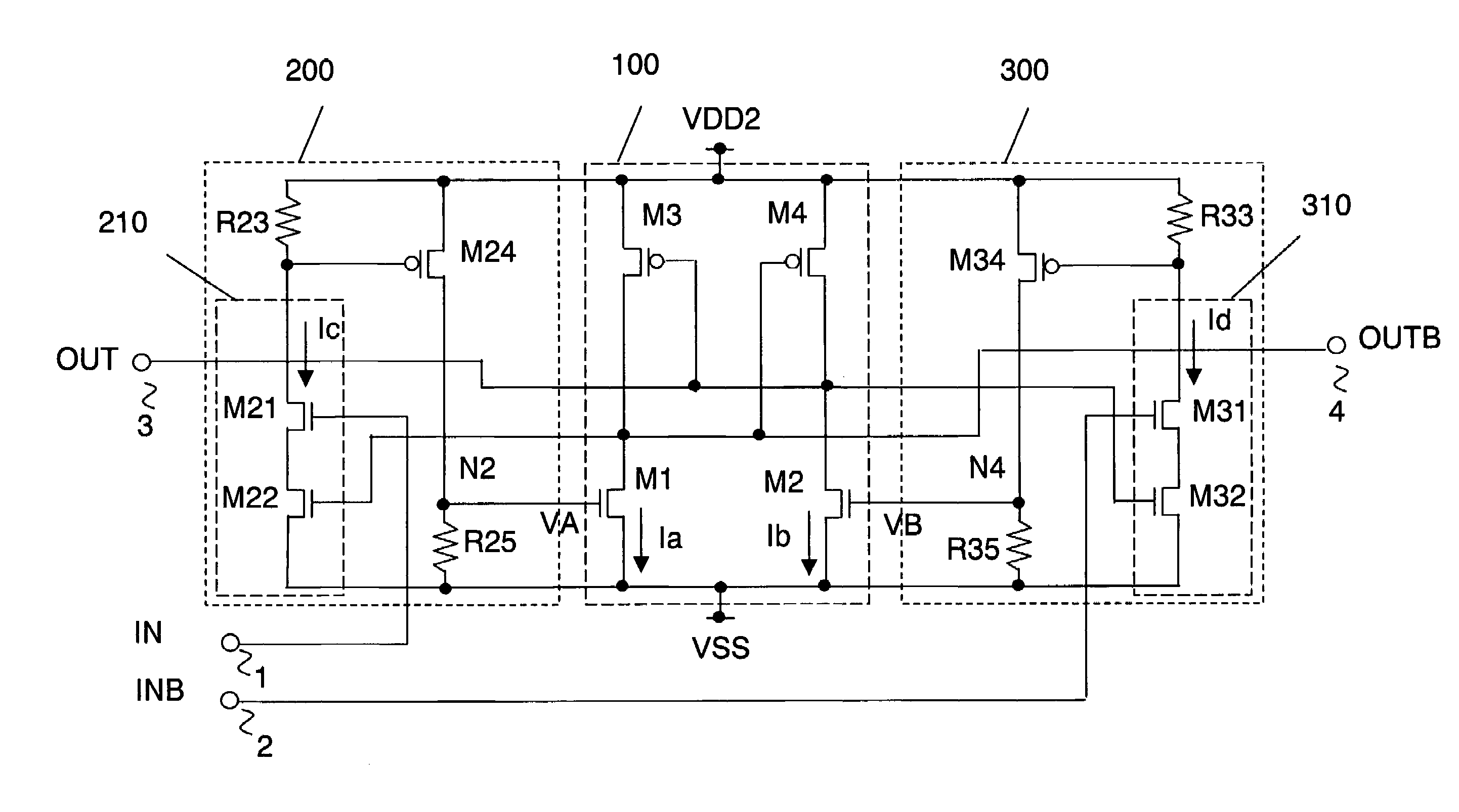

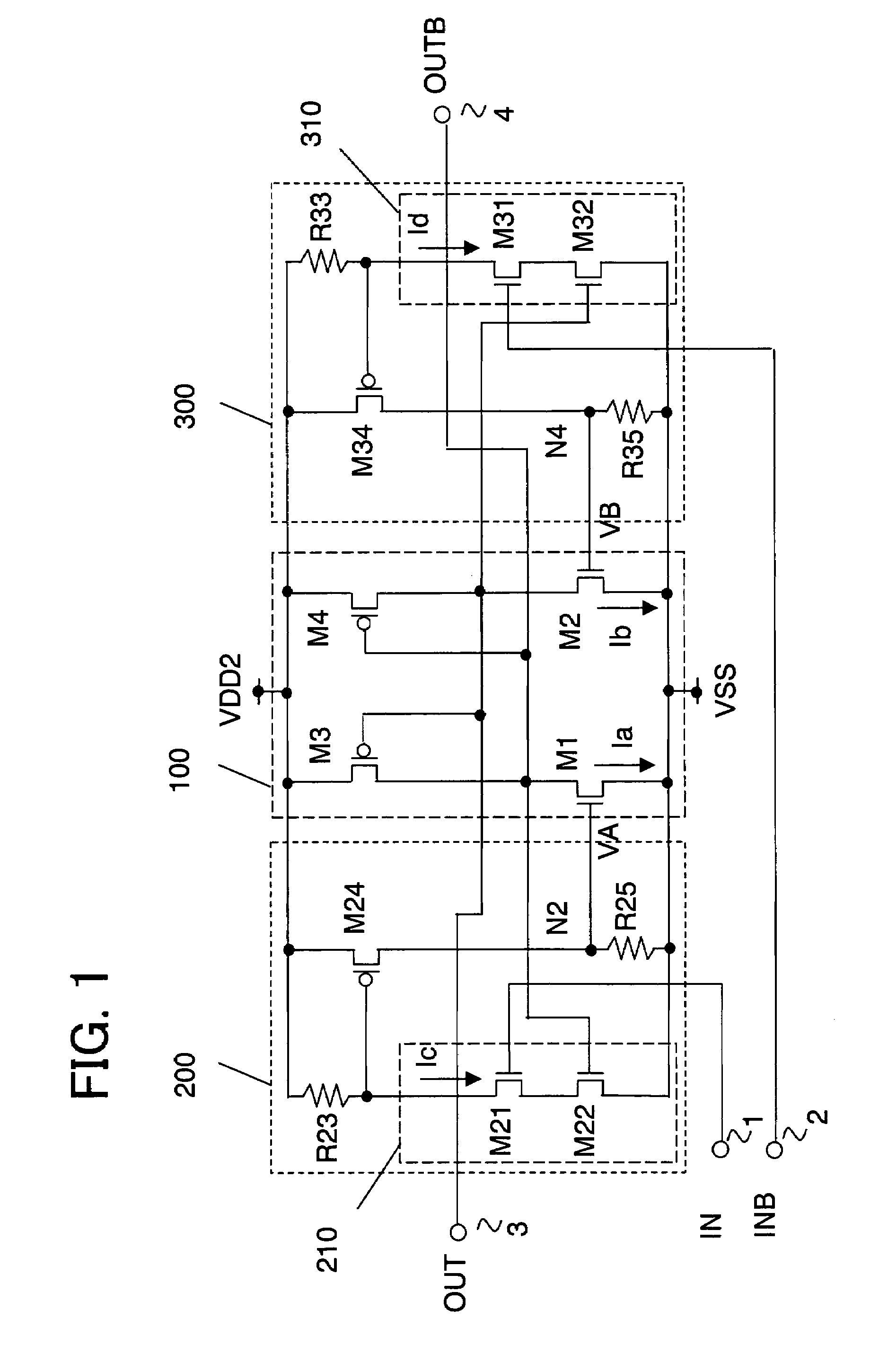

Level shift circuit and driver circuit using the same

InactiveUS20070146042A1Guaranteed uptimePrevent output delayPulse automatic controlElectric pulse generatorDriver circuitElectrical polarity

A level shift circuit operates normally when amplitude of input signal is small and amplitude of output signal is large. First and second terminals receive an input signal and its complementary signal having a first amplitude. Third and fourth terminals output an output signal and its complementary signal having a second amplitude, which is larger than the first amplitude. Output circuit comprises first and second transistors of first polarity respectively connected between first power supply and fourth and third terminals, respectively. Third and fourth transistors of second polarity, respectively, are connected between second power supply and fourth and third terminals, respectively, having control ends connected to the third and the fourth terminals, respectively. First current control circuit controls so that a current driving the fourth terminal flows through the first transistor according to the input signal and the complementary signal of the output signal. Second current control circuit controls so that a current driving the third terminal flows through the second transistor according to the complementary signal of the input signal and the output signal.

Owner:NEC CORP

MIMO-CDMA apparatus and the coding/decoding method thereof

InactiveUS20070133659A1Reduce output signalEnhanced signalMultiplex communicationDiversity/multi-antenna systemsDecoding methodsCode division multiple access

A Multiple-Output Multiple-Input Code-Division Multiple Access (MIMO-CDMA) apparatus and the coding method thereof. The apparatus includes a transmitter side and receiver side. Both of the transmitter side and the receiver side have a plurality of antennas for achieving the effect of multi-path transmission and receiving. In addition, at the receiver side, use preamble-spreading codes and space-time block coding technology to eliminate multi-path signal interference as well as to modify carrier frequency shift of the received signal.

Owner:NAT CHUNG SHAN INST SCI & TECH

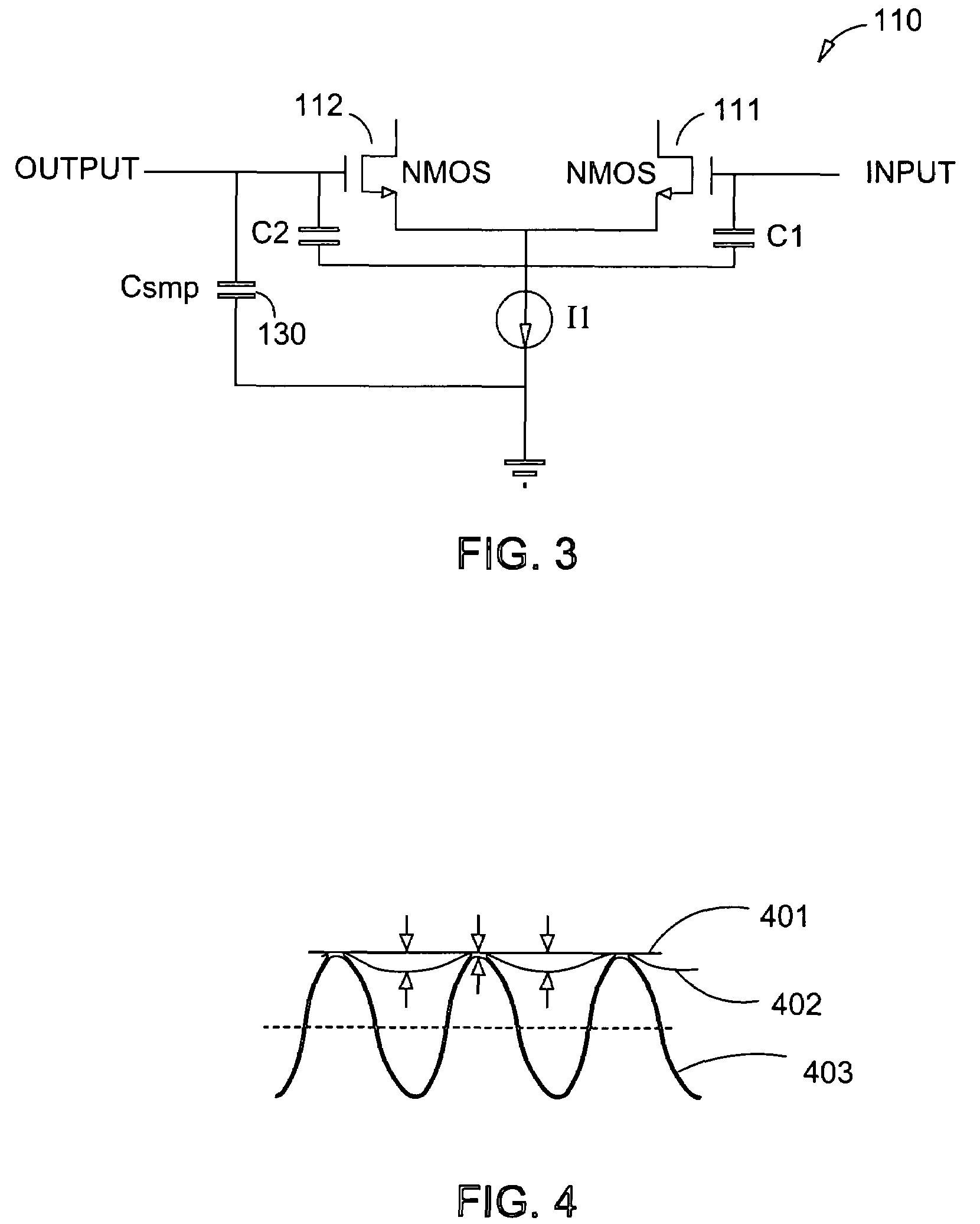

Differential peak detector

ActiveUS7525347B1High signal to noise ratioReduce output signalMultiple input and output pulse circuitsCurrent/voltage measurementTransconductancePeak value

Differential peak detection for outputting a signal indicative of a peak value of an input signal. The input signal is differentially amplified using common mode feedback and a common mode output is thereby output, wherein common mode level of the common mode output is substantially the same as a common mode voltage. The common mode output of such differential amplification is coupled to an input of a first common source input pair, and the common mode voltage and a feedback from the output signal across a sampling capacitor is coupled to an input of a second common source input pair. A summation of respective outputs of the first and second common source input pairs is coupled to an input of a transconductance stage, wherein an output of the transconductance stage controls charging of the sampling capacitor. In this manner, a more accurate output signal is provided.

Owner:MARVELL ASIA PTE LTD

Rotation angle detecting device

InactiveUS7078893B2Easy to detectImprove output linearityUsing electrical meansConverting sensor output electrically/magneticallyVertical planeEngineering

A rotation angle detecting device includes a magnet (4), a magnetic substance unit (5), and a non-contact magnetic detection element (7). The magnet (4) rotates with an object to be measured and includes two ends magnetized so as to have opposite polarities. The magnetic substance unit (5) forms a predetermined air gap with the two ends of the magnet (4) and is divided into magnetic members (6) so as to provide plane symmetry with respect to a vertical plane perpendicularly crossing a rotational center axis of the magnet (4) to form a magnetic detection gap (9) by the division. The non-contact magnetic detection element (7) is provided in the magnetic detection gap (9) between the magnetic members (6) so as to output a signal corresponding to a density of a magnetic flux passing through the magnetic detection gap (9). The rotation angle of the object to be measured is detected based on the output signal from the magnetic detection element (7). The magnetic members (6) include reverse warp parts (34) so that the air gap suddenly increases when the magnet (4) rotates at a predetermined rotation angle from a state where the air gap is minimum in a direction in which the air gap increases.

Owner:DENSO CORP

Capacitance type sensor

InactiveUS6867601B2Good reproducibilitySuppress errorCapacitance measurementsCapacitor with electrode area variationCapacitanceEngineering

A sensor unit having capacitance element electrodes and a displacement electrode being opposite thereto is disposed on a substrate. A detective button is supported onto the substrate in such a manner that the detective button is positioned above the sensor unit to define a specified space between the supporting member for supporting the detective button and the displacement electrode.

Owner:NITTA CORP

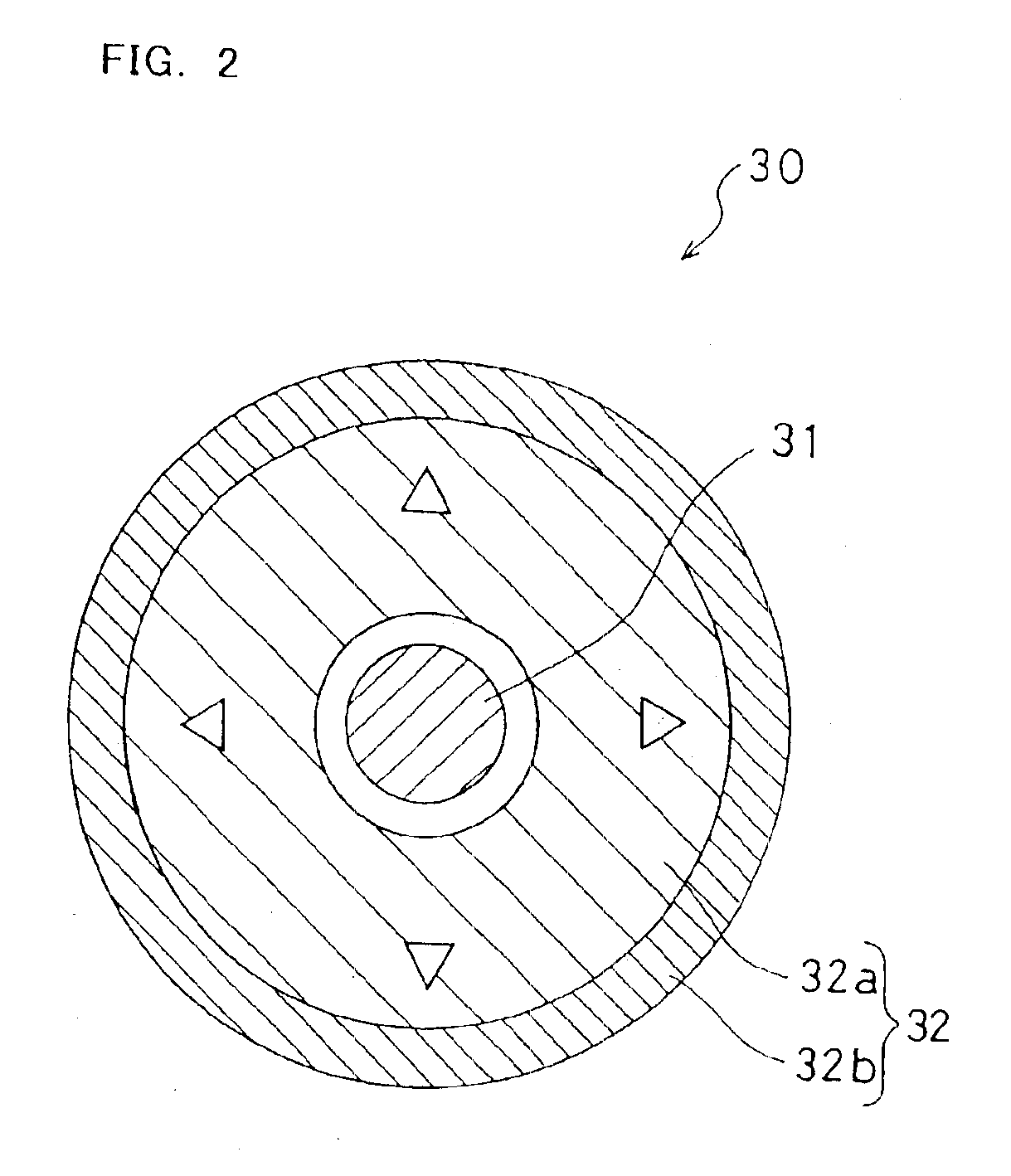

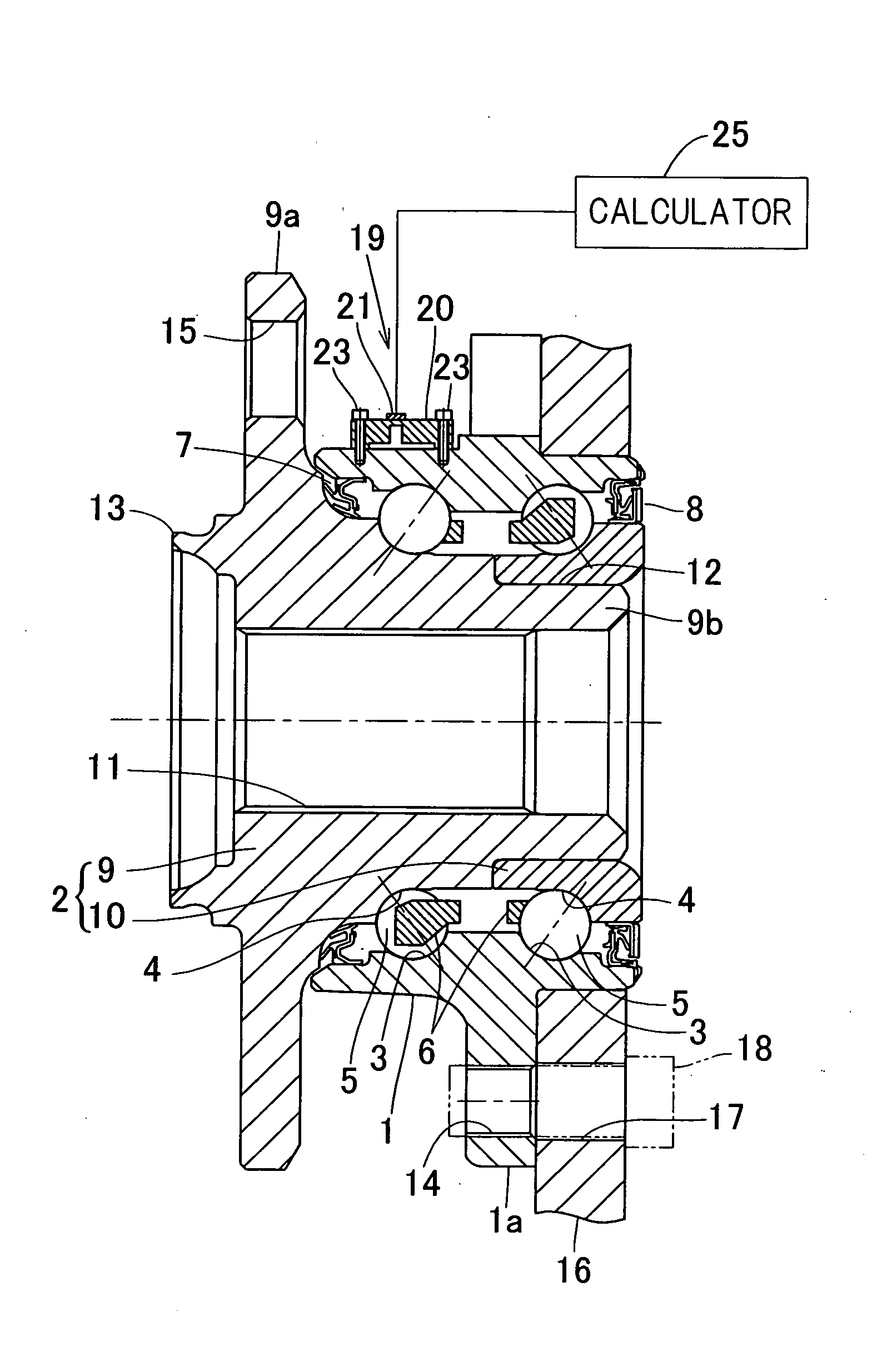

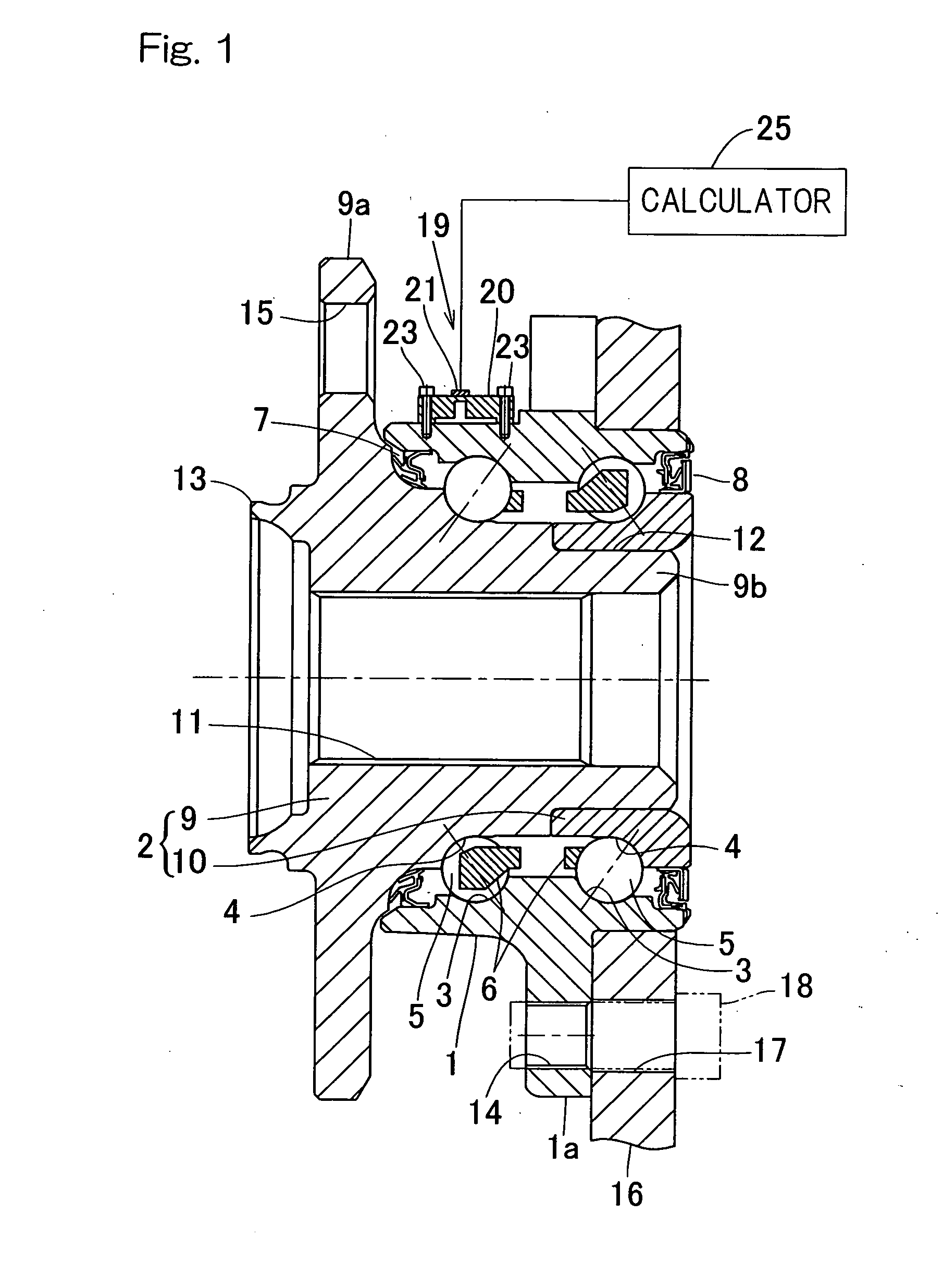

Sensor-equipped bearing for wheel

InactiveUS20100129017A1Easy to installReduce output signalRolling contact bearingsBearing assemblyHysteresisMechanical engineering

A sensor-equipped wheel support bearing assembly, in which a load imposed on the wheel can be accurately detected without influences from hysteresis is provided. This wheel support bearing assembly includes an outer member having a plurality of rolling surfaces, an inner member having rolling surfaces opposed respectively to the rolling surfaces of the outer member, and rolling elements between the rolling surfaces. A sensor unit is provided in a stationary member of one of the outer and inner members, which unit includes a strain generating member having two contact fixing segments to be fixed to the stationary member and a sensor fitted to the strain generating member for detecting a strain induced in this strain generating member. The two contact fixing segments are arranged at respective positions held at the same phase in a direction circumferentially of the stationary member.

Owner:NTN CORP

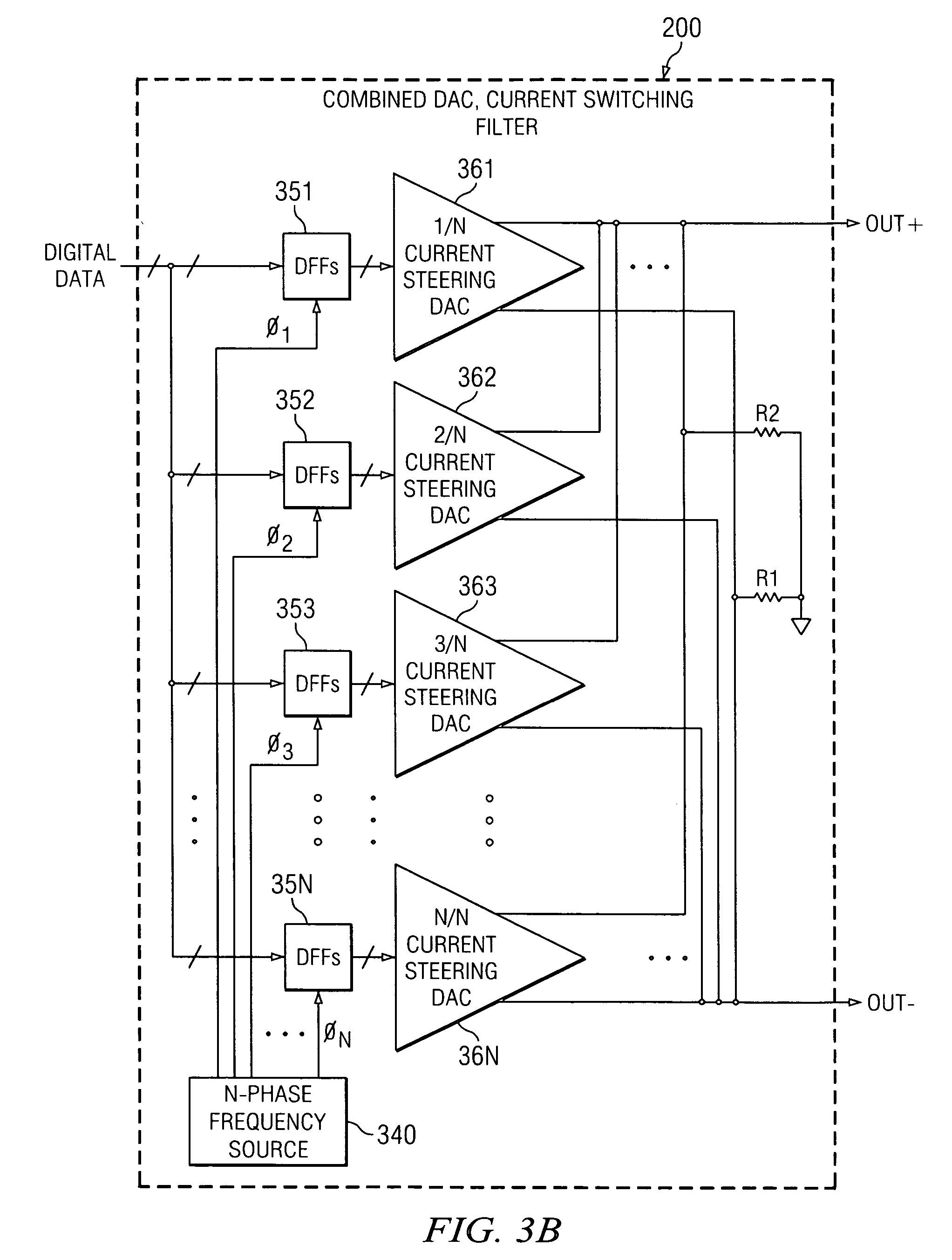

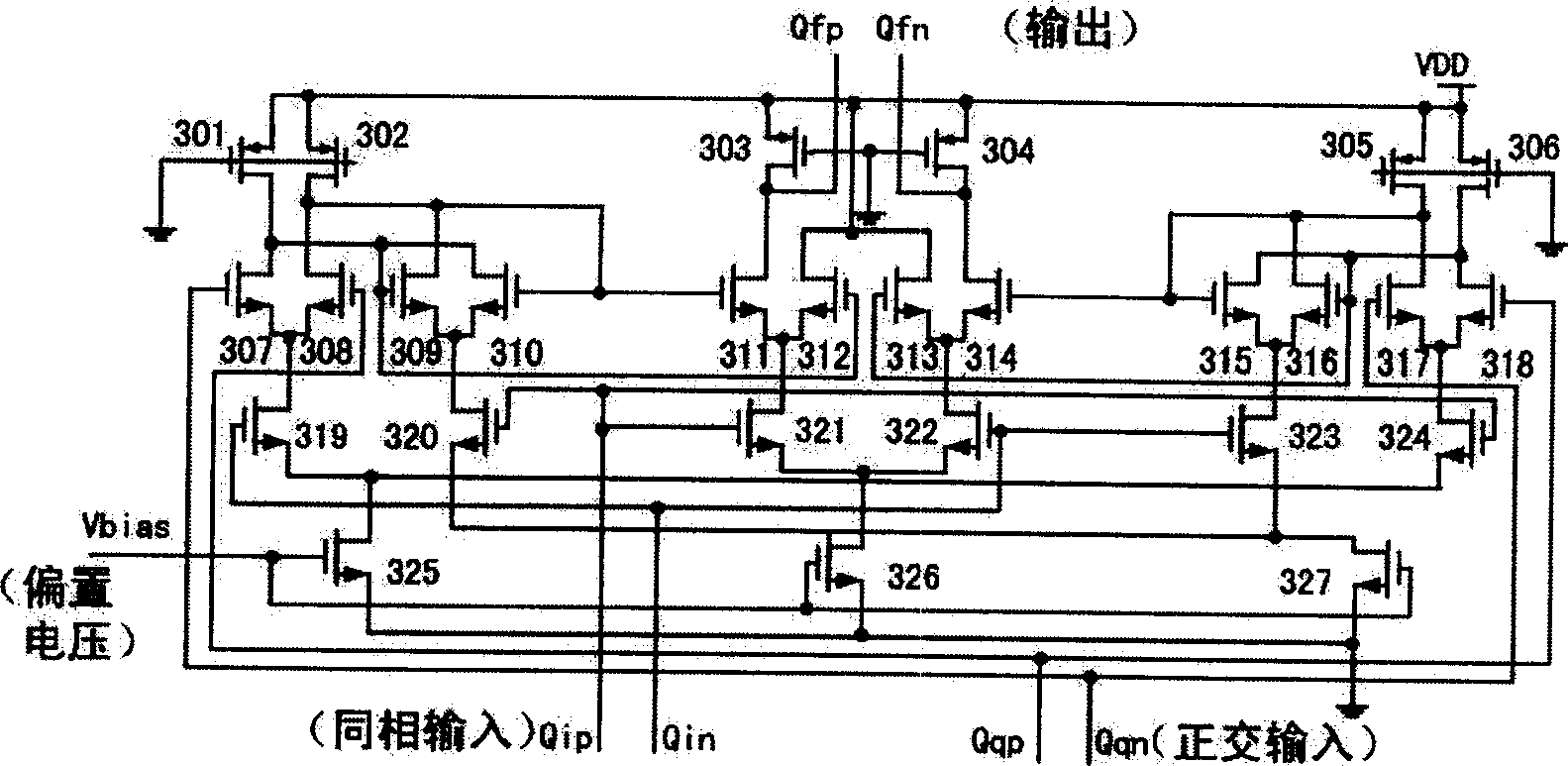

Current switching arrangement for D.A.C. reconstruction filtering

ActiveUS7098830B2Reduce harmonic contentReduce output signalElectric signal transmission systemsTransmissionDigital analog converterHarmonic

An arrangement provides a reduced harmonic content output signal that represents a value of a digital input signal. The arrangement includes plural storage devices 301 . . . configured to sample and store the digital input signal at different respective phases of a clock signal. The arrangement also has plural current steering digital-to-analog converters (DACs) 311 . . . configured to receive respective stored digital signals from respective ones of the plural storage devices, and to provide respective currents that represent the received stored digital signals. The arrangement also includes a combining arrangement configured to combine the currents from respective ones of the plural current steering DACs, so as to provide the reduced harmonic content output signal that represents the value of the digital input signal.

Owner:TEXAS INSTR INC

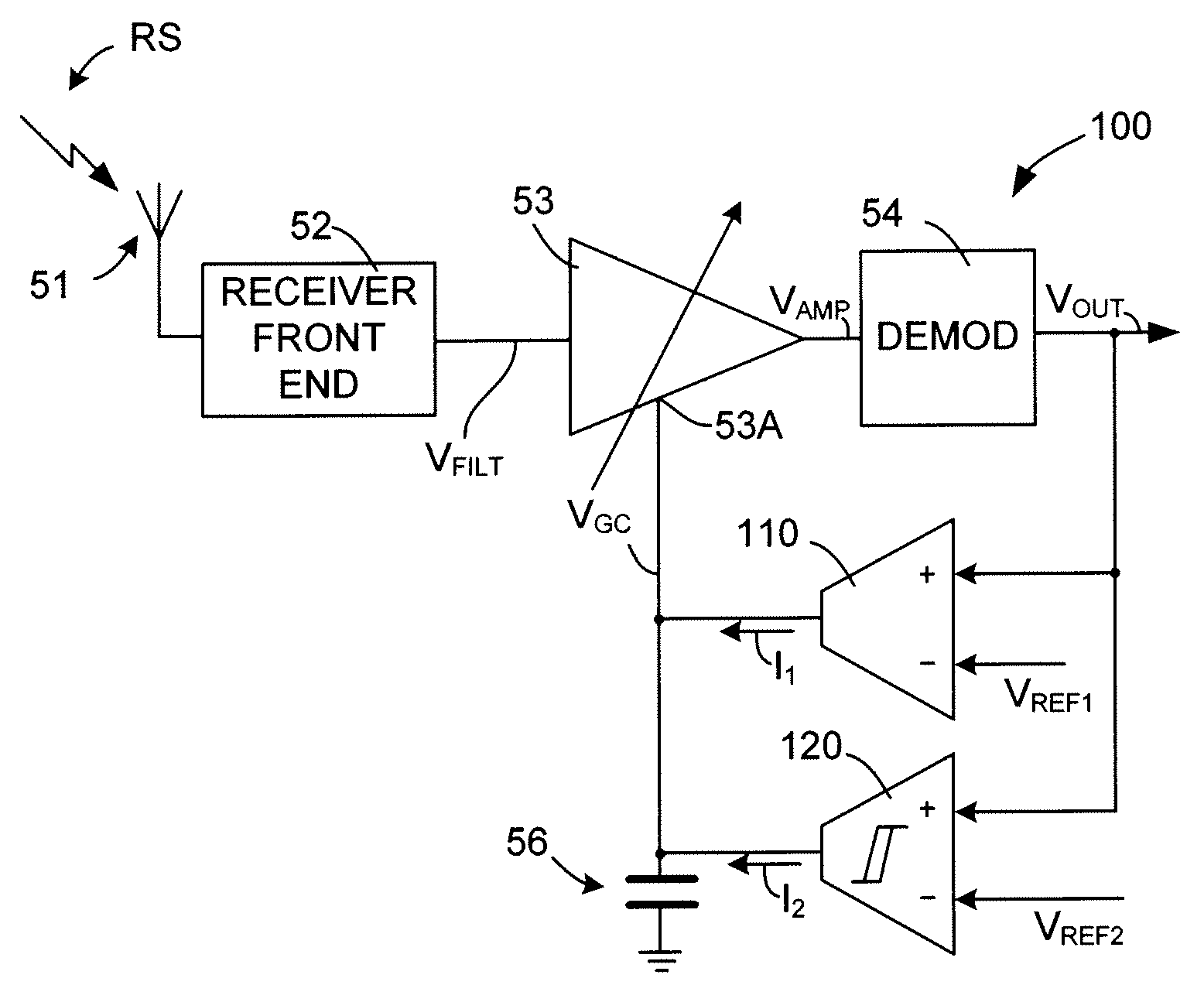

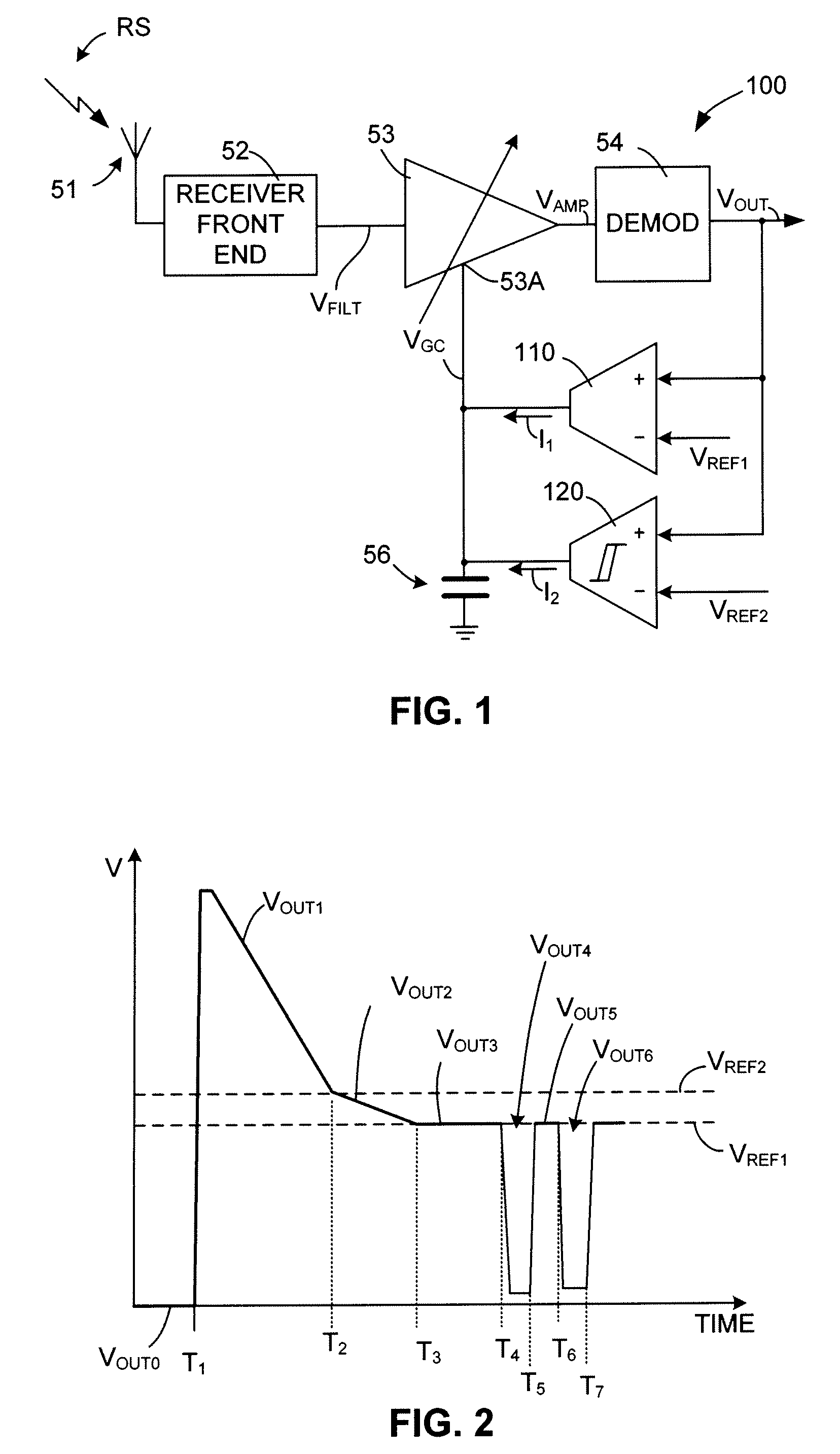

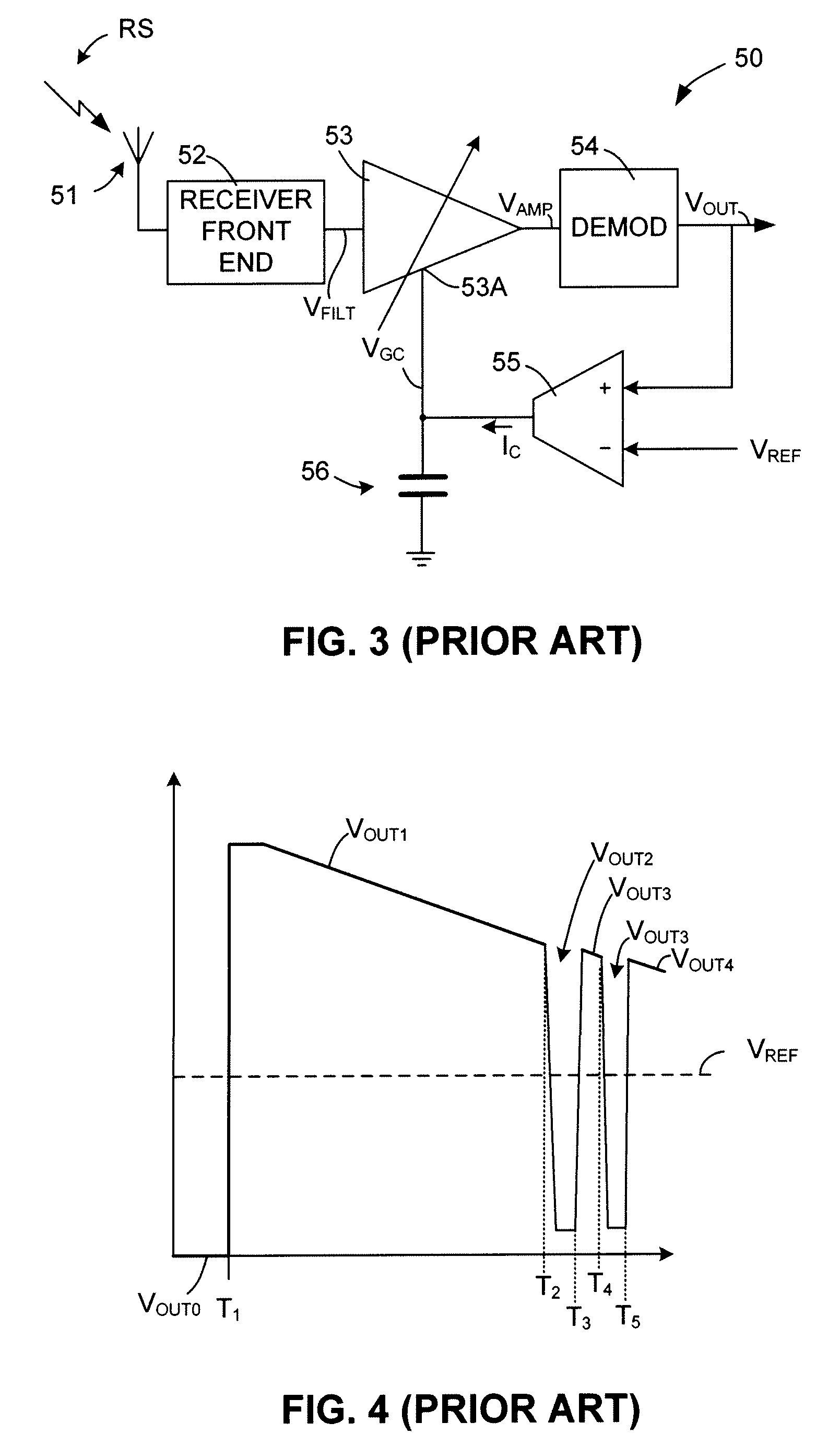

Fast Settling Radio Receiver Automatic Gain Control System

ActiveUS20090117868A1High output signalReduce delayGain controlRadio transmissionRadio receiverRadio reception

Owner:MICREL

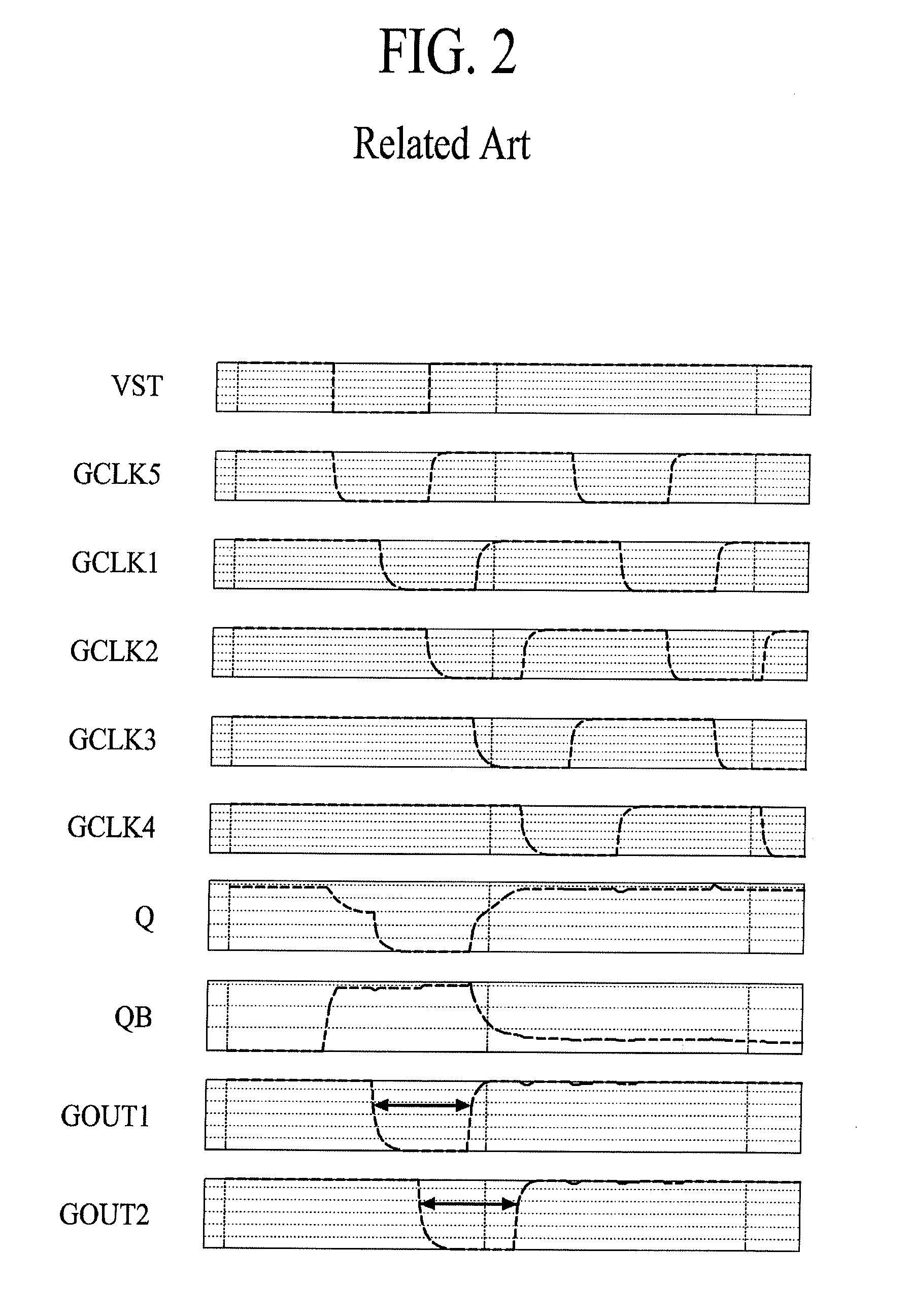

Shift register and method of driving the same

ActiveUS20140146031A1Reduce output signalCathode-ray tube indicatorsDigital storageShift registerDisplay device

A shift register for flat panel display devices includes a start signal unit configured to control a start of an output signal, an end signal unit configured to control an end of the output signal, and a plurality of stages configured to increase the output signal to a high-level driving voltage according to a signal supplied from a first node connected to the start signal unit, and decrease the output signal to a low-level driving voltage according to a signal supplied from a second node connected to the end signal unit. Each of the plurality of stages generates multi signals for diving a pixel circuit of a display device.

Owner:LG DISPLAY CO LTD

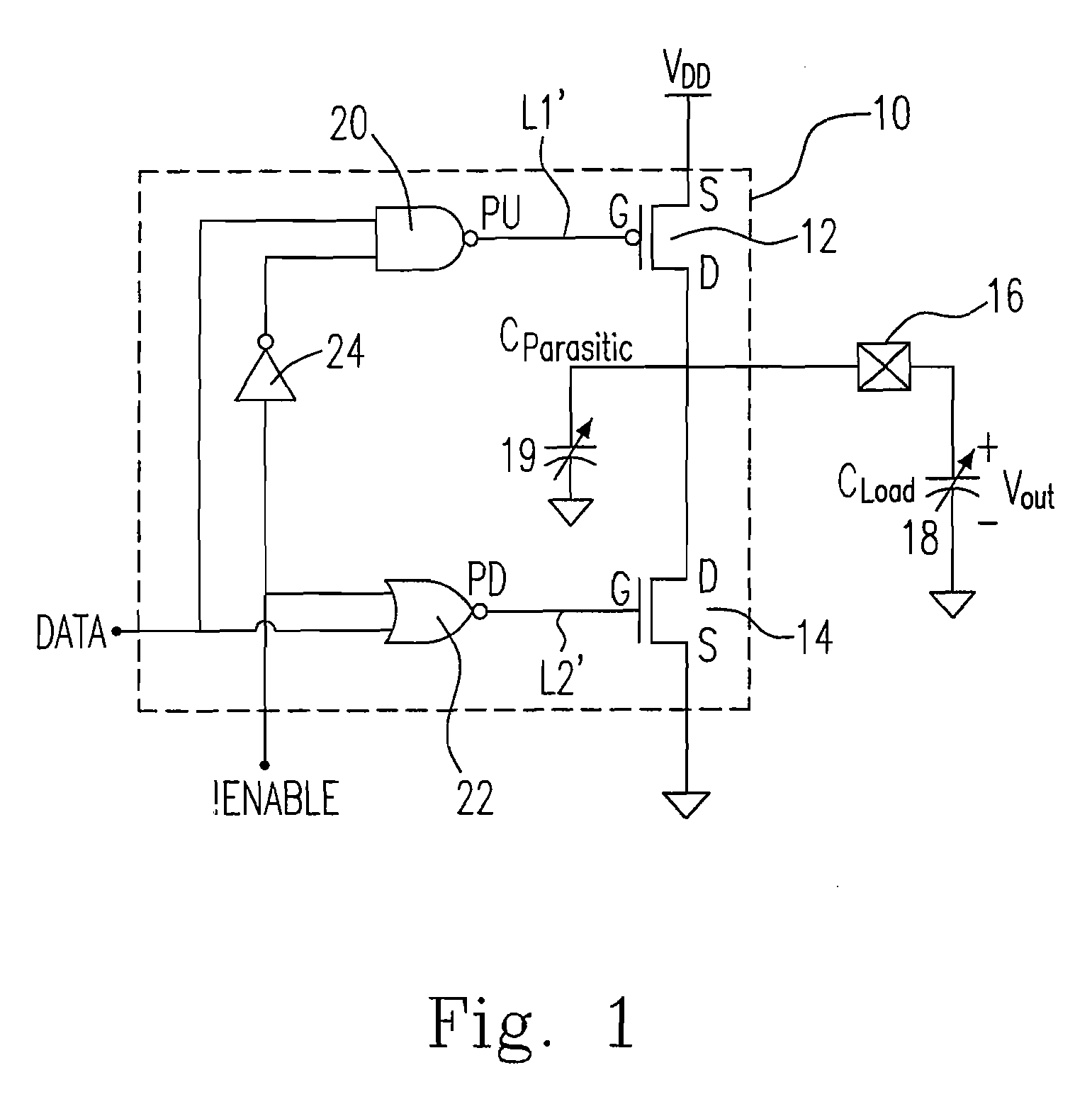

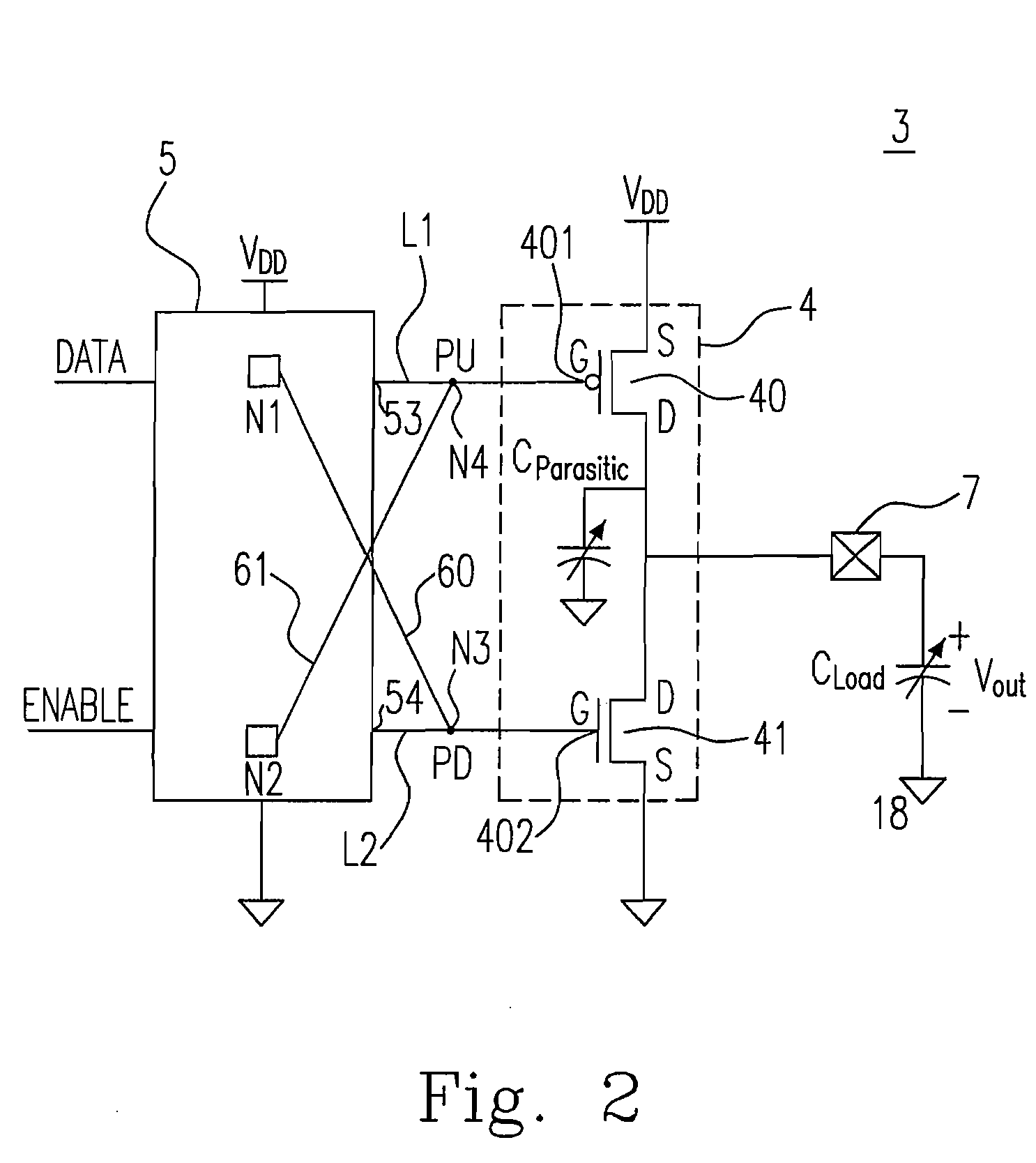

Output buffer device

ActiveUS20090195270A1Minimizing short-circuit currentReducing output signal ringingPower reduction in field effect transistorsDigital storageData bufferTime difference

A controlling output buffer slew rate method and an output buffer circuit for a memory device is provided. The output buffer include an output stage formed by a PMOS transistor and a NMOS transistor electrically connected in series, a pre-driver for respectively controlling each gate terminal of the PMOS transistor and the NMOS transistor in order to bring these transistors to the turning-on threshold, a first wire, for transmitting a pull-up signal, coupled between the output stage and the pre-driver, and a second wire, for transmitting a pull-down signal, coupled between the output stage and the pre-driver. After a DATA signal transition (logic state is changed from “H” to “L” or “L” from to “H”), the PMOS or NMOS transistor is turned off first, and then the NMOS or PMOS transistor is turned on due to the time difference between the pull-up signal and the pull-down signal.

Owner:MACRONIX INT CO LTD

Four path parallel clock data restoring circuit

InactiveCN1750400AReduce system complexityReduce complexityPulse automatic controlElectromagnetic transmissionClock recoveryPhase-locked loop

A four-channel parallel clock data resuming circuit includes a clock resuming phase-lock loop, three data delay phase-lock loops and a data resuming circuit, among which, the second channel input data is connected with the input of the clock resume phase-lock loop, which outputs the global clock signal, the global clock is aligned with the second channel input data and connected with the clock input ends of three data delay phase-lock loops, the input data of the other three channel input data are connected with the data input ends of the three data delay phase-lock loops, the three resume phase lock loops align the three channels of data signals with the global clock to realize the alignment of the four channels connected with the input of the resuming circuit, the global is connected with its clock input finally to output four channels of bit synchronous data signals and a global clock signal.

Owner:SOUTHEAST UNIV

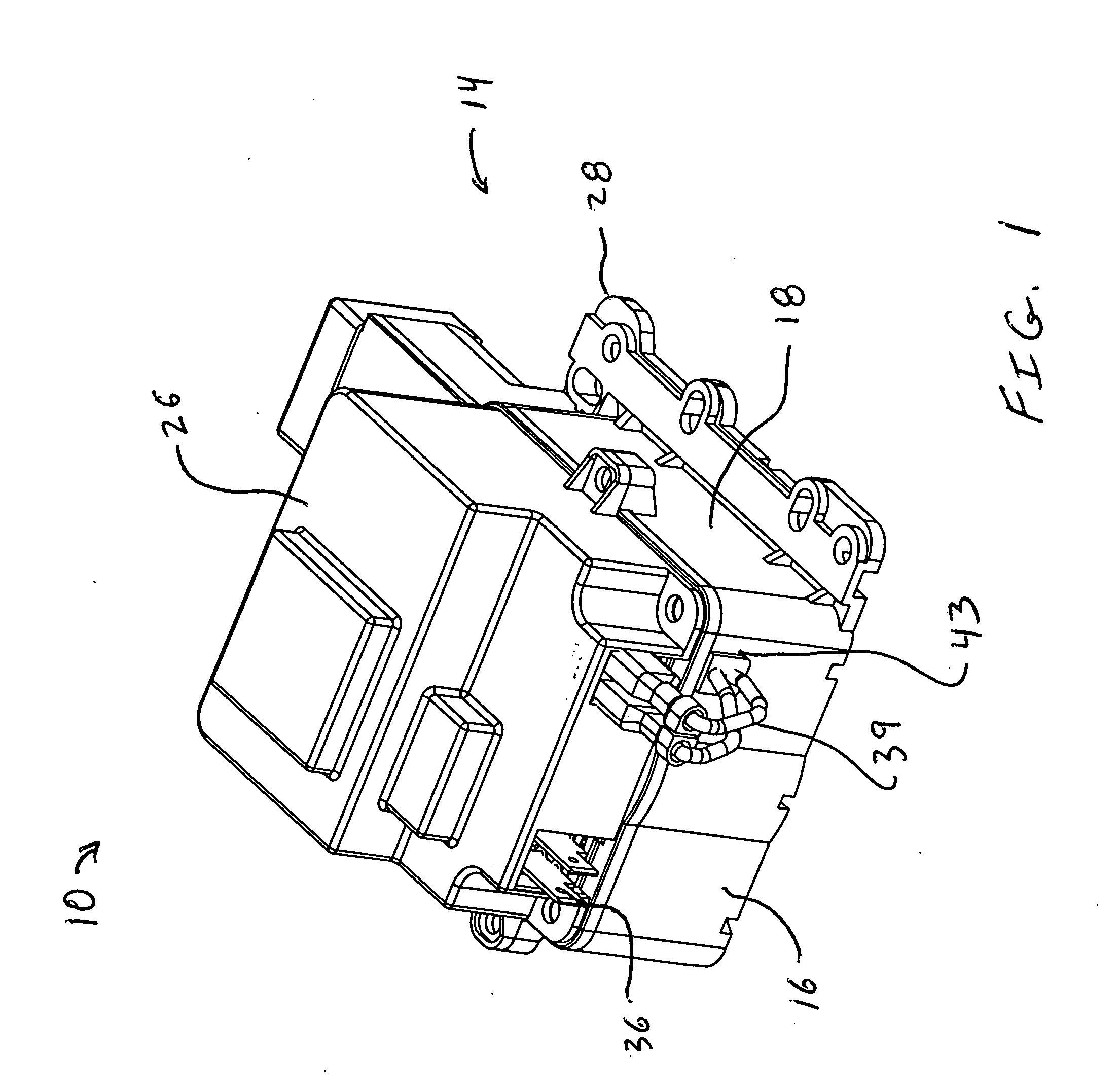

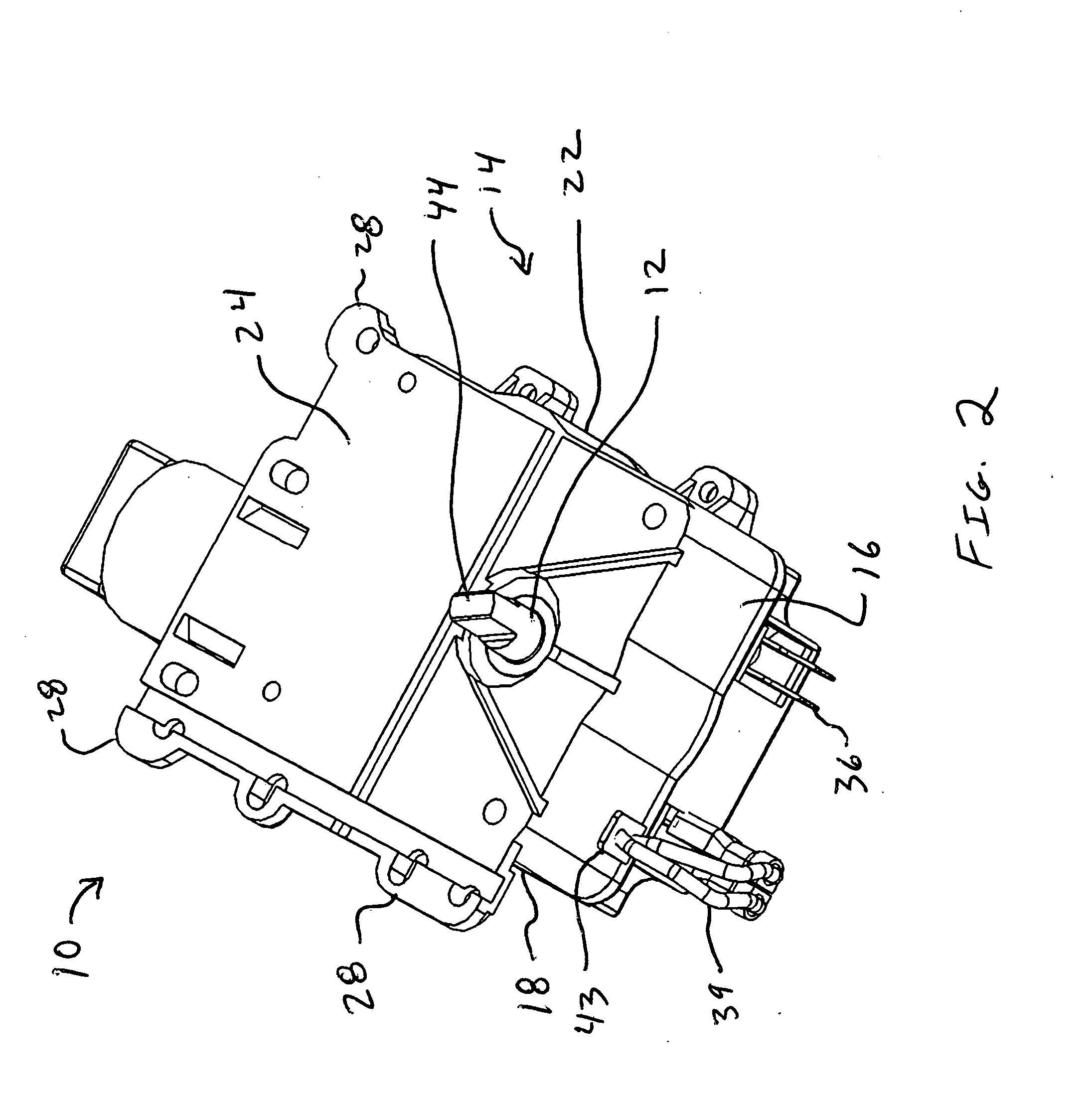

Drain valve actuators and methods of controlling drain valves

ActiveUS20090108220A1Reduce output signalOperating means/releasing devices for valvesDC motor speed/torque controlValve actuatorGear train

A valve actuator operates a valve, such as a drain valve of an industrial washing machine. The valve actuator has a permanent magnet DC motor which drives a gear train which rotatably drives an output shaft. The output shaft is engaged with the drain valve and moves the drain valve to open and closed positions as desired. The valve actuator also has a controller which controls operation of the valve actuator. The controller provides power to the motor only when needed to open and close the drain valve. The controller does not provide power to the motor when the drain valve is in the open and closed positions.

Owner:MOLON MOTOR & COLL

Output buffer device

ActiveUS7786761B2Minimise currentReduce output signalPower reduction in field effect transistorsDigital storageData signalEngineering

A controlling output buffer slew rate method and an output buffer circuit for a memory device is provided. The output buffer include an output stage formed by a PMOS transistor and a NMOS transistor electrically connected in series, a pre-driver for respectively controlling each gate terminal of the PMOS transistor and the NMOS transistor in order to bring these transistors to the turning-on threshold, a first wire, for transmitting a pull-up signal, coupled between the output stage and the pre-driver, and a second wire, for transmitting a pull-down signal, coupled between the output stage and the pre-driver. After a DATA signal transition (logic state is changed from “H” to “L” or “L” from to “H”), the PMOS or NMOS transistor is turned off first, and then the NMOS or PMOS transistor is turned on due to the time difference between the pull-up signal and the pull-down signal.

Owner:MACRONIX INT CO LTD

Three-axis accelerometer

InactiveUS20210215735A1Reduce distractionsReduce output signalAcceleration measurement using interia forcesSpeed/acceleration/shock instrument detailsCapacitanceRotational axis

A three-axis accelerometer measures acceleration in three axes by a single movable mass block, so that a more compact design of the three-axis accelerometer can be achieved. In addition, a plurality of detection capacitors, which forms differential capacitor pairs, are arranged in symmetric configuration with respect to a rotation axis of the movable mass block for sensing functions. Therefore, during sensing motion of a target axis direction, the all other unwanted capacitance changes in other axis direction may be cancelled.

Owner:MIRAMEMS SENSING TECH CO LTD

Low distortion digital to analog converter and digital signal synthesizer systems

InactiveUS7579971B2Increase sampling rateHigh resolutionDigital variable displayElectric signal transmission systems24-bitLow distortion

The present invention is a digital to analog converter circuit that provides significantly lower distortion than achieved by digital to analog converter circuits having comparable speed and resolution utilizing the present art. The present invention provides linear or higher order transitions between clock transition time points rather than step transitions used in the present art. Distortion reduction can exceed 30 dB in the embodiment with linear sample-to-sample transitions and greater in alternate embodiments with non-linear transitions. In other embodiments, the present invention can provide low distortion at resolutions from 16 to 24 bits or more at sample rates typical of high-speed 8-bit devices of the present art.

Owner:MASHHOON HAMID R

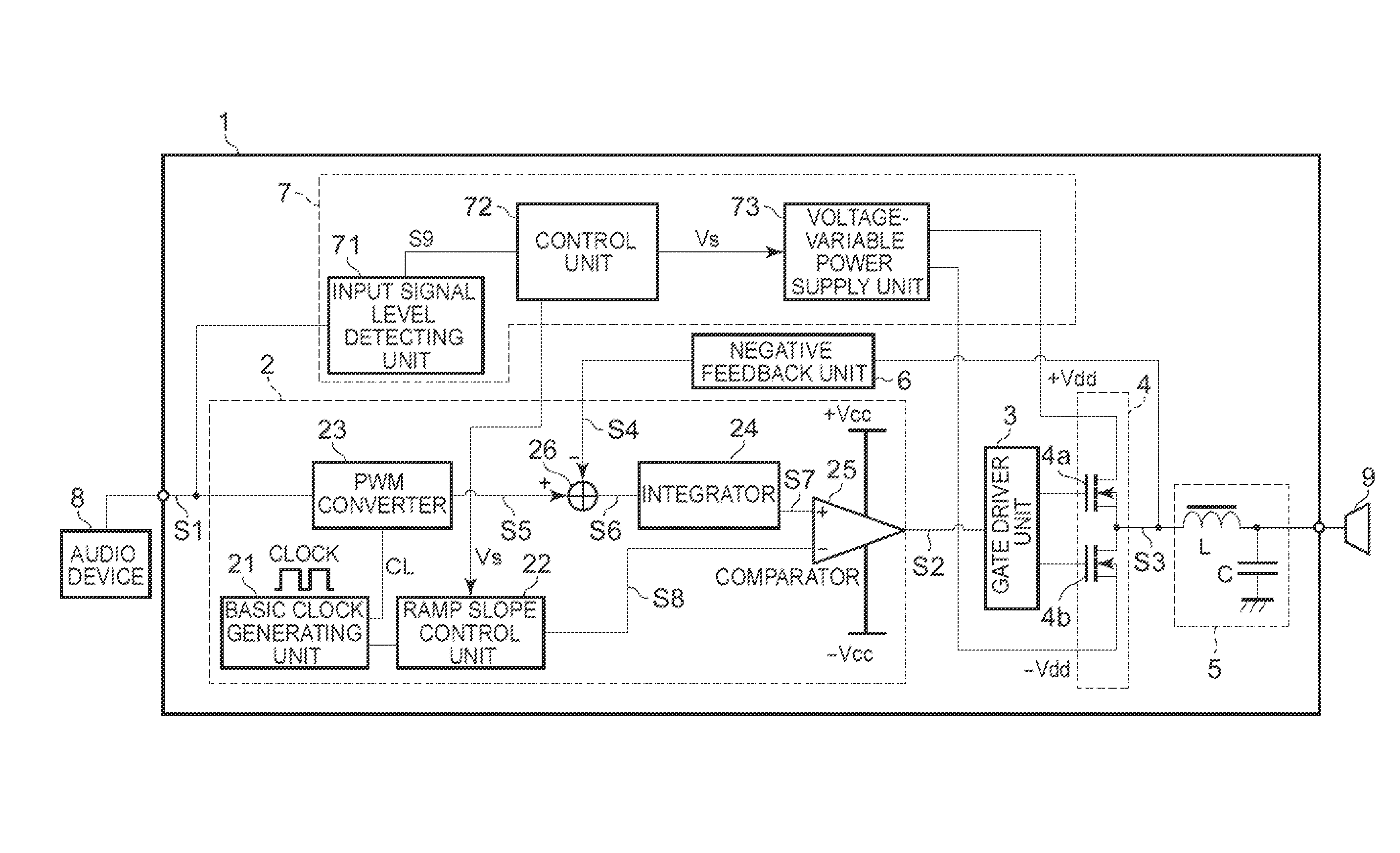

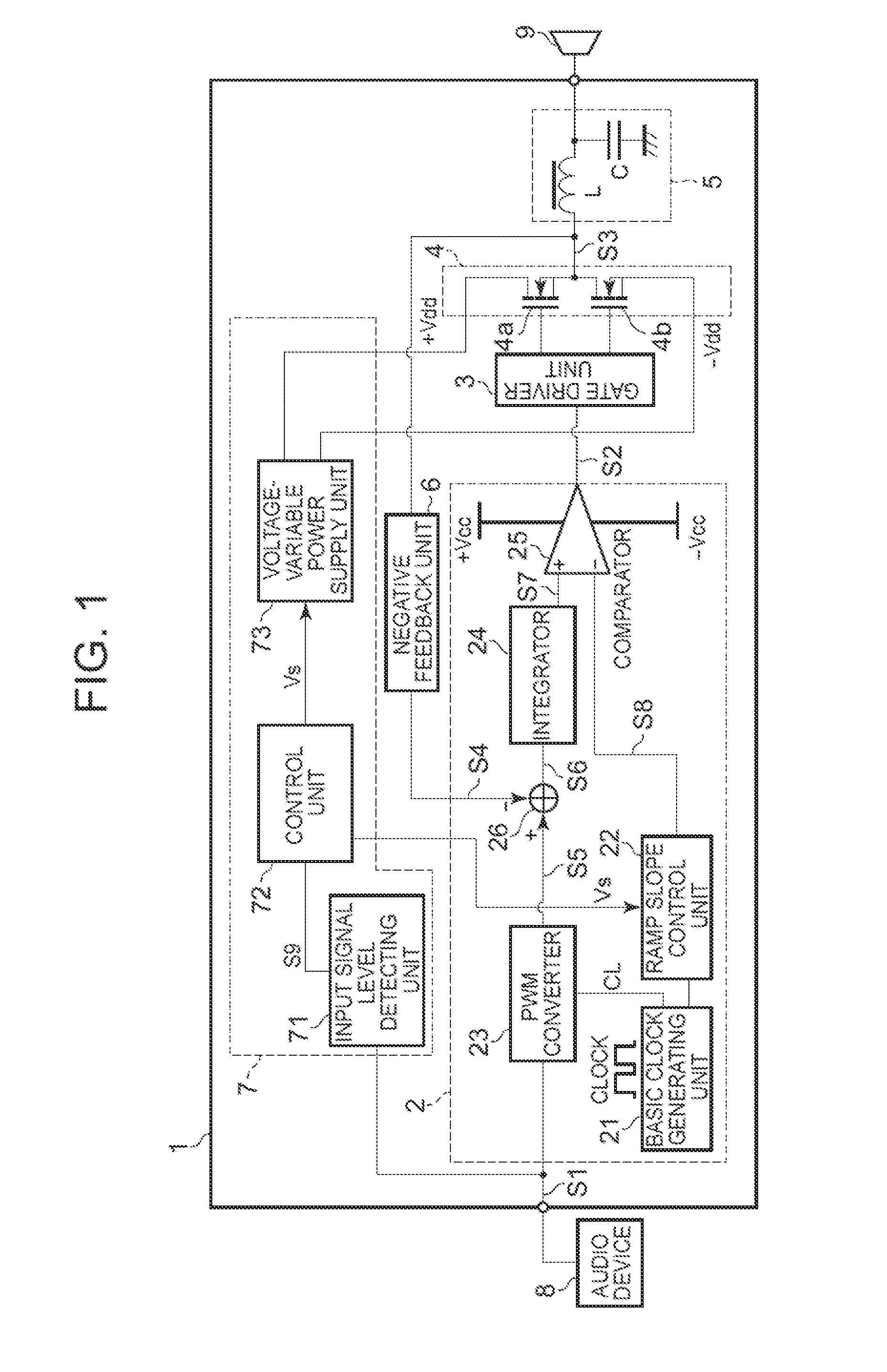

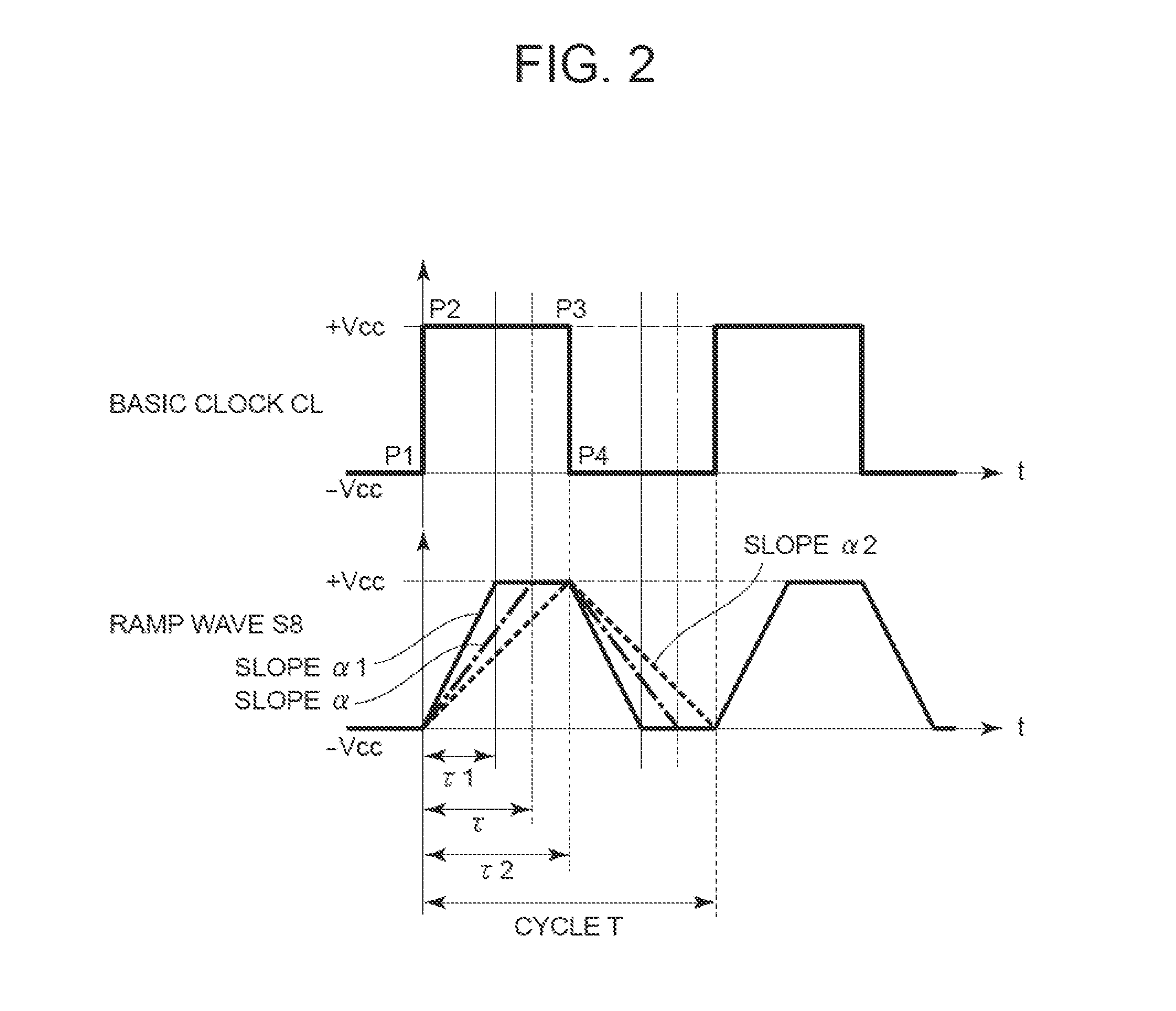

Amplifier apparatus

InactiveUS9036836B2Reduce noiseIncrease in sizeAmplifier modifications to reduce noise influencePower amplifiersAudio power amplifierPwm signals

Disclosed is a technique for reducing noise superimposed on an output signal while keeping loop gain constant without increasing the circuit scale and without changing the transfer function of the amplifier apparatus (frequency characteristics of gain and phase). According to the technique, there are included a power-supply voltage control unit 7 for detecting the amplitude level S9 of an input audio signal S1 and outputting power with a voltage value indicated by target set voltage value information Vs corresponding to this amplitude level S9, and a PWM modulation unit 2 including a PWM converter 23 for converting the pulse width of the input audio signal S1 and a correction unit for correcting the signal modulated by the PWM converter 23. The PWM modulation unit 2 corrects the pulse width of a PWM signal S5 modulated by the PWM converter 23 so that the correction unit will cancel out a change in amplification gain of a power amplification unit 4 according to the target set voltage value information Vs.

Owner:PANASONIC INTELLECTUAL PROPERTY MANAGEMENT CO LTD

Switching regulator configured to detect and shutdown reverse current

InactiveUS7936158B2Reduce output voltageReduce output signalEfficient power electronics conversionPower supply linesReverse currentEngineering

A switching regulator includes a first switch, an inductor, a second switch, a controller to control a switching operation by switching the first switch and switching the second switch complementally to the first switch, and a reverse current detector to detect a reverse current that flows from an output terminal toward the second switch. The reverse current detector generates a proportional voltage that is proportional to a voltage at a junction node between the second switch and the inductor, and detects a generation or an indication of the reverse current based on the proportional voltage. The controller turns the second switch off to create a shutdown state when the reverse current detector detects the generation or the indication of the reverse current.

Owner:RICOH ELECTRONIC DEVICES CO LTD

Level shift circuit and driver circuit using the same

InactiveUS7474138B2Reduce output signalGuaranteed uptimePulse automatic controlElectric pulse generatorDriver circuitElectrical polarity

A level shift circuit operates normally when amplitude of input signal is small and amplitude of output signal is large. First and second terminals receive an input signal and its complementary signal having a first amplitude. Third and fourth terminals output an output signal and its complementary signal having a second amplitude, which is larger than the first amplitude. Output circuit comprises first and second transistors of first polarity respectively connected between first power supply and fourth and third terminals, respectively. Third and fourth transistors of second polarity, respectively, are connected between second power supply and fourth and third terminals, respectively, having control ends connected to the third and the fourth terminals, respectively. First current control circuit controls so that a current driving the fourth terminal flows through the first transistor according to the input signal and the complementary signal of the output signal. Second current control circuit controls so that a current driving the third terminal flows through the second transistor according to the complementary signal of the input signal and the output signal.

Owner:NEC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com