Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

83results about How to "Overcome bias" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

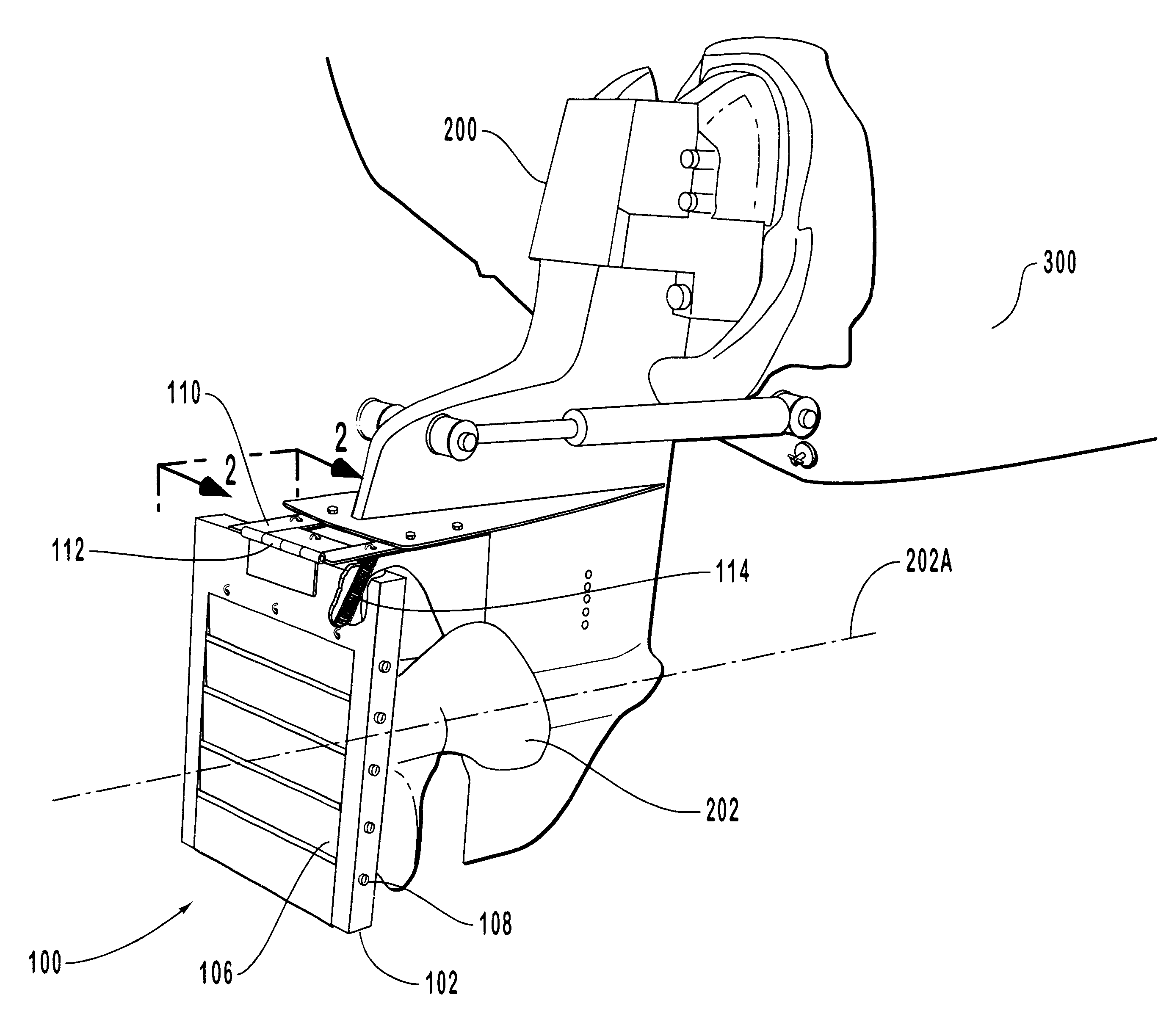

Weightlifting support assembly

A weightlifting system includes a weight bar frame rack which includes a multitude of openings along an upright to receive a weight support assembly at various positions along the frame rack. The support assembly includes a multitude of studs which extend from an inner surface of a U-shaped support plate to engage the openings and provide a robust weight support which will bear a significant quantity of weight. In use, the weight support assembly is pushed into and down the upright such that that the studs engage and are guided by the openings. Concurrent therewith, a spring bias is overcome until a latch member encounters a lock opening to securely lock the support into the desired position. To remove the weight support assembly a lock trigger is retracted and the weight support assembly is lifted up and out of the openings. The entire locking and unlocking of the weight support assembly is readily performed with one hand.

Owner:ROGERS ATHLETIC

Manual override for use with an electric safe

A manual override system for use with an electric safe. The manual override system permitting the safe to be opened in the event that an electrical system failure or other fault prevents controlling an electric lock. The manual override includes a slide plate and a mechanical lock connected to the slide plate. The electric lock is mounted to the slide plate such that it is moveable with movement of the slide plate. The manual lock is configured to move the slide plate, and thereby the electric lock, so as to permit the safe to be opened in the event of the electrical system failure or other fault prevents controlling the electric lock.

Owner:FIREKING INT

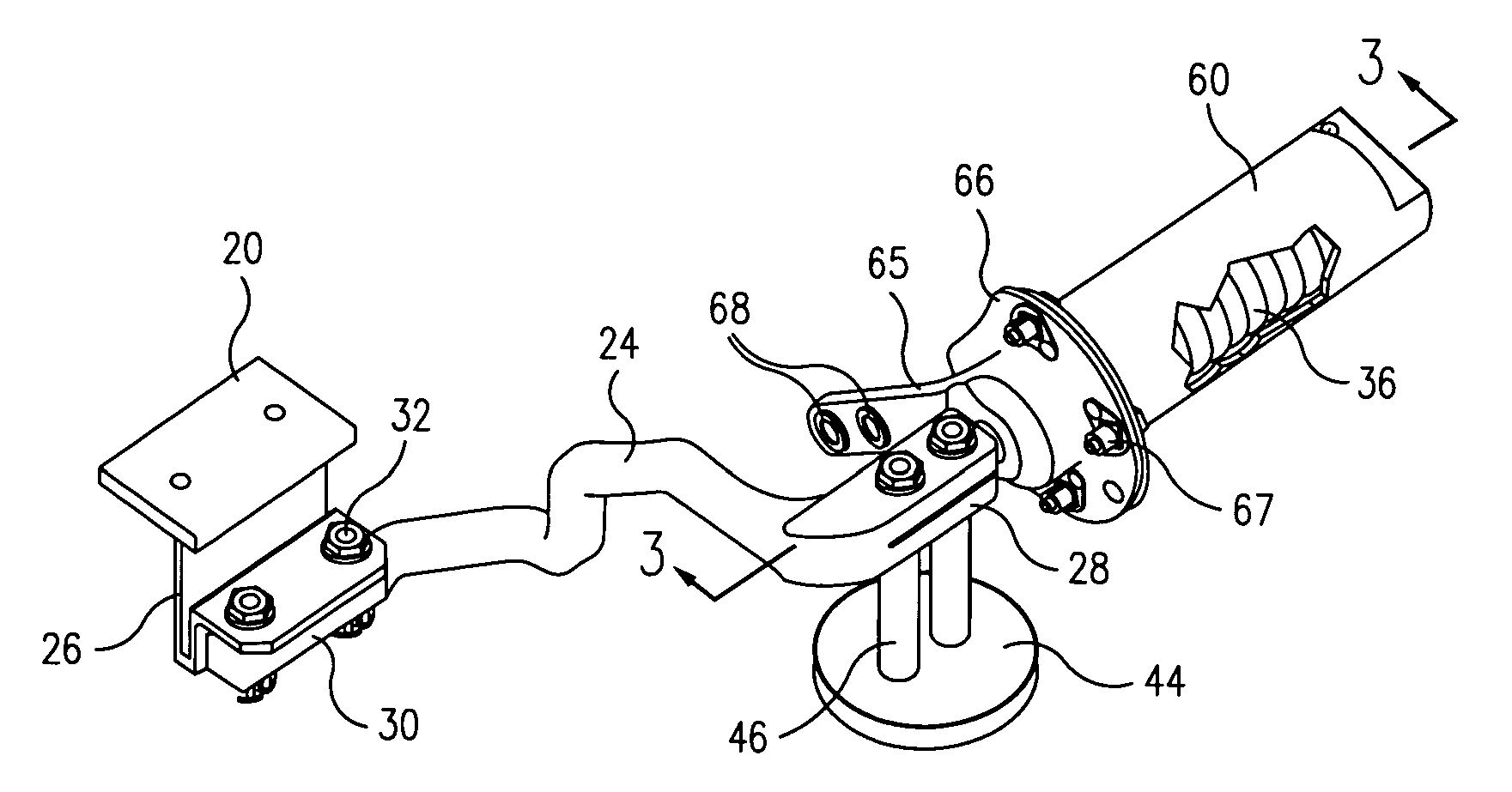

Archery rest system

ActiveUS8544457B1Little strengthOvercome biasBows/crossbowsCompressed gas gunsMechanical engineeringCircular segment

An archery rest system comprises a body mounted to the bow. A shaft is mounted within the body and a lever arm is secured to the shaft. An opening is formed in the body with an arrow launcher mounted to the shaft and extending through the opening. A spring biases the arrow launcher in an up position. A cord is secured to the lever arm. A securing mechanism secures the cord to the bow and an in-line dampening spring is mounted between the lever arm and the securing mechanism. With the bow at rest, the launcher moves to a down position out of contact with the arrow. Upon bow draw, the launcher moves into the up position contacting the arrow. Upon bow firing, the launcher moves to the down position with the spring absorbing load imparted on the cord when the shaft reaches a rotation travel limit.

Owner:HAMSKEA ARCHERY SOLUTIONS

Failsafe thermal bypass valve for cooling system

ActiveUS20100175640A1Overcome biasOperating means/releasing devices for valvesCoolant flow controlEngineeringActuator

A thermal bypass valve for a heat exchanger circuit includes a valve housing forming a valve chamber including a bypass passage and ports for the flow of heat exchange fluid into and out of the valve chamber as well as a bypass port defined by a valve seat. Two axially aligned thermally sensitive actuators are mounted in the chamber, each with an actuator body and its own movable piston extendible from one end of the body. One of these pistons operably engages the actuatory body associated with the other piston. Each actuator body is normally movable in the chamber in response to extension of its piston. One of the actuators extends its piston at a higher temperature than the temperature required for the other actuator to extend its piston. A bypass valve member is mounted on one of the actuators and can be moved by either actuator from an open position to a closed position.

Owner:DANA CANADA CORP

Failsafe thermal bypass valve for cooling system

ActiveUS8066197B2Overcome biasTemperature control without auxillary powerOperating means/releasing devices for valvesEngineeringActuator

A thermal bypass valve for a heat exchanger circuit includes a valve housing forming a valve chamber including a bypass passage and ports for the flow of heat exchange fluid into and out of the valve chamber as well as a bypass port defined by a valve seat. Two axially aligned thermally sensitive actuators are mounted in the chamber, each with an actuator body and its own movable piston extendible from one end of the body. One of these pistons operably engages the actuatory body associated with the other piston. Each actuator body is normally movable in the chamber in response to extension of its piston. One of the actuators extends its piston at a higher temperature than the temperature required for the other actuator to extend its piston. A bypass valve member is mounted on one of the actuators and can be moved by either actuator from an open position to a closed position.

Owner:DANA CANADA CORP

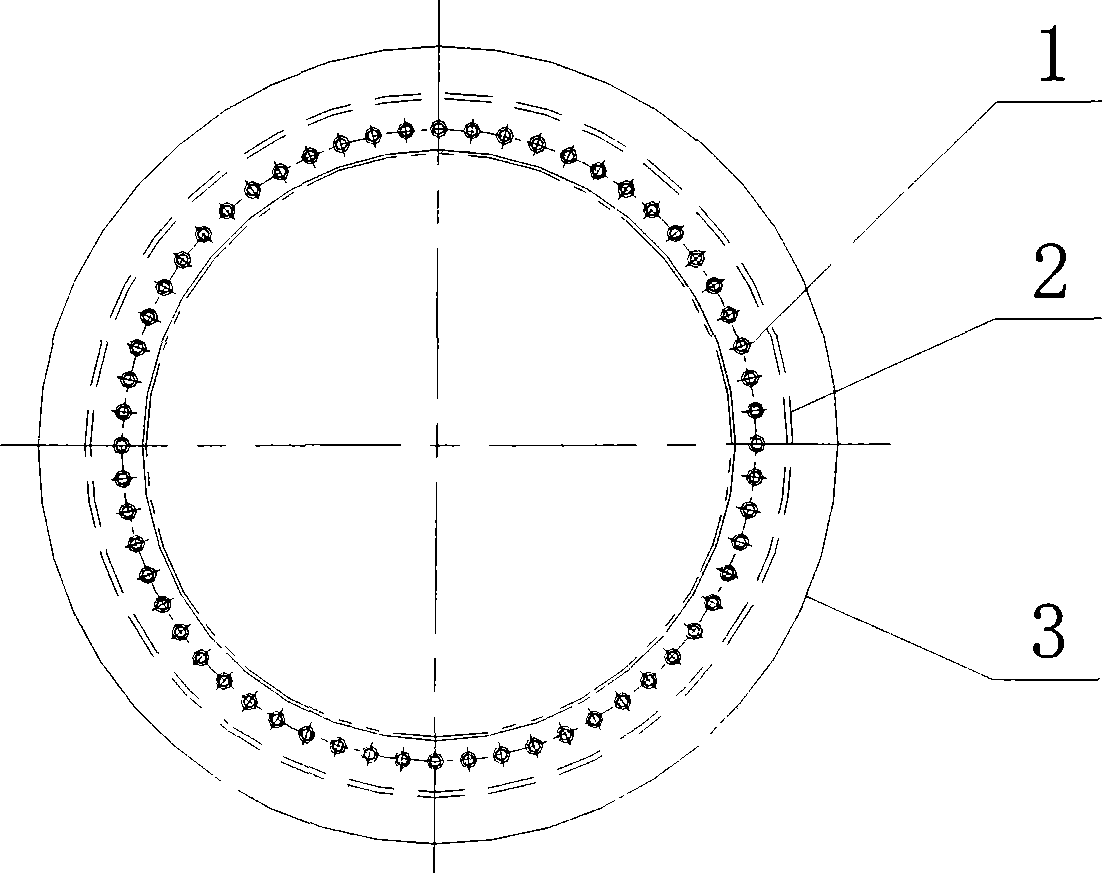

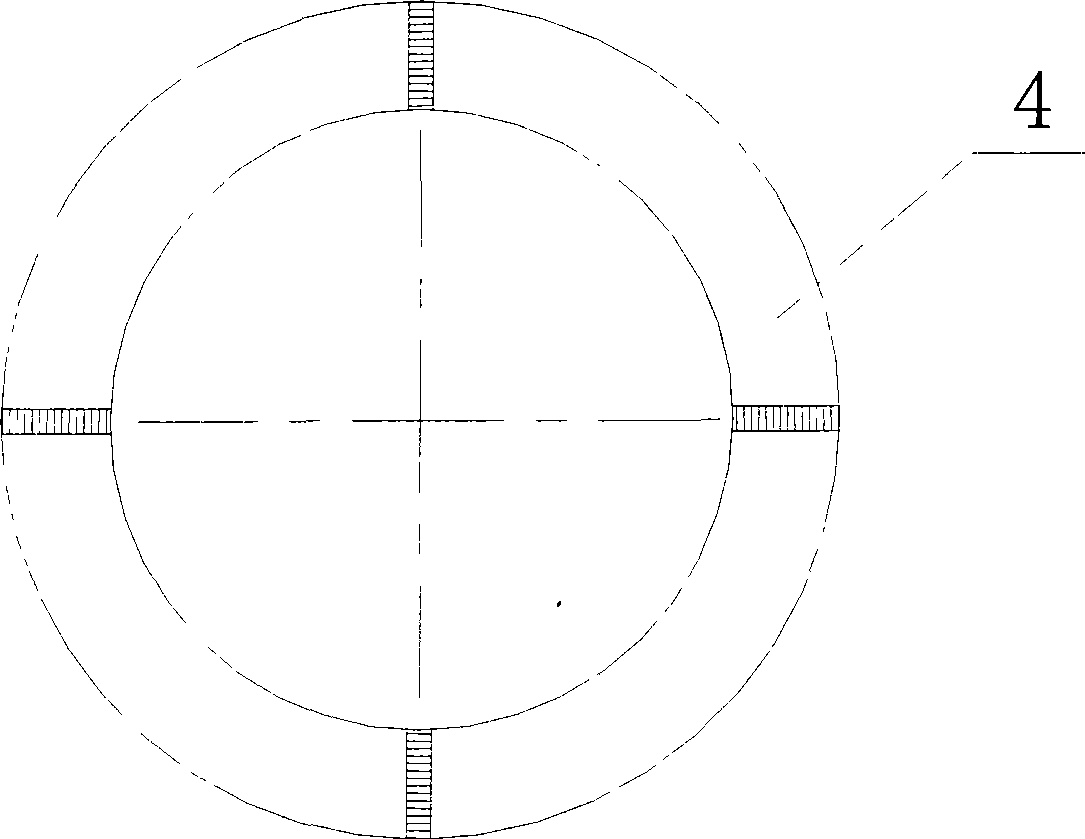

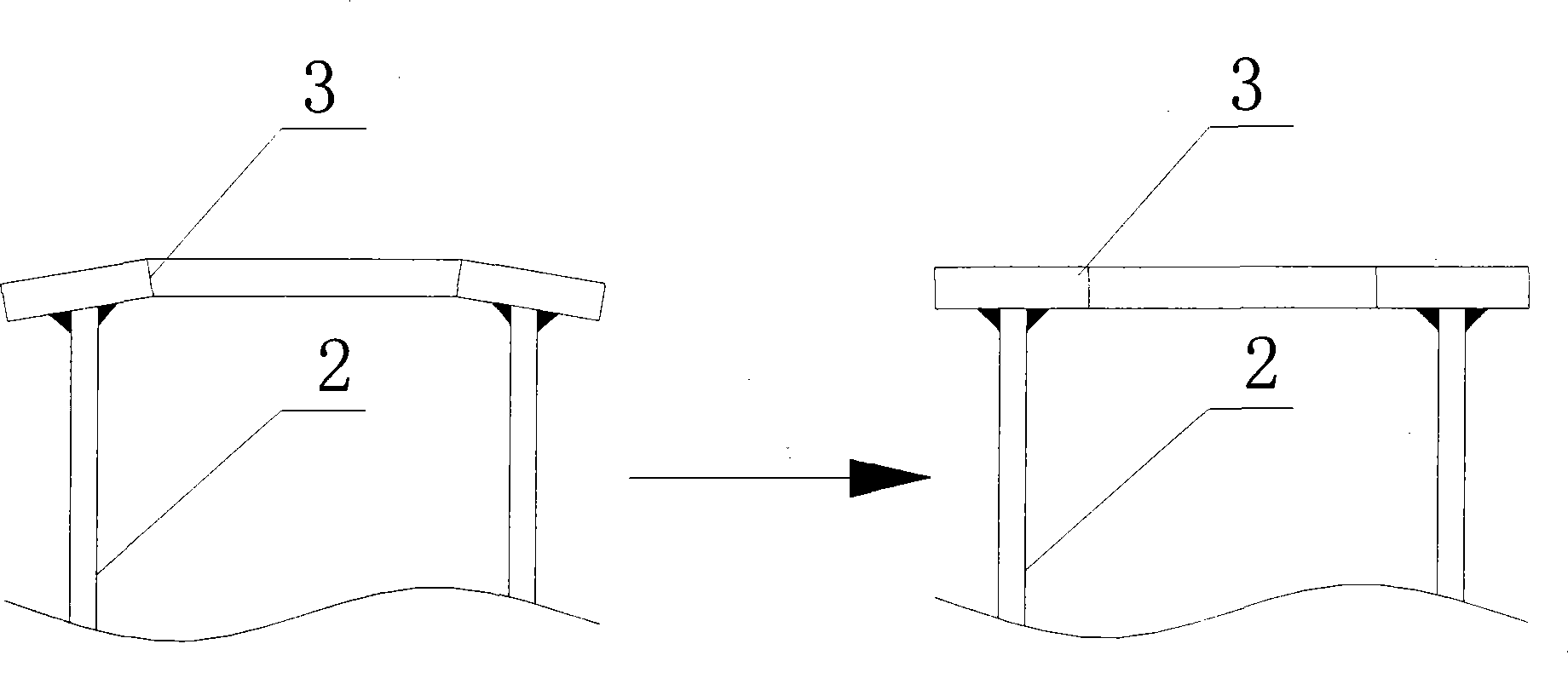

Manufacturing and mounting method of full-rotating rudder paddle base

InactiveCN101417703ASave material costOvercoming the problem of deviation caused by deformationPropulsion power plantsOutboard propulsion unitsDistortionPropeller

The invention discloses a manufacturing and mounting method for the foundation of a total-gyration rudder propeller. The method is as follows: a pre-processed steel plate is cut into four pieces of sector-shaped rings of the same size and a welding groove is cut; then a base faceplate is formed and after being annealed the base faceplate is planished with mechanical tools; after testing, the front, back, left and right marks are marked; the upper and lower sections and inner and outer circles of the base faceplate are processed; the scale is removed and the requirement by drawing is satisfied and a seam position should be taken into account simultaneously; after the size is checked, templates are fixed on the base faceplate according to the marks on the faceplate for drilling and facing; just two welding seams are welded on the base faceplate and the inner and outer sides of the left and right base cylinder to avoid full welding; the base is lifted before the total closing of a stern and is positioned well and reinforced after the total closing of the stern; and the level is checked once when one welding seam is welded till the final welding seam is completed in the welding process. The invention adopts the section blanking to displace the integral blanking so as to conserve the material cost and simultaneously overcome the technical problems of the focused stress in the base processing and manufacturing process, the welding distortion, etc..

Owner:CSSC HUANGPU WENCHONG SHIPBUILDING COMPANY

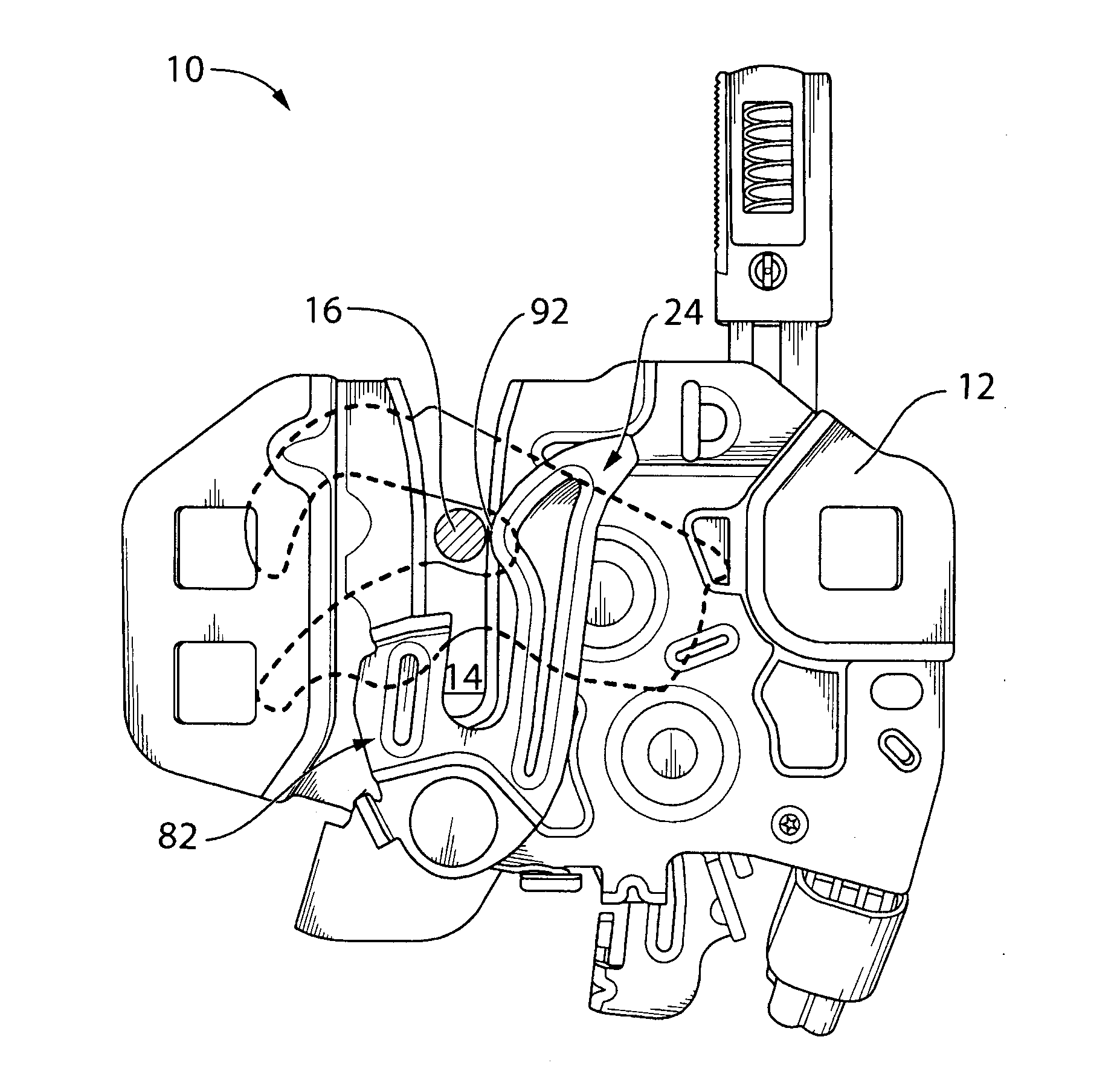

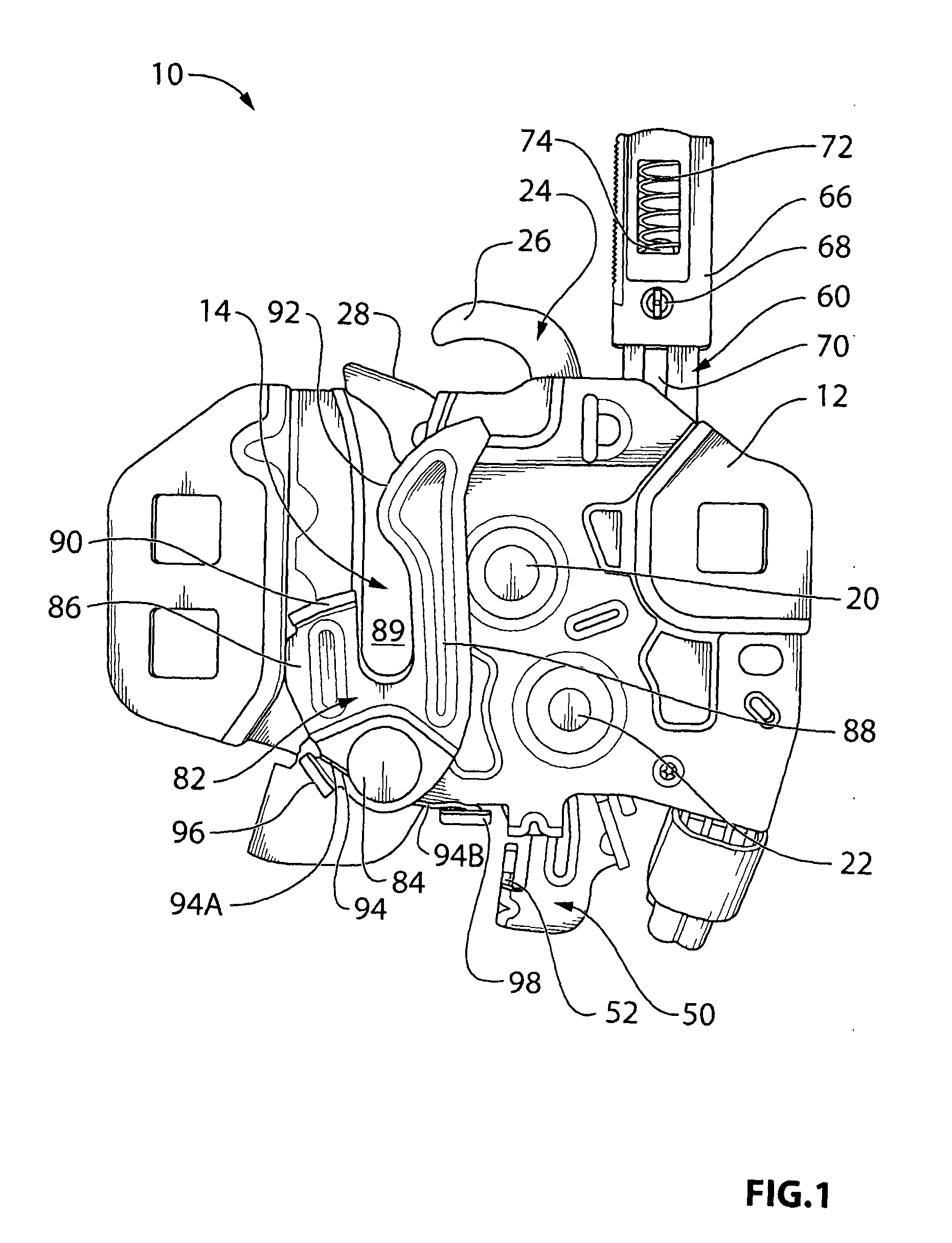

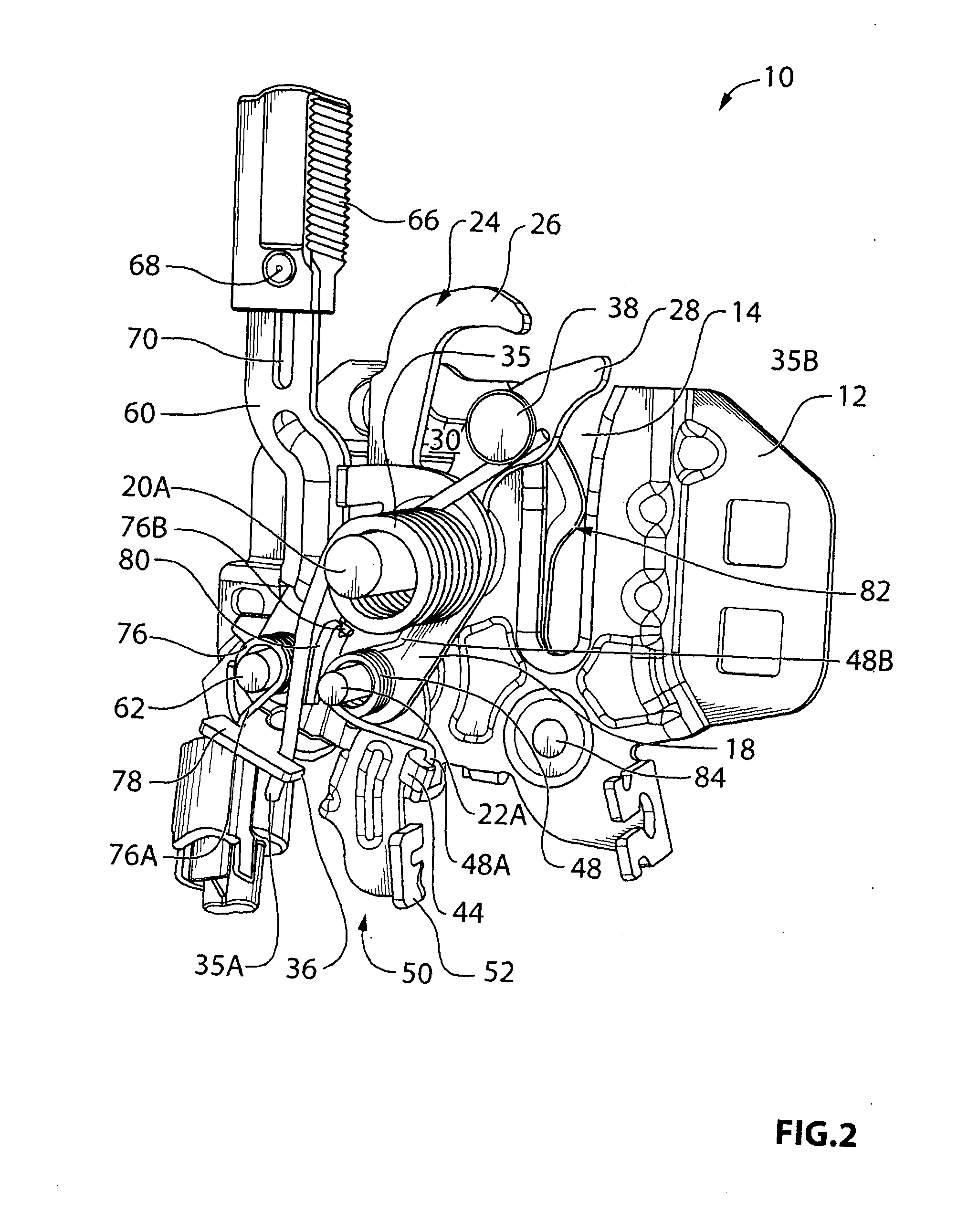

Over travel hood latch

ActiveUS20140015258A1Overcome biasSufficient forceNoise-prevention/anti-rattling lockingWing fastenersPedestrianElectrical and Electronics engineering

A hood latch having an extra-long fishmouth for enabling a vehicle hood to deflect downwardly upon impact, such as when hit by a pedestrian in a frontal crash. To prevent this deflection when the hood is slammed shut in ordinary use, a stop lever is pivotally mounted to the latch housing. The stop lever features first and second arms defining a slot therein. One arm has a proboscis thereon and is biased to align the slot with the fishmouth, with the proboscis jutting into the fishmouth. The proboscis receives an impact from the striker and rotates the stop lever to a blocking position wherein the non-proboscis arm intercepts the striker and prevents it from reaching the bottom end of the fishmouth. In the closed position the ratchet retains the striker at an intermediate depth in the fishmouth, enabling the striker to travel toward the bottom end thereof.

Owner:MAGNA CLOSURES INC

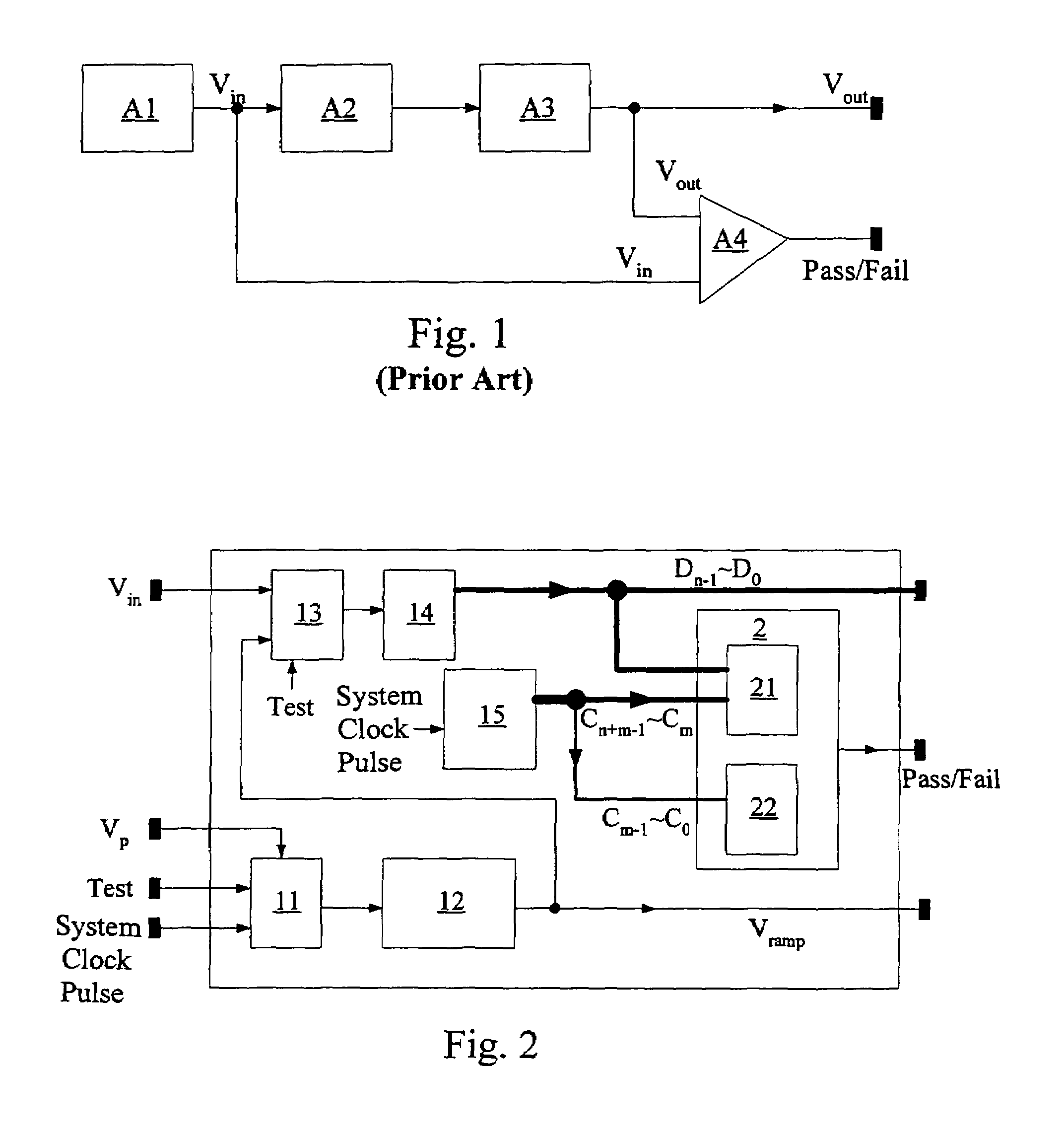

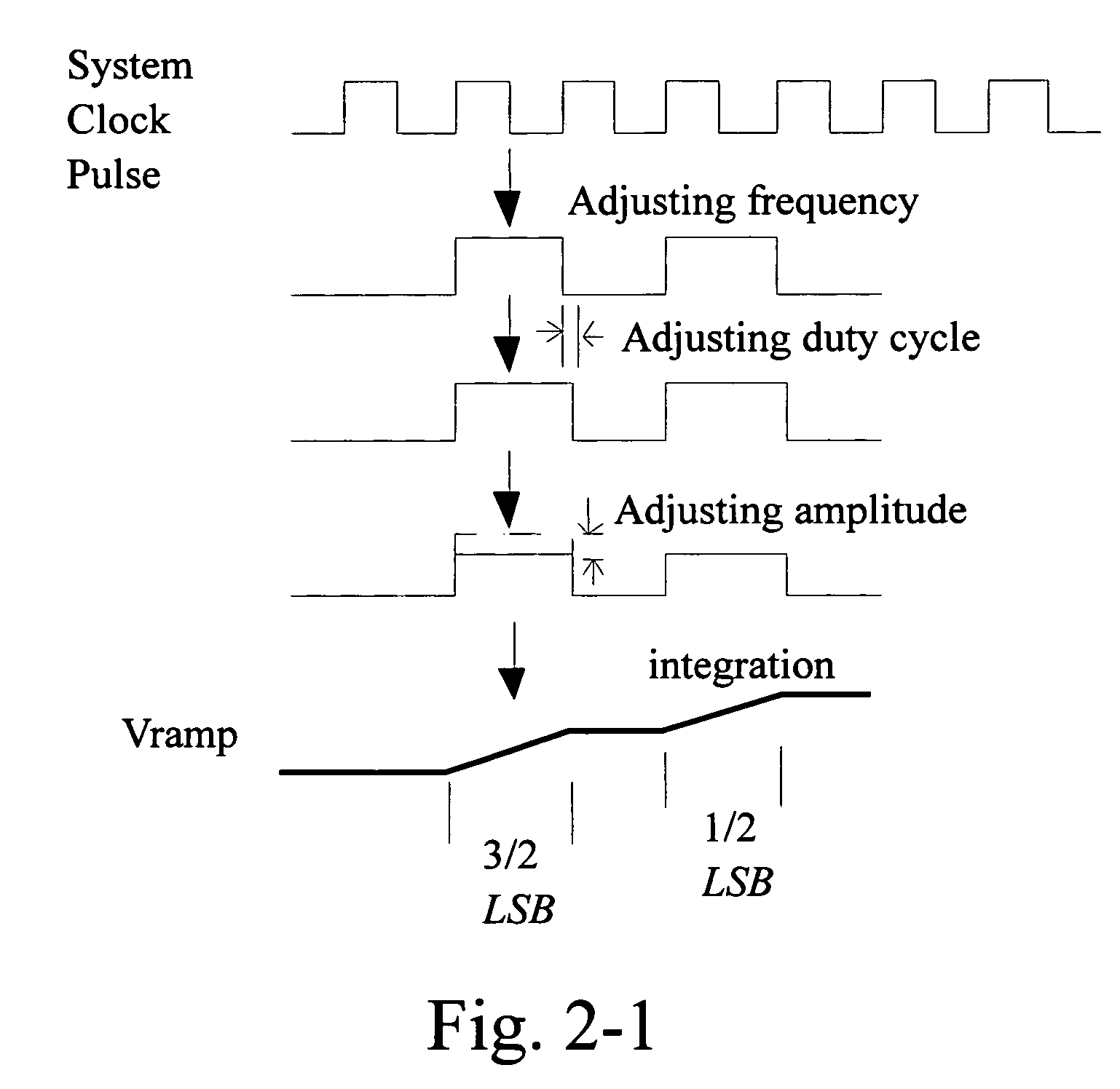

Scheme and method for testing Analog-to-Digital converters

InactiveUS7154422B2Simplify complexityLow costElectric signal transmission systemsAnalogue-digital convertersLinearityAnalog-to-digital converter

The invention provides a test scheme of analog-to-digital converters and method thereof. It comprises: a control circuit, a step-ramp signal generator, a multiplexer, an n+m-bit counter, and a test analyzing circuit, wherein m=1, 2, 3 . . . , based on desired accuracy of the test scheme. A clock pulse is coupled to the n+m-bit counter and a control circuit for regulating duty cycle, amplitude, and frequency. It is also coupled to a step-ramp signal generating circuit for being integrated as a test signal source. Therefore the step-ramp signal can synchronize with the n+m-bit counter, and the output codes are applied to compare with output codes of the n-bit ADCs for completely digitally analyzing ADC's parameters. The step-ramp signal is divided into several segments, each is integrated by the regulated clock signal with different duty cycles, which increases integrating time to compensate leakage currents of the capacitor and improve linearity of the step-ramp signal.

Owner:NAT CHENG KUNG UNIV

Automatic large-size workpiece measurement system based on machine vision

ActiveCN109612390AFill in the application gapEfficient removalImage enhancementImage analysisMachine visionSoftware system

The invention discloses an automatic large-size workpiece measurement system based on machine vision, and belongs to the technical field of machine vision measurement. The automatic large-size workpiece measurement system comprises an automatic large-size workpiece measurement hardware system and an automatic large-size workpiece measurement software system. The automatic large-size workpiece measurement hardware system comprises a light source, a camera, a lens and a high-accuracy moving device. The automatic large-size workpiece measurement software system comprises an image preprocessing algorithm, image data conversion modeling, a subpixel line / arc detection algorithm based on an improved RANSAC, and dimension calculation. The large-size workpiece can be measured by the system, and thesystem fills in the blank of application of machine vision in the field of large-size workpiece measurement. The software system can effectively eliminate noise and null points from an image and canrectify a non-uniform background. Production efficiency, stability and measurement accuracy of the system are improved.

Owner:江苏聚目科技有限公司

Hollow Core Floor and Deck Element

InactiveUS20080010943A1Improve carrying capacityOvercome biasConstruction materialFloorsHorizontal stressFloor slab

A stress-optimized structural support which may be utilized as a beam or assembled with similar supports to form a building floor or roof panel or a bridge deck utilizes an open core element, made preferably of suitably treated fluted paper, upper and lower thin skin sheets, preferably steel skins, and a layer of concrete poured over the top skin. Modules comprising the hollow core element and the upper and lower skin sheets are fabricated to lengths required for building floor, roof or bridge spans and, when joined by welding or otherwise joining the upper and lower skin sheets of adjacent elements along their full lengths, provide a floor or roof deck structure of a large span with horizontal stresses distributed omnidirectionally. A post-stressing tensile system redistributes and reduces the load on the roof deck by about one-half. Small building decks utilizing the stress redistribution system can be combined to build a large span roof in which multiple tensioning systems are coordinated to simultaneously effect the load redistribution.

Owner:MARSCHKE CARL R

Land roller

A land roller implement includes a wheel aligned with the respective gap between the inner roller and the outer roller of each wing in which the wheel is pivotal between a packing position in the working position of the rollers and a transport position supporting the rollers in the transport position of the implement. The wings can also include a drive motor associated with each transport wheel to drive forward rotation of the wheel for displacing the wings from the transport position to the working position without displacing the implement in a rearward direction. A leveling beam attachment and a seeding attachment can also optionally be used on the land roller implement. Optional latchable brace members pivotally supported on the wings may provide additional support to the wings when using the leveling beam attachment.

Owner:AG SHIELD LTD

Polyisocyanate modified with sulphamic acid, preparation method thereof and use thereof

ActiveUS20160280836A1Good water dispersibilityLong application periodPolyurea/polyurethane coatingsCross-linkAdhesive

A polyisocyanate modified with sulphamic acid and a mixture thereof, the preparation method thereof, and the use thereof in the production of polyurethane, especially as a cross-linking ingredient in the field of aqueous coatings and adhesives containing groups that are capable of reacting with isocyanate groups.

Owner:WANHUA CHEM GRP CO LTD +2

Boat motor trolling attachment

InactiveUS6397772B1Overcome biasShorten speedSteering by extensible flapsOutboard propulsion unitsPropellerForward speed

The present invention discloses a boat motor trolling attachment for use in conjunction with a boat motor and propeller to achieve effective trolling speeds. The boat motor trolling attachment includes a frame, defining an opening, and attached to a mounting bracket which is secured to the boat motor. Two springs are attached between the frame and the mounting bracket so as to bias the frame into a trolling position wherein the frame is disposed in a plane perpendicular to an axis defined by the propeller. Four control members are disposed horizontally across the opening and rotatably fixed to the frame so that a outflow of water impinging on the control members when the boat motor is in a forward gear automatically causes the control members to rotate in the frame so as to substantially close off the opening and form a continuous surface. The outflow of water generated by the propeller acts on the continuous surface and is transmitted thereby to the boat so as to resist forward motion of the boat. When the boat motor is in a reverse gear, the control members automatically rotate to allow a inflow of water to be generated by the propeller thereby facilitating control and maneuverability of the boat in reverse. At high forward speeds, the outflow of water generated by the propeller overcomes the bias imposed on the frame by the springs and automatically moves the frame to an inoperative position wherein the frame is disposed in a plane substantially parallel to the axis defined by the propeller.

Owner:CHRISTENSEN DALE

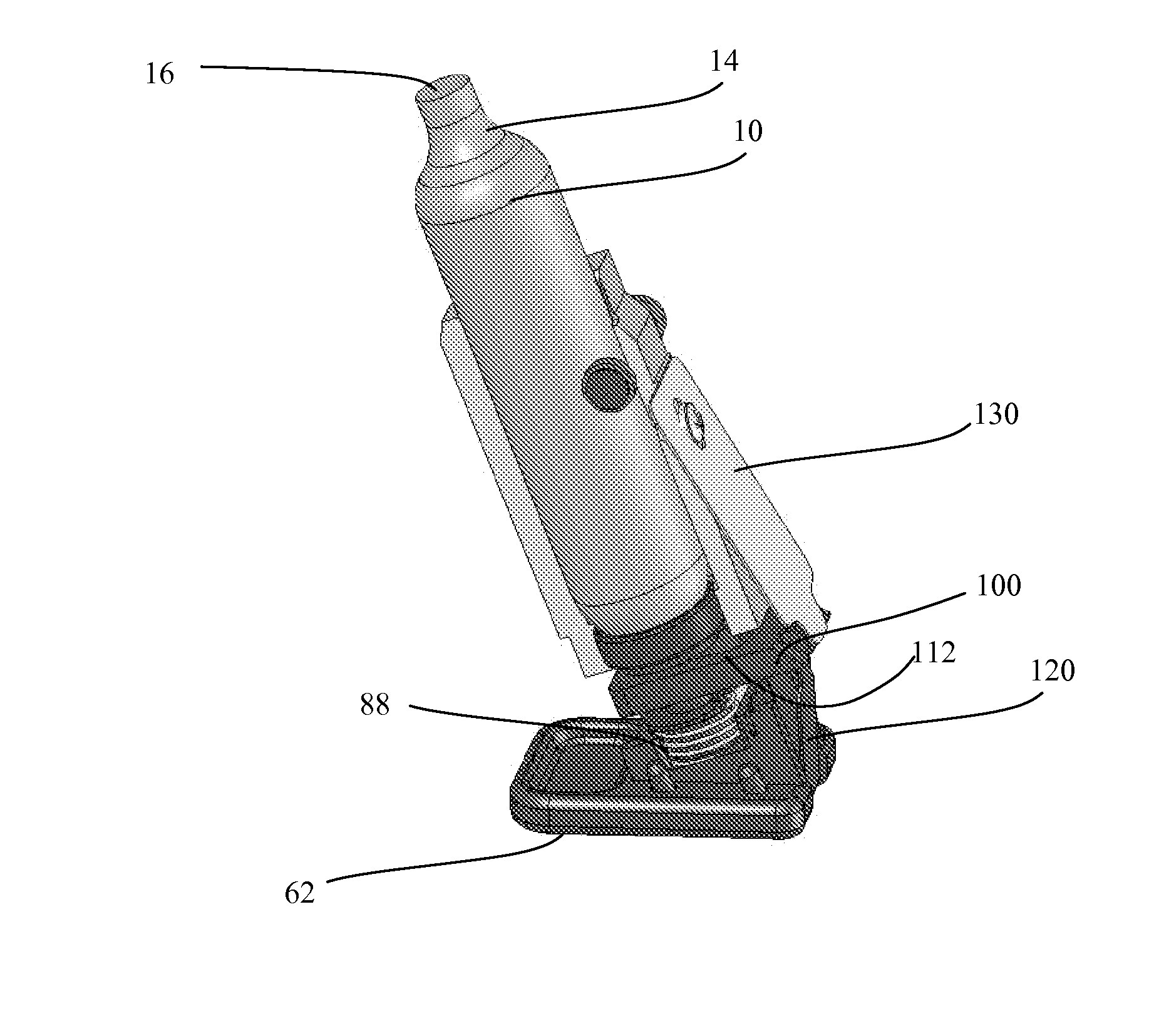

Water resistant keycard reader assembly for an electronic lock

InactiveUS20070163863A1Large range of motionOvercome biasElectric switchesIndividual entry/exit registersSurface mountingCard reader

An electronic lock includes a keycard sensing assembly which interacts with a keycard sensing switch surface mounted to a circuit board. The keycard sensing assembly is located adjacent a rear of a keycard slot such that when a key card is fully inserted into the keycard slot, the keycard activates the keycard sensing assembly. Such an arrangement permits a significant portion of the circuit board to be potted within a potting compound such that the keycard reader becomes essentially waterproof. Such a construction permits the insertion of a wet or damp keycard without concern for water damage to the keycard sensing assembly.

Owner:COMPIZED SECURITY SYST +1

Satellite platform flutter detection method based on TDICCD splicing zone image

ActiveCN107966137AHigh precisionDefine Quantitative RelationshipsImage analysisGeometric image transformationComputer visionSatellite

The invention discloses a satellite platform flutter detection method based on a TDICCD splicing zone image. The method comprises the following steps: 1) obtaining overlapped images, and using a timedelay and integration-charge coupled device splicing zone to obtain the overlapped images; 2) calculating a difference of relative imaging positions, performing accurate and dense coupling treatment on two overlapped images to obtain a homonymous matching point, and calculating the difference of the relative imaging positions of a same target in two overlapped images; and 3) estimating the satellite platform flutter according to the difference of the relative imaging positions. The method can effectively solve the problems of low flutter detection accuracy and only detection on several isolated frequency points, provides the flutter detection method with high precision and full coverage in a wide frequency range for a satellite platform, and increases the satellite attitude detection capability and extraction accuracy for the remote sensing image information.

Owner:ANHUI AGRICULTURAL UNIVERSITY

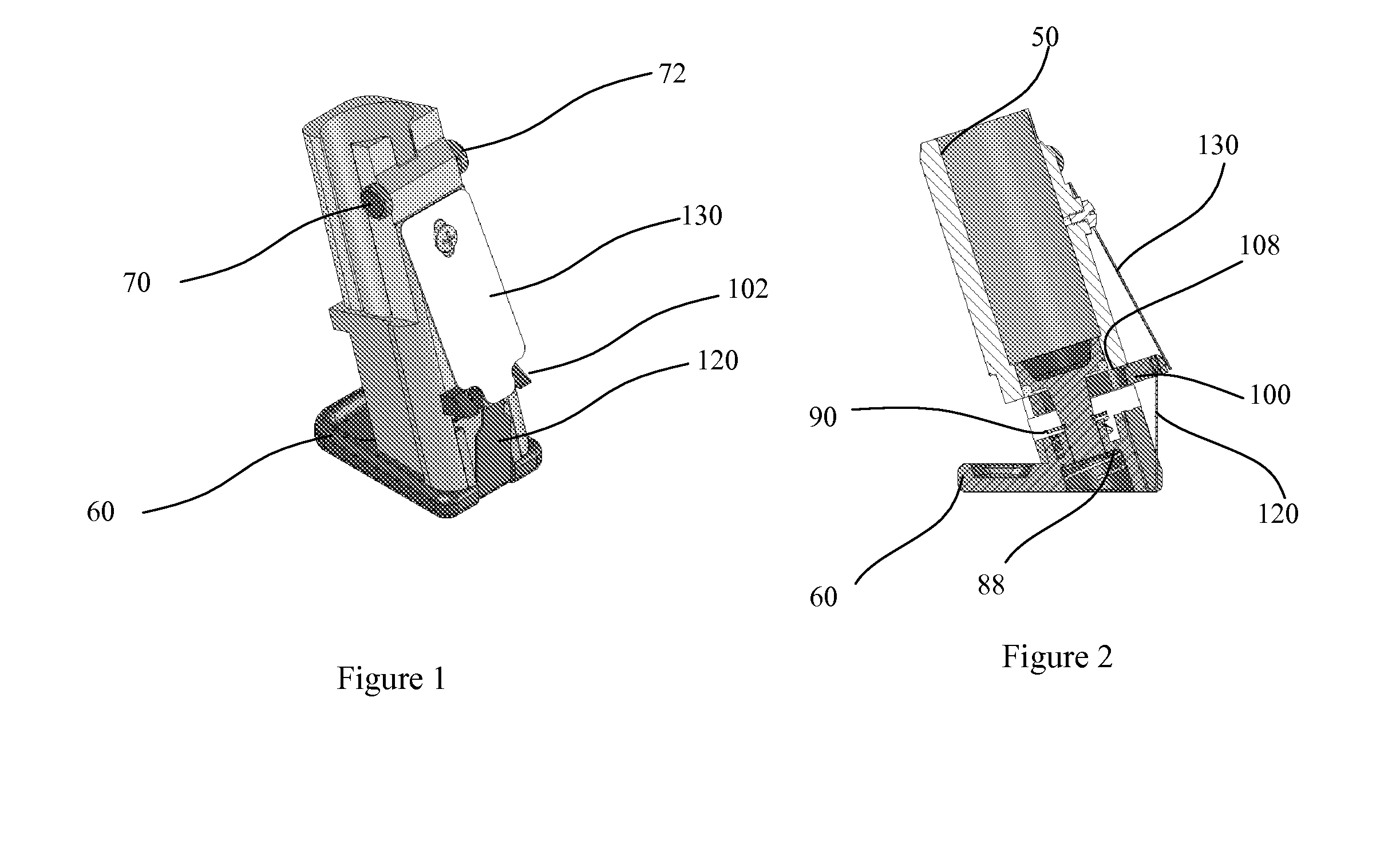

Magazine Assembly for Presenting a Pressure Cartridge to a Compressed Gas Powered Device

ActiveUS20080168974A1Bias on the interlock plate is overcomeOvercome biasAmmunition loadingCompressed gas gunsEngineeringLocking plate

A magazine assembly presents a pressure cartridge to a compressed gas powered device, such as a gun, wherein the magazine assembly has a cartridge support biased with respect to a magazine to urge the pressure cartridge to a short (or seated) position, wherein an interlock plate is biased to engage the cartridge support. The bias on the interlock plate is overcome during insertion of the magazine assembly into a magazine chamber, at which point the cartridge support moves relative to the magazine in response to a seated length of the pressure cartridge. The bias on the interlock plate then controls the positioning of the interlock plate to engage the cartridge support and retain the pressure cartridge relative to the magazine assembly. A lever connected to the gun then engages the magazine assembly to translate the magazine assembly relative to the gun and pierce the pressure cartridge.

Owner:CROSMAN CORP

Illuminated interface cable

InactiveUS20140140076A1Selective illumination of the connection areaPollution minimizationLighting support devicesLighting elementsEngineeringInterconnection

An illuminated interface cable with a connector interface on at least one end. A light circuit including a light and a mechanical switch, the light circuit configured to energize the light upon actuation of the mechanical switch. The light and momentary switch coupled to the connector interface, the light oriented to illuminate an interconnection area of the connector interface. The light may be provided, for example, as a light emitting diode.

Owner:XENTRIS WIRELESS

Flexible Mid-Section Float System for Protective Outerwear

InactiveUS20140090145A1Overcome biasEfficient use ofPersonal protection gearMetal working apparatusEngineeringLeather belt

The present invention provides, in part, a mid-section float system that can be used with protective outerwear, such as a protective, wearable carriage device, for example. The present invention also provides a quick attach / detach system for connecting belts or cumberbunds to an upper torso outerwear device. In one embodiment, the present invention includes a flexible connector having a base, a receiving strap and a spring connector component.

Owner:VELOCITY SYST

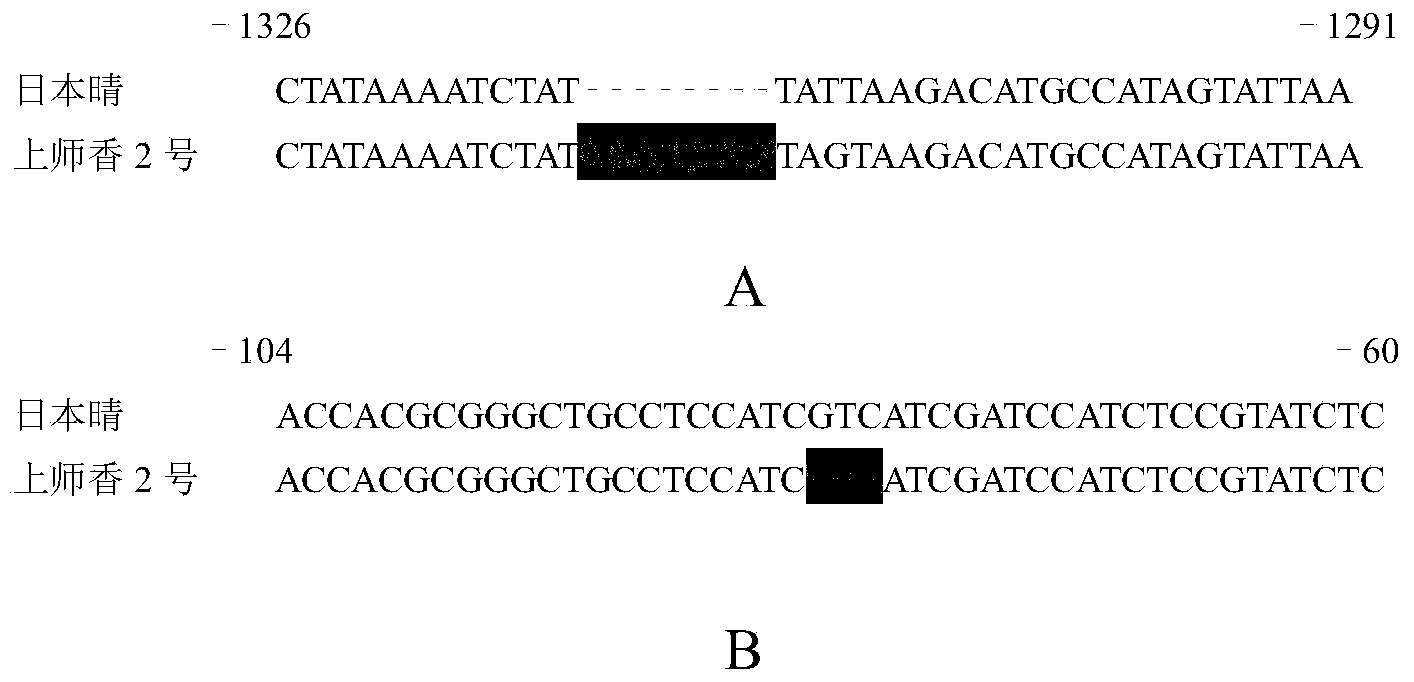

Betaine aldehyde dehydrogenase 2 fragrance gene in paddy rice, primer of molecular marker and screening method

InactiveCN103525840AMeet needsOvercome biasMicrobiological testing/measurementFermentationBiotechnologyNucleotide

The invention discloses a new betaine aldehyde dehydrogenase 2 gene enabling paddy rice to have the characteristic of light fragrance, and compared with non-fragrant paddy rice nipponbare, the mutation site is not located in coding strand but belongs to the mutation-type betaine aldehyde dehydrogenase 2 gene at the upstream of the coding strand. Three nucleotides are lost at the -81 site at the upstream of the first nucleotide of the initiation codon of the coding strand, and eight nucleotides are inserted into the -1314 site. A new light-fragrance type paddy rice species is cultivated once homozygous progeny is obtained by transferring the gene into non-fragrant paddy rice via hybridization. The invention also discloses a method for screening the paddy rice possessing the light-fragrance type characteristic and a primer of a molecular marker. The new gene is provided for cultivation of the light-fragrance type paddy rice; also the betaine aldehyde dehydrogenase 2 fragrance gene in paddy rice, the primer of molecular marker and the screening method help to perform assistant selection on plants containing light-fragrance gene, are beneficial to improve selection effect, and also help to identify whether the inbred progeny light-fragrance gene formed at the later stage of breeding is in a homozygous state, so that the breeding target can be realized rapidly and effectively.

Owner:SHANGHAI NORMAL UNIVERSITY

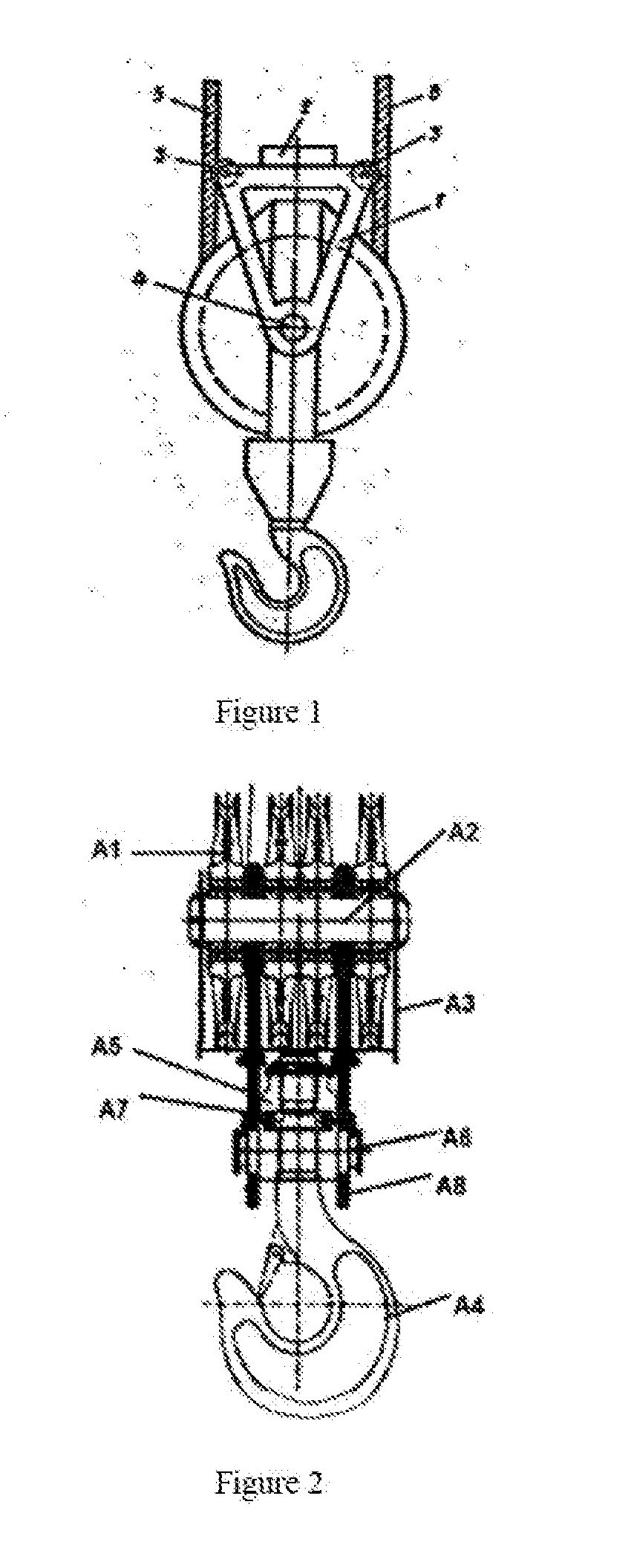

Lifting hook bias angle monitoring apparatus, vertical hoisting monitoring apparatus and mobile crane

InactiveUS20180009640A1Smooth changeAccurate detectionTelevision system detailsColor television detailsForce linesPull force

A lifting hook bias angle monitoring apparatus, a vertical hoisting monitoring apparatus, and a mobile crane. One method is that a lifting hook assembly serially connects connecting plates (b3) provided with hinge connection shafts (b2, b4) at two ends to a movable pulley component (b1) which bears a pulling force and a lifting hook component (b7) which bears a pulling force, and is also provided with a biaxial inclinometer (b9) on a platform surface (b8) of the connecting plates (b3) which is perpendicular to a lifting force line of action of the lifting pulley component, so as to detect a real-time lifting hook bias angle, and accordingly be developed into a mobile crane having a vertical hoisting monitoring function.

Owner:LIN HANDING

Cloud platform safety quantitative evaluation method based on improved VIKOR method

InactiveCN105512465AOvercome biasImprove accuracySpecial data processing applicationsInformaticsEvaluation resultIndex system

The invention discloses a cloud platform safety quantitative evaluation method based on an improved VIKOR method. The cloud platform safety quantitative evaluation method comprises the following steps of S1, determining the index system and attribute of cloud platform safety quantitative evaluation; S2, preprocessing index attribute data, and establishing an evaluation basis matrix; S3, converting the evaluation basis matrix into a standardized decision matrix; and S4, establishing a cloud platform safety evaluation model, and obtaining the evaluation result ranking index of each evaluation scheme in dependence on the evaluation model. Aiming the characteristic, of the cloud platform, that each evaluation factor has dynamic nature and relevance, a new decision matrix establishing method is provided, and therefore defects and deviations of a conventional VIKOR decision matrix processing method in the evaluation information set aspect can be overcome, scientificity, objectivity and comprehensiveness of safety evaluation can be obtained at the same time, and the accuracy of the cloud platform safety evaluation result can be improved.

Owner:赵鑫龙

Monitoring-point deviation adjustment circuit based on semi-path time sequence early-warning method and method

ActiveCN107357347AEfficient measurementMinimize Power Gain LossElectric variable regulationEngineeringCritical path method

The invention discloses a monitoring-point deviation adjustment circuit based on a semi-path time sequence early-warning method. The monitoring-point deviation adjustment circuit is composed of a monitoring-point-deviation-ratio detection module and a clock-duty-ratio adjustment module. The monitoring-point-deviation-ratio detection module detects a critical-path start point, a monitoring point and delay of a tail end point and the critical-path start point through a TDC, and the result is shown through the output stage number of the TDC; the TDC transmits an output signal to an ACU, then the calculated monitoring-point deviation ratio is compared with a threshold value through the ACU, and when the monitoring-point deviation ratio is larger than the threshold value, the adjusting signal of the clock duty ratio is pulled up. The clock-duty-ratio adjustment module increases the clock duty ratio step by step when the adjusting signal of the clock duty ratio is pulled up till a time sequence early-warning signal is pulled down; the clock duty ratio is stopped to be adjusted at this moment, and power consumption benefits lost by the path monitoring-point deviation are finally reduced.

Owner:SOUTHEAST UNIV

Scheme and method for testing analog-to digital converters

InactiveUS20060001560A1Accurate signalOvercome biasElectric signal transmission systemsAnalogue-digital convertersEngineeringLinearity

The invention provides a test scheme of analog-to-digital converters and method thereof. It comprises: a control circuit, a step-ramp signal generator, a multiplexer, an n+m-bit counter, and a test analyzing circuit, wherein m=1, 2, 3 . . . , based on desired accuracy of the test scheme. A clock pulse is coupled to the n+m-bit counter and a control circuit for regulating duty cycle, amplitude, and frequency. It is also coupled to a step-ramp signal generating circuit for being integrated as a test signal source. Therefore the step-ramp signal can synchronize with the n+m-bit counter, and the output codes are applied to compare with output codes of the n-bit ADCs for completely digitally analyzing ADC's parameters. The step-ramp signal is divided into several segments, each is integrated by the regulated clock signal with different duty cycles, which increases integrating time to compensate leakage currents of the capacitor and improve linearity of the step-ramp signal.

Owner:NAT CHENG KUNG UNIV

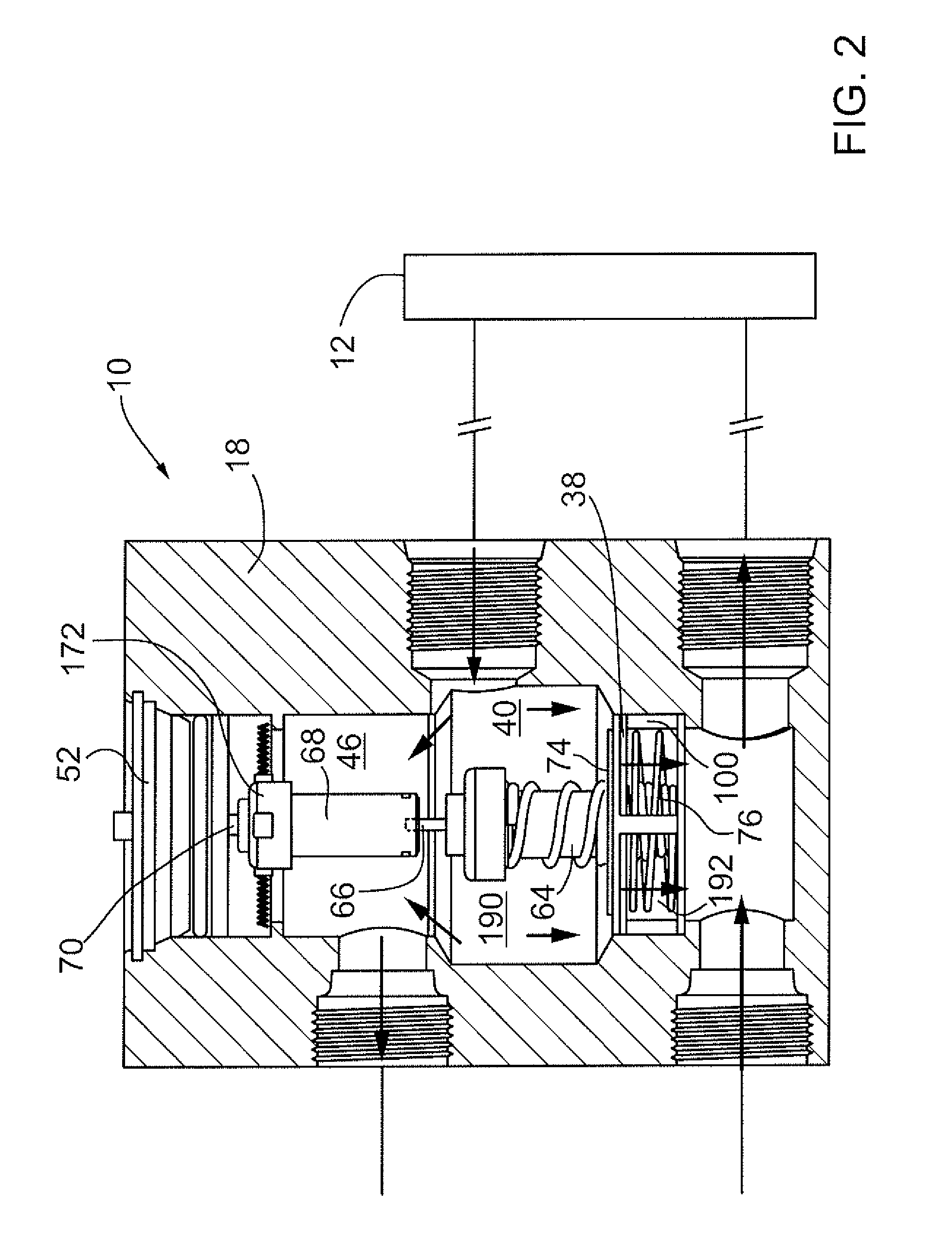

Solenoid-operated fluid valve and assembly incorporating same

InactiveUS20060243758A1Reduce coil heat buildupIncreasing duty cycleLiquid surface applicatorsOperating means/releasing devices for valvesMagnetic tension forceBobbin

A solenoid-operated valve and valve assembly. The valve may be made from a fluid tube that has a magnetizable plunger or armature movably positioned in the body. A coil of wire is directly wound to the fluid tube, thereby reducing the air gap between magnetic flux path and plunger to increase the magnetic force imparted to the plunger. Winding the coil to the valve body removes the need for a separate sleeve or bobbin, and additionally allows for tighter spacing and reduced air gap, thereby increasing magnetic flux by allowing more coil turns and closer coil spacing to the plunger. In one form, the valve is packaged into a narrow (for example, 15 millimeters wide) configuration for close valve-to-valve stackable centers, thereby allowing multiple valves to be placed side-by-side for adhesive or related fluid dispensing applications.

Owner:VALCO CINCINNATI

Mechanical command to arm fuze

A mechanical safe and arm device for rotating munitions reduces arming scatter so that the “no arm” and “all arm” distance are substantially the same. A first spring holds a flywheel, a pinion gear, and a drive gear against rotation until centrifugal forces cause the spring to release them. The drive gear then rotates, causing rotation of the pinion gear and the flywheel. A post depending from the flywheel strikes and unlocks a second spring that unlocks a pivotally-mounted rotor that carries a detonator. The rotor then pivots and brings the detonator into alignment with a firing pin.

Owner:AMTEC CORP

Intervertebral Implant Assembly and Instruments Therefor

PendingUS20200281736A1Small cross-sectional sizeOvercome biasSpinal implantsBone platesSpinal columnIliac screw

A spinal fusion system comprising an interbody device includes a leading end, trailing end, and opposed bone contacting sides extending therebetween. The trailing end defines a threaded opening that extends toward the leading end. The system also includes a bone plate that includes inner and outer surfaces and defines a first bone screw opening and connection screw opening extending therethrough. The system further includes a connection screw that includes a head and a threaded shaft. The head is positioned within the connection screw opening of the bone plate and is rotatably connected thereto such that the connection screw is rotatable about a longitudinal axis thereof but is prohibited from translational movement relative to the bone plate. The threaded shaft extends from the connection screw opening and is configured for threaded engagement with the threaded opening of interbody device.

Owner:K2M

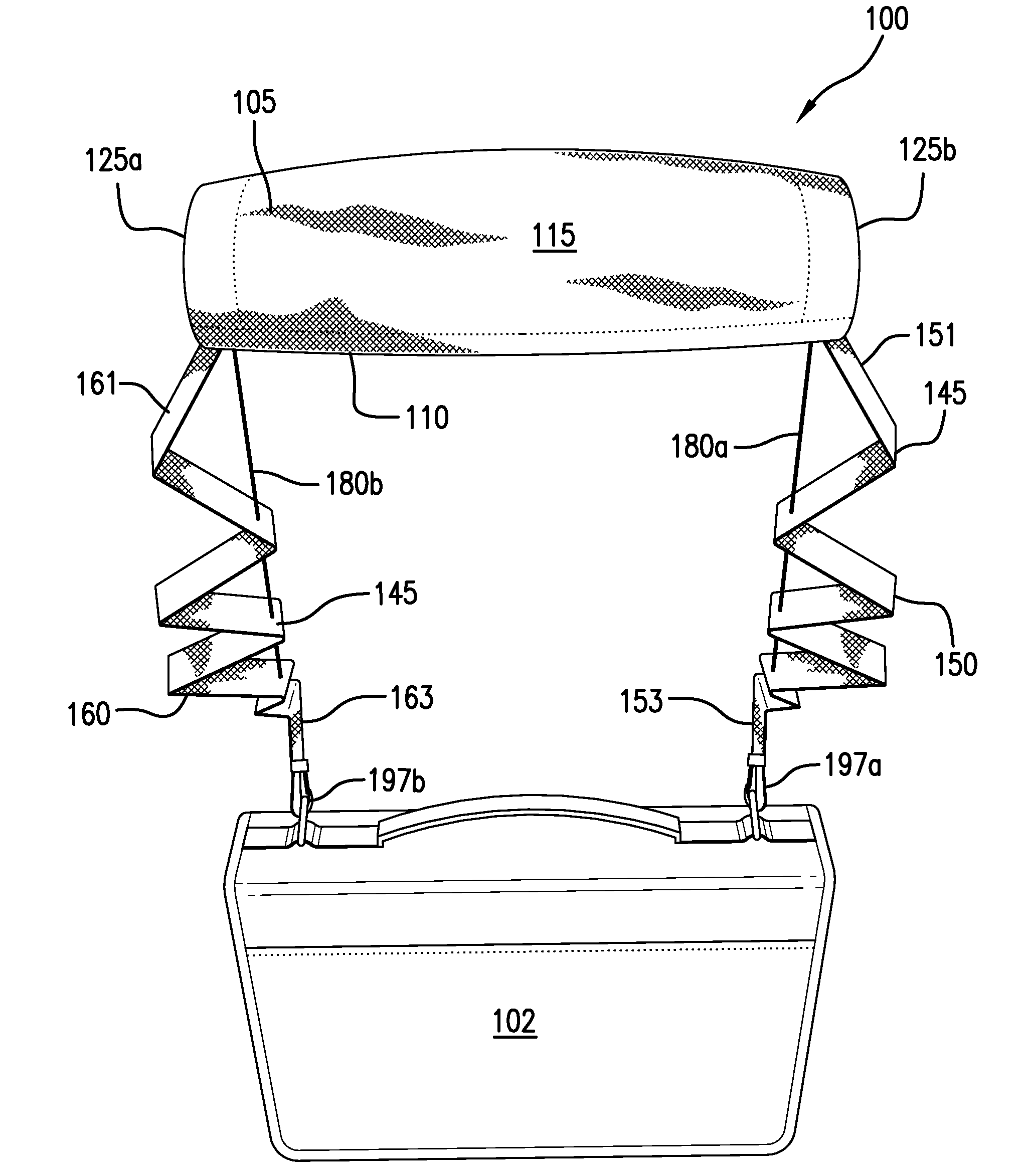

Retractable Shoulder Strap for Portable Objects

ActiveUS20160353863A1Overcome biasEasy to placeTravelling sacksTravelling carriersEngineeringGuide wires

A retractable shoulder strap for portable objects, such as bags, purses, briefcases or carry-on luggage, comprises a shoulder pad, an elongated strip of pliant material, a plurality of holes positioned at substantially uniform intervals along the length of the elongated strip, and retractors located inside the shoulder pad. Extendible guide wires passing through the plurality of holes connect the ends of the elongated strip to the retractors, which are spring-biased to automatically retract the guide wires and stow the elongated strip inside internal storage spaces in the shoulder pad, thereby eliminating slack in the strap when no tension is applied to the ends of the elongated strip. When tension is applied to the ends of the elongated strip, the portions of the elongated strip stowed in the internal storage spaces of the shoulder pad are automatically extracted, thereby increasing the length of the strap to facilitate normal over-the-shoulder use.

Owner:STEALTHSTRAP LLC

Precise positioning and sputtering-coating mechanical arm and positioning method thereof

InactiveCN101920495ACooperate accuratelyPositioning is preciseProgramme-controlled manipulatorVacuum evaporation coatingProduction lineMotor drive

The invention discloses a precise positioning and sputtering-coating mechanical arm, comprising a motor and a motor sleeve arm connected with the motor; the motor drives the motor sleeve arm to rotate; four sides of the motor sleeve are distributed with air cylinder blocks at equal diameter and equal distance; each air cylinder block is provided with an air cylinder; the piston rod of the air cylinder is vertically installed; the piston rod is detachably provided with a cover plate having a vacuum suction nozzle and used for placing light disk; the mechanical arm further comprises a positioning clamp for positioning the mounting position of the cover plate; the positioning clamp comprises a base; the center of the base is provided with a mounting hole; the housing of the motor is installed in the mounting hole of the positioning clamp; the base is provided with a station hole corresponding to the cover plate; the station hole is distributed at equal diameter and equal distance using the mounting hole as the center; the cover plate is installed in the station hole correspondingly to position the mounting position of the cover plate. The sputtering-coating mechanical arm greatly improves the production efficiency of light disk production line and simultaneously ensures low production cost; besides, the invention further discloses a positioning method.

Owner:HENAN KAIRUI DIGITAL

Droop stop mechanism for helicopter rotor blade

A droop stop mechanism for a helicopter rotor blade includes a pair of opposing stops disposed on opposite sides of the blade's flap hinge. An interposer is mounted at the end of an arm on a rotatable shaft for rotation in a plane perpendicular to the hinge. A torsion spring disposed concentrically about the shaft has a first end that is fixed and a second end coupled to the shaft to bias the interposer to a position disposed between the stops, thereby limiting blade droop. A weight is attached to the shaft such that, with rotation of the rotor, centrifugal forces acting on the weight cause the shaft and arm to rotate so as to overcome the bias of the spring and urge the interposer out from between the stops, thereby allowing greater blade droop. The spring and shaft are sealed in a canister for protection from the elements.

Owner:THE BOEING CO

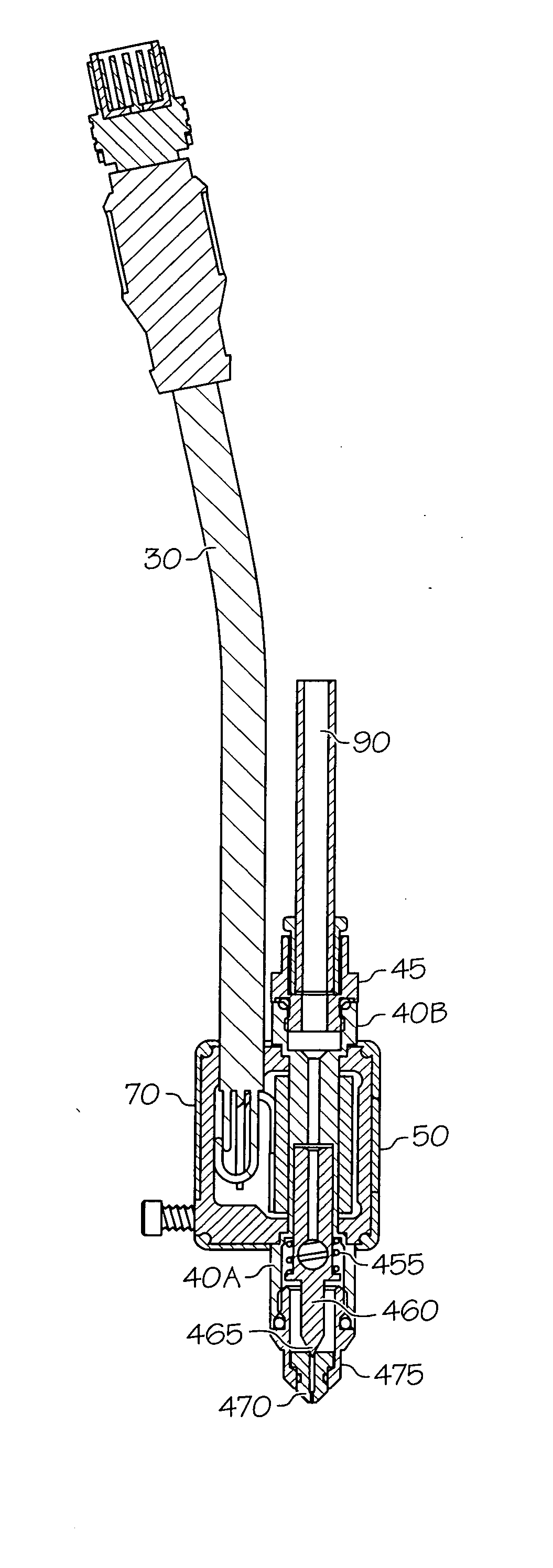

Fluid transfer apparatus

ActiveUS20050106048A1Reduce fluid pressureOvercome biasFlexible member pumpsSolid materialEngineeringValve seat

An apparatus for transferring a fluid from a supply container to a desired receptacle. The apparatus includes a conduit having a fluid passage with a valve seat and a flexible containment member. A moveable sealing member is coupled to the flexible containment member and is configured for sealingly engaging the valve seat. An activator is coupled to the sealing member for displacing the sealing member from the valve seat to effect the creation of a reduced fluid pressure in the fluid in the supply container.

Owner:SCEPTER US HLDG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com