Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Mitigate prospect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

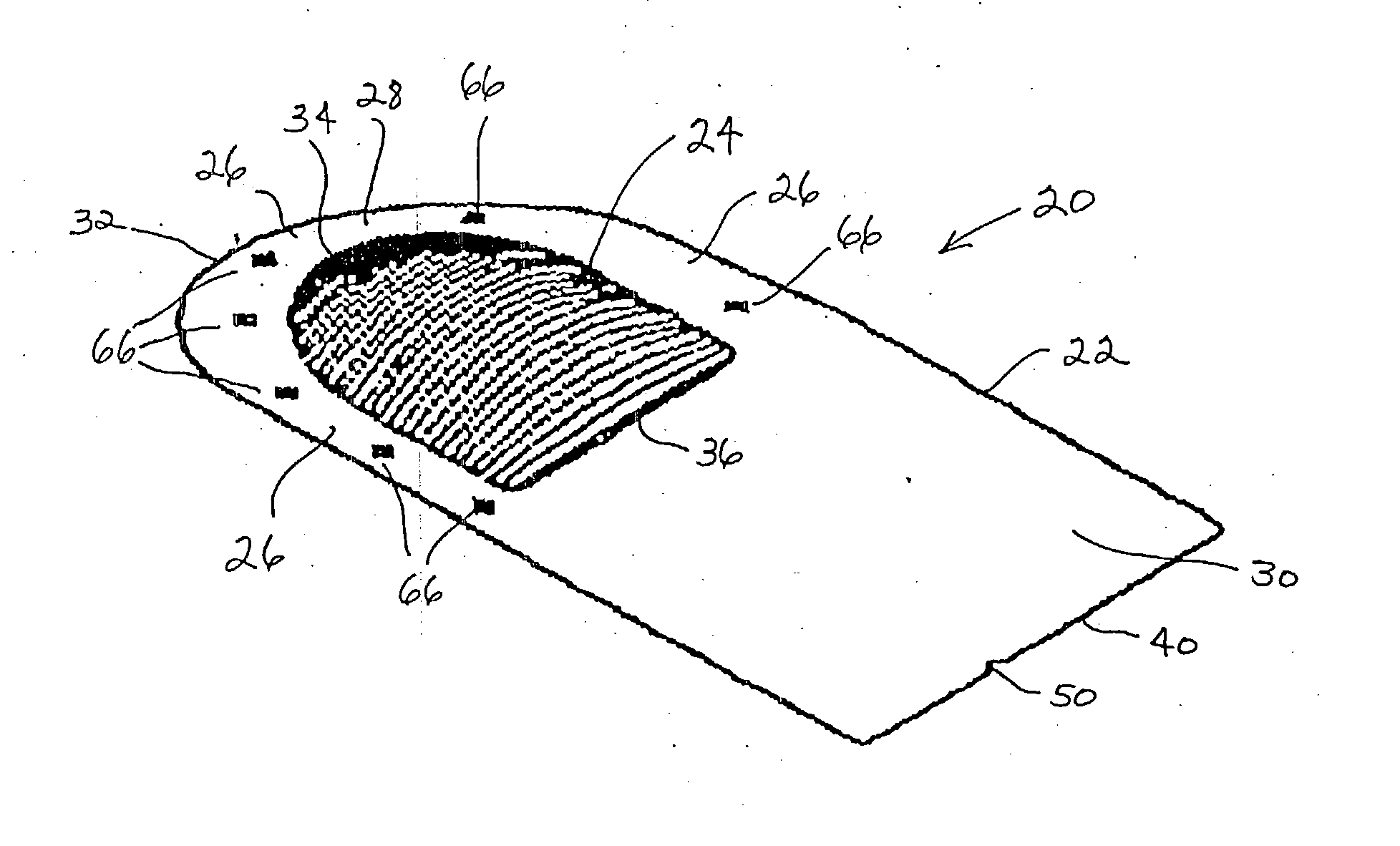

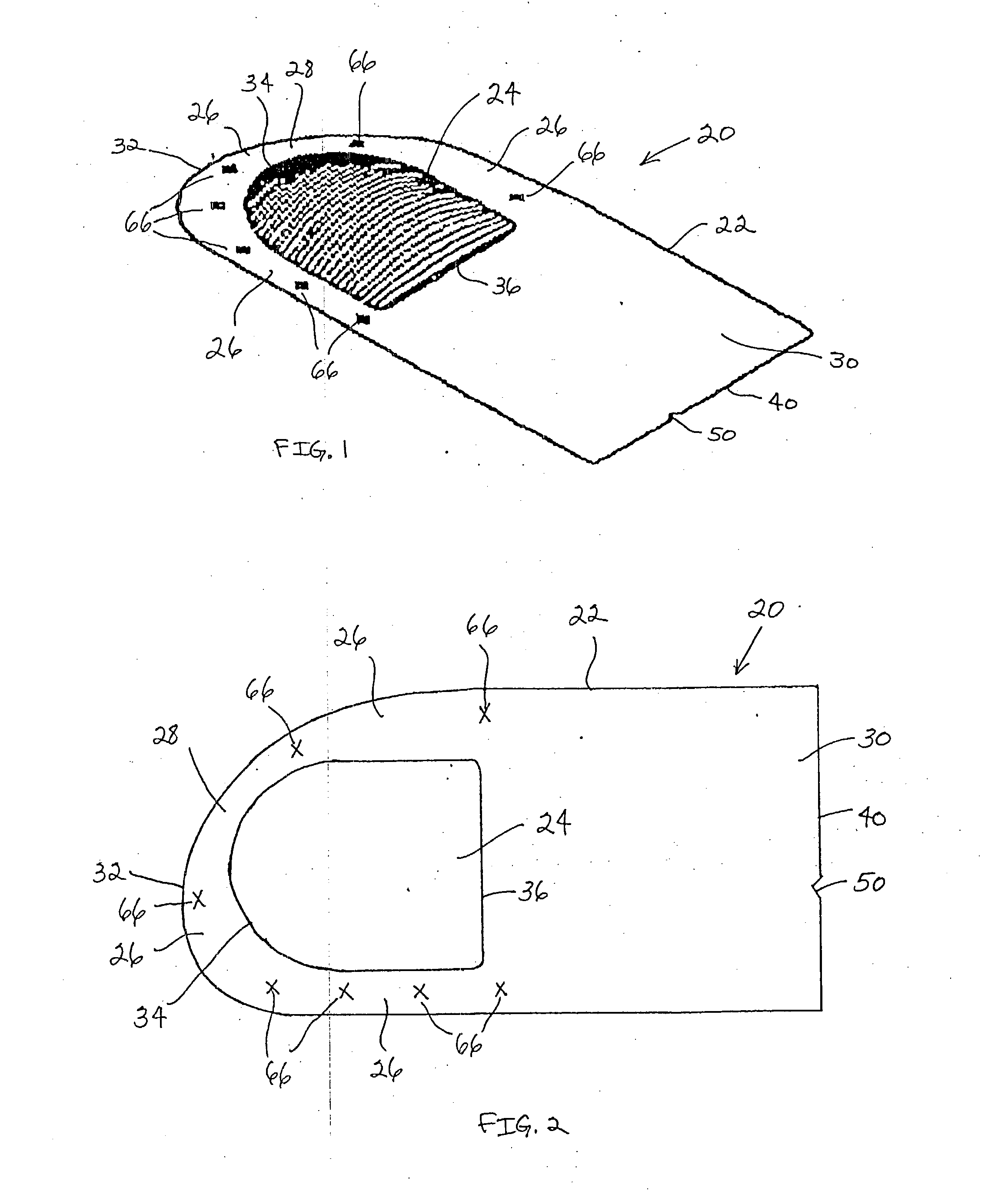

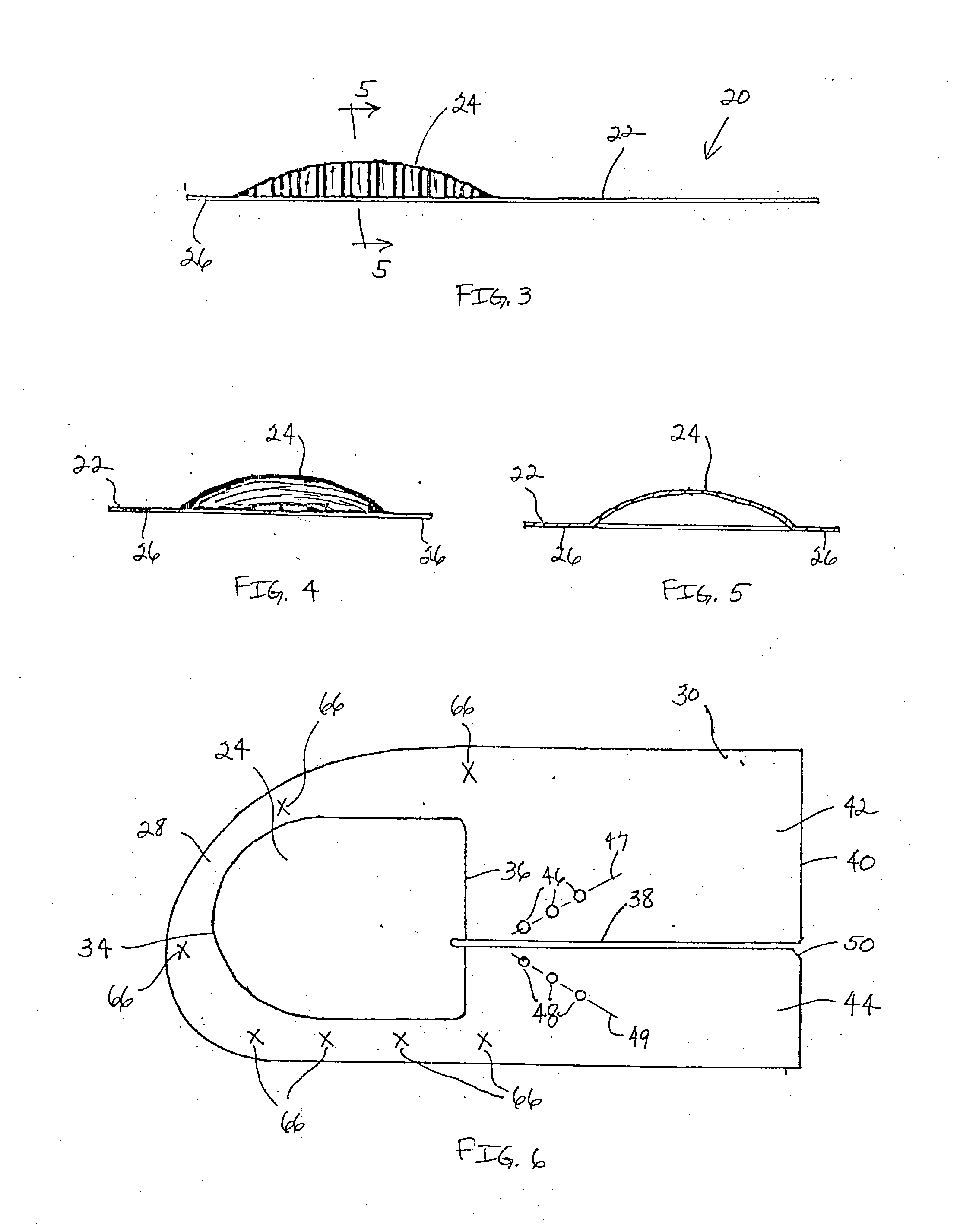

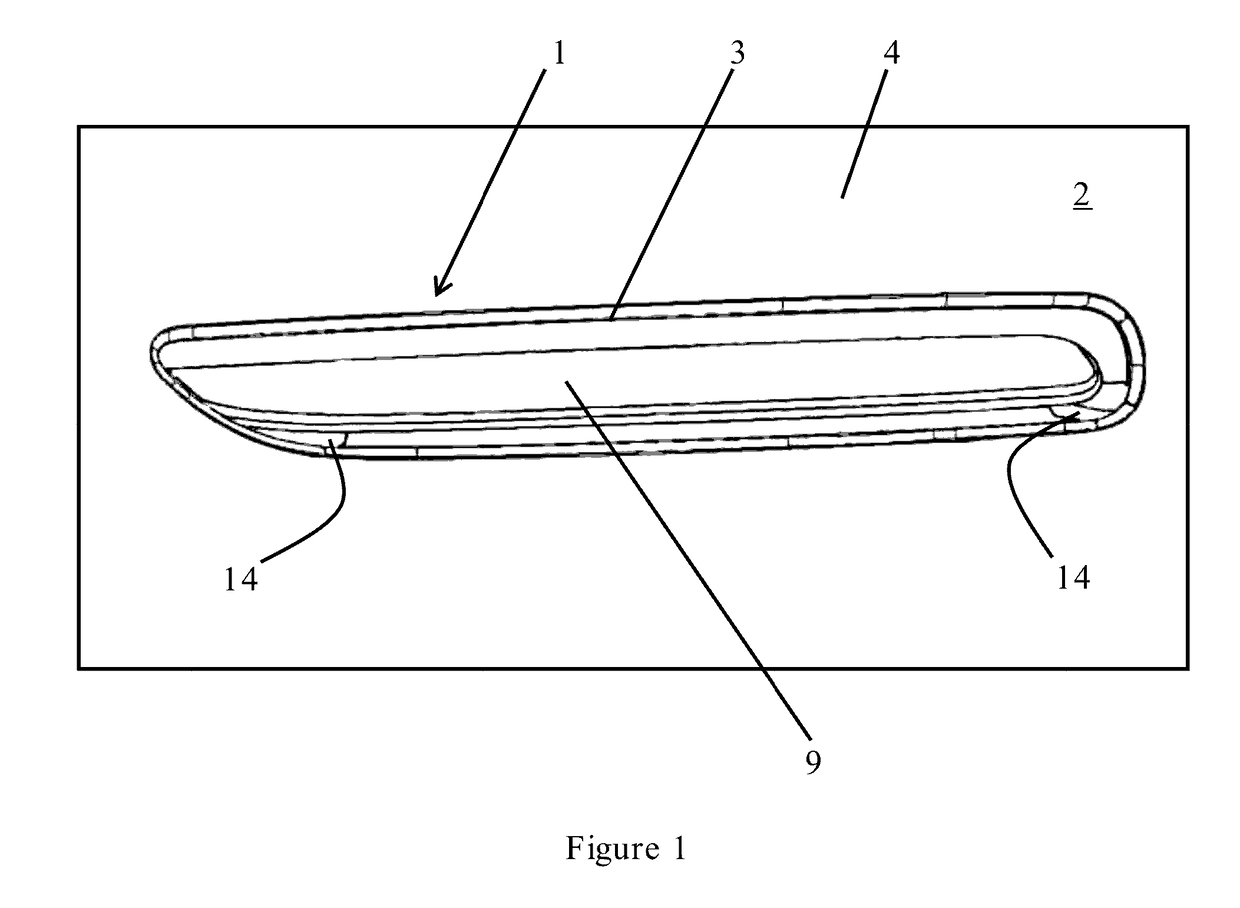

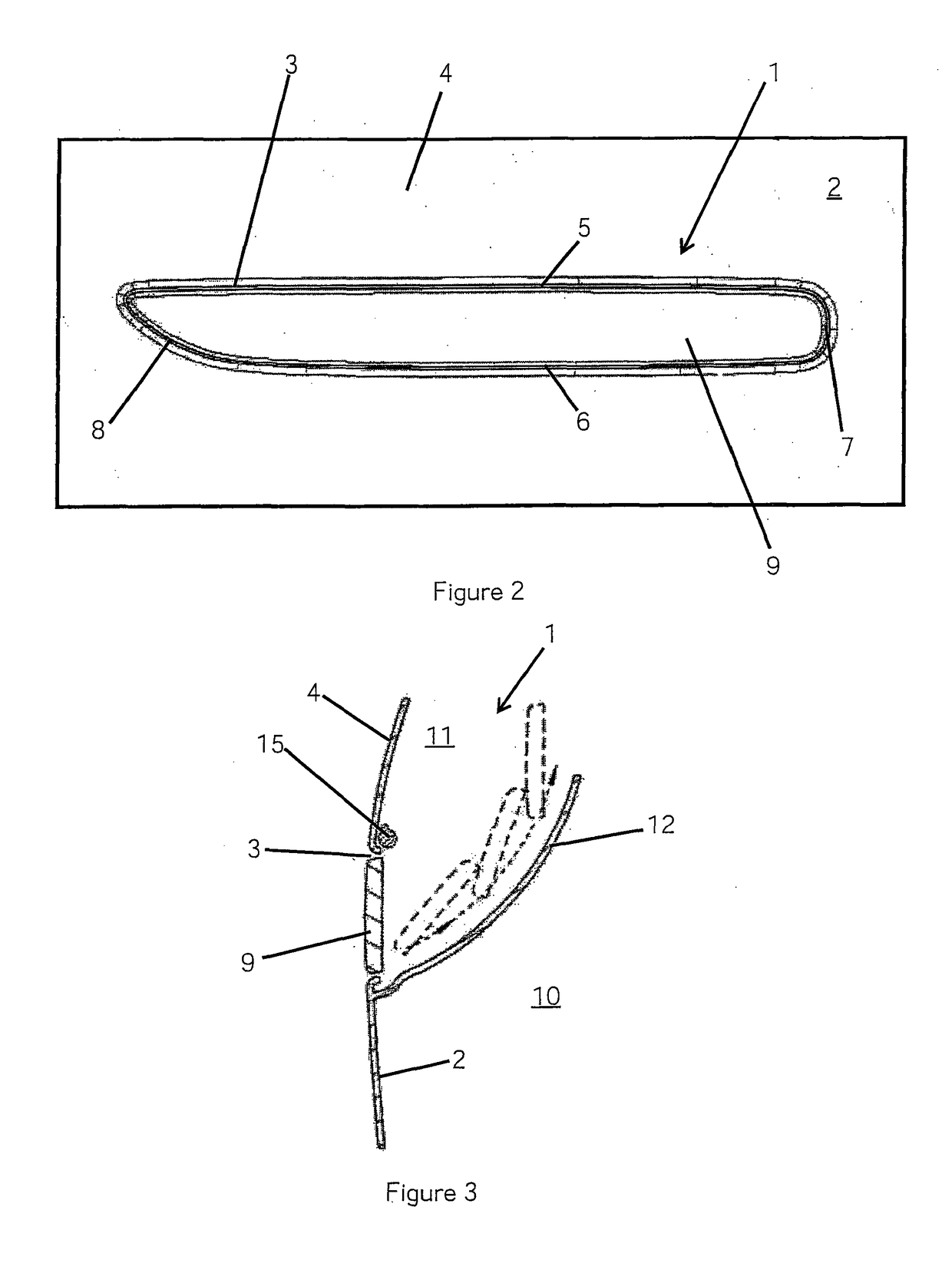

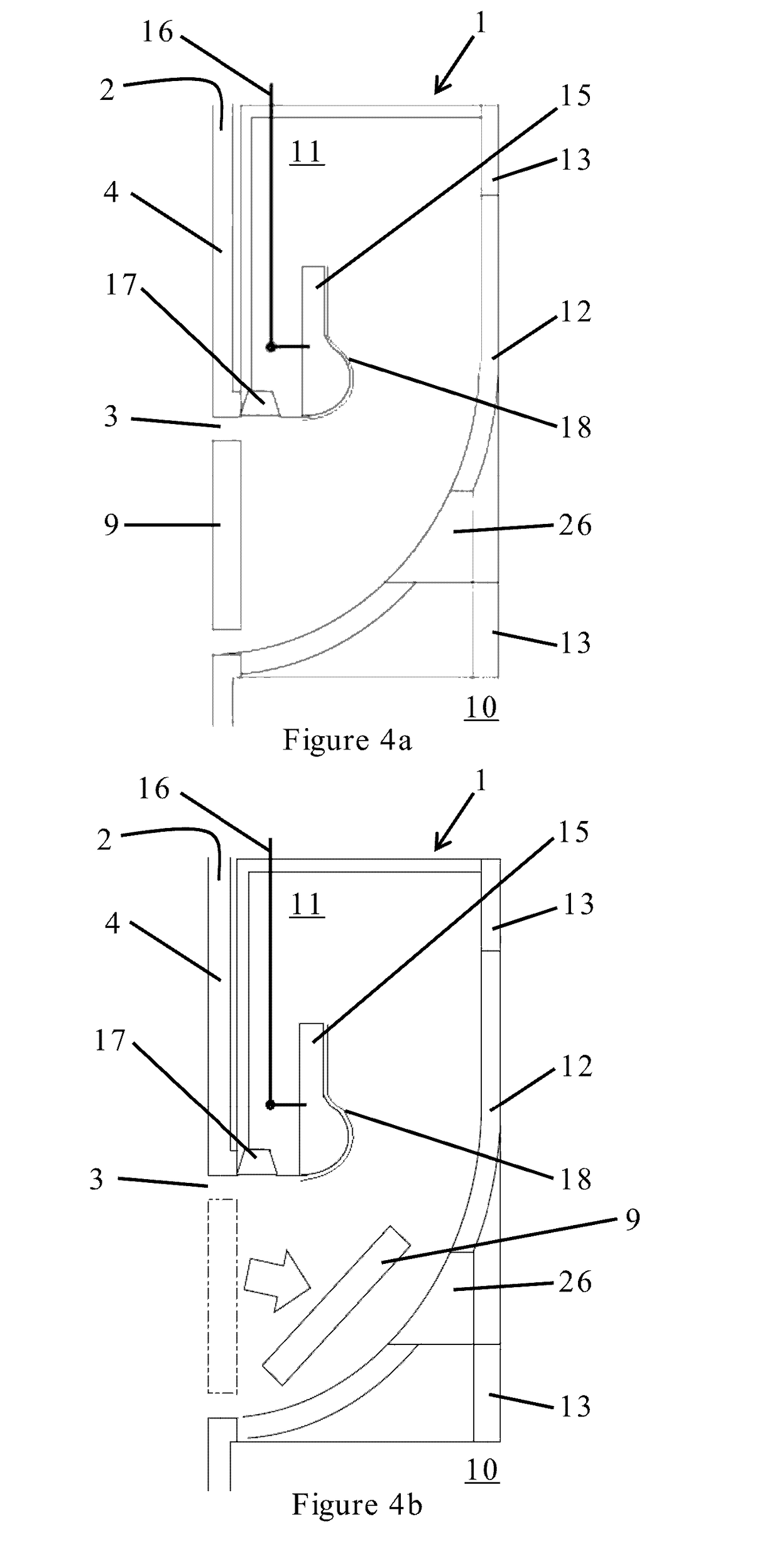

Implantable prosthesis

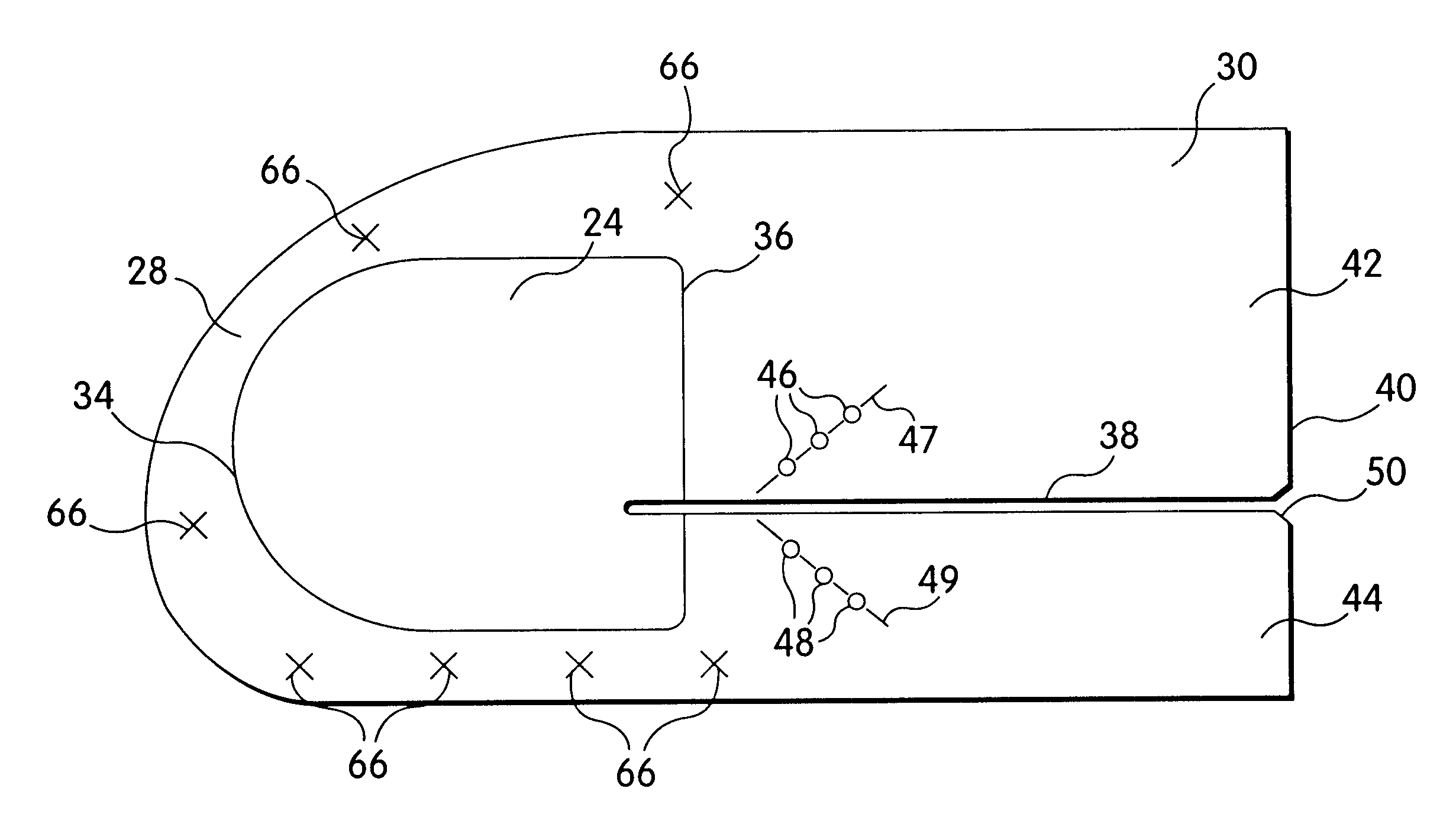

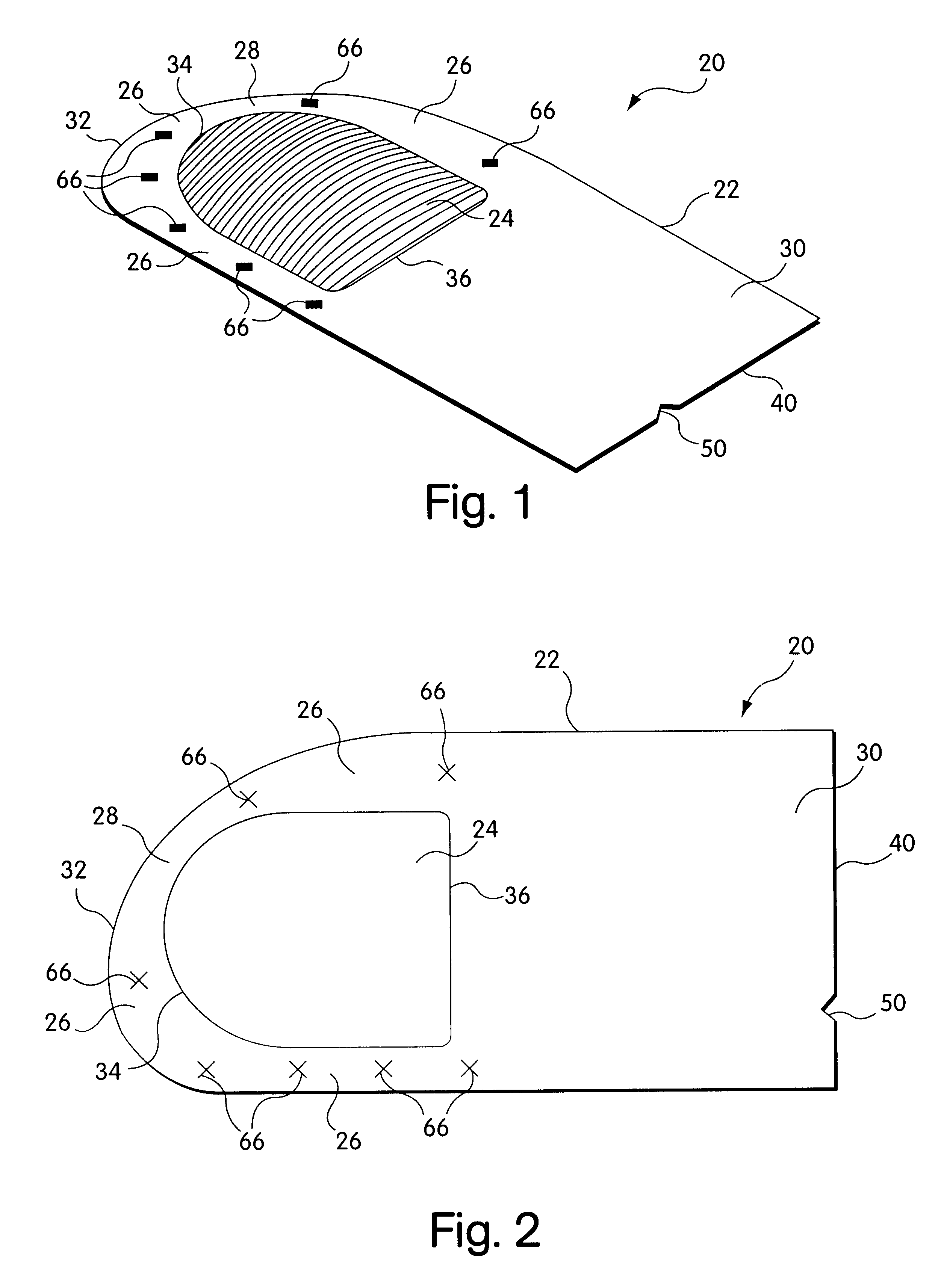

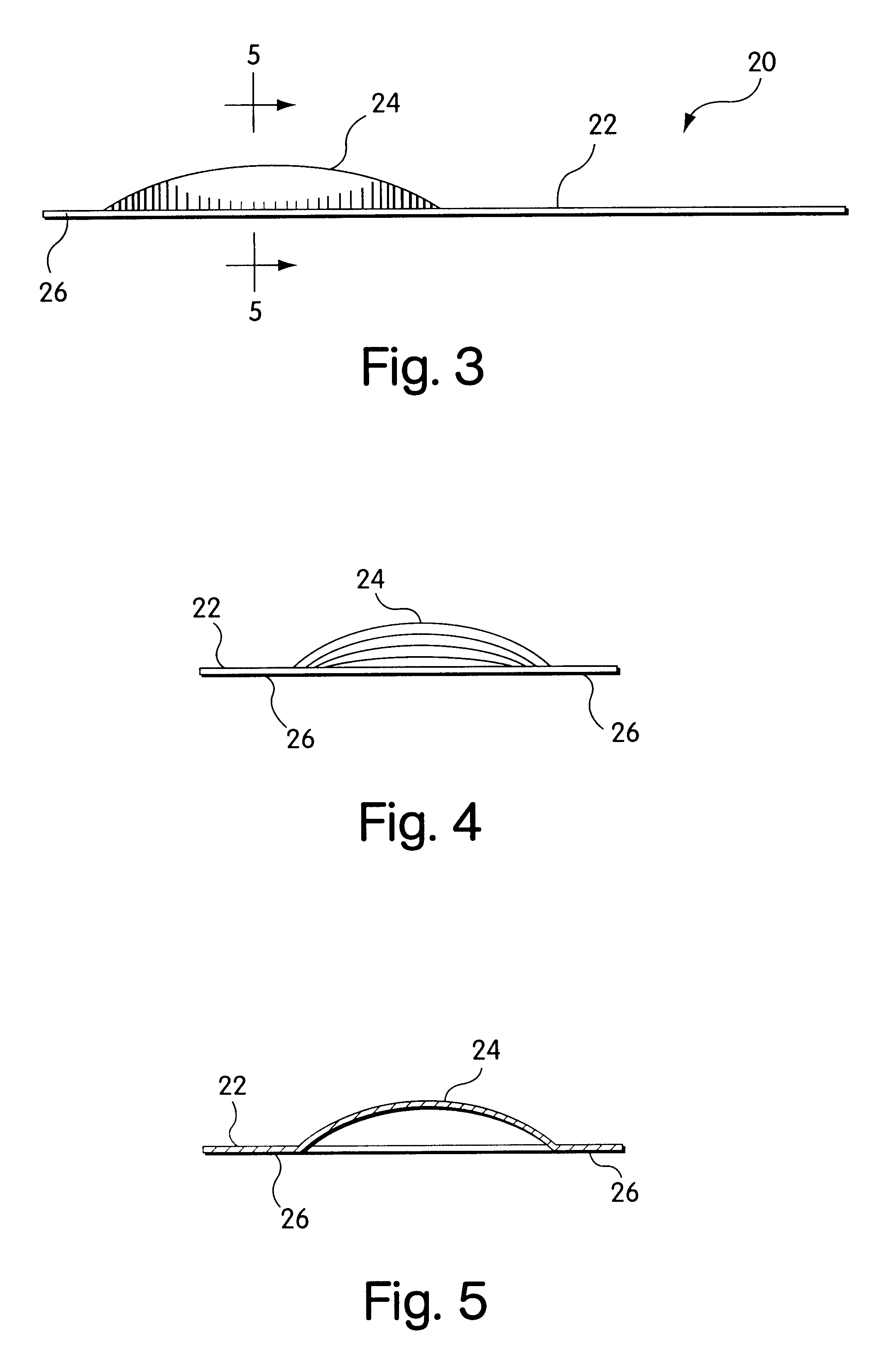

InactiveUS6610006B1Reduce the possibilityReduce postoperative painDiagnosticsLigamentsRepair siteIntraabdominal pressure

An implantable prosthesis for repairing an anatomical defect, such as a soft tissue and muscle wall defect. The prosthesis is configured to reduce the likelihood that an applied force at the repair site, such as due to intraabdominal pressure or tissue shrinkage, can lead to detrimental effects associated with tension at the anchoring locations between the prosthesis and host tissue and / or contraction of the prosthesis. In this regard, the prosthesis may be configured to limit the amount of tension at the anchoring locations caused by the application of a force or pressure to the prosthesis and / or contraction of the prosthesis. Alternatively, the prosthesis may be configured to compensate for contraction of the prosthesis due to tissue shrinkage at the repair site. The prosthesis may be configured to both limit tension at the anchoring locations and compensate for tissue shrinkage. The prosthesis may facilitate a reduction in postoperative discomfort, a recurrence of the defect, or the creation of a new defect associated with tension and / or prosthetic contraction.

Owner:CR BARD INC

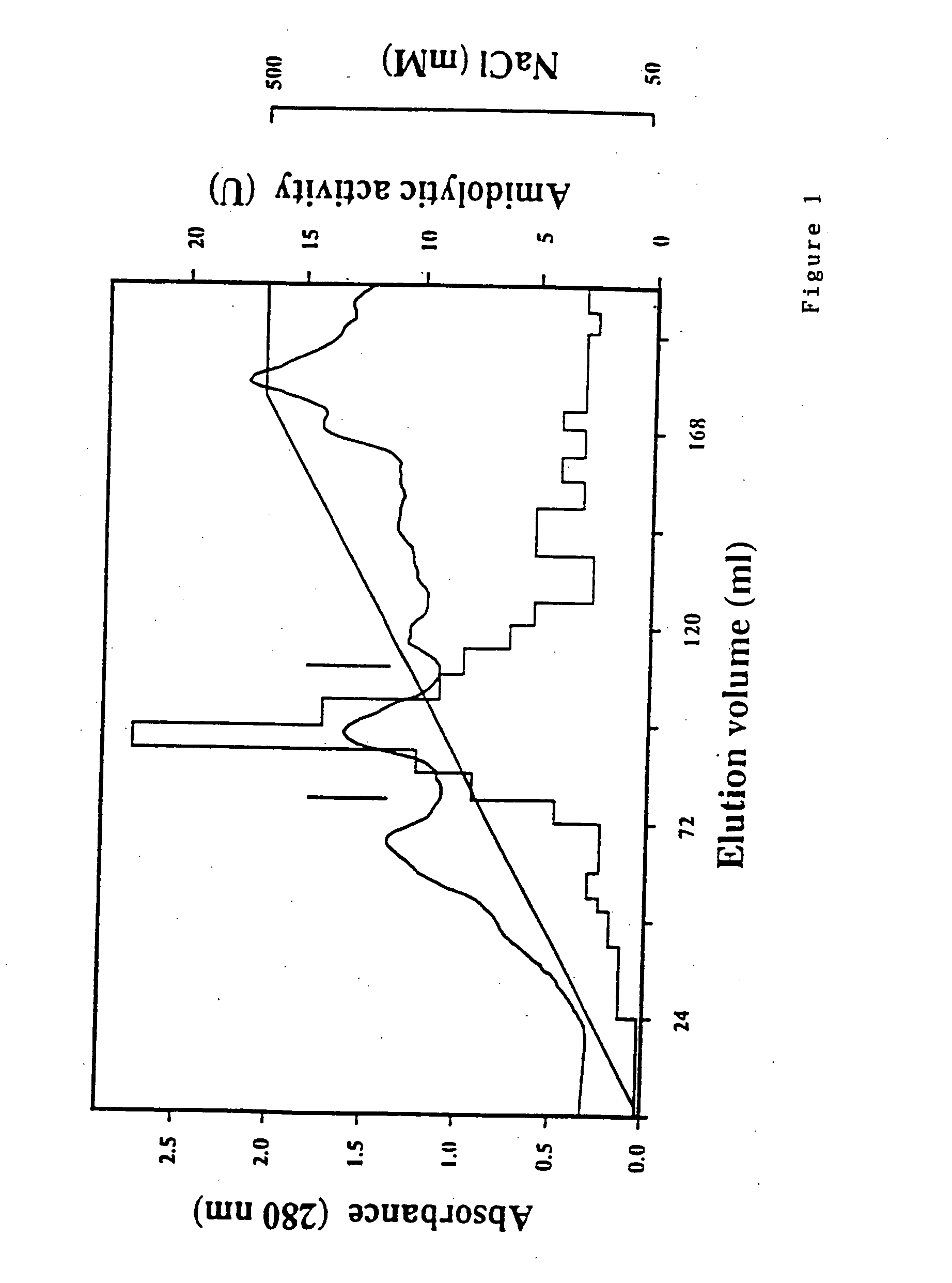

Iodinated matrices for disinfecting biological fluids

InactiveUS6096216ALarge capacityEfficient workAntibacterial agentsBiocideIon exchangeDrug biological activity

The present invention provides media for inactivating pathogens found within protein-containing biological fluids. The media of the present invention preserve the structural integrity and biological activity of labile proteins while simultaneously exhibiting potent disinfectant activity. The media of the present invention comprise iodinated chromatographic media, particularly ion exchange media. The invention further provides methods for disinfecting biological fluids.

Owner:AMERICAN NAT RED CROSS

Compositions and method for treatment and prophylaxis of inflammatory bowel disease

ActiveUS20120276201A1Promote healingPrevent relapseAntibacterial agentsOrganic active ingredientsSide effectHigh doses

Methods and compositions for treating inflammatory bowel disease involve the use of targeted antibiotics in combination with probiotic formulations. The probiotics mitigate many of the deleterious side effects associated with antibiotic use and permit the antibiotic to be administered at a higher dose and for a longer duration than would otherwise be possible in the absence of the probiotic. The practice of the invention may reduce or eliminate the use of immunosuppressants in the treatment and management of IBD.

Owner:TRACHTMAN IRA MILTON

Implantable prosthesis

InactiveUS20030187516A1Reduce the possibilityReduce postoperative painDiagnosticsSurgeryRepair siteIntraabdominal pressure

Owner:AMID PARVIZ K +1

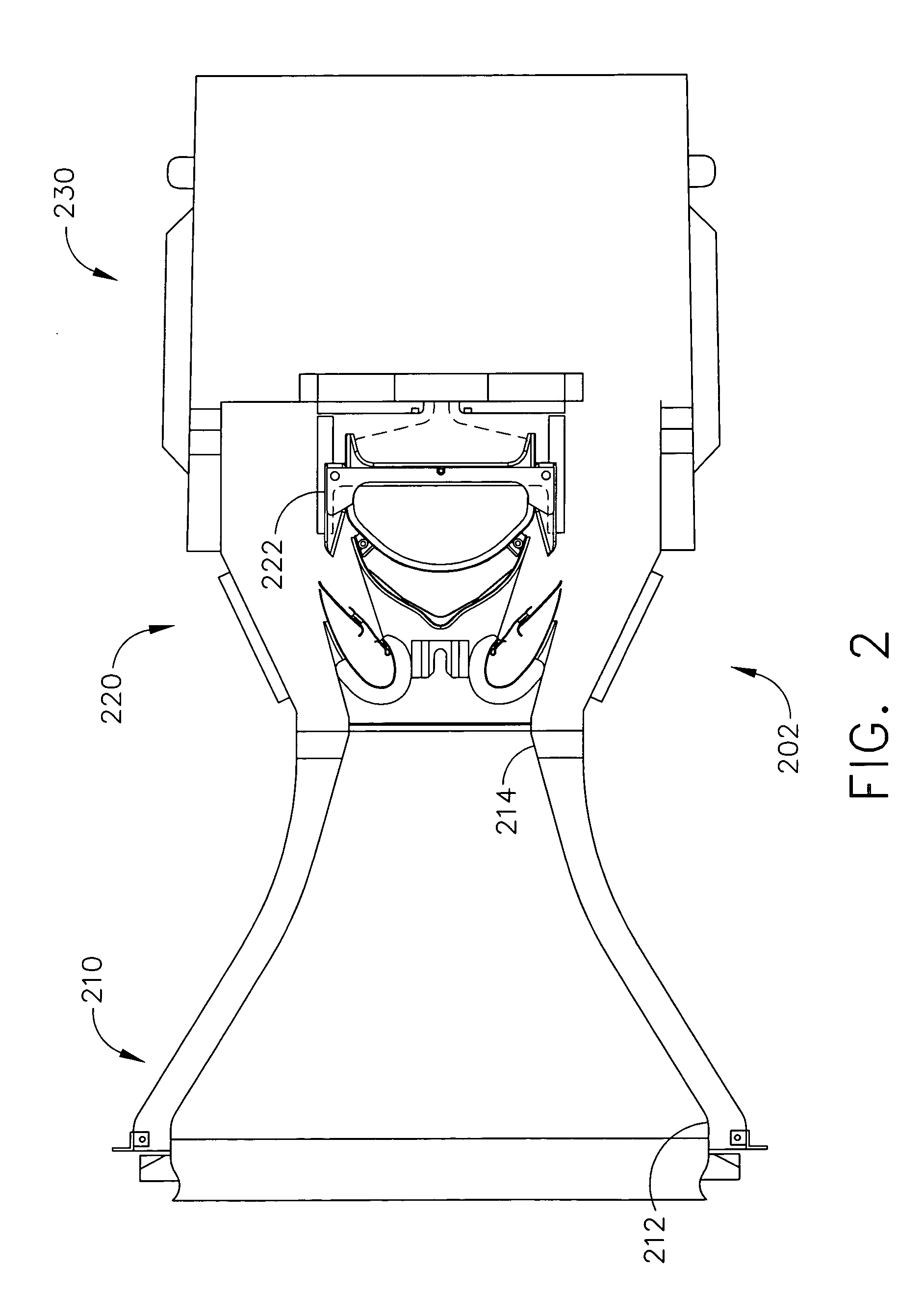

Mining Apparatus With Precision Navigation System

ActiveUS20070216216A1Clear operationRule out the possibilityDisloding machinesUnderground miningNavigation systemActuator

A mining apparatus includes a miner, a conveyor unit and a steering unit connecting the miner and conveyor unit. The apparatus also includes a heading sensor and a controller responsive to the heading sensor. A first actuator is carried on the miner, the control unit or the steering unit. The first actuator is positioned to a first side of a midline of the miner. Further a second actuator is carried on one of the miner, the conveyor unit and the steering unit. The second actuator is positioned to a second opposite side of the midline of the miner. The first and second actuators are utilized to adjust a connection angle between the miner and the conveyor unit either side of parallel in order to maintain the miner on the desired directional heading.

Owner:EAGLE HIGHWALL MINING SYST LLC

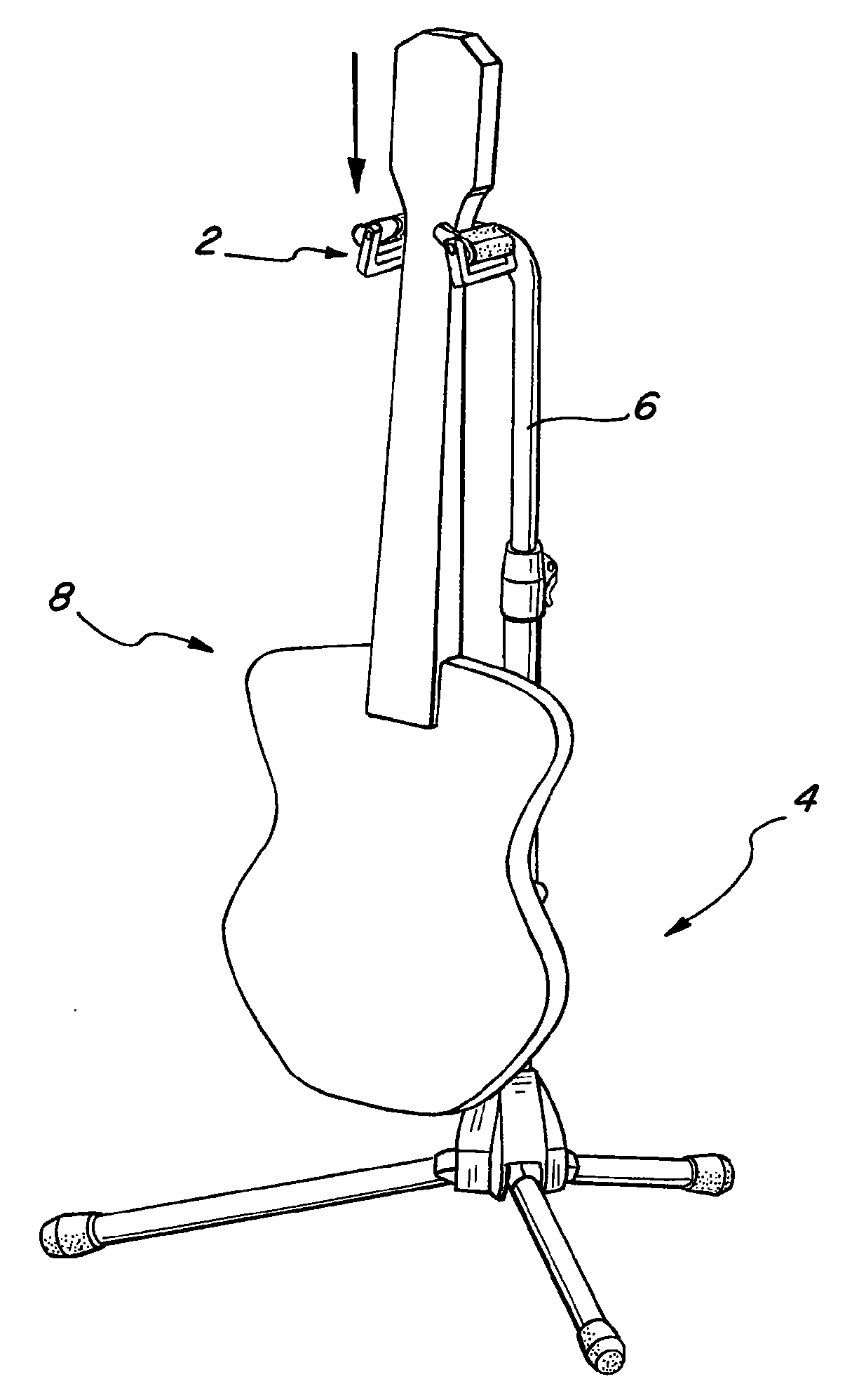

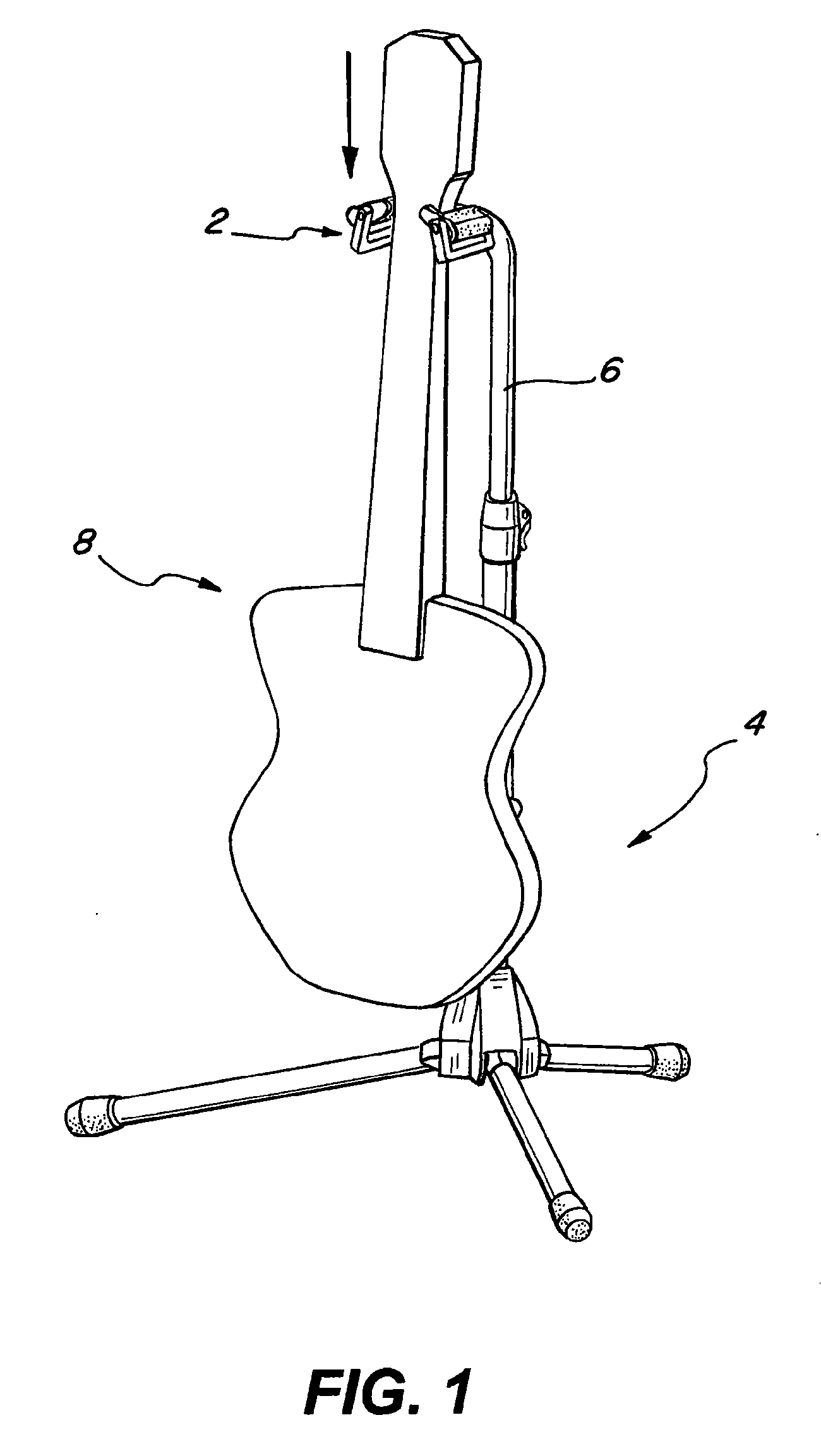

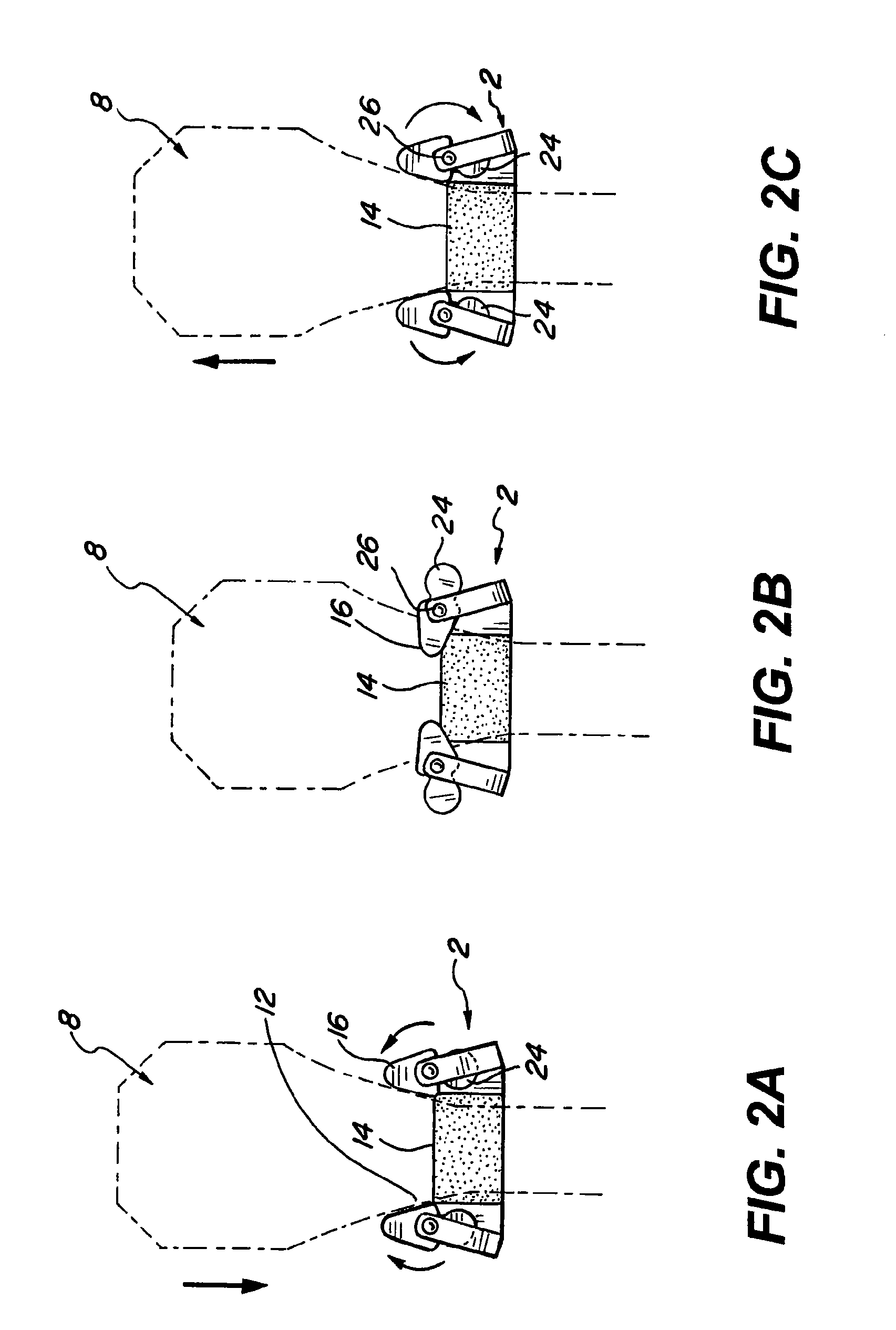

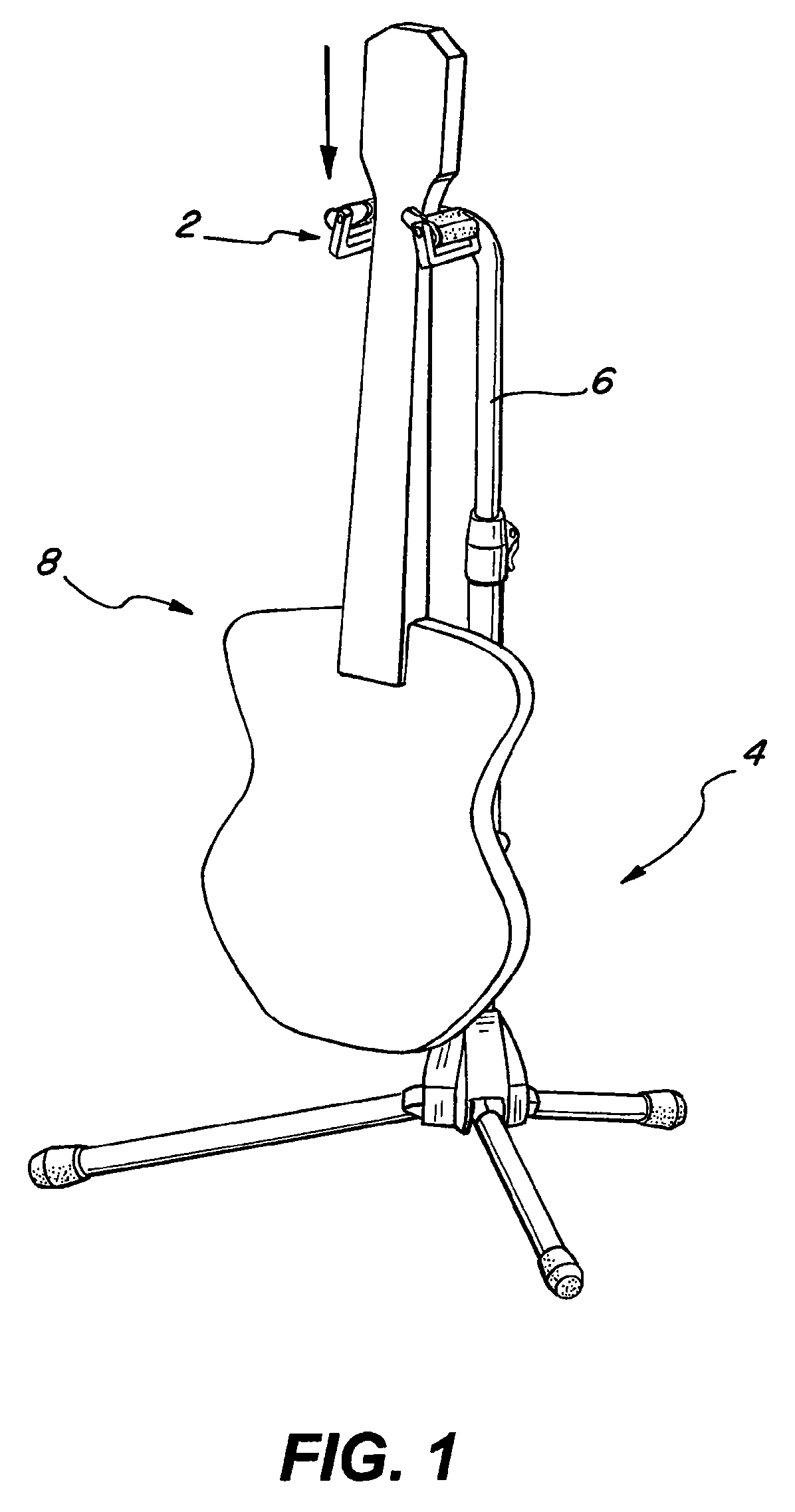

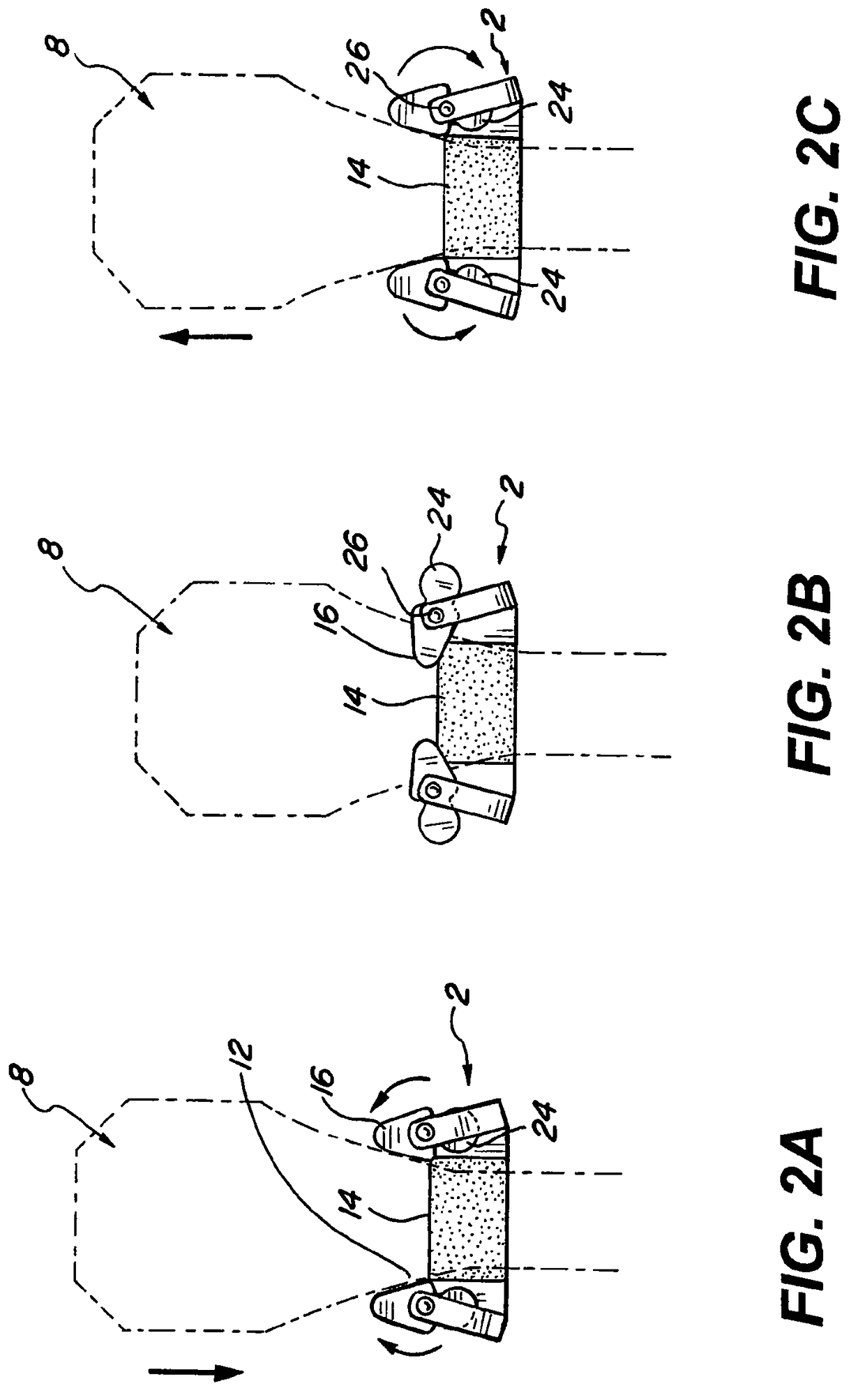

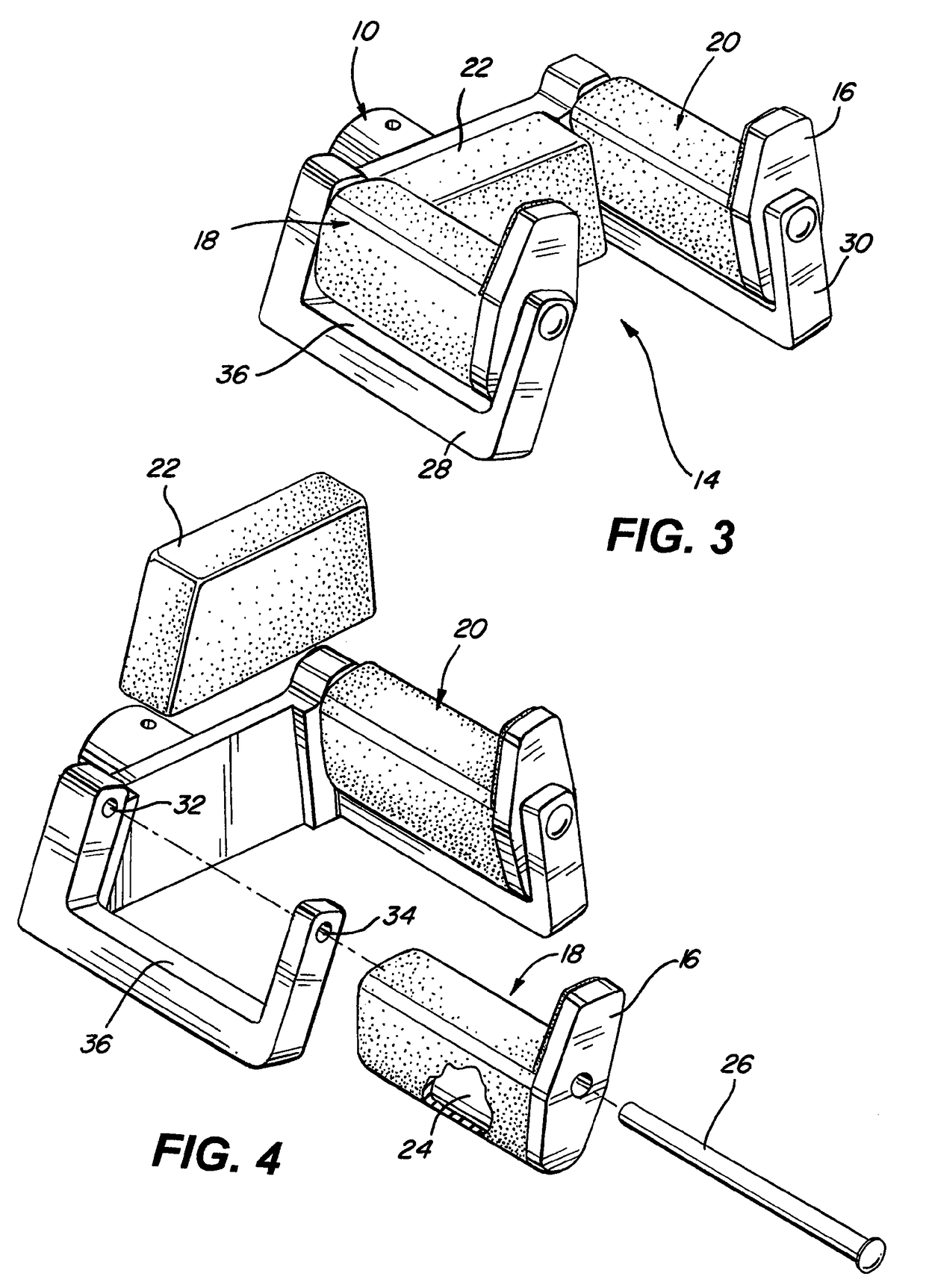

Locking device for retaining a musical instrument

InactiveUS20100163693A1Quickly and effectively placeSimple structurePipe supportsStringed musical instrumentsMechanical engineeringInstrumentation

A locking device for retaining a musical instrument can be attached to a stand assembly by a base member. A support unit with an entrance opening supports a portion of the instrument. A force such as gravitational can cause the support unit to rotate a biased locking member to close the entrance opening. Removal of the instrument permits a biasing force to open the locking member.

Owner:SOUNDKING GROUP

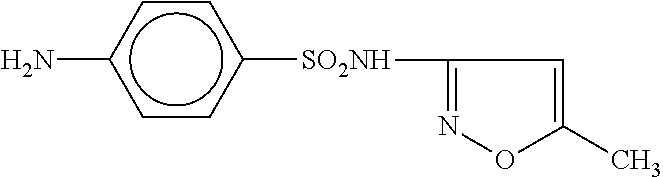

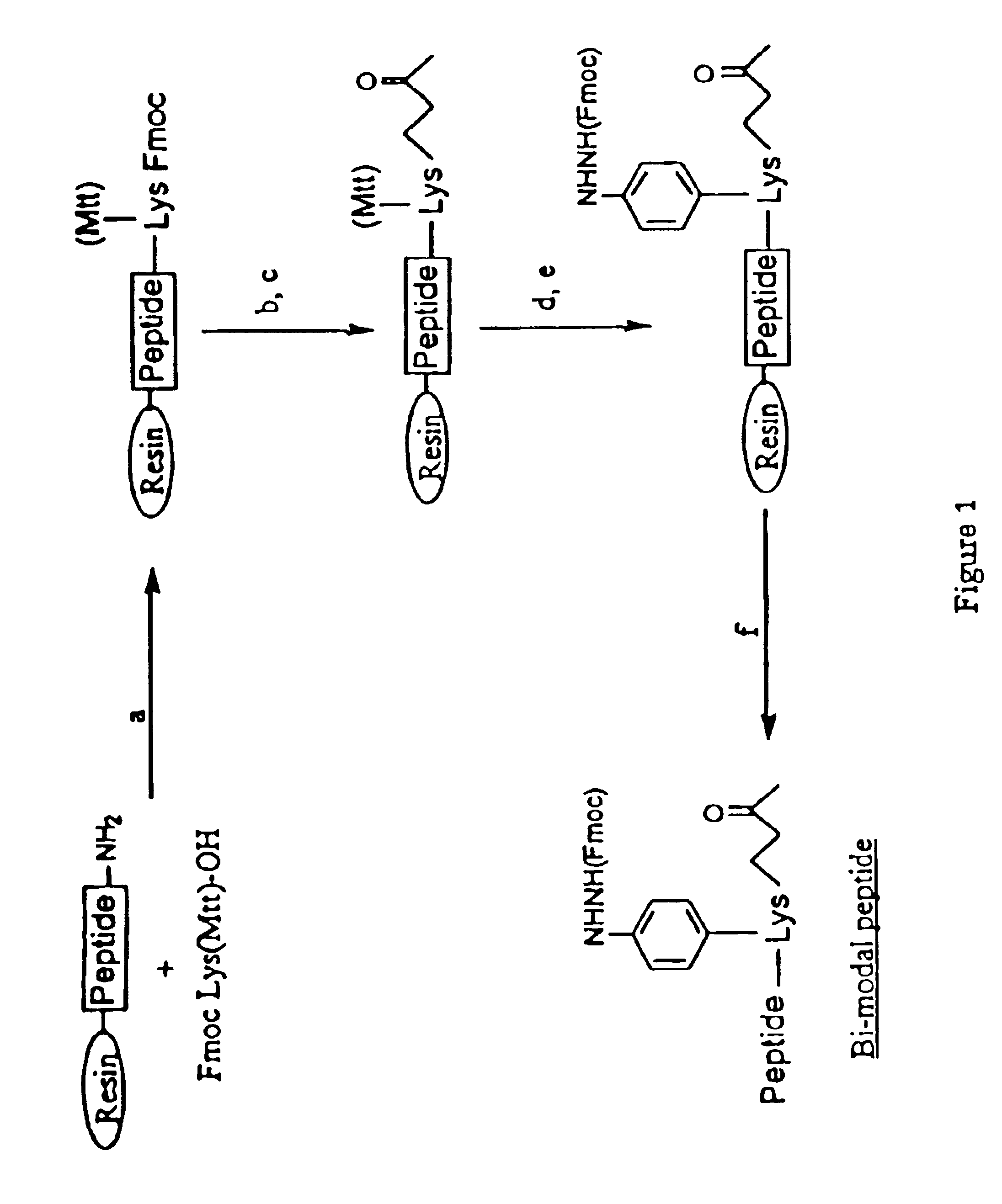

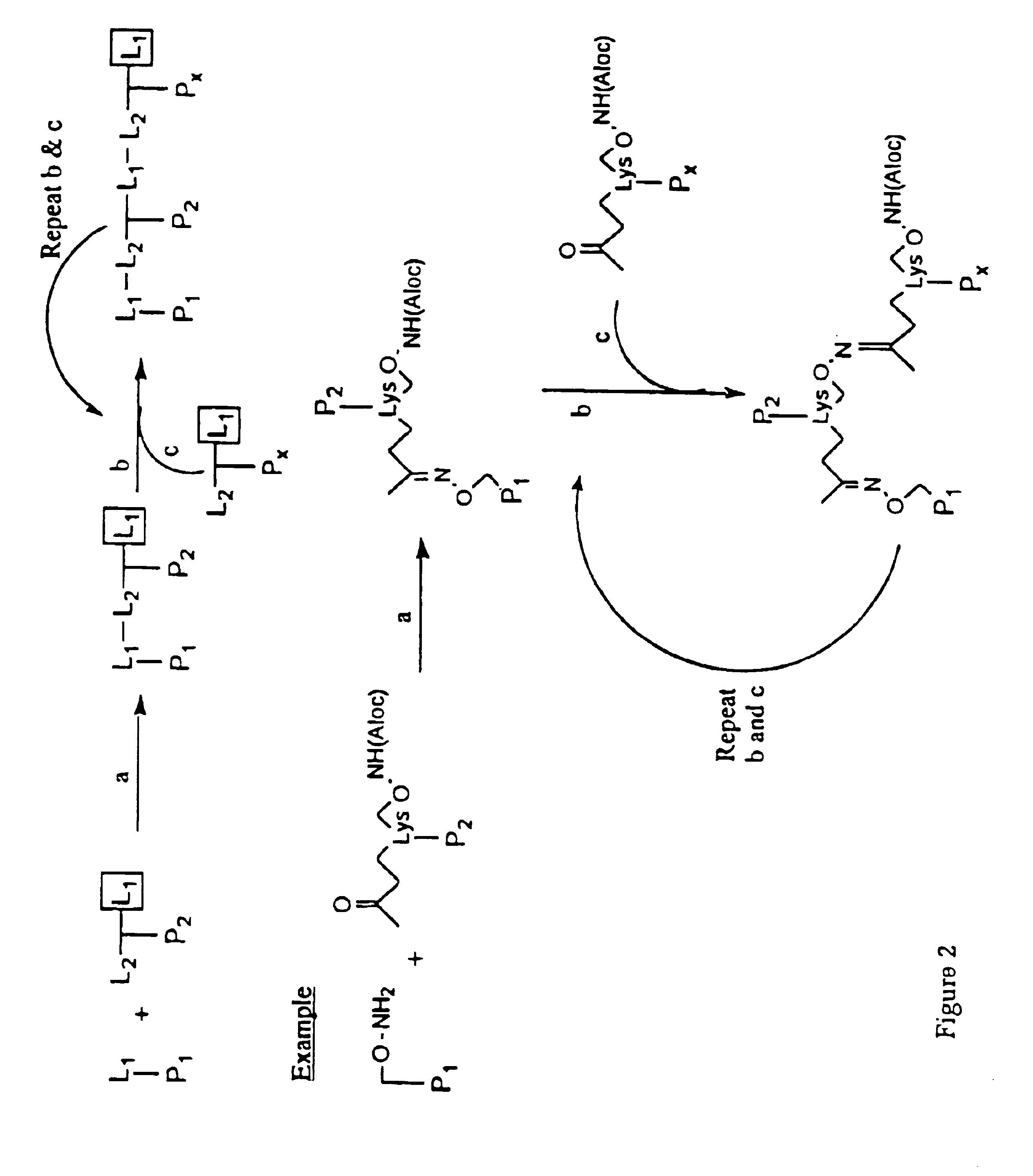

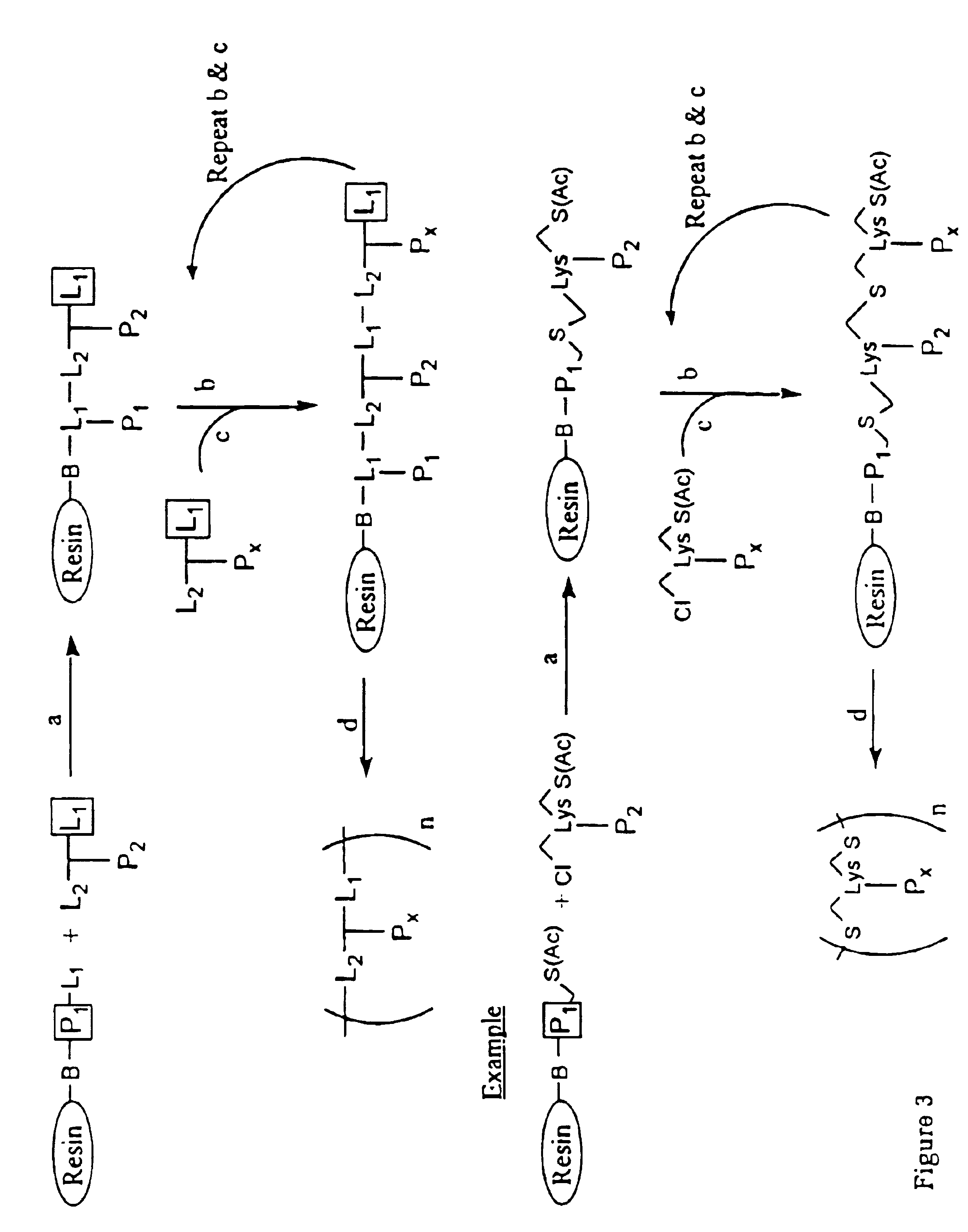

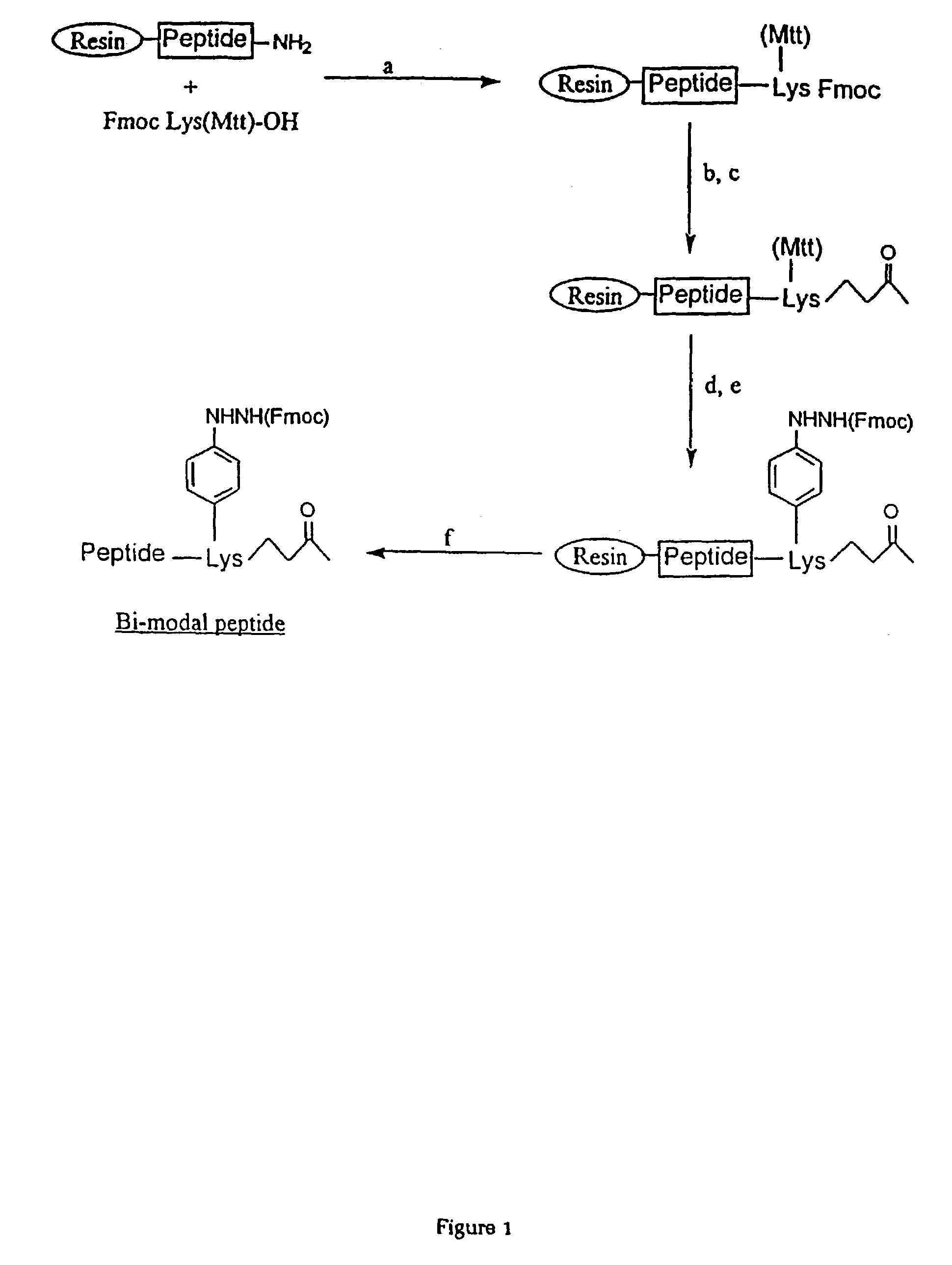

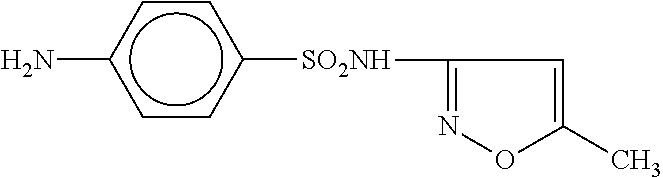

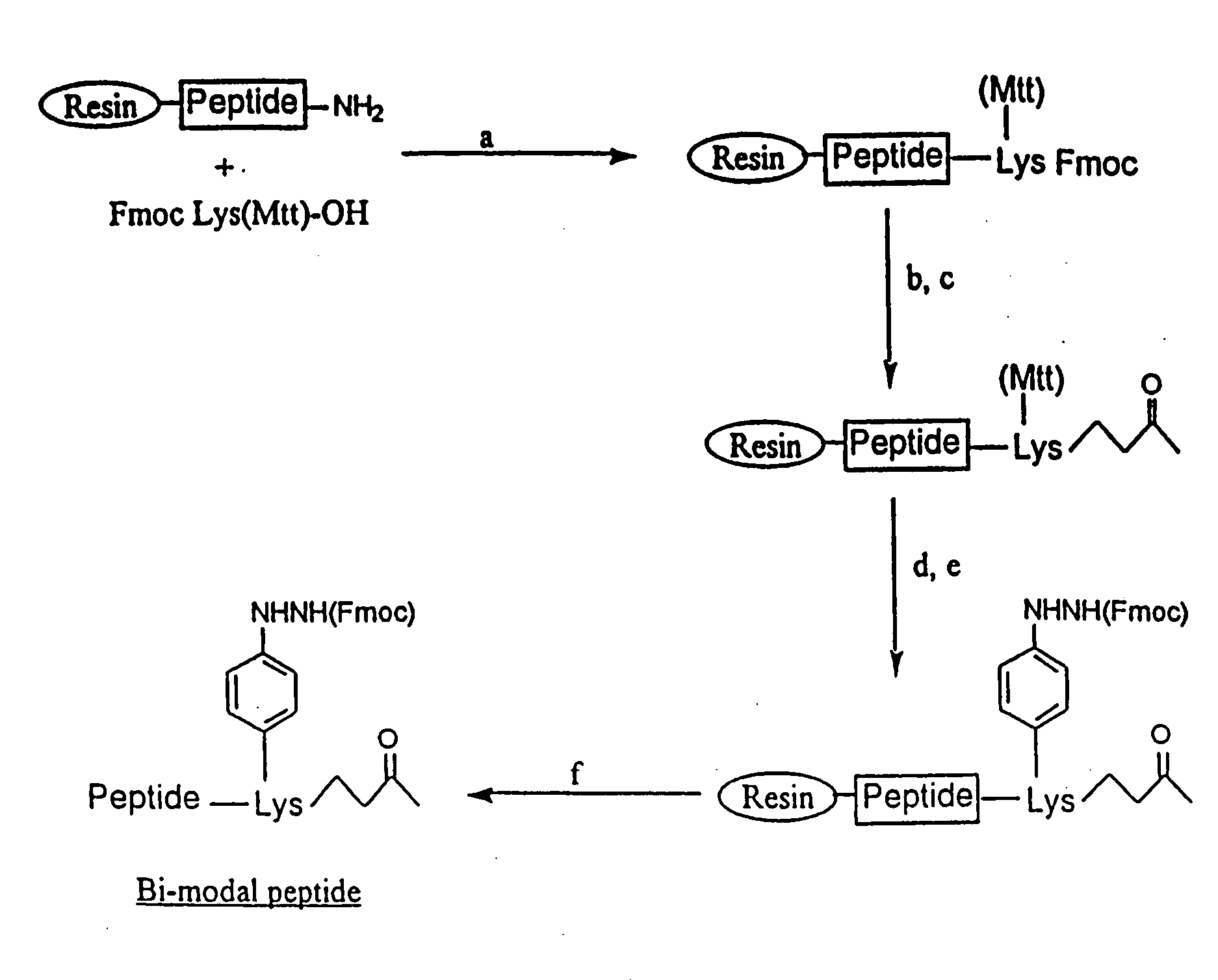

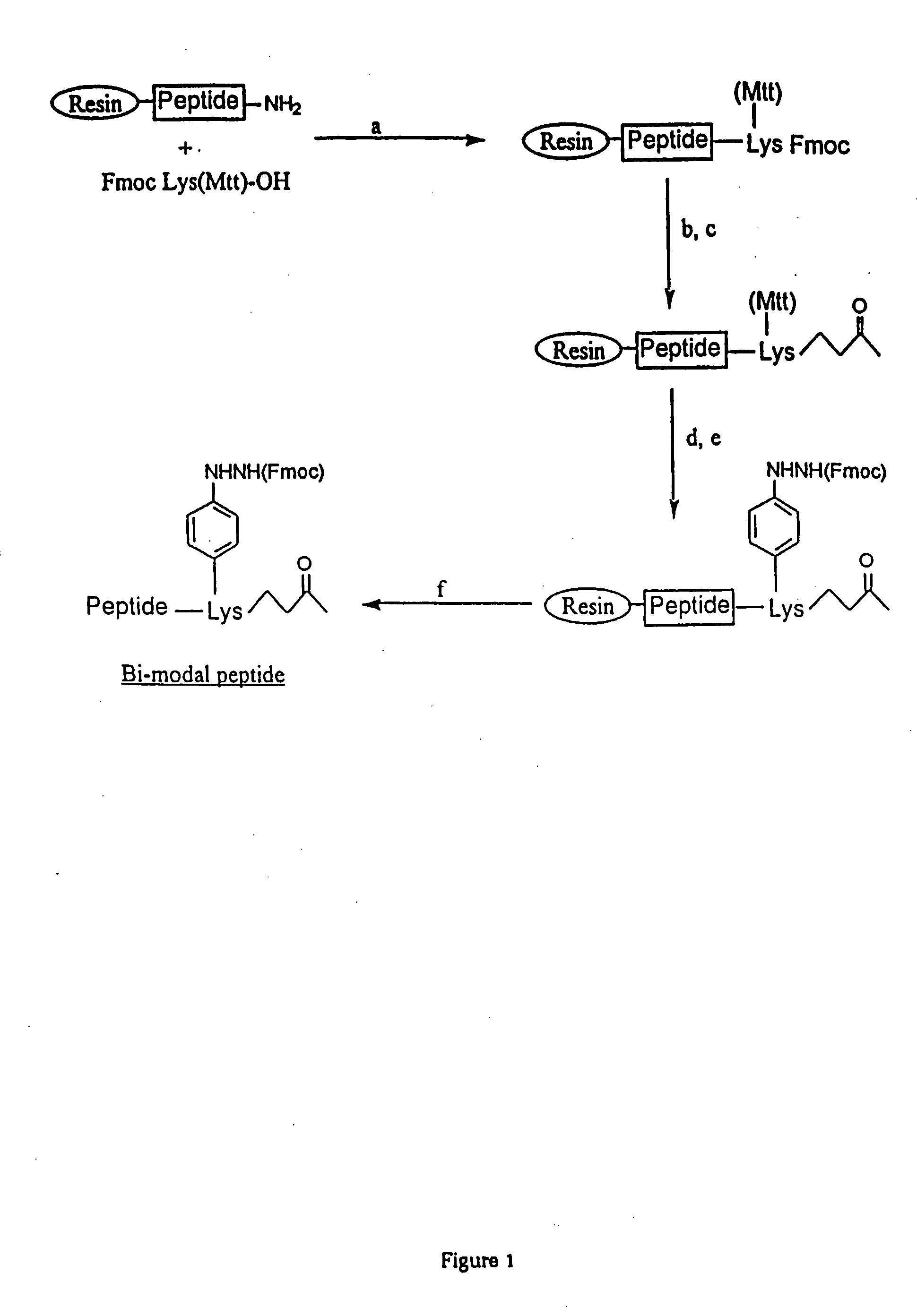

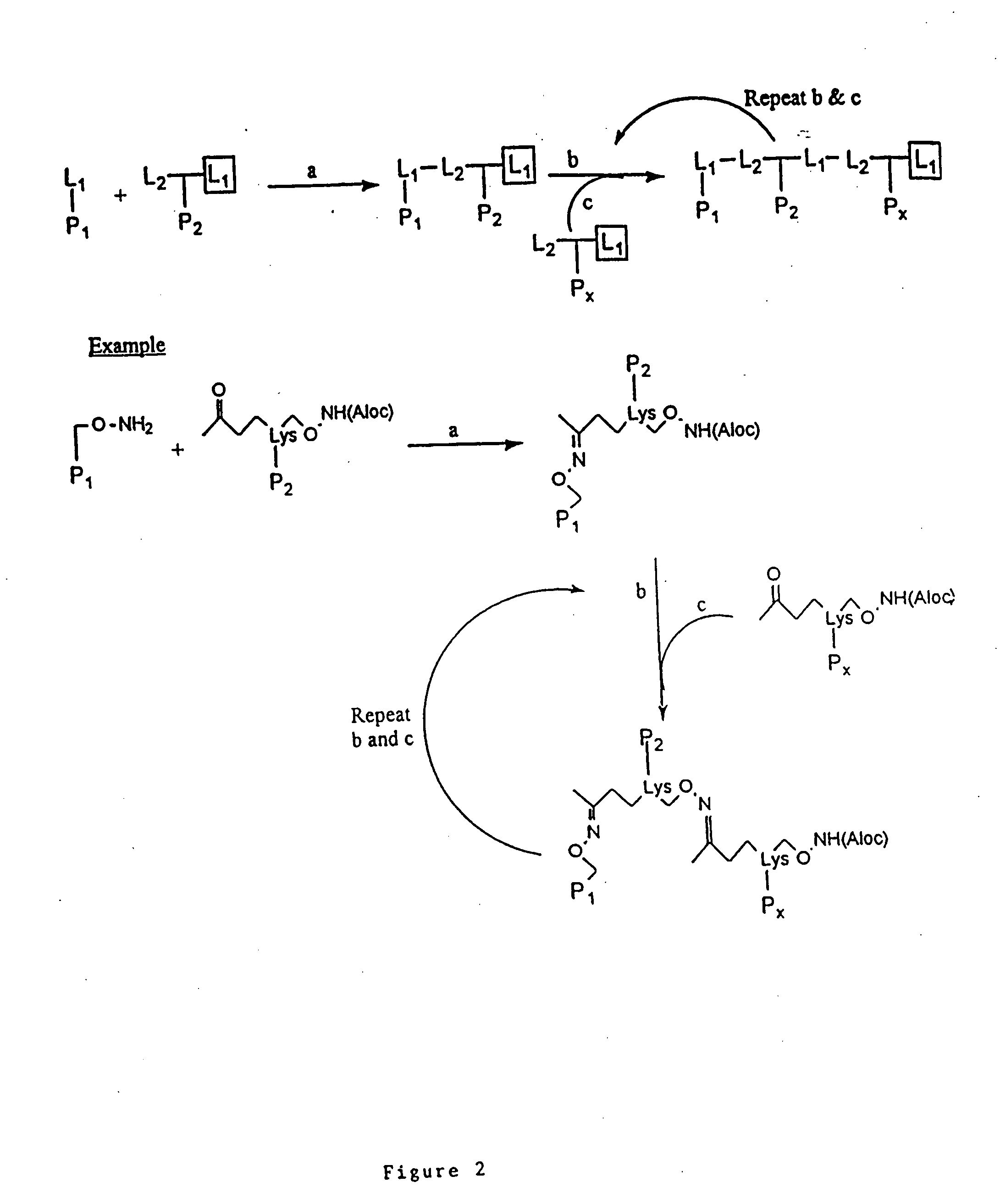

Synthetic peptides containing protective epitopes for the treatment and prevention of periodontitis associated with porphyromonas gingivalis

InactiveUS6962706B1Mitigate prospectEfficient inductionCosmetic preparationsImpression capsEpitopePorphyromonas gingivalis

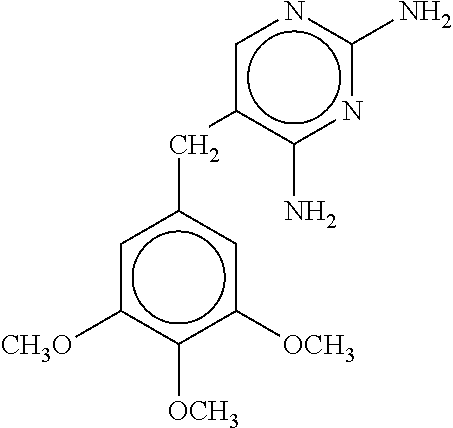

This invention relates to a peptide selected from the group: FLLDADHNTFGSVIPATGPLFTGTASS LYSANFESLIPANADPVVTTQNIIVTG LYSANFEYLIPANADPVVTTQNIIVTG TNPEPASGKMWIAGDGGNQP RYDDFTFEAGKKYTFTMRRAGMGDGTD DDYVFEAGKKYHFLLLMKKMGSGDGTE TNPEPASGKMWIAGDGGNQPARYDDFTFEAGKKYTFTMRRAGMGDGTD NTFGSVIPATGPL PASGKMWIAGDG EAGKKYTFTMRRA EAGKKYHFLMKKM. It also relates to compositions and use of these peptides for treating and testing Porphyromonas gingialis.

Owner:UNIVERSITY OF MELBOURNE +2

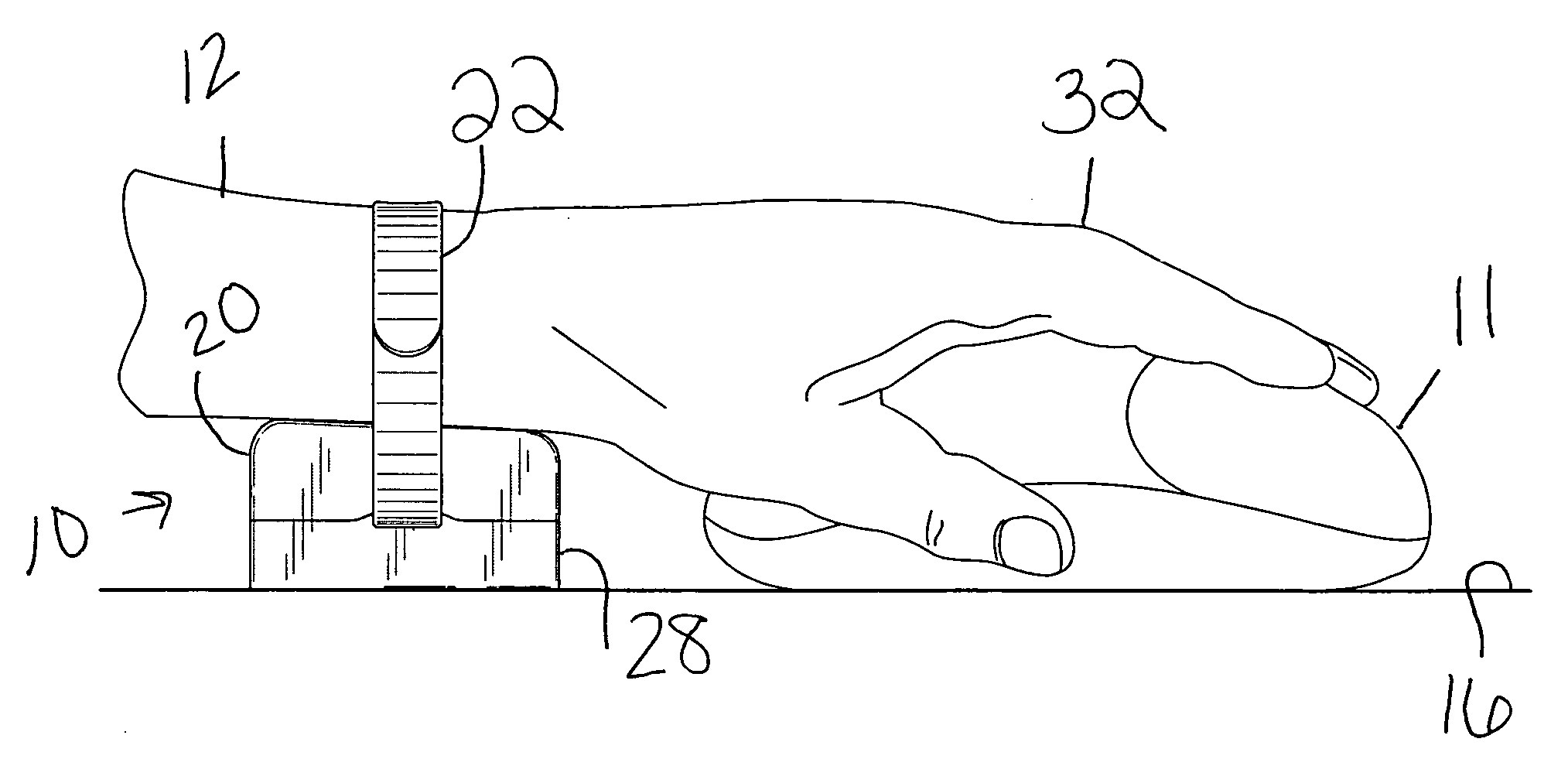

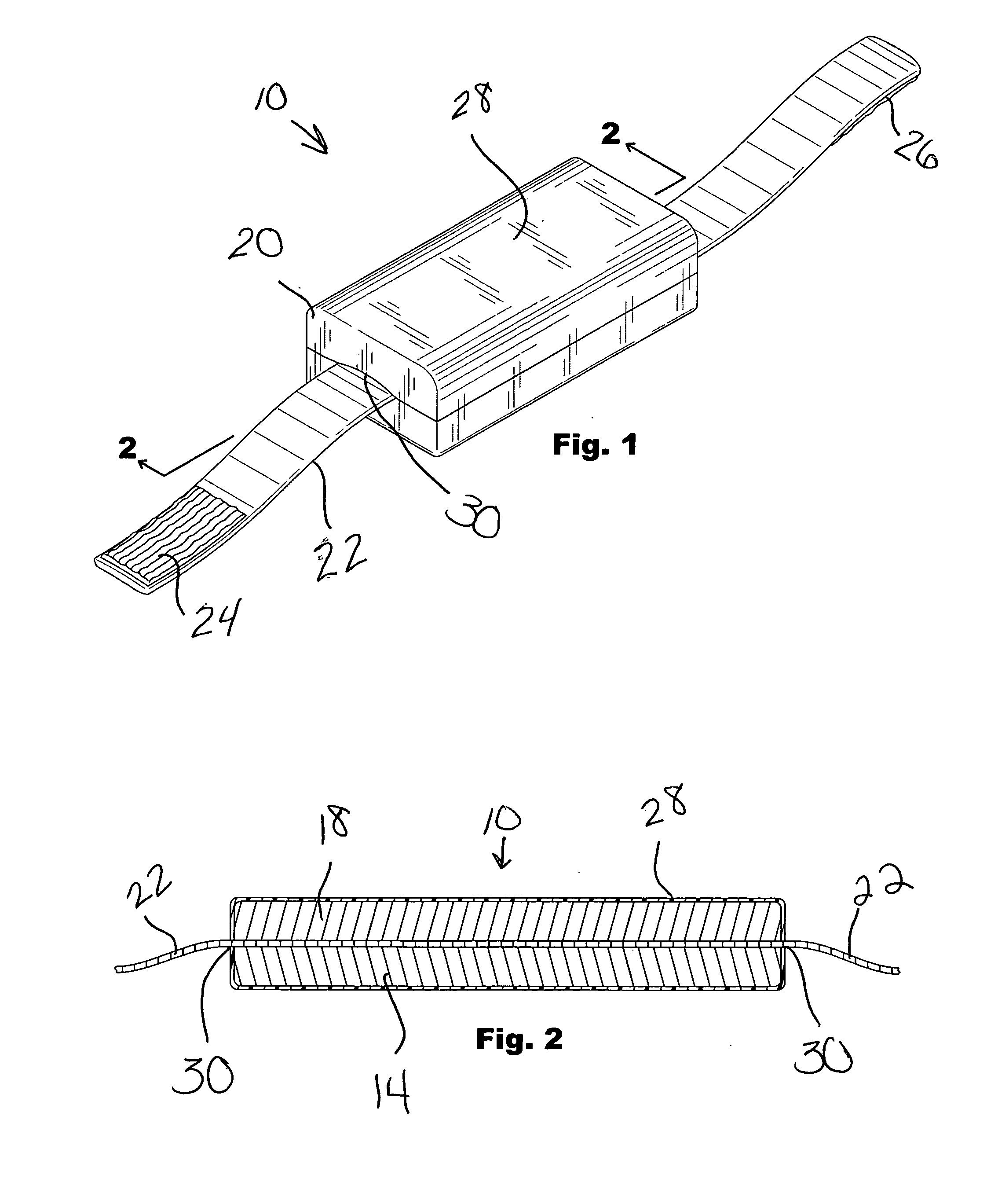

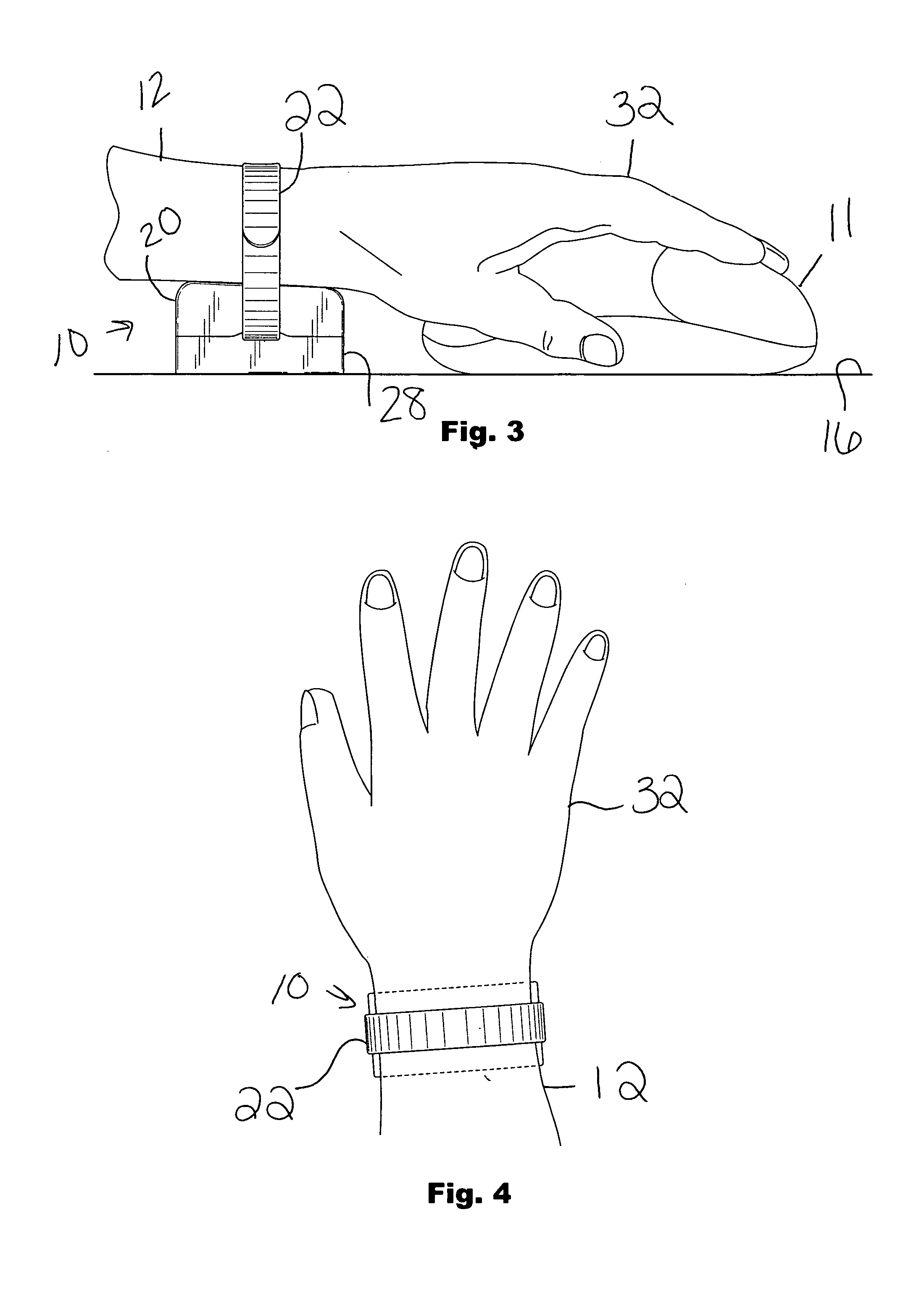

Portable wrist rest system

InactiveUS20050121562A1Avoid fatigueAvoid strainOffice tablesWriting supportsCTS - Carpal tunnel syndromeWrist support

A portable wrist resting pad for relieving and alleviating the strain and fatigue to the wrist and arm from repetitive and continual use of a computer mouse and keyboard includes a first support member for disposition on the desk surface, a second support member mounted to the first support member and having a density less than the first support member, and a wrist strap that extends outwardly from opposite ends of the support members for encompassing the wrist and attaching the support pad to the wrist. The wrist support pad elevates the wrist the appropriate distance from the work surface to relieve strain and fatigue to the wrist and arm for preventing carpal tunnel syndrome; and preferably one wrist support pad should be secured to each wrist to obtain maximum benefit from the portable wrist rest pads.

Owner:BAUMGARDNER DANNY D

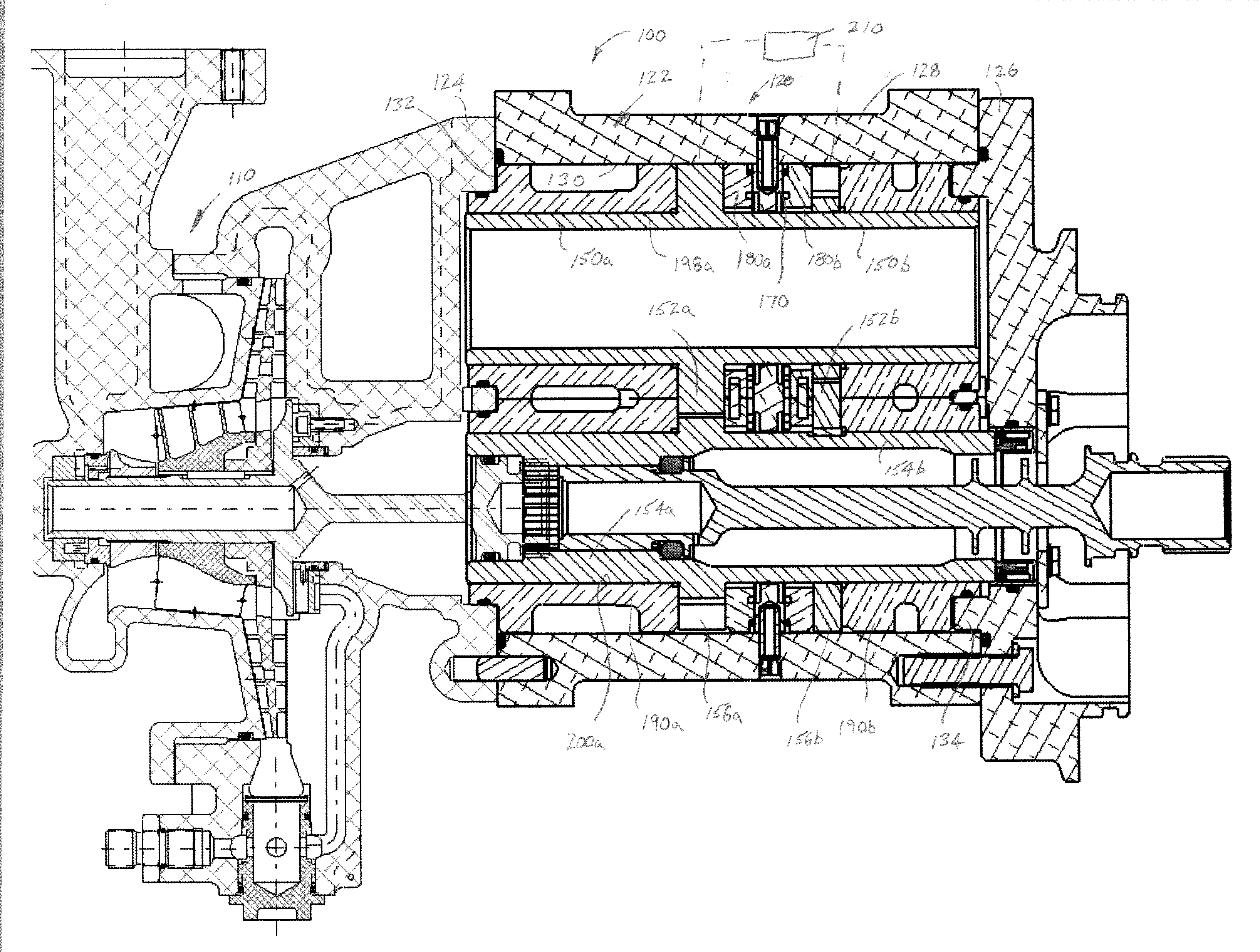

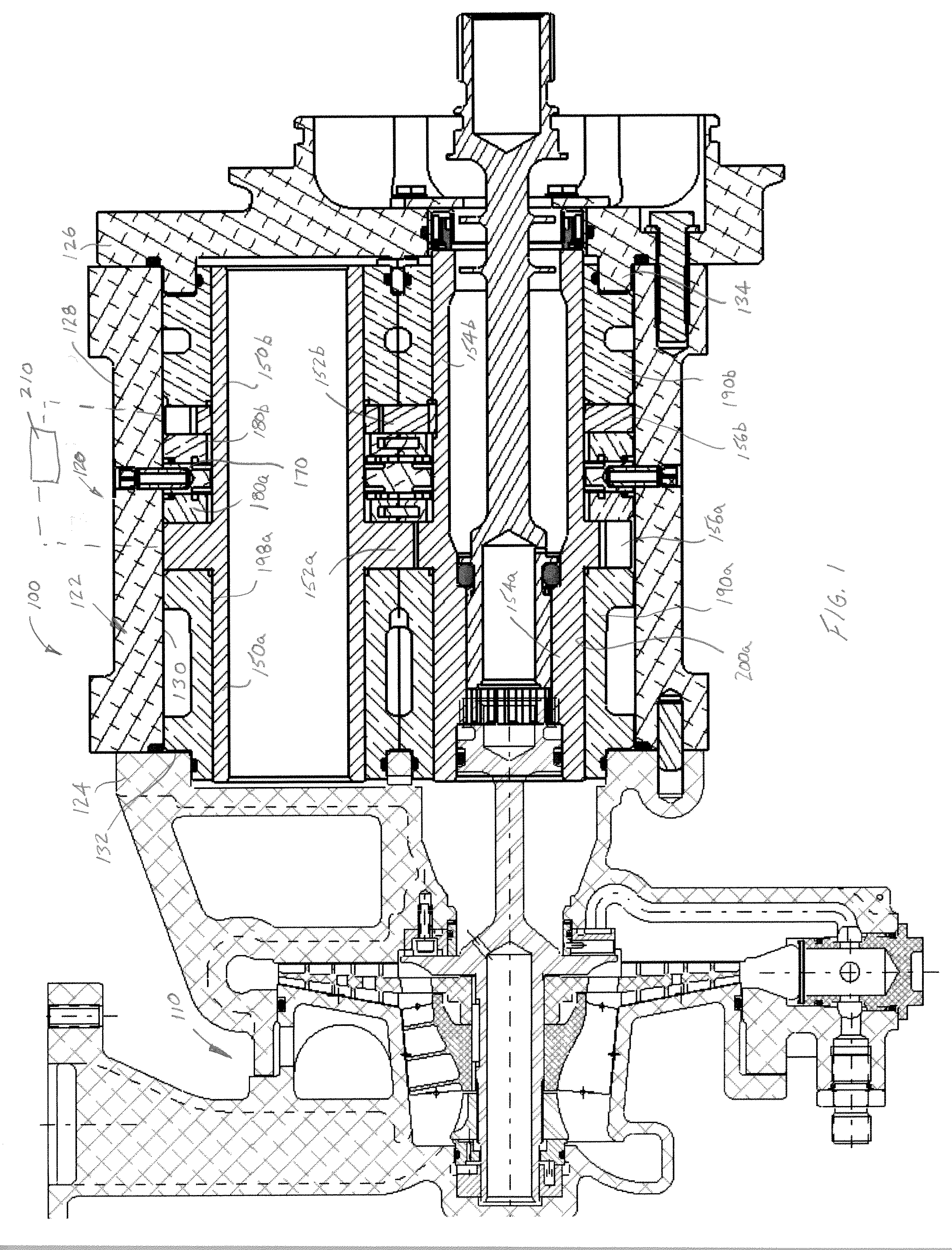

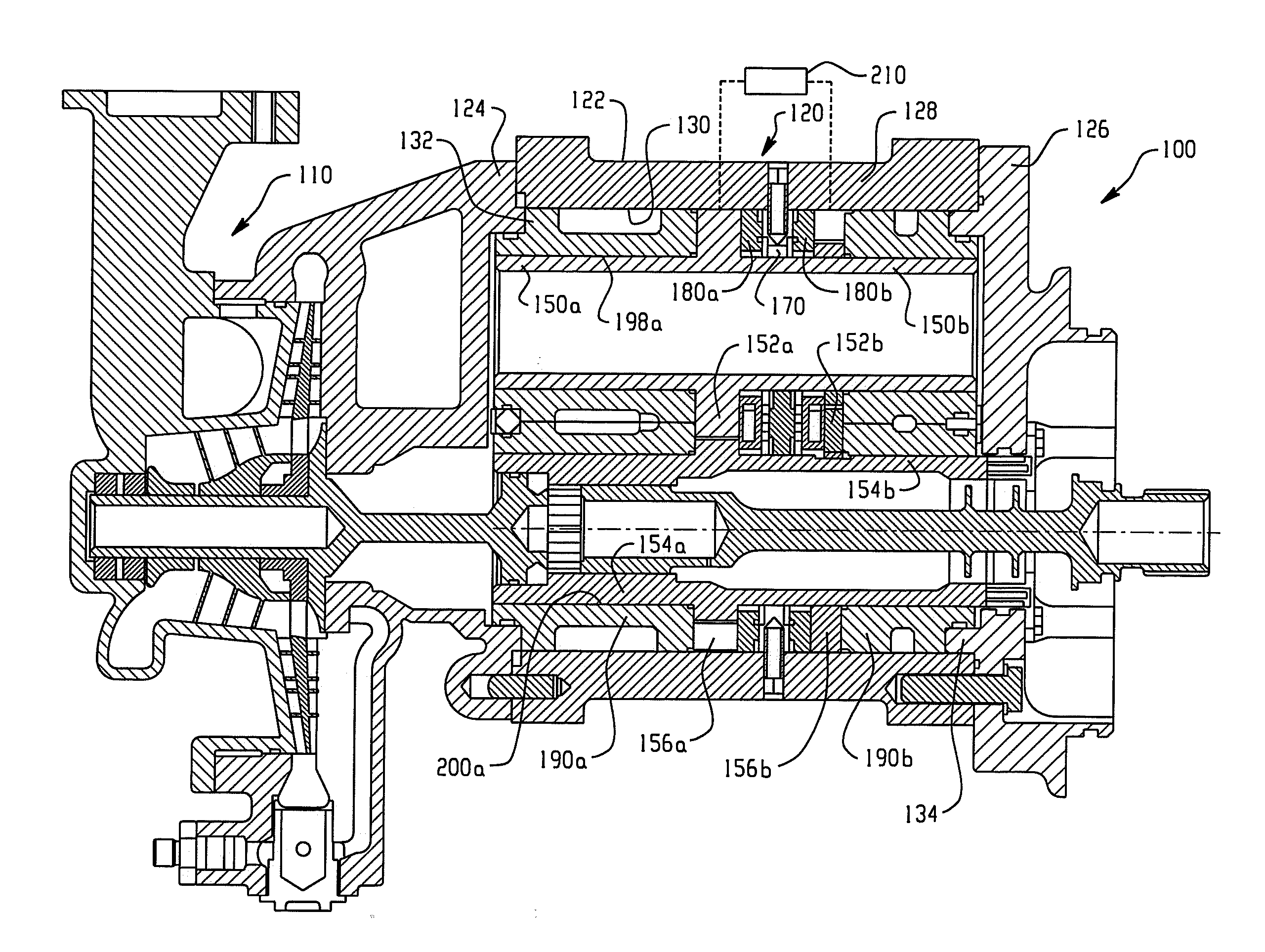

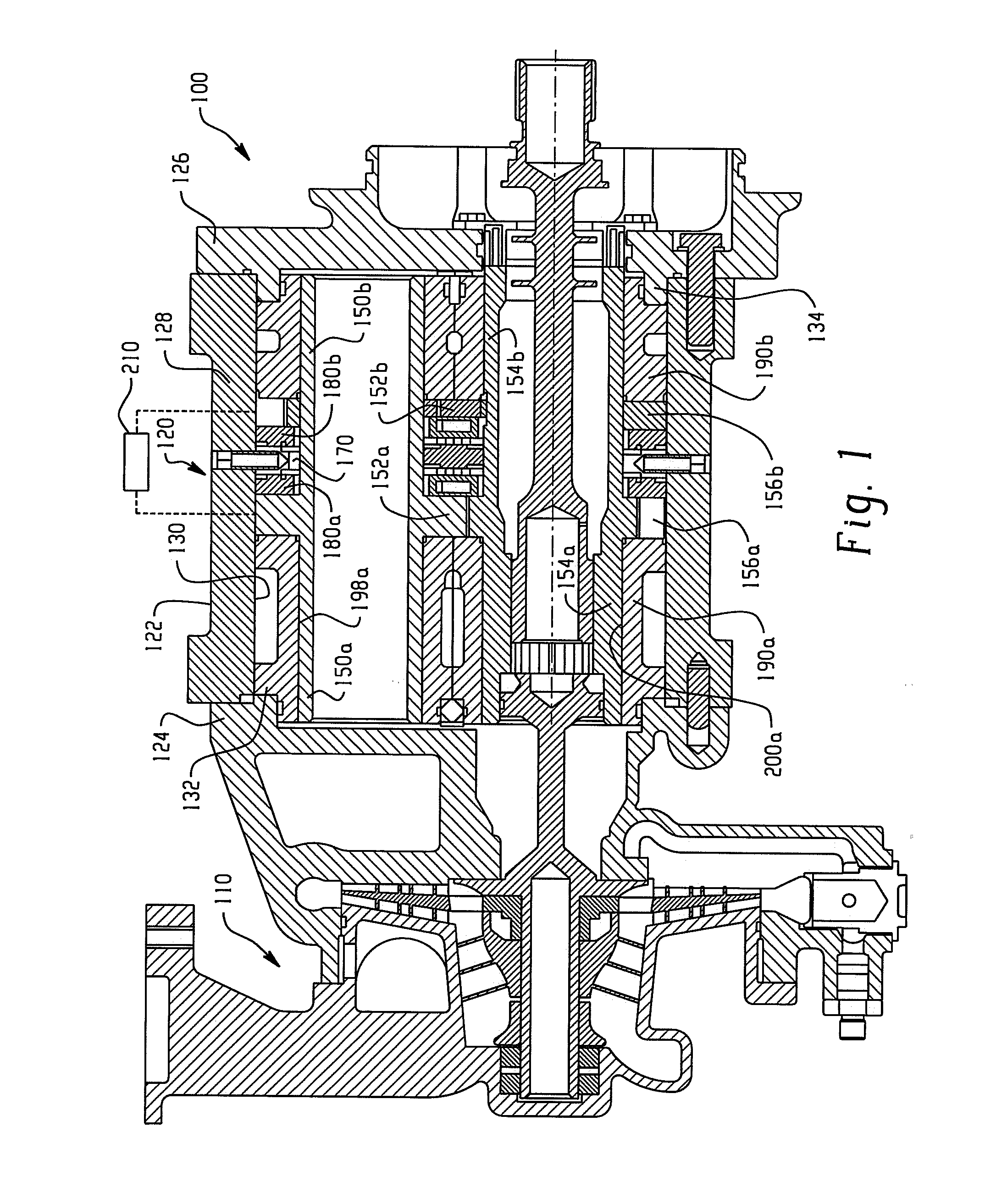

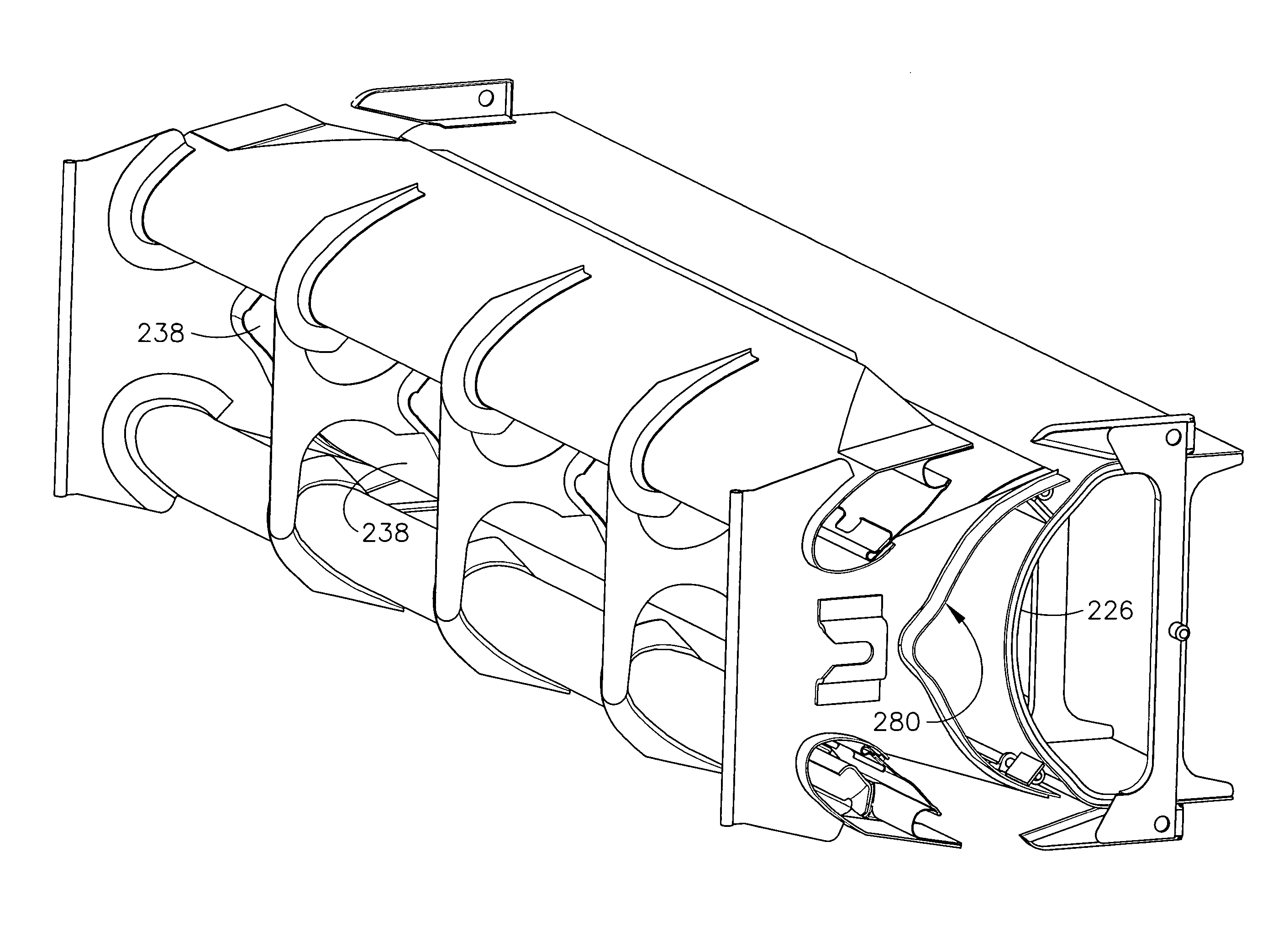

Aircraft main engine fuel pump with multiple gear stages using shared journals

InactiveUS20100266437A1Mitigate prospectLimit wearPump componentsOscillating piston enginesGear pumpEngineering

A multistage gear pump assembly includes first and second gear pumps that use common shafts and are axially separated by a spacer plate secured within a common bore and secured to the housing. Pressurized bearings are provided at opposite axial ends of the first and second gear pumps. The second gear pump handles cruise and idle operations of the aircraft while the first gear pump stage assists in meeting higher demand modes of engine operation. Otherwise, the first gear pump is maintained at a minimal pressure to reduce energy consumption and still provide desired stability and eliminate issues associated with bearing oil whirl associated with prior known arrangements. However, when additional assistance is required, such as during takeoff, climb, or windmill relight, the first gear pump advantageously contributes to the increased pressure.

Owner:EATON INDAL CORP

Aircraft main engine fuel pump with multiple gear stages using shared journals

ActiveUS20140003987A1Limit premature wearMinimize energy consumptionRotary/oscillating piston combinations for elastic fluidsOscillating piston enginesGear pumpEngineering

A multistage gear pump assembly includes first and second gear pumps that use common shafts and are axially separated by a fixed spacer within the housing. Pressurized bearings are provided at opposite axial ends of the first and second gear pumps. The second gear pump handles cruise and idle operations of the aircraft while the first gear pump stage assists in meeting higher demand modes of engine operation. Otherwise, the first gear pump is maintained at a minimal pressure to reduce energy consumption and still provide desired stability and eliminate issues associated with bearing oil whirl associated with prior known arrangements. When additional assistance is required, such as during takeoff, climb, or windmill relight, the first gear pump advantageously contributes to the increased pressure.

Owner:EATON INTELLIGENT POWER LIMITED

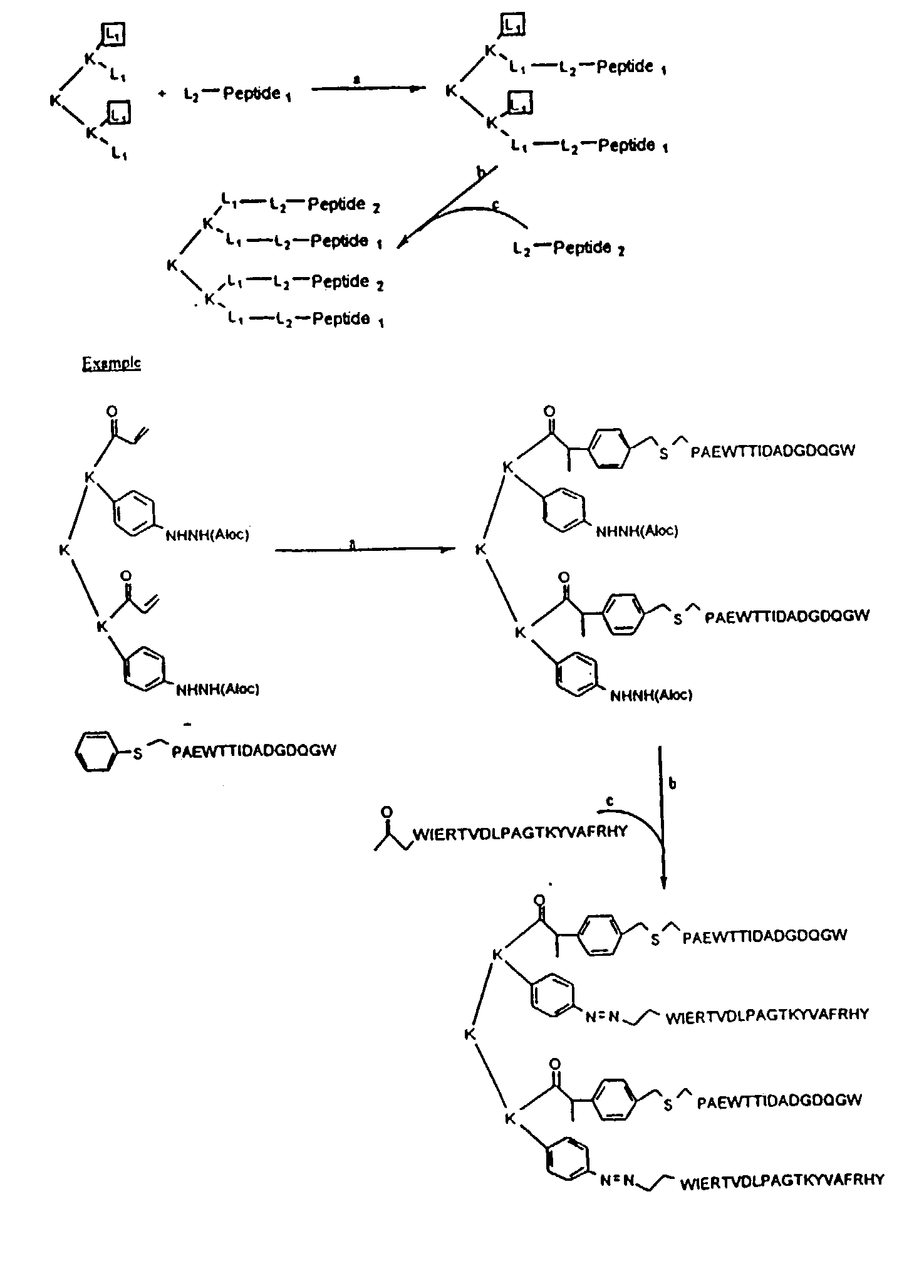

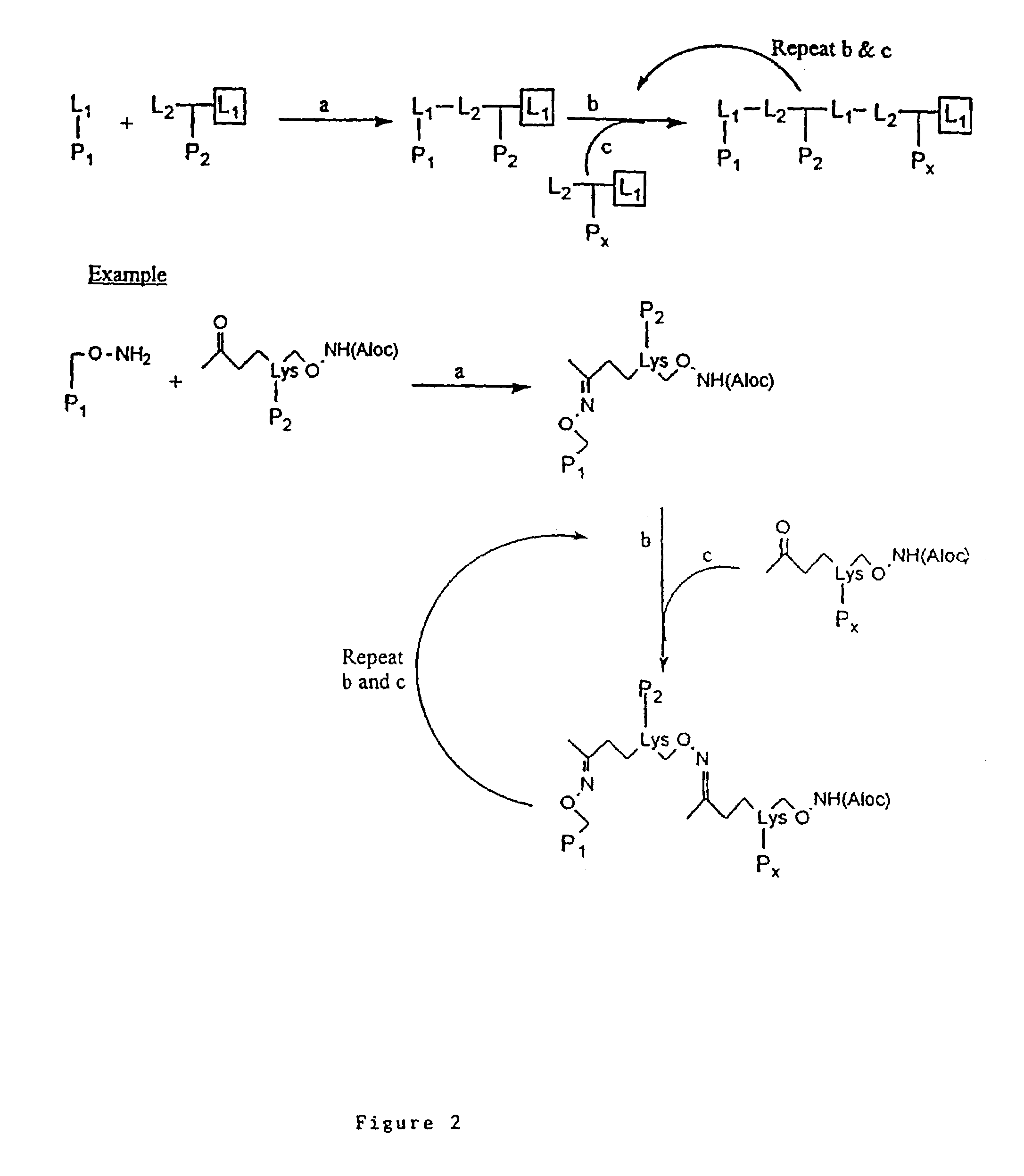

Synthetic peptide constructs for the diagnosis and treatment of periodontitis associated with Porphyromonas gingivalis

InactiveUS7262271B2Prevent diseaseReducing colonisationAntibacterial agentsCosmetic preparationsBacteroidesPorphyromonas gingivalis

The present invention relates to an oral composition and an immunogenic composition for the suppression of the pathogenic effects of the intra-oral bacterium Porphyromonas gingivalis associated with periodontal disease.

Owner:UNIVERSITY OF MELBOURNE

Locking device for retaining a musical instrument

InactiveUS7906717B2Quickly and effectively placeSimple structurePipe supportsStringed musical instrumentsEngineeringMechanical engineering

A locking device for retaining a musical instrument can be attached to a stand assembly by a base member. A support unit with an entrance opening supports a portion of the instrument. A force such as gravitational can cause the support unit to rotate a biased locking member to close the entrance opening. Removal of the instrument permits a biasing force to open the locking member.

Owner:SOUNDKING GROUP

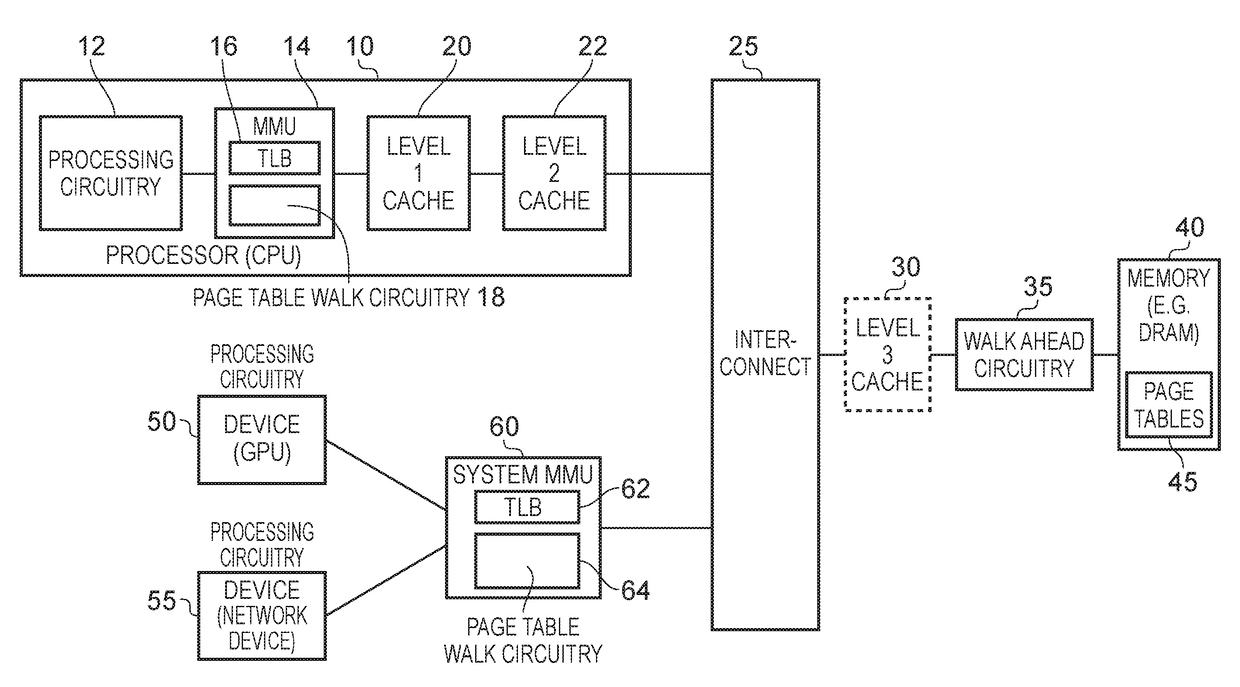

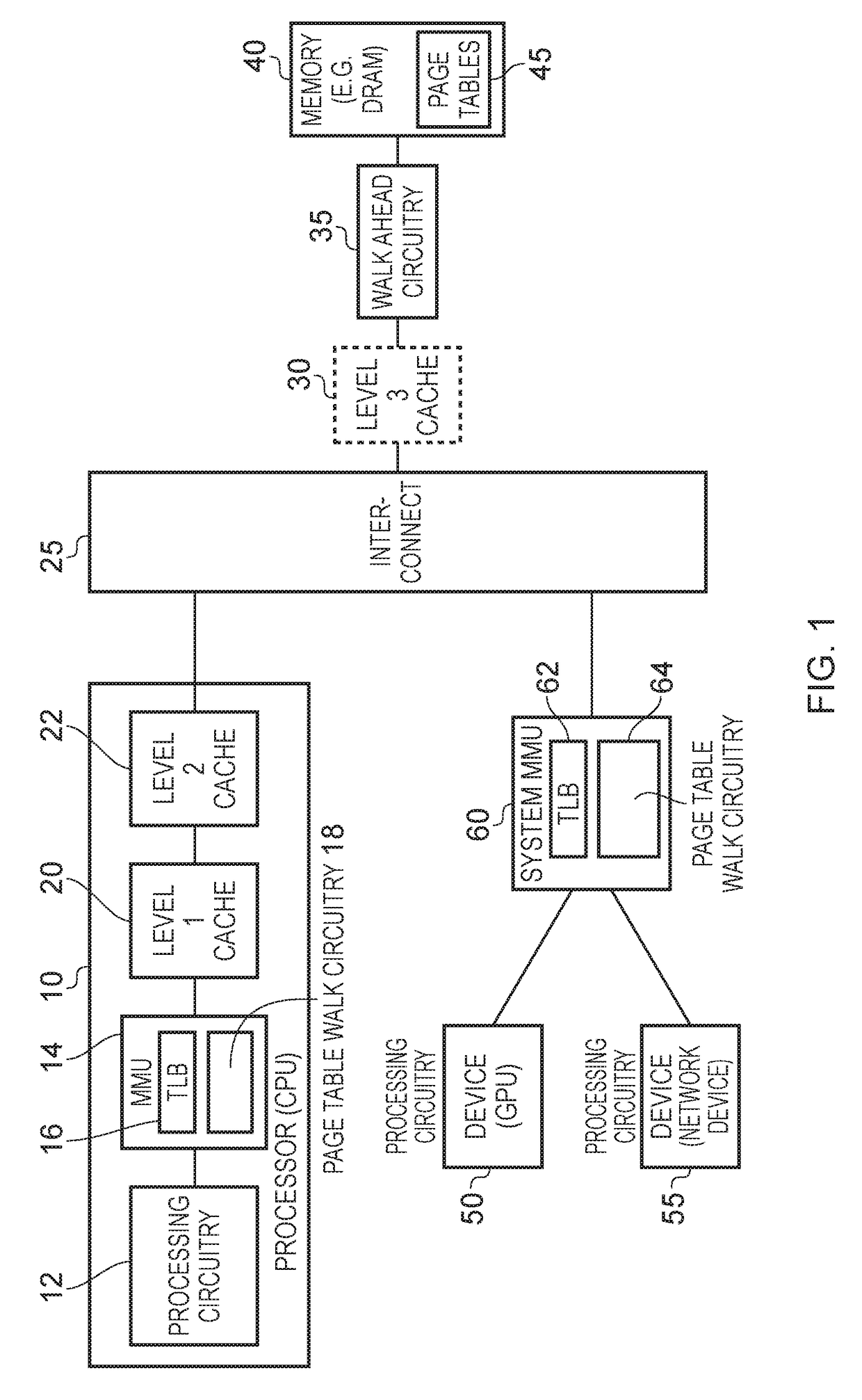

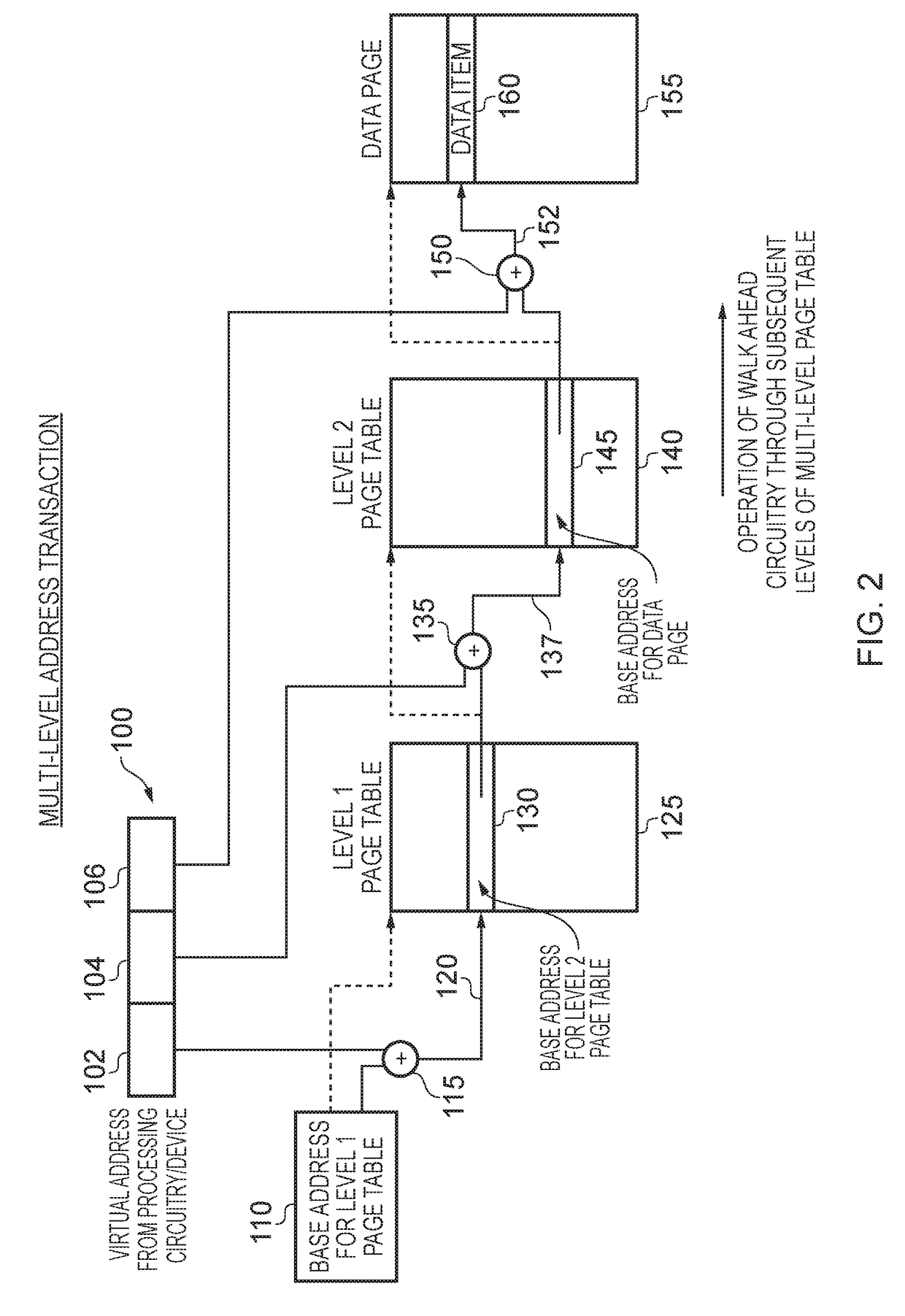

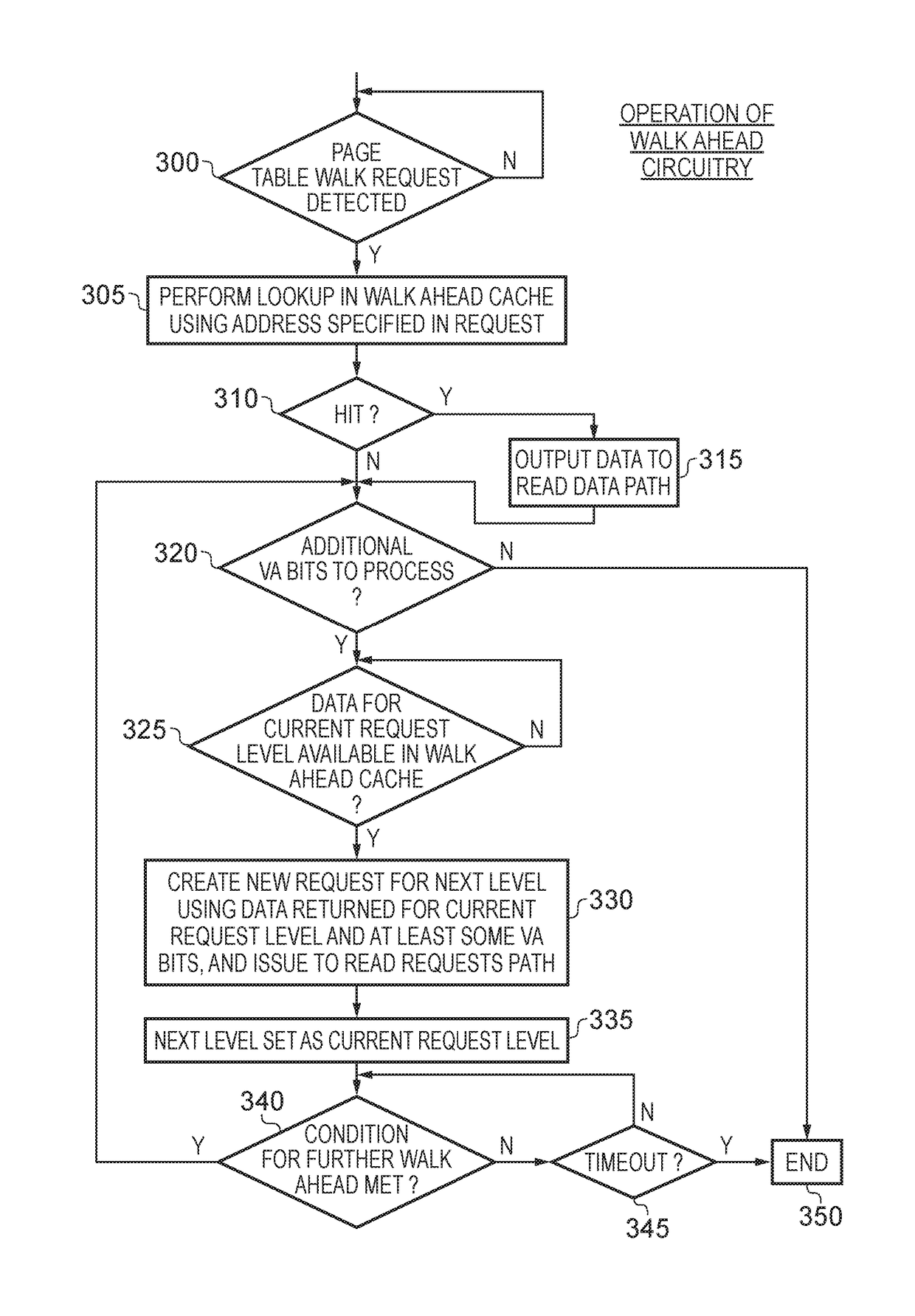

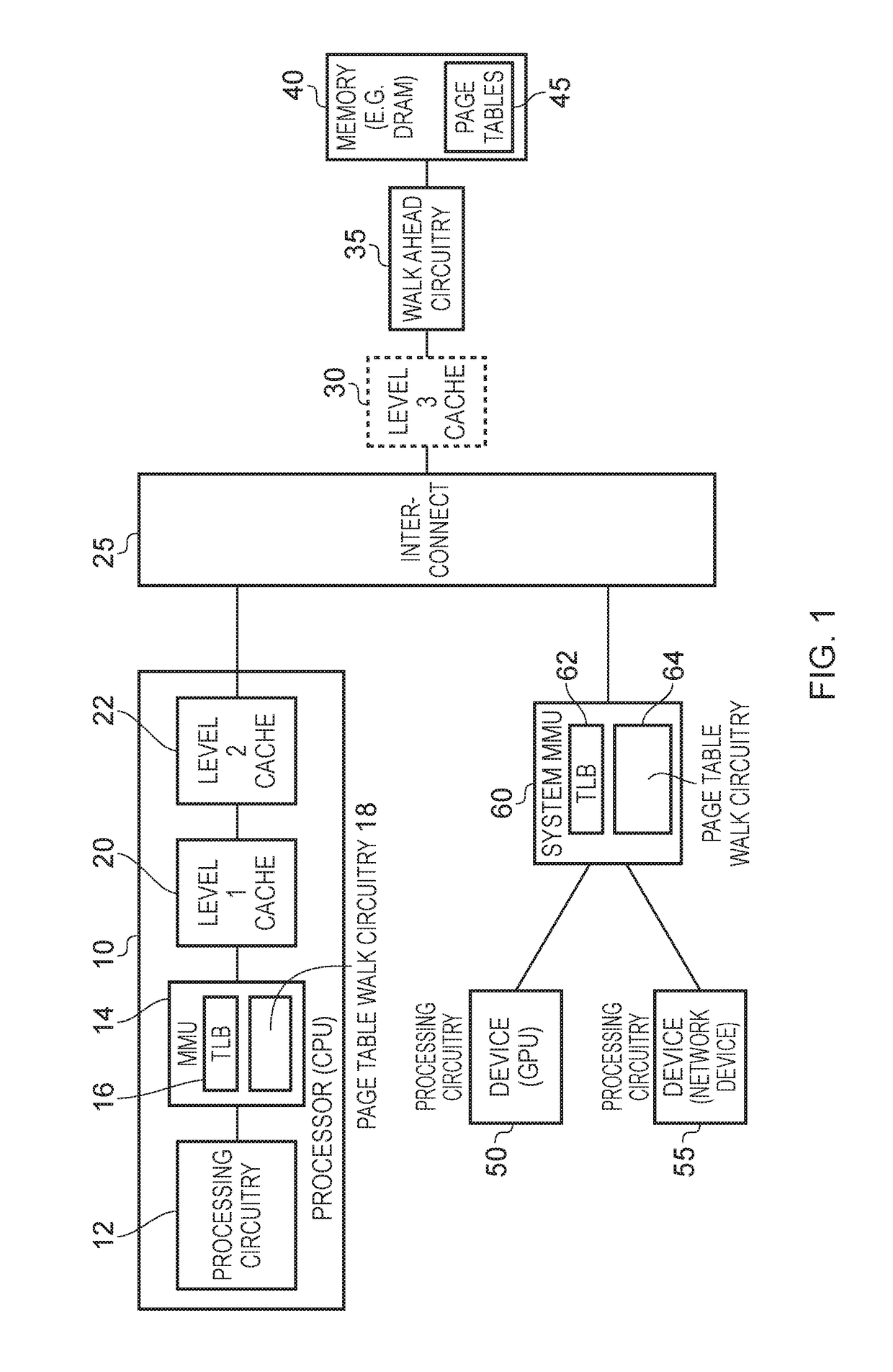

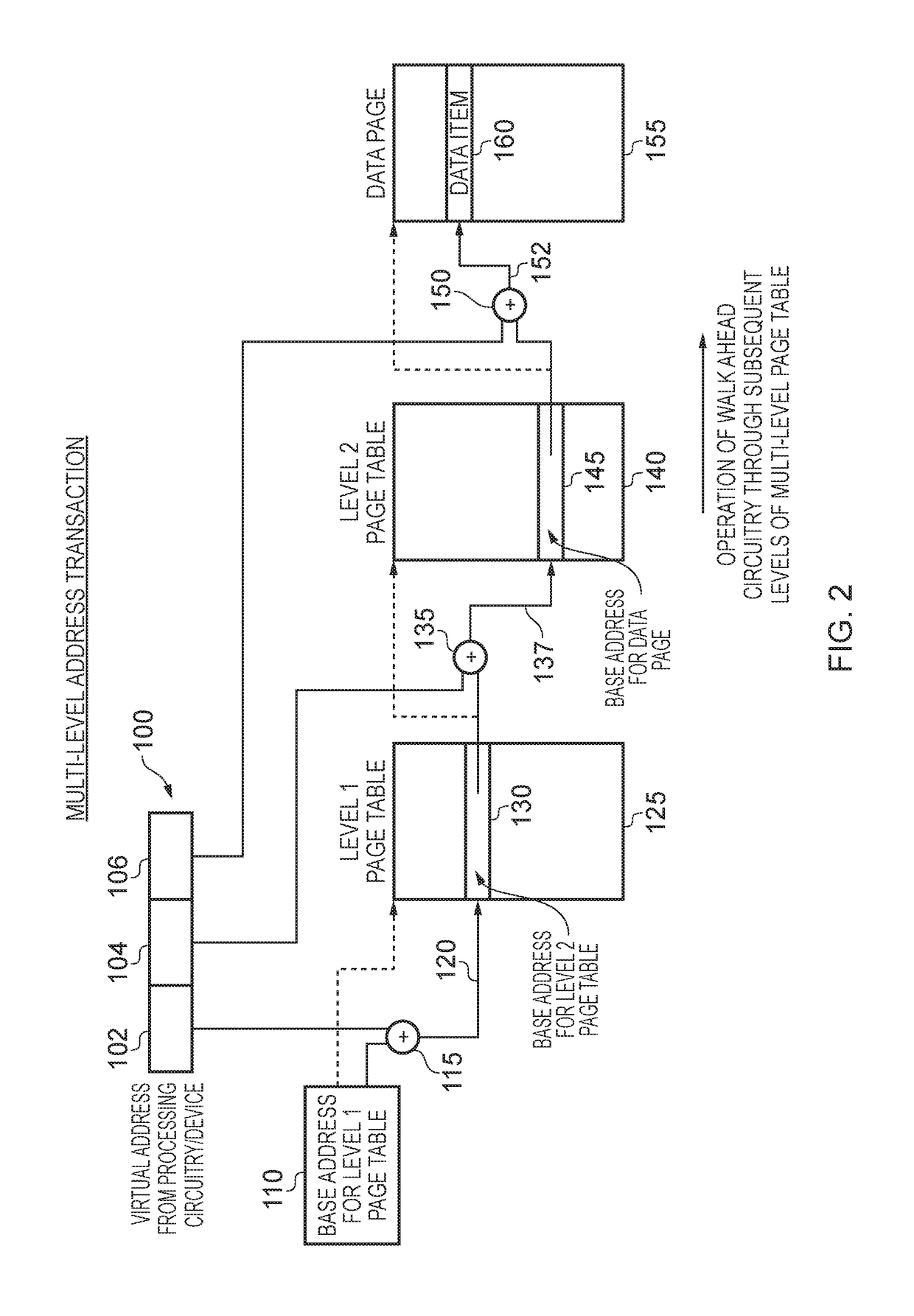

A data processing apparatus, and a method of handling address translation within a data processing apparatus

ActiveUS20170185528A1Easy to detectLess latencyMemory architecture accessing/allocationEnergy efficient computingPhysical addressNetwork address translation

A data processing apparatus and method are provided for performing address translation in response to a memory access request issued by processing circuitry of the data processing apparatus and specifying a virtual address for a data item. Address translation circuitry performs an address translation process with reference to at least one descriptor provided by at least one page table, in order to produce a modified memory access request specifying a physical address for the data item. The address translation circuitry includes page table walk circuitry configured to generate at least one page table walk request in order to retrieve the at least one descriptor required for the address translation process. In addition, walk ahead circuitry is located in a path between the address translation circuitry and a memory device containing the at least one page table. The walk ahead circuitry comprises detection circuitry used to detect a memory page table walk request generated by the page table walk circuitry of the address translation circuitry for a descriptor in a page table. In addition, the walk ahead circuitry has further request generation circuitry which is used to generate a prefetch memory request in order to prefetch data from the memory device at a physical address determined with reference to the descriptor requested by the detected memory page table walk request. This prefetched data may be another descriptor required as part of the address translation process, or may be the actual data item being requested by the processing circuitry. Such an approach can significantly reduce latency associated with the address translation process.

Owner:ARM LTD

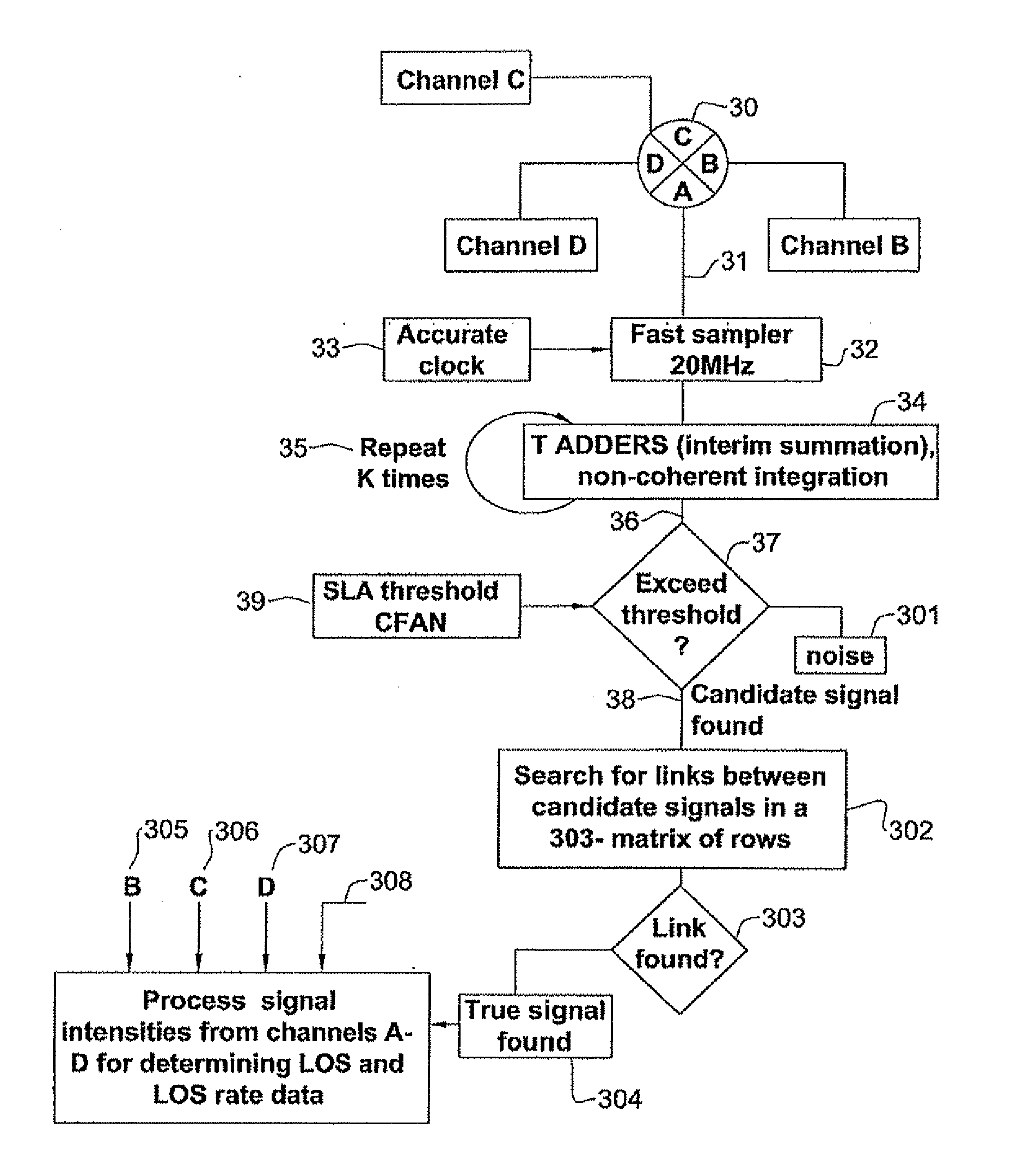

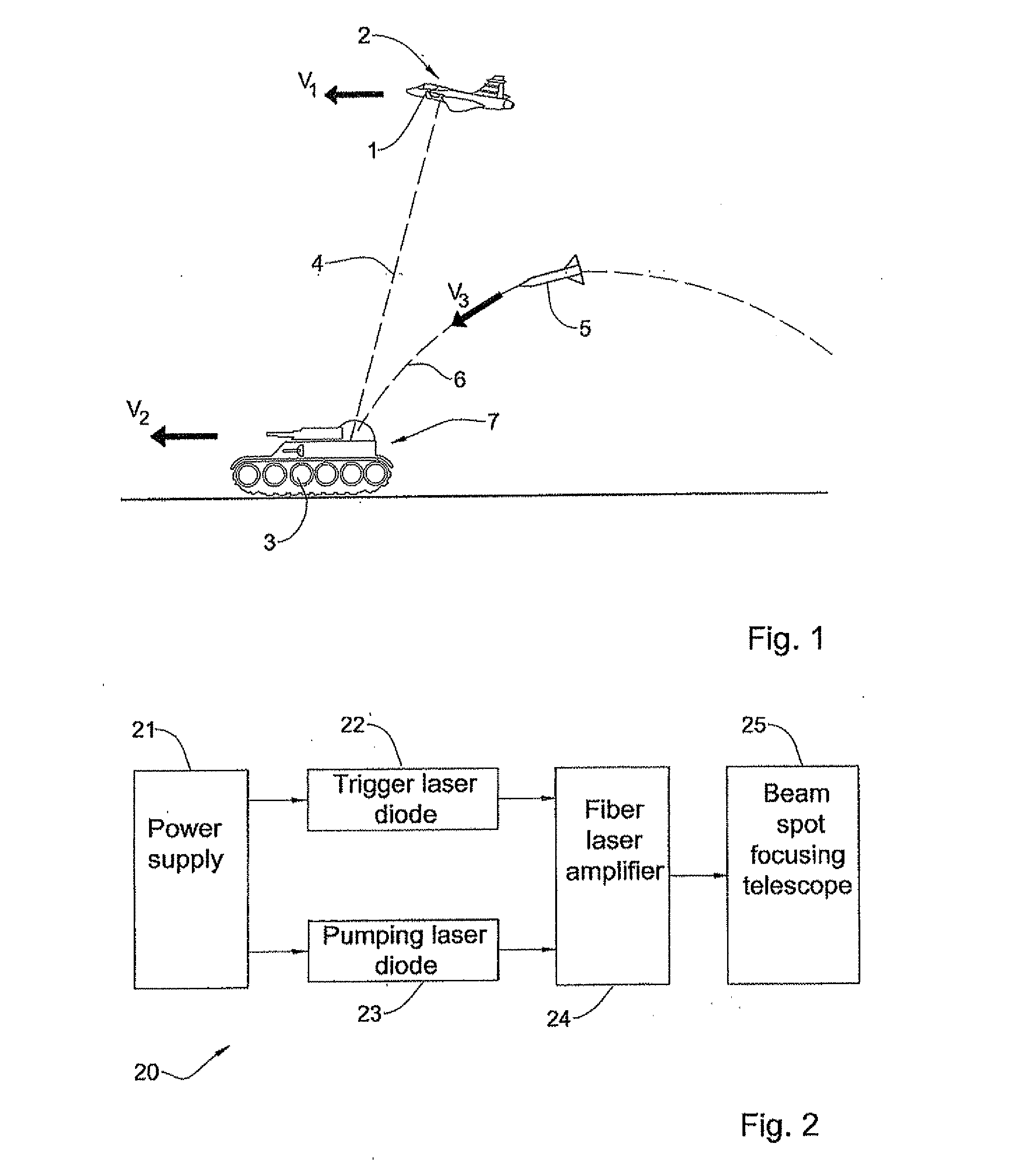

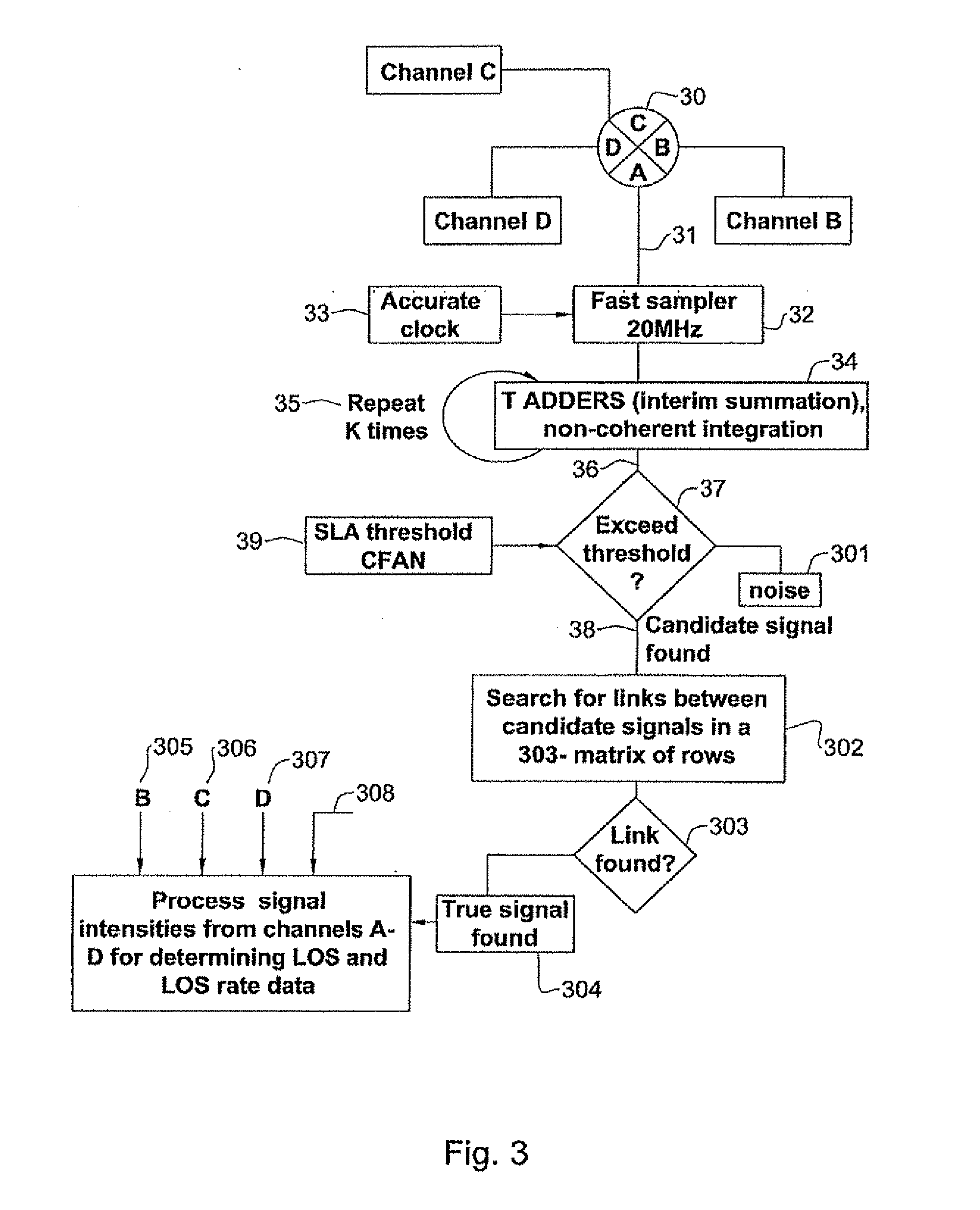

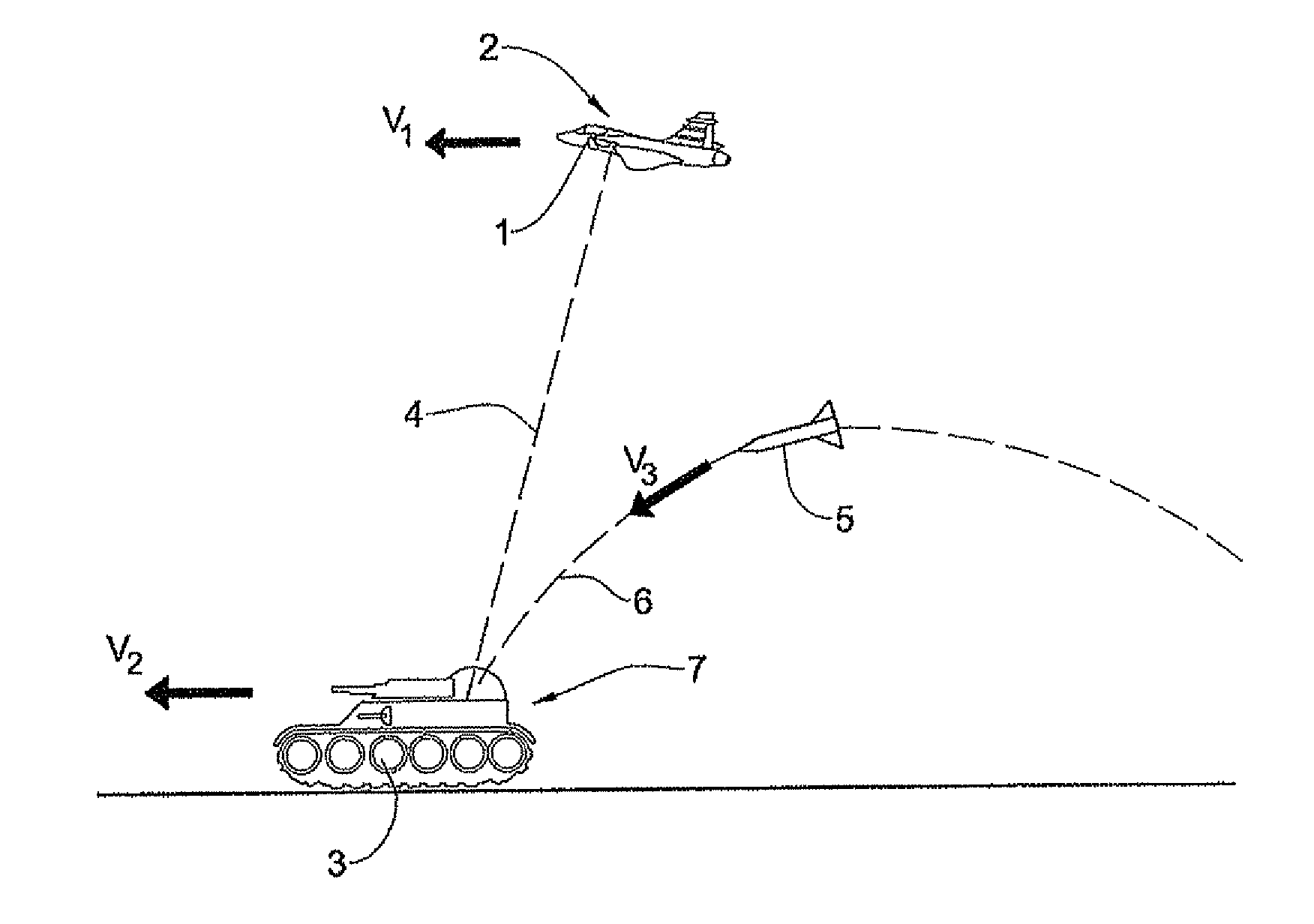

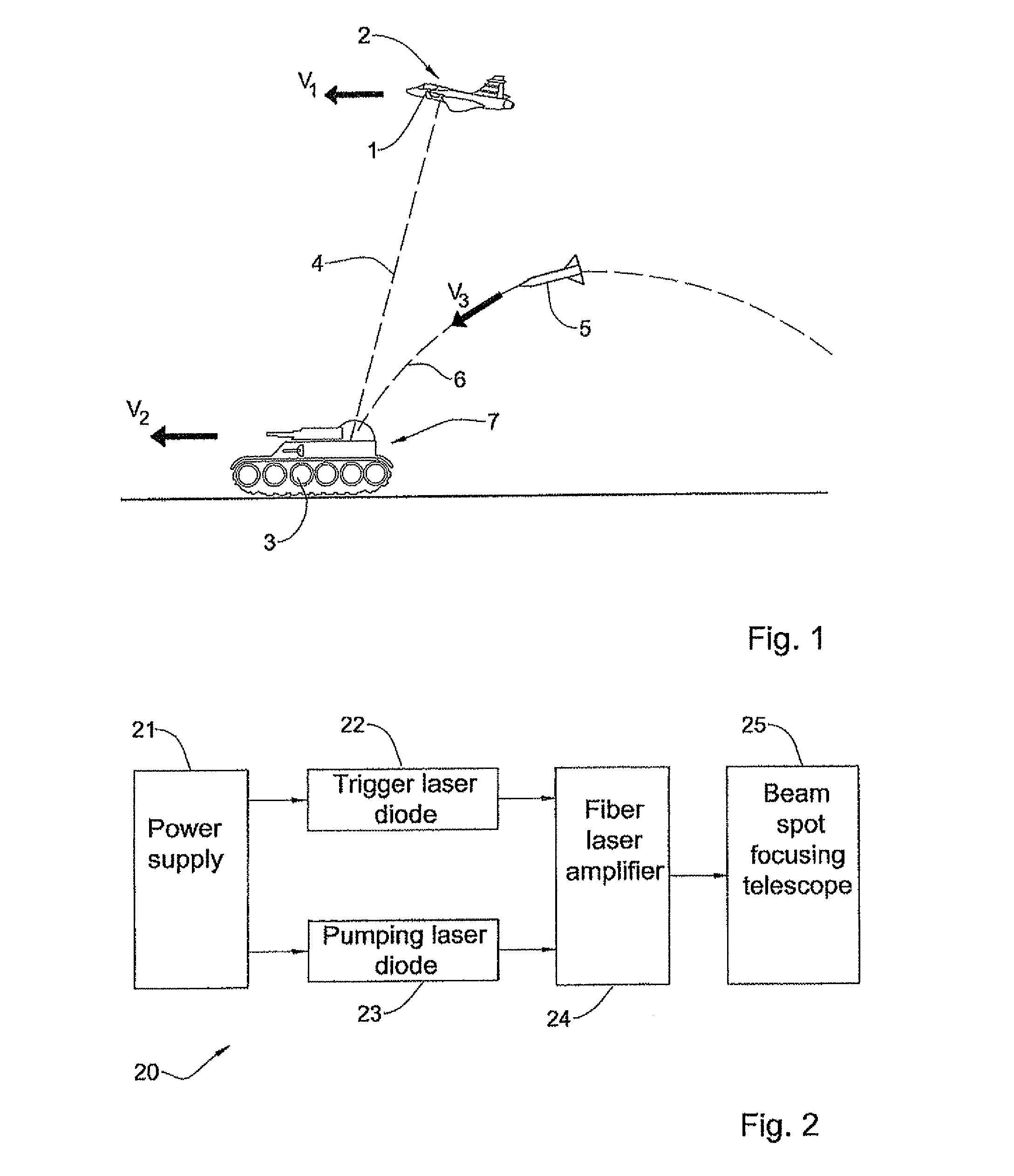

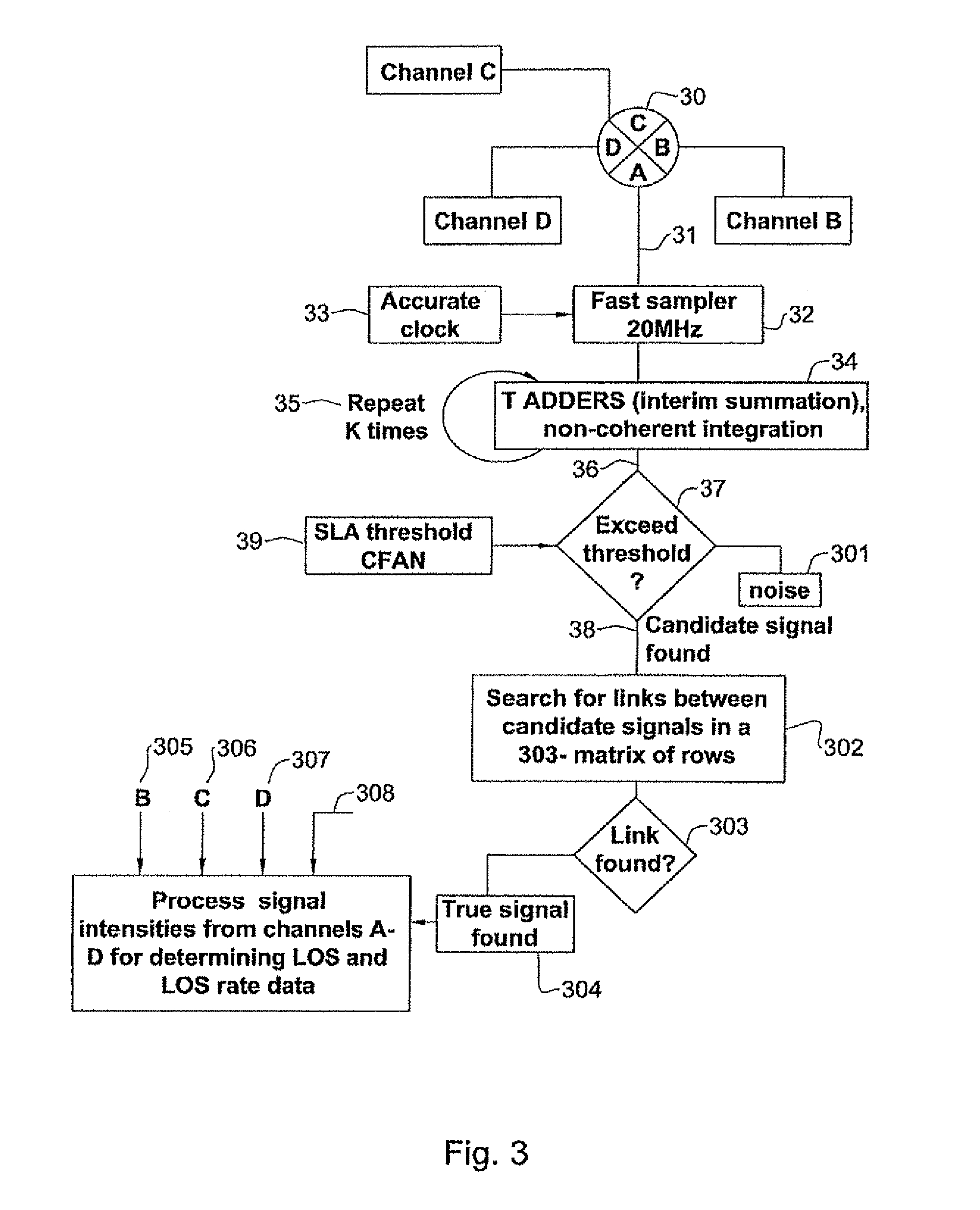

Method and system for designating a target and generating target-related action

ActiveUS20090323047A1Mitigate prospectReduce signal to noise ratioDirection controllersOptical rangefindersDistance to targetHandling system

A system that includes a laser designator configured to continuously designate a target with a pulsed laser spot. The system includes a sensor and associated processing system configured to receive a reflection of the laser spot, convert the received energy to plurality of signals, processing the signals for detecting true reflected signals and process the true reflected signals for generating target related action. The sensor and associated processor are configured to detect the true signals notwithstanding an inherent low Signal / Noise ratio of below 4 of the received signals from due to low pulse power of the laser designator and distance to target.

Owner:ISRAEL AEROSPACE IND

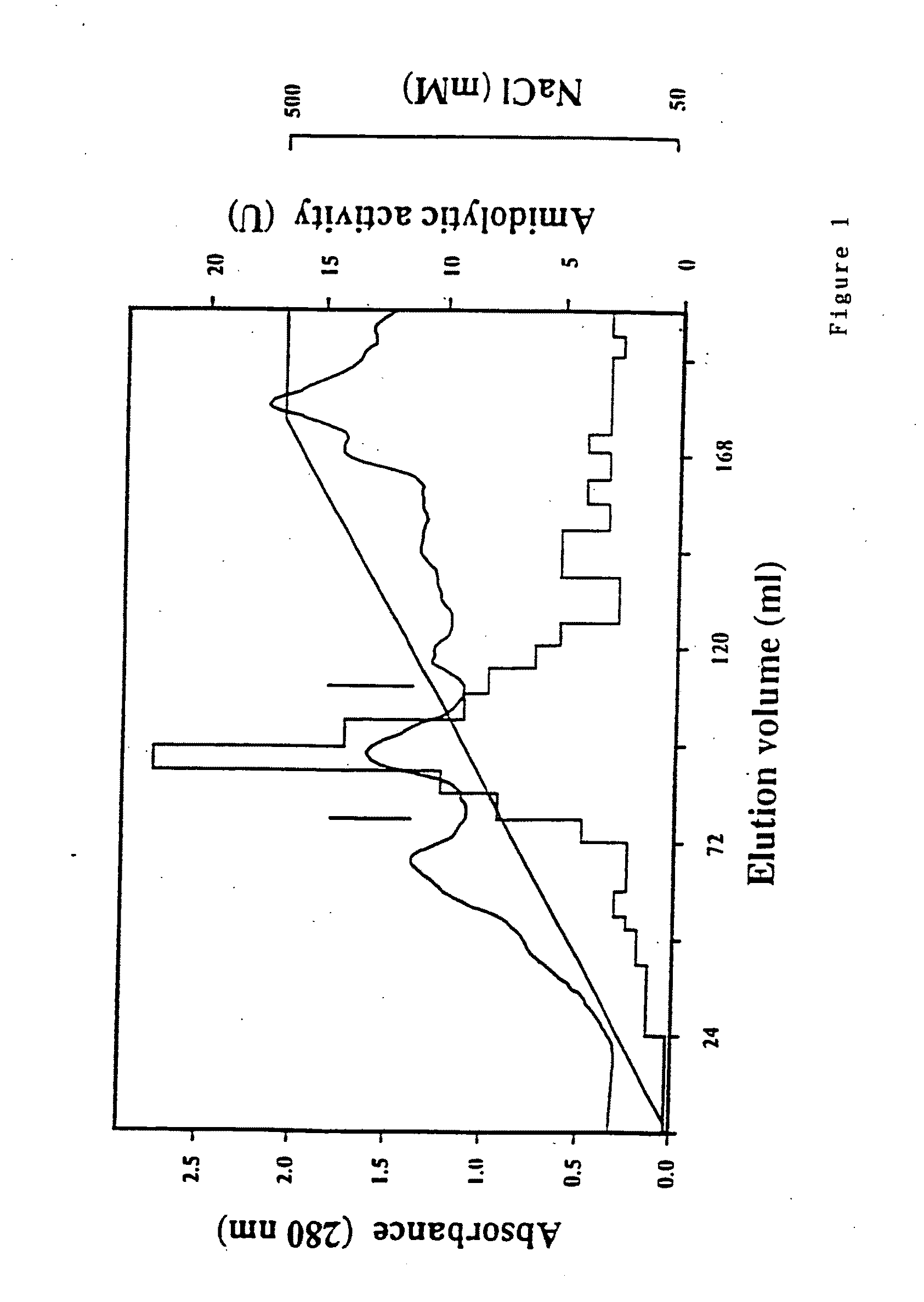

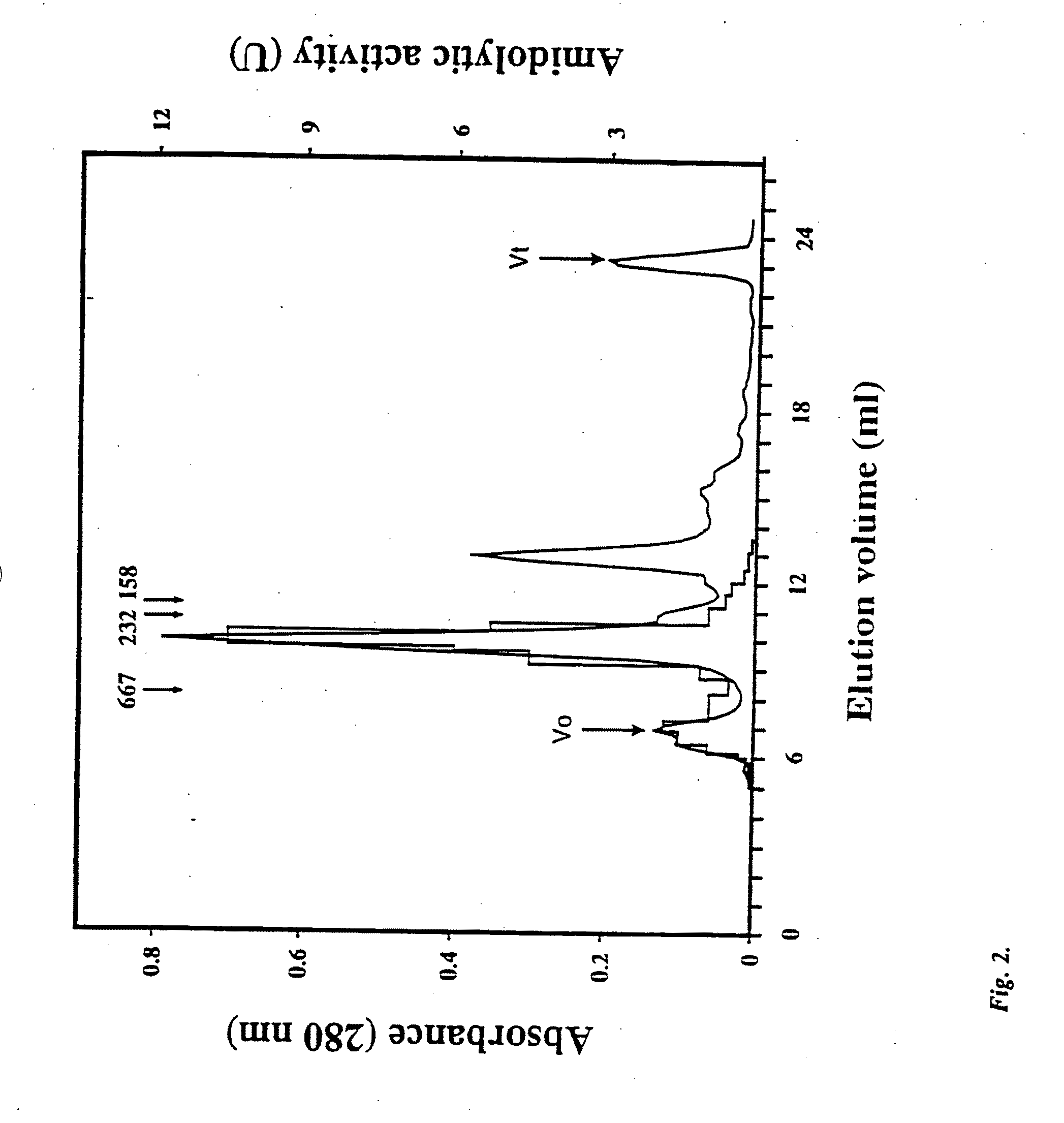

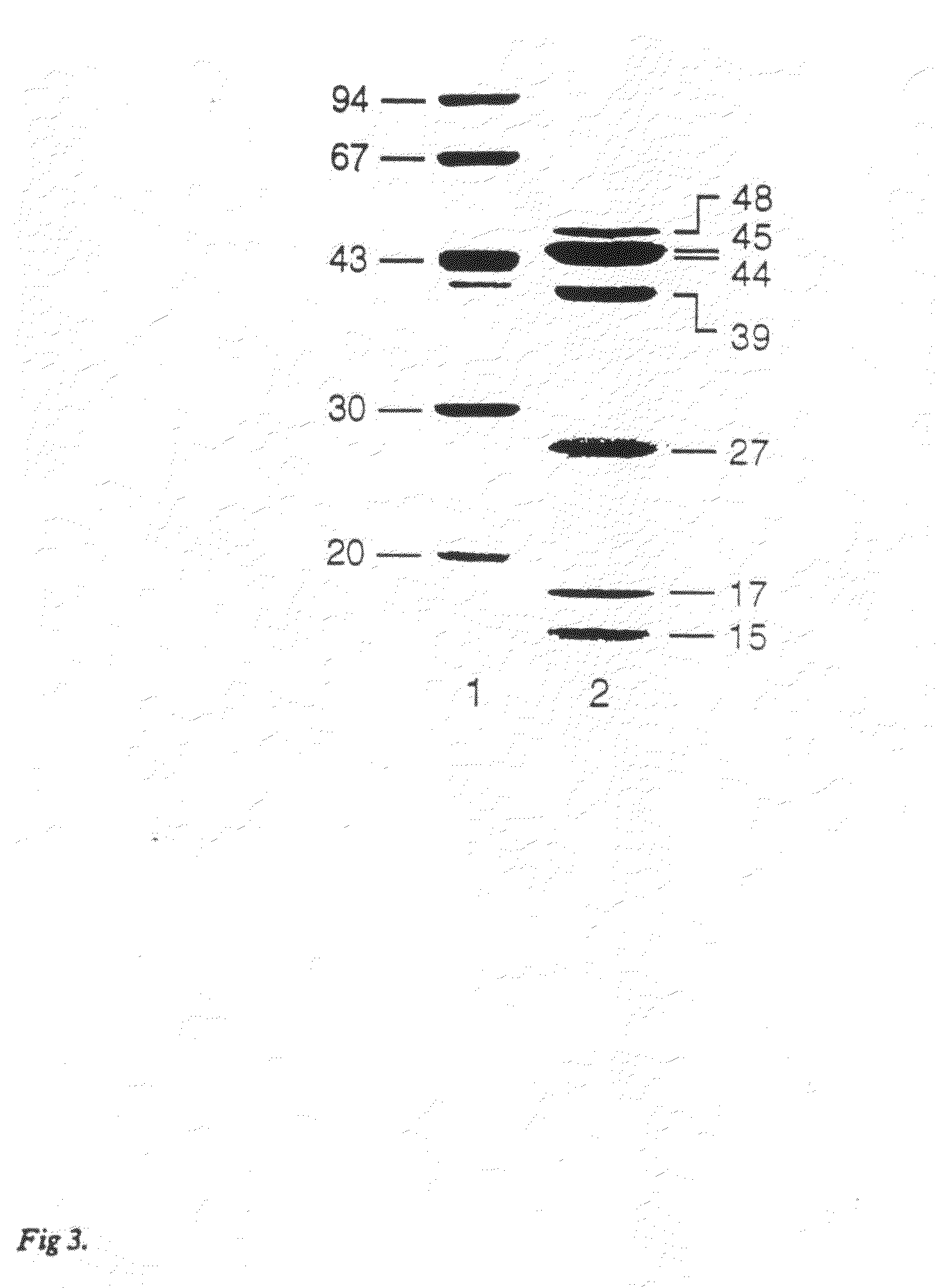

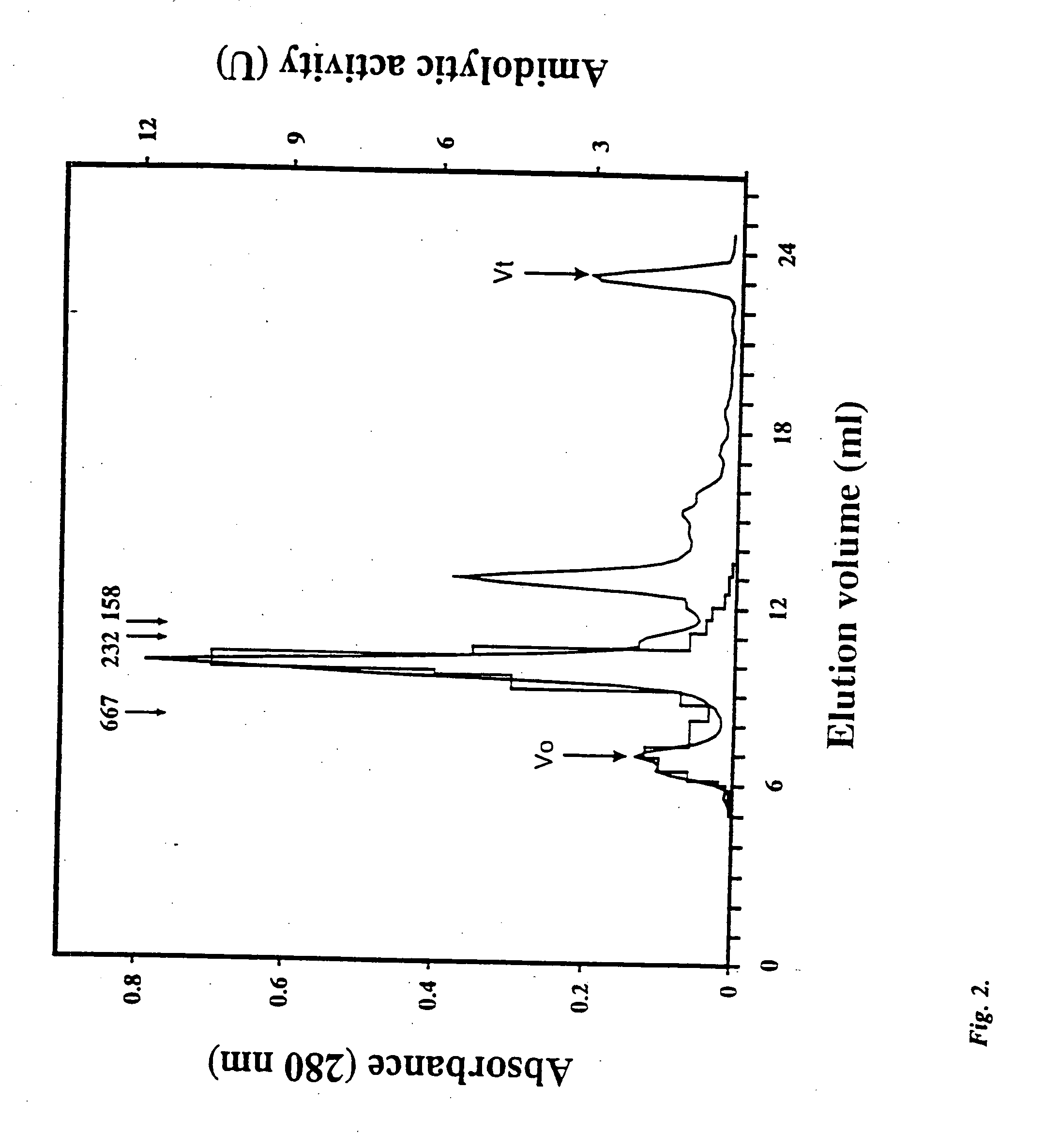

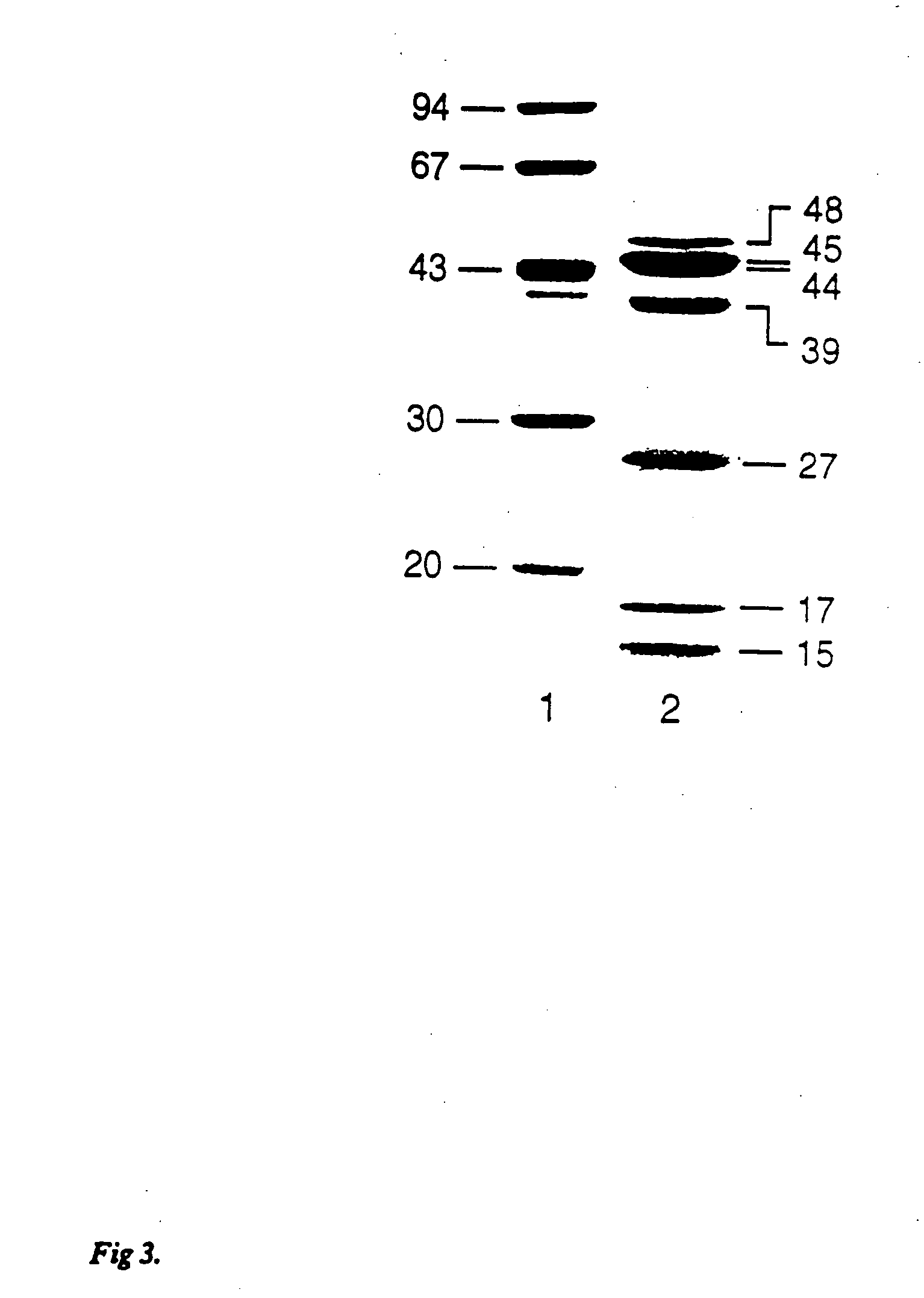

Diagnostics and treatments of periodontal disease

InactiveUS20110213129A1Mitigate prospectEfficient inductionCosmetic preparationsOrganic active ingredientsPorphyromonas gingivalisArginine

This invention relates to the PrtR-PrtK cell surface protein of Porphyromonas gingivalis and in particular a multimeric cell association protein complex comprising the PrtR and PrtK proteins. Accordingly the invention provides a substantially purified antigenic complex for use in raising an antibody response directed against Porphyromonas gingivalis. The complex comprises at least one multimeric protein complex of arginine-specific and lysine-specific thiol endopeptidases each containing at least one adhesin domain, the complex having a molecular weight of greater than about 200 kDa. The invention also relates to pharmaceutical compositions and associated agents based on said complex for the detection, prevention and treatment of Periodontal disease associated with P. gingivalis.

Owner:UNIVERSITY OF MELBOURNE

Compositions and methods for treatment and prophylaxis of gastrointestinal diseases

InactiveUS20160206564A1Prevent relapsePromote healingOrganic active ingredientsDigestive systemSide effectInflammatory bowel disease

Methods and compositions for treating inflammatory bowel disease, irritable bowel syndrome, and travelers' diarrhea involve the use of targeted antibiotics in combination with probiotic formulations. The probiotics mitigate many of the deleterious side effects associated with antibiotic use and permit the antibiotic to be administered at a higher dose and for a longer duration than would otherwise be possible in the absence of the probiotic. The practice of the invention may reduce or eliminate the use of immunosuppressants and other drugs in the treatment and management of inflammatory bowel disease, irritable bowel syndrome, travelers' diarrhea, and hepatic encephalopathy.

Owner:TRACHTMAN IRA MILTON

Data processing apparatus, and a method of handling address translation within a data processing apparatus

ActiveUS10133675B2Less latencyLower latencyMemory architecture accessing/allocationMemory adressing/allocation/relocationNetwork address translationPage table

A data processing apparatus and method are provided for performing address translation in response to a memory access request issued by processing circuitry of the data processing apparatus and specifying a virtual address for a data item. Address translation circuitry performs an address translation process with reference to at least one descriptor provided by at least one page table, in order to produce a modified memory access request specifying a physical address for the data item. The address translation circuitry includes page table walk circuitry configured to generate at least one page table walk request in order to retrieve the at least one descriptor required for the address translation process. In addition, walk ahead circuitry is located in a path between the address translation circuitry and a memory device containing the at least one page table. The walk ahead circuitry comprises detection circuitry used to detect a memory page table walk request generated by the page table walk circuitry of the address translation circuitry for a descriptor in a page table. In addition, the walk ahead circuitry has further request generation circuitry which is used to generate a prefetch memory request in order to prefetch data from the memory device at a physical address determined with reference to the descriptor requested by the detected memory page table walk request. This prefetched data may be another descriptor required as part of the address translation process, or may be the actual data item being requested by the processing circuitry. Such an approach can significantly reduce latency associated with the address translation process.

Owner:ARM LTD

Method and system for designating a target and generating target-related action

ActiveUS8054451B2Mitigate prospectReduce signal to noise ratioOptical rangefindersDirection controllersDistance to targetHandling system

A system that includes a laser designator configured to continuously designate a target with a pulsed laser spot. The system includes a sensor and associated processing system configured to receive a reflection of the laser spot, convert the received energy to plurality of signals, processing the signals for detecting true reflected signals and process the true reflected signals for generating target related action. The sensor and associated processor are configured to detect the true signals notwithstanding an inherent low Signal / Noise ratio of below 4 of the received signals from due to low pulse power of the laser designator and distance to target.

Owner:ISRAEL AEROSPACE IND

Diagnostics and treatments of Periodontal disease

InactiveUS20070189982A1Mitigate prospectEfficient inductionCosmetic preparationsOrganic active ingredientsPorphyromonas gingivalisArginine

This invention relates to the PrtR-PrtK cell surface protein of Porphyromonas gingivalis and in particular a multimeric cell association protein complex comprising the PrtR and PrtK proteins. Accordingly the invention provides a substantially purified antigenic complex for use in raising an antibody response directed against Porphyromonas gingivalis. The complex comprises at least one multimeric protein complex of arginine-specific and lysine-specific thiol endopeptidases each containing at least one adhesin domain, the complex having a molecular weight of greater than about 200 kDa. The invention also relates to pharmaceutical compositions and associated agents based on said complex for the detection, prevention and treatment of Periodontal disease associated with P. gingivalis.

Owner:UNIVERSITY OF MELBOURNE

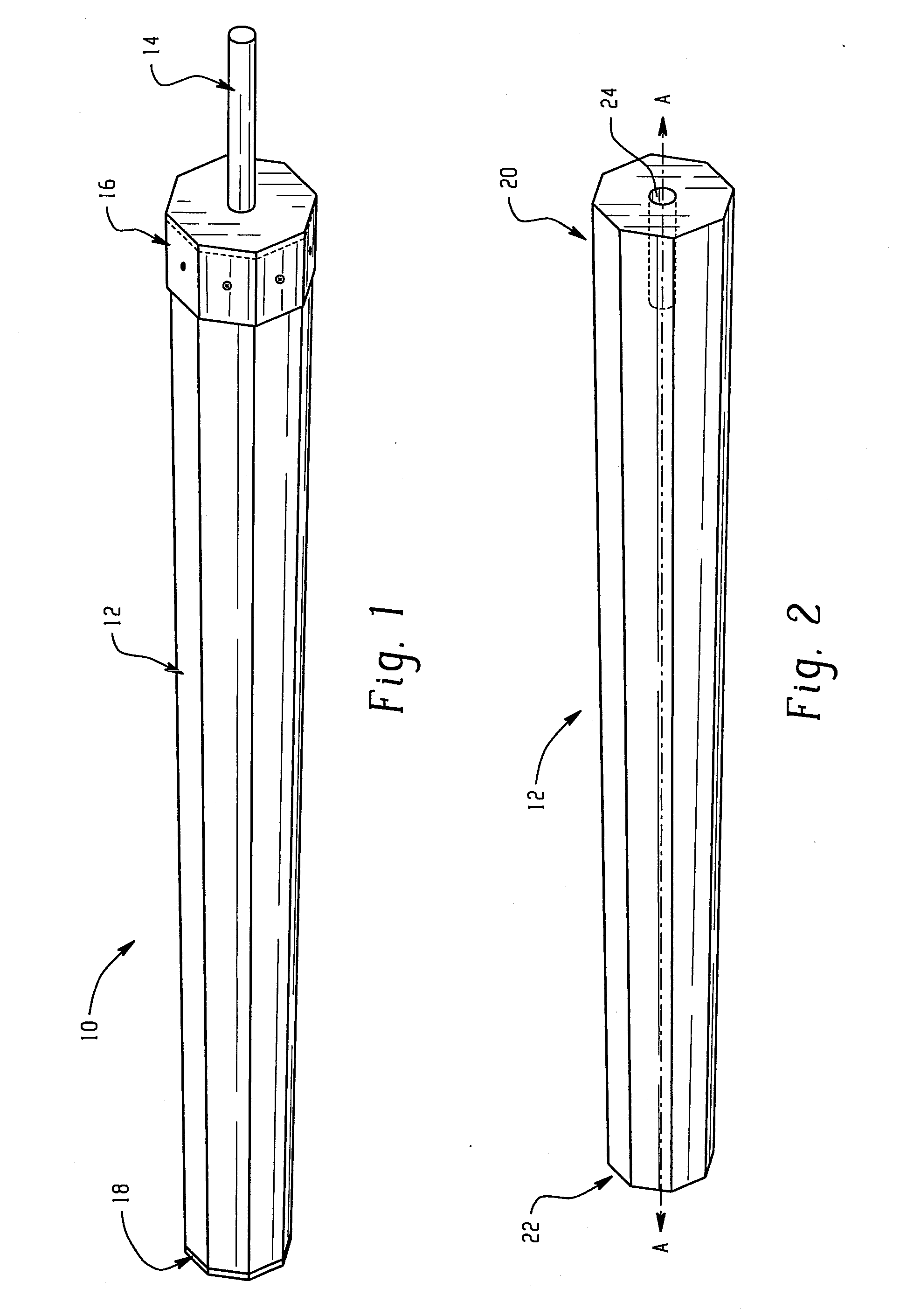

Tent pole apparatus with pin member and pole cap

InactiveUS20150176302A1High strengthImprove reinforcementTents/canopiesMetal working apparatusAdhesiveEngineering

A tent pole apparatus includes a tent pole member having a first, distal end spaced from a second, proximal end along a longitudinal axis thereof. A pin member is disposed at the distal end of the tent pole member. A proximal end of the pin member is at least partially inserted into a tent pole member cavity defined by a portion of the distal end of the tent pole member. A pole cap is affixed to a portion of the distal end of the tent pole member by each of an adhesive and welding. A portion of the pin member is welded to a portion of the pole cap.

Owner:DUQUM RAMSEY NASARR +1

Compositions and method for treatment and prophylaxis of inflammatory bowel disease

InactiveUS20150202238A1Prevent relapseRestorationBiocideOrganic active ingredientsSide effectHigh doses

Methods and compositions for treating inflammatory bowel disease involve the use of targeted antibiotics in combination with probiotic formulations. The probiotics mitigate many of the deleterious side effects associated with antibiotic use and permit the antibiotic to be administered at a higher dose and for a longer duration than would otherwise be possible in the absence of the probiotic. The practice of the invention may reduce or eliminate the use of immunosuppressants in the treatment and management of IBD.

Owner:TRACHTMAN IRA MILTON

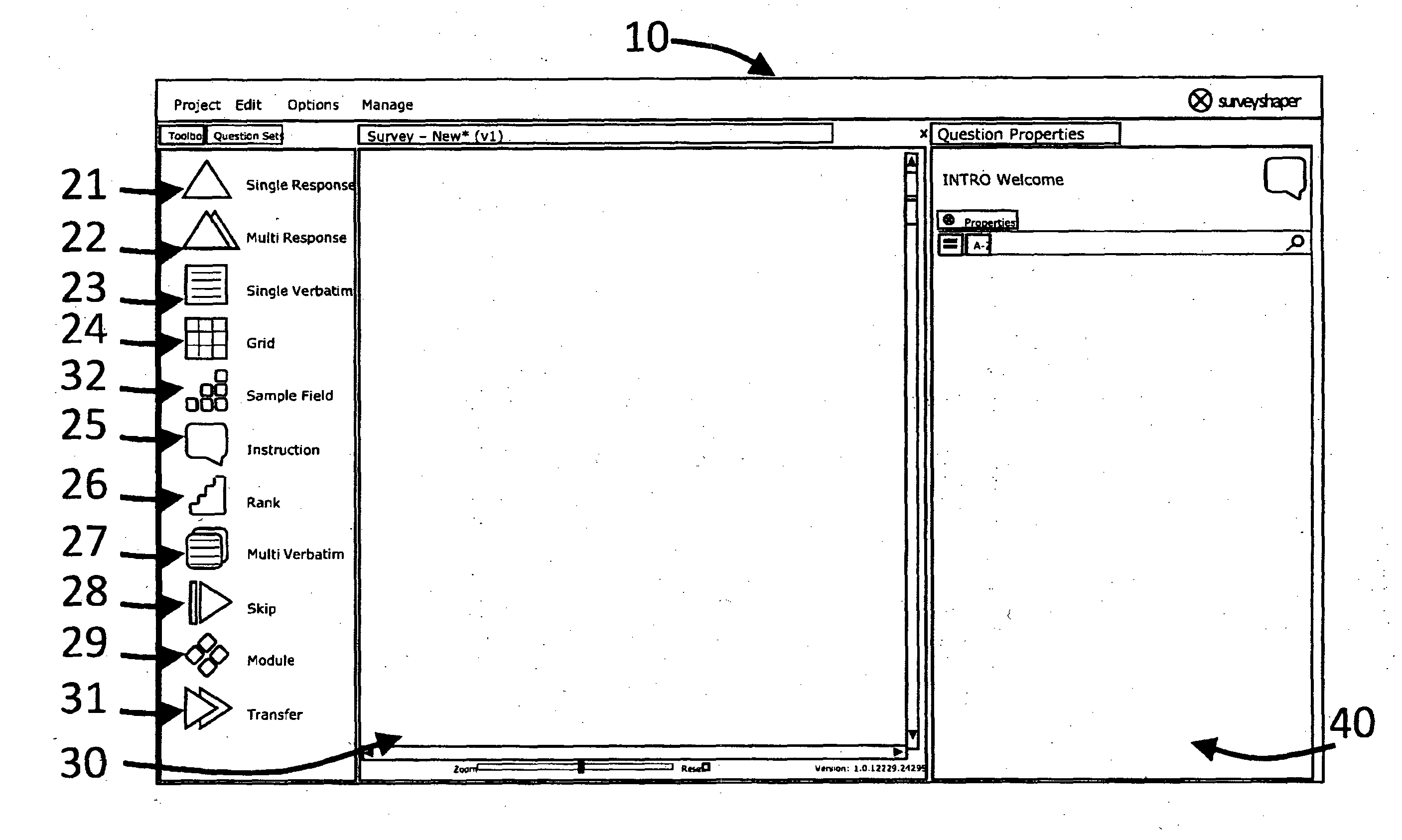

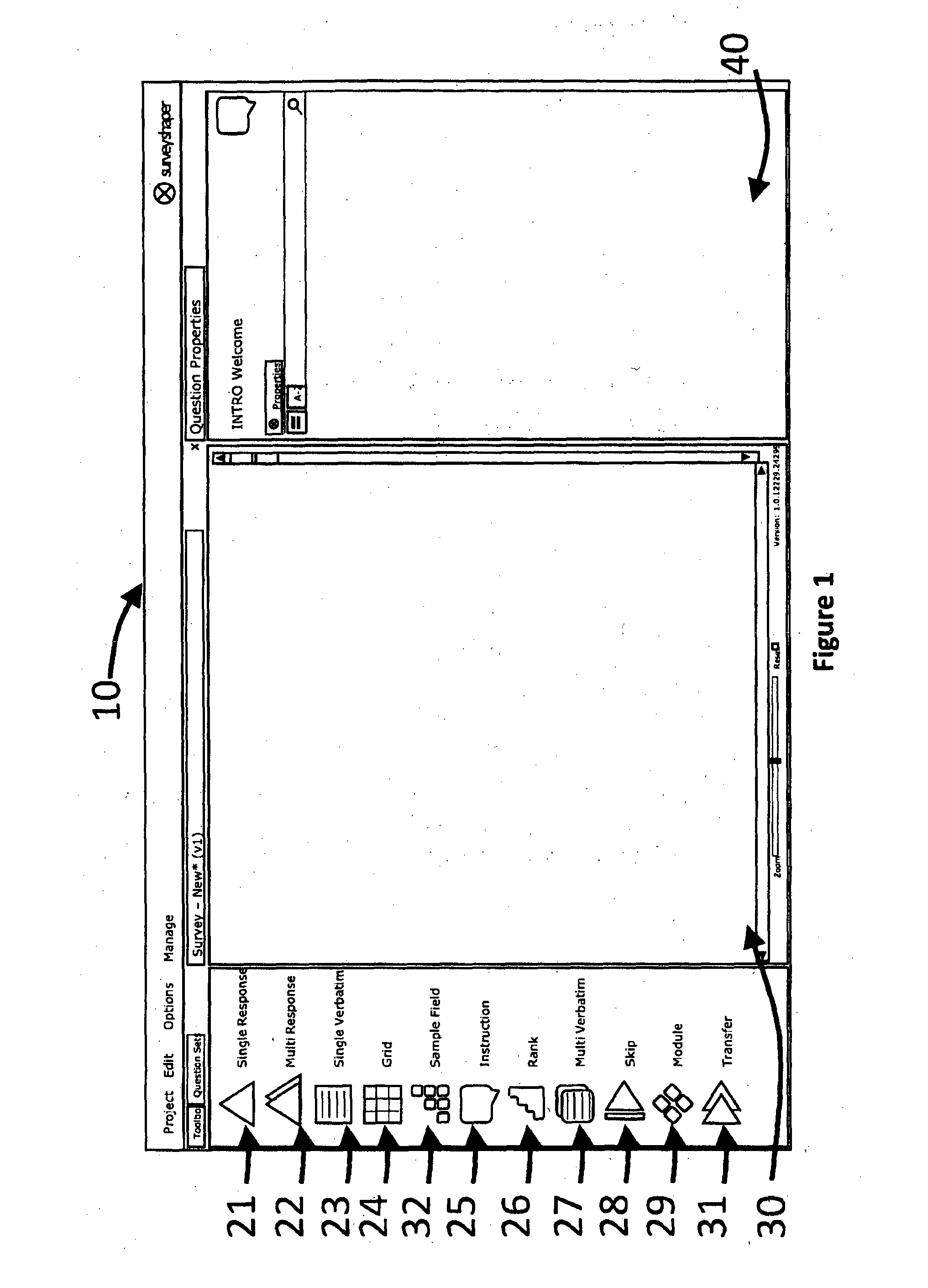

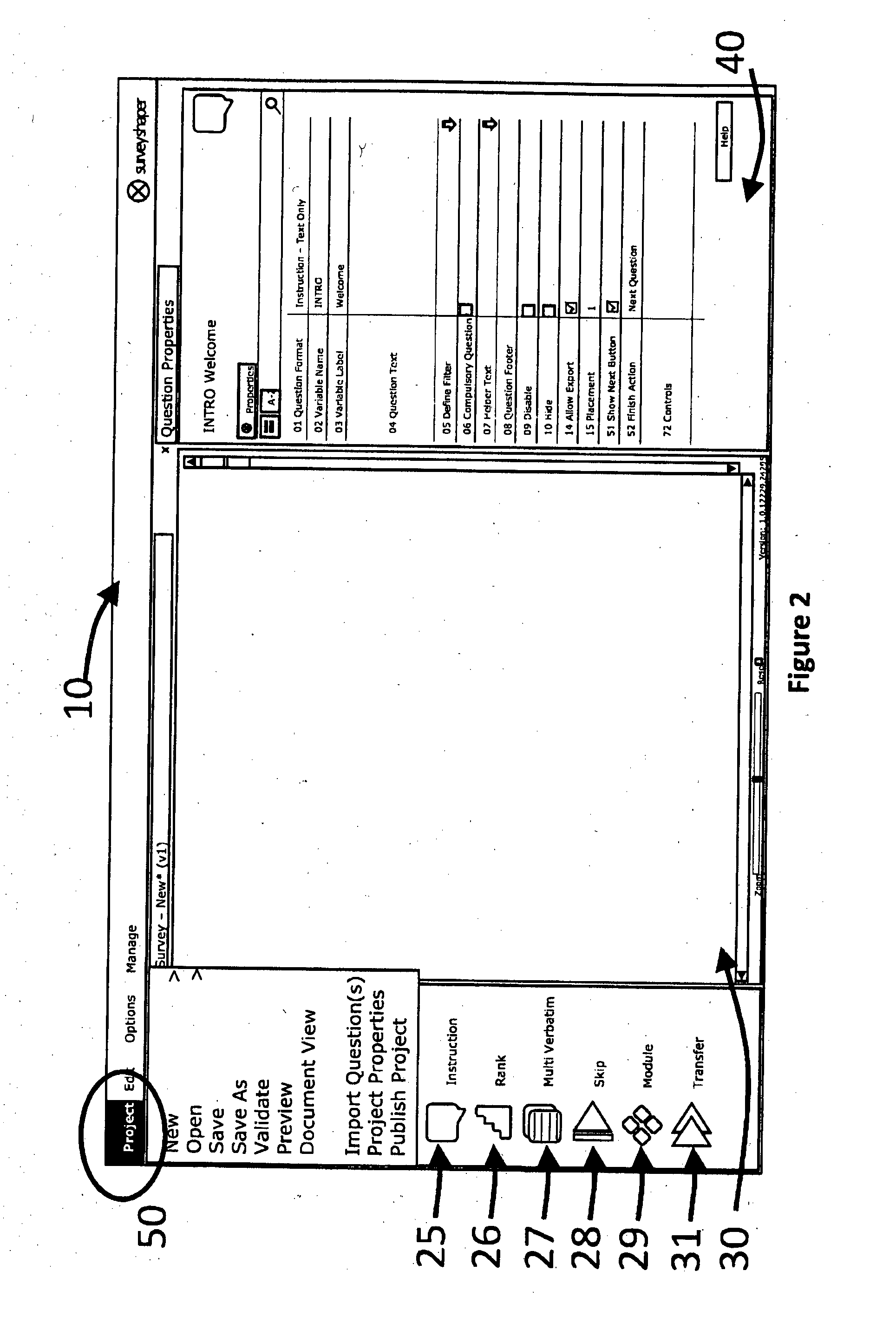

System and method of constructing on-line surveys

InactiveUS20150254691A1Quick identificationMitigate prospectMarket predictionsOffice automationGraphicsComputer science

A system and method of constructing on-line surveys is provided. In particular, the system and method assist a survey user in the construction of an on-line survey in that a graphical interface is presented to the user that includes graphical objects representing question types and / or formats, and the user is enabled to select graphical objects and to place the graphical objects representing pre-established survey components in a sequence, thereby defining a sequence of steps in an on-line survey. The sequence is further displayed to the user on the graphical interface, and once finalized, translated into computer readable format and deployed on-line to survey participants.

Owner:TWIST OF LEMON

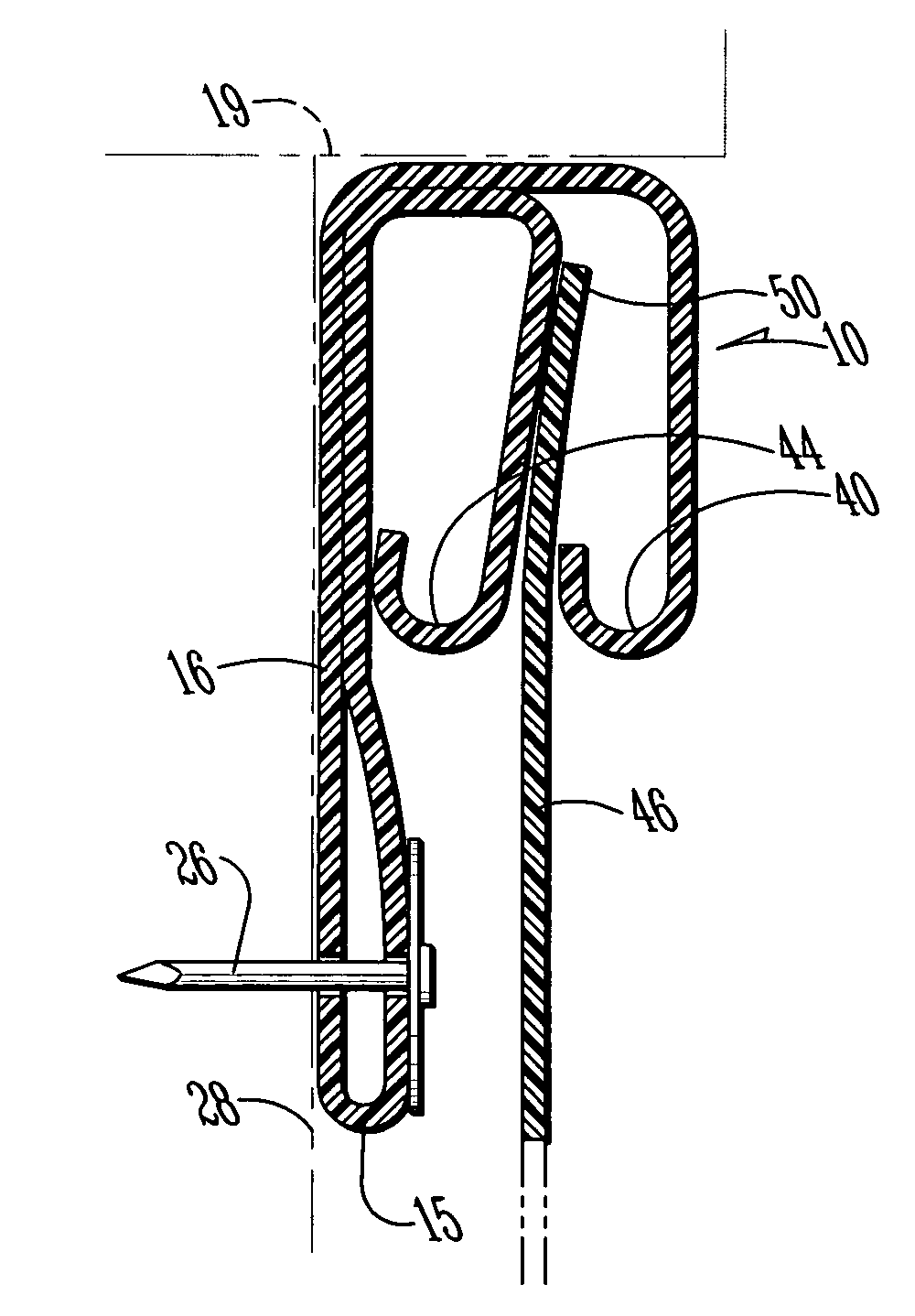

Door handle assembly

ActiveUS20190078360A1Big gapEasy to operateElectrical locking circuitsEngineeringElectrical and Electronics engineering

A door handle assembly is provided in the door of an automobile. The assembly includes an aperture in the outer skin of the door and a cover plate which closes off the aperture. The cover plate is retractable into a pocket behind the aperture, to open the aperture and allow a user to insert his / her fingers into the aperture. The user may then grab a latch release handle which is provided on the inner surface of the skin of the door, which senses the user's touch and releases a door latch, so that the door can be pulled open.

Owner:BENTLEY MOTORS

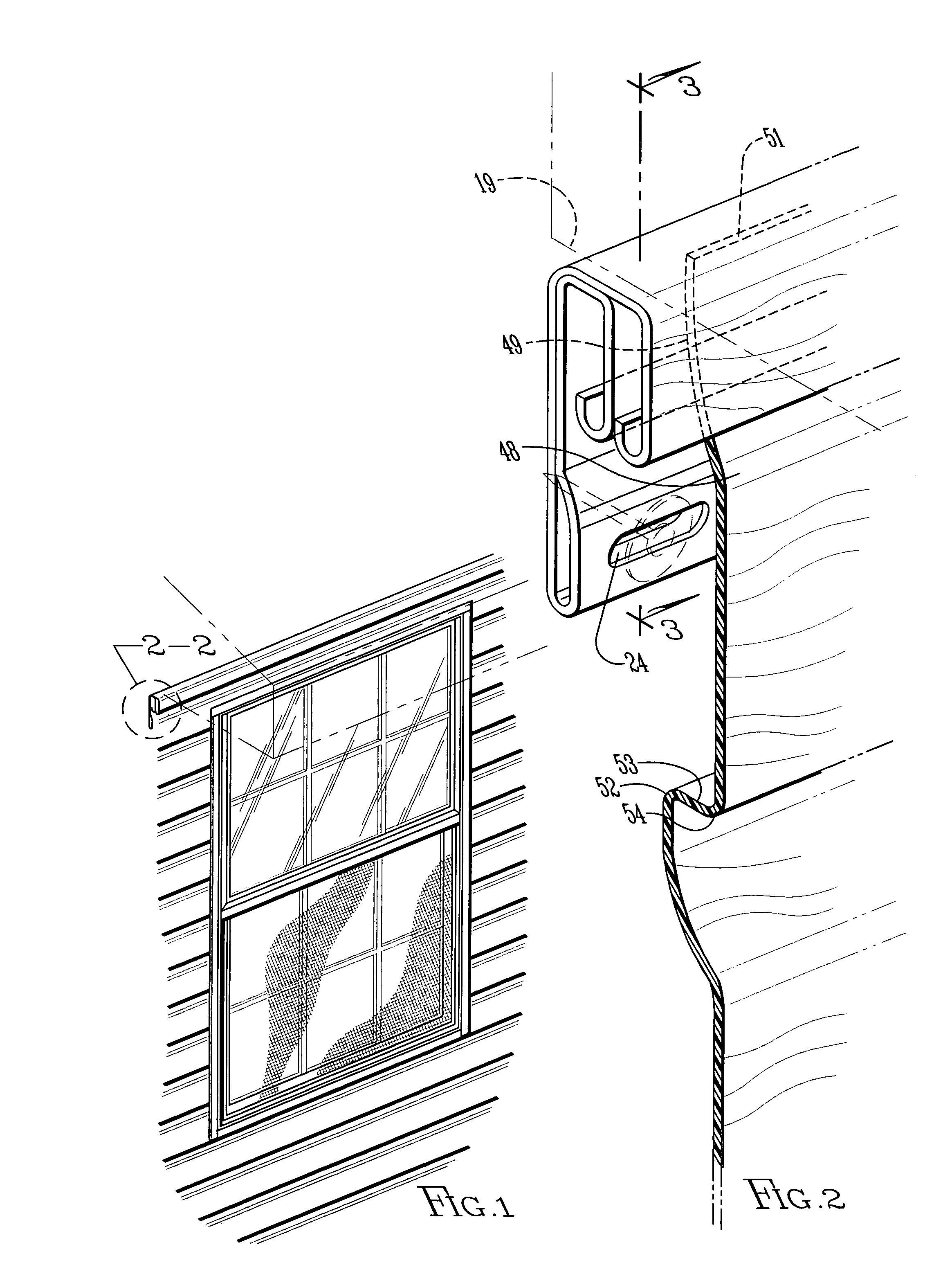

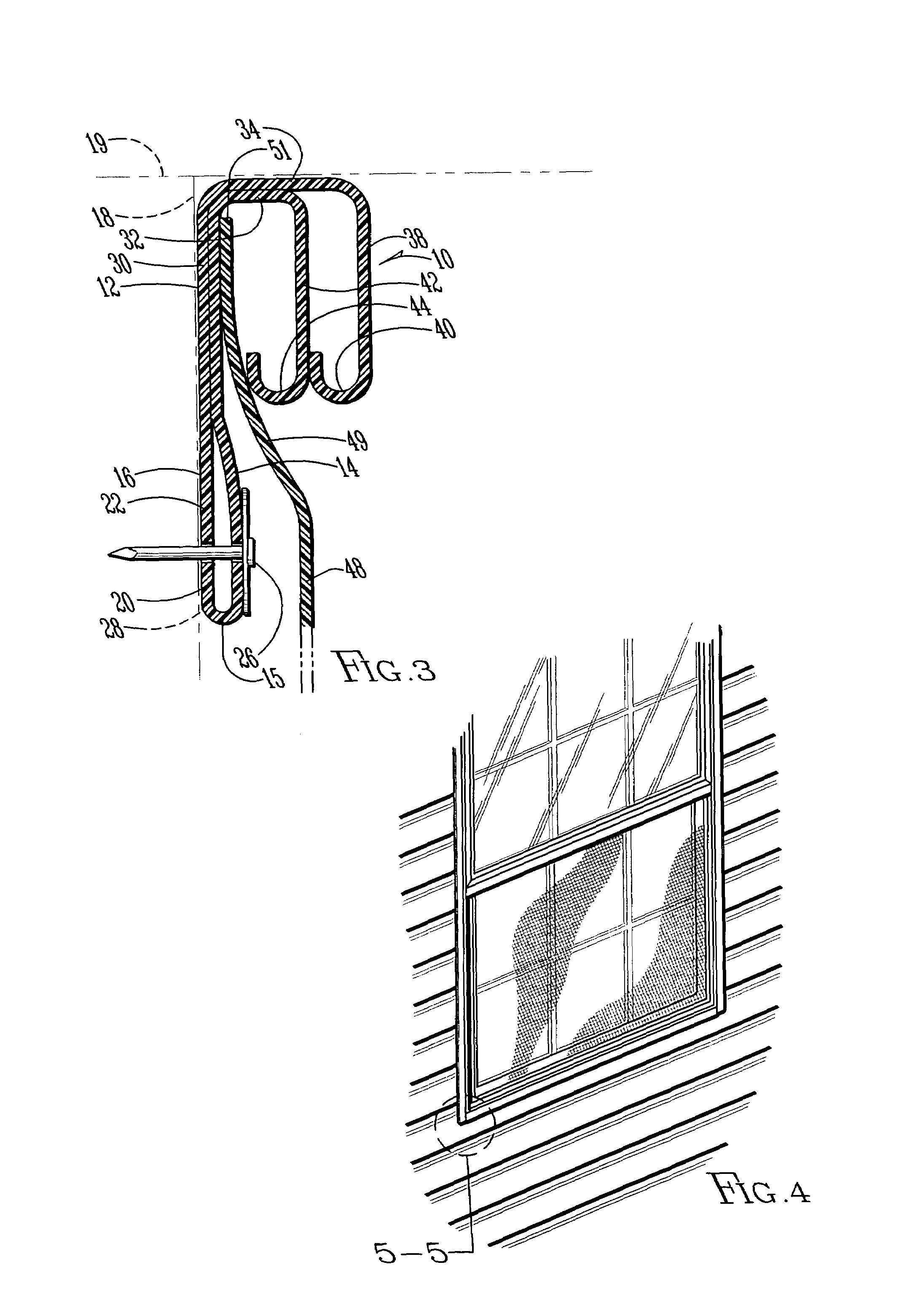

Method for extruding and product of the method

InactiveUS7424795B2Eliminate distractionsMitigate prospectRoof covering using tiles/slatesCovering/liningsEngineeringVinyl siding

A horizontally mounted siding component for finishing of a top course of a vinyl siding installation while minimizing the lateral deformation of the vinyl siding. The invention additionally relates to the method for post-form extruding a thermoplastic dual undersill trim with complex geometry including extensive folding of the extruded material in a series of fixtures.

Owner:ALCOA HOME EXTERIORS +10

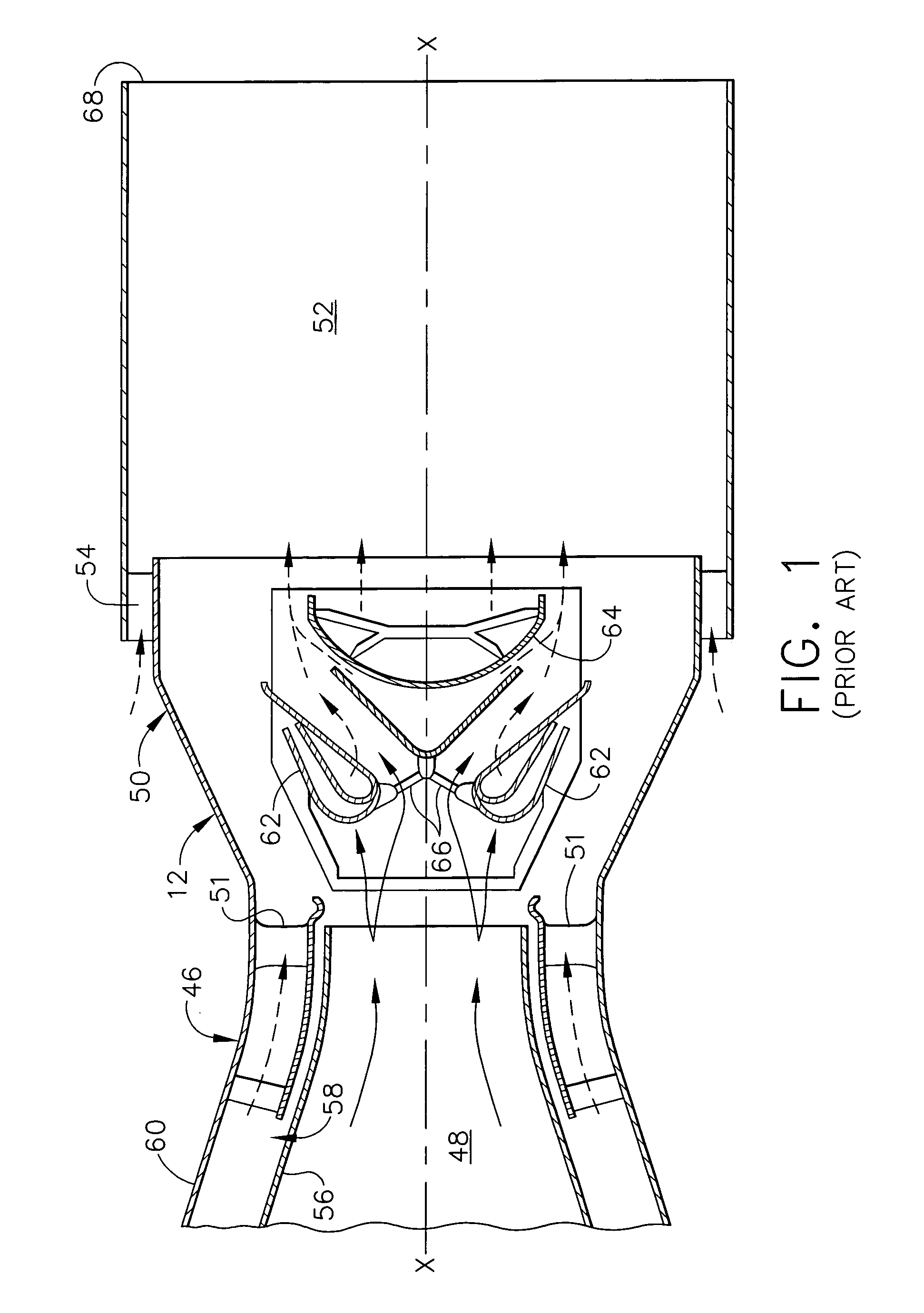

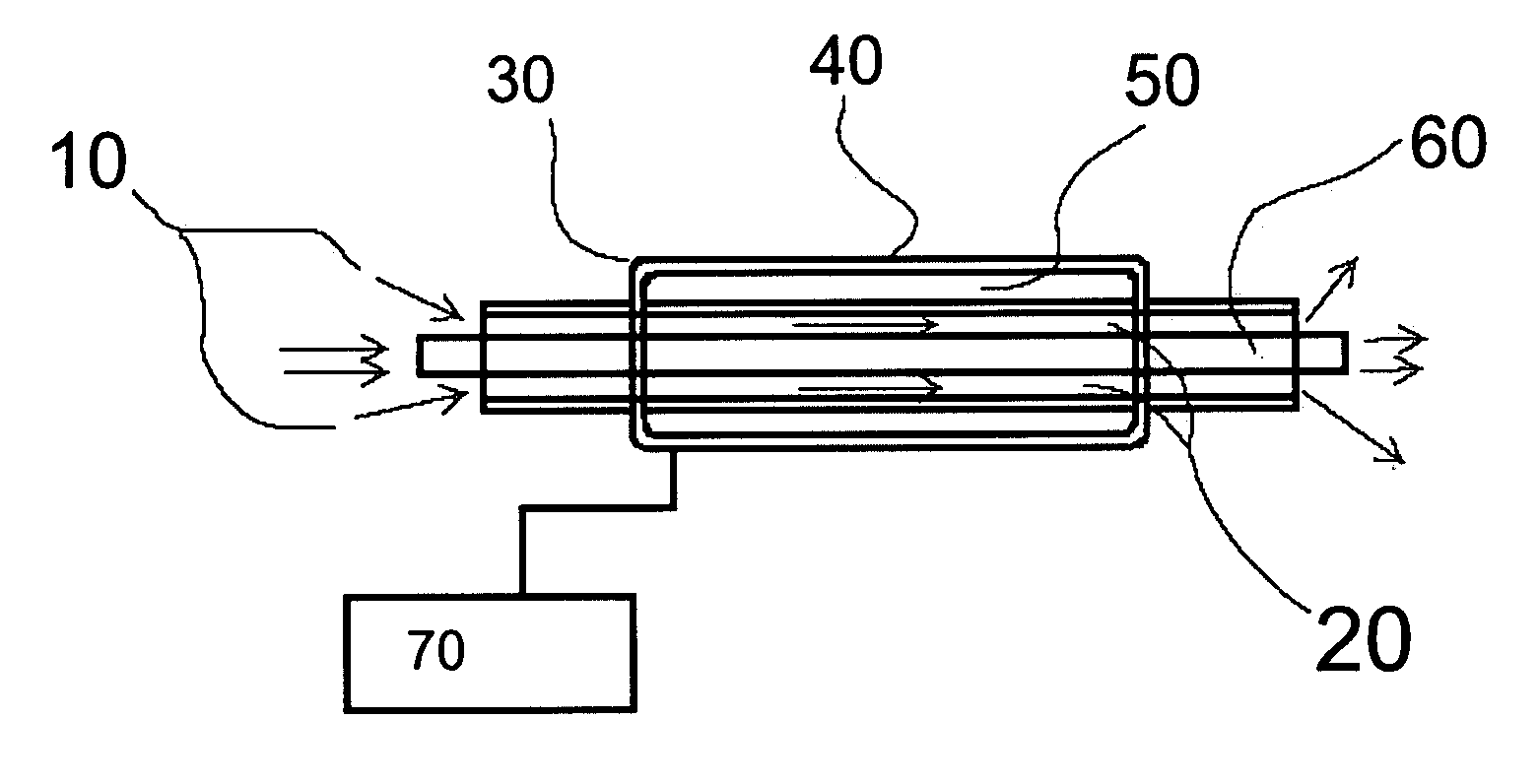

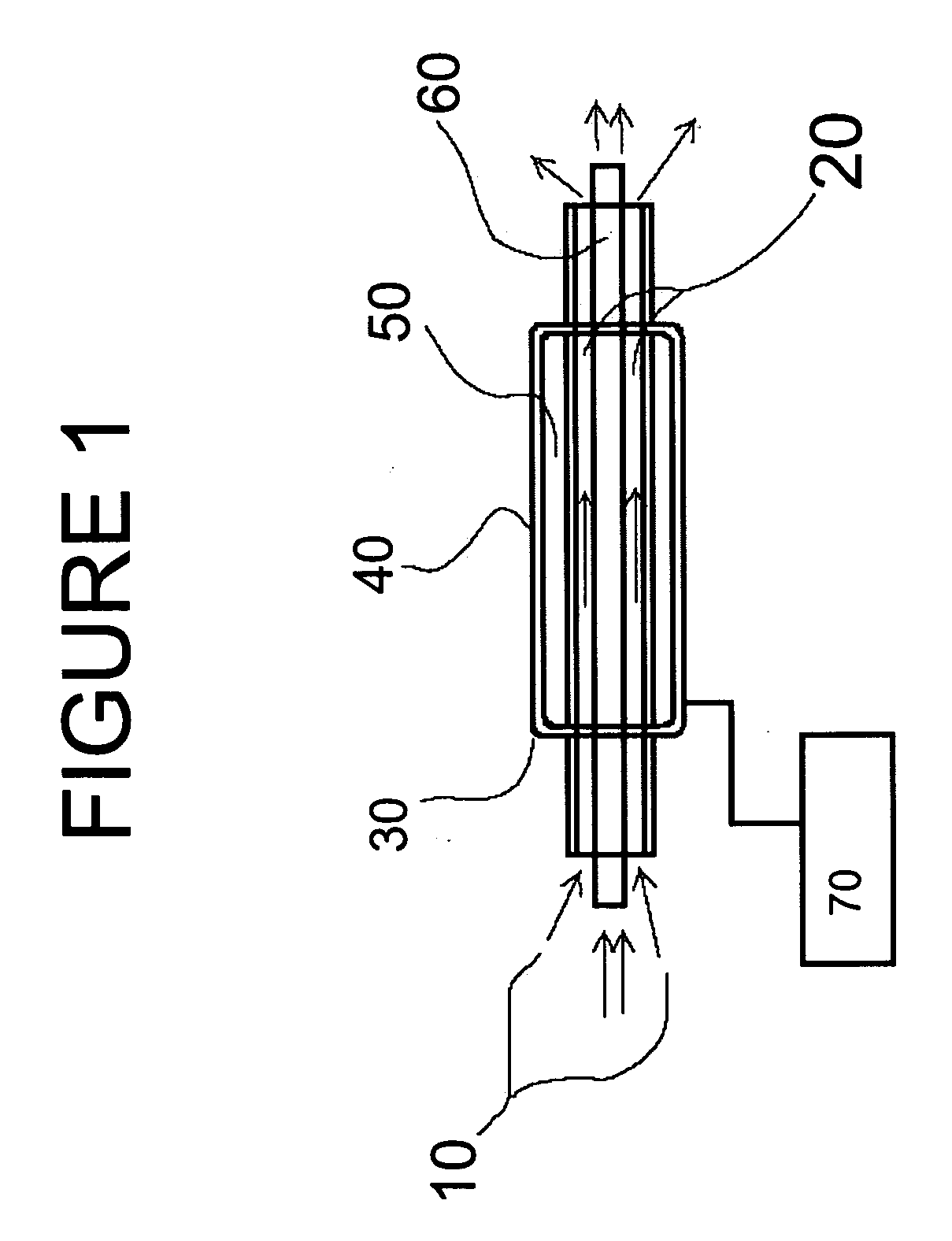

High reflectivity infrared coating applications for use in HIRSS applications

InactiveUS20060088727A1Improves IR performance of materialReducing and eliminating likelihoodPretreated surfacesLiquid/solution decomposition chemical coatingEngineeringHigh reflectivity

The present invention is a hover infrared suppression system for a gas turbine engine comprising a hover infrared suppression system having an upstream first stage, a second stage downstream of the first stage and a third stage downstream of the second stage, the engine operating at a temperature sufficient to cause the hover infrared suppression system to emit infrared radiation. The present invention further comprises a high reflectivity coating applied over a preselected area of at least one of the stages of the hover infrared suppression system to reduce the infrared radiation emitted from the engine, the high reflectivity coating being fired after application.

Owner:GENERAL ELECTRIC CO

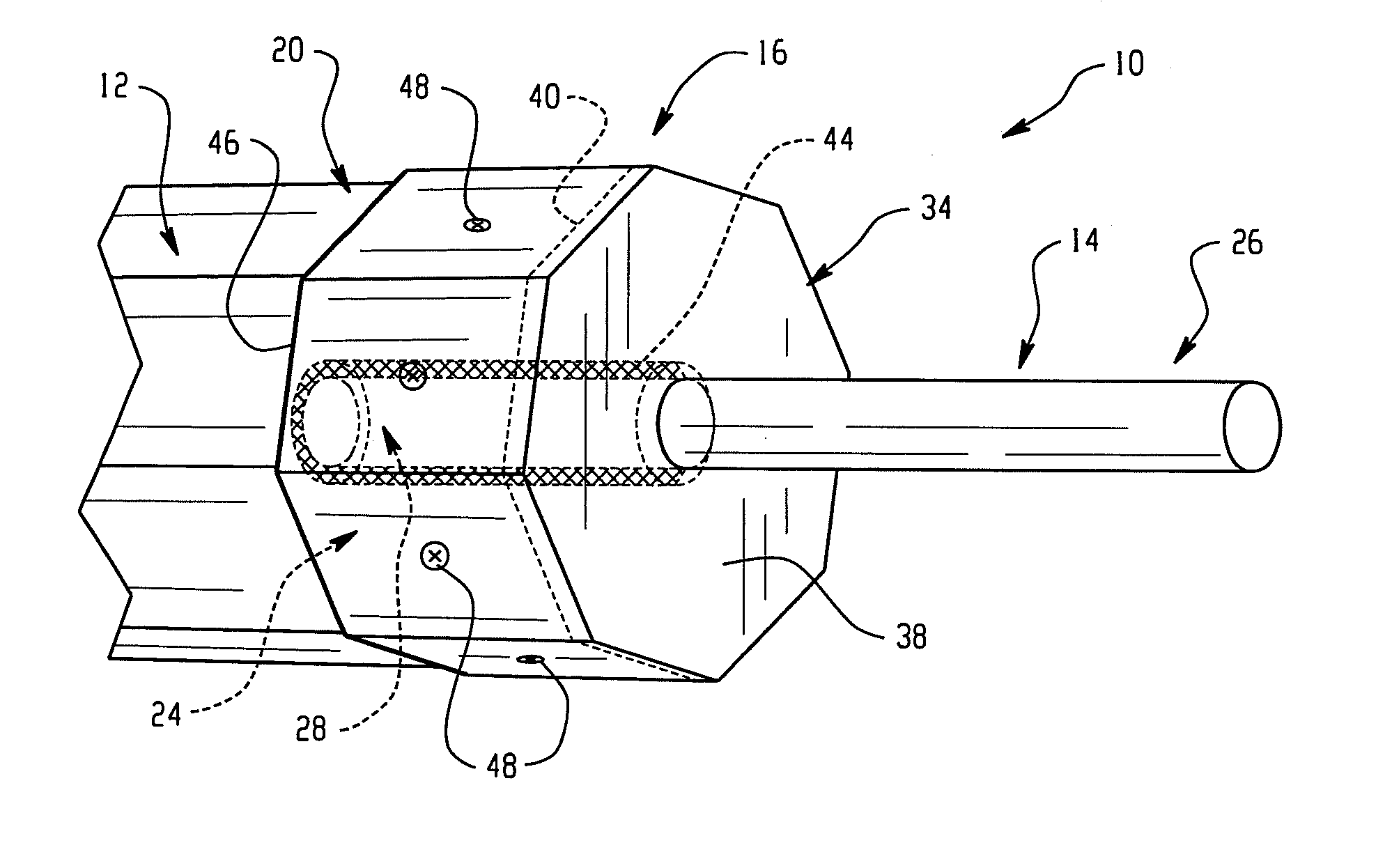

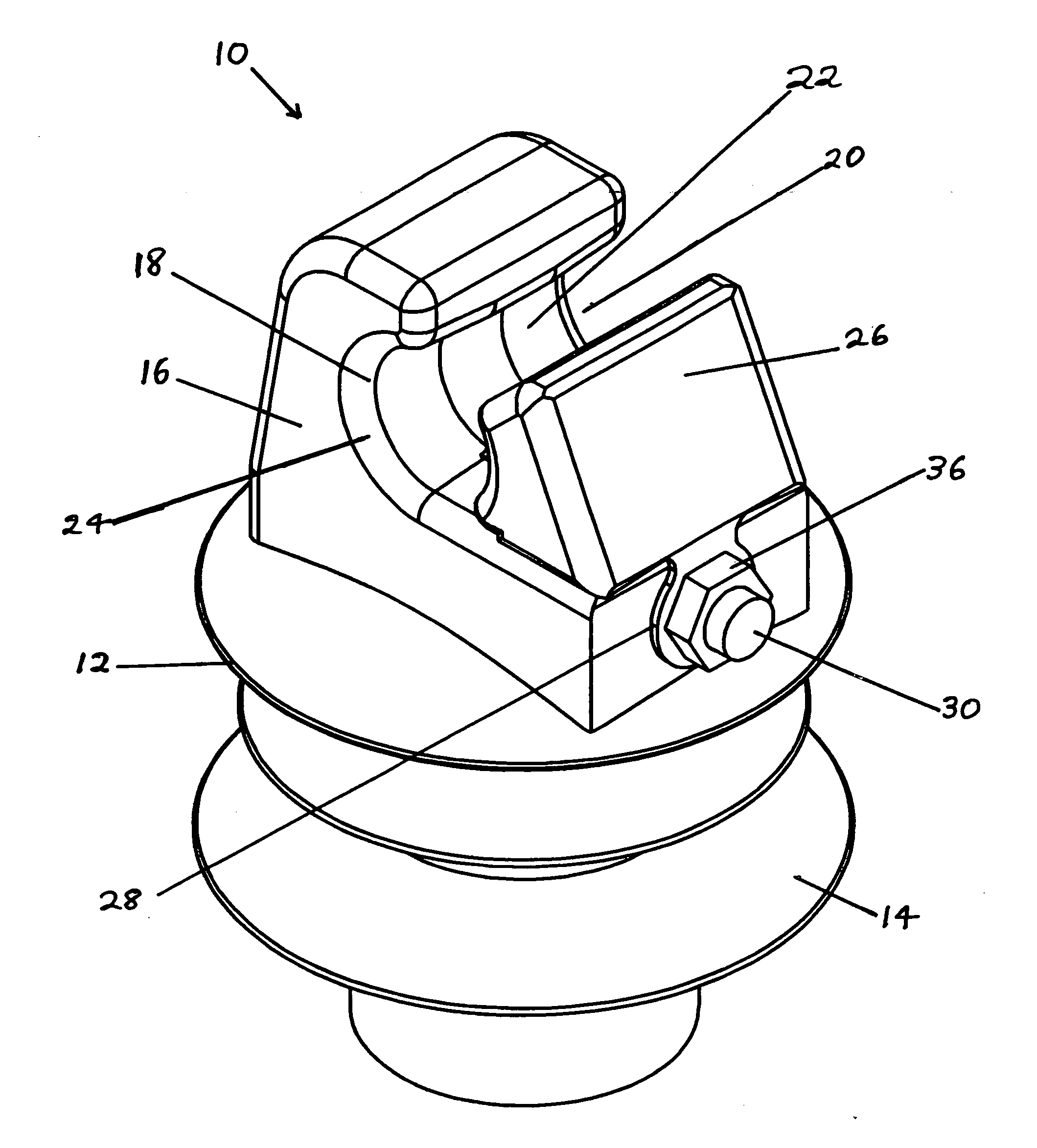

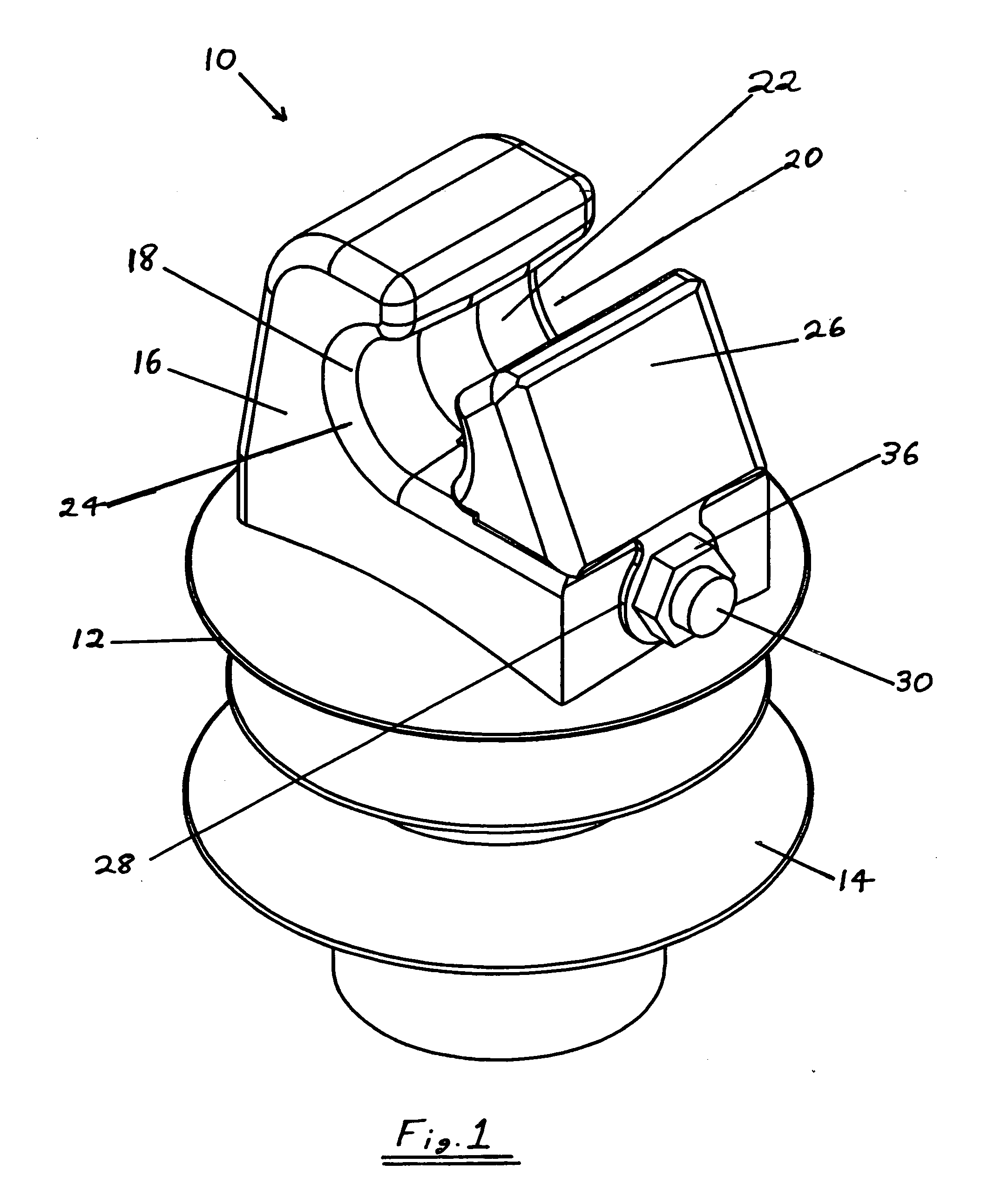

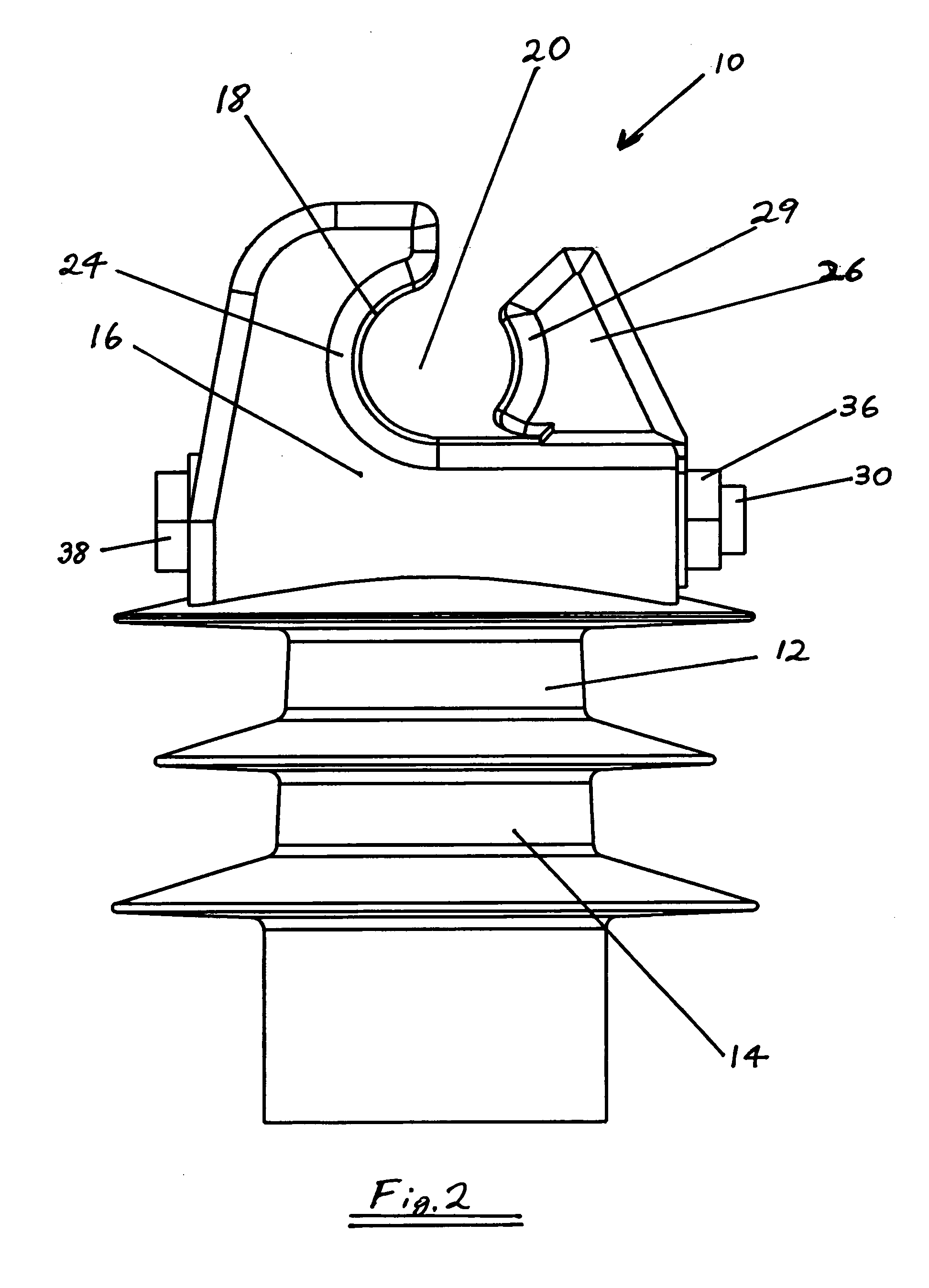

Integrated clamp insulators

InactiveUS20130032379A1Reduce probabilityUniform compositionOverhead installationSuspension/strain insulatorsElectrical conductorBiomedical engineering

An electrical insulator (12) comprising an insulator body (14) and a clamp (16) formed as an integral piece, wherein the insulator body has a base fitting for attachment to a support structure at one end with the clamp (16) being formed at the other end, said clamp having a body including a saddle (18) defining a hollow (20) for receiving an electrical conductor whether the electrical insulator is extending either substantially horizontally or substantially vertically from the support structure, and a bolt (30) upon which a keeper or retainer (26) is movable along a track (28) defined in the body of the clamp for securing an electrical conductor in the hollow (20).

Owner:PACIFIC POLYMERS

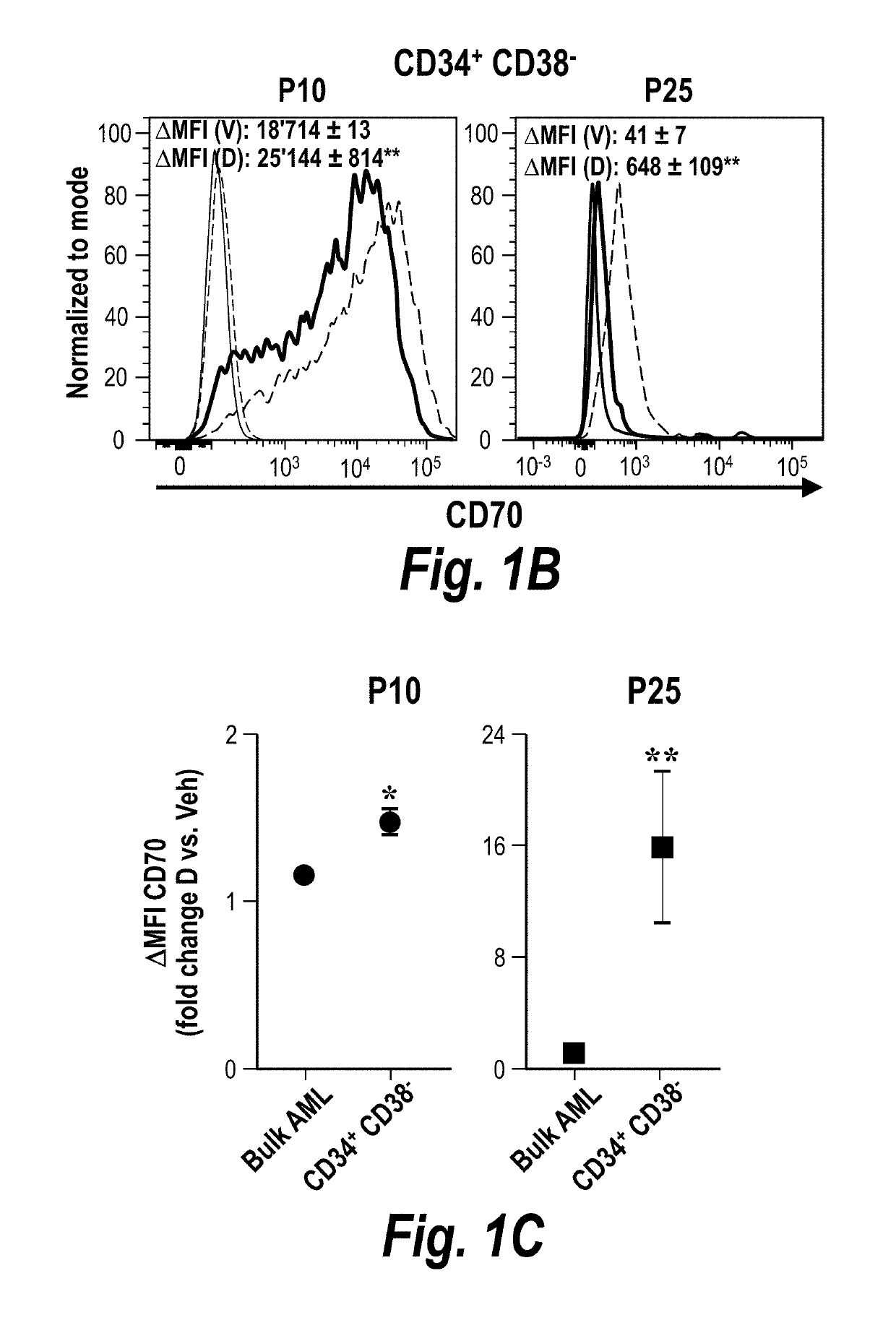

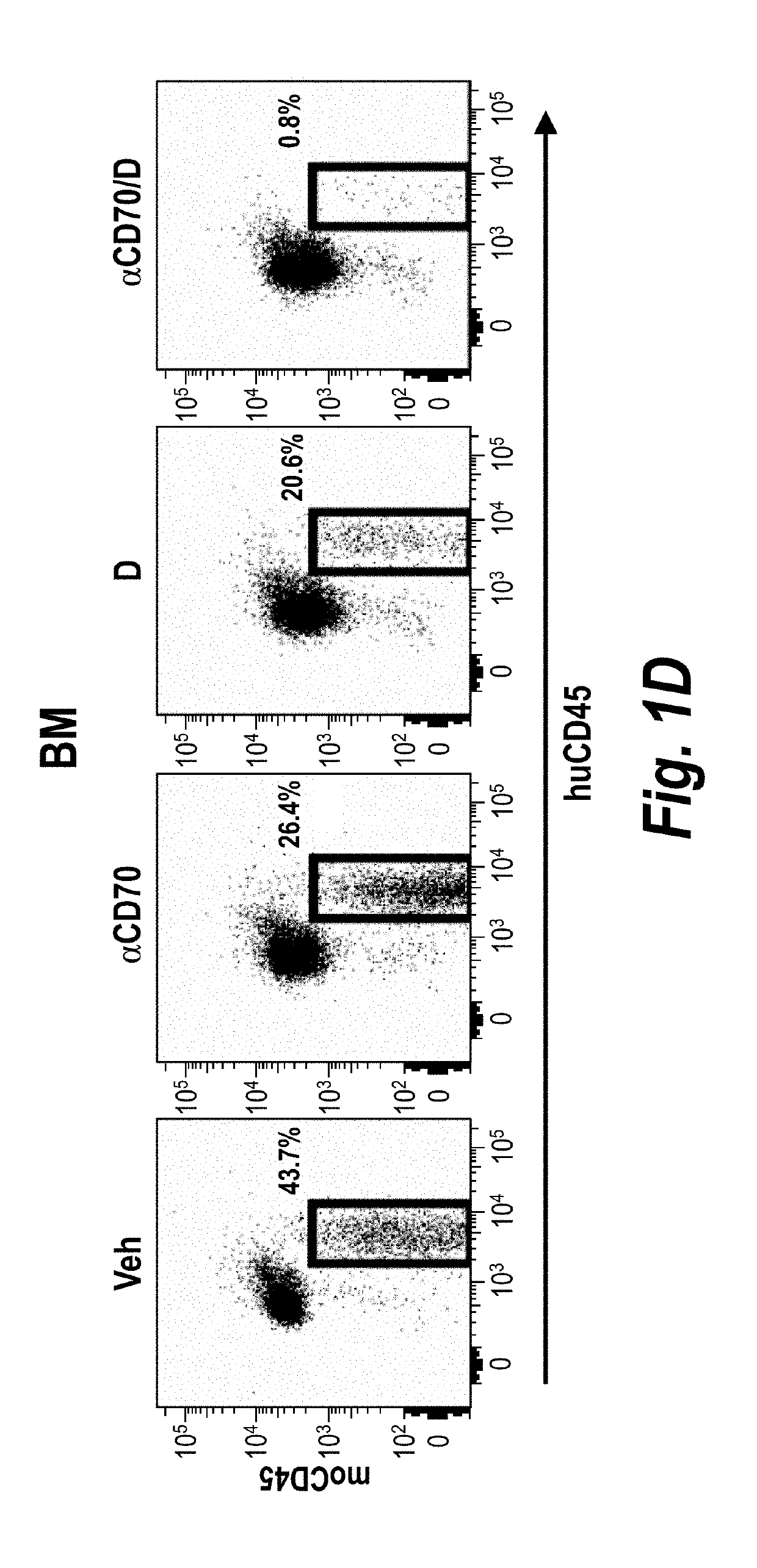

Treatment for acute myeloid leukemia

PendingUS20190106498A1Increase productionIncreased activationOrganic active ingredientsImmunoglobulins against cell receptors/antigens/surface-determinantsOncologySecondary Acute Myeloid Leukemia

Methods of treating acute myeloid leukemia (AML) or myelodysplastic syndrome (MDS) are provided, as are compositions and combinations suitable for use in said methods.

Owner:UNIVERSITY OF BERN +1

Compositions and method for treatment and prophylaxis of inflammatory bowel disease

InactiveUS9138441B2Promote healingPrevent relapseAntibacterial agentsOrganic active ingredientsSide effectInflammatory Bowel Diseases

Owner:TRACHTMAN IRA MILTON

Synthetic peptide constructs for the diagnosis and treatment of periodontitis associated with Porphyromonas gingivalis

InactiveUS20080124284A1Mitigate prospectEfficient inductionAntibacterial agentsCosmetic preparationsPorphyromonas gingivalisImmunogenicity

The present invention relates to an oral composition and an immunogenic composition for the suppression of the pathogenic effects of the intra-oral bacterium Porphyromonas gingivalis associated with periodontal disease.

Owner:UNIVERSITY OF MELBOURNE

Apparatus for Rapid Oxidation using UV Radiation

InactiveUS20090246101A1Promote fast reaction timeImprove efficiencyWater/sewage treatment by irradiationEnergy based chemical/physical/physico-chemical processesFluid intakeWater flow

An apparatus employing a UV reaction chamber that produces light for levying high-level amounts of hydroxyl radicals during the oxidation process. The flow passes through a fluid intake and into the UV reaction chamber. A metallic coating on the outer shell and quartz reactor work for increased efficiency during the oxidation process, as does a coolant tube. The apparatus is connected to a number of conceivable systems as the apparatus aids in the rapid oxidation process of the water flow.

Owner:POCHY ROCCO D +2

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com