Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43results about How to "Increase lock range" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

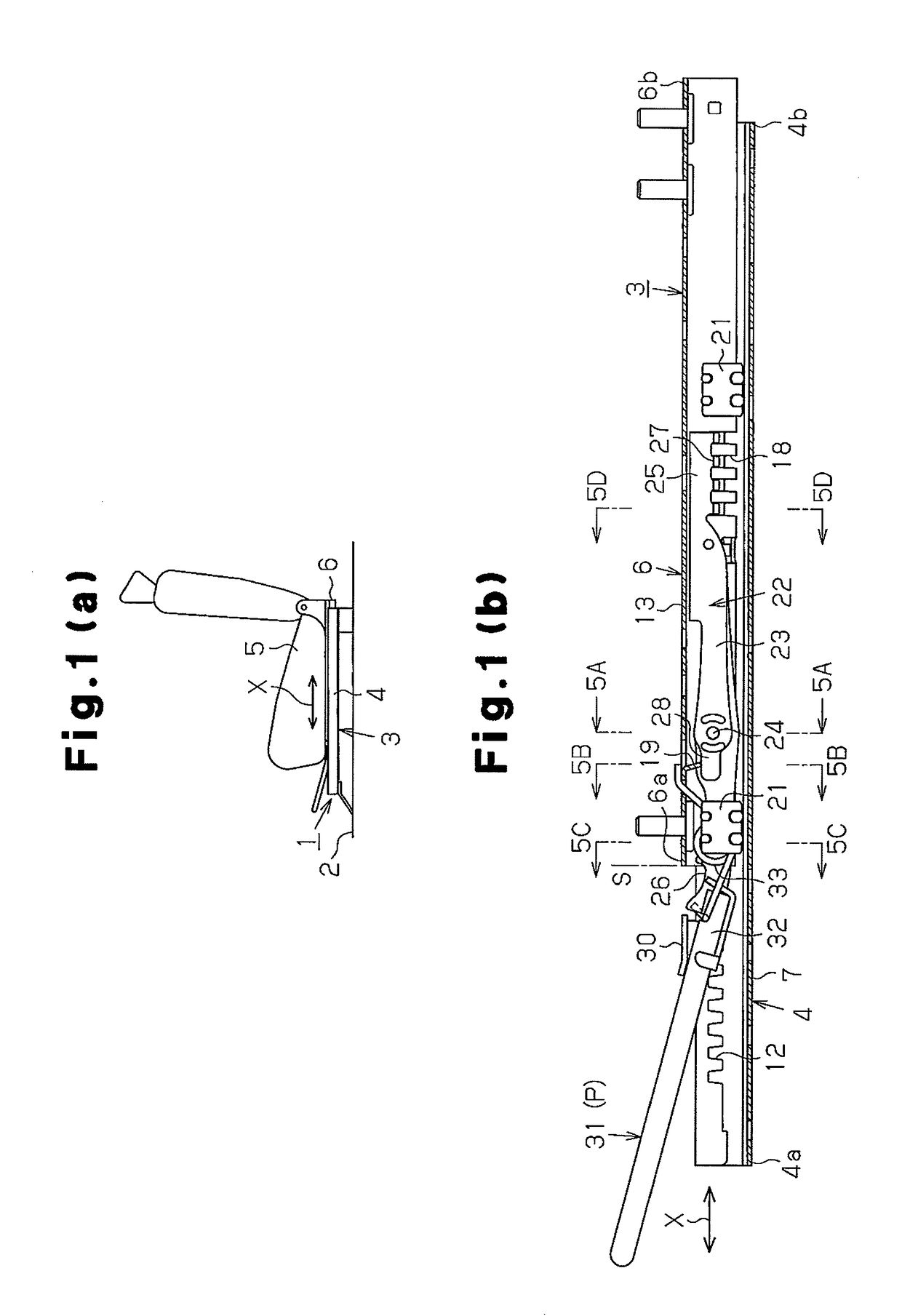

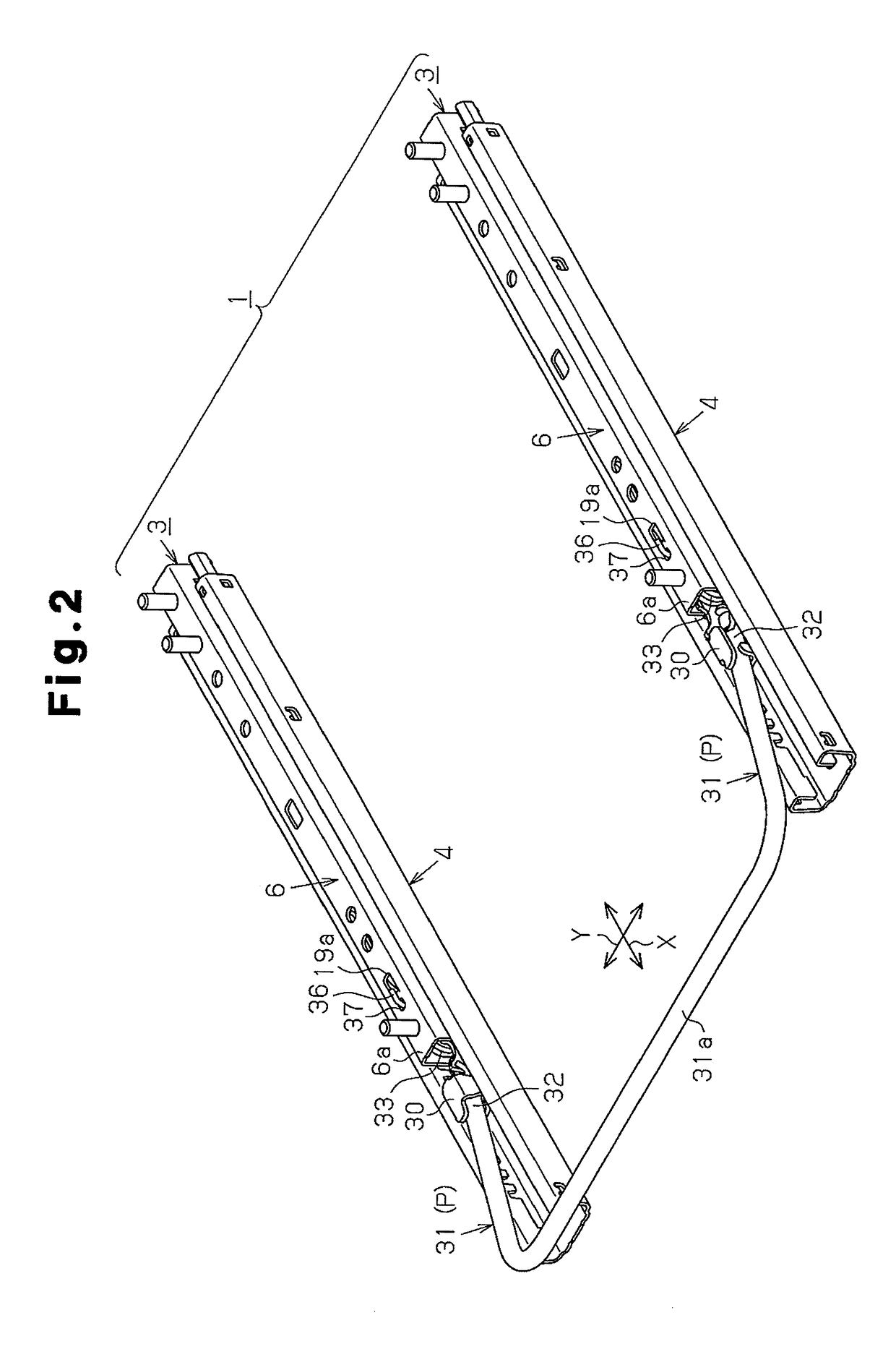

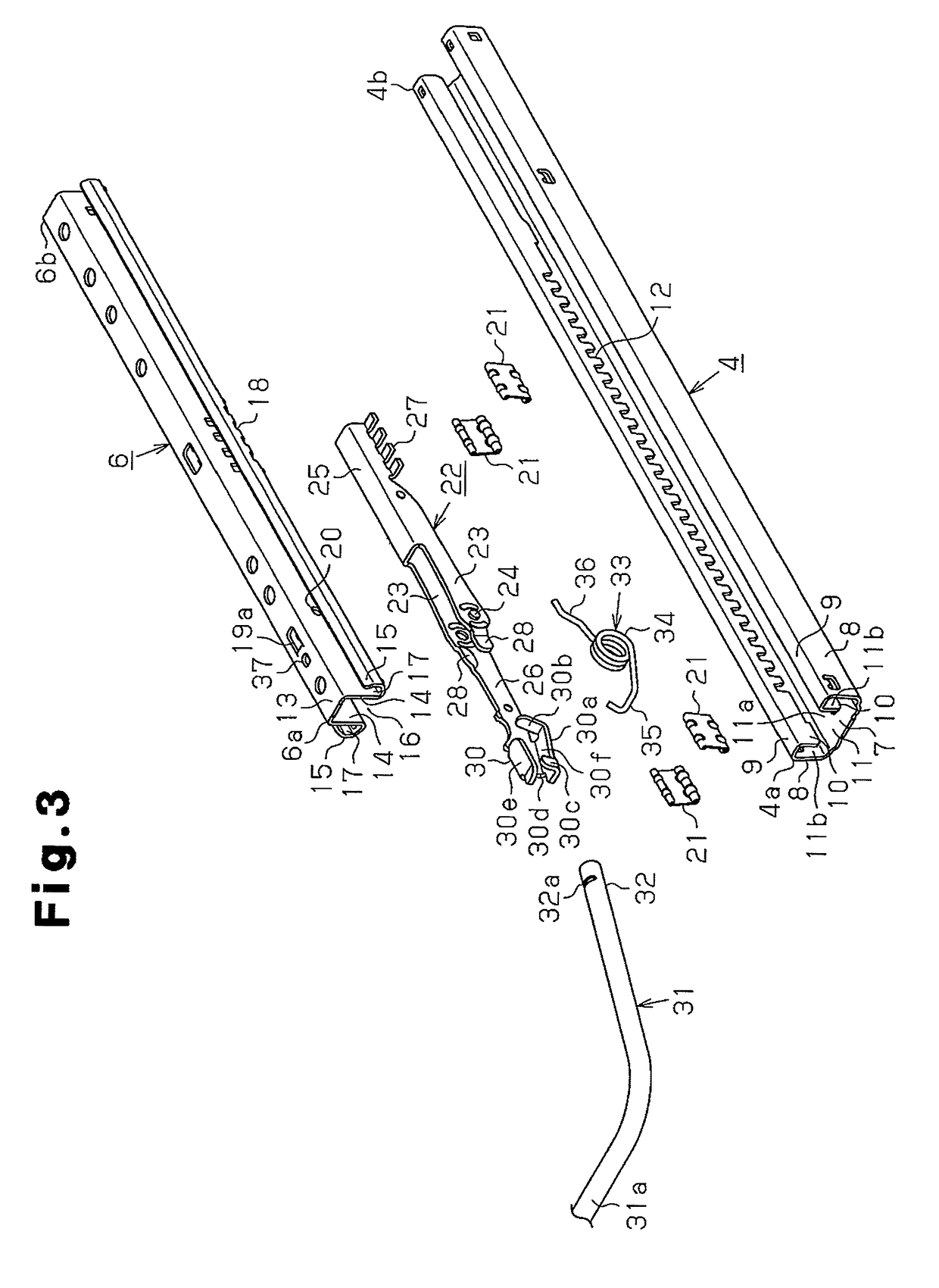

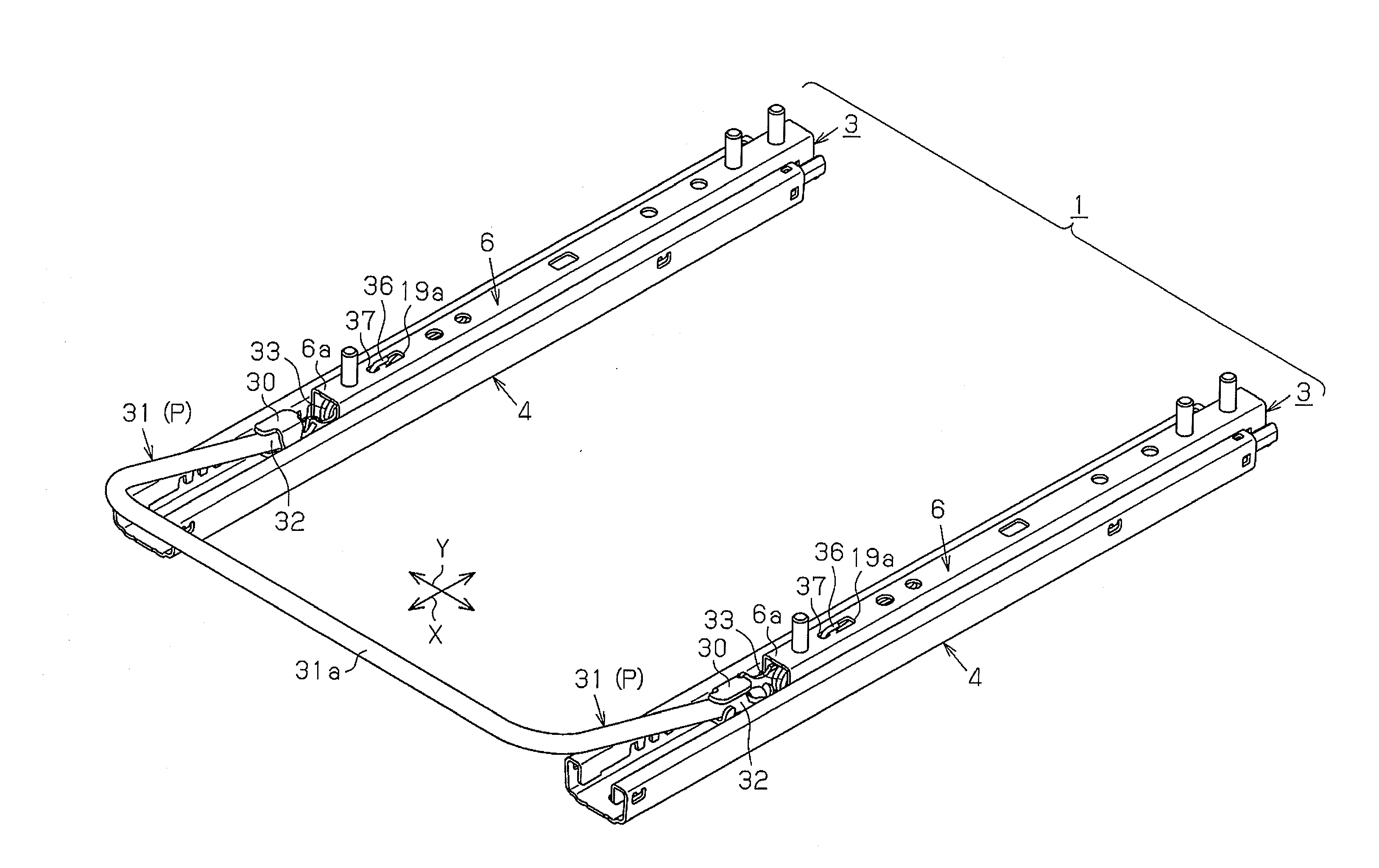

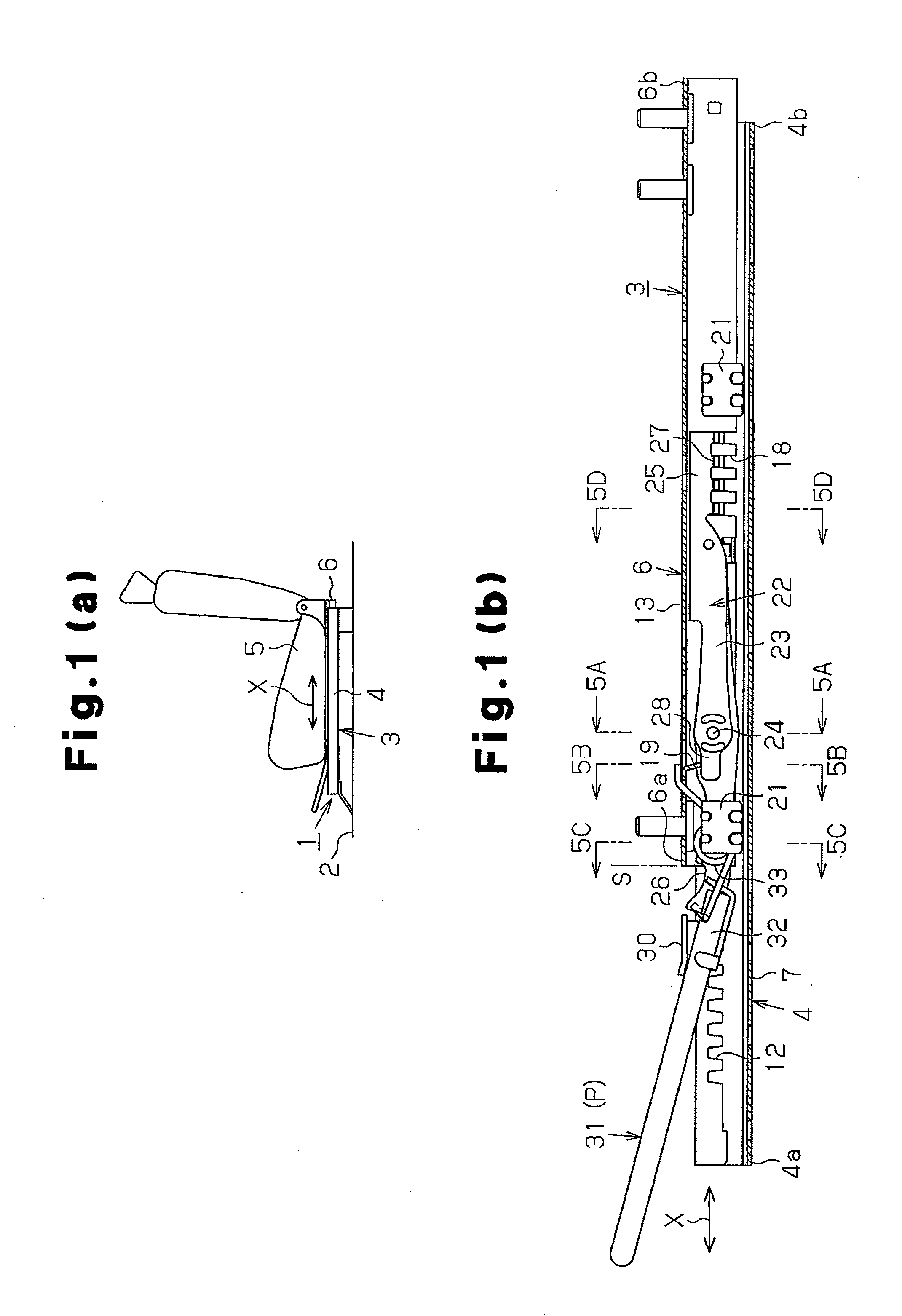

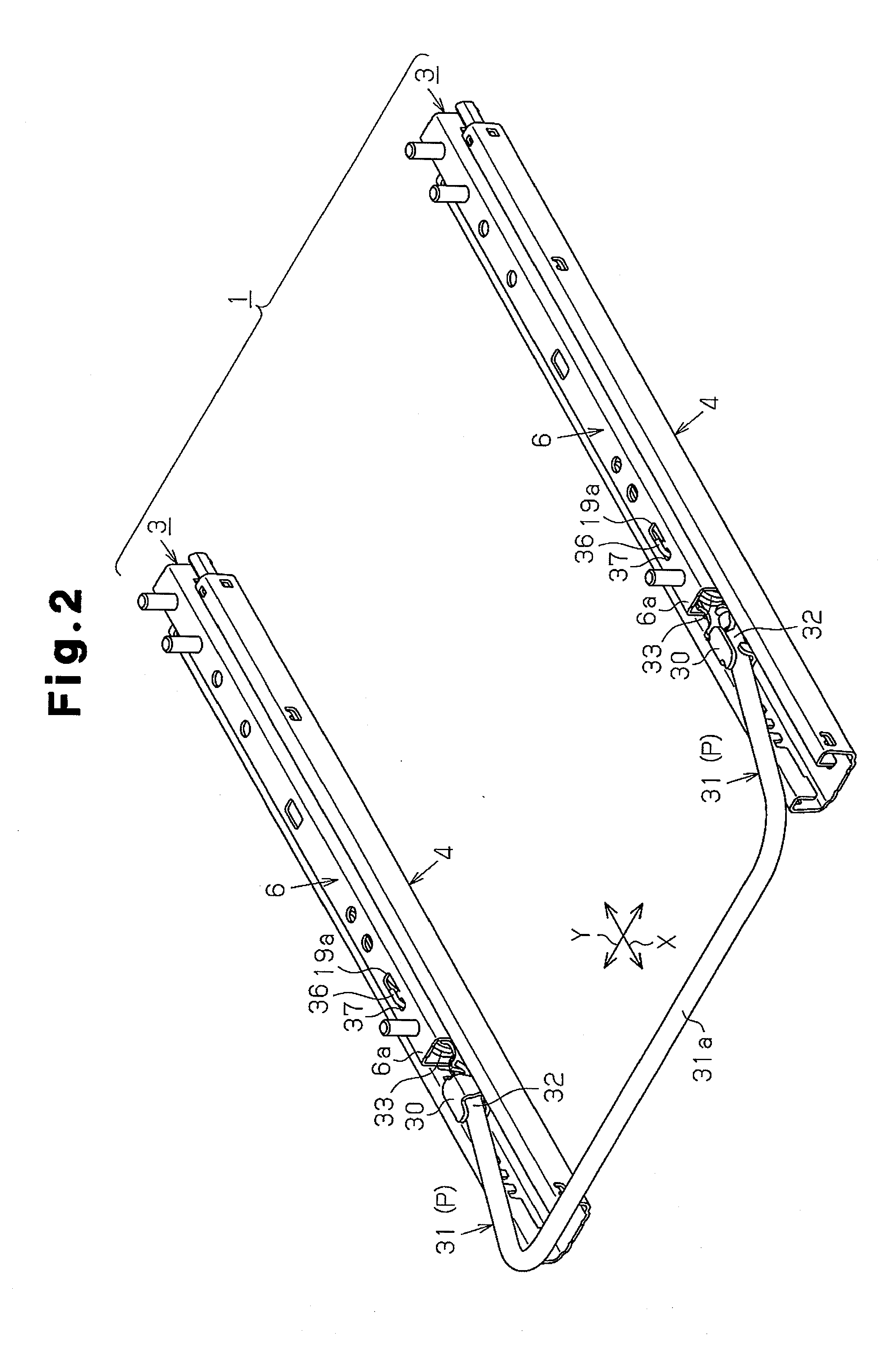

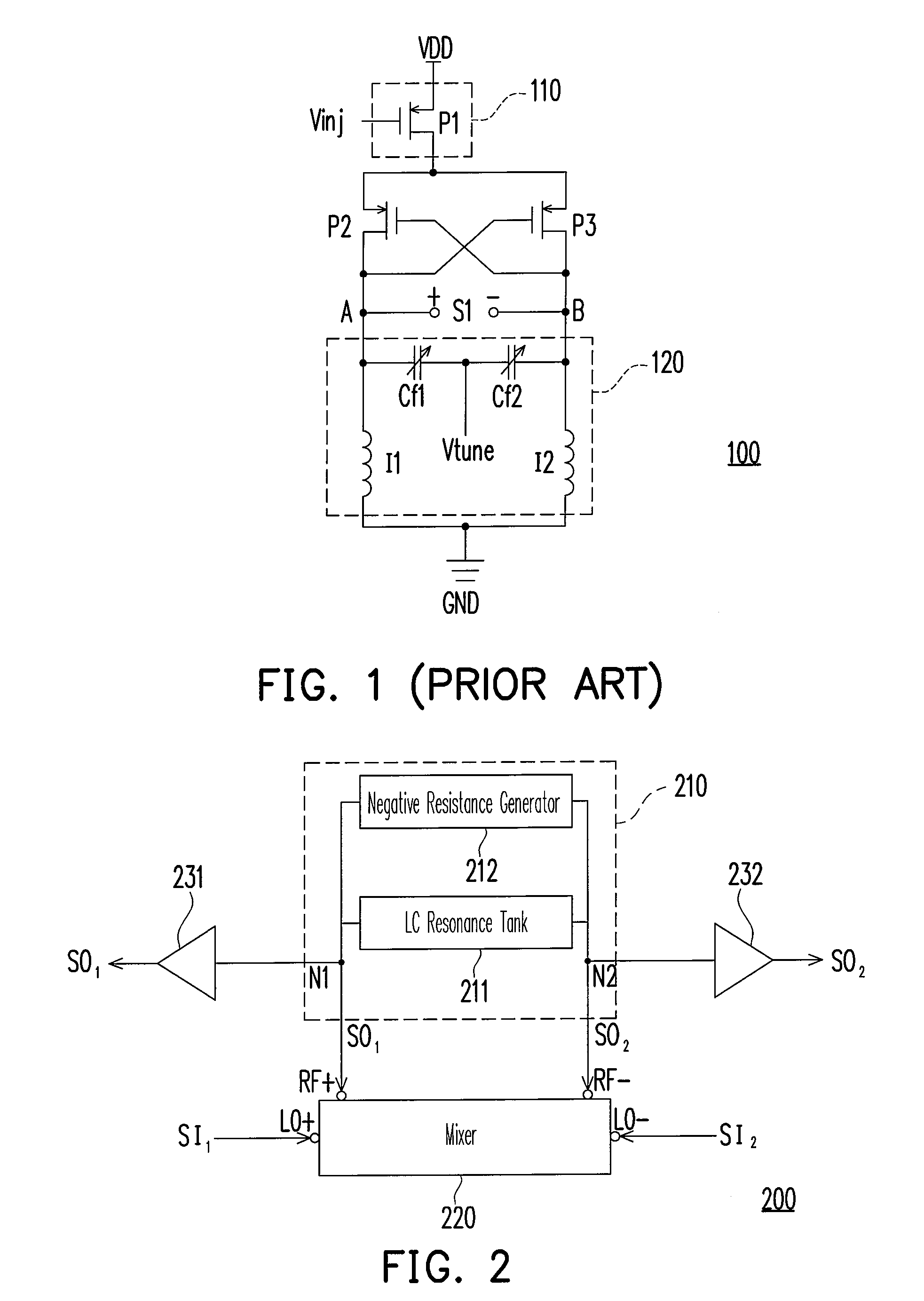

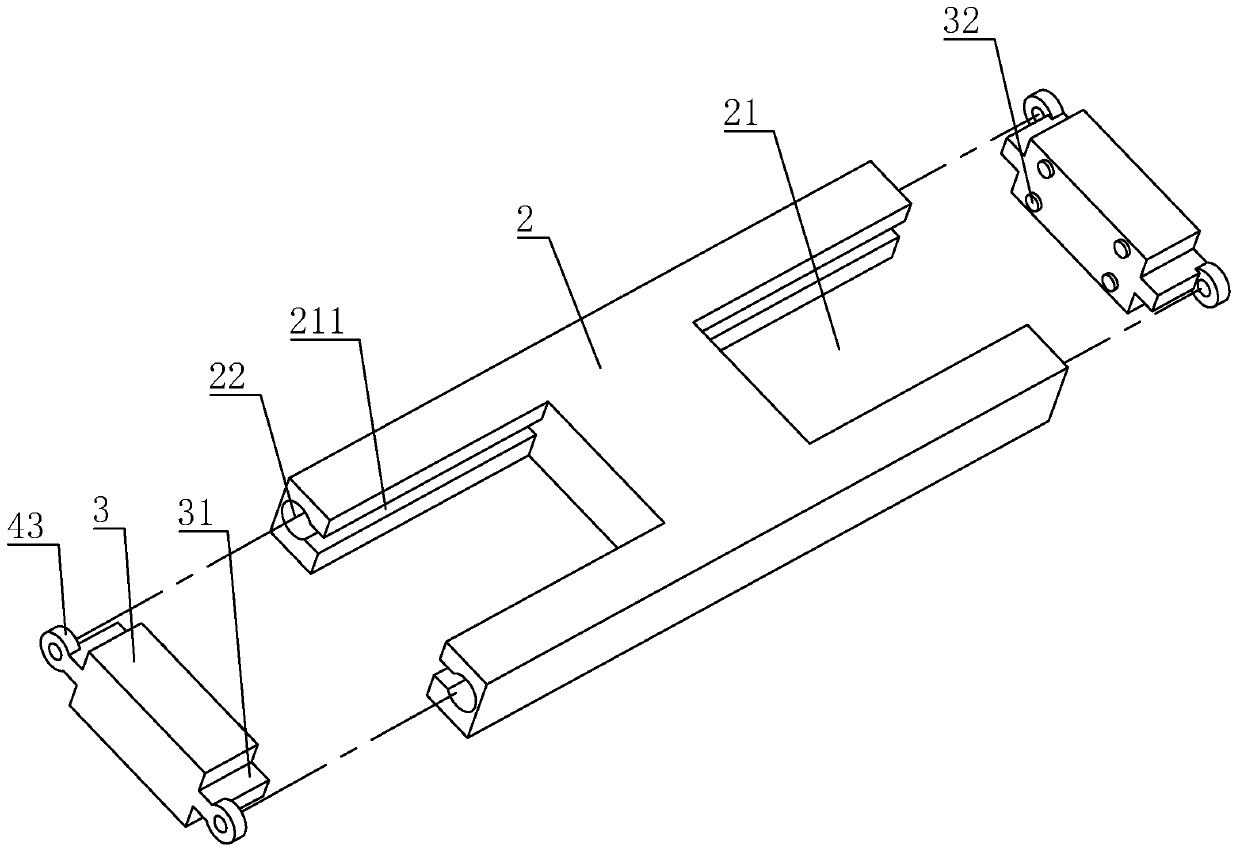

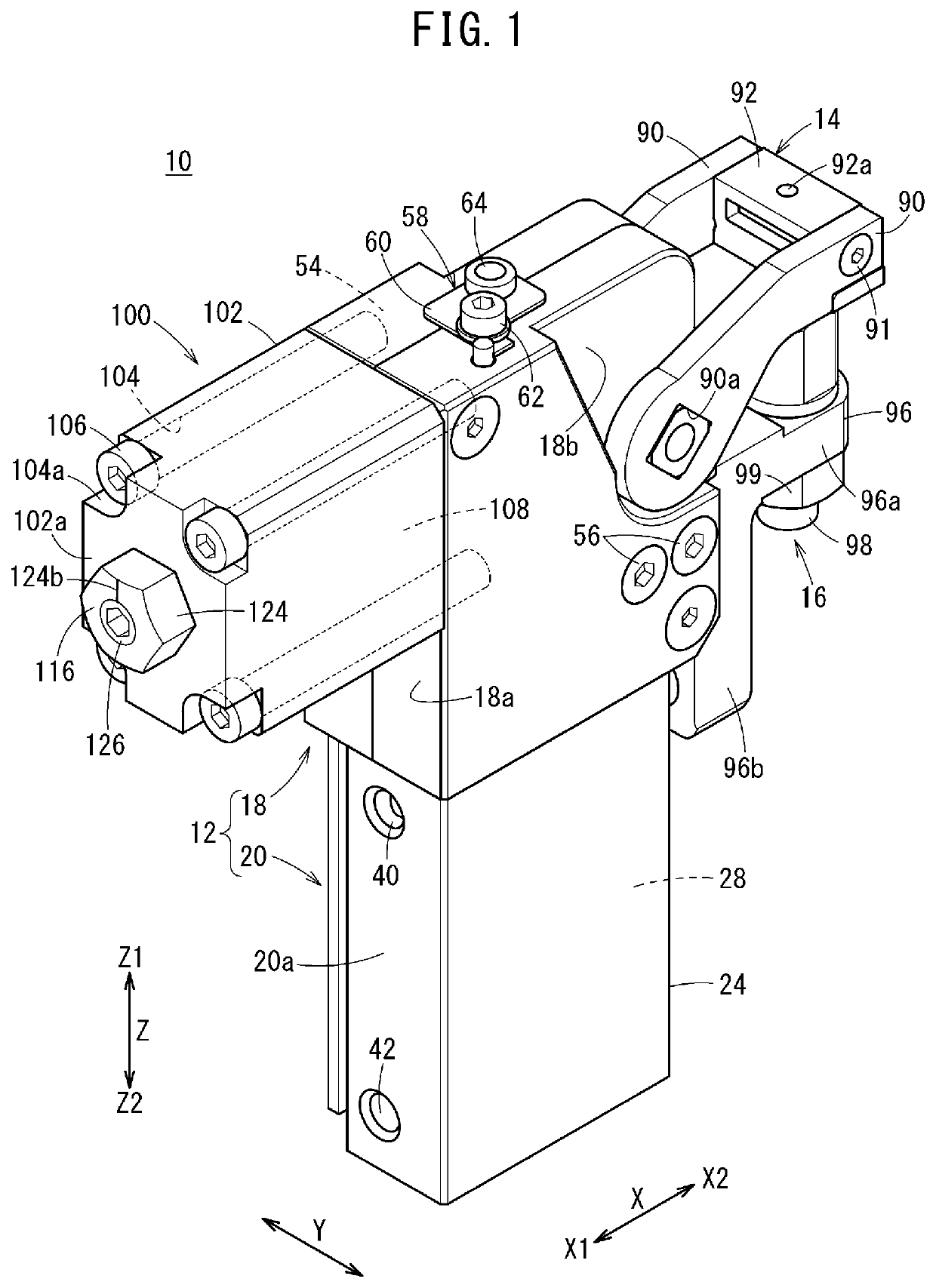

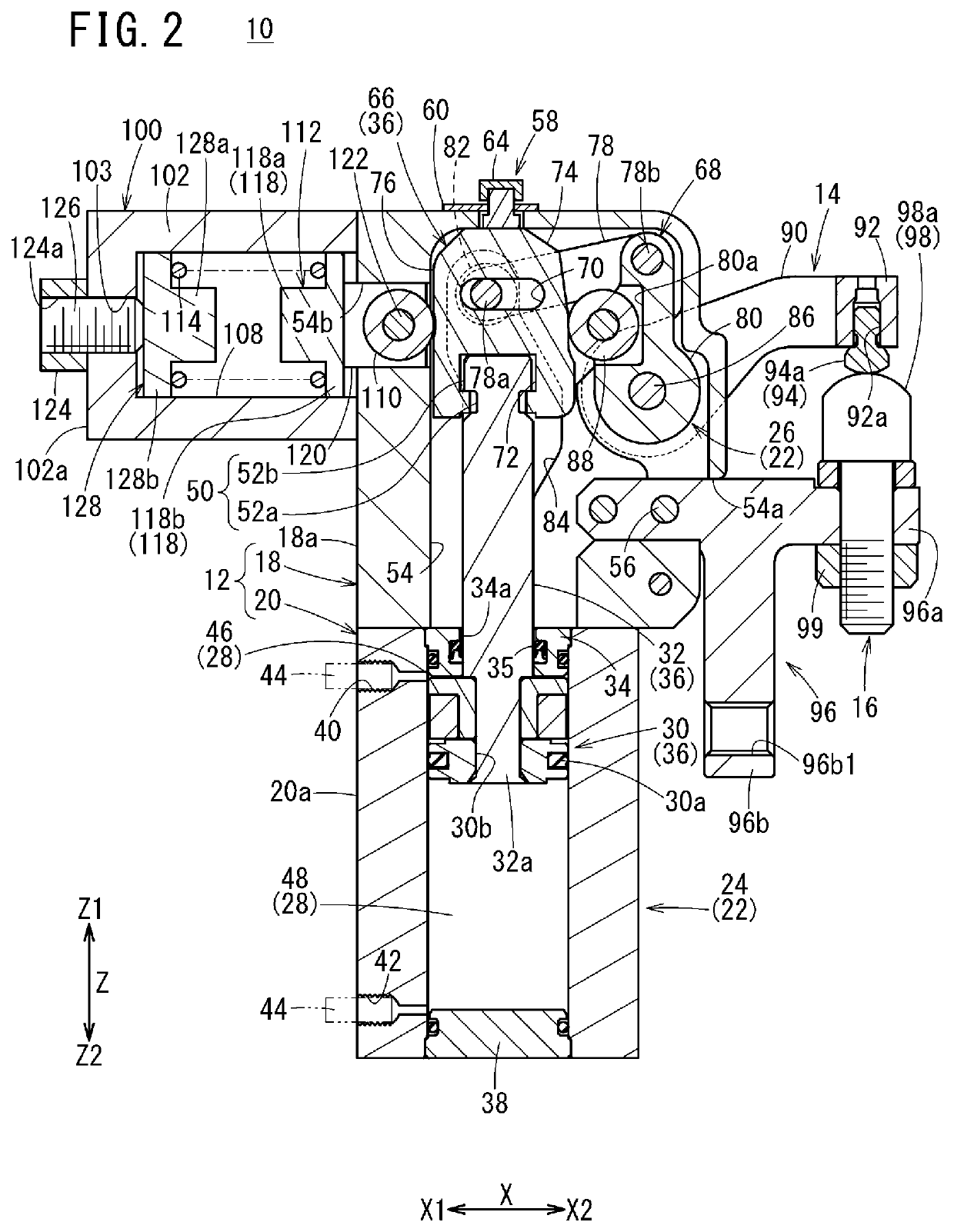

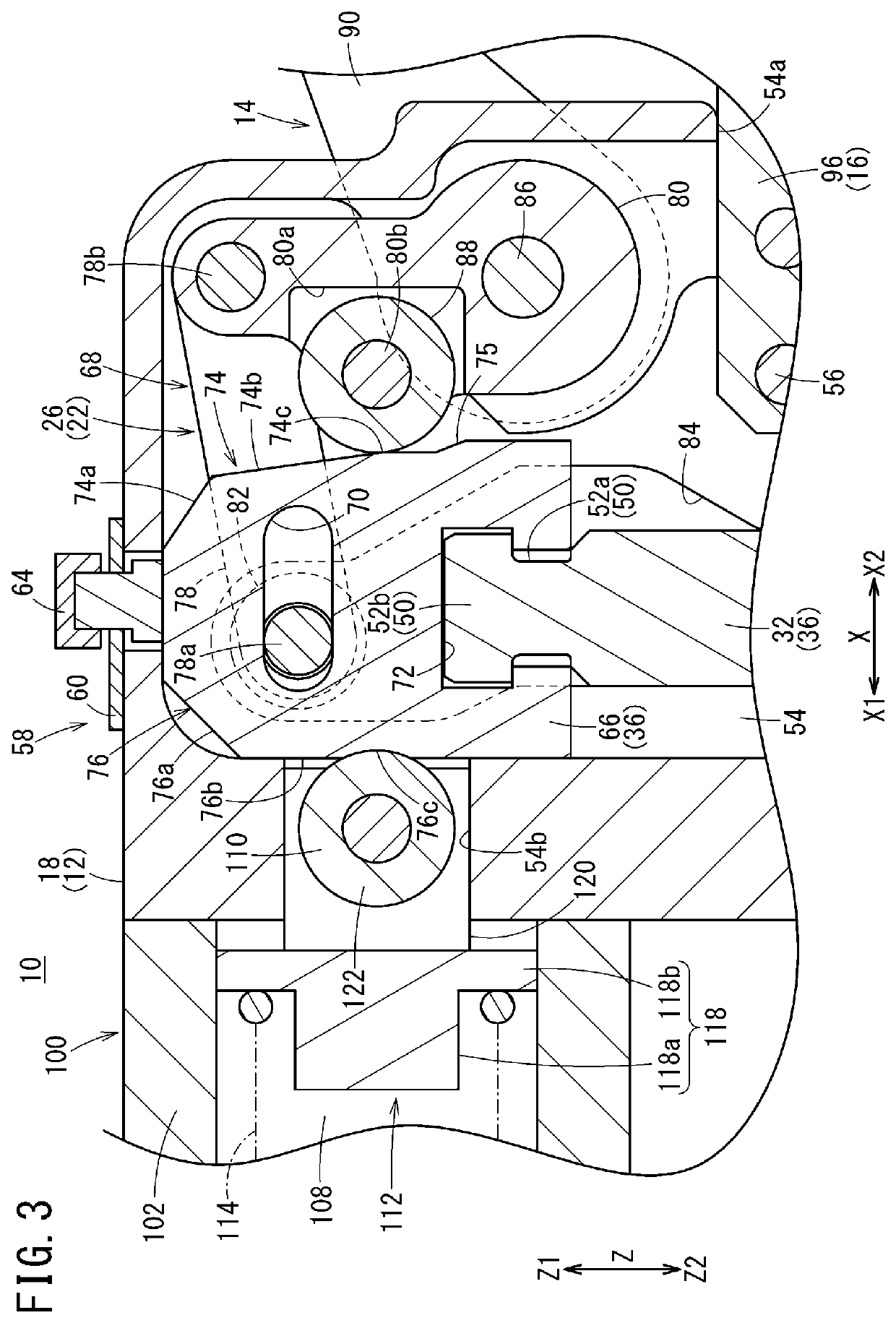

Lock mechanism for seat track slide device

ActiveUS8469328B2Improves unlocking prevention functionIncrease lock rangeVehicle seatsStands/trestlesLocking mechanismCoil spring

Owner:TOYOTA BODY SEIKO CO LTD

Lock mechanism for seat track slide device

ActiveUS20120132778A1Enlarge relative pivoting rangeImprove unlock prevention functionVehicle seatsStands/trestlesEngineeringCoil spring

A seat track slide device includes a pair of seat tracks. Each of the seat tracks has a lower rail, an upper rail, a lock lever, and a handle. Through manipulation of the handle, each seat track 3 is capable of switching the associated upper rail to a locking state and an unlocking state by selectively engaging and disengaging the lock lever with respect to the lower rail. Each lock lever is inserted into the corresponding upper rail and pivotally supported in the upper rail. An interlock support portion of the lock lever projects into an outer zone with respect to the front end of the upper rail. The interlock support portion of the lock lever supports an interlock support portion of the handle pivotally relative to each other. With the lock lever maintained in the locking state, the handle is allowed to pivot relative to the lock lever in the outer zone with respect to the front end of the upper rail against elastic force produced by a torsion coil spring arranged in the upper rail.

Owner:TOYOTA BODY SEIKO CO LTD

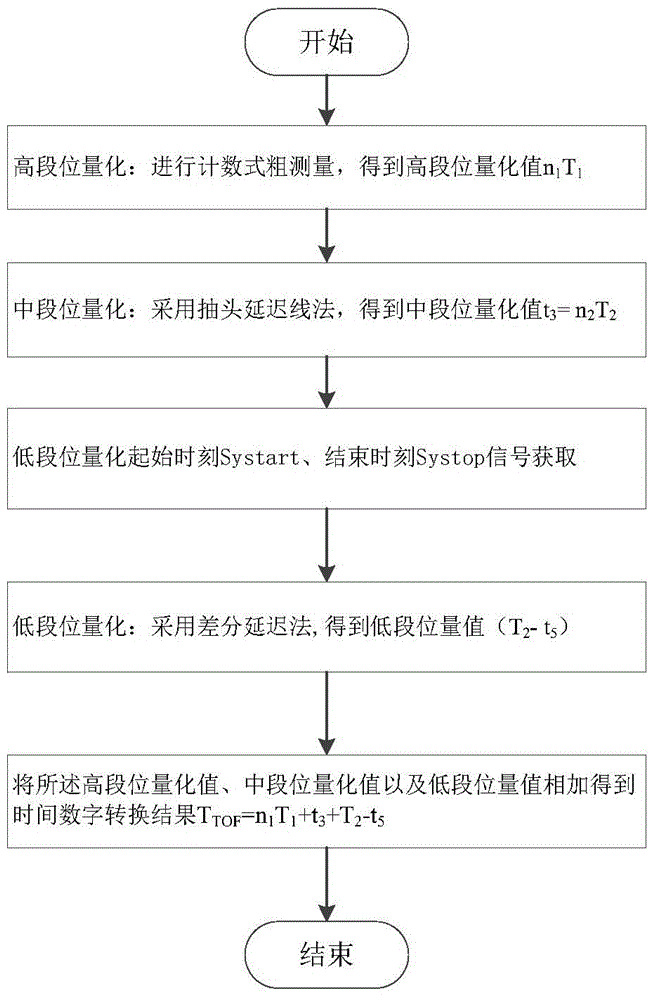

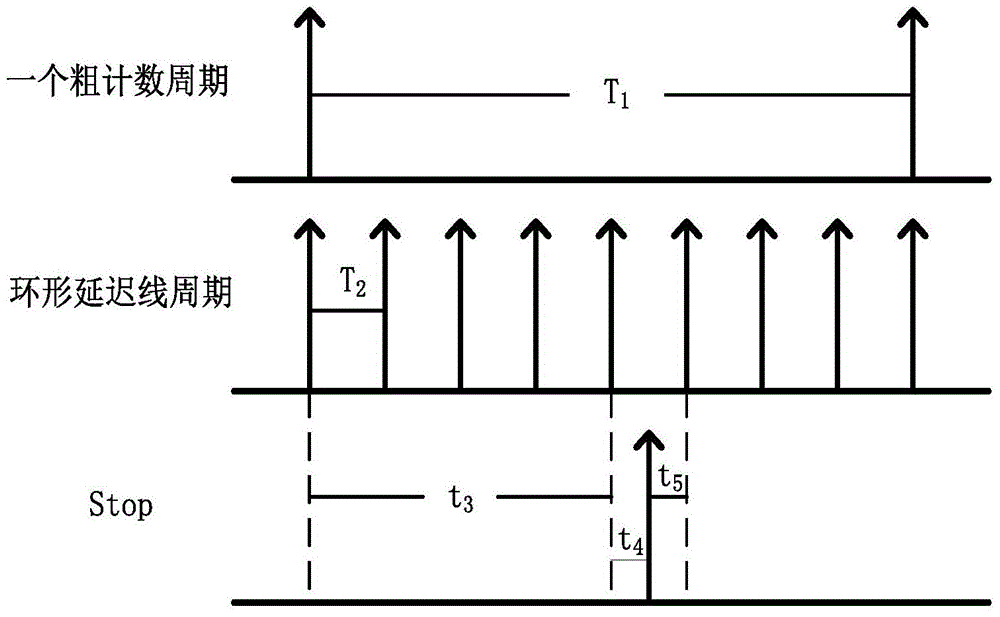

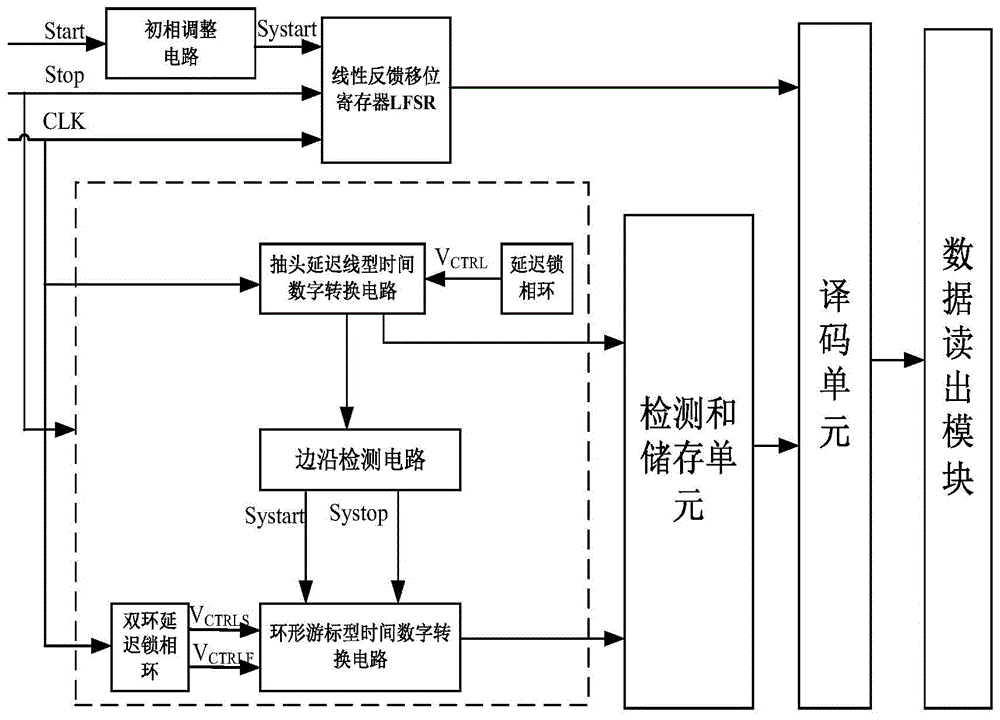

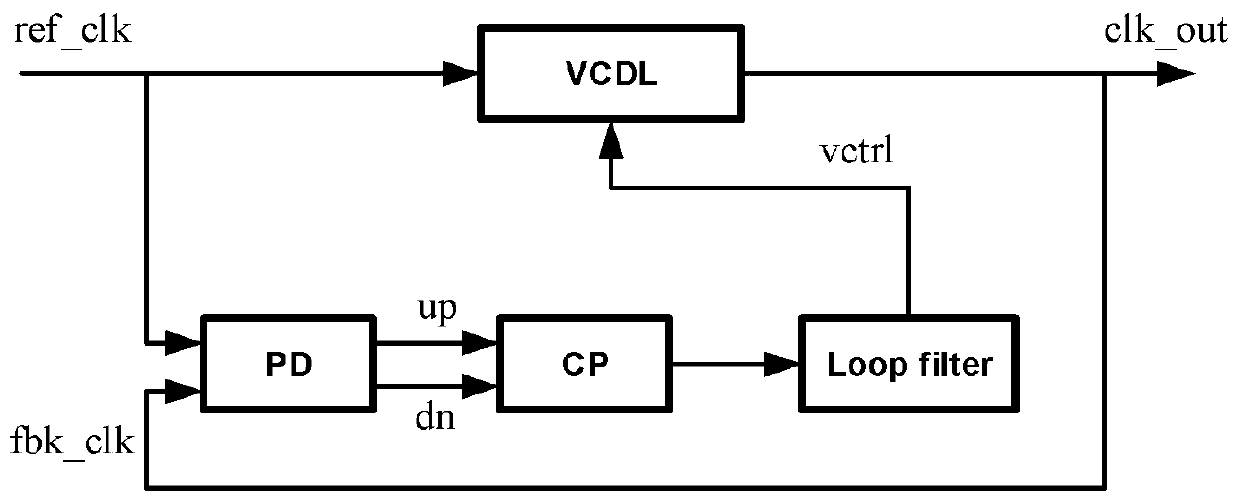

Dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit

InactiveCN104320130AHigh precision measurementImprove detection accuracyAnalogue/digital conversionElectric signal transmission systemsEngineeringVoltage control

The invention discloses a dual-loop DLL-based three-segment type high-precision time-to-digital conversion method and circuit. According to a measured time segment, a high-middle-low combined segmental type quantization method is adopted. A high-segment bit counting type quantizer in three-segment type TDC (time-to-digital conversion) is driven by a high-frequency stabilizing clock which is inputted from the outside, so that a wide-range stable distance measuring range can be realized; a middle-segment bit TDC is formed by a first DLL voltage controlled delay chain; high-segment bit subdivision can be realized through an asynchronous sampling mode, and repeatable uniform phase distinguishing can be accomplished in a stable clock period; a phase position at a termination time point is decoded, so that a middle-segment quantization function can be accomplished; and according to quantization errors generated by time-to-digital conversion in a middle-segment bit, error time is extracted, a low-segment bit accomplishes further quantization processing, and therefore, higher measurement precision can be realized.

Owner:SOUTHEAST UNIV

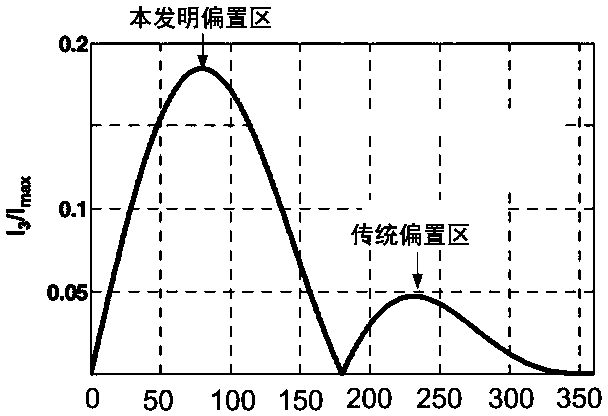

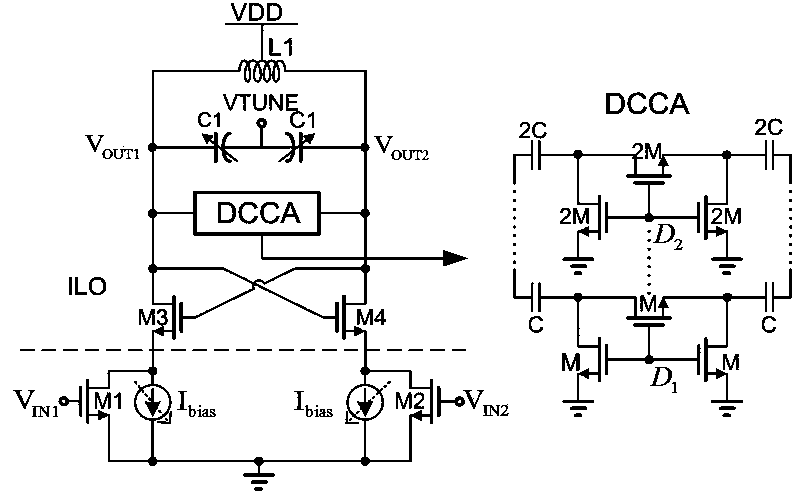

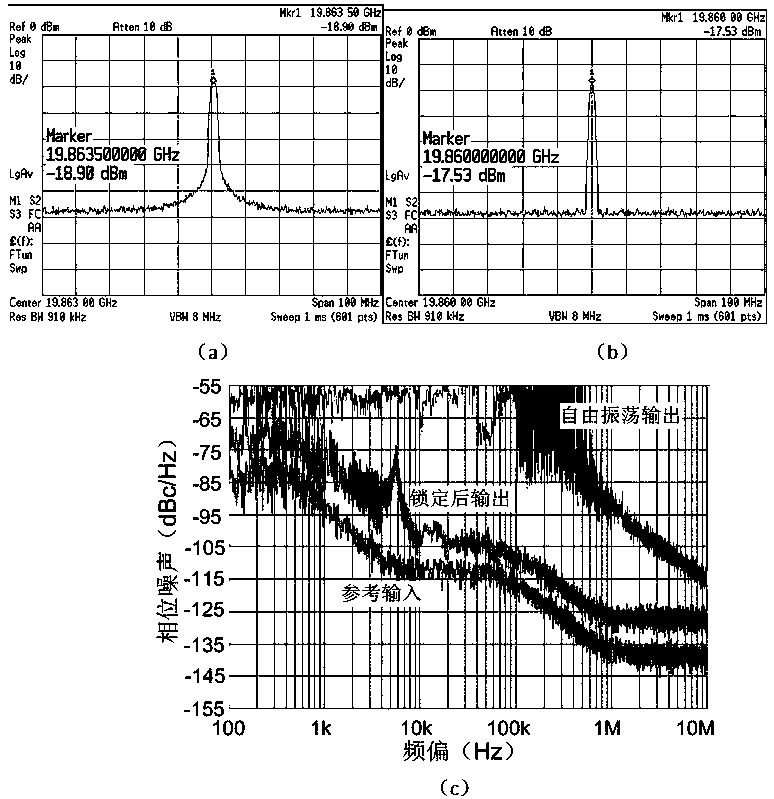

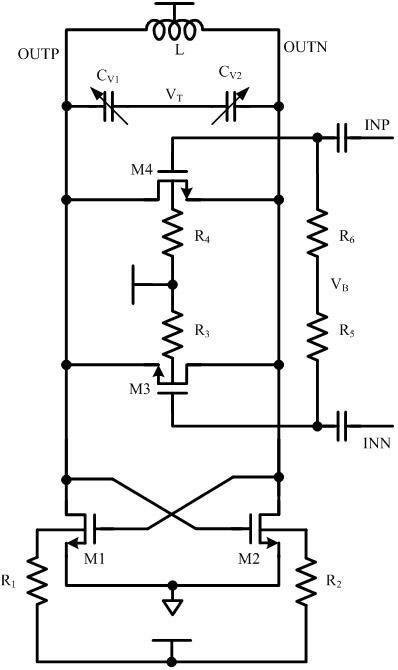

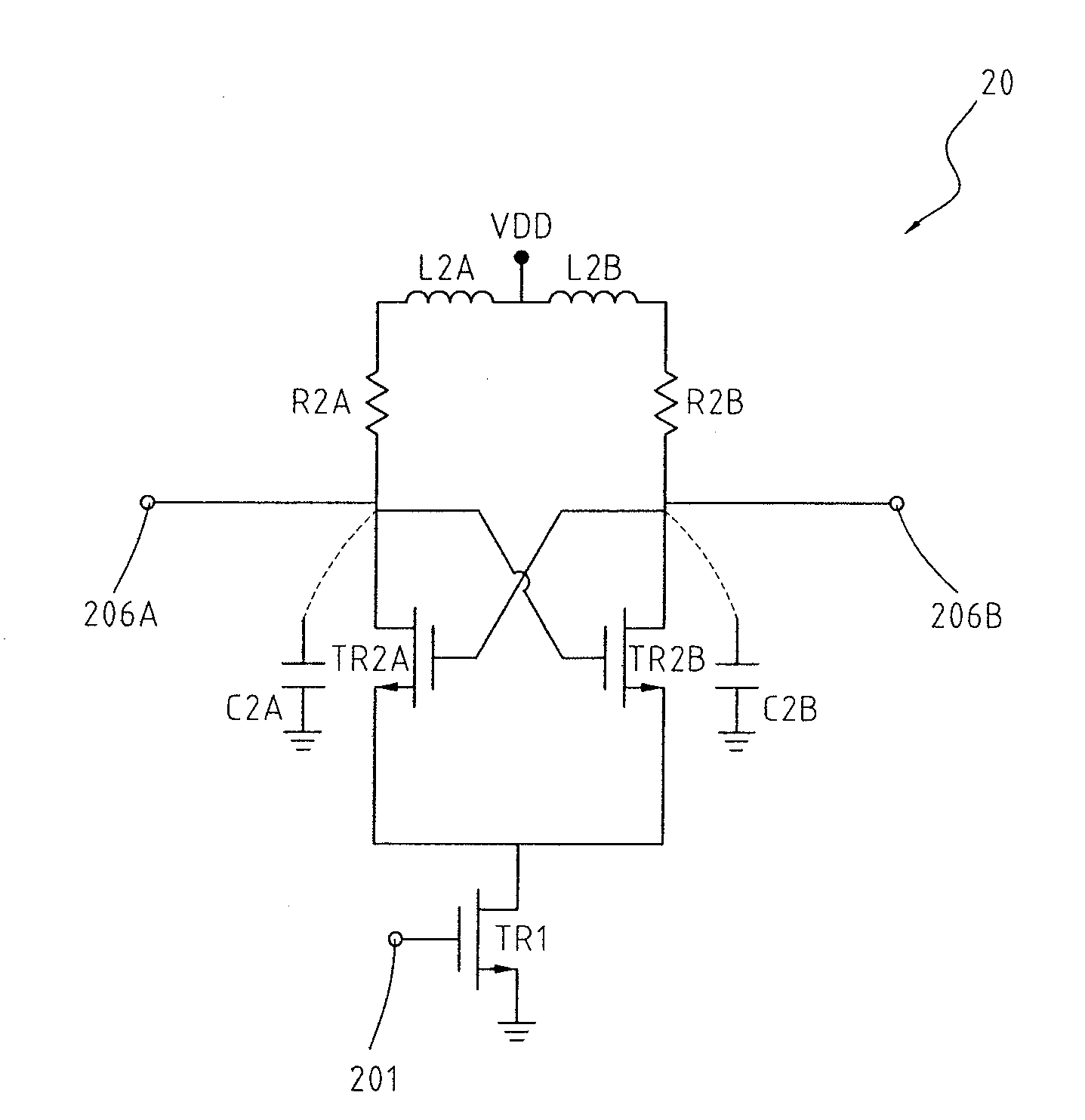

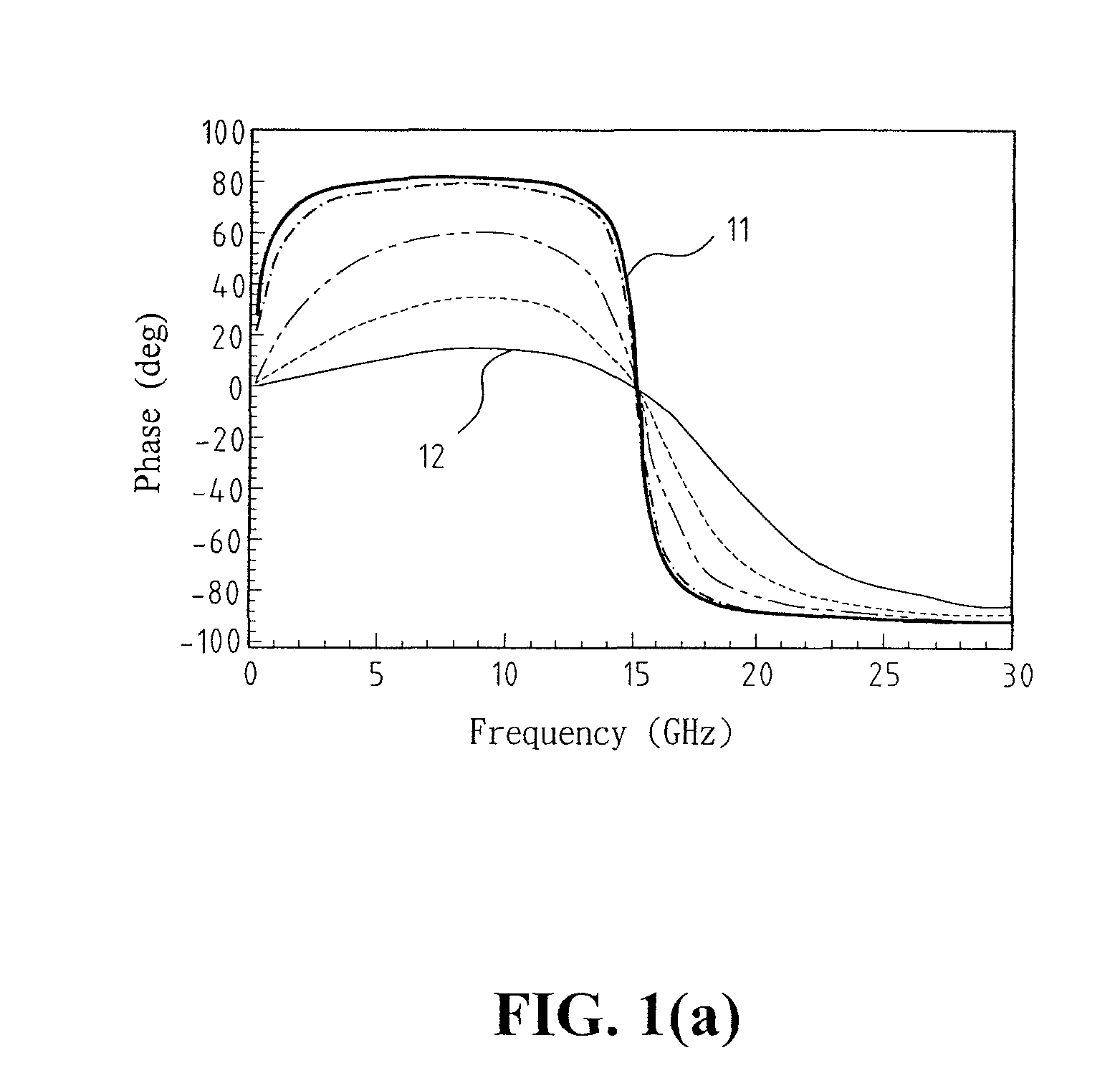

Low power consumption injection locked frequency tripler

InactiveCN103475310AIncrease the output frequency lock rangeReduced DC power consumptionOscillations generatorsPhysicsIntegrated circuit

The invention belongs to the technical field of integrated circuits of radiofrequency frequency synthesizers, and particularly relates to a low power consumption injection locked frequency tripler. A circuit comprises a harmonic wave generator and an injection locked oscillator. The harmonic wave generator is formed by a pair of NMOS tubes and is arranged in a weak inversion area in a bias mode, and triple frequency harmonic signals 3f0 with the maximum efficiency are generated by inputting fundamental frequency signals f0. The injection locked oscillator is composed of a pair of cross-coupled transistors, an inductor, a variable capacitor, a digital control capacitor array and an adjustable current source, and the working frequency of the injection locked oscillator is near the 3f0. In a free oscillation mode, the grid electrodes of the NMOS tubes have no input signals, bias currents of the injection locked oscillator are supplied by the adjustable current source, and self-oscillation frequency is output; in an injection locked mode, the grid electrodes of the NMOS tubes have fundamental frequency signals with frequency near the f0, an injection locked frequency tripler circuit is made to be locked at the frequency 3 f0, and the power consumption of the direct currents at the moment is extremely low. The power source voltages of the circuit are 0.8V, and the power consumption of the direct currents is only 0.16mW.

Owner:FUDAN UNIV

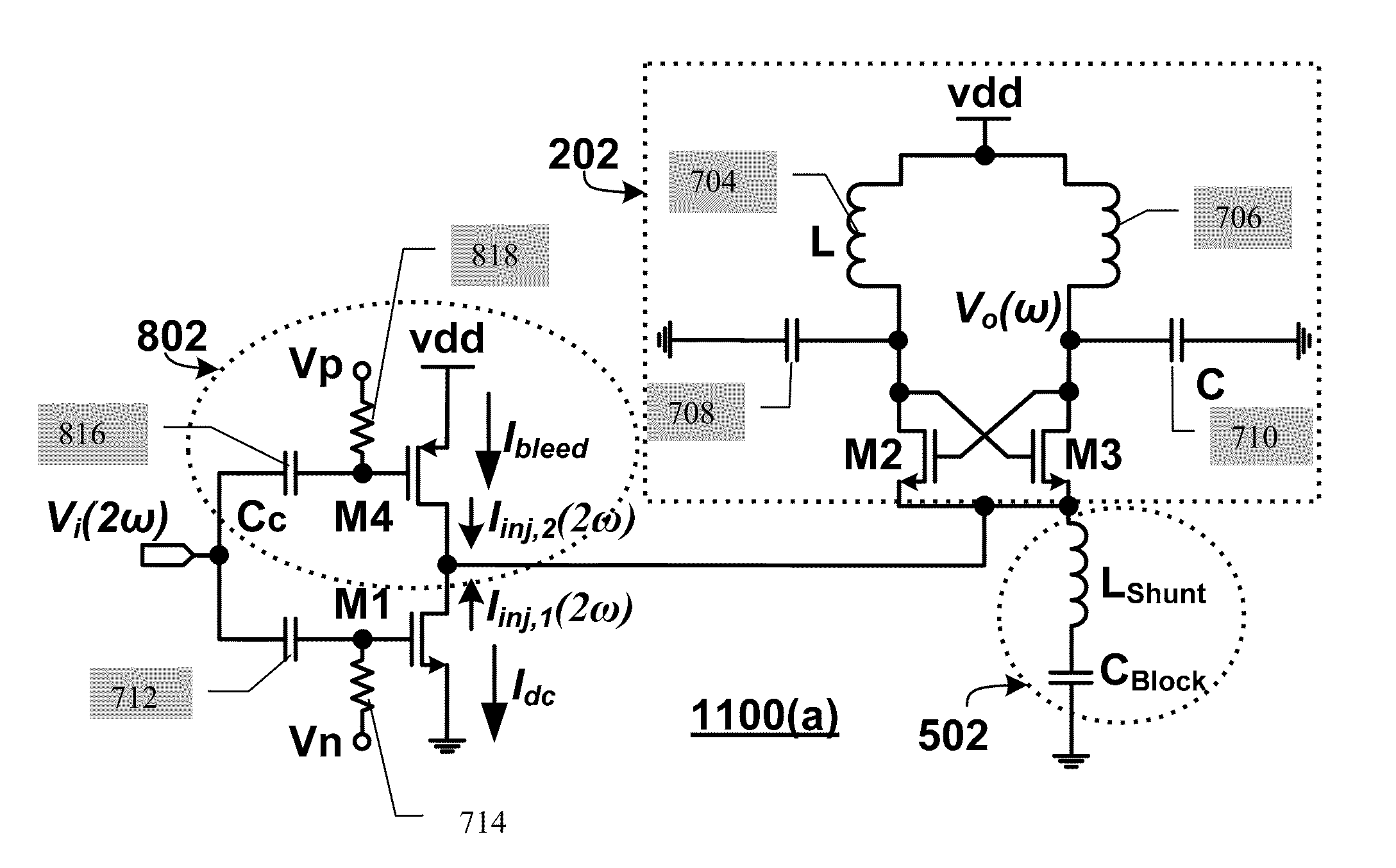

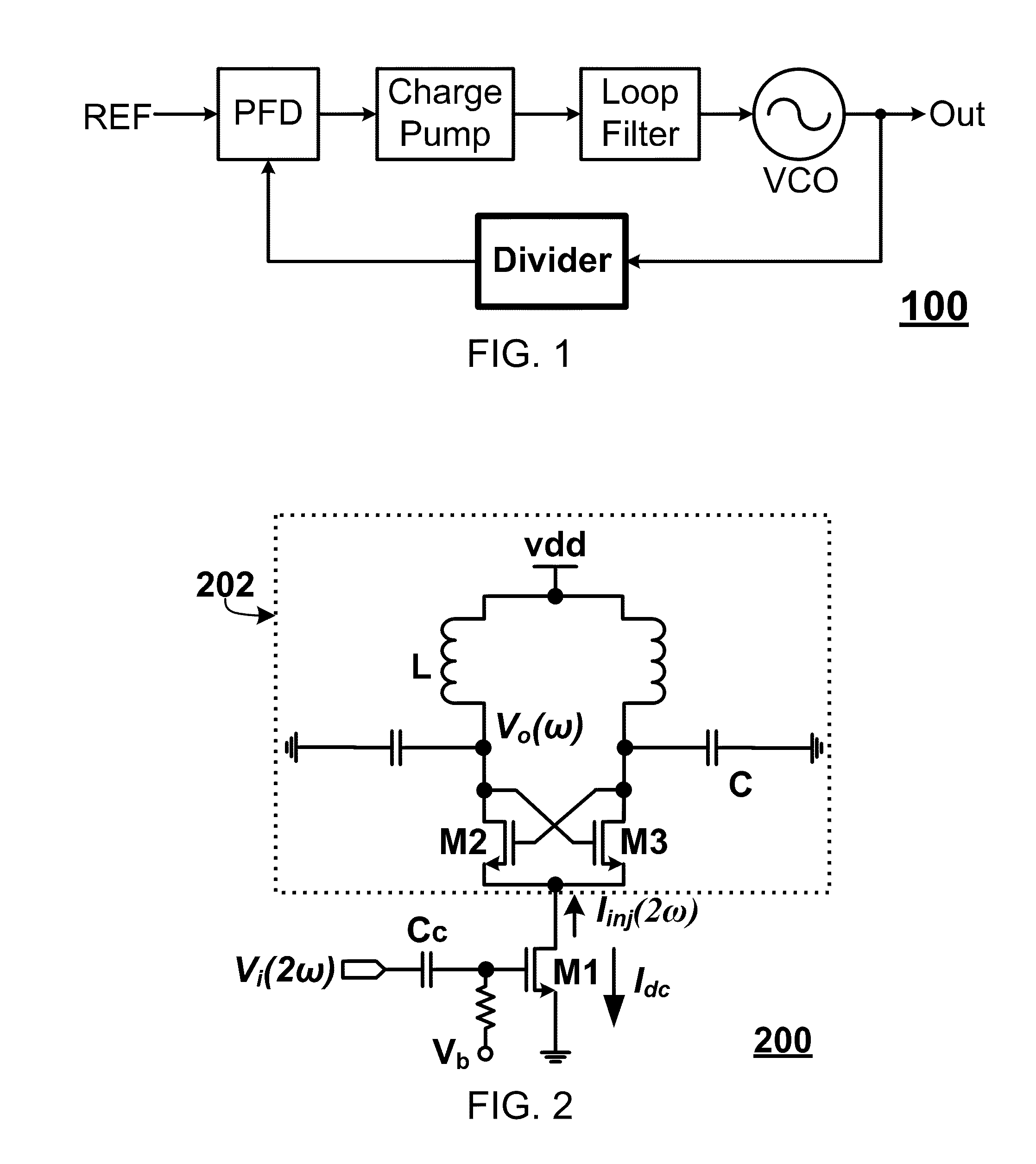

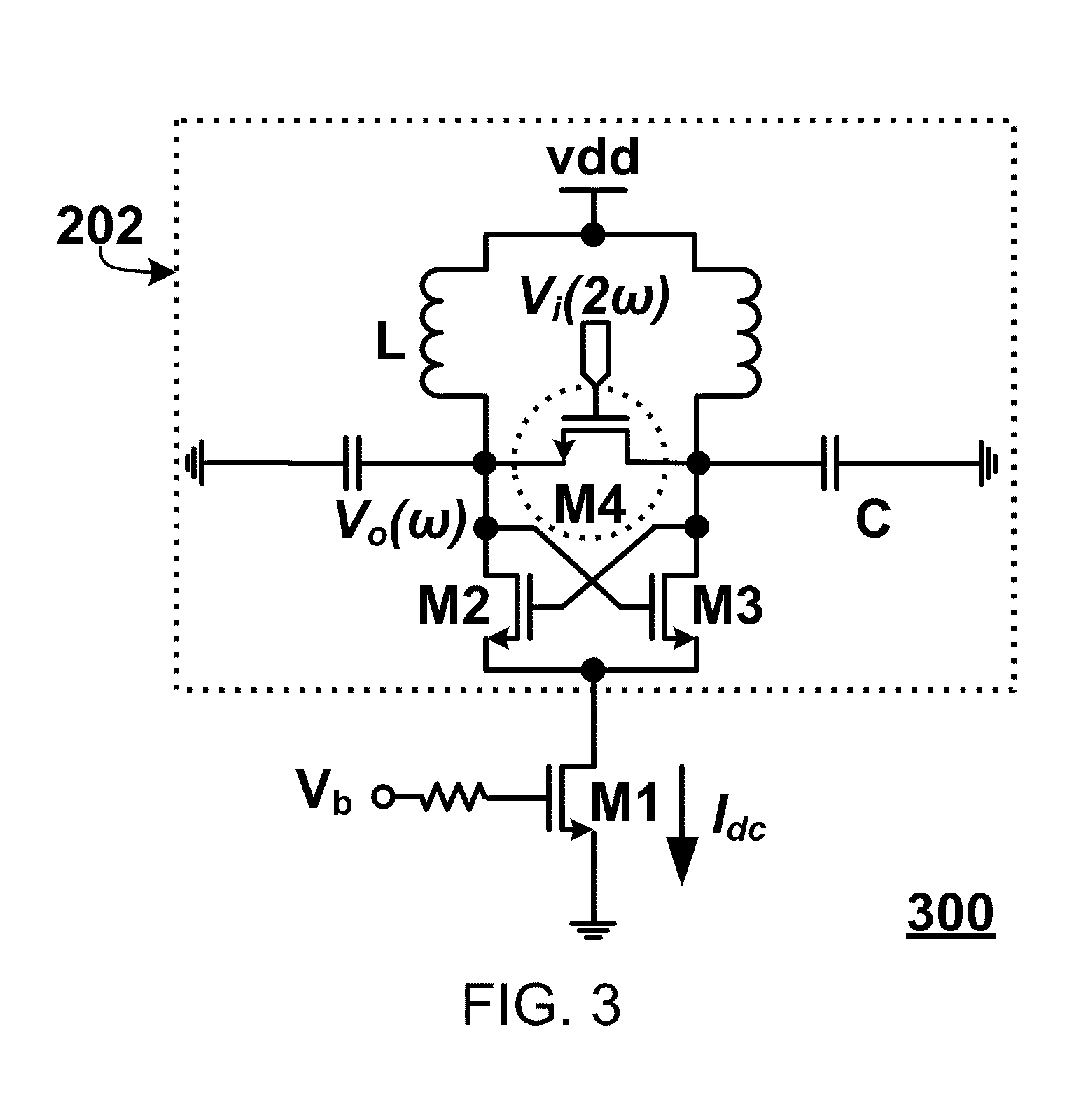

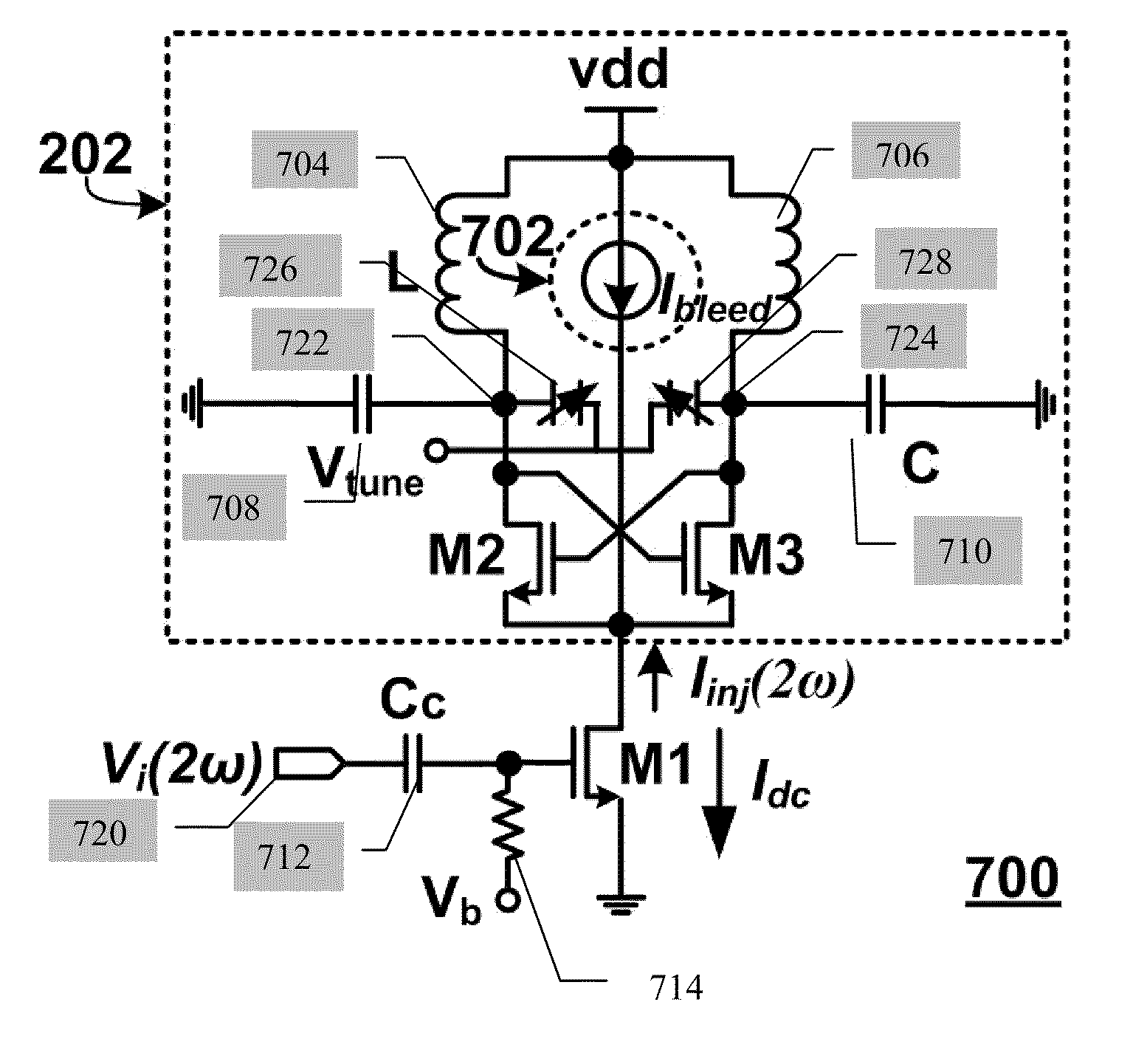

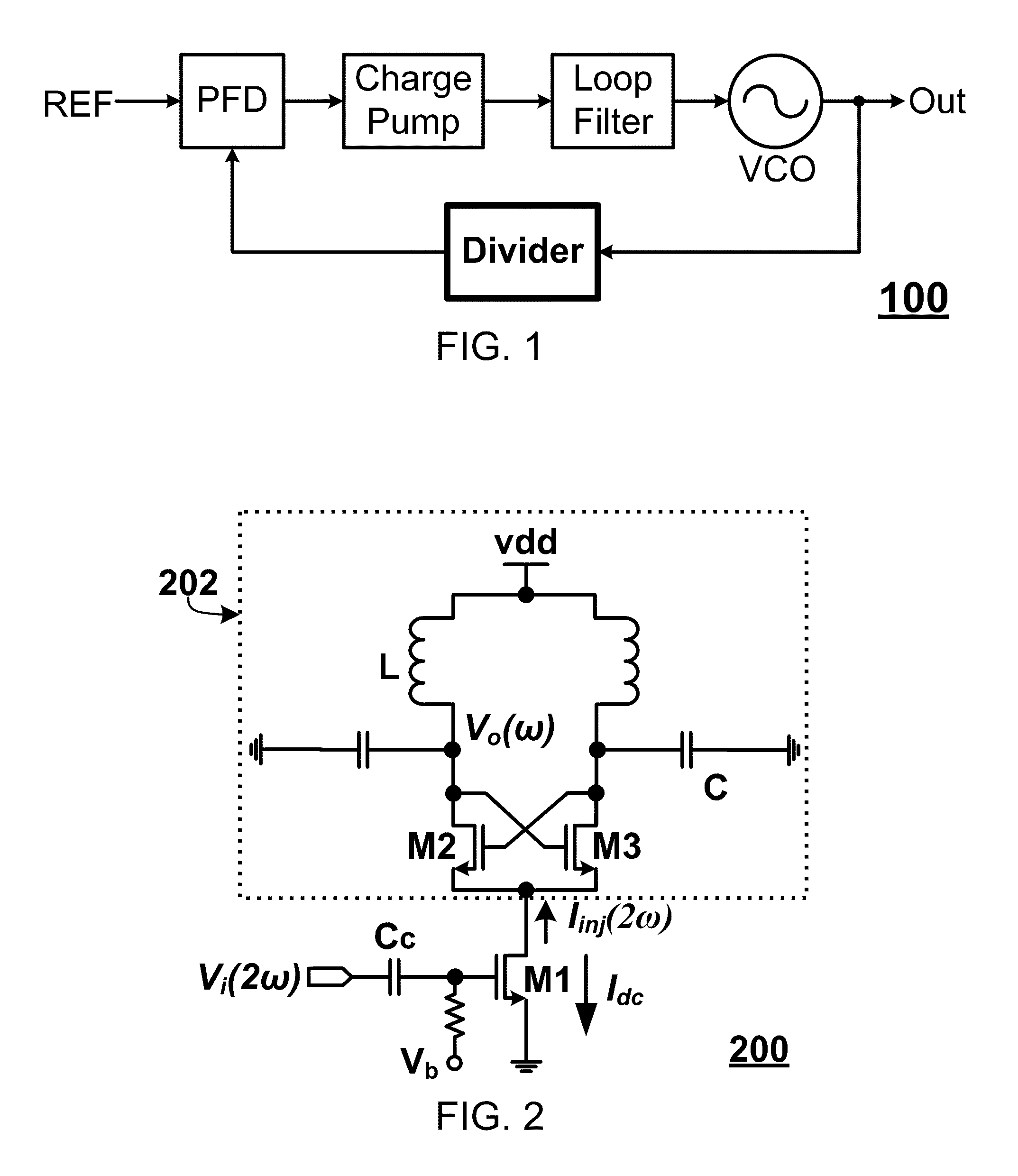

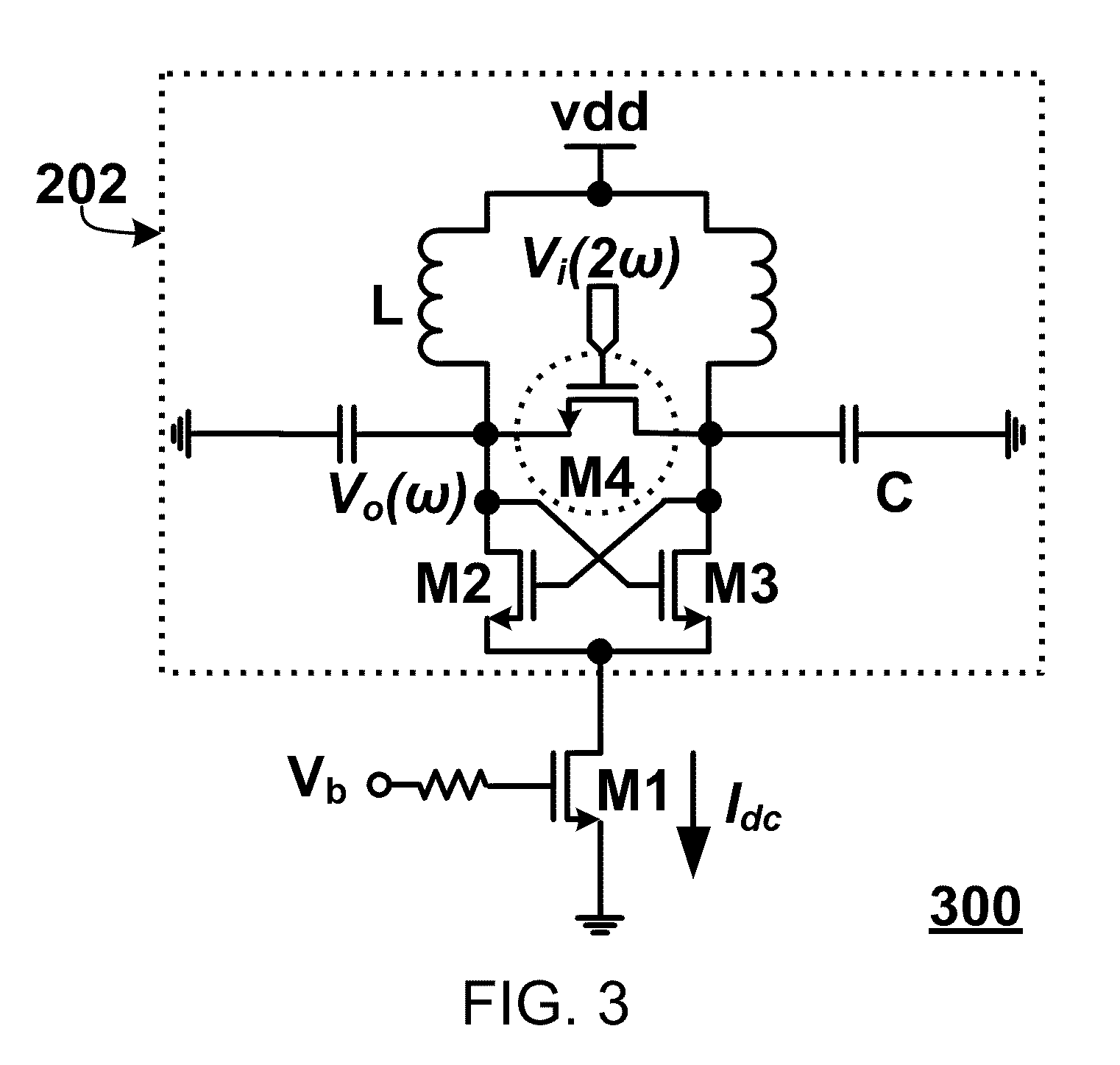

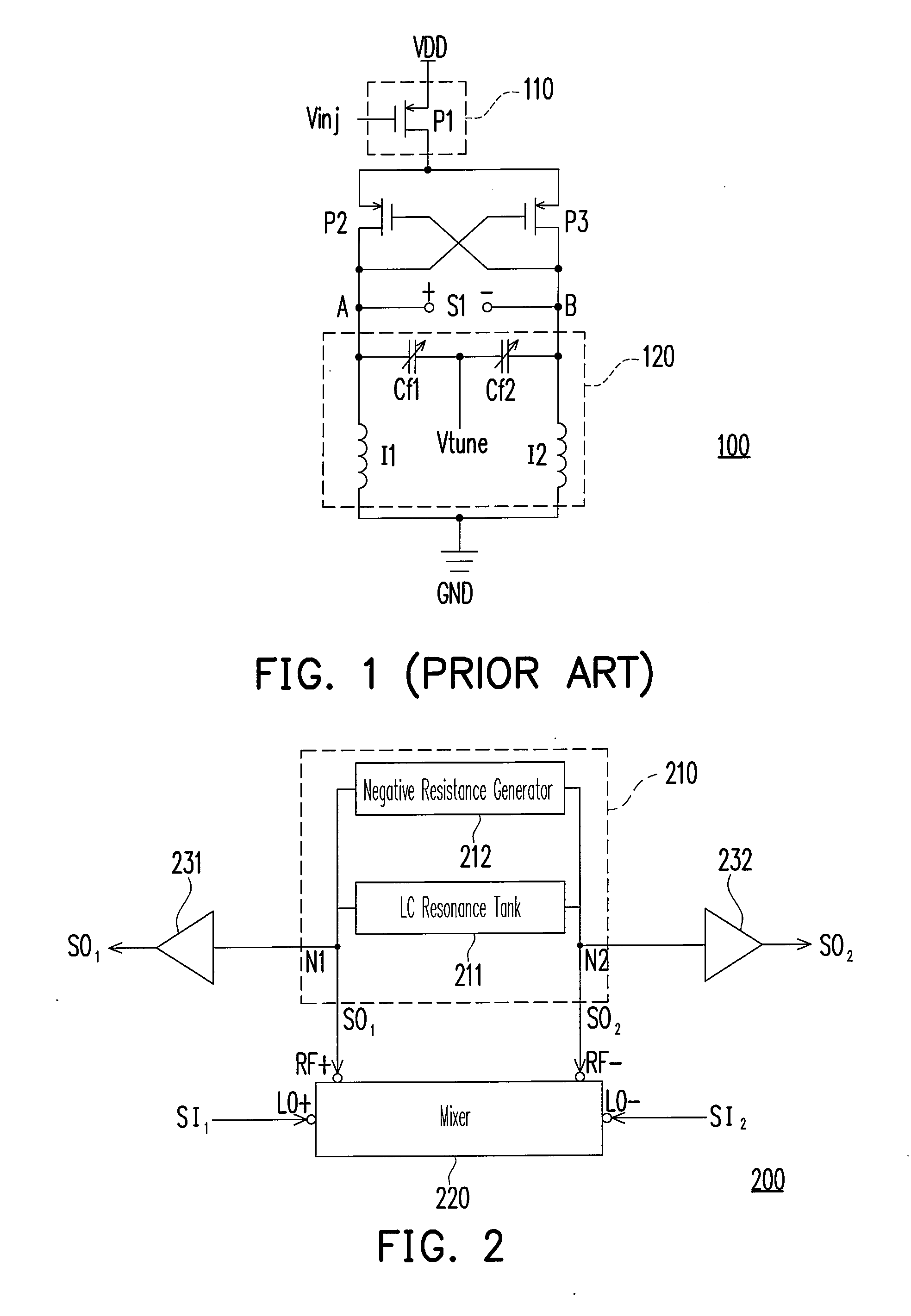

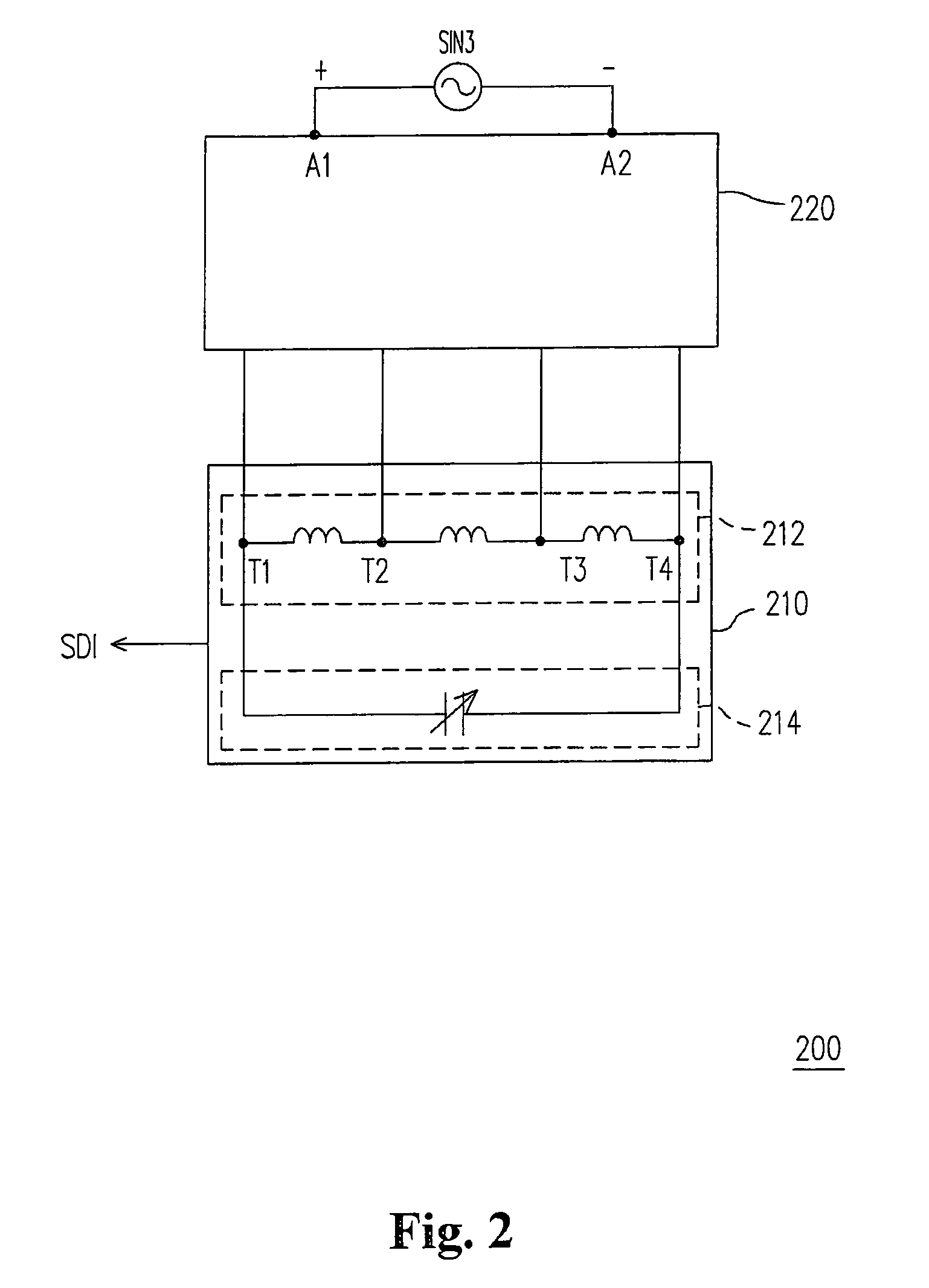

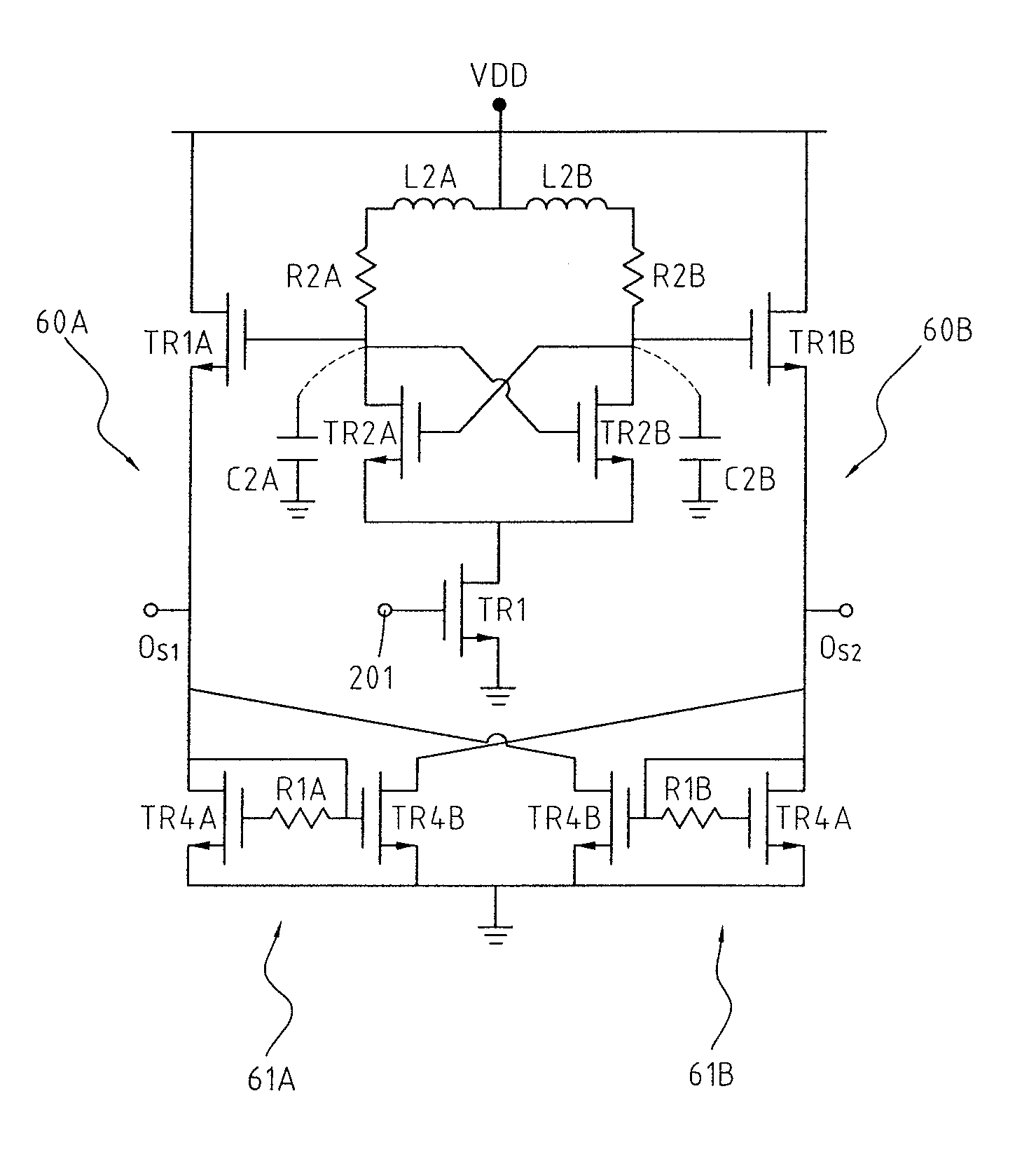

Frequency divider using an injection-locking-range enhancement technique

InactiveUS20100301955A1Increase lock rangePulse automatic controlElectric pulse generatorInjection lockedDc current

A locking range enhancement technique is described that steers away part of the DC current and reuses it to generate more injected AC current to the injection-locked resonator-based frequency dividers (ILFDs). The injection-enhanced ILFDs maintain the key features of ILFDs, which are high speed and low power consumption, without requiring any extra inductive component and thus extra chip area.

Owner:THE HONG KONG UNIV OF SCI & TECH

Frequency divider using an injection-locking-range enhancement technique

InactiveUS7961058B2Increase lock rangePulse automatic controlElectric pulse generatorInjection lockedPower flow

A locking range enhancement technique is described that steers away part of the DC current and reuses it to generate more injected AC current to the injection-locked resonator-based frequency dividers (ILFDs). The injection-enhanced ILFDs maintain the key features of ILFDs, which are high speed and low power consumption, without requiring any extra inductive component and thus extra chip area.

Owner:THE HONG KONG UNIV OF SCI & TECH

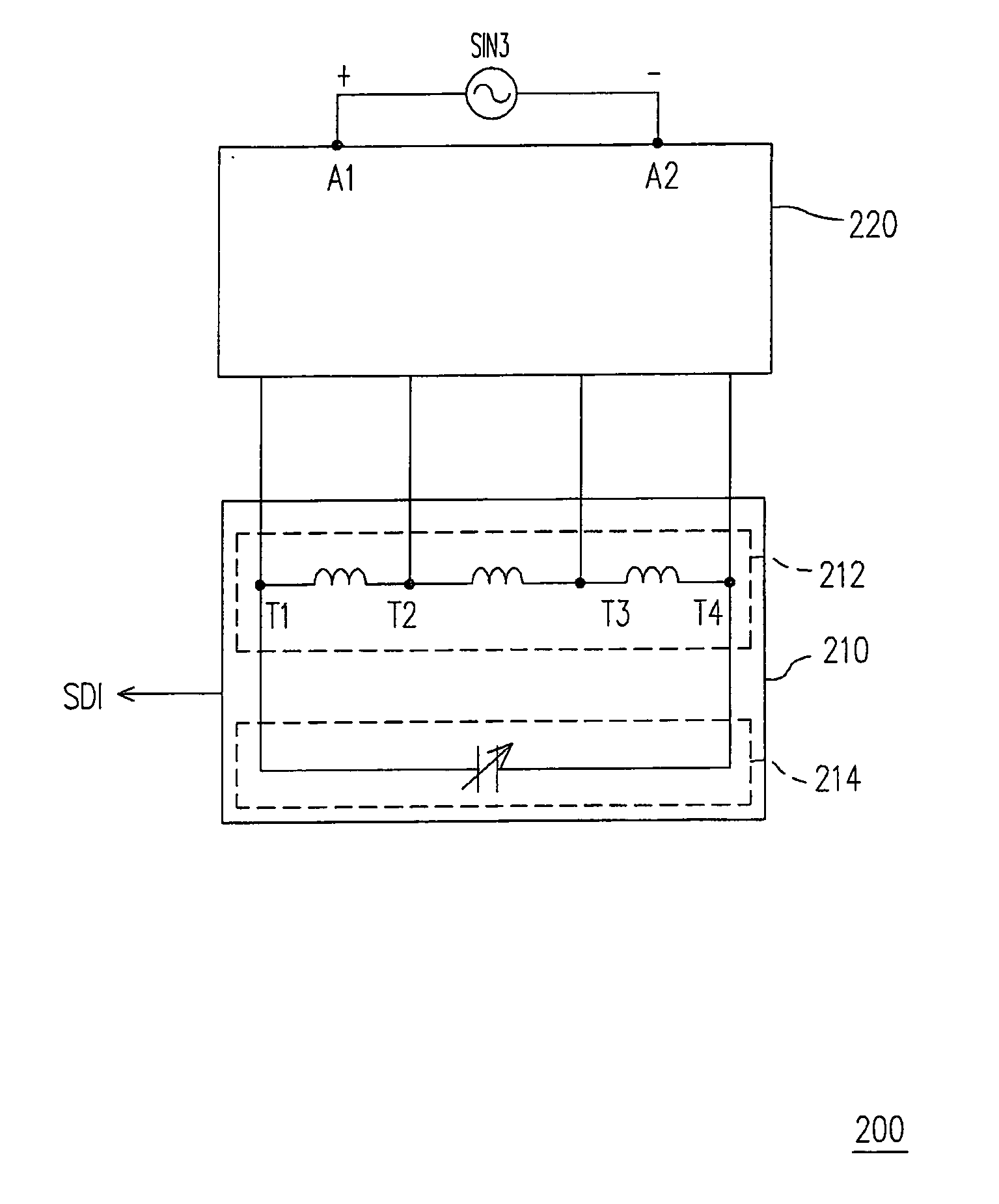

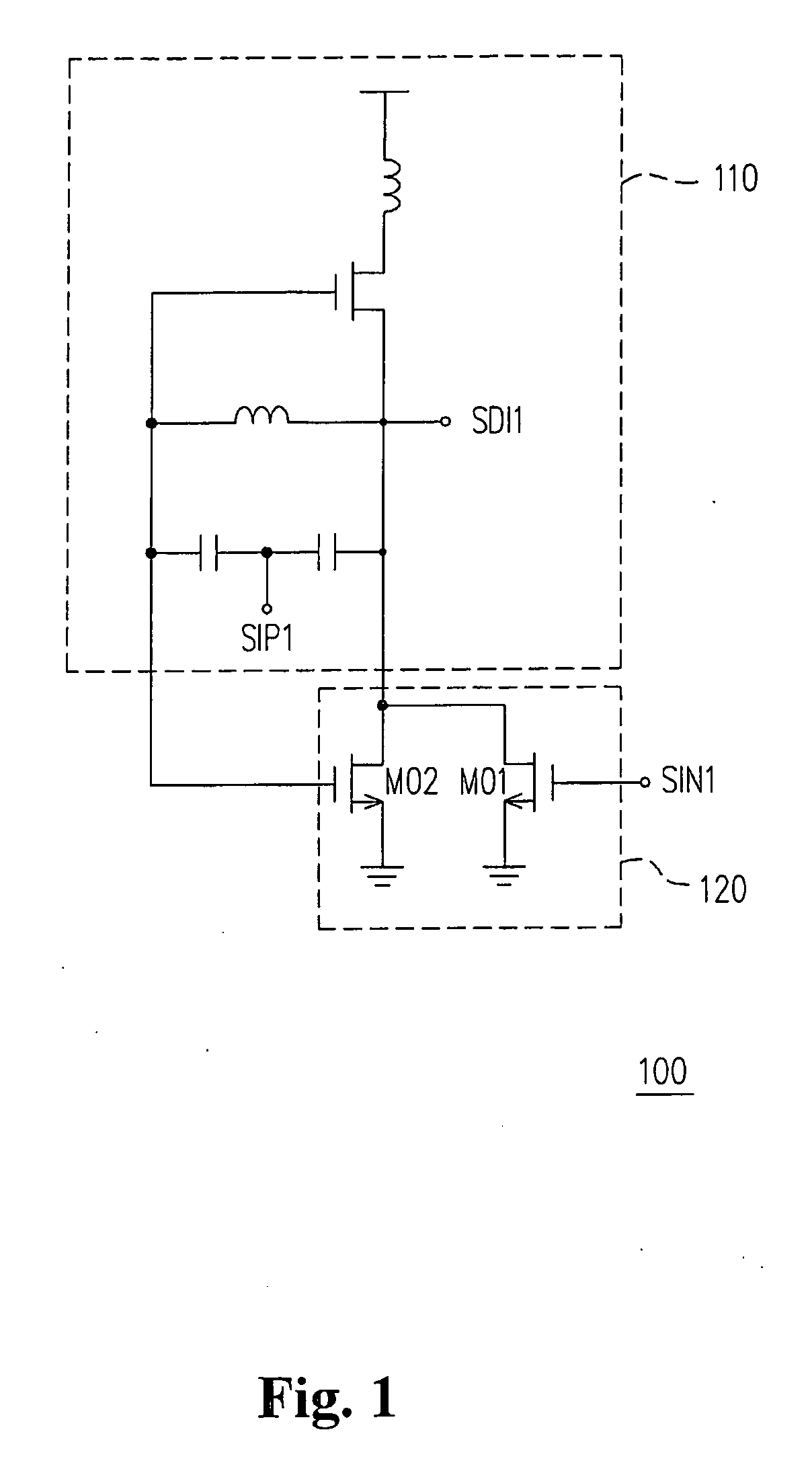

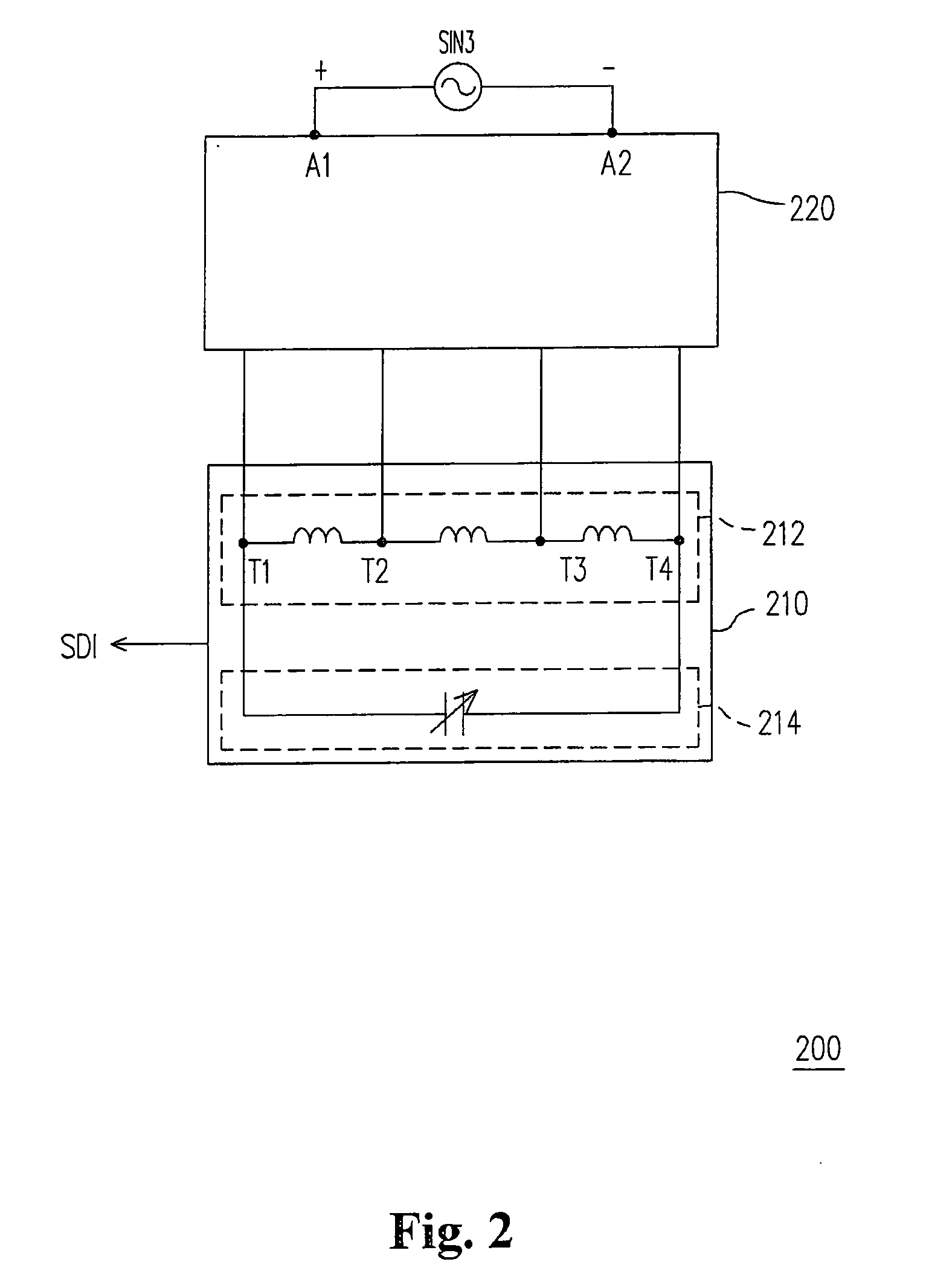

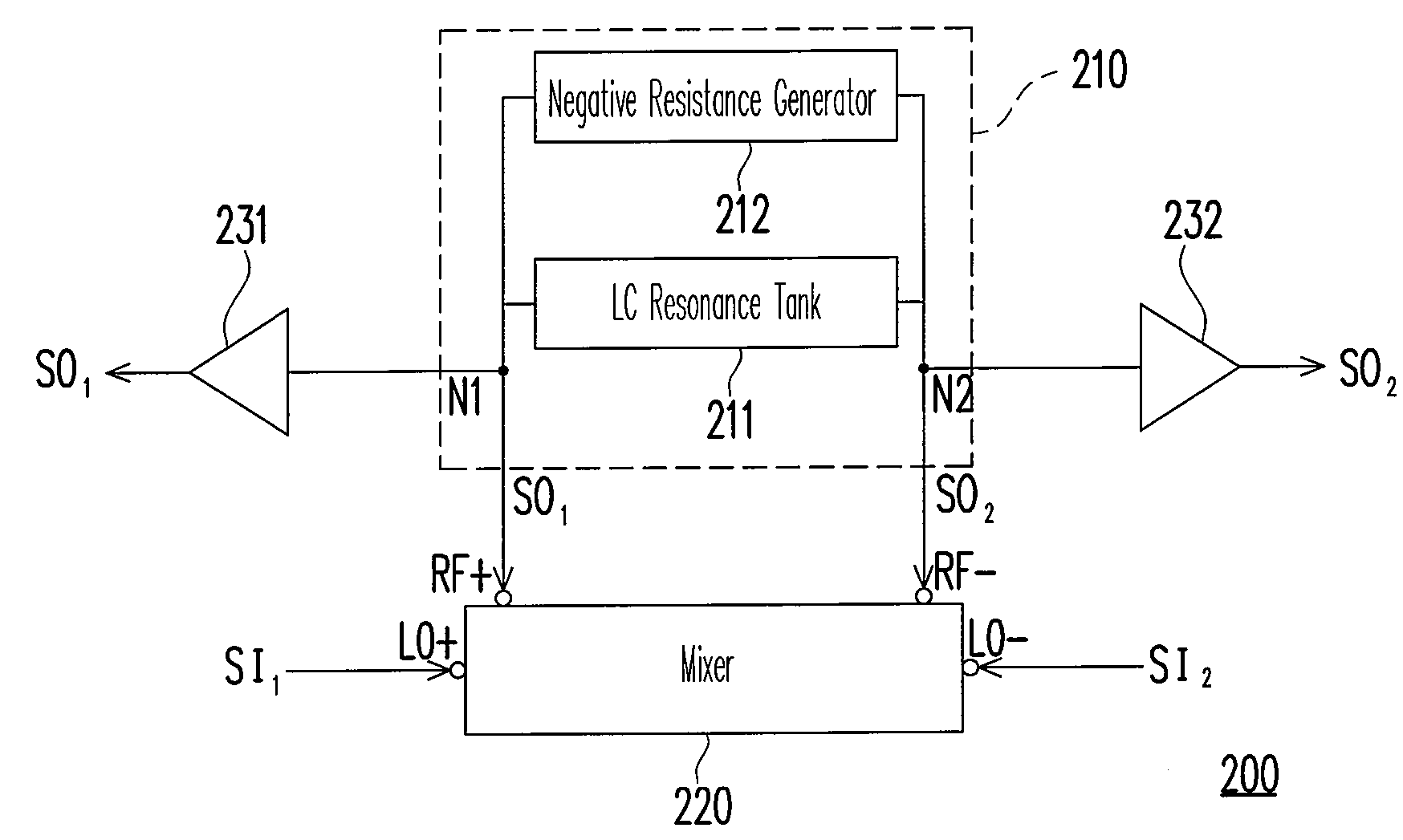

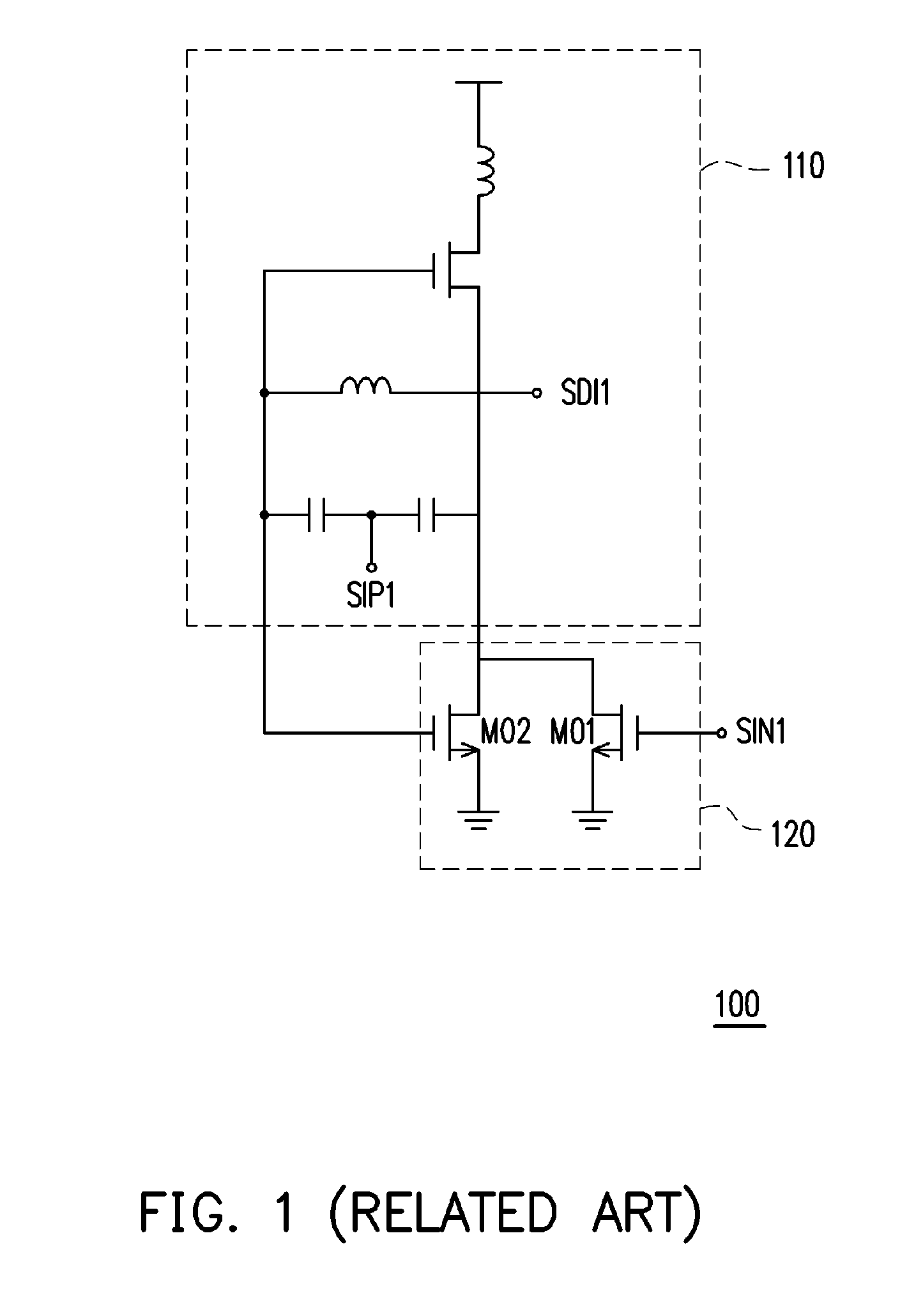

Injection-locked frequency divider

InactiveUS20090251177A1Low working voltageEasy to useOscillations generatorsInjection lockedCapacitance

An injection-locked frequency divider for dividing a frequency of an injection signal and obtaining a frequency divided signal is provided. The injection-locked frequency divider includes a signal injection unit and an oscillator. The signal injection unit includes a first input terminal and a second input terminal for receiving the injection signal. The received injection signal exhibits a phase difference of 180° between the first input terminal and the second input terminal. The oscillator includes an inductor unit and a variable capacitance unit. The injection-locked frequency divider is featured with a wide injection locking range, and can be realized with a low operation voltage, and therefore can be conveniently used in different kinds of hybrid ICs.

Owner:NAT TAIWAN UNIV OF SCI & TECH

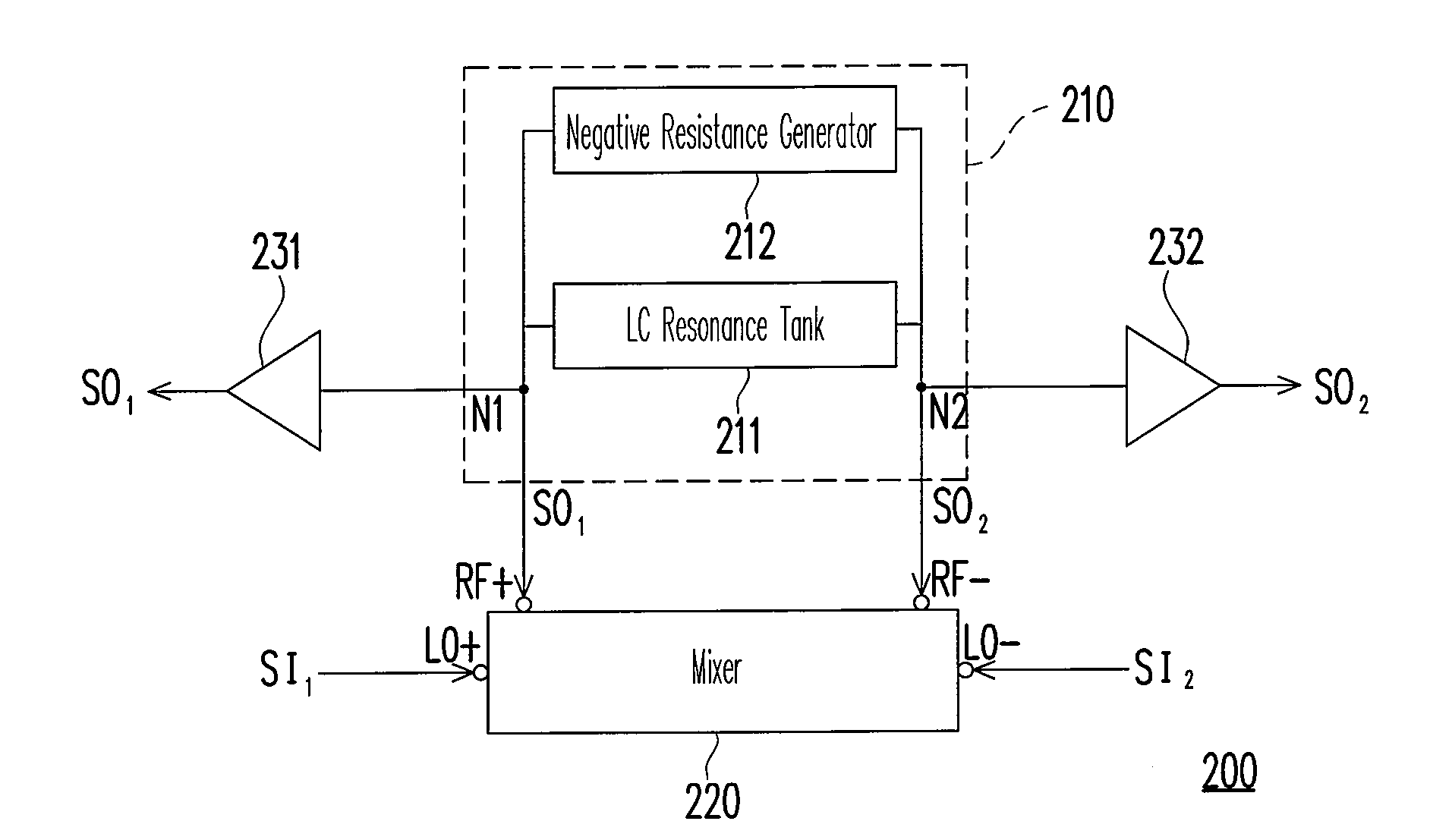

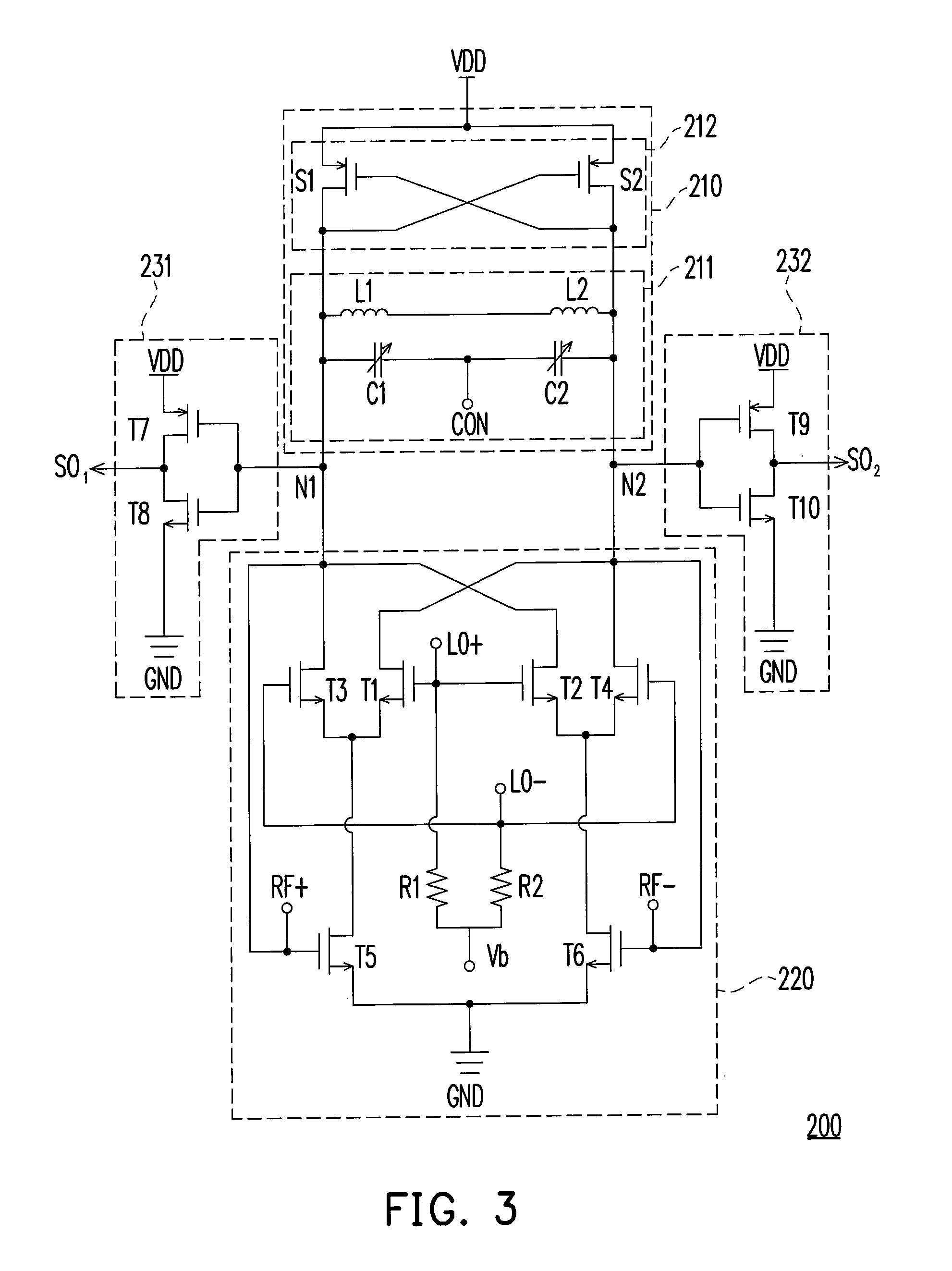

Injection-locked frequency divider

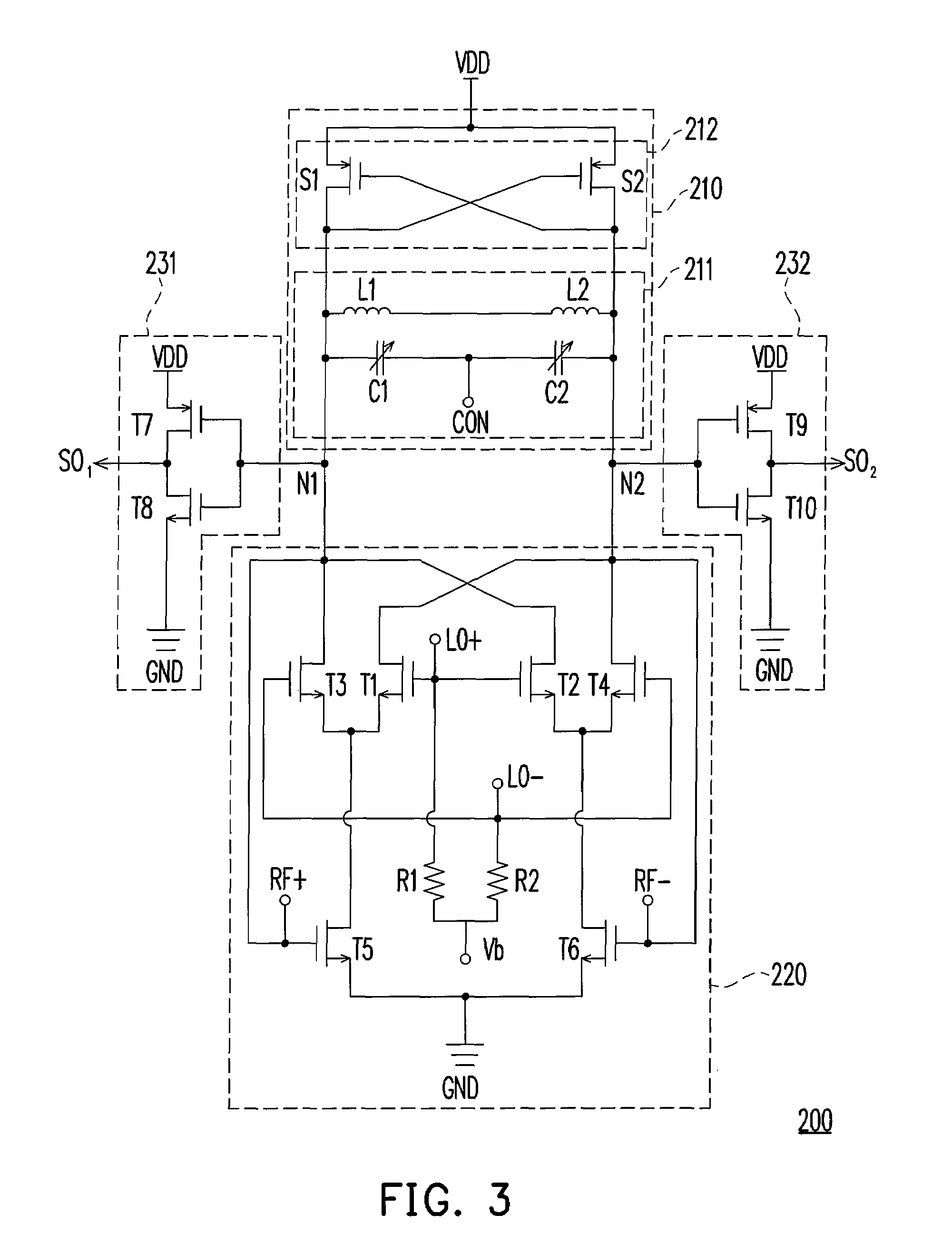

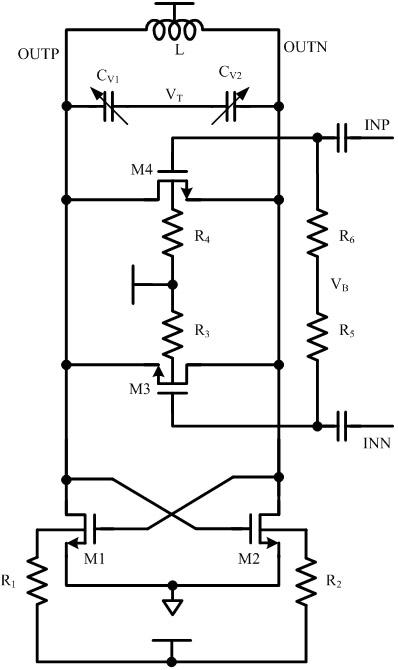

InactiveUS20090102565A1Increase lock rangeReduce phase noiseModulation transference balanced arrangementsOscillations generatorsInjection lockedFrequency mixer

An injection-locked frequency divider is provided. The injection-locked frequency divider includes a voltage control oscillator (VCO) and a mixer. The VCO includes a LC resonance tank and a negative-resistance generator for generating a differential oscillation signal including a first and a second oscillation signals. The LC resonance tank adjusts a VCO reactance and resonates for generating the differential oscillation signal. The negative-resistance generator coupled to the LC resonance tank eliminates an equivalent resistance generated by the LC resonance tank and maintains the VCO to continuously oscillate. The mixer has a first and a second local input terminals respectively receiving the first and second injected signals included in a differential injected signal, and the first and second radio frequency input terminals respectively receiving the first and second oscillation signals for mixing the differential injected signal with the differential oscillation signal to adjust the output frequency of the differential oscillation signal.

Owner:NAT TAIWAN UNIV OF SCI & TECH

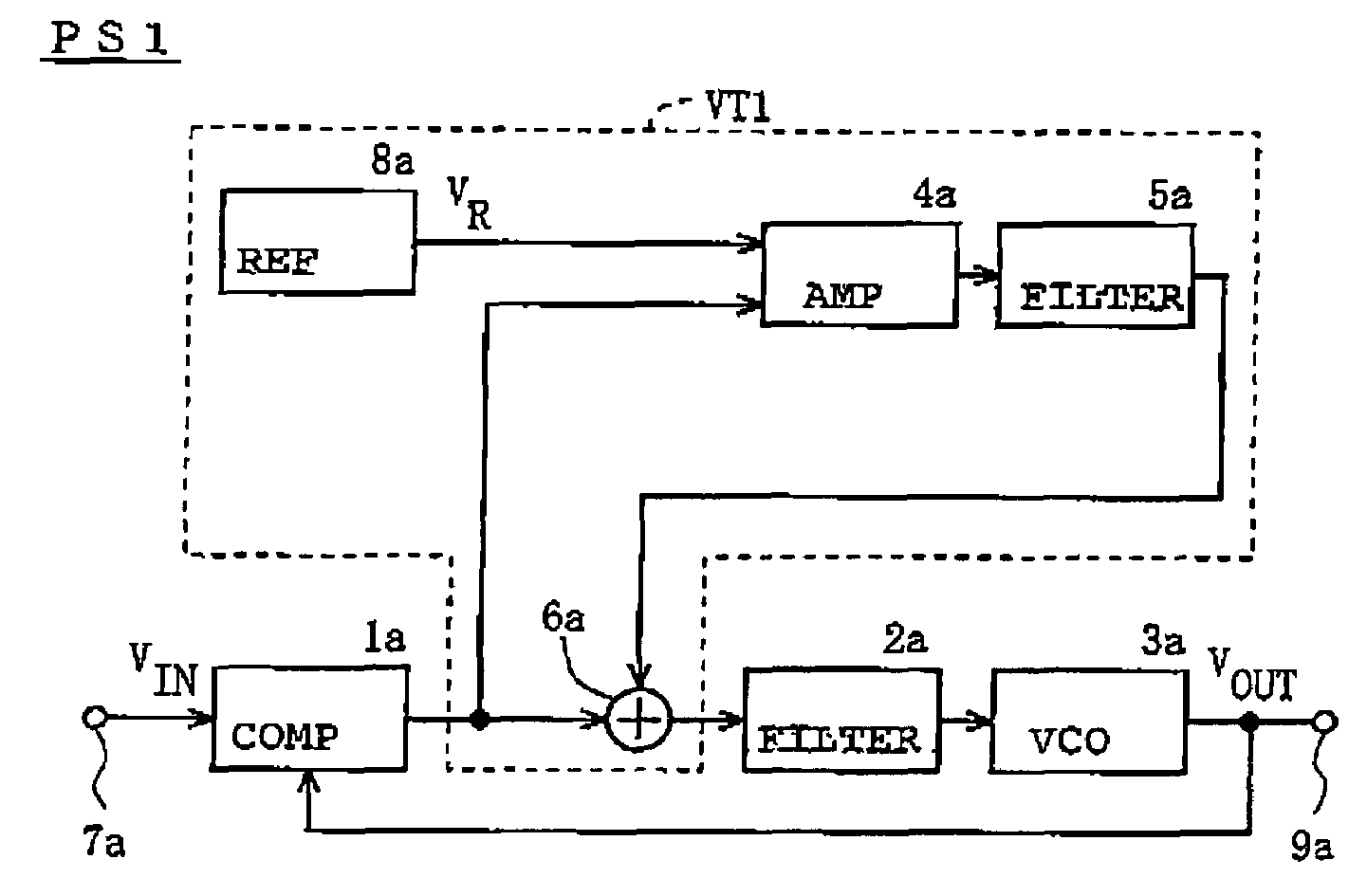

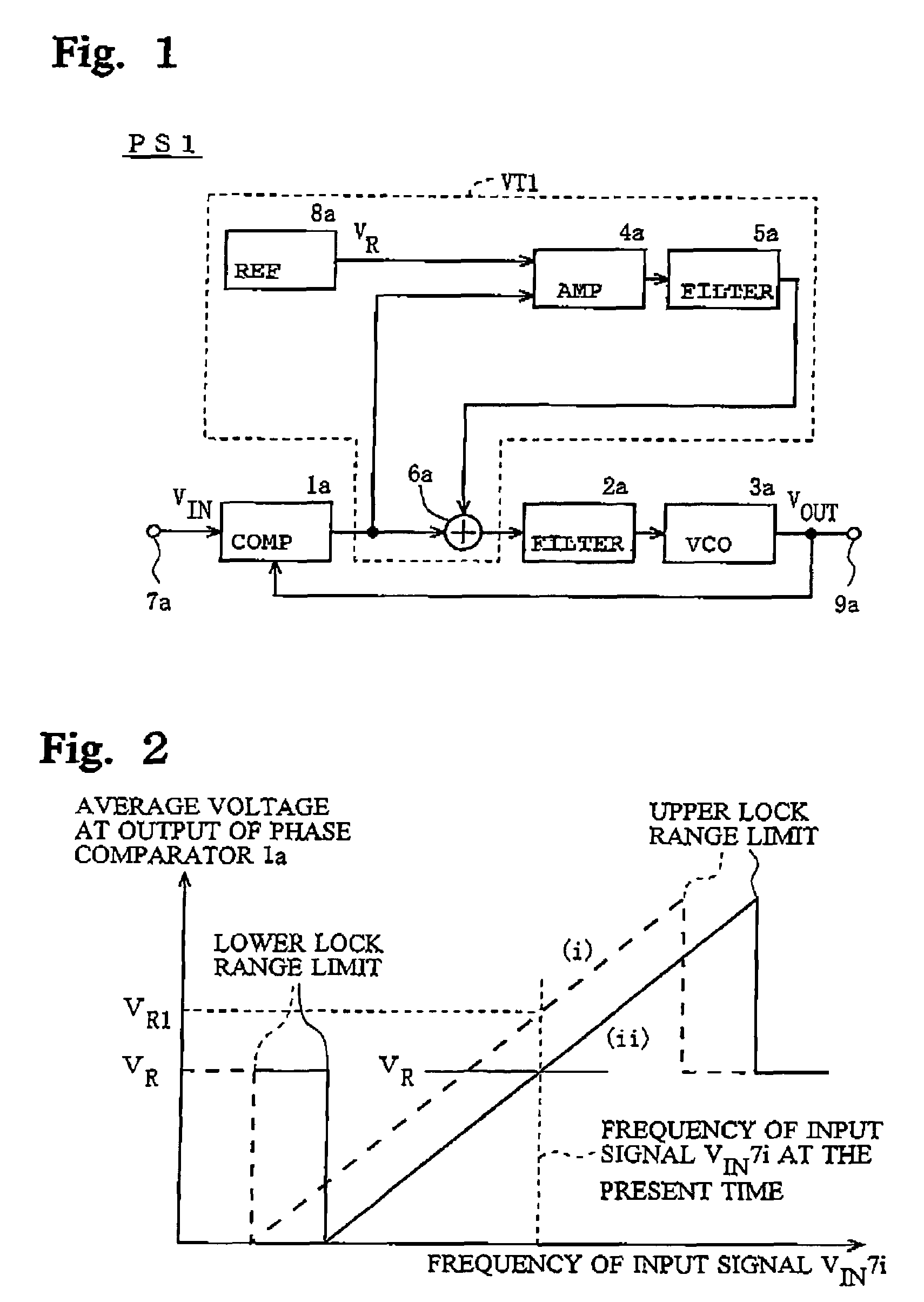

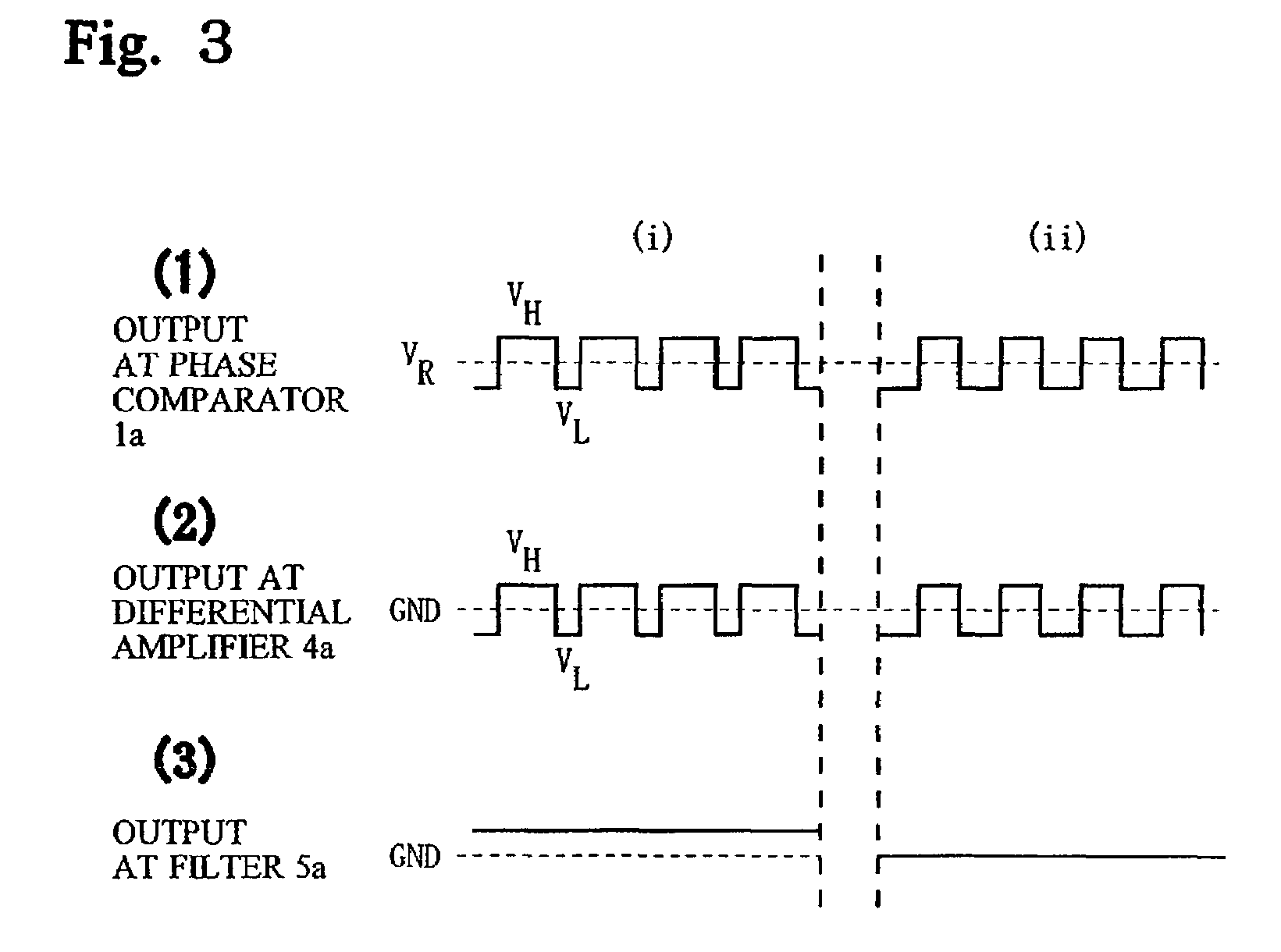

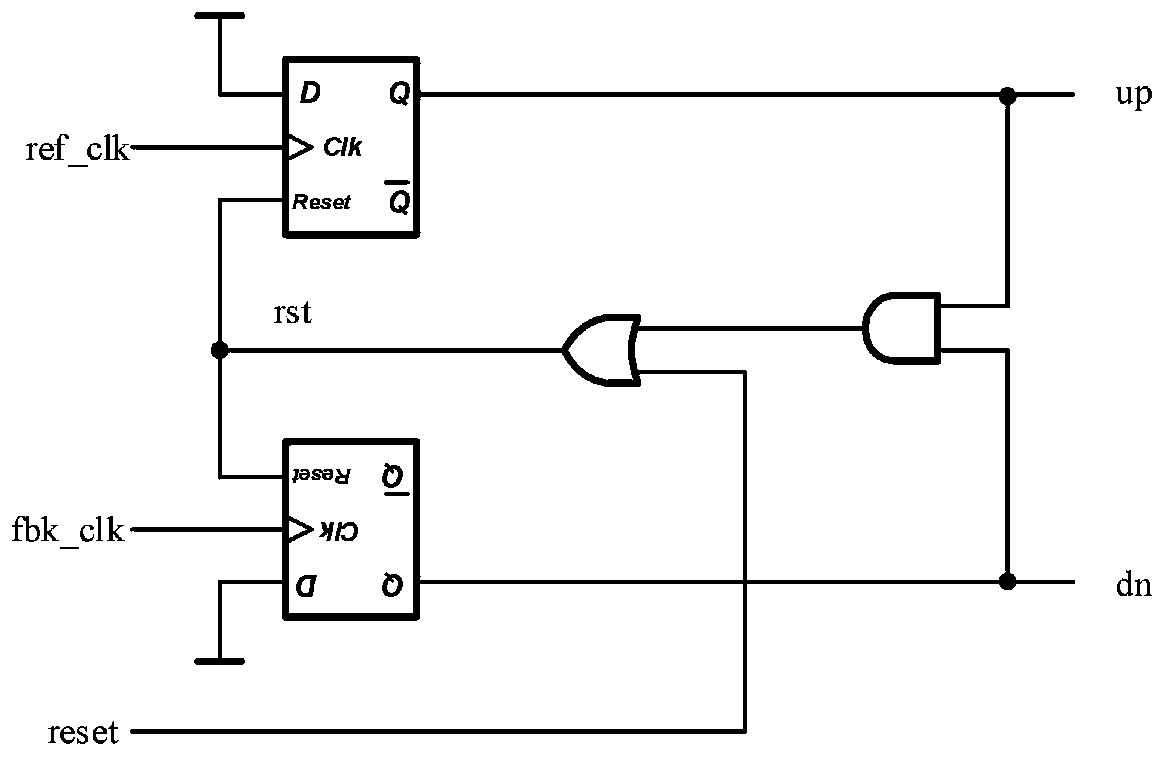

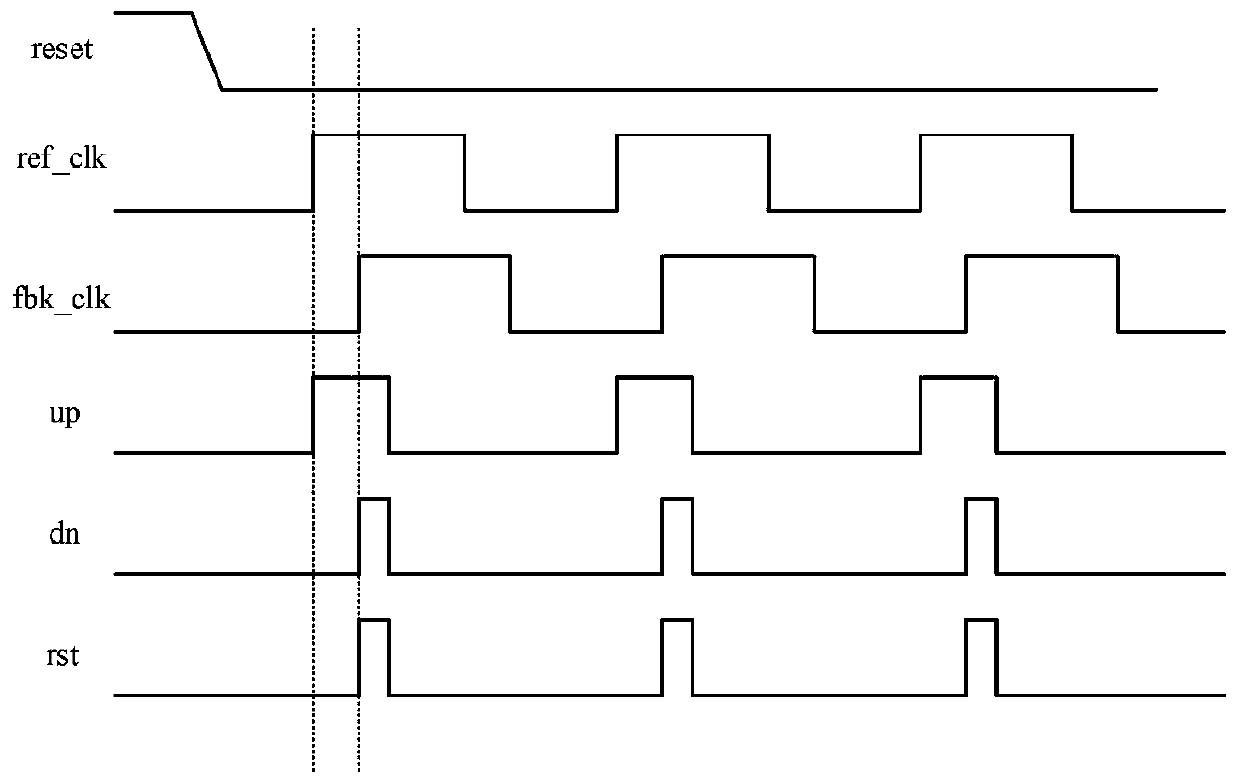

Phase-Locked Loop

InactiveUS7054403B2Increase lock rangePulse automatic controlAngle demodulation by phase difference detectionLoop filterVoltage reference

A phase lock circuit has a signal path to which a phase comparator, a loop filter and a voltage control oscillator are connected in series, the phase comparator being adapted to compare the phase of an input signal VIN with the phase in the output signal of the voltage control oscillator and to output its result of comparison, the loop filter being adapted to receive the output signal of the phase comparator and to output a DC voltage; the voltage control oscillator being adapted to control the output oscillation frequency depending on the DC output voltage of the loop filter, the phase lock circuit further comprising voltage tracking means for adding, to the voltage of the signal path, a signal causing the average voltage in the output voltage of the phase comparator to coincide with a predetermined reference voltage, whereby the voltage tracking means can enlarge the lock range in the phase lock circuit.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP +1

Injection-locked frequency divider

InactiveUS7659784B2Reduce phase noiseIncrease lock rangeModulation transference balanced arrangementsElectric pulse generatorInjection lockedResonance

An injection-locked frequency divider is provided. The injection-locked frequency divider includes a voltage control oscillator (VCO) and a mixer. The VCO includes a LC resonance tank and a negative-resistance generator for generating a differential oscillation signal including a first and a second oscillation signals. The LC resonance tank adjusts a VCO reactance and resonates for generating the differential oscillation signal. The negative-resistance generator coupled to the LC resonance tank eliminates an equivalent resistance generated by the LC resonance tank and maintains the VCO to continuously oscillate. The mixer has a first and a second local input terminals respectively receiving the first and second injected signals included in a differential injected signal, and the first and second radio frequency input terminals respectively receiving the first and second oscillation signals for mixing the differential injected signal with the differential oscillation signal to adjust the output frequency of the differential oscillation signal.

Owner:NAT TAIWAN UNIV OF SCI & TECH

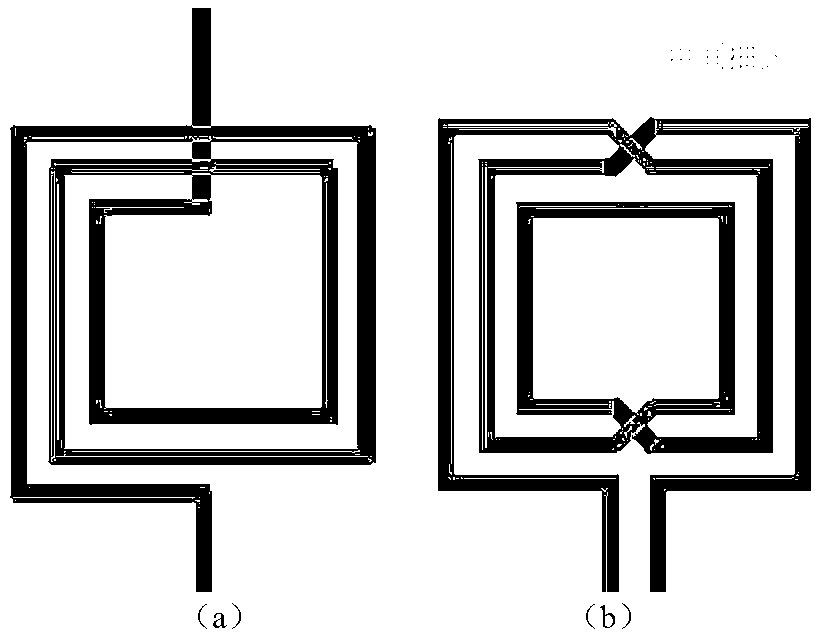

Very low voltage millimeter wave injection-locked dichotomous frequency divider

InactiveCN102158228AIncrease lock rangeReduce power consumptionPulse automatic controlCapacitanceInjection locked

The invention belongs to the technical field of millimeter wave integrated circuits and specifically relates to an injection-locked dichotomous frequency divider applied in an integrated circuit of a transceiver. The injection-locked dichotomous frequency divider comprises an inductance and capacitance oscillator, a tuning circuit and a signal injection circuit, wherein the tuning circuit is tuned by a varactor, the inductance and capacitance oscillator performs self-excited oscillation at certain frequency without external input excitation, and the signal injection circuit is used for injecting an input signal into a resonant cavity of the oscillator for realizing traction and locking of the self-excited frequency of the oscillator, thereby realizing dichotomous frequency division of the input signal. Compared with a traditional injection-locked circuit, an additional matching circuit is eliminated, the power consumption and the area required for a chip are significantly reduced, the injection efficiency is improved, and the locking range of the frequency divider is expanded. By using the forward body bias technology, the circuit can realize wider working frequency under lower voltage of a power supply, and the circuit can realize differential input.

Owner:FUDAN UNIV

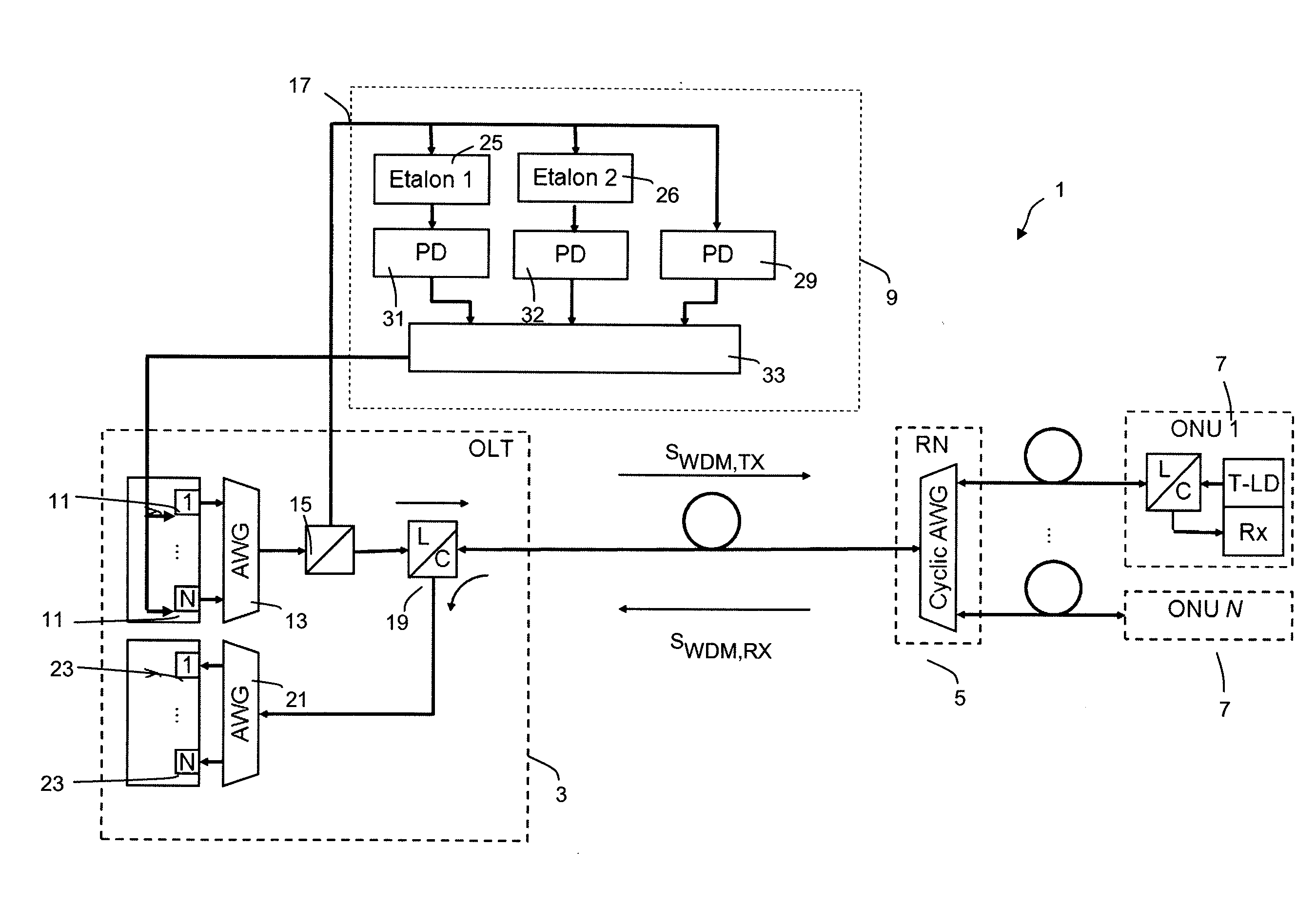

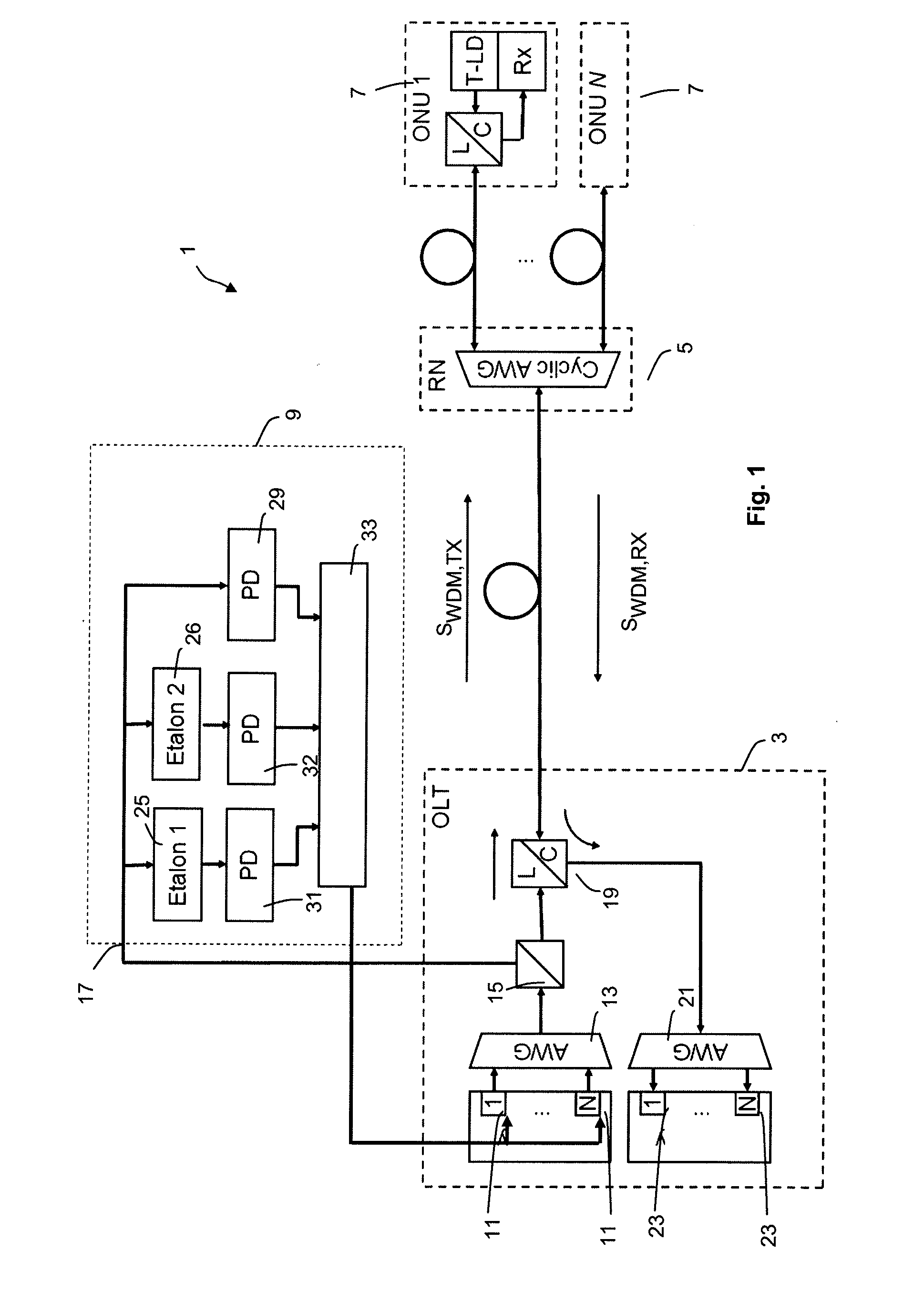

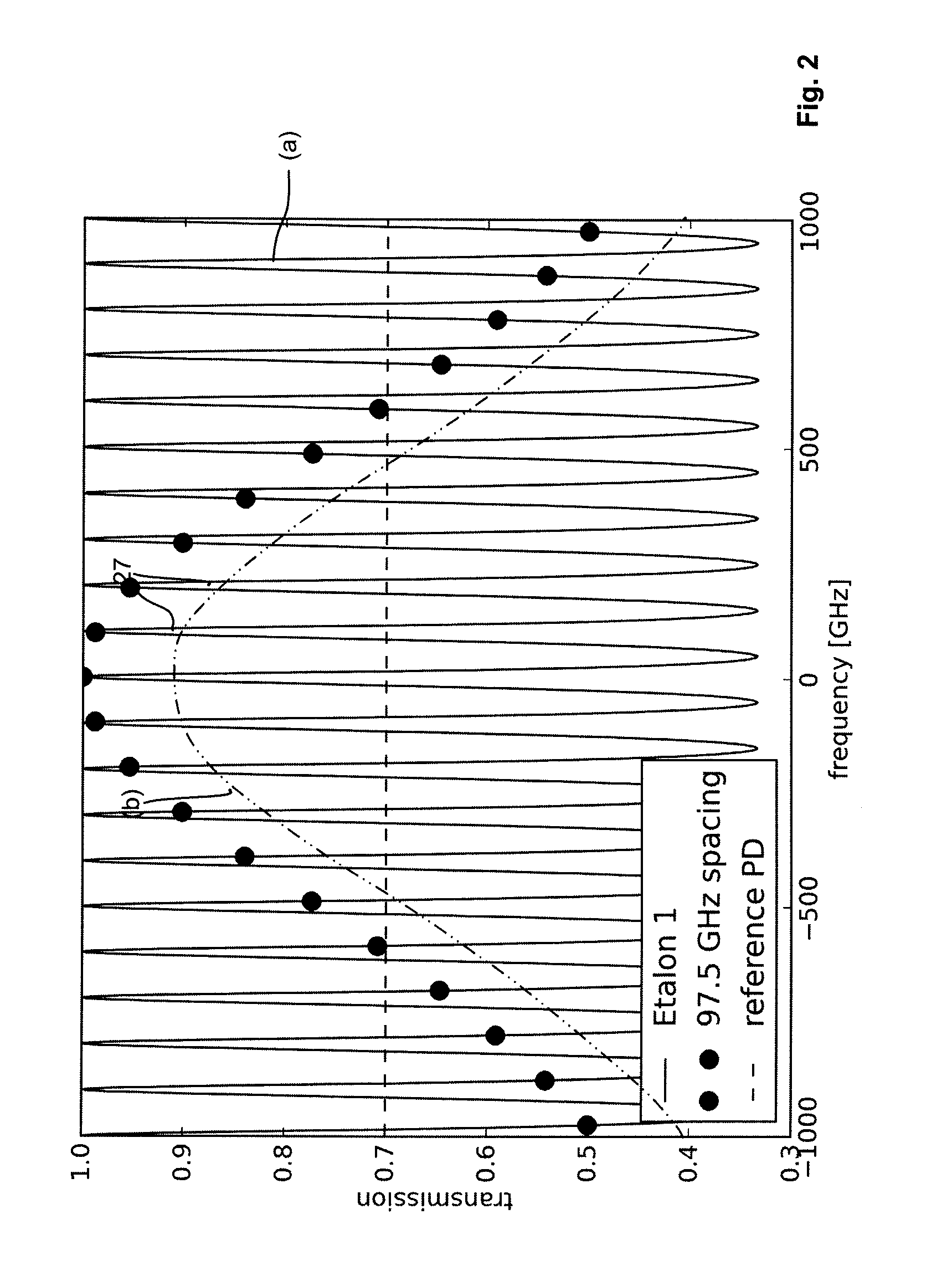

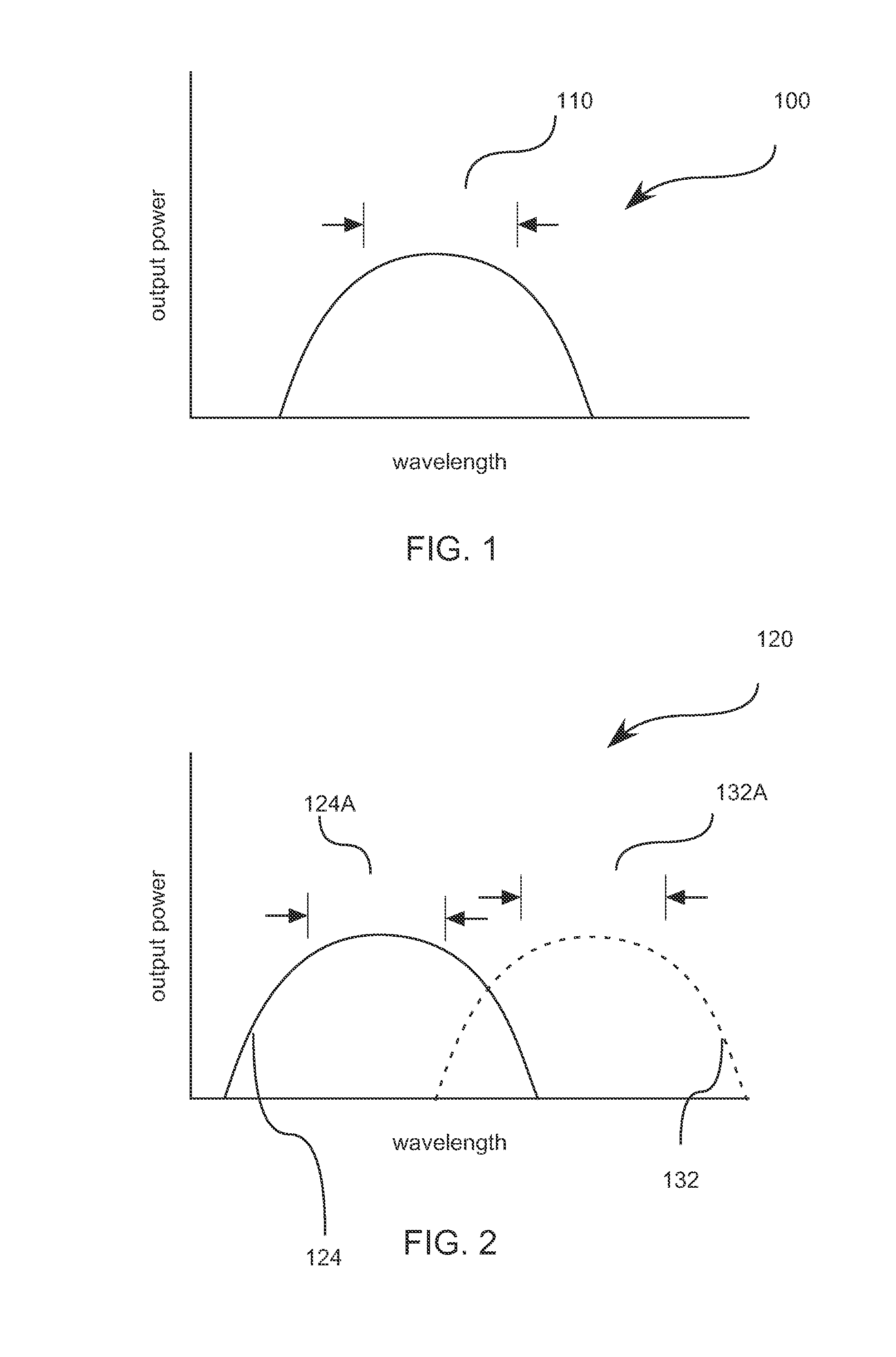

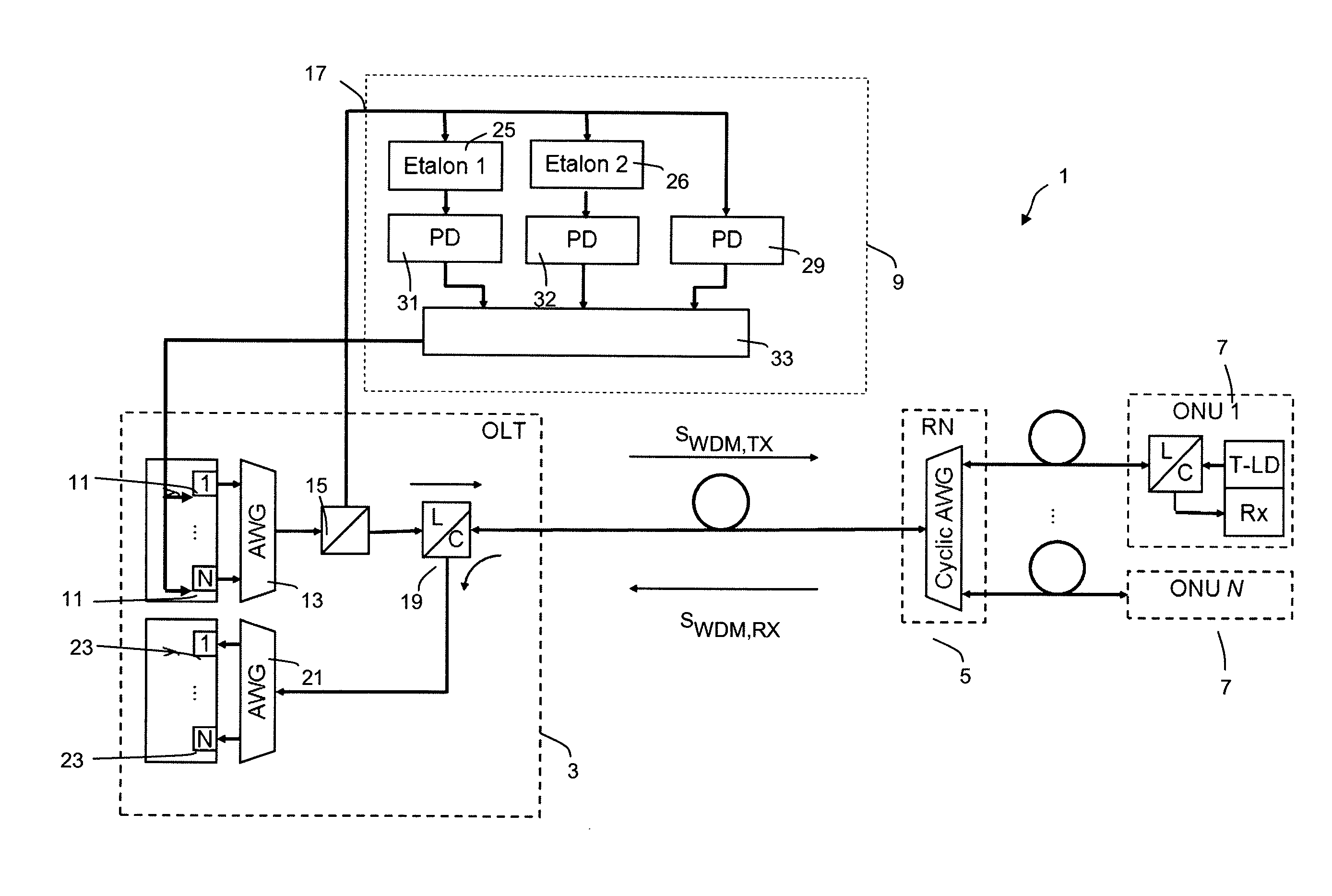

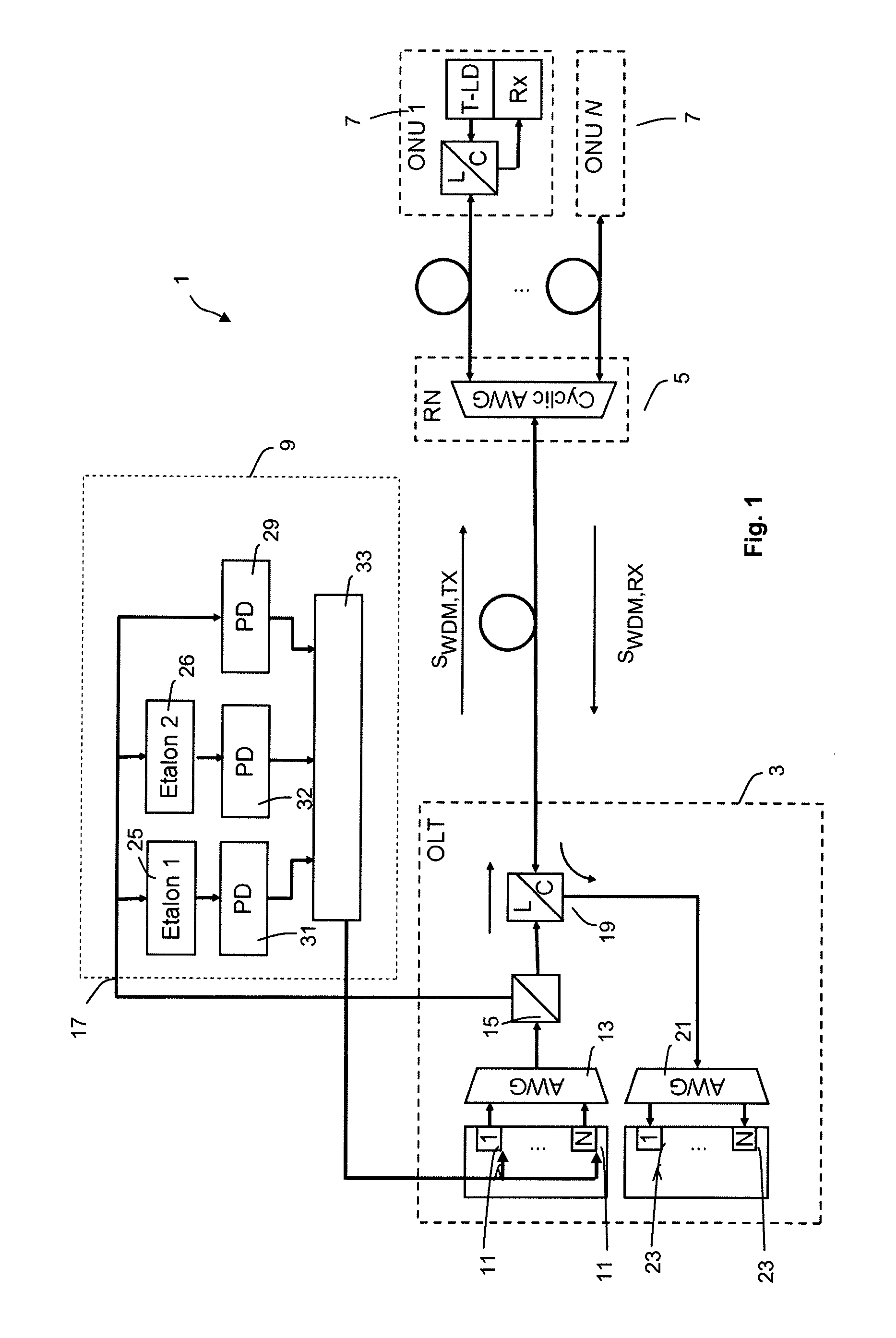

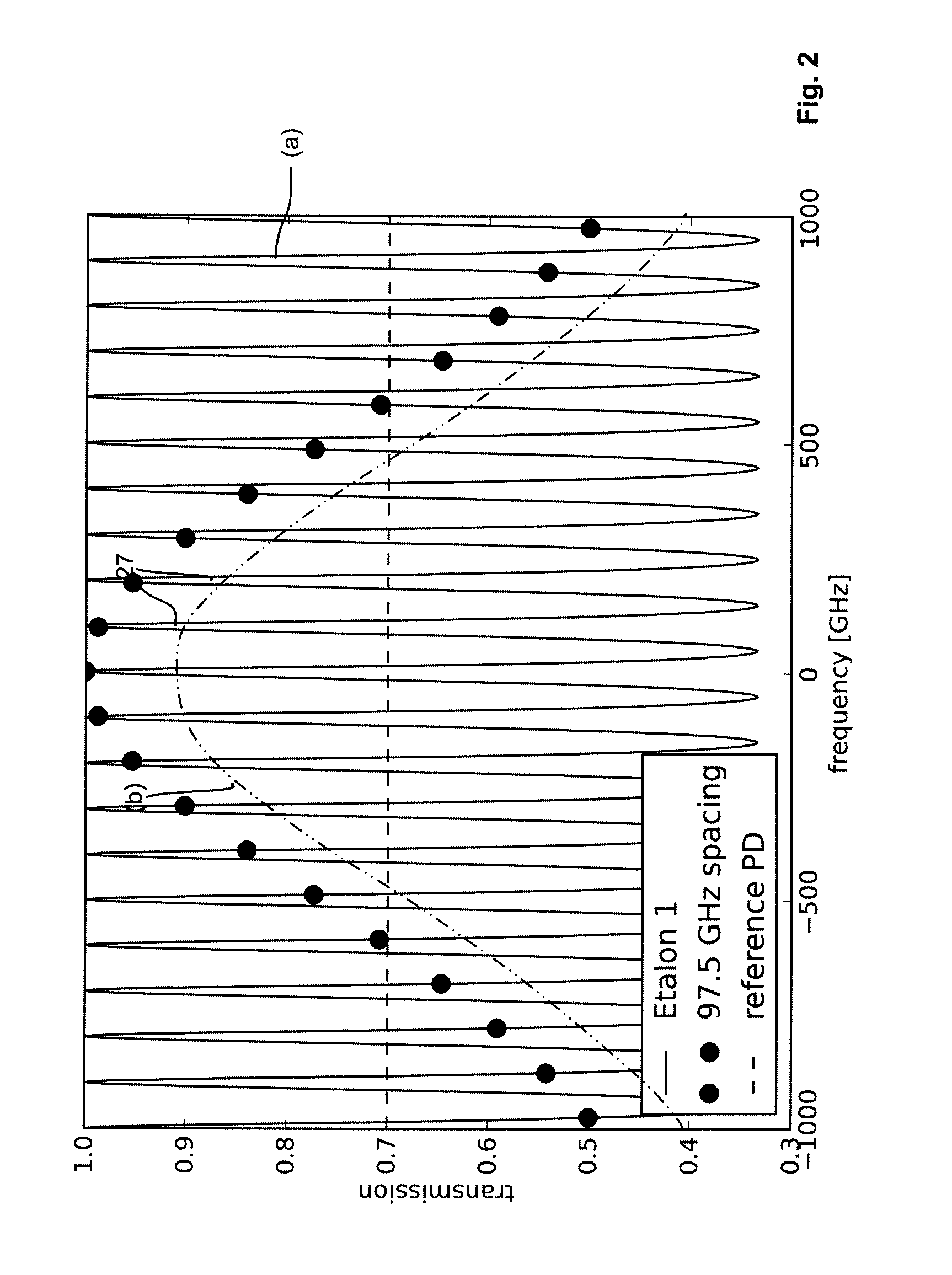

Optical frequency locking method and device for optical data transmission

ActiveUS20130064542A1Increase lock rangeMaximize rangeWavelength-division multiplex systemsTransmission monitoringOptical frequenciesOptical data transmission

An optical frequency locking method tunes each of a plurality of narrow-band optical channel transmit signals (having arbitrary channel frequency spacings) to a dedicated optical channel frequency. The method includes tapping-off a portion of the optical power of the respective channel transmit signal and filtering the tapped-off channel transmit signal using at least one optical filter device. The method also includes monitoring, as an optical input signal, the optical power of the respective channel transmit signal supplied to the at least one optical filter device and, as an optical output signal, the optical power of the filtered channel transmit signal. The method further includes tuning, within a predetermined locking range for the dedicated optical channel frequency, the optical frequency of the respective channel transmit signal such that a predetermined value for the ratio of the output signal and the input signal is reached.

Owner:ADVA OPTICAL NETWORKING SE

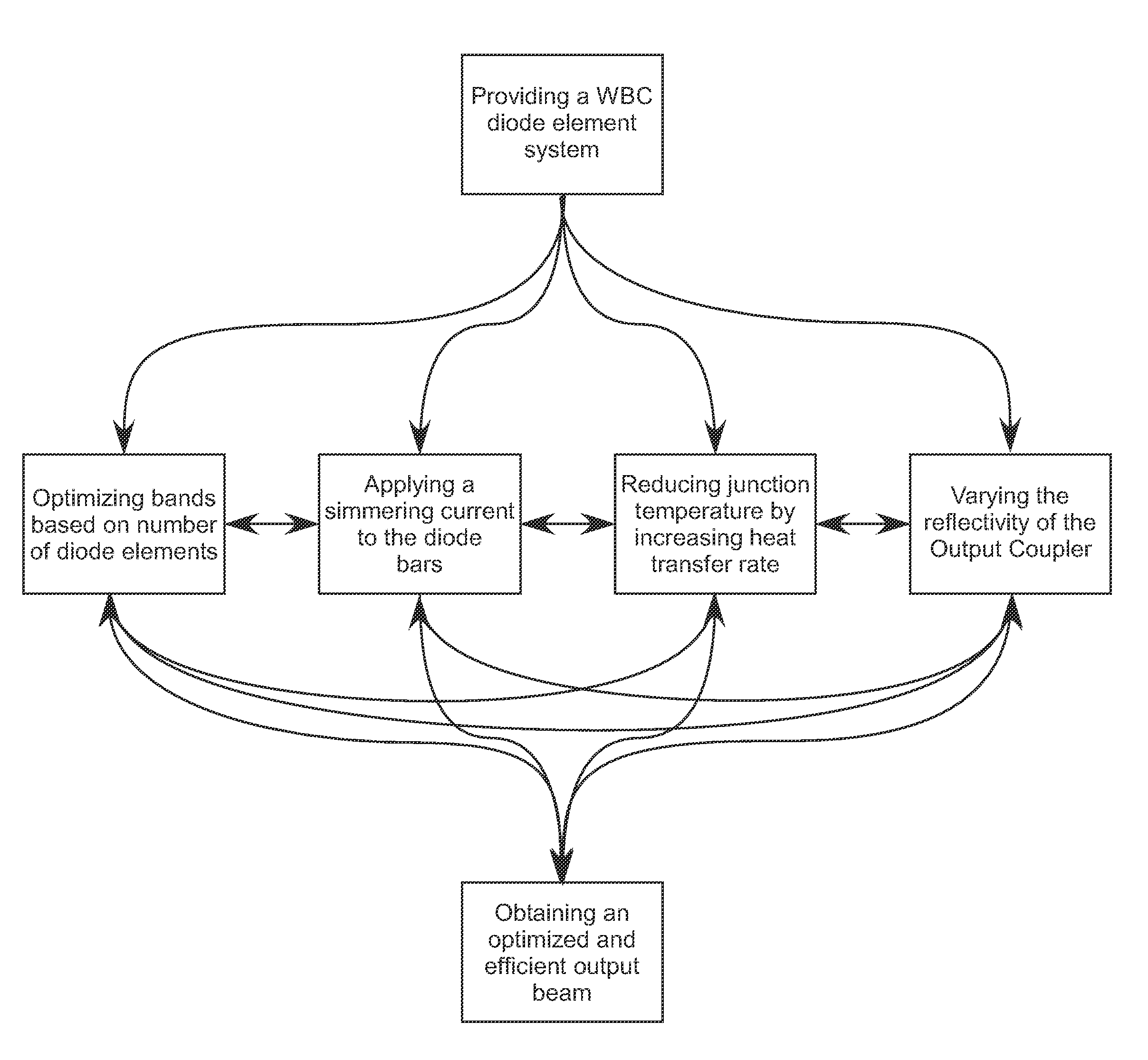

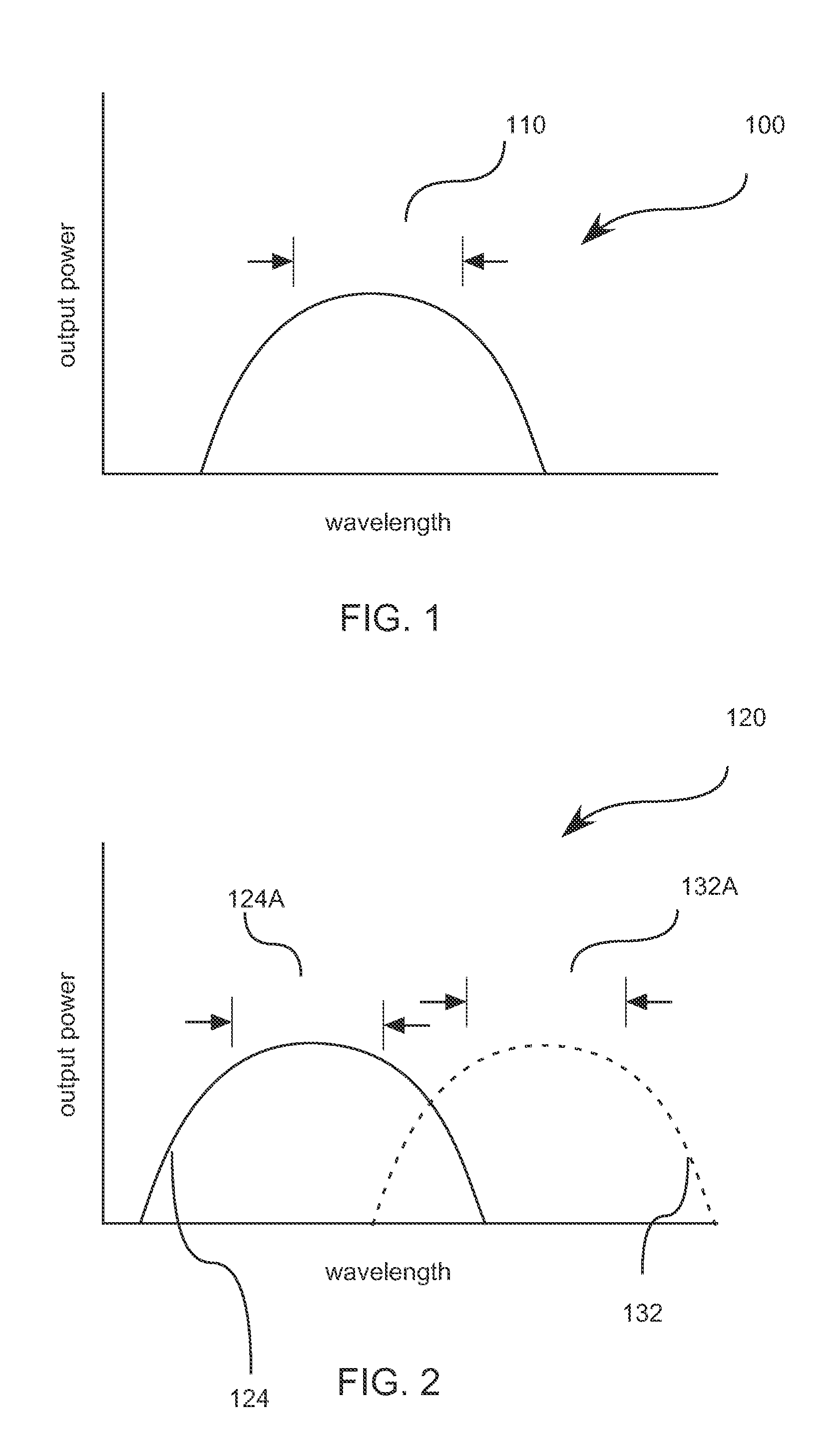

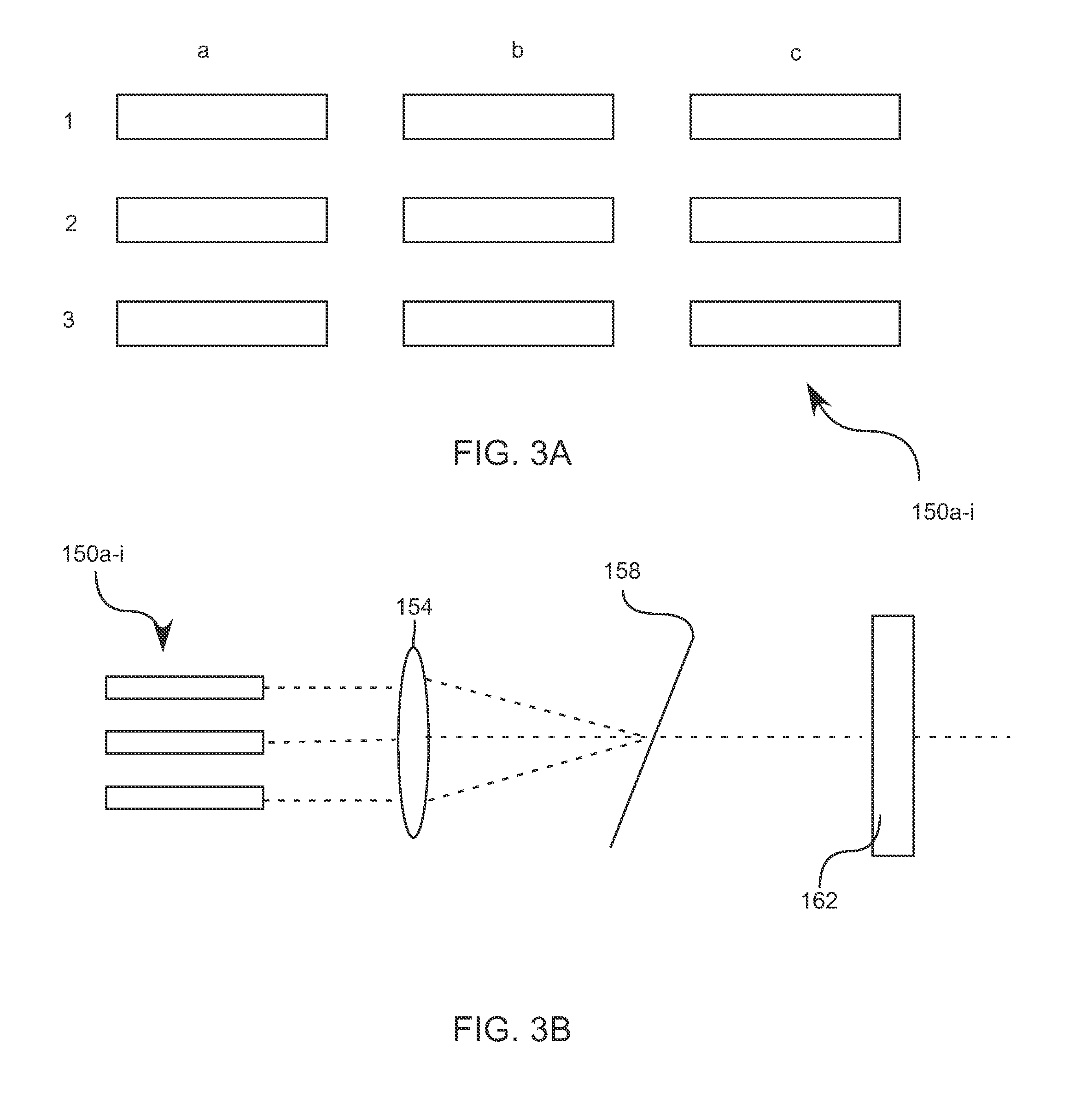

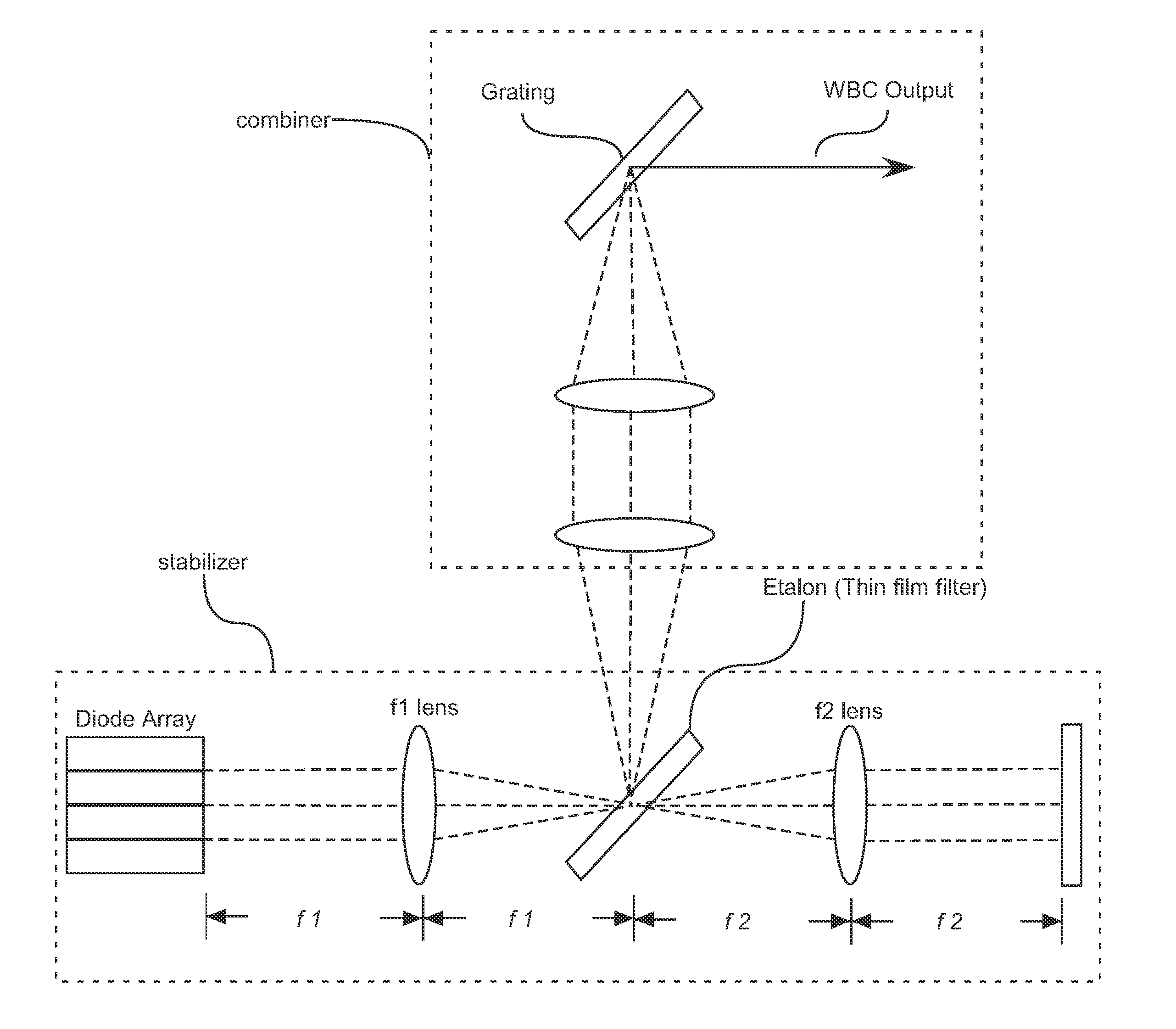

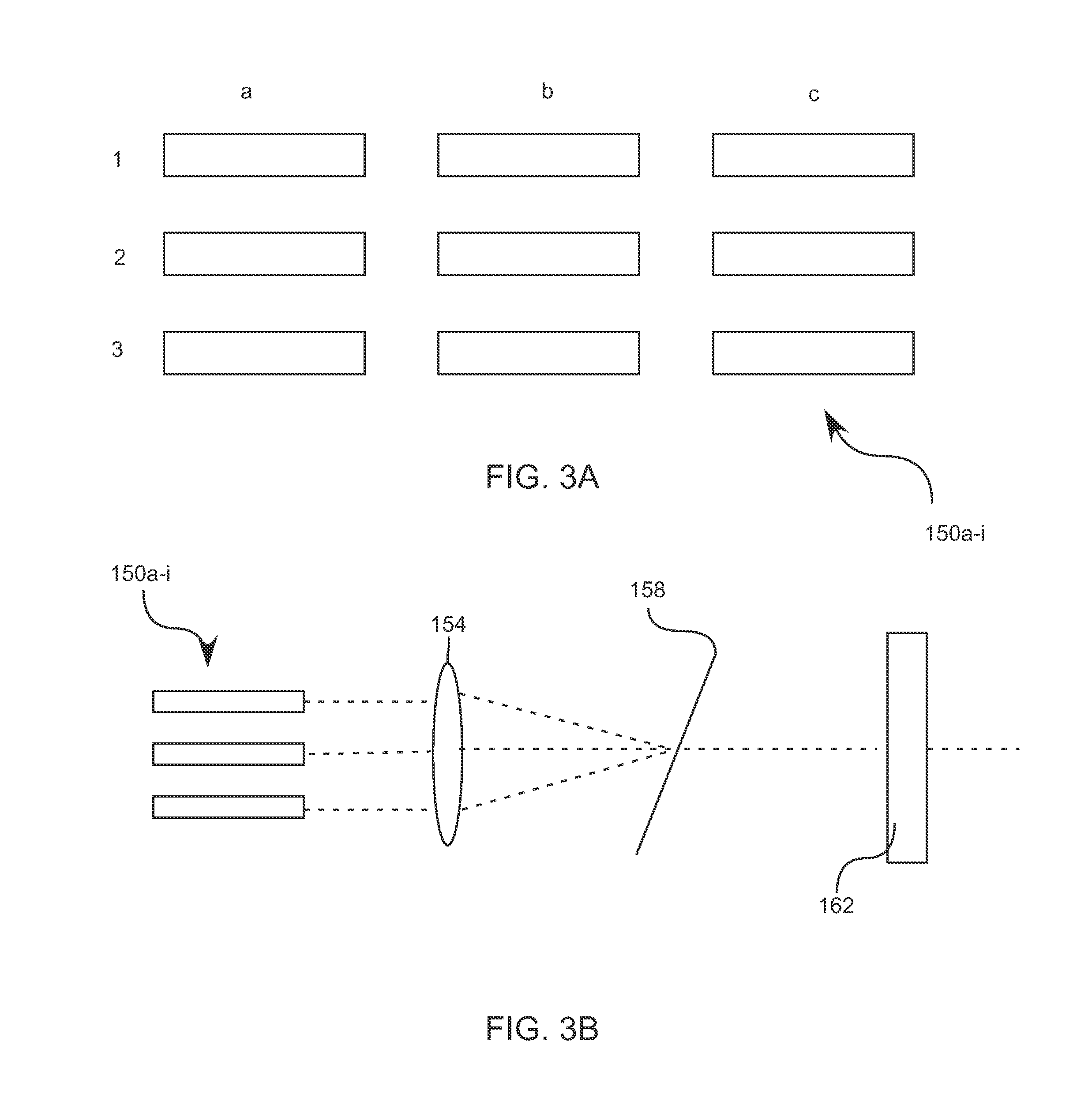

Method for improving performance of wavelength beam combining diode laser systems

ActiveUS9190807B2Fast turn-on time output powerImprove reflectivityLaser optical resonator constructionSemiconductor laser arrangementsLight beamLength wave

Owner:PANASONIC OF NORTH AMERICA

Harmonic suppression circuit, an injection-locked frequency divider circuit and associated methods

ActiveUS20090261868A1Harmonic reductionIncrease lock rangeOscillations generatorsTransmissionInjection lockedDifferential phase

The invention includes a harmonic suppression circuit, an injection-locked frequency divider circuit (ILFD) and associated methods. The harmonic suppression circuit comprises a source voltage, two suppression modules, two input terminals, two smoothed output terminals and a ground. The ILFD comprises a ground, an input transistor, an input terminal, two divider legs, two output terminals and a source voltage. The associated method to improve harmonic suppression comprises acts of synthesizing differential-phase signals and simultaneously suppressing second harmonics of in-phase signals. The method to extent an ILFD's locking range comprises acts of decreasing quality factor while keeping resonance frequency constant.

Owner:NAT TAIWAN UNIV

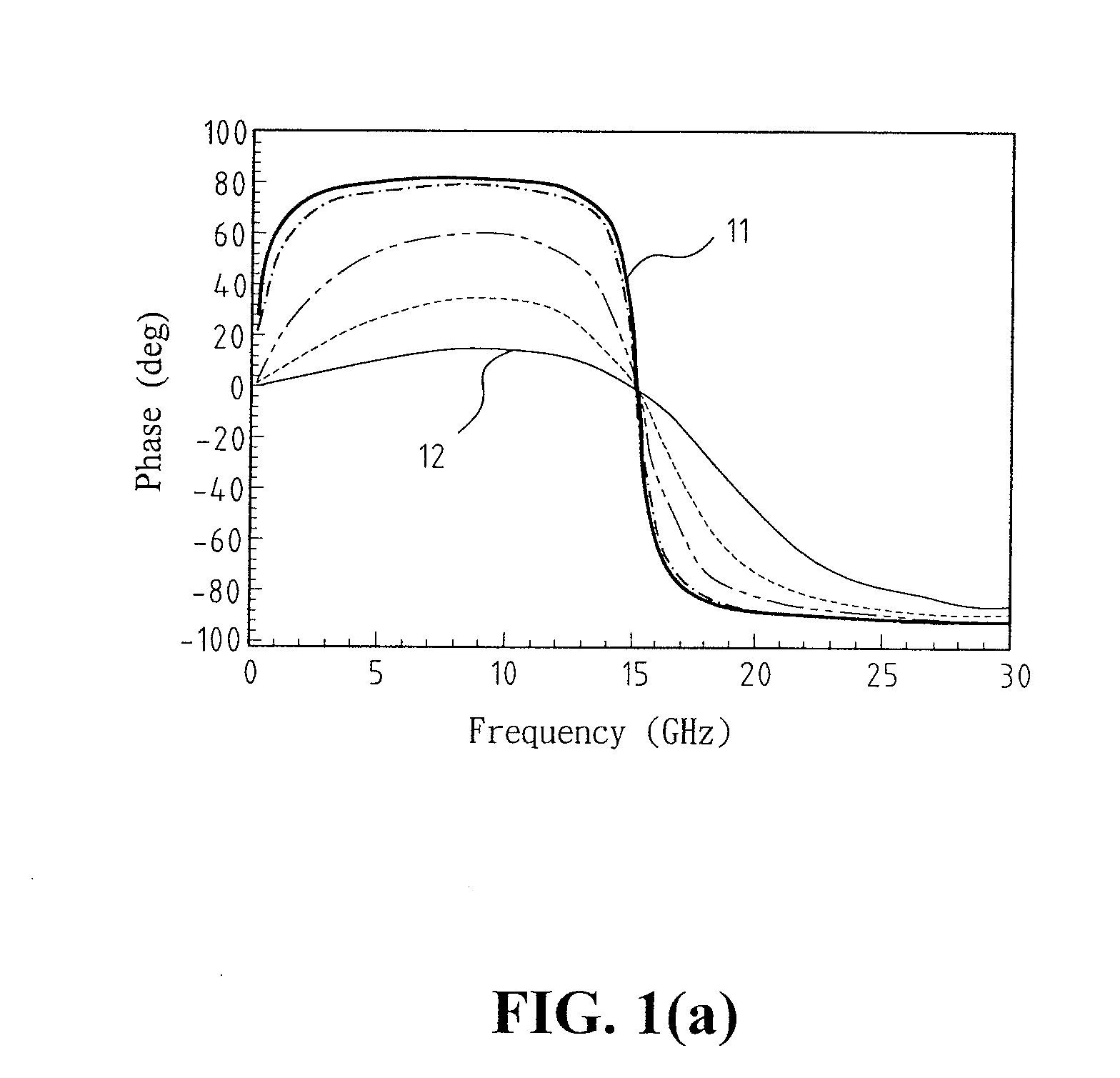

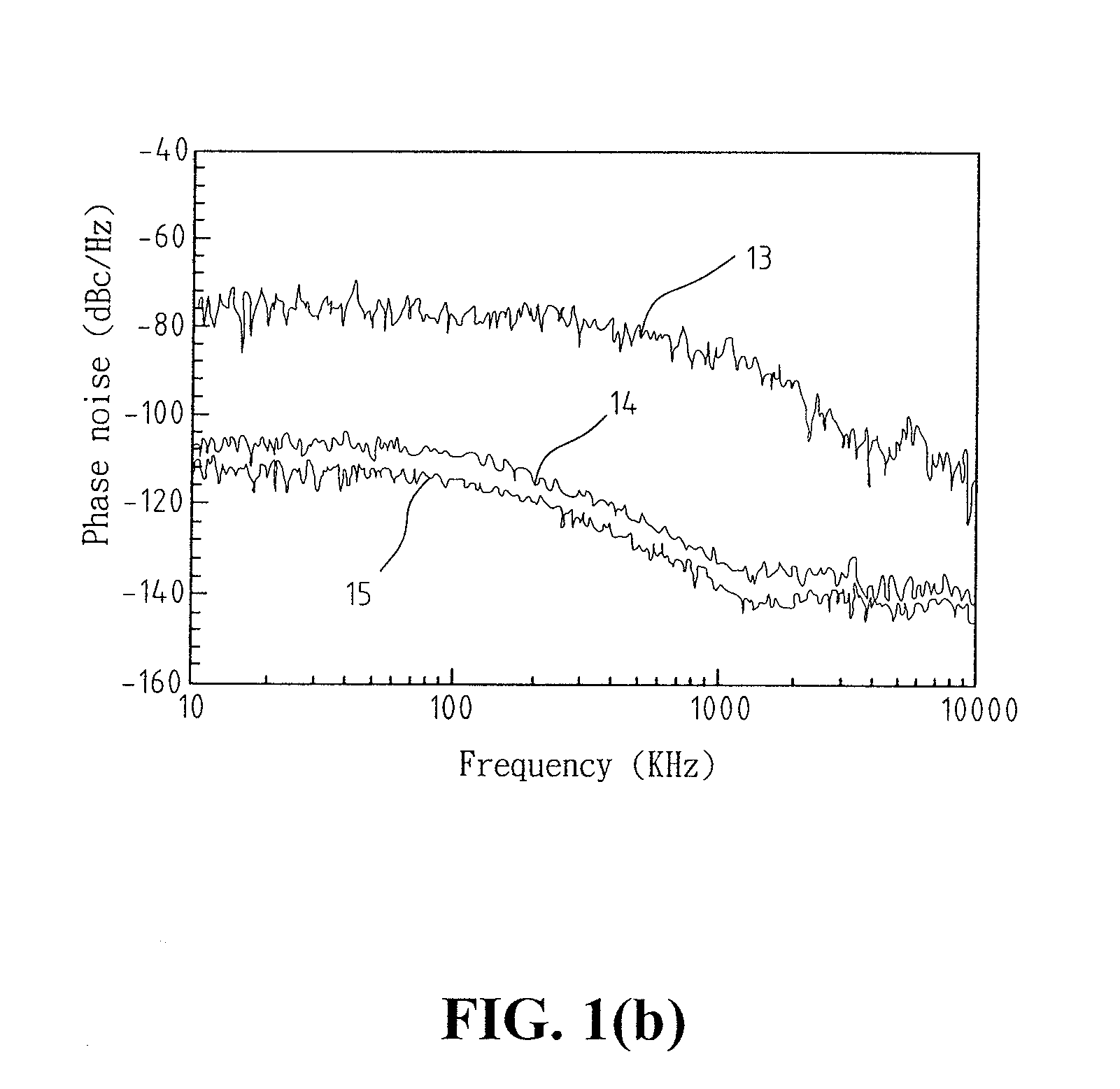

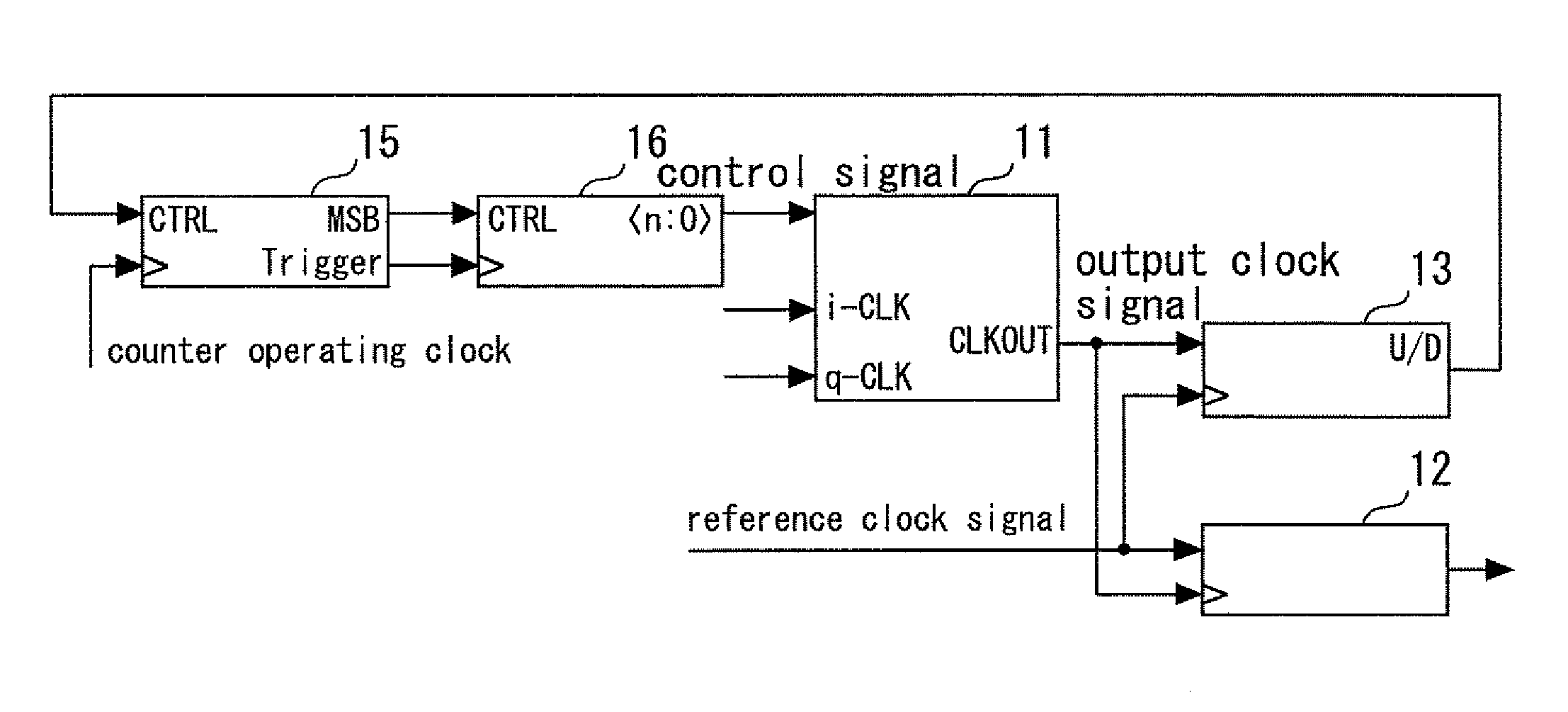

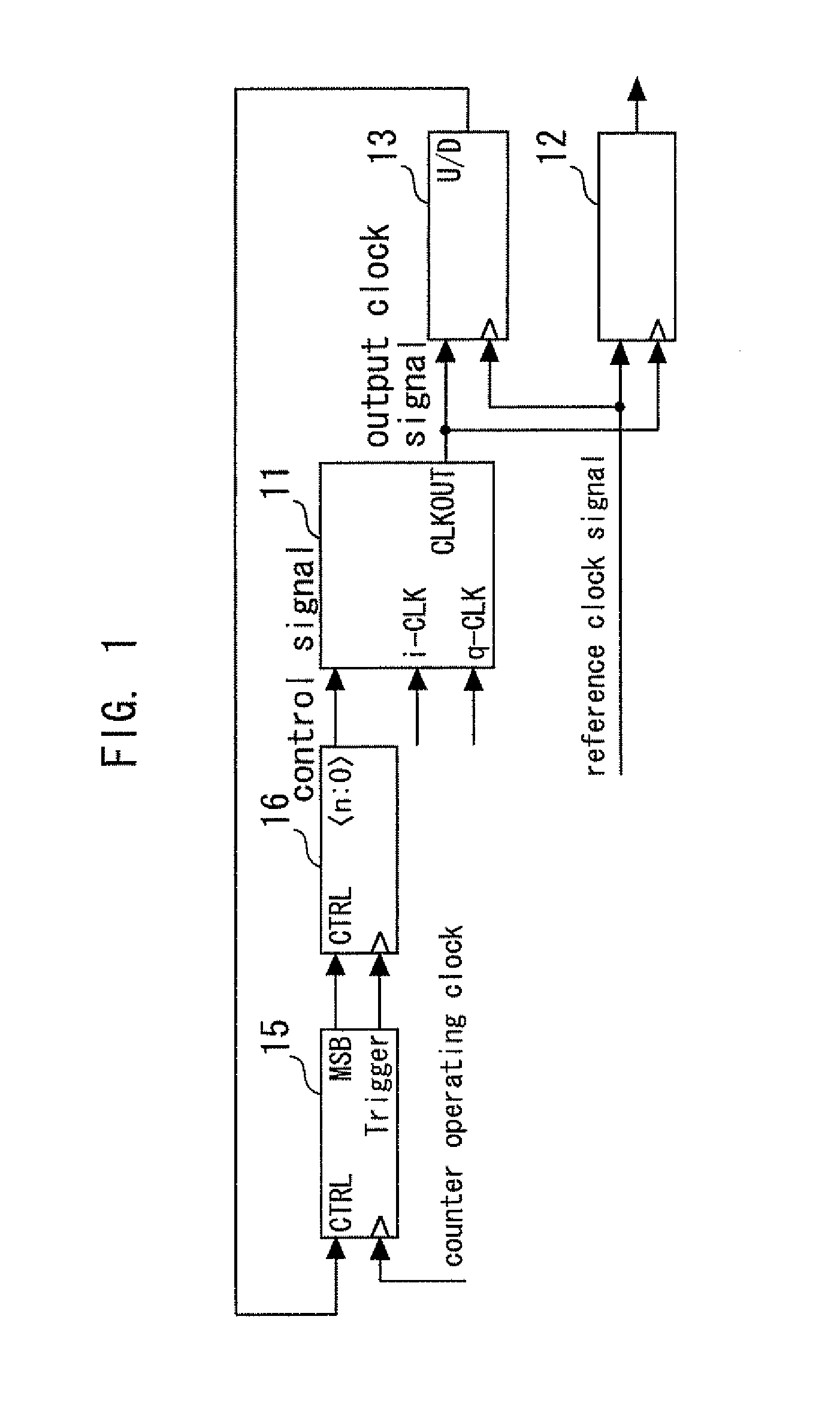

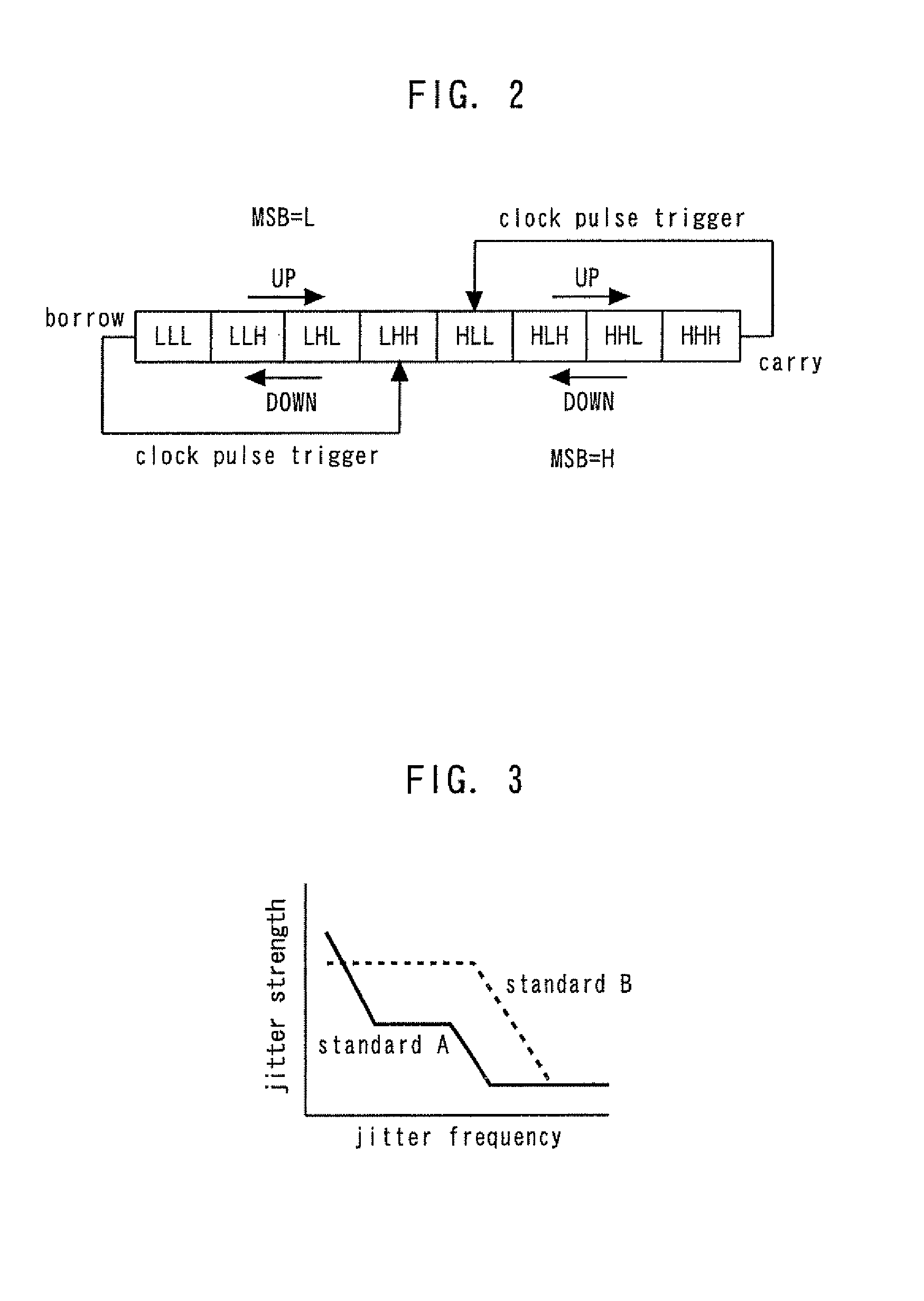

Digital-control-type phase-composing circuit system

InactiveUS7212049B2Increase resistanceIncrease lock rangePulse automatic controlControl signalPhase difference

A digital-control phase-composing circuit system has a phase-composing circuit which is supplied with two input clock signals having a phase difference therebetween and a control signal, and which composes an output clock signal having a phase between the phases of the two input clock signals on the basis of weighting through the control signal, a binary comparison circuit which compares the phase of the output clock signal to the phase of a reference clock signal, a first up / down counter which increments or decrements a first count value on the basis of the result of comparison made by the binary phase comparison circuit, outputs the most significant bit of the first count value, and outputs a clock pulse when a carry or a borrow occurs in the first count value, and a second up / down counter which operates on the basis of the clock pulse as an operating clock, increments or decrements a second count value on the basis of the most significant bit of the first count value, and outputs the second count value as the control signal.

Owner:MITSUBISHI ELECTRIC CORP

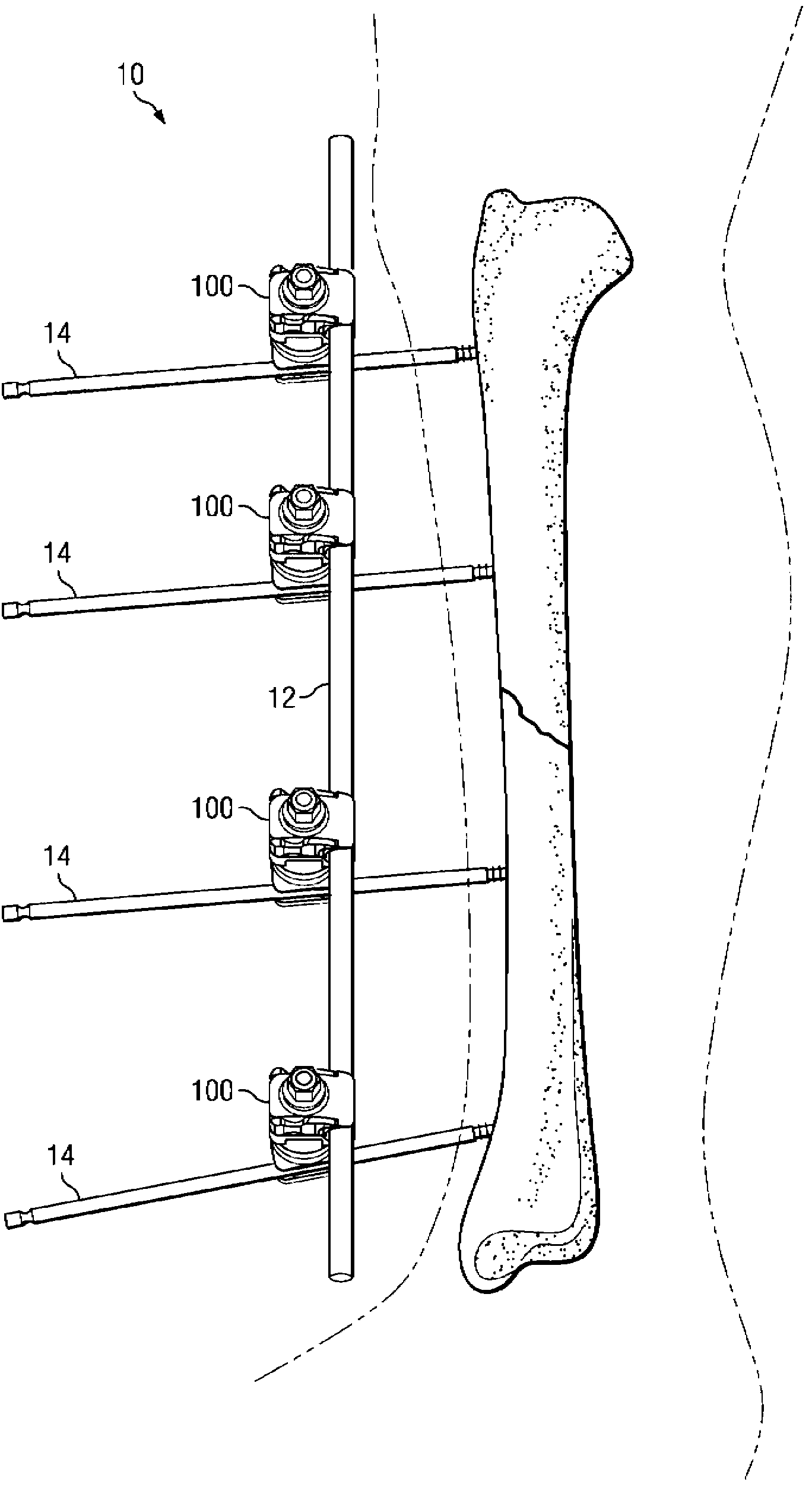

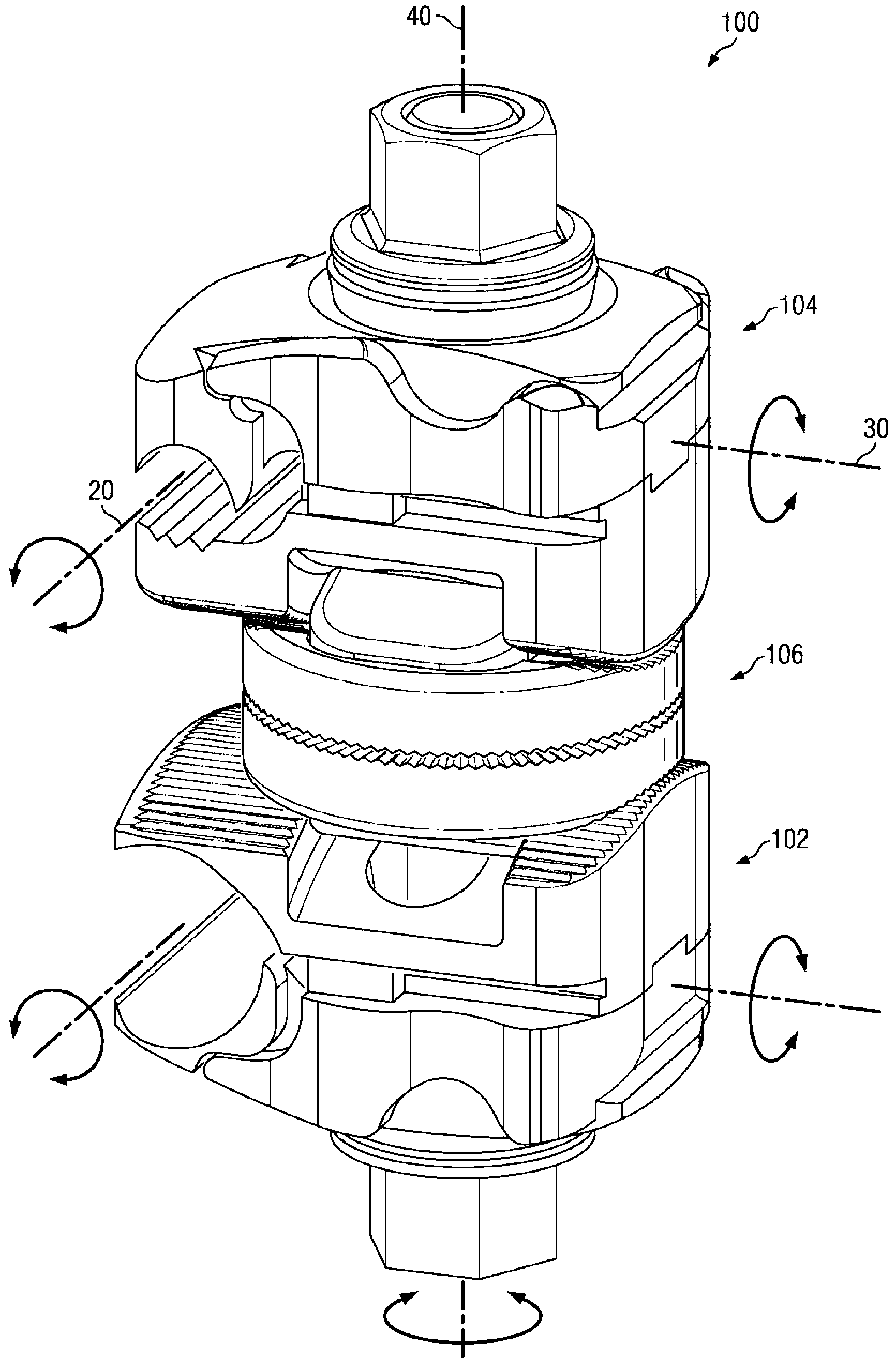

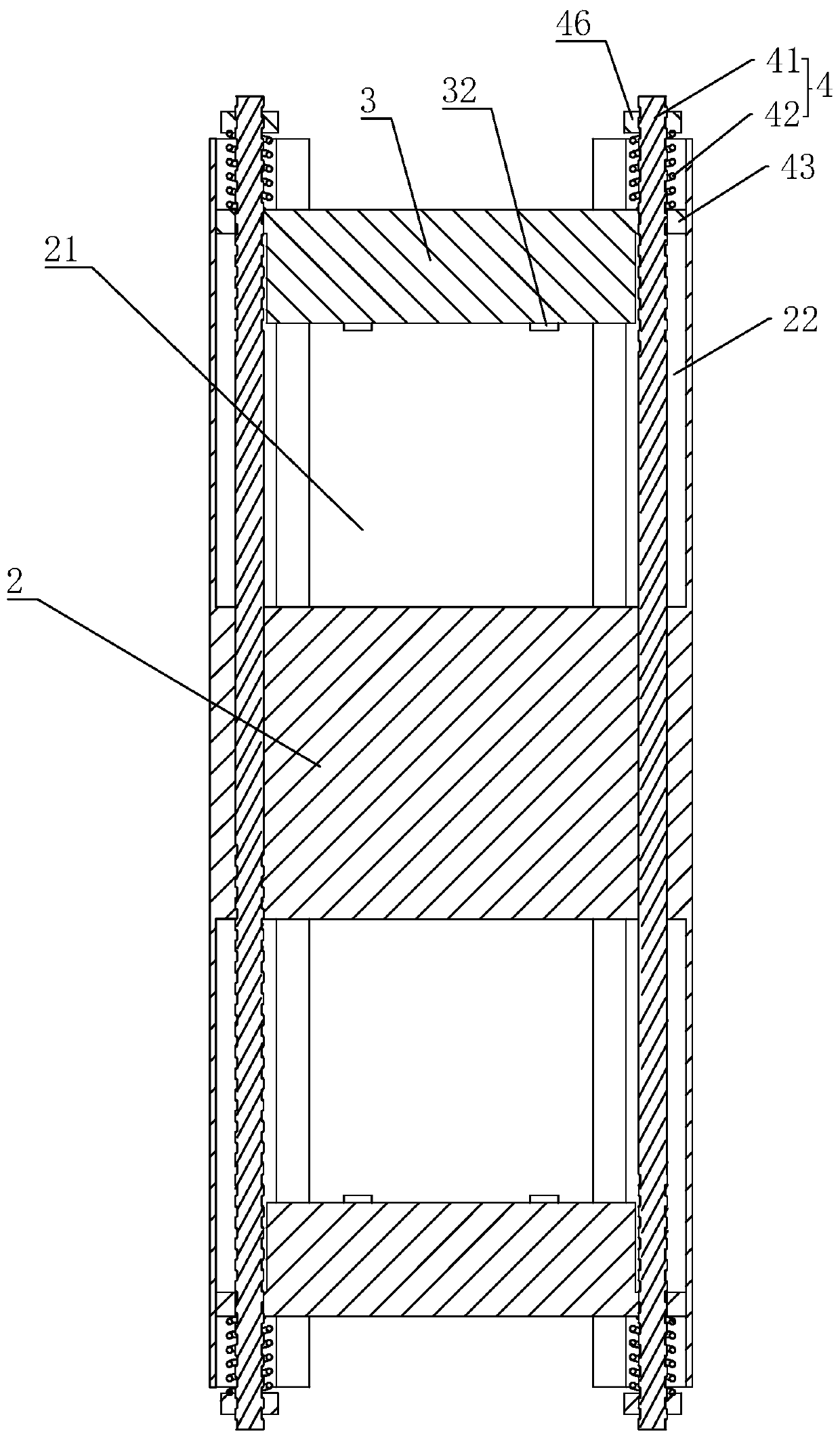

Multi-locking external fixation clamp

ActiveCN103260535AStable structureIncrease lock rangeExternal osteosynthesisBiomedical engineeringExternal fixation

A clamping device for attaching to an external fixation element of an external fixation system includes first and second jaws each having inner and outer surfaces, with the inner surface of the first jaw and the inner surface of the second jaw together forming a passage configured to receive the external fixation element. A locking system is engageable with the first and the second jaws. A portion of the locking system is moveable relative to the first and the second jaws between a first position where the locking arrangement is configured to prevent release of the external fixation element having a first size from between the first jaw and the second jaw and a second position where the locking arrangement is configured to prevent release of the external fixation element having a second size from between the first jaw and the second jaw.

Owner:ZIMMER INC

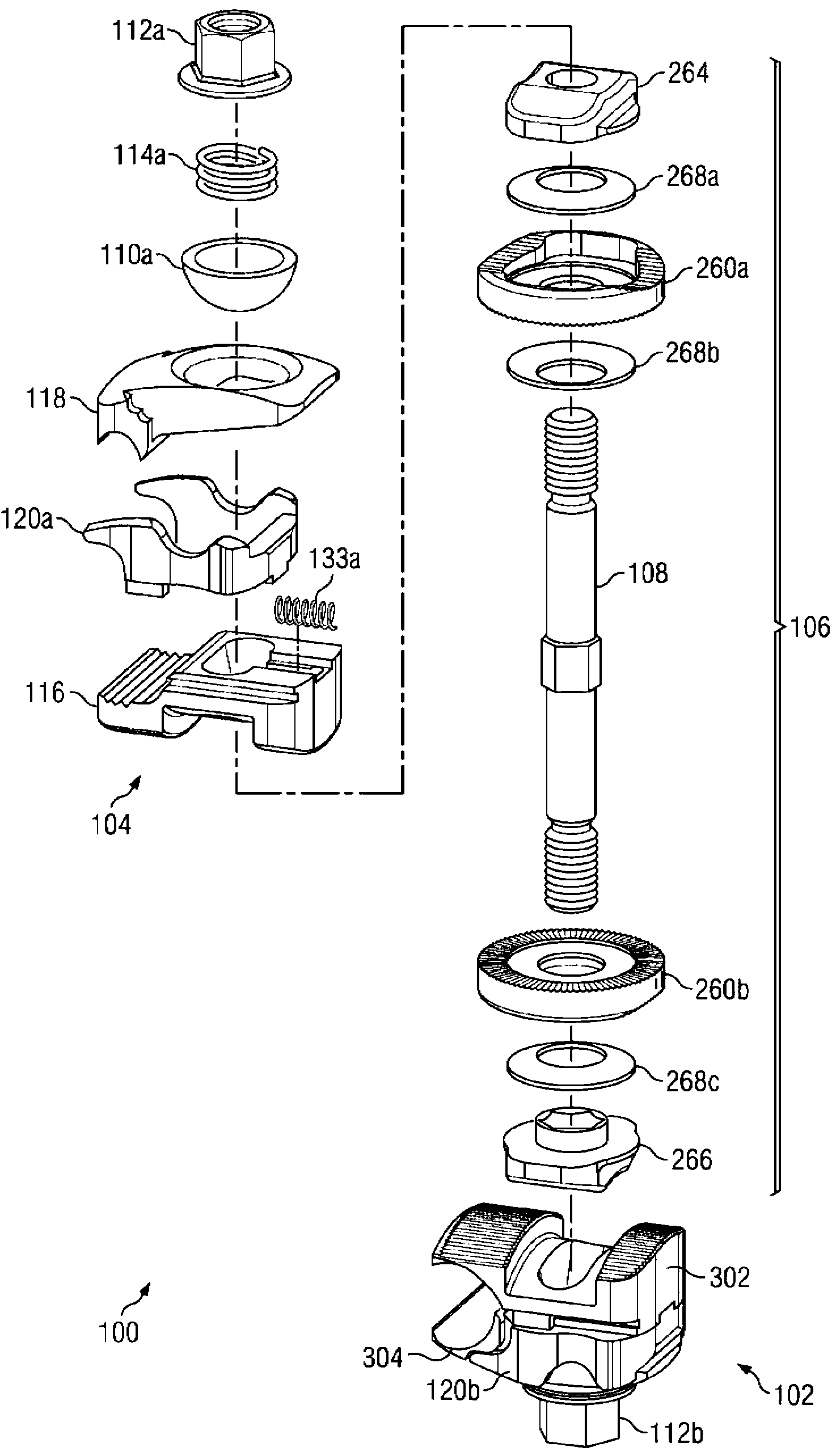

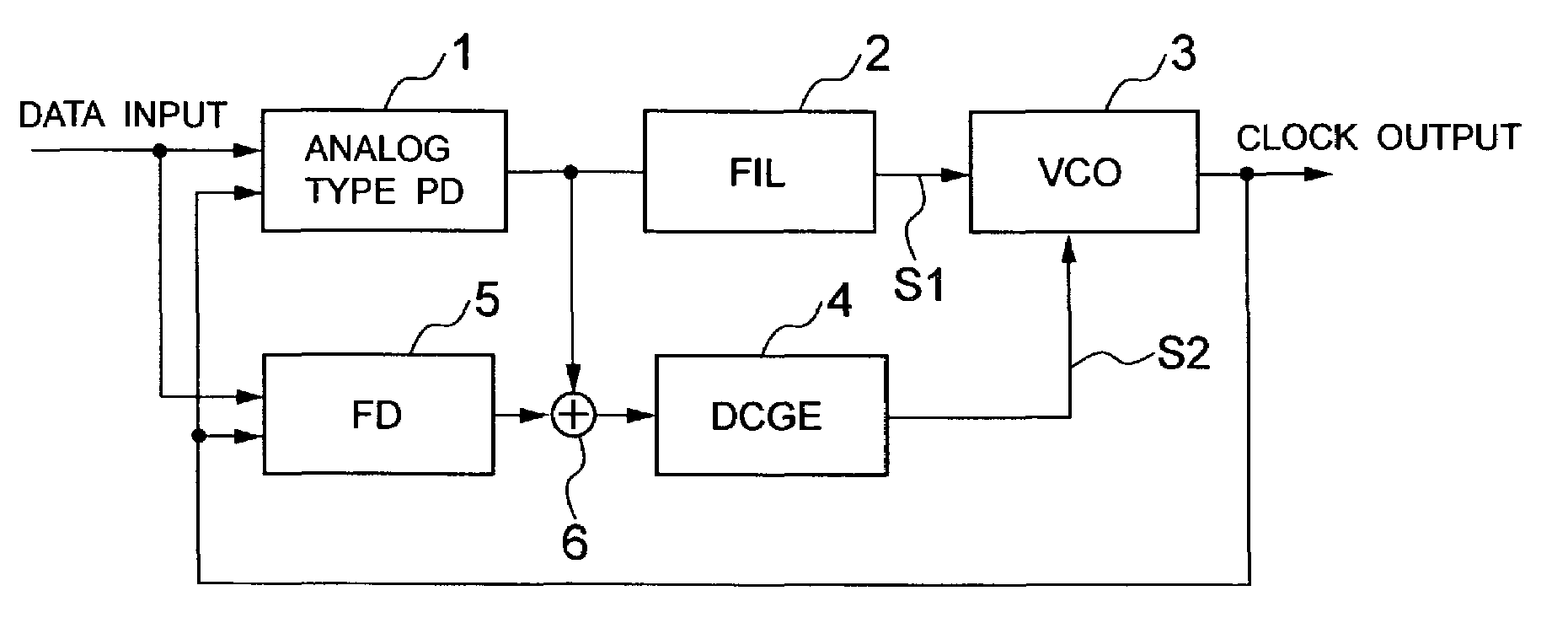

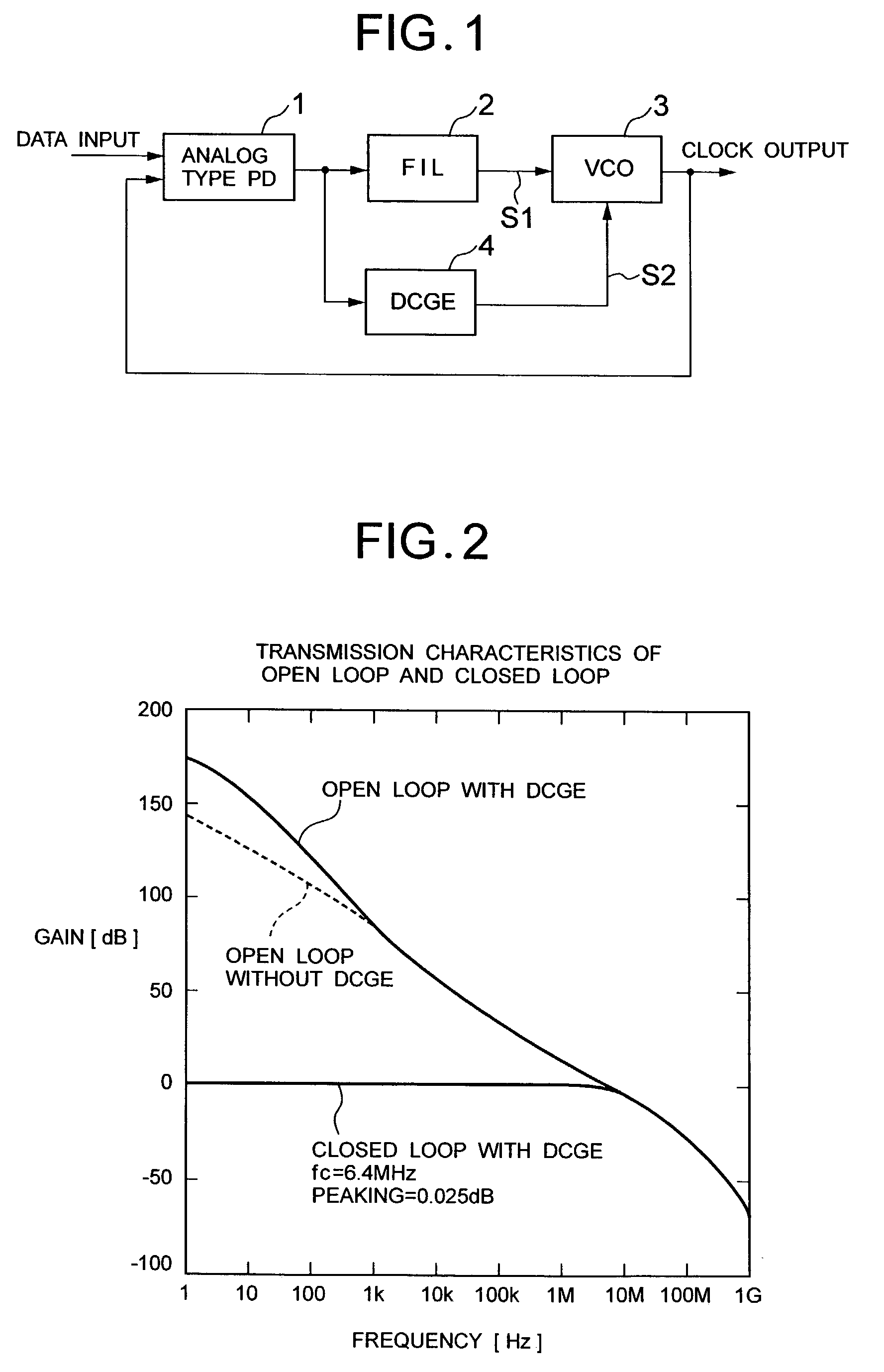

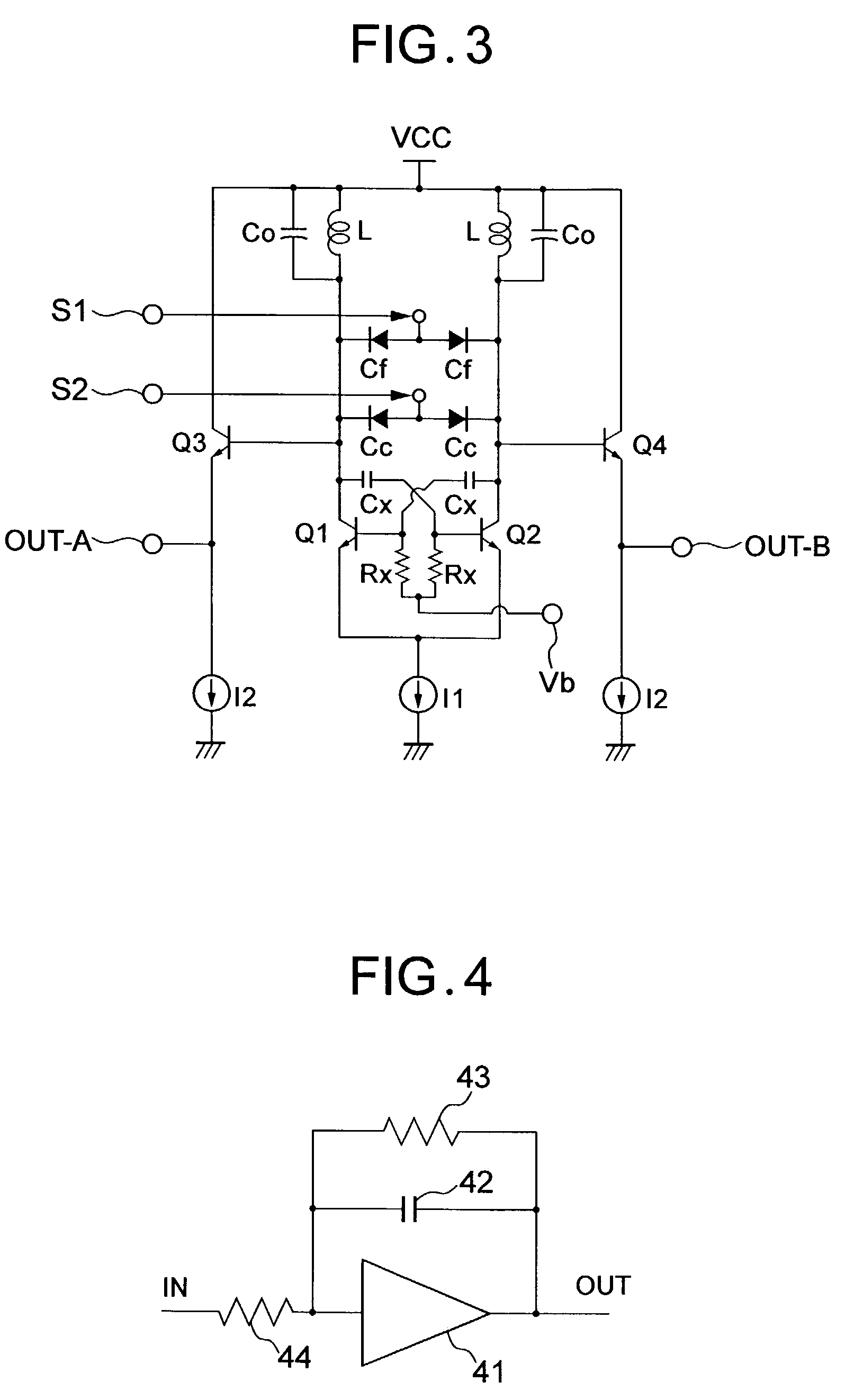

Phase locked loop circuit and clock reproduction circuit

InactiveUS7158602B2Wide locking rangeHigh gainPulse automatic controlOscillations generatorsLoop controlLow speed

A phase locked loop circuit and a clock reproduction circuit can operate stably with satisfying both of wide lock range and good jitter characteristics. The phase locked loop circuit for generating a clock signal in synchronized in phase with an input signal, has a phase comparator having an analog characteristics as a phase difference detection output characteristics and detecting a phase difference between the input signal and the clock signal, a first control loop controlled oscillation depending upon the phase difference detection output and a second control loop controlled oscillation depending upon a signal derived from the phase difference detection output with enhancing frequency components near a direct current component and performs low speed control in comparison with the first control loop.

Owner:NEC CORP

Method for Improving Performance of Wavelength Beam Combining Diode Laser Systems

ActiveUS20150229099A1Fast turn-on time output powerImprove reflectivityLaser detailsLaser optical resonator constructionLight beamLength wave

Owner:PANASONIC OF NORTH AMERICA

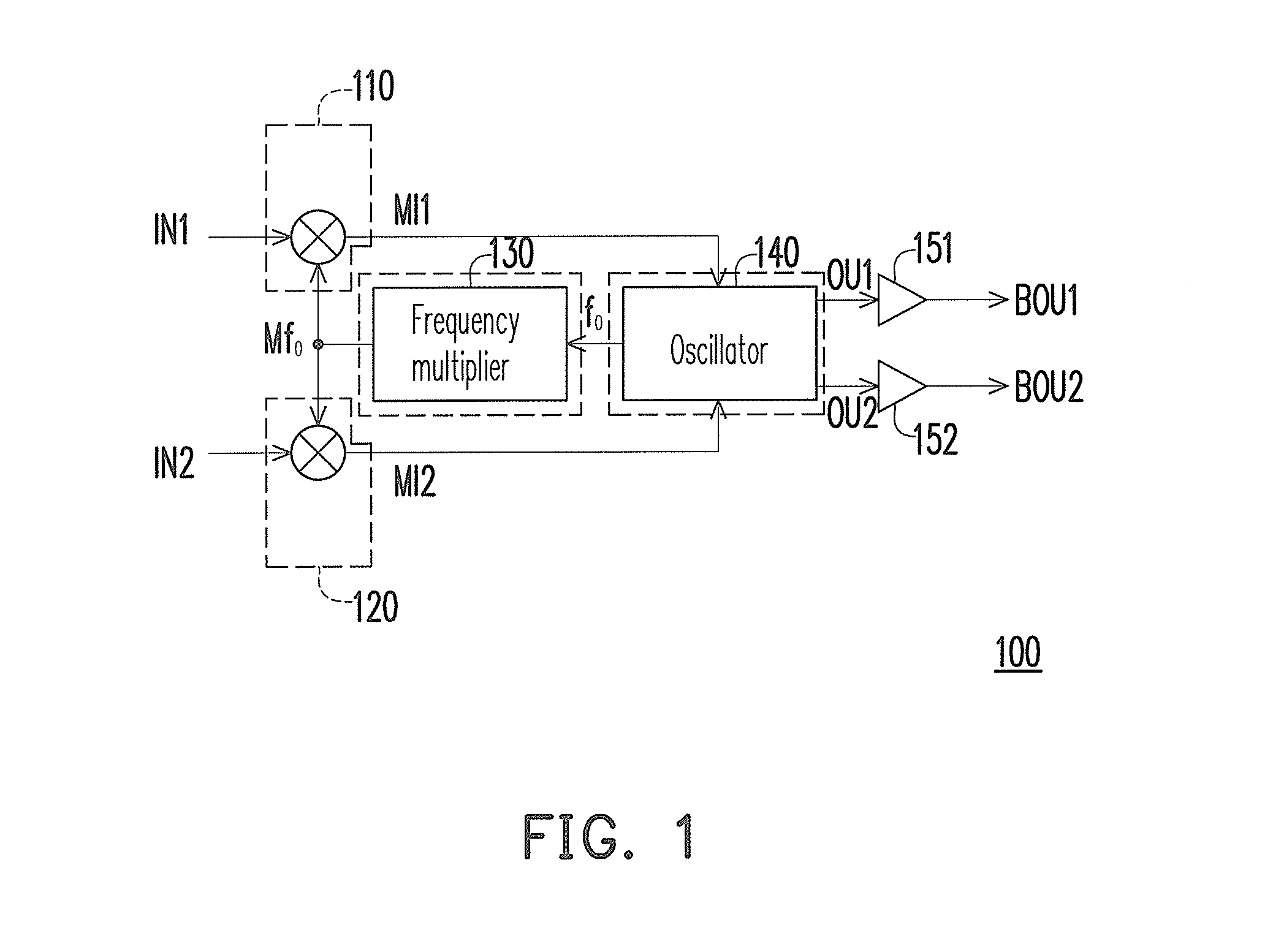

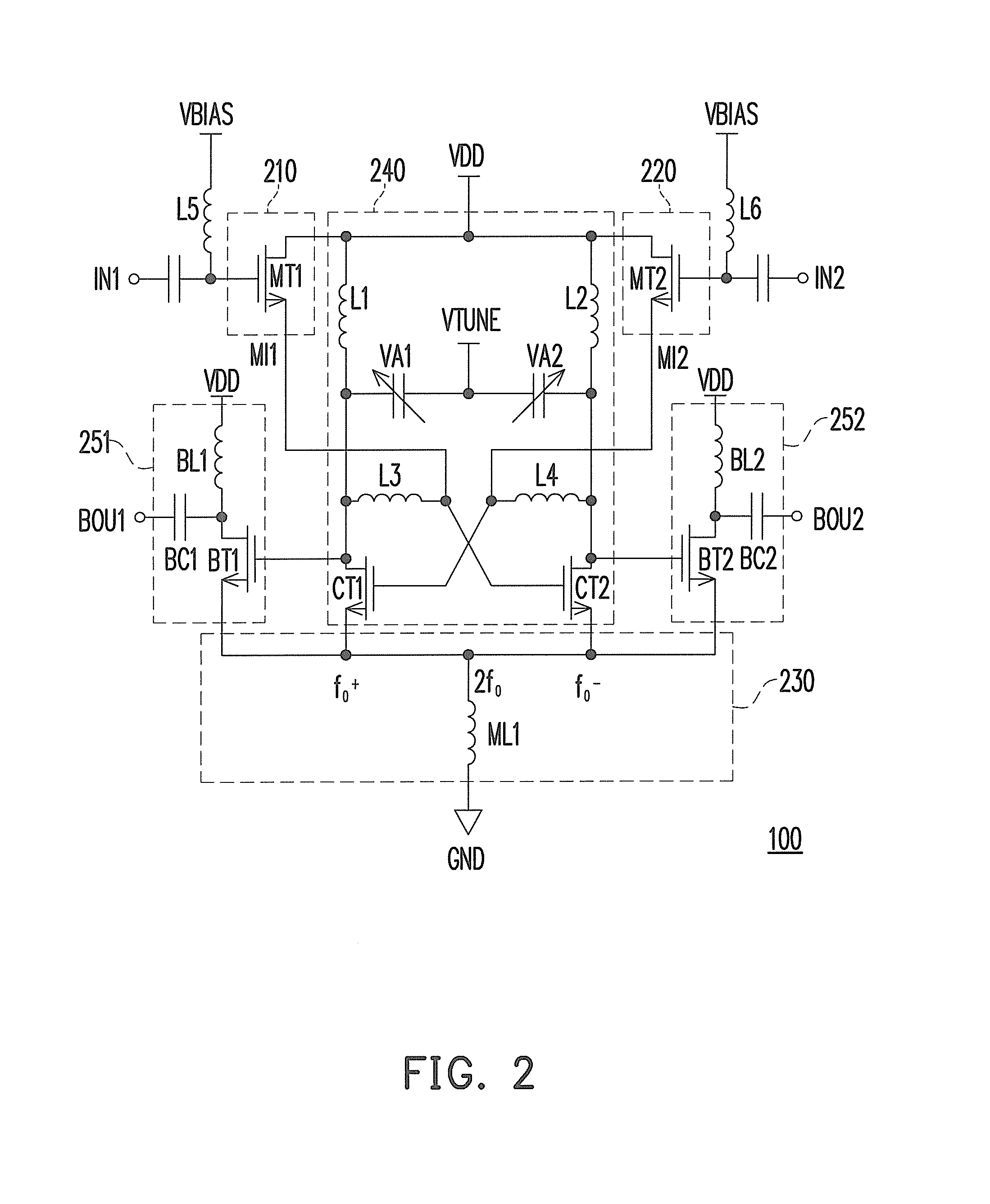

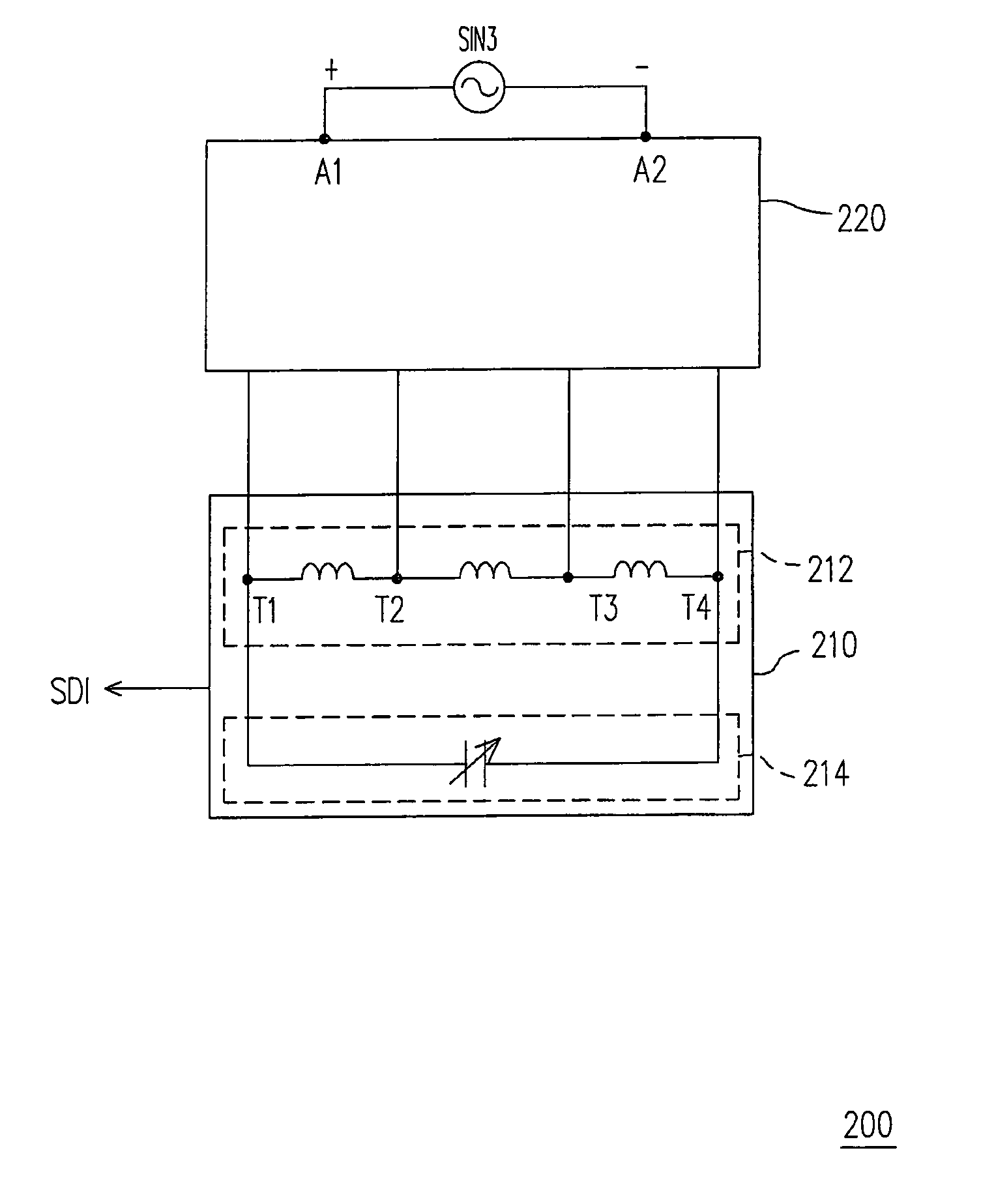

Injection-locked frequency dividing apparatus

InactiveUS8305116B2Easy to lockIncrease lock rangeCounting chain pulse countersPulse counters with static storageInjection lockedFrequency mixer

An injection-locked frequency dividing apparatus including a frequency multiplier, a first linear mixer, a second linear mixer, and an oscillator is disclosed. The frequency multiplier receives a frequency signal and generates a multiple-frequency signal accordingly. The first and the second linear mixer both receive the multiple-frequency signal and respectively receive a first input signal and a second input signal, wherein the phases of the first and the second input signal are complementary. The first and the second linear mixer respectively mix the multiple-frequency signal with the first and the second input signal to respectively generate a first mixed signal and a second mixed signal. The oscillator generates the frequency signal. The oscillator further receives the first and the second mixed signal and generates a first output signal and a second output signal accordingly, wherein the phases of the first and the second output signal are complementary.

Owner:NAT TAIWAN UNIV OF SCI & TECH

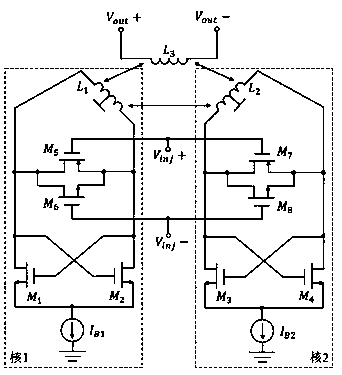

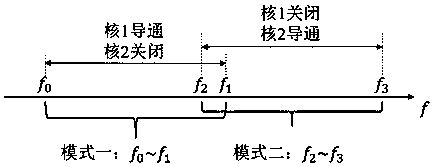

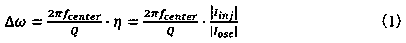

Switchable dual-core injection locking frequency divider with wide locking range

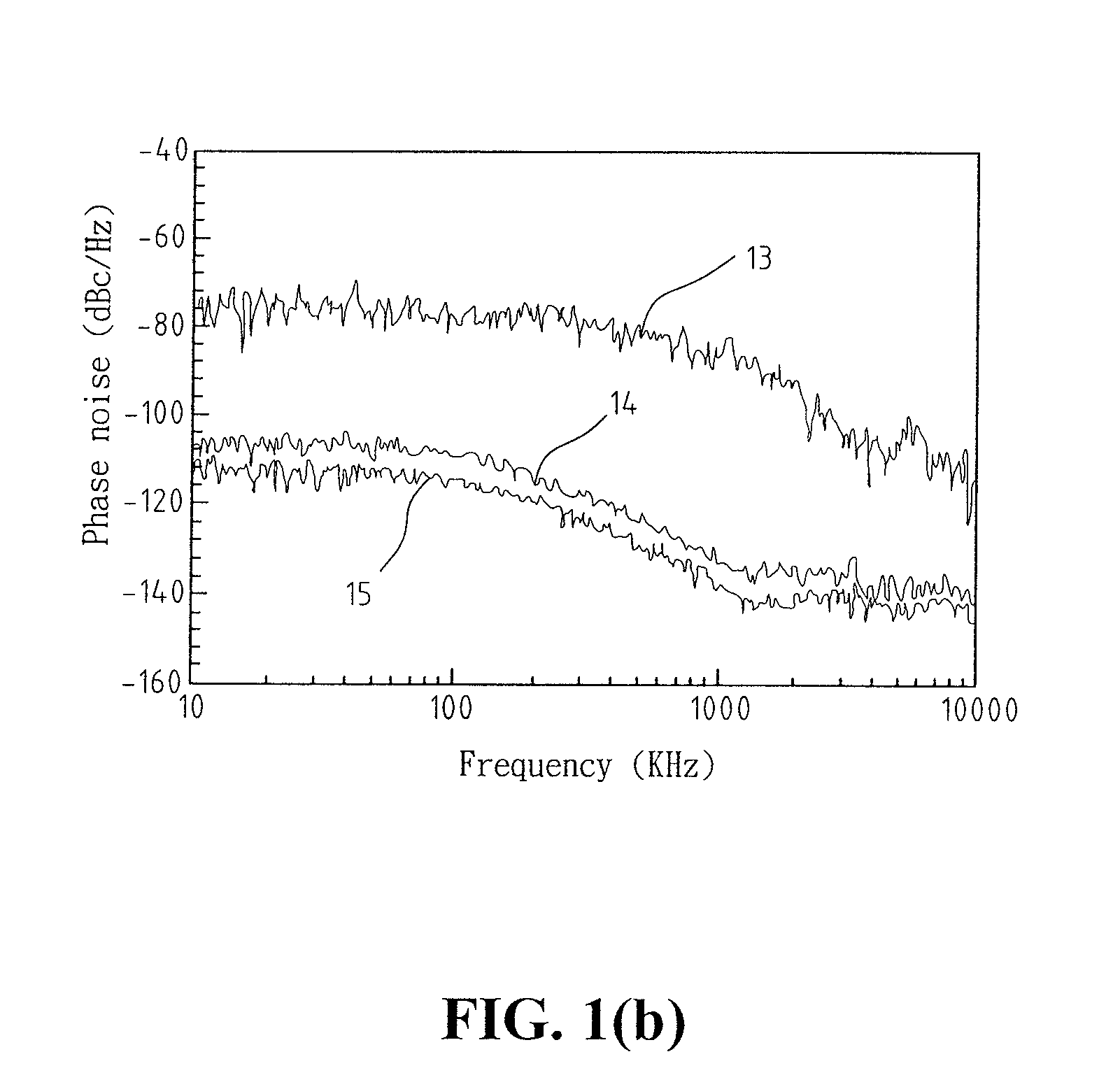

PendingCN111313892APhase Noise BoostIncrease lock rangePulse automatic controlHigh level techniquesParasitic capacitorResonance point

The invention discloses a switchable dual-core injection locking frequency divider with a wide locking range, and the frequency divider enables two self-resonant frequencies to be distributed at different frequencies through employing different parasitic capacitances of a cross coupling tube when two cores are connected and disconnected. The locking ranges in the two modes are added, so the overall locking range is greatly expanded; the resonant cavity oscillates at a lower resonance point of the transformer in two modes, the quality factor of the resonant cavity is optimized to improve the phase noise of the frequency divider, and the better overall performance can be achieved in the aspects of power consumption, output power and the like by optimizing the parameters of the transformer, the injection pipe, the cross coupling pipe and other elements. The structure is simple, and integration is facilitated.

Owner:TIANJIN UNIV MARINE TECH RES INST

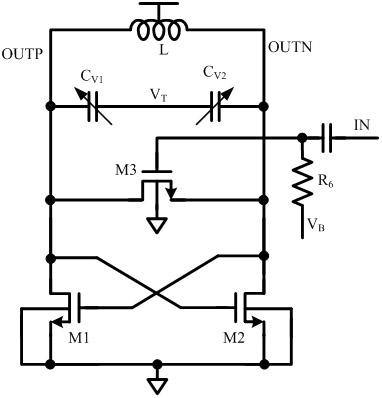

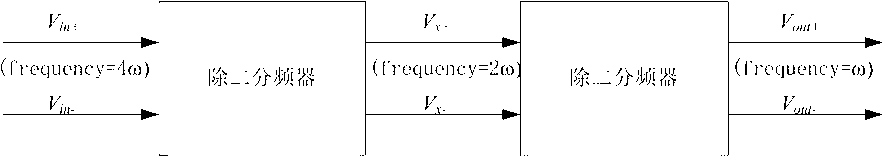

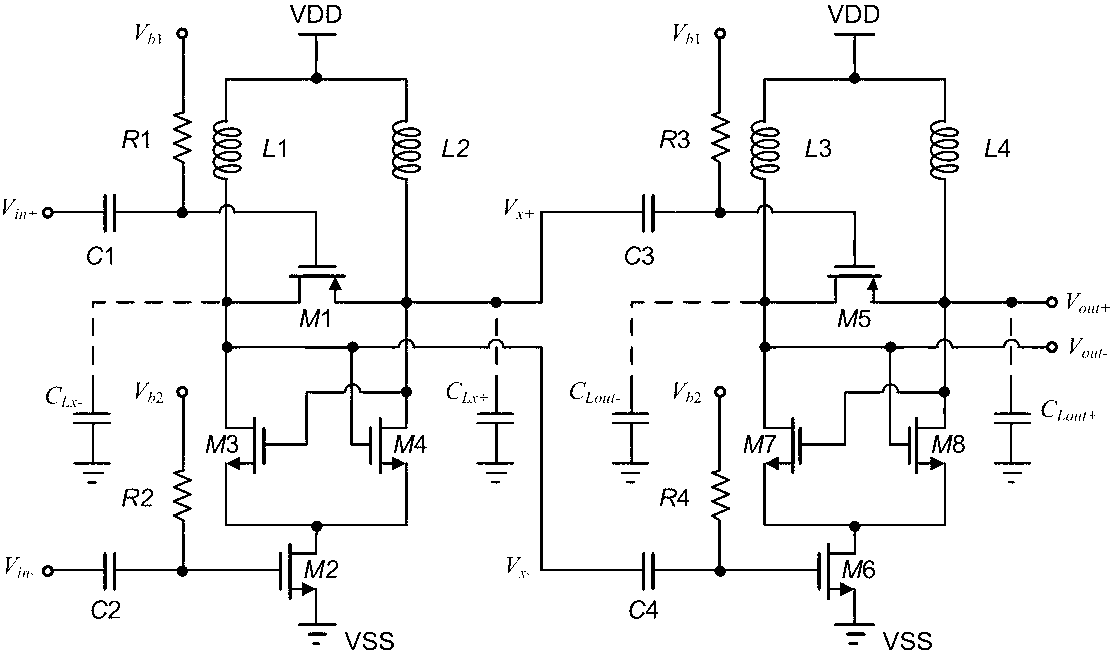

Divide-by-four injection locked frequency divider circuit with low power consumption and wide lock range

InactiveCN102710260AImprove injection efficiencyImprove output swingPulse automatic controlCapacitanceInjection locked

The invention belongs to the technical field of integrated circuits and particularly discloses a divide-by-four injection locked frequency divider circuit with low power consumption and wide lock range. The divide-by-four injection locked frequency divider circuit is composed of two stages of divide-by-two injection locked frequency dividers with identical structures, circuit stages are coupled by adopting a capacitor, and each circuit stage is composed of an inductor, a crossed coupling pipe, two injection pipes, a coupling capacitor and a biasing circuit. For the structure of the circuit, two injection manners including a direct injection manner and a tail current source injection manner are adopted at the same time, so that the circuit has the advantages of the two injection manners simultaneously, injection signals are inversion signals, an injection end is a grid electrode of an MOS (Metal Oxide Semiconductor) tube, and the divide-by-two injection locked frequency dividers can be directly cascaded. The circuit disclosed by the invention can be powered by dual-power-supply voltage, is suitable for a low power supply voltage environment, is low in direct-current power consumption and can be used to realize a wider lock range. The circuit is of a differential structure and can be realized by using CMOS (Complementary Metal Oxide Semiconductor), BiMOS (Bi-state Metal Oxide Semiconductor) and other processes.

Owner:FUDAN UNIV

Injection-locked frequency divider

InactiveUS7782101B2Increase lock rangeLow working voltageAngle modulation by variable impedenceCounting chain pulse countersCapacitanceInjection locked

An injection-locked frequency divider for dividing a frequency of an injection signal and obtaining a frequency divided signal is provided. The injection-locked frequency divider includes a signal injection unit and an oscillator. The signal injection unit includes a first input terminal and a second input terminal for receiving the injection signal. The received injection signal exhibits a phase difference of 180° between the first input terminal and the second input terminal. The oscillator includes an inductor unit and a variable capacitance unit. The injection-locked frequency divider is featured with a wide injection locking range, and can be realized with a low operation voltage, and therefore can be conveniently used in different kinds of hybrid ICs.

Owner:NAT TAIWAN UNIV OF SCI & TECH

C-type wingceltis bar and cross beam end adjustable connecting part

ActiveCN111441486AIncrease lock rangeRealize deadlockBuilding constructionsStructural engineeringMechanical engineering

Owner:JIANGSU JINHUI CONSTR & INSTALLATION ENG

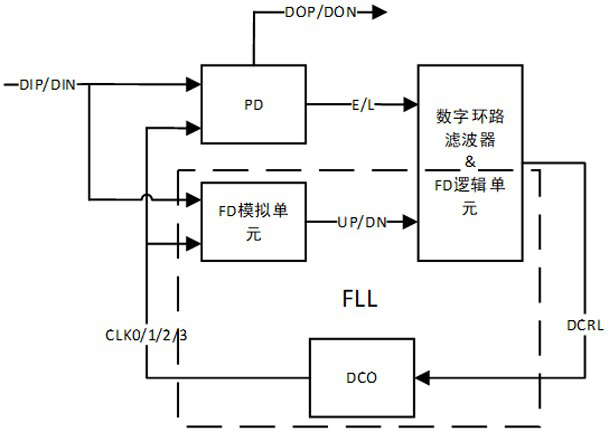

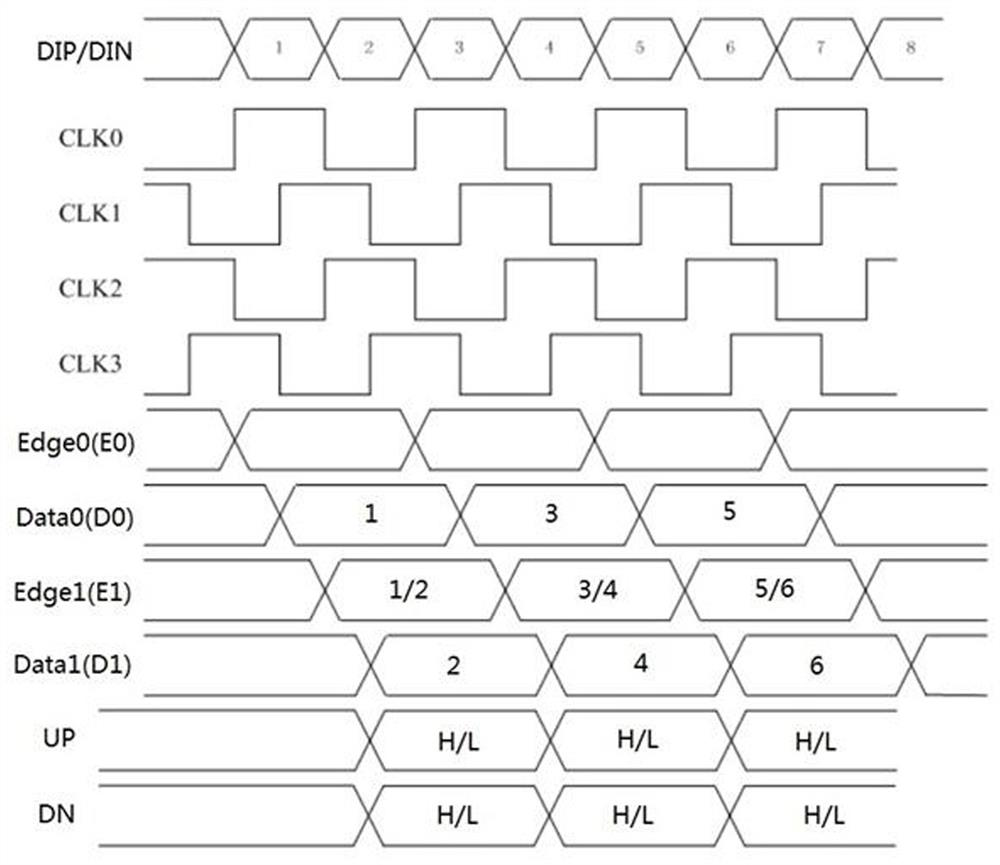

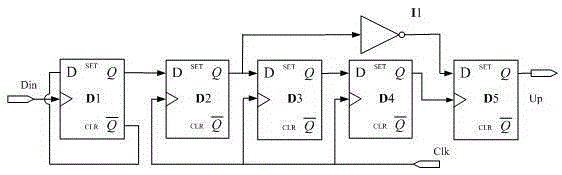

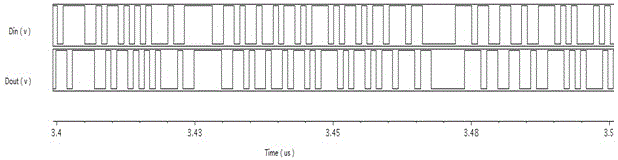

Frequency search and error correction method in clock data recovery circuit

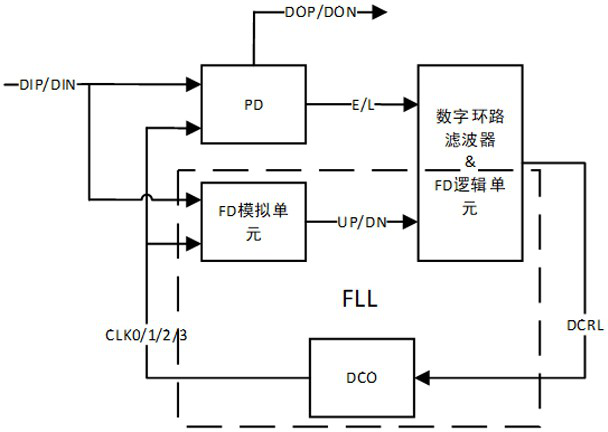

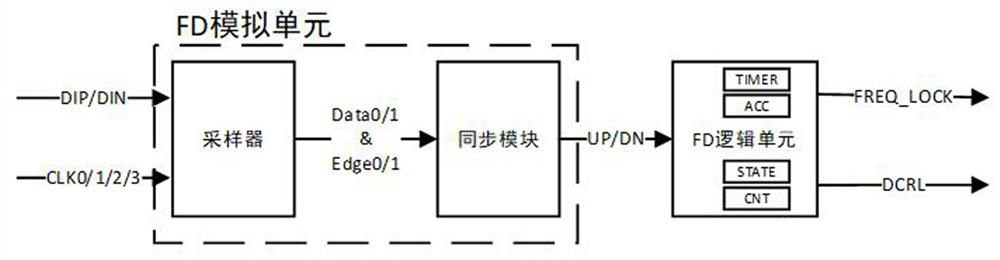

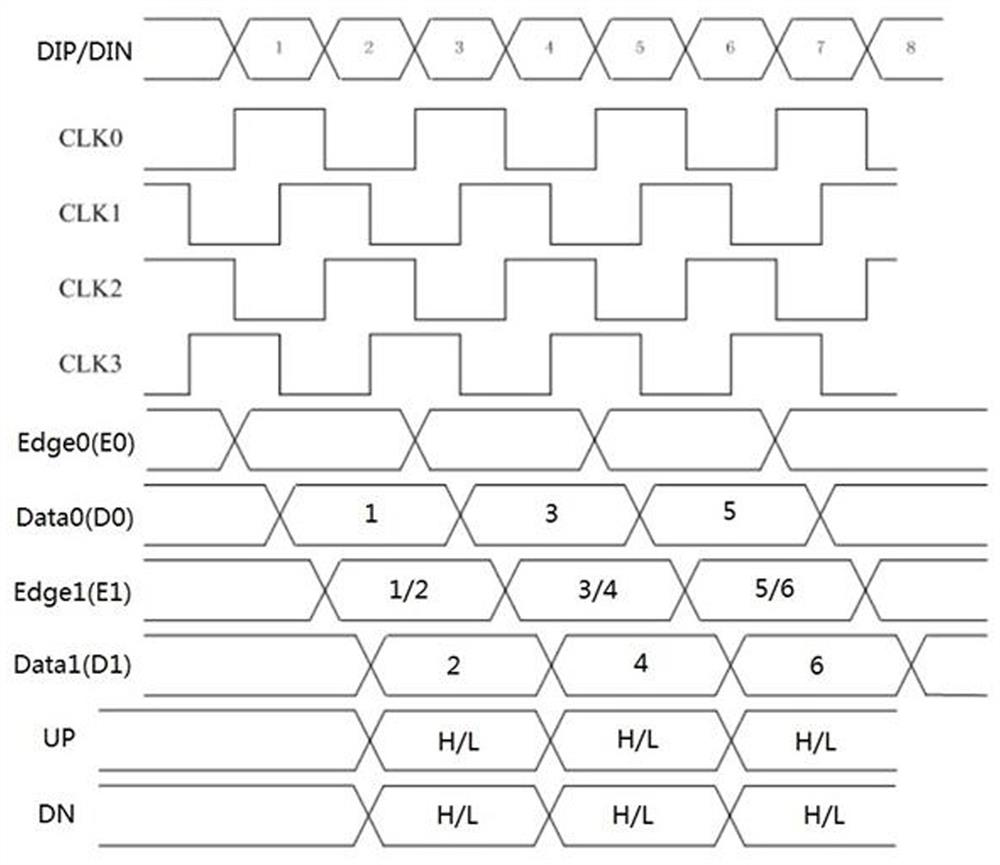

ActiveCN113938129AImprove compatibilityImprove usabilityPulse automatic controlControl theoryComputer science

The invention discloses a frequency search and error correction method in a clock data recovery circuit. The method comprises the following steps: initializing a frequency search algorithm parameter; processing a frequency error characteristic UP / DN signal according to the set algorithm parameters, starting frequency search, performing corresponding counting according to the frequency error characteristic UP / DN signal, when phase error signal conversion occurs, accumulating 1 to a jump parameter JUMP to obtain an accumulation parameter SUM, and further judging whether to output a frequency search result or not; and setting the number of times of repeated verification and a threshold parameter, obtaining a reset DCRL value verification frequency locking result, and outputting the result. The UP / DN pulse counting accuracy is improved, the stability and reliability of frequency locking are improved, false locking in frequency locking is prevented, the frequency locking time is prevented from being too long, the problem of frequency search misjudgment caused by random jitter is solved, frequency search and locking are accurately completed, and the problem that a CDR cannot work due to wrong frequency locking is solved.

Owner:EVERPRO TECH COMPANY

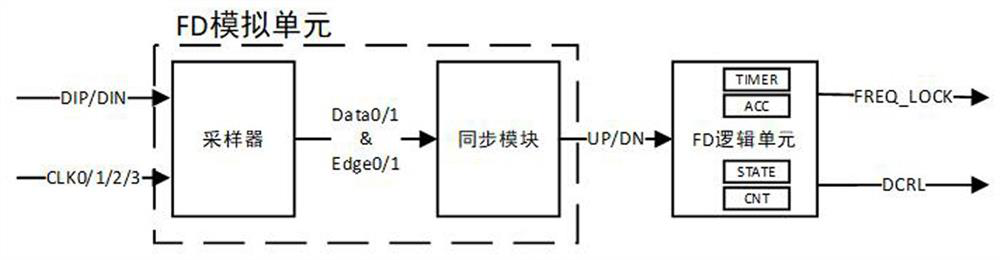

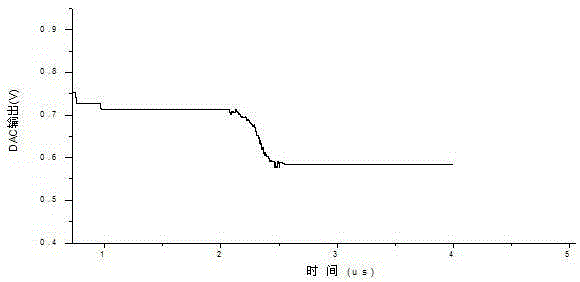

A semi-blind oversampling clock data recovery circuit with high locking range

The invention discloses a semi-blind oversampling clock data recovery circuit with a high locking range, which is mainly used for improving the range of application of the semi-blind oversampling clock data recovery circuit and avoiding generating error code during excessive continuous word time data recovery. The semi-blind oversampling clock data recovery circuit comprises a receiver (1) composed of a multi-path parallel oversampling circuit (11) and a frequency detector FD (12), a data recovery and frequency phase control circuit (2) composed of a filtering and shaping circuit (21), an edge detection circuit (22), a data recovery circuit (23), a phase information circuit (24), a byte adjustment circuit (25) and a frequency / phase adjustment circuit (26), and a feedback circuit (3) composed of a multi-phase VCO (Voltage Controlled Oscillator) circuit (31), a LPF (Low Pass Filter) circuit (32) and an DAC (Digital to Analog Converter) circuit (33). Through the adjustment, the frequency of the sampling clock just can sample the input data, the locking is realized, and the clock data recovery is further accomplished.

Owner:NANJING UNIV OF POSTS & TELECOMM INST AT NANJING CO LTD

Clamping device

Owner:SMC CORP

Optical frequency locking method and device for optical data transmission

ActiveUS9166695B2Increase lock rangeMaximize rangeSemiconductor laser arrangementsLaser output parameters controlOptical data transmissionOptical power

Owner:ADVA OPTICAL NETWORKING SE

Phase discrimination circuit of delay phase-locked loop

The invention provides a phase discriminator circuit of a delay phase-locked loop, which comprises a frequency dividing circuit, a retiming circuit, a reference time delay circuit and a phase discriminator main body circuit. The frequency dividing circuit is connected with the retiming circuit, the retiming circuit is connected with the reference time delay circuit, and the reference time delay circuit is connected with the phase discriminator main body circuit. The phase discrimination circuit of the delay phase-locked loo comprises the frequency division circuit, the retiming circuit, the reference time delay circuit and the phase discriminator main body circuit, wherein the frequency division circuit, the retiming circuit and the reference delay circuit are added on the basis of the phase discriminator main body circuit; thus the delayed frequency division reference clock can be aligned with the frequency division feedback clock, and the locking range of the phase-locked loop is expanded.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

Harmonic suppression circuit, an injection-locked frequency divider circuit and associated methods

ActiveUS8198923B2Increase lock rangeHarmonic reductionOscillations generatorsTransmissionInjection lockedDifferential phase

The invention includes a harmonic suppression circuit, an injection-locked frequency divider circuit (ILFD) and associated methods. The harmonic suppression circuit comprises a source voltage, two suppression modules, two input terminals, two smoothed output terminals and a ground. The ILFD comprises a ground, an input transistor, an input terminal, two divider legs, two output terminals and a source voltage. The associated method to improve harmonic suppression comprises acts of synthesizing differential-phase signals and simultaneously suppressing second harmonics of in-phase signals. The method to extent an ILFD's locking range comprises acts of decreasing quality factor while keeping resonance frequency constant.

Owner:NAT TAIWAN UNIV

A frequency search and error correction method in a clock data recovery circuit

ActiveCN113938129BImprove compatibilityImprove usabilityPulse automatic controlWrong frequencyControl theory

A frequency search and error correction method in a clock data recovery circuit, comprising: initializing frequency search algorithm parameters; processing the frequency error characteristic UP / DN signal according to the set algorithm parameters, and starting frequency search, wherein according to the frequency error characteristic UP The / DN signal is counted accordingly. When there is a phase error signal conversion, add 1 to the jump parameter JUMP to obtain the accumulated parameter SUM, and further judge whether to output the frequency search result; set the number of repeated verifications and threshold parameters to obtain the reset The DCRL value verifies the frequency lock result and outputs it. The invention improves the counting accuracy of UP / DN pulses, increases the stability and reliability of frequency locking, prevents false locking in frequency locking and avoids too long frequency locking time, and overcomes the problem of wrong judgment of frequency search caused by random jitter , Accurately complete frequency search and lock, avoiding the problem that CDR cannot work due to wrong frequency lock.

Owner:EVERPRO TECH COMPANY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com