Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

54results about How to "Improve substrate strength" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

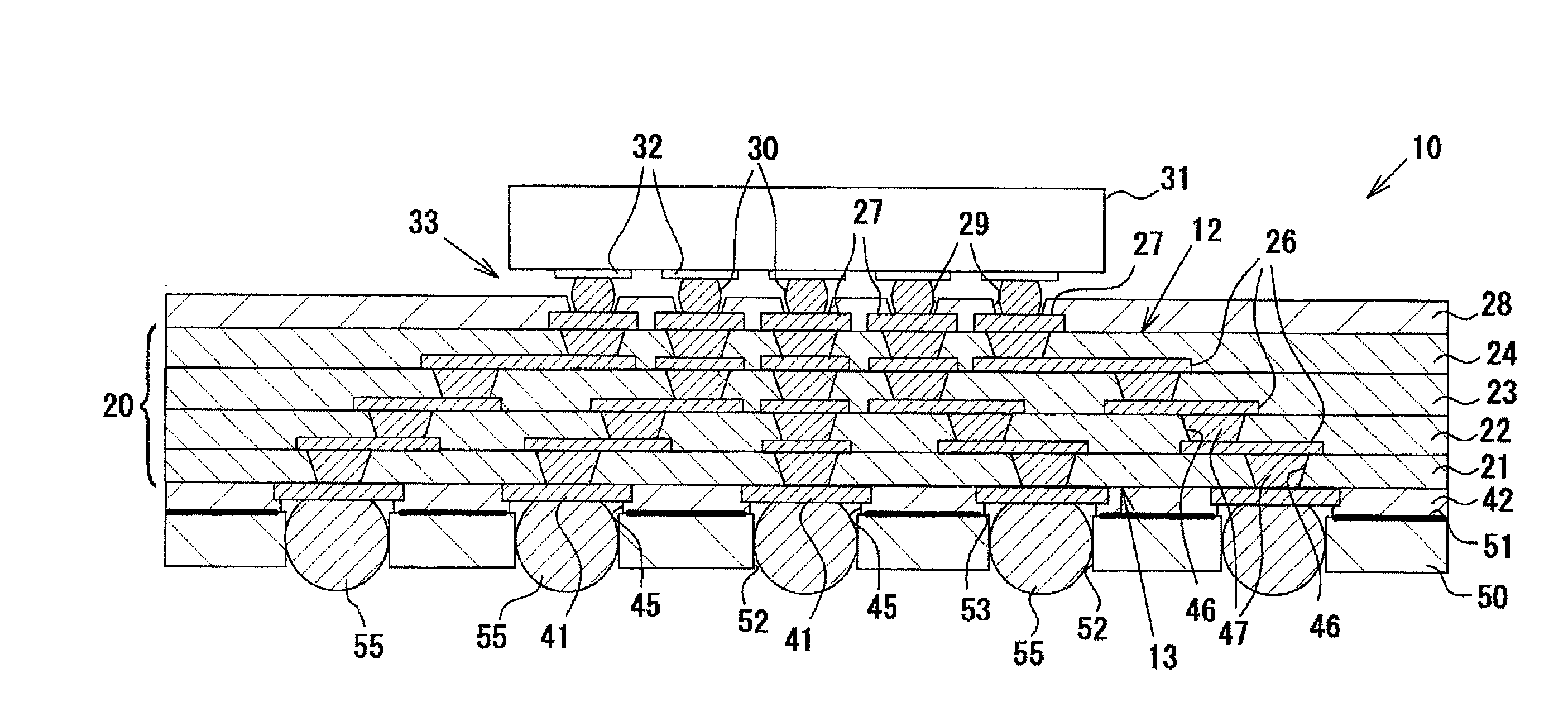

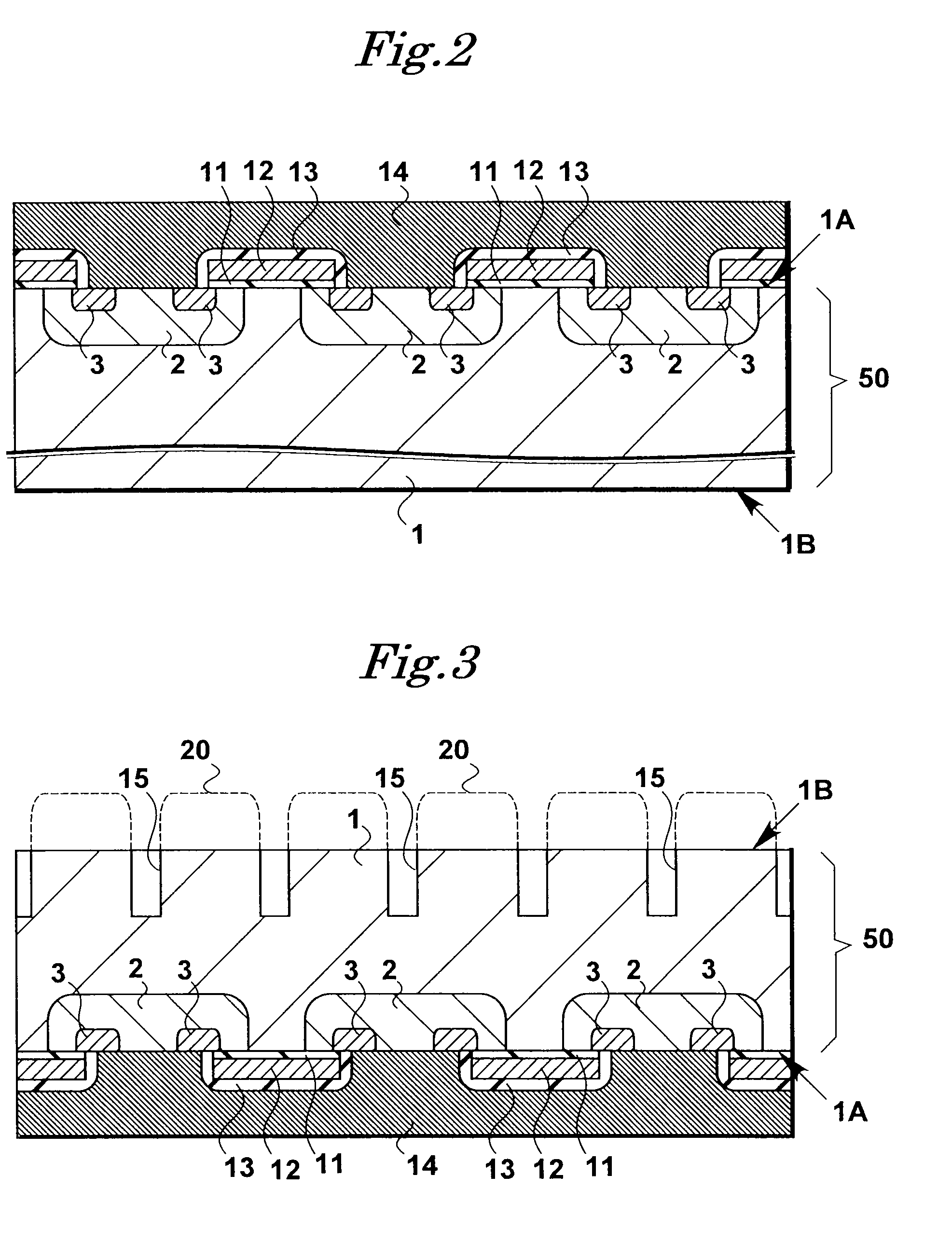

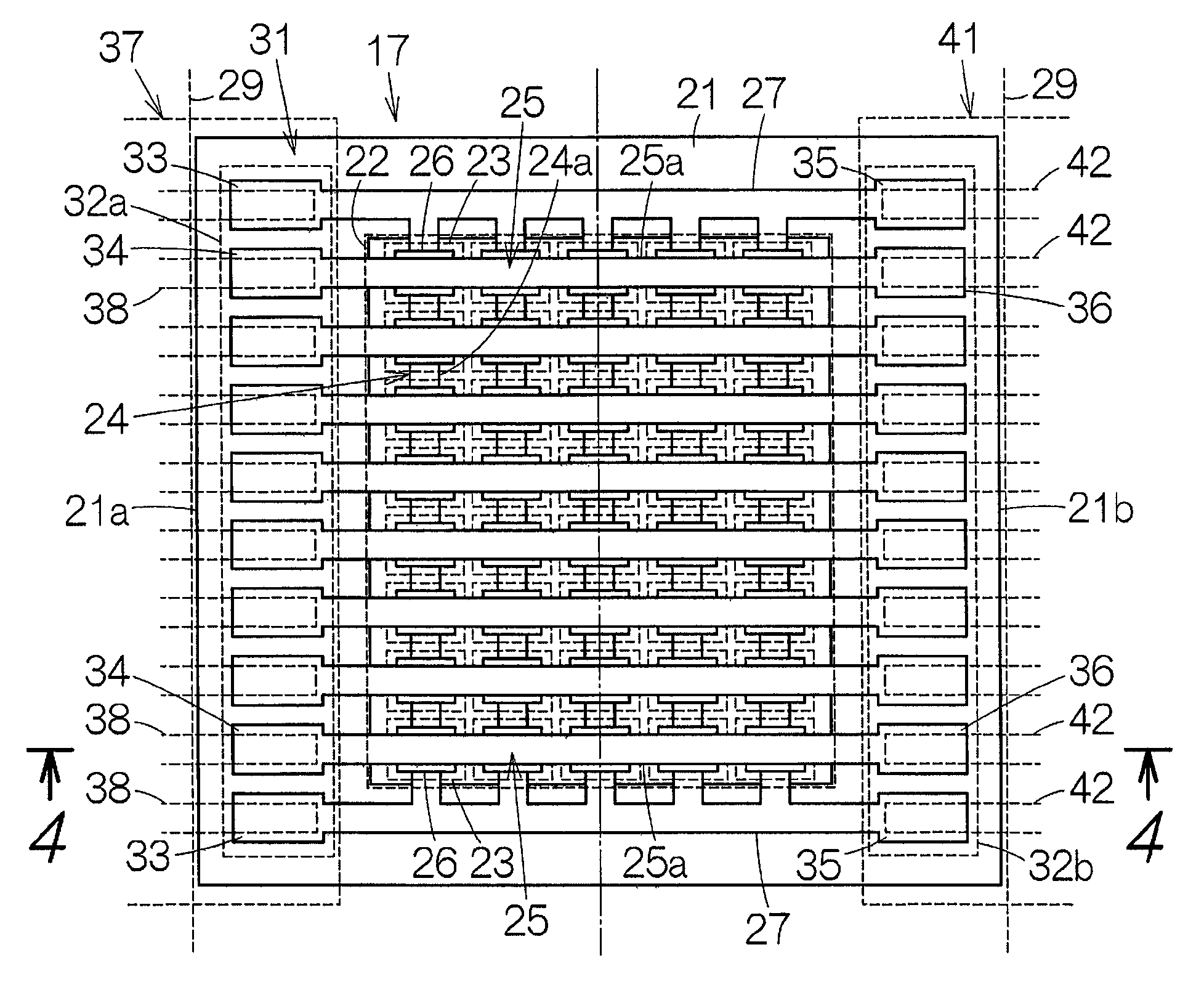

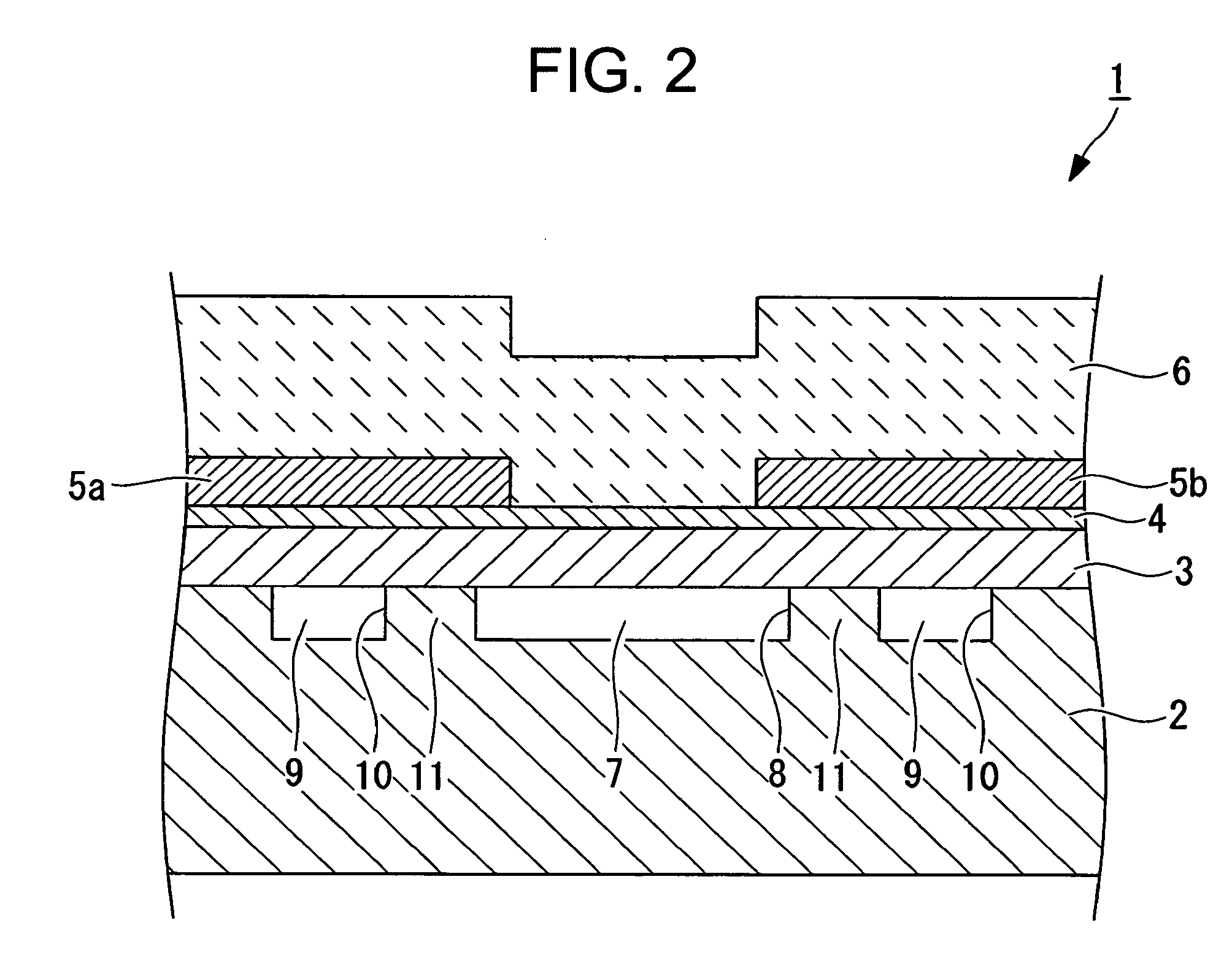

Multi-layer wiring board and method of manufacturing the same

InactiveUS20090242245A1High bonding strengthEasy to processFinal product manufactureSemiconductor/solid-state device detailsResistMetallic materials

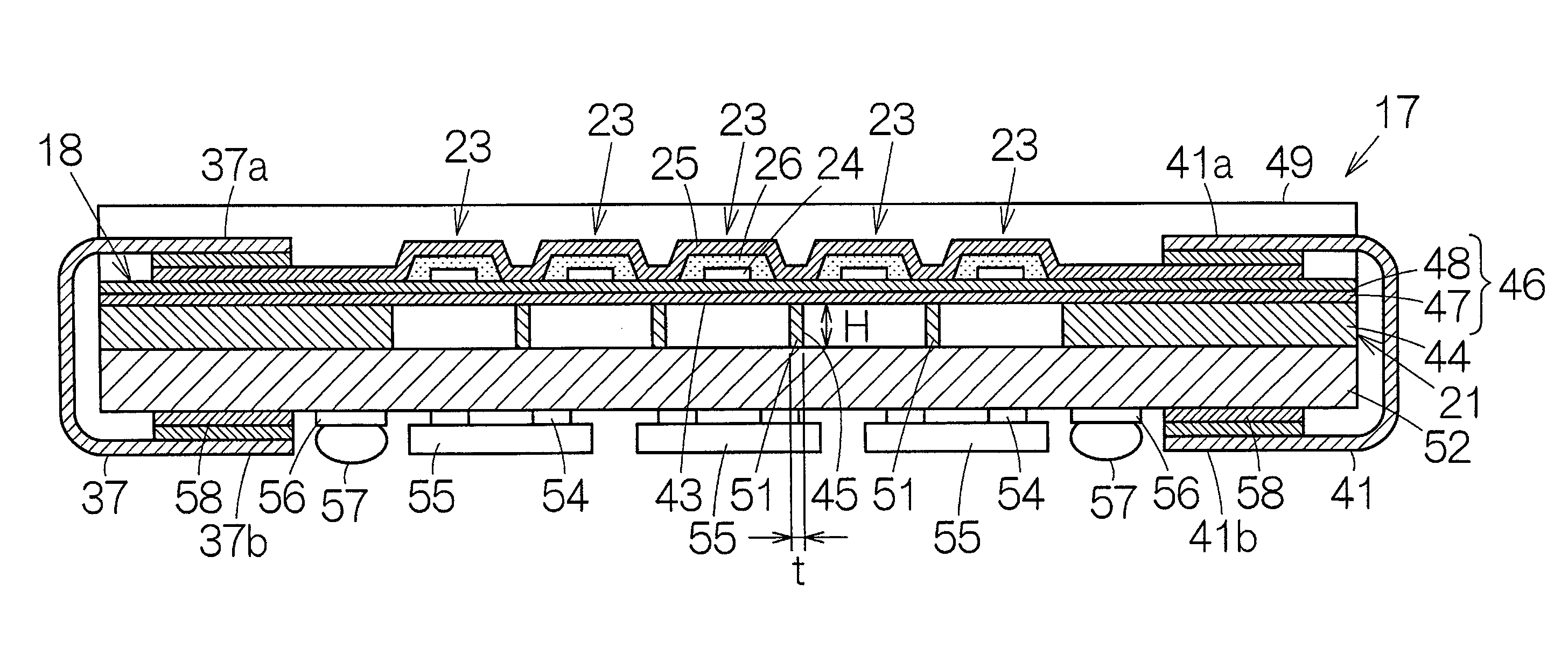

A multi-layer wiring board without a core substrate includes: a multi-layer laminated structure; first terminals provided on a front surface of the multi-layer laminated structure; second terminals provided on a rear surface of the multi-layer laminated structure; a solder resist which covers the rear surface and which has solder resist openings formed at positions corresponding to the second terminals; a reinforcing plate which is made of a non-metal material and which has reinforcing plate openings formed at positions corresponding to the second terminals; and an adhesive layer interposed between the solder resist and the reinforcing plate to fix the reinforcing plate to the solder resist and which includes adhesive layer openings formed at positions corresponding to the second terminals. A diameter of the solder resist openings and a diameter of the reinforcing plate openings are smaller than that of the adhesive layer openings.

Owner:NGK SPARK PLUG CO LTD

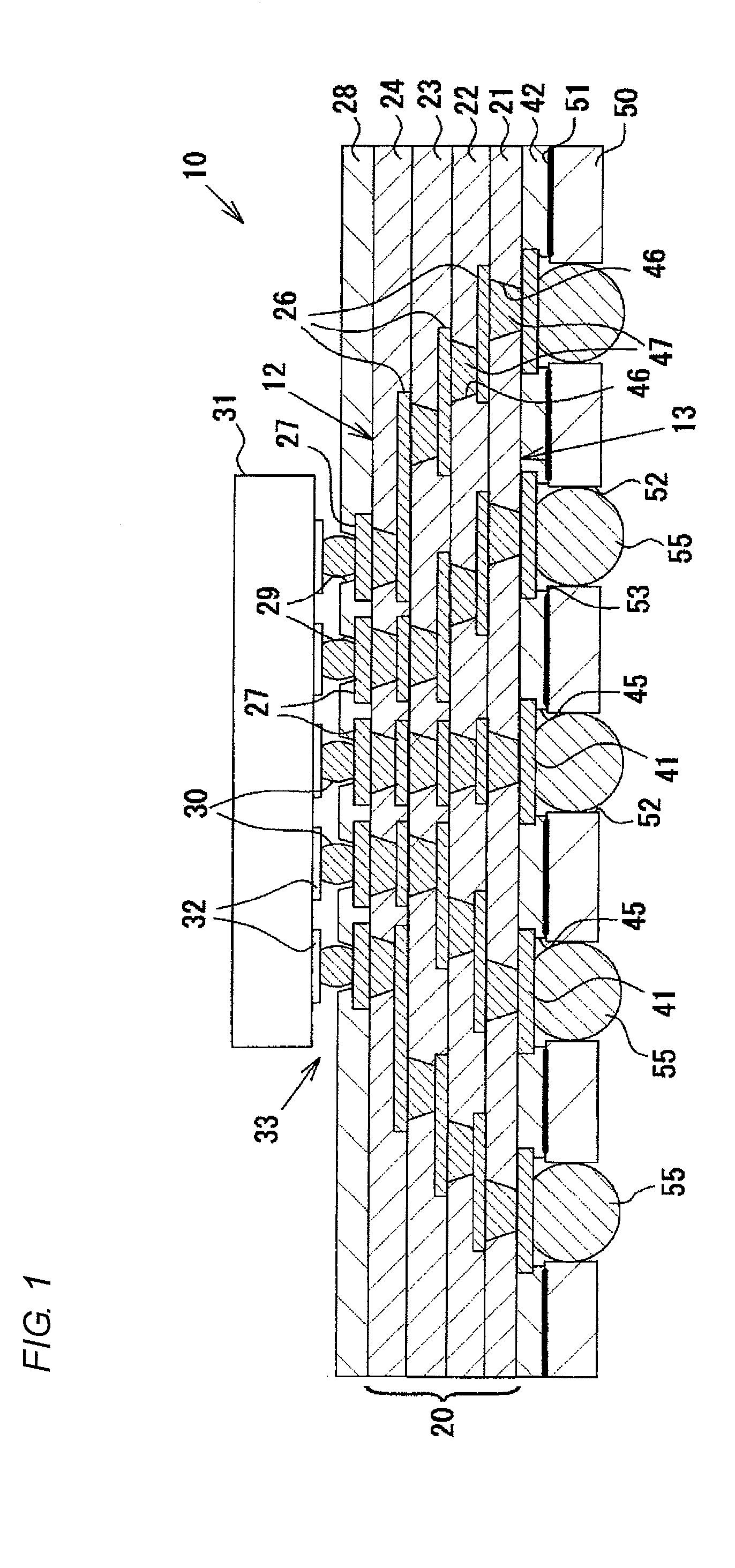

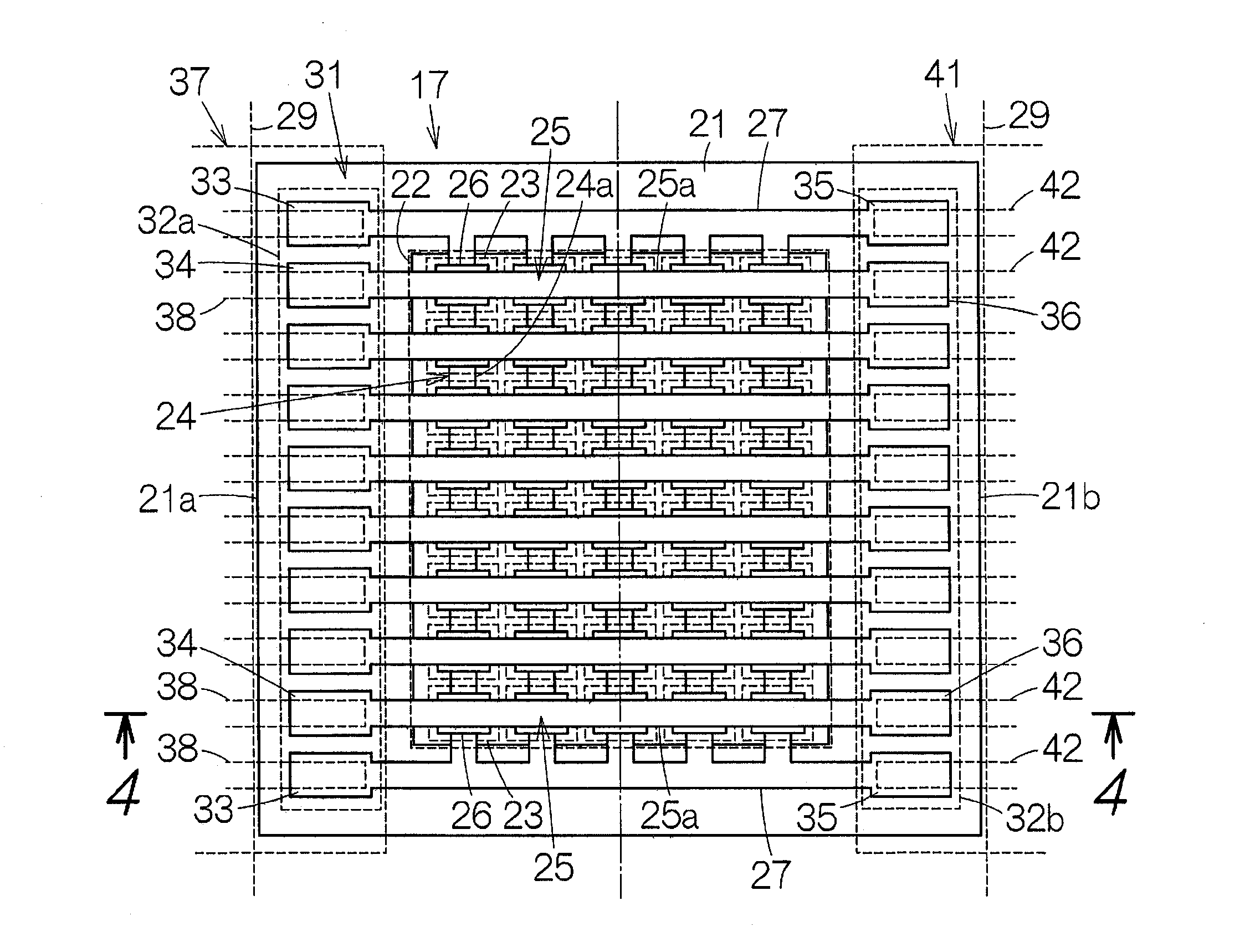

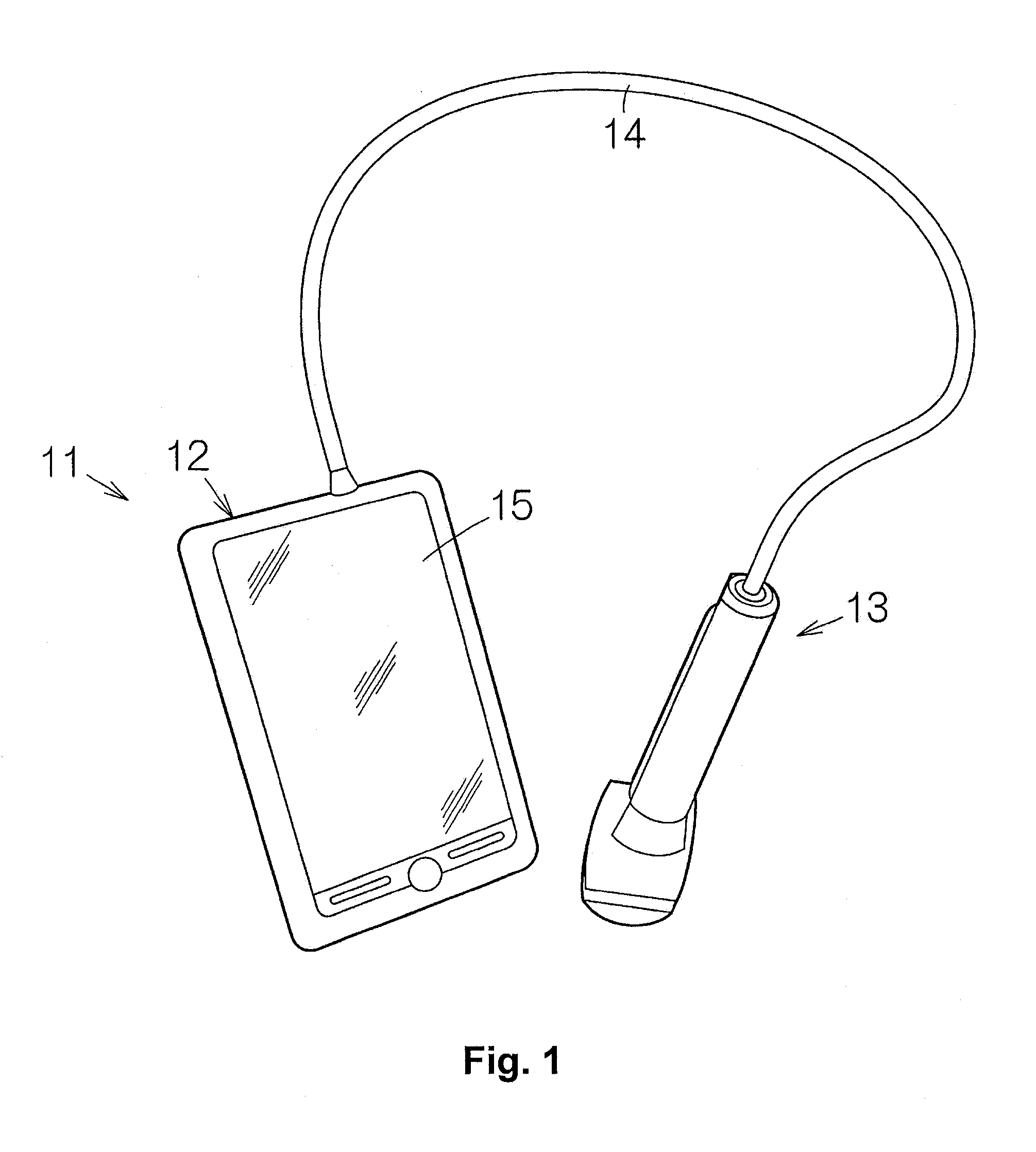

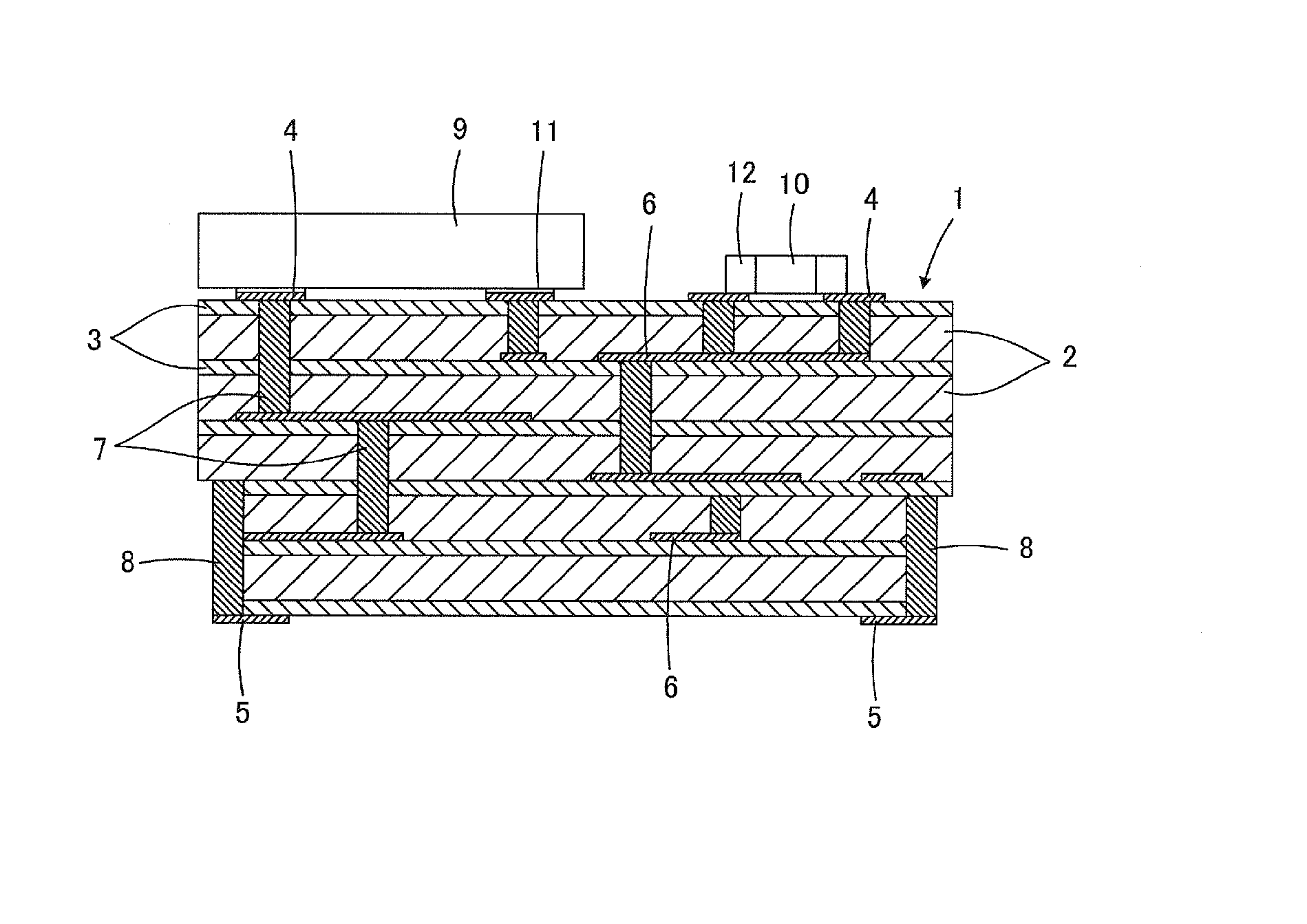

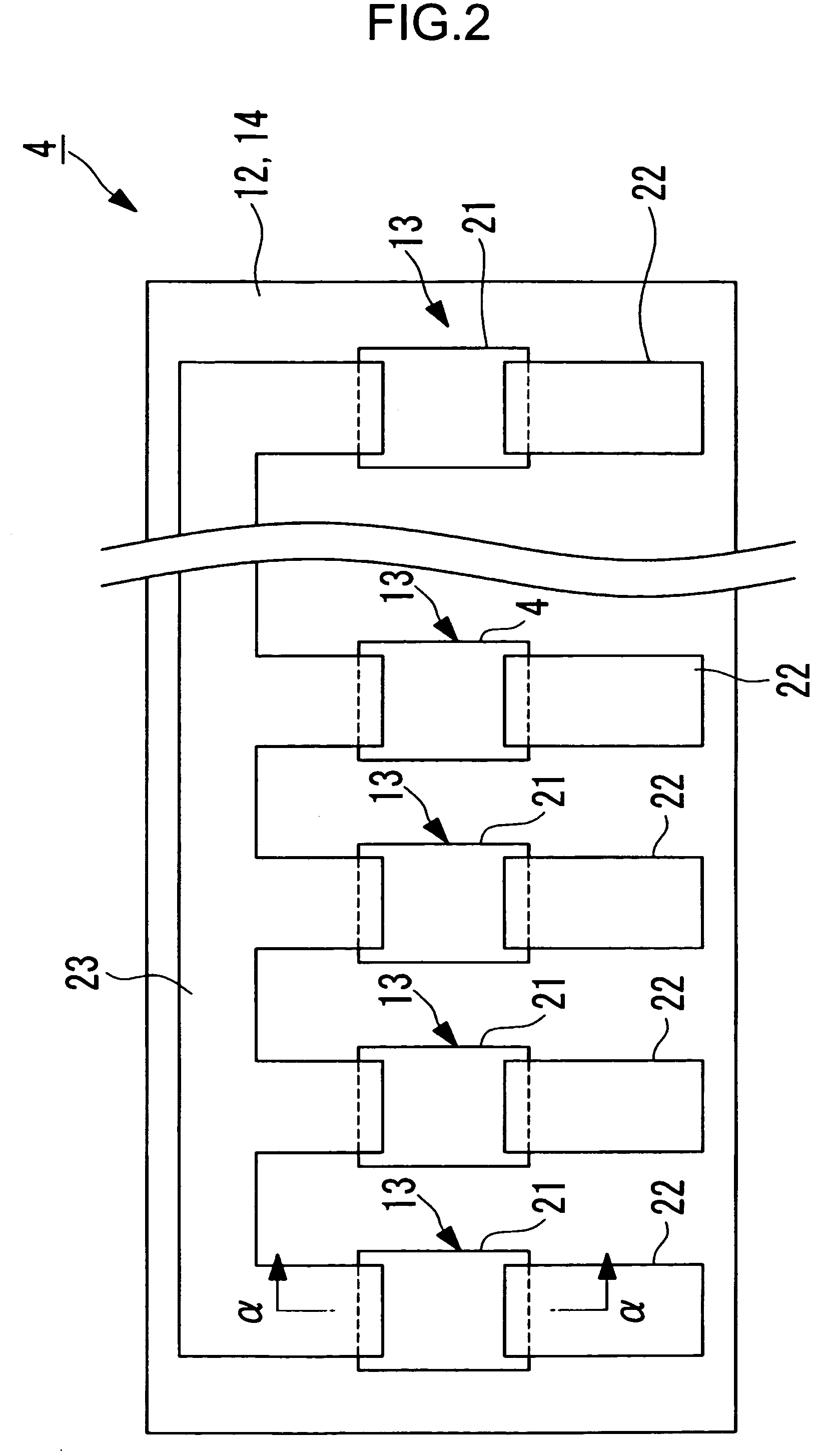

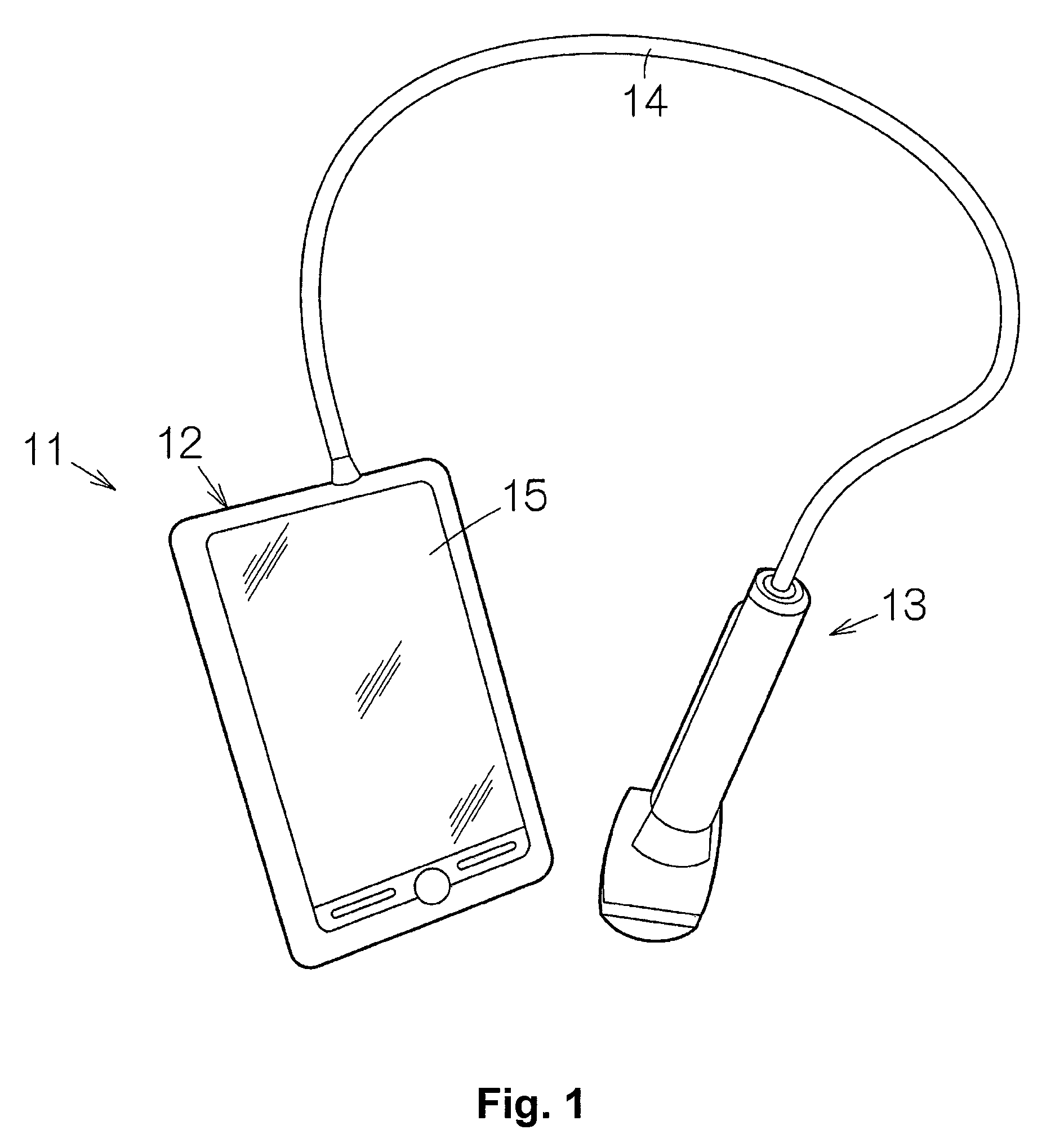

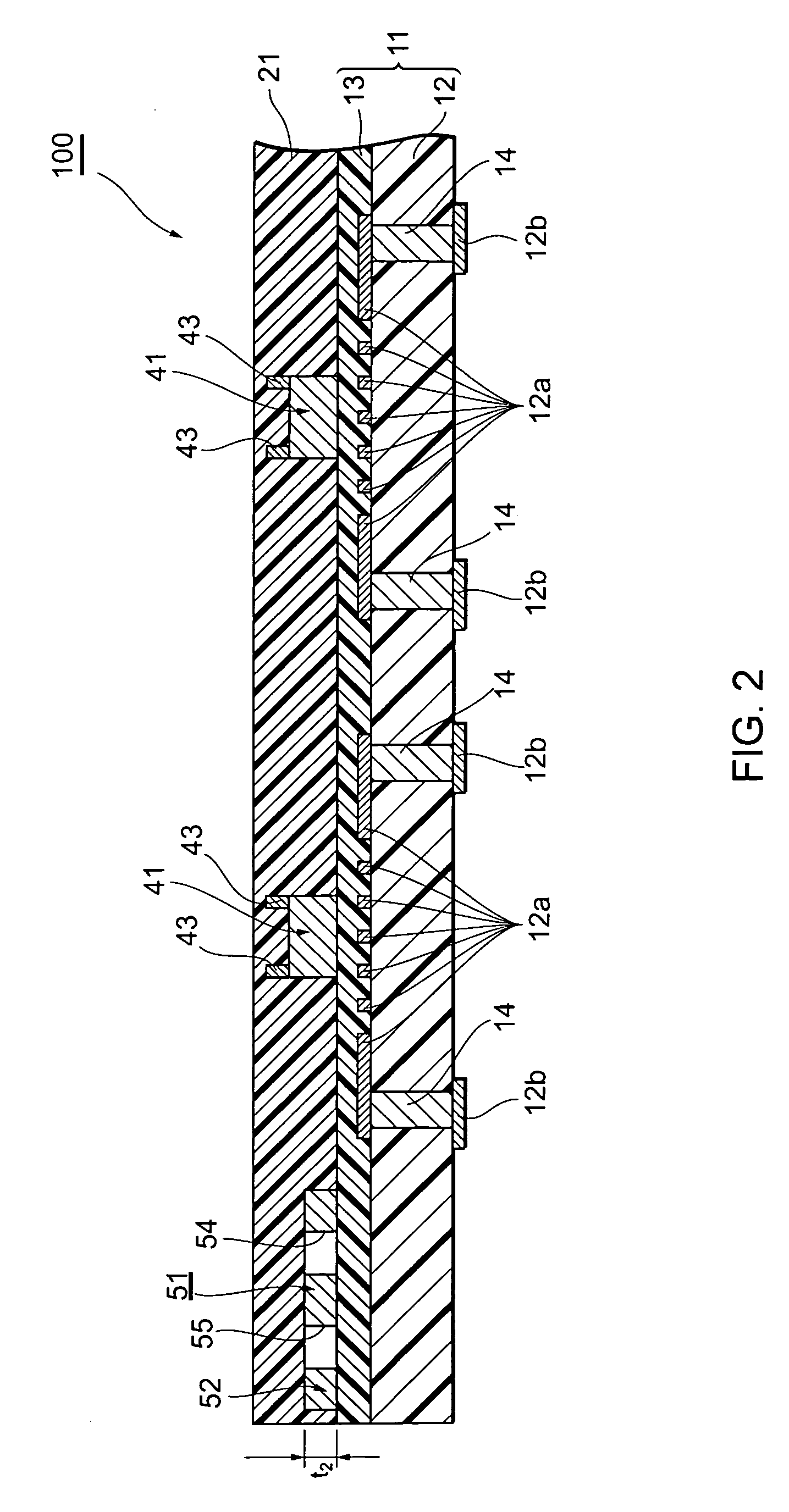

Ultrasonic transducer element chip, probe, electronic instrument, and ultrasonic diagnostic device

ActiveUS20130258803A1High strengthAvoid damageUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostriction/magnetostriction machinesUltrasonic sensorElectronic instrument

An ultrasonic transducer element chip includes a substrate, a plurality of ultrasonic transducer elements, a reinforcing member and a ventilation passage. The substrate defines a plurality of openings arranged in an array pattern. The ultrasonic transducer elements are respectively disposed at the openings on a first surface of the substrate. The reinforcing member is fixed on a second surface of the substrate opposite to the first surface of the substrate to reinforce the substrate. Through the ventilation passage, internal spaces of the openings and an external space of the substrate are in communication with each other.

Owner:SEIKO EPSON CORP

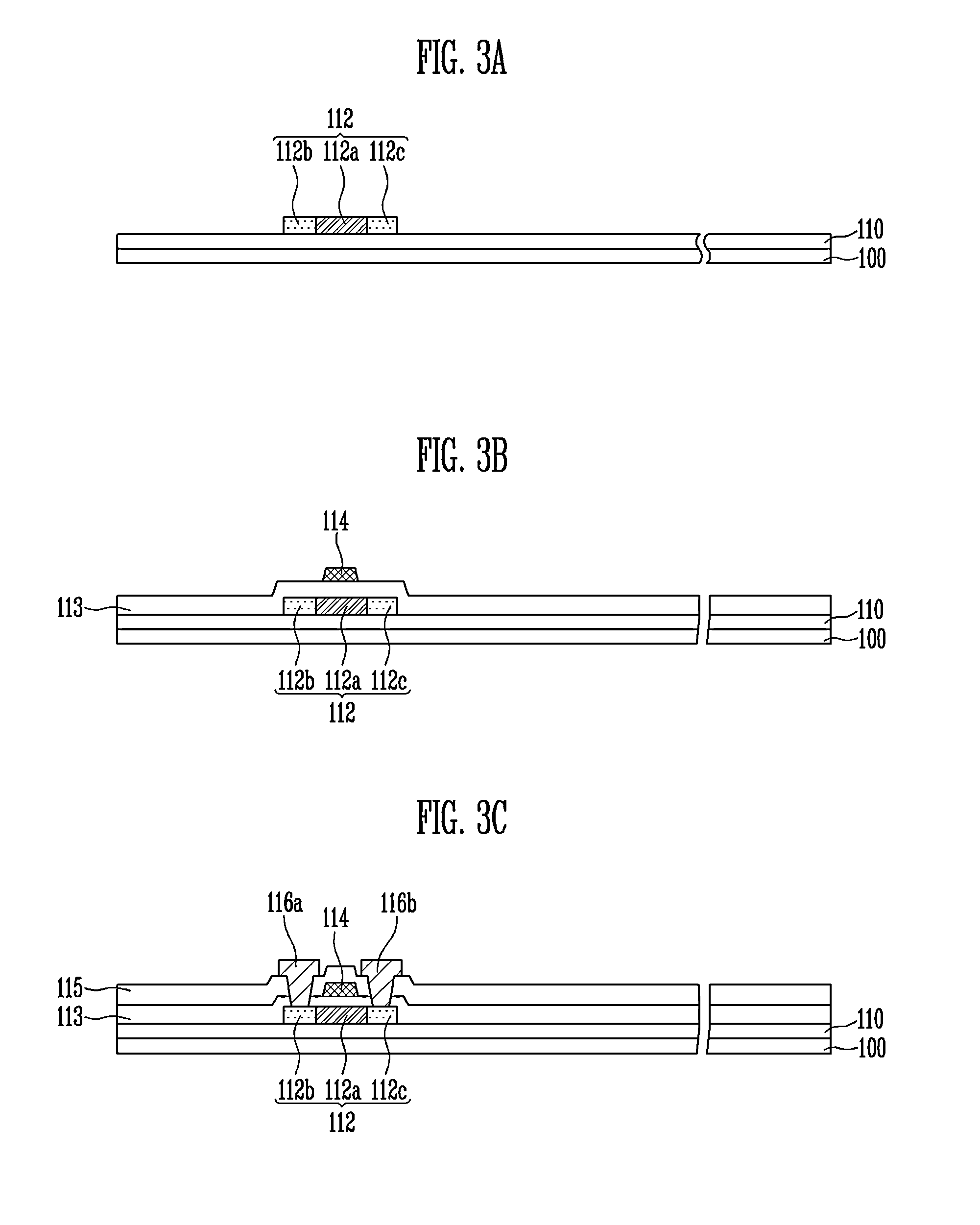

Touch panel

InactiveUS20120075209A1Good adhesivenessImprove propertiesInput/output processes for data processingOptical reflectionTransmittance

A touch panel, which contains a substrate, a mask layer, a sensing circuit layer and a barrier layer, is disclosed. The mask layer is disposed around the bottom surface of the substrate. The sensing circuit layer is located on the same side of the substrate with the mask layer, and the surrounding area of the sensing circuit layer is shielded by the mask layer. In addition, the area of the sensing circuit layer exposed from the mask layer is defined as a sensing region. Furthermore, the barrier layer is disposed between the substrate and the sensing circuit layer and between the mask layer and the sensing circuit layer. Concurrently, the barrier layer further provides separation between the mask layer and the sensing circuit layer. The barrier layer has a transparent appearance. Particularly, the barrier layer is provided for changing optical refraction and harmonizing optical reflection index and transmittance.

Owner:CATCHER TECH

Semiconductor package

InactiveUS20060081968A1High mechanical strengthRealize functionSemiconductor/solid-state device detailsSolid-state devicesContact padSemiconductor chip

The present invention discloses a semiconductor package comprising a substrate having a plurality of substrate units, a plurality of semiconductor chips respectively disposed on the substrate units, and a plurality of conductive guard lines each disposed between two adjacent substrate units. Each substrate unit is provided with a plurality of contact pads and a plurality of conductive leads respectively connected to the corresponding contact pads. The semiconductor chips are electrically connected to the plurality of contact pads through the conductive leads. Each substrate unit has at least one of the contact pads electrically connected to the conductive guard lines such that the semiconductor package of the present invention can efficiently achieve the function of electrostatic discharge (ESD) protection.

Owner:HIMAX TECH LTD

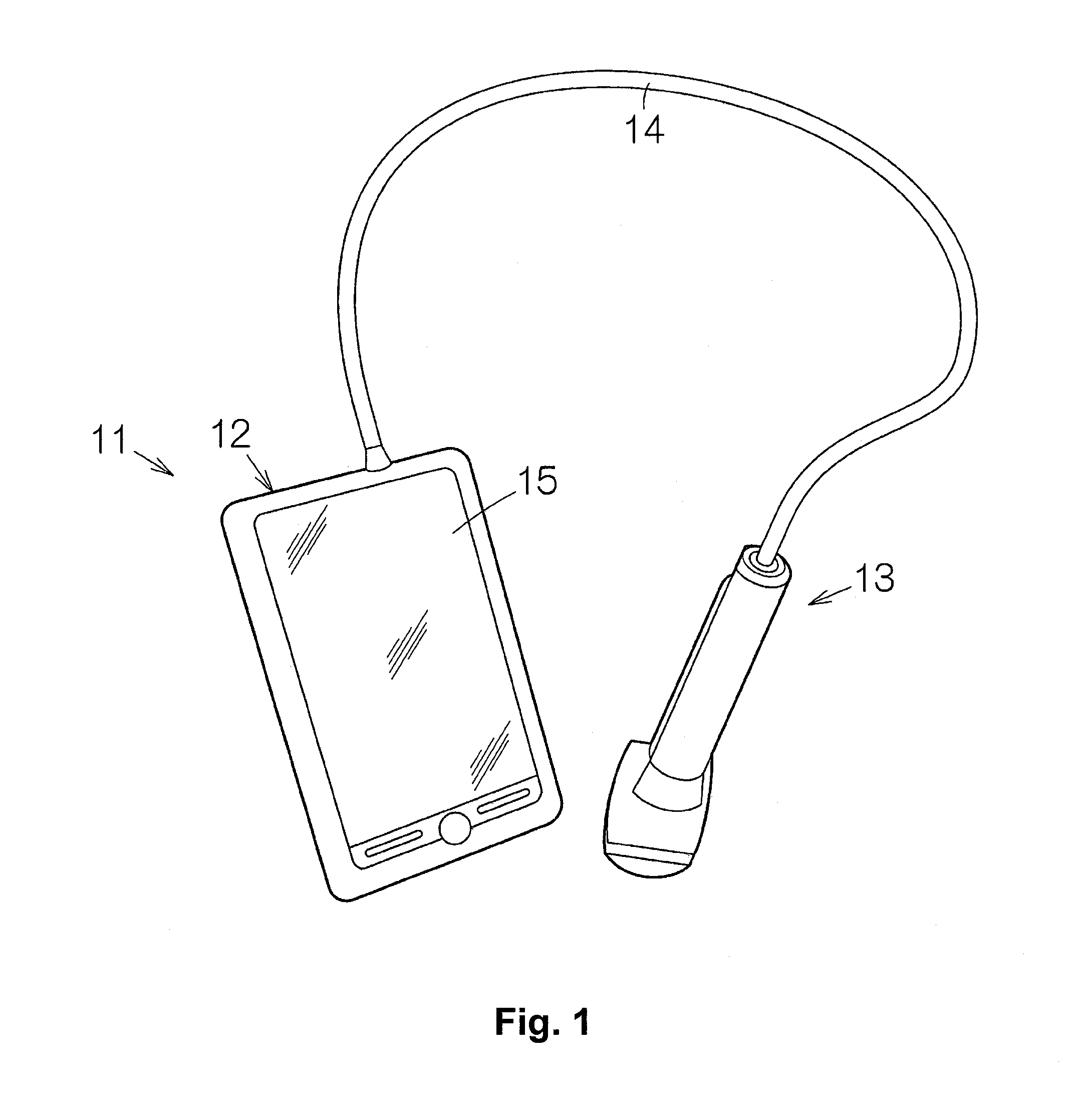

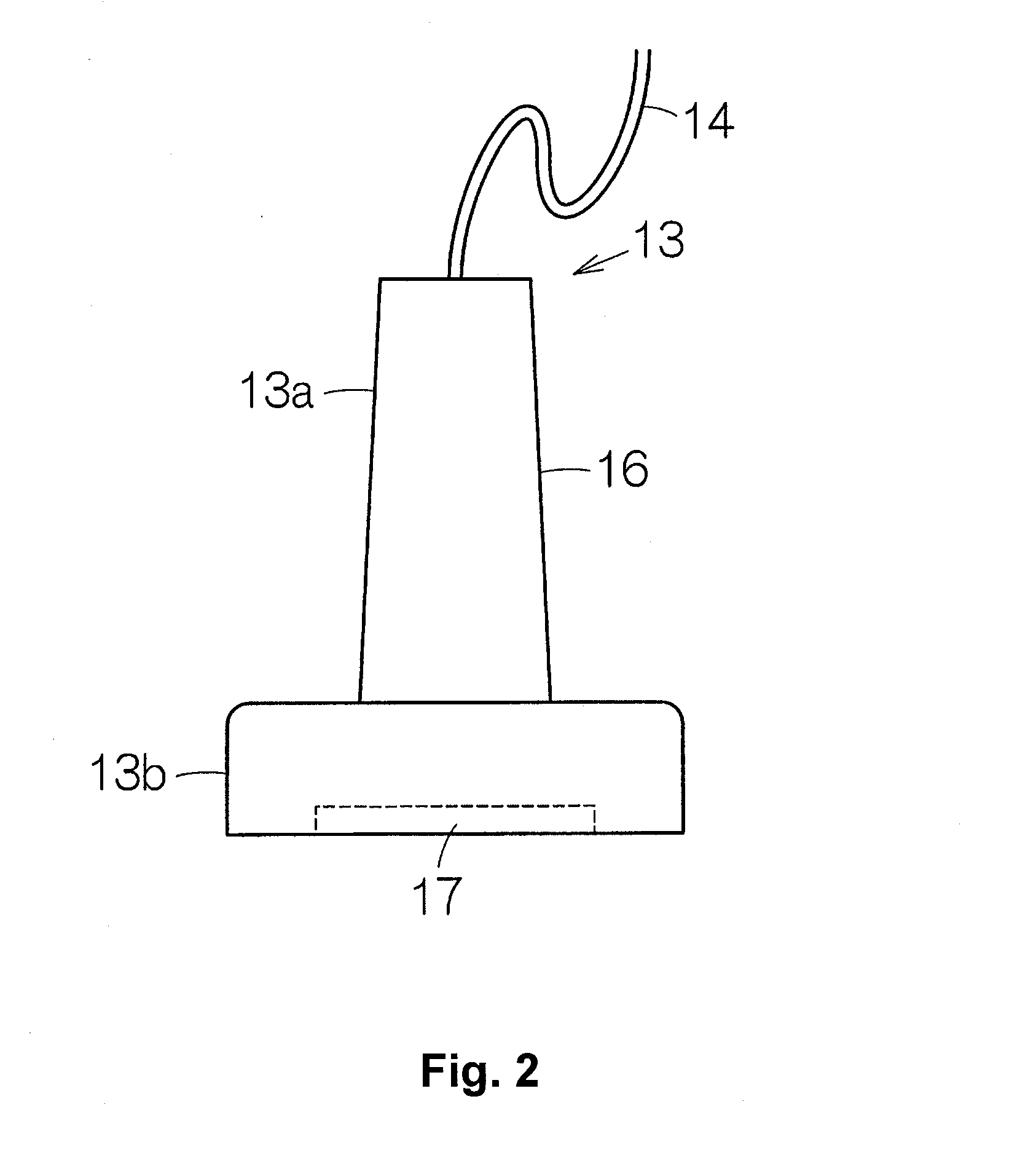

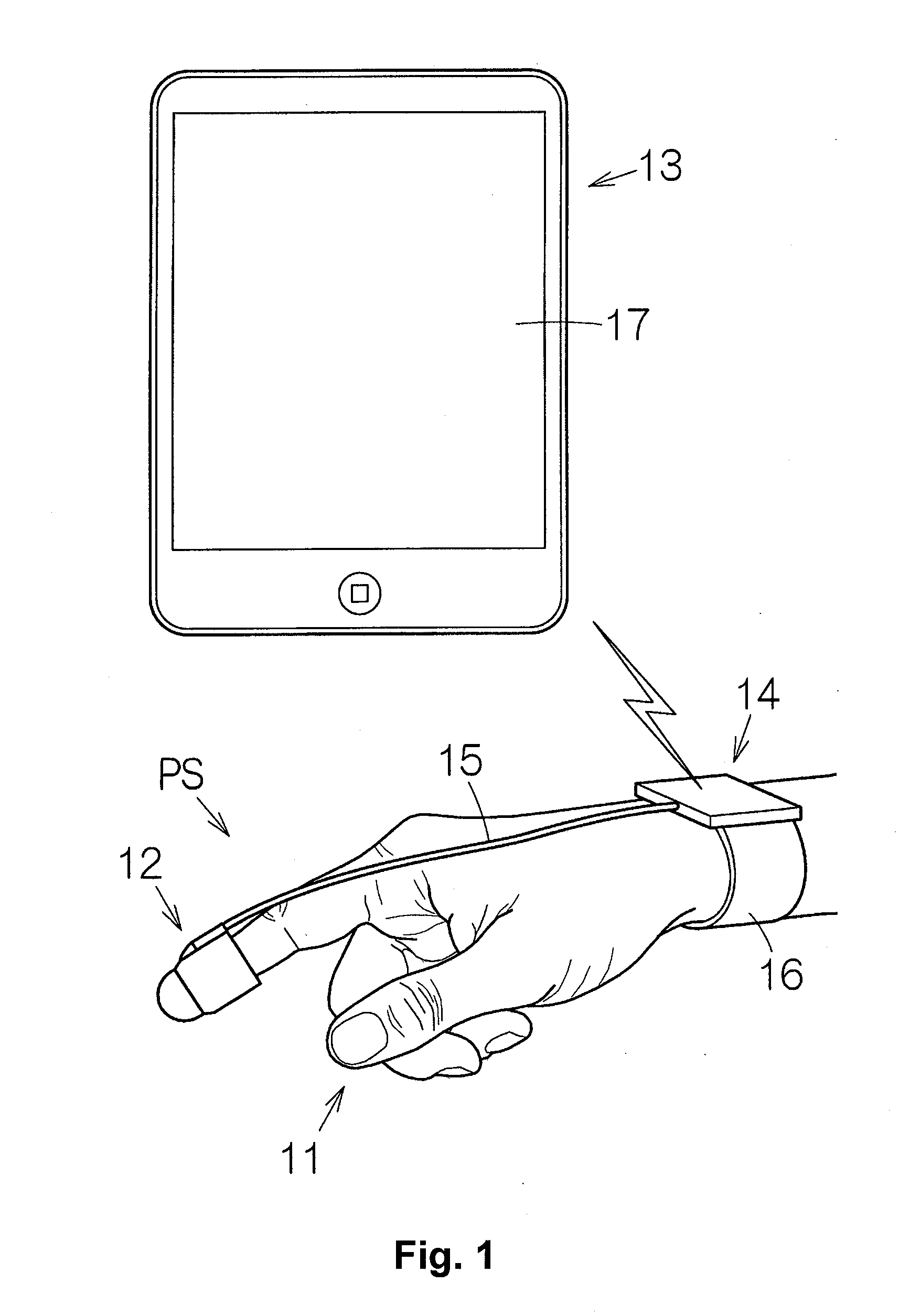

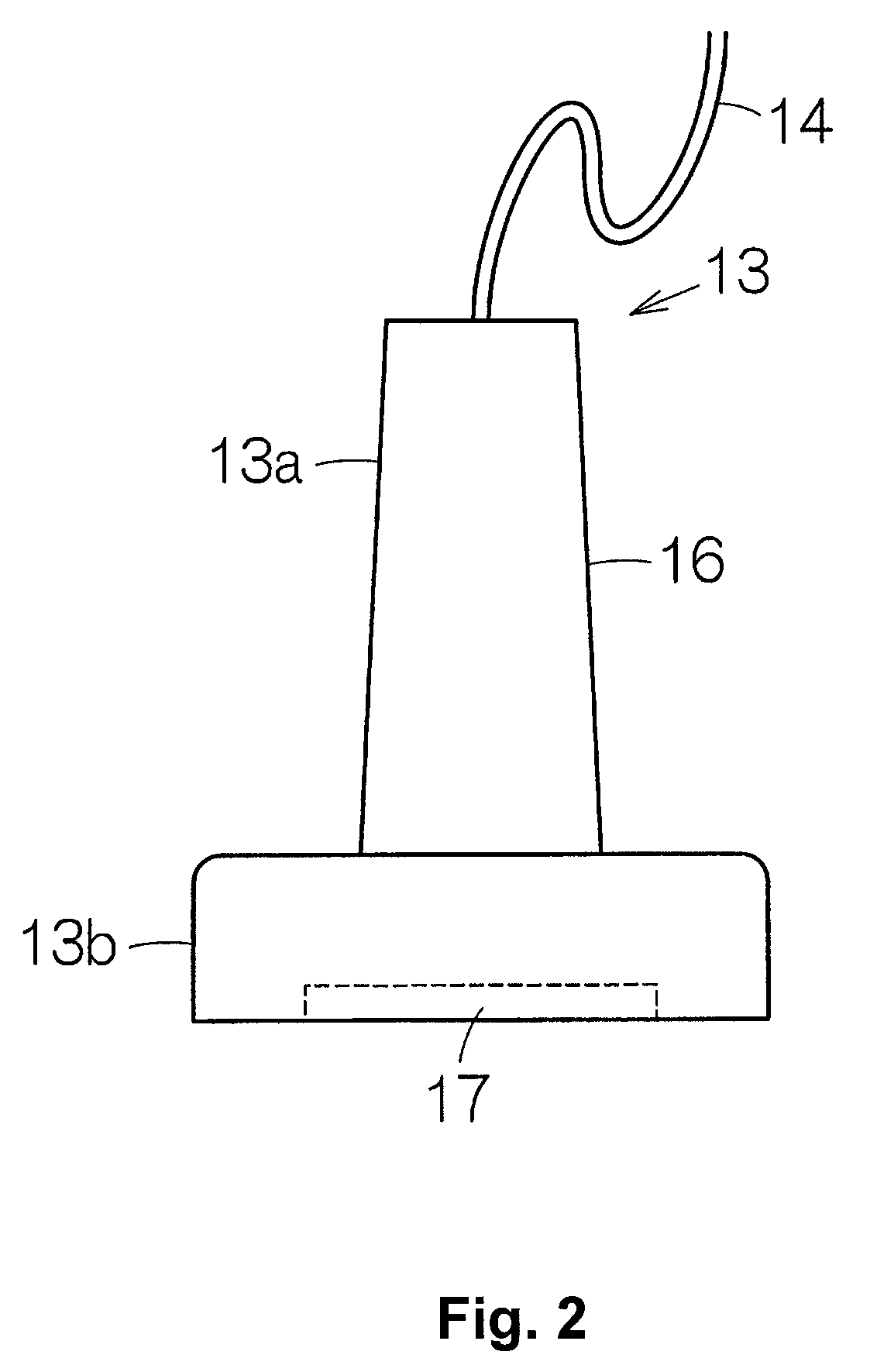

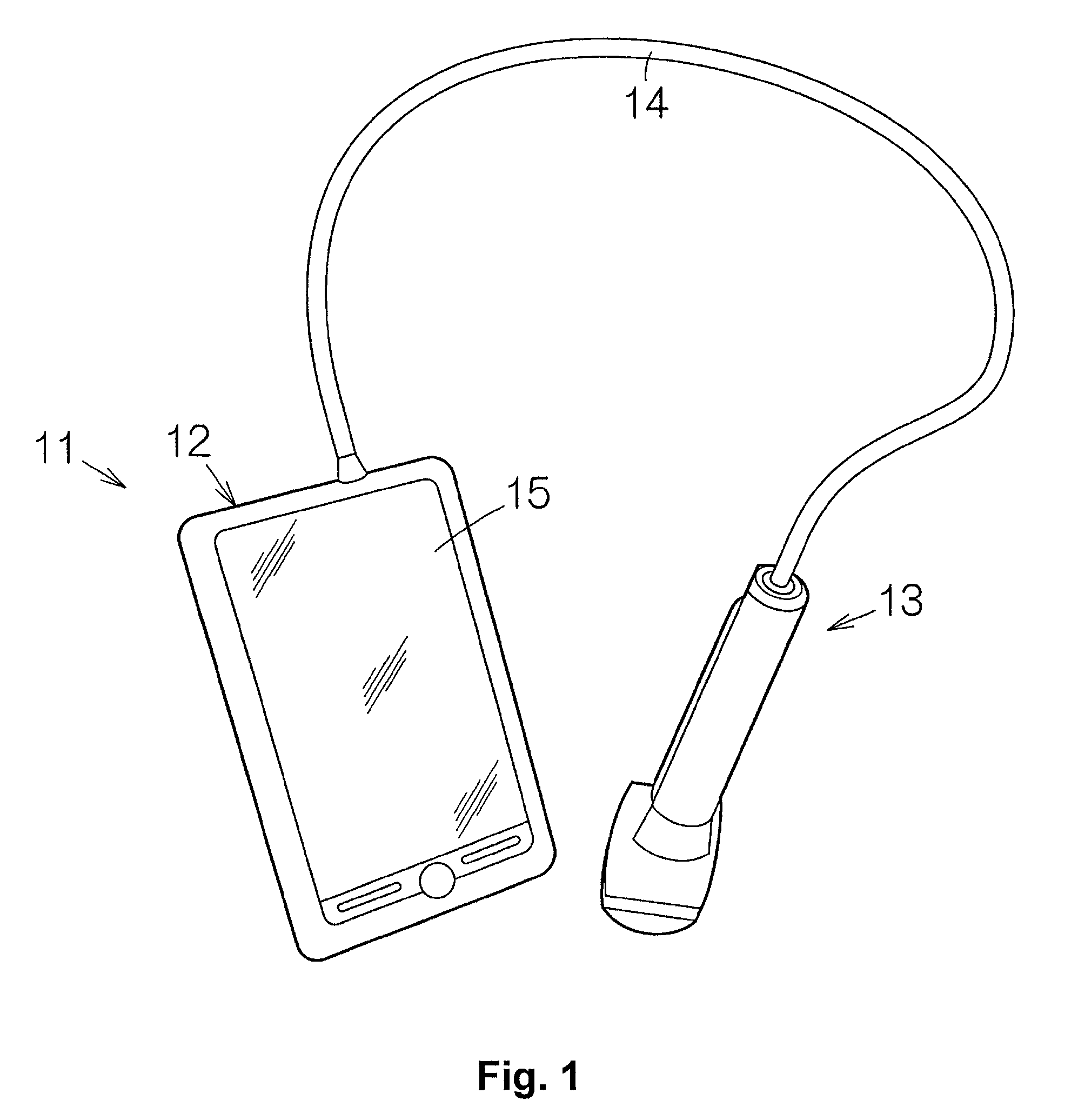

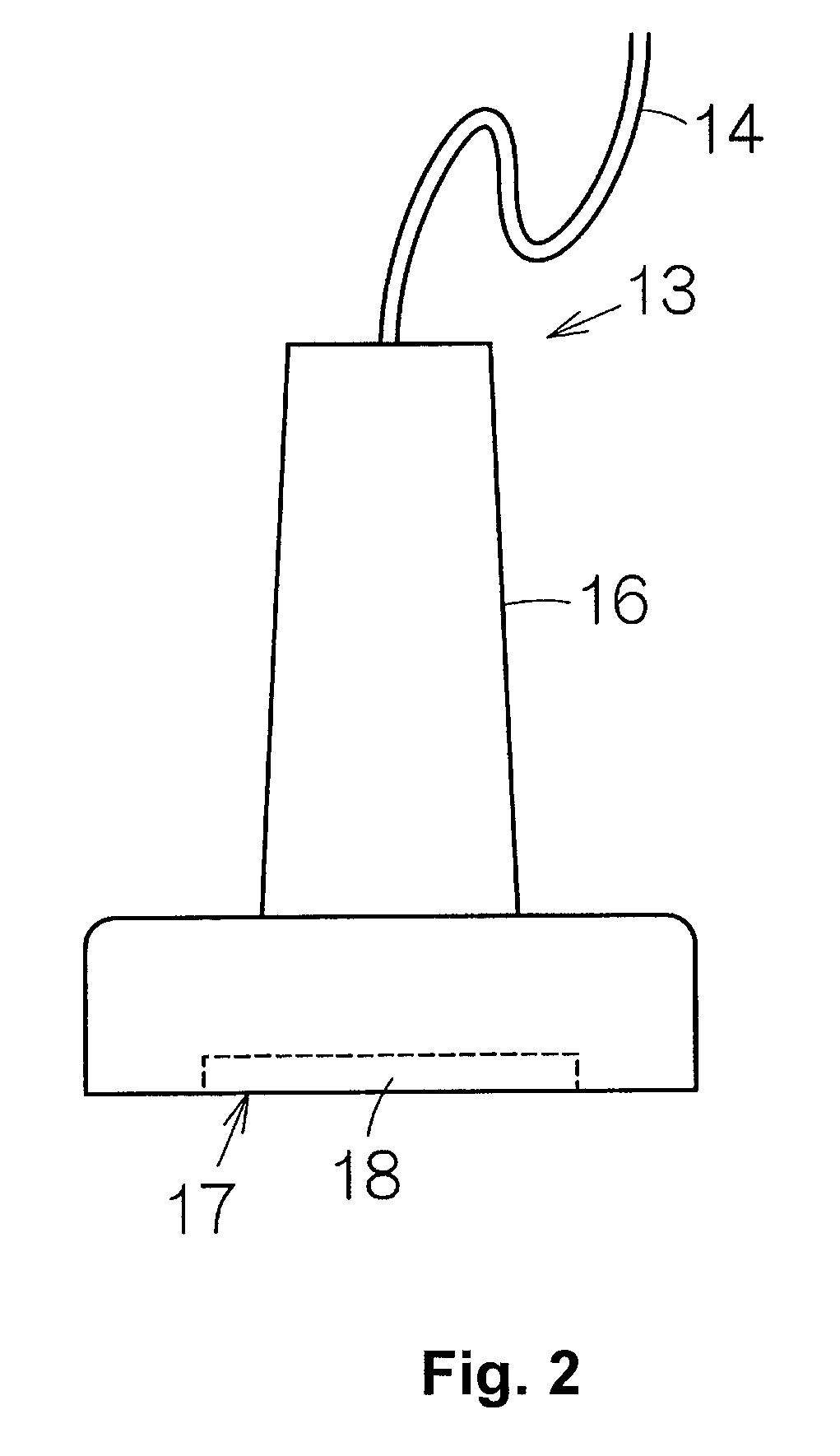

Ultrasonic probe, electronic instrument, and ultrasonic diagnostic device

InactiveUS20130261465A1Improve user friendlinessImprove rigidityUltrasonic/sonic/infrasonic diagnosticsMechanical vibrations separationElectronic instrumentEngineering

An ultrasonic probe includes an element chip, a flexible wiring member and a control circuit. The element chip includes a substrate forming a plurality of openings arranged in an array pattern and a plurality of ultrasonic transducer elements disposed at the openings. The flexible wiring member is connected to the element chip, and forming at least a part of an annular body surrounding a space. The control circuit is connected to the flexible wiring member and electrically connected to the ultrasonic transducer elements via the flexible wiring member.

Owner:SEIKO EPSON CORP

Ball grid array package structure

InactiveUS20080099890A1High mechanical strengthIncrease bumpSemiconductor/solid-state device detailsSolid-state devicesSealantBall grid array

A ball grid array package structure includes: a substrate having at least one chip bearing area on its upper surface and a plurality of electrical-connecting points on its lower surface; a plurality of chips are arranged on the chip bearing area and electrically connected with those electrical-connecting points; a plurality of through holes penetrating the substrate at the edge of chip bearing area; an encapsulant used to cover those chip and filling those through holes to form a strengthened bump surrounding the chip bearing area on the lower surface of the substrate; and a plurality of conductive balls are respectively arranged on those electrical-connecting points. The present invention utilizes the strengthened bump on the bottom of the substrate to enhance the structure strength of the substrate so as to avoid the warpage of the substrate caused from the stress due to the temperature variation during the package process to affect the following processes.

Owner:POWERTECH TECHNOLOGY

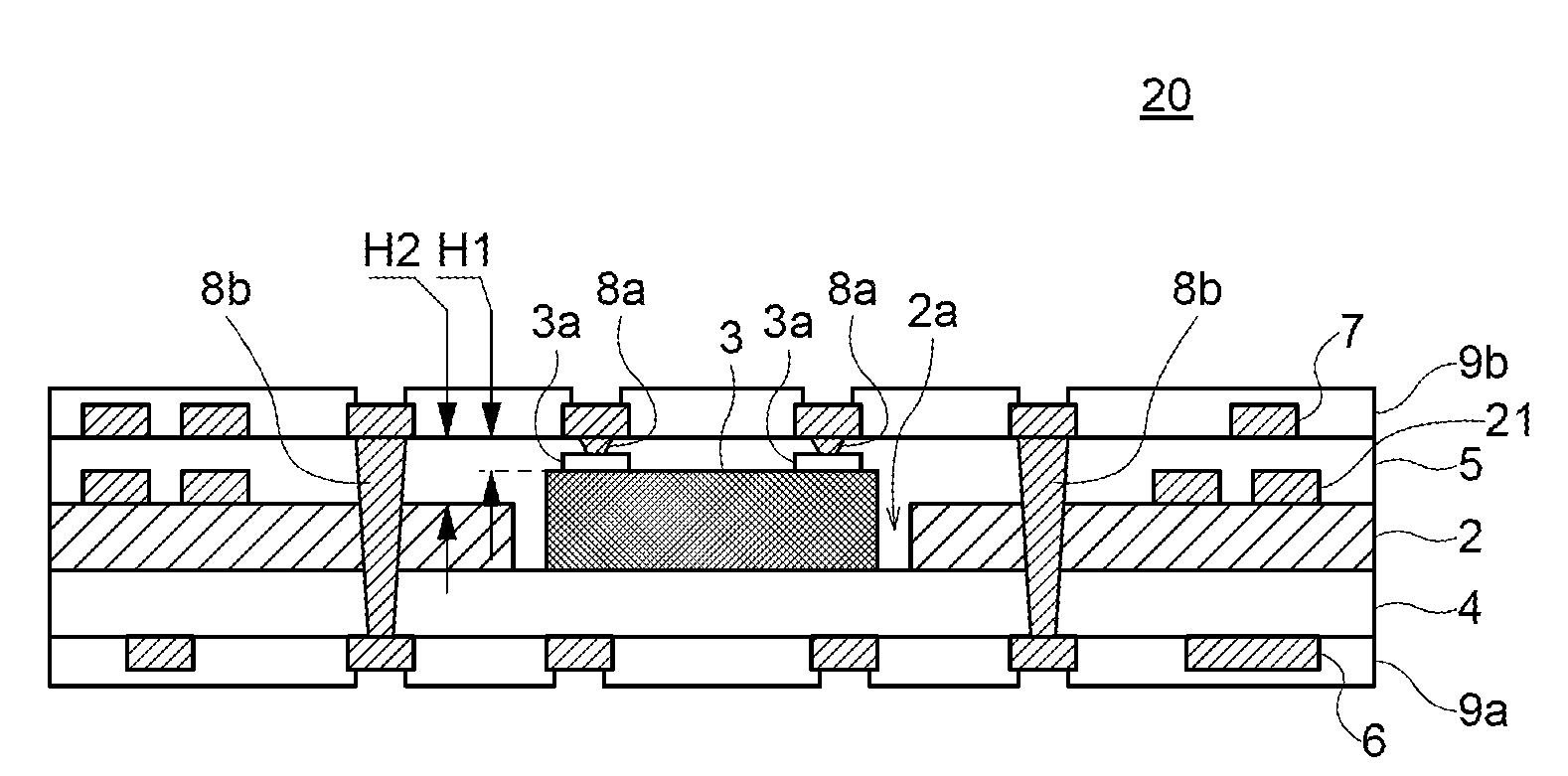

IC embedded substrate and method of manufacturing the same

ActiveUS20150145145A1High substrate strengthUniform thicknessSemiconductor/solid-state device detailsSolid-state devicesElectrical and Electronics engineering

Disclosed herein is an IC embedded substrate that includes a core substrate having an opening, an IC chip provided in the opening, a lower insulating layer, and upper insulating layer. The IC chip and the core substrate is sandwiched between the lower insulating layer and the upper insulating layer. The upper insulating layer is formed in such a way as to fill a gap between a side surface of the IC chip and an inner peripheral surface of the opening of the core substrate. A first distance from the upper surface of the IC chip to an upper surface of the upper insulating layer is shorter than a second distance from the upper surface of the core substrate to the upper surface of the upper insulating layer.

Owner:TDK CORPARATION

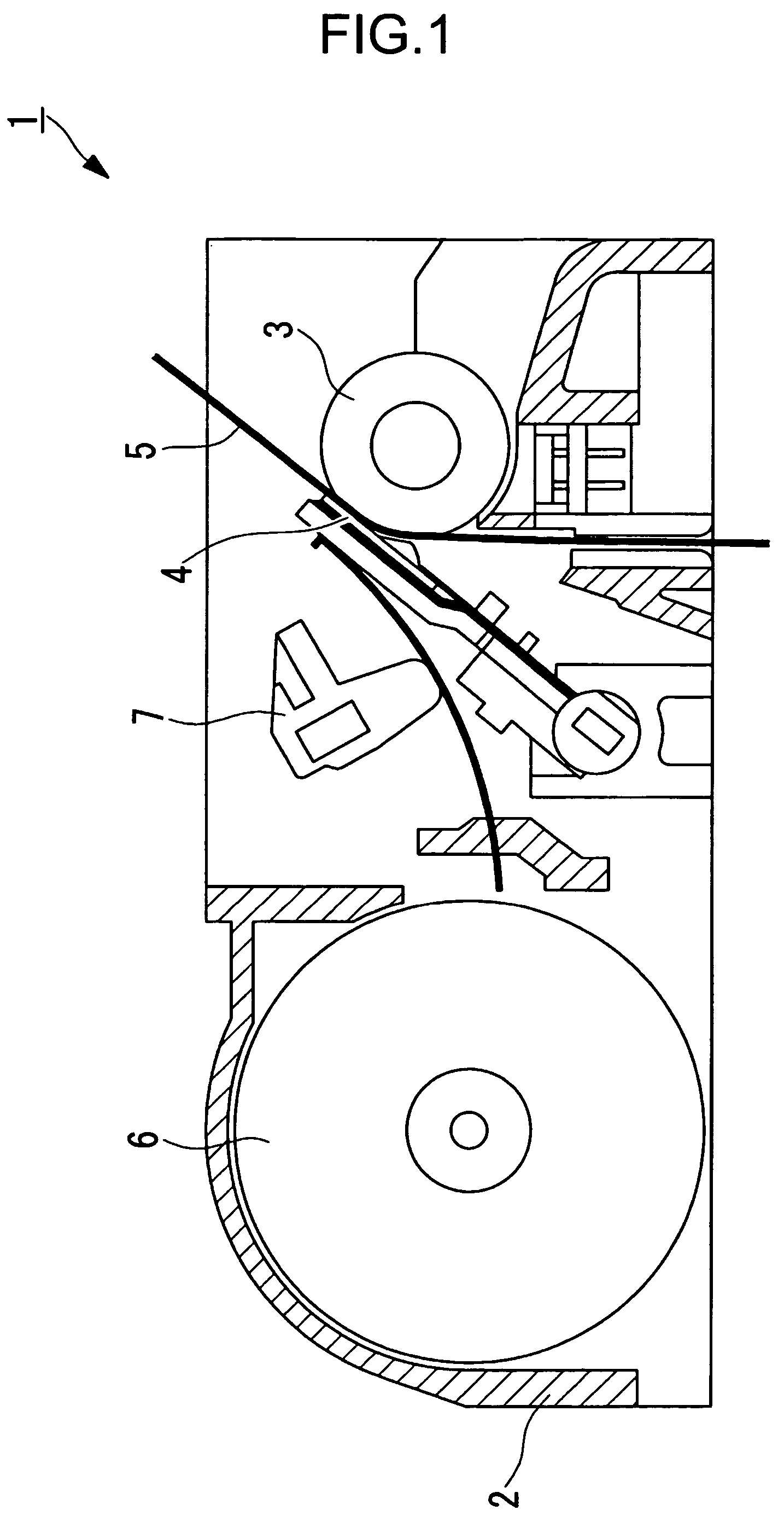

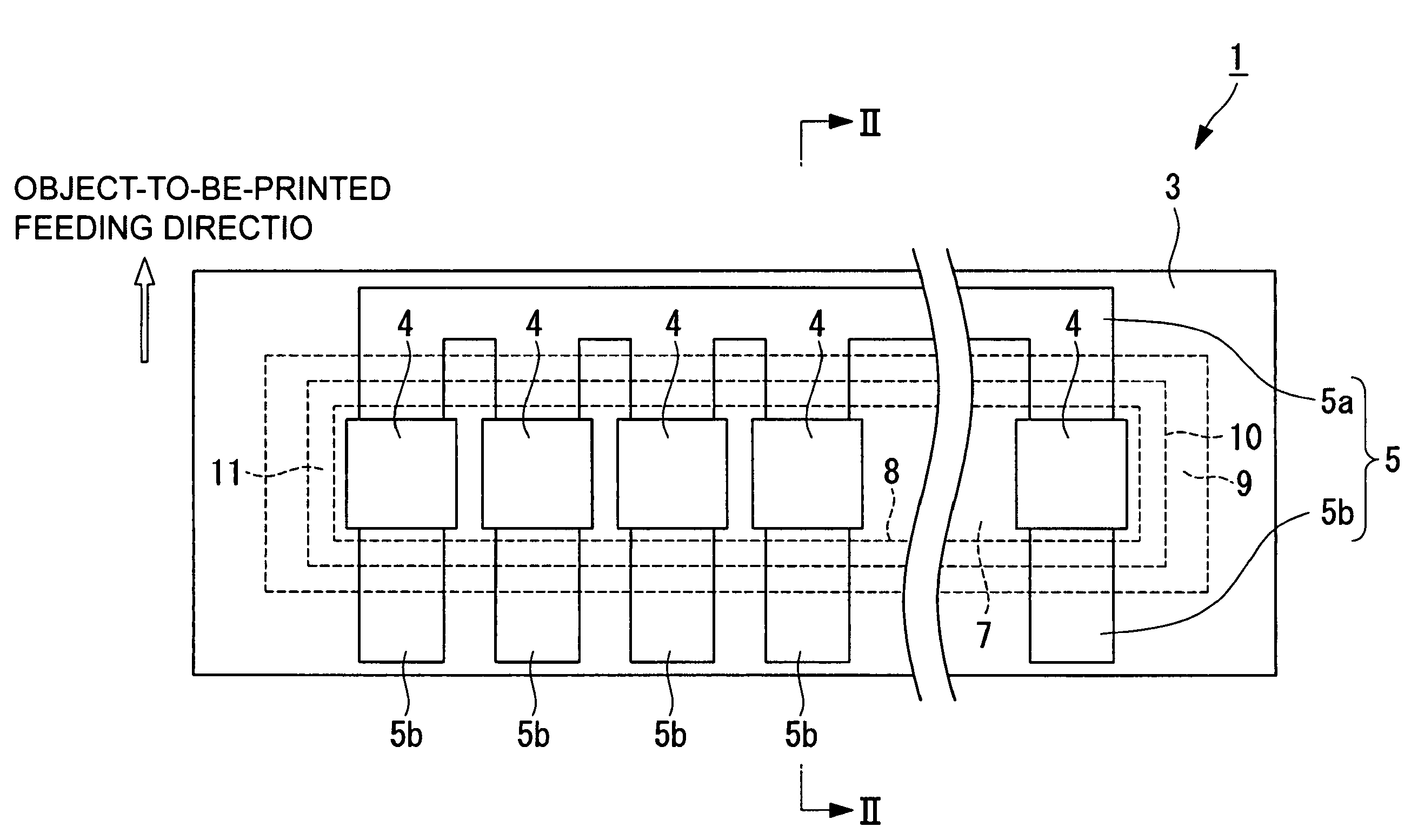

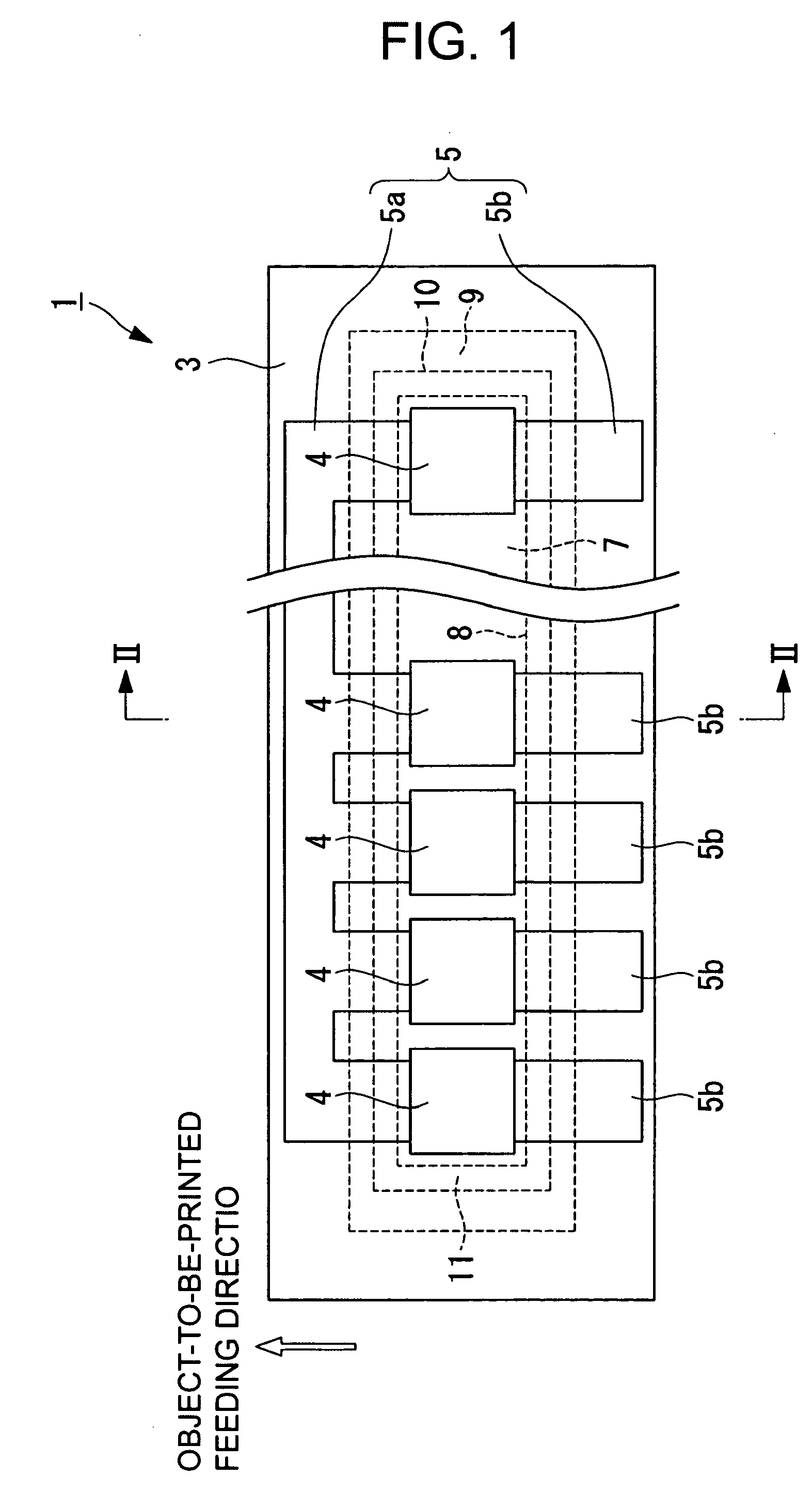

Heating resistance element, thermal head, printer, and method of manufacturing heating resistance element

InactiveUS20070091161A1Improve heating efficiencyReduce power consumptionPrintingElectrical resistance and conductanceLaser processing

A thermal head is structured to have a substrate, a thermal storage layer formed on one surface of the substrate and made of glass, and heating resistors provided on the thermal storage layer. A plurality of hollow portions are formed at a position spaced apart from a surface where the heating resistors are formed by laser processing using a femtosecond laser, in an area of the thermal storage layer which is opposed to the heating resistors. In this way, to provide a heating resistance element for improving heating efficiency of heating resistors to reduce power consumption, improving strength of a substrate under the heating resistors, and for enabling simple manufacture at a low cost, a thermal head and a printer using the same, and a method of manufacturing a heating resistance element.

Owner:SEIKO INSTR INC

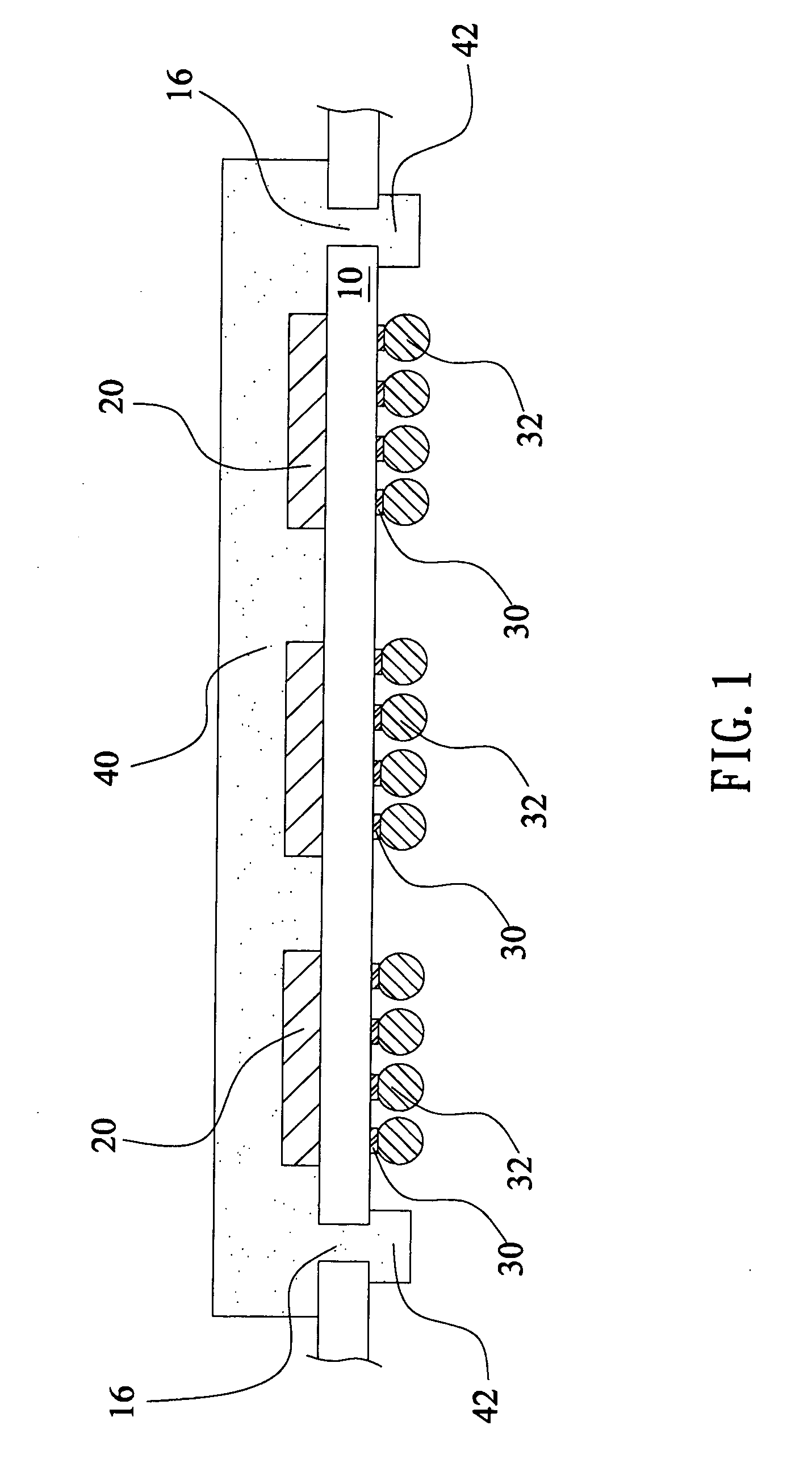

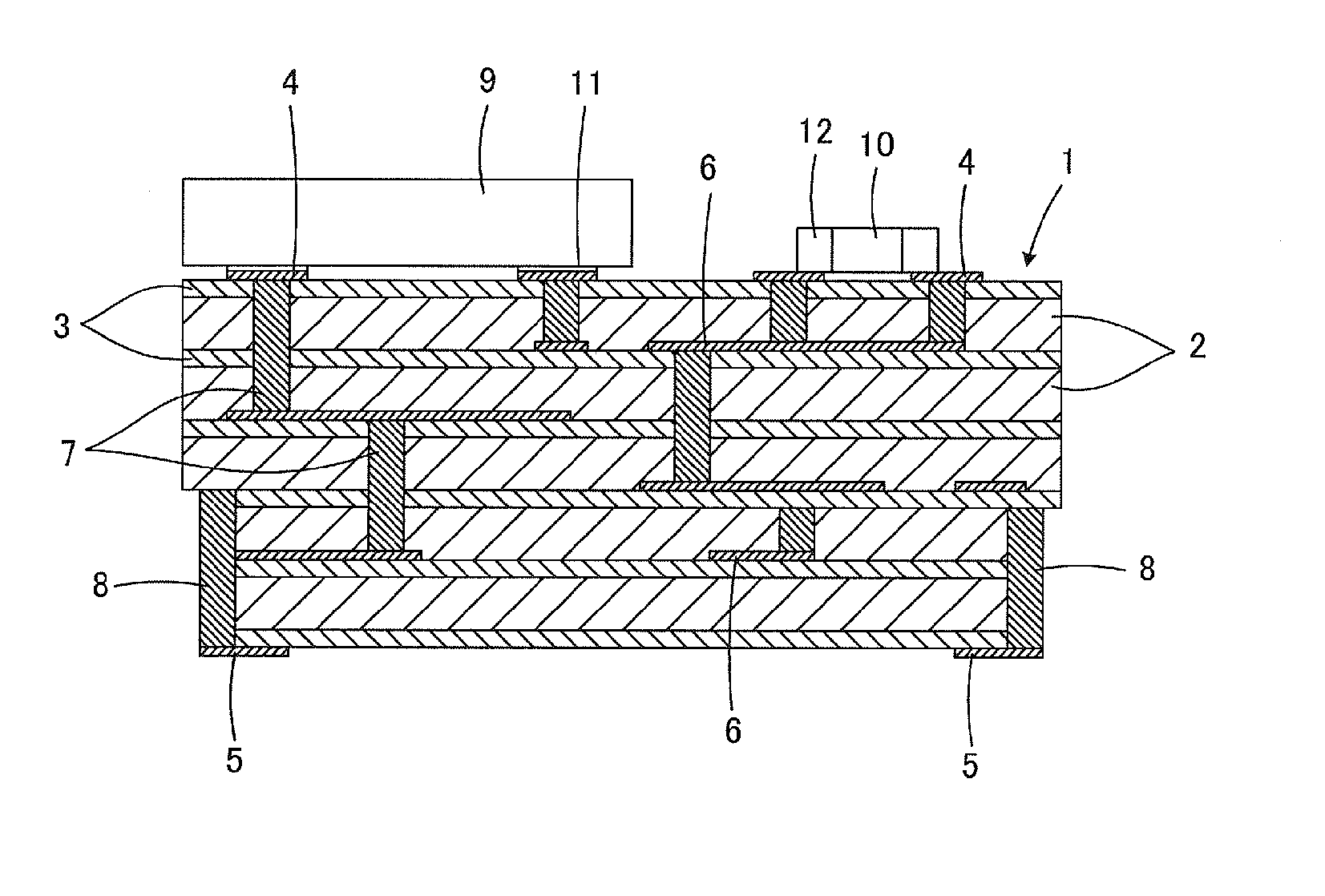

Ultrasonic transducer device, probe, electronic instrument, and ultrasonic diagnostic device

ActiveUS20130223192A1DistanceReduce thicknessPiezoelectric/electrostriction/magnetostriction machinesSonic/ultrasonic/infrasonic transmissionUltrasonic sensorElectronic instrument

An ultrasonic transducer device includes a substrate, a plurality of ultrasonic transducer elements, a wiring substrate and a wiring member. The substrate defines a plurality of openings arranged in an array pattern. Each of the ultrasonic transducer elements is provided in each of the openings on a first surface of the substrate. The wiring substrate is arranged to face a second surface of the substrate that is opposite from the first surface. The wiring substrate includes a first wiring part. The wiring member is connected to the substrate and the wiring substrate. The wiring member includes a second wiring part electrically connecting the ultrasonic transducer elements to the first wiring part.

Owner:SEIKO EPSON CORP

Semiconductor device and manufacturing method thereof

ActiveUS20090315071A1Improve effectManufacturing cost be reduceTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A manufacturing method of a semiconductor device 10 includes forming a plurality of second conductive second semiconductor regions at specific intervals on one main surface of a first conductive first semiconductor region, the plurality of second conductive second semiconductor regions being opposite to the first conductive first semiconductor region, forming a plurality of the first conductive third semiconductor regions on a main surface of the second semiconductor region, the plurality of the first conductive third regions being separated from each other, forming a plurality of holes at specific intervals on an another main surface which faces the one main surface of the first semiconductor region, the plurality of holes being separated from each other, forming a pair of adjacent second conductive fourth semiconductor regions which are alternately connected at a bottom part of the hole within the first semiconductor region, and burying an electrode within the hole.

Owner:SANKEN ELECTRIC CO LTD

Organic light emitting display device and method of manufacturing the same

InactiveUS20150144917A1High mechanical strengthEffectively blocking ambient oxygen and moistureSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOptoelectronics

An organic light emitting display device includes a first substrate, a second substrate, and an array of organic light emitting elements formed over the first substrate and interposed between the first and second substrate. The array comprises a pixel defining layer. The organic light emitting display device further includes a recess formed into the pixel defining layer, a sealing member, and a reinforcing member. The sealing member is formed along the edges of the first and second substrates and interconnects the first and second substrates. The reinforcing member comprises a first portion positioned in the recess and a second portion projected outside the recess toward the second substrate such that the second portion of the reinforcing member is capable of supporting the second substrate when the second substrate is pressed toward the first substrate by an external force.

Owner:SAMSUNG DISPLAY CO LTD

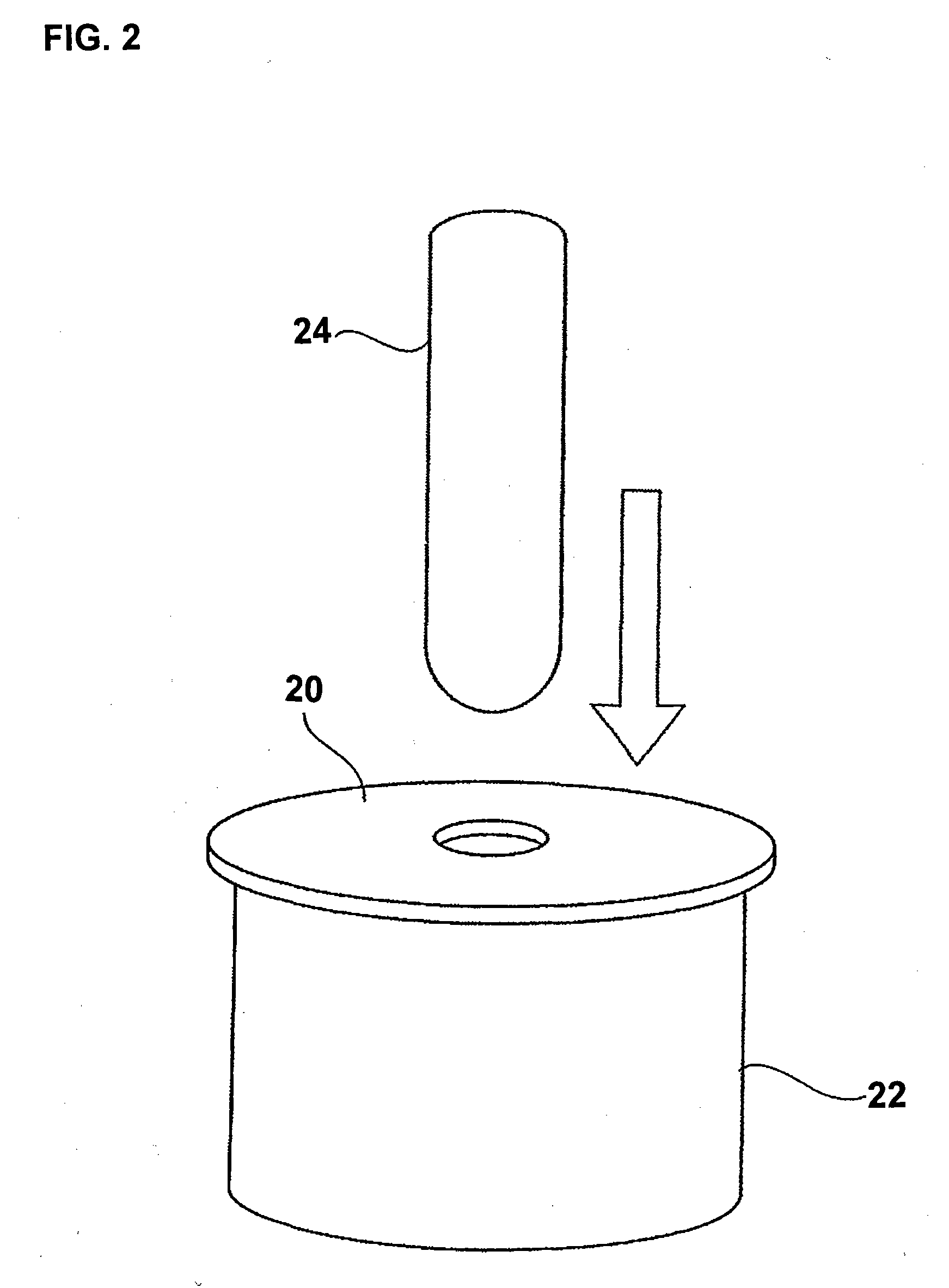

Method of manufacture of glass substrate for information recording medium, method of manufacture of magnetic recording disk, and magnetic recording disk

InactiveUS20080213626A1Suppress crackReduce amountDecorative surface effectsRecord information storageChemistryAlkaline elution

A method of manufacture of a glass substrate for a magnetic recording medium, which has both high substrate strength and low alkaline elution, includes an etching process of etching the inner-edge face of a donut-shaped glass substrate having an aluminosilicate composition, formed by removing the center portion of a die-molded disc-shaped glass substrate, and an alkali sealing process of performing alkali sealing treatment by proton substitution of alkali ions in the surface layer of the etched donut-shaped glass substrate. The process is used to manufacture a magnetic recording medium incorporating a glass substrate having a total alkaline elution amount of less than 3.1 μg / disk, wherein the magnetic recording medium has a transverse rupture strength greater than 132 N.

Owner:FUJI ELECTRIC DEVICE TECH CO

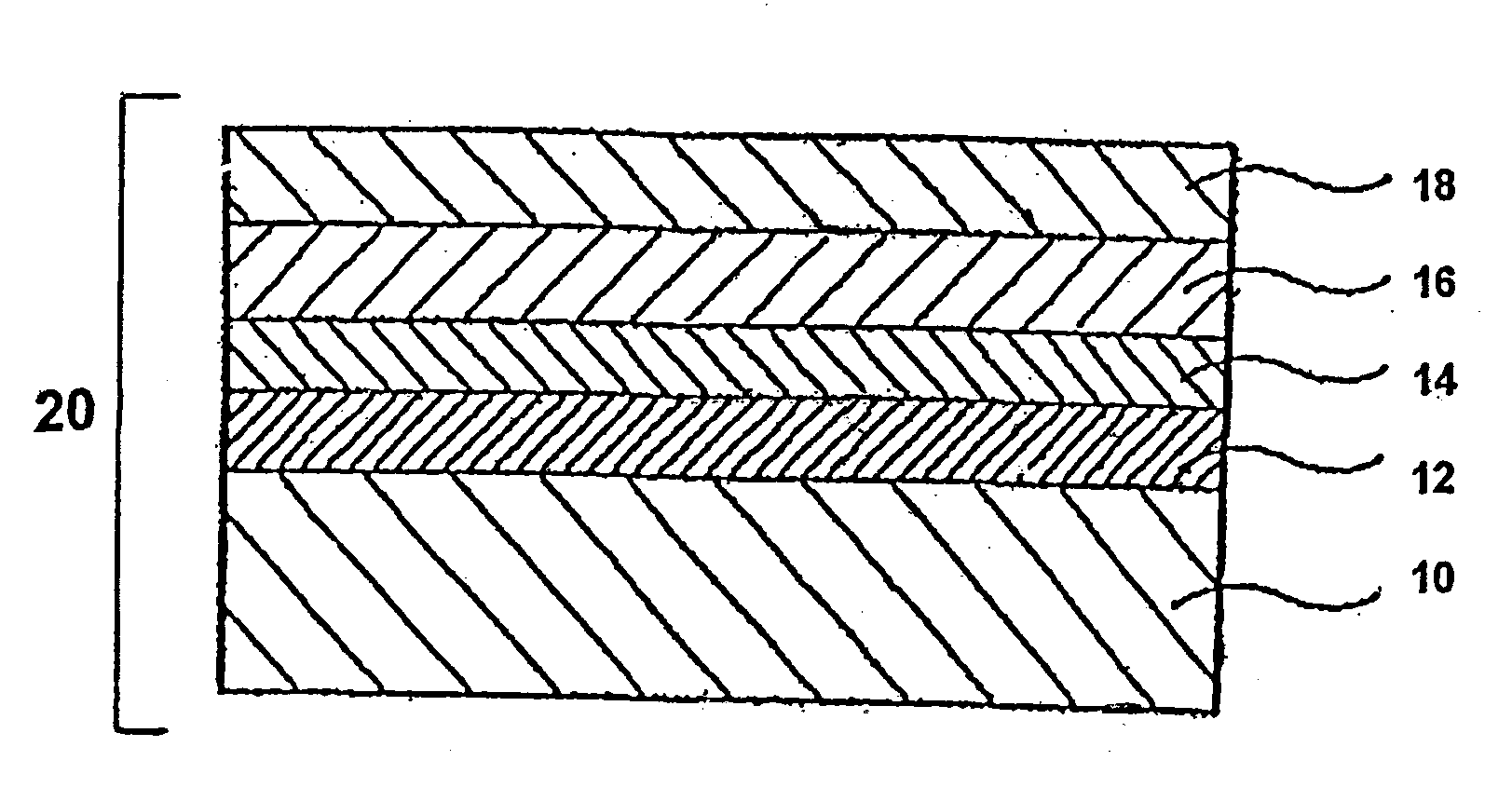

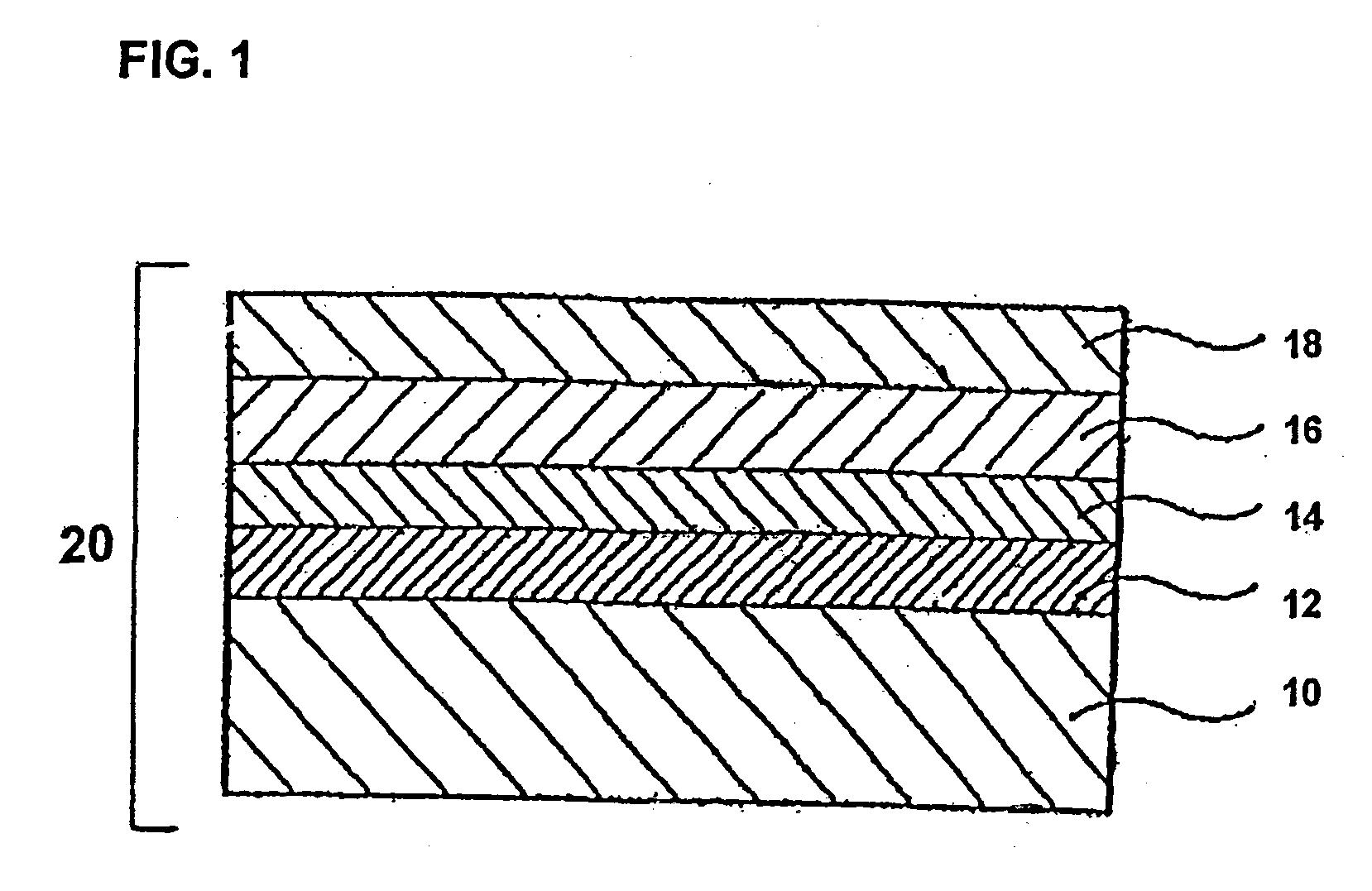

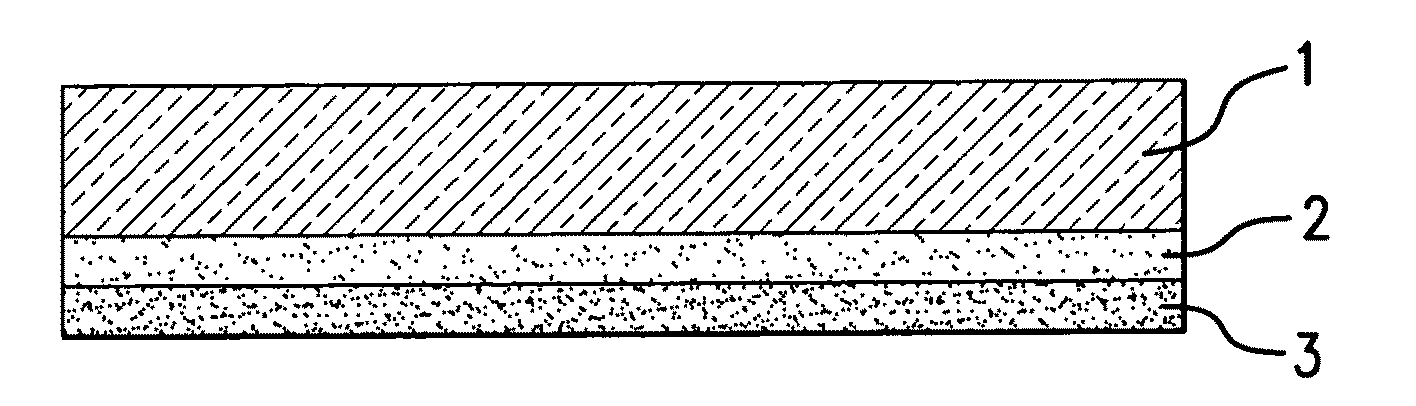

Multilayer ceramic substrate

ActiveUS20120003450A1High strengthImprove substrate strengthStacked capacitorsSynthetic resin layered productsCelsianUltimate tensile strength

In order to enable non-shrinkage firing, the strength of a multilayer ceramic substrate is increased which is obtained by a method in which alternately stacking a base material layer and a constrained layer which is not sintered at the sintering temperature for the base material layer, and in a firing step, allowing the material of the base material layer to flow into the constrained layer while subjecting the base material layer to sintering, thereby achieving densification of the constrained layer. The base material layer and the constrained layer each include celsian, and the abundance of celsian is lower in the base material layer than in the constrained layer. In order to increase the strength of the base material layer, the addition of a Ti component, rather than an increased content of Al component which interferes with sintering of the base material layer, causes fresnoite to be deposited in the base material layers. The presence of fresnoite in the base material layers increases crystal grain boundaries in the base material layers, and thus prevents cracking, thereby allowing the strength of the multilayer ceramic substrate to be improved.

Owner:MURATA MFG CO LTD

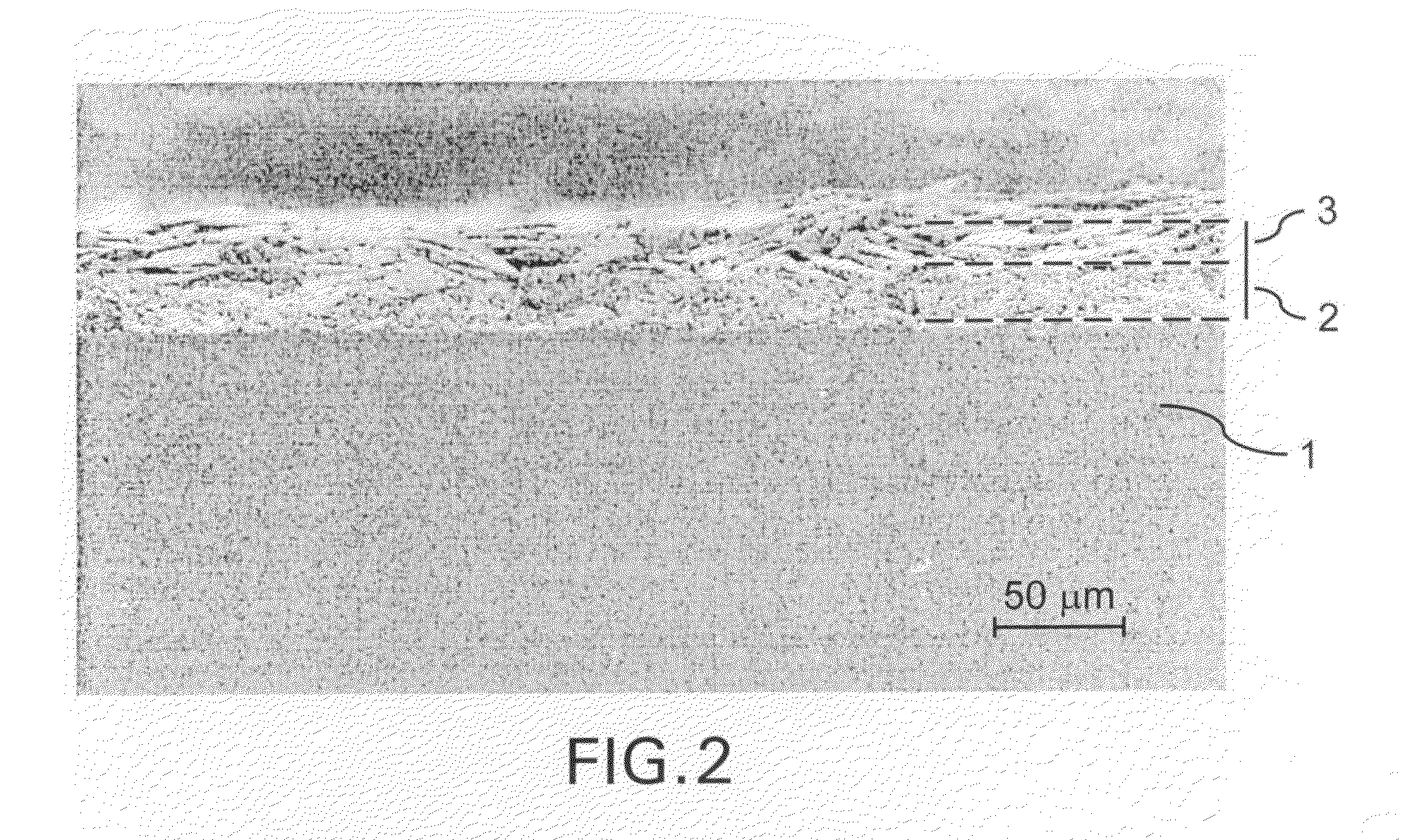

Substrate with High Fracture Strength

ActiveUS20100035022A1Improve substrate strengthHigh breaking strengthAfter-treatment detailsLayered productsBreaking strengthHigh fracture

The invention discloses a substrate with high fracture strength. The substrate according to the invention includes a plurality of nanostructures. The substrate has a first surface, and the nanostructures are protruded from the first surface. By the formation of the nanostructures, the fracture strength of the substrate is enhanced.

Owner:NATIONAL TSING HUA UNIVERSITY

Heating resistance element, thermal head, printer, and method of manufacturing heating resistance element

InactiveUS7522178B2Improve heating efficiencyReduce power consumptionPrintingElectrical resistance and conductanceLaser processing

A thermal head is structured to have a substrate, a thermal storage layer formed on one surface of the substrate and made of glass, and heating resistors provided on the thermal storage layer. A plurality of hollow portions are formed at a position spaced apart from a surface where the heating resistors are formed by laser processing using a femtosecond laser, in an area of the thermal storage layer which is opposed to the heating resistors. In this way, to provide a heating resistance element for improving heating efficiency of heating resistors to reduce power consumption, improving strength of a substrate under the heating resistors, and for enabling simple manufacture at a low cost, a thermal head and a printer using the same, and a method of manufacturing a heating resistance element.

Owner:SEIKO INSTR INC

Method of forming a modified layer in a substrate

ActiveUS20090149002A1Reduced strengthProcess stabilitySemiconductor/solid-state device manufacturingFine working devicesOptoelectronicsData storing

First, mapping data storing interrupted areas is obtained. In a first modified-layer forming step, before a stacked article is stacked on a front surface of a substrate, a laser beam is directed to the interrupted areas based on the mapping data to form modified layers only at the interrupted areas. After the stacked articles have been stacked on the substrate, in a second modified-layer forming step, the laser beam is directed at least to the predetermined dividing line formed with no modified layer in the first modified-layer forming step to form a modified layer.

Owner:DISCO CORP

Ultrasonic transducer element chip, probe, electronic instrument, and ultrasonic diagnostic device

ActiveUS9079220B2High strengthAvoid damageUltrasonic/sonic/infrasonic diagnosticsPiezoelectric/electrostrictive transducersUltrasonic sensorElectronic instrument

An ultrasonic transducer element chip includes a substrate, a plurality of ultrasonic transducer elements, a reinforcing member and a ventilation passage. The substrate defines a plurality of openings arranged in an array pattern. The ultrasonic transducer elements are respectively disposed at the openings on a first surface of the substrate. The reinforcing member is fixed on a second surface of the substrate opposite to the first surface of the substrate to reinforce the substrate. Through the ventilation passage, internal spaces of the openings and an external space of the substrate are in communication with each other.

Owner:SEIKO EPSON CORP

Mold structure for packaging LED chips and method thereof

InactiveUS20080160658A1Improve substrate strengthImprove structural strengthSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsEngineeringMechanical engineering

Owner:HARVATEK CORPORATION

Scratch-resistant silicone coating for cooktops made of glass or glass ceramic

InactiveUS20100167035A1Improve substrate strengthHigh bonding strengthSynthetic resin layered productsGlass/slag layered productsColloidal silicaSilicone coating

A functional element, in particular a cooktop or control panel, having a flat substrate composed of or of glass or glass ceramic, in which a coating that contains a crosslinked polysiloxane is applied to the substrate. In order to improve the scratch resistance of such a coating, according to this invention, a covering layer that contains an uncrosslinked polysiloxane is applied to the coating.

Owner:SCHOTT AG

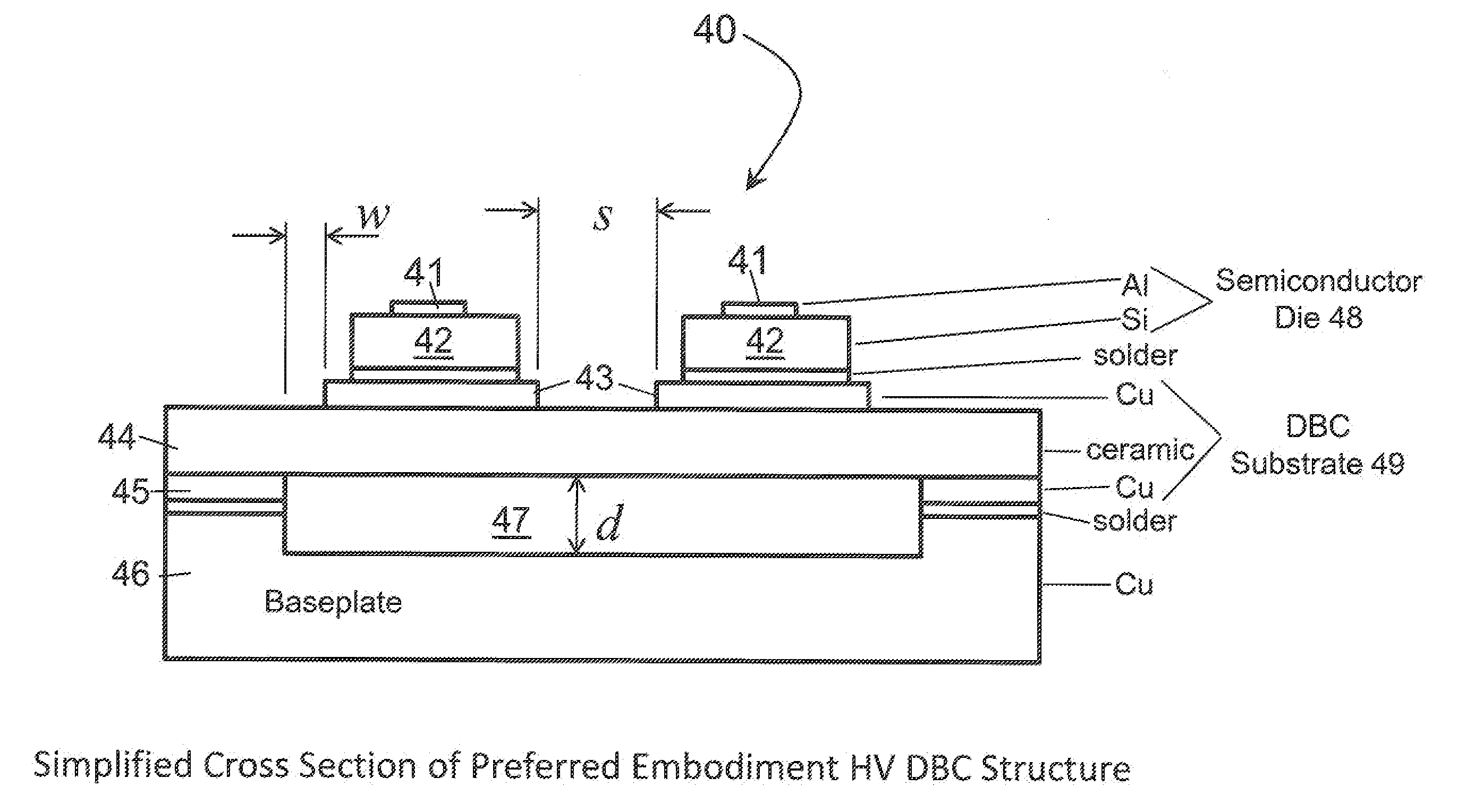

System and Method for Packaging of High-Voltage Semiconductor Devices

InactiveUS20130020672A1Reduction of electric fieldIncrease distanceSemiconductor/solid-state device detailsSolid-state devicesElectric field stressHigh pressure

A method and an electronic device structure comprising at least one access lead to adapted to be connected to an electrical circuit; at least one substrate region; at least one semiconductor die positioned on the substrate; the at least one semiconductor die being operatively connected to the at least one access lead; a dielectric region extending below the at least one semiconductor die; the dielectric region being formed by creating a cavity in the at least one substrate region; whereby the dielectric region operates to reduce electric field stresses produced by the at least one semiconductor die to thereby reduce the possibility of material failure and voltage breakdown. The method of making an electronic device structure comprises providing at least one substrate region; providing at least one semiconductor die located on the at least one substrate region; removing a portion of the at least one substrate region to provide a dielectric region within the substrate extending below the at least one semiconductor die; whereby the dielectric region within the at least one substrate region operates to reduce electric field stresses produced by the at least one semiconductor die to thereby reduce the possibility of material failure and voltage breakdown.

Owner:US SEC THE ARMY THE

Heating resistance element component and thermal printer

InactiveUS20090090703A1Improve heating efficiencyReduce power consumptionOhmic-resistance heating detailsPrintingElectrical resistance and conductanceHeat sensitive

Provided is a heating resistance element component, including: a supporting substrate; an insulating film laminated on the supporting substrate; a plurality of heating resistors arranged at intervals on the insulating film; a common wire connected to one end of each of the plurality of heating resistors; and individual wires each connected to another end of the each of the plurality of heating resistors, in which a surface of the supporting substrate is formed with a first concave portion and a second concave portion, the first concave portion being arranged in a region opposed to heating portions of the plurality of heating resistors, the second concave portion being arranged at an interval in a vicinity of the first concave portion. Accordingly, heating efficiency of the heating resistors can be increased to reduce power consumption, and a strength of the substrate under the heating resistors can be increased.

Owner:SEIKO INSTR INC

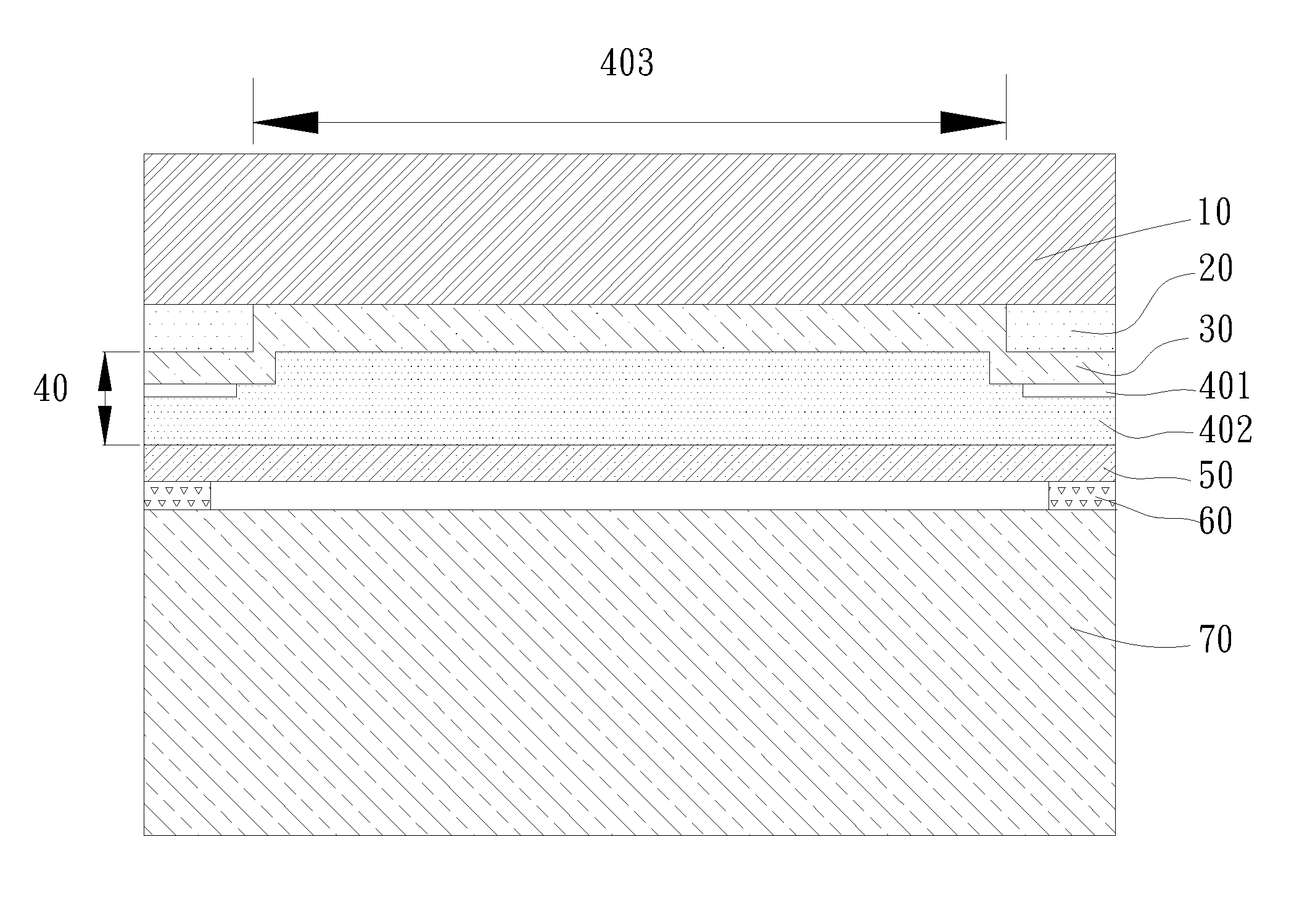

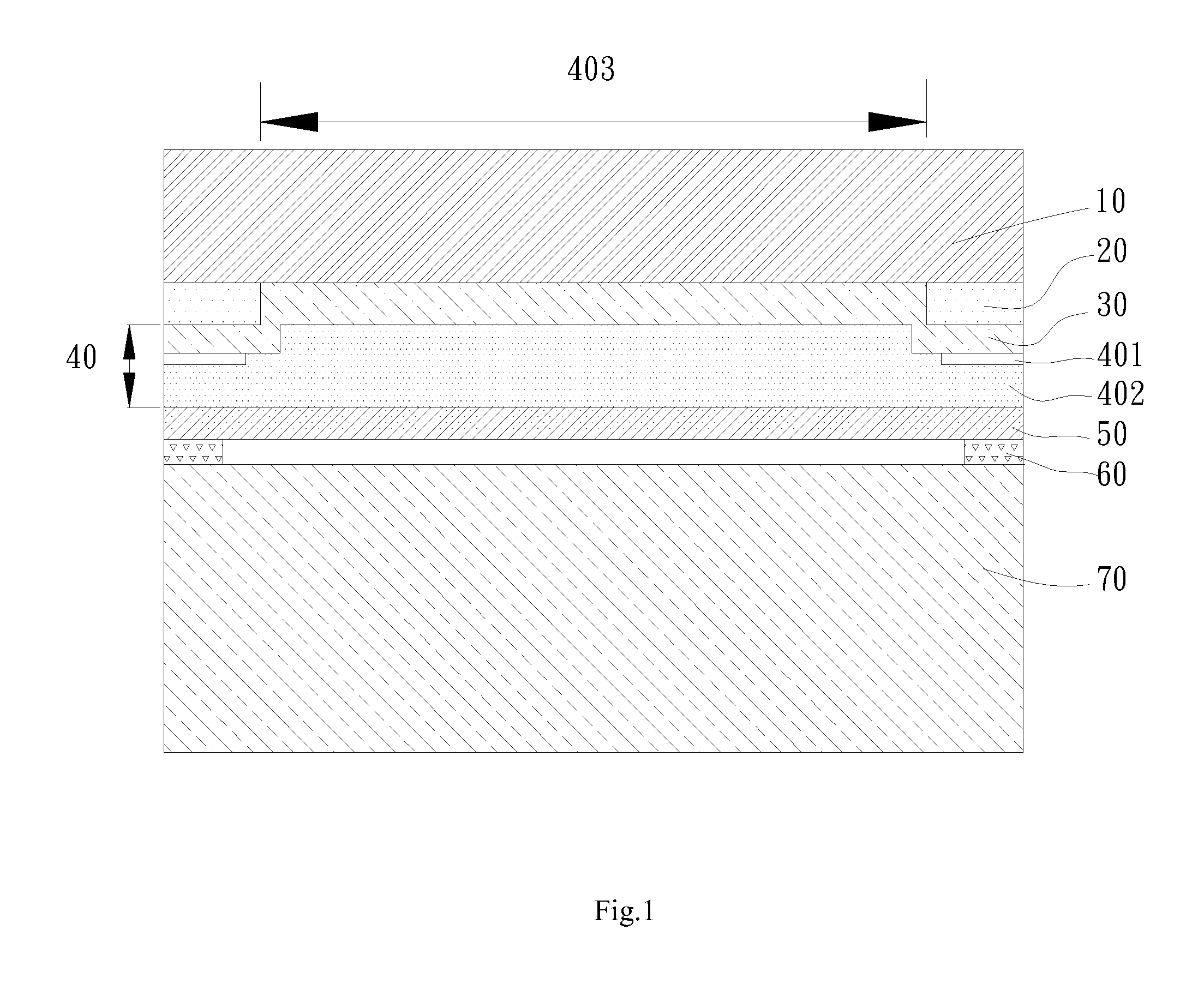

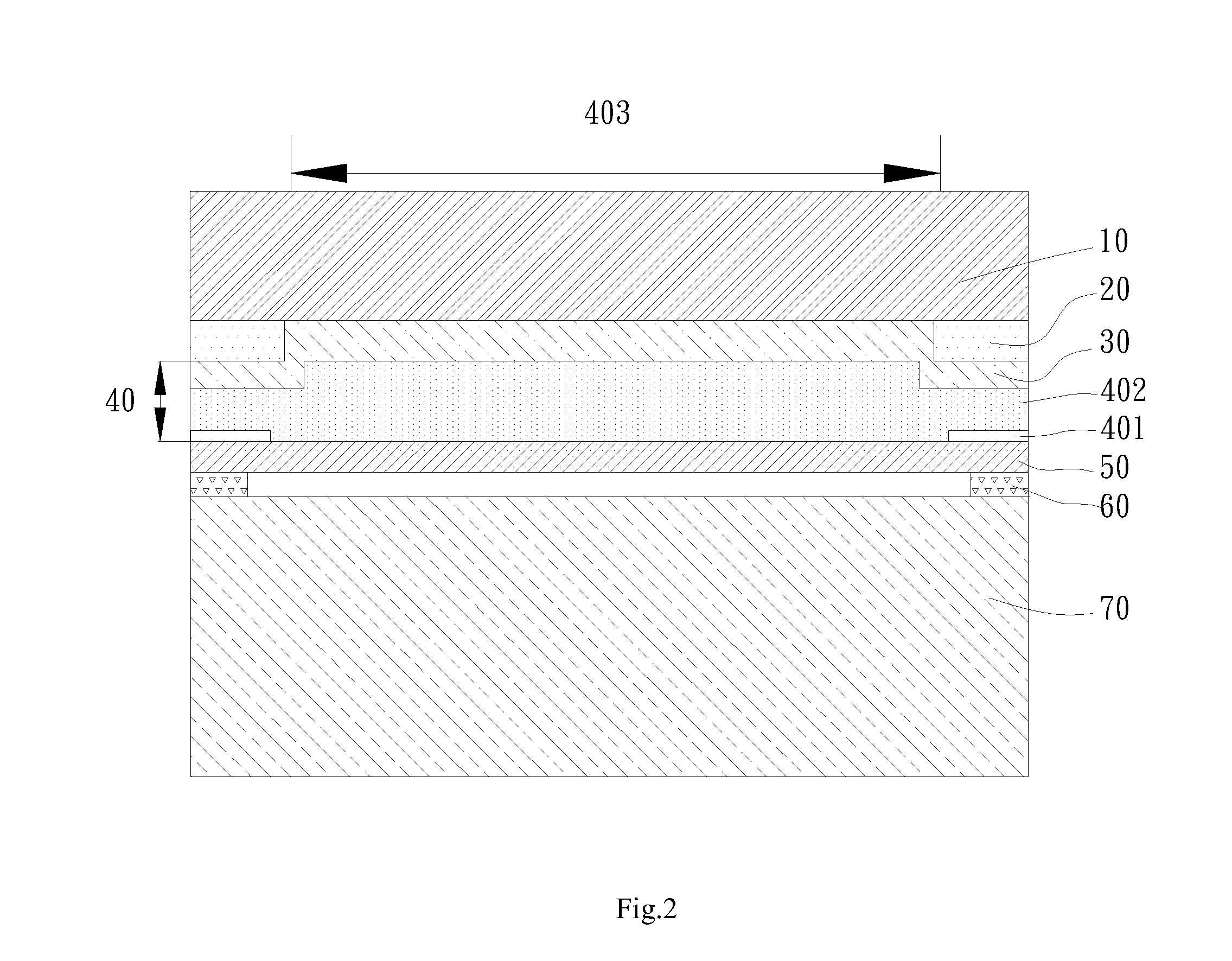

Display device and manufacturing method of display device

ActiveUS20140232952A1Reduce thicknessReduce the number of partsSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceLiquid crystal

Warpage deformation which is caused when substrates having mutually different linear expansion coefficients are bonded to sandwich a display functional layer is suppressed. A display device has a first substrate, a second substrate bonded to the first substrate so as to be opposed to the first substrate, and a liquid crystal layer serving as a display functional layer disposed between the first substrate and the second substrate. Also, a first linear expansion coefficient of the first substrate provided in the display device is larger than a second linear expansion coefficient of the second substrate, and a first thickness of the first substrate is larger than a second thickness of the second substrate.

Owner:JAPAN DISPLAY INC

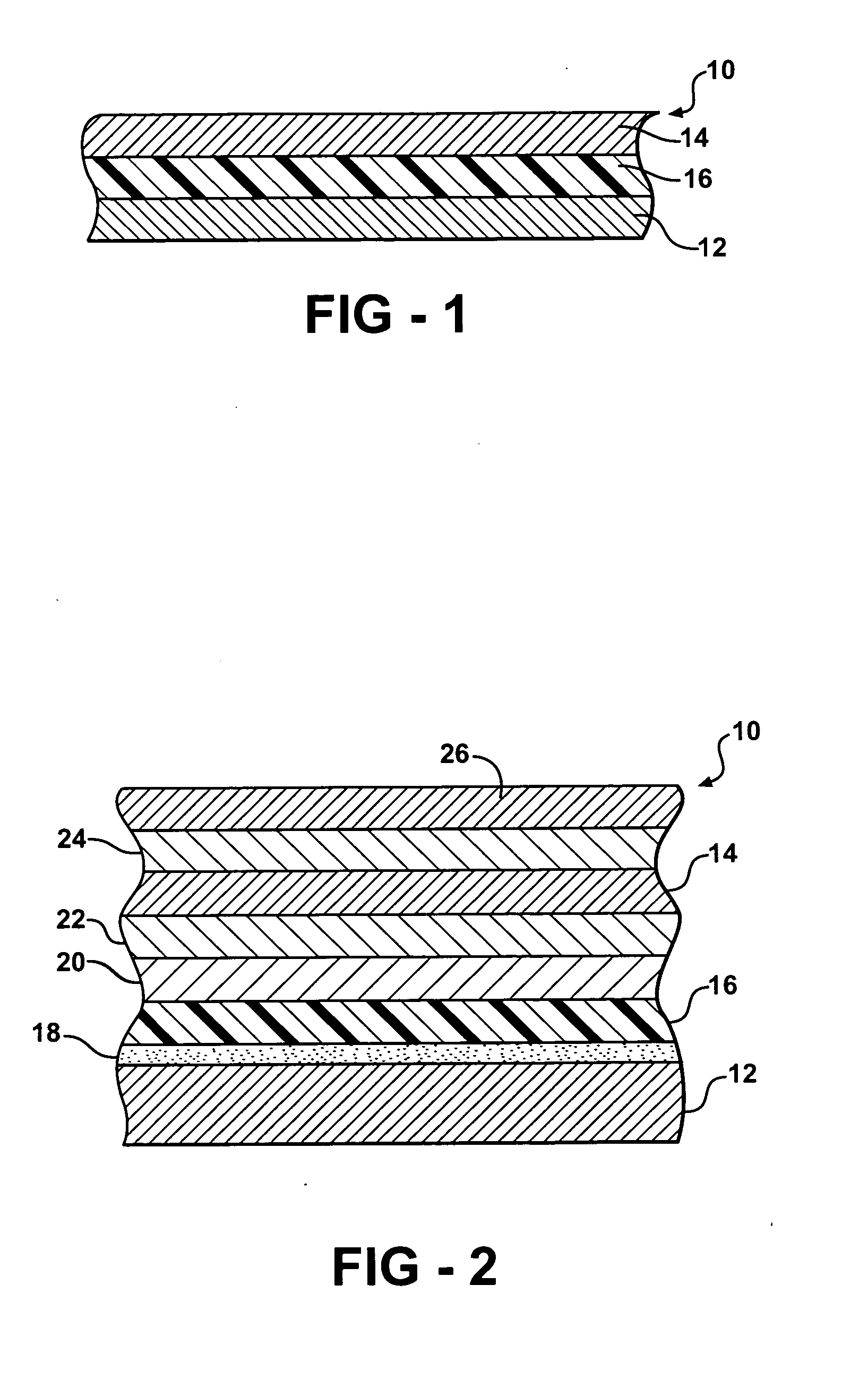

Composite Article Including a Cation-Sensitive Layer

InactiveUS20100051920A1Improve substrate strengthShorten the timeFilm/foil adhesivesElectroluminescent light sourcesMaterials scienceSilicone

A composite article includes a substrate having a surface, a cation-sensitive layer including a cation-sensitive material disposed on the surface of the substrate, and a silicone layer disposed between the substrate and the cation-sensitive layer. Cations are present on the surface of the substrate in an amount of at least 0.1 atomic weight percent based on the total atomic weight of the atoms on the surface of the substrate. The silicone layer includes a cured silicone composition for preventing cations from migrating from the substrate to the cation-sensitive layer. The inclusion of the silicone layer between the cation-sensitive layer and the substrate enables the use of materials for the substrate that have not been useable in the past due to the presence of excessive amounts of cations in the materials.

Owner:DOW CORNING CORP

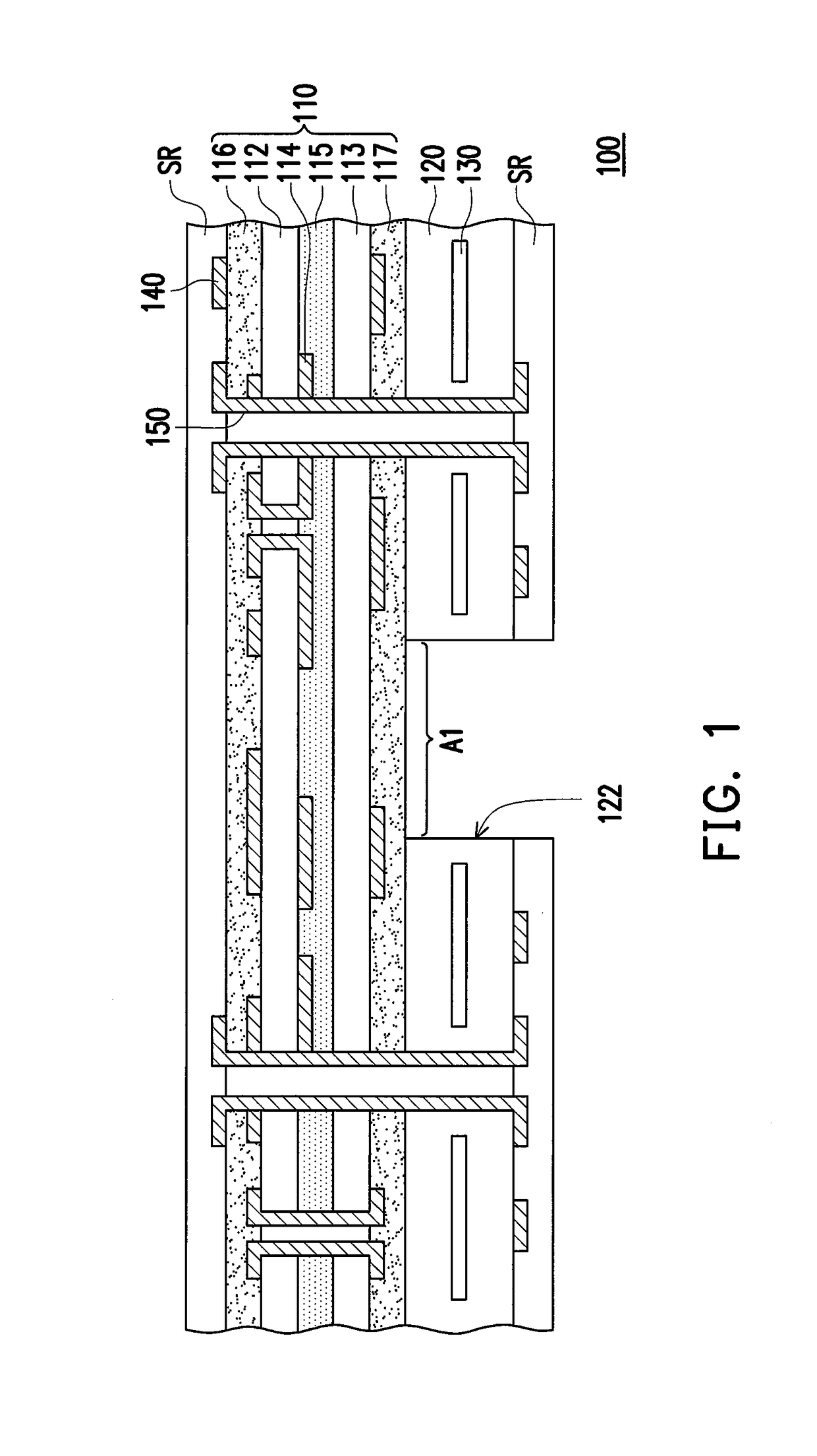

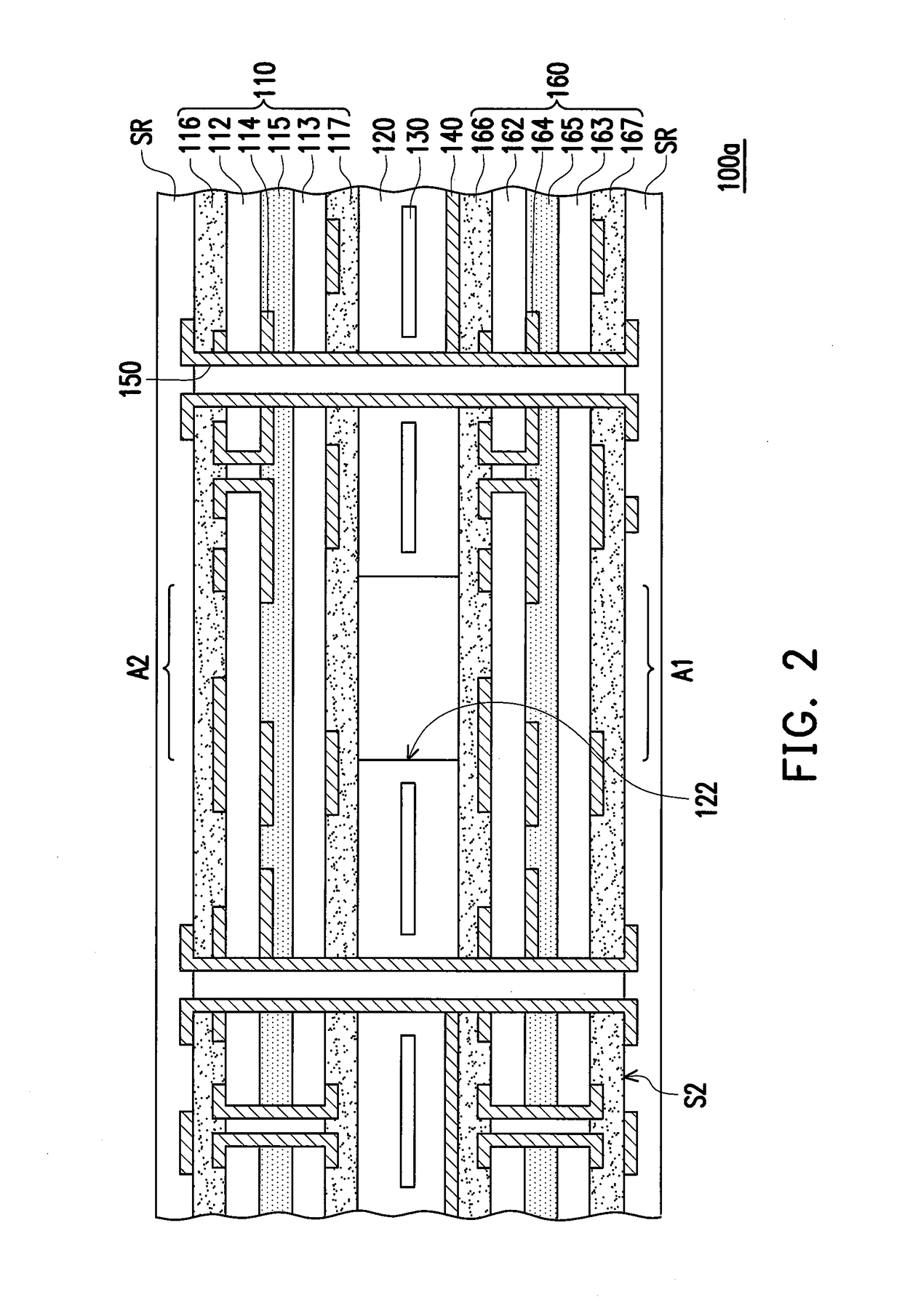

Rigid-flex board structure

ActiveUS9860978B1Improve flatnessStable structureCircuit bendability/stretchabilityStacked PCBsEngineeringFlexible electronics

A rigid-flex board structure includes a flexible printed circuit (FPC) board, a substrate, a reinforcing layer, a patterned circuit layer and a plurality of conductive vias. The FPC board includes at least one exposing area. The substrate is disposed on the FPC board and includes an opening exposing the exposing area. The reinforcing layer is embedded in the substrate and a rigidity of a material of the reinforcing layer is greater than a rigidity of a material of the substrate. The patterned circuit layer is disposed on the substrate. The conductive vias are configured to electrically connect the patterned circuit layer and the FPC board.

Owner:UNIFLEX TECH

Ultrasonic transducer device, probe, electronic instrument, and ultrasonic diagnostic device

ActiveUS9197331B2DistanceReduce thicknessMagnetostrictive device manufacture/assemblySonic/ultrasonic/infrasonic transmissionUltrasonic sensorElectronic instrument

An ultrasonic transducer device includes a substrate, a plurality of ultrasonic transducer elements, a wiring substrate and a wiring member. The substrate defines a plurality of openings arranged in an array pattern. Each of the ultrasonic transducer elements is provided in each of the openings on a first surface of the substrate. The wiring substrate is arranged to face a second surface of the substrate that is opposite from the first surface. The wiring substrate includes a first wiring part. The wiring member is connected to the substrate and the wiring substrate. The wiring member includes a second wiring part electrically connecting the ultrasonic transducer elements to the first wiring part.

Owner:SEIKO EPSON CORP

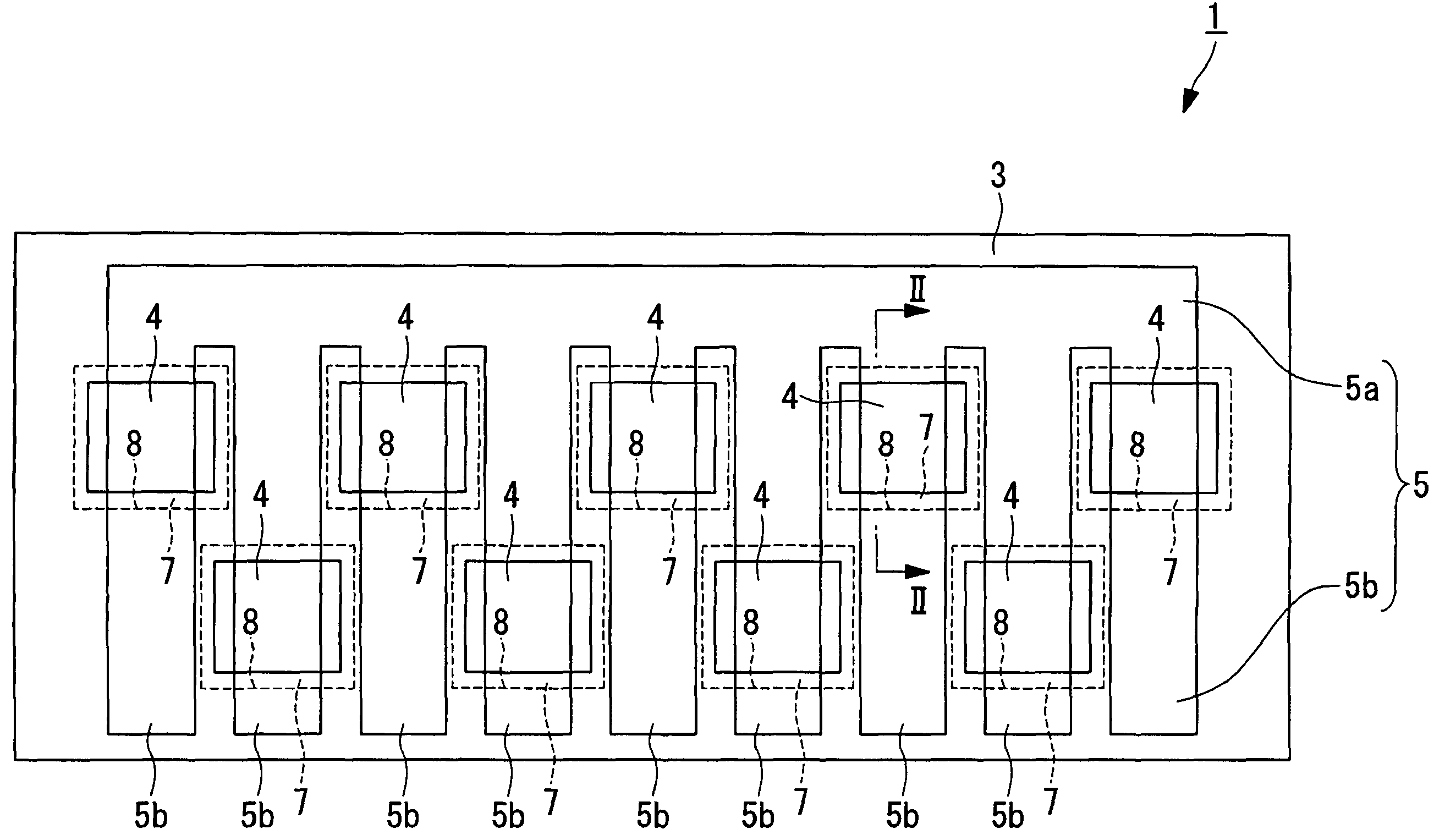

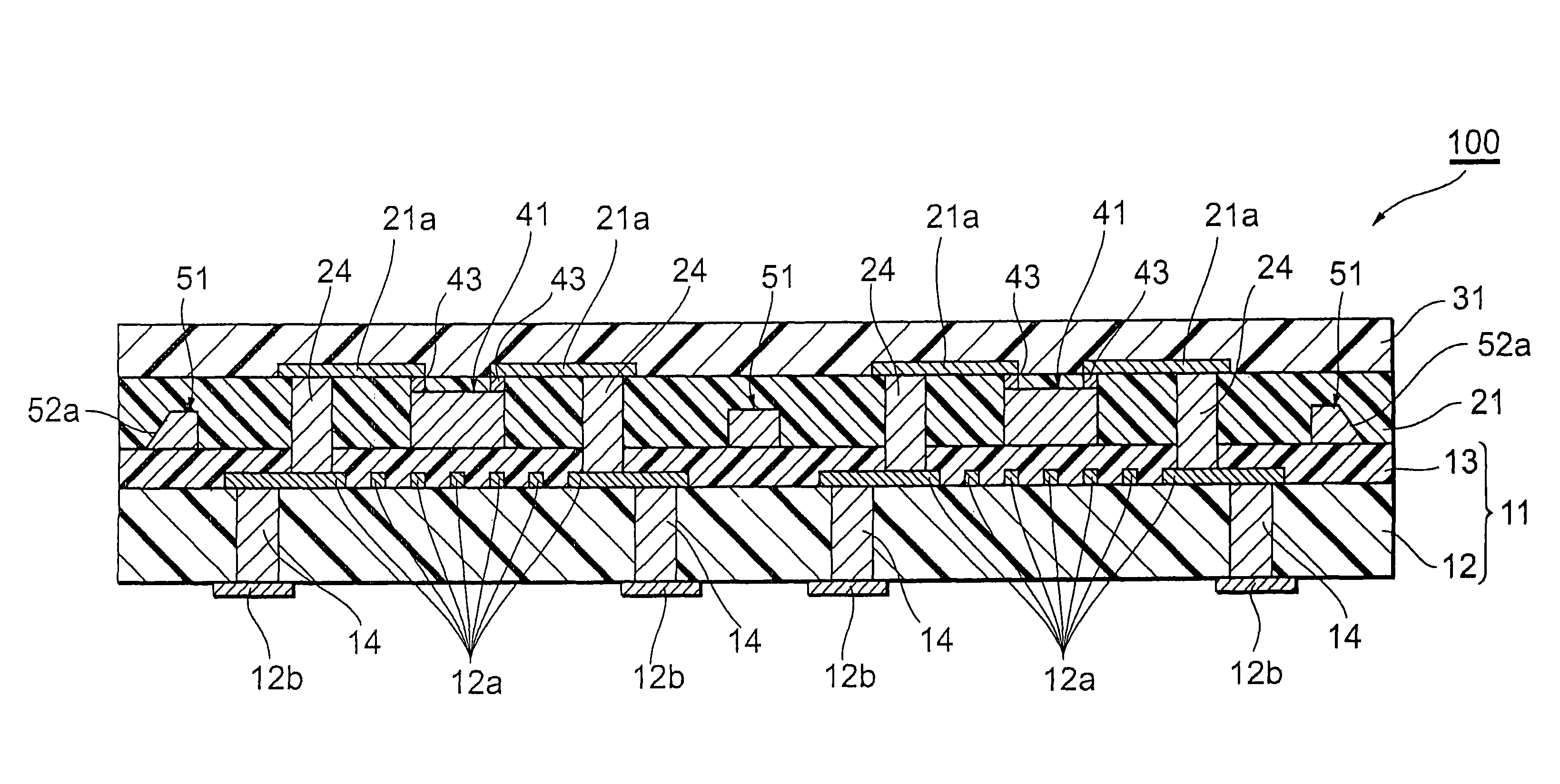

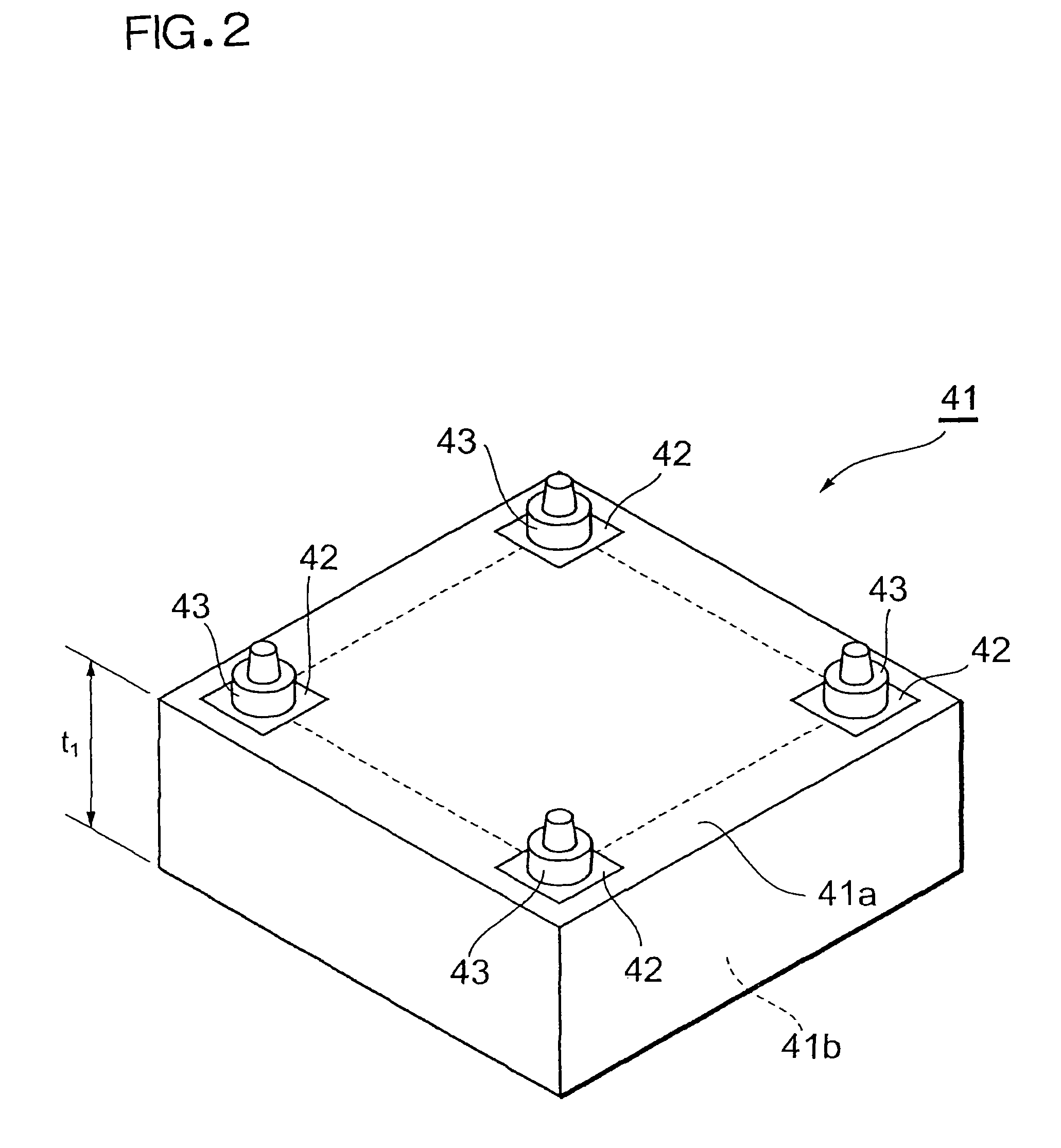

Assembly substrate and method of manufacturing the same

ActiveUS20090025965A1Low costReduce loadFinal product manufactureSemiconductor/solid-state device detailsProduction rateEngineering

The object of the present invention is to provide an assembly substrate which is easily handled and capable of suppressing occurrence of warpage, and offers high productivity and economic efficiency, and its manufacturing method. A work board 100 includes an insulating layer 21 on one surface of a substantially rectangular-shaped substrate 11, and electronic components 41 and a plate-like integrated frame 51 are embedded inside the insulating layer 21. The plate-like integrated frame 51 has a plurality of concave portions 53 arranged in parallel at its inner periphery wall 52a, and arranged on a non-placing area of the electronic components 41 so as to surround a plurality of the electronic components 41 (groups).

Owner:TDK CORPARATION

Multi-layer wiring board and method of manufacturing the same

InactiveUS8035035B2Improve substrate strengthReduce manufacturing costLine/current collector detailsFinal product manufactureSolder maskStructural engineering

A multi-layer wiring board without a core substrate includes: a multi-layer laminated structure; first terminals provided on a front surface of the multi-layer laminated structure; second terminals provided on a rear surface of the multi-layer laminated structure; a solder resist which covers the rear surface and which has solder resist openings formed at positions corresponding to the second terminals; a reinforcing plate which is made of a non-metal material and which has reinforcing plate openings formed at positions corresponding to the second terminals; and an adhesive layer interposed between the solder resist and the reinforcing plate to fix the reinforcing plate to the solder resist and which includes adhesive layer openings formed at positions corresponding to the second terminals. A diameter of the solder resist openings and a diameter of the reinforcing plate openings are smaller than that of the adhesive layer openings.

Owner:NGK SPARK PLUG CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS8039322B2Improve discharge performanceImprove substrate strengthTransistorSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A manufacturing method of a semiconductor device 10 includes forming a plurality of second conductive second semiconductor regions at specific intervals on one main surface of a first conductive first semiconductor region, the plurality of second conductive second semiconductor regions being opposite to the first conductive first semiconductor region, forming a plurality of the first conductive third semiconductor regions on a main surface of the second semiconductor region, the plurality of the first conductive third regions being separated from each other, forming a plurality of holes at specific intervals on an another main surface which faces the one main surface of the first semiconductor region, the plurality of holes being separated from each other, forming a pair of adjacent second conductive fourth semiconductor regions which are alternately connected at a bottom part of the hole within the first semiconductor region, and burying an electrode within the hole.

Owner:SANKEN ELECTRIC CO LTD

Heating resistance element component and printer

InactiveUS7852361B2Improve heating efficiencyReduce power consumptionPrintingElectrical resistance and conductanceEngineering

Provided is a heating resistance element component, including: a supporting substrate; an insulating film laminated on the supporting substrate; a plurality of heating resistors formed on the insulating film, the plurality of heating resistors being arranged in a zigzag shape along a main scanning direction and having a substantially square shape; a common wire connected to one end of each of the plurality of heating resistors; individual wires each connected to another end of the each of the plurality of heating resistors; and concave portions formed in regions which are opposed to the plurality of heating resistors and are located on a surface of the supporting substrate, in which an arrangement pitch of the plurality of heating resistors in a sub-scanning direction is larger than an arrangement pitch of the plurality of heating resistors in a main scanning direction.

Owner:SEIKO INSTR INC

Electronic component-embedded board and method of manufacturing the same

ActiveUS8237059B2High mechanical strengthShape variation is suppressedPrinted circuit assemblingPrinted electric component incorporationProduction rateElectronic component

Owner:TDK CORPARATION

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com