Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37results about How to "Easy and efficient and cost-effective" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

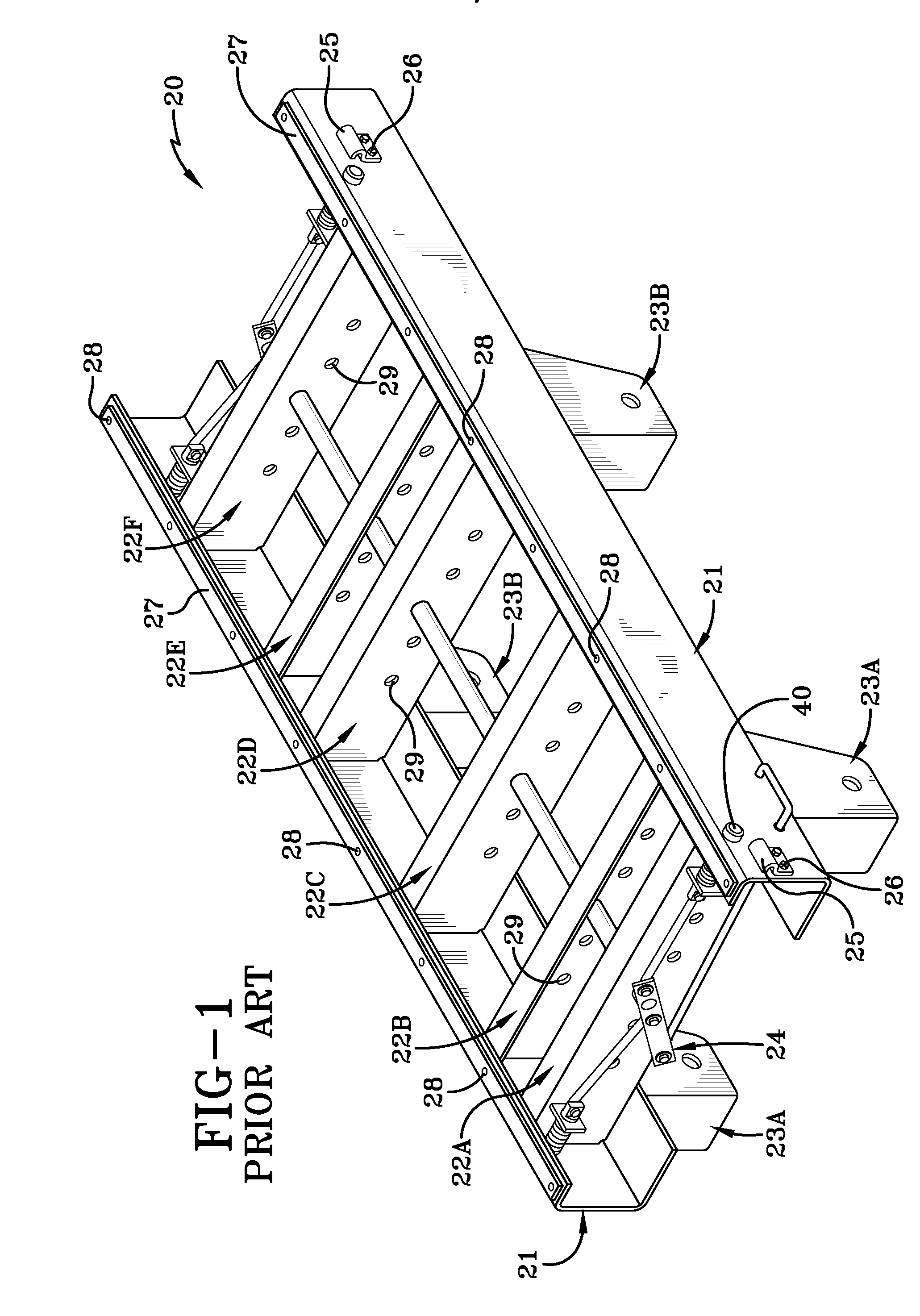

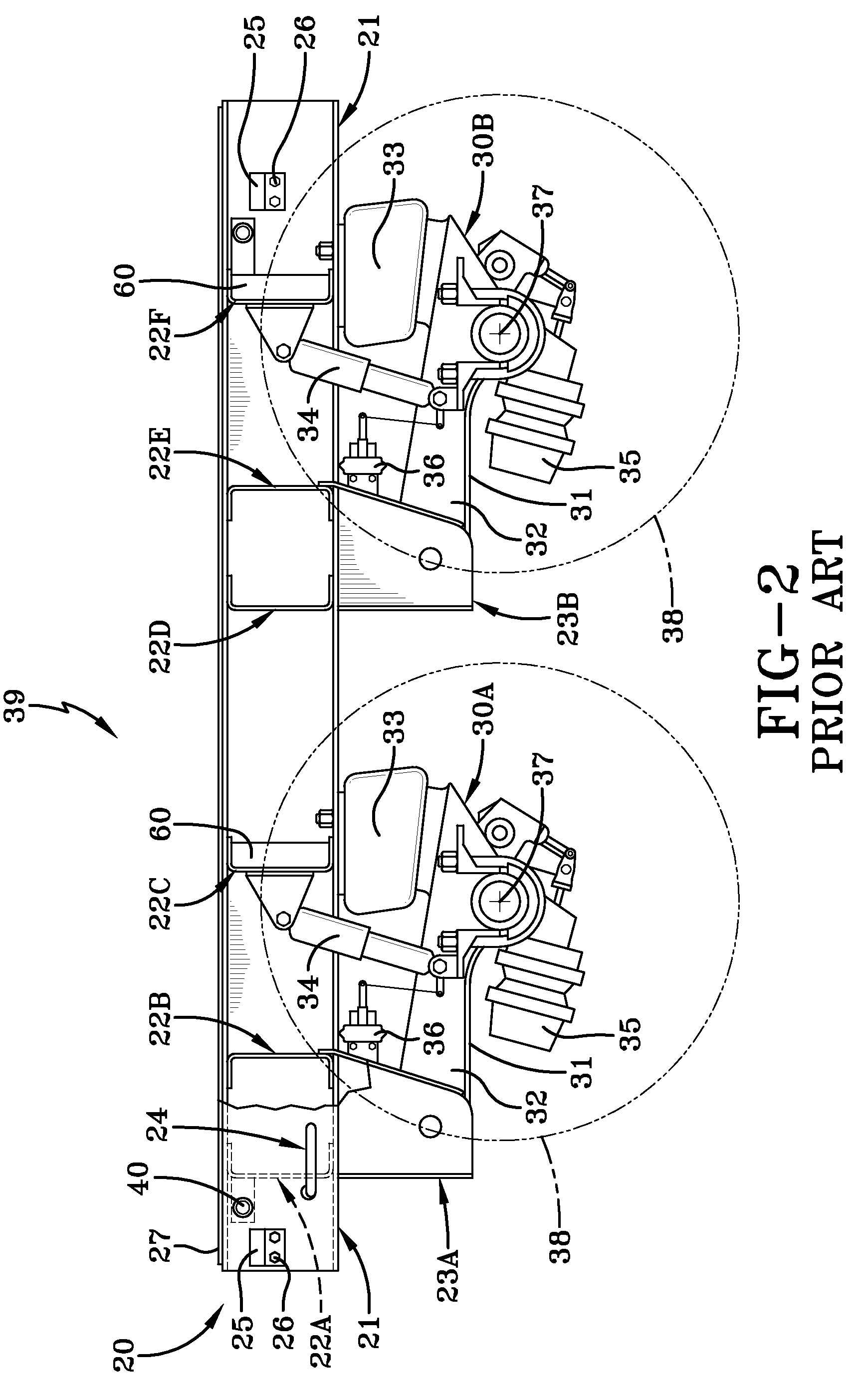

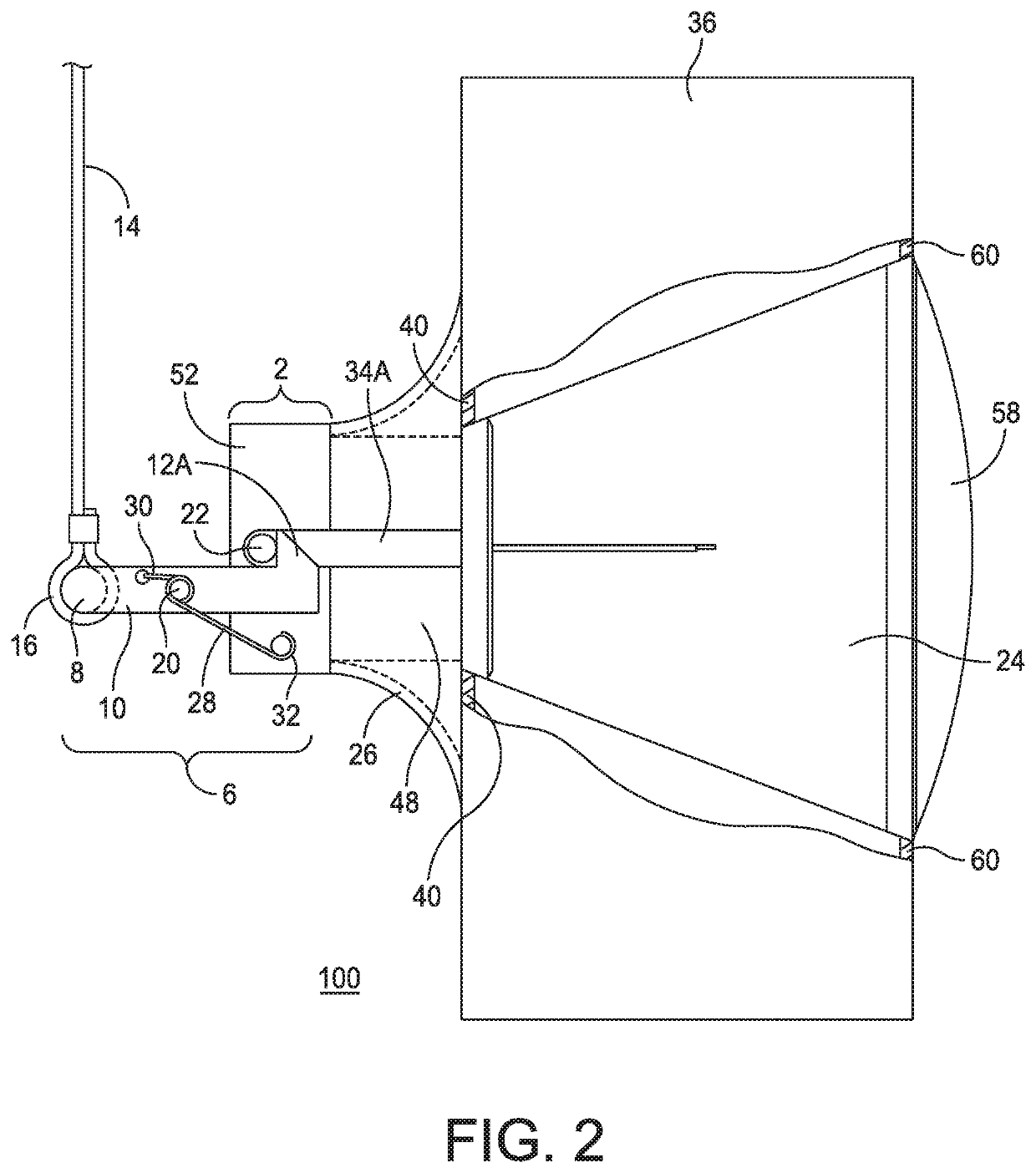

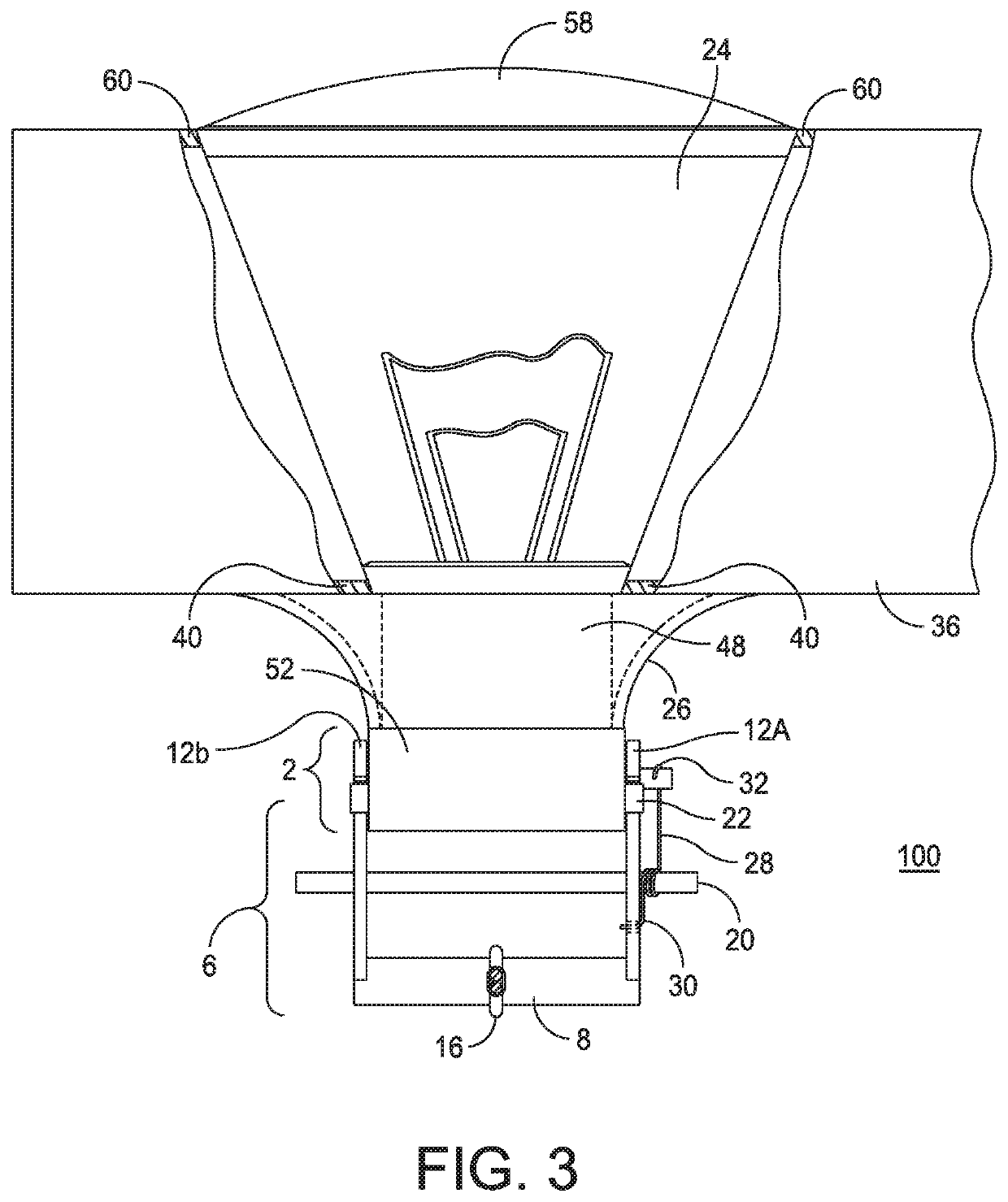

Frame for heavy-duty vehicles

InactiveUS20070126263A1Reduce harmEasy and efficient and cost-effectiveVehicle seatsSteering linkagesEngineeringHeavy duty

Owner:HENDRICKSON USA L L C

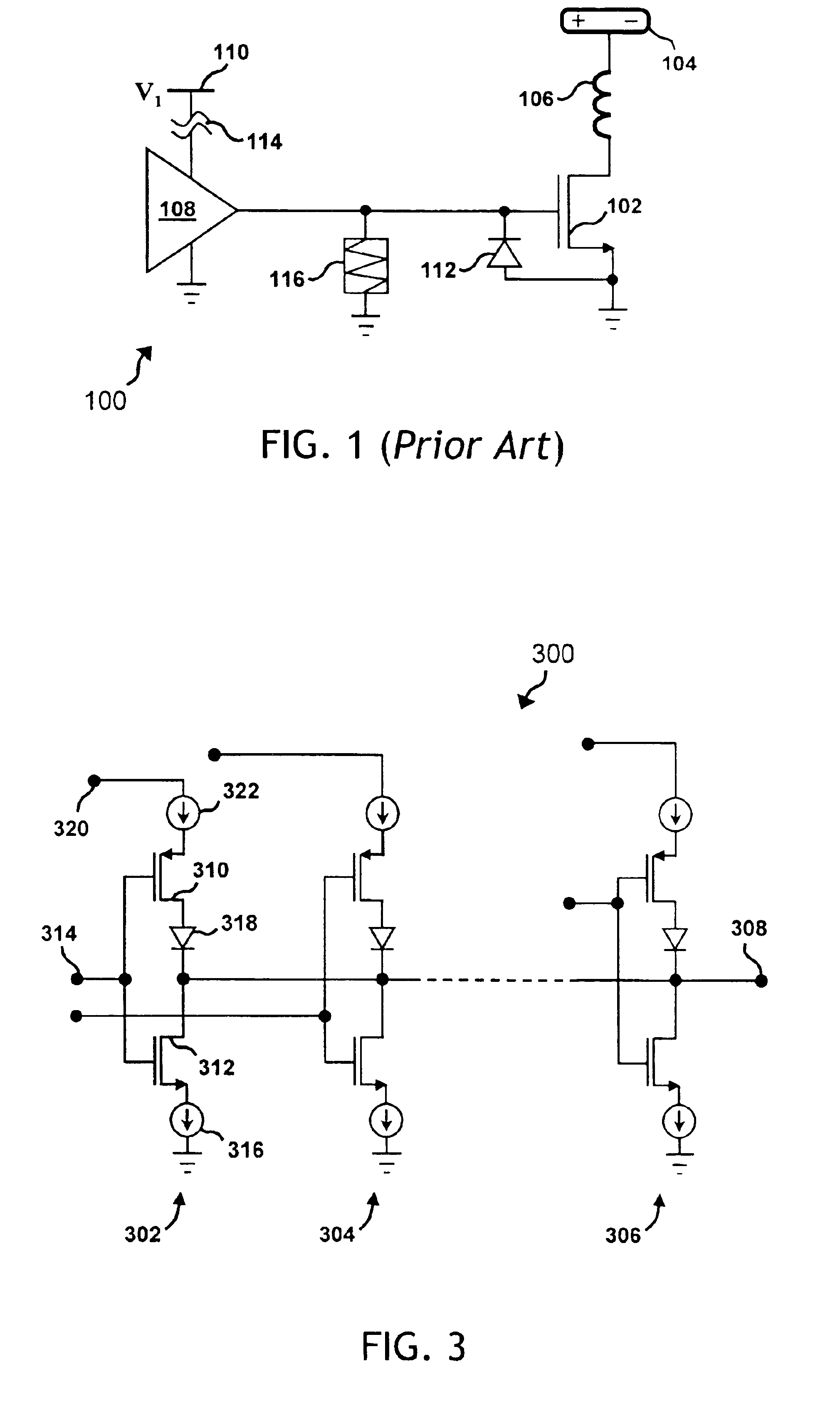

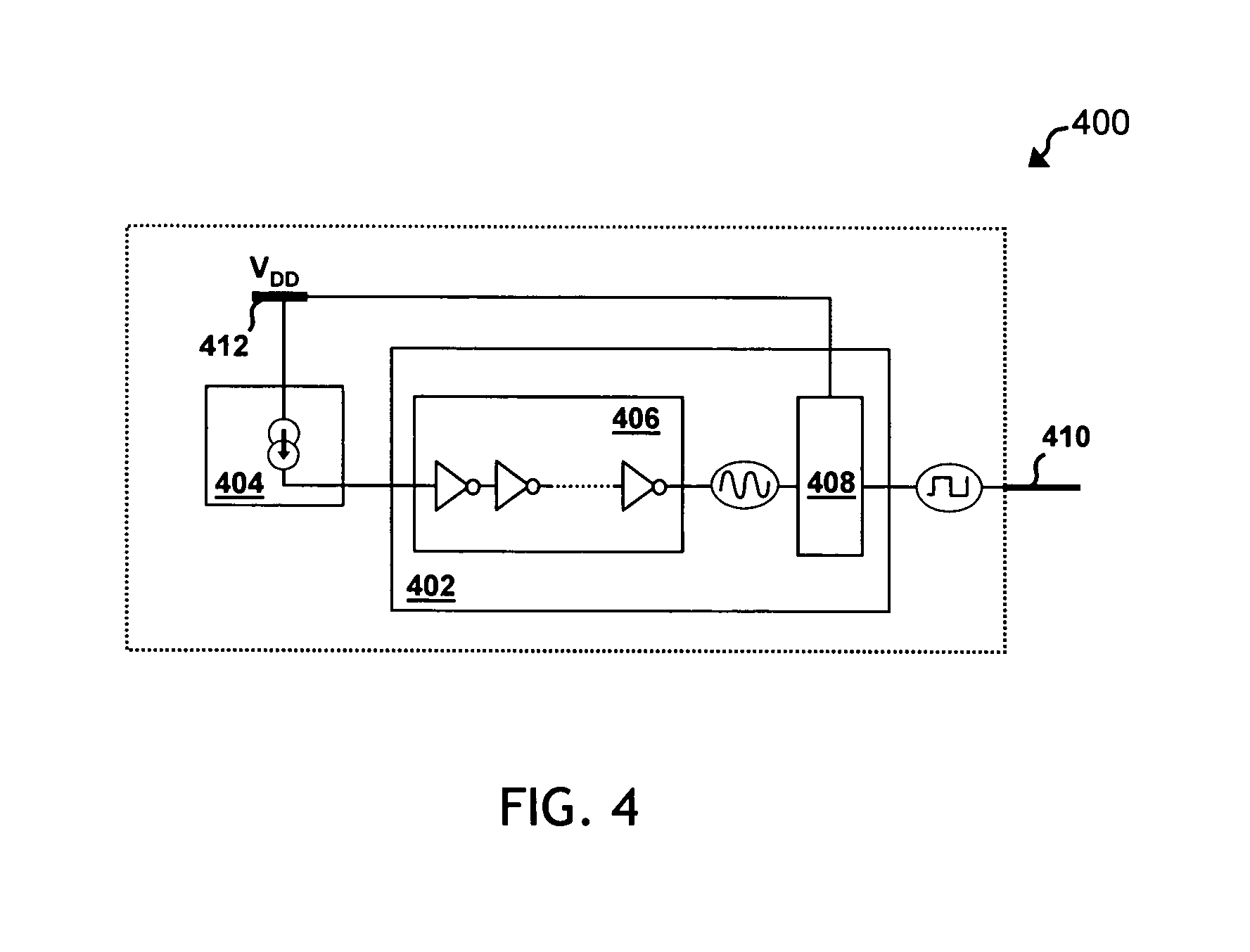

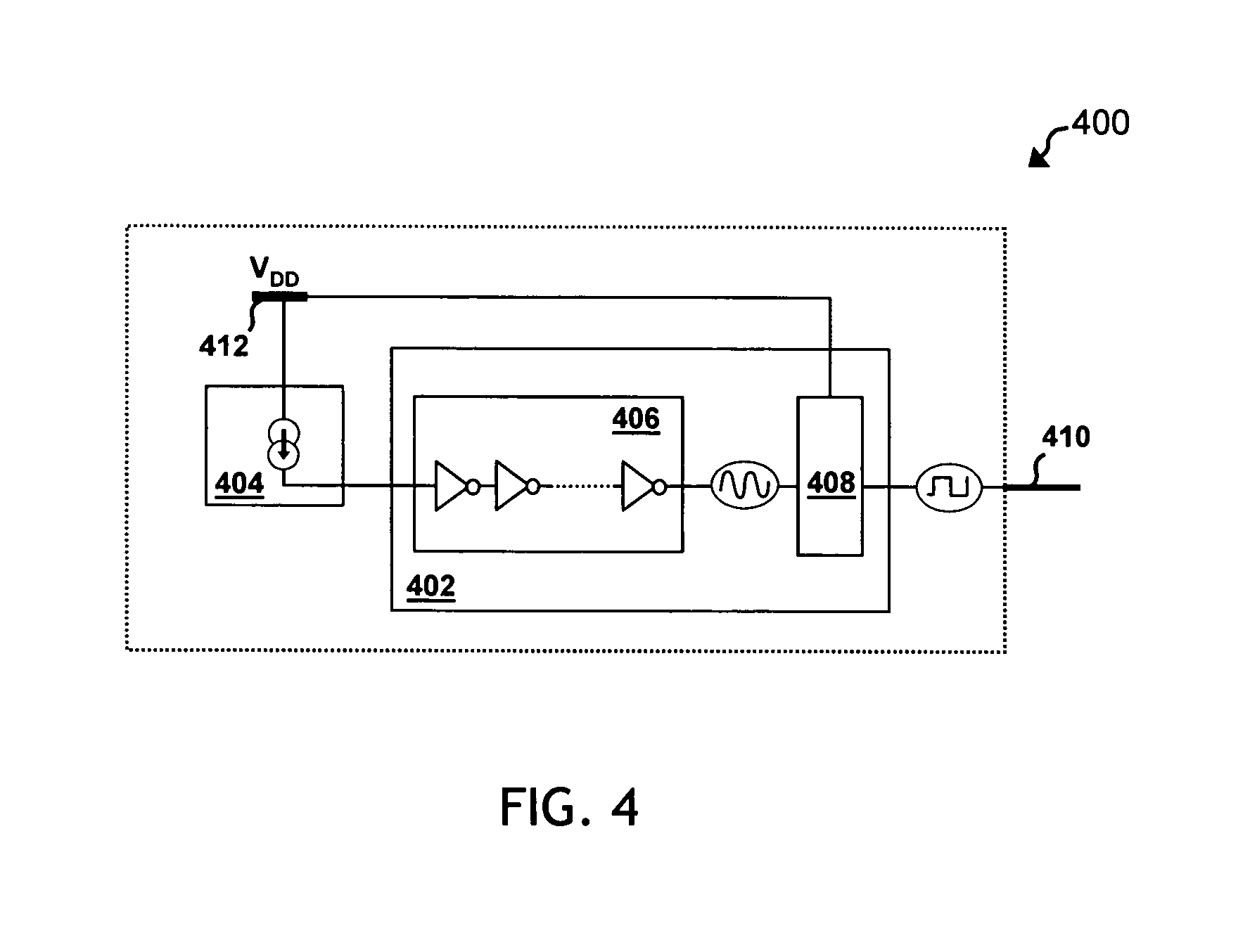

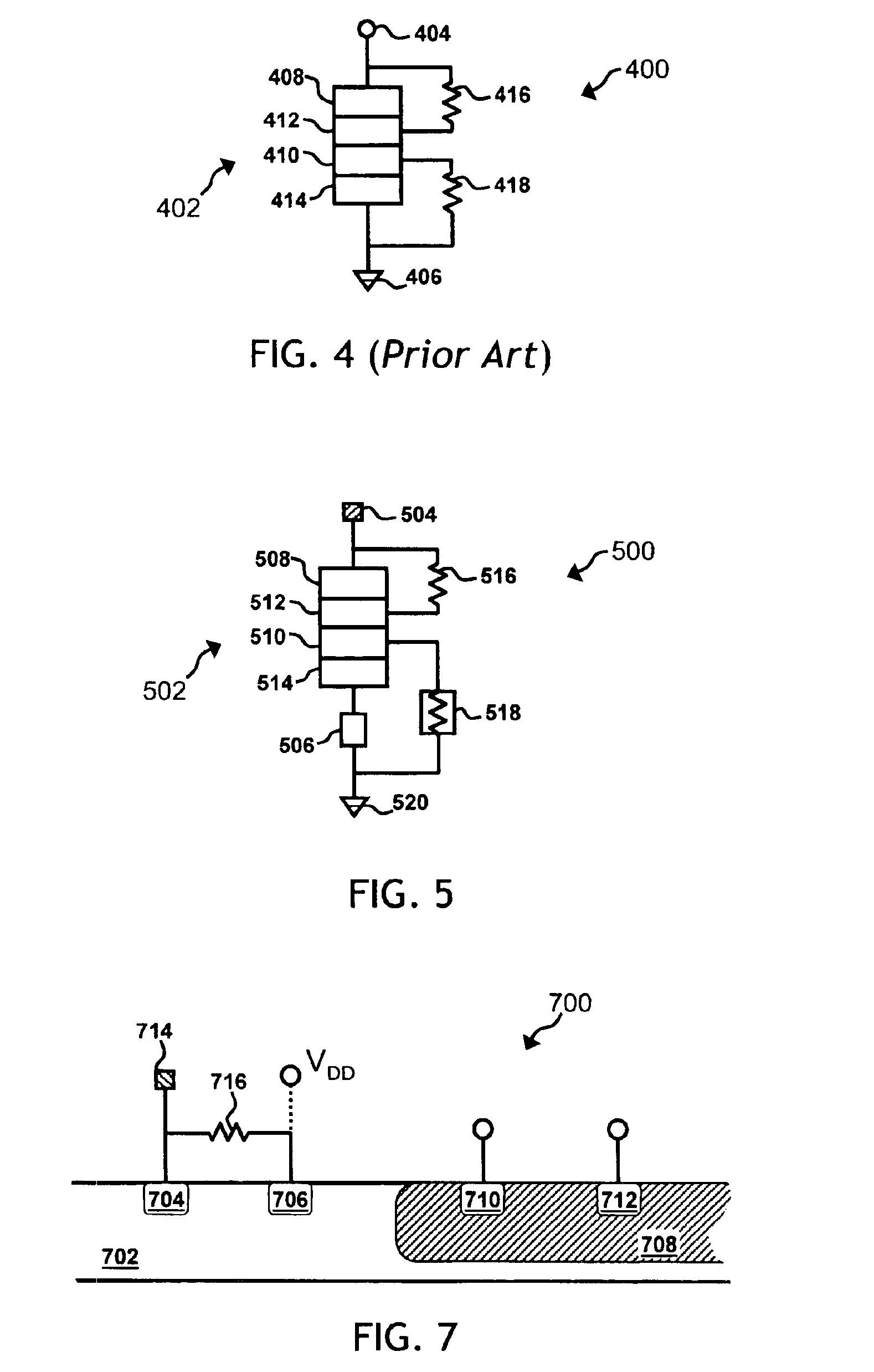

System for oxide stress testing

ActiveUS6864702B1Efficient and reliable assessmentEasy and efficient and cost-effectiveElectronic circuit testingIndividual semiconductor device testingControl signalEngineering

The present invention provides a system for stress testing an oxide structure to determine that structure's reliability in overstress conditions. The present invention provides an overstress test structure (400) that comprises a first transistor (406), having a first terminal coupled to ground, a second terminal coupled to a control signal (402), and a third terminal coupled to a first end of a first resistive element (412). A first voltage source (414) is coupled to the second end of the first resistive element. A second resistive element (416) is intercoupled between the second end of the first resistive element and ground. A second transistor (418) has a first terminal coupled to the second end of the first resistive element, a second terminal coupled to the first end of the first resistive element, and a third terminal coupled to a first node (420). A third resistive element (422) is intercoupled between the third terminal of the second transistor and ground; and a third transistor (424) has a first terminal coupled (426) to the oxide structure, a second terminal coupled to the first end of the first resistive elerment, and a third terminal coupled to a second voltage source (428).

Owner:TEXAS INSTR INC

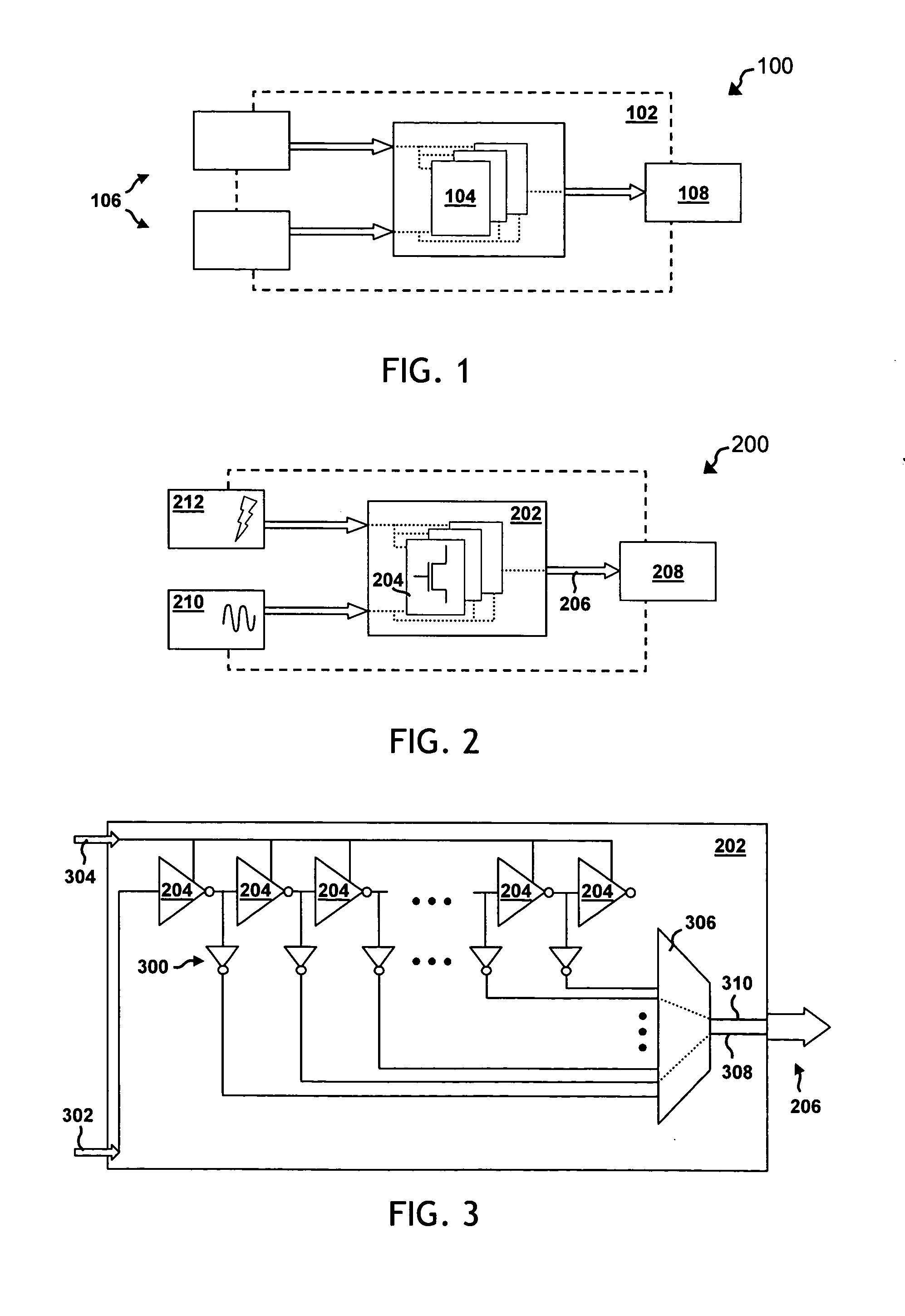

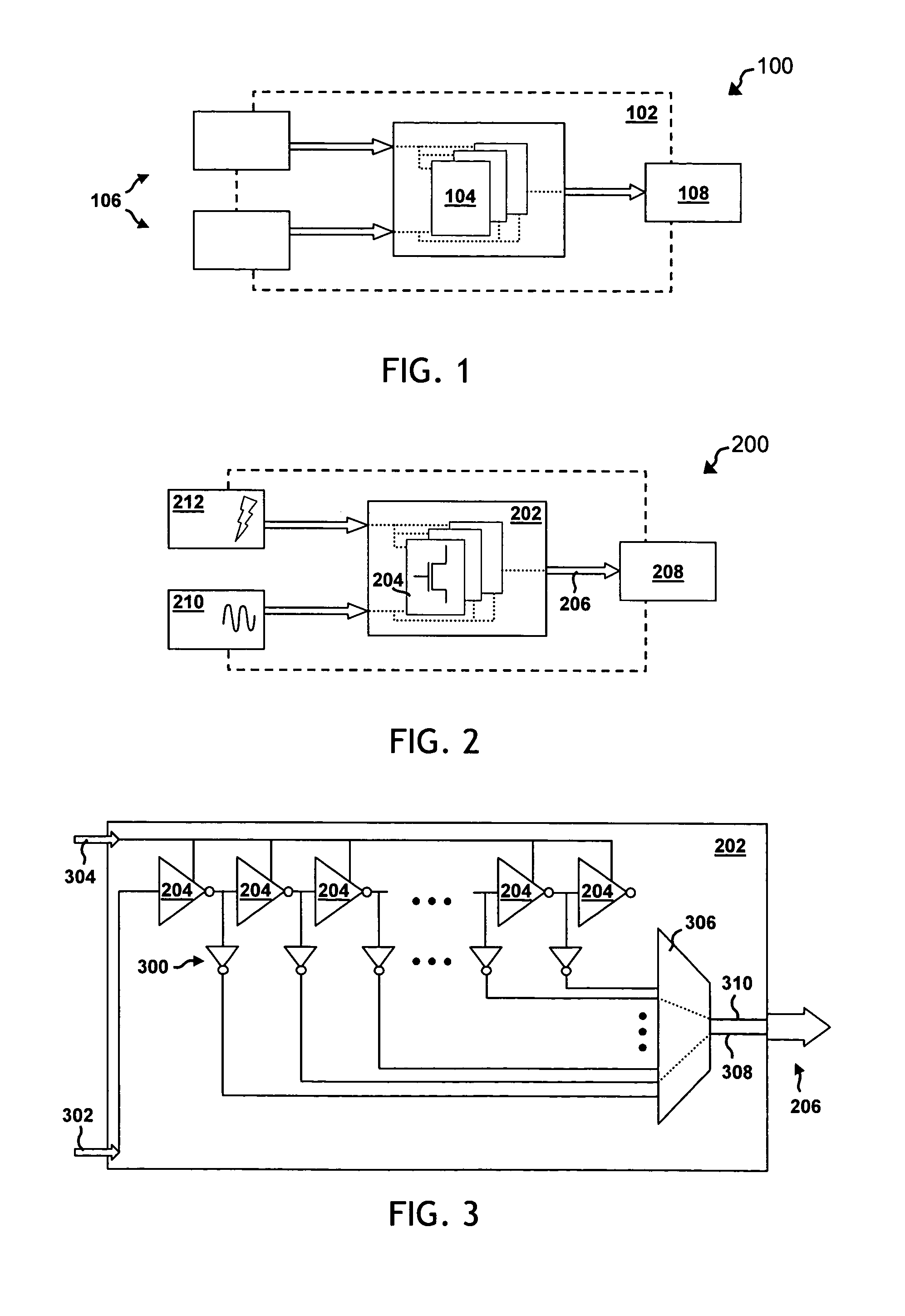

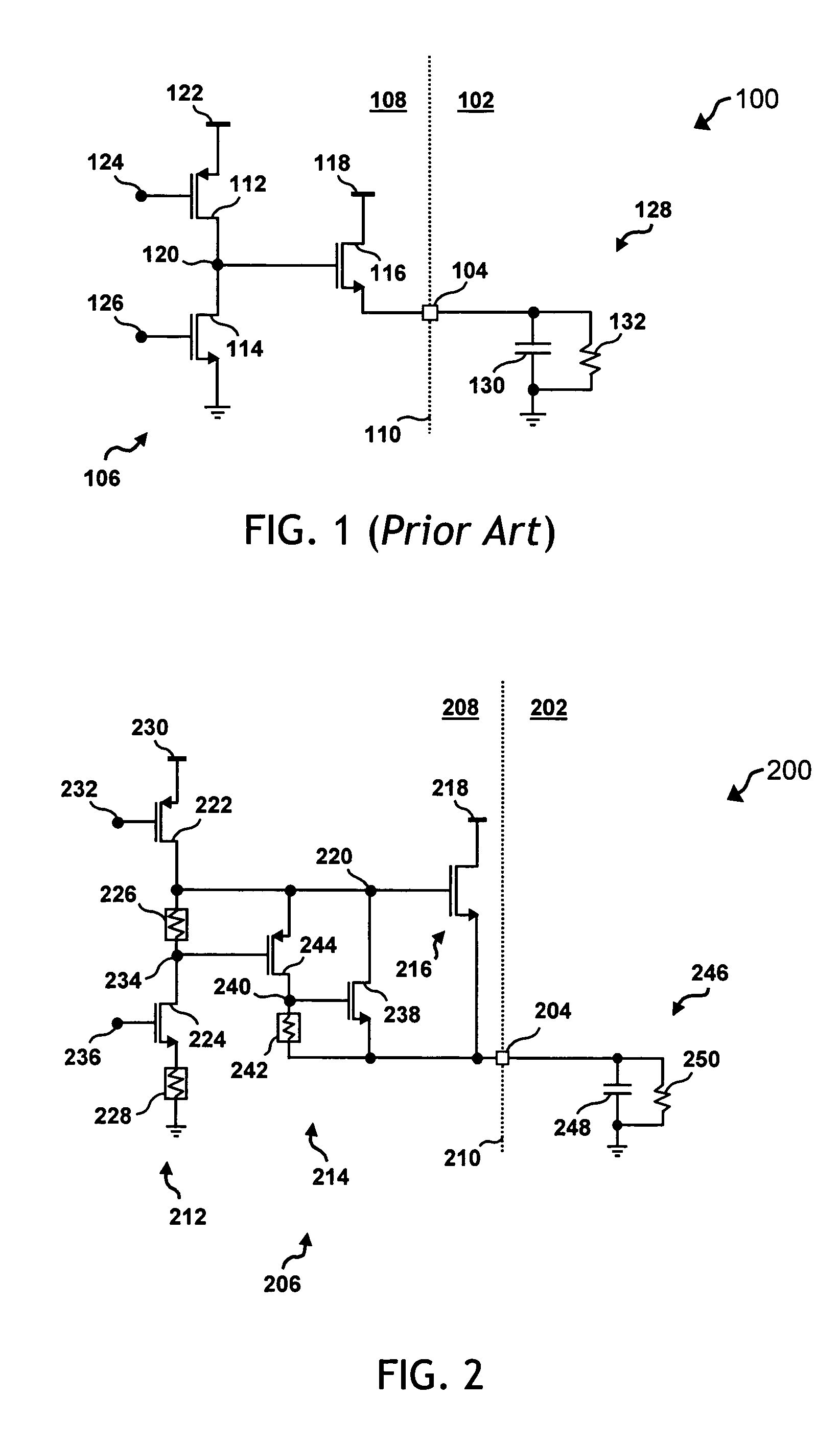

Versatile system for accelerated stress characterization of semiconductor device structures

ActiveUS20050280477A1Accelerates testEasy and efficientElectronic circuit testingPulse generation by logic circuitsEngineeringSemiconductor

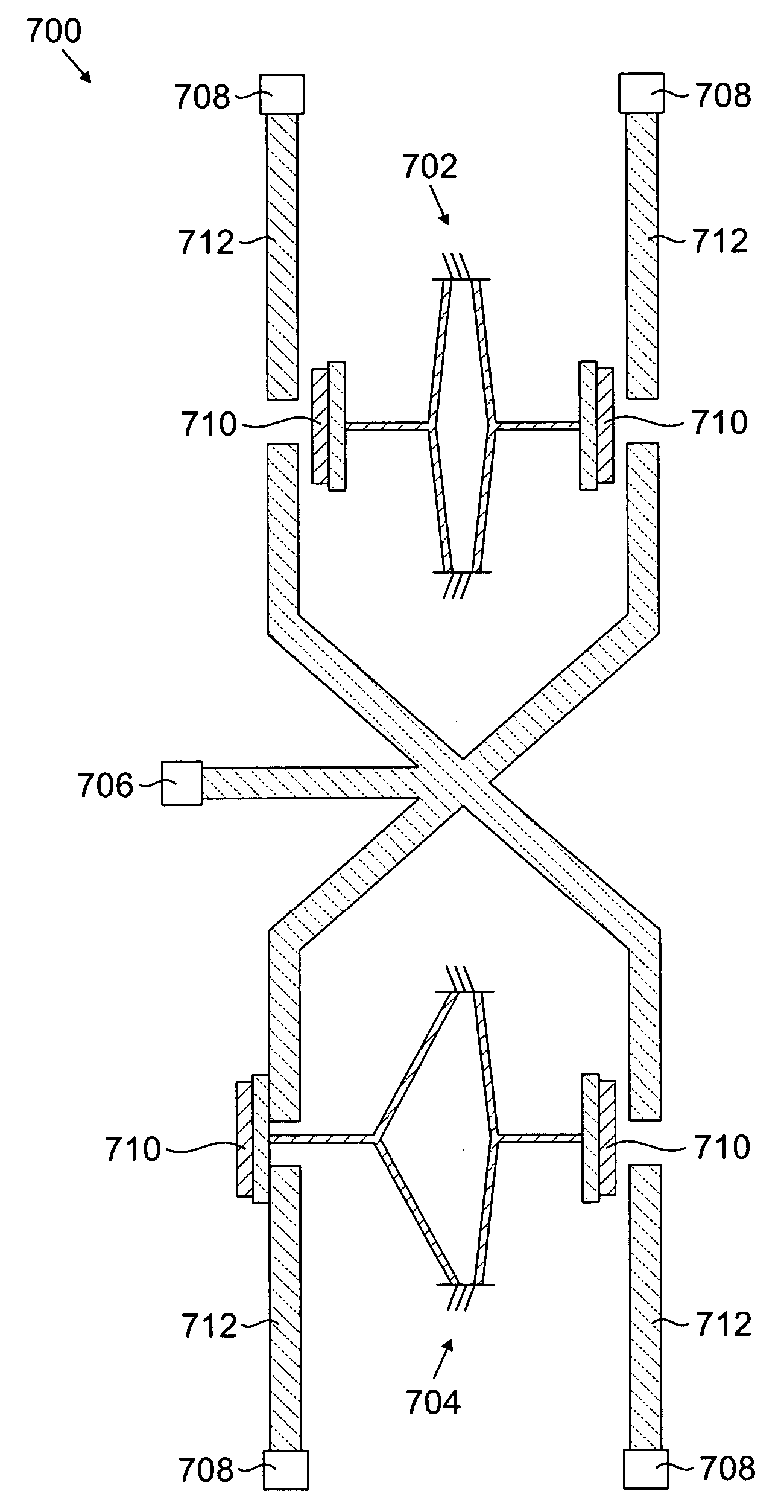

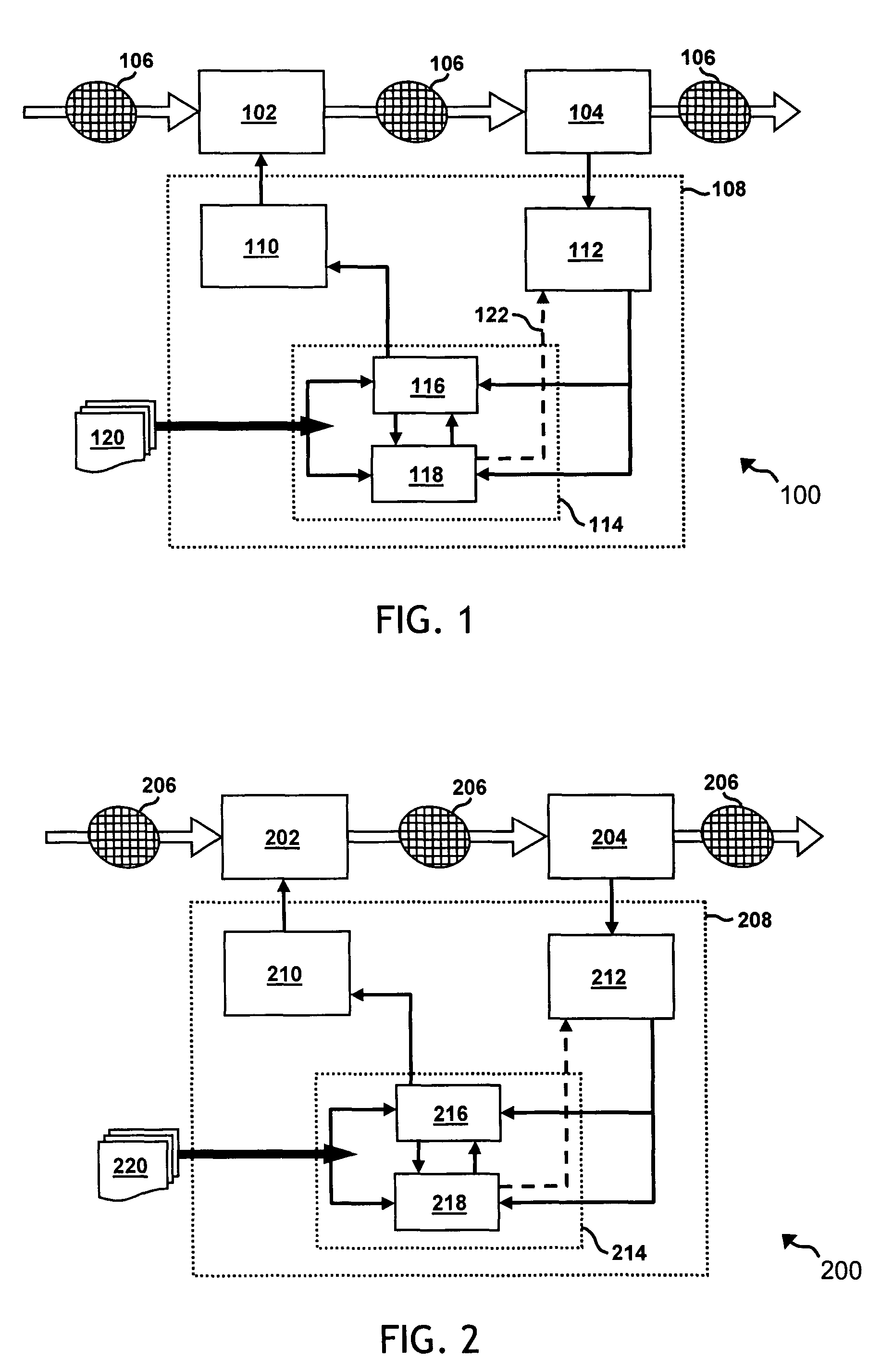

The present invention provides a system (200) for performing accelerated stress characterization of a given transistor (204). Inverter circuits, formed from the given transistor, are disposed in series with one another (202). A plurality of signal taps is operatively associated with each gap between adjacent inverter circuits. Selective circuitry is operatively coupled to the plurality of signal taps, and adapted to output (206) data from a first and a second of the plurality of signal taps. A controlled voltage component (212) is operatively coupled the plurality of inverter circuits, and adapted to supply a desired supply voltage. A controlled signal component (210) is operatively coupled the plurality of inverter circuits, and adapted to supply a signal of a desired frequency thereto. An evaluation component (208) receives signal data from the first and second signal taps for evaluation or processing.

Owner:TEXAS INSTR INC

Frame for heavy-duty vehicles

InactiveUS7658412B2Reduce harmEasy and efficient and cost-effectiveVehicle seatsSteering linkagesEngineeringHeavy duty

Owner:HENDRICKSON USA L L C

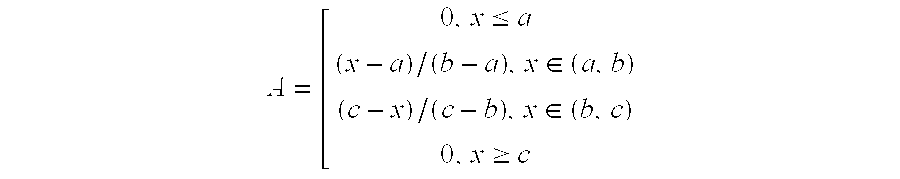

Fuzzy logic system for process control in chemical mechanical polishing

ActiveUS20070100489A1Easy and efficient and cost-effectiveEasy to integrateSemiconductor/solid-state device manufacturingLapping machinesMetrologyCompound (substance)

The present invention provides a versatile system for controlling chemical mechanical polishing in a semiconductor manufacturing process. The system of the present inventions utilizes an in-situ chemical mechanical polishing system, having some type of measurement or metrology function, to bulk polish a semiconductor wafer to a first target threshold. Once the first target has been reached, a fuzzy logic control function, communicatively coupled to the in-situ chemical mechanical polishing system, takes control of further polishing. Measurement data from the measurement function is processed by the fuzzy logic control function, which then adjusts additional polishing time for the polishing system to render a desired wafer topography.

Owner:SAMSUNG AUSTIN SEMICON +1

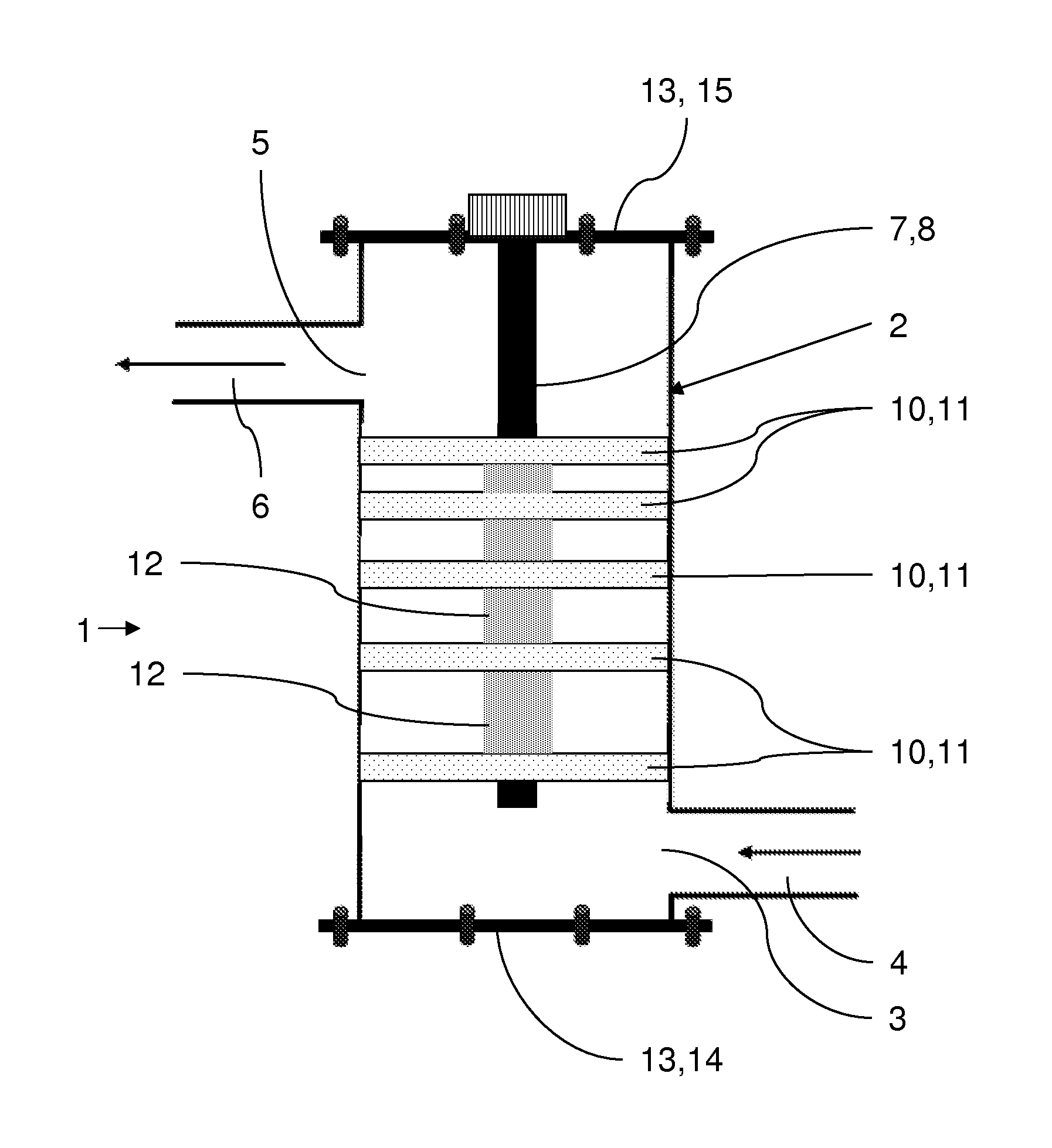

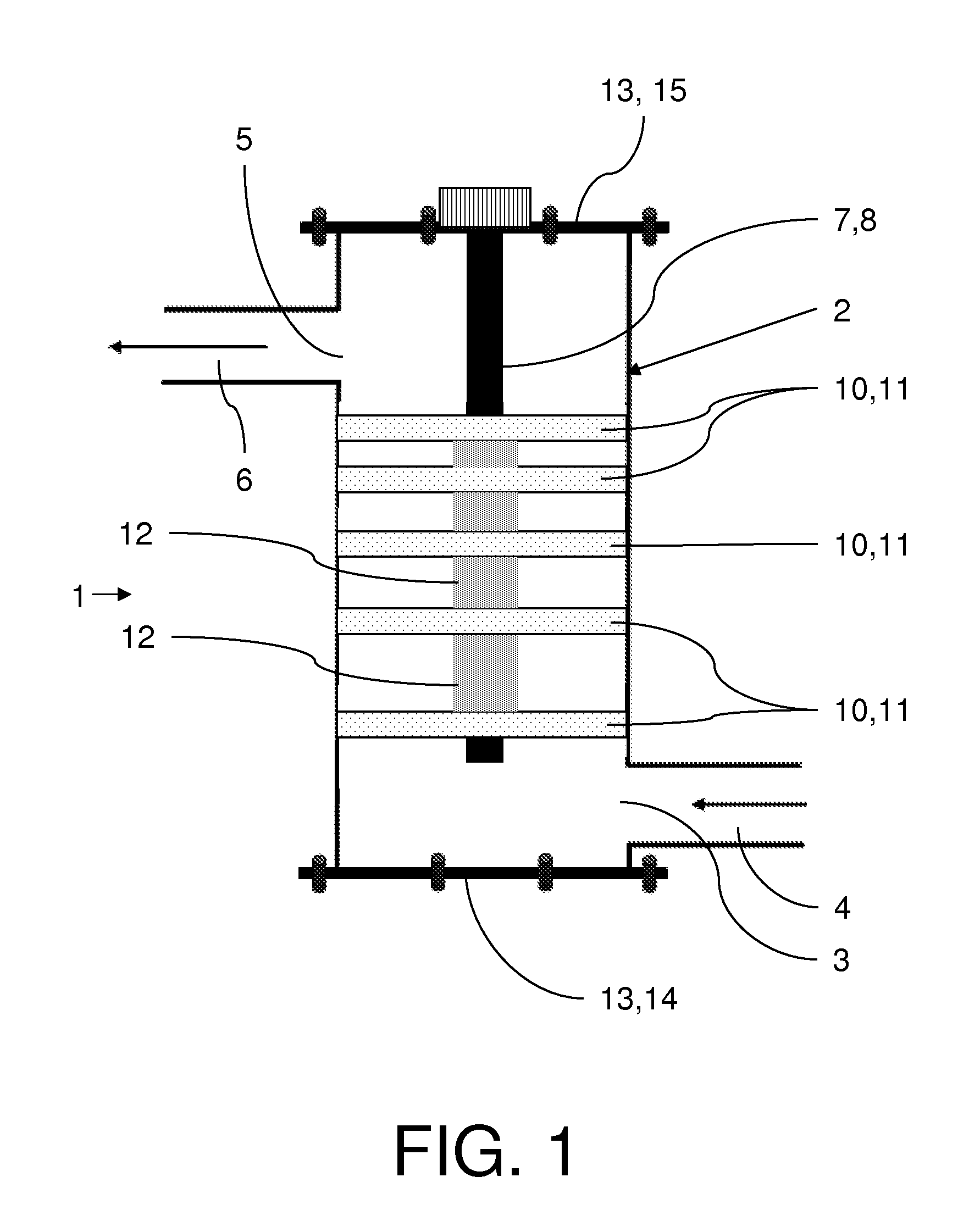

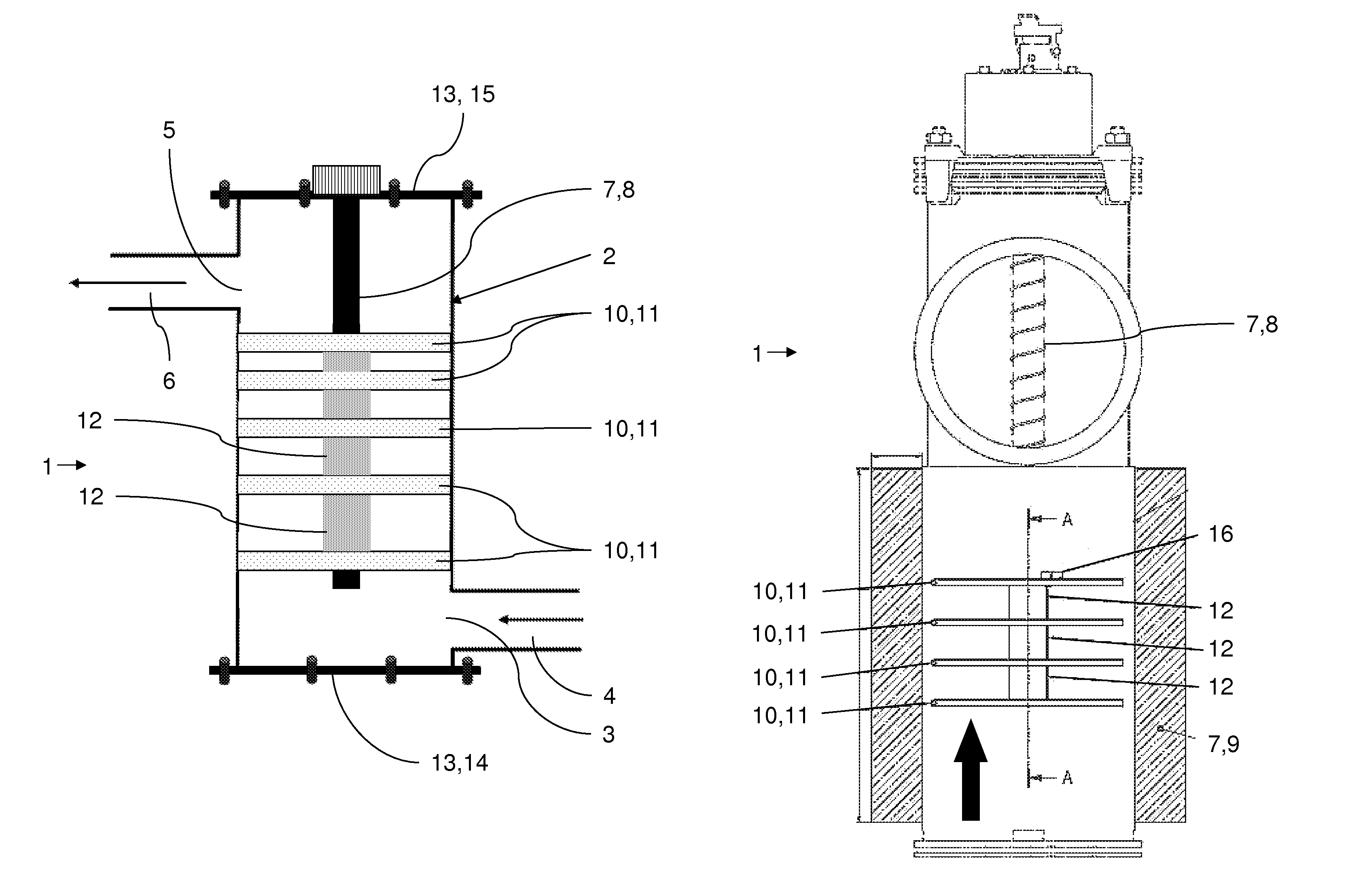

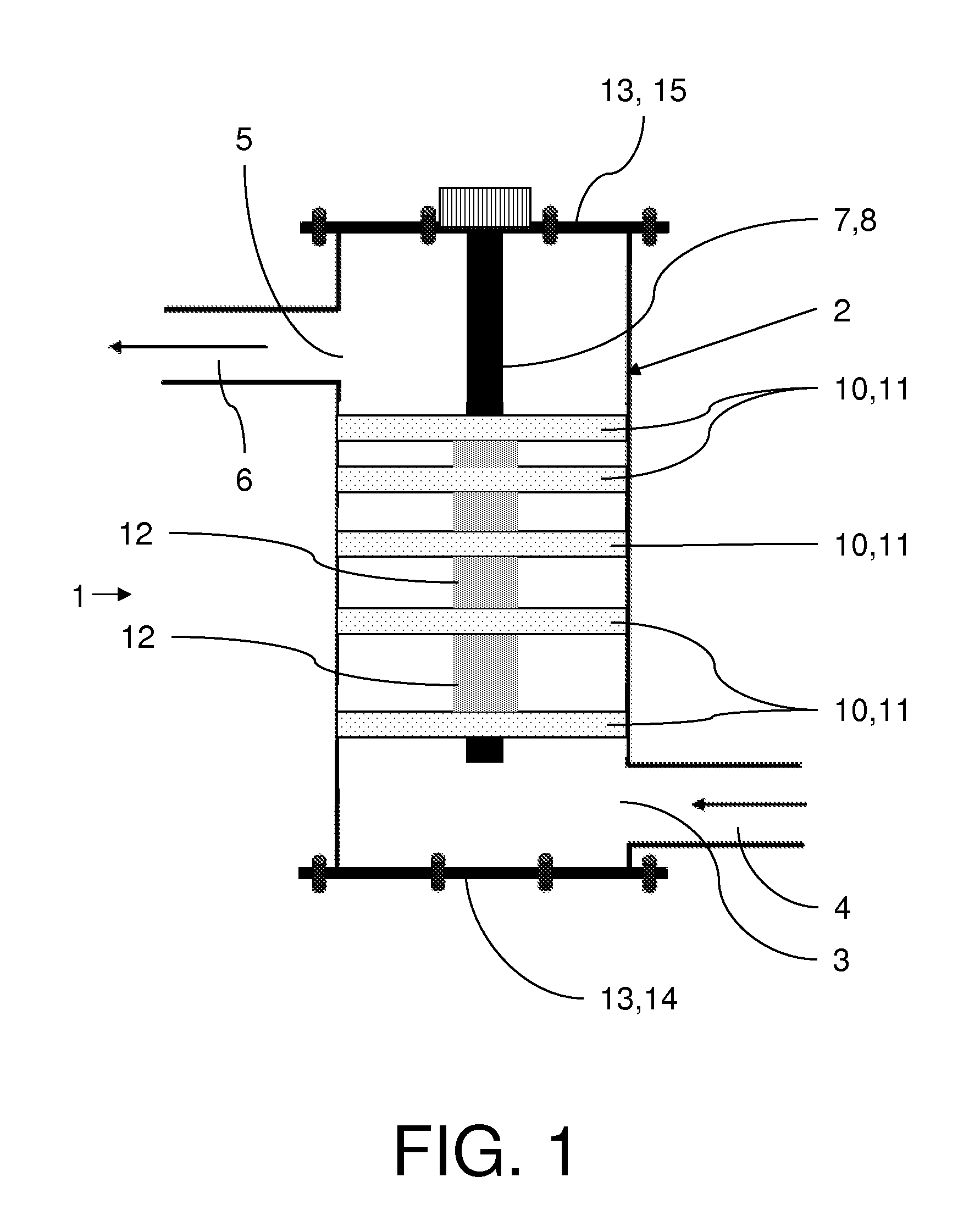

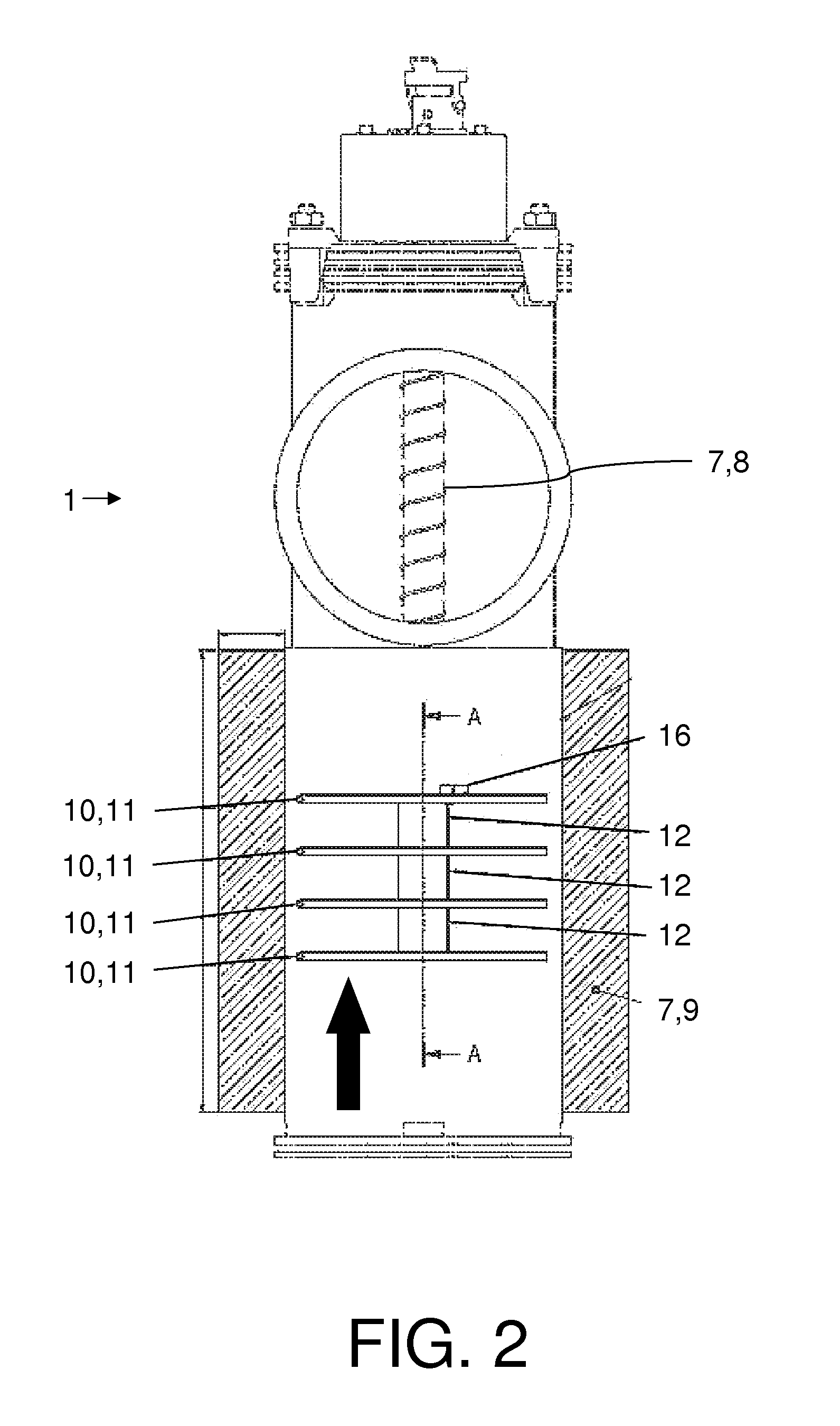

Hot-trap assembly for trapping unreacted gas by- products

InactiveUS20110252969A1Easy and efficient and cost-effective removalEasy and efficient and cost-effectiveCombination devicesAuxillary pretreatmentBiochemical engineeringProduct gas

The present invention provides a hot-trap device (1) comprising an enclosure (2) with at least one inlet (3), at least one outlet (5) at least one heating means (7) and at least one collector means (10) for the conversion of reaction by-products into products, wherein the collector means is arranged within the enclosure between the inlet and the outlet has a diameter that substantially matches the diameter of the enclosure and has at least one opening (18).

Owner:OERLIKON SOLAR AG (TRUEBBACH)

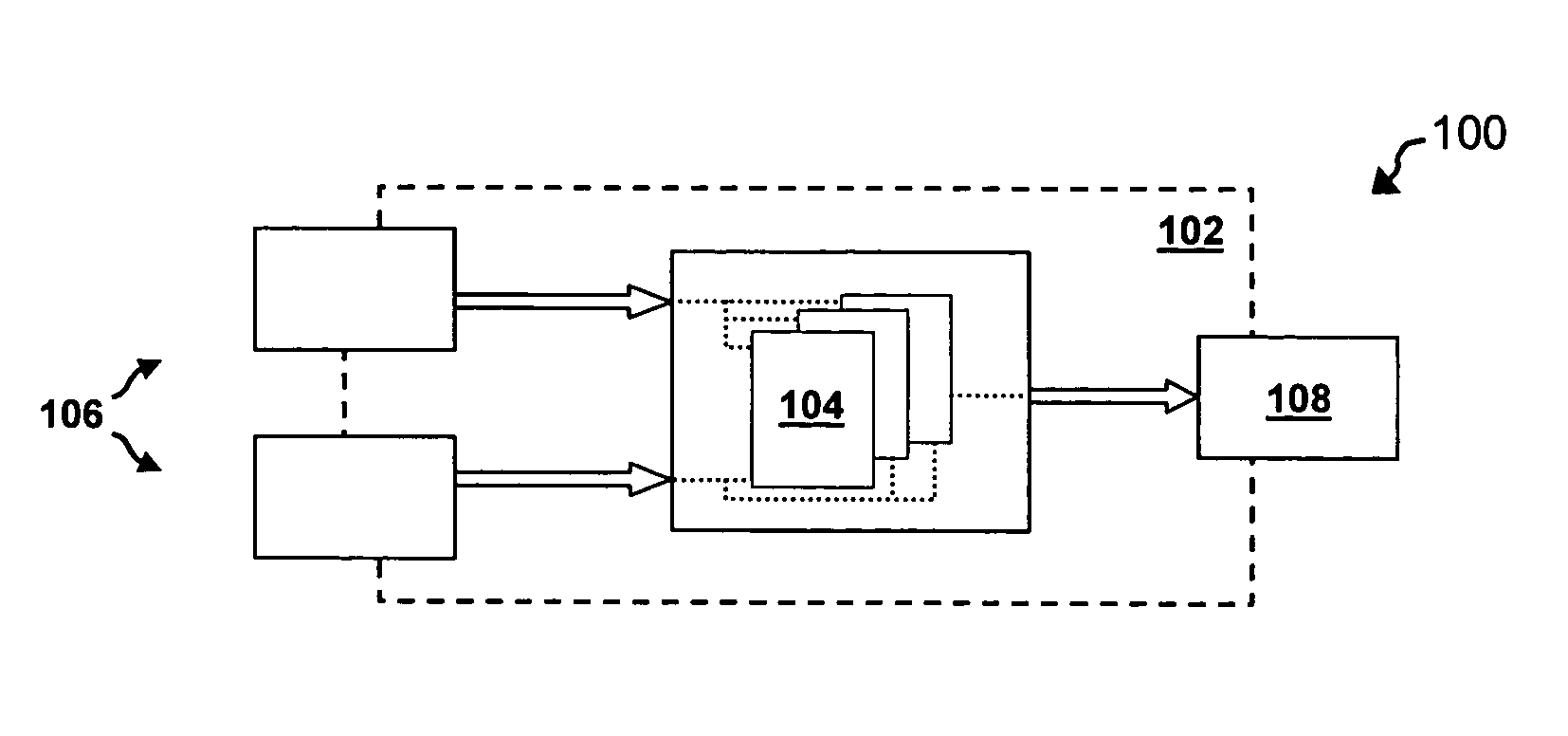

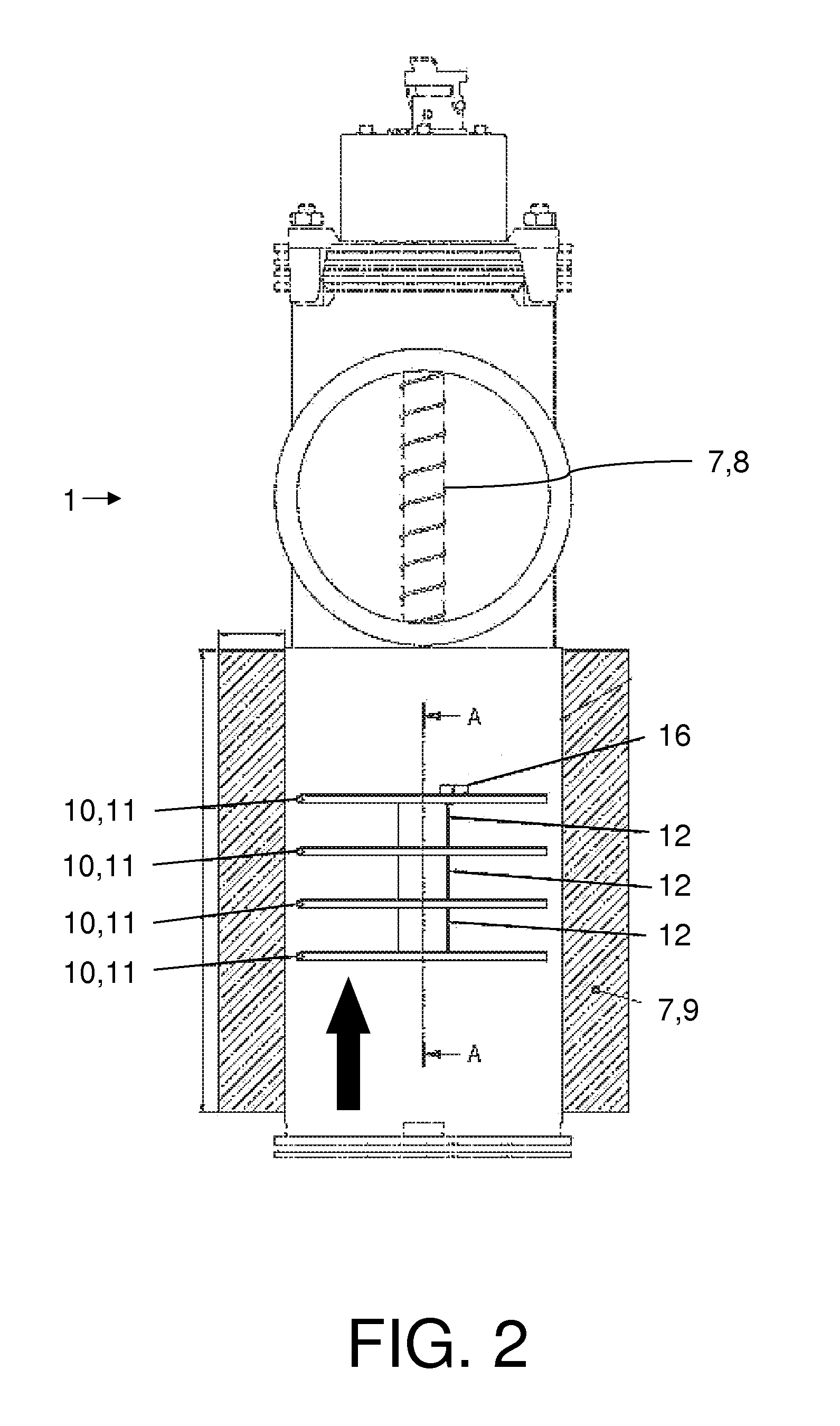

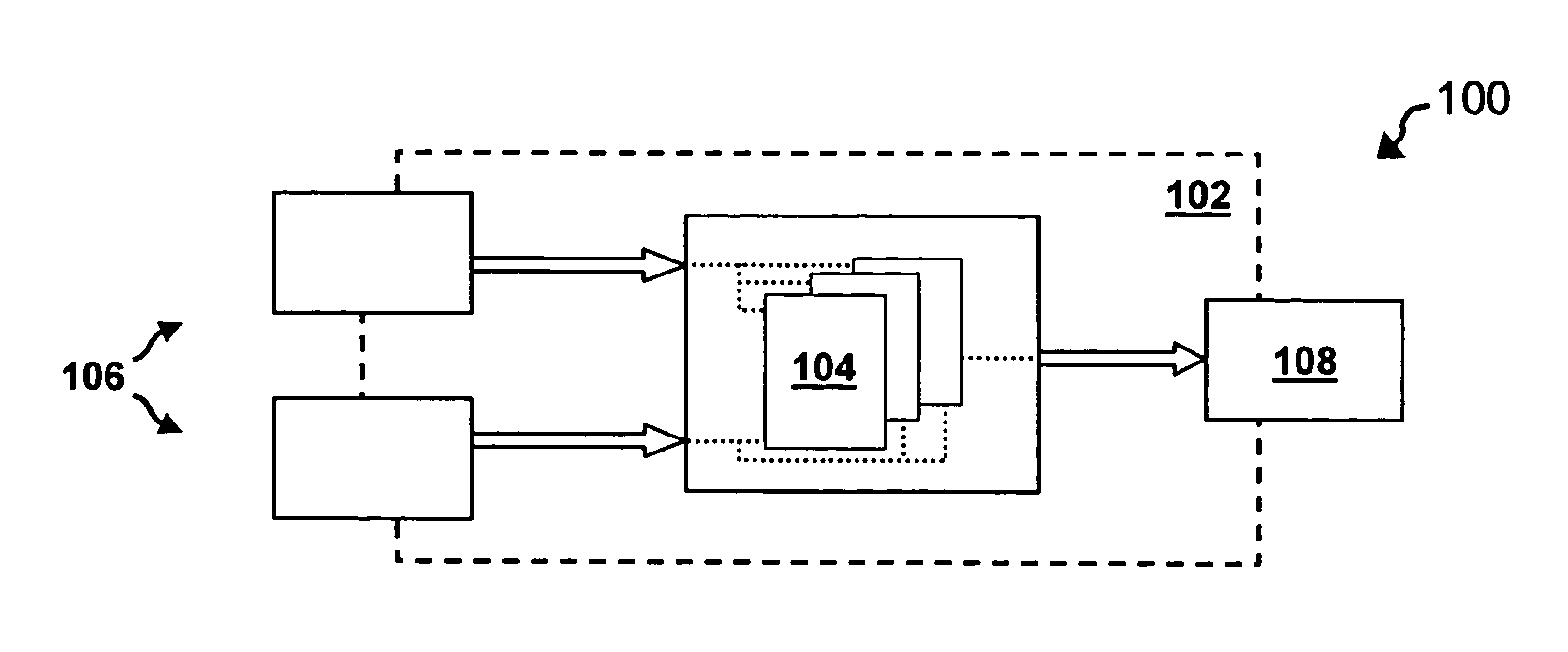

Versatile system for time-independent signal sampling

InactiveUS20060061349A1The signal is stable and accurateEasy and efficient and cost-effectiveDigital variable displayAnalog circuit testingEngineeringSimulation testing

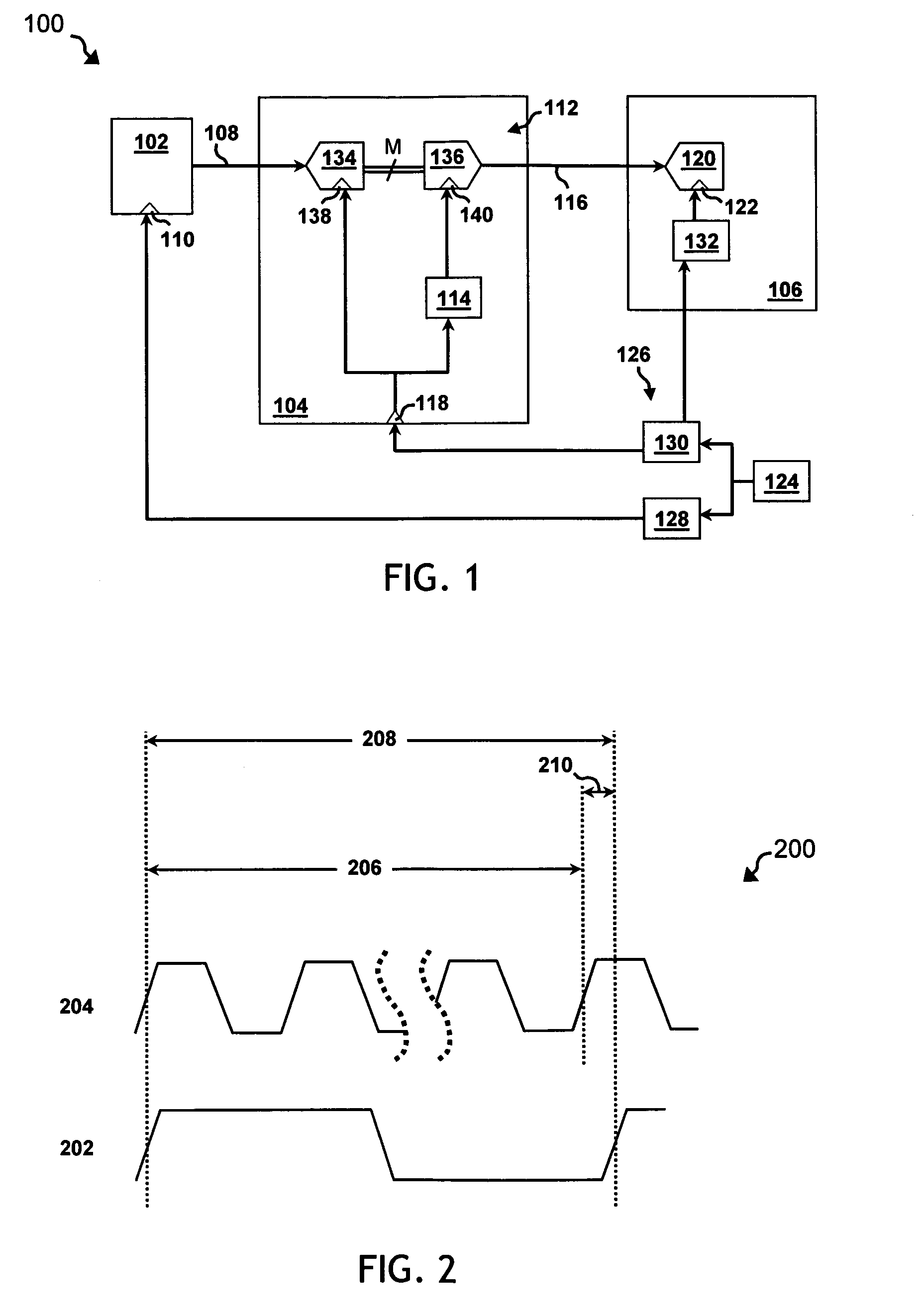

The present invention provides a system (100) that overcomes performance incongruities between a high-speed device (102) and commercial ATE (106). The system of the present invention provides an analog-to-analog sampler (104), having a clock input (118). The analog-to-analog sampler receives a first analog test signal (108) from the high-speed device, and converts it into a second analog test signal (116) at a desired rate, utilizing an analog-to-digital-to-analog conversion function (112) and a decimation function (114). The ATE system houses an analog capture component (120). The analog capture component has a clock input (122), and receives the second analog test signal for conversion into digital format. A series of clock signals (126) are generated from a common frequency reference source (124), to provide the necessary clock signals throughout the system.

Owner:TEXAS INSTR INC

Versatile system for a locking electro-thermal actuated MEMS switch

InactiveUS20060221430A1Easy to adaptGood equipment performanceElectrothermal relaysThermally actuated switchesActuatorClutch

A lockable MEMS switching architecture provided having a clutch assembly, a switching member, and an actuator. The clutch assembly has one or more engagement features located in proximity to the switching member - particularly one or more receiving features located upon the switching member. The clutch assembly is actuated to disengage the engagement features from the receiving features. The switching member is actuated to move in relation to the clutch assembly. Once the switching member is in a desired position, the clutch assembly is de-actuated, causing the engagement features to re-engage with the switching member, thereby restricting its further movement.

Owner:SAMSUNG ELECTRONICS CO LTD

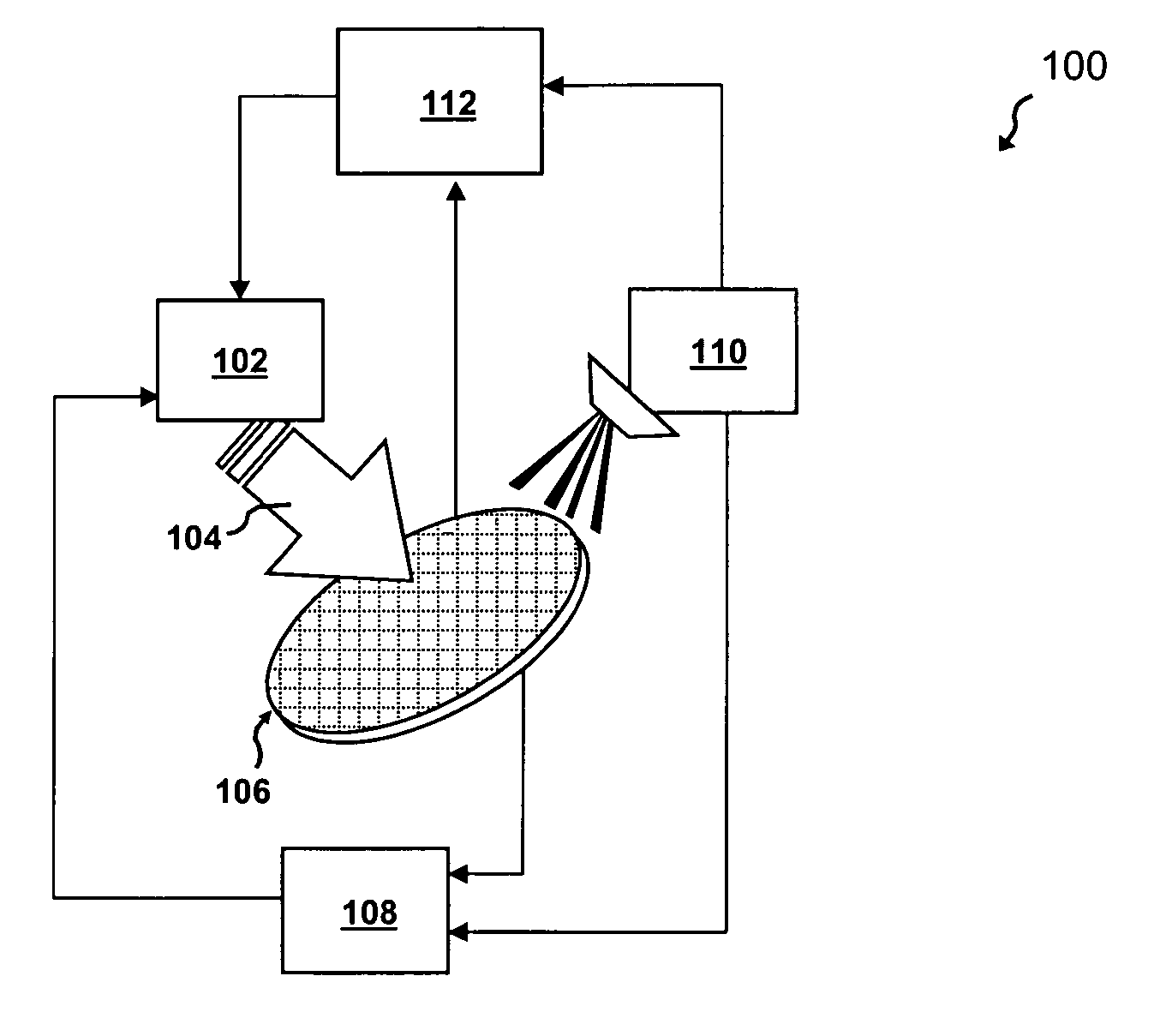

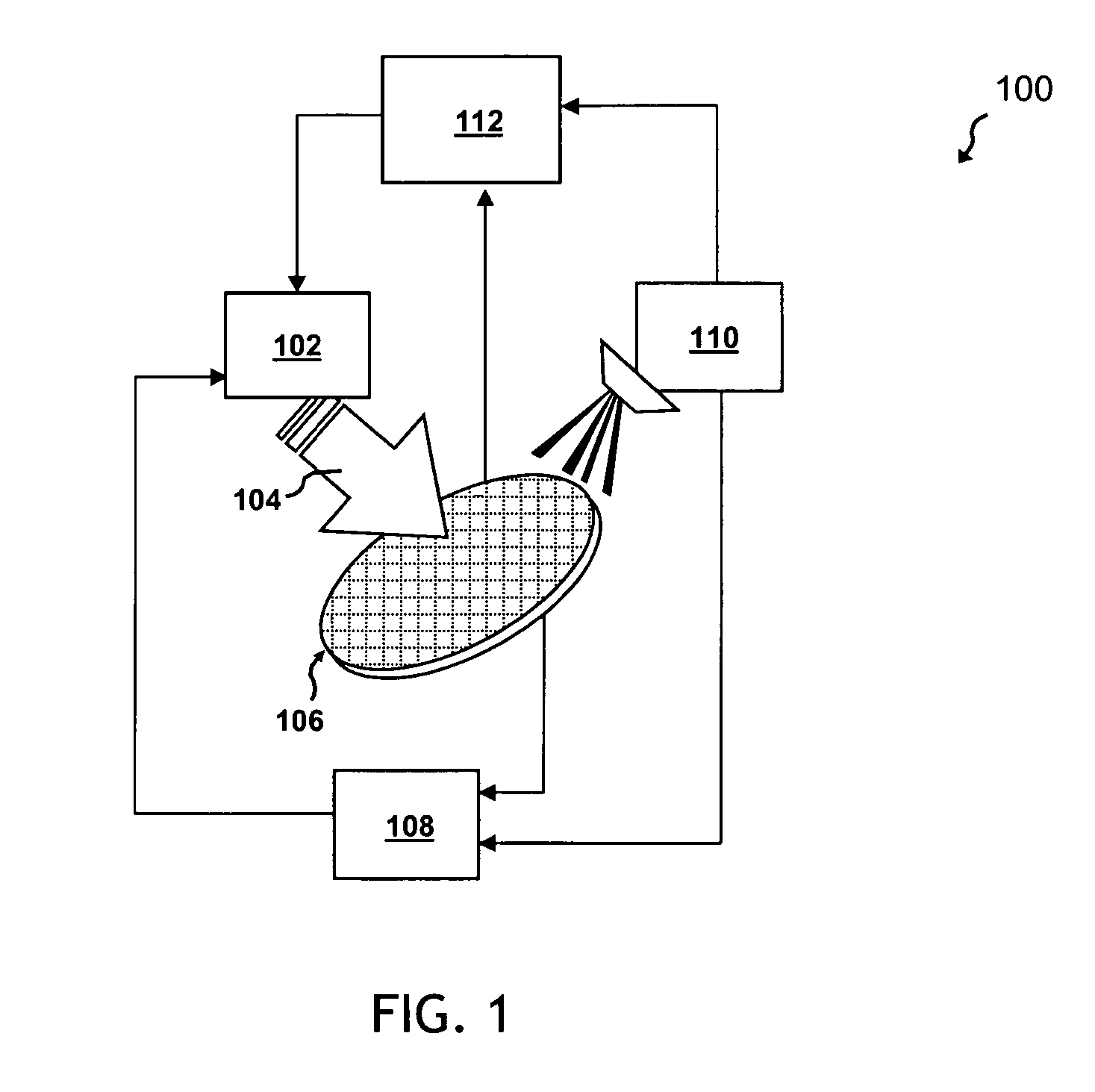

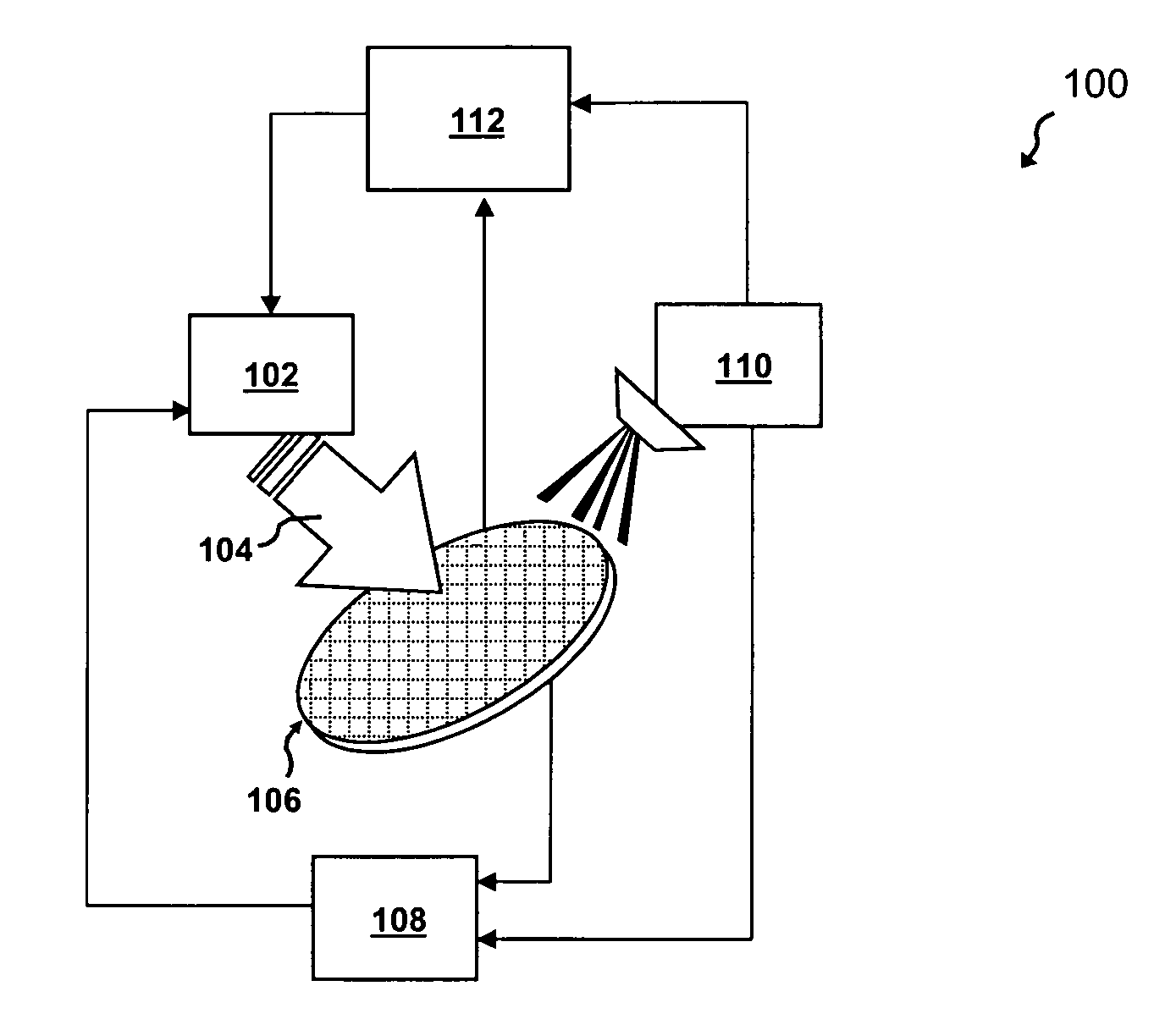

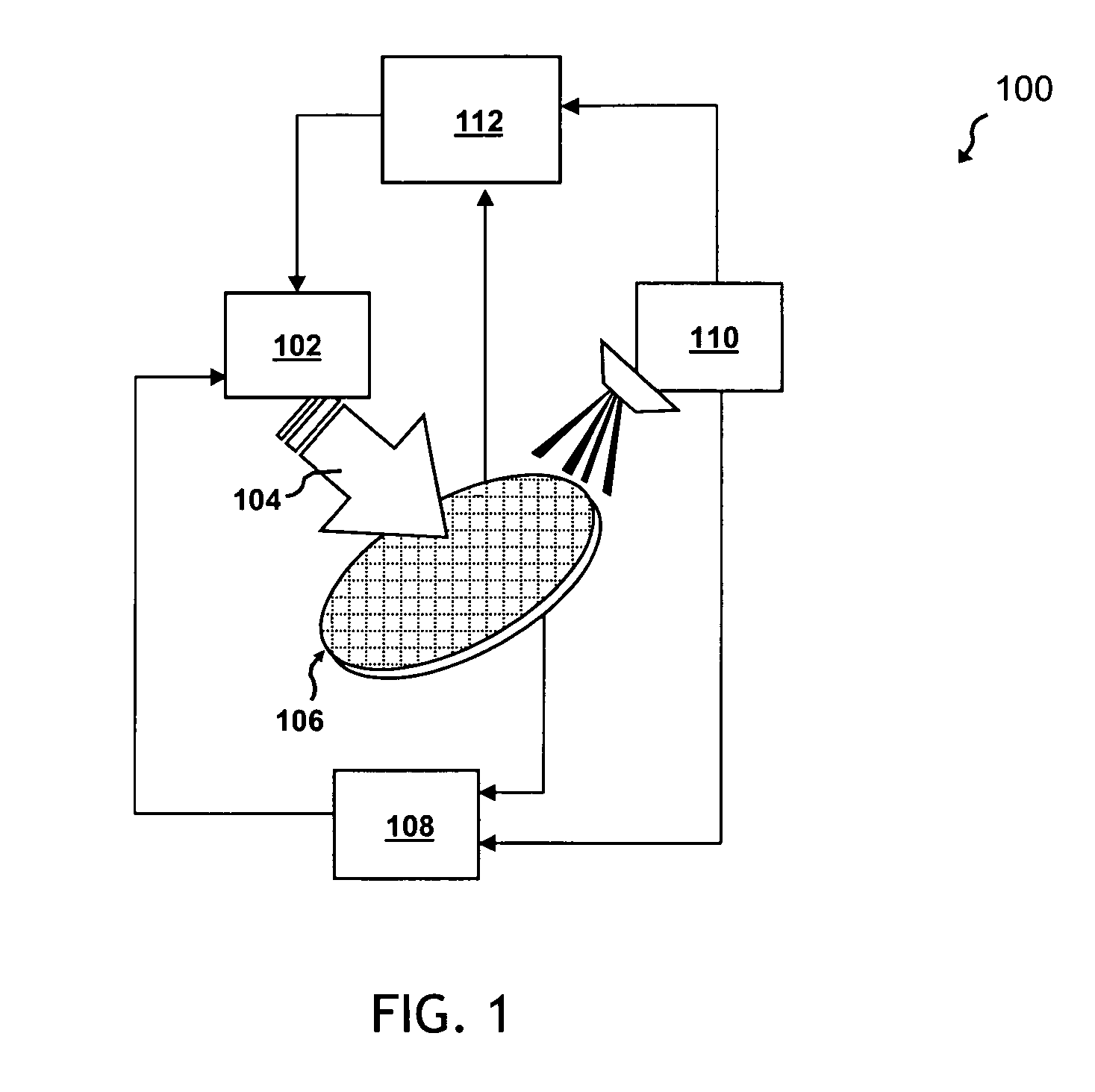

System for remediating cross contamination in semiconductor manufacturing processes

ActiveUS7200498B2Easy and efficient and cost-effectiveProcesses—efficiently streamlining cross-contamination testingSemiconductor/solid-state device testing/measurementMaterial analysis by electric/magnetic meansCopper contaminationEngineering

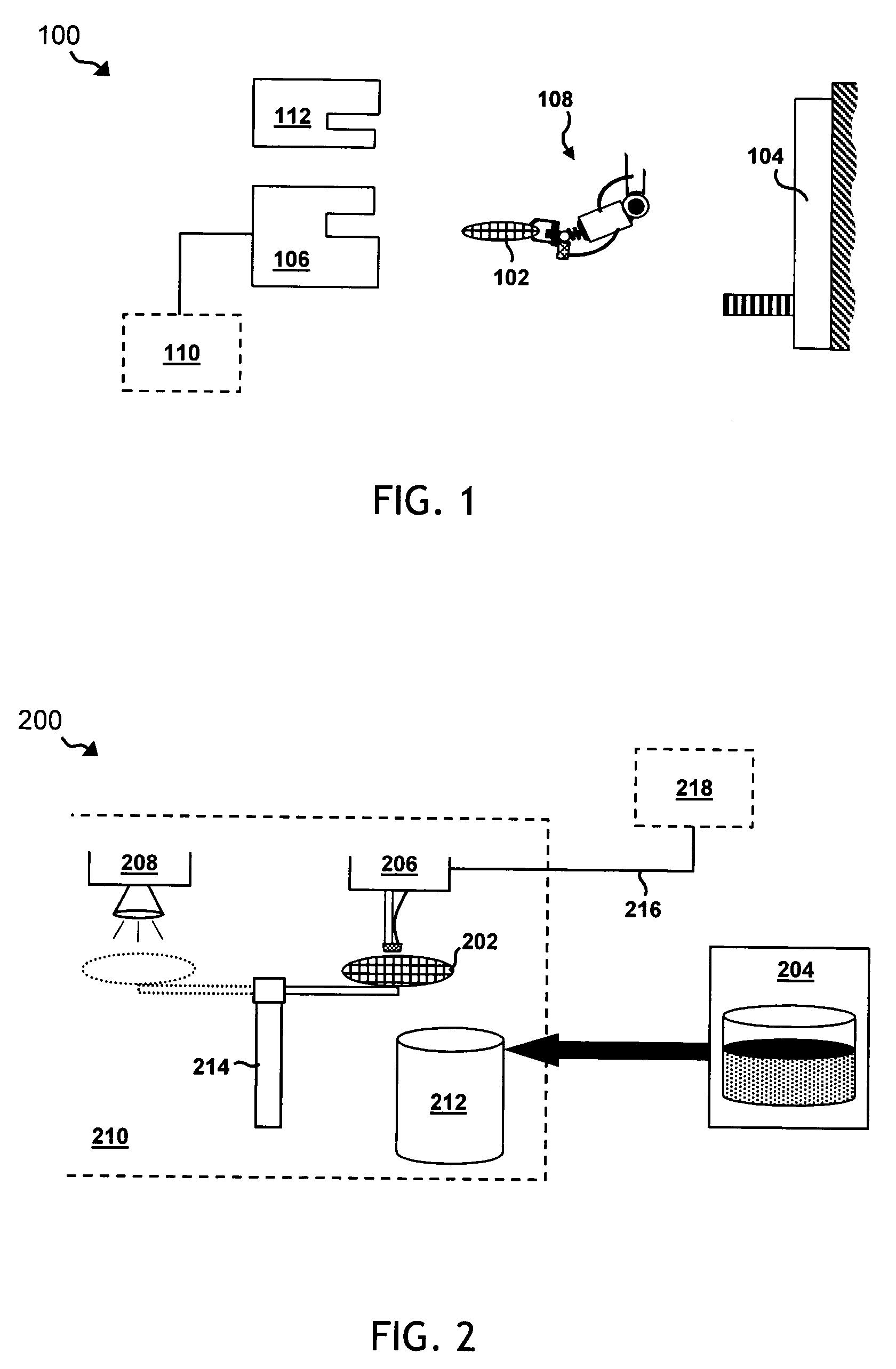

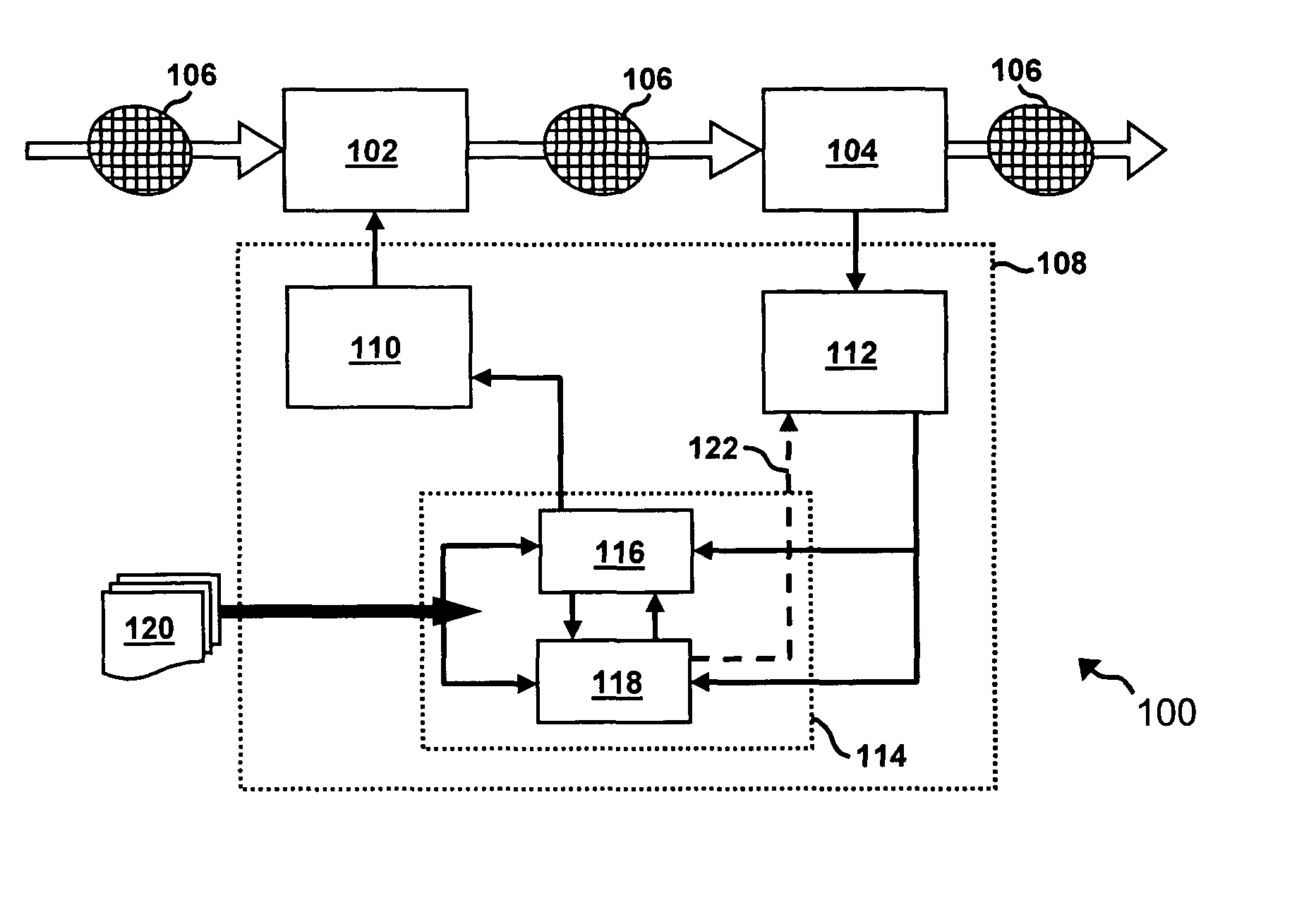

The present invention defines a system (100) for detecting copper contamination within a semiconductor manufacturing process. According to the present invention, a semiconductor wafer (102) is transferred (108) from a semiconductor manufacturing component (104), which may have exposed the wafer to copper contamination, to a measurement system (106). The measurement system measures an electrical value at a plurality of locations along a surface of the wafer, prior to and after exposure of the surface to an activation system (112). The activation system is provided to cause any copper contamination along the surface to form a precipitate thereon. An analysis component (110) is provided to receive electrical value and location information from the measurement system and to identify, from the measurements, the presence and location of copper contamination along the semiconductor wafer surface.

Owner:TEXAS INSTR INC

Versatile system for conditioning slurry in CMP process

ActiveUS20060026906A1Good conditionWell mixedPigmenting treatmentOther chemical processesEngineeringSlurry

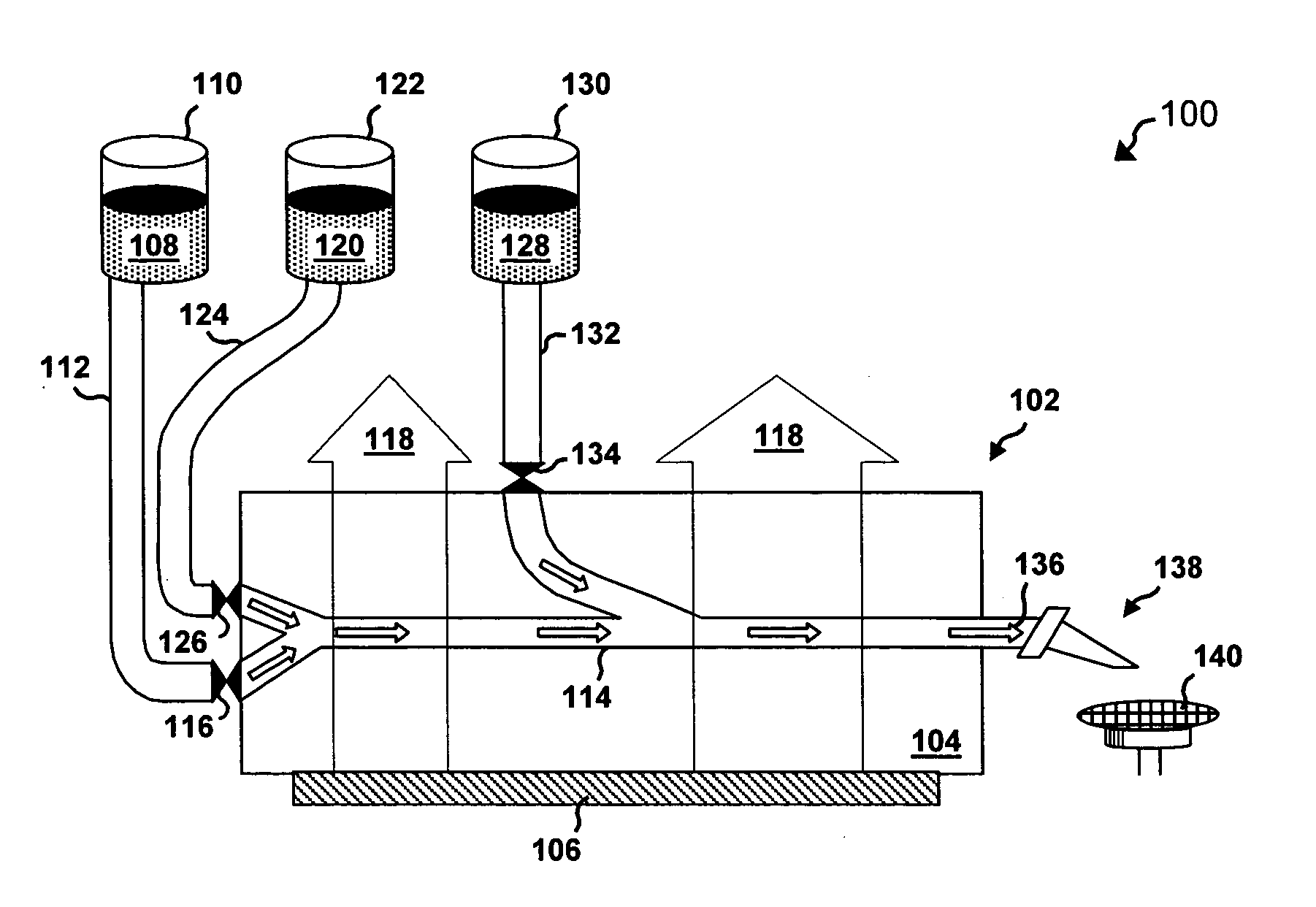

The present invention provides a system (100) for conditioning multi-component slurries utilized in chemical mechanical polishing (CMP) of semiconductor wafers (140). The system provides a first slurry component (108), and a second slurry component (120). A conditioning component (102) has first and second inlets, and an outlet operatively coupled to a dispensing system (138). First and second flow control components (116, 126) are operably intercoupled between the first and second inlets and the first and second slurry components, respectively. The system further provides a megasonic energy source (106), adapted to generate an energy field (118) across the conditioning component. A conveyance component (114) conducts the slurry components from the inlets through the energy field, and delivers a final mixture (136) of multi-component slurry to the outlet.

Owner:TEXAS INSTR INC

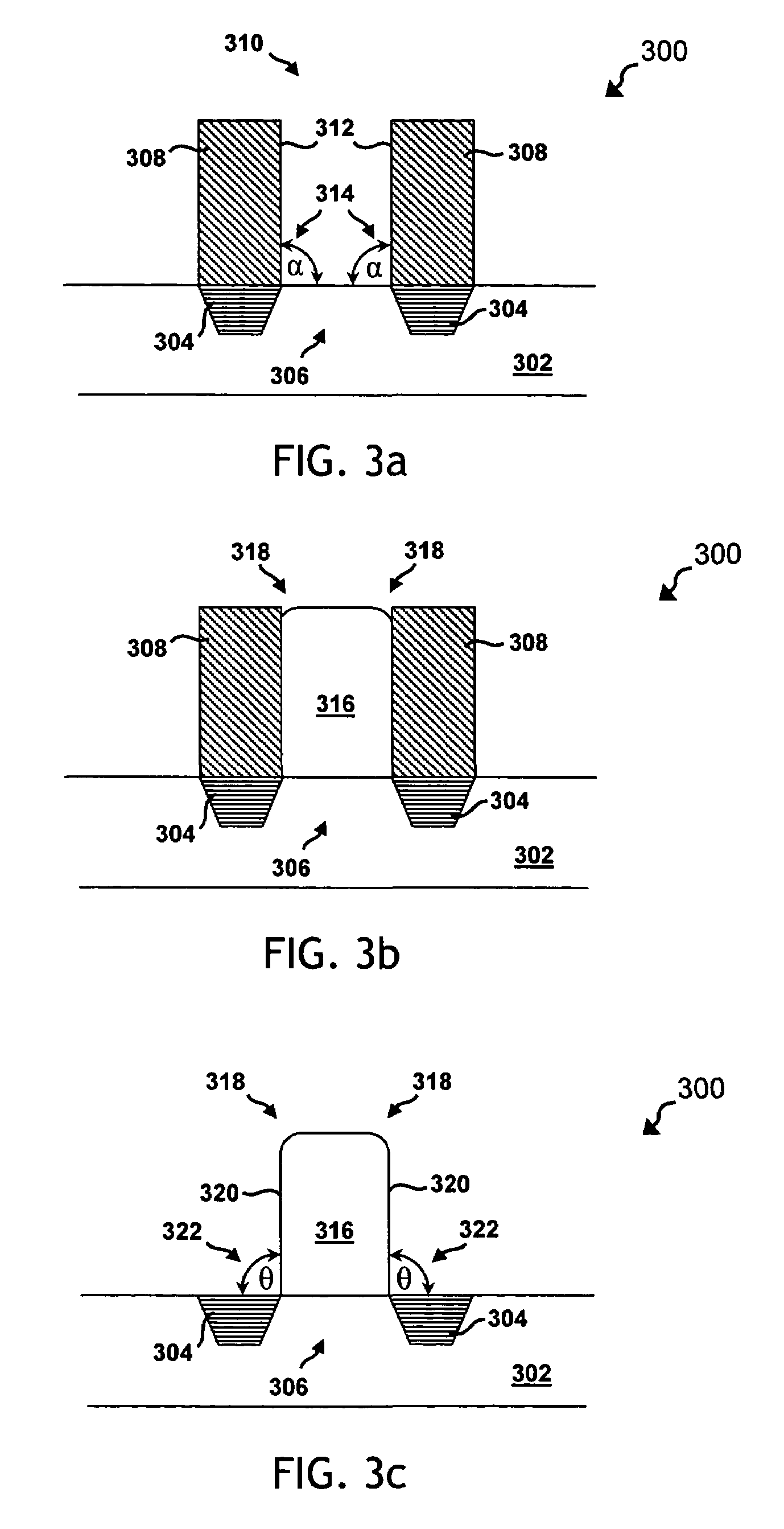

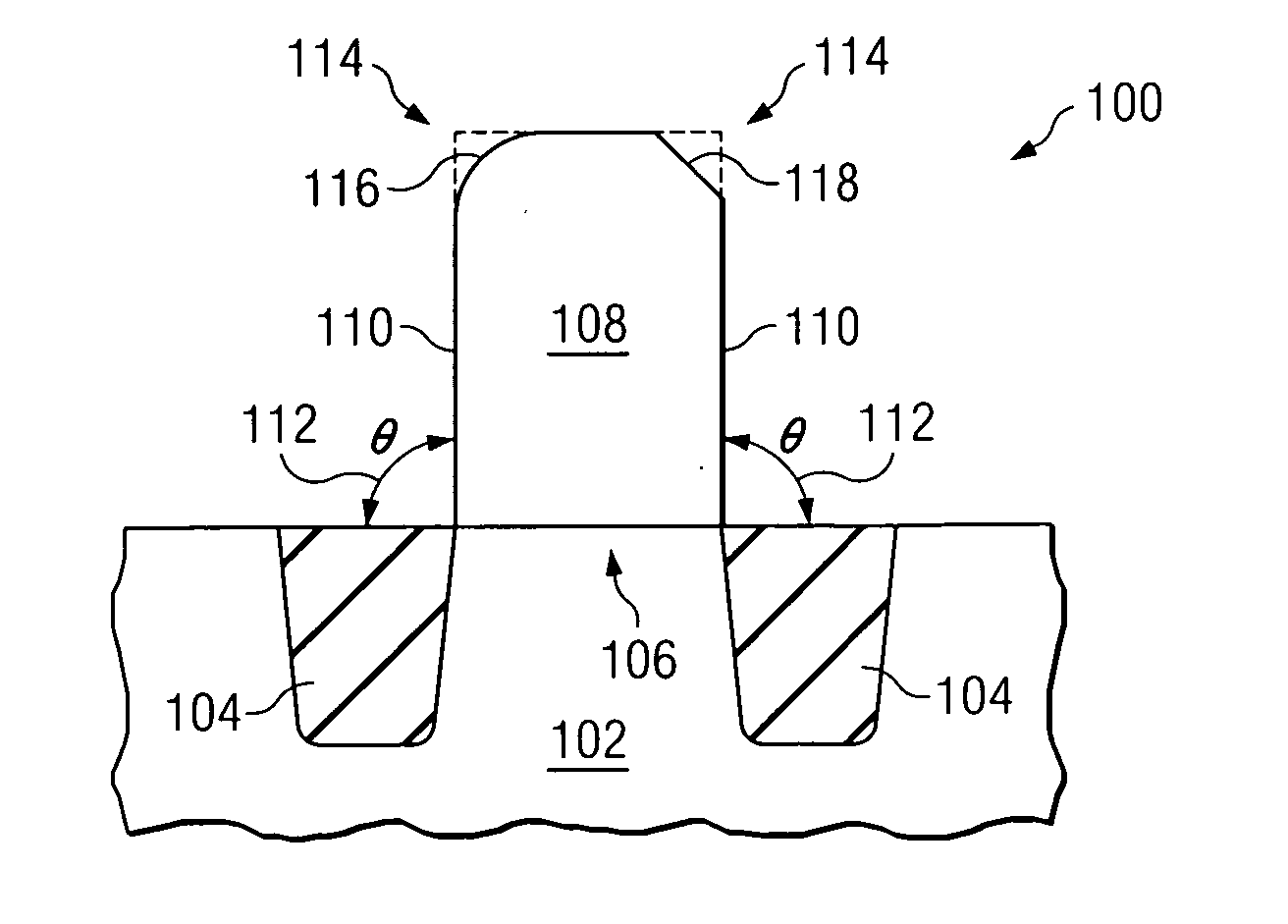

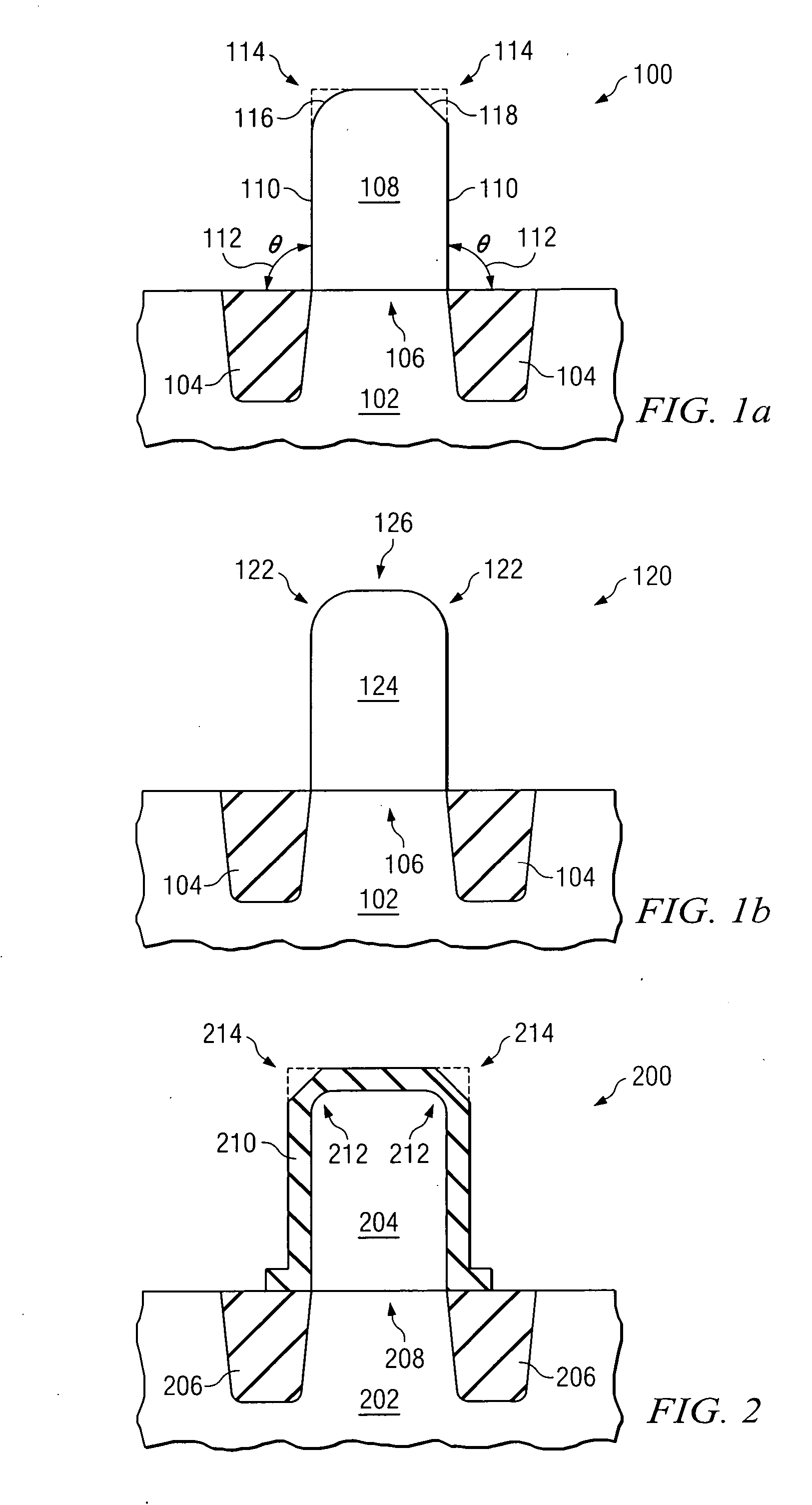

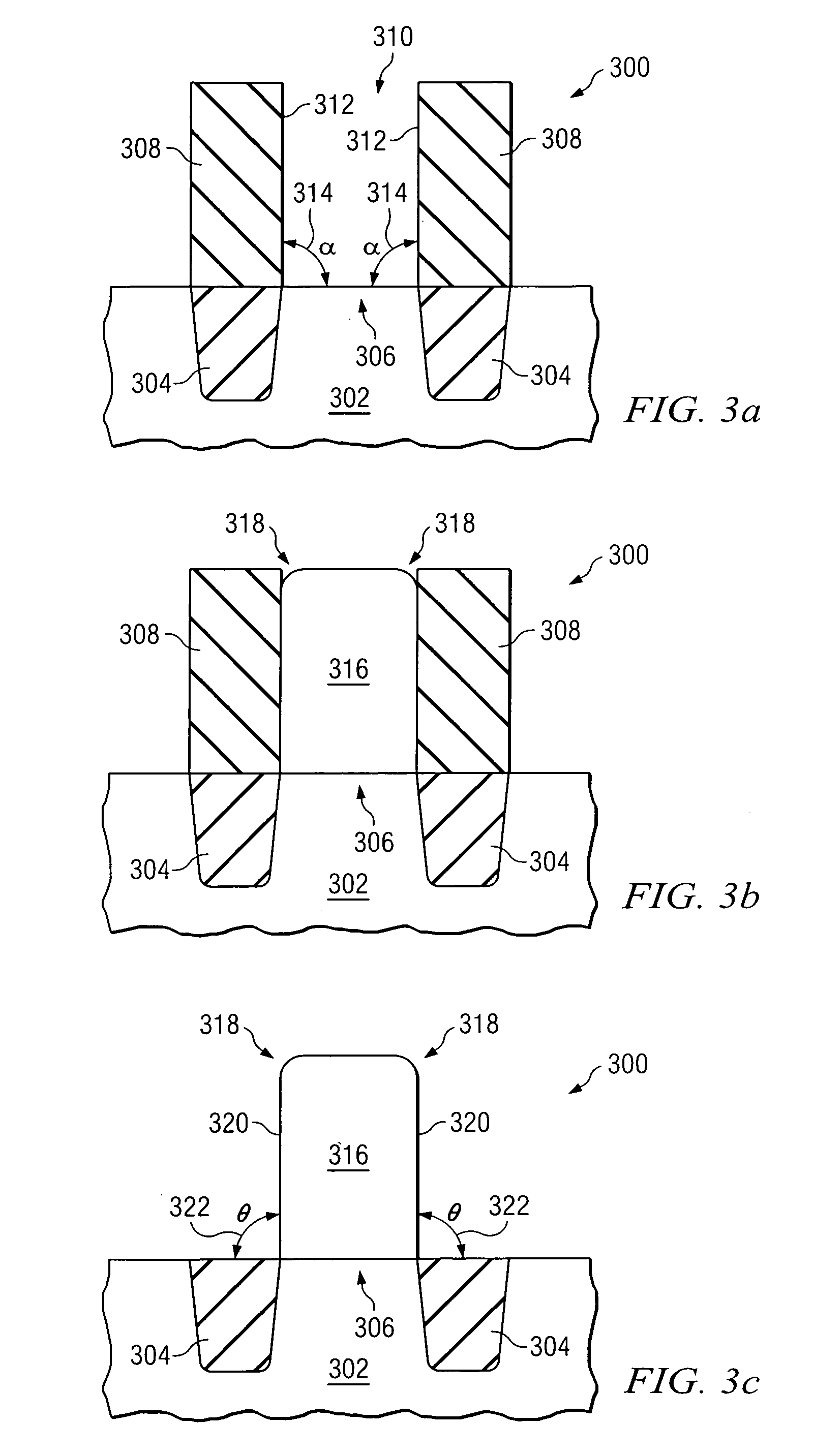

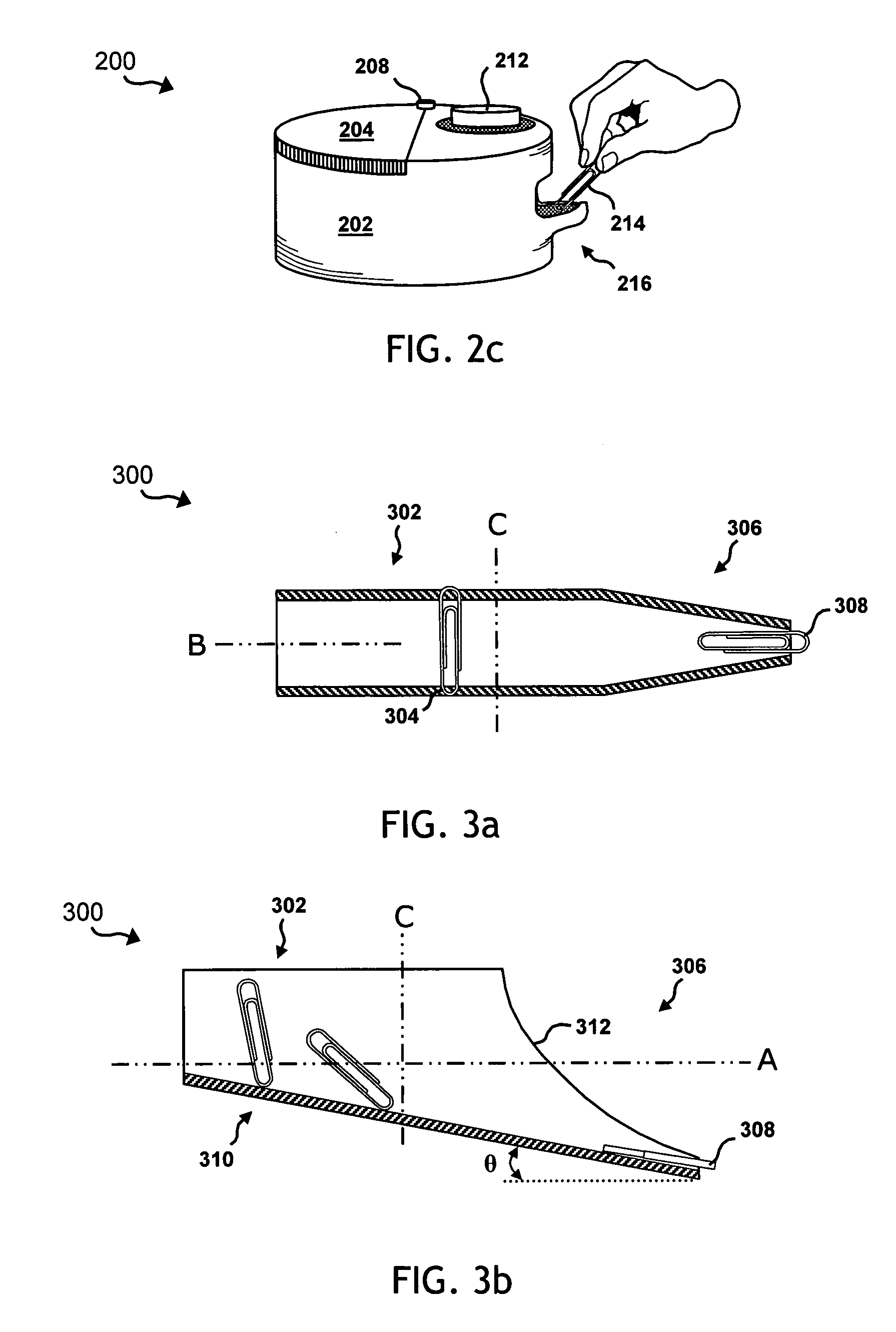

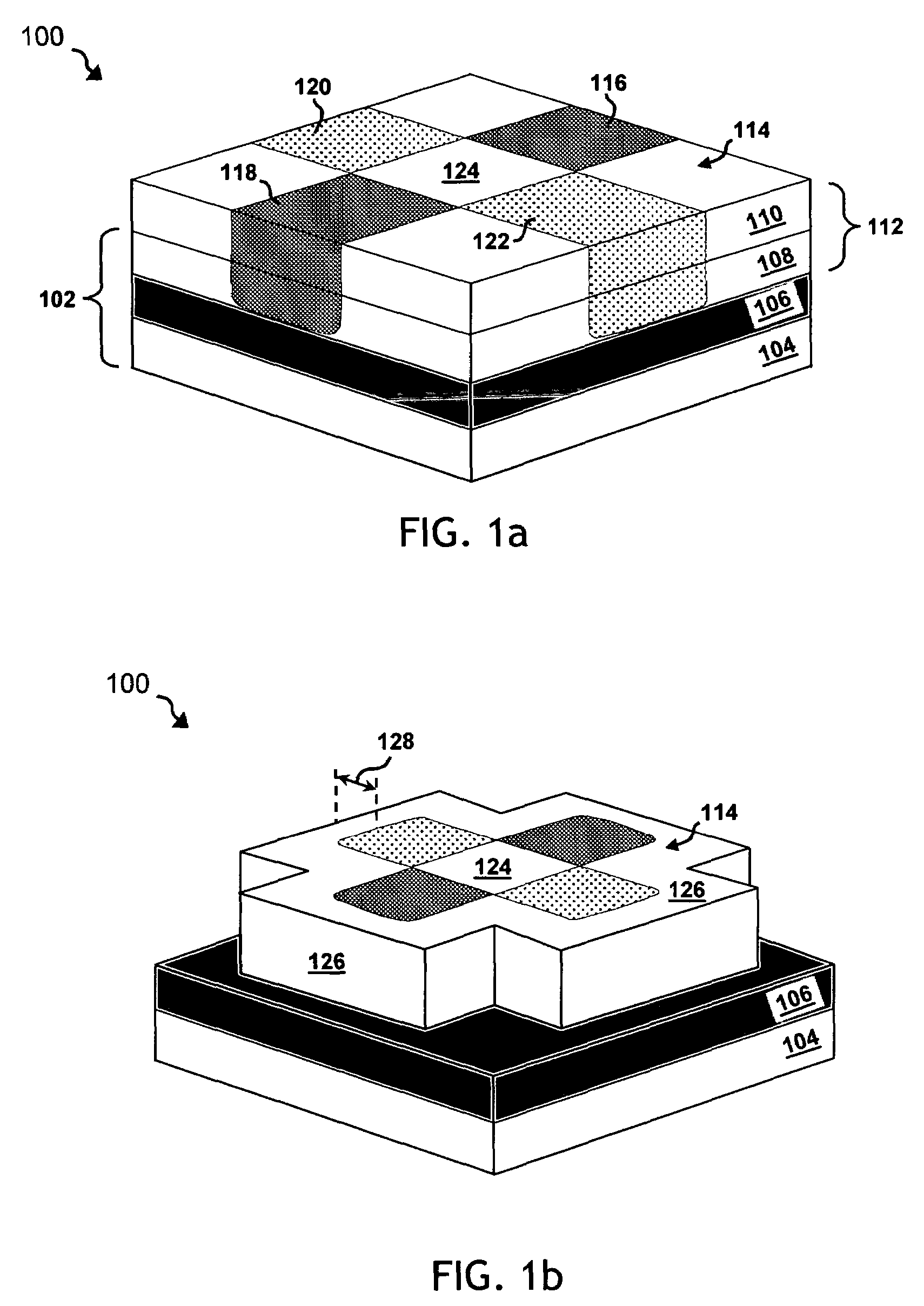

Versatile system for triple-gated transistors with engineered corners

ActiveUS6969644B1Readily implemented in and adaptableImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody areaSeparation relation

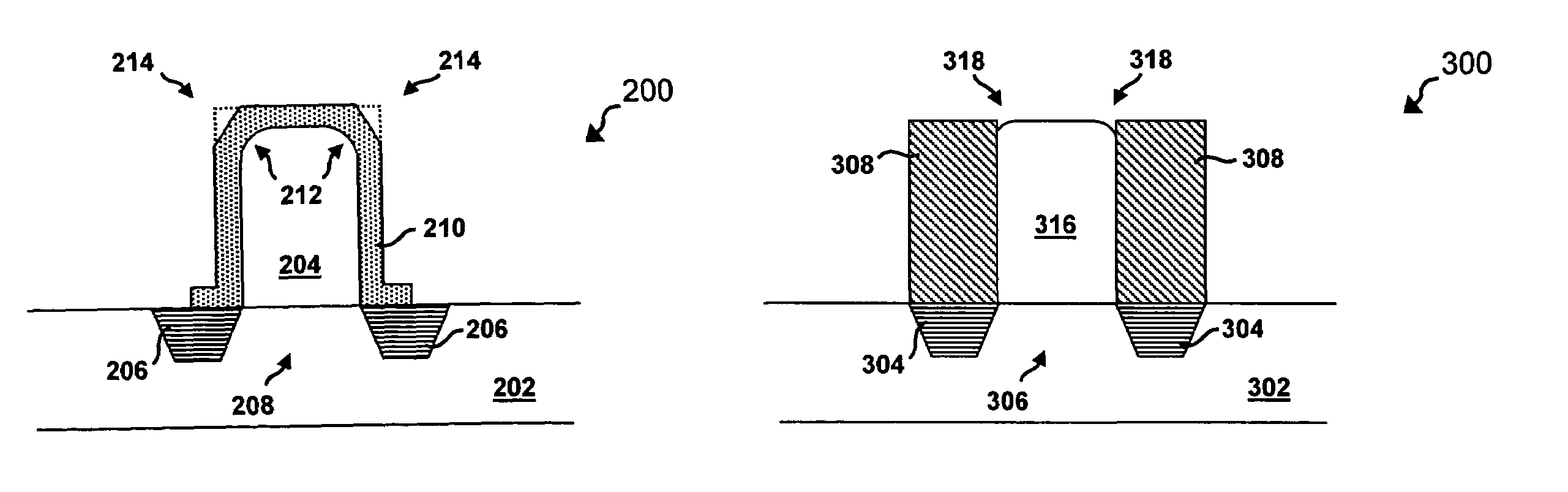

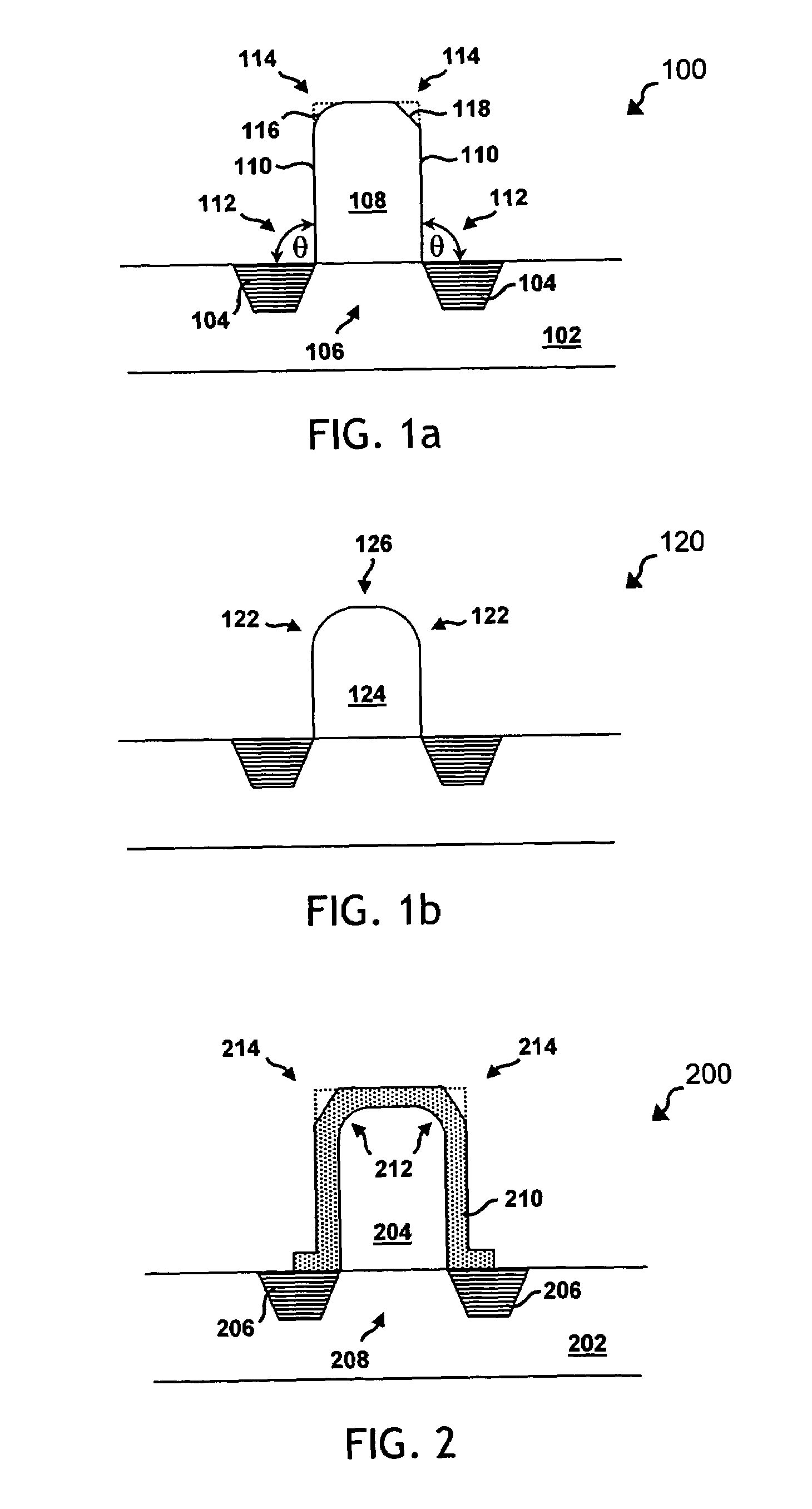

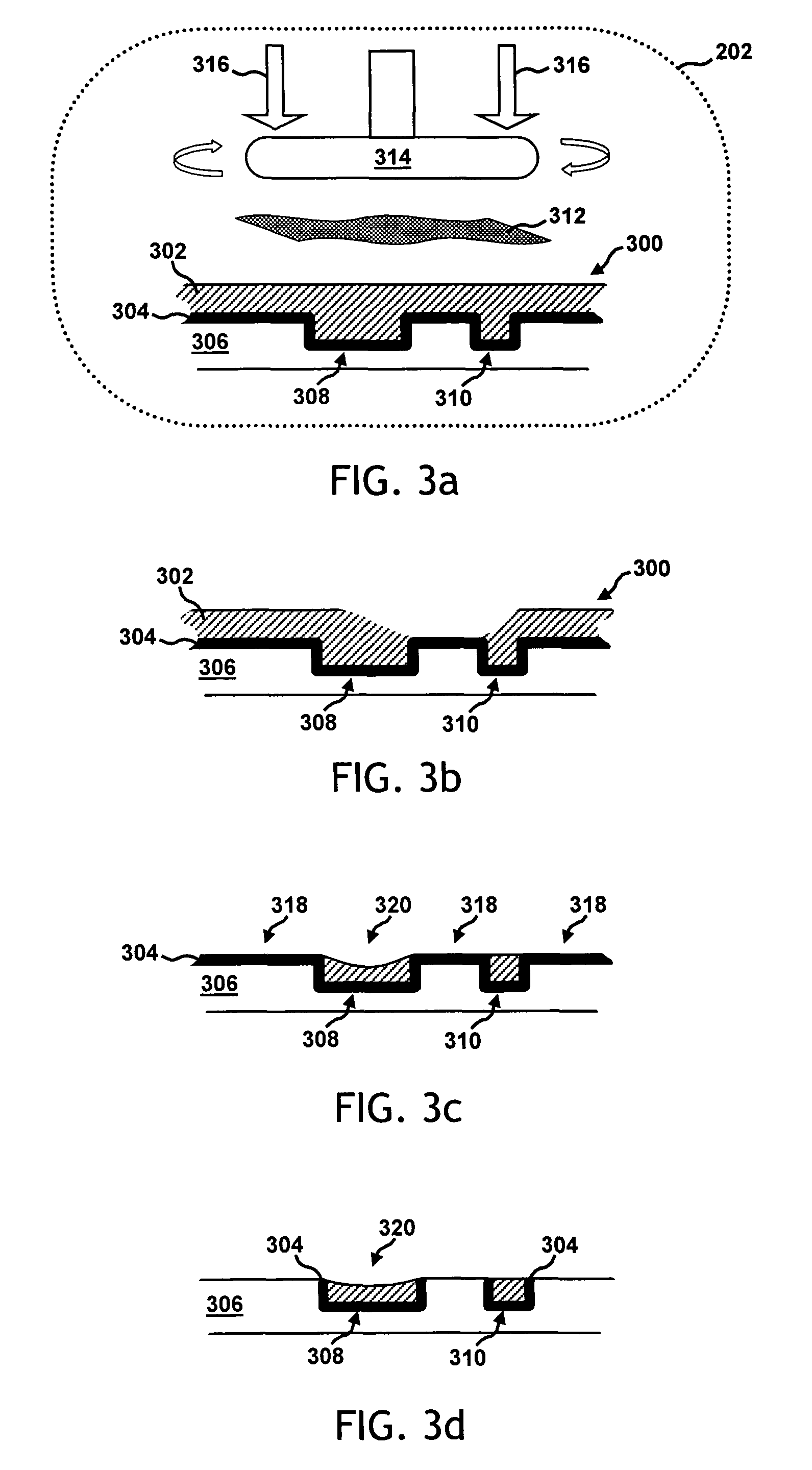

The present invention provides a system for producing a triple-gate transistor segment (300), utilizing a standard semiconductor substrate (302). The substrate has a plurality of isolation regions (304) formed along its upper surface in a distally separate relationship, defining a channel region (306). A form structure (308) is disposed atop the isolation regions, and defines a channel body area (310) over the channel region. A channel body structure (316) is disposed within the channel body area, and is engineered to provide a blunted corner or edge (318) along a perimeter of its upper exposed surface. The form structure is then removed, and subsequent processing is performed.

Owner:TEXAS INSTR INC

Versatile system for accelerated stress characterization of semiconductor device structures

ActiveUS7026838B2Effectively and accurately accelerated testing parameter independentlyWell representedElectronic circuit testingPulse generation by logic circuitsControl signalSemiconductor

The present invention provides a system (200) for performing accelerated stress characterization of a given transistor (204). Inverter circuits, formed from the given transistor, are disposed in series with one another (202). A plurality of signal taps is operatively associated with each gap between adjacent inverter circuits. Selective circuitry is operatively coupled to the plurality of signal taps, and adapted to output (206) data from a first and a second of the plurality of signal taps. A controlled voltage component (212) is operatively coupled the plurality of inverter circuits, and adapted to supply a desired supply voltage. A controlled signal component (210) is operatively coupled the plurality of inverter circuits, and adapted to supply a signal of a desired frequency thereto. An evaluation component (208) receives signal data from the first and second signal taps for evaluation or processing.

Owner:TEXAS INSTR INC

System for remediating cross contamination in semiconductor manufacturing processes

ActiveUS20050274805A1Easy and efficient and cost-effectiveProcesses—efficiently streamlining cross-contamination testingSemiconductor/solid-state device testing/measurementTransmission systemsCopper contaminationEngineering

The present invention defines a system (100) for detecting copper contamination within a semiconductor manufacturing process. According to the present invention, a semiconductor wafer (102) is transferred (108) from a semiconductor manufacturing component (104), which may have exposed the wafer to copper contamination, to a measurement system (106). The measurement system measures an electrical value at a plurality of locations along a surface of the wafer, prior to and after exposure of the surface to an activation system (112). The activation system is provided to cause any copper contamination along the surface to form a precipitate thereon. An analysis component (110) is provided to receive electrical value and location information from the measurement system and to identify, from the measurements, the presence and location of copper contamination along the semiconductor wafer surface.

Owner:TEXAS INSTR INC

Versatile system for triple-gated transistors with engineered corners

ActiveUS20060043524A1Readily implemented in and adaptableImprove performanceTransistorSemiconductor/solid-state device manufacturingBody areaEngineering

The present invention provides a system for producing a triple-gate transistor segment (300), utilizing a standard semiconductor substrate (302). The substrate has a plurality of isolation regions (304) formed along its upper surface in a distally separate relationship, defining a channel region (306). A form structure (308) is disposed atop the isolation regions, and defines a channel body area (310) over the channel region. A channel body structure (316) is disposed within the channel body area, and is engineered to provide a blunted corner or edge (318) along a perimeter of its upper exposed surface. The form structure is then removed, and subsequent processing is performed.

Owner:TEXAS INSTR INC

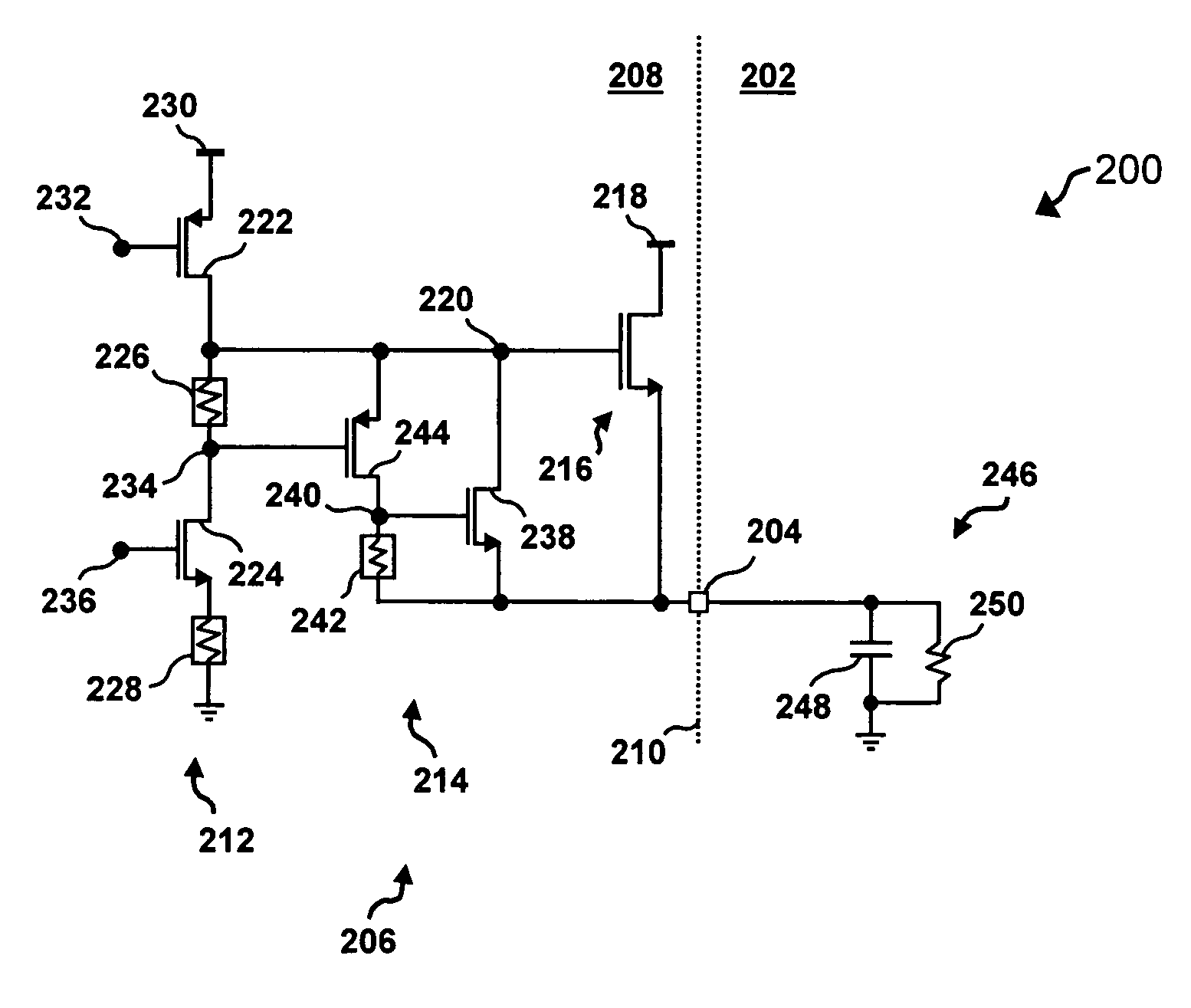

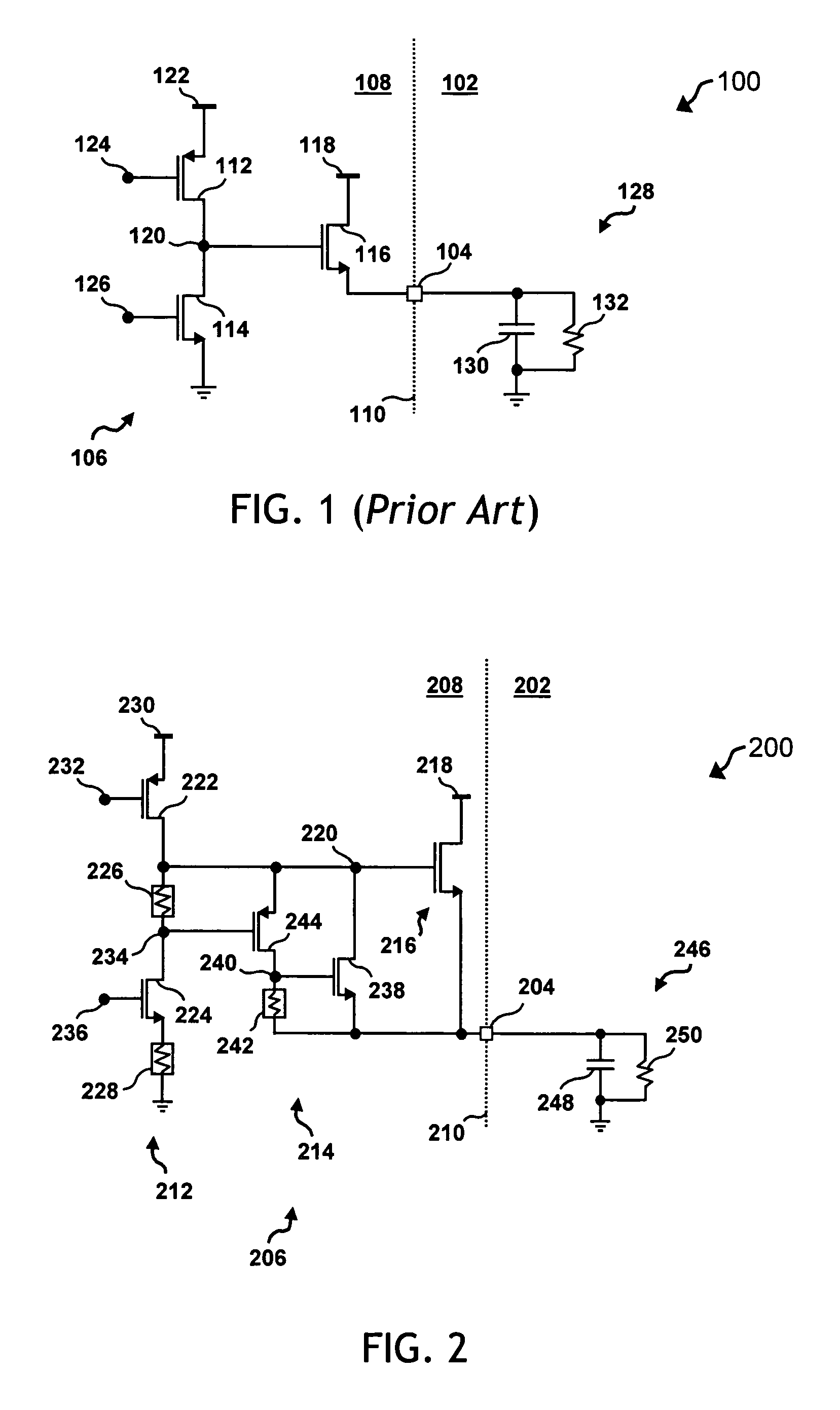

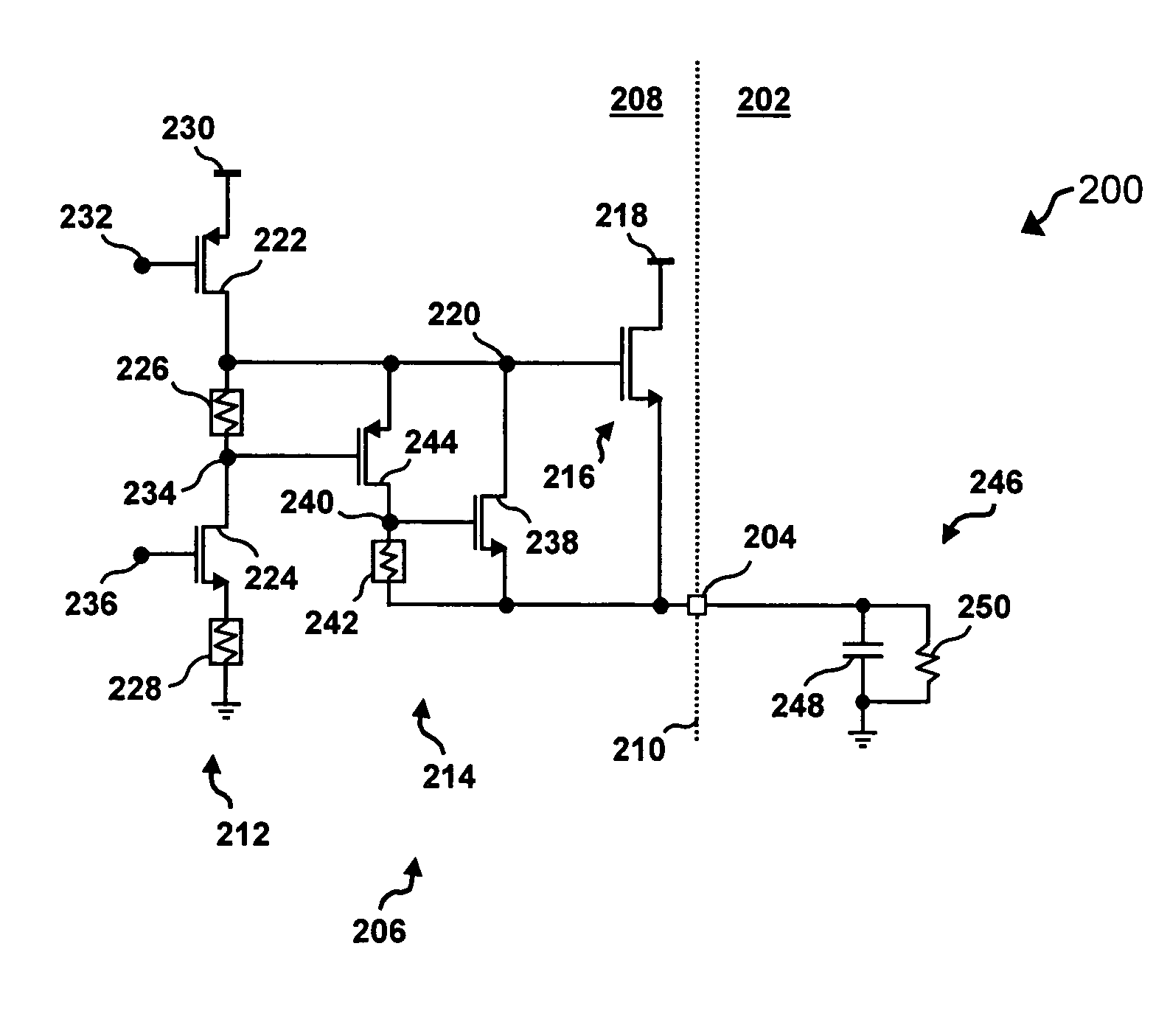

Versatile system for controlling driver signal timing

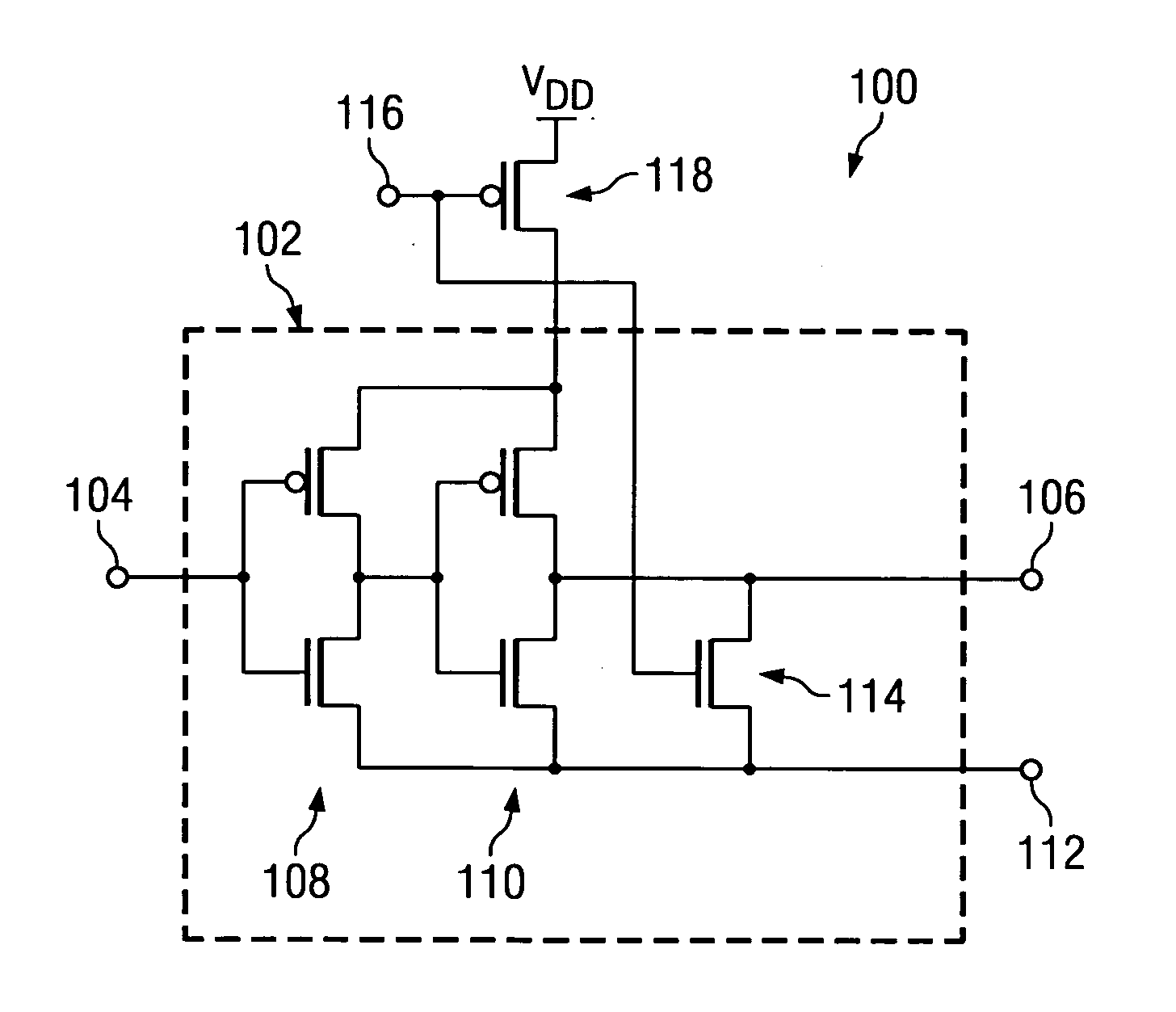

ActiveUS6952120B2Constrained and efficientGood equipment performanceTransistorElectronic switchingDriver circuitControl signal

The present invention provides a system (200) for controlling drive signal timing parameters of an output driver circuit (206). The present invention defines a driver circuit having an output interface (204), and a first transistor (222) coupled to a first voltage supply (230), a first control signal (232), and a first node (220). The circuit also has a first resistive element, coupled between the first node and a second node (234). A second resistive element (228) is coupled to ground. A second transistor (224) is coupled to the second node, to a second control signal (236), and the second resistive element. The circuit has a third transistor (244), coupled to the first and second nodes, and to a third node (240). A third resistive element (242) is coupled between the third node and the output interface. A fourth transistor (238) is coupled to the first and third nodes, and to the output interface. The circuit also has a fifth transistor (216), coupled to a second voltage supply (218), to the first node, and to the output interface.

Owner:TEXAS INSTR INC

Fuzzy logic system for process control in chemical mechanical polishing

ActiveUS7636611B2Easy and efficient and cost-effectiveEasy to integrateSemiconductor/solid-state device manufacturingLapping machinesMetrologyProcess engineering

The present invention provides a versatile system for controlling chemical mechanical polishing in a semiconductor manufacturing process. The system of the present inventions utilizes an in-situ chemical mechanical polishing system, having some type of measurement or metrology function, to bulk polish a semiconductor wafer to a first target threshold. Once the first target has been reached, a fuzzy logic control function, communicatively coupled to the in-situ chemical mechanical polishing system, takes control of further polishing. Measurement data from the measurement function is processed by the fuzzy logic control function, which then adjusts additional polishing time for the polishing system to render a desired wafer topography.

Owner:SAMSUNG AUSTIN SEMICON +1

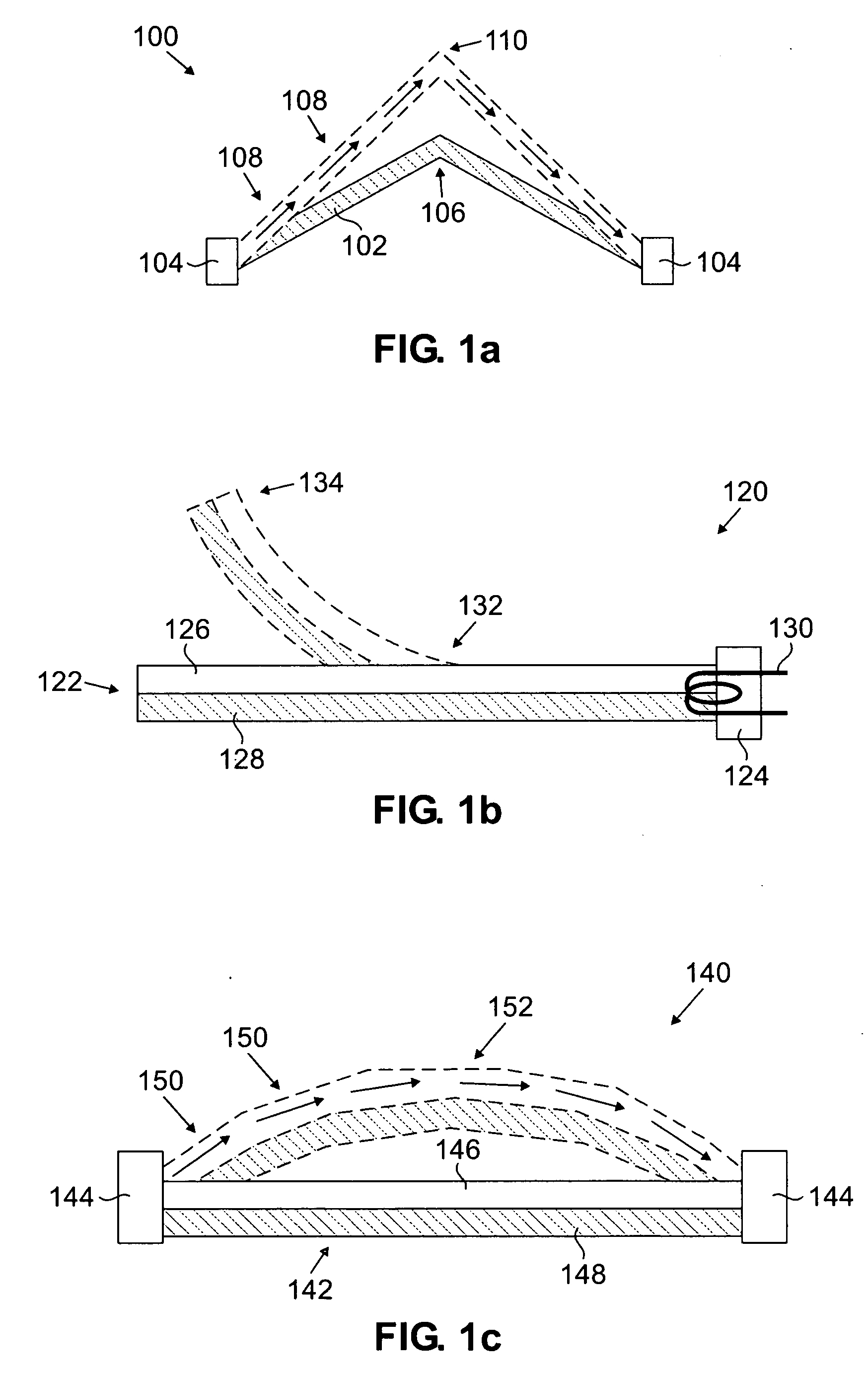

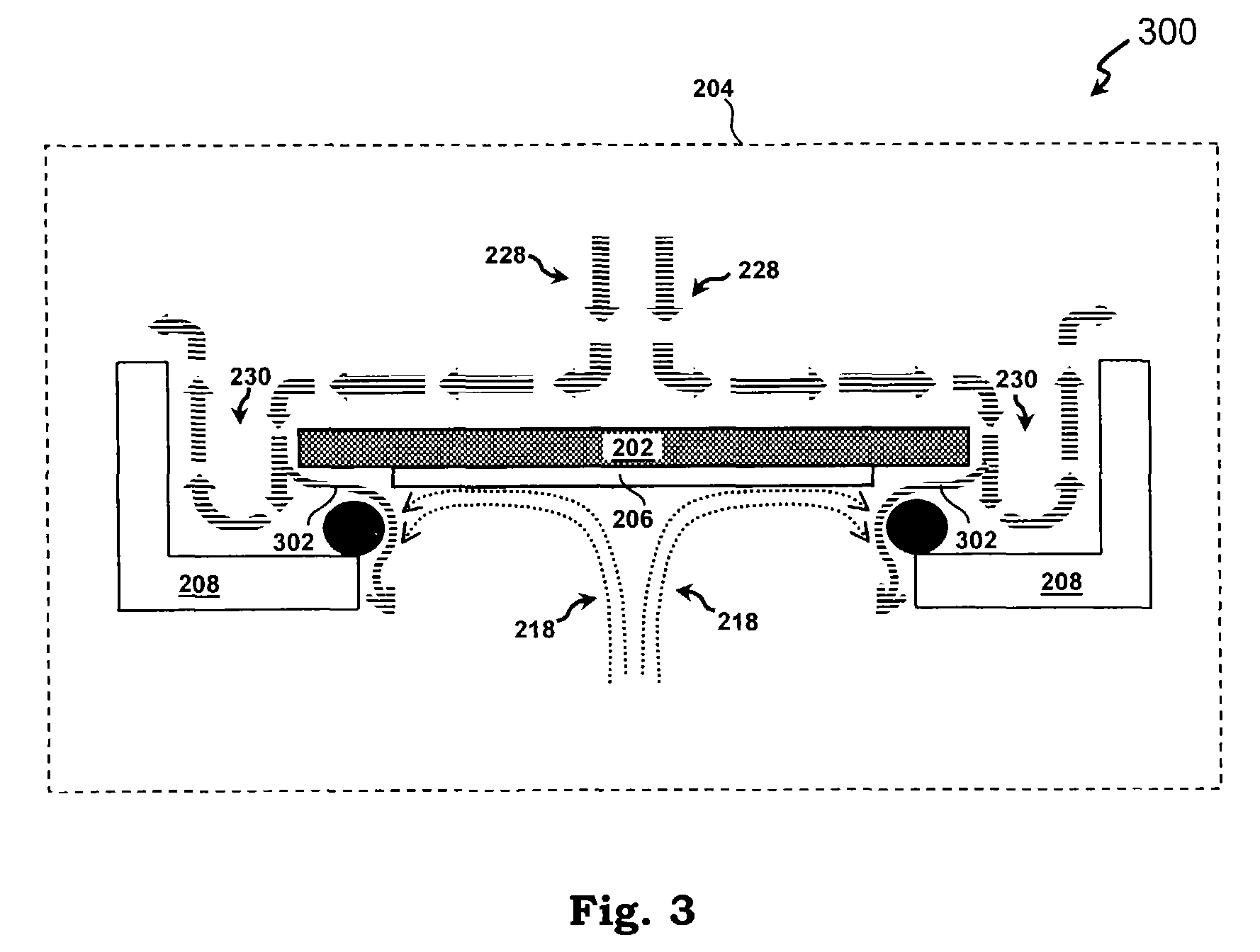

Versatile system for wafer edge remediation

ActiveUS7195679B2Improve production yieldSafely remediatesSemiconductor/solid-state device manufacturingCleaning using toolsEngineeringMechanical engineering

The present invention provides a system (200, 300) for remediating aberrations along the perimeter of a semiconductor wafer (202). The system includes a cleaning apparatus (204) within which the wafer is spun within a confined area. A chuck (208) defines the confined area, having a sidewall that extends above the upper surface (214) of the wafer and surrounds the perimeter of the wafer. The chuck also has a bottom wall, with an aperture formed therein, beneath the wafer. The system includes an isolation barrier (220), disposed atop the bottom wall of the chuck and around the aperture, in proximity to the lower surface so of the wafer. This forms a narrow gap (226) between the barrier and the wafer. A pressurized source forcefully directs a gas (218) at and along the lower surface of the wafer. The system also includes a remediation solution (228) that is applied to the upper surface of the wafer. The solution is forced into a well (230) formed between the chuck sidewall and the perimeter of the wafer, such that the solution bathes the perimeter of the wafer.

Owner:TEXAS INSTR INC

Hot-trap assembly for trapping unreacted gas by-products

InactiveUS8512452B2Easy and efficient and cost-effectiveCombination devicesAuxillary pretreatmentBiochemical engineeringProduct gas

The present invention provides a hot-trap device (1) comprising an enclosure (2) with at least one inlet (3), at least one outlet (5) at least one heating means (7) and at least one collector means (10) for the conversion of reaction by-products into products, wherein the collector means is arranged within the enclosure between the inlet and the outlet has a diameter that substantially matches the diameter of the enclosure and has at least one opening (18).

Owner:OERLIKON SOLAR AG (TRUEBBACH)

Versatile system for controlling semiconductor topography

ActiveUS7010381B2Easy and efficient and cost-effectiveDirect controlSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingData integrityEngineering

Owner:TEXAS INSTR INC

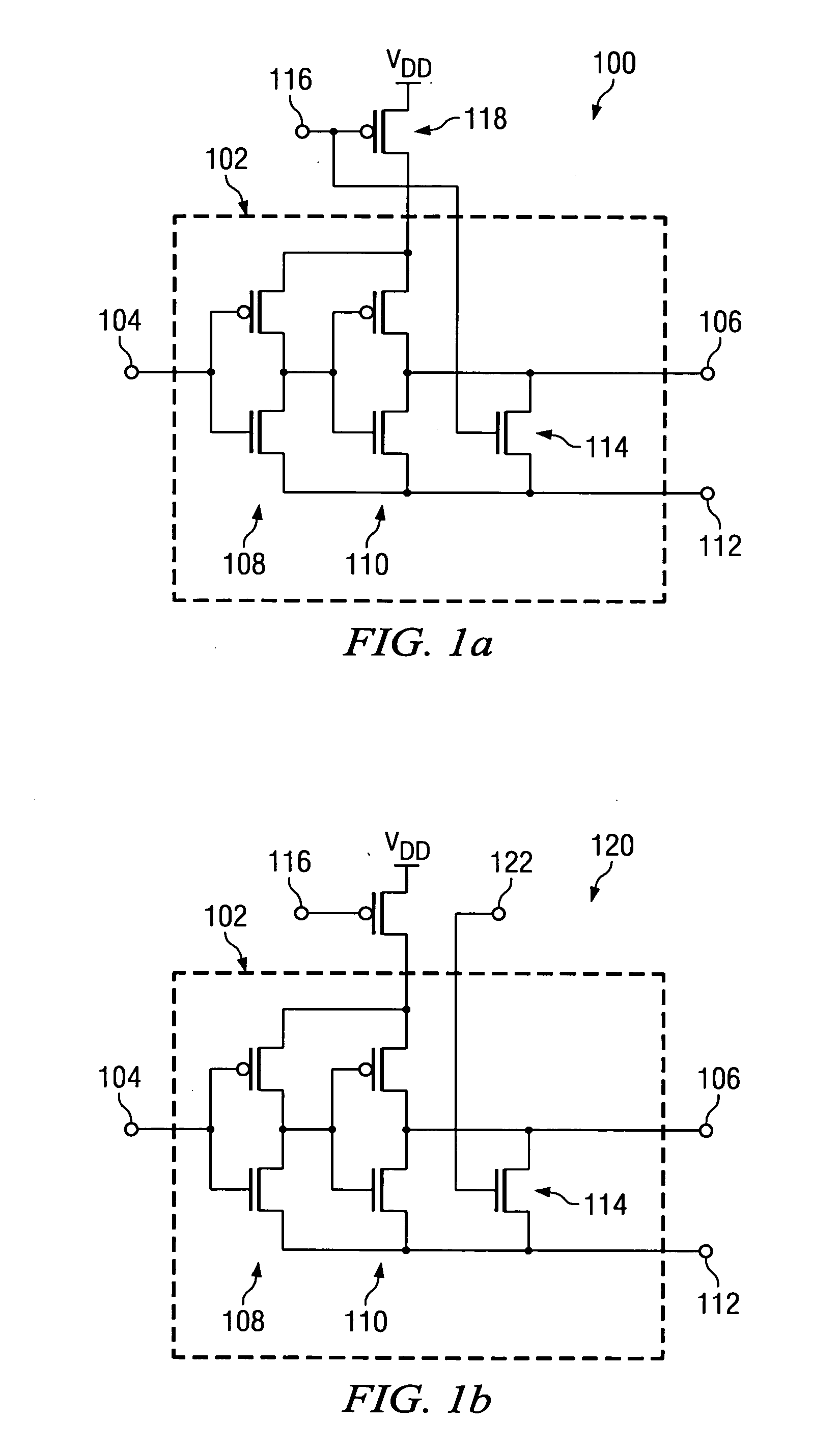

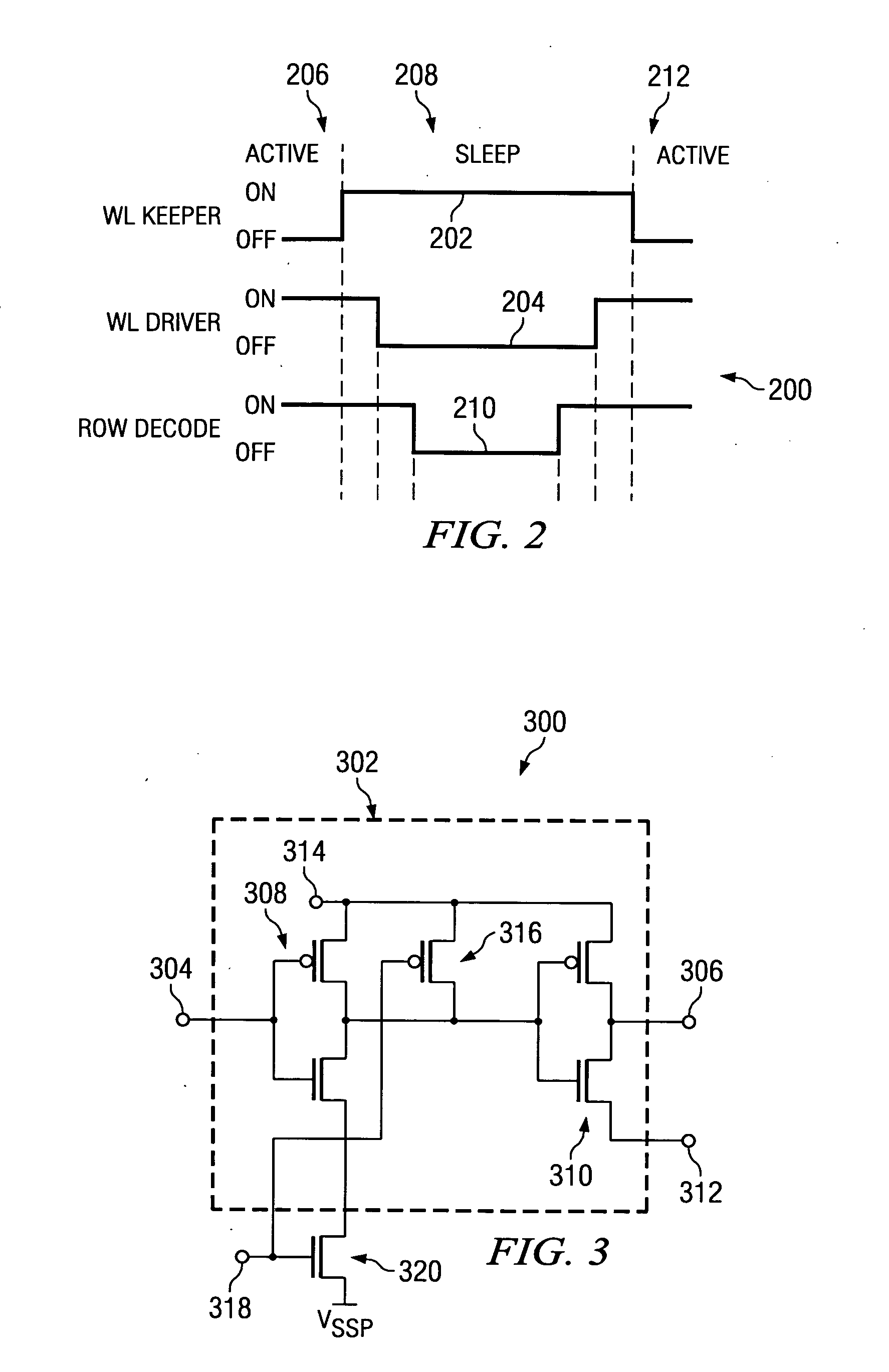

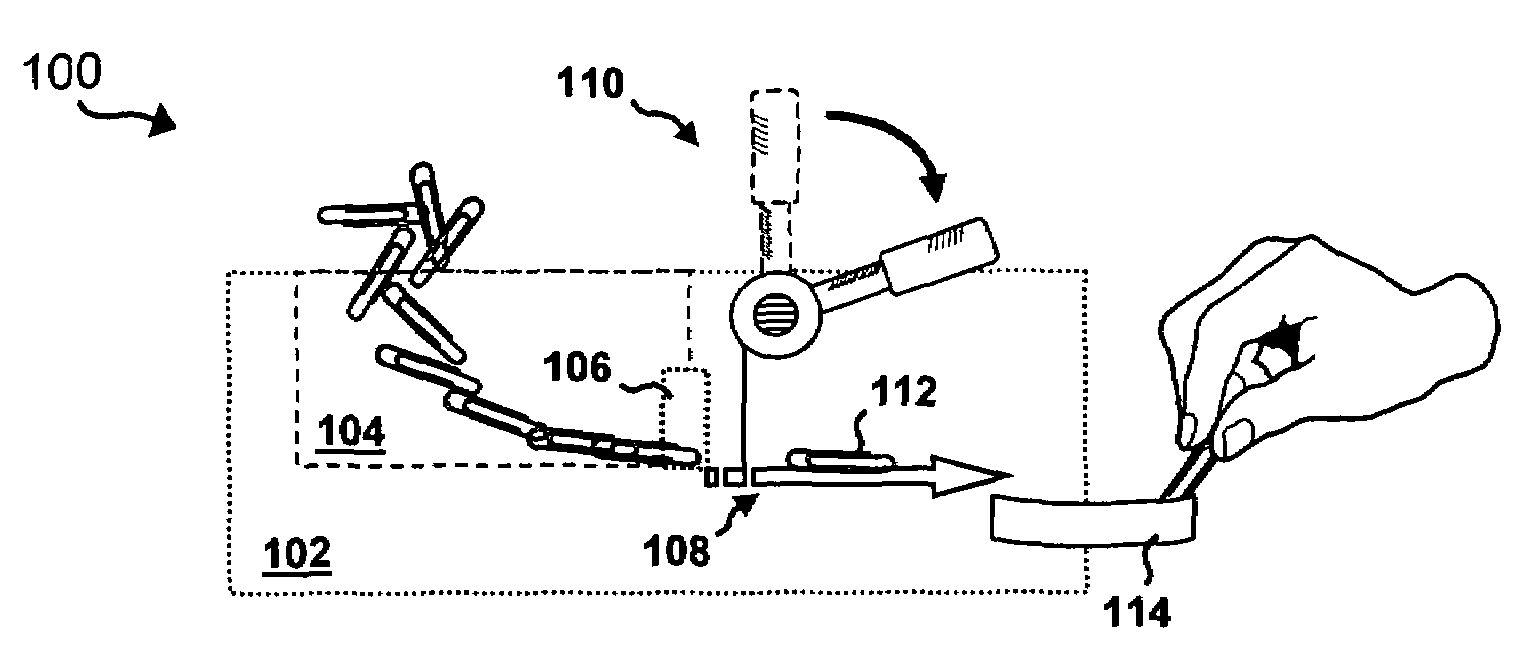

System for reducing row periphery power consumption in memory devices

ActiveUS20050036385A1Reducing row periphery power consumptionNegative impactDigital storageDriver circuitEngineering

The present invention provides a system for reducing row periphery power consumption in a semiconductor memory device, particularly during sleep mode operation. A memory device (100) according to the present invention has a row (106) of memory cells and driver circuitry (102) preceding the row of memory cells. The present invention provides an intervention circuit (114) instantiated within the driver circuitry proximal to the row of memory cells. The intervention circuit is operated to hold the row of memory cells at a desired state, while the driver circuitry (108, 110) preceding the intervention circuit is powered down.

Owner:TEXAS INSTR INC

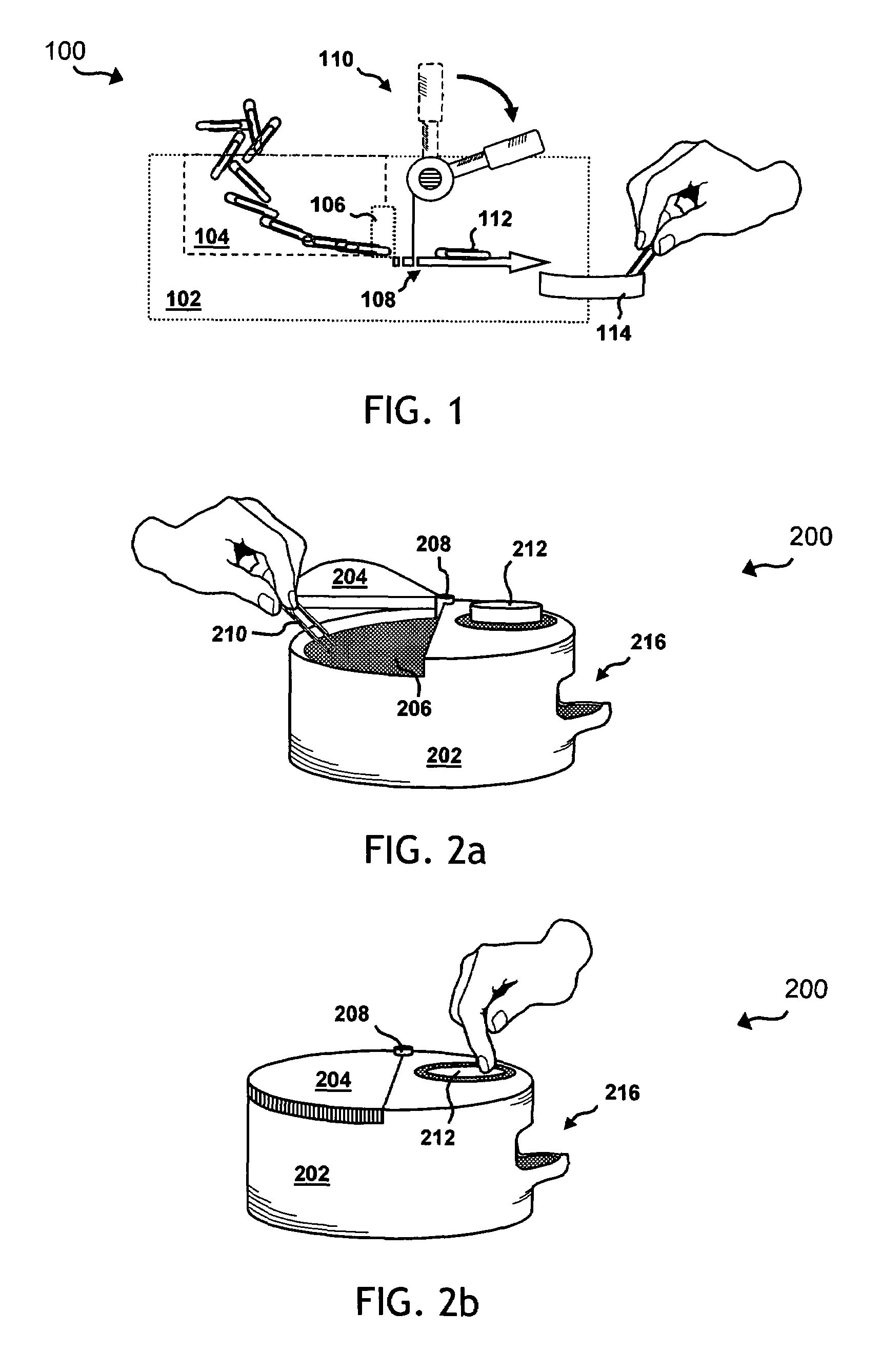

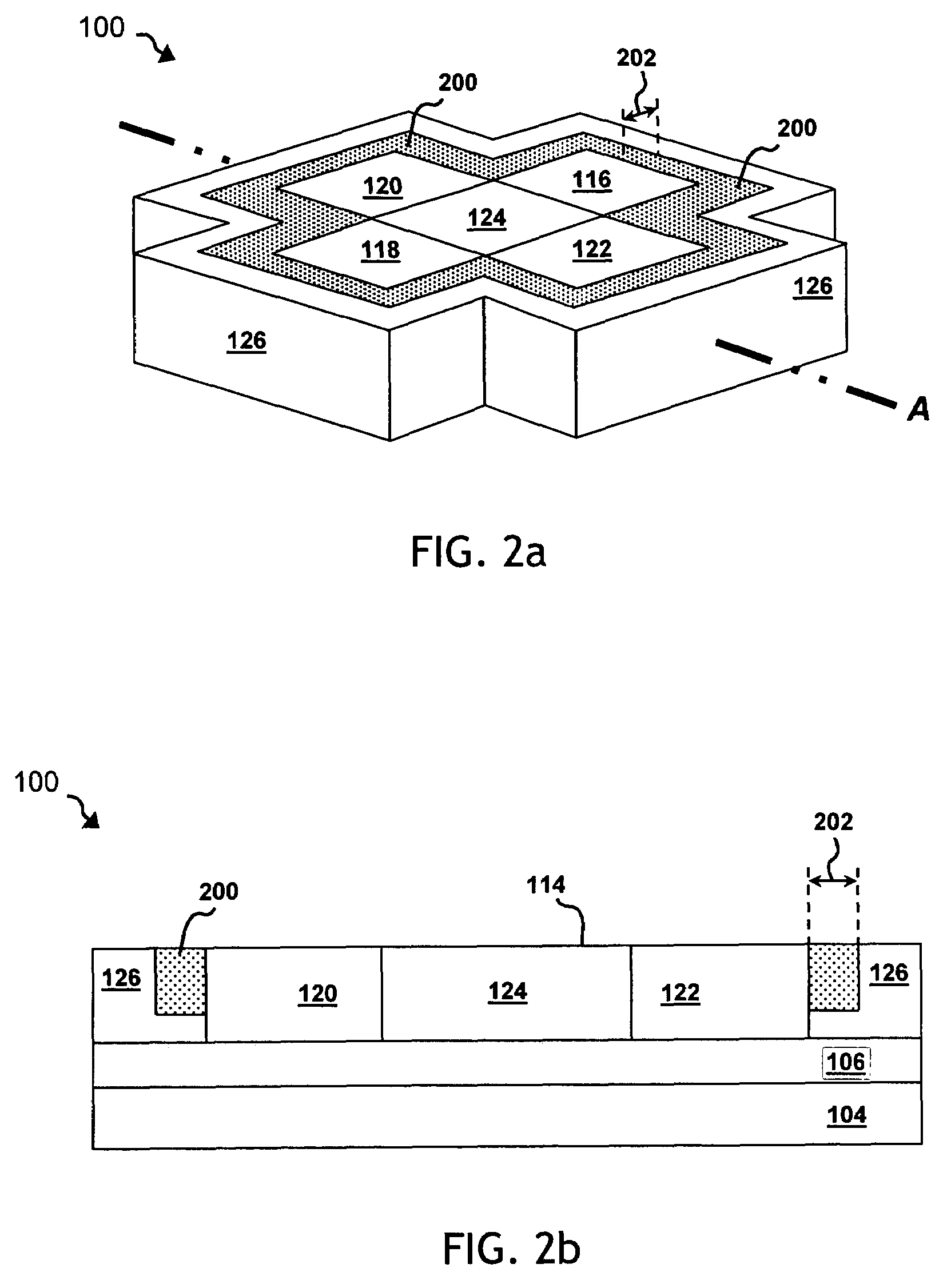

System for storing and dispensing paper clips

InactiveUS7299942B2Easy and economical mannerVersatile in formWriting accessoriesCoin-freed apparatus detailsPulp and paper industryBiological activation

The present invention defines a system (100) for one-at-a-time paper clip dispensing. The system includes a housing (102), and a retrieval receptacle (114) disposed somewhere along the exterior of the housing. A storage component (104) is disposed along or within the housing, and is adapted to receive loose paper clips. A gate component (106) is operably coupled to the storage component, and a sorting component is incorporated within the storage or gate component(s). An actuating system (110) is disposed somewhere within or along the housing. A retrieval system (112) is disposed between the receptacle and the storage component. The retrieval system is adapted to retrieve a single paper clip from the gate component, and deliver the paper clip to the receptacle, responsive to activation of the actuating system.

Owner:EDENS MICHELLE O

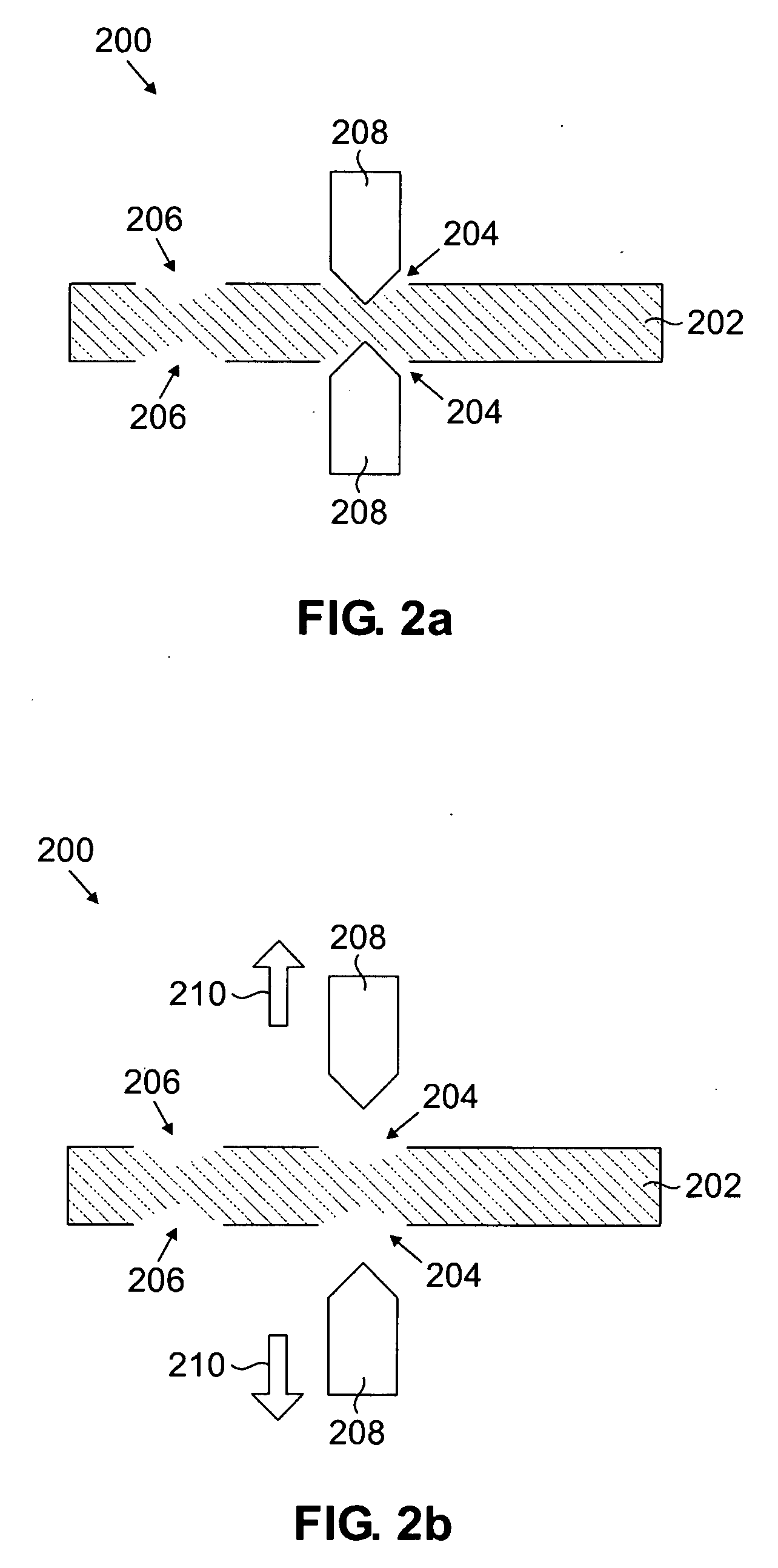

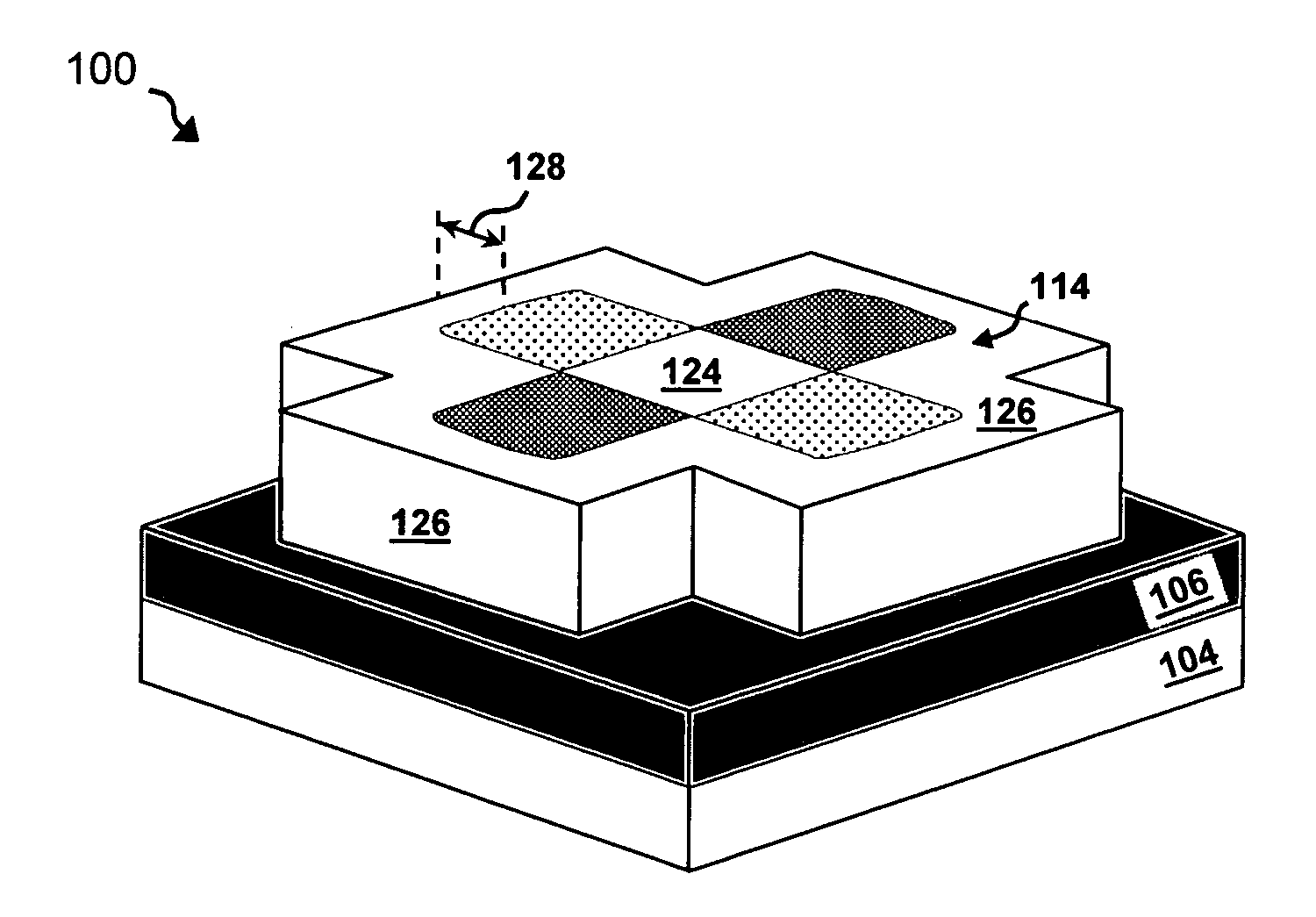

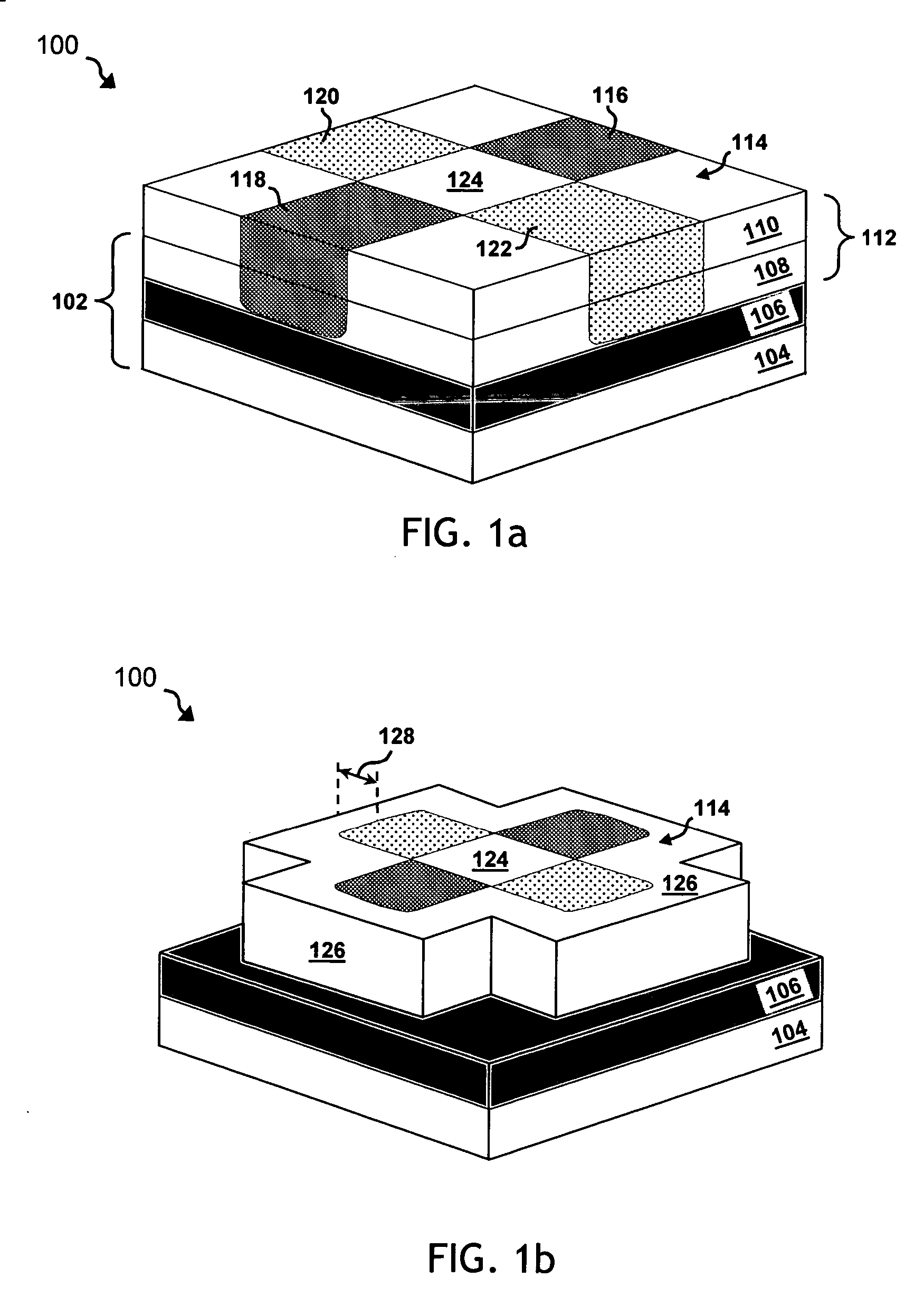

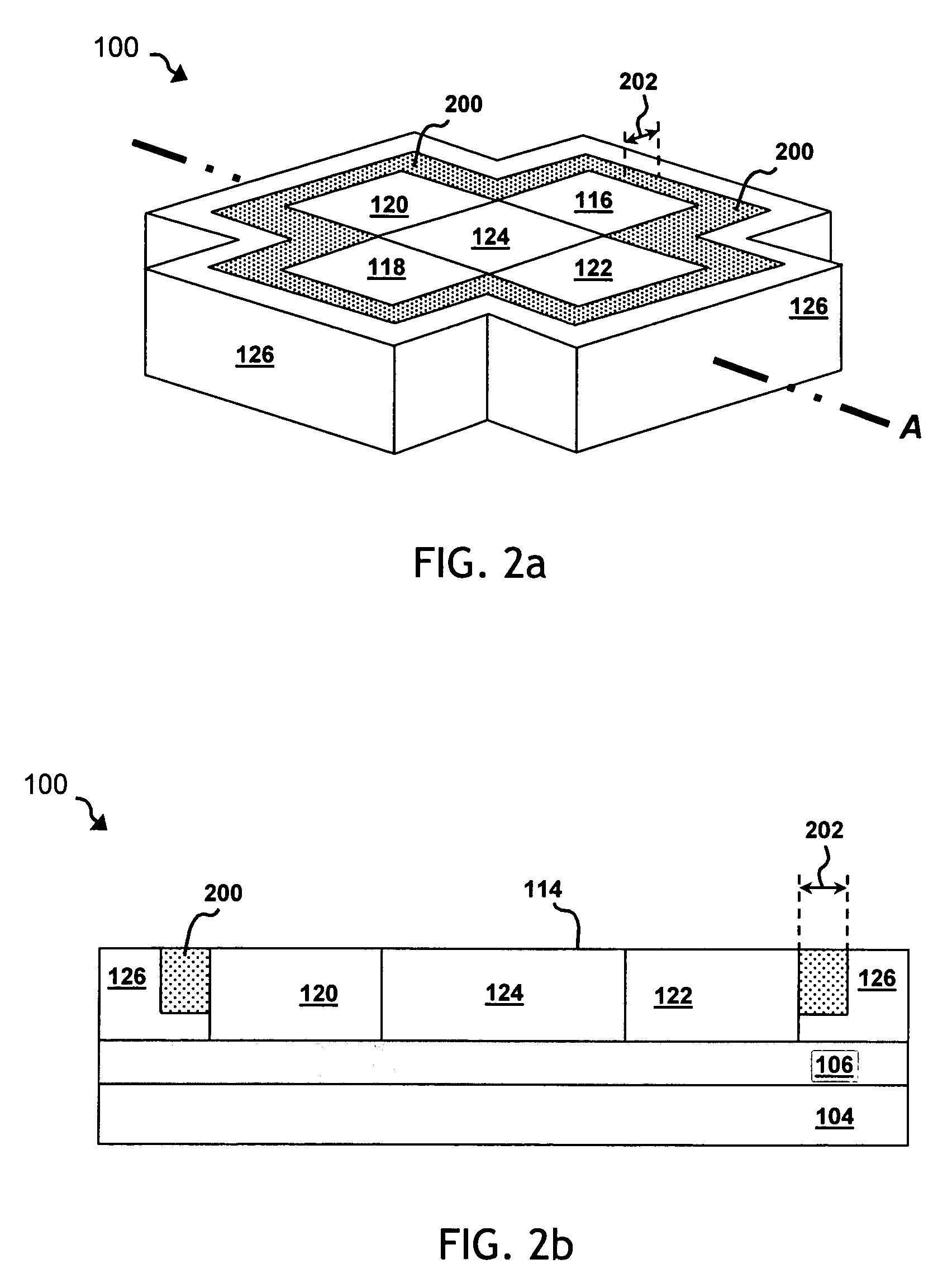

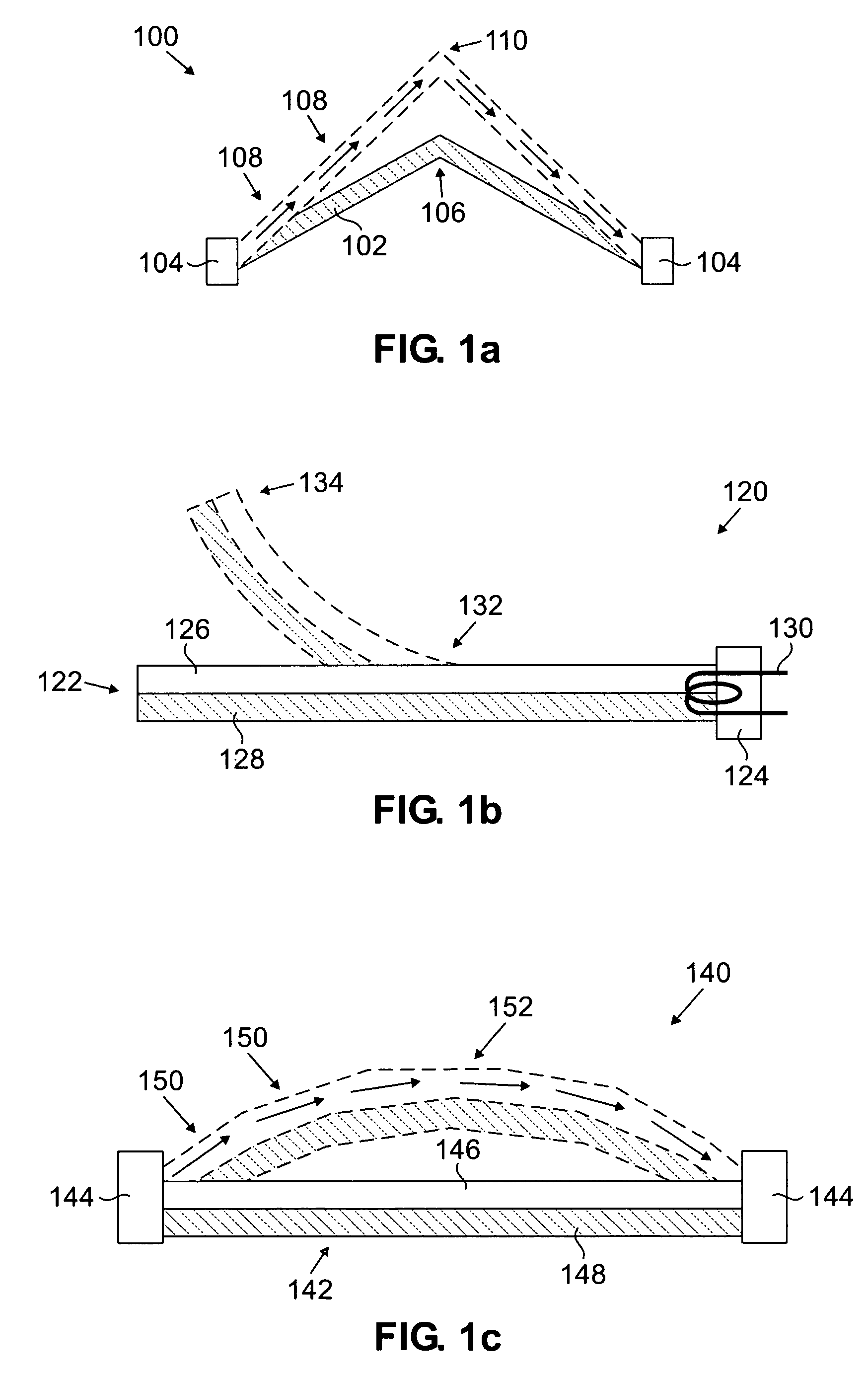

Versatile system for cross-lateral junction field effect transistor

ActiveUS7288800B2Easy to adaptEasy to produceThyristorSolid-state devicesField-effect transistorSemiconductor

The present invention provides a system for providing a cross-lateral junction field effect transistor (114) having desired high-performance desired voltage, frequency or current characteristics. The cross-lateral transistor is formed on a commercial semiconductor substrate (102). A channel structure (124) is formed along the substrate, having source (120) and drain (122) structures laterally formed on opposites sides thereof. A first gate structure (116) is formed along the substrate, laterally adjoining the channel structure orthogonal to the source and drain structures. A second gate structure (118) is formed along the substrate, laterally adjoining the channel structure, orthogonal to the source and drain structures and opposite the first gate structure.

Owner:TEXAS INSTR INC

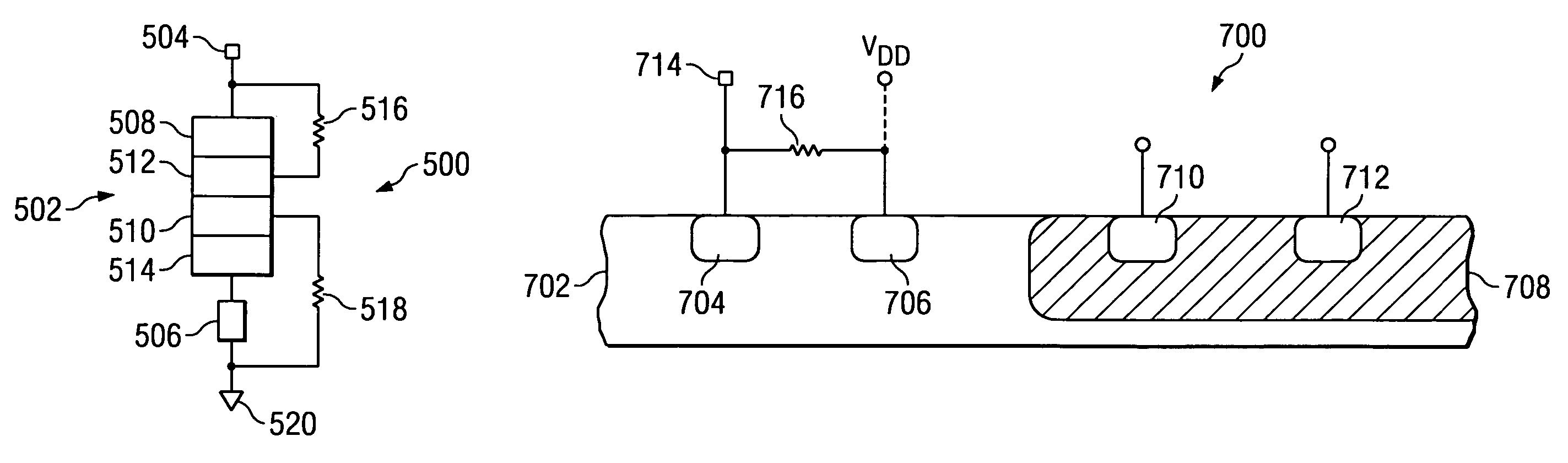

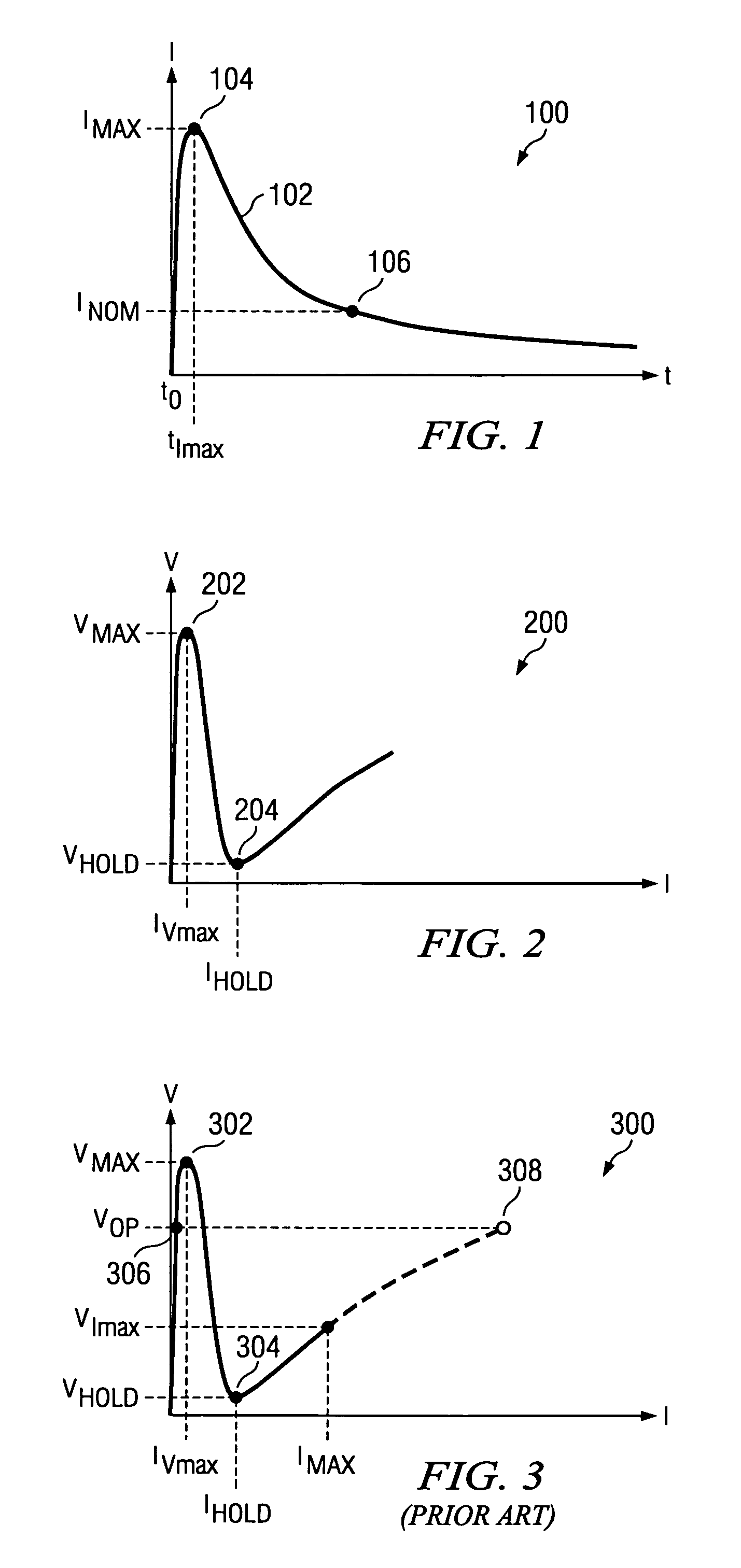

Versatile system for electrostatic discharge protection utilizing silicon controlled rectifier

InactiveUS7060538B2Easy to implementMinimize or eliminate SCR operational latch-up problemsTransistorThyristorSilicon-controlled rectifierSemiconductor

The present invention provides a system for electrostatic discharge protection in a semiconductor device, utilizing a silicon-controlled rectifier (502). The system includes the silicon controlled rectifier, which has a first p-type region (508) coupled to a voltage node (504), a first n-type region (512) having a first side adjoining the first p-type region, a second p-type region (510) having a first side adjoining a second side of the first n-type region, and a second n-type region (514) having a first side adjoining a second side of the second p-type region. A clamping structure (506) is intercoupled between the second n-type region and ground, to prevent the junction between the second p-type region and the second n-type region from retaining a forward bias. A switching structure (518) is intercoupled between the second p-type region and ground to ground the second p-type region during normal operation of the semiconductor device.

Owner:TEXAS INSTR INC

Versatile system for cross-lateral junction field effect transisor

ActiveUS20060151804A1Easy to adaptHighly versatileSolid-state devicesSemiconductor devicesEngineeringField-effect transistor

The present invention provides a system for providing a cross-lateral junction field effect transistor (114) having desired high-performance desired voltage, frequency or current characteristics. The cross-lateral transistor is formed on a commercial semiconductor substrate (102). A channel structure (124) is formed along the substrate, having source (120) and drain (122) structures laterally formed on opposites sides thereof. A first gate structure (116) is formed along the substrate, laterally adjoining the channel structure orthogonal to the source and drain structures. A second gate structure (118) is formed along the substrate, laterally adjoining the channel structure, orthogonal to the source and drain structures and opposite the first gate structure.

Owner:TEXAS INSTR INC

Versatile system for controlling driver signal timing

ActiveUS20050179471A1Constrained and efficientGood equipment performanceTransistorElectronic switchingDriver circuitControl signal

The present invention provides a system (200) for controlling drive signal timing parameters of an output driver circuit (206). The present invention defines a driver circuit having an output interface (204), and a first transistor (222) coupled to a first voltage supply (230), a first control signal (232), and a first node (220). The circuit also has a first resistive element, coupled between the first node and a second node (234). A second resistive element (228) is coupled to ground. A second transistor (224) is coupled to the second node, to a second control signal (236), and the second resistive element. The circuit has a third transistor (244), coupled to the first and second nodes, and to a third node (240). A third resistive element (242) is coupled between the third node and the output interface. A fourth transistor (238) is coupled to the first and third nodes, and to the output interface. The circuit also has a fifth transistor (216), coupled to a second voltage supply (218), to the first node, and to the output interface.

Owner:TEXAS INSTR INC

Versatile system for a locking electro-thermal actuated MEMS switch

InactiveUS7714691B2Easy to adaptProcesses—efficiently providing single or multi-throw switchesElectrothermal relaysThermally actuated switchesEngineeringActuator

A lockable MEMS switching architecture provided having a clutch assembly, a switching member, and an actuator. The clutch assembly has one or more engagement features located in proximity to the switching member—particularly one or more receiving features located upon the switching member. The clutch assembly is actuated to disengage the engagement features from the receiving features. The switching member is actuated to move in relation to the clutch assembly. Once the switching member is in a desired position, the clutch assembly is de-actuated, causing the engagement features to re-engage with the switching member, thereby restricting its further movement.

Owner:SAMSUNG ELECTRONICS CO LTD

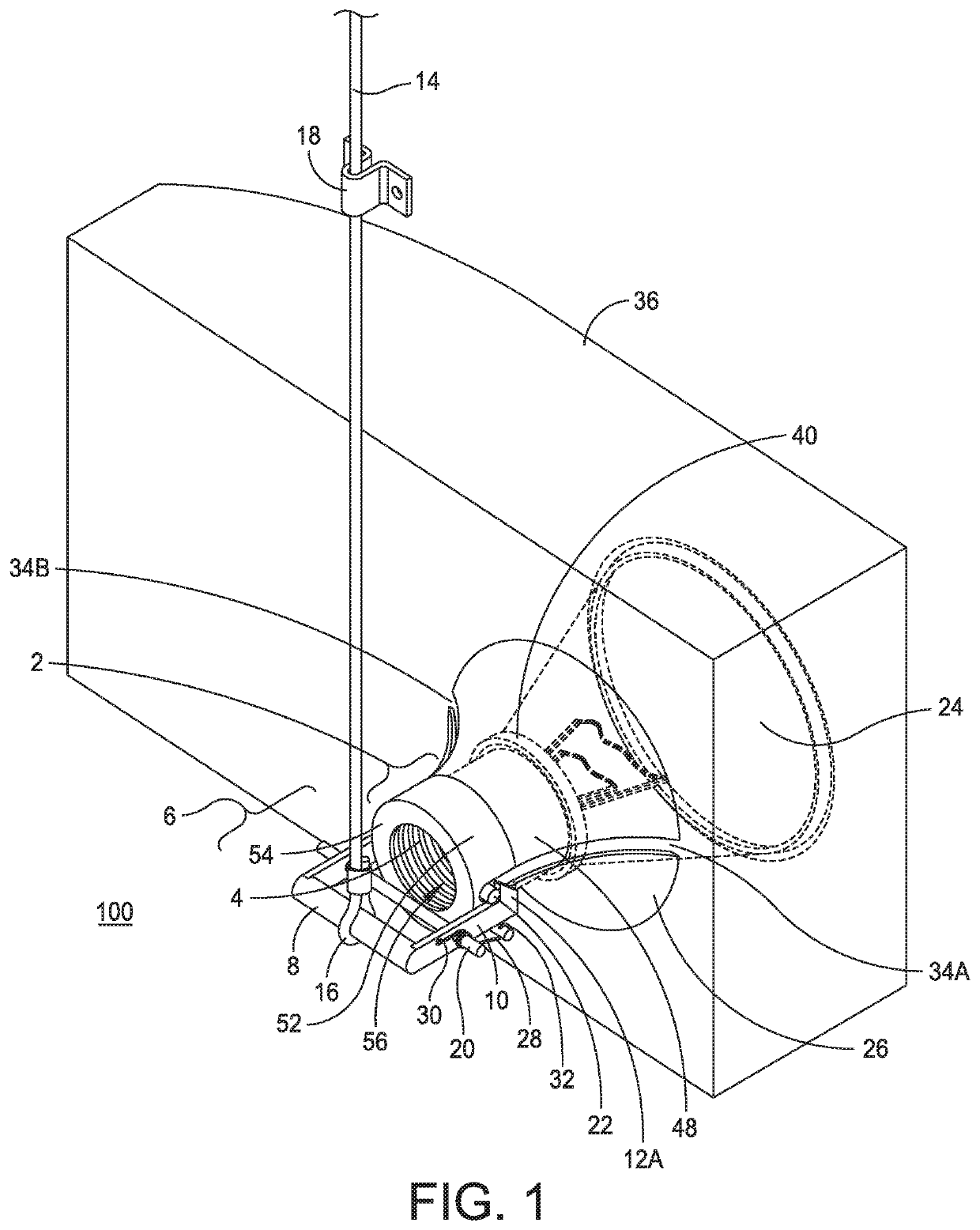

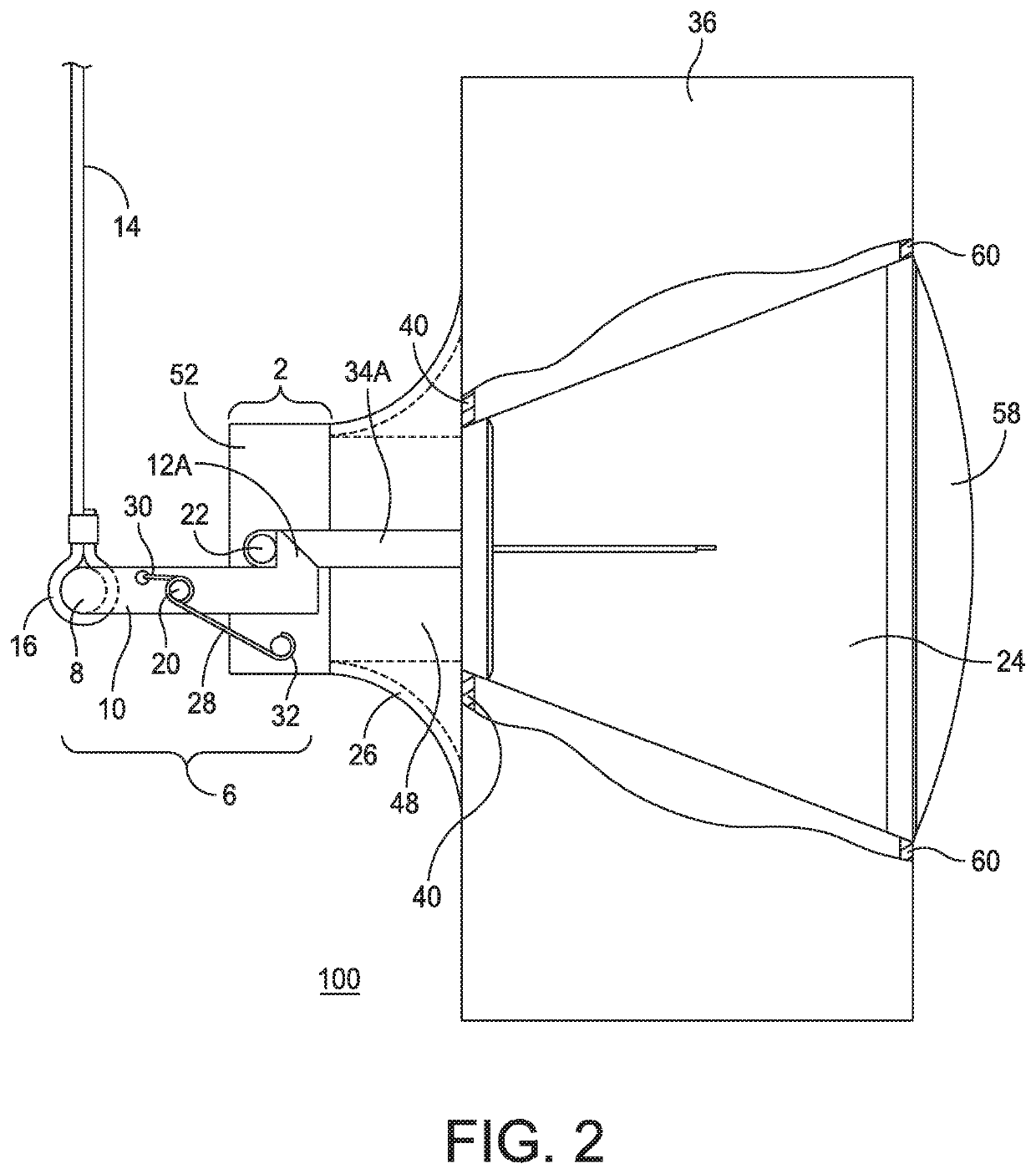

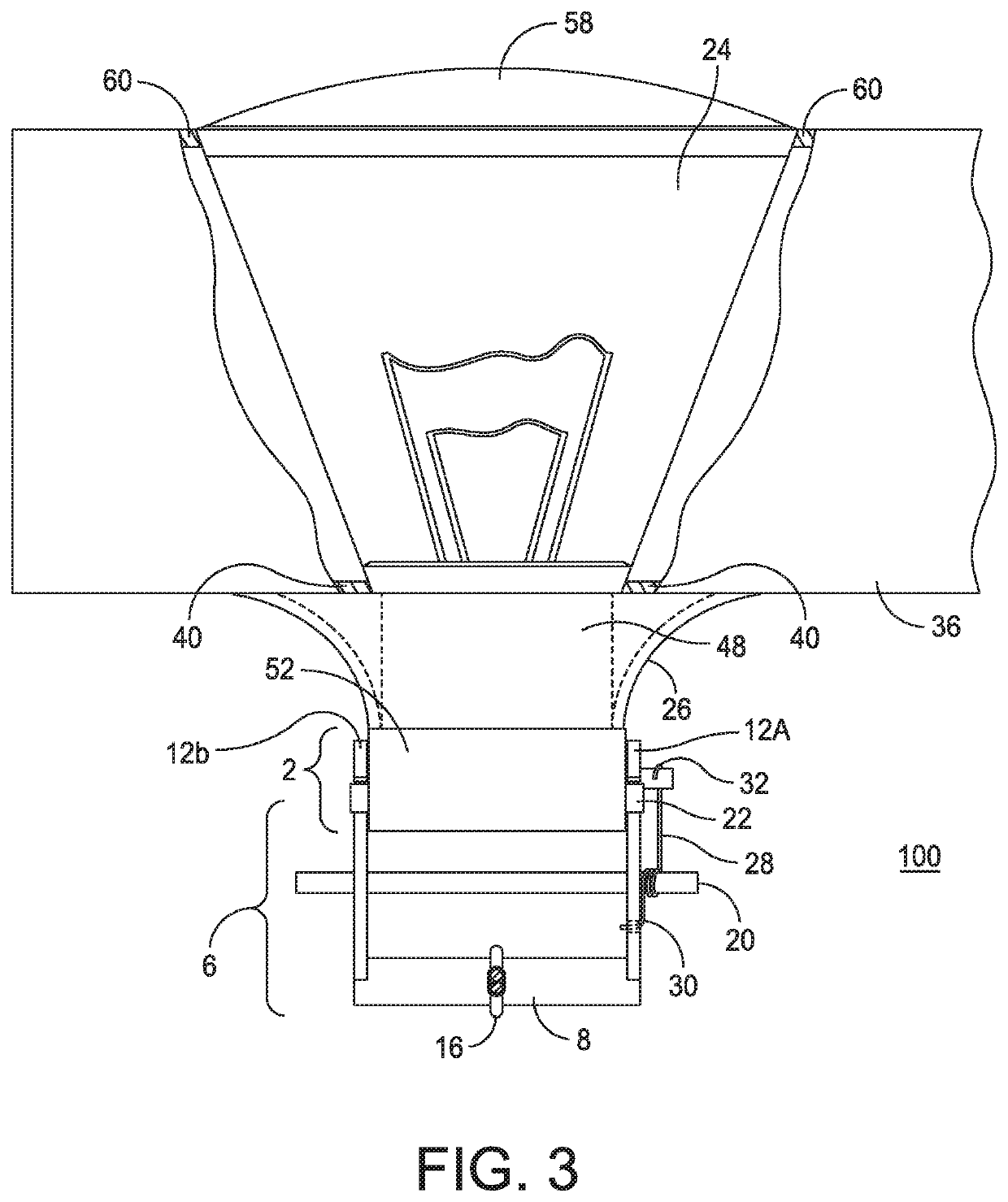

Vehicle Headlight Device Having An Ejectable And Replaceable Lightbulb Assembly

ActiveUS20210140600A1Easy accessEasy and efficient and cost-effectiveVehicle headlampsOptical signallingElectromagnetic radiationElectrical connector

The present invention relates to an ejectable headlight device for replacement of a lightbulb assembly from the front of a vehicle. The lightbulb assembly of the present invention has at least one lightbulb pin, a lightbulb base, a replaceable electromagnetic radiation source, an electrical connector, and a replaceable lens. The ejectable headlight device includes an ejector, a base that houses the ejector and has at least one guide for receiving the lightbulb pin. The device has a release arm that engages the lightbulb pin. The device further includes a pivot point and a pull attached to the release arm. When the release arm secures the lightbulb pin to the base, the device is in the locked position. When the pull engages the release arm to put the device in the unlocked position, the release arm pivots about the pivot point and disengages the lightbulb pin.

Owner:APARO JAMES M

Versatile system for electrostatic discharge protection utilizing silicon controlled rectifier

InactiveUS6949800B2Easy to implementMinimize or eliminate SCR operational latch-up problemsTransistorThyristorSilicon-controlled rectifierEngineering

The present invention provides a system for electrostatic discharge protection in a semiconductor device, utilizing a silicon-controlled rectifier (502). The system includes the silicon controlled rectifier, which has a first p-type region (508) coupled to a voltage node (504), a first n-type region (512) having a first side adjoining the first p-type region, a second p-type region (510) having a first side adjoining a second side of the first n-type region, and a second n-type region (514) having a first side adjoining a second side of the second p-type region. A clamping structure (506) is intercoupled between the second n-type region and ground, to prevent the junction between the second p-type region and the second n-type region from retaining a forward bias. A switching structure (518) is intercoupled between the second p-type region and ground to ground the second p-type region during normal operation of the semiconductor device.

Owner:TEXAS INSTR INC

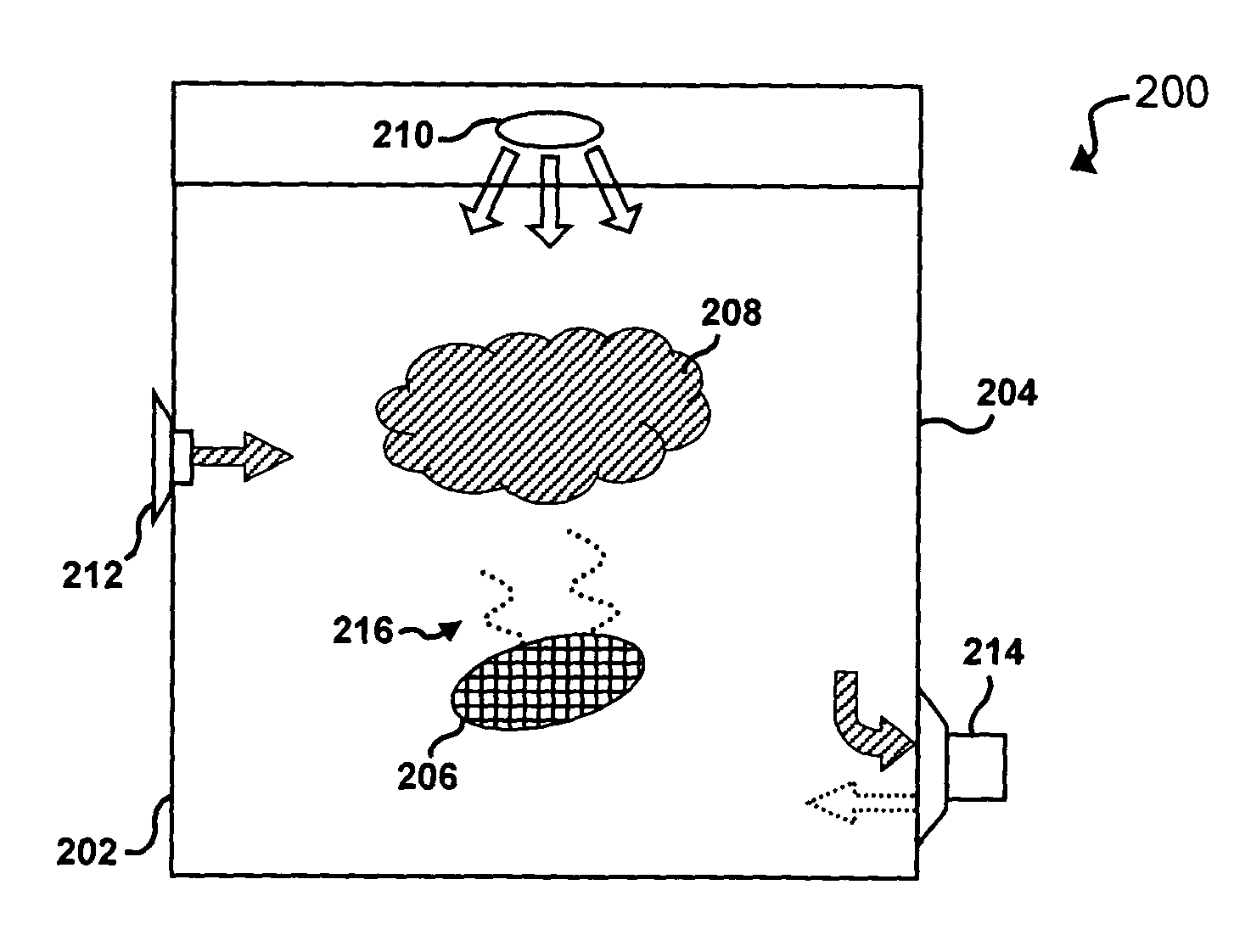

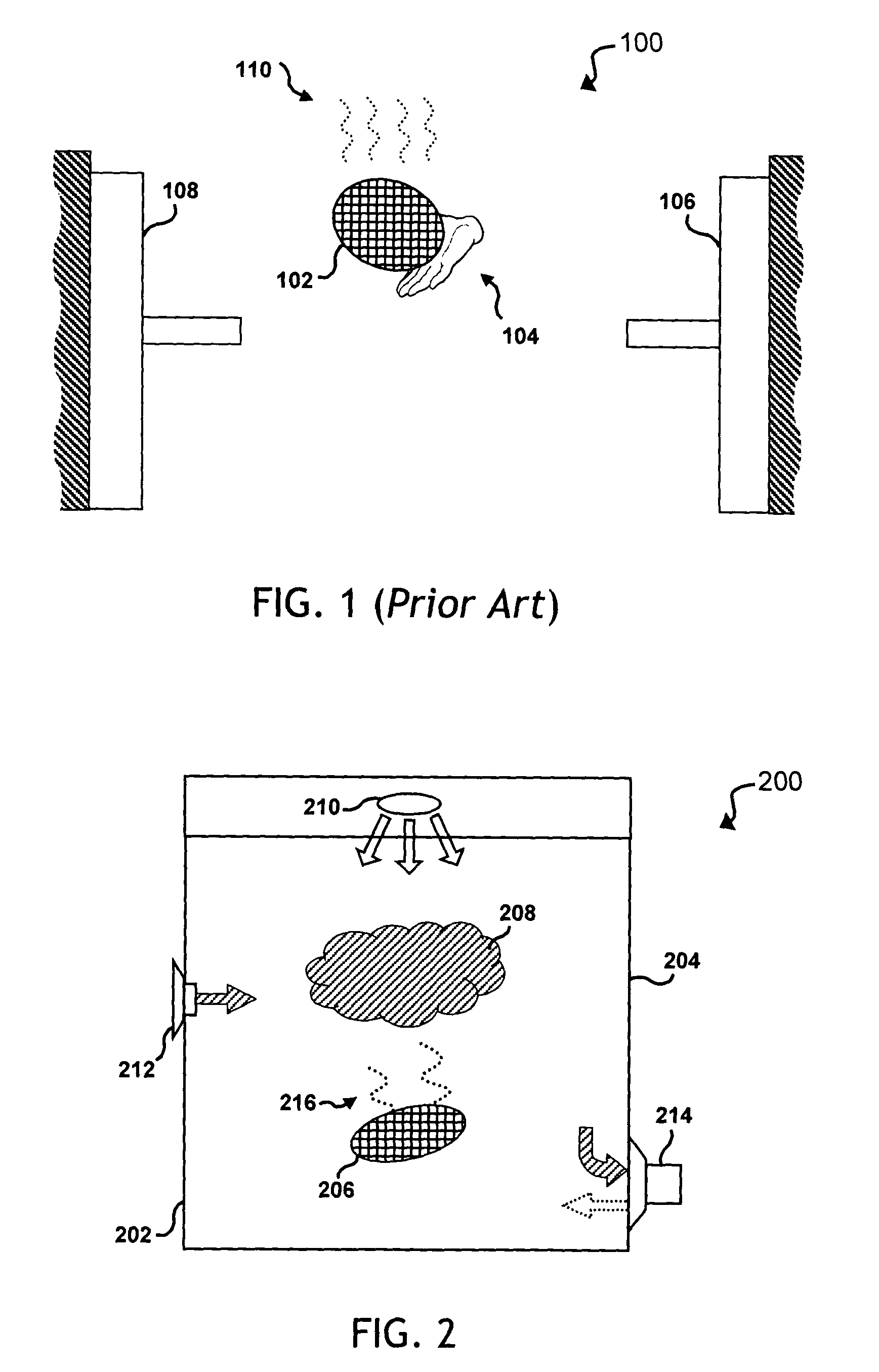

System for ultraviolet atmospheric seed layer remediation

InactiveUS7015568B2Easy and efficient and cost-effectiveNeutralize effectSemiconductor/solid-state device detailsSolid-state devicesAtmospheric airCopper

The present invention provides a system for removing organic contaminants (216) from a copper seed layer that has been deposited on a semiconductor substrate (206). The present invention provides a housing (204) to enclose the semiconductor substrate within. An ultraviolet radiation source (210) is disposed within the housing. A treatment medium (208) is also provided within the housing. The semiconductor substrate is enclosed within the housing and exposed to the treatment medium. The ultraviolet radiation source exposes the semiconductor substrate to ultraviolet radiation, desorbing the contaminants from the seed layer.

Owner:TEXAS INSTR INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com