Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

56results about How to "Cross-sectional area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

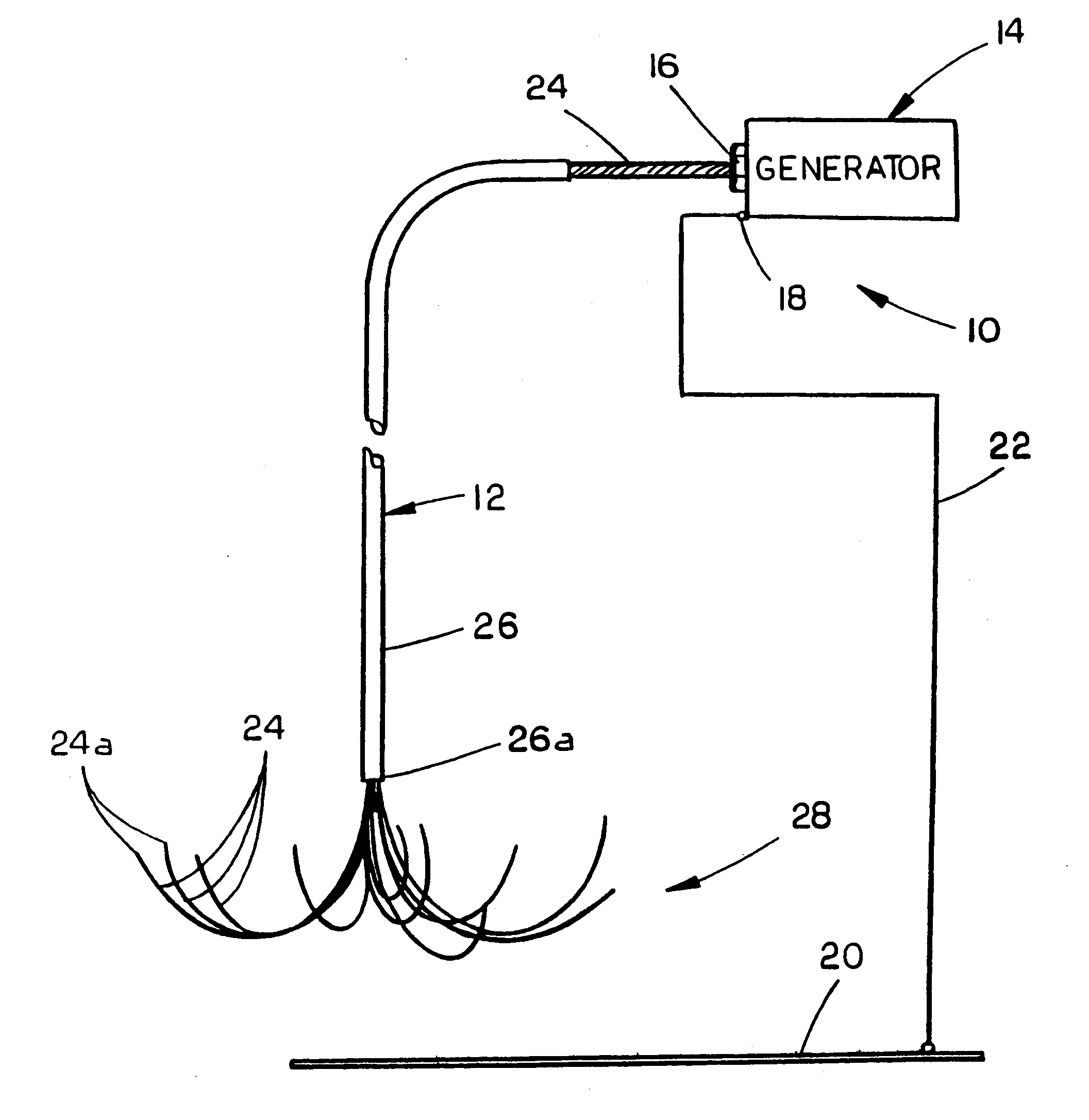

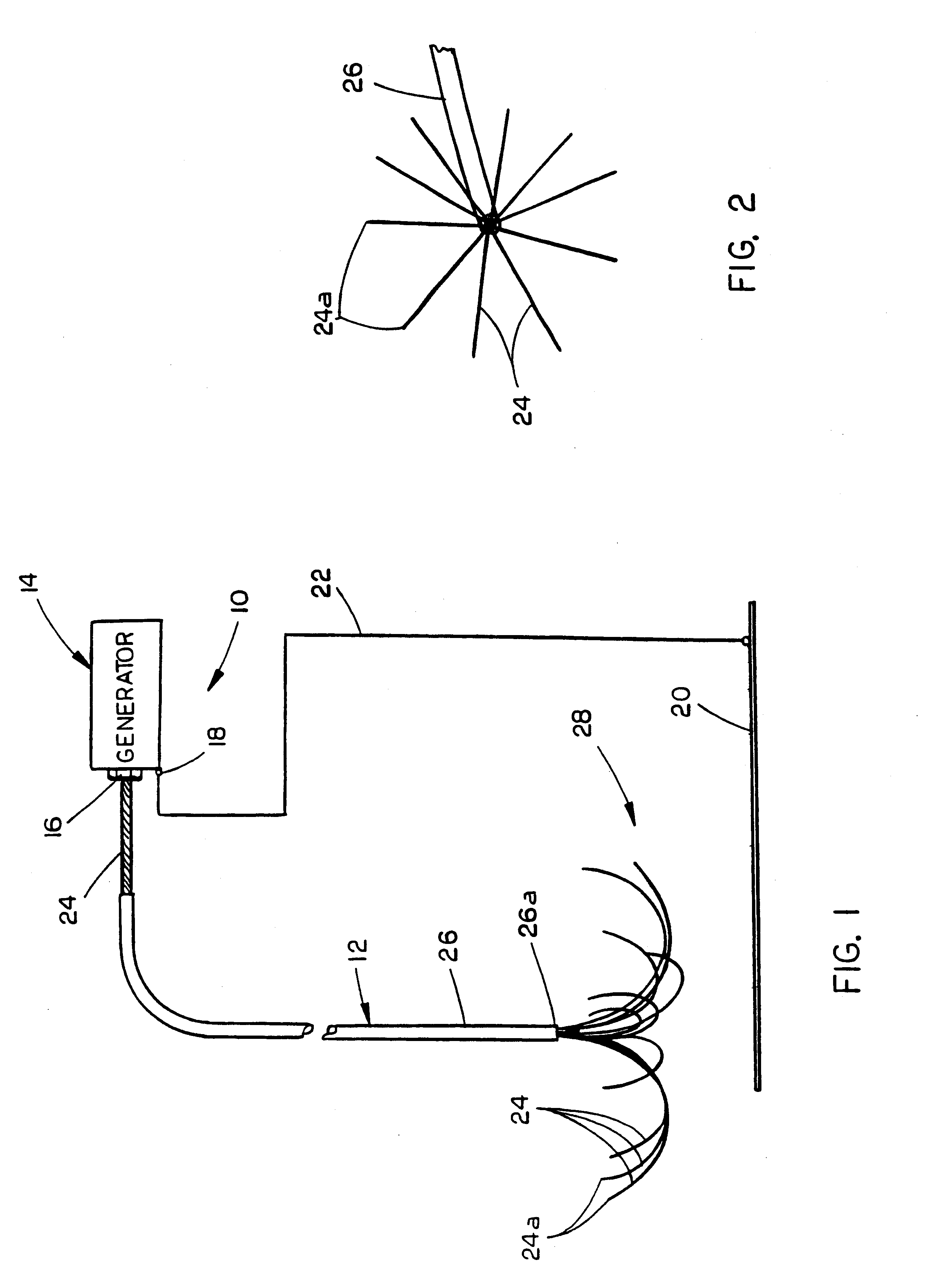

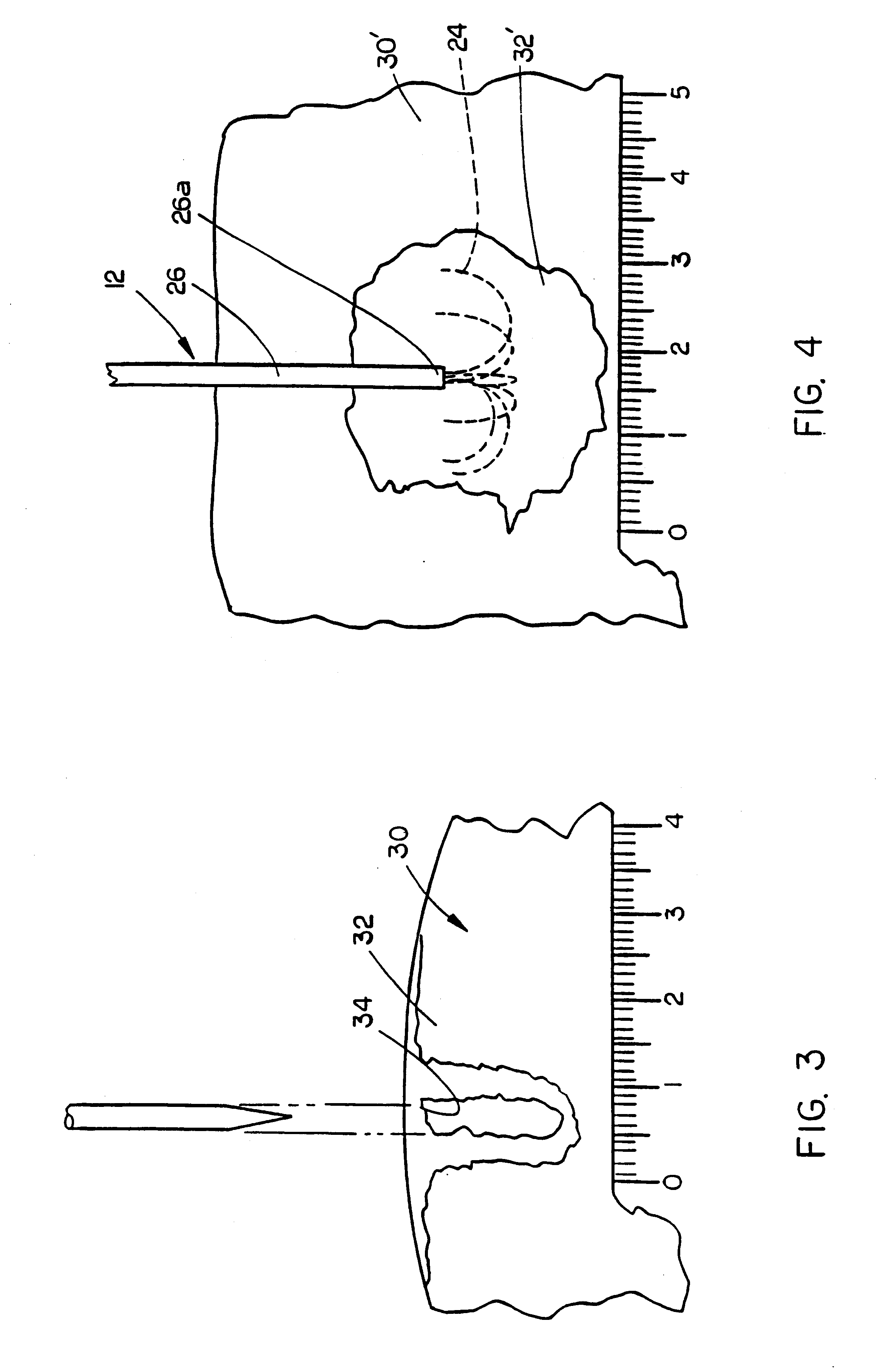

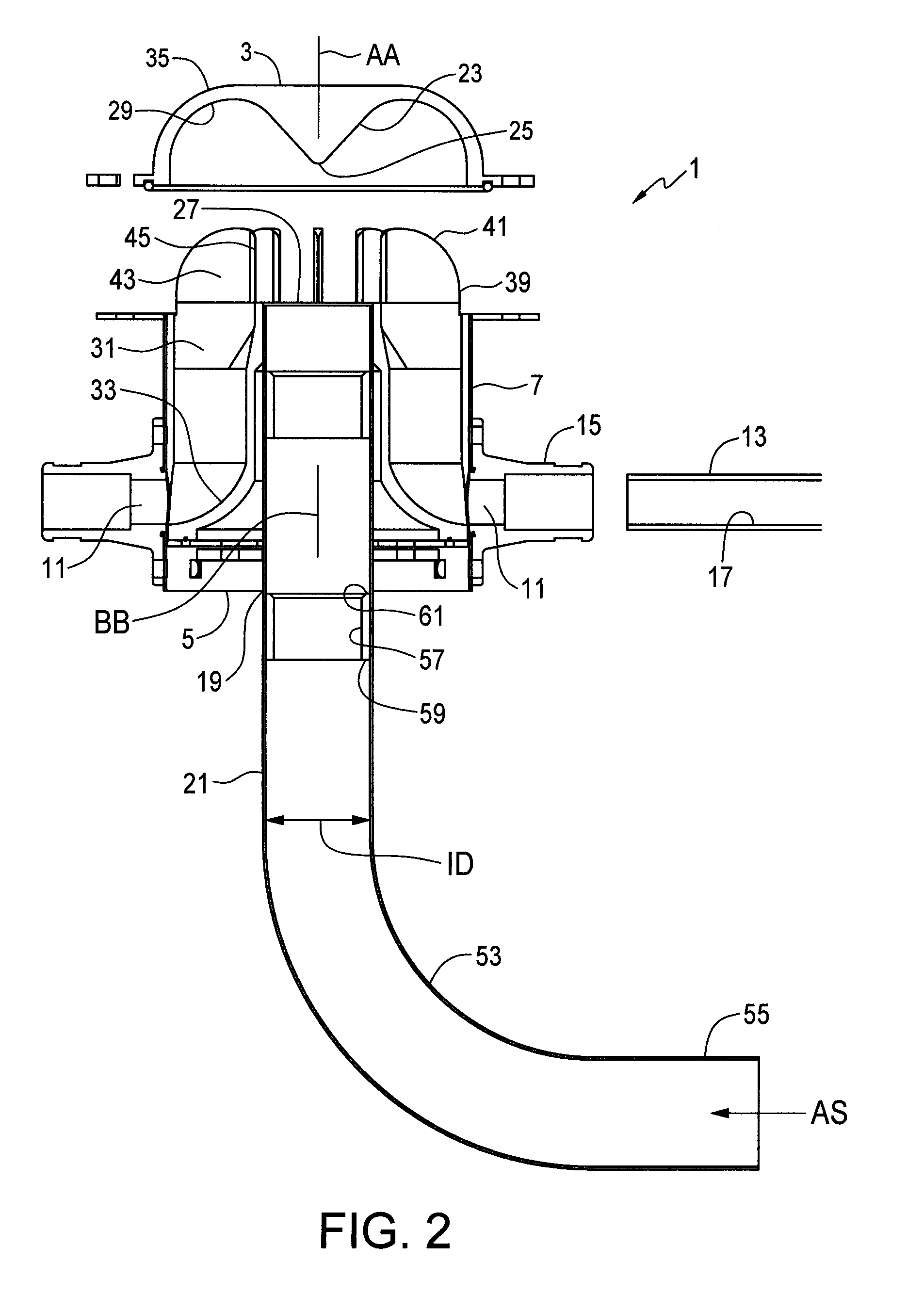

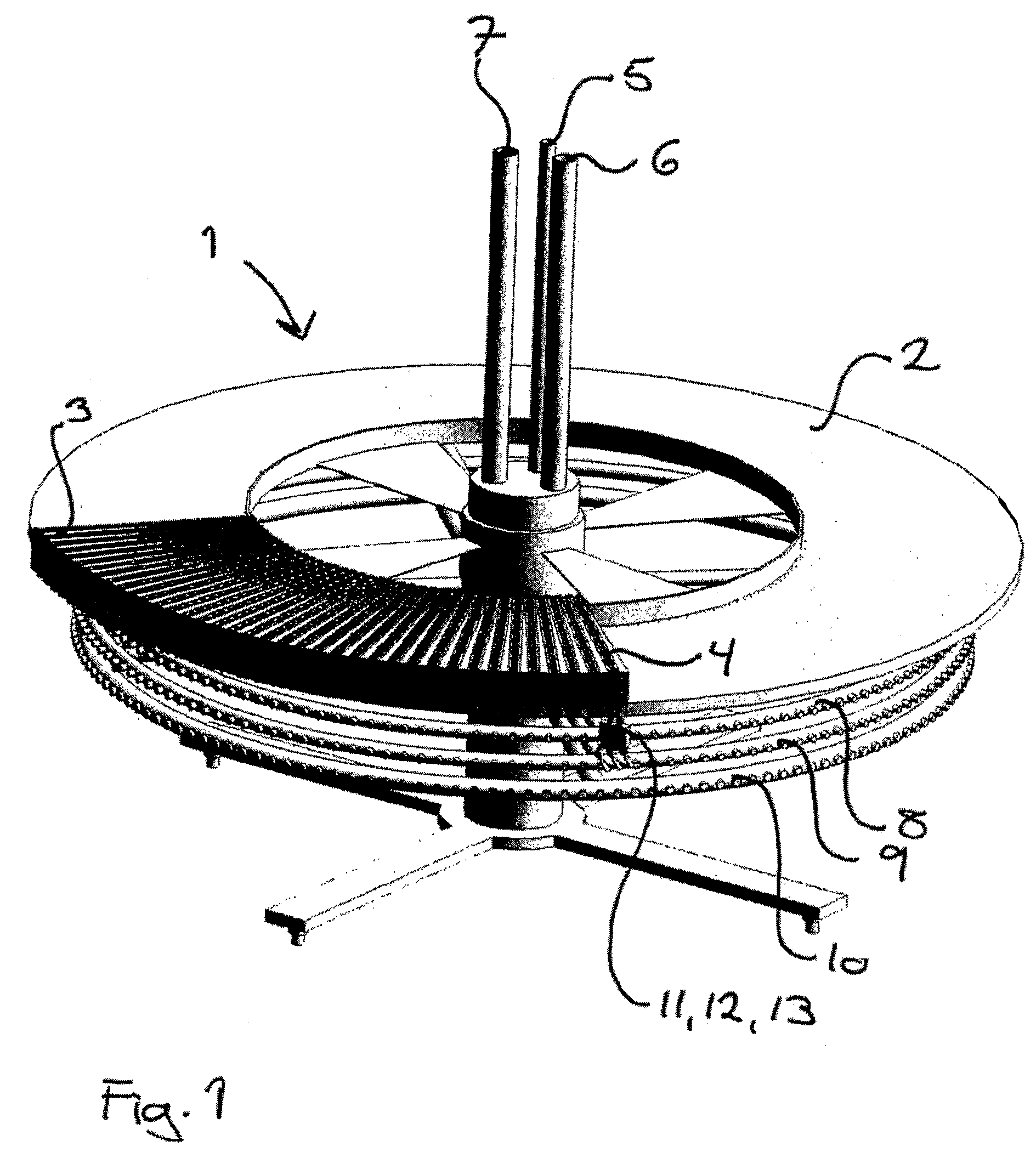

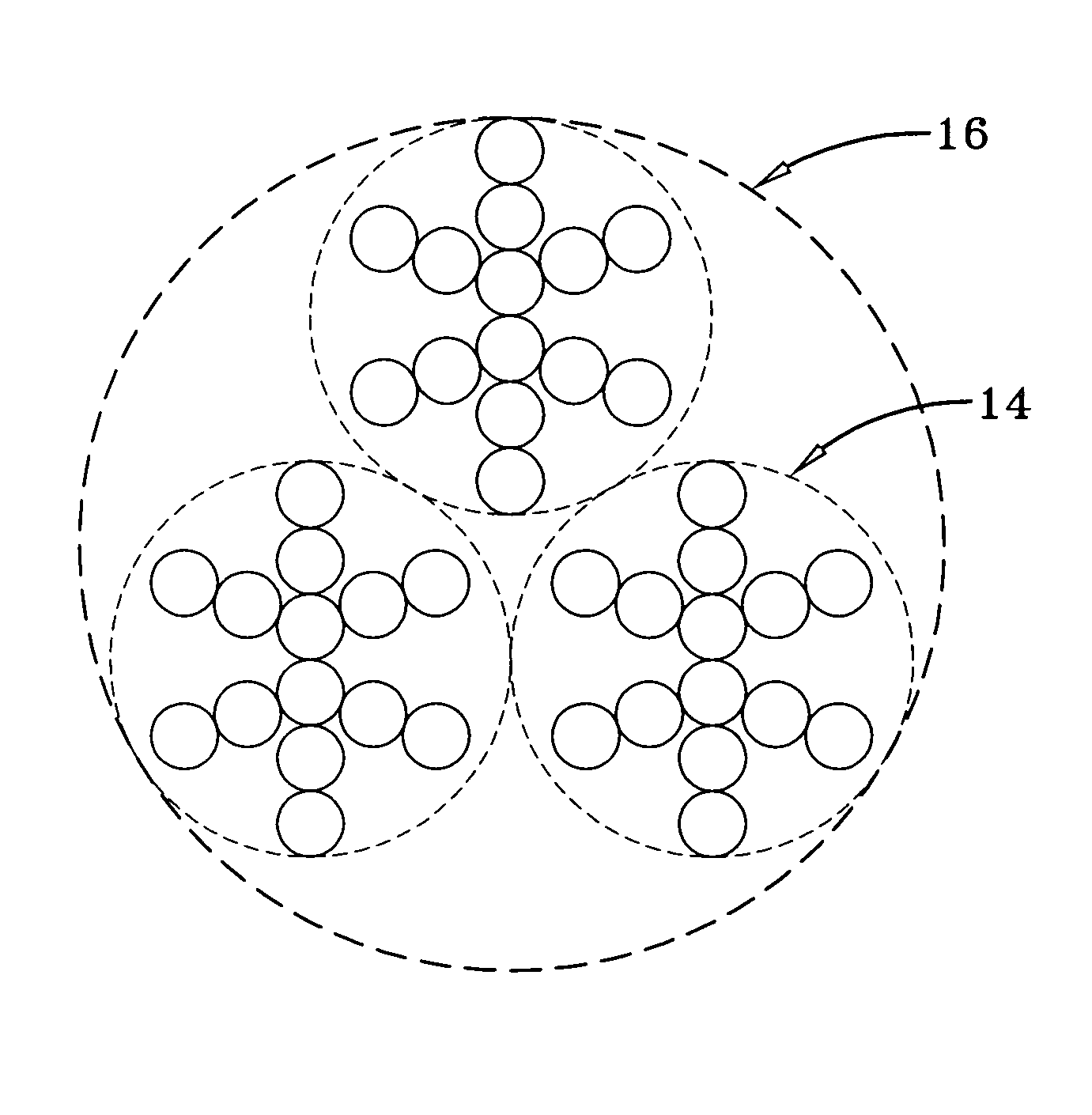

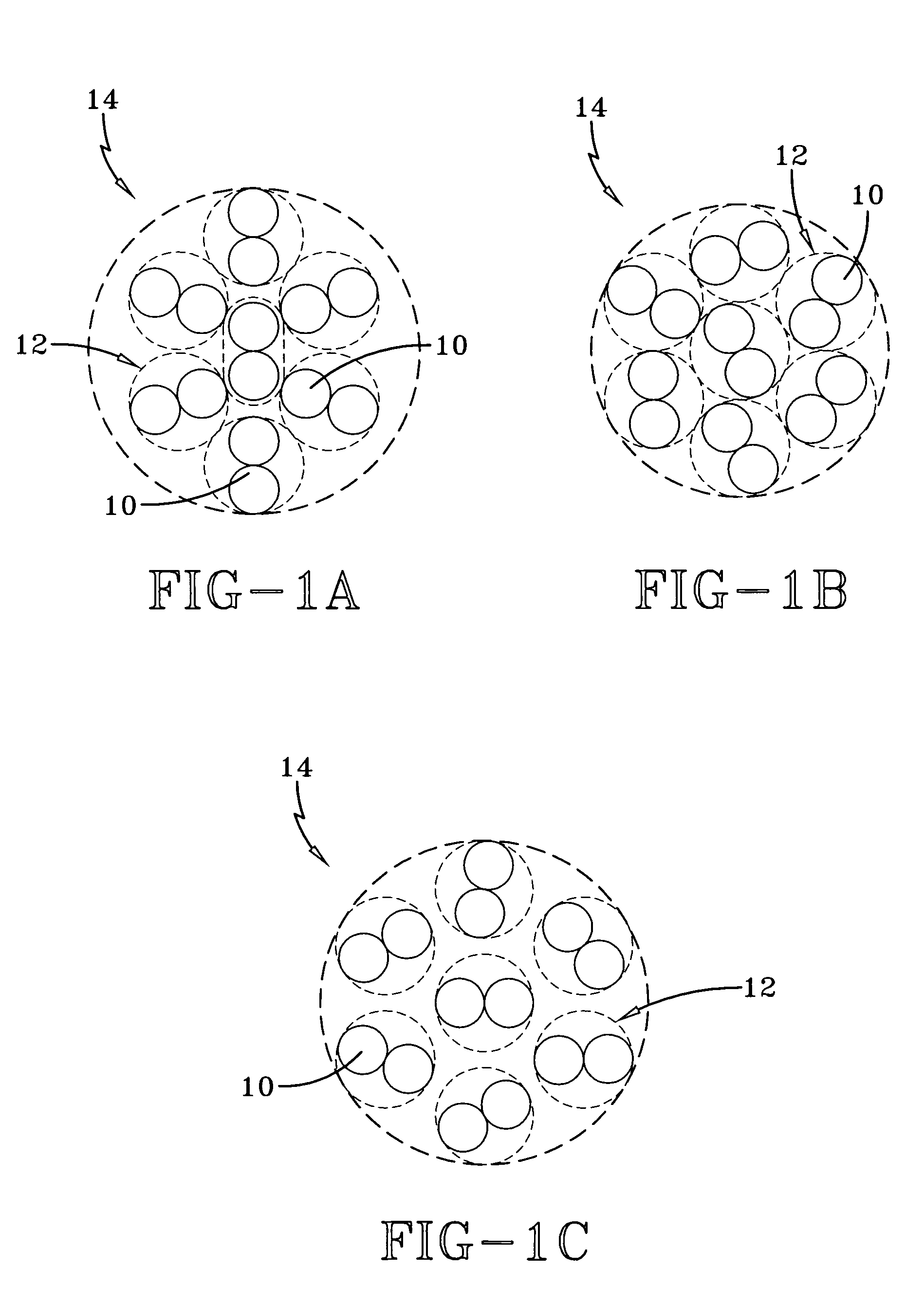

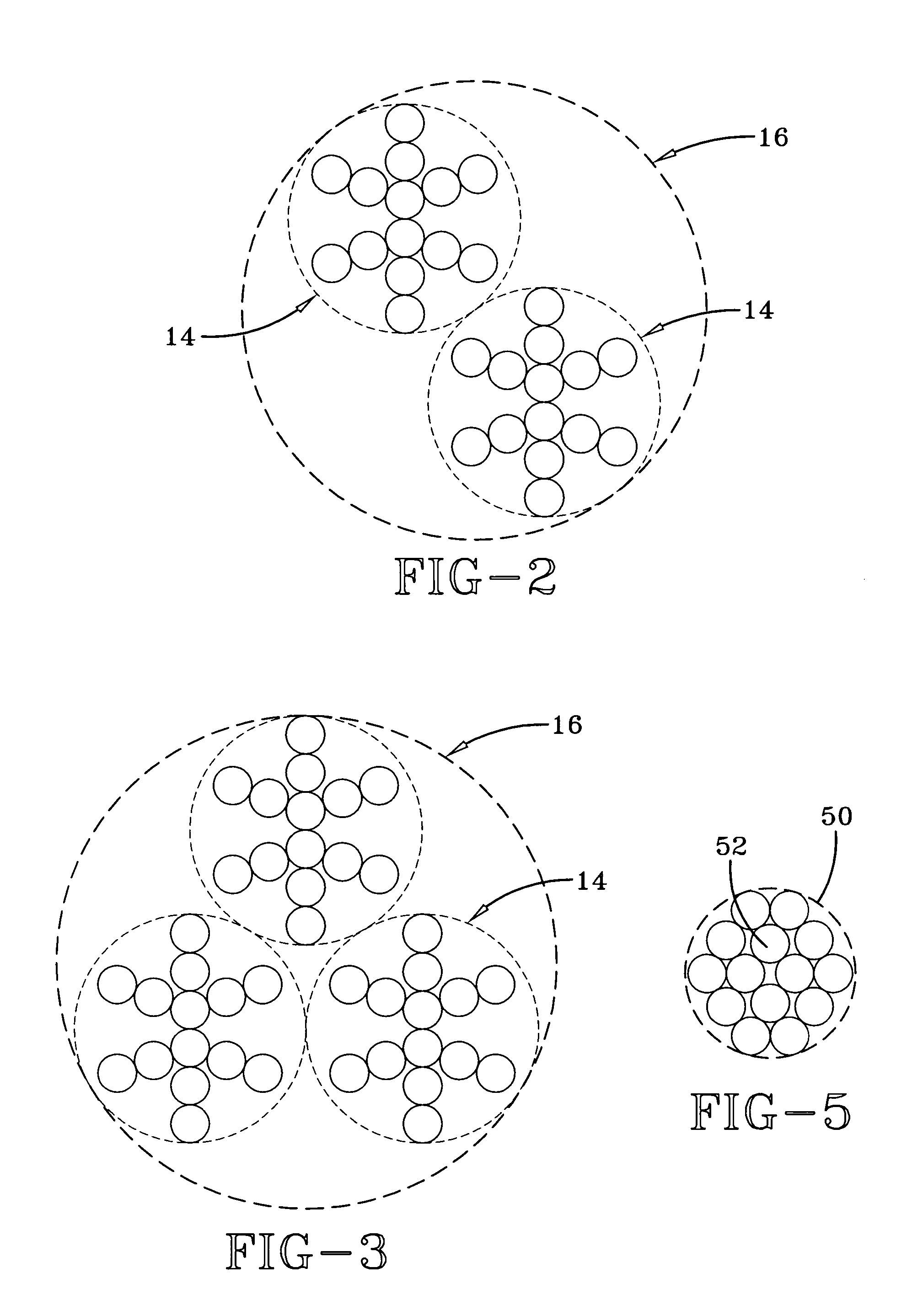

Method and systems for volumetric tissue ablation

InactiveUS6575967B1Uniform coverageImprove abilitiesElectrotherapySurgical needlesElectrical conductorTissue ablation

A volumetric tissue ablation apparatus includes a probe having a plurality of wires journaled through a catheter with a proximal end connected to the active terminal of a generator and a distal end projecting from a distal end of the catheter. The probe wire distal ends are arranged in an array with the distal ends located generally radially and uniformly spaced-apart from the catheter distal end. A conductor connected to the return terminal of the generator is located relative to the probe wire array to form a closed electrical circuit through tissue to be ablated. Preferably, the probe wire array includes 10 wires, each formed in an arch from the catheter distal end. The conductor can be either a conventional ground plate upon which the tissue is supported, or a conductor wire extending through the probe and electrically insulated from the probe wires.

Owner:BOARD OF RGT UNIV OF NEBRASKA

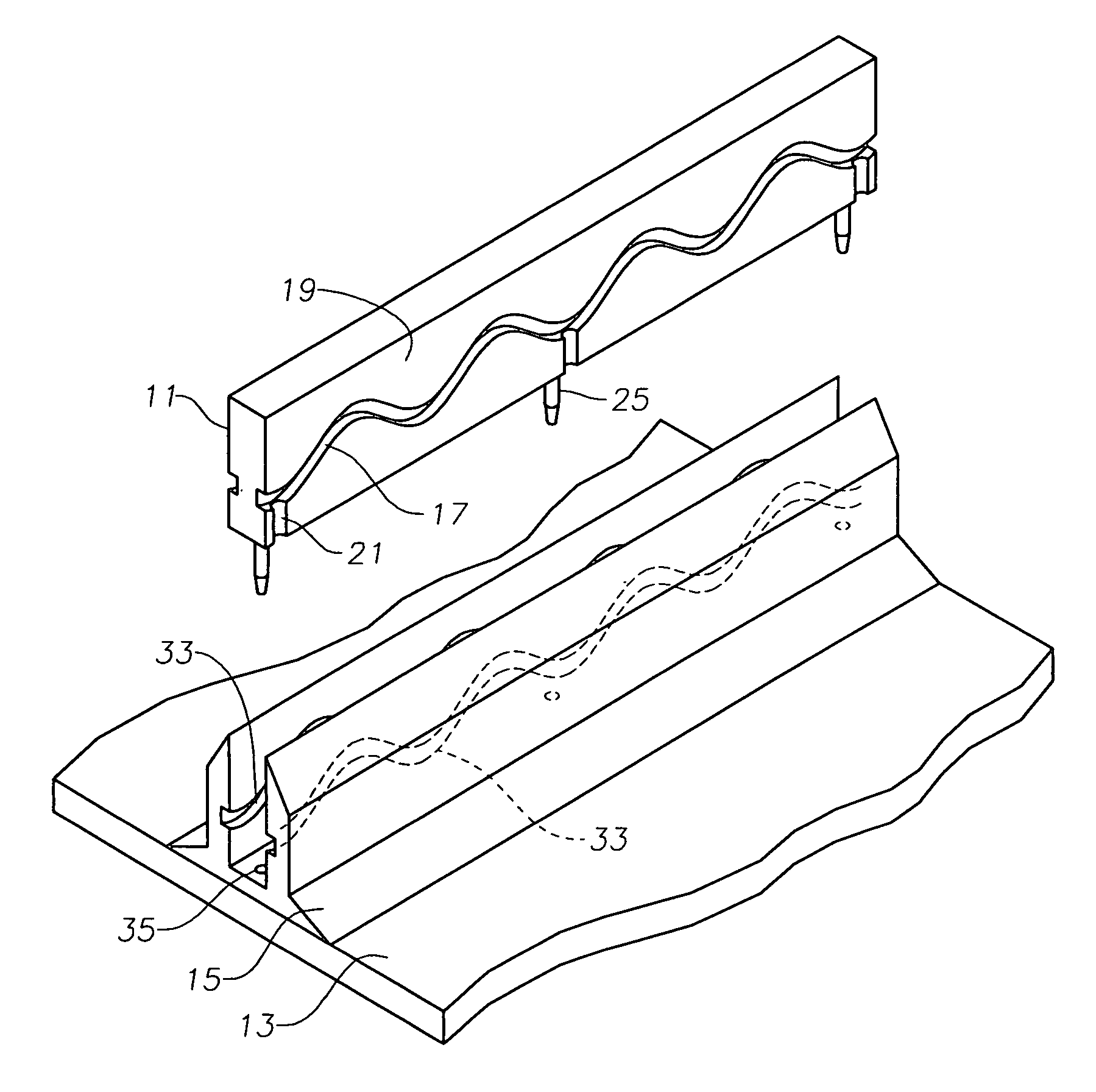

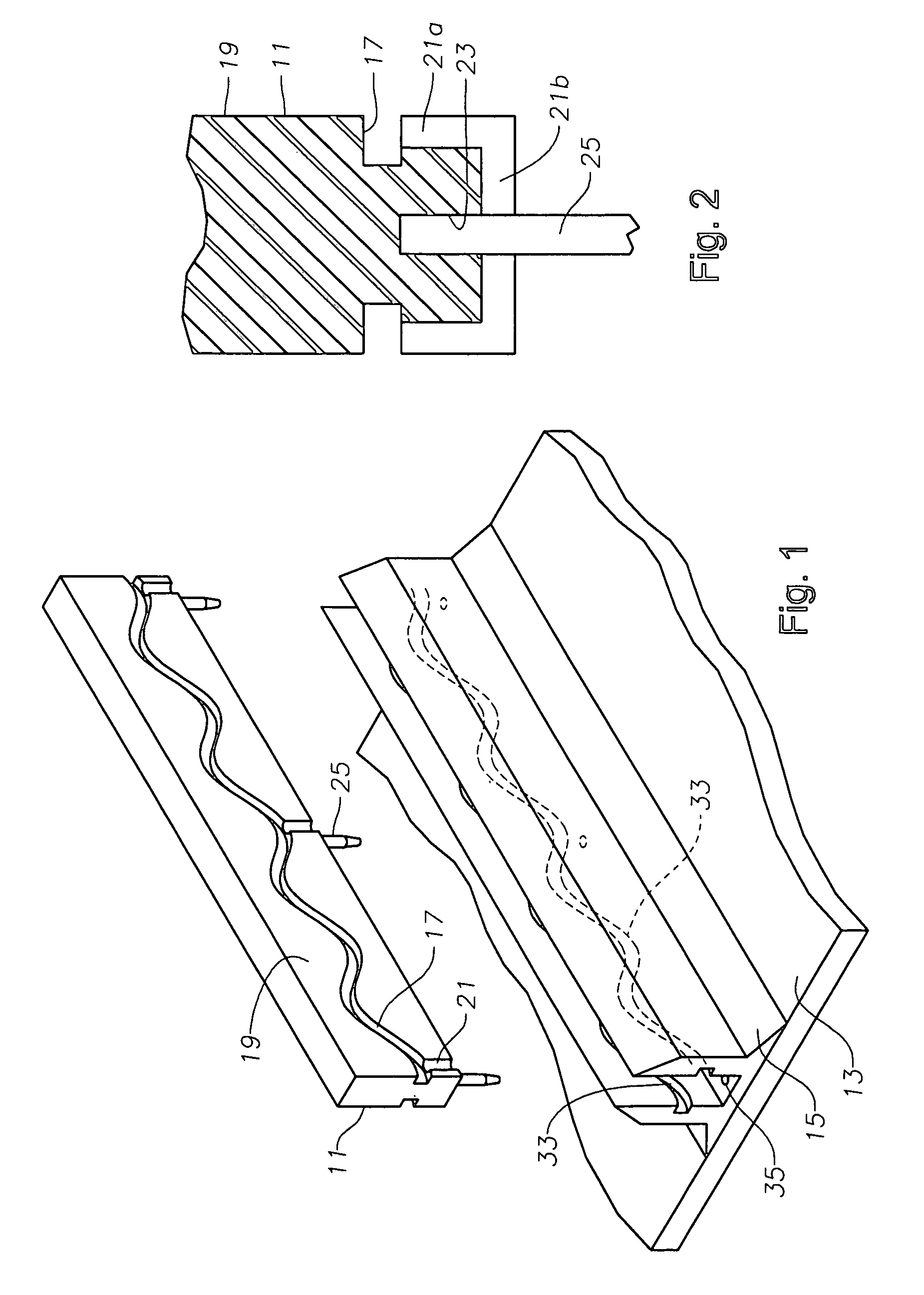

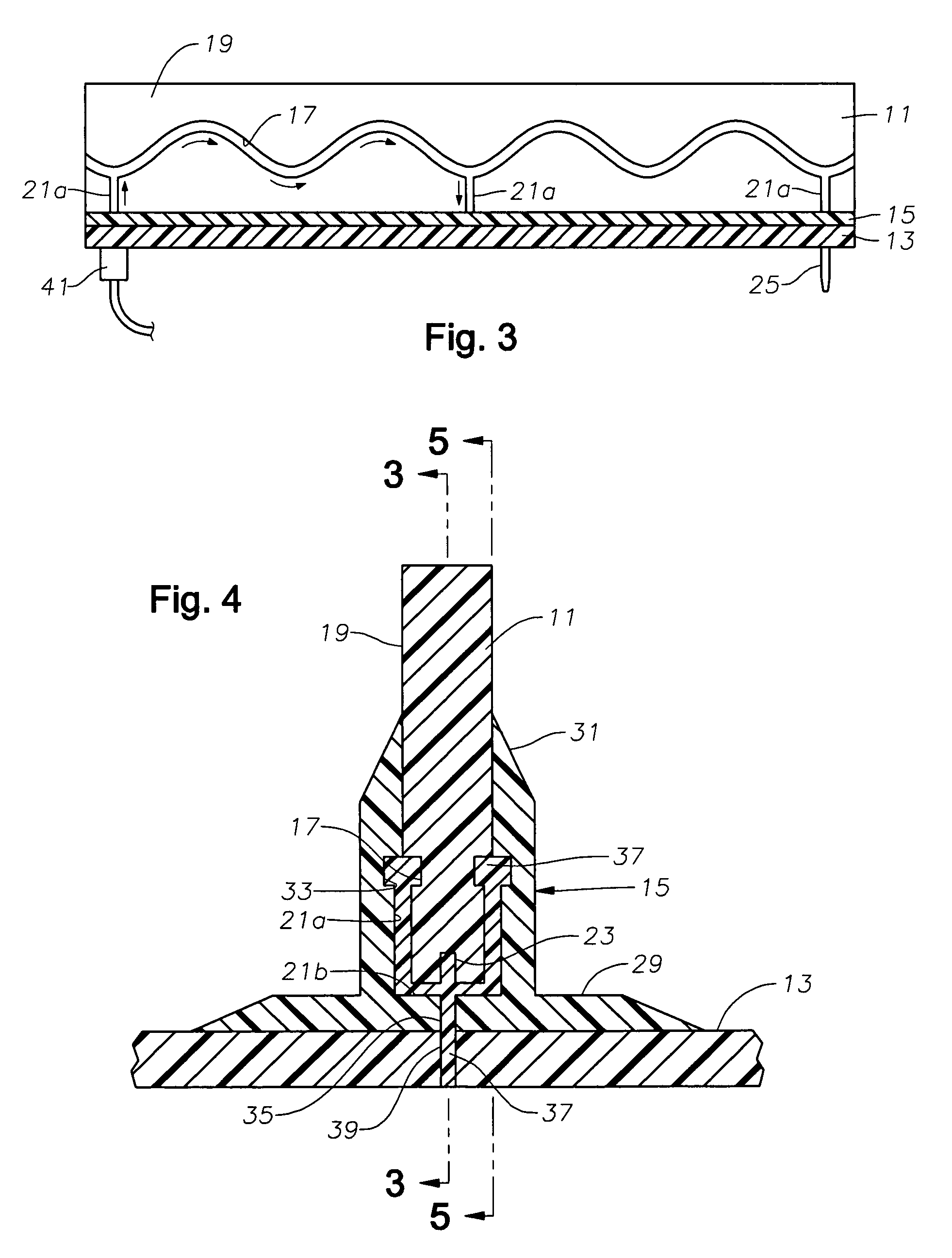

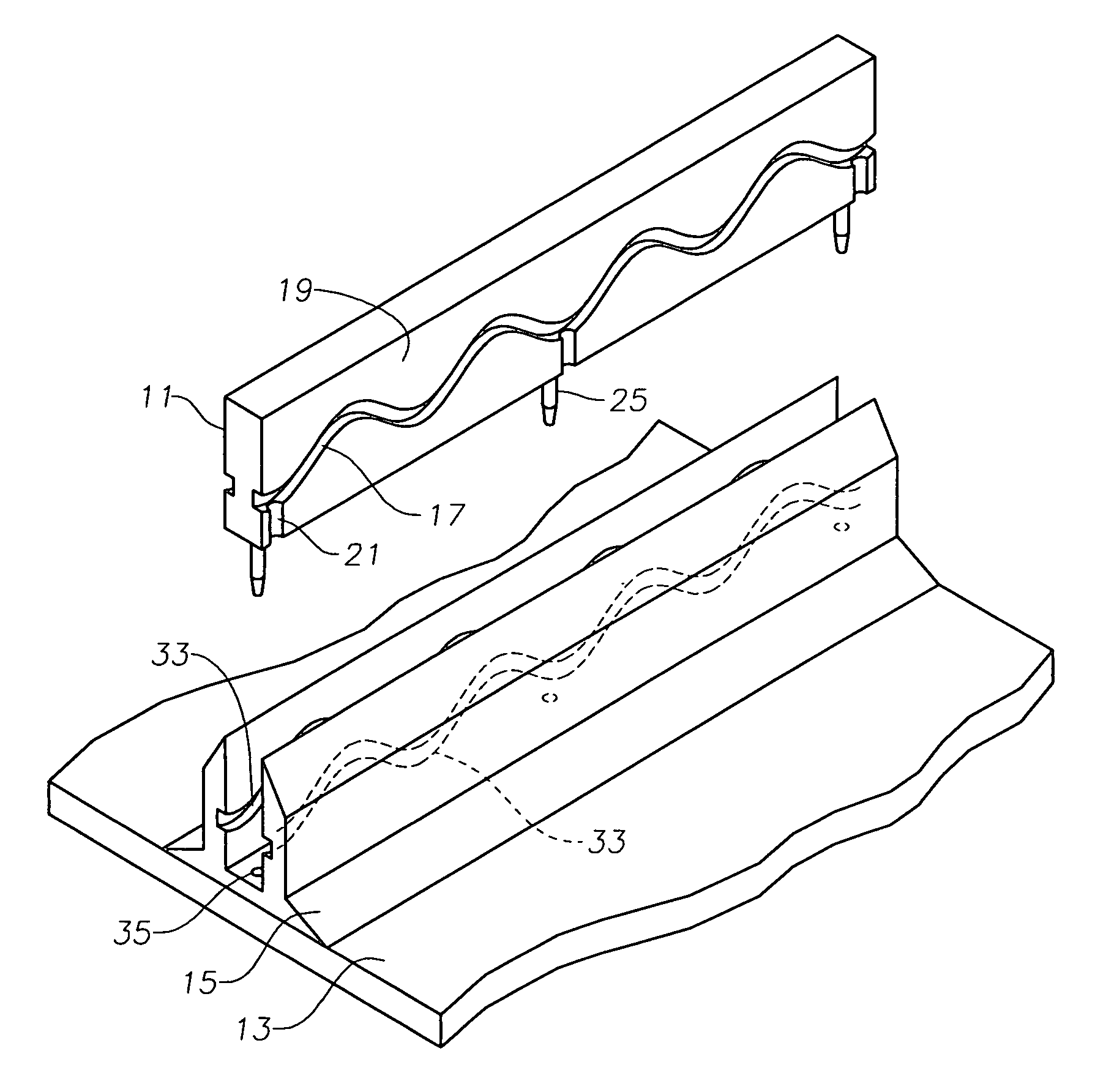

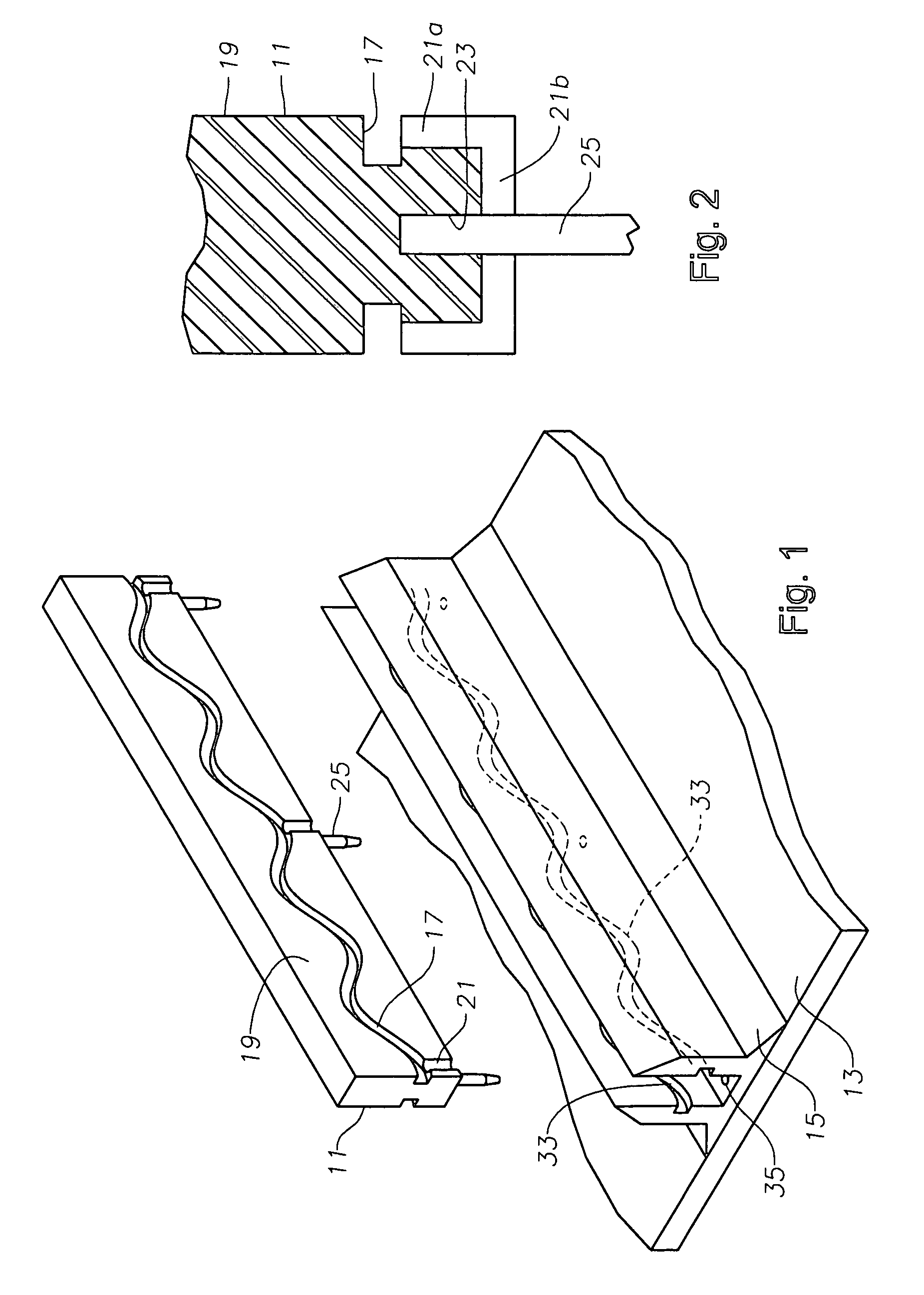

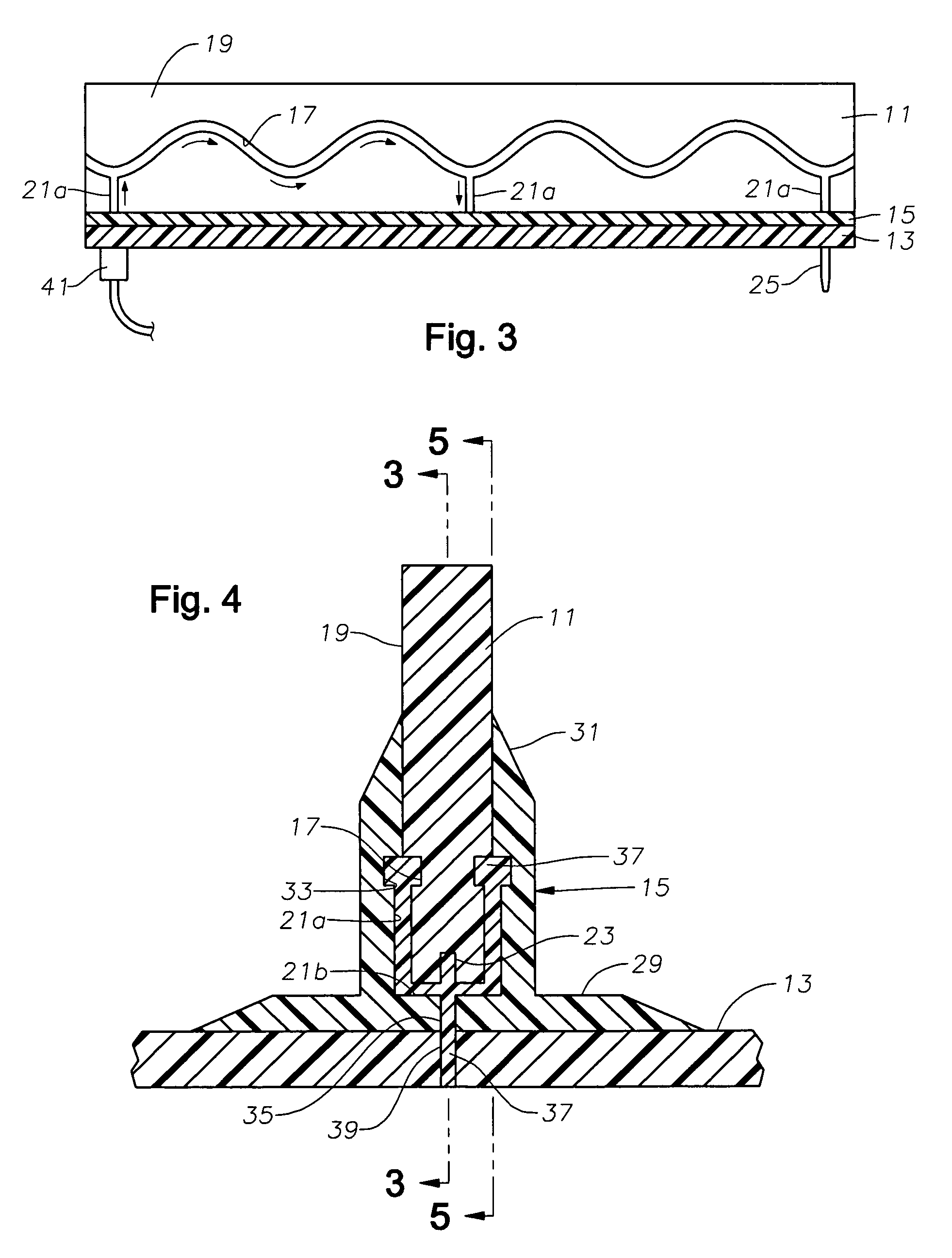

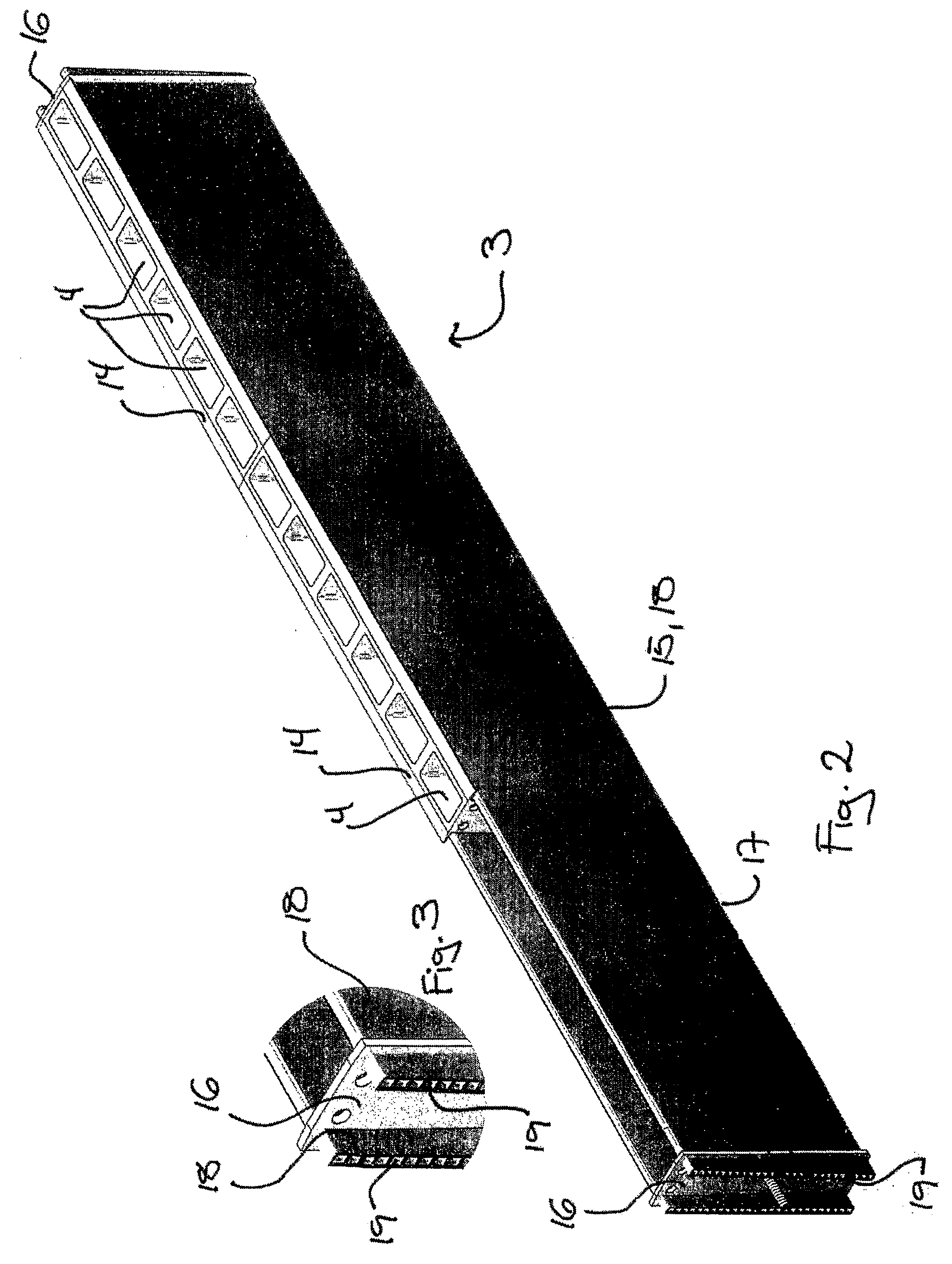

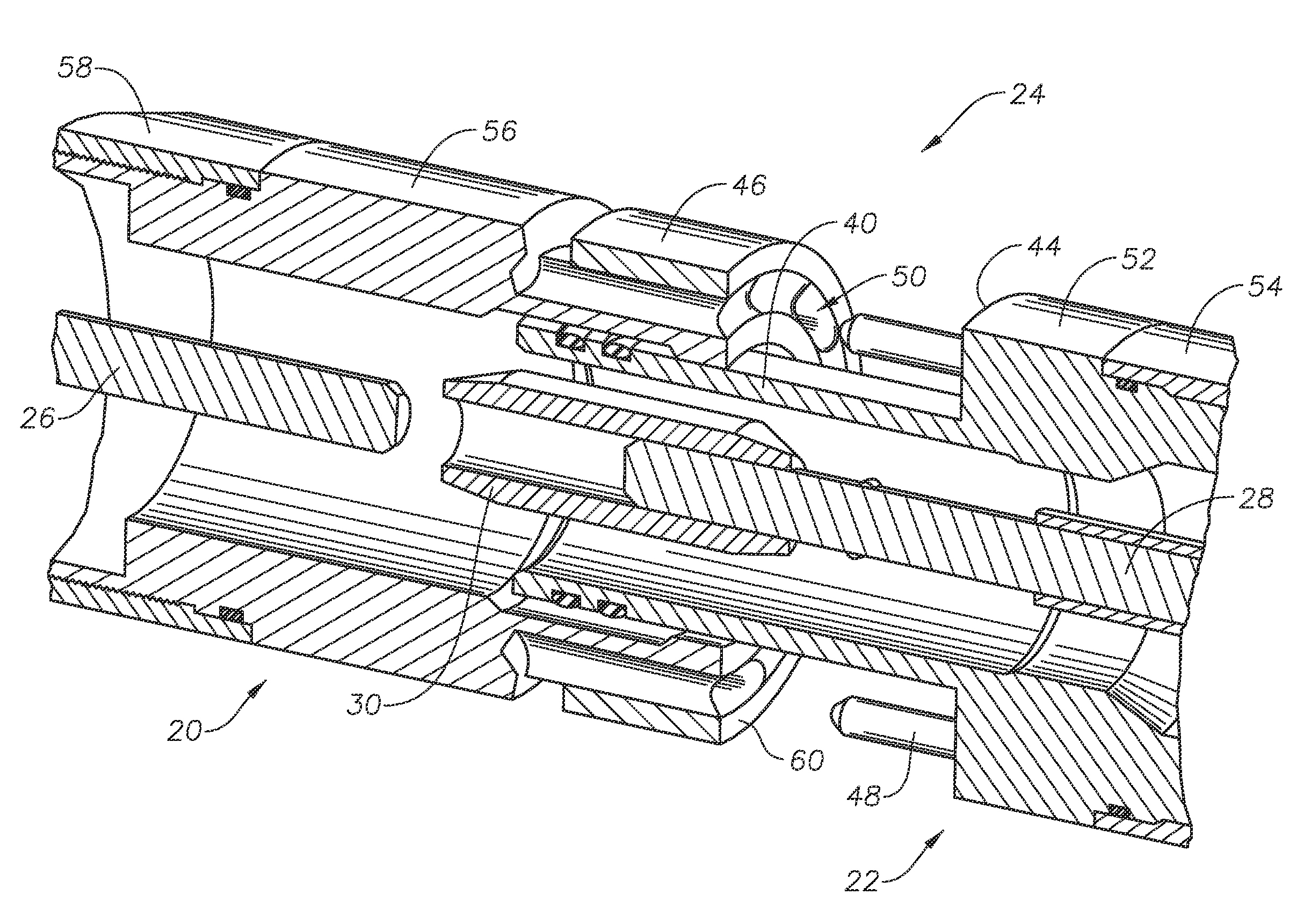

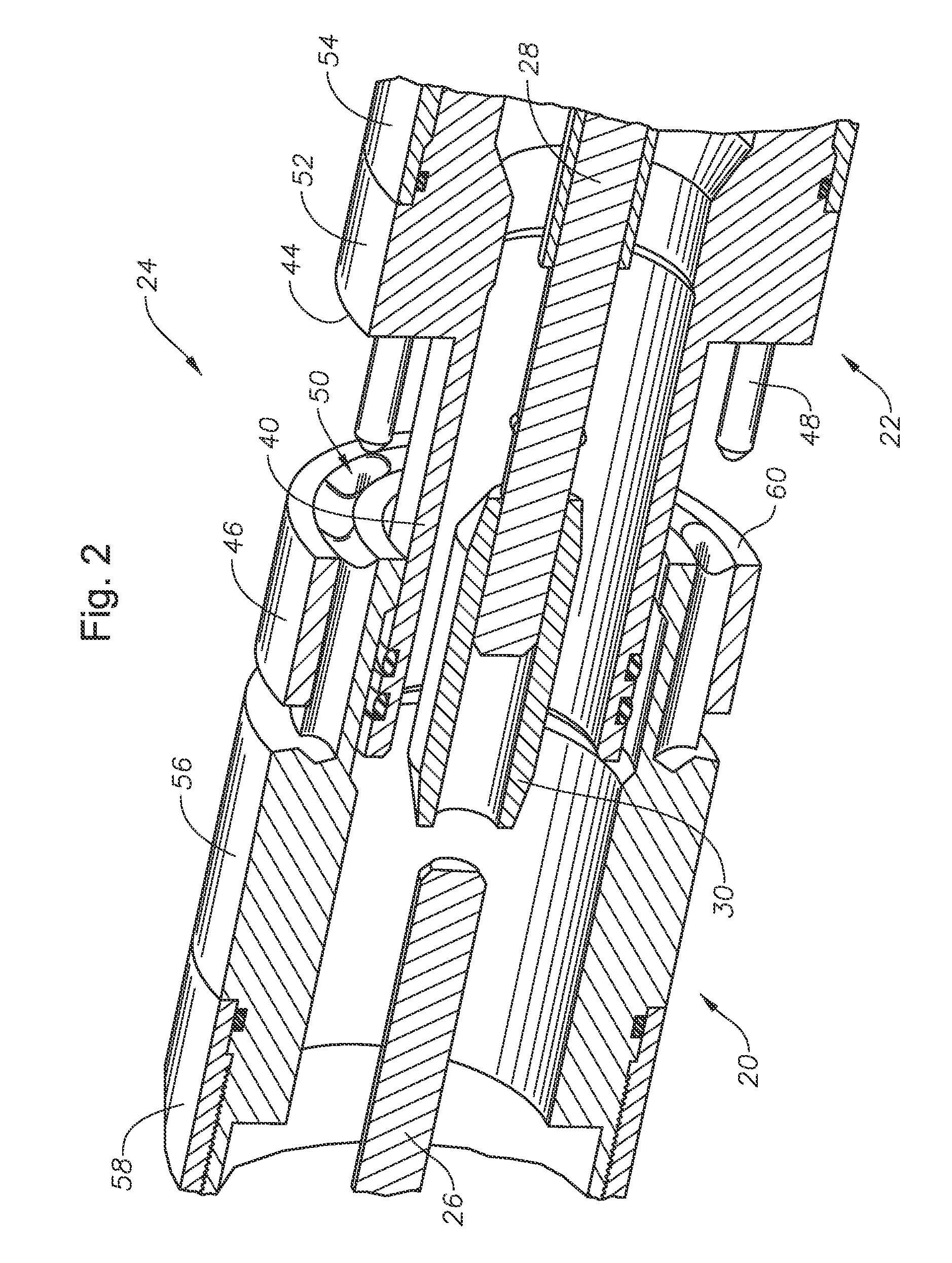

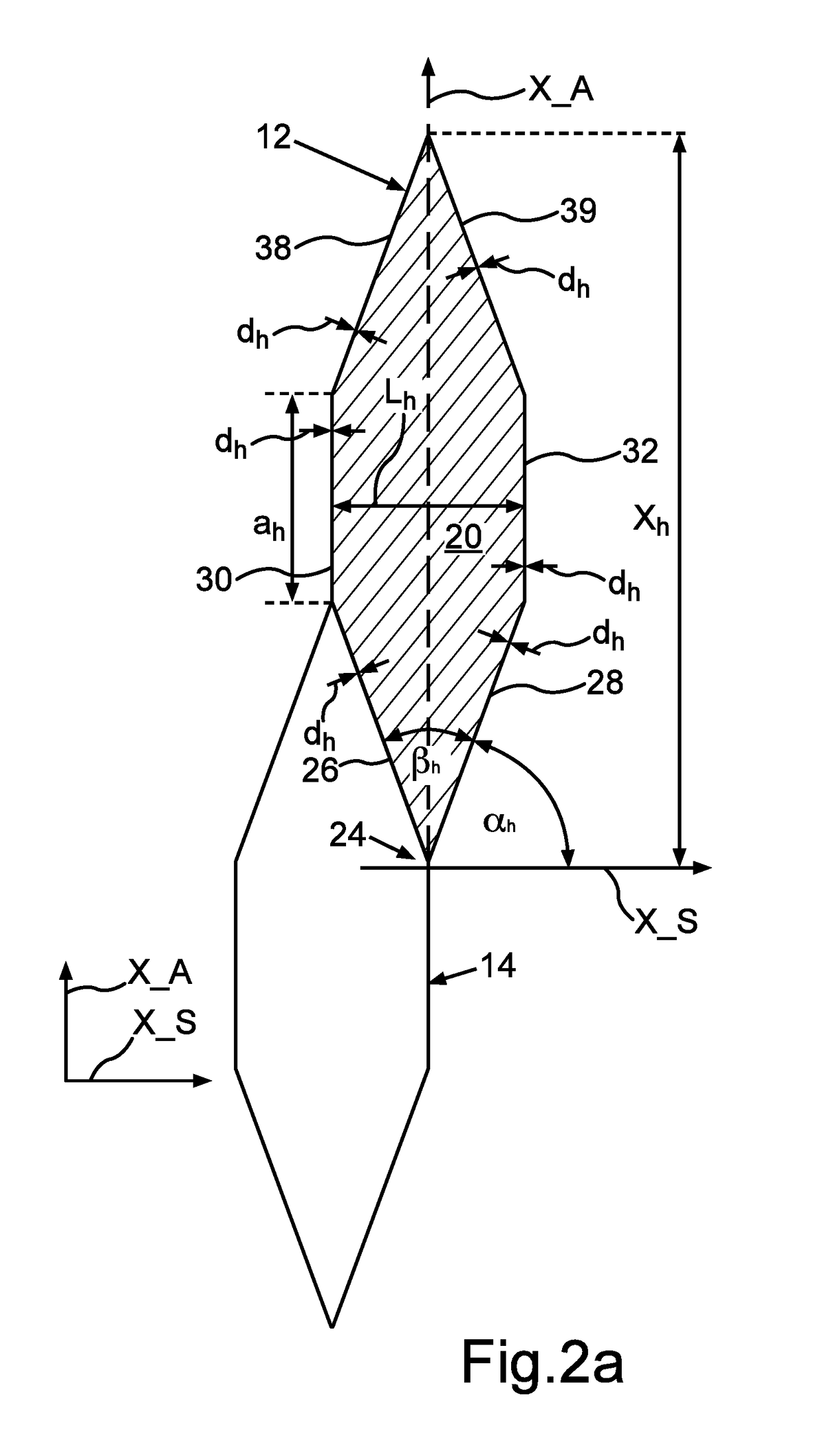

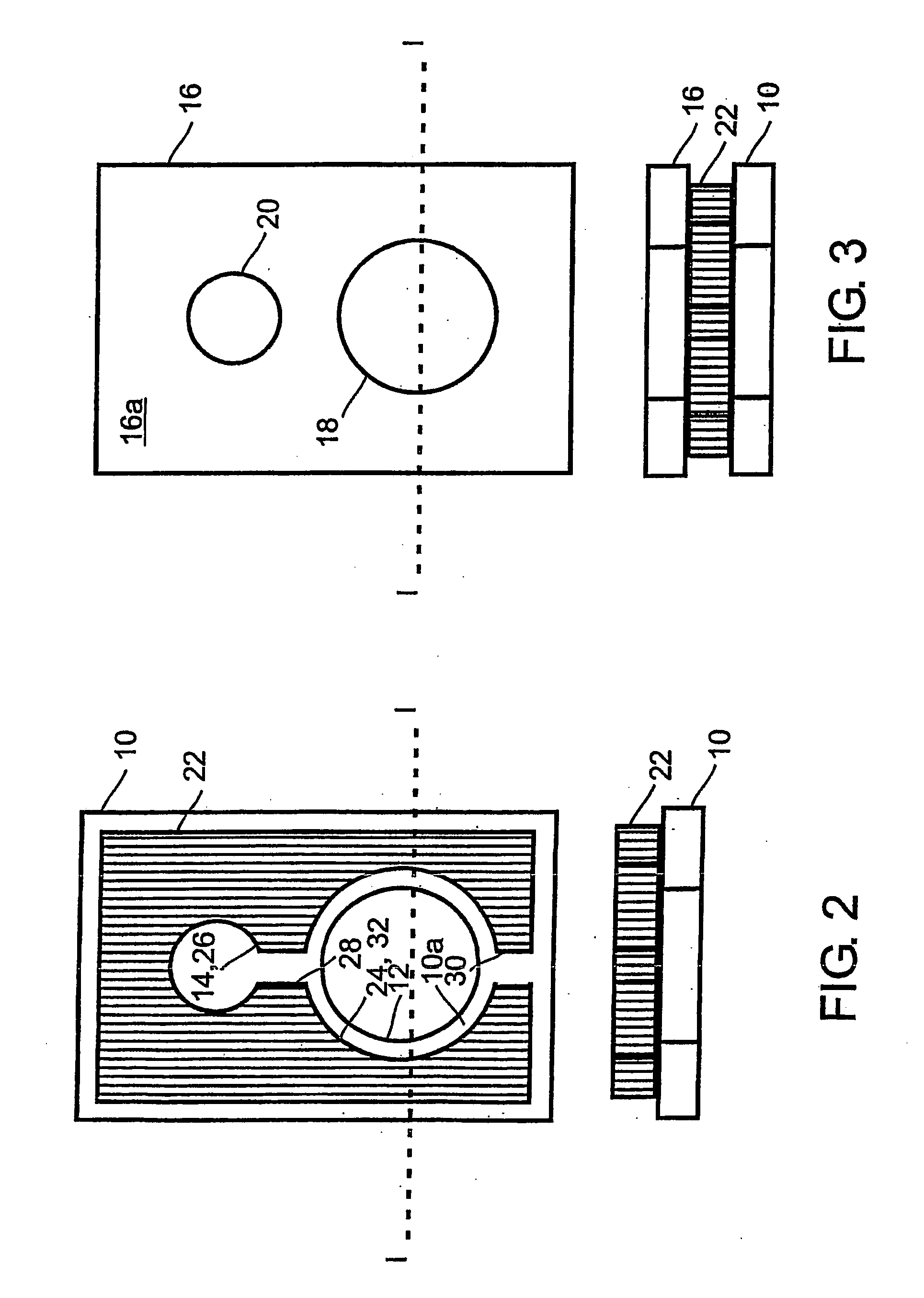

Failsafe injected adhesive joint

ActiveUS20070261787A1Convenient verificationCross sectional areaMaterial gluingCylinder headsAdhesion forceInjection port

A composite member is joined to another composite or noncomposite member, using liquid or paste adhesive resin that cures in the joint. The joint is configured in such a way that the adhesive forms an interlocking key within recesses in the joined members that prevents joint disassembly once the adhesive has cured and hardened. Both of the members are provided with recesses extending along their lengths in the joint. The recesses register with each other to define a cavity and may undulate. The recessed are designed in such a way as to take the full load capability if the joint, even if there is no adhesion to the joined members. Adhesive is injected into the cavity through injection ports spaced periodically along the length of the joint.

Owner:LOCKHEED MARTIN CORP

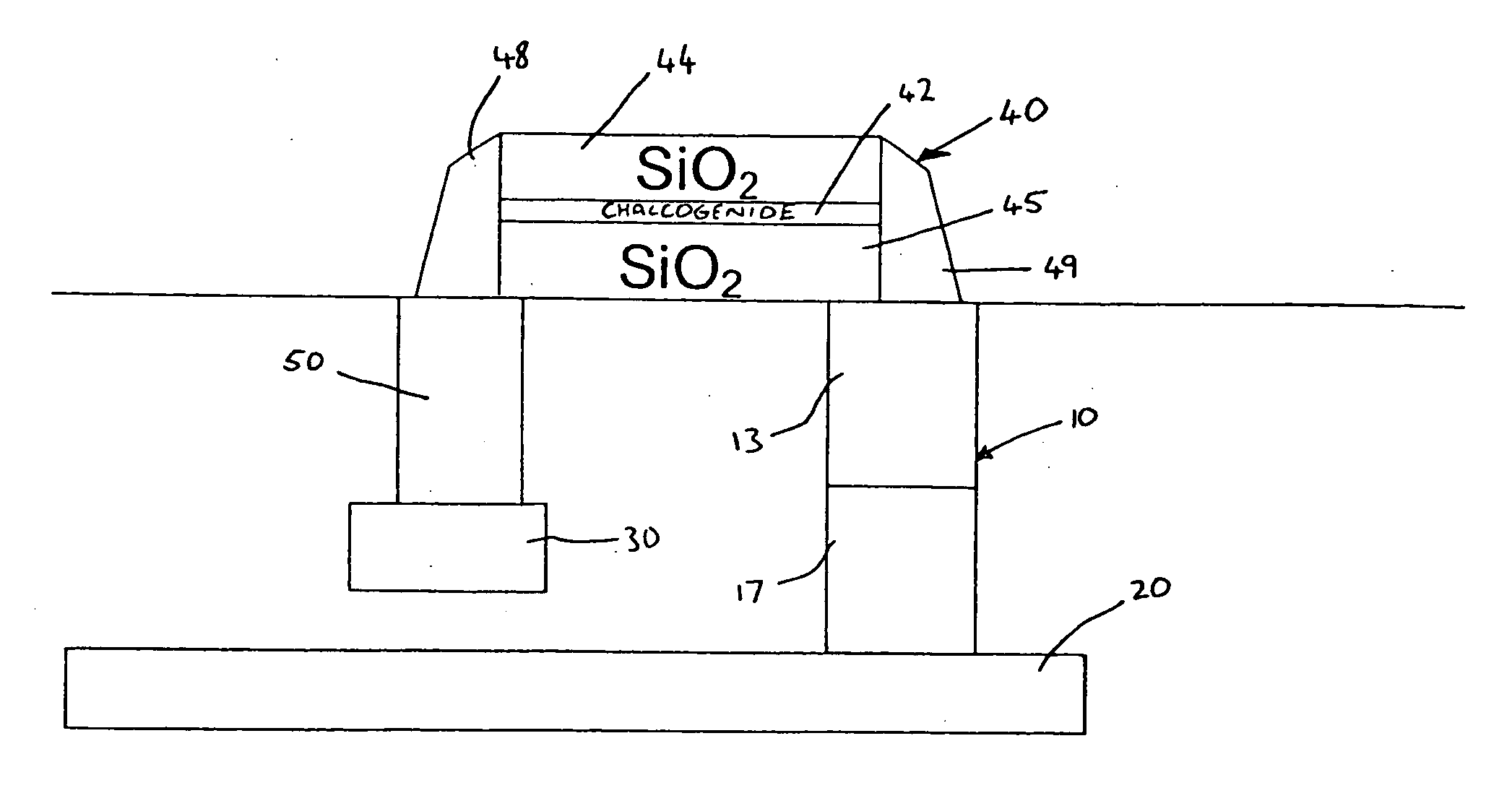

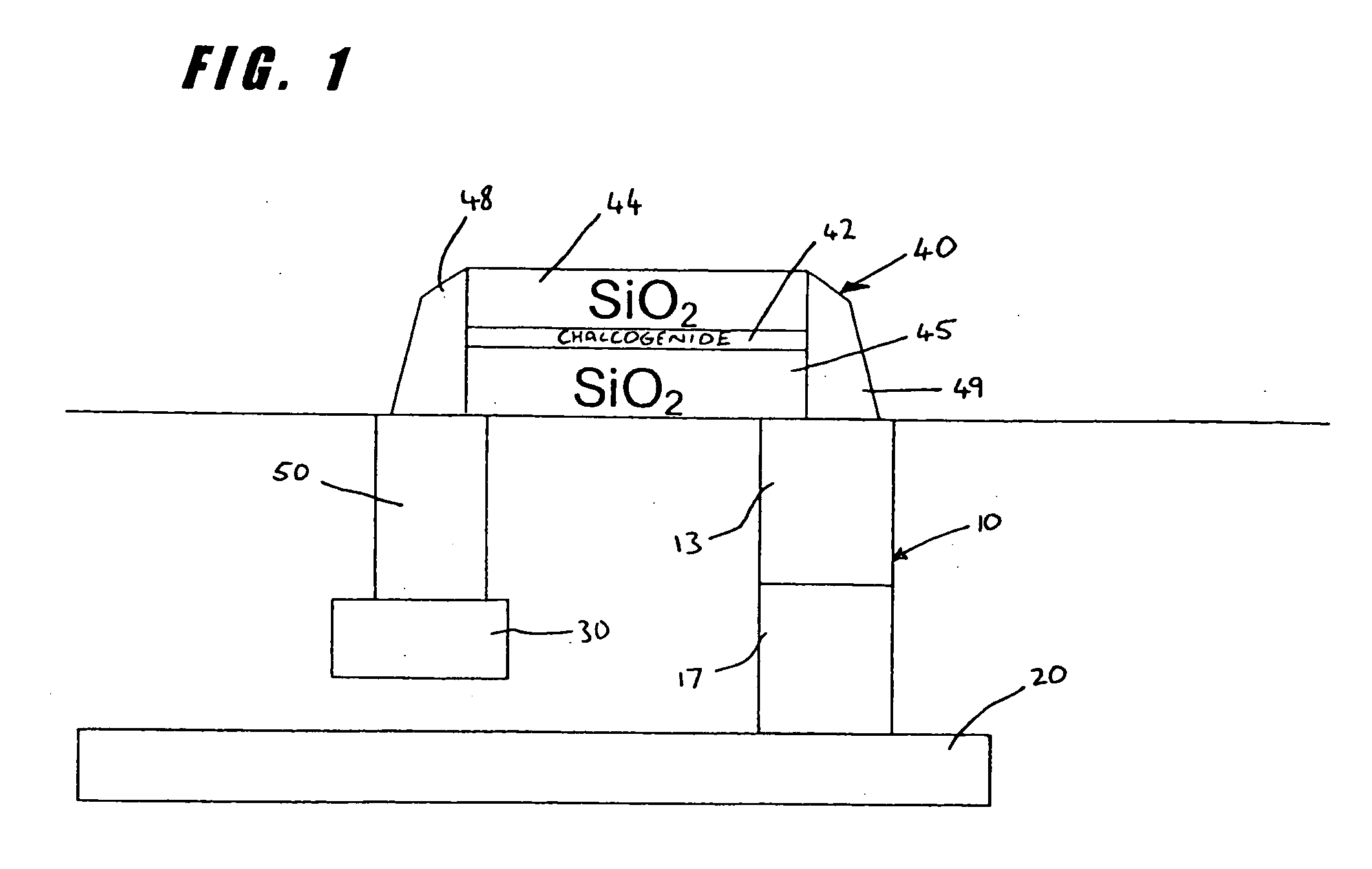

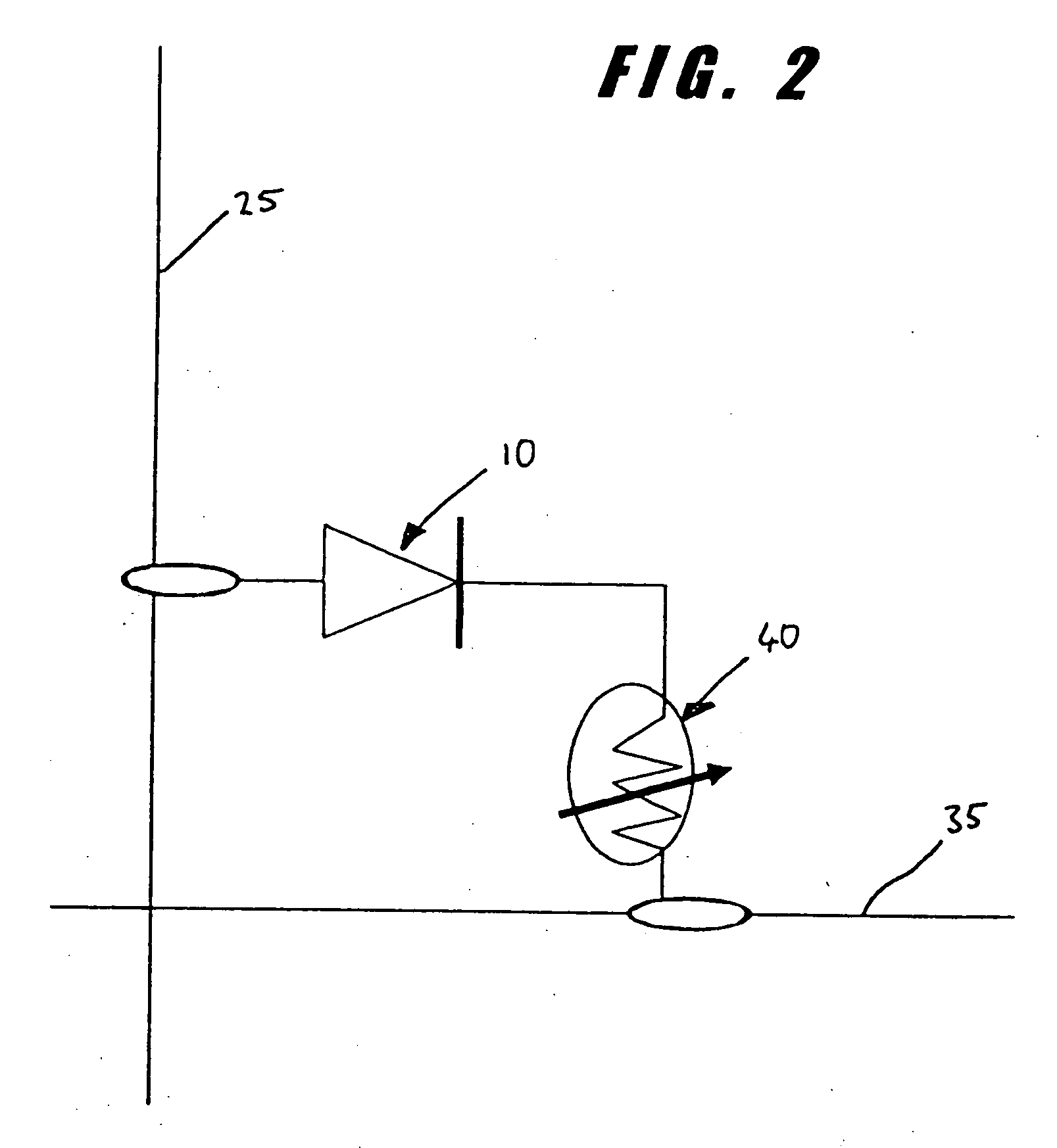

Thin film phase-change memory

ActiveUS20060258079A1Meet cutting requirementsCross-sectional area need no longer be limitedSolid-state devicesSemiconductor/solid-state device manufacturingBit lineCMOS

A memory cell comprises a chalcogenide random access memory (CRAM) cell and a CMOS circuit. The CMOS circuit accesses the CRAM cell. The CRAM cell has a cross-sectional area that is determined by a thin film process (e.g., a chalcogenide deposition thin film process) and by an iso-etching process. If desired, the chalcogenide structure may be implemented in series with a semiconductor device such as a diode or a selecting transistor. The diode drives a current through the chalcogenide structure. The selecting transistor drives a current through the chalcogenide structure when enabled by a voltage at a gate terminal of the selecting transistor. The selecting transistor has a gate terminal, a source terminal, and a drain terminal; the gate terminal may be operatively coupled to a word line of a memory array, the source terminal may be operatively coupled to a drive line of the memory array, and the drain terminal may be operatively coupled to a bit line of the memory array.

Owner:MACRONIX INT CO LTD

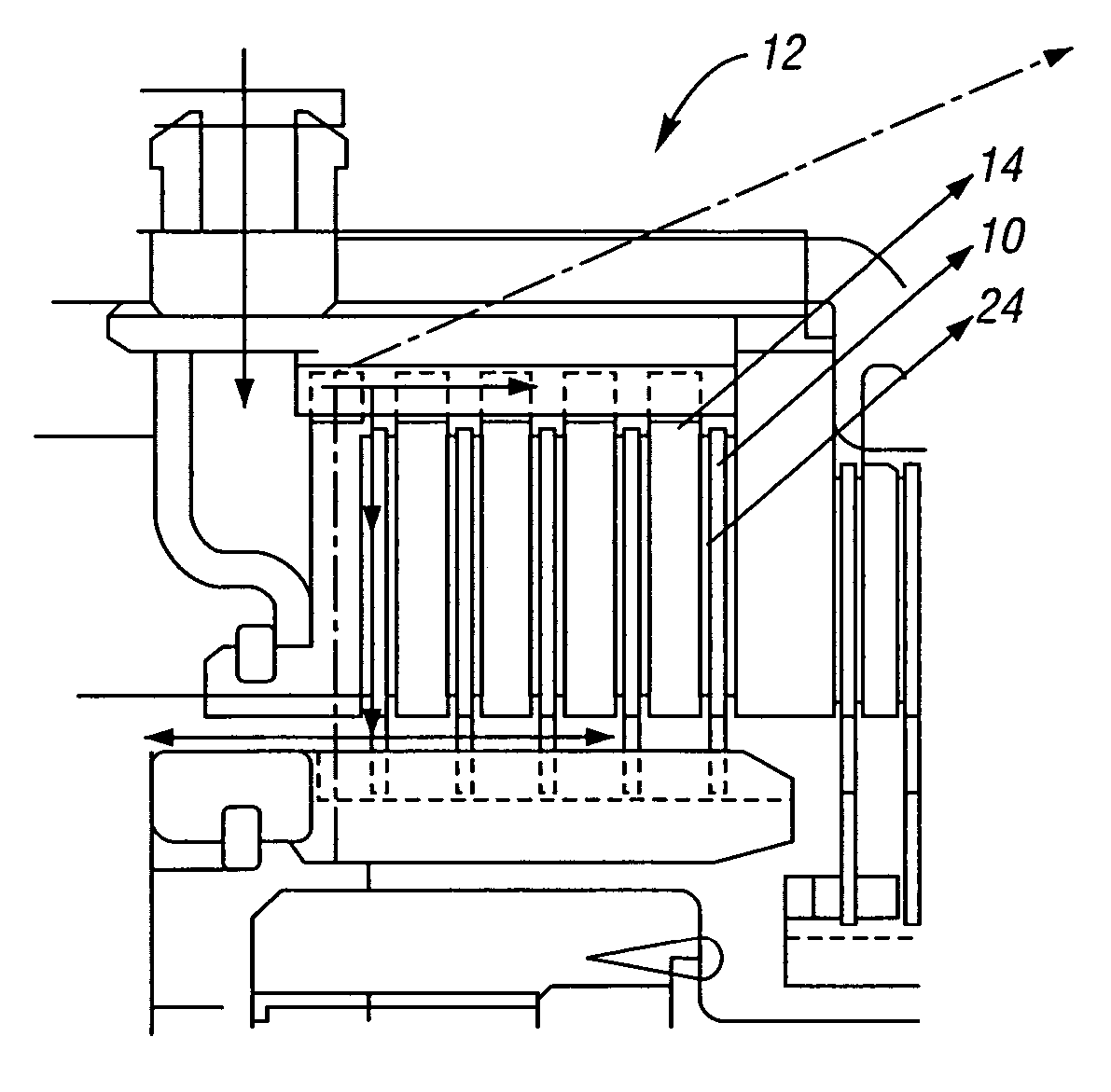

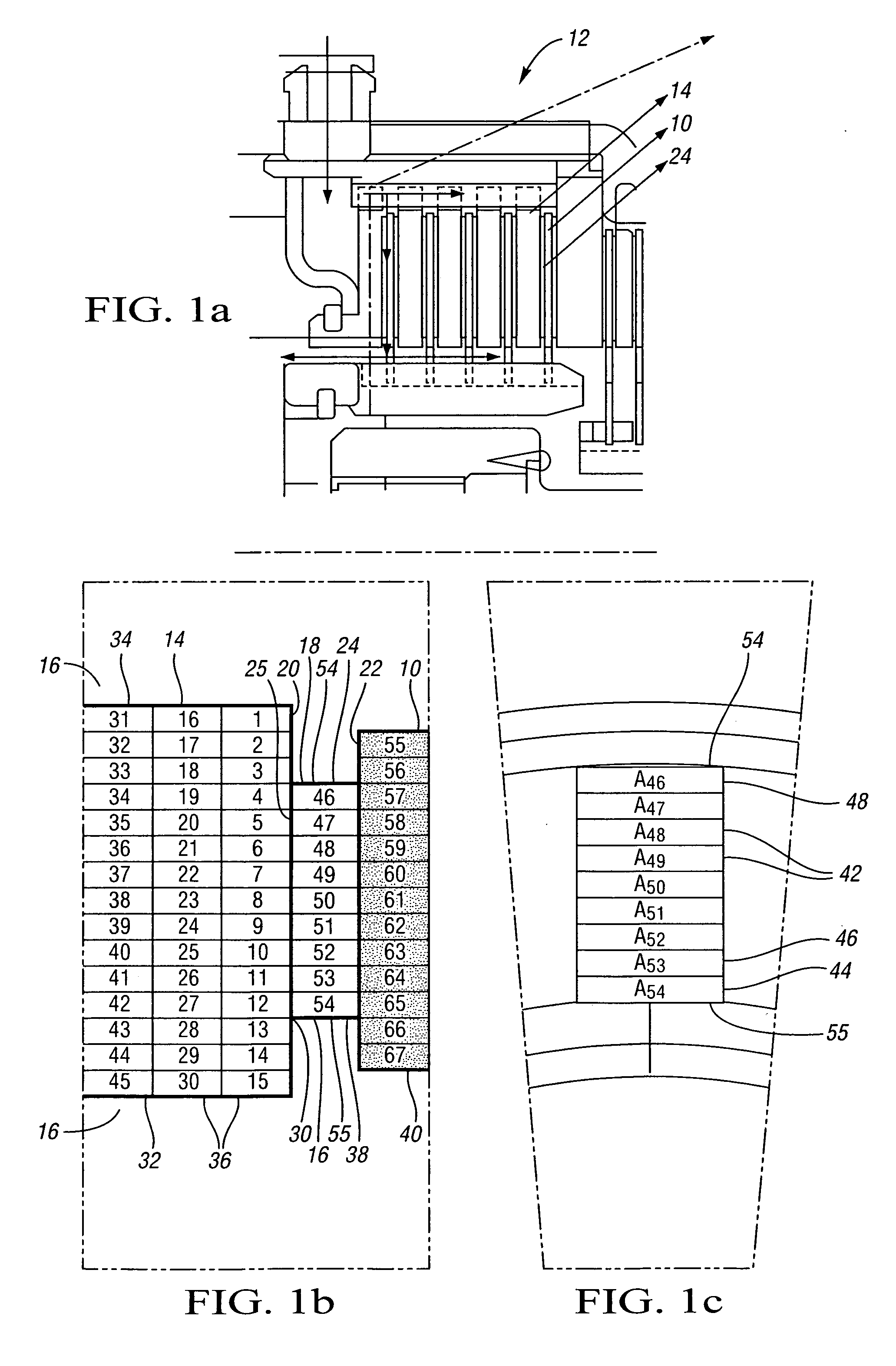

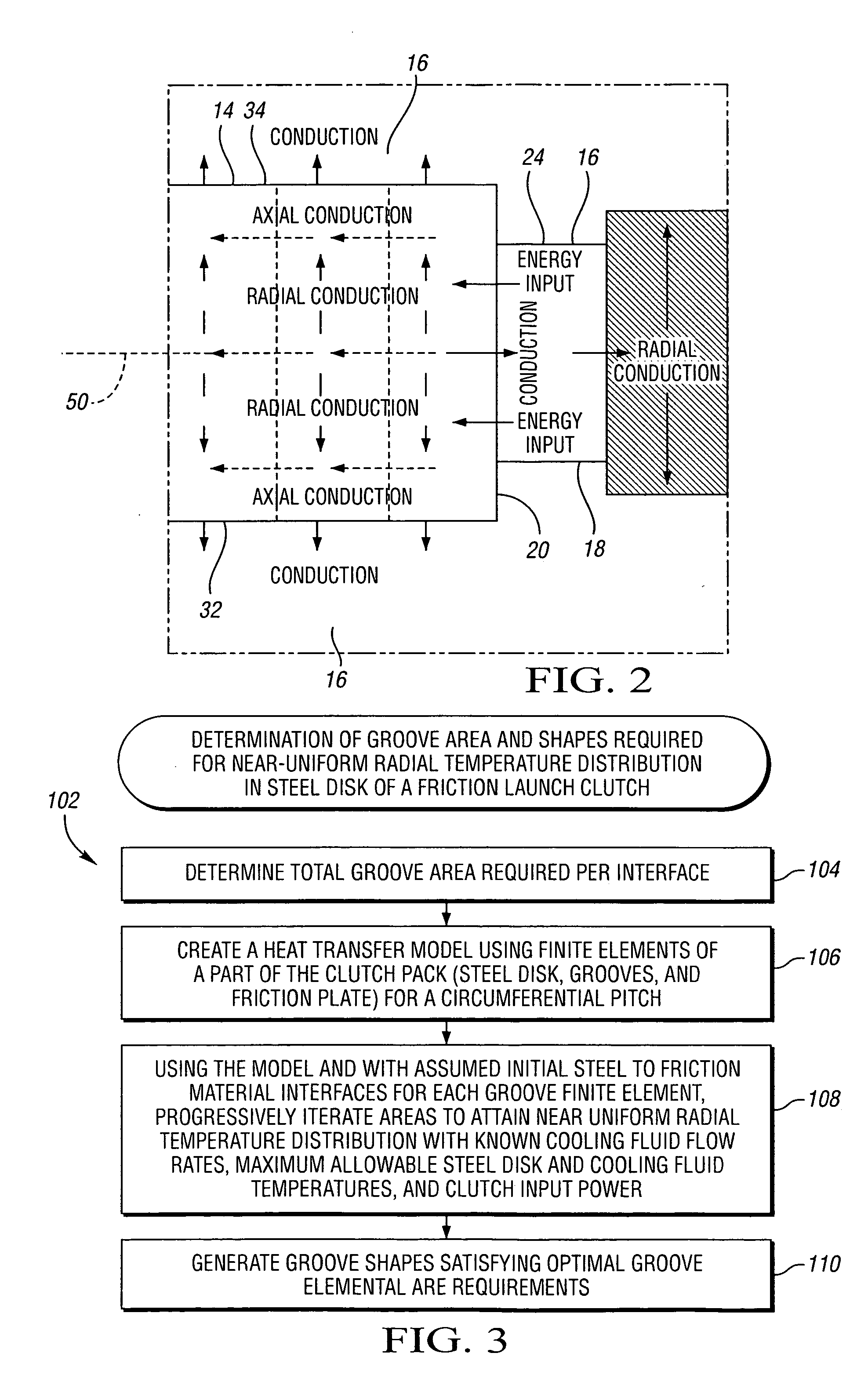

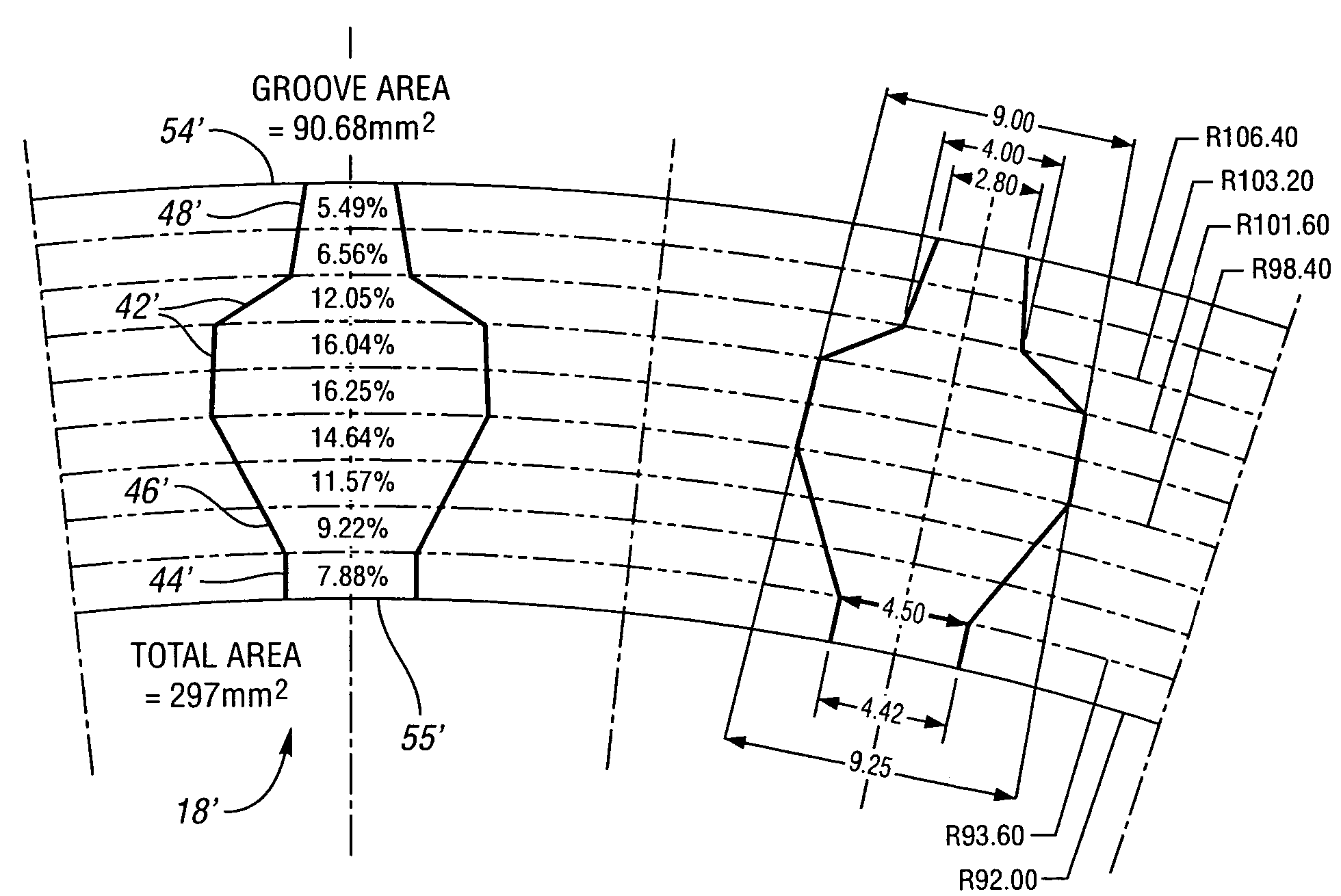

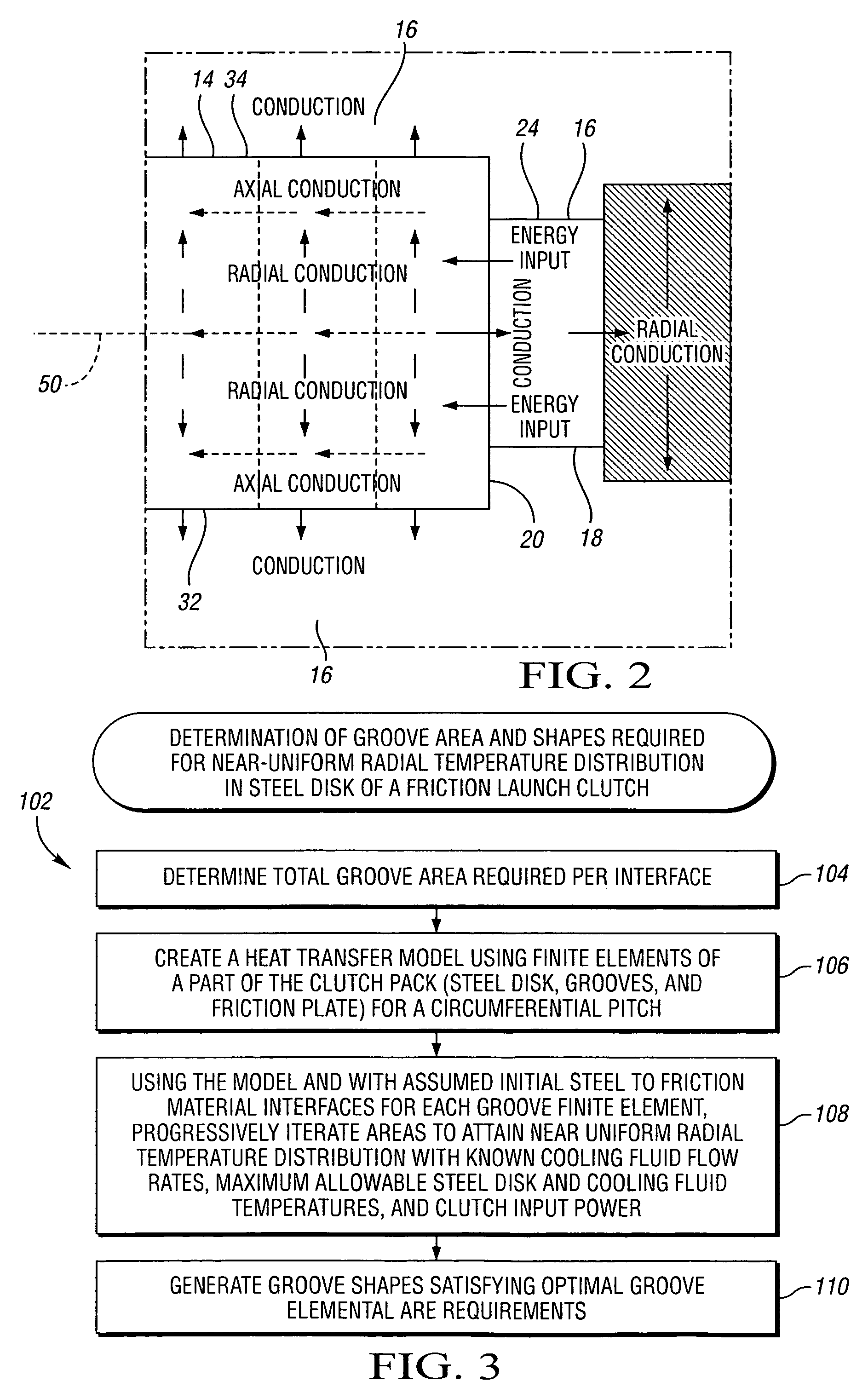

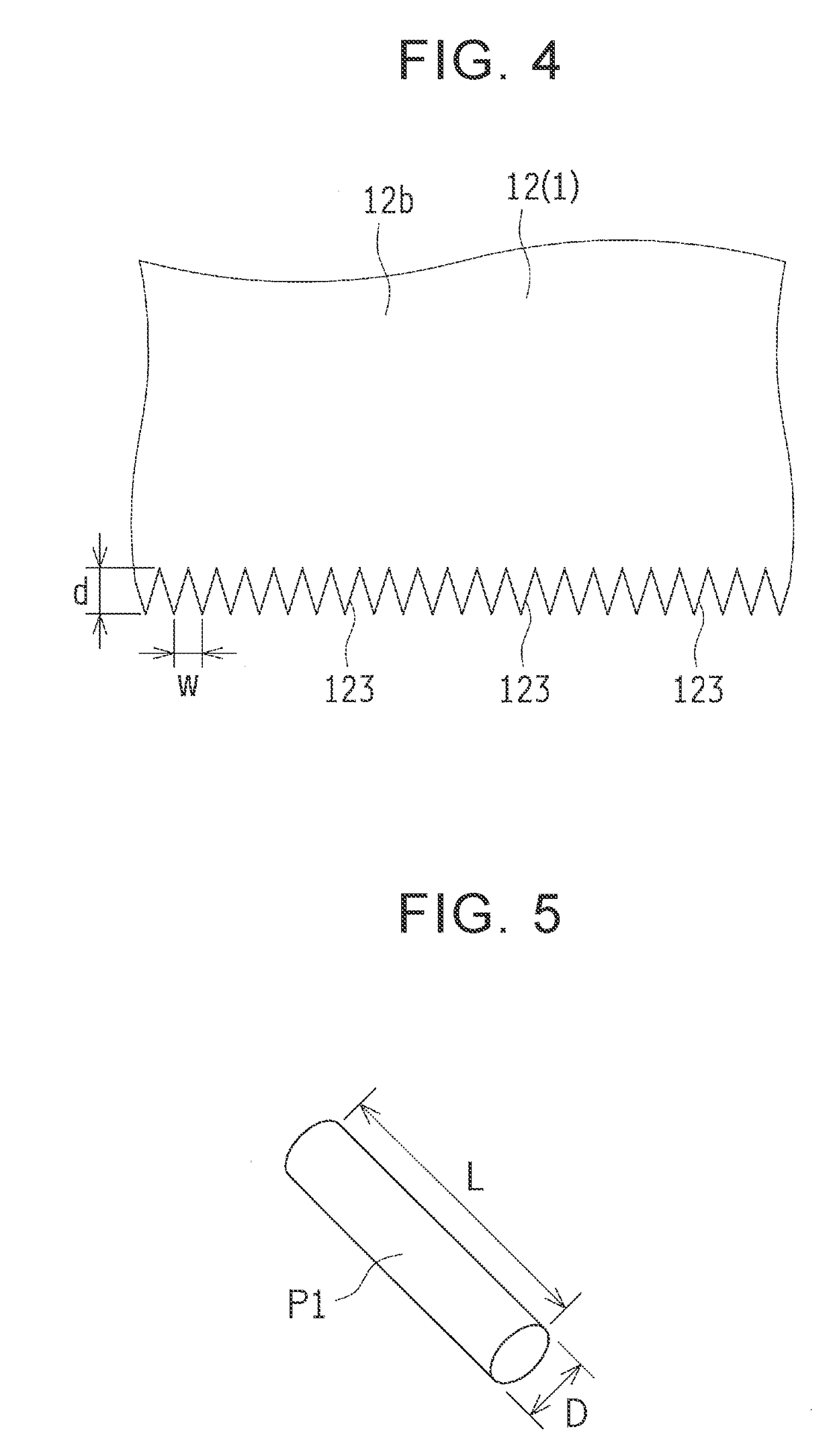

Clutch cooling grooves for uniform plate temperature in friction launch

InactiveUS20050284721A1Minimize heat distortionReduce the temperatureFluid actuated clutchesFriction clutchesEngineeringCooling fluid

Clutch cooling grooves formed on a friction plate are provided. The grooves are shaped to provide for substantially uniform steel disk temperatures in friction launch of a vehicle. The grooves are shaped such that the largest cross-sectional area is located adjacent to what would otherwise have been a hot area on the steel disk and the smallest cross-sectional area is located at the coolest location on the steel disk, at the cooling fluid inlet. Thus, the groove is shaped such that the smallest cross-sectional area is located at the cooling fluid inlet, the largest cross-sectional area is located between the cooling fluid inlet and the cooling fluid outlet, and the cooling fluid outlet has a cross-sectional area larger than the cooling fluid inlet and smaller than the cross-sectional area adjacent to the hot spot of the steel disk, between the cooling fluid inlet and the cooling fluid outlet.

Owner:GM GLOBAL TECH OPERATIONS LLC

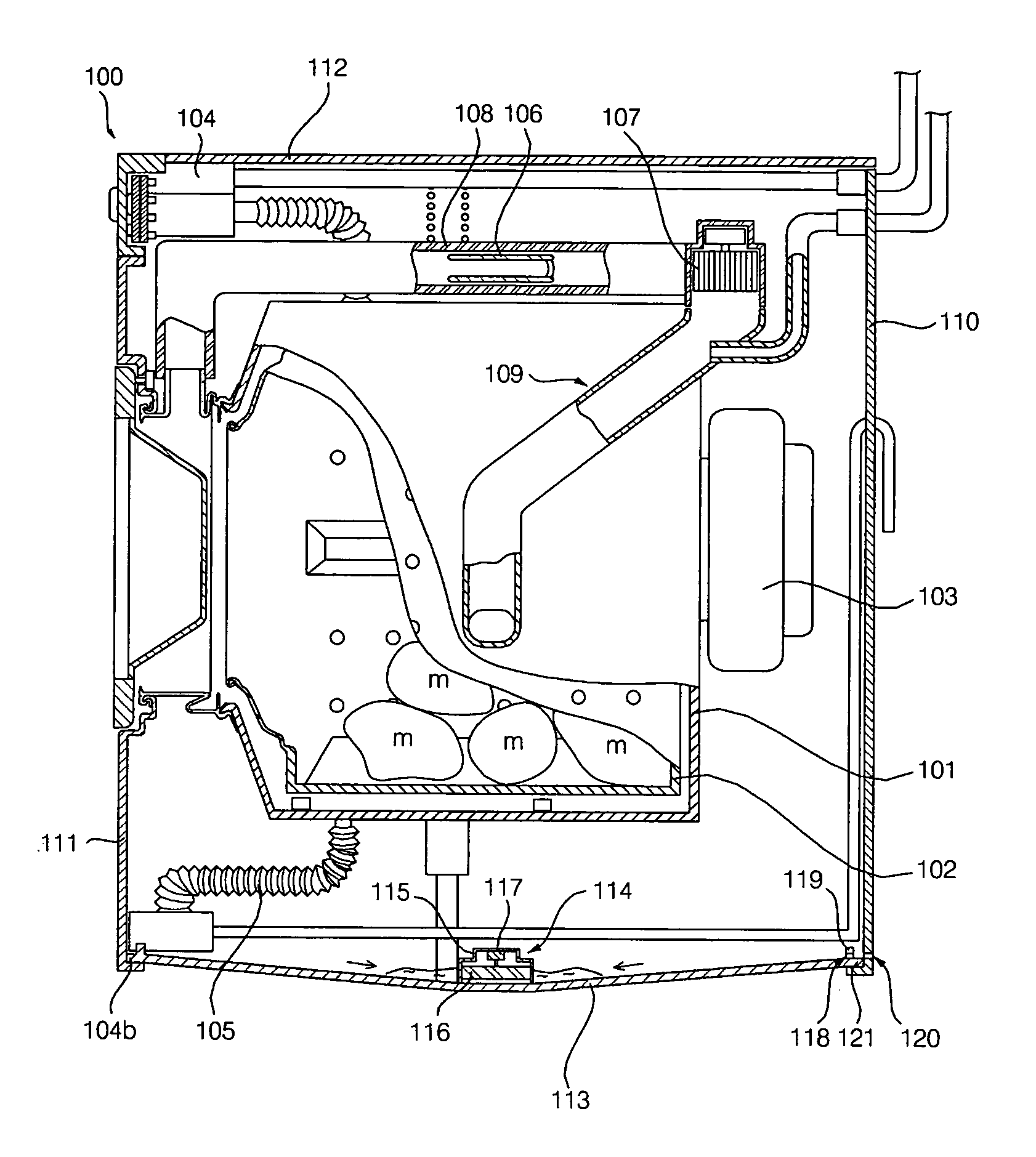

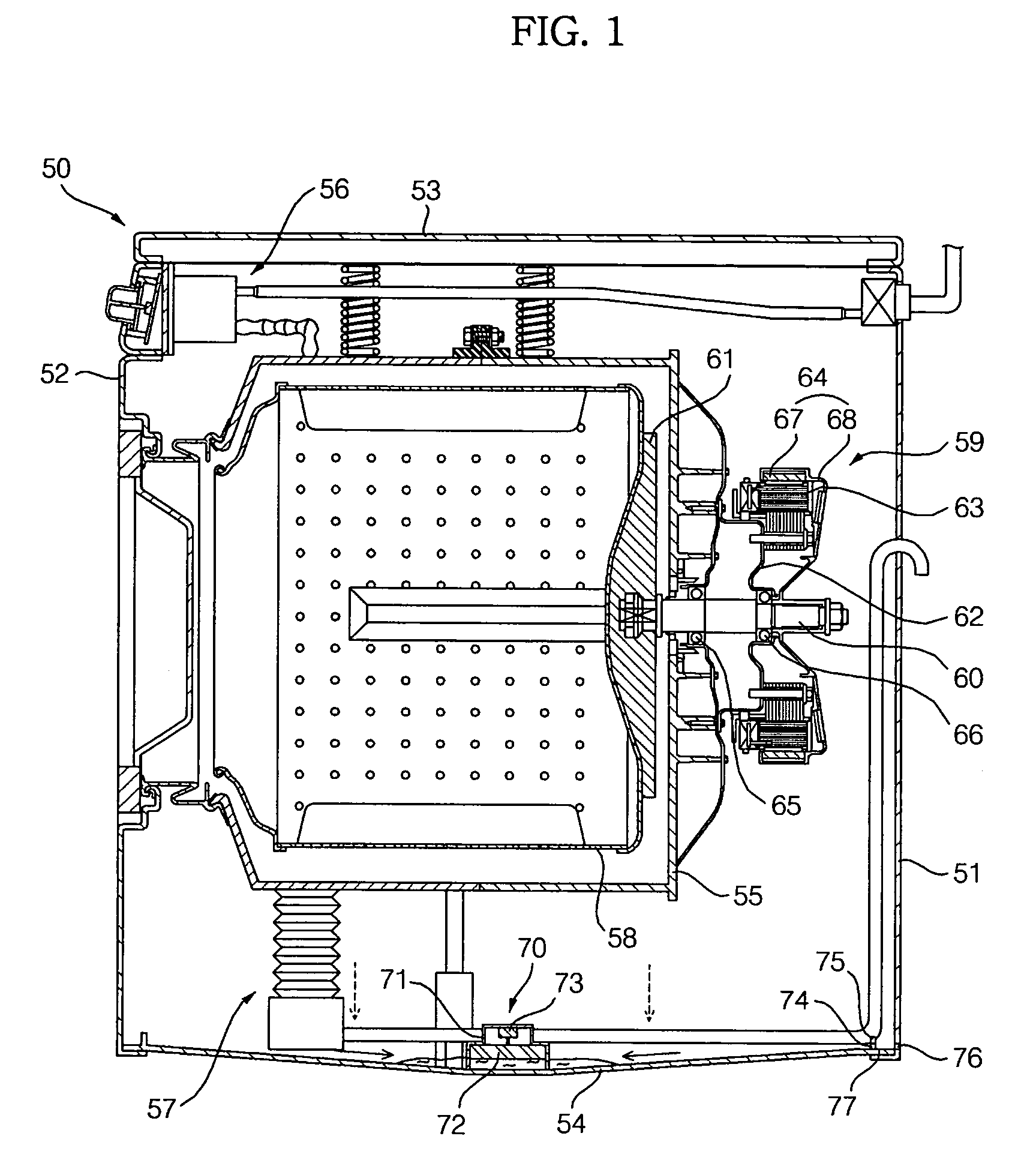

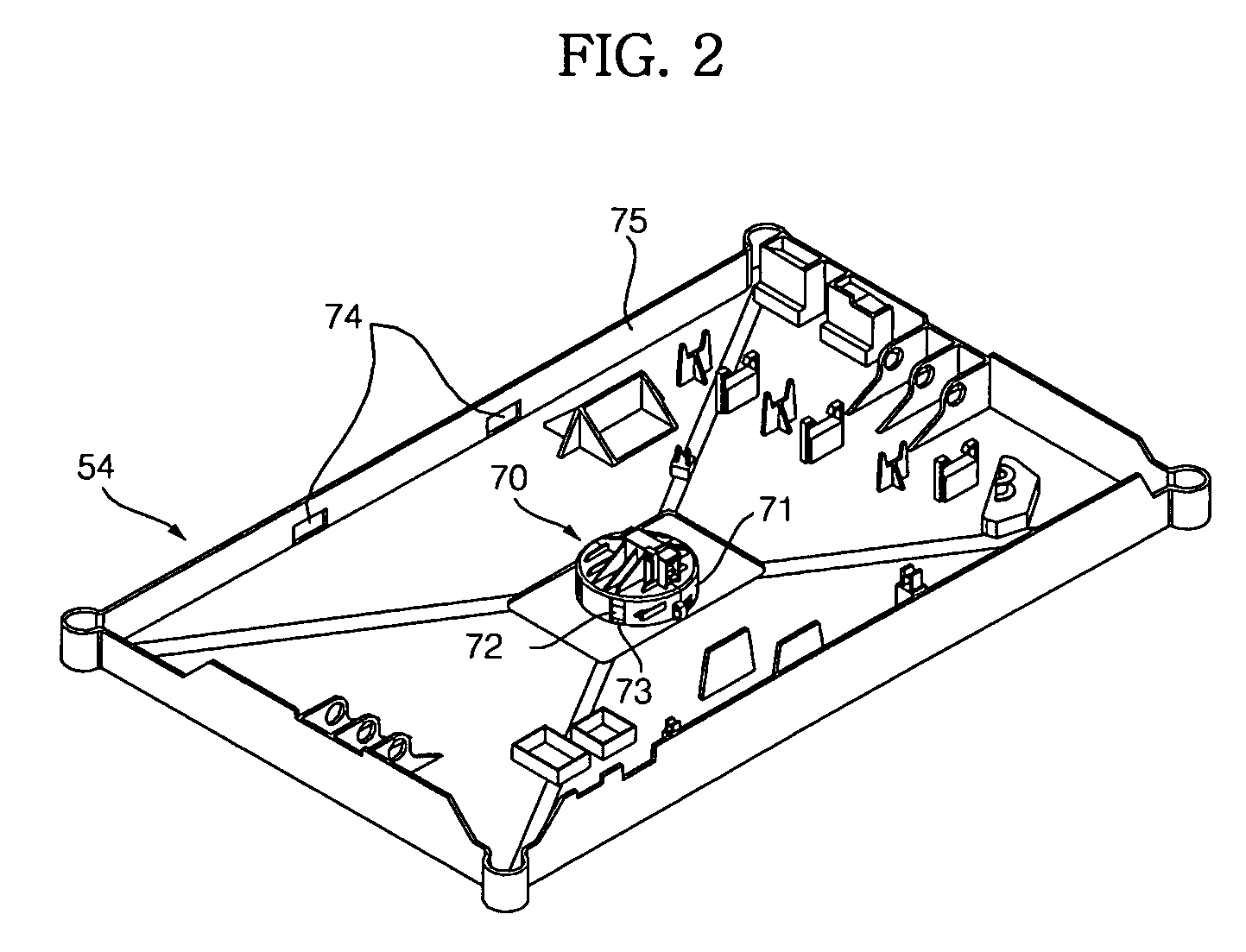

Washing apparatus

InactiveUS20060081014A1Reduce processing costsReduce material costsOther washing machinesControl devices for washing apparatusWater leakageWaste management

Disclosed herein is a washing apparatus in which the top of a base pan is inclined downward toward a mounting position of a water leakage sensor, so that water, dropped onto the base pan, is gathered toward the water leakage sensor regardless of a water drop position, thereby enabling prompt operation of the water leakage sensor and achieving an enhancement in reliability. Furthermore, the washing apparatus comprises holders by which the water leakage sensor is vertically caught after being vertically press fitted to the base pan, thereby enabling the water leakage sensor to be mounted to the base pan via a single vertical press-fitting operation, resulting in an enhancement in assembling efficiency.

Owner:LG ELECTRONICS INC

Failsafe injected adhesive joint

ActiveUS7670527B2Cross sectional areaImprove carrying capacityMaterial gluingCylinder headsAdhesion forceInjection port

A composite member is joined to another composite or noncomposite member, using liquid or paste adhesive resin that cures in the joint. The joint is configured in such a way that the adhesive forms an interlocking key within recesses in the joined members that prevents joint disassembly once the adhesive has cured and hardened. Both of the members are provided with recesses extending along their lengths in the joint. The recesses register with each other to define a cavity and may undulate. The recessed are designed in such a way as to take the full load capability if the joint, even if there is no adhesion to the joined members. Adhesive is injected into the cavity through injection ports spaced periodically along the length of the joint.

Owner:LOCKHEED MARTIN CORP

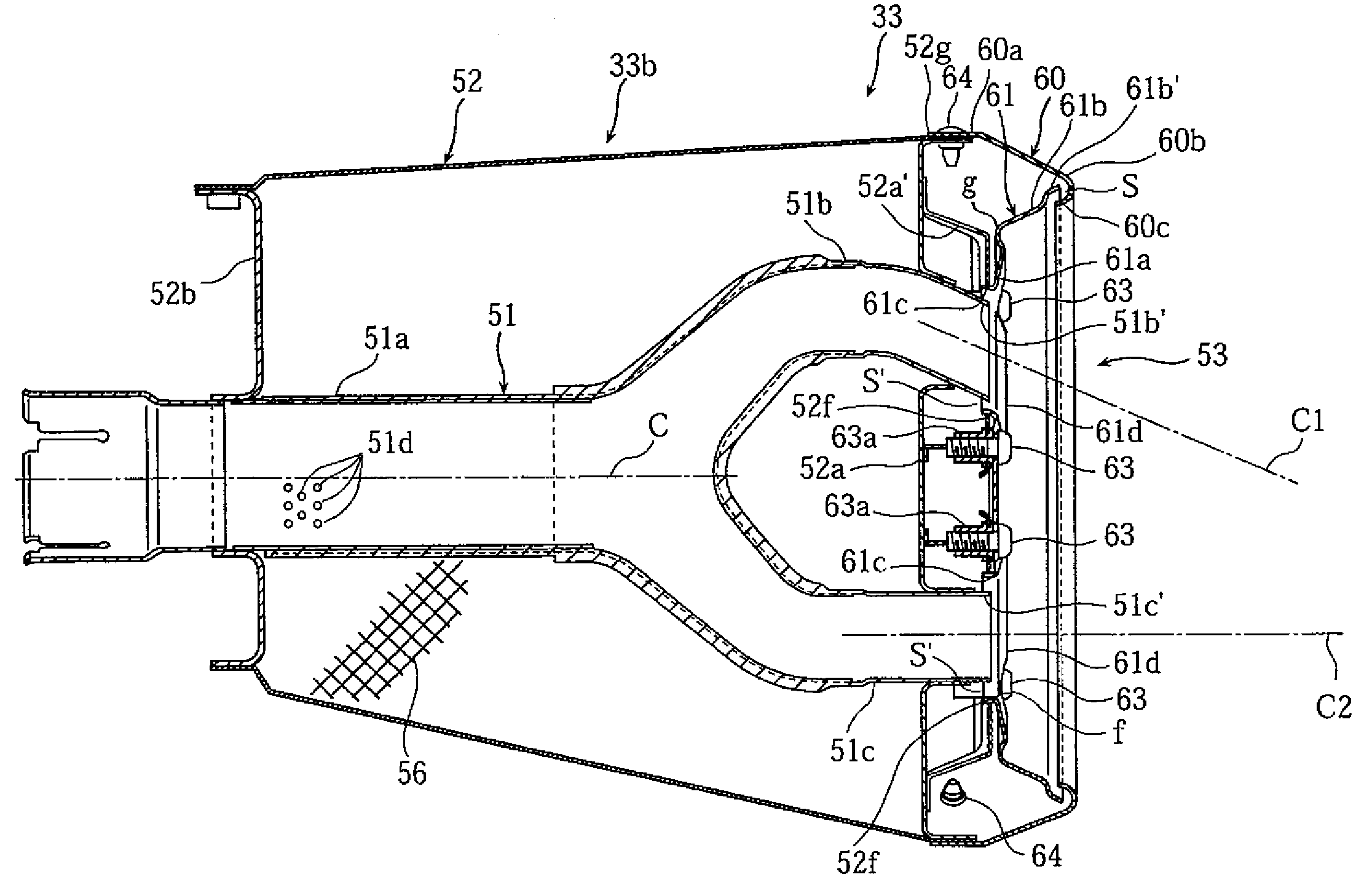

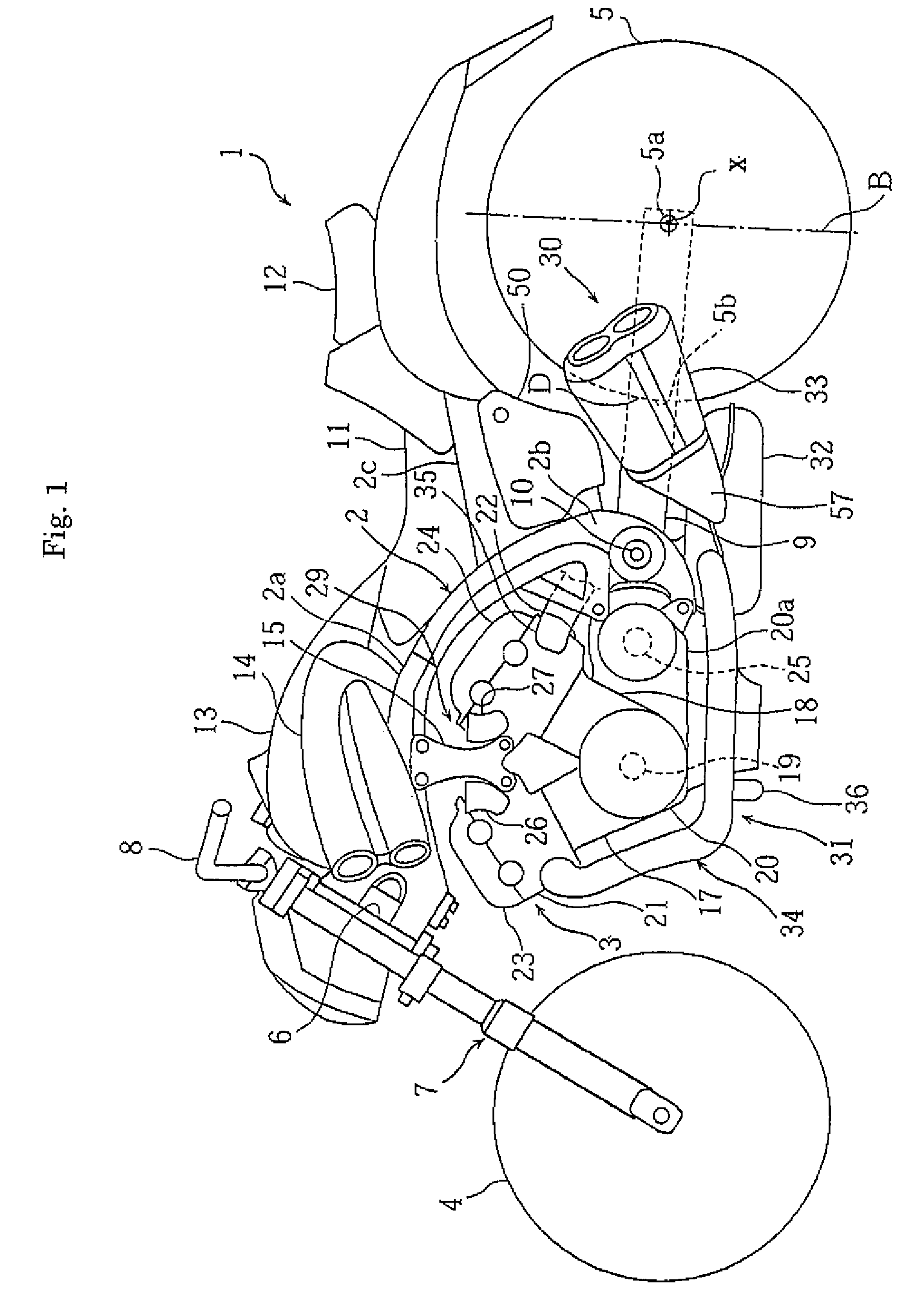

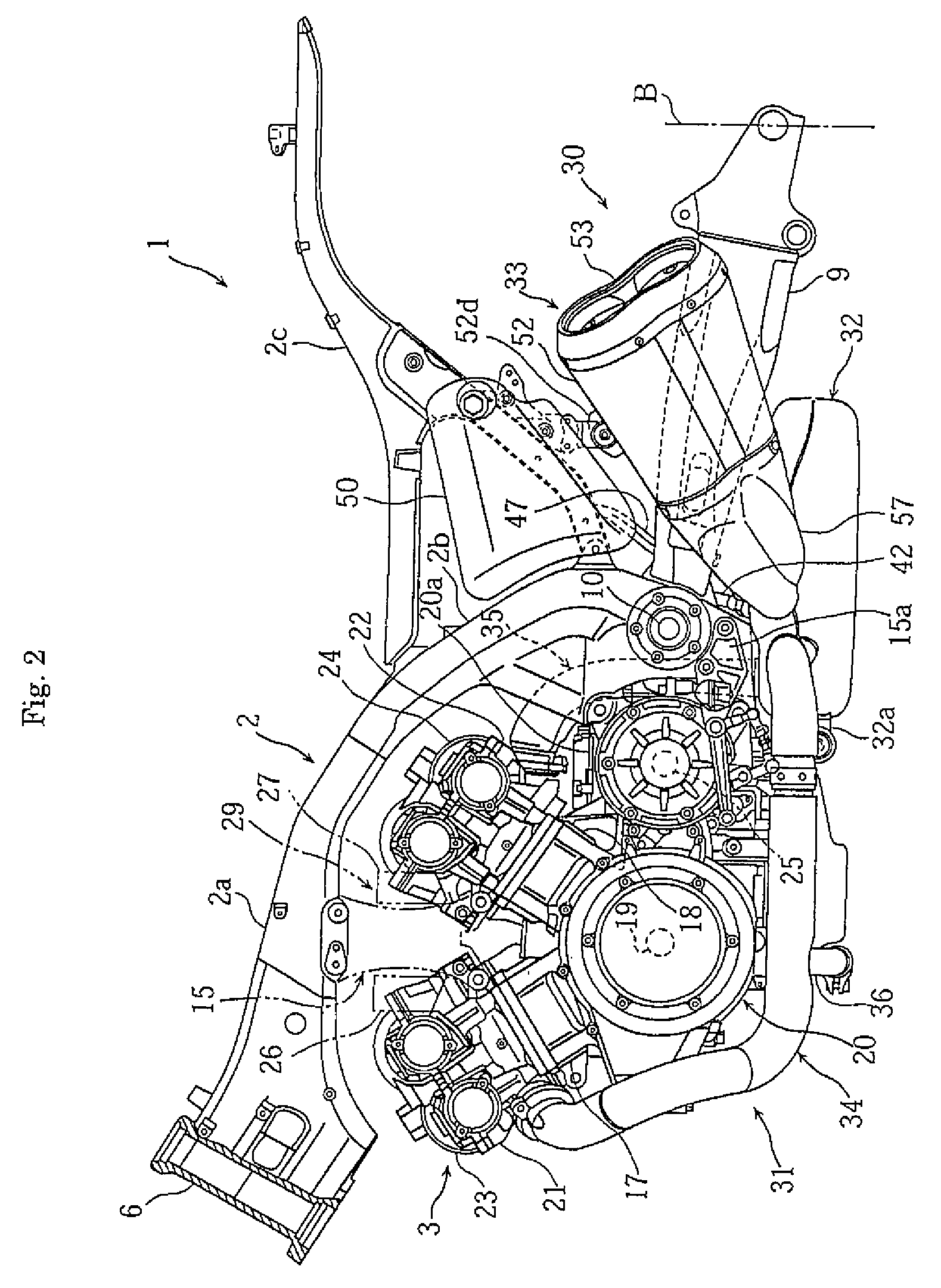

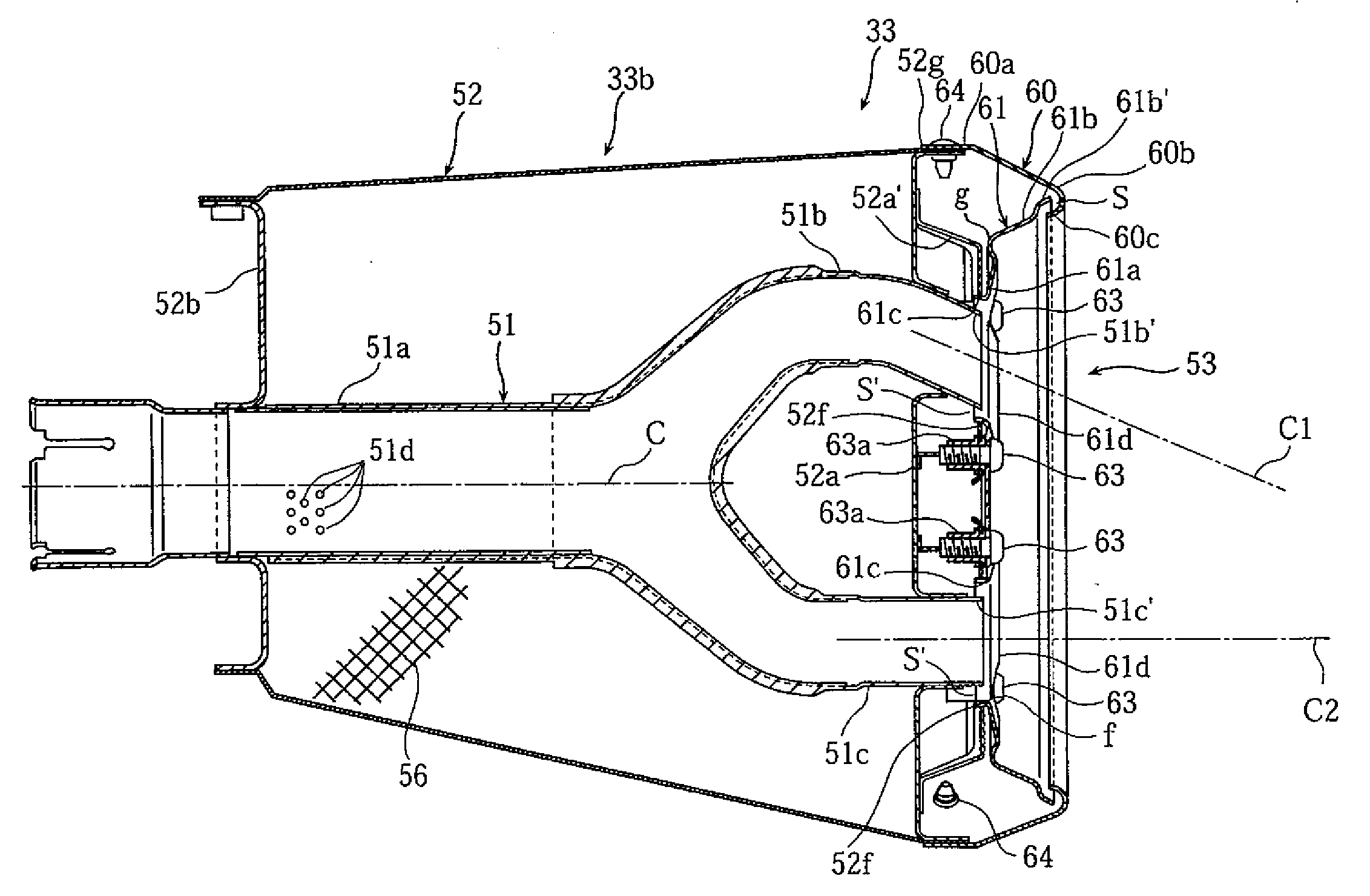

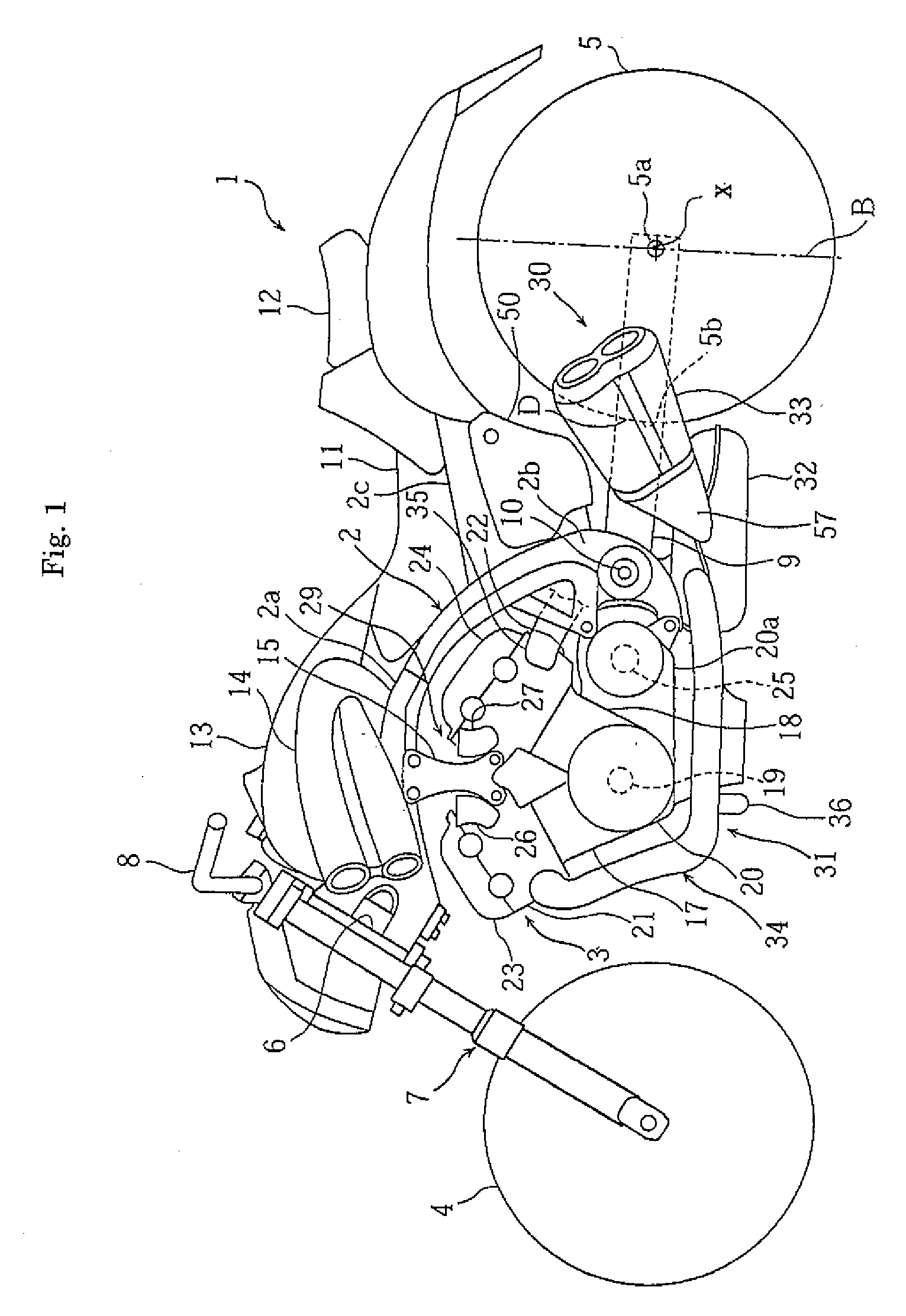

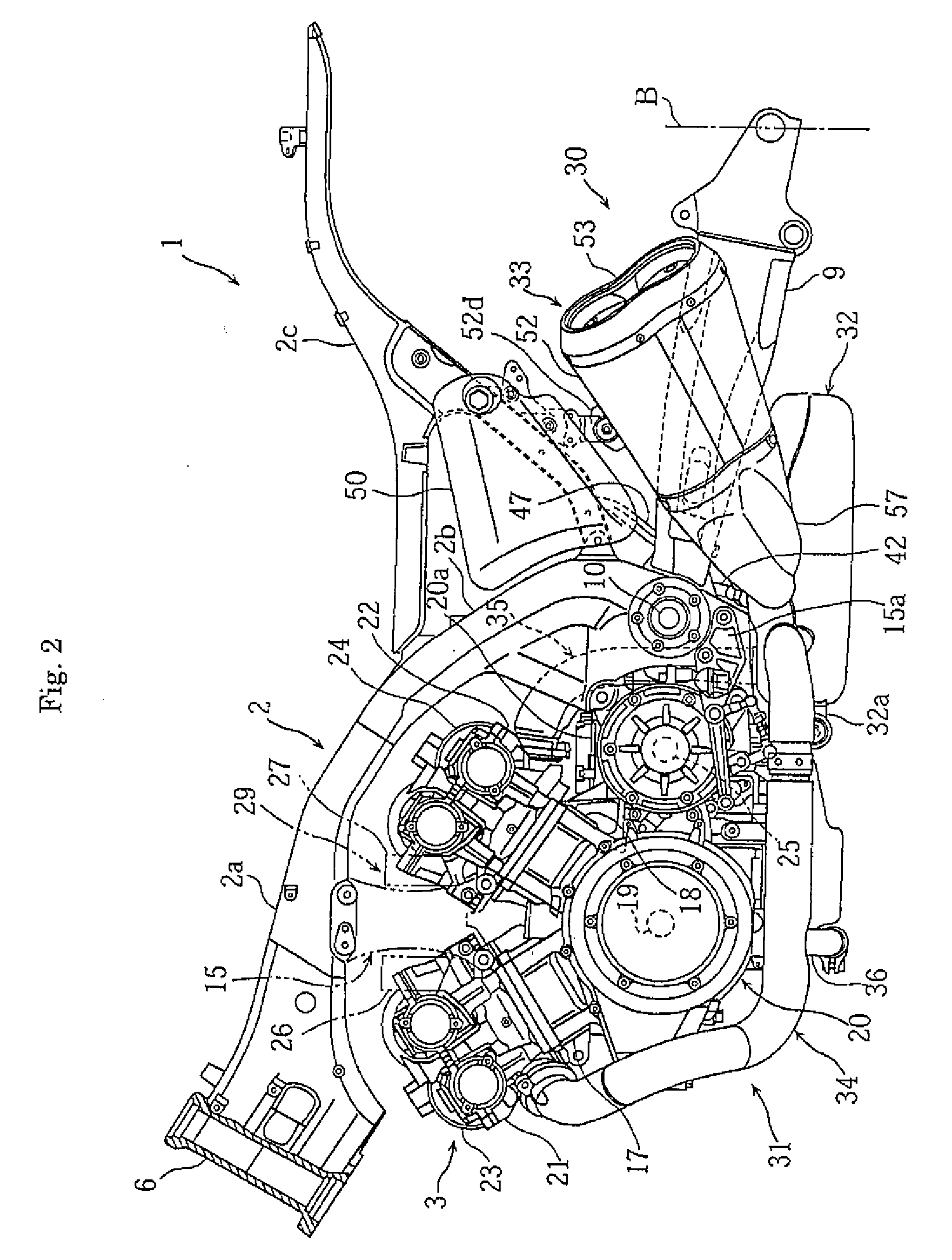

Exhaust system for motorcycle

ActiveUS7779963B2Cross sectional areaVolume of the area between the casing and the branch pipe section can be increasedSilencing apparatusThermometers using physical/chemical changesEngineeringMuffler

A motorcycle having a tail pipe formed from a pair of branch pipes that branch from a main pipe and that ensures a sound absorbing effect. A muffler has a casing that surrounds a rear section of an exhaust pipe, and a sound absorbing material that is filled between the casing and the rear section of the exhaust pipe. The rear section of the exhaust pipe includes a main pipe that is connected to the exhaust pipe and that extends to the rear, and first and second branch pipes that are connected to and branch from the main pipe and extend to the rear. A cross sectional area of the casing, when viewed from an exhaust gas flow direction becomes larger as the casing extends toward the branch pipe side.

Owner:YAMAHA MOTOR CO LTD

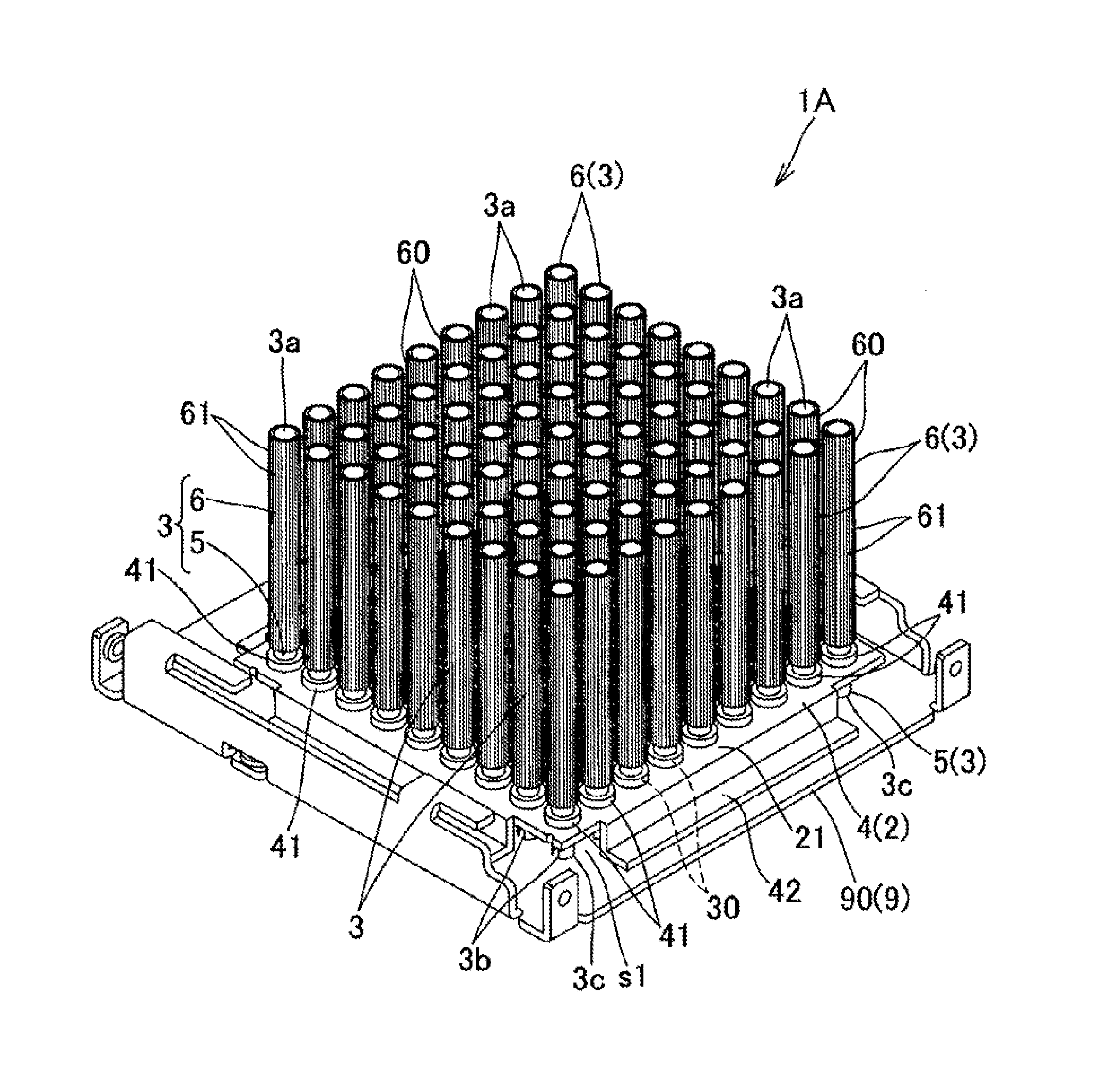

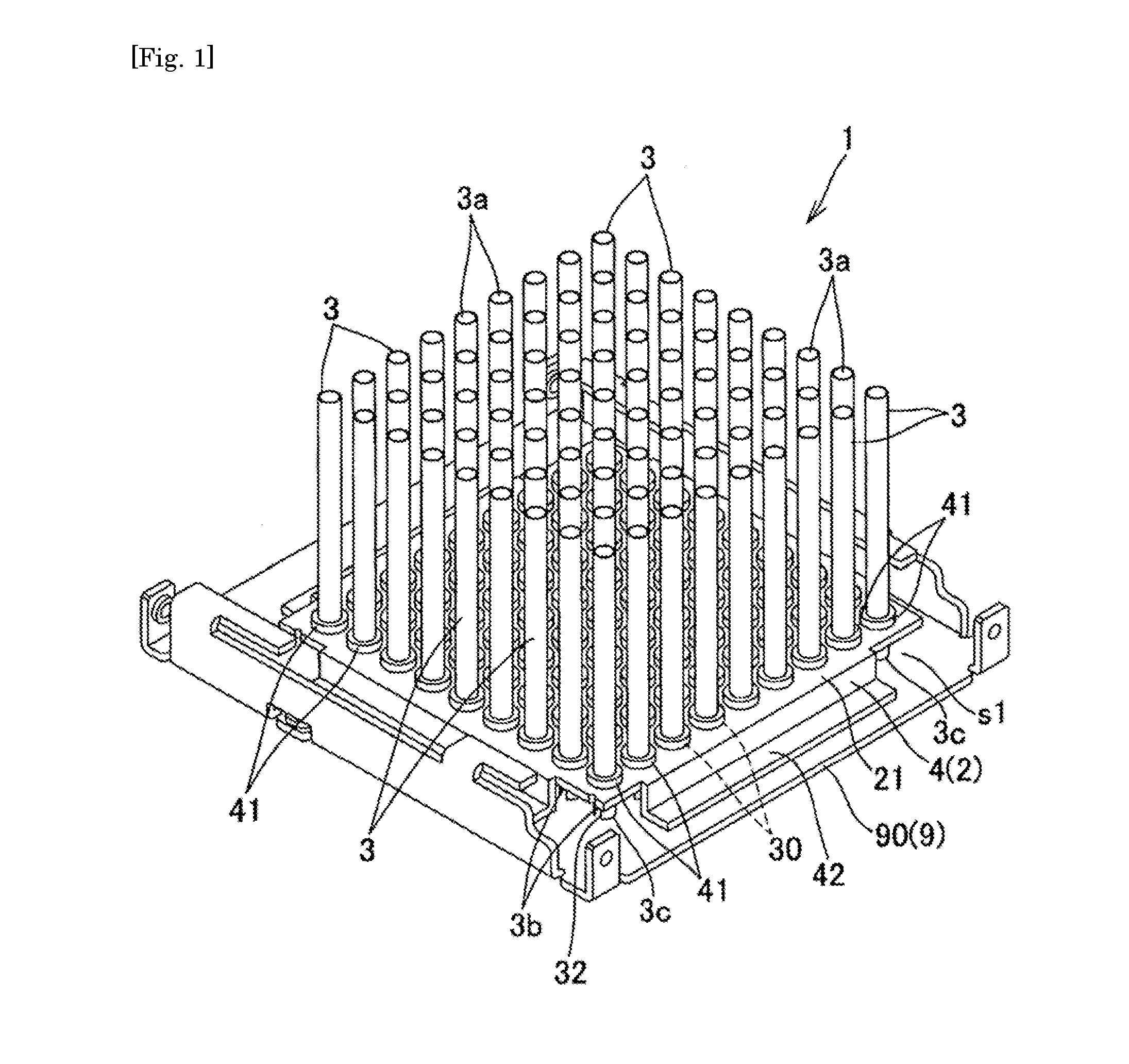

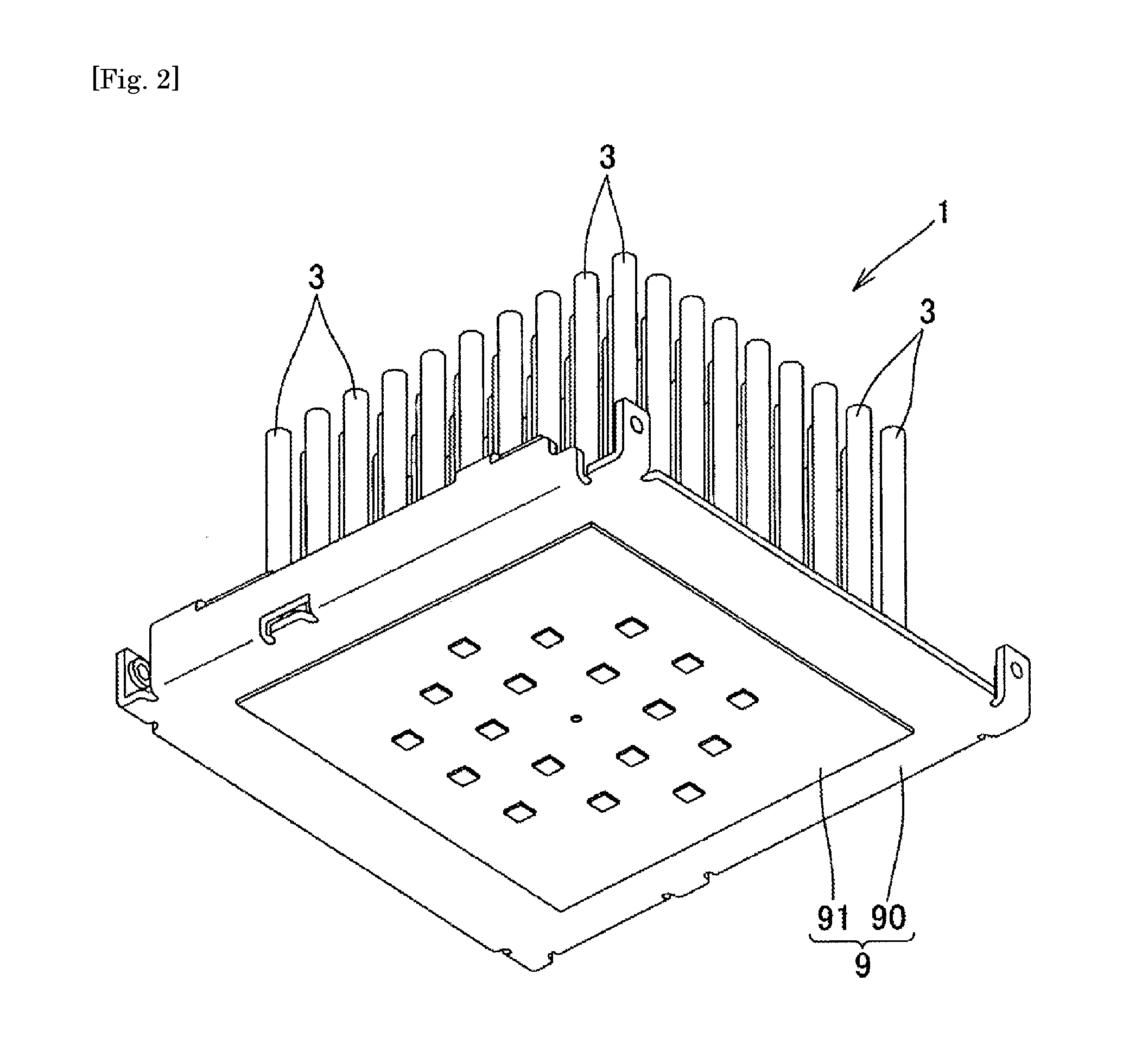

Heat sink

ActiveUS20160341492A1Increase freedomImprove cooling effectSemiconductor/solid-state device detailsLighting heating/cooling arrangementsInterior spaceEngineering

To provide a heat sink capable of enhancing heat dissipation performance.Cylindrical bodies 3 have openings 3a of which inner and outer sides are opened on front ends and are provided with through-holes 3b communicating the inner side and the outer side on side walls at the base end side. The cylindrical bodies 3 are provided in a standing manner in a state where portions at the base end side penetrate through a supporting main body 2 and project into a gap s1, the through-holes 3b are opened to the gap s1, and portions at the front end side also project from the surface of the supporting main body 2 at the opposite side to the gap s1. An atmosphere in the gap s1, which contains heat from a cooling target object 9, is capable of being made to flow into the cylindrical bodies 3 through the through-holes 3, circulate in inner spaces of the cylindrical bodies 3, and be released to the outside through the openings 3a on the front ends.

Owner:JAPAN

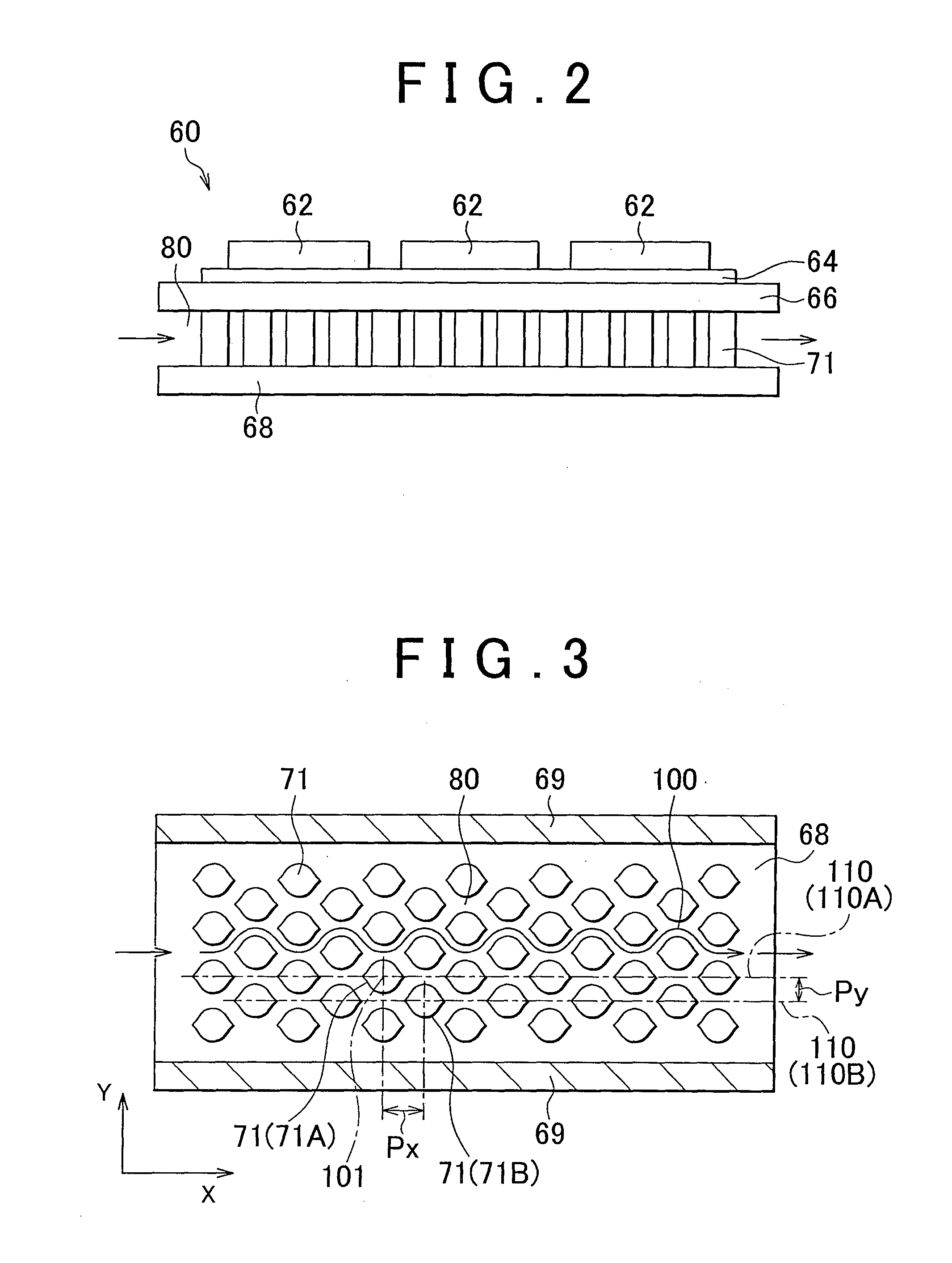

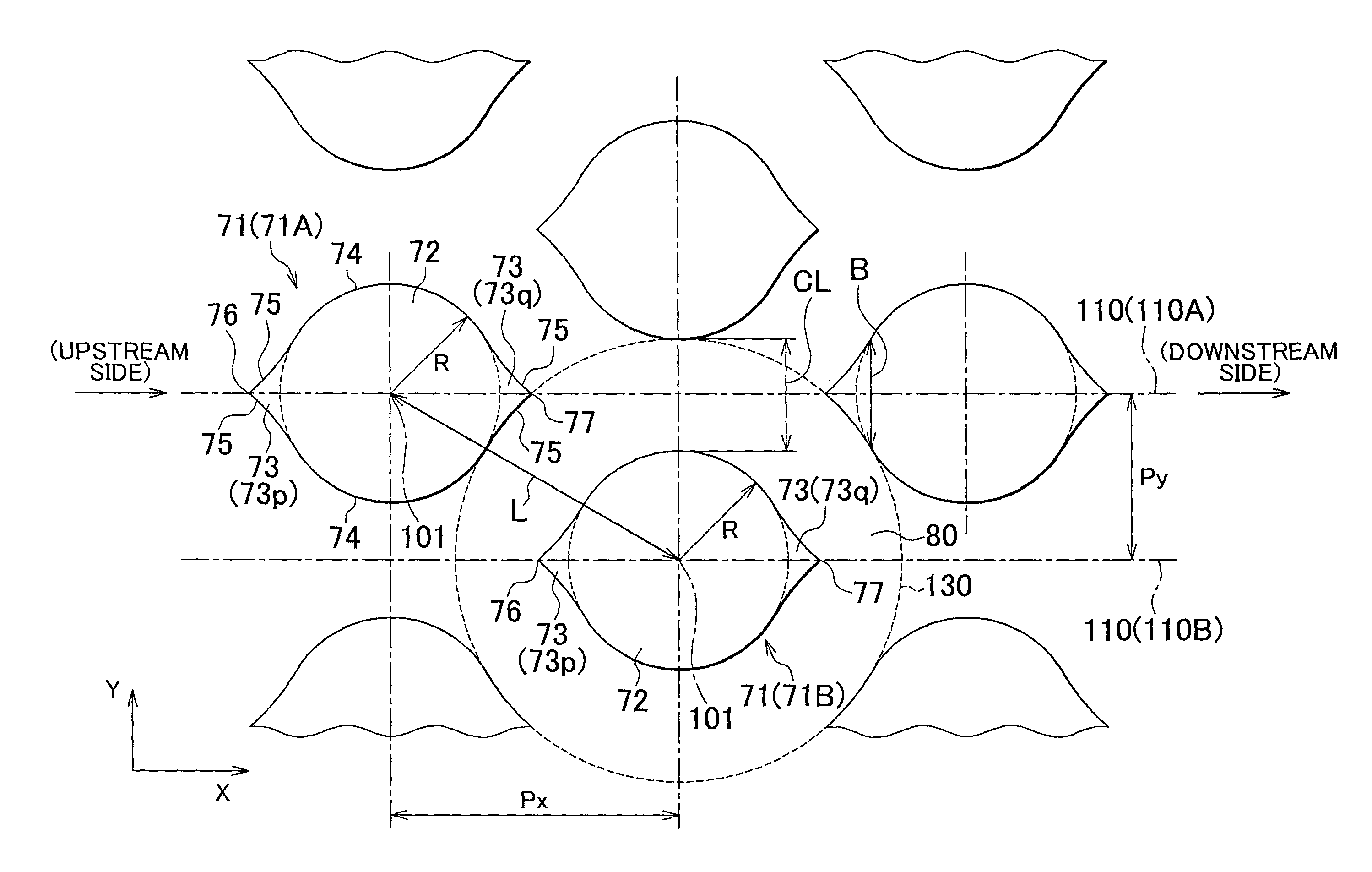

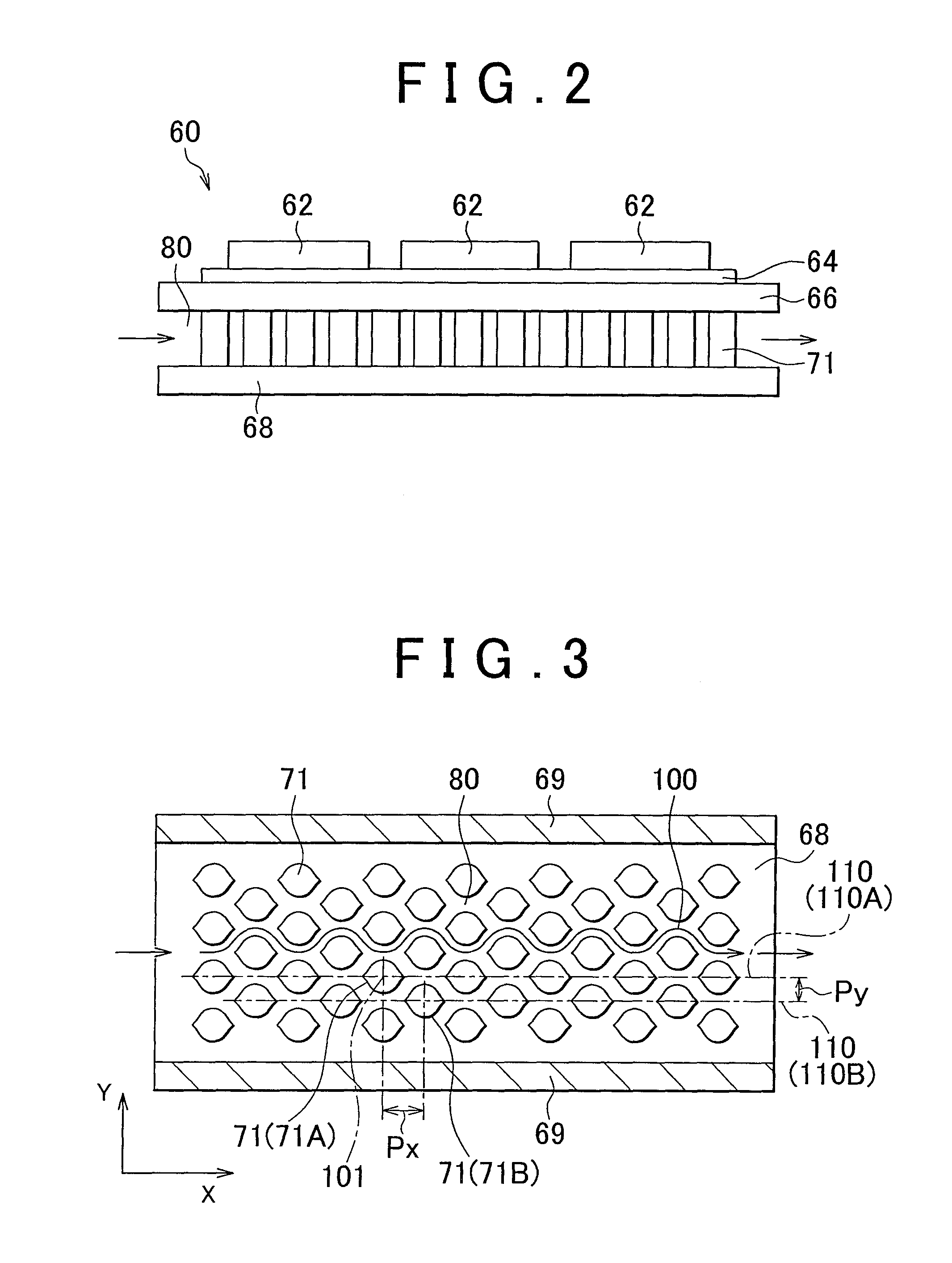

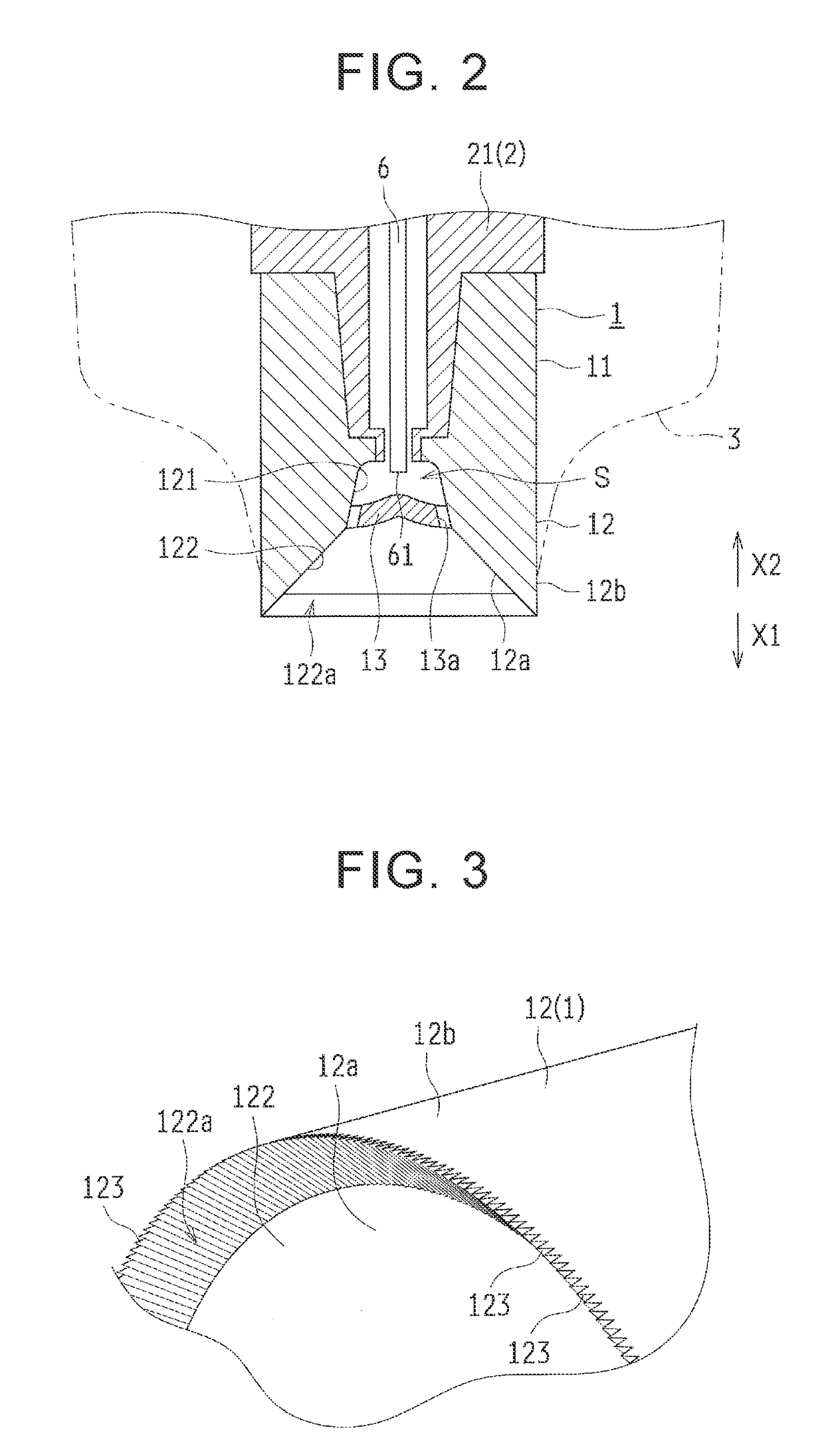

Cooling fin structure

ActiveUS20140138063A1Reduce total pressure lossImprove heat transfer efficiencySemiconductor/solid-state device detailsSolid-state devicesHeat sinkCoolant

A cooling fin structure used in a cooler for an electric device includes a plurality of pin fins (71) arranged in a zigzag form in a coolant passage (80). Each of the pin fins (71) has a circular portion (72) having a circular cross-section, and irregularly shaped portions (73) provided contiguously on the upstream and downstream sides of the circular portion (72) as viewed in a direction of flow of the coolant. The irregularly shaped portions (73) have an outer peripheral surface (75) that is formed along a circumference (130) having a center at a center point (101) of the circular portion (72) of a pin fin (71,71B) that is located adjacent to the pin fin (71, 71A) having the irregularly shaped portions (73), in an oblique direction relative to the direction of flow of the coolant.

Owner:TOYOTA JIDOSHA KK +1

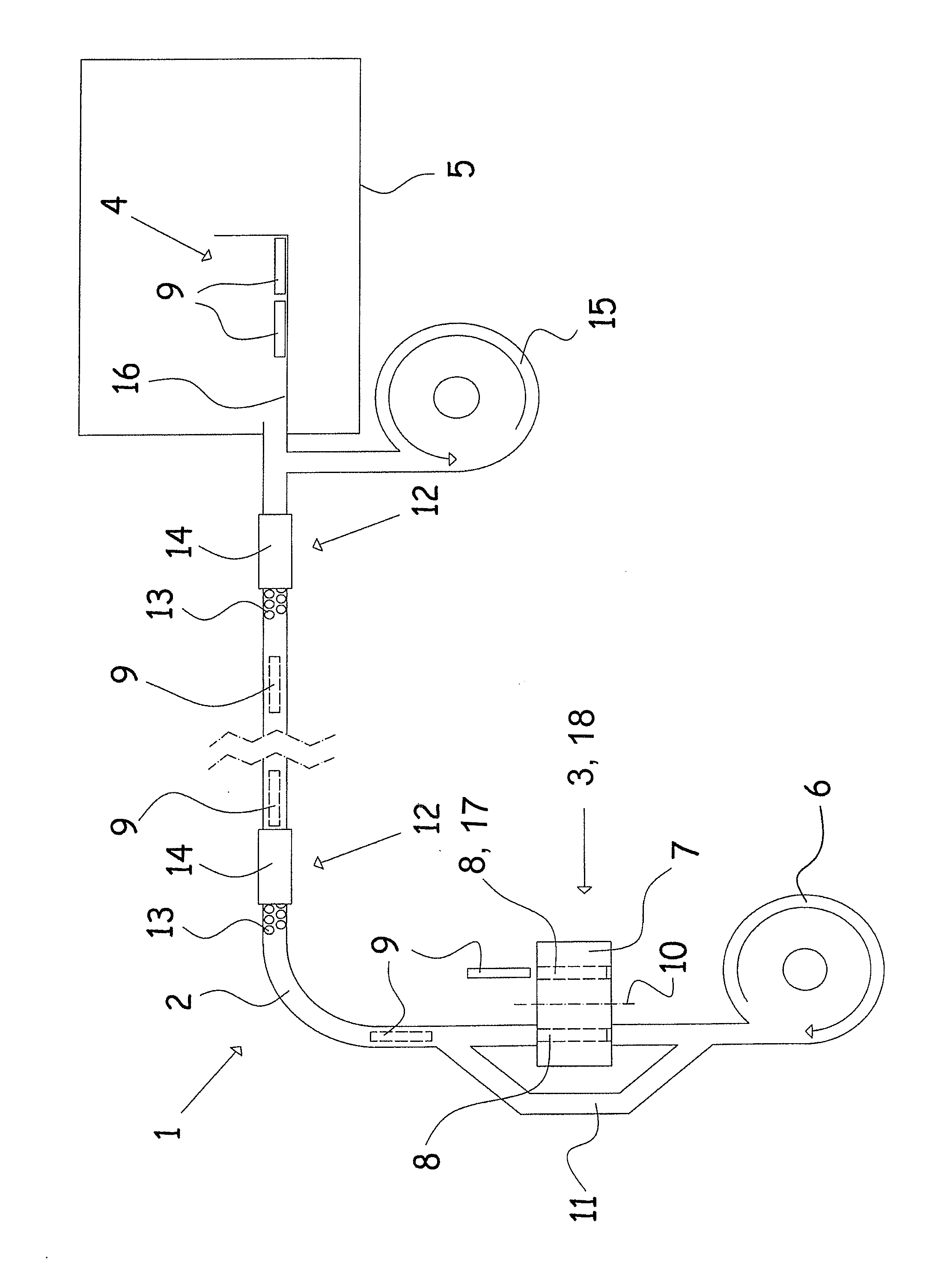

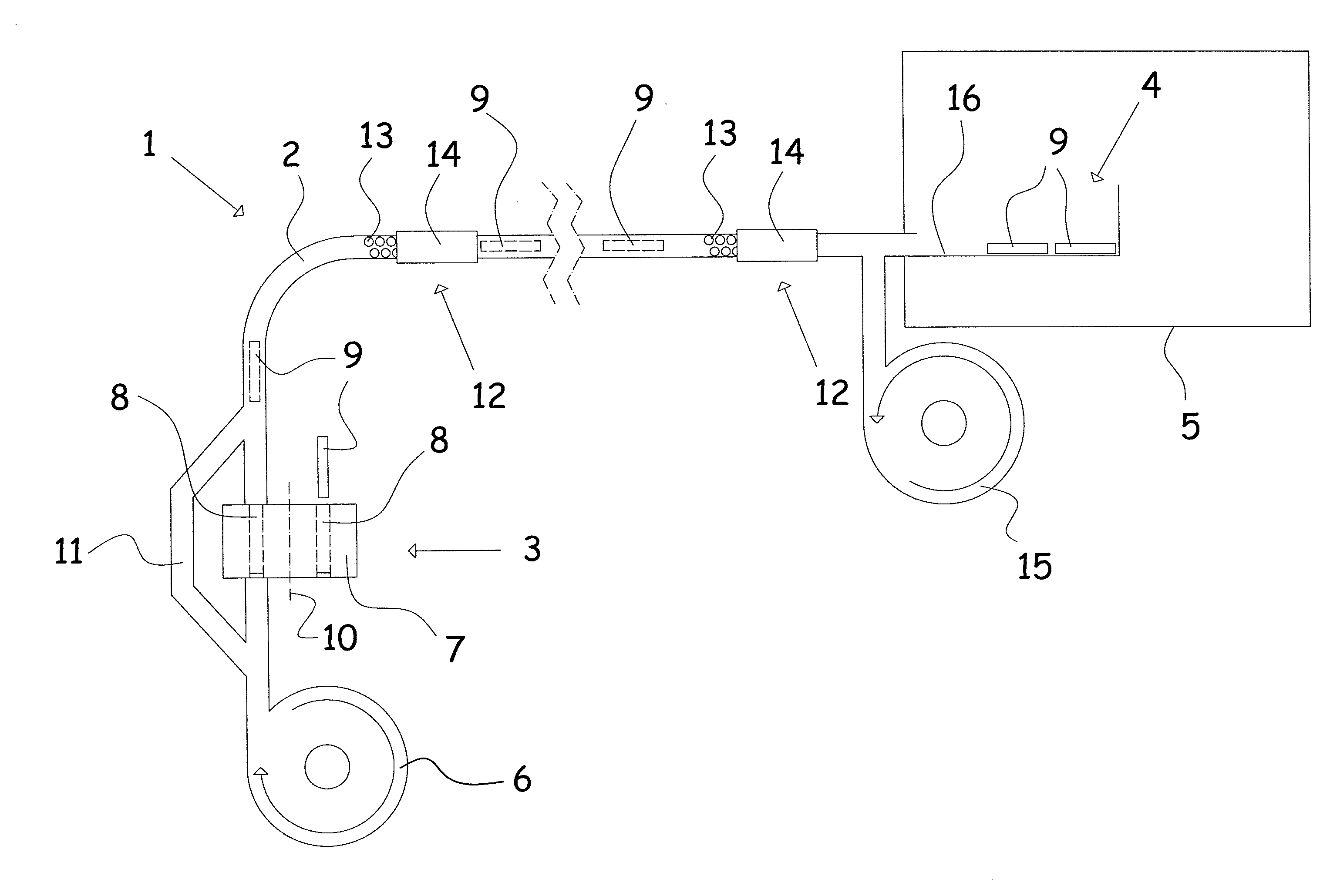

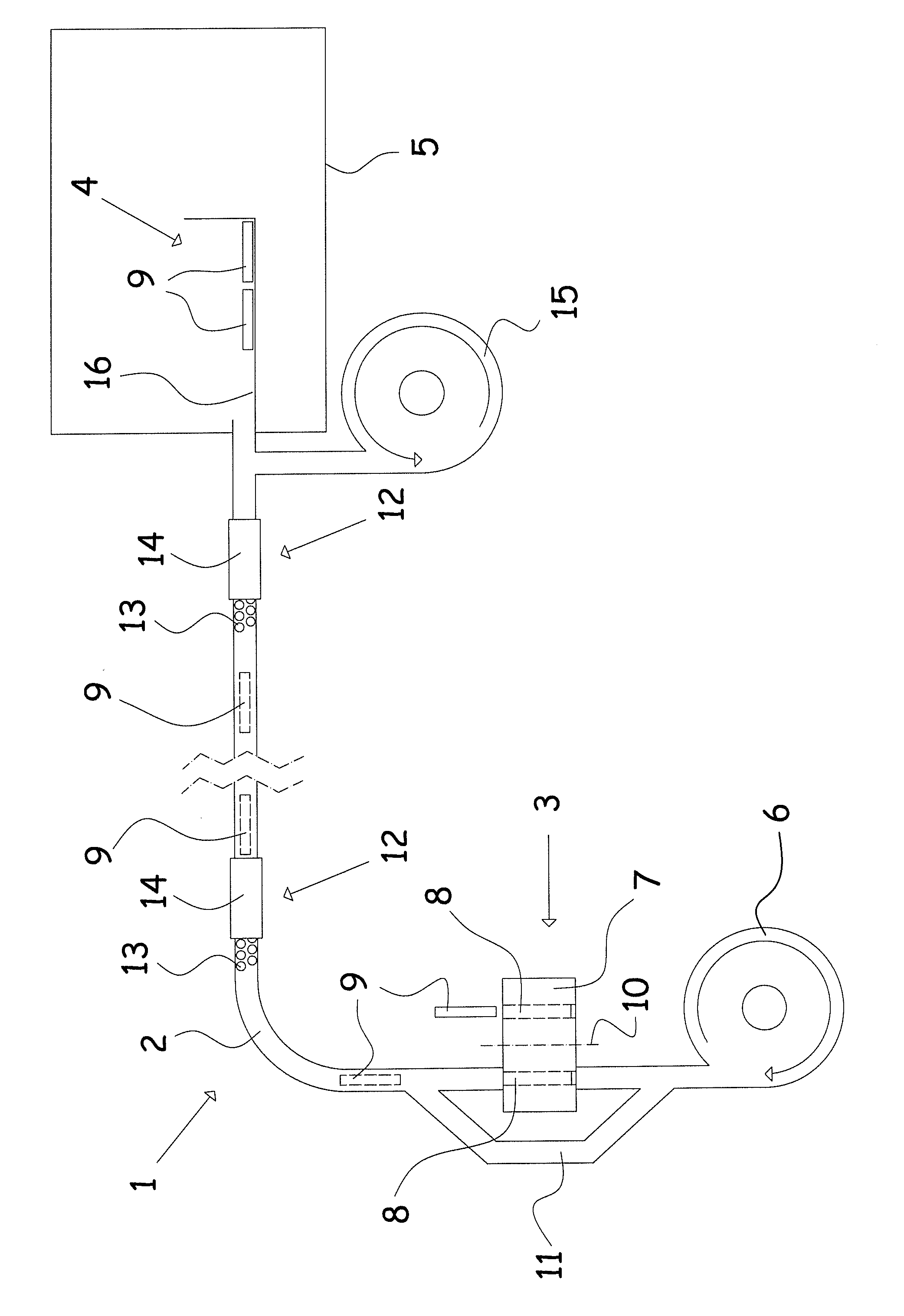

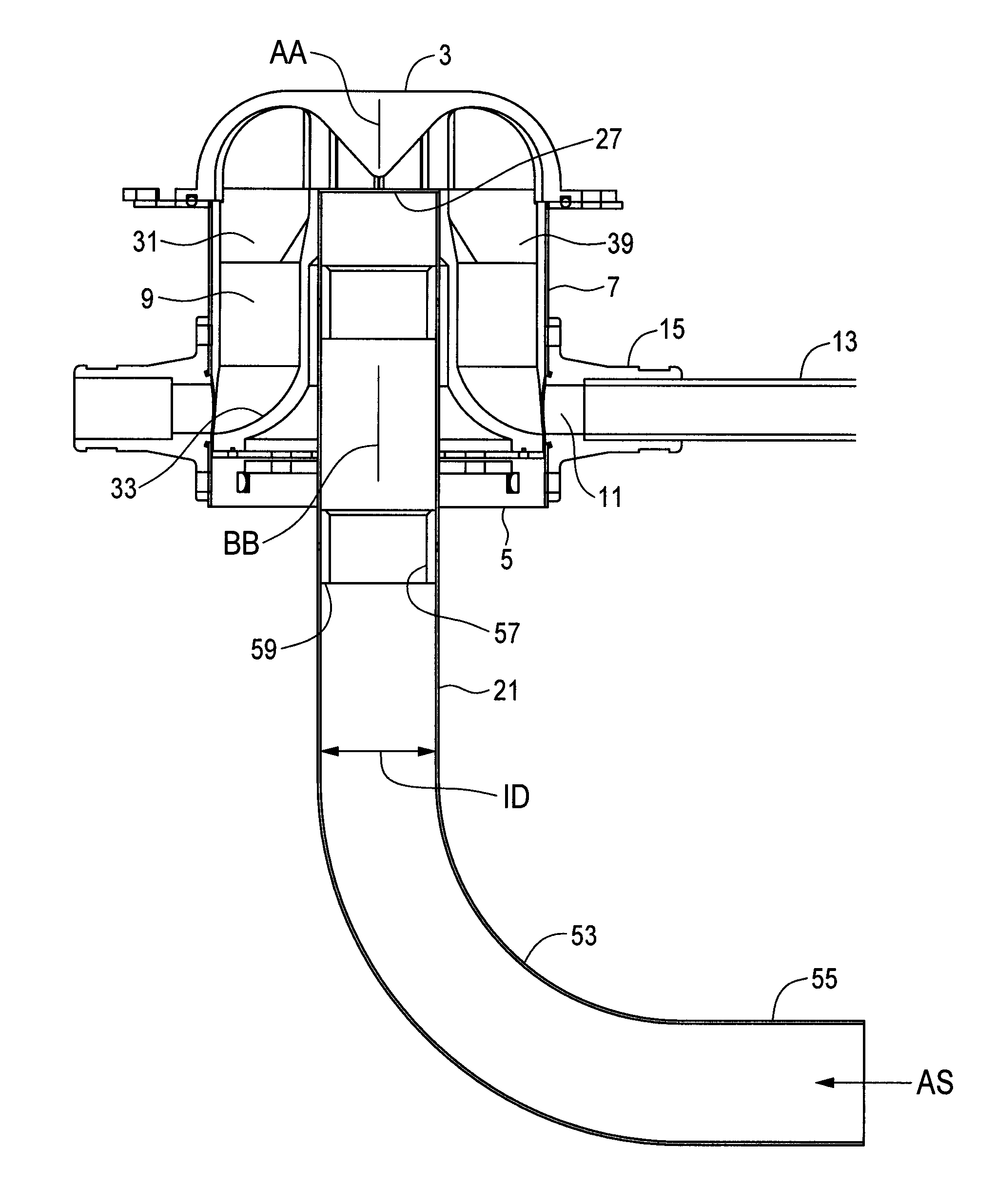

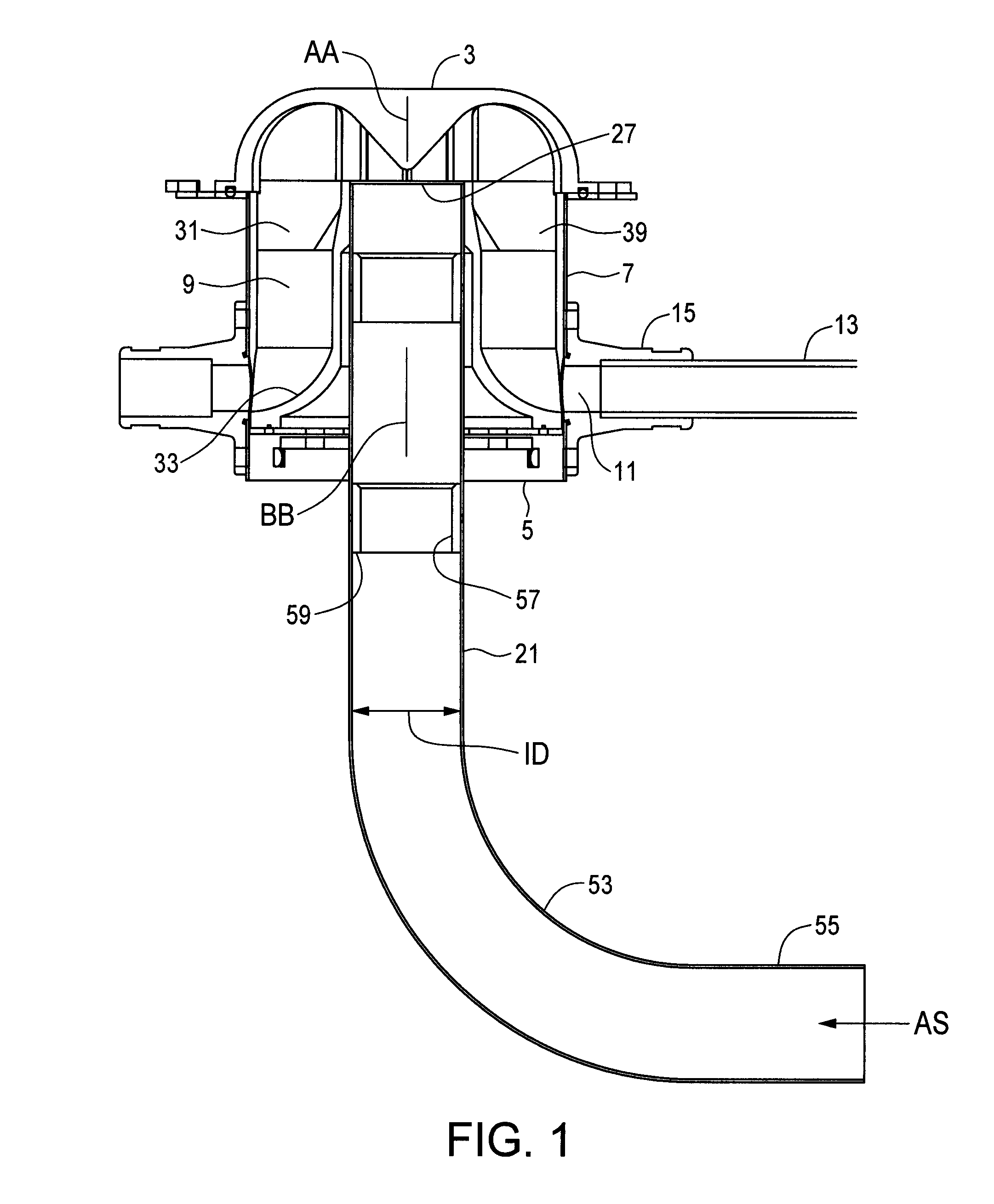

Pneumatic transport system

ActiveUS9309063B2Reduce workloadCross-sectional areaBulk conveyorsMaterial analysisTelecommunicationsTransport system

A conveying system including at least one tube connection, at least one dispatch station and at least one receiver station, where items are conveyed by an airflow in the direction of the airflow in the pipe connection from a dispatch station to a receiver station. The new feature of a conveying system is that the tube connection has an inner cross-sectional area, preferably a circular cross-sectional area, with a size greater than the largest cross-sectional area of an item, and which is preferably provided with at least twice the cross-sectional area compared with the largest cross-sectional area of an item. Hereby is achieved the advantage that several items may be conveyed in the same tube connection at the same time, where these items are sent individually and successively, corresponding to one item being sent immediately after another.

Owner:SARSTEDT APS

Pneumatic transport system

ActiveUS20120195698A1Gentle receptionIncrease speedBulk conveyorsMaterial analysisTelecommunicationsTransport system

A conveying system including at least one tube connection, at least one dispatch station and at least one receiver station, where items are conveyed by an airflow in the direction of the airflow in the pipe connection from a dispatch station to a receiver station. The new feature of a conveying system is that the tube connection has an inner cross-sectional area, preferably a circular cross-sectional area, with a size greater than the largest cross-sectional area of an item, and which is preferably provided with at least twice the cross-sectional area compared with the largest cross-sectional area of an item. Hereby is achieved the advantage that several items may be conveyed in the same tube connection at the same time, where these items are sent individually and successively, corresponding to one item being sent immediately after another.

Owner:SARSTEDT APS

Air seeder manifold apparatus

InactiveUS20150098767A1Cross sectional areaReduce morbidityBulk conveyorsAgriculture gas emission reductionSeederEngineering

A manifold apparatus for an air seeder has output ports spaced around a lower portion of the sidewall A vertically oriented input conduit extends upward through an input port defined in the bottom of the manifold into an upper portion of the manifold interior. A plurality of substantially vertical channels each extend downward from an inner top wall surface to one of the outlet ports and has an entrance opening at a top end thereof. The upper portion of the manifold interior is configured such that an air stream carrying entrained agricultural products passing out an open top end of the input conduit contacts the top wall and is directed outward into the entrance openings, and such that a substantially equal portion of the air stream and agricultural products flows into each entrance opening. Blunt edged pulsating rings can distribute agricultural products evenly across the input conduit.

Owner:SEEDMASTER MFG

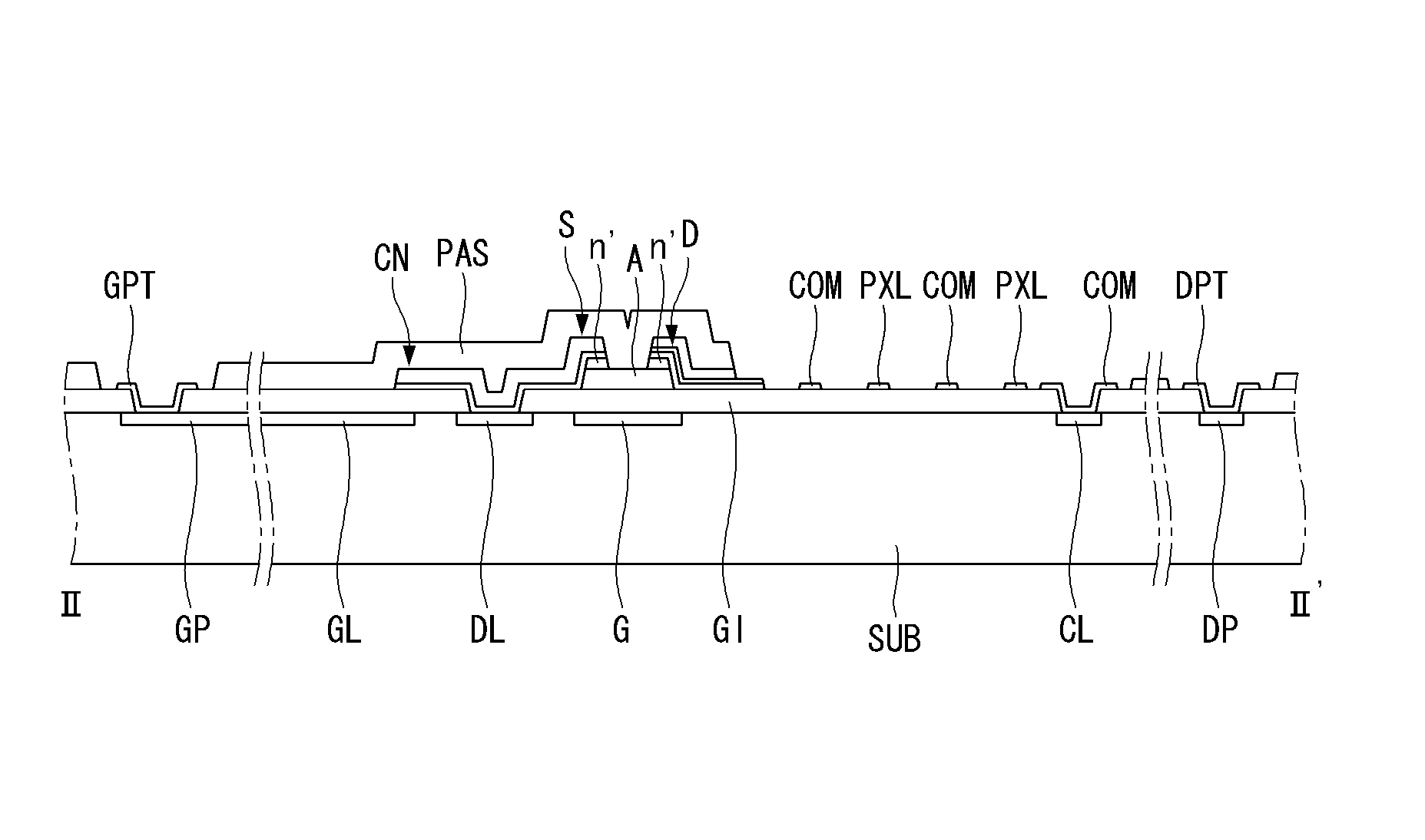

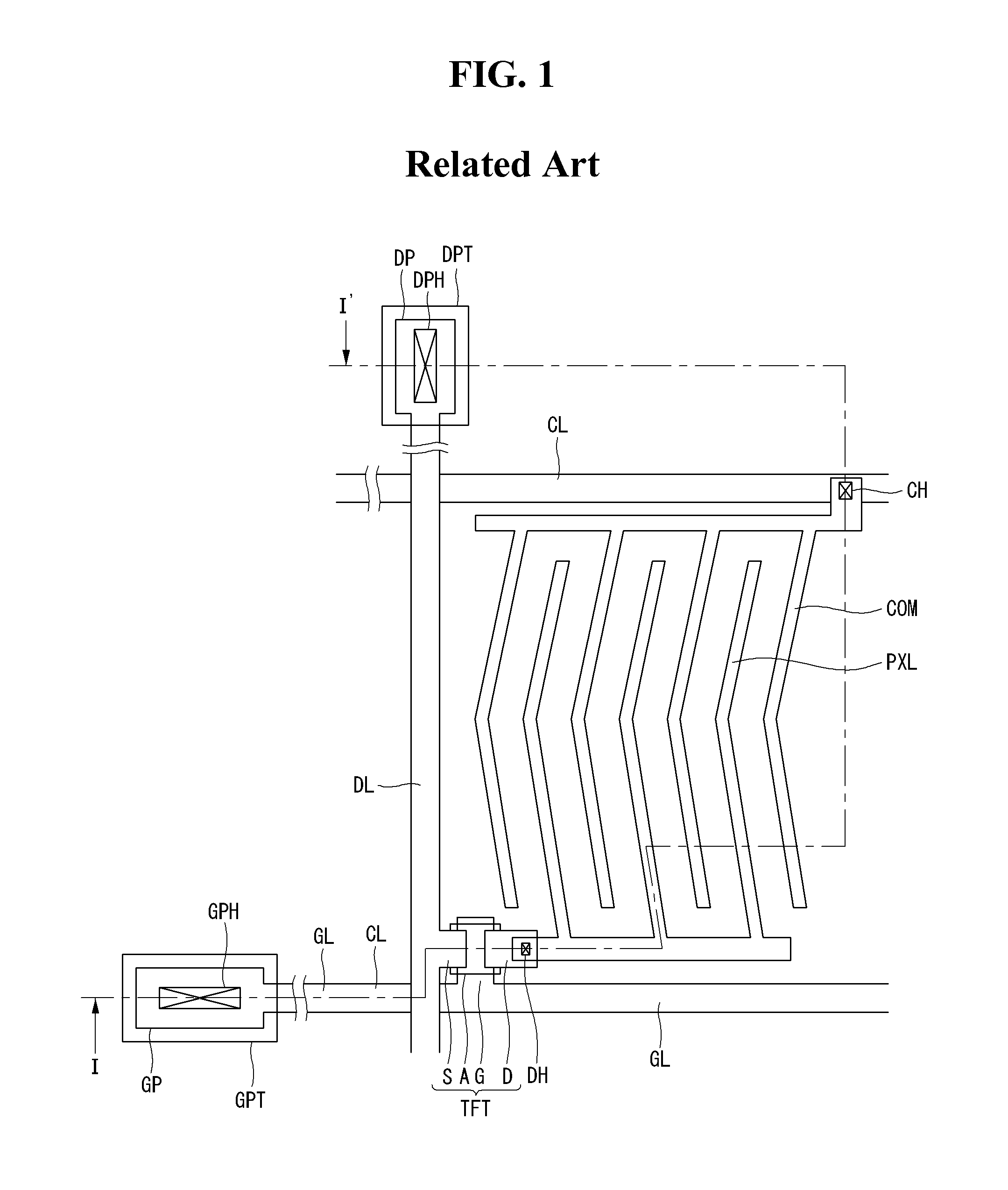

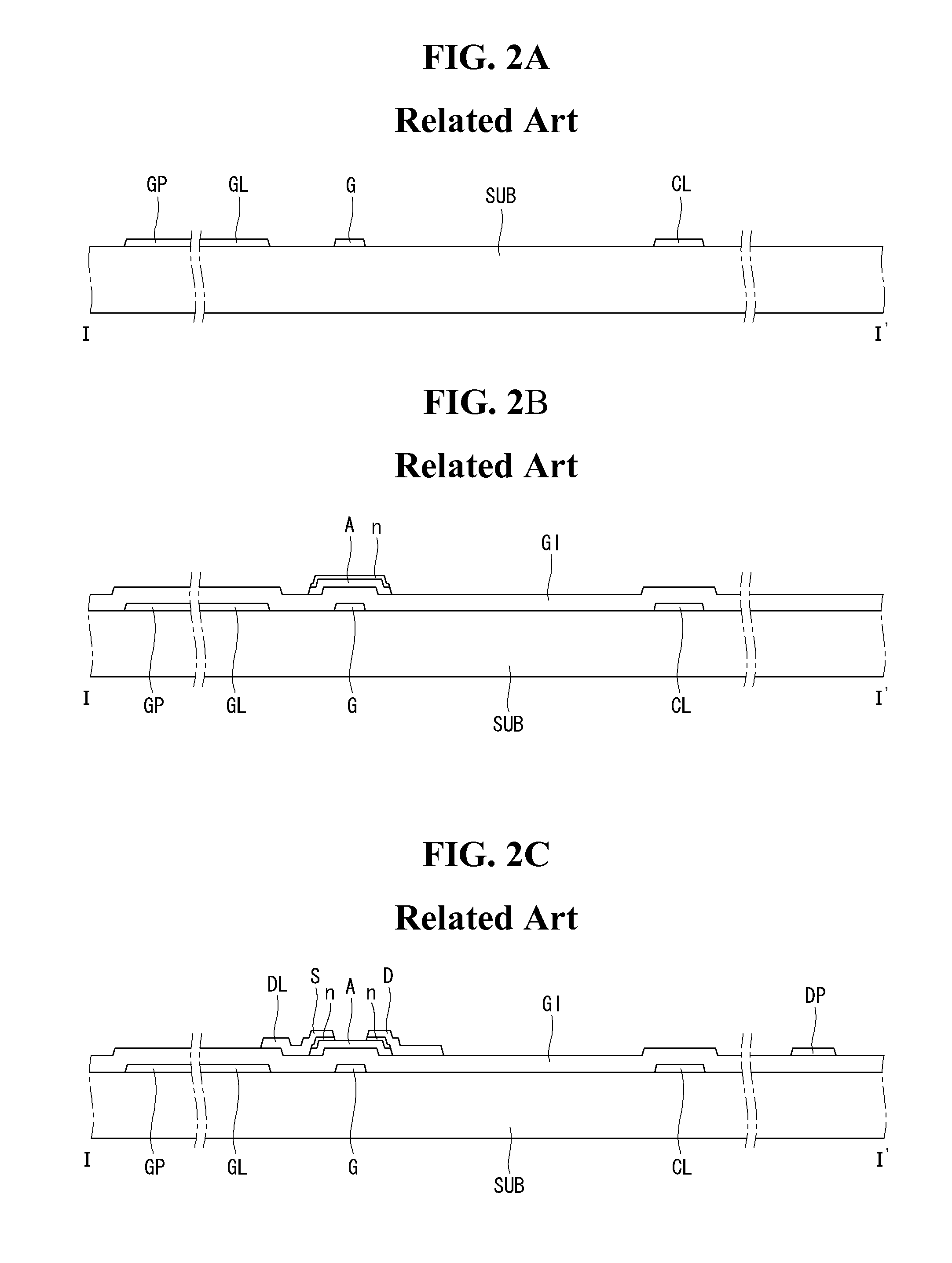

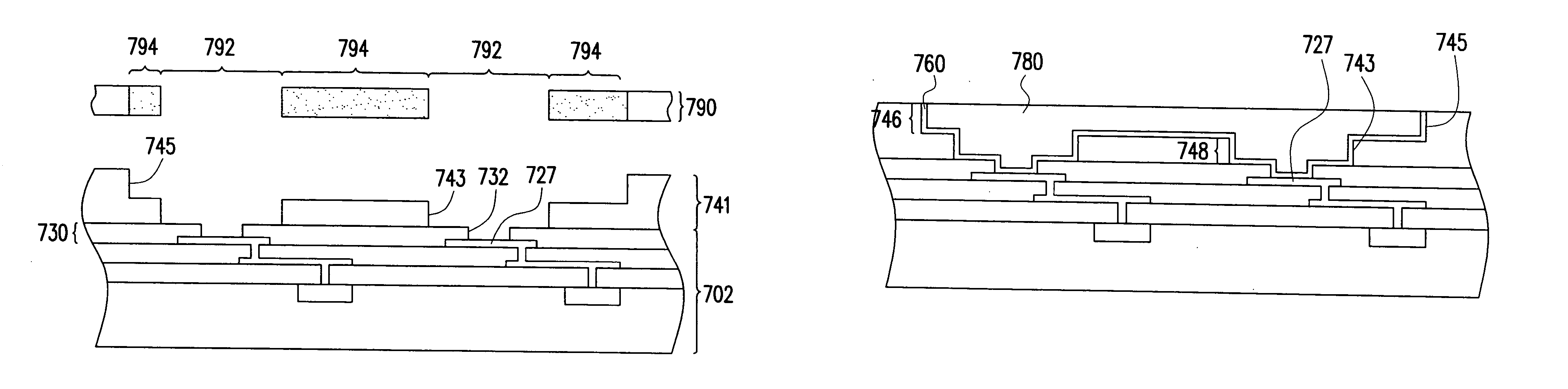

Method of manufacturing a thin film transistor including forming bus line patterns in a substrate and filling with metal

ActiveUS8592237B2Lower resistanceBus lineSolid-state devicesSemiconductor/solid-state device manufacturingLine resistanceEngineering

A method for manufacturing a thin film transistor substrate including forming bus lines by etching a surface of a substrate to form bus line patterns and filling the bus line patterns with a bus line metal; forming a semiconductor channel layer at one portion of a pixel area defined by the bus lines; and forming source-drain electrodes on the semiconductor channel layer, a pixel electrode extending from the drain electrode within the pixel area, and a common electrode parallel with the pixel electrode. The bus lines are formed as being thicker but the bus lines are buried in the substrate so that the line resistance can be reduced and the step difference due to the thickness of bus line does not affect the device.

Owner:LG DISPLAY CO LTD

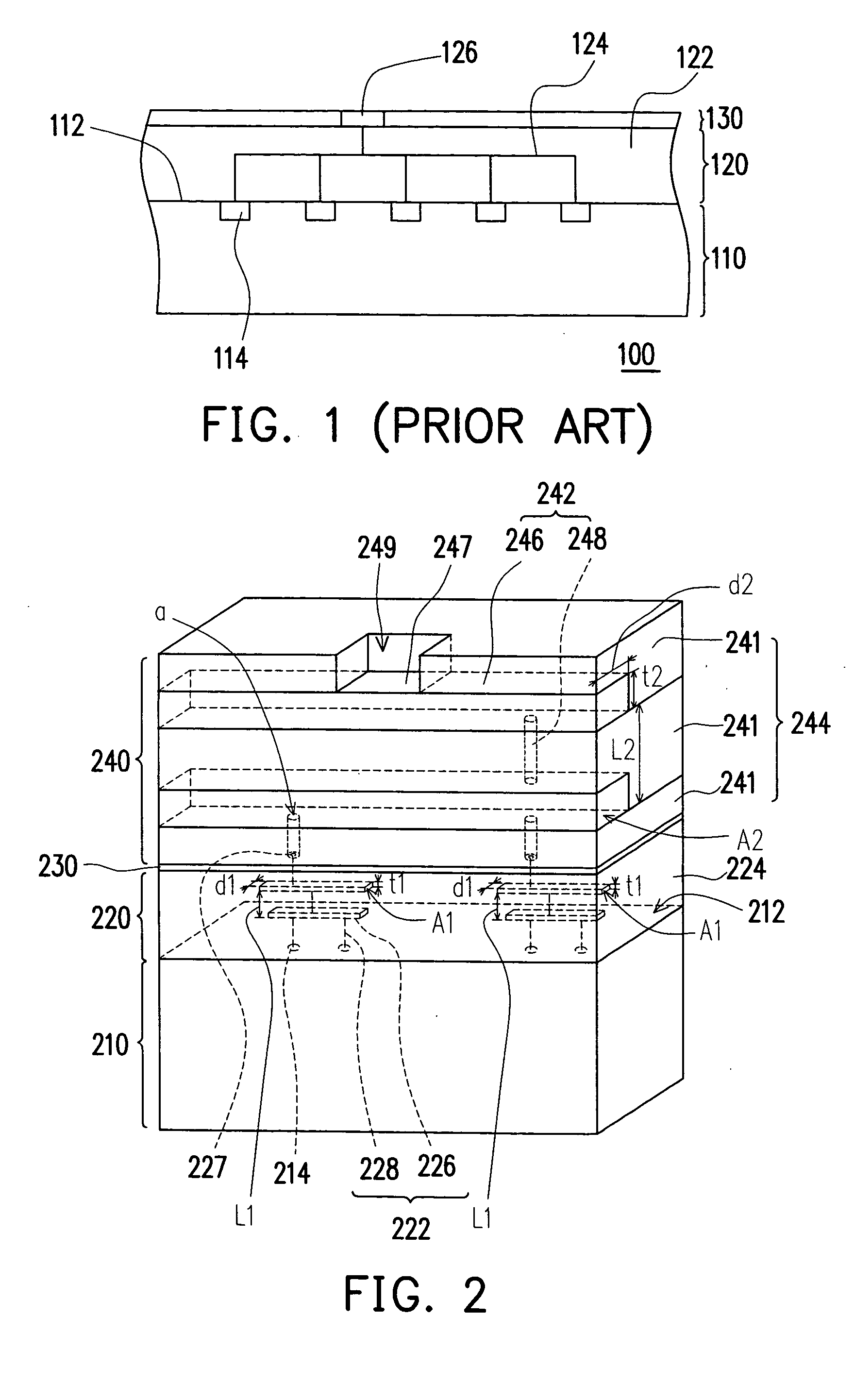

Chip structure and process for forming the same

InactiveUS20050032351A1Improves resistance-capacitance delayReduce energy lossSemiconductor/solid-state device detailsSolid-state devicesEngineeringInterconnection

A chip structure comprises a substrate, a first built-up layer, a passivation layer and a second built-up layer. The substrate includes many electric devices placed on a surface of the substrate. The first built-up layer is located on the substrate. The first built-up layer is provided with a first dielectric body and a first interconnection scheme, wherein the first interconnection scheme interlaces inside the first dielectric body and is electrically connected to the electric devices. The first interconnection scheme is constructed from first metal layers and plugs, wherein the neighboring first metal layers are electrically connected through the plugs. The passivation layer is disposed on the first built-up layer and is provided with openings exposing the first interconnection scheme. The second built-up layer is formed on the passivation layer. The second built-up layer is provided with a second dielectric body and a second interconnection scheme, wherein the second interconnection scheme interlaces inside the second dielectric body and is electrically connected to the first interconnection scheme. The second interconnection scheme is constructed from at least one second metal layer and at least one via metal filler, wherein the second metal layer is electrically connected to the via metal filler. The thickness, width, and cross-sectional area of the traces of the second metal layer are respectively larger than those of the first metal layers.

Owner:QUALCOMM INC +1

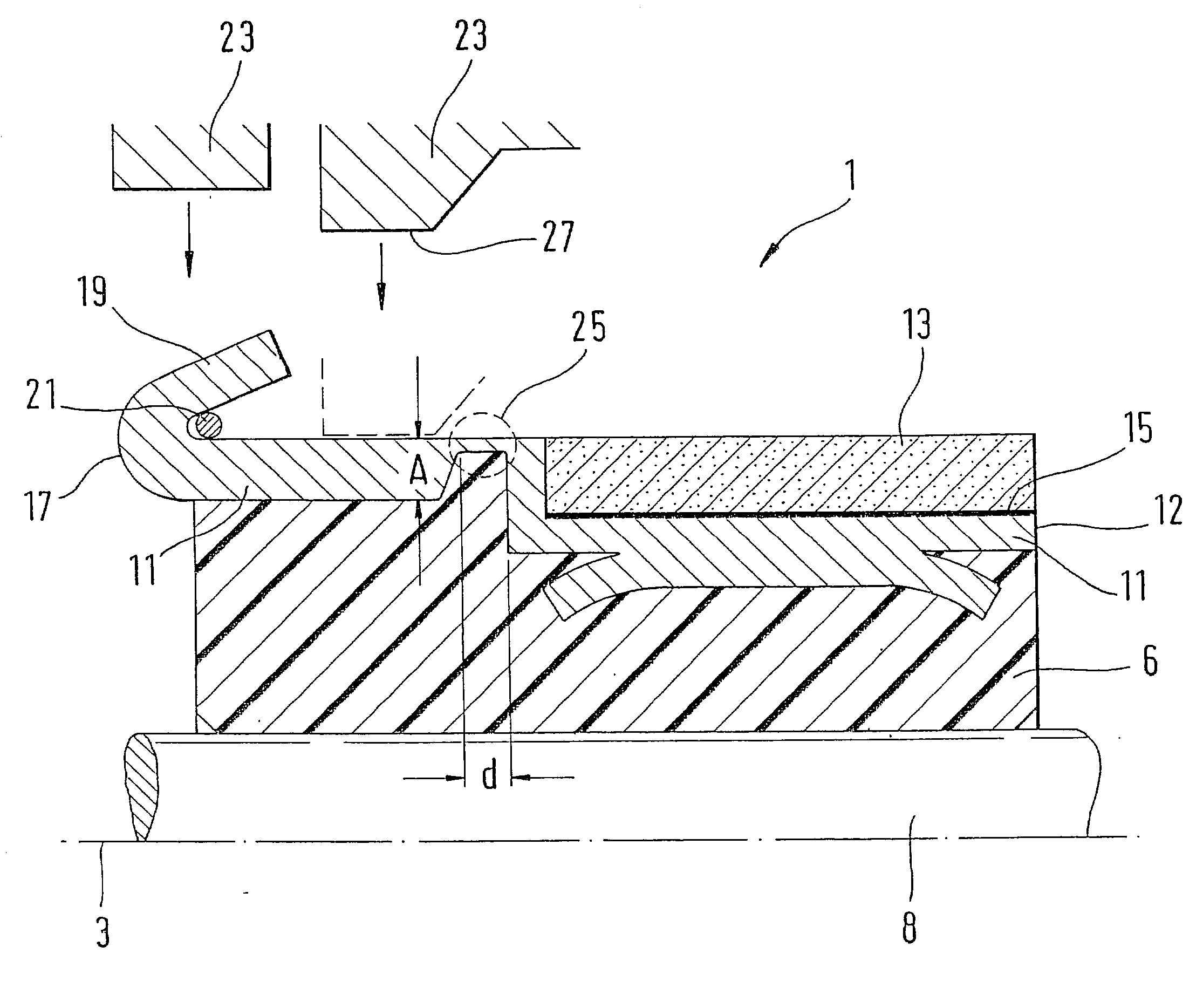

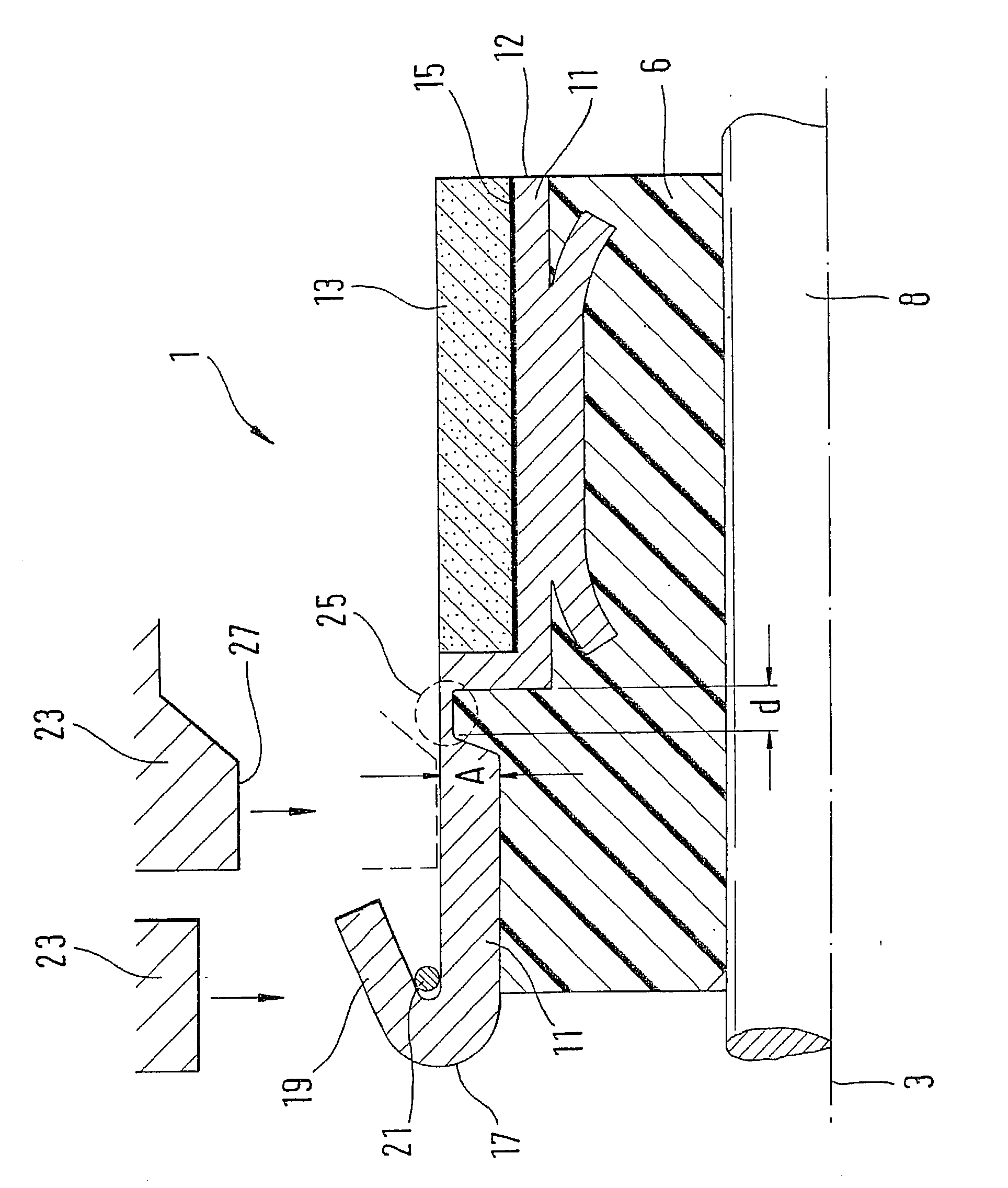

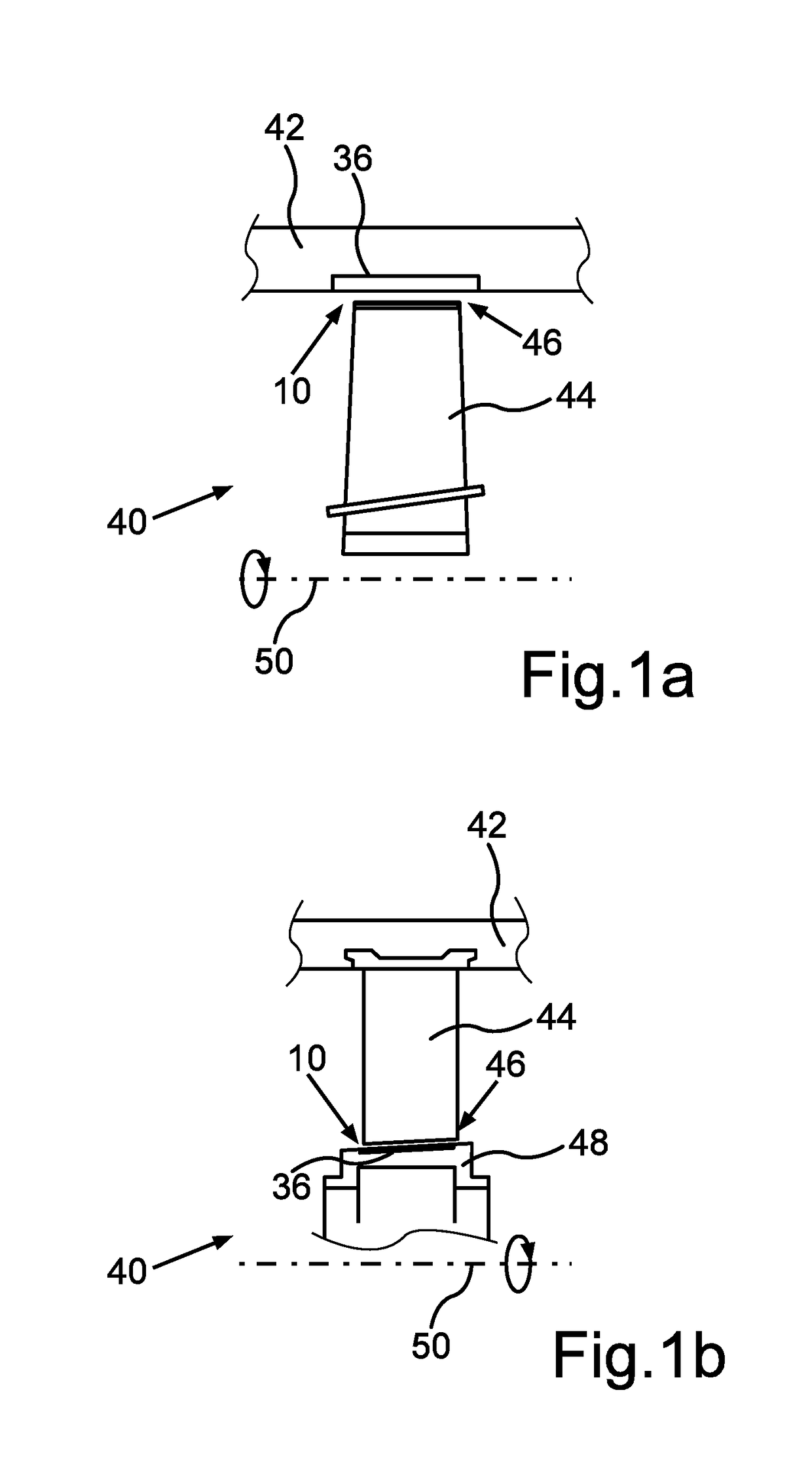

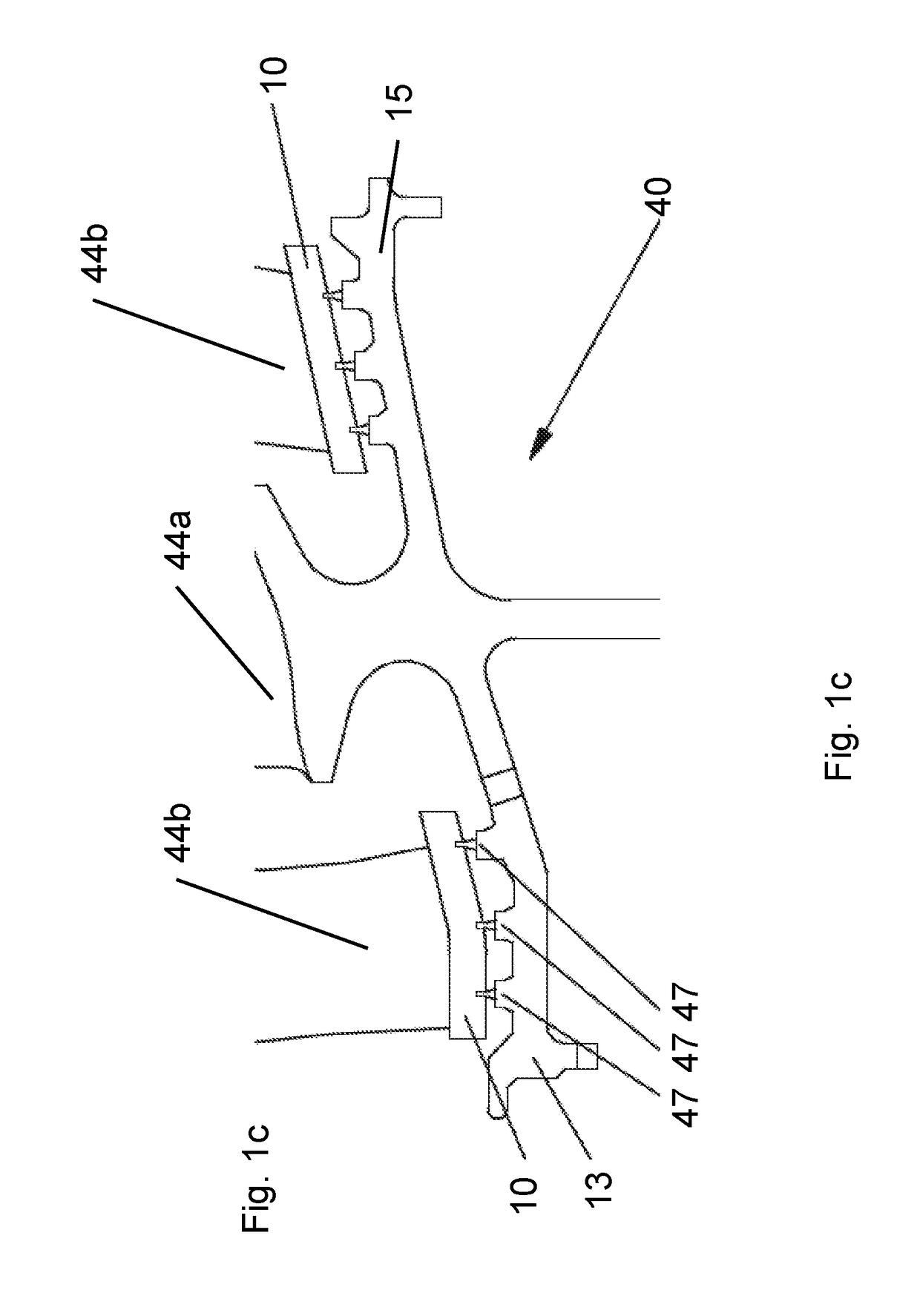

Hook commutator

InactiveUS20030020360A1Cross-sectional areaReduce heat transferRotary current collectorMagnetic circuitConductor CoilHigh heat

In a hook commutator of the prior art, a soldered connection (15), which connects a carbon segment (13) to a lamination (11) can become detached, since in the hot staking process for securing the winding wire, heat is produced. A hook commutator (1) of the invention has reduced thermal conduction in a region between the commutator hook (19) and the carbon segment (13), and thus the soldered connection (15) is protected against excessively high heat.

Owner:ROBERT BOSCH GMBH

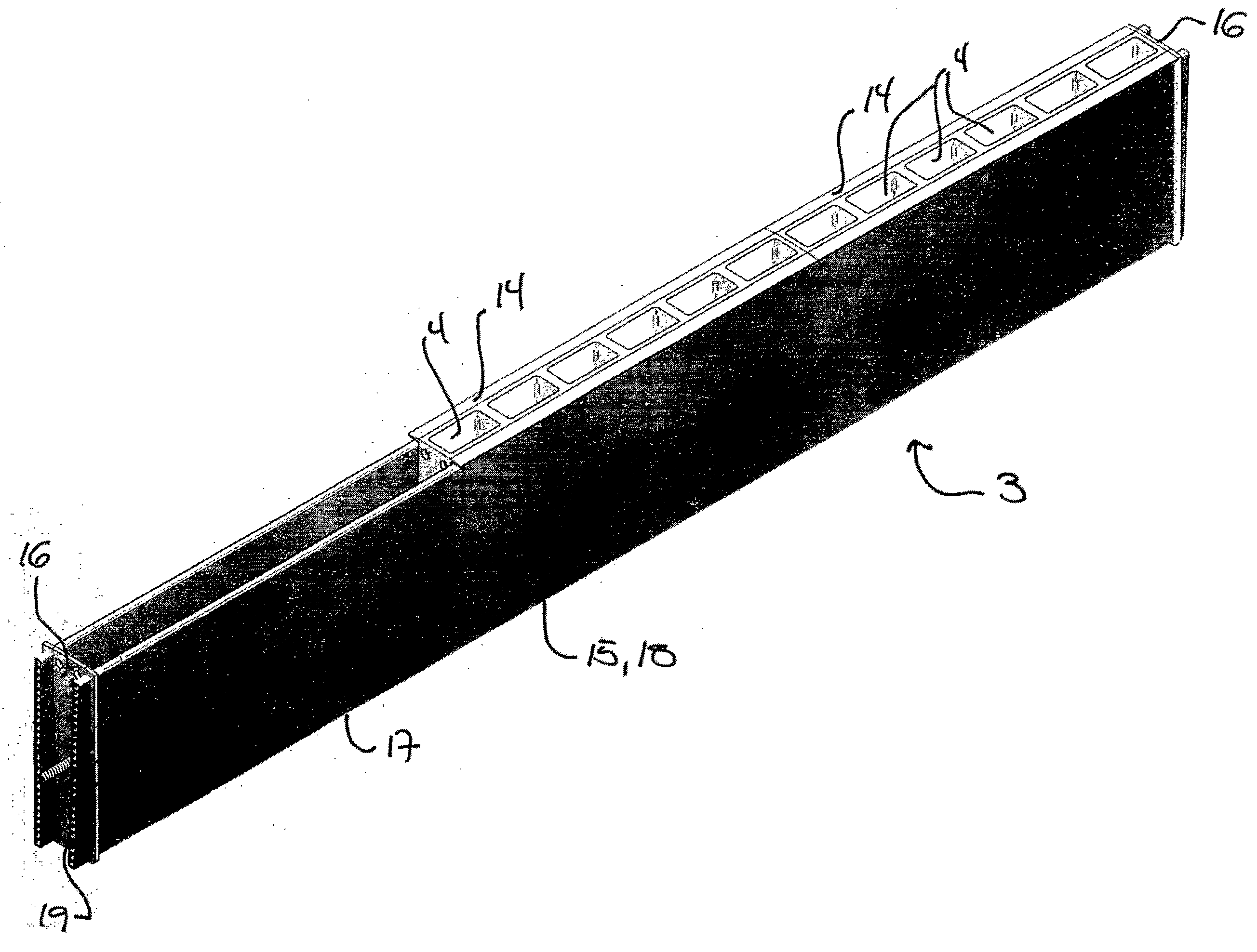

Freezer segment for a freezer for confectionary with segments including channels for direct evaporation of CO.sub.2

ActiveUS8763420B2Increase capacityCross sectional areaDomestic cooling apparatusLighting and heating apparatusSaline waterEvaporation

The present invention concerns a freezer segment for a freezer of the type used for casting confectionery in molds which are cooled for freezing and subsequently supplied with heat for a short period, whereafter stripping occurs. Cooling of the molds is effected by using direct evaporation of CO2. The advantage of such a freezer segment is that there is no use for both a primary and a secondary cooling circuit. Another advantage in using a system according to the invention is that working with temperatures down to about minus 50° C. is enabled, compared to about minus 40° C. with brine systems. The low freezing temperature entails that the capacity of a given system is increased by about 40%.

Owner:GRAM EQUIP

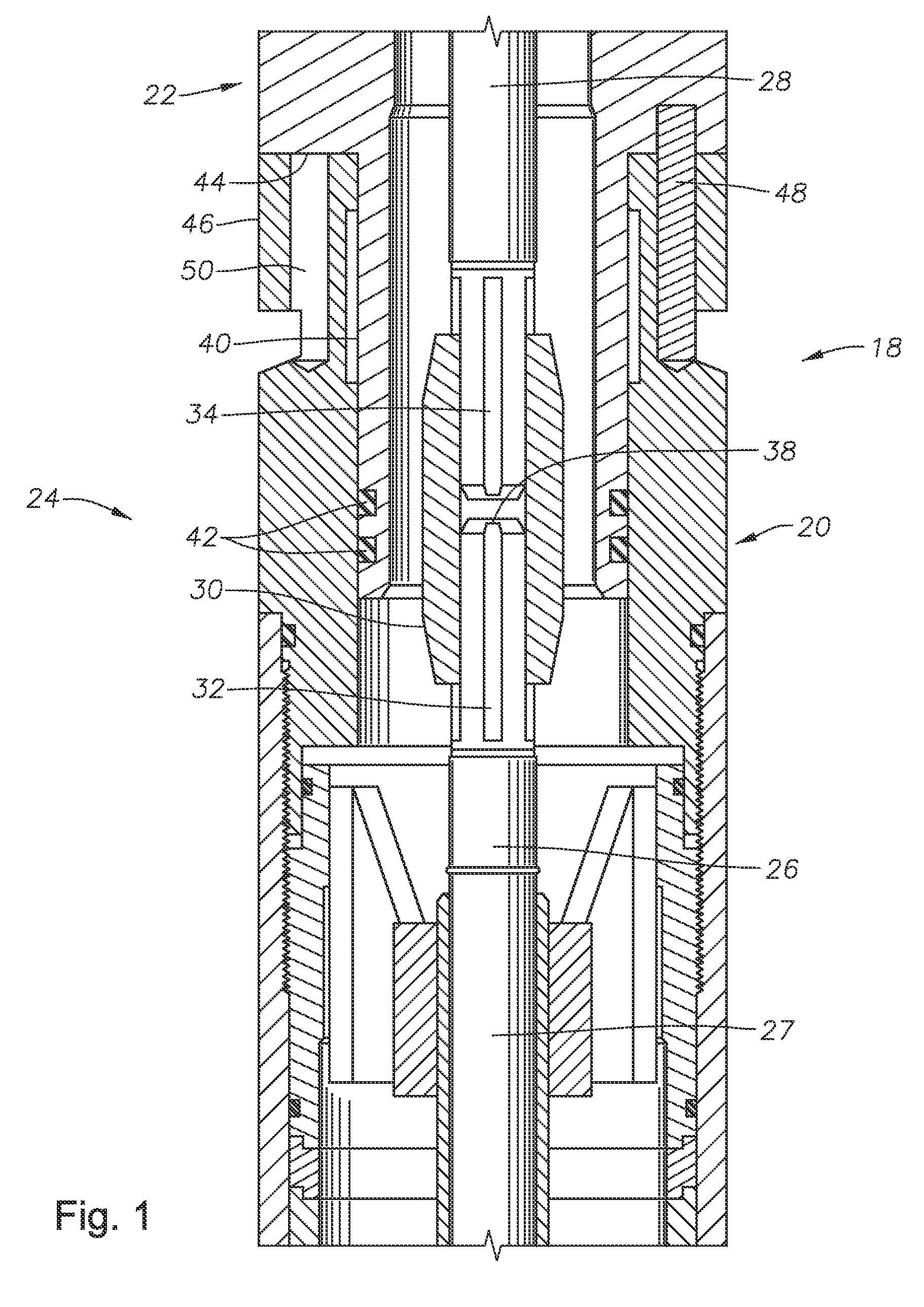

Connection assembly for through tubing conveyed submersible pumps

ActiveUS20120152563A1Cross sectional areaReduce the cross-sectional areaFluid removalElectrical and Electronics engineeringEnvironmental geology

An electrical submersible pumping (ESP) system for use in a wellbore that can be assembled in the wellbore. Upper and lower pump tandems are fitted with connectors that align the tandems when coupled in the wellbore. The connectors on the lower tandems have bores with enlarged openings on upward facing surfaces. Downward pointing pins are on lower facing surfaces of the connectors on the upper tandems. The cross sectional area of each bore decreases with distance away from the openings, so that as the pins insert into the bores the pins move along a helical path that in turn rotates the upper tandem into a designated azimuth and into alignment with the lower tandem. Properly aligning the upper and lower tandems couples respective drive and driven shafts in the tandems as the upper tandem lands on the lower tandem.

Owner:BAKER HUGHES INC

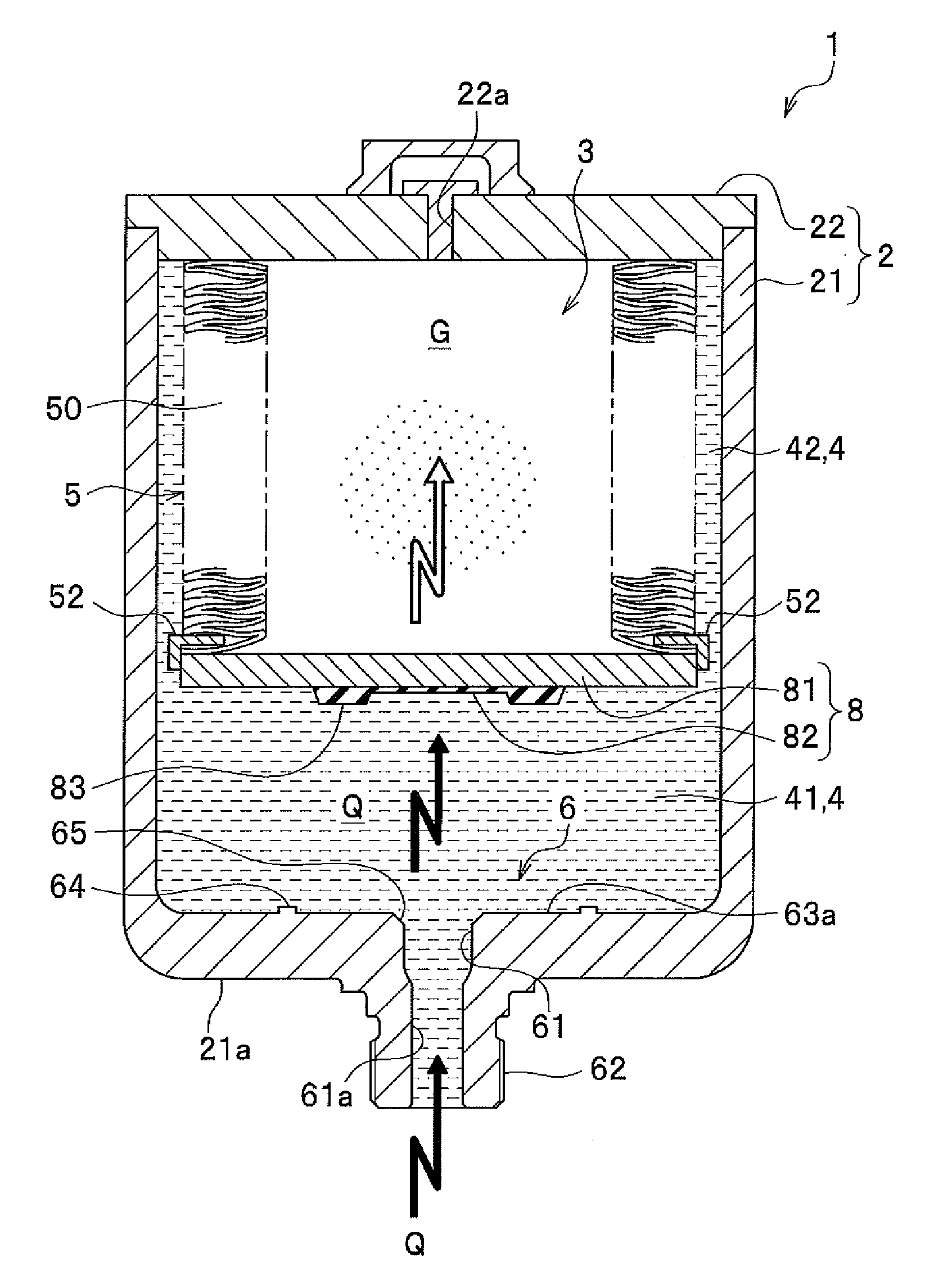

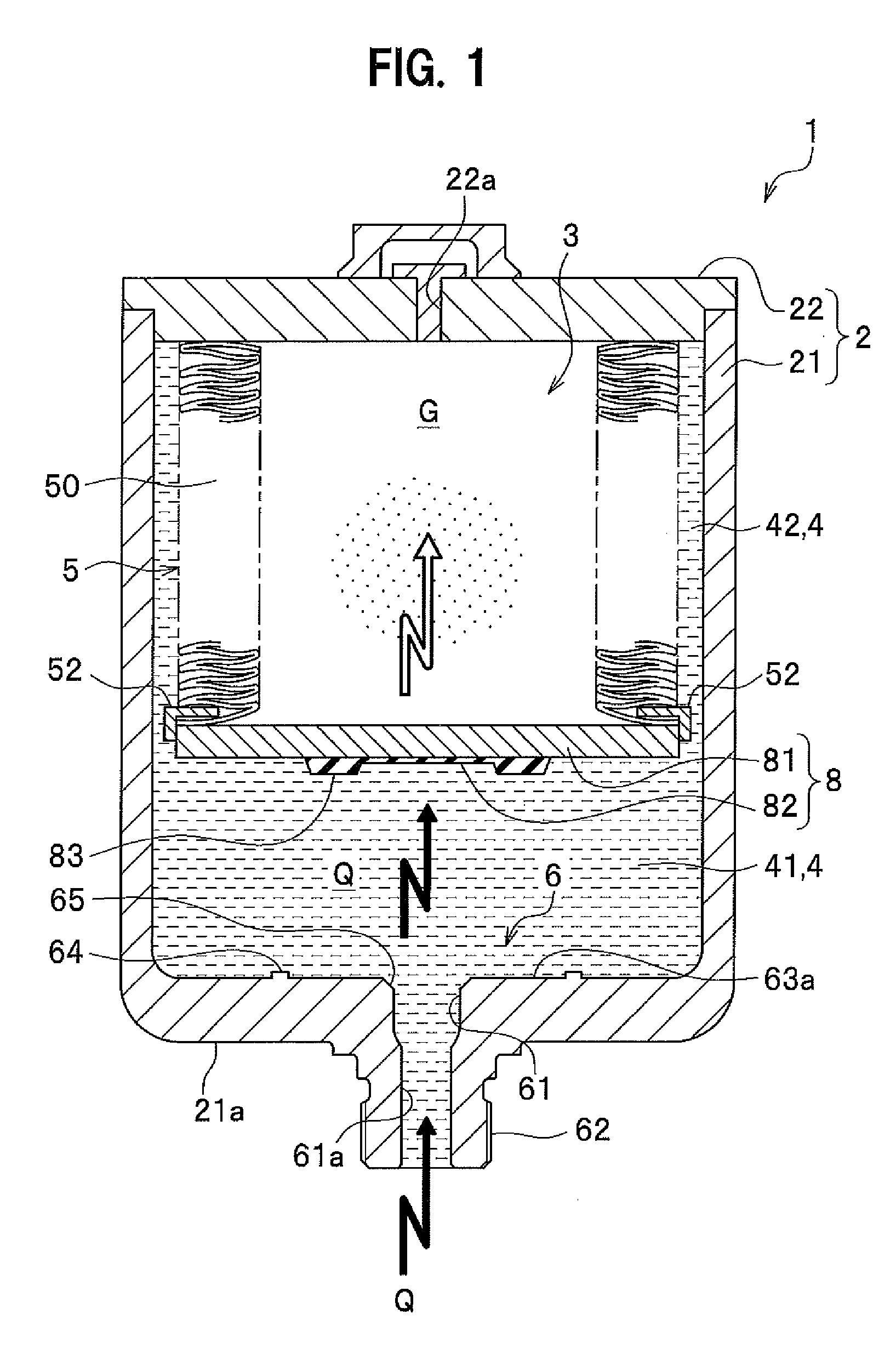

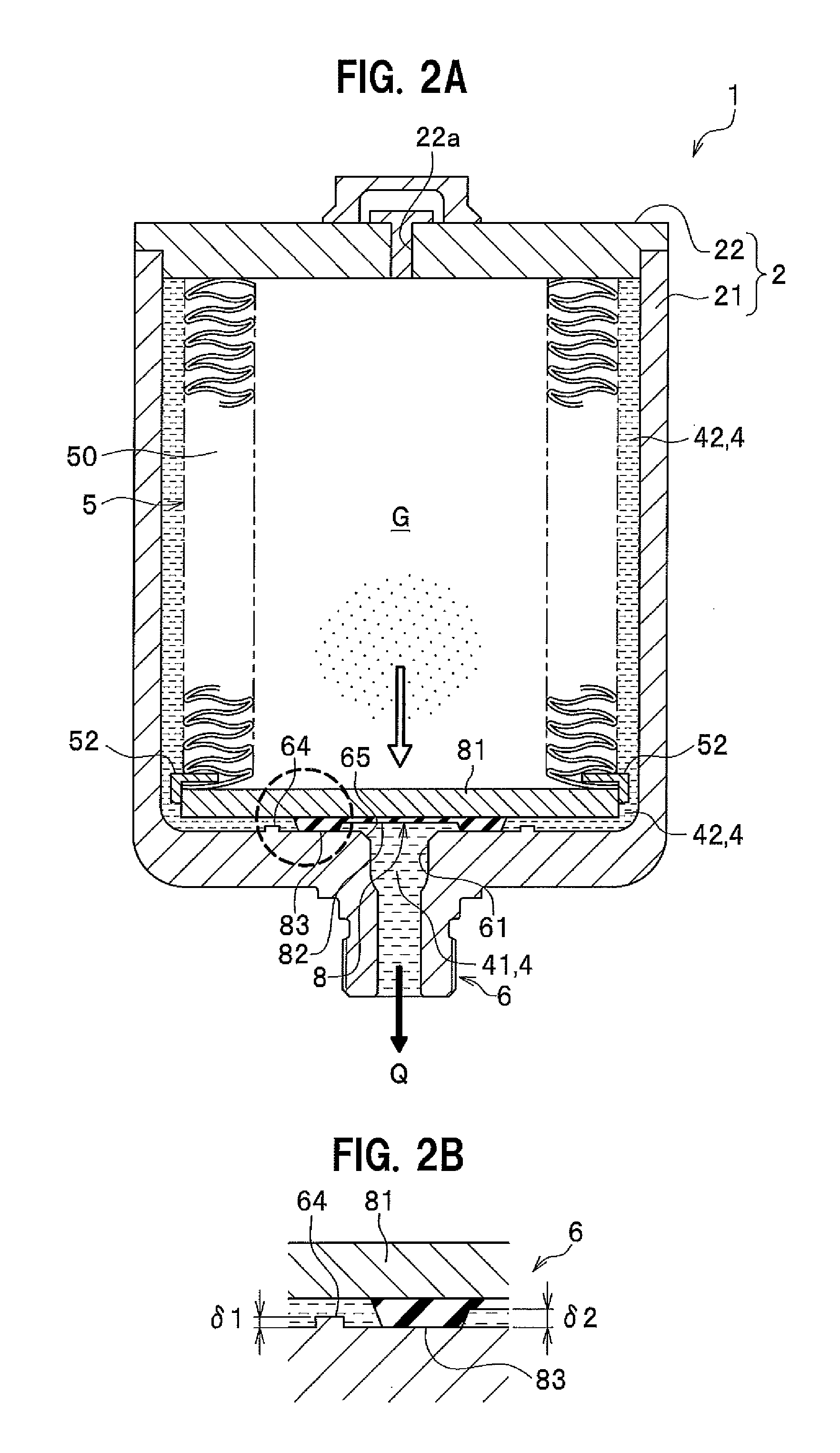

Accumulator

ActiveUS20150240839A1Improve sealingCross-sectional areaAccumulator installationsPipe elementsEngineeringAir chamber

An accumulator includes a bellows housed to freely expand and contract in a shell, a port part having a pressure fluid inflow port formed therein, and a self-sealing member arranged on a tip portion of the bellows to face the port part, in which when a pressure in the fluid chamber is lower than a predetermined pressure relative to an air chamber, the self-sealing member is allowed to abut onto a seal area of the port part to block the pressure fluid inflow port. The self-sealing member includes a resilient member arranged on a surface of a base material part, and an overhanging portion formed on the resilient member and allowed to abut onto the seal area for sealing. The port part includes a seal face having the seal area formed thereon, and a projecting portion arranged on a region other than the seal area on the seal face.

Owner:NHK SPRING CO LTD

Clutch cooling grooves for uniform plate temperature in friction launch

InactiveUS7448483B2Reduce the maximum temperatureMinimize distortionFluid actuated clutchesFriction clutchesEngineeringCooling fluid

Owner:GM GLOBAL TECH OPERATIONS LLC

Exhaust System for Motorcycle

ActiveUS20080110693A1Adequate sound absorbing effectFully filledSilencing apparatusThermometers using physical/chemical changesEngineeringMuffler

A motorcycle having a tail pipe formed from a pair of branch pipes that branch from a main pipe and that ensures a sound absorbing effect. A muffler has a casing that surrounds a rear section of an exhaust pipe, and a sound absorbing material that is filled between the casing and the rear section of the exhaust pipe. The rear section of the exhaust pipe includes a main pipe that is connected to the exhaust pipe and that extends to the rear, and first and second branch pipes that are connected to and branch from the main pipe and extend to the rear. A cross sectional area of the casing, when viewed from an exhaust gas flow direction becomes larger as the casing extends toward the branch pipe side.

Owner:YAMAHA MOTOR CO LTD

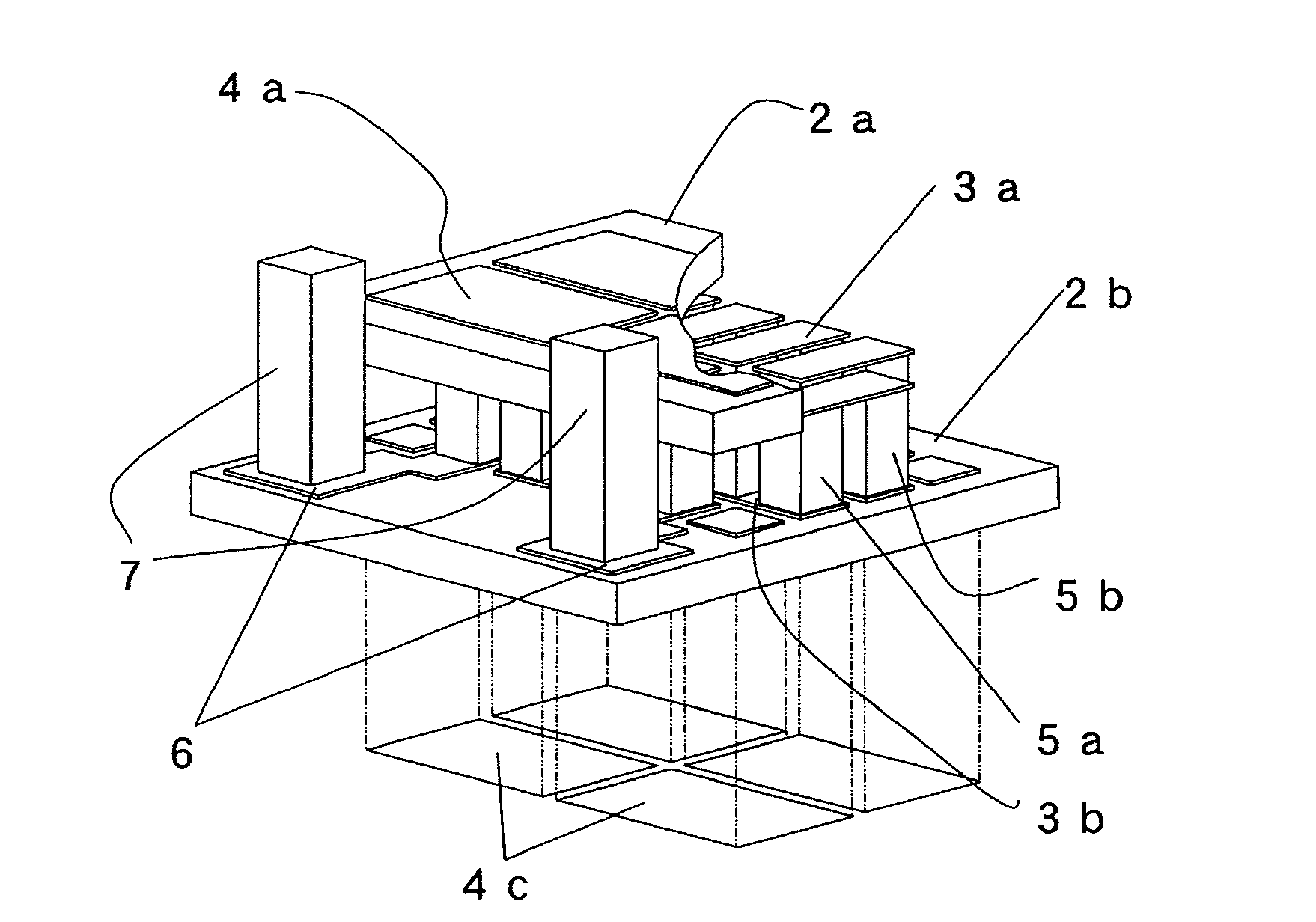

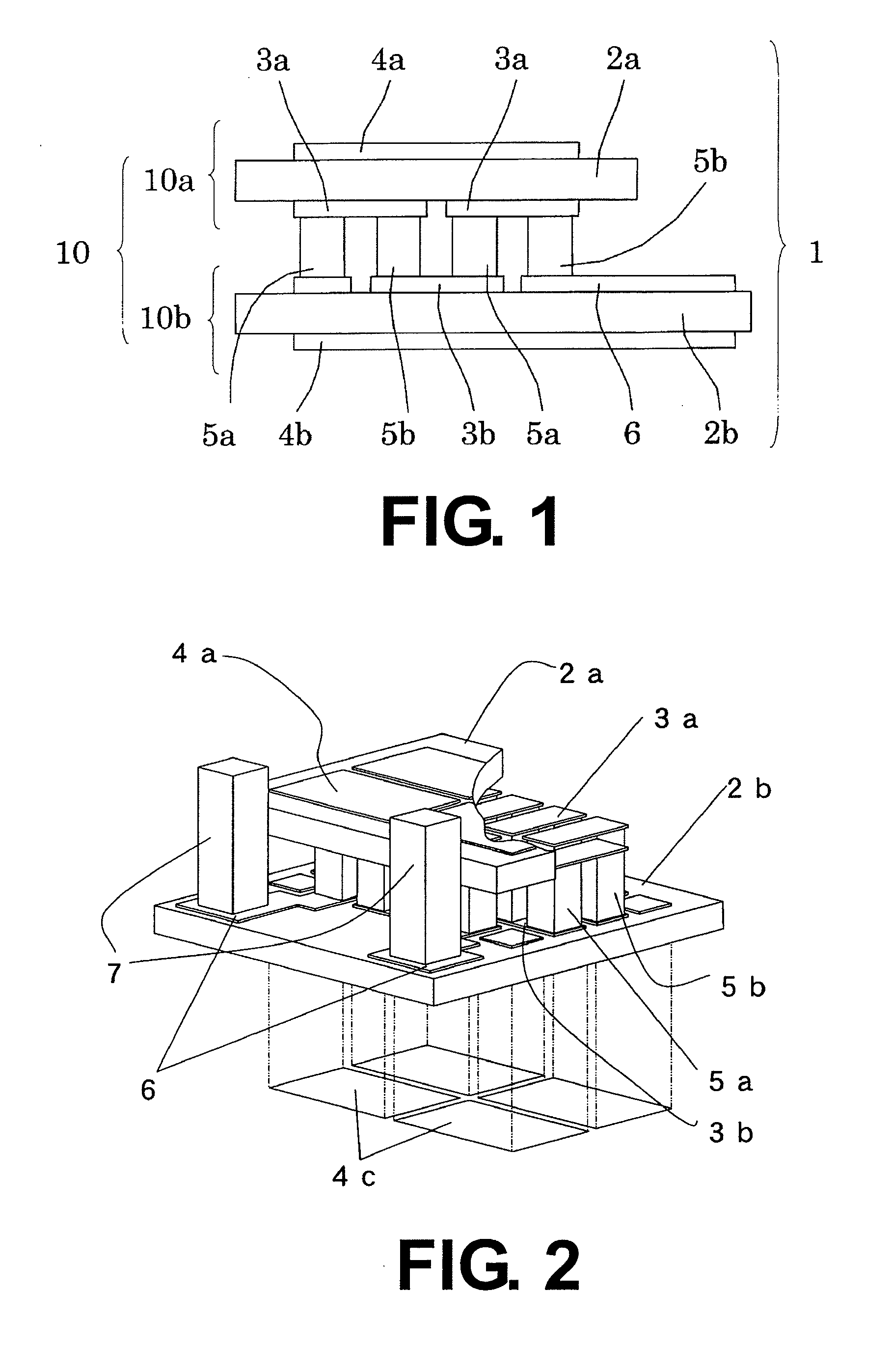

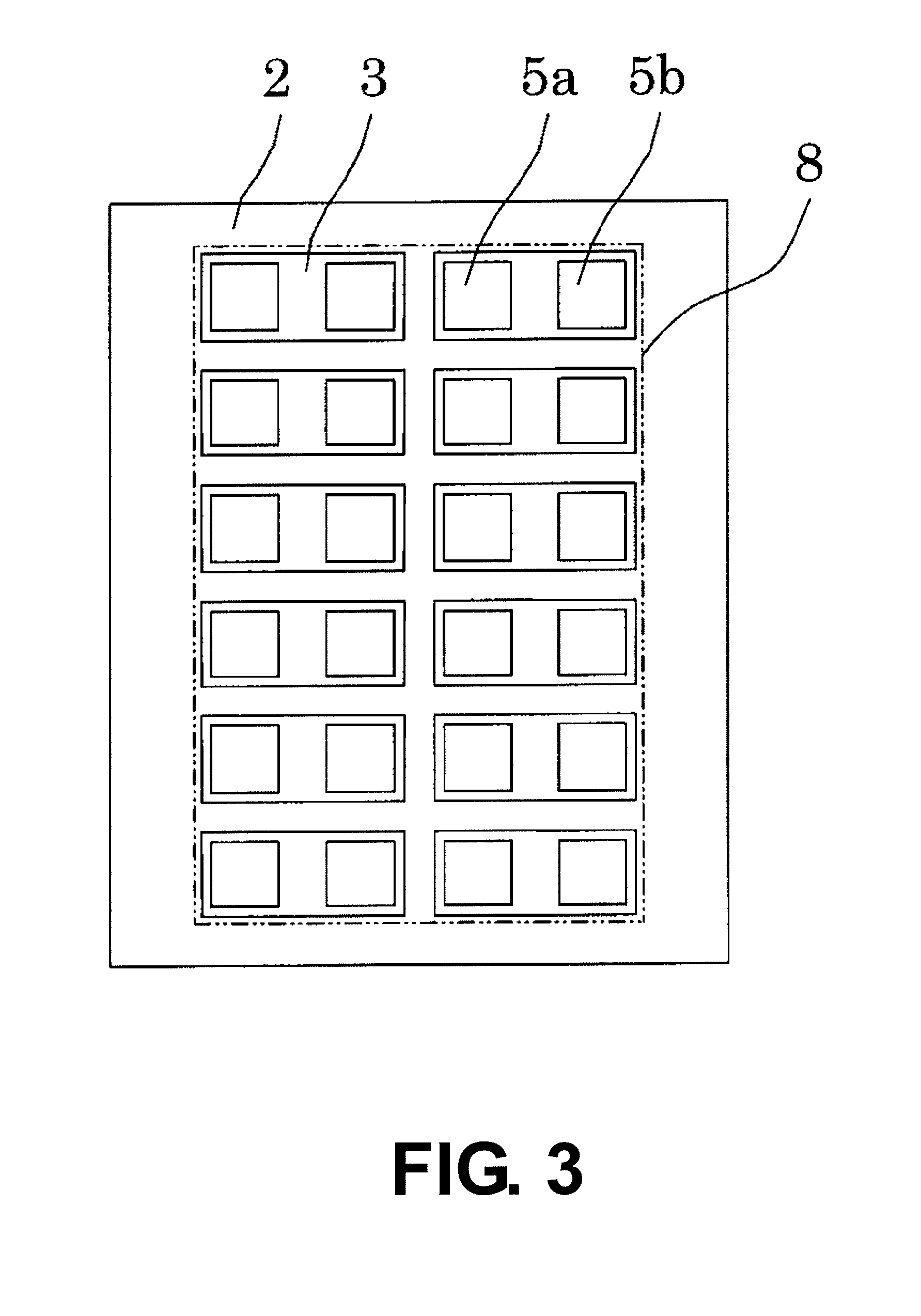

Thermoelectric module and metallized substrate

InactiveUS20100031989A1BreakageReduce the cross-sectional areaThermoelectric device with peltier/seeback effectSolid-state devicesTinningThermoelectric element

A thermoelectric module (1) utilizing the Peltier effect, exhibiting an element-occupied area ratio of 40% or below, the element-occupied area ratio defined as the ratio of the sum of cross-sectional areas, perpendicular to the direction of electric current passage, of thermoelectric elements (5a,5b) to the area of insulating substrate (2a) being in contact with an object to be cooled via a metalized layer (4a), wherein metalized layers (4a,4b) are provided with slits. In this construction, there can be prevented breakage of thermoelectric device by thermal stress occurring at assembly, or thermal stress occurring at pre-tinning conducted in advance for attaching an object to be cooled or at attaching package, etc.

Owner:KELK LTD

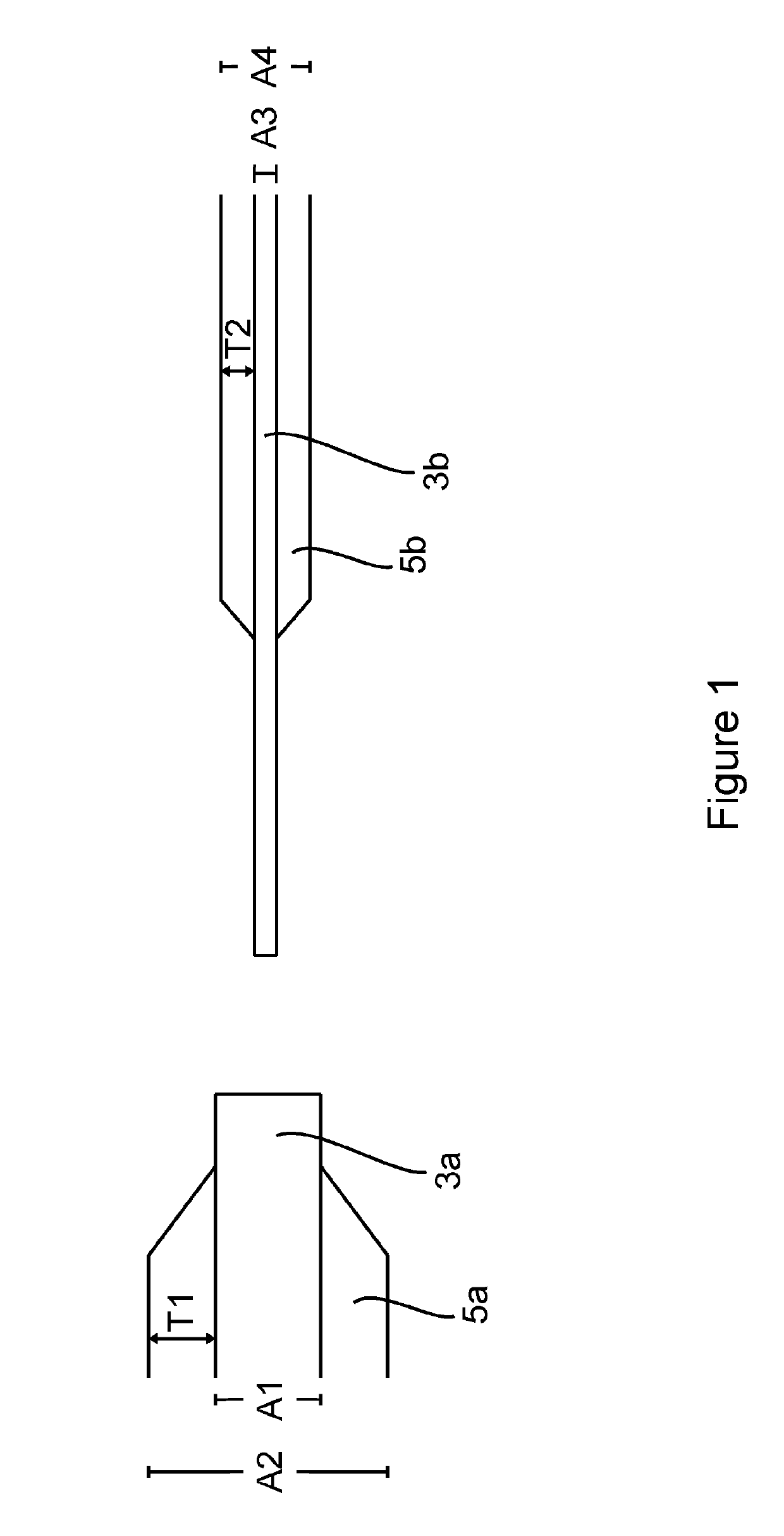

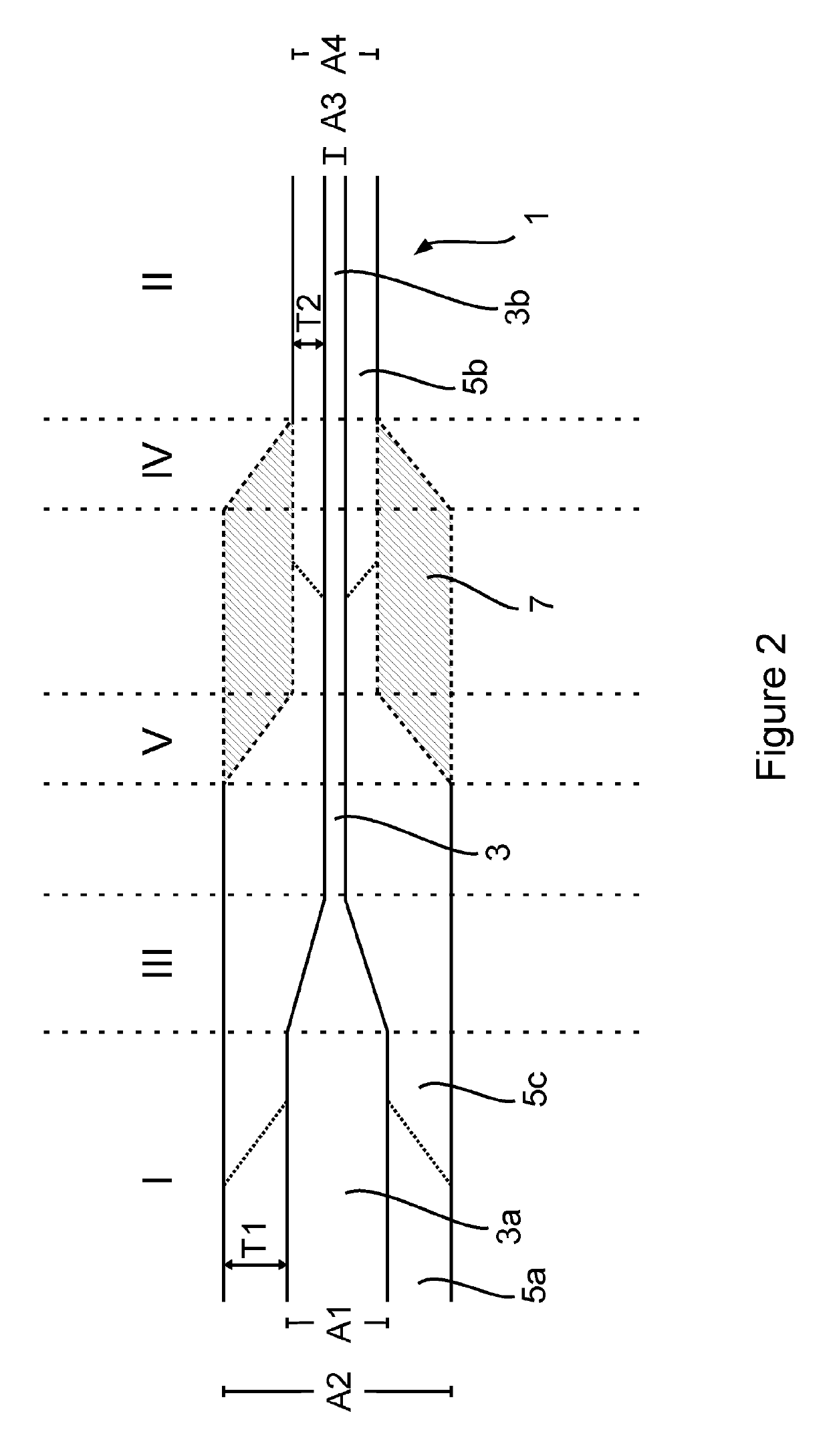

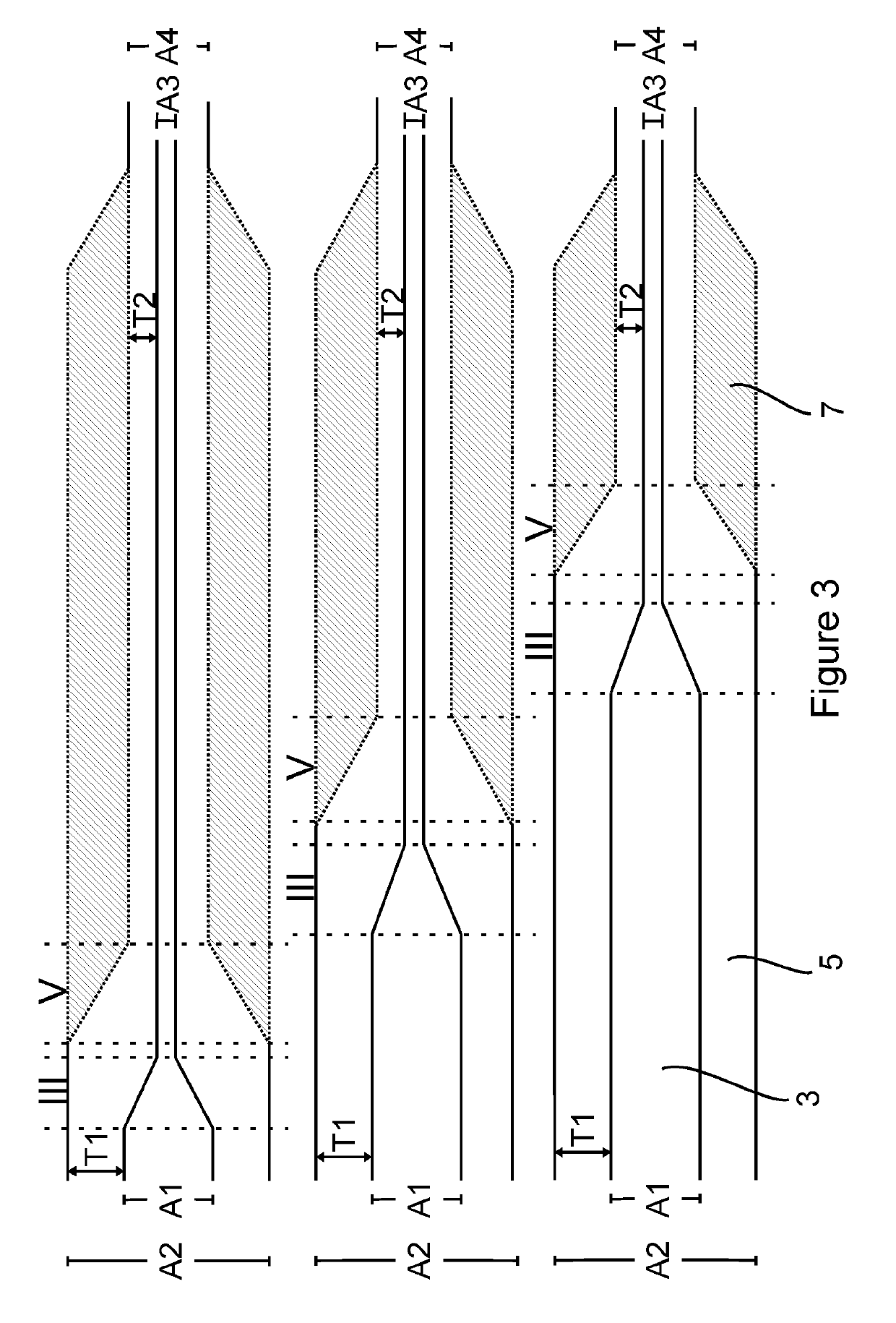

Insulated cable

ActiveUS20190237217A1Reduce variation in mechanical propertyCross-sectional areaPlastic/resin/waxes insulatorsSubmarine cablesElectrical and Electronics engineeringBond length

The invention relates to insulated submarine cables including conductive cores (3a, 3b) and insulating material (5a, 5b) surrounding the conductive cores (3a, 3b). Such an insulated cable includes a first length and a second length. The cable has a roughly constant core (3a) cross-sectional area A1 and a roughly constant insulating material (5a) thickness T1 along the first length, and a different roughly constant core (3b) cross-sectional area A3 and / or a different roughly constant insulating material (5b) thickness T2 along the second length. The cable may include one or more other lengths which join the first length and the second length to one another.

Owner:JDR CABLE SYST

Abradable structure for a turbomachine, turbomachine having an abradable structure, and method for manufacturing an abradable structure

InactiveUS20180355744A1Reduction in production timeSubstantial design freedomTurbinesAdditive manufacturing apparatusStructural elementEngineering

Owner:MTU AERO ENGINES GMBH

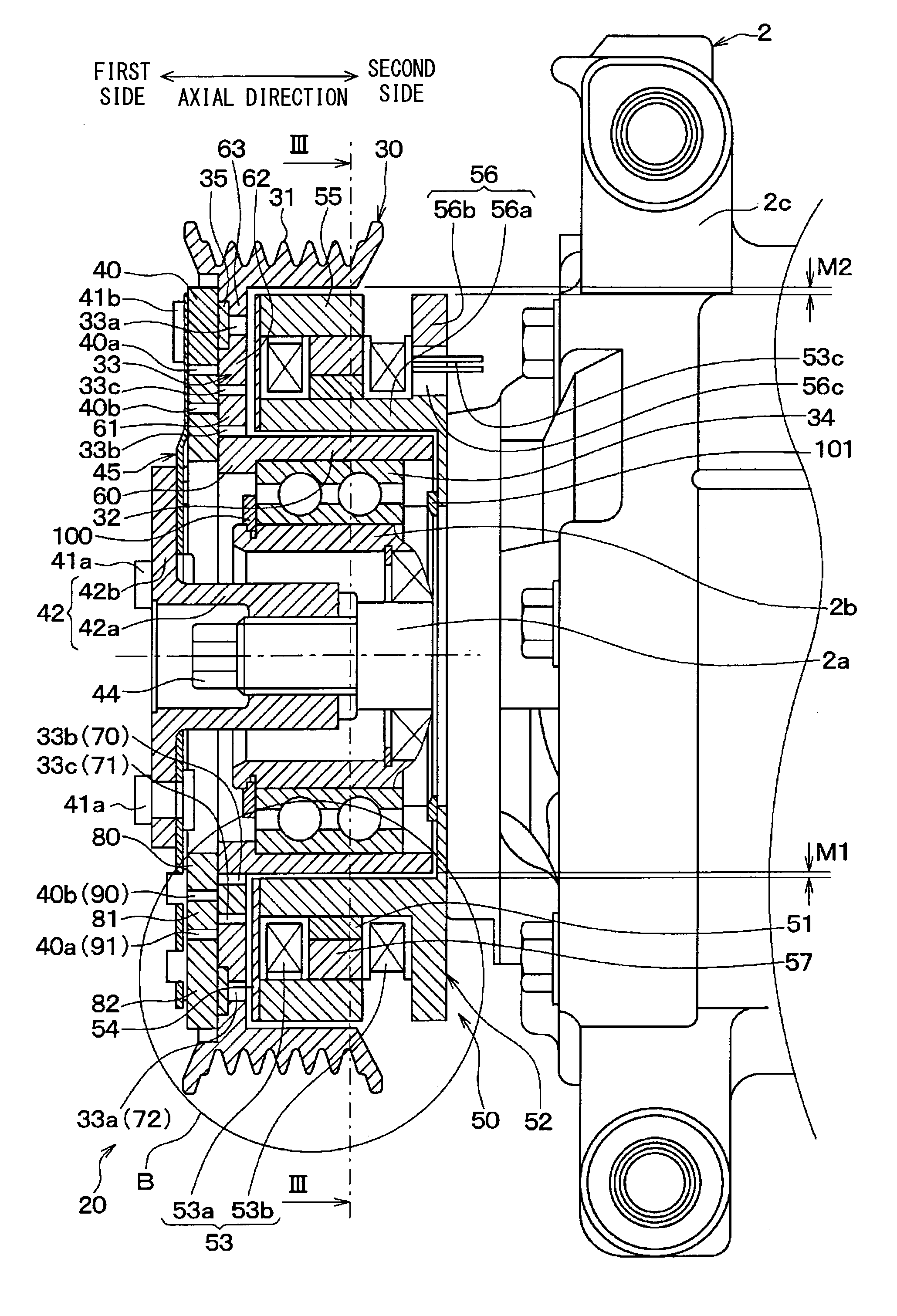

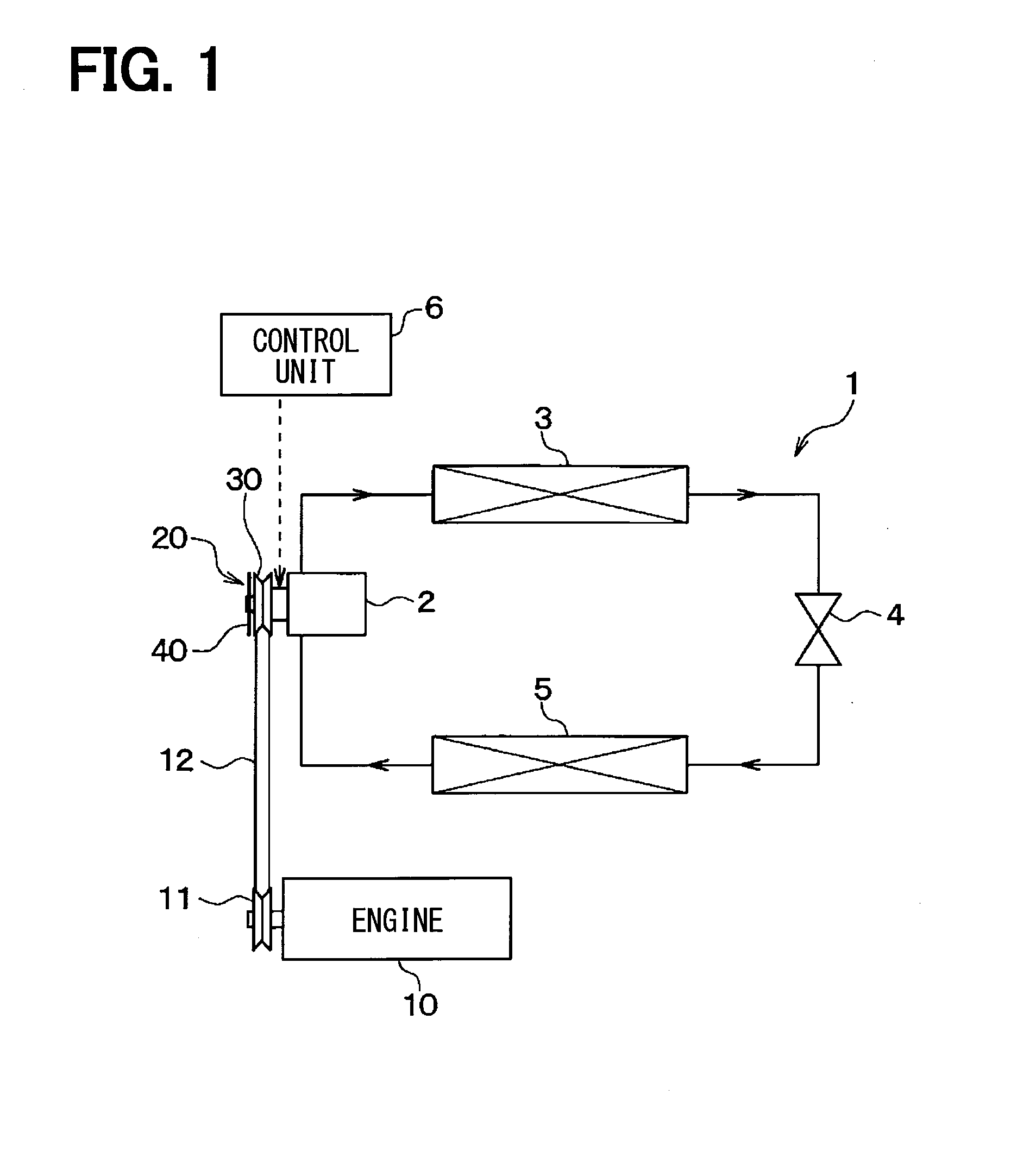

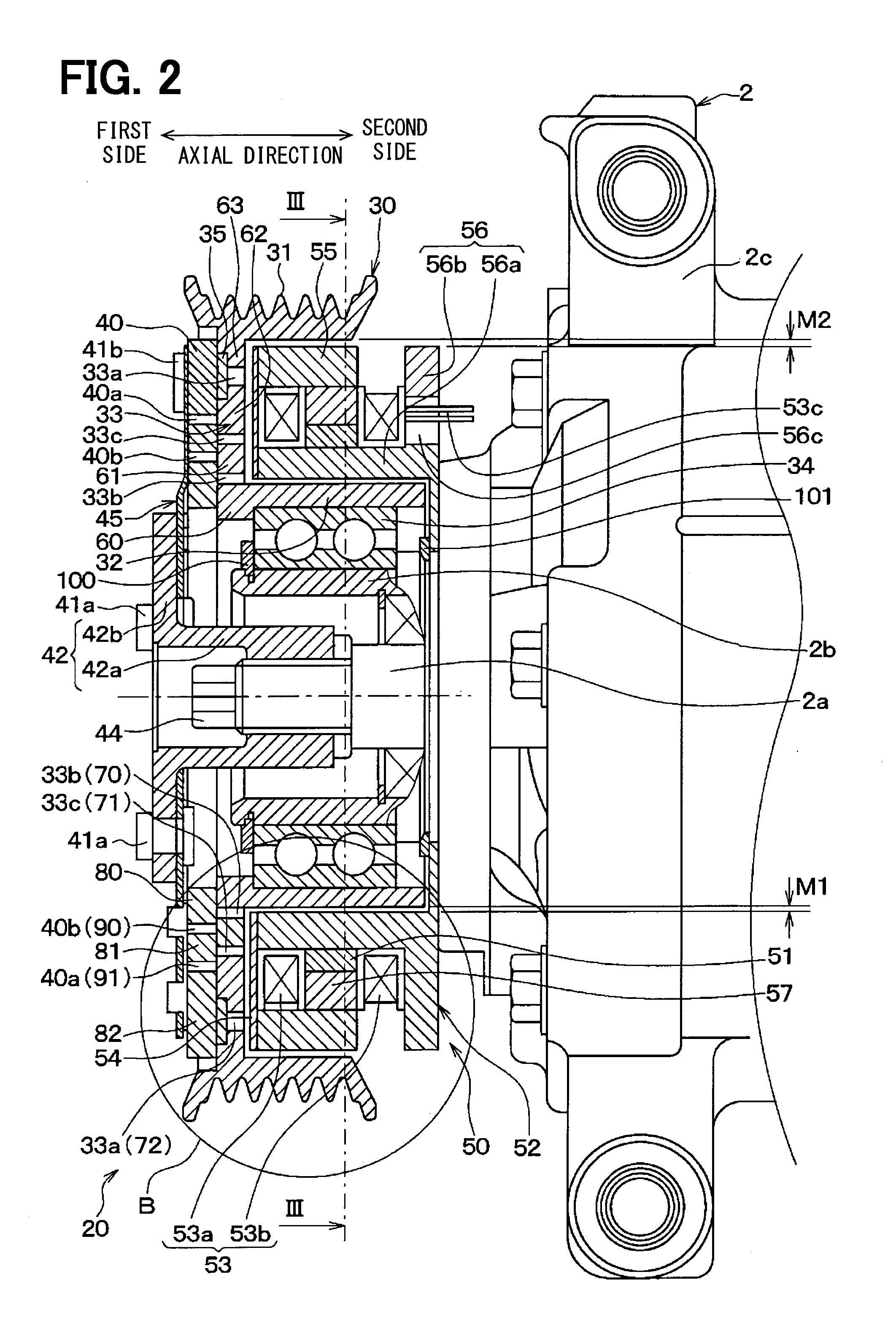

Clutch mechanism

InactiveUS20150300424A1Reduce physical sizeReduce power consumptionMagnetically actuated clutchesFriction clutchesEngineeringNon magnetic

In a clutch mechanism, non-magnetic portions of an armature and non-magnetic portions of a pulley are offset from one another in a radial direction of a rotating shaft. For this reason, in an attracting magnetic circuit, magnetic flux passes between an outer cylindrical portion and an inner cylindrical portion so as to avoid the non-magnetic portions of the armature and the non-magnetic portions of the pulley. Accordingly, magnetic flux passes through a boundary between the armature and the pulley six times. The number of poles of the attracting magnetic circuit is increased. The physical size of a permanent magnet can be reduced. For this reason, the physical size of the clutch mechanism is reduced. As a result, the power consumption of an electromagnetic coil can be reduced by increasing the cross-sectional areas of coil portions. The physical size of the clutch mechanism is reduced and the power consumed is reduced.

Owner:DENSO CORP

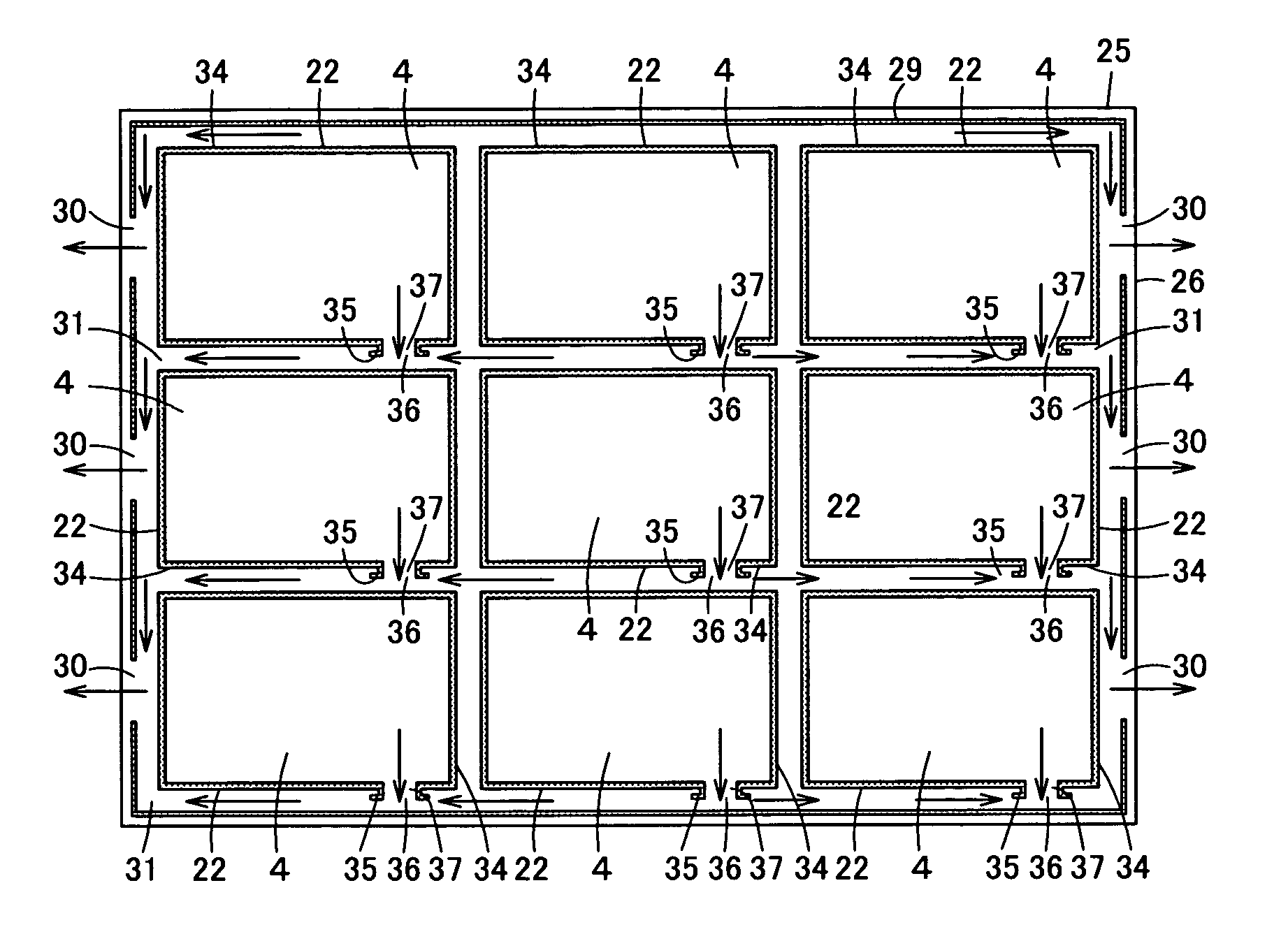

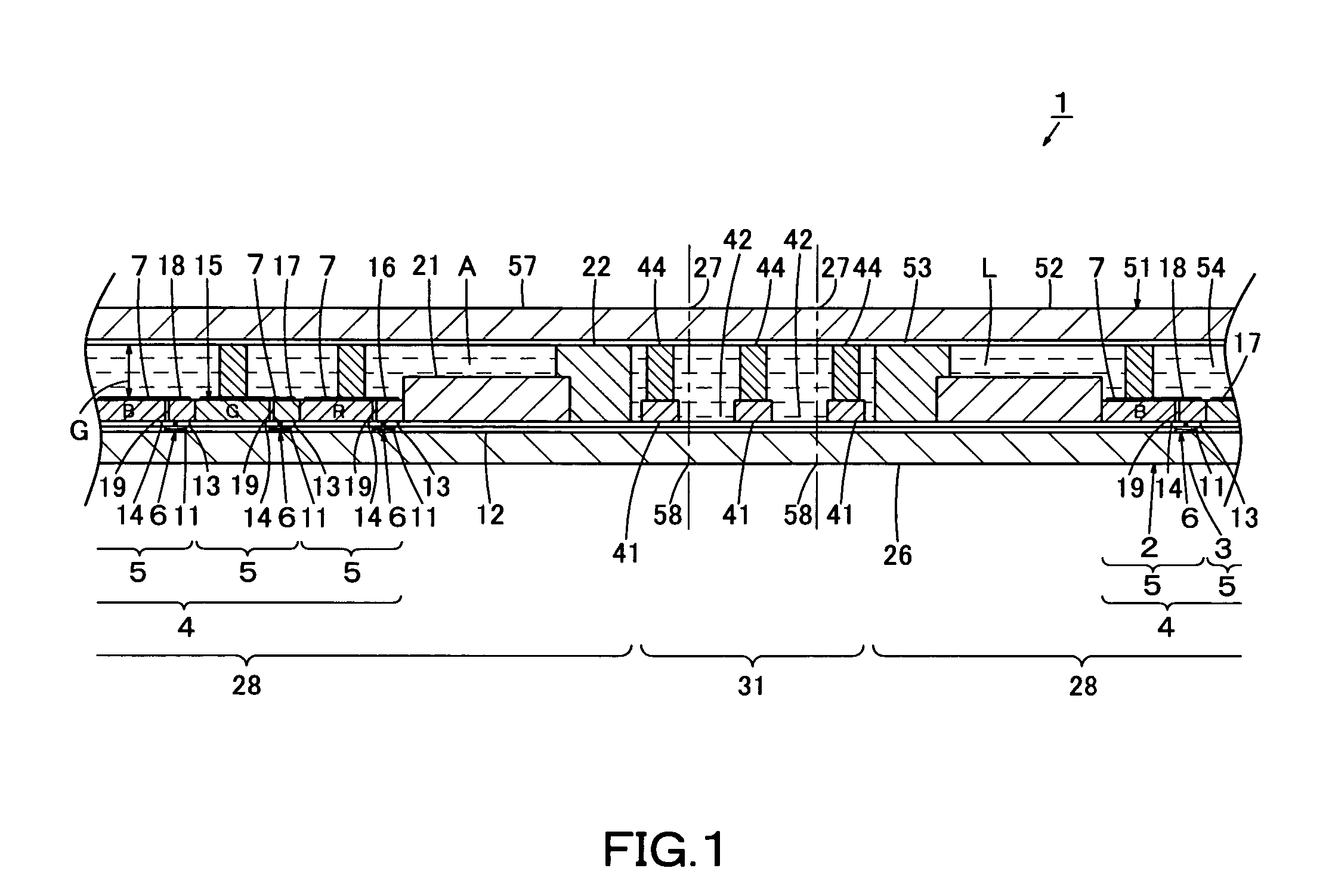

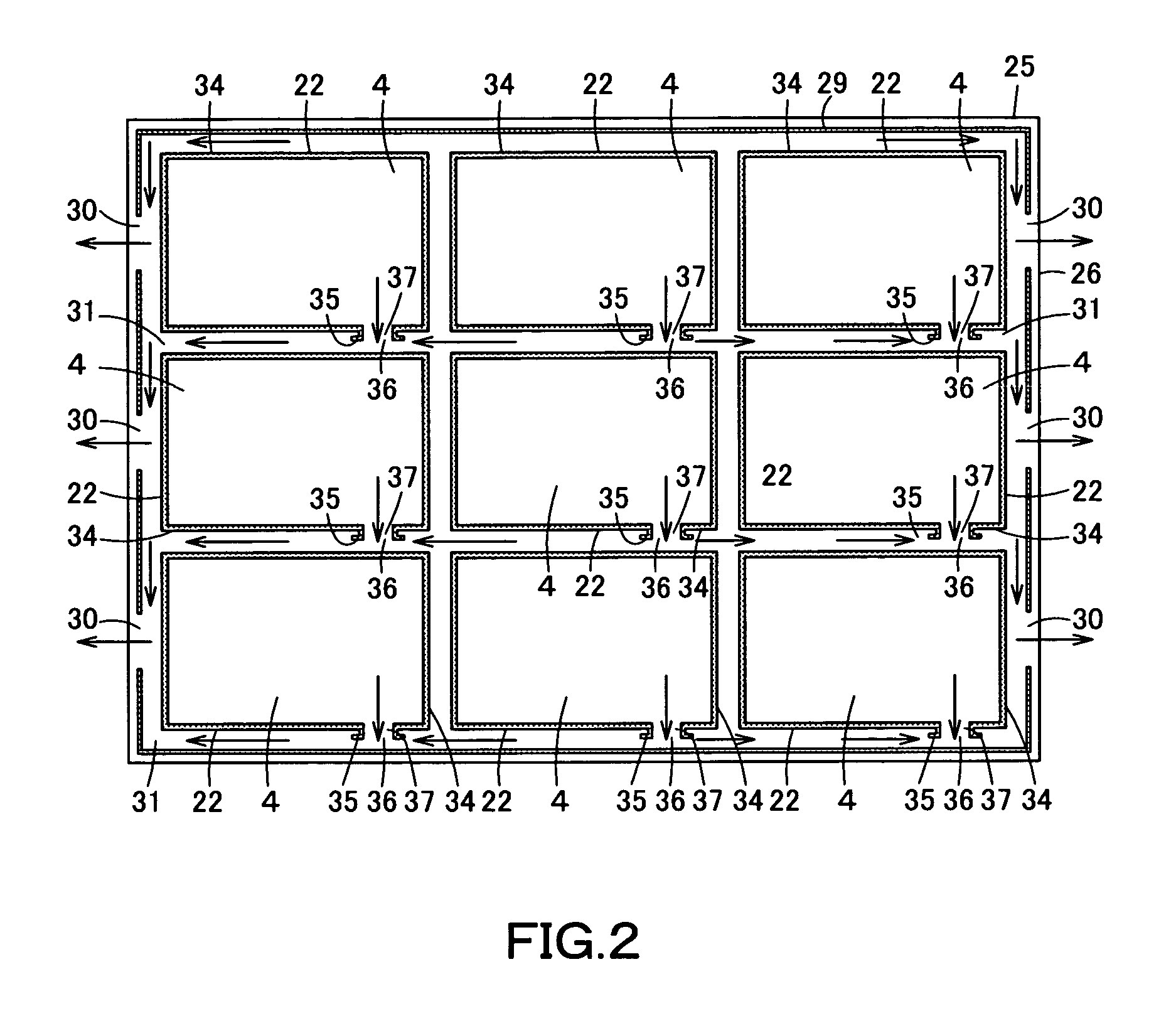

Board device and liquid crystal display device

InactiveUS7542123B2Cross-sectional areaImprove the display effectNon-linear opticsDischarge efficiencyProduction rate

Owner:JAPAN DISPLAY CENTRAL CO LTD

Cooling fin structure

ActiveUS9523541B2Reduce total pressure lossImprove heat transfer efficiencySemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat sink

A cooling fin structure used in a cooler for an electric device includes a plurality of pin fins (71) arranged in a zigzag form in a coolant passage (80). Each of the pin fins (71) has a circular portion (72) having a circular cross-section, and irregularly shaped portions (73) provided contiguously on the upstream and downstream sides of the circular portion (72) as viewed in a direction of flow of the coolant. The irregularly shaped portions (73) have an outer peripheral surface (75) that is formed along a circumference (130) having a center at a center point (101) of the circular portion (72) of a pin fin (71, 71B) that is located adjacent to the pin fin (71, 71A) having the irregularly shaped portions (73), in an oblique direction relative to the direction of flow of the coolant.

Owner:TOYOTA JIDOSHA KK +1

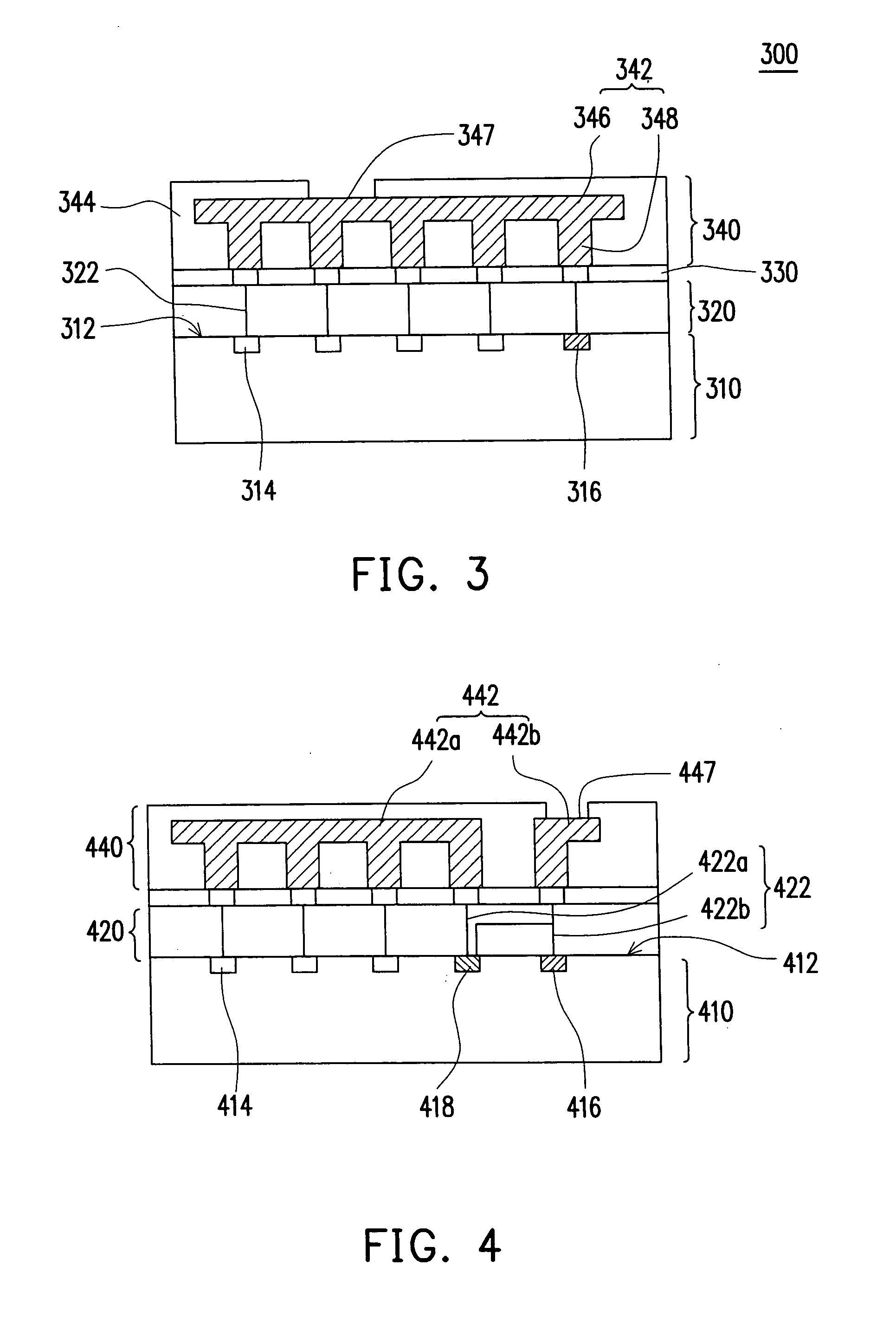

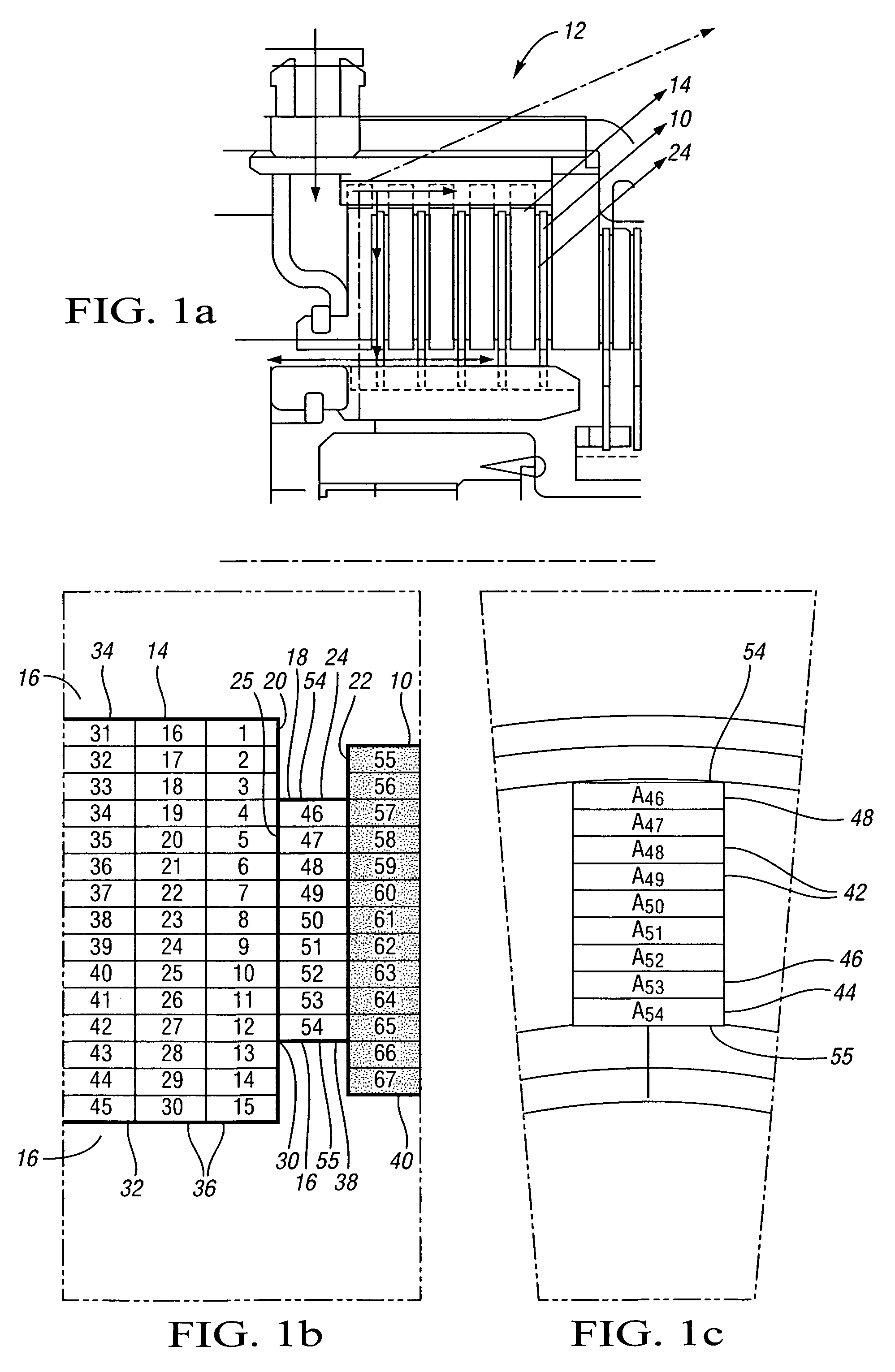

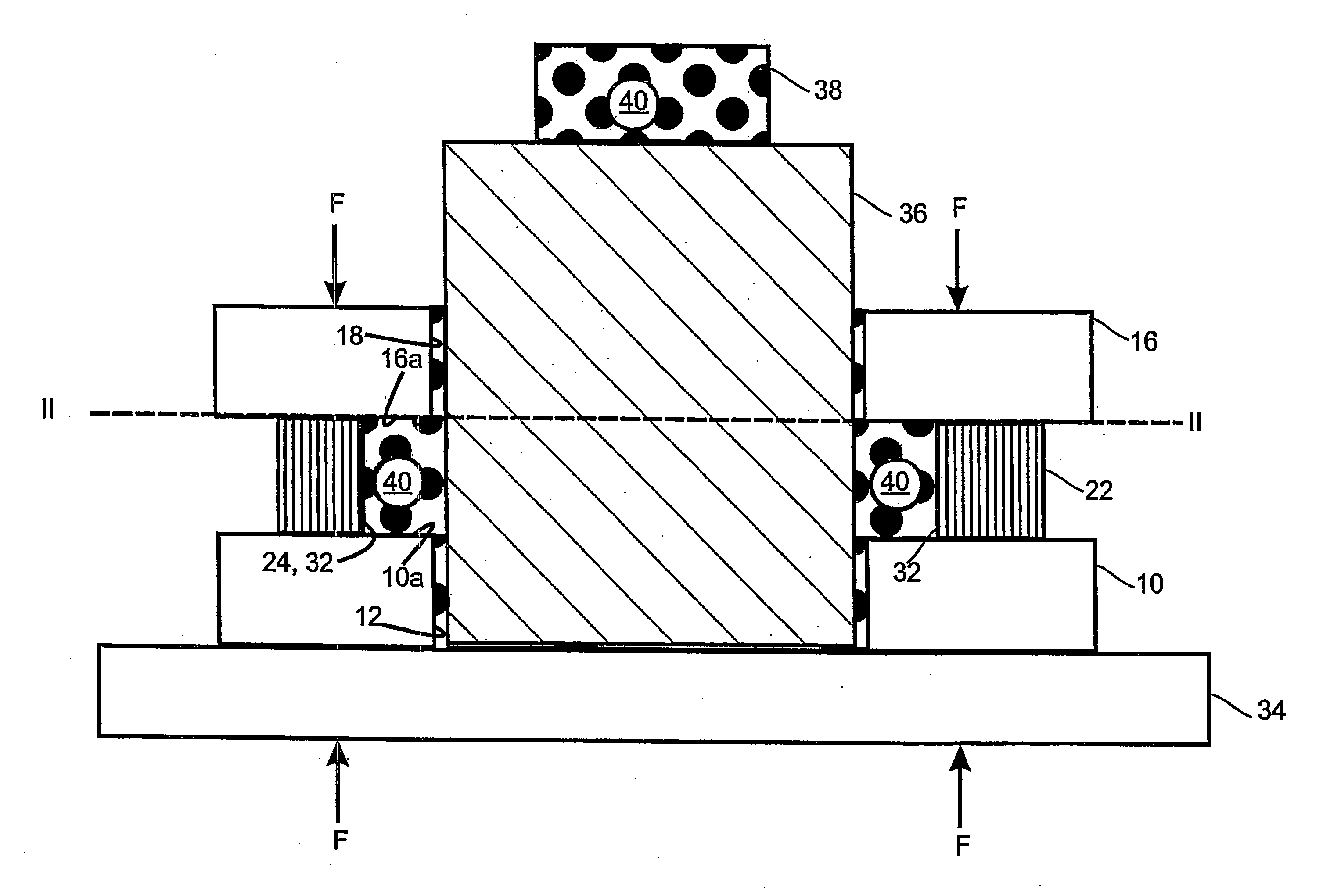

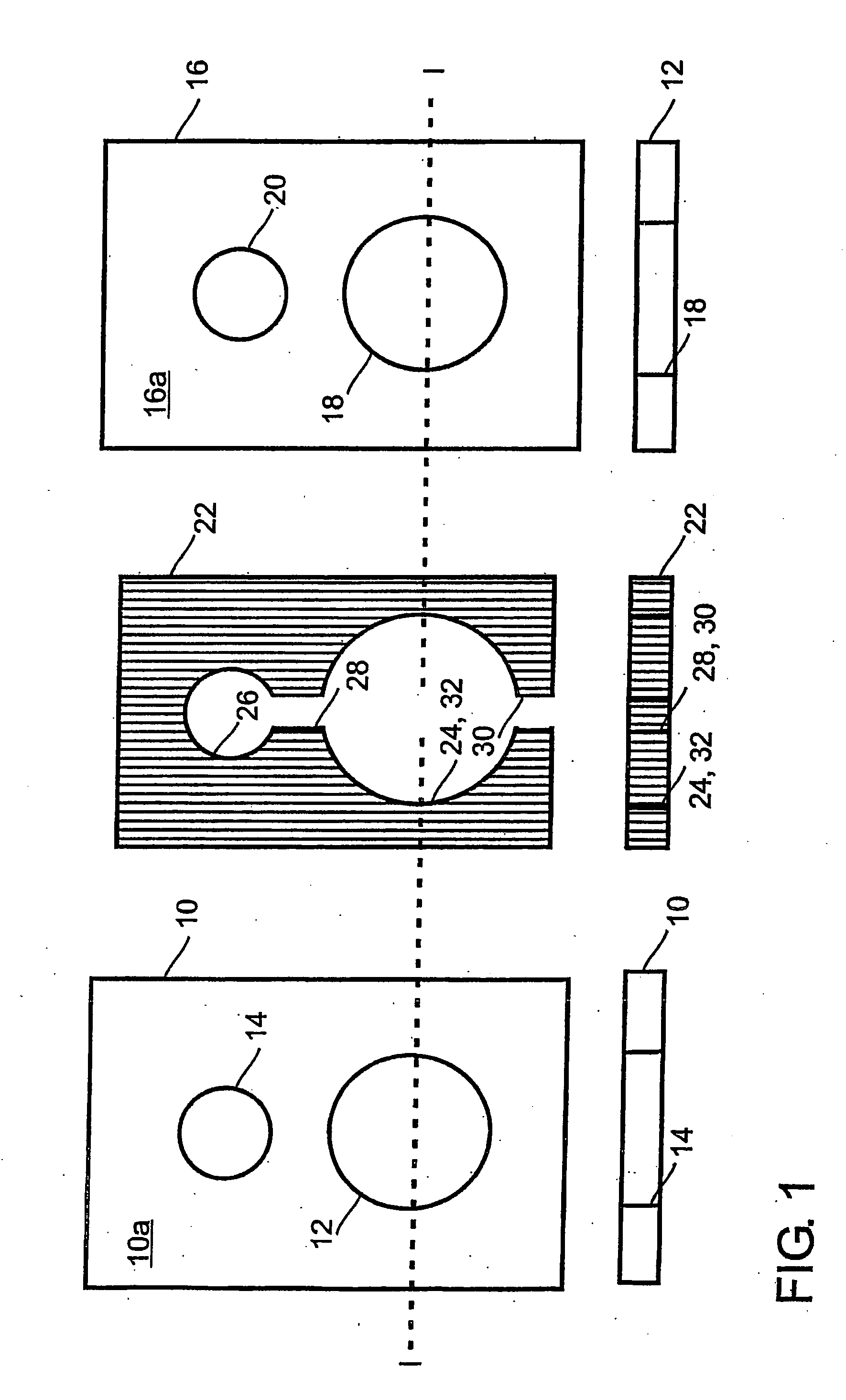

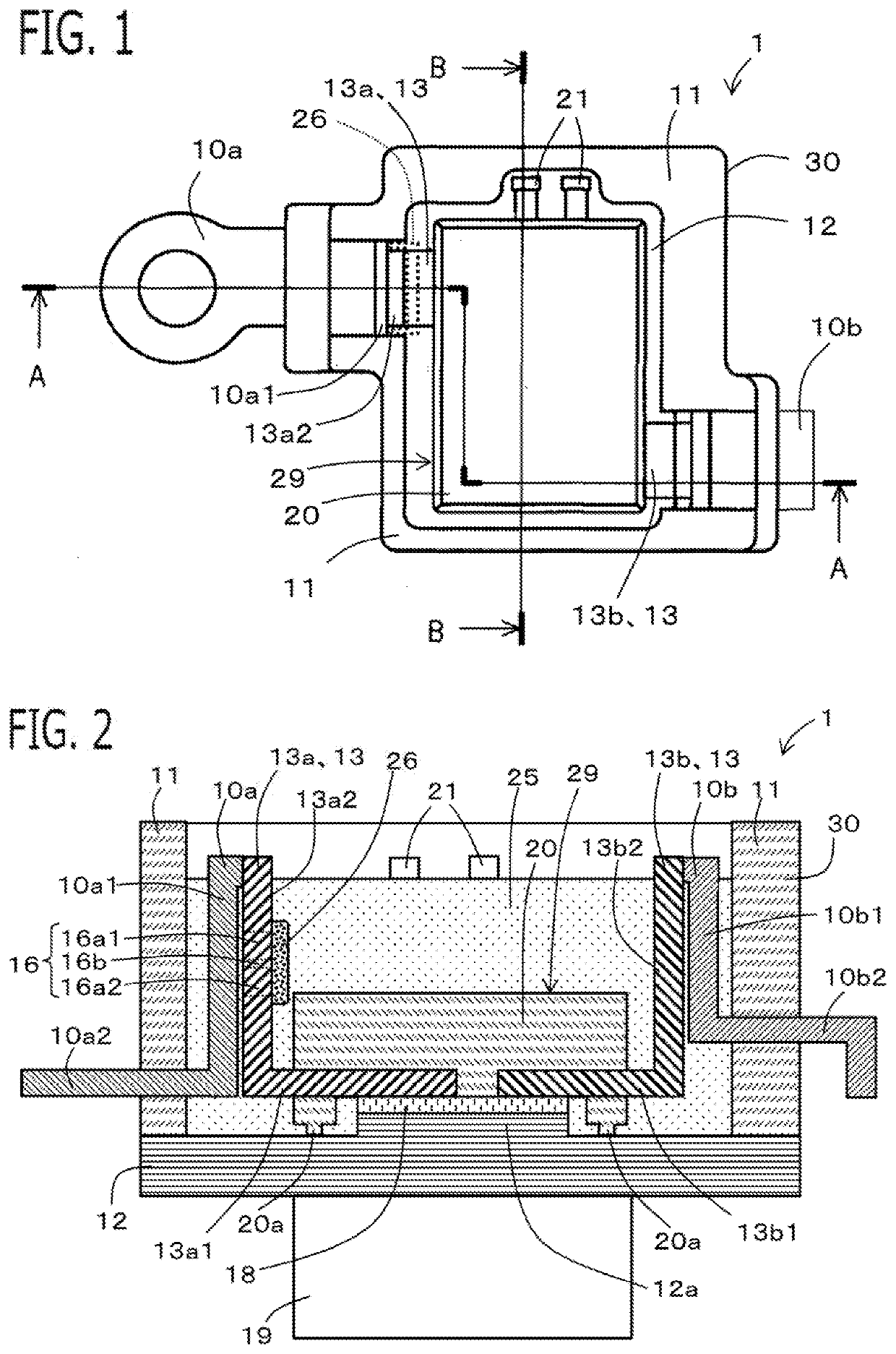

Method for Producing a Fuel Cell Stack

InactiveUS20080038620A1Low susceptibility to failureRapid and controlled assemblyFuel cells groupingPrimary cellsFuel cellsEngineering

A method for producing a fuel cell stack having the following steps: a) providing a first duplicating unit (10) with a first sealing surface (10a) and at least one second duplicating unit (16) with a second sealing surface (16a) and b) forming at least one sealing section (42) between the first sealing surface (10a) and the second sealing surface (16a). The step b) includes the steps of: b1) arranging a template (22) between the first sealing surface (10a) and the second sealing surface (16a), whereby the template (22) has at least one edge area (32) which is arranged adjacent to the sealing section to be formed (42), and b2) introducing a sealing compound (40) into an area which is defined by the first sealing surface (10a), the second sealing surface (16a) and the edge area (32) of the template (22).

Owner:STAXERA

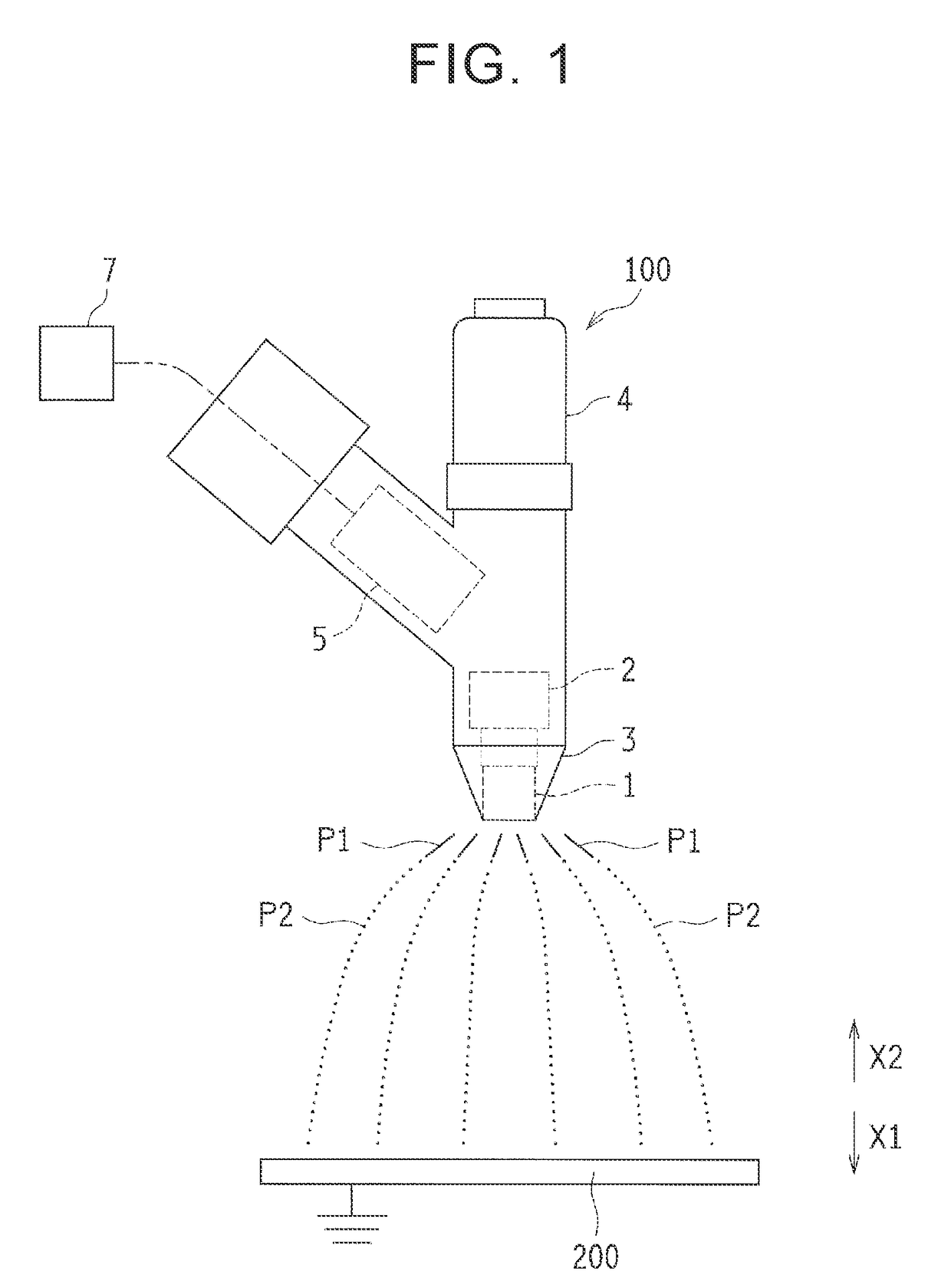

Coating device

ActiveUS20190083994A1Cross-sectional areaLiquid surface applicatorsSpraying power supplyEngineeringCentrifugal force

A coating device is equipped with a rotary head, a drive unit, and an electric power supply unit. The rotary head is configured to be supplied with a coating material. The rotary head includes a diffusion surface that is configured such that the coating material is diffused toward an outer edge portion of the diffusion surface by a centrifugal force, and a plurality of groove portions that are included in the outer edge portion. The rotary head is configured to discharge a threadlike coating material from the groove portions. Also, the coating device is configured such that a diameter of the threadlike coating material is set equal to or larger than 0.03 mm and equal to or smaller than 0.1 mm and that the threadlike coating material is electrostatically atomized.

Owner:TOYOTA JIDOSHA KK +1

Steel cord for reinforcement of off-the-road tires

InactiveUS7775247B2Improve cut resistanceImprove impact resistancePig casting plantsIngot casting plantsMetallurgyWire rope

Owner:THE GOODYEAR TIRE & RUBBER CO

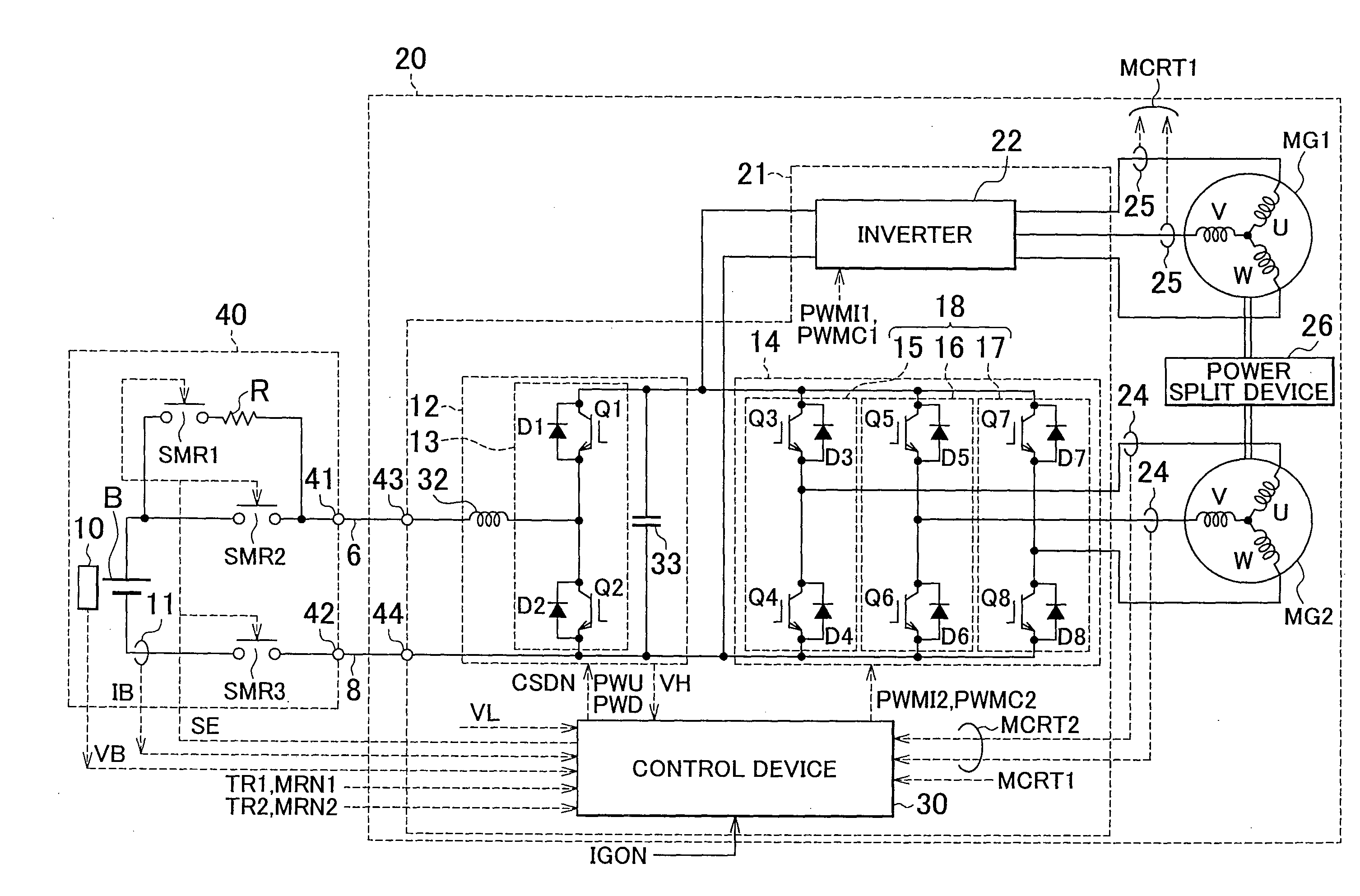

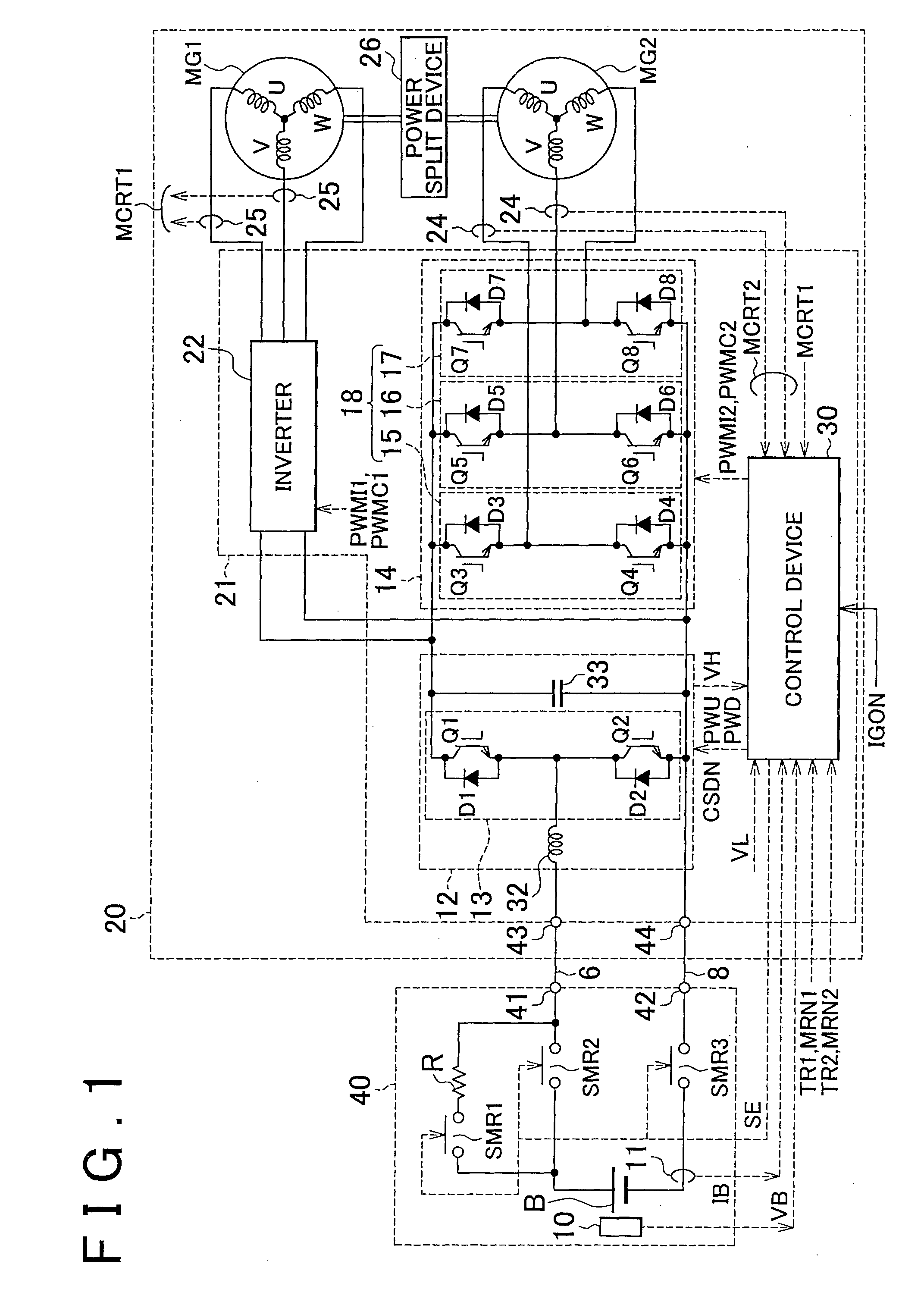

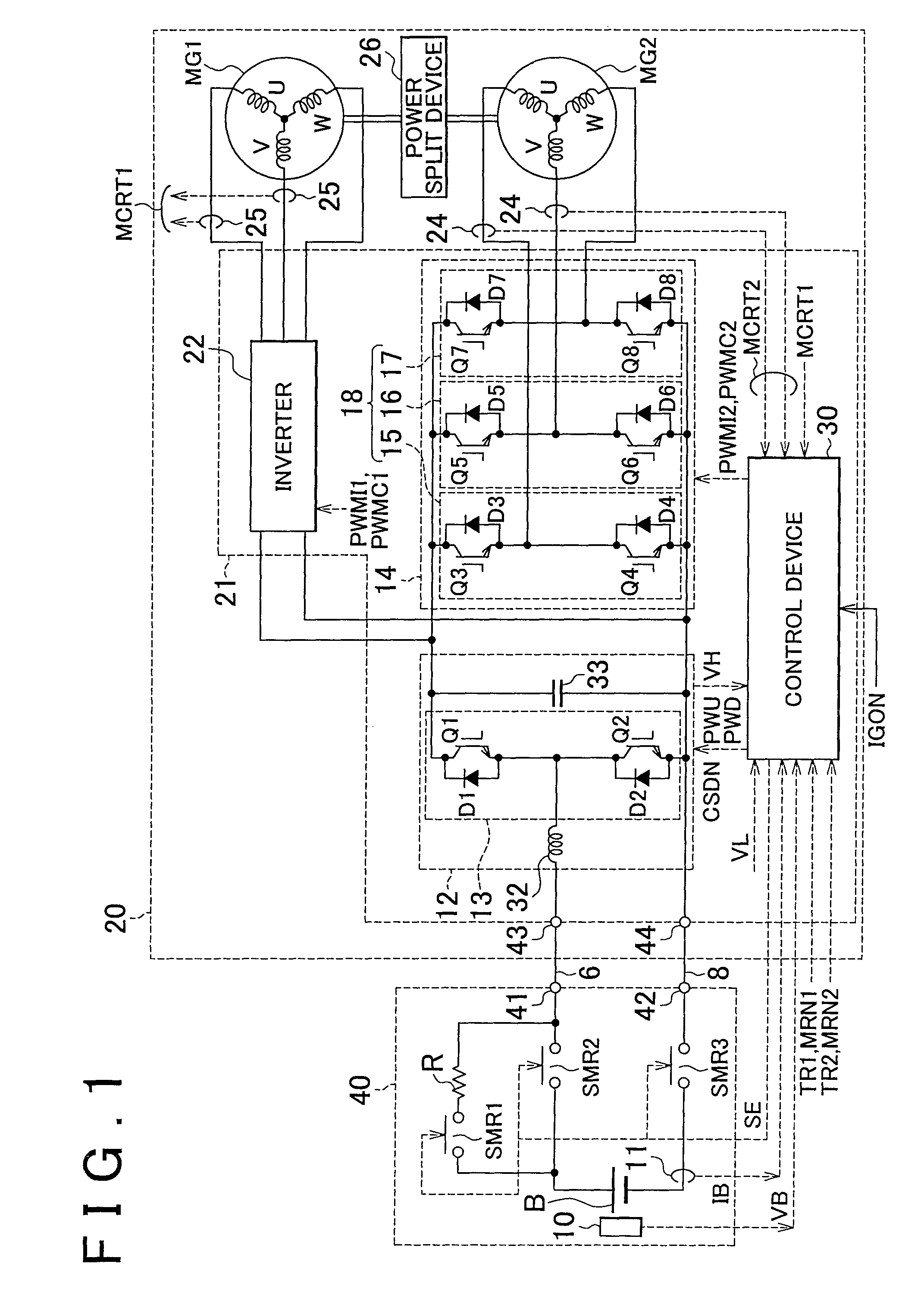

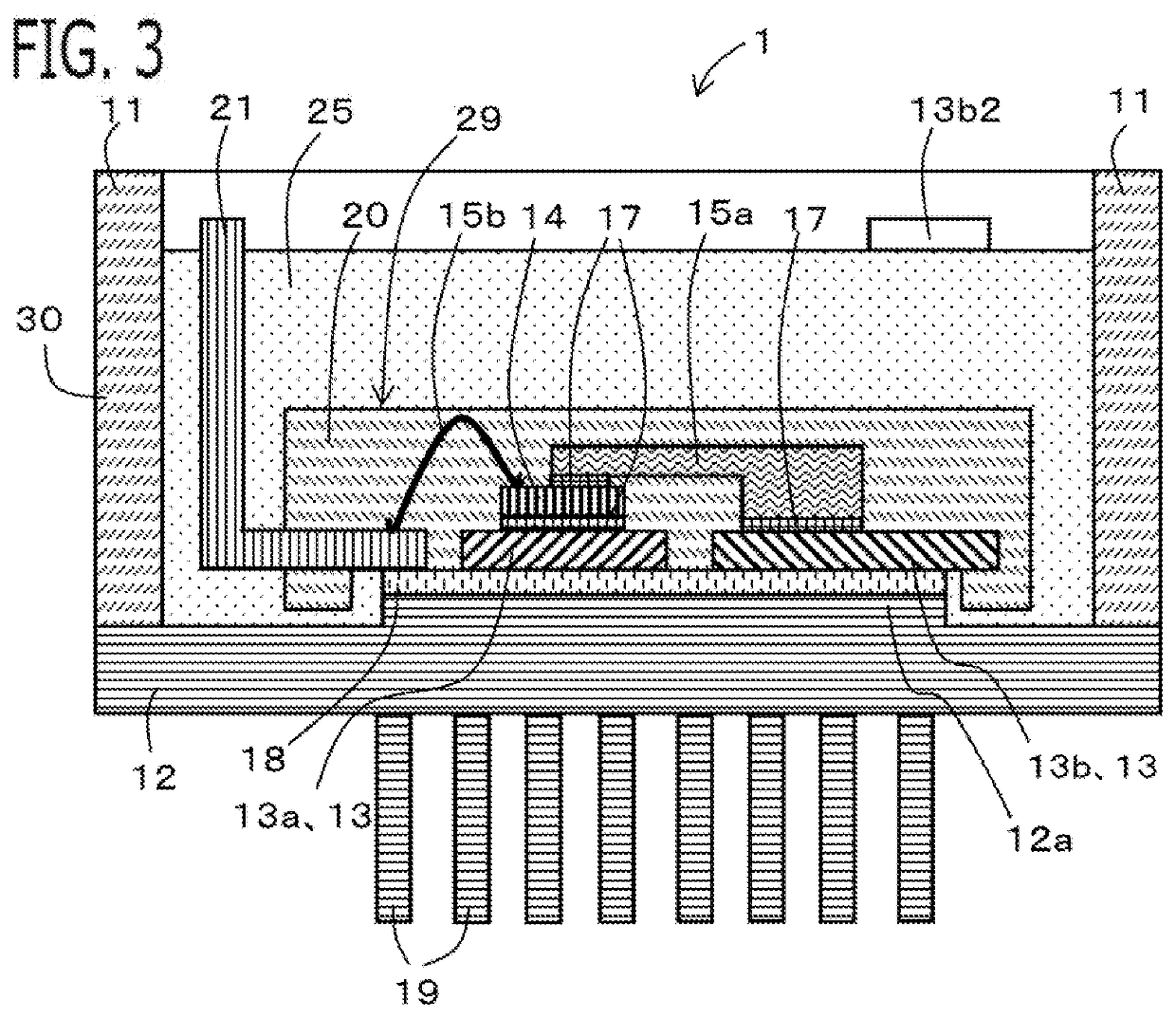

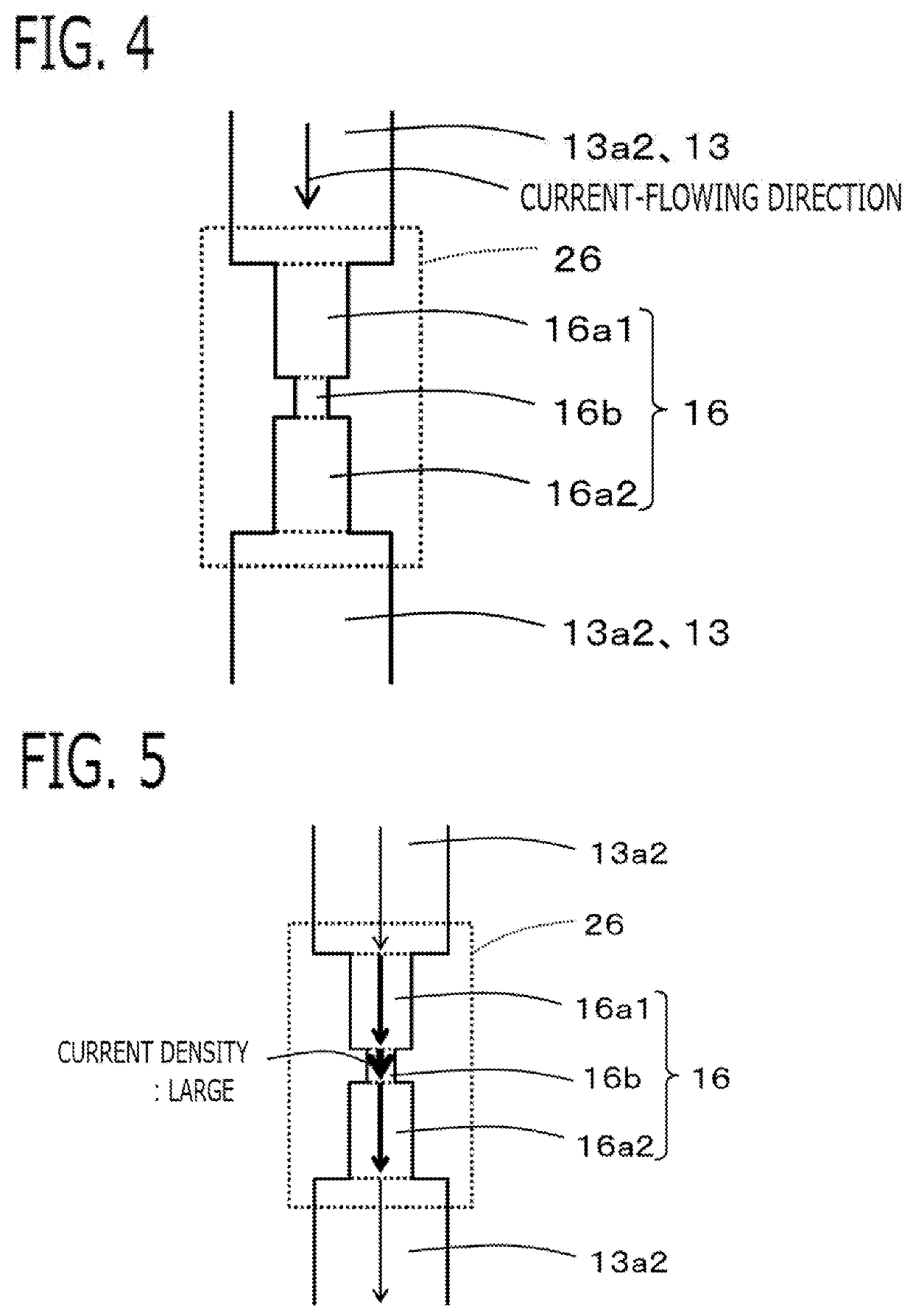

Electric-power conversion apparatus

ActiveUS20200234905A1Cost reductionAvoid scatterSemiconductor/solid-state device detailsSolid-state devicesPhysicsSemiconductor

There is provided an electric-power conversion apparatus in which smoke emission, a burnout, and short-circuiting can be suppressed even when a fuse portion is melted by an excessive current and in which it is made possible that heat generated in the fuse portion is less likely to be transferred to the electric power semiconductor device. The electric-power conversion apparatus includes a fuse portion formed in an electrode wiring member, a fuse resin member that covers the fuse portion, and a sealing resin member that seals an electric power semiconductor device and the fuse portion in a case. Along a current-flowing direction, the fuse portion includes an upstream-side first step portion whose cross-sectional area is smaller than that of the portion at the upstream side thereof, a second step portion whose cross-sectional area is smaller than that of the upstream-side first step portion, and a downstream-side first step portion whose cross-sectional area is larger than that of the second step portion but is smaller than that of the portion at the downstream side thereof.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com