Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

94 results about "Scale selection" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Remotely programmable integrated sensor transmitter

ActiveUS7223014B2Thermometer detailsThermometers using electric/magnetic elementsElectricityAnalog signal

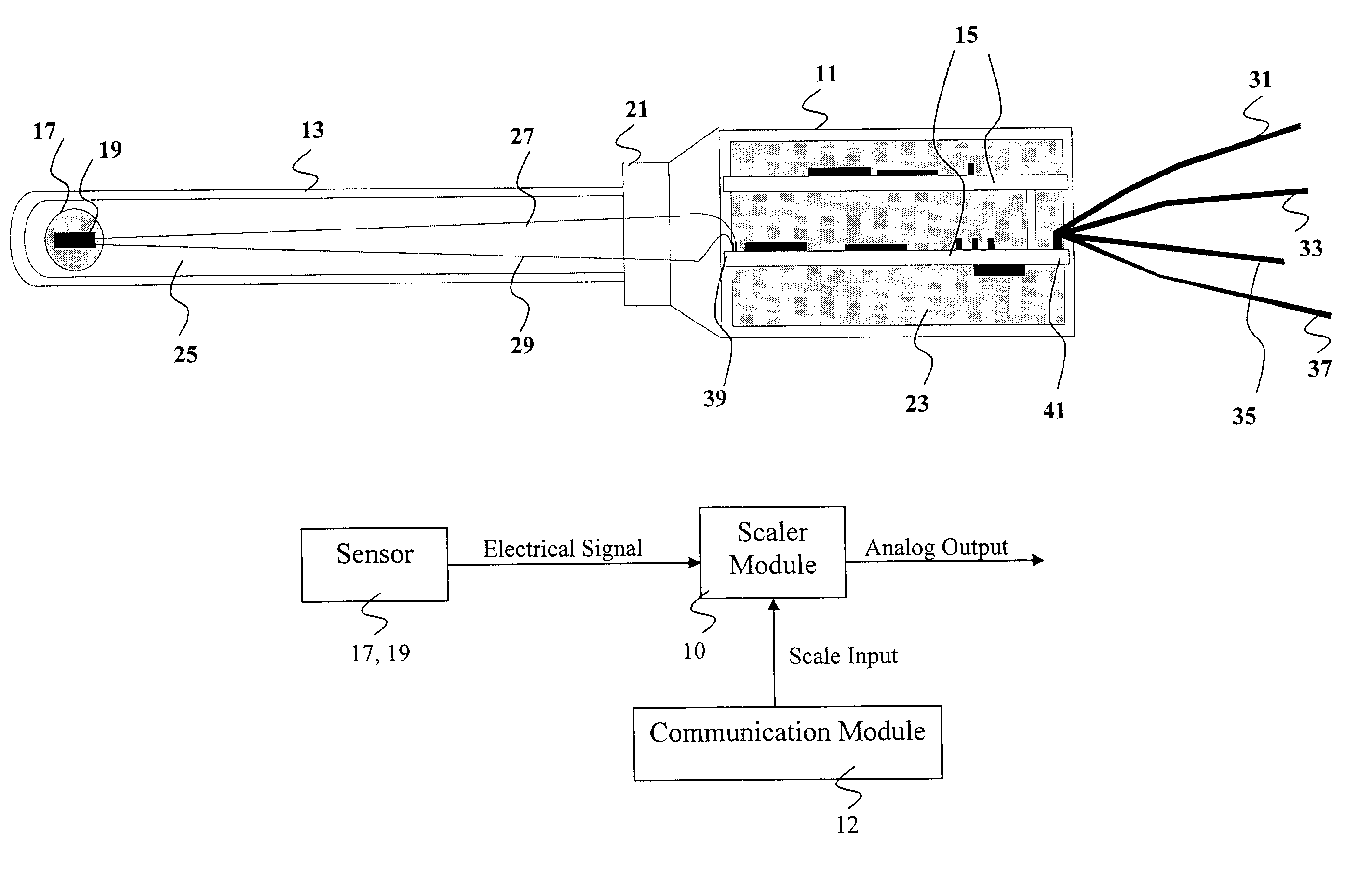

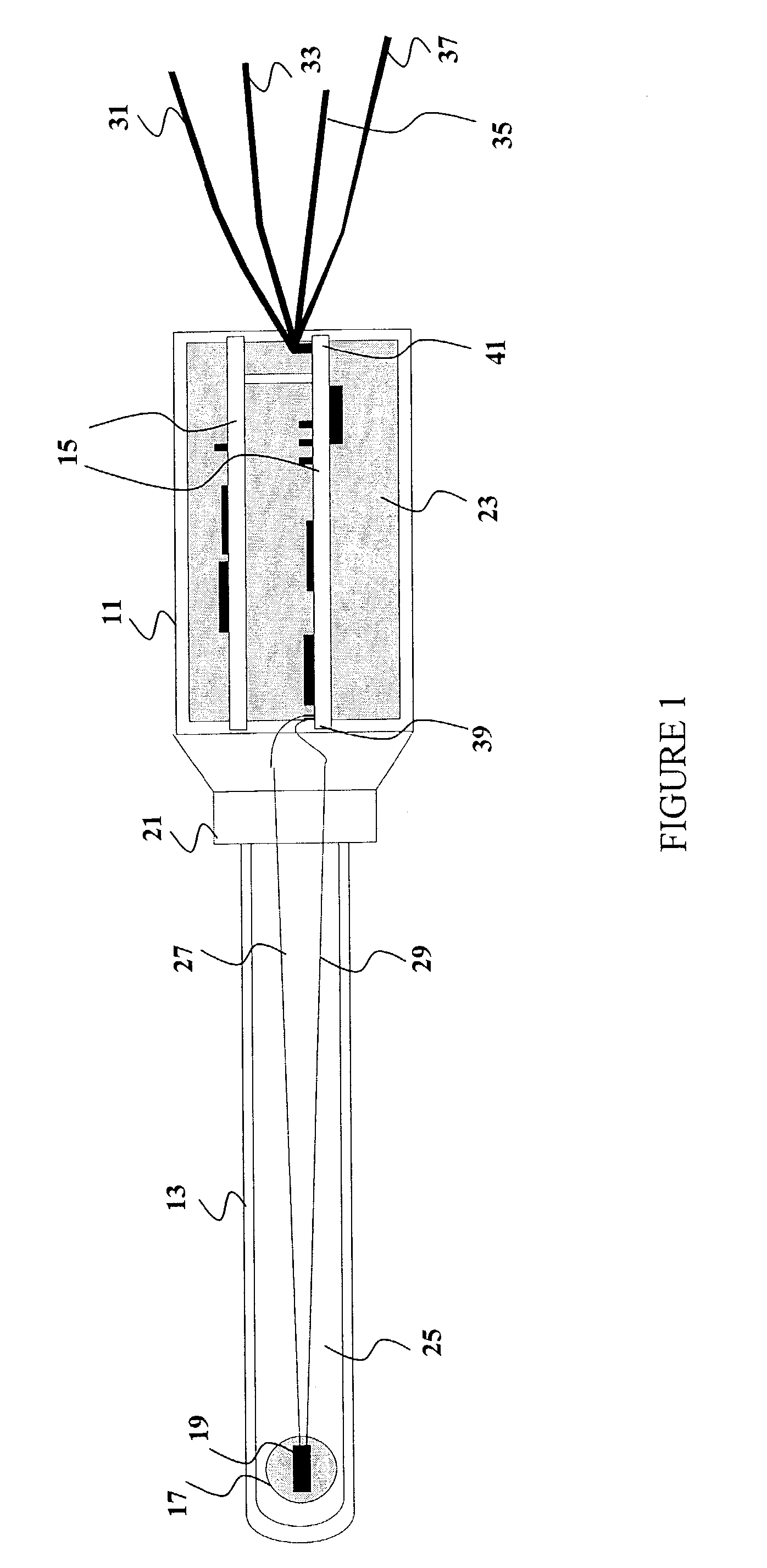

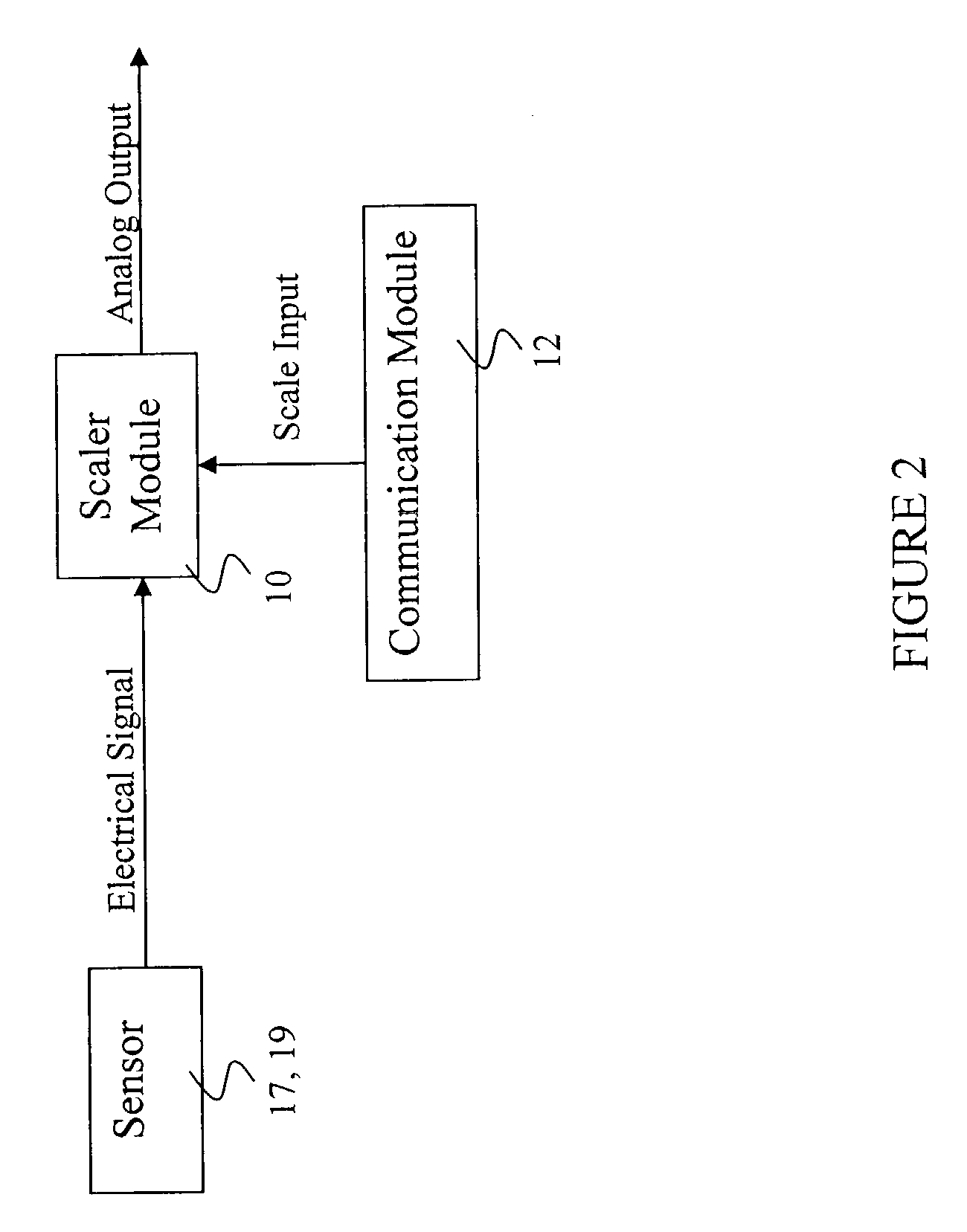

A remotely programmable integrated sensor transmitter device for measuring and reporting a physical quantity of a given medium comprises a sensor for measuring a physical quantity of a medium and providing an electrical output as a function of the property measured, a scaler module for receiving the electrical output and for producing a scaled analog signal as a function of the physical quantity and a scale selection input, and a data interface for receiving programming data from an external computer and for providing the scale selection output to the scaler module.

Owner:INTEMPCO CONTROLS

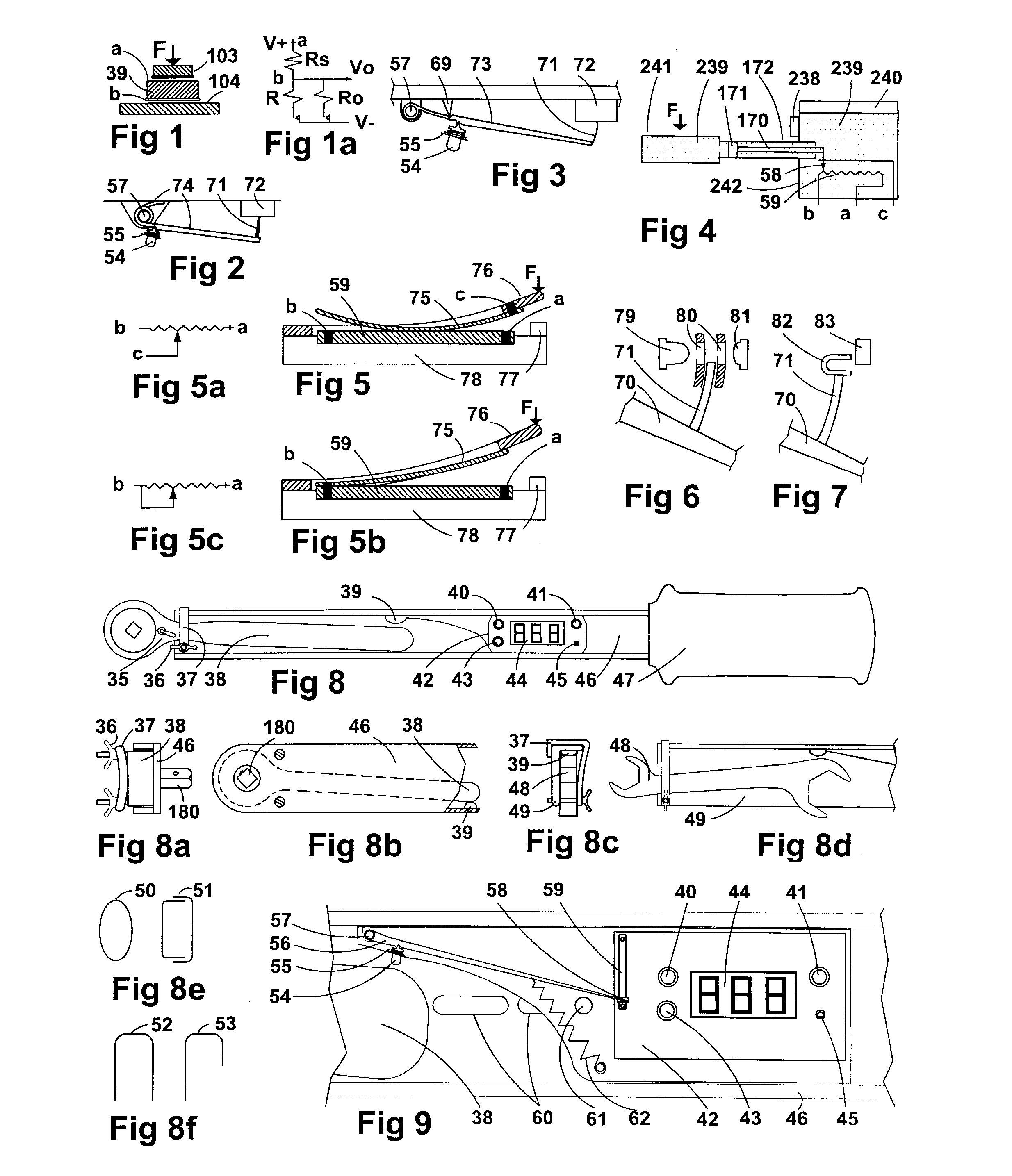

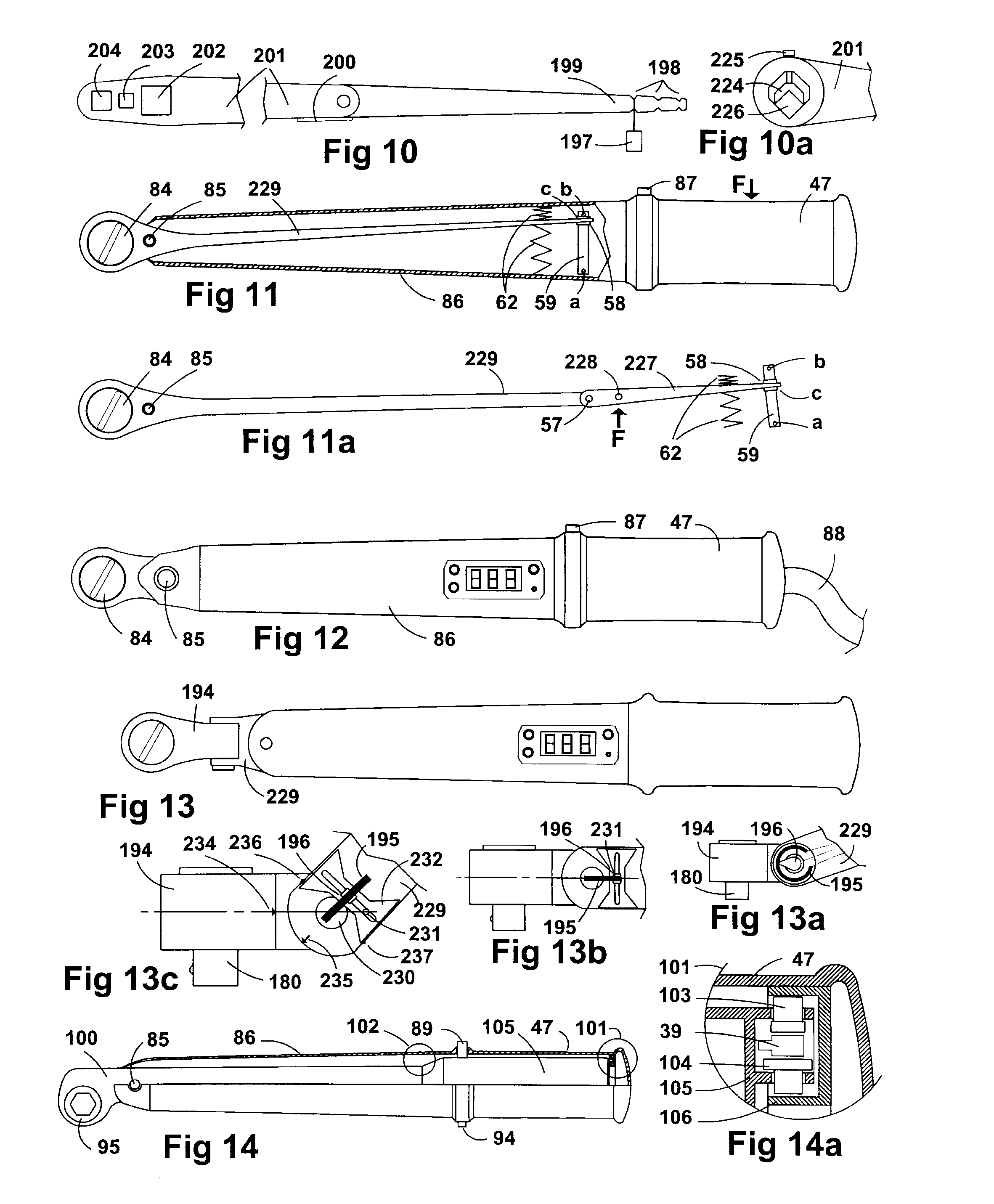

Force and Torque Measurements with Calibration and Auto Scale

InactiveUS20080127711A1Low costImprove reliabilityWeighing apparatus testing/calibrationSpannersPeak valueBiological activation

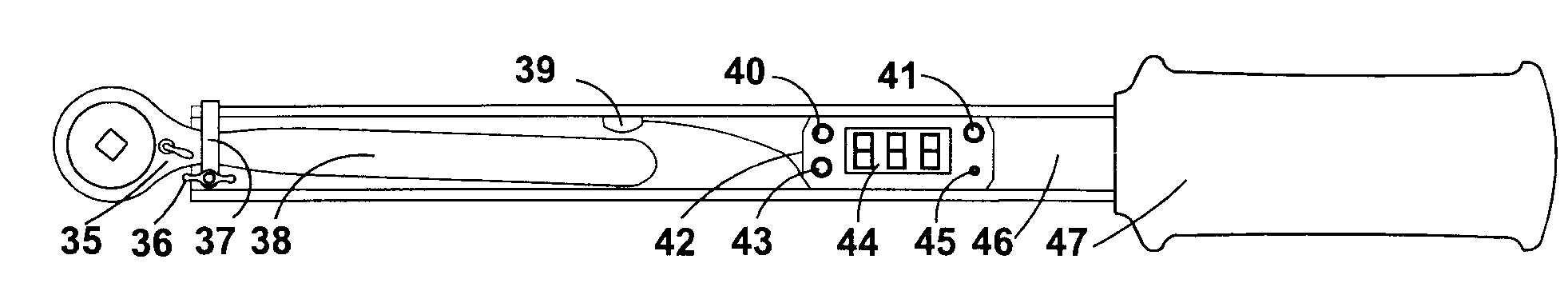

This invention is device and method for electronic measurements of the force and torque applied to a work piece. The measured values are visually displayed, audibly indicated, and / or transferred in electronic formats to other controlling devices. The values could be displayed in different physical measuring units, and as an average or peak. The device produces different output signals when the torque applied equals or exceeds predetermined values. This device and method provide an automatic, accurate, and easy calibration, which could be self-calibration or in-the-field calibration. It has protection from accidental activation of the switches, and provides a permanent record of the incidents in which the device was operated at conditions beyond its specifications. It provides a manual and / or automatic scale selection to improve the accuracy.

Owner:FARAG TAREK A Z

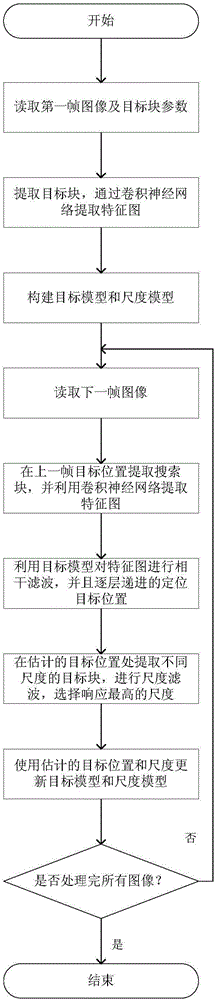

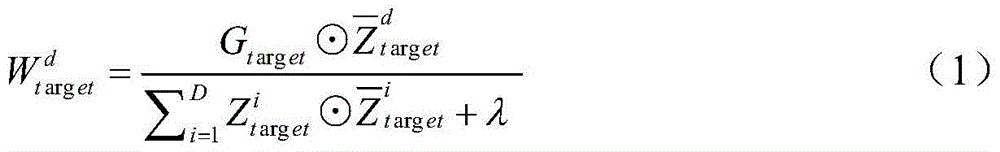

Robust target tracking method based on deep learning and multi-scale correlation filtering

ActiveCN105741316APrevent extractionRun fastImage enhancementImage analysisCorrelation filterScale dependent

The invention relates to a robust target tracking method based on deep learning and multi-scale correlation filtering. The tracking process is divided into a target location part and a scale selection part. In the target location part, the position of a target is located through a convolutional neural network and correlation filtering. In the scale selection part, a scale pyramid is used, and different scales are selected in a matching manner for targets through scale filtering. The multilayer characteristic of the convolutional neural network is taken as a representation model of targets, so the structural and semantic information of targets can be described robustly. Through use of the characteristics of correlation filtering, there is no need to train a classifier online, and the running speed of the algorithm is increased greatly. The idea of scale pyramid is adopted in scale, and correlation filtering matching is performed on targets of different scales to select the optimal scale. The method is of strong robustness to deformation, shading and scale change of targets.

Owner:XIAN ANMENG INTELLIGENT TECH CO LTD

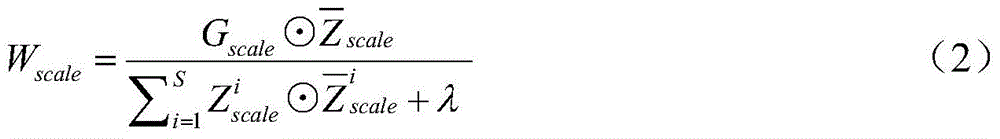

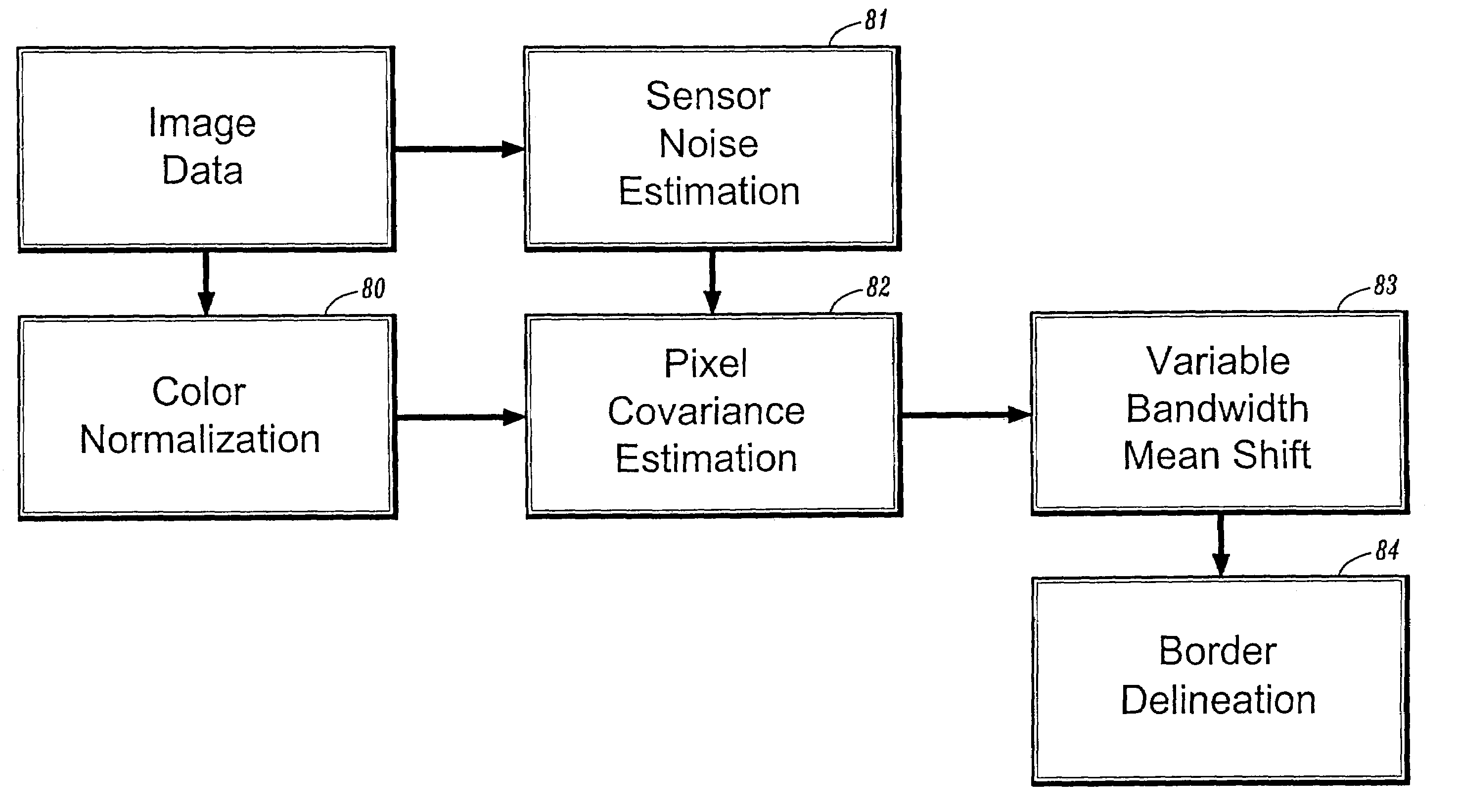

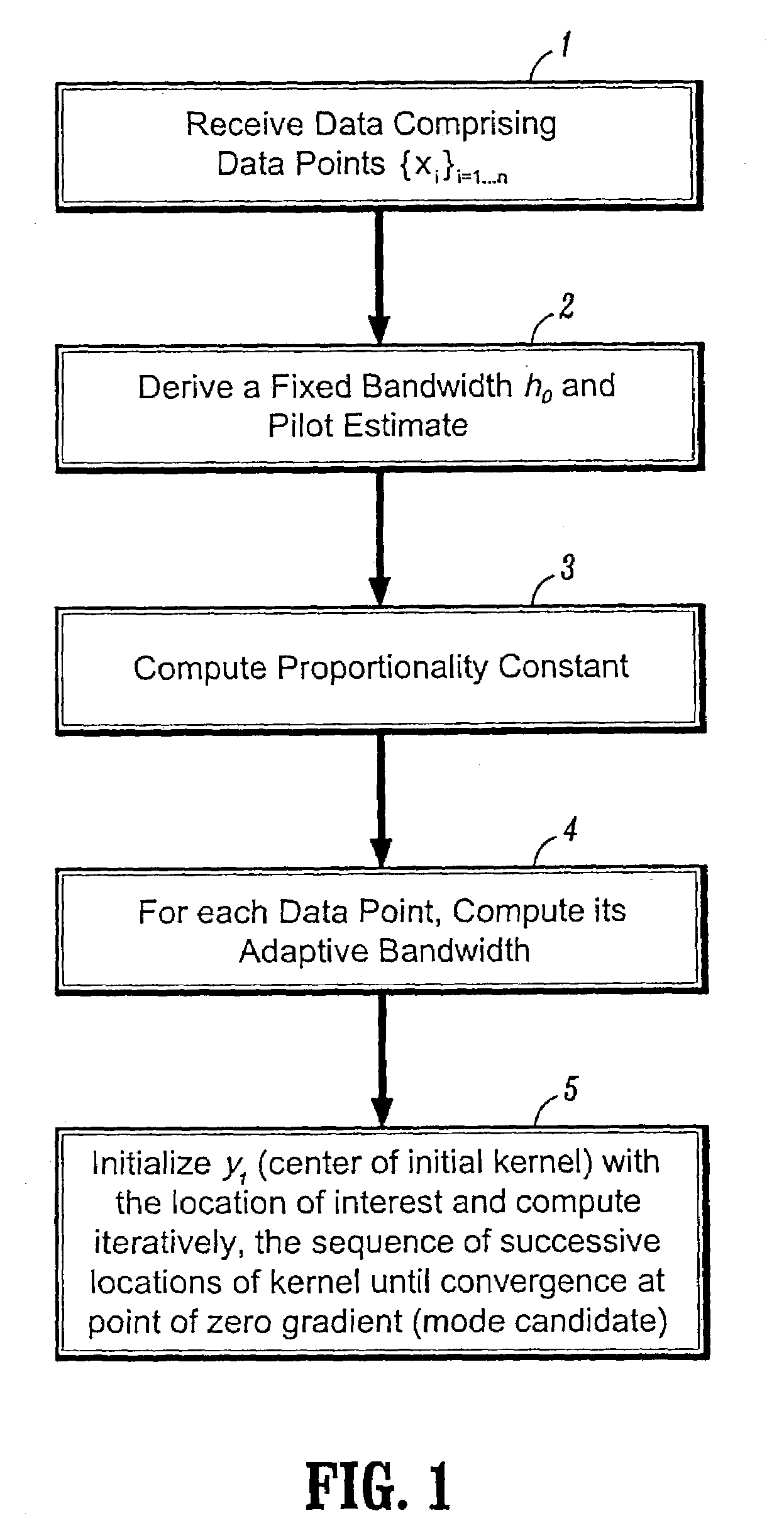

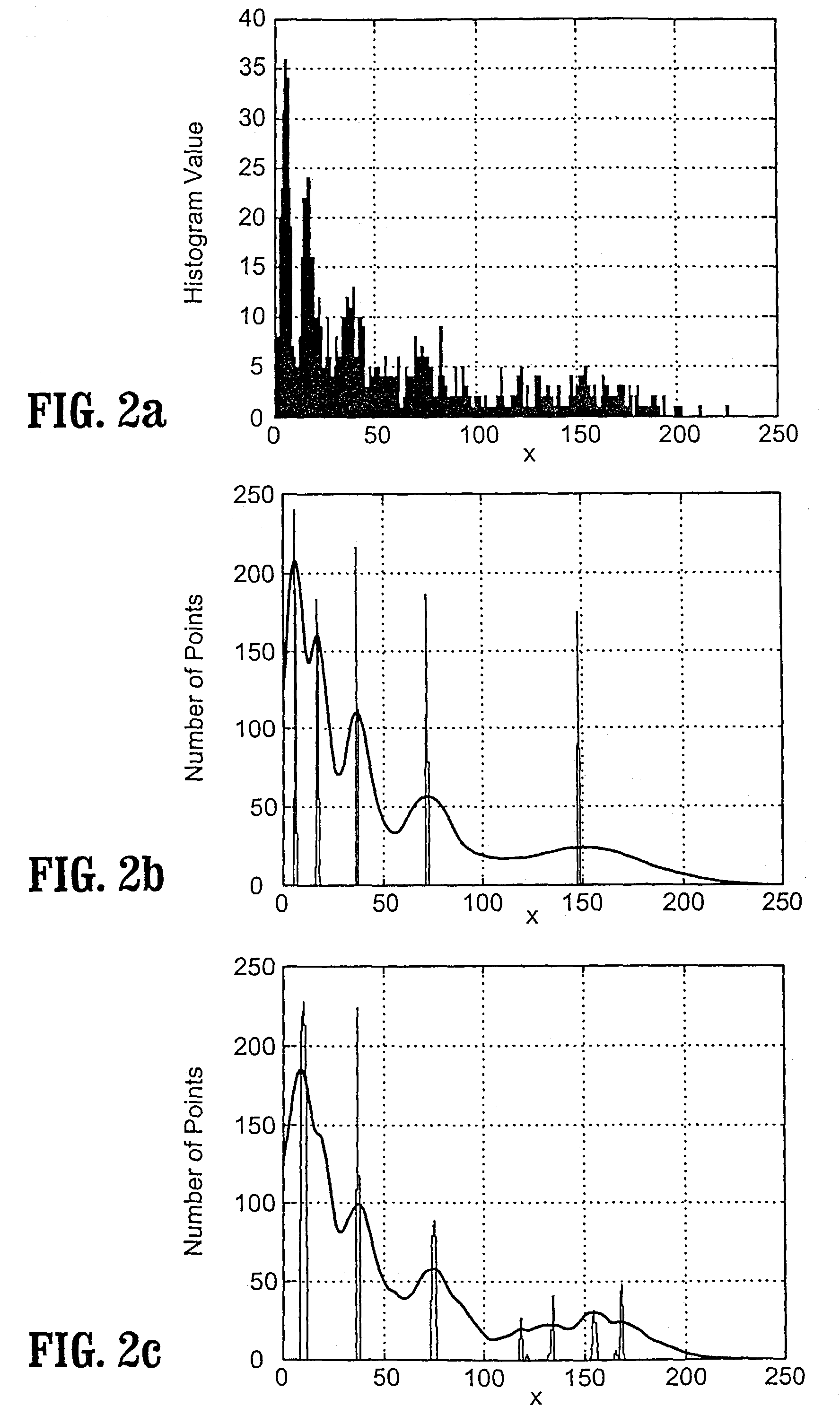

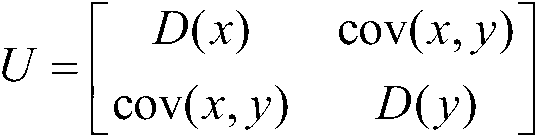

Systems and methods for automatic scale selection in real-time imaging

A system and method for automatic scale selection in real-time image and video processing and computer vision applications. In one aspect, a non-parametric variable bandwidth mean shift technique, which is based on adaptive estimation of a normalized density gradient, is used for detecting one or more modes in the underlying data and clustering the underlying data. In another aspect, a data-driven bandwidth (or scale) selection technique is provided for the variable bandwidth mean shift method, which estimates for each data point the covariance matrix that is the most stable across a plurality of scales. The methods can be used for detecting modes and clustering data for various types of data such as image data, video data speech data, handwriting data, etc.

Owner:IP3 2021 SERIES 600 OF ALLIED SECURITY TRUST I

Microprocessor with non-aligned circular addressing

A data processing system having a central processing unit (CPU) with address generation circuitry for accessing a circular buffer region in a non-aligned manner is provided. The CPU has an instruction set architecture that is optimized for intensive numeric algorithm processing. The CPU has dual load / store units connected to dual memory ports of a memory controller. The CPU can execute two aligned data transfers each having a length of one byte, two bytes, four bytes, or eight bytes in parallel by executing two load / store instructions. The CPU can also execute a single non-aligned data transfer having a length of four bytes or eight bytes by executing a non-aligned load / store instruction that utilizes both memory ports. A data transfer address for each load / store instruction is formed by fetching the instruction (600), decoding the instruction (610) to determine instruction type, transfer data size, addressing mode and scaling selection. For a non-aligned instruction, after selectively scaling (620) an offset provided by the instruction and combining the selectively scaled offset with a base address value the resultant address is then augmented (640) by a line size associated with the instruction. For circular addressing mode, both the resultant address and the augmented address are bounded (650, 651) to stay within the circular buffer region and two aligned data items are accessed in parallel (652, 653) and a non-aligned data item is extracted (654) from the two aligned data items, such that the non-aligned data item wraps around the boundary of the circular buffer region.

Owner:TEXAS INSTR INC

Cognitive assessment method and system based on virtual reality

InactiveCN106599558AChange assessment modeChange the traditional scale evaluation modeHealth-index calculationSpecial data processing applicationsCognitionMedical institution

The invention discloses a cognitive assessment method and system based on virtual reality. The system comprises an information inputting module, an intelligent conversion module, a processor module, a facial induction module, an electroencephalogram induction module and a VR (Virtual Reality) device module. On the basis of a traditional scale, the method overcomes the problems of the traditional scale on the aspects of application, operation, user experience and the like, in addition, the method combines scale assessment, micro-expression information and electroencephalogram information to judge a user cognition situation, a provided assessment result is more comprehensive, detailed and objective and is higher in reliability, and the method is the cognitive assessment method which has the advantages of being automatic in scale selection, simple in operation, good in user experience effects and good in assessment effects. The method exhibits wide applicability, has a low requirement on operation personnel, and is suitable to be popularized and used in basic medical institutions which lack professional medical care personnel.

Owner:WUHAN ZHIPU TIANCHUANG TECH CO LTD

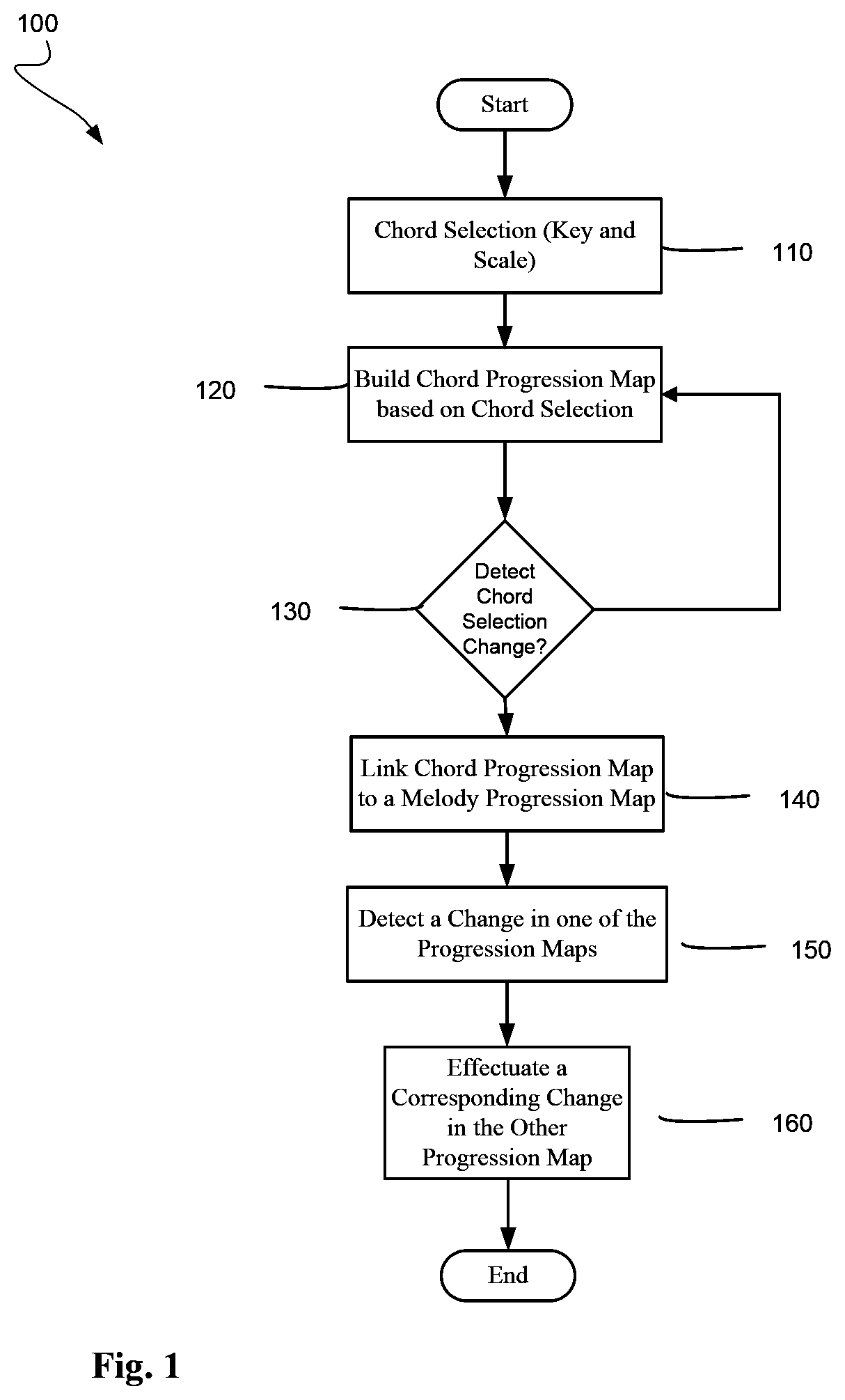

Apparatus, method, and computer-readable medium for generating musical pieces

An apparatus, method, and computer-readable storage medium that generate a harmonized musical piece. The method includes receiving a chord selection including a musical key and a scale selection, generating, within a digital audio work session, a chord progression sequence based on the received chord selection, in response to a detected chord selection change, modifying the chord progression sequence to include a chord progression corresponding to the chord selection change, setting the chord progression sequence as a master sequence, in response to detecting a second progression sequence within the digital audio work session, transmitting an identifier to the second progression sequence setting it as a slave sequence, and establishing a synchronized communication link between the master and the slave sequences such that changes made in the master sequence are automatically effectuated in the slave sequence, and combining the master sequence and the slave sequence to form a composed musical piece.

Owner:MIXED IN KEY

Mobile station and mobile communication method

The measurement frequency of a measurement procedure notified by a network is adjusted according to the speed of a mobile station. A mobile station UE according to the present invention includes: a speed detection unit 13 configured to detect the speed of the mobile station UE; and a parameter-scaling selection unit 14 (a determination unit) configured to determine a measurement frequency (specifically, a parameter used for calculating the measurement frequency) on the basis of the detected speed, the measurement frequency being a frequency at which the mobile station UE performs a measurement procedure.

Owner:NTT DOCOMO INC

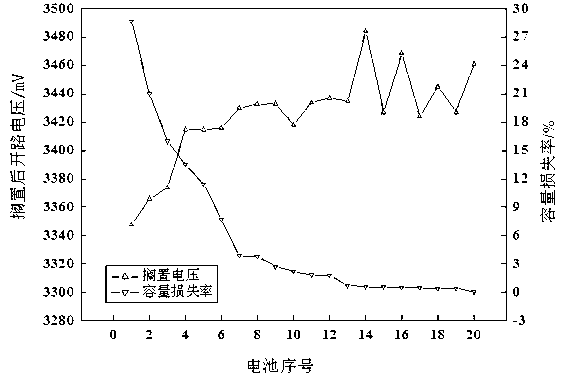

Method for quickly and effectively comparing self-discharge rates of batteries

The invention discloses a method for quickly and effectively comparing self-discharge rates of batteries. The method includes steps of 1), continuing charging the batteries in a constant-voltage and current-limiting manner when the batteries are in normal fully charged states, and stopping charging the batteries when charging currents are reduced to extremely low states or jump up and down at certain current values for a long time; 2), laying the batteries processed in the step 1) aside for a certain duration shorter than or equal to 7 days; 3), measuring open-circuit voltages of the batteries after the batteries are laid aside for the certain duration; and 4), comparing the open-circuit voltages measured in the step 3) to a standard value, determining that self-discharge of the batteries is abnormal if the open-circuit voltages are lower than the standard value, and determining that the self-discharge of the batteries are normal if the open-circuit voltages are higher than the standard value. The charging currents in the extremely low states are lower than or equal to 0.001C, and the long time is longer than or equal to 1 hour. Compared with the traditional method, the method for quickly and effectively comparing the self-discharge rates of the batteries has the advantages that the effectiveness for selecting the self-discharge rates of the batteries is obviously improved, and the method is applicable to large-scale selection, is high in selection efficiency and is effective.

Owner:JIANGSU HUAFU STORAGE NEW TECH DEV

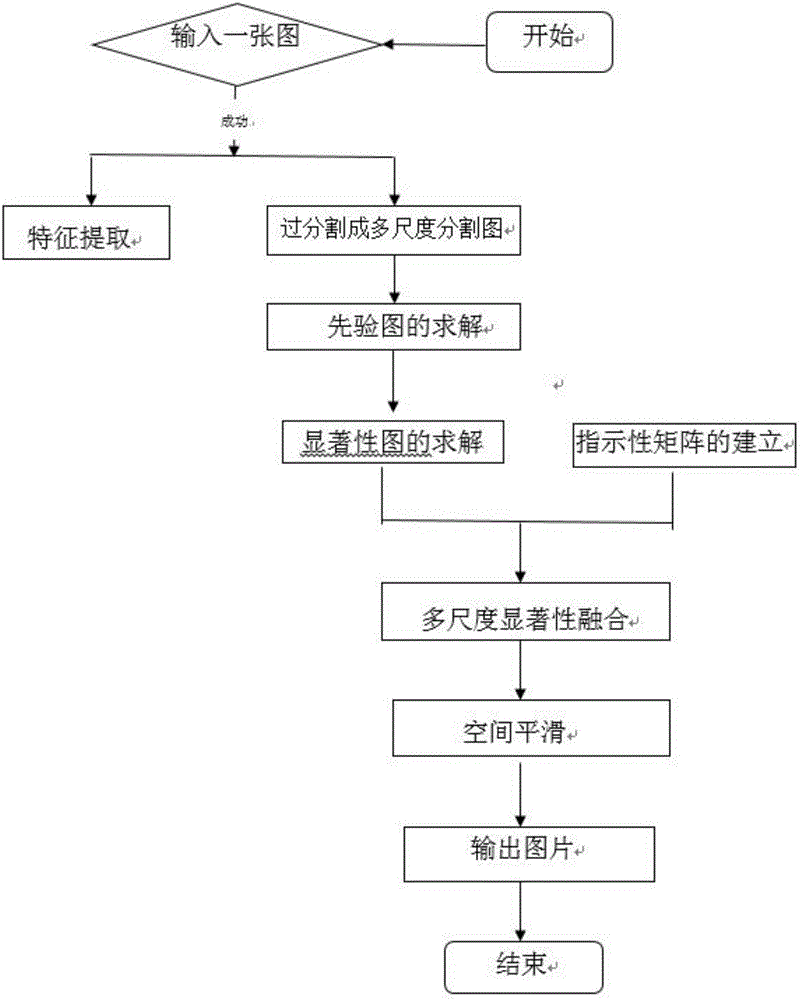

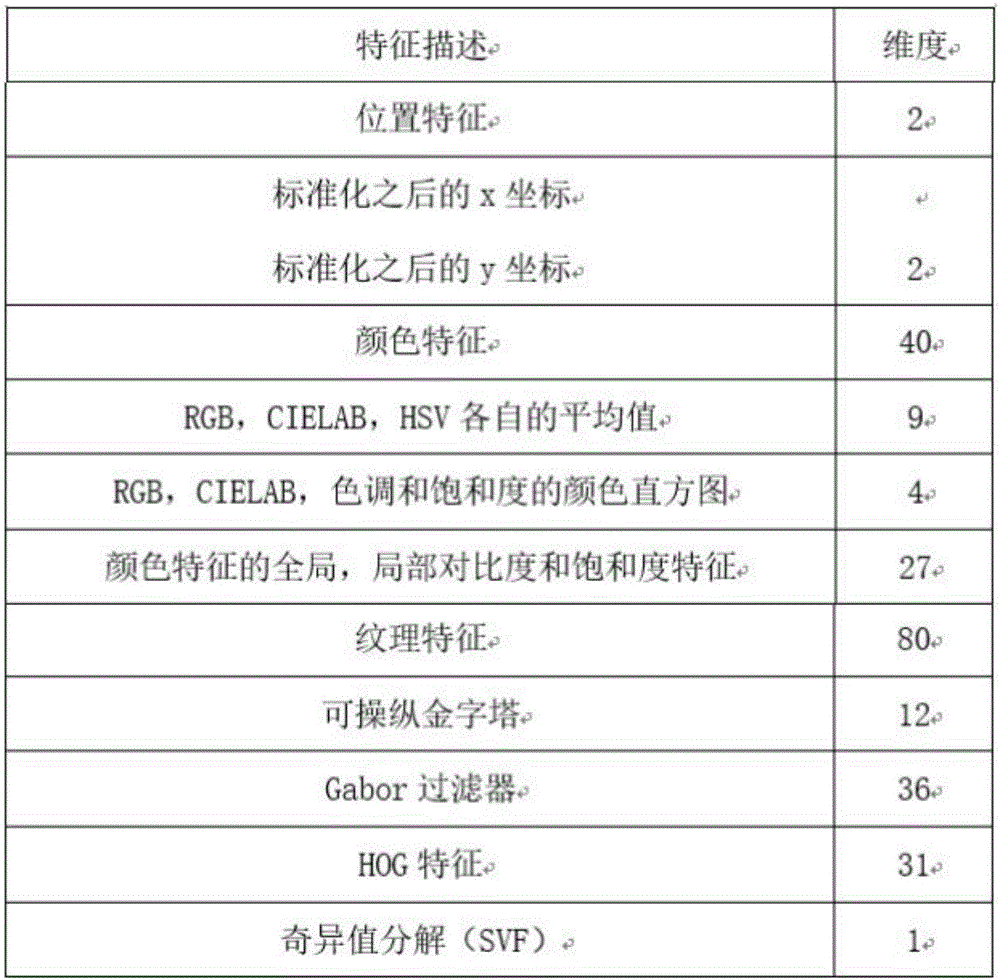

Low-rank multi-scale fusion-based image saliency detection method

InactiveCN106780450AEasy to handleSolve the problem of difficult scale selectionImage enhancementImage analysisSaliency mapCo operative

The invention relates to a low-rank multi-scale fusion-based image saliency detection method. The method is technically characterized by comprising the steps of performing single-scale saliency detection on an input image; performing multi-scale saliency fusion processing on the image subjected to the single-scale saliency detection, thereby obtaining a fused saliency map; and performing saliency detailing processing on the fused saliency map after the multi-scale saliency fusion processing to obtain a final cooperative saliency image. According to the method, a low-rank matrix recovery-based saliency detection method and a multi-scale saliency fusion method are applied to the saliency detection, and multi-scale low-rank saliency detection is generalized to cooperative saliency detection of multiple images by applying a GMM-based cooperative saliency priori to detect same or similar regions appearing in the images, so that the problem of difficulty in scale selection is solved, a more reliable saliency detection result is obtained, and the processing capability of the saliency detection is further improved.

Owner:TIANJIN UNIV

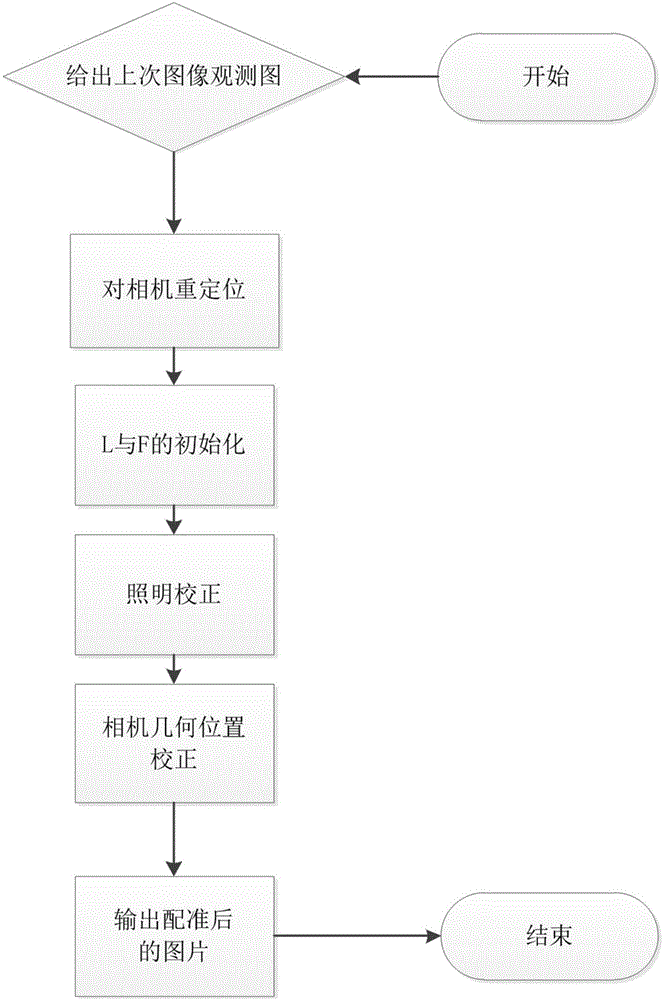

Method for high-precision registration of images under scene and illumination variation conditions

ActiveCN106780297ASolve the problem of difficult scale selectionReliable saliency detection resultsImage enhancementImage analysisMultiple imageScale selection

The invention relates to a method for high-precision registration of images under scene and illumination variation conditions. The method comprises the following steps of camera relocation, initialization of L and F, illumination correction and correction of a geometric position of a camera. The invention provides a multiscale low-rank significance testing method and applies GMM-based synergetic significance prior to popularize multiscale low-rank significance testing to synergetic significance testing of multiple images, so that the same or similar regions in multiple images are tested. Compared with the conventional significance testing method, a low-rank multiscale super-pixel fusion algorithm provided by the invention solves a problem of difficulty in scale selection and obtains a more reliable significance testing result.

Owner:TIANJIN UNIV

City water extraction method based on panchromatic remote sensing image

InactiveCN103761717AEfficient extractionCalculation method is simpleImage enhancementImage analysisComputer scienceGeographic information system

The invention discloses a city water extraction method based on a panchromatic remote sensing image. Water information of urban area needed to be extracted will be finally acquired through four procedures of remote sensing image preprocessing, the optimal scale selection, uniform texture generation, and the optical threshold segmentation. The city water extraction method based on a panchromatic remote sensing image is simple in calculating method, less in calculation, comparatively accurate in the final extracted results, and capable of being applied in several fields of urban planning, environmental sciences, geographic information mapping and the like.

Owner:HOHAI UNIV

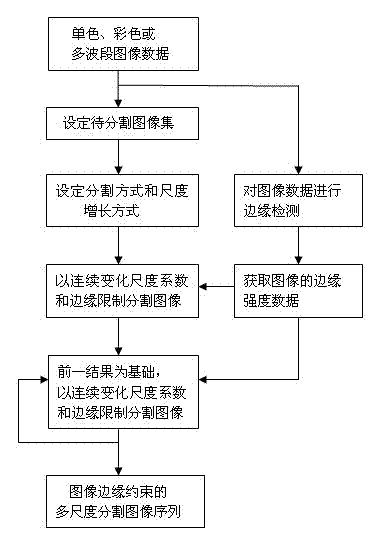

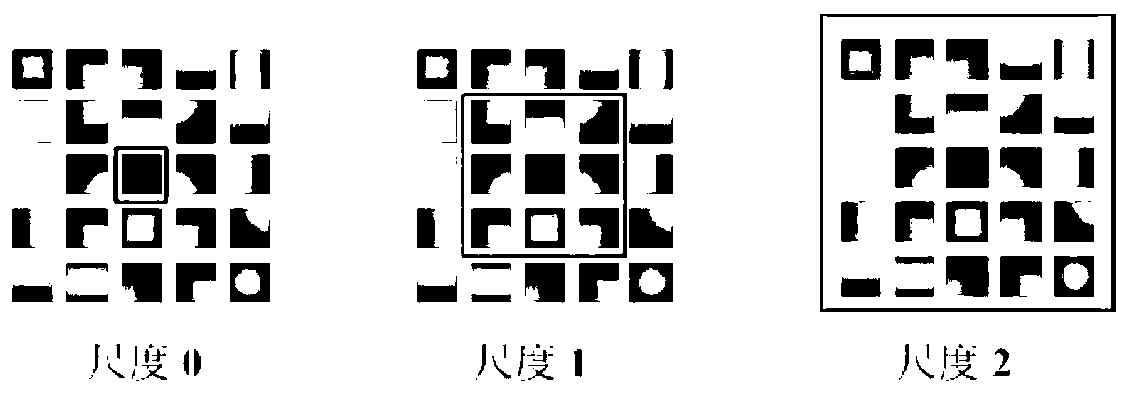

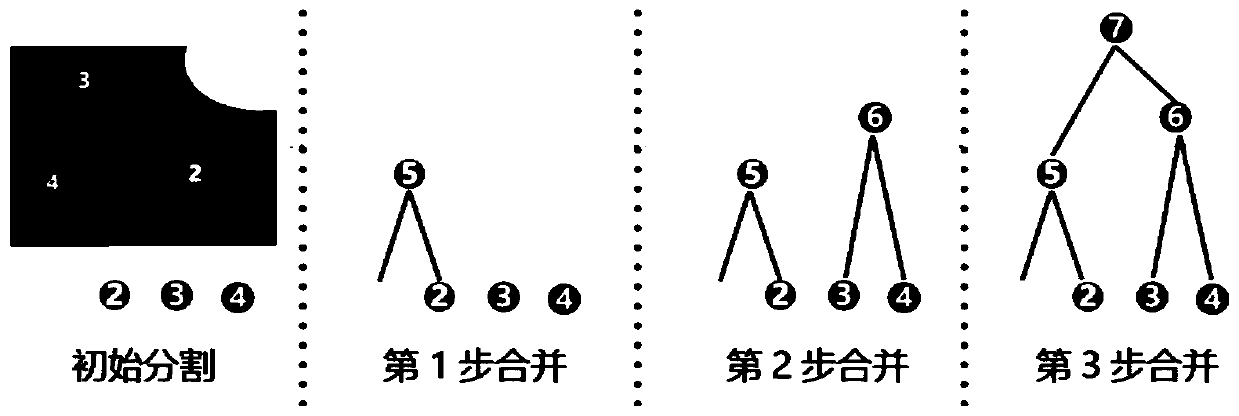

Image multi-scale segmentation method integrated with edge information

The invention discloses an image multi-scale segmentation method integrated with edge information. The method comprises the following steps: acquiring monochromatic, color or multiband image data; acquiring edge intensity data of the above image data; setting one or more image layer of the above image data as an image set to be segmented; setting an edge constrained condition, a segmentation method and a scale increase mode, and segmenting an image with a continuously increasing scale coefficient; carrying out image multi-scale segmentation under a scale coefficient, before merging of any patch, calculating statistics edge intensity in the patch after merging, and when the statistics edge intensity is larger than the edge constrained condition, not executing a merging process; changing the scale coefficient, and continuing to execute the multi-scale segmentation; repeating the previous step until completion of a scale increase process, and forming a multi-scale image segmentation result with image edge intensity as a constrained condition. According to the invention, an edge deletion problem in image segmentation is solved, and a scale selection mode is provided in image multi-scale segmentation.

Owner:陈建裕

Feature fusion block, convolutional neural network, pedestrian re-identification method and related equipment

ActiveCN111523470AImprove recognition accuracyBiometric pattern recognitionNeural architecturesEngineeringData mining

The invention discloses a multi-scale feature fusion block in combination with context information. The multi-scale feature fusion block comprises a forward hierarchical connection group, a backward hierarchical connection group and a channel multi-scale selection module, wherein the forward hierarchical connection group is used for progressive inter-scale information fusion; the backward hierarchical connection group is used for information fusion between spanning scales; and the channel multi-scale selection module is used for carrying out scale feature channel selection on the backward hierarchical connection group. The invention further discloses a convolutional neural network comprising the multi-scale feature fusion block in combination with the context information, so that effectivefusion of multi-scale features is realized. The invention further discloses a pedestrian re-identification method, device and equipment based on the convolutional neural network and a storage medium,and the pedestrian re-identification accuracy can be improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Scale-selection-based top-down visual saliency extraction method

InactiveCN102999763AReduce noise interferenceTest results are obviousCharacter and pattern recognitionSaliency mapNonlinear model

The invention discloses a scale-selection-based top-down visual saliency extraction method. The method includes a training stage, namely learning to obtain a nonlinear model and find an optimal scale in a multi-scale combination for calculation of saliency; and a saliency calculating stage, namely and extracting a saliency map according to the optimal scale and the non-linear model obtained in the training stage. The method fully considers people's intentions and takes advantage of context of multiple scales, and the region of visual saliency related to the people's intentions is effectively extracted. The scale-selection-based top-down visual saliency extraction method is applicable to the fields of object detections and the like.

Owner:SHANGHAI JIAO TONG UNIV

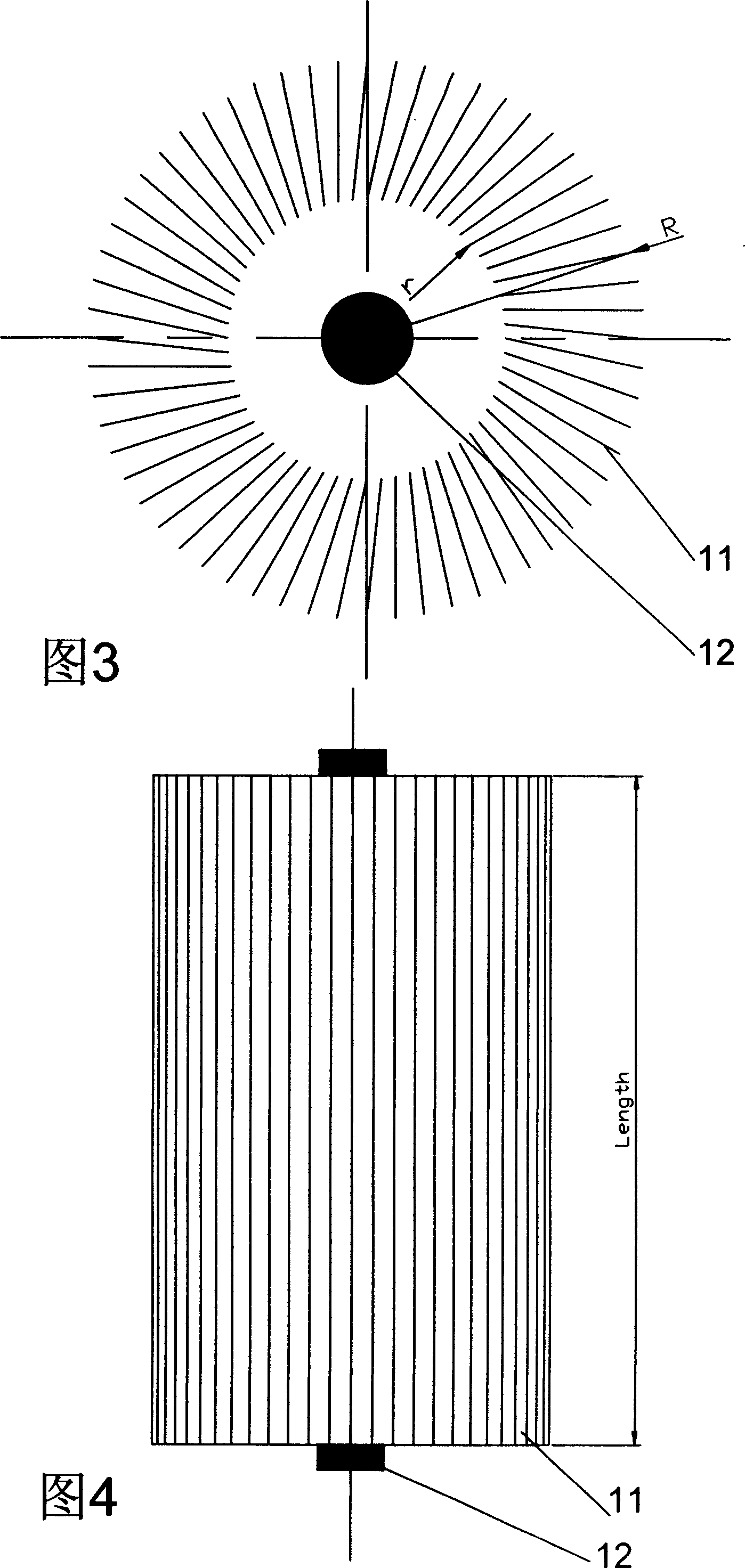

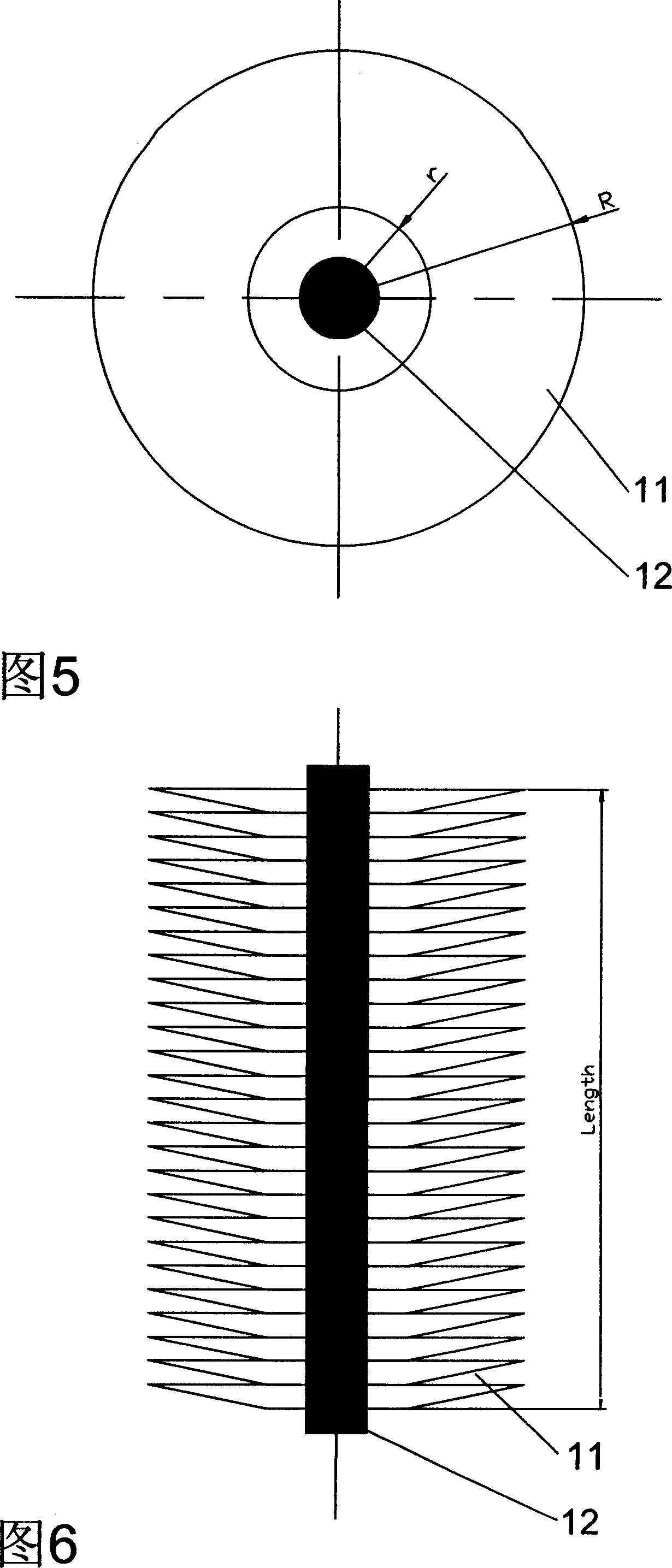

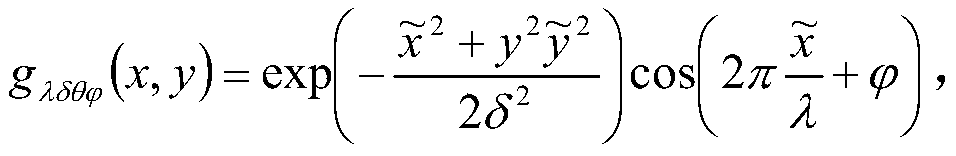

Toothpaste tube shoulder defect detection method based on Gabor filter

ActiveCN107945155ASmall amount of calculationAvoid interferenceImage enhancementImage analysisToothpasteVisual perception

The invention discloses a toothpaste tube shoulder defect detection method based on a Gabor filter. The method includes the following steps: carrying out pixel size calibration on a camera of a visionmeasurement system to obtain calibration data; acquiring a front image of a toothpaste tube shoulder through the camera; carrying out region-of-interest extraction for the above-mentioned image, andobtaining a to-be-detected region by dividing; carrying out Gabor filtering on the to-be-detected region to obtain a result graph; and according to an area / perimeter feature value in the result graph,judging whether a defect exists. According to the method, interference of other parts of workpieces is avoided through preprocessing the front image of the toothpaste tube shoulder, and the calculation amount of subsequent algorithm operations is decreased; and the Gabor filter is adopted, sensibility on edges of the image is realized, very good direction and scale selection can be provided, parameters are easy to adjust, very good illumination adaptability is realized, and a detection recognition speed and an accuracy rate are high. The toothpaste tube shoulder defect detection method basedon the Gabor filter provided by the invention can be widely applied to the field of product quality detection.

Owner:佛山缔乐视觉科技有限公司

Method for romancing and displaying character content in webpage by enlarging scaling of character style on mobile phone screen

InactiveCN101615189ASubstation equipmentSpecial data processing applicationsImage resolutionComputer graphics (images)

The invention relates to a method for scaling the character style in a webpage on a mobile phone screen. When romancing and displaying a webpage source file by the 100 percent of character style scaling on the mobile phone screen with the display resolution width being equal to or larger than 640 pixels, a mobile phone browser romances and displays partial corresponding character content in the webpage by a corresponding character style scaling larger than 100 percent and romances and displays the other character content in the webpage by the 100 percent of character style scaling according to a character content scaling selection functional module in mobile phone browser software or a character style scaling tab character string in the webpage source file.

Owner:魏新成

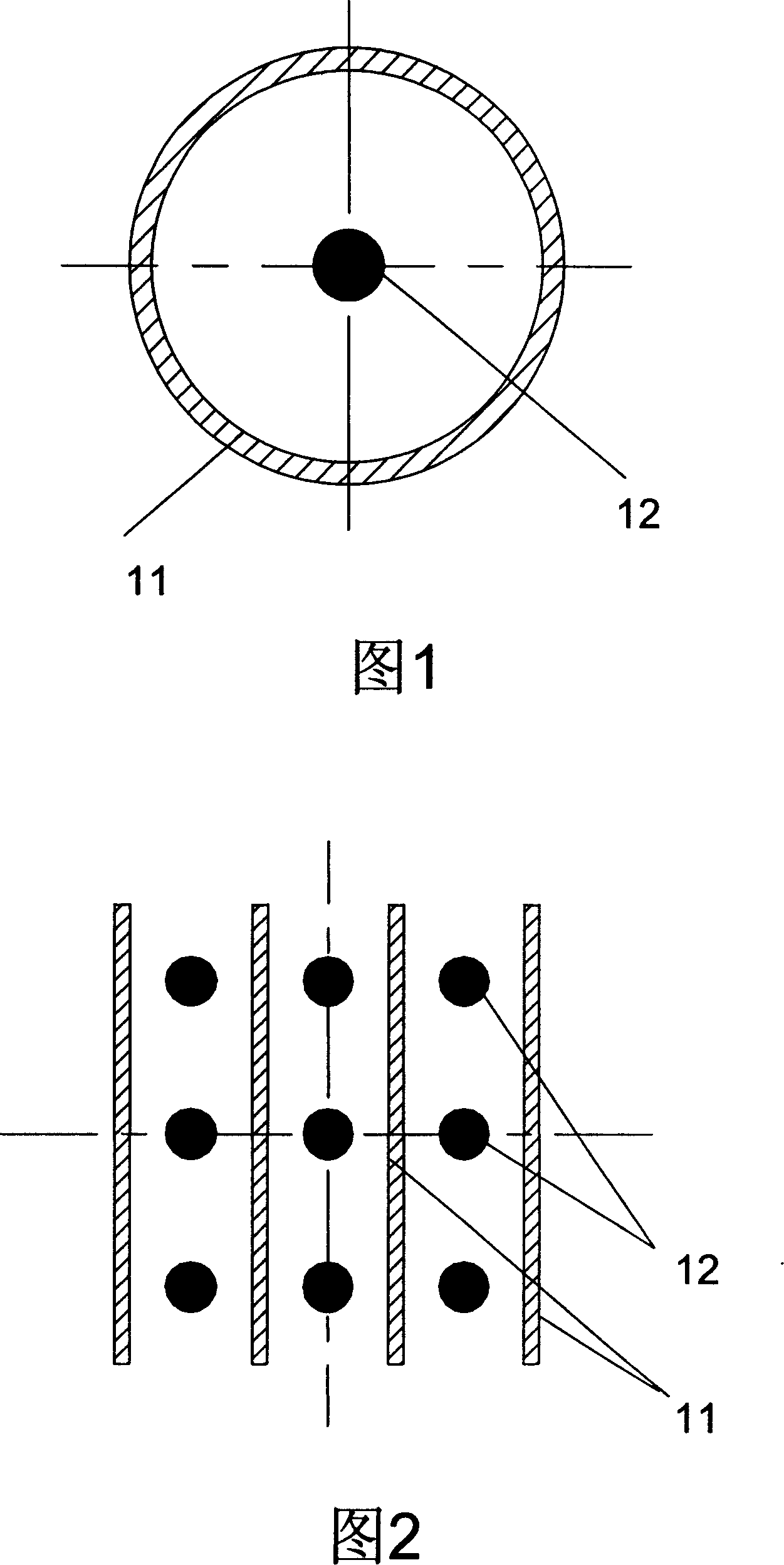

Module combined type photocatalyst pollutant disposal system

InactiveCN101112680ASimple designEasy to handleEnergy based chemical/physical/physico-chemical processesModular compositionStop time

The invention discloses a module combined-typed photocatalyst contamination processing system, which mainly arranges a plurality of photocatalytic carrier structure parts in a shell in the serial way or parallel way or serial and parallel way to constitute the photocatalyst contamination processing system. The contamination processing system can be combined in serial and / or parallel way by selecting and using independent processing modules with suitable quantity according to the design scale of the contamination processing system. The invention simplifies and facilitates the design of the photocatalyst contamination processing system which is the same convenient as the module combination. The contamination processing system with modularization design not only can increase the processing ability of the processing system to the contamination according to the requirement, but also can improve the circulation path of the contamination processing by simple modularization combination, and improve the stopping time of the contamination fluid in the processing system, namely the contacting reaction time with the photocatalyst carrier, thus obtaining more effective contamination processing system.

Owner:杨小明

Pixel circuit, driving method thereof and pixel array structure

The invention discloses a pixel circuit, a driving method thereof and a pixel array structure, aiming to reduce charging time of an OLED (organic light emitting diode) pixel circuit. The pixel circuit comprises a load control module, a load module, a gray scale selection module, a driving module and a light emitting element. The load control module is controlled by a first scanning signal line to store data signals at a first node and a second node. The load module is connected with a first power supply terminal, the driving module, the first node and the second node respectively, and is controlled by the first node signal and the second node signal to store analog data signals at the load module and provide the analog data signals to the driving module. The gray scale selection module is controlled by a second scanning signal line to transmit digital data signals to a third node of the gray scale selection module. The driving module is controlled by the second node signal and a third node signal to drive the light emitting element. The first end of the light emitting element is connected with a second power supply terminal while the second end of the same is connected with the driving module.

Owner:BOE TECH GRP CO LTD

Method for scale selection of microorganism alkaliproof related genes

InactiveCN101063174AAchieve high throughputAchieve scaleMicrobiological testing/measurementFermentationMicroorganismBacillus coli

The invention discloses a method to sieve scale microbe alkali proof relative gene in microbe engineering domain, which is characterized by the following: collecting typical basic environment soil sample; rough-extracting; purifying; getting macro-genom DNA of soil sample; electrization-inverting bacillus coli defect strain E with connecting product between macro-genom DNA part enzyme cutting fragment and carrier; sieving; getting positive colony; proceeding sub-clone and functional appraise for alkali proof related gene of positive clone. This invention can be used to breeding of alkali proof and molecule of microbe.

Owner:RUBBER RES INST CHINESE ACADEMY OF TROPICAL AGRI SCI

Method for detecting maximally stable extremal region of image based on scale space

InactiveCN103310439AImprove blur invarianceGood scale invarianceImage analysisMaximally stable extremal regionsScale space

The embodiment of the invention discloses a method for detecting a maximally stable extremal region of an image based on a scale space, comprising the following steps of S10, structuring the scale space of the image by adopting Gaussian kernel; S20, carrying out maximally stable extremal region detection on all scale-level images to obtain candidate region characteristics; S30, defining a scale selection function for each region characteristic, and screening the candidate region characteristics by judging whether the scale selection functions reach a local maximum value or not; and S40, removing repeated region characteristics of which the locations and the areas are similar to obtain final region characteristics with good invariance. According to the method for detecting the maximally stable extremal region of the image based on the scale space, an MSER (Maximally Stable Extremal Region) in the single scale space is expanded into a multiscale space, so that the invariance of the region characteristics is improved, and the defect that the invariance of the MSER in image blur variation is poorer is overcome.

Owner:ZHEJIANG UNIV

Workpiece surface defect feature extraction method

InactiveCN110348461AIncrease contrastImprove image qualityImage enhancementImage analysisFeature vectorFeature extraction

The invention discloses a workpiece surface defect feature extraction method. The method comprises the following steps: S1, source image acquisition; S2, preprocessing the source image; S3, thresholdvalue cutting; S4, positioning a workpiece area; S5, shearing; S6, filtering processing; S7, contour extraction; S8, feature extraction; and S9, feature vector identification. The method has the advantages that the adaptability to illumination change is good, the reverse selection and scale selection characteristics are good, and compared with an existing workpiece surface defect feature extraction method, the discrimination accuracy is improved, and meanwhile the robustness is also improved.

Owner:JIANGSU MARITIME INST

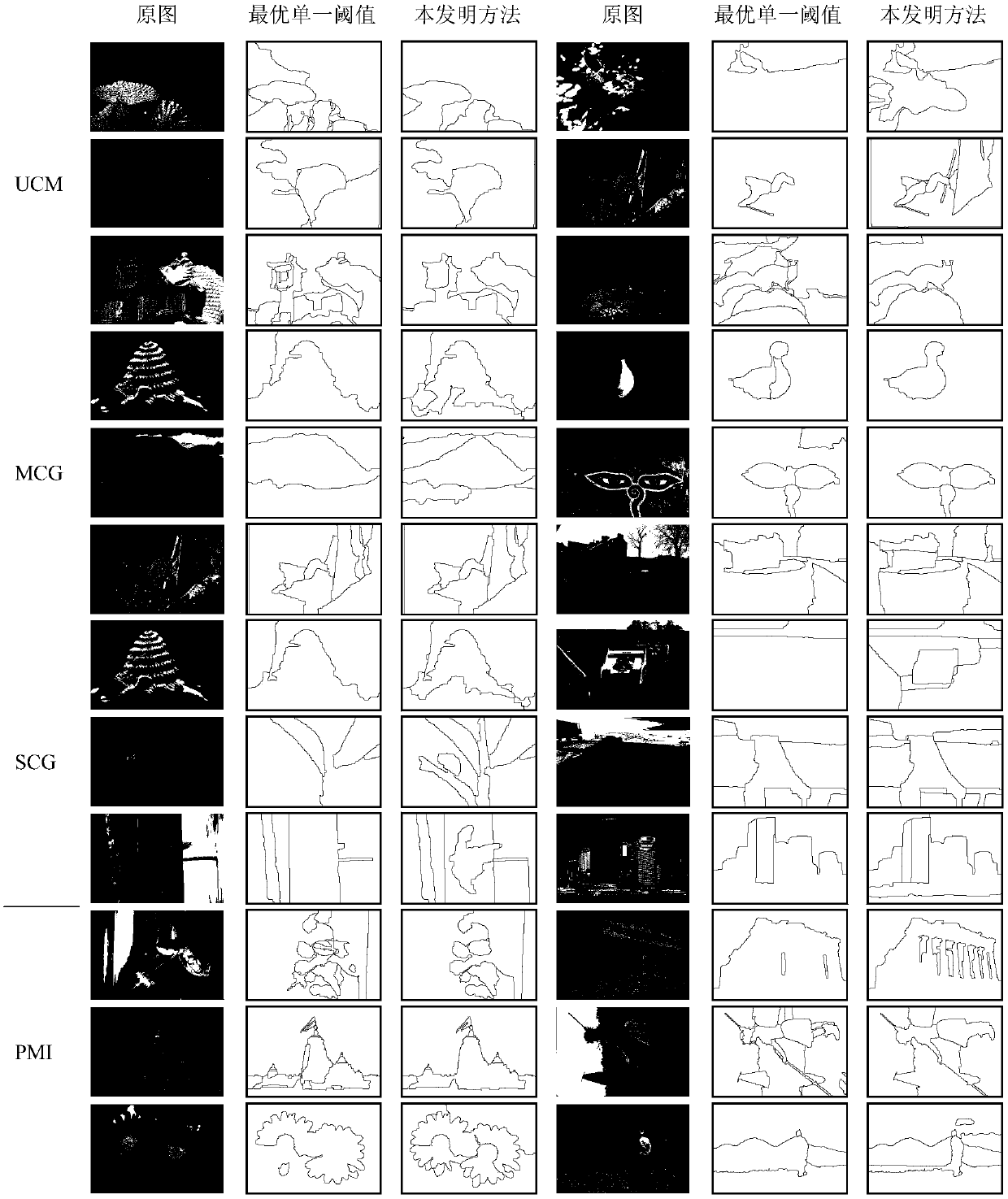

Method and device for achieving network planning

ActiveCN104581744AReasonable network planning resourcesReasonable planning resourcesNetwork planningThe InternetComputer science

The invention discloses a method and device for achieving network planning. The method comprises the steps that in a network planning area, user Internet surfing information of base stations of other systems except a first system is obtained within the preset duration; the analysis and statistics are carried out on the user Internet surfing information of all the base stations, and the Internet surfing flow of all user terminals which correspond to the base stations, support the first system and customize the first system service is obtained; the Internet surfing flow, obtained through the statistics, of the base stations is ranked, and the position of the base station with the Internet surfing flow ranked in front is selected according to a network planning scale for establishing a first system base station. When the network is planned, the Internet surfing flow of the user terminals which support the first system and customize the first system service in the Internet surfing flow of other base stations except the first system is analyzed, the position where the first system base station is established is determined, network planning resources are more reasonable, and the development of the first system service is promoted.

Owner:CHINA UNITED NETWORK COMM GRP CO LTD

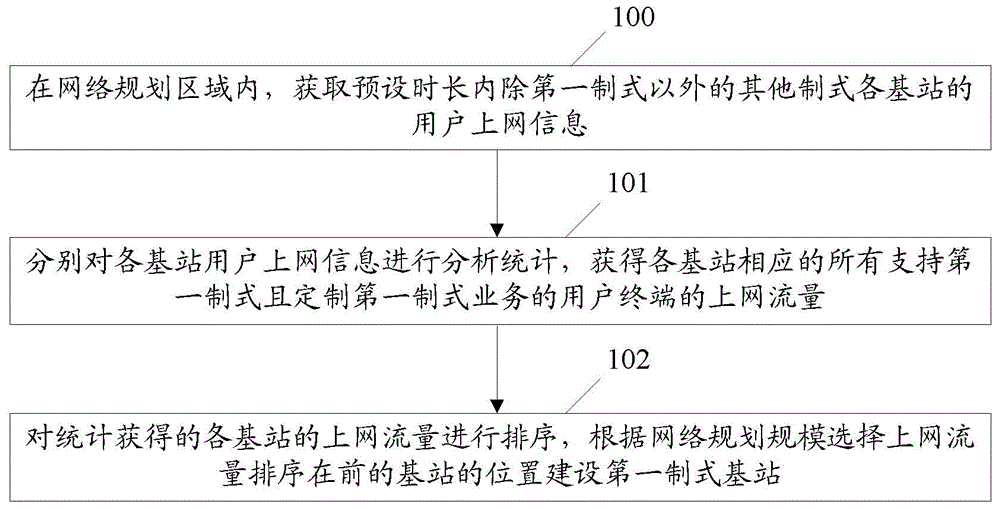

Image segmentation level selection method based on scale perception

ActiveCN109636809AImplement adaptive selectionOvercome limitationsImage enhancementImage analysisFeature vectorImage segmentation algorithm

The invention discloses an image segmentation level selection method based on scale perception, and aims to improve the segmentation quality of an overall image. The method comprises the following main steps: firstly, obtaining a segmentation result represented by a tree form by using a multi-level image segmentation algorithm; secondly, calculating feature vectors of all segmented regions in eachsegmentation layer, and performing quantitative description on region segmentation quality according to a visual format tower principle; thirdly, constructing a graph model of the multi-level segmented image by taking the hierarchical region with the finest segmentation granularity as a node, and finally, mapping a label to a region corresponding to the original hierarchy, and combining to obtaina final image segmentation result. According to the method, based on the scale selection principle of segmentation area quality, the problem of hierarchical selection of multi-level image segmentation is solved, and the limitation of traditional single hierarchical selection and the uncertainty of threshold parameters on segmentation hierarchical selection are overcome. As a post-processing means, the output quality of the multi-level image segmentation algorithm in a visual processing task can be improved.

Owner:南京方和网络科技有限公司 +1

Method and device for reconfiguration scale selection of reconfigurable manufacture system

ActiveCN103606012ABalance costForecastingManufacturing computing systemsDemarcation pointFrequency spectrum

The invention provides a method and a device for reconfiguration scale selection of a reconfigurable manufacture system. The device comprises a first acquiring module for acquiring production performance signals of the reconfigurable manufacture system; a processing module for carrying out Fourier transform to the signals to obtain a corresponding frequency spectrum Fn or a frequency spectrum density function F(omega) to obtain a spectrogram; a second acquiring module for acquiring the variation amount [delta] that the performance of the reconfigurable manufacture system (RMS) needs; a first inquiring module for finding the corresponding amplitude in the frequency spectrum in dependence on the variation amount [delta]; a second inquiring module for finding a corresponding frequency value [omega] in the frequency spectrum in dependence on the variation amount [delta]; a third acquiring module for acquiring a demarcation point frequency value of each scale reconfiguration in the frequency domain; and a determining module for determining the grade that a reconfiguration needing to be carried out belongs to in dependence on the comparative result of the frequency value [omega] and the demarcation point frequency value. According to the invention, the balance between reconfigurable usefulness and cost is guaranteed to some extent, the reconfigurable manufacture system (RMS) is optimized, and at the same time relative advantages are guaranteed.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Optimal scale selection method and device and computer readable storage medium

InactiveCN110097078AWide applicabilityMeet analysis needsCharacter and pattern recognitionSelection methodClassification result

Embodiments of the invention disclose an optimal scale selection method and device, and a computer readable storage medium. The method comprises the steps of generating the segmentation result graphsunder different scale parameters based on an input remote sensing image; selecting a training sample from the generated segmentation result graphs, training the training sample to obtain a multi-scaleclassification model, then carrying out multi-scale classification on the remote sensing image to be classified, and generating the classification result graphs under different scale parameters; selecting a plurality of target classification result graphs from the classification result graphs, and respectively calculating the classification precision associated with each target classification result graph; and carrying out optimal scale selection after classification precision statistics. By implementing the invention, the multi-scale classification result is used for precision evaluation, the optimal scale is selected according to the precision evaluation statistical result, the applicability is wider, the analysis requirements under more scenes can be met, the conversion from the optimal segmentation scale to the optimal classification scale is achieved, and the defects that the efficiency is low and the effect is poor when the analysis scale is selected at the segmentation stage are overcome.

Owner:SHENZHEN UNIV

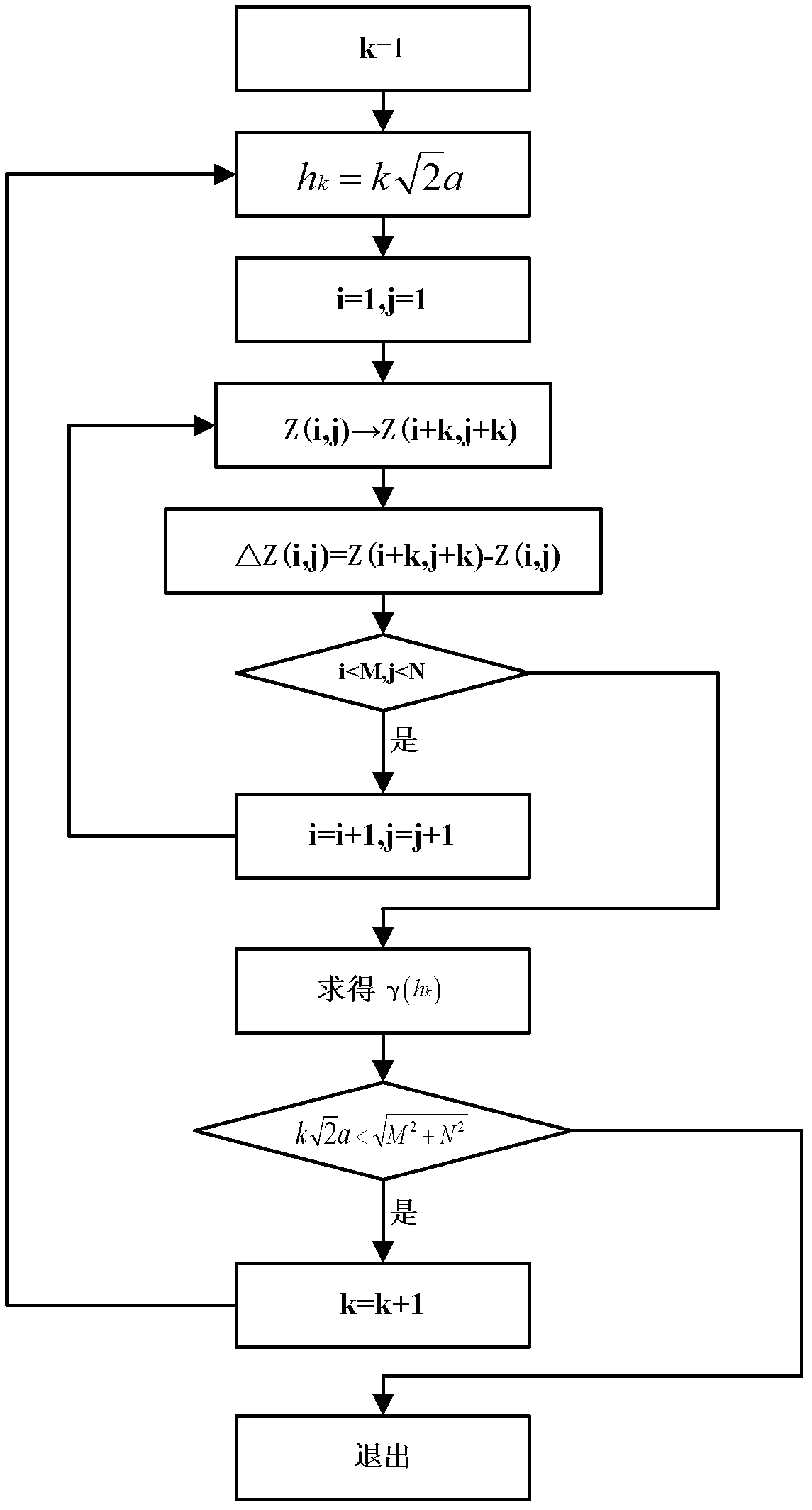

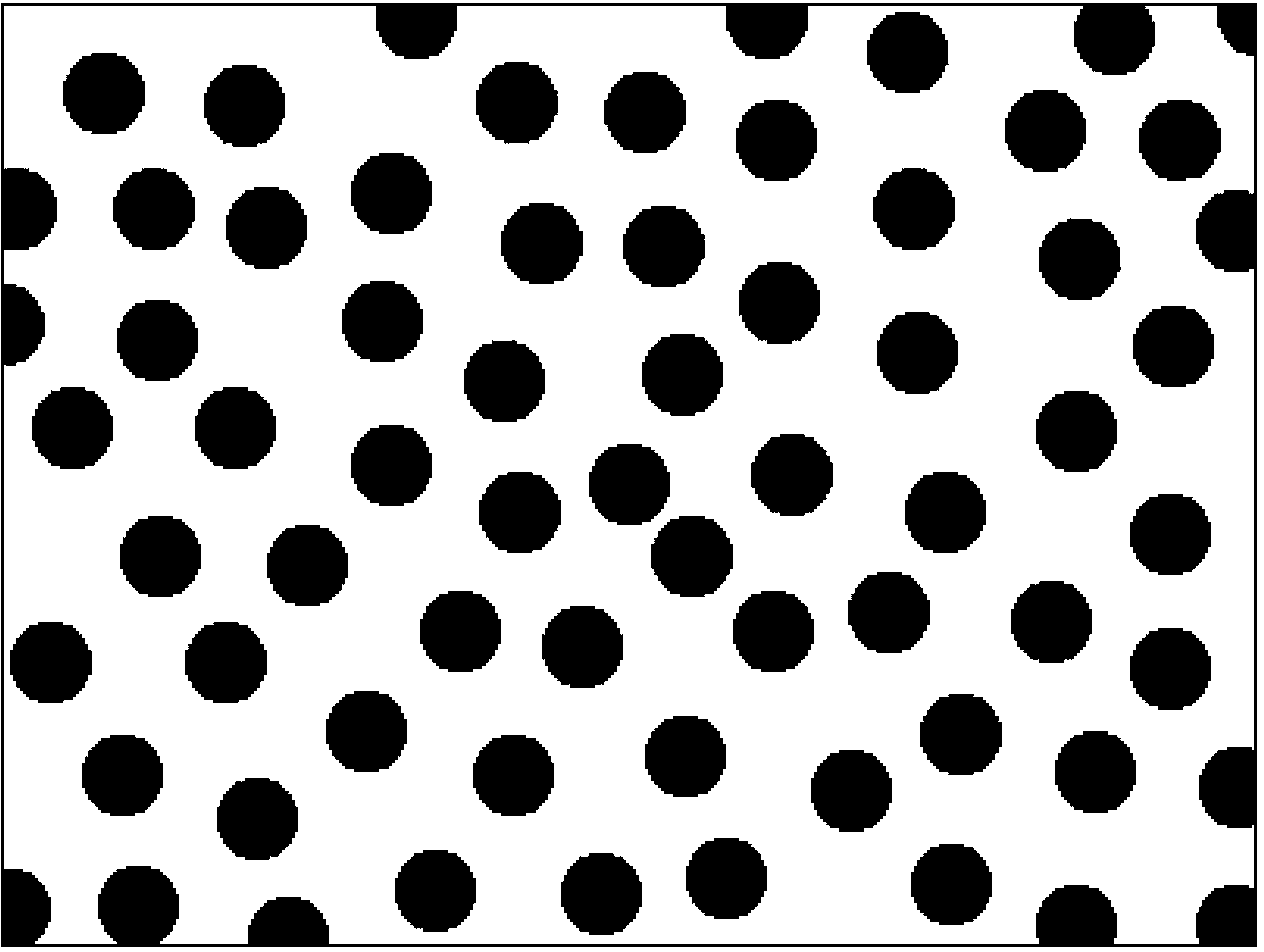

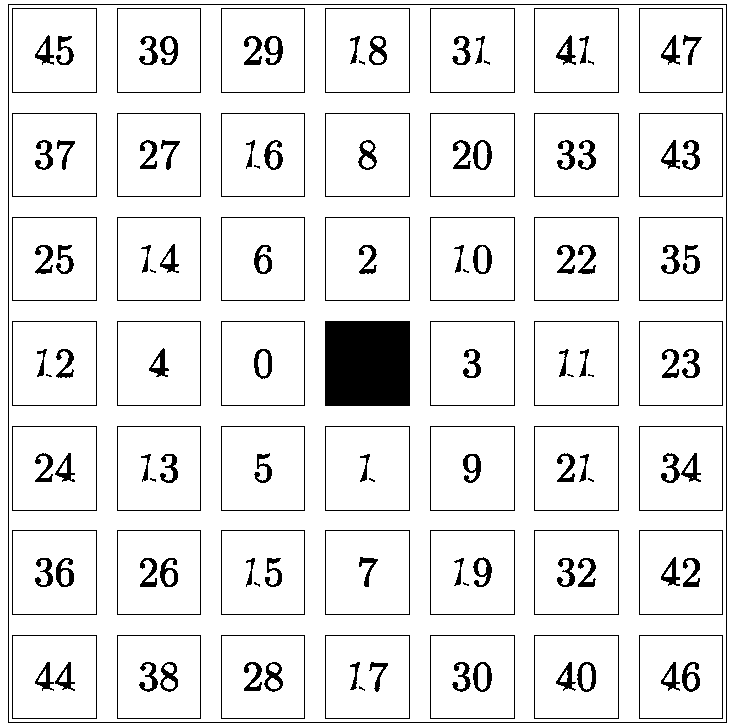

Omnidirectional search mechanism variogram based optimal remote sensing scale selection method

ActiveCN102354391ABig errorImprove accuracyImage data processing detailsLocal optimumComputer science

The invention relates to an omnidirectional search mechanism variogram based optimal remote sensing scale selection method, which comprises the following steps of: firstly, selecting a research area by using an obtained remote sensing image; then, calculating corresponding variogram values of the remote sensing image at different space intervals in each direction by using an omnidirectional search algorithm; on this basis, establishing a curvilinear relation between the space intervals and the variogram values of the space intervals, and then solving a corresponding local optimal space scale of the remote sensing image in each direction based on the spherical model regression fitting in a variogram model; and finally, taking the local optimal space scale corresponding to the direction with the maximum degree of fitting as the optimal space scale of the remote sensing image. By using the method disclosed by the invention, the problem of 'false' local optimal scales caused by that when a traditional variogram algorithm is used, in the process of selecting the optimal space scale of a remote sensing image, only an isotropic factor is taken into consideration is solved, thereby improving the accuracy of optimal scale selection.

Owner:WUHAN UNIV OF TECH

Method for geography phenomenon multi-point simulation spatial scale selection

InactiveCN103268423AEfficient use ofAvoid uncertaintySpecial data processing applicationsSpatial correlationShortest distance

A method for geography phenomenon multi-point simulation spatial scale selection comprises the steps of (1) calculating the shortest distance between a template center and a boundary, (2) calculating the critical distance, smaller than a predetermined threshold value, of the spatial correlation of a training image, and (3) determining the size of spatial scale needing to be considered, namely the number of multiple grids according to the shortest distance between the template center and the boundary and the critical distance of the spatial correlation. According to the method for the geography phenomenon multi-point simulation spatial scale selection, the size of the spatial scale needed can be determined according to the spatial correlation before multi-point simulation, and therefore subjectivity and uncertainty existing when spatial scale selection is achieved by using expert experience are avoided, and a parameter determining method of the number of the multiple grids is provided for relevant issues in production and life, such as petroleum reservoir simulation. The method for the geography phenomenon multi-point simulation spatial scale selection can be applied to fields such as geology and mineral products, weather, remote sensing, ocean research, military reconnaissance and environmental monitoring.

Owner:SHANXI UNIV +1

Systems and methods for automatic scale selection in real-time imaging

A system and method for automatic scale selection in real-time image and video processing and computer vision applications. In one aspect, a non-parametric variable bandwidth mean shift technique, which is based on adaptive estimation of a normalized density gradient, is used for detecting one or more modes in the underlying data and clustering the underlying data. In another aspect, a data-driven bandwidth (or scale) selection technique is provided for the variable bandwidth mean shift method, which estimates for each data point the covariance matrix that is the most stable across a plurality of scales. The methods can be used for detecting modes and clustering data for various types of data such as image data, video data speech data, handwriting data, etc.

Owner:PALO ALTO NETWORKS INC

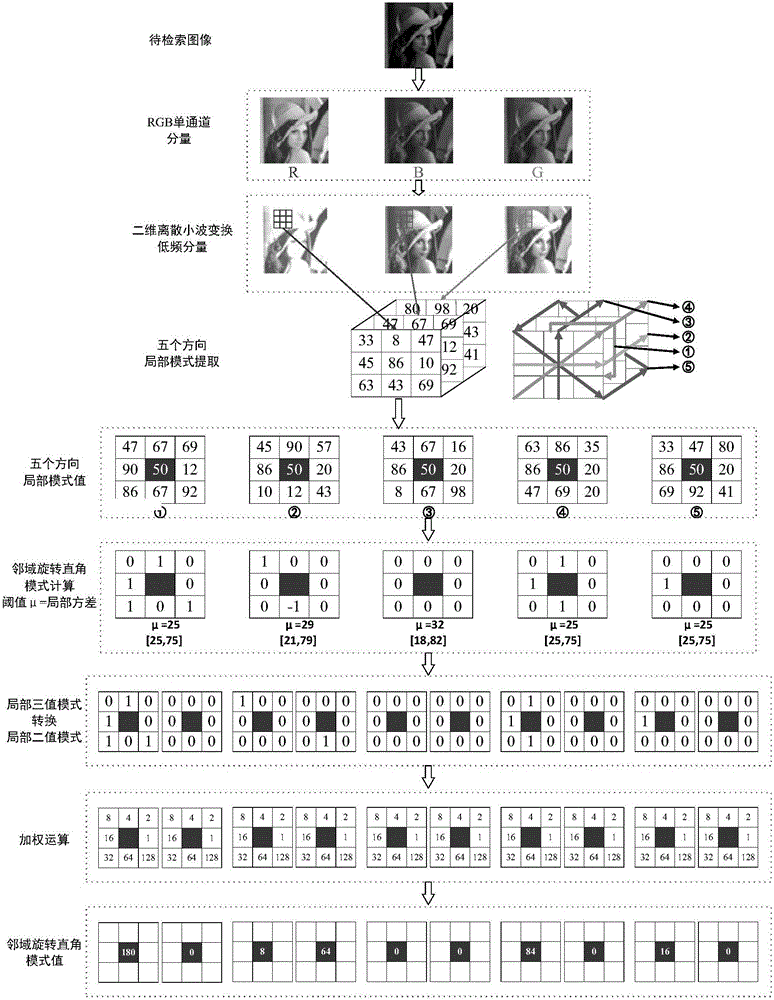

Image retrieval method based on neighborhood rotation right angle mode

ActiveCN106649611AEasy extractionLarge amount of informationCharacter and pattern recognitionSpecial data processing applicationsScale selectionLow frequency

The invention relates to an image retrieval method based on a neighborhood rotation right angle mode, and solves the problems that the prior art, a recall ratio and a precision ratio are low as threshold selection is limited and part of image information is lost in gray scale selection. The method comprises the following steps: I, separating three channel colors of R, G and B of a colorful image, and conducting two-dimensional discrete wavelet transform on the three channel colors respectively, and taking low frequency sub-bands of the three channel colors as a selected plane; II, based on a VLBP mode, extracting a local mode of the plane selected in step I; III, calculating a neighborhood rotation right angle mode value of the local mode according to the neighborhood rotation right angle mode; and III, conducting feature similarity measurement on a feature vector formed by the neighborhood rotation right angle mode value and an image data base, and evaluating an image retrieval result by using a recall ratio and a precision ratio. The invention is applied to the field of image retrieval.

Owner:HARBIN UNIV OF COMMERCE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com