Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

61 results about "Positive logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

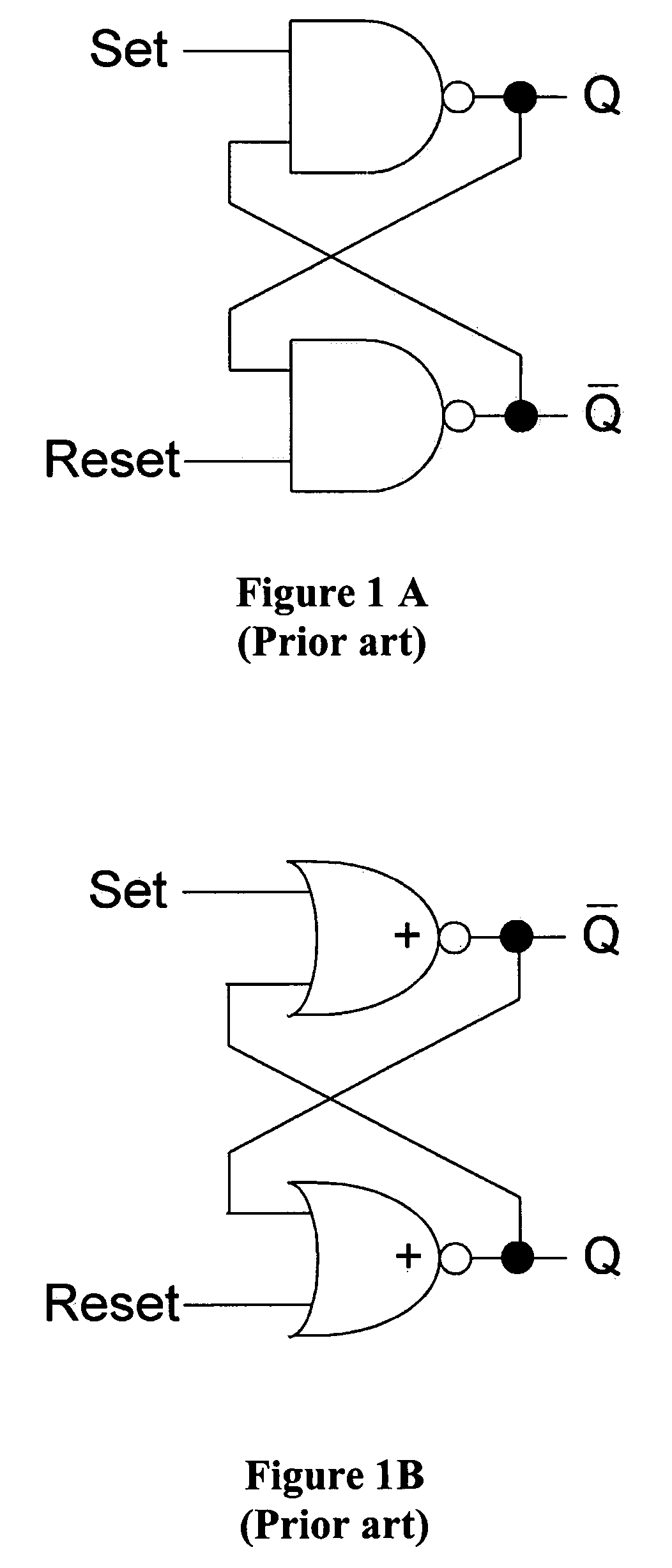

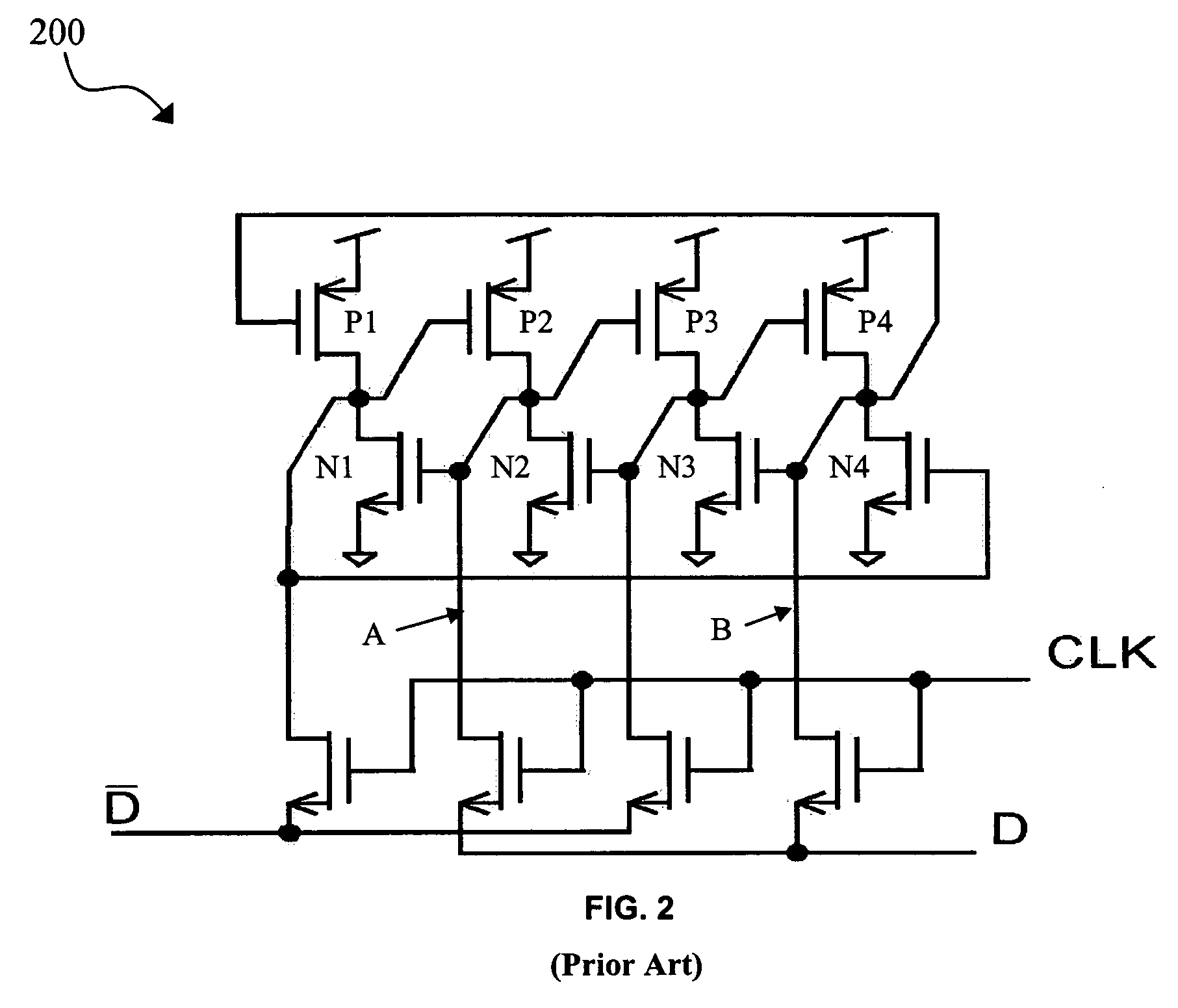

Redundant single event upset supression system

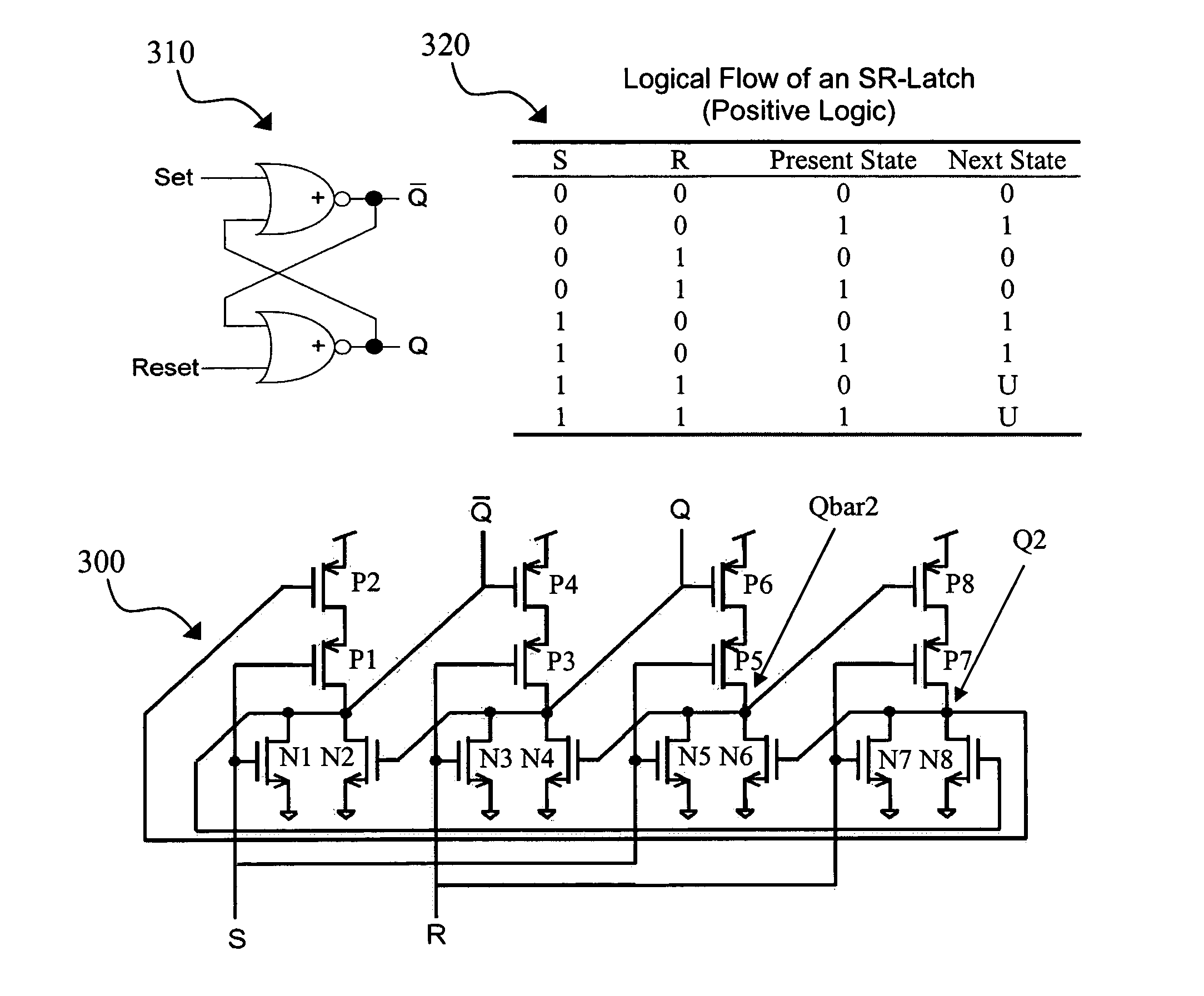

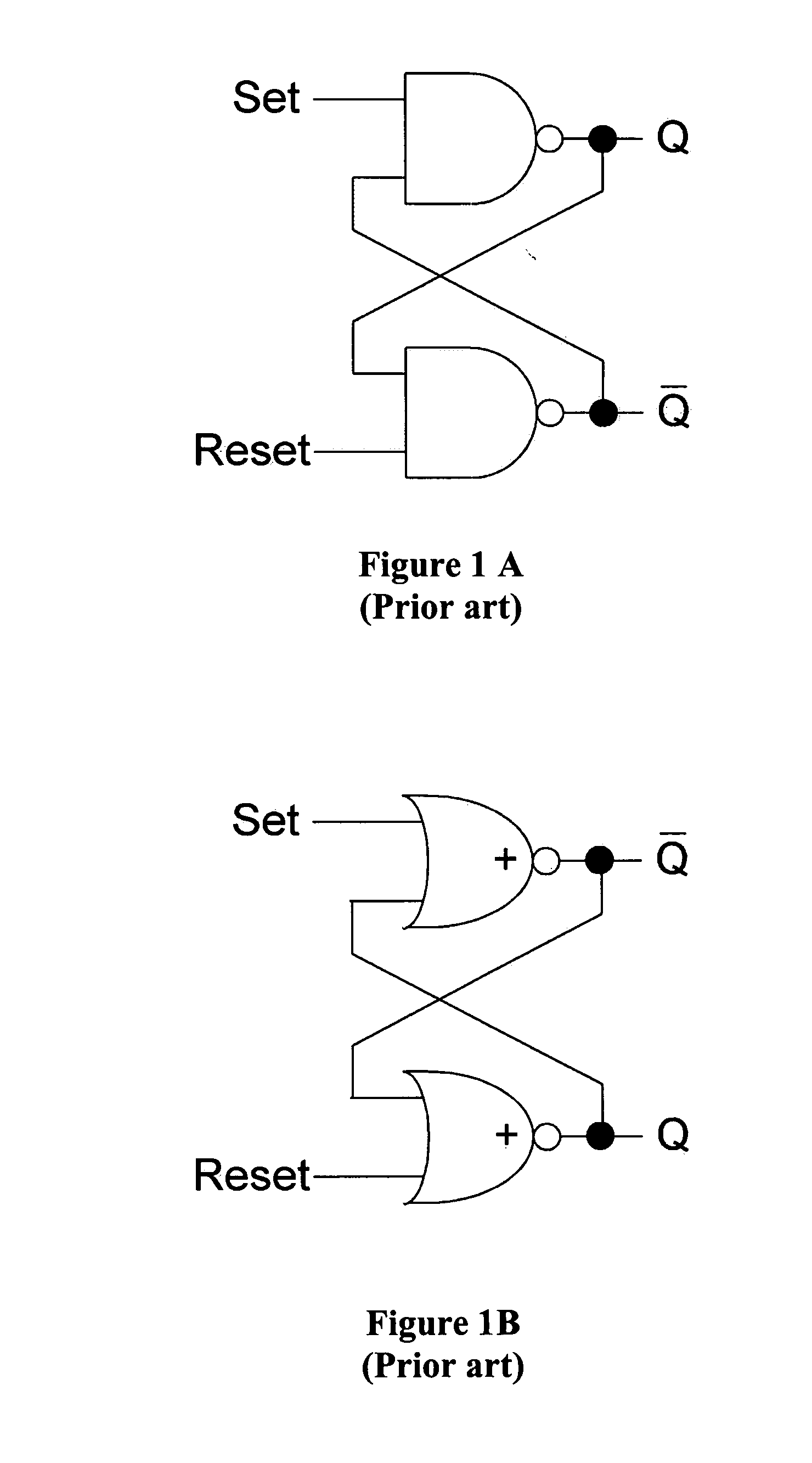

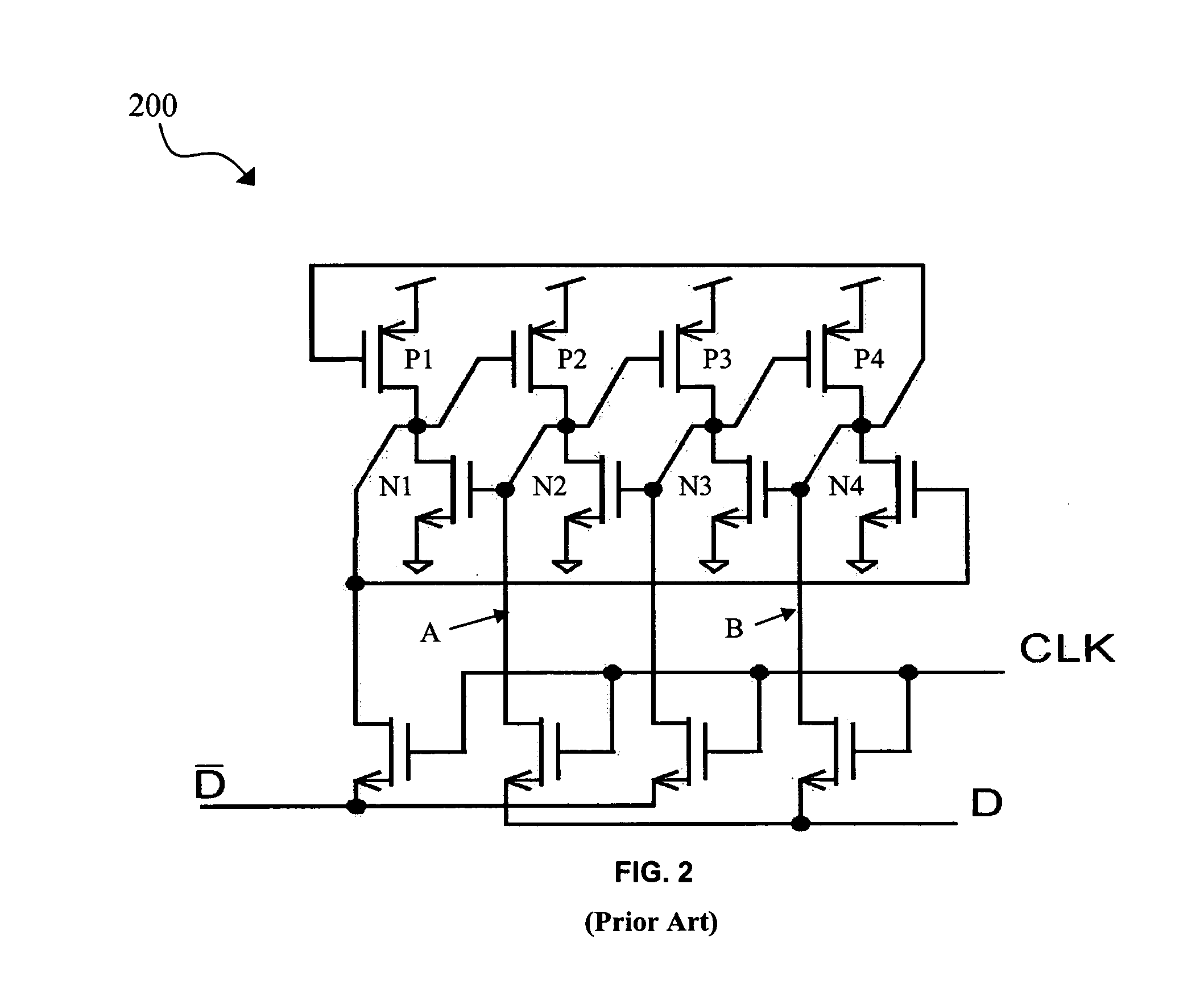

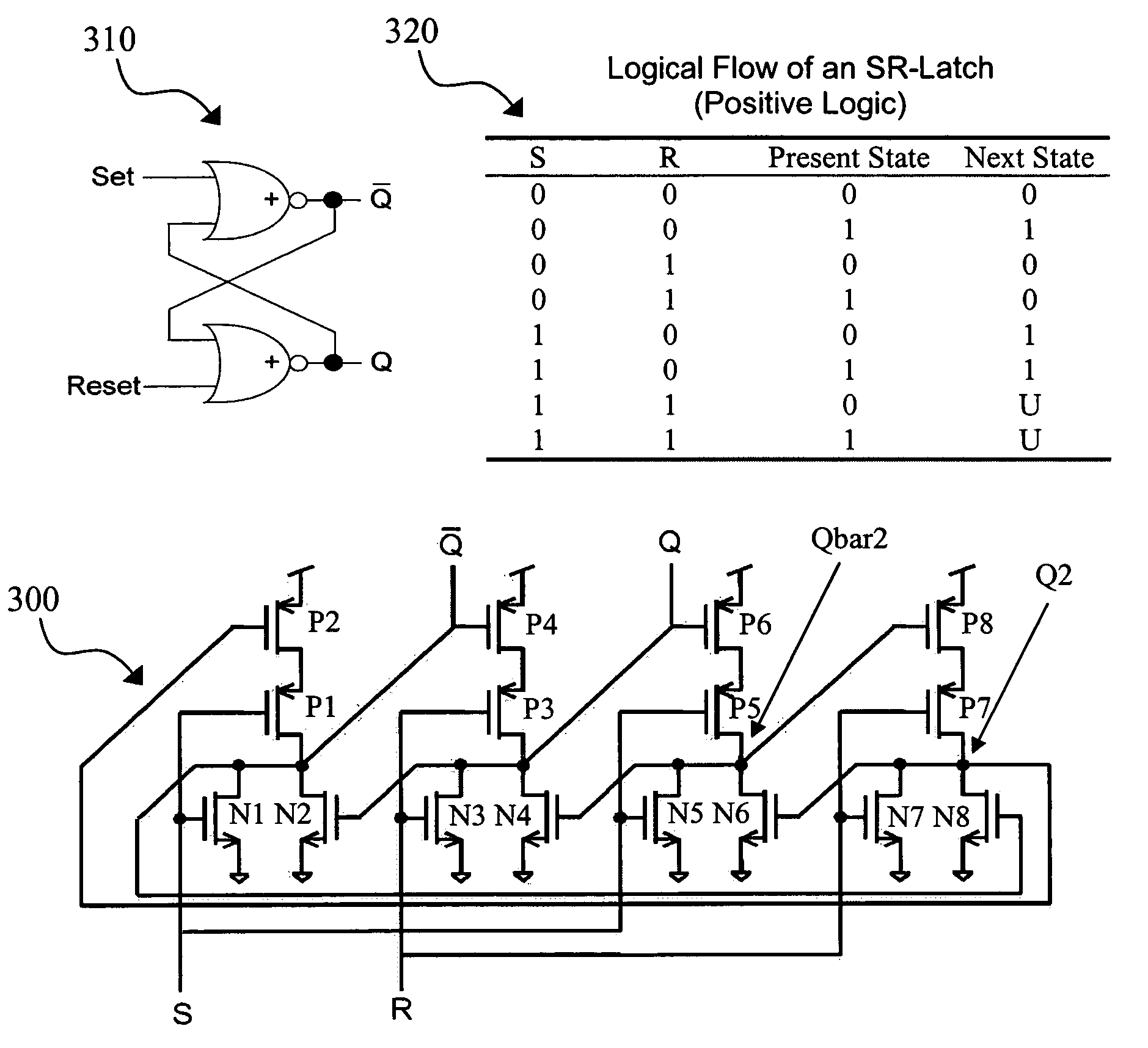

CMOS transistors are configured to operate as either a redundant, SEU-tolerant, positive-logic, cross-coupled Nor Gate SR-flip flop or a redundant, SEU-tolerant, negative-logic, cross-coupled Nand Gate SR-flip flop. The register can operate as a memory, and further as a memory that can overcome the effects of radiation. As an SR-flip flop, the invention can be altered into any known type of latch or flip-flop by the application of external logic, thereby extending radiation tolerance to devices previously incapable of radiation tolerance. Numerous registers can be logically connected and replicated thereby being electronically configured to operate as a redundant circuit.

Owner:FERMI RESEARCH ALLIANCE LLC

Redundant single event upset supression system

CMOS transistors are configured to operate as either a redundant, SEU-tolerant, positive-logic, cross-coupled Nor Gate SR-flip flop or a redundant, SEU-tolerant, negative-logic, cross-coupled Nand Gate SR-flip flop. The register can operate as a memory, and further as a memory that can overcome the effects of radiation. As an SR-flip flop, the invention can be altered into any known type of latch or flip-flop by the application of external logic, thereby extending radiation tolerance to devices previously incapable of radiation tolerance. Numerous registers can be logically connected and replicated thereby being electronically configured to operate as a redundant circuit.

Owner:FERMI RESEARCH ALLIANCE LLC

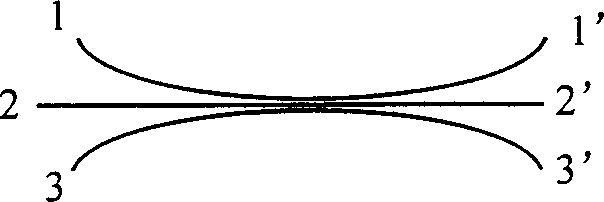

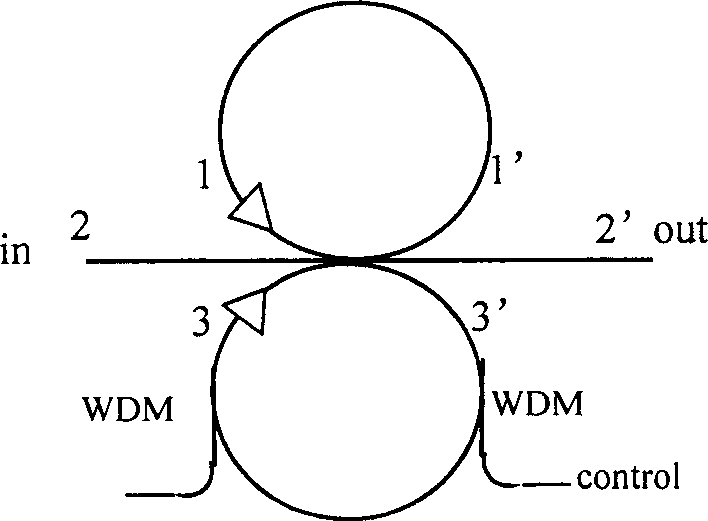

Double-ring coupled all optical buffer storage

InactiveCN1417604AExtended storage timeGood symmetryCoupling light guidesElectromagnetic transmissionFiber couplerPhase difference

The double-ring coupled all optical buffer storage based on 3x3 fiber coupler stores light signal has its read / write operation under control of one other light signal. Two side ports of the 3x3 fibercoupler constitute the double-ring structure via fiber feedback and the middle ports are used as the input and output of the buffer storage. Control light is led in and led out one fiber ring via twoWDM fiber coupler, and the phase difference between the two ring light signals is altered by means of cross phase modulation effect to realize the write-in and real-out of light signal in fiber ring.The control light signal may be positive logic one or negative logic one. If necessary, light amplifier may be added into the fiber ring for power compensation. Several buffer storages can be constituted into one parallel signal light buffer storage.

Owner:BEIJING JIAOTONG UNIV

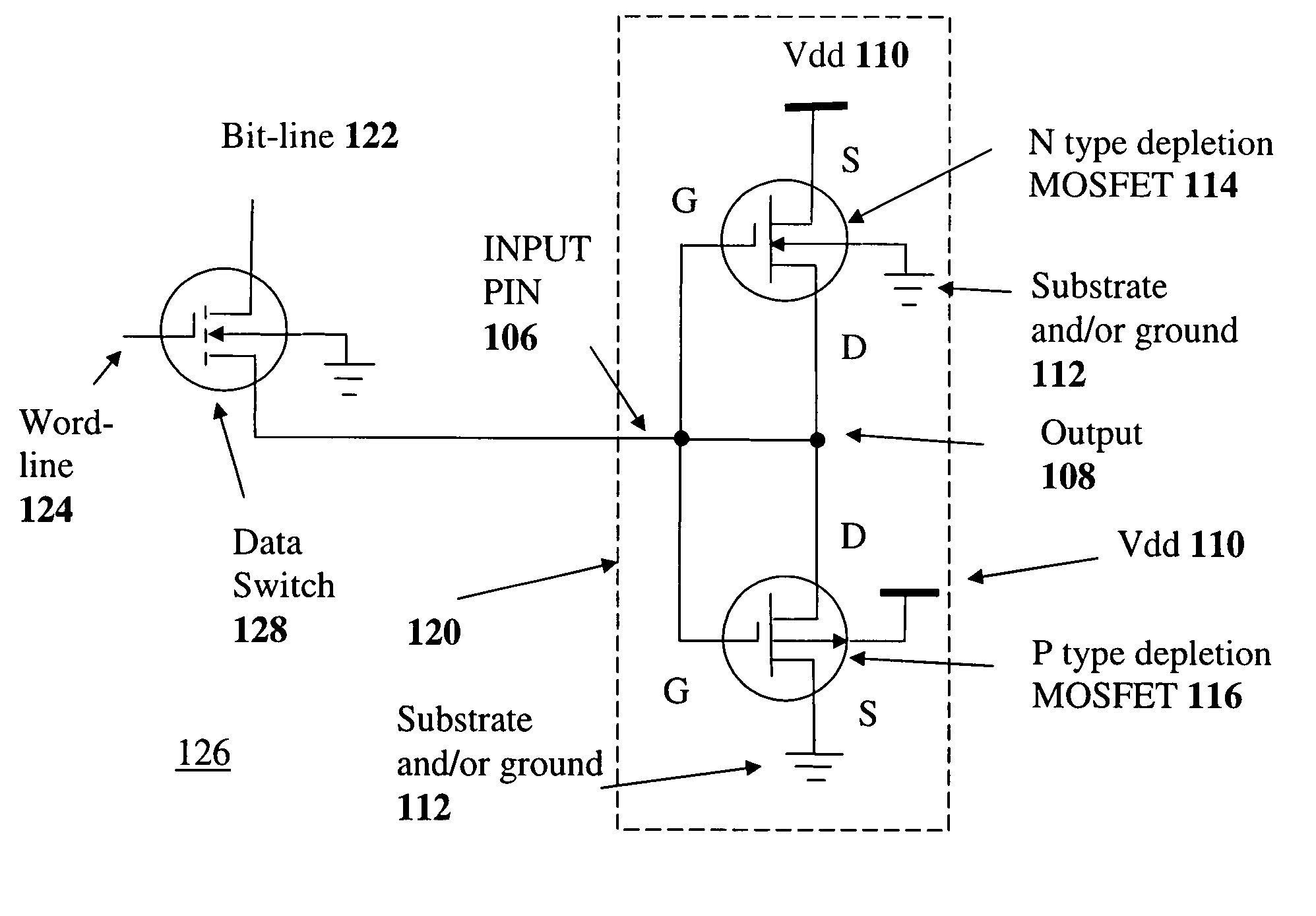

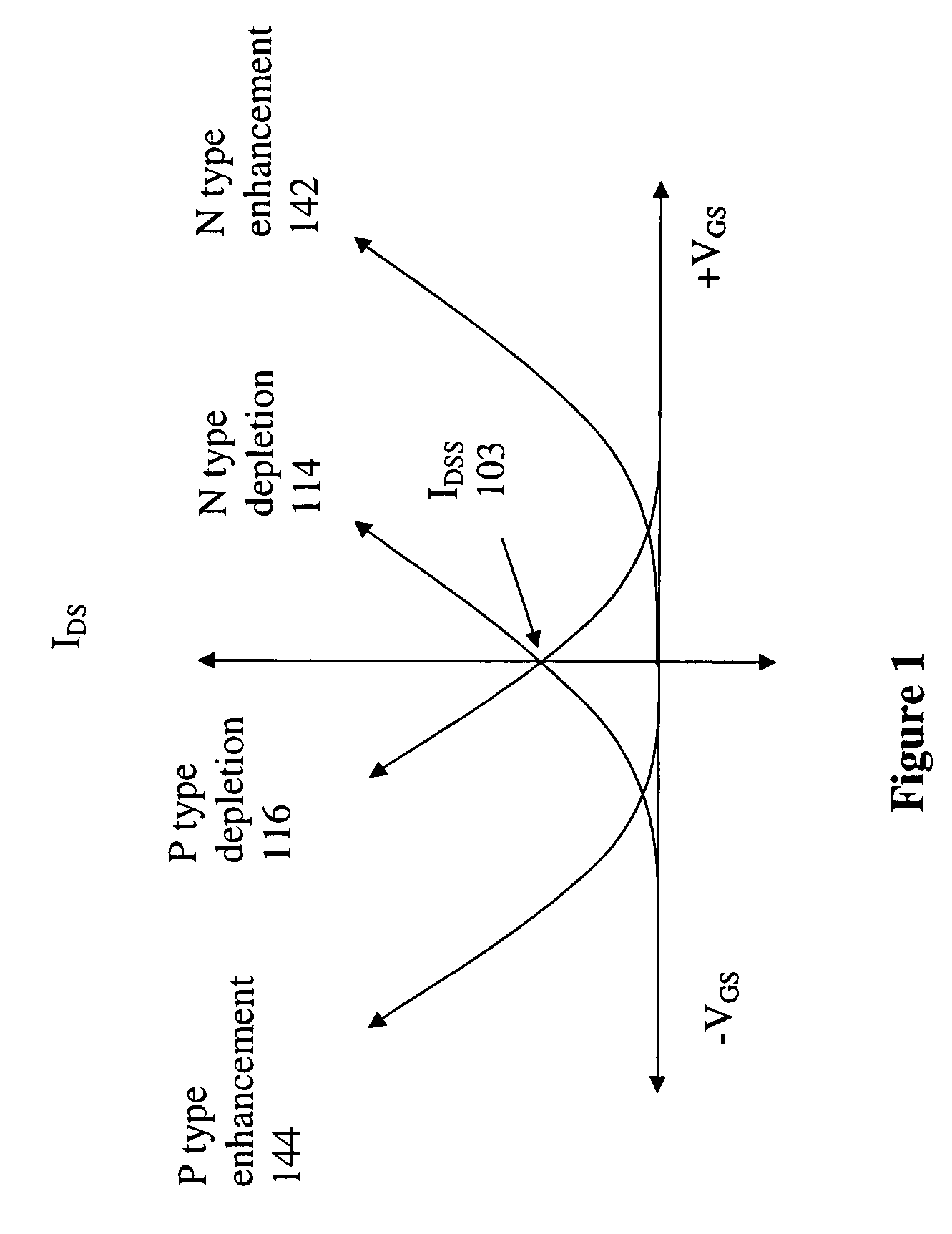

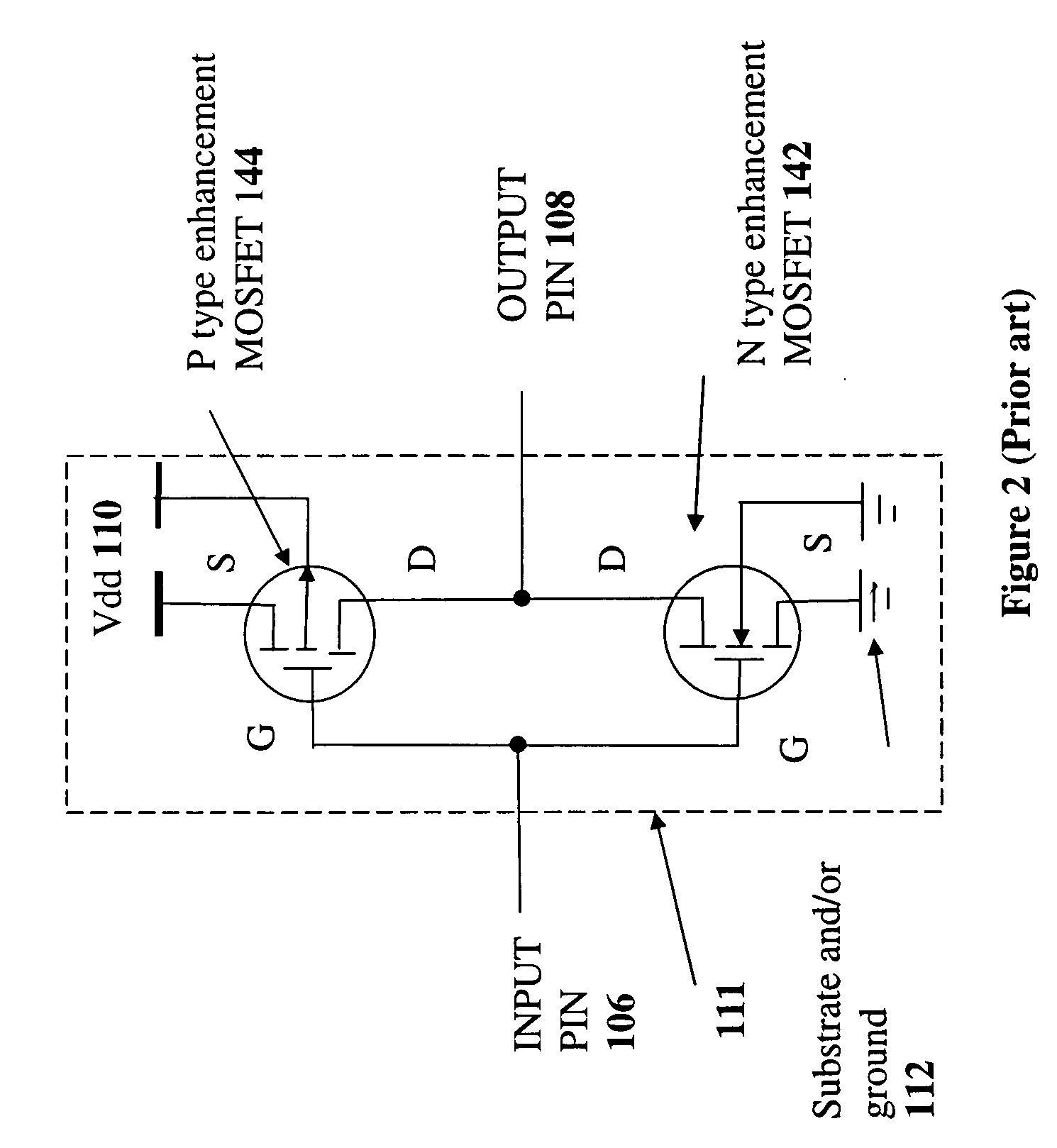

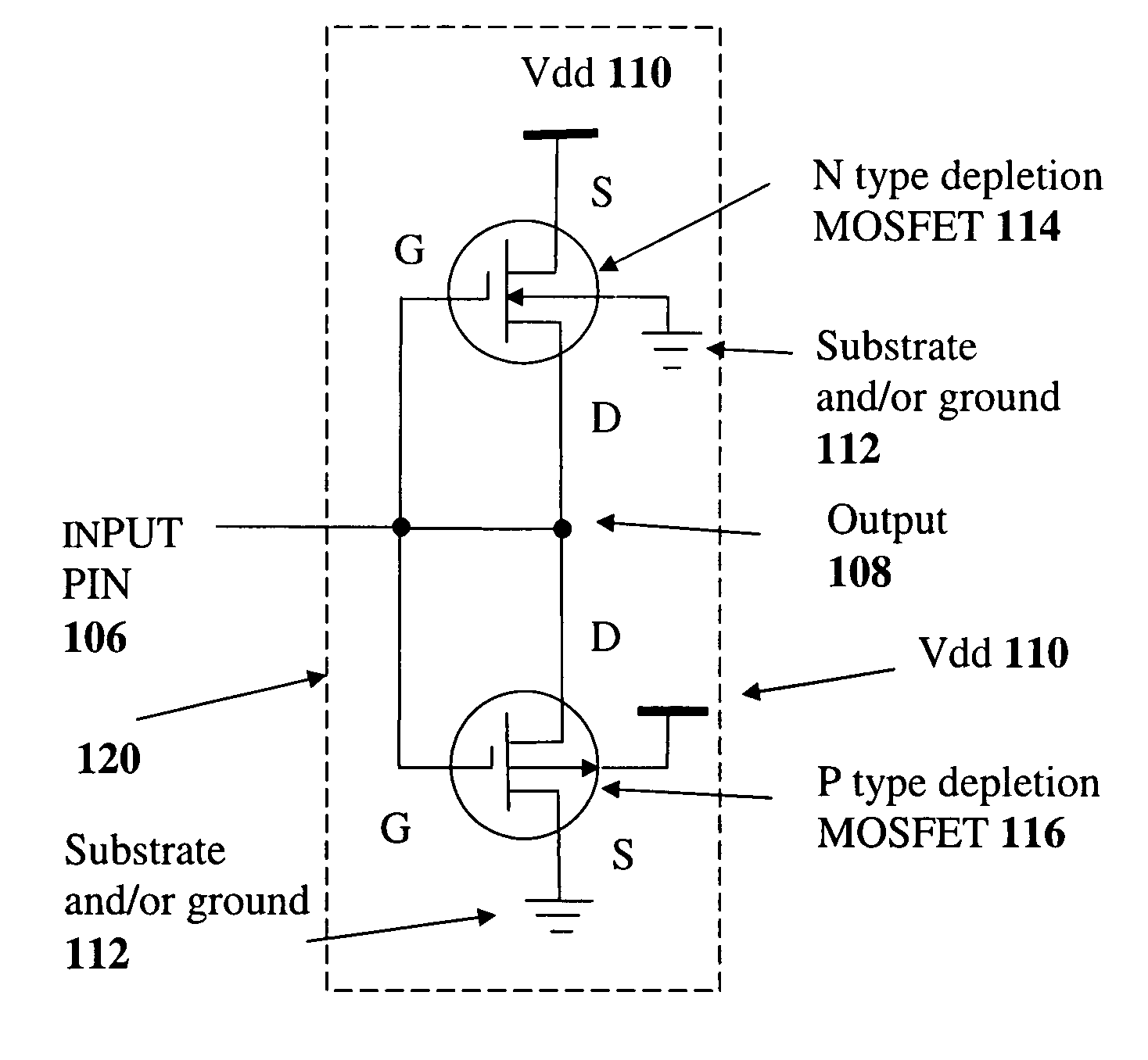

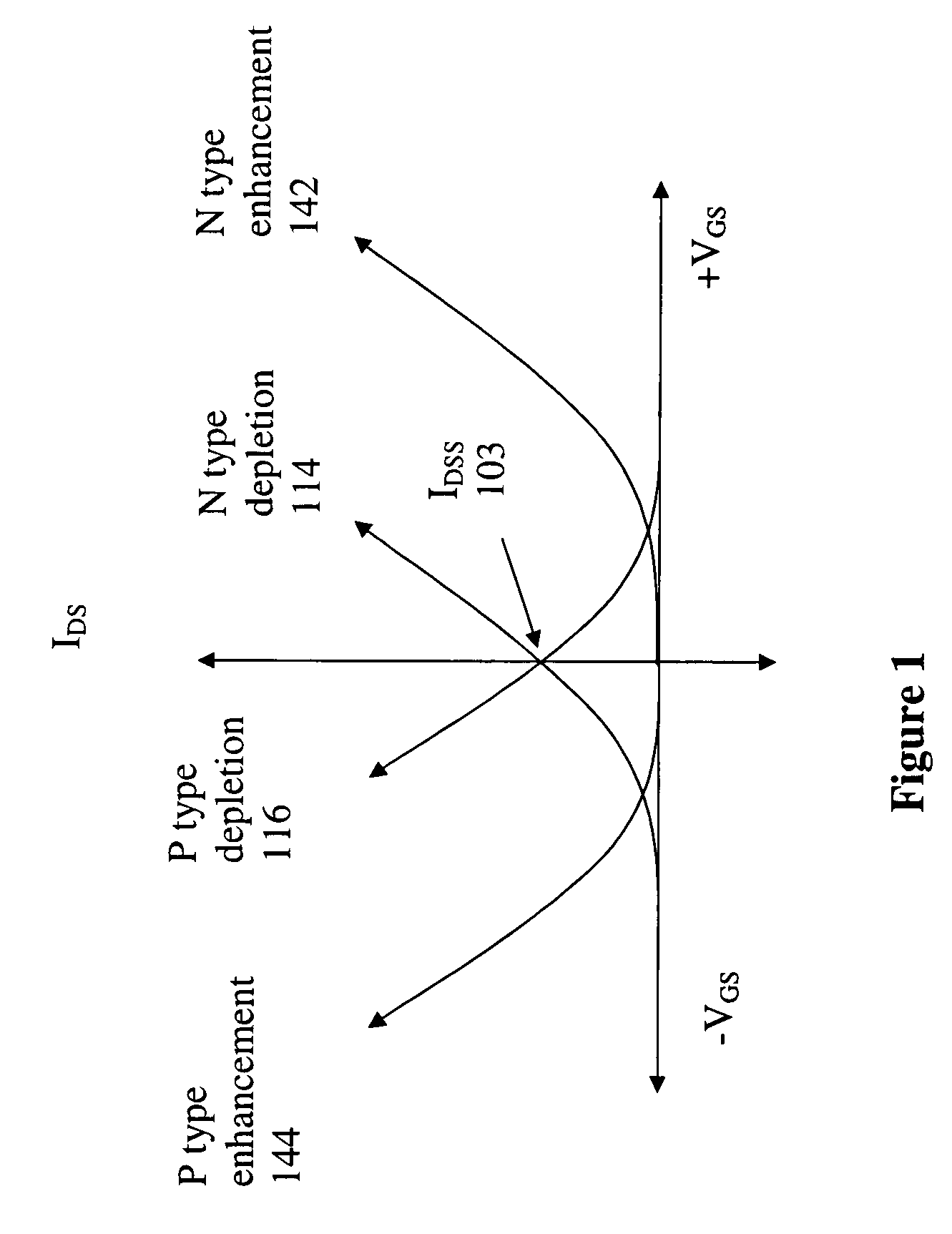

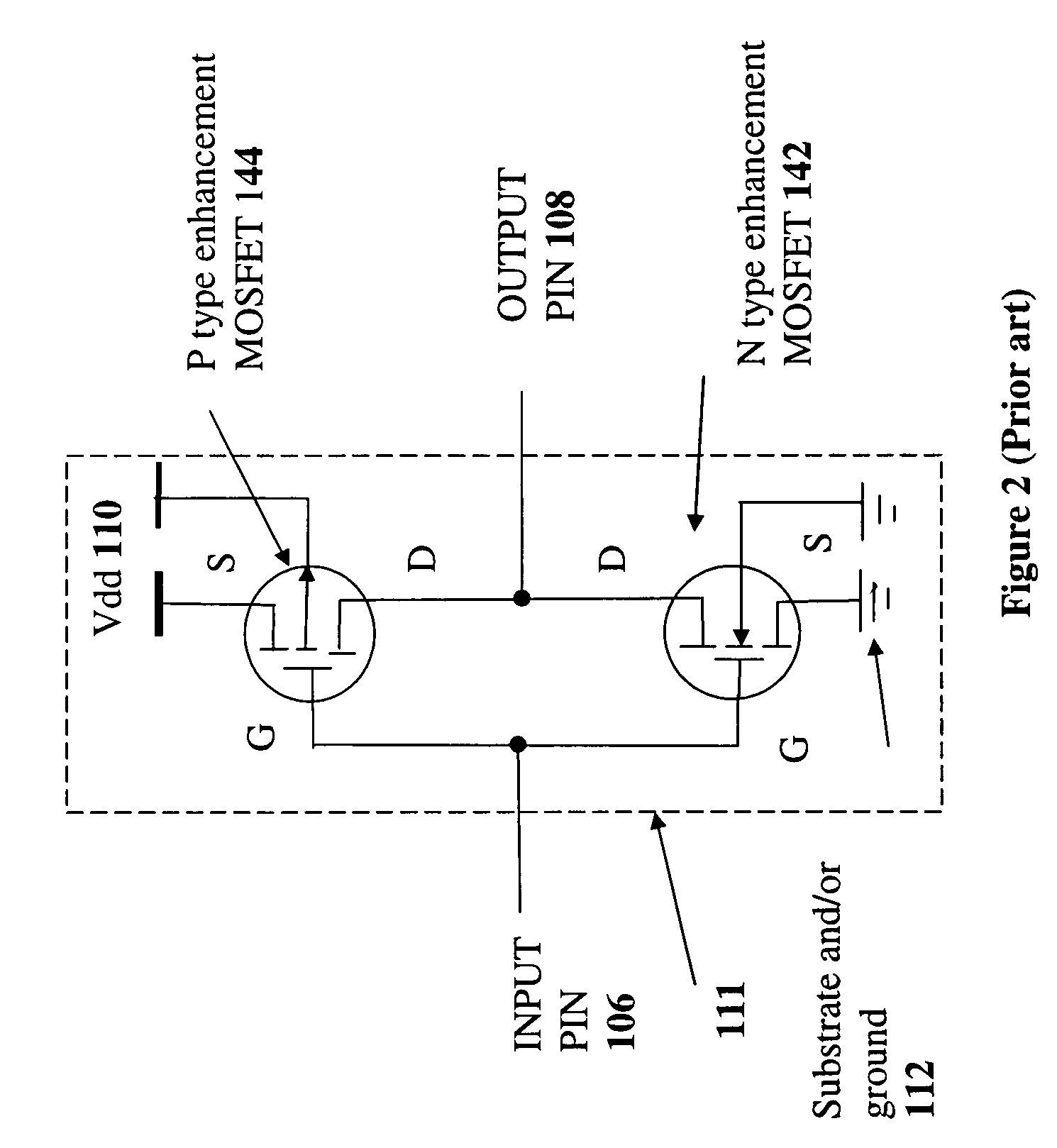

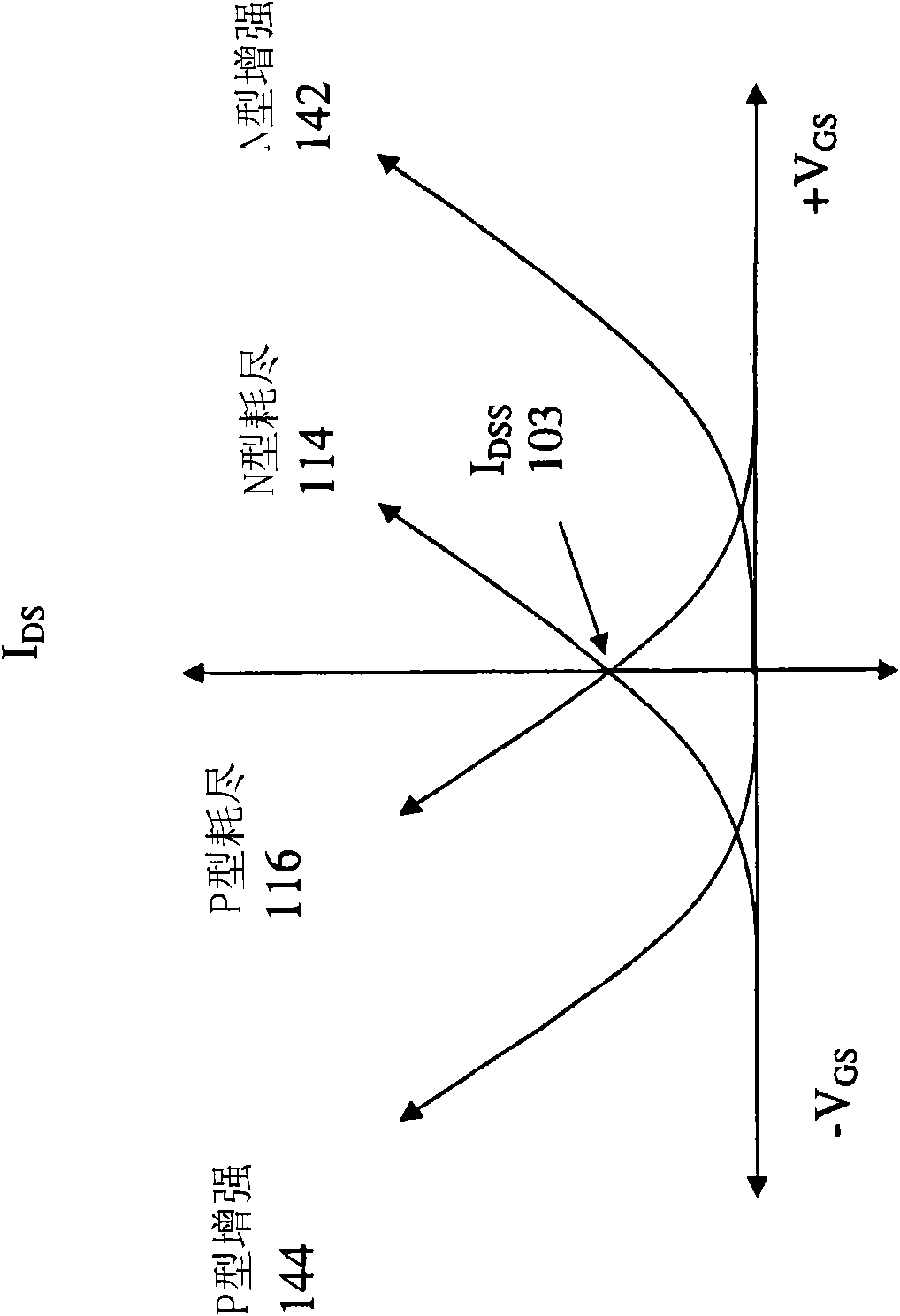

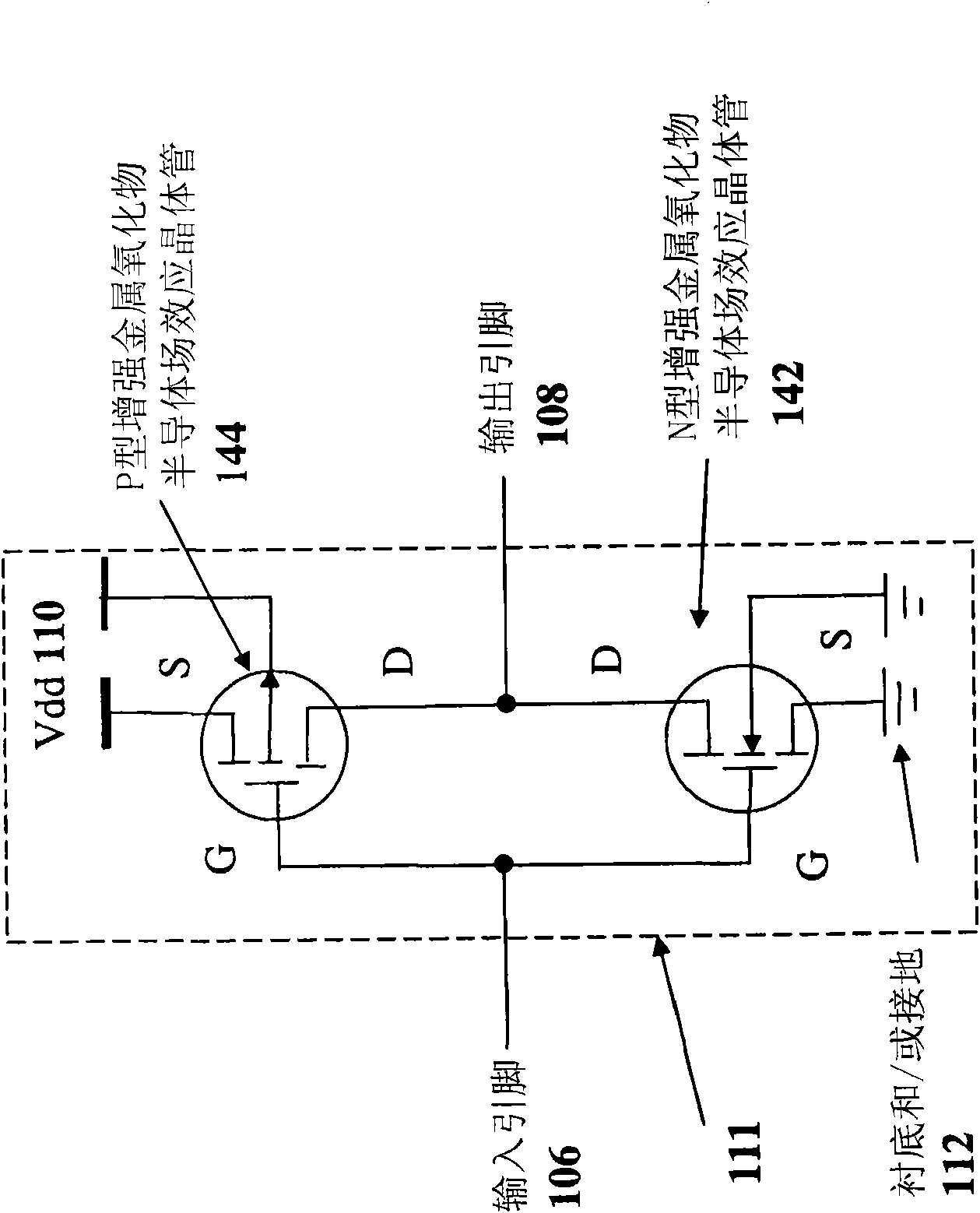

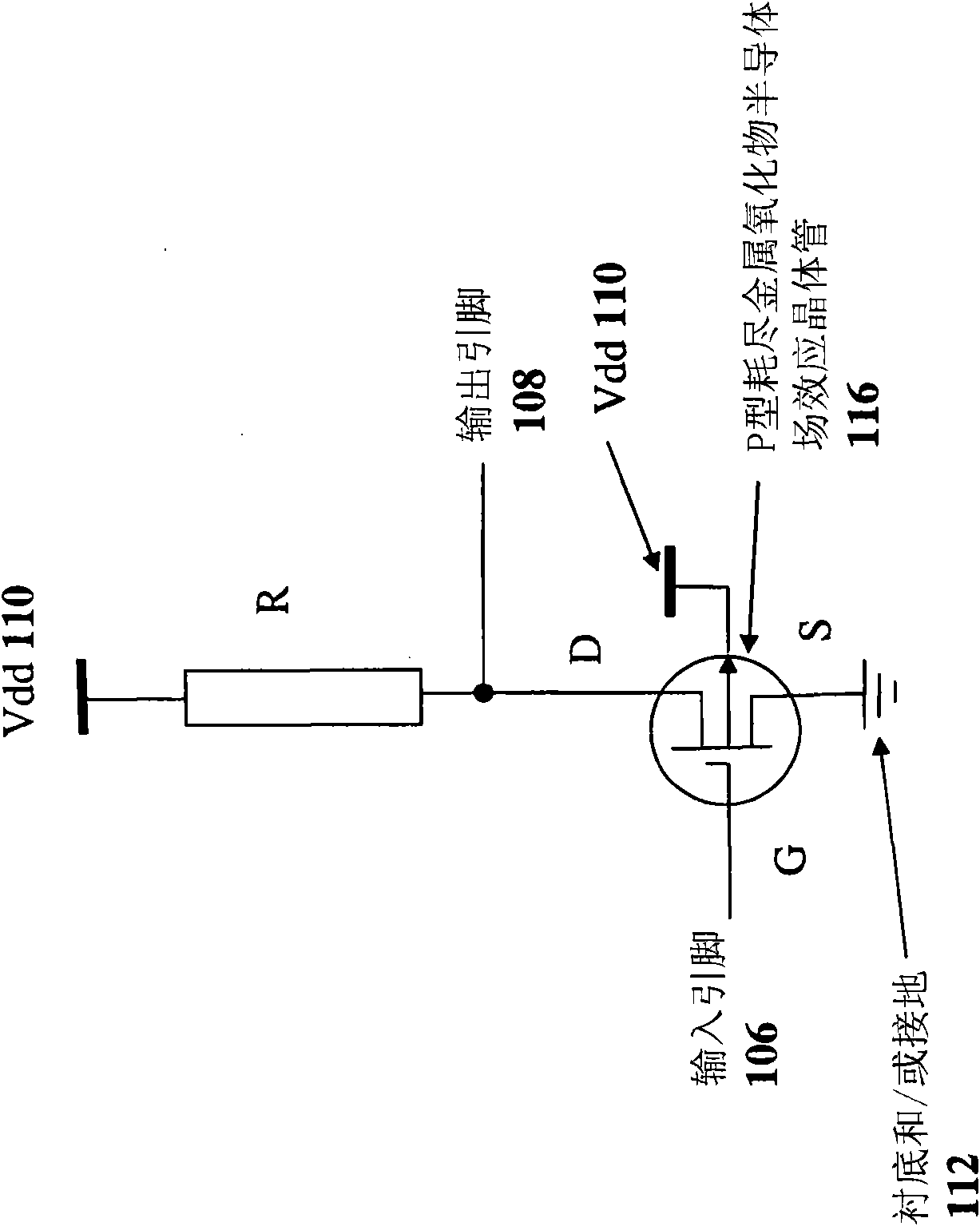

Depletion-mode mosfet circuit and applications

ActiveUS20080175045A1TransistorLogic circuits characterised by logic functionCMOSStatic random-access memory

Positive logic circuits, systems and methods using MOSFETs operated in a depletion-mode, including electrostatic discharge protection circuits (ESD), non-inverting latches and buffers, and one-to-three transistor static random access memory cells. These novel circuits supplement enhancement-mode MOSFET technology and are also intended to improve the reliability of the complementary metal-oxide-semiconductor (CMOS) integrated circuit (IC) products.

Owner:LIN WEN T

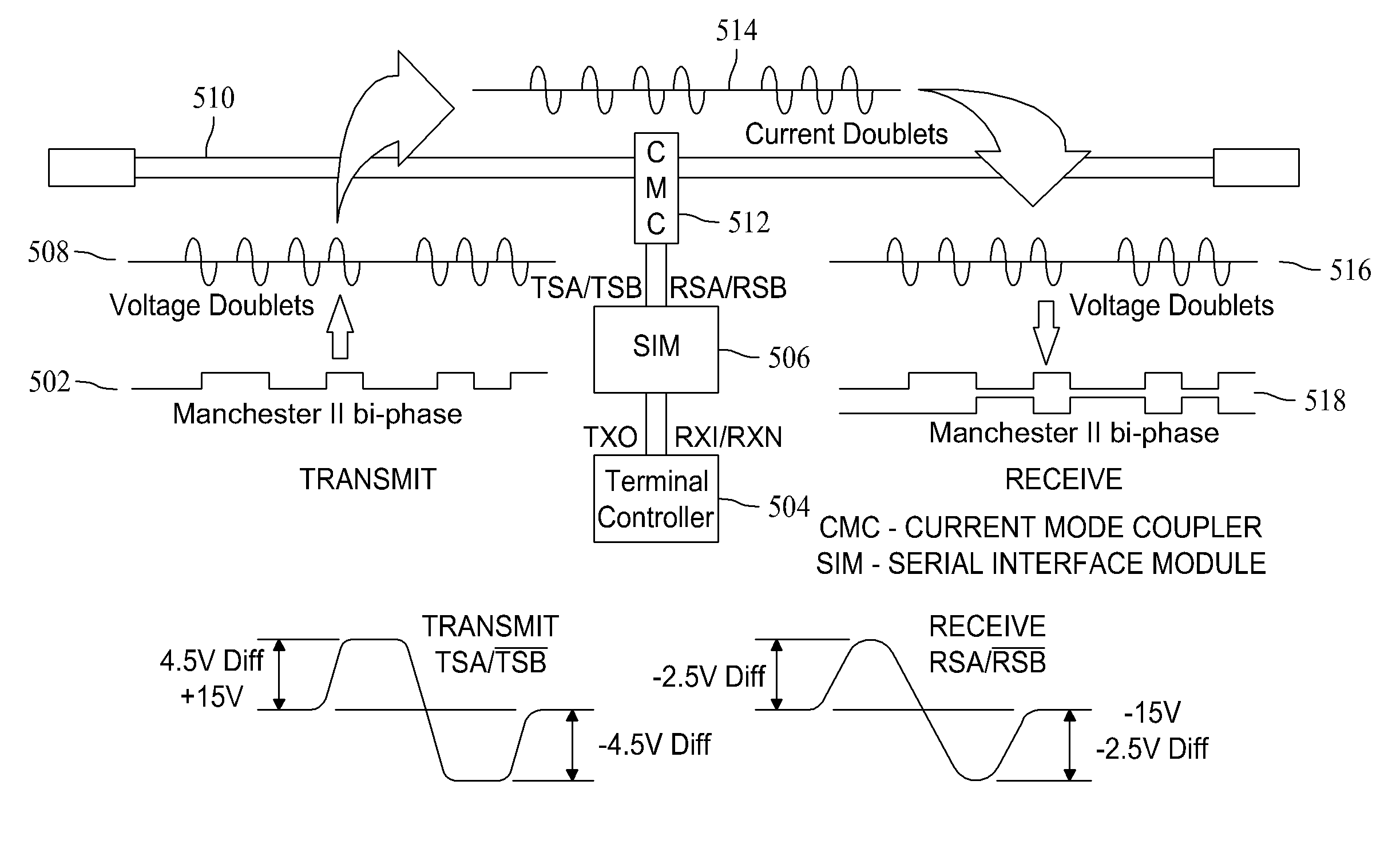

Burst mode optical media converter with fast analog conversion

A media converter for interfacing an optical fiber bus to an electrical interface of an electronic device is described. The media converter includes an interface circuit configured to convert electrical signals received from a transmitting channel of the electrical device in a voltage doublet format to positive logic electrical pulses and convert received electrical signals for application to a receiving channel of the electrical device from positive logic electrical pulses to a voltage doublet format, a DC coupled receiver comprising an optical interface operable for receiving optical signals from the optical fiber data bus, the receiver operable for converting the optical signals to positive logic electrical pulses for application to the interface circuit, a laser diode operable to transmit optical signals onto the optical bus, and a laser diode driver operable for receiving the positive logic electrical pulses from the interface circuit and converting the electrical signals to signals compatible for operating the laser diode.

Owner:THE BOEING CO

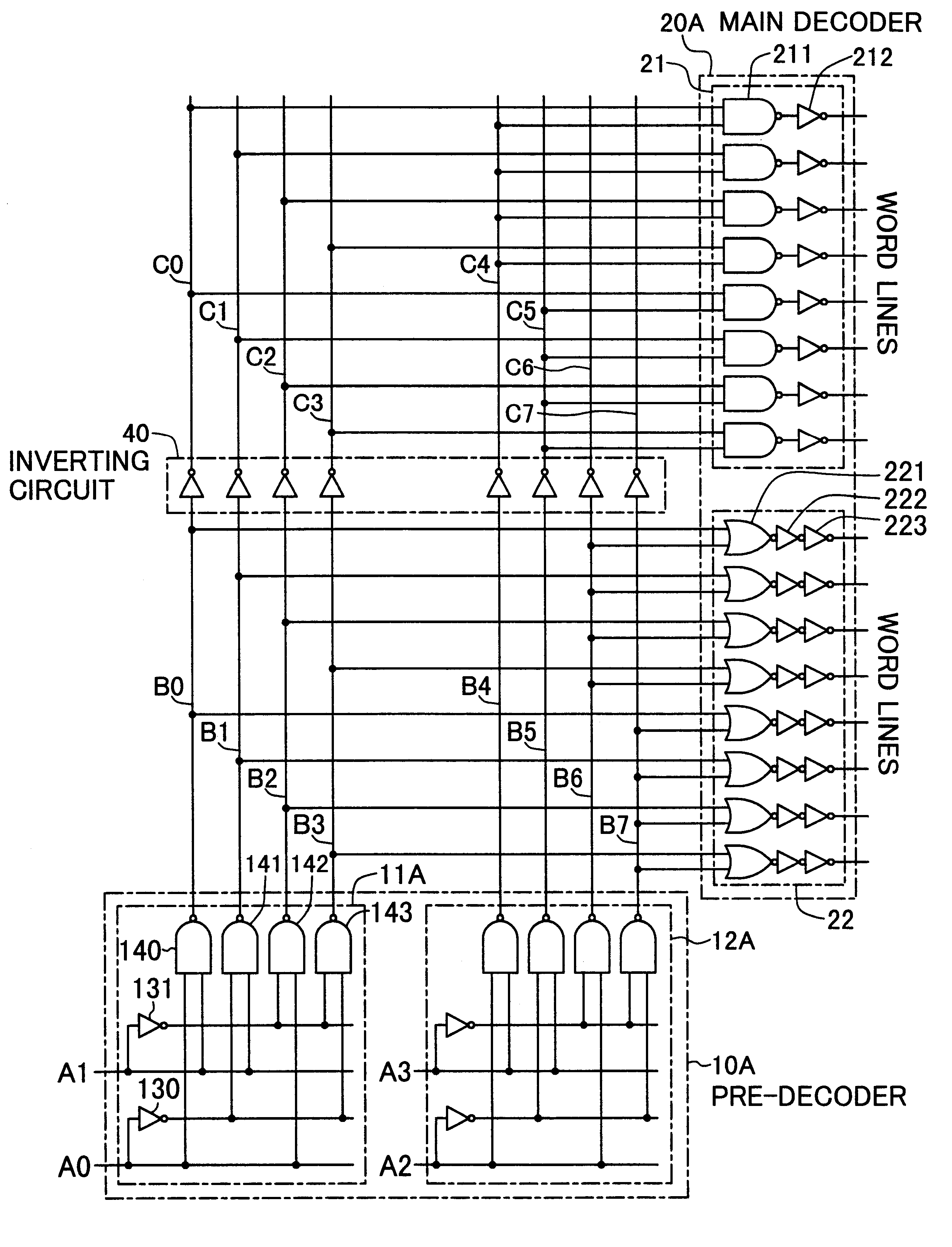

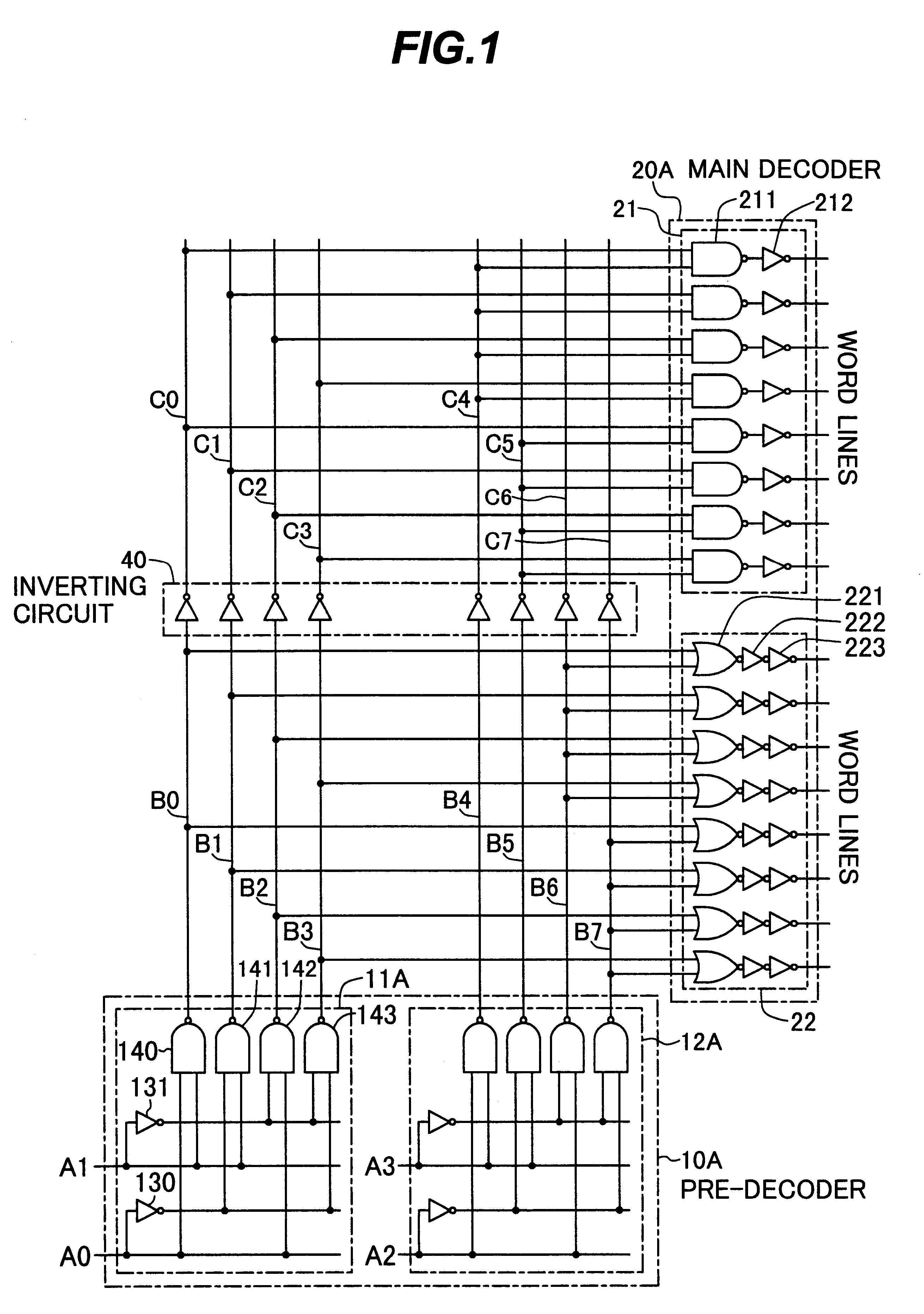

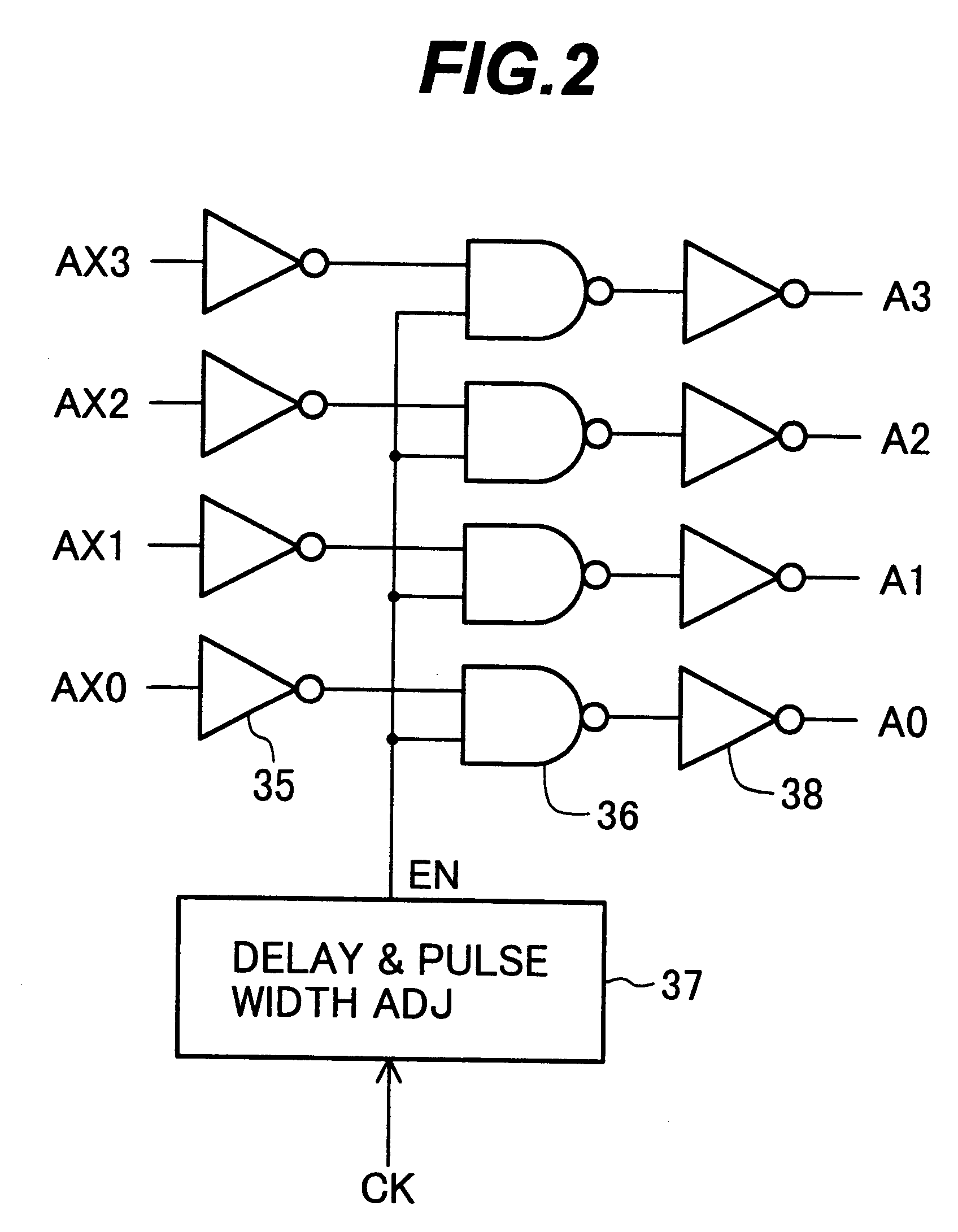

Semiconductor memory equipped with row address decoder having reduced signal propagation delay time

The output of a pre-decoder 10A is provided, on one side, to a main decoder 22 with the input of negative logic and on the other side, to a main decoder 21 with the input of positive logic through an inverting circuit 40. The number of gate stages from the output of the pre-decoder 10A to the output of the main decoder 21 is three which is equal to the number of gate stages from the output of the pre-decoder 10A to the output of the main decoder 22.

Owner:SOCIONEXT INC

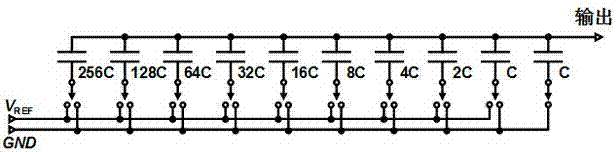

Successive approximation type analog-to-digital converter and error code detection based digital correction method thereof

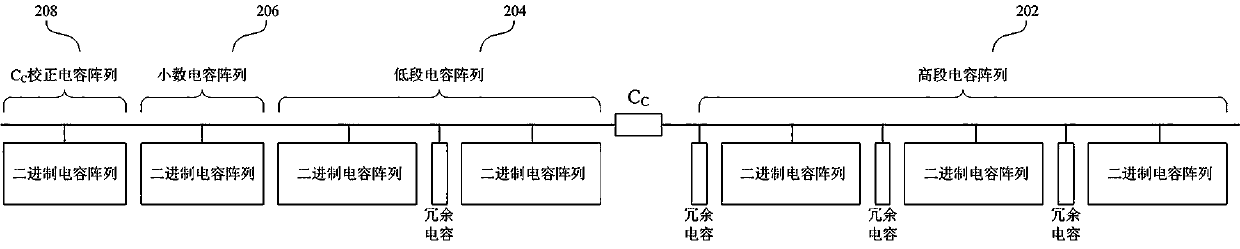

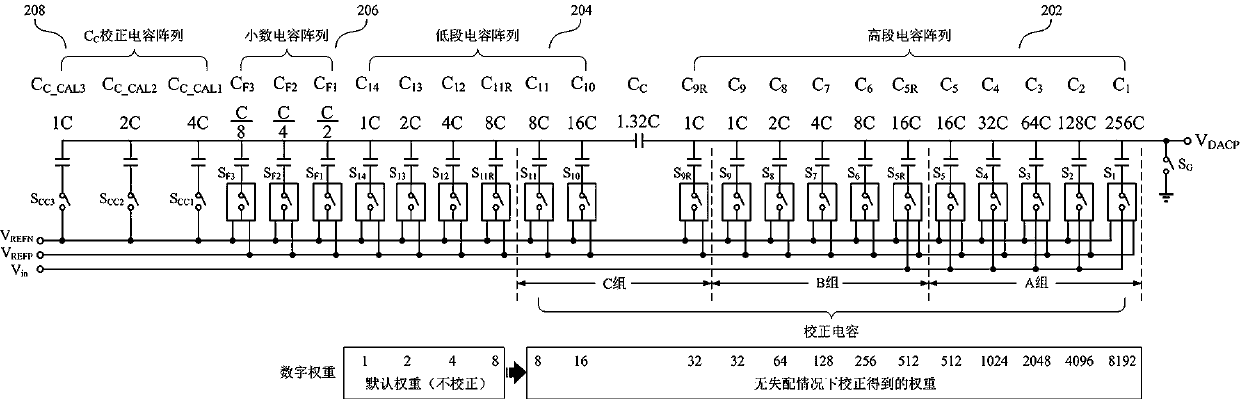

ActiveCN104779954ACutting costsReal-time correctionAnalogue/digital conversion calibration/testingCorrection methodCapacitance

The invention discloses a successive approximation type analog-to-digital converter and an error code detection based digital correction method thereof. The correction method comprises steps as follows: 1) an initial value of a correction capacitor is set; 2) a digital correction logic circuit randomly acquires digital output codes of a converter; 3) the output codes are divided into two groups, namely, a group A and a group B, and the output codes are counted by 8-bit counters A and B; 4) if the overflow speed of the 8-bit counter B is higher than that of the 8-bit counter A, the correction capacitor is increased by 0.5 C; if the overflow speed of the 8-bit counter A is higher than that of the 8-bit counter B, the correction capacitor is decreased by 0.5 C; if the overflow speed of the 8-bit counter B is equal to that of the 8-bit counter A, the value of the correction capacitor is unchanged; 5) after Step 4) is finished, the digital correction logic circuit clears the 8-bit counters A and B, and Steps 2)-4) are repeated. According to the correction method, the specific correction process and the conversion process of the successive approximation type analog-to-digital converter are conducted synchronously, no additional correction period or correction time is required, real-time response can be made to PVT change, and the method has the advantage of capability of realizing real-time correction.

Owner:ZHEJIANG UNIV

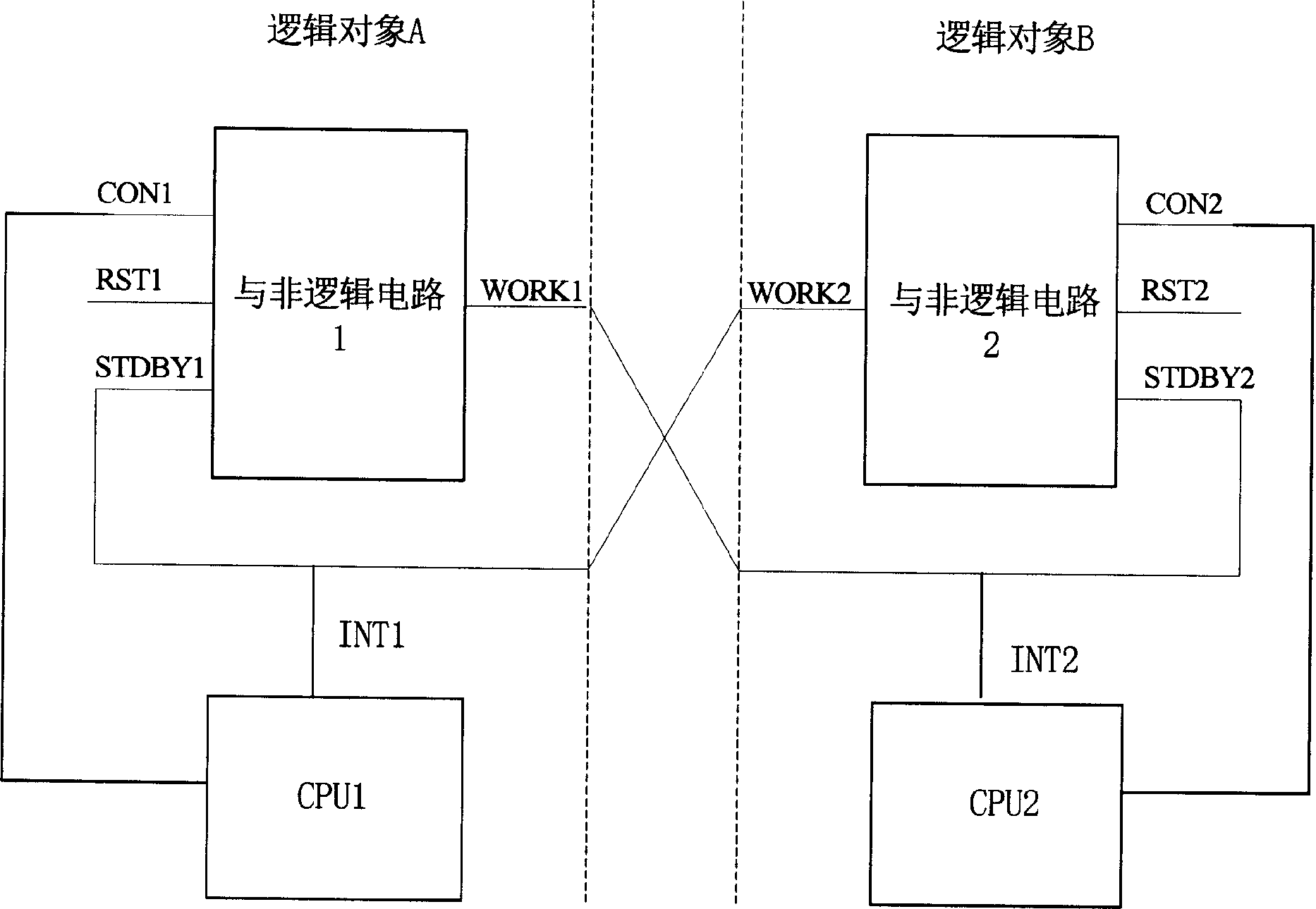

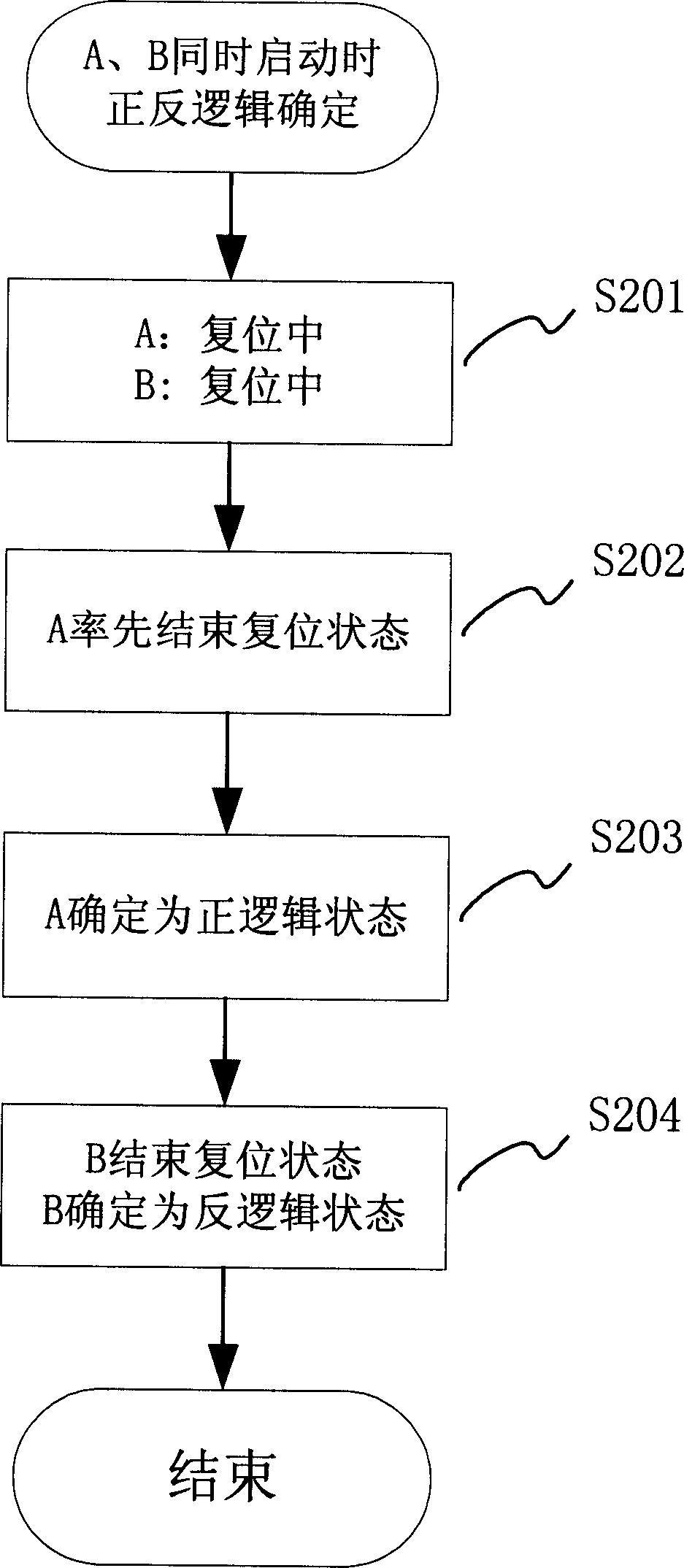

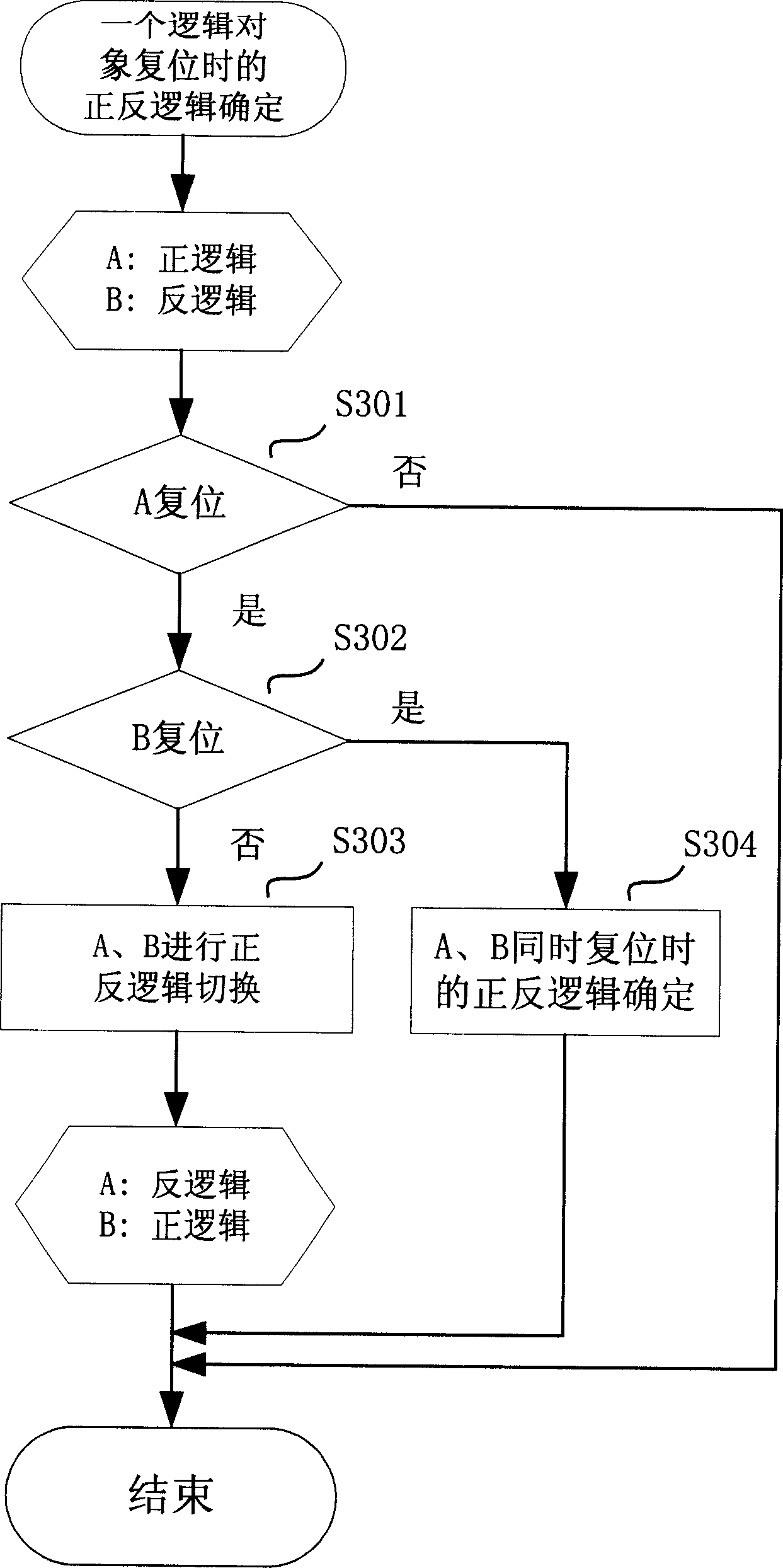

Redundant switching controlling method and circuit

InactiveCN1591348AQuickly determine positive and negative logic statesQuickly determine logic stateLogical operation testingControl signalPositive logic

The present invention relates to a redundancy switching control method and its circuit. Said method includes the following steps: detecting that logical object A of positive logic state produces abnormal state and notifying it to another logical object B; according to the failure extent of self-body another logical object B can define logical state; according to the logical state of logical object B logical object A can make failure extent comparison, and again define logical state of self-body; according to the requirement repeating the above-mentioned steps until the logical object with lighter failure extent can be defined into positive logical state. The correspondent control circuit includes a group of AND-NOT circuits and processor, said AND-NOT circuits are respectively correspondent to logical objects, have three input ends; first input end is used for transferring control signal; second input end is used for transferring reset signal; and third input end is used for transferring state signal, and is connected with output end of relative logical object and illogical circuit.

Owner:ZHEJIANG SUPCON TECH +1

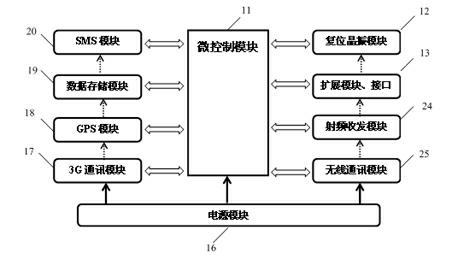

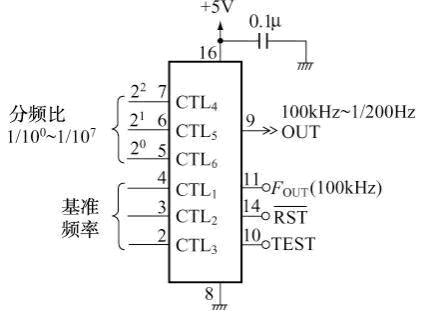

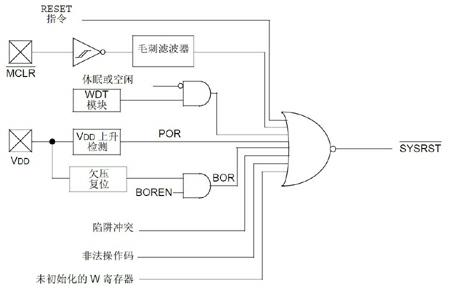

Gate of internet of things for implementing long-term operation in environment without electricity and implementation method

The invention discloses a gateway of an internet of things for implementing long-term operation in an environment without electricity and an implementation method. The gateway of the internet of things is used for receiving and transmitting acquired data of different sets of sensing equipment at a front end and comprises a microcontroller, a built-in power supply module, a reset crystal oscillator module and a communication interface module, wherein the built-in power supply module is used for supplying electricity; the reset crystal oscillator module comprises a crystal oscillator chip, a programmable frequency divider and a reset module; the crystal oscillator chip and the programmable frequency divider are used for acquiring a frequency of positive logic inputting by using a reference frequency pin of the crystal oscillator chip, and converting an output frequency into a low-frequency signal which is required by a preset clock by using a frequency dividing ratio and is used for providing a clock signal for the microcontroller regularly or in an event-triggered mode; the reset module is used for triggering the gateway to be reset; and the microcontroller is connected to the built-in power supply module and the reset crystal oscillator module respectively, and is used for receiving data and transmitting data to a back end interface through the communication interface module after being waken by the reset crystal oscillator module and then stopping working to enter a dormant state. By a timed uploading function of the gateway, the electricity quantity of a built-in battery can be used to the maximum extent to ensure that gateway equipment can work as long as possible, and the gateway can play an important role in particular environments and occasions with special requirements such as agriculture and forestry, mines and the like.

Owner:上海宜云健康管理咨询有限公司

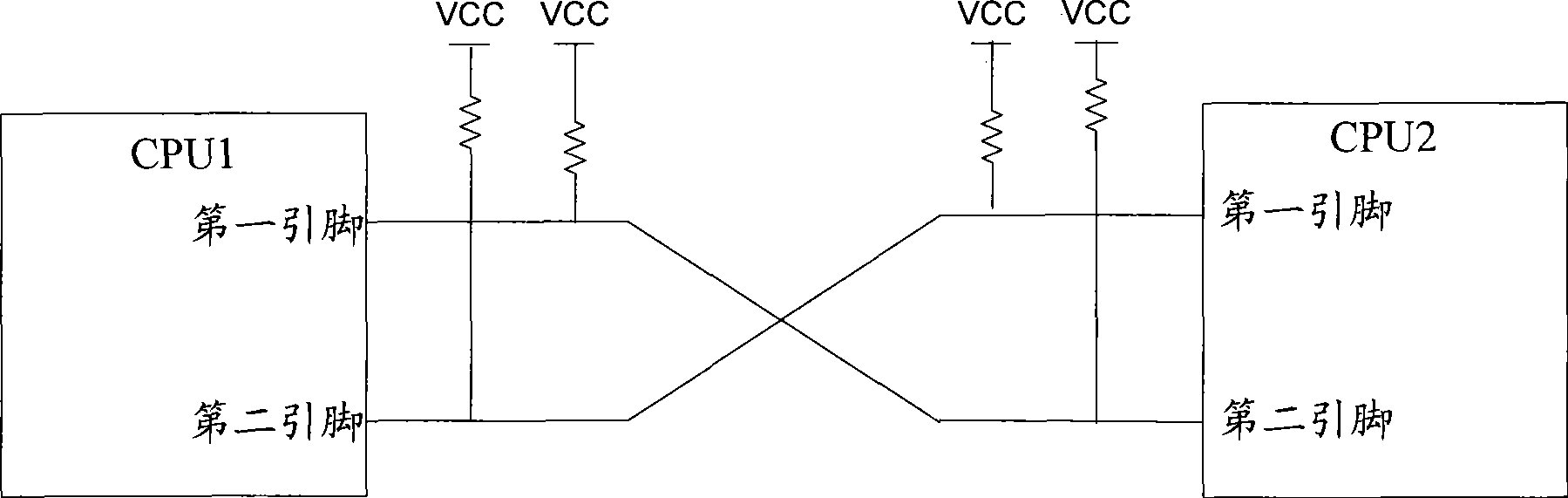

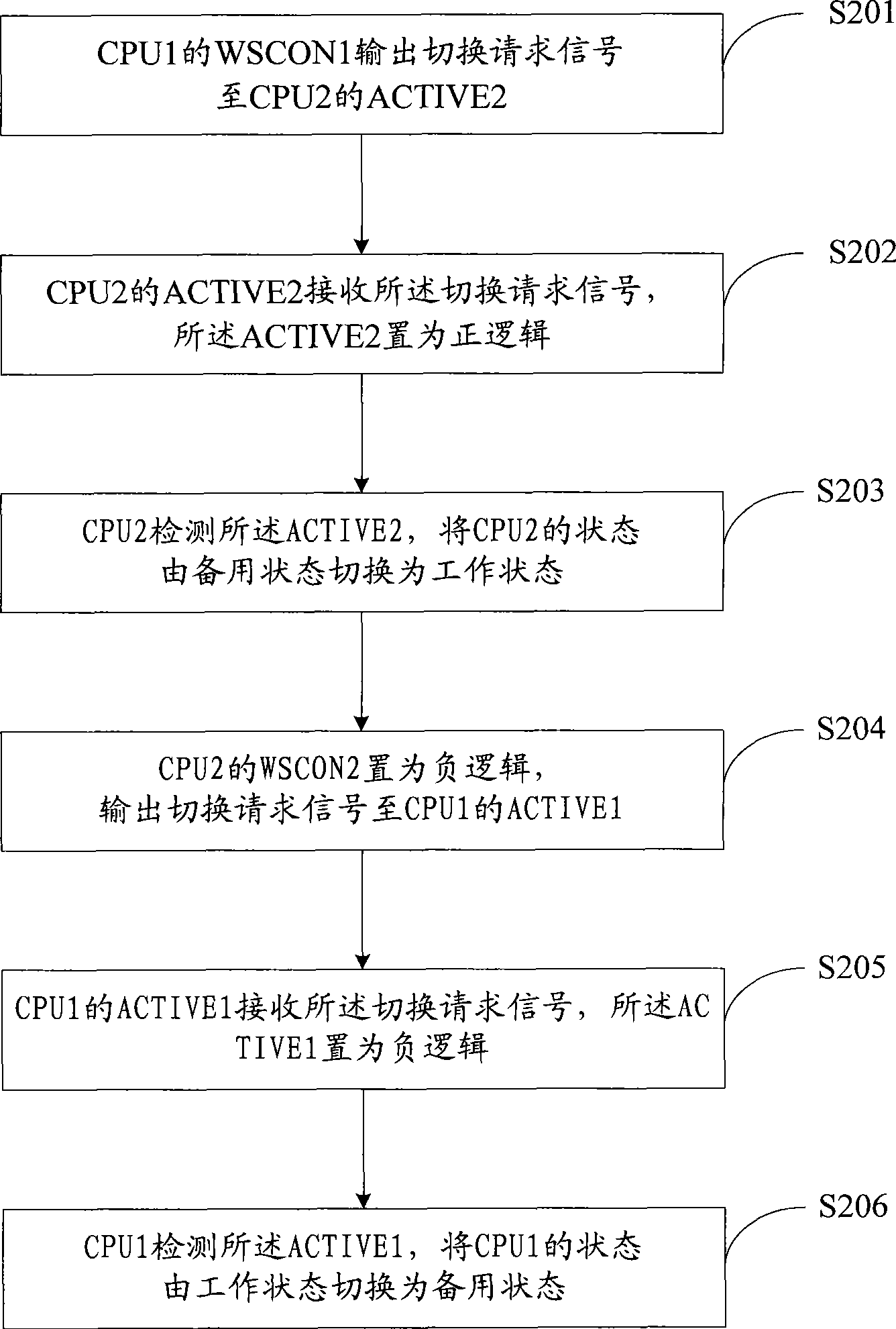

Redundant switch control circuit and method

ActiveCN101510081AReduce the probability of false switchingImprove reliabilityProgramme controlComputer controlPositive logicControl circuit

The invention discloses a redundant switch control circuit and a method thereof. In the embodiment of the redundant switch control method, CPU1 and CPU2 adoppt a hot standby redundant configuration way; the CPU1 is in a working state; the CPU2 is in a standby state; when the CPU1 in the working state is broken down, the method comprises: the CPU1 outputs a switching request signal to the CPU2; the CPU2 receives the switching request signal; a first pin of the switching CPU2 is set to positive logic and then is detected; the state of the CPU2 is switched from the standby state to the working state; a second pin of the CPU2 is set to negative logic; a switching request signal is output to the CPU1; the CPU1 receives the switching request signal; a first pin of the CPU1 is set to negative logic and then is detected; and the state of the CPU1 is switched from the working state to the standby state. The embodiment of the invention leads the false switching rate of the redundant switch control circuit to be reduced and the reliability to be improved.

Owner:ZHEJIANG SUPCON TECH

Burst mode optical media converter with fast analog conversion

A media converter for interfacing an optical fiber bus to an electrical interface of an electronic device is described. The media converter includes an interface circuit configured to convert electrical signals received from a transmitting channel of the electrical device in a voltage doublet format to positive logic electrical pulses and convert received electrical signals for application to a receiving channel of the electrical device from positive logic electrical pulses to a voltage doublet format, a DC coupled receiver comprising an optical interface operable for receiving optical signals from the optical fiber data bus, the receiver operable for converting the optical signals to positive logic electrical pulses for application to the interface circuit, a laser diode operable to transmit optical signals onto the optical bus, and a laser diode driver operable for receiving the positive logic electrical pulses from the interface circuit and converting the electrical signals to signals compatible for operating the laser diode.

Owner:THE BOEING CO

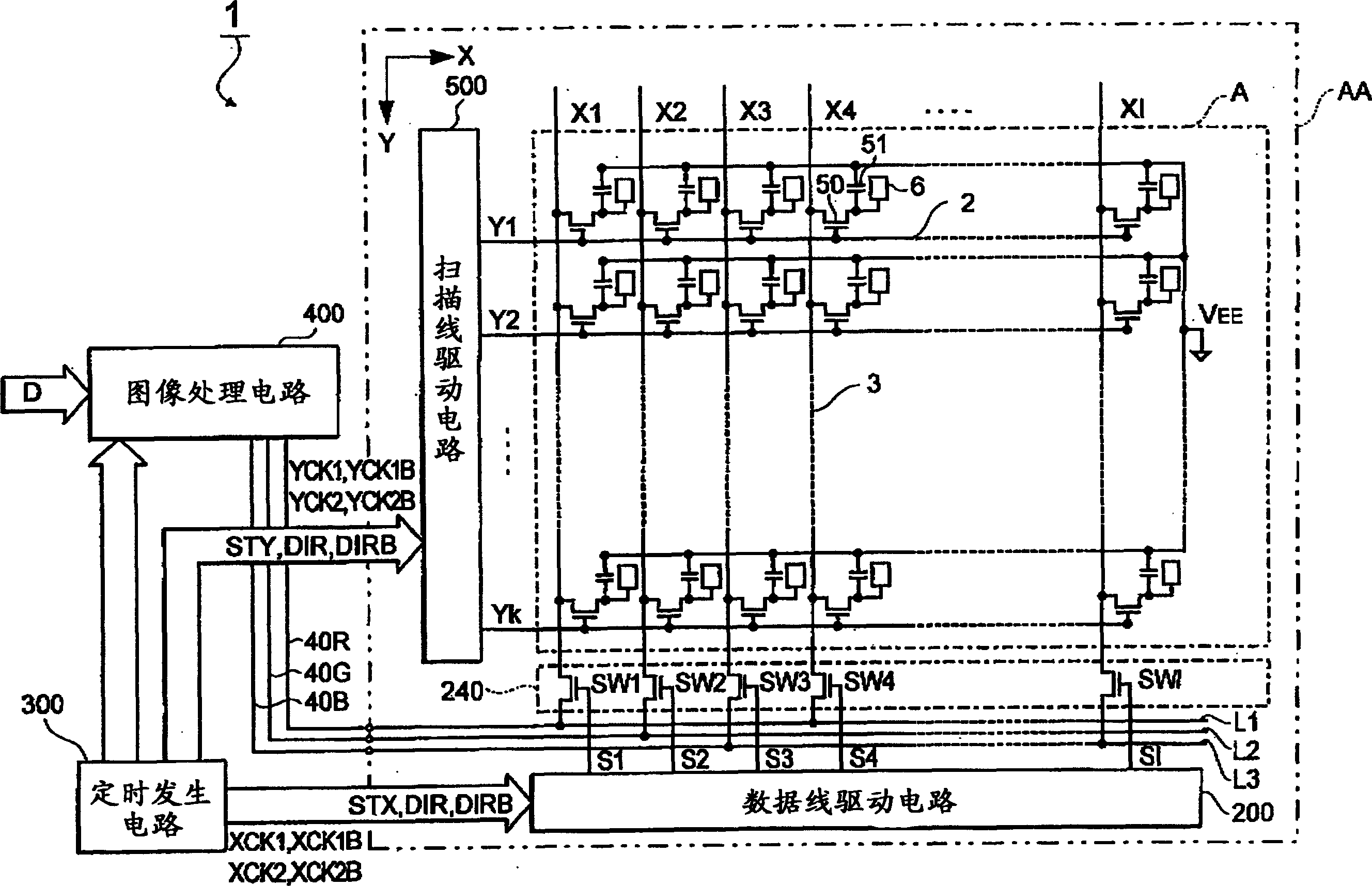

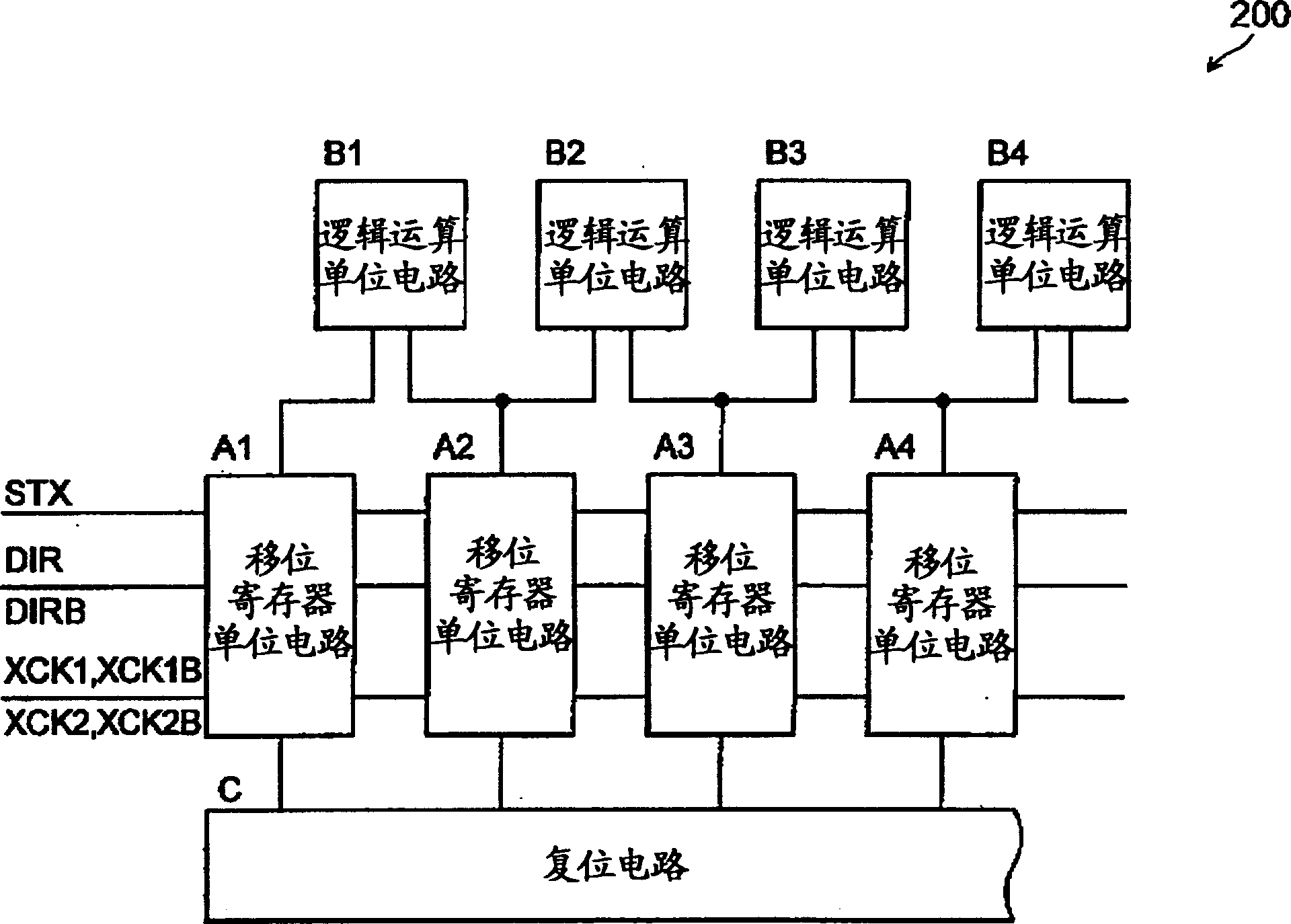

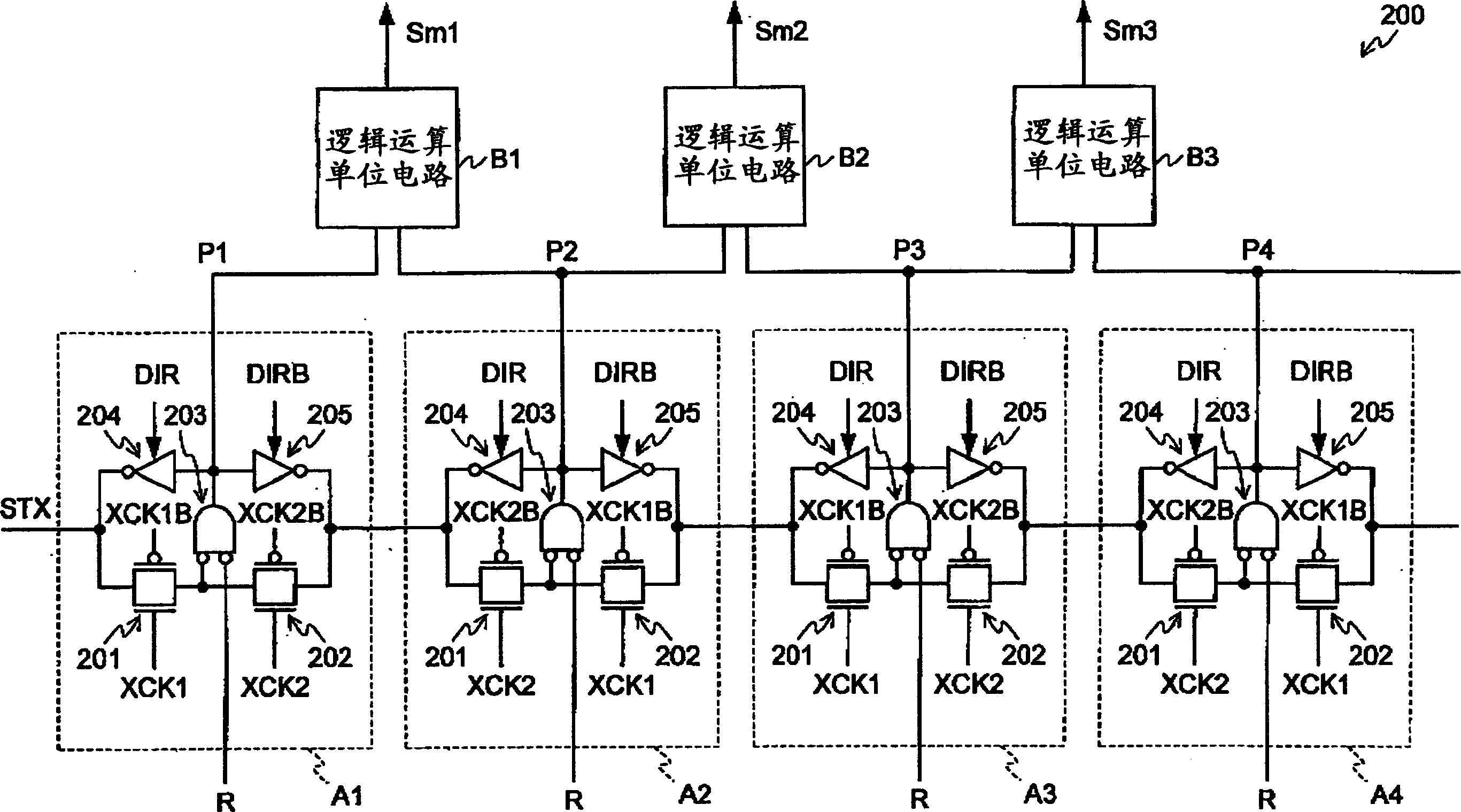

Bidirectional shift register

InactiveCN1825490AQuickly design jobsStatic indicating devicesDigital storageShift registerTransmission gate

The invention relates to a bidirectional shift register which can make the same of output signal pulse widths when it is formed by positive logic or passive logic, wherein the data line driving circuit (200) has multistage shift register unit circuit (A) which has the first and second transmission gates (201, 202) for synchronously transmitting the pulse STX with the X clock signal XCK and the reversed X clock signal XCKB; the first logic circuit (203) for reversed outputting input signal; and the first and second clock-control inverters (204, 205) for making the logic potential of transmission direction control signal DIR effective; the output of first logic circuit (203) is connected to the input of inverters (204, 205) whose outputs are connected to the input of first logic circuit (203) via the transmission doors (201, 202).

Owner:SEIKO EPSON CORP

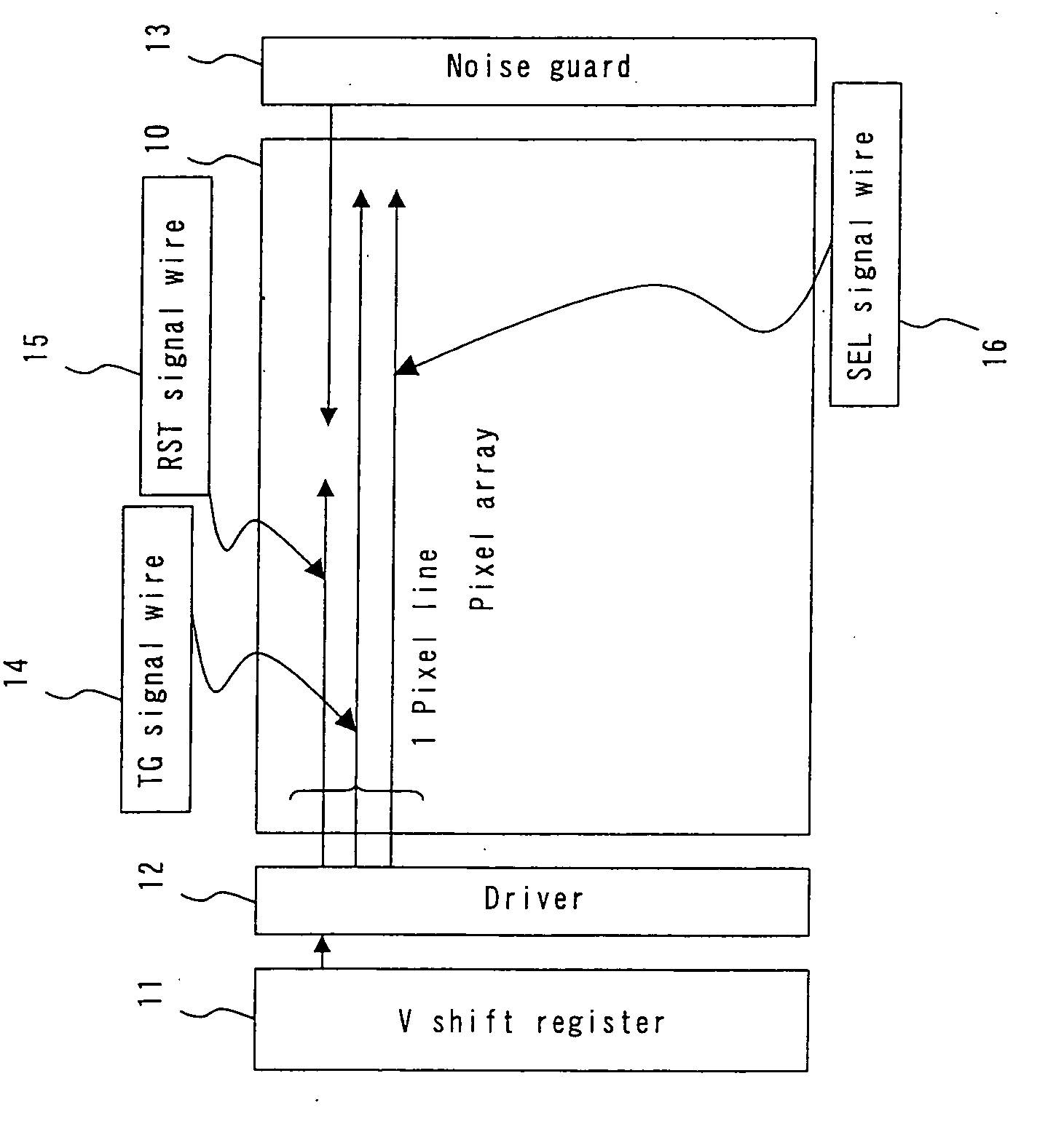

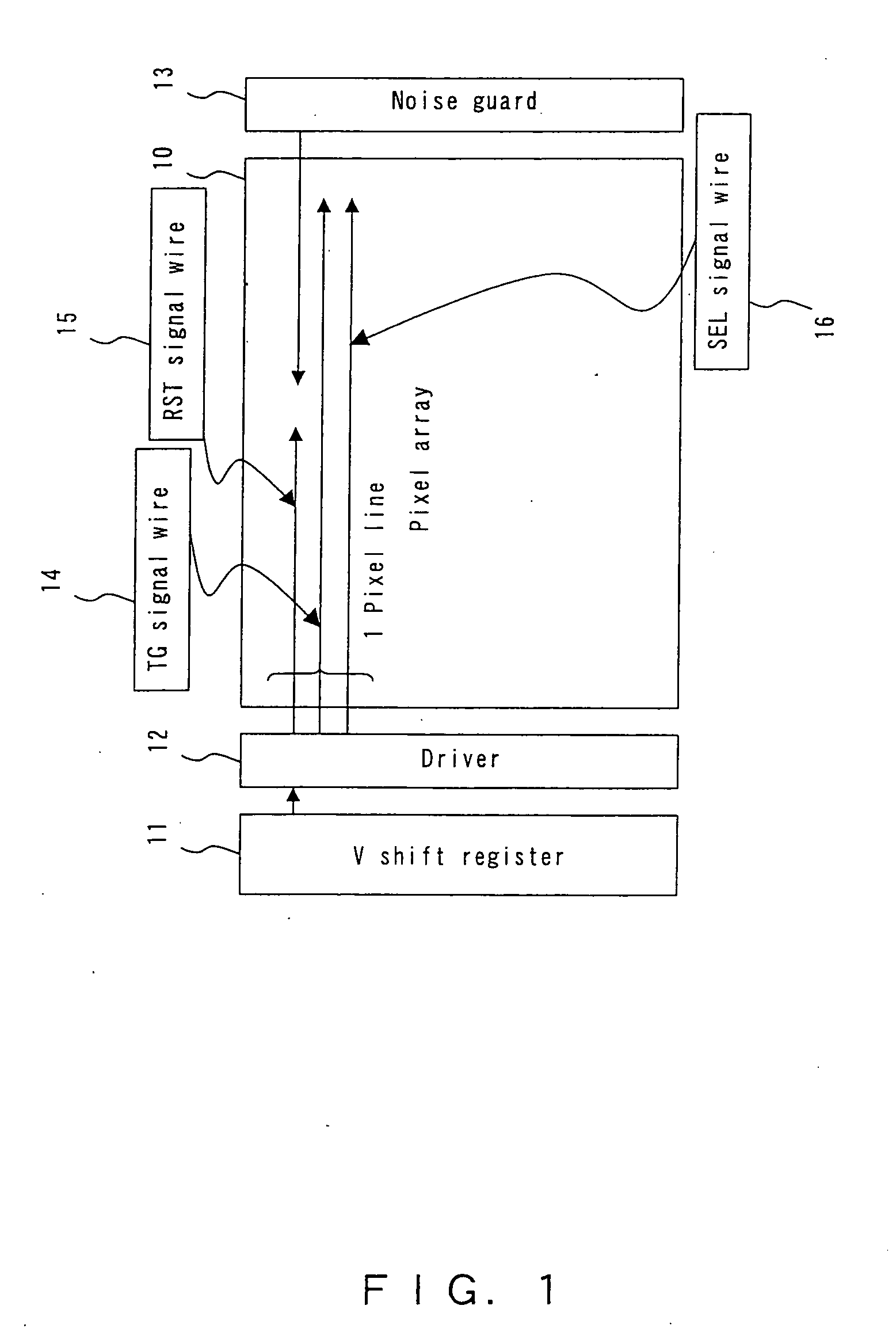

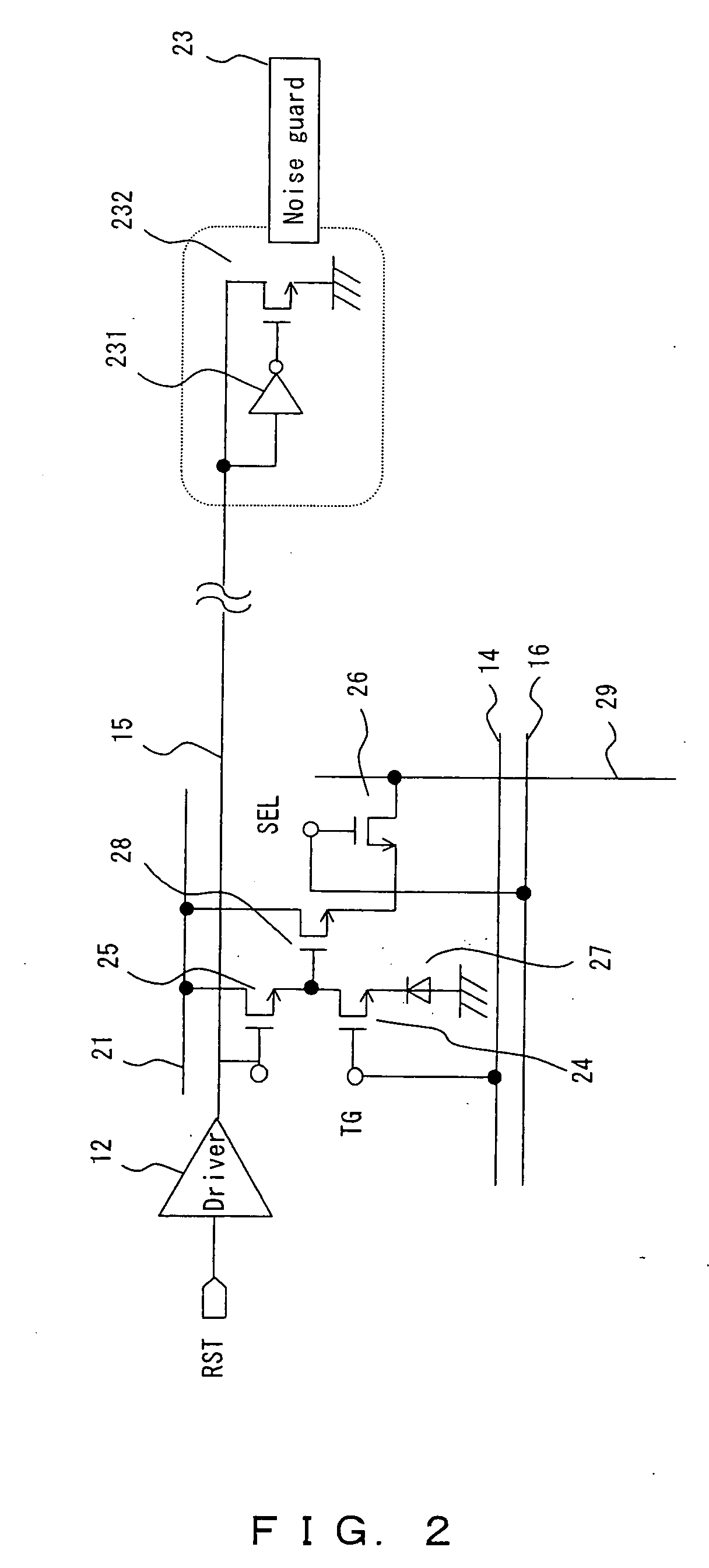

Semiconductor apparatus with crosstalk noise reduction circuit

InactiveUS20060176383A1Reduce chip areaIncrease chip areaTelevision system detailsTelevision system scanning detailsDriver circuitControl signal

In order to reduce crosstalk caused between control signal wires in a semiconductor apparatus without increasing the size of the semiconductor apparatus, a noise guard circuit is provided at the opposite end of the control signal wire to the driver circuit. The noise guard circuit controls in such a way as to increase the impedance between the relevant control signal wire and a fixed potential when the logic of the relevant control signal wire is positive logic for driving the element, and as to decrease the impedance between the relevant control signal wire and a fixed potential when the logic of the relevant control signal wire is negative logic for driving the element.

Owner:SOCIONEXT INC

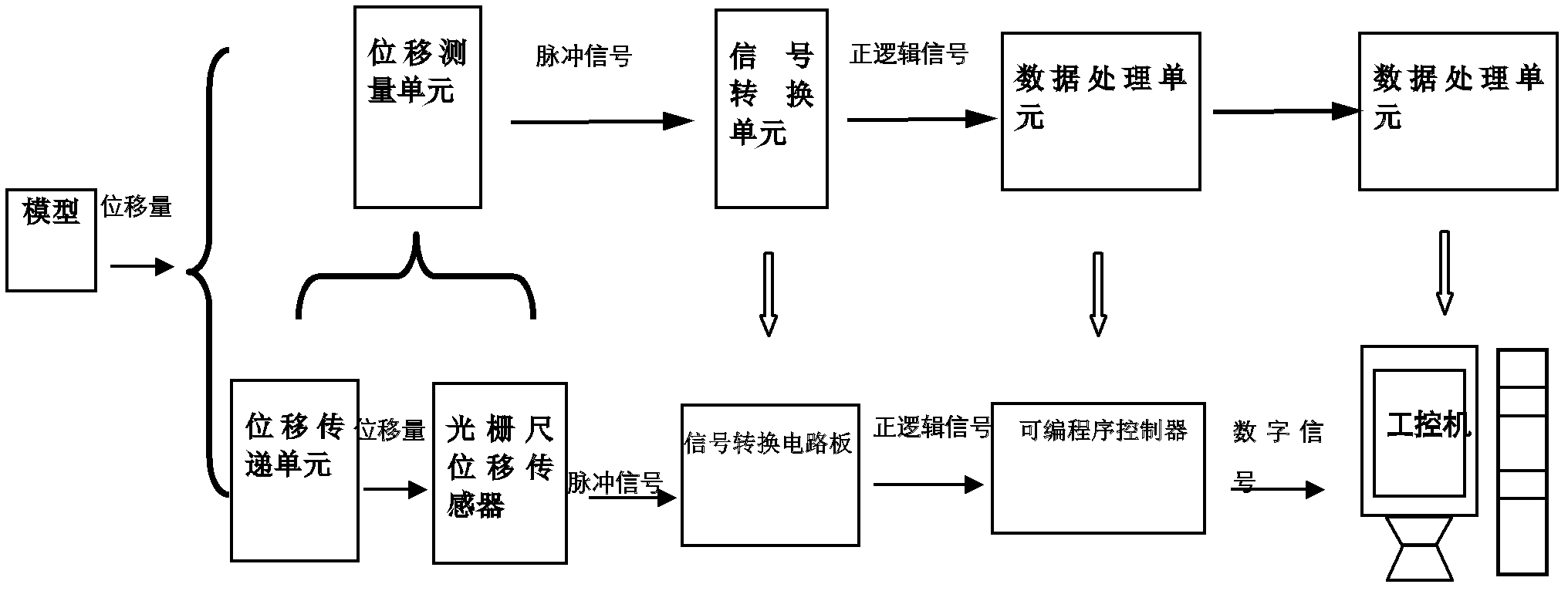

Automatic test system for model test displacement data and test method thereof

InactiveCN102322791AHigh precisionGo digitalUsing electrical meansProgramme control in sequence/logic controllersInteraction interfaceEngineering

The invention discloses an automatic test system for model test displacement data and a test method thereof. The automatic test system comprises a displacement transfer unit, a displacement measurement unit, a signal conversion unit, a data processing unit and a visualized human computer interaction interface system, wherein the displacement transfer unit is connected with a model; when the model body displaces, the displacement measurement unit outputs pulse signals of which the pulse number is in proportion to displacement amount; after the output pulse signals are received, processed and converted into an identifiable positive logic signal by the signal conversion unit, the identifiable positive logic signal is transmitted to the signal processing unit; the signal processing unit calculates the number of the pulse to calculate model displacement; and the model displacement is finally stored and displayed on the visualized human computer interaction interface system to automatically generate a model displacement time interval curve for testers to dynamically observe and monitor model displacement in real time. According to the automatic test system for model test displacement data and the test method thereof, the digitization, the visualization and the intellectualization of the automatic measurement of the model displacement in the underground engineering model test in the fields of hydropower, traffic, energy, resource and defence construction fields can be realized.

Owner:SHANDONG UNIV

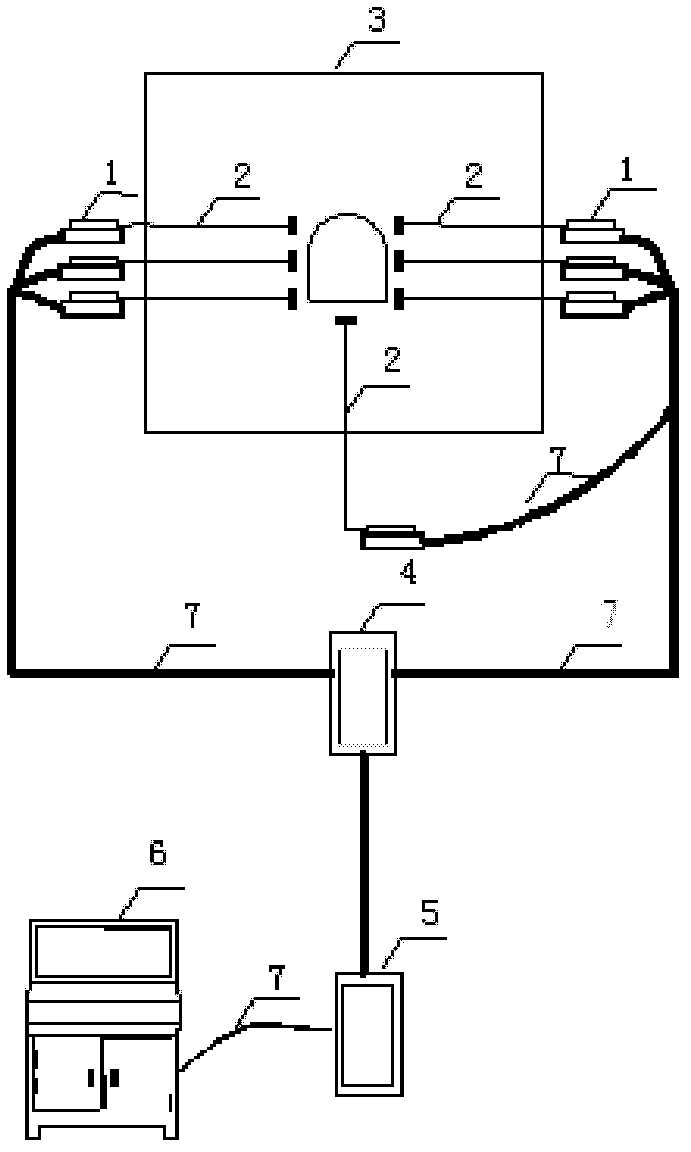

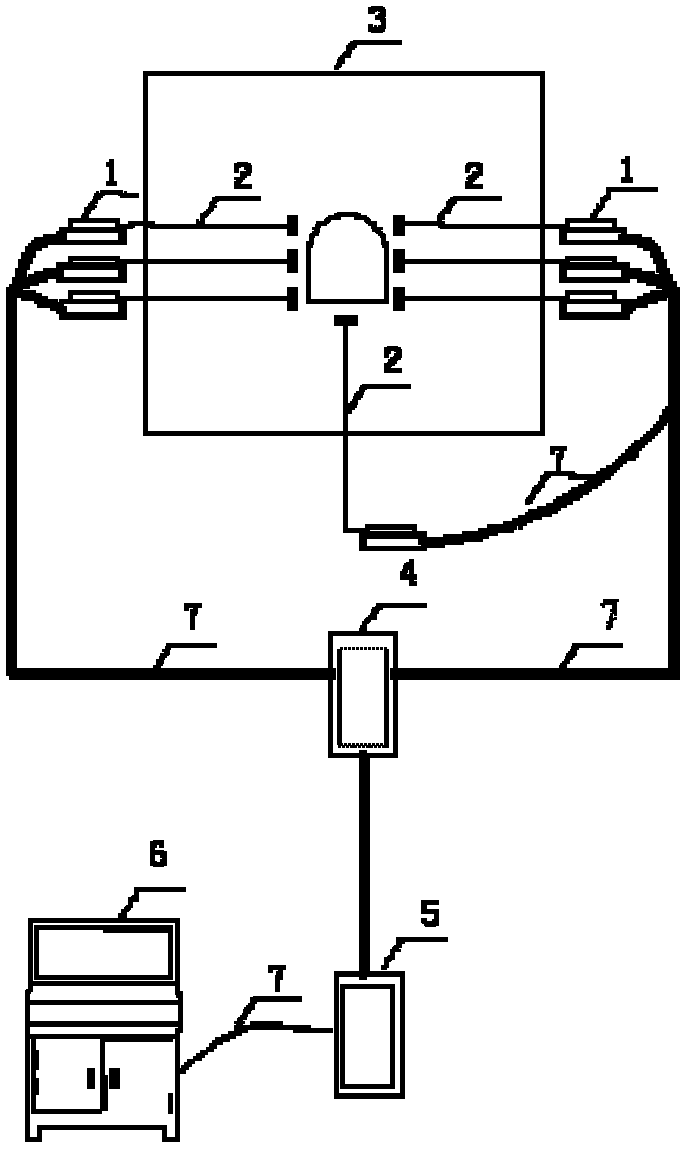

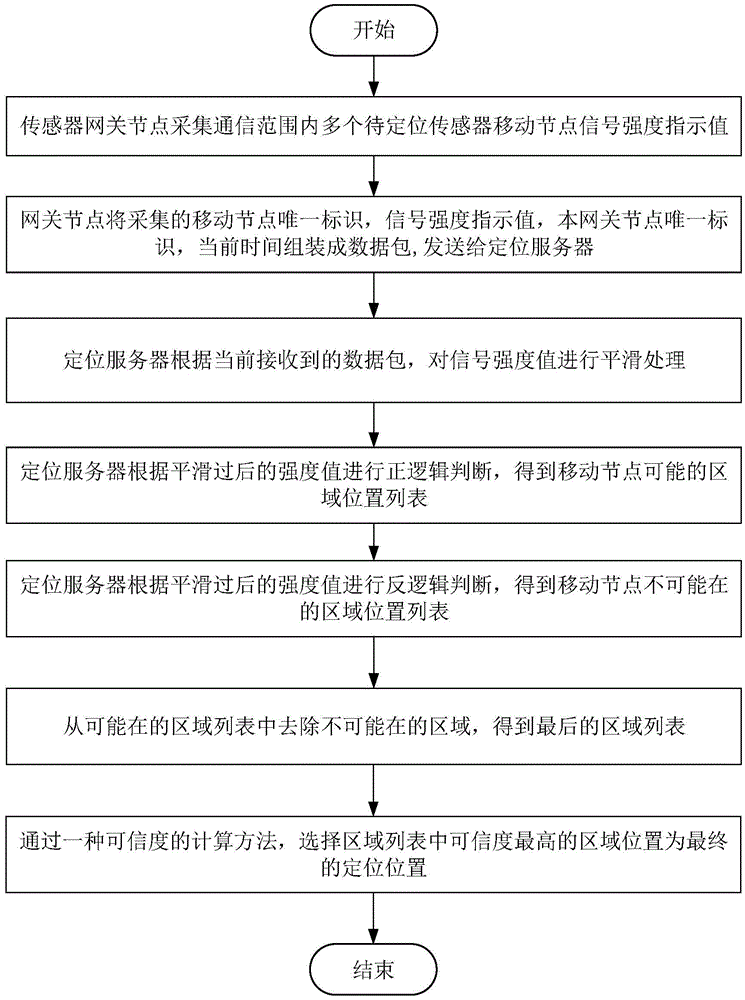

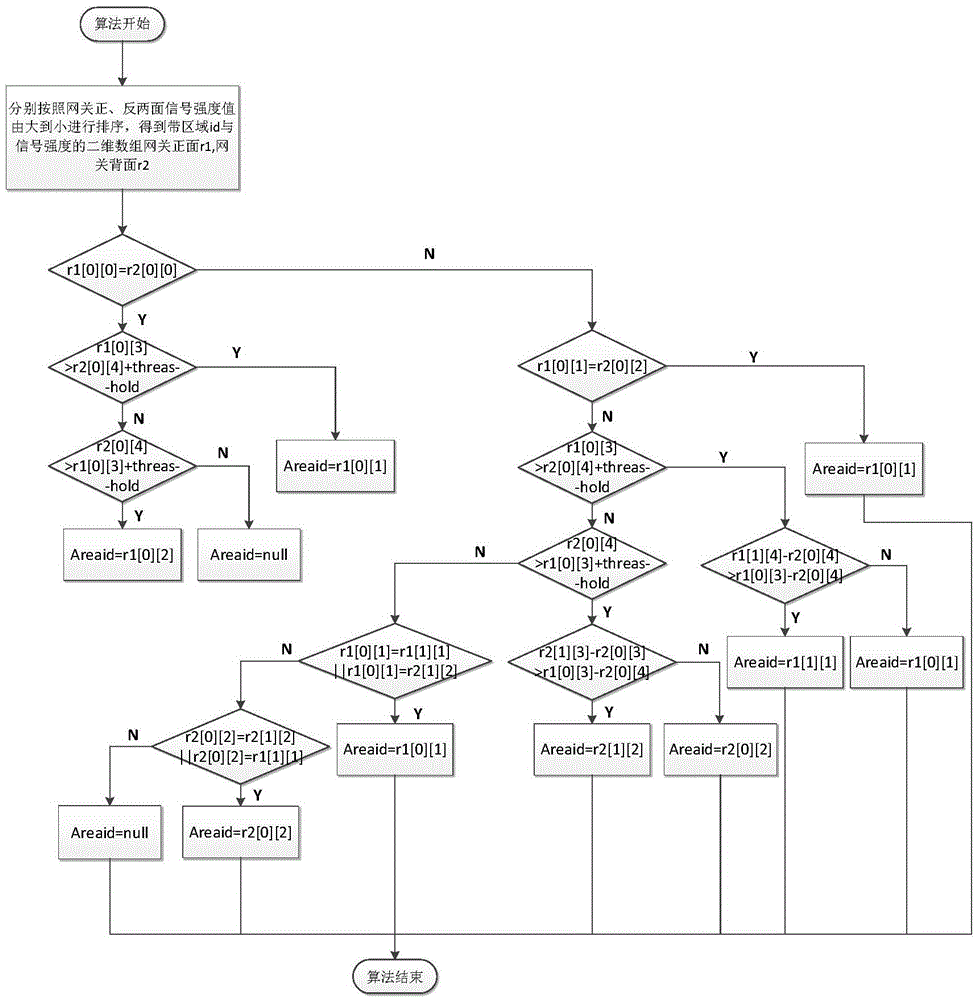

Method and system for positioning and optimizing indoor area

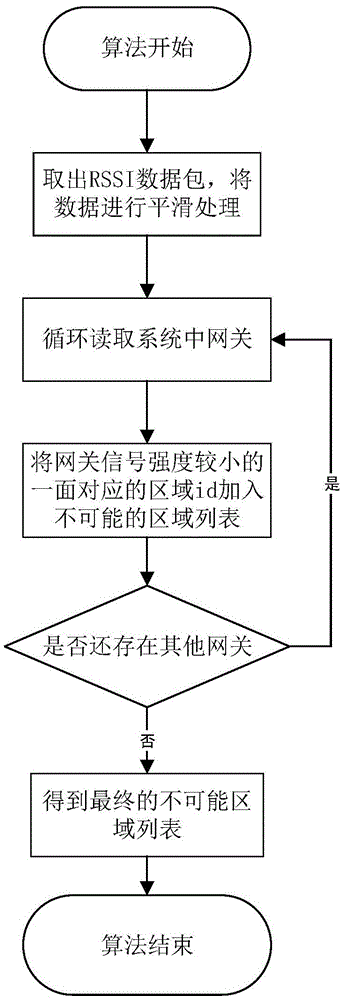

ActiveCN105554879AImprove positioning accuracySimplify the collection processUsing reradiationWireless commuication servicesNetwork packetUnique identifier

The invention relates to a method and a system for positioning and optimizing an indoor area. Signal strength indicators of multiple to-be-positioned sensor mobile nodes in a communication range are acquired; the acquired mobile node unique identifier, the signal strength indicators, the gateway node unique identifier and the current time are packaged into a data packet, and the data packet is sent to a positioning server; the positioning server carries out smoothing processing on the signal strength indicators according to the received data packet; positive logic judgment is carried out according to the strength indicator after smoothing to obtain a possible mobile node area position list; impossible areas are removed from the possible area position list, and a final area list is obtained; and through a reliability calculation method, the area position with the highest reliability in the area list is selected to be the final positioning position. Through introducing the mixed logic, the method and the system are used for indoor area positioning, and the indoor area positioning accuracy is improved.

Owner:INST OF INFORMATION ENG CHINESE ACAD OF SCI

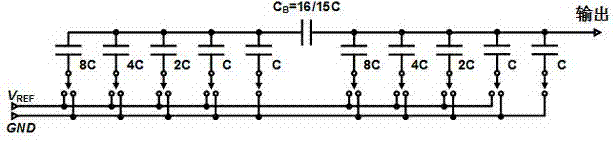

Successive approximation type analog-to-digital converter with capacitance mismatch correction function

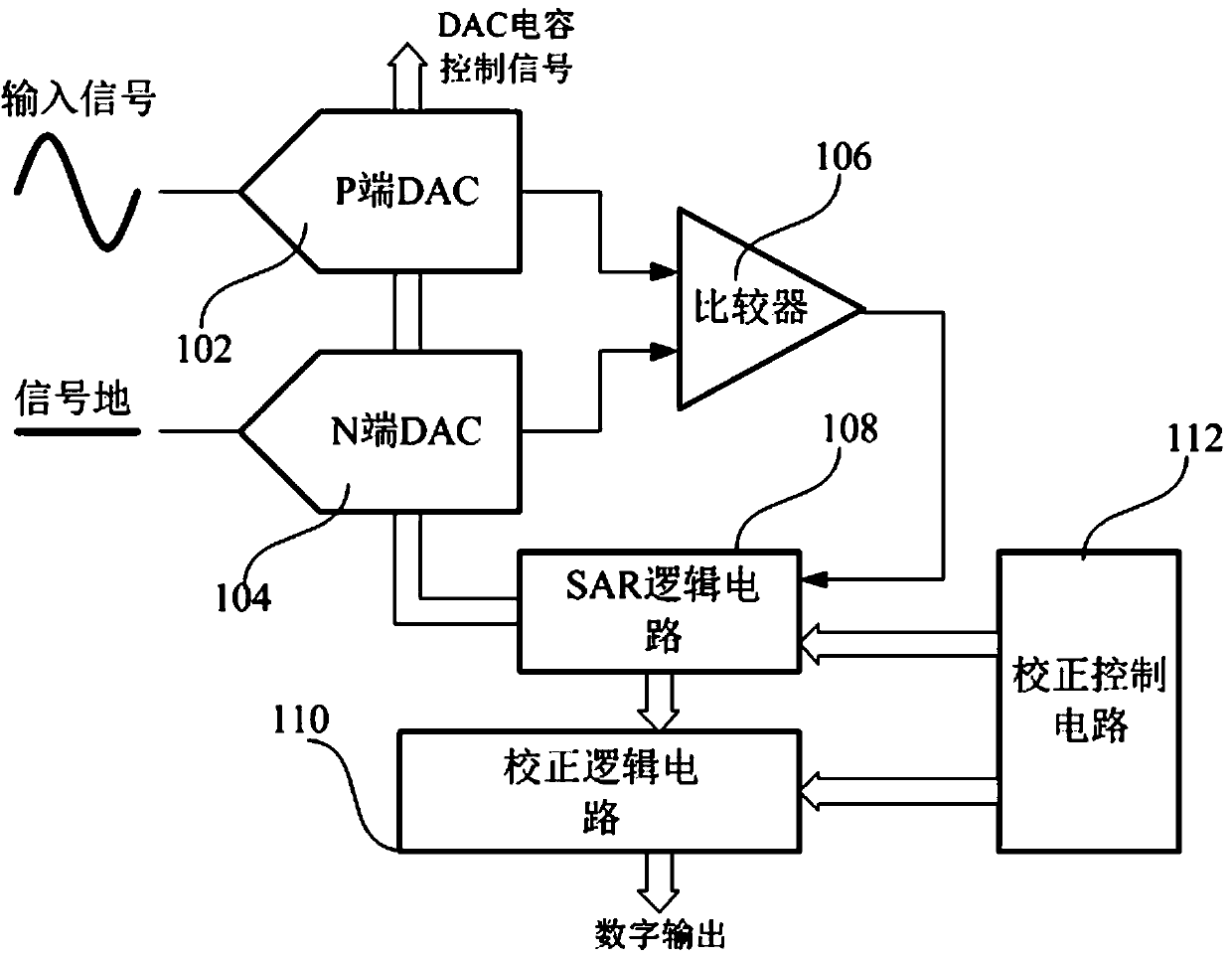

ActiveCN111431529ARealize digital self-calibrationLow costHigh level techniquesAnalogue/digital conversion calibration/testingCapacitanceA d converter

The invention discloses a successive approximation type analog-to-digital converter with a capacitor mismatch correction function. The circuit is provided with a P-end DAC (102), an N-end DAC (104), acomparator (106), an SAR logic circuit (108), a correction logic circuit (110) and a correction control circuit (112). The output end of the P-end DAC (102) and the output end of the N-end DAC (104)are respectively connected with two input ends of the comparator (106). Wherein the output of the comparator (106) is connected with the SAR logic circuit (108); the SAR logic circuit (108) is in control connection with the P-end DAC (102), the N-end DAC (104) and the correction logic circuit (110); and the correction control circuit (112) is in control connection with the SAR logic circuit (108)and the correction logic circuit (110).

Owner:成都铭科思微电子技术有限责任公司

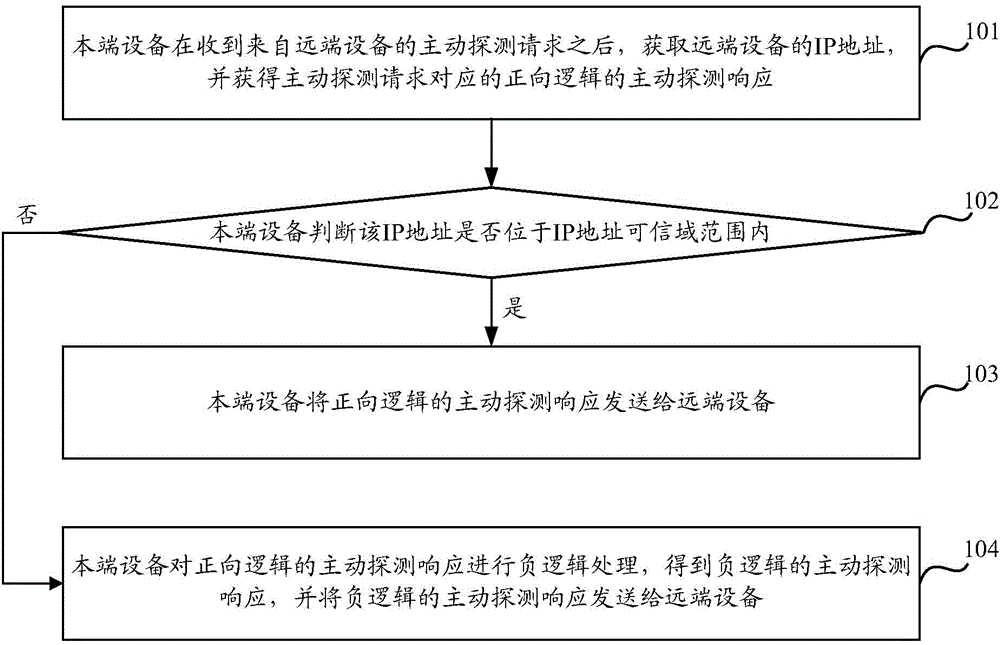

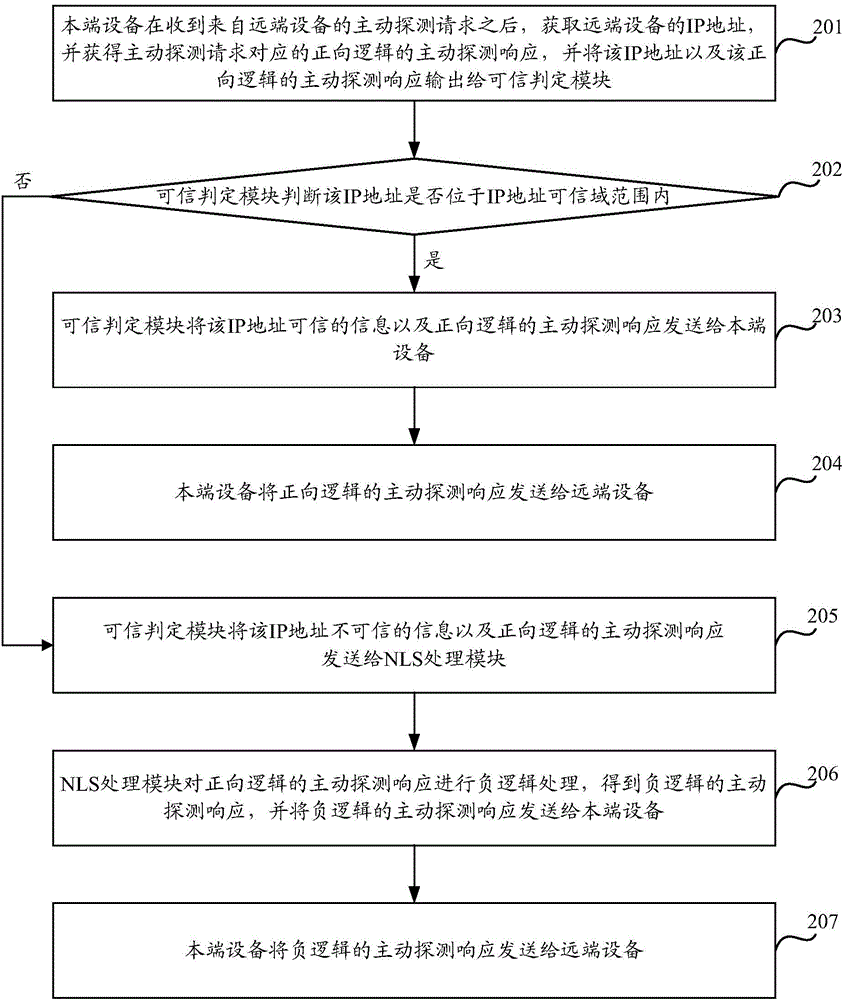

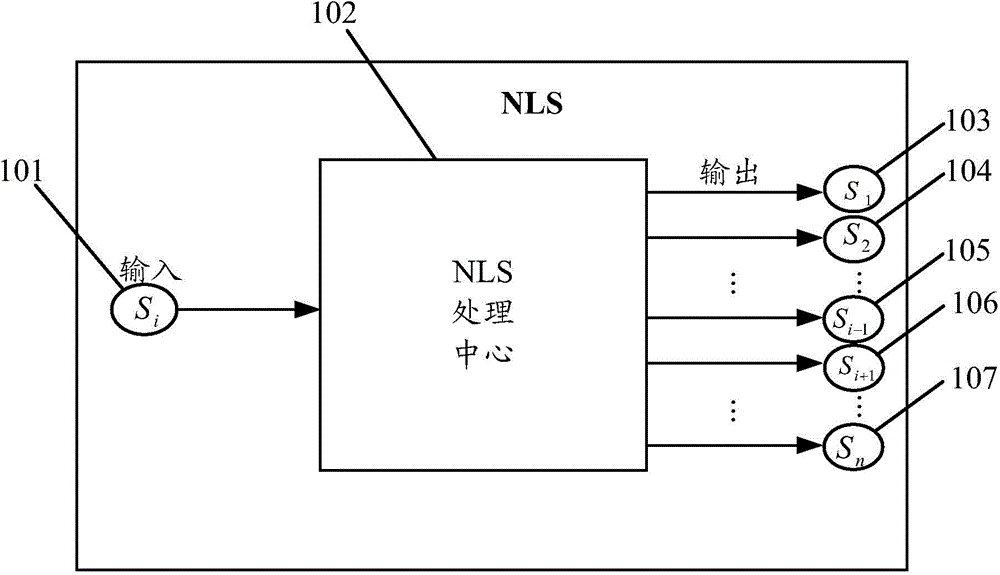

Method, equipment and system for processing active detection response

The invention discloses a method, equipment and a system for processing an active detection response. The method comprises the following steps: current equipment receives an active detection request from remote equipment, obtains an IP (internet protocol) address of the remote equipment and obtains the positive logic active detection response corresponding to the active detection request; the current equipment judges whether the IP address is within an IP address credible region range or not; if the IP address is within the IP address credible region range, the current equipment sends the positive logic active detection response to the remote equipment; if the IP address is not within the IP address credible region range, the current equipment performs negative logic treatment on the positive logic active detection response, obtains a negative logic active detection response and sends the negative logic active detection response to the remote equipment. According to the embodiment of the invention, an attacker can be prevented from mining key network data from the active detection response, so that an attack behavior cannot be made, the network security is improved, and insecurity, information leakage and the like caused by positive logic are avoided.

Owner:CHINA MOBILE COMM GRP CO LTD

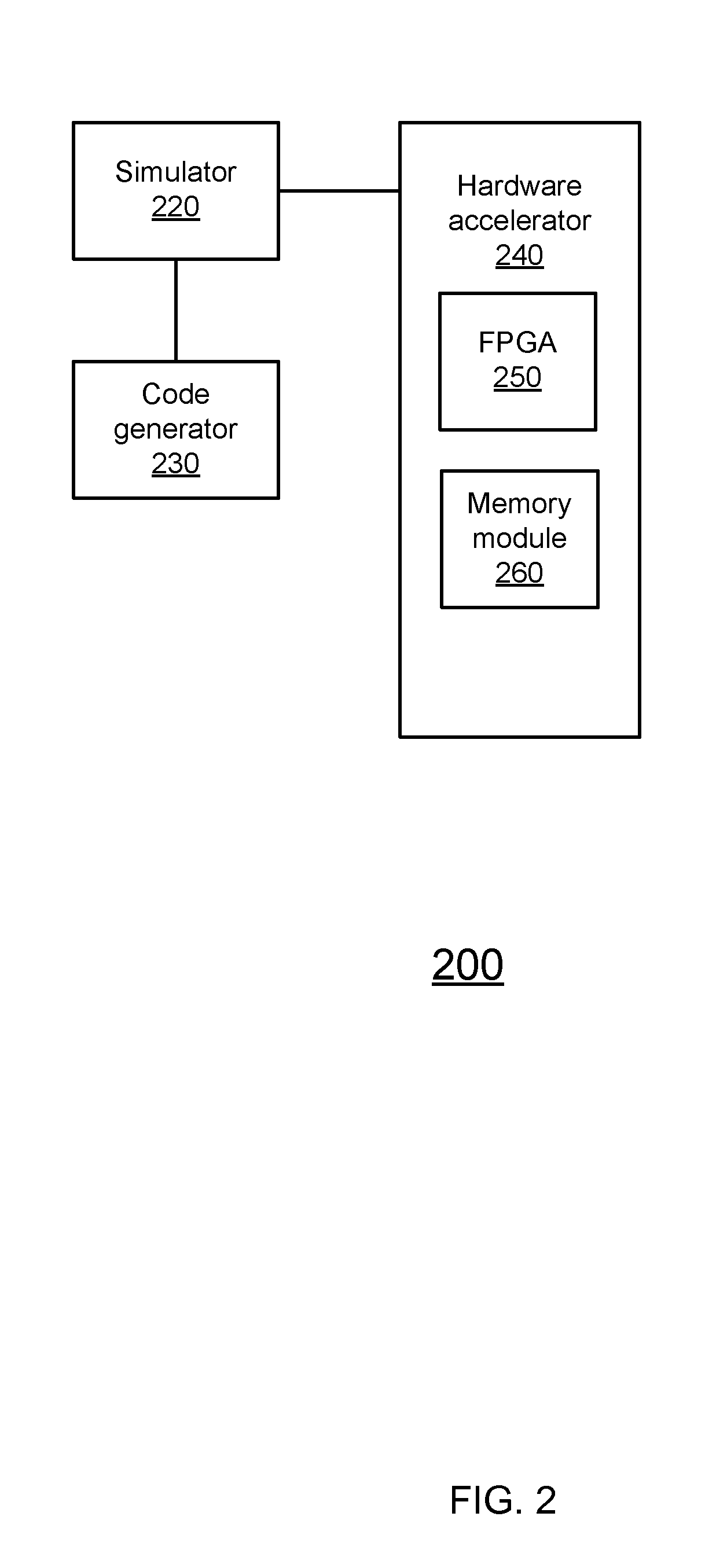

Method and system and computer program product for accelerating simulations

InactiveUS20120265515A1Computer aided designSpecial data processing applicationsParallel computingComputer science

Method, system, and computer program product. The method may include: receiving a model of a circuit that includes logic that is designed to receive sequence information and / or constants from input modules of the circuit. Updating the model or generating a new model that includes an interface and an initialization module. The initialization module may provide, to a hardware accelerator and during an initialization of a simulation of the circuit, the constants and / or the sequence information. The interface may interface between a simulator and a hardware accelerator that includes one or more FPGAs. Generating FPGA code of an amended logic that includes the logic and a programmable module; wherein the programmable module may receive, during the initialization of the simulation, the constants and / or the sequence information, and to provide during the simulation and to the logic, at least one out of the constants and a sequence represented by the sequence information.

Owner:WEINTRAUB REUVEN

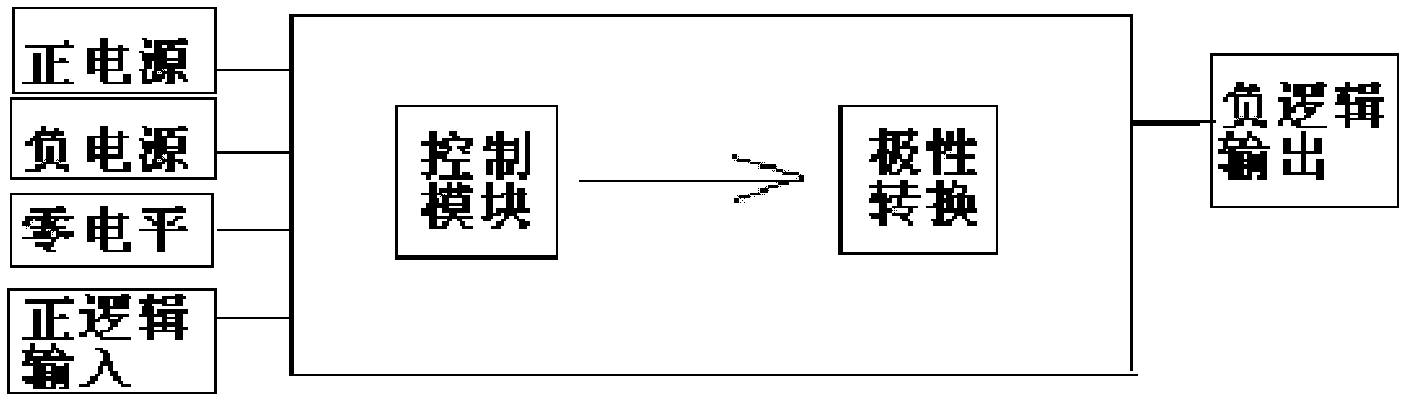

Single-power-supply positive and negative logic conversion circuit

ActiveCN102571069ALow costReduce wiring difficultyLogic circuits coupling/interface using field-effect transistorsNegative powerComputer module

The invention discloses a single-power-supply positive and negative logic conversion circuit, which comprises a power supply, a zero level, a positive logic input, a control circuit and a negative logic output, wherein the power supply only comprises a negative power supply; the control circuit comprises a voltage reducing module and a control module; the voltage reducing module comprises an MOS (Metal Oxide Semiconductor) tube voltage reducing module and an enabling control module; the output end of the MOS tube voltage reducing module is connected with a reshaping and amplifying circuit through a signal; the MOS tube voltage reducing module is formed by connecting a plurality of NMOS (N-channel Metal Oxide Semiconductor) tubes in series; the enabling control module consists of one NMOS tube; the input end of the MOS tube voltage reducing module is connected with the positive logic input; the output end of the MOS tube voltage reducing module is connected with the input end of the enabling control module and an internal negative logic signal; the output end of the enabling control module is connected with a negative level; and the internal negative logic signal is connected with the input end of the control module. The single-power-supply positive and negative logic conversion circuit has the advantages that: only a single power supply is required for supplying power, the chip cost and the wiring difficulty and cost of a power wire are reduced, and the entire logic conversion circuit is relatively simple.

Owner:WUXI I-MENG ELECTRONIC TECH CO LTD

Depletion-mode MOSFET circuit and applications

ActiveUS7817459B2TransistorLogic circuits characterised by logic functionCMOSStatic random-access memory

Owner:LIN WEN T

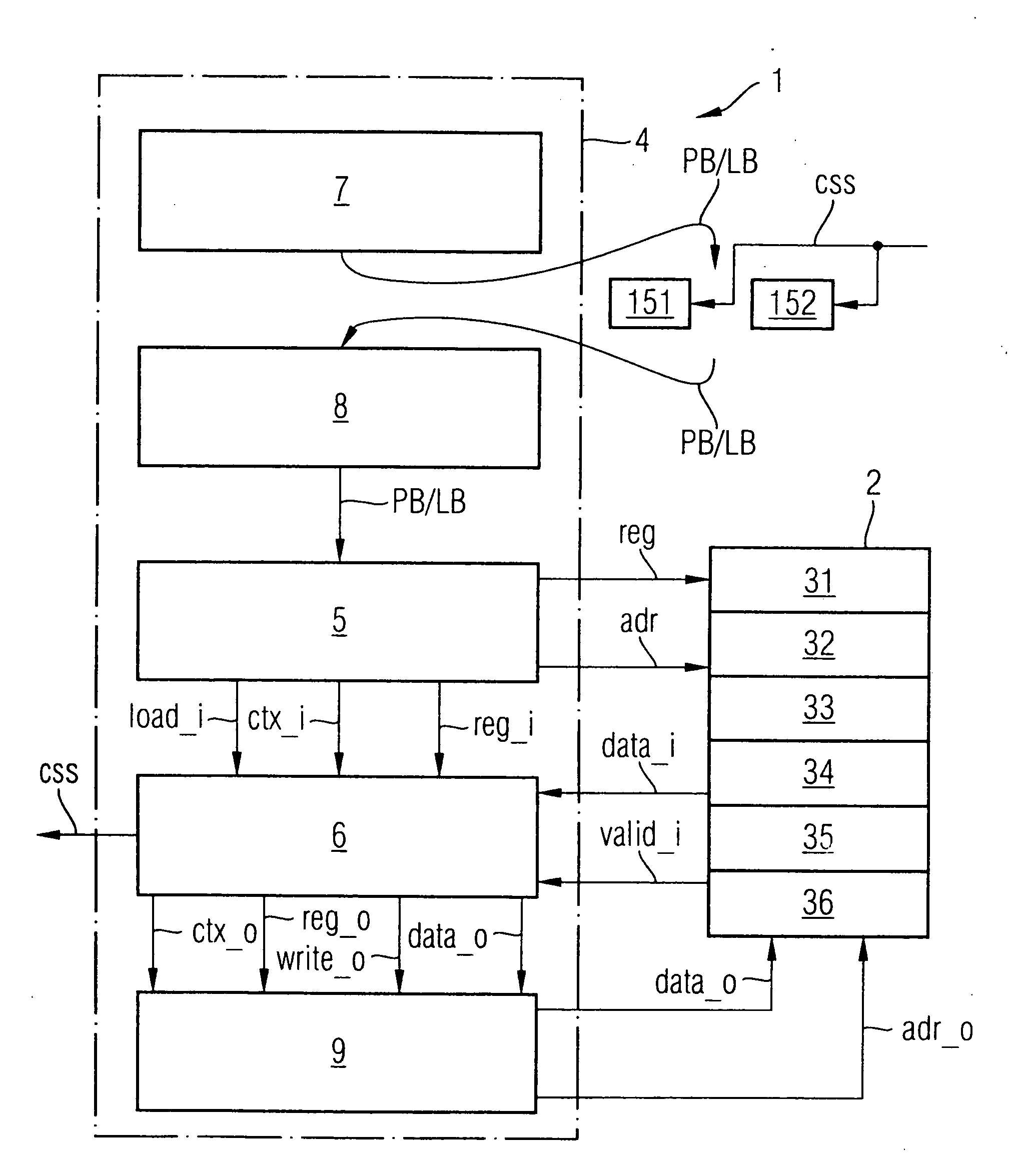

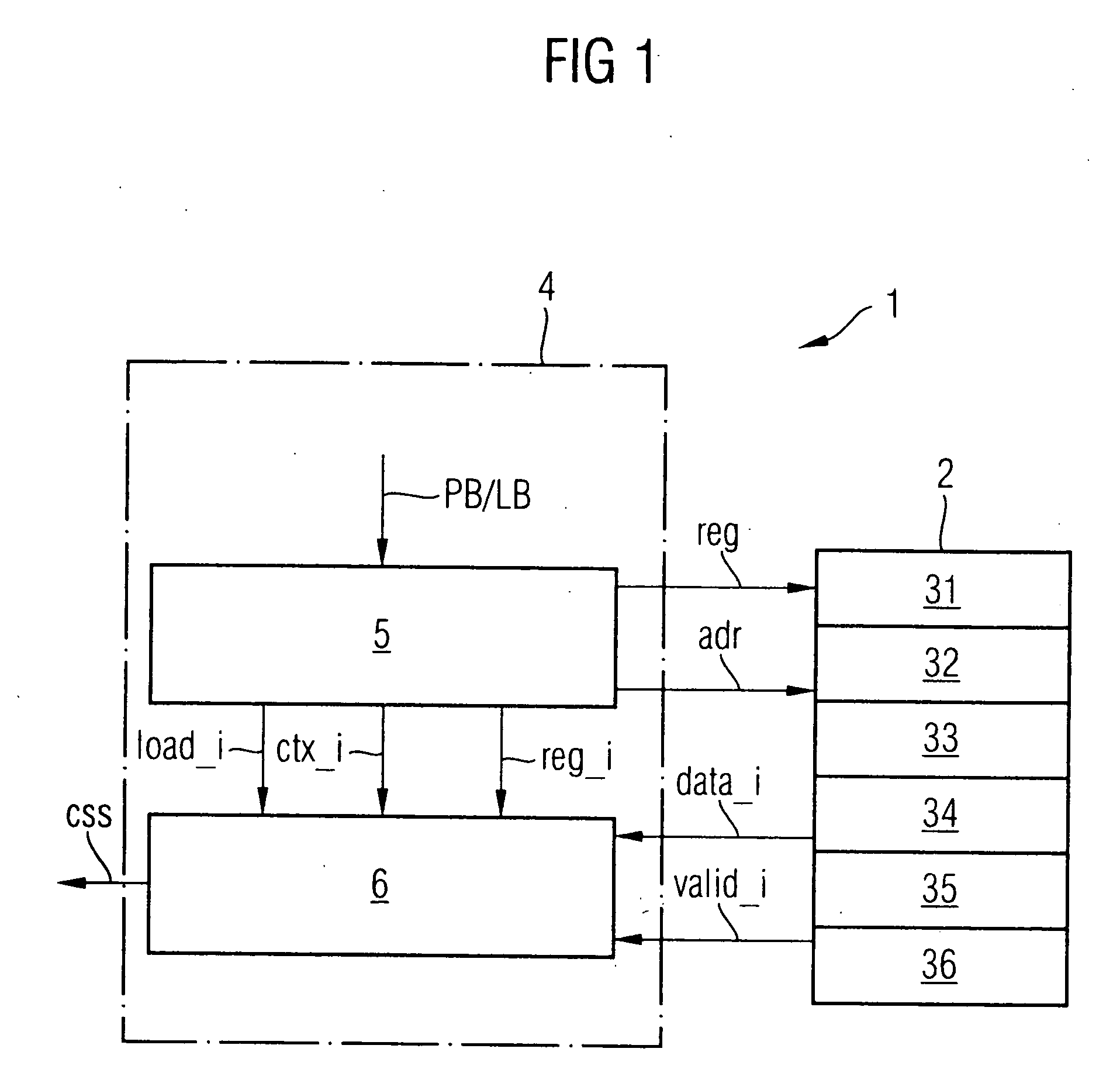

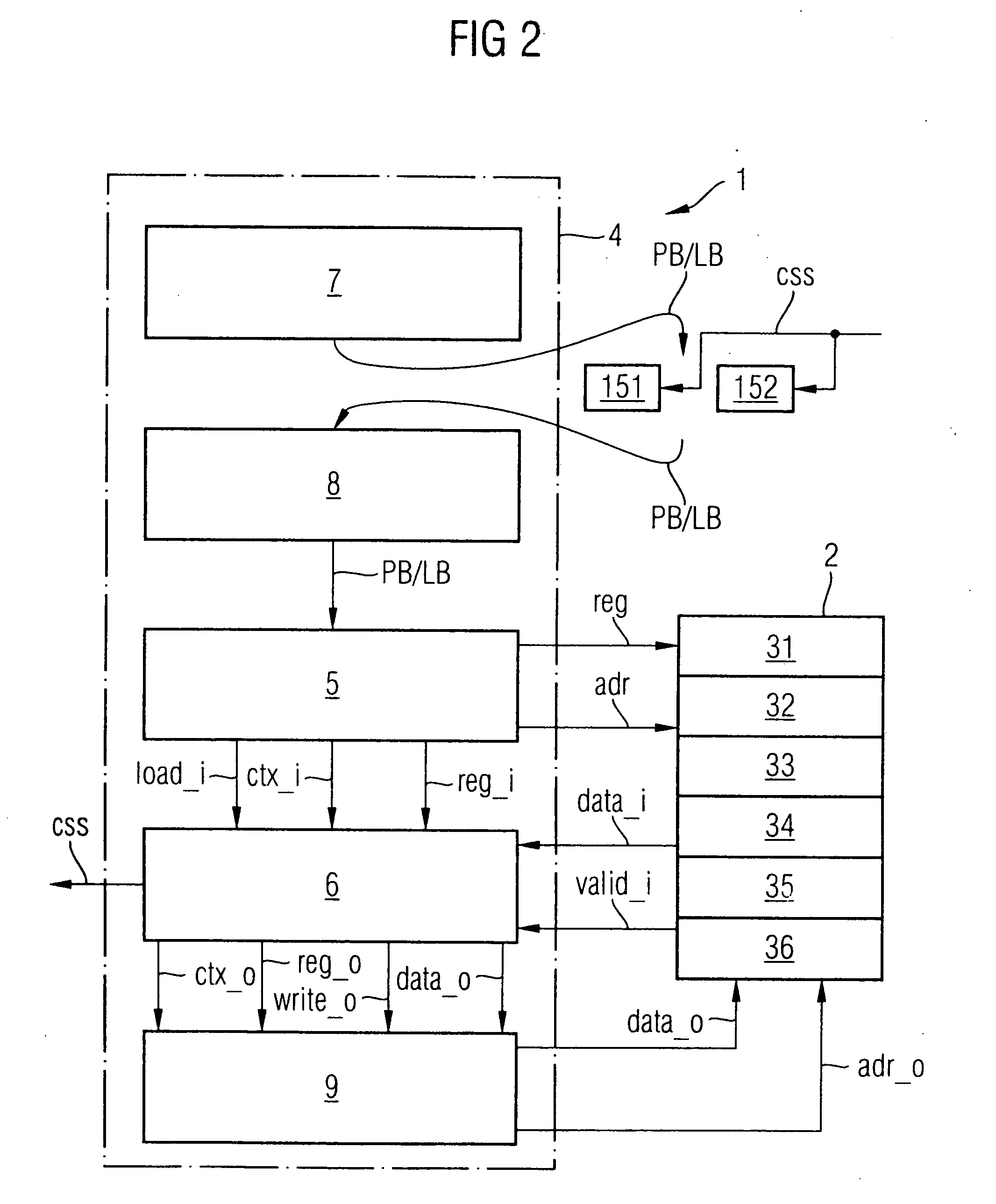

Multi-thread processor and method for operating such a processor

InactiveUS20060230258A1Save spaceSimplification of the driving of the processorDigital computer detailsSpecific program execution arrangementsLoad cyclePositive logic

A multithread processor with synchronization of a command flow, with an associated data flow and with generation of a memory-triggered context switch signal comprises a synchronization device configured, when receiving a load cycle indicator flag with a positive logic signal level from a memory read access unit, to load and buffer in a synchronized fashion an associated context identifier and a target register identifier and to forward the context identifier and the target register identifier to a downstream pipeline stage and, when receiving a validity signal with a positive logic signal level from a memory system, to load and buffer in a synchronized fashion an associated memory value, and to forward the memory value to the pipeline stage. The processor comprises further a logic circuit generating, when the load cycle indicator flag with a positive logic signal level and the validity signal are received, a context switch signal with a negative logic signal level.

Owner:INFINEON TECH AG

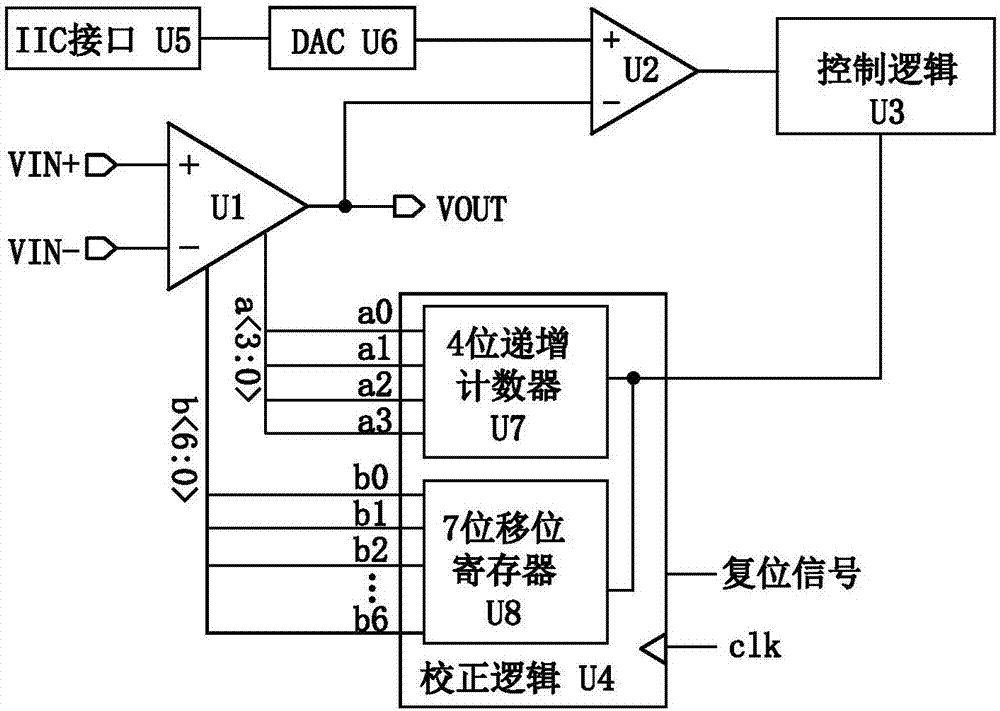

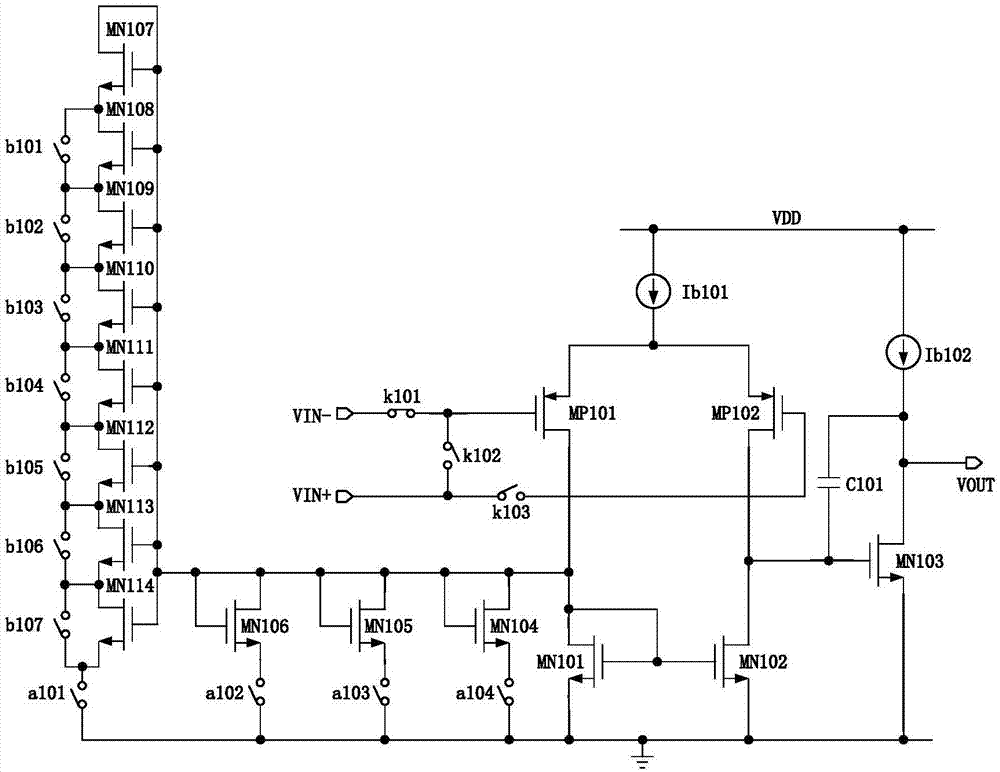

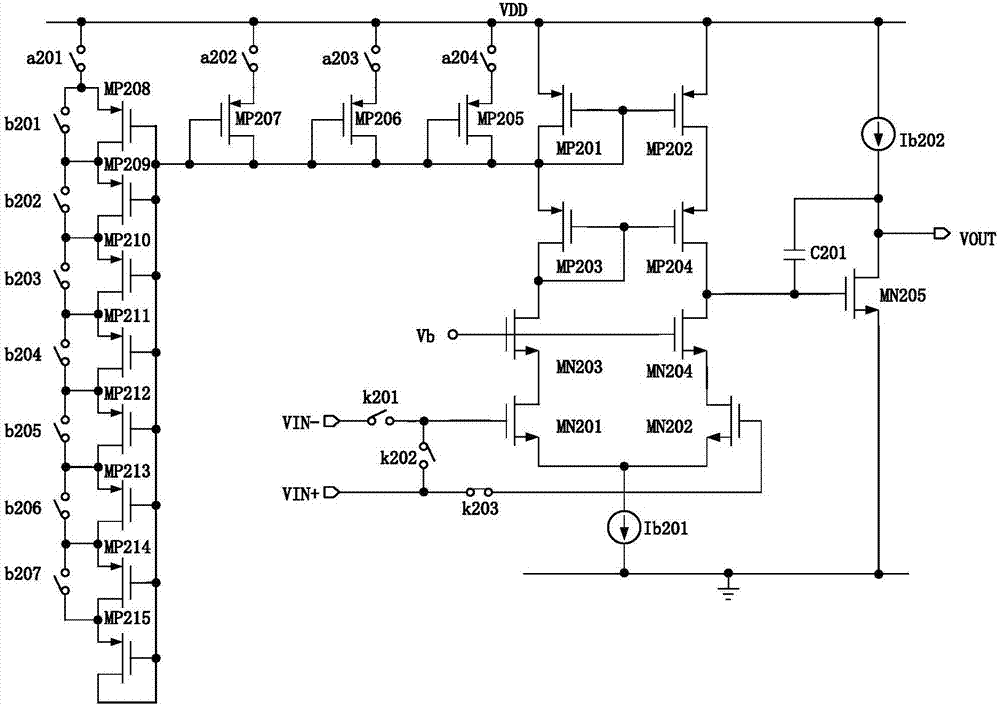

Operational amplifier for performing offset voltage correction on output working point

ActiveCN107346959AAdapt to requirementsHigh precisionNegative-feedback-circuit arrangementsGain controlSoftware engineeringPositive logic

The invention relates to an operational amplifier for performing offset voltage correction on an output working point. The operational amplifier comprises an operational amplifier module, a comparator module, a logic control module, a correction logic module, an inter-integrated circuit (IIC) interface and a digital-to-analogue converter (DAC) module, wherein the IIC interface is connected with the DAC module, and an output end of the DAC module is connected with an in-phase input end of the comparator module; an inverting input end of the comparator module is connected with an output end (VOUT) of the operational amplifier module; an input end of the logic control module is connected with an output end of the comparator module; an output end of the logic control module is connected with an input end of the correction logic module. An offset correction process of the operational amplifier comprises coarse adjustment and fine adjustment; the coarse adjustment is carried out in a way of transistor parallel connection, and the fine adjustment is carried out in a way of transistor series connection, so that the correction accuracy is improved.

Owner:西安华泰半导体科技有限公司

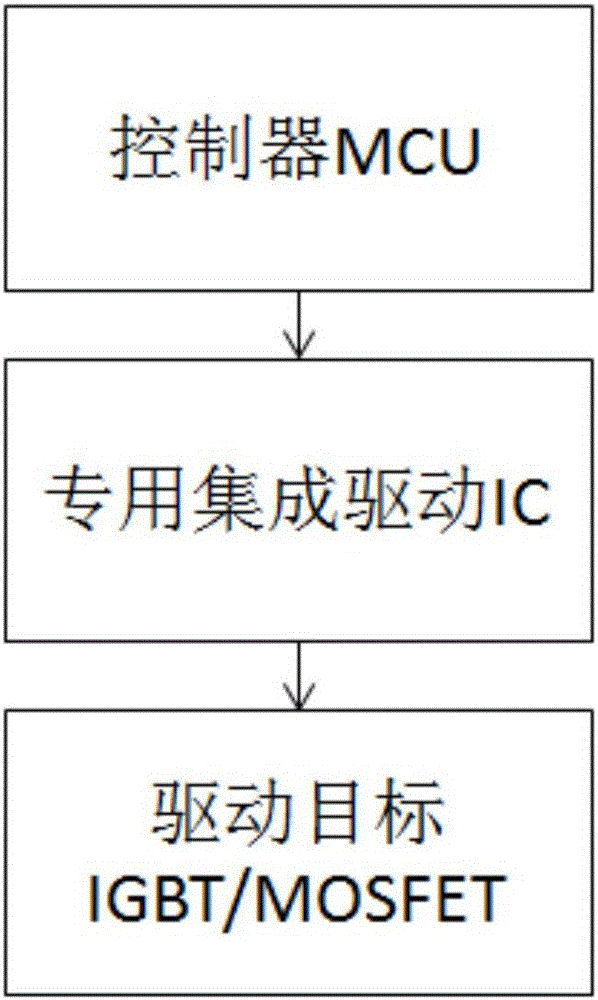

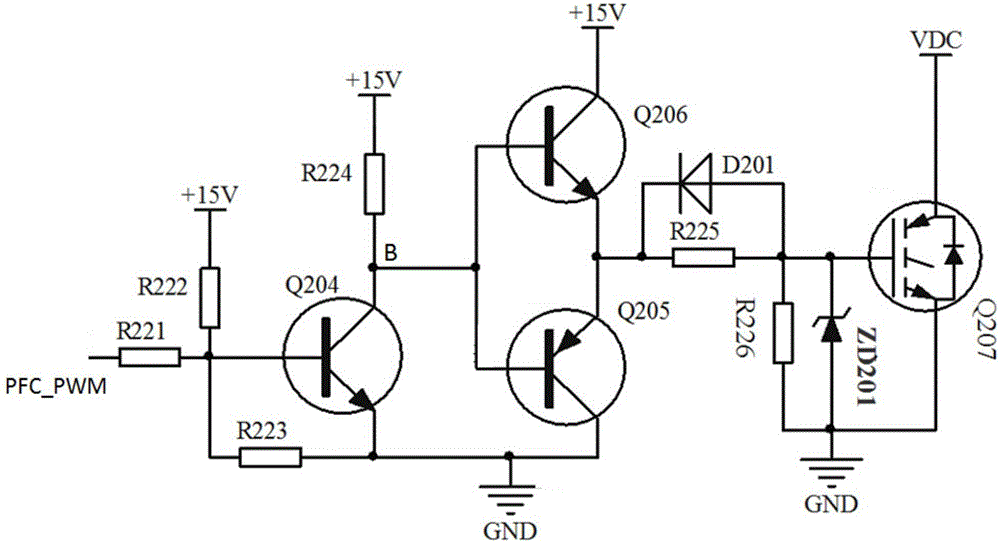

Negative-logical IGBT/MOSFET driving circuit, driving system and driving method, and air conditioner

InactiveCN105116804AReduce material costsReduce manufacturing costProgramme controlComputer controlMOSFETDriver circuit

The invention relates to a negative-logical IGBT / MOSFET driving circuit, driving system and driving method, and an air conditioner. The negative-logical IGBT / MOSFET driving circuit comprises two stages of driving circuits, i.e., a first stage of driving circuit and a second stage of driving circuit; the first stage of driving circuit is used for converting the I / O driving level of a low voltage MCU into a specific driving level, and the second stage of driving circuit is used for ensuring the saturation conduction of a driving object IGBT / MOSFET. According to the invention, a cheap and general two-stage triode replaces a routine special-purpose integrated driving IC to control a high current IGBT / MOSFET, thereby reducing the manufacture cost and risk of a control circuit designer under the condition of not changing original performances; in addition, compared with a positive logic driving circuit, the negative-logical driving circuit can greatly reduce material costs and the dependence on a provider under the condition of not changing original performances, thereby enhancing the competitive power of a control circuit provider.

Owner:GD MIDEA HEATING & VENTILATING EQUIP CO LTD +1

Depletion-mode MOSFET circuit and applications

Positive logic circuits, systems and methods using MOSFETs operated in a depletion-mode, including electrostatic discharge protection circuits (ESD), non-inverting latches and buffers, and one-to-three transistor static random access memory cells. These novel circuits supplement enhancement-mode MOSFET technology and are also intended to improve the reliability of the complementary metal-oxide-semiconductor (CMOS) integrated circuit (IC) products.

Owner:克伊斯通半导体有限公司

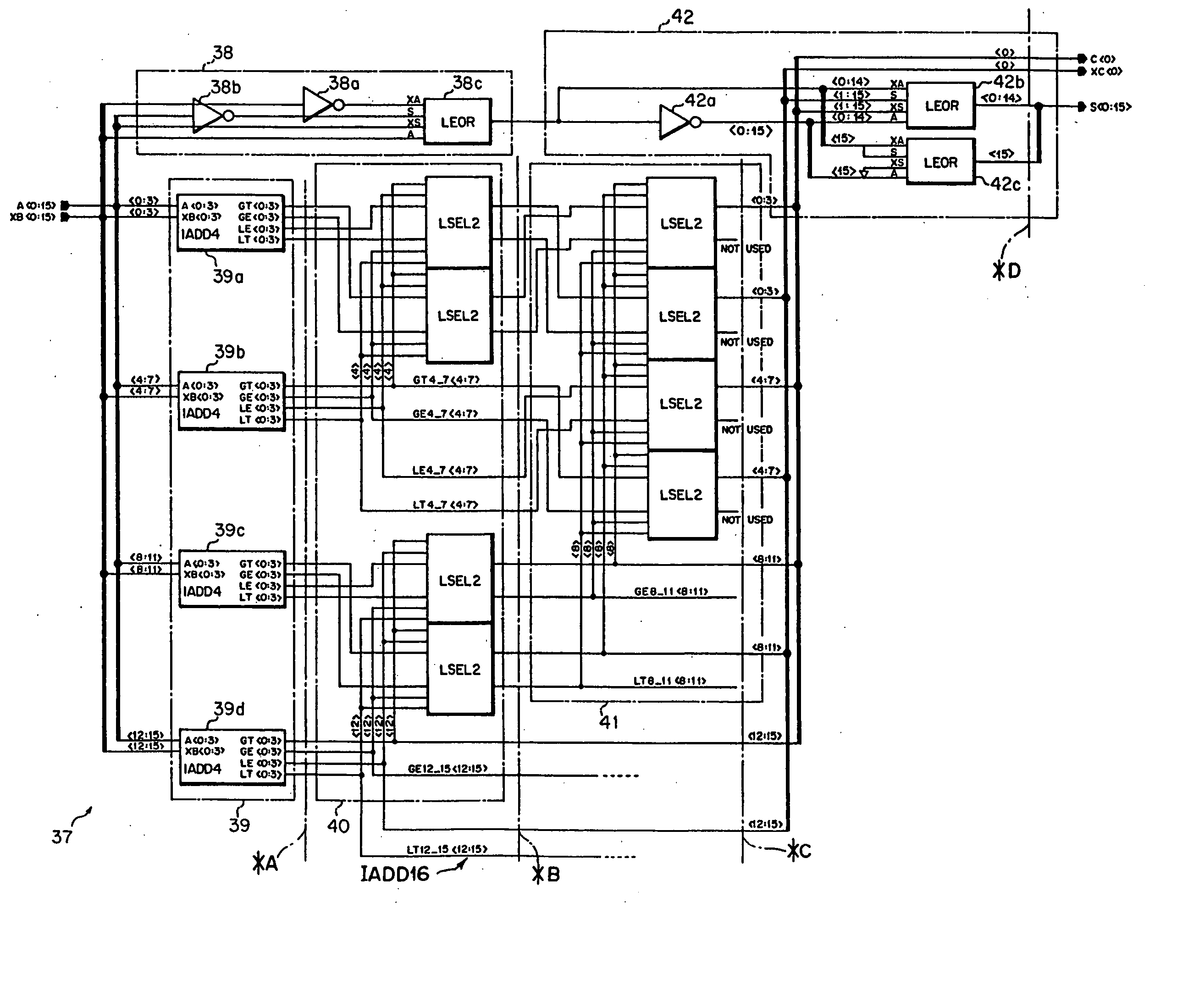

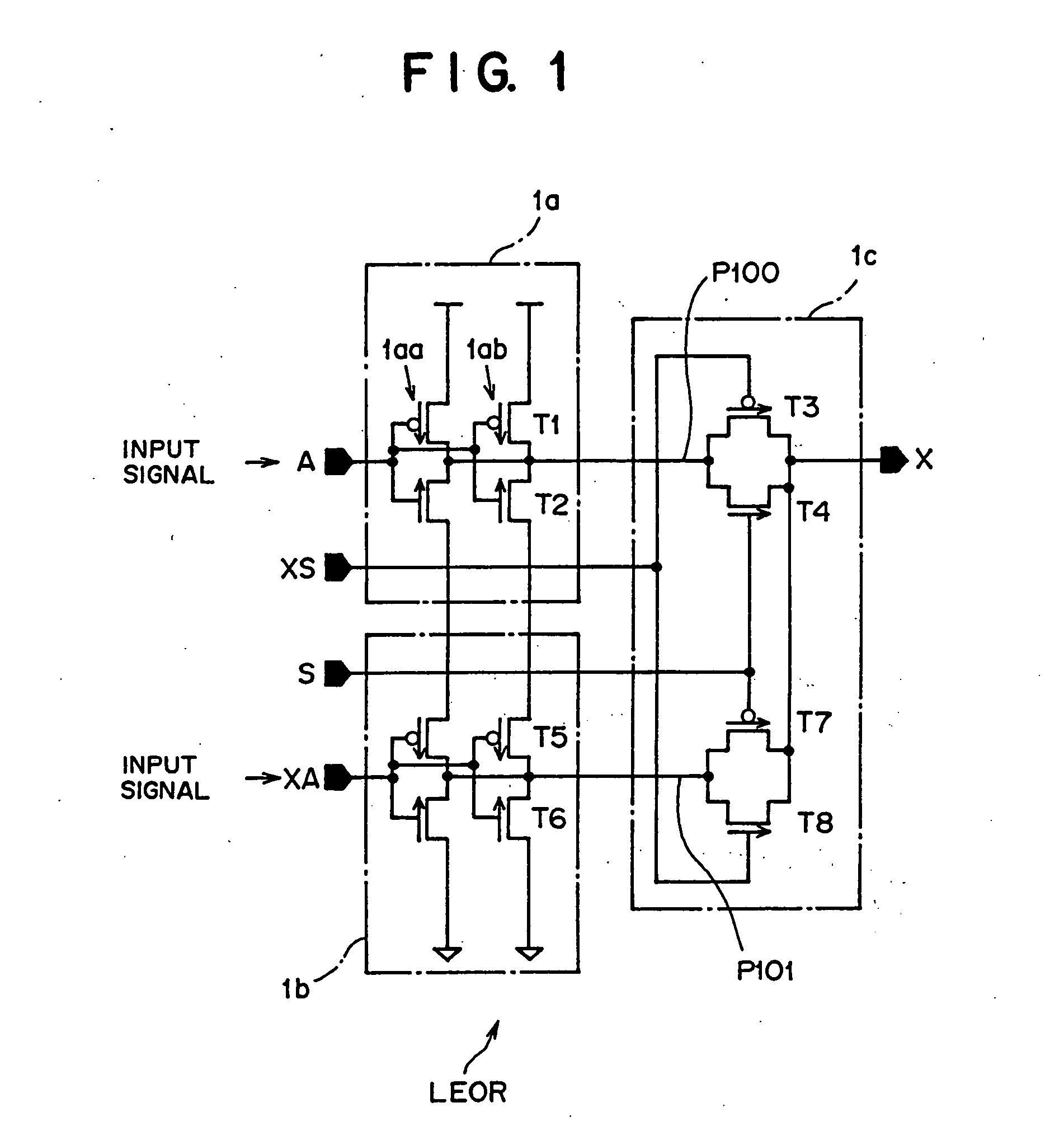

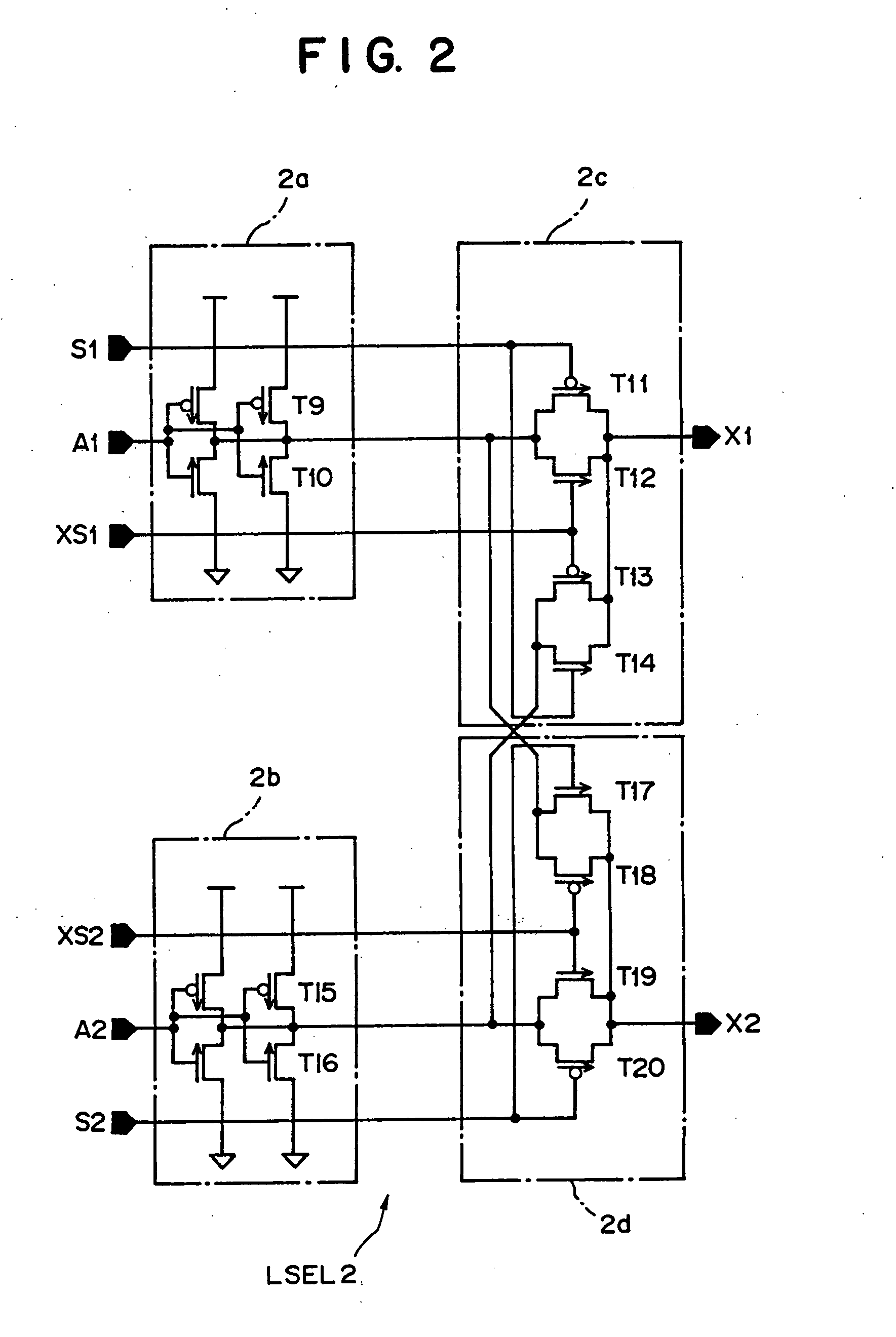

Logic circuit

InactiveUS20050193051A1Reduce the numberIncrease speedLogic circuits characterised by logic functionComputations using contact-making devicesCmos logic circuitsEngineering

A CMOS logic circuit is disclosed wherein the number of kinds of basic parts is suppressed to five to allow designing of a circuit which operates at a high speed and repetitiveness of wiring lines is increased to allow designing of a circuit which is simple in circuit scale and high in expandability and besides the time required for adjustment of components is reduced significantly to reduce the man-hours for arrangement significantly to reduce the man-hours for development significantly and the same basic parts are used so as to achieve augmentation of the yield and promote reduction of the production cost. A basic cell of the CMOS logic circuit includes a first inversion section for inverting a first input signal having one of positive logic and negative logic and outputting the inverted signal, a second inversion section for inverting a second input signal having the other of the positive logic and the negative logic and outputting the inverted signal, and a transmission section for selectively outputting one of the output of the first inversion section and the output of the second inversion section in accordance with a logical value which depends upon an externally controllable selection signal and an inverted signal of the selection signal.

Owner:FUJITSU LTD

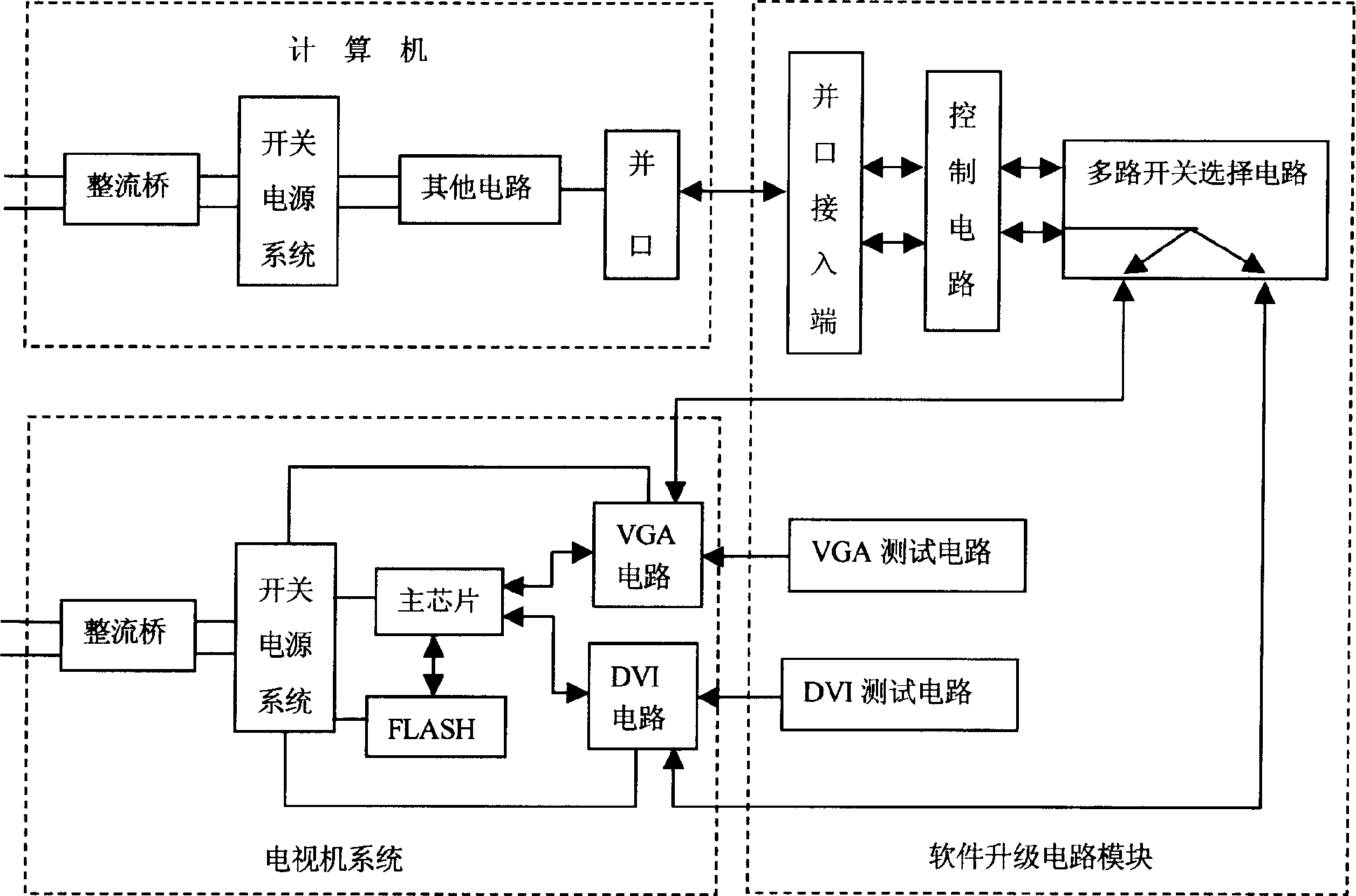

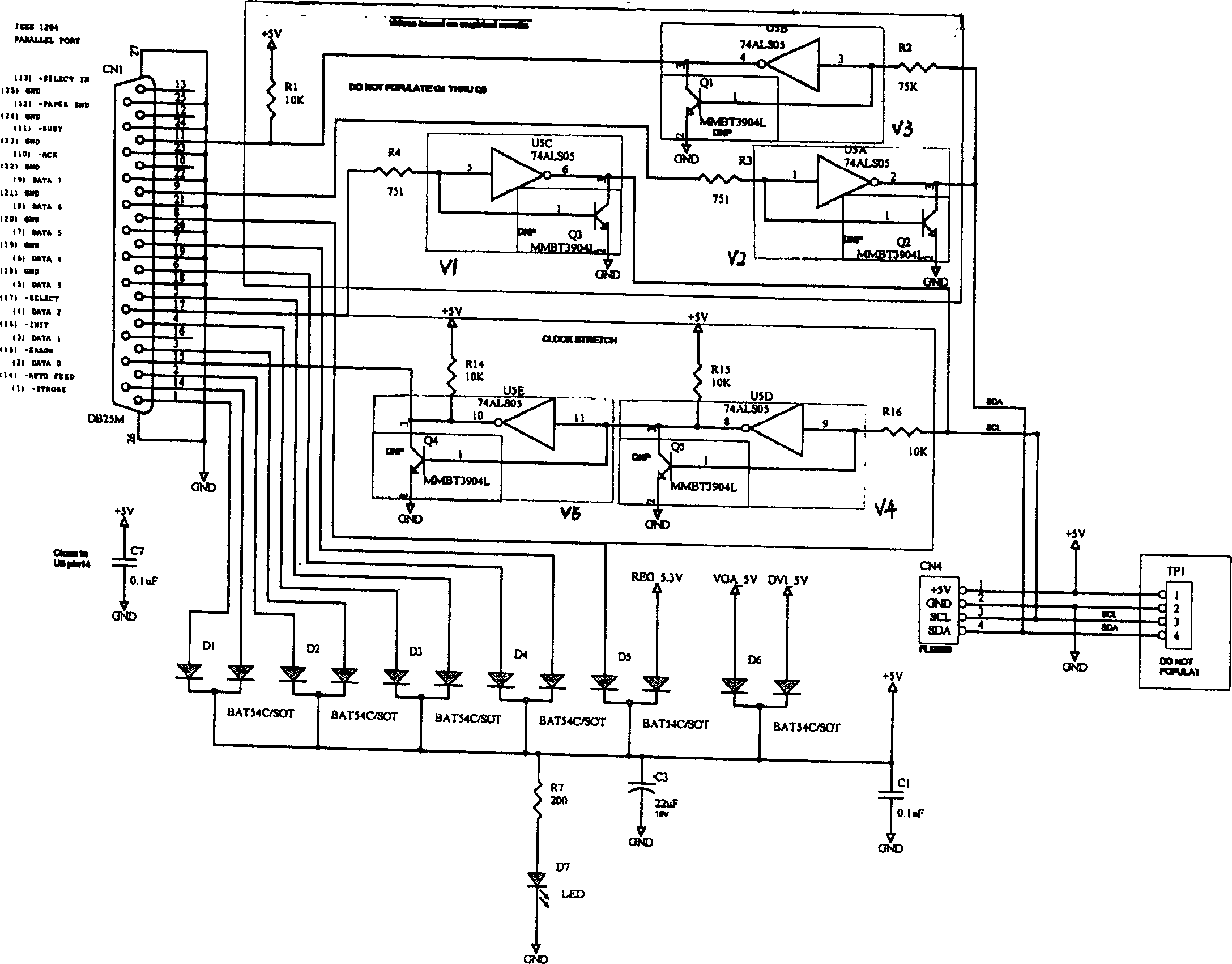

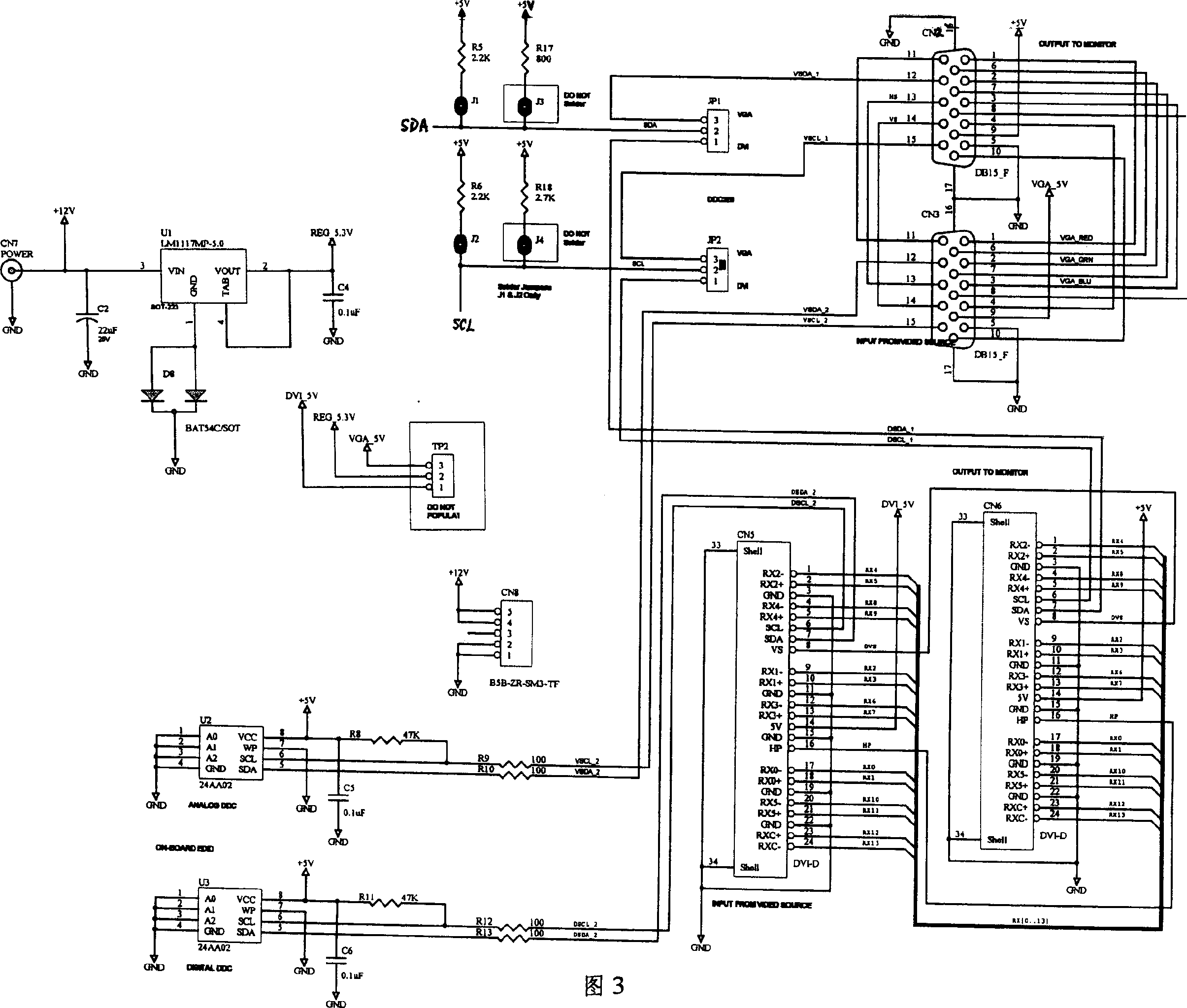

Software upgrading circuit module of TV set

ActiveCN1738380AImprove upgrade speedSimple designTelevision system detailsColor television detailsData signalComputer module

The invention discloses a software upgrading circuit module. The invention spurns the traditional serial port software upgrading mode, uses the parallel port upgrading mode, uses the I / O port with parallel 25 pins of computer to simulate the IIC bus, uses the control circuit of software upgrading circuit module to realize the switch from the positive logic bus data signal to the passive logic bus data signal, and uses the IIC bus of VGA or DVI plug of TV set to realize the communication between the main processing chips of the computer and TV set, so the writing program in parallel mode by controlling the FLASH chip is easy, while the upgrading speed of software and the producing efficiency are improved. The inventive software upgrading circuit module has simply design and high practicality. In addition, by setting the jump device of said module, any one of TV plugs can be selected to upgrade, so the versatility of said system is guaranteed.

Owner:HISENSE +1

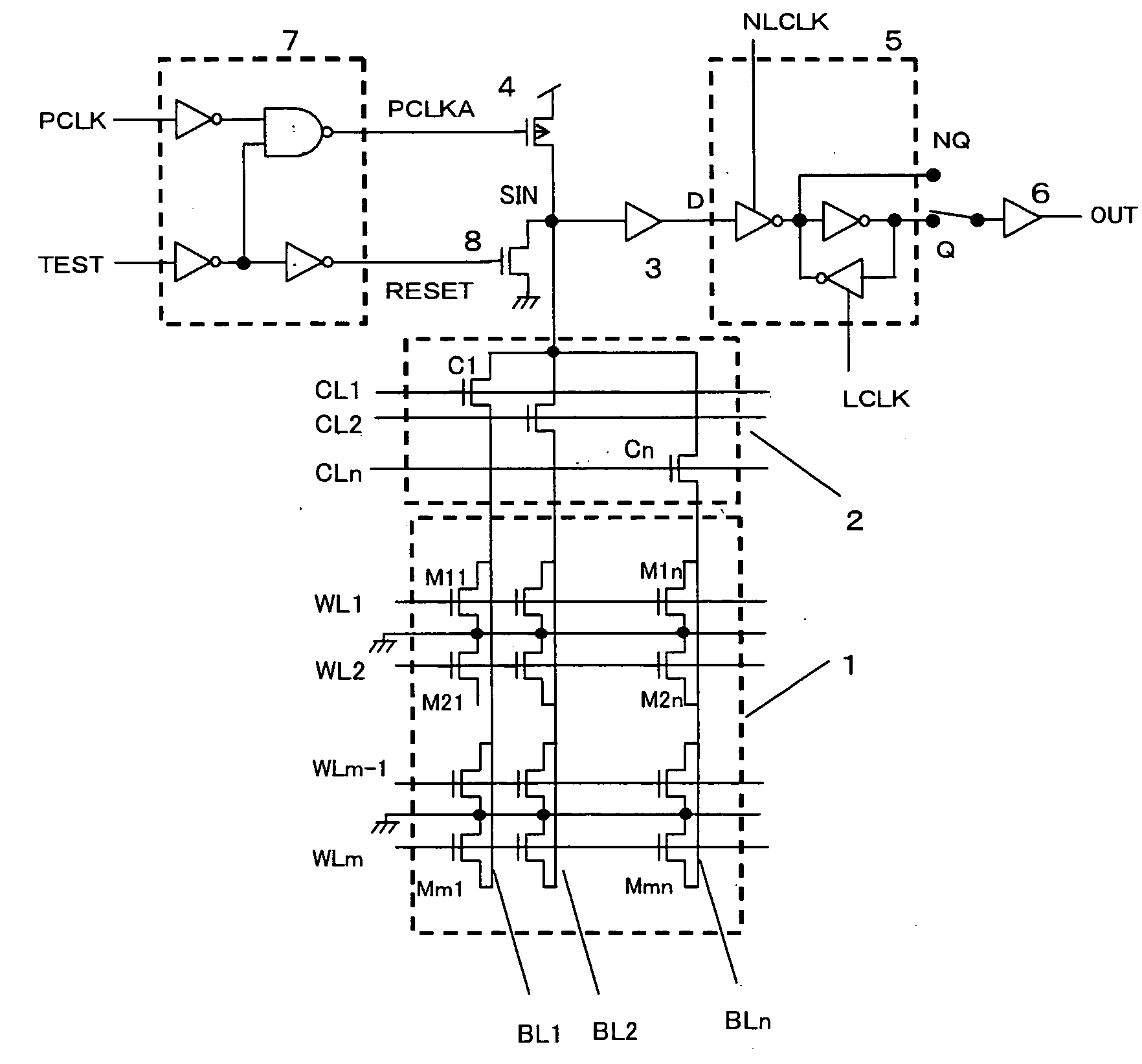

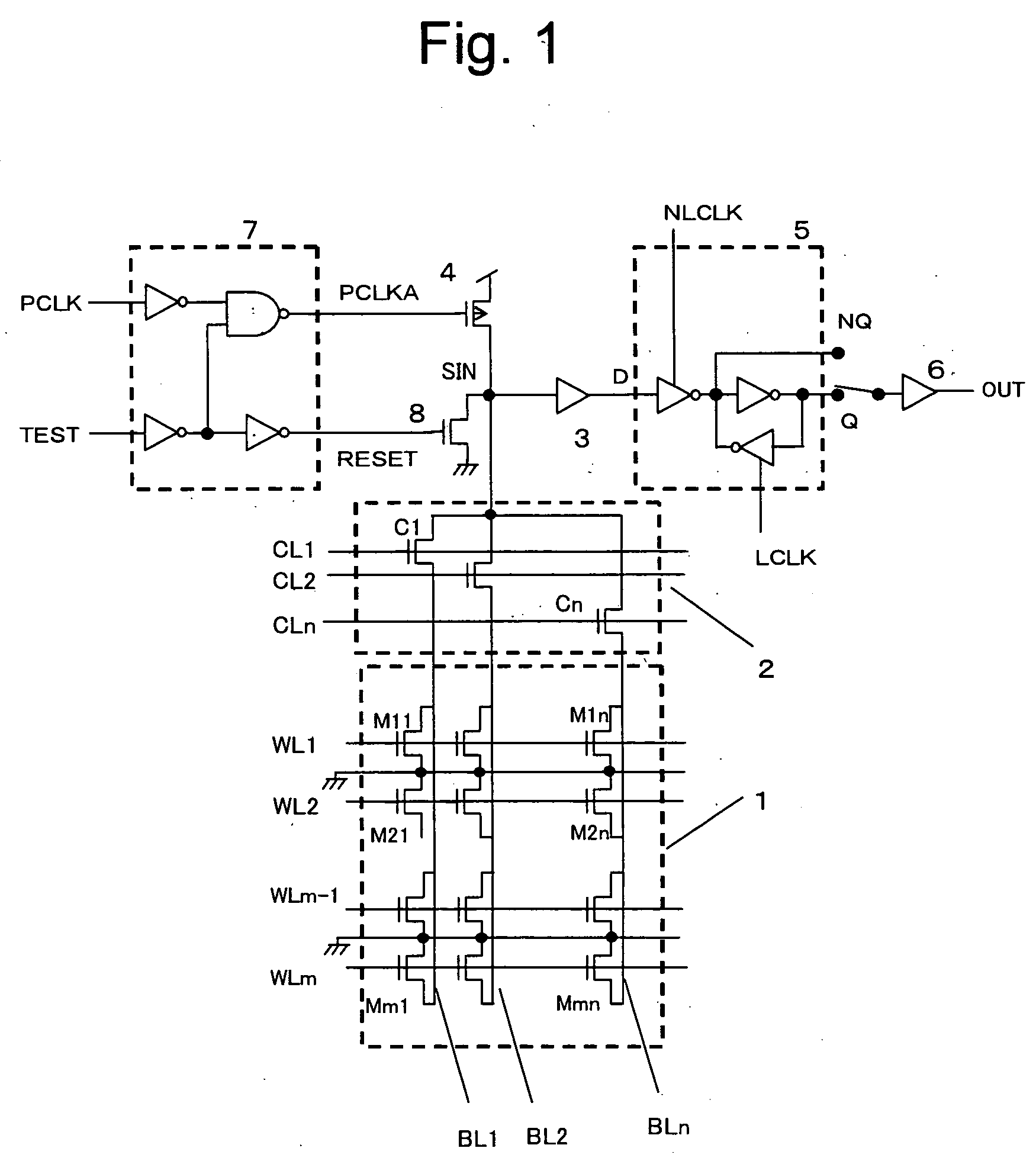

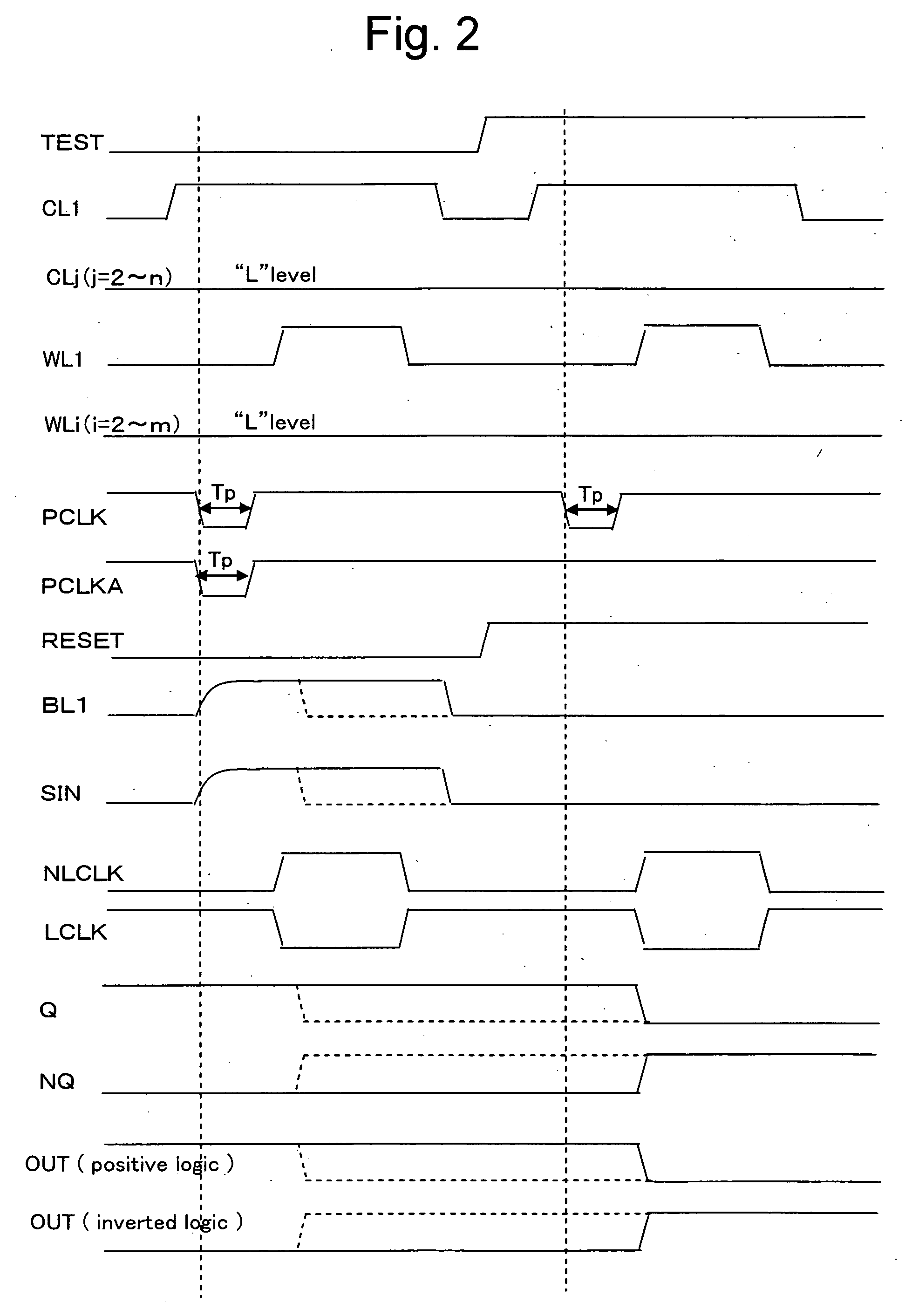

Semiconductor device

InactiveUS20060002212A1Avoid YieldReduce the number of connectionsElectronic circuit testingSolid-state devicesBit lineAudio power amplifier

An output end and an inverted output end of a latch circuit that is connected to an output buffer circuit are switched with each other, and thereby, the relationship between the data of “0” or “1” and the drain of a memory cell is connected or not connected to a bit line is changed. In addition, an input of a sense amplifier is fixed at the grounding potential by means of a test control signal, and thereby, positive logic is confirmed in the case where the output of the output buffer circuit is “L,” and negative logic is confirmed in the case where the output of the output buffer circuit is “H.”

Owner:PANASONIC CORP

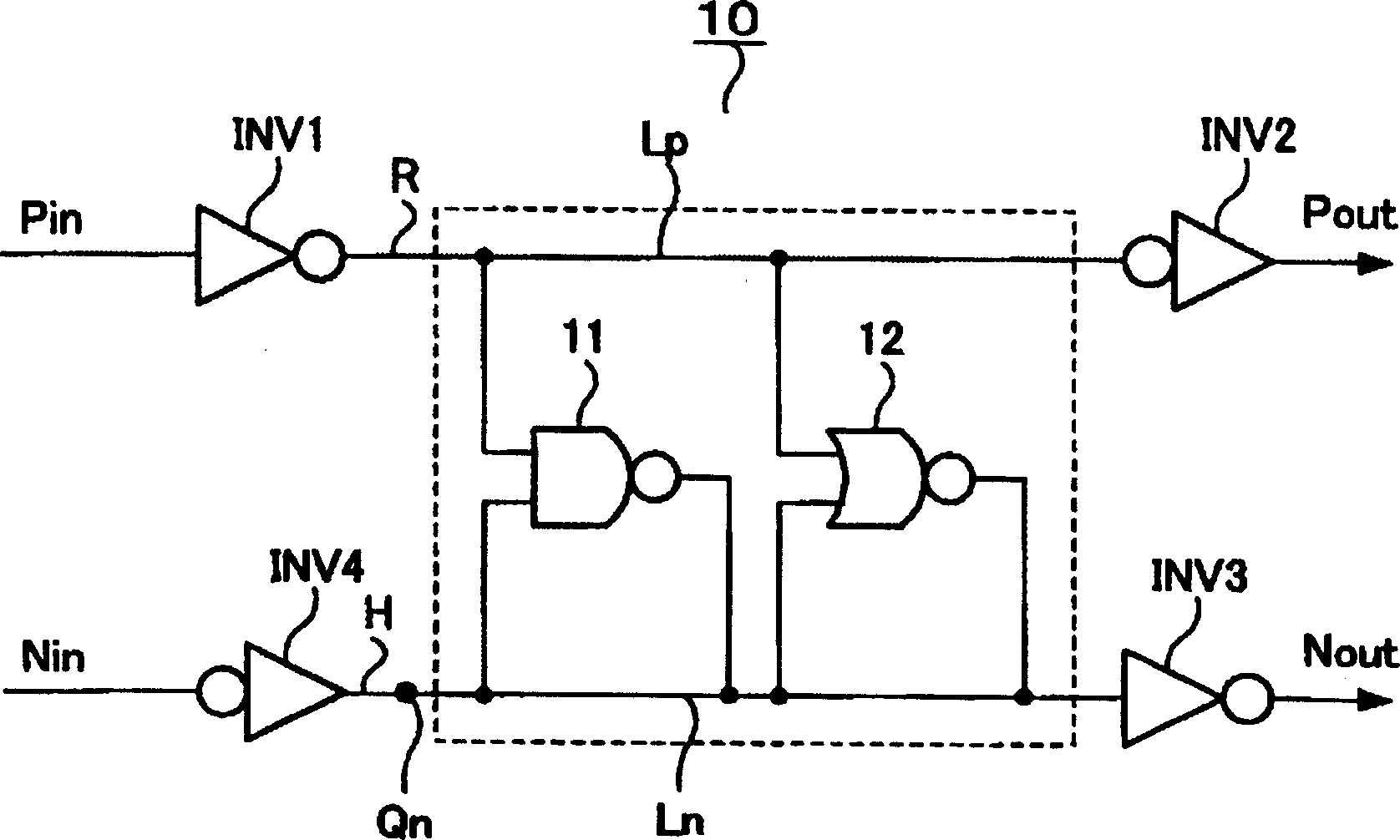

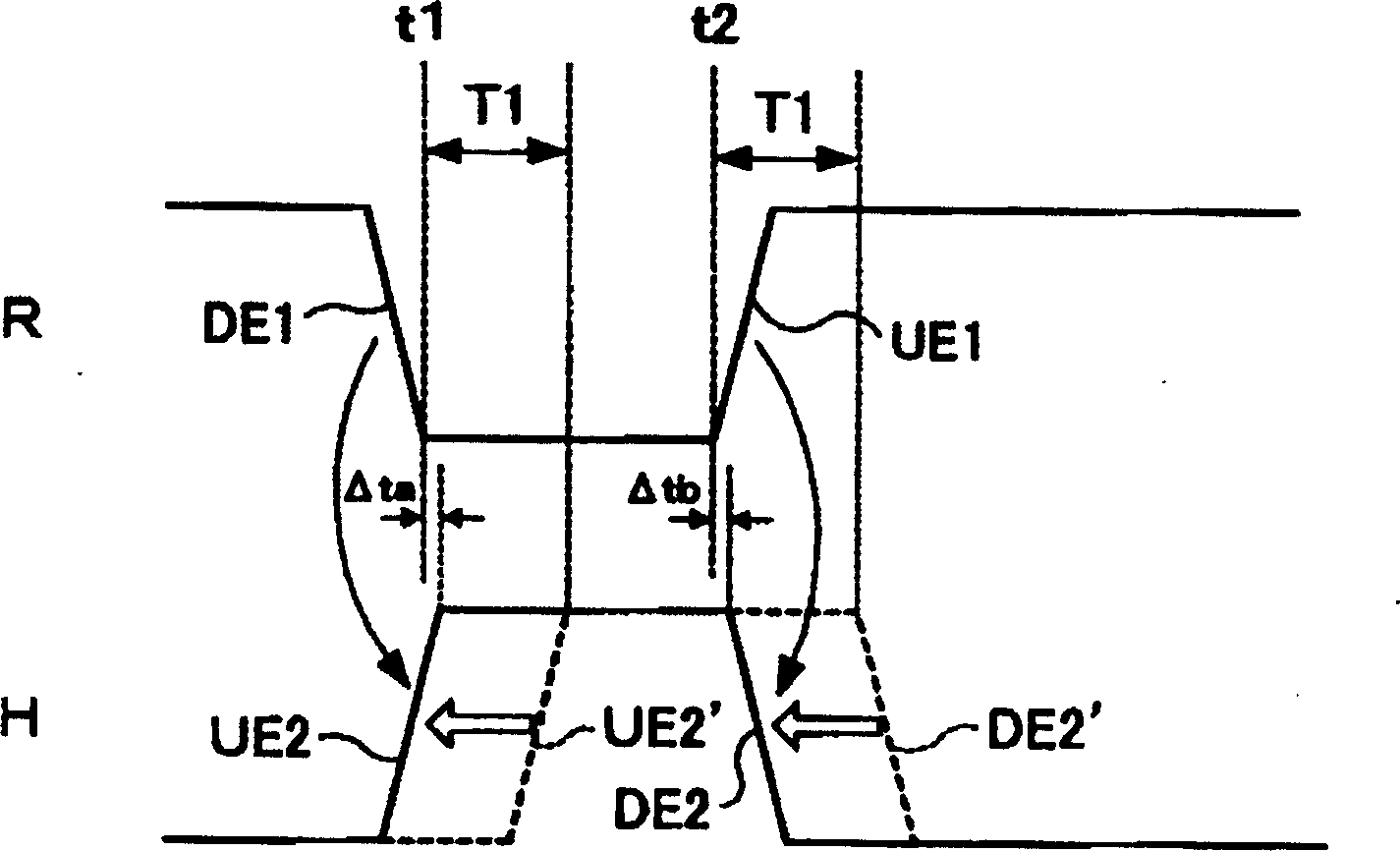

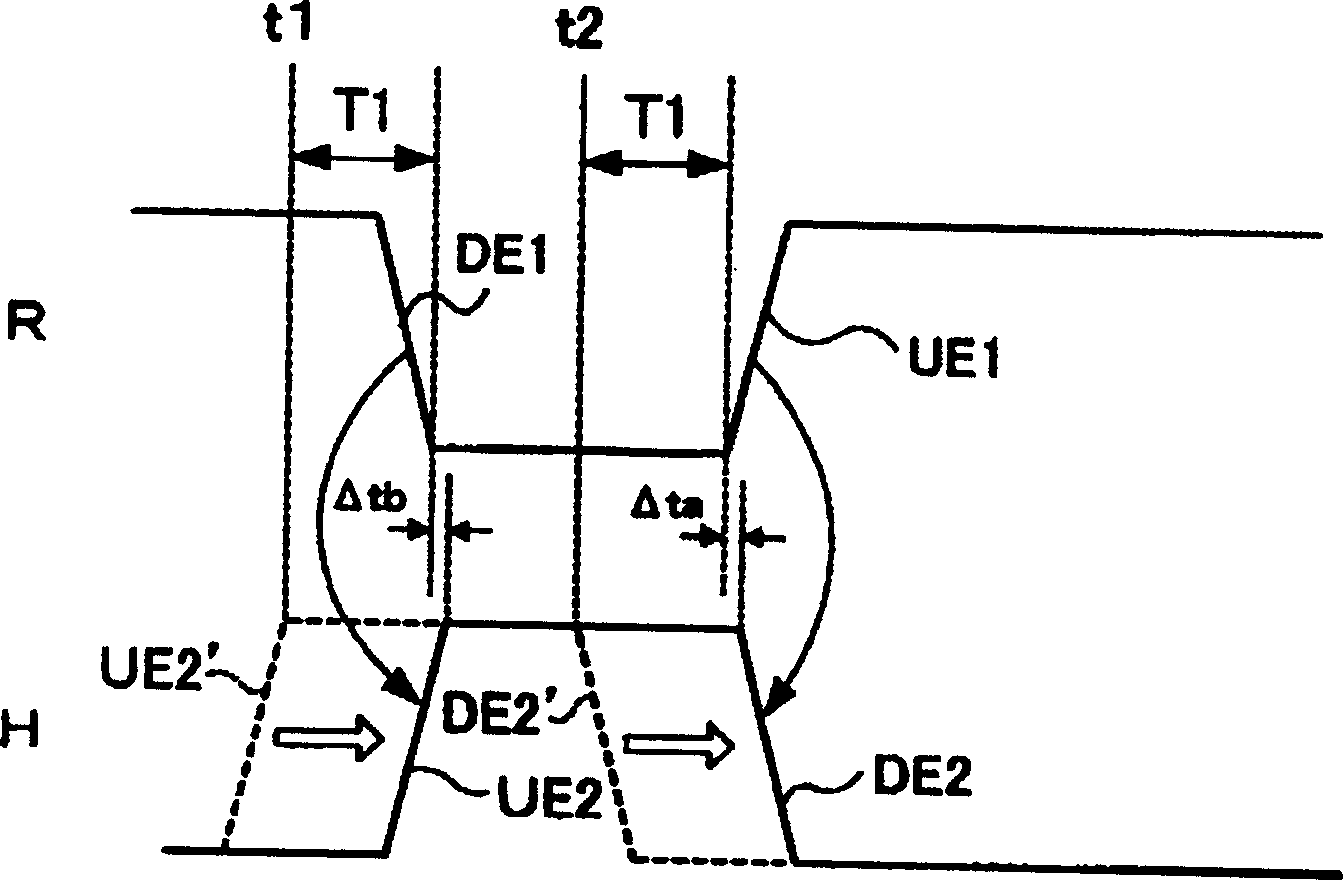

Pellicle

To facilitate the estimation of the delay time between an input and an output. Inverters INV1 and INV4 generate a reference signal R and a signal to-be-corrected H on the basis of an input positive-logic signal Pin and an input negative-logic signal Nin. Since the reference signal R is transferred through a wiring line Lp, it undergoes no delay in the process of the transfer. On the other hand, the signal to-be-corrected H undergoes the influence of the reference signal R and has its phase corrected by a NAND circuit 11 and a NOR circuit 12.

Owner:SEIKO EPSON CORP

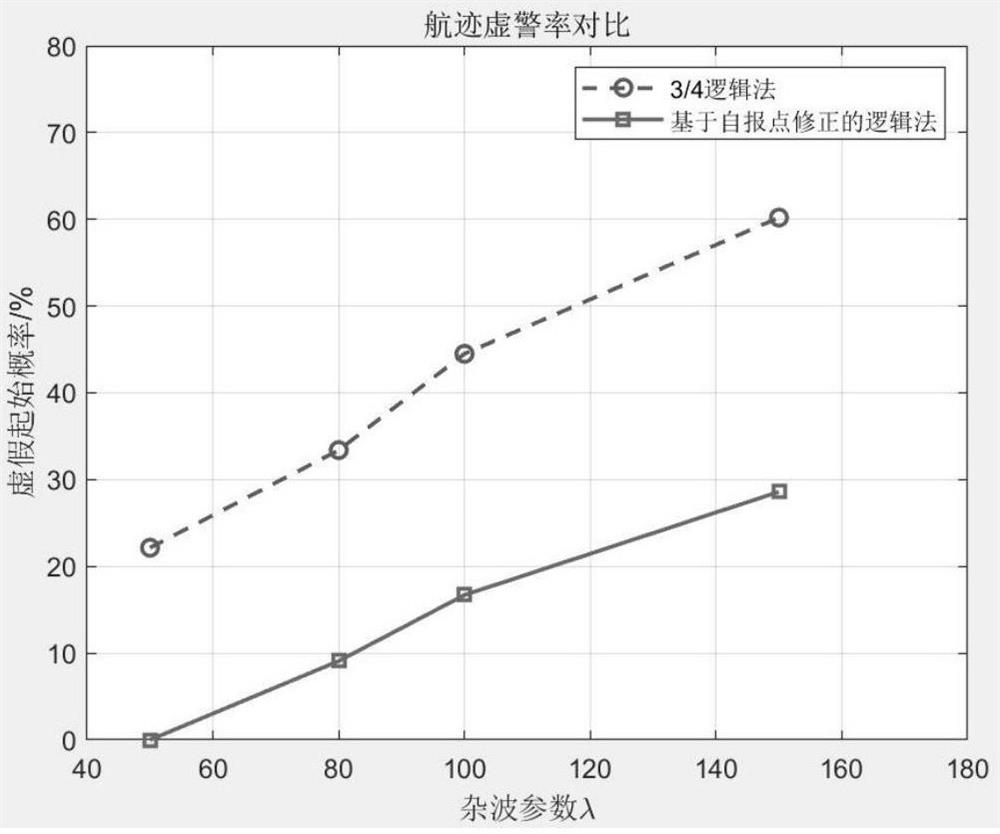

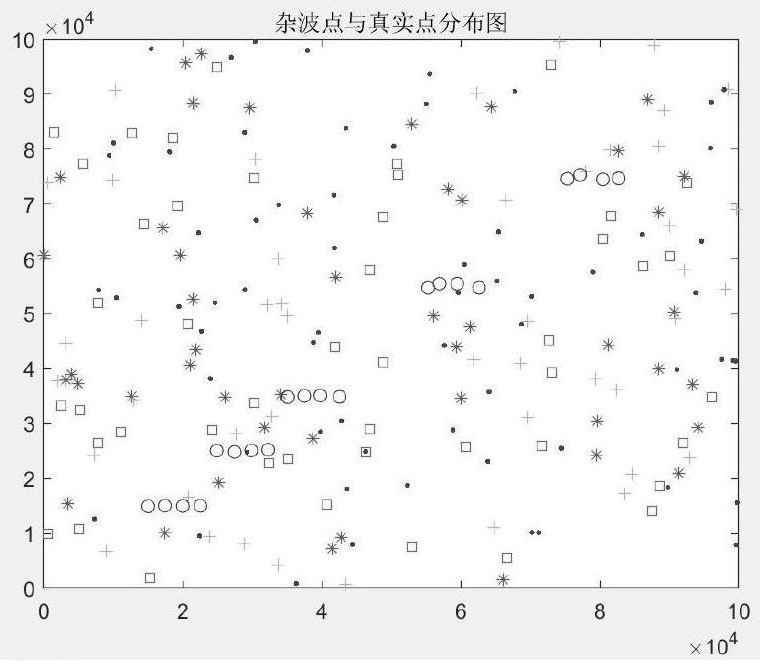

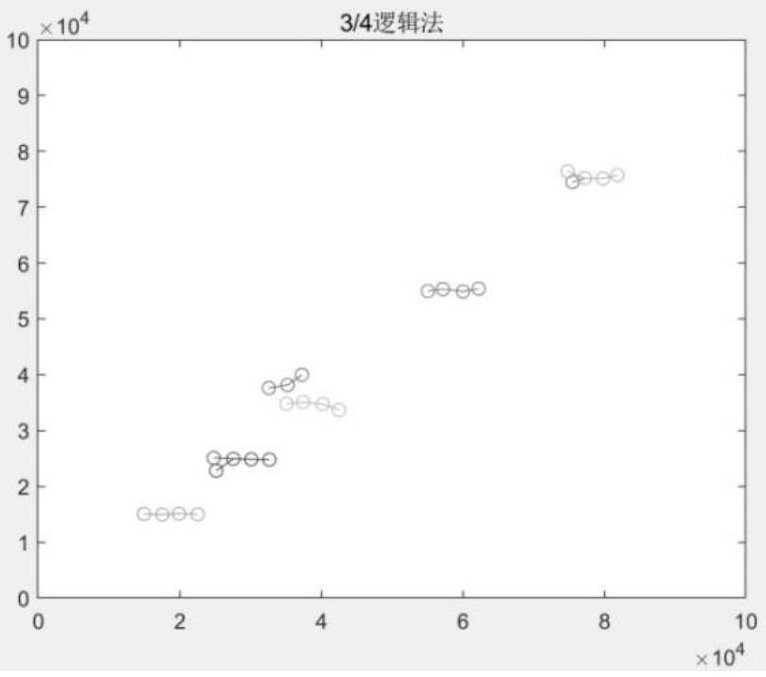

Correction logic method track initiation method based on self-reporting point

ActiveCN113340308AMultiple false numbersNavigational calculation instrumentsCharacter and pattern recognitionAlgorithmPositive logic

The invention provides a correction logic method track initiation method based on a self-reporting point, and belongs to the field of track initiation, and the method comprises the steps: building a temporary track; in the initial correlation gate, setting a clustering threshold by taking the self-reporting point as a core point, and forming a temporary track set according to a standard according to different position relationships of the measurement points in the clustering threshold and the initial correlation gate; extrapolating the temporary track, and adding an angle constraint threshold value to the third measurement falling into the prediction correlation gate; judging the relevance between the measurement and the temporary track, and selecting a corresponding point as a final relevance point according to a standard; and so on, until the start success condition is met or the start condition is not met until the track disappears. The logic starting correction method mainly aims at the unbalance problem that the number of real plots falling into the association gate is large but the false starting rate is low when the track of the m / n logic method starts, meanwhile, the number of the real plots falling into the association gate is not reduced, the false starting probability of the method is low through experimental verification, and the false number of initial tracks is small.

Owner:XIDIAN UNIV

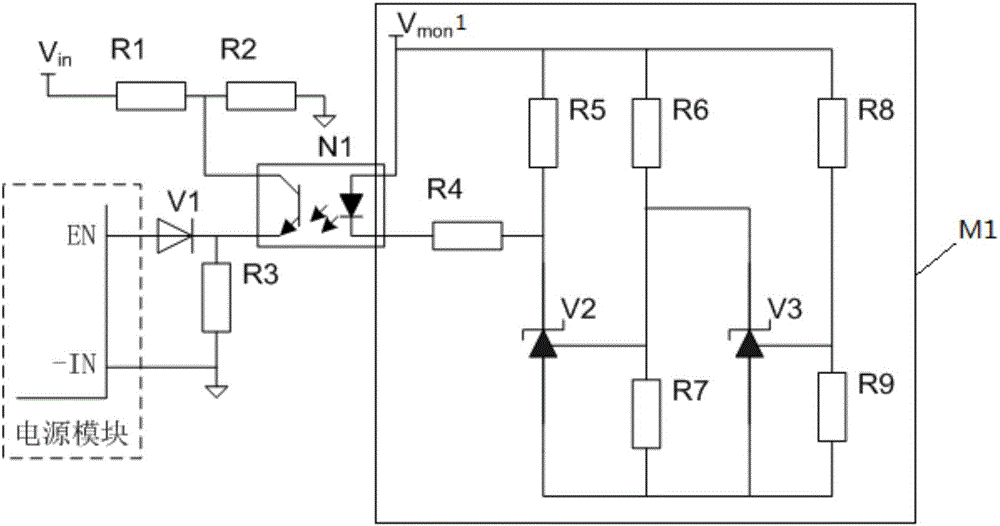

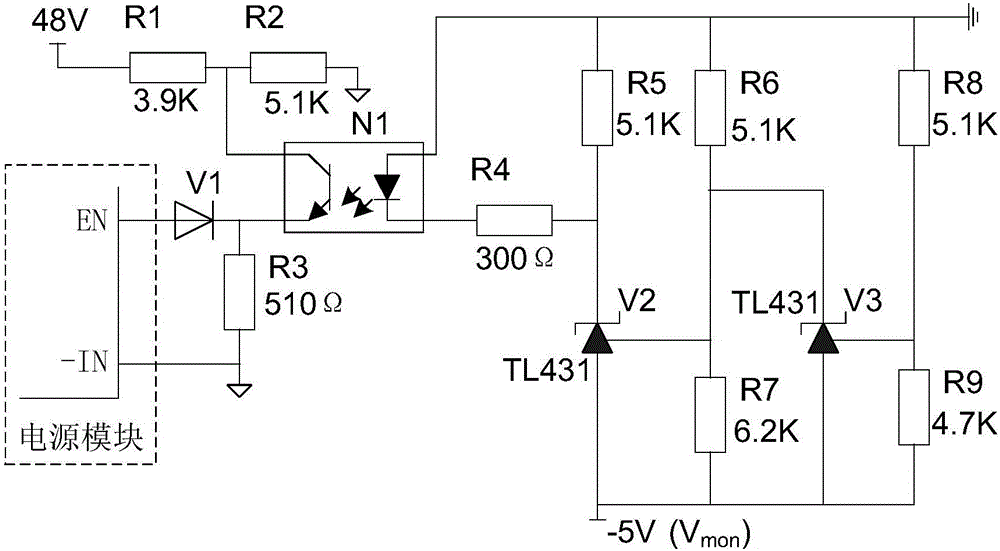

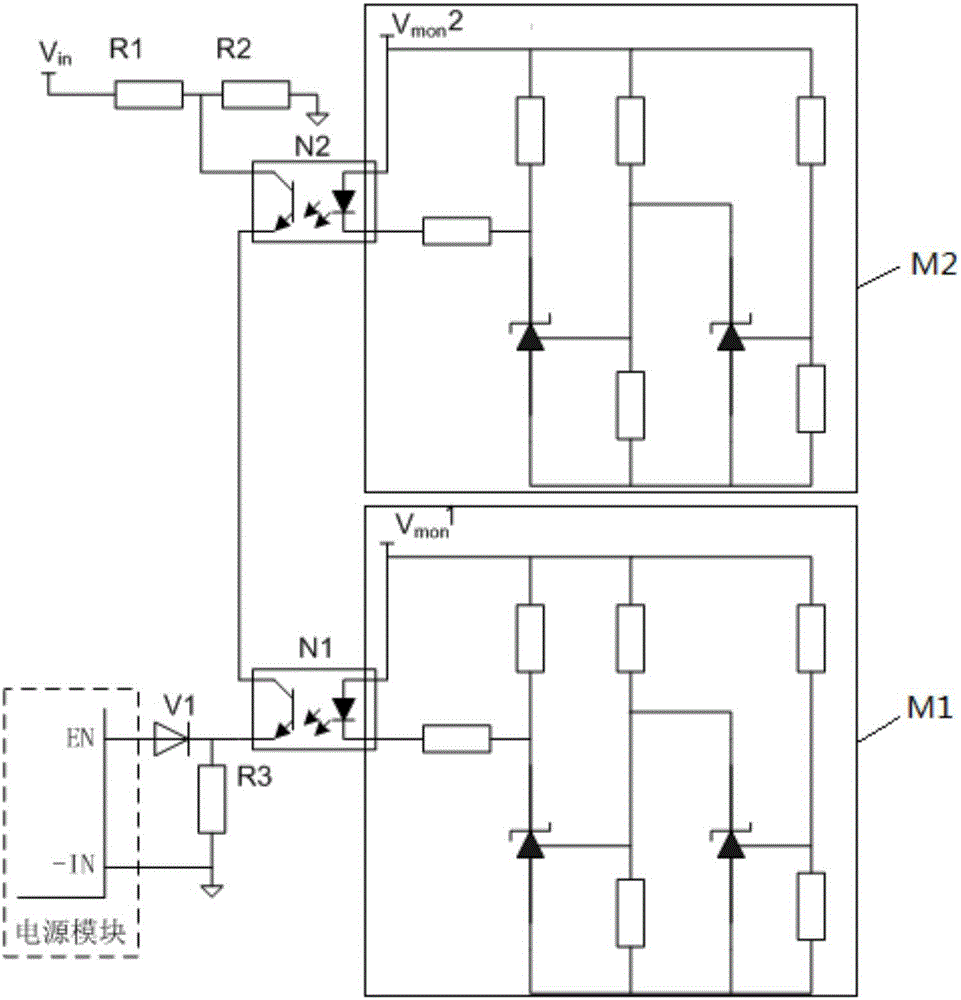

Positive logic enabling power-on control circuit of power supply module

ActiveCN106773639ADoes not affect isolationSimple structureIgnition automatic controlArrangements for smooth engagement/disengagementElectricityLower limit

The invention provides a positive logic enabling power-on control circuit of a power supply module. The positive logic enabling power-on control circuit comprises a diode circuit, a photoelectric isolation coupler, and a zone conduction control circuit. The positive terminal of the diode circuit is connected with an enabling terminal of a power supply module and the negative terminal of the diode circuit is connected with an input negative terminal of the power supply module. A collector of a triode of the photoelectric isolation coupler receives an input voltage and an emitter of the triode is connected with the negative terminal of the diode circuit. The zone conduction control circuit receiving a monitoring voltage of a monitored power supply is used for controlling a light-emitting diode of the photoelectric isolation coupler to be in conduction when the monitoring voltage exceeds a lower limit voltage and does not exceed an upper limit voltage, so that the triode of the photoelectric isolation coupler is in conduction and thus the enabling terminal of the power supply module is disconnected with the input negative terminal and the power supply module outputs the voltage. When the monitoring voltage exceeds the upper limit voltage, the zone conduction control circuit controls the light-emitting diode of the photoelectric isolation coupler to be cut off, so that the triode of the photoelectric isolation coupler is cut off and thus the enabling terminal of the power supply module is connected with the input negative terminal and the power supply module does not output the voltage. Therefore, the load damage resulted from power-on operation can be prevented.

Owner:SHANGHAI SPACEFLIGHT INST OF TT&C & TELECOMM

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com